- 低電源電圧範囲 : 1.8 V ~ 3.6 V

- 超低消費電力 :

- アクティブ・モード : 250  $\mu$ A (1 MHz、2.2 V)

- スタンバイ・モード : 0.7  $\mu$ A

- オフ・モード (RAM データ保持) : 0.1  $\mu$ A

- スタンバイ・モードから 1  $\mu$ s 以下の超高速ウェークアップ

- 16 ビット RISC アーキテクチャ、

65 ns インストラクション・サイクル・タイム

- Basic Clock モジュール構成

- 16 MHz までの内部周波数

(4 つの±1% に校正された周波数)

- 32 kHz クリスタル

- 16 MHz までの高周波数クリスタル

- レゾネータ

- 外部デジタル・クロック源

- 16 ビット タイマ\_A (3 つのキャプチャ/コンペア

・レジスタ付き)

- アナログ信号コンペア機能又はスロープ A/D 変換の

ためのオン・チップ・コンパレータ

- ブラウンアウト検出

- シリアル・オンボード・プログラミング、

外部プログラミング電圧不要、

セキュリティ・ヒューズによるプログラム可能な

コード保護

- ブートストラップ・ローダ

- オン・チップ・エミュレーション・モジュール

- ファミリ製品 :

- MSP430F2101: 1KB + 256B フラッシュ・メモリ、

128B RAM

- MSP430F2111: 2KB + 256B フラッシュ・メモリ、

128B RAM

- MSP430F2121: 4KB + 256B フラッシュ・メモリ、

256B RAM

- MSP430F2131: 8KB + 256B フラッシュ・メモリ、

256B RAM

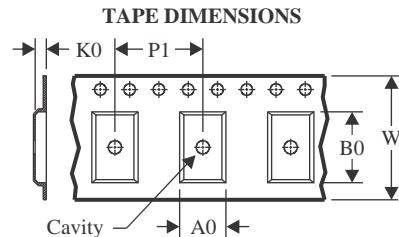

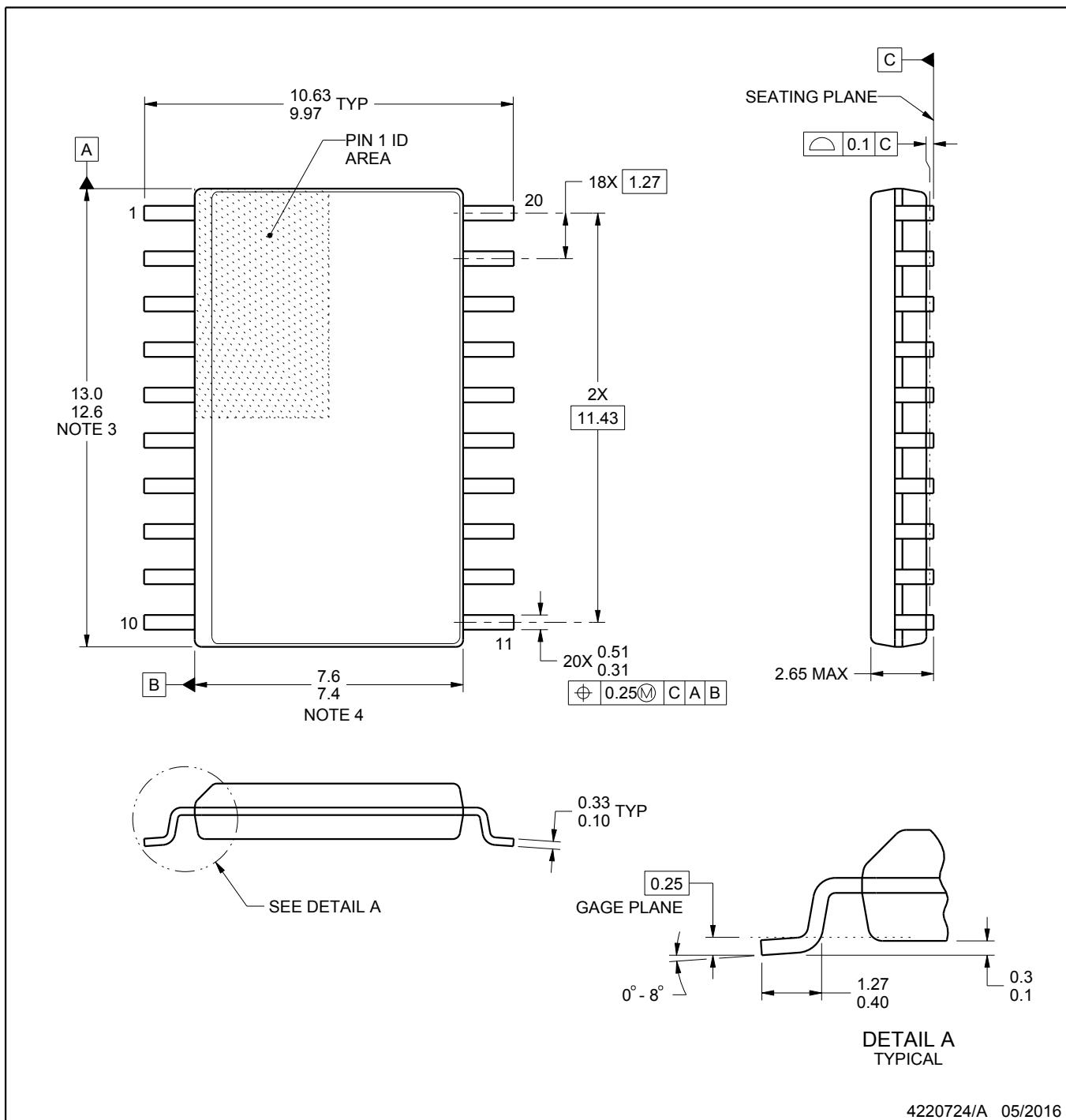

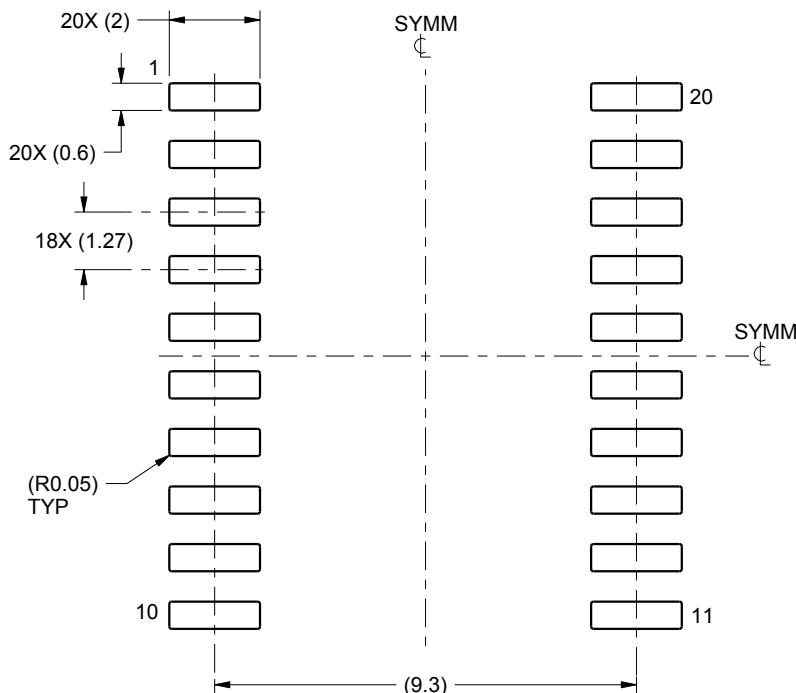

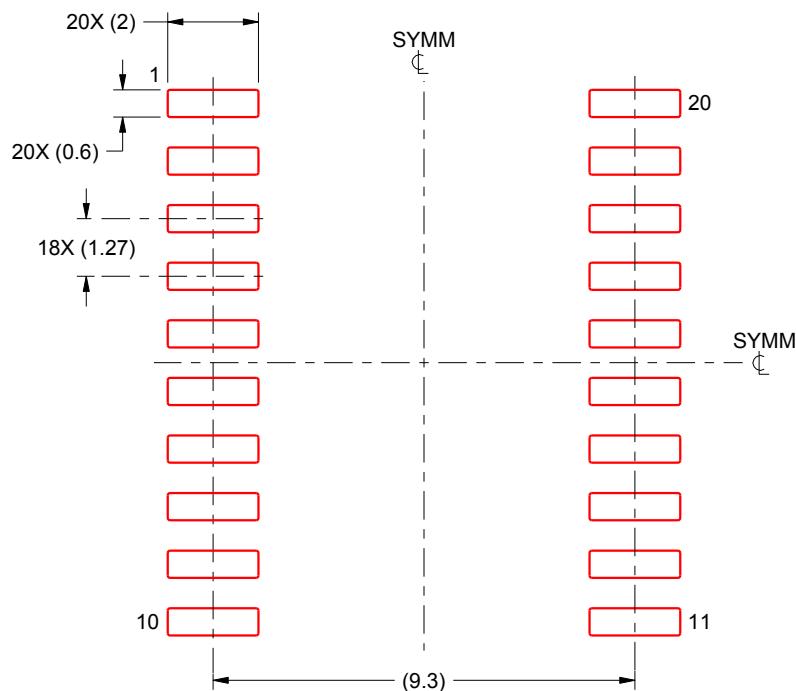

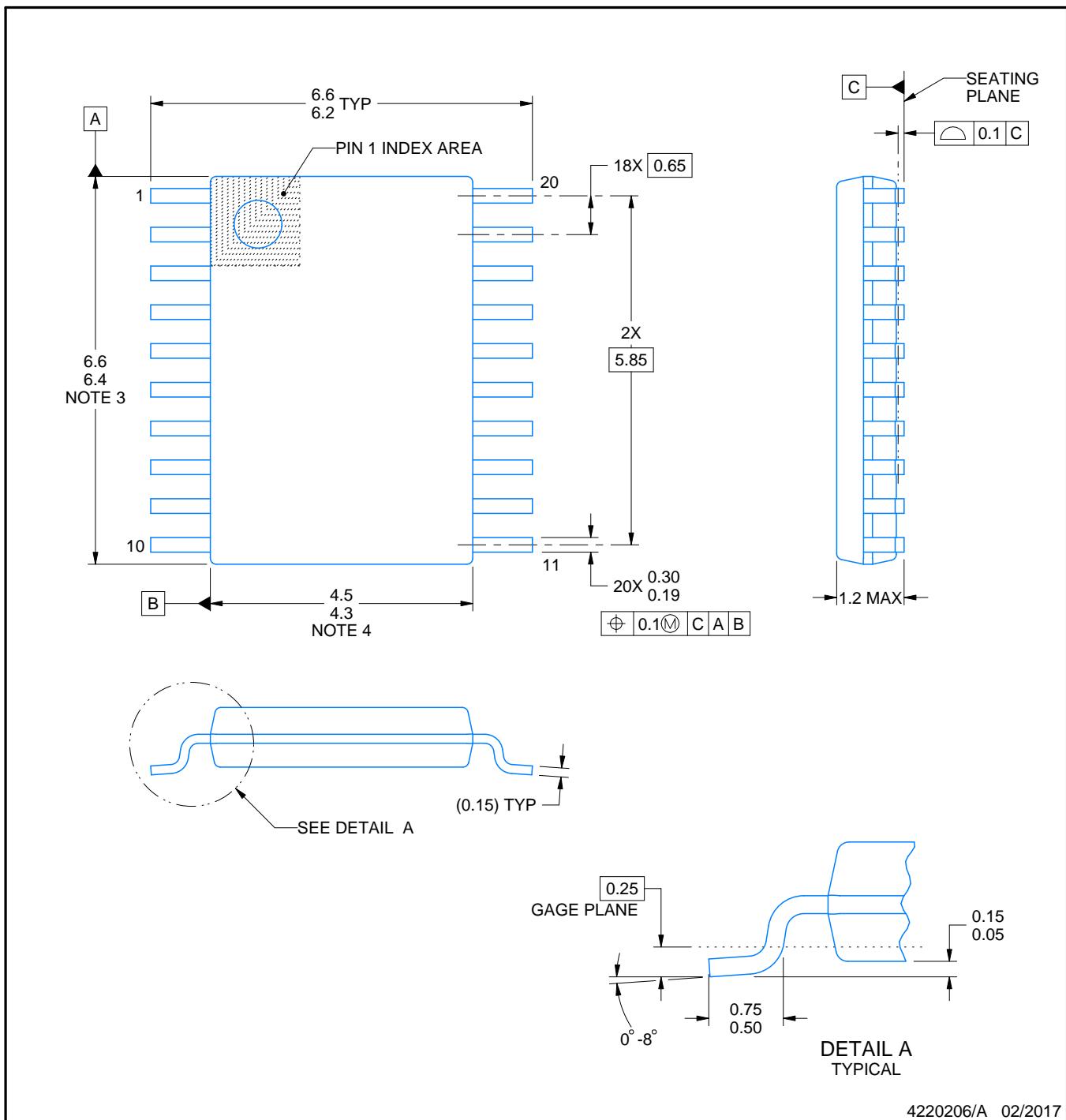

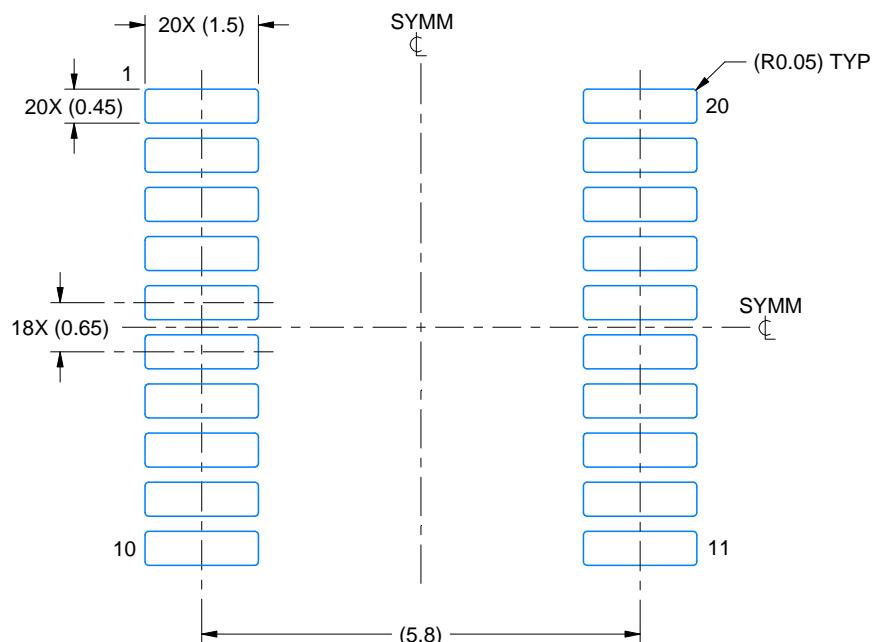

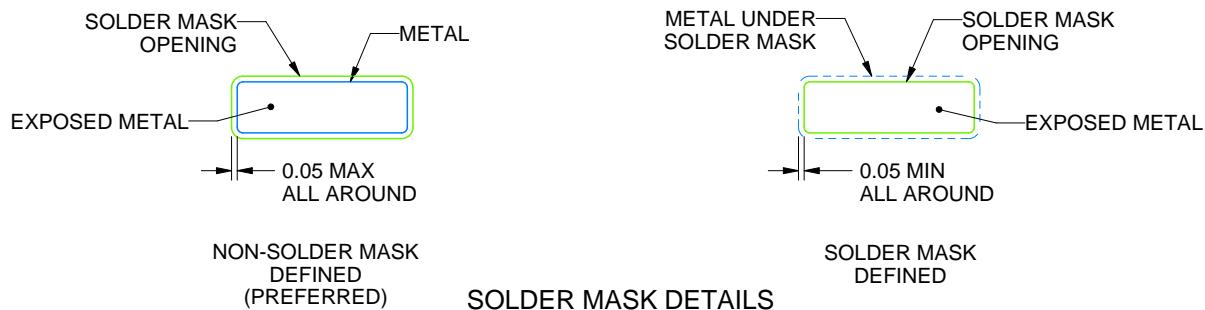

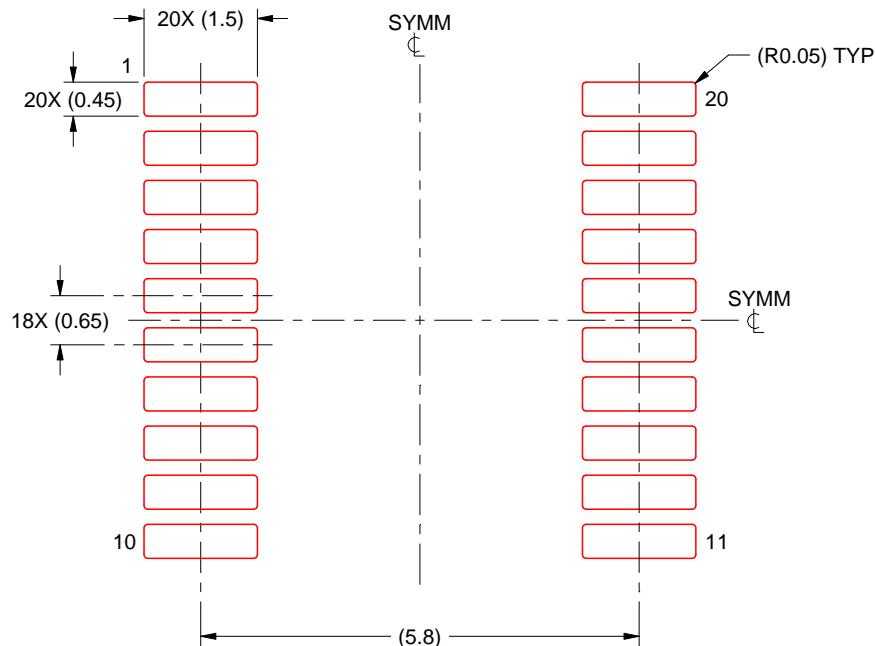

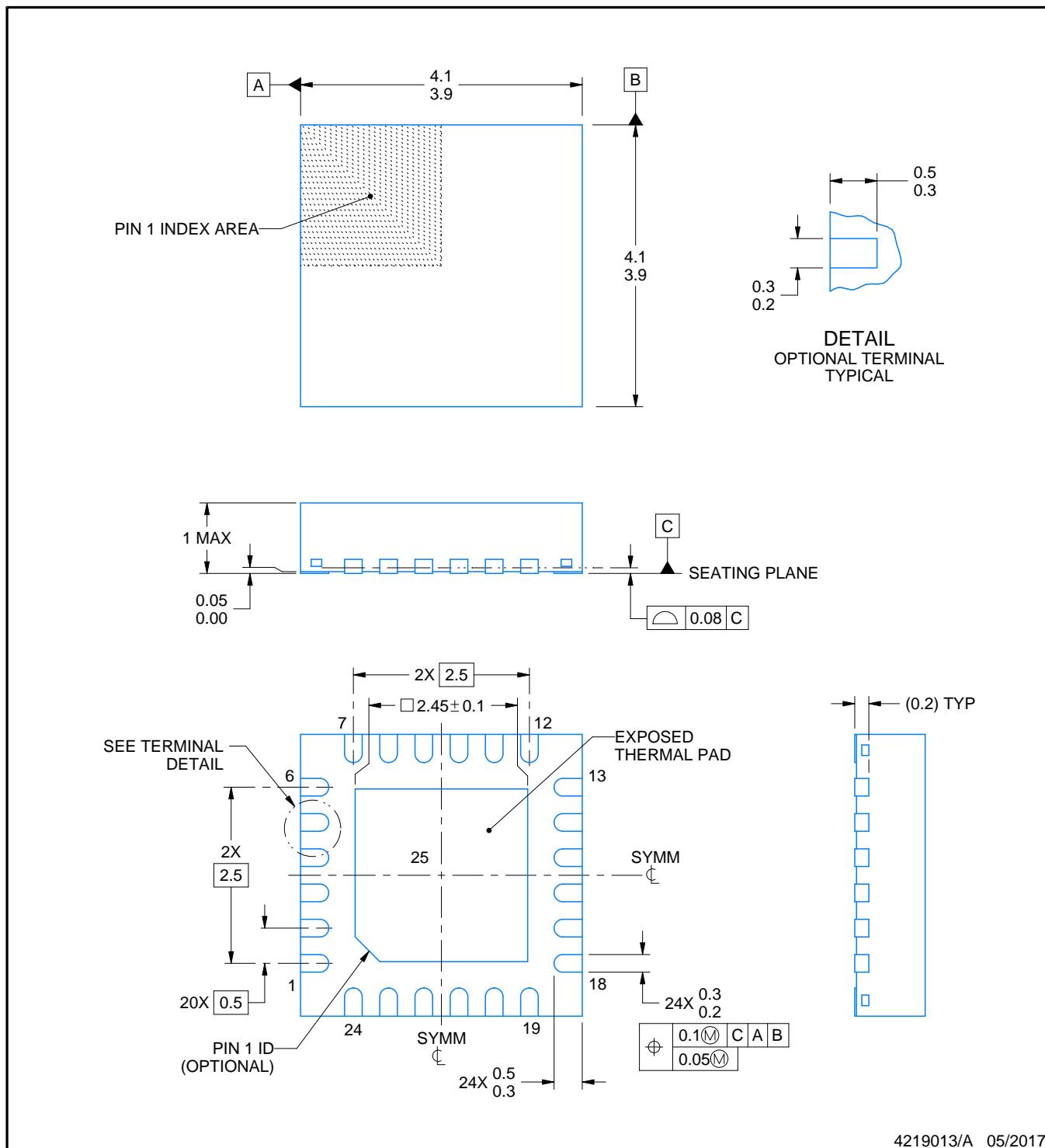

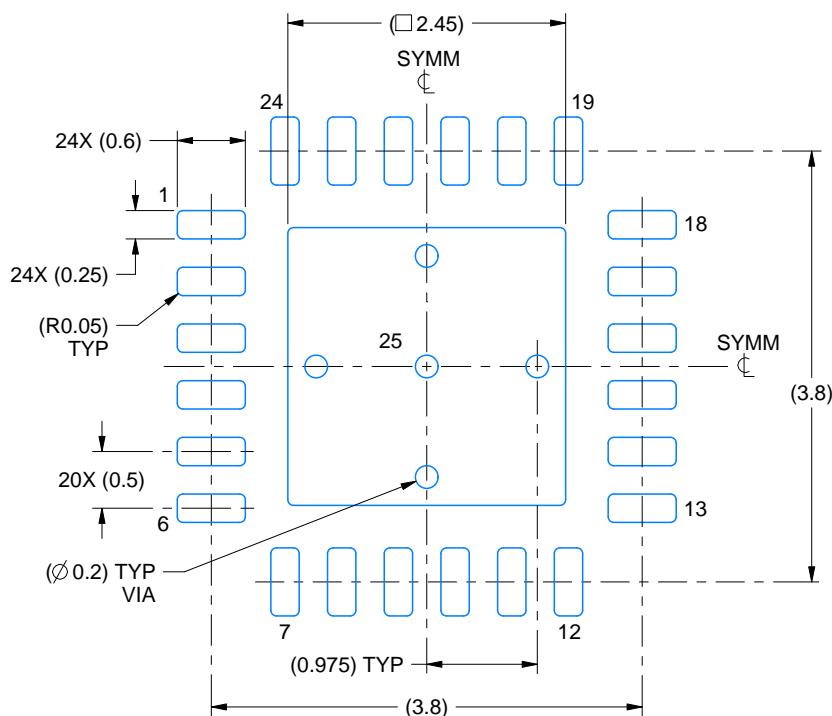

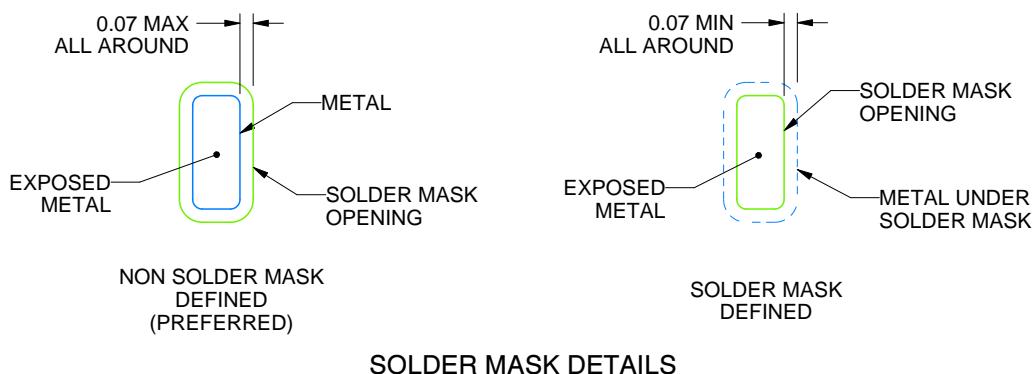

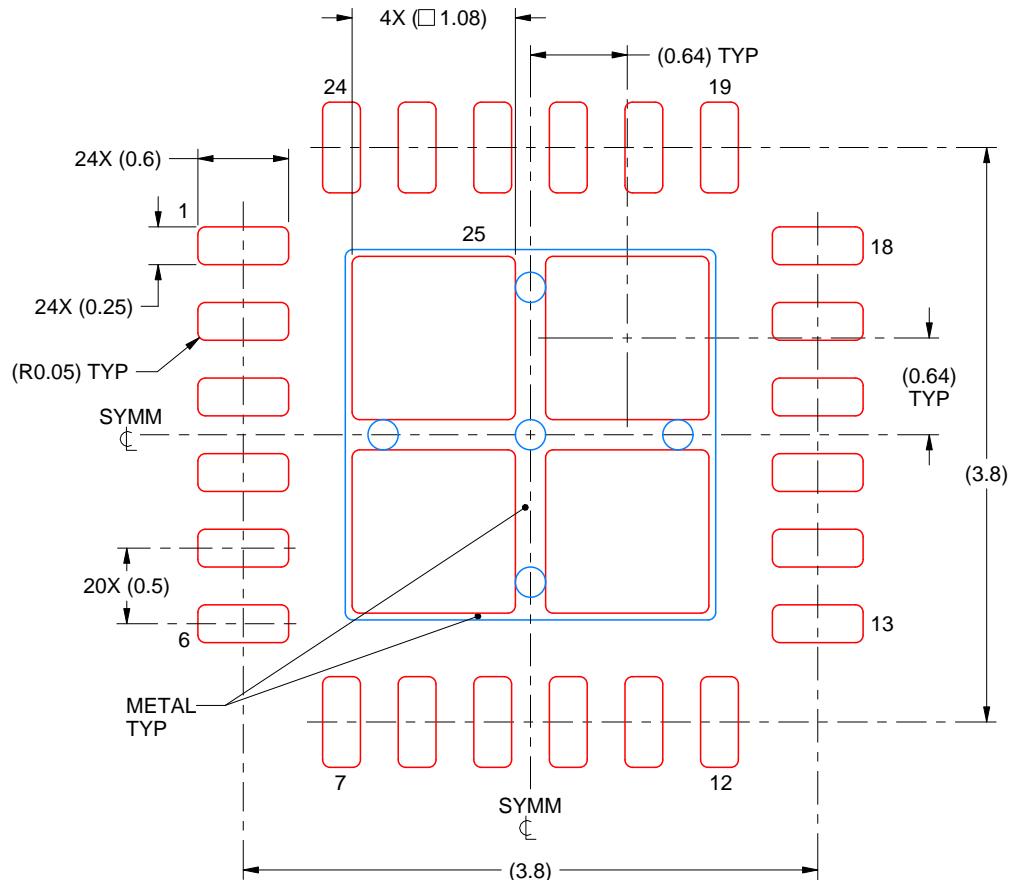

- 20 ピン プラスチック SOWB、20 ピン プラスチック

TSSOP、20 ピン TVSOP、及び 24 ピン QFN パッケージ

- モジュールの詳細は、MSP430x2xx ファミリ ユーザーズ・ガイド を参照して下さい。

## 概要

テキサス・インスツルメンツの超低消費電力マイクロコントローラ MSP430 ファミリは、色々なアプリケーションのための異なる種類のペリフェラル・デバイスで構成されています。5つの低消費電力モードを持ったアーキテクチャは、携帯型計測機器アプリケーションのバッテリ寿命を延ばすために最適化されています。デバイスには、パワフルな 16 ビット RISC CPU、16 ビット レジスタ、及び最大コード効率のためのコンスタント・ジェネレータが搭載されています。デジタル・コントロール・オシレータ (DCO) により、低消費電力モードからアクティブ・モードへのウェークアップが 1  $\mu$ s 以内で行われます。

MSP430x21x1 シリーズは、16 ビット タイマ、多用途アナログ・コンパレータ、及び 16 個の I/O 端子を内蔵した超低消費電力ミックスド・シグナル・マイクロコントローラです。

標準的なアプリケーションとしては、アナログ信号を取得し、デジタル値に変換し、表示のため又はホスト・システムへの送信のためにデータを処理するセンサ・システムがあります。もう 1 つのアプリケーションの分野では、スタンダード・アロン RF センサ・フロント・エンドがあります。アナログ・コンパレータにより、スロープ A/D 変換が可能です。

## 製品オプション

| T <sub>A</sub> | パッケージ・デバイス                                                           |                                                                      |                                                                          |                                                                          |

|----------------|----------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

|                | プラスチック<br>20 ピン SOWB<br>(DW)                                         | プラスチック<br>20 ピン TSSOP<br>(PW)                                        | プラスチック<br>20 ピン TVSOP<br>(DGV)                                           | プラスチック<br>24 ピン QFN<br>(RGE)                                             |

| -40°C ~ 85°C   | MSP430F2101IDW<br>MSP430F2111IDW<br>MSP430F2121IDW<br>MSP430F2131IDW | MSP430F2101IPW<br>MSP430F2111IPW<br>MSP430F2121IPW<br>MSP430F2131IPW | MSP430F2101IDGV<br>MSP430F2111IDGV<br>MSP430F2121IDGV<br>MSP430F2131IDGV | MSP430F2101IRGE<br>MSP430F2111IRGE<br>MSP430F2121IRGE<br>MSP430F2131IRGE |

テキサス・インスツルメンツの半導体製品の供給状況、標準保証、及び重大用途における使用に関しては、重要なご注意がこのデータ・シートの終わりに掲載されていますので、ご参照下さい。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討及びご採用にあたりましては、必ず正規英語版の最新情報をご確認下さい。TI及び日本TIは、正規英語版にて更新の情報を提供しているにも関わらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

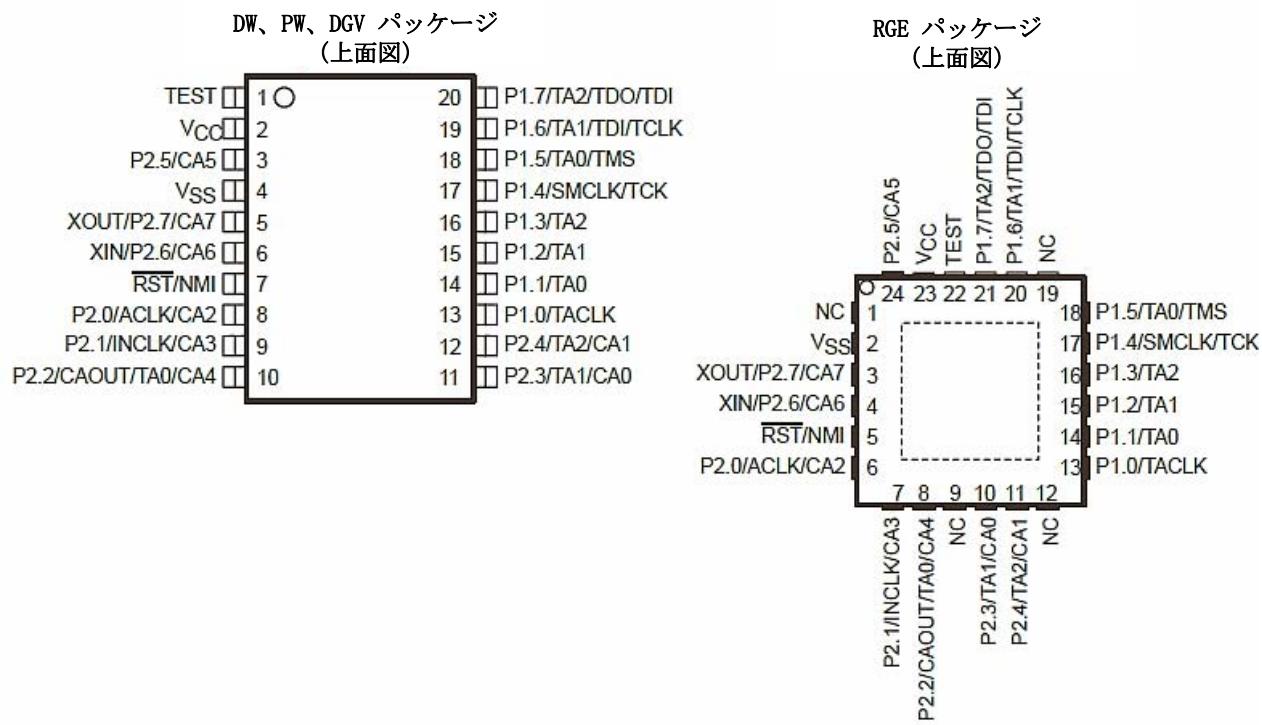

## デバイス ピン配置

(注) NC 端子は内部で接続されていません。

放熱パッドは V<sub>SS</sub> に接続することを推奨します。

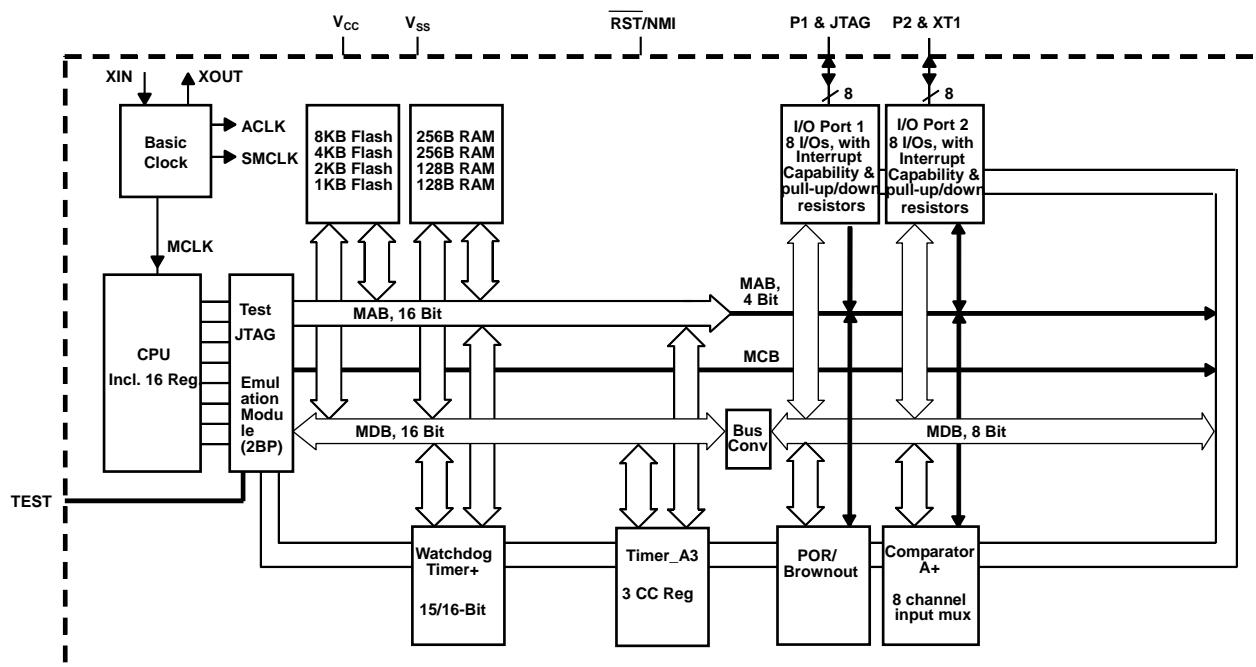

## 機能ブロック図

(注) I/O 情報の詳細は、ポート図のセクションを参照して下さい。

端子機能表

| 端子                 |                 |           |     | 機能                                                                            |

|--------------------|-----------------|-----------|-----|-------------------------------------------------------------------------------|

| 名前                 | DW、PW、DGV<br>番号 | RGE<br>番号 | I/O |                                                                               |

| P1.0/TACLK         | 13              | 13        | I/O | 汎用デジタル I/O / タイマ_A、クロック信号 TACLK 入力                                            |

| P1.1/TA0           | 14              | 14        | I/O | 汎用デジタル I/O / タイマ_A、キャプチャ: CCI0A 入力、コンペア: Out0 出力 / BSL 送信                     |

| P1.2/TA1           | 15              | 15        | I/O | 汎用デジタル I/O / タイマ_A、キャプチャ: CCI1A 入力、コンペア: Out1 出力                              |

| P1.3/TA2           | 16              | 16        | I/O | 汎用デジタル I/O / タイマ_A、キャプチャ: CCI2A 入力、コンペア: Out2 出力                              |

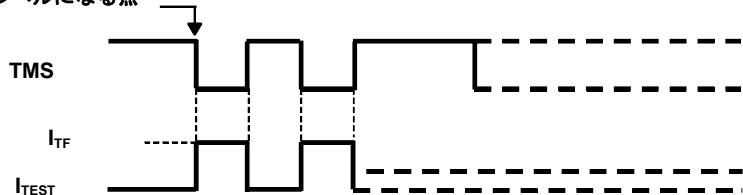

| P1.4/SMCLK/TCK     | 17              | 17        | I/O | 汎用デジタル I/O / SMCLK 信号出力 / テスト・クロック、デバイス・プログラミング及びテストのための入力                    |

| P1.5/TA0/TMS       | 18              | 18        | I/O | 汎用デジタル I/O / タイマ_A、コンペア: Out0 出力 / テスト・モード選択、デバイス・プログラミング及びテストのための入力          |

| P1.6/TA1/TDI/TCLK  | 19              | 20        | I/O | 汎用デジタル I/O / タイマ_A、コンペア: Out1 出力 / テスト・データ入力又はテスト・クロック入力                      |

| P1.7/TA2/TDO/TDI † | 20              | 21        | I/O | 汎用デジタル I/O / タイマ_A、コンペア: Out2 出力 / テスト・データ出力又はプログラミング時のデータ入力                  |

| P2.0/ACLK/CA2      | 8               | 6         | I/O | 汎用デジタル I/O / ACLK 出力 / コンパレータ_A+、CA2 入力                                       |

| P2.1/INCLK/CA3     | 9               | 7         | I/O | 汎用デジタル I/O / タイマ_A、INCLK クロック信号 / コンパレータ_A+、CA3 入力                            |

| P2.2/CAOUT/TA0/CA4 | 10              | 8         | I/O | 汎用デジタル I/O / タイマ_A、キャプチャ: CCI0B 入力 / コンパレータ_A+ 出力 / コンパレータ_A+、CA4 入力 / BSL 受信 |

| P2.3/CA0/TA1       | 11              | 10        | I/O | 汎用デジタル I/O / タイマ_A、コンペア: Out1 出力 / コンパレータ_A+、CA0 入力                           |

| P2.4/CA1/TA2       | 12              | 11        | I/O | 汎用デジタル I/O / タイマ_A、コンペア: Out2 出力 / コンパレータ_A+、CA1 入力                           |

| P2.5/CA5           | 3               | 24        | I/O | 汎用デジタル I/O / コンパレータ_A+、CA5 入力                                                 |

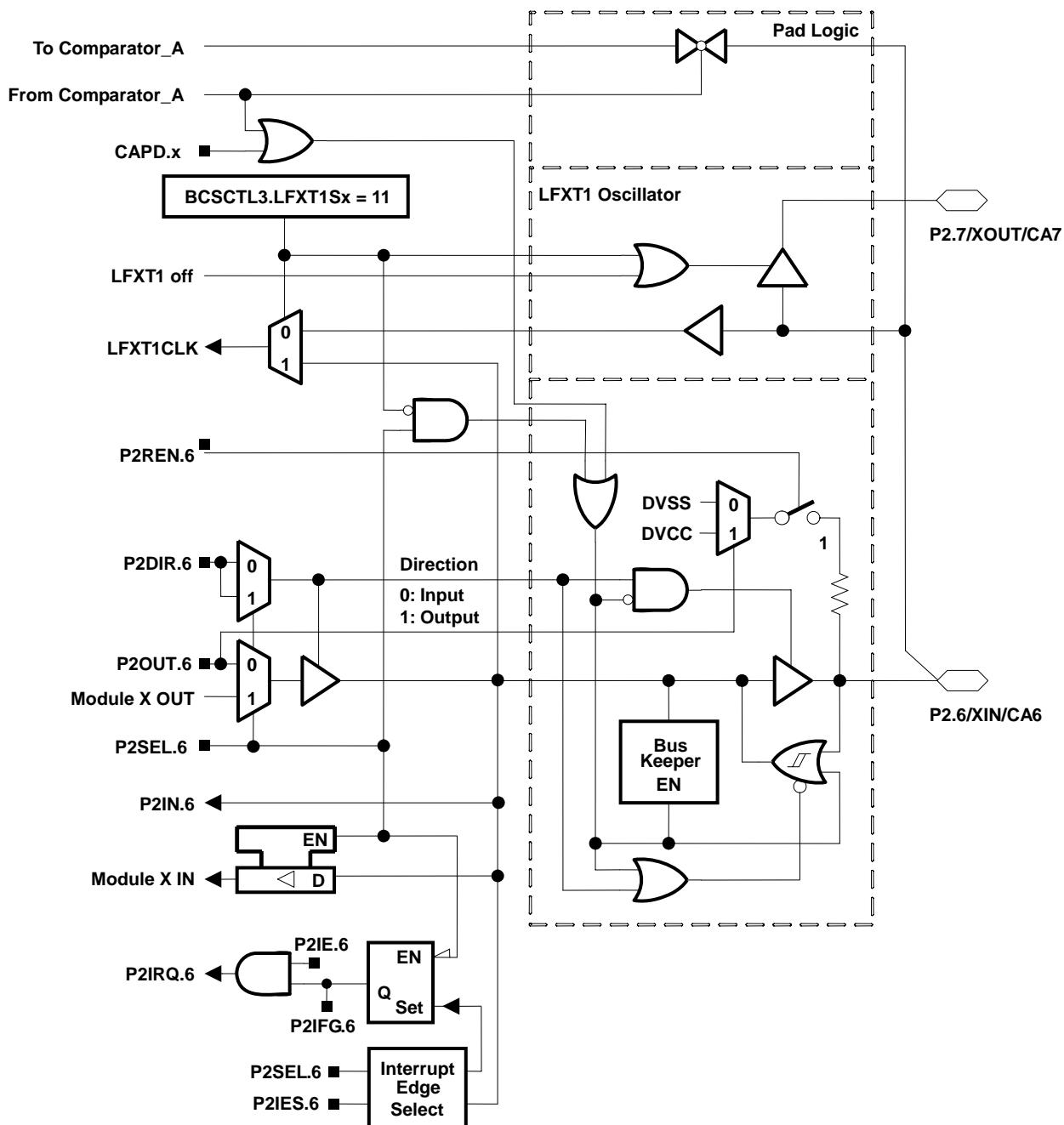

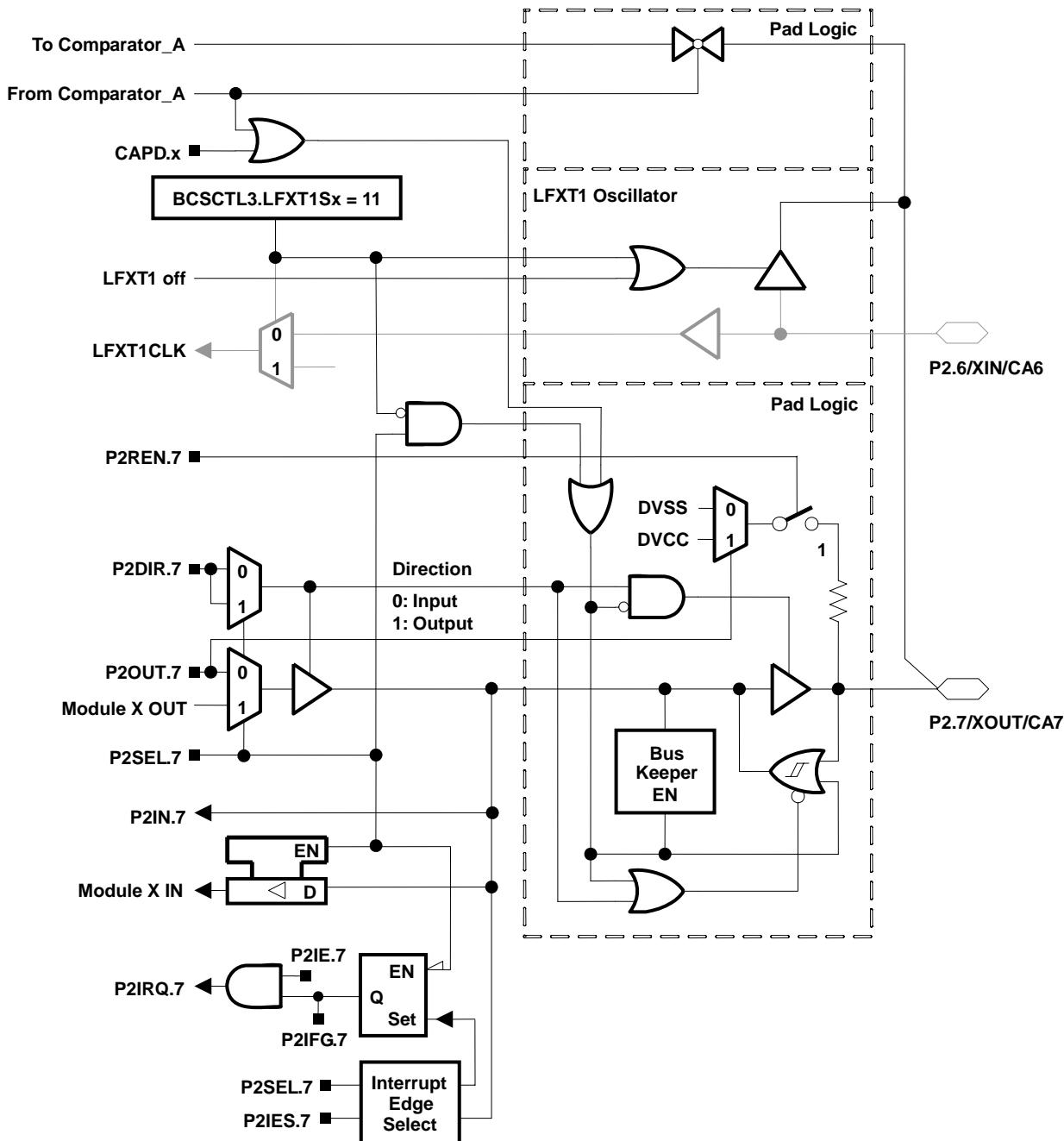

| XIN/P2.6/CA6       | 6               | 4         | I/O | クリスタル・オシレータ入力 / 汎用デジタル I/O / コンパレータ_A+、CA6 入力                                 |

| XOUT/P2.7/CA7      | 5               | 3         | I/O | クリスタル・オシレータ出力 / 汎用デジタル I/O / コンパレータ_A+、CA7 入力                                 |

| RST/NMI            | 7               | 5         | I   | リセット又はマスク不可能な割り込み入力                                                           |

| TEST               | 1               | 22        | I   | ポート1 JTAG 端子のテスト・モードの選択入力。デバイス保護ヒューズが TEST に接続されています。                         |

| V <sub>cc</sub>    | 2               | 23        |     | 電源                                                                            |

| V <sub>ss</sub>    | 4               | 2         |     | グランド基準                                                                        |

| QFN パッド            | NA              | パッケージ・パッド | NA  | QFN パッケージのパッドは V <sub>ss</sub> に接続することを推奨します。                                 |

† TDO 又は TDI は JTAG 命令によって選択されます。

(注) XOUT/P2.7/CA7 が入力として使用されている場合は、P2SEL.7 がクリアされるまでは過剰な電流が流れます。これは、リセットの後、オシレータの出力ドライバがこの端子に接続されるためです。

## 概要説明

## CPU

MSP430 CPU には、アプリケーションに適した 16 ビット RISC アーキテクチャを搭載しています。プログラム・プロセ・インストラクション以外のすべての動作は、ソース・オペランドのための 7 つのアドレッシング・モード及びデスティネーション・オペランドのための 4 つのアドレッシング・モードと共にレジスタ・オペレーションとして実行されます。

CPU は、命令実行時間を短縮する 16 個のレジスタを内蔵しています。レジスタ間のオペレーション実行時間は、CPU クロックの 1 サイクルです。

レジスタの内の 4 個 (R0～R3) は、それぞれプログラム・カウンタ、スタック・ポインタ、ステータス・レジスタ、及びコンスタント・ジェネレータ (定数発生回路) として割り当てられています。残りのレジスタは、汎用レジスタです。

ペリフェラルは、データ、アドレス、及びコントロール・バスを使って CPU に接続され、すべての命令によって取り扱うことができます。

## 命令セット

命令セットは 3 つのフォーマット及び 7 つのアドレス・モードを持った 51 の命令からなります。各々の命令は、ワード及びバイト・データに基づいて実行することができます。表 1 に命令フォーマットの 3 つのタイプの例を示します。表 2 にアドレス・モードを示します。

|               |           |

|---------------|-----------|

| プログラム・カウンタ    | PC/R0     |

| スタック・ポインタ     | SP/R1     |

| ステータス・レジスタ    | SR/CG1/R2 |

| コンスタント・ジェネレータ | CG2/R3    |

| 汎用レジスタ        | R4        |

| 汎用レジスタ        | R5        |

| 汎用レジスタ        | R6        |

| 汎用レジスタ        | R7        |

| 汎用レジスタ        | R8        |

| 汎用レジスタ        | R9        |

| 汎用レジスタ        | R10       |

| 汎用レジスタ        | R11       |

| 汎用レジスタ        | R12       |

| 汎用レジスタ        | R13       |

| 汎用レジスタ        | R14       |

| 汎用レジスタ        | R15       |

表 1. 命令ワード・フォーマット

|                            |              |                       |

|----------------------------|--------------|-----------------------|

| デュアル・オペランド (ソース-デスティネーション) | 例、ADD R4, R5 | R4 + R5 → R5          |

| シングル・オペランド (デスティネーションのみ)   | 例、CALL R8    | PC → (TOS), R8 → PC   |

| 相対ジャンプ (無条件/条件付き)          | 例、JNE        | Jump-on-equal bit = 0 |

表 2 アドレス・モード

| アドレス・モード       | S | D | 構文               | 例                 | 動作                            |

|----------------|---|---|------------------|-------------------|-------------------------------|

| レジスタ           | ● | ● | MOV Rs, Rd       | MOV R10, R11      | R10 → R11                     |

| インデックス         | ● | ● | MOV X(Rn), Y(Rm) | MOV 2(R5), 6(R6)  | M(2+R5) → M(6+R6)             |

| シンボリック (PC 対応) | ● | ● | MOV EDE, TONI    |                   | M(EDE) → M(TONI)              |

| 絶対             | ● | ● | MOV &MEM, &TCDAT |                   | M(MEM) → M(TCDAT)             |

| 間接             | ● |   | MOV @Rn, Y(Rm)   | MOV @R10, Tab(R6) | M(R10) → M(Tab+R6)            |

| 間接 (自動インクリメント) | ● |   | MOV @Rn+, Rm     | MOV @R10+, R11    | M(R10) → R11<br>R10 + 2 → R10 |

| 即時             | ● |   | MOV #X, TONI     | MOV #45, TONI     | #45 → M(TONI)                 |

(注) S = ソース、D = デスティネーション

## 動作モード

MSP430 には、1 つのアクティブ・モードと、ソフトウェアで選択可能な 5 つの低消費電力動作モードがあります。割り込みイベントにより、デバイスを 5 つの低消費電力モードのどれからでもウェークアップすることができ、要求に応え、そして、割り込みプログラムから戻るのに伴って低消費電力モードに戻ることができます。

以下の 6 つの動作モードを、ソフトウェアによって構成することができます：

- アクティブ・モード AM；

- すべてのクロックはアクティブ

- 低消費電力モード 0 (LPM0)；

- CPU はディスエーブル

- ACLK 及び SMCLK はアクティブのまま。MCLK はディスエーブル

- 低消費電力モード 1 (LPM1)；

- CPU はディスエーブル

- ACLK 及び SMCLK はアクティブのまま。MCLK はディスエーブル

- アクティブ・モードで DCO が使用されない場合は、DCO の DC 発生回路はディスエーブル

- 低消費電力モード 2 (LPM2)；

- CPU はディスエーブル

- MCLK 及び SMCLK はディスエーブル

- DCO の DC 発生回路はイネーブルのまま

- ACLK はアクティブのまま

- 低消費電力モード 3 (LPM3)；

- CPU はディスエーブル

- MCLK 及び SMCLK はディスエーブル

- DCO の DC 発生回路はディスエーブル

- ACLK はアクティブのまま

- 低消費電力モード 4 (LPM4)；

- CPU はディスエーブル

- ACLK はディスエーブル

- MCLK 及び SMCLK はディスエーブル

- DCO の DC 発生回路はディスエーブル

- クリスタル・オシレータは停止

## 割り込みベクタ・アドレス

割り込みベクタ及びパワー・アップの開始アドレスは、アドレス範囲 0FFFFh ~ 0FFC0h に位置します。ベクタは、適切な割り込み処理命令シーケンスの 16 ビット・アドレスを含みます。

もし、リセット・ベクタ（アドレス 0FFEh に配置）が 0FFFh を含む（すなわち、フラッシュ・メモリがプログラムされていない）場合、CPU はパワー・アップの直後に LPM4 に移行します。

| 割り込みソース                                                           | 割り込みフラグ                                     | システム割り込み                                  | ワード・アドレス          | 優先順位              |

|-------------------------------------------------------------------|---------------------------------------------|-------------------------------------------|-------------------|-------------------|

| パワー・アップ<br>外部リセット<br>ウォッチドッグ<br>フラッシュ・キー違反<br>PC アウト・オブ・レンジ (注 1) | PORIFG<br>RSTIFG<br>WDTIFG<br>KEYV<br>(注 2) | リセット                                      | 0FFEh             | 31<br>(最上位)       |

| NMI<br>オシレータ障害<br>フラッシュ・メモリ アクセス違反                                | NMIIFG<br>OFIFG<br>ACCVIFG<br>(注 2, 4)      | マスク可能 (不可能)<br>マスク可能 (不可能)<br>マスク可能 (不可能) | 0FFFCCh           | 30                |

|                                                                   |                                             |                                           | 0FFF8h            | 29                |

|                                                                   |                                             |                                           | 0FFF6h            | 28                |

| コンパレータ_A+                                                         | CAIFG                                       | マスク可能                                     | 0FFF4h            | 27                |

| ウォッチドッグ・タイマ                                                       | WDTIFG                                      | マスク可能                                     | 0FFF2h            | 26                |

| タイマ_A2                                                            | TACCR0 CCIFG (注 3)                          | マスク可能                                     | 0FFF0h            | 25                |

| タイマ_A2                                                            | TACCR1 CCIFG、<br>TAIFG (注 2, 3)             | マスク可能                                     | 0FFEh             | 24                |

|                                                                   |                                             |                                           | 0FFECh            | 23                |

|                                                                   |                                             |                                           | 0FFE2h            | 22                |

|                                                                   |                                             |                                           | 0FFE0h            | 21                |

|                                                                   |                                             |                                           | 0FFE8h            | 20                |

| I/O ポート P2<br>(8 つのフラグ)                                           | P2IFG.0 ~ P2IFG.7<br>(注 2, 3)               | マスク可能                                     | 0FFE6h            | 19                |

| I/O ポート P1<br>(8 つのフラグ)                                           | P1IFG.0 ~ P1IFG.7<br>(注 2, 3)               | マスク可能                                     | 0FFE4h            | 18                |

|                                                                   |                                             |                                           | 0FFE2h            | 17                |

|                                                                   |                                             |                                           | 0FFE0h            | 16                |

| (注 5)                                                             |                                             |                                           | 0FFDEh            | 15                |

| (注 6)                                                             |                                             |                                           | 0FFDCh ... 0FFC0h | 14 ... 0<br>(最下位) |

(注 1) CPU が、モジュールのレジスタ・メモリ・アドレス範囲 (0h ~ 01FFh) から命令をフェッチしようとした場合に、リセットが生成されます。

(注 2) 複数のソース・フラグ

(注 3) 割り込みフラグはモジュールの中にあります。

(注 4) マスク可能 (不可能)：個々の割り込みイネーブル・ビットにより、割り込みイベントをディスエーブルにすることができます。しかし、汎用割り込みイネーブルでは、それをディスエーブルにすることはできません。

(注 5) この場所は、ブートストラップ・ローダ・セキュリティ・キー (BSLSKEY) として使用されます。

この場所を 0AA55h の値にすると、BSL は完全にディスエーブルになります。

この場所を 0h の値にすると、無効なパスワードが入力された場合にフラッシュの消去をディスエーブルにします。

(注 6) アドレス 0FFDCh ~ 0FFC0h までの割り込みベクタは、このデバイスでは使用されませんが、必要な場合は通常のプログラム・コードとして使用することができます。

## スペシャル・ファンクション・レジスター

ほとんどの割り込み及びモジュール・インエーブル・ビットは、最も低いアドレス空間に集められています。機能の目的で割り当てられていないスペシャル・ファンクション・レジスタ・ビットは、物理的にデバイスの中に存在しませんので、この配列によってソフトウェアのアクセスが簡単になります。

## 割り込みイネーブル 1、2

Address 0h

|        | 7    | 6 | 5    | 4      | 3 | 2 | 1    | 0     |

|--------|------|---|------|--------|---|---|------|-------|

| ACCVIE |      |   |      | NMIIIE |   |   | OFIE | WDTIE |

|        | rw-0 |   | rw-0 |        |   |   | rw-0 | rw-0  |

WDTIE: ウオッチドッグ・タイマ割り込みイネーブル。ウォッチドッグ・モードが選択された場合はインアクティブとなります。ウォッチドッグ・タイマがインターバル・タイマ・モードとして構成された場合はアクティブとなります。

OFIE : オシレータ障害イネーブル

NMTTE: マスク可能な(不可能な)割り込みイネーブル

ACCYIE: フラッシュ・アクヤス違反割り込みイネーブル

A horizontal diagram showing memory address 01b. The address is divided into two bytes: 01 and b. The byte 01 is further divided into four nibbles: 0, 1, 2, and 3. The byte b is divided into four nibbles: 4, 5, 6, and 7. Each nibble is represented by a vertical line segment. The nibble 0 is at the bottom, followed by 1, 2, and 3 at the top. The nibble 4 is at the bottom, followed by 5, 6, and 7 at the top. The nibble 0 is at the bottom, followed by 1, 2, and 3 at the top. The nibble 4 is at the bottom, followed by 5, 6, and 7 at the top.

### 割り込みフラグ・レジスタ 1、2

| Address | 7 | 6 | 5 | 4      | 3      | 2      | 1     | 0      |

|---------|---|---|---|--------|--------|--------|-------|--------|

| 02h     |   |   |   | NMIIFG | RSTIFG | PORIFG | OFIFG | WDTIFG |

WDTIFG : ウオッチドッグ・タイマ・オーバーフロー (ウォッチドッグ・モード) 又はセキュリティ・ブレーカー

$V_{CC}$  パワー・アップ又はリセット・モードでの RST/NMI 端子のリセット条件でリセットされます。

OEIEC: オシレータ障害でフラグがセットされまく

RSTIFG: 外部リセット割り込みフラグ。リセット・モードでの RST/NMI 端子のリセット条件でセットされます。パワー・アップでリセットされます。

PORTEG: パワー・オン・リセット割り込みフラグ V. パワー・アップでセットされます。

NMT/REG : RST/NMT 端子でセットされます

## 說明

rw: ビットは 読み出し及び書き込みをすることができます

読み出しおよび書き込みをすることができます。PUC によりリセット又はセリットされます。

rw-(0,1): ビットは、読み出し及び書き込みをすることができます。POR によりリセット又はセットされます。

デバイスには、SFR ビットが存在しません。

## メモリ構成

|                                     |                       | MSP430F2101                                     | MSP430F2111                                     | MSP430F2121                                     | MSP430F2131                                     |

|-------------------------------------|-----------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| メモリ<br>メイン: 割り込みベクタ<br>メイン: コード・メモリ | サイズ<br>フラッシュ<br>フラッシュ | 1KB フラッシュ<br>0FFFFh - OFFE0h<br>0FFFFh - OFC00h | 2KB フラッシュ<br>0FFFFh - OFFE0h<br>0FFFFh - OF800h | 4KB フラッシュ<br>0FFFFh - OFFE0h<br>0FFFFh - OF000h | 8KB フラッシュ<br>0FFFFh - OFFE0h<br>0FFFFh - OE000h |

|                                     | サイズ<br>フラッシュ          | 256 バイト<br>010FFh - 01000h                      |

| 情報メモリ                               | サイズ<br>ROM            | 1KB<br>0FFFFh - 0C00h                           | 1KB<br>0FFFFh - 0C00h                           | 1KB<br>0FFFFh - 0C00h                           | 1KB<br>0FFFFh - 0C00h                           |

|                                     | RAM                   | 128 バイト<br>027Fh - 0200h                        | 128 バイト<br>027Fh - 0200h                        | 256 バイト<br>02FFh - 0200h                        | 256 バイト<br>02FFh - 0200h                        |

| ペリフェラル                              |                       | 16 ビット<br>8 ビット<br>8 ビット SFR                    | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h       | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h       | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h       |

## ブートストラップ・ローダ (BSL)

MSP430 ブートストラップ・ローダ (BSL) により、ユーザーは UART シリアル・インターフェースを使用してフラッシュ・メモリ又は RAM をプログラムすることができます。BSL を経由した MSP430 メモリへのアクセスは、ユーザーによって定義されたパスワードにより保護されています。BSL を完全にディスエーブルにしたり、無効なパスワードが入力された場合にフラッシュの消去をディスエーブルにしたりするために、ブートストラップ・ローダ・セキュリティ・キーがアドレス OFFDEh に用意されています。BSL 及びその実施方法の詳細は、アプリケーション・レポート *MSP430 ブートストラップ・ローダの特徴* "Features of the MSP430 Bootstrap Loader" (資料番号 SLAA089) を参照して下さい。

| BSLKEY | 動作                                      |

|--------|-----------------------------------------|

| 00000h | 無効なパスワードが入力された場合、ディスエーブルされたフラッシュ・メモリを消去 |

| 0AA55h | BSL はディスエーブル                            |

| その他の値  | BSL はイネーブル                              |

| BSL 機能 | DW、PW、DGV パッケージ・ピン | RGE パッケージ・ピン |

|--------|--------------------|--------------|

| データ送信  | 14 - P1.1          | 14 - P1.1    |

| データ受信  | 10 - P2.2          | 8 - P2.2     |

## フラッシュ・メモリ

フラッシュ・メモリは、JTAG ポート、ブートストラップ・ローダ、又は CPU によるイン・システムによりプログラムすることができます。CPU はフラッシュ・メモリに対して、1 バイト及び 1 ワードの書き込みを行うことができます。フラッシュ・メモリは、以下の特徴を持っています。:

- フラッシュ・メモリは、n セグメントのメイン・メモリ及び 4 セグメントのそれぞれ 64 バイトの情報メモリ (A ~ D) を持っています。メイン・メモリのそれぞれのセグメントのサイズは 512 バイトです。

- セグメント 0 ~ n は 1 ステップで消去が可能です。あるいは、それぞれのセグメントは個々に消去も可能です。

- セグメント A ~ D は、個々に又はセグメント 0 ~ n のグループとして消去することができます。セグメント A ~ D は、情報メモリとも呼ばれます。

- セグメント A にはキャリブレーション・データが含まれています。リセットの後、セグメント A はプログラミング又は消去に対して保護されています。そのロックは外すことができますが、キャリブレーション・データが必要な場合は、このセグメントを消去しないように注意しなければなりません。

## ペリフェラル

ペリフェラルは、データ、アドレス、及びコントロール・バスを通して CPU に接続され、すべての命令を使って取り扱うことができます。モジュールの詳細は、MSP430x2xx ファミリ ユーザーズ・ガイドを参照して下さい。

### オシレータ及びシステム・クロック

クロック・システムは、32768 Hz の時計用クリスタル・オシレータ、内部デジタル制御オシレータ (DCO)、及び高周波数クリスタル・オシレータのサポートを含む basic clock モジュールで構成されています。basic clock モジュールは、安いシステム・コストと低消費電力の必要条件を満たすように設計されています。内部 DCO は、高速ターン・オン・クロック・ソースを提供し、1  $\mu$ s 以内に安定します。basic clock モジュールは次のクロック信号を提供します：

- 補助クロック (ACLK) : 32768 Hz の時計用クリスタル又は高周波数クリスタルから供給

- メイン・クロック (MCLK) : CPU によって使用されるシステム・クロック

- サブ・メイン・クロック (SMCLK) : ペリフェラル・モジュールによって使用されるサブ・システム・クロック

| DCO キャリブレーション・データ<br>(フラッシュ情報メモリ・セグメント A に入れてメーカーから供給されます。) |                |     |        |

|-------------------------------------------------------------|----------------|-----|--------|

| DCO 周波数                                                     | キャリブレーション・レジスタ | サイズ | アドレス   |

| 1 MHz                                                       | CALBC1_1MHz    | バイト | 010FFh |

|                                                             | CALDC0_1MHz    | バイト | 010FEh |

| 8 MHz                                                       | CALBC1_8MHz    | バイト | 010FDh |

|                                                             | CALDC0_8MHz    | バイト | 010FCh |

| 12 MHz                                                      | CALBC1_12MHz   | バイト | 010FBh |

|                                                             | CALDC0_12MHz   | バイト | 010FAh |

| 16 MHz                                                      | CALBC1_16MHz   | バイト | 010F9h |

|                                                             | CALDC0_16MHz   | バイト | 010F8h |

## プラウンアウト

プラウンアウト回路は、パワー・オン及びパワー・オフ時にデバイスに適切な内部リセット信号を供給するため内蔵されています。

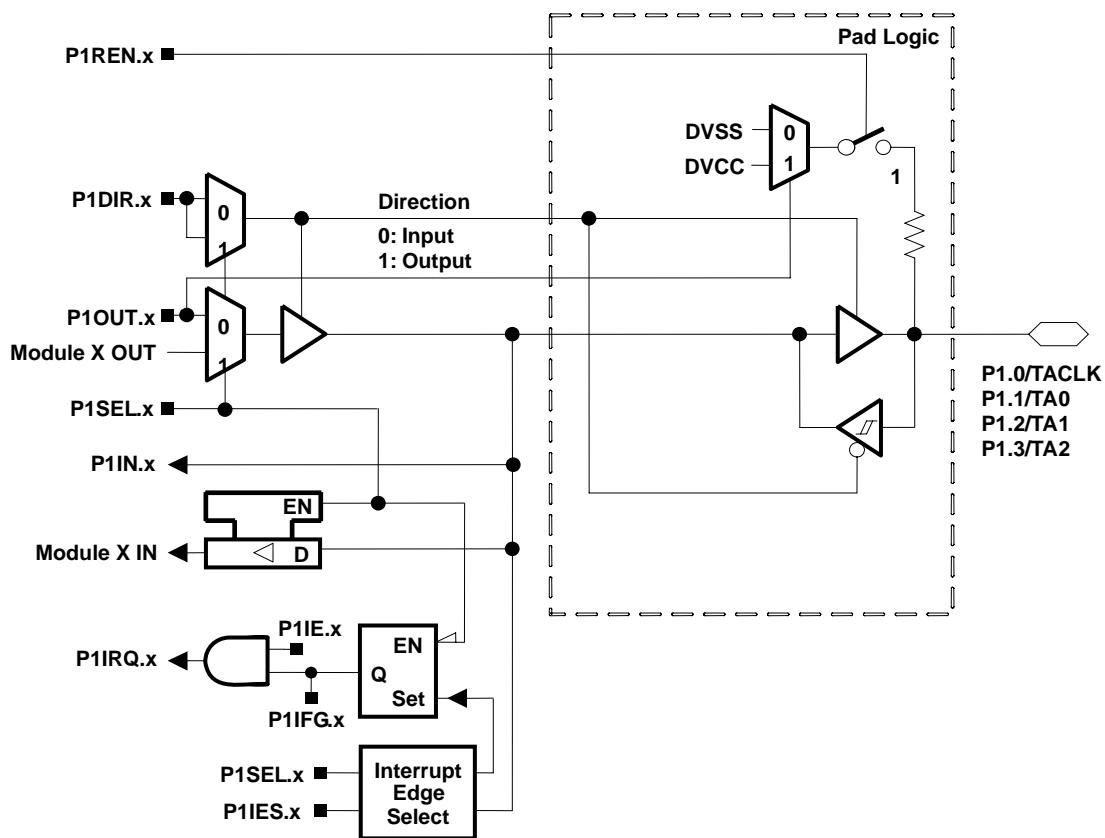

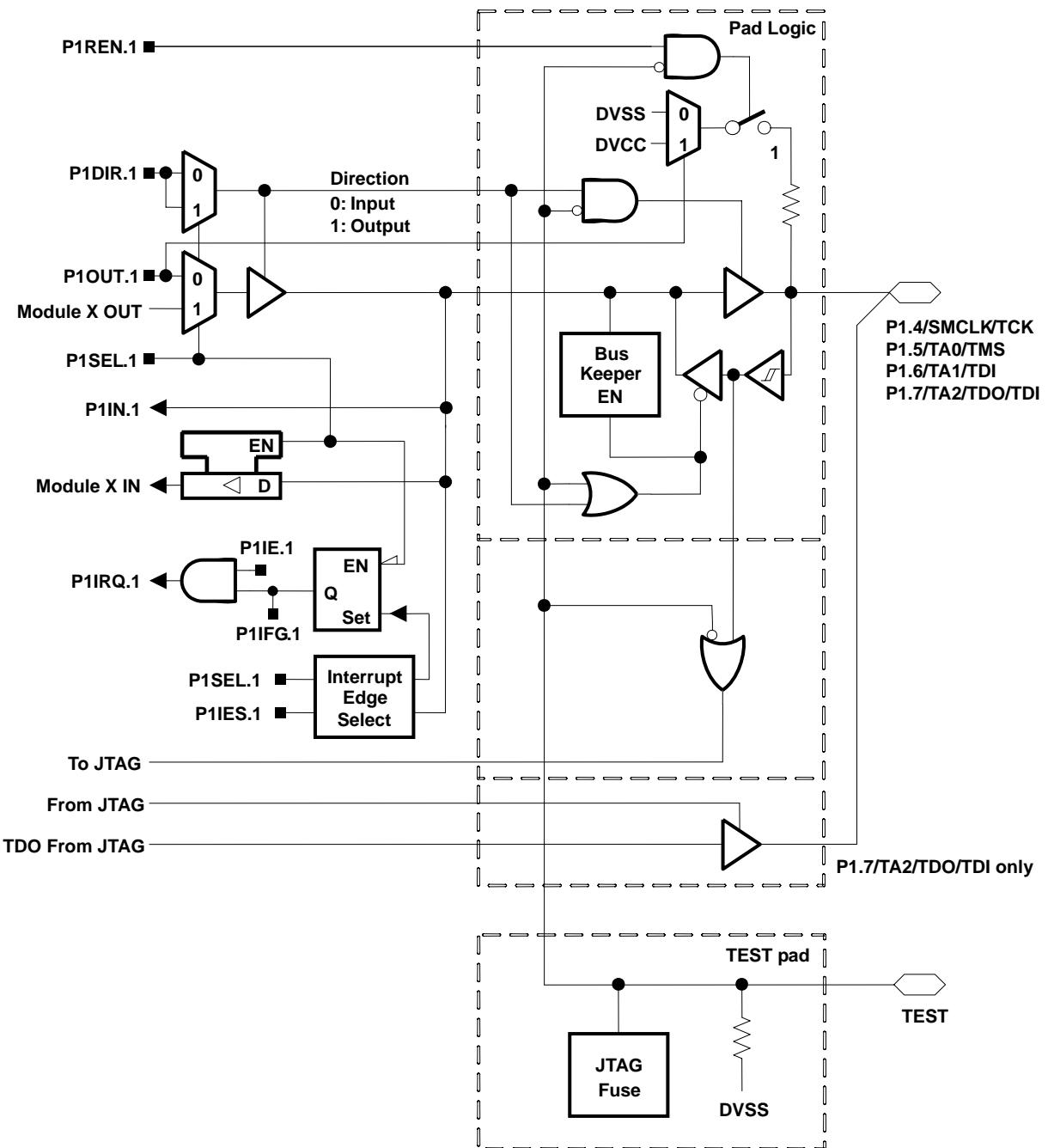

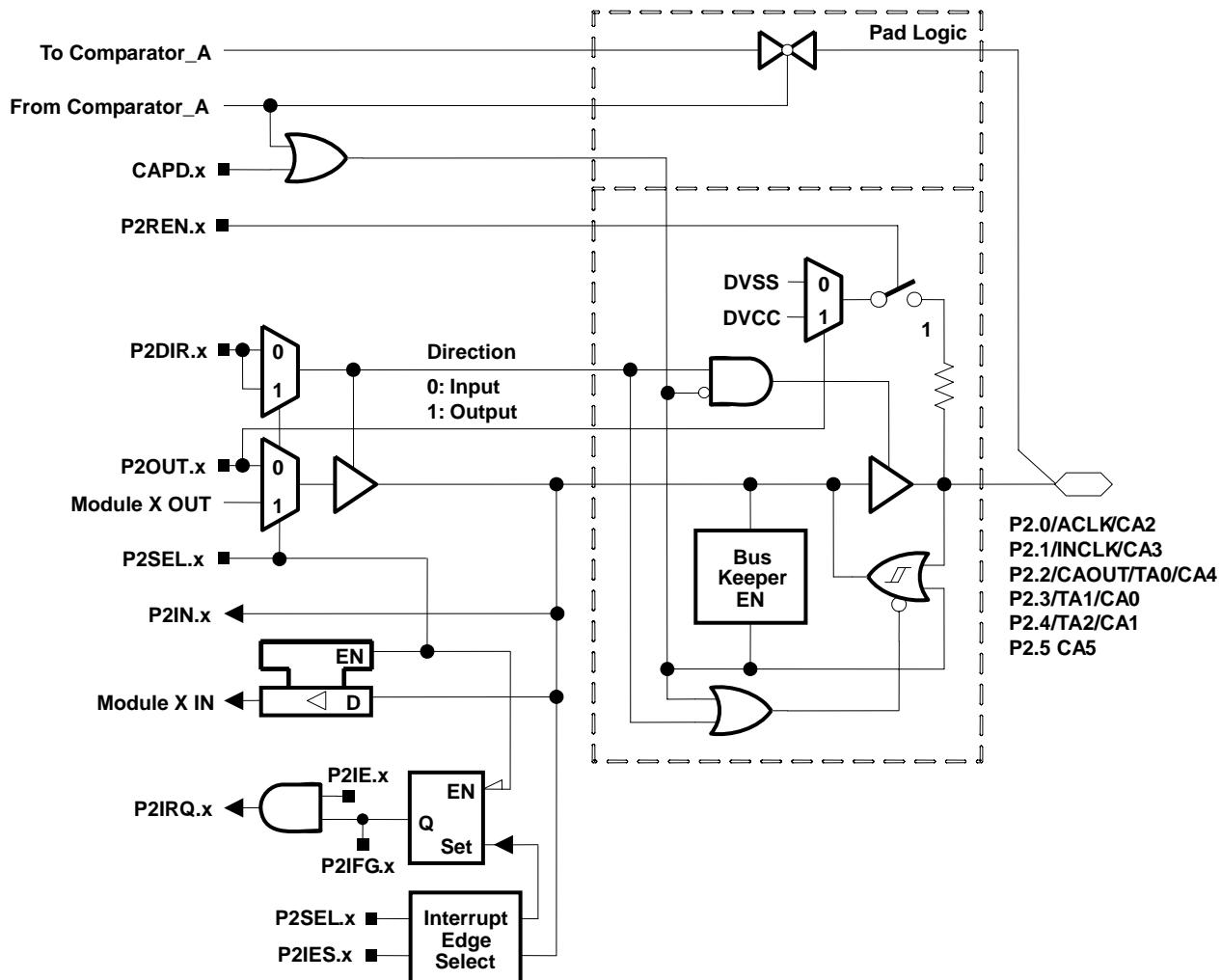

## デジタル I/O

2 つの 8 ビット I/O ポート内蔵：ポート P1 及び P2

- すべての個々の I/O ビットは、独立してプログラム可能です。

- 入力、出力、及び割り込み条件のどんな組み合わせでも可能です。

- ポート P1 及び P2 のすべての 8 ビットは、エッジ選択可能な割り込み入力です。

- ポート・コントロール・レジスタへの読み出し/書き込みアクセスは、すべての命令により可能です。

- それぞれの I/O ポートには、個別にプログラム可能なプルアップ/プルダウン抵抗があります。

## WDT+ ウオッチドッグ・タイマ

ウォッチドッグ・タイマ (WDT+) モジュールの基本的な機能は、ソフトウェア障害が発生した後、制御されたシステムの再開を行うことです。設定された時間間隔が経過すると、システム・リセットが生成されます。ウォッチドッグ機能が必要でないアプリケーションでは、モジュールはインターバル・タイマとして設定することができます。設定された時間間隔で割り込みを発生することができます。

## コンパレータ\_A+

コンパレータ\_A+ モジュールの基本的な機能は、高精度スロープ A/D 変換、バッテリ電圧監視、及び外部アナログ信号のモニタを行うことです。

## タイマ\_A3

タイマ\_A3 は、3 つのキャプチャ/コンペア・レジスタ付きの 16 ビット タイマ/カウンタです。タイマ\_A3 により、複数のキャプチャ/コンペア、PWM 出力、及びインターバル・タイミングを利用することができます。タイマ\_A3 にも、拡張割り込みの機能があります。割り込みは、オーバーフロー状態のカウンタから、及びキャプチャ/コンペア・レジスタのそれぞれから生成されることがあります。

| タイマ_A3 信号の接続 |           |                 |                 |                |               |           |           |

|--------------|-----------|-----------------|-----------------|----------------|---------------|-----------|-----------|

| 入力端子番号       |           | デバイス<br>入力信号    | モジュール<br>入力名    | モジュール・<br>ブロック | モジュール<br>出力信号 | 出力端子番号    |           |

| DW、PW、DGV    | RGE       |                 |                 |                |               | DW、PW、DGV | RGE       |

| 13 - P1.0    | 13 - P1.0 | TACLK           | TACLK           | タイマ            | NA            |           |           |

|              |           | ACLK            | ACLK            |                |               |           |           |

|              |           | SMCLK           | SMCLK           |                |               |           |           |

| 9 - P2.1     | 7 - P2.1  | INCLK           | INCLK           |                |               |           |           |

| 14 - P1.1    | 14 - P1.1 | TA0             | CCIOA           | CCR0           | TA0           | 14 - P1.1 | 14 - P1.1 |

| 10 - P2.2    | 8 - P2.2  | TA0             | CCIOB           |                |               | 18 - P1.5 | 18 - P1.5 |

|              |           | V <sub>ss</sub> | GND             |                |               |           |           |

|              |           | V <sub>cc</sub> | V <sub>cc</sub> |                |               |           |           |

| 15 - P1.2    | 15 - P1.2 | TA1             | CCI1A           | CCR1           | TA1           | 11 - P2.3 | 10 - P2.3 |

|              |           | CAOUT (内部)      | CCI1B           |                |               | 15 - P1.2 | 15 - P1.2 |

|              |           | V <sub>ss</sub> | GND             |                |               | 19 - P1.6 | 20 - P1.6 |

|              |           | V <sub>cc</sub> | V <sub>cc</sub> |                |               |           |           |

| 16 - P1.3    | 16 - P1.3 | TA2             | CCI2A           | CCR2           | TA2           | 12 - P2.4 | 11 - P2.4 |

|              |           | ACLK (内部)       | CCI2B           |                |               | 16 - P1.3 | 16 - P1.3 |

|              |           | V <sub>ss</sub> | GND             |                |               | 20 - P1.7 | 21 - P1.7 |

|              |           | V <sub>cc</sub> | V <sub>cc</sub> |                |               |           |           |

ペリフェラル・ファイル・マップ

| ワード・アクセスによるペリフェラル |                                                                                                                                                  |                                                                                     |                                                                               |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| タイマ_A             | キャプチャ/コンペア・レジスタ<br>キャプチャ/コンペア・レジスタ<br>キャプチャ/コンペア・レジスタ<br>タイマ_A レジスタ<br>キャプチャ/コンペア制御<br>キャプチャ/コンペア制御<br>キャプチャ/コンペア制御<br>タイマ_A 制御<br>タイマ_A 割り込みベクタ | TACCR2<br>TACCR1<br>TACCR0<br>TAR<br>TACCTL2<br>TACCTL1<br>TACCTL0<br>TACTL<br>TAIV | 0176h<br>0174h<br>0172h<br>0170h<br>0166h<br>0164h<br>0162h<br>0160h<br>012Eh |

| フラッシュ・メモリ         | フラッシュ制御 3<br>フラッシュ制御 2<br>フラッシュ制御 1                                                                                                              | FCTL3<br>FCTL2<br>FCTL1                                                             | 012Ch<br>012Ah<br>0128h                                                       |

| ウォッチドッグ+          | ウォッチドッグ・タイマ制御                                                                                                                                    | WDTCTL                                                                              | 0120h                                                                         |

| バイト・アクセスによるペリフェラル |                                                                                                                                                  |                                                                                     |                                                                               |

| コンパレータ_A+         | コンパレータ_A ポート デイス<br>エーブル<br>コンパレータ_A 制御 2<br>コンパレータ_A 制御 1                                                                                       | CAPD<br>CACTL2<br>CACTL1                                                            | 05Bh<br>05Ah<br>059h                                                          |

| Basic Clock       | Basic clock システム制御 3<br>Basic clock システム制御 2<br>Basic clock システム制御 1<br>DCO クロック周波数制御                                                            | BCSCTL3<br>BCSCTL2<br>BCSCTL1<br>DCOCTL                                             | 053h<br>058h<br>057h<br>056h                                                  |

| ポート P2            | ポート P2 抵抗イネーブル<br>ポート P2 選択<br>ポート P2 割り込みイネーブル<br>ポート P2 割り込みエッジ選択<br>ポート P2 割り込みフラグ<br>ポート P2 方向<br>ポート P2 出力<br>ポート P2 入力                     | P2REN<br>P2SEL<br>P2IE<br>P2IES<br>P2IFG<br>P2DIR<br>P2OUT<br>P2IN                  | 02Fh<br>02Eh<br>02Dh<br>02Ch<br>02Bh<br>02Ah<br>029h<br>028h                  |

| ポート P1            | ポート P1 抵抗イネーブル<br>ポート P1 選択<br>ポート P1 割り込みイネーブル<br>ポート P1 割り込みエッジ選択<br>ポート P1 割り込みフラグ<br>ポート P1 方向<br>ポート P1 出力<br>ポート P1 入力                     | P1REN<br>P1SEL<br>P1IE<br>P1IES<br>P1IFG<br>P1DIR<br>P1OUT<br>P1IN                  | 027h<br>026h<br>025h<br>024h<br>023h<br>022h<br>021h<br>020h                  |

| スペシャル・ファンクション     | SFR 割り込みフラグ 2<br>SFR 割り込みフラグ 1<br>SFR 割り込みイネーブル 2<br>SFR 割り込みイネーブル 1                                                                             | IFG2<br>IFG1<br>IE2<br>IE1                                                          | 003h<br>002h<br>001h<br>000h                                                  |

## 絶対最大定格 (特記無き場合) †

|                                          |                       |    |

|------------------------------------------|-----------------------|----|

| 印加電圧 ( $V_{cc}$ ~ $V_{ss}$ 間) .....      | -0.3 ~ 4.1            | V  |

| 印加電圧 (全端子) (注 1) .....                   | -0.3 ~ $V_{cc} + 0.3$ | V  |

| ダイオード電流 (全端子) .....                      | $\pm 2$               | mA |

| 保存温度範囲 未プログラムのデバイス (注 2) $T_{stg}$ ..... | -55 ~ 150             | °C |

| 保存温度範囲 プログラム済みデバイス (注 2) $T_{stg}$ ..... | -40 ~ 85              | °C |

† 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これは、ストレスの定格のみについて示してあり、この仕様書の「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(注 1) すべての電圧は  $V_{ss}$  を基準とします。JTAG ヒューズ切断電圧  $V_{pb}$  は、絶対最大定格を越えても構いません。JTAG ヒューズを切断する時、TEST 端子に電圧が印加されます。

(注 2) ピーク リフロー温度が、出荷箱又はリール上のデバイス ラベルで規定された温度より高くならない状態で、現在の JEDEC J-STD-020 規格に従ってプリント基板にはんだ付けする工程では、もっと高い温度を印加しても構いません。

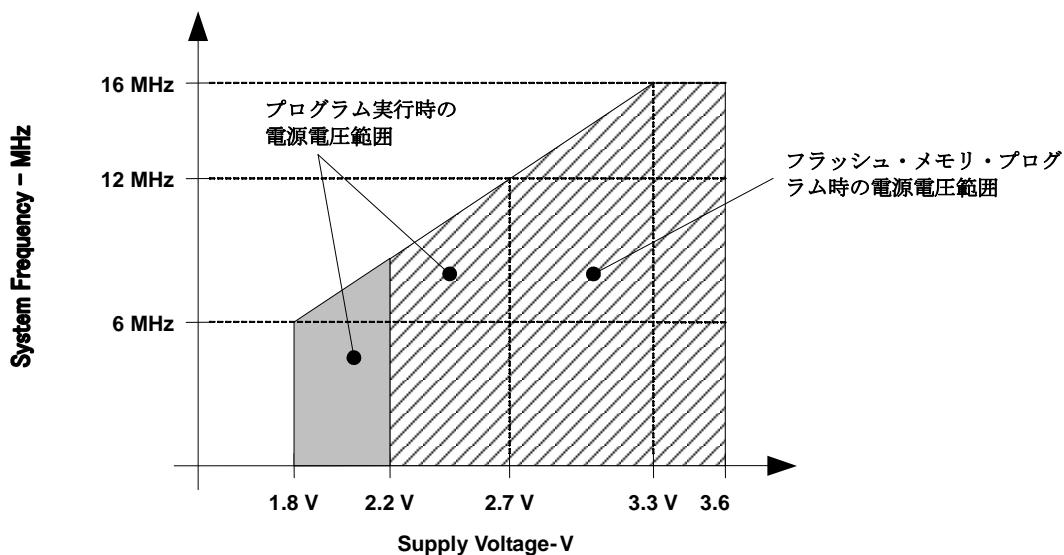

## 推奨動作条件

| 項目                                                         | 最小                                                | 標準  | 最大 | 単位  |

|------------------------------------------------------------|---------------------------------------------------|-----|----|-----|

| 電源電圧 (プログラム実行時)、 $V_{cc}$ (注 1)                            | 1.8                                               | 3.6 | V  |     |

| 電源電圧 (フラッシュ・メモリ プログラム/消去時)、 $V_{cc}$                       | 2.2                                               | 3.6 | V  |     |

| 電源電圧、 $V_{ss}$                                             | 0                                                 |     | V  |     |

| 動作周囲温度、 $T_A$                                              | -40                                               | 85  | °C |     |

| プロセッサ周波数 $f_{SYSTEM}$<br>(最大 MCLK 周波数)<br>(注 1、2 及び図 1 参照) | $V_{cc} = 1.8$ V、<br>デューティ比 = 50% $\pm 10\%$      | 0   | 6  | MHz |

|                                                            | $V_{cc} = 2.7$ V、デューティ比 =<br>50% $\pm 10\%$ (注 3) | 0   | 12 |     |

|                                                            | $V_{cc} = 3.3$ V、デューティ比 =<br>50% $\pm 10\%$ (注 4) | 0   | 16 |     |

(注 1) MSP430 CPU は、MCLK で直接クロックされます。

MCLK の上側及び下側位相は、規定された最大周波数のパルス幅を越えてはいけません。

(注 2) モジュールによって最大入力クロック周波数の規格が異なることがあります。このデータ・シートの各モジュールの規格を参照して下さい。

(注 3) これは、 $V_{cc} = 2.7$  V ~ 3.6 V 及び  $T_A = -40^\circ\text{C} \sim 85^\circ\text{C}$  の時の 12 MHz 用に提供された DCO キャリブレーション値を使用した場合です。

(注 4) これは、 $V_{cc} = 3.3$  V ~ 3.6 V 及び  $T_A = -40^\circ\text{C} \sim 85^\circ\text{C}$  の時の 16 MHz 用に提供された DCO キャリブレーション値を使用した場合です。

(注) 最小プロセッサ周波数は、システム・クロックによって決まります。フラッシュ・プログラム又は消去は、2.2 V の最小  $V_{cc}$  が必要です。

図 1. 動作範囲

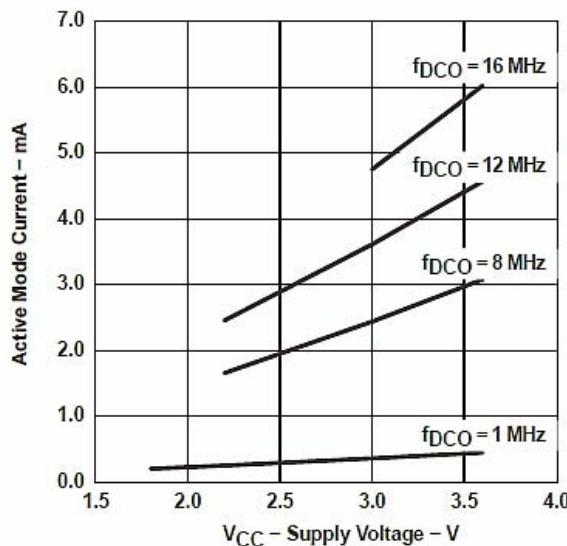

推奨電源電圧及び動作周囲温度における電気的特性 (特記無き場合)

アクティブ・モード電源電流 ( $V_{CC}$ ) (外部電流を除く) (注 1, 2)

| 項目                                           | 測定条件                                                                                                                                                                                                  | $V_{CC}$ | 最小 | 標準  | 最大  | 単位      |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|-----|-----|---------|

| $I_{AM, 1MHz}$ アクティブ・モード (AM) 電流 (1 MHz)     | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 1$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>フラッシュ・メモリのプログラム実行時、<br>BCSCTL1 = CALBC1_1MHz、<br>DCOCTL = CALDCO_1MHz、<br>CPUOFF = 0、SCG0 = 0、SCG1 = 0、OSCOFF = 0             | 2.2 V    |    | 250 | 300 | $\mu A$ |

|                                              |                                                                                                                                                                                                       | 3 V      |    | 350 | 410 |         |

| $I_{AM, 1MHz}$ アクティブ・モード (AM) 電流 (1 MHz)     | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 1$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>RAM のプログラム実行時、<br>BCSCTL1 = CALBC1_1MHz、<br>DCOCTL = CALDCO_1MHz、<br>CPUOFF = 0、SCG0 = 0、SCG1 = 0、OSCOFF = 0                  | 2.2 V    |    | 200 |     | $\mu A$ |

|                                              |                                                                                                                                                                                                       | 3 V      |    | 300 |     |         |

| $I_{AM, 4kHz}$ アクティブ・モード (AM) 電流 (4 kHz)     | $f_{MCLK} = f_{SMCLK} = f_{ACLK} = 32,768$ Hz/8 = 4,096 Hz、<br>$f_{DCO} = 0$ Hz、<br>フラッシュ・メモリのプログラム実行時、<br>SELMX = 11、SELS = 1、DIVMx = DIVSx = DIVAx = 11、<br>CPUOFF = 0、SCG0 = 1、SCG1 = 0、OSCOFF = 0 | 2.2 V    |    | 2   | 5   | $\mu A$ |

|                                              |                                                                                                                                                                                                       | 3 V      |    | 3   | 9   |         |

| $I_{AM, 100kHz}$ アクティブ・モード (AM) 電流 (100 kHz) | $f_{MCLK} = f_{SMCLK} = f_{DCO(0,0)} \approx 100$ kHz、<br>$f_{ACLK} = 0$ Hz、<br>フラッシュ・メモリのプログラム実行時、<br>RSELx = 0、DCOx = 0、<br>CPUOFF = 0、SCG0 = 0、SCG1 = 0、OSCOFF = 1                                 | 2.2 V    |    | 60  | 85  | $\mu A$ |

|                                              |                                                                                                                                                                                                       | 3 V      |    | 72  | 95  |         |

(注 1) すべての入力は、0 V 又は  $V_{CC}$  に接続します。出力にはソース電流、シンク電流を流しません。

(注 2) 電流は、負荷容量 9 pF の Micro Crystal CC4V-T1A SMD で特性評価されています。

内部及び外部負荷容量は、必要とされている 9 pF に厳密にマッチするように選ばれます。

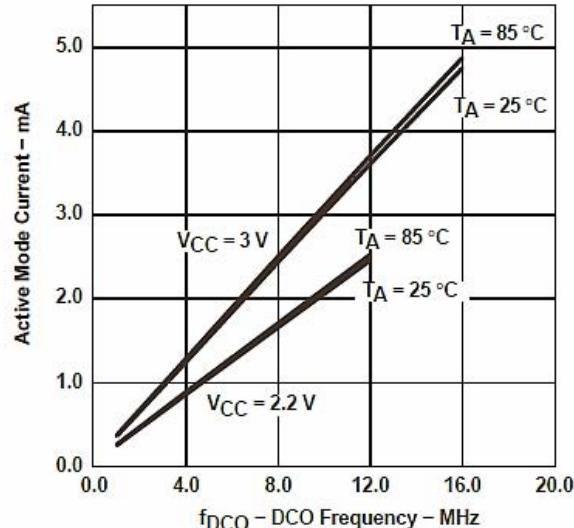

代表特性 - アクティブ・モード電源電流 ( $V_{CC}$ )

図 2.  $V_{CC}$  対アクティブ・モード電源電流、 $T_A = 25^\circ C$

図 3. DCO 周波数対アクティブ・モード電源電流

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）

ロー・パワー・モード電源電流 ( $V_{cc}$ ) (外部電流を除く) (注 1、2)

| 項目                                              | 測定条件                                                                                                                                                                           | $V_{cc}$  | 最小                  | 標準  | 最大  | 単位      |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|-----|-----|---------|

| $I_{LPM0, 1MHz}$ ロー・パワー・モード 0 電流 (LPM0) (注 3)   | $f_{MCLK} = 0$ MHz、<br>$f_{SMCLK} = f_{DCO} = 1$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>BCSCTL1 = CALBC1_1MHz、<br>DCOCTL = CALDCO_1MHz、<br>CPUOFF = 1、SCG0 = 0、SCG1 = 0、OSCOFF = 0 | 2.2 V     |                     | 65  | 80  | $\mu A$ |

|                                                 |                                                                                                                                                                                | 3 V       |                     | 85  | 100 |         |

| $I_{LPM0, 100kHz}$ ロー・パワー・モード 0 電流 (LPM0) (注 3) | $f_{MCLK} = 0$ MHz、<br>$f_{SMCLK} = f_{DCO(0, 0)} \approx 100$ kHz、 $f_{ACLK} = 0$ Hz、<br>RSELX = 0、DCOx = 0、<br>CPUOFF = 1、SCG0 = 0、SCG1 = 0、OSCOFF = 1                       | 2.2 V     |                     | 37  | 48  | $\mu A$ |

|                                                 |                                                                                                                                                                                | 3 V       |                     | 41  | 52  |         |

| $I_{LPM2}$ ロー・パワー・モード 2 電流 (LPM2) (注 4)         | $f_{MCLK} = f_{SMCLK} = 0$ MHz、 $f_{DCO} = 1$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>BCSCTL1 = CALBC1_1MHz、<br>DCOCTL = CALDCO_1MHz、<br>CPUOFF = 1、SCG0 = 0、SCG1 = 1、OSCOFF = 0    | 2.2 V     |                     | 22  | 29  | $\mu A$ |

|                                                 |                                                                                                                                                                                | 3 V       |                     | 25  | 32  |         |

| $I_{LPM3}$ ロー・パワー・モード 3 電流 (LPM3) (注 4)         | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 0$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>CPUOFF = 1、SCG0 = 1、<br>SCG1 = 1、OSCOFF = 0                                                            | 2.2 V     | $T_A = -40^\circ C$ | 0.7 | 1.2 | $\mu A$ |

|                                                 |                                                                                                                                                                                |           | $T_A = 25^\circ C$  | 0.7 | 1   |         |

|                                                 |                                                                                                                                                                                |           | $T_A = 85^\circ C$  | 1.6 | 2.3 |         |

|                                                 |                                                                                                                                                                                | 3 V       | $T_A = -40^\circ C$ | 0.9 | 1.2 |         |

|                                                 |                                                                                                                                                                                |           | $T_A = 25^\circ C$  | 0.9 | 1.2 |         |

|                                                 |                                                                                                                                                                                |           | $T_A = 85^\circ C$  | 1.6 | 2.8 |         |

| $I_{LPM4}$ ロー・パワー・モード 4 電流 (LPM4) (注 5)         | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 0$ MHz、<br>$f_{ACLK} = 32,768$ Hz、<br>CPUOFF = 1、SCG0 = 1、SCG1 = 1、<br>OSCOFF = 1                                                            | 2.2 V     | $T_A = 25^\circ C$  | 0.1 | 0.5 | $\mu A$ |

|                                                 |                                                                                                                                                                                | 2.2 V/3 V | $T_A = 85^\circ C$  | 0.8 | 1.9 |         |

(注 1) すべての入力は、0 V 又は  $V_{cc}$  に接続します。出力にはソース電流、シンク電流を流しません。

(注 2) 電流は、負荷容量 9 pF の Micro Crystal CC44V-T1A SMD で特性評価されています。

内部及び外部負荷容量は、必要とされている 9 pF に厳密にマッチするように選ばれます。

(注 3) SMCLK でクロックした時のプラウンアウト及び WDT の電流が含まれています。

(注 4) ACLK でクロックした時のプラウンアウト及び WDT の電流が含まれています。

(注 5) プラウンアウトの電流が含まれています。

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

シユミット・トリガ入力 - ポート P1 及び P2

| 項目                                                                 | 測定条件                                                                                   | V <sub>cc</sub> | 最小   | 標準 | 最大   | 単位              |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|------|----|------|-----------------|

| V <sub>IT+</sub> 立ち上がり入力スレッショルド電圧                                  |                                                                                        |                 | 0.45 |    | 0.75 | V <sub>cc</sub> |

|                                                                    |                                                                                        | 2.2 V           | 1    |    | 1.65 | V               |

|                                                                    |                                                                                        | 3 V             | 1.35 |    | 2.25 |                 |

| V <sub>IT-</sub> 立ち下がり入力スレッショルド電圧                                  |                                                                                        |                 | 0.25 |    | 0.55 | V <sub>cc</sub> |

|                                                                    |                                                                                        | 2.2 V           | 0.55 |    | 1.2  | V               |

|                                                                    |                                                                                        | 3 V             | 0.75 |    | 1.65 |                 |

| V <sub>hys</sub> 入力電圧ヒステリシス (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                                        | 2.2 V           | 0.2  |    | 1    | V               |

|                                                                    |                                                                                        | 3 V             | 0.3  |    | 1    |                 |

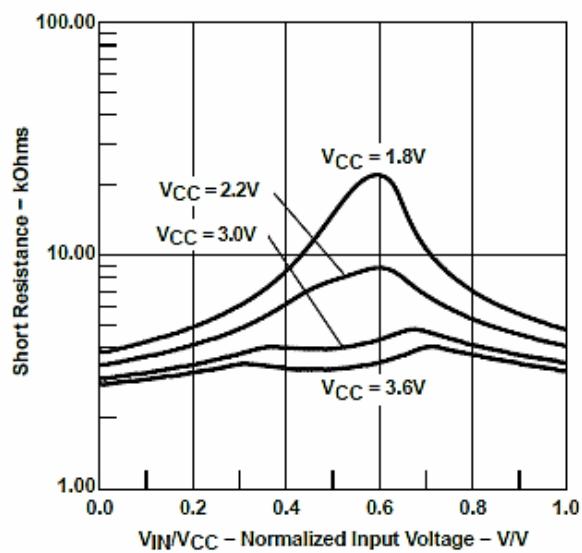

| R <sub>pull</sub> プルアップ/プルダウン抵抗                                    | プルアップ: V <sub>IN</sub> = V <sub>ss</sub> ;<br>プルダウン: V <sub>IN</sub> = V <sub>cc</sub> |                 | 20   | 35 | 50   | Ω               |

| C <sub>I</sub> 入力容量                                                | V <sub>IN</sub> = V <sub>ss</sub> 又は V <sub>cc</sub>                                   |                 |      |    | 5    | pF              |

入力 - ポート P1 及び P2

| 項目                             | 測定条件                                                   | V <sub>cc</sub> | 最小 | 標準 | 最大 | 単位 |

|--------------------------------|--------------------------------------------------------|-----------------|----|----|----|----|

| t <sub>(int)</sub> 外部割り込みタイミング | ポート P1、P2: P1.x ~ P2.x、割り込みフラグをセットするための外部トリガ・パルス幅(注 1) | 2.2 V/3 V       | 20 |    |    | ns |

(注 1) 外部信号は、最小割り込みパルス幅 t<sub>(int)</sub> が適合するたび毎に割り込みフラグをセットします。トリガ信号が t<sub>(int)</sub> より短い場合にもセットされることがあります。

リーク電流 - ポート P1 及び P2

| 項目                                      | 測定条件    | V <sub>cc</sub> | 最小 | 標準 | 最大  | 単位 |

|-----------------------------------------|---------|-----------------|----|----|-----|----|

| I <sub>1kg(Px.x)</sub> ハイ・インピーダンス リーク電流 | (注 1、2) | 2.2 V/3 V       |    |    | ±50 | nA |

(注 1) 特記無き場合、リーク電流は対応する端子に V<sub>ss</sub> 又は V<sub>cc</sub> を印加して測定します。

(注 2) デジタル・ポート端子のリーク電流は、個別に測定します。ポート端子は入力となるように選択し、プルアップ/プルダウン抵抗はディスエーブルとします。

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

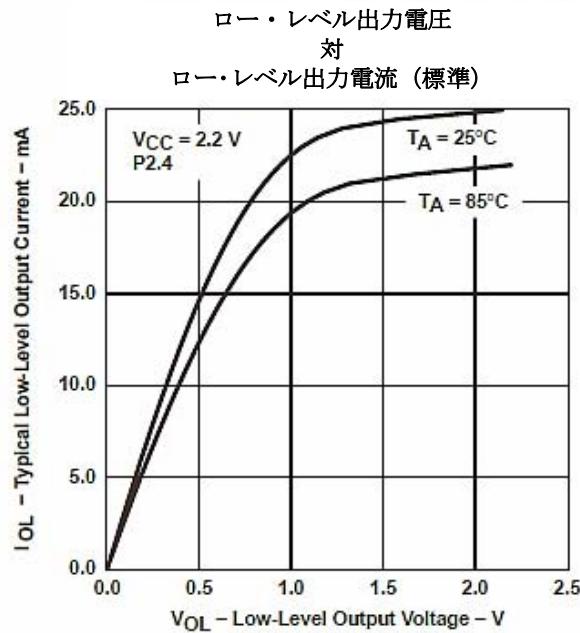

## 出力 - ポート P1 及び P2

| 項目                           | 測定条件                            | $V_{CC}$ | 最小              | 標準              | 最大       | 単位 |

|------------------------------|---------------------------------|----------|-----------------|-----------------|----------|----|

| $I_L$<br>最大負荷電流（ポート端子当たり）    |                                 |          |                 |                 | $\pm 6$  | mA |

| $I_{LT}$<br>最大合計負荷電流（全ポート端子） |                                 |          |                 |                 | $\pm 48$ | mA |

| $V_{OH}$<br>ハイ・レベル出力電圧       | $I_{(OHmax)} = -1.5$ mA (注 1、3) | 2.2 V    | $V_{CC} - 0.25$ | $V_{CC}$        |          | V  |

|                              | $I_{(OHmax)} = -6$ mA (注 2、3)   |          | $V_{CC} - 0.6$  | $V_{CC}$        |          |    |

|                              | $I_{(OHmax)} = -1.5$ mA (注 1、3) | 3 V      | $V_{CC} - 0.25$ | $V_{CC}$        |          |    |

|                              | $I_{(OHmax)} = -6$ mA (注 2、3)   |          | $V_{CC} - 0.6$  | $V_{CC}$        |          |    |

| $V_{OL}$<br>ロー・レベル出力電圧       | $I_{(OLmax)} = 1.5$ mA (注 1、3)  | 2.2 V    | $V_{SS}$        | $V_{SS} + 0.25$ |          | V  |

|                              | $I_{(OLmax)} = 6$ mA (注 2、3)    |          | $V_{SS}$        | $V_{SS} + 0.6$  |          |    |

|                              | $I_{(OLmax)} = 1.5$ mA (注 1、3)  | 3 V      | $V_{SS}$        | $V_{SS} + 0.25$ |          |    |

|                              | $I_{(OLmax)} = 6$ mA (注 2、3)    |          | $V_{SS}$        | $V_{SS} + 0.6$  |          |    |

(注 1) 全出力の最大電流  $I_{(OHmax)}$  と  $I_{(OLmax)}$  の合計は、規定の最大電圧降下を保持するため  $\pm 12$  mA を越えてはいけません。(注 2) 全出力の最大電流  $I_{(OHmax)}$  と  $I_{(OLmax)}$  の合計は、規定の最大電圧降下を保持するため  $\pm 48$  mA を越えてはいけません。

(注 3) 同時に 1 出力のみ負荷をかけます。

## 出力周波数 - ポート P1 及び P2

| 項目                               | 測定条件                                                       | $V_{CC}$ | 最小 | 標準 | 最大 | 単位  |

|----------------------------------|------------------------------------------------------------|----------|----|----|----|-----|

| $f_{Px,y}$<br>ポート出力周波数<br>(負荷付き) | P1.4/SMCLK、 $C_L = 20$ pF、 $R_L = 1$ k $\Omega$<br>(注 1、2) | 2.2 V    |    |    | 10 | MHz |

|                                  |                                                            | 3 V      |    |    | 12 |     |

| $f_{Port,CLK}$<br>クロック出力周波数      | P2.0/ACLK、P1.4/SMCLK、 $C_L = 20$ pF<br>(注 2)               | 2.2 V    |    |    | 12 | MHz |

|                                  |                                                            | 3 V      |    |    | 16 |     |

(注 1) 出力と  $V_{CC}$  及び  $V_{SS}$  間に 2 個の 0.5 k $\Omega$  抵抗デバイダを負荷として使用します。出力は、デバイダのセンター・タップに接続します。(注 2) 出力電圧は、規定のトグル周波数で少なくとも 10% 及び 90%  $V_{CC}$  まで届きます。

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

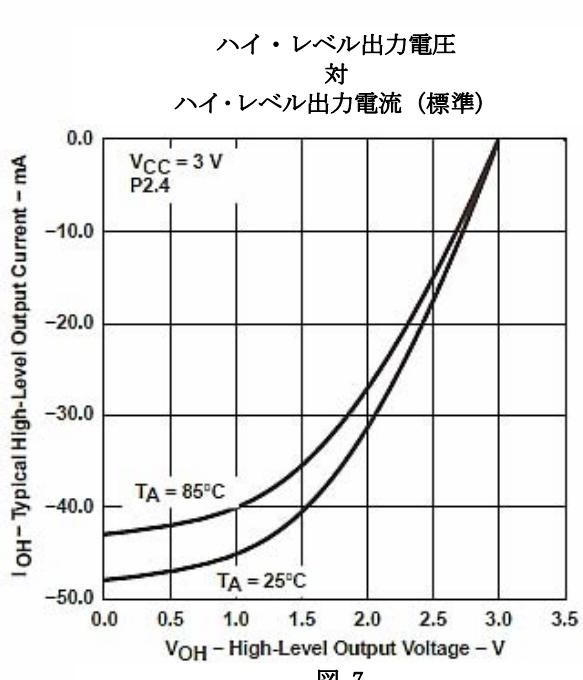

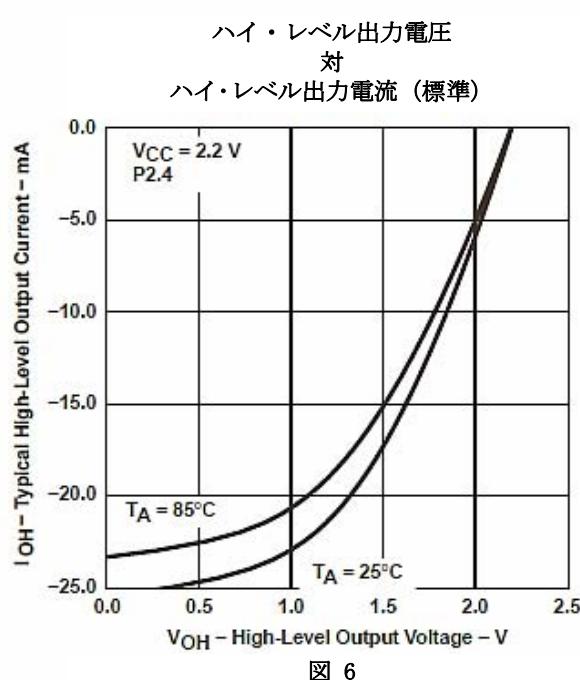

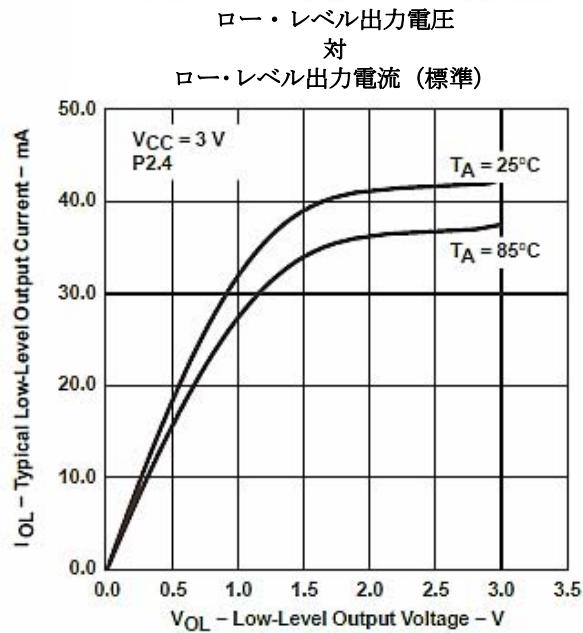

代表特性 - 出力

（注）同時に1出力のみ負荷をかけます。

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

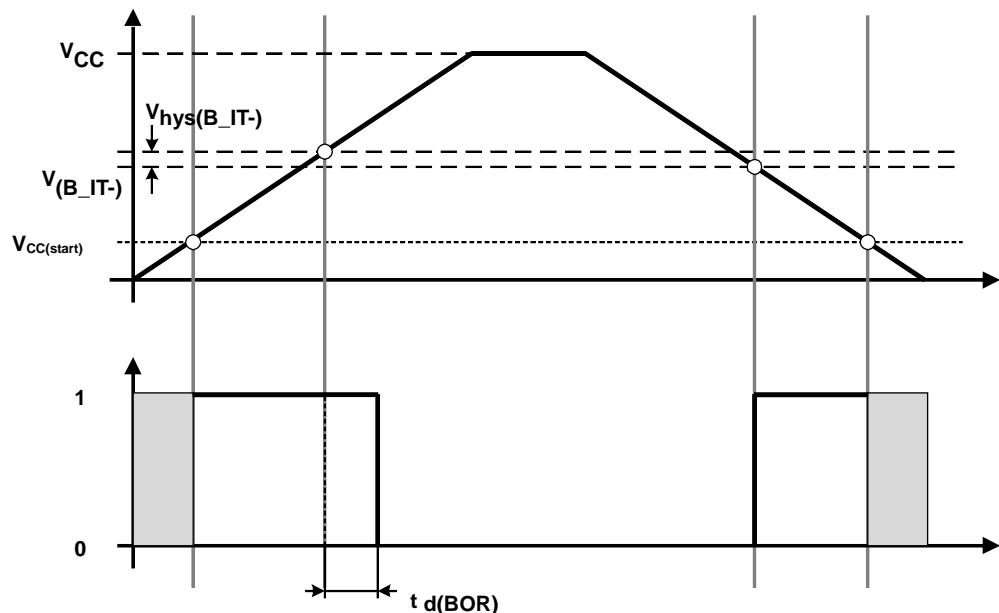

## POR/ブラウンアウト・リセット（BOR）（注1、2）

| 項目                                            | 測定条件                            | $V_{CC}$  | 最小                   | 標準  | 最大   | 単位            |

|-----------------------------------------------|---------------------------------|-----------|----------------------|-----|------|---------------|

| $V_{CC(start)}$ （図8参照）                        | $dV_{CC}/dt \leq 3 \text{ V/s}$ |           | 0.7 x $V_{(B\_IT-)}$ |     |      | V             |

| $V_{(B\_IT-)}$ （図8～図10参照）                     | $dV_{CC}/dt \leq 3 \text{ V/s}$ |           |                      |     | 1.71 | V             |

| $V_{hys(B\_IT-)}$ （図8参照）                      | $dV_{CC}/dt \leq 3 \text{ V/s}$ |           | 70                   | 130 | 180  | mV            |

| $t_d(BOR)$ （図8参照）                             |                                 |           |                      |     | 2000 | $\mu\text{s}$ |

| $t_{(reset)}$ 内部でリセットを受け付けるための RST/NMI 端子パルス幅 |                                 | 2.2 V/3 V | 2                    |     |      | $\mu\text{s}$ |

（注1） ブラウンアウト・モジュールの消費電流は、 $I_{CC}$  に含まれています。 $V_{(B\_IT-)} + V_{hys(B\_IT-)} \leq 1.8 \text{ V}$  とします。

（注2） パワーアップ時は、CPU は  $V_{CC} = V_{(B\_IT-)} + V_{hys(B\_IT-)}$  となった後、 $t_d(BOR)$  経過後にコードの実行を開始します。デフォルトの DCO の設定値は、 $V_{CC} \geq V_{CC(min)}$  となるまで変えてはいけません。 $V_{CC(min)}$  は、使用する動作周波数における最小電源電圧を表します。

図 8. 電源電圧対 POR / ブラウンアウト・リセット（BOR）

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

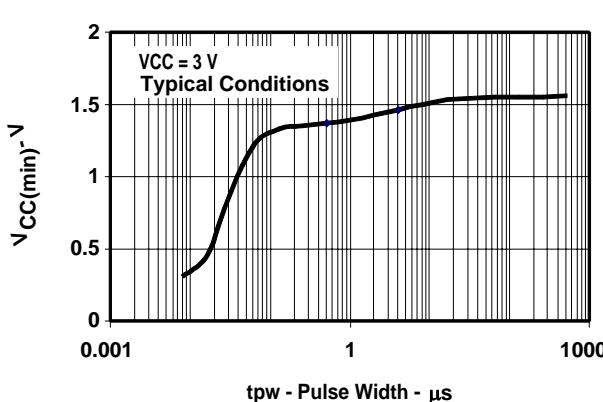

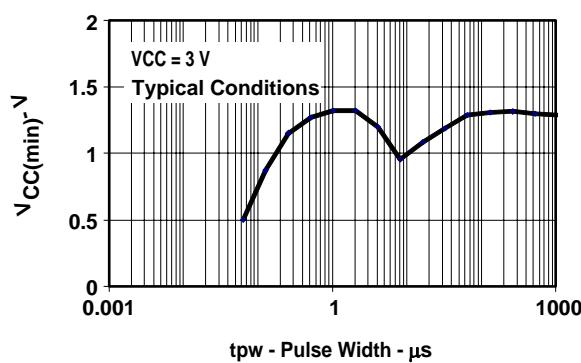

代表特性 - POR / ブラウンアウト・リセット (BOR)

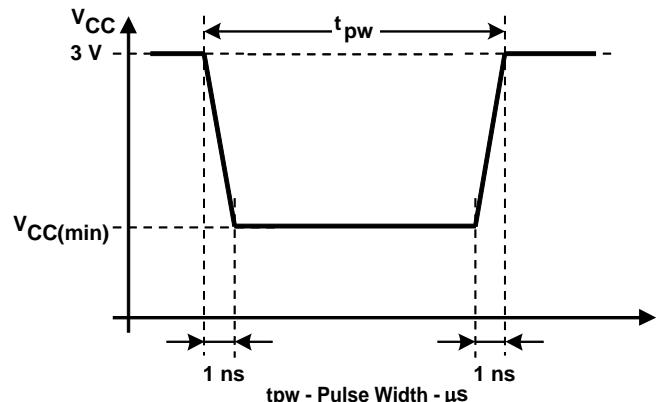

図 9. POR / ブラウンアウト信号を生成するための  $V_{CC(min)}$  レベル（矩形波電圧降下）

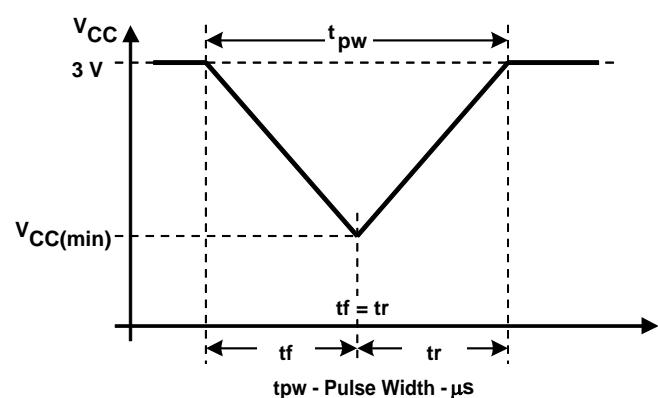

図 10. POR / ブラウンアウト信号を生成するための  $V_{CC(min)}$  レベル（三角波電圧降下）

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

## 主要 DCO 特性

- RSEL<sub>x</sub> によって選択されるすべての範囲は、RSEL<sub>x</sub> + 1 と重なります： RSEL<sub>x</sub> = 0 は RSEL<sub>x</sub> = 1 と重なります、... RSEL<sub>x</sub> = 14 は RSEL<sub>x</sub> = 15 と重なります。

- DCO コントロール・ビット DCO<sub>x</sub> は、パラメータ  $S_{DCO}$  によって定義されるステップ・サイズを持ちます。

- 変調制御ビット MOD<sub>x</sub> は、32 DCOCLK サイクルの期間で  $f_{DCO(RSEL, DCO+1)}$  が使用される頻度を選択します。周波数  $f_{DCO(RSEL, DCO+1)}$  は、残りのサイクルのために使用されます。この平均周波数は、次式で表されます。

$$f_{average} = \frac{32 \times f_{DCO(RSEL, DCO)} \times f_{DCO(RSEL, DCO+1)}}{MOD \times f_{DCO(RSEL, DCO)} + (32 - MOD) \times f_{DCO(RSEL, DCO+1)}}$$

## DCO 周波数

| 項目                                            | 測定条件                                                               | V <sub>CC</sub> | 最小   | 標準   | 最大   | 単位    |

|-----------------------------------------------|--------------------------------------------------------------------|-----------------|------|------|------|-------|

| V <sub>CC</sub><br>電源電圧                       | RSEL <sub>x</sub> < 14                                             |                 | 1.8  | 3.6  |      | V     |

|                                               | RSEL <sub>x</sub> = 14                                             |                 | 2.2  | 3.6  |      |       |

|                                               | RSEL <sub>x</sub> = 15                                             |                 | 3.0  | 3.6  |      |       |

| $f_{DCO(0, 0)}$<br>DCO 周波数 (0, 0)             | RSEL <sub>x</sub> = 0, DCO <sub>x</sub> = 0, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.06 | 0.14 | 0.14 | MHz   |

| $f_{DCO(0, 3)}$<br>DCO 周波数 (0, 3)             | RSEL <sub>x</sub> = 0, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.07 | 0.17 | 0.17 | MHz   |

| $f_{DCO(1, 3)}$<br>DCO 周波数 (1, 3)             | RSEL <sub>x</sub> = 1, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.10 | 0.20 | 0.20 | MHz   |

| $f_{DCO(2, 3)}$<br>DCO 周波数 (2, 3)             | RSEL <sub>x</sub> = 2, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.14 | 0.28 | 0.28 | MHz   |

| $f_{DCO(3, 3)}$<br>DCO 周波数 (3, 3)             | RSEL <sub>x</sub> = 3, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.20 | 0.40 | 0.40 | MHz   |

| $f_{DCO(4, 3)}$<br>DCO 周波数 (4, 3)             | RSEL <sub>x</sub> = 4, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.28 | 0.54 | 0.54 | MHz   |

| $f_{DCO(5, 3)}$<br>DCO 周波数 (5, 3)             | RSEL <sub>x</sub> = 5, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.39 | 0.77 | 0.77 | MHz   |

| $f_{DCO(6, 3)}$<br>DCO 周波数 (6, 3)             | RSEL <sub>x</sub> = 6, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.54 | 1.06 | 1.06 | MHz   |

| $f_{DCO(7, 3)}$<br>DCO 周波数 (7, 3)             | RSEL <sub>x</sub> = 7, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 0.80 | 1.50 | 1.50 | MHz   |

| $f_{DCO(8, 3)}$<br>DCO 周波数 (8, 3)             | RSEL <sub>x</sub> = 8, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 1.10 | 2.10 | 2.10 | MHz   |

| $f_{DCO(9, 3)}$<br>DCO 周波数 (9, 3)             | RSEL <sub>x</sub> = 9, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0  | 2.2 V/3 V       | 1.60 | 3.00 | 3.00 | MHz   |

| $f_{DCO(10, 3)}$<br>DCO 周波数 (10, 3)           | RSEL <sub>x</sub> = 10, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 2.2 V/3 V       | 2.50 | 4.30 | 4.30 | MHz   |

| $f_{DCO(11, 3)}$<br>DCO 周波数 (11, 3)           | RSEL <sub>x</sub> = 11, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 2.2 V/3 V       | 3.00 | 5.50 | 5.50 | MHz   |

| $f_{DCO(12, 3)}$<br>DCO 周波数 (12, 3)           | RSEL <sub>x</sub> = 12, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 2.2 V/3 V       | 4.30 | 7.30 | 7.30 | MHz   |

| $f_{DCO(13, 3)}$<br>DCO 周波数 (13, 3)           | RSEL <sub>x</sub> = 13, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 2.2 V/3 V       | 6.00 | 9.60 | 9.60 | MHz   |

| $f_{DCO(14, 3)}$<br>DCO 周波数 (14, 3)           | RSEL <sub>x</sub> = 14, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 2.2 V/3 V       | 8.60 | 13.9 | 13.9 | MHz   |

| $f_{DCO(15, 3)}$<br>DCO 周波数 (15, 3)           | RSEL <sub>x</sub> = 15, DCO <sub>x</sub> = 3, MOD <sub>x</sub> = 0 | 3 V             | 12.0 | 18.5 | 18.5 | MHz   |

| $f_{DCO(15, 7)}$<br>DCO 周波数 (15, 7)           | RSEL <sub>x</sub> = 15, DCO <sub>x</sub> = 7, MOD <sub>x</sub> = 0 | 3 V             | 16.0 | 26.0 | 26.0 | MHz   |

| $S_{RSEL}$<br>レンジ RSEL ~ RSEL+1 間<br>の周波数ステップ | $S_{RSEL} = f_{DCO(RSEL+1, DCO)} / f_{DCO(RSEL, DCO)}$             | 2.2 V/3 V       |      | 1.55 |      | ratio |

| $S_{DCO}$<br>タップ DCO ~ DCO+1 間の<br>周波数ステップ    | $S_{DCO} = f_{DCO(RSEL, DCO+1)} / f_{DCO(RSEL, DCO)}$              | 2.2 V/3 V       | 1.05 | 1.08 | 1.12 |       |

| デューティ比                                        | P1.4/SMCLK で測定                                                     | 2.2 V/3 V       | 40   | 50   | 60   | %     |

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

校正された DCO 周波数 - 校正時の公差

| 項目                          | 測定条件                                                              | T <sub>A</sub> | V <sub>CC</sub> | 最小    | 標準   | 最大    | 単位  |

|-----------------------------|-------------------------------------------------------------------|----------------|-----------------|-------|------|-------|-----|

| 校正時の周波数公差                   |                                                                   | 25°C           | 3 V             | -1    | ±0.2 | +1    | %   |

| $f_{CAL(1MHz)}$ 1 MHz 校正值   | BCSCTL1= CALBC1_1MHz;<br>DCOCTL = CALDCO_1MHz<br>ゲーティング時間: 5 ms   | 25°C           | 3 V             | 0.990 | 1    | 1.010 | MHz |

| $f_{CAL(8MHz)}$ 8 MHz 校正值   | BCSCTL1= CALBC1_8MHz;<br>DCOCTL = CALDCO_8MHz<br>ゲーティング時間: 5 ms   | 25°C           | 3 V             | 7.920 | 8    | 8.080 | MHz |

| $f_{CAL(12MHz)}$ 12 MHz 校正值 | BCSCTL1= CALBC1_12MHz;<br>DCOCTL = CALDCO_12MHz<br>ゲーティング時間: 5 ms | 25°C           | 3 V             | 11.88 | 12   | 12.12 | MHz |

| $f_{CAL(16MHz)}$ 16 MHz 校正值 | BCSCTL1= CALBC1_16MHz;<br>DCOCTL = CALDCO_16MHz<br>ゲーティング時間: 2 ms | 25°C           | 3 V             | 15.84 | 16   | 16.16 | MHz |

校正された DCO 周波数 - 温度範囲 0°C ~ 85°C の公差

| 項目                          | 測定条件                                                              | T <sub>A</sub> | V <sub>CC</sub> | 最小    | 標準   | 最大    | 単位  |

|-----------------------------|-------------------------------------------------------------------|----------------|-----------------|-------|------|-------|-----|

| 1 MHz 公差                    |                                                                   | 0°C ~ 85°C     | 3 V             | -2.5  | ±0.5 | +2.5  | %   |

| 8 MHz 公差                    |                                                                   | 0°C ~ 85°C     | 3 V             | -2.5  | ±1.0 | +2.5  | %   |

| 12 MHz 公差                   |                                                                   | 0°C ~ 85°C     | 3 V             | -2.5  | ±1.0 | +2.5  | %   |

| 16 MHz 公差                   |                                                                   | 0°C ~ 85°C     | 3 V             | -3.0  | ±2.0 | +3.0  | %   |

| $f_{CAL(1MHz)}$ 1 MHz 校正值   | BCSCTL1= CALBC1_1MHz;<br>DCOCTL = CALDCO_1MHz<br>ゲーティング時間: 5 ms   | 0°C ~ 85°C     | 2.2 V           | 0.970 | 1    | 1.030 | MHz |

|                             |                                                                   |                | 3 V             | 0.975 | 1    | 1.025 |     |

|                             |                                                                   |                | 3.6 V           | 0.970 | 1    | 1.030 |     |

| $f_{CAL(8MHz)}$ 8 MHz 校正值   | BCSCTL1= CALBC1_8MHz;<br>DCOCTL = CALDCO_8MHz<br>ゲーティング時間: 5 ms   | 0°C ~ 85°C     | 2.2 V           | 7.760 | 8    | 8.400 | MHz |

|                             |                                                                   |                | 3 V             | 7.800 | 8    | 8.200 |     |

|                             |                                                                   |                | 3.6 V           | 7.600 | 8    | 8.240 |     |

| $f_{CAL(12MHz)}$ 12 MHz 校正值 | BCSCTL1= CALBC1_12MHz;<br>DCOCTL = CALDCO_12MHz<br>ゲーティング時間: 5 ms | 0°C ~ 85°C     | 2.2 V           | 11.70 | 12   | 12.30 | MHz |

|                             |                                                                   |                | 3 V             | 11.70 | 12   | 12.30 |     |

|                             |                                                                   |                | 3.6 V           | 11.70 | 12   | 12.30 |     |

| $f_{CAL(16MHz)}$ 16 MHz 校正值 | BCSCTL1= CALBC1_16MHz;<br>DCOCTL = CALDCO_16MHz<br>ゲーティング時間: 2ms  | 0°C ~ 85°C     | 3 V             | 15.52 | 16   | 16.48 | MHz |

|                             |                                                                   |                | 3.6 V           | 15.00 | 16   | 16.48 |     |

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

校正された DCO 周波数 - 電源電圧  $V_{cc}$  の範囲の公差

| 項目                          | 測定条件                                                              | $T_A$ | $V_{cc}$      | 最小    | 標準 | 最大    | 単位  |

|-----------------------------|-------------------------------------------------------------------|-------|---------------|-------|----|-------|-----|

| 1 MHz 公差 ( $V_{cc}$ の範囲)    |                                                                   | 25°C  | 1.8 V ~ 3.6 V | -2.5  | ±2 | +2.5  | %   |

| 8 MHz 公差 ( $V_{cc}$ の範囲)    |                                                                   | 25°C  | 1.8 V ~ 3.6 V | -2.5  | ±2 | +2.5  | %   |

| 12 MHz 公差 ( $V_{cc}$ の範囲)   |                                                                   | 25°C  | 2.2 V ~ 3.6 V | -2.5  | ±2 | +2.5  | %   |

| 16 MHz 公差 ( $V_{cc}$ の範囲)   |                                                                   | 25°C  | 3 V ~ 3.6 V   | -3    | ±2 | +3    | %   |

| $f_{CAL(1MHz)}$ 1 MHz 校正值   | BCSCTL1= CALBC1_1MHz;<br>DCOCTL = CALDCO_1MHz<br>ゲーティング時間: 5 ms   | 25°C  | 1.8 V ~ 3.6 V | 0.970 | 1  | 1.030 | MHz |

| $f_{CAL(8MHz)}$ 8 MHz 校正值   | BCSCTL1= CALBC1_8MHz;<br>DCOCTL = CALDCO_8MHz<br>ゲーティング時間: 5 ms   | 25°C  | 1.8 V ~ 3.6 V | 7.760 | 8  | 8.240 | MHz |

| $f_{CAL(12MHz)}$ 12 MHz 校正值 | BCSCTL1= CALBC1_12MHz;<br>DCOCTL = CALDCO_12MHz<br>ゲーティング時間: 5 ms | 25°C  | 2.2 V ~ 3.6 V | 11.64 | 12 | 12.36 | MHz |

| $f_{CAL(16MHz)}$ 16 MHz 校正值 | BCSCTL1= CALBC1_16MHz;<br>DCOCTL = CALDCO_16MHz<br>ゲーティング時間: 2 ms | 25°C  | 3 V ~ 3.6 V   | 15.00 | 16 | 16.48 | MHz |

## 校正された DCO 周波数 - 総合公差

| 項目                          | 測定条件                                                              | $T_A$        | $V_{cc}$      | 最小    | 標準 | 最大    | 単位  |

|-----------------------------|-------------------------------------------------------------------|--------------|---------------|-------|----|-------|-----|

| 1 MHz 総合公差                  |                                                                   | -40°C ~ 85°C | 1.8 V ~ 3.6 V | -5    | ±2 | +5    | %   |

| 8 MHz 総合公差                  |                                                                   | -40°C ~ 85°C | 1.8 V ~ 3.6 V | -5    | ±2 | +5    | %   |

| 12 MHz 総合公差                 |                                                                   | -40°C ~ 85°C | 2.2 V ~ 3.6 V | -5    | ±2 | +5    | %   |

| 16 MHz 総合公差                 |                                                                   | -40°C ~ 85°C | 3 V ~ 3.6 V   | -6    | ±3 | +6    | %   |

| $f_{CAL(1MHz)}$ 1 MHz 校正值   | BCSCTL1= CALBC1_1MHz;<br>DCOCTL = CALDCO_1MHz<br>ゲーティング時間: 5ms    | -40°C ~ 85°C | 1.8 V ~ 3.6 V | 0.950 | 1  | 1.050 | MHz |

| $f_{CAL(8MHz)}$ 8 MHz 校正值   | BCSCTL1= CALBC1_8MHz;<br>DCOCTL = CALDCO_8MHz<br>ゲーティング時間: 5 ms   | -40°C ~ 85°C | 1.8 V ~ 3.6 V | 7.600 | 8  | 8.400 | MHz |

| $f_{CAL(12MHz)}$ 12 MHz 校正值 | BCSCTL1= CALBC1_12MHz;<br>DCOCTL = CALDCO_12MHz<br>ゲーティング時間: 5 ms | -40°C ~ 85°C | 2.2 V ~ 3.6 V | 11.40 | 12 | 12.60 | MHz |

| $f_{CAL(16MHz)}$ 16 MHz 校正值 | BCSCTL1= CALBC1_16MHz;<br>DCOCTL = CALDCO_16MHz<br>ゲーティング時間: 2 ms | -40°C ~ 85°C | 3 V ~ 3.6 V   | 15.00 | 16 | 17.00 | MHz |

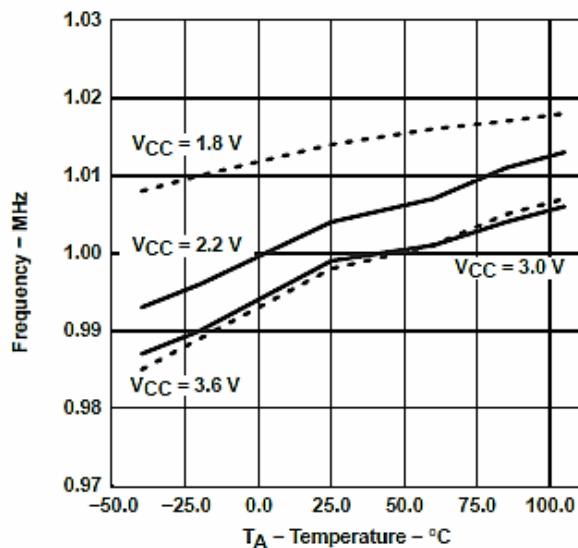

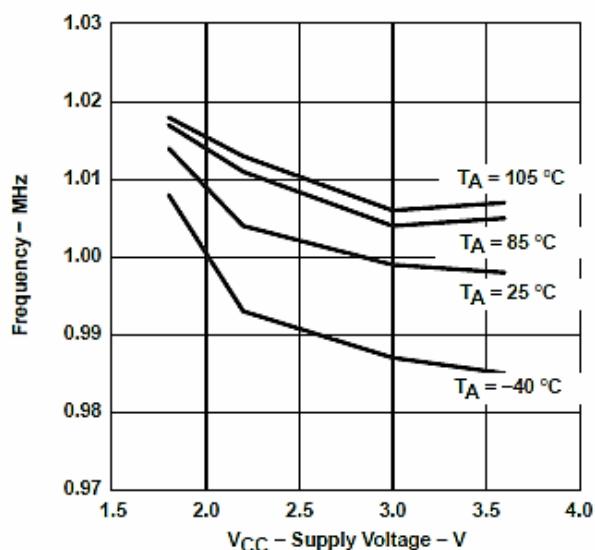

代表特性 - 校正された 1 MHz DCO 周波数

図 11. 温度対校正された 1 MHz 周波数

図 12. V<sub>CC</sub> 対校正された 1 MHz 周波数

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

## 低消費電力モード（LPM3/4）からのウェークアップ

| 項目                                                          | 測定条件                                            | V <sub>CC</sub> | 最小 | 標準                                                     | 最大  | 単位 |

|-------------------------------------------------------------|-------------------------------------------------|-----------------|----|--------------------------------------------------------|-----|----|

| t <sub>DCO, LPM3/4</sub> LPM3/4 からの DCO クロック・ウェークアップ時間（注 1） | BCSCTL1= CALBC1_1MHz;<br>DCOCTL = CALDCO_1MHz   | 2.2 V/3 V       |    |                                                        | 2   | μs |

|                                                             | BCSCTL1= CALBC1_8MHz;<br>DCOCTL = CALDCO_8MHz   | 2.2 V/3 V       |    |                                                        | 1.5 |    |

|                                                             | BCSCTL1= CALBC1_12MHz;<br>DCOCTL = CALDCO_12MHz | 2.2 V/3 V       |    |                                                        | 1   |    |

|                                                             | BCSCTL1= CALBC1_16MHz;<br>DCOCTL = CALDCO_16MHz | 3 V             |    |                                                        | 1   |    |

| t <sub>CPU, LPM3/4</sub> LPM3/4 からの CPU ウェークアップ時間（注 2）      |                                                 |                 |    | 1/f <sub>MCLK</sub><br>+<br>t <sub>Clock, LPM3/4</sub> |     |    |

（注 1） DCO クロック・ウェークアップ時間は、外部ウェークアップ信号（すなわちポート割り込み）のエッジから、クロック端子（MCLK 又は SMCLK）で外部から観測される最初のクロック・エッジまでを測定します。

（注 2） パラメータは、DCOCLK が MCLK として使用された場合のみに適用されます。

## 代表特性 - LPM3/4 からの DCO クロック・ウェークアップ時間

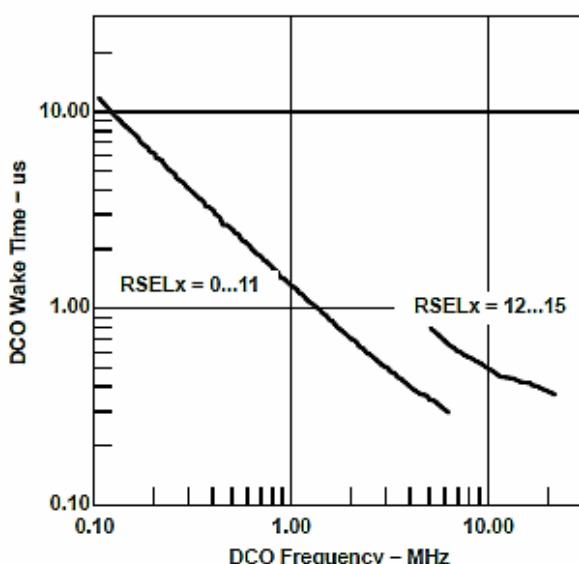

図 13. DCO 周波数対 LPM3 からのクロック・ウェークアップ時間

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

クリスタル・オシレータ、LFXT1、低周波数モード（注4）

| 項目                                                                    | 測定条件                                                                           | $V_{CC}$      | 最小     | 標準     | 最大     | 単位        |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|--------|--------|--------|-----------|

| $f_{LFXT1, LF}$<br>LFXT1 オシレータ クリスタル<br>周波数、LF モード 0, 1               | XTS = 0, LFXT1Sx = 0 又は 1                                                      | 1.8 V ~ 3.6 V |        | 32,768 |        | Hz        |

| $f_{LFXT1, LF, logic}$<br>LFXT1 オシレータ ロジック・<br>レベル矩形波入力周波数、<br>LF モード | XTS = 0, LFXT1Sx = 3                                                           | 1.8 V ~ 3.6 V | 10,000 | 32,768 | 50,000 | Hz        |

| $OA_{LF}$<br>LF クリスタル発振許容値                                            | XTS = 0, LFXT1Sx = 0;<br>$f_{LFXT1, LF} = 32,768$ kHz、<br>$C_{L, eff} = 6$ pF  |               |        | 500    |        | $k\Omega$ |

|                                                                       | XTS = 0, LFXT1Sx = 0;<br>$f_{LFXT1, LF} = 32,768$ kHz、<br>$C_{L, eff} = 12$ pF |               |        | 200    |        |           |

| 内部有効負荷容量、<br>LF モード<br>(注1)                                           | XTS = 0, XCAPx = 0                                                             |               | 1      |        |        | $pF$      |

|                                                                       | XTS = 0, XCAPx = 1                                                             |               | 5.5    |        |        |           |

|                                                                       | XTS = 0, XCAPx = 2                                                             |               | 8.5    |        |        |           |

|                                                                       | XTS = 0, XCAPx = 3                                                             |               | 11     |        |        |           |

| デューティ 比<br>LF モード                                                     | XTS = 0, P1.4/ACLK で測定、<br>$f_{LFXT1, LF} = 32,768$ Hz                         | 2.2 V/3 V     | 30     | 50     | 70     | %         |

| $f_{Fault, LF}$<br>オシレータ障害周波数、<br>LF モード（注3）                          | XTS = 0, LFXT1Sx = 3<br>(注2)                                                   | 2.2 V/3 V     | 10     |        | 10,000 | Hz        |

- (注1) ボンド及びパッケージの寄生容量を含みます。（約 2 pF/端子）

プリント基板には容量が付加されますので、ACLK 周波数を測定することによって正確な負荷を検証することを推奨します。

正確な測定のため、有効負荷容量は常に使用するクリスタルの規格に適合しなければなりません。

- (注2) ロジック・レベル入力周波数で測定しますが、クリスタルでの動作にも適用されます。

- (注3) 規格の最小値より低い周波数では障害フラグがセットされ、最大値より高い周波数では障害フラグがセットされません。

その間の周波数では障害フラグがセットされることもあります。

- (注4) LFXT1 オシレータの EMI を改善するため、次のガイドラインに従って下さい。

- デバイスとクリスタルの間の配線はできるだけ短くする。

- オシレータ端子の周辺は、良好なグランド・プレーンとなるように設計する。

- 他のクロック又はデータ・ラインからオシレータ端子 XIN 及び XOUT へのクロストークを防止する。

- XIN 及び XOUT 端子の下側又は近くにプリント基板の配線を走らせないようにする。

- オシレータ端子 XIN 及び XOUT の寄生負荷を防止するための組み立て材料及び組み立て方法を使用する。

- コーティングを使用する場合は、それがオシレータ端子間に容量／抵抗リレークを誘導しないこと。

- シリアル・プログラミング・アダプタを使用するために、XOUT ラインを JTAG ヘッダへ配線しない。

この信号は、シリアル・プログラミング・アダプタには必要ありません。

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

## クリスタル・オシレータ、LFXT1、高周波数モード（注5）

| 項目                                                                           | 測定条件                                                                                    | V <sub>CC</sub> | 最小  | 標準   | 最大  | 単位  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|-----|------|-----|-----|

| f <sub>LFXT1, HF0</sub><br>LFXT1 オシレータ クリスタル<br>周波数、HF モード 0                 | XTS = 1、LFXT1Sx = 0                                                                     | 1.8 V ~ 3.6 V   | 0.4 |      | 1   | MHz |

| f <sub>LFXT1, HF1</sub><br>LFXT1 オシレータ クリスタル<br>周波数、HF モード 1                 | XTS = 1、LFXT1Sx = 1                                                                     | 1.8 V ~ 3.6 V   | 1   |      | 4   | MHz |

| f <sub>LFXT1, HF2</sub><br>LFXT1 オシレータ クリスタル<br>周波数、HF モード 2                 | XTS = 1、LFXT1Sx = 2                                                                     | 1.8 V ~ 3.6 V   | 2   |      | 10  | MHz |

|                                                                              |                                                                                         | 2.2 V ~ 3.6 V   | 2   |      | 12  |     |

|                                                                              |                                                                                         | 3 V ~ 3.6 V     | 2   |      | 16  |     |

| f <sub>LFXT1, HF, logic</sub><br>LFXT1 オシレータ ロジック・レ<br>ベル矩形波入力周波数、<br>HF モード | XTS = 1、LFXT1Sx = 3                                                                     | 1.8 V ~ 3.6 V   | 0.4 |      | 10  | MHz |

|                                                                              |                                                                                         | 2.2 V ~ 3.6 V   | 0.4 |      | 12  |     |

|                                                                              |                                                                                         | 3 V ~ 3.6 V     | 0.4 |      | 16  |     |

| OA <sub>HF</sub><br>HF クリスタル発振許容値<br>(図 14、15 参照)                            | XTS = 0、LFXT1Sx = 0、<br>f <sub>LFXT1, HF</sub> = 1 MHz、<br>C <sub>L, eff</sub> = 15 pF  |                 |     | 2700 |     | Ω   |

|                                                                              | XTS = 0、LFXT1Sx = 1、<br>f <sub>LFXT1, HF</sub> = 4 MHz、<br>C <sub>L, eff</sub> = 15 pF  |                 |     | 800  |     |     |

|                                                                              | XTS = 0、LFXT1Sx = 2、<br>f <sub>LFXT1, HF</sub> = 16 MHz、<br>C <sub>L, eff</sub> = 15 pF |                 |     | 300  |     |     |

| C <sub>L, eff</sub><br>内部有効負荷容量、<br>HF モード<br>(注 1)                          | XTS = 1 (注 2)                                                                           |                 |     | 1    |     | pF  |

| デューティ<br>比                                                                   | XTS = 1、P1.4/ACLK で測定、<br>f <sub>LFXT1, HF</sub> = 10 MHz                               | 2.2 V/3 V       | 40  | 50   | 60  | %   |

|                                                                              | XTS = 1、P1.4/ACLK で測定、<br>f <sub>LFXT1, HF</sub> = 16 MHz                               | 2.2 V/3 V       | 40  | 50   | 60  |     |

| f <sub>Fault, HF</sub><br>オシレータ障害周波数、<br>HF モード (注 4)                        | XTS = 1、LFXT1Sx = 3<br>(注 3)                                                            | 2.2 V/3 V       | 30  |      | 300 | kHz |

- (注 1) ボンド及びパッケージの寄生容量を含みます。（約 2 pF/端子）

プリント基板には容量が付加されますので、ACLK 周波数を測定することによって正確な負荷を検証することを推奨します。

正確な測定のため、有効負荷容量は常に使用するクリスタルの規格に適合しなければなりません。

- (注 2) ロジック・レベル入力周波数で測定しますが、クリスタルでの動作にも適用されます。

- (注 3) 規格の最小値より低い周波数では障害フラグがセットされ、最大値より高い周波数では障害フラグがセットされません。

その間の周波数では障害フラグがセットされることもあります。

- (注 4) LFXT1 オシレータの EMI を改善するため、次のガイドラインに従って下さい。

– デバイスとクリスタルの間の配線はできるだけ短くする。

– オシレータ端子の周辺は、良好なグランド・プレーンとなるように設計する。

– 他のクロック又はデータ・ラインからオシレータ端子 XIN 及び XOUT へのクロストークを防止する。

– XIN 及び XOUT 端子の下側又は近くにプリント基板の配線を走らせないようにする。

– オシレータ端子 XIN 及び XOUT の寄生負荷を防止するための組み立て材料及び組み立て方法を使用する。

– コーティングを使用する場合は、それがオシレータ端子間に容量／抵抗リードを誘導しないこと。

– シリアル・プログラミング・アダプタを使用するため、XOUT ラインを JTAG ヘッダへ配線しない。

この信号は、シリアル・プログラミング・アダプタには必要ありません。

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

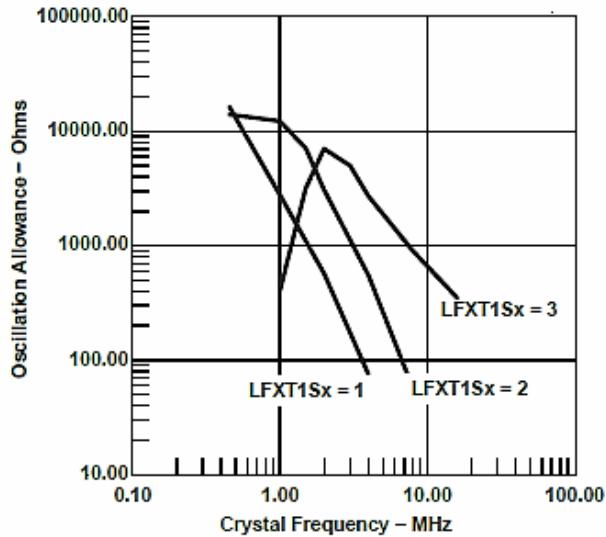

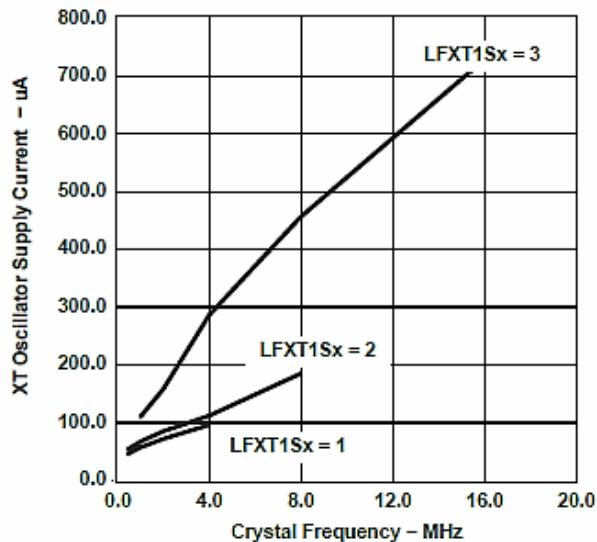

代表特性 - LFXT1 オシレータ HF モード (XTS = 1)

図 14. クリスタル周波数対発振許容値、 $C_{L_{\text{eff}}} = 15 \text{ pF}$ ,  $T_A = 25^\circ\text{C}$

図 15. クリスタル周波数対 XT オシレータ電源電流、 $C_{L_{\text{eff}}} = 15 \text{ pF}$ ,  $T_A = 25^\circ\text{C}$

## 推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

## タイマ\_A

| 項目                   |                       | 測定条件                                                     | V <sub>cc</sub> | 最小 | 標準 | 最大 | 単位  |

|----------------------|-----------------------|----------------------------------------------------------|-----------------|----|----|----|-----|

| f <sub>TA</sub>      | タイマ_A クロック周波数         | 内部: SMCLK、ACLK;<br>外部: TACLK、INCLK;<br>デューティ比 = 50% ±10% | 2.2 V           |    |    | 10 | MHz |

|                      |                       |                                                          | 3 V             |    |    | 16 |     |

| t <sub>TA, cap</sub> | タイマ_A、<br>キャプチャ・タイミング | TA0、TA1、TA2                                              | 2.2 V/3 V       | 20 |    |    | ns  |

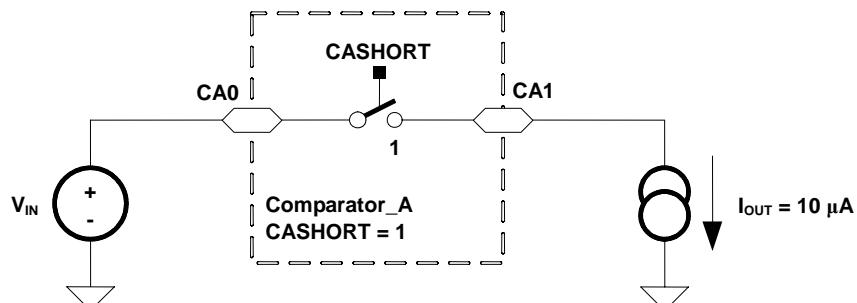

## コンパレータ\_A+（注 1）

| 項目                                |                                                        | 測定条件                                                                                          | V <sub>cc</sub> | 最小   | 標準                  | 最大   | 単位 |

|-----------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|------|---------------------|------|----|

| I <sub>(DD)</sub>                 |                                                        | CAON = 1、CARSEL = 0、CAREF = 0                                                                 | 2.2 V           |      | 25                  | 40   | μA |

|                                   |                                                        |                                                                                               | 3 V             |      | 45                  | 60   |    |

| I <sub>(RefLadder/RefDiode)</sub> |                                                        | CAON = 1、CARSEL = 0、<br>CAREF = 1/2/3、P2.3/CA0/TA1 及び<br>P2.4/CA1/TA2 は無負荷                    | 2.2 V           |      | 30                  | 50   | μA |

|                                   |                                                        |                                                                                               | 3 V             |      | 45                  | 71   |    |

| V <sub>(IC)</sub>                 | 同相入力電圧                                                 | CAON = 1                                                                                      | 2.2 V/3 V       | 0    | V <sub>cc</sub> - 1 |      | V  |

| V <sub>(Ref025)</sub>             | Voltage @ 0.25 V <sub>CC</sub> node<br>V <sub>CC</sub> | PCA0 = 1、CARSEL = 1、<br>CAREF = 1、P2.3/CA0/TA1 及び<br>P2.4/CA1/TA2 は無負荷                        | 2.2 V/3 V       | 0.23 | 0.24                | 0.25 |    |

| V <sub>(Ref050)</sub>             | Voltage @ 0.5 V <sub>CC</sub> node<br>V <sub>CC</sub>  | PCA0 = 1、CARSEL = 1、CAREF = 2、<br>P2.3/CA0/TA1 及び P2.4/CA1/TA2 は無<br>負荷                       | 2.2 V/3 V       | 0.47 | 0.48                | 0.5  |    |

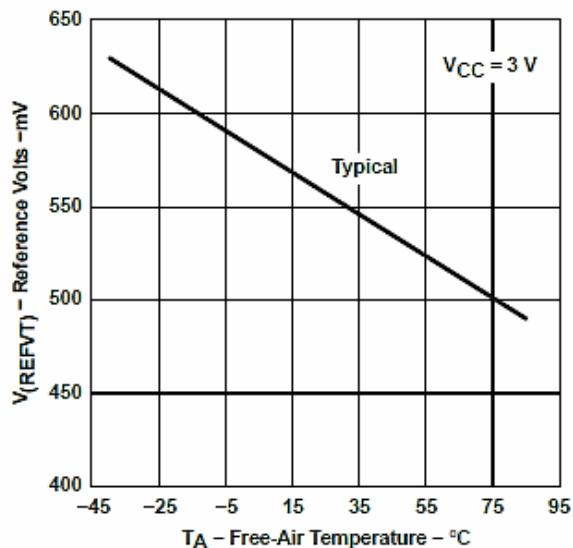

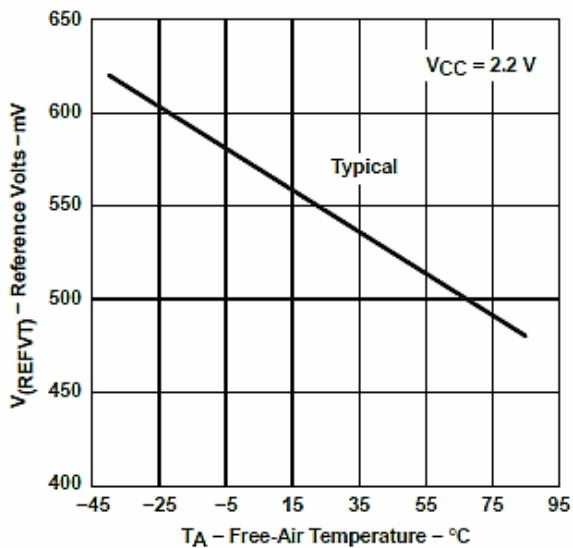

| V <sub>(RefVT)</sub>              | (図 19、20 参照)                                           | PCA0 = 1、CARSEL = 1、CAREF = 3、<br>P2.3/CA0/TA1 及び P2.4/CA1/TA2 は無<br>負荷、T <sub>A</sub> = 85°C | 2.2 V           | 390  | 480                 | 540  | mV |

| V <sub>(offset)</sub>             | オフセット電圧                                                | (注 2)                                                                                         | 2.2 V/3 V       | -30  |                     | 30   |    |

| V <sub>hys</sub>                  | 入力ヒステリシス                                               | CAON = 1                                                                                      | 2.2 V/3 V       | 0    | 0.7                 | 1.4  | mV |

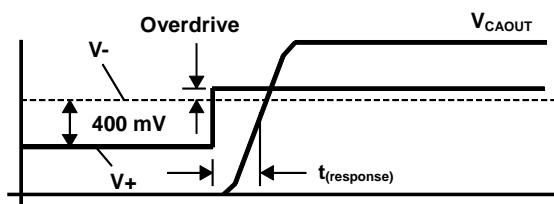

| t <sub>(response)</sub>           | 応答時間<br>(ロー・レベル ~ ハイ・レ<br>ベル及びハイ・レベル ~ ロ<br>ー・レベル)     | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>フィルタなし: CAF = 0<br>(注 3) (図 16、17 参照)                | 2.2 V           | 80   | 165                 | 300  | ns |

|                                   |                                                        |                                                                                               | 3 V             | 70   | 120                 | 240  |    |

|                                   |                                                        | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>Wフィルタ付き: CAF = 1<br>(注 3) (図 16、17 参照)               | 2.2 V           | 1.4  | 1.9                 | 2.8  | μs |

|                                   |                                                        |                                                                                               | 3 V             | 0.9  | 1.5                 | 2.2  |    |

(注 1) コンパレータ\_A+ 端子のリーク電流は、I<sub>lkg(Px,x)</sub> 規格と同じです。

(注 2) 入力オフセット電圧は、連続して測定する毎に CAEX ビットを使ってコンパレータ\_A+ 入力を反転させることにより、キヤンセルすることができます。2 つの連続した測定値を加算します。

(注 3) 応答時間は P2.2/CAOUT で測定します。

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

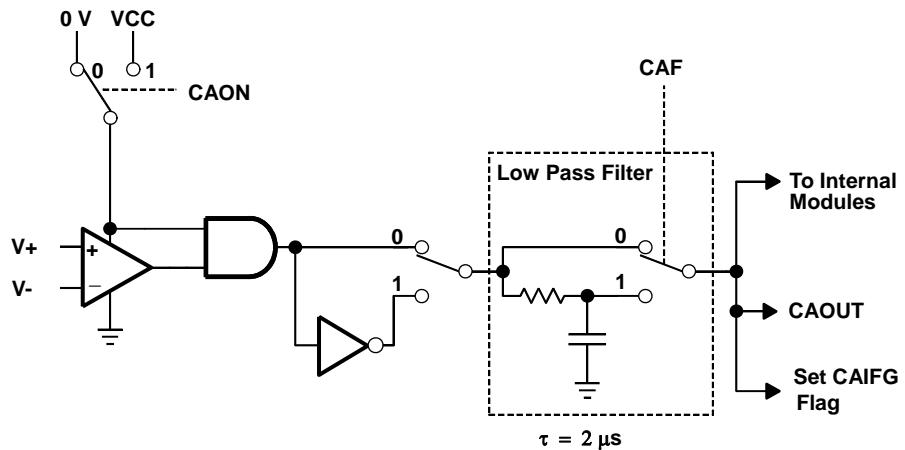

図 16. コンパレータ\_A+ モジュール ブロック図

図 17. オーバードライブの定義

図 18. コンパレータ\_A+ 短絡抵抗測定条件

推奨電源電圧及び動作周囲温度における電気的特性（特記無き場合）（続き）

代表特性 - コンパレータ\_A+

図 19. 温度対  $V_{(REFVT)}$ 、 $V_{CC} = 3\text{ V}$ 図 20. 温度対  $V_{(REFVT)}$ 、 $V_{CC} = 2.2\text{ V}$ 図 21.  $V_{IN}/V_{CC}$  対短絡抵抗

推奨電源電圧及び動作周囲温度における電気的特性 (特記無き場合) (続き)

フラッシュ・メモリ

| 項目                                         | 測定条件                     | $V_{CC}$    | 最小              | 標準              | 最大  | 単位     |

|--------------------------------------------|--------------------------|-------------|-----------------|-----------------|-----|--------|

| $V_{CC(PGM/ERASE)}$ プログラム及び消去時電源電圧         |                          |             | 2.2             |                 | 3.6 | V      |

| $f_{FTG}$ フラッシュ・タイミング発生器周波数                |                          |             | 257             |                 | 476 | kHz    |

| $I_{PGM}$ プログラム時消費電流 ( $V_{CC}$ )          |                          | 2.2 V/3.6 V | 3               | 5               |     | mA     |

| $I_{ERASE}$ 消去時消費電流 ( $V_{CC}$ )           |                          | 2.2 V/3.6 V | 3               | 7               |     | mA     |

| $t_{CPT}$ 累積プログラム時間                        | (注 1)                    | 2.2 V/3.6 V |                 |                 | 4   | ms     |

| $t_{CMErase}$ 累積一括消去時間                     |                          | 2.2 V/3.6 V | 20              |                 |     | ms     |

| プログラム/消去回数                                 |                          |             | 10 <sup>4</sup> | 10 <sup>5</sup> |     | cycles |

| $t_{Retention}$ データ保持期間                    | $T_J = 25^\circ\text{C}$ |             | 100             |                 |     | years  |

| $t_{Word}$ ワード又はバイト・プログラム時間                | (注 2)                    |             | 30              | $t_{FTG}$       |     |        |

| $t_{Block, 0}$ 先頭バイト又はワードのブロック・プログラム時間     |                          |             | 25              |                 |     |        |

| $t_{Block, 1-63}$ 各後続バイト又はワードのブロック・プログラム時間 |                          |             | 18              |                 |     |        |