**OPA1677, OPA1678, OPA1679**

JAJSCZ4E - JANUARY 2017 - REVISED DECEMBER 2022

# OPA167x 低歪オーディオ・オペアンプ

# 1 特長

低いノイズ:1 kHz 時に 4.5nV/√Hz

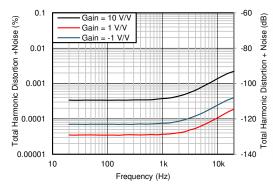

低歪:1kHz 時に 0.0001%

高いオープン・ループ・ゲイン: 114dB

大きい同相除去比:110dB

低い静止電流:

- チャネルごとに 2mA

低い入力バイアス電流:10pA (標準値)

スルーレート:9V/µs

広いゲイン帯域幅:16 MHz (G = 1)

ユニティ・ゲイン安定

レール・ツー・レール出力

広い電源電圧範囲:

±2.25V~±18V、または 4.5V~36V

シングル、デュアル、およびクワッド・チャネル・バージョ

利用可能なパッケージ:

シングル: SOIC-8、SOT-23

- デュアル:SOIC-8、小型 SON-8、VSSOP-8

- クワッド:小型 QFN-16、SO-14、TSSOP-14

• 温度範囲:-40℃~+85℃

# 2 アプリケーション

• 業務用マイクとワイヤレス・システム

業務用オーディオ・ミキサ/制御卓

ギターアンプ / その他楽器用アンプ

AV レシーバ

車載用外部アンプ

### 3 概要

シングル・チャネル OPA1677、デュアル・チャネル OPA1678 およびクワッド・チャネル OPA1679 (OPA167x) オペアンプは、オーディオ回路での一般的な 使用において、従来型のオペアンプよりも高いシステム・レ ベルの性能を実現します。

OPA167x アンプは、ノイズ密度が 4.5nV/√Hz と低く、歪 みも 1kHz で 0.0001% と低いため、オーディオ信号の忠 実度が向上します。また、2kΩ 負荷で電源の 800mV 内 側までのレール・ツー・レール出力が可能なため、ヘッドル ームが増大し、ダイナミック・レンジが最大化されます。

OPA167x は、多くの種類のオーディオ製品の電源に対 応するために、わずか 2mA の電源電流で、±2.25V~ ±18V (または 4.5V~36V) の非常に広い電源電圧範囲 で動作します。これらのオペアンプは安定したユニティ・ゲ インを持ち、広い範囲の負荷条件についてダイナミック特 性が非常に優れているため、多くのオーディオ回路で使 用できます。

OPA167x アンプは、オーバードライブまたは過負荷時で も、チャネル間のクロストークが最小限になるように、完全 に独立した内部回路を使用しています。

### デバイス情報

| ノハイベ門報  |      |                      |  |  |  |

|---------|------|----------------------|--|--|--|

| 部品番号    | チャネル | パッケージ <sup>(1)</sup> |  |  |  |

| OPA1677 | シンゲル | SOIC (8)             |  |  |  |

|         |      | SOT-23 (5)           |  |  |  |

|         |      | SOIC (8)             |  |  |  |

| OPA1678 | デュアル | VSSOP (8)            |  |  |  |

|         |      | SON (8)              |  |  |  |

|         |      | SOIC (14)            |  |  |  |

| OPA1679 | クワッド | TSSOP (14)           |  |  |  |

|         |      | QFN (16)             |  |  |  |

利用可能なパッケージについては、データシートの末尾にあるパ ッケージ・オプションについての付録を参照してください。

THD+N と周波数との関係 (2kΩ 負荷)

# **Table of Contents**

| 1 特長                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                    | 7.3 Feature Description                                                | 14                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------|

| 2アプリケーション                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      | 7.4 Device Functional Modes                                            | 18                            |

| 3 概要                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      | 8 Application and Implementation                                       | 19                            |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      | 8.1 Application Information                                            | 19                            |

| 5 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                             |                                                                      | 8.2 Typical Applications                                               | <mark>2</mark> 0              |

| 6 Specifications                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      | 8.3 Power Supply Recommendations                                       | 26                            |

| 6.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      | 8.4 Layout                                                             |                               |

| 6.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      | 9 Device and Documentation Support                                     | 28                            |

| 6.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                          |                                                                      | 9.1 Device Support                                                     | 28                            |

| 6.4 Thermal Information: OPA1677                                                                                                                                                                                                                                                                                                                                                                              |                                                                      | 9.2 Documentation Support                                              |                               |

| 6.5 Thermal Information: OPA1678                                                                                                                                                                                                                                                                                                                                                                              |                                                                      | 9.3ドキュメントの更新通知を受け取る方法                                                  | <mark>2</mark> 9              |

| 6.6 Thermal Information: OPA1679                                                                                                                                                                                                                                                                                                                                                                              |                                                                      | 9.4 サポート・リソース                                                          | 29                            |

| 6.7 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                    | 9.5 Trademarks                                                         | 29                            |

| 6.8 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                    | 9.6 静電気放電に関する注意事項                                                      | 29                            |

| 7 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      | 9.7 用語集                                                                |                               |

| 7.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      | 10 Mechanical, Packaging, and Orderable                                |                               |

| 7.2 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                   | Information                                                            | 29                            |

| <b>4 Revision History</b><br>資料番号末尾の英字は改訂を表しています。そ                                                                                                                                                                                                                                                                                                                                                            |                                                                      |                                                                        | <b>D</b>                      |

| 資料番号末尾の英字は改訂を表しています。 そ<br>Changes from Revision D (December 202                                                                                                                                                                                                                                                                                                                                               | 1) to Revisi                                                         | ion E (December 2022)                                                  | Page                          |

| 資料番号末尾の英字は改訂を表しています。 そ<br>Changes from Revision D (December 202                                                                                                                                                                                                                                                                                                                                               | 1) to Revisi                                                         |                                                                        |                               |

| 資料番号末尾の英字は改訂を表しています。 そ<br>Changes from Revision D (December 202                                                                                                                                                                                                                                                                                                                                               | 11) to Revisi<br>ューから量産                                              | ion E (December 2022)<br>ミデータ (アクティブ) に変更                              |                               |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to I                                                                                                                                                                                                                                                                 | 1) to Revisi<br>ューから量産<br>Revision D                                 | ion E (December 2022)<br>ミデータ (アクティブ) に変更                              | Page                          |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to I<br>文書全体の表、図、相互参照の採番方法を                                                                                                                                                                                                                                            | 1) to Revisi<br>ューから量産<br>Revision D<br>更新                           | ion E (December 2022)<br>ミデータ (アクティブ) に変更<br>(December 2021)           | Page                          |

| 資料番号末尾の英字は改訂を表しています。そ<br><b>Changes from Revision D (December 202</b><br>• OPA1677 D (SOIC、8) パッケージをプレビ<br><b>Changes from Revision C (April 2019) to I</b><br>• 文書全体の表、図、相互参照の採番方法を<br>• OPA1677 の量産データ (アクティブ) デバイ                                                                                                                                                                                          | 1) to Revision D<br>更新                                               | ion E (December 2022)<br>Eデータ (アクティブ) に変更<br>(December 2021)<br>S内容を追加 | Page                          |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to<br>・ 文書全体の表、図、相互参照の採番方法を<br>・ OPA1677 の量産データ (アクティブ) デバイ<br>Changes from Revision B (June 2018) to                                                                                                                                                                | 1) to Revision D<br>更新イスと関連する                                        | ion E (December 2022)<br>ミデータ (アクティブ) に変更                              | Page1                         |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to I<br>・ 文書全体の表、図、相互参照の採番方法を<br>・ OPA1677 の量産データ (アクティブ) デバイ<br>Changes from Revision B (June 2018) to I<br>・ OPA1679 QFN パッケージのステータスを「                                                                                                                             | 1) to Revision D<br>更新イスと関連する<br>Revision C<br>Revision C<br>量産データ」  | ion E (December 2022)<br>Eデータ (アクティブ) に変更<br>(December 2021)<br>S内容を追加 | Page1 Page                    |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to I<br>・ 文書全体の表、図、相互参照の採番方法を<br>・ OPA1677 の量産データ (アクティブ) デバイ<br>Changes from Revision B (June 2018) to I<br>・ OPA1679 QFN パッケージのステータスを「<br>・ Changed GPN BUF634A in Figure 8-6, C                                                                                   | 1) to Revision D<br>更新イスと関連する<br>Revision C<br>配産データ」<br>Composite H | ion E (December 2022)<br>ミデータ (アクティブ) に変更                              | Page1 Page1 Page1             |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to D<br>・ 文書全体の表、図、相互参照の採番方法を<br>・ OPA1677 の量産データ (アクティブ) デバイ<br>Changes from Revision B (June 2018) to D<br>・ OPA1679 QFN パッケージのステータスを「<br>・ Changed GPN BUF634A in Figure 8-6, C<br>Changes from Revision A (May 2018) to F                                        | 1) to Revision D<br>更新イスと関連する<br>Revision C<br>量産データ」<br>Composite H | ion E (December 2022)<br>ミデータ (アクティブ) に変更                              | Page1 Page1 Page1 Page1       |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (December 202<br>・ OPA1677 D (SOIC、8) パッケージをプレビ<br>Changes from Revision C (April 2019) to D<br>・ 文書全体の表、図、相互参照の採番方法を<br>・ OPA1677 の量産データ (アクティブ) デバイ<br>Changes from Revision B (June 2018) to D<br>・ OPA1679 QFN パッケージのステータスを「<br>・ Changed GPN BUF634A in Figure 8-6, C<br>Changes from Revision A (May 2018) to F                                        | 1) to Revision D 更新                                                  | ion E (December 2022)<br>医データ (アクティブ) に変更                              | Page1 Page1 Page1 Page1       |

| 資料番号末尾の英字は改訂を表しています。そ Changes from Revision D (December 202  OPA1677 D (SOIC、8) パッケージをプレビ  Changes from Revision C (April 2019) to I  文書全体の表、図、相互参照の採番方法を  OPA1677 の量産データ (アクティブ) デバイ  Changes from Revision B (June 2018) to I  OPA1679 QFN パッケージのステータスを「  Changed GPN BUF634A in Figure 8-6, C  Changes from Revision A (May 2018) to I  プレビュー版 QFN (RUM) パッケージについ  Changes from Revision * (February 2017) | 1) to Revision D 更新                                                  | ion E (December 2022)<br>医データ (アクティブ) に変更                              | Page1 Page1 Page1 Page1 Page1 |

# **5 Pin Configuration and Functions**

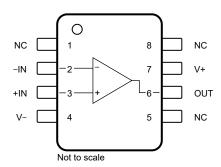

図 5-1. OPA1677: D Package, 8-Pin SOIC (Top View)

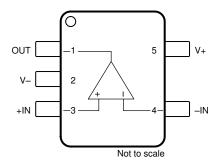

図 5-2. OPA1677: DBV Package, 5-Pin SOT-23 (Top View)

**Pin Functions: OPA1677**

|      | PIN         |                 |                  |                                 |  |

|------|-------------|-----------------|------------------|---------------------------------|--|

|      | NO.         |                 | TYPE             | DESCRIPTION                     |  |

| NAME | D<br>(SOIC) | DBV<br>(SOT-23) | · · · · <u>-</u> |                                 |  |

| -IN  | 2           | 4               | Input            | Inverting input                 |  |

| +IN  | 3           | 3               | Input            | Noninverting input              |  |

| OUT  | 6           | 1               | Output           | Output                          |  |

| V-   | 4           | 2               | Power            | Negative (lowest) power supply  |  |

| V+   | 7           | 5               | Power            | Positive (highest) power supply |  |

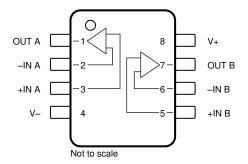

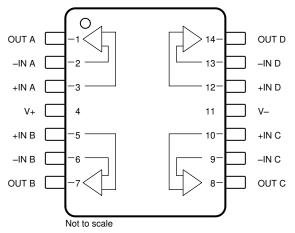

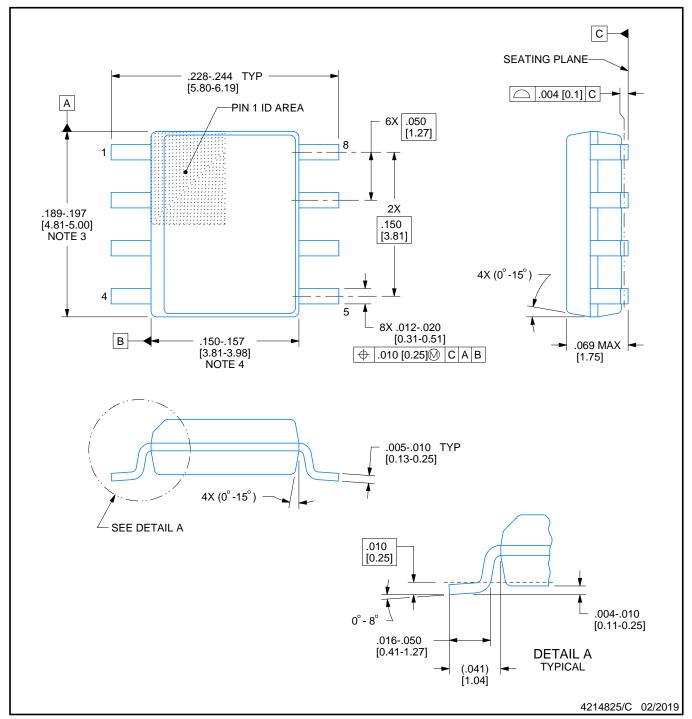

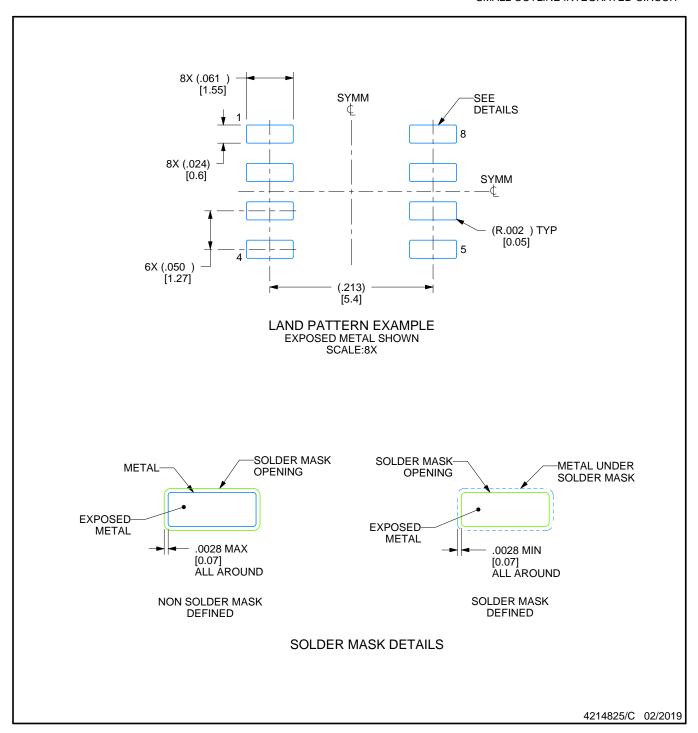

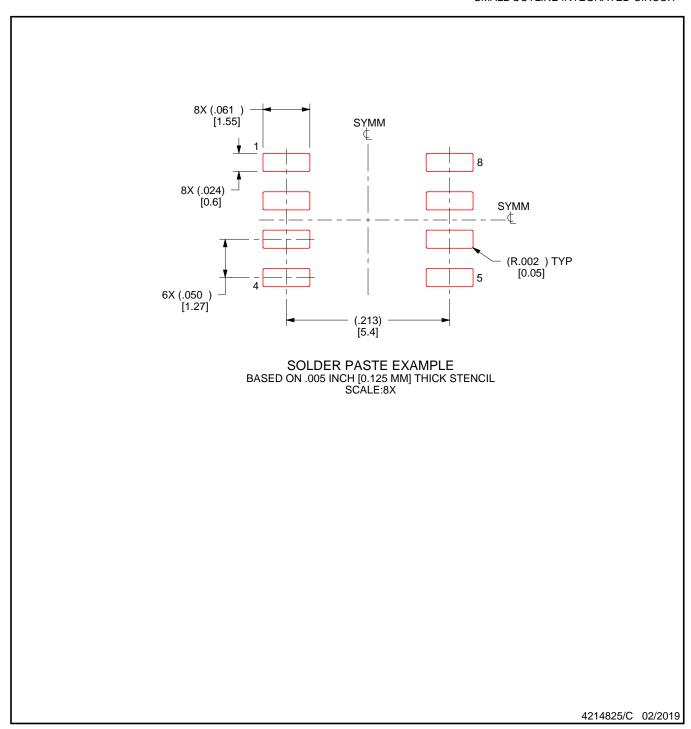

図 5-3. OPA1678: D Package, 8-Pin SOIC and DGK Package, 8-Pin VSSOP (Top View)

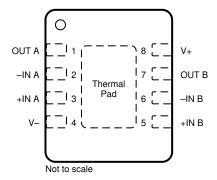

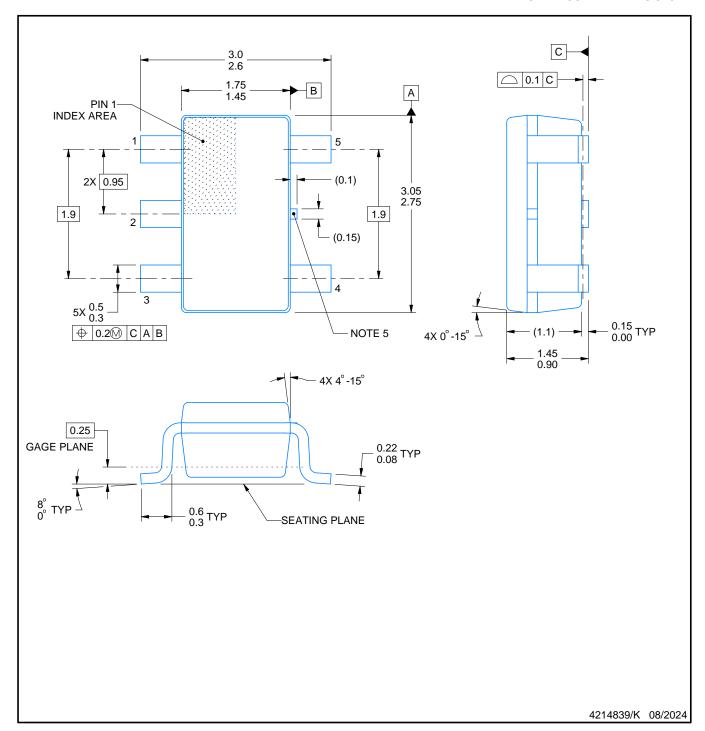

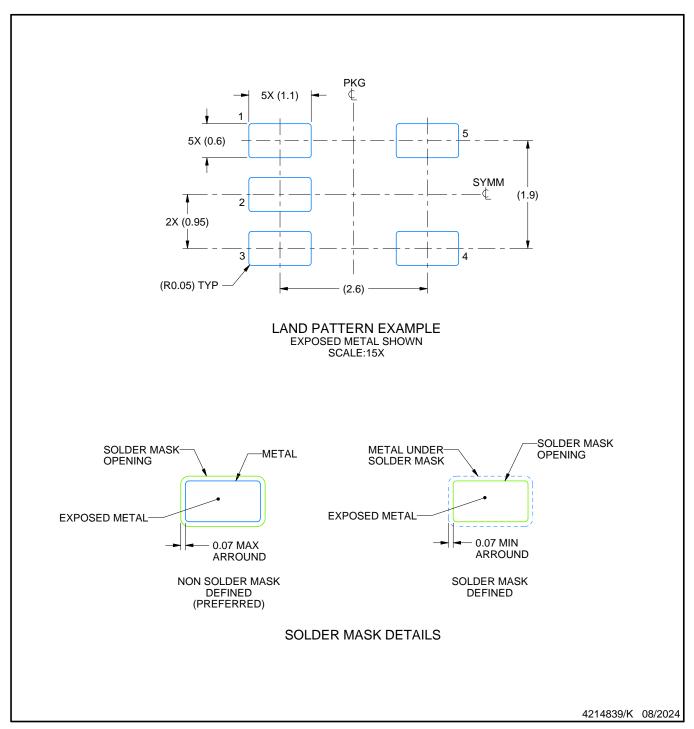

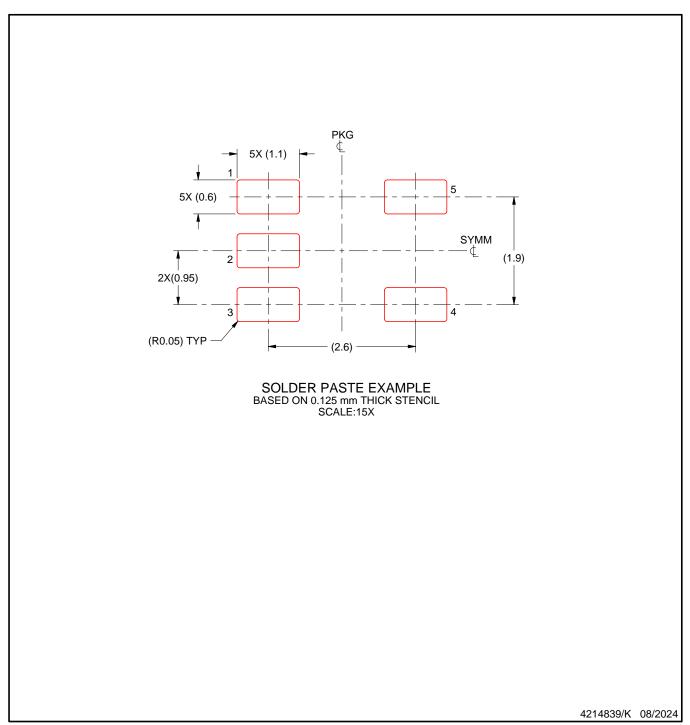

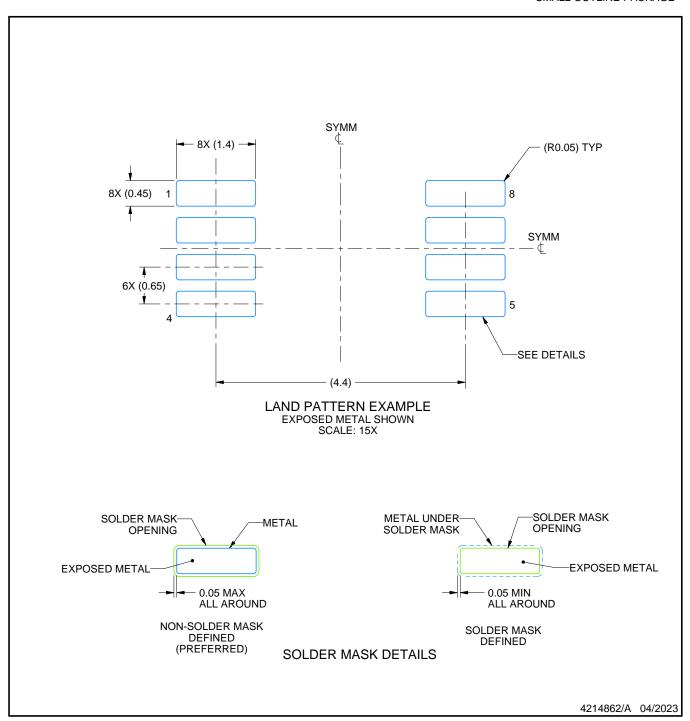

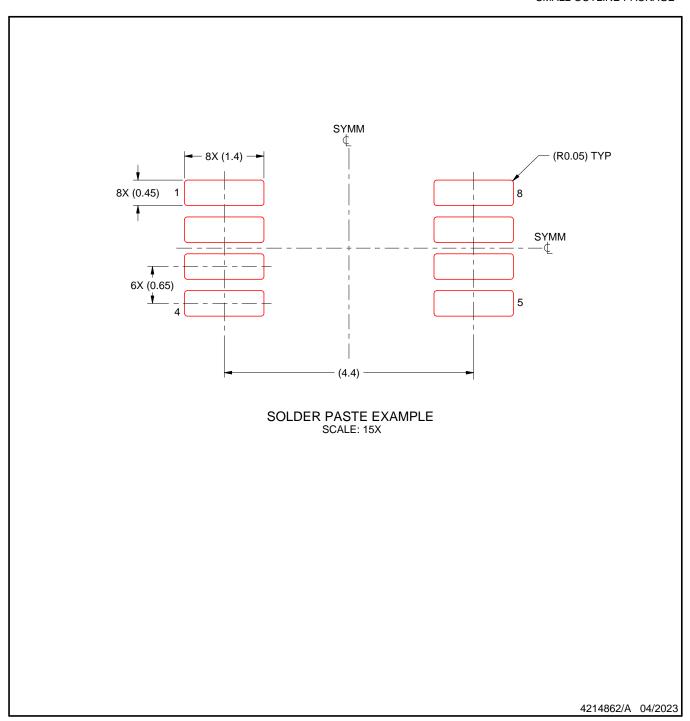

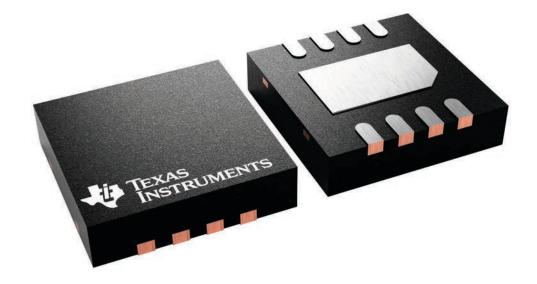

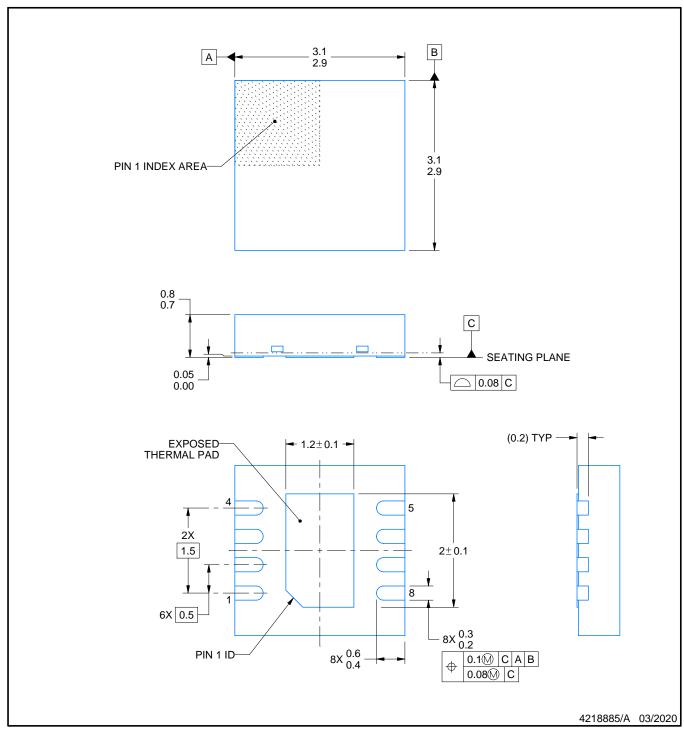

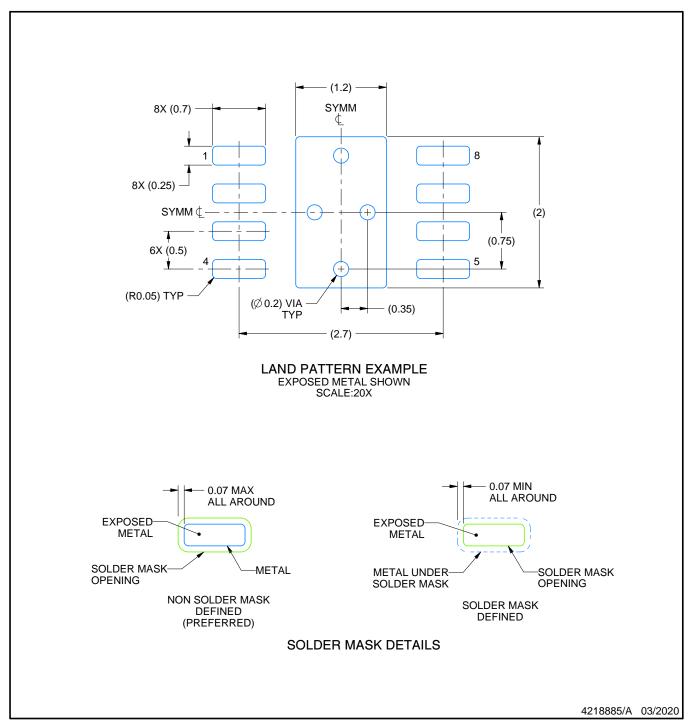

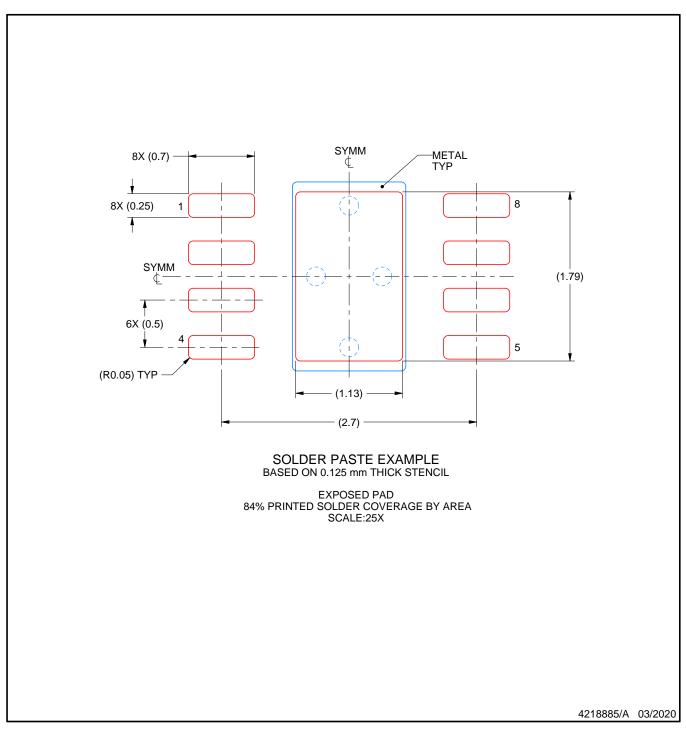

図 5-4. OPA1678: DRG Package, 8-Pin SON With Exposed Thermal Pad (Top View)

### **Pin Functions: OPA1678**

| PIN         |             | TYPE   | DESCRIPTION                                                                                                                                                                         |  |  |

|-------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.         | ITPE   | DESCRIPTION                                                                                                                                                                         |  |  |

| −IN A       | 2           | Input  | Inverting input, channel A                                                                                                                                                          |  |  |

| +IN A       | 3           | Input  | Noninverting input, channel A                                                                                                                                                       |  |  |

| –IN B       | 6           | Input  | Inverting input, channel B                                                                                                                                                          |  |  |

| +IN B       | 5           | Input  | ninverting input, channel B                                                                                                                                                         |  |  |

| OUT A       | 1           | Output | Output, channel A                                                                                                                                                                   |  |  |

| OUT B       | 7           | Output | Output, channel B                                                                                                                                                                   |  |  |

| V-          | 4           | Power  | Negative (lowest) power supply                                                                                                                                                      |  |  |

| V+          | 8           | Power  | Positive (highest) power supply                                                                                                                                                     |  |  |

| Thermal Pad | Thermal pad | _      | For DRG (SON-8) package. Exposed thermal die pad on underside. Connect thermal die pad to V–. Solder the thermal pad to improve heat dissipation and provide specified performance. |  |  |

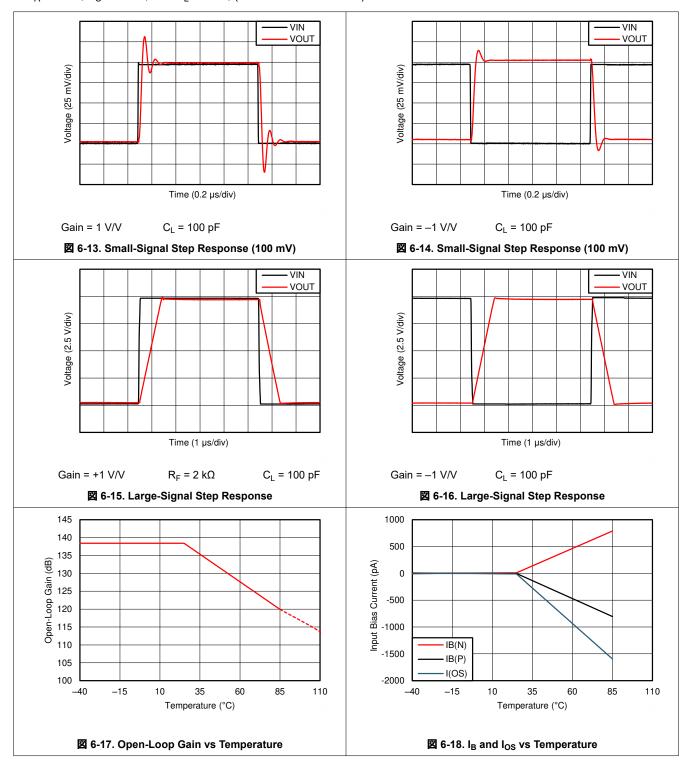

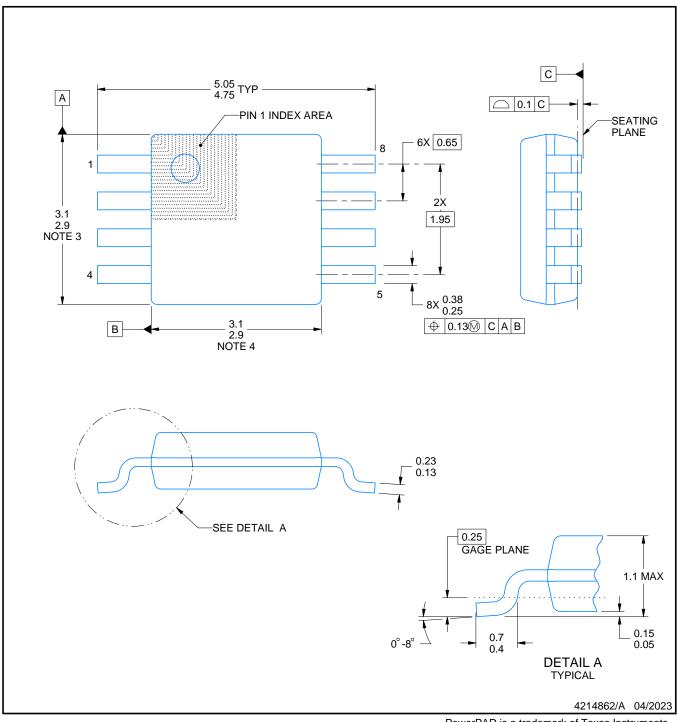

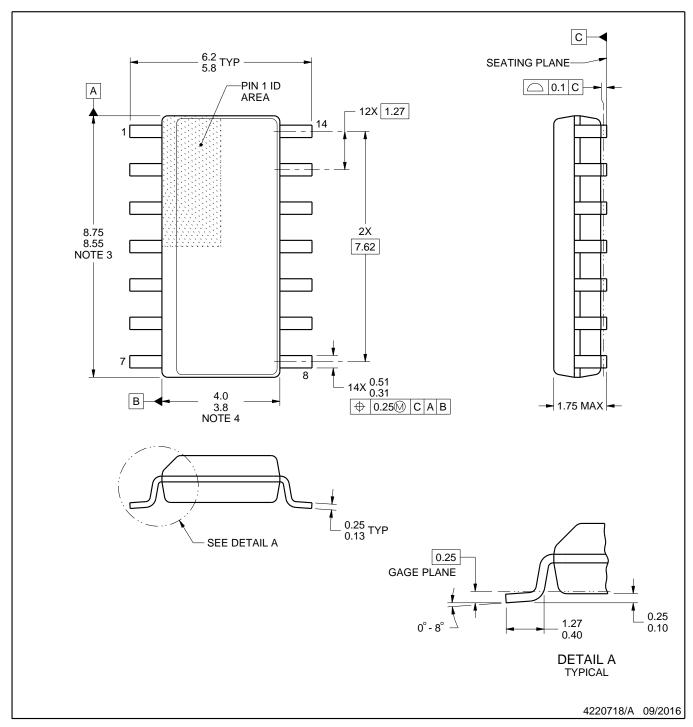

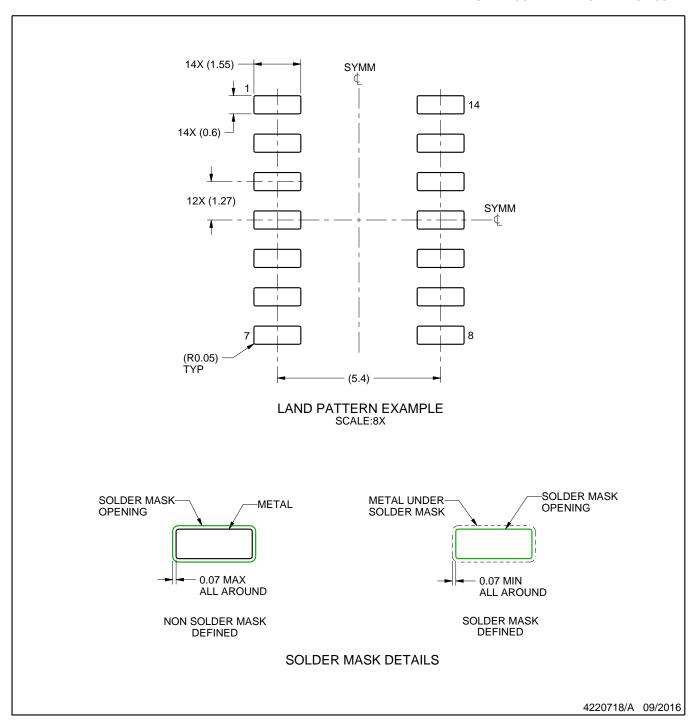

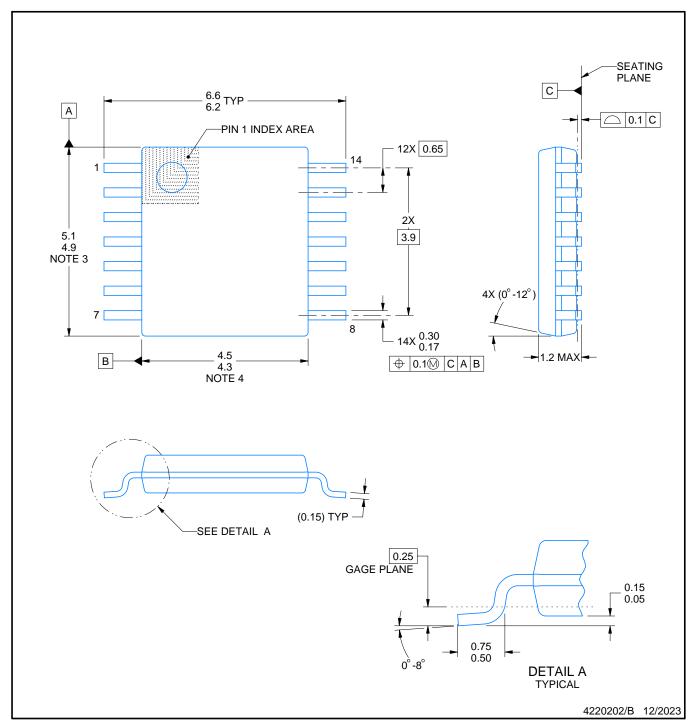

図 5-5. OPA1679: D Package, 14-Pin SOIC and PW Package, 14-Pin TSSOP (Top View)

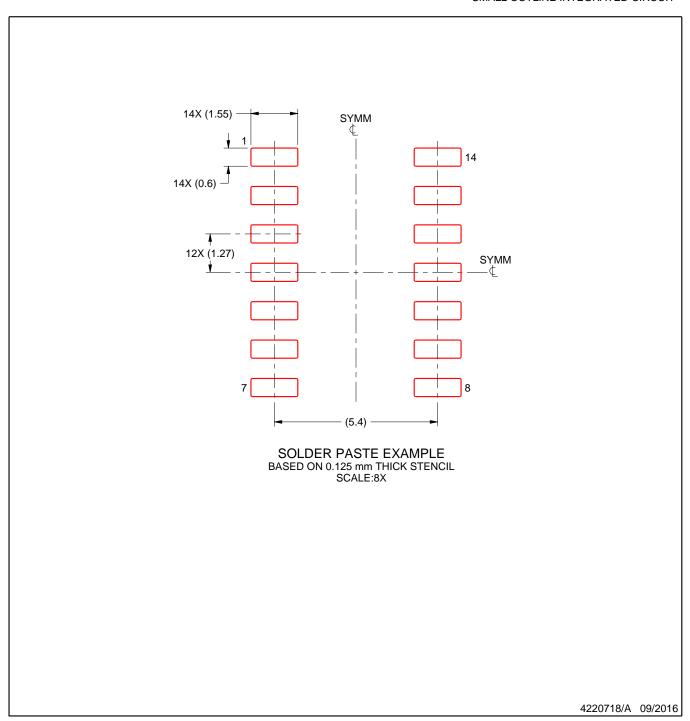

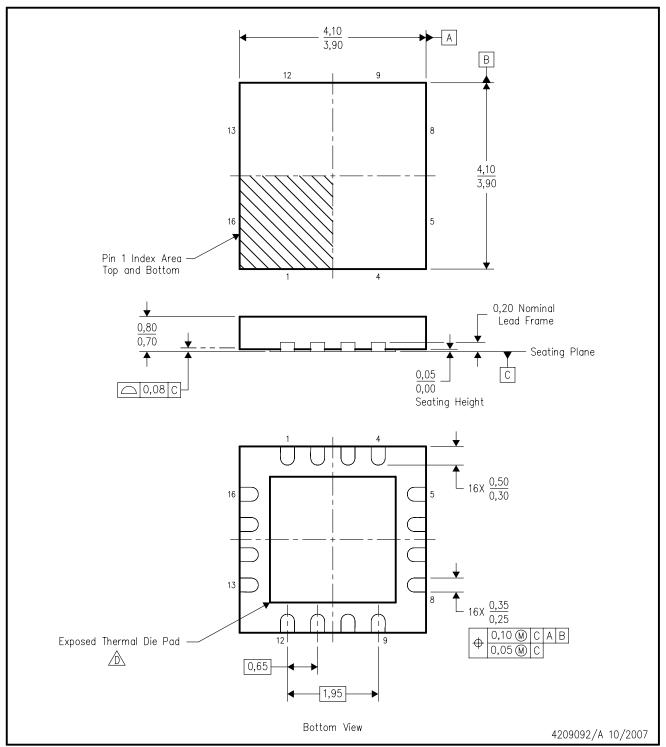

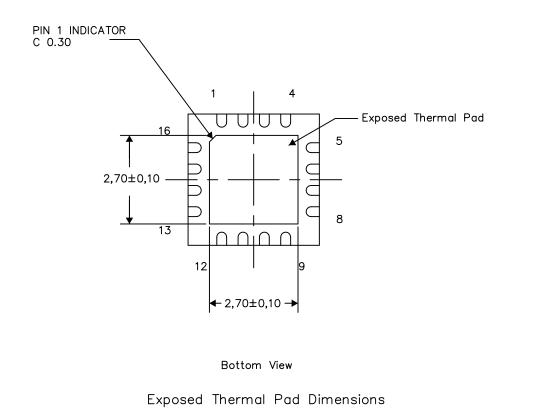

図 5-6. OPA1679: RUM Package, 16-Pin QFN With Exposed Thermal Pad (Top View)

**Pin Functions: OPA1679**

|             |                        |             | 1 111 1 | UNCTIONS: OPA1679                                                                                                                                          |

|-------------|------------------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | PIN                    |             |         |                                                                                                                                                            |

|             | NO.                    |             | TYPE    | DESCRIPTION                                                                                                                                                |

| NAME        | D (SOIC)<br>PW (TSSOP) | RUM (QFN)   |         |                                                                                                                                                            |

| –IN A       | 2                      | 1           | Input   | Inverting input, channel A                                                                                                                                 |

| +IN A       | 3                      | 2           | Input   | Noninverting input, channel A                                                                                                                              |

| –IN B       | 6                      | 5           | Input   | Inverting input, channel B                                                                                                                                 |

| +IN B       | 5                      | 4           | Input   | Noninverting input, channel B                                                                                                                              |

| –IN C       | 9                      | 8           | Input   | Inverting input, channel C                                                                                                                                 |

| +IN C       | 10                     | 9           | Input   | Noninverting input, channel C                                                                                                                              |

| –IN D       | 13                     | 12          | Input   | Inverting input, channel D                                                                                                                                 |

| +IN D       | 12                     | 11          | Input   | Noninverting input, channel D                                                                                                                              |

| NC          | _                      | 13          | _       | No connect                                                                                                                                                 |

| NC          | _                      | 16          | _       | No connect                                                                                                                                                 |

| OUT A       | 1                      | 15          | Output  | Output, channel A                                                                                                                                          |

| OUT B       | 7                      | 6           | Output  | Output, channel B                                                                                                                                          |

| OUT C       | 8                      | 7           | Output  | Output, channel C                                                                                                                                          |

| OUT D       | 14                     | 14          | Output  | Output, channel D                                                                                                                                          |

| V+          | 4                      | 3           | Power   | Positive (highest) power supply                                                                                                                            |

| V-          | 11                     | 10          | Power   | Negative (lowest) power supply                                                                                                                             |

| Thermal Pad | _                      | Thermal pad | _       | Exposed thermal die pad on underside. Connect thermal die pad to V–. Solder the thermal pad to improve heat dissipation and provide specified performance. |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                      |                                                   | MIN        | MAX        | UNIT |

|------------------|----------------------|---------------------------------------------------|------------|------------|------|

|                  | Voltage              | Supply voltage, $V_S = (V+) - (V-)$               |            | 40         | V    |

|                  |                      | Input voltage                                     | (V-) - 0.5 | (V+) + 0.5 | V    |

|                  | Current              | Input current (all pins except power-supply pins) | -10        | 10         | mA   |

|                  |                      | Output short-circuit current <sup>(2)</sup>       | Continu    | ious       |      |

| T <sub>A</sub>   | Operating tem        | perature                                          | -55        | 125        | °C   |

| $T_{J}$          | Junction temperature |                                                   |            | 150        | °C   |

| T <sub>stg</sub> | Storage temperature  |                                                   | -65        | 150        | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Short-circuit to V<sub>S</sub> / 2 (ground in symmetrical dual-supply setups), one amplifier per package.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

|                    |                         | Machine model (MM) <sup>(3)</sup>                                              | ±200  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) Machine Model was not tested on OPA1679IRUM.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                       |             | MIN   | NOM MAX | UNIT |

|----------------|-----------------------|-------------|-------|---------|------|

|                | Single supply         | 4.5         | 36    |         |      |

| Vs             | Supply voltage        | Dual supply | ±2.25 | ±18     | V    |

| T <sub>A</sub> | Operating temperature |             | -40   | 125     | °C   |

# 6.4 Thermal Information: OPA1677

|                       |                                              | OPA         | 1677            |      |

|-----------------------|----------------------------------------------|-------------|-----------------|------|

|                       | THERMAL METRIC(1)                            | D<br>(SOIC) | DBV<br>(SOT-23) | UNIT |

|                       |                                              | 8 PINS      | 5 PINS          |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 132.9       | 180.5           | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 74.0        | 78.5            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 76.3        | 47.3            | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 24.9        | 20.4            | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 75.6        | 47.0            | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | N/A             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Thermal Information: OPA1678

|                       |                                              |             | OPA1678        |              |      |

|-----------------------|----------------------------------------------|-------------|----------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D<br>(SOIC) | DGK<br>(VSSOP) | DRG<br>(SON) | UNIT |

|                       |                                              | 8 PINS      | 8 PINS         | 8 PINS       |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 144         | 219            | 66.9         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 77          | 79             | 54.5         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 62          | 104            | 40.4         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 28          | 15             | 1.9          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 61          | 102            | 40.4         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | N/A            | 10.8         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.6 Thermal Information: OPA1679

|                       | THERMAL METRIC <sup>(1)</sup>                | D<br>(SOIC) | PW<br>(TSSOP) | RUM<br>(QFN) | UNIT |

|-----------------------|----------------------------------------------|-------------|---------------|--------------|------|

|                       |                                              | 14 PINS     | 14 PINS       | 16 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 90          | 127           | 38.5         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 55          | 47            | 34.4         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 44          | 59            | 17.4         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 20          | 55            | 0.6          | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 44          | 58            | 17.4         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | N/A           | 7.1          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.7 Electrical Characteristics**

at  $V_S = \pm 15 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $R_L = 2 \text{ k}\Omega$ , and  $V_{CM} = V_{OUT} = \text{midsupply}$  (unless otherwise noted)

|                  | PARAMETER                            |                                                                                                          | TEST CONDITIONS                          | MIN        | TYP      | MAX        | UNIT               |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|------------|----------|------------|--------------------|

| AUDIO PEI        | RFORMANCE                            |                                                                                                          |                                          |            |          |            |                    |

| T.I.D. 1.1       |                                      |                                                                                                          | 2006                                     | 0.         | 0001%    |            |                    |

| THD+N            | Total harmonic distortion + noise    | $G = 1, R_L = 6$                                                                                         | 00 Ω, f = 1 kHz, $V_O = 3 V_{RMS}$       |            | -120     |            | dB                 |

|                  |                                      |                                                                                                          | SMPTE/DIN two-tone, 4:1                  | 0.         | 0001%    |            |                    |

|                  |                                      |                                                                                                          | (60 Hz and 7 kHz)                        |            | -120     |            | dB                 |

|                  |                                      | G = 1                                                                                                    | DIM 30                                   | 0.         | 0001%    |            |                    |

| IMD              | Intermodulation distortion           | $V_O = 3 V_{RMS}$                                                                                        | (3-kHz square wave and 15-kHz sine wave) |            | -120     |            | dB                 |

|                  |                                      |                                                                                                          | CCIF twin-tone                           | 0.         | 0001%    |            |                    |

|                  |                                      |                                                                                                          | (19 kHz and 20 kHz)                      |            | -120     |            | dB                 |

| FREQUEN          | CY RESPONSE                          |                                                                                                          |                                          |            |          |            |                    |

| GBW              | Gain-bandwidth product               | G = 1                                                                                                    |                                          |            | 16       |            | MHz                |

| SR               | Slew rate                            | G = -1                                                                                                   |                                          |            | 9        |            | V/µs               |

|                  | Full power bandwidth <sup>(1)</sup>  | V <sub>O</sub> = 1 V <sub>P</sub>                                                                        |                                          |            | 1.4      |            | MHz                |

|                  | Overload recovery time               | G = -10                                                                                                  |                                          |            | 1        |            | μs                 |

|                  | Channel separation (dual and quad)   | f = 1 kHz                                                                                                |                                          |            | -130     |            | dB                 |

| NOISE            |                                      | 1                                                                                                        |                                          |            |          |            |                    |

| on               | Input voltage poice                  | f = 20 Hz to 2                                                                                           | 0 kHz                                    |            | 5.4      |            |                    |

| en               | Input voltage noise                  | f = 0.1 Hz to                                                                                            | f = 0.1 Hz to 10 Hz                      |            | 1.74     |            | - μV <sub>PP</sub> |

|                  | Input voltage noise density          | f = 1 kHz                                                                                                |                                          |            | 4.5      |            | nV/√Hz             |

| i <sub>n</sub>   | Input current noise density          | f = 1 kHz                                                                                                |                                          | 3          |          |            | fA/√Hz             |

| OFFSET V         | OLTAGE                               |                                                                                                          |                                          |            |          |            |                    |

| Vos              | Input offset voltage                 | $V_S = \pm 2.25 \text{ V}$                                                                               |                                          |            | ±0.5     | ±2         | mV                 |

| *05              | input chest voltage                  | $V_S = \pm 2.25 \text{ V to } \pm 18 \text{ V}, T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}^{(2)}$ |                                          |            | 2        |            | μV/°C              |

| PSRR             | Power-supply rejection ratio         | V <sub>S</sub> = ±2.25 V                                                                                 | to ±18 V                                 |            | 3        | 8          | μV/V               |

| INPUT BIA        | S CURRENT                            |                                                                                                          |                                          |            |          |            |                    |

| I <sub>B</sub>   | Input bias current                   | V <sub>CM</sub> = 0 V                                                                                    |                                          |            | ±10      |            | pA                 |

| los              | Input offset current                 | V <sub>CM</sub> = 0 V                                                                                    |                                          |            | ±10      |            | pA                 |

| INPUT VOL        | LTAGE RANGE                          |                                                                                                          |                                          |            |          |            |                    |

| V <sub>CM</sub>  | Common-mode voltage range            |                                                                                                          |                                          | (V-)+0.5   |          | (V+) – 2   | V                  |

| CMRR             | Common-mode rejection ratio          |                                                                                                          |                                          | 100        | 110      |            | dB                 |

| INPUT IMP        |                                      |                                                                                                          |                                          |            |          |            |                    |

|                  | Differential                         |                                                                                                          |                                          |            | 100    6 |            | MΩ    pF           |

|                  | Common-mode                          |                                                                                                          |                                          | 60         | 000    2 |            | GΩ    pF           |

| OPEN-LOC         |                                      | 04 ) 00::                                                                                                | 4)/ 40//) 00//                           | 400        | 4        |            |                    |

| A <sub>OL</sub>  | Open-loop voltage gain               | (V-) + 0.8 V s                                                                                           | $\leq V_{O} \leq (V+) - 0.8 \text{ V}$   | 106        | 114      |            | dB                 |

| OUTPUT           | Outrot well-                         |                                                                                                          | 1                                        | 0/ ) . 0 0 |          | ()(1)      |                    |

| V <sub>o</sub>   | Output voltage                       |                                                                                                          |                                          | (V-) + 0.8 |          | (V+) - 0.8 |                    |

| I <sub>OUT</sub> | Output Current                       |                                                                                                          |                                          |            | ション 6.8  |            | mA                 |

| Zo               | Open-loop output impedance           | f = 1 MHz                                                                                                |                                          | See セク     | ション 6.8  |            | Ω                  |

| I <sub>SC</sub>  | Short-circuit current <sup>(3)</sup> |                                                                                                          |                                          |            | ±50      |            | mA                 |

| CL               | Capacitive load drive                |                                                                                                          |                                          |            | 100      |            | pF                 |

| POWER SU         | JPPLY                                | 1                                                                                                        |                                          |            |          | -          |                    |

| IQ               | Quiescent current (per channel)      | I <sub>O</sub> = 0 A                                                                                     | (0)                                      |            | 2        | 2.5        | mA                 |

| •                |                                      | I <sub>O</sub> = 0 A, T <sub>A</sub> =                                                                   | =-40°C to 125°C <sup>(2)</sup>           |            |          | 2.8        |                    |

- (1) Full-power bandwidth = SR /  $(2\pi \times V_P)$ , where SR = slew rate.

- (2) Specified by design and characterization.

- (3) One channel at a time.

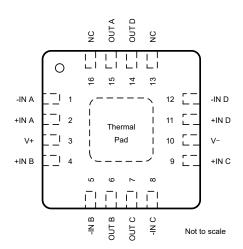

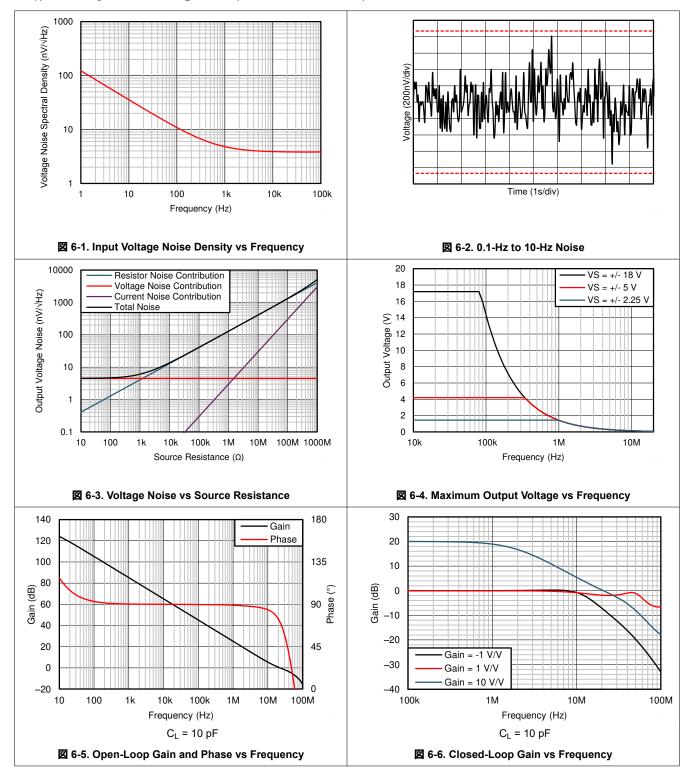

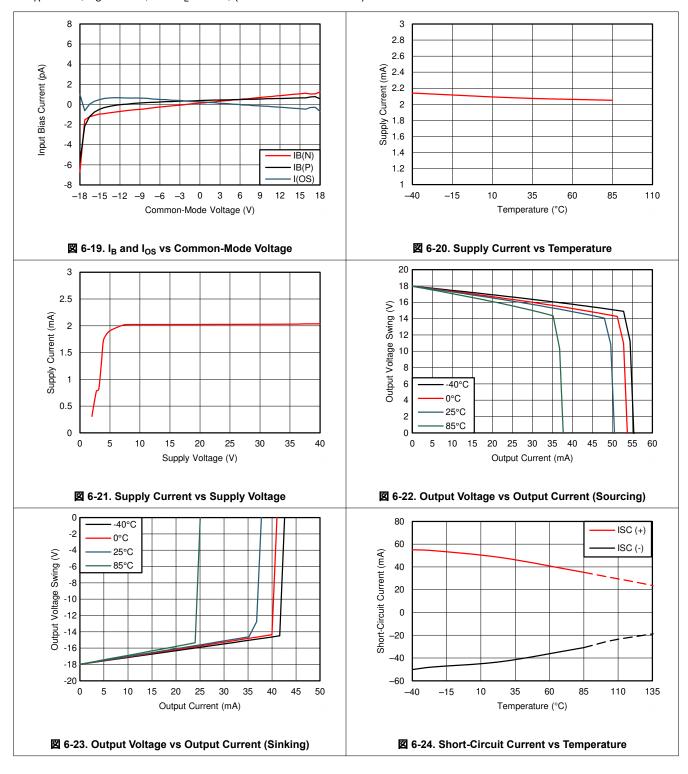

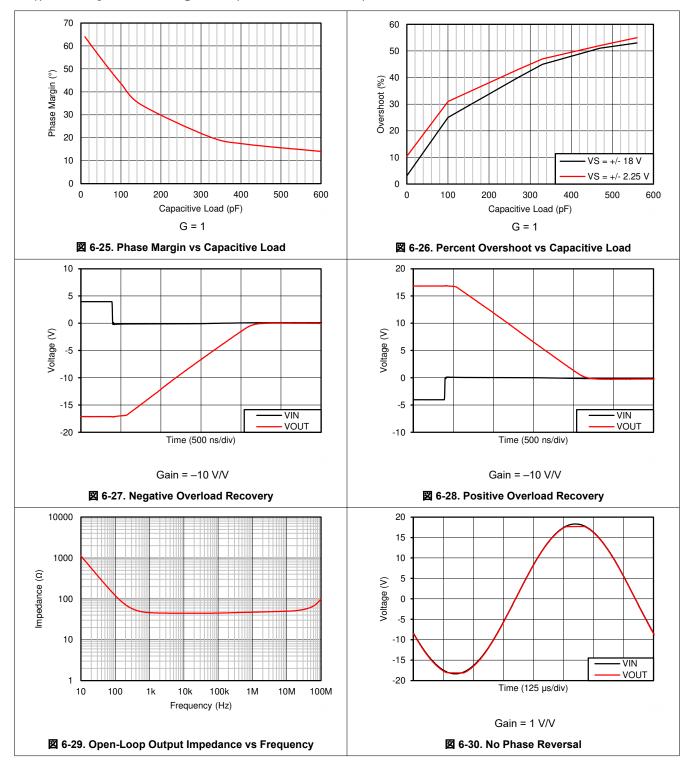

# **6.8 Typical Characteristics**

# 7 Detailed Description

## 7.1 Overview

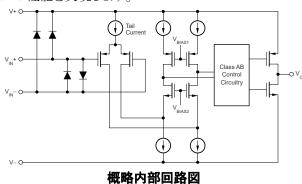

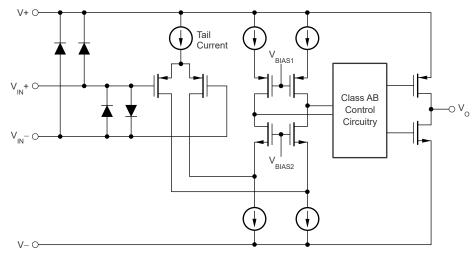

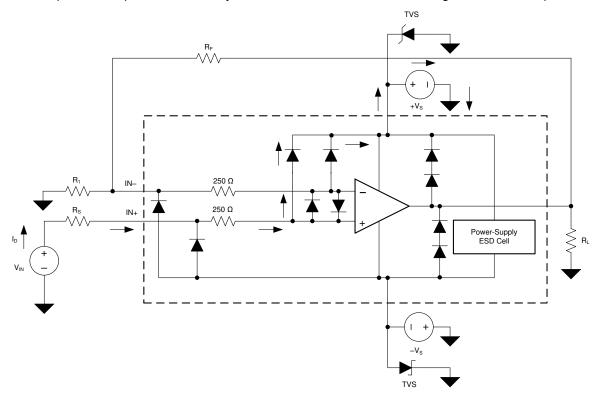

The OPA167x devices are unity-gain stable, dual-channel and quad-channel op amps with low noise and distortion. #7>=> 7.2 shows a simplified schematic of the OPA167x (one channel shown). These devices consist of a low-noise input stage with a folded cascode and a rail-to-rail output stage. This topology exhibits excellent noise and distortion performance across a wide range of supply voltages that are not delivered by legacy, commodity, audio operational amplifiers.

## 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Phase Reversal Protection

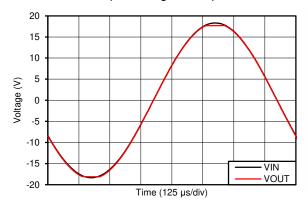

The OPA167x family has internal phase-reversal protection. Many op amps exhibit phase reversal when the input is driven beyond the linear common-mode range. This condition is most often encountered in noninverting circuits when the input is driven beyond the specified common-mode voltage range, causing the output to reverse into the opposite rail. The input of the OPA167x prevents phase reversal with excessive common-mode voltage. Instead, the appropriate rail limits the output voltage. This performance is shown in  $\boxtimes$  7-1.

図 7-1. Output Waveform Devoid of Phase Reversal During an Input Overdrive Condition

#### 7.3.2 Electrical Overstress

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but can involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown

characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

A good understanding of this basic ESD circuitry and the relevance to an electrical overstress event is helpful.

7-2 illustrates the ESD circuits contained in the OPA167x (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where the diodes meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

図 7-2. Equivalent Internal ESD Circuitry Relative to a Typical Circuit Application

An ESD event produces a short-duration, high-voltage pulse that is transformed into a short-duration, high-current pulse when discharging through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent damage. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more amplifier device pins, current flows through one or more steering diodes. Depending on the path that the current takes, the absorption device can activate. The absorption device has a trigger, or threshold voltage, that is greater than the normal operating voltage of the OPA167x but less than the device breakdown voltage level. When this threshold is exceeded, the absorption device quickly activates and clamps the voltage across the supply rails to a safe level.

When the operational amplifier connects into a circuit (see 🗵 7-2), the ESD protection components are intended to remain inactive and do not become involved in the application circuit operation. However, circumstances can arise where an applied voltage exceeds the operating voltage range of a given pin. If this condition occurs, there is a risk that some internal ESD protection circuits can turn on and conduct current. Any such current flow occurs through steering-diode paths and rarely involves the absorption device.

☑ 7-2 shows a specific example where the input voltage (V<sub>IN</sub>) exceeds the positive supply voltage (V+) by 500 mV or more. Much of what happens in the circuit depends on the supply characteristics. If V+ can sink the current, one of the upper input steering diodes conducts and directs current to V+. Excessively high current

levels can flow with increasingly higher  $V_{IN}$ . As a result, the data sheet specifications recommend that applications limit the input current to 10 mA.

If the supply is not capable of sinking the current,  $V_{IN}$  can begin sourcing current to the operational amplifier and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings.

Another common question involves what happens to the amplifier if an input signal is applied to the input when the power supplies (V+ or V-) are at 0 V. Again, this question depends on the supply characteristic when at 0 V, or at a level less than the input signal amplitude. If the supplies appear as high impedance, then the input source supplies the operational amplifier current through the current-steering diodes. This state is not a normal bias condition; most likely, the amplifier does not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

If there is any uncertainty about the ability of the supply to absorb this current, add external Zener diodes to the supply pins; see  $\boxtimes$  7-2. Select the Zener voltage so that the diode does not turn on during normal operation. However, the Zener voltage must be low enough so that the Zener diode conducts if the supply pin begins to rise above the safe-operating, supply-voltage level.

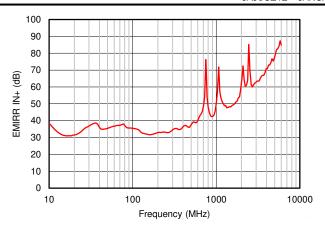

### 7.3.3 EMI Rejection Ratio (EMIRR)

The electromagnetic interference (EMI) rejection ratio, or EMIRR, describes the EMI immunity of operational amplifiers. An adverse effect that is common to many operational amplifiers is a change in the offset voltage as a result of RF signal rectification. An operational amplifier that is more efficient at rejecting this change in offset as a result of EMI has a higher EMIRR and is quantified by a decibel value. Measuring EMIRR can be performed in many ways, but this document provides the EMIRR IN+, which specifically describes the EMIRR performance when the RF signal is applied to the noninverting input pin of the operational amplifier. In general, only the noninverting input is tested for EMIRR for the following three reasons:

- Operational amplifier input pins are known to be the most sensitive to EMI, and typically rectify RF signals better than the supply or output pins.

- The noninverting and inverting operational amplifier inputs have symmetrical physical layouts and exhibit nearly matching EMIRR performance.

- EMIRR is easier to measure on noninverting pins than on other pins because the noninverting input pin can be isolated on a printed-circuit-board (PCB). This isolation allows the RF signal to be applied directly to the noninverting input pin with no complex interactions from other components or connecting PCB traces.

A more formal discussion of the EMIRR IN+ definition and test method is shown in the *EMI Rejection Ratio of Operational Amplifiers* application report, available for download at www.ti.com.

The EMIRR IN+ of the OPA167x is plotted versus frequency in  $\boxtimes$  7-3. The dual and quad operational amplifier device versions have approximately identical EMIRR IN+ performance. The OPA167x unity-gain bandwidth is 16 MHz. EMIRR performance below this frequency denotes interfering signals that fall within the operational amplifier bandwidth.

図 7-3. OPA167x EMIRR vs Frequency

表 7-1 lists the EMIRR IN+ values for the OPA167x at particular frequencies commonly encountered in real-world applications. Applications listed in 表 7-1 can be centered on or operated near the particular frequency shown. This information can be of special interest to designers working with these types of applications, or working in other fields likely to encounter RF interference from broad sources, such as the industrial, scientific, and medical (ISM) radio band.

| 表 7-1. OPA167x EMIRR IN+ for Frequencies of Inte | rest |

|--------------------------------------------------|------|

|                                                  |      |

| FREQUENCY | APPLICATION OR ALLOCATION                                                                                 | EMIRR IN+ |

|-----------|-----------------------------------------------------------------------------------------------------------|-----------|

| 400 MHz   | Mobile radio, mobile satellite, space operation, weather, radar, UHF                                      | 36 dB     |

| 900 MHz   | GSM, radio communication and navigation, GPS (to 1.6 GHz), ISM, aeronautical mobile, UHF                  | 42 dB     |

| 1.8 GHz   | GSM, mobile personal comm. broadband, satellite, L-band                                                   | 52 dB     |

| 2.4 GHz   | 802.11b/g/n, Bluetooth™, mobile personal comm., ISM, amateur radio and satellite, S-band                  | 64 dB     |

| 3.6 GHz   | Radiolocation, aero comm./nav., satellite, mobile, S-band                                                 | 67 dB     |

| 5 GHz     | 802.11a/n, aero communication and navigation, mobile communication, space and satellite operation, C-band | 77 dB     |

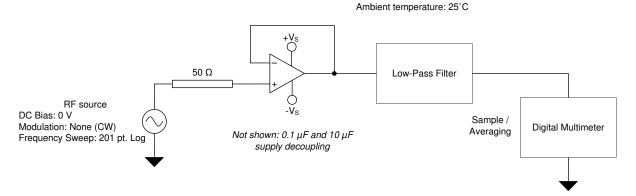

### 7.3.3.1 EMIRR IN+ Test Configuration

☑ 7-4 shows the circuit configuration for testing the EMIRR IN+. An RF source is connected to the operational amplifier noninverting input pin using a transmission line. The operational amplifier is configured in a unity-gain buffer topology with the output connected to a low-pass filter (LPF) and a digital multimeter (DMM). A large impedance mismatch at the operational amplifier input causes a voltage reflection; however, this effect is characterized and accounted for when determining the EMIRR IN+. The resulting dc offset voltage is sampled and measured by the multimeter. The LPF isolates the multimeter from residual RF signals that can interfere with multimeter accuracy. See the *EMI Rejection Ratio of Operational Amplifiers* application report for more details.

図 7-4. EMIRR IN+ Test Configuration Schematic

### 7.4 Device Functional Modes

## 7.4.1 Operating Voltage

The OPA167x series op amps operate from  $\pm 2.25$  V to  $\pm 18$  V supplies while maintaining excellent performance. The OPA167x series can operate with as little as 4.5 V between the supplies and with up to 36 V between the supplies. However, some applications do not require equal positive and negative output voltage swing. With the OPA167x series, power-supply voltages are not required to be equal. For example, the positive supply can be set to 25 V with the negative supply at -5 V.

In all cases, the common-mode voltage must be maintained within the specified range. In addition, key parameters are specified over the temperature range of  $T_A = -40^{\circ}\text{C}$  to +85°C. Parameters that vary significantly with operating voltage or temperature are shown in  $200^{\circ}$  6.8.

# 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 8.1 Application Information

## 8.1.1 Capacitive Loads

The dynamic characteristics of the OPA167x series are optimized for commonly encountered gains, loads, and operating conditions. The combination of low closed-loop gain and high capacitive loads decreases the phase margin of the amplifier, and can lead to gain peaking or oscillations. As a result, heavier capacitive loads must be isolated from the output. The simplest way to achieve this isolation is to add a small resistor ( $R_S$  equal to 50  $\Omega$ , for example) in series with the output.

This small series resistor also prevents excess power dissipation if the output of the device short-circuits. For more details about analysis techniques and application circuits, see the *Feedback Plots Define Op Amp AC Performance* application report, available for download from the TI website (www.ti.com).

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# 8.2 Typical Applications

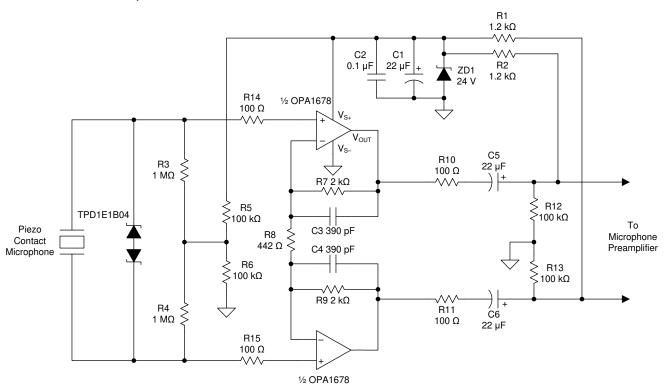

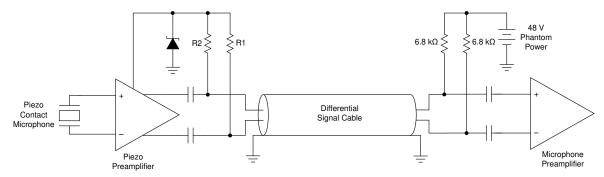

## 8.2.1 Phantom-Powered Preamplifier for Piezo Contact Microphones

Contact microphones are useful for amplifying the sound of musical instruments that do not contain electric pickups, such as acoustic guitars and violins. Most contact microphones use a piezo element to convert vibrations in the body of the musical instrument to a voltage which can be amplified or recorded. The low noise and low input bias current of the OPA1678 make the device an excellent choice for high impedance preamplifiers for piezo elements. This preamplifier circuit provides high input impedance for the piezo element but has low output impedance for driving long cable runs. The circuit is also designed to be powered from 48-V phantom power which is commonly available in professional microphone preamplifiers and recording consoles.

A TINA-TI™ simulation schematic of the circuit below is available in the *Tools and Software* section of the OPA1678 or OPA1679 product folder.

**28** 8-1. Phantom-Powered Preamplifier for Piezo Contact Microphones

### 8.2.1.1 Design Requirements

- –3-dB bandwidth: 20 Hz to 20 kHz

- Gain: 20 dB (10 V/V)

- Piezo element capacitance: 8 nF (9-kHz resonance)

# 8.2.1.2 Detailed Design Procedure

### **8.2.1.2.1 Power Supply**

In professional audio systems, phantom power is applied to the two signal lines that carry a differential audio signal from the microphone. 🗵 8-2 is a diagram of the system showing 48-V phantom power applied to the differential signal lines between the piezo preamplifier output and the input of a professional microphone preamplifier.

図 8-2. System Diagram Showing the Application of Phantom Power to the Audio Signal Lines

A voltage divider is used to extract the common-mode phantom power from the differential audio signal in this type of system. The voltage at center point of the voltage divider formed by R1 and R2 does not change when audio signals are present on the signal lines (assuming R1 and R2 are matched). A Zener diode forces the voltage at the center point of R1 and R2 to a regulated voltage. The values of R1 and R2 are determined by the allowable voltage drop across these resistors from the current delivered to both op amp channels and the Zener diode. There are two power supply current pathways in parallel, each sharing half the total current of the op amp and Zener diode. Resistors R1 and R2 can be calculated using  $\overrightarrow{x}$  1:

$$\frac{V_{ZD}}{\left(\frac{I_{OPA}}{2} + \frac{I_{ZD}}{2}\right)} - 6.8 \text{ k}\Omega = R_{PS}$$

(1)

A 24-V Zener diode is selected for this design, and 1 mA of current flows through the diode at idle conditions to maintain the reverse-biased condition of the Zener diode. The maximum idle power supply current of both op amp channels is 5 mA. Inserting these values into  $\pm$  1 gives the values for R1 and R2 shown in  $\pm$  2.

$$\frac{24V}{\left(\frac{I_{OPA}}{2} + \frac{I_{ZD}}{2}\right)} - 6.8 \text{ k}\Omega = \frac{24V}{\left(\frac{5.0 \text{ mA}}{2} + \frac{1.0 \text{ mA}}{2}\right)} - 6.8 \text{ k}\Omega = 1.2 \text{ k}\Omega = R_{PS}$$

(2)

Using a value of 1.2  $k\Omega$  for resistors R1 and R2 establishes a 1-mA current through the Zener diode and properly regulate the node to 24 V. Capacitor C1 forms a low-pass filter with resistors R1 and R2 to filter the Zener diode noise and any residual differential audio signals. Mismatch in the values of R1 and R2 causes a portion of the audio signal to appear at the voltage divider center point. The corner frequency of the low-pass filter must be set below the audio band, as shown in  $\gtrsim 3$ .

$$C_1 \geq \frac{1}{2 \cdot \pi \cdot R_1 \mid\mid R_2 \cdot f_{-3dB}} \geq \frac{1}{2 \cdot \pi \cdot 600 \Omega \cdot 20 \text{ Hz}} \geq 13 \text{ } \mu\text{F} \rightarrow 22 \text{ } \mu\text{F} \tag{3}$$

A 22- $\mu$ F capacitor is selected because the capacitor meets the requirements for power supply filtering and is a widely available denomination. A 0.1- $\mu$ F capacitor (C2) is added in parallel with C1 as a high-frequency bypass capacitor.

#### 8.2.1.2.2 Input Network

Resistors R3 and R4 provide a pathway for the input bias current of the OPA1678 while maintaining the high input impedance of the circuit. The contact microphone capacitance and the required low-frequency response determine the values of R3 and R4. The -3-dB frequency formed by the microphone capacitance and amplifier input impedance is shown in Equation 4:

$$F_{-3dB} = \frac{1}{2 \cdot \pi \cdot (R_3 + R_4) \cdot C_{MIC}} \le 20 \text{ Hz}$$

(4)

A piezo element with 8 nF of capacitance was selected for this design because the 9-kHz resonance is towards the upper end of the audible bandwidth, and is less likely to affect the frequency response of many musical instruments. The minimum value for resistors R3 and R4 is then calculated with Equation 5:

$$R_{1N} \ge \frac{1}{4 \cdot \pi \cdot F_{-3dB} \cdot C_{MIC}} \ge \frac{1}{4 \cdot \pi \cdot 20 \text{ Hz} \cdot 8 \text{ nF}} \ge 497.4 \text{ k}\Omega$$

(5)

$1\text{-}M\Omega$  resistors are selected for R3 and R4 to make sure the circuit meets the design requirements for -3-dB bandwidth. The center point of resistors R3 and R4 is biased to half the supply voltage through the voltage divider formed by R5 and R6. This sets the input common-mode voltage of the circuit to a value within the input voltage range of the OPA1678. Piezo elements can produce very large voltages if the elements are struck with sufficient force. To prevent damage, the input of the OPA1678 is protected by a transient voltage suppressor (TVS) diode placed across the preamplifier inputs. The TPD1E1B04 TVS was selected due to low capacitance and the 6.4-V clamping voltage does not clamp the desired low amplitude vibration signals. Resistors R14 and R15 limit current flow into the amplifier inputs in the event that the internal protection diodes of the amplifier are forward-biased.

#### 8.2.1.2.3 Gain

R7, R8, and R9 determines the gain of the preamplifier circuit. The gain of the circuit is shown in Equation 6:

$$A_{V} = 1 + \frac{R_7 + R_9}{R_8} = 10 \text{ V/V}$$

(6)

Resistors R7 and R9 are selected with a value of 2  $k\Omega$  to avoid loading the output of the OPA1678 and producing distortion. The value of R8 is then calculated in Equation 7:

$$R_8 = \frac{R_7 + R_9}{A_V - 1} = \frac{2 k\Omega + 2 k\Omega}{10 - 1} = 444.4 \Omega \rightarrow 442 \Omega$$

(7)

Capacitors C3 and C4 limit the bandwidth of the circuit so that signals outside the audio bandwidth are not amplified. The corner frequency produced by capacitors C3 and C4 is shown in Equation 8. This corner frequency must be above the desired –3-dB bandwidth point to avoid attenuating high-frequency audio signals.

$$\begin{split} &C_{3} = C_{4} = C_{FB} \\ &C_{FB} \leq \frac{1}{2 \cdot \pi \cdot F_{-3dB} \cdot R_{7/9}} \leq \frac{1}{2 \cdot \pi \cdot 20 \text{ kHz} \cdot 2 \text{ k}\Omega} \leq 3.98 \text{ nF} \end{split} \tag{8}$$

C3 and C4 are 390-pF capacitors, which places the corner frequency approximately 1 decade above the desired –3-dB bandwidth point. Capacitors C3 and C4 must be NP0 or C0G type ceramic capacitors or film capacitors. Other ceramic dielectrics, such as X7R, are not suitable for these capacitors and produce distortion.

#### 8.2.1.2.4 Output Network

The audio signal is ac-coupled onto the microphone signal lines through capacitors C5 and C6. The value of capacitors C5 and C6 are determined by the low-frequency design requirements and the input impedance of the microphone preamplifier that connect to the output of the circuit.  $\not\equiv$  9 shows an approximation of the capacitor value requirements, and neglects the effects of R10, R11, R12, and R13 on the frequency response. The microphone preamplifier input impedance ( $R_{IN\ MIC}$ ) uses a typical value of 4.4 k $\Omega$  for the calculation.

$$C_{5} = C_{6} = C_{OUT}$$

$$C_{OUT} \ge \frac{2}{2 \cdot \pi \cdot R_{IN\_MIC} \cdot 20 \text{ Hz}} \ge \frac{2}{2 \cdot \pi \cdot 4.4 \text{ k}\Omega \cdot 20 \text{ Hz}} \ge 3.6 \text{ \muF}$$

(9)

For simplicity, the same 22- $\mu$ F capacitors selected for the power supply filtering are selected for C5 and C6 to satisfy  $\not \equiv 9$ . At least 50-V rated capacitors must be used for C5 and C6. If polarized capacitors are used, the positive terminal must be oriented towards the microphone preamplifier. Resistors R10 and R11 isolate the op amp outputs from the capacitance of long cables that can cause instability. R12 and R13 discharge ac-coupling capacitors C4 and C5 when phantom power is removed.

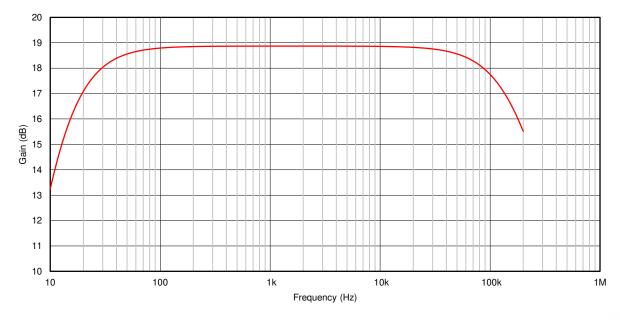

### 8.2.1.3 Application Curves

The frequency response of the preamplifier circuit is shown in  $\boxtimes$  8-3. The -3-dB frequencies are 15.87 Hz and 181.1 kHz, which meet the design requirements. The gain within the passband of the circuit is 18.9 dB, slightly less than the design goal of 20 dB. The reduction in gain is a result of the voltage division between the output resistors of the piezo preamplifier circuit and the input impedance of the microphone preamplifier. The A-weighted noise of the circuit (referred to the input) is 842.2 nV<sub>RMS</sub> or -119.27 dBu.

図 8-3. Frequency Response of the Preamplifier Circuit for a 8-nF Piezo Element

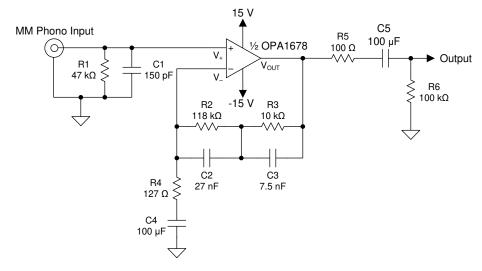

### 8.2.2 Phono Preamplifier for Moving Magnet Cartridges

The noise and distortion performance of the OPA167x family of amplifiers is exceptional in applications with high source impedances, which makes these devices a viable choice in preamplifier circuits for moving magnet (MM) phono cartridges.

8-4 shows a preamplifier circuit for MM cartridges with 40 dB of gain at 1 kHz.

図 8-4. Phono Preamplifier for Moving Magnet Cartridges (Single-Channel Shown)

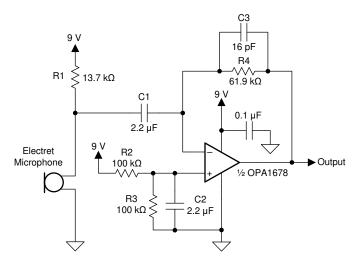

### 8.2.3 Single-Supply Electret Microphone Preamplifier

The preamplifier circuit shown in 🗵 8-5 operates the OPA1678 as a transimpedance amplifier that converts the output current from the electret microphone internal JFET into a voltage. Resistor R4 determines the gain of the circuit. Resistors R2 and R3 bias the input voltage to half the power supply voltage for proper functionality on a single-supply.

**図 8-5. Single-Supply Electret Microphone Preamplifier**

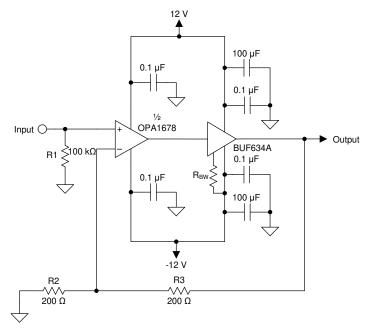

## 8.2.4 Composite Headphone Amplifier

⊠ 8-6 shows the BUF634A buffer inside the feedback loop of the OPA1678 to increase the available output current for low-impedance headphones. If the BUF634A is used in wide-bandwidth mode, no additional components besides the feedback resistors are required to maintain loop stability.

図 8-6. Composite Headphone Amplifier (Single-Channel Shown)

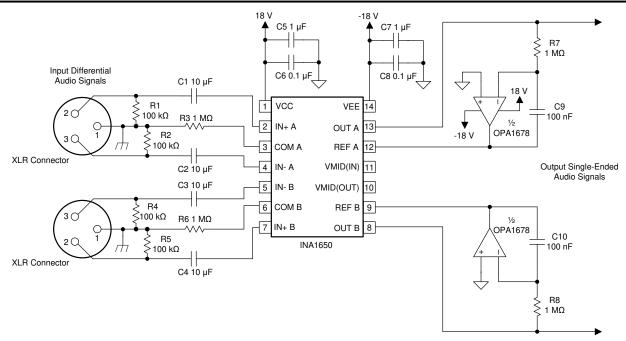

## 8.2.5 Differential Line Receiver With AC-Coupled Outputs

⊠ 8-7 shows the OPA1678 used as an integrator that drives the reference pin of the INA1650, which forces the output dc voltage to 0 V. This configuration is an alternative to large ac-coupling capacitors that can distort at high output levels. The low input bias current and low input offset voltage of the OPA1678 make the device an excellent choice for integrator applications.

図 8-7. Differential Line Receiver With AC-Coupled Outputs

# 8.3 Power Supply Recommendations

The OPA167x devices are specified for operation from 4.5 V to 36 V ( $\pm 2.25$  V to  $\pm 18$  V); many specifications apply from  $-40^{\circ}$ C to  $+85^{\circ}$ C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are shown in 2000 6.8. Applications with noisy or high-impedance power supplies require decoupling capacitors close to the device pins. In most cases, 0.1- $\mu$ F capacitors are adequate.

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

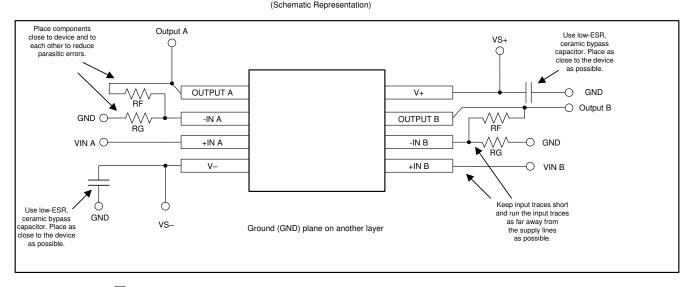

For best operational performance of the device, use good printed-circuit board (PCB) layout practices, including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole and of op amp itself. Bypass capacitors are used to reduce the coupled noise by providing low-impedance power sources local to the analog circuitry.

- Connect low-ESR, 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for singlesupply applications.

- Separate grounding for analog and digital portions of circuitry is one of the simplest and most-effective

methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes.

A ground plane helps distribute heat and reduces electromagnetic interference (EMI) noise pickup. Physically

separate digital and analog grounds, observing the flow of the ground current.

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If these traces cannot be kept separate, crossing the sensitive trace perpendicular is much better as opposed to in parallel with the noisy trace.

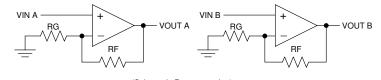

- Place the external components as close to the device as possible. As shown in ⊠ 8-8, keeping R<sub>F</sub> and R<sub>G</sub> close to the inverting input minimizes parasitic capacitance.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

- Cleaning the PCB following board assembly is recommended for best performance.

www.tij.co.jp

Any precision integrated circuit can experience performance shifts resulting from moisture ingress into the plastic package. Following any aqueous PCB cleaning process, bake the PCB assembly to remove moisture introduced into the device packaging during the cleaning process. A low temperature, post-cleaning bake at 85°C for 30 minutes is sufficient for most circumstances.

# 8.4.1.1 Power Dissipation

The OPA167x series op amps are capable of driving 2-kΩ loads with a power-supply voltage up to ±18 V and full operating temperature range. Internal power dissipation increases when operating at high supply voltages. Copper leadframe construction used in the OPA167x series op amps improves heat dissipation compared to conventional materials. Circuit board layout can also help minimize junction temperature rise. Wide copper traces help dissipate the heat by acting as an additional heat sink. Temperature rise can be further minimized by soldering the devices to the circuit board rather than using a socket.

### 8.4.2 Layout Example

図 8-8. Operational Amplifier Board Layout for Noninverting Configuration

# 9 Device and Documentation Support

# 9.1 Device Support

## 9.1.1 Development Support

## 9.1.1.1 PSpice® for TI

PSpice® for TI は、アナログ回路の性能評価に役立つ設計およびシミュレーション環境です。レイアウトと製造に移る前に、サブシステムの設計とプロトタイプ・ソリューションを作成することで、開発コストを削減し、市場投入までの期間を短縮できます。

## 9.1.1.2 TINA-TI™ シミュレーション・ソフトウェア (無償ダウンロード)

TINA-TI™ シミュレーション・ソフトウェアは、SPICE エンジンをベースにした単純かつ強力な、使いやすい回路シミュレーション・プログラムです。TINA-TI シミュレーション・ソフトウェアは、TINA™ ソフトウェアのすべての機能を持つ無償バージョンで、パッシブ・モデルとアクティブ・モデルに加えて、マクロモデルのライブラリがプリロードされています。TINA-TI シミュレーション・ソフトウェアには、SPICE の標準的な DC 解析、過渡解析、周波数ドメイン解析などの全機能に加え、追加の設計機能が搭載されています。

TINA-TI シミュレーション・ソフトウェアは設計ツールとシミュレーション Web ページから無料でダウンロードでき、ユーザーが結果をさまざまな方法でフォーマットできる、広範な後処理機能を備えています。仮想計測器により、入力波形を選択し、回路ノード、電圧、および波形をプローブして、動的なクイック・スタート・ツールを作成できます。

注

これらのファイルを使用するには、TINA ソフトウェアまたは TINA-TI ソフトウェアがインストールされている必要があります。 TINA-TI™ ソフトウェア・フォルダから、無償の TINA-TI シミュレーション・ソフトウェアをダウンロードしてください。

## 9.1.1.3 DIP アダプタ評価基板

DIP アダプタ評価基板は、オペアンプの迅速なプロトタイプ製作とテストを可能にする評価基板です。小型の表面実装デバイスとのインターフェイスを迅速、容易、低コストで実現します。付属の Samtec 端子ストリップか、直接配線により既存の回路へサポートされているオペアンプを接続します。DIP アダプタ評価基板キットは、以下の業界標準パッケージをサポートしています。D または U (SOIC-8)、PW (TSSOP-8)、DGK (VSSOP-8)、DBV (SOT-23-6、SOT-23-5、およびSOT-23-3)、DCK (SC70-6 およびSC70-5)、およびDRL (SOT563-6)。

## 9.1.1.4 **DIYAMP-EVM**

DIYAMP-EVM は、実際のアンプ回路を提供する独自の評価基板 (EVM) であり、設計コンセプトの迅速な評価とシミュレーションの検証を実現します。この評価基板は、3 つの業界標準パッケージ (SC70、SOT23、SOIC) で供給されており、シングル / デュアル電源向けに、アンプ、フィルタ、安定性補償、コンパレータの各構成など、12 の一般的なアンプ構成が可能です。

### 9.1.1.5 TI のリファレンス・デザイン

TI のリファレンス・デザインは、TI の高精度アナログ・アプリケーション専門家により作成されたアナログ・ソリューションです。TI のリファレンス・デザインは、動作原理、部品の選択、シミュレーション、完全な PCB 回路図およびレイアウト、部品表、測定済みの性能を提供します。TI のリファレンス・デザインは、http://www.ti.com/ww/en/analog/precision-designs/からオンラインで入手できます。

### 9.1.1.6 フィルタ設計ツール

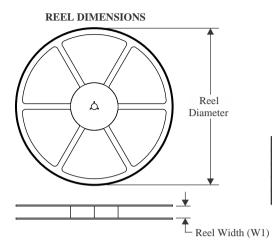

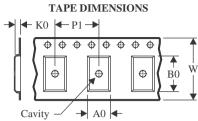

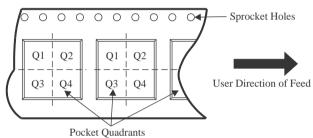

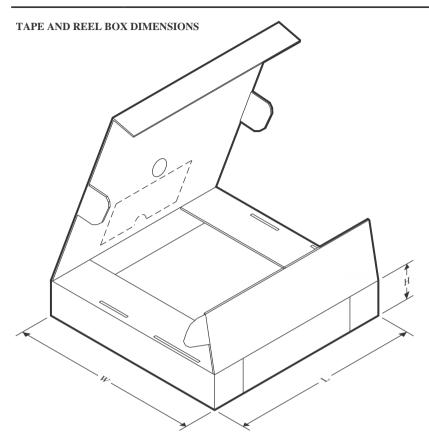

フィルタ設計ツールは単純で強力な、使いやすいアクティブ・フィルタ設計プログラムです。フィルタ設計ツールを使用すると、TI のベンダ・パートナーからの TI 製オペアンプやパッシブ・コンポーネントを使用して、最適なフィルタ設計を作成できます。