**OPA2333-Q1**

JAJSIN9B - DECEMBER 2008-REVISED FEBRUARY 2020

# OPA2333-Q1 車載用、1.8V、マイクロパワー、CMOS、ゼロドリフトの オペアンプ

#### 1 特長

車載アプリケーション用に AEC 認定済み温度グレード 1:-40℃~+125℃、T<sub>Δ</sub>

低いオフセット電圧: 23μV 以下0.01Hz~10Hzのノイズ: 1.1μV<sub>PP</sub>

静止電流:17μA単一電源動作

電源電圧: 1.8 V~5.5 Vレール・ツー・レール入出力

• パッケージ: 8 ピン SOIC および VSSOP

#### 2 アプリケーション

ポンプ

• 位置センサ

• 車両占有検出センサ

ブレーキ・システム

• エアバッグ

#### 3 概要

OPA2333-Q1 CMOS オペアンプは、独自の自動較正技 術を採用することで、非常に低いオフセット電圧 (10μV 以下) を実現しながら、時間経過および温度変動に対するドリフトをほぼゼロに抑えています。これらの小型、高精度、低静止電流のオペアンプは、レールを 100mV 上回る同相範囲を持つ高インピーダンス入力と、レールの 50mV 以内までスイングするレール・ツー・レール出力を備えています。最低 1.8V (±0.9V)、最高 5.5V (±2.75V) のシングルまたはデュアル電源が使用できます。このデバイスは、低電圧の単一電源で動作するように最適化されています。

OPA2333-Q1 は、従来の相補入力段に見られるクロスオーバーを持たず、同相除去比 (CMRR) が優れています。この設計により、アナログ/デジタル・コンバータ(ADC)の微分直線性の低下がなく、優れたADC駆動性能が得られます。

**OPA2333-Q1** は、**-40**°C~**+125**°C で動作が規定されています。

#### 製品情報(1)

| 型番         | パッケージ     | 本体サイズ(公称)     |

|------------|-----------|---------------|

| OPA2333-Q1 | SOIC (8)  | 4.90mm×3.91mm |

| UPA2333-Q1 | VSSOP (8) | 3.00mm×3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にあるパッケージ・オプションについての付録を参照してくださ い

#### 0.1Hz~10Hzのノイズ

# 目次

| 1 | 特長1                                                             | 7.4 Device Functional Modes        |

|---|-----------------------------------------------------------------|------------------------------------|

| 2 | アプリケーション1                                                       | 8 Application and Implementation 1 |

| 3 | 概要1                                                             | 8.1 Application Information 1      |

| 4 | 改訂履歴2                                                           | 8.2 Typical Application 1          |

| 5 | Pin Configuration and Functions                                 | 9 Power Supply Recommendations 1   |

| 6 | Specifications4                                                 | 10 Layout 1                        |

| • | 6.1 Absolute Maximum Ratings 4                                  | 10.1 Layout Guidelines 1           |

|   | 6.2 ESD Ratings                                                 | 10.2 Layout Example 1              |

|   | 6.3 Recommended Operating Conditions                            | 11 デバイスおよびドキュメントのサポート              |

|   | 6.4 Thermal Information4                                        | 11.1 ドキュメントのサポート1                  |

|   | 6.5 Electrical Characteristics: V <sub>S</sub> = 1.8 V to 5.5 V | 11.2 ドキュメントの更新通知を受け取る方法            |

|   | 6.6 Typical Characteristics6                                    | 11.3 サポート・リソース1                    |

| 7 | Detailed Description9                                           | 11.4 商標1                           |

| - | 7.1 Overview 9                                                  | 11.5 静電気放電に関する注意事項 1               |

|   | 7.2 Functional Block Diagram9                                   | 11.6 Glossary1                     |

|   | 7.3 Feature Description9                                        | 12 メカニカル、パッケージ、および注文情報 1           |

# 4 改訂履歴

### Revision A (June 2010) から Revision B に変更

Page

| • | 「製品情報」表、「ピンの機能」表、「 <i>ESD 定</i> 格」表、「推奨動作条件」表、「熱に関する情報」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを 追加 |     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed input offset voltage (over full temp range) from 22 µV to 15 µV in Electrical Characteristics table                                                                                       | . ! |

| • | Added maximum value of 0.05 $\mu$ V/°C to the V <sub>OS</sub> drift parameter in the <i>Electrical Characteristics</i> table                                                                      | . ! |

| • | Deleted Thermal resistance parameter from Flectrical Characteristics table                                                                                                                        | ,   |

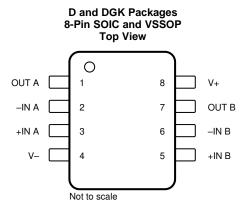

# **5 Pin Configuration and Functions**

#### **Pin Functions**

| PIN |       | 1/0 | DESCRIPTION                       |  |  |  |  |  |  |

|-----|-------|-----|-----------------------------------|--|--|--|--|--|--|

| NO. | NAME  | I/O | DESCRIPTION                       |  |  |  |  |  |  |

| 1   | OUT A | 0   | Channel A output                  |  |  |  |  |  |  |

| 2   | –IN A | I   | Channel A inverting input         |  |  |  |  |  |  |

| 3   | +IN A | I   | Channel A noninverting input      |  |  |  |  |  |  |

| 4   | V-    | _   | Negative (lowest) supply voltage  |  |  |  |  |  |  |

| 5   | +IN B | 1   | Channel B noninverting input      |  |  |  |  |  |  |

| 6   | –IN B | I   | Channel B inverting input         |  |  |  |  |  |  |

| 7   | OUT B | 0   | Channel B output                  |  |  |  |  |  |  |

| 8   | V+    | _   | Positive (highest) supply voltage |  |  |  |  |  |  |

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                 | MIN      | MAX        | UNIT |

|------------------|-------------------------------------------------|----------|------------|------|

| $V_{CC}$         | Supply voltage                                  |          | 7          | ٧    |

| VI               | Input voltage, signal input pins <sup>(2)</sup> | -0.3     | (V+) + 0.3 | ٧    |

|                  | Output short-circuit <sup>(3)</sup>             | Continuo | ous        |      |

| T <sub>A</sub>   | Operating free-air temperature                  | -40      | 125        | °C   |

| TJ               | Operating virtual-junction temperature          |          | 150        | °C   |

| T <sub>stg</sub> | Storage temperature                             | -65      | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                                                                                        |                                                                              | VALUE | UNIT |

|--------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|------|

| V                  | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> HBM ESD classification level 2 |                                                                              | ±2000 | V    |

| V <sub>(ESD)</sub> |                                                                                        | Charged-device model (CDM), per AEC Q100-011 CDM ESD Classification Level C6 | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN | NOM MAX | UNIT |

|----------------|--------------------------------|-----|---------|------|

| V <sub>S</sub> | Specified supply voltage       | 1.8 | 5.5     | V    |

| T <sub>A</sub> | Specified free-air temperature | -40 | 125     | °C   |

#### 6.4 Thermal Information

|                      |                                              | OPA      | OPA2333-Q1  |      |  |  |

|----------------------|----------------------------------------------|----------|-------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (VSSOP) | UNIT |  |  |

|                      |                                              | 8 PINS   | 8 PINS      |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 124.0    | 180.3       | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 73.7     | 48.1        | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 64.4     | 100.9       | °C/W |  |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 18.0     | 2.4         | °C/W |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 63.9     | 99.3        | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A      | N/A         | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Input terminals are diode clamped to the power-supply rails. Input signals that can swing more than 0.3 V beyond the supply rails should be current limited to 10 mA or less.

<sup>(3)</sup> Short circuit to ground, one amplifier per package

# 6.5 Electrical Characteristics: $V_S = 1.8 \text{ V to } 5.5 \text{ V}$

At  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$  connected to  $V_S/2$ ,  $V_{CM}$  =  $V_S/2$ , and  $V_{OUT}$  =  $V_S/2$  (unless otherwise noted).

|                                  | PARAMETER                          | TEST CONDITIONS                                                                                                                          | MIN        | TYP              | MAX        | UNIT               |

|----------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|------------|--------------------|

| OFFSET \                         | VOLTAGE                            |                                                                                                                                          |            |                  |            |                    |

| \ /                              | land offert valtage                | V <sub>S</sub> = 5 V                                                                                                                     |            | 2                | 10         | μV                 |

| V <sub>OS</sub>                  | Input offset voltage               | $V_S = 5 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                  |            |                  | 15         | μV                 |

| dV <sub>OS</sub> /d <sub>T</sub> | V <sub>OS</sub> drift              | $V_S = 5 \text{ V}, T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                                                   |            | 0.02             | 0.05       | μV/°C              |

| PSRR                             | Power-supply rejection ratio       | V <sub>S</sub> = 1.8 V to 5.5 V,<br>T <sub>A</sub> = -40°C to +125°C                                                                     |            | 1                | 6          | μV/V               |

|                                  | Long-term stability <sup>(1)</sup> |                                                                                                                                          |            | 1 <sup>(1)</sup> |            | μV                 |

|                                  | Channel separation, dc             |                                                                                                                                          |            | 0.1              |            | $\mu V/V$          |

| INPUT BI                         | AS CURRENT                         |                                                                                                                                          |            |                  |            |                    |

|                                  | land him adment                    |                                                                                                                                          |            | ±70              | ±200       | pА                 |

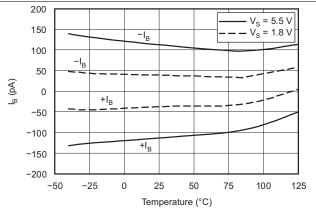

| I <sub>B</sub>                   | Input bias current                 | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                           |            | ±150             |            | рА                 |

| Ios                              | Input offset current               | ut offset current ±140                                                                                                                   |            |                  |            |                    |

| NOISE                            |                                    | •                                                                                                                                        | •          |                  |            |                    |

|                                  | land distance asian                | f = 0.01 Hz to 1 Hz                                                                                                                      |            | 0.3              |            | $\mu V_{PP}$       |

|                                  | Input voltage noise                | f = 0.1 Hz to 10 Hz                                                                                                                      |            | 1.1              |            | $\mu V_{PP}$       |

| i <sub>n</sub>                   | Input current noise                | f = 10 Hz                                                                                                                                |            | 100              |            | fA/√ <del>Hz</del> |

| INPUT VC                         | DLTAGE                             |                                                                                                                                          |            |                  | <u> </u>   |                    |

| V <sub>CM</sub>                  | Common-mode supply voltage         |                                                                                                                                          | (V-) - 0.1 |                  | (V+) + 0.1 | V                  |

| CMRR                             | Common-mode rejection ratio        | $(V-) - 0.1 V < V_{CM} < (V+) + 0.1 V,$<br>$T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                | 102        | 130              |            | dB                 |

| INPUT CA                         | APACITANCE                         |                                                                                                                                          | 1          |                  | "          |                    |

|                                  | Differential                       |                                                                                                                                          |            | 2                |            | pF                 |

|                                  | Common-mode                        |                                                                                                                                          |            | 4                |            | pF                 |

| OPEN-LO                          | OP GAIN                            |                                                                                                                                          | !          |                  | *          |                    |

| <b>A</b> <sub>OL</sub>           | Open-loop voltage gain             | $(V-) + 100 \text{ mV} < V_O < (V+) - 100 \text{ mV},$<br>$R_L = 10 \text{ k}\Omega, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 104        | 130              |            | dB                 |

| FREQUE                           | NCY RESPONSE                       |                                                                                                                                          |            |                  | <u> </u>   |                    |

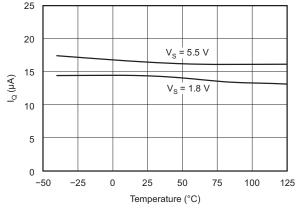

| GBW                              | Gain-bandwidth product             | C <sub>L</sub> = 100 pF                                                                                                                  |            | 350              |            | kHz                |

| SR                               | Slew rate                          | G = 1                                                                                                                                    |            | 0.16             |            | V/μs               |

| OUTPUT                           |                                    |                                                                                                                                          |            |                  | *          |                    |

|                                  |                                    | $R_L = 10 \text{ k}\Omega$                                                                                                               |            | 30               | 50         | mV                 |

|                                  | Voltage output swing from rail     | $R_L = 10 \text{ k}\Omega, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                           |            |                  | 85         | mV                 |

| I <sub>SC</sub>                  | Short-circuit current              |                                                                                                                                          |            | ±5               |            | mA                 |

| C <sub>L</sub>                   | Capacitive load drive              |                                                                                                                                          |            |                  |            |                    |

|                                  | (2)Open-loop output impedance      | f = 350 kHz, I <sub>O</sub> = 0 A                                                                                                        |            | 2                |            | kΩ                 |

| POWER S                          | SUPPLY                             | -                                                                                                                                        | I          |                  |            |                    |

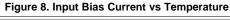

|                                  |                                    | I <sub>O</sub> = 0 A                                                                                                                     |            | 17               | 25         | μА                 |

| lQ                               | Quiescent current per amplifier    | $I_O = 0 \text{ A}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                  |            |                  | 30         | <u>.</u><br>μΑ     |

|                                  | Turn-on time                       | V <sub>S</sub> = 5 V                                                                                                                     |            | 100              |            | <br>μs             |

<sup>(1) 300-</sup>hour life test at 150°C demonstrated randomly distributed variation of approximately 1  $\mu$ V. (2) See the *Typical Characteristics* section.

# TEXAS INSTRUMENTS

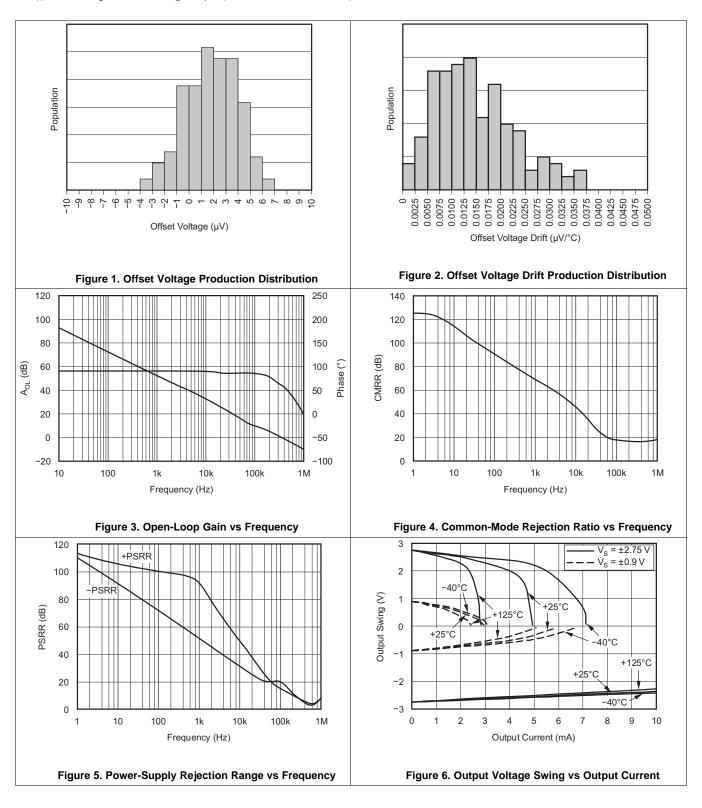

#### 6.6 Typical Characteristics

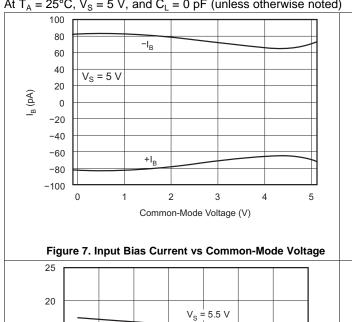

At  $T_A = 25$ °C,  $V_S = 5$  V, and  $C_L = 0$  pF (unless otherwise noted)

### **Typical Characteristics (continued)**

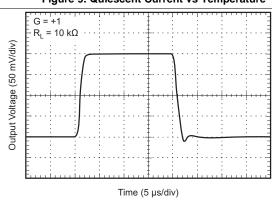

Figure 9. Quiescent Current vs Temperature

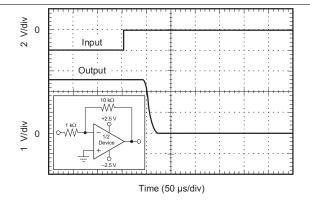

Figure 10. Large-Signal Step Response

Figure 11. Small-Signal Step Response

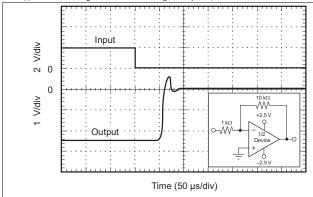

Figure 12. Positive Over-Voltage Recovery

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

At  $T_A = 25$ °C,  $V_S = 5$  V, and  $C_L = 0$  pF (unless otherwise noted)

Figure 13. Negative Over-Voltage Recovery

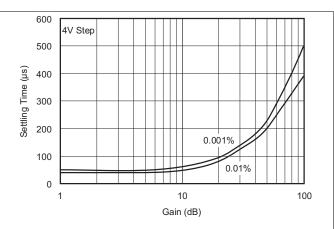

Figure 14. Settling Time vs Closed-Loop Gain

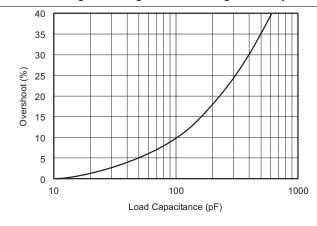

Figure 15. Small-Signal Overshoot vs Load Capacitance

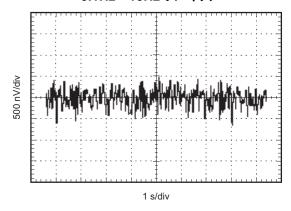

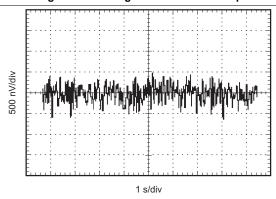

Figure 16. 0.1-Hz to 10-Hz Noise

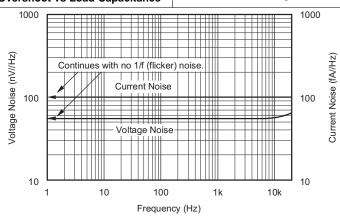

Figure 17. Current and Voltage Spectral Density vs Frequency

#### 7 Detailed Description

#### 7.1 Overview

The OPA2333-Q1 device is a zero-drift, low-power, rail-to-rail input and output operational amplifier. The device operates from 1.8 V to 5.5 V, is unity-gain stable, and is designed for a wide range of general-purpose applications. The zero-drift architecture provides ultra-low offset voltage and near-zero offset voltage drift.

The OPA2333-Q1 is unity-gain stable and free from unexpected output phase reversal. The device uses a proprietary auto-calibration technique to provide low offset voltage and very low drift over time and temperature.

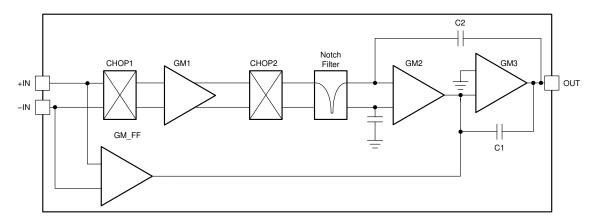

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Rail-to-Rail Input Voltage

The OPA2333-Q1 input common-mode voltage range extends 0.1 V beyond the supply rails. The device is designed to cover the full range without the troublesome transition region found in some other rail-to-rail amplifiers.

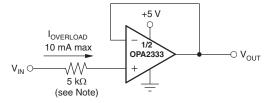

Normally, input bias current is approximately 70 pA; however, input voltages exceeding the power supplies can cause excessive current to flow into or out of the input pins. Momentary voltages greater than the power supply can be tolerated if the input current is limited to 10 mA. This limitation is easily accomplished with an input resistor (see Figure 18).

NOTE: A current-limiting resistor required if the input voltage exceeds the supply rails by ≥ 0.5 V.

Figure 18. Input Current Protection

#### 7.3.2 Internal Offset Correction

The OPA2333-Q1 op amps use an auto-calibration technique with a time-continuous 350-kHz op amp in the signal path. This amplifier is zero corrected every 8  $\mu$ s using a proprietary technique. At power up, the amplifier requires approximately 100  $\mu$ s to achieve the specified  $V_{OS}$  accuracy. This design has no aliasing or flicker noise.

#### 7.4 Device Functional Modes

The OPA2333-Q1 has a single functional mode. The device is powered on as long as the power-supply voltage is between 1.8 V ( $\pm 0.9$  V) and 5.5 V ( $\pm 2.75$  V).

#### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. Ti's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The OPA2333-Q1 is a unity-gain stable, precision operational amplifier with very low offset voltage drift. The device is also free from output phase reversal. Applications with noisy or high-impedance power supplies require decoupling capacitors close to the device power-supply pins. In most cases, 0.1-μF capacitors are adequate.

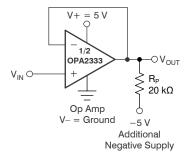

#### 8.1.1 Achieving Output Swing to the Op Amp Negative Rail

Some applications require output voltage swings from 0 V to a positive full-scale voltage (such as 2.5 V) with excellent accuracy. With most single-supply op amps, problems arise when the output signal approaches 0 V, near the lower output swing limit of a single-supply op amp. A good single-supply op amp may swing close to single-supply ground, but does not reach ground. The output of the OPA2333-Q1 can be made to swing to ground or slightly below on a single-supply power source. To do so requires the use of another resistor and an additional, more negative, power supply than the op amp negative supply. A pulldown resistor may be connected between the output and the additional negative supply to pull the output down below the value that the output would otherwise achieve (see Figure 19).

Figure 19. V<sub>OUT</sub> Range to Ground

The OPA2333-Q1 has an output stage that allows the output voltage to be pulled to its negative supply rail, or slightly below, using the technique previously described. This technique only works with some types of output stages. The OPA2333-Q1 has been characterized to perform with this technique; however, the recommended resistor value is approximately 20 k $\Omega$ .

#### **NOTE**

This configuration increases the current consumption by several hundreds of microamps.

Accuracy is excellent down to 0 V and as low as -2 mV. Limiting and nonlinearity occurs below -2 mV, but excellent accuracy returns as the output is again driven above -2 mV. Lowering the resistance of the pulldown resistor allows the op amp to swing even further below the negative rail. Resistances as low as 10 k $\Omega$  can be used to achieve excellent accuracy down to -10 mV.

#### 8.2 Typical Application

#### 8.2.1 High-Side Voltage-to-Current (V-I) Converter

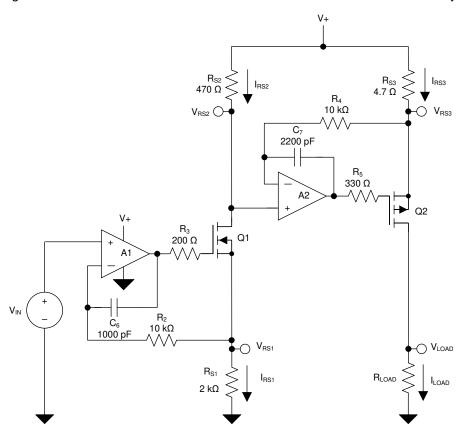

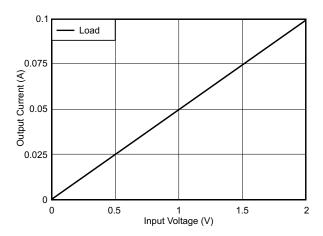

The circuit shown in Figure 20 is a high-side voltage-to-current (V-I) converter. It translates in input voltage of 0 V to 2 V to and output current of 0 mA to 100 mA. Figure 21 shows the measured transfer function for this circuit. The low offset voltage and offset drift of the OPA333-Q1 device facilitate excellent dc accuracy for the circuit.

Figure 20. High-Side Voltage-to-Current (V-I) Converter

#### **Typical Application (continued)**

#### 8.2.1.1 Design Requirements

The design requirements are as follows:

Supply voltage: 5 V dcInput: 0 V to 2 V dc

Output: 0 mA to 100 mA dc

#### 8.2.1.2 Detailed Design Procedure

The V-I transfer function of the circuit is based on the relationship between the input voltage,  $V_{IN}$ , and the three current sensing resistors,  $R_{S1}$ ,  $R_{S2}$ , and  $R_{S3}$ . The relationship between  $V_{IN}$  and  $R_{S1}$  determines the current that flows through the first stage of the design. The current gain from the first stage to the second stage is based on the relationship between  $R_{S2}$  and  $R_{S3}$ .

For a successful design, pay close attention to the dc characteristics of the operational amplifier chosen for the application. To meet the performance goals, this application benefits from an operational amplifier with low offset voltage, low temperature drift, and rail-to-rail output. The OPA2333-Q1 CMOS operational amplifier is a high-precision, 5- $\mu$ V offset, 0.05- $\mu$ V/°C drift amplifier optimized for low-voltage, single-supply operation with an output swing to within 50 mV of the positive rail. The OPA2333-Q1 uses chopping techniques to provide low initial offset voltage and near-zero drift over time and temperature. Low offset voltage and low drift reduce the offset error in the system, making these devices appropriate for precise dc control. The rail-to-rail output stage of the OPA2333-Q1 makes sure that the output swing of the operational amplifier is able to fully control the gate of the MOSFET devices within the supply rails.

A detailed error analysis, design procedure, and additional measured results are given in the *High-Side V-I Converter* reference design.

#### 8.2.1.3 Application Curve

Figure 21. Measured Transfer Function for High-Side V-I Converter

#### **Typical Application (continued)**

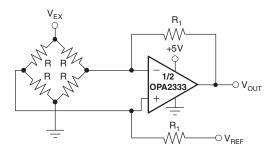

#### 8.2.1.4 Single Op Amp Bridge Amplifier

Figure 22 shows the basic configuration for a bridge amplifier.

Figure 22. Single Op-Amp Bridge Amplifier

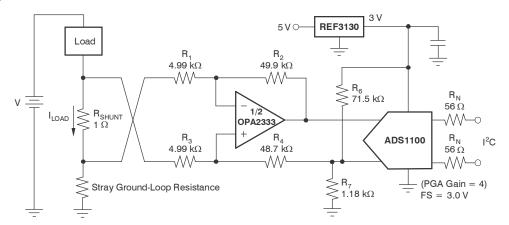

#### 8.2.1.5 Low-Side Current Monitor

A low-side current shunt monitor is shown in Figure 23.  $R_N$  are operational resistors used to isolate the ADS1100 from the noise of the digital  $I^2C$  bus. Because the ADS1100 is a 16-bit converter, a precise reference is essential for maximum accuracy. If absolute accuracy is not required, and the 5-V power supply is sufficiently stable, the REF3130 may be omitted.

NOTE: 1% resistors provide adequate common-mode rejection at small ground-loop errors.

Figure 23. Low-Side Current Monitor

#### **Typical Application (continued)**

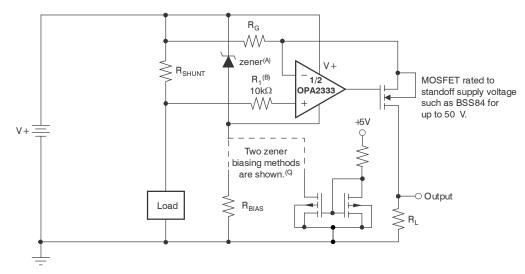

#### 8.2.1.6 High-Side Current Monitor

Figure 24 shows the use case for a precision single-supply amplifier for a high-side current sensing circuit.

- A. Zener rated for op amp supply capability (that is, 5.1 V for the OPA2333).

- B. Current-limiting resistor.

- C. Choose a Zener biasing resistor or dual NMOSFETs (FDG6301N, NTJD4001N, or Si1034).

Figure 24. High-Side Current Monitor

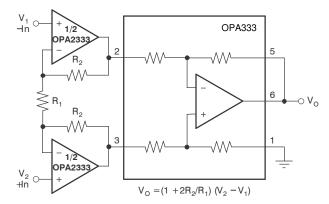

#### 8.2.1.7 Precision Instrumentation Amplifier

Figure 25 shows a three op amp implementation for a high-CMRR instrumentation amplifier..

Figure 25. Precision Instrumentation Amplifier

#### 9 Power Supply Recommendations

The OPA2333-Q1 is specified for operation from 1.8 V to 5.5 V (±0.9 V to ±2.75 V); many specifications apply from –40°C to +125°C. The *Typical Characteristics* section presents parameters that can exhibit significant variance with regard to operating voltage or temperature.

#### **CAUTION**

Supply voltages greater than 7 V can permanently damage the device (see the *Absolute Maximum Ratings* table).

Place  $0.1-\mu F$  bypass capacitors near the power-supply pins to reduce coupling errors from noisy or high-impedance power supplies. For more details on bypass capacitor placement, see the *Layout* section.

#### 10 Layout

#### 10.1 Layout Guidelines

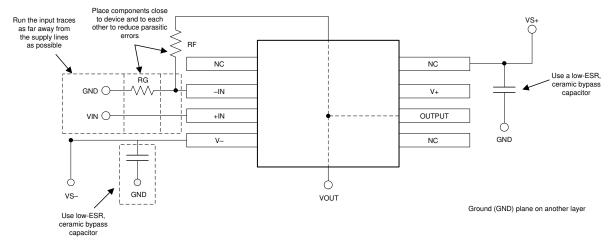

Pay attention to good layout practices. Keep traces short and when possible, use a printed-circuit-board (PCB) ground plane with surface-mount components placed as close to the device pins as possible. Place a 0.1- $\mu$ F capacitor closely across the supply pins. Apply these guidelines throughout the analog circuit to improve performance and provide benefits, such as reducing the electromagnetic interference (EMI) susceptibility.

Operational amplifiers vary in susceptibility to radio frequency interference (RFI). RFI can generally be identified as a variation in offset voltage or dc signal levels with changes in the interfering RF signal. The OPA2333-Q1 is specifically designed to minimize susceptibility to RFI and demonstrates remarkably low sensitivity compared to previous generation devices. Strong RF fields may still cause varying offset levels.

For lowest offset voltage and precision performance, optimize circuit layout and mechanical conditions. Avoid temperature gradients that create thermoelectric (Seebeck) effects in the thermocouple junctions formed from connecting dissimilar conductors. Cancel these thermally-generated potentials by assuring they are equal on both input terminals. Other layout and design considerations include:

- Use low-thermoelectric-coefficient connections (avoid dissimilar metals).

- Thermally isolate components from power supplies or other heat sources.

- Shield operational amplifier and input circuitry from air currents, such as cooling fans.

Following these guidelines reduces the likelihood of junctions being at different temperatures, which can cause thermoelectric voltages of 0.1  $\mu$ V/°C or higher, depending on materials used.

#### 10.2 Layout Example

Figure 26. Layout Example

#### 11 デバイスおよびドキュメントのサポート

#### 11.1 ドキュメントのサポート

#### 11.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『ADS1100 Self-Calibrating, 16-Bit ANALOG-TO-DIGITAL CONVERTER』データシート(英語)

- テキサス・インスツルメンツ、『REF31xx 15ppm/°C Maximum, 100-μA, SOT-23 Series Voltage Reference』データシート (英語)

- テキサス・インスツルメンツ、『INAx321 microPower, Single-Supply, CMOS Instrumentation Amplifier』データシート (英語)

- テキサス・インスツルメンツ、『INA32x Precision, Rail-to-Rail I/O INSTRUMENTATION AMPLIFIER』データシート (英語)

#### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 11.3 サポート・リソース

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 11.4 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | ( )    | ( )           |                 |                       | (-)  | (4)                           | (5)                        |              | (-,              |

| OPA2333AQDGKRQ1       | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -            | OCOQ             |

| OPA2333AQDGKRQ1.A     | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | OCOQ             |

| OPA2333AQDRQ1         | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 02333Q           |

| OPA2333AQDRQ1.A       | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 02333Q           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA2333-Q1:

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

• Catalog : OPA2333

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

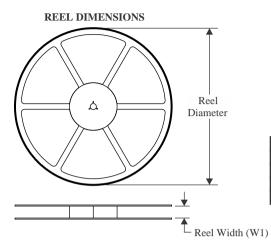

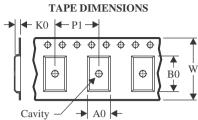

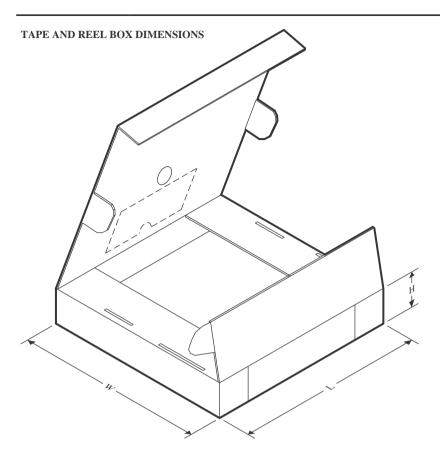

#### TAPE AND REEL INFORMATION

|    | -                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

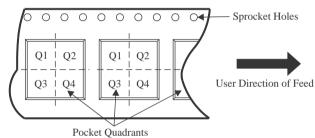

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA2333AQDGKRQ1 | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| OPA2333AQDRQ1   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA2333AQDGKRQ1 | VSSOP        | DGK             | 8    | 2500 | 367.0       | 367.0      | 38.0        |

| OPA2333AQDRQ1   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

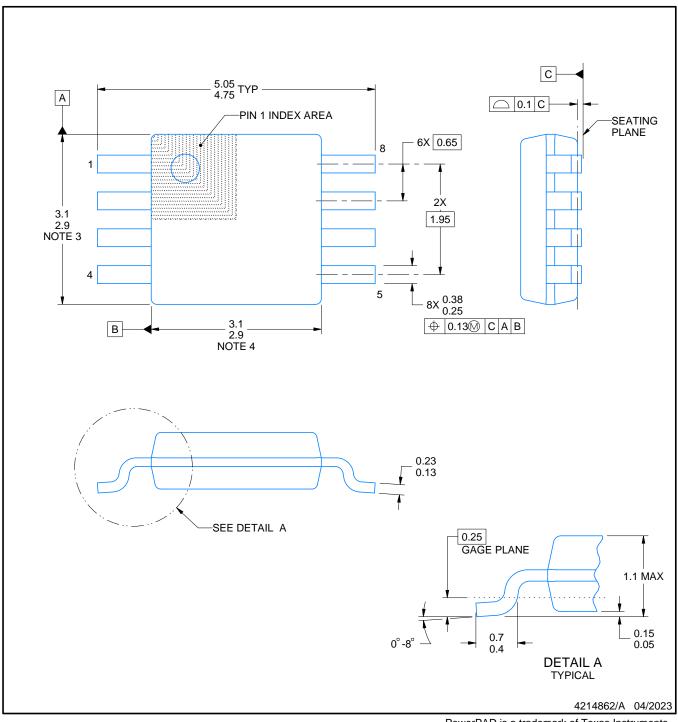

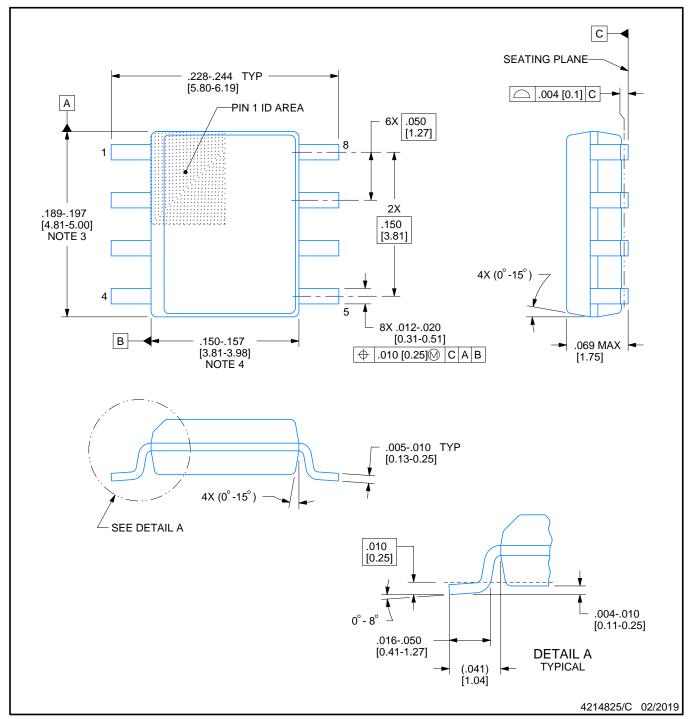

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

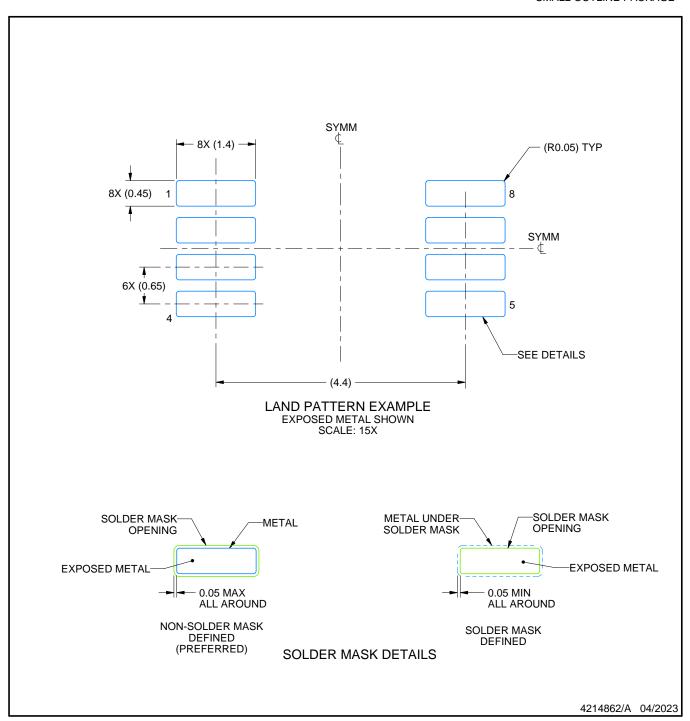

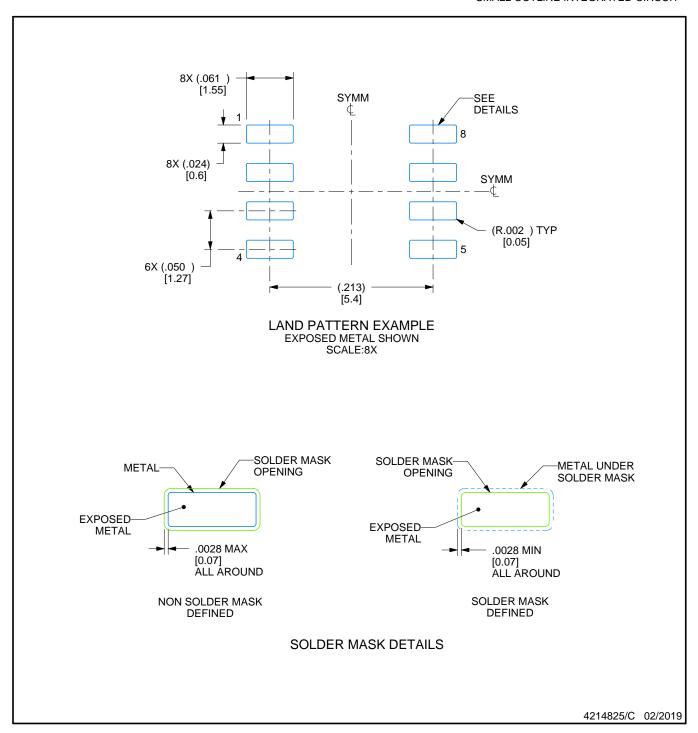

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

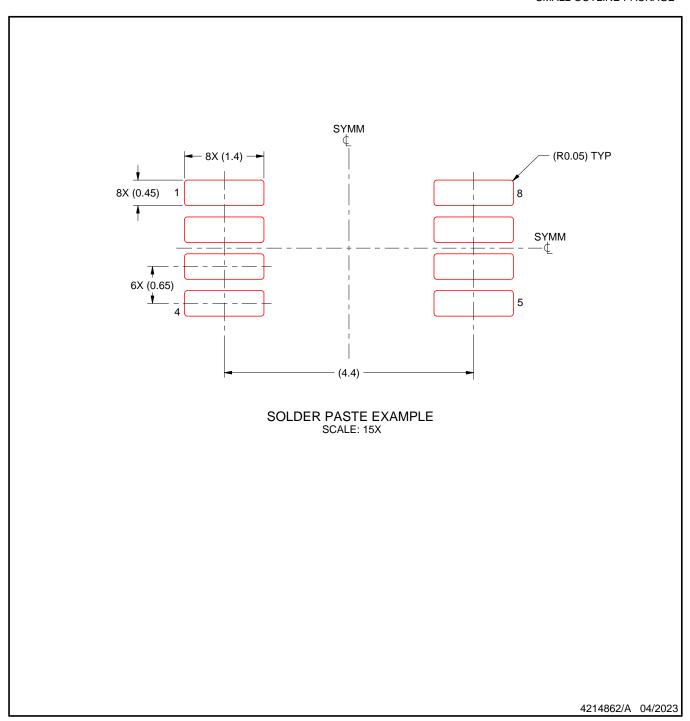

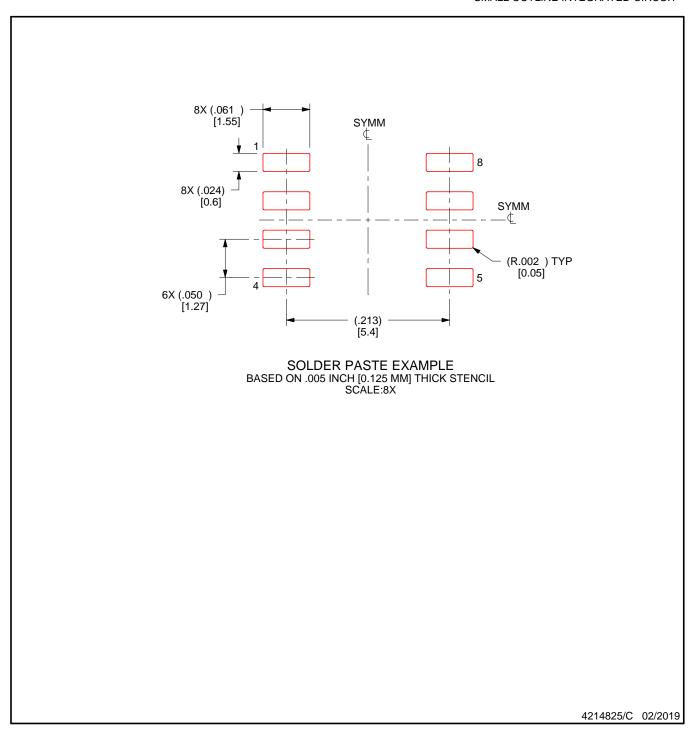

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月