## 高精度、高速 トランスインピーダンス・アンプ

### 特 長

- トランスインピーダンス帯域幅 > 1MHz

- 優れた長時間V<sub>OS</sub>安定性

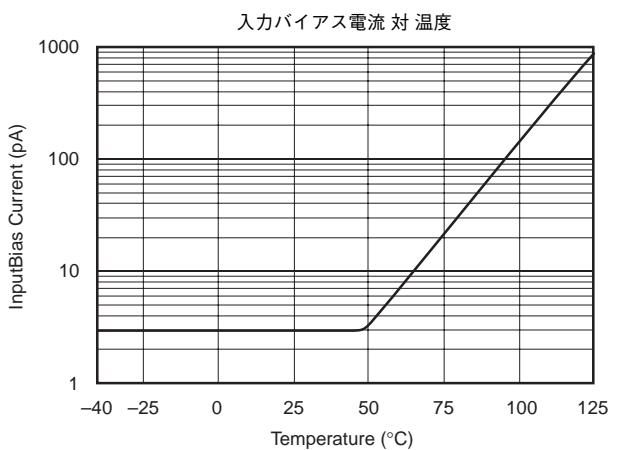

- バイアス電流 : 50pA(最大)

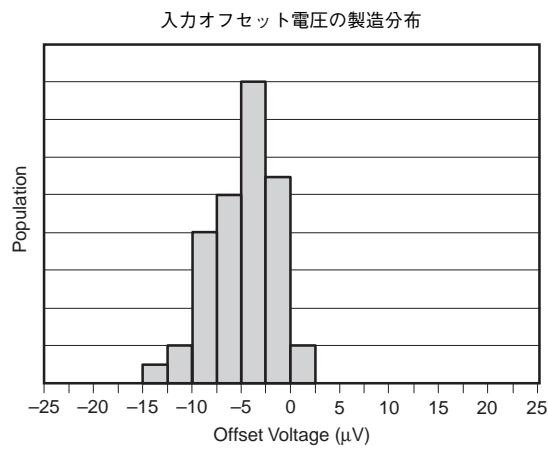

- オフセット電圧 : 25μV(最大)

- 入力電流範囲 : 10nAから1mA

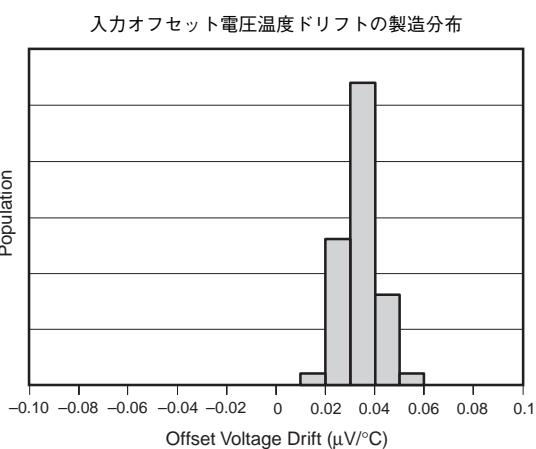

- 温度ドリフト : 0.1μV/°C(最大)

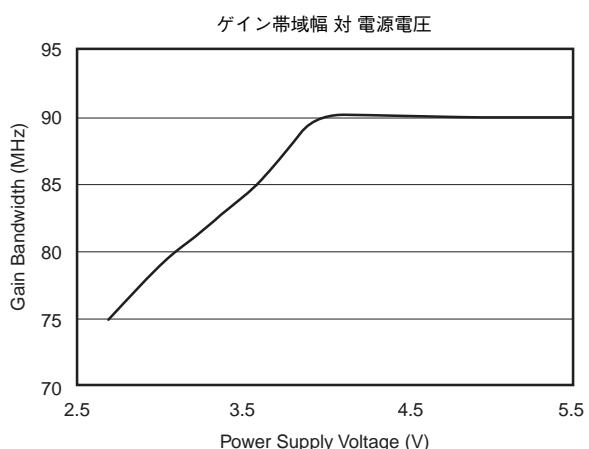

- 帯域幅 : 90MHz

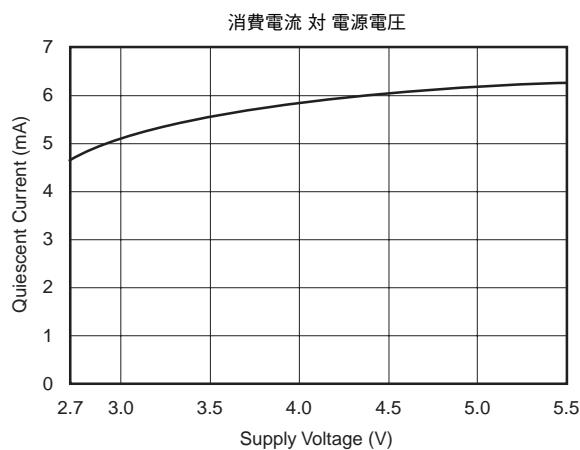

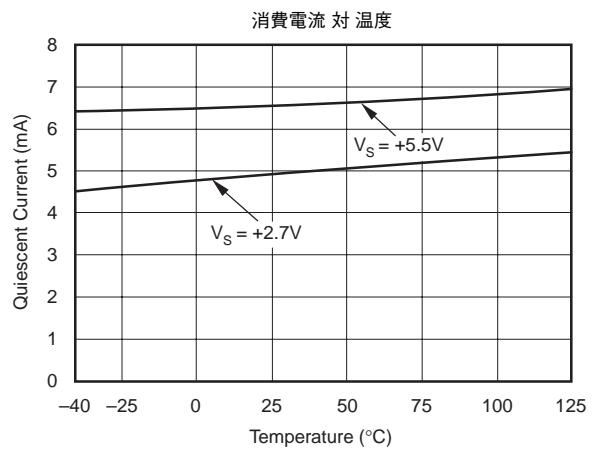

- 消費電流 : 6.5mA

- 電源電圧範囲 : 2.7Vから5.5V

- シングルおよびデュアル版

- MicroSizeパッケージ : MSOP-8

### ア プ リ ケ シ ョ ン

- フォトダイオードのモニタリング

- 高精度のI/V変換

- 光アンプ

- CATスキャナのフロントエンド

### 解 説

トランスインピーダンス・アンプのOPA380ファミリーは、高精度、長時間安定性、極めて低い1/fノイズとともに高速動作(90MHzゲイン帯域幅[GBW])を提供します。まさに高速フォトダイオードのアプリケーションに最適です。OPA380は25μVのオフセット電圧、0.1μV/°Cのオフセット電圧の温度ドリフト、および50pAの入力バイアス電流を特長とします。OPA380はオフセット、ドリフトおよびノイズ特性において、従来のJFETオペアンプをはるかに凌駕します。

トランスインピーダンス・アンプの信号帯域幅は、帰還抵抗とともにアンプのGBWとフォトダイオードの寄生容量に大きく依存します。帯域幅が90MHzのOPA380は、ほとんどの回路構成においてトランスインピーダンス帯域幅 > 1MHzを実現します。OPA380は、光ファイバーのパワーレベルでの高速制御ループに理想的です。

OPA380は、その高精度および低ノイズの2特性によって、5ディケードのダイナミックレンジを実現します。そのため、1段のI/V変換で10nAから1mAまでのオーダーの電流測定が可能です。ログアンプとは対照的に、OPA380は全ダイナミックレンジにおいて非常な広帯域幅を提供します。また、-5Vに接続した外部プルダウン抵抗を使用すると、出力電圧範囲を0Vまで拡張できます。

OPA380(シングル版)は、MSOP-8およびSO-8パッケージで提供しています。またOPA2380(デュアル版)は、小型のMSOP-8パッケージで提供する予定です。全製品とも-40°Cから+125°Cの温度範囲で規定されています。

### OPA380 RELATED DEVICES

| PRODUCT  | FEATURES                                     |

|----------|----------------------------------------------|

| OPA300   | 150MHz CMOS, 2.7V to 5.5V Supply             |

| OPA350   | 500V V OS, 38MHz, 2.5V to 5V Supply          |

| OPA335   | 10V V OS, Zero-Drift, 2.5V to 5V Supply      |

| OPA132   | 16MHz GBW, Precision FET Op Amp, ±15V        |

| OPA656/7 | 230MHz, Precision FET, ±5V                   |

| LOG112   | LOG amp, 7.5 decades, ±4.5V to ±18V Supply   |

| LOG114   | LOG amp, 7.5 decades, ±2.25V to ±5.5V Supply |

| IVC102   | Precision Switched Integrator                |

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## ABSOLUTE MAXIMUM RATINGS (1)

|                                                 |       |                      |

|-------------------------------------------------|-------|----------------------|

| Voltage Supply                                  | ..... | +7V                  |

| Signal Input Terminals <sup>(2)</sup> , Voltage | ..... | -0.5V to (V+) + 0.5V |

| Current                                         | ..... | ±10mA                |

| Short-Circuit Current <sup>(3)</sup>            | ..... | Continuous           |

| Operating Temperature Range                     | ..... | -40°C to +125°C      |

| Storage Temperature Range                       | ..... | -65°C to +150°C      |

| Junction Temperature                            | ..... | +150°C               |

| Lead Temperature (soldering, 10s)               | ..... | +300°C               |

| ESD Rating (Human Body Model)                   | ..... | 2000V                |

- (1) これらの定格以上のストレスは、デバイスの永久破壊を生じることがあります。絶対最大定格の条件下でデバイスを長期間置くと、その信頼性を劣化させることができます。これらはストレスのみに関する定格であり、推奨動作条件を超える条件でのデバイスの機能動作を含むものではありません。

- (2) 入力ピンはダイオードで電源およびグランドにクランプしています。電源およびグランドを0.5V以上超える入力信号は、その電流を10mA以下に制限する必要があります。

- (3) グランドへの短絡電流であり、1パッケージあたり1アンプとします。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## PACKAGE/ORDERING INFORMATION

| PRODUCT                | PACKAGE-LEAD | PACKAGE DESIGNATOR <sup>(1)</sup> | SPECIFIED TEMPERATURE RANGE | PACKAGE MARKING | ORDERING NUMBER | TRANSPORT MEDIA, QUANTITY |

|------------------------|--------------|-----------------------------------|-----------------------------|-----------------|-----------------|---------------------------|

| OPA380                 | MSOP-8       | DGK                               | -40°C to +125°C             | AUN             | OPA380AIDGKT    | Tape and Reel, 250        |

|                        |              |                                   |                             |                 | OPA380AIDGKR    | Tape and Reel, 2500       |

| OPA380                 | SO-8         | D                                 | -40°C to +125°C             | OPA380A         | OPA380AID       | Rails, 100                |

|                        |              |                                   |                             |                 | OPA380AIDR      | Tape and Reel, 2500       |

| OPA2380 <sup>(2)</sup> | MSOP-8       | DGK                               | -40°C to +125°C             | BBX             | OPA2380AIDGKT   | Rails, 250                |

|                        |              |                                   |                             |                 | OPA2380AIDGKR   | Tape and Reel, 2500       |

(1) 最新の仕様およびパッケージに関する情報は、弊社ウェブサイトのwww.ti.comを参照願います。

(2) 2004年の第2四半期に入手可能です。

## PIN ASSIGNMENTS

| Top View                          |                                            |

|-----------------------------------|--------------------------------------------|

| <p>OPA380</p> <p>MSOP-8, SO-8</p> | <p>OPA2380<sup>(2)</sup></p> <p>MSOP-8</p> |

NOTES: (1)NC indicates no internal connection.

(2)Available Q 22004.

## ELECTRICAL CHARACTERISTICS: $V_S = 2.7V$ to $5.5V$

**Boldface** limits apply over the temperature range,  $T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .

All specifications at  $T_A = +25^\circ\text{C}$ ,  $R_L = 2\text{k}\Omega$  connected to  $V_S/2$ , and  $V_{\text{OUT}} = V_S/2$ , unless otherwise noted.

| PARAMETER                                                | CONDITION           | OPA380, OPA2380                                                                                                                                                |            |            | UNITS                        |

|----------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------------------------|

|                                                          |                     | MIN                                                                                                                                                            | TYP        | MAX        |                              |

| <b>OFFSET VOLTAGE</b>                                    |                     |                                                                                                                                                                |            |            |                              |

| Input Offset Voltage                                     | $V_{\text{OS}}$     |                                                                                                                                                                |            |            | $\mu\text{V}$                |

| Drift vs Power Supply                                    | $dV_{\text{OS}}/dT$ |                                                                                                                                                                |            |            | $\mu\text{V}/^\circ\text{C}$ |

| Over Temperature                                         | $\text{PSRR}$       |                                                                                                                                                                |            |            | $\mu\text{V/V}$              |

| Long-Term Stability <sup>(1)</sup>                       |                     |                                                                                                                                                                |            |            | $\mu\text{V/V}$              |

| Channel Separation, dc                                   |                     |                                                                                                                                                                |            |            | $\mu\text{V/V}$              |

| <b>INPUT BIAS CURRENT</b>                                |                     |                                                                                                                                                                |            |            |                              |

| Input Bias Current                                       | $I_B$               |                                                                                                                                                                |            |            | $\text{pA}$                  |

| Over Temperature                                         |                     |                                                                                                                                                                |            |            |                              |

| Input Offset Current                                     | $I_{\text{OS}}$     |                                                                                                                                                                |            |            | $\text{pA}$                  |

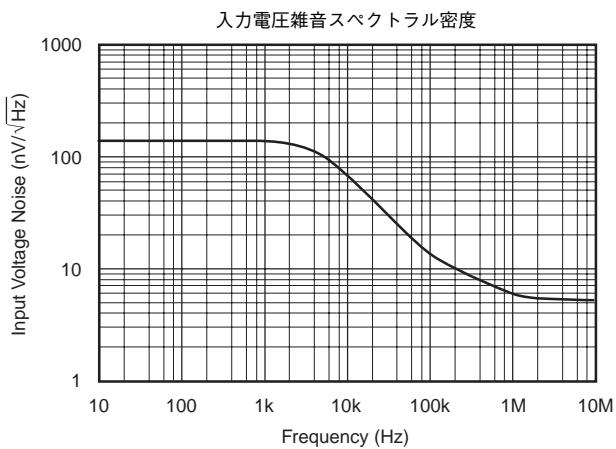

| <b>NOISE</b>                                             |                     |                                                                                                                                                                |            |            |                              |

| Input Voltage Noise, $f = 0.1\text{Hz}$ to $10\text{Hz}$ | $e_n$               |                                                                                                                                                                |            |            | $\mu\text{VPP}$              |

| Input Voltage Noise Density, $f = 10\text{kHz}$          | $e_n$               |                                                                                                                                                                |            |            | $\text{nV}/\sqrt{\text{Hz}}$ |

| Input Voltage Noise Density, $f > 1\text{MHz}$           | $e_n$               |                                                                                                                                                                |            |            | $\text{nV}/\sqrt{\text{Hz}}$ |

| Input Current Noise Density, $f = 10\text{kHz}$          | $i_n$               |                                                                                                                                                                |            |            | $\text{fA}/\sqrt{\text{Hz}}$ |

| <b>INPUT VOLTAGE RANGE</b>                               |                     |                                                                                                                                                                |            |            |                              |

| Common-Mode Voltage Range                                | $V_{\text{CM}}$     |                                                                                                                                                                |            |            | $\text{V}$                   |

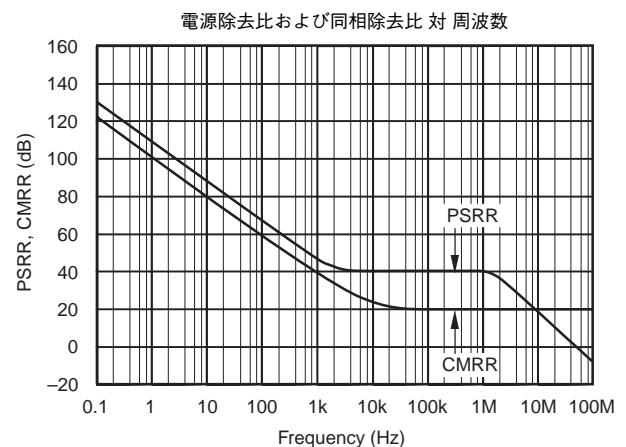

| Common-Mode Rejection Ratio                              | $\text{CMRR}$       |                                                                                                                                                                |            |            | $\text{dB}$                  |

| <b>INPUT IMPEDANCE</b>                                   |                     |                                                                                                                                                                |            |            |                              |

| Differential Capacitance                                 |                     |                                                                                                                                                                |            |            | $\text{pF}$                  |

| Common-Mode Resistance and Inverting                     |                     |                                                                                                                                                                |            |            |                              |

| Input Capacitance                                        |                     |                                                                                                                                                                |            |            | $\Omega \parallel \text{pF}$ |

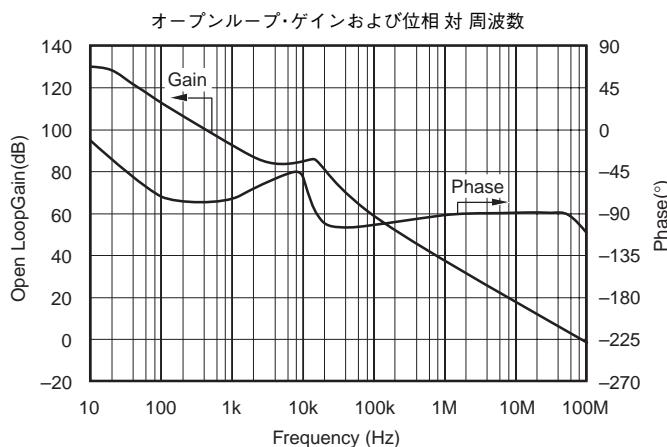

| <b>OPEN-LOOP GAIN</b>                                    |                     |                                                                                                                                                                |            |            |                              |

| Open-Loop Voltage Gain                                   | $A_{\text{OL}}$     | $0.1\text{V} < V_O < (V+) - 0.7, V_{\text{CM}} = V_S/2$                                                                                                        | <b>110</b> | <b>130</b> | $\text{dB}$                  |

|                                                          |                     | $0.1\text{V} < V_O < (V+) - 0.6, V_{\text{CM}} = V_S/2, T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$                                                        | <b>110</b> | <b>130</b> | $\text{dB}$                  |

|                                                          |                     | $0\text{V} < V_O < (V+) - 0.7\text{V}, V_{\text{CM}} = 0\text{V}, R_P = 2\text{k}\Omega$ to $-5\text{V}^{(2)}$                                                 | <b>106</b> | <b>120</b> | $\text{dB}$                  |

|                                                          |                     | $0\text{V} < V_O < (V+) - 0.6\text{V}, V_{\text{CM}} = 0\text{V}, R_P = 2\text{k}\Omega$ to $-5\text{V}^{(2)}, T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$ | <b>106</b> | <b>120</b> | $\text{dB}$                  |

| <b>FREQUENCY RESPONSE</b>                                |                     | $C_L = 50\text{pF}$                                                                                                                                            |            |            |                              |

| Gain-Bandwidth Product                                   | $\text{GBW}$        |                                                                                                                                                                |            |            | $\text{MHz}$                 |

| Slew Rate                                                | $\text{SR}$         | $G = +1$                                                                                                                                                       |            |            | $\text{V}/\mu\text{s}$       |

| Settling Time, 0.015% <sup>(3)</sup>                     | $t_S$               | $V_S = +5\text{V}, 4\text{V Step}, G = +1$                                                                                                                     |            |            | $\mu\text{s}$                |

| Overload Recovery Time <sup>(4), (5)</sup>               |                     | $V_{\text{IN}} \bullet G = > V_S$                                                                                                                              |            |            | $\text{ns}$                  |

| <b>OUTPUT</b>                                            |                     |                                                                                                                                                                |            |            |                              |

| Voltage Output Swing from Positive Rail                  |                     | $R_L = 2\text{k}\Omega$                                                                                                                                        |            |            | $\text{mV}$                  |

| Voltage Output Swing from Negative Rail                  |                     | $R_L = 2\text{k}\Omega$                                                                                                                                        |            |            | $\text{mV}$                  |

| Voltage Output Swing from Positive Rail                  |                     | $R_P = 2\text{k}\Omega$ to $-5\text{V}^{(2)}$                                                                                                                  |            |            | $\text{mV}$                  |

| Voltage Output Swing from Negative Rail                  |                     | $R_P = 2\text{k}\Omega$ to $-5\text{V}^{(2)}$                                                                                                                  |            |            | $\text{mV}$                  |

| Output Current                                           | $I_{\text{OUT}}$    |                                                                                                                                                                |            |            |                              |

| Short-Circuit Current                                    | $I_{\text{SC}}$     |                                                                                                                                                                |            |            |                              |

| Capacitive Load Drive                                    | $C_{\text{LOAD}}$   |                                                                                                                                                                |            |            |                              |

| Open-Loop Output (resistance)                            |                     | $f = 1\text{MHz}, I_O = 0\text{V}$                                                                                                                             |            |            | $\Omega$                     |

(1)  $150^\circ\text{C}$ , 300時間の寿命試験では、測定再現性のある約 $1\mu\text{V}$ のランダムに分布する変動を示しました。

(2) 図5に示すように、 $V_{\text{OUT}}$ と $-5\text{V}$ 間に接続したブルダウン抵抗 $R_P$ だけを負荷とする出力でテストしました。アプリケーション節の「グランド・レベルの出力振幅の実現」も参照願います。

(3)  $1\text{MHz}$ のトランシスインピーダンス周波数。

(4) リニア動作の回復に要する時間。

(5) 正電源電圧から回復する時間。

## ELECTRICAL CHARACTERISTICS: $V_S = 2.7V$ to $5.5V$ (continued)

**Boldface** limits apply over the temperature range,  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

All specifications at  $T_A = +25^{\circ}\text{C}$ ,  $R_L = 2\text{k}\Omega$  connected to  $V_S/2$ , and  $V_{\text{OUT}} = V_S/2$ , unless otherwise noted.

| PARAMETER                         | CONDITION     | OPA380, OPA2380 |     |            | UNITS                       |

|-----------------------------------|---------------|-----------------|-----|------------|-----------------------------|

|                                   |               | MIN             | TYP | MAX        |                             |

| <b>POWER SUPPLY</b>               |               |                 |     |            |                             |

| Specified Voltage Range           | $V_S$         |                 |     | 2.7        | V                           |

| Quiescent Current (per amplifier) | $I_Q$         | $I_O = 0V$      |     | 6.5        | mA                          |

| <b>Over Temperature</b>           |               |                 |     | 8.3        | mA                          |

|                                   |               |                 |     | <b>8.8</b> | <b>mA</b>                   |

| <b>TEMPERATURE RANGE</b>          |               |                 |     |            |                             |

| Specified Range                   |               |                 |     | $-40$      | $^{\circ}\text{C}$          |

| Operating Range                   |               |                 |     | $-40$      | $^{\circ}\text{C}$          |

| Storage Range                     |               |                 |     | $-65$      | $^{\circ}\text{C}$          |

| Thermal Resistance                | $\theta_{JA}$ |                 |     | 150        | $^{\circ}\text{C}/\text{W}$ |

| MSOP-8                            |               |                 |     | 150        | $^{\circ}\text{C}/\text{W}$ |

| SO-8                              |               |                 |     |            |                             |

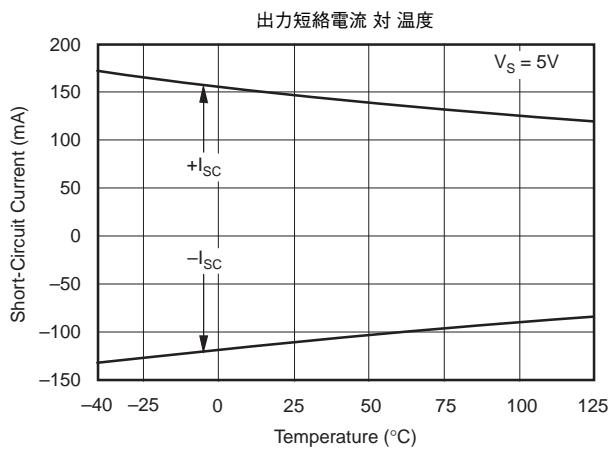

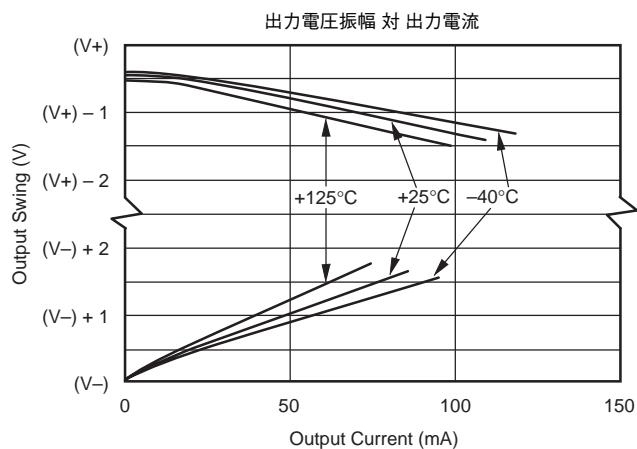

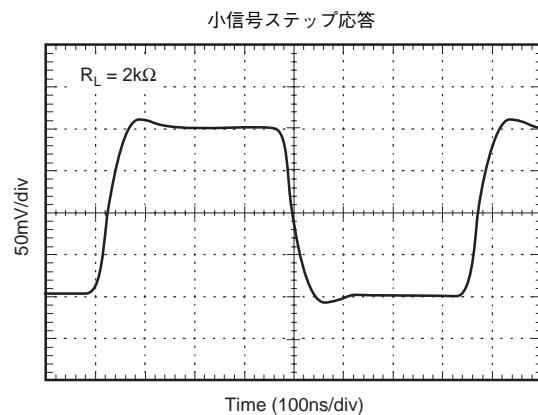

代表的特性:  $V_S = +2.7V$  to  $+5.5V$

All specifications at  $T_A = +25^\circ C$ ,  $R_L = 2k\Omega$  connected to  $V_S/2$ , and  $V_{OUT} = V_S/2$ , unless otherwise noted.

## 代表的特性: $V_S = +2.7V$ to $+5.5V$ (continued)

All specifications at  $T_A = +25^\circ\text{C}$ ,  $R_L = 2\text{k}\Omega$  connected to  $V_S/2$ , and  $V_{\text{OUT}} = V_S/2$ , unless otherwise noted.

## 代表的特性: $V_S = +2.7V$ to $+5.5V$ (continued)

All specifications at  $T_A = +25^\circ C$ ,  $R_L = 2k\Omega$  connected to  $V_S/2$ , and  $V_{OUT} = V_S/2$ , unless otherwise noted.

## 代表的特性: $V_S = +2.7V$ to $+5.5V$ (continued)

All specifications at  $T_A = +25^\circ C$ ,  $R_L = 2k\Omega$  connected to  $V_S/2$ , and  $V_{OUT} = V_S/2$ , unless otherwise noted.

# アプリケーション情報

## 基本動作

OPA380は1/fノイズが非常に低い高性能トランジンピーダンス・アンプです。そのユニークなアーキテクチャーにより、OPA380の長時間入力オフセット電圧安定性は150°C、300時間の試験でもわずか1μV程度の変動です。

OPA380の特性は、内部のオートゼロ・アンプと高速アンプの組み合わせにより得られていますが、従来の複合的アプローチに比べ過負荷回復時間およびセトリング・タイムを改善するように設計しました。また、特に0V動作が可能な回路オプション(図3参照)に対応した設計も本デバイスの特長です。

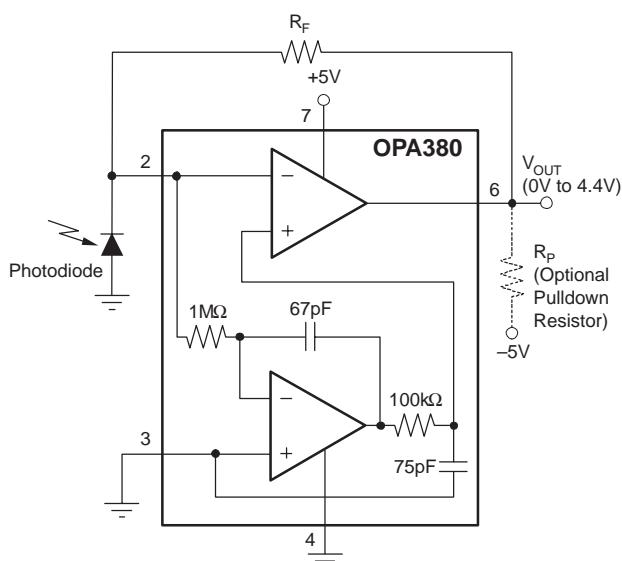

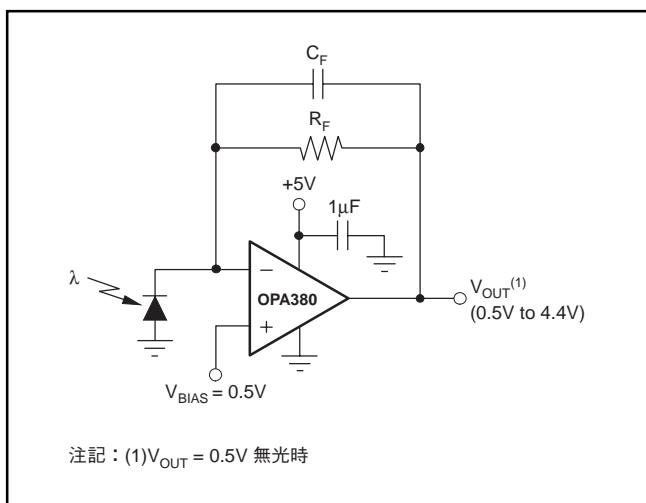

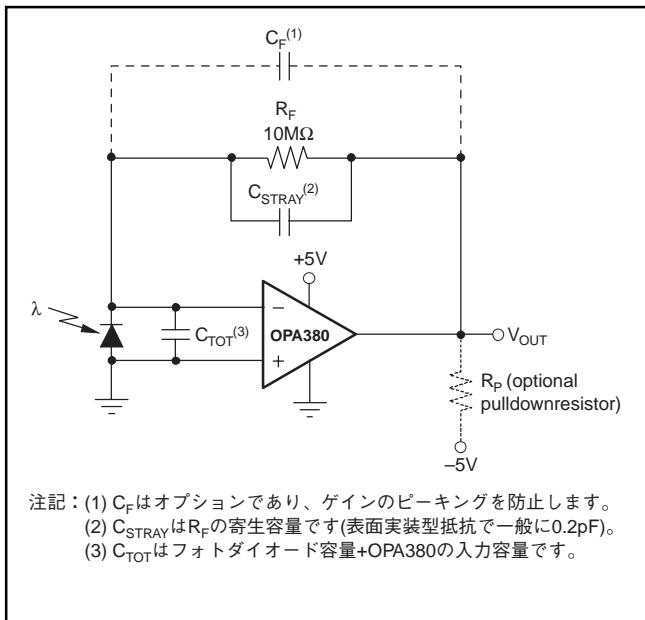

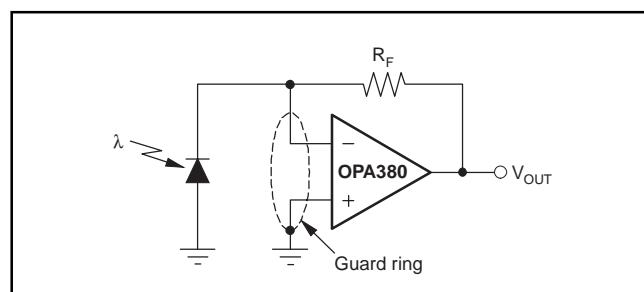

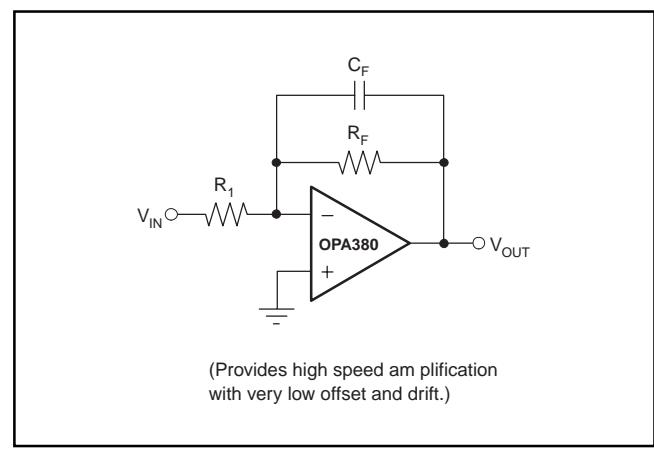

OPA380は反転アンプの構成で使用し、非反転入力は固定バイアス点として使用します。図1に代表的なOPA380の回路構成を示します。電源ピンは1μFのセラミックあるいはタンタル・コンデンサでバイパスします。電解コンデンサはお奨めできません。

図1. OPA380の代表的回路構成

## 電源電圧

OPA380シリーズのオペアンプは、-40°Cから+125°Cの温度範囲において、2.7Vから5.5Vの電源電圧で規定されています。電源電圧と温度によって著しく変化するパラメータは、「代表的特性グラフ」に示してあります。

## 内部オフセット補正

OPA380はその信号路中に、タイム・コンティニュアス(連続時間)な90MHzのオペアンプによるオートゼロ回路を使用しています。本アンプは独自の技術によって100μsごとにゼロ補正を行っています。電源投入時では、本アンプはV<sub>OS</sub>を仕様内の精度に合わせるために、約400μsのオート・ゼロ・サイクルを1回必要とします。この時間が経過するまでは、アンプの機能は適正ですが、入力オフセット電圧は規定できません。

本デバイスのエイリアシングとノイズは特筆すべき小さい値です。ゼロ補正是10kHzのレートで実施されますが、その周波数における基本ノイズはほとんどありません。すべての用途に対しても、本デバイスのあらゆるグリッチノイズは20MHz以上にあり、必要なら簡単にフィルタで除去できますが、ほとんどのアプリケーションはそのような高周波ノイズに敏感ではなく、フィルタをする必要がありません。

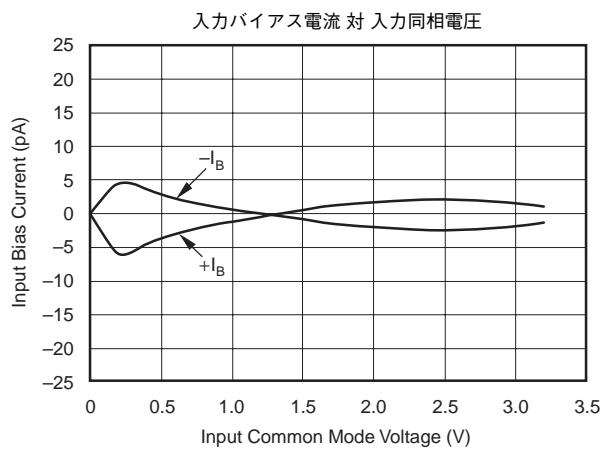

## 入力電圧

OPA380シリーズの入力同相電圧範囲は、V-から(V+) -1.8Vです。この同相範囲外の入力信号に対しては、本アンプは適正な出力値になりませんが、ラッチや反転をすることはありません。

## 入力過電圧保護

本デバイスの入力はESDダイオードで保護されており、入力電圧が電源電圧を約500mV以上超えると、このESDダイオードが導通します。電源電圧を500mV以上超える瞬間的な入力電圧は、その電流が10mAに制限されなければ許容できます。OPA380シリーズは、入力が電源電圧を超えて、その電流が制限されれば位相反転しないことを特長としています。

## 出力範囲

OPA380は、正電源から最小600mVおよび負電源から最小100mVの振幅で2kΩ負荷時に優れたリニアリティを示します。リニアリティを保ちながらの負電源への振幅は、0ボルトまで拡張することができます。これについては、「グランド・レベルの出力振幅の実現」の節を参照願います。また、代表的特性の「出力電圧振幅 対 出力電流」も参照願います。

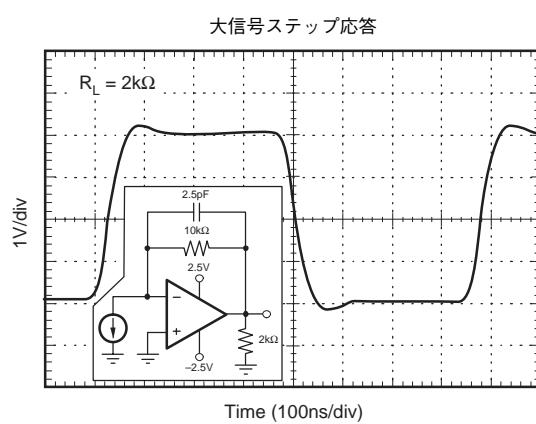

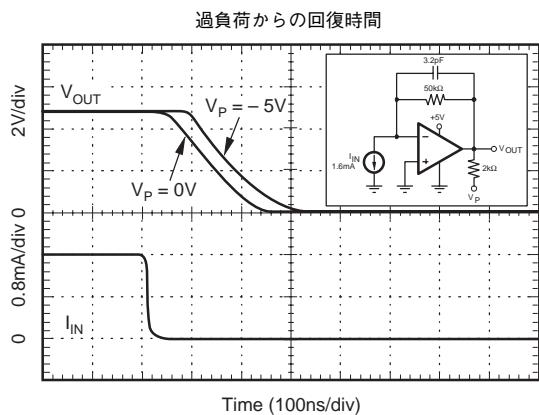

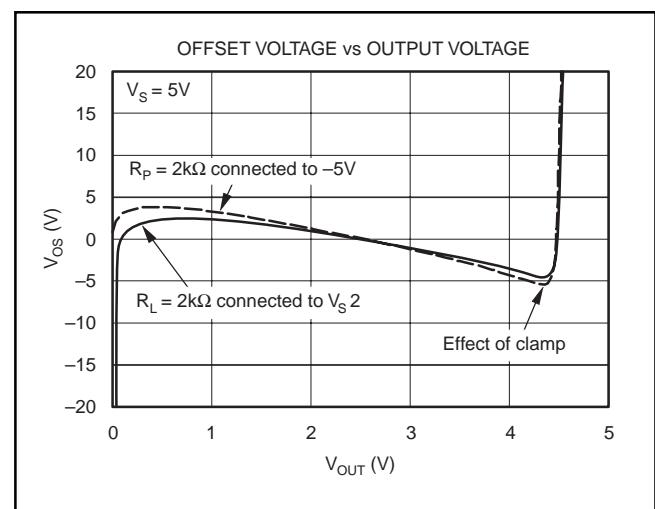

OPA380の出力振幅は、正電源への仕様値よりもわずかに正電源側へ接近できます。しかし、その場合リニアリティが損なわれます。また、高速過負荷回復クランプが出力電圧振幅の正電源への接近可能な範囲を制限します(図2参照)。

図2. 高速過負荷回復クランプによる出力電圧への影響

## 過負荷回復時間

OPA380は出力の飽和を防止するように設計されています。正電源へオーバードライブされた後、リニア動作に戻るのに要する時間はわずか100ns(代表値)です。負電源への過負荷回復に要する時間は、「グランド・レベルの出力振幅の実現」を用いないかぎり、もっと長い時間になります。

## 出力振幅のオペアンプ負電源までの到達

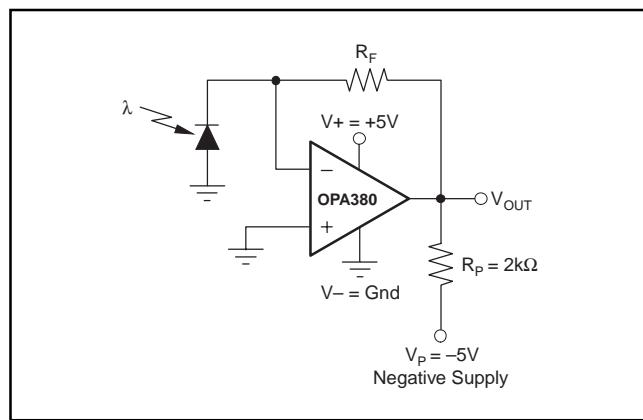

アプリケーションによっては、0Vから正のフルスケール電圧(例えば+4.096V)までの出力電圧振幅が優れた精度で必要になります。ほとんどの単電源オペアンプでは、出力が0Vすなわち出力振幅の下限に接近すると問題が発生します。良くできた単電源のオペアンプは、単電源のグラウンド近くまで振幅が得られるかもしれません、グラウンドには達しません。OPA380およびOPA2380の出力振幅は、単電源でもグラウンドあるいはそのわずか下まで達するようにできます。そのためには、別の抵抗および本アンプの負電源より低い別の負電源が必要になります。図3に示すように1個のプルダウン抵抗を出力と別の負電源間に接続すると、出力をその値以下まで引き下げることができます。

図3. オプションのプルダウン抵抗を用いて $V_{OUT}=0V$ を得たアンプ

## グランド・レベルの出力振幅の実現

OPA380には、この手法で出力電圧を負電源まで下げられる出力段があります。しかし、この手法はある種の出力段のみに可能です。OPA380は、この手法が十分機能するように設計されています。信頼性の高い動作が0Vまで、仕様の温度範囲内で保証されています。

## 単電源回路におけるフォトダイオードのバイアス

+IN入力は正のDC電圧をバイアスして、出力電圧にオフセットを与えます。また、そのバイアスによりアンプ出力は、フォトダイオードに光を与えない場合におけるフォトダイオード測定の真のゼロ値を示します。さらに、負電源から戻るための遅れ時間を防止します。このバイアス電圧はフォトダイオードの両端に印加され、高速動作のための逆バイアスになります。このバイアス点に接続するRCフィルタは、ノイズを低減します(図4参照)。また、このバイアス電圧は、グランド・レベルを含まないADCのオフセット・バイアス点としての役割もできます。

図4. フィルタした逆バイアス電圧

## トランスインピーダンス・アンプ

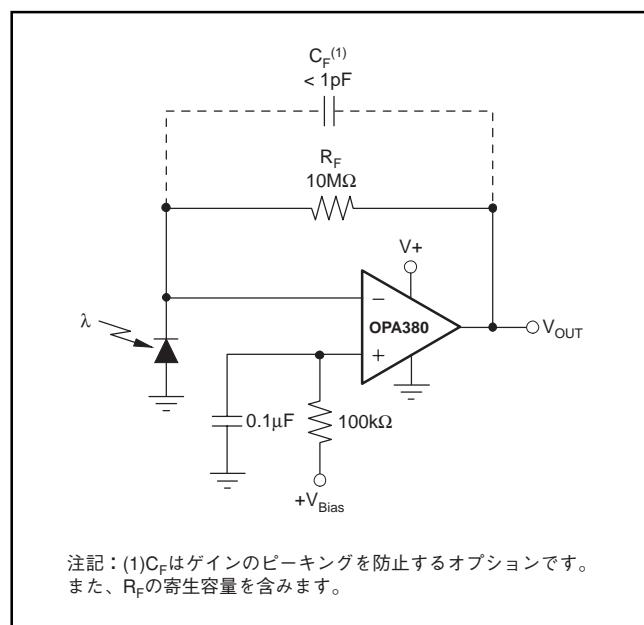

広帯域幅、低入力バイアス電流、低入力電圧・電流ノイズにより、OPA380は理想的な広帯域フォトダイオード用トランスインピーダンス・アンプです。フォトダイオード容量が回路の実効雑音ゲインを高周波時に増加させるため、アンプの電圧ノイズが低いことは重要です。

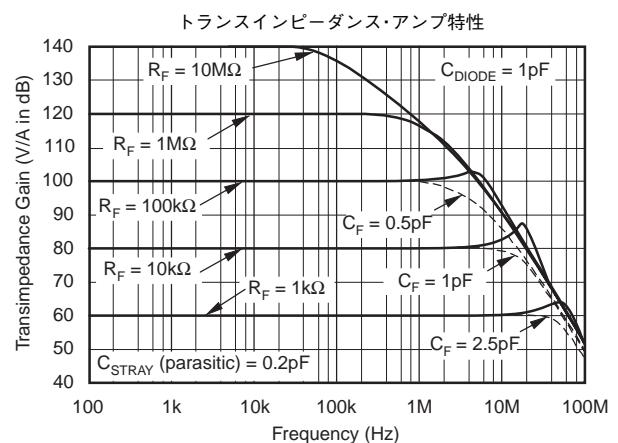

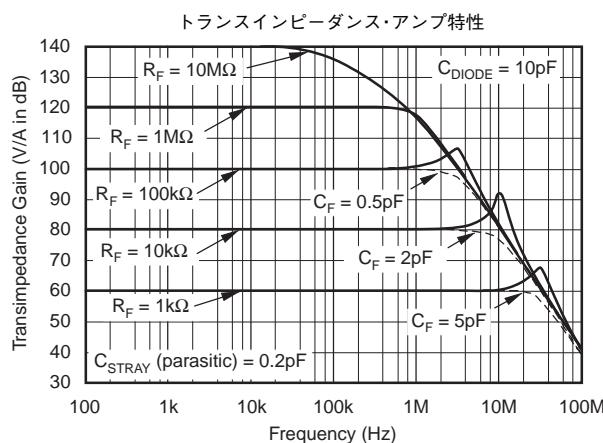

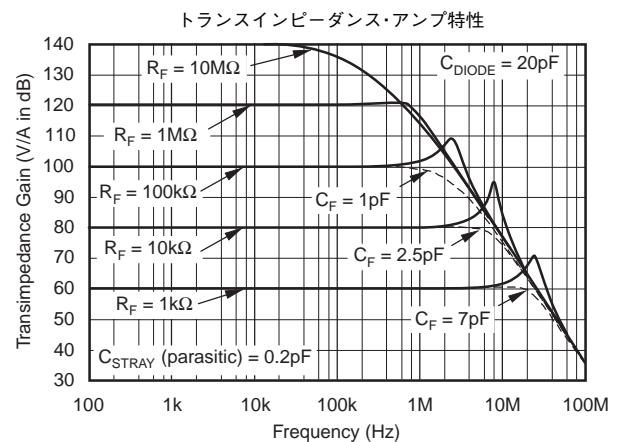

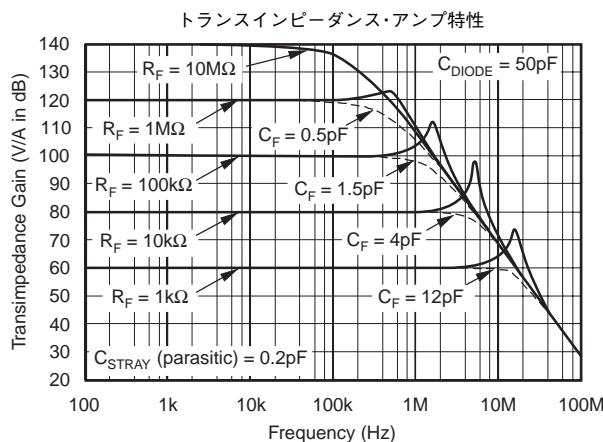

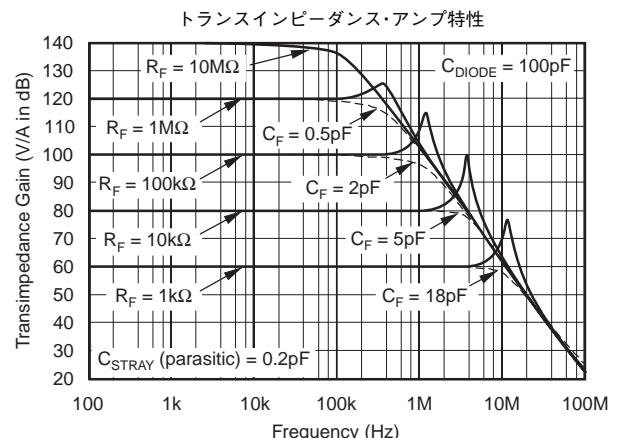

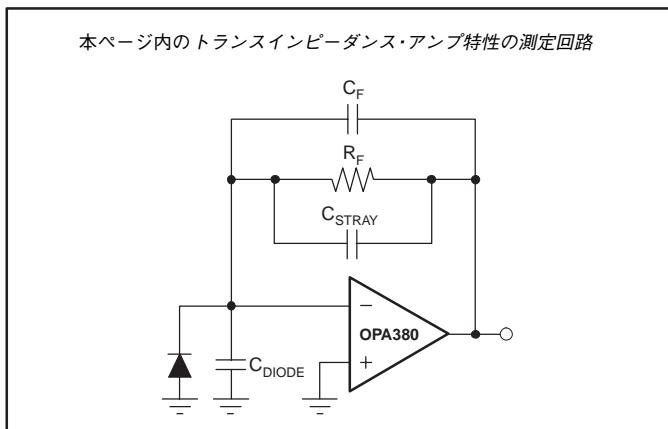

トランスインピーダンス設計に関するキーとなる要素は図5に示してあります。

- 全入力容量( $C_{TOT}$ )。これは、フォトダイオード容量( $C_{DIODE}$ )と寄生の同相および差動モード入力容量の和(OPA380の場合、3pF+1.1pF)；

- 所要のトランスインピーダンスのゲイン( $R_F$ )；

- OPA380のゲイン帯域幅積(GBW, 90MHz)

になります。

これら3変数のセットにより、帰還容量値( $C_F$ )は周波数応答を制御するように設定できます。 $C_{STRAY}$ は $R_F$ の寄生容量であり、代表的な表面実装型の抵抗で0.2pFです。

最大限に平坦な2次のバタワース周波数応答を得るには、帰還ポールを次のように設定します：

$$\frac{1}{2\pi R_F(C_F + C_{STRAY})} = \sqrt{\frac{GBW}{4\pi R_F C_{TOT}}} \quad (1)$$

帯域幅は次のように計算され：

$$f_{3dB} = \sqrt{\frac{GBW}{2\pi R_F C_{TOT}}} \text{ Hz} \quad (2)$$

この2式により、最大トランスインピーダンス帯域幅が求まります。より高いトランスインピーダンス帯域幅には、高速CMOSのOPA300(180MHzのGBW)あるいはOPA656(230MHzのGBW)が使用できます。

より詳細な情報は、Application Bulletin AB-050(SBOA055)の「Compensate Transimpedance Amplifiers Intuitively」を参照願います。これはwww.ti.comからダウンロードして入手できます。

図5. トランシングピーダンス・アンプ

### トランシングピーダンス帯域幅とノイズ

$R_F$ によって設定されるゲインを制限すると、トランシングピーダンス回路の出力におけるノイズを低減できます。しかし、必要なゲインはトランシングピーダンス段で得るべきです。トランシングピーダンス・アンプ以降でゲインを得ると、一般にノイズ特性が悪化するからです。信号はリニアに増加しますが、 $R_F$ により発生する雑音スペクトル密度は  $R_F$  の平方根に比例します。したがって、トランシングピーダンス段で必要な全ゲインを得れば、SN比は改善されます。

全ノイズは帯域幅の増加とともに増加します。したがって、回路の帯域幅を所要の値のみに制限します。容量  $C_F$  を帰還抵抗  $R_F$  に並列に接続し、帯域幅を制限します。安定性に問題がなくても、全出力雑音が問題の場合はこのようにします。

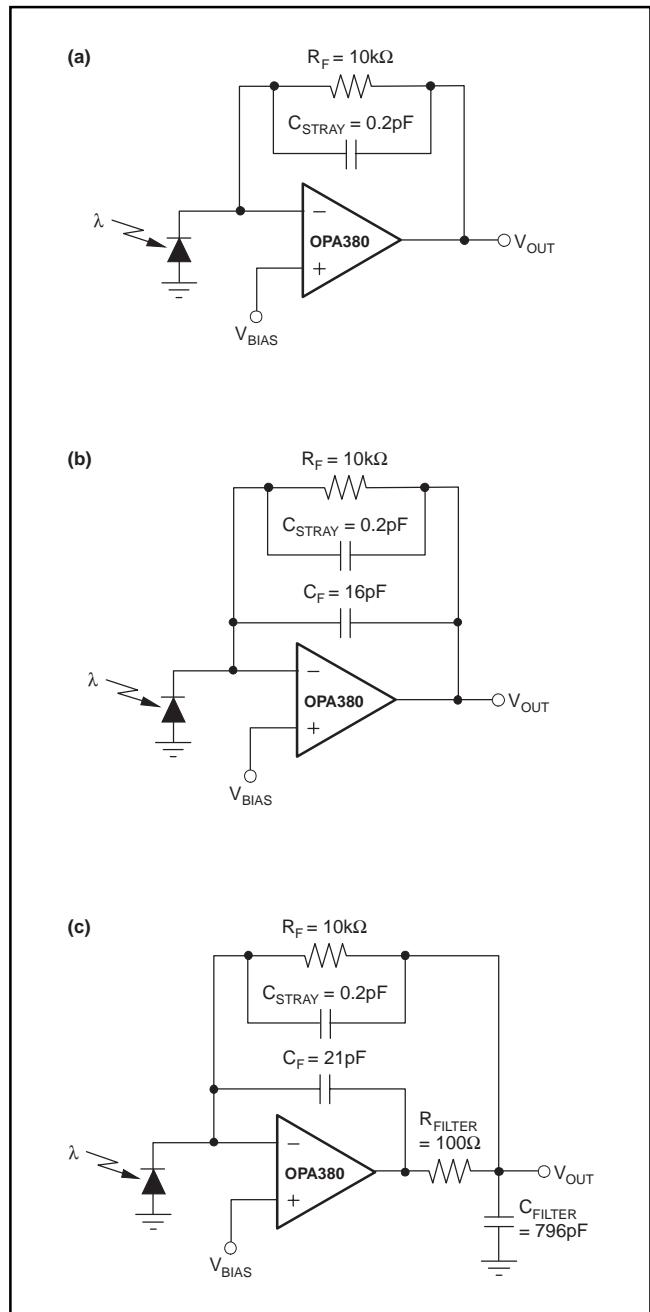

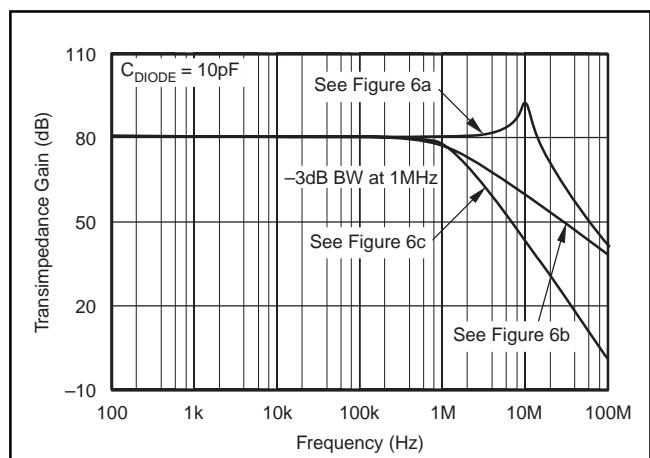

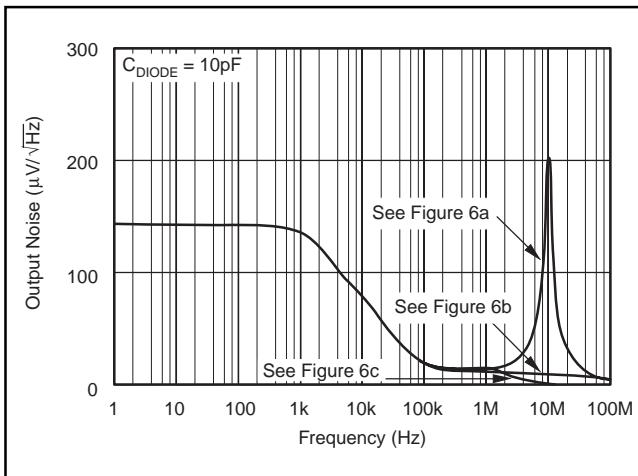

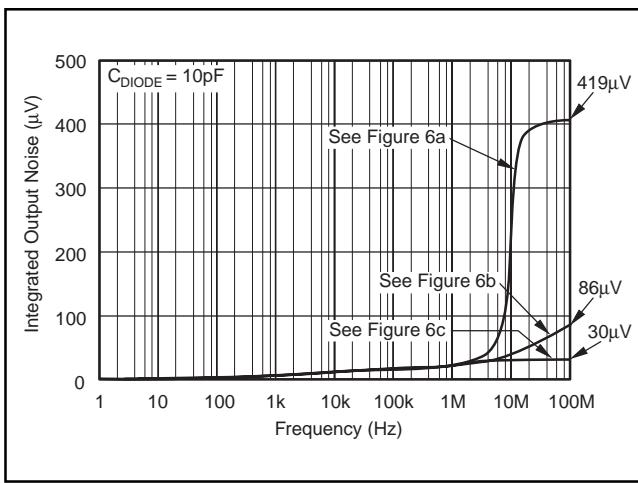

図6 aは帰還容量のないトランシングピーダンス回路を示します。この回路のトランシングピーダンス・ゲインを図7に示します。その-3dBポイントは約10MHzです。これに16pFの帰還容量(図6 b)を付けると帯域幅を制限し、-3dBポイントが約1MHzになります(図7参照)。出力ノイズは、第2ポールを生ずるフィルタ(図6 cの  $R_{FILTER}$  および  $C_{FILTER}$ )の付加により、さらに低減されます。この第2ポールは帰還ループ内に配置し、アンプの低出力インピーダンスを保ちます。(もし、このポールを帰還ループ外に配置すると、別のバッファを必要とし、ノイズとDC誤差が増加するでしょう。)

ダイオードの等価抵抗を表す  $R_{DIODE}$  と、等価ダイオード容量+OPA380の入力容量を  $C_{TOT}$  として両者を用いると、ノイズのゼロの周波数  $f_Z$  は次のように計算されます。

$$f_Z = \frac{(R_{DIODE} + R_F)}{2\pi R_{DIODE} R_F (C_{TOT} + C_F)} \quad (3)$$

これらの回路構成による出力ノイズへの影響を図8に、積分出力ノイズへの影響を図9に示します。次式を用いてフィルタ定数を選択すると、2ポールのバタワース・フィルタ(平坦な通過域が

図6. 全ノイズおよび積分ノイズ・ゲインを変化したトランシングピーダンス回路

図7. トランシングピーダンス・ゲイン(図6の回路)

図8. 出力ノイズ(図6の回路)

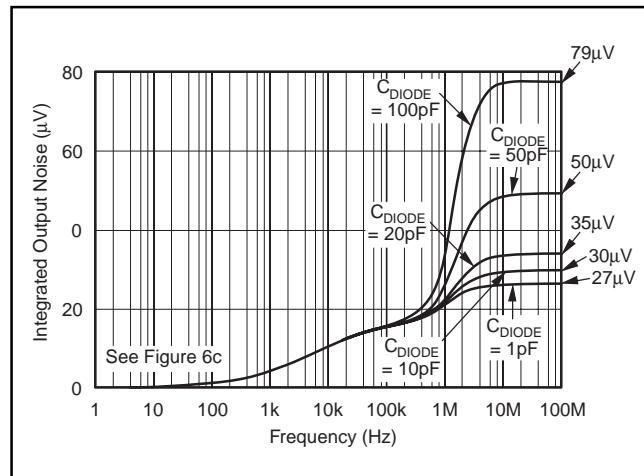

図10. いろいろな値のC<sub>DIODE</sub>についての積分出力ノイズ(図6cの回路)

図9. 積分出力ノイズ(図6の回路)

最大になる)が得られます。

$$C_F R_F = 2 C_{\text{FILTER}} R_{\text{FILTER}} \quad (4)$$

また、

$$f_{-3dB} = \frac{1}{2\pi\sqrt{R_F R_{\text{FILTER}} C_F C_{\text{FILTER}}}} \quad (5)$$

図6 bの回路は20dB/decadeで減衰します。別のフィルタを加えた図6 cの回路は40dB/decadeで減衰し、その結果ノイズ特性を改善します。

図10は、図6 cの回路におけるダイオード容量の積分出力ノイズへの影響を示します。

さらなる情報は、「FET Transimpedance Amplifiers(SBOA060)」および「Noise Analysis for High Speed Op Amps(SBOA066)」を参照願います。これらはTIウェブサイトからダウンロードして入手できます。

## 基板レイアウト

フォトダイオード容量と加算点(反転入力)の寄生容量を最小化します。これらの容量は、オペアンプの電圧ノイズを増幅する原因になります(高周波における増幅を高めます)。低ノイズの電圧源でフォトダイオードに逆バイアスをかけると、その容量を著しく低減できます。小さなフォトダイオードほど、その容量は小さくなります。小さなフォトダイオードに光を集中する光学部品を使用します。

回路基板のリーク電流は、本来よく設計されているアンプでも、その特性を劣化させます。回路基板は注意深くきれいにします。回路基板のアンプ入力を取り囲むガード・リングを等電位でドライブすると、リーク電流の制御に役立ちます。これについては図11を参照願います。

図11. 入力ガードの配線

## 他の微小電流測定方法

ログアンプを用いて、非常に広いダイナミックレンジの入力電流をより狭い範囲に圧縮します。8ディケードすなわち100pAから10mAまでの広い入力ダイナミックレンジは、12ビットADCへの入力で対処できます。(対象製品: LOG101, LOG102, LOG104, LOG112)

極度に微小な電流は、コンデンサーの積分電流で正確に測定できます。(対象製品: IVC102)

入手可能な製品の範囲に関する詳細な情報は、上記に指定した製品名あるいは、transimpedanceおよびlogarithmicをキーワードにして、www.ti.comで検索願います。

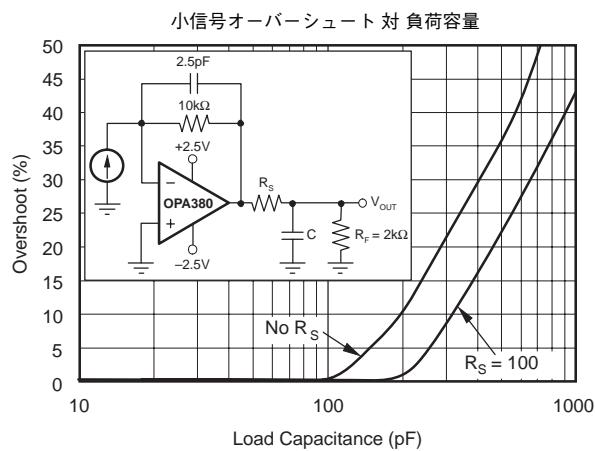

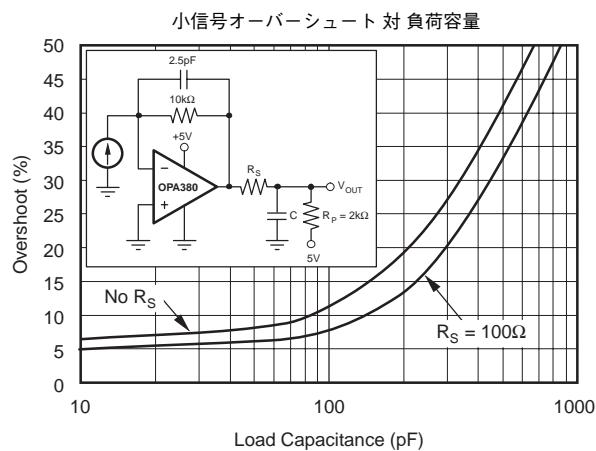

### 容量性負荷および安定性

OPA380シリーズのオペアンプは、最大500pFまでの純容量性負荷をドライブできます。ゲインを高めると、アンプの大容量性負荷へのドライブ能力が強化されます。(代表的特性の「小信号オーバーシュート対負荷容量」の曲線を参照願います。)

ユニティ・ゲイン(ボルテージ・フォロワ)構成での容量性負荷ドライブを改善する1つの方法は、負荷と直列に10Ωから20Ωの抵抗を挿入することです。これはDC精度を保ちつつ、大容量性負荷によるリングギングを低減します。

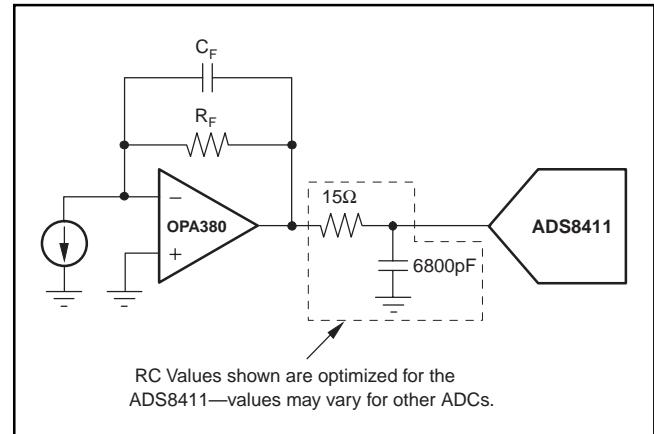

### 高速16ビットADC(アナログ-デジタル変換器)のドライブ

OPA380シリーズは、ADS8411のような高速16ビットADCのドライブに最適です。OPA380オペアンプはADCの入力容量をバッファし、信号ゲインを与える一方で電荷注入を行います。図12はシングルエンドでADS8411(16ビット、2MSPS、ADC)をインターフェイスするOPA380を示します。詳細な情報については、ADS8411のデータシートを参照願います。

図12. 16ビットADCのドライブ

図13. OPA380の反転アンプ回路

4073329/D 12/03

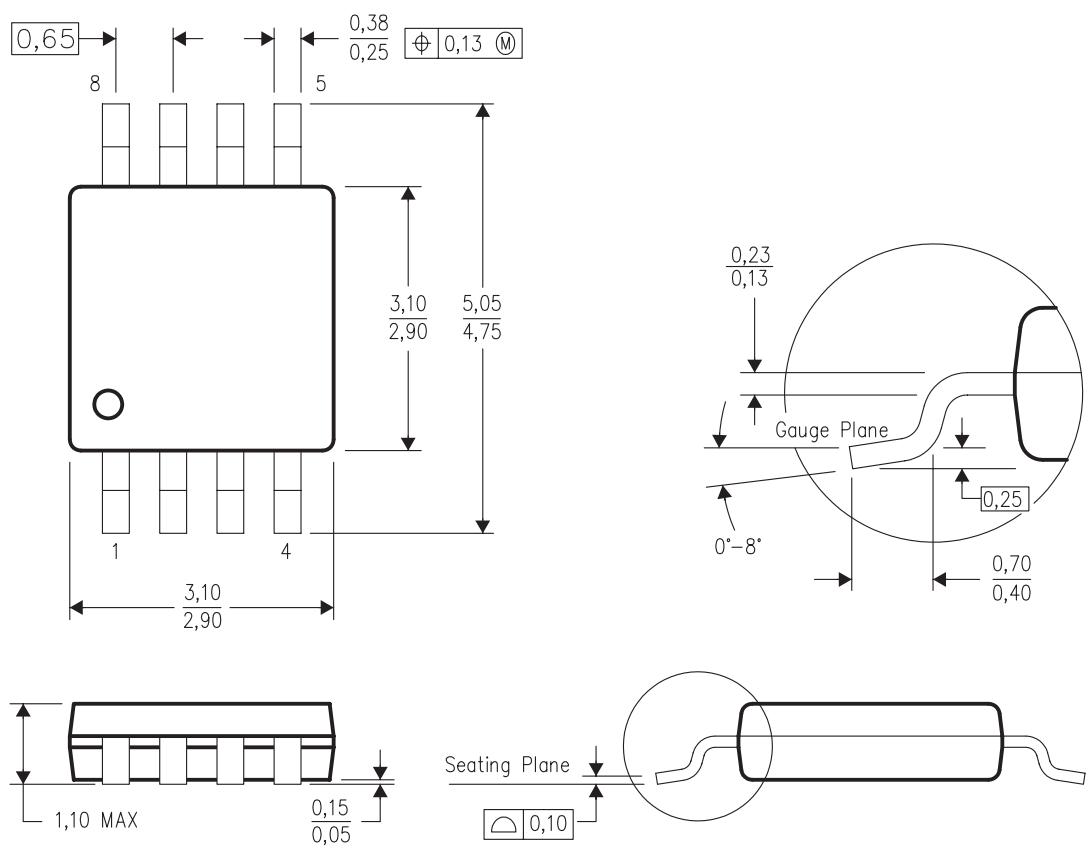

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187 variation AA.

# 外觀

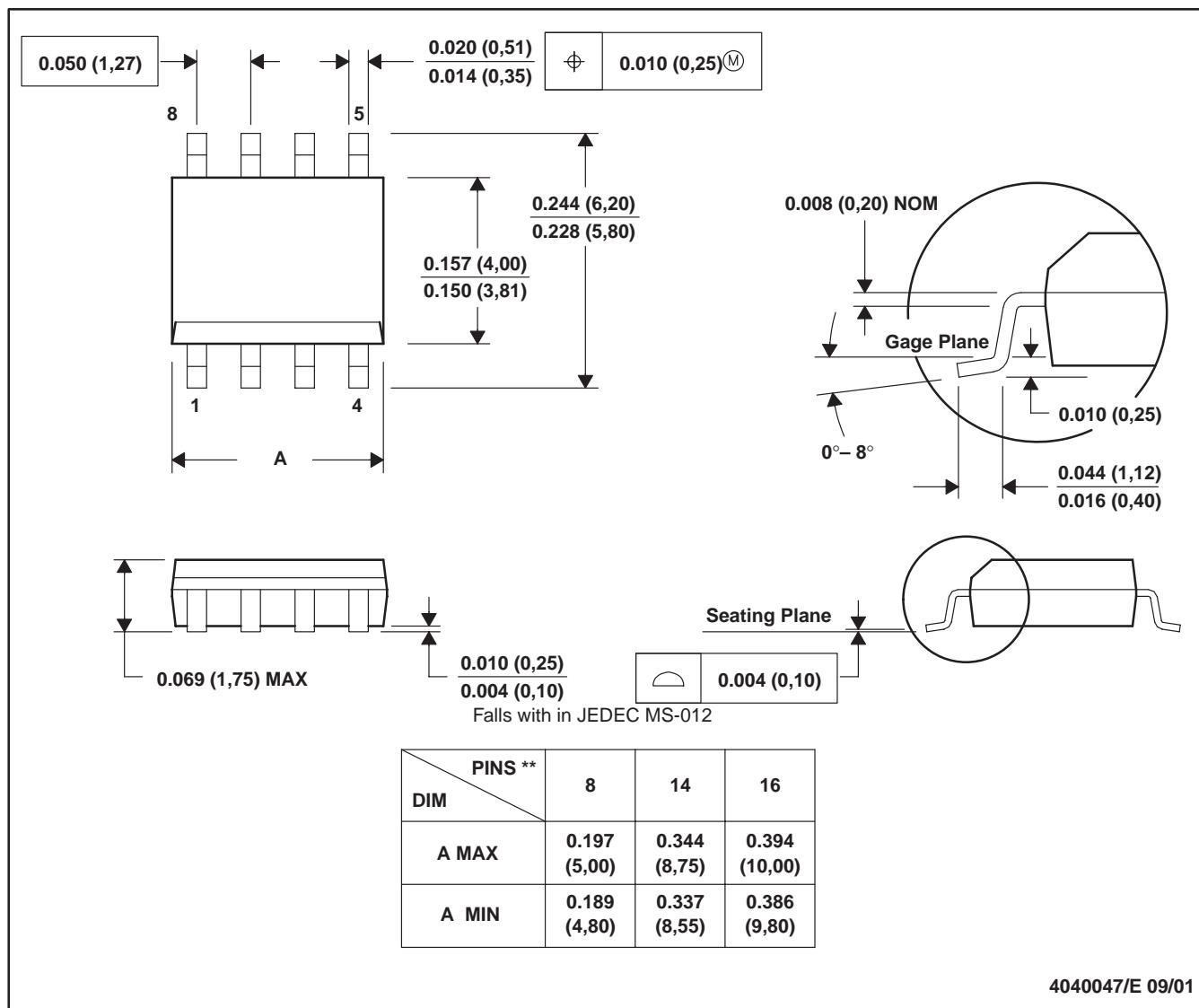

D (R-PDSO-G\*\*)

8 PINS SHOWN

PLASTIC SMALL-OUTLINE PACKAGE

4040047/E 09/01

- NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| OPA2380AIDGKR         | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug                    | Level-2-260C-1 YEAR               | -40 to 125   | BBX                 |

| OPA2380AIDGKR.B       | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | BBX                 |

| OPA2380AIDGKT         | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI   Nipdaug                    | Level-2-260C-1 YEAR               | -40 to 125   | BBX                 |

| OPA2380AIDGKT.B       | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | BBX                 |

| OPA2380AIDGKTG4       | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | BBX                 |

| OPA380AID             | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

| OPA380AID.B           | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

| OPA380AIDG4           | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

| OPA380AIDGKR          | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Sn   Nipdaug               | Level-2-260C-1 YEAR               | -40 to 125   | AUN                 |

| OPA380AIDGKR.B        | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | AUN                 |

| OPA380AIDGKT          | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI   Sn   Nipdaug               | Level-2-260C-1 YEAR               | -40 to 125   | AUN                 |

| OPA380AIDGKT.B        | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | AUN                 |

| OPA380AIDGKTG4        | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI                              | Level-2-260C-1 YEAR               | -40 to 125   | AUN                 |

| OPA380AIDR            | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

| OPA380AIDR.B          | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

| OPA380AIDRG4          | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | OPA<br>380A         |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

**(4) Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**(5) MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

**(6) Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

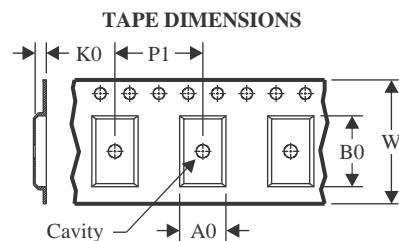

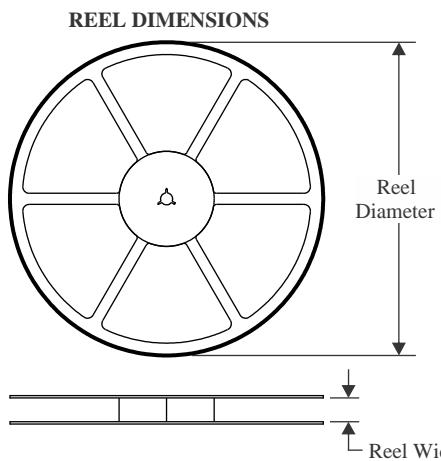

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

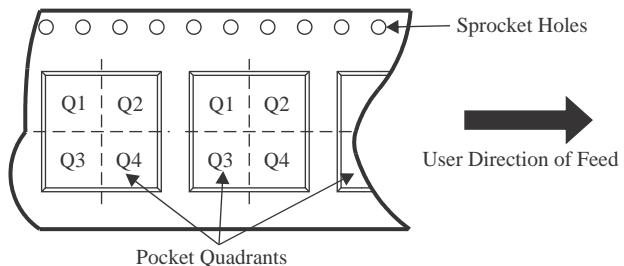

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| OPA2380AIDGKR | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2380AIDGKT | VSSOP        | DGK             | 8    | 250  | 180.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA380AIDR    | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

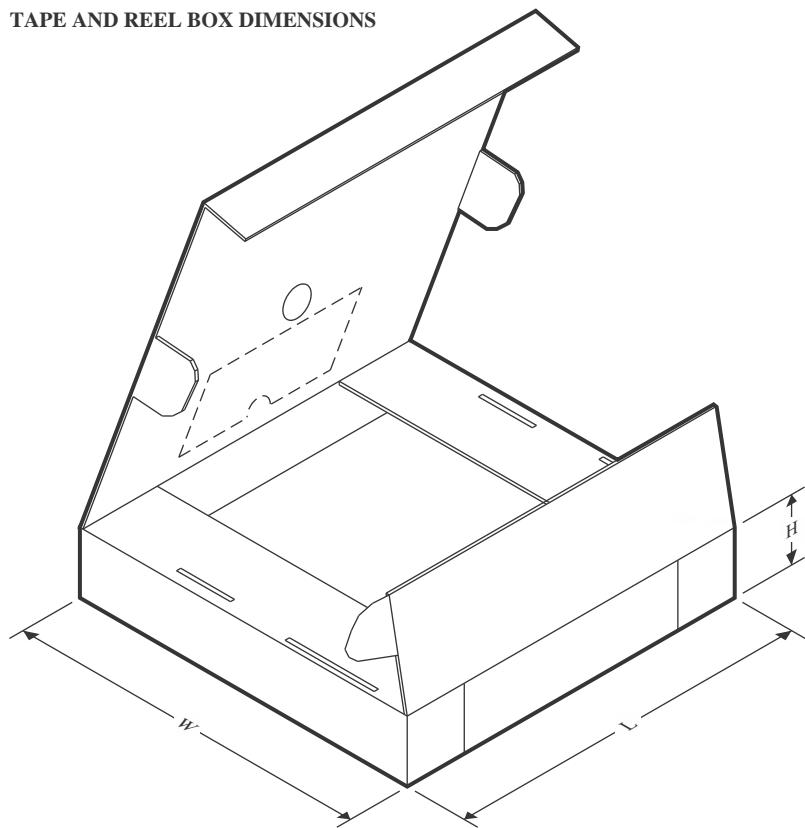

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA2380AIDGKR | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA2380AIDGKT | VSSOP        | DGK             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| OPA380AIDR    | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

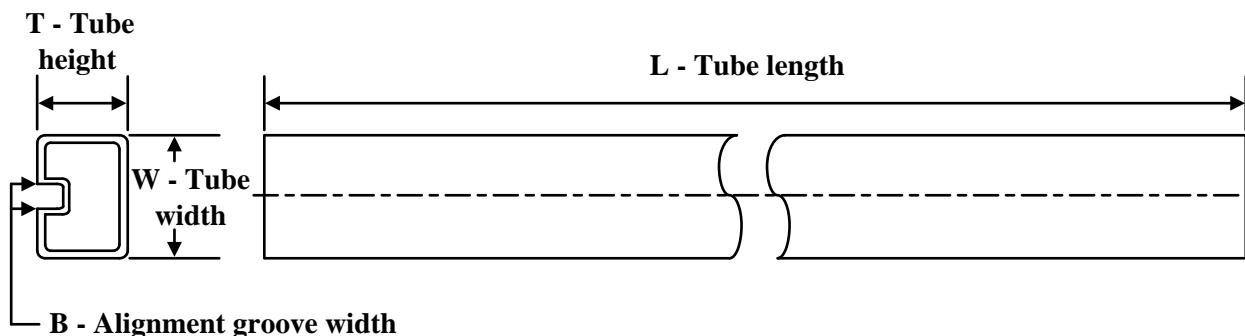

**TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (μm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| OPA380AID   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA380AID.B | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA380AIDG4 | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月