# PGA302 0V~5V レシオメトリック出力搭載のセンサ シグナルコンディショナー

## 1 特長

- アナログ機能:

- デュアルチャネルのアナログ フロントエンド

- オンチップ温度センサ

- 最大 200V/V のゲインをプログラム可能

- 16ビットシグマ デルタ A/D コンバータ

- デジタル機能:

- 3次線形補正アルゴリズム

- デバイス構成、較正データ、ユーザー データ用の EEPROM メモリ

- I<sup>2</sup>C インターフェイス

- 電力線経由の単線式インターフェイス

- 一般的な機能:

- AFE センサ入力、電源、および出力バッファの診断

- メモリの組み込みセルフ テスト (MBIST)

- ウオッチドッグ

- パワー マネージメント制御

## 2 アプリケーション

- 圧力トランスマッタ

- 温度トランスマッタ

- 流量トランスマッタ

- レベルトランスマッタ

## 3 概要

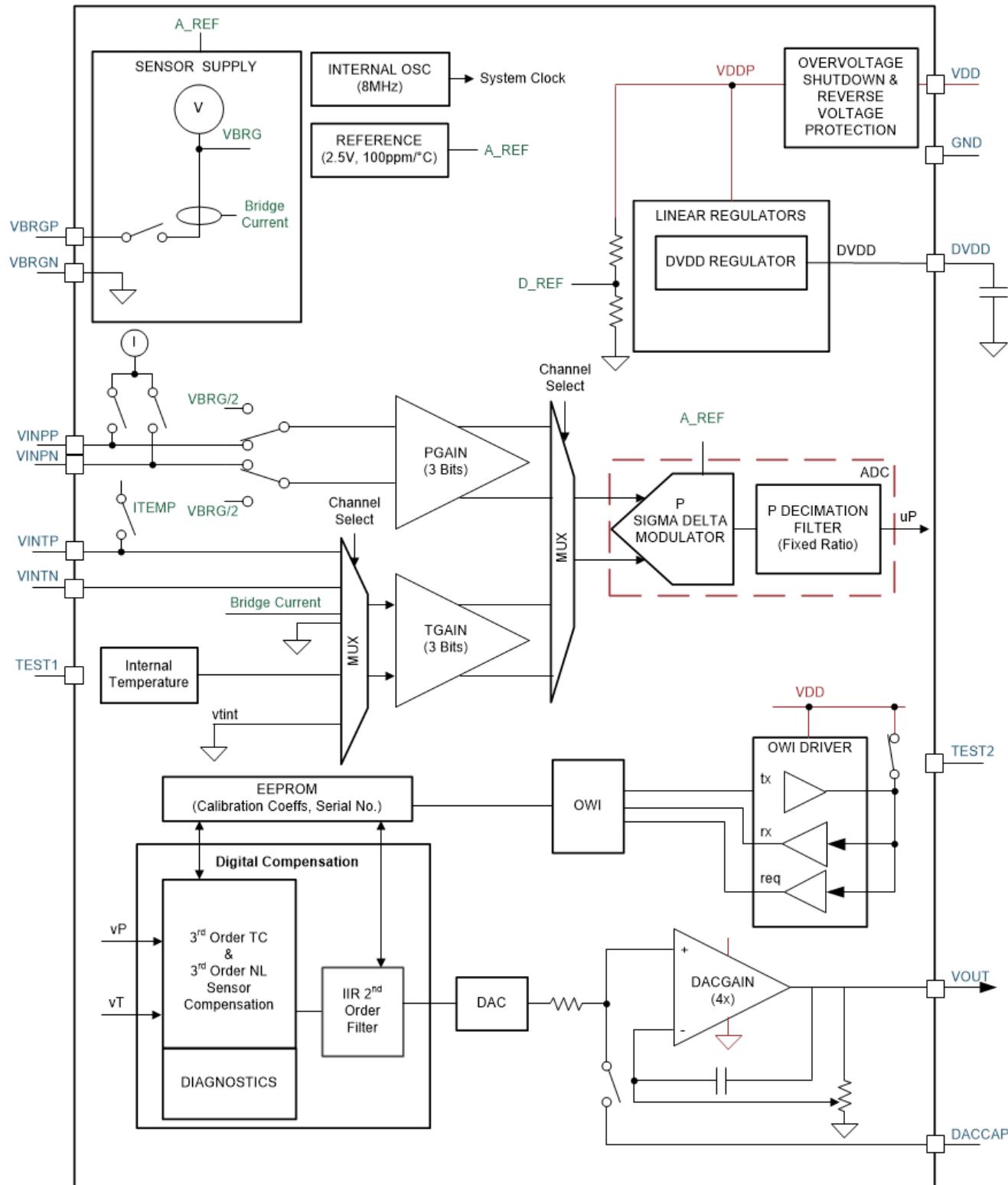

PGA302 は低ドリフト係数、低ノイズのプログラム可能な信号コンディショナー デバイスで、圧力、温度、およびレベル センシング アプリケーションなど各種の抵抗性ブリッジ センシング アプリケーション用に設計されています。また、PGA302 は流量測定アプリケーション、張力ゲージ負荷セルを使用する重量計および圧力センシング アプリケーション、その他一般的な抵抗性ブリッジ信号コンディショニング アプリケーションにも対応しています。

PGA302 はブリッジ励起電圧が 2.5V で、電流出力ソースは出力電流を最大 1mA にプログラム可能です。デバイスの入力には 2 つの同一なアナログ フロントエンド(AFE) チャネルが搭載されており、16 ビットのシグマ-デルタ ADC に続いています。AFE の各チャネルには、専用のプログラム可能なゲイン アンプがあり、最大ゲインは 200V/V です。

さらに、チャネルの 1 つにはセンサ オフセット補償機能が組み込まれており、他のチャネルには内部温度センサが組み込まれています。

デバイスの出力には 1.25V、14 ビットの DAC があり、レシオメトリック電圧の電源出力バッファに続いており、このゲインは 4V/V で、0~5V のレシオメトリック電圧のシステム出力が可能になります。PGA302 デバイスには、3 次の温度ドリフト係数(TC)および非線形性(NL)デジタル補償アルゴリズムが実装されており、アナログ出力信号の較正を行います。線形化アルゴリズムに必要なすべてのパラメータ、および他のユーザー データは、内蔵の EEPROM メモリに保存されます。

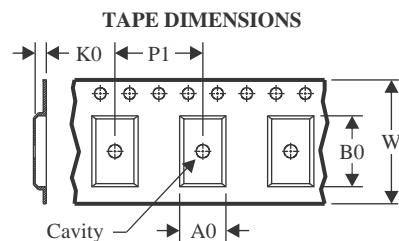

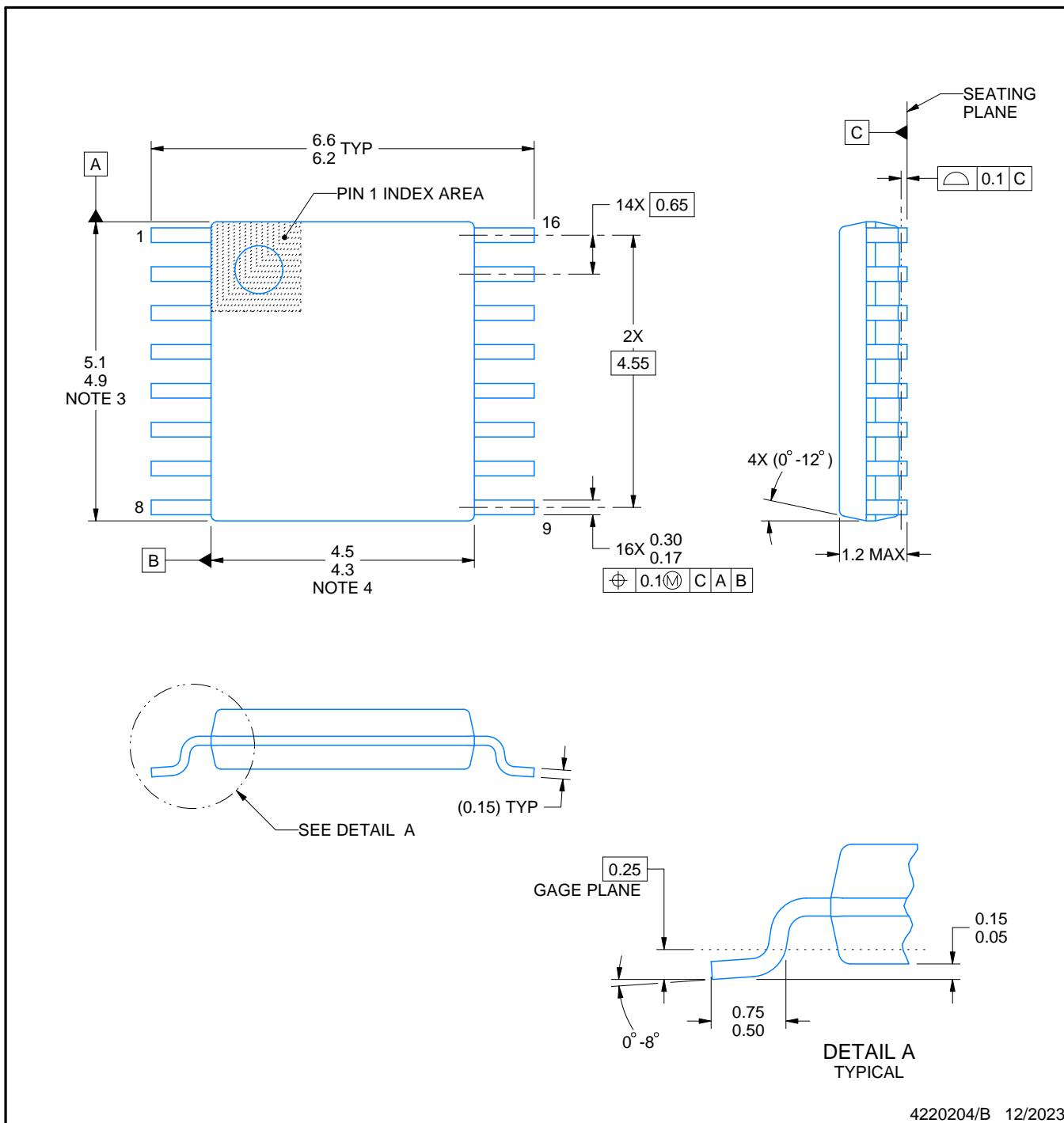

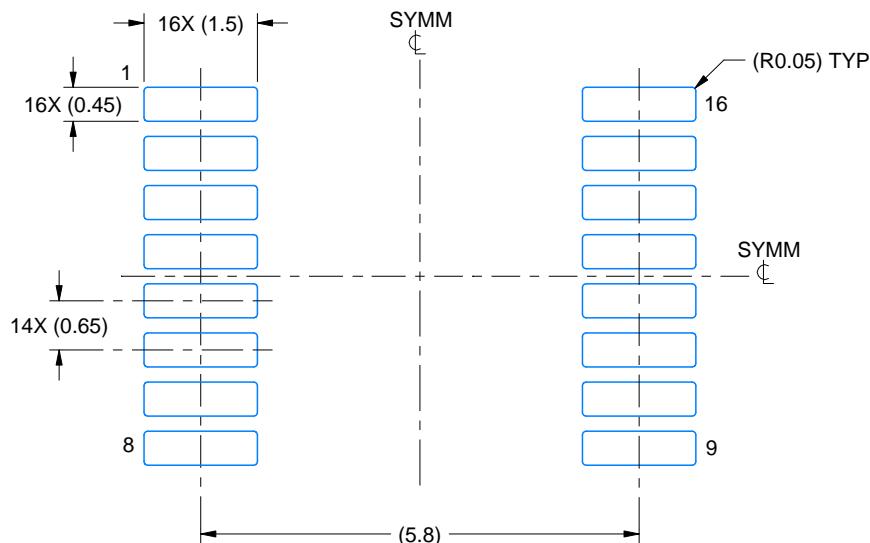

### パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------|----------------------|--------------------------|

| PGA302 | PW (TSSOP, 16)       | 5mm × 6.4mm              |

(1) 詳細については、[メカニカル、パッケージ、および注文情報](#)をご覧ください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLDS216](#)

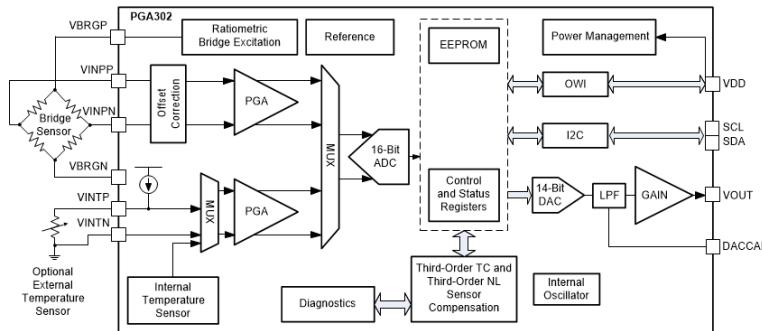

PGA302 の概略ブロック図

システム接続性のため、PGA302 デバイスには I<sup>2</sup>C インターフェイスと、単線式インターフェイス (OWI) が組み込まれており、最終的なシステム較正プロセスにおいて、電源ラインによる通信と構成をサポートします。励起出力ソース、AFE への入力、およびデバイス内の電源に、診断機能が実装されています。センサのオープンや短絡などのシステム診断機能もサポートされています。

PGA302 は、ピエゾ抵抗素子、セラミック膜、張力ゲージ、スチール薄膜など、各種のセンシング素子タイプに対応しています。このデバイスは、加速度計、湿度センサの信号コンディショニング アプリケーションに加えて、いくつかの電流センシング、シャント ベースのアプリケーションにも使用できます。

## 目次

|                                   |          |                               |           |

|-----------------------------------|----------|-------------------------------|-----------|

| <b>1 特長</b>                       | <b>1</b> | 5.19 不揮発性メモリ                  | <b>17</b> |

| <b>2 アプリケーション</b>                 | <b>1</b> | 5.20 診断- PGA30x               | <b>17</b> |

| <b>3 概要</b>                       | <b>1</b> | 5.21 代表的特性                    | <b>18</b> |

| <b>4 ピン構成および機能</b>                | <b>4</b> | <b>6 詳細説明</b>                 | <b>19</b> |

| <b>5 仕様</b>                       | <b>5</b> | 6.1 概要                        | <b>19</b> |

| 5.1 絶対最大定格                        | 5        | 6.2 機能ブロック図                   | <b>20</b> |

| 5.2 ESD 定格                        | 5        | 6.3 機能説明                      | <b>21</b> |

| 5.3 推奨動作条件                        | 5        | 6.4 デバイスの機能モード                | <b>43</b> |

| 5.4 熱に関する情報                       | 6        | <b>7 レジスタ マップ</b>             | <b>44</b> |

| 5.5 過電圧および逆電圧保護                   | 6        | 7.1 プログラマーのモデル                | <b>44</b> |

| 5.6 リニアレギュレータ                     | 6        | <b>8 アプリケーションと実装</b>          | <b>70</b> |

| 5.7 内部リファレンス                      | 6        | 8.1 アプリケーション情報                | <b>70</b> |

| 5.8 内部発振器                         | 6        | 8.2 代表的なアプリケーション              | <b>71</b> |

| 5.9 ブリッジセンサ電源                     | 7        | 8.3 電源に関する推奨事項                | <b>73</b> |

| 5.10 温度センサ電源                      | 7        | 8.4 レイアウト                     | <b>73</b> |

| 5.11 ブリッジオフセットキャンセル               | 9        | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>75</b> |

| 5.12 P ゲインおよび T ゲイン入力アンプ(チョッパ安定化) | 9        | 9.1 ドキュメントの更新通知を受け取る方法        | <b>75</b> |

| 5.13 A/D コンバータ                    | 10       | 9.2 サポート・リソース                 | <b>75</b> |

| 5.14 内部温度センサ                      | 12       | 9.3 商標                        | <b>75</b> |

| 5.15 ブリッジ電流測定                     | 12       | 9.4 静電気放電に関する注意事項             | <b>75</b> |

| 5.16 1 ワンワイヤインターフェイス              | 13       | 9.5 用語集                       | <b>75</b> |

| 5.17 DAC 出力                       | 13       | <b>10 改訂履歴</b>                | <b>75</b> |

| 5.18 DAC 出力の DAC ゲイン              | 13       | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>75</b> |

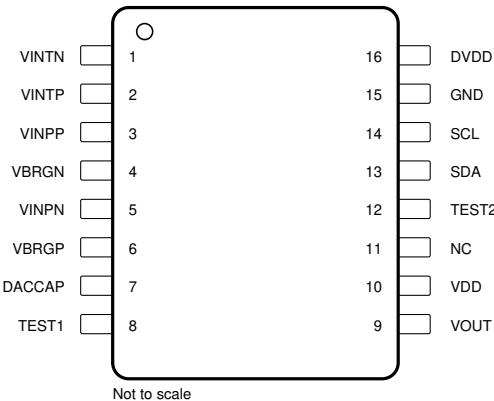

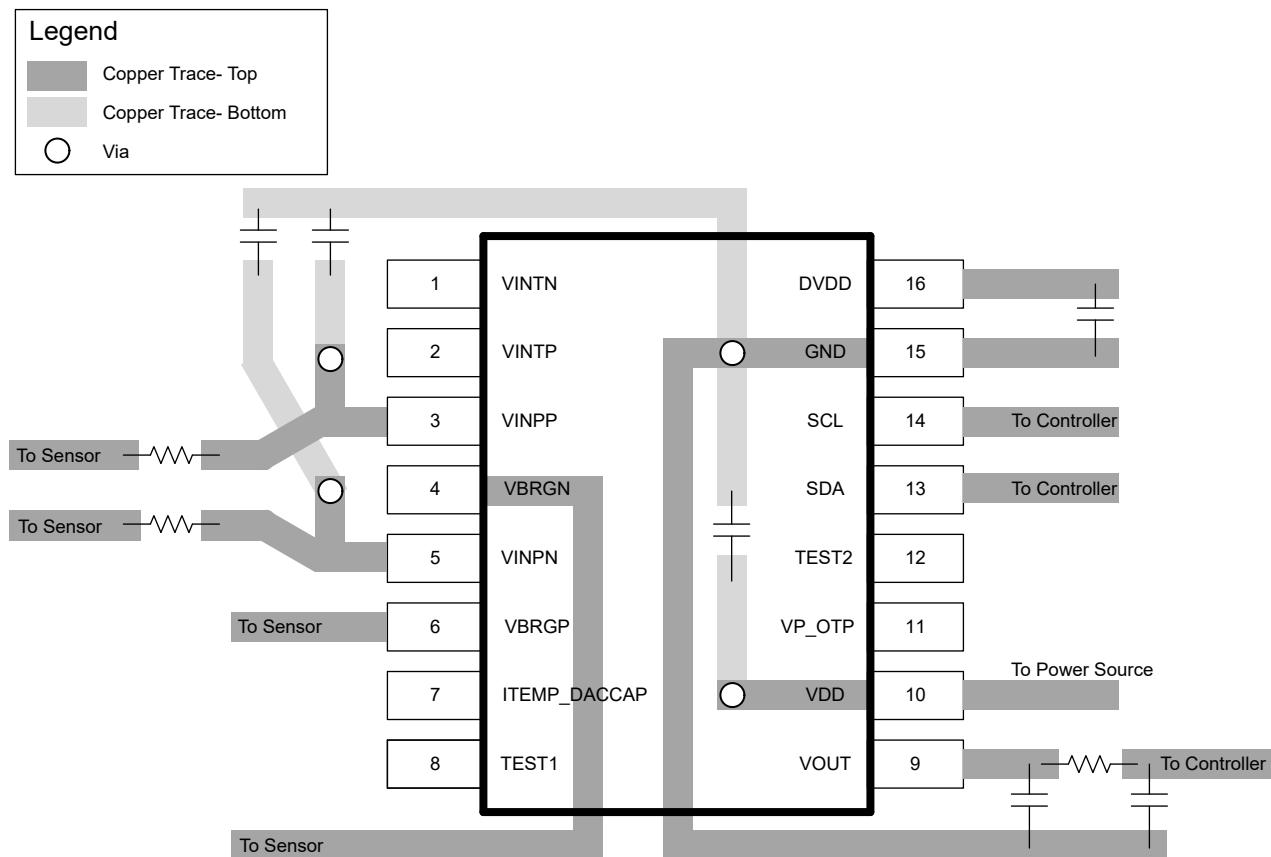

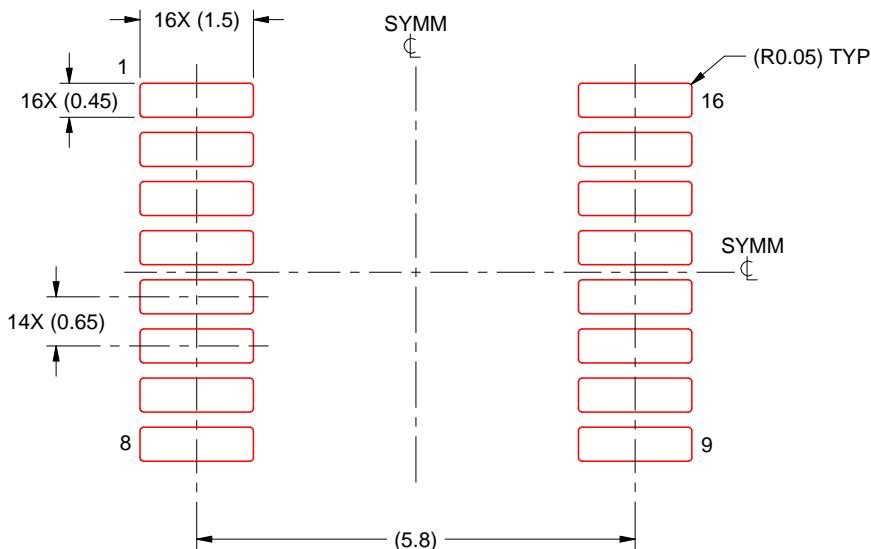

## 4 ピン構成および機能

図 4-1. PGA302 PW パッケージ、16 ピン TSSOP (上面図)

表 4-1. ピンの機能

| ピン |        | タイプ | 説明                                  |

|----|--------|-----|-------------------------------------|

| 番号 | 名称     |     |                                     |

| 1  | VINTN  | I   | 外部温度センサ - 負入力                       |

| 2  | VINTP  | I   | 外部温度センサ-正入力                         |

| 3  | VINPP  | I   | 抵抗性センサ-正入力                          |

| 4  | VBRGN  | O   | ブリッジドライブ負                           |

| 5  | VINPN  | I   | 抵抗性センサ-負入力                          |

| 6  | VBRGP  | O   | ブリッジドライブ正                           |

| 7  | DACCAP | I/O | DAC LPF コンデンサ                       |

| 8  | TEST1  | O   | テストピン 1                             |

| 9  | VOUT   | O   | アナログ電圧出力(DAC ゲインアンプから)              |

| 10 | VDD    | P   | 電源電圧                                |

| 11 | NC     | -   | 無接続                                 |

| 12 | TEST2  | O   | テストピン 2                             |

| 13 | SDA    | I/O | I <sup>2</sup> C インターフェイスシリアルデータピン  |

| 14 | SCL    | I   | I <sup>2</sup> C インターフェイスシリアルクロックピン |

| 15 | GND    | P   | グラウンド                               |

| 16 | DVDD   | P   | デジタルロジックレギュレータコンデンサ                 |

## 5 仕様

### 5.1 絶対最大定格

(1) 参照

|                              |                  | 最小値  | 最大値 | 単位 |

|------------------------------|------------------|------|-----|----|

| VDD                          | VDD 電圧           | -20  | 20  | V  |

| VOUT                         | VOUT 電圧          | -20  | 20  | V  |

|                              | VP_OTP の電圧       | -0.3 | 8   | V  |

|                              | センサ入力および駆動ピンでの電圧 | -0.3 | 5   | V  |

|                              | 任意の I/O ピンの電圧    | -0.3 | 2   | V  |

| I <sub>DD</sub> 、VOUT<br>短絡時 | 電源電流             |      | 25  | mA |

| T <sub>Jmax</sub>            | 最大接合部温度          |      | 155 | °C |

| T <sub>stg</sub>             | 保存温度             | -40  | 150 | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス評価であり、データシートの「推奨動作条件」に示された値と等しい、またはそれを超える条件で本製品が正しく動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置ぐと、本製品の信頼性に影響を与えることがあります。

### 5.2 ESD 定格

|                    |      |                                                         | 値                     | 単位    |

|--------------------|------|---------------------------------------------------------|-----------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | 9 と 10 を除くすべてのピン      | ±2000 |

|                    |      |                                                         | ピン 9 および 10           | ±4000 |

|                    |      | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | 1, 8, 9, 16 を除くすべてのピン | ±500  |

|                    |      |                                                         | ピン 1, 8, 9, 16        | ±750  |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |                            |                                                    | 最小値 | 公称値 | 最大値                | 単位   |

|-----------------|----------------------------|----------------------------------------------------|-----|-----|--------------------|------|

| V <sub>DD</sub> | 電源電圧                       |                                                    | 4.5 | 5   | 5.5 <sup>(1)</sup> | V    |

|                 | スルーレート                     | V <sub>DD</sub> = 0~5 V、VDD 上のデカップリングコンデンサ = 10 nF |     |     | 5                  | V/ns |

| I <sub>DD</sub> | 電流電源-通常動作                  | VBRG 上に無負荷、DAC 上に無負荷                               |     | 6.5 | 10                 | mA   |

| T <sub>A</sub>  | 動作時の周囲温度                   |                                                    | -40 |     | 150                | °C   |

|                 | プログラミング温度                  | EEPROM                                             | -40 |     | 140                | °C   |

|                 | スタートアップ時間(アナログとデジタルの両方を含む) | VDD ランプ レート ≤ 1V/μs                                |     |     | 250                | μs   |

|                 | VDD ピン上のコンデンサ              | 直列抵抗は含まない                                          |     |     | 100                | nF   |

- (1) VDD>OVP の場合、デバイスのアナログ回路はオフになります。ただし、デバイス内部のデジタルロジックは引き続き動作します。本デバイスは、VDD < VDD\_ABSMAX に損傷なしで耐えられます

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | PGA302     | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | PW (TSSOP) |      |

|                       |                   | 16 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 96.8       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 27.3       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 43.3       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 1.2        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 42.7       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、[IC パッケージの熱評価基準](#)アプリケーション レポートをご覧ください。

## 5.5 過電圧および逆電圧保護

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ           | テスト条件         | 最小値  | 標準値 | 最大値 | 単位 |

|-----------------|---------------|------|-----|-----|----|

| 逆電圧             |               | -20  |     |     | V  |

| 過電圧アノログ シャットダウン | -40°C ~ 150°C | 5.65 |     |     | V  |

## 5.6 リニア レギュレータ

| パラメータ                 | テスト条件                         | 最小値                 | 標準値  | 最大値 | 単位   |

|-----------------------|-------------------------------|---------------------|------|-----|------|

| V <sub>DVDD</sub>     | DVDD 電圧 - 動作中                 | DVDD ピンのコンデンサ=100nF | 1.75 | 1.8 | 1.86 |

| V <sub>DVDD_POR</sub> | DVDD 電圧 - デジタル POR            |                     | 1.4  | 1.6 | 1.75 |

|                       | DVDD 電圧 - デジタル POR ヒス<br>テリシス |                     |      | 0.1 | V    |

| V <sub>VDD_POR</sub>  | VDD 電圧 - デジタル POR             |                     | 4    |     | V    |

|                       | VDD 電圧 - デジタル POR ヒス<br>テリシス  |                     |      | 0.1 | V    |

## 5.7 内部リファレンス

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                   | テスト条件                                                                                                                                                                            | 最小値   | 標準値 | 最大値  | 単位     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|--------|

| リファレンス電圧(リファレンスバッファを含む) |                                                                                                                                                                                  | 2.5   |     |      | V      |

| リファレンスの初期誤差             |                                                                                                                                                                                  | -0.5% |     | 0.5% |        |

| 基準電圧 TC                 |                                                                                                                                                                                  | -250  |     | 250  | ppm/°C |

| PSRR                    | VDD のリップル条件:<br>• VDD DC レベル= 5V<br>• VDD リップル振幅= 100mV<br>• VDD リップル周波数範囲: 30Hz ~ 50KHz<br>の式を使用して PSRR を計算します。<br>$20\log_{10}(\text{基準電圧}/\text{電圧の振幅} / \text{VDD リップルの振幅})$ |       | -35 |      | dB     |

## 5.8 内部発振器

| パラメータ     | テスト条件                 | 最小値 | 標準値 | 最大値 | 単位 |

|-----------|-----------------------|-----|-----|-----|----|

| 内部発振器     |                       |     |     |     |    |

| 内部発振器の周波数 | T <sub>A</sub> = 25°C | 8   |     | MHz |    |

| パラメータ         | テスト条件           | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|-----------------|-----|-----|-----|----|

| 内部発振器の周波数変動公差 | 動作温度範囲全体で求められます | -3% |     | 3%  |    |

## 5.9 ブリッジセンサ電源

| パラメータ                      | テスト条件                                | 最小値                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 標準値  | 最大値  | 単位                    |

|----------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------|

| <b>抵抗性ブリッジセンサの VBRG 電源</b> |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      |                       |

| $V_{BRGP} - V_{BRGN}$      | ブリッジ電源電圧                             | $I_{LOAD} = 0 \sim 8.5\text{mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.4  | 2.5  | 2.6                   |

| $P_{ミスマッチ}$                | ブリッジ電源電圧、温度変動、および ADC 基準温度の変動間のミスマッチ | ドリフトミスマッチを計算する手順:<br>1. $VDD = 5\text{V}$<br>2. $5\text{mV}$ 出力の $5\text{-K}\Omega$ ゼロ TC ブリッジをデバイスに接続します<br>3. $P GAIN = 200\text{V/V}$ に設定します<br>4. 温度設定 = $25^\circ\text{C}$ 、<br>ADC コードを測定<br>512 サンプルを平均化<br>5. 温度設定 = $-40^\circ\text{C}$ 、<br>ADC コードを測定<br>512 サンプルを平均化<br>6. 温度設定 = $125^\circ\text{C}$ 、<br>ADC コードを測定<br>512 サンプルを平均化<br>7. 次の式を使用してドリフトを計算します:(温度での ADC コード - $25^\circ\text{C}$ での ADC コード) / (( $25^\circ\text{C}$ での ADC コード) × (温度 - 25)) | -250 | +250 | ppm/ $^\circ\text{C}$ |

| $I_{BRG}$                  | ブリッジへの電流供給                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.5  |      | mA                    |

|                            | ブリッジ短絡電流制限                           | $T_A = 25^\circ\text{C}; V_{VDD} = 5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                              | 9    | 25   | mA                    |

| $C_{BRG}$                  | 容量性負荷                                | $R_{BRG} = 5\text{k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 2    | nF                    |

## 5.10 温度センサ電源

| パラメータ                                 | テスト条件      | 最小値           | 標準値 | 最大値  | 単位            |

|---------------------------------------|------------|---------------|-----|------|---------------|

| <b>温度センサー用 ITEMP 電源<sup>(1)</sup></b> |            |               |     |      |               |

| $I_{TEMP}$                            | 温度センサ用電流電源 | 制御ビット = 0b000 | 45  | 50   | 55            |

|                                       |            | 制御ビット = 0b001 | 90  | 100  | 110           |

|                                       |            | 制御ビット = 0b010 | 180 | 200  | 220           |

|                                       |            | 制御ビット = 0b011 | 850 | 1000 | 1150          |

|                                       |            | 制御ビット = 0b1xx |     | オフ   | $\mu\text{A}$ |

## 5.10 溫度センサ電源 (続き)

| パラメータ          | テスト条件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 最小値           | 標準値  | 最大値  | 単位                          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|-----------------------------|

| $T_{MISMATCH}$ | <p>ドリフトミスマッチを計算する手順:</p> <ol style="list-style-type: none"> <li>1. <math>VDD = 5\text{ V}</math></li> <li>2. <math>1-\text{k}\Omega</math>、ゼロ温度係数抵抗をデバイスの温度入力ピンに接続します</li> <li>3. <math>T GAIN = 1.33\text{V/V}</math> に設定します</li> <li>4. <math>ITEMP = 100\ \mu\text{A}</math> に設定します</li> <li>5. 温度= <math>25^\circ\text{C}</math> に設定、平均 512 サンプルで ADC コードを測定します</li> <li>6. 温度= <math>-40^\circ\text{C}</math> に設定、平均 512 サンプルで ADC コードを測定します</li> <li>7. 温度= <math>125^\circ\text{C}</math> に設定、平均 512 サンプルで ADC コードを測定します</li> <li>8. 次の式を使用してドリフトを計算します:<br/> <math display="block">(\text{温度での ADC コード} - 25^\circ\text{C} \text{での ADC コード}) / ((25^\circ\text{C} \text{での ADC コード}) \times (\text{温度} - 25))</math> </li> </ol> |               | -250 | +250 | $\text{ppm}/^\circ\text{C}$ |

| $Z_{OUT}$      | 出力インピーダンス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 設計により保証されています | 15   |      | $\text{M}\Omega$            |

| $C_{TEMP}$     | 容量性負荷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |      | 100  | $\text{nF}$                 |

(1) 8-ピンのパッケージ オプションは該当しません

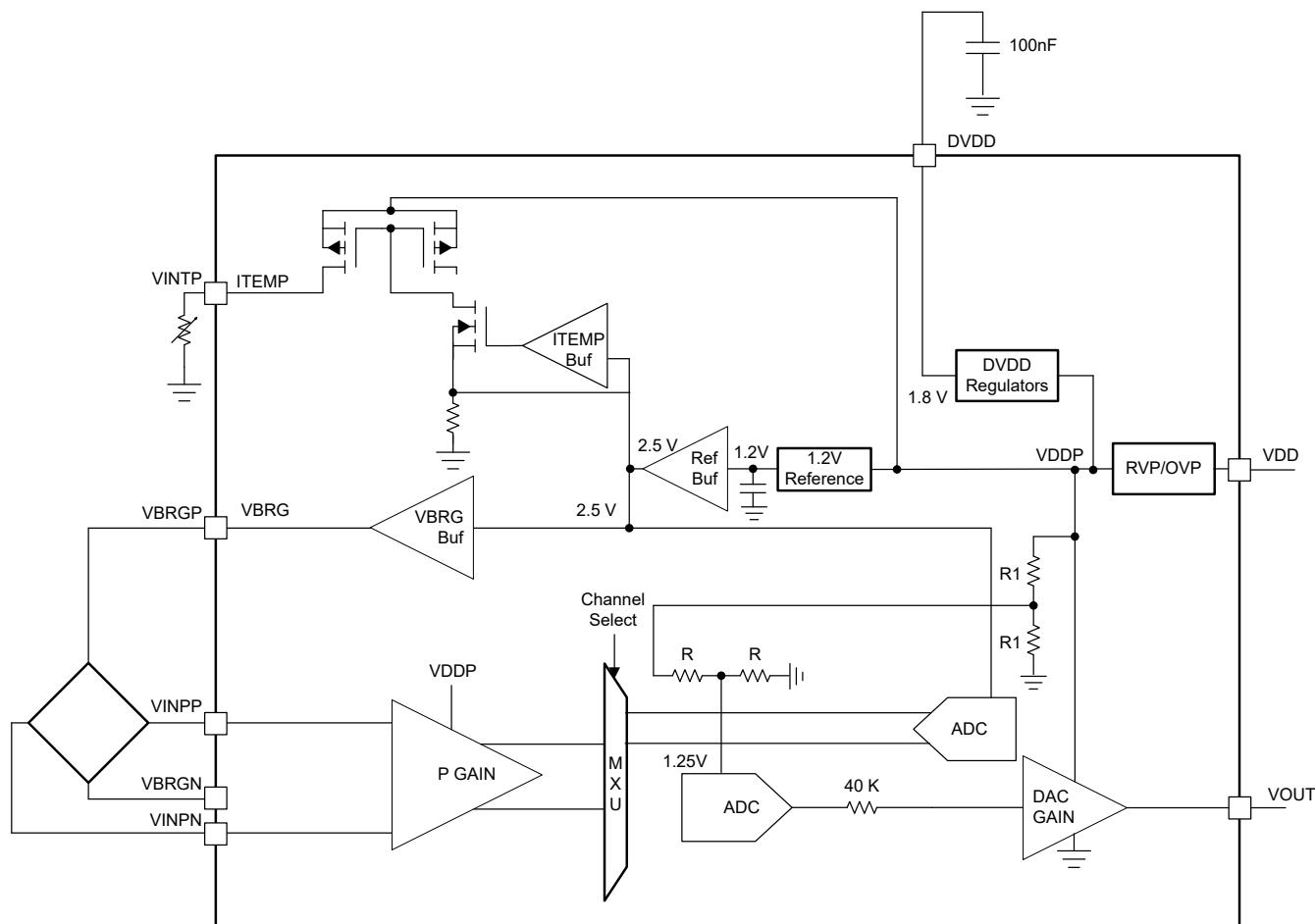

図 5-1. ブリッジ電源と ADC リファレンスはレシオメトリックです

### 5.11 ブリッジオフセットキャンセル

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ               | テスト条件 | 最小値    | 標準値    | 最大値 | 単位 |

|---------------------|-------|--------|--------|-----|----|

| オフセットキャンセル範囲        |       | -54.75 | +54.75 |     | mV |

| オフセットキャンセル公差        |       | -10%   | +10%   |     |    |

| オフセットキャンセル分解能(4ビット) |       | 10     |        |     | mV |

### 5.12 P ゲインおよび T ゲイン入力アンプ (チョッパ安定化)

| パラメータ         | テスト条件    | 最小値  | 標準値  | 最大値  | 単位  |

|---------------|----------|------|------|------|-----|

| ゲインステップ(3ビット) | DC で 000 | 1.31 | 1.33 | 1.35 | V/V |

|               | 001      | 1.97 | 2    | 2.03 |     |

|               | 010      | 3.92 | 4    | 4.08 |     |

|               | 011      | 9.6  | 10   | 10.4 |     |

|               | 100      | 19   | 20   | 21   |     |

|               | 101      | 38   | 40   | 42   |     |

|               | 110      | 96   | 100  | 104  |     |

|               | 111      | 185  | 200  | 215  |     |

| パラメータ         | テスト条件                                  | 最小値                                                   | 標準値  | 最大値 | 単位     |

|---------------|----------------------------------------|-------------------------------------------------------|------|-----|--------|

| 帯域幅           | PGAIN = 1.33                           | 680                                                   |      |     | kHz    |

|               | PGAIN = 2                              | 470                                                   |      |     |        |

|               | PGAIN = 4                              | 250                                                   |      |     |        |

|               | PGAIN = 10                             | 104                                                   |      |     |        |

|               | PGAIN = 20                             | 80                                                    |      |     |        |

|               | PGAIN = 40                             | 72                                                    |      |     |        |

|               | PGAIN = 100                            | 30                                                    |      |     |        |

|               | PGAIN = 200                            | 15                                                    |      |     |        |

| 入力オフセット電圧     |                                        | 14                                                    |      |     | µV     |

| 温度によるゲインのドリフト | ゲイン = 200 V/V                          | -250                                                  | +250 |     | ppm/°C |

| 入力バイアス電流      |                                        | 5                                                     |      |     | nA     |

| 同相電圧範囲        |                                        | 選択された<br>ゲイン、ブリ<br>ッジ電源、<br>センサ スペ<br>ンにより異<br>なる (1) |      |     | V      |

| 同相除去比         | F <sub>CM</sub> = 50 Hz; 設計により保証されています | 110                                                   |      |     | dB     |

| 入力インピーダンス     | 設計により保証されています                          | 10                                                    |      |     | MΩ     |

(1) P ゲイン入力および出力のコモンモード:

- a. ゲイン入力における正/負ピンのシングルエンド電圧は+0.02V～+4.38V とする必要があります

## 5.13 A/D コンバータ

| パラメータ                               | テスト条件            | 最小値                 | 標準値 | 最大値 | 単位  |

|-------------------------------------|------------------|---------------------|-----|-----|-----|

| シグマ デルタ 変調器の周波数                     |                  | 4                   |     |     | MHz |

| ADC 電圧 入力範囲                         |                  | -2.5                | 2.5 |     | V   |

| ビット数                                |                  | 16                  |     |     | ビット |

| -2.5-V 差分入力についての、<br>ADC の 2 の補数コード | 2 の補数            | 8000 <sub>hex</sub> |     |     | LSB |

| 0-V 差分入力についての、<br>ADC の 2 の補数コード    |                  | 0000 <sub>hex</sub> |     |     | LSB |

| 2.5-V 差分入力についての、<br>ADC の 2 の補数コード  |                  | 7FFF <sub>hex</sub> |     |     | LSB |

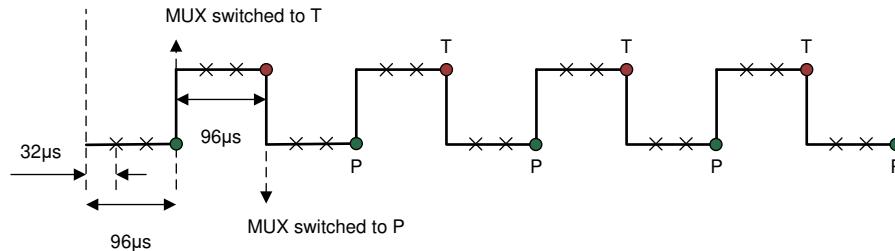

| 出力サンプル期間(レイテンシなし)                   | サンプル期間制御ビット=0b00 | 96                  |     |     | µs  |

| ADC マルチプレクサのスイッチング時間                |                  | 1                   |     |     | µs  |

## 5.13 A/D コンバータ (続き)

| パラメータ                                | テスト条件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 最小値 | 標準値  | 最大値 | 単位  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----|

| 有効ビット数 (ENOB)                        | <p>ENOB を計算する手順:</p> <ol style="list-style-type: none"> <li>1. VDD = 5 V</li> <li>2. 温度 = -40°C、25°C、125°C、150°C</li> <li>3. 5k Ω、ゼロ TC ブリッジを、差動電圧がほぼゼロの圧力入力ピン デバイスに接続します</li> <li>4. P GAIN = 200V/V に設定</li> <li>5. ADC のサンプル期間を 96 μs に設定します</li> <li>6. 入力 MUX を圧力チャネルに設定します</li> <li>7. ADC 測定</li> <li>8. 次の式を使用して ENOB を計算します。<math>20\log_{10}(32768/2/\sqrt{2})/(ADC \text{ コード RMS})/6.02</math></li> </ol>                                                                                                                      |     | 11.4 |     | ビット |

| P チャネルと T チャネルの間のクロストークが存在する場合の ENOB | <p>クロストークが存在する場合の ENOB を計算する手順:</p> <ol style="list-style-type: none"> <li>1. VDD = 5 V</li> <li>2. 温度 = -40°C、25°C、125°C、150°C</li> <li>3. 5k Ω、ゼロ TC ブリッジを圧力入力ピン デバイスに接続します</li> <li>4. P GAIN = 200V/V に設定</li> <li>5. ADC のサンプル期間を 96 μs に設定します</li> <li>6. 温度入力ピンのデバイスに、1kHz、1.25-V 同相、100 Ω のソース インピーダンスで 1Vpp の正弦波を接続します</li> <li>7. T GAIN = 1.33V/V に設定します</li> <li>8. 入力 MUX を圧力チャネルに設定します</li> <li>9. ADC 測定</li> <li>10. 次の式を使用して ENOB を計算します。<math>20\log_{10}(32768/2/\sqrt{2})/(ADC \text{ コード RMS})/6.02</math></li> </ol> |     | 11.4 |     | ビット |

## 5.13 A/D コンバータ (続き)

| パラメータ | テスト条件                                                                                                                                                                                                                                               | 最小値 | 標準値  | 最大値 | 単位  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----|

| 直線性   | 直線性を計算する手順:<br>1. VDD = 5 V<br>2. 温度 = 25°C<br>3. 5k Ω、ゼロ TC ブリッジを 30% FS ~ 70% FS 入力電圧でデバイスの圧力入力ピンに接続します<br>4. ゲイン = 200V/V<br>5. ADC のサンプル期間を 96 μs に設定します<br>6. 入力 MUX を圧力チャネルに設定します<br>7. P ADC を測定します<br>8. エンドポイント FIT を使用して、最大偏差として直線性を計算します |     | ±0.8 |     | %FS |

## 5.14 内部温度センサ

| パラメータ                           | テスト条件      | 最小値  | 標準値 | 最大値 | 単位     |

|---------------------------------|------------|------|-----|-----|--------|

| 内部温度センサ範囲                       |            | -40  | 150 |     | °C     |

| (1)のゲイン                         | 16 ビット ADC | 20   |     |     | LSB/°C |

| オフセット                           |            | 5700 |     |     | LSB    |

| 典型的なゲインおよびオフセット値を用いた較正後の合計誤差(2) |            | ±6   |     |     | °C     |

(1)  $ADC = \text{ゲイン} \times \text{温度} + \text{オフセット}$

(2) TI ではセンサのキャリブレーションを行いません。ユーザーは、製造ラインで内部温度センサを較正する必要があります。

## 5.15 ブリッジ電流測定

| パラメータ                          | テスト条件 | 最小値 | 標準値  | 最大値 | 単位     |

|--------------------------------|-------|-----|------|-----|--------|

| ブリッジの電流範囲                      |       | 0   | 8500 |     | μA     |

| T ゲインが 1.33 ゲインに構成されている場合のゲイン  |       |     | 2250 |     | LSB/mA |

| オフセット T ゲインは 1.33 ゲインに構成されています |       |     | 2075 |     | LSB    |

| パラメータ    | テスト条件                                                                                                                                                                                                                                                                                                                                               | 最小値 | 標準値 | 最大値 | 単位     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| 合計温度ドリフト | 合計温度ドリフトの計算手順:<br>1. VDD = 5 V<br>2. 温度=−40°C、25°C、125°C、150°C<br>3. 5k Ω、ゼロ TC ブリッジを、差動電圧がほぼゼロの圧力入力ピン デバイスに接続します<br>4. T GAIN = 1.33V/V に設定します<br>5. 入力 MUX をブリッジ電流に設定します<br>6. T ADC を測定します<br>7. 10Hz の 1 次フィルタを使用して ADC コードをフィルタ処理します<br>8. 次の式を使用して合計温度ドリフトを計算します:(<br>温度の ADC コード –<br>25°C の ADC コード)/(温度 – 25°C)/(<br>25°C の ADC コード) × 1e6 |     | 600 |     | ppm/°C |

## 5.16 1 ワンワイヤ インターフェイス

| パラメータ    | テスト条件                        | 最小値                 | 標準値     | 最大値  | 単位    |

|----------|------------------------------|---------------------|---------|------|-------|

| 通信ポーレート  |                              | 2400                | 9600    |      | ビット/秒 |

| OWI_ENH  | OWI アクティベーション high           |                     | OWI_ENL |      | V     |

| OWI_ENL  | OWI アクティベーション low            |                     |         | 6.8  | V     |

| OWI_LOW  | アクティベーション信号パルス low 時間        | OWI_DGL_CNT_SEL = 0 | 1       |      | ms    |

|          |                              | OWI_DGL_CNT_SEL = 1 | 10      |      |       |

| OWI_HIGH | アクティベーション信号パルス high 時間       | OWI_DGL_CNT_SEL = 0 | 1       |      | ms    |

|          |                              | OWI_DGL_CNT_SEL = 1 | 10      |      |       |

| OWI_VIH  | OWI トランシーバ Rx の high スレッショルド |                     | 5.3     |      | V     |

| OWI_VIL  | OWI トランシーバ Rx の low スレッショルド  |                     |         | 4.7  | V     |

| OWI_IOH  | OWI トランシーバ Tx の high スレッショルド |                     | 900     | 1300 | μA    |

| OWI_IOL  | OWI トランシーバ Tx の low スレッショルド  |                     | 2       | 5    | μA    |

## 5.17 DAC 出力

| パラメータ     | テスト条件          | 最小値 | 標準値         | 最大値 | 単位  |

|-----------|----------------|-----|-------------|-----|-----|

| DAC の基準電圧 | レシオメトリックリファレンス |     | 0.25 × Vddp |     | V   |

| DAC 分解能   |                |     | 14          |     | ビット |

## 5.18 DAC 出力の DAC ゲイン

| パラメータ              | テスト条件               | 最小値 | 標準値 | 最大値 | 単位  |

|--------------------|---------------------|-----|-----|-----|-----|

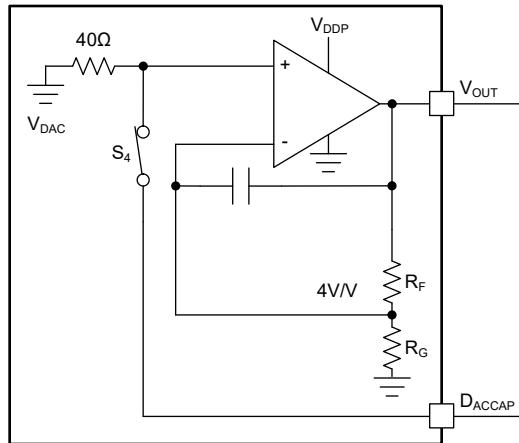

| バッファゲイン(図 5-2 を参照) |                     | 3.9 | 4   | 4.3 | V/V |

| ゲイン帯域幅積            | 無負荷、DACCAP なし、公称ゲイン |     | 1   |     | MHz |

## 5.18 DAC 出力の DAC ゲイン (続き)

| パラメータ               | テスト条件                                                                                                                                                                                                                                                                                                                                                          | 最小値 | 標準値  | 最大値 | 単位    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| オフセット誤差(DAC 誤差を含む)  | <p>VDD = 5 V および 25°C でのゲイン非直線性を次のように計算します。</p> <ol style="list-style-type: none"> <li>DAC コード=819d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=8192d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=15564d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>線形曲線 - エンドポイント法を使用して 3 つの測定値をフィットさせ、オフセットを決定します</li> </ol>                                   |     | ±20  |     | mV    |

| ゲインの非線形性(DAC 誤差を含む) | <p>VDD = 5 V および 25°C でのゲイン非直線性を次のように計算します。</p> <ol style="list-style-type: none"> <li>DAC コード=819d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=8192d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=15564d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>線形曲線-エンドポイント法を使用して 3 つの測定値を当てはめ、非直線性を決定します</li> </ol>                                        |     | ±600 |     | μV    |

| 総合未調整誤差             | <p>VDD = 5 V および 25°C でのゲイン非直線性を次のように計算します。</p> <ol style="list-style-type: none"> <li>DAC コード=819d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=8192d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>DAC コード=15564d を 25°C、0mA 負荷に印加して、VOUT の電圧を測定します</li> <li>線形曲線-エンドポイント法を使用して 3 つの測定値を当てはめ、値を理想的な線と比較して総合的な未調整誤差を判定します。エラーは w.r.t. です 4V FS。</li> </ol> | -2  | 2    |     | FSO 率 |

## 5.18 DAC 出力の DAC ゲイン (続き)

| パラメータ                                             | テスト条件                                                                                                                                                                                                                                                | 最小値                           | 標準値                           | 最大値                           | 単位   |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|------|

| DAC コードの温度および負荷電流変化によるレシオメトリックエラー = 819d～~15564d  | VDD = 5V で、DAC コードでのレシオメトリック誤差は次のように計算します。<br>1. 25°C と 0mA 負荷に DAC コードを印加し、VOUT の電圧を測定します<br>2. 温度を -40°C～150°C の間で変化させ、VOUT の電圧を測定します<br>3. 0 mA から 2.5 mA への負荷電流を変化させ、VOUT の電圧を測定します<br>4. レシオメトリックエラー = ((負荷時 温度時の VOUT) - (0mA 時 25°C 時の VOUT)) | -10                           | 10                            | 10                            | mV   |

| DAC コード = 819d から 15564d の VDD の変更によるレシオメトリックエラー。 | DAC コードでのレシオメトリック誤差は、次のように計算します。<br>1. 25°C と 0mA 負荷に DAC コードを印加し、VOUT の電圧を測定します<br>2. VDD を 4.5V と 5.5V の間で変更し、VOUT の電圧を測定します<br>3. 温度を -40°C～150°C の間で変化させ、VOUT の電圧を測定します<br>4. レシオメトリックエラー = ((VDD、T での VOUT) - (5V、25°C での VOUT) × VDD / 5V)     | -12                           | 12                            | 12                            | mV   |

| セトリング時間(1 次応答)                                    | DAC コード 819d～~15564d ステップ、CLOAD = 100nF。出力は最終値の 99% です                                                                                                                                                                                               | 100                           | 100                           | 100                           | μs   |

| ゼロコード電圧                                           | DAC コード = 0000h<br>、I DAC = 1 mA                                                                                                                                                                                                                     | 100 <sup>(1)</sup>            | 100 <sup>(1)</sup>            | 100 <sup>(1)</sup>            | mV   |

|                                                   | DAC コード = 0000h<br>、I DAC = 2.5 mA                                                                                                                                                                                                                   | 250                           | 250                           | 250                           | mV   |

| フル コード電圧                                          | DAC コードが 3FFFh のときの出力、<br>I DAC = -1 mA                                                                                                                                                                                                              | Vddp -<br>0.15 <sup>(1)</sup> | Vddp -<br>0.15 <sup>(1)</sup> | Vddp -<br>0.15 <sup>(1)</sup> | V    |

|                                                   | DAC コードが 3FFFh のときの出力、<br>I DAC = -2.5 mA                                                                                                                                                                                                            | Vddp -<br>0.28                | Vddp -<br>0.28                | Vddp -<br>0.28                | V    |

| 出力電流                                              | DAC コード = 3FFFh、DAC コード = 0000h                                                                                                                                                                                                                      |                               |                               | ±2.5                          | mA   |

| 短絡出力電流                                            | DAC コード = 3FFFh                                                                                                                                                                                                                                      | 10                            | 10                            | 40                            | mA   |

| 短絡吸収力電流                                           | DAC コード = 0000h                                                                                                                                                                                                                                      | 10                            | 10                            | 40                            | mA   |

| 出力電圧ノイズ(ゲイン = 4x)                                 | f = 10 Hz～1 KHz、VDD = 4.5 V、DAC コード = 1FFFh、DACCAP ピンにコンデンサなし、温度 = 25°C                                                                                                                                                                              | 80                            | 80                            | 80                            | μVpp |

| プルアップ抵抗                                           |                                                                                                                                                                                                                                                      | 2                             | 2                             | 47                            | kΩ   |

| プルダウン抵抗                                           |                                                                                                                                                                                                                                                      | 2                             | 2                             | 47                            | kΩ   |

| 容量                                                |                                                                                                                                                                                                                                                      | 0.1                           | 0.1                           | 1000                          | nF   |

(1) 電圧出力帯域については、図 5-2 をご覧ください。

図 5-2. PGA302 出力バッファ

## 5.19 不揮発性メモリ

| パラメータ  |             | テスト条件     | 最小値 | 標準値  | 最大値 | 単位   |

|--------|-------------|-----------|-----|------|-----|------|

| EEPROM | サイズ         |           |     | 128  |     | バイト  |

|        | 消去/書き込みサイクル |           |     | 1000 |     | サイクル |

|        | プログラミング時間   | 12 バイトページ |     | 8    |     | ms   |

|        | データ保持期間     |           |     | 10   |     | 年    |

## 5.20 診断- PGA30x

| パラメータ          |                                        | テスト条件                                 | 最小値  | 標準値   | 最大値 | 単位   |

|----------------|----------------------------------------|---------------------------------------|------|-------|-----|------|

| VBRG_OV        | 抵抗式ブリッジ センサの電源過電圧スレッショルド               |                                       | 7.5% |       |     | VBRG |

| VBRG_UV        | 抵抗式ブリッジ センサの 低電圧スレッショルド                |                                       |      | -4%   |     | VBRG |

| VDD_OV         | VDD OV スレッショルド                         |                                       | 5.51 |       |     | V    |

| DVDD_OV        | DVDD OV スレッショルド                        |                                       | 1.85 |       |     | V    |

| REF_OV         | リファレンス過電圧スレッショルド                       |                                       | 2.69 |       |     | V    |

| REF_UV         | リファレンス低電圧スレッショルド                       |                                       |      | 2.42  |     | V    |

| P_DIAG_PD      | ゲイン入力診断プルダウン抵抗の値                       | VINPP および VINPN、それぞれにプルダウン抵抗付き        | 1    | MΩ    |     |      |

| T_DIAG_PD      | T ゲイン入力診断プルダウン抵抗の値                     |                                       | 2    |       |     |      |

|                |                                        |                                       | 3    |       |     |      |

|                |                                        |                                       | 4    |       |     |      |

| VINP_OV        | P ゲイン入力過電圧スレッショルド値                     | VINPP および VINPN、それぞれにスレッショルド コンバレータ付き | 1    | MΩ    |     |      |

| VINT_OV        | T ゲイン入力過電圧                             |                                       | 90%  | VBRDG |     |      |

| VINT_UV        | T ゲイン入力のアンダーボルテージ                      |                                       | 84%  |       |     |      |

| PGAIN_OV       | P ゲイン出力過電圧                             |                                       | 78%  |       |     |      |

| PGAIN_UV       | P ゲイン出力低電圧                             |                                       | 70%  | VBRDG |     |      |

| TGAIN_OV       | T ゲイン出力過電圧                             |                                       | 10%  |       |     |      |

| TGAIN_UV       | T ゲイン出力電圧(低電圧)                         |                                       | 16%  |       |     |      |

| HARNESS_FAULT1 | オープン線 VOUT 電圧- VDD、VOUT にプルアップ付き       | プルアップ抵抗は 2k Ω~47k Ω±5% です。全温度範囲       | 24%  |       |     |      |

| HARNESS_FAULT2 | オープン 線 VOUT 電圧 - GND オープン、VOUT プルダウン付き | プルダウン抵抗は、全温度範囲で 2k ~47k Ω±5% です       | 30%  | VDD   |     |      |

|                |                                        |                                       | 95%  | VDD   |     |      |

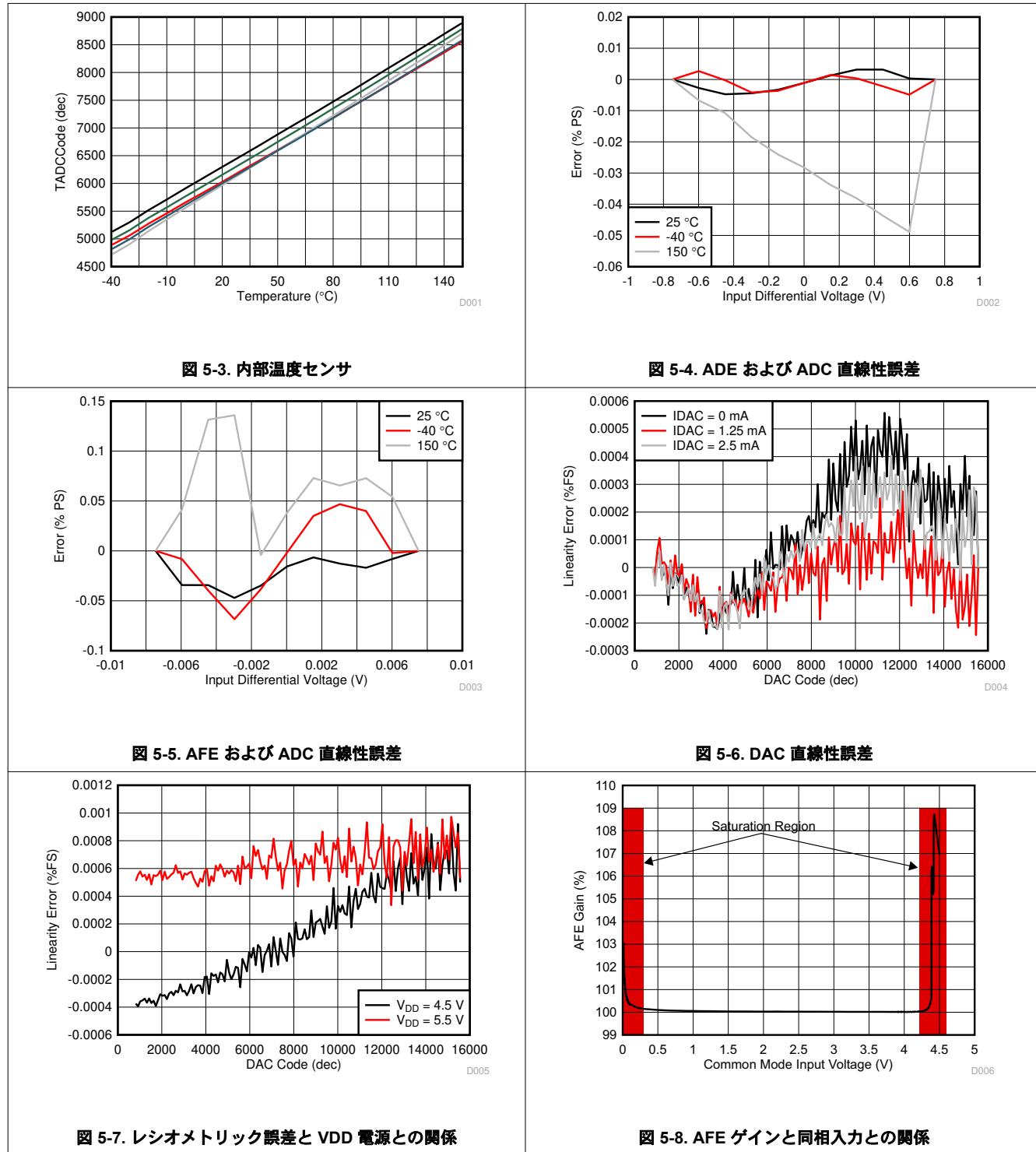

## 5.21 代表的特性

## 6 詳細説明

### 6.1 概要

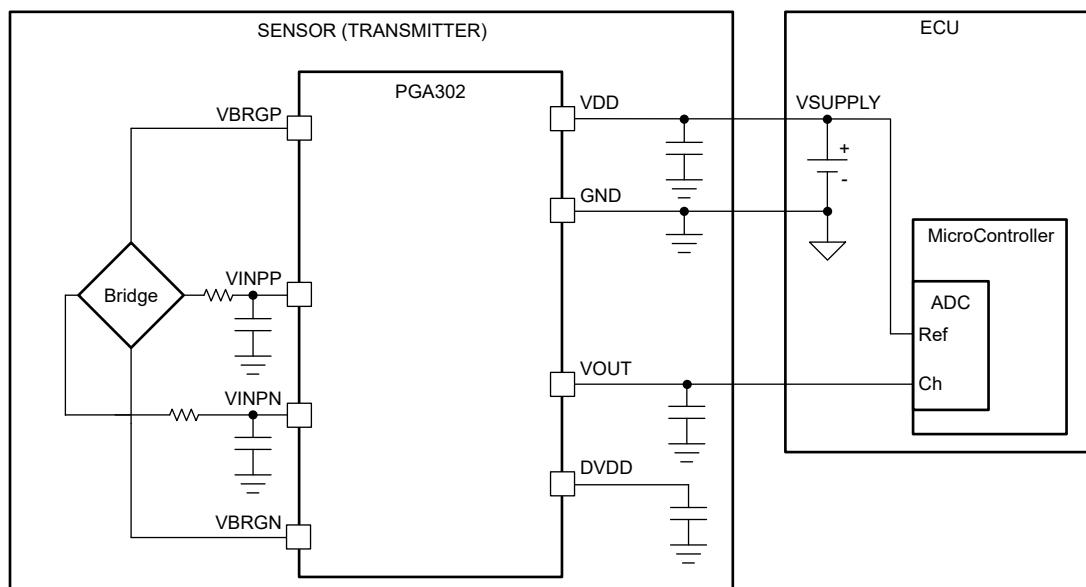

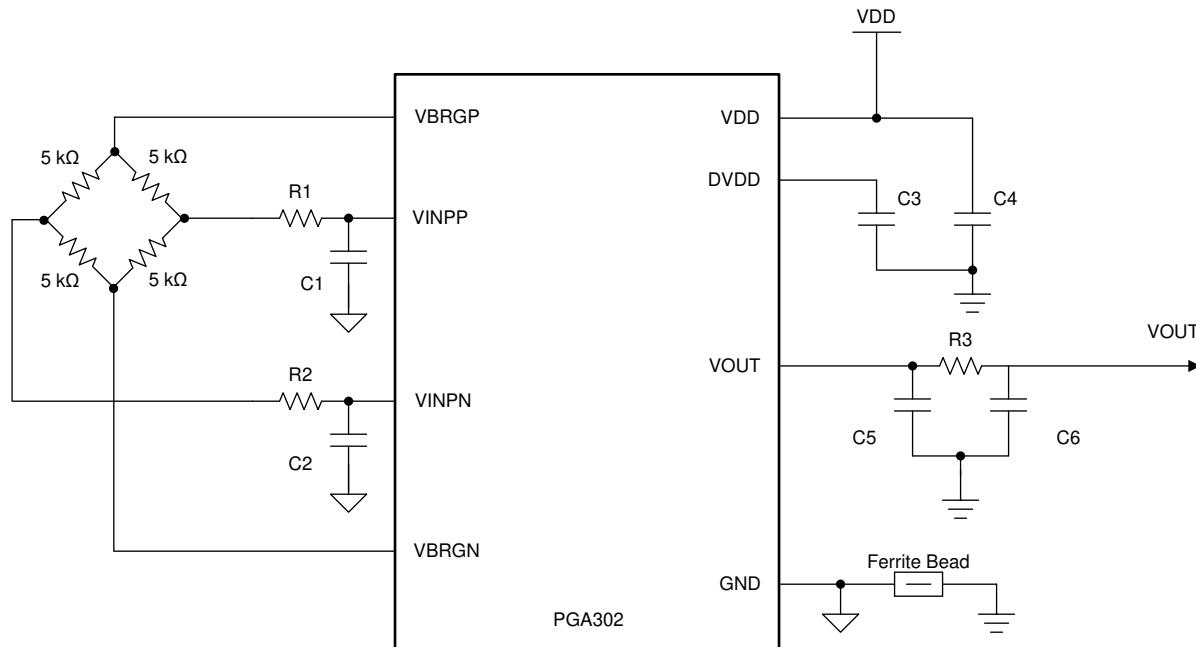

PGA302 は、高精度、低ドリフト、低ノイズ、低消費電力、多用途の信号コンディショナ車載グレード認定デバイスで、抵抗性ブリッジ圧力および温度センシング・アプリケーション用です。この PGA302 は、ピエゾ抵抗素子、セラミック膜、スチール薄膜など、各種のセンシング素子タイプに対応しています。代表的なアプリケーションとしては、圧力センサトランスマッタ、トランスデューサ、液位計、流量計、歪み計、重量計、熱電対、サーミスタ、2 線抵抗温度計(RTD)、抵抗式フィールドトランスミッタなどがサポートされています。また、加速度計や湿度センサの信号コンディショニング・アプリケーションにも使用できます。PGA302 は 2.5 V のブリッジ励起電圧を提供します。PGA302 は、センサおよび温度信号を、アナログのフロントエンド チェーンを介して増幅とデジタル化によって調整して、。調整された信号は、アナログ形式で出力できます。信号データは、I<sub>2</sub>C デジタル インターフェイスおよび GPIO ポートからもアクセスできます。また、デジタル インターフェイスは、デバイス内の他の機能ブロックを構成するためにも使用できます。PGA302 には、独自の単線式インターフェイス(OWI)が搭載され、電源線経由で通信と構成をサポートします。この機能により、配線の数を最小化できます。

この PGA302 には、抵抗ブリッジ入力と温度検出入力用の 2 つの独立したアナログ フロントエンド(AFE)チェーンが搭載されています。各 AFE チェーンには、独自のゲイン アンプがあります。抵抗式ブリッジ入力 AFE チェーンは、ゲインを 1.33V/V から 200V/V まで、8 ステップにプログラム可能です。温度センシング入力 AFE チェーンについて、PGA302 は、オプションの外部温度センシング用に最大 1000 μA を供給できる電流源を備えています。この電流ソースは、定電流ブリッジ励起としても使用できます。さらに、PGA302 には、内部温度センサが内蔵されており、温度センシング AFE チェーンの入力として構成できます。

ADC デシメーション フィルタ後のデジタル化された信号は、送信され、線形化および補正の計算のデジタル信号ロジックが行われます。には 128 バイトの EEPROM が PGA302 に内蔵されており、センサの較正係数と、必要に応じて構成設定を保存できます。

PGA302 は、14 ビットの DAC を備えており、その後に 4-V/N のバッファゲイン段が接続されています。業界規格のレンオメトリック電圧に対応。

診断機能により、電源の過電圧、電圧不足、オープン AFE フォルト、DAC フォルトなどの動作状況が監視され、DAC ループバック オプションにより信号チェーンの整合性をチェックできます。PGA302 は発振器と電力管理も統合しています。PGA302 は、-40°C から 150°C の広範囲の周囲温度で動作します。小型のパッケージ サイズで、PGA302 抵抗性ブリッジ センシング アプリケーションに必要なすべての機能が内蔵されているため、PCB の面積を最小化し、アプリケーション全体の設計を簡素化できます。

## 6.2 機能ブロック図

## 6.3 機能説明

このセクションでは、各機能ブロックについてご説明します。

### 6.3.1 過電圧および逆電圧保護

PGA302 は過電圧保護機能を内蔵しています。このブロックは、外部電源の過電圧状態からデバイスを保護し、デバイス動作をシャットオフします。

PGA302 は、逆電圧保護ブロックを内蔵しています。このブロックは、外部電源のバッテリが逆方向になっている状況で、デバイスを保護します。

### 6.3.2 リニア レギュレータ

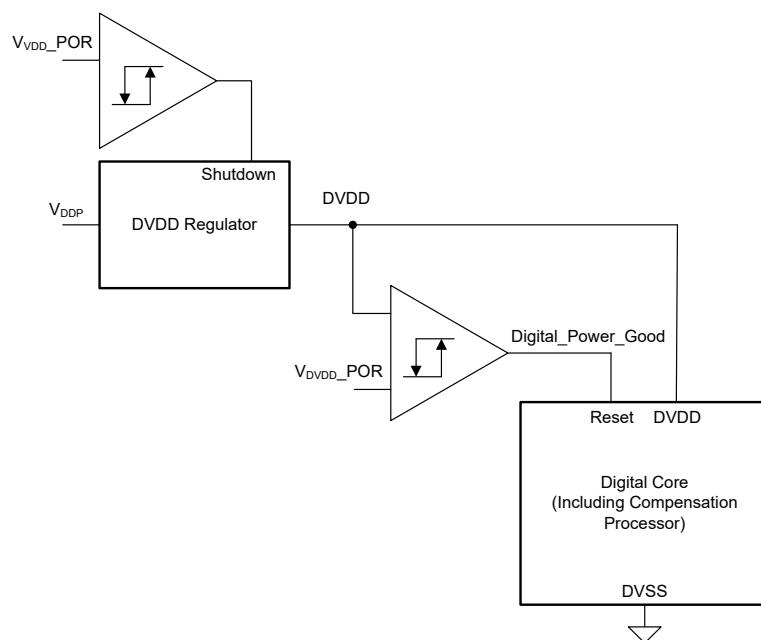

PGA302 には、デジタル回路へ 1.8-V にレギュレートされた電圧を供給する DVDD レギュレータが内蔵されています。

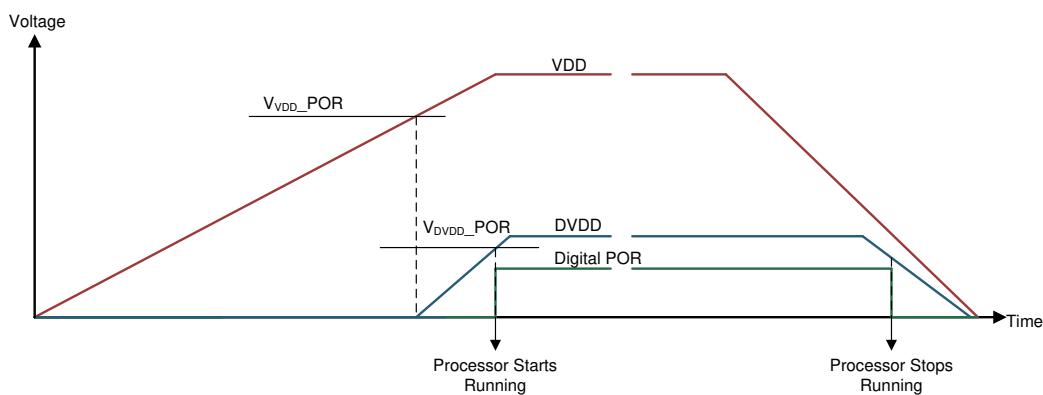

デジタル コアへのパワーオンリセット(POR)信号は、DVDD がレギュレートされているときにアサート解除されます。**図 6-1** はデジタルパワーオンリセット(POR)信号生成のブロック図を示し、**図 6-2** は VDD ランプアップおよびランプダウン時のデジタル POR 信号のアサートおよびアサート解除のタイミングを示します。このタイミングは、電源オン時には、DVDD が安定したレベルになるまで、デジタルコアとプロセッサはリセット状態に保持されることを示しています。

**図 6-1. デジタルパワーオンリセット信号の生成**

**図 6-2. デジタルパワーオンリセット信号の生成**

### 6.3.3 内部リファレンス

PGA302 は内部バンドギャップ リファレンスを内蔵しています。

リファレンスを使用して、ADC リファレンス電圧とブリッジ駆動電圧を生成します。

#### 注

正確なリファレンスは、電源オン時にデジタルコアが開始してから 50  $\mu$ s 後に有効になります。

### 6.3.4 内部発振器

デバイスには、内部発振器が内蔵されています。この発振器は、PGA302 のさまざまな回路に必要な内部クロックを提供します。

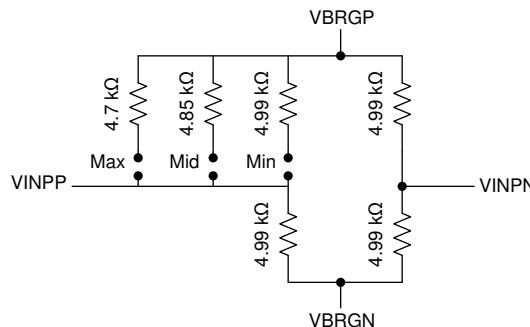

### 6.3.5 抵抗性ブリッジ用の VBRGP および VBRGN 電源

抵抗性ブリッジセンサに電源を供給する PGA302 のセンサ電圧供給ブロック。PGA302 のセンサ供給は、公称出力供給 2.5-V です。この公称供給量は、正確な内部基準である Accurate Reference にレシオメトリックです。

### 6.3.6 温度センサの ITEMP 電源

PGA302 の ITEMP ブロックは、PTC などの外部温度センサにプログラマブル電流を供給します。温度センサ電流源は、リファレンスに対してレシオメトリックです。

電流値は、TEMP\_CTRL レジスタの ITEMP\_CTRL ビットを使用してプログラムできます。

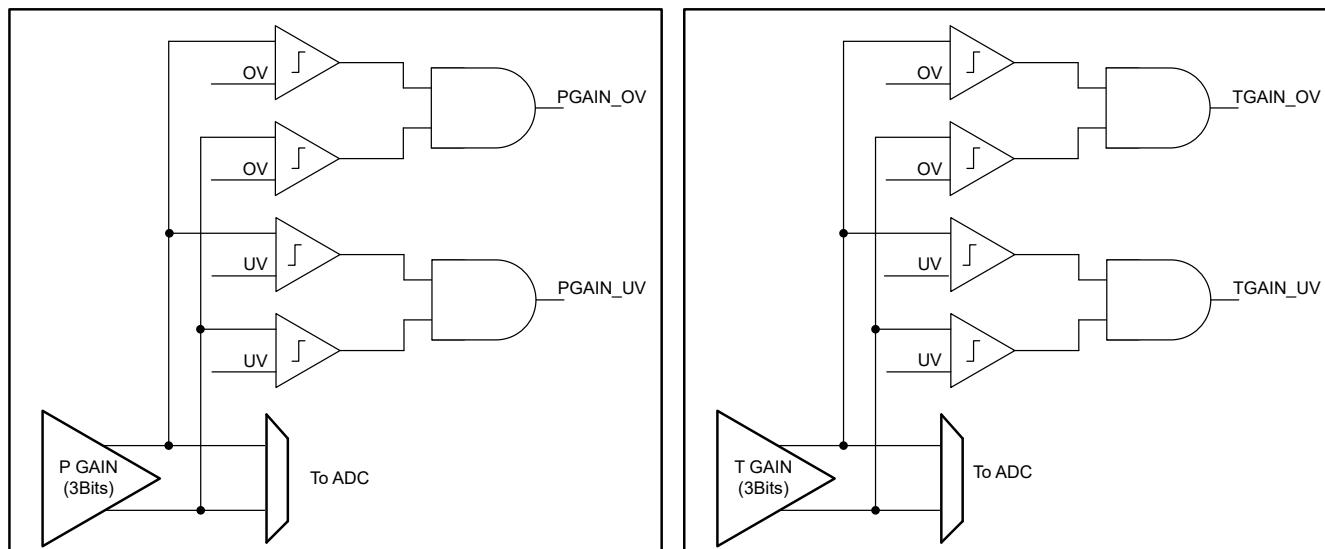

### 6.3.7 P ゲイン

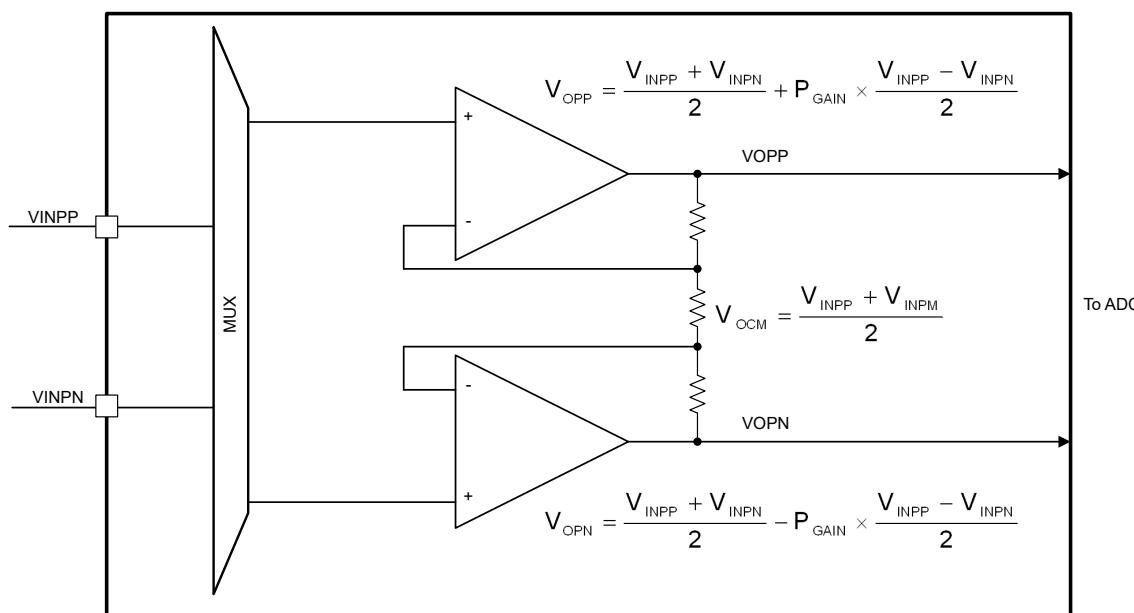

P ゲイン設計には、高精度、低ドリフト、低フリッカーノイズ、チョッパー安定化アンプが組み込まれています。P ゲインは、図 6-3 に示すように計測アンプとして実装されています。

このステージのゲインは、広範な信号スパンを持つ検出素子に対応するため、P\_GAIN\_SELECT レジスタの 3 ビットを使用して調整できます。

P ゲインアンプは、ハーフブリッジ出力を測定するよう構成できます。この場合、ハーフブリッジは VINPP ピンか VINPN ピンのいずれかに接続でき、もう一方のピンは VBRG/2 に内部で接続されます。

図 6-3. P ゲイン

### 6.3.8 T ゲイン

T ゲイン設計には、高精度、低ドリフト、低フリッカーノイズ、チョッパー安定化アンプが組み込まれています。T ゲインはアーキテクチャにおいて P ゲインと同一です。

このステージのゲインは、広範な信号スパンを持つセンサ素子に対応するため、T\_GAIN\_SELECT レジスタの 3 ビットで調整できます。

T ゲインアンプは、以下のサンプルを測定するよう構成できます。

- 差動モードでの VINTP-VINTN

- シングルエンドモードでの VINTP-GND

- シングルエンドモードでの内蔵温度センサの電圧

- シングルエンドモードでのブリッジ電流

### 6.3.9 ブリッジオフセットキャンセル

PGA302 デバイスは、大きなセンサブリッジ オフセットを相殺するため、P ゲインの入力にブリッジ オフセット キャンセル回路を実装しています。AFE のゲイン前に、ブリッジの一方のノードに小さな電流を導入することで、PGA302 を実現します。オフセットの選択は OFFSET\_Cancel レジスタによって決定され、オフセット値を [表 6-1](#) に示します。

**表 6-1. PGA302 オフセットの実装をキャンセルします**

| OFFSET_CANCEL 値 | 適用されるオフセット電圧[mV] |

|-----------------|------------------|

| 0x00            | 0 [オフ]           |

| 0x01            | 3.65             |

| 0x02            | 7.3              |

| 0x03            | 10.95            |

| 0x04            | 14.6             |

| 0x05            | 18.28            |

| 0x06            | 21.9             |

| 0x07            | 25.55            |

| 0x08            | 29.2             |

| 0x09            | 32.85            |

| 0x0A            | 36.5             |

| 0x0B            | 40.15            |

| 0x0C            | 43.8             |

| 0x0D            | 47.45            |

| 0x0E            | 51.1             |

| 0x0F            | 54.75            |

さらに、正のオフセットの場合は OFFSET\_CANCEL\_SEL ビットを設定し、負のオフセットの場合は同ビットをクリアすることで、適用されるオフセットの極性を変更できます。

### 6.3.10 A/D コンバータ

A/D コンバータは、P および T ゲイン アンプの出力をデジタル化するものです。デジタル化された値は、それぞれのチャネル ADC レジスタで利用できます。

#### 6.3.10.1 シグマ デルタ 変調器 (ADC)

ADC 用のシグマ-デルタ モジュレータは、4 MHz、2 次、3 ビット量子化のシグマ-デルタ 変調器です。シグマ-デルタ 変調器は、ADC\_CFG\_1 レジスタを使用して停止できます。

### 6.3.10.2 ADC 向け デシメーション フィルタ

デシメーション フィルタの出力レートは、96  $\mu$ s、128  $\mu$ s、192  $\mu$ s、256  $\mu$ s のいずれかに構成できます。

デシメーションフィルタの出力は、16 ビットの符号付き 2 の補数値です。シグマ-デルタ 変調器の入力において与えられる差分電圧について、デシメーション出力コードのいくつかの例を、表 6-2 に示します。

表 6-2. ADC の入力電圧と出力カウントの関係

| シグマ-デルタ モジュレータの差分<br>入力電圧 | 16-BIT ノイズフリーデシメータ出力 |

|---------------------------|----------------------|

| -2.5 V                    | -32768 (0x8000)      |

| -1.25 V                   | -16384 (0xC000)      |

| 0 V                       | 0 (0x0000)           |

| 1.25 V                    | 16383 (0x3FFF)       |

| 2.5 V                     | 32767 (0x7FFF)       |

### 6.3.10.3 内蔵温度センサ ADC 変換

T ゲイン = 4 V/V について、デバイスの接合部温度と 16 ビット TGAIN ADC コードとの公称の関係を 式 1 に示します

$$T \text{ ADC Code} = 20 \times \text{TEMP} + 5700 \quad (1)$$

ここで、

- TEMP は温度(°C)です

表 6-3 に、接合部温度の値の ADC 出力例をいくつか示します。

表 6-3. 内蔵温度センサと ADC の値

| 内部温度  | 16-BIT ADC 公称値 |

|-------|----------------|

| -40°C | 4900 (0x1324)  |

| 0°C   | 5700 (0x1644)  |

| 150°C | 8700 (0x21FC)  |

### 6.3.10.4 ADC スキャンモード

ADC は圧力と温度の信号を周期的に変換するオートスキャンモードに設定されています。

#### 6.3.10.4.1 自動スキャン モードでの P-T マルチプレクサのタイミング

PGA302 にはマルチプレクサがあり、P チャンネルと T チャンネルを 1 つの ADC にマルチプレクスします。図 6-4 に、マルチプレクシング方式を示します。

- P ADC Interrupt Every 96 $\mu$ s

- P-T MUX switched to T every P ADC Sample

ADC Enabled at Power up

図 6-4. P-T マルチプレクシング

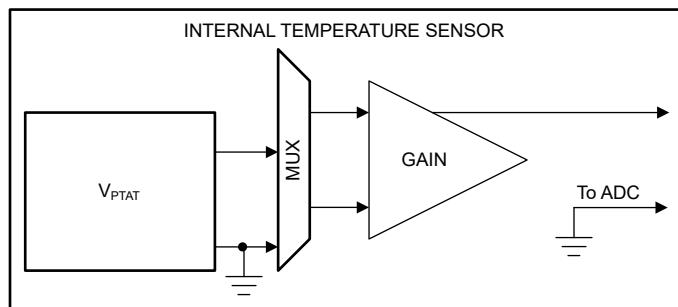

### 6.3.11 内部温度センサ

PGA302 は、内部温度センサを搭載しており、その電圧出力は ADC によってデジタル化され、プロセッサで利用できます。このデジタル化された値は、温度補正アルゴリズムの実装に使用します。内蔵温度センサで生成される電圧は、接合部温度に比例することに注意してください。

図 6-5 に、内蔵温度センサの AFE を示します。

図 6-5. 温度センサの AFE

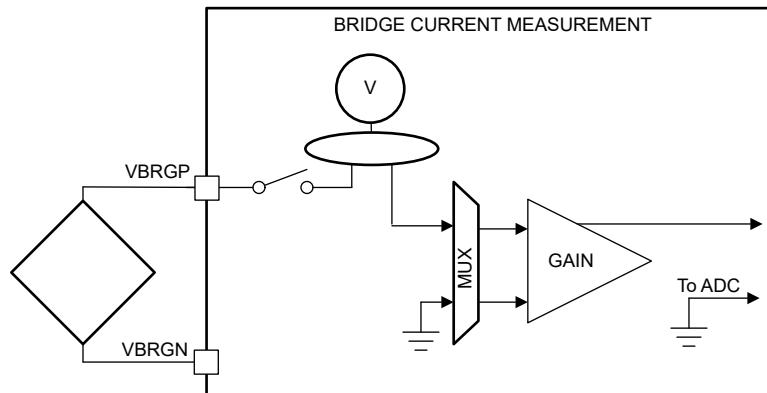

### 6.3.12 ブリッジ電流測定

PGA302 はブリッジ電流測定方式を採用しています。このデジタル化された値は、温度補正アルゴリズムの実装に使用できます。生成される電圧はブリッジ電流に比例することに注意してください。

図 6-6 はブリッジ電流の AFE を示します。

図 6-6. ブリッジ電流測定

### 6.3.13 デジタルインターフェイス

デジタルインターフェイスは、内部メモリ空間へアクセス(読み出しおよび書き込み)するために使用されます。デバイスには、次の通信モードがあります：

- 1 線式インターフェイス (OWI)に対応

このドキュメントでは、PGA302 によってサポートされている通信モードをまとめて、デジタルインターフェイスと表記します。通信モードでは、PGA302 デバイスはターゲットデバイスとして作動します。

### 6.3.14 OWI

デバイスには、OWI デジタル通信インターフェイスが搭載されています。OWI の機能は、OWI アクセスが可能な PGA302 の内部のすべてのメモリ位置に対して、書き込みおよび読み出しを可能にすることです。

### 6.3.14.1 OWI インターフェイスの概要

OWI デジタル通信はコントローラーターゲット通信リンクであり、そこでは PGA302 がターゲット デバイスとしてのみ作動します。コントローラ デバイスは、データ伝送の開始時/終了時を制御します。ターゲット デバイスは、コントローラからデータを送り返すよう命令されるまで、コントローラにデータを送り返しません。

PGA302 の VDD ピンは OWI として使用されるため、PGA302 がシステム モジュール内に埋め込まれているとき、通信には(VDD と GND)の 2 つのピンしか必要ありません。OWI コントローラは、VDD ピンの電圧を変調することで PGA302 と通信しながら、VDD ピンの電流を変調することで PGA302 はコントローラと通信します。PGA302 マイクロプロセッサには、VDD ピン上で駆動される OWI アクティベーション パルスに基いて OWI インターフェイスのアクティブ化と非アクティブ化を制御する能力があります。

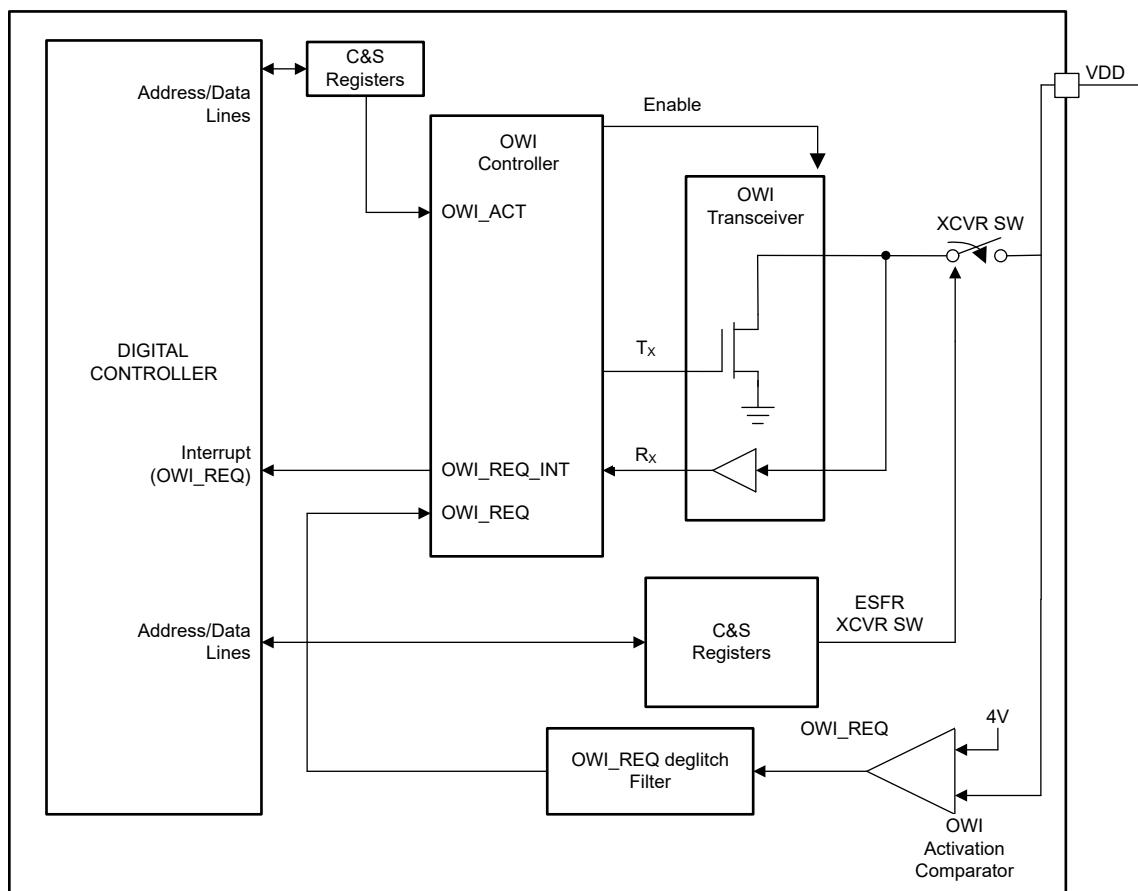

図 6-7 には、OWI 回路の構造のための機能的に等価な回路を示します。

図 6-7. OWI のシステム コンポーネント

### 6.3.14.2 OWI インターフェイスのアクティブ化と非アクティブ化

#### 6.3.14.2.1 OWI 通信のアクティブ化

OWI コントローラは、VDD ピン上に OWI アクティブ化パルスを生成して、OWI 通信を開始します。PGA302 が有効な OWI アクティブ化パルスを受信すると、OWI 通信の準備を独自で行います。

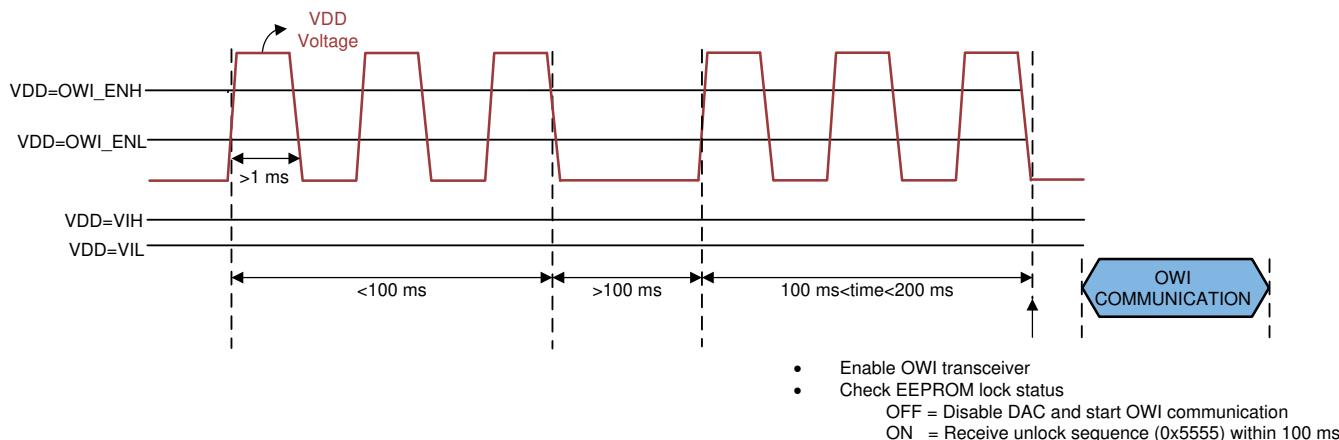

OWI 通信をアクティブにするには、OWI コントローラは VDD ピン上に OWI アクティブ化パルスを生成する必要があります。図 6-8 に、コントローラによって生成される OWI アクティブ化パルスを示します。

図 6-8. 過電圧の駆動による OWI のアクティブ化

#### 6.3.14.2.2 OWI 通信の非アクティブ化

OWI 通信を非アクティブ化して内部でプロセッサを再起動するには PGA302(リセット中の場合)、OWI コントローラで次の手順を実行する必要があります

- MICRO\_INTERFACE\_CONTROL レジスタの MICRO\_RESET ビットに 0 を書き込んでプロセッサのリセットをデアサートし、MICRO\_INTERFACE\_CONTROL レジスタの IF\_SEL ビットに 0 を書き込んでデジタル・インターフェイスへのアクセスをディセーブルする必要があります。

#### 6.3.14.3 OWI プロトコル

##### 6.3.14.3.1 OWI フレームの構造

###### 6.3.14.3.1.1 標準的なフィールド構造 :

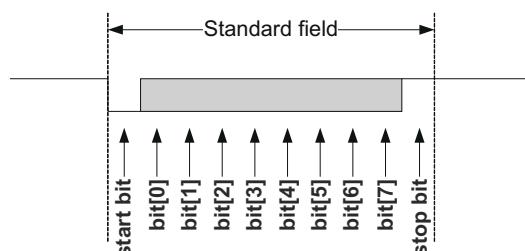

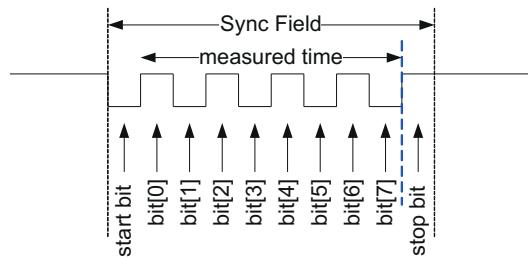

データは、バイトサイズのパケットで 1-wire のインターフェイス上で伝送されます。パケットフィールドの最初のビットは、スタートビットです。フィールドの次の 8 ビットは、OWI 制御ロジックで処理されるデータビットです。フィールドの最後のビットは、ストップビットです。フィールドのグループにより、伝送フレームが構成されます。伝送フレームは、1-wire インターフェイス上で 1 つの伝送動作を完了するために必要なフィールドで構成されます。1-wire フィールドの標準的なフィールド構造を、図 6-9 に示します

図 6-9. 標準的な OWI フィールド

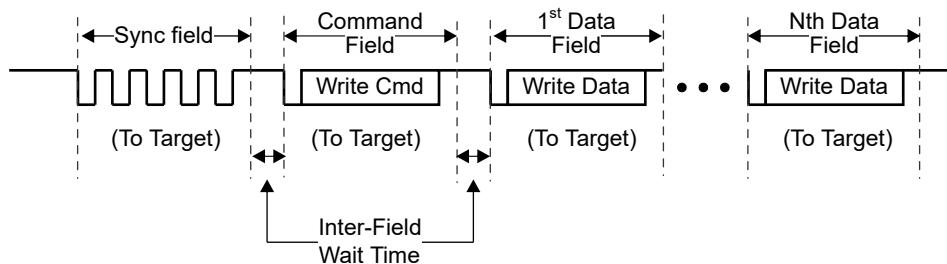

### 6.3.14.3.1.2 フレーム構造

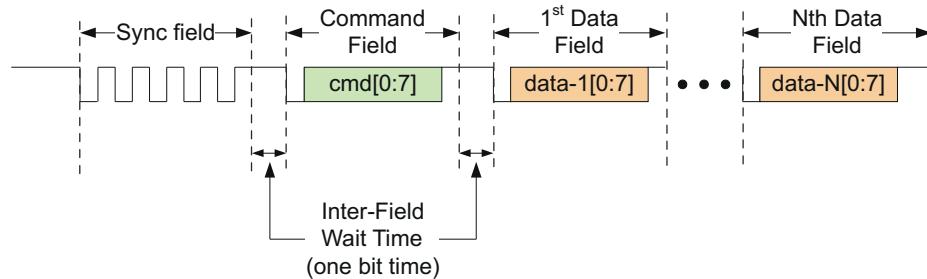

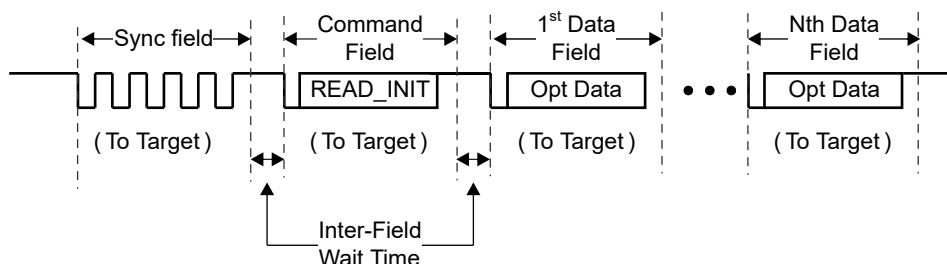

完全な単線データ伝送動作は、図 6-10 に示す構造のフレーム内で行われます。

図 6-10. OWI 伝送フレーム、N = 1~8

それぞれの传送フレームには、同期フィールドとコマンドフィールドに続き、その後に 0~8 個のデータフィールドが続きます。同期フィールドとコマンドフィールドは、常にコントローラから送信されます。データフィールドは、コマンドフィールドに指定されているコマンドに応じて、コントローラまたはターゲットのいずれかにより送信されます。コマンドフィールドによって、データフィールドの移動方向(コントローラからターゲットへ、またはターゲットからコントローラへ)が決まります。传送されるデータフィールドの数も、コマンドフィールドのコマンドによって決まります。フィールド間の待機時間は任意であり、ターゲットまたはコントローラが受信したデータを処理するために必要な場合があります。

OWI が論理 0 または論理 1 の状態で 15ms を超えてアイドルのまま維持されると、PGA302 の通信はリセットされ、コントローラから次のデータ伝送の同期フィールドが送られるのを待ちます。

### 6.3.14.3.1.3 同期フィールド

同期フィールドは、コントローラから传送されるすべてのフレームについて、最初のフィールドです。同期フィールドは、ターゲットデバイスがコントローラにより传送されるビット幅を計算するために使用します。このビット幅は、コントローラにより传送される以後のフィールドすべてを正確に受信するために使用されます。図 6-11 に、同期フィールドの形式を示します。

図 6-11. OWI 同期フィールド。

### 注

連続した同期フィールドビットを測定し、比較することによって、有効な同期フィールドが PGA302 に送信されているかどうかを判定します。同期フィールドで連続するいずれかの 2 ビットについて、ビット幅の差異が +/-25% を超える場合、PGA302 は、OWI フレームの以後の部分を無視します。すなわち、PGA302 は、その OWI メッセージに反応しません。

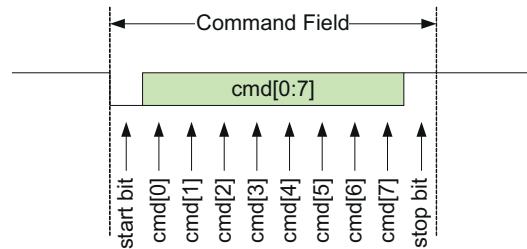

### 6.3.14.3.1.4 コマンドフィールド

コマンドフィールドは、マスターから送信される各フレームの中で 2 番目のフィールドです。コマンドフィールドには、どのような動作をすべきかについての命令と、ターゲットへ伝送されるデータをどこへ送信すべきかの命令が含まれています。コマンドフィールドは、読み取り動作中に、データをコントローラへ送り返すようにターゲットへ指示することもできます。传送

されるデータフィールドの数も、コマンドフィールドのコマンドにより決定されます。コマンドフィールドのフォーマットは [図 6-12](#) に示されています。

**図 6-12. OWI コマンド フィールド。**

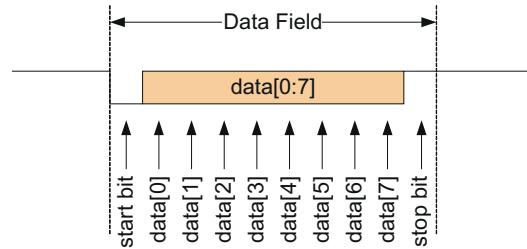

#### 6.3.14.3.1.5 データフィールド

コントローラが伝送フレームのコマンドフィールドを送信した後、ゼロ個以上のデータフィールドがターゲットへ(書き込み動作の場合)またはコントローラへ(読み出し動作の場合)送信されます。データフィールドは EEPROM のデータそのものか、データを保管するアドレスとなる場合があります。データのフォーマットは、コマンドフィールドのコマンドにより決定されます。[図 6-13](#) に、データフィールドの代表的なフォーマットを表示します。

**図 6-13. OWI データ フィールド。**

#### 6.3.14.3.2 OWI コマンド

PGA302 でサポートされている 5 つの OWI コマンドのリストは以下の通りです：

1. OWI 書き込み

2. OWI 読み取り初期化

3. OWI 読み取り応答

4. EEPROM キャッシュの OWI バースト書き込み

5. EEPROM キャッシュからの OWI バースト読み取り

#### 6.3.14.3.2.1 OWI 書き込みコマンド

| フィールドの位置   | 概要           | ビット 7 | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0 |

|------------|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| コマンドフィールド  | 基本的な書き込みコマンド | 0     | P2    | P1    | P0    | 0     | 0     | 0     | 1     |

| データフィールド 1 | 送信先アドレス      | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

| データフィールド 2 | 書き込むデータバイト   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

コマンドフィールドの P2、P1、P0 の各ビットは、OWI によってアクセスされるメモリページを決定します。メモリページのデコードは [表 6-4](#) に示されています。

**表 6-4. OWI メモリ ページのデコード**

| P2 | P1 | P0 | メモリ ページ                                   |

|----|----|----|-------------------------------------------|

| 0  | 0  | 0  | 制御およびステータスレジスタ、<br>DI_PAGE_ADDRESS = 0x00 |

| 0  | 1  | 0  | 制御およびステータスレジスタ、<br>DI_PAGE_ADDRESS = 0x02 |

| 1  | 0  | 1  | EEPROM のキャッシュ/セル                          |

| 1  | 1  | 0  | 予約済み                                      |

| 1  | 1  | 1  | 制御およびステータスレジスタ、<br>DI_PAGE_ADDRESS = 0x07 |

**6.3.14.3.2.2 OWI 読み取り初期化コマンド**

| フィールドの場所    | 概要             | ビット 7 | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0 |

|-------------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| コマンド フィールド  | 読み取り Init コマンド | 0     | P2    | P1    | P0    | 0     | 0     | 1     | 0     |

| データ フィールド 1 | アドレスをフェッチする    | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

コマンド フィールドの P2、P1、P0 の各ビットは、OWI によってアクセスされるメモリ ページを決定します。メモリページ デコードを [表 6-4](#) に示します。

**6.3.14.3.2.3 OWI 読み取り応答コマンド**

| フィールドの位置    | 概要                          | ビット 7 | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0 |

|-------------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| コマンド フィールド  | レスポンスコマンドを読み取る              | 0     | 1     | 1     | 1     | 0     | 0     | 1     | 1     |

| データ フィールド 1 | 取得されたデータ (OWI によりデータが送出される) | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

コマンド フィールドの P2、P1、P0 の各ビットは、OWI によってアクセスされるメモリ ページを決定します。メモリページ デコードは [表 6-4](#) に示されています。

**6.3.14.3.2.4 OWI パースト書き込みコマンド (EEPROM キャッシュへのアクセス)**

| フィールドの場所    | 概要                                 | ビット 7 | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0 |

|-------------|------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| コマンド フィールド  | EE_CACHE write コマンドのキャッシュ バイト(0~7) | 1     | 1     | 0     | 1     | 0     | 0     | 0     | 0     |

| データ フィールド 1 | 書き込む最初のデータ バイト                     | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| データ フィールド 2 | 書き込む 2 番目のデータ バイト                  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

**6.3.14.3.2.5 OWI パースト読み取りコマンド (EEPROM キャッシュへのアクセス)**

| フィールドの位置    | 概要                          | ビット 7 | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0 |

|-------------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| コマンド フィールド  | パースト読み取り応答 (8 バイト)          | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 1     |

| データ フィールド 1 | 1 番目のデータバイト取得 EE キャッシュバイト 0 | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| データ フィールド 2 | 2 番目のデータバイト取得 EE キャッシュバイト 1 | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

### 6.3.14.3.3 OWI での動作

#### 6.3.14.3.3.1 書き込み動作

ワンワイヤ インターフェースの書き込み動作は極めて簡単です。コマンド フィールドでは、ターゲットに保存する後続のデータ バイトの書き込み操作と、送信するデータフィールドの数を指定します。必要に応じて、最初の数データフィールドに追加のコマンド指示を送信することができます。書き込み動作を 図 6-14 に示します。

図 6-14. 書き込み動作、N = 1~8。

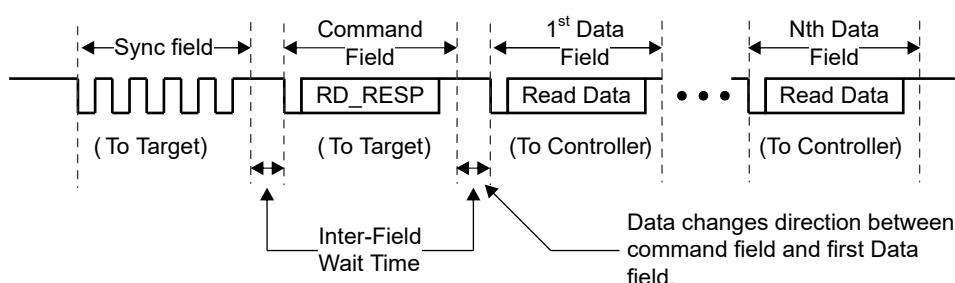

#### 6.3.14.3.3.2 読み出し動作

読み取り動作では、データをターゲットからコントローラへ移動するために、2 つの連続した送信フレームが必要です。最初のフレームは、Read Initialization フレームです。これは、ターゲット デバイス内の特定の場所からデータを取得し、OWI 経由で送信する準備をするようターゲットに指示します。データの場所は、コマンド フィールドで指定される場合もありますが、完全なデータの場所を指定するには、追加のデータフィールドが必要になる場合もあります。コントローラが読み出し応答フレームと呼ばれる次のフレームで指示するまで、データは送信されません。Read Response フレームでは、Read Response コマンド フィールドの送信直後に、データの方向がコントローラ → ターゲットから ターゲット → コントローラへ変化します。コマンド フィールドとデータ フィールドとの間には、信号ドライバが方向を切り替えるための十分な時間が空けられます。この待ち時間は 20  $\mu$ s で、この待ち時間のタイマーはターゲットデバイス上にあります。待ち時間の完了後、ターゲットは要求されたデータを送信します。コントローラ デバイスは信号ドライバを切り替えており、データの受信準備ができるはずです。Read フレームを 図 6-15 に示します。

図 6-15. Read Initialization フレーム、N = 1~8。

図 6-16. Read Response フレーム、N = 1~8

#### 6.3.14.3.3.3 EEPROM バースト書き込み

EEPROM バースト書き込みは、1つの OWI フレームを使用して 2 バイトのデータを EEPROM キャッシュに書き込みするために使用します。これによって、製造ラインで EEPROM を高速でプログラミングできます。EEPROM メモリ セルの内容を EEPROM キャッシュへ転送する前に、EEPROM ページを選択する必要があることに注意してください。

#### 6.3.14.3.3.4 EEPROM バースト読み取り

EEPROM バースト読み取りは、1つの OWI フレームを使用して 2 バイトのデータを EEPROM キャッシュに読み取りるために使用します。Burst Read コマンドは、製造ラインで EEPROM キャッシュの内容を高速で読み出すために使用されます。この読み出しプロセスは、EEPROM キャッシュへの書き込みを検証するために使用されます。

#### 6.3.14.4 OWI 通信エラーステータス

PGA302 は、OWI 通信のエラーを検出します。OWI\_ERROR\_STATUS\_LO および OWI\_ERROR\_STATUS\_HI レジスタには、OWI 通信エラーのビットが含まれています。検出される通信エラーには次のものがあります

- 通信ボーレートの範囲外です

- 無効な SYNC フィールドです

- コマンドおよびデータの無効な STOP ビット

- 無効な OWI コマンドです

#### 6.3.15 I<sup>2</sup>C インターフェイス

このデバイスには、I<sup>2</sup>C (Inter-Integrated Circuit) デジタル通信インターフェイスが搭載されています。I<sup>2</sup>C の主な機能は、I<sup>2</sup>C アクセスが可能なすべてのアドレスに対して、書き込みおよび読み出しを可能にすることです。

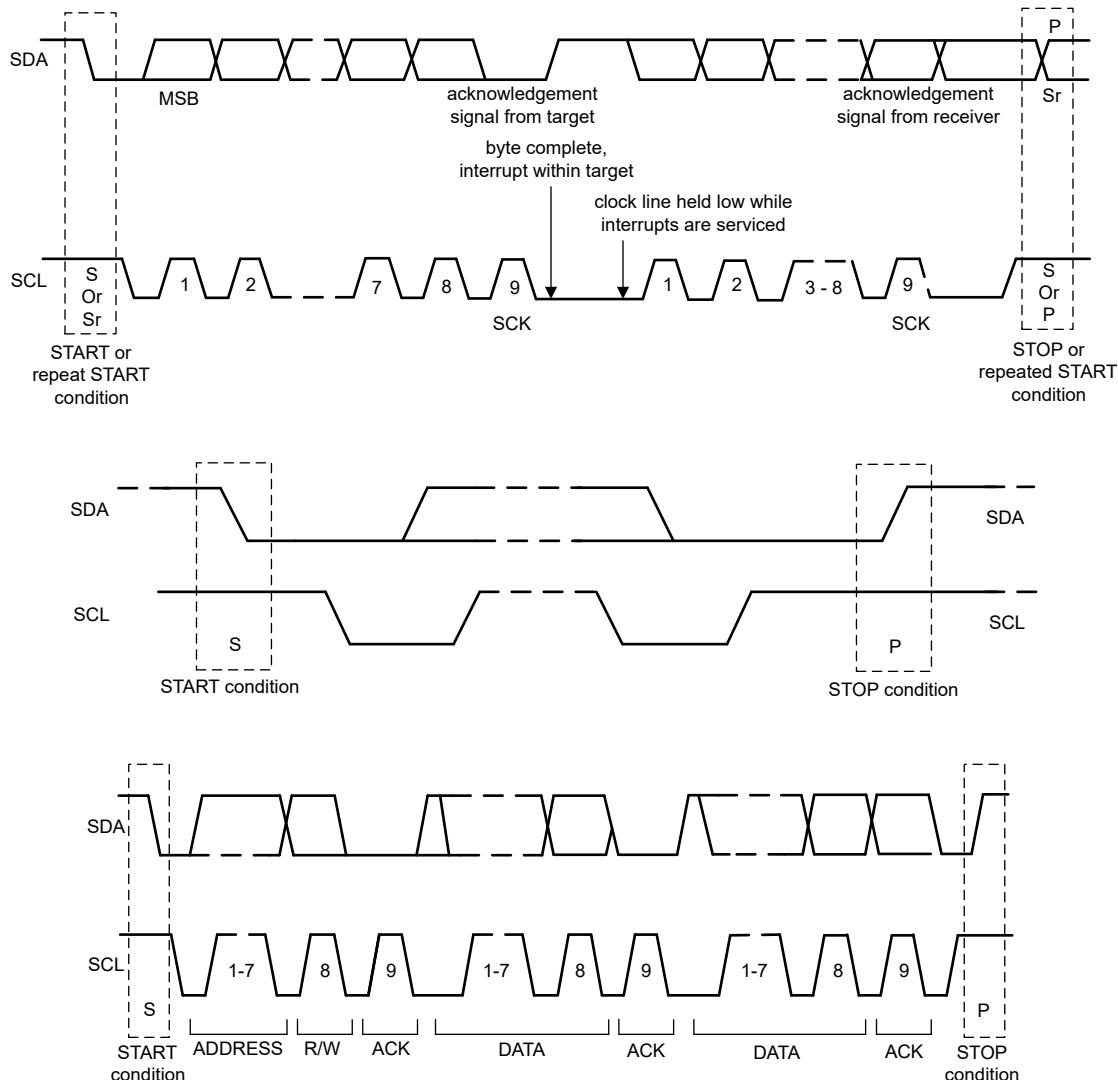

##### 6.3.15.1 I<sup>2</sup>C インターフェイスの概要

I<sup>2</sup>C は、同期シリアル通信標準で、通信のために次の 2 つのピンが必要です。

- SDA: I<sup>2</sup>C シリアル データ ライン

- SCL: I<sup>2</sup>C のシリアル クロック ライン (SCL)

I<sup>2</sup>C 通信はコントローラ/ターゲット形式の通信バスで行われ、コントローラである 1 つのデバイスのみがデータ伝送を開始できます。デバイスは I<sup>2</sup>C 通信において常にターゲット デバイスとして動作し、PGA900 と通信する外部のデバイスがマスターとして動作します。コントローラ デバイスは、SDA ライン上で通信を開始し、SCL ライン上でクロック信号を供給する必要があります。I<sup>2</sup>C の SDA ラインが low にプルされると、論理 0 とみなされ、I<sup>2</sup>C の SDA ラインが high でフローティング状態のとき、論理 1 とみなされます。I<sup>2</sup>C インターフェイスがテスト レジスタ空間以外のメモリ位置へアクセスするには、MICRO\_INTERFACE\_CONTROL レジスタの IF\_SEL ビットを論理 1 にセットする必要があります。

##### 6.3.15.2 I<sup>2</sup>C インターフェイスプロトコル

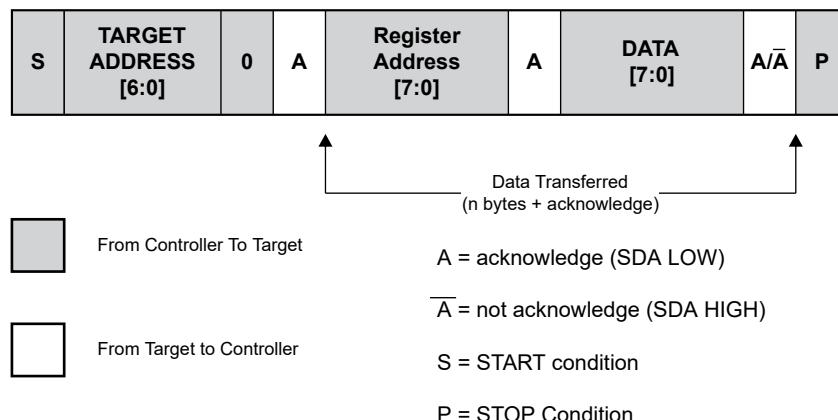

書き込み動作の I<sup>2</sup>C フレームの基本的なプロトコルを図 6-17 に示します。

**図 6-17. I<sup>2</sup>C 書き込み動作コントローラ トランスマッタから、7 ビットのターゲットアドレスにより PGA302 ターゲットをアドレス指定する**

この図は、I<sup>2</sup>C SDA ポートとの間でやり取りされるデータを表しています。

基本的なデータ転送では、指定されたターゲットアドレスへ 2 バイトのデータが送信されます。最初のデータフィールドはレジスタアドレス、2 番目のデータフィールドは送信または受信されるデータです。

I<sup>2</sup>C ターゲットアドレスは、どのメモリページが参照されるかを決定するために使用されます。**表 6-5 ターゲットアドレスからメモリページへのマッピング**を示したものです。

**表 6-5. ターゲットアドレス**

| ターゲットアドレス | PGA302 メモリページ                             |

|-----------|-------------------------------------------|

| 0x40      | テストレジスタ                                   |

| 0x42      | 制御およびステータスレジスタ、<br>DI_PAGE_ADDRESS = 0x02 |

| 0x45      | EEPROM のキャッシュ/セル                          |

| 0x46      | 予約済み                                      |

| 0x47      | 制御およびステータスレジスタ、<br>DI_PAGE_ADDRESS = 0x07 |

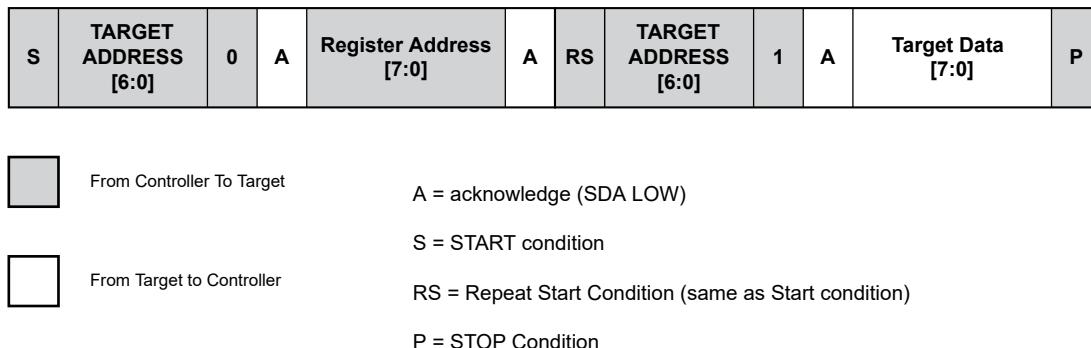

読み取り動作の基本的な PGA302 I<sup>2</sup>C プロトコルを**図 6-18** に示します。

**図 6-18. I<sup>2</sup>C 読み取り動作コントローラ トランスマッタから、7 ビットのターゲットアドレスにより PGA302 ターゲットをアドレス指定する**

ターゲットアドレスはメモリページを決定します。R/W ビットを 0 に設定します。

レジスタ アドレスは、要求されるデータの 8 ビット アドレスを指定します。

繰り返し START 条件が、上述の Write 操作の説明における書き込みデータに置き換わります。これにより、Write 操作の代わりに Read 操作が行われることを PGA302 デバイスに通知します。

2 番目の ターゲット アドレスには、データが取得される元のメモリ ページが含まれています。R/W ビット (A15) を 1 に設定します。

ターゲット データは、コントローラによりアクノリッジが受信された後で送信されます。

表 6-6 に、I<sup>2</sup>C 転送のいくつかの例を示します。

**表 6-6. I<sup>2</sup>C 転送の例**

| コマンド                                            | I <sup>2</sup> C SDA 上でコントローラからターゲット データ                       |

|-------------------------------------------------|----------------------------------------------------------------|

| COM MCU_TO_DIF_B0 を読み出します                       | ターゲット アドレス: 100 0000<br>レジスタ アドレス: 0000 0100                   |

| 制御およびステータス レジスタの 0x30 (DAC_REG0_1) に 0x80 を書き込む | ターゲット アドレス: 100 0010<br>レジスタ アドレス: 0011 0000<br>データ: 1000 0000 |

| EEPROM のバイト 7 から読み出し                            | ターゲット アドレス: 100 0101<br>レジスタ アドレス: 0000 0111                   |

### 6.3.15.3 I<sup>2</sup>C インターフェイスのクロック概要

このデバイスは、SCL ラインが high の立ち上がりエッジのときに SDA ラインのデータをサンプリングし、SCL ラインが low のときに変更されます。この動作に対する唯一の例外は、図 6-19 に示すように、起動、停止、および繰り返し起動条件です。

図 6-19. I2C のクロック概要

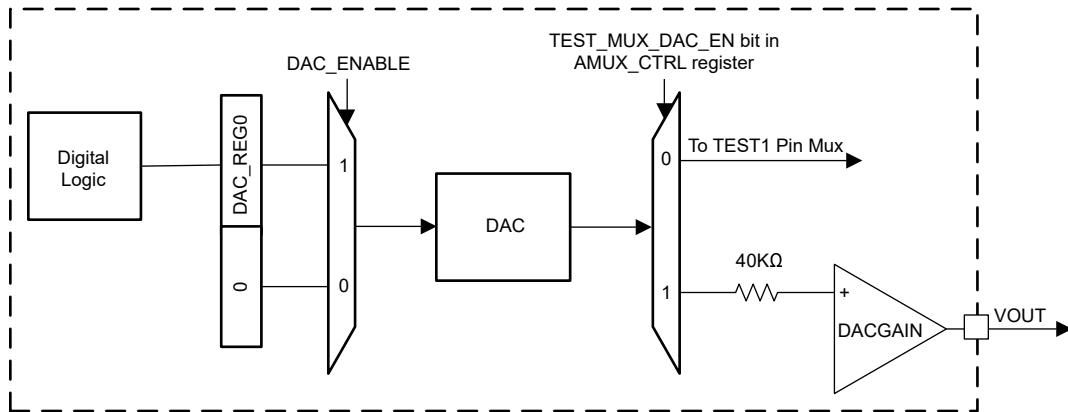

### 6.3.16 DAC 出力

このデバイスには、14 ビットの D/A コンバータが搭載されており、VDD 電源を基準にしてレシオメトリック出力電圧を生成します。DAC\_CTRL\_STATUS レジスタの DAC\_ENABLE ビットに 0 を書き込むことで DAC を無効にできます。

プロセッサがリセットを行うと、DAC レジスタは 0x000 コードに設定されます。

### 6.3.17 DAC 出力の DAC ゲイン

DAC ゲイン バッファは、DAC 出力の構成可能なバッファステージです。DAC ゲインの最終ステージは、Vddp とグラウンドに接続されています。これによって、VOUT 電圧を VDD 電圧付近まで駆動できます。

#### 6.3.17.1 DAC 出力を DAC GAIN 入力へ接続する

DAC 出力は、図 6-20 に示すように TEST1 テストピン、または DAC GAIN 入力へ接続できます。AMUX\_CTRL レジスタの TEMP\_MUX\_DAC\_EN ビットを 1 にセットすると、DAC 出力を DAC GAIN 入力へ接続できます。

図 6-20. DAC を DAC GAIN に接続

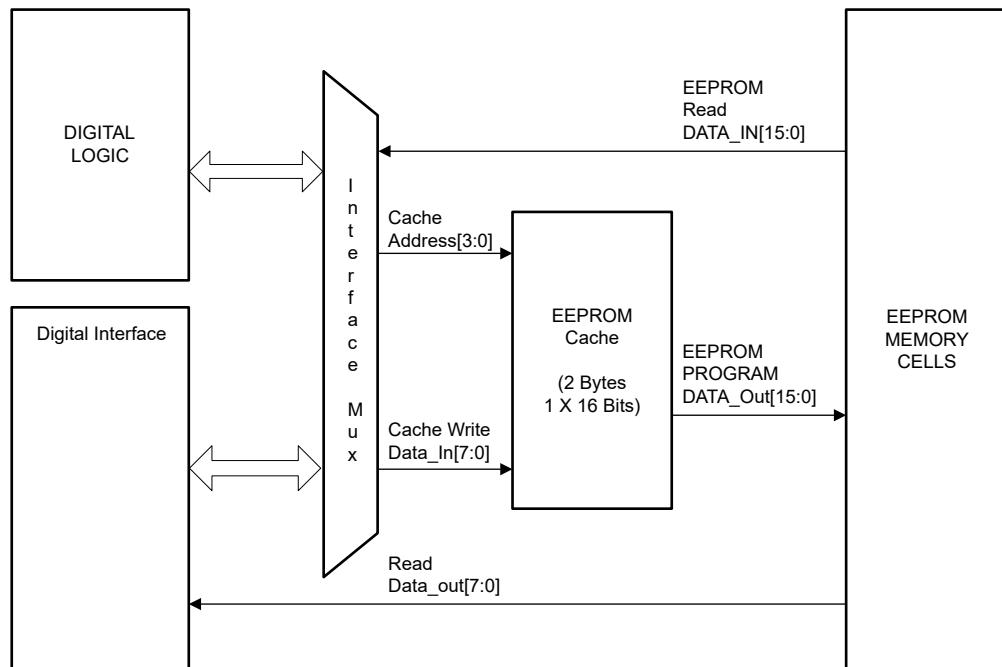

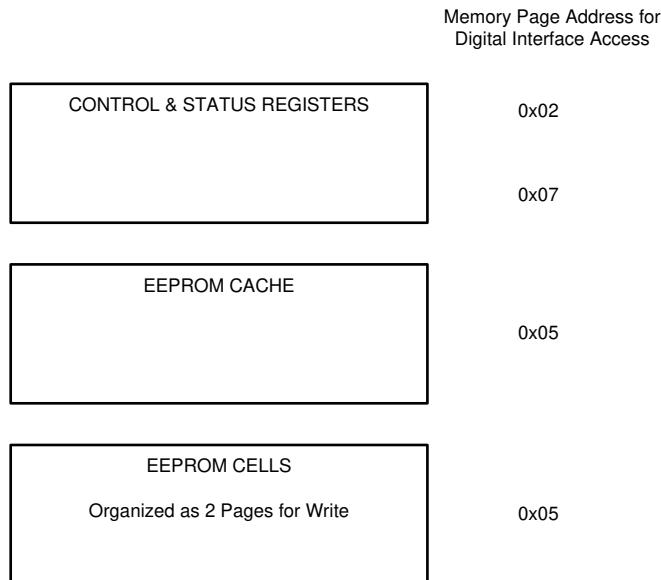

### 6.3.18 メモリ

#### 6.3.18.1 EEPROM メモリ

図 6-21 は EEPROM の構造を示します。各 EEPROM の内容は、書き込み前に EEPROM キャッシュへ転送する必要があります(つまり、EEPROM は 1 度に 2 バイトずつプログラムできます)。EEPROM の読み出しへは、EEPROM キャッシュを使用せずに実行されます。

図 6-21. EEPROM インターフェイスの構造

##### 6.3.18.1.1 EEPROM キャッシュ

EEPROM キャッシュは、プログラミング処理のときに、選択された EEPROM の位置へ転送されるデータの一時的な保存場所として機能します。

##### 6.3.18.1.2 EEPROM のプログラミング手順

EEPROM をプログラミングするために、EEPROM は各 2 バイトの 64 ページで構成されています。2 バイト EEPROM キャッシュへ書き込むことで、EEPROM メモリセルをプログラムできます。キャッシュの内容は、EEPROM メモリ ページを選択することにより、EEPROM メモリセルへ転送されます。

1. 7 ビット EEPROM のうち上位 6 ビットを EEPROM\_PAGE\_ADDRESS レジスタへ書き込み、EEPROM ページを選択します。

2. EEPROM\_CACHE レジスタへ書き込み、2 バイト EEPROM キャッシュをロードします。

3. ユーザーは、EEPROM\_CTRL レジスタの ERASE ビットに 1 を、EEPROM\_CTRL レジスタの PROGAM ビットに 1 を同時に書き込むことで、消去できます。

#### 6.3.18.1.3 EEPROM プログラミング電流

EEPROM のプログラミング プロセスの関係で、プログラミングの持続時間中は VDD ピンの電流が 1.5 mA 増えます。

#### 6.3.18.1.4 CRC

EEPROM メモリの最後のバイトは、CRC 用に予約されています。この CRC 値は、EEPROM メモリのすべてのデータに対応しています。最後のバイトがプログラムされるたびに、CRC 値が自動的に計算され、検証されます。この検証プロセスでは、計算された CRC 値に対して、EEPROM メモリセルにプログラムされた最後のバイトがチェックされます。計算された CRC が、この最後のバイトにプログラムされた値と一致していれば、EEPROM\_CRC\_STATUS レジスタの CRC\_GOOD ビットが設定されます。

CRC チェックは、EEPROM\_CRC レジスタの CALCULATE\_CRC ビットをセットすれば、いつでも開始できます。CRC 計算のステータスは EEPROM\_CRC\_STATUS レジスタの CRC\_CHECK\_IN\_PROG ビットで確認できるのに対し、CRC 検証の結果は EEPROM\_CRC\_STATUS レジスタの CRC\_GOOD ビットで確認できます。

CRC 計算を疑似コードで表現すると、次のようにになります：

```

currentCRC8 = 0xFF; // Current value of CRC8

for NextData;

D = NextData;

C = currentCRC8;

begin

nextCRC8_BIT0 = D_BIT7 ^ D_BIT6 ^ D_BIT0 ^ C_BIT0 ^ C_BIT6 ^ C_BIT7;

nextCRC8_BIT1 = D_BIT6 ^ D_BIT1 ^ D_BIT0 ^ C_BIT0 ^ C_BIT1 ^ C_BIT6;

nextCRC8_BIT2 = D_BIT6 ^ D_BIT2 ^ D_BIT1 ^ D_BIT0 ^ C_BIT0 ^ C_BIT1 ^ C_BIT2 ^ C_BIT6;

nextCRC8_BIT3 = D_BIT7 ^ D_BIT3 ^ D_BIT2 ^ D_BIT1 ^ C_BIT1 ^ C_BIT2 ^ C_BIT3 ^ C_BIT7;

nextCRC8_BIT4 = D_BIT4 ^ D_BIT3 ^ D_BIT2 ^ D_BIT1 ^ C_BIT2 ^ C_BIT3 ^ C_BIT4;

nextCRC8_BIT5 = D_BIT5 ^ D_BIT4 ^ D_BIT3 ^ C_BIT3 ^ C_BIT4 ^ C_BIT5;

nextCRC8_BIT6 = D_BIT6 ^ D_BIT5 ^ D_BIT4 ^ C_BIT4 ^ C_BIT5 ^ C_BIT6;

nextCRC8_BIT7 = D_BIT7 ^ D_BIT6 ^ D_BIT5 ^ C_BIT5 ^ C_BIT6 ^ C_BIT7;

end

currentCRC8 = nextCRC8_D8;

endfor

```

---

#### 注

EEPROM の CRC の計算は、電源オン時にデジタルコアが開始してから 340  $\mu$ s 後に完了します。

---

#### 6.3.19 診断

このセクションでは、診断機能について説明します。

##### 6.3.19.1 電源の診断

このデバイスには、電源のフォルトを監視するためのモジュールが搭載されています。次の内部電力レールが監視対象となります：

1. VDD 電圧、スレッショルドは、高電圧リファレンスを使用して生成されます

2. DVDD 電圧、スレッショルドは、高電圧リファレンスを使用して生成されます

3. ブリッジ電源電圧、スレッショルドは高電圧リファレンスを使用して生成されます

4. 内部発振器電源電圧、スレッショルドは、高電圧リファレンスを使用して生成されます

5. リファレンス出力電圧、スレッショルドは、高電圧リファレンスを使用して生成されます

電気的仕様には、各電力レールについて電圧スレッショルドが記載されています。

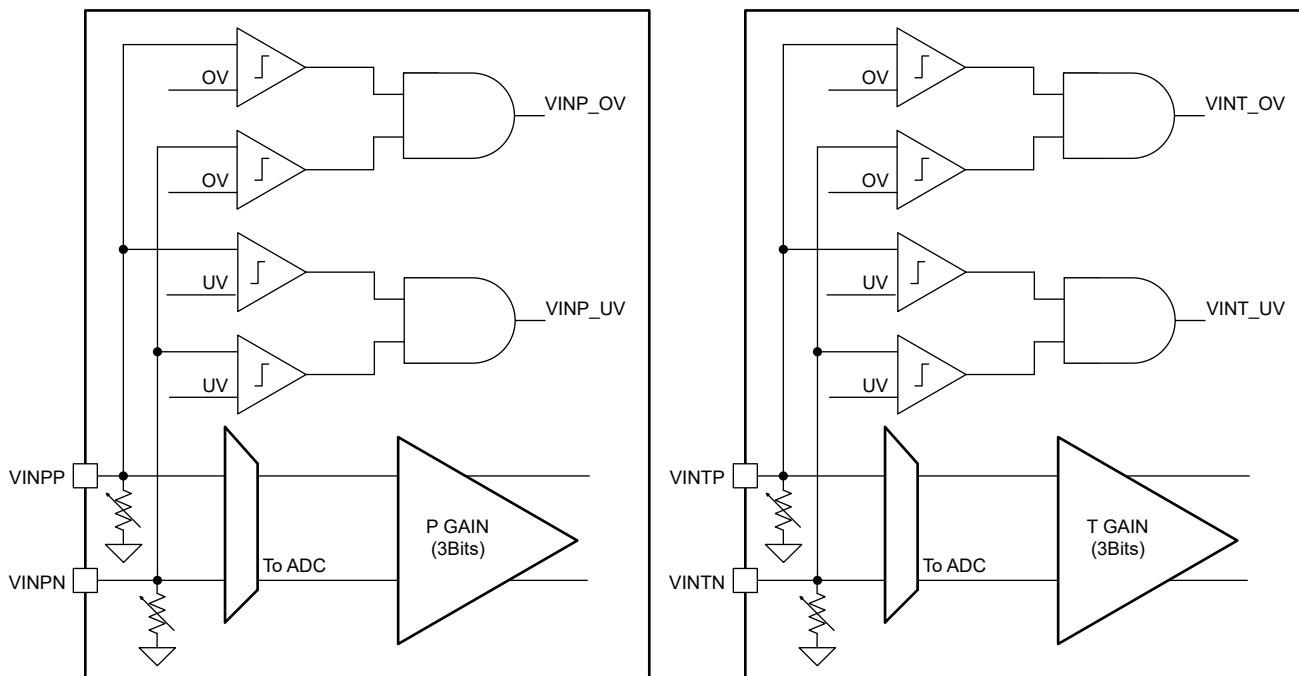

### 6.3.19.2 センサ接続性/ゲイン入力の故障

このデバイスには、ブリッジ接続性と温度センサ接続性の故障を監視する回路が搭載されています。温度センサとの接続性の故障は、16 ピンのパッケージ・オプションでのみ監視されます。具体的には、デバイスはブリッジ ピンのオープン状態(センサーからの接続消失を含む)、グラウンドへの短絡、およびセンサー電源への短絡を監視します。

**表 6-7. センサ接続性/ゲイン入力の故障具合 (診断抵抗がアクティブ)**

| 故障番号 | フォルト モード                   | チップの動作                                  |

|------|----------------------------|-----------------------------------------|

| 1    | VBRGP オープン                 | VINP_UV および PGAIN_UV フラグがセットされます        |

| 2    | VBRGN オープン                 | 該当なし                                    |

| 3    | VINPP オープン                 | VINP_UV および PGAIN_UV フラグがセットされます        |

| 4    | VINPN オープン                 | VINP_UV および PGAIN_UV フラグがセットされます        |

| 5    | VBRGP が VBRGN に短絡          | VBRG_UV, VINP_UV, PGAIN_UV のフラグがセットされます |

| 6    | VBRGP が VBRGN に短絡          | VINP_OV フラグおよび PGAIN_OV フラグが設定される       |

| 7    | VBRGP を VINPN に短絡          | VINP_OV フラグおよび PGAIN_OV フラグが設定される       |

| 8    | VINPP を VINPN に短絡          | 該当なし                                    |

| 9    | VINNPP を VBRGN に短絡         | VINP_UV および PGAIN_UV フラグがセットされます        |

| 10   | 温度パスは差動、VINTP オープン         | TGAIN_UV フラグがセットされる                     |

| 11   | 温度パスは差動、VINTN オープン         | VINT_OV および TGAIN_OV フラグが設定される          |

| 12   | 温度パスは差動、VINTP を VINTN に短絡  | 該当なし                                    |

| 13   | 温度パスはシングルエンド、VINTP オープン    | TGAIN_UV フラグがセットされる                     |

| 14   | 温度パスはシングルエンド、VINTN グラウンド短絡 | TGAIN_UV フラグがセットされる                     |

接続性故障のスレショルドは VBRDG 電圧から取得されます。

**図 6-22. ブリッジ接続性診断のプロック図**

### 6.3.19.3 ゲイン出力診断

このデバイスには、各ゲインの出力信号が特定の範囲内であることを確認するモジュールが搭載されています。これによって、信号チェーンのゲインステージが正しく動作していることを保証できます。AVDD電圧を使用して、比較のためのスレッショルド電圧が生成されます。

故障が検出されると、AFEDIAGレジスタの対応するビットがセットされます。故障条件が取り除かれても、故障ビットはラッチしたまま維持されます。故障を取り除くには、M0ソフトウェアが故障ビットを読み出し、そのビットに論理ゼロを書き戻す必要があります。また、システムリセットでも故障はクリアされます。

図 6-23. ゲイン出力診断のブロック図

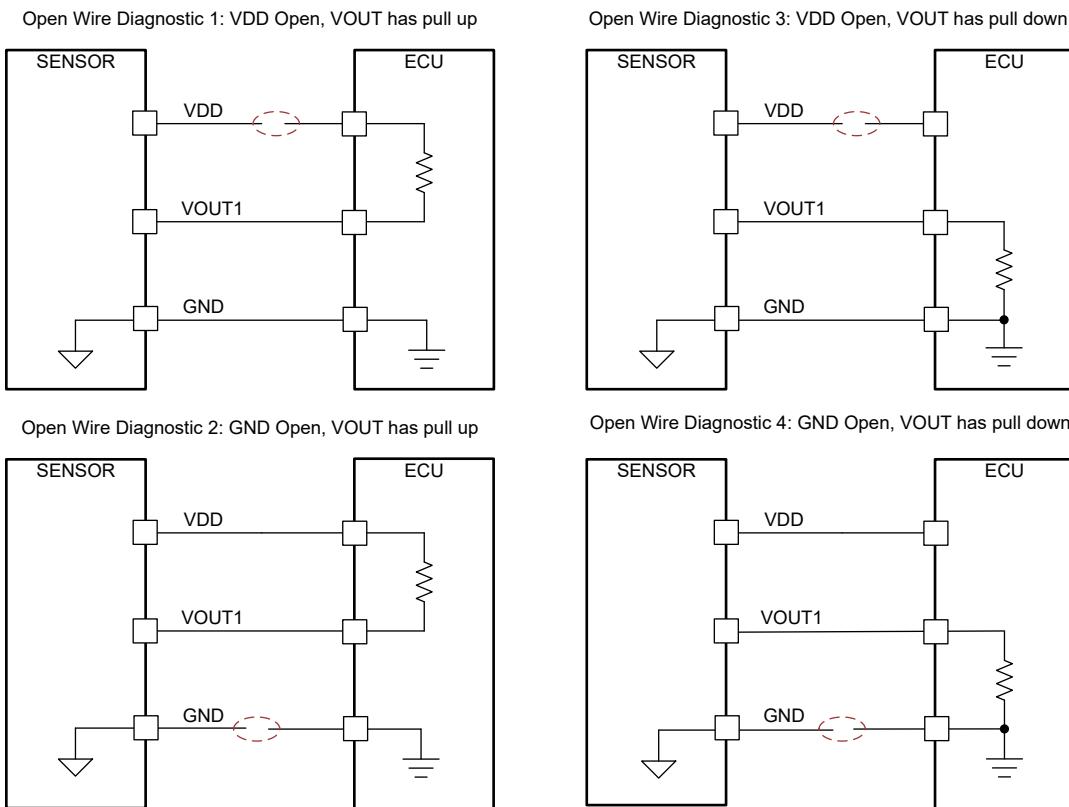

### 6.3.19.4 PGA302 ハーネスオープン線式診断

PGA302により、ECUでオープンワイヤ診断を実行できます。具体的には、ECUはVOUTラインにプルアップまたはプルダウンを設置して、オープンなVDDまたはオープンなGND線を検出できます。

表 6-8. PGA302 ハーネスの不具合

| 故障番号 | デバイス VDD | デバイス GND | デバイス VOUT          | 注記                               | 障害の削除後のデバイスステータス |

|------|----------|----------|--------------------|----------------------------------|------------------|

| 1    | 5 V      | 0V       | VDD にプルアップ         | VOUT を VDD にプルする通常接続             | 通常動作を再開します       |

| 2    | 5 V      | 0V       | GND にプルダウン         | VOUT を GND にプルする通常接続             | デバイスリセット         |

| 3    | 20 V     | 0 V      | GND から VDD へ       | オーバーボルテージ                        | デバイスリセット         |

| 4    | オープン     | 0 V      | VDD = 5V にプルアップします | VOUT を VDD にプルした状態で VDD をオープン    | デバイスリセット         |

| 5    | オープン     | 0 V      | GND にプルダウン         | VOUT が GND にプルされた状態で VDD をオープンする | デバイスリセット         |

| 6    | 5 V      | オープン     | VDD = 5V にプルアップします | VOUT が VDD にプルされた状態で GND をオープンする | デバイスリセット         |

| 7    | 5 V      | オープン     | GND にプルダウン         | VOUT を GND にプルした状態で GND をオープン    | デバイスリセット         |

| 8    | 0 V      | 20 V     | VDD にプルアップ         | VOUT が VDD にプルされているときの逆電圧        | デバイスリセット         |

| 9    | 0 V      | 20 V     | GND にプルダウン         | VOUT が GND にプルされた状態の逆電圧          | 物理的損傷の恐れがあります    |

表 6-8. PGA302 ハーネスの不具合 (続き)

| 故障番号 | デバイス VDD | デバイス GND | デバイス VOUT  | 注記                                 | 障害の削除後のデバイスステータス       |

|------|----------|----------|------------|------------------------------------|------------------------|

| 10   | 0 V      | 0V       | VDD にプルアップ | VOUT が VDD にプルされた状態で VDD が GND に短絡 | デバイスリセット               |

| 11   | 0 V      | 0V       | GND にプルダウン | VOUT が GND にプルされた状態で VDD が GND に短絡 | デバイスリセット               |

| 12   | 20 V     | 20 V     | VDD にプルアップ | VOUT が VDD にプルされた状態で GND が VDD に短絡 | デバイスリセット。物理的損傷の恐れがあります |

| 13   | 20 V     | 20 V     | GND にプルダウン | VOUT が GND にプルされた状態で GND が VDD に短絡 | デバイスリセット               |

| 14   | 20 V     | 0 V      | 20 V       | Vout を VDD に短絡                     | デバイスリセット。物理的損傷の恐れがあります |

| 15   | 20 V     | 0 V      | 0V         | Vout を GND に短絡                     | 通常動作を再開します             |

図 6-24 は、VDD および GND ピンで想定されるハーネスオープン線のフォルトを示したものです。

図 6-24. ハーネス オープン線式診断

表 6-9 に、線式診断と、ECU がオープンハーネスフォルトを検出できる対応する抵抗プル値をまとめます。

表 6-9. 標準的な内部プルダウン設定

| ハーネスを開きます | ECU のプル方向 | プル値 ( $k\Omega$ ) | フォルト条件中の PGA302 の状態                  | ECU 電圧レベル (VOUT/OWI ピン) |

|-----------|-----------|-------------------|--------------------------------------|-------------------------|

| VDD       | プルアップ     | 50                | PGA302 がオフになっています。存在するリーク電流(特に高温の場合) | VDD-(Ileak1×プルアップ)      |

表 6-9. 標準的な内部プルダウン設定 (続き)

| ハーネスを開きます | ECU のプル方向 | プル値 ( $k\Omega$ ) | フォルト条件中の PGA302 の状態                                    | ECU 電圧レベル (VOUT/OWI ピン)                   |

|-----------|-----------|-------------------|--------------------------------------------------------|-------------------------------------------|

| GND       | プルアップ     | 該当なし              | PGA302 はオフになっており、すべての電源レールが VDD にプルアップされています           | VDD                                       |

| VDD       | プルダウン     | 該当なし              | PGA302 はオフになっており、すべての電源レールがグラウンドにプルダウンされることを意味します      | GND                                       |

| GND       | プルダウン     | 50                | PGA302 がオフであり、リーク電流は VOUT ピンにプッシュされます (チップのグラウンドを介して)。 | GND + ( $I_{leak2} \times R_{pulldown}$ ) |

### 6.3.19.5 EEPROM CRC および TRIM エラー

EEPROM の最後のバイトには、EEPROM 内の全データの CRC が格納されています。

ユーザーはいつでも EEPROM CRC を検証できます。EEPROM に最後のバイトがプログラムされると、デバイスは自動的に CRC を計算し、EEPROM CRC ステータス レジスタの CRC\_GOOD ビットを更新します。CRC の有効性は、EEPROM\_CRC レジスタの制御ビット CACULATE\_CRC ビットを設定して CRC チェックを開始することでも検証できます。

また、デバイスにはアナログトリム値も存在します。アナログトリム値の有効性は、電源オン時に検証されます。トリム値の有効性は、TRIM\_CRC\_STATUS レジスタの CRC\_GOOD ビットを使用して推測できます。

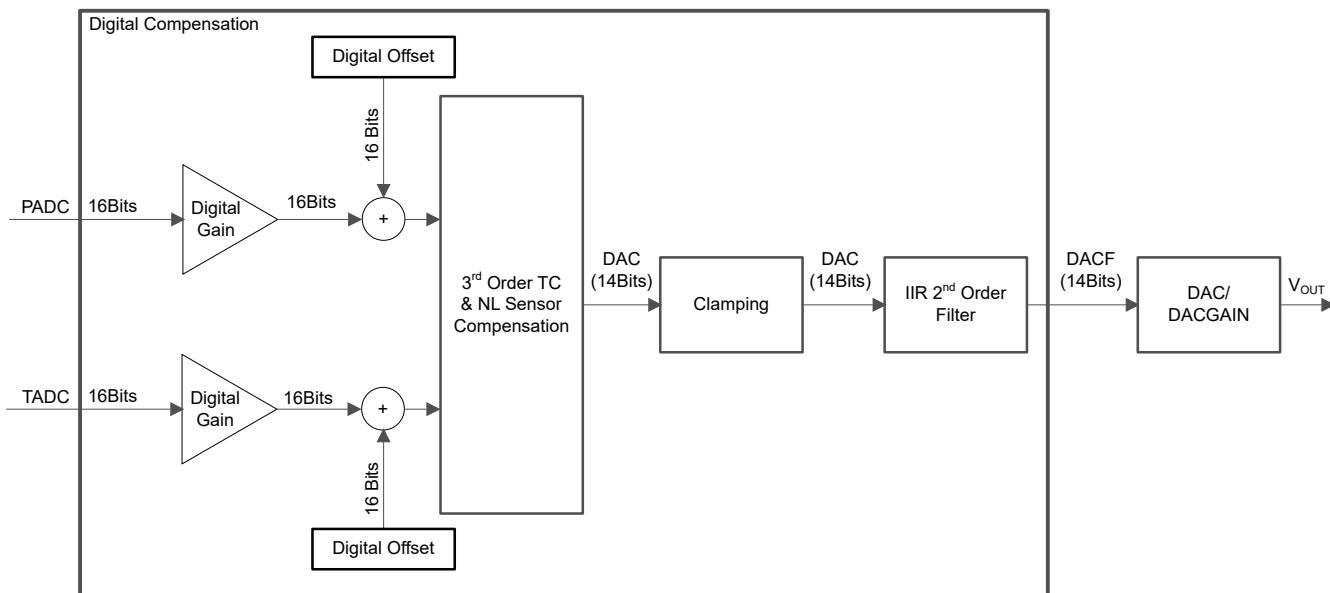

### 6.3.20 デジタル補償およびフィルタ

PGA300 は、圧力入力の 2 次オーダー TC および NL 補正を実装しています。補正された出力は、2 次オーダー IIR フィルタを使用してフィルタ処理され、出力レジスタに書き込まれます。

図 6-25. デジタル補償の計算式

#### 6.3.20.1 デジタルゲインおよびオフセット

デジタル補償は、式 2 および式 3 に示すデジタルゲインとオフセットを実行します：

$$P = a_0(PADC + b_0) \quad (2)$$

ここで、

- $a_0$  はデジタルゲインです

- また、 $b_0$  は PADC のデジタルオフセットです

$$T = a_1(TADC + b_1) \quad (3)$$

ここで、

- $a_1$  はデジタルゲインです

- and  $b_1$  は TADC のデジタルオフセットです。

### 6.3.20.2 TC および NL 修正

その補償を 式 4 に示します：

$$\text{OUTPUT} = \frac{(h_0 + h_1 \times T + h_2 \times T^2 + h_3 \times T^3) + (g_0 + g_1 \times T + g_2 \times T^2 + g_3 \times T^3) \times P + (n_0 + n_1 \times T + n_2 \times T^2 + n_3 \times T^3) \times P^2}{(m_0 + m_1 \times T + m_2 \times T^2 + m_3 \times T^3) \times P^3} \quad (4)$$

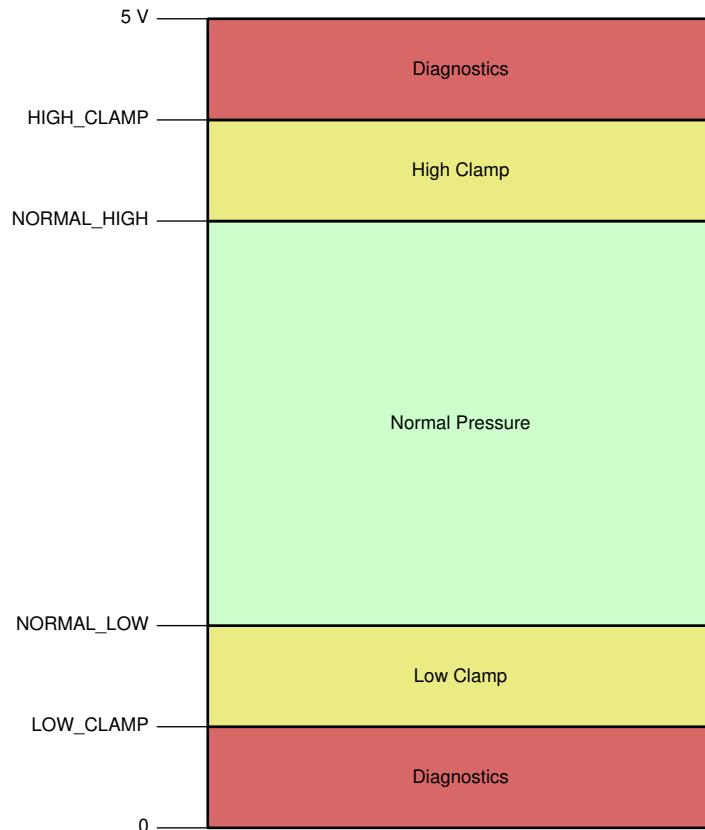

### 6.3.20.3 クランピング

補償の出力はクランプされます。ローおよびハイクランプ値はプログラム可能です。

図 6-26. PGA302 出力のクランピング

### 6.3.20.4 フィルタ

IIR フィルタを 式 5 と 式 6 に示します。

$$w(n) = (a_0 \times \text{OUTPUT}(n) + a_1 \times w(n-1) + a_2 w(n-2)) \quad (5)$$

$$\text{OUTPUT\_FF}(n) = (b_0 \times w(n) + b_1 \times w(n-1) + b_2 w(n-2)) \quad (6)$$

### 6.3.21 リビジョン ID

PGA302 リビジョン ID レジスタを含む。これらのレジスタは読み出し専用で、デバイスのリビジョンを表しており、特定のリビジョンであるすべてのデバイスについて一意のものではありません。

## 6.4 デバイスの機能モード

PGA302 には 2 つの機能モードがあります：のデジタル処理ロジックが有効である場合の動作モードと、デジタル処理ロジックがリセット状態にあるリセットモードです。

実行モードでは、I<sup>2</sup>C および OWI デジタルインターフェイスは、PGA302 デバイスのメモリ空間へのアクセスを許可しません。デバイスとの唯一の通信は、COMBUF 通信バッファレジスタにアクセスすることで確立できます。

リセットモードは一般に、PGA302 デバイス構成に使用されます。このモードでは、I<sup>2</sup>C または OWI インターフェースによるデバイスマモリへの読み書きが許可されます。このモードでは、のデジタル処理ロジックがリセットされます。つまり、デバイスの内部信号処理は実行されないため、デバイス自体から出力データは生成されません。

## 7 レジスタ マップ

### 7.1 プログラマーのモデル

#### 7.1.1 メモリ マップ

図 7-1. メモリ マップ

## 7.1.2 制御およびステータス レジスタ

**表 7-1. PGA302 制御およびステータス レジスタ**

| レジスタ名  | DI ページ<br>アドレス | DI オフセット<br>アドレス | EEPROM アド<br>レス | R/W | D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------|----------------|------------------|-----------------|-----|-----------|----|----|----|----|----|----|----|

| H0_LSB | 該当なし           | 該当なし             | 0x40000000      | RW  | H0 [7:0]  |    |    |    |    |    |    |    |

| H0_MSB | 該当なし           | 該当なし             | 0x40000001      | RW  | H0 [15:8] |    |    |    |    |    |    |    |

| H1_LSB | 該当なし           | 該当なし             | 0x40000002      | RW  | H1 [7:0]  |    |    |    |    |    |    |    |

| H1_MSB | 該当なし           | 該当なし             | 0x40000003      | RW  | H1 [15:8] |    |    |    |    |    |    |    |

| H2_LSB | 該当なし           | 該当なし             | 0x40000004      | RW  | H2 [7:0]  |    |    |    |    |    |    |    |

| H2_MSB | 該当なし           | 該当なし             | 0x40000005      | RW  | H2 [15:8] |    |    |    |    |    |    |    |

| H3_LSB | 該当なし           | 該当なし             | 0x40000006      | RW  | H3 [7:0]  |    |    |    |    |    |    |    |

| H3_MSB | 該当なし           | 該当なし             | 0x40000007      | RW  | H3 [15:8] |    |    |    |    |    |    |    |

| G0_LSB | 該当なし           | 該当なし             | 0x40000008      | RW  | G0 [7:0]  |    |    |    |    |    |    |    |

| G0_MSB | 該当なし           | 該当なし             | 0x40000009      | RW  | G0 [15:8] |    |    |    |    |    |    |    |

| G1_LSB | 該当なし           | 該当なし             | 0x4000000A      | RW  | G1 [7:0]  |    |    |    |    |    |    |    |

| G1_MSB | 該当なし           | 該当なし             | 0x4000000B      | RW  | G1 [15:8] |    |    |    |    |    |    |    |

| G2_LSB | 該当なし           | 該当なし             | 0x4000000C      | RW  | G2 [7:0]  |    |    |    |    |    |    |    |

| G2_MSB | 該当なし           | 該当なし             | 0x4000000D      | RW  | G2 [15:8] |    |    |    |    |    |    |    |

| G3_LSB | 該当なし           | 該当なし             | 0x4000003E      | RW  | G3 [7:0]  |    |    |    |    |    |    |    |

| G3_MSB | 該当なし           | 該当なし             | 0x4000003F      | RW  | G3 [15:8] |    |    |    |    |    |    |    |

| N0_LSB | 該当なし           | 該当なし             | 0x40000010      | RW  | N0 [7:0]  |    |    |    |    |    |    |    |

| N0_MSB | 該当なし           | 該当なし             | 0x40000011      | RW  | N0 [15:8] |    |    |    |    |    |    |    |

| N1_LSB | 該当なし           | 該当なし             | 0x40000012      | RW  | N1 [7:0]  |    |    |    |    |    |    |    |