## SN65HVD888 IEC-ESD 保護機能付きバス極性補正 RS-485 トランシーバ

### 1 特長

- EIA-485 規格の要件を上回る性能

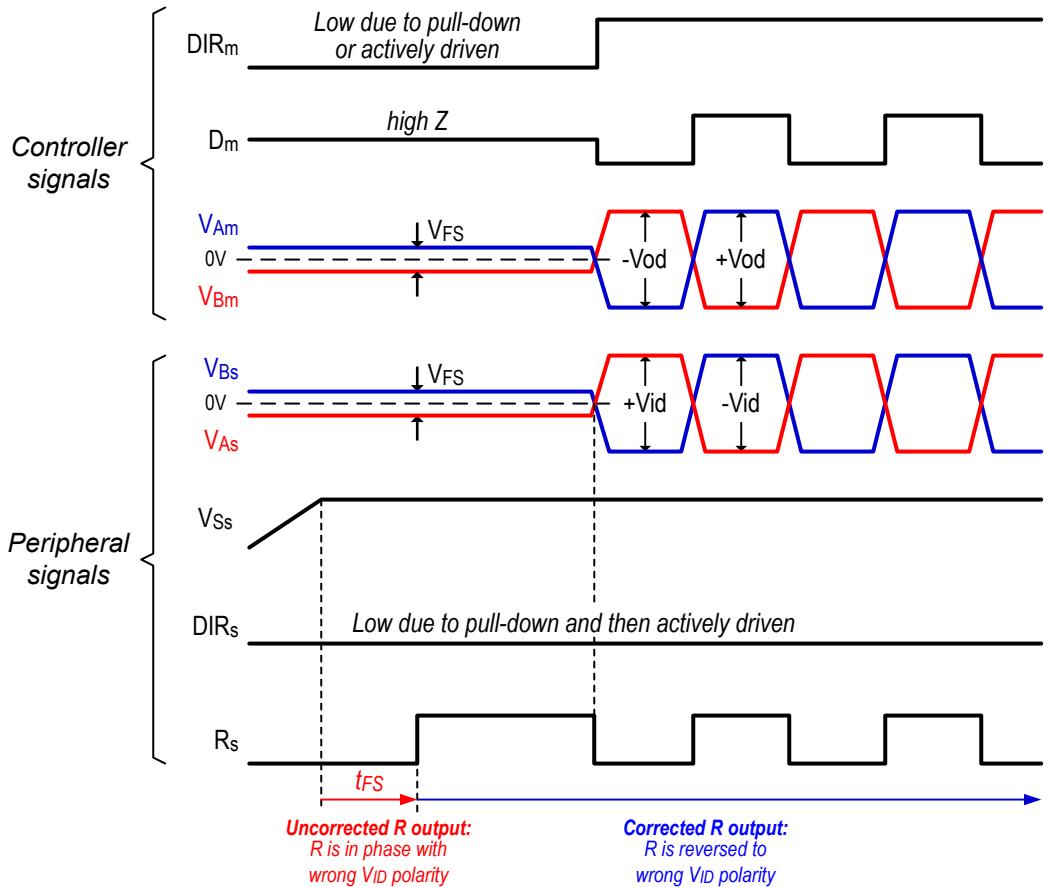

- 76ms ( $t_{FS}$ ) 以内のバス極性補正

- データレート: 300bps ~ 250kbps

- 次の 2 つの構成で動作します:

- フェイルセーフ抵抗のみ

- フェイルセーフ終端抵抗と差動終端抵抗

- バスに最大 256 ノード (1/8 ユニット負荷) を接続可能

- 下位互換性を持つ SOIC-8 パッケージ

- バスピン保護:

- $\pm 16\text{kV}$  の HBM 保護

- $\pm 12\text{kV}$  IEC61000-4-2、接触放電

- +4kV IEC61000-4-4 高速過渡バースト

### 2 アプリケーション

- e メータ ネットワーク

- 産業用オートメーション

- HVAC (エアコン) システム

- DMX512 ネットワーク

- プロセス制御

- バッテリ駆動アプリケーション

- モーション制御

- 通信機器

### 3 説明

SN65HVD888 は、バス極性自動補正機能と過渡保護機能を備えた低消費電力 RS-485 トランシーバです。ホットプラグ時に、76ms 以内のバスアイドル時間で、バス極性の検出と訂正を行います。オンチップ過渡保護により、デバイスは IEC61000 の ESD および EFT 過渡から保護されます。このデバイスは、要求の厳しい産業用途向けに堅牢なドライバとレシーバを備えています。バスピンは静電放電 (ESD) に対して堅牢であり、人体モデル (HBM)、エアギャップ放電、および接触放電の規格に対して高い保護レベルを備えています。

このデバイスは差動ドライバと差動レシーバを組み合わせたもので、単一の 5V 電源により動作します。ドライバの差動出力とレシーバの差動入力は内部的に接続され、半二重 (2 線式バス) 通信に適したバスポートを形成しています。同相電圧範囲が広いことから、このデバイスは長いケーブルを使用するマルチポイント アプリケーションに適しています。SN65HVD888 は SOIC-8 パッケージで提供され、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で特性評価されています。

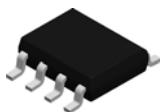

#### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| SN65HVD888 | SOIC (8)             | 4.9mm × 6mm              |

(1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はビンを含みます。

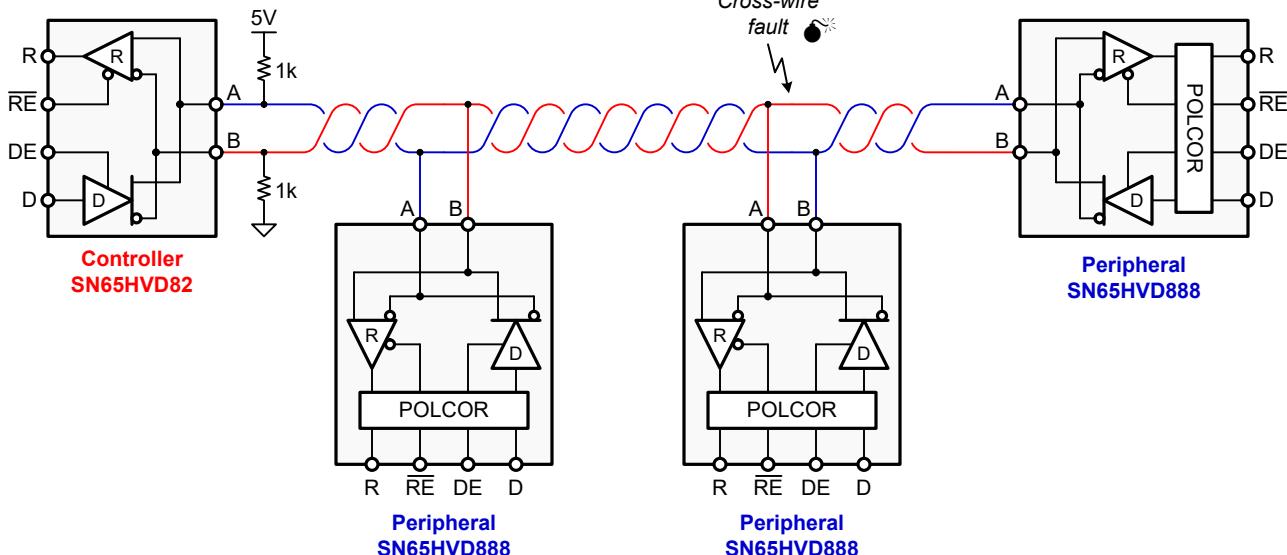

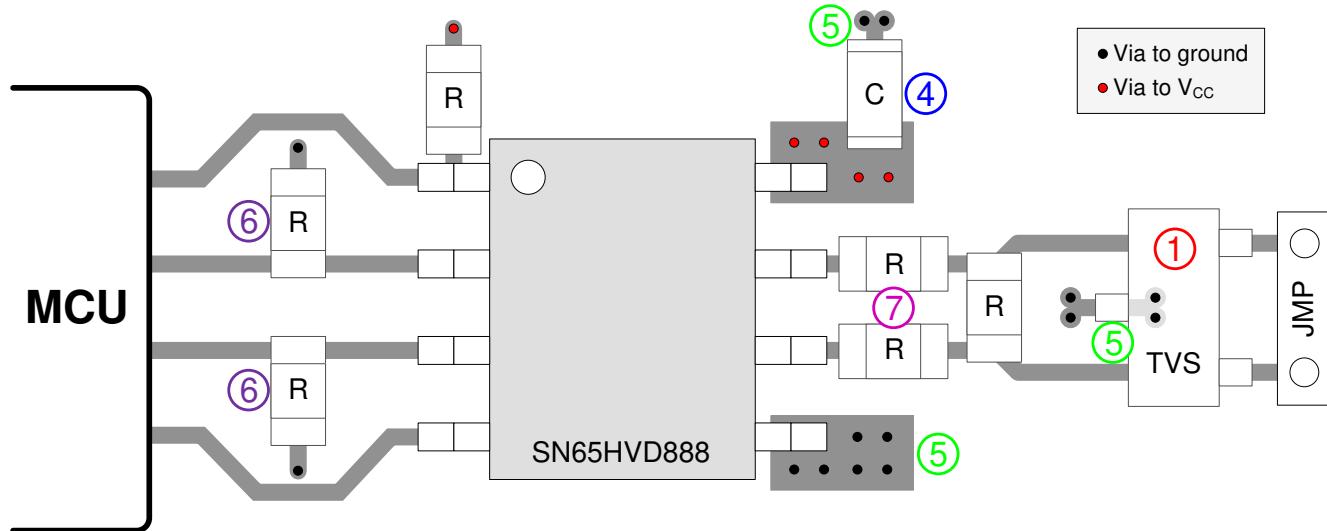

極性訂正機能(POLCOR)を備えた標準的なネットワーク アプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLLSEH3](#)

## 目次

|                       |    |                        |    |

|-----------------------|----|------------------------|----|

| 1 特長                  | 1  | 7.2 機能ブロック図            | 11 |

| 2 アプリケーション            | 1  | 7.3 機能説明               | 11 |

| 3 説明                  | 1  | 7.4 デバイスの機能モード         | 13 |

| 4 ピン構成および機能           | 3  | 8 アプリケーションと実装          | 15 |

| 5 仕様                  | 4  | 8.1 アプリケーション情報         | 15 |

| 5.1 絶対最大定格            | 4  | 8.2 代表的なアプリケーション       | 21 |

| 5.2 ESD 定格: JEDEC の仕様 | 4  | 8.3 電源に関する推奨事項         | 22 |

| 5.3 ESD 定格: IEC の仕様   | 4  | 8.4 レイアウト              | 22 |

| 5.4 推奨動作条件            | 5  | 9 デバイスおよびドキュメントのサポート   | 24 |

| 5.5 熱に関する情報           | 5  | 9.1 デバイス サポート          | 24 |

| 5.6 電気的特性             | 6  | 9.2 ドキュメントの更新通知を受け取る方法 | 24 |

| 5.7 消費電力特性            | 7  | 9.3 サポート・リソース          | 24 |

| 5.8 スイッチング特性          | 7  | 9.4 商標                 | 24 |

| 5.9 代表的特性             | 8  | 9.5 静電気放電に関する注意事項      | 24 |

| 6 パラメータ測定情報           | 9  | 9.6 用語集                | 24 |

| 7 詳細説明                | 11 | 10 改訂履歴                | 24 |

| 7.1 概要                | 11 | 11 メカニカル、パッケージ、および注文情報 | 25 |

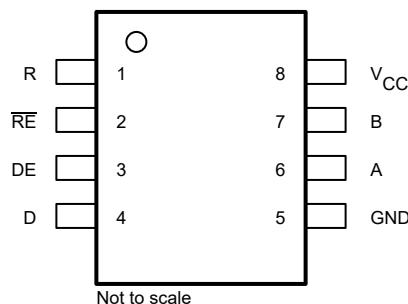

## 4 ピン構成および機能

図 4-1. D パッケージ、8 ピン SOIC

(上面図)

表 4-1. ピンの機能

| ピン              |    | I/O       | 説明                      |

|-----------------|----|-----------|-------------------------|

| 名称              | 番号 |           |                         |

| A               | 6  | バス入力 / 出力 | ドライバ出力またはレシーバ入力 (B を補完) |

| B               | 7  | バス入力 / 出力 | ドライバ出力またはレシーバ入力 (A を補完) |

| D               | 4  | デジタル入力    | ドライバー データ入力             |

| DE              | 3  | デジタル入力    | ドライバイニーブル、アクティブ High    |

| GND             | 5  | リファレンス電位  | ローカル デバイスのグランド          |

| R               | 1  | デジタル出力    | 受信データ出力                 |

| RE              | 2  | デジタル入力    | レシーバイニーブル、アクティブ Low     |

| V <sub>CC</sub> | 8  | 電源        | 4.5V ~ 5.5V を供給         |

## 5 仕様

### 5.1 絶対最大定格

([\(1\)](#) を参照)

|           |                                      | 最小値                  | 最大値 | 単位 |

|-----------|--------------------------------------|----------------------|-----|----|

| $V_{CC}$  | 電源電圧                                 | -0.5                 | 7   | V  |

|           | 任意のロジックピンの入力電圧                       | -0.3                 | 5.7 | V  |

|           | 電圧入力、過渡パルス、A および B、 $100\Omega$ を経由し | -100                 | 100 | V  |

|           | A または B 入力での電流                       | -18                  | 18  | V  |

|           | レシーバ出力電流                             | -24                  | 24  | mA |

|           | 連続総許容損失                              | (熱に関する情報) 表を参照してください |     |    |

| $T_J$     | 接合部温度                                |                      |     |    |

|           |                                      | 170                  |     |    |

| $T_{STG}$ | 保存温度                                 | -65                  | 150 | °C |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス評価であり、このデータシートの「[セクション 5.4](#)」に示された値と等しい、またはそれを超える条件で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格 : JEDEC の仕様

|             |                                                              | 値          | 単位 |

|-------------|--------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <a href="#">(1)</a>    | $\pm 8000$ | V  |

|             | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <a href="#">(2)</a> | $\pm 1500$ |    |

|             | マシン モデル (MM)                                                 | $\pm 100$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 ESD 定格 : IEC の仕様

|             |                                           | 値           | 単位 |

|-------------|-------------------------------------------|-------------|----|

| $V_{(ESD)}$ | IEC 61000-4-2 ESD (接触放電)、バス端子と GND        | $\pm 12000$ | V  |

|             | IEC 61000-4-4 EFT (高速過渡またはバースト) バス端子と GND | $\pm 4000$  |    |

|             | IEC 60749-26 ESD (HBM)、バス端子、GND           | $\pm 16000$ |    |

## 5.4 推奨動作条件

|                      |                                                        | 最小値 | 公称値 | 最大値      | 単位       |

|----------------------|--------------------------------------------------------|-----|-----|----------|----------|

| $V_{CC}$             | 電源電圧                                                   | 4.5 | 5   | 5.5      | V        |

| $V_{ID}$             | 差動入力電圧                                                 | -12 |     | 12       | V        |

| $V_I$                | 任意のバス端子での入力電圧 (個別モードまたは同相モード) <sup>(1)</sup>           | -7  |     | 12       | V        |

| $V_{IH}$             | High レベル入力電圧 (ドライバ、ドライバ イネーブル、レシーバ イネーブル入力)            | 2   |     | $V_{CC}$ | V        |

| $V_{IL}$             | Low レベル入力電圧 (ドライバ、ドライバ イネーブル、レシーバ イネーブル入力)             | 0   |     | 0.8      | V        |

| $I_o$                | 出力電流                                                   | -60 |     | 60       | mA       |

|                      | ドライバ                                                   |     | -8  |          |          |

| $C_L$                | 差動負荷容量                                                 |     | 50  |          | pF       |

| $R_L$                | 差動負荷抵抗                                                 |     | 60  |          | $\Omega$ |

| $1/t_{UI}$           | 信号速度                                                   | 0.3 |     | 250      | kbps     |

| $T_J$                | 接合部温度                                                  | -40 |     | 150      | °C       |

| $T_A$ <sup>(2)</sup> | 自由気流での動作温度 (さらなる情報については <a href="#">セクション 5.5</a> を参照) | -40 |     | 125      | °C       |

(1) このデータシートでは、最も小さい正 (最も大きな負の) 制限を最小として指定する代数的規約を使用します。

(2) 動作は、内部 (接合部) 温度が最大 150°C で規定されています。各アプリケーションでは、内部消費電力による自己発熱を考慮する必要があります。最大接合部温度は、サーマル シャットダウン (TSD) 回路によって内部的に制限され、接合部温度が 170°C に達すると、ドライバ出力はディセーブルされます。

## 5.5 熱に関する情報

| 熱評価基準 <sup>(1)</sup> | <b>SN65HVD888</b>   | 単位    |

|----------------------|---------------------|-------|

|                      | D (SOIC)            |       |

|                      | 8 ピン                |       |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 116.1 |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 60.8  |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 57.1  |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 13.9  |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 56.5  |

(1) 従来および最新の熱測定基準の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準』、[SPRA953](#) を参照してください。

## 5.6 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                                      | テスト条件                                                  |                                             | 最小値  | 標準値            | 最大値 | 単位      |

|------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|------|----------------|-----|---------|

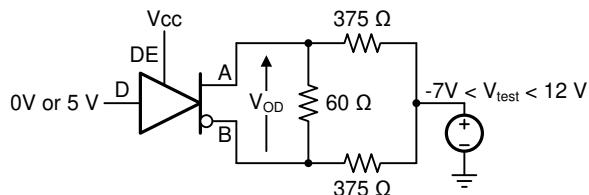

| $ V_{OD} $<br>ドライバの差動出力電圧の大きさ                              | $RL = 60\Omega$ 、各出力に $375\Omega$ 、 $-7V \sim +12V$    | 図 6-1 を参照                                   | 1.5  | 2.5            |     | V       |

|                                                            | $RL = 54\Omega$ (RS-485)                               | 図 6-2 を参照                                   | 1.5  | 2.5            |     |         |

|                                                            | $RL = 100\Omega$ (RS-422)                              | 図 6-2 を参照                                   | 2    | 3              |     |         |

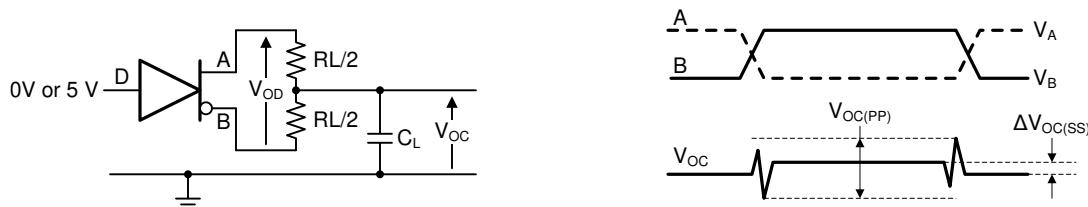

| $\Delta V_{OD} $<br>ドライバの差動出力電圧の大きさの変化                     | $RL = 54\Omega$ 、 $CL = 50pF$                          | 図 6-2 を参照                                   | -0.2 | 0              | 0.2 | V       |

| $V_{OC(ss)}$<br>定常同相出力電圧                                   | 2 本の $27\Omega$ 負荷抵抗の中央                                | 図 6-2 を参照                                   | 1    | $V_{CC} / 2$   | 3   | V       |

| $\Delta V_{OC}$<br>差動ドライバの同相出力電圧の変化                        | 2 本の $27\Omega$ 負荷抵抗の中央                                | 図 6-2 を参照                                   | -0.2 | 0              | 0.2 | mV      |

| $V_{OC(PP)}$<br>ピーク ツー ピークのドライバの同相出力電圧                     | 2 本の $27\Omega$ 負荷抵抗の中央                                | 図 6-2 を参照                                   |      | 850            |     | mV      |

| $C_{OD}$<br>差動出力容量                                         |                                                        |                                             |      | 8              |     | pF      |

| $V_{IT+}$<br>正方向のレシーバ差動入力電圧スレッショルド                         |                                                        |                                             |      | 35             | 100 | mV      |

| $V_{IT-}$<br>負方向のレシーバ差動入力電圧スレッショルド                         |                                                        |                                             | -100 | -35            |     | mV      |

| $V_{HYS}$ (1)<br>( $V_{IT+} - V_{IT-}$ )                   |                                                        |                                             | 40   | 60             |     | mV      |

| $V_{OH}$<br>レシーバの High レベル出力電圧                             | $I_{OH} = -8mA$                                        |                                             | 2.4  | $V_{CC} - 0.3$ |     | V       |

| $V_{OL}$<br>レシーバの Low レベル出力電圧                              | $I_{OL} = 8mA$                                         |                                             |      | 0.2            | 0.4 | V       |

| $I_I$<br>ドライバ入力、ドライバイネーブル、レシーバイネーブル入力電流                    |                                                        |                                             | -2   |                | 2   | $\mu A$ |

| $I_{OZ}$<br>レシーバのハイインピーダンス出力電流                             | $VO = 0V$ または $V_{CC} = \bar{RE} = V_{CC}$             |                                             | -10  |                | 10  | $\mu A$ |

| $ I_{OS} $<br>ドライバの短絡出力電流                                  | $ I_{OS} $ 、 $V_A$ または $V_B = -7V \sim +12V$           |                                             |      |                | 150 | mA      |

| $I_I$<br>バス入力電流 (終端無効)                                     | $V_{CC} = 4.5 \sim 5.5V$ または $V_{CC} = 0V$ 、 $DE = 0V$ | $V_I = 12V$                                 |      | 75             | 125 | $\mu A$ |

|                                                            |                                                        | $V_I = -7V$                                 | -100 | -40            |     |         |

| $I_{CC}$<br>消費電流 (静止時)<br>$-40^{\circ}C \sim 85^{\circ}C$  | ドライバとレシーバはイネーブル                                        | $DE = V_{CC}$ 、 $RE = GND$ 、無負荷             |      | 750            | 900 | $\mu A$ |

|                                                            | ドライバはイネーブル、レシーバはディセーブル                                 | $DE = V_{CC}$ 、 $RE = V_{CC}$ 、無負荷          |      |                | 650 |         |

|                                                            | ドライバはディセーブル、レシーバはイネーブル                                 | $DE = GND$ 、 $RE = GND$ 、無負荷                |      |                | 750 |         |

|                                                            | ドライバとレシーバはディセーブル                                       | $DE = GND$ 、 $D = GND$ 、 $RE = V_{CC}$ 、無負荷 |      | 0.4            | 5   |         |

| $I_{CC}$<br>消費電流 (静止時)<br>$-40^{\circ}C \sim 125^{\circ}C$ | ドライバとレシーバはイネーブル                                        | $DE = V_{CC}$ 、 $RE = GND$ 、無負荷             |      | 750            | 990 | $\mu A$ |

|                                                            | ドライバはイネーブル、レシーバはディセーブル                                 | $DE = V_{CC}$ 、 $RE = V_{CC}$ 、無負荷          |      |                | 715 |         |

|                                                            | ドライバはディセーブル、レシーバはイネーブル                                 | $DE = GND$ 、 $RE = GND$ 、無負荷                |      |                | 825 |         |

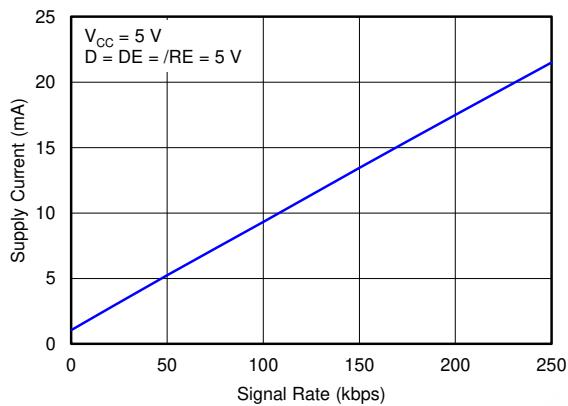

| 消費電流 (動的)                                                  | 図 5-3 を参照                                              |                                             |      |                |     |         |

(1) 特定の条件では、 $V_{IT+}$  は  $V_{IT-}$  よりも  $V_{HYS}$  以上高いことが指定されます。

## 5.7 消費電力特性

| パラメータ |                                                                                                               | テスト条件                                               | 値                                                   | 単位  |    |

|-------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----|----|

| PD    | 電力消費<br>ドライバおよびレシーバ有効、<br>$V_{CC} = 5.5V$ 、 $T_J = 150^{\circ}C$ 、<br>デューティ比 50% の方形波信号、<br>信号速度 250kbps の場合： | 未終端                                                 | $R_L = 300\Omega$ 、<br>$C_L = 50 \text{ pF}$ (ドライバ) | 164 | mW |

|       | RS-422 の負荷                                                                                                    | $R_L = 100\Omega$ 、<br>$C_L = 50 \text{ pF}$ (ドライバ) | 247                                                 |     |    |

|       | RS-485 の負荷                                                                                                    | $R_L = 54\Omega$ 、<br>$C_L = 50 \text{ pF}$ (ドライバ)  | 316                                                 |     |    |

## 5.8 スイッチング特性

3.3ms > ビット時間 > 4μs (特に記述のない限り)

| パラメータ                                                |                                      | テスト条件                      | 最小値                 | 標準値 | 最大値  | 単位   |    |

|------------------------------------------------------|--------------------------------------|----------------------------|---------------------|-----|------|------|----|

| <b>ドライバ</b>                                          |                                      |                            |                     |     |      |      |    |

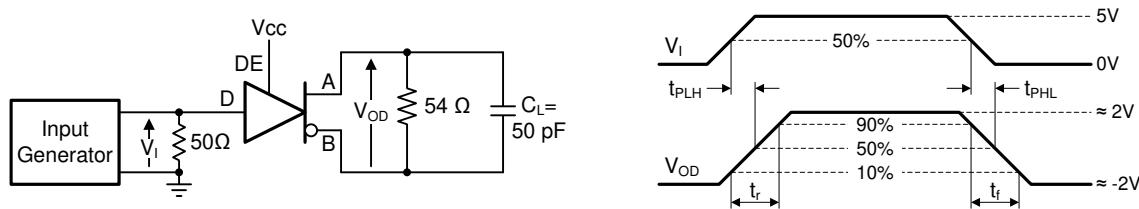

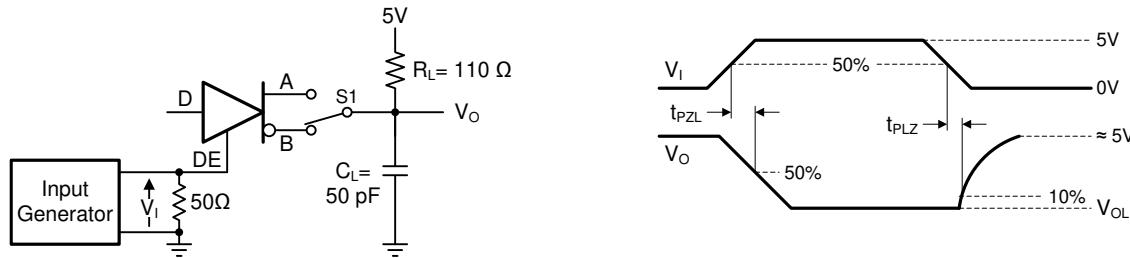

| $t_r, t_f$                                           | ドライバの差動出力の立ち上がり時間と立ち下がり時間            | $RL = 54\Omega, CL = 50pF$ | 図 6-3 を参照           | 400 | 700  | 1200 | ns |

| $t_{PHL}, t_{PLH}$                                   | ドライバの伝搬遅延                            | $RL = 54\Omega, CL = 50pF$ | 図 6-3 を参照           | 90  | 700  | 1000 | ns |

| $t_{SK(P)}$                                          | ドライバのパルス スキュー、 $ t_{PHL} - t_{PLH} $ | $RL = 54\Omega, CL = 50pF$ | 図 6-3 を参照           | 25  | 200  | ns   |    |

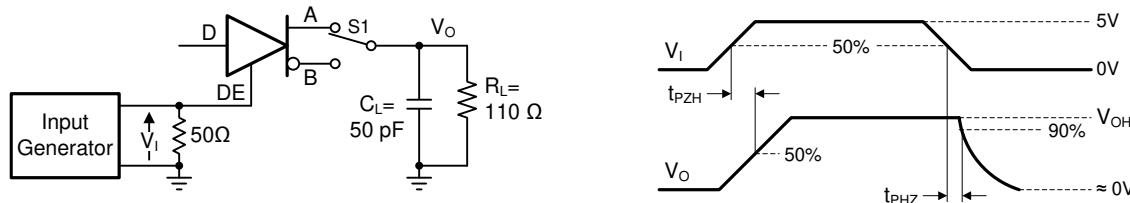

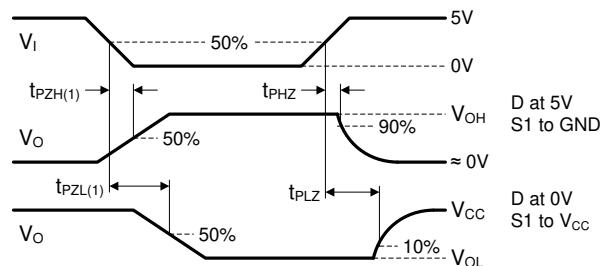

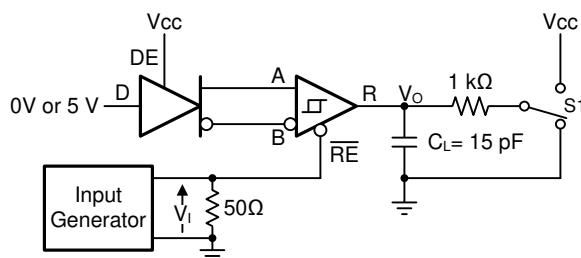

| $t_{PHZ}, t_{PLZ}$                                   | ドライバ ディスエーブル時間                       |                            | 図 6-4 および 図 6-5 を参照 | 50  | 500  | ns   |    |

| $t_{PHZ}, t_{PLZ}$                                   | ドライバ イネーブル時間                         | レシーバ イネーブル                 | 図 6-4 および 図 6-5 を参照 | 500 | 1000 | ns   |    |

|                                                      |                                      | レシーバが無効                    | 図 6-4 および 図 6-5 を参照 | 3   | 9    | μs   |    |

| <b>レシーバ</b>                                          |                                      |                            |                     |     |      |      |    |

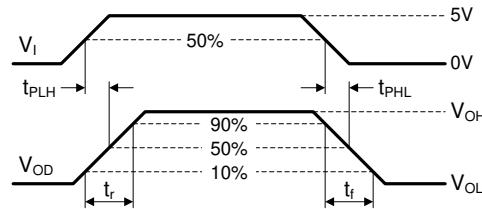

| $t_r, t_f$                                           | レシーバの出力立ち上がりおよび立ち下がり時間               | $CL = 15pF$                | 図 6-6 を参照           | 18  | 30   | ns   |    |

| $t_{PHL}, t_{PLH}$                                   | レシーバの伝搬遅延時間                          | $CL = 15pF$                | 図 6-6 を参照           | 85  | 195  | ns   |    |

| $t_{SK(P)}$                                          | レシーバのパルス スキュー、 $ t_{PHL} - t_{PLH} $ | $CL = 15pF$                | 図 6-6 を参照           | 1   | 15   | ns   |    |

| $t_{PHZ}, t_{PLZ}$                                   | レシーバ ディスエーブル時間                       |                            |                     | 50  | 500  |      |    |

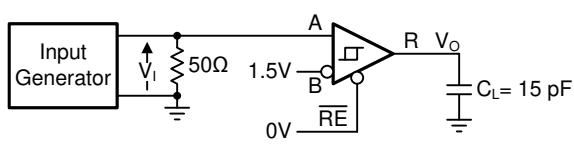

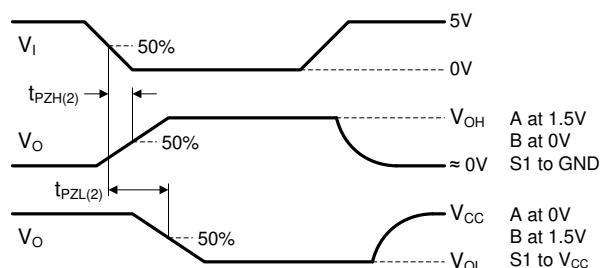

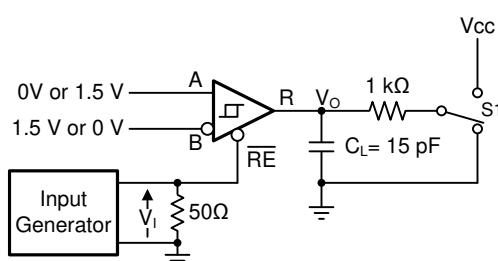

| $t_{PZL(1)}, t_{PZH(1)}$<br>$t_{PZL(2)}, t_{PZH(2)}$ | レシーバ イネーブル時間                         | ドライバがイネーブル                 | 図 6-7 を参照           | 20  | 130  | ns   |    |

|                                                      |                                      | ドライバが無効                    | 図 6-8 を参照           | 2   | 8    | μs   |    |

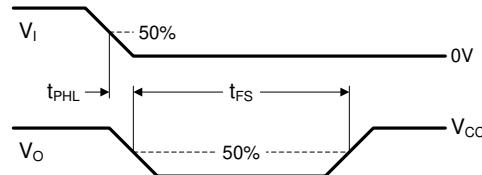

| $t_{FS}$                                             | バスのフェイルセーフ時間                         | ドライバが無効                    | 図 6-9 を参照           | 44  | 58   | 76   | ms |

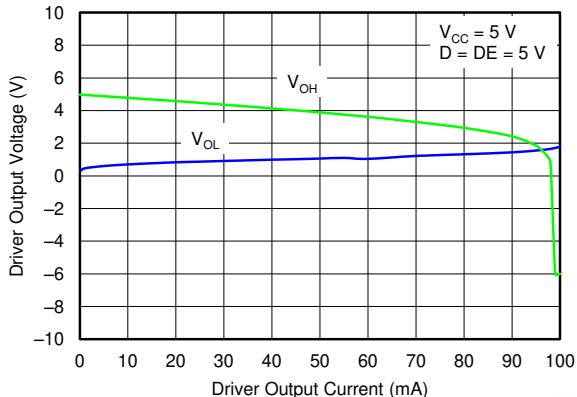

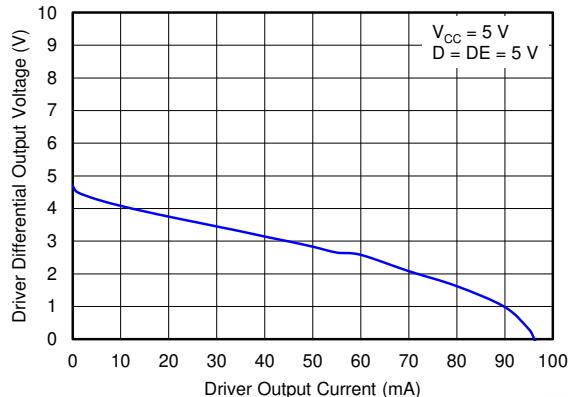

## 5.9 代表的特性

図 5-1. ドライバ出力電圧とドライバ出力電流との関係

図 5-2. ドライバ差動出力電圧とドライバ出力電流との関係

図 5-3. 電源電流と信号速度との関係

## 6 パラメータ測定情報

ドライバ

図 6-1. 同相モード負荷でのドライバ差動出力電圧の測定

図 6-2. RS-485 負荷を使用したドライバ差動および同相モード出力の測定

図 6-3. ドライバの差動出力の立ち上がり / 立ち下がり時間と伝搬遅延の測定

図 6-4. アクティブハイ出力およびプルダウン負荷でのドライバのイネーブルおよびディセーブル時間の測定

図 6-5. アクティブ Low 出力およびプルアップ負荷でのドライバのイネーブルおよびディセーブル時間の測定

レシーバ

図 6-6. レシーバ出力の立ち上がり / 立ち下がり時間と伝搬遅延の測定

図 6-7. ドライバを有効にした状態でのレシーバのイネーブル / ディセーブル時間の測定

図 6-8. ドライバを無効にした状態でのレシーバのイネーブル時間の測定

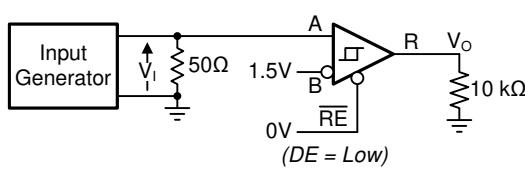

図 6-9. ドライバ無効時のレシーバ極性補正時間の測定

## 7 詳細説明

### 7.1 概要

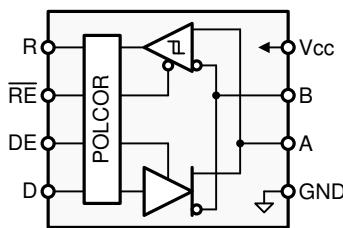

SN65HVD888 デバイスは、ツイストペア ケーブルなどの制御インピーダンス伝送媒体上で最大 250kbps のデータ伝送に適したハーフ デュプレックス RS-485 トランシーバです。このデバイスは高レベルの内部過渡保護を備え、IEC 61000-4-2 に基づく 12kV の ESD ストライクおよび IEC 61000-4-4 に基づく 4kV の EFT 過渡に対しても、損傷なく耐性を発揮します。SN65HVD82 はバス入力電流が低いため、最大 256 台まで同一の RS-485 バスに接続可能です。このデバイスには自動極性補正機能があり、スタートアップ時のバスの誤配線を検出し、必要に応じてバスの A と B を半分に交換します。

### 7.2 機能ブロック図

Copyright © 2018, Texas Instruments Incorporated

### 7.3 機能説明

#### 7.3.1 低消費電力のスタンバイ モード

ドライバとレシーバの両方が無効化された場合 (DE = Low, RE = High)、デバイスはスタンバイ モードに入ります。イネーブル入力が無効状態になる時間がごく短い場合 (例: 100ns 未満)、デバイスはスタンバイ モードに入らず、ドライバまたはレシーバのイネーブル処理中に SN65HVD888 がスタンバイ モードへ移行するのを防ぎます。イネーブル入力が 300ns 以上の間無効状態に保持された場合にのみ、デバイスは低消費電力スタンバイ モードに入ります。このモードでは内部回路の大部分が電源オフとなり、定常状態の電源電流は通常 400nA 未満になります。ドライバまたはレシーバのいずれかが再度イネーブルになると、内部回路がアクティブになります。V<sub>CC</sub> の立ち上げ時、デバイスがドライバおよびレシーバ無効モードに設定されている場合、容量の充電効果により I<sub>CC</sub> 無効電流が 5μA を超えることがあります。この条件は、V<sub>CC</sub> パワーアップ時にのみ発生します。

#### 7.3.2 バス極性補正

SN65HVD888 は、クロスワイヤ故障によって生じたバス信号の極性の誤りを自動的に修正します。バスの極性を検出するには、以下の 3 つの条件すべてを満たす必要があります:

- フェイル セーフ バイアス ネットワーク (一般にコントローラ ノードで) は、バスの信号極性を定義する必要があります

- ペリフェラル ノードはレシーバをイネーブルにし、ドライバをディセーブルにする必要があります ( $\overline{RE} = DE = Low$ )

- バスはフェイルセーフ時間 t<sub>FS-max</sub> の間アイドル状態にする必要があります

フェイルセーフ時間が経過すると、極性補正が完了し、受信チャネルと送信チャネルの両方に適用されます。バス極性のステータスはトランシーバ内でラッ奇され、その後のデータ送信時に保持されます。

#### 注

データ ストリングの持続時間が 0 または 1 秒連続して t<sub>FS-min</sub> を超えると、誤って極性補正がトリガされる可能性があるため、回避する必要があります。

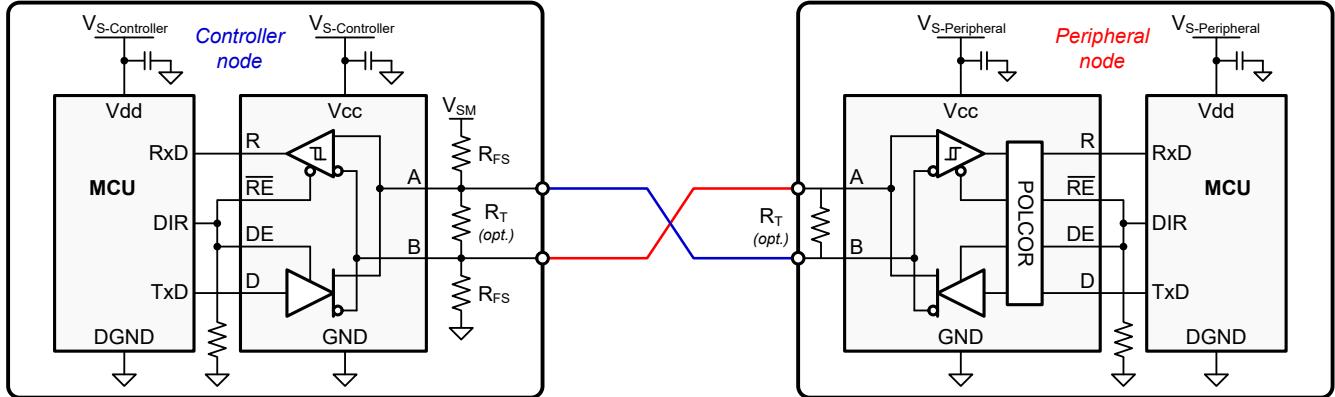

図 7-1 に、コントローラ ノードとペリフェラル ノードとの間の単純なポイントツー ポイント データリンクを示します。フェイル セーフ バイアス ネットワークを備えたコントローラ ノードがバス上の信号極性を決定するため、SN65HVD82 のような極性補正機能のない RS-485 トランシーバで十分です。その他のすべてのバスノードは通常ペリフェラルとして動作し、極性補正機能付きの SN65HVD888 トランシーバが必要です。

図 7-1. クロスワイヤ故障のあるポイントツー ポイント データ リンク

データ転送を開始する前に、コントローラトランシーバは、ペリフェラルトランシーバの最大フェイルセーフ時間  $t_{FS-max}$  を超える期間、アイドル状態にする必要があります。このアイドル時間は、方向制御ライン DIR を Low に駆動することで実現されます。一定時間  $t > t_{FS-max}$  が経過すると、コントローラはデータの送信を開始します。

コントローラとペリフェラル間に示されたクロスワイヤ故障のため、ペリフェラルノードは極性が反転したバス信号を受信します。ペリフェラルノードがバスに接続されたばかりの場合、電源投入時に方向制御ピンはプルダウンされ、その後ペリフェラル MCU によって積極的に Low に駆動されます。極性補正は、ペリフェラル電源が確立されるとすぐに開始し、約 44~76ms 後に終了します。

図 7-2. データ送信前の極性補正タイミング

初期状態では、ペリフェラル受信回路は入力に正しいバス極性が印加されていると仮定し、極性反転は行いません。バスフェイルセーフ電圧は逆極性なので、ペリフェラル レシーバの出力  $R_S$  は Low になります。 $t_{FS}$  が経過し、レシーバが誤ったバス極性を検出すると、内部 POLCOR ロジックが入力信号を反転し、 $R_S$  が High になります。

この時点では、極性を反転したすべての受信バスデータの極性がトランシーバ内で訂正されます。極性補正は送信経路にも適用されるため、ペリフェラル MCU から送信されたデータは POLCOR ロジックによって反転され、その後ドライバに入力されます。

ペリフェラル MCU からの反転データは、バス内のクロスワイヤ故障によって再度反転され、コントローラ側で正しいバス極性が復元されます。

このプロセスは、デバイスが起動し、誤ったバス極性を検出するたびに繰り返されます。

## 7.4 デバイスの機能モード

**表 7-1. ドライバ ピン機能**

| 入力                           | イネーブル | 出力 |    | 説明                   |

|------------------------------|-------|----|----|----------------------|

|                              |       | D  | DE |                      |

| <b>通常モード</b>                 |       |    |    |                      |

| H                            | H     | H  | L  | バスをアクティブに High に駆動   |

| L                            | H     | L  | H  | バスをアクティブに Low に駆動    |

| X                            | L     | Z  | Z  | ドライバが無効              |

| X                            | オープン  | Z  | Z  | ドライバはデフォルトで無効になっています |

| オープン                         | H     | H  | L  | バスをアクティブに High に駆動   |

| <b>極性補正モード<sup>(1)</sup></b> |       |    |    |                      |

| H                            | H     | L  | H  | バスをアクティブに Low に駆動    |

| L                            | H     | H  | L  | バスをアクティブに High に駆動   |

| X                            | L     | Z  | Z  | ドライバが無効              |

| X                            | オープン  | Z  | Z  | ドライバはデフォルトで無効になっています |

| オープン                         | H     | L  | H  | バスをアクティブに Low に駆動    |

- (1) 極性補正モードに移行するのは、 $V_{ID} < V_{IT-}$  および  $t > t_{FS}$  および  $DE = \text{low}$  のときです。 $\overline{RE}$  が Low から High になると、この状態はラッチされます。

**表 7-2. レシーバ ピンの機能**

| 差動入力                         | イネーブル           | 出力 | 説明               |

|------------------------------|-----------------|----|------------------|

| $V_{ID} = V_A - V_B$         | $\overline{RE}$ | R  |                  |

| <b>通常モード</b>                 |                 |    |                  |

| $V_{IT+} < V_{ID}$           | L               | H  | 有効なバスを High で受信  |

| $V_{IT-} < V_{ID} < V_{IT+}$ | L               | ?  | 不定のバス状態          |

| $V_{ID} < V_{IT-}$           | L               | L  | 有効なバスを Low で受信し  |

| X                            | H               | Z  | レシーバが無効          |

| X                            | オープン            | Z  | レシーバが無効          |

| オープン、短絡、アイドル パス              | L               | ?  | 不定のバス状態          |

| <b>極性補正モード<sup>(1)</sup></b> |                 |    |                  |

| $V_{IT+} < V_{ID}$           | L               | L  | 有効なバスを Low で受信し  |

| $V_{IT-} < V_{ID} < V_{IT+}$ | L               | ?  | 不定のバス状態          |

| $V_{ID} < V_{IT-}$           | L               | H  | 受信極性訂正されたバス High |

| X                            | H               | Z  | レシーバが無効          |

| X                            | オープン            | Z  | レシーバが無効          |

表 7-2. レシーバ ピンの機能 (続き)

| 差動入力                 | イネーブル | 出力 | 説明      |

|----------------------|-------|----|---------|

| $V_{ID} = V_A - V_B$ | RE    | R  |         |

| オープン、短絡、アイドル バス      | L     | ?  | 不定のバス状態 |

- (1) 極性補正モードに移行するのは、 $V_{ID} < V_{IT-}$  および  $t > t_{FS}$  および  $DE = \text{low}$  のときです。 $\overline{RE}$  が Low から High になると、この状態はラッチされます。

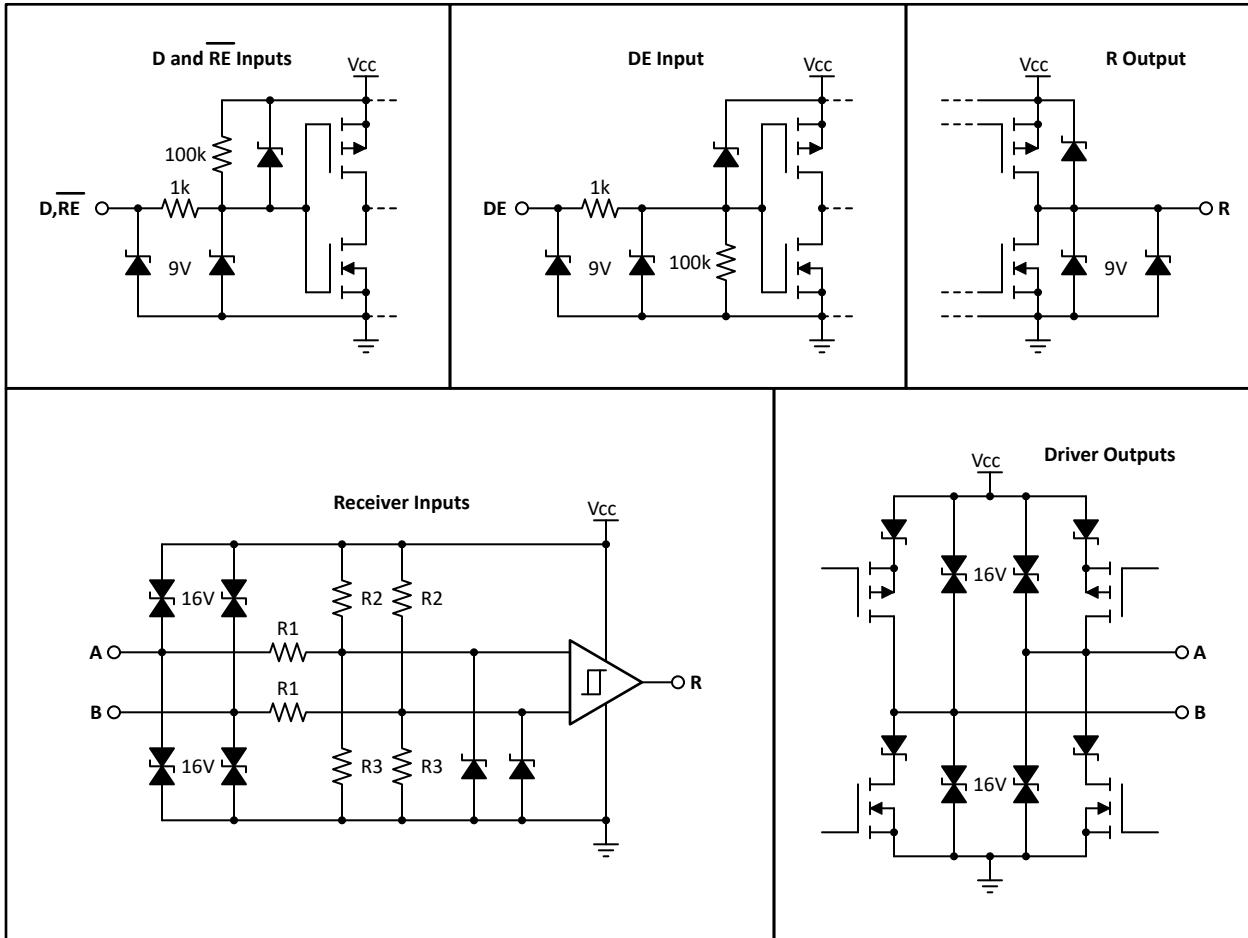

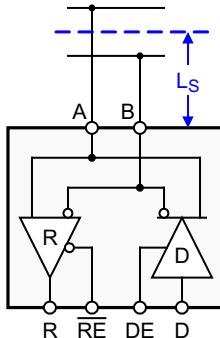

図 7-3. 等価な入力および出力回路図

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

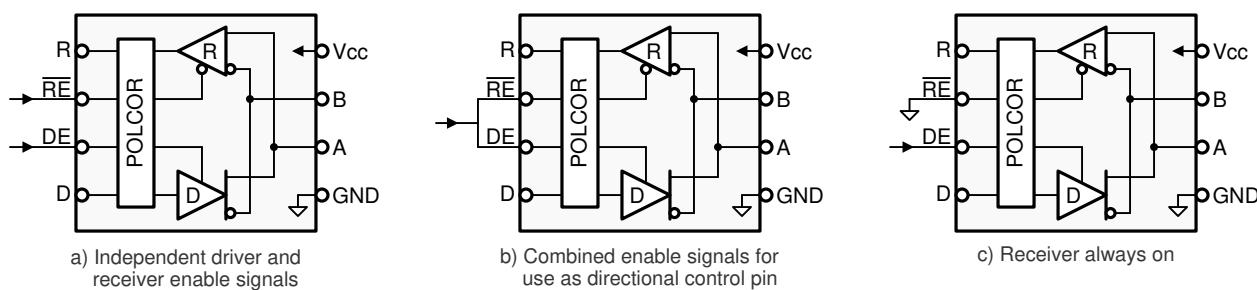

#### 8.1.1 デバイス設定

SN65HVD888 は、単一の  $5V \pm 10\%$  電源で動作するハーフ デュプレックス RS-485 トランシーバです。ドライバおよびレシーバのイネーブル ピンによって、さまざまな動作モードを構成できます。

Copyright © 2018, Texas Instruments Incorporated

図 8-1. トランシーバの設定

独立したイネーブル ラインを使用すると、ドライバとレシーバを個別にオン/オフできるため、最も柔軟な制御が可能になります。この構成では 2 本の制御ラインが必要ですが、ドライバがデータを送信しているかどうかに関わらず、バストラフィックを選択的に受信できます。SN65HVD888 が低消費電力スタンバイ モードに入れるのはこの構成のみであり、ドライバとレシーバを同時に無効化できるためです。

イネーブル信号を組み合わせると、単一の方向制御信号を形成することでコントローラとのインターフェイスが簡素化されます。したがって、方向制御ラインが High のとき、トランシーバはドライバとして構成され、Low のときはレシーバとして動作します。

レシーバ イネーブルをグランドに接続し、ドライバ イネーブル入力のみを制御する方法でも、制御ラインは 1 本だけで済みます。この構成では、ノードは他のノードからバスに送信されたデータを受信するだけでなく、自らがバスに送信したデータも受信するため、正しいデータが送信されたかを検証できます。

#### 8.1.2 バス設計

RS-485 バスは、バス ケーブルと並列に接続する複数のトランシーバで構成されています。ラインの反射を除去するために、各ケーブルの端は終端抵抗  $RT$  で終端します。この抵抗の値は、ケーブルの特性インピーダンス  $Z_0$  と一致します。この方式は並列終端と呼ばれ、比較的長いケーブル長にわたって高いデータ レートを実現できます。

一般的に使用されるケーブルは、 $Z_0 = 100\Omega$  の低コスト CAT-5 ケーブルのような 非シールド ツイストペア (UTP) や、 $Z_0 = 120\Omega$  の RS-485 ケーブルです。代表的なケーブル サイズは AWG22 と AWG24 です。

最大バス長は通常 4000 フィート (1200m) とされ、これは終端抵抗値に近いケーブル抵抗を持つ AWG24 ケーブルの長さを表します。その結果、バス信号は半分、すなわち 6dB 減衰します。実際に使用可能な最大ケーブル長は、信号速度、ケーブル特性、および環境条件によって異なります。

**表 8-1. フェイルセーフ ネットワークとバス終端機能を搭載した VID**

| V <sub>CC</sub> | R <sub>L</sub> 差動終端 | R <sub>FS</sub> プルアップ | R <sub>FS</sub> プルダウン | V <sub>ID</sub> |

|-----------------|---------------------|-----------------------|-----------------------|-----------------|

| 5V              | 54 Ω                | 560 Ω                 | 560 Ω                 | 230mV           |

|                 |                     | 1KΩ                   | 1KΩ                   | 131mV           |

|                 |                     | 4.7KΩ                 | 4.7KΩ                 | 29mV            |

|                 |                     | 10KΩ                  | 10KΩ                  | 13mV            |

アイドル バス状態でもフェイルセーフ動作を保証するため、外部フェイルセーフ抵抗ネットワークの使用が必須です。バスがアクティブに駆動されていないとき、差動レシーバ入力がフローティングになり、レシーバ出力がランダムな出力になります。適切なフェイルセーフ ネットワークがあると、レシーバ入力が強制的に V<sub>IT</sub> スレッショルドを超えると、SN65HVD888 レシーバ出力は強制的にフェイルセーフ (high) 状態になります。**表 8-1** に、54Ω の差動バス終端を持つ各種フェイルセーフ回路の差動入力電圧 (V<sub>ID</sub>) を示します。

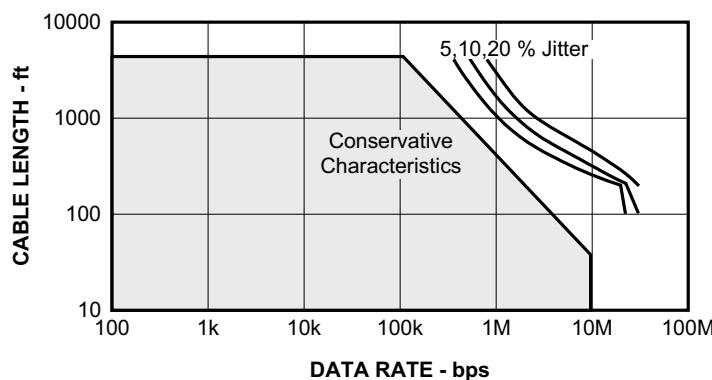

### 8.1.3 ケーブル長とデータ レートとの関係

データ レートとケーブル長の間には逆関係があります。つまり、データ レートが高くなると、ケーブル長が短くなります。逆に、データ レートが低くなると、ケーブル長が長くなります。ほとんどの RS-485 システムは 10kbps から 100kbps のデータ レートを使用しますが、e-メータリングのようなアプリケーションでは、距離が 4000 ft を超えても最大 250kbps のレートで動作することがよくあります。最大 5 または 10% の小信号ジッタを許容することで、より長い距離を実現できます。

**図 8-2. ケーブル長とデータ レート特性との関係**

### 8.1.4 スタブ長

ノードをバスに接続するときは、トランシーバ入力とケーブルトランクの間の距離 (スタブと呼ばれます) をできるだけ短くする必要があります。短距離である必要があるのは、スタブが非終端のバス線分となり、長すぎると反射を生じる可能性があるためです。一般的なガイドラインとして、スタブの電気的長さ、つまり往復遅延は、ドライバの立ち上がり時間の 1/10 未満にする必要があります。これにより、式 1 に示すように、物理的なスタブの最大長が得られます。

$$L_{Stub} \leq 0.1 \times t_r \times v \times c \quad (1)$$

ここで、

- t<sub>r</sub> は、ドライバの 10/90 の立ち上がり時間です

- c は光の速度 ( $3 \times 10^8$  m/s または  $9.8 \times 10^8$  ft/s) です

- v はケーブルの信号伝搬速度 ( $v = 78\%$ ) または配線の信号伝搬速度 ( $v = 45\%$ ) であり、光速 c に対する比率です

式 1 に基づき、最小立ち上がり時間 400ns で、SN65HVD888 の最大ケーブル スタブ長を式 2 に示します。

$$L_{Stub} \leq 0.1 \times 400 \times 10^{-9} \times 3 \times 10^8 \times 0.78 = 9.4 \text{ m (or } 30.6 \text{ ft}) \quad (2)$$

図 8-3. スタブ長

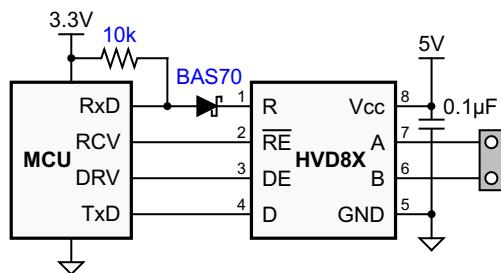

#### 8.1.5 3 ~ 5V インターフェイス

SN65HVD888 と 3V コントローラのインターフェイスは容易です。トランシーバの 5V ロジック入力は 3V の入力信号を受け付けるため、コントローラの I/O に直接接続できます。ただし、5V レシーバ出力 R をコントローラ入力に接続する場合は、ショットキーダイオードと 10k 抵抗によるレベルシフトが必要です(図 8-4 を参照)。R が high の場合、ダイオードは逆バイアスとなり、コントローラの電源電位が RxD 入力に印加されます。R が low のとき、ダイオードは順バイアス状態で導通します。この場合、コントローラの RxD 入力には、0.2V のダイオードの順方向電圧のみが存在します。

図 8-4. 3-V から 5-V へのインターフェイス

#### 8.1.6 ノイズ耐性

標準的な RS -485 トランシーバの入力感度は  $\pm 200\text{mV}$  です。差動入力電圧  $V_{ID}$  が  $+200\text{mV}$  を超えると、レシーバ出力は High になります。 $V_{ID} < -200\text{mV}$  の場合、レシーバ出力は Low になります。

SN65HVD888 トランシーバは、35mV の代表的な正方向入力スレッショルドと 40mV の最小ヒステリシスを持ち、高い受信ノイズ耐性を実現します。したがって、ノイズの多い入力条件が発生した場合、レシーバの出力が high から low に変化しないように、最大  $40\text{mV}_{PP}$  の差動ノイズ電圧が存在する可能性があります。

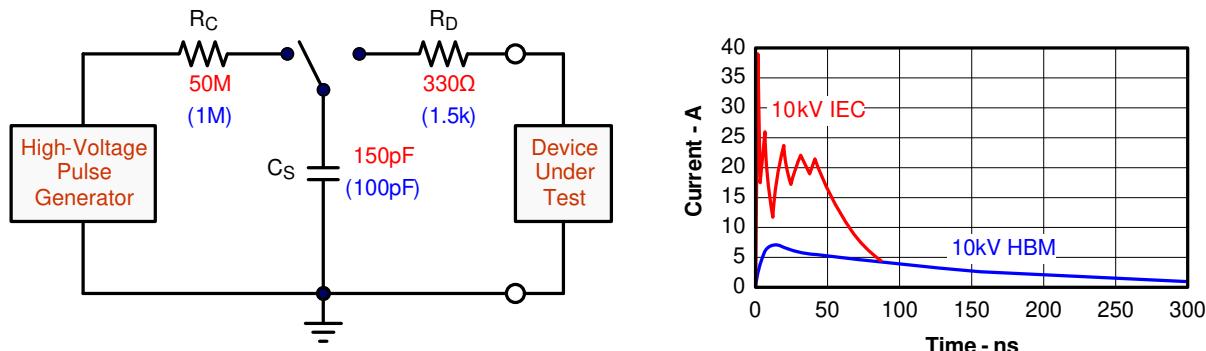

#### 8.1.7 過渡保護

SN65HVD888 トランシーバ ファミリのバス端子は、 $\pm 16\text{kV}$  HBM および  $\pm 12\text{kV}$  IEC61000-4-2 接触放電に対するオンチップ ESD 保護を備えています。国際電気標準会議 (IEC) の ESD テストは、HBM ESD テストよりはるかに厳しいものです。IEC モデルでは、充電容量  $C_{(S)}$  が 50% 高く、放電抵抗  $R_{(D)}$  が 78% 低いため、HBM モデルよりも放電電流が大幅に大きくなります。

IEC 61000-4-2 規格で規定されているように、接触放電は推奨される過渡保護試験方法です。IEC のエアギャップ試験は接触試験に比べて再現性が低いものの、エア放電の保護レベルは接触放電試験の結果から推定されます。

Copyright © 2016, Texas Instruments Incorporated

**図 8-5. HBM と IEC の ESD モデルと比較時の電流 (HBM 値は括弧内)**

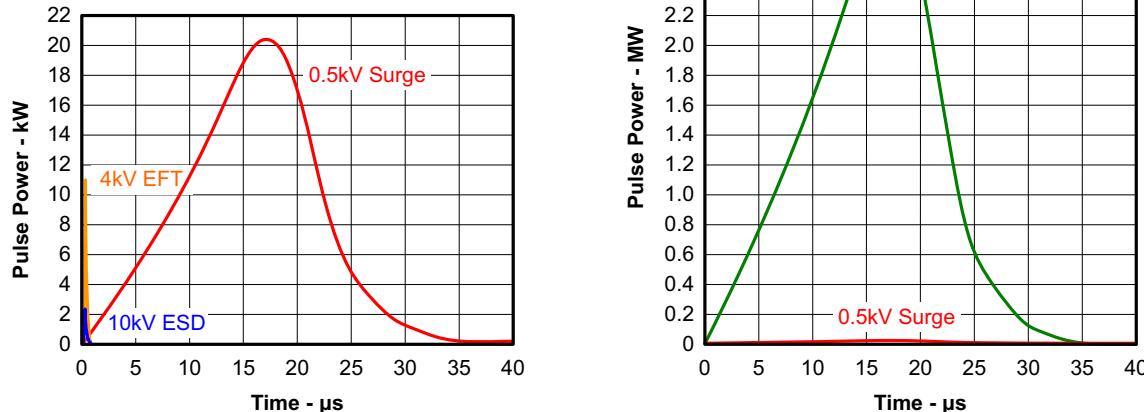

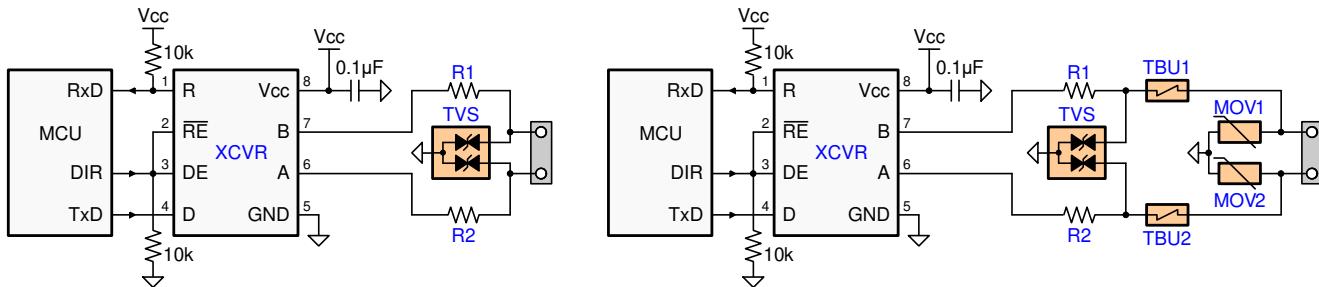

IEC ESD 保護のオンチップ実装により、機器の堅牢性が大幅に向上します。一般的な放電イベントは、コネクタやケーブルに人が接触したことが原因で発生します。設計者は、サーボ過渡と呼ばれる長期的な過渡に対する保護を実装することもできます。図 6-9 は、ESD と電気的高速過渡 (EFT) の過渡に加えて、短時間および長時間のサーボ過渡に対する保護を実現する 2 つの回路設計を推奨しています。表 8-2 に、外部保護デバイスの部品表を示します。

一般に、EFT はリレー接触型バウンスまたは誘導性負荷の中断によって発生します。サーボ過渡は多くの場合、落雷 (電圧と電流を誘導する直接衝撃または間接衝撃)、または負荷の変化や短絡のスイッチングを含む電源システムのスイッチングに起因します。これらの過渡は、ファクトリ オートメーションや電力グリッド システムなどの産業用環境でよく発生します。

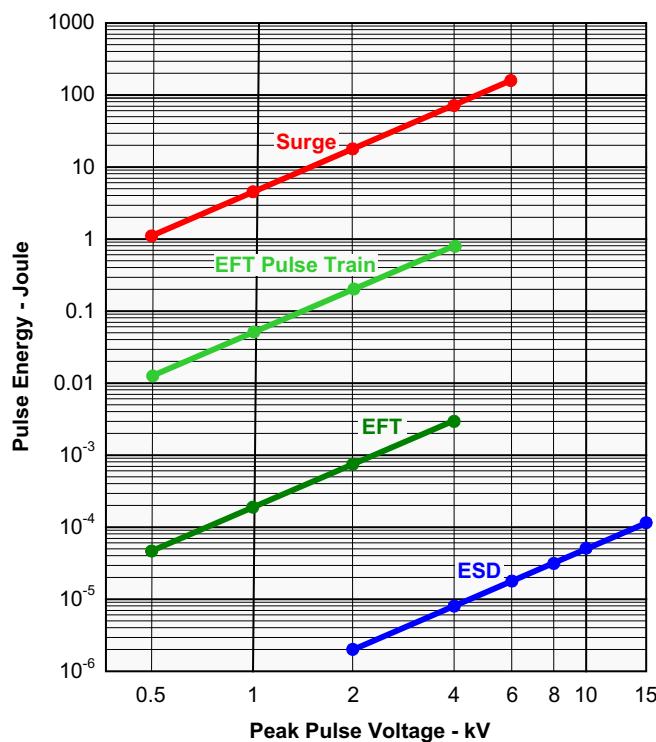

図 8-6 は、EFT のパルス電力とサーボ過渡を、IEC ESD 過渡に起因する電力と比較したものです。図 8-6 の左側の図で、左下隅にある小さな青い突起は 10kV の ESD 過渡の電力を示しています。これはすでに大きい EFT の電力スパイクと比べてごく小さく、まして 500V のサーボ過渡と比べるとさらに微小です。この種の過渡電力は、産業用およびプロセス自動化における工場環境をよく反映しています。図 8-6 の右側の図は、発電システムや電力網システムの e-マーティリング用途で発生する可能性が高い 6kV サーボ過渡の莫大な電力を、前述の 500V サーボ過渡と比較しています。

**注**

パルス電力の単位は kW から MW に変わり、その結果 500V サーボ過渡の電力はほとんどスケールから外れてしまいます。

**図 8-6. ESD、EFT、サーボ過渡の電力比較**

サーボ過渡の場合、高エネルギーであることはパルス幅が長く、パルス電力の減衰が遅いことで示されます

トランシーバの内部保護セルに投入される過渡の電気エネルギーは、熱エネルギーに変換されます。この熱エネルギーによって保護セルは加熱され、文字通り破壊されます。その結果、トランシーバ自体も破壊されます。図 8-7 は、単一の ESD、EFT、サーボ過渡、および適合性試験で一般的に印加される EFT パルス列における過渡エネルギーの大きな違いを示しています。

図 8-7. 過渡エネルギーの比較

表 8-2. 部品表

| デバイス       | 機能                                       | 発注型番               | 製造元    |

|------------|------------------------------------------|--------------------|--------|

| XCVR       | 5V、250kbps RS-485 トランシーバ                 | SN65HVD888         | TI     |

| R1, R2     | 10Ω、パルス耐性のある厚膜抵抗                         | CRCW0603010RJNEAHP | Vishay |

| TVS        | 双方向 400W 過渡サプレッサ                         | CDSOT23-SM712      | Bourns |

| TBU1, TBU2 | 双方向。                                     | TBU-CA-065-200-WH  | Bourns |

| MOV1, MOV2 | 200mA トランジエント ブロッキング ユニット 200V、金属酸化膜バリスタ | MOV-10D201K        | Bourns |

1. 「サードパーティー製品に関する免責事項」をご覧ください。

Copyright © 2016, Texas Instruments Incorporated

図 8-8. ESD、EFT、サージ過渡に対する過渡保護

図 8-8 に示される左側の回路は 500V 以上の過渡に対するサージ保護を提供し、右側の保護回路は 5kV のサージ過渡に耐えることができます。

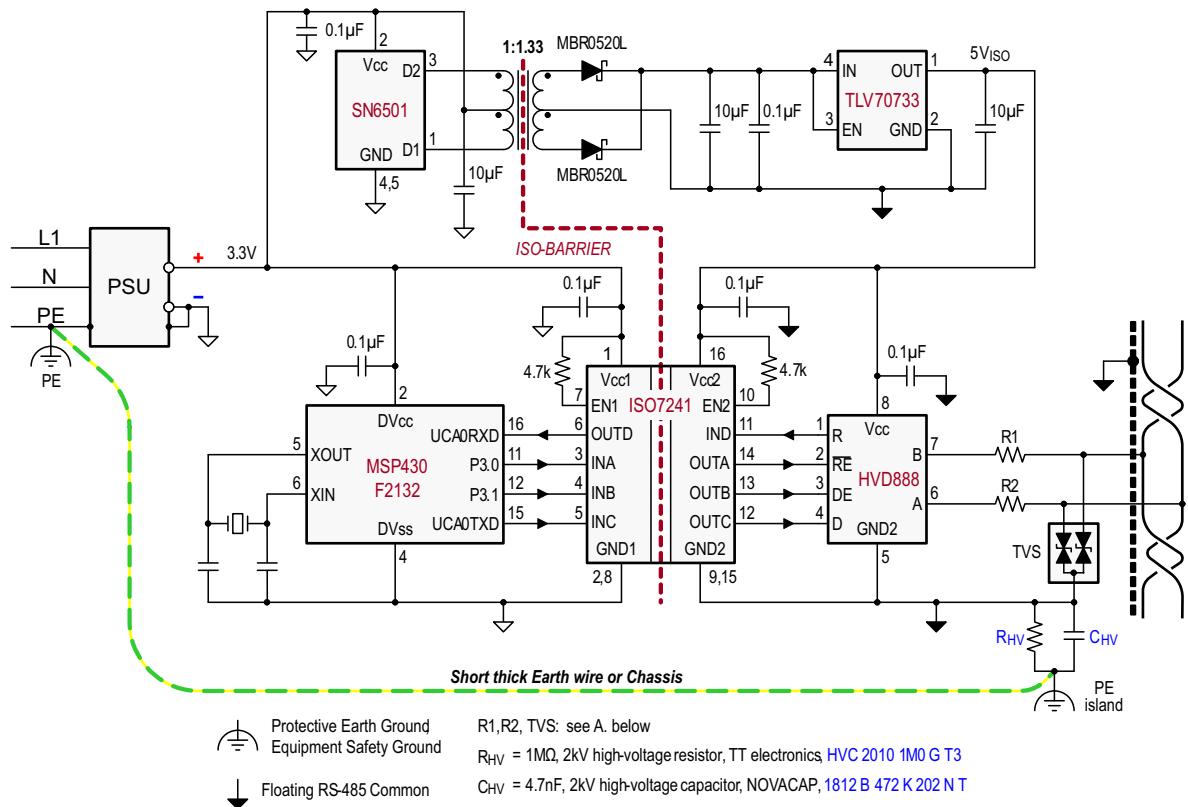

## 8.2 代表的なアプリケーション

多くの RS-485 ネットワークでは、不要なグランド ループの形成と、それによる信号品質への悪影響を防ぐために、絶縁化されたバス ノードが使用されています。絶縁化されたバス ノードには通常、マイコンが含まれており、マルチチャネル デジタル アイソレータ (図 8-9) を介してバストランシーバに接続されます。

A. 表 8-2 を参照してください。

図 8-9. 過渡保護機能付きの絶縁型バス ノード

### 8.2.1 設計要件

サンプル アプリケーション: 過渡保護機能付きの絶縁型バス ノード

- RS-485 準拠のバスインターフェイス (フルロード条件下 — すなわち最大ノード数が接続され、かつ  $120\Omega$  終端が 2 本ある状態 — で、少なくとも 1.5V の差動信号振幅が必要)。

- 信号ラインおよび電源ラインの両方のガルバニック絶縁。

- (IEC 61000-4-2 準拠の) 12kV ESD 過渡および (IEC 61000-4-4 準拠の) 4kV EFT に対して耐性を有します。

- (ハーフ デュプレックス通信における) 競合防止のため、バス上のデータフローを完全に制御できます。

### 8.2.2 詳細な設計手順

電力絶縁は、ブッシュプル型トランジスタドライバ SN6501 と、低コスト LDO の TLV70733 により実現されます。

信号絶縁には、クワッド デジタル アイソレータ ISO7241 を使用します。イネーブル入力 EN1 と EN2 は、 $4.7k\Omega$  の抵抗でプルアップされており、過渡イベント発生時の入力電流を制限します。

過渡保護は 図 8-8 (左図の回路) と同様ですが、追加された高耐圧コンデンサにより、フローティング RS-485 コモンの過渡エネルギーが保護接地 (PE) に迂回されます。この迂回は、バス上のノイズ過渡が通常、アース電位を基準として扱われるため必要となります。

$R_{HV}$  は高電圧抵抗のことと、一部のアプリケーションではバリスタを意味します。この抵抗は、通常動作中にフローティング グラウンドが危険な電位に帶電するのを防ぐために適用されます。

高速過渡によって  $C_{HV}$  を高電位に充電する可能性が想定される場合、 $C_{HV}$  を高速放電するために、抵抗の代わりにバリスタが使用されることがあります。

PE アイランドは、電源ユニット (PSU) の入り口でこのアイランドを PE グラウンドに接続する短く太いアース線を設けるための、PCB 上の銅アイランドを表しています。

シャーシを使用する機器設計では、通常、PE 接続はシャーシ自体を経由して行われます。通常、PE 導体は一方の端でシャーシに接続され、高電圧コンポーネント  $C_{HV}$  および  $R_{HV}$  はもう一方の端のシャーシに接続されます。

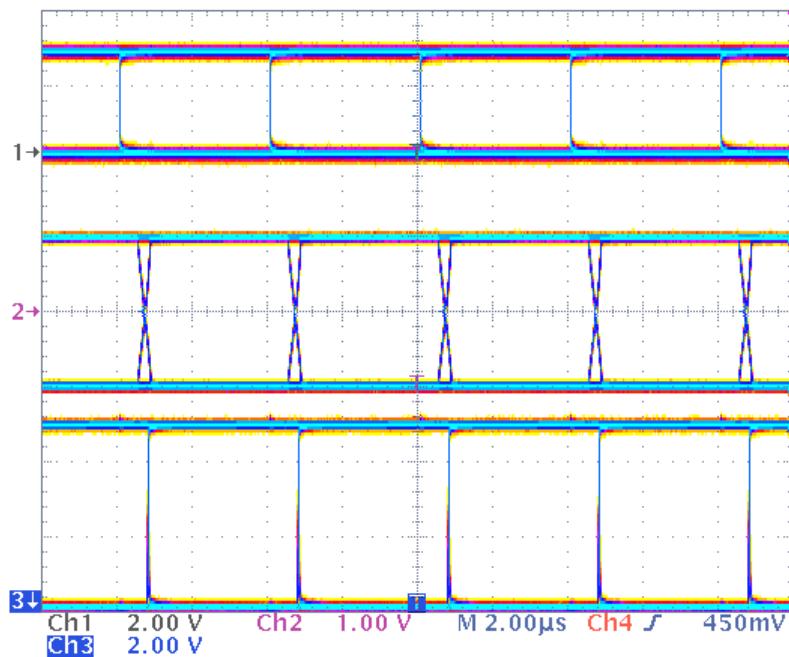

### 8.2.3 アプリケーション曲線

図 8-10. SN65HVD888 の D 入力 (上)、差動出力 (中央)、および R 出力 (下)、250kbps 動作、PRBS データ パターン

## 8.3 電源に関する推奨事項

すべてのデータレートと電源電圧で信頼性の高い動作を確保するため、電源ピンのできるだけ近くに  $100\text{nF}$  セラミックコンデンサを配置して、各電源をデカッピングする必要があります。これにより、スイッチ モード電源の出力に存在する電源電圧リップルを低減し、PCB 電源プレーンの抵抗とインダクタンスを補償するのに役立ちます。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

#### 8.4.1.1 過渡保護の設計およびレイアウトに関する考慮事項

ESD および EFT の過渡現象は、およそ 3MHz から 3GHz にわたる広い周波数帯域を持つため、PCB 設計時には高周波レイアウト技術を適用する必要があります。

PCB 設計を成功させるためには、保護回路の設計を念頭に置いて始める必要があります。

1. 保護回路をバス コネクタの近くに配置し、ノイズ過渡が基板に伝播するのを防止します。

2.  $V_{cc}$  およびグランド プレーンを使用して、低インダクタンスを実現します。高周波電流は、最小インダクタンスの経路を通り、最小インピーダンスの経路を通るわけではないことに注意してください。

3. 信号路の方向に向けて保護部品を設計します。過渡電流を信号路から強制的に迂回させて保護デバイスに到達させないでください。

4. 基板上のトランシーバ、UART、コントローラ IC の V<sub>CC</sub> ピンにできるだけ近い位置に、100nF ~ 220nF のバイパスコンデンサを配置します。

5. 実効ビアインダクタンスを最小化するため、バイパスコンデンサと保護デバイスの V<sub>CC</sub> およびグランド接続には少なくとも 2 つのビアを使用します。

6. 過渡イベント時にこれらのラインのノイズ電流を制限するには、イネーブル ラインに 1k ~ 10k のプルアップまたはプルダウン抵抗を使用します。

7. TVS クランプ電圧がトランシーババスピンの規定最大電圧よりも高い場合は、A と B の各バスラインにパルス耐性抵抗を挿入します。これらの抵抗は、トランシーバへの残留クランプ電流を制限し、ラッチアップを防止します。

- 純粋な TVS 保護は最大 1kV のサージ過渡に十分ですが、過渡電圧が高い場合は、数百ボルトのクランプ電圧に過渡を低減する金属酸化物バリスタ (MOV) と、過渡電流を 200mA に制限する過渡ブロッキング ユニット (TBU) が必要です。

#### 8.4.2 レイアウト例

図 8-11. SN65HVD888 のレイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。右上の【アラートを受け取る】をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

[テキサス・インスツルメンツ E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision C (January 2018) to Revision D (September 2025)</b> | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| • すべての古い用語をコントローラおよびペリフェラルに変更。                                               | 1           |

| • 図 7-3 の R 出力の 1K 抵抗を削除                                                     | 13          |

| <b>Changes from Revision B (June 2017) to Revision C (January 2018)</b> | <b>Page</b> |

|-------------------------------------------------------------------------|-------------|

| • 「製品情報」表をパッケージ情報表に変更                                                   | 1           |

| • 3.3V <sub>ISO</sub> を「5V <sub>ISO</sub> 」に変更 (図 8-9)                  | 21          |

| <b>Changes from Revision A (September 2015) to Revision B (June 2017)</b>                                                                       | <b>Page</b> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 「概要」のテキストを「 $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ の特性を規定」から: 説明において $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ の範囲で特製評価済みに変更..... | 1           |

| • $t_A$ の MAX 値を変更: $85^{\circ}\text{C}$ から $125^{\circ}\text{C}$ に変更 (推奨動作条件表).....                                                            | 5           |

| • 電気的特性表において、 $I_{CC}$ を $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ および $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ の温度範囲の値を示すよう変更.....   | 6           |

| <b>Changes from Revision * (July 2013) to Revision A (September 2015)</b>                                                                                                 | <b>Page</b> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加..... | 1           |

| • JEDEC 規格 22 の試験方法 A114 (HBM) を $\pm 4\text{kV}$ から $\pm 8\text{kV}$ に変更。.....                                                                                           | 4           |

| • JEDEC 規格 22 の試験方法 A115 (機械モデル) を $\pm 100\text{V}$ から $\pm 200\text{V}$ に変更。.....                                                                                       | 4           |

| • 図 7-3 の「D/ $\overline{RE}$ 入力」回路および「DE 入力」回路を変更.....                                                                                                                    | 13          |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">SN65HVD888D</a>  | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

| SN65HVD888D.A                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

| SN65HVD888D.B                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

| <a href="#">SN65HVD888DR</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

| SN65HVD888DR.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

| SN65HVD888DR.B               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | HVD888              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

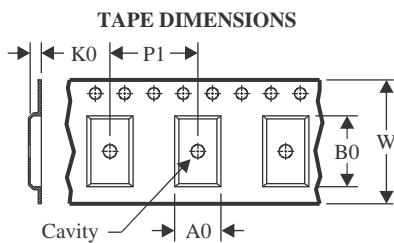

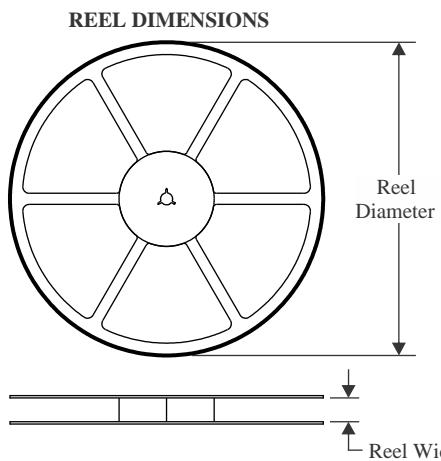

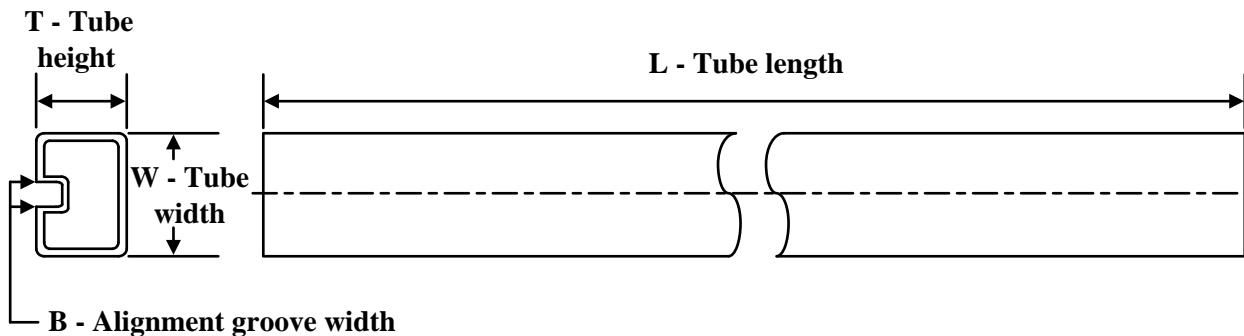

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

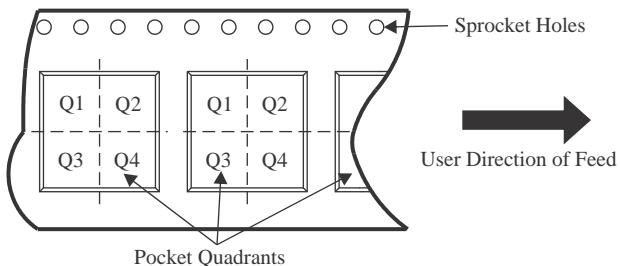

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| SN65HVD888DR | SOIC         | D               | 8    | 2500 | 330.0              | 12.5               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVD888DR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| SN65HVD888D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| SN65HVD888D.A | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| SN65HVD888D.B | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

D0008A

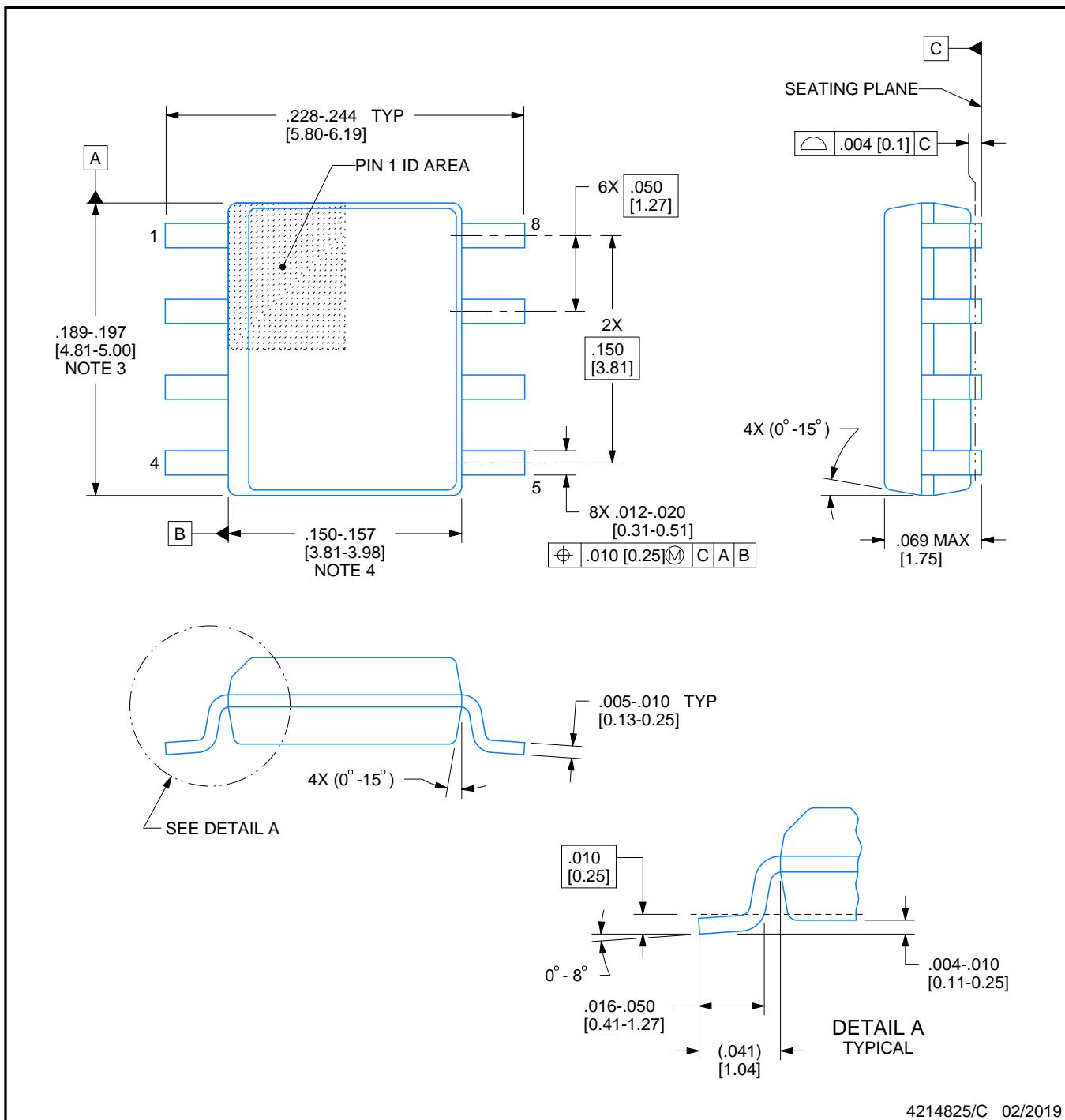

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches.

- Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

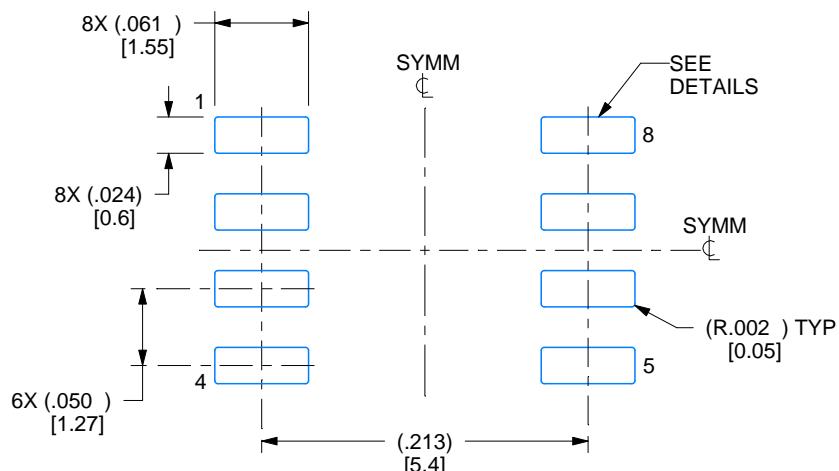

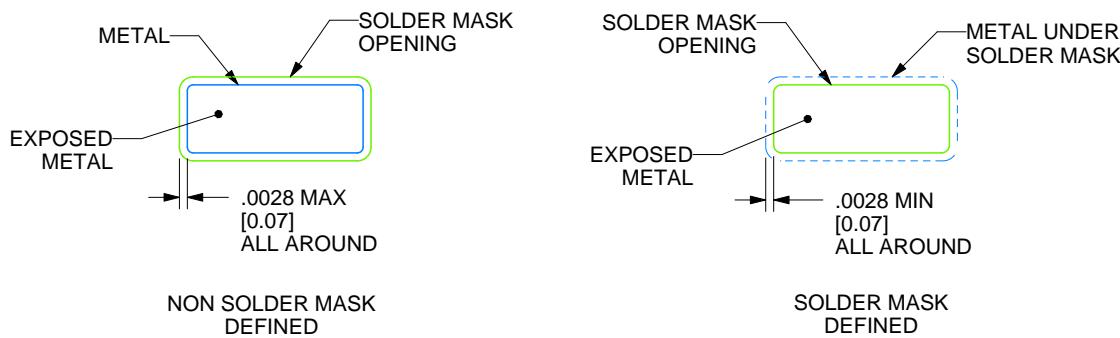

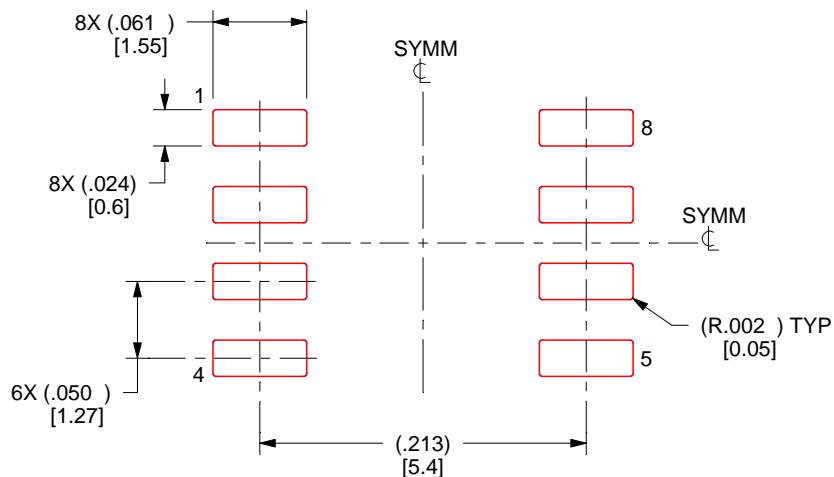

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月