**SN75LVPE5412**

# SN75LVPE5412 PCle® 5.0 32Gbps 4 チャネル リニア リドライバ、1:2 デマルチ プレクサ

## 1 特長

Texas

INSTRUMENTS

- 1:2 デマルチプレクサを内蔵したクワッド チャネル PCle 5.0 リニア リドライバ / リピータ

- PCIe, UPI, CCIX, NVLink, DisplayPort, SAS, SATA、XFI 互換のプロトコル非依存リニアドライバ

- 単一の 3.3V 電源 PCIe 電源レール使用可能

- 4 チャネル動作用 720mW 低起動消費電力

- ヒートシンク不要

- 16GHz において最高 24dB のイコライゼーションを実

- 8~16GHz に対して -10dB の卓越した RX/TX 差動 RL

- PRBS データによる 55fs RMS の低い追加 RJ

- 短いレイテンシ: 90ps

- 自動レシーバ検出機能と、PCIeリンクトレーニングの シームレスなサポート

- ピン制御または SMBus/I<sup>2</sup>C によるデバイス構成

- ピンによる Demux の選択

- 内部電圧レギュレータによる電源ノイズへの耐性

- 信頼性の高い製造を実現するための高速な製造テスト

- 1 つまたは複数のデバイスを使用して x4、x8、x16 バ ス幅をサポート

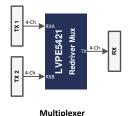

- マルチプレクサ製品 SN75LVPE5421

- 温度範囲:-40℃~85℃

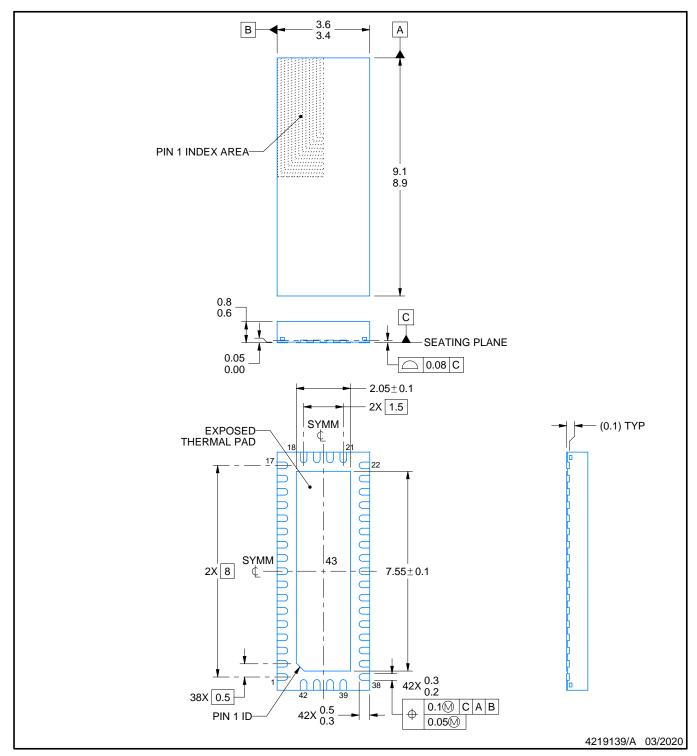

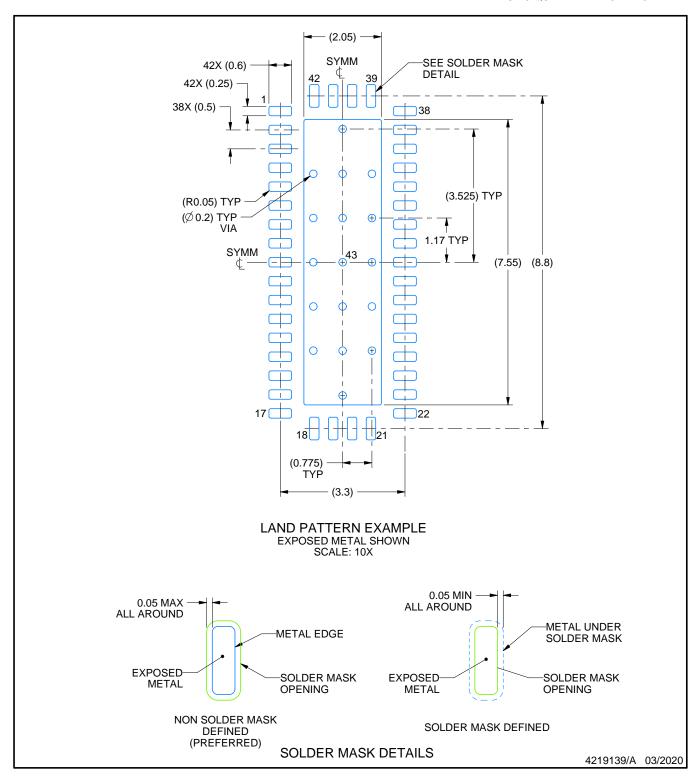

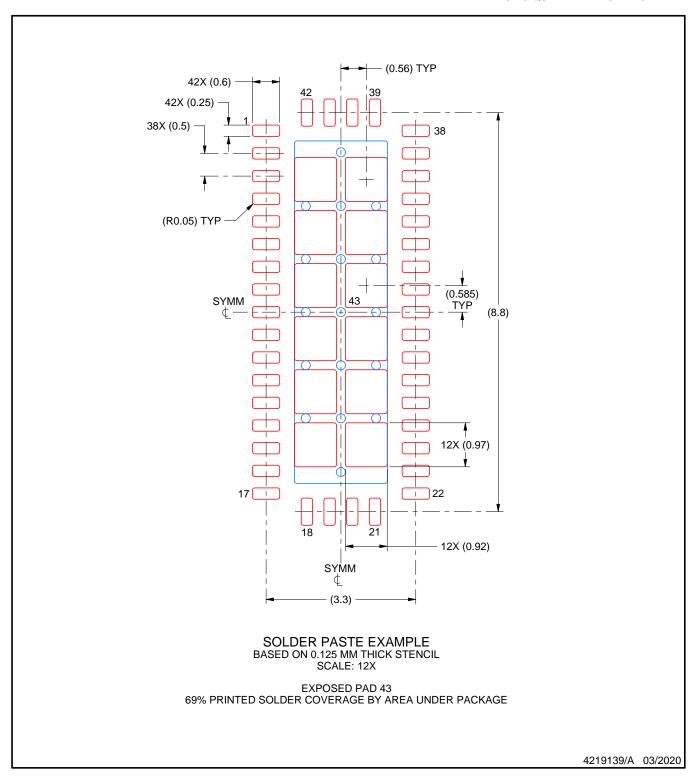

- 3.5mm × 9mm 42 ピン、0.5mm ピッチの WQFN パッ ケージ

## 2 アプリケーション

- デスクトップ PC とマザーボード

- ディスプレイ・パネル、ゲーム・コンソール

- ラック・サーバー、マイクロサーバー、タワー・サーバー

- 高性能コンピューティング、ハードウェア・アクセラレ

- データ・ストレージ、ネットワーク接続ストレージ

- ストレージ・エリア・ネットワーク (SAN) とホスト・バス・ア ダプタ (HBA) カード

- ネットワーク・インターフェイス・カード (NIC)

## 3 概要

SN75LVPE5412 は、4 チャネルのリニア リドライバで、デ マルチプレクサ (demux) が内蔵されています。低消費電 カ高性能リニア リドライバは、PCIe 5.0 や最大 32Gbps の他のインターフェイスをサポートするよう設計されていま

SN75LVPE5412 レシーバは、連続時間リニア イコライザ (CTLE)を搭載し、高周波数での昇圧を実現しています。 イコライザは、相互接続媒体 (例:PCB 配線、ケーブル) に起因する符号間干渉 (ISI) によって完全に閉じた入力 アイ パターンを開くことができます。 PCIe リンク トレーニン グの間に、リニア リドライバとルート コンプレックス (RC) -エンドポイント (EP) 間受動チャネルが全体として最良の 送信および受信イコライゼーション設定を持つように調整 され、結果的に最良の電気的リンクが得られます。チャネ ル間のクロストークが小さく、追加ジッタが小さく、リターン ロスが非常に優れているため、デバイスはリンク内でほぼ パッシブ要素になることができます。このデバイスは、内部 リニア電圧レギュレータを備えており、高速データ パス用 にクリーンな電源を供給し、基板上の電源ノイズへの高い 耐性を実現します。

SN75LVPE5412 は、量産時に高速テストを実施してお り、信頼性の高い大量生産に対応しています。また、この デバイスは AC および DC ゲインの変動が小さいため、大 容量プラットフォームを展開する際の一貫したイコライゼー ションにも対応しています。

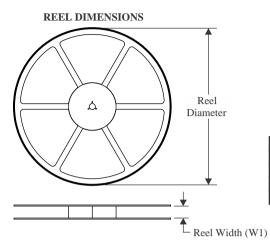

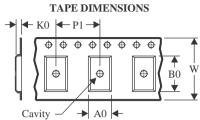

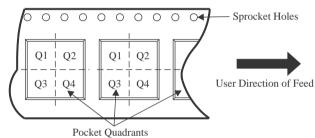

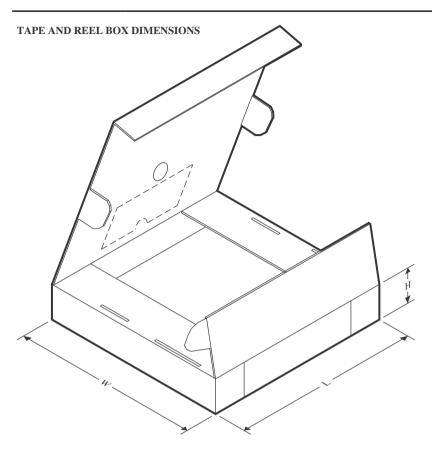

#### パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |  |

|--------------|----------------------|--------------------------|--|

| SN75LVPE5412 | RUA (WQFN, 42)       | 9mm×3.5mm                |  |

- 詳細については、セクション 10 を参照してください。 (1)

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

アプリケーション使用事例

## **Table of Contents**

| 1 特長1                                     | 6.3 Feature Description | 13              |

|-------------------------------------------|-------------------------|-----------------|

| 2 アプリケーション1                               |                         |                 |

| 3 概要 1                                    | 0 F D .                 | 15              |

| 4 Pin Configuration and Functions         |                         | 20              |

| 5 Specifications                          |                         | 20              |

| 5.1 Absolute Maximum Ratings              |                         | 20              |

| 5.2 ESD Ratings6                          | 7 0 D 0   -   D   -   - | <mark>24</mark> |

| 5.3 Recommended Operating Conditions      | 7 1 1                   | 24              |

| 5.4 Thermal Information                   | 0 D D                   | <mark>26</mark> |

| 5.5 DC Electrical Characteristics         |                         | 26              |

| 5.6 High Speed Electrical Characteristics | 8.2 サポート・リソース           | 26              |

| 5.7 SMBUS/I2C Timing Characteristics      |                         |                 |

| 5.8 Typical Characteristics10             |                         | 26              |

| 5.9 Typical Jitter Characteristics11      |                         |                 |

| 6 Detailed Description12                  |                         |                 |

| 6.1 Overview                              |                         |                 |

| 6.2 Functional Block Diagram12            |                         | 26              |

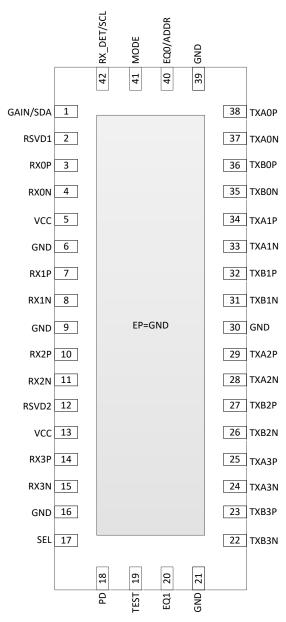

## **4 Pin Configuration and Functions**

図 4-1. RUA Package, 42-Pin WQFN (Top View)

3

## 表 4-1. Pin Functions

| PI          | N                        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                      | ITPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MODE        | 41                       | I, 5-level          | Sets device control configuration modes. The 5-level IO pin is defined in 表 6-1. The pin can be exercised at device power up or in normal operation mode. L0: <i>Pin Mode</i> – device control configuration is done solely by strap pins. L1 or L2: <i>SMBus/l</i> <sup>2</sup> <i>C Mode</i> – device control configuration is done by an external controller with SMBus/l <sup>2</sup> <i>C</i> primary. This pin along with ADDR pin sets devices secondary address. L3 and L4 (Float): RESERVED – TI internal test modes. |

| EQ0 /ADDR   | 40                       | I, 5-level          | In Pin Mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EQ1         | 20                       | I, 5-level          | The EQ0 and EQ1 pins sets receiver linear equalization CTLE (AC gain) for all channels according to 表 6-2. These pins are sampled at device power-up only. In SMBus/I <sup>2</sup> C Mode:  The ADDR pin in conjunction with MODE pin sets SMBus / I <sup>2</sup> C secondary address according to 表 6-5. The pin is sampled at device power-up only.                                                                                                                                                                          |

| GAIN /SDA   | 1                        | I, 5-level / IO     | In Pin Mode: Flat gain (broadband gain – DC and AC) from the input to the output of the device for all channels. Note: the device also provides AC (high frequency) gain in the form of equalization controlled by EQ pins or SMBus/I²C registers. The pin is sampled at device power-up only.  In SMBus/I²C Mode: 3.3V SMBus/I²C data. External pullup resistor such as 4.7 kΩ required for operation.                                                                                                                        |

| GND         | EP, 6, 9, 16, 21, 30, 39 | Р                   | Ground reference for the device.  EP: the Exposed Pad at the bottom of the QFN package. It is used as the GND return for the device. The EP should be connected to one or more ground planes through the low resistance path. A via array provides a low impedance path to GND. The EP also improves thermal dissipation.                                                                                                                                                                                                      |

| PD          | 18                       | I, 3.3V LVCMOS      | 2-level logic controlling the operating state of the redriver. Active in both <i>Pin Mode</i> and <i>SMBus/l</i> <sup>2</sup> <i>C Mode</i> . The pin is used part of PCIe RX_DET state machine as outlined in 表 6-4. High: power down for all channels Low: power up, normal operation for all channels                                                                                                                                                                                                                       |

| RSVD1, 2    | 2, 12                    | _                   | Reserved pins – for best signal integrity performance connect the pins to GND. Alternate option would be 0 $\Omega$ resistors from pins to GND.                                                                                                                                                                                                                                                                                                                                                                                |

| RX_DET /SCL | 42                       | I, 5-level / IO     | In <i>Pin Mode:</i> Sets receiver detect state machine options according to 表 6-4. The pin is sampled at device power-up only. In <i>SMBus</i> / <i>I</i> <sup>2</sup> <i>C Mode:</i> 3.3V SMBus/ <i>I</i> <sup>2</sup> <i>C clock.</i> External pullup resistor such as 4.7 kΩ required for operation.                                                                                                                                                                                                                        |

| RX0N        | 4                        | I                   | Inverting differential RX inputs. Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RX0P        | 3                        | I                   | Noninverting differential RX inputs. Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX1N        | 8                        | I                   | Inverting differential RX inputs. Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RX1P        | 7                        | I                   | Noninverting differential RX inputs. Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX2N        | 11                       | I                   | Inverting differential RX inputs. Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RX2P        | 10                       | I                   | Noninverting differential RX inputs. Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX3N        | 15                       | I                   | Inverting differential RX inputs. Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RX3P        | 14                       | 1                   | Noninverting differential RX inputs. Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SEL         | 17                       | I, 3.3V LVCMOS      | Selects the mux path. Active in both <i>Pin Mode</i> and <i>SMBus/l</i> <sup>2</sup> <i>C Mode</i> . The pin has a weak internal pull-down resistor. Note: the SEL pin must be exercised in system implementations for mux selection between Port A vs Port B. The pin is used for PCIe RX_DET state machine as outlined in 表 6-4. L: Port A selected. H: Port B selected.                                                                                                                                                     |

| TXA0N       | 37                       | 0                   | Inverting differential TX output – Port A, Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXA0P       | 38                       | 0                   | Non-inverting differential TX output – Port A, Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## 表 4-1. Pin Functions (続き)

| PIN NAME NO. |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                           |  |

|--------------|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

|              |       | ITPE\"              | DESCRIPTION                                                                                                                           |  |

| TXA1N        | 33    | 0                   | Inverting differential TX output – Port A, Channel 1.                                                                                 |  |

| TXA1P        | 34    | 0                   | Non-inverting differential TX output – Port A, Channel 1.                                                                             |  |

| TXA2N        | 28    | 0                   | Inverting differential TX output – Port A, Channel 2.                                                                                 |  |

| TXA2P        | 29    | 0                   | Non-inverting differential TX output – Port A, Channel 2.                                                                             |  |

| TXA3N        | 24    | 0                   | Inverting differential TX output – Port A, Channel 3.                                                                                 |  |

| TXA3P        | 25    | 0                   | Non-inverting differential TX output – Port A, Channel 3.                                                                             |  |

| TXB0N        | 35    | 0                   | Inverting differential TX output – Port B, Channel 0.                                                                                 |  |

| TXB0P        | 36    | 0                   | Non-inverting differential TX output – Port B, Channel 0.                                                                             |  |

| TXB1N        | 31    | 0                   | Inverting differential TX output – Port B, Channel 1.                                                                                 |  |

| TXB1P        | 32    | 0                   | Non-inverting differential TX output – Port B, Channel 1.                                                                             |  |

| TXB2N        | 26    | 0                   | Inverting differential TX output – Port B, Channel 2.                                                                                 |  |

| TXB2P        | 27    | 0                   | Non-inverting differential TX output – Port B, Channel 2.                                                                             |  |

| TXB3N        | 22    | 0                   | Inverting differential TX output – Port B, Channel 3.                                                                                 |  |

| TXB3P        | 23    | 0                   | Non-inverting differential TX output – Port B, Channel 3.                                                                             |  |

| TEST         | 19    | 0                   | TI internal test pin. Keep no connect.                                                                                                |  |

| VCC          | 5, 13 | Р                   | Power supply, VCC = 3.3V ± 10%. The VCC pins on this device should be connected through a low-resistance path to the board VCC plane. |  |

<sup>(1)</sup> I = input, O = output, P = power, GND = ground

5

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                             |                                        | MIN  | MAX  | UNIT |

|-----------------------------|----------------------------------------|------|------|------|

| VCC <sub>ABSMAX</sub>       | Supply voltage (VCC)                   | -0.5 | 4.0  | V    |

| VIO <sub>CMOS,ABSMAX</sub>  | 3.3V LVCMOS and open drain I/O voltage | -0.5 | 4.0  | V    |

| VIO <sub>5LVL,ABSMAX</sub>  | 5-level input I/O voltage              | -0.5 | 2.75 | V    |

| VIO <sub>HS-RX,ABSMAX</sub> | High-speed I/O voltage (RXnP, RXnN)    | -0.5 | 3.2  | V    |

| VIO <sub>HS-TX,ABSMAX</sub> | High-speed I/O voltage (TXnP, TXnN)    | -0.5 | 2.75 | V    |

| T <sub>J,ABSMAX</sub>       | Junction temperature                   |      | 150  | °C   |

| T <sub>stg</sub>            | Storage temperature range              | -65  | 150  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Rating may cause permanent device damage. Absolute Maximum Rating do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Condition. If used outside the Recommended Operating Condition but within the Absolute Maximum Rating, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|    |       |                         |                                                                       | VALUE | UNIT       |

|----|-------|-------------------------|-----------------------------------------------------------------------|-------|------------|

| \/ | (ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | \ <u>'</u> |

| "  | (ESD) | Liectiostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | · •        |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2 kV may actually have higher performance.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                                                                             | ,                                               | MIN   | NOM | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|-------|-----|------|------|

| VCC                   | Supply voltage, VCC to GND                                                                  | DC plus AC power should not exceed these limits | 3.0   | 3.3 | 3.6  | V    |

|                       |                                                                                             | DC to <50 Hz, sinusoidal <sup>1</sup>           |       |     | 250  | mVpp |

|                       |                                                                                             | 50 Hz to 500 kHz, sinusoidal <sup>1</sup>       |       |     | 100  | mVpp |

| $N_{VCC}$             | Supply noise tolerance                                                                      | 500 kHz to 2.5 MHz, sinusoidal <sup>1</sup>     |       |     | 33   | mVpp |

|                       |                                                                                             | Supply noise, >2.5 MHz, sinusoidal <sup>1</sup> |       |     | 10   | mVpp |

| T <sub>RampVCC</sub>  | VCC supply ramp time                                                                        | From 0V to 3.0V                                 | 0.150 |     | 100  | ms   |

| T <sub>J</sub>        | Operating junction temperature                                                              |                                                 | -40   |     | 115  | °C   |

| T <sub>A</sub>        | Operating ambient temperature                                                               |                                                 | -40   |     | 85   | °C   |

| PW <sub>LVCMOS</sub>  | Minimum pulse width required for<br>the device to detect a valid signal<br>on LVCMOS inputs | PD and SEL                                      | 200   |     |      | μs   |

| VCC <sub>SMBUS</sub>  | SMBus/I <sup>2</sup> C SDA and SCL open drain termination voltage                           | Supply voltage for open drain pull-up resistor  |       |     | 3.6  | V    |

| F <sub>SMBus</sub>    | SMBus/I <sup>2</sup> C clock (SCL) frequency in SMBus secondary mode                        |                                                 | 10    |     | 400  | kHz  |

| VID <sub>LAUNCH</sub> | Source differential launch amplitude                                                        |                                                 | 800   |     | 1200 | mVpp |

| DR                    | Data rate                                                                                   |                                                 | 1     |     | 32   | Gbps |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.4 Thermal Information**

|                         | THERMAL METRIC <sup>(1)</sup>                |              | UNIT |

|-------------------------|----------------------------------------------|--------------|------|

|                         |                                              | RUA, 42 Pins |      |

| R <sub>θJA-High K</sub> | Junction-to-ambient thermal resistance       | 26.1         | °C/W |

| R <sub>0</sub> JC(top)  | Junction-to-case (top) thermal resistance    | 14.1         | °C/W |

| R <sub>0JB</sub>        | Junction-to-board thermal resistance         | 8.7          | °C/W |

| ΨЈТ                     | Junction-to-top characterization parameter   | 1.6          | °C/W |

| ΨЈВ                     | Junction-to-board characterization parameter | 8.6          | °C/W |

| R <sub>0JC(bot)</sub>   | Junction-to-case (bottom) thermal resistance | 2.6          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

### 5.5 DC Electrical Characteristics

over operating free-air temperature and voltage range (unless otherwise noted)

|                                     | PARAMETER                                                  | TEST CONDITIONS                                                    | MIN  | TYP | MAX  | UNIT |

|-------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|------|-----|------|------|

| Power                               |                                                            |                                                                    |      |     |      |      |

| P <sub>ACT</sub>                    | Device active power                                        | All channels enabled (PD = L)                                      |      | 720 | 970  | mW   |

| P <sub>STBY</sub>                   | Device power consumption in standby power mode             | All channels disabled (PD = H)                                     |      | 23  | 36   | mW   |

| Control IO                          |                                                            |                                                                    |      |     | -    |      |

| V <sub>IH</sub>                     | High level input voltage                                   | SDA, SCL, PD, SEL pins                                             | 2.1  |     |      | V    |

| V <sub>IL</sub>                     | Low level input voltage                                    | SDA, SCL, PD, SEL pins                                             |      |     | 1.08 | V    |

| V <sub>OH</sub>                     | High level output voltage                                  | $R_{\text{pull-up}} = 4.7 \text{ k}\Omega \text{ (SDA, SCL pins)}$ | 2.1  |     |      | V    |

| V <sub>OL</sub>                     | Low level output voltage                                   | I <sub>OL</sub> = -4 mA (SDA, SCL pins)                            |      |     | 0.4  | V    |

| I <sub>IH,SEL</sub>                 | Input high leakage current for SEL pins                    | V <sub>Input</sub> = VCC, for SEL pin                              |      |     | 100  | μΑ   |

| I <sub>IH</sub>                     | Input high leakage current                                 | V <sub>Input</sub> = VCC, (SCL, SDA, PD pins)                      |      |     | 10   | μA   |

| I <sub>IL</sub>                     | Input low leakage current                                  | V <sub>Input</sub> = 0V, (SCL, SDA, PD, SEL pins)                  | -10  |     |      | μΑ   |

| I <sub>IH,FS</sub>                  | Input high leakage current for fail safe input pins        | V <sub>Input</sub> = 3.6V, VCC = 0V, (SCL, SDA, PD, SEL pins)      |      |     | 200  | μΑ   |

| C <sub>IN-CTRL</sub>                | Input capacitance                                          | SCL, SDA, PD, SEL pins                                             |      | 1.6 |      | pF   |

| 5 Level IOs (                       | MODE, GAIN, EQ1, EQ0, RX_DET pins                          |                                                                    |      |     | •    |      |

| I <sub>IH_5L</sub>                  | Input high leakage current, 5 level IOs                    | VIN = 2.5V                                                         |      |     | 10   | μA   |

| I <sub>IL_5L</sub>                  | Input low leakage current for all 5 level IOs except MODE. | VIN = GND                                                          | -10  |     |      | μΑ   |

| I <sub>IL_5L,MODE</sub>             | Input low leakage current for MODE pin                     | VIN = GND                                                          | -200 |     |      | μA   |

| Receiver                            |                                                            |                                                                    |      |     | •    |      |

| V <sub>RX-DC-CM</sub>               | RX DC common mode (CM) voltage                             | Device is in active or standby state                               |      | 1.4 |      | V    |

| Z <sub>RX-DC</sub>                  | Rx DC single-ended impedance                               |                                                                    |      | 50  |      | Ω    |

| Z <sub>RX-HIGH-IMP-</sub><br>DC-POS | DC input CM input impedance during Reset or power-down     | Inputs are at V <sub>RX-DC-CM</sub> voltage                        | 20   |     |      | kΩ   |

| Transmitter                         |                                                            |                                                                    |      |     |      |      |

| Z <sub>TX-DIFF-DC</sub>             | DC differential Tx impedance                               | Impedance of Tx during active signaling, VID,diff = 1Vpp           |      | 100 |      | Ω    |

| V <sub>TX-DC-CM</sub>               | Tx DC common mode voltage                                  |                                                                    |      | 1.0 |      | V    |

| I <sub>TX-SHORT</sub>               | Tx short circuit current                                   | Total current the Tx can supply when shorted to GND                |      | 70  |      | mA   |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

1

uct Folder Links: SN/5LVPE5412

English Data Sheet: SNLS693

## **5.6 High Speed Electrical Characteristics**

over operating free-air temperature and voltage range (unless otherwise noted)

|                                | PARAMETER                                                          | TEST CONDITIONS                                                                                                                                | MIN | TYP | MAX | UNIT |

|--------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Receiver                       |                                                                    |                                                                                                                                                |     |     |     |      |

|                                |                                                                    | 50 MHz to 1.25GHz                                                                                                                              |     | -22 |     | dB   |

|                                |                                                                    | 1.25GHz to 2.5GHz                                                                                                                              | ,   | -22 |     | dB   |

| RL <sub>RX-DIFF</sub>          | Input differential return loss                                     | 2.5GHz to 4.0GHz                                                                                                                               | ,   | -20 |     | dB   |

|                                |                                                                    | 4.0GHz to 8.0GHz                                                                                                                               | ,   | -13 |     | dB   |

|                                |                                                                    | 8.0GHz to 16GHz                                                                                                                                |     | -9  |     | dB   |

|                                |                                                                    | 50 MHz to 2.5GHz                                                                                                                               |     | -20 |     | dB   |

| RL <sub>RX-CM</sub>            | Input common-mode return loss                                      | 2.5GHz to 8.0GHz                                                                                                                               | ,   | -14 |     | dB   |

|                                |                                                                    | 8.0GHz to 16GHz                                                                                                                                | ,   | -9  |     | dB   |

| XT <sub>RX</sub>               | Receive-side pair-to-pair isolation                                | Minimum over 10 MHz to 16GHz range                                                                                                             |     | -45 |     | dB   |

| Transmitter                    |                                                                    |                                                                                                                                                |     | -   |     |      |

| V <sub>TX-AC-CM-PP</sub>       | Tx AC peak-to-peak common mode voltage                             | Measured with lowest EQ, GAIN = L4;<br>PRBS-7, 32Gbps, over at least 10 <sup>6</sup> bits<br>using a bandpass filter from 30 kHz to<br>500 MHz |     |     | 50  | mVpp |

| V <sub>TX-RCV-</sub><br>DETECT | Amount of voltage change allowed during receiver detection         | Measured while Tx is sensing whether a low-impedance receiver is present. No load is connected to the driver output                            | 0   |     | 600 | mV   |

|                                |                                                                    | 50 MHz to 1.25GHz                                                                                                                              | ,   | -22 |     | dB   |

|                                |                                                                    | 1.25GHz to 2.5GHz                                                                                                                              |     | -22 |     | dB   |

| RL <sub>TX-DIFF</sub>          | Output differential return loss                                    | 2.5GHz to 4.0GHz                                                                                                                               |     | -21 |     | dB   |

|                                |                                                                    | 4.0GHz to 8.0GHz                                                                                                                               |     | -15 |     | dB   |

|                                |                                                                    | 8.0GHz to 16GHz                                                                                                                                |     | -10 |     | dB   |

|                                |                                                                    | 50 MHz to 2.5GHz                                                                                                                               |     | -16 |     | dB   |

| RL <sub>TX-CM</sub>            | Output common-mode return loss                                     | 2.5GHz to 8.0GHz                                                                                                                               |     | -12 |     | dB   |

|                                |                                                                    | 8.0GHz to 16GHz                                                                                                                                |     | -10 |     | dB   |

| XT <sub>TX</sub>               | Transmit-side pair-to-pair isolation; port A or port B             | Minimum over 10 MHz to 16GHz range                                                                                                             |     | -50 |     | dB   |

| Device Datap                   | path                                                               |                                                                                                                                                |     |     |     |      |

| T <sub>PLHD/PHLD</sub>         | Input-to-output latency (propagation delay) through a data channel | For either low-to-high or high-to-low transition.                                                                                              |     | 90  | 130 | ps   |

| L <sub>TX-SKEW</sub>           | Lane-to-lane output skew                                           | Between any two lanes within a single transmitter.                                                                                             |     |     | 20  | ps   |

| T <sub>RJ-DATA</sub>           | Additive random jitter with data                                   | Jitter through redriver minus the calibration trace. 32Gbps PRBS15. 800 mVpp-diff input swing.                                                 |     | 55  |     | fs   |

| T <sub>RJ-INTRINSIC</sub>      | Intrinsic additive random jitter with clock                        | Jitter through redriver minus the calibration trace. 32GHz clock. 800 mVpp-diff input swing.                                                   |     | 35  |     | fs   |

| JITTER <sub>TOTAL</sub> -      | Additive total jitter with data                                    | Jitter through redriver minus the calibration trace. 32Gbps PRBS15. 800 mVpp-diff input swing.                                                 |     | 1.0 |     | ps   |

| JITTER <sub>TOTAL</sub>        | Intrinsic additive total jitter with clock                         | Jitter through redriver minus the calibration trace. 16GHz clock. 800 mVpp-diff input swing.                                                   |     | 0.1 |     | ps   |

Copyright © 2024 Texas Instruments Incorporated

8

## 5.6 High Speed Electrical Characteristics (続き)

over operating free-air temperature and voltage range (unless otherwise noted)

|                       | PARAMETER                                                            | TEST CONDITIONS                               | MIN | TYP  | MAX | UNIT |

|-----------------------|----------------------------------------------------------------------|-----------------------------------------------|-----|------|-----|------|

|                       |                                                                      | Minimum EQ, GAIN1/0=L0                        |     | -5.6 |     | dB   |

|                       | GAIN Broadband DC and AC flat gain - input to output, measured at DC | Minimum EQ, GAIN1/0=L1                        |     | -3.8 |     | dB   |

| FLAT-GAIN             |                                                                      | Minimum EQ, GAIN1/0=L2                        |     | -1.2 |     | dB   |

|                       |                                                                      | Minimum EQ, GAIN1/0=L3                        |     | 2.6  |     | dB   |

|                       |                                                                      | Minimum EQ, GAIN1/0=L4 (Float)                |     | 0.6  |     | dB   |

| EQ-MAX <sub>16G</sub> | EQ boost at max setting (EQ INDEX = 19)                              | AC gain at 16GHz relative to gain at 100 MHz. |     | 24.0 |     | dB   |

| LINEARITY-<br>DC      | Output DC linearity.                                                 | at 0dB flat gain                              |     | 1700 |     | mVpp |

| LINEARITY-<br>AC      | Output AC linearity at 32Gbps                                        | at 0dB flat gain                              |     | 930  |     | mVpp |

## 5.7 SMBUS/I2C Timing Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                                         | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|--|--|--|

| Secondary           | Secondary Mode                                                                                    |                                     |     |     |     |      |  |  |  |

| t <sub>SP</sub>     | Pulse width of spikes which must be suppressed by the input filter                                |                                     |     |     | 50  | ns   |  |  |  |

| t <sub>HD-STA</sub> | Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated |                                     | 0.6 |     |     | μs   |  |  |  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                       |                                     | 1.3 |     |     | μs   |  |  |  |

| T <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                      |                                     | 0.6 |     |     | μs   |  |  |  |

| t <sub>SU-STA</sub> | Set-up time for a repeated START condition                                                        |                                     | 0.6 |     |     | μs   |  |  |  |

| t <sub>HD-DAT</sub> | Data hold time                                                                                    |                                     | 0   |     |     | μs   |  |  |  |

| T <sub>SU-DAT</sub> | Data setup time                                                                                   |                                     | 0.1 |     |     | μs   |  |  |  |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                             | Pull-up resistor = 4.7kΩ, Cb = 10pF |     | 120 |     | ns   |  |  |  |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                             | Pull-up resistor = 4.7kΩ, Cb = 10pF |     | 2   |     | ns   |  |  |  |

| t <sub>SU-STO</sub> | Set-up time for STOP condition                                                                    |                                     | 0.6 |     |     | μs   |  |  |  |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                                  |                                     | 1.3 |     |     | μs   |  |  |  |

| t <sub>VD-DAT</sub> | Data valid time                                                                                   |                                     |     |     | 0.9 | μs   |  |  |  |

| t <sub>VD-ACK</sub> | Data valid acknowledge time                                                                       |                                     |     |     | 0.9 | μs   |  |  |  |

| C <sub>b</sub>      | Capacitive load for each bus line                                                                 |                                     |     |     | 400 | pF   |  |  |  |

9

## **5.8 Typical Characteristics**

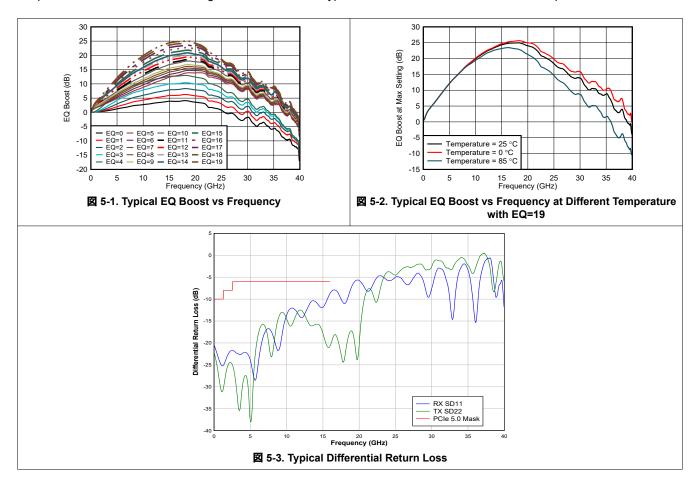

☑ 5-1 shows typical EQ gain curves versus frequency for different EQ settings. ☑ 5-2 shows EQ gain variation over temperature for maximum EQ setting of 19. ☑ 5-3 shows typical differential return loss for Rx and Tx pins.

## **5.9 Typical Jitter Characteristics**

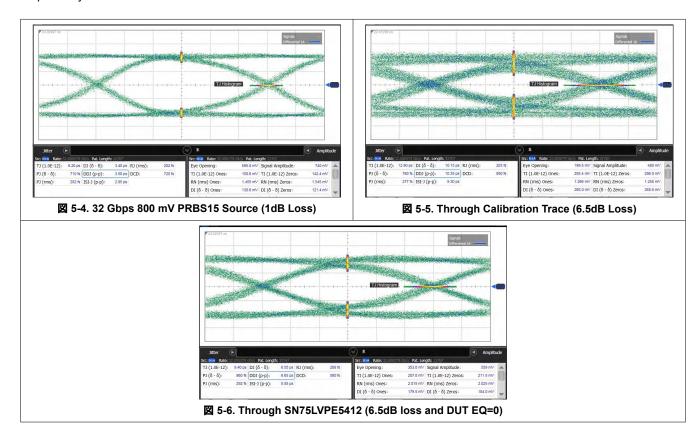

$\boxtimes$  5-4,  $\boxtimes$  5-5, and  $\boxtimes$  5-6 illustrate eye diagrams at source, through calibration traces, and through SN75LVPE5412 respectively.

## **6 Detailed Description**

### 6.1 Overview

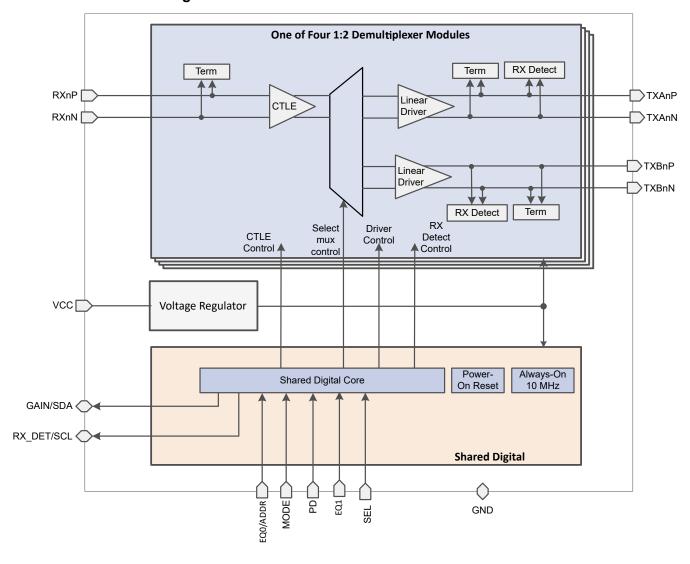

The SN75LVPE5412 is a four channel linear redriver with integrated demultiplexer (demux). The low-power high-performance linear repeater or redriver is designed to support PCle 1.0, 2.0, 3.0, 4.0, and 5.0. The device is a protocol agnostic linear redriver that can operate for other AC-coupled interface up to 32Gbps.

The signal channels of the SN75LVPE5412 operate independently from one another. Each channel includes a continuous-time linear equalizer (CTLE) and a linear output driver, which together compensate for a lossy transmission channel between the source transmitter and the final receiver. The linearity of the data path is specifically designed to preserve any transmit equalization while keeping PCle receiver's (either from Root Complex or Endpoint) equalization effective.

The SN75LVPE5412 can be configured in two different ways:

**Pin Mode** – device control configuration is done solely by strap pins. Pin mode is expected to be good enough for many system implementation needs.

**SMBus/I<sup>2</sup>C Secondary Mode** – provides most flexibility. Requires an external SMBus/I<sup>2</sup>C primary device to configure SN75LVPE5412 though writing to its secondary address.

### 6.2 Functional Block Diagram

## **6.3 Feature Description**

### 6.3.1 Five-Level Control Inputs

The SN75LVPE5412 has five 5-level inputs pins (EQ1, EQ0, GAIN, MODE, and RX\_DET) that are used to control the configuration of the device. These 5-level inputs use a resistor divider to help set the 5 valid levels and provide a wider range of control settings. External resistors must be of 10% tolerance or better. The EQ0, EQ1, GAIN, and RX DET pins are sampled at power-up only. The MODE pin can be exercised at device power up or in normal operation mode.

| 表 | 6-1. | 5-Level | Control | Pin | Settings |

|---|------|---------|---------|-----|----------|

|---|------|---------|---------|-----|----------|

| LEVEL | SETTING        |

|-------|----------------|

| LO    | 1 kΩ to GND    |

| L1    | 8.25 kΩ to GND |

| L2    | 24.9 kΩ to GND |

| L3    | 75 kΩ to GND   |

| L4    | F (Float)      |

#### 6.3.2 Linear Equalization

The SN75LVPE5412 receivers feature a continuous-time linear equalizer (CTLE) that applies high-frequency boost and low-frequency attenuation to help equalize the frequency-dependent insertion loss effects of a passive channel. The receivers implement two stage linear equalizer for wide range of equalization capability. The equalizer stages also provide flexibility to make subtle modifications of mid-frequency boost for best EQ gain profile match with wide range of channel media characteristics. The EQ profile control feature is only available in SMBus/I<sup>2</sup>C Mode. In Pin Mode the settings are optimized for FR4 traces.

表 6-2 shows available equalization boost through EQ control pins or SMBus/I<sup>2</sup>C registers. In Pin Control mode EQ1 and EQ0 pins set equalization boost for all channels. In I<sup>2</sup>C Mode individual channels can be independently programmed for EQ boost.

表 6-2. Equalization Control Settings

|          | EQUALIZATION SETTING |       |               |               |                     | TYPICAL EQ       | BOOST (dB) |           |

|----------|----------------------|-------|---------------|---------------|---------------------|------------------|------------|-----------|

|          | Pin N                | /lode |               | SMBus/I       | <sup>2</sup> C Mode |                  |            |           |

| EQ INDEX | EQ1                  | EQ0   | eq_stage1_3:0 | eq_stage2_2:0 | eq_profile_3:0      | eq_stage1_bypass | At 8 GHz   | At 16 GHz |

| 0        | L0                   | L0    | 0             | 0             | 0                   | 1                | 2.0        | 4.0       |

| 1        | L0                   | L1    | 1             | 0             | 0                   | 1                | 4.0        | 6.0       |

| 2        | L0                   | L2    | 3             | 0             | 0                   | 1                | 5.0        | 8.0       |

| 3        | L0                   | L3    | 7             | 0             | 0                   | 1                | 7.0        | 10.0      |

| 4        | L0                   | L4    | 7             | 1             | 0                   | 1                | 8.0        | 12.0      |

| 5        | L1                   | L0    | 0             | 0             | 1                   | 0                | 7.0        | 12.0      |

| 6        | L1                   | L1    | 1             | 0             | 1                   | 0                | 7.5        | 13.0      |

| 7        | L1                   | L2    | 2             | 0             | 1                   | 0                | 8.0        | 14.0      |

| 8        | L1                   | L3    | 3             | 0             | 3                   | 0                | 9.0        | 15.0      |

| 9        | L1                   | L4    | 4             | 0             | 3                   | 0                | 10.0       | 15.5      |

| 10       | L2                   | L0    | 5             | 1             | 7                   | 0                | 10.5       | 16.0      |

| 11       | L2                   | L1    | 6             | 1             | 7                   | 0                | 11.0       | 17.0      |

| 12       | L2                   | L2    | 8             | 1             | 7                   | 0                | 12.0       | 17.5      |

Product Folder Links: SN75LVPE5412

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

13

| 表 6-2. Equalization Control Settings | (続き) |

|--------------------------------------|------|

|--------------------------------------|------|

|          | EQUALIZATION SETTING |       |               |               |                     | TYPICAL EQ       | BOOST (dB) |           |

|----------|----------------------|-------|---------------|---------------|---------------------|------------------|------------|-----------|

|          | Pin N                | /lode |               | SMBus/I       | <sup>2</sup> C Mode |                  |            |           |

| EQ INDEX | EQ1                  | EQ0   | eq_stage1_3:0 | eq_stage2_2:0 | eq_profile_3:0      | eq_stage1_bypass | At 8 GHz   | At 16 GHz |

| 13       | L2                   | L3    | 10            | 1             | 7                   | 0                | 12.5       | 18.5      |

| 14       | L2                   | L4    | 10            | 2             | 15                  | 0                | 13.0       | 19.0      |

| 15       | L3                   | L0    | 11            | 3             | 15                  | 0                | 14.0       | 20.0      |

| 16       | L3                   | L1    | 12            | 4             | 15                  | 0                | 15.0       | 21.0      |

| 17       | L3                   | L2    | 13            | 5             | 15                  | 0                | 16.0       | 22.0      |

| 18       | L3                   | L3    | 14            | 6             | 15                  | 0                | 16.5       | 23.0      |

| 19       | L3                   | L4    | 15            | 7             | 15                  | 0                | 17.0       | 24.0      |

#### 6.3.3 Flat Gain

The GAIN pin can be used to set the overall datapath flat gain (broadband gain including high frequency) of the SN75LVPE5412 when the device is in Pin Mode. The pin GAIN sets the Flat-Gain for all channels. In  $I^2$ C Mode each channel can be independently set.  $\pm$  6-3 shows flat gain control configuration settings. The default recommendation for most systems will be GAIN = L4 (float) that provides flat gain of 0dB.

The flat gain and equalization of the SN75LVPE5412 must be set such that the output signal swing at DC and high frequency does not exceed the DC and AC linearity ranges of the devices, respectively.

表 6-3. Flat Gain Configuration Settings

| Pin Mode<br>GAIN | I <sup>2</sup> C Mode<br>flat_gain_2:0 | Flat Gain                       |

|------------------|----------------------------------------|---------------------------------|

| L0               | 0                                      | -5.6dB                          |

| L1               | 1                                      | −3.8dB                          |

| L2               | 3                                      | −1.2dB                          |

| L3               | 7                                      | +2.6dB                          |

| L4 (float)       | 5                                      | +0.6dB (default recommendation) |

### 6.3.4 Receiver Detect State Machine

The SN75LVPE5412 deploys an RX detect state machine that governs the RX detection cycle as defined in the PCI express specifications. At device power up or through manually triggered event using PD or SEL pin or writing to the relevant I²C/SMBus register, the redriver determines whether or not a valid PCI express termination is present at the far end of the link. The RX\_DET pin of SN75LVPE5412 provides additional flexibility for system designers to appropriately set the device in desired mode according to 表 6-4. For the PCIe application the RX\_DET pin can be left floating for default settings.

Note: power up ramp or PD/SEL event triggers RX detect for all four channels. In applications where SN75LVPE5412 channels are used for multiple PCle links, the RX detect function can be performed for individual channels through writing in appropriate I<sup>2</sup>C/SMBus registers.

表 6-4. Receiver Detect State Machine Settings

| PD | RX_DET | RX Common-mode Impedance | COMMENTS                                                                                                                                                    |  |  |  |

|----|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| L  | L0     | Always 50 Ω              | PCI Express RX detection state machine is disabled. Recommended for non PCIe interface use case where the SN75LVPE5412 is used as buffer with equalization. |  |  |  |

|                                      | o, 10 o. 12 . D |               |

|--------------------------------------|-----------------|---------------|

|                                      |                 |               |

|                                      |                 |               |

| _                                    |                 |               |

| 表 6-4. Receiver Detect State Machine | C-44:           | ///<br>/<br>/ |

| ₹ 6-4. Receiver Detect State Machine | Seminas         |               |

| PD | RX_DET     | RX Common-mode Impedance               | COMMENTS                                                                                                                                                                                       |

|----|------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L  | L1         | Pre Detect: Hi-Z<br>Post Detect: 50 Ω. | Outputs polls until 3 consecutive valid detections                                                                                                                                             |

| L  | L2         | Pre Detect: Hi-Z<br>Post Detect: 50 Ω. | Outputs polls until 2 consecutive valid detections                                                                                                                                             |

| L  | L3         | Pre Detect: Hi-Z<br>Post Detect: 50 Ω. | Reserved                                                                                                                                                                                       |

| L  | L4 (Float) | Pre Detect: Hi-Z<br>Post Detect: 50 Ω. | TX polls every ≅150 µs until valid termination is detected. RX CM impedance held at Hi-Z until detection Reset by asserting PD high for 200 µs then low. Recommended default setting for PCIe. |

| Н  | X          | Hi-Z                                   | Reset Channels and set their RX impedance to Hi-Z                                                                                                                                              |

#### 6.4 Device Functional Modes

#### 6.4.1 Active PCIe Mode

The device is in normal operation with PCle state machine enabled by RX\_DET = L4 (float). This mode is recommended for PCle use cases. In this mode, the PD pin is driven low in a system (for example, by PCle connector *PRSNT* signal). In this mode, the device redrives and equalizes PCle RX or TX signals to provide better signal integrity.

#### 6.4.2 Active Buffer Mode

The device is in normal operation with PCIe state machine disabled by RX\_DET = L0. This mode is recommended for non-PCIe use cases. In this mode, the device is working as a buffer to provide linear equalization to improve signal integrity.

#### 6.4.3 Standby Mode

The device is in standby mode invoked by PD = H. In this mode, the device is in standby mode conserving power.

#### 6.5 Programming

#### 6.5.1 Pin Mode

The SN75LVPE5412 can be fully configured through pin-strap pins. In this mode the device uses 2-level and 5-level pins for device control and signal integrity optimum settings.

### 6.5.2 SMBUS/I<sup>2</sup>C Register Control Interface

If MODE = L2 (SMBus /  $I^2$ C secondary control mode), the SN75LVPE5412 is configured for best signal integrity through a standard  $I^2$ C or SMBus interface that may operate up to 400 kHz. The secondary address of the SN75LVPE5412 is determined by the pin strap settings on the ADDR and MODE pins. 表 6-5 provides the eight possible secondary addresses (7-bit) for each channel banks of the device. In SMBus/ $I^2$ C modes the SCL, SDA pins must be pulled up to a 3.3V supply with a pull-up resistor. The value of the resistor depends on total bus capacitance. 4.7k $\Omega$  is a good first approximation for a bus capacitance of 10pF.

表 6-5. SMBUS/I2C Secondary Address Settings

| MODE | ADDR | 7-bit Secondary Address<br>Channels 0-1 | 7-bit Secondary Address<br>Channels 2-3 |

|------|------|-----------------------------------------|-----------------------------------------|

| L1   | L0   | 0x18                                    | 0x19                                    |

| L1   | L1   | 0x1A                                    | 0x1B                                    |

| L1   | L2   | 0x1C                                    | 0x1D                                    |

| L1   | L3   | 0x1E                                    | 0x1F                                    |

| X    | L4   | Reserved                                | Reserved                                |

| L2   | L0   | 0x20                                    | 0x21                                    |

| L2   | L1   | 0x22                                    | 0x23                                    |

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

## 表 6-5. SMBUS/I2C Secondary Address Settings (続き)

| MODE | ADDR | 7-bit Secondary Address<br>Channels 0-1 | 7-bit Secondary Address<br>Channels 2-3 |

|------|------|-----------------------------------------|-----------------------------------------|

| L2   | L2   | 0x24                                    | 0x25                                    |

| L2   | L3   | 0x26                                    | 0x27                                    |

The SN75LVPE5412 has two types of registers:

- **Shared Registers:** These registers can be accessed at any time and are used for device-level configuration, status read back, control, or to read back the device ID information.

- Channel Registers: These registers are used to control and configure specific features for each individual channel. All channels have the same register set and can be configured independent of each other or configured as a group through broadcast writes to Bank 0 or Bank 1.

The SN75LVPE5412 features two banks of channels, Bank 0 (Channels 0-1) and Bank 1 (Channels 2-), each featuring a separate register set and requiring a unique SMBus secondary address.

| Channel Registers Base<br>Address | Channel Bank 0 Access                                              | Channel Bank 1 Access                                              |

|-----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| 0x00                              | Channel 0 registers                                                | Channel 2 registers                                                |

| 0x20                              | Channel 0 registers                                                | Channel 2 registers                                                |

| 0x40                              | Channel 1 registers                                                | Channel 3 registers                                                |

| 0x60                              | Channel 1 registers                                                | Channel 3 registers                                                |

| 0x80                              | Broadcast write channel Bank 0 registers, read channel 0 registers | Broadcast write channel Bank 1 registers, read channel 2 registers |

| 0xE0                              | Bank 0 Share registers                                             | Bank 1 Share registers                                             |

### 6.5.2.1 Shared Registers

### 表 6-6. General Registers (Offset = 0xE2)

| Bit | Field        | Туре   | Reset  | Description                                                                      |

|-----|--------------|--------|--------|----------------------------------------------------------------------------------|

| 7   | RESERVED     | R      | 0x0    | Reserved                                                                         |

| 6   | rst_i2c_regs | R/W/SC | 0x0    | Device reset control: Reset all I2C registers to default values (self-clearing). |

| 5   | rst_i2c_mas  | R/W/SC | 0x0    | Reset I <sup>2</sup> C Primary (self-clearing).                                  |

| 4-0 | RESERVED     | R      | 0x0000 | Reserved                                                                         |

#### 表 6-7. DEVICE\_ID0 Register (Offset = 0xF0)

| Bit | Field        | Туре | Reset  | Description           |

|-----|--------------|------|--------|-----------------------|

| 7-4 | RESERVED     | R    | 0x0001 | Reserved              |

| 3   | device_id0_3 | R    | 0x1    | Device ID0 [3:1]: 111 |

| 2   | device_id0_2 | R    | 0x1    | see MSB               |

| 1   | device_id0_1 | R    | 0x1    | see MSB               |

| 0   | RESERVED     | R    | X      | Reserved              |

#### 表 6-8. DEVICE ID1 Register (Offset = 0xF1)

| Bit | Field        | Туре | Reset | Description                       |

|-----|--------------|------|-------|-----------------------------------|

| 7   | device_id[7] | R    | 0x0   | Device ID 0010 1000: SN75LVPE5412 |

| 6   | device_id[6] | R    | 0x0   | see MSB                           |

| 5   | device_id[5] | R    | 0x1   | see MSB                           |

| 4   | device_id[4] | R    | 0x0   | see MSB                           |

| 3   | device_id[3] | R    | 0x1   | see MSB                           |

Product Folder Links: SN75LVPE5412

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

表 6-8. DEVICE\_ID1 Register (Offset = 0xF1) (続き)

| Bit | Field        | Туре | Reset | Description |

|-----|--------------|------|-------|-------------|

| 2   | device_id[2] | R    | 0x0   | see MSB     |

| 1   | device_id[1] | R    | 0x0   | see MSB     |

| 0   | device_id[0] | R    | 0x1   | see MSB     |

17

## 6.5.2.2 Channel Registers

## 表 6-9. RX Detect Status Register (Channel Register Base + Offset = 0x00)

| Bit | Field         | Туре | Reset | Description                                                                            |

|-----|---------------|------|-------|----------------------------------------------------------------------------------------|

| 7   | RX_det_comp_p | R    | 0x0   | RX Detect positive data pin status: 0: Not detected 1: Detected – the value is latched |

| 6   | RX_det_comp_n | R    | 0x0   | RX Detect negative data pin status: 0: Not detected 1: Detected – the value is latched |

| 5-0 | RESERVED      | R    | 0x0   | Reserved                                                                               |

## 表 6-10. EQ Gain Control Register (Channel Register Base + Offset = 0x01)

| Bit | Field            | Туре | Reset | Description               |

|-----|------------------|------|-------|---------------------------|

| 7   | eq_stage1_bypass | R/W  | 0x0   | Enable EQ stage 1 bypass: |

|     |                  |      |       | 0: Bypass disabled        |

|     |                  |      |       | 1: Bypass enabled         |

| 6   | eq_stage1_3      | R/W  | 0x0   | EQBoost stage 1 control   |

| 5   | eq_stage1_2      | R/W  | 0x0   | See 表 6-2 for details     |

| 4   | eq_stage1_1      | R/W  | 0x0   |                           |

| 3   | eq_stage1_0      | R/W  | 0x0   |                           |

| 2   | eq_stage2_2      | R/W  | 0x0   | EQ Boost stage 2 control  |

| 1   | eq_stage2_1      | R/W  | 0x0   | See 表 6-2 for details     |

| 0   | eq_stage2_0      | R/W  | 0x0   |                           |

## 表 6-11. EQ Gain / Flat Gain Control Register (Channel Register Base + Offset = 0x03)

| Bit | Field        | Туре | Reset | Description                    |

|-----|--------------|------|-------|--------------------------------|

| 7   | RESERVED     | R    | 0x0   | Reserved                       |

| 6   | eq_profile_3 | R/W  | 0x0   | EQ mid-frequency boost profile |

| 5   | eq_profile_2 | R/W  | 0x0   | See 表 6-2 for details          |

| 4   | eq_profile_1 | R/W  | 0x0   |                                |

| 3   | eq_profile_0 | R/W  | 0x0   |                                |

| 2   | flat_gain_2  | R/W  | 0x1   | Flat gain select:              |

| 1   | flat_gain_1  | R/W  | 0x0   | See 表 6-3 for details          |

| 0   | flat_gain_0  | R/W  | 0x1   |                                |

## 表 6-12. RX Detect Control Register (Channel Register Base + Offset = 0x04)

| Bit | Field           | Туре | Reset | Description                                                                                                                                                      |

|-----|-----------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 | RESERVED        | R    | 0x0   | Reserved                                                                                                                                                         |

| 2   | mr_RX_det_man   | R/W  | 0x0   | Manual override of RX_detect_p/n decision: 0: RX detect state machine is enabled 1: RX detect state machine is overridden – always valid RX termination detected |

| 1   | en_RX_det_count | R/W  | 0x0   | Enable additional RX detect polling 0: Additional RX detect polling disabled 1: Additional RX detect polling enabled                                             |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

## 表 6-12. RX Detect Control Register (Channel Register Base + Offset = 0x04) (続き)

| Bit | Field            | Туре | Reset | Description                                                      |

|-----|------------------|------|-------|------------------------------------------------------------------|

| 0   | sel_RX_det_count | R/W  | 0x0   | Select number of valid RX detect polls – gated by                |

|     |                  |      |       | en_RX_det_count = 1                                              |

|     |                  |      |       | 0: Device transmitters poll until 2 consecutive valid detections |

|     |                  |      |       | 1: Device transmitters poll until 3 consecutive valid detections |

## 表 6-13. PD Override Register (Channel Register Base + Offset = 0x05)

| Bit | Field              | Type | Reset    | Description                                                                                                                                   |

|-----|--------------------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | device_en_override | R/W  | 0x0      | Enable power down overrides thorugh SMBus/I <sup>2</sup> C 0: Manual override disabled 1: Manual override enabled                             |

| 6-0 | device_en          | R/W  | 0x111111 | Manual power down of redriver various blocks – gated by device_en_override = 1 111111: All blocks are enabled 000000: All blocks are disabled |

## 表 6-14. RX Detect Reset Register (Channel Register Base + Offset = 0x0A)

|     | <b>200</b> 1 11 10 1 2 0 10 |      | , (   | ioi regioto: Duoc i onoci oxori,                                                                                                                                                  |

|-----|-----------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field                       | Type | Reset | Description                                                                                                                                                                       |

| 7-3 | RESERVED                    | R    | 0x0   | Reserved                                                                                                                                                                          |

| 2   | mr_RX_det_rst               | R/W  | 0x0   | RX Detect state machine reset. Toggle the bit if RX Detect machine needs to be reset in I <sup>2</sup> C mode  0: state machine is not reset  1: RX detect state machine is reset |

| 1-0 | RESERVED                    | R/W  | 0x0   | Reserved                                                                                                                                                                          |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

## 7 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 7.1 Application Information

The SN75LVPE5412 is a high-speed linear repeater with integrated demux. The device extends the reach of differential channels impaired by loss from transmission media like PCBs and cables. It can be deployed in a variety of different systems. The following sections outline typical applications and their associated design considerations.

### 7.2 Typical Applications

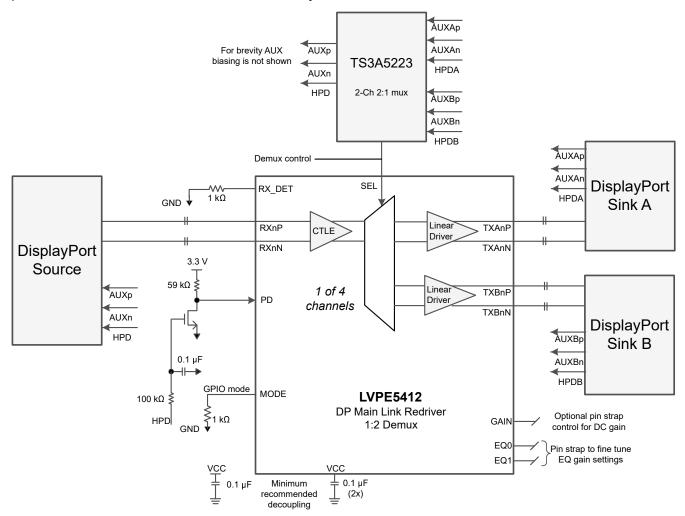

The SN75LVPE5412 is a PCI Express linear redriver that can also be configured as interface agnostic redriver by disabling its RX detect feature. The device can be used in a wide range of interfaces including:

- **PCI Express**

- Ultra Path Interconnect (UPI)

- SATA

- SAS

20

DisplayPort

資料に関するフィードバック(ご意見やお問い合わせ)を送信 Product Folder Links: SN75LVPE5412

English Data Sheet: SNLS693

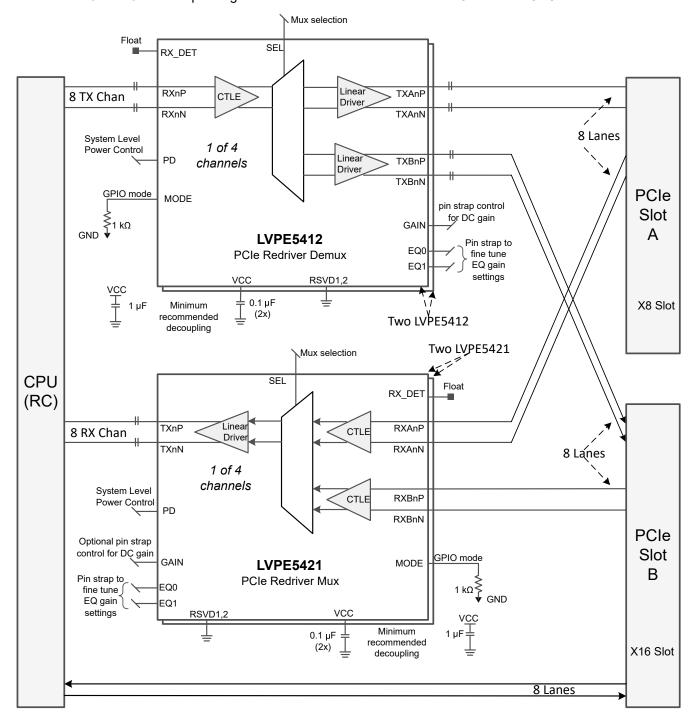

### 7.2.1 PCIe x8 Lane Switching

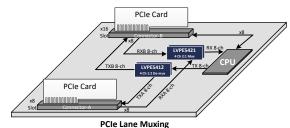

The SN75LVPE5412 and SN75LVPE5421 can be used to switch PCle lanes from a CPU into one of the two PCle CEM connectors. ☒ 7-1 shows a simplified schematic for the following configuration:

- Two SN75LVPE5412 demultiplex eight TX channels from the CPU into one of the two PCIe slots.

- Two SN75LVPE5421 multiplex eight RX channels from one of the two PCIe slots to CPU.

図 7-1. Simplified Schematic for PCle Lane Switching

### 7.2.1.1 Design Requirements

As with any high-speed design, there are many factors which influence the overall performance. The following list indicates critical areas for consideration during design:

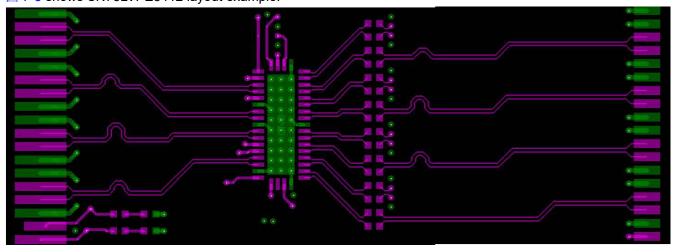

- Use 85 Ω impedance traces when interfacing with PCIe CEM connectors. Length matching on the P and N traces should be done on the single-ended segments of the differential pair.

- Use a uniform trace width and trace spacing for differential pairs.

- Place AC-coupling capacitors near to the receiver end of each channel segment to minimize reflections.

- For Gen 3.0, 4.0, and 5.0, AC-coupling capacitors of 220 nF are recommended, set the maximum body size to 0402, and add a cutout void on the GND plane below the landing pad of the capacitor to reduce parasitic capacitance to GND.

- Back-drill connector vias and signal vias to minimize stub length.

- · Use reference plane vias to ensure a low inductance path for the return current.

### 7.2.1.2 Detailed Design Procedure

In PCIe Gen 3.0, 4.0, and 5.0 applications, the specification requires RX-TX link training to establish and optimize signal conditioning settings at 8.0, 16.0, and 32.0Gbps, respectively. In link training, the RX partner requests a series of FIR – pre-shoot and de-emphasis coefficients (10 presets) from the TX partner. The RX partner includes CTLE and DFE. The link training would pre-condition the signal, with an equalized link between the Root Complex and Endpoint.

Note: there is no link training in PCle Gen 1.0 (2.5Gbps) or PCle Gen 2.0 (5.0Gbps) applications. The SN75LVPE5412 is placed in between the TX and RX. It helps extend the PCB trace reach distance by boosting the attenuated signals with its equalization, which allows the user to recover the signal by the downstream RX more easily.