# TCAL6416R 16 ビット変換 I<sup>2</sup>C バス / SMBus I/O エクスパンダ、割り込み出力、リセット入力、Agile I/O 構成用スティッキー レジスタ付き

## 1 特長

- 1.08V~3.6V の動作電源電圧範囲

- 1.2V、1.8V、2.5V、3.3V I<sup>2</sup>C バスと P ポートとの間の 双方向電圧レベル変換と GPIO 拡張が可能

- 低いスタンバイ消費電流: 1μA (標準値、1.8V 時)

- 1MHz のファストモードプラス I<sup>2</sup>C バス

- ハードウェアアドレスピンにより、同じ I<sup>2</sup>C/SMBus バス上に 2 つのデバイスを接続可能

- アクティブ Low のリセット入力 (RESET)

- RESET によって本デバイスがリセットされると、ステイッキー レジスタが値を保持

- I<sup>2</sup>C 機能ステートマシンがリセット

- オープンドレインのアクティブ Low 割り込み出力 (INT)

- 入力 / 出力構成レジスタ

- 極性反転レジスタ

- 構成可能な I/O 駆動強度レジスタ

- 10kΩ プルアップおよびプルダウン抵抗構成レジスタ

- パワーオンリセット内蔵

- ソフトウェアリセット呼び出しのサポート

- SCL または SDA 入力のノイズフィルタ

- 大電流の最大駆動能力を持つラッチ付き出力により LED を直接駆動

- JESD 78、Class II 準拠で 100mA 超のラッチアップ性能

- JESD 22 を上回る ESD 保護

- 4000V、人体モデル (A114-A)

- 荷電デバイスモデルで 1000V (C101)

## 2 アプリケーション

- サーバー

- ルーター (テレコム・スイッチング機器)

- パーソナル・コンピュータ

- パーソナル・エレクトロニクス

- 産業用オートメーション

- ゲーム機

- GPIO が制限されたプロセッサを使用する製品

## 3 概要

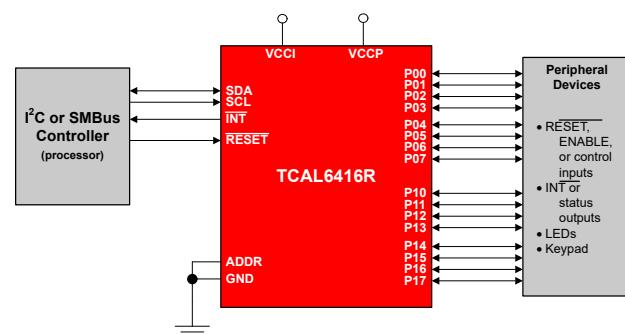

TCAL6416R は、2 線式双方向 I<sup>2</sup>C バス (または SMBus) プロトコルに対応する汎用パラレル入出力 (I/O) 拡張機能を備えています。このデバイスは、I<sup>2</sup>C バス側 ( $V_{CCI}$ ) で 1.08V~3.6V、P ポート側 ( $V_{CCP}$ ) で 1.08V~3.6V の電源電圧で動作します。

このデバイスは、100kHz (スタンダードモード)、400kHz (ファストモード)、1MHz (ファストモードプラス) の I<sup>2</sup>C クロック周波数をサポートしています。TCAL6416R をはじめとする I/O エクスパンダは、スイッチ、センサ、プッシュボタン、LED、ファンなどに I/O を追加する必要がある場合に、簡単なソリューションとして使用できます。

TCAL6416R には、速度、消費電力、EMI に関して I/O 性能を向上させる追加機能を備えた Agile I/O ポートが付いています。追加機能として、プログラム可能な出力駆動強度、プログラム可能なプルアップおよびプルダウン抵抗、ラッチ可能な入力、マスク可能な割り込み、割り込みステータスレジスタ、プログラム可能なオープンドレインまたはプッシュプル出力があります。

I<sup>2</sup>C ステートマシンがスタックした場合、RESET ピンでそのステートマシンをリセットするだけで、その I<sup>2</sup>C に再びアクセスできるようになります。I<sup>2</sup>C が再度初期化されている間、I/O ピンとスティッキー レジスタは最後に設定された状態を保持しています。

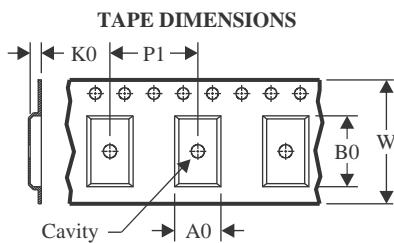

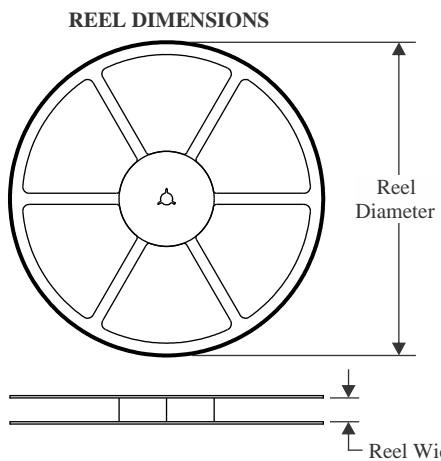

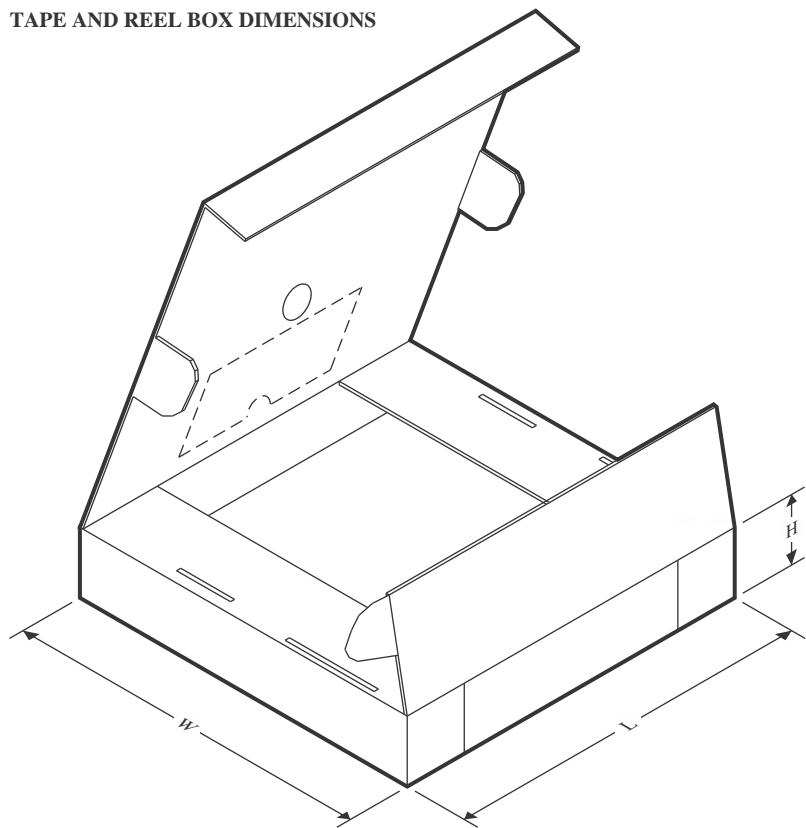

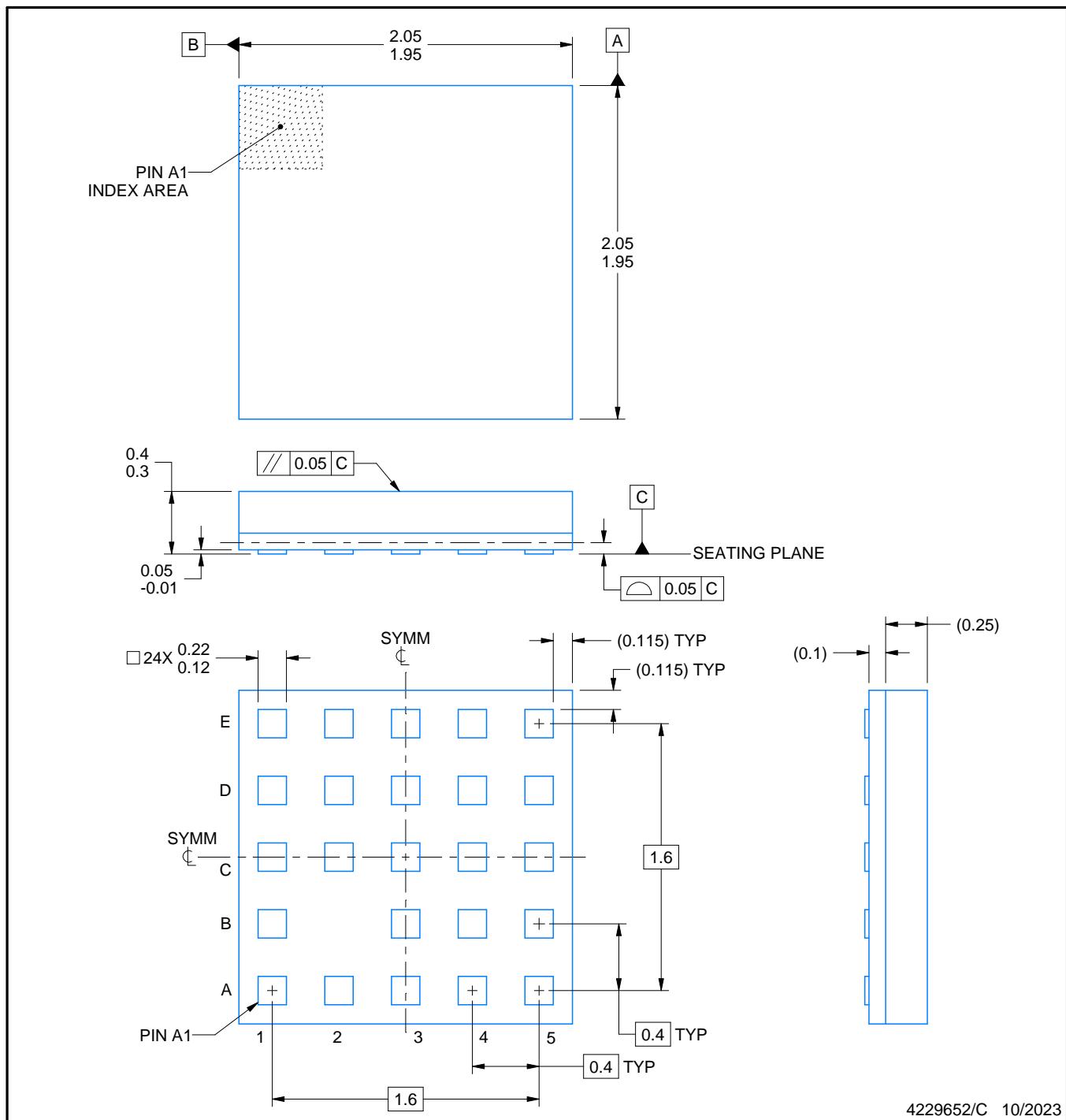

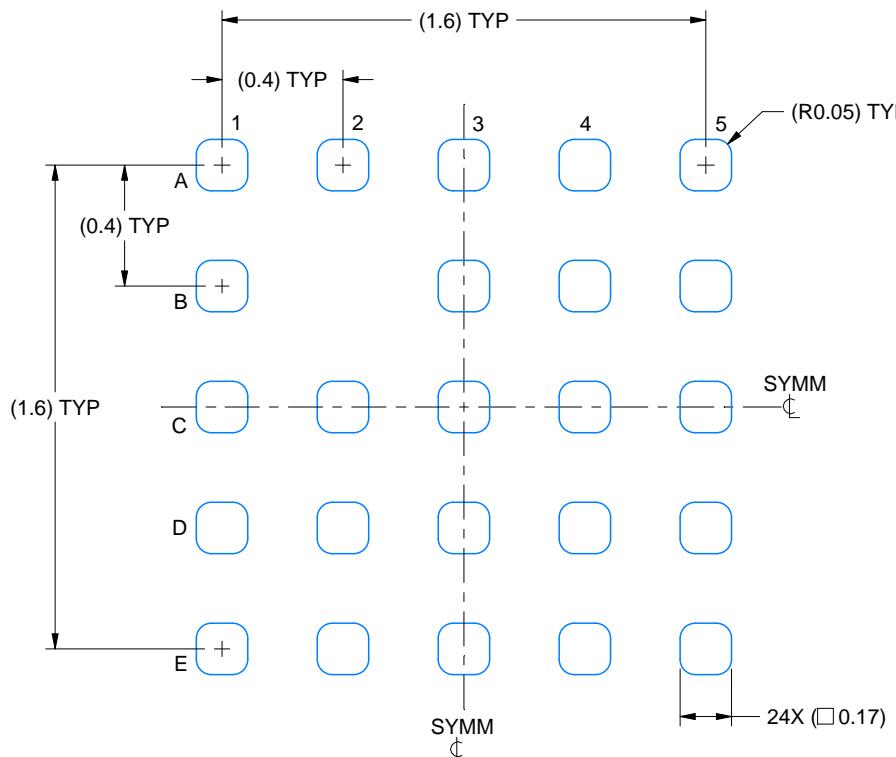

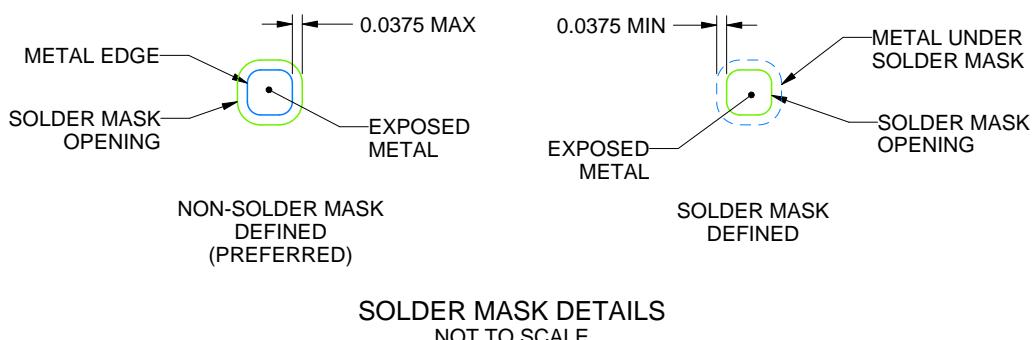

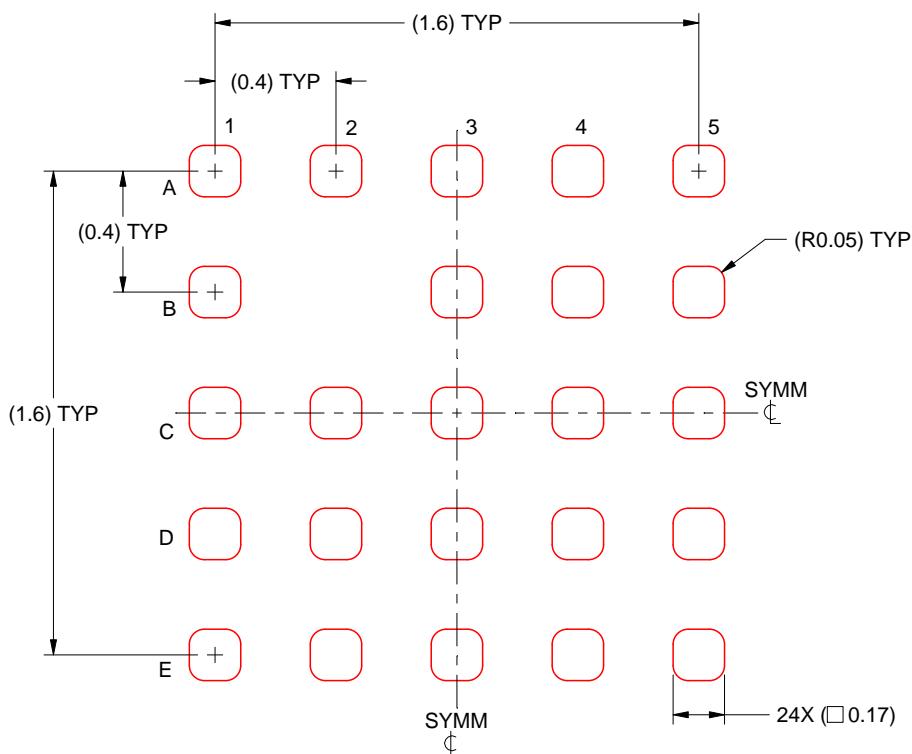

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-----------|----------------------|-------------------------|

| TCAL6416R | DTO (X2QFN, 24)      | 2mm × 2mm               |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                |           |                               |           |

|--------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                    | <b>1</b>  | 7.3 機能説明                      | <b>20</b> |

| <b>2 アプリケーション</b>              | <b>1</b>  | 7.4 デバイスの機能モード                | <b>22</b> |

| <b>3 概要</b>                    | <b>1</b>  | 7.5 プログラミング                   | <b>22</b> |

| <b>4 ピン構成および機能</b>             | <b>3</b>  | 7.6 レジスタ マップ                  | <b>24</b> |

| <b>5 仕様</b>                    | <b>5</b>  | <b>8 アプリケーションと実装</b>          | <b>33</b> |

| 5.1 絶対最大定格                     | 5         | 8.1 アプリケーション情報                | 33        |

| 5.2 ESD 定格                     | 5         | 8.2 代表的なアプリケーション              | 33        |

| 5.3 推奨動作条件                     | 6         | 8.3 電源に関する推奨事項                | 36        |

| 5.4 熱に関する情報                    | 6         | 8.4 レイアウト                     | 38        |

| 5.5 電気的特性                      | 7         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>39</b> |

| 5.6 タイミング要件                    | 8         | 9.1 ドキュメントの更新通知を受け取る方法        | 39        |

| 5.7 I <sup>2</sup> C バスタイミング要件 | 9         | 9.2 サポート・リソース                 | 39        |

| 5.8 スイッチング特性                   | 10        | 9.3 商標                        | 39        |

| 5.9 代表的特性                      | 10        | 9.4 静電気放電に関する注意事項             | 39        |

| <b>6 パラメータ測定情報</b>             | <b>14</b> | 9.5 用語集                       | 39        |

| <b>7 詳細説明</b>                  | <b>18</b> | <b>10 改訂履歴</b>                | <b>39</b> |

| 7.1 概要                         | 18        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>39</b> |

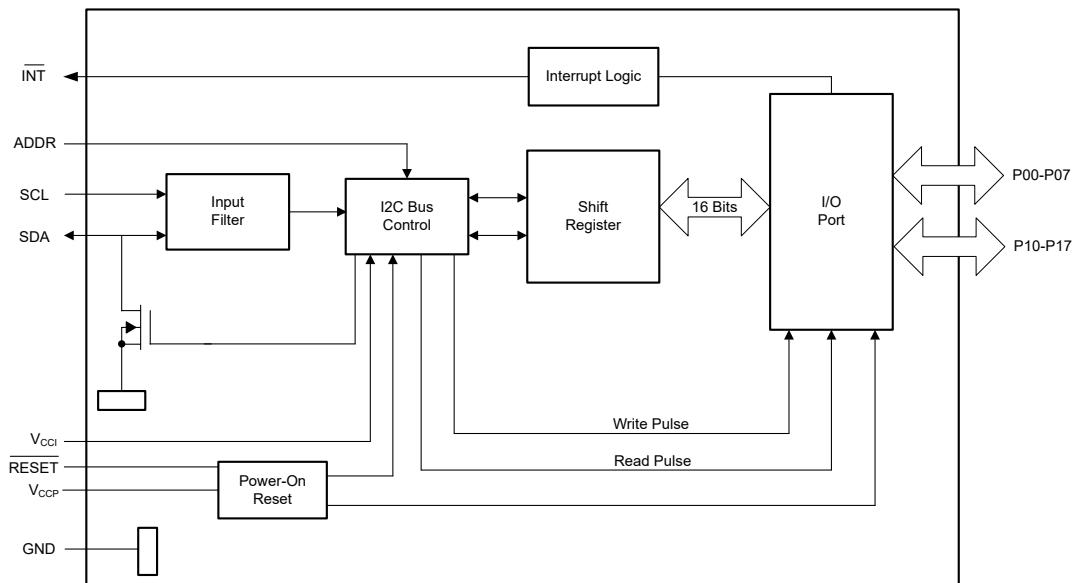

| 7.2 機能ブロック図                    | 19        |                               |           |

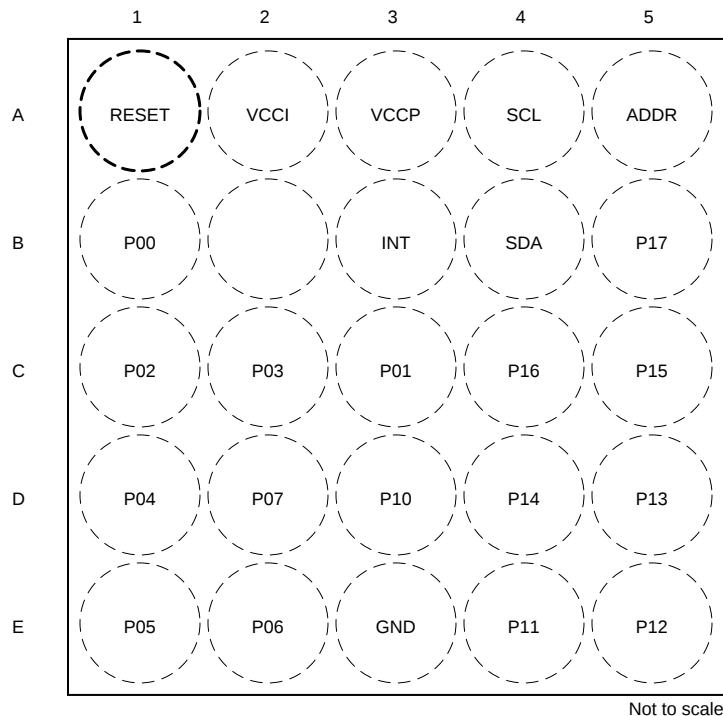

## 4 ピン構成および機能

図 4-1. DTO パッケージ、24 ピン X2QFN (上面図)

**表 4-1. ピンの機能**

| ピン               |    | タイプ <sup>(1)</sup> | 説明                                                                          |

|------------------|----|--------------------|-----------------------------------------------------------------------------|

| 名称               | 番号 |                    |                                                                             |

| INT              | B3 | O                  | 割り込み出力。プルアップ抵抗を介して V <sub>CCI</sub> または V <sub>CCP</sub> に接続します             |

| V <sub>CCI</sub> | A2 | —                  | I <sup>2</sup> C バスの電源電圧。外部 I <sup>2</sup> C コントローラの電源電圧に直接接続します            |

| RESET            | A1 | I                  | アクティブ Low のリセット入力。アクティブな接続が使用されていない場合は、プルアップ抵抗を経由して V <sub>CCI</sub> に接続します |

| P00              | B1 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P00 は入力として構成されます                          |

| P01              | C3 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P01 は入力として構成されます                          |

| P02              | C1 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P02 は入力として構成されます                          |

| P03              | C2 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P03 は入力として構成されます                          |

| P04              | D1 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P04 は入力として構成されます                          |

| P05              | E1 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P05 は入力として構成されます                          |

| P06              | E2 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P06 は入力として構成されます                          |

| P07              | D2 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P07 は入力として構成されます                          |

| GND              | E3 | —                  | グランド                                                                        |

| P10              | D3 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P10 は入力として構成されます                          |

| P11              | E4 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P11 は入力として構成されます                          |

| P12              | E5 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P12 は入力として構成されます                          |

| P13              | D5 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P13 は入力として構成されます                          |

| P14              | D4 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P14 は入力として構成されます                          |

| P15              | C5 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P15 は入力として構成されます                          |

| P16              | C4 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P16 は入力として構成されます                          |

| P17              | B5 | I/O                | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P17 は入力として構成されます                          |

| ADDR             | A5 | I                  | アドレス入力。V <sub>CCP</sub> またはグランドに直接接続します                                     |

| SCL              | A4 | I                  | シリアル クロック バス。プルアップ抵抗を経由して V <sub>CCI</sub> に接続します                           |

| SDA              | B4 | I/O                | シリアル データ バス。プルアップ抵抗を経由して V <sub>CCI</sub> に接続します                            |

| V <sub>CCP</sub> | A3 | —                  | P ポート用 TCAL6416R の電源電圧                                                      |

(1) I = 入力、O = 出力

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                       |                             |           | 最小値                           | 最大値      | 単位  |    |

|-----------------------|-----------------------------|-----------|-------------------------------|----------|-----|----|

| $V_{CC1}$ 、 $V_{CCP}$ | 電源電圧                        |           | -0.5                          | 4        | V   |    |

| $V_I$                 | 入力電圧 <sup>(2)</sup>         |           | -0.5                          | 4        | V   |    |

| $V_O$                 | 出力電圧 <sup>(2)</sup>         |           | -0.5                          | 4        | V   |    |

| $I_{IK}$              | 入力クランプ電流                    | $V_I < 0$ |                               | -20      | mA  |    |

| $I_{OK}$              | 出力クランプ電流                    | $V_O < 0$ |                               | -20      | mA  |    |

| $I_{IOK}$             | 入力 / 出力クランプ電流               | P ポート     | $V_O < 0$ または $V_O > V_{CCP}$ | $\pm 20$ | mA  |    |

|                       |                             | SDA       | $V_O < 0$ または $V_O > V_{CCI}$ | $\pm 20$ |     |    |

| $I_{OL}$              | 連続出力 Low 電流 <sup>(3)</sup>  | P ポート     | $V_O = 0 \sim V_{CCP}$        | 50       | mA  |    |

|                       |                             | SDA       | $V_O = 0 \sim V_{CCI}$        | 25       |     |    |

| $I_{OH}$              | 連続出力 High 電流 <sup>(3)</sup> | P ポート     | $V_O = 0 \sim V_{CCP}$        | -50      | mA  |    |

| $I_{CC}$              | GND を流れる連続電流                |           |                               | -200     | mA  |    |

| $I_{CC}$              | $V_{CCP}$ を流れる連続電流          |           |                               | 160      | mA  |    |

|                       | $V_{CCI}$ を流れる連続電流          |           |                               | 10       |     |    |

| $T_J$                 | 接合部温度                       |           |                               | 130      | °C  |    |

| $T_{stg}$             | 保存温度                        |           |                               | -65      | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 入力と出力の電流の定格を順守しても、入力の負電圧と出力電圧の定格を超えることがあります。

- (3) このピンが出力に設定されている場合、IO ピンを GND に直接接続することはできません。これにより 150mA を超える電流が発生し、デバイスに損傷を与える可能性があります。IO ピンを GND に接続する場合は、10kΩ を超えるプルダウン抵抗を IO ピンに接続することを推奨します。

### 5.2 ESD 定格

|             |      |                                                                     | 値          | 単位 |

|-------------|------|---------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>        | $\pm 4000$ | V  |

|             |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC 仕様 JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 1000$ |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

外気温度範囲での動作時 (特に記述がない限り)

|                       |                                               |               | 最小値                  | 最大値                  | 単位 |

|-----------------------|-----------------------------------------------|---------------|----------------------|----------------------|----|

| $V_{CC1}$ 、 $V_{CCP}$ | 電源電圧                                          |               | 1.08                 | 3.6                  | V  |

| $V_{IH}$              | High レベル入力電圧                                  | SCL、SDA、RESET | $0.7 \times V_{CC1}$ | 3.6                  | V  |

|                       |                                               | P00~P17、ADDR  | $0.7 \times V_{CCP}$ | 3.6                  |    |

| $V_{IL}$              | Low レベル入力電圧                                   | SCL、SDA、RESET | -0.5                 | $0.3 \times V_{CC1}$ | V  |

|                       |                                               | P00~P17、ADDR  | -0.5                 | $0.3 \times V_{CCP}$ | V  |

| $I_{OH}$              | High レベル出力電流 ( $V_{CCP} - V_{OH} \leq 0.3V$ ) | P00~P17       |                      | -10                  | mA |

| $I_{OH}$ (全ポートの合計)    | High レベル出力電流 ( $V_{CCP} - V_{OH} \leq 0.3V$ ) | P00~P17       |                      | -160                 | mA |

| $I_{OL}$              | Low レベル出力電流 ( $V_{OL} \leq 0.3V$ )            | P00~P17       |                      | 25                   | mA |

| $I_{OL}$ (全ポートの合計)    | Low レベル出力電流 ( $V_{OL} \leq 0.3V$ )            | P00~P17       |                      | 160                  | mA |

| $T_A$                 | 周囲温度                                          |               | -40                  | 125                  | °C |

| $T_{PCB}$             | 基板の温度 (デバイスから 1mm 離れた場所で測定)                   |               | -40                  | 120                  | °C |

| $T_J$                 | 接合部温度                                         |               |                      | 125                  | °C |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | パッケージ       | 単位   |

|----------------------|-------------------|-------------|------|

|                      |                   | DTO (X2QFN) |      |

|                      |                   | ピン          |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 150.4       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 48.1        | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 89.4        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 1.0         | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 89.2        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ             |                                   | テスト条件                                                                                                                                                                         | V <sub>CCP</sub>                                                                                                                                                          | 最小値          | 標準値  | 最大値 | 単位 |

|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-----|----|

| V <sub>IK</sub>   | 入力ダイオード クランプ電圧                    | I <sub>I</sub> = -18mA                                                                                                                                                        | 1.08V ~ 3.6V                                                                                                                                                              | -1.2         |      |     | V  |

| V <sub>PORR</sub> | パワーONリセット電圧、V <sub>CC</sub> 立ち上がり | V <sub>I</sub> = V <sub>CC</sub> または GND, I <sub>O</sub> = 0                                                                                                                  |                                                                                                                                                                           |              | 0.85 | 1.0 | V  |

| V <sub>PORF</sub> | パワーONリセット電圧、V <sub>CC</sub> 立ち下がり | V <sub>I</sub> = V <sub>CC</sub> または GND, I <sub>O</sub> = 0                                                                                                                  |                                                                                                                                                                           | 0.6          | 0.75 |     | V  |

| V <sub>OH</sub>   | P ポート High レベル出力電圧                | I <sub>OH</sub> = -8mA, CC-XX = 11b                                                                                                                                           | 1.08V                                                                                                                                                                     | 0.8          |      |     | V  |

|                   |                                   |                                                                                                                                                                               | 1.65V                                                                                                                                                                     | 1.4          |      |     |    |

|                   |                                   |                                                                                                                                                                               | 2.3V                                                                                                                                                                      | 2.1          |      |     |    |

|                   |                                   |                                                                                                                                                                               | 3V                                                                                                                                                                        | 2.8          |      |     |    |

|                   |                                   | I <sub>OH</sub> = -2.5mA および CC-XX = 00b,<br>I <sub>OH</sub> = -5mA および CC-XX = 01b,<br>I <sub>OH</sub> = -7.5mA および CC-XX = 10b,<br>I <sub>OH</sub> = -10mA および CC-XX = 11b, | 1.08V                                                                                                                                                                     | 0.75         |      |     |    |

|                   |                                   |                                                                                                                                                                               | 1.65V                                                                                                                                                                     | 1.4          |      |     |    |

|                   |                                   |                                                                                                                                                                               | 2.3V                                                                                                                                                                      | 2.1          |      |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           |              |      |     |    |

|                   |                                   |                                                                                                                                                                               | 3V                                                                                                                                                                        | 2.8          |      |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           |              |      |     |    |

| V <sub>OL</sub>   | Low レベル出力電圧                       | P ポート                                                                                                                                                                         | I <sub>OL</sub> = 8mA, CC-XX = 11b                                                                                                                                        | 1.08V        | 0.2  |     | V  |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 1.65V        | 0.15 |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 2.3V         | 0.1  |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 3.0V         | 0.1  |     |    |

|                   |                                   | P ポート                                                                                                                                                                         | I <sub>OL</sub> = 2.5mA および CC-XX = 00b,<br>I <sub>OL</sub> = 5mA および CC-XX = 01b,<br>I <sub>OL</sub> = 7.5mA および CC-XX = 10b,<br>I <sub>OL</sub> = 10mA および CC-XX = 11b, | 1.08V        | 0.25 |     | V  |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 1.65V        | 0.15 |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 2.3V         | 0.1  |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           | 3.0V         | 0.1  |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           |              |      |     |    |

|                   |                                   |                                                                                                                                                                               |                                                                                                                                                                           |              |      |     |    |

| I <sub>OL</sub>   | Low レベル出力電流                       | SDA                                                                                                                                                                           | V <sub>OL</sub> = 0.4 V                                                                                                                                                   | 1.08V ~ 3.6V | 20   |     | mA |

|                   |                                   | INT                                                                                                                                                                           | V <sub>OL</sub> = 0.4 V                                                                                                                                                   |              | 4    |     |    |

| I <sub>I</sub>    | 入力リーク電流                           | P ポート                                                                                                                                                                         | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                  | 1.08V ~ 3.6V |      | ±1  | μA |

|                   |                                   |                                                                                                                                                                               | V <sub>I</sub> = 3.6V                                                                                                                                                     | 0V           |      | ±1  |    |

| I <sub>I</sub>    | 入力リーク電流                           | SCL、SDA、RESET                                                                                                                                                                 | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                  | 1.08V ~ 3.6V |      | ±1  |    |

| I <sub>I</sub>    | 入力リーク電流                           | ADDR                                                                                                                                                                          | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                  | 1.08V ~ 3.6V |      | ±1  | μA |

## 5.5 電気的特性 (続き)

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ                               |              | テスト条件                                                                                                                                                                                       | V <sub>CCP</sub>                                                                                                                                                             | 最小値          | 標準値 | 最大値           | 単位            |

|-------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|---------------|---------------|

| $I_{CC}$<br>( $I_{CCI} + I_{CCP}$ ) | 静止時電流        | 動作モード<br>(400kHz)                                                                                                                                                                           | SDA, $\overline{RESET} = V_{CCI}$ 、<br>P ポート、ADDR = V <sub>CCP</sub> または<br>GND、<br>I/O = 入力、 $f_{SCL} = 400\text{kHz}$ 、<br>$-40^\circ\text{C} < T_A \leq 85^\circ\text{C}$ | 3.6V         | 7   | 15            | $\mu\text{A}$ |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 2.7V         | 5   | 11            |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.95V        | 4   | 8             |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.32V        | 2   | 6             |               |

|                                     |              | 動作モード<br>(1MHz)                                                                                                                                                                             | SDA, $\overline{RESET} = V_{CCI}$ 、<br>P ポート、ADDR = V <sub>CCP</sub> または<br>GND、<br>I/O = 入力、 $f_{SCL} = 1\text{MHz}$ 、<br>$-40^\circ\text{C} < T_A \leq 85^\circ\text{C}$   | 3.6V         | 7   | 24            | $\mu\text{A}$ |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 2.7V         | 5   | 18            |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.95V        | 4   | 14            |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.32V        | 2   | 11            |               |

|                                     |              | スタンバイ モード                                                                                                                                                                                   | SDA, $\overline{RESET} = V_{CCI}$ 、<br>P ポート、ADDR = V <sub>CCP</sub> または<br>GND、<br>I/O = 入力、 $f_{SCL} = 1\text{MHz}$ 、<br>$85^\circ\text{C} < T_A \leq 125^\circ\text{C}$   | 3.6V         | 34  |               | $\mu\text{A}$ |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 2.7V         | 24  |               |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.95V        | 18  |               |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.32V        | 12  |               |               |

|                                     |              | SCL, SDA, $\overline{RESET} = V_{CCI}$ 、<br>P ポート、ADDR = V <sub>CCP</sub> または<br>GND、<br>I/O = 入力、 $I_O = 0$ 、 $f_{SCL} = 0\text{kHz}$ 、<br>$-40^\circ\text{C} < T_A \leq 85^\circ\text{C}$ | 3.6V                                                                                                                                                                         | 42           |     | $\mu\text{A}$ |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 2.7V         | 30  |               |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.95V        | 22  |               |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.32V        | 16  |               |               |

|                                     |              | SCL, SDA, $\overline{RESET} = V_{CCI}$ 、<br>P ポート、ADDR = V <sub>CCP</sub> または<br>GND、<br>I/O = 入力、 $I_O = 0$ 、 $f_{SCL} = 0\text{kHz}$ 、<br>$85^\circ\text{C} < T_A \leq 125^\circ\text{C}$ | 3.6V                                                                                                                                                                         | 1.5          | 4   | $\mu\text{A}$ |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 2.7V         | 1.2 | 3             |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.95V        | 0.6 | 3             |               |

|                                     |              |                                                                                                                                                                                             |                                                                                                                                                                              | 1.32V        | 0.6 | 3             |               |

| R <sub>pu(int)</sub>                | 内部プルアップ抵抗    | P ポート                                                                                                                                                                                       |                                                                                                                                                                              |              |     |               | k $\Omega$    |

| R <sub>pd(int)</sub>                | 内部プルダウン抵抗    |                                                                                                                                                                                             |                                                                                                                                                                              |              |     |               |               |

| C <sub>I</sub>                      | 入力ピン容量       | SCL                                                                                                                                                                                         | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                     | 1.08V ~ 3.6V | 2.5 | 5             | pF            |

| C <sub>IO</sub>                     | 入力 / 出力ピンの容量 | SDA                                                                                                                                                                                         | V <sub>IO</sub> = V <sub>CC</sub> または GND                                                                                                                                    | 1.08V ~ 3.6V | 6   | 8             | pF            |

|                                     |              | P ポート                                                                                                                                                                                       | V <sub>IO</sub> = V <sub>CC</sub> または GND                                                                                                                                    | 1.08V ~ 3.6V | 6   | 8.5           |               |

## 5.6 タイミング要件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |                         |  | 最小値 | 最大値 | 単位 |

|--------------------|-------------------------|--|-----|-----|----|

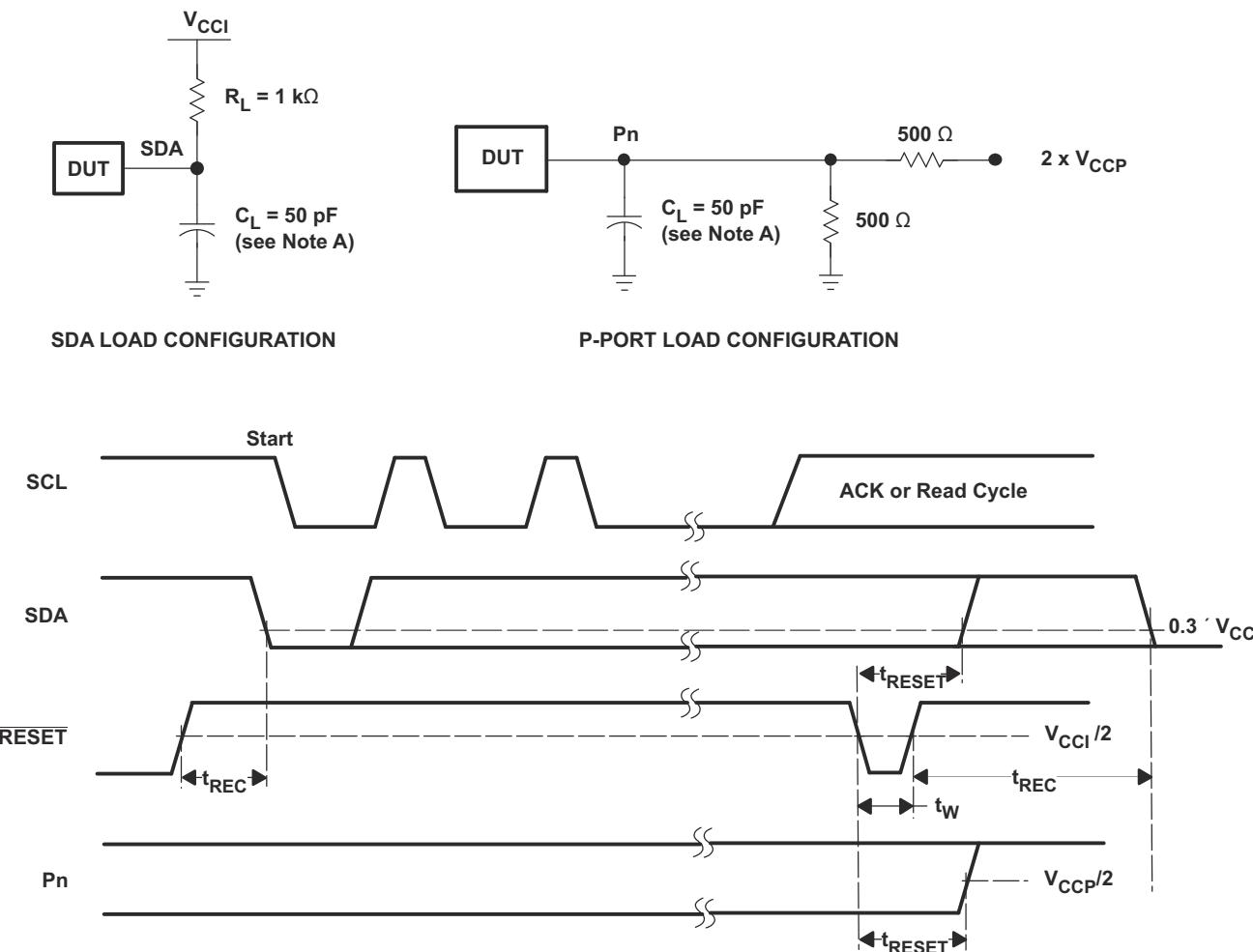

| t <sub>w</sub>     | リセット パルス時間              |  | 80  |     | ns |

| t <sub>REC</sub>   | リセット復帰時間                |  | 0   |     | ns |

| t <sub>RESET</sub> | リセットまでの時間               |  | 400 |     | ns |

| P ポート              |                         |  |     |     |    |

| t <sub>PH</sub>    | 割り込みを発生させる P ポートの最小パルス幅 |  | 30  |     | ns |

## 5.7 I<sup>2</sup>C バス タイミング要件

外気温度範囲での動作時 (特に記述がない限り)

|                                       |                                           |                                   | 最小値                           | 最大値  | 単位  |

|---------------------------------------|-------------------------------------------|-----------------------------------|-------------------------------|------|-----|

| <b>I<sup>2</sup>C バス - スタンダード モード</b> |                                           |                                   |                               |      |     |

| $f_{scl}$                             | I <sup>2</sup> C クロック周波数                  |                                   | 0                             | 100  | kHz |

| $t_{sch}$                             | I <sup>2</sup> C クロックの High 時間            |                                   | 4                             |      | μs  |

| $t_{scl}$                             | I <sup>2</sup> C クロックの Low 時間             |                                   | 4.7                           |      | μs  |

| $t_{sp}$                              | I <sup>2</sup> C スパイク時間                   |                                   | 50                            |      | ns  |

| $t_{sds}$                             | I <sup>2</sup> C シリアル データ セットアップ時間        |                                   | 250                           |      | ns  |

| $t_{sdh}$                             | I <sup>2</sup> C シリアル データ ホールド時間          |                                   | 0                             |      | ns  |

| $t_{icr}$                             | I <sup>2</sup> C 入力の立ち上がり時間               |                                   |                               | 1000 | ns  |

| $t_{icf}$                             | I <sup>2</sup> C 入力の立ち下がり時間               |                                   |                               | 300  | ns  |

| $t_{ocf}$                             | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF~400pF バス                     |                               | 300  | ns  |

| $t_{buf}$                             | STOP と START 間の I <sup>2</sup> C バスのフリー時間 |                                   | 4.7                           |      | μs  |

| $t_{sts}$                             | I <sup>2</sup> C START または反復 START 条件の設定  |                                   | 4.7                           |      | μs  |

| $t_{sth}$                             | I <sup>2</sup> C START または反復 START 条件ホールド |                                   | 4                             |      | μs  |

| $t_{sps}$                             | I <sup>2</sup> C STOP 条件の設定               |                                   | 4                             |      | μs  |

| $t_{vd(data)}$                        | 有効データ時間                                   | SCL Low から SDA 出力有効まで             |                               | 3.45 | μs  |

| $t_{vd(ack)}$                         | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 |                               | 3.45 | μs  |

| $C_b$                                 | I <sup>2</sup> C バスの容量性負荷                 |                                   |                               | 400  | pF  |

| <b>I<sup>2</sup>C バス - ファスト モード</b>   |                                           |                                   |                               |      |     |

| $f_{scl}$                             | I <sup>2</sup> C クロック周波数                  |                                   | 0                             | 400  | kHz |

| $t_{sch}$                             | I <sup>2</sup> C クロックの High 時間            |                                   | 0.6                           |      | μs  |

| $t_{scl}$                             | I <sup>2</sup> C クロックの Low 時間             |                                   | 1.3                           |      | μs  |

| $t_{sp}$                              | I <sup>2</sup> C スパイク時間                   |                                   | 50                            |      | ns  |

| $t_{sds}$                             | I <sup>2</sup> C シリアル データ セットアップ時間        |                                   | 100                           |      | ns  |

| $t_{sdh}$                             | I <sup>2</sup> C シリアル データ ホールド時間          |                                   | 0                             |      | ns  |

| $t_{icr}$                             | I <sup>2</sup> C 入力の立ち上がり時間               |                                   | 20                            | 300  | ns  |

| $t_{icf}$                             | I <sup>2</sup> C 入力の立ち下がり時間               |                                   | 20 × (V <sub>CC</sub> / 5.5V) | 300  | ns  |

| $t_{ocf}$                             | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF~400pF バス                     | 20 × (V <sub>CC</sub> / 5.5V) | 300  | ns  |

| $t_{buf}$                             | STOP と START 間の I <sup>2</sup> C バスのフリー時間 |                                   | 1.3                           |      | μs  |

| $t_{sts}$                             | I <sup>2</sup> C START または反復 START 条件の設定  |                                   | 0.6                           |      | μs  |

| $t_{sth}$                             | I <sup>2</sup> C START または反復 START 条件ホールド |                                   | 0.6                           |      | μs  |

| $t_{sps}$                             | I <sup>2</sup> C STOP 条件の設定               |                                   | 0.6                           |      | μs  |

| $t_{vd(data)}$                        | 有効データ時間                                   | SCL Low から SDA 出力有効まで             |                               | 0.9  | μs  |

| $t_{vd(ack)}$                         | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 |                               | 0.9  | μs  |

| $C_b$                                 | I <sup>2</sup> C バスの容量性負荷                 |                                   |                               | 400  | pF  |

| <b>I<sup>2</sup>C バス - 高速モード プラス</b>  |                                           |                                   |                               |      |     |

| $f_{scl}$                             | I <sup>2</sup> C クロック周波数                  |                                   | 0                             | 1000 | kHz |

| $t_{sch}$                             | I <sup>2</sup> C クロックの High 時間            |                                   | 0.26                          |      | μs  |

## 5.7 I<sup>2</sup>C バス タイミング要件 (続き)

外気温度範囲での動作時 (特に記述がない限り)

|                |                                           | 最小値                               | 最大値                           | 単位  |    |

|----------------|-------------------------------------------|-----------------------------------|-------------------------------|-----|----|

| $t_{scl}$      | I <sup>2</sup> C クロックの Low 時間             | 0.5                               |                               | μs  |    |

| $t_{sp}$       | I <sup>2</sup> C スパイク時間                   |                                   | 50                            | ns  |    |

| $t_{sds}$      | I <sup>2</sup> C シリアル データ セットアップ時間        | 50                                |                               | ns  |    |

| $t_{sdh}$      | I <sup>2</sup> C シリアル データ ホールド時間          | 0                                 |                               | ns  |    |

| $t_{icr}$      | I <sup>2</sup> C 入力の立ち上がり時間               |                                   | 120                           | ns  |    |

| $t_{icf}$      | I <sup>2</sup> C 入力の立ち下がり時間               | 20 × (V <sub>CC</sub> / 5.5V)     | 120                           | ns  |    |

| $t_{ocf}$      | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF~550pF バス                     | 20 × (V <sub>CC</sub> / 5.5V) | 120 | ns |

| $t_{buf}$      | STOP と START 間の I <sup>2</sup> C バスのフリー時間 | 0.5                               |                               | μs  |    |

| $t_{sts}$      | I <sup>2</sup> C START または反復 START 条件の設定  | 0.26                              |                               | μs  |    |

| $t_{sth}$      | I <sup>2</sup> C START または反復 START 条件ホールド | 0.26                              |                               | μs  |    |

| $t_{sps}$      | I <sup>2</sup> C STOP 条件の設定               | 0.26                              |                               | μs  |    |

| $t_{vd(data)}$ | 有効データ時間                                   | SCL Low から SDA 出力有効まで             | 0.45                          | μs  |    |

| $t_{vd(ack)}$  | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 | 0.45                          | μs  |    |

| $C_b$          | I <sup>2</sup> C バスの容量性負荷                 |                                   | 550                           | pF  |    |

## 5.8 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    |                | 始点 (入力) | 終点 (出力) | 最小値 | 標準値 | 最大値 | 単位 |

|----------|----------------|---------|---------|-----|-----|-----|----|

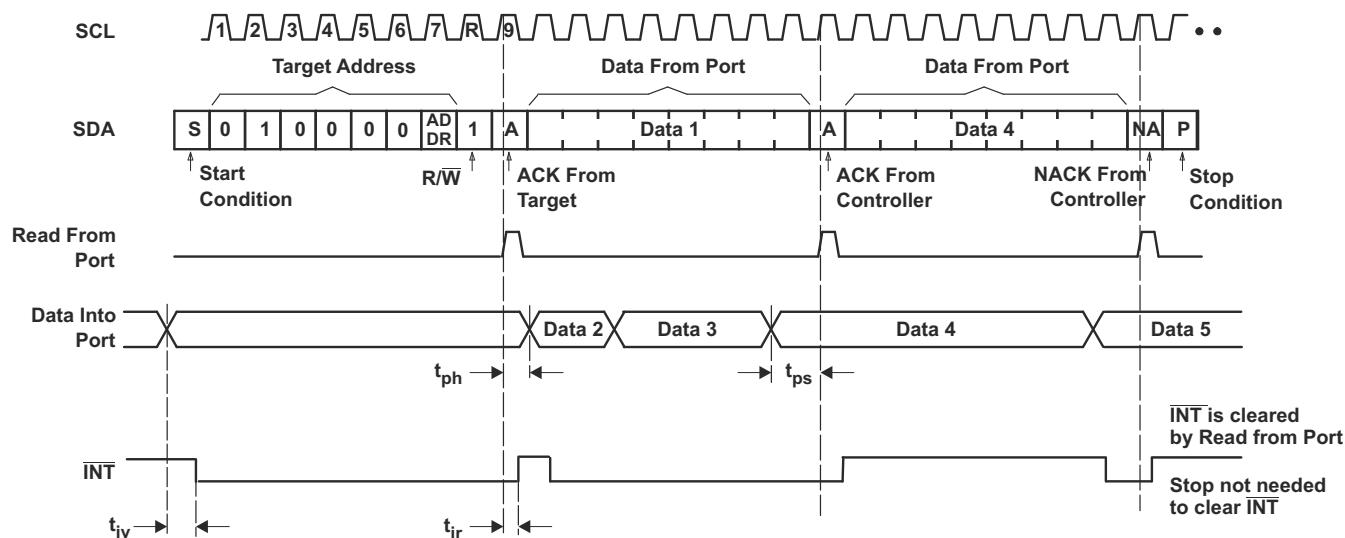

| $t_{lv}$ | 割り込み有効時間       | P ポート   | INT     |     | 1   |     | μs |

| $t_{lr}$ | 割り込みリセット遅延時間   | SCL     | INT     |     | 1   |     | μs |

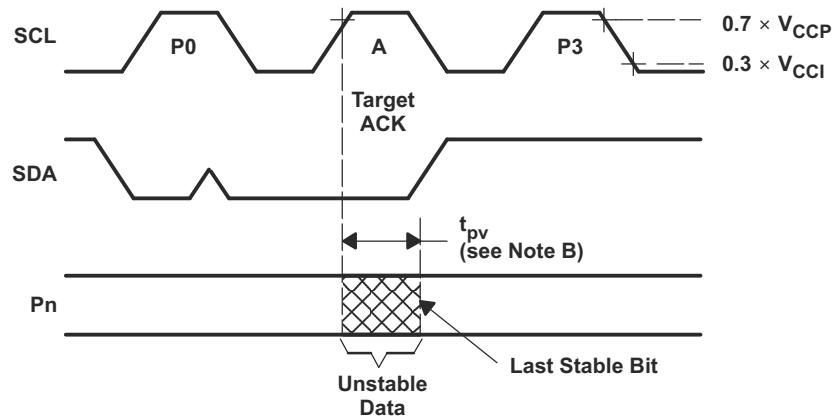

| $t_{pv}$ | 出力データ有効時間      | SCL     | P ポート   |     | 400 |     | ns |

| $t_{ps}$ | 入力データ セットアップ時間 | P ポート   | SCL     | 0   |     |     | ns |

| $t_{ph}$ | 入力データ ホールド時間   | P ポート   | SCL     | 300 |     |     | ns |

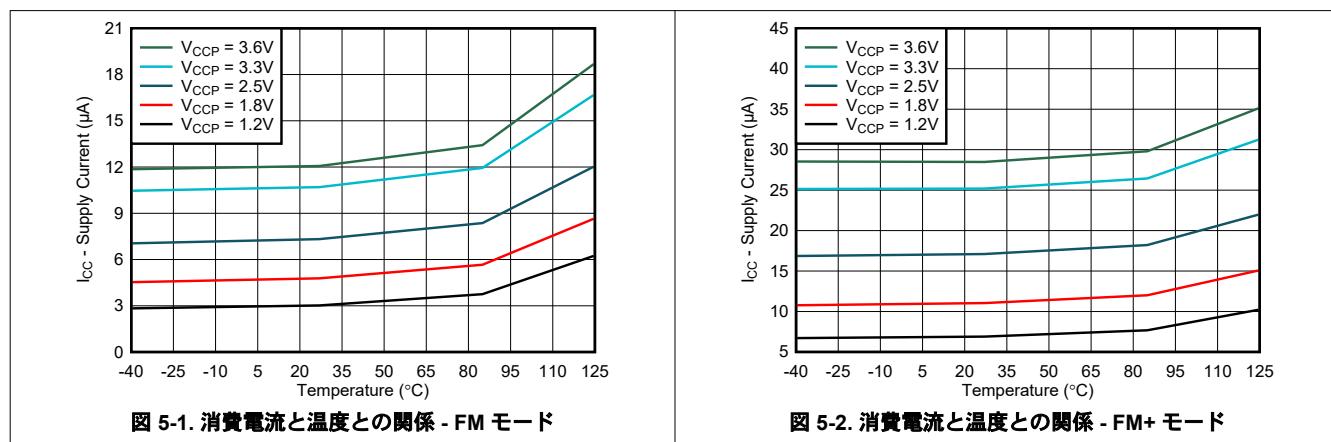

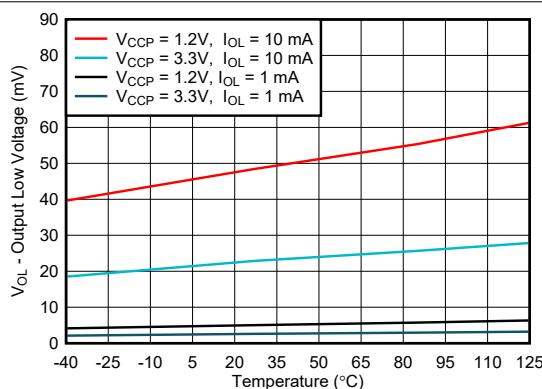

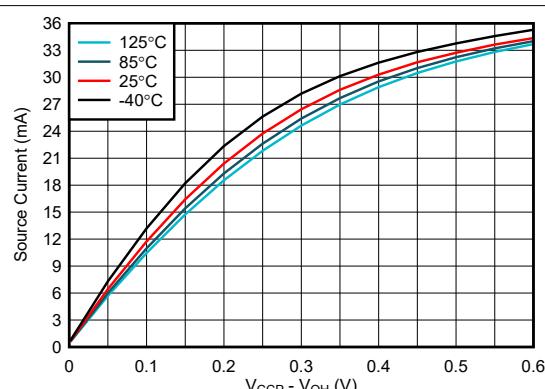

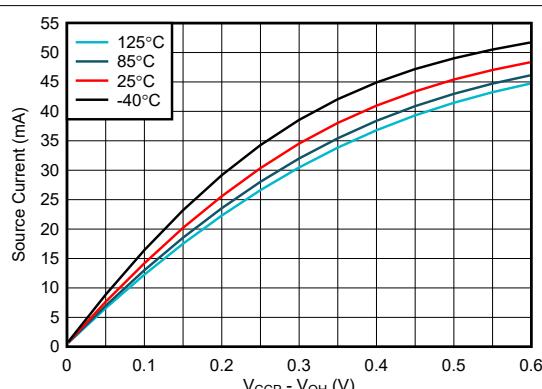

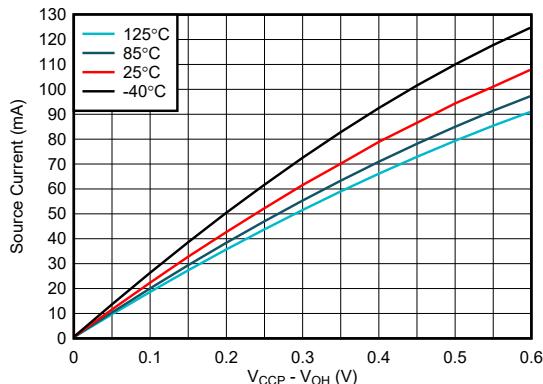

## 5.9 代表的特性

T<sub>A</sub> = 25°C (特に記述のない限り)

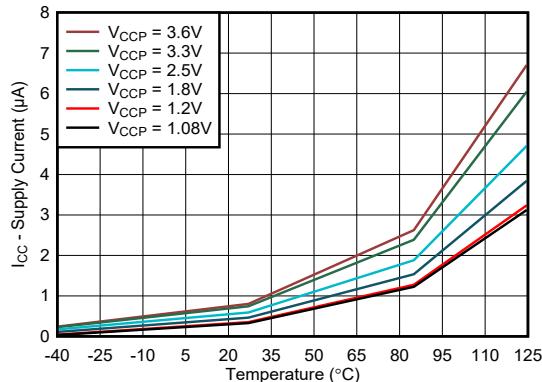

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 5-3. スタンバイ消費電流と温度との関係

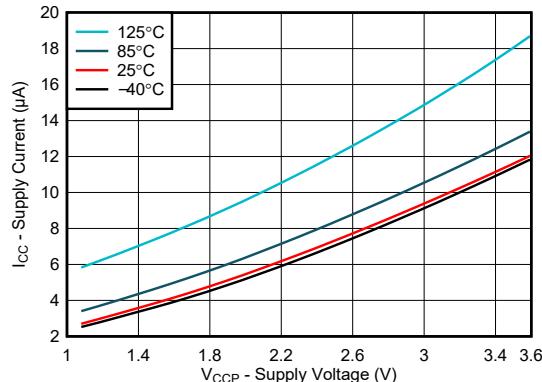

図 5-4. 消費電流と電源電圧との関係 - FM モード

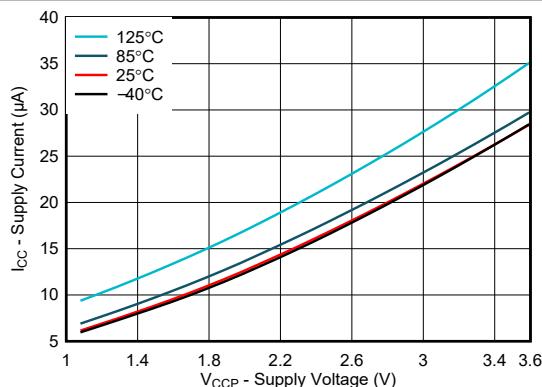

図 5-5. 消費電流と電源電圧との関係 - FM+ モード

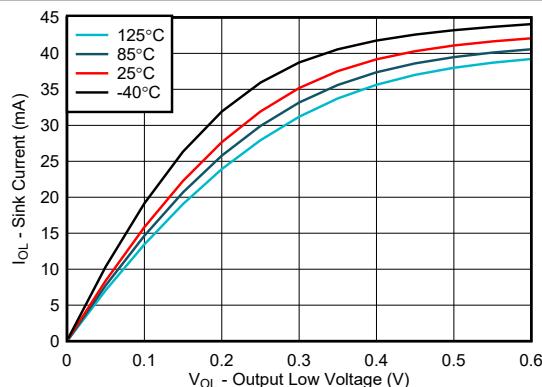

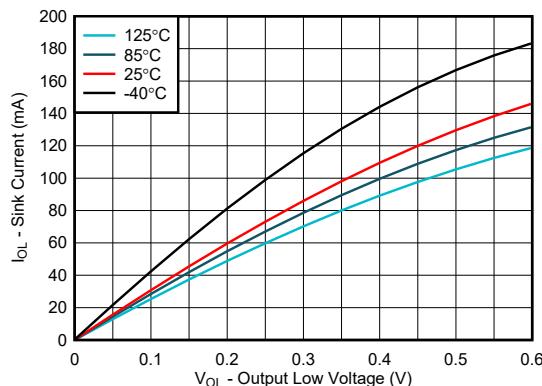

図 5-6. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 1.08\text{V}$

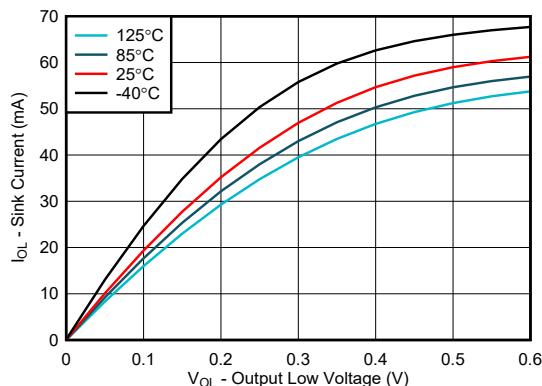

図 5-7. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 1.2\text{V}$

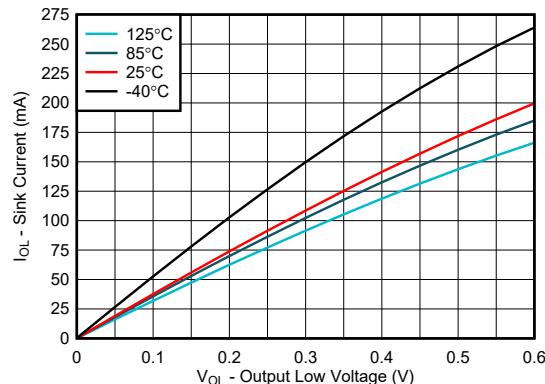

図 5-8. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 1.8\text{V}$

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 5-9. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 2.5\text{V}$

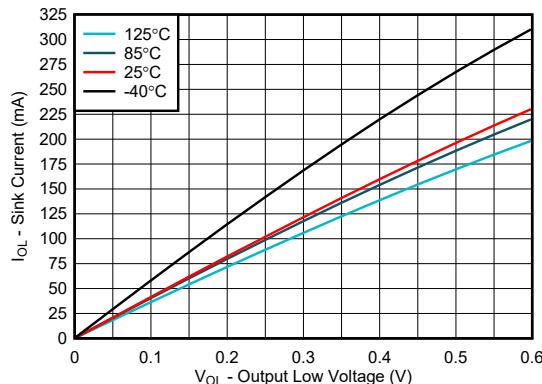

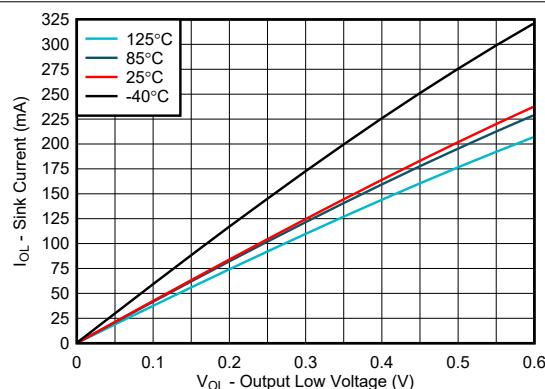

図 5-10. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 3.3\text{V}$

図 5-11. I/O シンク電流と出力 Low 電圧との関係、 $V_{CCP} = 3.6\text{V}$

図 5-12. I/O Low 電圧と温度との関係

図 5-13. I/O ソース電流と出力 High 電圧との関係、 $V_{CCP} = 1.08\text{V}$

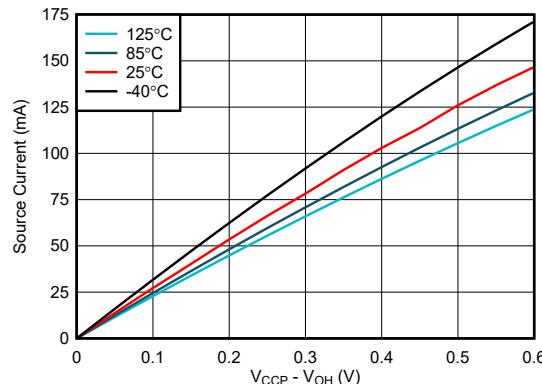

図 5-14. I/O ソース電流と出力 High 電圧との関係、 $V_{CCP} = 1.2\text{V}$

## 5.9 代表的特性 (続き)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 5-15. I/O ソース電流と出力 High 電圧との関係、

$V_{CCP} = 1.8\text{V}$

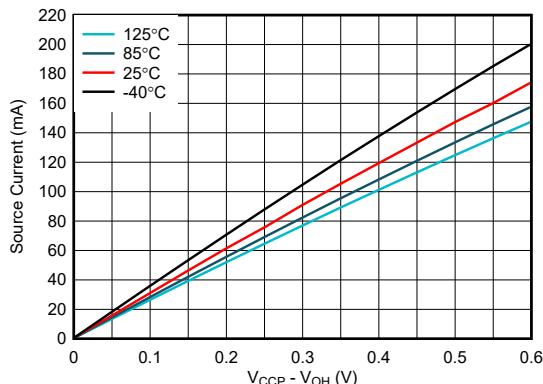

図 5-16. I/O ソース電流と出力 High 電圧との関係、

$V_{CCP} = 2.5\text{V}$

図 5-17. I/O ソース電流と出力 High 電圧との関係、

$V_{CCP} = 3.3\text{V}$

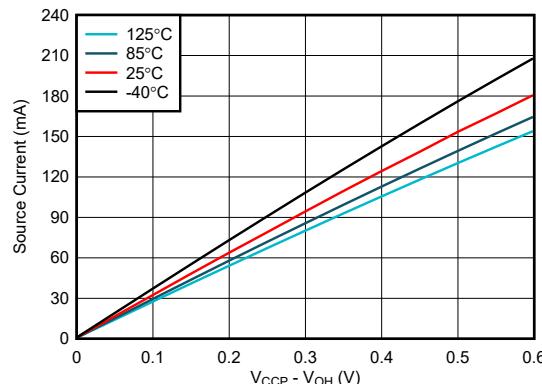

図 5-18. I/O ソース電流と出力 High 電圧との関係、

$V_{CCP} = 3.6\text{V}$

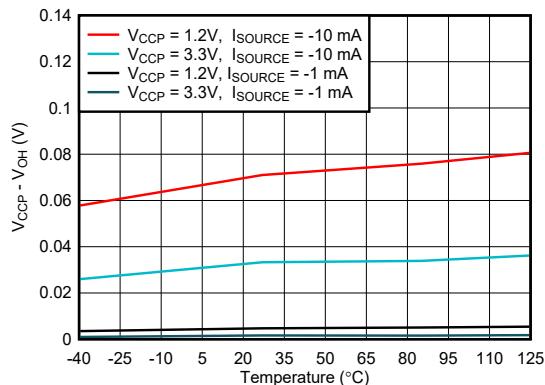

図 5-19. I/O High 電圧と温度との関係

## 6 パラメータ測定情報

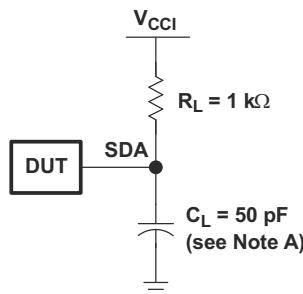

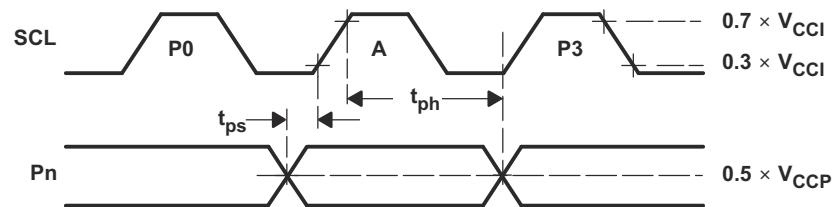

SDA LOAD CONFIGURATION

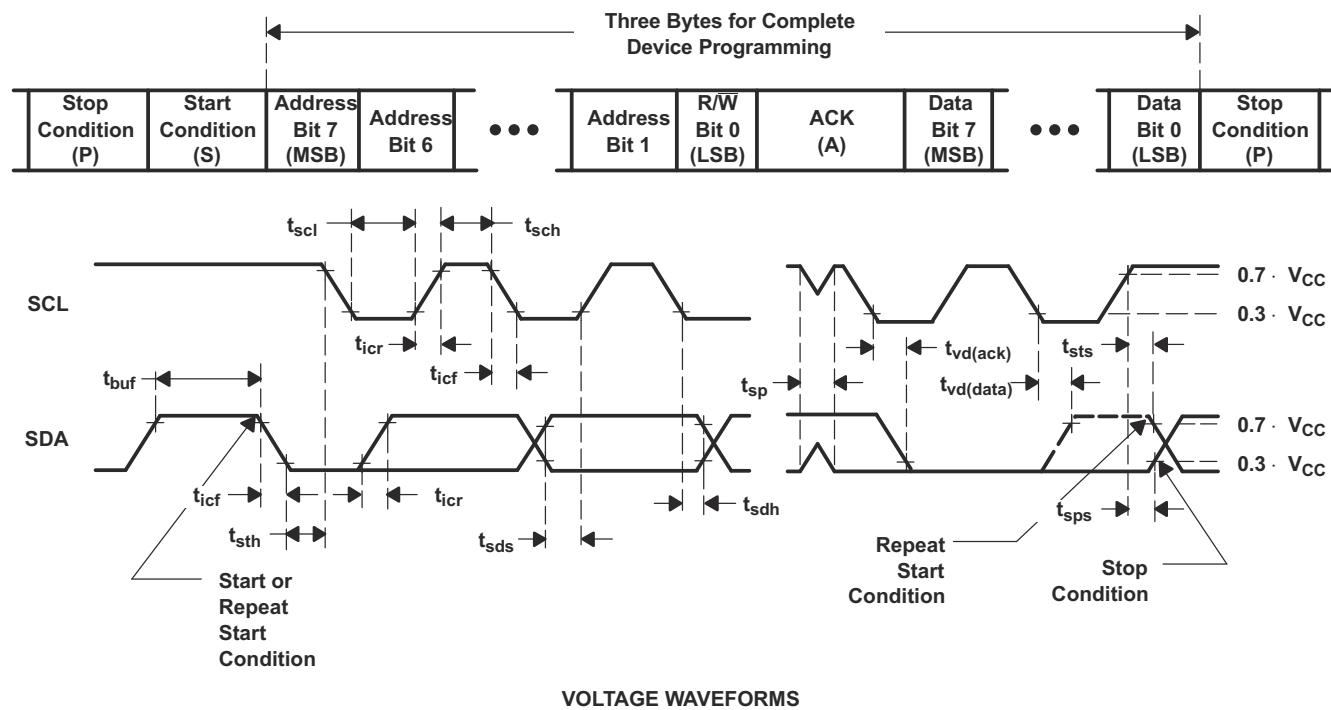

VOLTAGE WAVEFORMS

| BYTE | DESCRIPTION              |

|------|--------------------------|

| 1    | I <sup>2</sup> C address |

| 2, 3 | P-port data              |

- A.  $C_L$  にはプローブと治具の容量が含まれます。 $t_{ocf}$  は、10pF または 400pF の  $C_L$  で測定されます。

- B. すべての入力は、以下の特性を持つジエネレータから供給されます: PRR ≤ 10MHz,  $Z_O = 50\Omega$ ,  $t_f/t_r \leq 30\text{ns}$ 。

- C. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 6-1. I<sup>2</sup>C インターフェイスの負荷回路と電圧波形

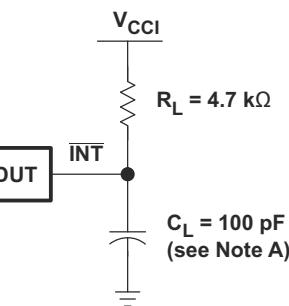

INTERRUPT LOAD CONFIGURATION

- A.  $C_L$  にはプローブと治具の容量が含まれます。

- B. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_O = 50\Omega$ ,  $t_r/t_f \leq 30\text{ns}$ 。

- C. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 6-2. 割り込み負荷回路および電圧波形

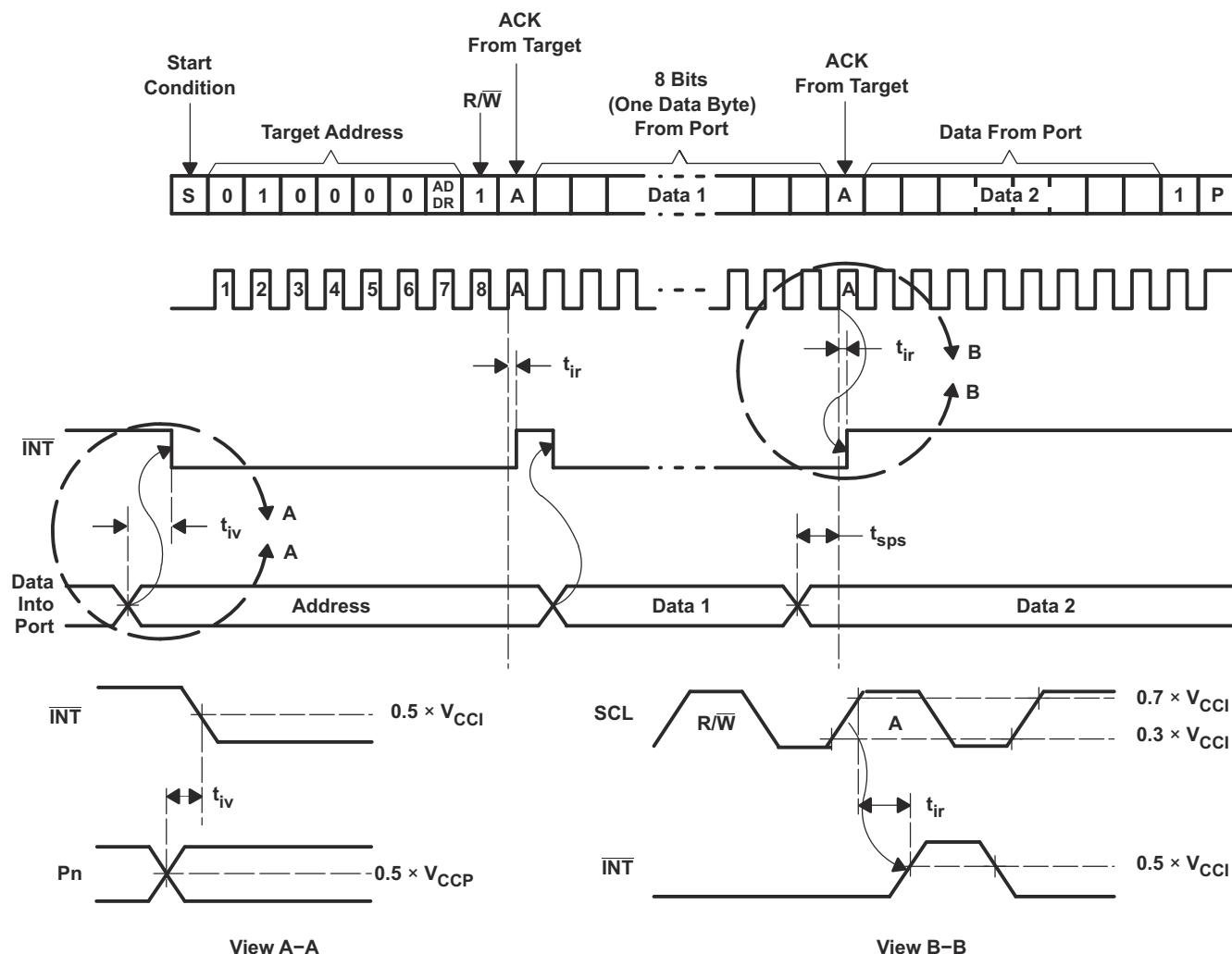

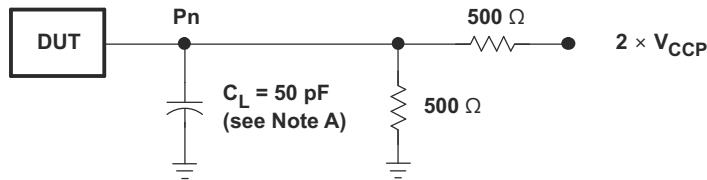

P-PORT LOAD CONFIGURATION

WRITE MODE ( $R/\bar{W} = 0$ )READ MODE ( $R/\bar{W} = 1$ )

- A.  $C_L$  にはプローブと治具の容量が含まれます。

- B.  $t_{pv}$  は、SCL で  $0.7 \times V_{CC}$  から 50% の I/O (On) 出力まで測定されます。

- C. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_O = 50\Omega$ ,  $t_r/t_f \leq 30\text{ns}$ 。

- D. 出力は一度に 1 つずつ測定され、測定するたびに 1 回遷移します。

- E. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 6-3. P ポートの負荷回路およびタイミング波形

- A.  $C_L$  にはプローブと治具の容量が含まれます。

- B. すべての入力は、以下の特性を持つジェネレータから供給されます: PRR  $\leq$  10MHz,  $Z_0 = 50\Omega$ ,  $t_f/t_r \leq 30\text{ns}$ .

- C. 出力は一度に 1 つずつ測定され、測定するたびに 1 回遷移します。

- D. I/O は入力として構成されます。

- E. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 6-4. リセット負荷回路および電圧波形

## 7 詳細説明

### 7.1 概要

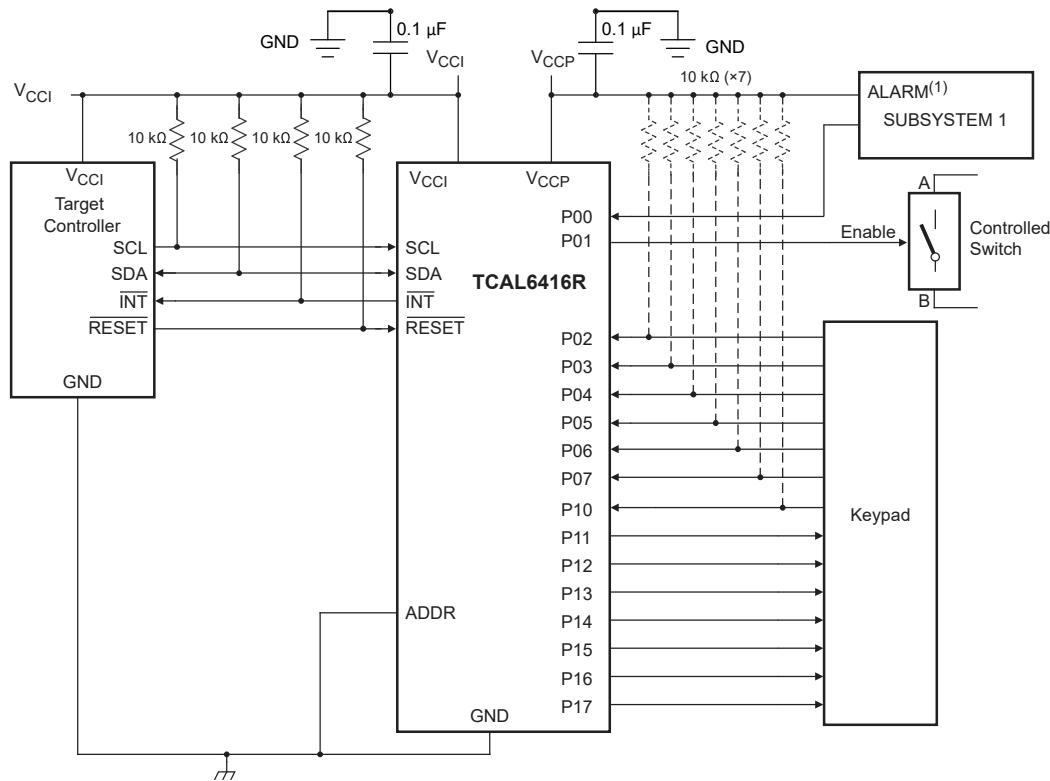

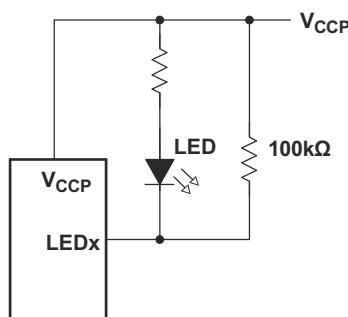

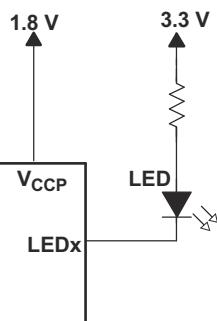

TCAL6416R は、広い電源電圧範囲にわたる電圧変換に対応しています。そのため、デバイスは I<sup>2</sup>C 側で最新のプロセッサとのインターフェイスが可能となり、電源レベルが低くなるため、消費電力の節約になります。プロセッサの電源電圧が低下している一方で、LED など一部の PCB 部品は依然として高い電圧の電源を必要とします。

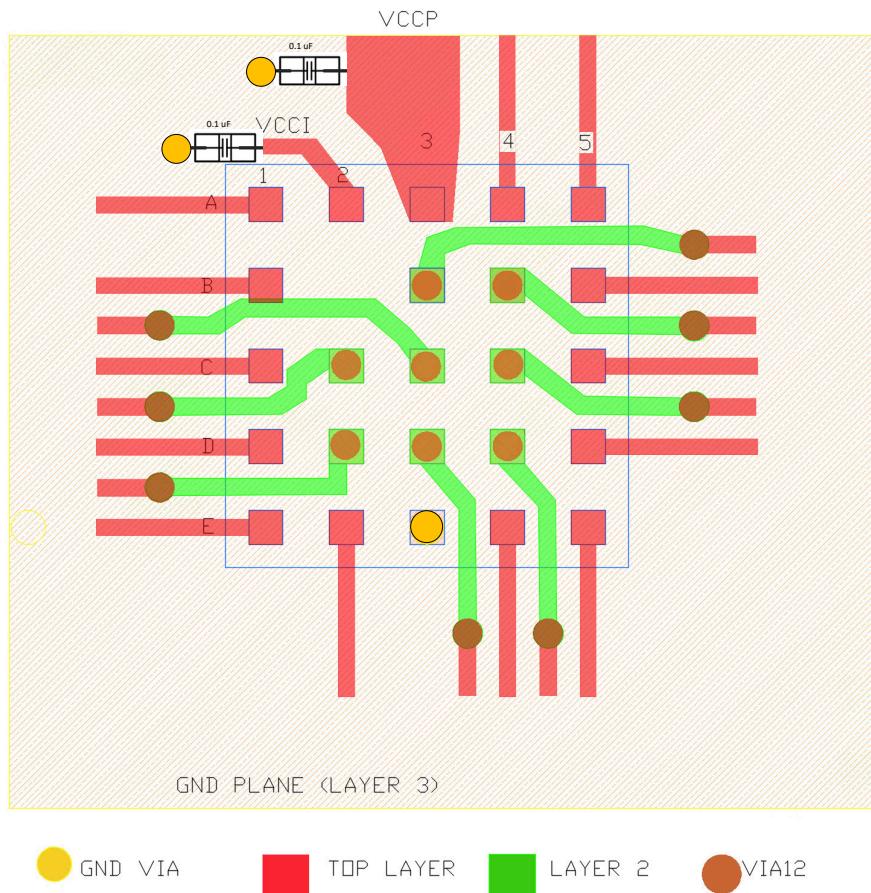

V<sub>CC1</sub> ピンは I<sup>2</sup>C バスの電源となるため、SCL、SDA、RESET ピンに接続されたプルアップ抵抗は V<sub>CC1</sub> で終端する必要があります。INT 出力にはオープンドレイン構造があり、アプリケーションに応じて、V<sub>CCP</sub> または V<sub>CC1</sub> への外部プルアップ抵抗が必要です。V<sub>CCP</sub> ピンは、P ポートへの電源となります。いずれかの P ポートで外部プルアップ抵抗が使用されている場合、または、いずれかの P ポートで LED が駆動されている場合、P00-P07 と P10-P17 に接続された 1 つまたは複数の抵抗または LED は、V<sub>CCP</sub> で終端する必要があります。デバイスの P ポートを出力として構成すると、LED を直接駆動するために最大 25mA までシンクできますが、追加の外部抵抗により電流を制限する必要があります。

TCAL6416R のデジタル コアは 8 ビットのデータ レジスタで構成されており、それらのレジスタを使ってユーザーは I/O ポートの特性を設定できます。電源投入時、またはソフトウェアリセット呼び出しの後に、I/O は入力として構成されます。ただし、Configuration レジスタに書き込むことにより、システム コントローラは I/O を入力または出力のどちらにも構成することができます。各入力または出力のデータは、対応する入力ポート レジスタまたは出力ポート レジスタに保持されます。入力ポート レジスタの極性は、極性反転 レジスタで反転できます。システム コントローラはすべてのレジスタを読み取ることができます。さらに、TCAL6416R には、I/O ポートの強化に特化した Agile I/O 機能が搭載されています。Agile I/O 機能とレジスタには、プログラム可能な出力駆動強度、プログラム可能なプルアップ抵抗とプルダウン抵抗、ラッチ可能な入力、マスク可能な割り込み、割り込みステータス レジスタ、プログラム可能なオープンドレインまたはプッシュプル出力が含まれています。これらの構成 レジスタにより柔軟性が向上するため、I/O は強化され、ユーザーは消費電力、スピード、EMI などの設計を最適化できるようになります。

デバイスの他の機能には、入力ポートの状態が変化するたびに INT ピンで発生する割り込みがあります。デバイスをデフォルトの状態にリセットするには、ソフトウェアリセットコマンドを送信するか、またはデバイスの電源を一度切ってパワーオンリセットを行います。ADDR ハードウェアセレクタブル アドレス ピンを使用することで、2 つの TCAL6416R デバイスを同じ I<sup>2</sup>C バスに接続することができます。

TCAL6416R のオープンドレイン割り込み (INT) 出力は、いずれかの入力状態が対応する Input Port レジスタの状態と異なる場合にアクティブになって、入力状態が変化したことをシステム コントローラに示すために使用されます。INT ピンは、プロセッサの割り込み入力に接続することができます。このラインで割り込み信号を送信することにより、デバイスは I<sup>2</sup>C バスで通信しなくとも、リモート I/O ポートに受信データがあるかどうかをプロセッサに通知することができます。そのため、シンプルなターゲット デバイスとして機能できます。

システム コントローラは、タイムアウトまたはその他の不適切な動作が発生した場合、スティッキー レジスタをデフォルト値にリセットせず、RESET 入力ピンを Low にアサートすることで、I<sup>2</sup>C/SMBus ステートマシンを再初期化できます。

1 本のハードウェア ピン (ADDR) を使用すると、固定 I<sup>2</sup>C アドレスをプログラムして変更することができ、2 つのデバイスで同じ I<sup>2</sup>C バスや SMBus を共有することができます。

## 7.2 機能ブロック図

A. すべての I/O は、電源投入時に入力に設定されます。

図 7-1. 論理図 (正論理)

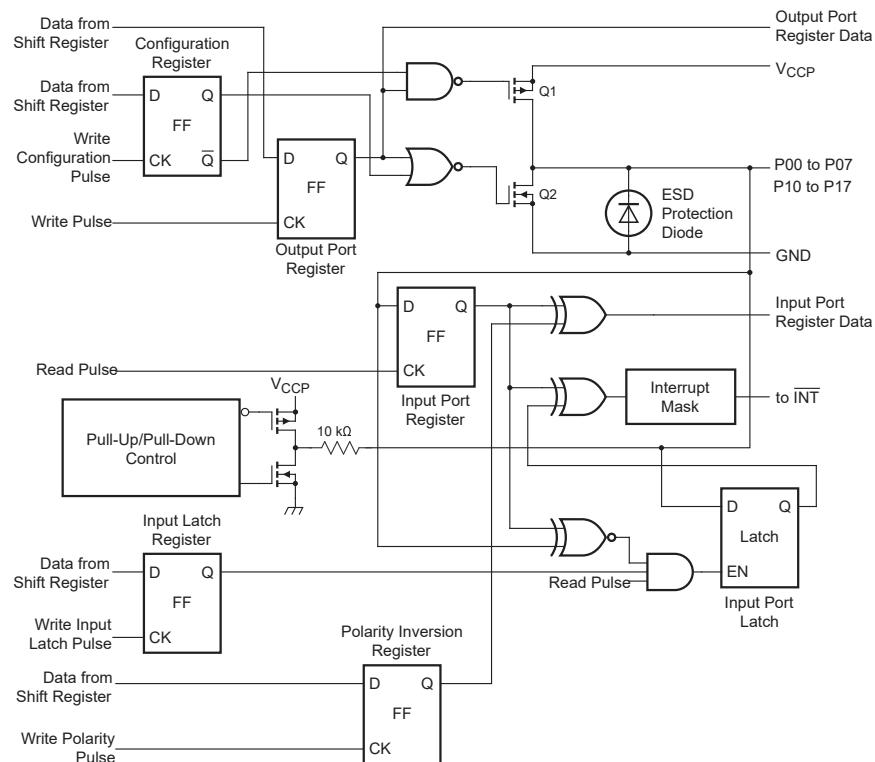

A. 電源オン時、またはソフトウェアリセット呼び出しの後で、すべてのレジスタがデフォルト値に戻ります。

図 7-2. P00 から P17 の概略回路図

## 7.3 機能説明

### 7.3.1 電圧変換

表 7-1 に、TCAL6416R でサポートされる I<sup>2</sup>C バス ( $V_{CC1}$ ) と P ポート ( $V_{CCP}$ ) 用のすべての電源電圧レベル オプションの組み合わせを示します。

表 7-1. 電圧変換

| $V_{CC1}$ (I <sup>2</sup> C コントローラの SDA および SCL)<br>(V) | $V_{CCP}$ (P ポート)<br>(V) |

|---------------------------------------------------------|--------------------------|

| 1.2                                                     | 1.2                      |

| 1.2                                                     | 1.8                      |

| 1.2                                                     | 2.5                      |

| 1.2                                                     | 3.3                      |

| 1.8                                                     | 1.2                      |

| 1.8                                                     | 1.8                      |

| 1.8                                                     | 2.5                      |

| 1.8                                                     | 3.3                      |

| 2.5                                                     | 1.2                      |

| 2.5                                                     | 1.8                      |

| 2.5                                                     | 2.5                      |

| 2.5                                                     | 3.3                      |

| 3.3                                                     | 1.2                      |

| 3.3                                                     | 1.8                      |

| 3.3                                                     | 2.5                      |

| 3.3                                                     | 3.3                      |

### 7.3.2 I/O ポート

I/O が入力として構成されている場合、FET Q1 と Q2 はオフになり (セクション 7.2 を参照)、高インピーダンス入力が生成されます。入力電圧は、電源電圧より高い、最大 3.6V まで上昇させることができます。

I/O が出力として構成されている場合、Q1 または Q2 は出力ポートレジスタの状態に応じてイネーブルになります。この場合、I/O ピンと電源または GND の間に低インピーダンスのパスがあります。この I/O ピンに印加される外部電圧は、適切に動作させるために推奨レベルを超えないようにする必要があります。

### 7.3.3 調整可能な出力駆動強度

出力駆動強度レジスタを使用すると、GPIO の駆動レベルを制御することができます。各 GPIO は、4 種類の電流レベルのいずれか 1 つに個別に構成できます。これらのビットをプログラムすることにより、ユーザーはトランジスタペアの数か I/O パッドを駆動する「フィンガー」数を変更します。図 7-3 に、出力段の概略図を示します。パッドの動作は、構成レジスタ、出力ポートのデータ、出力駆動強度レジスタの影響を受けます。出力駆動制御レジスタビットを 01b にプログラムすると、2 つのフィンガーのみアクティブになります。電流駆動能力は 50% 低下します。

図 7-3. 出力段の概略図

出力駆動選択機能は、出力が切り替わる際にピーク電流を発生させます。電流駆動能力を下げる、発生するシステムノイズを減らすことができます。このピーク電流は電源と GND パッケージのインダクタンスを経由して流れ、ノイズ（一部は放射されますが、多くは影響の大きな同時スイッチングノイズ (SSN)）を生成します。つまり、同時に多くの出力を切り替えるとグランドノイズと電源ノイズが発生します。出力駆動強度を出力駆動強度レジスタで制御することにより、ユーザーは外部の部品を追加することなく、SSN の問題を低減することができます。

#### 7.3.4 割り込み出力 (INT)

割り込み機能がマスクされていない場合、入力モードでのポート入力のすべての立ち上がりエッジまたは立ち下がりエッジによって割り込みが生成されます。 $t_V$  時間が経過すると、INT 信号は有効になります。割り込み回路は、ポート上のデータが元の設定に戻されたとき、または割り込みを生成したポートからデータが読み取られたときにリセットされます。リセットは、読み取りモード時に SCL 信号の立ち上がりエッジの後のアクリッジ (ACK) ビットで発生します。ACK クロックパルス中に発生する割り込みは、このパルス中に割り込みがリセットされるため、失われる（または非常に短くなる）ことがあります。リセット後に I/O の各変化が検出され、INT として送信されます。

他のデバイスとの間での読み取りや書き込みは、割り込み回路に影響しません。また、出力として構成されたピンが割り込みを発生させることはできません。I/O を出力から入力に変更すると、ピンの状態が入力ポートレジスタの内容と一致しない場合、誤って割り込みが発生する可能性があります。

INT 出力にはオープンドレイン構造があり、割り込み機能が必要な場合は  $V_{CC}$  への外部プルアップ抵抗が必要です。それ以外の場合は、フローティングのままにできます。

#### 7.3.5 リセット入力 (RESET)

$V_{CC}$  電源を動作レベルに保持しながら、RESET 入力をアサートすると、I<sup>2</sup>C ステートマシンが初期化されます。

ステートマシンをリセットするには、 $t_W$  の最小時間の間、RESET ピンを Low に保持します。

RESET がトグルされると、TCAL6416R のレジスタはスティッキーになり、I<sup>2</sup>C ステートマシンの初期化中、最後に設定された状態を保持します。RESET 入力が Low になると、アドレスポインタ（コマンドバイト）はデフォルト値に戻ります。

アクティブ接続が使用されない場合、この入力には  $V_{CC1}$  へのプルアップ抵抗が必要です。

TCAL6416R のパワー サイクル (電源を一度切って再度投入すること) を行わずにレジスタをリセットする方法については、[セクション 7.3.6](#) を参照してください。

### 7.3.6 ソフトウェアリセット呼び出し

ソフトウェアリセット呼び出しは、I<sup>2</sup>C バス上のコントローラから送信されるコマンドで、このコマンドに対応しているすべてのデバイスに対して電源投入時のデフォルト状態にリセットするよう指示を出します。想定どおりに機能させるためには、I<sup>2</sup>C バスの機能を有効にして、このバスにデバイスがぶらさがっていない状態にする必要があります。

ソフトウェアリセット呼び出しは、以下の手順で定義されます。

1. I<sup>2</sup>C バスコントローラが START 条件を送信します。

2. 使用するアドレスは、予約済みのゼネラルコールの I<sup>2</sup>C バスアドレス「0000 0000」で、R/W ビットは 0 にセットします。送信されるバイトは、0x00 です。

3. ゼネラルコール機能をサポートしているすべてのデバイスは、ACK を送信します。R/W ビットが 1 (読み出し) にセットされているなら、デバイスは NACK を送信します。

4. ゼネラルコールアドレスがアクノリッジされると、コントローラは 0x06 に等しいデータの 1 バイトのみを送信します。データバイトが他の値の場合、デバイスはアクノリッジしないか、リセットします。1つよりも多いバイトが送信された場合、2番目以降のバイトはアクノリッジされず、デバイスは無効と判断して I<sup>2</sup>C メッセージを無視します。

5. データ (0x06) の 1 バイトが送信されると、コントローラはソフトウェアリセットシーケンスを終了させるために STOP 条件を送信します。本デバイスは繰り返し START 条件を無視し、リセットは実行されません。

上記の手順がすべて完了すると、デバイスはリセットを実行します。これにより、すべてのレジスタ値はクリアされ、電源投入時のデフォルト値に戻ります。

## 7.4 デバイスの機能モード

### 7.4.1 パワーオンリセット

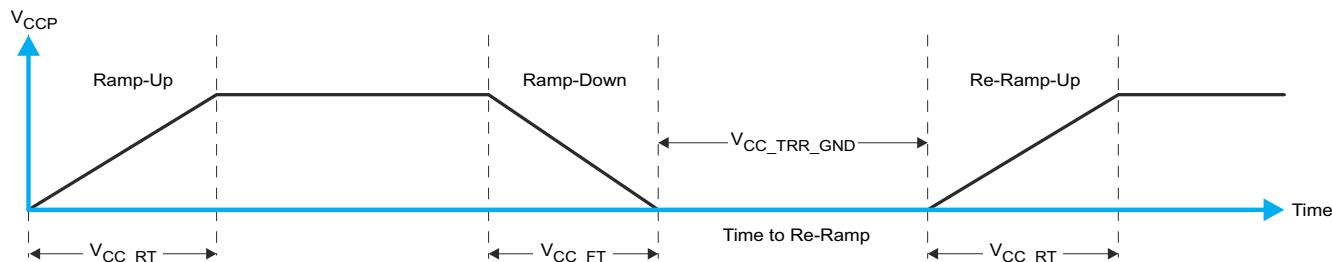

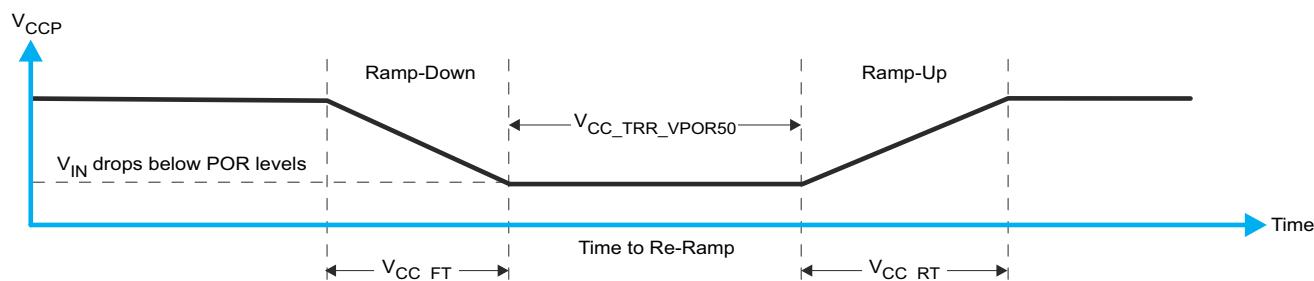

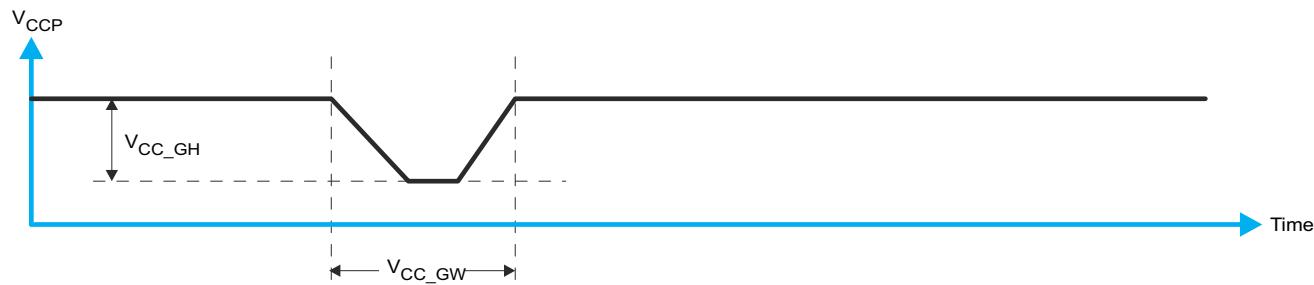

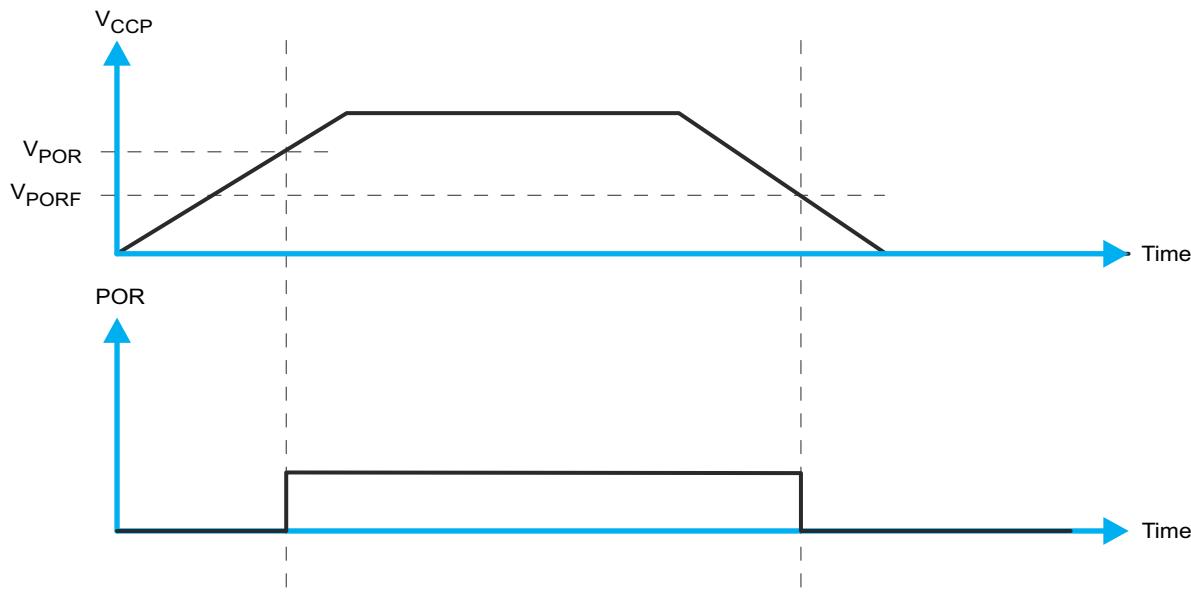

$V_{CCP}$  に電力 (0V~) を印加すると、電源電圧が  $V_{POR}$  に到達するまで、内部のパワーオンリセットにより TCAL6416R はリセット状態に保持されます。このとき、リセット状態は解除され、TCAL6416R のレジスタと I<sup>2</sup>C/SMBus のステートマシンはそれぞれのデフォルト状態に初期化されます。パワーリセットサイクルを行うには、その後で  $V_{CCP}$  を  $V_{PORF}$  未満に下げてから、再び動作電圧まで戻す必要があります。

## 7.5 プログラミング

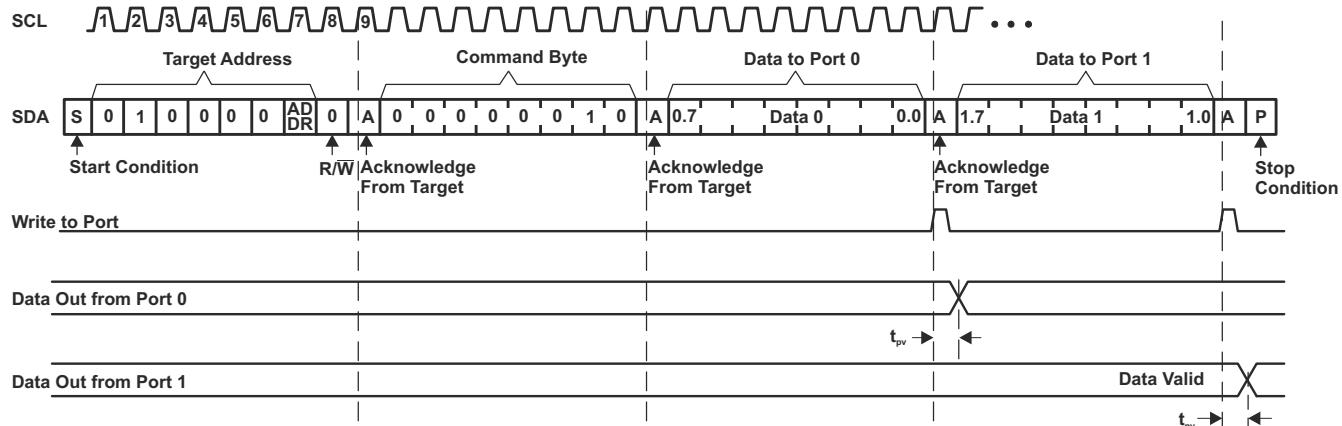

### 7.5.1 I<sup>2</sup>C インターフェイス

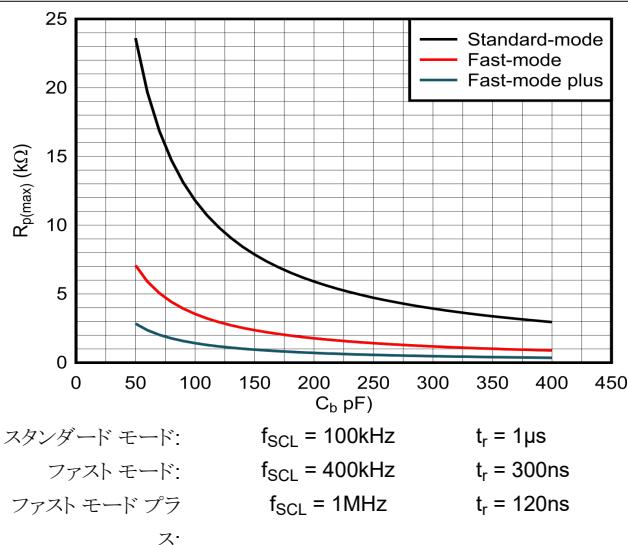

双方向 I<sup>2</sup>C バスは、シリアルクロック (SCL) ラインとシリアルデータ (SDA) ラインで構成されます。デバイスの出力段に接続するときは、両方のラインをプルアップ抵抗経由で正の電源に接続する必要があります。データ転送は、バスがビジ一状態でないときにのみ開始できます。

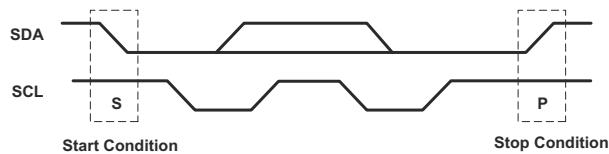

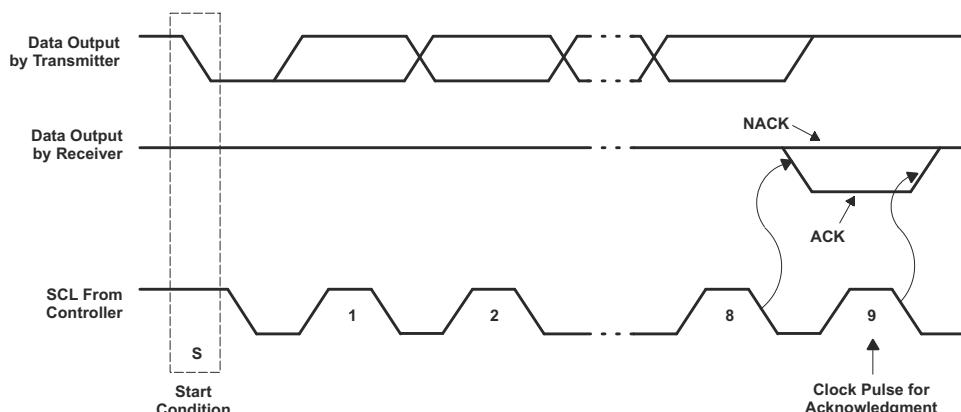

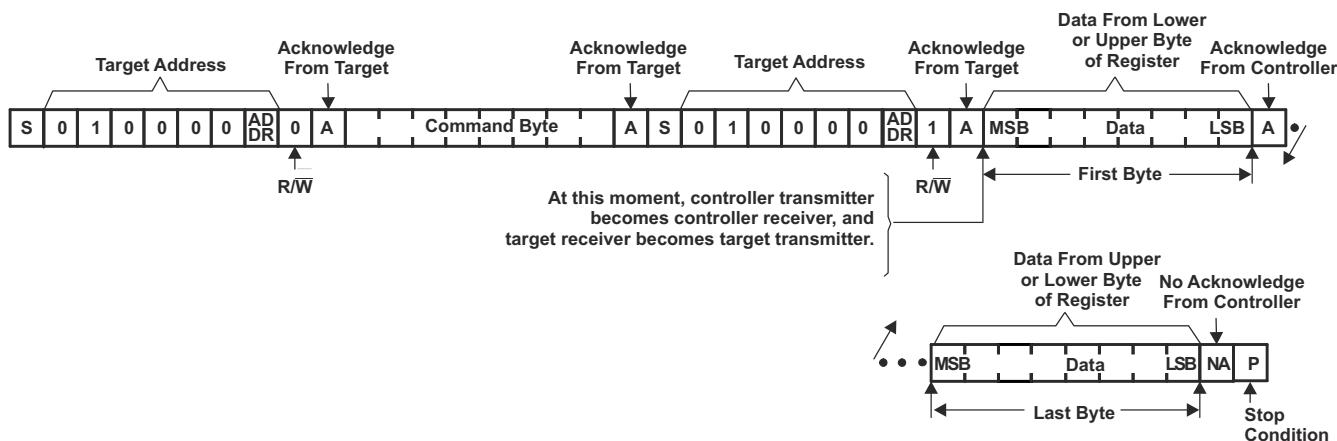

コントローラは、START 条件を送信することで、このデバイスとの I<sup>2</sup>C 通信を開始します。START 条件とは、SCL 入力が High のときに、SDA 入力 / 出力が High から Low に遷移することです ([図 7-4](#) を参照)。START 条件の後、デバイスのアドレスバイトが送信されます。最初は、データ方向ビット (R/W) を含む最上位ビット (MSB) が最初に送信されます。

有効なアドレスバイトを受信すると、このデバイスは、ACK 関連のクロックパルスが High のときに SDA 入力 / 出力を Low にするアクノリッジ (ACK) で応答します。ターゲットデバイスのアドレス入力を START 条件と STOP 条件の間で変更することはできません。

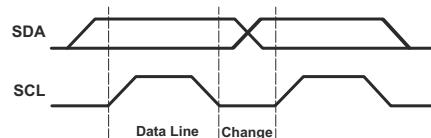

I<sup>2</sup>C バスでは、各クロックパルスの間に 1 つのデータビットのみが転送されます。SDA ラインのデータは、クロック周期の High パルス中は安定している必要があります。この時点でデータラインが変化すると、制御コマンド (START または STOP) として解釈されるためです ([図 7-5](#) を参照)。

コントローラは STOP 条件を送信します。STOP 条件とは、SCL 入力が High のときに SDA 入力 / 出力が Low から High に遷移することです ([図 7-4](#) を参照)。

START 条件と STOP 条件の間に、トランシミッタからレシーバへ任意の数のデータ バイトを転送できます。8 ビットの各バイトの後に 1 つの ACK ビットが続きます。レシーバが ACK ビットを送信する前に、トランシミッタは SDA ラインを解放する必要があります。アクノリッジを行うデバイスは、ACK 関連のクロック周期が High パルスのときは SDA ラインが安定して Low を維持できるように、ACK クロック パルスの間は SDA ラインをプルダウンする必要があります (図 7-6 を参照)。ターゲットのレシーバがアドレス指定されている場合、各バイトを受信した後に ACK を生成する必要があります。同様に、コントローラはターゲットのトランシミッタから受信した各バイトの後に ACK を生成する必要があります。適切な動作のために、セットアップ時間とホールド時間の条件を満たす必要があります。

コントローラのレシーバは、最後のバイトがターゲットからクロック出力された後、アクノリッジ (NACK) を生成せずに、データの終了をターゲットのトランシミッタに通知します。コントローラのレシーバは、SDA ラインを High に保持することでこれを行います。この場合、コントローラが STOP 条件を生成できるように、トランシミッタはデータ ラインを解放する必要があります。

図 7-4. START 条件と STOP 条件の定義

図 7-5. ピット転送

図 7-6. I<sup>2</sup>C バスのアクノリッジ

表 7-2. インターフェイスの定義

| バイト                         | ビット     |     |     |     |     |     |      |         |

|-----------------------------|---------|-----|-----|-----|-----|-----|------|---------|

|                             | 7 (MSB) | 6   | 5   | 4   | 3   | 2   | 1    | 0 (LSB) |

| デバイスの I <sup>2</sup> C アドレス | L       | H   | L   | L   | L   | L   | ADDR | R/W     |

| I/O データ バス                  | P07     | P06 | P05 | P04 | P03 | P02 | P01  | P00     |

|                             | P17     | P16 | P15 | P14 | P13 | P12 | P11  | P10     |

## 7.6 レジスタ マップ

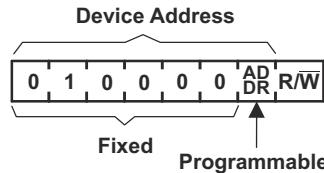

### 7.6.1 デバイス アドレス

図 7-7 に、TCAL6416R のアドレスを示します。

図 7-7. TCAL6416R のアドレス

表 7-3. アドレス参照

| ADDR | I <sup>2</sup> C パスのターゲットのアドレス |

|------|--------------------------------|

| L    | 32 (10 進)、20 (16 進)            |

| H    | 33 (10 進)、21 (16 進)            |

ターゲットのアドレスの最後のビットにより、実行する動作 (読み取りまたは書き込み) が定義されます。High (1) を選択すると読み取り動作、Low (0) を選択すると書き込み動作となります。

### 7.6.2 複数の電源オンのデフォルト条件

TCAL6416R の下には、それぞれ異なるレジスタ起動値を持つ 2 つの追加デバイスがあります。これは、さまざまなパワーアップ要件を持つシステムを支援し、初期化ソフトウェアに適合させるために行われます。表 7-4 に、デバイスの名前と起動時の値の変更を示します。TCAL6416RADTOR (セクション 7.6.3 およびセクション 7.6.4 では TCAL6416RA と記載) は、出力ポートおよび構成レジスタの電源オン時の値が更新されています。TCAL6416RBDTOR (セクション 7.6.3 およびセクション 7.6.4 で TCAL6416RB として参照) は、極性反転、プルアップ/プルダウン・イネーブル、および割り込みマスク・レジスタについてパワーアップ値が更新されています。

表 7-4. デバイスとそれらの起動値

| 発注用製品型番 (Orderable Part Number) | レジスタの起動値を変更                                              | コマンド バイト (16 進) 変更            |

|---------------------------------|----------------------------------------------------------|-------------------------------|

| TCAL6416RDTOR                   | デフォルトの電源オン値を使用                                           | 該当なし                          |

| TCAL6416RADTOR                  | 出力ポート 0 & 1<br>構成 0 & 1                                  | 02 & 03<br>06 & 07            |

| TCAL6416RBDTOR                  | 極性反転 0 & 1<br>プルアップ / プルダウン イネーブル 0 & 1<br>割り込みマスク 0 & 1 | 04 & 05<br>46 & 47<br>4A & 4B |

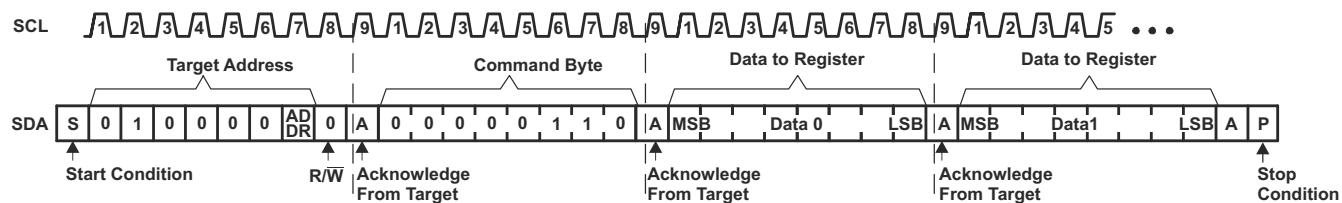

### 7.6.3 制御レジスタとコマンドバイト

アドレス バイトのアクノリッジが成功すると、バス コントローラはコマンド バイトを送信します。このバイトは TCAL6416R の制御レジスタに保存されます。このデータ バイトの下位 3 ビットは、影響を受ける内部レジスタ（入力、出力、極性反転、または構成）を反映しています。ビット 6 とコマンド バイトの下位 4 ビットは、デバイスの拡張機能 (Agile IO) を指すために組み合わせて使用されます。コマンド バイトは、書き込み転送中にのみ送信されます。

新しいコマンドが送信されると、アドレス指定されたレジスタは、新しいコマンド バイトが送信されるまで、読み取りによってアクセスが継続されます。電源投入時、ハードウェアリセット時、またはソフトウェアリセット時に、制御レジスタはデフォルトで 00h に設定されます。

**RESET** 入力が Low になると、アドレス ポインタ（コマンド バイト）はデフォルト値に戻ります。

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|----|----|----|----|----|----|----|----|

図 7-8. 制御レジスタ ビット

表 7-5. コマンド バイト

| 制御レジスタ ビット |    |    |    |    |    |    |    | コマンド バイト<br>(16 進) | レジスタ     | プロトコル           | 電源投入時<br>のデフォルト<br>値 | 電源投入時<br>の<br>TCAL6416R<br>A | 電源投入時<br>の<br>TCAL6416R<br>B |

|------------|----|----|----|----|----|----|----|--------------------|----------|-----------------|----------------------|------------------------------|------------------------------|

| B7         | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                    |          |                 |                      |                              |                              |

| 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00                 | 入力ポート 0  | バイトの読み取り        | xxxx xxxx            | xxxx xxxx                    | xxxx xxxx                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01                 | 入力ポート 1  | バイトの読み取り        | xxxx xxxx            | xxxx xxxx                    | xxxx xxxx                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02                 | 出力ポート 0  | バイトの読み取り / 書き込み | 1111 1111            | 0000 0000                    | 1111 1111                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03                 | 出力ポート 1  | バイトの読み取り / 書き込み | 1111 1111            | 0000 0000                    | 1111 1111                    |

| 0          | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 04                 | 極性反転 0   | バイトの読み取り / 書き込み | 0000 0000            | 0000 0000                    | 1111 1111                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 05                 | 極性反転 1   | バイトの読み取り / 書き込み | 0000 0000            | 0000 0000                    | 1111 1111                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 06                 | 構成 0     | バイトの読み取り / 書き込み | 1111 1111            | 0000 0000                    | 1111 1111                    |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 07                 | 構成 1     | バイトの読み取り / 書き込み | 1111 1111            | 0000 0000                    | 1111 1111                    |

| 0          | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 40                 | 出力駆動強度 0 | バイトの読み取り / 書き込み | 1111 1111            | 1111 1111                    | 1111 1111                    |

| 0          | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 41                 | 出力駆動強度 0 | バイトの読み取り / 書き込み | 1111 1111            | 1111 1111                    | 1111 1111                    |

| 0          | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 42                 | 出力駆動強度 1 | バイトの読み取り / 書き込み | 1111 1111            | 1111 1111                    | 1111 1111                    |

| 0          | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 43                 | 出力駆動強度 1 | バイトの読み取り / 書き込み | 1111 1111            | 1111 1111                    | 1111 1111                    |

**表 7-5. コマンド バイト (続き)**

| 制御レジスタ ビット |    |    |    |    |    |    |    |    | コマンド バイト<br>(16 進)         | レジスタ            | プロトコル     | 電源投入時<br>のデフォルト<br>値 | 電源投入時<br>の<br>TCAL6416R<br>A | 電源投入時<br>の<br>TCAL6416R<br>B |

|------------|----|----|----|----|----|----|----|----|----------------------------|-----------------|-----------|----------------------|------------------------------|------------------------------|

| B7         | B6 | B5 | B4 | B3 | B2 | B1 | B0 |    |                            |                 |           |                      |                              |                              |

| 0          | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 44 | 入力ラッチ レジスタ 0               | バイトの読み取り / 書き込み | 0000 0000 | 0000 0000            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 45 | 入力ラッチ レジスタ 1               | バイトの読み取り / 書き込み | 0000 0000 | 0000 0000            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 46 | プルアップ / プルダウン イネーブル レジスタ 0 | バイトの読み取り / 書き込み | 0000 0000 | 0000 0000            | 1111 1111                    |                              |

| 0          | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 47 | プルアップ / プルダウン イネーブル レジスタ 1 | バイトの読み取り / 書き込み | 0000 0000 | 0000 0000            | 1111 1111                    |                              |

| 0          | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 48 | プルアップ / プルダウン 選択 レジスタ 0    | バイトの読み取り / 書き込み | 1111 1111 | 1111 1111            | 1111 1111                    |                              |

| 0          | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 49 | プルアップ / プルダウン 選択 レジスタ 1    | バイトの読み取り / 書き込み | 1111 1111 | 1111 1111            | 1111 1111                    |                              |

| 0          | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 4A | 割り込みマスク レジスタ 0             | バイトの読み取り / 書き込み | 1111 1111 | 1111 1111            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 4B | 割り込みマスク レジスタ 1             | バイトの読み取り / 書き込み | 1111 1111 | 1111 1111            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 4C | 割り込みステータス レジスタ 0           | バイトの読み取り        | 0000 0000 | 0000 0000            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 4D | 割り込みステータス レジスタ 1           | バイトの読み取り        | 0000 0000 | 0000 0000            | 0000 0000                    |                              |

| 0          | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 4F | 出力ポート構成 レジスタ               | バイトの読み取り / 書き込み | 0000 0000 | 0000 0000            | 0000 0000                    |                              |

#### 7.6.4 レジスタの説明

TCAL6416R にはステッキー レジスタがあり、RESET が Low にアサートされたとき、直前の値を保持します。本レジスタは、デバイスの電源をオフにしてから再度オンにした場合、またはソフトウェアリセット呼び出しが発行された場合にのみ、電源投入時のデフォルト値に戻ります。

入力ポート レジスタ (レジスタ 0 および 1) には、構成 レジスタによって入力と出力のどちらにピンが定義されているかに関係なく、ピンに入ってくるロジック レベルが反映されます。入力ポート レジスタは、読み取り専用です。これらのレジスタに書き込みを行っても、影響はありません。外部的に印加されるロジック レベルによって、デフォルト値 (X) が決まります。読み取り動作の前に、書き込み転送が送信され、それと同時に、次に入力ポート レジスタがアクセスされることを I<sup>2</sup>C デバイスに通知するコマンド バイトも送信されます。

**表 7-6. レジスタ 0 および 1 (入力ポート レジスタ) (1)**

| ビット   | I-07 | I-06 | I-05 | I-04 | I-03 | I-02 | I-01 | I-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | X    | X    | X    | X    | X    | X    | X    | X    |

| ビット   | I-17 | I-16 | I-15 | I-14 | I-13 | I-12 | I-11 | I-10 |

| デフォルト | X    | X    | X    | X    | X    | X    | X    | X    |

出力ポートレジスタ(レジスタ2および3)には、構成レジスタで出力として定義されているピンから出していくロジックレベルが示されます。これらのレジスタのビット値は、入力として定義されたピンには影響しません。そして、これらのレジスタから読み出した値は、実際のピンの値ではなく、出力選択を制御しているフリップフロップの値を反映しています。

**表 7-7. レジスタ2および3(出力ポートレジスタ)**

| ビット               | O-07 | O-06 | O-05 | O-04 | O-03 | O-02 | O-01 | O-00 |

|-------------------|------|------|------|------|------|------|------|------|

| デフォルト             | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| <b>TCAL6416RA</b> | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット               | O-17 | O-16 | O-15 | O-14 | O-13 | O-12 | O-11 | O-10 |

| デフォルト             | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| <b>TCAL6416RA</b> | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

極性反転レジスタ(レジスタ4および5)は、構成レジスタで入力として定義されたピンの極性を反転することができます。これらのレジスタのビットをセットする(1を書き込む)と、対応するポートピンの極性が反転します。これらのレジスタのビットをクリアする(0を書き込む)と、対応するポートピンの元の極性が保持されます。

**表 7-8. レジスタ4および5(極性反転レジスタ)**

| ビット               | P-07 | P-06 | P-05 | P-04 | P-03 | P-02 | P-01 | P-00 |

|-------------------|------|------|------|------|------|------|------|------|

| デフォルト             | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| <b>TCAL6416RB</b> | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| ビット               | P-17 | P-16 | P-15 | P-14 | P-13 | P-12 | P-11 | P-10 |

| デフォルト             | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| <b>TCAL6416RB</b> | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

構成レジスタ(レジスタ6および7)は、I/Oピンの方向を構成します。これらのレジスタのビットを1にセットすると、対応するポートピンは高インピーダンス出力ドライバを持つ入力としてイネーブルになります。これらのレジスタのビットを0にクリアすると、対応するポートピンは出力としてイネーブルになります。ポートの構成を入力から出力に変更すると、クリアされたポートに関連する割り込みが発生します。

**表 7-9. レジスタ6および7(構成レジスタ)**

| ビット               | C-07 | C-06 | C-05 | C-04 | C-03 | C-02 | C-01 | C-00 |

|-------------------|------|------|------|------|------|------|------|------|

| デフォルト             | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| <b>TCAL6416RA</b> | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット               | C-17 | C-16 | C-15 | C-14 | C-13 | C-12 | C-11 | C-10 |

| デフォルト             | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| <b>TCAL6416RA</b> | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

出力駆動強度レジスタは、PポートのGPIOバッファの出力駆動レベルを制御します。各GPIOは、2つのレジスタの制御ビットを使用して、目標の出力電流レベルに個別に構成することができます。たとえば、レジスタ0x41h(ビット7および6)はポートP07を制御し、レジスタ0x41h(ビット5および4)はポートP06を制御します(以下同様)。GPIOの出力駆動レベルは、00b = 0.25xの駆動強度、01b = 0.5xの駆動強度、10b = 0.75xの駆動強度、11b = 完全駆動強度の能力を持つ1xにプログラムされます。詳細については、[V](#)を参照してください。

**表 7-10. レジスタ0x40h、0x41h、0x42h、0x43h(出力駆動強度レジスタ)**

| ビット   | CC-03 | CC-03 | CC-02 | CC-02 | CC-01 | CC-01 | CC-00 | CC-00 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット   | CC-07 | CC-07 | CC-06 | CC-06 | CC-05 | CC-05 | CC-04 | CC-04 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

**表 7-10. レジスタ 0x40h、0x41h、0x42h、0x43h (出力駆動強度レジスタ) (続き)**

| ビット   | CC-03 | CC-03 | CC-02 | CC-02 | CC-01 | CC-01 | CC-00 | CC-00 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ビット   | CC-13 | CC-13 | CC-12 | CC-12 | CC-11 | CC-11 | CC-10 | CC-10 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット   | CC-17 | CC-17 | CC-16 | CC-16 | CC-15 | CC-15 | CC-14 | CC-14 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

入力ラッチ レジスタは、P ポートの GPIO ピンの入力ラッチ機能をイネーブル / ディセーブルにします。これらのレジスタは、このピンが入力ポートとして構成されている場合にのみ有効です。Input Latch レジスタ ビットが 0 のとき、対応する入力ピンの状態はラッチされません。対応する入力ピンの状態が変化すると、割り込みが発生します。入力レジスタの読み出しを行うと、割り込みはクリアされます。入力が最初のロジック状態に戻ってから、入力ポートレジスタを読み出すと、割り込みはクリアされます。

Input Latch レジスタ ビットが 1 にセットされると、対応する入力ピンの状態がラッチされます。入力状態が変化すると、割り込みが発生し、入力ロジック値が入力ポートレジスタ (レジスタ 0 および 1) の対応ビットにロードされます。入力ポートレジスタを読み出すと、割り込みはクリアされます。ただし、入力ポートレジスタを読み出す前に、入力ピンが元のロジック状態に戻ると、割り込みはクリアされず、入力ポートレジスタの対応するビットには、割り込みが開始されたロジック値が保持されます。

たとえば、P04 入力がロジック 0 状態にあり、それからロジック 1 状態に遷移して、再びロジック 0 状態に戻ると、入力ポート 0 レジスタはこの変化を捉えて、割り込みが生成されます (マスクされていない場合)。入力ポート 0 レジスタで読み出しが実行されると、それ以外の入力が変化していないければ、割り込みはクリアされ、入力ポート 0 レジスタのビット 4 の読み出し値は「1」です。入力ポートレジスタのビット 4 の次の読み出し値は、この時点で「0」になります。

ラッチされていない入力とラッチされた入力の状態が同時に切り替わり、それから元の状態に戻ると、割り込みはアクティブのままとなります。入力レジスタを読み出すと、ラッチされた入力の状態変化のみが反映され、割り込みもクリアされます。入力ラッチ レジスタがラッチされた構成からラッチされていない構成に変わると、入力のロジック値が元の状態に戻れば、割り込みはクリアされます。

入力ピンがラッチされた入力からラッチされていない入力に変わると、入力ポートレジスタからの読み出しには、現在のポートロジック レベルが反映されます。入力ピンがラッチされていない入力からラッチされた入力に変わると、入力レジスタからの読み出しにはラッチされたロジック レベルが反映されます。

**表 7-11. レジスタ 0x44h および 0x45h (入力ラッチ レジスタ)**

| ビット   | L-07 | L-06 | L-05 | L-04 | L-03 | L-02 | L-01 | L-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット   | L-17 | L-16 | L-15 | L-14 | L-13 | L-12 | L-11 | L-10 |

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

プルアップ / プルダウン イネーブル レジスタを使用すると、GPIO ピンのプルアップ / プルダウン抵抗をイネーブル / ディセーブルにすることができます。ビットをロジック 1 にセットすると、プルアップ / プルダウン抵抗を選択することができます。ビットをロジック 0 にセットすると、GPIO ピンからプルアップ / プルダウン抵抗が切断されます。GPIO ピンを出力として構成すると、抵抗はディセーブルになります。プルアップ / プルダウン選択レジスタを使用すると、プルアップ抵抗またはプルダウン抵抗のいずれかを選択することができます。

**表 7-12. レジスタ 0x46h および 0x47h (プルアップ / プルダウン イネーブル レジスタ)**

| ビット        | PE-07 | PE-06 | PE-05 | PE-04 | PE-03 | PE-02 | PE-01 | PE-00 |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| デフォルト      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| TCAL6416RB | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット        | PE-17 | PE-16 | PE-15 | PE-14 | PE-13 | PE-12 | PE-11 | PE-10 |

| デフォルト      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

**表 7-12. レジスタ 0x46h および 0x47h (プルアップ / プルダウン イネーブル レジスタ) (続き)**

| ビット               | PE-07 | PE-06 | PE-05 | PE-04 | PE-03 | PE-02 | PE-01 | PE-00 |

|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| <b>TCAL6416RB</b> | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

**Pull-Up/Pull-Down Selection** レジスタを使用すると、それぞれのレジスタ ビットをプログラムすることにより、各 GPIO のプルアップ抵抗やプルダウン抵抗を構成することができます。ビットをロジック 1 に設定すると、その GPIO ピンに対して  $10\text{k}\Omega$  のプルアップ抵抗が選択されます。ビットをロジック 0 に設定すると、その GPIO ピンに対して  $10\text{k}\Omega$  のプルダウン抵抗が選択されます。レジスタ 0x46h と 0x47h を使用してプルアップ / プルダウン機能をディセーブルにすると、これらのレジスタに書き込みを行っても GPIO ピンに影響はありません。

**表 7-13. レジスタ 0x48h および 0x49h (プルアップ / プルダウン選択レジスタ)**

| ビット   | PUD-07 | PUD-06 | PUD-05 | PUD-04 | PUD-03 | PUD-02 | PUD-01 | PUD-00 |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| デフォルト | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

| ビット   | PUD-17 | PUD-16 | PUD-15 | PUD-14 | PUD-13 | PUD-12 | PUD-11 | PUD-10 |

| デフォルト | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

電源投入時には、割り込みマスク レジスタはデフォルトのロジック 1 にセットされ、システムの起動時に割り込みはディセーブルになります。割り込みをイネーブルにするには、対応するマスクビットをロジック 0 にセットします。

入力状態が変化し、割り込みマスク レジスタの対応ビットが 1 にセットされると、割り込みはマスクされ、割り込みピンはアサートされません。割り込みマスク レジスタの対応ビットが 0 にセットされると、割り込みピンがアサートされます。

入力状態が変化し、その結果として発生した割り込みがマスクされたとき、割り込みマスク レジスタ ビットを 0 にセットすると、割り込みピンがアサートされます。現時点ですでに割り込みのソースになっている入力の割り込みマスク ビットが 1 にセットされると、割り込みピンのアサートは解除されます。