# THS4541 負レール入力、レールツー レール出力、高精度、850MHz 完全差動アンプ

## 1 特長

- 完全差動アンプ (FDA) アーキテクチャ

- 帯域幅: 500MHz (G = 2V/V)

- ゲイン帯域幅積: 850MHz

- スルーレート: 1500V/μs

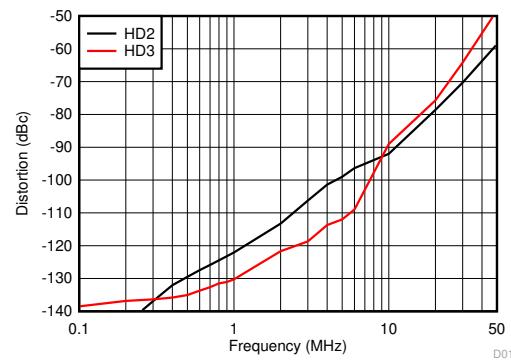

- HD<sub>2</sub>: -95dBc (10MHz, 2V<sub>PP</sub>, R<sub>L</sub> = 500Ω)

- HD<sub>3</sub>: -90dBc (10MHz, 2V<sub>PP</sub>, R<sub>L</sub> = 500Ω)

- 入力電圧ノイズ: 2.2nV/√Hz (f > 100kHz)

- 小さいオフセットドリフト: ±0.5μV/°C (標準値)

- 負のレール入力 (NRI)

- レールツー レール出力 (RRO)

- R<sub>load</sub> ≥ 50Ω で確実に動作

- 出力同相モード制御

- 電源:

- 単一電源電圧範囲: 2.7V ~ 5.4V

- 両電源電圧範囲: ±1.35V ~ ±2.7V

- 静止電流: 10.1mA (5V 電源)

- パワーダウン機能: 2μA (標準値)

## 2 アプリケーション

- 低消費電力、高性能の ADC ドライバ:

- SAR, ΔΣ, パイプライン

- 低消費電力、高性能 (DC または AC 結合):

- シングルエンド入力 / 差動出力アンプ

- 差動 / 差動アンプ

- 差動アクティブ フィルタ

- DAC 出力の差動トランジスインピーダンス

- ADC3xxx ファミリ 低消費電力、高性能 ADC との DC または AC 結合インターフェイス

- ADA4932-1 とピン互換 (VQFN-16)

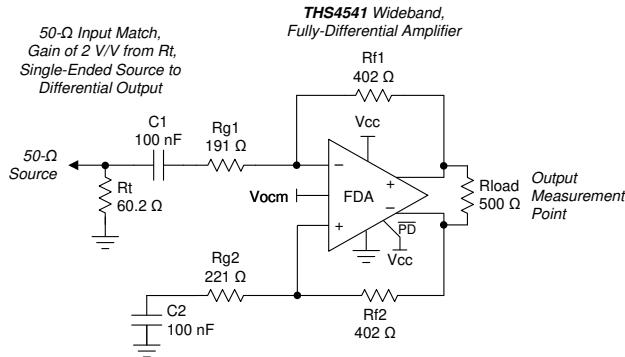

概略回路図

## 3 概要

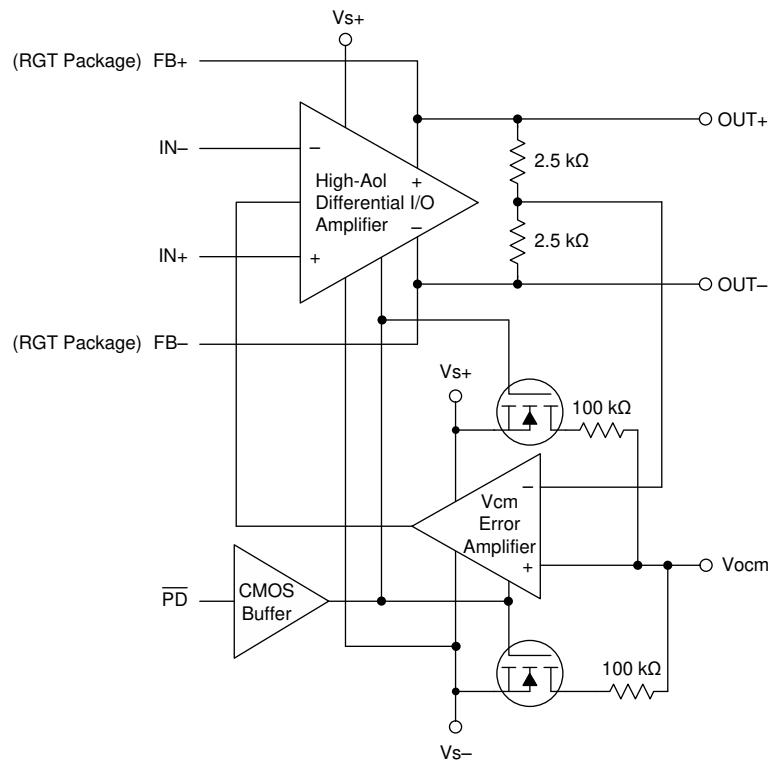

THS4541 は、負のレールおよびレールツー レール出力未満の入力同相範囲を備えた、低消費電力、電圧フィードバック、全差動アンプ (FDA) です。THS4541 は、高性能な A/D コンバータ (ADC) または D/C コンバータ (DAC) のインターフェイス設計において高密度が重要な低消費電力のデータ アクイジション システム向けに設計されています。

THS4541 は、DC 結合、グランド中心、ソース信号のインターフェイスに必要とされる負のレール入力を備えています。このレールツー レール出力を備えた負のレール入力を使うことで、シングルエンド、グランド基準のバイポーラ信号源とさまざまな逐次比較レジスタ (SAR)、デルタシグマ (ΔΣ)、またはパイプライン ADC との間を 2.7V ~ 5.4V の単一電源を使用して簡単に接続できます。

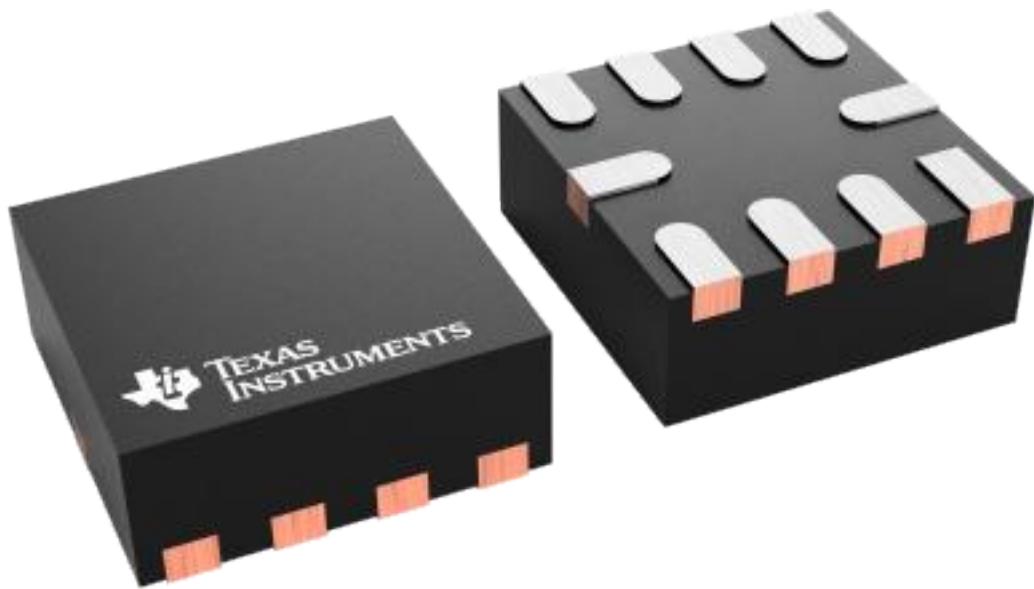

THS4541 は、-40°C ~ +125°C の広い温度範囲にわたって動作が規定されており、16 ピンの VQFN および 10 ピンの WQFN パッケージで供給されます。

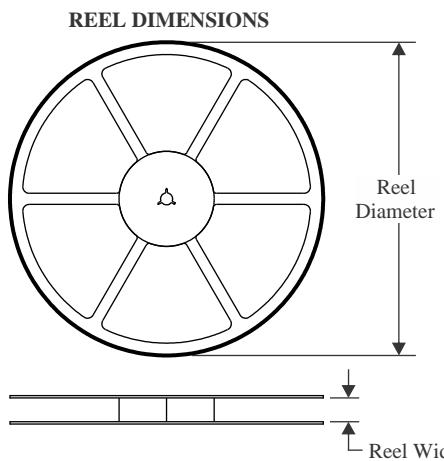

### パッケージ情報

| 部品番号 (1) | パッケージ (2)      | パッケージ サイズ (3) |

|----------|----------------|---------------|

| THS4541  | RGT (VQFN, 16) | 3mm × 3mm     |

|          | RUN (WQFN, 10) | 2mm × 2mm     |

(1) セクション 4 を参照

(2) 詳細については、セクション 12 を参照してください。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

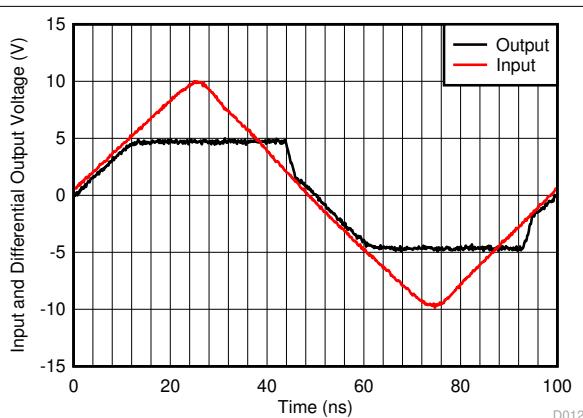

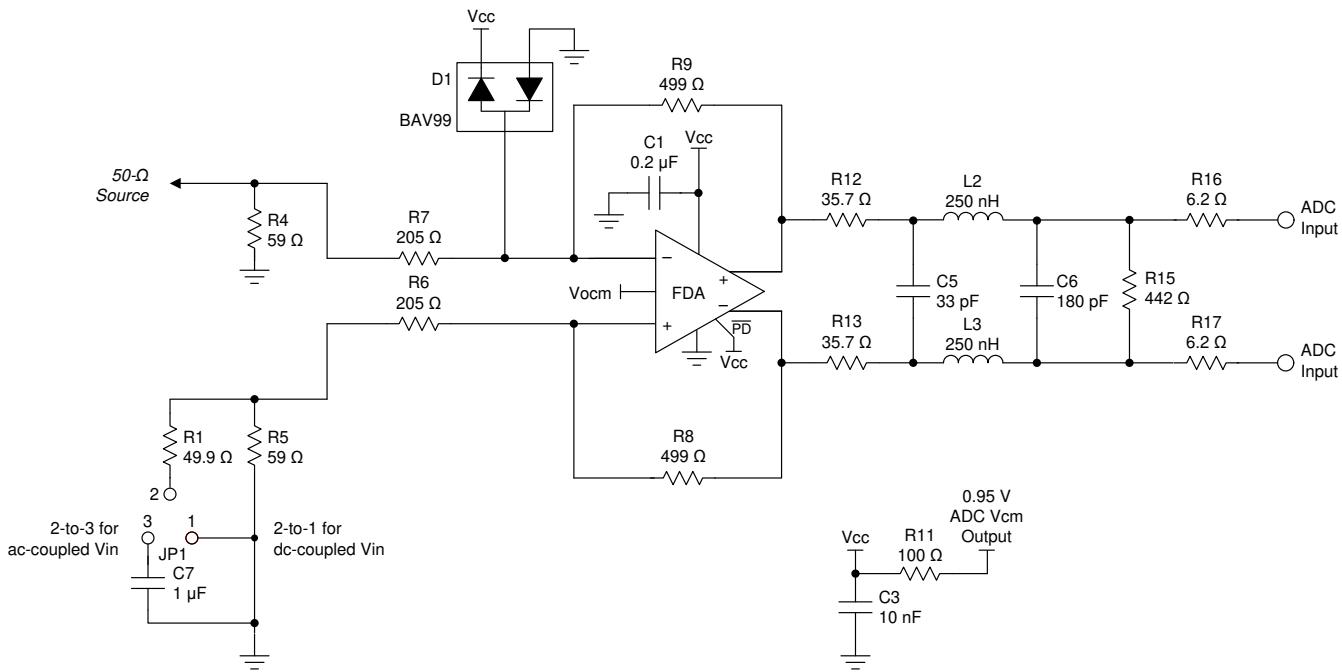

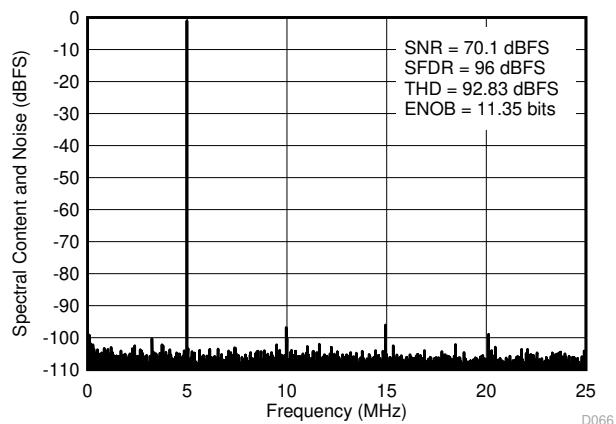

シングルから差動へ、ゲイン = 2、2V<sub>PP</sub> 出力

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                    |           |                               |           |

|------------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                        | <b>1</b>  | 7.7 容量性負荷の駆動                  | <b>33</b> |

| <b>2 アプリケーション</b>                  | <b>1</b>  | 7.8 熱解析                       | <b>34</b> |

| <b>3 概要</b>                        | <b>1</b>  | <b>8 詳細説明</b>                 | <b>35</b> |

| <b>4 デバイス比較表</b>                   | <b>2</b>  | 8.1 概要                        | <b>35</b> |

| <b>5 ピン構成および機能</b>                 | <b>3</b>  | 8.2 機能ブロック図                   | <b>37</b> |

| <b>6 仕様</b>                        | <b>4</b>  | 8.3 機能説明                      | <b>37</b> |

| 6.1 絶対最大定格                         | 4         | 8.4 デバイスの機能モード                | 38        |

| 6.2 ESD 定格                         | 4         | <b>9 アプリケーションと実装</b>          | <b>47</b> |

| 6.3 推奨動作条件                         | 4         | 9.1 アプリケーション情報                | 47        |

| 6.4 熱に関する情報                        | 4         | 9.2 代表的なアプリケーション              | 47        |

| 6.5 電気的特性: $(Vs+) - Vs- = 5V$      | 5         | 9.3 電源に関する推奨事項                | 52        |

| 6.6 電気的特性: $(Vs+) - Vs- = 3V$      | 8         | 9.4 レイアウト                     | 52        |

| 6.7 代表的特性 (5V 単一電源)                | 11        | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>54</b> |

| 6.8 代表的特性: 3V 単一電源                 | 14        | 10.1 デバイスのサポート                | 54        |

| 6.9 代表的特性: 電源電圧範囲: 3V~5V           | 18        | 10.2 ドキュメントのサポート              | 54        |

| <b>7 パラメータ測定情報</b>                 | <b>23</b> | 10.3 ドキュメントの更新通知を受け取る方法       | 54        |

| 7.1 特性評価回路の例                       | 23        | 10.4 サポート・リソース                | 55        |

| 7.2 周波数応答の形状係数                     | 25        | 10.5 商標                       | 55        |

| 7.3 I/O ヘッドルームに関する検討事項             | 28        | 10.6 静電気放電に関する注意事項            | 55        |

| 7.4 出力 DC 誤差およびドリフトの計算値と、抵抗の不均衡の影響 | 29        | 10.7 用語集                      | 55        |

| 7.5 ノイズ解析                          | 32        | <b>11 改訂履歴</b>                | <b>55</b> |

| 7.6 高調波歪みに影響を与える要因                 | 33        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>55</b> |

## 4 デバイス比較表

| デバイス     | 帯域幅 (MHz) | $I_Q$ (mA) | THD (dBc) 2V <sub>PP</sub> , 100kHz 時 | 入力ノイズ電圧: 11nV/√Hz | レールツー レール |

|----------|-----------|------------|---------------------------------------|-------------------|-----------|

| THS4531A | 36        | 0.25       | -104                                  | 10                | 出力        |

| THS4521  | 145       | 0.95       | -102                                  | 4.6               | 出力        |

| THS4520  | 620       | 14.2       | -107                                  | 2                 | 出力        |

## 5 ピン構成および機能

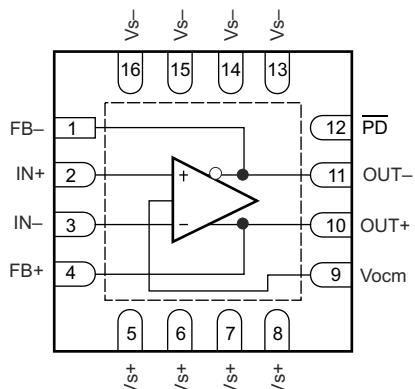

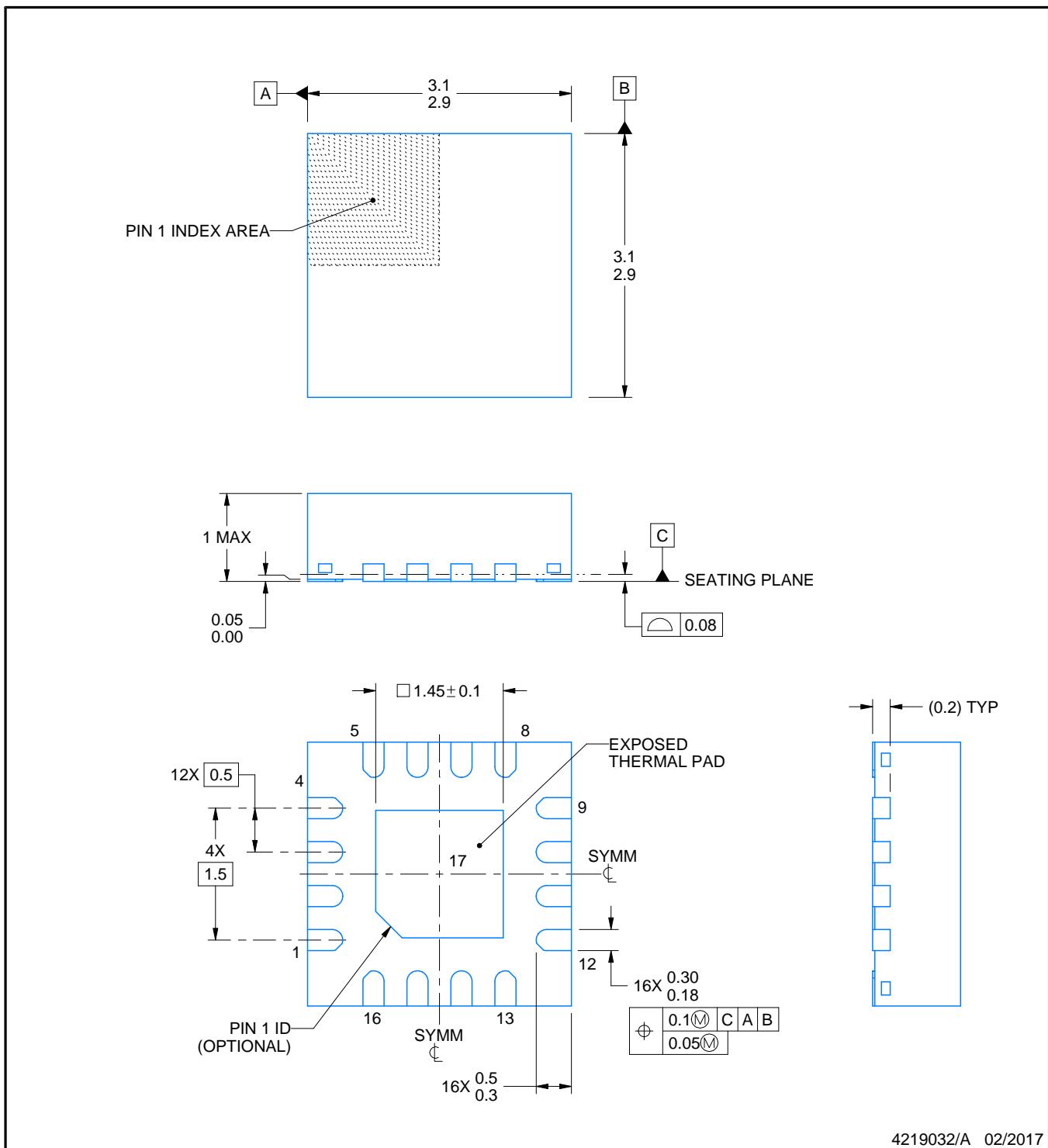

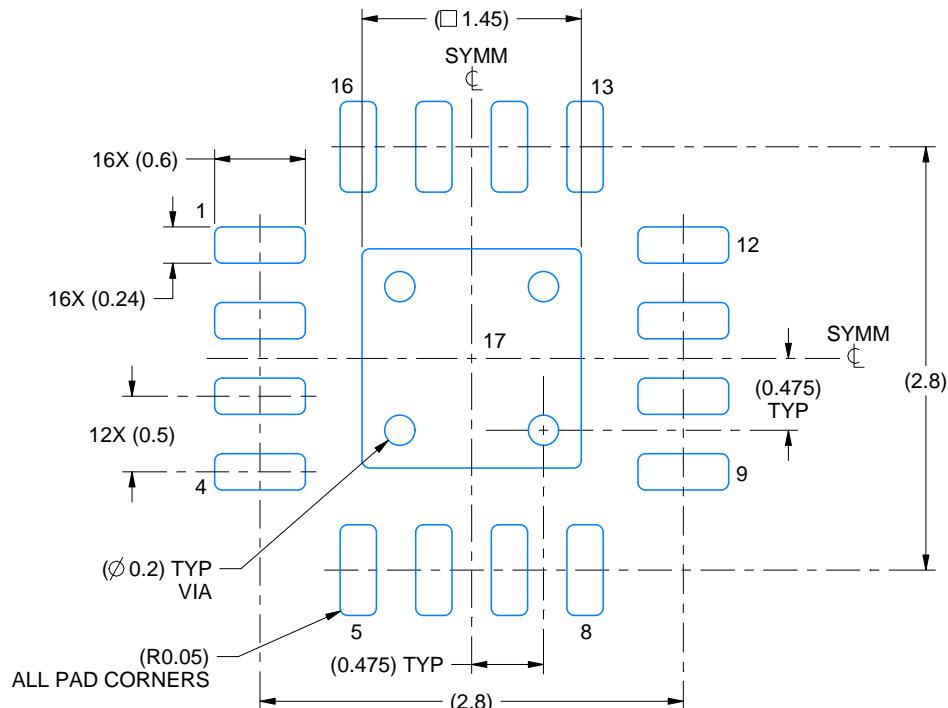

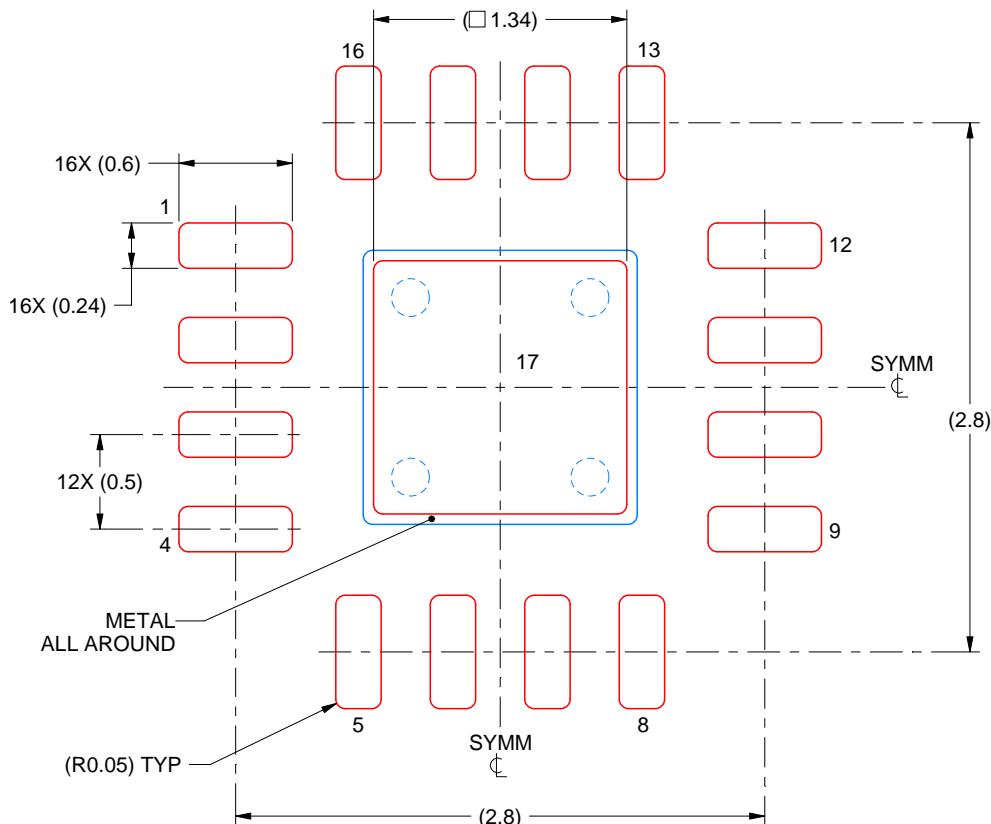

図 5-1. RGT パッケージ

16 ピン VQFN (露出サーマル パッド付き)

上面図

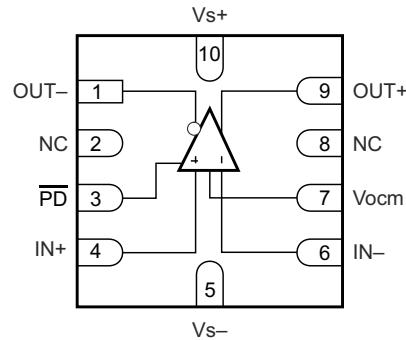

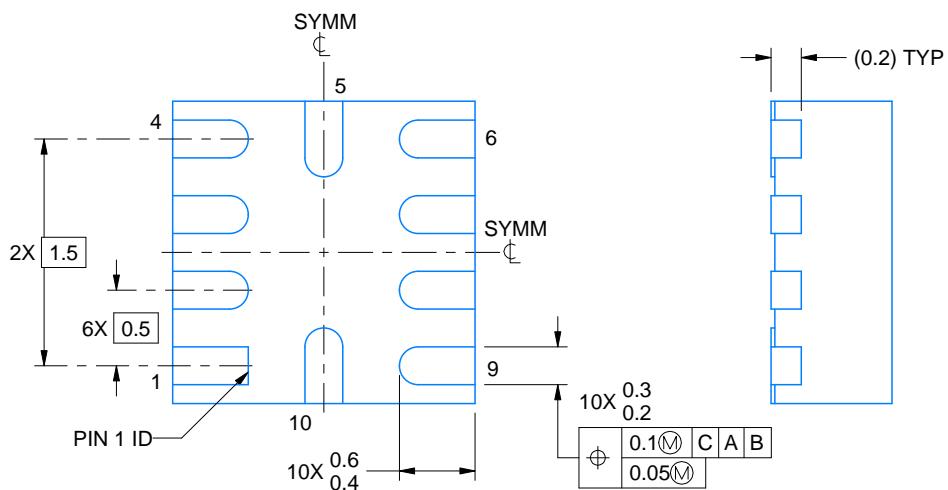

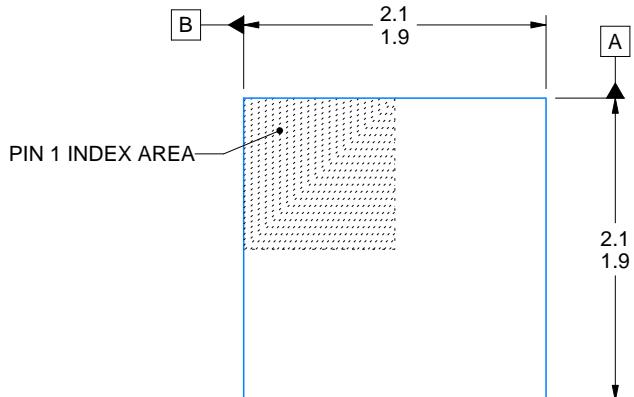

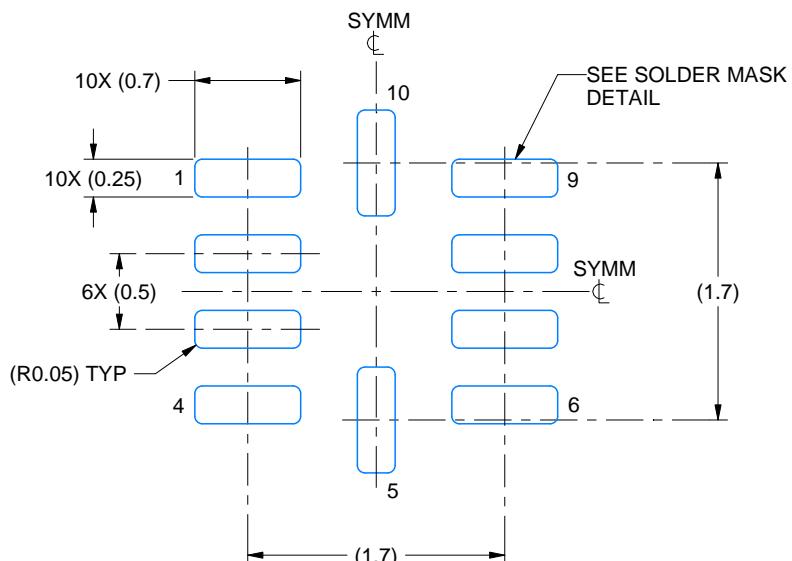

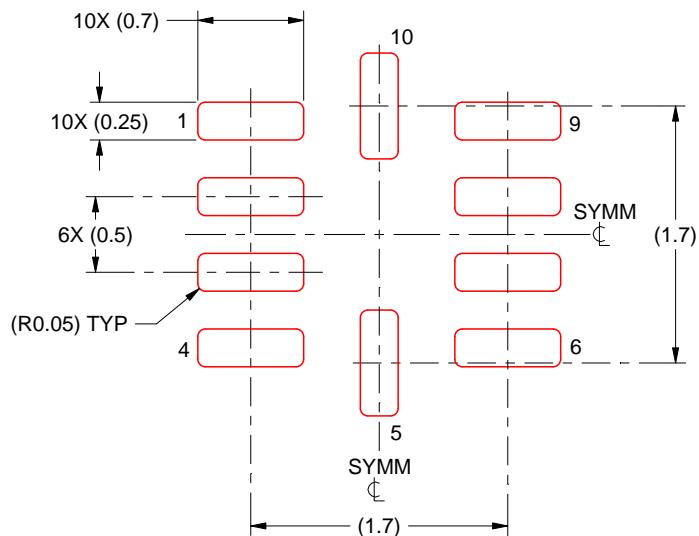

図 5-2. RUN パッケージ

10 ピン WQFN

上面図

表 5-1. ピンの機能

| ピン   |                | タイプ | 説明                                                                            |

|------|----------------|-----|-------------------------------------------------------------------------------|

| 名称   | 番号 (1)         |     |                                                                               |

| FB+  | 4              | 出力  | 非反転(正)出力帰還                                                                    |

| FB-  | 1              | 出力  | 反転(負)出力帰還                                                                     |

| IN+  | 2              | 入力  | 非反転(正)アンプ入力                                                                   |

| IN-  | 3              | 入力  | 反転(負)アンプ入力                                                                    |

| NC   | —              | —   | 内部接続なし                                                                        |

| OUT+ | 10             | 出力  | 非反転(正)アンプ出力                                                                   |

| OUT- | 11             | 出力  | 反転(負)アンプ出力                                                                    |

| PD   | 12             | 入力  | パワーダウン。 $\overline{PD}$ = 論理 Low = 電源オフモード、 $\overline{PD}$ = 論理 High = 通常動作。 |

| Vocm | 9              | 入力  | 同相モード電圧入力                                                                     |

| Vs+  | 5, 6, 7, 8     | 入力  | 正電源入力                                                                         |

| Vs-  | 13, 14, 15, 16 | 入力  | 負電源入力                                                                         |

(1) 露出サーマルパッドを熱拡散の電力またはグランドプレーンに半田付けします。このパッドはダイと電気的に絶縁されていますが、オープンではなく電源またはグランドプレーンに接続する必要があります。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |         |                  | 最小値                         | 最大値         | 単位 |

|------------------|---------|------------------|-----------------------------|-------------|----|

| 電圧               |         | 電源電圧、(Vs+) – Vs– |                             | 5.5         | V  |

|                  |         | 入力 / 出力電圧範囲      | (Vs–) – 0.5                 | (Vs+) + 0.5 |    |

|                  |         | 差動入力電圧           |                             | ±1          |    |

| 電流               |         | 連続入力電流           |                             | ±20         | mA |

|                  |         | 連続出力電流           |                             | ±80         |    |

|                  |         | 連続消費電力           | セクション 6.4 および セクション 7.8 を参照 |             |    |

|                  | 接合部     |                  |                             | 150         | °C |

|                  | 動作時自由気流 |                  | -40                         | 125         |    |

| T <sub>stg</sub> | 保存      |                  | -65                         | 150         |    |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD 定格

|                    |      |                                                               | 値     | 単位 |

|--------------------|------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>  | ±2000 | V  |

|                    |      | デバイス帯電モデル (CDM)、JEDEC仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

|                    |      | マシン モデル <sup>(2)</sup>                                        | ±150  |    |

(1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |           | 最小  | 公称 | 最大  | 単位 |

|-----------------|-----------|-----|----|-----|----|

| V <sub>s+</sub> | 単一電源電圧    | 2.7 | 5  | 5.4 | V  |

| T <sub>J</sub>  | ジヤンクション温度 | -40 | 25 | 125 | °C |

### 6.4 熱に関する情報

| 熱特性 <sup>(1)</sup>    |                     | THS4541    |            | 単位   |

|-----------------------|---------------------|------------|------------|------|

|                       |                     | RGT (VQFN) | RUN (WQFN) |      |

|                       |                     | 16 ピン      | 10 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 52         | 146        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 69         | 75         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 25         | 39         | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への評価パラメータ    | 2.7        | 14         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への評価パラメータ    | 25         | 105        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 9.3        | 47         | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

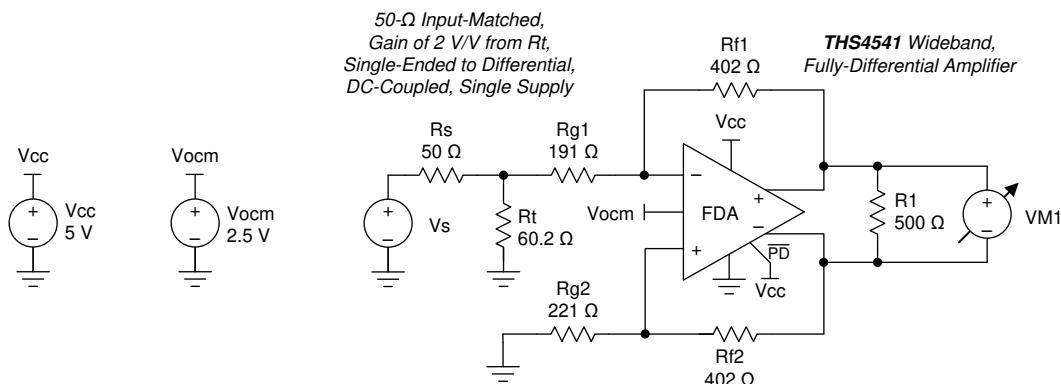

## 6.5 電気的特性 : ( $V_{S+}$ ) – $V_{S-}$ = 5V

$T_A \approx 25^\circ\text{C}$ 、 $V_{OCM}$  = オープン (デフォルトは中間電位)、 $V_{OUT} = 2V_{PP}$ 、 $R_f = 402\Omega$ 、 $R_{LOAD} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $G = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\bar{PD} = +Vs$  (特に記述のない限り)。AC 結合でゲイン 2V/V のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン 2V/V のテスト回路については、図 7-3 を参照してください。

| パラメータ                 | テスト条件                                                                                      | 最小値  | 代表値 | 最大値 | 単位     | テストレベル<br>(1) |

|-----------------------|--------------------------------------------------------------------------------------------|------|-----|-----|--------|---------------|

| <b>AC 特性</b>          |                                                                                            |      |     |     |        |               |

| 小信号帯域幅                | $V_{OUT} = 100mV_{PP}$ 、 $G = 1$                                                           | 620  |     |     | MHz    | C             |

|                       | $V_{OUT} = 100mV_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                               | 500  |     |     |        | C             |

|                       | $V_{OUT} = 100mV_{PP}$ 、 $G = 5$                                                           | 210  |     |     |        | C             |

|                       | $V_{OUT} = 100mV_{PP}$ 、 $G = 10$                                                          | 125  |     |     |        | C             |

| ゲイン帯域幅積               | $V_{OUT} = 100mV_{PP}$ 、 $G = 20$                                                          | 850  |     |     | MHz    | C             |

| 大信号帯域幅                | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                                  | 340  |     |     | MHz    | C             |

| 0.1dB 平坦度の帯域幅         | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                                  | 100  |     |     | MHz    | C             |

| スルーレート <sup>(2)</sup> | $V_{OUT} = 2V_{PP}$ 、 $FPBW$ (図 7-1 を参照)                                                   | 1500 |     |     | V/μs   | C             |

| 立ち上がり / 立ち下がり時間       | $V_{OUT} = 2V$ ステップ、 $G = 2$ 入力 $\leq 0.3ns$ $t_r$ (図 7-3 を参照)                             | 1.4  |     |     | ns     | C             |

| セトリング時間               | $\sim 1\%$ 、 $V_{OUT} = 2V$ ステップ、 $t_r = 2ns$ 、 $G = 2$ (図 7-3 を参照)                        | 4    |     |     | ns     | C             |

|                       | $\sim 0.1\%$ 、 $V_{OUT} = 2V$ ステップ、 $t_r = 2ns$ 、 $G = 2$ (図 7-3 を参照)                      | 8    |     |     |        | C             |

| オーバーシュートとアンダーシュート     | $V_{OUT} = 2V$ ステップ $G = 2$ 、入力 $\leq 0.3ns$ $t_r$ (図 7-3 を参照)                             | 10%  |     |     |        | C             |

| 100kHz の高調波歪み         | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ 、HD2 (図 7-1 を参照)                                             | -140 |     |     | dBc    | C             |

|                       | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ 、HD3 (図 7-1 を参照)                                             | -140 |     |     |        | C             |

| 10MHz の高調波歪み          | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ 、HD2 (図 7-1 を参照)                                             | -95  |     |     | dBc    | C             |

|                       | $V_{OUT} = 2V_{PP}$ 、 $G = 2$ 、HD3 (図 7-1 を参照)                                             | -90  |     |     |        | C             |

| 2 次相互変調歪              | $f = 10MHz$ 、 $100kHz$ トーン間隔、 $V_{OUT}$ エンベロープ = $2V_{PP}$ (トーン当たり $1V_{pp}$ ) (図 7-1 を参照) | -90  |     |     | dBc    | C             |

| 3 次相互変調歪              | $f = 10MHz$ 、 $100kHz$ トーン間隔、 $V_{OUT}$ エンベロープ = $2V_{PP}$ (トーン当たり $1V_{pp}$ ) (図 7-1 を参照) | -85  |     |     | dBc    | C             |

| 入力電圧ノイズ               | $f > 100kHz$                                                                               | 2.2  |     |     | nV/√Hz | C             |

| 入力電流ノイズ               | $f > 1 MHz$                                                                                | 1.9  |     |     | pA/√Hz | C             |

| オーバードライブの復帰時間         | 2 倍の出力オーバードライブ、どちらの極性にも対応                                                                  | 20   |     |     | ns     | C             |

| 閉ループ出力インピーダンス         | $f = 10MHz$ (差動)                                                                           | 0.1  |     |     | Ω      | C             |

## 6.5 電気的特性 : (Vs+) – Vs– = 5V (続き)

$T_A \approx 25^\circ\text{C}$ 、 $\text{Vocm}$  = オープン (デフォルトは中間電位)、 $\text{Vout} = 2\text{V}_{\text{PP}}$ 、 $\text{Rf} = 402\Omega$ 、 $\text{Rload} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $\text{G} = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\overline{\text{PD}} = +\text{Vs}$  (特に記述のない限り)。AC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-3 を参照してください。

| パラメータ                        | テスト条件                                             | 最小値                                               | 代表値                    | 最大値                    | 単位                                   | テストレベル<br>(1) |

|------------------------------|---------------------------------------------------|---------------------------------------------------|------------------------|------------------------|--------------------------------------|---------------|

| <b>DC 特性</b>                 |                                                   |                                                   |                        |                        |                                      |               |

| $\text{A}_{\text{OL}}$       | 開ループ電圧ゲイン                                         | 100                                               | 119                    |                        | dB                                   | A             |

| 入力換算オフセット電圧                  | $T_A = 25^\circ\text{C}$                          | -450                                              | $\pm 100$              | 450                    | $\mu\text{V}$                        | A             |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -600                                              | $\pm 100$              | 600                    |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -700                                              | $\pm 100$              | 700                    |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -850                                              | $\pm 100$              | 850                    |                                      | B             |

| 入力オフセット電圧ドリフト <sup>(3)</sup> | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -2.4                                              | $\pm 0.5$              | 2.4                    | $\mu\text{V}/^\circ\text{C}$         | B             |

| 入力バイアス電流<br>(ノードから外方向を正とする)  | $T_A = 25^\circ\text{C}$                          |                                                   | 10                     | 13                     | $\mu\text{A}$                        | A             |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     |                                                   | 11                     | 13.5                   |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  |                                                   | 12                     | 14                     |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | 12                     | 14.5                   |                                      | B             |

| 入力バイアス電流ドリフト <sup>(3)</sup>  | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | 6                      | 15                     | $\text{nA}/^\circ\text{C}$           | B             |

| 入力オフセット電流                    | $T_A = 25^\circ\text{C}$                          | -500                                              | $\pm 150$              | 500                    | $\text{nA}$                          | A             |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -550                                              | $\pm 150$              | 550                    |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -580                                              | $\pm 150$              | 580                    |                                      | B             |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -620                                              | $\pm 150$              | 620                    |                                      | B             |

| 入力オフセット電流ドリフト <sup>(3)</sup> | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -1.3                                              | $\pm 0.3$              | 1.3                    | $\text{nA}/^\circ\text{C}$           | B             |

| <b>入力</b>                    |                                                   |                                                   |                        |                        |                                      |               |

| コモン モード入力 Low                | 中間電位からの同相信号除去比の低下は $3\text{dB}$ 未満                | $T_A = 25^\circ\text{C}$                          | $(\text{Vs}^-) - 0.2$  | $(\text{Vs}^-) - 0.1$  | V                                    | A             |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(\text{Vs}^-) - 0.1$  | $\text{Vs}^-$          |                                      | B             |

| コモン モード入力 High               | 中間電位からの同相信号除去比の低下は $3\text{dB}$ 未満                | $T_A = 25^\circ\text{C}$                          | $(\text{Vs}^+) - 1.3$  | $(\text{Vs}^+) - 1.2$  | V                                    | A             |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(\text{Vs}^+) - 1.3$  |                        |                                      | B             |

| 同相除去比                        | $((\text{Vs}^+) - \text{Vs}^-) / 2$ の入力ピン         | 85                                                | 100                    |                        | dB                                   | A             |

| 入力インピーダンス差動モード               | $((\text{Vs}^+) - \text{Vs}^-) / 2$ の入力ピン         |                                                   | 110                    | $\parallel 0.85$       | $\text{k}\Omega \parallel \text{pF}$ | C             |

| <b>出力</b>                    |                                                   |                                                   |                        |                        |                                      |               |

| 出力電圧 Low                     | $T_A = 25^\circ\text{C}$                          |                                                   | $(\text{Vs}^-) + 0.2$  | $(\text{Vs}^-) + 0.25$ | V                                    | A             |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(\text{Vs}^-) + 0.2$  | $(\text{Vs}^-) + 0.25$ |                                      | B             |

| 出力電圧 High                    | $T_A = 25^\circ\text{C}$                          |                                                   | $(\text{Vs}^+) - 0.25$ | $(\text{Vs}^+) - 0.2$  | V                                    | A             |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(\text{Vs}^+) - 0.25$ | $(\text{Vs}^+) - 0.2$  |                                      | B             |

| 出力電流駆動                       | $T_A = 25^\circ\text{C}$                          |                                                   | $\pm 75$               | $\pm 100$              | mA                                   | A             |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | $\pm 75$               |                        |                                      | B             |

## 6.5 電気的特性 : (Vs+) – Vs– = 5V (続き)

$T_A \approx 25^\circ\text{C}$ 、 $\text{Vocm}$  = オープン (デフォルトは中間電位)、 $\text{Vout} = 2\text{V}_{\text{PP}}$ 、 $\text{Rf} = 402\Omega$ 、 $\text{Rload} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $\text{G} = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\overline{\text{PD}} = +\text{Vs}$  (特に記述のない限り)。AC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-3 を参照してください。

| パラメータ                                               | テスト条件                                                                             | 最小値                                               | 代表値     | 最大値     | 単位                                   | テストレベル <sup>(1)</sup> |

|-----------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|---------|---------|--------------------------------------|-----------------------|

| <b>電源</b>                                           |                                                                                   |                                                   |         |         |                                      |                       |

| 仕様動作電圧                                              |                                                                                   | 2.7                                               | 5       | 5.4     | V                                    | B                     |

| 静止時動作電流                                             | $T_A = 25^\circ\text{C}$ 、 $\text{Vs} = 5\text{V}$                                | 9.7                                               | 10.1    | 10.5    | mA                                   | A                     |

|                                                     | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                 | 9.4                                               | 10.1    | 11      |                                      | B                     |

| $\pm\text{PSRR}$                                    | どちらかの電源ピンから差動 $\text{Vout}$ まで                                                    | 85                                                | 100     |         | dB                                   | A                     |

| <b>パワーダウン</b>                                       |                                                                                   |                                                   |         |         |                                      |                       |

| 電圧スレッショルド有効化                                        |                                                                                   | $(\text{Vs}^-) + 1.7$                             |         |         | V                                    | A                     |

| 電圧スレッショルド無効化                                        |                                                                                   | $(\text{Vs}^-) + 0.7$                             |         |         | V                                    | A                     |

| ディスエーブルピンのバイアス電流                                    | $\overline{\text{PD}} = \text{Vs}^- \rightarrow \text{Vs}^+$                      | 20                                                | 50      |         | nA                                   | B                     |

| パワーダウン静止時電流                                         | $\overline{\text{PD}} = (\text{Vs}^-) + 0.7\text{V}$                              | 6                                                 | 30      |         | $\mu\text{A}$                        | A                     |

|                                                     | $\overline{\text{PD}} = \text{Vs}^-$                                              | 2                                                 | 8       |         |                                      | A                     |

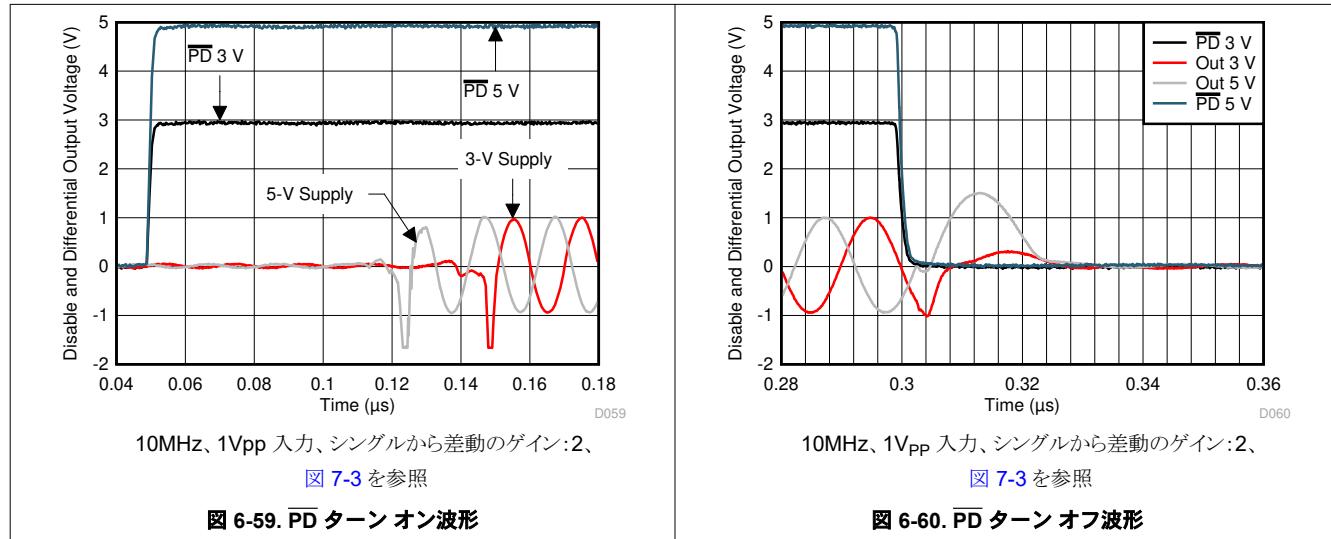

| ターンオン時間の遅延                                          | $\overline{\text{PD}} = \text{Low}$ から $\text{Vout} = \text{最終値の } 90\%$ になるまでの時間 | 100                                               |         |         | ns                                   | C                     |

| ターンオフ時間の遅延                                          | $\overline{\text{PD}} = \text{Low}$ から $\text{Vout} = \text{最終値の } 10\%$ になるまでの時間 | 60                                                |         |         | ns                                   | C                     |

| <b>出力コモンモード電圧制御<sup>(4)</sup></b>                   |                                                                                   |                                                   |         |         |                                      |                       |

| 小信号帯域幅                                              | $\text{Vocm} = 100\text{mV}_{\text{PP}}$                                          | 150                                               |         |         | MHz                                  | C                     |

| スルーレート <sup>(2)</sup>                               | $\text{Vocm} = 2\text{V}$ ステップ                                                    | 400                                               |         |         | V/ $\mu\text{s}$                     | C                     |

| ゲイン                                                 |                                                                                   | 0.975                                             | 0.982   | 0.995   | V/V                                  | A                     |

| 入力バイアス電流                                            | ノードから外方向を正とする                                                                     | -0.7                                              | 0.1     | 0.7     | $\mu\text{A}$                        | A                     |

| 入力インピーダンス                                           | $((\text{Vs}^+) - \text{Vs}^-) / 2$ に駆動される $\text{Vocm}$ 入力                       | $47 \parallel 1.2$                                |         |         | $\text{k}\Omega \parallel \text{pF}$ | C                     |

| $((\text{Vs}^+) - \text{Vs}^-) / 2$ からのデフォルト電圧オフセット | $\text{Vocm}$ ピンはオープン                                                             | -40                                               | $\pm 8$ | 40      | mV                                   | A                     |

| CM $\text{Vos}$                                     | コモンモードオフセット電圧                                                                     | $T_A = 25^\circ\text{C}$                          | -5      | $\pm 2$ | 5                                    | mV                    |

|                                                     |                                                                                   | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -6      | $\pm 2$ | 5.8                                  |                       |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -6.2    | $\pm 2$ | 6.2                                  |                       |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -7      | $\pm 2$ | 7.08                                 |                       |

| コモンモードオフセット電圧ドリフト <sup>(3)</sup>                    | $((\text{Vs}^+) - \text{Vs}^-) / 2$ に駆動される $\text{Vocm}$ 入力                       | -20                                               | $\pm 4$ | +20     | $\mu\text{V}/^\circ\text{C}$         | B                     |

| 負電源までのコモンモードループ電源のヘッドルーム                            | 中間電位 CM $\text{Vos}$ から $\pm 12\text{mV}$ 未満のシフト                                  | $T_A = 25^\circ\text{C}$                          | 0.88    |         | V                                    | A                     |

|                                                     |                                                                                   | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | 0.91    |         |                                      | B                     |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | 0.94    |         |                                      | B                     |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | 0.94    |         |                                      | B                     |

| 正電源までのコモンモードループ電源のヘッドルーム                            | 中間電位 CM $\text{Vos}$ から $\pm 12\text{mV}$ 未満のシフト                                  | $T_A = 25^\circ\text{C}$                          | 1.1     |         | V                                    | A                     |

|                                                     |                                                                                   | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | 1.15    |         |                                      | B                     |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | 1.2     |         |                                      | B                     |

|                                                     |                                                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | 1.2     |         |                                      | B                     |

(1) テストレベル (特性とシミュレーションにより設定されたすべての値):(A)  $T_A \approx 25^\circ\text{C}$  (特性とシミュレーションによる過熱制限) 時に 100% テスト済み。(B) 実製品ではテストされていません。特性とシミュレーションにより設定される制約あり。(C) 情報のための標準値。

(2) このスルーレートは、大信号帯域幅から以下の式によって推定される立ち上がり時間と立ち下がり時間の平均です。 $(V_P / \sqrt{2}) \cdot 2\pi \cdot f_{-3\text{dB}}$

(3) 入力オフセット電圧ドリフト、入力バイアス電流ドリフト、入力オフセット電流ドリフト、および  $\text{Vocm}$  ドリフトは、環境温度エンドポイントの最大範囲で取得したデータを使用して差を算出し、温度範囲で割った平均値です。最大ドリフトは、デバイスの多数のサンプリングの分布により設定されます。ドリフトは、テスト、または QA サンプル テストでは規定されません。

(4) 仕様は、入力  $\text{Vocm}$  ピンから差動出力の平均電圧までです。

## 6.6 電気的特性 : ( $V_{S+}$ ) – $V_{S-}$ = 3 V

$T_A \approx 25^\circ\text{C}$ 、 $V_{OCM}$  = オープン (デフォルトは中間電位)、 $V_{OUT} = 2V_{PP}$ 、 $R_f = 402\Omega$ 、 $R_{LOAD} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $G = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\bar{PD} = +Vs$  (特に記述のない限り)。AC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-3 を参照してください。

| パラメータ                 | テスト条件                                                                                                        | 最小値  | 代表値 | 最大値 | 単位                     | テストレベル<br>(1) |

|-----------------------|--------------------------------------------------------------------------------------------------------------|------|-----|-----|------------------------|---------------|

| <b>AC 特性</b>          |                                                                                                              |      |     |     |                        |               |

| 小信号帯域幅                | $V_{out} = 100\text{mV}_{PP}$ 、 $G = 1$                                                                      | 600  |     |     | MHz                    | C             |

|                       | $V_{out} = 100\text{mV}_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                                          | 500  |     |     |                        | C             |

|                       | $V_{out} = 100\text{mV}_{PP}$ 、 $G = 5$                                                                      | 200  |     |     |                        | C             |

|                       | $V_{out} = 100\text{mV}_{PP}$ 、 $G = 10$                                                                     | 120  |     |     |                        | C             |

| ゲイン帯域幅積               | $V_{out} = 100\text{mV}_{PP}$ 、 $G = 20$                                                                     | 850  |     |     | MHz                    | C             |

| 大信号帯域幅                | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                                             | 300  |     |     | MHz                    | C             |

| 0.1dB 平坦度の帯域幅         | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ (図 7-1 を参照)                                                             | 90   |     |     | MHz                    | C             |

| スルーレート <sup>(2)</sup> | $V_{out} = 2\text{V}$ ステップ、FPBW (図 7-1 を参照)                                                                  | 1300 |     |     | V/ $\mu$ s             | C             |

| 立ち上がり / 立ち下がり時間       | $V_{out} = 2\text{V}$ ステップ、 $G = 2$ 、入力 $\leq 0.3\text{ns}$ $t_r$ (図 7-3 を参照)                                | 1.8  |     |     | ns                     | C             |

| セトリング時間               | $\sim 1\%$ 、 $V_{out} = 2\text{V}$ ステップ、 $t_r = 2\text{ns}$ 、 $G = 2$ (図 7-3 を参照)                            | 5    |     |     | ns                     | C             |

|                       | $\sim 0.1\%$ 、 $V_{out} = 2\text{V}$ ステップ、 $t_r = 2\text{ns}$ 、 $G = 2$ (図 7-3 を参照)                          | 8    |     |     |                        | C             |

| オーバーシュートとアンダーシュート     | $V_{out} = 2\text{V}$ ステップ $G = 2$ 、入力 $\leq 0.3\text{ns}$ $t_r$ (図 7-3 を参照)                                 | 10%  |     |     |                        | C             |

| 100kHz の高調波歪み         | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ 、HD2 (図 7-1 を参照)                                                        | -140 |     |     | dBc                    | C             |

|                       | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ 、HD3 (図 7-1 を参照)                                                        | -140 |     |     |                        | C             |

| 10MHz の高調波歪み          | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ 、HD2 (図 7-1 を参照)                                                        | -92  |     |     | dBc                    | C             |

|                       | $V_{out} = 2\text{V}_{PP}$ 、 $G = 2$ 、HD3 (図 7-1 を参照)                                                        | -89  |     |     |                        | C             |

| 2 次相互変調歪              | $f = 10\text{MHz}$ 、100kHz トーン間隔、 $V_{out}$ エンベロープ = $2\text{V}_{PP}$ (トーン当たり $1\text{V}_{pp}$ ) (図 7-1 を参照) | -89  |     |     | dBc                    | C             |

| 3 次相互変調歪              | $f = 10\text{MHz}$ 、100kHz トーン間隔、 $V_{out}$ エンベロープ = $2\text{V}_{PP}$ (トーン当たり $1\text{V}_{pp}$ ) (図 7-1 を参照) | -87  |     |     | dBc                    | C             |

| 入力電圧ノイズ               | $f > 100\text{kHz}$                                                                                          | 2.2  |     |     | nV/ $\sqrt{\text{Hz}}$ | C             |

| 入力電流ノイズ               | $f > 1\text{MHz}$                                                                                            | 1.9  |     |     | pA/ $\sqrt{\text{Hz}}$ | C             |

| オーバードライブの復帰時間         | 2 倍の出力オーバードライブ、どちらの極性にも対応                                                                                    | 20   |     |     | ns                     | C             |

| 閉ループ出力インピーダンス         | $f = 10\text{MHz}$ (差動)                                                                                      | 0.1  |     |     | $\Omega$               | C             |

## 6.6 電気的特性 : $(Vs+) - Vs- = 3\text{ V}$ (続き)

$T_A \approx 25^\circ\text{C}$ 、 $V_{\text{ocm}} = \text{オープン}$  (デフォルトは中間電位)、 $V_{\text{out}} = 2V_{\text{pp}}$ 、 $R_f = 402\Omega$ 、 $R_{\text{load}} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $G = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\overline{PD} = +Vs$  (特に記述のない限り)。AC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-3 を参照してください。

| パラメータ                        | テスト条件                                             | 最小値                                               | 代表値            | 最大値            | 単位                                   | テスト レベル<br>(1) |

|------------------------------|---------------------------------------------------|---------------------------------------------------|----------------|----------------|--------------------------------------|----------------|

| <b>DC 特性</b>                 |                                                   |                                                   |                |                |                                      |                |

| $A_{\text{OL}}$              | 開ループ電圧ゲイン                                         | 100                                               | 119            |                | dB                                   | A              |

| 入力換算オフセット電圧                  | $T_A = 25^\circ\text{C}$                          | -450                                              | $\pm 100$      | 400            | $\mu\text{V}$                        | A              |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -600                                              | $\pm 100$      | 600            |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -700                                              | $\pm 100$      | 700            |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -850                                              | $\pm 100$      | 850            |                                      | B              |

| 入力オフセット電圧ドリフト <sup>(3)</sup> | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -2.4                                              | $\pm 0.5$      | 2.4            | $\mu\text{V}/^\circ\text{C}$         | B              |

| 入力バイアス電流<br>(ノードから外方向を正とする)  | $T_A = 25^\circ\text{C}$                          |                                                   | 9              | 12             | $\mu\text{A}$                        | A              |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     |                                                   | 9              | 12.5           |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  |                                                   | 9              | 13             |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | 9              | 13.5           |                                      | B              |

| 入力バイアス電流ドリフト <sup>(3)</sup>  | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | -5             | 15             | $\text{nA}/^\circ\text{C}$           | B              |

| 入力オフセット電流                    | $T_A = 25^\circ\text{C}$                          | -500                                              | $\pm 150$      | 500            | $\text{nA}$                          | A              |

|                              | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -550                                              | $\pm 150$      | 550            |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -580                                              | $\pm 150$      | 580            |                                      | B              |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -620                                              | $\pm 150$      | 620            |                                      | B              |

| 入力オフセット電流ドリフト <sup>(3)</sup> | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -1.3                                              | $\pm 0.3$      | 1.3            | $\text{nA}/^\circ\text{C}$           | B              |

| <b>入力</b>                    |                                                   |                                                   |                |                |                                      |                |

| コモン モード入力 Low                | 中間電位からの同相信号除去比の低下は $3\text{dB}$ 未満                | $T_A = 25^\circ\text{C}$                          | $(Vs-) - 0.2$  | $(Vs-) - 0.1$  | V                                    | A              |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(Vs-) - 0.1$  | $Vs-$          |                                      | B              |

| コモン モード入力 High               | 中間電位からの同相信号除去比の低下は $3\text{dB}$ 未満                | $T_A = 25^\circ\text{C}$                          | $(Vs+) - 1.3$  | $(Vs+) - 1.2$  | V                                    | A              |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(Vs+) - 1.3$  |                |                                      | B              |

| 同相除去比                        | $((Vs+) - Vs-) / 2$ の入力ピン                         |                                                   | 85             | 100            | dB                                   | A              |

| 入力インピーダンス差動モード               | $((Vs+) - Vs-) / 2$ の入力ピン                         |                                                   | 110    0.85    |                | $\text{k}\Omega \parallel \text{pF}$ | C              |

| <b>出力</b>                    |                                                   |                                                   |                |                |                                      |                |

| 出力電圧 Low                     |                                                   | $T_A = 25^\circ\text{C}$                          | $(Vs-) + 0.2$  | $(Vs-) + 0.25$ | V                                    | A              |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(Vs-) + 0.2$  | $(Vs-) + 0.25$ |                                      | B              |

| 出力電圧 High                    |                                                   | $T_A = 25^\circ\text{C}$                          | $(Vs+) - 0.25$ | $(Vs+) - 0.2$  | V                                    | A              |

|                              |                                                   | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | $(Vs+) - 0.25$ | $(Vs+) - 0.2$  |                                      | B              |

| 出力電流駆動                       | $T_A = 25^\circ\text{C}$                          |                                                   | $\pm 55$       | $\pm 60$       | mA                                   | A              |

|                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ |                                                   | $\pm 55$       |                |                                      | B              |

## 6.6 電気的特性 : $(V_{s+}) - V_{s-} = 3\text{ V}$ (続き)

$T_A \approx 25^\circ\text{C}$ 、 $V_{ocm} = \text{オープン}$  (デフォルトは中間電位)、 $V_{out} = 2V_{pp}$ 、 $R_f = 402\Omega$ 、 $R_{load} = 499\Omega$ 、 $50\Omega$  入力マッチング、 $G = 2\text{V/V}$ 、シングルエンド入力、差動出力、および  $\bar{PD} = +V_s$  (特に記述のない限り)。AC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-1 を参照してください。DC 結合でゲイン  $2\text{V/V}$  のテスト回路については、図 7-3 を参照してください。

| パラメータ                                     | テスト条件                                                                            | 最小値                                               | 代表値      | 最大値     | 単位                            | テストレベル<br>(1) |   |

|-------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------|----------|---------|-------------------------------|---------------|---|

| <b>電源</b>                                 |                                                                                  |                                                   |          |         |                               |               |   |

| 仕様動作電圧                                    |                                                                                  | 2.7                                               | 3        | 5.4     | V                             | B             |   |

| 静止時動作電流                                   | $T_A = 25^\circ\text{C}$ 、 $V_s = 3\text{ V}$                                    | 9.3                                               | 9.7      | 10.1    | mA                            | A             |   |

|                                           | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                | 9                                                 | 9.7      | 10.6    |                               | B             |   |

| $\pm PSRR$                                | どちらかの電源ピンから差動 $V_{out}$ まで                                                       | 85                                                | 100      |         | dB                            | A             |   |

| <b>パワーダウン</b>                             |                                                                                  |                                                   |          |         |                               |               |   |

| 電圧スレッショルド有効化                              |                                                                                  | $(V_{s-}) + 1.7$                                  |          |         | V                             | A             |   |

| 電圧スレッショルド無効化                              |                                                                                  | $(V_{s-}) + 0.7$                                  |          |         | V                             | A             |   |

| ディスエーブルピンのバイアス電流                          | $\bar{PD} = V_{s-} \rightarrow V_{s+}$                                           | 20                                                | 50       |         | nA                            | B             |   |

| パワーダウン静止時電流                               | $\bar{PD} = (V_{s-}) + 0.7\text{V}$                                              | 2                                                 | 30       |         | $\mu\text{A}$                 | A             |   |

|                                           | $\bar{PD} = V_{s-}$                                                              | 1.0                                               | 8.0      |         |                               | A             |   |

| ターンオン時間の遅延                                | $\bar{PD} = \text{Low} \text{ から } V_{out} = \text{最終値の } 90\% \text{ になるまでの時間}$ | 100                                               |          |         | ns                            | C             |   |

| ターンオフ時間の遅延                                | $\bar{PD} = \text{Low} \text{ から } V_{out} = \text{最終値の } 10\% \text{ になるまでの時間}$ | 60                                                |          |         | ns                            | C             |   |

| <b>出力コモンモード電圧制御<sup>(4)</sup></b>         |                                                                                  |                                                   |          |         |                               |               |   |

| 小信号帯域幅                                    | $V_{ocm} = 100\text{mV}_{pp}$                                                    | 140                                               |          |         | MHz                           | C             |   |

| スルーレート <sup>(2)</sup>                     | $V_{ocm} = 1\text{V}$ ステップ                                                       | 350                                               |          |         | $\text{V}/\mu\text{s}$        | C             |   |

| ゲイン                                       |                                                                                  | 0.975                                             | 0.987    | 0.990   | V/V                           | A             |   |

| 入力バイアス電流                                  | ノードから外方向を正とする                                                                    | -0.7                                              | 0.1      | 0.7     | $\mu\text{A}$                 | A             |   |

| 入力インピーダンス                                 | $((V_{s+}) - V_{s-}) / 2$ に駆動される $V_{ocm}$ 入力                                    | 47    1.2                                         |          |         | $\text{k}\Omega    \text{pF}$ | C             |   |

| $((V_{s+}) - V_{s-}) / 2$ からのデフォルト電圧オフセット | $V_{ocm}$ ピンはオープン                                                                | -40                                               | $\pm 10$ | 40      | mV                            | A             |   |

| CM $V_{os}$                               | コモンモードオフセット電圧                                                                    | $T_A = 25^\circ\text{C}$                          | -5       | $\pm 2$ | 5                             | mV            | A |

|                                           |                                                                                  | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | -5.8     | $\pm 2$ | 5.8                           |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -6.2     | $\pm 2$ | 6.2                           |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | -7       | $\pm 2$ | 7                             |               | B |

| コモンモードオフセット電圧ドリフト <sup>(3)</sup>          | $((V_{s+}) - V_{s-}) / 2$ に駆動される $V_{ocm}$ 入力                                    | -20                                               | $\pm 4$  | 20      | $\mu\text{V}/^\circ\text{C}$  | B             |   |

| 負電源までのコモンモードループ電源のヘッドルーム                  | 中間電位 $CM V_{os}$ から $\pm 12\text{mV}$ 未満のシフト                                     | $T_A = 25^\circ\text{C}$                          | 0.88     |         |                               | V             | A |

|                                           |                                                                                  | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | 0.91     |         |                               |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | 0.94     |         |                               |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | 0.94     |         |                               |               | B |

| 正電源までのコモンモードループ電源のヘッドルーム                  | 中間電位 $CM V_{os}$ から $\pm 12\text{mV}$ 未満のシフト                                     | $T_A = 25^\circ\text{C}$                          | 1.1      |         |                               | V             | A |

|                                           |                                                                                  | $T_A = 0^\circ\text{C} \sim 70^\circ\text{C}$     | 1.15     |         |                               |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | 1.2      |         |                               |               | B |

|                                           |                                                                                  | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ | 1.2      |         |                               |               | B |

- (1) テストレベル (特性とシミュレーションにより設定されたすべての値):(A)  $T_A \approx 25^\circ\text{C}$  (特性とシミュレーションによる過熱制限) 時に 100% テスト済み。(B) 実製品ではテストされていません。特性とシミュレーションにより設定される制約あり。(C) 情報のための標準値。

- (2) このスルーレートは、大信号帯域幅から以下の式によって推定される立ち上がり時間と立ち下がり時間の平均です。 $(V_p / \sqrt{2}) \cdot 2\pi \cdot f_{-3\text{dB}}$

- (3) 入力オフセット電圧ドリフト、入力バイアス電流ドリフト、入力オフセット電流ドリフト、および  $V_{ocm}$  ドリフトは、環境温度エンドポイントの最大範囲で取得したデータを使用して差を算出し、温度範囲で割った平均値です。最大ドリフトは、デバイスの多数のサンプリングの分布により設定されます。ドリフトは、テスト、または QA サンプル テストでは規定されません。

- (4) 仕様は、入力  $V_{ocm}$  ピンから差動出力平均電圧までとなります。

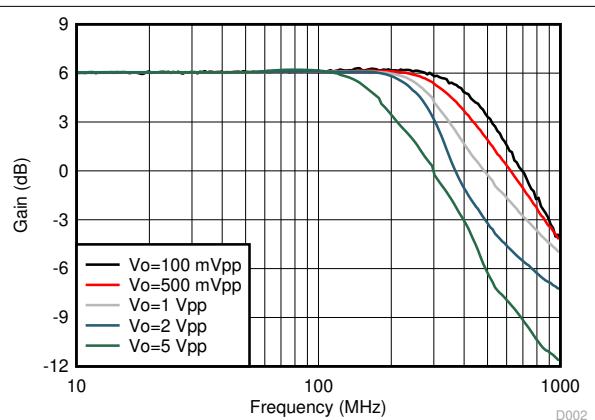

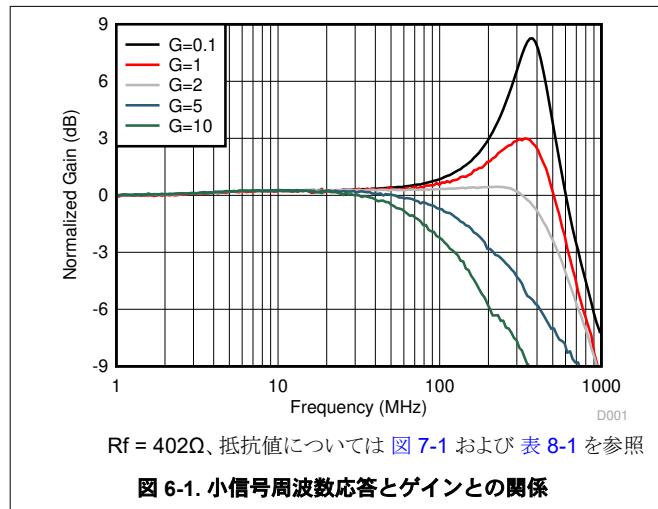

## 6.7 代表的特性 (5V 単一電源)

$V_{s+} = 5V$ ,  $V_{s-} = GND$ ,  $V_{ocm}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ ,  $R_{load} = 500\Omega$ ,  $TA \approx 25^\circ C$

(特に記述のない限り)

## 6.7 代表的特性 (5V 単一電源) (続き)

$V_{S+} = 5V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ 、 $R_{LOAD} = 500\Omega$ 、 $TA \approx 25^\circ C$

(特に記述のない限り)

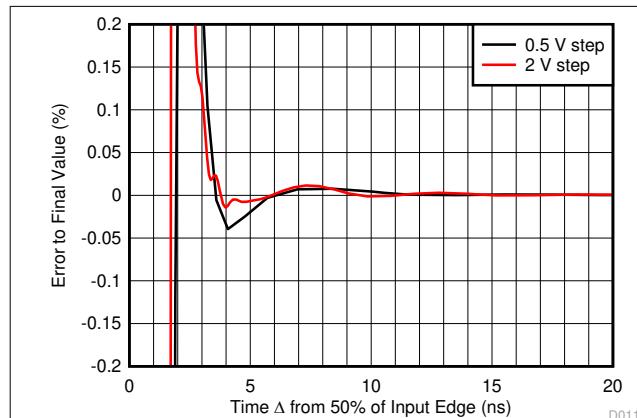

## 6.7 代表的特性 (5V 単一電源) (続き)

$V_{s+} = 5V$ ,  $V_{s-} = GND$ ,  $V_{ocm}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V,  $R_{load} = 500\Omega$ ,  $TA \approx 25^\circ C$

(特に記述のない限り)

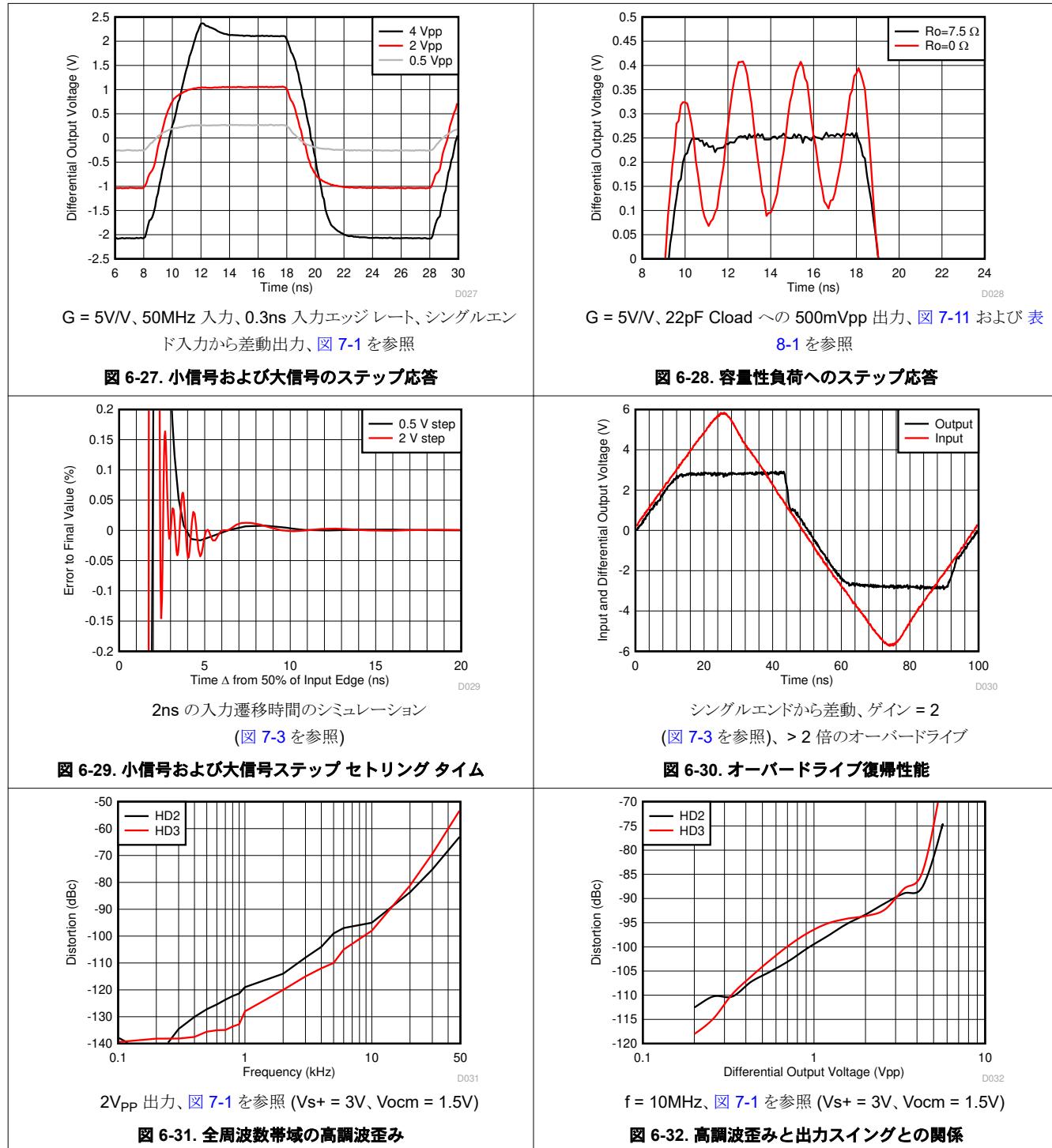

2ns の入力遷移時間のシミュレーション (図 7-3 を参照)

図 6-11. 小信号および大信号ステップセトリングタイム

シングルエンドから差動、ゲイン = 2 (図 7-3 を参照)、2 倍の入力オーバードライブ

図 6-12. オーバードライブ復帰性能

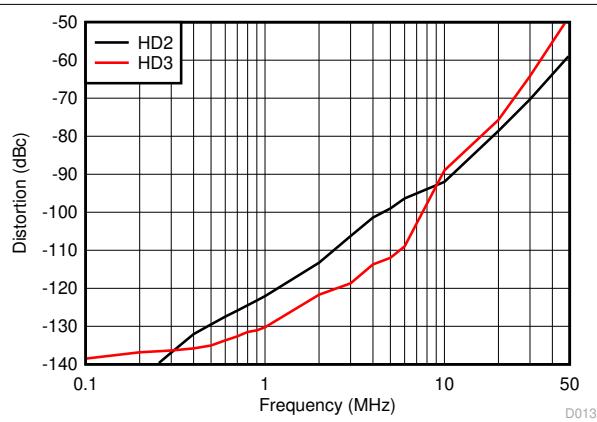

$V_o = 2V_{pp}$ 、図 7-1 を参照

図 6-13. 全周波数帯域の高調波歪み

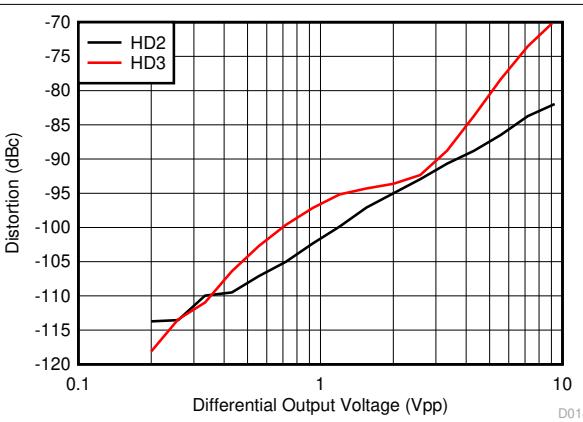

$f = 10MHz$ 、図 7-1 を参照

図 6-14. 高調波歪みと出力スイングとの関係

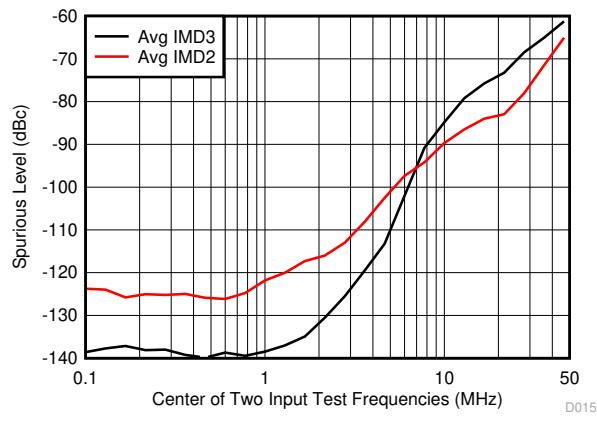

$1V_{pp}$  (各トーン)、図 7-1 を参照

図 6-15. 全周波数帯域の IMD2 と IM3

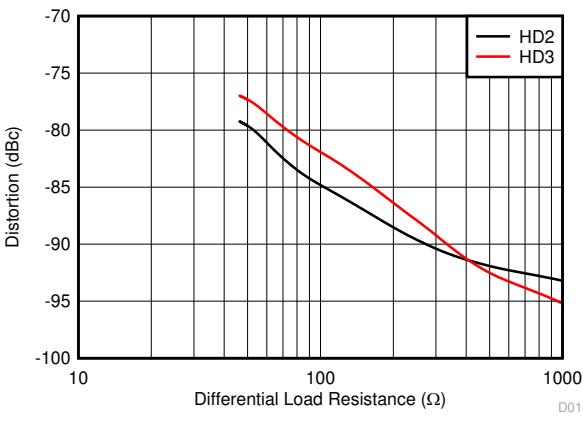

$f = 10MHz$ 、図 7-1 を参照、 $R_{load}$  は調整済み

図 6-16. 高調波歪みと  $R_{load}$  との関係

## 6.7 代表的特性 (5V 単一電源) (続き)

$V_{S+} = 5V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

## 6.8 代表的特性 : 3V 単一電源

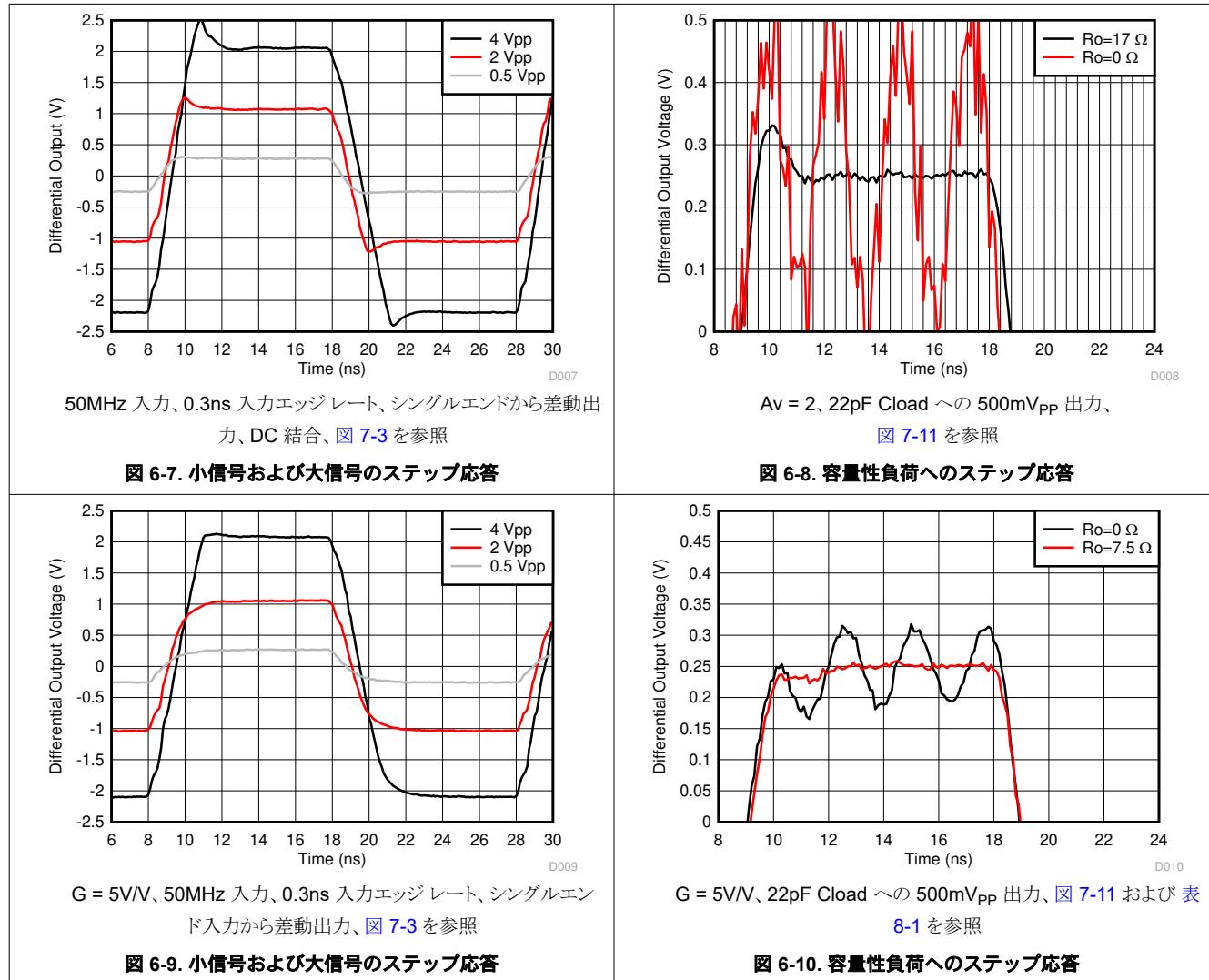

$V_{S+} = 3V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

## 6.8 代表的特性：3V 単一電源 (続き)

$V_{s+} = 3V$ 、 $V_{s-} = GND$ 、 $V_{ocm}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{load} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

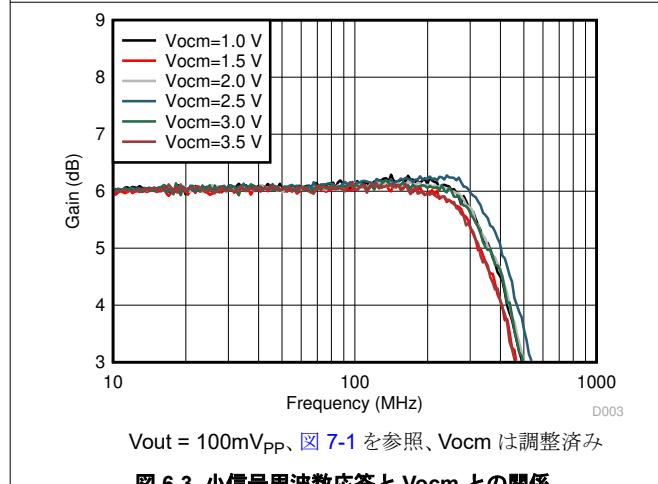

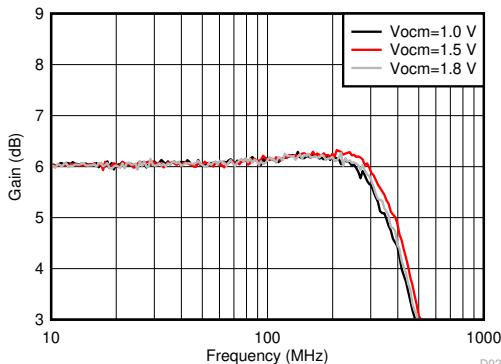

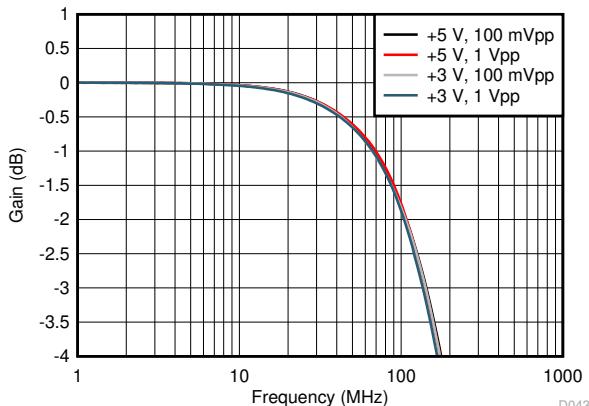

$V_{out} = 100mV_{PP}$ 、図 7-1 を参照、 $V_{ocm}$  は調整済み

図 6-21. 小信号周波数応答と  $V_{ocm}$  との関係

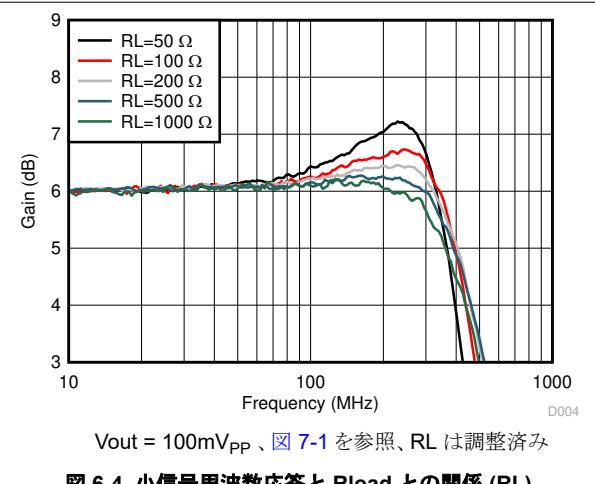

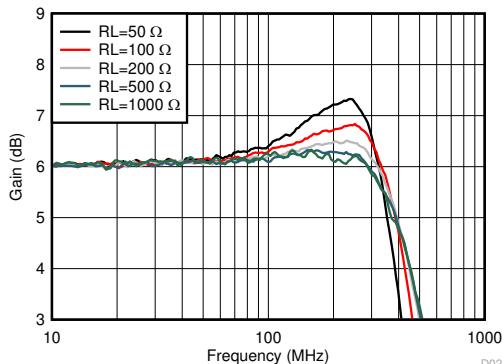

$V_{out} = 100mV_{PP}$ 、図 7-1 を参照、 $R_{load}$  は調整済み

図 6-22. 小信号周波数応答と  $R_{load}$  との関係

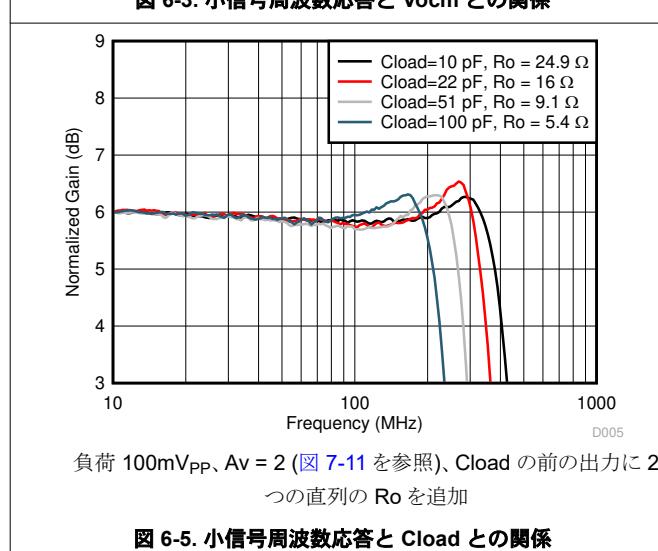

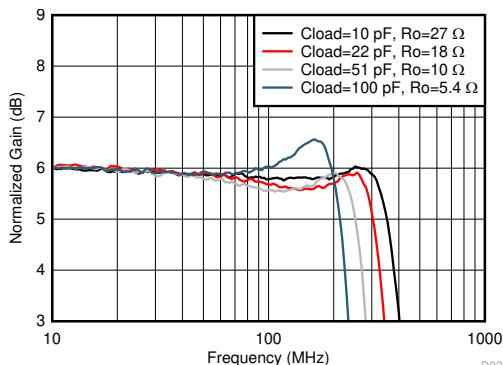

負荷  $100mV_{PP}$ 、 $Av = 2$  (図 7-11 を参照)、 $Cload$  の前の出力に 2 つの直列の  $Ro$  を追加

図 6-23. 小信号周波数応答と  $Cload$  との関係

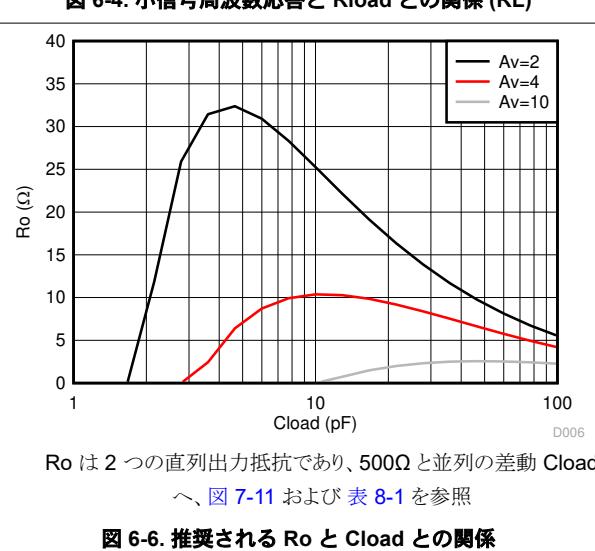

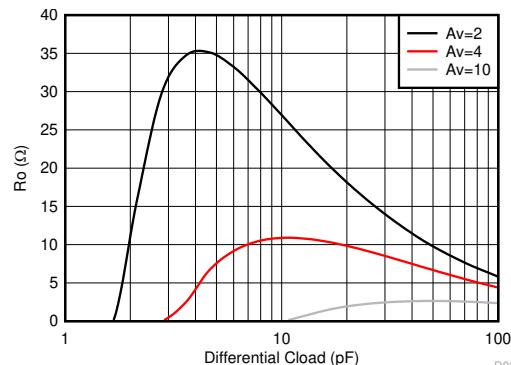

出力の 2 つの  $Ro$  と  $500\Omega$  と並列の差動  $Cload$ 、図 7-11 および表 8-1 を参照

図 6-24. 推奨される  $Ro$  と  $Cload$  との関係

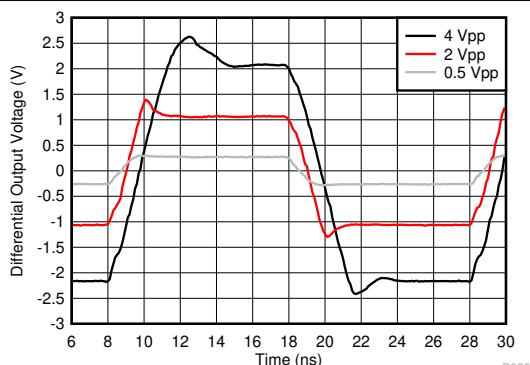

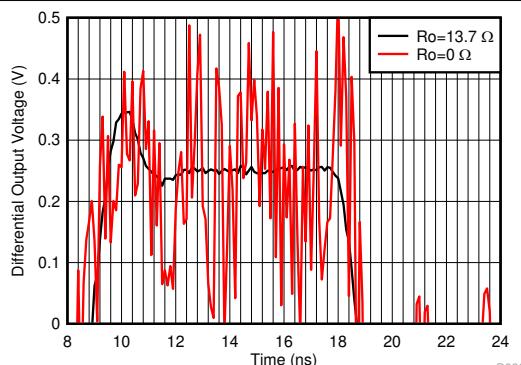

50MHz 入力、0.3ns 入力エッジレート、シングルエンド入力から差動出力、DC 結合、図 7-3 を参照

図 6-25. 小信号および大信号のステップ応答

22pF  $Cload$  への  $500mV_{PP}$  出力、図 7-11 を参照 ( $V_{s+} = 3V$ 、 $V_{ocm} = 1.5V$ )

図 6-26. 容量性負荷へのステップ応答

## 6.8 代表的特性：3V 単一電源 (続き)

$V_{S+} = 3V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

## 6.8 代表的特性：3V 単一電源 (続き)

$V_{S+} = 3V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

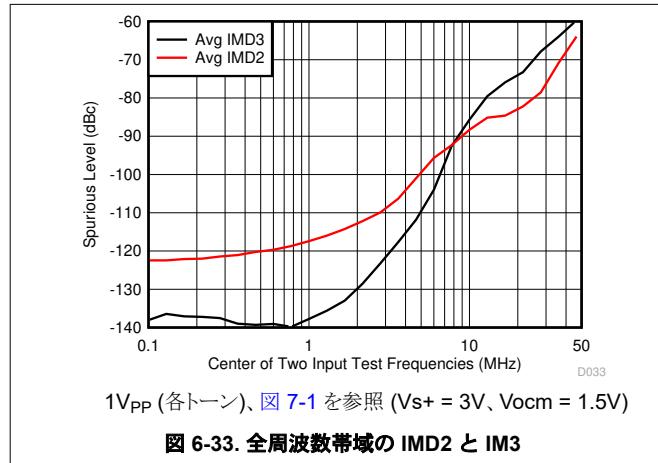

1V<sub>PP</sub> (各トーン)、図 7-1 を参照 ( $V_{S+} = 3V$ 、 $V_{OCM} = 1.5V$ )

図 6-33. 全周波数帯域の IMD2 と IMD3

$f = 10MHz$ 、図 7-1 を参照 ( $V_{S+} = 3V$ 、 $V_{OCM} = 1.5V$ )

図 6-34. 高調波歪みと  $R_{LOAD}$  との関係

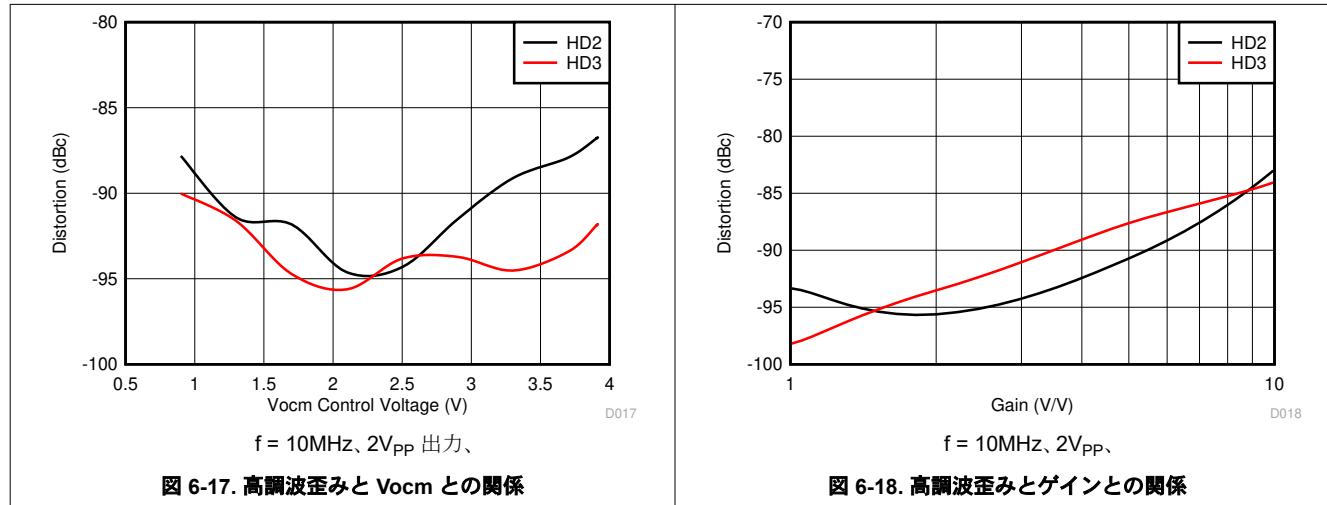

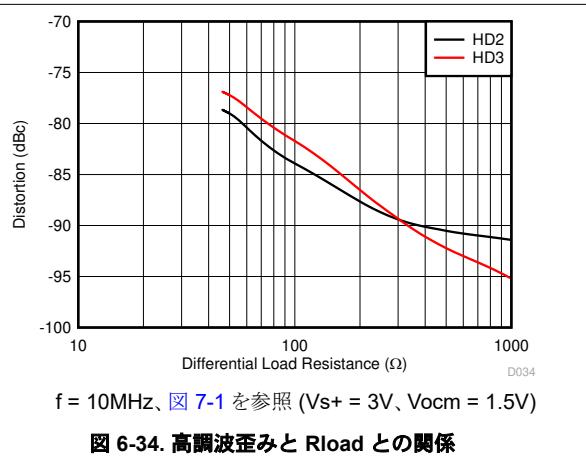

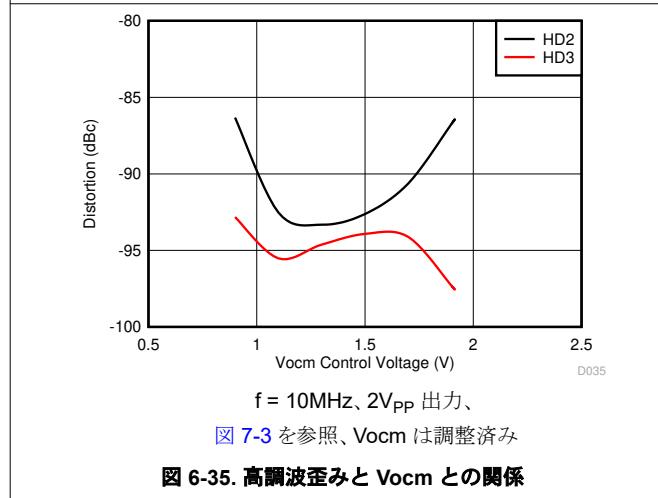

$f = 10MHz$ 、2V<sub>PP</sub> 出力、

図 7-3 を参照、 $V_{OCM}$  は調整済み

図 6-35. 高調波歪みと  $V_{OCM}$  との関係

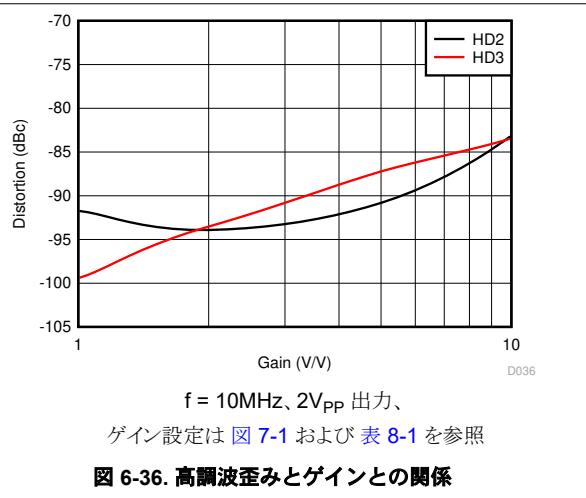

$f = 10MHz$ 、2V<sub>PP</sub> 出力、

ゲイン設定は 図 7-1 および 表 8-1 を参照

図 6-36. 高調波歪みとゲインとの関係

## 6.9 代表的特性：電源電圧範囲：3V～5V

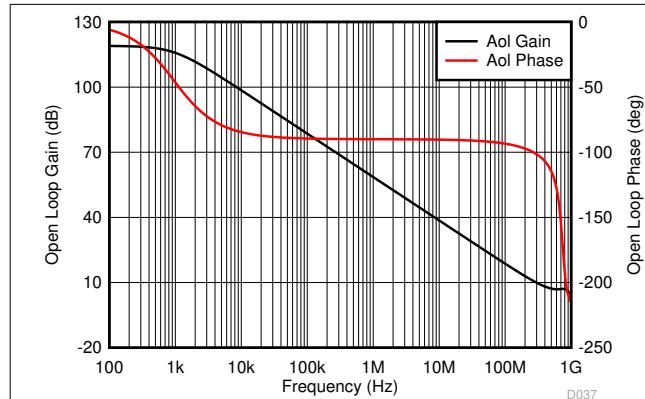

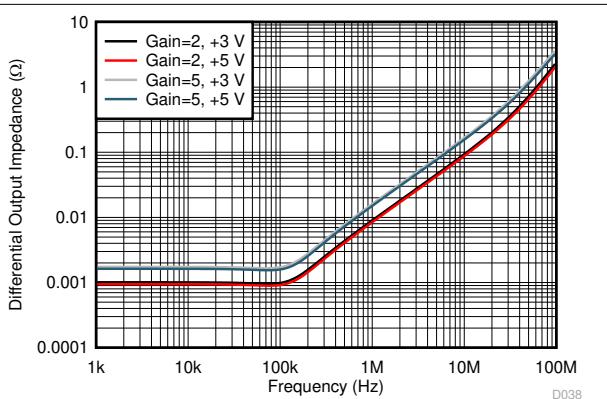

$V_{S+} = 3V$  および  $5V$ 、 $V_{S-} = GND$ 、 $V_{COM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ 、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

図 6-37. メイン アンプ差動開ループ ゲインおよび位相と周波数との関係

シングルエンド入力から差動出力、差動出力インピーダンスのシミュレーション

(閉ループ) ゲイン = 2 および 5、図 7-1 を参照

図 6-38. 閉ループ出力インピーダンス

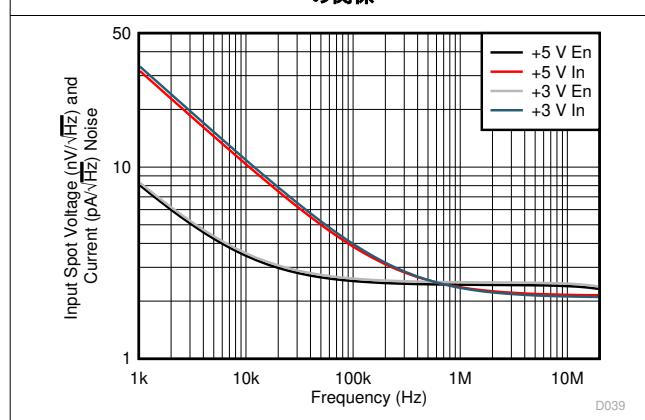

図 6-39. 全周波数帯域の入力スポットノイズ

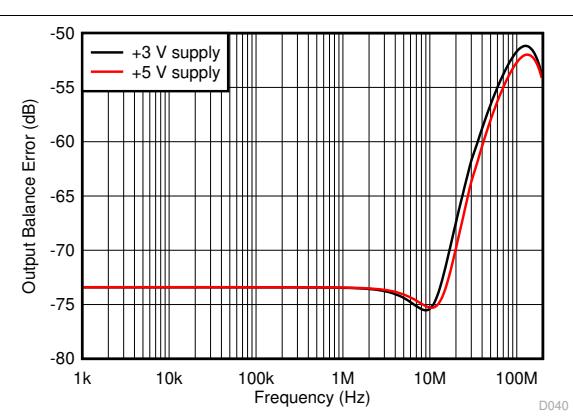

シングルエンド入力から差動出力、ゲイン = 2

(図 7-1 を参照)、1% 抵抗のシミュレーション、ワーストケースのミスマッチ

図 6-40. 全周波数帯域の出力バランス誤差

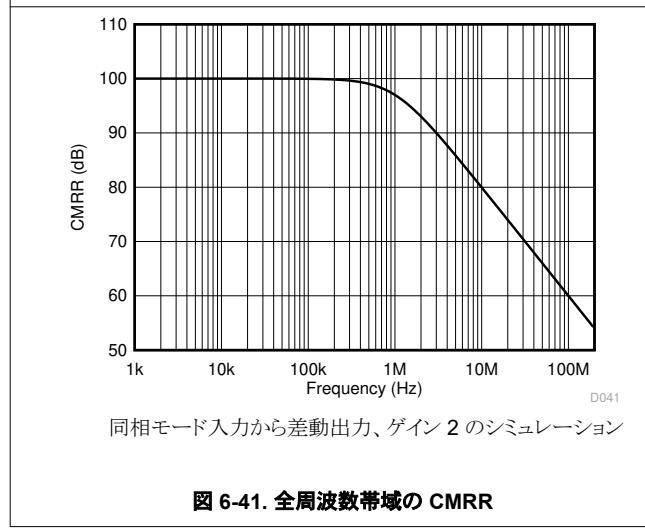

同相モード入力から差動出力、ゲイン 2 のシミュレーション

図 6-41. 全周波数帯域の CMRR

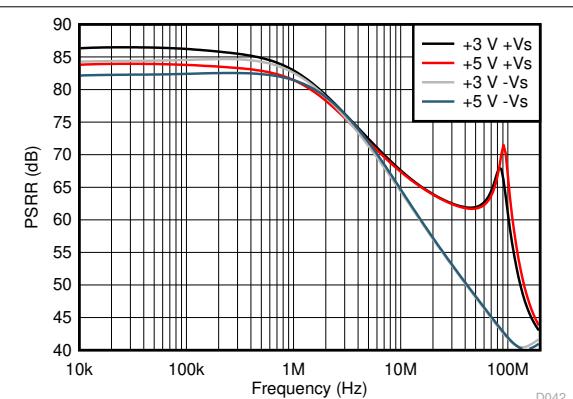

シングルエンドから差動、ゲイン = 2 (図 7-1 を参照)

の差動出力への PSRR シミュレーション

図 6-42. 全周波数帯域の PSRR

## 6.9 代表的特性：電源電圧範囲：3V～5V (続き)

$V_{S+} = 3V$  および  $5V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ 、 $R_{load} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

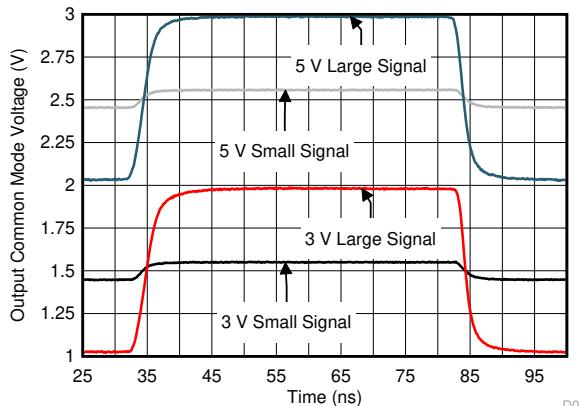

図 6-43. 同相モード、小信号および大信号応答 ( $V_{OCM}$  ピン駆動)

図 6-44. 同相モード、小ステップ応答および大ステップ応答 ( $V_{OCM}$  ピン駆動)

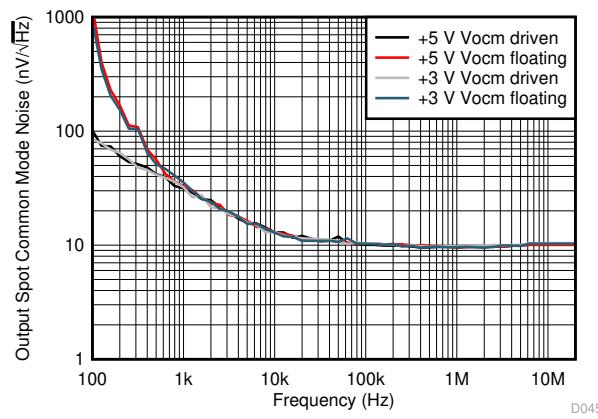

$V_{OCM}$  入力は、低インピーダンスのソースにより中電圧に駆動するか、またはオープンでデフォルトの中電圧とすることが可能

図 6-45. 出力同相モード ノイズ

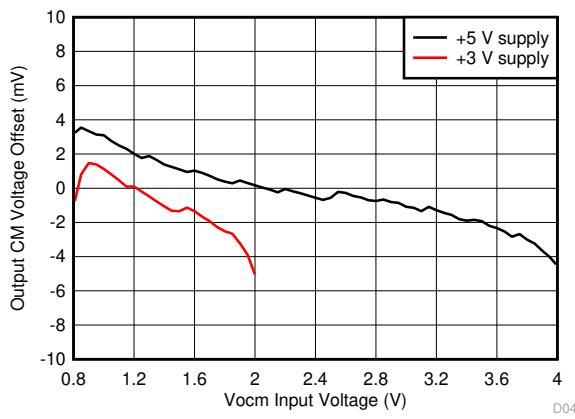

37 ユニットの  $V_{OCM}$  出力オフセットの平均、標準偏差

2.5mV 未満、図 7-3 を参照

図 6-46.  $V_{OCM}$  オフセットと  $V_{OCM}$  設定との関係

## 6.9 代表的特性：電源電圧範囲：3V～5V (続き)

$V_{S+} = 3V$  および  $5V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ 、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

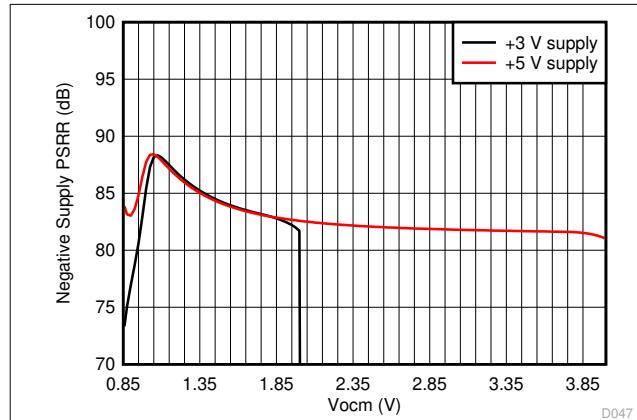

シングルエンドから差動、ゲイン:2 (図 7-1 を参照)、差動出力に対する負電源からの PSRR (1kHz シミュレーション)

図 6-47. -PSRR と  $V_{S-}$  に近づいていく  $V_{OCM}$  との関係

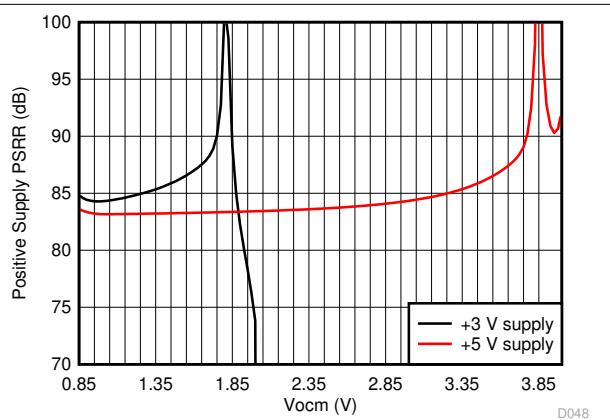

シングルエンドから差動、ゲイン:2 (図 7-1 を参照)、差動出力に対する正電源からの PSRR (1kHz シミュレーション)

図 6-48. +PSRR と  $V_{S+}$  に近づいていく  $V_{OCM}$  との関係

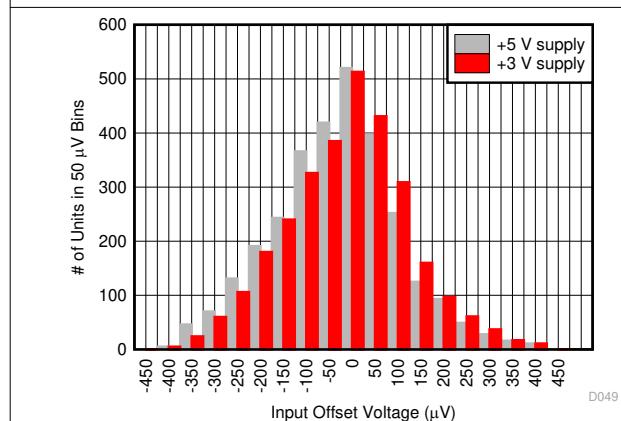

図 6-49. 入力オフセット電圧

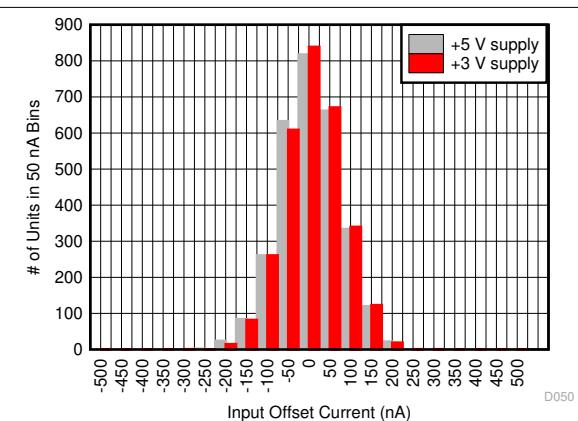

図 6-50. 入力オフセット電流

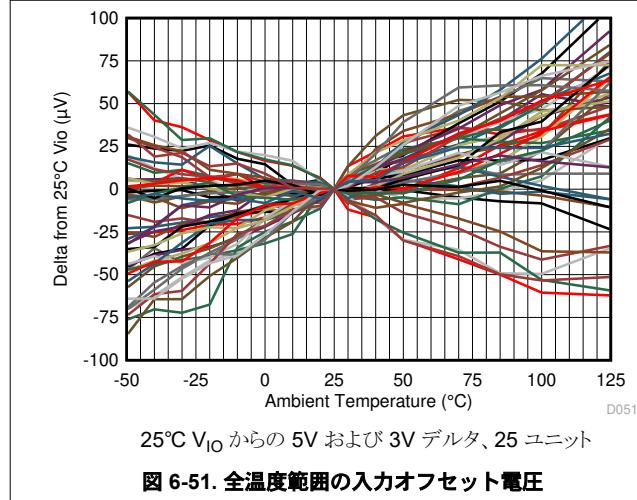

図 6-51. 全温度範囲の入力オフセット電圧

図 6-52. 全温度範囲の入力オフセット電流

## 6.9 代表的特性：電源電圧範囲：3V～5V (続き)

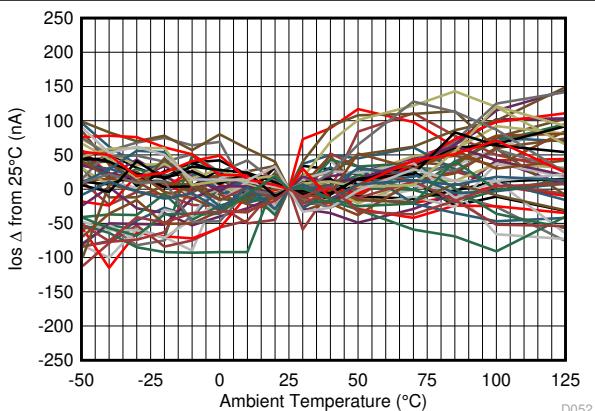

$V_{S+} = 3V$  および  $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン = 2V/V、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

## 6.9 代表的特性：電源電圧範囲：3V～5V (続き)

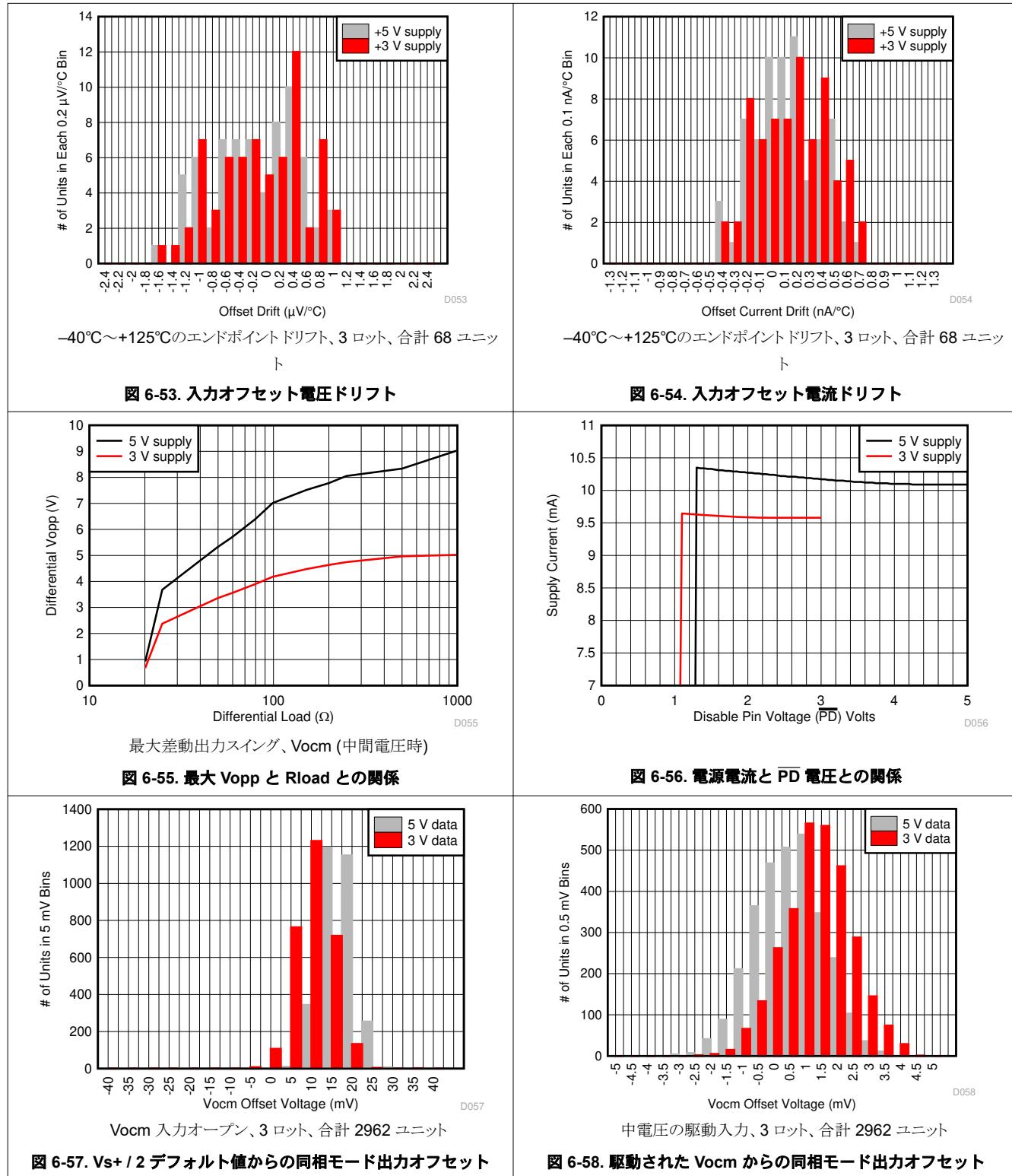

$V_{S+} = 3V$  および  $5V$ 、 $V_{S-} = GND$ 、 $V_{OCM}$  はオープン、 $50\Omega$  シングルエンド入力から差動出力、ゲイン =  $2V/V$ 、 $R_{LOAD} = 500\Omega$ 、 $T_A \approx 25^\circ C$  (特に記述のない限り)

## 7 パラメータ測定情報

### 7.1 特性評価回路の例

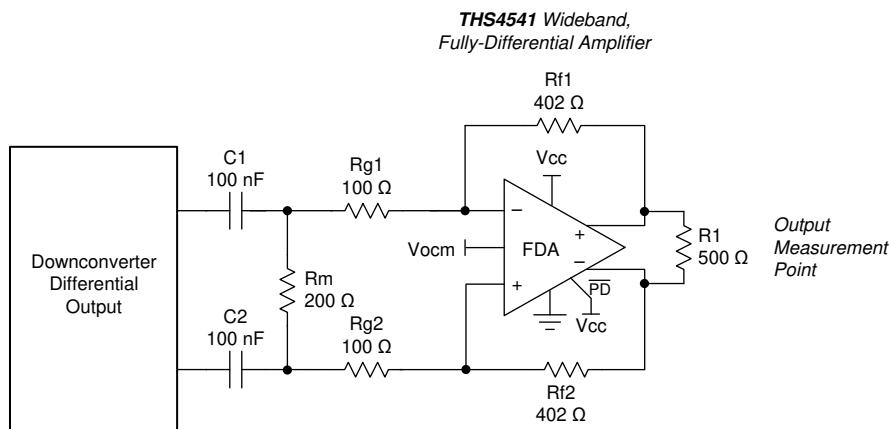

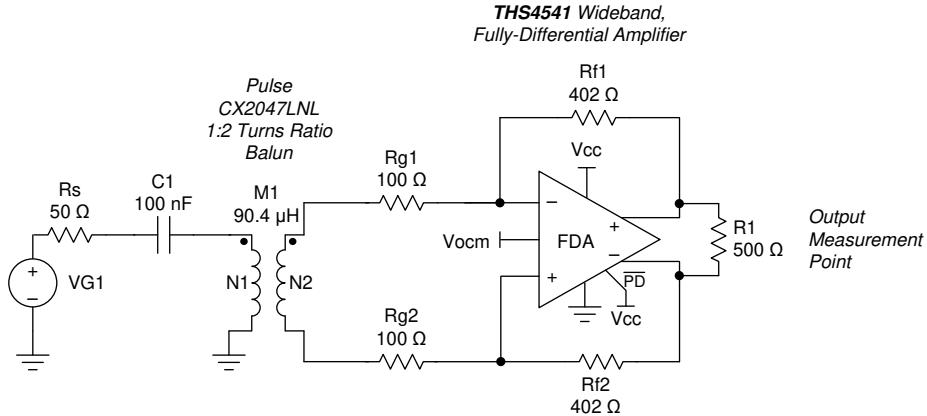

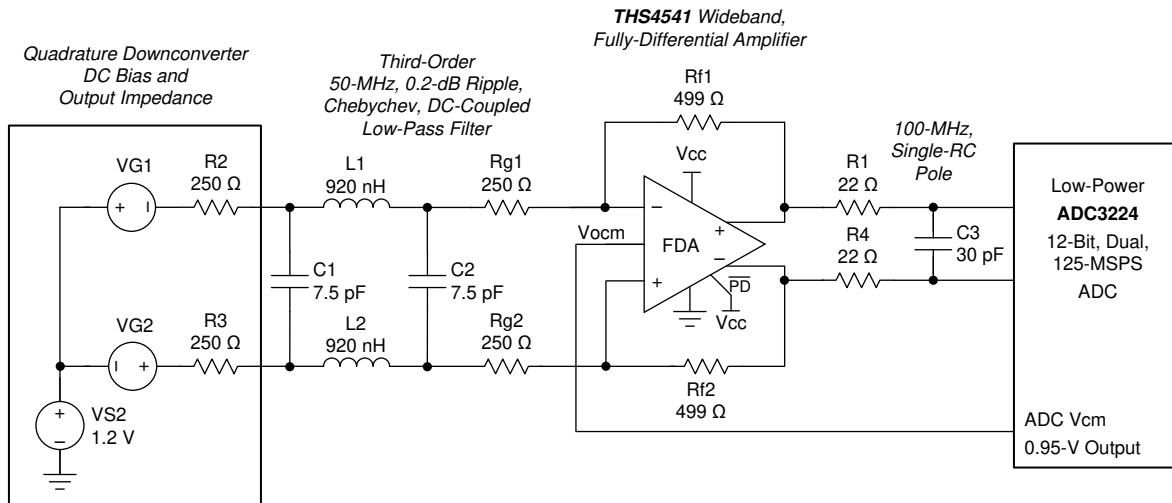

THS4541 は、高精度オペアンプのトリムされた入力オフセット電圧を備えた完全差動アンプ (FDA) 設計の利点を提供します。FDA は非常にフレキシビリティの高いデバイスであり、設定可能な出力コモン モード レベルの中心に純粋な差動出力信号を供給することができます。主な選択肢として、シングルエンドまたは差動入力、AC 結合またはDC 結合の信号パス、ゲイン目標値、および抵抗値などを選択できます。図 6-1 ~ 図 6-36 に、より厳しいアプリケーション要件として、シングルエンドから差動への設計に重点を置いた特性を示します。差動信号源は確実にサポートされるため、多くの場合、実装と分析が容易です。

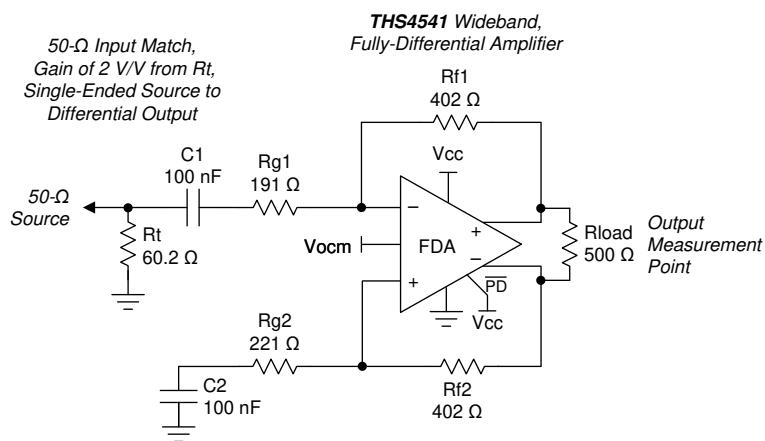

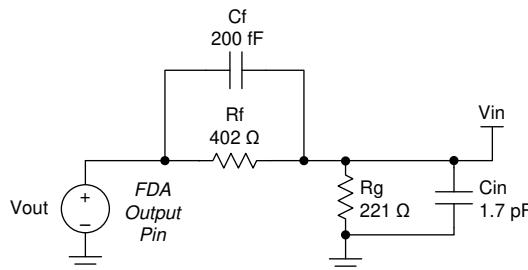

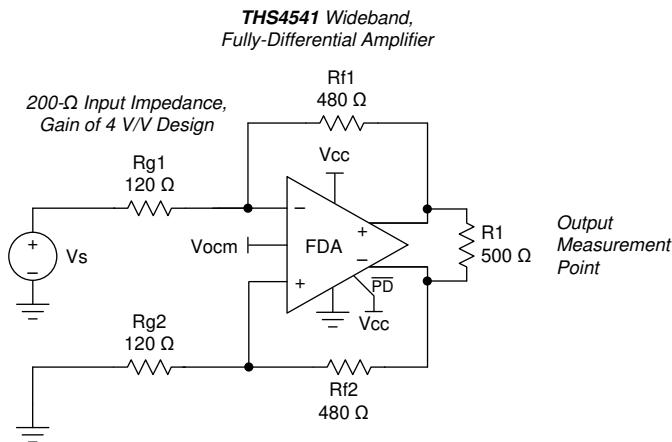

ほとんどの実験機器はシングルエンドであるため、特性回路は、通常、シングルエンドでマッチングのとれた  $50\Omega$  入力終端で動作し、FDA 出力ピンで差動出力となります。その後、テストと周波数範囲に応じて、さまざまなバラン (またはトランジス) を介して出力をシングルエンドに戻します。DC 結合、ステップ応答テストでは、トレース演算付きの  $50\Omega$  スコープ入力を 2 つ使用します。図 7-1 に、シングルエンドから差動への AC 結合特性評価グラフの出発点となる回路を示します。

図 7-1. AC 結合されたシングルエンド ソースから 2V/V の差動ゲインへのテスト回路

図 7-1 は、 $402\Omega$  での  $R_f$  ( $R_{f1} = R_{f2}$ ) の値が決定される一般的な特性プロットを示しています。この素子の値はアプリケーションでは完全にフレキシブルですが、 $402\Omega$  はこの値に関連する寄生的な問題に十分に妥協することができます。具体的には次のような点があります。

- 出力負荷を追加。FDA は、出力全体に追加した負荷として両方の帰還抵抗を備えた反転オペアンプ設計のように動作します。図 7-1 に、合計差動負荷の概算値が  $500\Omega \parallel 804\Omega = 308\Omega$  であることを示します。

- 抵抗値に起因するノイズの寄与。これらの抵抗は、 $4kT/R$  項、および入力電流ノイズへのゲイン供給の両方に寄与します (セクション 7.5 を参照)。

- 入力加算ノードの寄生帰還極。この極は帰還  $R$  の値と  $0.85\text{pF}$  の差動入力容量 (任意の基板レイアウトの寄生値と同じ) により形成されているため、ほとんどの状況ではノイズ ゲインがゼロになり、位相マージンが減少します。この影響は、最適な周波数応答平坦度、またはステップ応答オーバーシュートを実現するために管理する必要があります。選択された  $402\Omega$  の値は、より低い値において位相マージンがわずかに低下しますが、出力ピン全体の公称値  $500\Omega$  から負荷が大幅に減少することはありません。

図 7-1 に、周波数ドメイン特性曲線の出発点となる回路を示します。そこからさまざまな素子を変更して、次に示す種々の設計目標への影響を調べます。

- ゲイン設定は、 $R_t$  および 2 つの  $R_g$  素子を調整することによって変更されます (50Ω の入力マッチングを維持したまま)。

- 抵抗性負荷と容量性負荷の両方を含む出力負荷でテストしています。

- 電源設定。多くの場合、単一電源 +5V のテストでは  $\pm 2.5V$  電源を使用し、+3V のテストでは  $\pm 1.5V$  電源を使用します。

- アクティブ チャネル テストでは、ディセーブル制御ピンを  $V_{S+}$  に接続します。

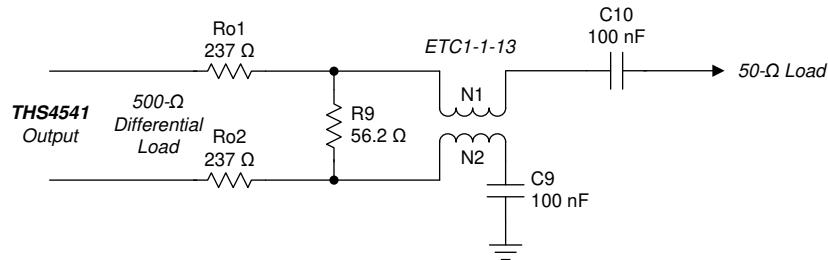

ほとんどのネットワーク アナライザおよびスペクトラム アナライザはシングルエンド入力であるため、THS4541 の特性テストの出力回路では、通常、対象となる負荷としては、バランを介してシングルエンド 50Ω 負荷に接続されています。これはバラン出力からの 50Ω のソースが、バランに戻る状況を示しています。たとえば、図 7-2 に、図 7-1 で使用される広帯域 MA/Com バランを示します。この回路では THS4541 に 500Ω の差動負荷が示されていますが、ネットワーク アナライザには AC 結合された 50Ω のソースが供給されます。通常、歪みテストでは、図 7-2 のようなより広い帯域のインターフェイスから 90° 回転した低周波数の DC 絶縁バラン (TT1-6T など) を使用します。

図 7-2. 500Ω 負荷から、シングルエンド、二重終端、AC 結合、50Ω へのインターフェイスの例

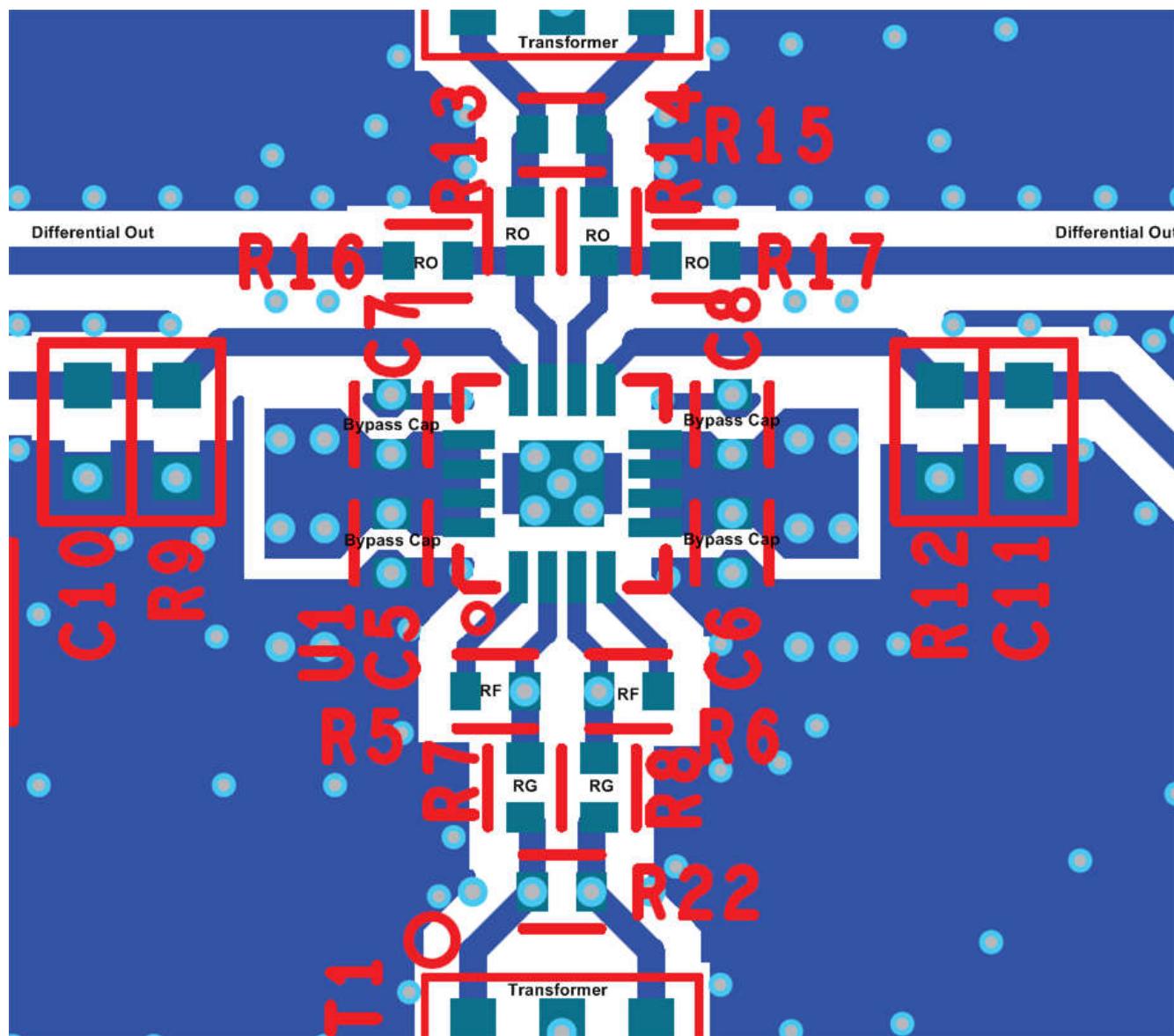

このアプローチにより、大きい差動負荷が可能になりますが、広帯域 50Ω の出力マッチングは、信号路の挿入によって相当な損失が発生します。この損失は特性評価では許容可能であり、特性化曲線を示す際には正規化されます。

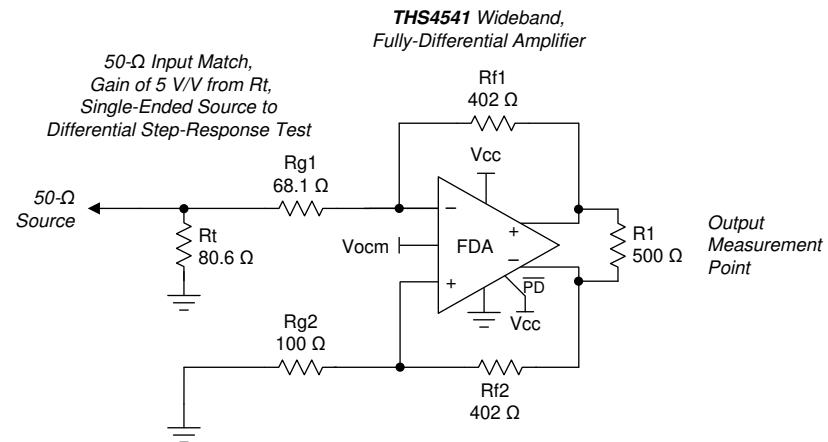

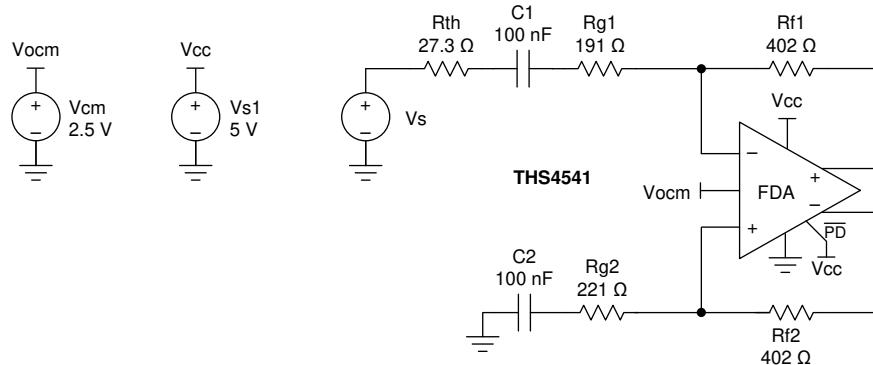

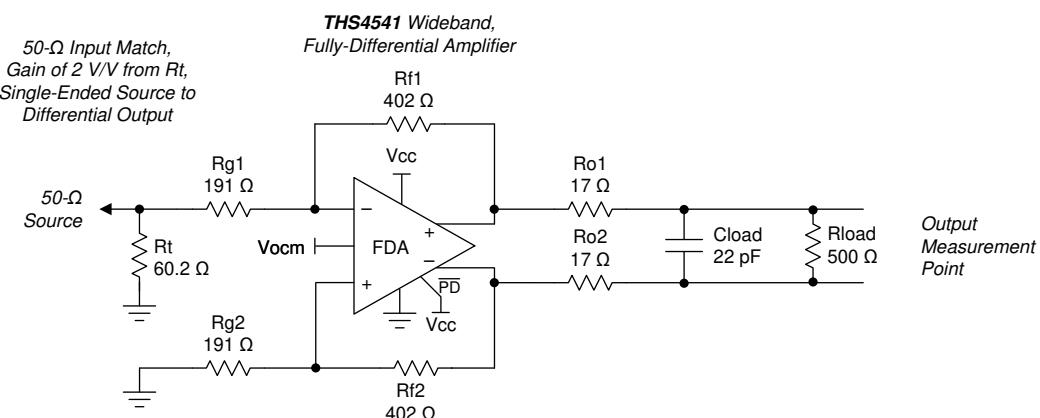

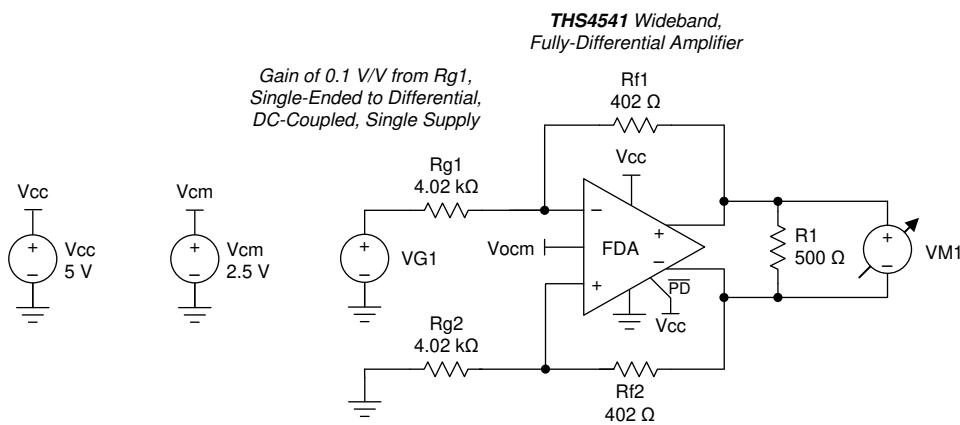

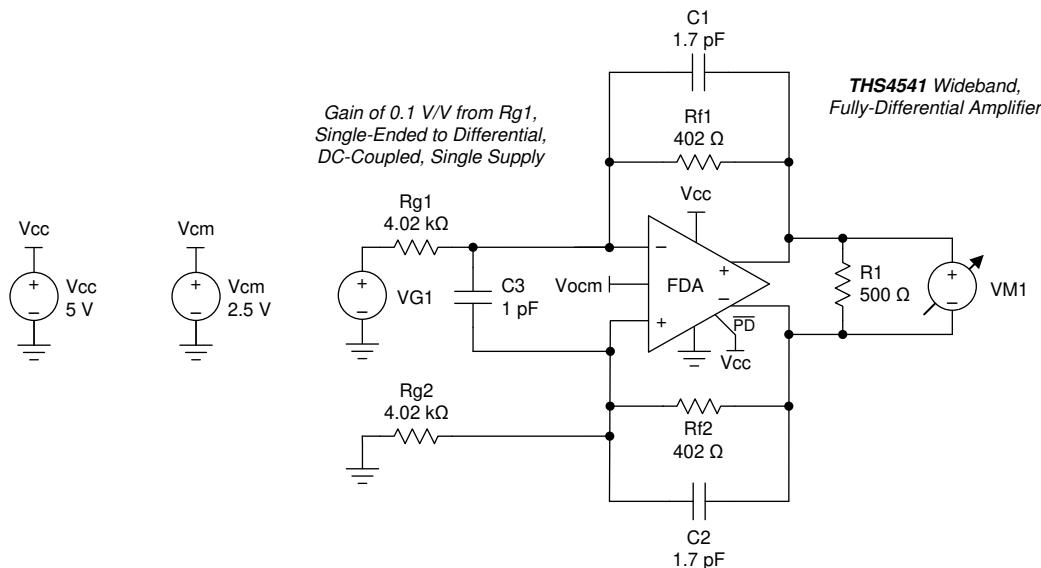

図 7-3 に、時間ドメインまたは DC 結合テストの開始点として使用する回路を示します。ここでは、図 6-25 および 図 6-27 で使用される 5V/V のゲイン設定を示しています。

図 7-3. DC 結合、シングルエンドから差動、ゲイン 5V/V に設定した基本的なテスト回路

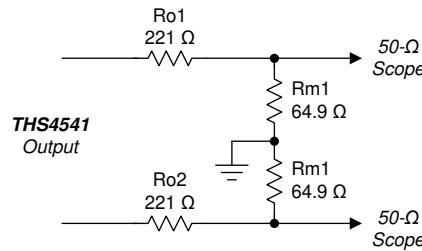

ここでは、入力は DC 結合で、ソースに  $50\Omega$  の入力マッチングがあり、差動出力に  $5V/V$  のゲインが設定されており、ここでも公称値  $500\Omega$  の負荷を駆動しています。単一電源を使用すると、 $V_{ocm}$  の制御入力をフローティング（デフォルトは中間電位）、または、 $V_{ocm}$  ループの許容範囲内で駆動することができます（ $V_{ocm}$  のヘッドルームの制限については、[電気的特性](#)の表を参照）。この回路をステップ応答の測定に使用するには、2つの出力をそれぞれ  $250\Omega$  回路の負荷に接続し、 $50\Omega$  のソースインピーダンスに変換して2つの  $50\Omega$  スコープ入力に接続します。次に、スコープ入力の差分によって、[図 6-9](#) および [図 6-27](#) のステップ応答を生成します。[図 7-4](#) に、出力インターフェイス回路を示します。この接地されたインターフェイスにより、単一電源動作では、出力  $V_{ocm}$  の電圧から DC 負荷電流が流れ込みます。平衡型のバイポーラ電源でこのテストを実行すると、この DC 負荷電流がなくなり、同様の波形が得られます。

**図 7-4.  $500\Omega$  負荷から、差動、二重終端、DC 結合された  $50\Omega$  スコープへのインターフェイスの例**

## 7.2 周波数応答の形状係数

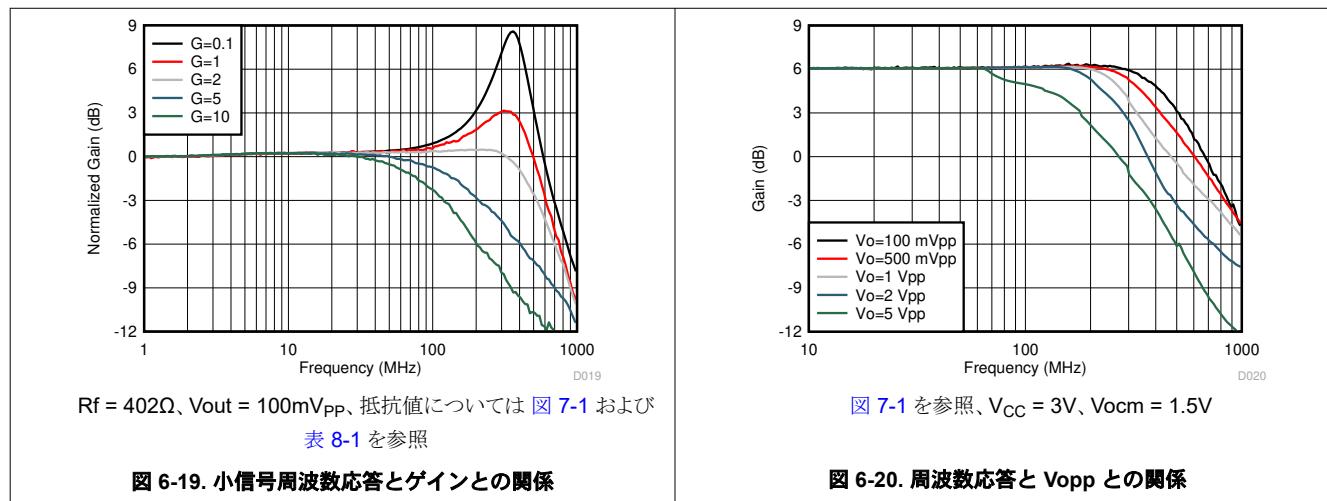

[図 6-1](#) は、[図 7-1](#) の回路で  $402\Omega$  固定の帰還抵抗を使用した場合の、ゲインに対する小信号応答を示しています。電圧フィードバックは FDA に基づいているため、THS4541 はゲイン設定によって変化する応答形状を示しています。この応答形状は、主にクロスオーバー時におけるループゲインのクロスオーバー周波数と位相マージンによって決定されます。このループゲインのクロスオーバー周波数は、開ループ応答とノイズゲインが交差する点（ループゲインが 1 に低下する点）です。ノイズゲインは出力から差動入力への分割電圧の逆数であり、各フィードバックパスでの平衡分圧比を使用します。一般に、ノイズゲイン（NG）は、ソースインピーダンスから入力マッチングを供給する設計においては、信号ゲインと同じではありません。NG は、 $1 + R_f / (反転加算接合部からグランドまでの総インピーダンス)$  によって求めることができます。[表 8-1](#) のゲインスイープで算出した抵抗値を使用して、NG を示すスイープを繰り返すことにより、[表 7-1](#) を求めることができます。ここでは、厳密な R ソリューション飲みを示しています。

**表 7-1.  $R_f = 402\Omega$  で掃引されたゲインの抵抗値とノイズゲイン<sup>(1)</sup>**

| 信号ゲイン | Rt, EXACT ( $\Omega$ ) | Rg1, EXACT ( $\Omega$ ) | Rg2, EXACT ( $\Omega$ ) | ノイズゲイン |

|-------|------------------------|-------------------------|-------------------------|--------|

| 1     | 55.2                   | 399                     | 425                     | 1.94   |

| 2     | 60.1                   | 191                     | 218                     | 2.85   |

| 3     | 65.6                   | 124                     | 153                     | 3.63   |

| 4     | 72                     | 89.7                    | 119                     | 4.37   |

| 5     | 79.7                   | 67.8                    | 98.3                    | 5.09   |

| 6     | 89.1                   | 54.2                    | 86.5                    | 5.65   |

| 7     | 101                    | 43.2                    | 76.6                    | 6.25   |

| 8     | 117                    | 35.2                    | 70.1                    | 6.74   |

| 9     | 138                    | 29                      | 65.8                    | 7.11   |

| 10    | 170                    | 23.6                    | 62.5                    | 7.44   |

| 11    | 220                    | 18.7                    | 59.3                    | 7.78   |

| 12    | 313                    | 14.6                    | 57.7                    | 7.97   |

| 13    | 545                    | 10.8                    | 56.6                    | 8.11   |

| 14    | 2209                   | 7.26                    | 56.1                    | 8.16   |

NG は、帯域幅およびすべての出力誤差項 (DC オフセットやノイズなど) にとって非常に重要です。低速デバイスの場合、通常は DC ノイズ ゲインのみを考慮します。ただし、THS4541 の場合、300MHz 以上のループ ゲイン クロスオーバーでは、帰還回路により差動加算接合部への寄生極が生成され、ノイズ ゲインは周波数とともに増加します。この極によって、ループ周辺に位相シフトが追加され、想定よりも低いクロスオーバー周波数となります。402Ω の帰還抵抗上にある 0.2pF の寄生が示すように、図 7-5 の帰還回路 (シングルエンド) を考慮します。THS4541 の 0.85pF の差動入力容量は、この片面分析回路の場合、1.7pF の寄生としてシングルエンドに変換されます (ここに示す  $R_g$  は 図 7-1 の  $R_g$  )。

図 7-5. 402Ω を使用して 50Ω ソースにマッチングさせた 2 構成のゲインに対する帰還回路

図 7-5 における  $V_{out}$  から  $V_{in}$  までの応答形状には、極とゼロがあります。NG については、図 7-5 の  $V_{in}$  と  $V_{out}$  をラプラス変換して、その逆数をとることによって、式 1 のように周波数依存の NG 応答が求められます。この式ではゼロが最初に求まり、次に極が求まります。

$$NG = \left( 1 + \frac{C_{in}}{C_f} \right) \frac{\frac{s + \frac{R_f}{R_g}}{s + \frac{1}{R_f \cdot C_f}}}{s + \frac{R_f (C_f + C_{in})}{R_g}} \quad (1)$$

ゼロの位置は重要です。図 7-5 の 2 つのゲイン値を使用した場合、NG の推定されるゼロは 588MHz です。加算接合部での寄生容量をグランドまたはパワー プレーンに制限することは、差動と信号エンドのいずれの場合でも、基板レイアウトにおいて重要です。

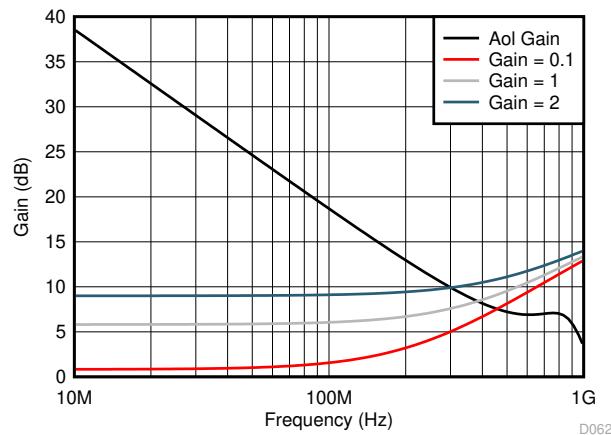

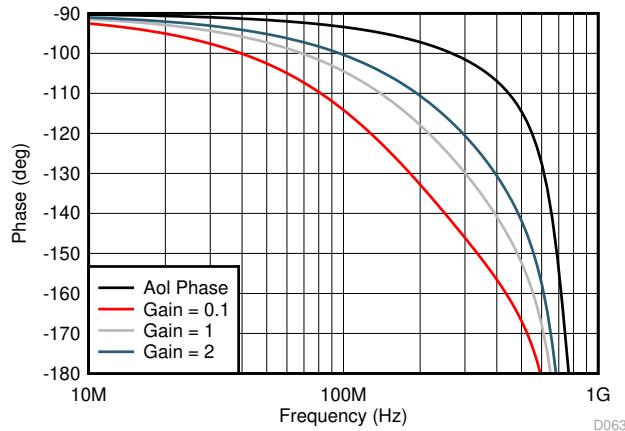

THS4541 に対して、この帰還モデル、開ループ ゲイン、および位相データを使用することで、図 7-6 に示されるように、全周波数帯域の AOL および NG 曲線が描かれます。ここでは、ノイズ ゲインのピークによって交点は周波数内に引き戻されます。

図 7-6. 図 7-1 の低ゲインに対する AOL およびノイズ ゲインのプロット

閉ループ帯域幅とピークをするには、THS4541 の AOL 位相からノイズ ゲイン位相を除去して、図 7-7 に示すように、ループ周辺の合計位相を得る必要があります。

図 7-7. 図 6-1 の 3 つの低ゲインに対するループ ゲイン位相

図 7-6 および 図 7-7 より 表 7-2 を使用して、これらのクロスオーバーにおけるループ ゲインのクロスオーバー周波数と位相マージンを表にすると、図 6-1 の応答形状を説明することができます。

表 7-2. 図 6-1 におけるゲイン 0.1、1、2 の推定クロスオーバー周波数と位相マージン

| ゲイン | DC NG (V/V) | 0dB LG (MHz) | 位相マージン (°) |

|-----|-------------|--------------|------------|

| 0.1 | 1.1         | 457          | 18         |

| 1   | 1.94        | 380          | 41         |

| 2   | 2.85        | 302          | 59         |

これらのクロスオーバー (または 0dB のループ ゲイン) 周波数から、 $f_{-3dB}$  の適切な近似値はクロスオーバー周波数と 1.6 (位相マージンが 65° 未満の場合) を掛けることにより求められます。理想的には、ループ ゲインのクロスオーバーで 65° の位相マージンを確保すると、平坦なバターワース閉ループ応答を実現できます。ゲイン 2 に対して 59° の位相マージンを設定すると、この条件におけるほぼフラットな応答は、 $f_{-3dB}$  から  $1.6 \times 302\text{MHz} = 483\text{MHz}$  と算出され、これは測定された 500MHz の SSBW にほぼ一致しています。

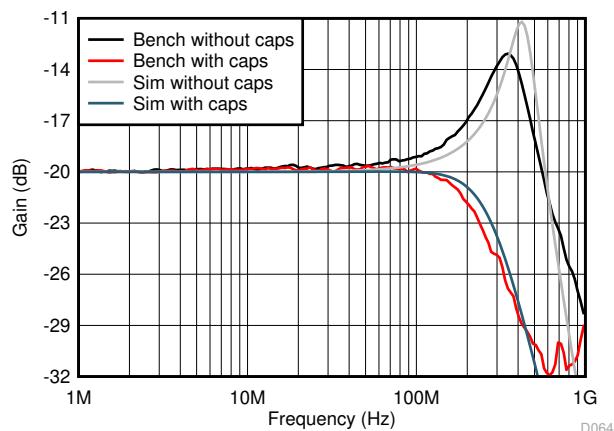

アッテネータに 0.1V/V と超低位相マージンを設定すると、図 6-1 に示すようにピーク応答が高くなります。このピークは、セクション 9.2.1 に示すように、帰還コンデンサと入力間の差動コンデンサを使用することで、簡単に補償できます。

ループ ゲイン分析の一部としてノイズ ゲインのゼロを考慮すると、帰還抵抗値を比較的小さくし、THS4541 の入力ピン上のレイアウト寄生容量を最小限に抑えることが、この帰還極の影響を低減するために重要であることがわかります。TINA モデルは、このような問題を予測するのに適しています (このモデルは 0.85pF の差動内部容量を考慮しています)。シミュレーションの加算接合部に外部寄生容量の推定値を追加し、応答形状をより正確に予測します。

## 7.3 I/O ヘッドルームに関する検討事項

ほとんどの設計の開始点は、通常、出力コモン モード電圧を割り当てることです。AC 結合の信号パスでは、この電圧はデフォルトの中間電位となることが多く、これにより  $V_{OCM}$  を中心として駆動可能な最も大きい出力振幅が得られます。DC 結合設計では、この電圧は、 $V_{OCM}$  制御の仕様に示されるように、電源に必要な最小ヘッドルームを考慮して設定します。次に、目標の出力  $V_{OCM}$  から、必要な出力差動  $V_{PP}$  が電源電圧内に収まっていることを確認します。必要な差動  $V_{OPP}$  に対して、式 2 と式 3 による出力ピンのスイングが絶対最大定格内であることを確認し、さらに、差動  $V_{OPP}$  がこのレールツーレール (RR) 出力デバイスの電源レール内に収まっていることを確認してください。

$$V_{O_{min}} = V_{OCM} - \frac{V_{OPP}}{4} \quad (2)$$

$$V_{O_{max}} = V_{OCM} + \frac{V_{OPP}}{4} \quad (3)$$

例えば、ADC3223 を 3.3V の単一電源を使用して 0.95V<sub>CM</sub> 制御で駆動する場合、最大出力スイングは、0.95V<sub>CM</sub> から、グランドより +0.2V 高い電圧へ向かって下降する信号によって設定されます。この 0.75V の片側スイングは、公称値 0.95V<sub>CM</sub> の出力コモン モードの周囲で  $4 \times 0.75V = 3V_{PP}$  の差動として供給されます。ハイサイドの最大出力は、 $0.95 + 0.75 = 1.7V$  です。この結果は、 $3.3V - 0.2V = 3.1V$  と許容最大値内に十分収まります。この  $3V_{PP}$  も、この ADC に必要な最大値  $2V_{PP}$  のフルスケール差動入力を十分超えています。ただし、この余分なスイング範囲は、ADC への段間フィルタによって挿入損失が加わる場合に有用です。

出力ヘッドルームが確定したら、入力結合部も動作範囲内に収まるようにします。入力範囲は負電源電圧まで拡張されています (全動作温度範囲で)。そのため、入力範囲の制限は通常、正電源電圧に近づいたときにのみ現れます。ここでは、全動作温度範囲にわたって最大 1.3V のヘッドルームが必要となります。

入力ピンは、外部の回路設計、必要な出力  $V_{OCM}$ 、および入力信号特性によって設定される電圧で動作します。差動 – 差動設計では、入力電圧  $V_{ICM}$  は入力信号とともに変動しないため、次の 2 つの構成を考慮する必要があります。

- AC 結合の差動入力設計では、 $V_{ICM}$  は出力  $V_{OCM}$  と同じです。入力  $V_{ICM}$  には、正電源に対して約 1.3V のヘッドルームが必要です。そのため、その値に対する最大  $V_{OCM}$  は、 $V_{OCM}$  の正のヘッドルームの要件である 1.2V から入力ピンに必要な 1.3V に低減されます。出力  $V_{OCM}$  の下限は、全動作温度範囲にわたり負電源に対して約 0.95V であり、入力  $V_{ICM}$  の最小ヘッドルーム 0V 以内に十分収まっています。

- DC 結合の差動入力設計では、ソース  $V_{CM}$  から THS4541  $V_{OCM}$  の設定までの分割電圧を確認し、結果として得られた分割電圧によって入力  $V_{ICM}$  が許容範囲内に収まっていることを確認します。ソース  $V_{CM}$  がいざれかの電圧範囲で変動する可能性がある場合は、この結果をその範囲で検証してください。

シングルエンド入力から差動出力への設計では、外部構成により設定される DC  $V_{ICM}$  電圧があり、その電圧を中心にして小信号に関連するスイングが発生します。次の 2 つの条件を考慮する必要があります。

- AC 結合のシングルエンド入力から差動への設計では、出力  $V_{OCM}$  の電圧と同じ平均入力  $V_{ICM}$  が印加され、入力電圧に応じてその  $V_{OCM}$  を中心にして AC 結合のスイングが発生します。

- DC 結合のシングルエンド入力から差動への設計では、ソース信号コモン モードによって設定される公称入力  $V_{ICM}$  と出力  $V_{OCM}$  の設定が得られ、分圧器で設定される DC  $V_{ICM}$  レベルを中心にして小信号に関連するスイングが発生します。

シングルエンド入力から差動出力への設計において、 $V_{ICM}$  の電圧範囲を得る方法の 1 つは、FDA 出力の非信号入力側の電圧スイングを決定し、それぞれの分圧器の信号を入力ピンからグランドに戻すか、またはこちら側で使用される DC リファレンス電圧へと戻すことです。この例の解析を 図 7-8 に示します。ここで、図 7-1 の回路はテブナンの定理に基づいたソース インピーダンスを示すため簡略化しています。

図 7-8. テブナンの定理によるソースを使用した図 7-1 からの入力スイング解析回路

この AC 結合入力解析では、公称 DC 入力  $V_{icm}$  が単純に出力  $V_{ocm}$  になります (この設計例では 2.5V)。次に、帰還回路の下側を考慮すると、必要な最大出力差動  $V_{pp}$  は、 $R_{g2}$  および  $R_{f2}$  の結合部で既知の AC  $V_{pp}$  を生成します。例えば、設計の意図として最大 4V<sub>pp</sub> の差動出力を想定している場合、各 FDA 出力ピンは  $V_{ocm}$  を中心にして  $\pm 1V$  (= 2.5V) となり、それが  $V_{icm}$  に戻ります。これにより、 $V_{ocm}$  の DC 設定値を中心にして  $\pm 1V \times 221 / (221 + 402) = \pm 0.355V$  の電圧が生成されます。これはシングルエンドから差動への設計の場合に、入力  $V_{icm}$  の範囲を評価する簡単な手法であり、入力側の回路を信号ソースとグランド、または非信号入力側の電圧リファレンスに分割して低減させることにより、FDA を使用しているすべての設計に適用することができます。

## 7.4 出力 DC 誤差およびドリフトの計算値と、抵抗の不均衡の影響

THS4541 は、トリムされた入力オフセット電圧と、 $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  の温度範囲全体にわたる非常に低いオフセットのドリフトを実現しています。このオフセット電圧は、他のいくつかの誤差寄与項と組み合わされて、初期の  $25^{\circ}\text{C}$  の差動オフセット誤差帯域が発生し、その結果、温度に対するドリフトが発生します。各誤差項に対して、その項にゲインを割り当てる必要があります。この解析では、DC 結合信号路のみを検討します。FDA の 2 つの側の抵抗値と比率のミスマッチによる影響から、新しい出力誤差のソース (標準的なオペアンプ解析と比較して) が発生します。同相モード電圧またはドリフトは、外付け帰還抵抗とゲイン設定抵抗の公差、および標準値に対する近似に起因するわずかなミスマッチにより、差動出力誤差が生じます。

誤差項 (25°C およびドリフト)、および出力差動電圧へのゲインには、次のものが含まれます。

- 入力オフセット電圧 - この電圧のゲインは、ノイズ・ゲインまたは  $1 + R_f / R_g$  に等しくなります。ここで、 $R_g$  は入力ピンからソースまでの合計 DC インピーダンス、または DC リファレンス電圧 (通常はグランド) です。

- 入力オフセット電流 - この電流には、平均帰還抵抗値を介しての差動出力へのゲインがあります。

残りの項は、絶対帰還抵抗のミスマッチと FDA の両側の分圧比におけるミスマッチの両方の想定する範囲から発生します。これらの抵抗ミスマッチで最初の項は、 $R_f$  のミスマッチに起因して差動出力オフセットを生じる入力バイアス電流です。単純化のため、上側の  $R_f$  および  $R_g$  値は  $R_{f1}$  および  $R_{g1}$  と呼び、比率は  $R_{f1} / R_{g1} \equiv G_1$  になります。下側の素子は  $R_{f2}$  および  $R_{g2}$  として定義され、比率は  $R_{f2} / R_{g2} \equiv G_2$  になります。ワーストケースの寄与を計算するには、設計抵抗の公差の最大変動を絶対値と比のミスマッチに使用します。たとえば、公差  $\pm 1\%$  の抵抗を想定する場合、ワーストケースの  $G_1$  は公称値より 2% 高くなり、 $G_2$  は公称値より 2% 低くなり、同様にワーストケースの  $R_f$  値は 2% のミスマッチになります。シングルエンドから差動段への  $R_t$  および  $R_{g1}$  でマッチングされたインピーダンス設計の場合、この初期比のミスマッチに対して、標準値近似により抵抗公差の初期帰還比の固定のミスマッチが生じ、ミスマッチが追加されます。選択する外部抵抗の公差を  $\pm T$  と定義します (公差 1% の抵抗、 $T = 0.01$ )。

- バイアス電流誤差の合計ゲイン:  $\pm 2 \times T \times R_{fnom}$

出力同相レベルを発生させるもの、または温度変化に応じてシフトするものはすべて、2つの帰還比 (G1 および G2) が等しくない場合に出力差動誤差項を発生させます。出力同相モードでのシフトを発生させることになる誤差は、同相モード制御ループによってオーバーライドされます。この場合、帰還比のミスマッチにより、 $V_{OCM}$  の出力周りに平衡な差動誤差が発生します。

同相モード項と帰還比のミスマッチから差動誤差を発生させる項には、望ましい  $V_{ocm}$  電圧、ソース同相モード電圧のすべて、 $V_{ocm}$  制御ピンへのリファレンス電圧バイアスのドリフトのすべて、 $V_{ocm}$  制御パスの内部オフセットとドリフトのすべてが含まれます。

出力同相モード制御とソース同相モード電圧 (V<sub>icm</sub>) だけを考慮すると、出力差動オフセットへの変換は次の [式 4](#) を使用します。

$$V_{od} = \frac{V_{ocm}(G1 - G2) - V_{icm}(G1 - G2)}{1 + \frac{G1 + G2}{2}} \quad (4)$$

標準値の近似のために  $G_1$  と  $G_2$  のミスマッチを無視すると、これら 2 項の変換ゲインは 式 5 に示すように、公称  $R_f / R_g \equiv G$  および公差  $T$  の項で計算できます。 $G$  が増加すると、この変換ゲインは  $4T$  に近づきます。これは、これらの項が差動オフセットを出力するワーストケースのゲインです。

$$\frac{V_{od}}{V_{ocm}} = \frac{G}{(1+G)} \cdot \frac{4T}{(1-T^2)} \quad (5)$$

この差動出力誤差に対する変換ゲインは、次の 2 つの誤差項に適用されます。V<sub>com</sub> (入力制御ピンが駆動され、フローティングではないことを想定) と、ソース V<sub>com</sub> 電圧です。この例では、ソース同相モード電圧が 0V であると仮定しています。そうではない場合は、目的のアプリケーションのソースの同相モードの値または範囲にこのゲインを適用します。

これらの項を使用して、ワーストケースの出力の  $25^{\circ}\text{C}$  の誤差帯域と、ワーストケースのドリフト (すべての誤差項を個別に追加する) を推定する詳細な例として、 $R_f = 402\Omega$  の 図 7-3 の 2V/V 構成のゲインを使用し、図 7-9 で使用する標準値で抵抗の公差が  $\pm 1\%$  と仮定します。

図 7-9. 2 の DC 結合ゲイン、 $R_f = 402\Omega$ 、シングルエンドから差動へのマッピング入力  $50\Omega$  インピーダンス

信号入力側の標準値近似では、実際には抵抗の公差に加えて  $G$  ミスマッチが追加されます。図 7-9 では、 $G2 = 402 / 221 = 1.819$ 、 $G1 = 402 / 218.3 = 1.837$  (公称) で、1% の抵抗を使用する場合は、 $G2$  および  $G1$  (初期値ミスマッチ) に対して +2% の公差を持ちます。

最高 25°C の誤差項の使用、V<sub>com</sub> の制御ピンに対する公称 2.5V 入力により、誤差項、出力差動誤差 (V<sub>od</sub>) に対するゲイン、25°C での合計出力誤差帯域 表 7-3 が得られます

表 7-3. ワーストケースの出力  $V_{od}$  誤差帯域

| 誤差項                        | 25°C最大値        | $V_{od}$ に対するゲイン | 出力誤差           |

|----------------------------|----------------|------------------|----------------|

| 入力 $V_{io}$                | $\pm 0.45mV$   | 2.85V/V          | $\pm 1.2825mV$ |

| 入力 $I_{os}$                | $\pm 0.5\mu A$ | 402Ω             | $\pm 0.201mV$  |

| 入力 $I_{bcm}$ 、 $R_f$ ミスマッチ | 13μA           | $\pm 8.04\Omega$ | $\pm 0.105mV$  |

| $V_{ocm}$ 入力、 $G$ ミスマッチ    | 2.5V           | $\pm 0.0322$     | $\pm 80.5mV$   |

|                            |                | 合計               | $\pm 82.09mV$  |

$G$  比率ミスマッチに対する 0.03222 の変換ゲインはワーストケースであり、標準値の近似のため最初に大きい  $G1$  値から始まり、その比率の  $R_f$  素子と  $R_g$  素子で  $\pm 1\%$  の公差を使用します。実際の  $V_{ocm}$  の変換ゲイン範囲は対称ではありませんが、ここではそのように表示しています。最初の 25°Cのワーストケースの誤差帯域は、 $V_{od}$  に対する帰還抵抗比のミスマッチによる  $V_{ocm}$  の変換が支配的な要素になります。この  $G$  マッチングと公差を改善して、この項を低減します。

通常、出力の  $V_{od}$  で予想されるドリフトは、初期誤差帯域よりも重要です。[表 7-4](#) は、これらの項とワーストケースのドリフトを得るためにすべての項を個別に追加した合計の結果を示します。

表 7-4. ワーストケースの出力  $V_{od}$  ドリフト帯域

| 誤差項                        | ドリフト最大値                  | $V_{od}$ に対するゲイン | 出力誤差                       |

|----------------------------|--------------------------|------------------|----------------------------|

| 入力 $V_{io}$                | $\pm 2.4\mu V/^{\circ}C$ | 2.85V/V          | $\pm 6.84\mu V/^{\circ}C$  |

| 入力 $I_{os}$                | $\pm 1.3nA/^{\circ}C$    | 402Ω             | $\pm 0.522\mu V/^{\circ}C$ |

| 入力 $I_{bcm}$ 、 $R_f$ ミスマッチ | 15nA/^{\circ}C           | $\pm 8.04\Omega$ | $\pm 0.121\mu V/^{\circ}C$ |

| $V_{ocm}$ 入力、 $G$ ミスマッチ    | $\pm 12\mu V/^{\circ}C$  | $\pm 0.0322$     | $\pm 0.386\mu V/^{\circ}C$ |

|                            |                          | 合計               | $\pm 7.86\mu V/^{\circ}C$  |

この計算では、入力オフセット電圧ドリフトが出力差動オフセットのドリフトの支配的な要素になります。最後の項では、 $V_{ocm}$  のパスのドリフトは、同相モード・パスの内部オフセットのドリフトのみになります。 $V_{ocm}$  入力のソースの追加の外部ドリフトについても検討してください。

THS4541 の絶対精度とドリフトは、非常に優れています。 $V_{ocm}$  制御入力の高ドリフトと組み合わされたミスマッチの抵抗帰還比は、実際に出力  $V_{od}$  ドリフトの支配的な要素になる可能性があります。出力の差動の精度が入力マッチング精度よりも重要な場合、公称の  $G1$  と  $G2$  のマッチングを改善するために 2 つの入力側のネットワークのマッチングを検討してください。 $402\Omega$  の帰還値を使用するこの設計例では、入力バイアス電流誤差項のゲインは比較的低くなっています。 $R_f$  値が大きいほど、これらの項のゲインは大きくなります。[表 7-4](#) では、より小さい出力ドリフトの控えめな評価が、各項の相関関係がなく、各項のワーストケース・スパンの RMS の半分であると見なしていることが示されています。この例の計算を実行すると、出力オフセットのドリフトの値が  $\pm 3.42\mu V/^{\circ}C$  と小さくなることが推定され、基本的に入力オフセットのドリフトのワーストケース・スパンの半分になります。外部構成の出力差動オフセットとドリフトを推定するには、これらの手順に従います。

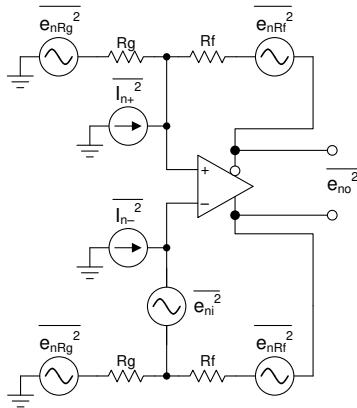

## 7.5 ノイズ解析

図 7-10 は、出力ノイズ解析の最初のステップを示しています。それは、アプリケーション回路を最も単純な形に削減して、グランドに対して、フィードバックおよびゲイン設定素子を等しくすることです。ここでは、FDA および抵抗のノイズ項を考慮します。

図 7-10. FDA ノイズ解析回路

それぞれの項にノイズ電力が示されています。 $R_f$  と  $R_g$  の項がそれぞれの側で一致している場合は、差動出力の合計ノイズはこれらの個別の項の RSS になります。式 6 に、 $NG \equiv 1 + R_f / R_g$  を使用した総出力ノイズを示します。各抵抗ノイズの項は、 $4kT R$  電力です。

$$e_{no} = \sqrt{(e_{ni}NG)^2 + 2(i_nR_f)^2 + 2(4kT R_f NG)} \quad (6)$$