## 自動フロー制御付き UART

### 特長

- プログラマブル自動-RTS および自動-CTS 機能

- 自動-CTS モード時 CTS によるトランスマッチタ制御機能

- 自動-RTS モード時、RTS による受信 FIFO コンテンツおよび閾値制御機能

- 同一電源時における、シリアルデータおよびモデムコントロール出力の RJ11 ケーブルを直接駆動可能

- 既存のすべての TL16C450 ソフトウェアが動作可能

- リセット後、すべてのレジスタは TL16C450 レジスタセットと同一

- Vcc 5V の場合、最大動作周波数は 24-MHz で 1.5-Mbaud まで動作可能

- Vcc 3.3 V の場合、最大動作周波数は 20-MHz で 1.25-Mbaud まで動作可能

- Vcc 2.5 V の場合、最大動作周波数 16-MHz で 1-Mbaud まで動作可能

- TL16C450 モード時、ホールド・レジスタとソフト・レジスタが CPU とシリアル・データ間の正確な同期を実現

- 入力リファレンス・クロックをプログラマブル・ボーレート・ジェネレータで、1 から ( $2^{16} - 1$ ) まで分周機能および内部 16 × クロック生成機能

- 標準非同期通信ビット(スタートビット、ストップビット、パリティビット)を付加、またはシリアル・データストリームから剥離機能

- 5-V、3.3-V、および 2.5-V 動作

- 独立受信クロック入力

- 送信、受信、ラインステータス、データセット割り込みの個別制御機能

- 完全なプログラマブル・シリアル・インターフェースの特徴:

- 5-, 6-, 7-, または、8-ビットキャラクタ

- 偶数-, 奇数-, または、パリティビットなしの生成および検出

- 1-, 1 1/2-, または、2-ストップビット生成

- ボー・レート ジェネレーション(dc から 1 Mbit/s)機能

- 誤スタート・ビット検出機能

- 完了ステータスレポート機能

- 双方向データバスおよび制御バスの 3-ステート出力の TTL ドライブ機能

- ライン・ブレーク生成および検出機能

- 内部診断機能:

- 通信リンク障害分離用ループ・バック制御

- ブレーク、パリティ、オーバーランおよびフレーミング・エラー・シミュレーション

- 完全な優先割り込み制御機能

- モデム制御機能(CTS、RTS、DSR、DTR、RI、および DCD)

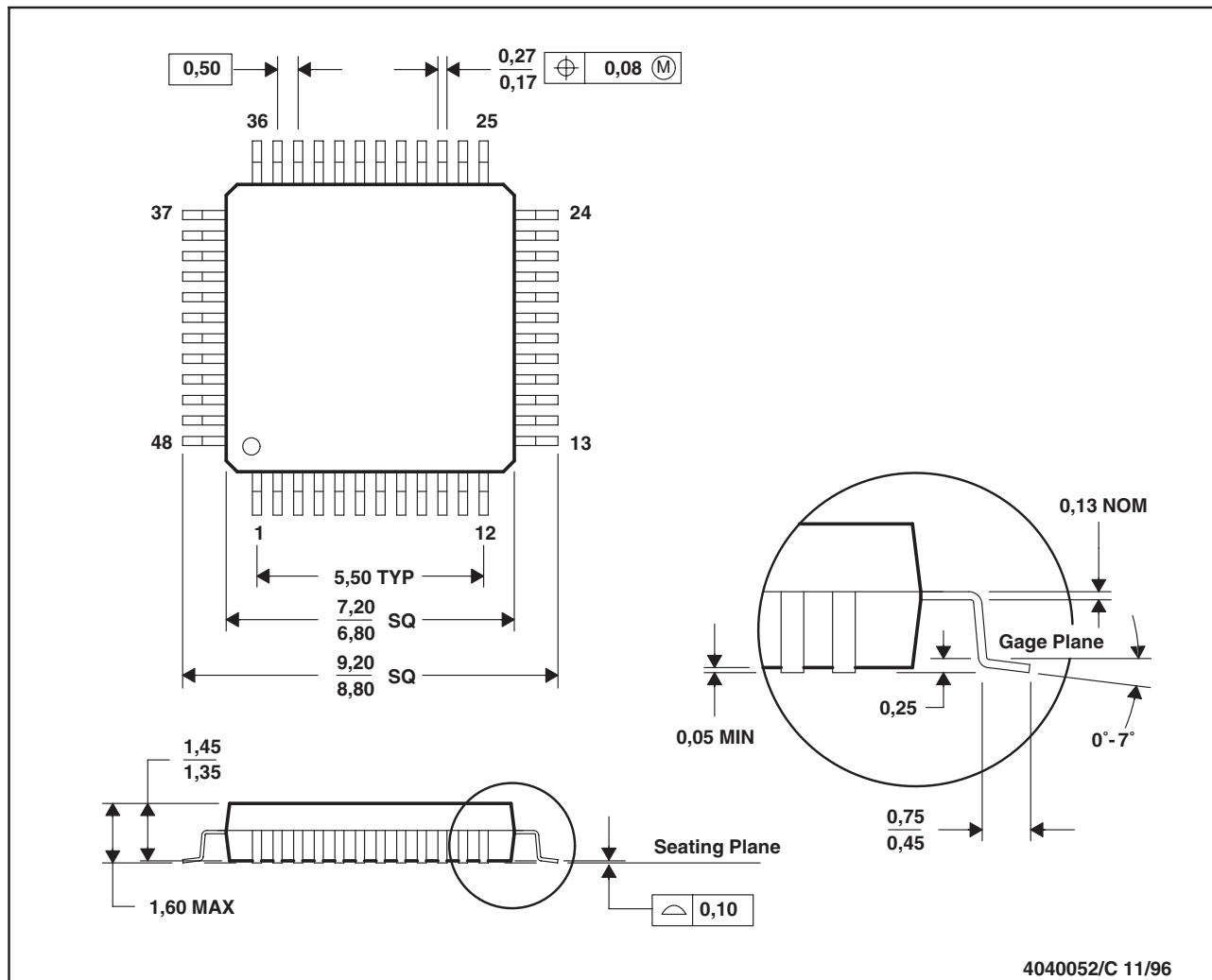

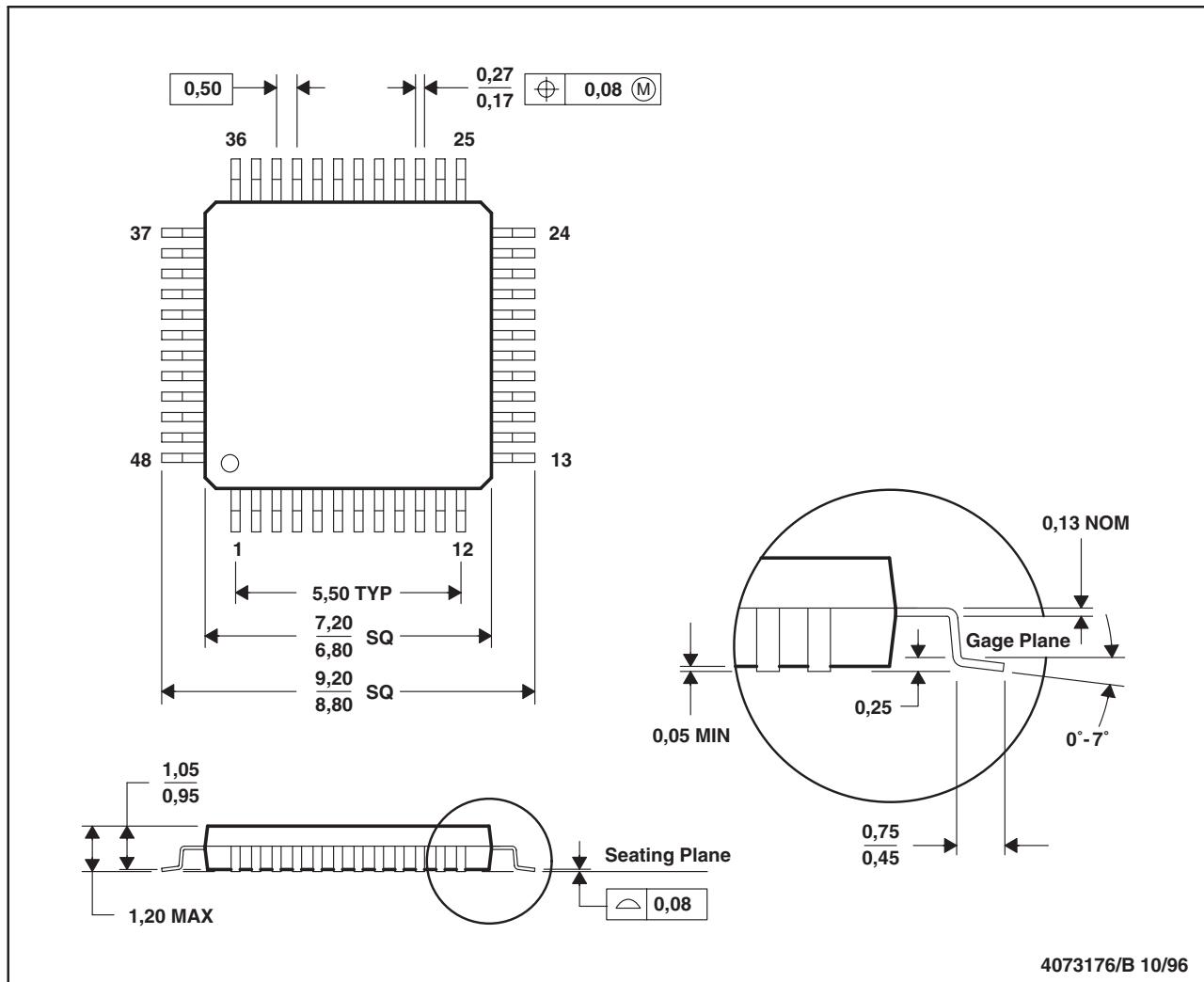

- パッケージ: 48-ピン QFP (PT)、48-ピン TQFP (PFB)、および 32-ピン QFN (RHB)

### 概要

TL16C550D および TL16C550DI は、TL16C550C の動作速度と動作電圧のアップグレード(機能的には同等)バージョンです。また TL16C450 の機能アップグレードバージョンもあります。パワーアップ時には TL16C450 と同じ機能(キャラクタ、つまり TL16C450 モード)ですが、TL16C550D および TL16C550DI は TL16C550C と同じように、FIFO モードとしても使うことができます。この機能で送受信キャラクタをバッファリングすることにより CPU の過剰なソフトウェア実行負荷を緩和します。送受信 FIFO は、受信 FIFO にある 1 バイトあたり 3 つのエラー・ステータス・ビット含め、16 バイトまでデータを貯めることができます。FIFO モードでは、RTS 出力および CTS 入力信号を使用したシリアルデータフローを自動的に制御することで、かなりのソフトウェアオーバーロードを減らし、システムの効率性を増やすことができる選択可能自動フロー制御機能があります。

TL16C550D および TL16C550DI は、周辺デバイスから受信したデータをシリアル・パラレル変換または、CPU から受信したデータをパラレル・シリアル変換します。CPU は、いつでも UART ステータスを読み取ることができます。UART は、通信リンクのソフトウェア管理を最小限にできる完全なモデム制御機能とプロセッサ割り込み制御機能を持っています。

本データシートの終わりにある、製品の有効性、標準保証、Texas Instruments 半導体製品のアプリケーションでの使用、免責に関するご注意をお読みください。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本 TI)が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本 TI による和文資料は、あくまでも TI 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TI および日本 TI は、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# TL16C550D

# TL16C550DI

## UART

SLLS698

TL16C550D および TL16C550DI UART は共に、1 から 65535 までのディバイザでリファレンス・クロックを分周し、内部トランスマッタ回路に 16×リファレンス・クロックを供給することの出来るプログラマブル・ボーレート・ジェネレータを持っています。またレシーバ回路に対してもこの 16×クロックを使用します。UART は、1.5-Mbaud までのシリアル・転送レート(24-MHz 入力クロック)を行うことが出来ます。この時ビット時間は、667ns、通常のキャラクタ時間は、6.7 $\mu$ s(スタートビット、8 データビット、トップビットの場合)となります。

TL16C450 ピンのうち二つのピンは、TL16C550D および TL16C550DI では、TXRDY と RXRDY に変更されていて、DMA コントローラに信号を伝える機能ピンとなっています。

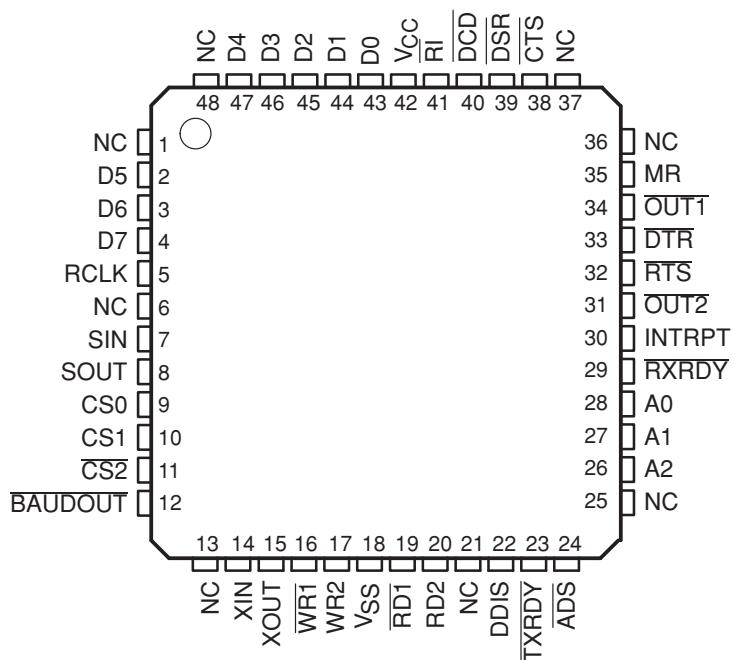

PT/PFB PACKAGE

(TOP VIEW)

NC- 内部接続無し

LQFP

TQFP

**TL16C550D**

**TL16C550DI**

**UART**

SLLS698

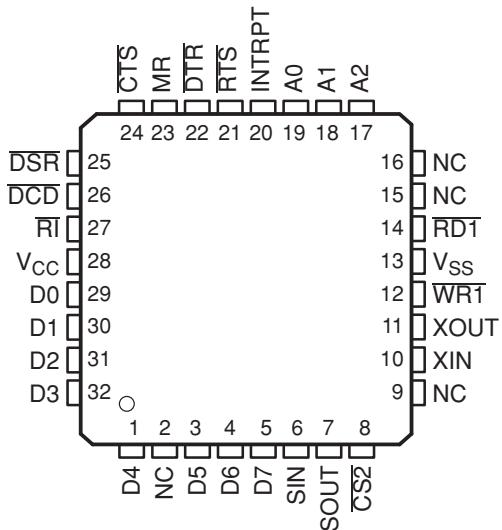

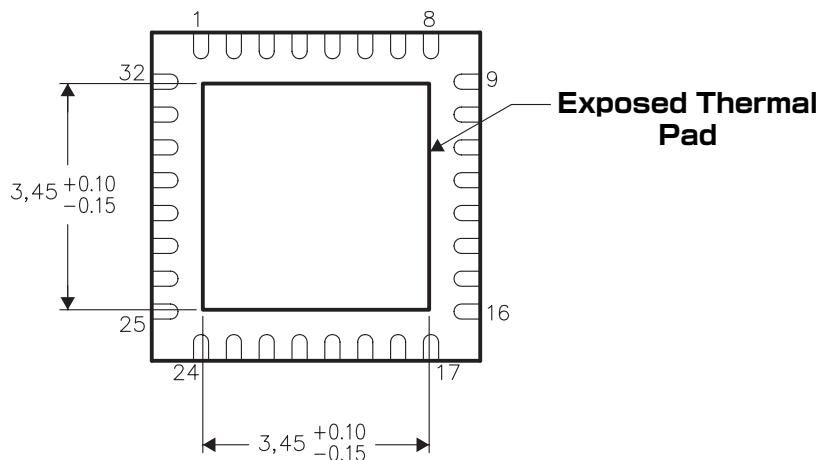

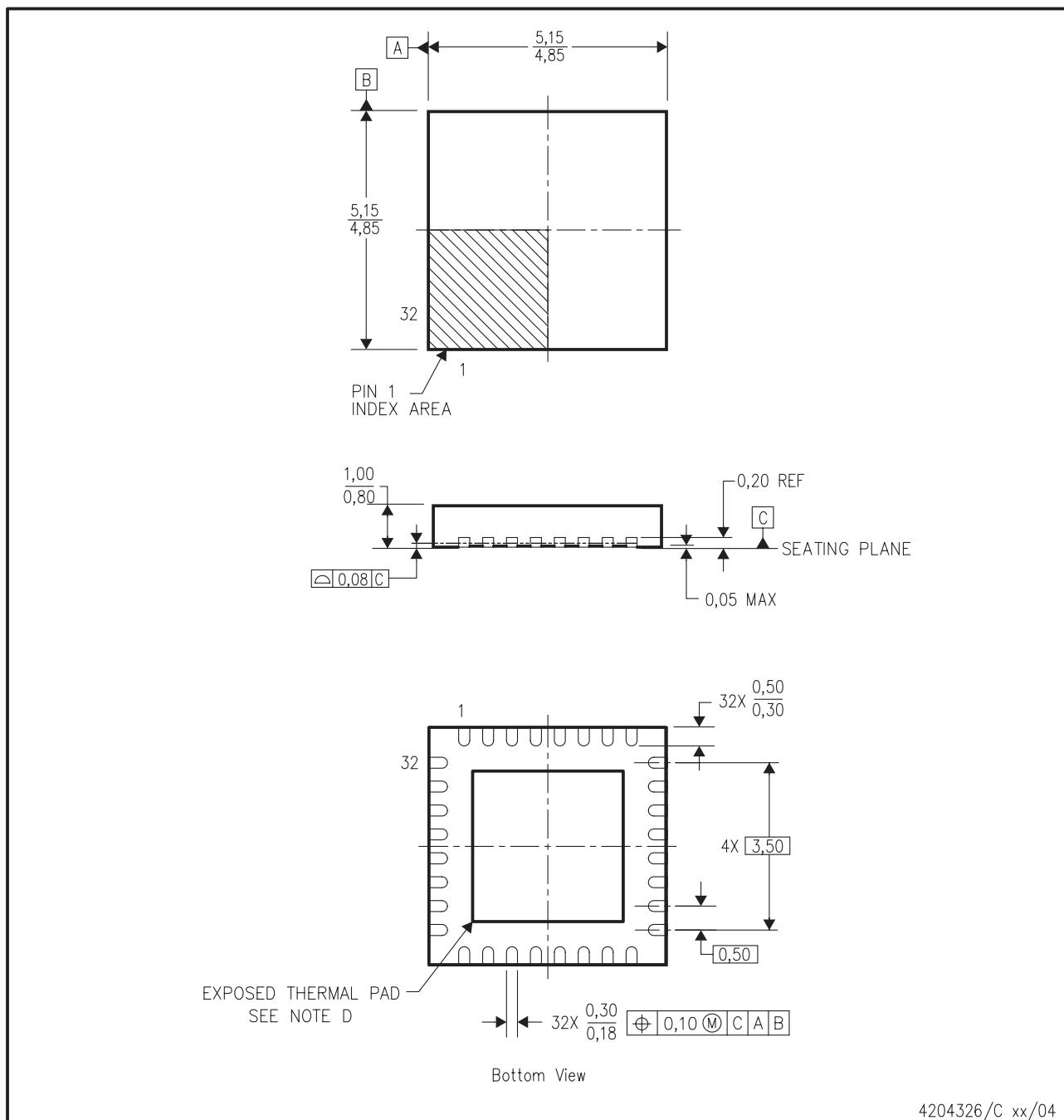

RHB PACKAGE

(TOP VIEW)

NC- 内部接続無し

QFN

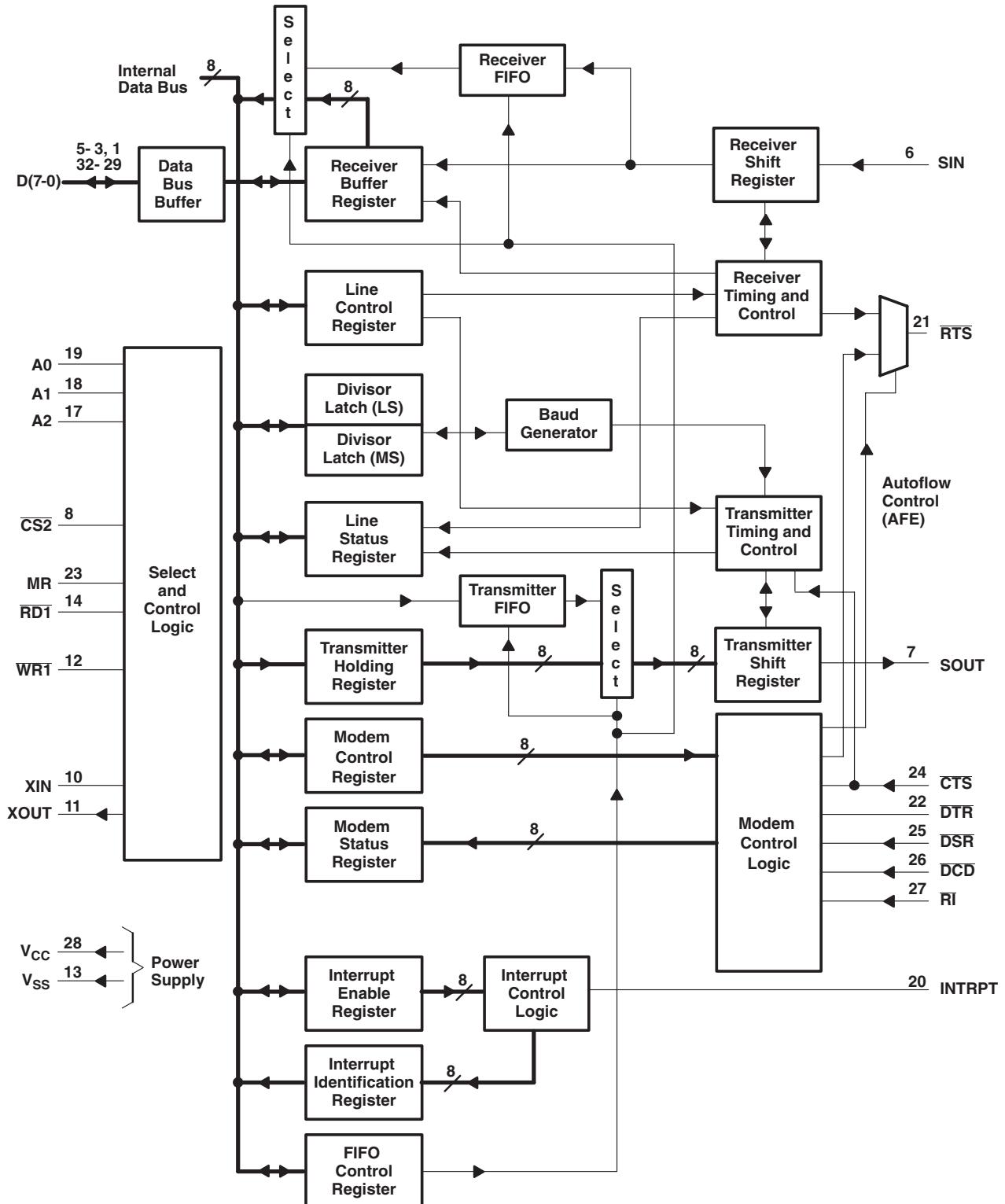

TL16C550Dは、ピン数を減らした32-ピンRHB (QFN) パッケージを持っています。これは、あるアプリケーションには必要とされないピンを減らすことで達成されています。これらは、CS0、CS1、 $\overline{AD5}$ 、RD2、WR2、RCLKの各入力信号およびDDIS、TXRDY、RXRDY、OUT1、OUT2、およびBAUDOUTの各出力信号です。BAUDOUTおよびRCLKは、内部で接続されています。

TL16C550Dの機能すべては、RHBパッケージでも変わりません。

## 詳細説明

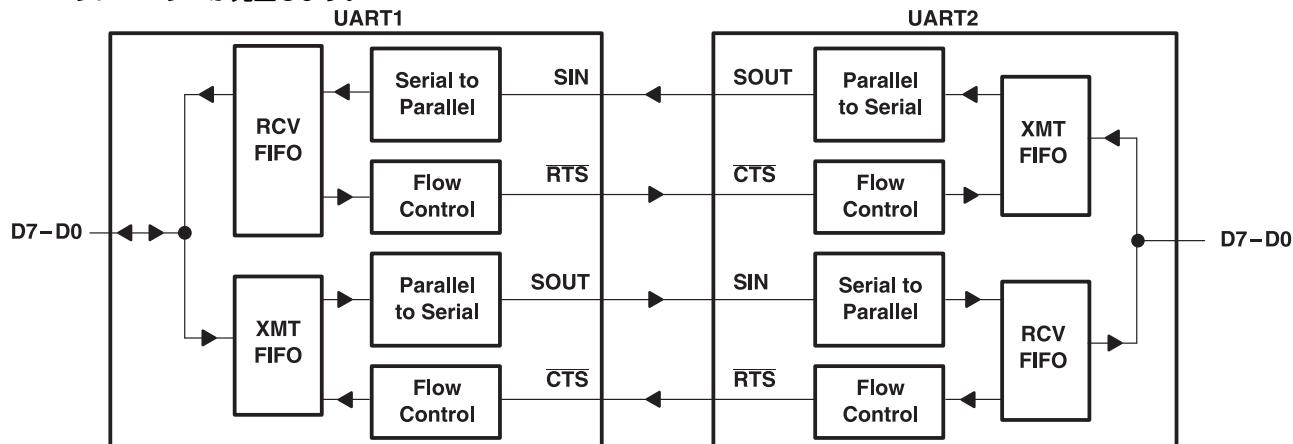

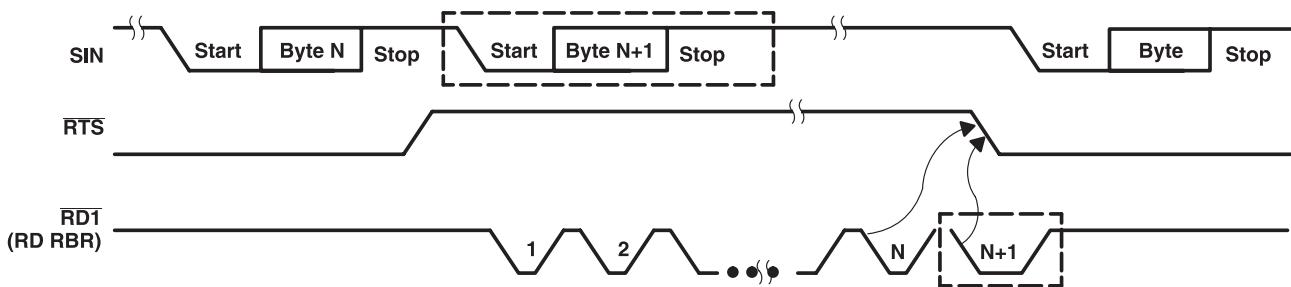

### 自動フロー制御(図 1 参照)

自動フロー制御は、自動-CTS および自動-RTS から構成されます。自動-CTS 機能では、CTS 入力はトランスマッタ FIFO がデータを送信できるようになる前に、アクティブである必要があります。自動-RTS 機能では、レシーバがデータを受けることが出来るようになると、送信シリアル・デバイスにそのことを通知するために、RTS がアクティブになります。RTS と CTS を接続する場合、データ送信はレシーバ側の FIFO にデータ用スペースができるまで起こりません。したがって、自動フロー制御を使用可能にした TL16C550D の UART1 と UART2 を使うことで、オーバーラン・エラーを防ぐことができます。さもなくば、トランスマッタ・データ転送速度がレシーバ FIFO 読み取りの遅れ時間を越えた場合に、オーバーラン・エラーが発生します。

図 1. 自動フロー制御(自動-RTS および自動-CTS) 例

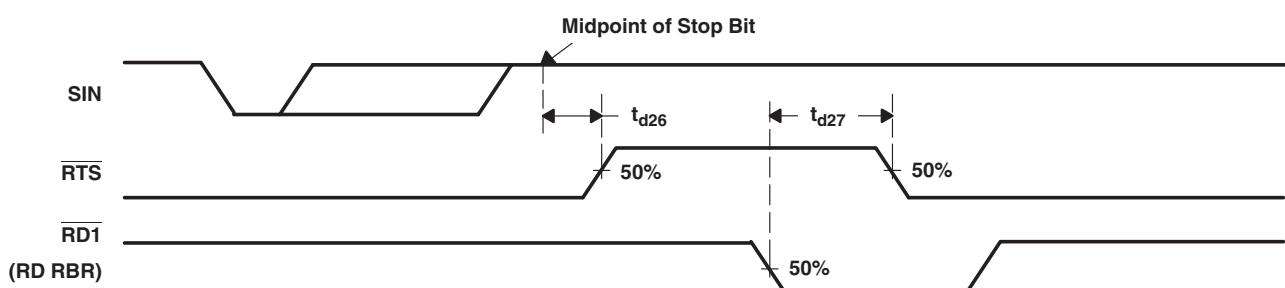

### 自動-RTS (図 1 参照)

自動-RTS データ・フロー制御は、レシーバのタイミングと制御ブロック（機能ブロックダイアグラム参照）およびプログラムされたレシーバ FIFO トリガー・レベルに関連しています。レシーバ FIFO レベルがトリガー・レベル 1、4、または 8(図 3 参照)に達した場合、RTS はディアサートされます。トリガー・レベル 1、4、および 8 では、送信 UART には、トリガー・レベルに達した後にもう一バイトを送信する可能性があります(送信 UART には、送信できるバイトがあると仮定します)。というのは、もう一バイトの追加送信が開始した後でも、RTS のディアサートを認識しないことがあります。一旦 RCV FIFO がレシーバ・バッファ・レジスタの読み取りで空になると、RTS は、自動的にリアサートされます。

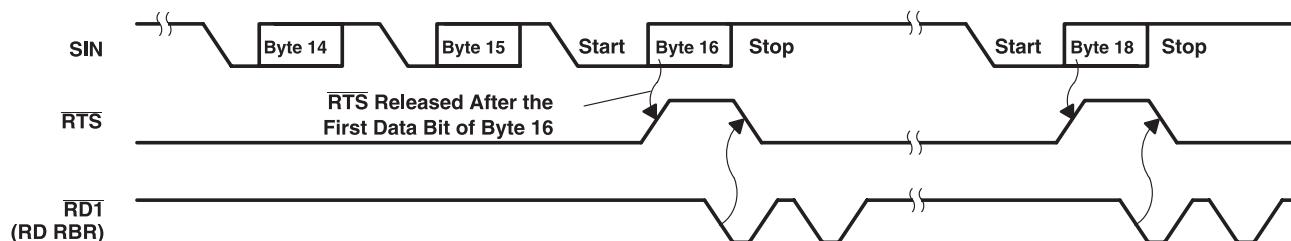

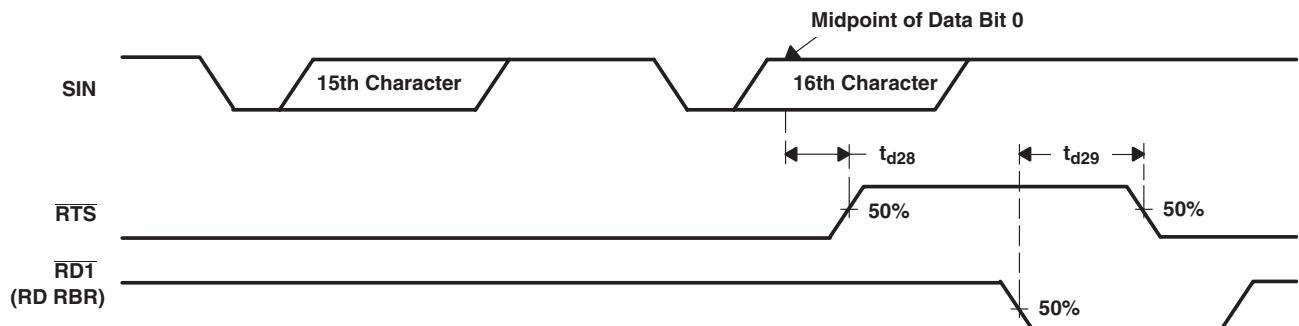

トリガー・レベルが 14 の場合(図 4 参照)、RTS は 16 番目のキャラクタの最初のデータ・ビットが SIN ラインに現れた後、ディアサートされます。RTS は、RCV FIFO が少なくとも一個の受信可能なバイト・スペースがあれば、リアサートされます。

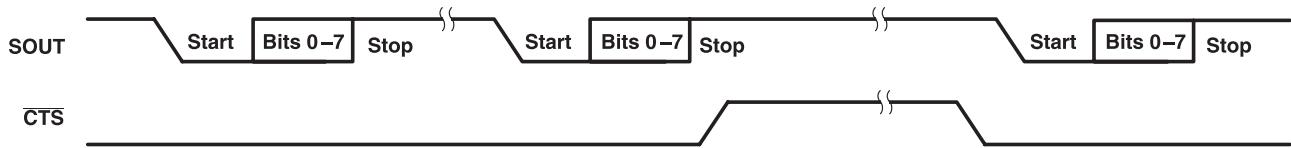

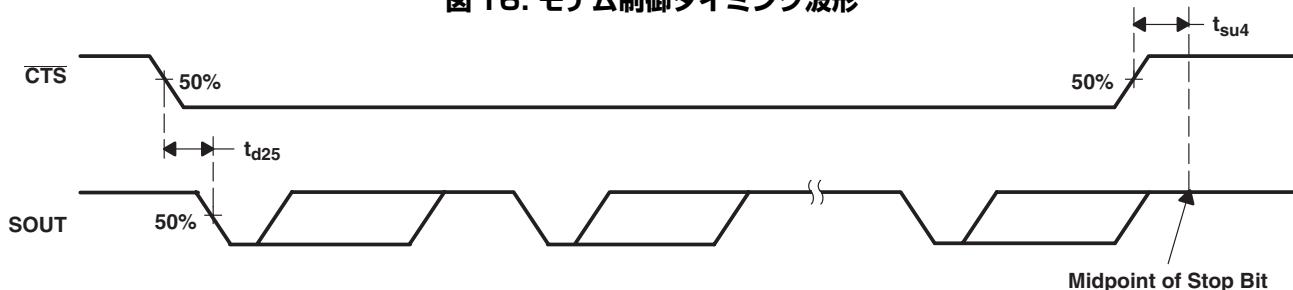

### 自動-CTS(図 1 参照)

トランスマッタ回路は、次のバイトデータ送信前にCTS を調べます。CTS がアクティブな場合、次のバイトを送信します。トランスマッタに次のバイトの送信を停止させるには、現在送信中の最後のストップ・ビットの途中より前でCTS をディスイネーブルにする必要があります(図 2 参照)。自動-CTS 機能は、ホストシステムの割り込み負荷を低減させます。フロー制御がイネーブルの場合、デバイス自体が自動的にそのトランスマッタを制御するため、CTS レベルの変化は、ホストへの割り込みのトリガーにはなりません。自動-CTS を使用しないと、トランスマッタは送信 FIFO にあるデータをいつでも送信てしまい、レシーバ側がオーバーラン・エラーを起こす可能性があります。

### 自動フロー制御および自動-CTS 使用方法

自動フロー制御は、モード制御レジスタのビット 5 (AutoFlow Enable つまり AFE) およびビット 1 (RTS)を 1 に設定して使用可能に出来ます。自動フローは自動-RTS および自動-CTS の両方を使うことが出来ます。自動-CTS のみを使う場合は、モード制御レジスタのビット 1 をクリアする必要があります。(この時、制御信号がCTS をドライブしていると仮定します。)

## 自動-CTS および自動-RTS 機能タイミング

- A. CTS がローの時、トランスマッタはシリアル・データを送信し続けます。

- B. CTS が現在のバイトの最後のストップ・ビットの真ん中より前にハイになった場合、トランスマッタは現在のバイト送信を終えて、次のバイトを送信することはありません。

- C. CTS がハイからローに変化した場合、トランスマッタは再びデータ送信を開始します。

図 2. CTS 機能タイミング・ウェーブ・フォーム

レシーバ FIFO トリガー・レベルは、1、4、8、または 14 バイトに設定できます。これらは、図 3 および図 4 に説明されています。

- A. N = RCV FIFO トリガー・レベル(1、4、または 8 バイト)

- B. ダッシュラインで囲まれた二つのブロックは、自動-RTS セクションで説明したとおり、追加バイトが送信される場合を説明しています。

図 3. RTS 機能タイミング・ウェーブ・フォーム、RCV FIFO トリガー・レベル=1、4、または 8 バイト

- A. RTS は、レシーバが 16 番目のバイトの最初のデータビットを受信した時、ディアサートされます。受信 FIFO は、16 番目のバイトを受信した後フルになります。

- B. RTS は、最低 1 バイトのスペースが空きかつバイトの受信中ではない場合か、2 バイト以上の空きが在る場合に再度アサートされます。

- C. 受信 FIFO がフルの場合、受信バッファレジスタを一度でもリードすると RTS は、アサートされます。

図 4. RTS 機能タイミング・ウェーブ・フォーム、RCV FIFO トリガー・レベル=14 バイト

# TL16C550D

# TL16C550DI

## UART

SLLS698

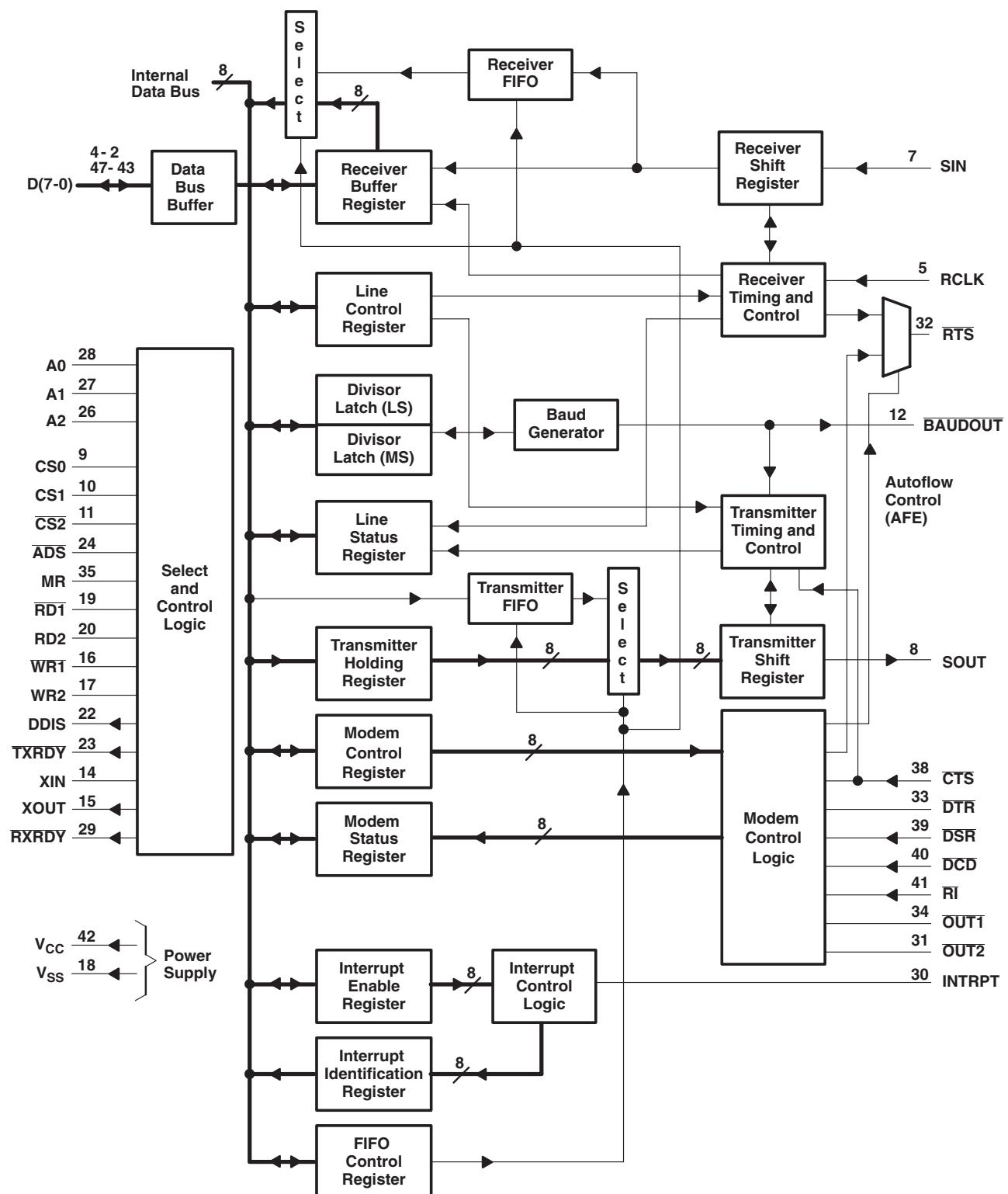

### 機能ブロックダイヤグラム(PT および PFB パッケージ用)

機能ブロックダイヤグラム(RHB パッケージ用)

# TL16C550D

## TL16C550DI

### UART

SLLS698

### ピン構成(PT および PFB パッケージ用)

| ピン構成<br>名称                                   | ピン番号                                      | I/O | 説明                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------|-------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO<br>A1<br>A2                               | 28<br>27<br>26                            | I   | レジスタ選択端子。AO-A2は、読み取り・書き込み動作に使用されます。読み取りや書き込みをするUARTレジスタを選択します。レジスタ・アドレスについては表1およびADS説明を参照してください。                                                                                                                                                                                                                                |

| ADS                                          | 24                                        | I   | アドレス・ストローブ端子。 <u>ADS</u> がアクティブ(ロー)の場合、AO、A1、およびA2およびCS0、CS1、および <u>CS2</u> は、内部選択ロジックを直接ドライプします。 <u>ADS</u> がハイの場合、レジスタ選択信号およびチップ選択信号は、 <u>ADS</u> がハイからローに変化した時の値を保持します。                                                                                                                                                      |

| BAUDOUT                                      | 12                                        | O   | ボーラウト端子。 <u>BAUDOUT</u> は、UARTのトランシミッタで使用される16×クロック信号です。クロック周波数は、ボーラウト・ディバイザ・ラッチに設定された値で、外部発信器の周波数を分周することによって決ります。 <u>BAUDOUT</u> は、この出力をRCLKに繋ぐことで、レシーバにも使用できます。                                                                                                                                                               |

| CS0<br>CS1<br>CS2                            | 9<br>10<br>11                             | I   | チップ選択端子。CS0およびCS1がハイ、 <u>CS2</u> がローの場合、これら三つの入力はUARTを選択します。これらの入力のいずれかが非アクティブな場合、UARTは非アクティブのままになります(ADS説明参照)。                                                                                                                                                                                                                 |

| CTS                                          | 38                                        | I   | 送信クリア端子。 <u>CTS</u> は、モデル・ステータス信号です。そのステータスは、モデル・ステータス・レジスタのビット4( <u>CTS</u> )を読み取ることでチェックできます。モデル・ステータス・レジスタのビット0(ΔCTS)は、モデル・ステータス・レジスタからの最後の読み取り後 <u>CTS</u> のステータスが変化したことを示します。 <u>CTS</u> のレベルが変化し、自動- <u>CTS</u> モードがディスイネーブルで、モデル・ステータス割り込みがイネーブルの場合、割り込みが起こります。 <u>CTS</u> は、また自動- <u>CTS</u> モードで使用されトランシミッタをコントロールします。 |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 43<br>44<br>45<br>46<br>47<br>2<br>3<br>4 | I/O | データバス端子。3-ステートの双方向データライン8本で、UARTとCPU間でデータ、制御情報、ステータス情報をやり取りします。                                                                                                                                                                                                                                                                 |

| DCD                                          | 40                                        | I   | データキャリア検出端子。 <u>DCD</u> は、モデルステータス信号です。そのステータスは、モデル・ステータス・レジスタのビット7( <u>DCD</u> )を読み取ることでチェックできます。モデル・ステータス・レジスタのビット3(Δ <u>DCD</u> )は、モデル・ステータス・レジスタからの最後の読み取り後、 <u>DCD</u> のステータスが変化したことを示します。 <u>DCD</u> のレベルが変化し、モデル・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                          |

| DDIS                                         | 22                                        | O   | ドライバ・ディスイネーブル端子。DDISは、CPUがデータ読み取りをしていない時にアクティブ(ハイ)です。アクティブな場合、DDISは外部トランシーバを使用不能にすることができます。                                                                                                                                                                                                                                     |

| DSR                                          | 39                                        | I   | データ設定レディ端子。 <u>DSR</u> は、モデル・ステータス信号です。そのステータスは、モデル・ステータス・レジスタのビット5( <u>DSR</u> )を読み取ることでチェックできます。モデル・ステータス・レジスタのビット1(Δ <u>DSR</u> )は、モデル・ステータス・レジスタからの最後の読み取り後、 <u>DSR</u> のステータスが変化したことを示します。 <u>DSR</u> のレベルが変化し、モデル・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                          |

| DTR                                          | 33                                        | O   | データ・ターミナル・レディ端子。アクティブ(ロー)の場合、 <u>DTR</u> でモデルやデータ機器にUARTが通信の準備ができる事を知らせます。 <u>DTR</u> は、モデル制御レジスタのDTRを設定することによりアクティブにすることが出来ます。 <u>DTR</u> は、マスタリセット、ループ・モード設定時、またはDTRビットのクリアのいずれかで、非アクティブになります。                                                                                                                                |

| INTRPT                                       | 30                                        | O   | 割り込み端子。アクティブ(ハイ)の場合、INTRPTはUARTに処理されるべき割り込みがあることをCPUに通知します。割り込みを生じる条件は以下の4通りです。レシーバ・エラー、データ受信または受信データタイムアウト(FIFOモードのみ)、トランシミッタ・ホールディング・レジスタ・エンブティ、またはイネーブルされたモデル・ステータス割り込み。INTRPTは、割り込みがサービス要求時またはマスタリセットでリセット(ディスイネーブル)されます。                                                                                                   |

| MR                                           | 35                                        | I   | マスター・リセット端子。アクティブ(ハイ)の場合、MRはほとんどのUARTレジスタをクリアし、出力信号の値を設定します(表2参照)。                                                                                                                                                                                                                                                              |

| NC                                           | 1, 6, 13,<br>21, 25, 36<br>37, 48         | I   | NC端子。内部での接続はありません。                                                                                                                                                                                                                                                                                                              |

| OUT1<br>OUT2                                 | 34<br>31                                  | O   | 出力1および出力2端子。これらは、それぞれのモデル制御レジスタ(MCR)ビット(OUT1およびOUT2)で設定することにより、アクティブ(ローレベル)に設定することの出来るユーザー指定出力端子です。OUT1およびOUT2は、ループ・モード設定時またはMCRのビット2(OUT1)またはビット3(OUT2)をクリアすること、またはマスター・リセットによりイナクティブ(ハイ)に設定されます。                                                                                                                              |

| RCLK                                         | 5                                         | I   | レシーバ・クロック信号。RCLKは、UARTのレシーバ用の16×ボーレート・クロックです。                                                                                                                                                                                                                                                                                   |

## ピン構成(PT および PFB パッケージについて) (続き)

| 名称          | ピン構成<br>ピン番号 | I/O | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD1<br>RD2  | 19<br>20     | I   | リード端子。RD1 または RD2 がアクティブ (それぞれローまたはハイ) の場合、UART が選択され、CPU はステータスまたは選択した UART レジスタからデータを読み取ることができます。これらの入力のうちひとつだけが、データの読み取り時に必要になります。他の入力は非アクティブにする必要があります(例えば、RD2 はローまたは RD1 をハイにします)。                                                                                                                                                                                                                                                                                                                                                                                     |

| RI          | 41           | I   | リング・インジケータ端子。RI は、モデム・ステータス信号です。そのステータスは、モデム・ステータス・レジスタのビット 6(RI)を読み取ることでチェックできます。モデム・ステータス・レジスタのビット 2(TERI)は、モデム・ステータス・レジスタの最後の読み取り後、RI がローからハイレベルへ遷移したことを示します。遷移した時、モデム・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                                                                                                                                                                                                                                                                                                                    |

| RTS         | 32           | O   | 送信リクエスト端子。アクティブの場合、RTS は UART がデータ受信準備ができていることをモデムまたはデータ器機へ知らせます。RTS は、RTS モデム制御レジスタビットを設定することでアクティブ・レベルに設定され、マスクリセットまたはループ・モード時または MCR のビット 1(RTS)をクリアすることで、非アクティブ (ハイ) に設定されます。自動 RTS モードでは、RTS はレシーバ閾値制御回路で非アクティブになるレベルに設定されます。                                                                                                                                                                                                                                                                                                                                          |

| RXRDY       | 29           | O   | レシーバ・レディ端子。レシーバの直接メモリアクセス(DMA)が、RXRDY を使うことで可能となります。FIFO モード時、FIFO 制御レジスタ・ビット 3 (FCR3)を使用して DMA 制御信号の二つのタイプのうちのひとつは選択することができます。TL16C450 モードで動作する場合、DMA モード 0 のみが可能です。モード 0 は、CPU バス・サイクル間で転送を行う単一転送 DMA をサポートしています。モード 1 は、レシーバ FIFO が空になるまで継続的に行われる複数転送 DMA をサポートしています。DMA モード 0 (FCR0 = 0 または FCR0 = 1、FCR3=0) は、レシーバ FIFO またはレシーバ保持レジスタに最低ひとつのキャラクタがある時、RXRDY はアクティブ(ロー)です。RXRDY がアクティブであって、FIFO または保持レジスタにキャラクタがなくなった場合、RXRDY は非アクティブ (ハイ) になります。DMA モード 1 (FCR0 = 1、FCR3=1) では、トリガー・レベルまたはタイムアウトになった時、RXRDY はアクティブ (ロー) になり、FIFO または保持レジスタにキャラクタがない場合、非アクティブ(ハイ)になります。 |

| SIN         | 7            | I   | シリアルデータ入力端子。SIN は、接続した通信デバイスからのシリアルデータ入力です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOUT        | 8            | O   | シリアルデータ出力端子。SOUT は、接続した通信デバイスに対するシリアルデータ出力です。SOUT は、マスクリセットの後マーキングレベル (ハイ) となります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TXRDY       | 23           | O   | トランスマッタ・レディ端子。トランスマッタ DMA 制御には、TXRDY が使用できます。FIFO モードの場合、DMA 制御信号の 2 つのタイプの内 1 つを、FCR3 を使って設定できます。TL16C450 モードで動作する場合、DMA モード 0 のみが設定可能です。モード 0 は、CPU バス・サイクル間で転送を行う単一転送 DMA をサポートしています。モード 1 は、転送 FIFO が一杯になるまで継続的に行われる複数転送 DMA をサポートしています。                                                                                                                                                                                                                                                                                                                                |

| Vcc         | 42           |     | 2.25V から 5.5V までの電圧を供給します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vss         | 18           |     | グランド端子。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| WR1<br>WR2  | 16<br>17     | I   | 入力書き込み端子。WR1 または WR2 のどちらかがアクティブ (それぞれローまたはハイ) の時、UART が選択され、CPU は選択した UART レジスタに制御データまたはデータを書き込むことができます。これらの入力のうちひとつだけが、データの書き込み時に必要になります。他の入力は非アクティブ・レベルにする必要があります(例えば、WR2 はローまたは WR1 をハイにします)。                                                                                                                                                                                                                                                                                                                                                                           |

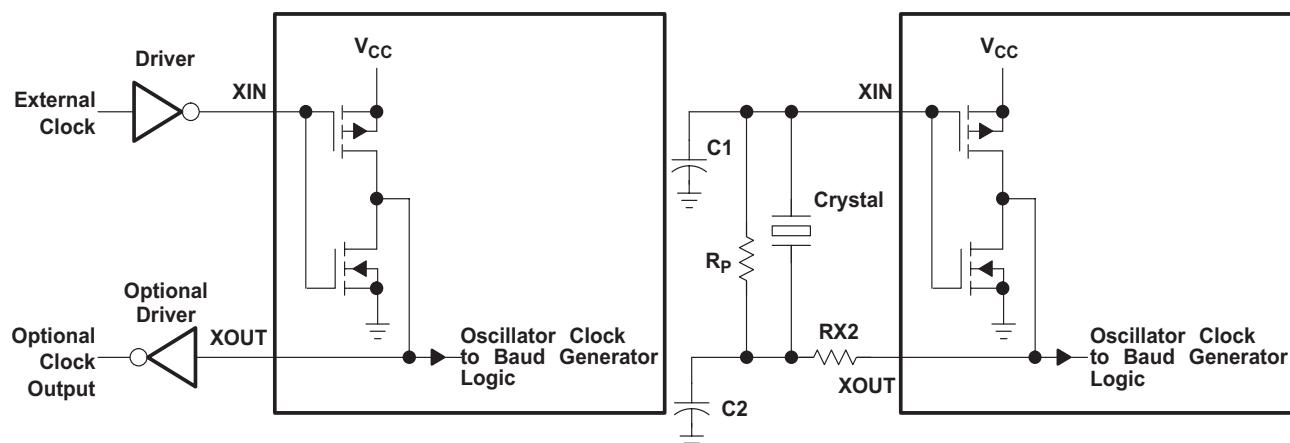

| XIN<br>XOUT | 14<br>15     | I/O | 外部クロック端子。XIN および XOUT は、UART のメイン・タイミング・リファレンスに接続されています。(クロックまたは水晶)。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# TL16C550D

# TL16C550DI

## UART

SLLS698

### ピン構成 (RHB パッケージ)

| 名称                                           | ピン番号                                     | I/O | 説明                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO<br>A1<br>A2                               | 19<br>18<br>17                           | I   | レジスタ選択端子。AO-A2は、読み取り・書き込み動作に使用されます。読み取りや書き込みをするUARTレジスタを選択します。レジスタ・アドレスについては表1およびADS説明を参照してください。                                                                                                                                                                                                                                        |

| CS2                                          | 8                                        | I   | チップ選択端子。 $\overline{CS2}$ がローの場合、UARTが選択されます。 $\overline{CS2}$ がハイの場合、UARTは非アクティブです。                                                                                                                                                                                                                                                    |

| CTS                                          | 24                                       | I   | 送信クリア端子。 $\overline{CTS}$ は、モデム・ステータス信号です。そのステータスは、モデム・ステータス・レジスタのビット4(CTS)を読み取ることでチェックできます。モデム・ステータス・レジスタのビット0( $\Delta CTS$ )は、モデム・ステータス・レジスタからの最後の読み取り後 $\overline{CTS}$ のステータスが変化したことを示します。 $\overline{CTS}$ のレベルが変化し、自動-CTSモードがディスイネーブルで、モデム・ステータス割り込みがイネーブルの場合、割り込みが起こります。 $\overline{CTS}$ は、また自動-CTSモードで使用されトランスマッチタをコントロールします。 |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 29<br>30<br>31<br>32<br>1<br>3<br>4<br>5 | I/O | データバス端子。3-ステートの双方向データライン8本で、UARTとCPU間でデータ、制御情報、ステータス情報をやり取りします。                                                                                                                                                                                                                                                                         |

| DCD                                          | 26                                       | I   | データキャリア検出端子。 $\overline{DCD}$ は、モデムステータス信号です。そのステータスは、モデム・ステータス・レジスタのビット7(DCD)を読み取ることでチェックできます。モデム・ステータス・レジスタのビット3( $\Delta DCD$ )は、モデム・ステータス・レジスタからの最後の読み取り後、 $\overline{DCD}$ のステータスが変化したことを示します。 $\overline{DCD}$ のレベルが変化し、モデム・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                        |

| DSR                                          | 25                                       | I   | データ設定レディー端子。 $\overline{DSR}$ は、モデム・ステータス信号です。そのステータスは、モデム・ステータス・レジスタのビット5(DSR)を読み取ることでチェックできます。モデム・ステータス・レジスタのビット1( $\Delta DSR$ )は、モデム・ステータス・レジスタからの最後の読み取り後、 $\overline{DSR}$ のステータスが変化したことを示します。DSRのレベルが変化し、モデム・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                                      |

| DTR                                          | 22                                       | O   | データ・ターミナル・レディー端子。アクティブ(ロー)の場合、 $\overline{DTR}$ でモデルやデータ機器にUARTが通信の準備ができたことを知らせます。 $\overline{DTR}$ は、モデル制御レジスタのDTRを設定することによりアクティブにすることができます。 $\overline{DTR}$ は、マスタリセット、ループ・モード設定時、またはDTRビットのクリアのいずれかで、非アクティブになります。                                                                                                                    |

| INTRPT                                       | 20                                       | O   | 割り込み端子。アクティブ(ハイ)の場合、INTRPTはUARTに処理されるべき割り込みがあることをCPUに通知します。割り込みを生じる条件は以下の4通りです。レシバ・エラー、データ受信または受信データタイムアウト(FIFOモードのみ)、トランスマッチ・ホールディング・レジスタ・エンブティ、またはイネーブルされたモデムステータス割り込み。INTRPTは、割り込みがサービス要求時またはマスタリセットでリセット(ディスイネーブル)されます。                                                                                                             |

| MR                                           | 23                                       | I   | マスター・リセット端子。アクティブ(ハイ)の場合、MRはほとんどのUARTレジスタをクリアし、出力信号の値を設定します(表2参照)。                                                                                                                                                                                                                                                                      |

| NC                                           | 2, 9,<br>15, 16                          | -   | NC端子。内部での接続はありません。                                                                                                                                                                                                                                                                                                                      |

| RD1                                          | 14                                       | I   | リード端子。 $\overline{RD1}$ がアクティブ(ロー)の場合、UARTが選択され、CPUはステータスまたは選択したUARTレジスタからデータを読み取ることができます。                                                                                                                                                                                                                                              |

| RI                                           | 27                                       | I   | リング・インジケータ端子。 $\overline{RI}$ は、モデム・ステータス信号です。そのステータスは、モデム・ステータス・レジスタのビット6(RI)を読み取ることでチェックできます。モデム・ステータス・レジスタのビット2(TERI)は、モデム・ステータス・レジスタからの最後の読み取り後、 $\overline{RI}$ がローからハイレベルへ遷移したことを示します。遷移した時、モデム・ステータス割り込みがイネーブルの場合、割り込みが起こります。                                                                                                    |

| RTS                                          | 21                                       | O   | 送信リクエスト端子。アクティブの場合、RTSはUARTがデータ受信準備ができていることをモデルまたはデータ器機へ知らせます。RTSは、RTSモデル制御レジスタビットを設定することでアクティブ・レベルに設定され、マスタリセットまたはループ・モード時またはMCRのビット1(RTS)をクリアすることで、非アクティブ(ハイ)に設定されます。自動RTSモードでは、RTSはレシバ閾値制御回路で非アクティブになるレベルに設定されます。                                                                                                                    |

## ピン構成 (RHB パッケージ)(続き)

| 名称              | ピン構成<br>ピン番号 | I/O | 説明                                                                                          |

|-----------------|--------------|-----|---------------------------------------------------------------------------------------------|

| SIN             | 6            | I   | シリアルデータ入力端子。SINは、接続した通信デバイスからのシリアルデータ入力です。                                                  |

| SOUT            | 7            | O   | シリアルデータ出力端子。SOUTは、接続した通信デバイスに対するシリアルデータ出力です。SOUTは、マスター・リセットの後マーキングレベル(ハイ)となります。             |

| V <sub>cc</sub> | 28           |     | 2.25V から 5.5V までの電圧を供給します。                                                                  |

| V <sub>ss</sub> | 13           |     | グランド端子。                                                                                     |

| WR1             | 12           | I   | 入力書き込み端子。 $\overline{WR1}$ がアクティブ(ロー)の時、UARTが選択され、CPUは選択したUARTレジスタに制御データまたはデータを書き込むことができます。 |

| XIN             | 10           | I   | 外部クロック端子。XINおよびXOUTは、UARTのメイン・タイミング・リファレンスに接続されています。                                        |

| XOUT            | 11           | O   | (クロックまたは水晶)。                                                                                |

## 絶対最大定格 (特に記載のない限り)<sup>†</sup>

|                                                            |                                  |               |

|------------------------------------------------------------|----------------------------------|---------------|

| 電源電圧範囲                                                     | V <sub>cc</sub> (注 1 参照) .....   | -0.5V ~ 7V    |

| 任意の入力値における入力電圧範囲                                           | V <sub>i</sub> .....             | -0.5V ~ 7V    |

| 出力電圧範囲                                                     | V <sub>o</sub> .....             | -0.5V ~ 7V    |

| 動作周囲温度範囲                                                   | T <sub>A</sub> , TL16C550D ..... | 0°C ~ 70°C    |

|                                                            | TL16C550DI .....                 | -40°C ~ 85°C  |

| 保存温度範囲                                                     | T <sub>stg</sub> .....           | -65°C ~ 150°C |

| ケースから 1.6 mm (1/16 インチ)、10 秒間の半田温度: PT および PFB パッケージ ..... |                                  | 260°C         |

†「絶対最大定格」に記載された値を超えるストレスはデバイスを永久に損傷することがあります。この定格はストレスだけに適用され、この値または「推奨動作条件」に示された値以上の条件でデバイスの機能動作を保証するものではありません。絶対最大条件下に長時間置いた場合は、デバイスの信頼性が低下することがあります。

注 1:すべての電圧値は V<sub>ss</sub> を基準としています。

# TL16C550D

# TL16C550DI

## UART

SLLS698

## 推奨動作条件

### 2.5 V ±10%

|                              | 最小   | 標準       | 最大       | 単位  |

|------------------------------|------|----------|----------|-----|

| 電源電圧 $V_{CC}$                | 2.25 | 2.5      | 2.75     | V   |

| 入力電圧 $V_I$                   | 0    | $V_{CC}$ | $V_{CC}$ | V   |

| ハイレベル入力電圧、 $V_{IH}$          | 1.8  | 2.75     | 2.75     | V   |

| ローレベル入力電圧、 $V_{IL}$          | -0.3 | 0.6      | 0.6      | V   |

| 出力電圧、 $V_O$                  | 0    | $V_{CC}$ | $V_{CC}$ | V   |

| ハイレベル出力電流、 $I_{OH}$ (すべての出力) |      | 1        | 1        | mA  |

| ローレベル出力電流、 $I_{OL}$ (すべての出力) |      | 2        | 2        | mA  |

| 発振 / クロック速度                  |      | 16       | 16       | MHz |

### 3.3 V ±10%

|                              | 最小           | 標準           | 最大           | 単位  |

|------------------------------|--------------|--------------|--------------|-----|

| 電源電圧 $V_{CC}$                | 3            | 3.3          | 3.6          | V   |

| 入力電圧 $V_I$                   | 0            | $V_{CC}$     | $V_{CC}$     | V   |

| ハイレベル入力電圧、 $V_{IH}$          | 0.7 $V_{CC}$ |              |              | V   |

| ローレベル入力電圧、 $V_{IL}$          |              | 0.3 $V_{CC}$ | 0.3 $V_{CC}$ | V   |

| 出力電圧、 $V_O$                  | 0            | $V_{CC}$     | $V_{CC}$     | V   |

| ハイレベル出力電流、 $I_{OH}$ (すべての出力) |              | 1.8          | 1.8          | mA  |

| ローレベル出力電流、 $I_{OL}$ (すべての出力) |              | 3.2          | 3.2          | mA  |

| 発振 / クロック速度                  |              | 20           | 20           | MHz |

### 5 V ±10%

|                              | 最小      | 標準           | 最大       | 単位  |

|------------------------------|---------|--------------|----------|-----|

| 電源電圧 $V_{CC}$                | 4.5     | 5            | 5.5      | V   |

| 入力電圧 $V_I$                   | 0       | $V_{CC}$     | $V_{CC}$ | V   |

| ハイレベル入力電圧、 $V_{IH}$          | XIN を除く | 2            |          | V   |

|                              | XIN     | 0.7 $V_{CC}$ |          |     |

| ローレベル入力電圧、 $V_{IL}$          | XIN を除く | 0.8          |          | V   |

|                              | XIN     | 0.3 $V_{CC}$ |          |     |

| 出力電圧、 $V_O$                  | 0       | $V_{CC}$     | $V_{CC}$ | V   |

| ハイレベル出力電流、 $I_{OH}$ (すべての出力) |         | 4            | 4        | mA  |

| ローレベル出力電流、 $I_{OL}$ (すべての出力) |         | 4            | 4        | mA  |

| 発振 / クロック速度                  |         | 24           | 24       | MHz |

## 推奨電源電圧および推奨動作温度範囲の電気的特性(特に記載のない限り)

### 2.5 V 公称値

| パラメータ                         | テスト条件                                                                                                                                                    | 最小  | 標準† | 最大       | 単位            |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|---------------|

| $V_{OH}^{\dagger}$ ハイ・レベル出力電圧 | $I_{OH} = -1 \text{ mA}$                                                                                                                                 | 1.8 |     |          | V             |

| $V_{OL}^{\dagger}$ ロー・レベル出力電圧 | $I_{OL} = 2 \text{ mA}$                                                                                                                                  |     | 0.5 |          | V             |

| $I_i$ 入力電流                    | $V_{CC} = 3.6V$ $V_{SS} = 0$<br>$V_i = 0 \sim 3.6V$<br>他のすべての端子は、フローティング                                                                                 |     |     | 10       | $\mu\text{A}$ |

| $I_{OZ}$ ハイ・インピーダンス出力電流       | $V_{CC} = 3.6V$ $V_{SS} = 0$<br>$V_o = 0 \sim 3.6V$<br>書き込みモードでチップを選択またはチップは、非選択。                                                                        |     |     | $\pm 20$ | $\mu\text{A}$ |

| $I_{CC}$ 電源電流                 | $V_{CC} = 3.6V$ $T_A = 25^\circ\text{C}$<br>$SIN, DSR, DCD, CTS$ および $RI$ は $2V$<br>他のすべての入力は $0.8V$ 、XTAL1は $4\text{ MHz}$ 、出力に負荷無し、ボーレート = $50$ kbit/s |     | 8   |          | mA            |

| $C_i(\text{CLK})$ クロック入力容量    | $k\text{bit/s}$<br>$V_{CC} = 0, V_{SS} = 0,$<br>$f = 1\text{MHz}$<br>$T_A = 25^\circ\text{C}$<br>他のすべての端子はグランド接続                                         | 15  | 20  |          | pF            |

| $C_o(\text{CLK})$ クロック出力容量    |                                                                                                                                                          | 20  | 30  |          | pF            |

| $C_i$ 入力容量                    |                                                                                                                                                          | 6   | 10  |          | pF            |

| $C_o$ 出力容量                    |                                                                                                                                                          | 10  | 20  |          | pF            |

† すべての標準値は  $V_{CC} = 2.5V$  および  $T_A = 25^\circ\text{C}$  です。

‡ これらのパラメータは XOUT 以外のすべての出力に適用されます。

### 3.3 V 公称値

| パラメータ                         | テスト条件                                                                                                                                                    | 最小  | 標準† | 最大       | 単位            |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|---------------|

| $V_{OH}^{\dagger}$ ハイ・レベル出力電圧 | $I_{OH} = -1.8 \text{ mA}$                                                                                                                               | 2.4 |     |          | V             |

| $V_{OL}^{\dagger}$ ロー・レベル出力電圧 | $I_{OL} = 3.2 \text{ mA}$                                                                                                                                |     | 0.5 |          | V             |

| $I_i$ 入力電流                    | $V_{CC} = 3.6V$ $V_{SS} = 0$<br>$V_i = 0 \sim 3.6V$<br>他のすべての端子は、フローティング                                                                                 |     | 10  |          | $\mu\text{A}$ |

| $I_{OZ}$ ハイ・インピーダンス出力電流       | $V_{CC} = 3.6V$ $V_{SS} = 0$<br>$V_o = 0 \sim 3.6V$<br>書き込みモードでチップを選択またはチップは、非選択。                                                                        |     |     | $\pm 20$ | $\mu\text{A}$ |

| $I_{CC}$ 電源電流                 | $V_{CC} = 3.6V$ $T_A = 25^\circ\text{C}$<br>$SIN, DSR, DCD, CTS$ および $RI$ は $2V$<br>他のすべての入力は $0.8V$ 、XTAL1は $4\text{ MHz}$ 、出力に負荷無し、ボーレート = $50$ kbit/s |     | 8   |          | mA            |

| $C_i(\text{CLK})$ クロック入力容量    | $V_{CC} = 0, V_{SS} = 0,$<br>$f = 1\text{MHz}$<br>$T_A = 25^\circ\text{C}$<br>他のすべての端子はグランド接続                                                            | 15  | 20  |          | pF            |

| $C_o(\text{CLK})$ クロック出力容量    |                                                                                                                                                          | 20  | 30  |          | pF            |

| $C_i$ 入力容量                    |                                                                                                                                                          | 6   | 10  |          | pF            |

| $C_o$ 出力容量                    |                                                                                                                                                          | 10  | 20  |          | pF            |

† すべての標準値は  $V_{CC} = 3.3V$  および  $T_A = 25^\circ\text{C}$  です。

‡ これらのパラメータは XOUT 以外のすべての出力に適用されます。

# TL16C550D

# TL16C550DI

## UART

SLLS698

### 推奨電源電圧および推奨動作温度範囲の電気的特性(特に記載のない限り)(続き)

#### 5 V公称値

| パラメータ                         | テスト条件                                                                                                                               | 最小  | 標準†      | 最大 | 単位      |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------|----|---------|

| $V_{OH}^{\dagger}$ ハイ・レベル出力電圧 | $I_{OH} = -4\text{mA}$                                                                                                              | 4.0 |          |    | V       |

| $V_{OL}^{\dagger}$ ロー・レベル出力電圧 | $I_{OL} = 4\text{mA}$                                                                                                               |     | 0.4      |    | V       |

| $I_i$ 入力電流                    | $V_{CC} = 5.25V$ $V_{SS} = 0$<br>$V_i = 0 \sim 5.25V$<br>他のすべての端子は、フローティング                                                          |     | 10       |    | $\mu A$ |

| $I_{OZ}$ ハイ・インピーダンス出力電流       | $V_{CC} = 5.25V$ $V_{SS} = 0$<br>$V_o = 0 \sim 5.25V$<br>書き込みモードでチップを選択またはチップは、非選択。                                                 |     | $\pm 20$ |    | $\mu A$ |

| $I_{CC}$ 電源電流                 | $V_{CC} = 5.25V$ $T_A = 25^\circ C$<br>$SIN, DSR, DCD, CTS$ および $RI$ は $2V$<br>他のすべての入力は $0.8V$ 、XTAL1 は $4MHz$ 、出力に負荷無し、ボーレート = 50 |     | 10       |    | mA      |

| $C_i(CLK)$ クロック入力容量           | kbit/s<br>$V_{CC} = 0, V_{SS} = 0,$<br>$f = 1MHz$<br>他のすべての端子はグランド接続                                                                | 15  | 20       |    | pF      |

| $C_o(CLK)$ クロック出力容量           |                                                                                                                                     | 20  | 30       |    | pF      |

| $C_i$ 入力容量                    |                                                                                                                                     | 6   | 10       |    | pF      |

| $C_o$ 出力容量                    |                                                                                                                                     | 10  | 20       |    | pF      |

†すべての標準値は  $V_{CC} = 5V$  および  $T_A = 25^\circ C$  です。

‡これらのパラメータは XOUT 以外のすべての出力に適用されます。

## 推奨電源電圧および推奨動作温度範囲のシステム・タイミング条件

| パラメータ                                               | 略号        | 図番   | テスト条件                                        | 最小 | 最大 | 単位            |

|-----------------------------------------------------|-----------|------|----------------------------------------------|----|----|---------------|

| $t_{cR}$ サイクルタイム、読み取り( $t_{w7} + t_{d8} + t_{d9}$ ) | RC        |      |                                              | 87 |    | ns            |

| $t_{cW}$ サイクルタイム、書き込み( $t_{w6} + t_{d5} + t_{d6}$ ) | WC        |      |                                              | 87 |    | ns            |

| $t_{w1}$ パルス期間、クロック・ハイ                              | $t_{XH}$  | 5    | $f = 16 \text{ MHz Max.}$<br>$V_{cc} = 2.5V$ | 25 |    | ns            |

| $t_{w2}$ パルス期間、クロック・ロー                              | $t_{XL}$  |      |                                              |    |    |               |

| $t_{w1}$ パルス期間、クロック・ハイ                              | $t_{XH}$  | 5    | $f = 20 \text{ MHz Max.}$<br>$V_{cc} = 3.3V$ | 20 |    | ns            |

| $t_{w2}$ パルス期間、クロック・ロー                              | $t_{XL}$  |      |                                              |    |    |               |

| $t_{w1}$ パルス期間、クロック・ハイ                              | $t_{XH}$  | 5    | $f = 24 \text{ MHz Max.}$<br>$V_{cc} = 5V$   | 18 |    | ns            |

| $t_{w2}$ パルス期間、クロック・ロー                              | $t_{XL}$  |      |                                              |    |    |               |

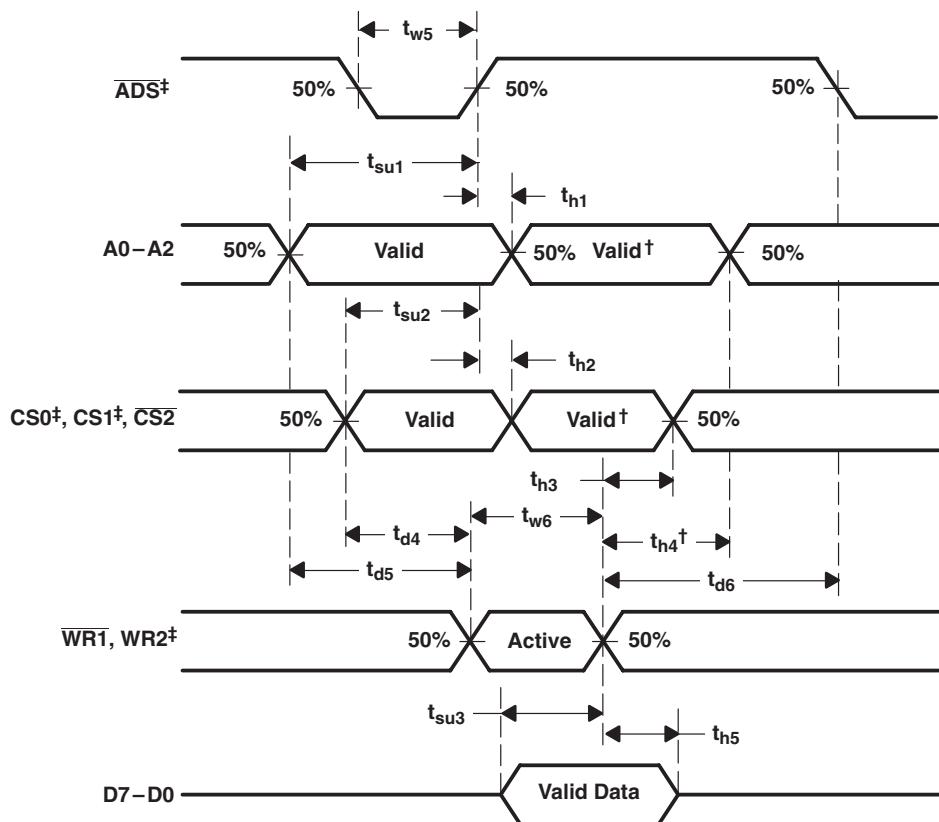

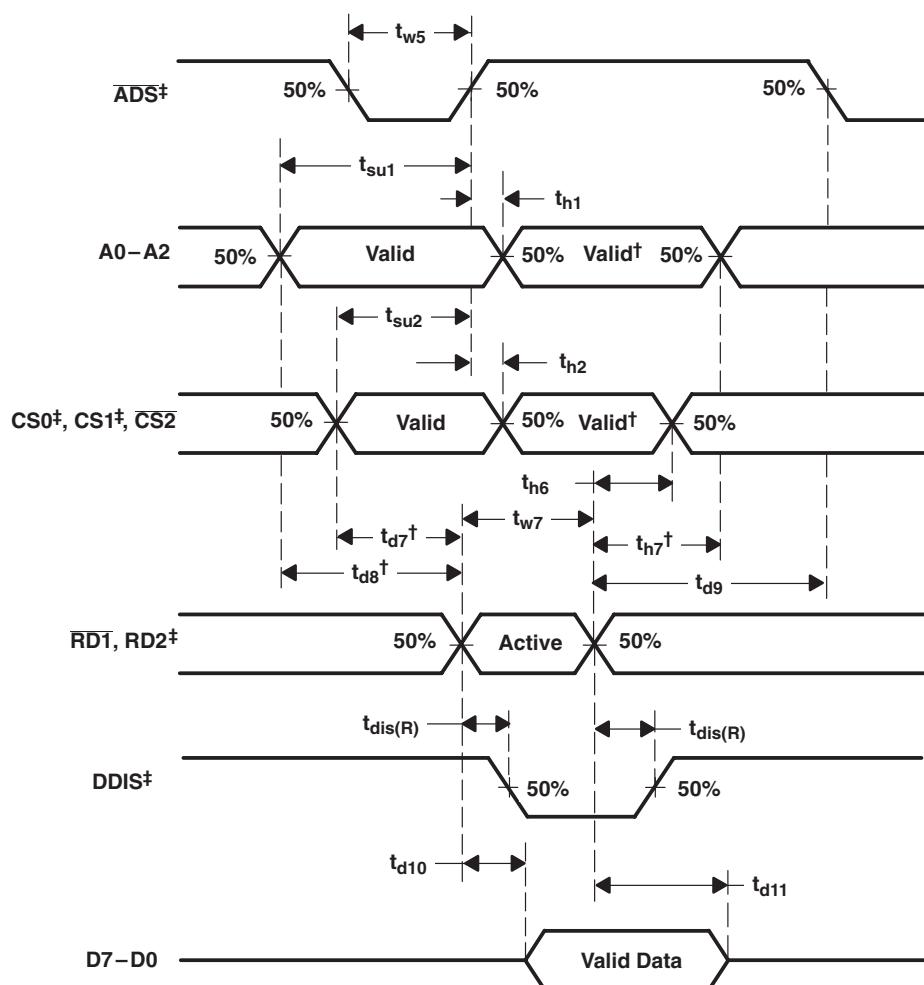

| $t_{w5}$ パルス期間、ADS ロー                               | $t_{ADS}$ | 6, 7 |                                              | 9  |    | ns            |

| $t_{w6}$ パルス期間、WR                                   | $t_{WR}$  | 6    |                                              | 40 |    | ns            |

| $t_{w7}$ パルス期間、RD                                   | $t_{RD}$  | 7    |                                              | 40 |    | ns            |

| $t_{w8}$ パルス期間、MR                                   | $t_{MR}$  |      |                                              | 1  |    | $\mu\text{s}$ |

| $t_{su1}$ セットアップ時間、ADS ↑前に有効なアドレス                   | $t_{AS}$  | 6, 7 |                                              | 8  |    | ns            |

| $t_{su2}$ セットアップ時間、ADS ↑前に有効な CS アドレス               | $t_{CS}$  |      |                                              |    |    |               |

| $t_{su3}$ セットアップ時間、WR1 ↑または WR2 ↓前に有効なデータ           | $t_{DS}$  | 6    |                                              | 15 |    | ns            |

| $t_{su4}$ セットアップ時間、ストップビットの真ん中前の CTS ↑              |           | 17   |                                              | 10 |    | ns            |

| $t_{h1}$ ホールド時間、ADS ↑後のアドレス・ロー                      | $t_{AH}$  | 6, 7 |                                              | 0  |    | ns            |

| $t_{h2}$ ホールド時間、ADS ↑後に有効な CS                       | $t_{CH}$  |      |                                              |    |    |               |

| $t_{h3}$ ホールド時間、WR1 ↑または WR2 ↓後に有効な CS              | $t_{WCS}$ | 6    |                                              | 10 |    | ns            |

| $t_{h4}$ ホールド時間、WR1 ↑または WR2 ↓後に有効なアドレス             | $t_{WA}$  |      |                                              |    |    |               |

| $t_{h5}$ ホールド時間、WR1 ↑または WR2 ↓後に有効なデータ              | $t_{DH}$  | 6    |                                              | 5  |    | ns            |

| $t_{h6}$ ホールド時間、RD1 ↑または RD2 ↓後に有効な CS              | $t_{RCS}$ | 7    |                                              | 10 |    | ns            |

| $t_{h7}$ ホールド時間、RD1 ↑または RD2 ↓後に有効なアドレス             | $t_{RA}$  | 7    |                                              | 20 |    | ns            |

| $t_{d4}^+$ 遅延時間、WR1 ↑または WR2 ↓前に有効な CS              | $t_{CSW}$ | 6    |                                              | 7  |    | ns            |

| $t_{d5}^+$ 遅延時間、WR1 ↑または WR2 ↓前に有効なアドレス             | $t_{AW}$  |      |                                              |    |    |               |

| $t_{d6}^+$ 遅延時間、ライトサイクル、ADS ↓に対する WR1 ↑または WR2 ↓    | $t_{WC}$  | 6    |                                              | 40 |    | ns            |

| $t_{d7}^+$ 遅延時間、RD1 ↓または RD2 ↑への有効な CS              | $t_{CSR}$ | 7    |                                              | 7  |    | ns            |

| $t_{d8}^+$ 遅延時間、RD1 ↓または RD2 ↑への有効なアドレス             | $t_{AR}$  |      |                                              |    |    |               |

| $t_{d9}^+$ 遅延時間、リードサイクル、ADS ↓に対する RD1 ↑または RD2 ↓    | $t_{RC}$  | 7    |                                              | 40 |    | ns            |

| $t_{d10}^+$ 遅延時間、有効データへの RD1 ↓または RD2 ↑             | $t_{RVD}$ | 7    | $C_L = 75 \text{ pF}$                        | 45 |    | ns            |

| $t_{d11}^+$ 遅延時間、フローティングデータへの RD1 ↑または RD2 ↓        | $t_{HZ}$  | 7    | $C_L = 75 \text{ pF}$                        | 20 |    | ns            |

† ADS が低い場合のみ適用します。

## 推奨電源電圧および推奨動作温度範囲のシステム・スイッチング特性(注2 参照)

| パラメータ                                              | 略号        | 図番 | テスト条件                 | 最小 | 最大 | 単位 |

|----------------------------------------------------|-----------|----|-----------------------|----|----|----|

| $t_{dis(R)}$ ディスイネーブル時間、DDIS ↑↓への RD1 ↓↑または RD2 ↑↓ | $t_{RDD}$ | 7  | $C_L = 75 \text{ pF}$ | 20 |    | ns |

注 2: 充電・放電時間は  $V_{OL}$ 、 $V_{OH}$ 、および外部負荷で決まります。

# TL16C550D

# TL16C550DI

## UART

SLLS698

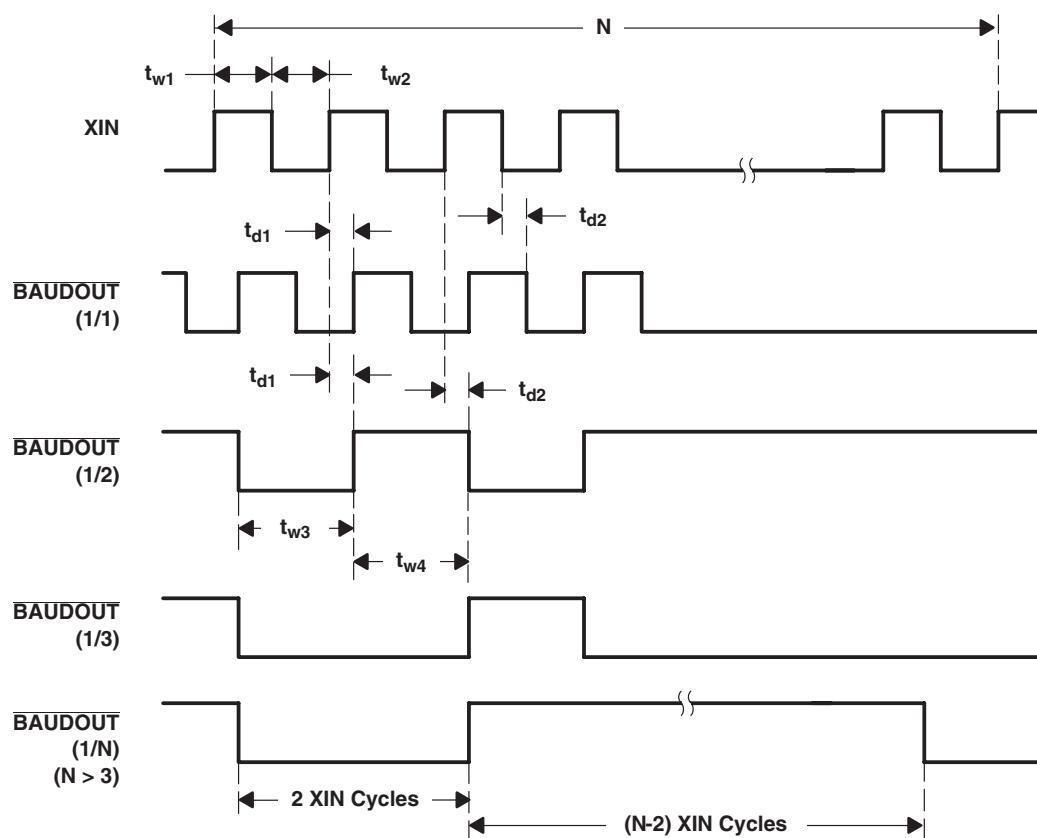

### 推奨電源電圧および推奨動作温度範囲および $C_L = 75\text{pF}$ でのボーナス・ジェネレータのスイッチング特性(PT および PFB パッケージのみ)

| パラメータ                                                                         | 略号        | 図番 | テスト条件                                                               | 最小 | 最大 | 単位 |

|-------------------------------------------------------------------------------|-----------|----|---------------------------------------------------------------------|----|----|----|

| $t_{w3}$ パルス期間、 $\overline{\text{BAUDOUT}}$ ロー                                | $t_{LW}$  | 5  | $f = 24\text{ MHz}$ ,<br>$\text{CLK} \div 2$ , $V_{CC} = 5\text{V}$ | 35 |    | ns |

| $t_{w4}$ パルス期間、 $\overline{\text{BAUDOUT}}$ ハイ                                | $t_{HW}$  | 5  |                                                                     |    |    |    |

| $t_{d1}$ 遅延時間、 $XIN \uparrow$ に対する $\overline{\text{BAUDOUT}}$ $\uparrow$     | $t_{BLD}$ | 5  |                                                                     | 45 |    | ns |

| $t_{d1}$ 遅延時間、 $XIN \downarrow$ に対する $\overline{\text{BAUDOUT}}$ $\downarrow$ | $t_{BHD}$ | 5  |                                                                     | 45 |    | ns |

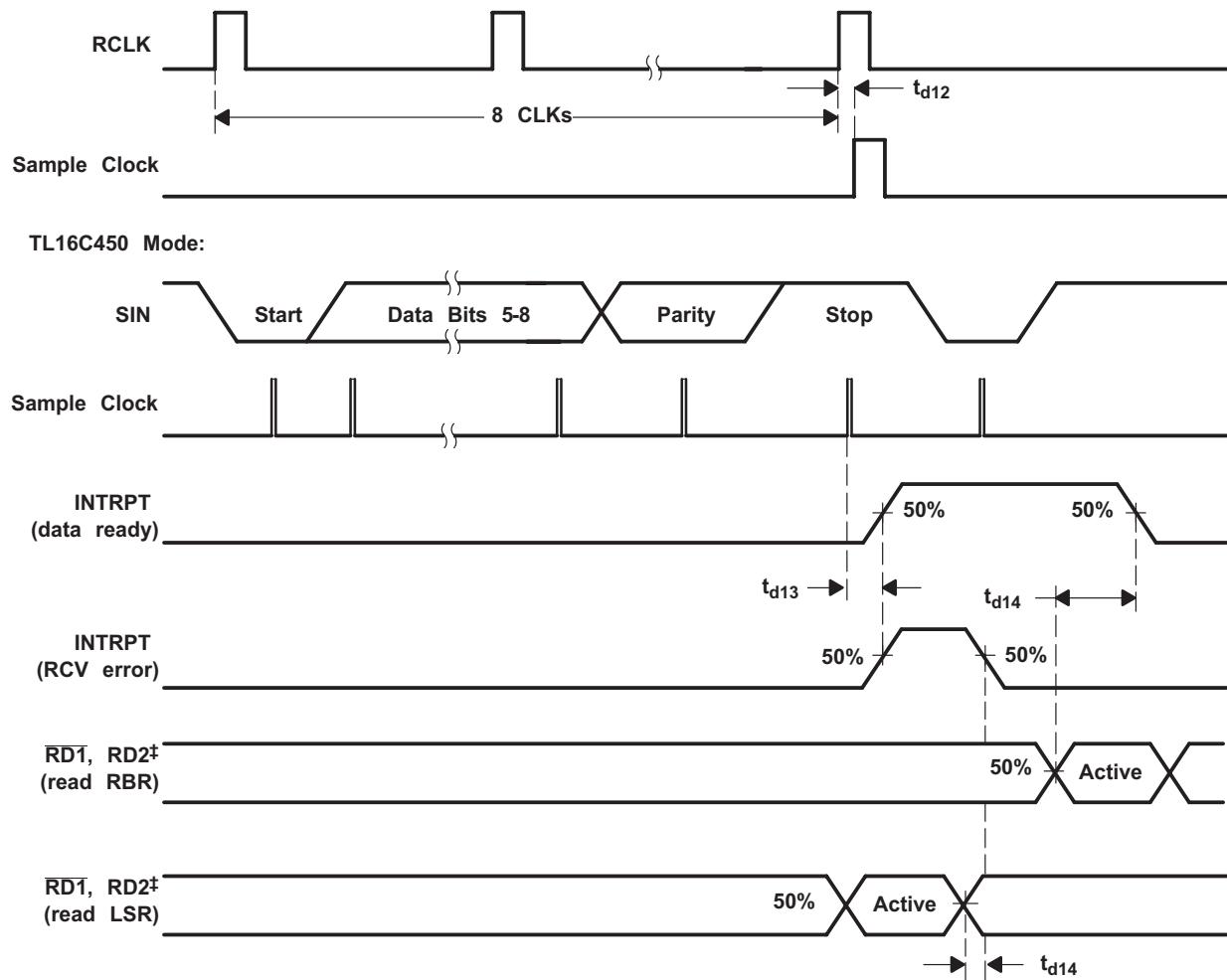

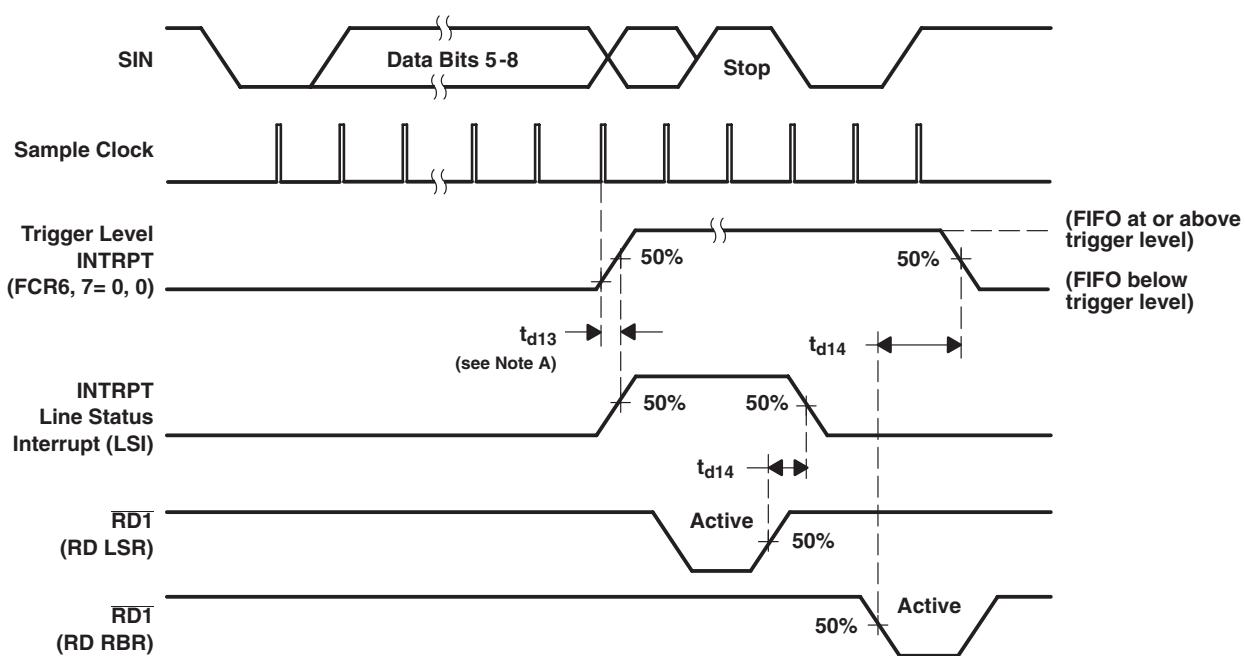

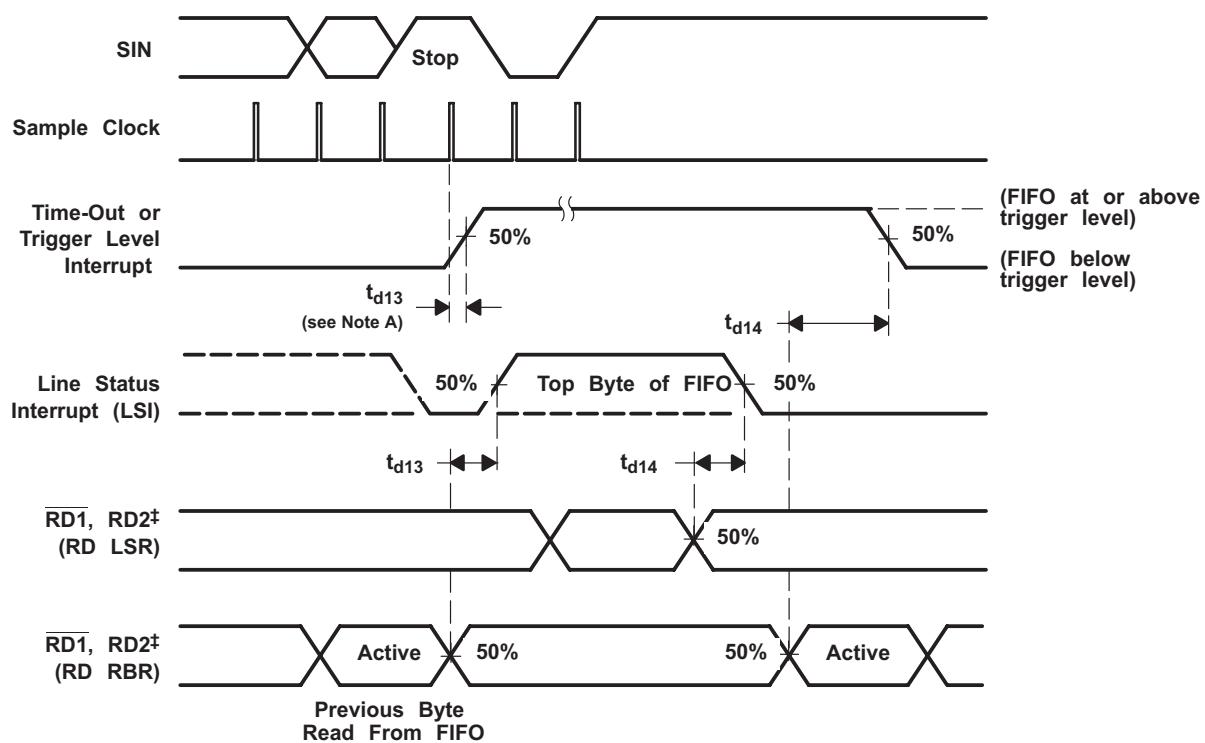

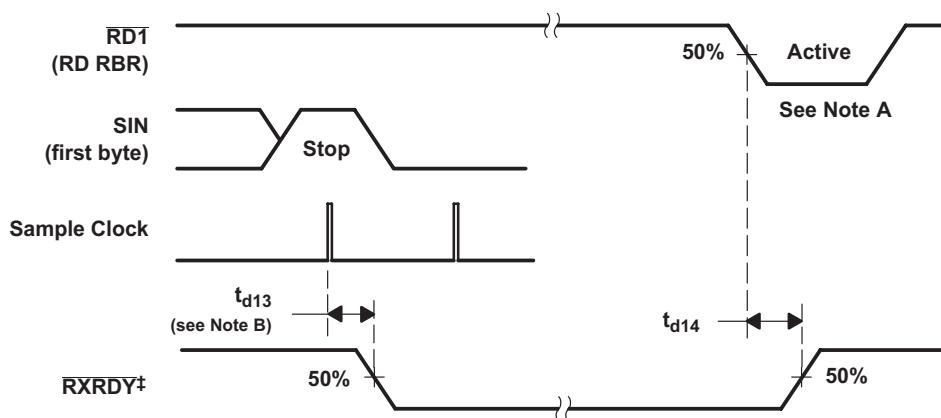

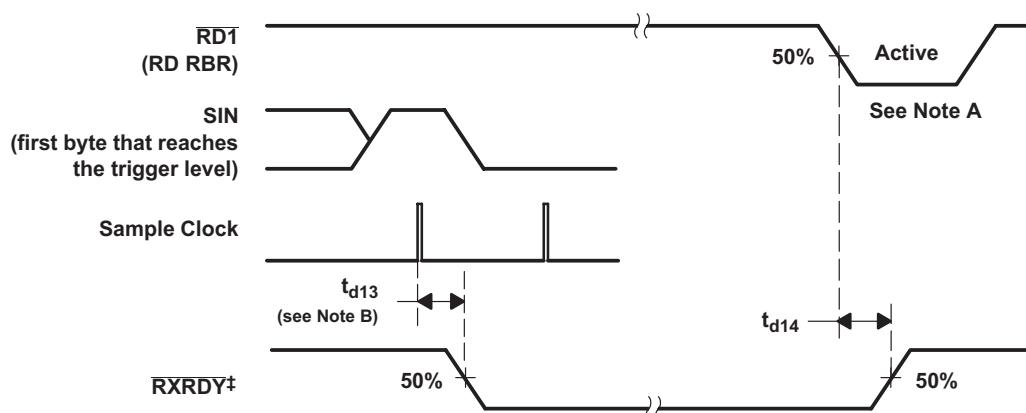

### 推奨電源電圧および推奨動作温度範囲でのレシーバのスイッチング特性(注 3 参照)

| パラメータ                                                                                              | 略号         | 図番                  | テスト条件                | 最小 | 最大 | 単位           |

|----------------------------------------------------------------------------------------------------|------------|---------------------|----------------------|----|----|--------------|

| $t_{d12}$ 遅延時間、 $\text{RCLK}$ に対するサンプル                                                             | $t_{SCD}$  | 8                   |                      | 10 |    | ns           |

| $t_{d13}$ 遅延時間、Stop から INTRPT または RBR 読み取りから LSI 割り込み、Stop から $\overline{\text{RXRDY}} \downarrow$ | $t_{SINT}$ | 8, 9, 10,<br>11, 12 |                      | 1  |    | RCLK<br>サイクル |

| $t_{d14}$ 遅延時間、RBR/LSR 読み取りから INTRPT のリセット                                                         | $t_{RINT}$ | 8, 9, 10,<br>11, 12 | $C_L = 75\text{ pF}$ | 70 |    | ns           |

注 3: FIFOモードでは、受信FIFOおよびステータスレジスタ(割り込み識別レジスタまたはライン・ステータス・レジスタ)の読み取りサイクル( $RC = 425\text{ ns}$  (min))。

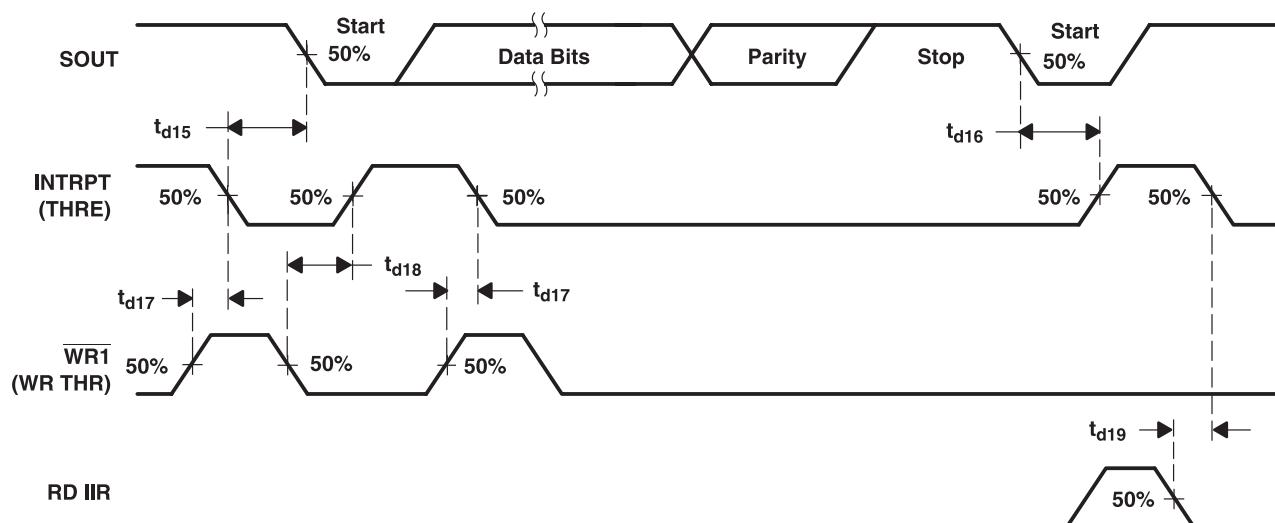

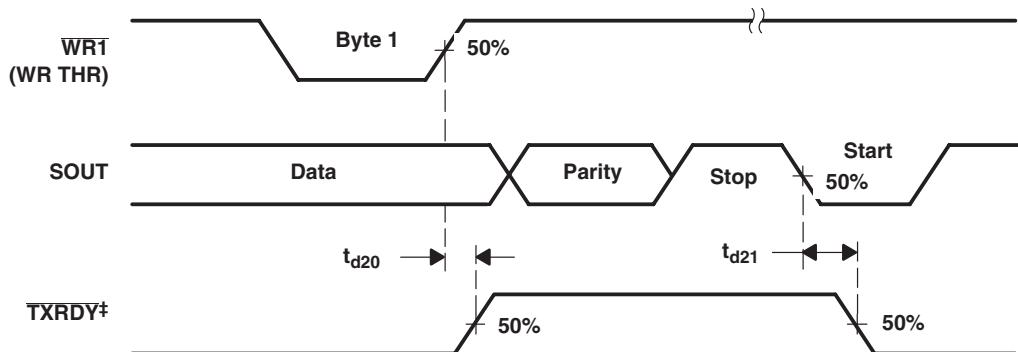

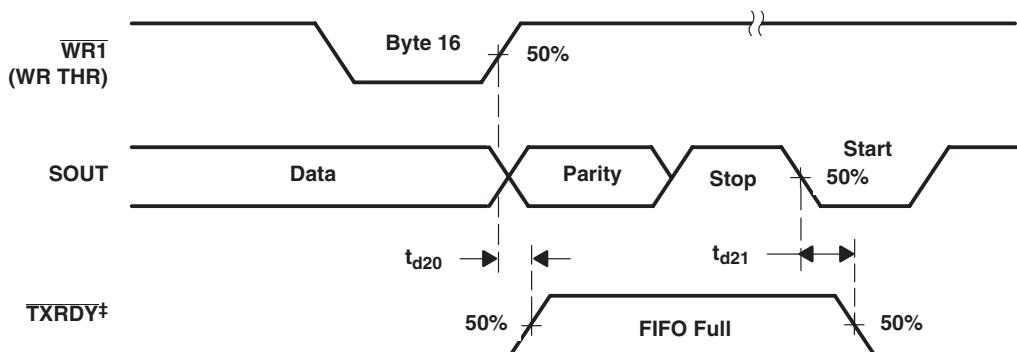

### 推奨電源電圧および推奨動作温度範囲でのトランスマッタのスイッチング特性

| パラメータ                                                                  | 略号        | 図番     | テスト条件                | 最小 | 最大 | 単位             |

|------------------------------------------------------------------------|-----------|--------|----------------------|----|----|----------------|

| $t_{d15}$ 遅延時間、初期書き込みから送信開始                                            | $t_{IRS}$ | 13     |                      | 8  | 24 | ボーアウト・<br>サイクル |

| $t_{d16}$ 遅延時間、INTRPT 開始                                               | $t_{STI}$ | 13     |                      | 8  | 10 | ボーアウト・<br>サイクル |

| $t_{d17}$ 遅延時間、 $\overline{\text{WR1}}(\text{WR THR})$ から INTRPT をリセット | $t_{HR}$  | 13     | $C_L = 75\text{ pF}$ | 50 |    | ns             |

| $t_{d18}$ 遅延時間、初期書き込みから INTRPT (THRE <sup>†</sup> )                    | $t_{SI}$  | 13     |                      | 16 | 34 | ボーアウト・<br>サイクル |

| $t_{d19}$ 遅延時間、IIR + 読み取りから INTRPT (THRE <sup>†</sup> )をリセット           | $t_{IR}$  | 13     | $C_L = 75\text{ pF}$ | 35 |    | ns             |

| $t_{d20}$ 遅延時間、書き込みから $\overline{\text{TXRDY}}$ 非アクティブ                 | $t_{WXI}$ | 14, 15 | $C_L = 75\text{ pF}$ | 35 |    | ns             |

| $t_{d21}$ 遅延時間、書き込み開始から $\overline{\text{TXRDY}}$ アクティブ                | $t_{SXA}$ | 14, 15 | $C_L = 75\text{ pF}$ | 9  |    | ボーアウト・<br>サイクル |

† THRE = トランスマッタ・ホールディング・レジスタ・エンブティ、IIR = 割り込み識別レジスタ

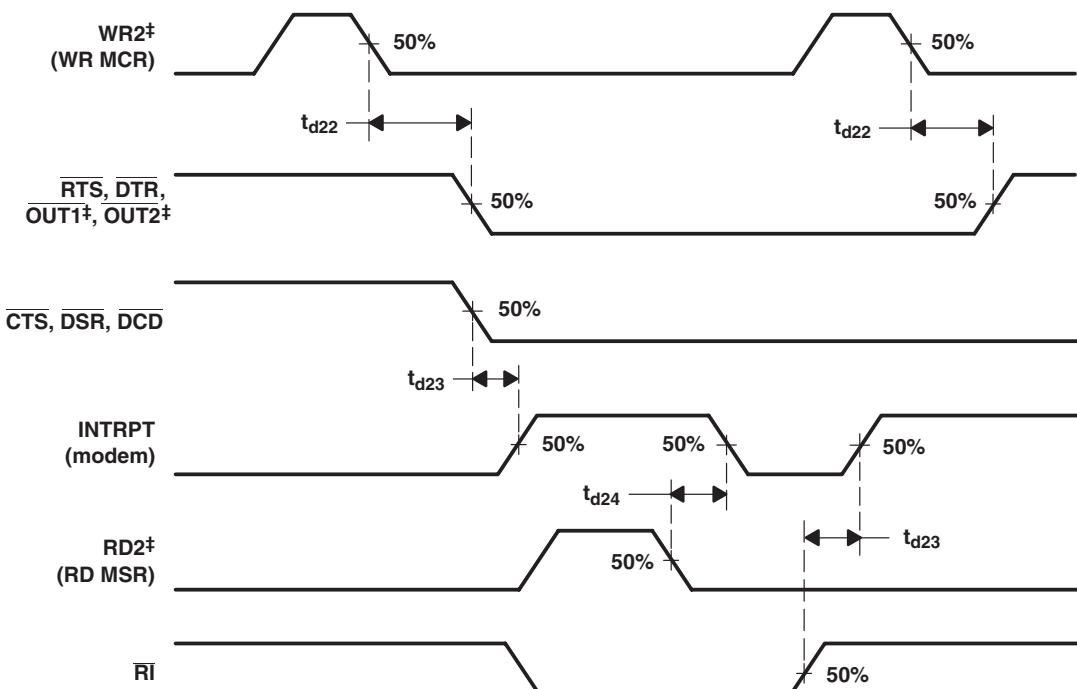

**推奨電源電圧および推奨動作温度範囲の特徴を切り替えるモード制御、 $C_L=75\text{pF}$**

| パラメータ                                                            | 略号        | 図番 | 最小 | 最大 | 単位          |

|------------------------------------------------------------------|-----------|----|----|----|-------------|

| $t_{d22}$ 遅延時間、WR2 MCR から OUTPUT                                 | $t_{MDO}$ | 16 | 50 | ns |             |

| $t_{d23}$ 遅延時間、モデム割り込みから INTRPT セット                              | $t_{SIM}$ | 16 | 35 | ns |             |

| $t_{d24}$ 遅延時間、RD2 MSR から INTRPT リセット                            | $t_{RIM}$ | 16 | 40 | ns |             |

| $t_{d25}$ 遅延時間、 $\overline{\text{CTS}}$ ローから SOUT ↓              |           | 17 | 24 |    | ポートアウト・サイクル |

| $t_{d26}$ 遅延時間、RCV 閾値バイトから $\overline{\text{RTS}}$ ↑             |           | 18 | 2  |    | ポートアウト・サイクル |

| $t_{d27}$ 遅延時間、受信 FIFO の最終バイトの読み取りから $\overline{\text{RTS}}$ ↓   |           | 18 | 2  |    | ポートアウト・サイクル |

| $t_{d28}$ 遅延時間、16 番目のキャラクタの最初のデータビットから $\overline{\text{RTS}}$ ↑ |           | 19 | 2  |    | ポートアウト・サイクル |

| $t_{d29}$ 遅延時間、RBR リードから $\overline{\text{RTS}}$ ↓               |           | 19 | 2  |    | ポートアウト・サイクル |

## パラメータ測定情報

図5. ボー・ジェネレータ・タイミング波形(PTおよびPFBパッケージのみ)

## パラメータ測定情報

†  $\overline{ADS}$  がローの時にのみ適用されます。

‡  $\overline{ADS}$ , CS0, CS1 および WR2 信号は、PT および PFB パッケージにのみ適用されます。

図 6. 書き込みサイクル・タイミング波形

## パラメータ測定情報

†  $\overline{ADS}$  がローの時にのみ適用されます。

‡  $\overline{ADS}$ , CS0, CS1, DDIS および RD2 信号は、PT および PFB パッケージにのみ適用されます。

**図 7. 読み取りサイクル・タイミング波形**

## パラメータ測定情報

‡ RD2 信号は、PT および PFB パッケージにのみ適用されます。

図 8. レシーバ・タイミング波形

## パラメータ測定情報

注A: タイムアウト割り込みについて、 $t_{d13} = 9$  RCLKs.

図9. 受信 FIFO ファースト・バイト(DR ビットセット) 波形

### パラメータ測定情報

‡ RD2 信号は、PT および PFB パッケージにのみ適用されます。

注 A: タイムアウト割り込みについて、 $t_{d13} = 9$  RCLKs.

図 10. ファーストバイト以外の受信 FIFO バイト(すでに設定済みの DR 内部ビット)波形

‡ RXRDY 信号は、PT および PFB パッケージにのみ適用されます。

注: A. これは、FIFO の最後のバイトの読み取りです。

B: タイムアウト割り込みについて、 $t_{d13} = 9$  RCLKs.

図 11. レシーバ・レディ(RXRDY)波形、FCR0 = 0 または FCR0 = 1 および FCR3 = 0 (モード 0)

## パラメータ測定情報

† RXRDY 信号は、PT および PFB パッケージにのみ適用されます。

注: A. これは、FIFO の最後のバイトの読み取りです。

B: タイムアウト割り込みについて、 $t_{d13} = 9$  RCLKs.

図 12. レシーバ・レディ (RXRDY) 波形、FCR0 = 1 および FCR3 = 1 (モード 1)

図 13. トランスマッタ・タイミング波形

### パラメータ測定情報

‡ TXRDY 信号は、PT および PFB パッケージにのみ適用されます。

図 14. トランスマッタ・レディ(TXRDY)波形、

FCR0 = 0 または FCR0 = 1 および FCR3 = 0 (モード 0)

‡ TXRDY 信号は、PT および PFB パッケージにのみ適用されます。

図 15. トランスマッタ・レディ(TXRDY)波形、FCR0 = 1 および FCR3 = 1 (モード 1)

## パラメータ測定情報

‡ OUT1、OUT2、RD2 および WR2 信号は、PT および PFB パッケージにのみ適用されます。

図 16. モデム制御タイミング波形

図 17. CTS および SOUT 自動フロー制御タイミング(開始およびストップ)波形

図 18. RCV 閾値 1、4、または 8 の時の自動-RTS タイミング波形

## パラメータ測定情報

図 19. RCV 閾値 14 の時の自動 -RTS タイミング波形

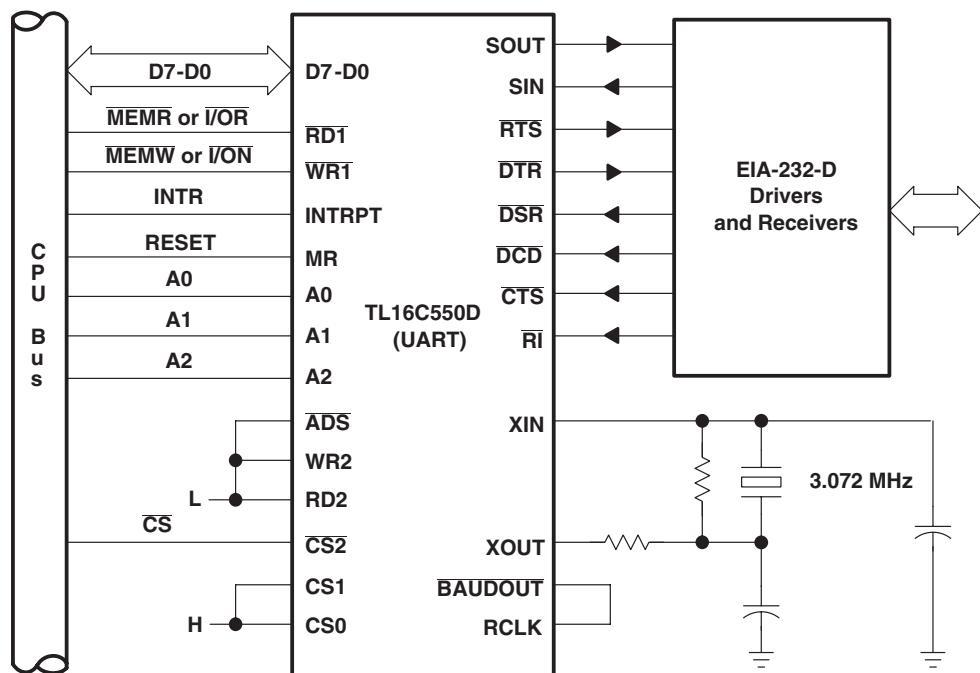

## アプリケーション情報

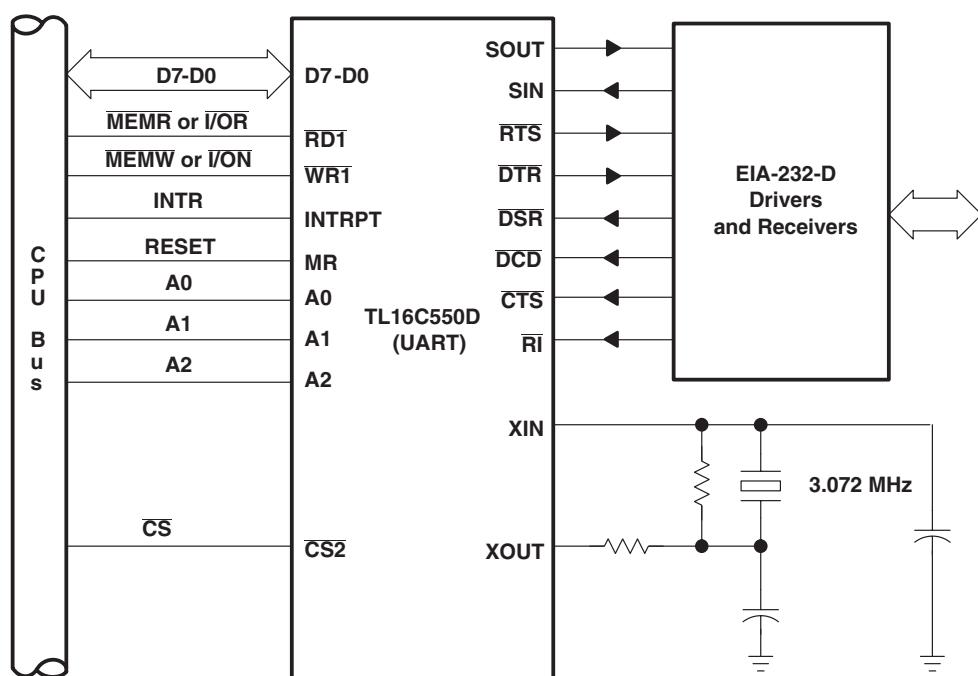

図 20. 基本 TL16C550D コンフィギュレーション (PT および PFB パッケージ用)

## アプリケーション情報

図21. 基本TL16C550Dコンフィギュレーション(RHBパッケージ用)

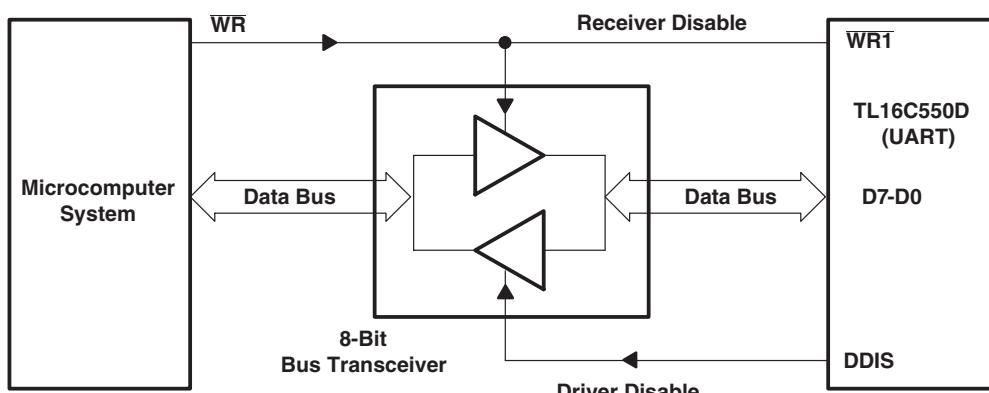

図22. 高負荷データバスの代表的なインターフェース例

## アプリケーション情報

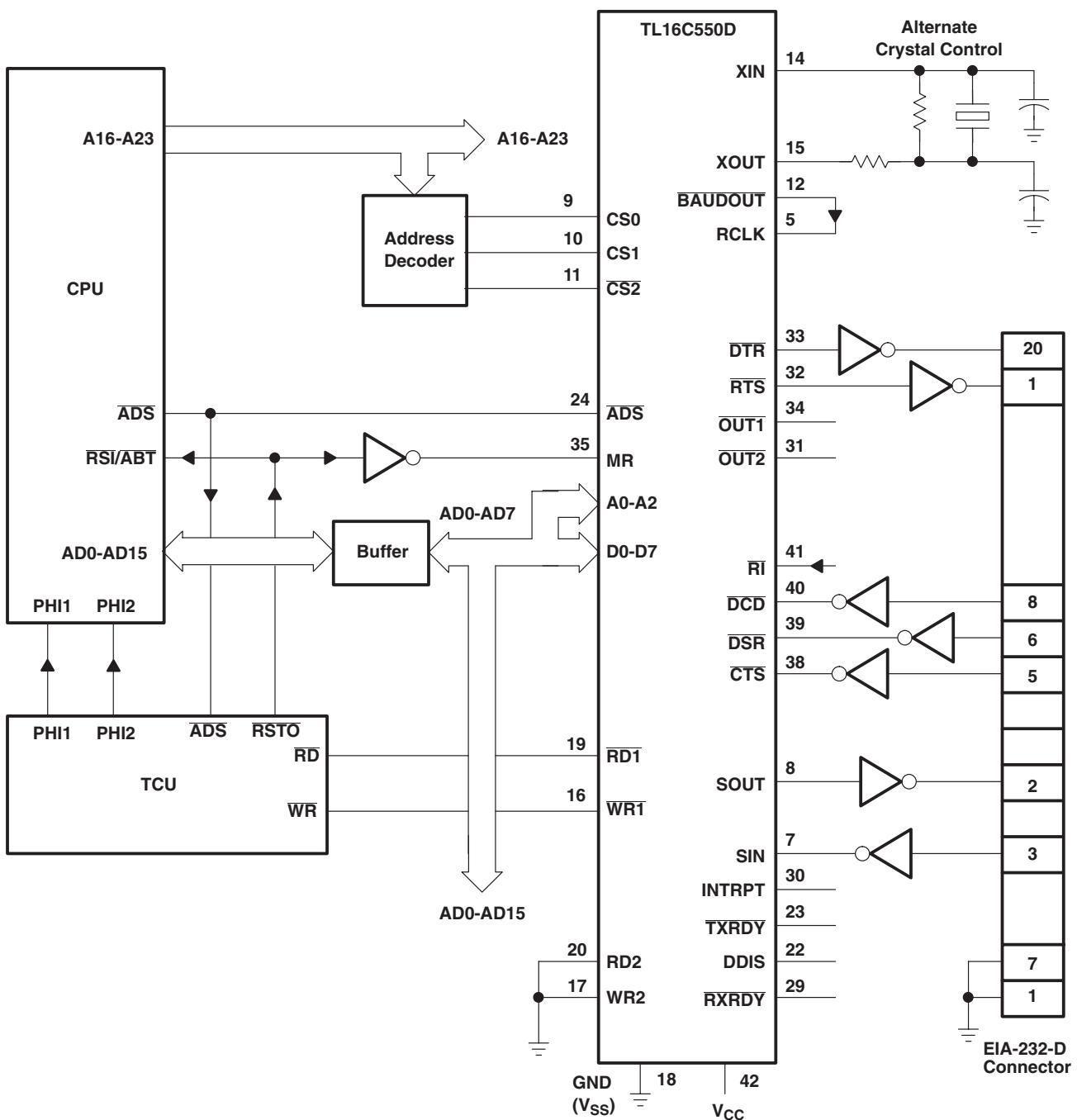

図 23. TL16C550D の CPU への代表的な接続例(PT および PFB パッケージ用)

## アプリケーション情報

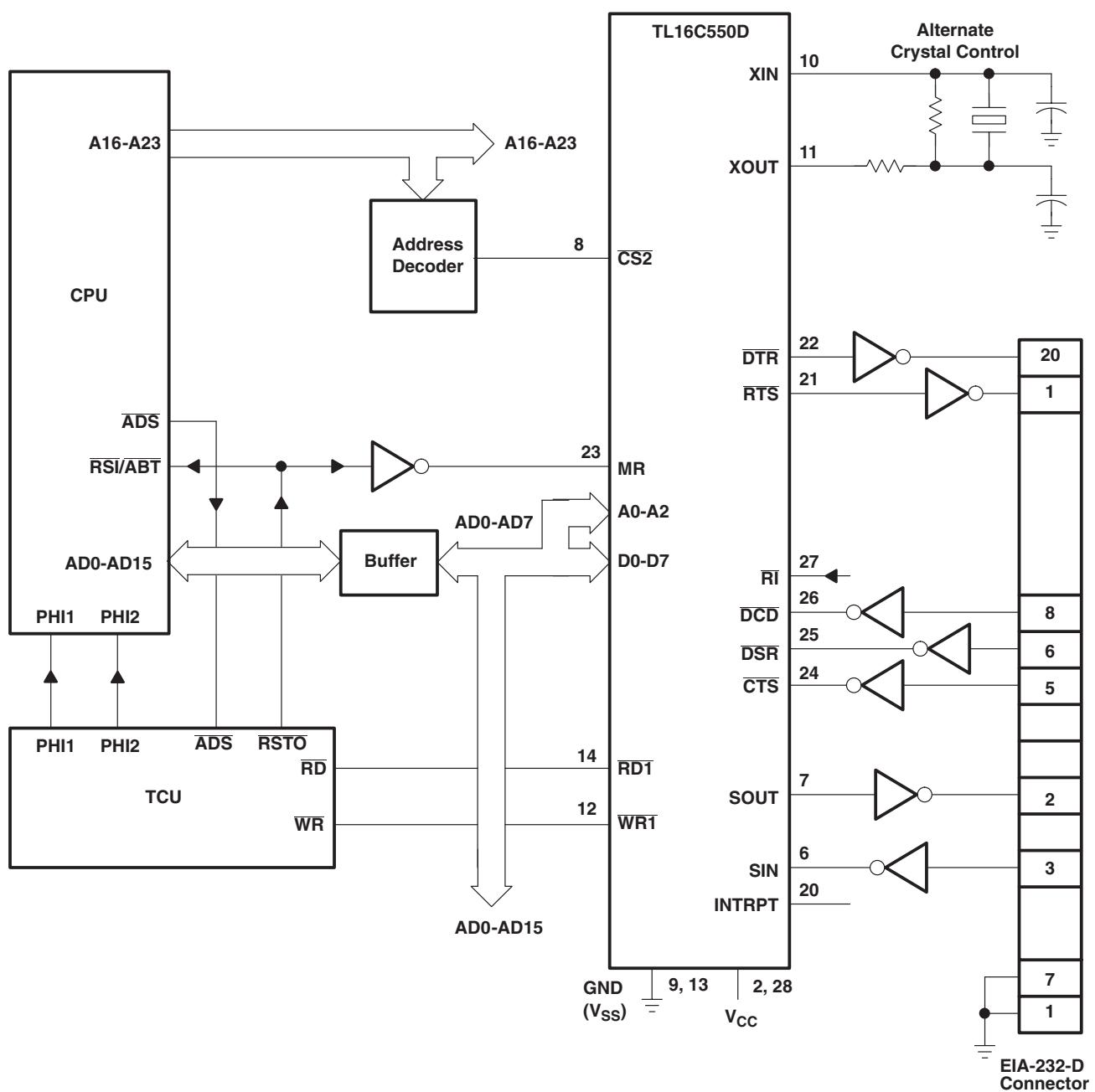

図 24. TL16C550D の CPU への代表的な接続例(RHB パッケージ用)

## 操作方法

**表 1. レジスタ選択**

| DLAB <sup>†</sup> | A2 | A1 | AO | レジスタ                                       |

|-------------------|----|----|----|--------------------------------------------|

| 0                 | L  | L  | L  | レシーバ・バッファ(読み取り)、トランスマッタ・ホールディング・レジスタ(書き込み) |

| 0                 | L  | L  | H  | 割り込みイネーブルレジスタ                              |

| X                 | L  | H  | L  | 割り込み識別レジスタ(読み取り)                           |

| X                 | L  | H  | L  | FIFO 制御レジスタ(書き込み)                          |

| X                 | L  | H  | H  | ライン制御レジスタ                                  |

| X                 | H  | L  | L  | モデム制御レジスタ                                  |

| X                 | H  | L  | H  | ライン・ステータス・レジスタ                             |

| X                 | H  | H  | L  | モデム・ステータス・レジスタ                             |

| X                 | H  | H  | H  | スクラッチ・レジスタ                                 |

| 1                 | L  | L  | L  | ディバイザ・ラッチ(LSB)                             |

| 1                 | L  | L  | H  | ディバイザ・ラッチ(MSB)                             |

† ディバイザ・ラッチ・アクセスビット(DLAB)は、ライン制御レジスタのMSBビットです。このビットへ書き込むことで DLAB 信号は、制御されます。(表 3 参照)。

**表 2. UART リセット機能**

| レジスタ / 信号                           | リセット制御                | リセット時の状態                                            |

|-------------------------------------|-----------------------|-----------------------------------------------------|

| 割り込みイネーブルレジスタ                       | マスター・リセット             | すべてのビットがクリアされます(0-3 強制および 4-7 常に 0)                 |

| 割り込み認識レジスタ                          | マスター・リセット             | ビット 0 が設定され、ビット 1、2、3、6、および 7 がクリアされ、ビット 4-5 は常に 0。 |

| FIFO 制御レジスタ                         | マスター・リセット             | すべてのビットがクリアされます。                                    |

| ライン制御レジスタ                           | マスター・リセット             | すべてのビットがクリアされます。                                    |

| モデム制御レジスタ                           | マスター・リセット             | すべてのビットがクリアされます。(6-7 は常に 0)                         |

| ライン・ステータス・レジスタ                      | マスター・リセット             | ビット 5 および 6 がセットされ、他のすべてのビットがクリアされる。                |

| モデム・ステータス・レジスタ                      | マスター・リセット             | ビット 0-3 はクリアされる。ビット 4-7 は入力信号です。                    |

| SOUT                                | マスター・リセット             | ハイ                                                  |

| INTRPT (レシーバ・エラー・フラグ)               | LSR/MR 読み取り           | ロー                                                  |

| INTRPT (受信データ在り)                    | RBR/MR 読み取り           | ロー                                                  |

| INTRPT (トランスマッタ・ホールディング・レジスタ・エンブティ) | IR 読み取り / THR/MR 書き込み | ロー                                                  |

| INTRPT (モデム・ステータス変化)                | MSR/MR 読み取り           | ロー                                                  |

| OUT2                                | マスター・リセット             | ハイ                                                  |

| RTS                                 | マスター・リセット             | ハイ                                                  |

| DTR                                 | マスター・リセット             | ハイ                                                  |

| OUT1                                | マスター・リセット             | ハイ                                                  |

| スクラッチ・レジスタ                          | マスター・リセット             | 変化無し                                                |

| ディバイザ・ラッチ(LSB および MSB)レジスタ          | マスター・リセット             | 変化無し                                                |

| レシーバ・バッファ・レジスタ                      | マスター・リセット             | 変化無し                                                |

| トランスマッタ・ホールディング・レジスタ                | マスター・リセット             | 変化無し                                                |

| RCVR FIFO                           | MR/FCR1- FCRO/ΔFCRO   | すべてのビットがクリアされます。                                    |

| XMIT FIFO                           | MR/FCR2- FCRO/ΔFCRO   | すべてのビットがクリアされます。                                    |

# TL16C550D

# TL16C550DI

## UART

SLLS698

## 操作方法

### アクセス可能なレジスタ

CPUを使用するシステム・プログラマは、表2でまとめたUARTレジスタへのアクセスと制御を行います。これらのレジスタはUART動作、受信データ、送信データを制御します。これらのレジスタを表3にまとめます。

表3. アクセス可能なレジスタ要約

| ビット番号 | レジスタ・アドレス              |                              |                                            |                      |                    |                         |                    |                            |                            |            |                |                |

|-------|------------------------|------------------------------|--------------------------------------------|----------------------|--------------------|-------------------------|--------------------|----------------------------|----------------------------|------------|----------------|----------------|

|       | 0 DLAB = 0             | 0 DLAB = 0                   | 1 DLAB = 0                                 | 2                    | 2                  | 3                       | 4                  | 5                          | 6                          | 7          | 0 DLAB = 1     | 1 DLAB = 1     |

|       | レシーバ・バッファ・レジスタ(読み取りのみ) | トランスマッタ・ホールディング・レジスタ(書き込みのみ) | 割り込みイネーブルレジスタ                              | 割り込み識別レジスタ(読み取りのみ)   | FIFO制御レジスタ(書き込みのみ) | ライン制御レジスタ               | モデム制御レジスタ          | ライン・ステータス・レジスタ             | モデム・ステータス・レジスタ             | スクラッチ・レジスタ | ディバイザ・ラッチ(LSB) | ディバイザ・ラッチ(MSB) |

|       | RBR                    | THR                          | IER                                        | IIR                  | FCR                | LCR                     | MCR                | LSR                        | MSR                        | SCR        | DLL            | DLM            |

| 0     | データビット0†               | データビット0                      | 受信データ在り割り込みイネーブル(ERBI)                     | 0の場合<br>ペンドイング割り込み在り | FIFOイネーブル          | ワード長選択ビット0(WLS0)        | データ・ターミナル・レディ(DTR) | データ・レディ(DR)                | デルタ送信クリア(△CTS)             | ビット0       | ビット0           | ビット8           |

| 1     | データビット1                | データビット1                      | トランスマッタ・ホールディング・レジスタ・エンブティ割り込みイネーブル(ETBEI) | 割り込みIDビット1           | レシーバFIFOリセット       | ワード長選択ビット1(WLS1)        | 送信リクエスト(RTS)       | オーバーラン・エラー(OE)             | デルタ・データ設定レディ(△DSR)         | ビット1       | ビット1           | ビット9           |

| 2     | データビット2                | データビット2                      | レシーバライン・ステータス割り込みイネーブル(ELSI)               | 割り込みIDビット2           | トランスマッタFIFOリセット    | ストップ・ビット数(STB)          | OUT1               | パリティ・エラー(PE)               | トレーリング・エッジリング・インジケータ(TERI) | ビット2       | ビット2           | ビット10          |

| 3     | データビット3                | データビット3                      | モデム・ステータス割り込みイネーブル(EDSSI)                  | 割り込みIDビット3(注意4参照)    | DMAモード選択           | パリティ・イネーブル許可(PEN)       | OUT2               | フレーミング・エラー(FE)             | デルタ・データ・キャリア検出(△DCD)       | ビット3       | ビット3           | ビット11          |

| 4     | データビット4                | データビット4                      | 0                                          | 0                    | 予約                 | 偶数パリティ選択(EPS)           | ループ                | ブレーク割り込み(BI)               | 送信クリア(CTS)                 | ビット4       | ビット4           | ビット12          |

| 5     | データビット5                | データビット5                      | 0                                          | 0                    | 予約                 | スティック・パリティ              | 自動フロー制御イネーブル(AFE)  | トランスマッタ・ホールディング・レジスタ(THRE) | データ設定レディ(DSR)              | ビット5       | ビット5           | ビット13          |

| 6     | データビット6                | データビット6                      | 0                                          | FIFO使用イネーブル(注4参照)    | レシーバ・トリガー(LSB)     | ブレーク制御                  | 0                  | 送信エンブティ(TEMPT)             | リング・インジケータ(RI)             | ビット6       | ビット6           | ビット14          |

| 7     | データビット7                | データビット7                      | 0                                          | FIFO使用イネーブル(注4参照)    | レシーバ・トリガー(MSB)     | ディバイザ・ラッチ・アクセスビット(DLAB) | 0                  | RCVR FIFOエラー(注意4参照)        | データ・キャリア検出(DCD)            | ビット7       | ビット7           | ビット15          |

† ビット0が LSB ビットです。送信または受信される最初のビットです。

注4: これらのビットは、TL16C450モードでは必ず0です。

## 操作方法

### FIFO制御レジスタ(FCR)

FCRは、読み取り専用のIIRと同じアドレスにある、書き込み専用のレジスタです。FCRでFIFOをイネーブルやクリアしたり、レシーバFIFOトリガー・レベルを設定、DMA信号タイプを選択します。

- ビット0: このビットは、設定時、トランスマッタおよびレシーバFIFOをイネーブルします。他のFCRビットに書き込むためには、ビット0を設定することが必要です。そうでなければ、プログラムすることができません。このビットを変更することで、FIFOをクリアします。

- ビット1: このビットをセットするとレシーバFIFOの全バイトがクリアされ、そのカウンタもクリアされます。シフトレジスタはクリアされません。このビットに書き込まれた1は、セルフクリアします。

- ビット2: このビットをセットすると送信FIFOの全バイトがクリアされ、そのカウンタもクリアされます。シフトレジスタはクリアされません。このビットに書き込まれた1は、セルフクリアします。

- ビット3: FCROが1にセットされた場合、FCR3を1にすると、RXRDYおよびTXRDYがレベル0からレベル1に変わります。

- ビット4および5: これら二つのビットは、将来の使用に備えて予約されています。

- ビット6および7: これら二つのビットは、レシーバFIFO割り込みのトリガー・レベルを設定します（表4参照）。

表4. レシーバFIFOトリガー・レベル

| ビット7 | ビット6 | レシーバFIFOトリガー・レベル(バイト) |

|------|------|-----------------------|

| 0    | 0    | 01                    |

| 0    | 1    | 04                    |

| 1    | 0    | 08                    |

| 1    | 1    | 14                    |

### FIFO割り込みモード操作

レシーバFIFOとレシーバ割り込みがイネーブルされた場合(FCRO = 1、IER0 = 1、IER2 = 1)、レシーバ割り込みは以下のように起こります。

- FIFOがプログラムされたトリガー・レベルに達すると、受信データ在り割り込みが、マイクロプロセッサに対して起ります。FIFOがプログラムしたトリガー・レベルより落ちるとクリアされます。

- 同様に FIFO トリガー・レベルに達すると、IIR 受信データ在りも表示されます。割り込みの場合と同様に、FIFO がトリガー・レベルより落ちるとクリアされます。

- レシーバ・ライン・ステータス割り込み (IIR=06)は、受信データ在り(IIR=04)割り込みより優先順位が高く設定されています。

- キャラクタがシフト・レジスタからレシーバFIFOへ送信されると、データ・レディ・ビット(LSR0)がセットされます。FIFOがエンブティになるとクリアされます。

## 操作方法

### FIFO割り込みモード操作（続き）

レシーバFIFOとレシーバ割り込みがイネーブルの場合

1. 以下の条件で、FIFO タイムアウト割り込みが起こります。

- a. 少なくともひとつのキャラクタが FIFO にある。

- b. 最新のシリアル・キャラクタは、連続する4回のキャラクタ時間より前に受信した。(2つのストップ・ビットが設定されていると、2つ目のSTOPビットの時間もキャラクタ時間に含まれます。)

- c. マイクロプロセッサによる最新のFIFO読み取りが、4連続キャラクタ時間より以前である。キャラクタを受信してからタイムアウト割り込みまでの時間は、12ビット・キャラクタで300-ボーレートの場合、160msとなります。

2. キャラクタ時間は、クロック信号のRCLK 入力を使用して計算されます（ボーレートに比例して遅くなります）。

3. タイムアウト割り込みが起こっている時、マイクロプロセッサがレシーバFIFOから1個のキャラクタを読み取ると、タイマーは、クリアされます。

4. タイムアウト割り込みが起こっていない時、タイムアウト・タイマーは新しいキャラクタを受信した後、またはマイクロプロセッサがレシーバFIFO の読み取り後にクリアされます。

送信 FIFO および THRE 割り込みがイネーブルの時に(FCRO = 1、 IER1 = 1)、送信割り込みは以下のように起こります。

1. トランスマッタ・ホールディング・レジスタ・エンプティ割り込み[IIR (3-0) = 2]は、送信 FIFO がエンプティの時起こります。THRが書き込まれる(この割り込み処理中、1から16キャラクタが送信 FIFO に書き込みされるかもしれません。)かまたは IIR が読み取りされた時、クリアされます[IIR (3-0) = 1]

2. トランスマッタ・ホールディング・レジスタ・エンプティ割り込みは、最後に FIFO が空になってから、トランスマッタ FIFO に最低2バイトなかった場合に、1キャラクタ時間引く最後のストップビット時間分遅れます。FCRO 変更後最初のトランスマッタ割り込みは、イネーブルにされているとすぐに起こります。

### FIFO ポーリング・モード操作

FCRO = 1 (トランスマッタおよびレシーバFIFOイネーブル時)の時、IER0、IER1、IER2、IER3の4つのビットをクリアすると、UARTをFIFOポーリング・モードとして使うことが出来ます。レシーバおよびトランスマッタは別々に制御されるため、一方または両方のいずれかを、ポーリング・モードで操作出来ます。

このモードでは、ユーザー・プログラムは、レシーバおよびトランスマッタのステータスを、LSRを使ってチェックします。前述のとおり、以下のようになります。

- LSR0 は、レシーバFIFO にバイトがひとつでもあるとセットされます。

- LSR1 から LSR4 でのエラーが起ったかが判ります。キャラクタ・エラー・ステータスは、割り込みモードの時と同じように扱われます。IIR は、IER2 = 0 なので影響を受けません。

- LSR5 は THR がエンプティであることを示します。

- LSR6 は THR および TSR 両方がエンプティであることを示します。

- LSR7 は、エラーがレシーバFIFO にあるかどうかを示します。

FIFO ポーリング・モードでは、トリガー・レベルへの到達またはタイムアウトは起こりません。しかし、レシーバとトランスマッタ FIFO は、少なくともキャラクタを保持することが出来ます。

## 操作方法

### 割り込みイネーブルレジスタ(IER)

IERは、5つのタイプの割り込みをイネーブルにし(表5参照)、割り込みが起こると INTRPT が応答できるようにすることができます。IERは、ビット0から3までクリアすることで、割り込みシステムをディスイネーブルすることもできます。このレジスタの内容は、表3にまとめられ、以下の黒丸で説明されます。

- ビット0: 設定する時は、このビットは受信データ在り割り込みをイネーブルにします。

- ビット1: 設定する時は、このビットは THRE に割り込みをイネーブルにします。

- ビット2: 設定する時は、このビットはレシーバライン・ステータス割り込みをイネーブルにします。

- ビット3: 設定する時は、このビットはモデム・ステータス割り込みをイネーブルにします。

- ビット4から7: これらのビットは使用されていません (必ずクリアされています)。

### 割り込み識別レジスタ(IIR)

UARTは、最もよく使われるマイクロプロセッサとフレキシブルなインターフェースを可能にするオンチップ割り込み発生機能と割り込み優先順位機能を持っています。

UARTは、4つの割り込み優先順位レベルを持っています。

- 優先1 - レシーバライン・ステータス (最優先)

- 優先2 - レシーバデータ在りまたはレシーバ・キャラクタ・タイムアウト

- 優先3 - トランスマッチ・ホールディング・レジスタ・エンプティ

- 優先4 - モデム・ステータス(最低優先)

割り込みが起こると、IIRは、割り込みがペンドィング状態であることを示し、IIRの下位3ビットで (ビット0、1、2) 割り込みタイプをエンコードします。このレジスタの内容は、表3にまとめられ、表5で説明されています。各ビットの詳細は以下のとおりです。

- ビット0: このビットは、ハードウェア優先またはポーリング割り込みシステムのどちらかで使用されます。ビット0が0の時、割り込みがペンドィング状態です。ビット1の時は、割り込みがペンドィングではありません。

- ビット1および2: これら二つのビットは、最優先の割り込みのペンドィングを表3に示します。

- ビット3: このビットは、TL16C450モードで必ずクリアされています。FIFOモードでは、ビット3はビット2と一緒にセットされると、タイムアウト割り込みがペンドィングであることを示します。

- ビット4および5: これら2つのビットは使用されていません (必ずクリアされています)。

- ビット6および7: これらのビットは、必ずTL16C450モードでクリアされます。これらは、FIFO制御レジスタのビット0がセットされた場合、セットされます。

## 操作方法

### 割り込み識別レジスタ(IIR)(続き)

表 5. 割り込み制御機能

| 割り込み識別レジスタ |      |      |      | 優先順位 | 割り込みタイプ                                                                                                | 割り込みソース                                                                                | 割り込みリセット方法 |

|------------|------|------|------|------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------|

| ビット3       | ビット2 | ビット1 | ビット0 |      |                                                                                                        |                                                                                        |            |

| 0          | 0    | 0    | 1    | 無し   | 無し                                                                                                     | 無し                                                                                     | 無し         |

| 0          | 1    | 1    | 0    | 1    | レシーバライン・ステータス<br>オーバーラン・エラー、パリティ・エラー、フレーミング・エラー、またはブレーク割り込み                                            | ライン・ステータス・レジスタの読み取り                                                                    |            |

| 0          | 1    | 0    | 0    | 2    | 受信データ在り<br>TL16C450 モードでレシーバデータ在りまたはFIFOモードでトリガーレベル到達                                                  | レシーバ・バッファ・レジスタの読み取り                                                                    |            |

| 1          | 1    | 0    | 0    | 2    | キャラクタ・タイムアウト<br>最後の4キャラクタ期間中、レシーバFIFOからキャラクタが取り除かれることなく、入力されたキャラクタもありません。この期間中、最低1つのキャラクタがFIFOの中にあります。 | レシーバ・バッファ・レジスタを読み取り                                                                    |            |

| 0          | 0    | 1    | 0    | 3    | トランスマッタ・ホールディング・レジスタ・エンプティ<br>トランスマッタ・ホールディング・レジスタ・エンプティ                                               | トランスマッタ・ホールディング・レジスタ・エンプティ<br>割り込み識別レジスタを読み取り(割り込みソースの場合)、またはトランスマッタ・ホールディング・レジスタに書き込み |            |

| 0          | 0    | 0    | 0    | 4    | モデム・ステータス<br>送信クリア、データ設定レディ、リング・インジケータ、またはデータキャリア検出                                                    | モデム・ステータス・レジスタの読み取り                                                                    |            |

### ライン制御レジスタ(LCR)

システムプログラマは、LCRを通して非同期データ通信交換フォーマットを決めます。さらに、プログラマはLCRの内容を検索、点検、修正することができます。このことで、システムメモリにラインの特徴を別個に保存する必要性がなくなります。このレジスタの内容は、表3にまとめられ、以下の黒丸リストで説明されます。

- ビット0および1: これら二つのビットは、各送受信シリアル・キャラクタのビット数を指定します。これらのビットは、表6に示されたとおりエンコードされます。

表 6. シリアル・キャラクタのワード長

| ビット1 | ビット0 | ワード長 |

|------|------|------|

| 0    | 0    | 5ビット |

| 0    | 1    | 6ビット |

| 1    | 0    | 7ビット |

| 1    | 1    | 8ビット |

- ビット2: このビットで、1、1.5、または2のストップビットを各送信キャラクタに付加します。ビット2がクリアされると、1ストップビットがデータに付加されます。ビット2がセットされると、付加されるストップビット数はビット0および1で選択されたワード長に依存します。レシーバは、選択されているストップビット数にかかわらず、最初のストップビットのみクロックします。ワード長およびビット2に関して付加されるストップビット数は表7に示されています。

## 操作方法

### ライン制御レジスタ(LCR)(続き)

表7. 生成されるストップビット数

| ビット2 | ビット1および2で選択されたワード長 | 付加されるストップビット数 |

|------|--------------------|---------------|

| 0    | 任意のワード長            | 1             |

| 1    | 5ビット               | 1 1/2         |

| 1    | 6ビット               | 2             |

| 1    | 7ビット               | 2             |

| 1    | 8ビット               | 2             |

- ビット3: このビットはパリティイネーブルビットです。ビット3がセットされると、送信されているデータの最後のデータ・ワードビットと最初のストップビットの間に、パリティビットが付加されます。受信データに対しては、ビット3がセットされているとパリティがチェックされます。ビット3がクリアされていると、パリティの付加、チェックは一切ありません。

- ビット4: このビットは偶数パリティ選択ビットです。パリティがイネーブルで(ビット3がセット)、ビット4がセットされると、偶数パリティ(データとパリティビットの論理1の数が偶数個)が選択されます。パリティがイネーブルで、ビット4がクリアされると、奇数パリティ(論理1の数が奇数個)が選択されます。

- ビット5: このビットはスティック・パリティビットです。ビット3、4、5がセットされると、パリティビットは0として送信されます。ビット3、5がセットされると、ビット4がクリアされ、パリティビットが1として送信されます。ビット5がクリアされると、スティック・パリティはディスイネーブルになります。

- ビット6: このビットはブレーク制御ビットです。ビット6をセットすると強制的にブレークするように設定されます。つまり、SOUTを強制的にスペーシング(クリア)状態にする条件です。ビット6がクリアされると、ブレークはディスイネーブルになり、トランスマッタ回路には影響しません。この機能は、SOUTだけに影響します。

- ビット7: このビットは、ディバイザ・ラッチ・アクセスピット(DLAB)です。ビット7は、ボーメネレータのディバイザ・ラッチにアクセスするため、読み取りまたは書き込み中にセットが必要です。ビット7は、レシーバ・バッファ、THR、またはIERにアクセスするため、読み取りまたは書き込み中にクリアする必要があります。

### ライン・ステータス・レジスタ(LSR)<sup>†</sup>

LSRは、データ・トランスファ中のステータス情報をCPUへ提供します。このレジスタの内容は、表3にまとめられ、以下の黒丸リストに説明されています。

- ビット0: このビットは、レシーバ用データ・レディー(DR)インジケータです。DRは、完全なキャラクタを受信し、RBRまたはFIFOに送る時にセットされます。DRは、RBRまたはFIFOのデータすべてを読み取ることでクリアされます。

- ビット1<sup>‡</sup>: このビットは、オーバーラン・エラー(OE)インジケータです。OEがセットされると、RBRの中のキャラクタが読み取られる前に、レジスタに送信された次のキャラクタでそのキャラクタが上書きされることを示します。OEは、CPUがLSRの内容を読み取るたびにクリアされます。FIFOモードでは、データが、トリガー・レベルを超えてFIFOに受信し続けた場合、FIFOがいっぱいになり、次のキャラクタが完全にシフトレジスタで受信された後のみオーバーラン・エラーが発生します。オーバーラン・エラーは、発生したらすぐCPUに示されます。シフトレジスタのキャラクタは上書きされますが、FIFOには転送されません。

<sup>†</sup> ライン・ステータス・レジスタは、読み取り操作のみを目的としています。このレジスタへの書き込みは、工場試験環境以外では推奨されません。

<sup>‡</sup> ビット1から4は、レシーバライン・ステータス割り込みを起こすエラー条件です。

## 操作方法

### ライン・ステータス・レジスタ(LSR)(続き) †

- ビット2#: このビットは、パリティエラー(PE)インジケータです。PEがセットされると、受信データキャラクタのパリティがLCR(ビット4)で選択したパリティに合わないことを示します。PEは、CPUがLSRの内容を読み取るたびにクリアされます。FIFOモードでは、このエラーは個々のFIFO内のキャラクタに関連しています。このエラーは、エラーを持ったキャラクタがFIFOのトップにある時に、CPUに示されます。

- ビット3#: このビットは、フレーミングエラー(FE)インジケータです。FEがセットされると、受信キャラクタが有効(設定された)ストップビットを持っていないことを示します。FEは、CPUがLSRの内容を読み取るたびにクリアされます。FIFOモードでは、このエラーは個々のFIFO内のキャラクタに関連しています。このエラーは、エラーを持ったキャラクタがFIFOのトップにある時に、CPUに示されます。UART(内部回路)は、フレーミングエラー後、再同期化しようとします。これを達成するためには、フレーミングエラーは次のスタートビットによるものであると想定されています。エラーを持ったUARTは、このスタートビットを2度サンプリングし、その後入力データを受け付けます。

- ビット4#: このビットは、ブレーク割り込み(BI)インジケータです。BIがセットされると、受信データ入力はフルワード送信時間より長い間、ローに保持されたことを示します。フルワード送信時間は、スタート、データ、パリティおよびストップビットを送信する合計時間として定義されます。BIは、CPUがLSRの内容を読み取るたびにクリアされます。FIFOモードでは、このエラーは個々のFIFO内のキャラクタに関連しています。このエラーは、エラーを持ったキャラクタがFIFOのトップにある時に、CPUに示されます。ブレークが発生すると、0キャラクタが1つFIFOにロードされます。次のキャラクタ送信は、SINが最低2RCLKサンプル間マーキングステートになった後、次の有効なスタートビットを受信した時、可能になります。

- ビット5: このビットはTHREインジケータです。THREは、THRがエンプティの場合セットされ、UARTが新しいキャラクタを受ける用意ができていることを示します。THREがセットされ、THRE割り込みがイネーブルな場合、割り込みが発生します。THREは、THRの内容がTSRに送信された時セットされます。THREは、CPUがTHRにロードすると同時にクリアされます。FIFOモードでは、THREは送信FIFOがエンプティの場合セットされます。最低1バイトが送信FIFOに書き込まれるとクリアされます。

- ビット6: このビットは、トランスマッタエンプティ(TEMPT)インジケータです。TEMPTビットは、THRとTSRの両方がエンプティの時にセットされます。THRまたはTSRのどちらかが、データキャラクタを含む場合、TEMPTはクリアされます。FIFOモードでは、TEMPTはトランスマッタFIFOとシフトレジスタが両方ともエンプティの場合セットされます。

- ビット7: TL16C550Dモードでは、このビットは必ずクリアされます。TL16C450モードでは、このビットは必ずクリアされます。FIFOモードでは、LSR7はFIFOに最低1パリティ、フレーミングまたはブレークエラーがある場合セットされます。マイクロプロセッサがLSRを読み取り、引き続きFIFOの中にエラーがない場合クリアされます。

### モデム制御レジスタ(MCR)

MCRは、8ビットレジスタです。モデム、データ器機、モデムをエミュレートする周辺デバイスとのインタフェースを制御します。このレジスタの内容は、表3にまとめられ、以下の黒丸リストに説明されています。

- ビット0: このビット(DTR)は $\overline{DTR}$ 出力を制御します。

- ビット1: このビット(RTS)は $\overline{RTS}$ 出力を制御します。

- ビット2: このビット(OUT1)は、ユーザー指定出力信号の $\overline{OUT1}$ を制御します。

- ビット3: このビット(OUT2)は、ユーザー指定出力信号の $\overline{OUT2}$ を制御します。

0から3までのビットのどれかをセットすると、そのビットに関連した出力はロー・レベルになります。これらのビットがクリアされると、それらの出力はハイ・レベルになります。

† ライン・ステータス・レジスタは、読み取り操作のみを目的としています。このレジスタへの書き込みは、工場試験環境以外では推奨されません。

‡ ビット1から4は、レシーバライン・ステータス割り込みを起こすエラー条件です。

## 操作方法

### モデム制御レジスタ(MCR)(続き)

- ビット4: このビット(LOOP)は、UARTの自己診断テスト用のローカル・ループバック機能を備えています。LOOPが設定されると、以下が発生します。

- トランスマッタ SOUT がハイに設定されます。

- レシーバ SIN の接続は、解除されます。

- TSR の出力は、レシーバシフト・レジスタ入力にループバックされます。

- 4つのモデム制御入力(CTS、DSR、DCD、およびRI)の接続は、解除されます。

- 4つのモデム制御出力(DTR、RTS、OUT1、およびOUT2)は、4つのモデム制御入力に接続されます。

- 4つのモデム制御出力は、非アクティブ(ハイ) レベルになります。

- ビット5: このビット(AFE)は、自動フロー制御イネーブルです。セットされると、詳細説明で説明された自動フロー制御がイネーブルになります。

自己診断モードでは、送信されたデータはすぐに受信されます。このことにより、プロセッサはUARTへの送受信データパスを検証できます。レシーバとトランスマッタの割り込みは完全に動作可能です。モデム制御割り込みも動作できますが、しかしモデム制御割り込みのソースは、4つのモデム制御入力ではなく、MCRの下位4つのビットです。すべての割り込みは、IERによって制御されます。

UART自動フロー制御は、表8に示されているとおり MCR のビット1および5をプログラミングすることで設定できます。

表8. 自動フロー制御設定

| MCR ビット5<br>(AFE) | MCR ビット1<br>(RTS) | 機能                                 |

|-------------------|-------------------|------------------------------------|

| 1                 | 1                 | 使用可能自動-RTS および自動-CTS(自動フロー制御イネーブル) |

| 1                 | 0                 | 自動-CTS のみイネーブル                     |

| 0                 | ×                 | 自動-RTS および自動-CTS ディスイネーブル          |

### モデム・ステータスレジスタ(MSR)

MSRは、8ビットレジスタです。モデム、データ機器、モデムをエミュレートする周辺デバイスのステータスをCPUに伝えることができます。さらに、このレジスタの4つのビットは、情報の変更を伝えます。モデムからの制御入力が状態を変化した場合、対応するビットがセットされます。4つのビットすべては、CPUがMSRを読み取った時にクリアされます。このレジスタの内容は、表3にまとめられ、以下の黒丸リストで説明されています。

- ビット0: このビットは、送信クリア( $\Delta$  CTS)変化のインジケータです。 $\Delta$  CTSは、それがCPUに最後に読み取られてから、CTS入力の状態が変化したことを示します。 $\Delta$  CTSがセットされると(自動フロー制御がディスイネーブルで、モデムステータス割り込みがイネーブルの時)、モデムステータス割り込みが起こります。自動フロー制御がイネーブルの時、( $\Delta$  CTSがクリアされても。) 割り込みは、起こりません。

- ビット1: このビットは、データセットレディー( $\Delta$  DSR)変化のインジケータです。 $\Delta$  DSRは、それがCPUに最後に読み取られてから、DSR入力の状態が変化したことを示します。 $\Delta$  DSRがセットされ、モデムステータス割り込みがイネーブルの時、モデムステータス割り込みが起こります。

- ビット2: このビットは、リング・インジケータ・トレーディング・エッジ・ディテクタービットです.TERIは、チップへのRI入力がローからハイへ変化したことを示します.TERIがセットされ、モデム・ステータス割り込みがイネーブルの時、モデム・ステータス割り込みが起こります。

## 操作方法

### モデム・ステータスレジスタ(MSR)(続き)

- ビット3: このビットは、データキャリア ( $\Delta$  DCD) 変化インジケータです。 $\Delta$  DCD は、それが CPU に最後に読み取られてから、 $\overline{DCD}$  端子の状態が変化したことを示します。 $\Delta$  DCD がセットされ、モデム・ステータス割り込みがインペルの時、モデム・ステータス割り込みが起こります。

- ビット4: このビットは、送信クリア (CTS) 端子の補数です。UART が自己診断モードの時 (LOOP[MCR4]=1)、このビットは MCR ビット1 (RTS)と同じです。

- ビット5: このビットは、データセットレディー ( $\overline{DSR}$ ) 端子の補数です。UART が自己診断モードの時 (LOOP[MCR4]=1)、このビットは MCR ビット0 (DTR)と同じです。

- ビット6: このビットは、リング・インジケータ (RI) 端子の補数です。UART が自己診断モードの時 (LOOP[MCR4]=1)、このビットは MCR ビット2 (OUT1)と同じです。

- ビット7: このビットは、データキャリア検出 (DCD) 端子の補数です。UART が自己診断モードの時 (LOOP[MCR4]=1)、このビットは MCR ビット3 (OUT2)と同じです

### プログラマブル・ポー・ジェネレータ

UART は、DC から 16MHzまでのクロックを入力として、それをディバイザで 1 から( $2^{16}-1$ )の範囲で分周するプログラマブル・ポー・ジェネレータを持っています。ポー・ジェネレータの出力周波数は、ボーレートの 16 倍(16 ×)です。ディバイザの値を求める式は以下のとおりです。

$$\text{ディバイザ} = \text{XIN 周波入力} \div (\text{求めるボーレート} \times 16)$$

ディバイザ・ラッチと呼ばれる 2つの8-ビットレジスタに、16-ビット・バイナリ・フォーマットでディバイザ値を保存します。これらのディバイザ・ラッチは、ポー・ジェネレータの正しい動作を保証するため、UART の初期化中ロードすることが必要です。ディバイザ・ラッチのいずれかがロードされると、16ビット・ポー・カウンタもロードされ、初期ロードでの長いカウントを防ぎます。

表9 および 10 は、1.8432 MHz および 3.072 MHz のそれぞれの水晶周波数を使った時のポー・ジェネレータの使用法を説明します。38.4 kbits/s およびそれ以下のボーレートについては、エラーは小さくなります。選択したボーレートの精度は、選択した水晶周波数に依存します(図 25 代表的なクロック回路の例を参照)。

## 操作方法

### プログラマブル・ポート・ジェネレータ (続き)

表 9. 1.8432-MHz 水晶を使用するポート

| 必要<br>ポート | 16 × クロックを発<br>生するために使用す<br>るディバイザ値 | 必要と実際の<br>ポートの差異の<br>パーセントエラー |

|-----------|-------------------------------------|-------------------------------|

| 50        | 2304                                |                               |

| 75        | 1536                                |                               |

| 110       | 1047                                | 0.026                         |

| 134.5     | 857                                 | 0.058                         |

| 150       | 768                                 |                               |

| 300       | 384                                 |                               |

| 600       | 192                                 |                               |

| 1200      | 96                                  |                               |

| 1800      | 64                                  |                               |

| 2000      | 58                                  | 0.69                          |

| 2400      | 48                                  |                               |

| 3600      | 32                                  |                               |

| 4800      | 24                                  |                               |

| 7200      | 16                                  |                               |

| 9600      | 12                                  |                               |

| 19200     | 6                                   |                               |

| 38400     | 3                                   |                               |

| 56000     | 2                                   | 2.86                          |

表 10. 3.072-MHz 水晶を使用するポート

| 必要<br>ポート | 16 × クロックを発<br>生るために使用す<br>るディバイザ値 | 必要と実際の<br>ポートの差異の<br>パーセントエラー |

|-----------|------------------------------------|-------------------------------|

| 50        | 3840                               |                               |

| 75        | 2560                               |                               |

| 110       | 1745                               | 0.026                         |

| 134.5     | 1428                               | 0.034                         |

| 150       | 1280                               |                               |

| 300       | 640                                |                               |

| 600       | 320                                |                               |