# TL28L92 3.3V~5V デュアル、ユニバーサル非同期レシーバ / トランスマッタ

## 1 特長

- 3.3V~5V、-40°~85°C および 68xxx または 80xxx バスインターフェイス

- デュアル、全二重、独立した非同期レシーバ / トランスマッタ、各レシーバおよびトランスマッタに 16 文字の FIFO

- ピンプログラミングにより 68xxx または 80xxx バスインターフェイスを選択

- プログラマブル データフォーマット

- 5 データビットから 8 データビット + パリティ

- 奇数、偶数、パリティなし、または強制パリティ

- 1 ストップ、1.5 ストップ、または 2 ストップビットを 1/16 ビットインクリメントでプログラム可能

- 16 ビットのプログラマブル カウンタおよびタイマ

- 各レシーバおよびトランスマッタは次の範囲でボーレートをプログラム可能:

- 28 固定レート: 50Bd~230.4kBd

- その他のボーレートは 16 倍の 1MHz まで

- プログラマブル カウンタとタイマから求めた、プログラマブルなユーザー定義のレート

- 外部 1x または 16x クロック

- パリティ、フレーミング、オーバーラン エラー検出

- 不正スタートビットの検出

- ラインブレーク検出と生成

- プログラマブル チャネル モード

- 通常 (全二重)

- 自動エコー

- ローカル ループバック

- リモート ループバック

- マルチファンクション、7 ビット入力ポート (IACKN を含む)

- クロック入力または制御入力として機能可能

- 4 つの入力の状態変化を検出するには、通常は > 100kΩ のプルアップ抵抗を使用します

- モデム制御用の状態変化検出器

- マルチファンクションの 8 ビット出力ポート

- 個別のビット設定およびリセット機能

- 出力をステータス信号および割り込み信号にプログラム可能

- DMA インターフェイスの FIFO ステータス

- 汎用割り込みシステム

- 8 つのマスク可能割り込み条件を持つ单一割り込み出力

- 出力ポートは、OR 接続可能な合計 5 つまでの個別の割り込み出力を供給するように構成可能

- 各 FIFO は、4 つの異なる割り込みレベルにプログラム可能

– 各レシーバのウォッチドッグ タイマ

- 最大データ転送レート: 1x – 1Mbit/s, 16x – 1Mbit/s

- 開始 / 終了ブレーク割り込みおよびステータス

- キャラクタの途中で発生するブレークを検出

- オンチップの水晶発振器

- パワーダウン モード

- レシーバのタイムアウト モード

- 3.3V または 5V の単一電源電圧

- JEDEC 14C ESD の要件を満たす (または上回る) 性能

## 2 概要

TL28L92 は 3.3V または 5V 電源で動作し、追加機能とより深い FIFO を備えています。パワーアップ時の構成は、16 文字のレシーバ、16 文字の送信 FIFO、各レシーバのウォッチドッグ タイマ、モードレジスタ 0 の追加、拡張ボーレートと全体的な高速化、プログラム可能なレシーバ、トランスマッタ割り込みです。

ピンプログラミングにより、デバイスは Motorola または Intel バスインターフェイスで動作可能です。MR0A レジスタのビット 3 により、デバイスは 8 バイト FIFO モードで動作可能です。

テキサス・インスツルメンツの TL28L92 デュアル ユニバーサル非同期レシーバ / トランスマッタ (DUART) は、シングルチップの CMOS-LSI 通信デバイスで、2 つの全二重非同期レシーバ / トランスマッタ チャネルを 1 つのパッケージに搭載しています。このデバイスはマイクロプロセッサと直接接続して、モデムおよび DMA インターフェイスを備えたポーリングまたは割り込み駆動のシステムで使用できます。

各チャネルの動作モードとデータ フォーマットは、別々にプログラム可能です。さらに、各レシーバおよびトランスマッタは、28 の固定ボーレート、プログラム可能なカウンタ / タイマから生成された 16x クロック、または外部の 1x または 16x クロックのいずれかを動作速度に選択できます。ボーレート ジェネレータおよびカウンタ / タイマは、水晶振動子、または外部クロック入力で直接動作できます。レシーバとトランスマッタの動作速度を別々にプログラムできるため、DUART はクラスタ化された端末システムなどのデュアルスピード チャネル アプリケーションで使用すると特に能力を発揮します。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

各レシーバおよびトランスマッタは、8 文字または 16 文字の FIFO でバッファされ、レシーバのオーバーラン、トランスマッタのアンダーランの可能性を最小限に抑え、割り込み駆動システムでの割り込みオーバーヘッドを低減します。さらに、レシーバ バッファがフルになったときにリモートトランスマッタをディスエーブルするために、RTS/CTS 信号によってフロー制御機能が提供されます。TL28L92 には、多目的の 7 ビット入力ポートと多目的の 8 ビット出力ポートも搭載されています。これらは汎用 I/O ポートとして使用することも、プログラム制御の下で特定の機能 (クロック入力、ステータス / 割り込み出力など) を割り当てることもできます。

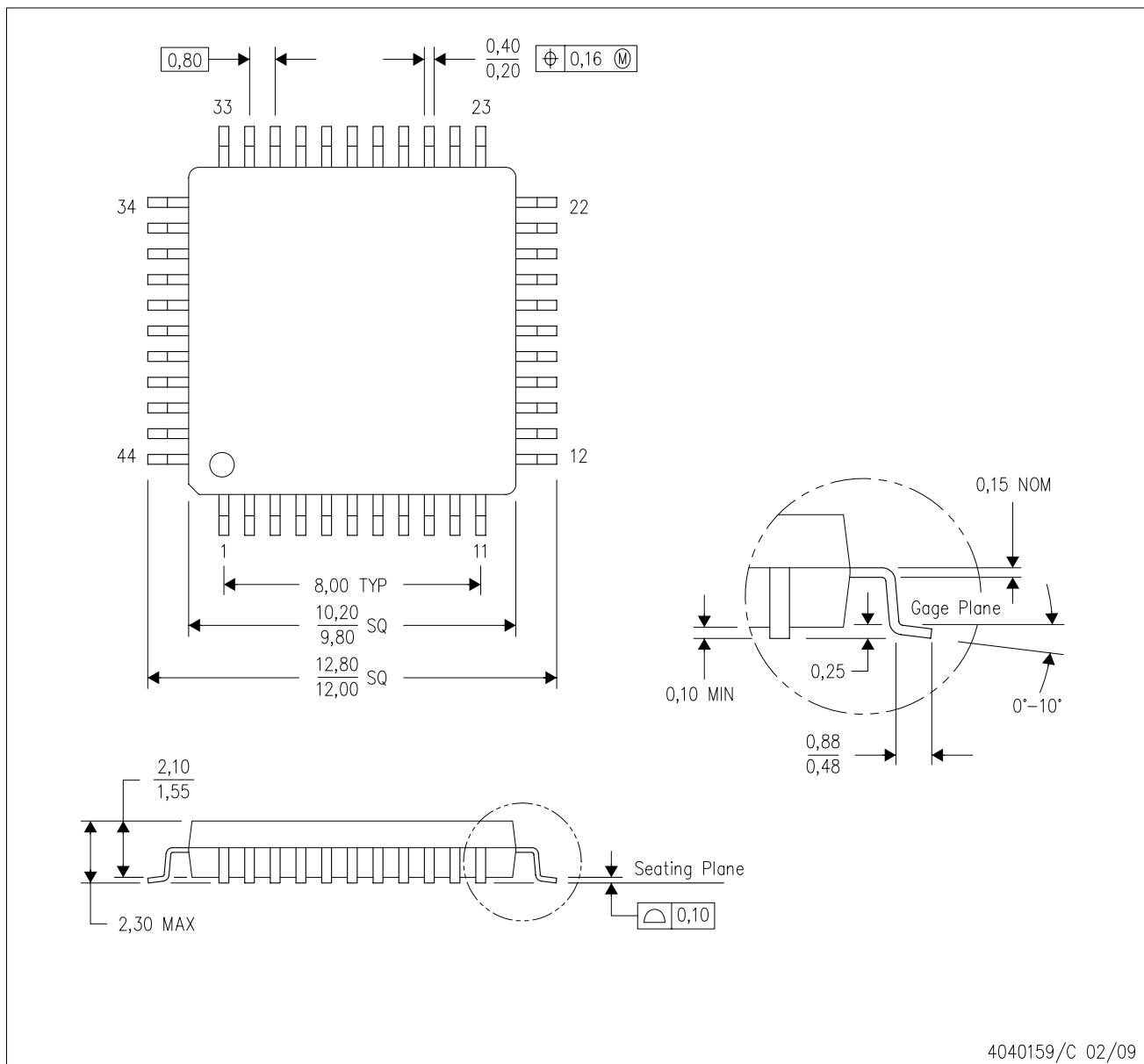

TL28L92 は、現在 44 ピンの QFP (FR) で供給されています。

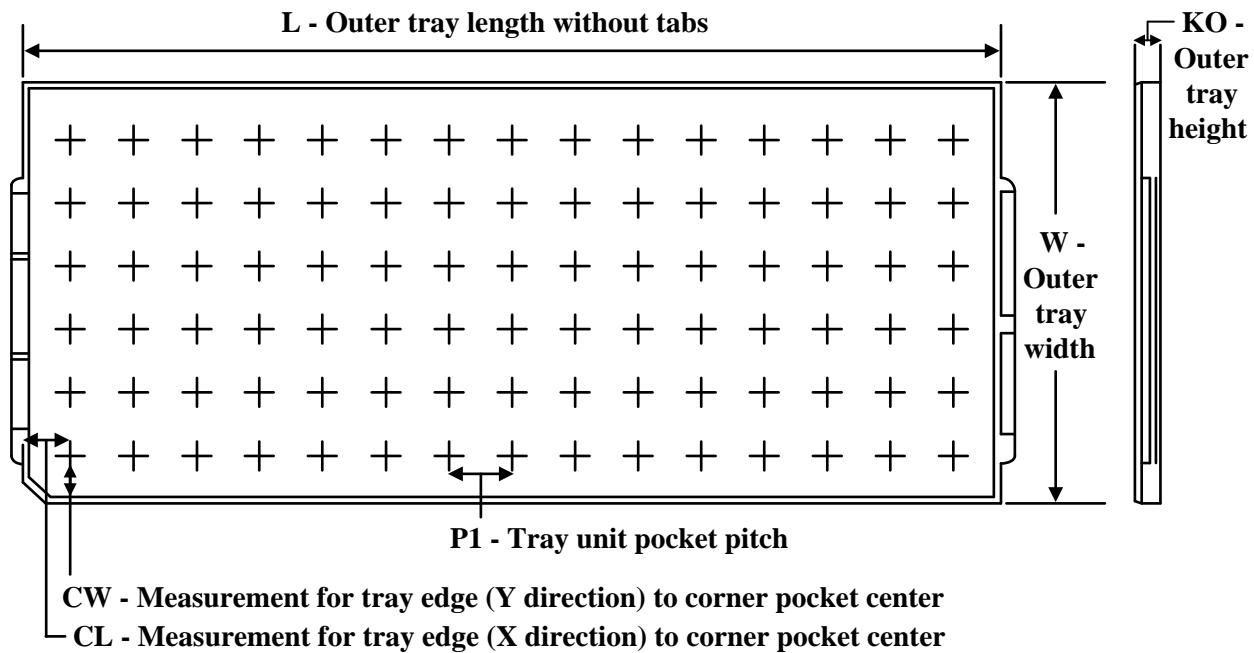

#### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| TL28L92 | QFP (FR)             | 12.4mm x 12.4mm          |

(1) 詳細については、[セクション 9](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

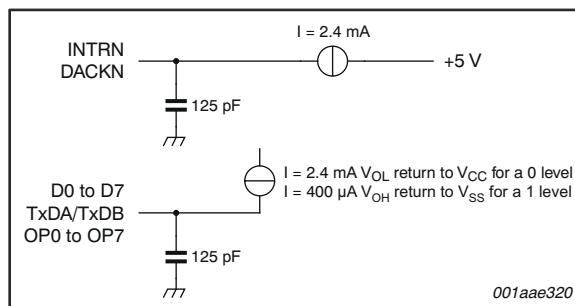

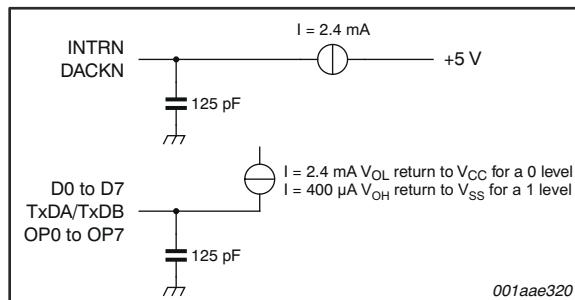

#### 出力のテスト条件

## Table of Contents

|                                                |    |                                                    |    |

|------------------------------------------------|----|----------------------------------------------------|----|

| 1 特長                                           | 1  | 5.3 Feature Description                            | 23 |

| 2 概要                                           | 1  | 6 Programming                                      | 30 |

| 3 Pin Configurations and Functions             | 3  | 6.1 Register Overview                              | 30 |

| 4 Electrical Specifications                    | 8  | 6.2 Condensed Register Bit Formats                 | 31 |

| 4.1 Absolute Maximum Ratings                   | 8  | 6.3 Register Descriptions                          | 33 |

| 4.2 Static Characteristics for 5V Operation    | 8  | 6.4 Output Port Notes                              | 51 |

| 4.3 Static Characteristics for 3.3V Operation  | 9  | 6.5 CTS, RTS, CTS Enable Tx Signals                | 51 |

| 4.4 Dynamic Characteristics for 5V Operation   | 10 | 7 Device and Documentation Support                 | 52 |

| 4.5 Dynamic Characteristics for 3.3V Operation | 12 | 7.1 ドキュメントの更新通知を受け取る方法                             | 52 |

| 4.6 Typical Performance                        | 14 | 7.2 サポート・リソース                                      | 52 |

| 4.7 Timing Diagrams                            | 14 | 7.3 Trademarks                                     | 52 |

| 4.8 Test Information                           | 20 | 7.4 静電気放電に関する注意事項                                  | 52 |

| 5 Detailed Description                         | 21 | 7.5 用語集                                            | 52 |

| 5.1 Overview                                   | 21 | 8 Revision History                                 | 52 |

| 5.2 Functional Block Diagram                   | 21 | 9 Mechanical, Packaging, and Orderable Information | 53 |

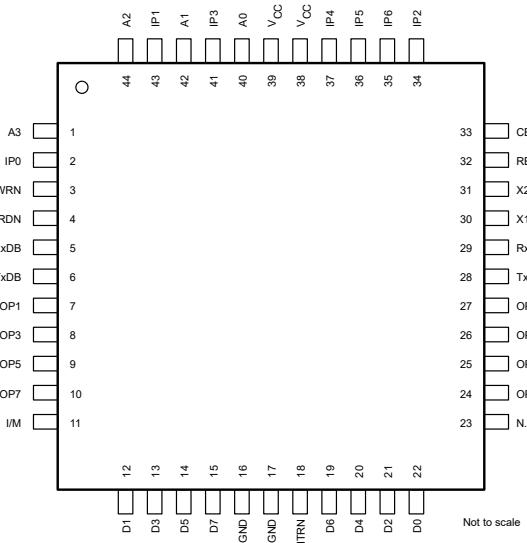

## 3 Pin Configurations and Functions

図 3-1. 80xxx Mode FR (QFP) Package

(Top View)

表 3-1. Pin Functions for 80xxx Interface

| PINS              |                     | TYPE | DESCRIPTION                                                                                                                                                                                                                            |

|-------------------|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | QFP (FR)<br>PIN NO. |      |                                                                                                                                                                                                                                        |

| A0, A1,<br>A2, A3 | 40, 42,<br>44, 1    | I    | Address inputs: Select the DUART internal registers and ports for read/write operations.                                                                                                                                               |

| CEN               | 33                  | I    | Chip enable: active LOW input signal. When LOW, data transfers between the CPU and the DUART are enabled on D0 to D7 as controlled by the WRN, RDN and A0 to A3 inputs. When HIGH, places the D0 to D7 lines in the 3-state condition. |

表 3-1. Pin Functions for 80xxx Interface (続き)

| PINS                                    |                                         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                              |

|-----------------------------------------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                    | QFP (FR)<br>PIN NO.                     |      |                                                                                                                                                                                                                                                                                          |

| D0, D1,<br>D2, D3,<br>D4, D5,<br>D6, D7 | 22, 12,<br>21, 13,<br>20, 14,<br>19, 15 | I/O  | Data bus: Bidirectional 3-state data bus used to transfer commands, data and status between the DUART and the CPU. D0 is the least significant bit.                                                                                                                                      |

| GND                                     | 16, 17                                  | Pwr  | Ground                                                                                                                                                                                                                                                                                   |

| IP0                                     | 2                                       | I    | Input 0: General purpose input or channel A clear to send active LOW input (CTSAN).                                                                                                                                                                                                      |

| IP1                                     | 43                                      | I    | Input 1: General purpose input or channel B clear to send active LOW input (CTSBN).                                                                                                                                                                                                      |

| IP2                                     | 34                                      | I    | Input 2: General-purpose input or counter/timer external clock input.                                                                                                                                                                                                                    |

| IP3                                     | 41                                      | I    | Input 3: General purpose input or channel A transmitter external clock input (TxCA). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock.                                                                               |

| IP4                                     | 37                                      | I    | Input 4: General purpose input or channel A receiver external clock input (RxC). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock.                                                                                          |

| IP5                                     | 36                                      | I    | Input 5: General purpose input or channel B transmitter external clock input (TxCB). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock.                                                                               |

| IP6                                     | 35                                      | I    | Input 6: General purpose input or channel B receiver external clock input (RxCB). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock.                                                                                         |

| I/M                                     | 11                                      | I    | Bus configuration: When HIGH or not connected configures the bus interface to the conditions shown in this table.                                                                                                                                                                        |

| INTRN                                   | 18                                      | O    | Interrupt request: Active LOW, open-drain, output which signals the CPU that one or more of the eight maskable interrupting conditions are true. This pin requires a pull-up device.                                                                                                     |

| N.C.                                    | 23                                      | –    | Not connected                                                                                                                                                                                                                                                                            |

| OP0                                     | 27                                      | O    | Output 0: General purpose output or channel A request to send (RTSAN, active LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                              |

| OP1                                     | 7                                       | O    | Output 1: General-purpose output or channel B request to send (RTSBN, active LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                              |

| OP2                                     | 26                                      | O    | Output 2: General purpose output, or channel A transmitter 1× or 16× clock output, or channel A receiver 1× clock output.                                                                                                                                                                |

| OP3                                     | 8                                       | O    | Output 3: General purpose output or open-drain, active LOW counter/timer output or channel B transmitter 1× clock output, or channel B receiver 1× clock output.                                                                                                                         |

| OP4                                     | 25                                      | O    | Output 4: General purpose output or channel A open-drain, active LOW, RxA interrupt ISR[1] output.                                                                                                                                                                                       |

| OP5                                     | 9                                       | O    | Output 5: General-purpose output or channel B open-drain, active LOW, RxB interrupt ISR[5] output.                                                                                                                                                                                       |

| OP6                                     | 24                                      | O    | Output 6: General purpose output or channel A open-drain, active LOW, TxA interrupt ISR[0] output.                                                                                                                                                                                       |

| OP7                                     | 10                                      | O    | Output 7: General-purpose output, or channel B open-drain, active LOW, TxB interrupt ISR[4] output.                                                                                                                                                                                      |

| RDN                                     | 4                                       | I    | Read strobe: When LOW and CEN is also LOW, causes the contents of the addressed register to be presented on the data bus. The read cycle begins on the falling edge of RDN.                                                                                                              |

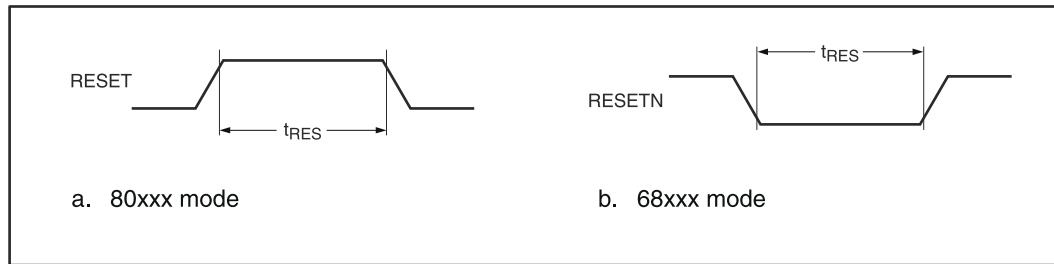

| RESET                                   | 32                                      | I    | Reset: A HIGH level clears internal registers (SRA, SRB, IMR, ISR, OPR and OPCR), puts OP0 to OP7 in the HIGH state, stops the counter/timer, and puts channels A and B in the inactive state, with the TxD and TxD outputs in the mark (HIGH) state. Sets MR pointer to MR1. See 図 4-2. |

**表 3-1. Pin Functions for 80xxx Interface (続き)**

| PINS            |                     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                |

|-----------------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | QFP (FR)<br>PIN NO. |      |                                                                                                                                                                                                                                                                                            |

| RxD A           | 29                  | I    | Channel A receiver serial data input: The least significant bit is received first. See note on drive levels at block diagram ( <a href="#">図 5-1</a> ).                                                                                                                                    |

| RxD B           | 5                   | I    | Channel B receiver serial data input: The least significant bit is received first. See note on drive levels at block diagram ( <a href="#">図 5-1</a> ).                                                                                                                                    |

| TxD A           | 28                  | O    | Channel A transmitter serial data output: The least significant bit is transmitted first. This output is held in the Mark condition when the transmitter is disabled, Idle or when operating in local loopback mode. See note on drive levels at block diagram ( <a href="#">図 5-1</a> ).  |

| TxD B           | 6                   | O    | Channel B transmitter serial data output: The least significant bit is transmitted first. This output is held in the Mark condition when the transmitter is disabled, Idle, or when operating in local loopback mode. See note on drive levels at block diagram ( <a href="#">図 5-1</a> ). |

| V <sub>CC</sub> | 38, 39              | Pwr  | Power supply: 3.3 V ± 10% or 5 V ± 10 % supply input.                                                                                                                                                                                                                                      |

| WRN             | 3                   | I    | Write strobe: When LOW and CEN is also LOW, the contents of the data bus is loaded into the addressed register. The transfer occurs on the rising edge of the signal.                                                                                                                      |

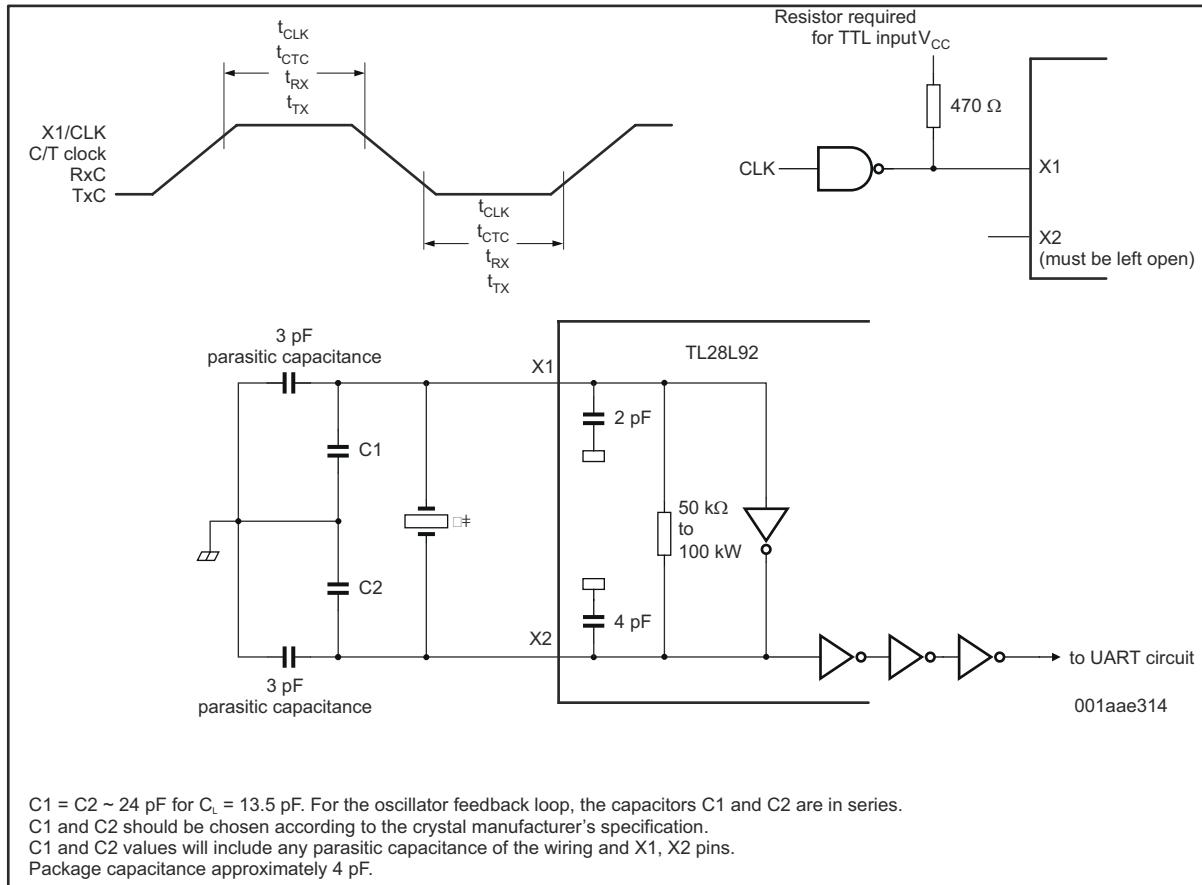

| X1/CLK          | 30                  | I    | Crystal 1: Crystal or external clock input. A crystal or clock of the specified limits must be supplied at all times. When a crystal is used, a capacitor must be connected from this pin to ground (see <a href="#">図 4-9</a> ).                                                          |

| X2              | 31                  | O    | Crystal 2: Connection for other side of the crystal. When a crystal is used, a capacitor must be connected from this pin to ground (see <a href="#">図 4-9</a> ). If X1/CLK is driven from an external source, this pin must be left open.                                                  |

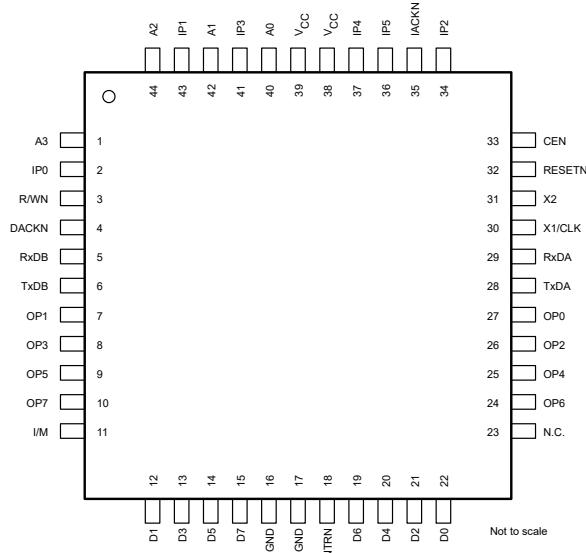

**図 3-2. 68xxx Mode FR (QFP) Package

(Top View)**

**表 3-2. Pin Functions for 68xxx Interface**

| PINS                                    |                                         | TYPE | DESCRIPTION                                                                                                                                                                                                                                           |

|-----------------------------------------|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                    | QFP (FR)<br>PIN NO.                     |      |                                                                                                                                                                                                                                                       |

| A0, A1,<br>A2, A3                       | 40, 42,<br>44, 1                        | I    | Address inputs: Select the DUART internal registers and ports for read/write operations.                                                                                                                                                              |

| CEN                                     | 33                                      | I    | Chip enable: active LOW input signal. When LOW, data transfers between the CPU and the DUART are enabled on D0 to D7 as controlled by the WRN, RDN and A0 to A3 inputs. When HIGH, places the D0 to D7 lines in the 3-state condition.                |

| DACKN                                   | 4                                       | O    | Data transfer acknowledge. Active low output. DACKN is asserted low during a write, read, or interrupt. Acknowledge cycle to indicate data transfer between the CPU and the TL28L92.                                                                  |

| D0, D1,<br>D2, D3,<br>D4, D5,<br>D6, D7 | 22, 12,<br>21, 13,<br>20, 14,<br>19, 15 | I/O  | Data bus: Bidirectional 3-state data bus used to transfer commands, data and status between the DUART and the CPU. D0 is the least significant bit.                                                                                                   |

| GND                                     | 16, 17                                  | Pwr  | Ground                                                                                                                                                                                                                                                |

| IACKN                                   | 35                                      | I    | Interrupt acknowledge. An active low input indicates an interrupt acknowledge cycle. Typically asserted by the CPU in response to an interrupt request. When IACKN is asserted, the TL28L92 places the interrupt vector on the bus and asserts DACKN. |

| IP0                                     | 2                                       | I    | Input 0: General purpose input or channel A clear to send active LOW input (CTSAN).                                                                                                                                                                   |

| IP1                                     | 43                                      | I    | Input 1: General purpose input or channel B clear to send active LOW input (CTSBN).                                                                                                                                                                   |

| IP2                                     | 34                                      | I    | Input 2: General-purpose input or counter/timer external clock input.                                                                                                                                                                                 |

| IP3                                     | 41                                      | I    | Input 3: General purpose input or channel A transmitter external clock input (TxCA). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock.                                            |

| IP4                                     | 37                                      | I    | Input 4: General purpose input or channel A receiver external clock input (RxC). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock.                                                       |

| IP5                                     | 36                                      | I    | Input 5: General purpose input or channel B transmitter external clock input (TxCB). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock.                                            |

**表 3-2. Pin Functions for 68xxx Interface (続き)**

| PINS            |                     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                      |

|-----------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | QFP (FR)<br>PIN NO. |      |                                                                                                                                                                                                                                                                                                                  |

| I/M             | 11                  | I    | Bus configuration: When HIGH or not connected configures the bus interface to the conditions shown in this table.                                                                                                                                                                                                |

| INTRN           | 18                  | O    | Interrupt request: Active LOW, open-drain, output which signals the CPU that one or more of the eight maskable interrupting conditions are true. This pin requires a pull-up device.                                                                                                                             |

| N.C.            | 23                  | –    | Not connected                                                                                                                                                                                                                                                                                                    |

| OP0             | 27                  | O    | Output 0: General purpose output or channel A request to send (RTSAN, active LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                                                      |

| OP1             | 7                   | O    | Output 1: General-purpose output or channel B request to send (RTSBN, active LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                                                      |

| OP2             | 26                  | O    | Output 2: General purpose output, or channel A transmitter 1× or 16× clock output, or channel A receiver 1× clock output.                                                                                                                                                                                        |

| OP3             | 8                   | O    | Output 3: General purpose output or open-drain, active LOW counter/timer output or channel B transmitter 1× clock output, or channel B receiver 1× clock output.                                                                                                                                                 |

| OP4             | 25                  | O    | Output 4: General purpose output or channel A open-drain, active LOW, RxA interrupt ISR[1] output.                                                                                                                                                                                                               |

| OP5             | 9                   | O    | Output 5: General-purpose output or channel B open-drain, active LOW, RxB interrupt ISR[5] output.                                                                                                                                                                                                               |

| OP6             | 24                  | O    | Output 6: General purpose output or channel A open-drain, active LOW, TxA interrupt ISR[0] output.                                                                                                                                                                                                               |

| OP7             | 10                  | O    | Output 7: General-purpose output, or channel B open-drain, active LOW, TxB interrupt ISR[4] output.                                                                                                                                                                                                              |

| RESETN          | 32                  | I    | Reset. Active low. When RESETN is asserted the following registers are cleared: SRA, SRB, IMR, ISR, OPR, and OPCR. Outputs OP0 and OP7 are driven to a logic high state, the counter/timer is stopped, and channels A and B are placed in the inactive state with the TxD A and TxD B outputs in the high state. |

| RxD A           | 29                  | I    | Channel A receiver serial data input: The least significant bit is received first. See note on drive levels at block diagram (図 5-2).                                                                                                                                                                            |

| RxD B           | 5                   | I    | Channel B receiver serial data input: The least significant bit is received first. See note on drive levels at block diagram (図 5-2).                                                                                                                                                                            |

| R/WN            | 3                   | I    | Read/Write: Input. When CEN is low and R/WN input is high this indicates a read cycle. When CEN is low and R/WN is low this indicates a write cycle.                                                                                                                                                             |

| TxD A           | 28                  | O    | Channel A transmitter serial data output: The least significant bit is transmitted first. This output is held in the Mark condition when the transmitter is disabled, Idle or when operating in local loopback mode. See note on drive levels at block diagram (図 5-2).                                          |

| TxD B           | 6                   | O    | Channel B transmitter serial data output: The least significant bit is transmitted first. This output is held in the Mark condition when the transmitter is disabled, Idle, or when operating in local loopback mode. See note on drive levels at block diagram (図 5-2).                                         |

| V <sub>CC</sub> | 38, 39              | Pwr  | Power supply: 3.3 V ± 10% or 5 V ± 10 % supply input.                                                                                                                                                                                                                                                            |

| X1/CLK          | 30                  | I    | Crystal 1: Crystal or external clock input. A crystal or clock of the specified limits must be supplied at all times. When a crystal is used, a capacitor must be connected from this pin to ground (see 図 4-9).                                                                                                 |

| X2              | 31                  | O    | Crystal 2: Connection for other side of the crystal. When a crystal is used, a capacitor must be connected from this pin to ground (see 図 4-9). If X1/CLK is driven from an external source, this pin must be left open.                                                                                         |

## 4 Electrical Specifications

### 4.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|           |                                                   |                 | MIN  | MAX            | UNIT  |

|-----------|---------------------------------------------------|-----------------|------|----------------|-------|

| $T_{amb}$ | Ambient temperature <sup>(2)</sup> <sup>(3)</sup> |                 | -40  | 85             | °C    |

| $T_{stg}$ | Storage temperature                               |                 | -65  | 150            | °C    |

| $V_{CC}$  | Voltage from $V_{CC}$ to GND <sup>(3)</sup>       |                 | -0.5 | 7              | V     |

| $V_S$     | Voltage from any pin to GND <sup>(3)</sup>        |                 | -0.5 | $V_{CC} + 0.5$ | V     |

| $P_D$     | Package power dissipation                         | QFP44 package   |      | 1.78           | W     |

|           |                                                   | HVQFN48 package |      | 0.5            |       |

| $P_{der}$ | Dissipation derating factor (above 25°C)          | QFP44 package   |      | 14             | mW/°C |

|           |                                                   | HVQFN48 package |      | 28             |       |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) For operation at elevated temperatures, the device must be derated based on 150°C maximum junction temperature.

(3) Parameters are valid over specified temperature range.

### 4.2 Static Characteristics for 5V Operation

$V_{CC} = 5V \pm 10\%$ ;  $T_{amb} = -40^\circ\text{C}$  to  $85^\circ\text{C}$  (unless otherwise noted) <sup>(1)</sup> <sup>(2)</sup>

| SYMBOL        | PARAMETER                                           | TEST CONDITIONS                                                          |                                | MIN                 | TYP  | MAX | UNIT          |

|---------------|-----------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|---------------------|------|-----|---------------|

| $V_{IL}$      | Low-level input voltage                             |                                                                          |                                |                     |      | 0.8 | V             |

| $V_{IH}$      | High-level input voltage                            | Except pin X1/CLK                                                        |                                | 2.4                 | 1.5  |     | V             |

|               |                                                     | Pin X1/CLK                                                               |                                | $0.8 \times V_{CC}$ | 2.4  |     |               |

| $V_{OL}$      | Low-level output voltage                            | $I_{OL} = 2.4\text{mA}$                                                  |                                |                     | 0.2  | 0.4 | V             |

| $V_{OH}$      | High-level output voltage                           | Except open-drain outputs <sup>(3)</sup> ;<br>$I_{OH} = -400\mu\text{A}$ |                                | $V_{CC} - 0.5$      |      |     | V             |

| $I_{I(1XPD)}$ | Power-down mode input current on pin X1/CLK         | $V_I = 0\text{V}$ to $V_{CC}$                                            |                                | 0.5                 | 0.05 | 0.5 | $\mu\text{A}$ |

| $I_{IL(X1)}$  | Low-level operating input current on pin X1/CLK     | $V_I = 0\text{V}$                                                        |                                |                     |      | 0   | $\mu\text{A}$ |

| $I_{IH(X1)}$  | High-level operating input current on pin X1/CLK    | $V_I = V_{CC}$                                                           |                                |                     |      | 130 | $\mu\text{A}$ |

| $I_I$         | Input leakage current                               | $V_I = 0\text{V}$ to $V_{CC}$                                            | All except input port pins     | -0.5                | 0.05 | 0.5 | $\mu\text{A}$ |

|               |                                                     |                                                                          | Input port pins <sup>(4)</sup> | -8                  | -2   | 0.5 |               |

| $I_{OZH}$     | High-level output OFF current (3-state data bus)    | $V_I = V_{CC}$                                                           |                                |                     |      | 0.5 | $\mu\text{A}$ |

| $I_{OZL}$     | Low-level output OFF current (3-state data bus)     | $V_I = 0\text{V}$                                                        |                                |                     | -0.5 |     | $\mu\text{A}$ |

| $I_{ODL}$     | Low-level output current in OFF state (open drain)  | $V_I = 0\text{V}$                                                        |                                |                     | -0.5 |     | $\mu\text{A}$ |

| $I_{ODH}$     | High-level output current in OFF state (open drain) | $V_I = V_{CC}$                                                           |                                |                     |      | 0.5 | $\mu\text{A}$ |

| $I_{CC}$      | Power supply current                                | CMOS input levels,<br><sup>(5)</sup>                                     | Operating mode                 |                     | 7    | 10  | $\text{mA}$   |

|               |                                                     |                                                                          | Power-down mode                |                     | 25   | 40  | $\mu\text{A}$ |

(1) All voltage measurements are referenced to ground. For testing, all inputs swing between 0.4V and 3V with a transition time of 5ns maximum. For X1/CLK this swing is between 0.4V and  $0.8 \times V_{CC}$ . All time measurements are referenced at input voltages of 0.8V and 2V, and output voltages of 0.8V and 2V, as appropriate.

(2) Typical values are at  $25^\circ\text{C}$ , typical supply voltages, and typical processing parameters.

(3) Test conditions for outputs:  $C_L = 125\text{pF}$ , except open-drain outputs. Test conditions for open-drain outputs:  $C_L = 125\text{pF}$ , constant current source = 2.6mA.

(4) Input port pins have active pull-up transistors that will source a typical 2 $\mu\text{A}$  from  $V_{CC}$  when the input pins are at VSS. Input port pins at  $V_{CC}$  source 0 $\mu\text{A}$ .

(5) All outputs are disconnected. Inputs are switching between CMOS levels of  $V_{CC} - 0.2\text{V}$  and  $V_{SS} + 0.2\text{V}$ .

### 4.3 Static Characteristics for 3.3V Operation

$V_{CC} = 3.3V \pm 10\%$ ;  $T_{amb} = -40^\circ\text{C}$  to  $85^\circ\text{C}$  (unless otherwise noted)<sup>(1)</sup> <sup>(2)</sup>

| SYMBOL        | PARAMETER                                           | TEST CONDITIONS                                                          |                                | MIN                           | TYP                 | MAX | UNIT          |

|---------------|-----------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------|-----|---------------|

| $V_{IL}$      | Low-level input voltage                             |                                                                          |                                | 0.65                          | $0.2 \times V_{CC}$ |     | V             |

| $V_{IH}$      | High-level input voltage                            |                                                                          |                                | 2.4                           | 1.7                 |     | V             |

| $V_{OL}$      | Low-level output voltage                            | $I_{OL} = 2.4\text{mA}$                                                  |                                |                               | 0.2                 | 0.4 | V             |

| $V_{OH}$      | High-level output voltage                           | except open-drain outputs <sup>(3)</sup> ;<br>$I_{OH} = -400\mu\text{A}$ |                                | $V_{CC} - 0.5$ $V_{CC} - 0.2$ |                     |     | V             |

| $I_{I(1XPD)}$ | Power-down mode input current on pin X1/CLK         | $V_I = 0\text{V}$ to $V_{CC}$                                            |                                | 0.5                           | 0.05                | 0.5 | $\mu\text{A}$ |

| $I_{IL(X1)}$  | Low-level operating input current on pin X1/CLK     | $V_I = 0\text{V}$                                                        |                                | 0                             |                     |     | $\mu\text{A}$ |

| $I_{IH(X1)}$  | High-level operating input current on pin X1/CLK    | $V_I = V_{CC}$                                                           |                                | 130                           |                     |     | $\mu\text{A}$ |

| $I_I$         | Input leakage current                               | $V_I = 0\text{V}$ to $V_{CC}$                                            | all except input port pins     | -0.5                          | 0.05                | 0.5 | $\mu\text{A}$ |

|               |                                                     |                                                                          | input port pins <sup>(4)</sup> | -8                            | -2                  | 0.5 |               |

| $I_{OZH}$     | High-level output OFF current (3-state data bus)    | $V_I = V_{CC}$                                                           |                                | 0.5                           |                     |     | $\mu\text{A}$ |

| $I_{OZL}$     | Low-level output OFF current (3-state data bus)     | $V_I = 0\text{V}$                                                        |                                | -0.5                          |                     |     | $\mu\text{A}$ |

| $I_{ODL}$     | Low-level output current in OFF state (open drain)  | $V_I = 0\text{V}$                                                        |                                | -0.5                          |                     |     | $\mu\text{A}$ |

| $I_{ODH}$     | High-level output current in OFF state (open drain) | $V_I = V_{CC}$                                                           |                                | 0.5                           |                     |     | $\mu\text{A}$ |

| $I_{CC}$      | Power supply current                                | CMOS input levels, <sup>(5)</sup>                                        | Operating mode                 | 4                             | 6                   |     | $\text{mA}$   |

|               |                                                     |                                                                          | Power-down mode                | 15                            | 25                  |     | $\mu\text{A}$ |

- (1) All voltage measurements are referenced to ground. For testing, all inputs swing between 0.4V and 3V with a transition time of 5ns maximum. For X1/CLK this swing is between 0.4V and  $0.8 \times V_{CC}$ . All time measurements are referenced at input voltages of 0.8V and 2V, and output voltages of 0.8V and 2V, as appropriate.

- (2) Typical values are at  $25^\circ\text{C}$ , typical supply voltages, and typical processing parameters.

- (3) Test conditions for outputs:  $C_L = 125\text{pF}$ , except open-drain outputs. Test conditions for open-drain outputs:  $C_L = 125\text{pF}$ , constant current source = 2.6mA.

- (4) Input port pins have active pull-up transistors that will source a typical 2  $\mu\text{A}$  from  $V_{CC}$  when the input pins are at VSS. Input port pins at  $V_{CC}$  source 0  $\mu\text{A}$ .

- (5) All outputs are disconnected. Inputs are switching between CMOS levels of  $V_{CC} - 0.2\text{V}$  and  $V_{SS} + 0.2\text{V}$ .

## 4.4 Dynamic Characteristics for 5V Operation

over operating free-air temperature range (unless otherwise noted) (1) (2) (3) (4)

| PARAMETER                                                          | TEST CONDITIONS                                          | MIN              | TYP | MAX | UNIT |

|--------------------------------------------------------------------|----------------------------------------------------------|------------------|-----|-----|------|

| <b>Reset Timing</b> (see <a href="#">图 4-2</a> )                   |                                                          |                  |     |     |      |

| $t_{RES}$ Reset pulse width                                        |                                                          | 100              | 18  |     | ns   |

| <b>Bus Timing<sup>(5)</sup></b> (see <a href="#">图 4-3</a> )       |                                                          |                  |     |     |      |

| $t_{AS}$ A0 to A3 set-up time to RDN, WRN LOW                      |                                                          | 10               | 6   |     | ns   |

| $t_{AH}$ A0 to A3 hold time from RDN, WRN LOW                      |                                                          | 20               | 12  |     | ns   |

| $t_{CS}$ CEN set-up time to RDN, WRN LOW                           |                                                          | 0                |     |     | ns   |

| $t_{CH}$ CEN hold time from RDN, WRN LOW                           |                                                          | 0                |     |     | ns   |

| $t_{RW}$ WRN, RDN pulse width (LOW time)                           |                                                          | 15               | 8   |     | ns   |

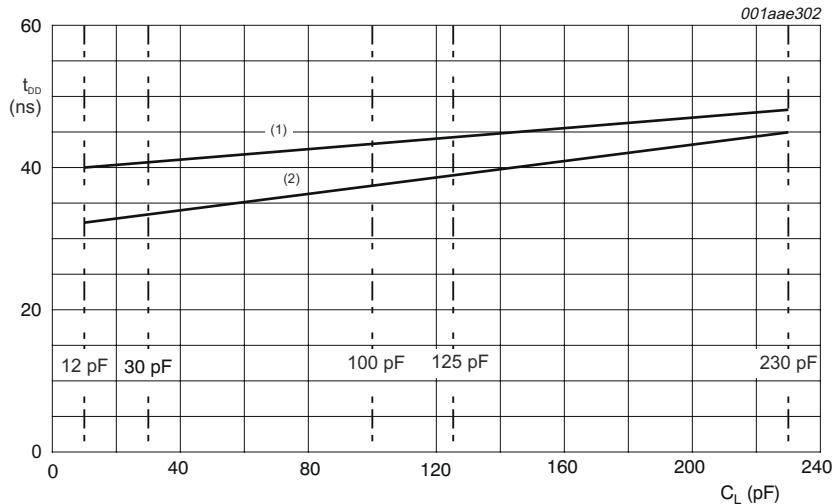

| $t_{DD}$ Data valid after RDN LOW                                  | 125 pF load; see <a href="#">图 4-1</a> for smaller loads |                  | 40  | 55  | ns   |

| $t_{DA}$ RDN LOW to data bus active                                |                                                          | 0 <sup>(6)</sup> |     |     | ns   |

| $t_{DF}$ data bus floating after RDN or CEN HIGH                   |                                                          |                  | 20  |     | ns   |

| $t_{DI}$ RDN or CEN HIGH to data bus invalid                       |                                                          | 0                |     |     | ns   |

| $t_{DS}$ Data bus set-up time before WRN or CEN HIGH (write cycle) |                                                          | 25               | 17  |     | ns   |

| $t_{DH}$ Data hold time after WRN HIGH                             |                                                          | 0                | -12 |     | ns   |

| $t_{RWD}$ HIGH time between read and/or write cycles               |                                                          | 17               | 10  |     | ns   |

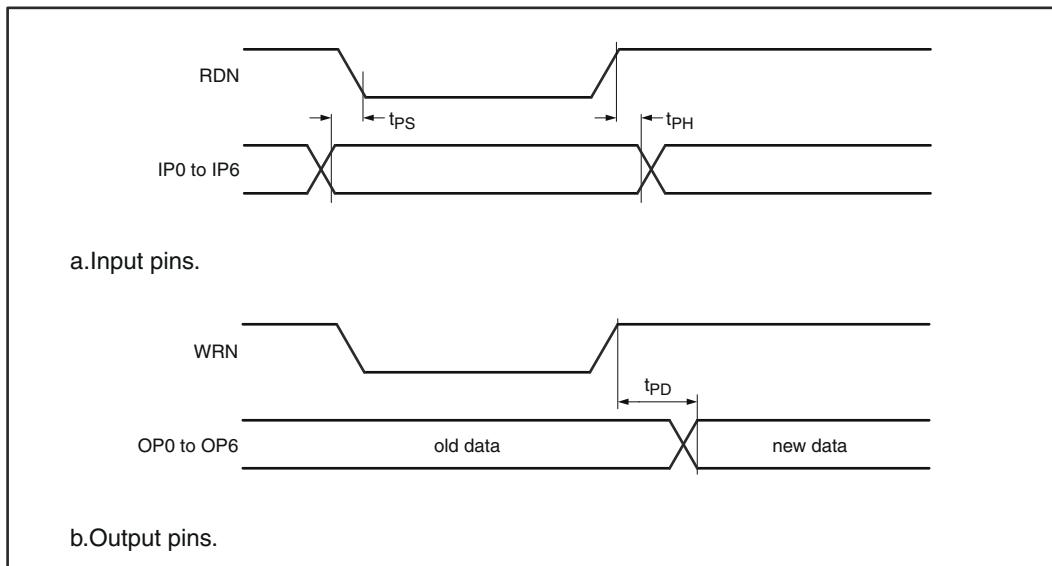

| <b>Port Timing<sup>(5)</sup></b> (see <a href="#">图 4-7</a> )      |                                                          |                  |     |     | ns   |

| $t_{PS}$ Port in set-up time before RDN LOW (Read IP ports cycle)  |                                                          | 0                | -20 |     | ns   |

| $t_{PH}$ Port in hold time after RDN HIGH                          |                                                          | 0                | -20 |     |      |

| $t_{PD}$ OP port valid after WRN or CEN HIGH (OPR write cycle)     |                                                          |                  | 40  | 60  |      |

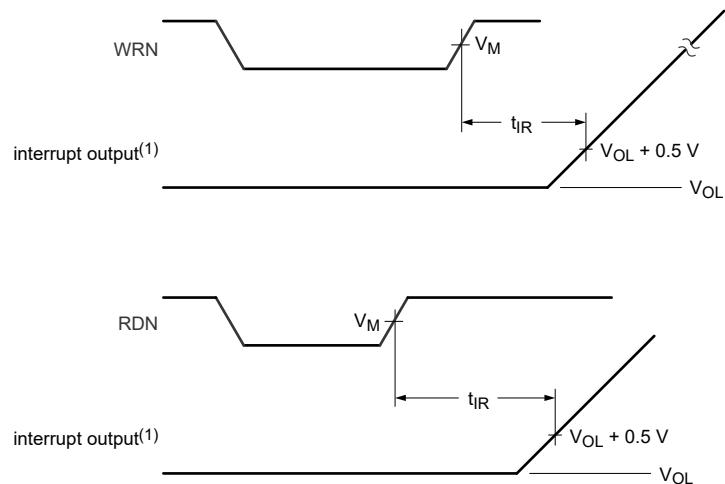

| <b>Interrupt Timing</b> (see <a href="#">图 4-8</a> )               |                                                          |                  |     |     |      |

| $t_{IR}$ INTRN (or OP3 to OP7 when used as interrupts)             | Read Rx FIFO (RxRDY/FFULL interrupt)                     | 40               | 60  |     | ns   |

|                                                                    | Write Tx FIFO (TxRDY interrupt)                          | 40               | 60  |     |      |

|                                                                    | Reset command (delta break change interrupt)             | 40               | 60  |     |      |

|                                                                    | Stop C/T command (counter/timer interrupt)               | 40               | 60  |     |      |

|                                                                    | Read IPCR (delta input port change interrupt)            | 40               | 60  |     |      |

|                                                                    | Write IMR (clear of change interrupt mask bit(s))        | 40               | 60  |     |      |

## 4.4 Dynamic Characteristics for 5V Operation (続き)

over operating free-air temperature range (unless otherwise noted) (1) (2) (3) (4)

| PARAMETER                                                                       | TEST CONDITIONS                                                | MIN                       | TYP                | MAX   | UNIT  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------|--------------------|-------|-------|

| <b>Clock Timing (see 図 4-9)</b>                                                 |                                                                |                           |                    |       |       |

| $t_{CLK}$                                                                       | X1/CLK HIGH or LOW time                                        |                           | 30                 | 20    | ns    |

| $f_{CLK}$                                                                       | X1/CLK frequency                                               |                           | 0.1 <sup>(7)</sup> | 3.686 | 8 MHz |

| $t_{CTC}$                                                                       | C/T clock (IP2) HIGH or LOW time<br>(C/T external clock input) |                           | 30                 | 10    |       |

| $f_{CTC}$                                                                       | C/T clock (IP2) frequency                                      |                           | 0 <sup>(7)</sup>   | 8     | MHz   |

| $t_{RX}$                                                                        | RxC HIGH or LOW time                                           | 16 $\times$               | 30                 | 10    | ns    |

| $f_{RX}$                                                                        | RxC frequency                                                  | 16 $\times$               | 0 <sup>(7)</sup>   | 16    | MHz   |

|                                                                                 |                                                                | 1 $\times$ <sup>(8)</sup> | 0 <sup>(7)</sup>   | 1     |       |

| $t_{TX}$                                                                        | TxC HIGH or LOW time                                           | 16 $\times$               | 30                 | 10    | ns    |

| $f_{TX}$                                                                        | TxC frequency                                                  | 16 $\times$               |                    | 16    | MHz   |

|                                                                                 |                                                                | 1 $\times$ <sup>(8)</sup> | 0 <sup>(8)</sup>   | 1     |       |

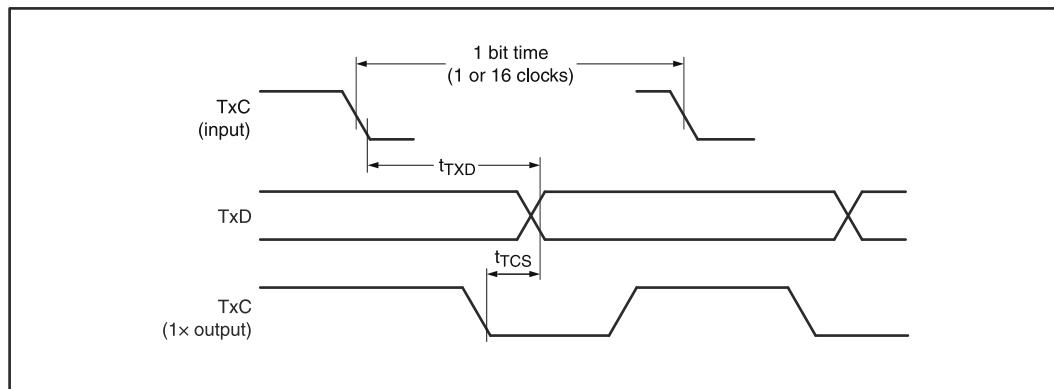

| <b>Transmitter Timing, External Clock (see 図 4-10)</b>                          |                                                                |                           |                    |       |       |

| $t_{TxD}$                                                                       | TxD output delay from TxC LOW (TxC input pin)                  |                           | 40                 | 60    | ns    |

| $t_{TCS}$                                                                       | Output delay from TxC output pin LOW to TxD data output        |                           | 6                  | 30    | ns    |

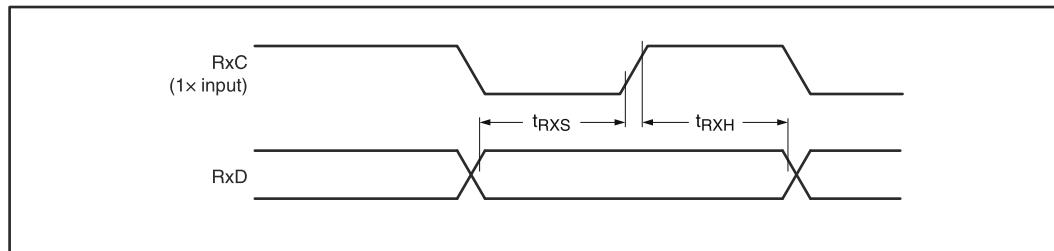

| <b>Receiver Timing, External Clock (see 図 4-11)</b>                             |                                                                |                           |                    |       |       |

| $t_{RXS}$                                                                       | RxD data set-up time to RxC HIGH                               |                           | 50                 | 40    | ns    |

| $t_{RXH}$                                                                       | RxD data hold time from RxC HIGH                               |                           | 50                 | 40    | ns    |

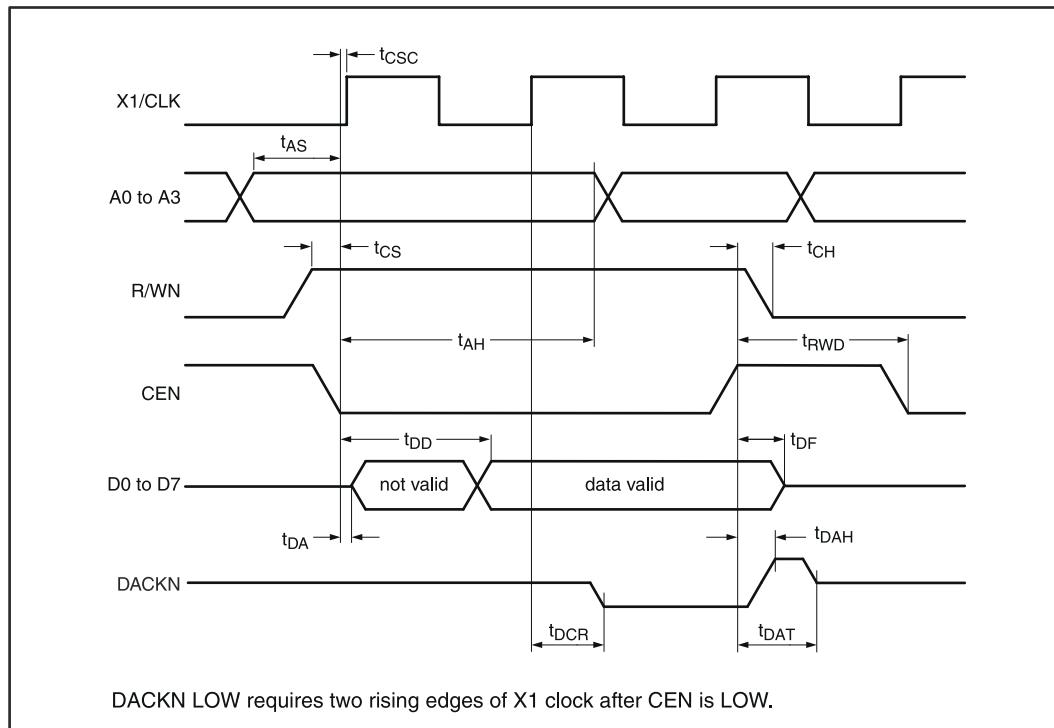

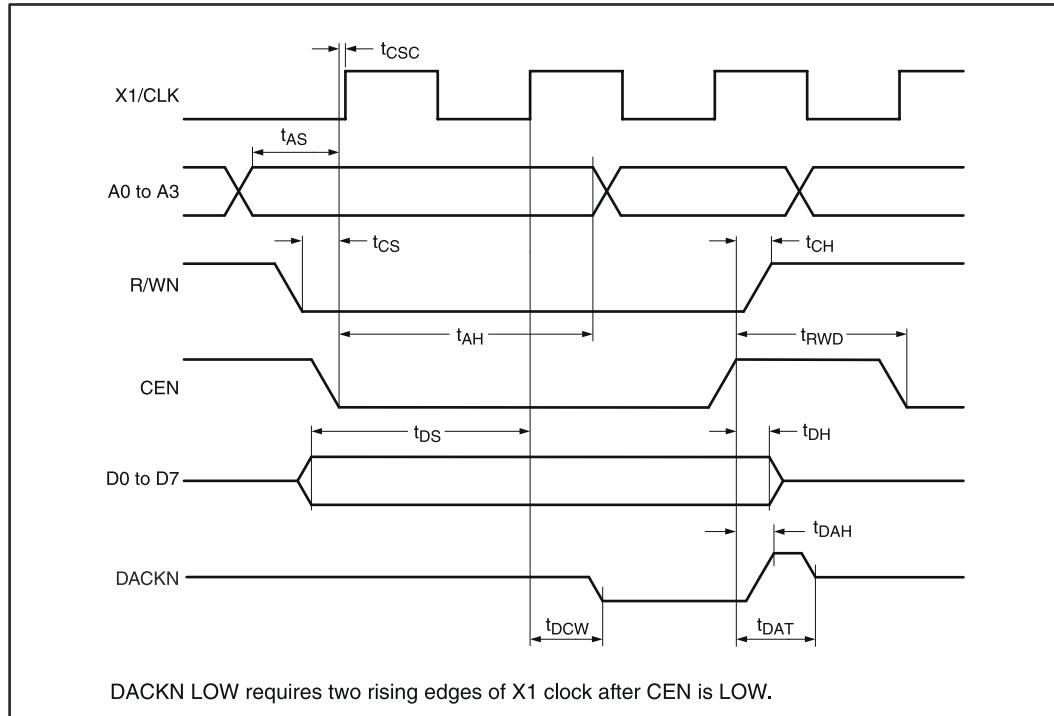

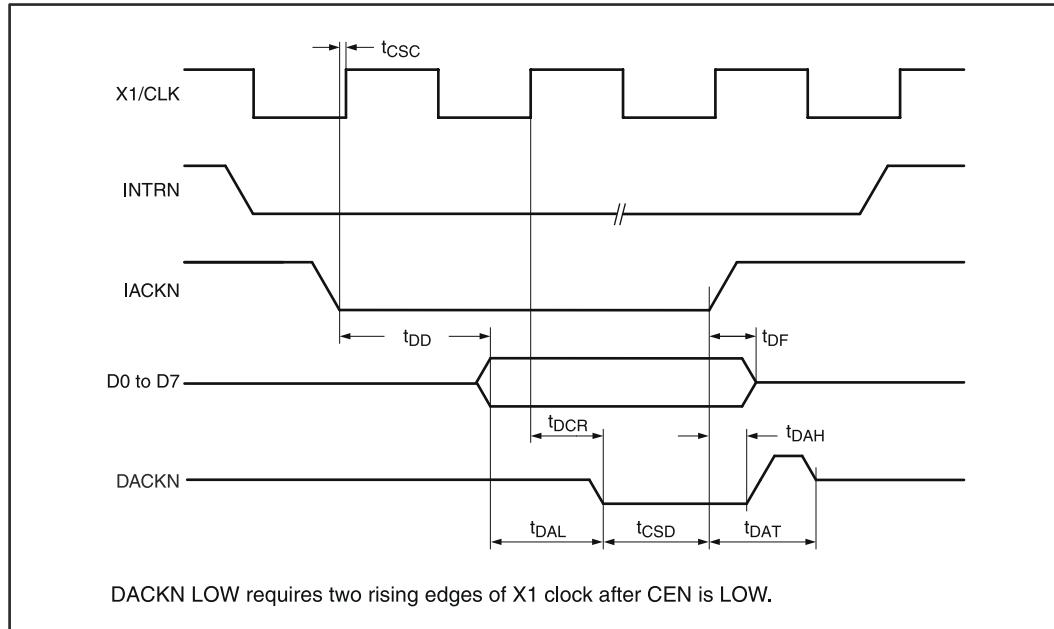

| <b>68xxx or Motorola Bus Timing (see 図 4-3, 図 4-4, and 図 4-5)<sup>(9)</sup></b> |                                                                |                           |                    |       |       |

| $t_{DCR}$                                                                       | DACKN LOW (read cycle) from X1 HIGH                            |                           | 15                 | 35    | ns    |

| $t_{DCW}$                                                                       | DACKN LOW (write cycle) from X1 HIGH                           |                           | 15                 | 35    | ns    |

| $t_{DAT}$                                                                       | DACKN high-impedance from CEN or IACKN HIGH                    |                           | 8                  | 10    | ns    |

| $t_{CSC}$                                                                       | CEN or IACKN set-up time to X1 HIGH for minimum DACKN cycle    |                           | 16                 | 8     | ns    |

- (1) Parameters are valid over specified temperature and voltage range.

- (2) All voltage measurements are referenced to ground. For testing, all inputs swing between 0.4V and 3V with a transition time of 5ns maximum. For X1/CLK this swing is between 0.4V and 0.8  $\times$   $V_{CC}$ . All time measurements are referenced at input voltages of 0.8V and 2V, and output voltages of 0.8V and 2V, as appropriate.

- (3) Test conditions for outputs:  $C_L = 125\text{pF}$ , except open-drain outputs. Test conditions for open-drain outputs:  $C_L = 125\text{pF}$ , constant current source = 2.6mA.

- (4) Typical values are the average values at 25°C and 5V.

- (5) Timing is illustrated and referenced to the WRN and RDN Inputs. Also, CEN may be the strobing input. CEN and RDN (also CEN and WRN) are ORed internally. The signal asserted last initiates the cycle and the signal negated first terminates the cycle.

- (6) Specified by characterization of sample units.

- (7) Minimum frequencies are not tested but are specified by design.

- (8) Clocks for 1 $\times$  mode should maintain a 60/40 duty cycle or better.

- (9) Minimum DACKN time is (( $t_{DCR}$  or  $t_{DCW}$ )  $t_{CSC}$  + 2 X1 edges + rise time over 5ns). Two X1 edges is 273ns at 3.6864MHz. For faster bus cycles, the 80xxx bus timing may be used while in the 68xxx mode. It is not necessary to wait for DACKN to insure the proper operation of the SC28C92. In all cases, the data is written to the TL28L92 on the falling edge of DACKN or the rise of CEN. The fall of CEN initializes the bus cycle. The rise of CEN ends the bus cycle. DACKN LOW or CEN HIGH completes the write cycle.

## 4.5 Dynamic Characteristics for 3.3V Operation

over operating free-air temperature range (unless otherwise noted)<sup>(1) (2) (3) (4)</sup>

| PARAMETER                                                          | TEST CONDITIONS                                         | MIN              | TYP | MAX | UNIT |

|--------------------------------------------------------------------|---------------------------------------------------------|------------------|-----|-----|------|

| <b>Reset Timing</b> (see <a href="#">图 4-2</a> )                   |                                                         |                  |     |     |      |

| $t_{RES}$ Reset pulse width                                        |                                                         | 100              | 20  |     | ns   |

| <b>Bus Timing<sup>(5)</sup></b> (see <a href="#">图 4-3</a> )       |                                                         |                  |     |     |      |

| $t_{AS}$ A0 to A3 set-up time to RDN, WRN LOW                      |                                                         | 10               | 6   |     | ns   |

| $t_{AH}$ A0 to A3 hold time from RDN, WRN LOW                      |                                                         | 33               | 16  |     | ns   |

| $t_{CS}$ CEN set-up time to RDN, WRN LOW                           |                                                         | 0                |     |     | ns   |

| $t_{CH}$ CEN hold time from RDN, WRN LOW                           |                                                         | 0                |     |     | ns   |

| $t_{RW}$ WRN, RDN pulse width (LOW time)                           |                                                         | 20               | 10  |     | ns   |

| $t_{DD}$ Data valid after RDN LOW                                  | 125pF load; see <a href="#">图 4-1</a> for smaller loads |                  | 46  | 75  | ns   |

| $t_{DA}$ RDN LOW to data bus active                                |                                                         | 0 <sup>(6)</sup> |     |     | ns   |

| $t_{DF}$ data bus floating after RDN or CEN HIGH                   |                                                         | 15               | 20  |     | ns   |

| $t_{DI}$ RDN or CEN HIGH to data bus invalid                       |                                                         | 0                |     |     | ns   |

| $t_{DS}$ Data bus set-up time before WRN or CEN HIGH (write cycle) |                                                         | 43               | 20  |     | ns   |

| $t_{DH}$ Data hold time after WRN HIGH                             |                                                         | 0                | -15 |     | ns   |

| $t_{RWD}$ HIGH time between read and/or write cycles               |                                                         | 27               | 10  |     | ns   |

| <b>Port Timing<sup>(5)</sup></b> (see <a href="#">图 4-7</a> )      |                                                         |                  |     |     | ns   |

| $t_{PS}$ Port in set-up time before RDN LOW (Read IP ports cycle)  |                                                         | 0                | -20 |     | ns   |

| $t_{PH}$ Port in hold time after RDN HIGH                          |                                                         | 0                | -20 |     |      |

| $t_{PD}$ OP port valid after WRN or CEN HIGH (OPR write cycle)     |                                                         | 50               | 75  |     |      |

| <b>Interrupt Timing</b> (see <a href="#">图 4-8</a> )               |                                                         |                  |     |     |      |

| $t_{IR}$ INTRN (or OP3 to OP7 when used as interrupts)             | Read Rx FIFO (RxRDY/FFULL interrupt)                    | 40               | 79  |     | ns   |

|                                                                    | Write Tx FIFO (TxRDY interrupt)                         | 40               | 79  |     |      |

|                                                                    | Reset command (delta break change interrupt)            | 40               | 79  |     |      |

|                                                                    | Stop C/T command (counter/timer interrupt)              | 40               | 79  |     |      |

|                                                                    | Read IPCR (delta input port change interrupt)           | 40               | 79  |     |      |

|                                                                    | Write IMR (clear of change interrupt mask bit(s))       | 40               | 79  |     |      |

## 4.5 Dynamic Characteristics for 3.3V Operation (続き)

over operating free-air temperature range (unless otherwise noted)<sup>(1) (2) (3) (4)</sup>

| PARAMETER                                                                       | TEST CONDITIONS                                             | MIN                       | TYP                | MAX   | UNIT  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------|--------------------|-------|-------|

| <b>Clock Timing (see 図 4-9)</b>                                                 |                                                             |                           |                    |       |       |

| $t_{CLK}$                                                                       | X1/CLK HIGH or LOW time                                     |                           | 35                 | 25    | ns    |

| $f_{CLK}$                                                                       | X1/CLK frequency                                            |                           | 0.1 <sup>(7)</sup> | 3.686 | 8 MHz |

| $t_{CTC}$                                                                       | C/T clock (IP2) HIGH or LOW time (C/T external clock input) |                           | 30                 | 15    |       |

| $f_{CTC}$                                                                       | C/T clock (IP2) frequency                                   |                           | 0 <sup>(7)</sup>   | 8     | MHz   |

| $t_{RX}$                                                                        | RxC HIGH or LOW time                                        | 16 $\times$               | 30                 | 10    | ns    |

| $f_{RX}$                                                                        | RxC frequency                                               | 16 $\times$               | 0 <sup>(7)</sup>   | 16    | MHz   |

|                                                                                 |                                                             | 1 $\times$ <sup>(8)</sup> | 0 <sup>(7)</sup>   | 1     |       |

| $t_{TX}$                                                                        | TxC HIGH or LOW time                                        | 16 $\times$               | 30                 | 15    | ns    |

| $f_{TX}$                                                                        | TxC frequency                                               | 16 $\times$               |                    | 16    | MHz   |

|                                                                                 |                                                             | 1 $\times$ <sup>(8)</sup> | 0 <sup>(8)</sup>   | 1     |       |

| <b>Transmitter Timing, External Clock (see 図 4-10)</b>                          |                                                             |                           |                    |       |       |

| $t_{TxD}$                                                                       | TxD output delay from TxC LOW (TxC input pin)               |                           | 40                 | 78    | ns    |

| $t_{TCS}$                                                                       | Output delay from TxC output pin LOW to TxD data output     |                           | 8                  | 30    | ns    |

| <b>Receiver Timing, External Clock (see 図 4-11)</b>                             |                                                             |                           |                    |       |       |

| $t_{RXS}$                                                                       | RxD data set-up time to RxC HIGH                            |                           | 50                 | 10    | ns    |

| $t_{RXH}$                                                                       | RxD data hold time from RxC HIGH                            |                           | 50                 | 10    | ns    |

| <b>68xxx or Motorola Bus Timing (see 図 4-3, 図 4-4, and 図 4-5)<sup>(9)</sup></b> |                                                             |                           |                    |       |       |

| $t_{DCR}$                                                                       | DACKN LOW (read cycle) from X1 HIGH                         |                           | 18                 | 57    | ns    |

| $t_{DCW}$                                                                       | DACKN LOW (write cycle) from X1 HIGH                        |                           | 18                 | 57    | ns    |

| $t_{DAT}$                                                                       | DACKN high-impedance from CEN or IACKN HIGH                 |                           | 10                 | 15    | ns    |

| $t_{CSC}$                                                                       | CEN or IACKN set-up time to X1 HIGH for minimum DACKN cycle |                           | 30                 | 10    | ns    |

- (1) Parameters are valid over specified temperature and voltage range.

- (2) All voltage measurements are referenced to ground. For testing, all inputs swing between 0.4V and 3V with a transition time of 5ns maximum. For X1/CLK this swing is between 0.4V and 0.8  $\times$   $V_{CC}$ . All time measurements are referenced at input voltages of 0.8V and 2V, and output voltages of 0.8V and 2V, as appropriate.

- (3) Test conditions for outputs:  $C_L$  = 125pF, except open-drain outputs. Test conditions for open-drain outputs:  $C_L$  = 125pF, constant current source = 2.6mA.

- (4) Typical values are the average values at 25°C and 5V.

- (5) Timing is illustrated and referenced to the WRN and RDN Inputs. Also, CEN may be the strobing input. CEN and RDN (also CEN and WRN) are ORed internally. The signal asserted last initiates the cycle and the signal negated first terminates the cycle.

- (6) Specified by characterization of sample units.

- (7) Minimum frequencies are not tested but are specified by design.

- (8) Clocks for 1 $\times$  mode should maintain a 60/40 duty cycle or better.

- (9) Minimum DACKN time is (( $t_{DCR}$  or  $t_{DCW}$ )  $t_{CSC}$  + 2 X1 edges + rise time over 5ns). Two X1 edges is 273ns at 3.6864MHz. For faster bus cycles, the 80xxx bus timing may be used while in the 68xxx mode. It is not necessary to wait for DACKN to insure the proper operation of the SC28C92. In all cases, the data is written to the TL28L92 on the falling edge of DACKN or the rise of CEN. The fall of CEN initializes the bus cycle. The rise of CEN ends the bus cycle. DACKN LOW or CEN HIGH completes the write cycle.

## 4.6 Typical Performance

(1)  $V_{CC} = 3.3$  V;  $T_{amb} = 25^\circ\text{C}$

(2)  $V_{CC} = 5.0$  V;  $T_{amb} = 25^\circ\text{C}$

Bus cycle times:

80xxx mode:  $t_{DD} + t_{RWD} = 70$  ns for  $V_{CC} = 5$  V or 40 ns for  $V_{CC} = 3.3$  V + rise and fall time of control signals.

68XXX mode:  $t_{CSC} + t_{DAT} + 1$  cycle of the X1 clock for = 70 ns for  $V_{CC} = 5$  V + rise and fall time of control signals.

**図 4-1. Port Timing as a Function of Capacitive Loading at Typical Conditions**

## 4.7 Timing Diagrams

**図 4-2. Reset Timing**

図 4-3. Bus Timing (80xxx Mode)

図 4-4. Bus Timing, Read Cycle (68xxx Mode)

図 4-5. Bus Timing, Write Cycle (68xxx Mode)

図 4-6. Interrupt Cycle Timing (68xxx Mode)

図 4-7. Port Timing

The test for open-drain outputs is intended to switch the output transistor. Measurement of this response is referenced from the midpoint of the switching signal,  $V_M$ , to a point 0.2V above  $V_{OL}$ . This point represents noise margin that assures true switching has occurred. Beyond this level, the effects of external circuitry and test environment are pronounced and can greatly affect the resultant measurement.

(1) IRQN or OP3toOP7 when used as interrupt outputs.

図 4-8. Interrupt Timing (80xxx Mode)

图 4-9. Clock Timing

图 4-10. Transmitter External Clocks

図 4-11. Receiver External Clocks

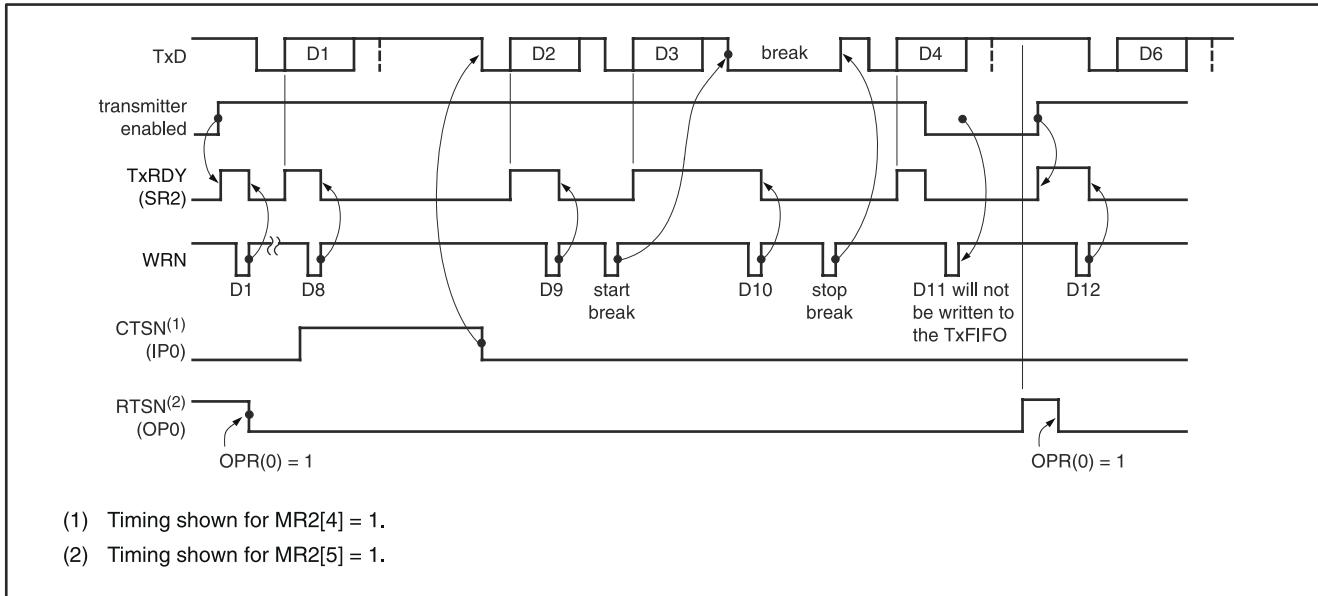

図 4-12. Transmitter Timing

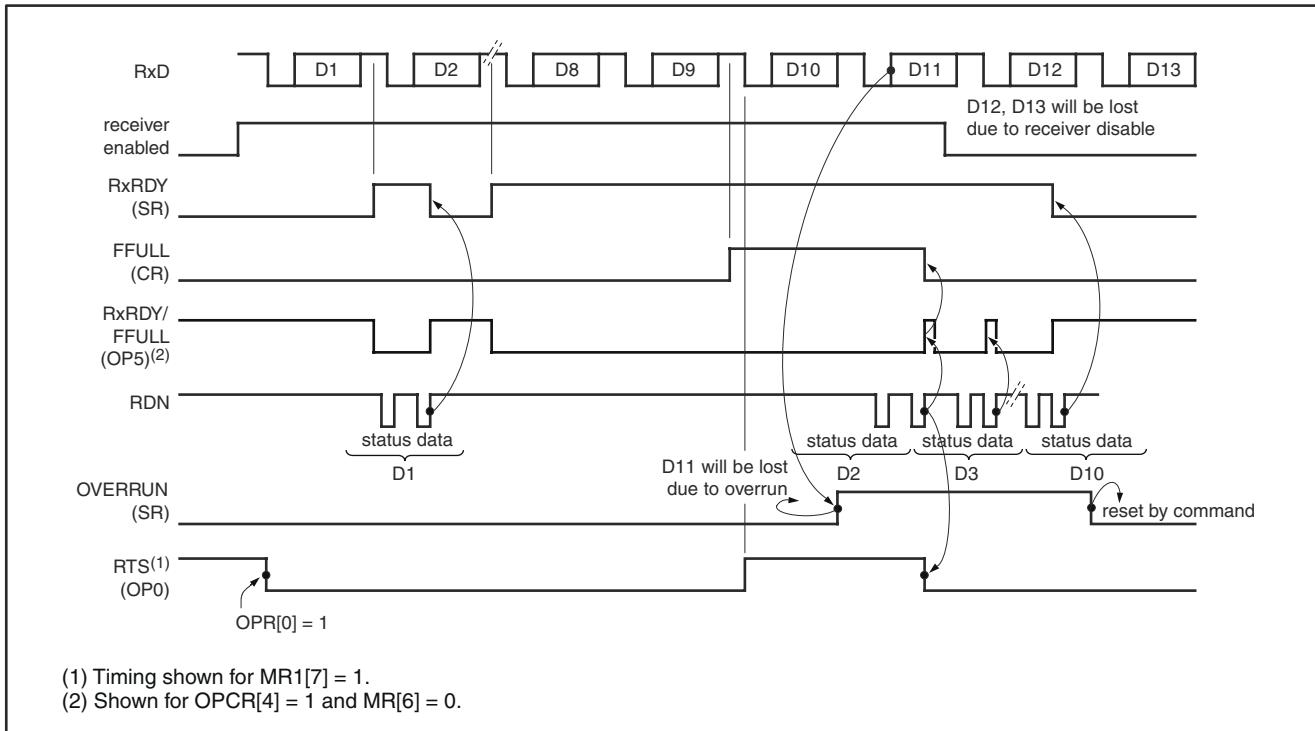

図 4-13. Receiver Timing

#### 4.8 Test Information

図 4-14. Test Conditions on Outputs

## 5 Detailed Description

## 5.1 Overview

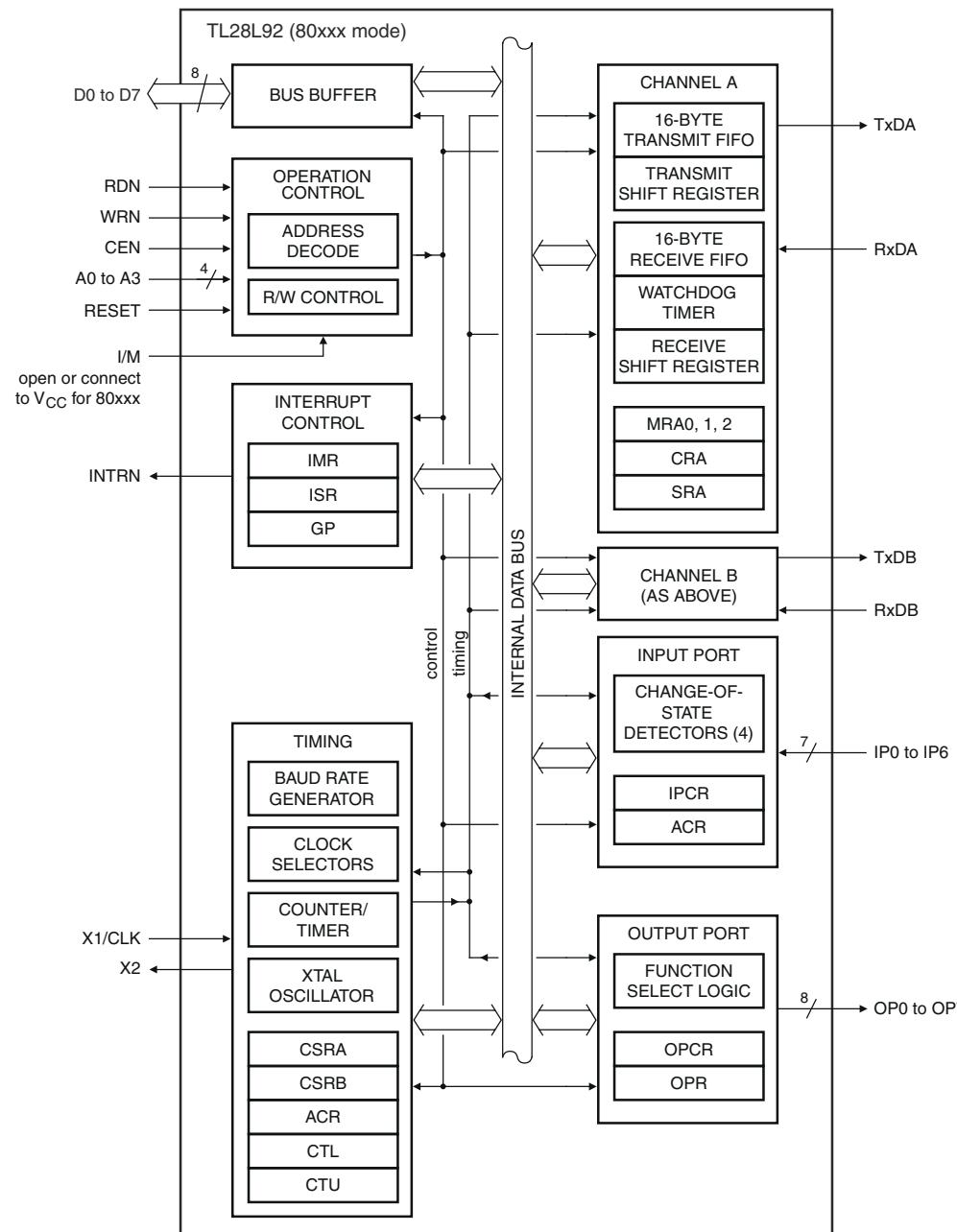

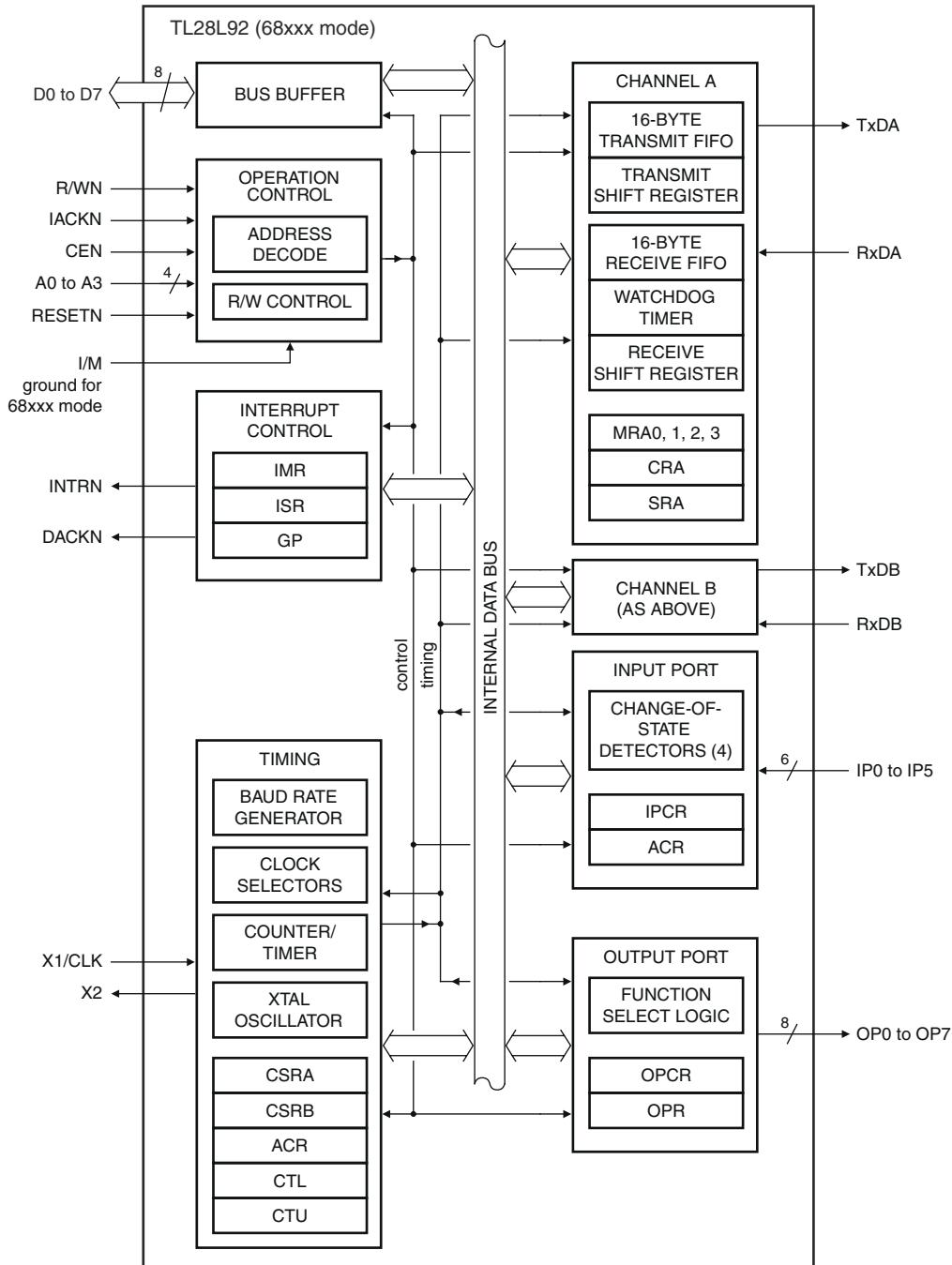

The TL28L92 DUART consists of the following eight major sections: data bus buffer, operation control, interrupt control, timing, communications channels A and B, input port and output port. See [図 5-1](#) and [図 5-2](#) .

## 5.2 Functional Block Diagram

A. The data pins TxD and RxD are considered idle at the logic 1 (HIGH) level when inactive, or active when at the logic 0 (LOW) level. Comments about these levels when RS232 is referenced often refer to Mark and Space levels. Mark usually means inactive and Space means active. The voltage levels represented by the terms Mark and Space are often reversed from those above: Mark is low voltage, and Space is high voltage.

図 5-1. Block Diagram (80xxx Mode)

A. The data pins TxD and RxD are considered idle at the logic 1 (HIGH) level when inactive, or active when at the logic 0 (LOW) level. Comments about these levels when RS232 is referenced often refer to Mark and Space levels. Mark usually means inactive and Space means active. The voltage levels represented by the terms Mark and Space are often reversed from those above: Mark is low voltage, and Space is high voltage.

図 5-2. Block Diagram (68xxx Mode)

## 5.3 Feature Description

### 5.3.1 Data Bus Buffer

The data bus buffer provides the interface between the external and internal data buses. It is controlled by the operation control block to allow read and write operations to take place between the controlling CPU and the DUART.

### 5.3.2 Operation Control

The operation control logic receives operation commands from the CPU and generates appropriate signals to internal sections to control device operation. It contains address decoding and read and write circuits to permit communications with the microprocessor via the data bus.

### 5.3.3 Interrupt Control

A single active LOW interrupt output (INTRN) is provided which is activated upon the occurrence of any of eight internal events. Associated with the interrupt system are the Interrupt Mask Register (IMR) and the Interrupt Status Register (ISR). The IMR can be programmed to select only certain conditions to cause INTRN to be asserted. The ISR can be read by the CPU to determine all currently active interrupting conditions. Outputs OP3 to OP7 can be programmed to provide discrete interrupt outputs for the transmitter, receivers, and counter/timer. When OP3 to OP7 are programmed as interrupts, their output buffers are changed to the open-drain active LOW configuration. The OP pins may be used for DMA and modem control as well (see [セクション 6.4](#)).

### 5.3.4 FIFO Configuration

Each receiver and transmitter has a 16 byte FIFO. These FIFOs may be configured to operate at a fill capacity of either 8 bytes or 16 bytes. The 8 byte or 16 byte mode is controlled by the MR0A[3] bit. A logic 0 value for this bit sets the 8-bit mode (the default); a logic 1 sets the 16 byte mode. MR0A bit 3 sets the FIFO size for both channels.

The FIFO fill interrupt level automatically follow the programming of the MR0A[3] bit. See [表 6-22](#) and [表 6-23](#).

### 5.3.5 68xxx Mode

When the I/M pin is connected to GND (ground), the operation of the TL28L92 switches to the bus interface compatible with the Motorola bus interfaces. Several of the pins change their function as follows:

- IP6 becomes IACKN input

- RDN becomes DACKN

- WRN becomes R/WN

The interrupt vector is enabled and the interrupt vector is placed on the data bus when IACKN is asserted LOW. The interrupt vector register is located at address 0xC. The contents of this register are set to 0x0F on the application of RESETN.

The generation of DACKN uses two positive edges of the X1 clock as the DACKN delay from the falling edge of CEN. If the CEN is withdrawn before two edges of the X1 clock occur, the generation of DACKN is terminated. Systems not strictly requiring DACKN may use the 68xxx mode with the bus timing of the 80xxx mode greatly decreasing the bus cycle time.

### 5.3.6 Timing Circuits

#### 5.3.6.1 Crystal Clock

The timing block consists of a crystal oscillator, a baud rate generator, a programmable 16-bit counter/timer, and four clock selectors. The crystal oscillator operates directly from a crystal connected across the X1/CLK and X2 inputs. If an external clock of the appropriate frequency is available, it may be connected to X1/CLK. The clock serves as the basic timing reference for the Baud Rate Generator (BRG), the counter/timer, and other internal circuits. A clock signal within the limits specified in the specifications section of this data sheet must always be supplied to the DUART. If an external clock is used instead of a crystal, X1 should be driven using a configuration similar to the one in [図 4-9](#). Nominal crystal rate is 3.6864 MHz. Rates up to 8 MHz may be used.

### 5.3.6.2 Baud Rate Generator

The baud rate generator operates from the oscillator or external clock input at the X1 input and is capable of generating 28 commonly used data communications baud rates ranging from 50kBd to 38.4kBd. Programming bit 0 of MR0 to a logic 1 gives additional baud rates of 57.6kBd, 115.2kBd and 230.4kBd (500 kHz with X1 at 8MHz). Note that the MR0A[2:0] control this change and that the change applies to both channels. MR0B[2:0] are reserved.

The baud rates are based on an input frequency of 3.6864MHz. Changing the X1 frequency changes all baud rates by ratio of 3.6864MHz to the new frequency. All rates generated by the BRG is in the 16 $\times$  mode. The clock outputs from the BRG are at 16 $\times$  the actual baud rate.

The counter/timer can be used as a timer to produce a 16 $\times$  clock for any other baud rate by counting down the crystal clock or an external clock. The four clock selectors allow the independent selection, for each receiver and transmitter, of any of these baud rates or external timing signal. The use of the counter/timer also requires the generation of a frequency 16 $\times$  of the baud rate. See [セクション 5.3.6.3](#).

### 5.3.6.3 Counter/Timer

The Counter/timer is a 16-bit programmable divider that operates in one of three modes: counter, timer and time-out. In the timer mode it generates a square wave. In the counter mode, it generates a time delay. In the time-out mode, it monitors the time between received characters. The C/T uses the numbers loaded into the Counter/Timer Lower Register (CTLR) and the Counter/Timer Upper Register (CTUR) as its divisor.