# TLC6C598 8ビット・シフト・レジスタLEDドライバ

## 1 特長

- 3V～5.5Vの広い $V_{CC}$

- 出力最大定格40V

- 8個のパワーDMOSトランジスタにより、 $V_{CC} = 5V$ で50mAの連続電流を出力、または1ms未満の単一パルス期間および50mA未満の平均電流で200mAのPWM電流を出力

- サーマル・シャットダウン保護機能

- 拡張カスケードにより複数のステージが可能

- 単一の入力ですべてのレジスタをクリア

- 低消費電力

- 低速なスイッチング時間( $t_r$ および $t_f$ )により、EMIを大幅に低減

- 16ピンのTSSOP-PWパッケージ

## 2 アプリケーション

- 家電機器用ディスプレイ・パネル

- エレベータ用ディスプレイ・パネル

- PLC用機能インジケータ

- 7セグメント・ディスプレイ

## 3 概要

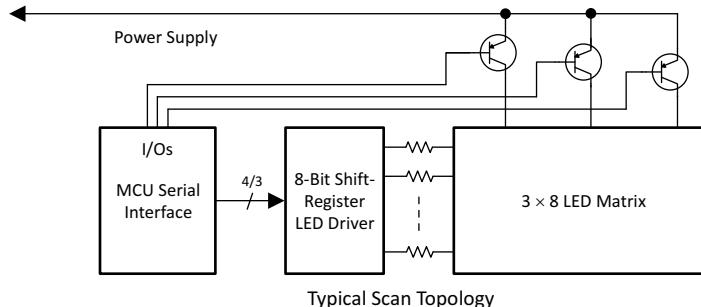

TLC6C598は、モノリシックで中程度の電圧、低電流出力の8ビット・シフト・レジスタで、LEDなど、比較的中程度の負荷電力を必要とするシステムで使用するよう設計されています。

このデバイスには、8ビットのシリアル・イン、パラレル・アウトのシフト・レジスタが内蔵されており、8ビットのDタイプ・ストレージ・レジスタへデータを供給します。シフト・レジスタとストレージ・レジスタの両方に、それぞれ独立したクロックが供給されます。出力はローサイドのオープン・ドレインDMOSトランジスタで、出力定格は40Vです。 $V_{CC} = 5V$ のとき、50mAの連続シンク電流、または1ms未満の単一パルス期間および50mA未満の平均電流で200mAのPWM電流を出力します。デバイスにはサーマル・シャットダウン保護が内蔵されており、人体モデルを使用したテストで2000V、マシン・モデルでは200VまでのESD保護を提供します。

TLC6C598の特性は、-40°C～105°Cの動作時周辺温度範囲での動作についてのものです。

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ      | 本体サイズ(公称)     |

|----------|------------|---------------|

| TLC6C598 | TSSOP (16) | 5.00mm×4.40mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

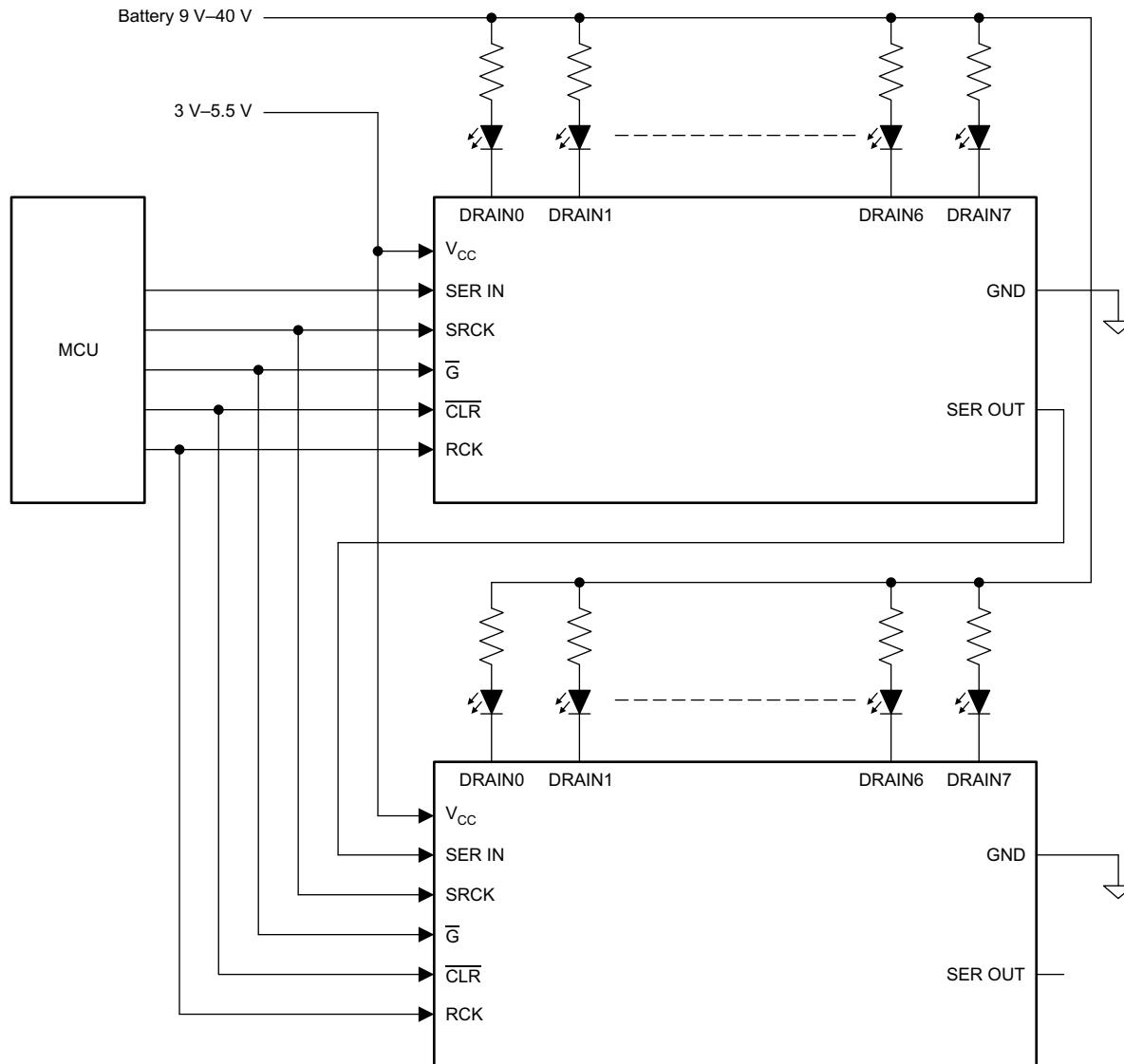

### 代表的なアプリケーションの回路図

Copyright © 2016, Texas Instruments Incorporated

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、[www.ti.com](http://www.ti.com)で閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: **SLIS177**

## 目次

|                                            |    |                                         |    |

|--------------------------------------------|----|-----------------------------------------|----|

| <b>1 特長</b>                                | 1  | 8.1 Overview                            | 11 |

| <b>2 アプリケーション</b>                          | 1  | 8.2 Functional Block Diagram            | 11 |

| <b>3 概要</b>                                | 1  | 8.3 Feature Description                 | 12 |

| <b>4 改訂履歴</b>                              | 2  | 8.4 Device Functional Modes             | 12 |

| <b>5 Pin Configuration and Functions</b>   | 3  | <b>9 Application and Implementation</b> | 13 |

| <b>6 Specifications</b>                    | 4  | 9.1 Application Information             | 13 |

| 6.1 Absolute Maximum Ratings               | 4  | 9.2 Typical Application                 | 13 |

| 6.2 ESD Ratings                            | 4  | <b>10 Power Supply Recommendations</b>  | 16 |

| 6.3 Recommended Operating Conditions       | 4  | <b>11 Layout</b>                        | 16 |

| 6.4 Thermal Information                    | 4  | 11.1 Layout Guidelines                  | 16 |

| 6.5 Electrical Characteristics             | 5  | 11.2 Layout Example                     | 16 |

| 6.6 Timing Requirements                    | 5  | <b>12 デバイスおよびドキュメントのサポート</b>            | 17 |

| 6.7 Switching Characteristics              | 6  | 12.1 コミュニティ・リソース                        | 17 |

| 6.8 Timing Waveforms                       | 7  | 12.2 商標                                 | 17 |

| 6.9 Typical Characteristics                | 8  | 12.3 静電気放電に関する注意事項                      | 17 |

| <b>7 Parameter Measurement Information</b> | 9  | 12.4 Glossary                           | 17 |

| <b>8 Detailed Description</b>              | 11 | <b>13 メカニカル、パッケージ、および注文情報</b>           | 17 |

## 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2016年5月 | *    | 初版 |

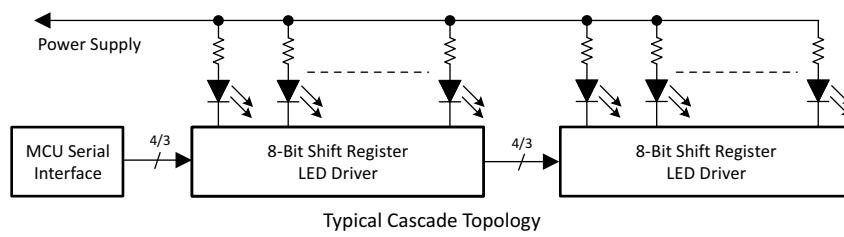

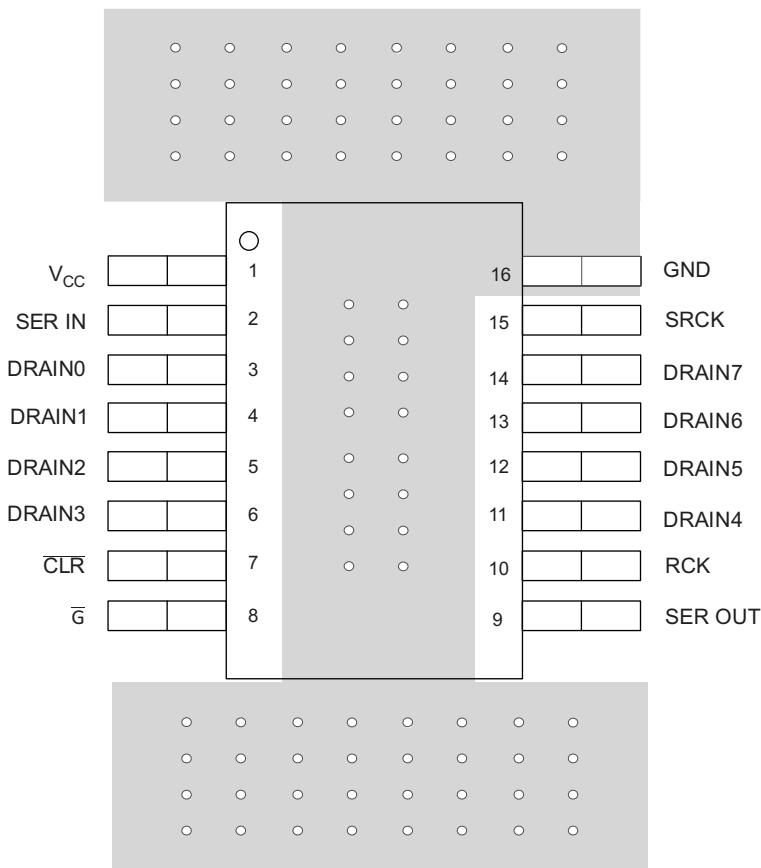

## 5 Pin Configuration and Functions

### Pin Functions

| PIN             |     | I/O | DESCRIPTION                                                                                                                                                                                                |

|-----------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. |     |                                                                                                                                                                                                            |

| CLR             | 7   | I   | Shift register clear, active-low. The storage register transfers data to the output buffer when CLR is high. Driving CLR low clears all the registers in the device.                                       |

| DRAIN0          | 3   | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN1          | 4   | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN2          | 5   | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN3          | 6   | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN4          | 11  | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN5          | 12  | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN6          | 13  | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| DRAIN7          | 14  | O   | Open-drain output, LED current-sink channel, connect to LED cathode                                                                                                                                        |

| $\overline{G}$  | 8   | I   | Output enable, active-low. LED-channel enable and disable input pin. Having $\overline{G}$ low enables all drain channels according to the output-latch register content. When high, all channels are off. |

| GND             | 16  | —   | Power ground, the ground reference pin for the device. This pin must connect to the ground plane on the PCB.                                                                                               |

| RCK             | 10  | I   | Register clock. The data in each shift register stage transfers to the storage register at the rising edge of RCK.                                                                                         |

| SER IN          | 2   | I   | Serial data input. Data on SER IN loads into the internal register on each rising edge of SRCK.                                                                                                            |

| SER OUT         | 9   | O   | Serial data output of the 8-bit serial shift register. The purpose of this pin is to cascade several devices on the serial bus.                                                                            |

| SRCK            | 15  | I   | Serial clock input. On each rising SRCK edge, data transfers from SER IN to the internal serial shift registers.                                                                                           |

| V <sub>CC</sub> | 1   | I   | Power supply pin for the device. TI recommends adding a 0.1- $\mu$ F ceramic capacitor close to the pin.                                                                                                   |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|           |                                      | MIN                                     | MAX | UNIT |

|-----------|--------------------------------------|-----------------------------------------|-----|------|

| $V_{CC}$  | Logic supply voltage                 | -0.3                                    | 8   | V    |

| $V_I$     | Logic input-voltage range            | -0.3                                    | 8   | V    |

| $V_{DS}$  | Power DMOS drain-to-source voltage   | -0.3                                    | 42  | V    |

|           | Continuous total dissipation         | See <a href="#">Thermal Information</a> |     |      |

| $T_J$     | Operating junction temperature range | -40                                     | 125 | °C   |

| $T_{stg}$ | Storage temperature range            | -55                                     | 165 | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under [Recommended Operating Conditions](#). Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|             |                         |                                                         | VALUE                         | UNIT |

|-------------|-------------------------|---------------------------------------------------------|-------------------------------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000                         | V    |

|             |                         | Charged device model (CDM), per AEC Q100-011            | All pins                      |      |

|             |                         |                                                         | Corner pins (1, 8, 9, and 16) |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

|          |                               | MIN | MAX | UNIT |

|----------|-------------------------------|-----|-----|------|

| $V_{CC}$ | Supply voltage                | 3   | 5.5 | V    |

| $V_{IH}$ | High-level input voltage      | 2.4 |     | V    |

| $V_{IL}$ | Low-level input voltage       |     | 0.7 | V    |

| $T_A$    | Operating ambient temperature | -40 | 105 | °C   |

### 6.4 Thermal Information

|                             | THERMAL METRIC <sup>(1)</sup>                | TLC6C598   | UNIT |

|-----------------------------|----------------------------------------------|------------|------|

|                             |                                              | PW (TSSOP) |      |

|                             |                                              | 16 PINS    |      |

| $R_{\theta JA}$             | Junction-to-ambient thermal resistance       | 129.4      | °C/W |

| $R_{\theta JC(\text{top})}$ | Junction-to-case (top) thermal resistance    | 55.4       | °C/W |

| $R_{\theta JB}$             | Junction-to-board thermal resistance         | 65.8       | °C/W |

| $\psi_{JT}$                 | Junction-to-top characterization parameter   | 9.9        | °C/W |

| $\psi_{JB}$                 | Junction-to-board characterization parameter | 65.2       | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report ([SPRA953](#)).

## 6.5 Electrical Characteristics

$V_{CC} = 5 \text{ V}$ ,  $T_A = 25^\circ\text{C}$  (unless otherwise noted)

| PARAMETER                                 | TEST CONDITIONS                         |                                                                                                  | MIN                    | TYP   | MAX   | UNIT             |  |  |

|-------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|------------------------|-------|-------|------------------|--|--|

| DRAIN0 to DRAIN7. Drain-to-source voltage |                                         |                                                                                                  |                        |       | 40    | V                |  |  |

| $V_{OH}$                                  | High-level output voltage, SER OUT      | $I_{OH} = -20 \mu\text{A}$                                                                       | $V_{CC} = 5 \text{ V}$ | 4.9   | 4.99  | V                |  |  |

|                                           |                                         | $I_{OH} = -4 \text{ mA}$                                                                         |                        | 4.5   | 4.69  | V                |  |  |

| $V_{OL}$                                  | Low-level output voltage, SER OUT       | $I_{OH} = 20 \mu\text{A}$                                                                        | $V_{CC} = 5 \text{ V}$ | 0.001 | 0.01  | V                |  |  |

|                                           |                                         | $I_{OH} = 4 \text{ mA}$                                                                          |                        | 0.25  | 0.4   | V                |  |  |

| $I_{IH}$                                  | High-level input current                | $V_{CC} = 5 \text{ V}$ , $V_I = V_{CC}$                                                          |                        |       | 0.2   | $\mu\text{A}$    |  |  |

| $I_{IL}$                                  | Low-level input current                 | $V_{CC} = 5 \text{ V}$ , $V_I = 0$                                                               |                        |       | -0.2  | $\mu\text{A}$    |  |  |

| $I_{CC}$                                  | Logic supply current                    | $V_{CC} = 5 \text{ V}$ , no clock signal                                                         | All outputs off        | 0.1   | 1     | $\mu\text{A}$    |  |  |

|                                           |                                         |                                                                                                  | All outputs on         | 88    | 160   |                  |  |  |

| $I_{CC(FRQ)}$                             | Logic supply current at frequency       | $f_{SRCK} = 5 \text{ MHz}$ , $C_L = 30 \text{ pF}$                                               | All outputs on         |       | 200   | $\mu\text{A}$    |  |  |

| $I_{DSx}$                                 | Off-state drain current                 | $V_{DS} = 30 \text{ V}$                                                                          | $V_{CC} = 5 \text{ V}$ |       | 0.1   | $\mu\text{A}$    |  |  |

|                                           |                                         | $V_{DS} = 30 \text{ V}$ , $T_C = 105^\circ\text{C}$                                              | $V_{CC} = 5 \text{ V}$ |       | 0.15  |                  |  |  |

| $r_{DS(on)}$                              | Static drain-source on-state resistance | $I_D = 20 \text{ mA}$ , $V_{CC} = 5 \text{ V}$ , $T_A = 25^\circ\text{C}$ , Single channel ON    |                        | 6     | 7.41  | 8.6              |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 5 \text{ V}$ , $T_A = 25^\circ\text{C}$ , All channels ON      |                        | 6.7   | 8.3   | 9.6              |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 3.3 \text{ V}$ , $T_A = 25^\circ\text{C}$ , Single channel ON  |                        | 7.9   | 9.34  | 11.2             |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 3.3 \text{ V}$ , $T_A = 25^\circ\text{C}$ , All channels ON    |                        | 8.7   | 10.25 | 12.3             |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 5 \text{ V}$ , $T_A = 105^\circ\text{C}$ , Single channel ON   |                        | 9.1   | 11.13 | 12.9             |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 5 \text{ V}$ , $T_A = 105^\circ\text{C}$ , All channels ON     |                        | 10.3  | 12.28 | 14.5             |  |  |

|                                           |                                         | $I_D = 20 \text{ mA}$ , $V_{CC} = 3.3 \text{ V}$ , $T_A = 105^\circ\text{C}$ , Single channel ON |                        | 11.6  | 13.69 | 16.4             |  |  |

| $T_{SHUTDOWN}$                            | Thermal shutdown trip point             |                                                                                                  |                        | 150   | 175   | 200              |  |  |

|                                           | $^\circ\text{C}$                        |                                                                                                  |                        |       | 15    | $^\circ\text{C}$ |  |  |

## 6.6 Timing Requirements

|          |                                      | MIN | NOM | MAX | UNIT |

|----------|--------------------------------------|-----|-----|-----|------|

| $t_{su}$ | Setup time, SER IN high before SRCK↑ | 15  |     |     | ns   |

| $t_h$    | Hold time, SER IN high after SRCK↑   | 15  |     |     | ns   |

| $t_w$    | SER IN pulse duration                | 40  |     |     | ns   |

## 6.7 Switching Characteristics

$V_{CC} = 5 \text{ V}$ ,  $T_A = 25^\circ\text{C}$

| PARAMETER                                                                            | TEST CONDITIONS                               | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------------------------------------------|-----------------------------------------------|------|-----|-----|------|

| $t_{PLH}$<br>Propagation delay time from $\overline{G}$ to output, low-to-high level | $C_L = 30 \text{ pF}$ , $I_D = 48 \text{ mA}$ | 220  |     |     | ns   |

| $t_{PHL}$<br>Propagation delay time from $\overline{G}$ to output, high-to-low level |                                               | 75   |     |     | ns   |

| $t_r$<br>Rise time, drain output                                                     |                                               | 210  |     |     | ns   |

| $t_f$<br>Fall time, drain output                                                     |                                               | 128  |     |     | ns   |

| $t_{pd}$<br>Propagation delay time, SRCK $\downarrow$ to SER OUT                     | $C_L = 30 \text{ pF}$ , $I_D = 48 \text{ mA}$ | 49.4 |     |     | ns   |

| $t_{or}$<br>SER OUT rise time (10% to 90%)                                           | $C_L = 30 \text{ pF}$                         | 20   |     |     | ns   |

| $t_{of}$<br>SER OUT fall time (90% to 10%)                                           | $C_L = 30 \text{ pF}$                         | 20   |     |     | ns   |

| $f_{(SRCK)}$<br>Serial clock frequency                                               | $C_L = 30 \text{ pF}$ , $I_D = 20 \text{ mA}$ |      | 10  |     | MHz  |

| $t_{SRCK\_WH}$<br>SRCK pulse duration, high                                          |                                               | 30   |     |     | ns   |

| $t_{SRCK\_WL}$<br>SRCK pulse duration, low                                           |                                               | 30   |     |     | ns   |

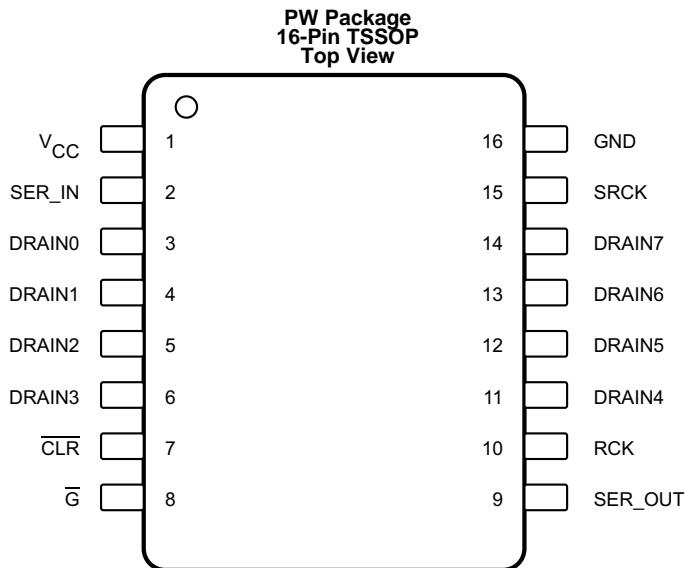

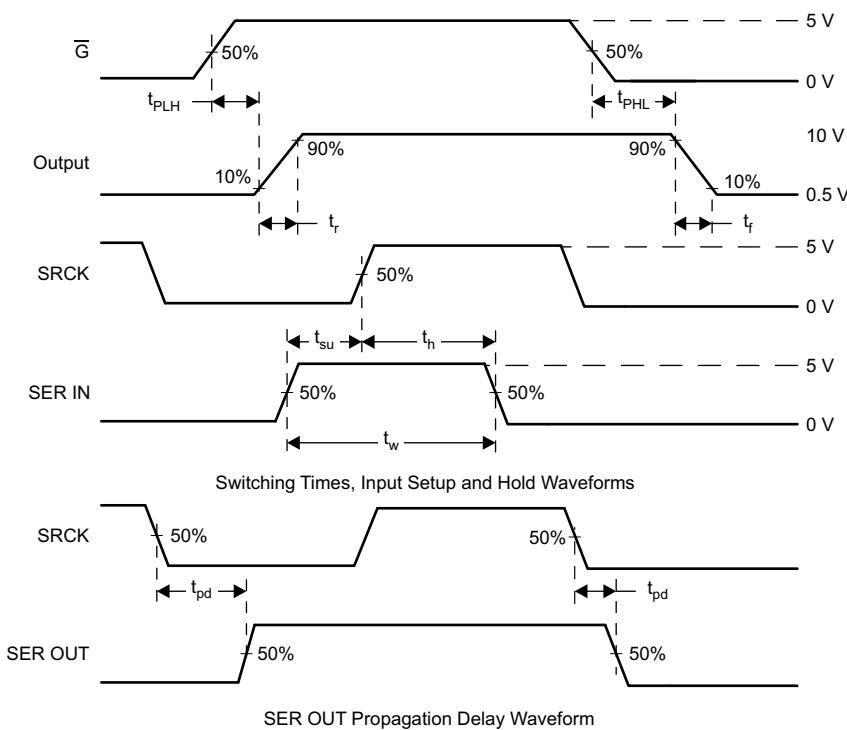

## 6.8 Timing Waveforms

図 1 shows the SER IN to SER OUT waveform. The output signal appears on the falling edge of the shift register clock (SRCK) because there is a phase inverter at SER OUT (see 図 13). As a result, it takes seven and a half periods of SRCK for data to transfer from SER IN to SER OUT.

図 1. SER IN to SER OUT Waveform

図 2 shows the switching times and voltage waveforms. Tests for all these parameters took place using the test circuit shown in 図 11.

図 2. Switching Times and Voltage Waveforms

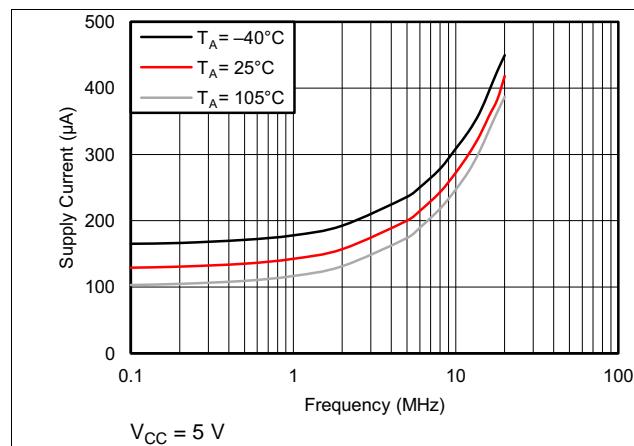

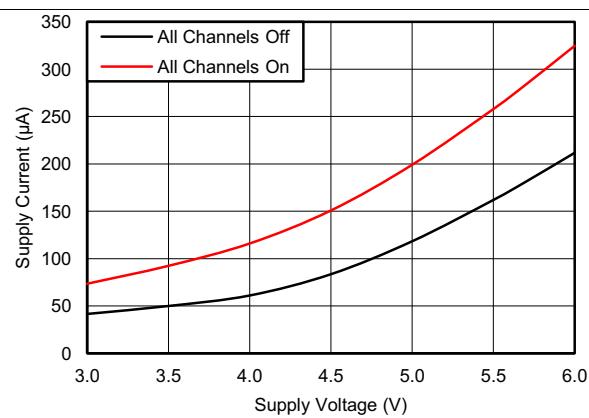

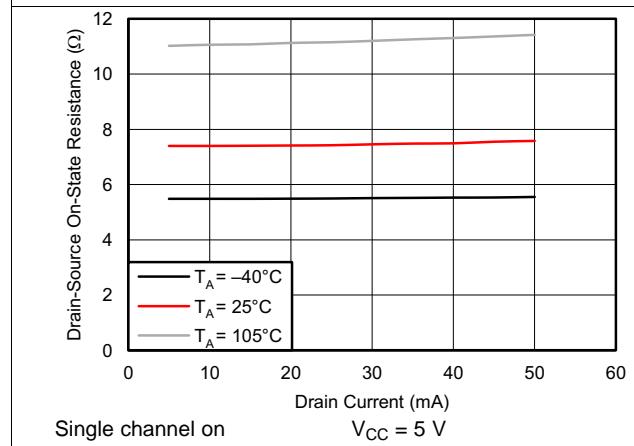

## 6.9 Typical Characteristics

图 3. Supply Current vs Frequency

图 4. Supply Current vs Supply Voltage

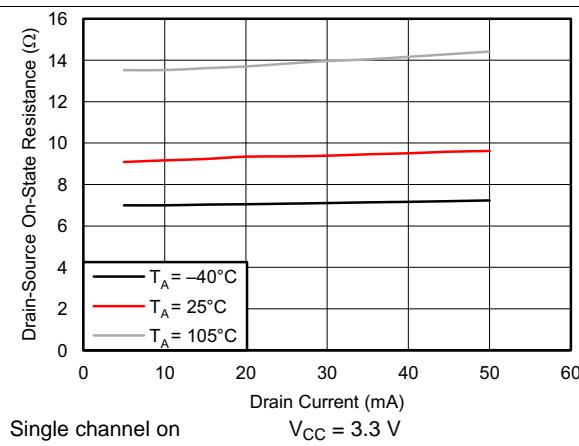

图 5. Drain-to-Source On-State Resistance vs Drain Current

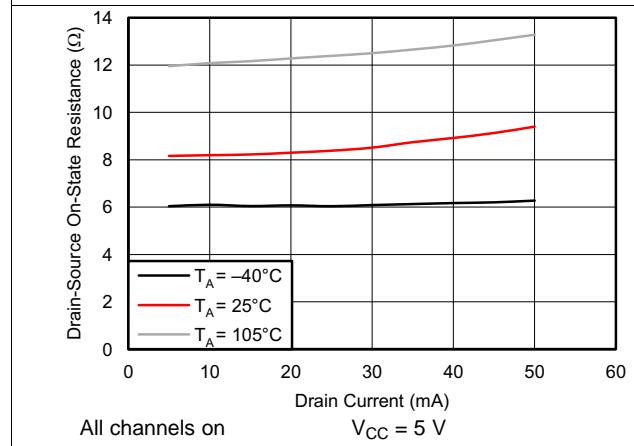

图 6. Drain-to-Source On-State Resistance vs Drain Current

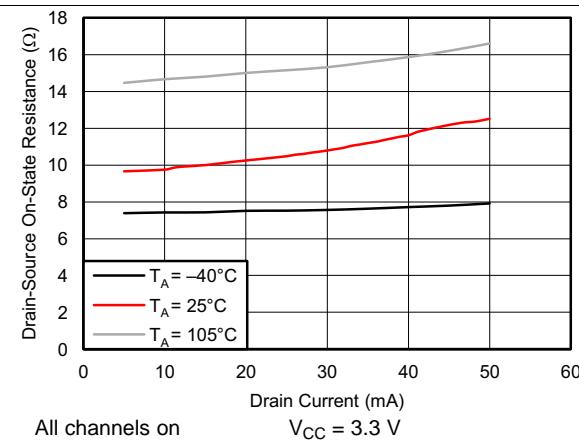

图 7. Drain-to-Source On-State Resistance vs Drain Current

图 8. Drain-to-Source On-State Resistance vs Drain Current

## Typical Characteristics (continued)

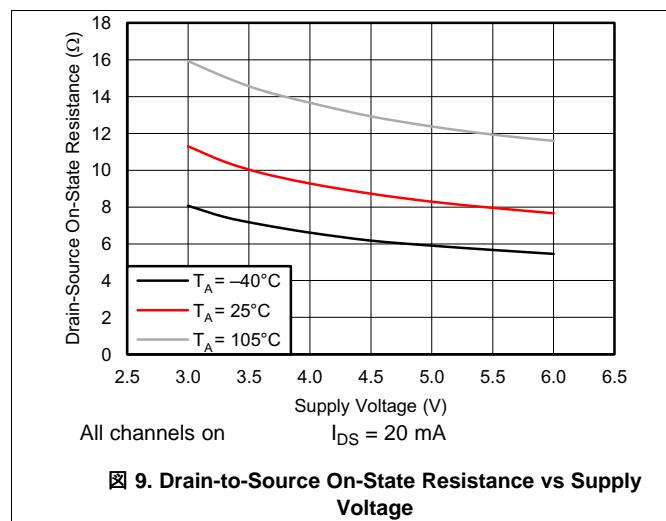

図 9. Drain-to-Source On-State Resistance vs Supply Voltage

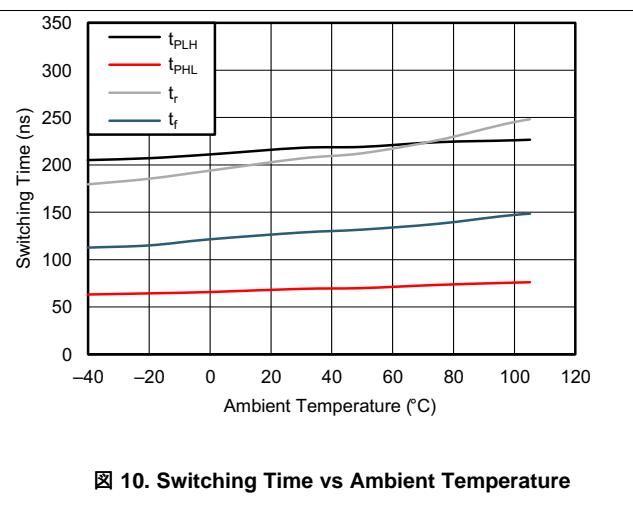

図 10. Switching Time vs Ambient Temperature

## 7 Parameter Measurement Information

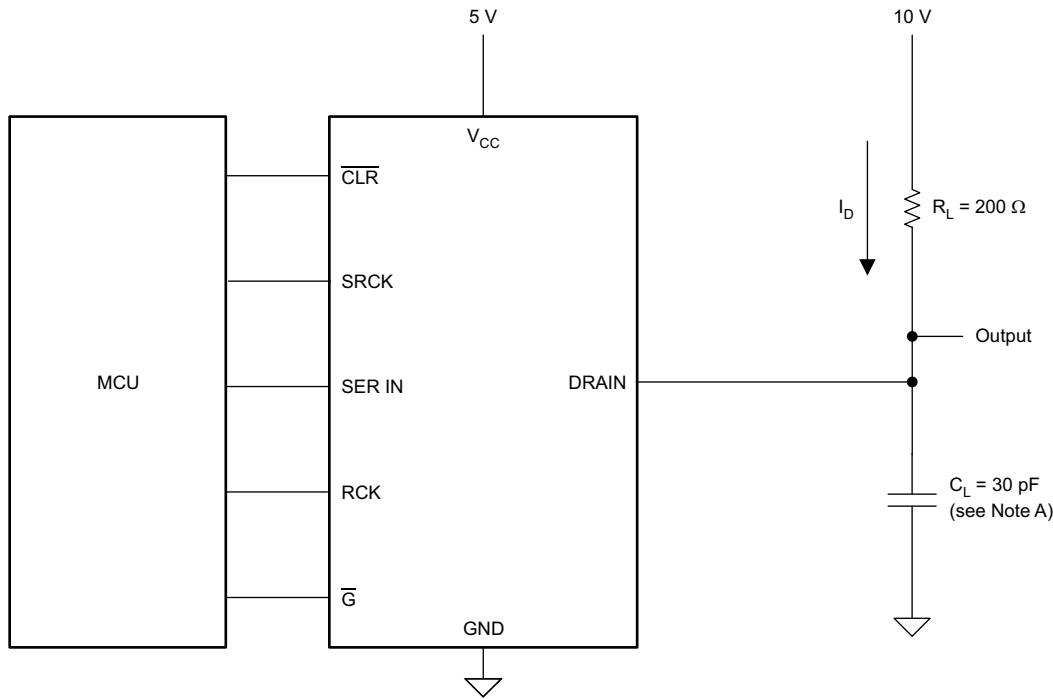

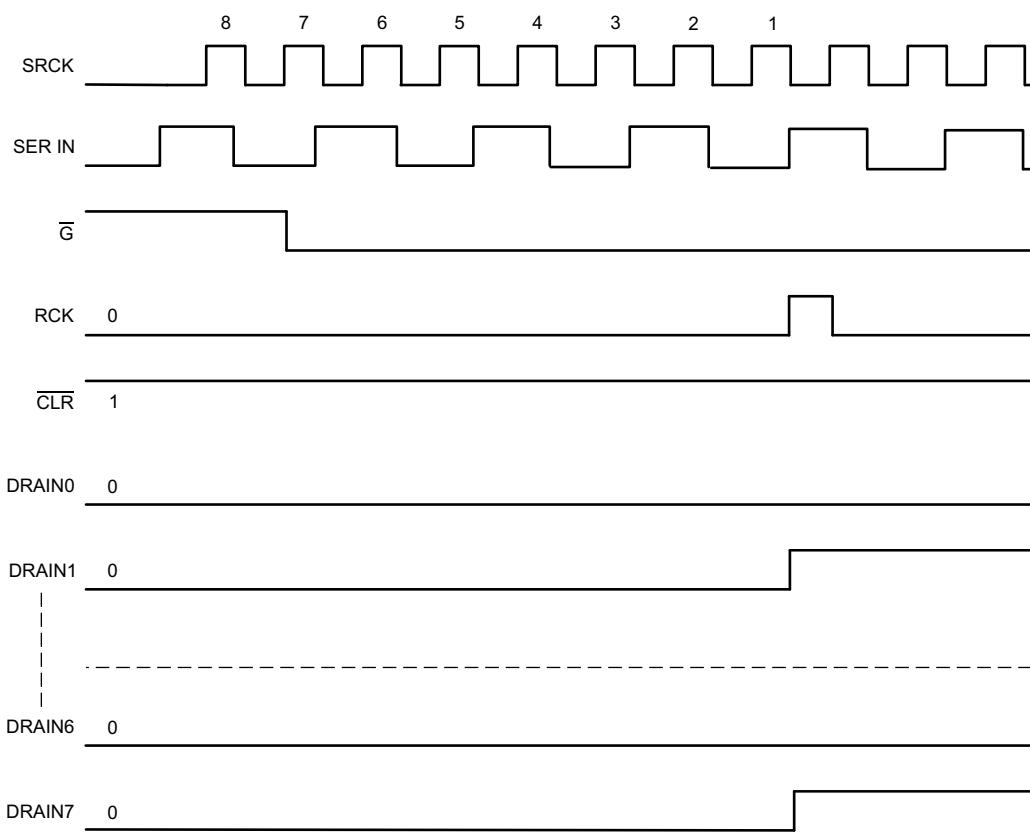

図 11 and 図 12 show the resistive-load test circuit and voltage waveforms. One can see from 図 12 that with  $\overline{G}$  held low and  $\overline{CLR}$  held high, the status of each drain changes on the rising edge of the register clock, indicating the transfer of data to the output buffers at that time.

Copyright © 2016, Texas Instruments Incorporated

A.  $C_L$  includes probe and jig capacitance.

図 11. Resistive-Load Test Circuit

**Parameter Measurement Information (continued)**

**図 12. Voltage Waveforms**

## 8 Detailed Description

## 8.1 Overview

The TLC6C598 device is a monolithic, medium-voltage, low-current 8-bit shift register designed to drive relatively moderate load power such LEDs. The device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Thermal shutdown protection is also built-into the device.

## 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

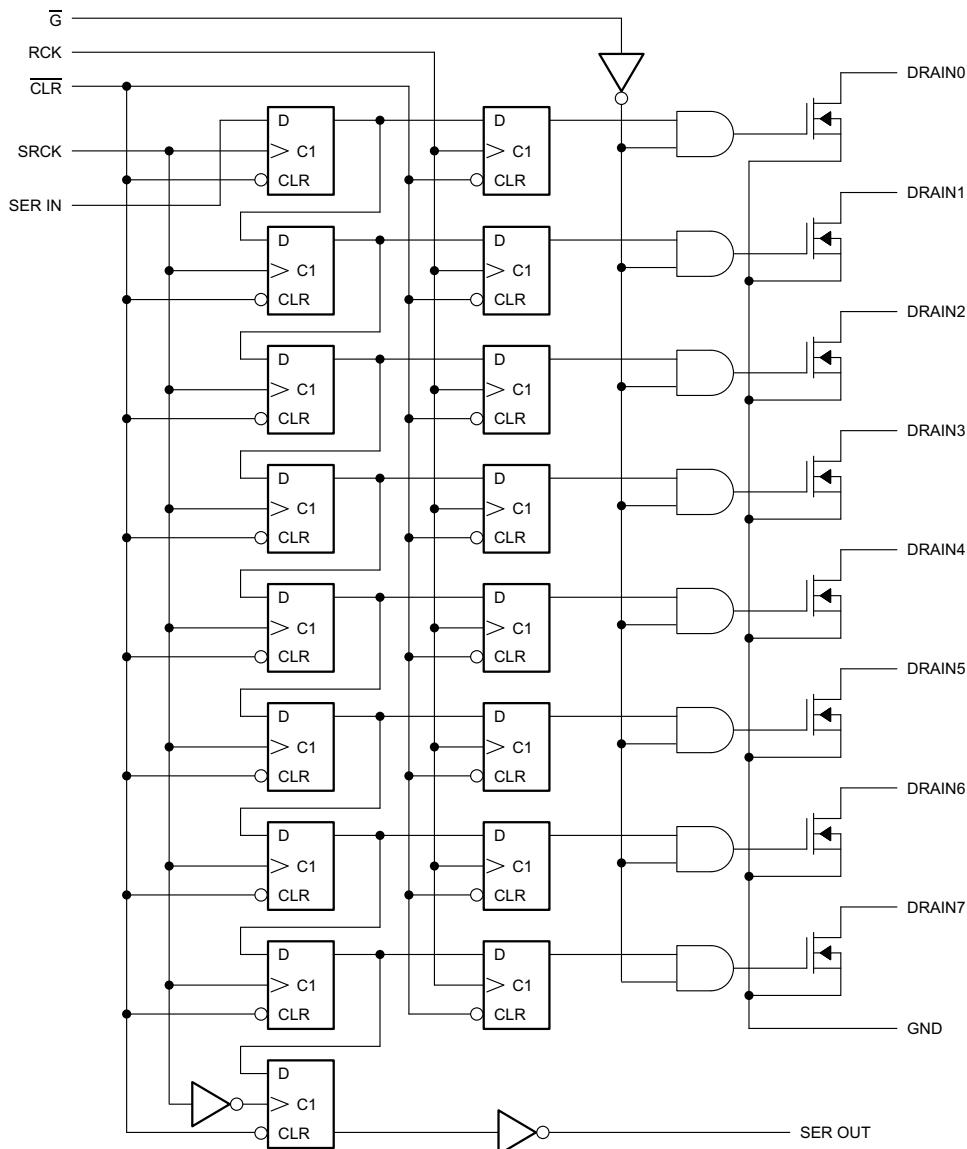

図 13. Logic Diagram (Positive) of TLC6C598

## 8.3 Feature Description

### 8.3.1 Thermal Shutdown

The device implements an internal thermal shutdown to protect itself if the junction temperature exceeds 175°C (typical). The thermal shutdown forces the device to have an open state when the junction temperature exceeds the thermal trip threshold. Once the junction temperature decreases below 160°C (typical), the device begins to operate again.

### 8.3.2 Serial-In Interface

The TLC6C598 device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Data transfer through the shift and storage registers is on the rising edge of the shift register clock (SRCK) and the register clock (RCK), respectively. The storage register transfers data to the output buffer when shift-register clear (CLR) is high.

### 8.3.3 Clear Registers

A logic low on the  $\overline{\text{CLR}}$  pin clears all registers in the device. TI suggests clearing the device during power up or initialization.

### 8.3.4 Output Channels

DRAIN0–DRAIN7. These pins can survive up to 40-V LED supply voltage.

### 8.3.5 Register Clock

RCK is the storage-register clock. Data in the storage register appears at the output whenever the output enable ( $\overline{G}$ ) input signal is high.

### 8.3.6 Cascade Through SER OUT

By connecting the SER OUT pin to the SER IN input of the next device on the serial bus in cascade, the data transfers to the next device on the falling edge of SRCK. This connection can improve the cascade application reliability, as it can avoid the issue that the second device receives SRCK and data input on the same rising edge of SRCK.

### 8.3.7 Output Control

Holding the output enable (pin  $\overline{G}$ ) high holds all data in the output buffers low, and all drain outputs are off. Holding  $\overline{G}$  low makes data from the storage register transparent to the output buffers. When data in the output buffers is low, the DMOS transistor outputs are off. When data is high, the DMOS transistor outputs are capable of sinking current. This pin also can be used for global PWM dimming.

## 8.4 Device Functional Modes

### 8.4.1 Operation With $V_{CC} < 3$ V

This device works normally within the range  $3 \text{ V} \leq V_{CC} \leq 5.5 \text{ V}$ . When the operating voltage is lower than 3 V, correct behavior of the device, including communication interface and current capability, is not assured.

### 8.4.2 Operation With $5.5 \text{ V} \leq V_{CC} \leq 8$ V

The device works normally in this voltage range, but reliability issues may occur if the device works for a long time in this voltage range.

## 9 Application and Implementation

---

### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

---

### 9.1 Application Information

The TLC6C598 device is a serial-in, parallel-out, power and logic, 8-bit shift register with low-side open-drain DMOS output ratings of 40-V and 50-mA continuous sink-current capabilities when  $V_{CC} = 5$  V. The device is designed to drive resistive loads and is particularly well-suited as an interface between a microcontroller and LEDs or lamps. The device also provides up to 2000 V of ESD protection when tested using the human body model and 200 V when using the machine model.

### 9.2 Typical Application

图 14 shows a typical cascade application circuit with two TLC6C598 chips configured in cascade topology. The MCU generates all the input signals.

## Typical Application (continued)

Copyright © 2016, Texas Instruments Incorporated

**图 14. Typical Application Circuit**

### 9.2.1 Design Requirements

| DESIGN PARAMETER                                               | EXAMPLE VALUE |

|----------------------------------------------------------------|---------------|

| $V_{\text{Battery}}$                                           | 9 V to 40 V   |

| $V_{\text{CC\_1}}$                                             | 3.3 V         |

| $I(D0), I(D1), I(D2), I(D3), I(D4), I(D5), I(D6), I(D7)$       | 30 mA         |

| $V_{\text{CC\_2}}$                                             | 5 V           |

| $I(D8), I(D9), I(D10), I(D11), I(D12), I(D13), I(D14), I(D15)$ | 50 mA         |

## 9.2.2 Detailed Design Procedure

To begin the design process, the designer must decide on a few parameters, as follows:

- $V_{\text{supply}}$ : LED supply voltage

- $V_{\text{Dx}}$ : LED forward voltage

- $I$ : LED current

With these parameters determined, the resistor in series with the LED can be calculated by using the following equation:

$$R_X = (V_{\text{Supply}} - V_{\text{Dx}}) / I \quad (1)$$

## 9.2.3 Application Curve

図 15. TLC6C598 Application Waveform

## 10 Power Supply Recommendations

The TLC6C598 device is designed to operate with an input voltage supply range from 3 V to 5.5 V. This input supply should be well regulated. TI recommends placing the ceramic bypass capacitors near the V<sub>CC</sub> pin.

## 11 Layout

### 11.1 Layout Guidelines

There are no special layout requirements for the digital signal pins. The only requirement is placing the ceramic bypass capacitors near the corresponding pins.

Maximize the copper coverage on the PCB to increase the thermal conductivity of the board. The major heat-flow path from the package to the ambient is through the copper on the PCB. Maximizing the copper coverage is extremely important when the design does not include heat sinks attached to the PCB on the other side of the package.

Add as many thermal vias as possible directly under the package ground pad to optimize the thermal conductivity of the board.

All thermal vias should be either plated shut or plugged and capped on both sides of the board to prevent solder voids. To ensure reliability and performance, the solder coverage should be at least 85%.

### 11.2 Layout Example

図 16. TLC6C598 Example Layout

## 12 デバイスおよびドキュメントのサポート

### 12.1 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™ Online Community** *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At [e2e.ti.com](http://e2e.ti.com), you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.2 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 12.3 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 12.4 Glossary

[SLYZ022 — TI Glossary.](#)

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TLC6C598PWR           | Active        | Production           | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 105   | 6C598I              |

| TLC6C598PWR.A         | Active        | Production           | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 105   | 6C598I              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TLC6C598 :**

- Automotive : [TLC6C598-Q1](#)

---

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

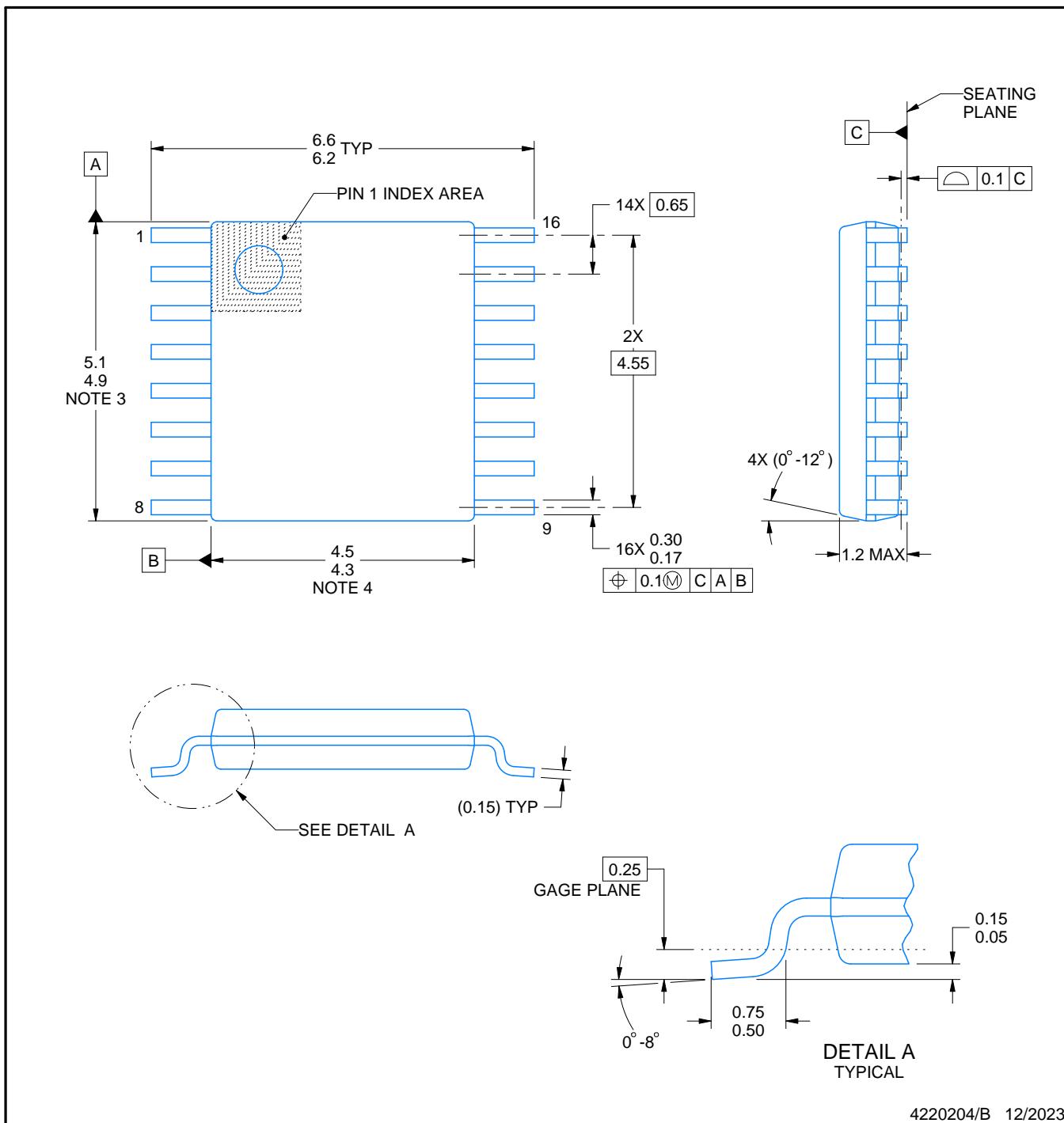

## PACKAGE OUTLINE

**PW0016A**

## **TSSOP - 1.2 mm max height**

## SMALL OUTLINE PACKAGE

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-153.

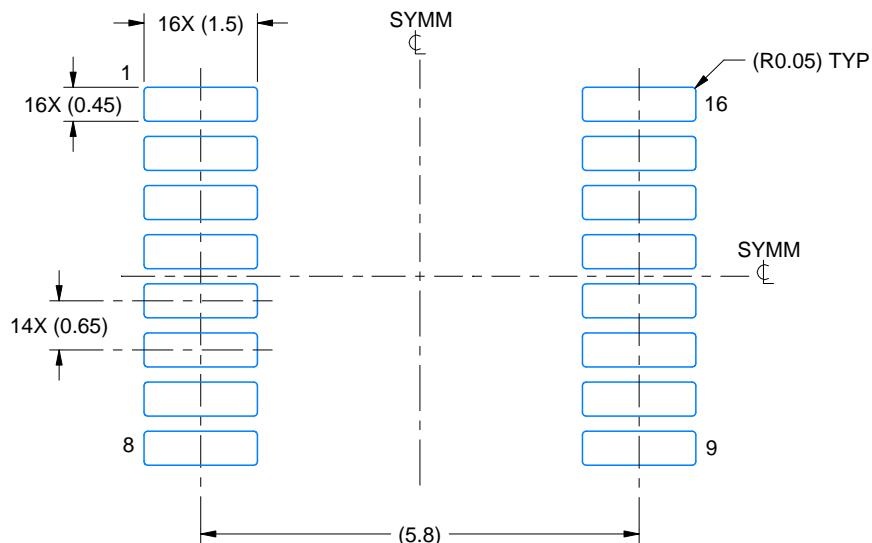

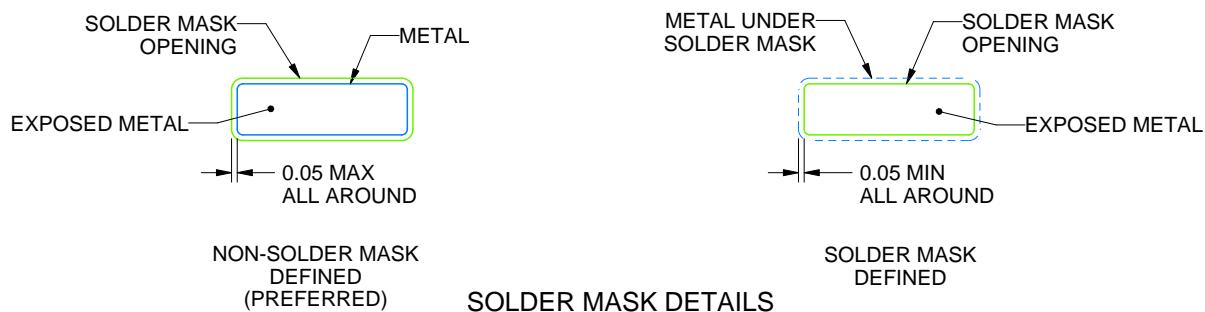

# EXAMPLE BOARD LAYOUT

PW0016A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

4220204/B 12/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

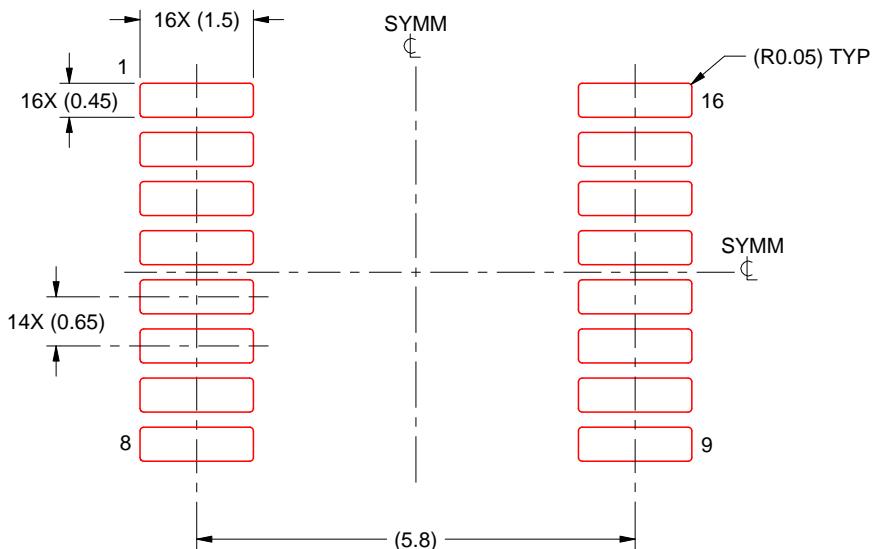

# EXAMPLE STENCIL DESIGN

PW0016A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4220204/B 12/2023

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月