# TLVx888 低ノイズ、ゼロドリフト、広帯域幅、マルチプレクサ対応オペアンプ

## 1 特長

- 高い DC 精度:

- ゼロドリフト:  $0.01\mu\text{V}/^\circ\text{C}$

- 低いオフセット電圧:  $3\mu\text{V}$

- 高 PSRR:  $150\text{ dB}$

- 高い CMRR:  $150\text{ dB}$

- 優れた AC 性能:

- ゲイン帯域幅:  $14\text{MHz}$

- スルーレート:  $40\text{V}/\mu\text{s}$

- 低ノイズ:  $7.5\text{nV}/\sqrt{\text{Hz}}$

- 負レールへの入力、レールツーレール出力

- 低い静止電流:  $1.5\text{mA}$

- RFI および EMI フィルタ付き入力

- 電源電圧範囲:  $4.5\text{V} \sim 36\text{V}$

- 温度:  $-40^\circ\text{C} \sim +125^\circ\text{C}$

## 2 アプリケーション

- PC 電源およびゲーム機

- 商用 DC/DC

- 流量トランスマッタ

- 圧力トランスマッタ

- 商用バッテリ チャージャ

- 電気メータ

## 3 説明

TLV888、TLV2888、TLV4888 (TLVx888) は、広帯域幅、低ノイズのゼロドリフトのオペアンプです。これらのオペアンプのオフセット電圧は、わずか  $15\mu\text{V}$  (最大値) であり、温度範囲全体でのオフセット電圧ドリフトは、わずか  $0.05\mu\text{V}/^\circ\text{C}$  (最大値) です。

TLVx888 は広いゲイン帯域幅と非常に高いスルーレートにより、非常に短いセッティング時間を特長としています。独自の MUX 対応入力アーキテクチャを使用することで、マルチチャネルシステムではセッティングタイムがさらに短縮されます。

高精度、高速セッティング、低ノイズを兼ね備えた TLVx888 は、信号測定、高精度計測機器、データ アクイジションなど広範なアプリケーションに最適です。

TLVx888 は、業界標準のパッケージと超小型のパッケージで利用可能、スペースの制約が厳しいアプリケーションに適しています。これらのデバイスの動作範囲は、 $-40^\circ\text{C} \sim +125^\circ\text{C}$  に指定されています。

### パッケージ情報

| 部品番号    | チャネル数 | パッケージ (1)                        | パッケージ サイズ (2)   |

|---------|-------|----------------------------------|-----------------|

| TLV888  | シングル  | D (SOIC、8)                       | 4.90mm × 6.00mm |

|         |       | DBV (SOT-23、5)                   | 2.90mm × 2.80mm |

|         |       | DRL (SOT、5) <sup>(3)</sup>       | 1.60mm × 1.60mm |

| TLV2888 | デュアル  | D (SOIC、8)                       | 4.90mm × 6.00mm |

|         |       | DDF (SOT-23、8)<br><sup>(3)</sup> | 2.90mm × 2.80mm |

|         |       | DGK (VSSOP、8)                    | 3.00mm × 4.90mm |

|         |       | DSG (WSON、8) <sup>(3)</sup>      | 2.00mm × 2.00mm |

| TLV4888 | クワッド  | D (SOIC、14)                      | 8.65mm × 6.00mm |

|         |       | PW (TSSOP-14)                    | 5.00mm × 6.40mm |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 開発中製品の情報 (製品データではありません)。

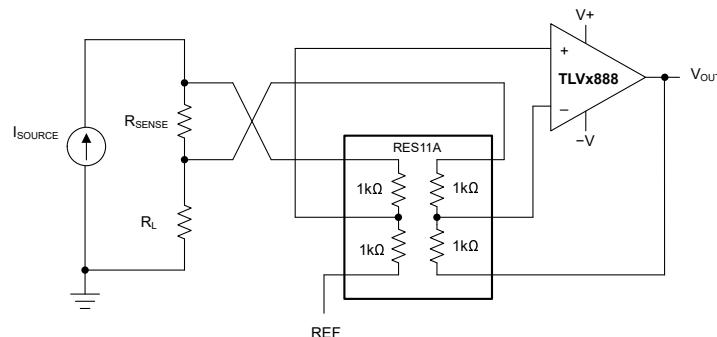

ハイサイド電流シャント モニタ アプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SBOSAG5](#)

## 目次

|                      |    |                        |    |

|----------------------|----|------------------------|----|

| 1 特長                 | 1  | 6.4 デバイスの機能モード         | 20 |

| 2 アプリケーション           | 1  | 7 アプリケーションと実装          | 21 |

| 3 説明                 | 1  | 7.1 アプリケーション情報         | 21 |

| 4 ピン構成および機能          | 2  | 7.2 代表的なアプリケーション       | 24 |

| 5 仕様                 | 5  | 7.3 電源に関する推奨事項         | 28 |

| 5.1 絶対最大定格           | 5  | 7.4 レイアウト              | 28 |

| 5.2 ESD 定格           | 5  | 8 デバイスおよびドキュメントのサポート   | 30 |

| 5.3 推奨動作条件           | 5  | 8.1 デバイスサポート           | 30 |

| 5.4 熱に関する情報: TLV888  | 6  | 8.2 ドキュメントのサポート        | 30 |

| 5.5 熱に関する情報: TLV2888 | 6  | 8.3 ドキュメントの更新通知を受け取る方法 | 30 |

| 5.6 熱に関する情報: TLV4888 | 6  | 8.4 サポート・リソース          | 31 |

| 5.7 電気的特性            | 7  | 8.5 商標                 | 31 |

| 5.8 代表的特性            | 9  | 8.6 静電気放電に関する注意事項      | 31 |

| 6 詳細説明               | 17 | 8.7 用語集                | 31 |

| 6.1 概要               | 17 | 9 改訂履歴                 | 31 |

| 6.2 機能ブロック図          | 17 | 10 メカニカル、パッケージ、および注文情報 | 31 |

| 6.3 機能説明             | 17 |                        |    |

## 4 ピン構成および機能

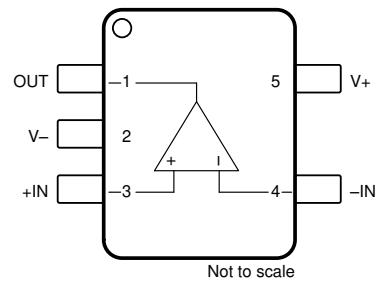

図 4-1. TLV888 : D パッケージ、8 ピン SOIC (上面図) 図 4-2. TLV888 : DBV パッケージ、5 ピン SOT-23 (上面図)

表 4-1. ピンの機能 : TLV888

| 名称  | ピン      |     | タイプ | 説明                   |  |  |

|-----|---------|-----|-----|----------------------|--|--|

|     | 番号      |     |     |                      |  |  |

|     | D       | DBV |     |                      |  |  |

| -IN | 2       | 4   | 入力  | 反転入力                 |  |  |

| +IN | 3       | 3   | 入力  | 非反転入力                |  |  |

| NC  | 1, 8, 5 | -   | -   | 接続なし (フローティングのままでも可) |  |  |

| OUT | 6       | 1   | 出力  | 出力                   |  |  |

| V-  | 4       | 2   | 電源  | 負 (最低) 電源            |  |  |

| V+  | 7       | 5   | 電源  | 正 (最高) 電源            |  |  |

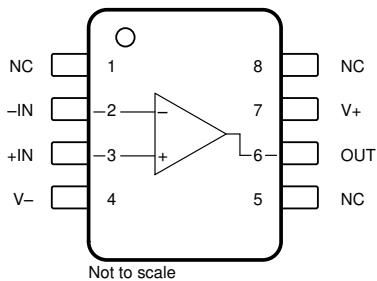

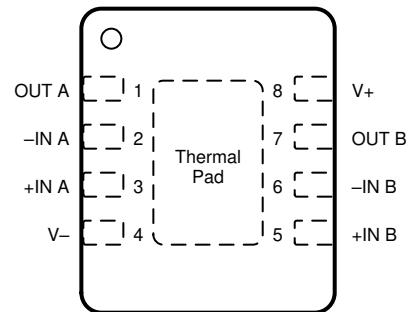

図 4-3. TLV2888 : D パッケージ、8 ピン SOIC および

DGK パッケージ、8 ピン VSSOP (上面図)

図 4-4. DSG パッケージ、8 ピン WSON (露出サーマル

パッド付き) (上面図)

表 4-2. ピンの機能 : TLV2888

| ピン                      |    | タイプ | 説明                                                             |

|-------------------------|----|-----|----------------------------------------------------------------|

| 名称                      | 番号 |     |                                                                |

| -IN A                   | 2  | 入力  | 反転入力、チャネル A                                                    |

| -IN B                   | 6  | 入力  | 反転入力、チャネル B                                                    |

| +IN A                   | 3  | 入力  | 非反転入力、チャネル A                                                   |

| +IN B                   | 5  | 入力  | 非反転入力、チャネル B                                                   |

| OUT A                   | 1  | 出力  | 出力チャネル A                                                       |

| OUT B                   | 7  | 出力  | 出力チャネル B                                                       |

| V-                      | 4  | 電源  | 負電源                                                            |

| V+                      | 8  | 電源  | 正電源                                                            |

| サーマル パッド <sup>(1)</sup> | -  | -   | サーマル パッドを負電源 (V-) に接続します。詳細については、「露出サーマル パッド付きパッケージ」も参照してください。 |

(1) DSG パッケージのみ

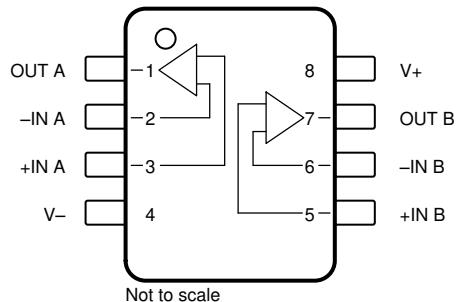

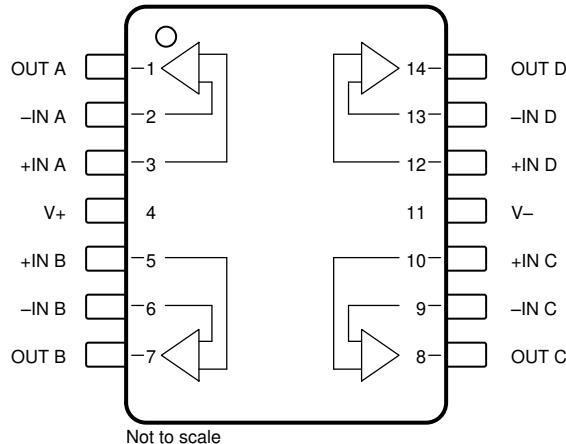

図 4-5. TLV4888 : D パッケージ、14 ピン SOIC および PW パッケージ、14 ピン TSSOP (上面図)

表 4-3. ピン機能 : TLV4888

| ピン    |    | タイプ | 説明           |

|-------|----|-----|--------------|

| 名称    | 番号 |     |              |

| -IN A | 2  | 入力  | 反転入力、チャネル A  |

| -IN B | 6  | 入力  | 反転入力、チャネル B  |

| -IN C | 9  | 入力  | 反転入力、チャネル C  |

| -IN D | 13 | 入力  | 反転入力、チャネル D  |

| +IN A | 3  | 入力  | 非反転入力、チャネル A |

| +IN B | 5  | 入力  | 非反転入力、チャネル B |

| +IN C | 10 | 入力  | 非反転入力、チャネル C |

| +IN D | 12 | 入力  | 非反転入力、チャネル D |

| OUT A | 1  | 出力  | 出力チャネル A     |

| OUT B | 7  | 出力  | 出力チャネル B     |

| OUT C | 8  | 出力  | 出力チャネル C     |

| OUT D | 14 | 出力  | 出力チャネル D     |

| V-    | 11 | 電源  | 負電源          |

| V+    | 4  | 電源  | 正電源          |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                     |       |    | 最小値          | 最大値           | 単位 |

|---------------------|-------|----|--------------|---------------|----|

| $V_S$               | 電源電圧  |    |              | 40            | V  |

| 信号入力電圧              |       | 同相 | $(V-) - 0.5$ | $(V+) + 0.5$  | V  |

|                     |       | 差動 |              | $(V+) - (V-)$ |    |

| 電流                  |       |    |              | $\pm 10$      | mA |

| 出力短絡 <sup>(2)</sup> |       |    | 連続           |               |    |

| $T_A$               | 動作温度  |    | -55          | 150           | °C |

| $T_J$               | 接合部温度 |    |              | 150           | °C |

| $T_{stg}$           | 保存温度  |    | -65          | 150           | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

- (2) グランドへの短絡、パッケージあたり 1 台のアンプ。

### 5.2 ESD 定格

|                                               |      |                                                          | 値          | 単位 |

|-----------------------------------------------|------|----------------------------------------------------------|------------|----|

| $V_{(ESD)}$                                   | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | $\pm 4000$ | V  |

| <b>TLV2888D, TLV2888DGK, TLV888D, TLV4888</b> |      |                                                          |            |    |

| $V_{(ESD)}$                                   | 静電放電 | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 250$  | V  |

| <b>TLV888DBV</b>                              |      |                                                          |            |    |

| $V_{(ESD)}$                                   | 静電放電 | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 500$  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|       |                     |        | 最小値        | 公称値      | 最大値 | 単位 |

|-------|---------------------|--------|------------|----------|-----|----|

| $V_S$ | 供給電圧、 $(V+) - (V-)$ | 単一電源   | 4.5        | 36       | V   |    |

|       |                     | デュアル電源 | $\pm 2.25$ | $\pm 18$ |     |    |

| $T_A$ | 動作温度                |        | -40        | 125      | °C  |    |

## 5.4 熱に関する情報 : TLV888

| 熱評価基準 <sup>(1)</sup>  |                     | TLV888   |             | 単位   |

|-----------------------|---------------------|----------|-------------|------|

|                       |                     | D (SOIC) | DBV (SOT23) |      |

|                       |                     | 8 ピン     | 5 ピン        |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 144.1    | 197.3       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 81.9     | 96.0        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 88.9     | 64.8        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 26.2     | 32.5        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 88.3     | 64.4        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 該当なし     | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 熱に関する情報 : TLV2888

| 熱評価基準 <sup>(1)</sup>  |                     | TLV2888  |             | 単位   |

|-----------------------|---------------------|----------|-------------|------|

|                       |                     | D (SOIC) | DGK (VSSOP) |      |

|                       |                     | 8 ピン     | 8 ピン        |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 132.3    | 158.7       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 72.2     | 53.0        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 81.7     | 93.2        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 19.6     | 2.4         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 80.6     | 91.6        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 該当なし     | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.6 熱に関する情報 : TLV4888

| 熱評価基準 <sup>(1)</sup>  |                     | TLV4888  |            | 単位   |

|-----------------------|---------------------|----------|------------|------|

|                       |                     | D (SOIC) | PW (TSSOP) |      |

|                       |                     | 14 ピン    | 14 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 94.8     | 102.3      | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 56.0     | 36.6       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 54.0     | 60.6       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 18.2     | 9.1        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 53.5     | 59.9       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 該当なし     | 該当なし       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.7 電気的特性

$T_A = 25^\circ\text{C}$ 、 $V_S = 4.5\text{V} \sim 36\text{V}$ 、 $V_{CM} = V_{OUT} = V_S/2$ 、および  $R_{LOAD} = 10\text{k}\Omega$  を  $V_S/2$  に接続 (特に記述のない限り)

| パラメータ            |                              | テスト条件                                                                                                                        | 最小値                      | 標準値             | 最大値                          | 単位                                   |

|------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|------------------------------|--------------------------------------|

| <b>オフセット電圧</b>   |                              |                                                                                                                              |                          |                 |                              |                                      |

| $V_{OS}$         | 入力オフセット電圧 <sup>(1)</sup>     | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                                                            | $\pm 3$                  | $\pm 15$        | $\mu\text{V}$                |                                      |

|                  |                              |                                                                                                                              |                          | $\pm 20$        |                              |                                      |

| $dV_{OS}/dT$     | 入力オフセット電圧ドリフト <sup>(1)</sup> | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                                                            | $\pm 0.01$               | $\pm 0.05$      | $\mu\text{V}/^\circ\text{C}$ |                                      |

| $PSRR$           | 電源除去比 <sup>(1)</sup>         | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                                                            | $\pm 0.03$               | $\pm 0.5$       | $\mu\text{V}/\text{V}$       |                                      |

| <b>入力バイアス電流</b>  |                              |                                                                                                                              |                          |                 |                              |                                      |

| $I_B$            | 入力バイアス電流 <sup>(1)</sup>      | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                                                            | $\pm 50$                 | $\pm 350$       | $\text{pA}$                  |                                      |

|                  |                              |                                                                                                                              |                          | $\pm 7$         | $\text{nA}$                  |                                      |

| $I_{OS}$         | 入力オフセット電流 <sup>(1)</sup>     | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$                                                                            | $\pm 100$                | $\pm 600$       | $\text{pA}$                  |                                      |

|                  |                              |                                                                                                                              |                          | $\pm 3$         | $\text{nA}$                  |                                      |

| <b>ノイズ</b>       |                              |                                                                                                                              |                          |                 |                              |                                      |

| $E_n$            | 入力電圧ノイズ                      | $f = 0.1\text{Hz} \sim 10\text{Hz}$                                                                                          | 0.180                    |                 |                              | $\mu\text{V}_{\text{PP}}$            |

| $e_n$            | 入力電圧ノイズ密度                    | $f = 10\text{Hz}$                                                                                                            | 7.6                      |                 |                              | $\text{nV}/\sqrt{\text{Hz}}$         |

|                  |                              | $f = 100\text{Hz}$                                                                                                           | 7.6                      |                 |                              |                                      |

|                  |                              | $f = 1\text{kHz}$                                                                                                            | 7.5                      |                 |                              |                                      |

| $i_n$            | 入力電流ノイズ密度                    | $f = 1\text{kHz}$                                                                                                            | 175                      |                 |                              | $\text{fA}/\sqrt{\text{Hz}}$         |

| <b>入力電圧</b>      |                              |                                                                                                                              |                          |                 |                              |                                      |

| $V_{CM}$         | 同相電圧                         |                                                                                                                              | $(V-) - 0.1$             | $(V+) - 1.7$    |                              | $\text{V}$                           |

| $CMRR$           | 同相除去比                        | $(V-) - 0.1\text{V} \leq V_{CM} \leq (V+) - 1.7\text{V}$                                                                     | $V_S = \pm 2.25\text{V}$ | 118             | 135                          | $\text{dB}$                          |

|                  |                              |                                                                                                                              | $V_S = \pm 18\text{V}$   | 140             | 150                          |                                      |

|                  |                              | $(V-) - 0.1\text{V} \leq V_{CM} \leq (V+) - 1.7\text{V}$<br>$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ <sup>(1)</sup> | $V_S = \pm 2.25\text{V}$ | 118             | 130                          |                                      |

|                  |                              |                                                                                                                              | $V_S = \pm 18\text{V}$   | 140             | 150                          |                                      |

| <b>入力インピーダンス</b> |                              |                                                                                                                              |                          |                 |                              |                                      |

| $Z_{id}$         | 差動入力インピーダンス                  |                                                                                                                              | 100                      | $\parallel 1.6$ |                              | $\text{M}\Omega \parallel \text{pF}$ |

| $Z_{ic}$         | コモンモード入力インピーダンス              |                                                                                                                              | 1                        | $\parallel 1.9$ |                              | $\text{T}\Omega \parallel \text{pF}$ |

| <b>開ループゲイン</b>   |                              |                                                                                                                              |                          |                 |                              |                                      |

| $A_{OL}$         | 開ループ電圧ゲイン                    | $V_S = \pm 15\text{V}$ ,<br>$(V-) + 0.6\text{V} < V_O < (V+) - 0.6\text{V}$ ,<br>$R_{LOAD} = 10\text{k}\Omega$               |                          | 130             | 148                          | $\text{dB}$                          |

|                  |                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ <sup>(1)</sup>                                                             |                          | 130             |                              |                                      |

|                  |                              | $V_S = \pm 15\text{V}$ ,<br>$(V-) + 1.7\text{V} < V_O < (V+) - 1.7\text{V}$ ,<br>$R_{LOAD} = 2\text{k}\Omega$                |                          | 130             | 144                          |                                      |

|                  |                              | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ <sup>(1)</sup>                                                             |                          | 130             |                              |                                      |

## 5.7 電気的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = 4.5\text{V} \sim 36\text{V}$ 、 $V_{CM} = V_{OUT} = V_S/2$ 、および  $R_{LOAD} = 10\text{k}\Omega$  を  $V_S/2$  に接続 (特に記述のない限り)

| パラメータ        | テスト条件             |                                                                                                          | 最小値                                                              | 標準値        | 最大値 | 単位               |

|--------------|-------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------|-----|------------------|

| <b>周波数応答</b> |                   |                                                                                                          |                                                                  |            |     |                  |

| GBW          | ゲイン帯域幅積           |                                                                                                          | 14                                                               |            |     | MHz              |

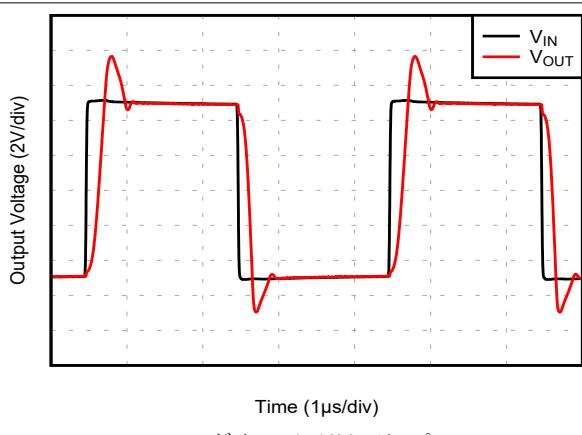

| SR           | スルーレート            | ゲイン = 1, 10V ステップ                                                                                        | 40                                                               |            |     | V/ $\mu\text{s}$ |

| THD+N        | 全高調波歪み + ノイズ      | ゲイン = 1, $f = 1\text{kHz}$ 、 $V_{OUT} = 4\text{V}_{RMS}$                                                 | 0.00012%                                                         |            |     |                  |

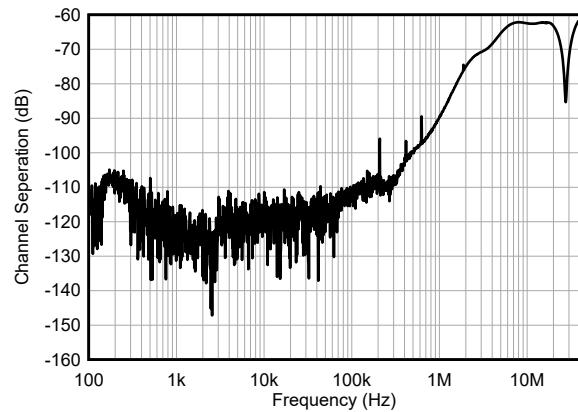

|              | クロストーク            | $f = 100\text{kHz}$                                                                                      | 110                                                              |            |     | dB               |

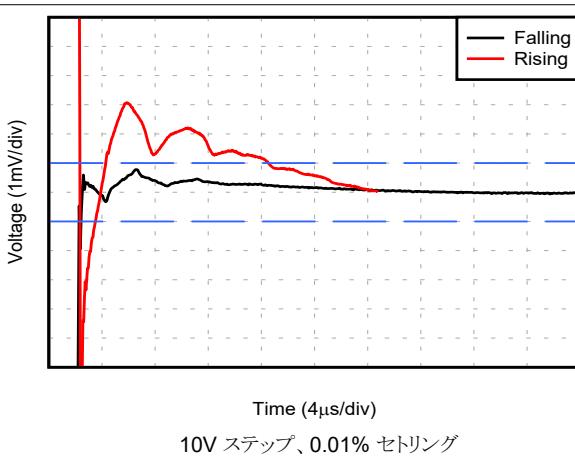

| $t_S$        | セトリング タイム         | $V_S = \pm 18\text{V}$ , ゲイン = 1, 10V ステップ                                                               | 0.1% まで                                                          | 1          |     | $\mu\text{s}$    |

|              |                   |                                                                                                          | 0.01% まで                                                         | 15         |     |                  |

| $t_{OR}$     | 過負荷回復時間           | $V_{IN} \times \text{ゲイン} = V_S = \pm 18\text{V}$                                                        | 460                                                              |            |     | ns               |

| <b>出力</b>    |                   |                                                                                                          |                                                                  |            |     |                  |

| $V_O$        | 電圧出力スイング (レールから)  | 正のレール、<br>$V_S = 30\text{V}$                                                                             | 無負荷 <sup>(1)</sup>                                               | 26         | 40  | mV               |

|              |                   |                                                                                                          | $R_{LOAD} = 10\text{k}\Omega$                                    | 122        | 150 |                  |

|              |                   |                                                                                                          | $R_{LOAD} = 2\text{k}\Omega$                                     | 500        | 575 |                  |

|              |                   | 負のレール、<br>$V_S = 30\text{V}$                                                                             | 無負荷 <sup>(1)</sup>                                               | 26         | 40  |                  |

|              |                   |                                                                                                          | $R_{LOAD} = 10\text{k}\Omega$                                    | 120        | 135 |                  |

|              |                   |                                                                                                          | $R_{LOAD} = 2\text{k}\Omega$                                     | 515        | 575 |                  |

|              |                   | $R_{LOAD} = 10\text{k}\Omega$ , $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、両方のレール <sup>(1)</sup> |                                                                  |            | 250 |                  |

|              |                   |                                                                                                          |                                                                  |            |     |                  |

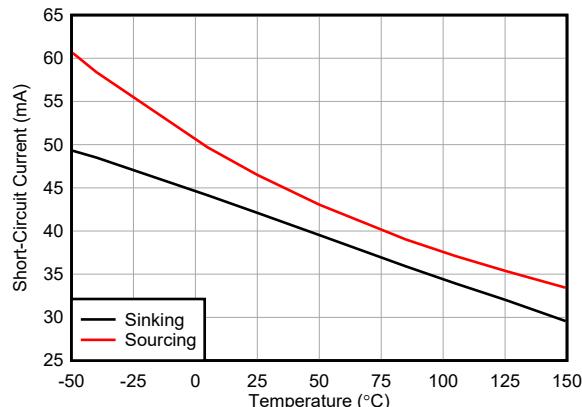

| $I_{SC}$     | 短絡電流              |                                                                                                          |                                                                  | ±42        |     | mA               |

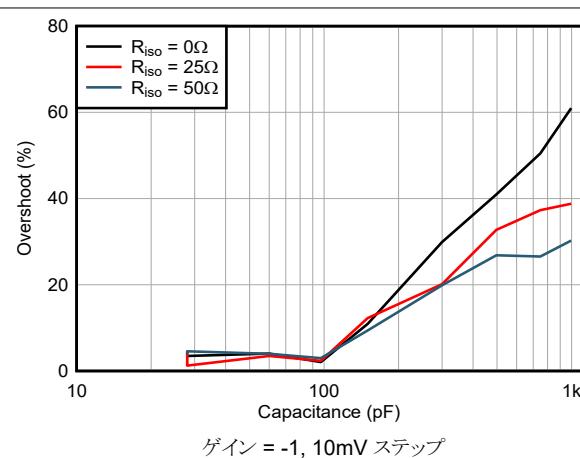

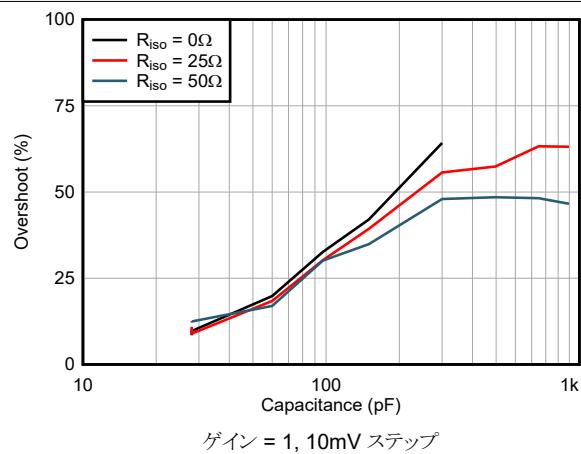

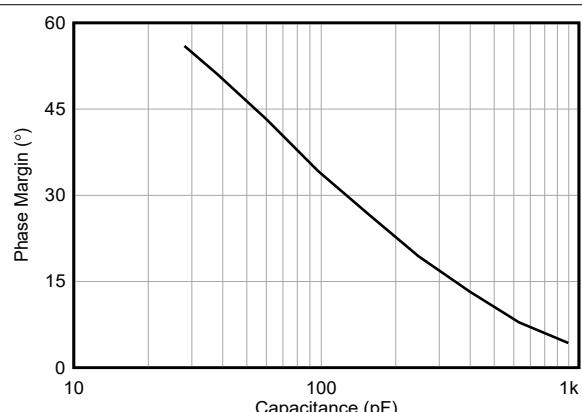

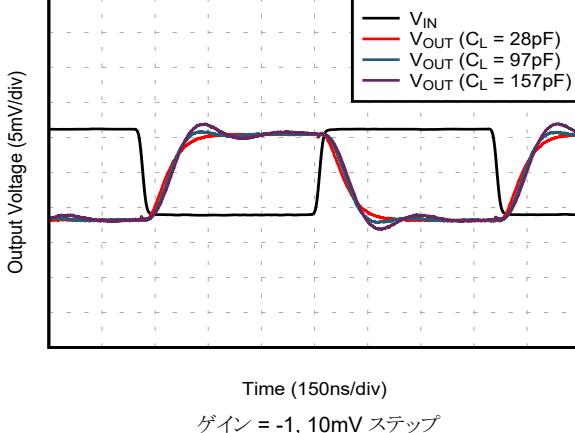

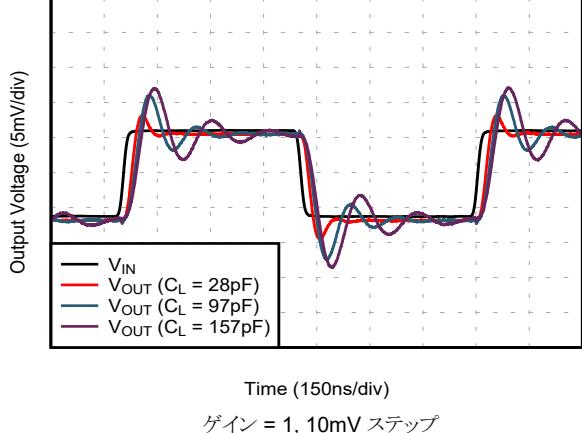

| $C_{LOAD}$   | 容量性負荷駆動能力         |                                                                                                          |                                                                  | 「代表的特性」を参照 |     | pF               |

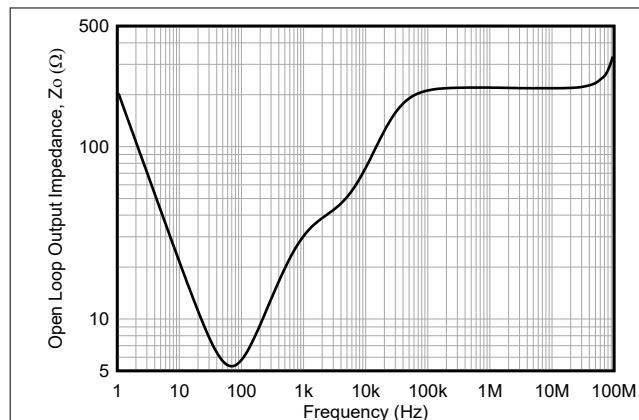

| $Z_O$        | オープン ループ出力インピーダンス | $f = 1\text{MHz}$                                                                                        |                                                                  | 220        |     | $\Omega$         |

| <b>電源</b>    |                   |                                                                                                          |                                                                  |            |     |                  |

| $I_Q$        | アンプごとの静止電流        | $V_S = \pm 2.25\text{V}$ ( $V_S = 4.5\text{V}$ )、 $I_O = 0\text{A}$                                      |                                                                  | 1.5        | 1.8 | mA               |

|              |                   |                                                                                                          | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ <sup>(1)</sup> | 1.5        | 1.9 |                  |

|              |                   | $V_S = \pm 18\text{V}$ ( $V_S = 36\text{V}$ )、 $I_O = 0\text{A}$                                         |                                                                  | 1.5        | 1.8 |                  |

|              |                   |                                                                                                          | $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ <sup>(1)</sup> | 1.5        | 1.9 |                  |

(1) 複数のロットにわたるデバイスの母集団ベンチ システムの測定から確立された仕様。

## 5.8 代表的特性

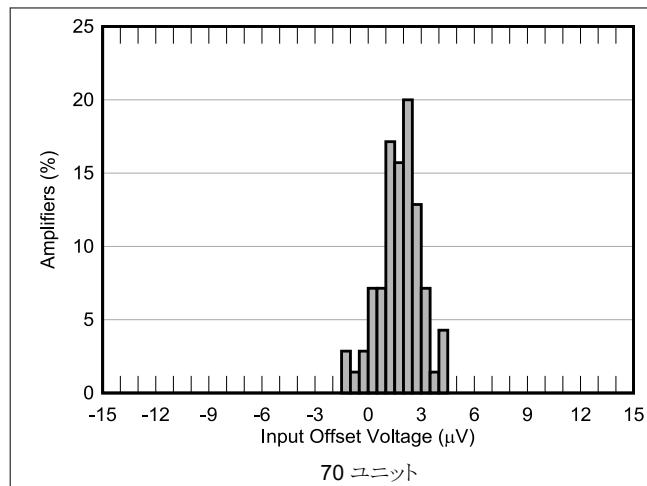

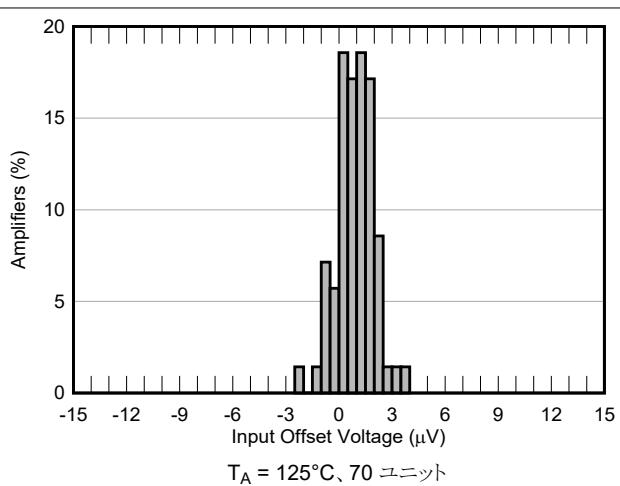

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

図 5-1. オフセット電圧の分布

図 5-2. オフセット電圧の分布

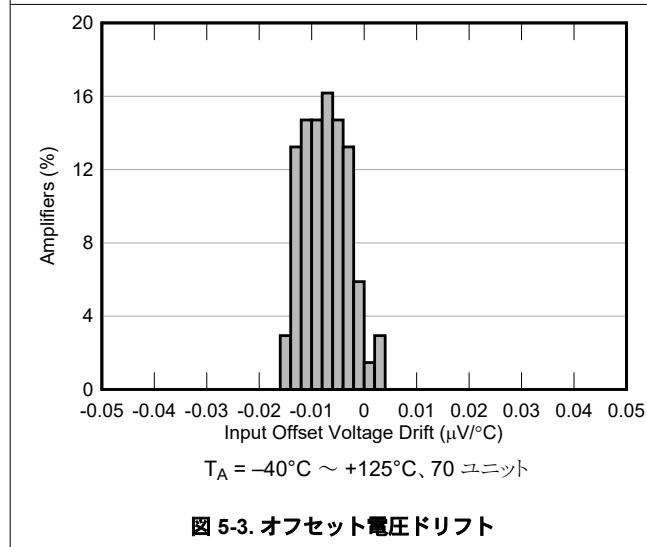

図 5-3. オフセット電圧ドリフト

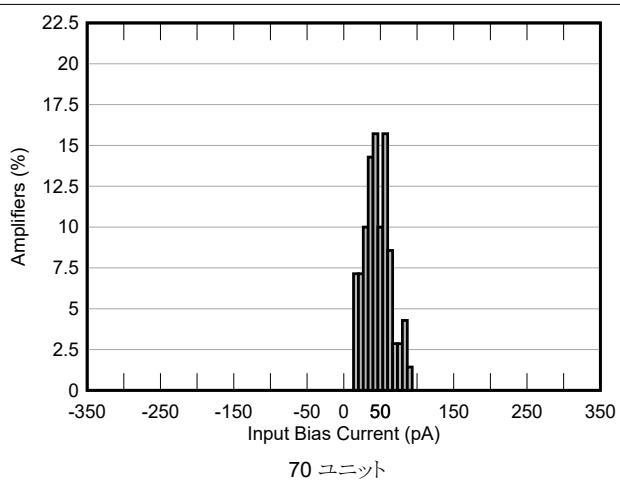

図 5-4. 入力バイアス電流の分布、 $I_{BN}$

## 5.8 代表的特性 (続き)

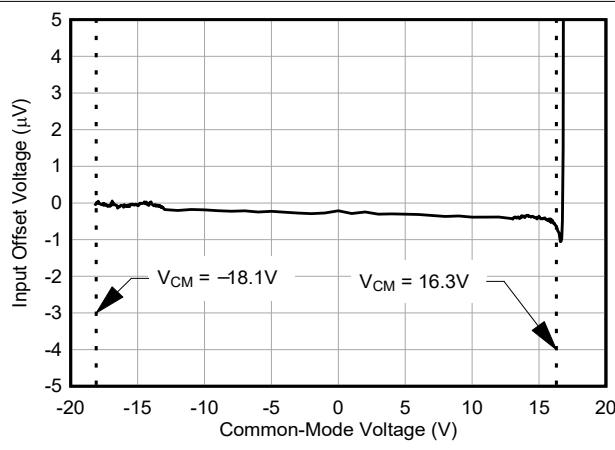

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

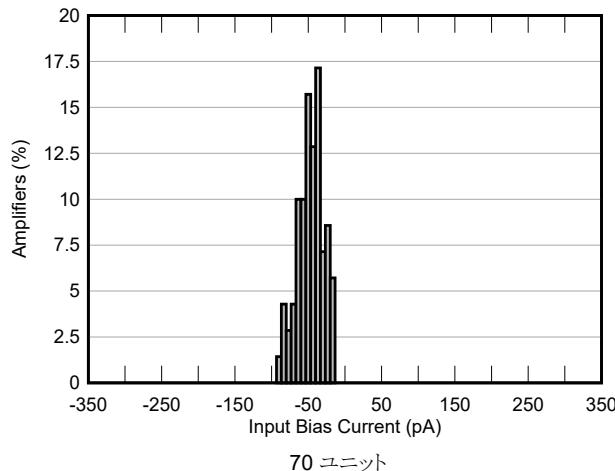

図 5-5. 入力バイアス電流の分布、 $I_{BP}$

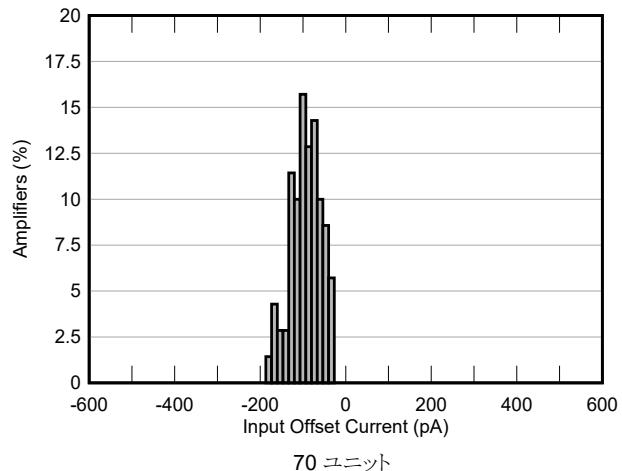

図 5-6. 入力オフセット電流の分布

図 5-7. オフセット電圧と同相電圧との関係

図 5-8. オフセット電圧と同相電圧との関係

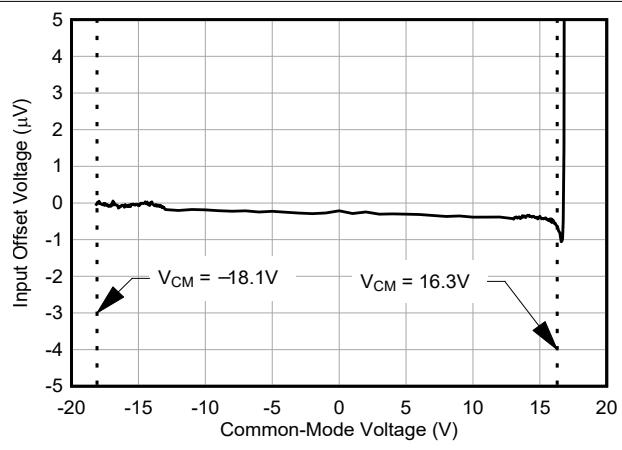

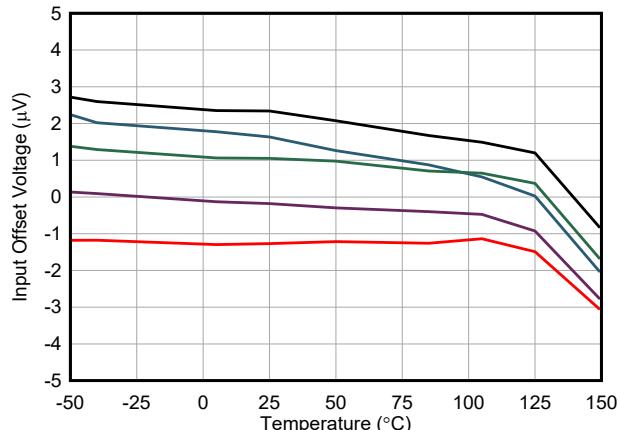

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

5 個の代表的なユニット

図 5-9. オフセット電圧と温度との関係

5 個の代表的なユニット

図 5-10. オフセット電圧と電源電圧との関係

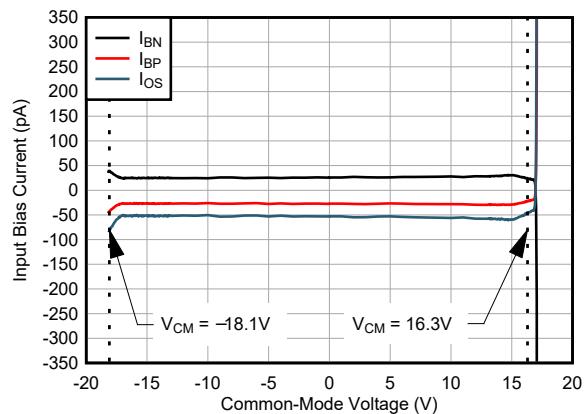

図 5-11. 入力バイアス電流と同相電圧との関係

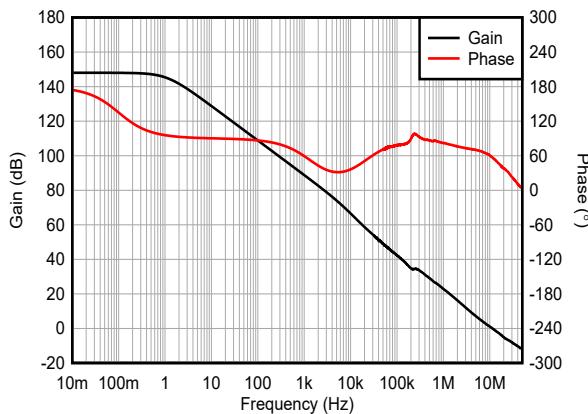

図 5-12. 開ループゲインおよび位相と周波数との関係

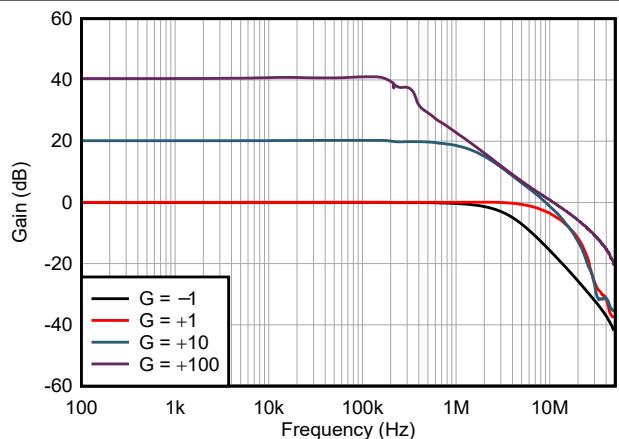

図 5-13. 閉ループゲインと周波数との関係

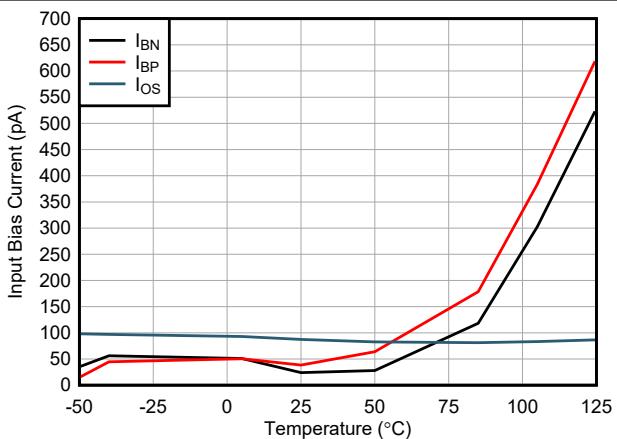

図 5-14. 入力バイアス電流およびオフセット電流と温度との関係

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{\text{CM}} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

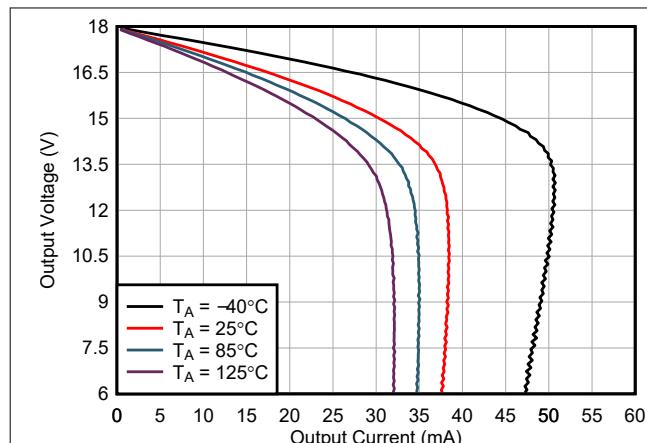

図 5-15. 出力電圧スイングと

出力電流との関係 (ソース)

図 5-16. 出力電圧スイングと

出力電流との関係 (シンク)

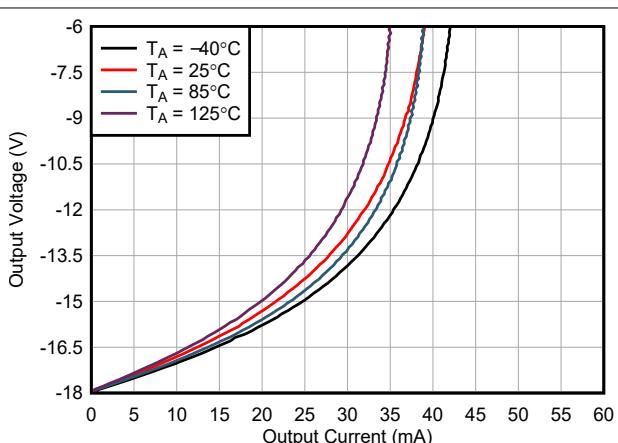

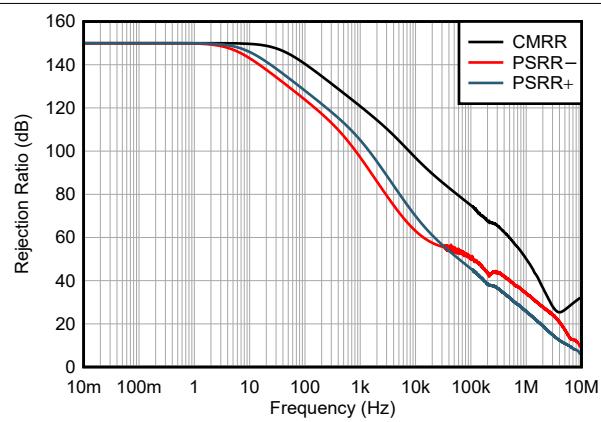

図 5-17. CMRR および PSRR と周波数との関係

図 5-18. CMRR と温度との関係

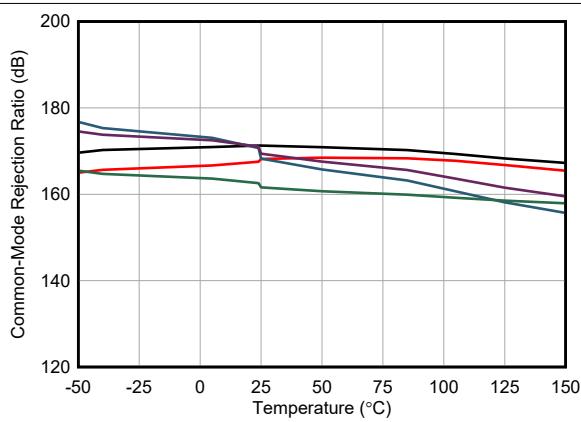

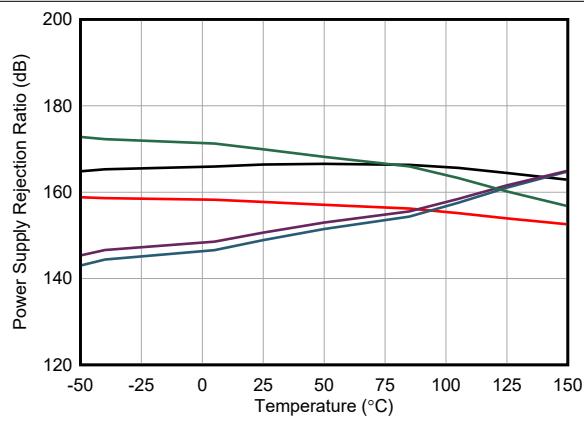

5 個の代表的なユニット

図 5-19. PSRR と温度との関係

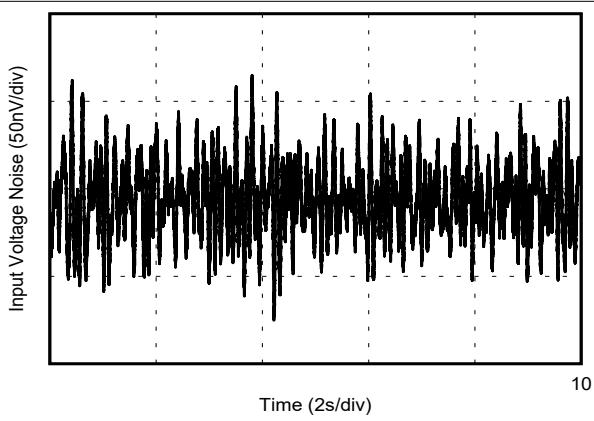

図 5-20. 0.1Hz~10Hz の電圧ノイズ

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{\text{CM}} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

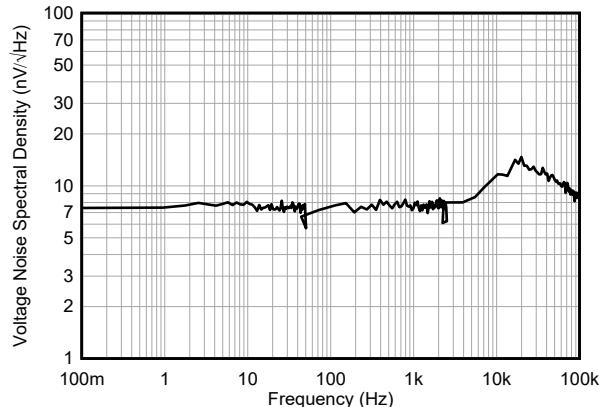

図 5-21. 入力電圧ノイズ スペクトル密度と周波数との関係

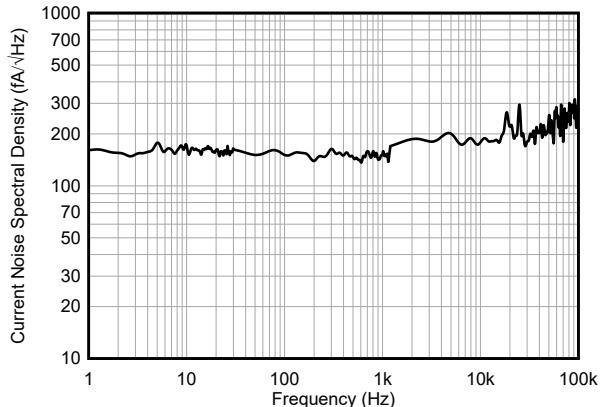

図 5-22. 入力電流ノイズ スペクトル密度と周波数との関係

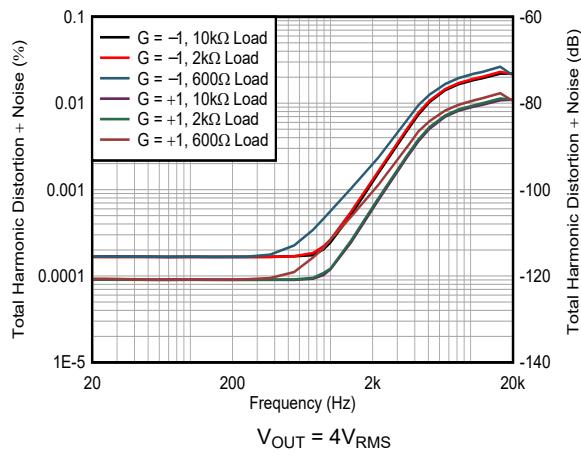

図 5-23. THD+N と周波数との関係

図 5-24. THD+N と出力振幅との関係

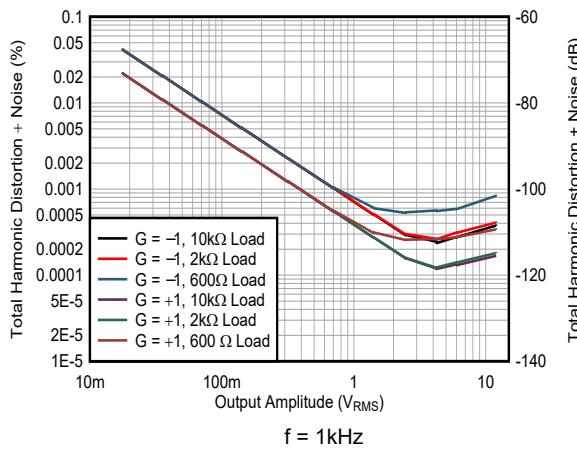

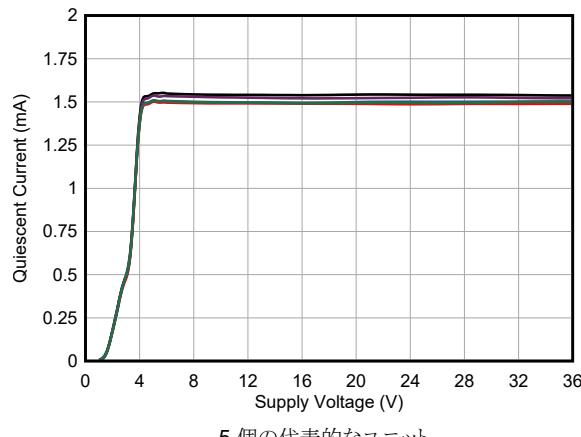

図 5-25. 静止電流と電源電圧との関係

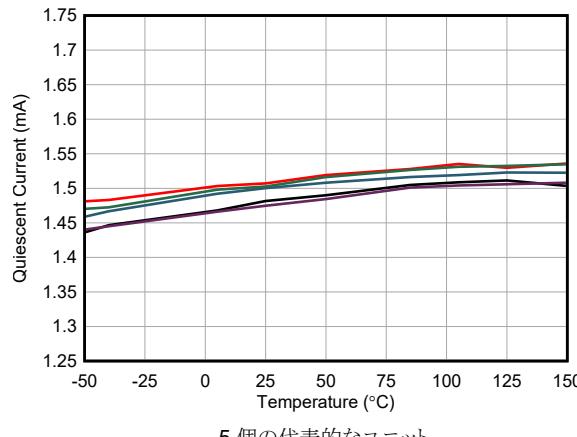

図 5-26. 静止電流と温度との関係

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

図 5-27. 開ループ出力インピーダンスと周波数との関係

図 5-28. 小信号オーバーシュートと

容量性負荷との関係

図 5-29. 小信号オーバーシュートと

容量性負荷との関係

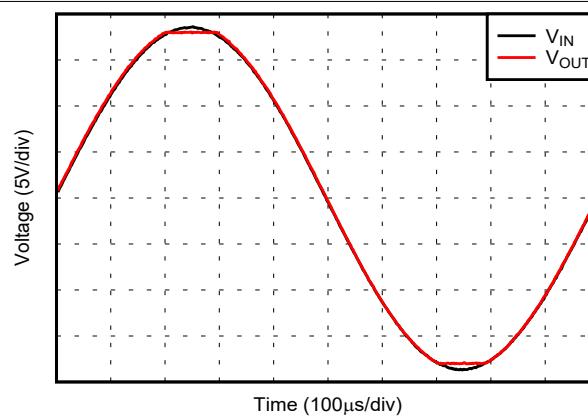

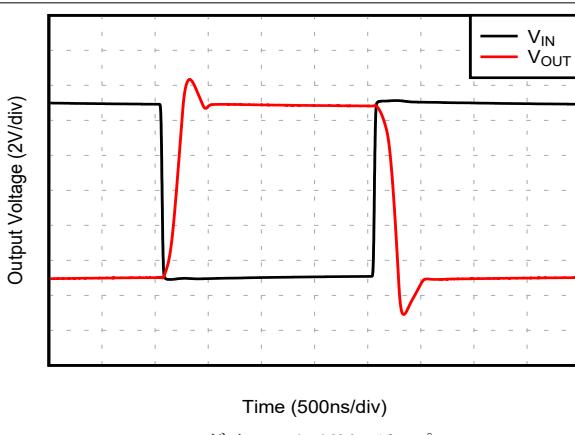

図 5-30. 位相反転が発生しない

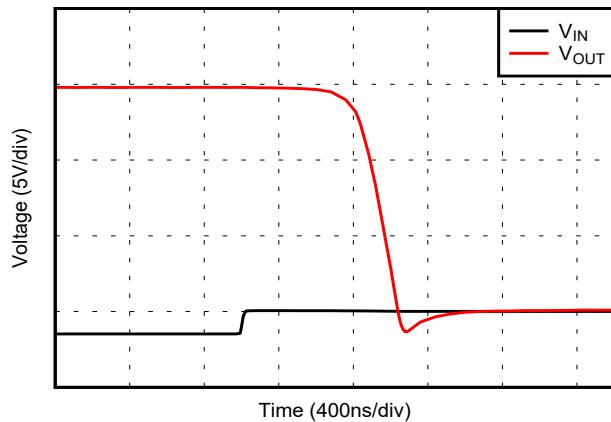

図 5-31. 正の過負荷からの回復

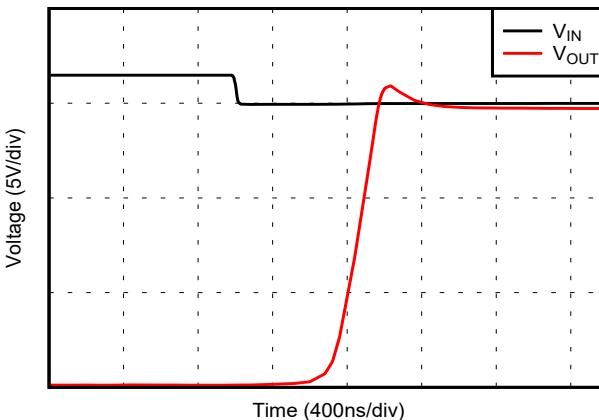

図 5-32. 負の過負荷からの回復

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

## 5.8 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $V_{CM} = V_S / 2$ 、 $R_L = 10\text{k}\Omega$  (特に記述のない限り)

図 5-39. 短絡電流と温度との関係

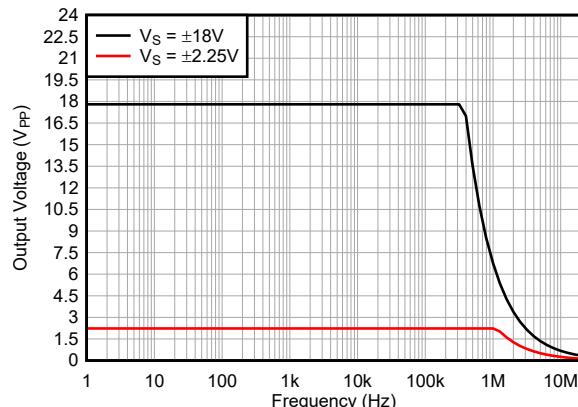

図 5-40. 最大出力電圧と周波数との関係

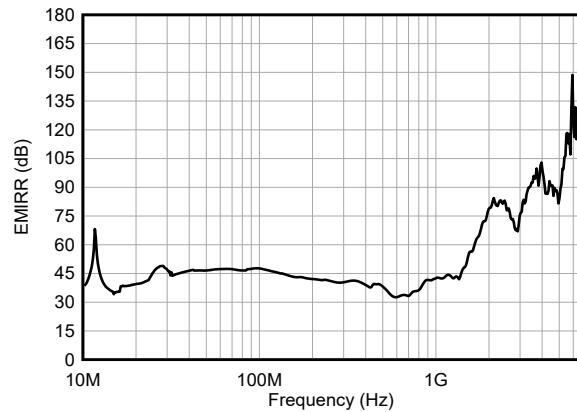

図 5-41. EMIRR と周波数との関係

図 5-42. チャネル セパレーション

## 6 詳細説明

### 6.1 概要

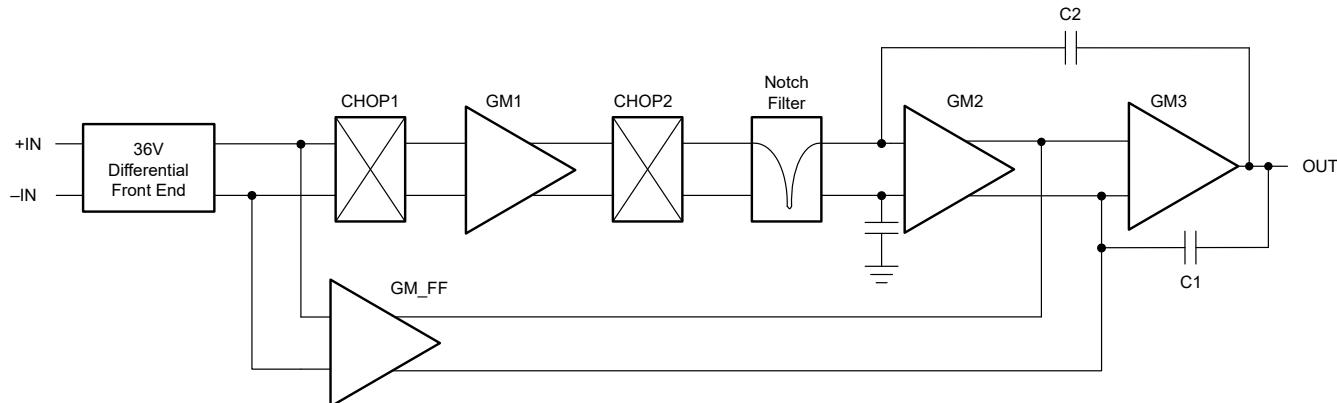

TLVx888 オペアンプは、高精度のオフセットとドリフト、優れた全体的性能を兼ね備えているため、多くの高精度アプリケーションに最適です。 $0.01\mu\text{V}/^\circ\text{C}$  という高精度のオフセットのドリフトにより、 $-40^\circ\text{C} \sim +125^\circ\text{C}$  の全動作温度範囲にわたって安定性が提供されます。さらに、このデバイスは CMRR、PSRR、 $A_{OL}$  が高く、優れた線形性能を提供します。すべてのアンプと同様に、ノイズの多い、または高インピーダンスの電源を使用するアプリケーションでは、デバイスのピンの近くにデカップリング コンデンサが必要です。通常は、 $0.1\mu\text{F}$  のコンデンサが適しています。詳細およびレイアウト例については、「[セクション 7.4](#)」を参照してください。

TLVx888 は、ゼロドリフト、マルチプレクサ対応オペアンプ ファミリの製品です。このデバイスは  $4.5\text{V} \sim 36\text{V}$  で動作し、ユニティゲインで安定しており、さまざまな汎用かつ高精度のアプリケーション用に設計されています。ゼロドリフトアーキテクチャにより、入力オフセット電圧が非常に低く、さらに、温度変化および時間の経過に伴う入力オフセット電圧ドリフトがほぼゼロになっています。また、このアーキテクチャの選択により、非常に低い広帯域ノイズ、ゼロフリッカーノイズ、チョッパ周波数未満で動作する際にも優れた歪み性能など、優れた AC 性能を実現します。

次のセクションは、独自の TLVx888 アーキテクチャを示しています。

### 6.2 機能ブロック図

### 6.3 機能説明

TLVx888 オペアンプは、独自の定期的な自動キャリブレーション技術を使用して、非常に低い入力オフセット電圧を実現するとともに、時間の経過および温度変化に伴う入力オフセット電圧ドリフトを非常に低く抑えます。このデバイスは、さまざまなアプリケーションにおいて高い精度を維持するために役立つ、いくつかの統合機能を備えています。これには、位相反転の防止、EMI 除去、電気的オーバーストレスの防止、マルチプレクサ対応入力などがあります。

TLVx888 の規定性能を維持するためのいくつかの設計手法および検討事項については、『[チョッパ アンプの精度の最適化](#)』アプリケーション ノートと『[オペアンプのオフセット電圧とバイアス電流の制限](#)』アプリケーション ノートに詳しく記載されています。

#### 6.3.1 入力同相範囲

TLVx888 は、 $4.5\text{V} \sim 36\text{V}$  ( $\pm 2.25\text{V} \sim \pm 18\text{V}$ ) で動作することが規定されています。TLVx888 は、負のレールを含む広い入力同相電圧 ( $V_{CM}$ ) 範囲を提供しているため、単一電源動作に最適です。入力同相電圧の正のレールに対する範囲は  $(V+) - 1.7\text{V}$  に制限されます。規定性能を維持するためには、入力同相電圧を  $(V-) - 0.1\text{V} \leq V_{CM} \leq (V+) - 1.7\text{V}$  に制限します。

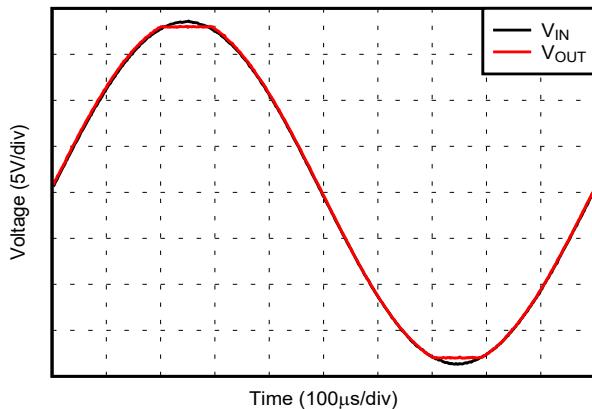

### 6.3.2 位相反転保護

TLVx888 には、位相反転保護が内蔵されています。一部のオペアンプでは、入力がリニア同相範囲を超えて駆動されると、位相反転が発生します。この条件が最も多く発生するのは非反転回路で、規定された同相電圧範囲を超えて入力を駆動すると、出力は逆のレールに反転します。TLVx888 入力は、過剰な同相電圧による位相反転を防止します。代わりに、出力は適切なレールに制限されます。図 6-1 にこの特性を示します。

図 6-1. 位相反転が発生しない

### 6.3.3 チョッピングによる過渡現象

TLVx888 などのゼロドリフトアンプは、入力のスイッチングアーキテクチャを使用して、アンプ固有のオフセットとドリフトを補正します。入力の内蔵スイッチからのチャージインジェクションがあると、アンプの入力バイアス電流に短い過渡現象が発生する可能性があります。パルスの持続時間が非常に短いため、このパルスは増幅されません。ただし、フィードバック回路を経由して、パルスがアンプの出力に結合される可能性があります。アンプ出力における入力過渡現象の影響を最小限に抑えるには、低い値の抵抗を使用します。過渡現象による追加ノイズを最小限に抑えるには、RC ネットワークなどのローパスフィルタを使用します。TLVx888 のチョッピング周波数は通常 200kHz です。

### 6.3.4 EMI 除去

TLVx888 は、内蔵の電磁干渉(EMI)フィルタを使用して、ワイヤレス通信や、アナログ信号チェーンとデジタル部品を組み合わせた高密度実装のボードなどから発生する EMI 干渉の影響を低減します。EMI 耐性は、回路設計手法により改善可能です。TLVx888 は、このような設計の改善を活用しています。

帯域幅外のスペクトル成分を持つ信号に対しては、それを補正するためのアンプのループゲインが不十分なため、いずれかのオペアンプに対して高周波信号が伝導または放射されると、悪影響が発生する可能性があります。入力、電源、または出力で伝導または放射による EMI があると、予期しない DC オフセット、過渡電圧、その他の未知の動作が発生する可能性があります。ノイズの多い無線信号、デジタルクロック、インターフェイスから、敏感なアナログノードを適切にシールドし、分離するように注意してください。

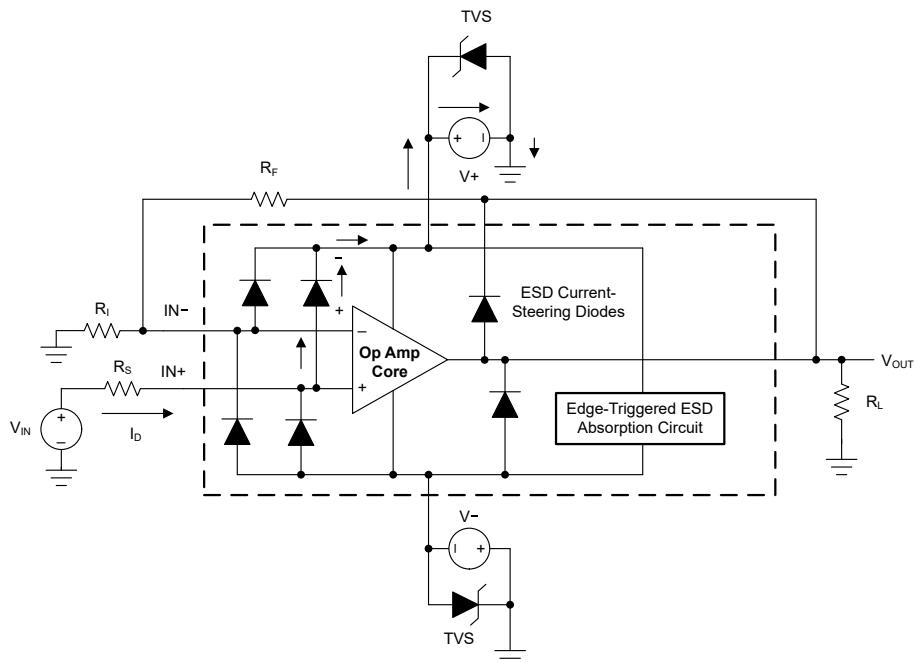

### 6.3.5 電気的オーバーストレス

設計者は、オペアンプが電気的オーバーストレスにどの程度耐えられるのかという質問をすることがよくあります。これらの質問は、主にデバイスの入力に関するものですが、電源電圧ピンや、さらに出力ピンにも関係する場合があります。これらの各ピンの機能には、特定の半導体製造プロセスの電圧ブレークダウン特性と、ピンに接続された特定の回路とで決まる電気的ストレスの制限値があります。また、これらの回路には内部に静電気放電 (ESD) 保護機能が組み込まれており、製品の組み立て前にも組み立て中にも、偶発的な ESD イベントから保護します。

この基本的な ESD 回路と、電気的オーバーストレスイベントとの関連性を十分に理解しておくと役に立ちます。TLVx888 に含まれる ESD 回路の図を、図 6-2 に示します (破線で囲まれている部分)。ESD 保護回路には、いくつかの電流ステアリングダイオードが含まれており、入力ピンや出力ピンから内部の電源ラインへ戻るよう配線されています。さらに、これらのダイオードは、オペアンプ内部の吸収デバイスにも接続されます。この保護回路は、回路が通常動作している間は非アクティブになるように設計されています。

ESD イベントがあると、短時間の高電圧パルスが発生し、それが半導体デバイスを通じて放電する際に、短時間の大電流パルスに変わります。ESD 保護回路は、オペアンプコアを迂回する電流経路を提供して、損傷を防止するように設計されています。保護回路によって吸収されたエネルギーは、熱として放散されます。

2つ以上のアンプデバイスピンの間に ESD 電圧が発生すると、電流は1つまたは複数のステアリングダイオードを流れます。電流が流れる経路に応じて、吸収デバイスがアクティブになります。吸収デバイスのトリガまたはスレッショルド電圧は、TLVx888 の通常動作電圧より高く、デバイスのブレークダウン電圧レベルよりも低くなっています。このスレッショルドを超えると、吸収デバイスが迅速にアクティブになり、電源レールの電圧を安全なレベルにクランプします。

図 6-2 は、オペアンプを回路に接続したとき、ESD 保護部品は非アクティブのままであり、アプリケーション回路の動作に関与しないことを示しています。ただし、印加された電圧が特定のピンの動作電圧範囲を超える状況が発生する可能性があります。この状況が発生した場合、一部の内部 ESD 保護回路のバイアスがオンになって電流が流れるリスクがあります。このような電流の流れは、ステアリングダイオードパスを経由して発生し、吸収デバイスが関係することはほとんどありません。

注:  $V_{IN} = (V+) + 500\text{mV}$ 。

TVS:  $V+ < V_{TWSBR(\text{min})} < 40\text{V}$ 。ここで、 $V_{TWSBR(\text{min})}$  は、TVS のブレークダウン電圧の最小規定値です。

$R_s$  の推奨値は、過電圧状態でのおよそ  $5\text{k}\Omega$  です。

図 6-2. 代表的な回路アプリケーションと比較して等価な内部 ESD 回路

図 6-2 に、入力電圧 ( $V_{IN}$ ) が正電源電圧 ( $V_+$ ) を 500mV 以上上回る具体的な例を示します。この回路で発生する現象の多くは、電源の特性によって異なります。 $V_+$  が電流をシンクできる場合、上側の入力ステアリング ダイオードの 1 つが導通し、電流を  $+V_S$  へ導きます。 $V_{IN}$  が高くなると、非常に高いレベルの電流が流れる可能性があります。その結果、データシートの仕様では、アプリケーションが入力電流を 10mA に制限することを推奨しています。

電源が電流をシンクできない場合、 $V_{IN}$  はオペアンプへの電流ソースを開始し、その後、正の電源電圧供給を引き継ぐことができます。この場合の危険は、電圧がオペアンプの絶対最大定格を超えるレベルまで上昇する可能性があることです。

よくある質問として、「電源  $V_+$  または  $V_-$  が 0V のときに入力信号を加えるとどうなるか」というものもあります。ここでも、電源が 0V または入力信号の振幅より低いレベルにあるときの電源特性によって状況が変わります。見かけ上、電源のインピーダンスが高い場合、オペアンプの電源電流は、入力ソースから電流ステアリング ダイオードを経由して供給できます。このような状態はアンプにとって通常のバイアス条件ではなく、特性の劣化や異常な動作につながる可能性があります。電源のインピーダンスが低い場合には、ステアリング ダイオードを流れる電流が非常に大きくなる可能性があります。電流レベルは、入力ソースが電流を供給できる能力と、入力バスに存在する抵抗によって異なります。

この電流を吸収する電源の能力が不確実である場合は、外部過渡電圧サプレッサ (TVS) ダイオードを電源ピンに追加します (図 6-2 も参照)。このブレークダウン電圧は、通常動作中にダイオードがオンにならないように選択する必要があります。ただし、電源ピンが安全な動作電源電圧レベルを超えそうになった場合には TVS ダイオードが導通する程度に、ブレークダウン電圧を低くする必要があります。

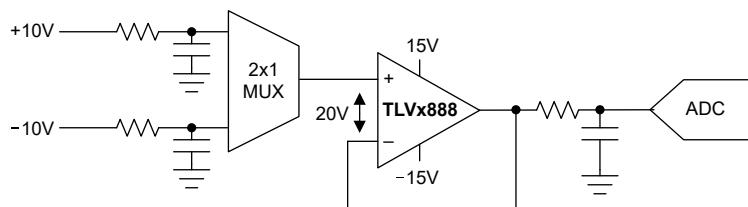

### 6.3.6 MUX 対応入力

TLVx888 には独自の入力段設計が採用されており、高い入力インピーダンスを維持しながら、入力差動電圧を印加できます。通常、高電圧の CMOS またはバイポーラ接合入力アンプには、半導体プロセスの最大値を超えていてデバイスに永続的な損傷を与える可能性のある、大きい  $V_{GS}$  電圧から入力トランジスタを保護する逆並列ダイオードが搭載されています。大きいステップ入力を印加したとき、またはチャネル間を切り替えたとき、またはアンプをコンパレータとして使う場合、大きい  $V_{GS}$  電圧が発生してしまう可能性があります。

TLVx888 は、大きい差動電圧が印加されたときに大きい入力バイアス電流が発生することを防止するスイッチ入力手法により、これらの問題を解決します。この入力アーキテクチャは、スイッチングまたは多重化アプリケーションで見られる多くの問題に対応します。これらのアプリケーションでは、大きな電位間を高速にスイッチングすることにより、RC フィルタリング ネットワークに大きな乱れが生じます。図 6-3 は、マルチプレクサ対応入力でセトリング タイム性能を向上できる代表的なアプリケーションを示しています。TLVx888 は、これらの設計の革新により、優れたセトリング性能を得るとともに、スルーレートの向上と広い帯域幅を実現しています。TLVx888 は、コンパレータとしても使用できます。差動および同相入力電圧範囲は引き続き適用されます。

図 6-3. 多重化アプリケーション

### 6.4 デバイスの機能モード

TLVx888 には単一機能モードがあり、電源電圧が 4.5V ( $\pm 2.25V$ ) を上回ると動作します。TLVx888 の推奨電源電圧は 36V ( $\pm 18V$ ) です。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TLVx888 オペアンプは、高精度のオフセットとドリフト、優れた全体的性能を兼ね備えているため、多くの高精度アプリケーションに最適です。オフセットドリフトの精度は、わずか  $0.01\mu\text{V}/^\circ\text{C}$  で、温度範囲全体にわたって安定性が得られます。さらに、これらのデバイスは、優れた CMRR、PSRR、および  $A_{OL}$  dc 性能と、優れた低ノイズ動作を組み合わせています。すべてのアンプと同様に、ノイズの多い、または高インピーダンスの電源を使用するアプリケーションでは、デバイスのピンの近くにデカップリング コンデンサが必要です。通常は、 $0.1\mu\text{F}$  のコンデンサが適しています。

#### 7.1.1 ノイズの基本的な計算

低ノイズ回路設計では、すべてのノイズ源を慎重に分析する必要があります。多くの場合、外部ノイズ源が支配的な要素になることがあるため、ソース抵抗がオペアンプのノイズ性能全体に与える影響を考慮します。回路全体のノイズは、すべてのノイズ要素の二乗和平方根に等しくなります。

ソースインピーダンスの抵抗の部分では、抵抗の平方根に比例する熱ノイズが発生します。ソースインピーダンスは一般に固定されているため、ノイズ全体への寄与を最小限に抑えるオペアンプおよび帰還抵抗を選定します。

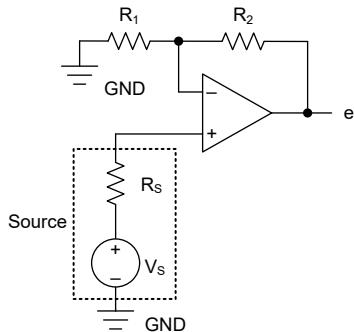

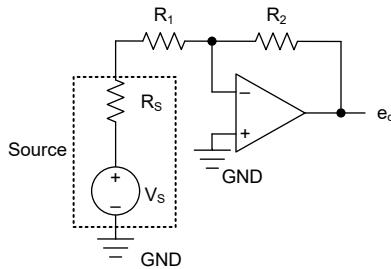

図 7-1 は、ゲインが存在する非反転型オペアンプ回路構成を示しています。図 7-2 は、ゲインが存在する反転型オペアンプ回路構成を示しています。ゲインが存在する回路構成では、帰還ネットワーク抵抗もノイズの原因となります。一般に、オペアンプの電流ノイズは帰還抵抗に反応して、追加のノイズを発生させます。ただし、TLVx888 の電流ノイズは低いため、電流ノイズの寄与は無視できます。

一般的には、帰還抵抗の値を選択して、これらのノイズ発生源を無視できる程度まで下げるることができます。低インピーダンスの帰還抵抗は、アンプの出力に負荷をかけます。両方の構成について、合計ノイズの計算式を示します。

ノイズ計算に関する追加リソースについては、[TI Precision Labs](#) を参照してください。

図 7-1. 非反転型ゲイン構成のノイズの計算

$$E_o = e_o \sqrt{BW_N} [V_{RMS}] \quad (1)$$

$$e_o = \left(1 + \frac{R_2}{R_1}\right) \sqrt{e_S^2 + e_N^2 + (e_{R_1} || R_2)^2 + (i_N R_S)^2 + \left(i_N \frac{R_1 R_2}{R_1 + R_2}\right)^2} \left[ \frac{V}{\sqrt{Hz}} \right] \quad (2)$$

$$e_S = \sqrt{4k_B T(K) R_S} \left[ \frac{V}{\sqrt{Hz}} \right] \quad (3)$$

$$e_{R_1} || R_2 = \sqrt{4k_B T(K) \left( \frac{R_1 R_2}{R_1 + R_2} \right)} \left[ \frac{V}{\sqrt{Hz}} \right] \quad (4)$$

$$k_B = 1.38065 \times 10^{-23} \left[ \frac{J}{K} \right] \quad (5)$$

$$T(K) = 2.3715 + T(^{\circ}C) [K] \quad (6)$$

ここで、

- $e_n$  はアンプの電圧ノイズ スペクトル密度。TLVx888 の場合、 $e_n = 7.5\text{nV}/\sqrt{\text{Hz}}$  (1kHz 時)

- $e_o$  は合計ノイズ密度

- $e_S$  は、 $R_S$  の熱ノイズ

- $e_{R_1} || R_2$  は、 $R_1 || R_2$  の熱ノイズ

- $k_B$  はボルツマン定数

- $T(K)$  は温度 (ケルビン)

図 7-2. 反転型ゲイン構成のノイズの計算

$$E_o = e_o \sqrt{BW_N} [V_{RMS}] \quad (7)$$

$$e_o = \left( 1 + \frac{R_2}{R_S + R_1} \right) \sqrt{e_N^2 + (e_{R1} + R_S || R_2)^2 + \left( i_N \frac{(R_S + R_1)R_2}{R_S + R_1 + R_2} \right)^2} \left[ \frac{V}{\sqrt{Hz}} \right] \quad (8)$$

$$e_{R1 + R_S || R_2} = \sqrt{4k_B T(K) \left( \frac{(R_S + R_1)R_2}{R_S + R_1 + R_2} \right)} \left[ \frac{V}{\sqrt{Hz}} \right] \quad (9)$$

$$k_B = 1.38065 \times 10^{-23} \left[ \frac{J}{K} \right] \quad (10)$$

$$T(K) = 2.37.15 + T(^{\circ}C) [K] \quad (11)$$

ここで、

- を参照してください。

- $e_n$  はアンプの電圧ノイズ スペクトル密度。TLVx888 の場合、 $e_n = 7.5nV/\sqrt{Hz}$  (1kHz 時)

- $e_o$  は合計ノイズ密度

- $e_S$  は、 $R_S$  の熱ノイズ

- $e_{(R_1 + R_S) || R_2}$  は  $(R_1 + R_S) || R_2$  の熱ノイズ

- $k_B$  はボルツマン定数

- $T(K)$  は温度 (ケルビン)

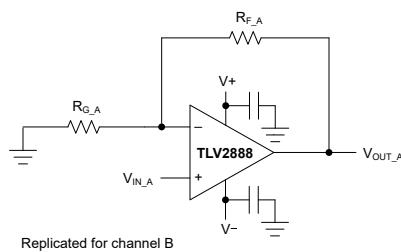

## 7.2 代表的なアプリケーション

### 7.2.1 ハイサイド電流センシング

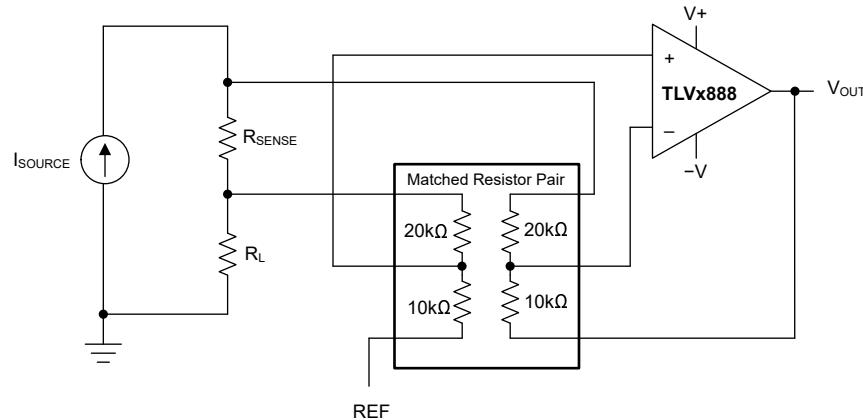

図 7-3. ハイサイド電流監視

#### 7.2.1.1 設計要件

一般的なシステム要件として、負荷に供給される電流を監視することが挙げられます。監視により、通常の電流レベルが維持されていることを確認でき、過電流状態が発生した場合には警告を出すこともできます。

幸い、TLVx888 のような高精度オペアンプを使用すると、比較的簡単な電流モニタ回路を実現できます。このデバイスは、非常に高いゲイン構成にも対応できる優れた精度と広いゲイン帯域幅を備えています。

TLVx888 は、あらかじめゲインが決定された差動アンプとして構成されます。差動アンプの入力は、負荷電流が流れるセンス抵抗の両端に接続されます。このセンス抵抗は、負荷電流が流れる回路のハイサイドまたはローサイドに接続できます。一般的には、ハイサイド電流検出が適用されます。図 7-3 に、適用可能な TLVx888 の構成を示します。ローサイド電流検出は、負荷とグランドの間にセンス抵抗を配置できる場合も適用できます。

この設計例では、以下のパラメータを使用します。

- デュアル電源:  $\pm 15V$

- リニア出力電圧範囲:  $0V \sim 5V$

- 負荷電流、 $I_L$ :  $1mA \sim 100mA$

以下の設計の詳細と式は、各種の出力電圧範囲や負荷電流に合わせてこの設計を再構成するために使用できます。

### 7.2.1.2 詳細な設計手順

ハイサイド電流モニタ回路の設計は、アンプの電気的特性を注意深く検討し、リニア動作が維持されるようにすれば、単純に行えます。システムを構成する際には、電流監視ステージの後の A/D コンバータ (ADC) の入力電圧範囲など、他の追加特性も考慮する必要があります。

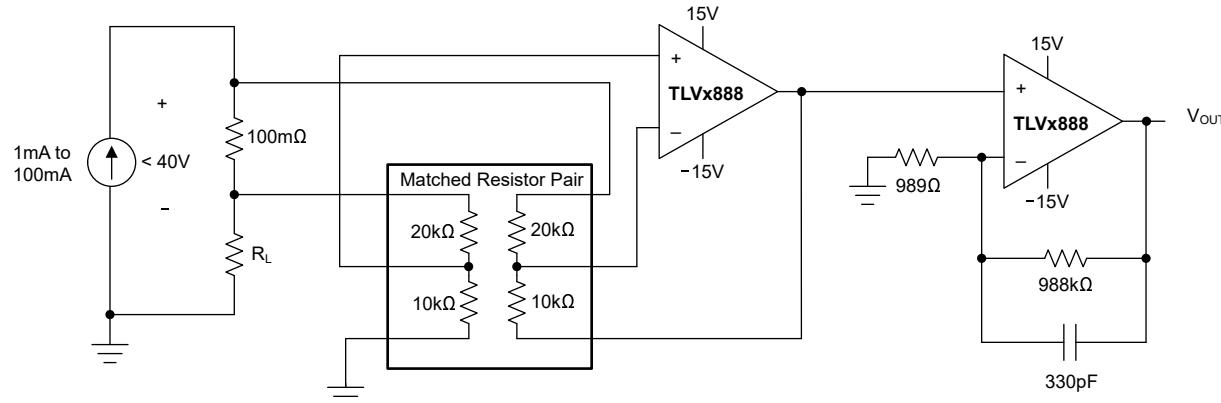

図 7-4. ゲインステージによるハイサイド電流センス

たとえば、ADC のフルスケール入力範囲が 0V ~ 5V に設定されている場合に対応するように出力電圧範囲を調整した、TLVx888 を用いたハイサイド電流監視回路の設計を考えてみます。TLVx888 はレールツーレール出力アンプとして規定されていますが、すべてのアンプと同様に、線形出力動作範囲は電源レールの端まで完全には拡張されません。この線形動作範囲を考慮する必要があります。

この設計例では、TLVx888 は  $\pm 15V$  で駆動されており、0V ~ 5V のスイングは容易に実現可能です。ADC の入力範囲がより広い場合は、それ以上も可能です。

オペアンプの線形出力電圧範囲を評価する最良の指標は、「電気的特性」表に記載された開ループ電圧ゲイン ( $A_{OL}$ ) の仕様値です。 $A_{OL}$  のテスト条件では、各電源レールから 600mV 離れた範囲での線形スイングが指定されています ( $R_L = 10k\Omega$ )。

この例では、公称負荷電流 ( $I_L$ ) として 100mA が使用されています。ただし、ほとんどのアプリケーションでは、100mA よりはるかに小さい電流レベルをモニタする機能が実用的です。

電流センス抵抗  $R_S$  の選択は、最大電流時に許容できる電圧降下量と、許容される電力損失または消費電力に基づいて行います。100mA の検出用途であれば、 $R_S$  に 100mΩ を選ぶと性能と損失のバランスが取れます。この値では、消費電力は 1mW、100mA における電圧降下は 10mV となります。

次に、TLVx888 の差動アンプ回路のゲインを決定します。100mA の最大電流が 100mΩ のセンス抵抗を流れるとき、抵抗両端には 100mV が発生します。差動アンプのゲインは、必要な入力同相電圧によって制限されます。たとえば、ゲインを 1/2 にすると、回路で観測されるハイサイド電圧は 1/3 に減衰されます。この減衰により、入力同相は TLVx888 の範囲 ( $V_+ - 1.7V$ ) に収まります。

TLVx888 の差動アンプ回路の入力に印加される差動電圧は差動アンプによって減衰され、適切なスケーリングにはゲインステージが必要です。便利なことに、TLV2888 の 2 番目のチャネルを使用できます。超低オフセットと広帯域幅により、非常に高いゲイン構成が可能です。この例では、1000V/V のゲインにより、0V ~ 5V の出力に必要なスケーリングが実現されます。

TLVx888 の出力電圧は意図的に 5V に制限されています。ただし、 $\pm 15V$  の電源により、出力電圧ははるかに高くでき、より広いダイナミックレンジを持つ高電圧データコンバータに対応可能です。

TLVx888 の出力は、他の CMOS 出力アンプと同様に、単一電源構成において線形出力パラメータが示す範囲よりも 0V に近づく傾向があります。電圧出力スイング  $V_O$  ('電気的特性'表を参照) は、線形出力範囲を示すものではなく、出力がどこまで電源レールに近づけるかを示す値です。この領域では、アンプ出力が飽和に近づき、アンプは線形に動作

しなくなります。したがって、電流監視アプリケーションでは、電流測定能力は 600mV 出力レベルよりはるかに低い範囲でも継続できます。ただし、直線性誤差が大きくなる点を考慮してください。

最後に、ハイサイド電流監視の性能を最大化するための注意点をいくつか挙げます。

1. 正確なゲイン結果を得るには、すべての抵抗値が重要です。同相の不一致による誤差を最小限に抑えるために、**[R1 と R3] および [R2 と R4]** の抵抗ペアを可能な限り厳密にマッチングします。許容誤差 0.1% 以下を使用してください。多くの場合、リール上で隣接する 2 つの抵抗を選択すると、ランダムに選択した場合よりもマッチングが良好になります。**RES21A** を使用すれば、個別の 0.1% 抵抗を使うよりも、性能の良い洗練された回路設計が可能です。

2. 差動アンプの閉ループゲイン **G** は、ゲイン誤差を抑え、帯域幅を最大化するために適切な値に設定します。**TLVx888** の高帯域は、非常に高いゲイン構成を可能にします。

3. 電流監視は、通常は DC 電源電流の測定に使用されますが、AC 電流も監視できます。この回路の **-3dB** カットオフ周波数には特に注意が必要です。

アンプベースのハイサイド電流監視の詳細については、[『TI アナログエンジニア向け回路クックブック: アンプ』](#)を参照してください。

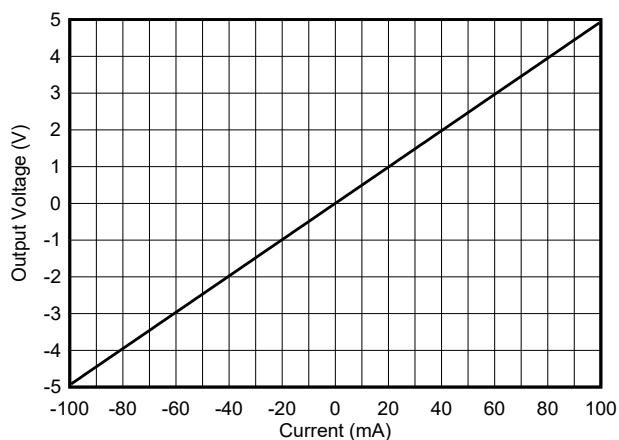

#### 7.2.1.3 アプリケーション曲線

図 7-5. 電流センス測定結果

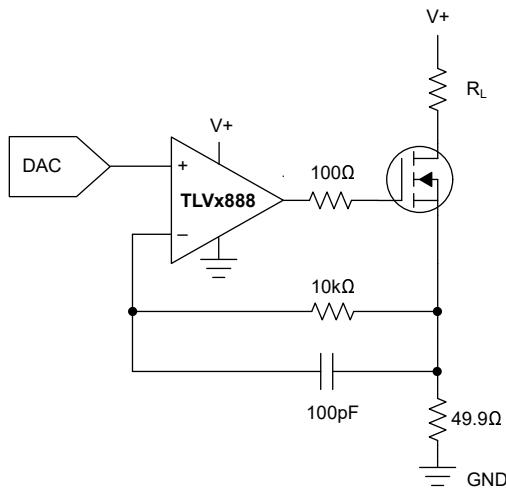

### 7.2.2 プログラマブル電流ソース

図 7-6 は、TLVx888 を使用した高精度電流源の基本構成を示しています。この回路は、フローティング負荷に対して構成可能な電流源を提供します。図 7-6 では、電流レベルを設定するために D/A コンバータ (D/A) を使用しています。たとえば、アンプ入力に 5V のフルスケール電圧を印加すると、100mA の電流源が得られます。

図 7-6. プログラマブル、高精度電流源

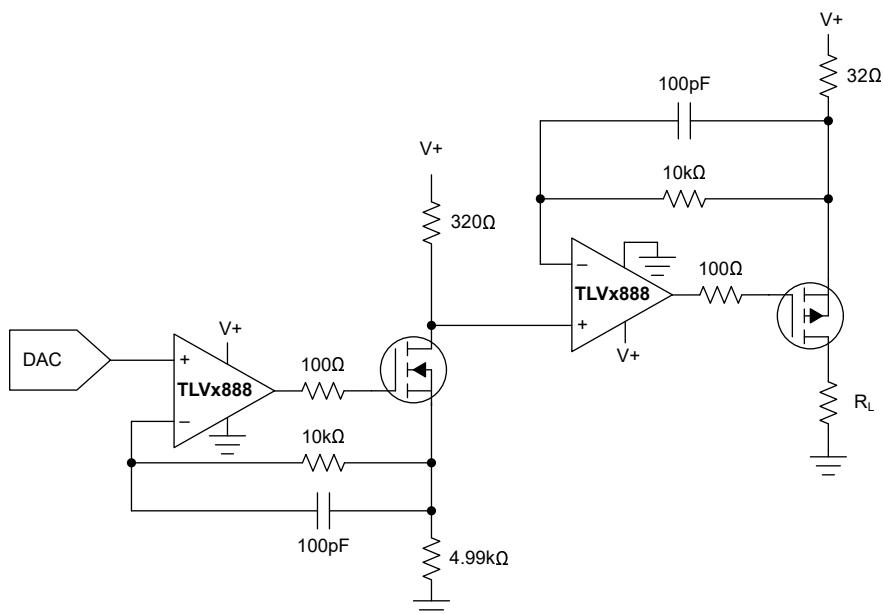

### 7.2.3 接地された負荷用のプログラマブル電流源

図 7-7 は、グランドリファレンス負荷用にプログラマブル電流源として構成された TLVx888 を示しています。単一電源動作を実現するために、2 段構成が採用されています。最初の段はリファレンス電流を設定し、2 番目の段はゲイン付き電流ミラーとして機能します。TLVx888 は両段において、トランジスタから供給される電流を制御するために使用されます。

図 7-7. グランドリファレンス負荷用の単一電源、プログラマブル電流源

## 7.3 電源に関する推奨事項

TLVx888 は、4.5V～36V ( $\pm 2.25V \sim \pm 18V$ ) で動作することが規定されています。TLVx888 は、シングル電源とデュアル電源の両方で動作します。TLVx888 は対称電源を必要とせず、オペアンプは動作に最低 4.5V の電圧のみを必要とします。

### 注意

40V を超える電源電圧を印加すると、デバイスに永続的な損傷を与える可能性があります。「絶対最大定格」表を参照してください。

電源ピンの近くに  $0.1\mu F$  のバイパスコンデンサを配置すると、ノイズの多い電源や高インピーダンスの電源からの誤差を低減できます。バイパスコンデンサの配置の詳細については、[セクション 7.4](#) を参照してください。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

デバイスで最高の動作性能を実現するには、適切な PCB レイアウト手法を使用してください。

- オフセット電圧を最小限に抑えるため、異なる導体の接続部に形成される熱電対接合部で熱電効果 (ゼーベック効果) が発生するような温度勾配を避けます。また、

- 熱電係数の低い条件を使用します (異なる金属は避けてください)。

- 電源や他の熱源から部品を熱的に絶縁します。

- オペアンプおよび入力回路を、冷却ファンなどの空気流から遮蔽します。

- ノイズは、オペアンプの電源ピンや回路全体を通じてアナログ回路に伝播する可能性があります。バイパスコンデンサは、アナログ回路に対して局所的に Low インピーダンスの電源を供給することにより、結合ノイズを低減します。

- 各電源ピンとグランドの間に Low ESR  $0.1\mu F$  のセラミックバイパスコンデンサを接続し、可能な限りデバイスの近くに配置します。単一電源アプリケーションの場合は、V+ からグランドに対して 1 つのバイパスコンデンサを接続します。

- 回路のアナログ部分とデジタル部分のグランドを分離することは、ノイズを抑制する最も簡単かつ効果的な方法の 1 つです。通常、多層 PCB のうち 1 つ以上の層はグランドプレーン専用です。グランドプレーンは熱の分散に役立つとともに、EMI ノイズを拾う可能性を低減します。グランド電流の流れに注意して、デジタルグランドとアナロググランドを物理的に分離します。詳細については、[PCB はオペアンプ設計のコンポーネント](#) / [Analog Design Journal](#) を参照してください。

- 寄生カップリングを低減するには、入力配線を電源配線または出力配線からできるだけ離して配置します。これらのトレースを離して配置できない場合、感度の高いトレースをノイズの多いトレースと平行にするのではなく、垂直に交差させます。

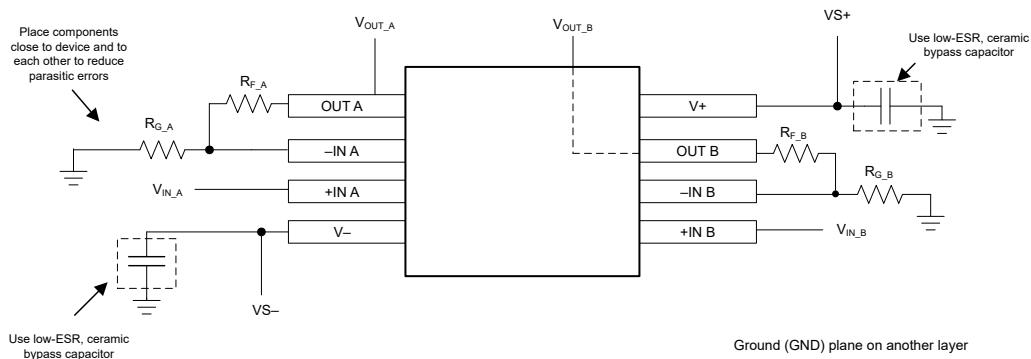

- デカップリングコンデンサをデバイスのできるだけ近くに配置します。図 7-9 が示すように、帰還抵抗 (R3) とゲイン抵抗 (R4) は反転入力の近くに配置して、寄生容量を最小限に抑えます。

- 入力トレースは、できる限り短くします。反転入力へのトレースを短くすると、反転入力の寄生容量を最小限に抑えることができます。入力トレースは、回路の中でも最も影響を受けやすい部分であることに常に注意してください。

- 最高の性能を得るために、基板組立後には PCB を清掃します。

- 高精度の集積回路では、プラスチックパッケージへの水分の侵入により性能が変化する場合があります。PCB を水で洗浄した後で、PCB アセンブリをベーキングして、洗浄中にデバイスのパッケージに取り込まれた水分を除去します。ほとんどの状況では、クリーニング後に  $85^{\circ}\text{C}$  で 30 分間の低温ベーキングを行えば十分です。

#### 7.4.2 レイアウト例

図 7-8. 回路図

図 7-9. 非反転型アンプ構成のオペアンプ基板のレイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 開発サポート

##### 8.1.1.1 PSpice® for TI

PSpice® for TI は、アナログ回路の性能評価に役立つ設計およびシミュレーション環境です。レイアウトと製造に移る前に、サブシステムの設計とプロトタイプの設計を作成することで、開発コストを削減し、市場投入までの期間を短縮できます。

##### 8.1.1.2 TINA-TI™ シミュレーション ソフトウェア (無償ダウンロード)

TINA-TI™ シミュレーション ソフトウェアは、SPICE エンジンをベースにした単純かつ強力な、使いやすい回路シミュレーション プログラムです。TINA-TI シミュレーション ソフトウェアは、TINA™ ソフトウェアのすべての機能を持つ無償バージョンで、パッシブ モデルとアクティブ モデルに加えて、マクロモデルのライブラリがプリロードされています。TINA-TI シミュレーション ソフトウェアには、SPICE の標準的な DC 解析、過渡解析、周波数ドメイン解析などの全機能に加え、追加の設計機能が搭載されています。

TINA-TI シミュレーション ソフトウェアは [設計およびシミュレーション ツール](#) Web ページから [無料でダウンロード](#) でき、ユーザーが結果をさまざまな形式で処理できる、広範な後処理機能を備えています。仮想計測器により、入力波形を選択し、回路ノード、電圧、および波形をプローブして、動的なクイック スタートツールを作成できます。

#### 注

これらのファイルを使用するには、TINA ソフトウェアまたは TINA-TI ソフトウェアがインストールされている必要があります。TINA-TI™ ソフトウェア フォルダから、無償の TINA-TI シミュレーション ソフトウェアをダウンロードしてください。

### 8.2 ドキュメントのサポート

#### 8.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『ゼロドリフト アンプ: 特長と利点』アプリケーション ブリーフ

- テキサス・インスツルメンツ、『PCB はオペアンプ設計のコンポーネント』アプリケーション ノート

- テキサス・インスツルメンツ、『オペアンプのゲイン安定性、第3部: AC ゲイン誤差の分析』

- テキサス・インスツルメンツ、『オペアンプのゲイン安定性、第2部: DC ゲイン誤差の分析』

- テキサス・インスツルメンツ、『完全差動アクティブ フィルタにおける無限ゲイン、MFB フィルタトポロジの使用』アプリケーション ノート

- テキサス・インスツルメンツ、『オペアンプの性能分析』

- テキサス・インスツルメンツ、『オペアンプの単一電源動作』アプリケーション ノート

- テキサス・インスツルメンツ、『鉛フリー仕上げ部品の保管寿命評価』アプリケーション ノート

- テキサス・インスツルメンツ、『フィードバック プロットによるオペアンプ AC 性能の定義』アプリケーション ノート

- テキサス・インスツルメンツ、『オペアンプの EMI 除去率』アプリケーション ノート

- テキサス・インスツルメンツ、『測温抵抗体のアナログ線形化』アプリケーション ノート

- テキサス・インスツルメンツ、『TI 高精度設計 TIPD102 ハイサイド電圧-電流 (V-I) コンバータ』

### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

## 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

## 8.5 商標

TINA-TI™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

TINA™ is a trademark of DesignSoft, Inc.

PSpice® is a registered trademark of Cadence Design Systems, Inc.

すべての商標は、それぞれの所有者に帰属します。

## 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (September 2025) to Revision B (December 2025)                                | Page |

|-------------------------------------------------------------------------------------------------------|------|

| • TLV888 の DBV (SOT-23, 5)、および TLV4888 D (SOIC, 14) および PW (TSSOP, 14) をプレビューから量産データ (アクティブ) に変更..... | 1    |

| • 「ESD 定格」で人体モデル (HBM) を $\pm 1000V$ から $\pm 4000V$ に変更.....                                          | 5    |

| Changes from Revision * (December 2024) to Revision A (September 2025)      | Page |

|-----------------------------------------------------------------------------|------|

| • TLV888D (SOIC) と TLV2888 DGK (VSSOP) のパッケージをプレビューから量産データ (アクティブ) に変更..... | 1    |

| • 「概要」のアプリケーション回路を更新 .....                                                  | 1    |

| • 「概要」のオフセット電圧ドリフトの値を更新して誤字を修正.....                                         | 1    |

| • TLV2888 (D, SOIC-8) の「熱に関する情報」を更新.....                                    | 6    |

| • $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ の同相信号除去比に注 1 を追加.....    | 7    |

| • $R_{\text{LOAD}} = 2\text{k}\Omega$ のテスト条件の開ループ電圧ゲインを更新.....              | 7    |

| • $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ の開ループ電圧ゲインに注 1 を追加..... | 7    |

| • 無負荷時の電圧出力スイング (レールから) に注 1 を追加.....                                       | 7    |

| • 無負荷時の電圧出力スイング (レールから) を更新.....                                            | 7    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TLV2888DGKR           | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 3VBS                |

| TLV2888DR             | Active        | Production           | SOIC (D)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TL2888              |

| TLV2888DR.A           | Active        | Production           | SOIC (D)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TL2888              |

| TLV4888DR             | Active        | Production           | SOIC (D)   14   | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TLV4888             |

| TLV4888PWR            | Active        | Production           | TSSOP (PW)   14 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TLV4888             |

| TLV888DR              | Active        | Production           | SOIC (D)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TL888               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

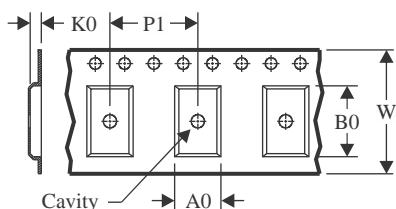

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

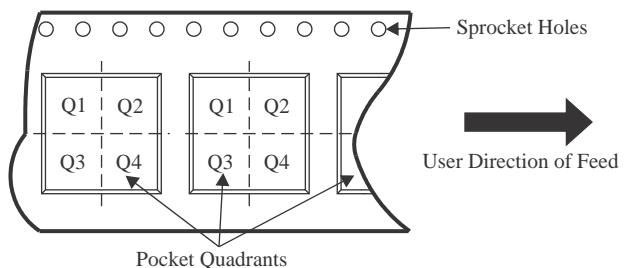

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TLV2888DGKR | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| TLV4888PWR  | TSSOP        | PW              | 14   | 3000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV2888DGKR | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| TLV4888PWR  | TSSOP        | PW              | 14   | 3000 | 353.0       | 353.0      | 32.0        |

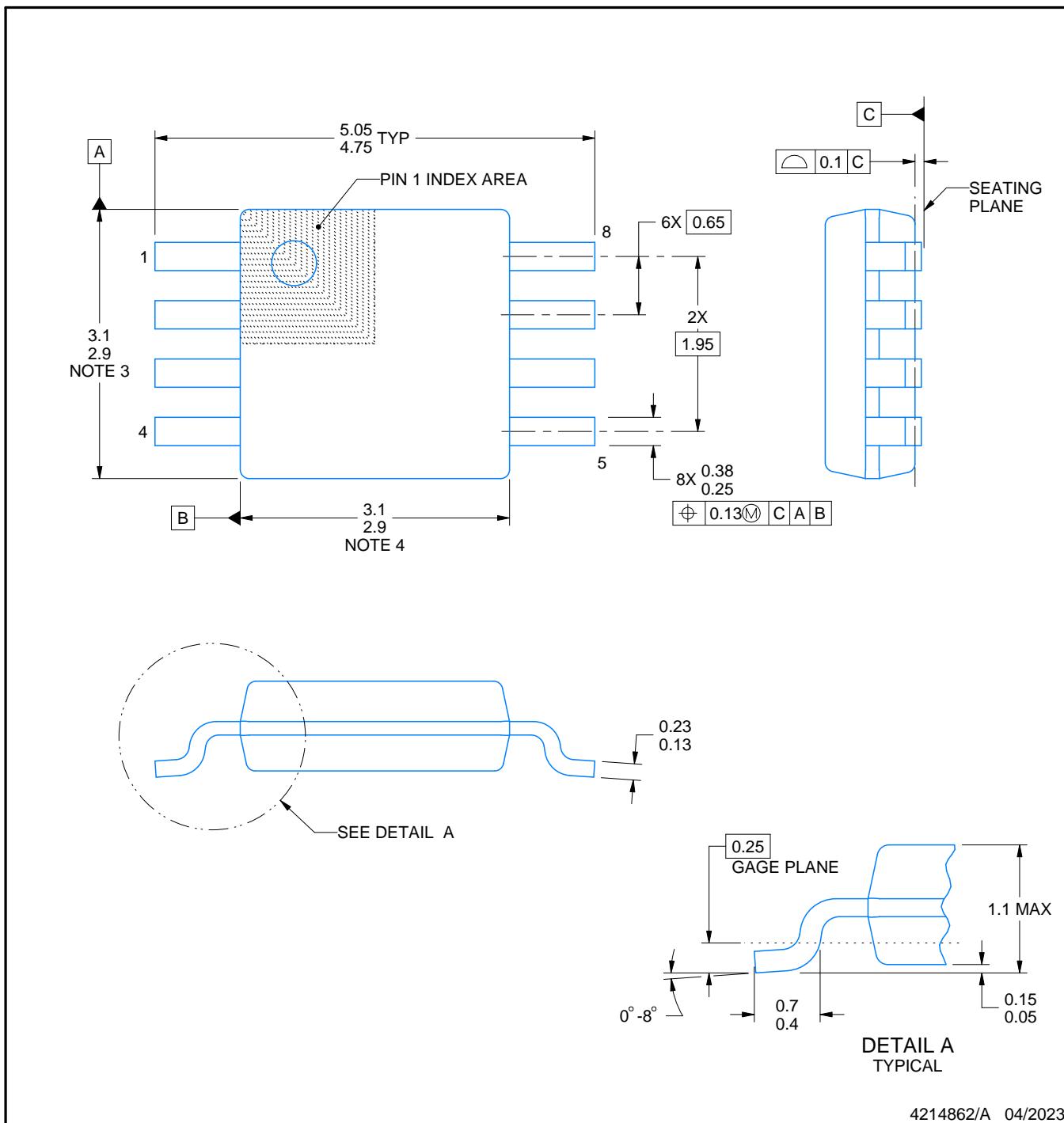

# PACKAGE OUTLINE

DGK0008A

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-187.

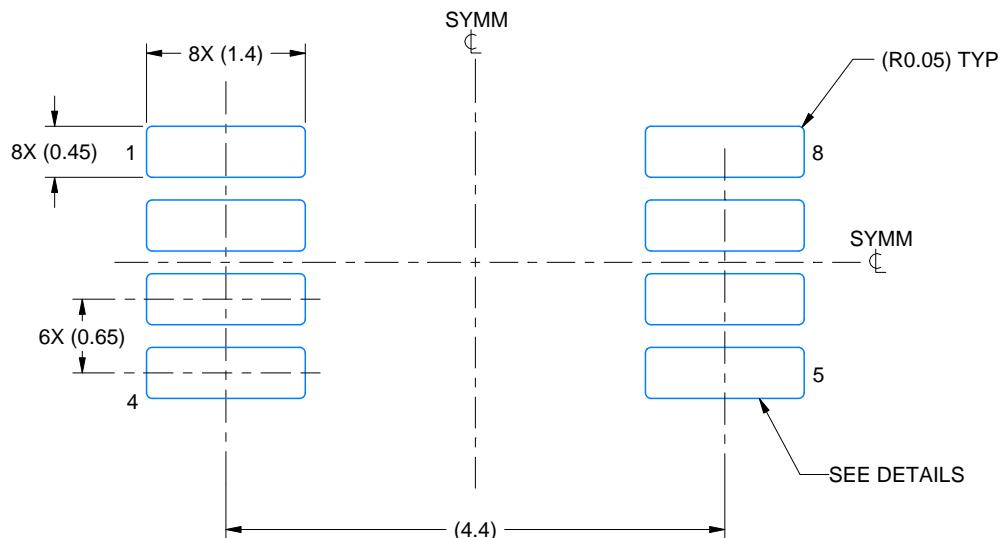

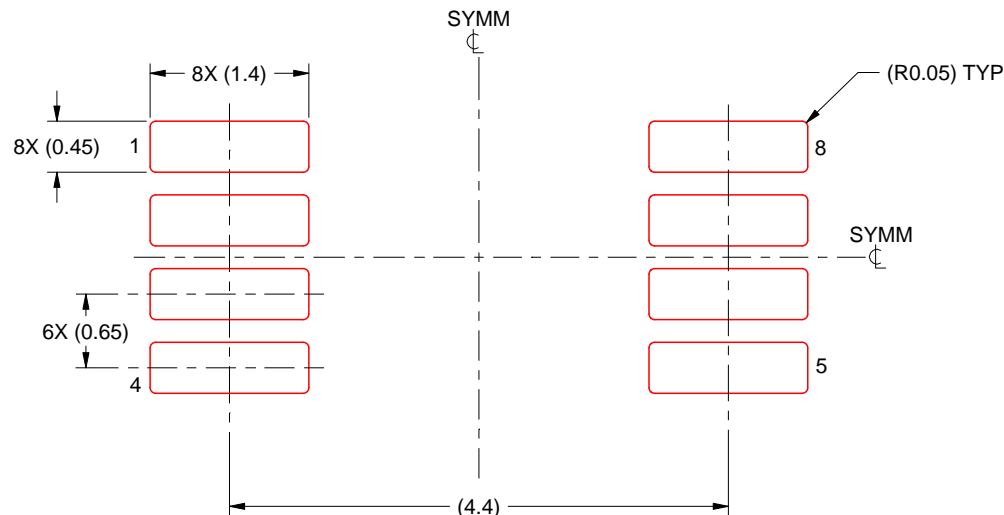

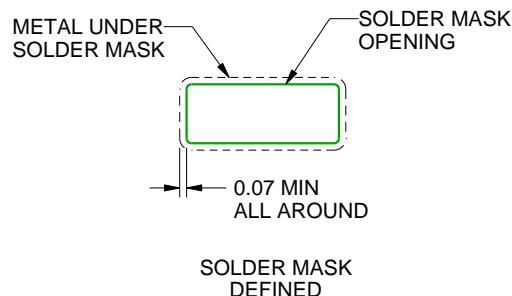

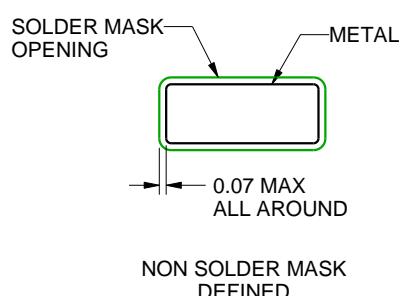

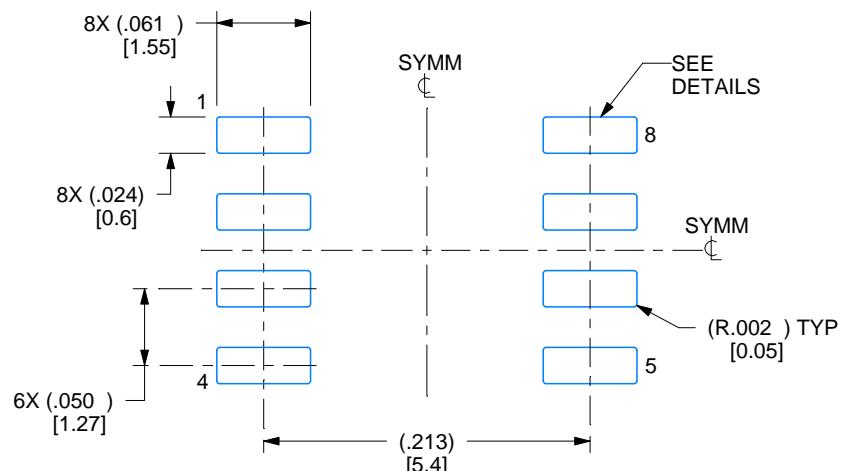

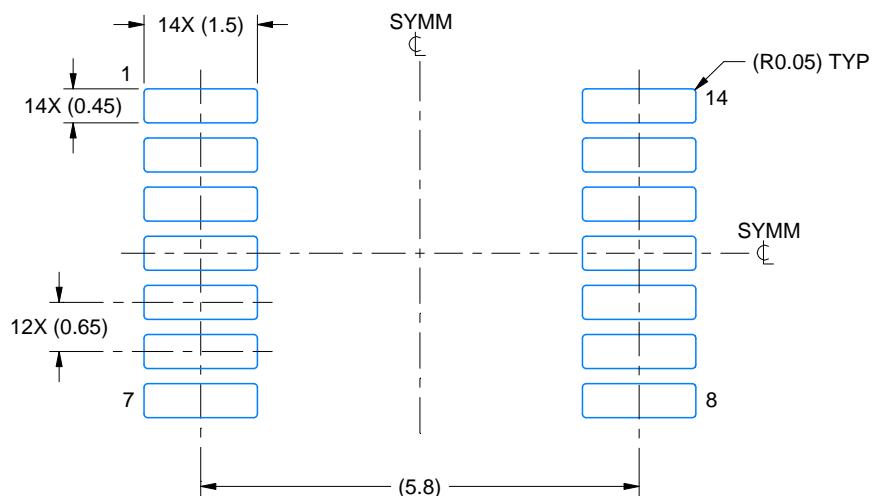

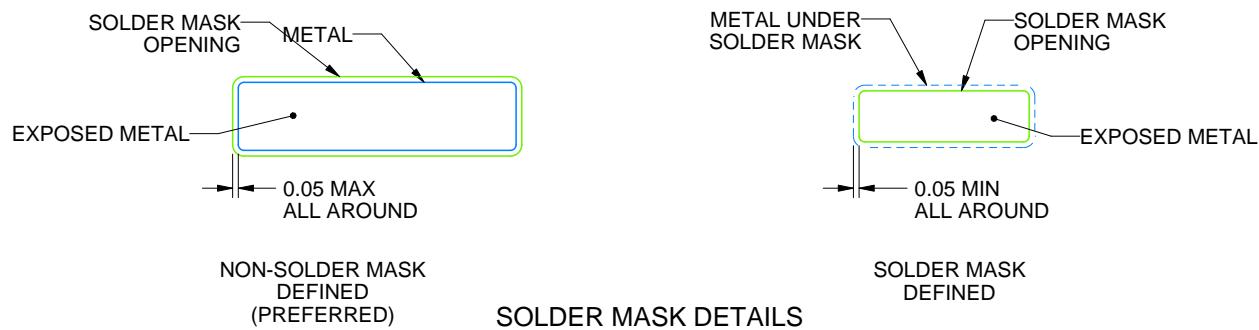

# EXAMPLE BOARD LAYOUT

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 15X

SOLDER MASK DETAILS

4214862/A 04/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

9. Size of metal pad may vary due to creepage requirement.

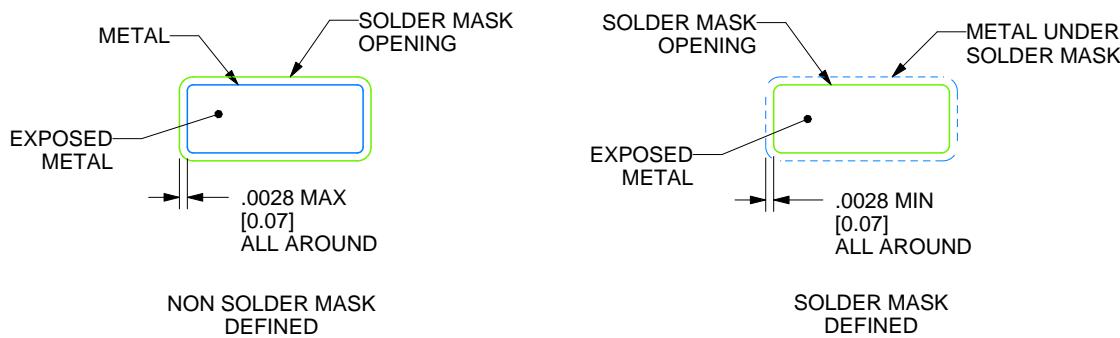

# EXAMPLE STENCIL DESIGN

DGK0008A

<sup>TM</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

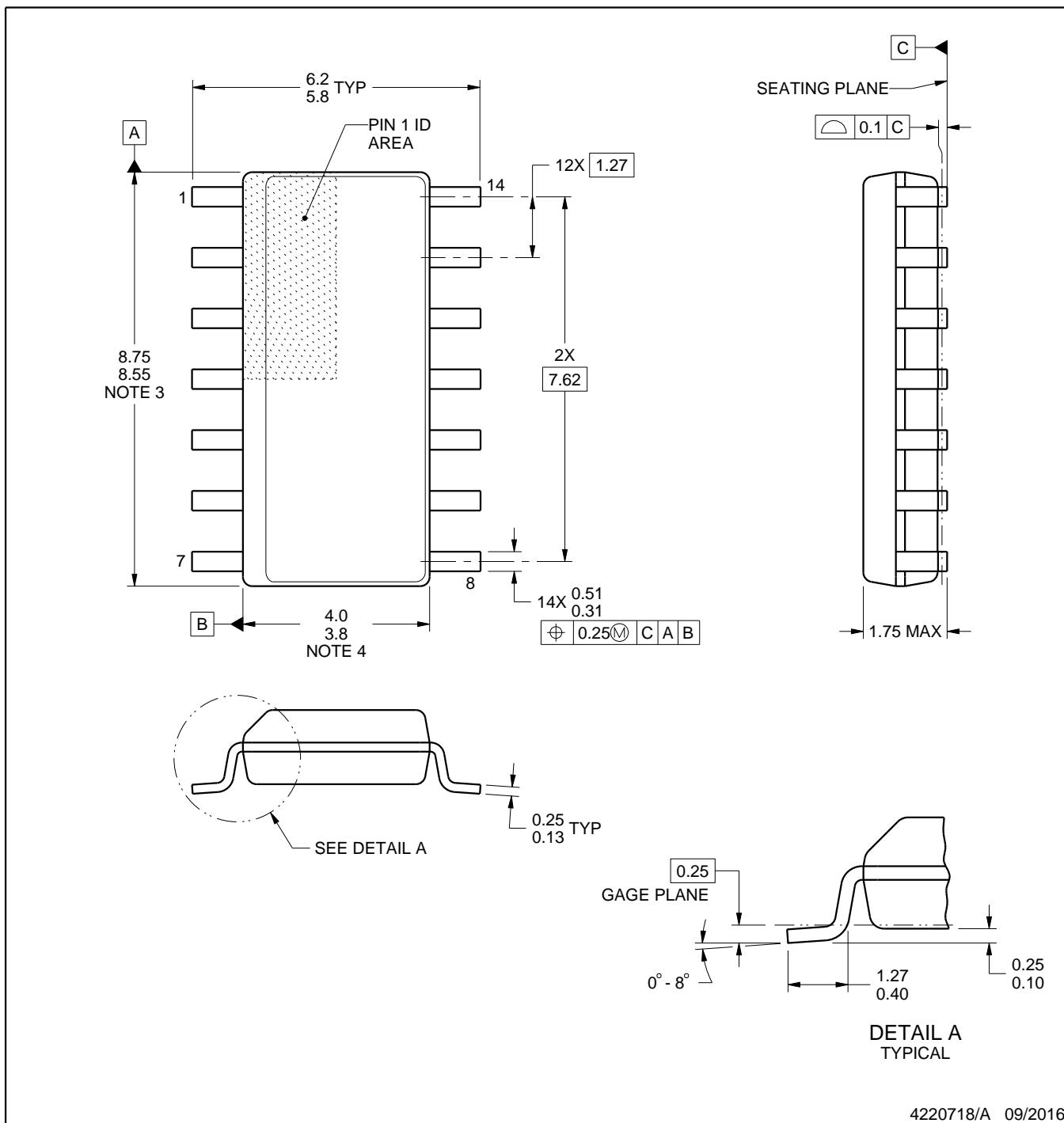

# PACKAGE OUTLINE

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4220718/A 09/2016

NOTES:

1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

5. Reference JEDEC registration MS-012, variation AB.

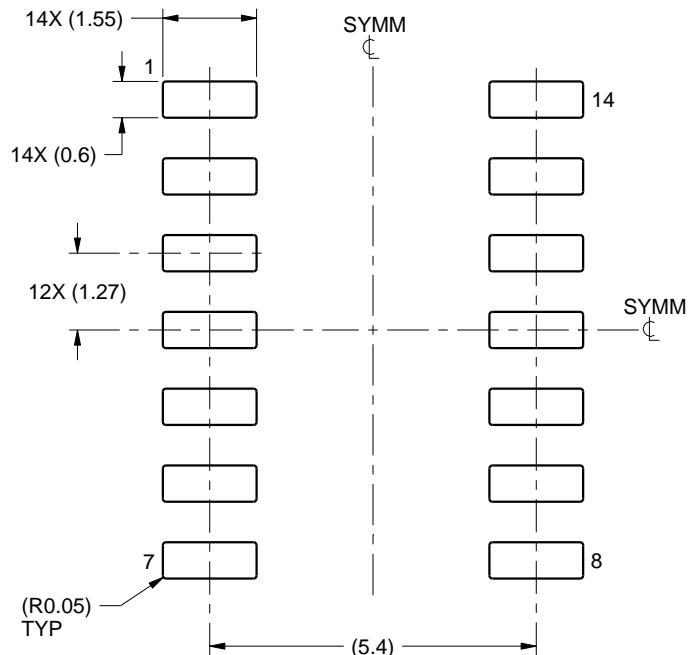

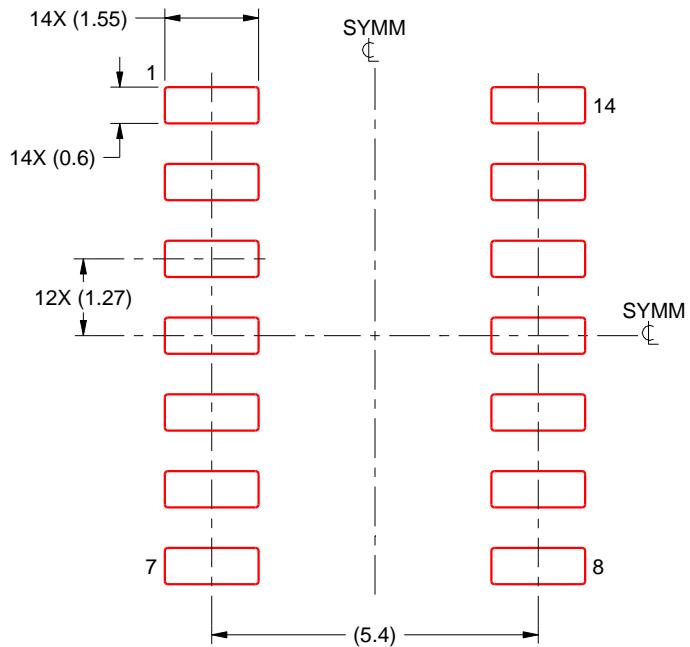

# EXAMPLE BOARD LAYOUT

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

SCALE:8X

SOLDER MASK DETAILS

4220718/A 09/2016

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:8X

4220718/A 09/2016

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

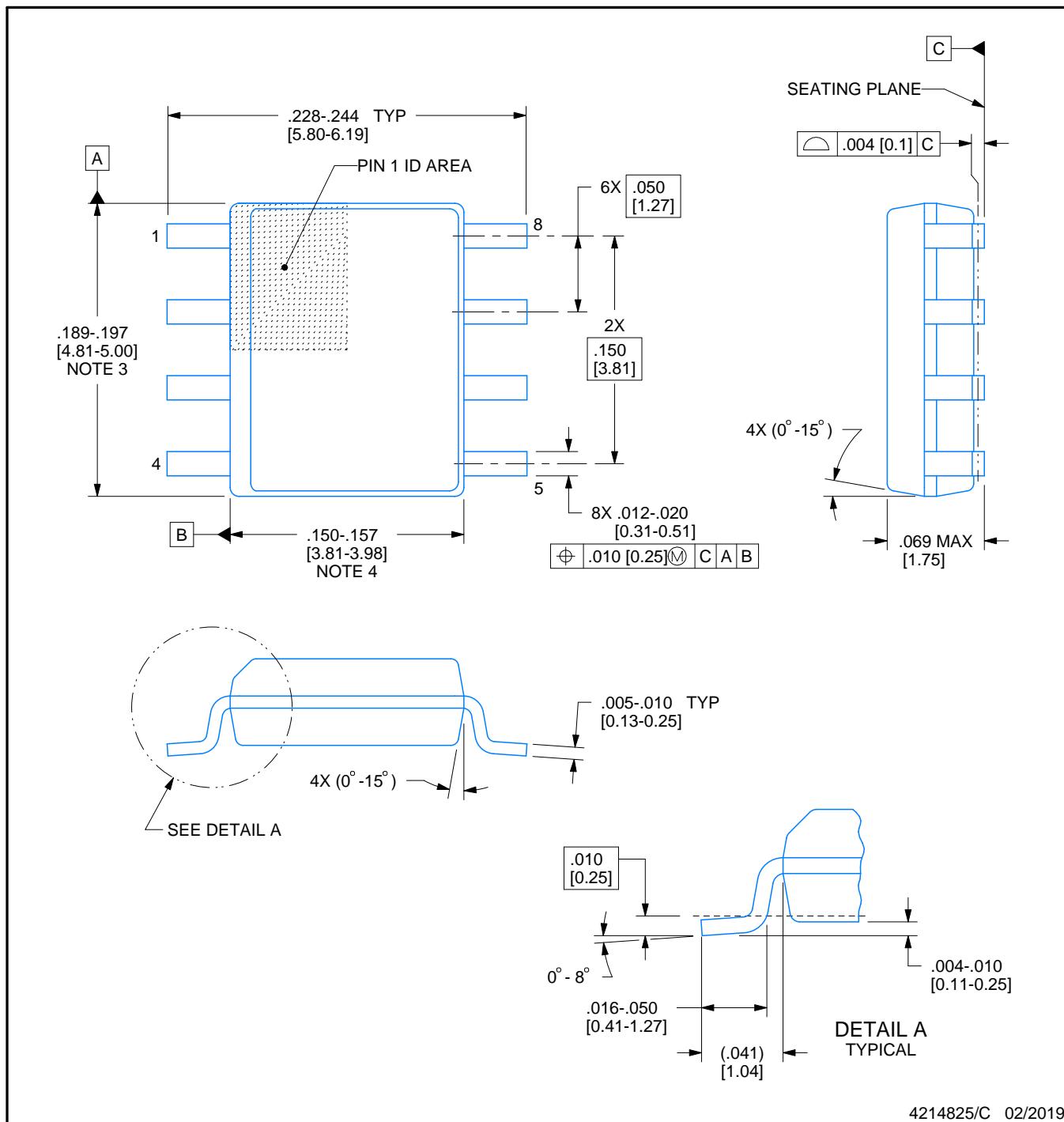

## PACKAGE OUTLINE

**D0008A**

## SOIC - 1.75 mm max height

## SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

## NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

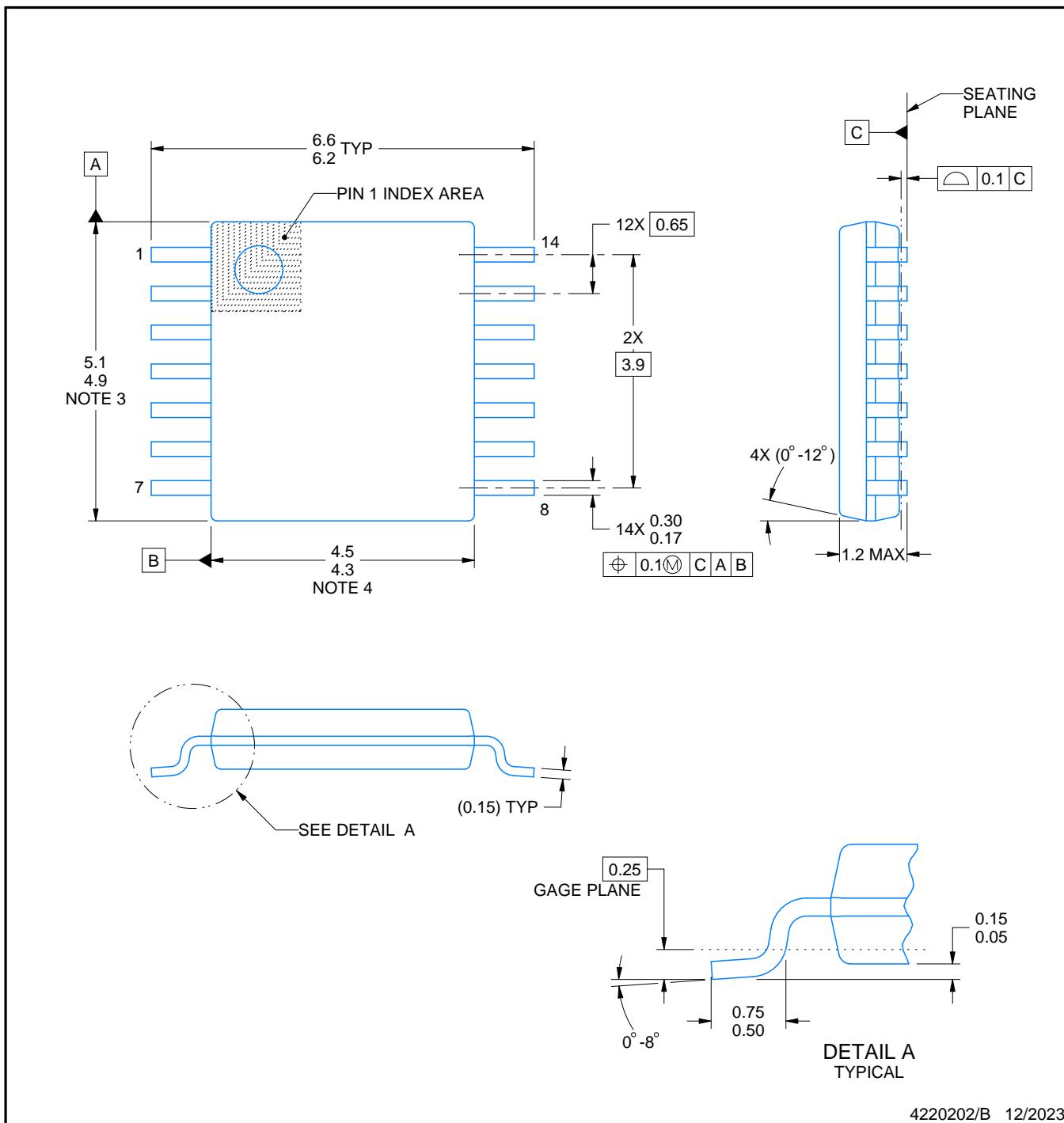

## PACKAGE OUTLINE

**PW0014A**

## **TSSOP - 1.2 mm max height**

## SMALL OUTLINE PACKAGE

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-153.

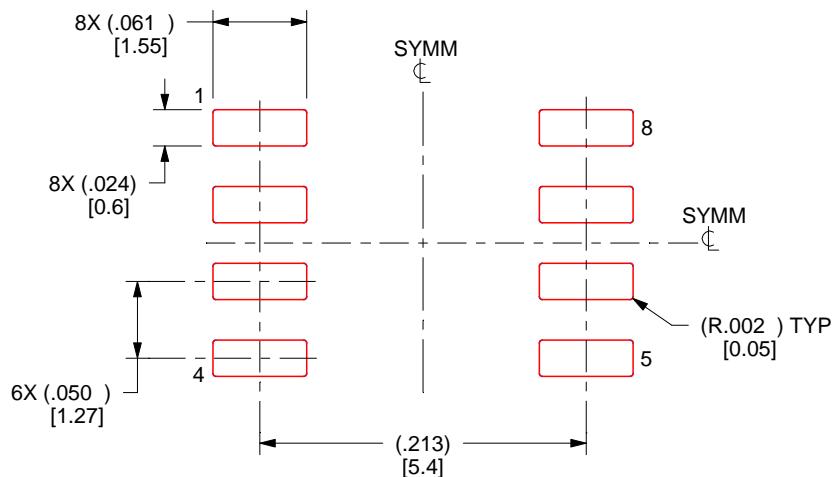

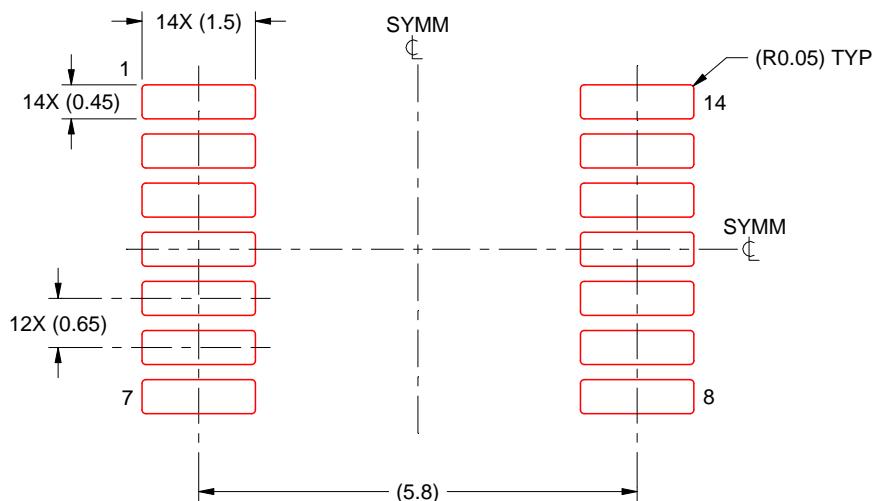

# EXAMPLE BOARD LAYOUT

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月