TLV9041, TLV9042, TLV9044

# JAJSIO2G - MARCH 2020 - REVISED MARCH 2022

# TLV904x 1.2V 超低電圧、10µA マイクロパワー RRIO アンプ 電力の制約が厳しいアプリケーション向け

## 1 特長

- コスト最適化アプリケーション向け低消費電力 CMOS

- 最低 1.2V の電源電圧で動作

- 低い入力バイアス電流:標準値 1pA、最大値 12pA

- 低い静止電流:10µA/Ch

- 0.1Hz~10Hz で 6.5µV<sub>p-p</sub> の低い積分ノイズ

- レール・ツー・レール入出力

- 高い GB 積:350kHz

- 熱ノイズ・フロア:64nV/√Hz

- 低い入力オフセット電圧:±0.6mV

- ユニティ・ゲイン安定

- 100pF の負荷容量を確実に駆動

- 内部 RFI および EMI フィルタ付きの入力ピン

- 広い動作温度範囲:-40℃~125℃

## 2 アプリケーション

- ポータブル・エレクトロニクス

- ウェアラブル・フィットネスおよびアクティビティ・モニタ

- ヘッドセット、ヘッドホン、小型イヤホン

- パーソナル・エレクトロニクス

- ビル・オートメーション

- ウェアラブル (医療以外)

- モーション検出器 (PIR、uWave など)

- 電子 POS (ePOS)

- 単一電源、ローサイド、単方向電流センシング回路

#### 3 概要

低消費電力 TLV904x ファミリには、レール・ツー・レール の入出力スイングが可能な、シングル (TLV9041)、デュア ル (TLV9042)、クワッド (TLV9044) チャネルの超低電圧 (1.2V~5.5V) オペアンプがあります。TLV904x は、低い 静止電流 (10µA、標準値) と最小 1.2V の電源電圧で動 作可能であることから、1.5V のコイン型電池アプリケーショ ンに対応できる、業界でも数少ないアンプの 1 つです。シ ャットダウン・モード (TLV9041S、TLV9042S、 TLV9044S)を使えば、消費電力をさらに削減できます。こ のモードでは、アンプをオフにして標準消費電流 150nA 未満のスタンバイ・モードに移行できます。これらのデバイ スは、バッテリ駆動の IoT デバイス、ウェアラブル電子機 器、低電圧での動作が重要なパーソナル電子機器など、 電力とスペースの制約が厳しいアプリケーション向けに、コ スト効率の優れたアンプ・ソリューションを提供します。

TLV904x ファミリは堅牢に設計されているため、回路設計 を簡素化できます。これらのオペアンプには、RFI および EMI 除去フィルタ、ユニティ・ゲイン安定、入力オーバード ライブ状態で位相反転がない、という特長があります。ま た、350kHz のゲイン帯域幅と 100pF の高い容量性負荷 駆動という優れた AC 性能を備えており、性能向上および 消費電力低減を可能にします。

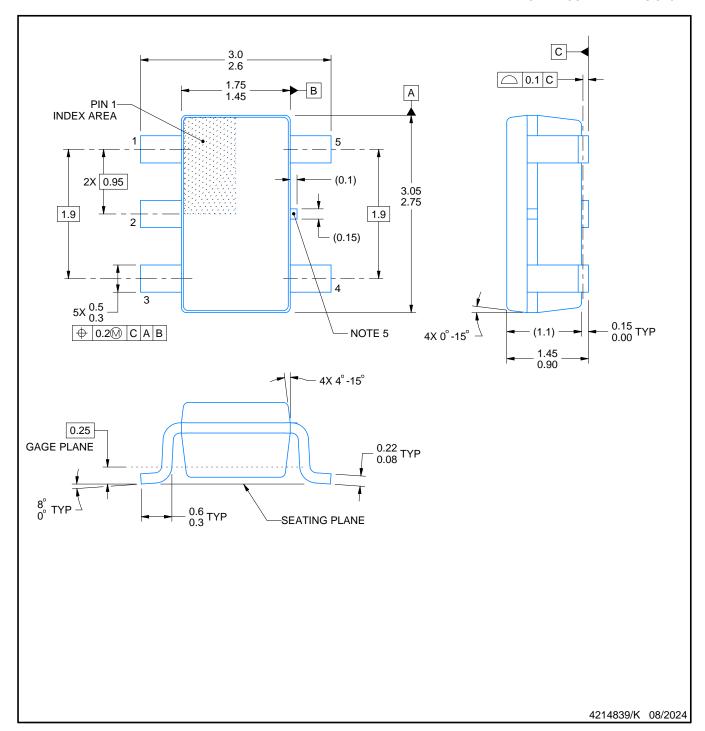

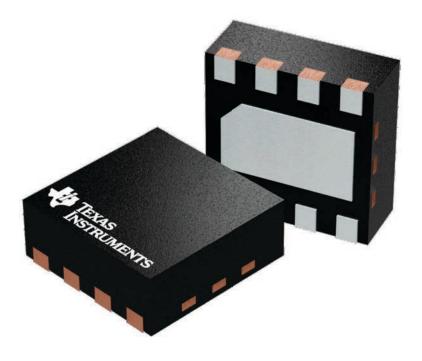

すべてのチャネル・バリアント (シングル、デュアル、クワッ ド) が、X2QFN や WSON など省スペースのマイクロサイ ズ・パッケージと、SOIC、VSSOP、TSSOP、SOT-23 など の業界標準パッケージで供給されます。

#### 製品情報

| 部品番号 <sup>(1) (2)</sup> | パッケージ       | 本体サイズ (公称)      |  |  |  |

|-------------------------|-------------|-----------------|--|--|--|

|                         | SOT-23 (5)  | 1.60mm × 2.90mm |  |  |  |

| TLV9041                 | SC70 (5)    | 1.25mm × 2.00mm |  |  |  |

|                         | X2SON (5)   | 0.80mm × 0.80mm |  |  |  |

| TLV9041S                | SOT-23 (6)  | 1.60mm × 2.90mm |  |  |  |

|                         | SOIC (8)    | 3.91mm × 4.90mm |  |  |  |

|                         | SOT-23 (8)  | 1.60mm × 2.90mm |  |  |  |

| TLV9042                 | WSON (8)    | 2.00mm × 2.00mm |  |  |  |

|                         | VSSOP (8)   | 3.00mm × 3.00mm |  |  |  |

|                         | TSSOP (8)   | 3.00mm × 4.40mm |  |  |  |

| TLV9042S                | X2QFN (10)  | 1.50mm × 2.00mm |  |  |  |

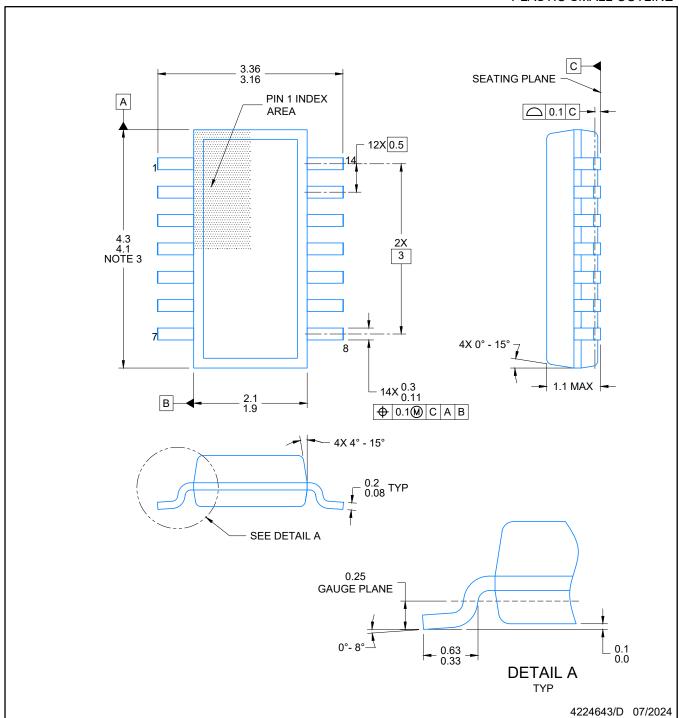

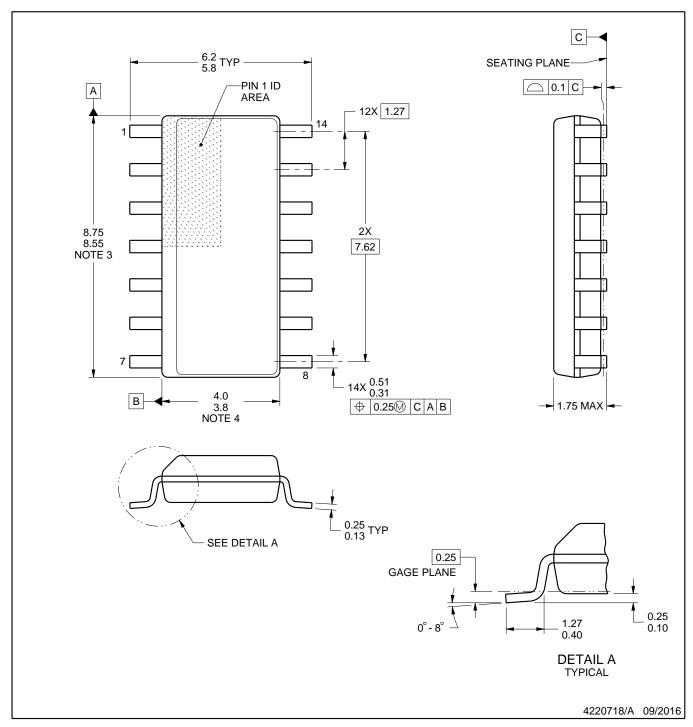

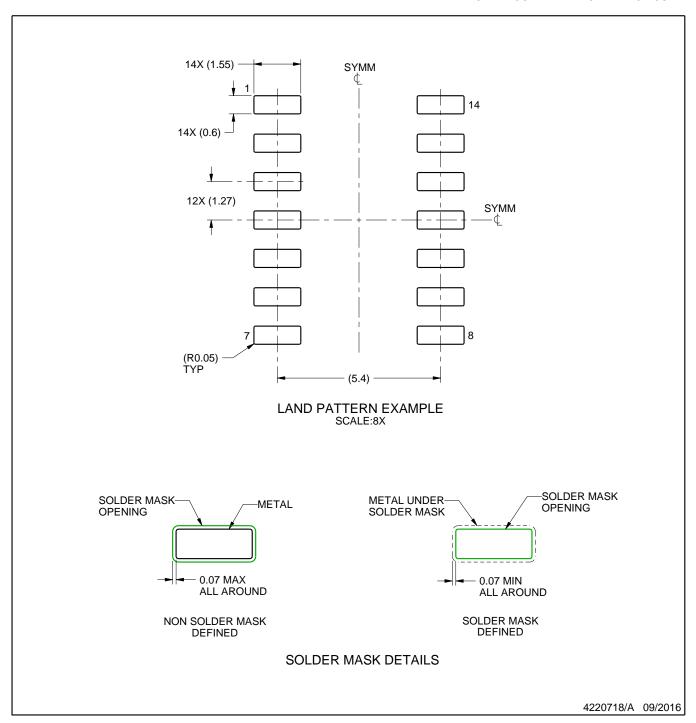

|                         | SOIC (14)   | 8.65mm × 3.91mm |  |  |  |

| TLV9044                 | TSSOP (14)  | 4.40mm × 5.00mm |  |  |  |

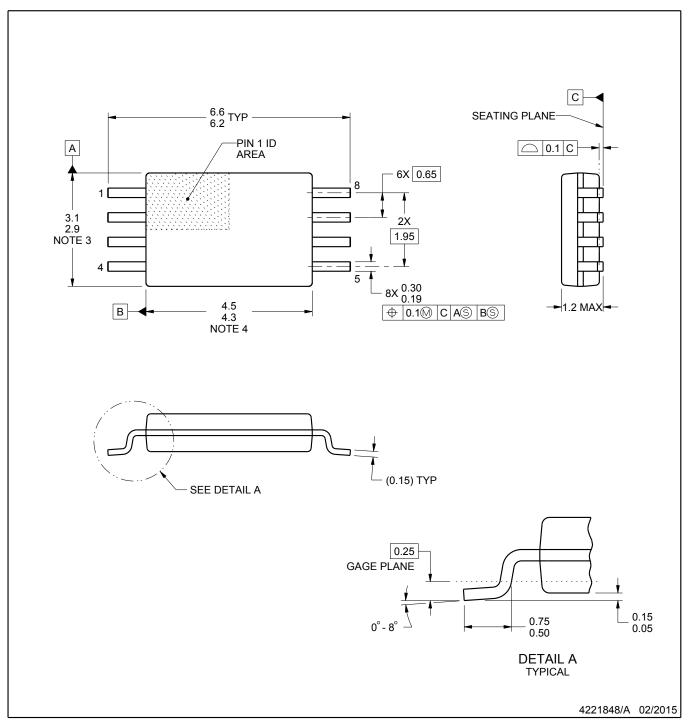

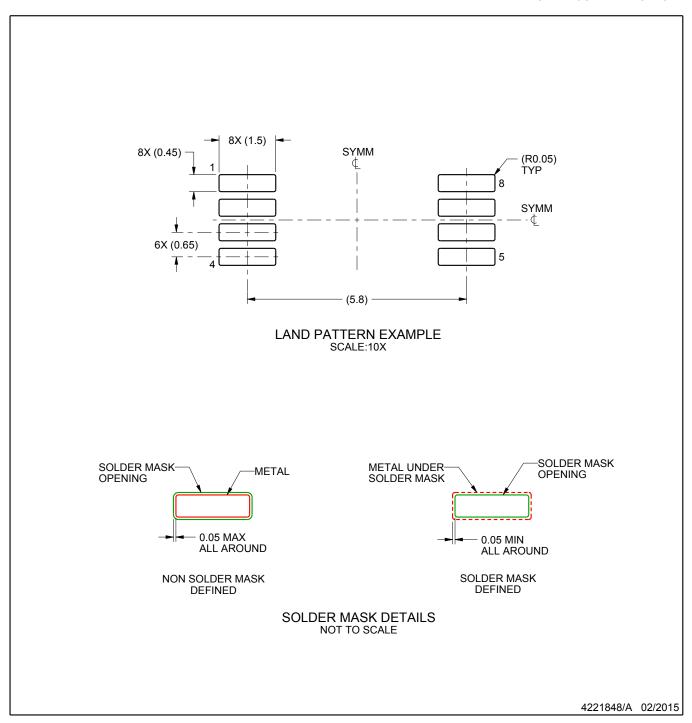

|                         | SOT-23 (14) | 4.20mm × 1.90mm |  |  |  |

- 利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

- 他のシングル・チャネルおよびデュアル・チャネルのパッケージ版 も近日リリース予定です。

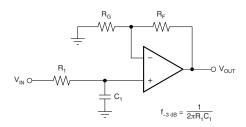

$\frac{V_{OUT}}{V_{IN}} = \left(1 + \frac{R_F}{R_G}\right) \left(\frac{1}{1 + sR_1C_1}\right)$

単極ローパス・フィルタ

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 ▼ www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SBOS836

## **Table of Contents**

| 1 特長                                                         | 1 8.3 Feature Description                                         | 20                      |

|--------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|

| 2 アプリケーション                                                   | 1 8.4 Device Functional Modes                                     |                         |

| 3 概要                                                         |                                                                   | ation25                 |

| 4 Revision History                                           | 2 9.1 Application Information                                     |                         |

| 5 Device Comparison Table                                    | 3 9.2 Typical Application                                         |                         |

| 6 Pin Configuration and Functions                            | 3 10 Power Supply Recommen                                        |                         |

| 7 Specifications                                             | <sub>7</sub> 11 Layout                                            |                         |

| 7.1 Absolute Maximum Ratings                                 | 7 11.1 Layout Guidelines                                          | 29                      |

| 7.2 ESD Ratings                                              | 7 11.2 Layout Example                                             | 29                      |

| 7.3 Recommended Operating Conditions                         |                                                                   | າ Support31             |

| 7.4 Thermal Information for Single Channel                   | <sub>7</sub> 12.1 Documentation Support                           | 31                      |

| 7.5 Thermal Information for Dual Channel                     | 8 12.2 Receiving Notification o                                   | Documentation Updates31 |

| 7.6 Thermal Information for Quad Channel                     |                                                                   | 31                      |

| 7.7 Electrical Characteristics                               |                                                                   | Caution31               |

| 7.8 Typical Characteristics                                  |                                                                   | 31                      |

| 8 Detailed Description                                       |                                                                   |                         |

| 8.1 Overview                                                 |                                                                   |                         |

| 8.2 Functional Block Diagram                                 |                                                                   |                         |

| 資料番号末尾の英字は改訂を表しています。その                                       |                                                                   | _                       |

| Changes from Revision F (February 2022) t                    |                                                                   | Page                    |

| <ul><li>「製品情報」セクションの X2SON (5) RTM を見</li></ul>              | 更新                                                                |                         |

| <ul> <li>Updated Device Comparison section for TL</li> </ul> | V9041IDPWR RTM                                                    | 3                       |

| <ul> <li>Added Thermal Information for TLV9041 DI</li> </ul> | PW nackage to the Thermal Information                             | for Single Channel      |

| section                                                      |                                                                   |                         |

| 3601011                                                      |                                                                   |                         |

| Changes from Revision E (August 2021) to                     | Revision F (February 2022)                                        | Page                    |

| <ul> <li>Updated Device Comparison section for TL</li> </ul> | V9044IDYYR RTM                                                    | 3                       |

| <ul> <li>Added Thermal Information for TLV9044 D</li> </ul>  |                                                                   |                         |

|                                                              |                                                                   |                         |

| Changes from Povision D (August 2024) to                     |                                                                   |                         |

| CHARLES HUILINEVISION D (MUUUSL 2021) LU                     | Pavision F (August 2021)                                          | Dano                    |

| <ul> <li>Added Thermal Information for TLV9042 Do</li> </ul> | Revision E (August 2021)  GK package to the Thermal Information : | Page                    |

## **5 Device Comparison Table**

|                 | NO. OF      | PACKAGE LEADS |               |               |                 |                               |             |              |                            |             |                             |              |              |    |

|-----------------|-------------|---------------|---------------|---------------|-----------------|-------------------------------|-------------|--------------|----------------------------|-------------|-----------------------------|--------------|--------------|----|

| DEVICE CHANNELS | SC70<br>DCK | SOIC<br>D     | SOT-23<br>DBV | SOT-23<br>DYY | SOT-23-8<br>DDF | SOT-553<br>DRL <sup>(1)</sup> | TSSOP<br>PW | VSSOP<br>DGK | WQFN<br>RTE <sup>(1)</sup> | WSON<br>DSG | X2QFN<br>RUC <sup>(1)</sup> | X2SON<br>DPW | X2QFN<br>RUG |    |

| TLV9041         | 1           | 5             | _             | 5             | _               | _                             | 5           | _            | _                          | _           | _                           | _            | 5            | _  |

| TLV9041S        | 1           | _             | _             | 6             | _               | _                             | _           | _            | _                          | _           | _                           | _            | _            | _  |

| TLV9042         | 2           | _             | 8             | _             | _               | 8                             | _           | 8            | 8                          | _           | 8                           | _            | _            | _  |

| TLV9042S        | 2           | _             | _             | _             | _               | _                             | _           | _            | _                          | _           | _                           | _            | _            | 10 |

| TLV9044         | 4           | _             | 14            | _             | 14              | _                             | _           | 14           | _                          | 16          | _                           | 14           | _            | _  |

(1) Package is preview only.

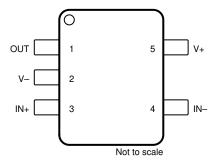

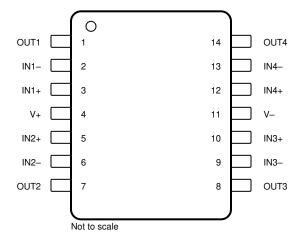

## **6 Pin Configuration and Functions**

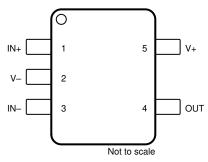

図 6-1. TLV9041 DBV Package 5-Pin SOT-23 Top View

図 6-3. TLV9041 DCK Package 5-Pin SC70 Top View

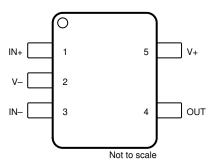

図 6-2. TLV9041U DBV Package 5-Pin SOT-23 Top View

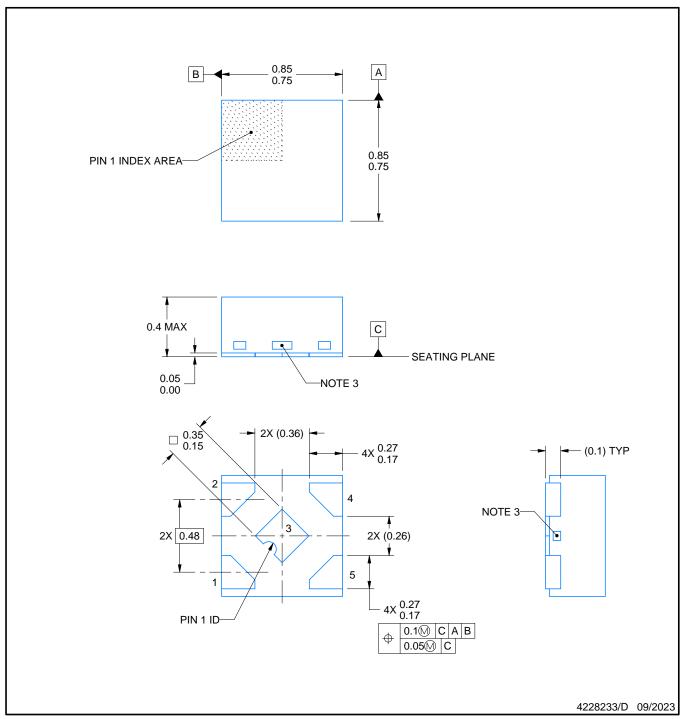

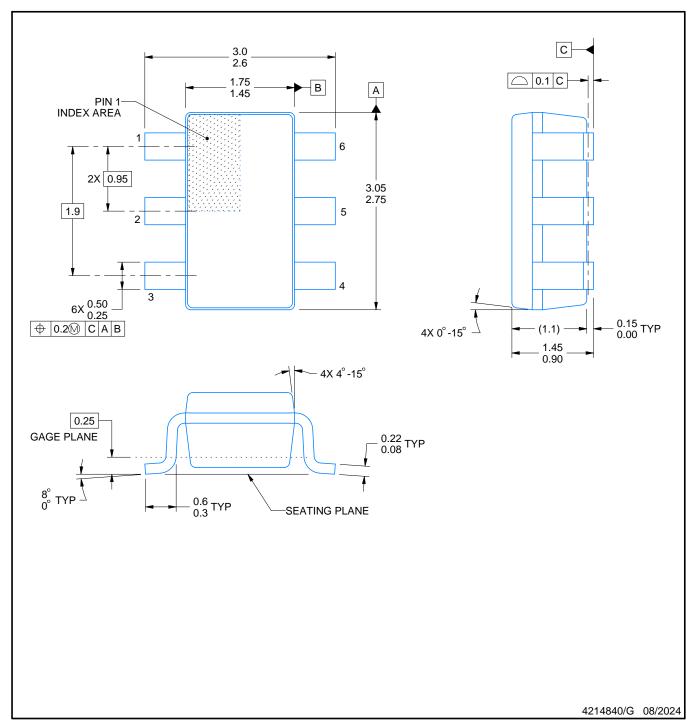

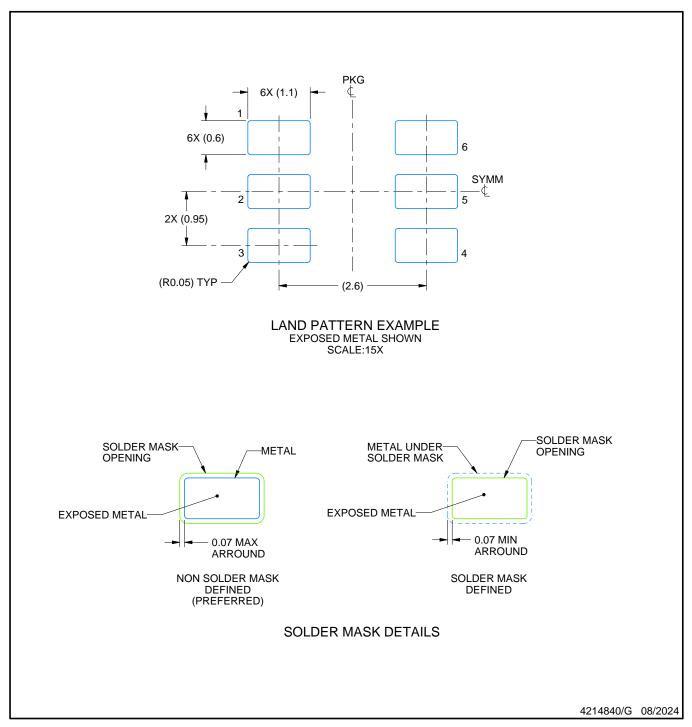

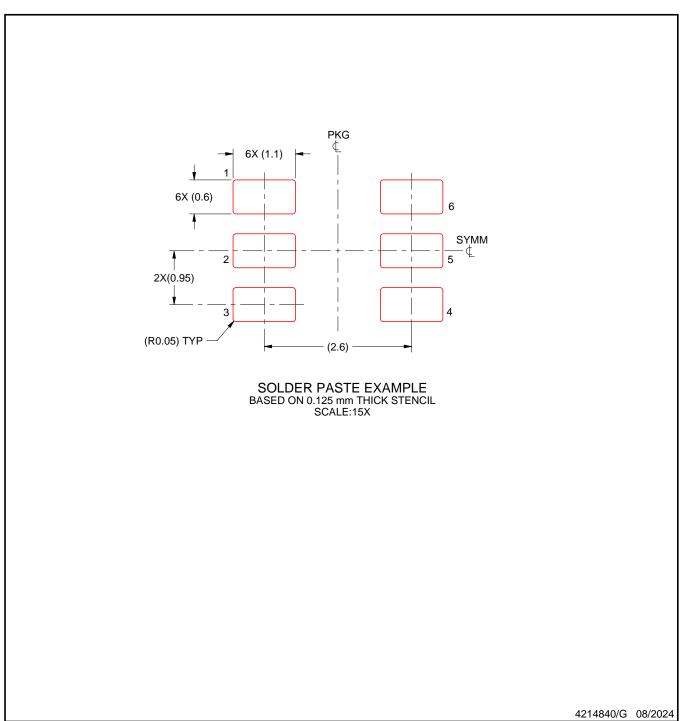

図 6-4. TLV9041 DPW Package 5-Pin X2SON Top View

表 6-1. Pin Functions: TLV9041 and TLV9041U

|      |        | PIN     |       |          |        |                                                               |  |

|------|--------|---------|-------|----------|--------|---------------------------------------------------------------|--|

|      |        | N       | 0.    |          | 1/0    | DESCRIPTION                                                   |  |

| NAME |        | TLV9041 |       | TLV9041U | 1/0    | DESCRIPTION                                                   |  |

|      | SOT-23 | SC70    | X2SON | SOT-23   |        |                                                               |  |

| IN-  | 4      | 3       | 2     | 3        | - 1    | Inverting input                                               |  |

| IN+  | 3      | 1       | 4     | 1        | I      | Noninverting input                                            |  |

| OUT  | 1      | 4       | 1     | 4        | 0      | Output                                                        |  |

| V-   | 2      | 2       | 3     | 2        | I or — | Negative (low) supply or ground (for single-supply operation) |  |

| V+   | 5      | 5       | 5     | 5        | I      | Positive (high) supply                                        |  |

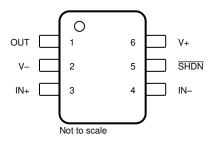

図 6-5. TLV9041S DBV Package 6-Pin SOT-23 Top View

表 6-2. Pin Functions: TLV9041S

| PIN  |     | I/O    | DESCRIPTION                                                   |  |  |

|------|-----|--------|---------------------------------------------------------------|--|--|

| NAME | NO. | 1/0    | DESCRIPTION                                                   |  |  |

| IN-  | 4   | I      | Inverting input                                               |  |  |

| IN+  | 3   | I      | Ioninverting input                                            |  |  |

| OUT  | 1   | 0      | utput                                                         |  |  |

| SHDN | 5   | I      | Shutdown (low), enabled (high)                                |  |  |

| V-   | 2   | l or — | Negative (low) supply or ground (for single-supply operation) |  |  |

| V+   | 6   | I      | Positive (high) supply                                        |  |  |

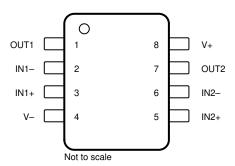

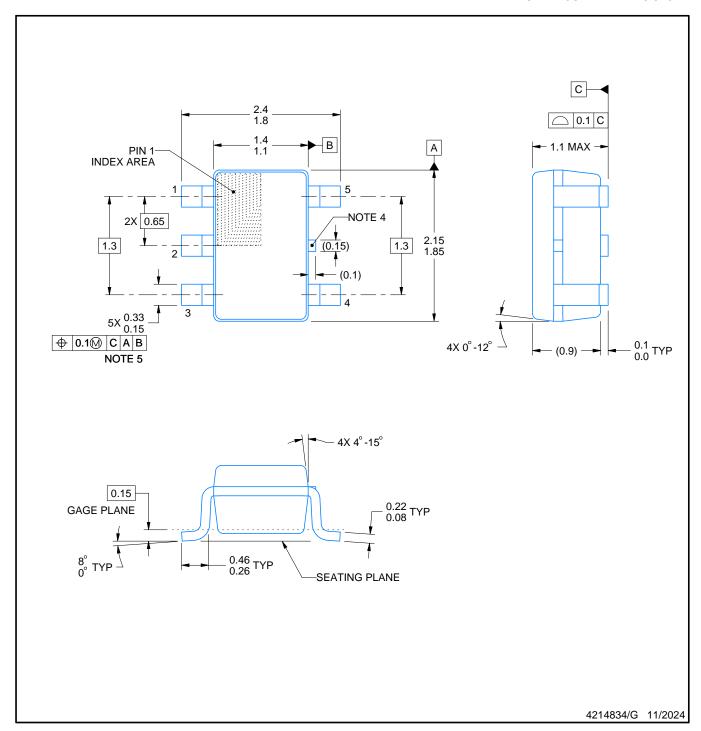

図 6-6. TLV9042 D, DDF, DGK, and PW Package 8-Pin SOIC, SOT-23 8, VSSOP, and TSSOP Top View

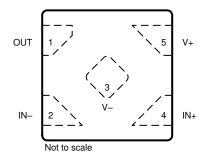

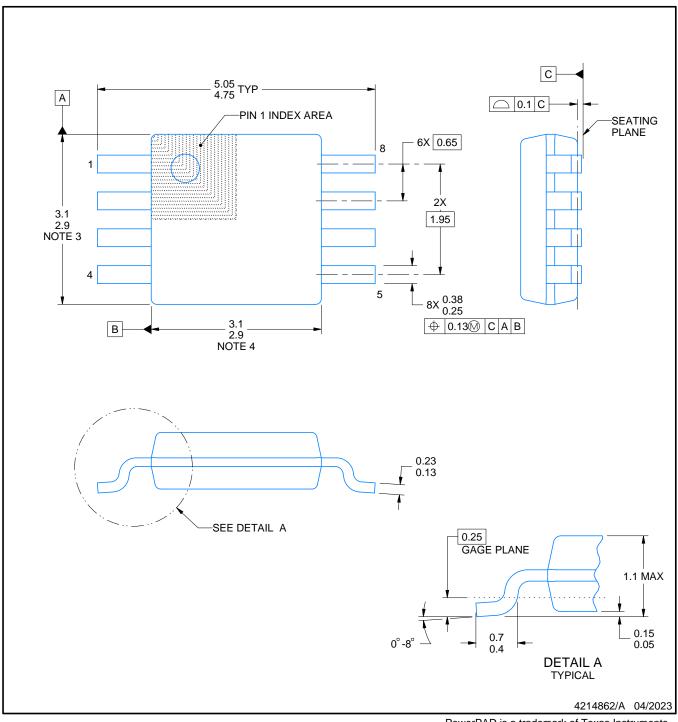

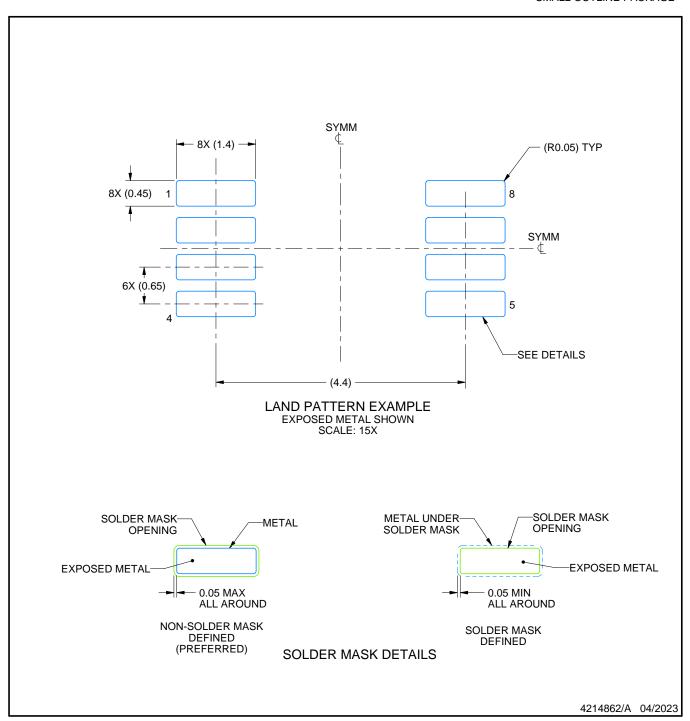

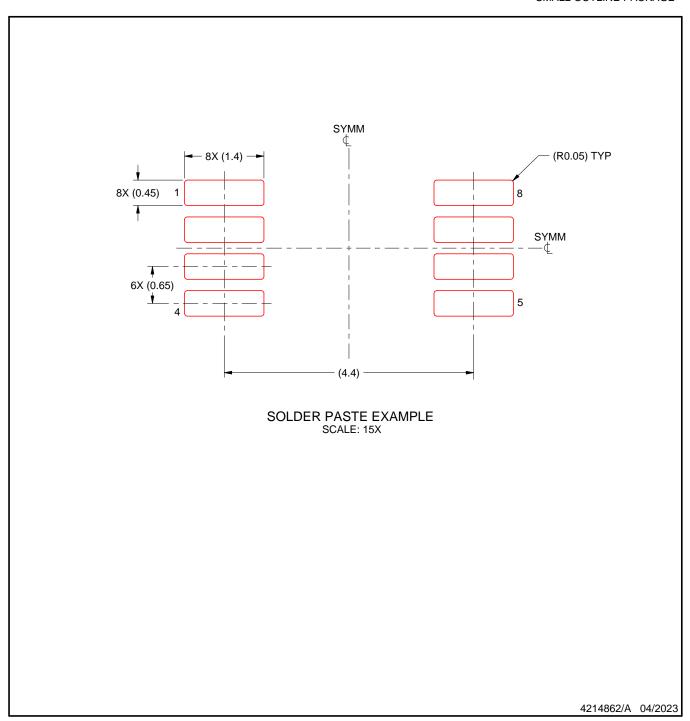

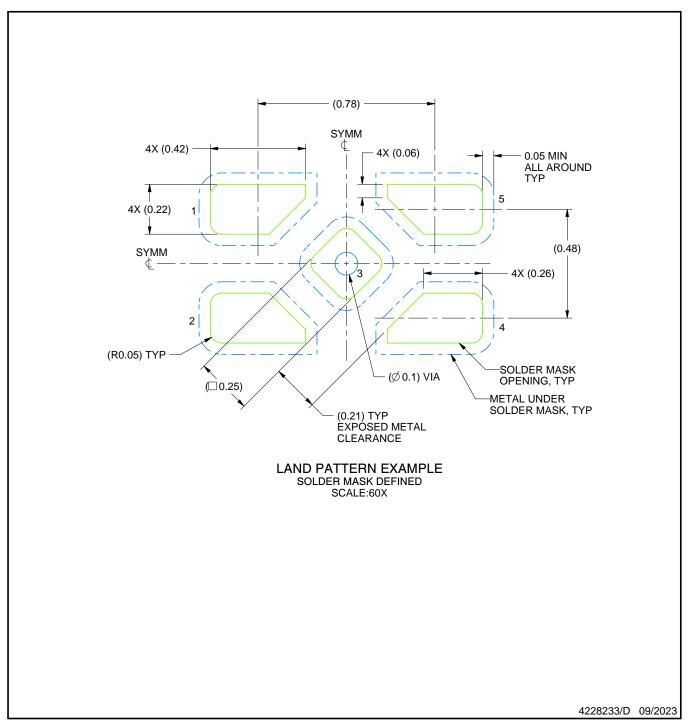

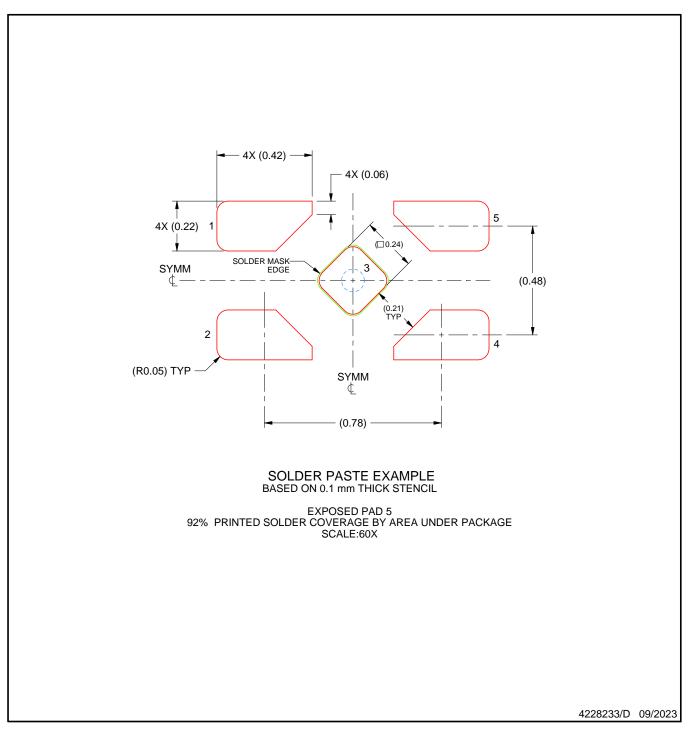

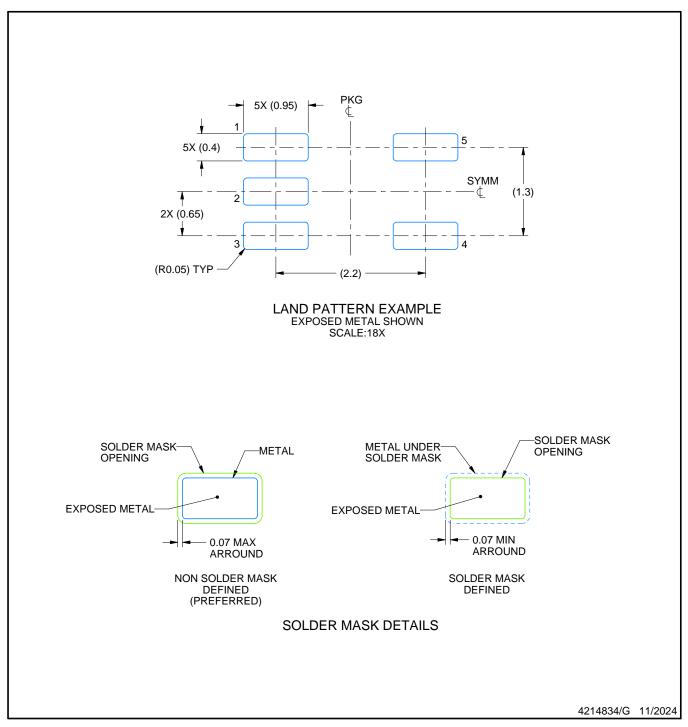

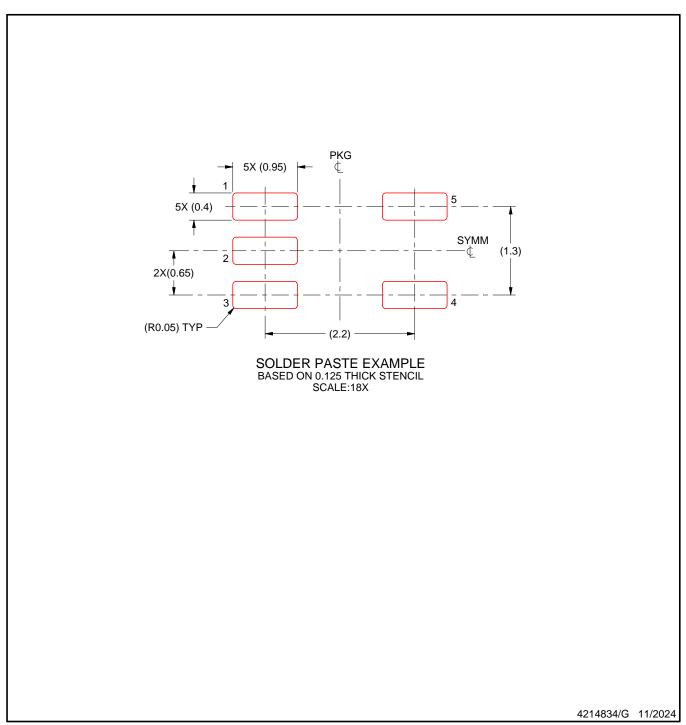

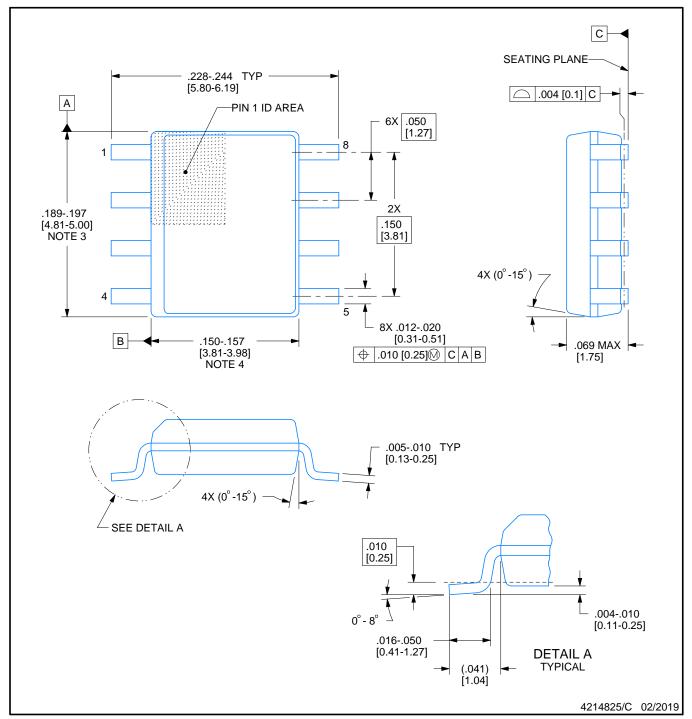

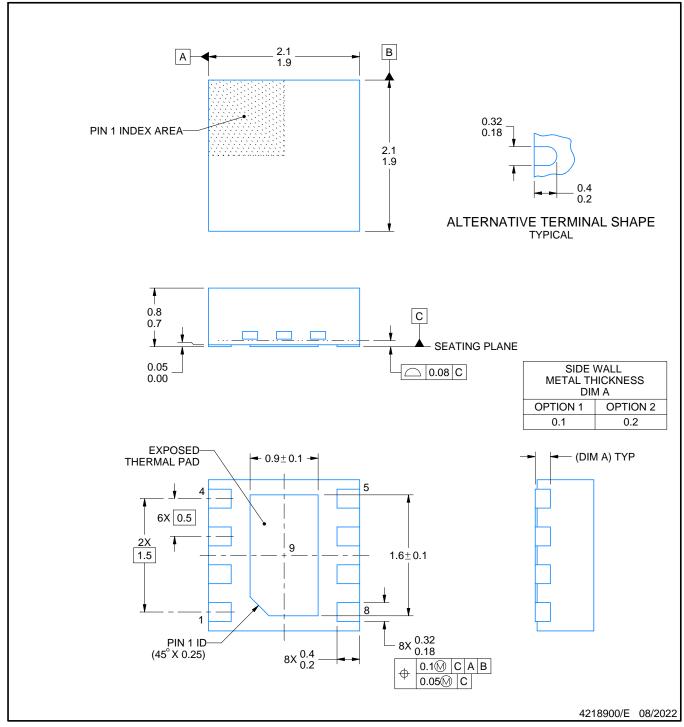

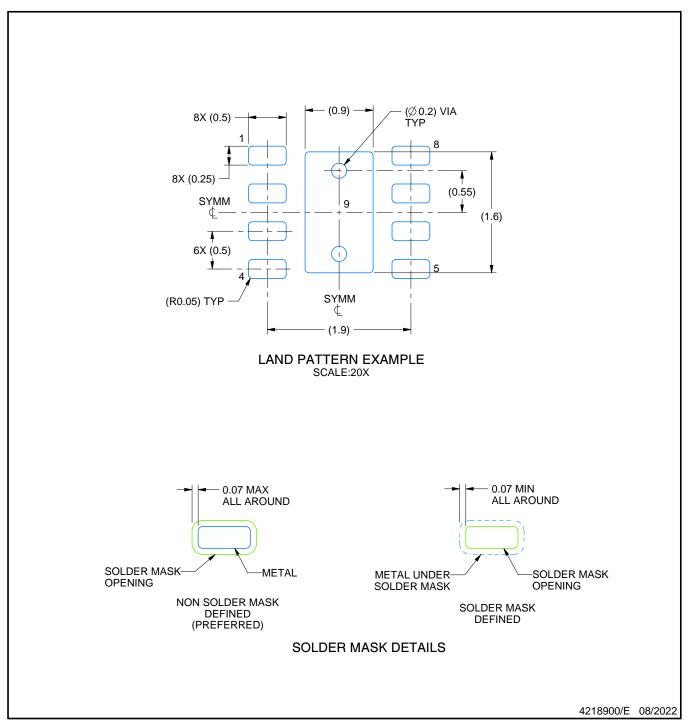

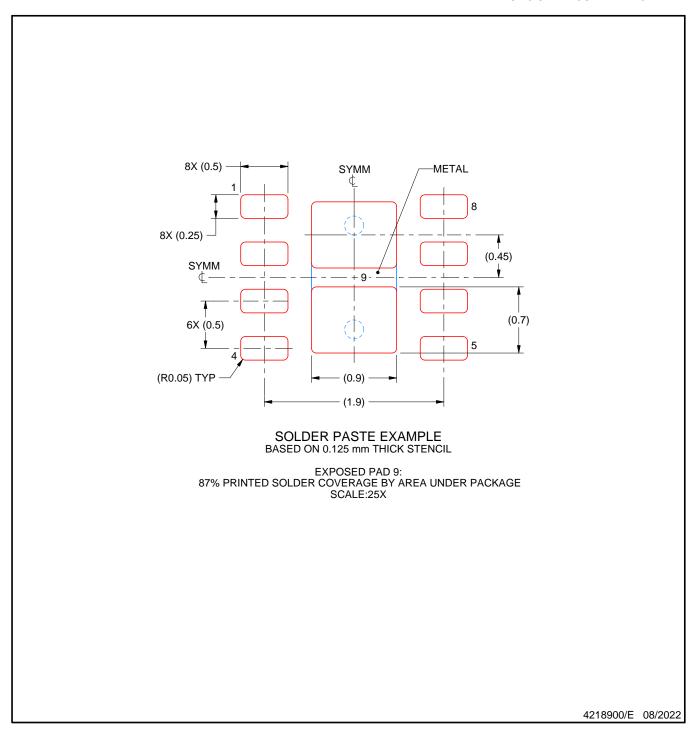

## 図 6-7. TLV9042 DSG Package 8-Pin WSON With Exposed Thermal Pad Top View

表 6-3. Pin Functions: TLV9042

| P    | 'IN | 1/0 | DESCRIPTION                                                   |  |  |  |

|------|-----|-----|---------------------------------------------------------------|--|--|--|

| NAME | NO. |     | DESCRIPTION                                                   |  |  |  |

| IN1- | 2   | I   | Inverting input, channel 1                                    |  |  |  |

| IN1+ | 3   | I   | Noninverting input, channel 1                                 |  |  |  |

| IN2- | 6   | I   | Inverting input, channel 2                                    |  |  |  |

| IN2+ | 5   | I   | Noninverting input, channel 2                                 |  |  |  |

| OUT1 | 1   | 0   | Output, channel 1                                             |  |  |  |

| OUT2 | 7   | 0   | Output, channel 2                                             |  |  |  |

| V-   | 4   | I   | Negative (low) supply or ground (for single-supply operation) |  |  |  |

## 表 6-3. Pin Functions: TLV9042 (continued)

| P    | PIN |     | DESCRIPTION            |  |  |  |

|------|-----|-----|------------------------|--|--|--|

| NAME | NO. | I/O | DESCRIPTION            |  |  |  |

| V+   | 8   | I   | Positive (high) supply |  |  |  |

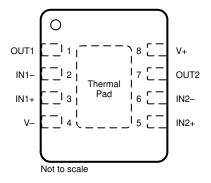

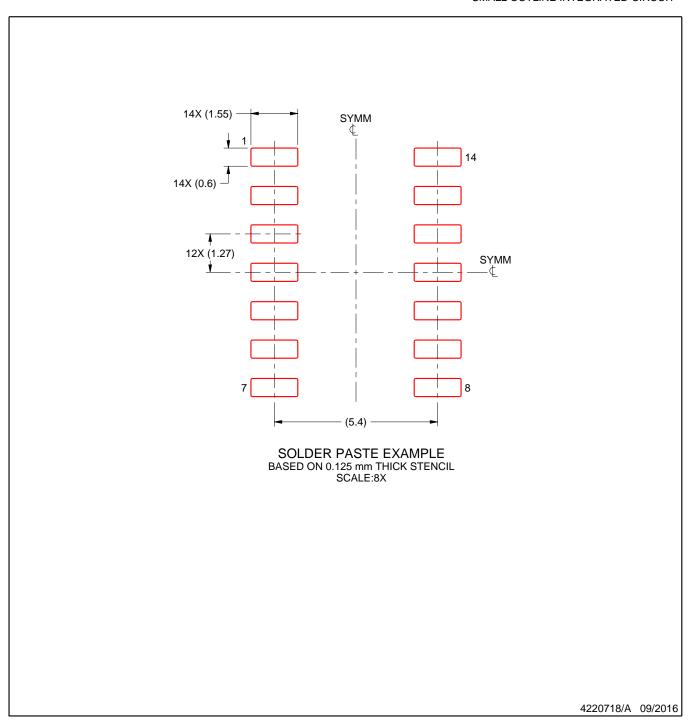

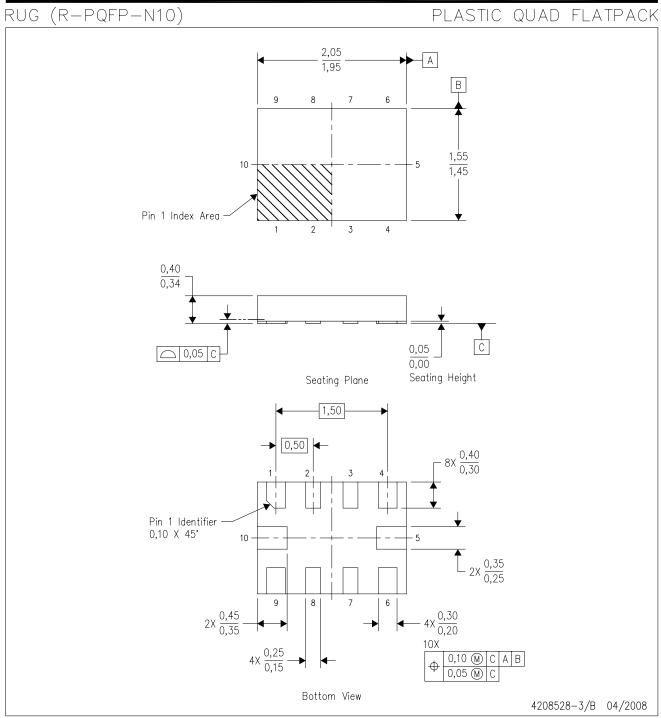

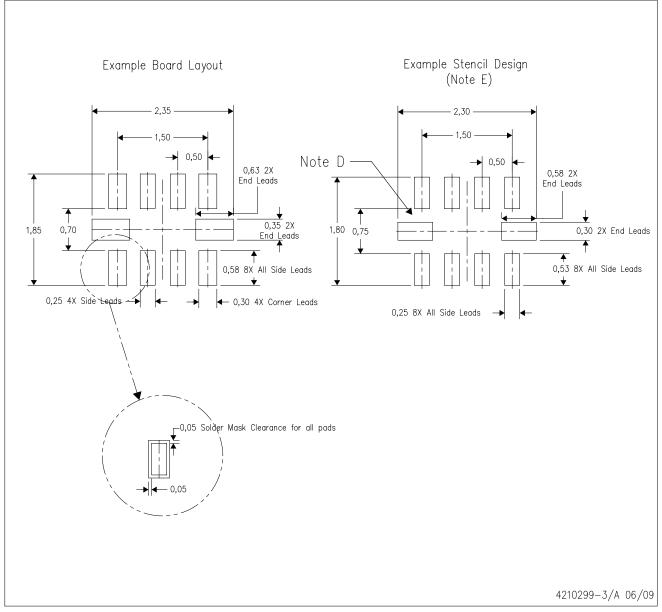

図 6-8. TLV9042S RUG Package 10-Pin X2QFN Top View

表 6-4. Pin Functions: TLV9042S

| PII   | N   | I/O | DESCRIPTION                                                   |  |

|-------|-----|-----|---------------------------------------------------------------|--|

| NAME  | NO. | 1/0 | DESCRIPTION                                                   |  |

| IN1-  | 9   | I   | Inverting input, channel 1                                    |  |

| IN1+  | 10  | I   | Noninverting input, channel 1                                 |  |

| IN2-  | 5   | I   | Inverting input, channel 2                                    |  |

| IN2+  | 4   | I   | Noninverting input, channel 2                                 |  |

| OUT1  | 8   | 0   | Output, channel 1                                             |  |

| OUT2  | 6   | 0   | Output, channel 2                                             |  |

| SHDN1 | 2   | I   | Shutdown – low = disabled, high = enabled, channel 1          |  |

| SHDN2 | 3   | I   | Shutdown – low = disabled, high = enabled, channel 2          |  |

| V-    | 1   | I   | Negative (low) supply or ground (for single-supply operation) |  |

| V+    | 7   | I   | Positive (high) supply                                        |  |

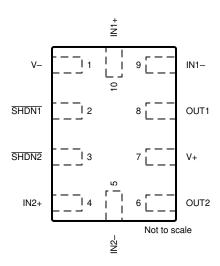

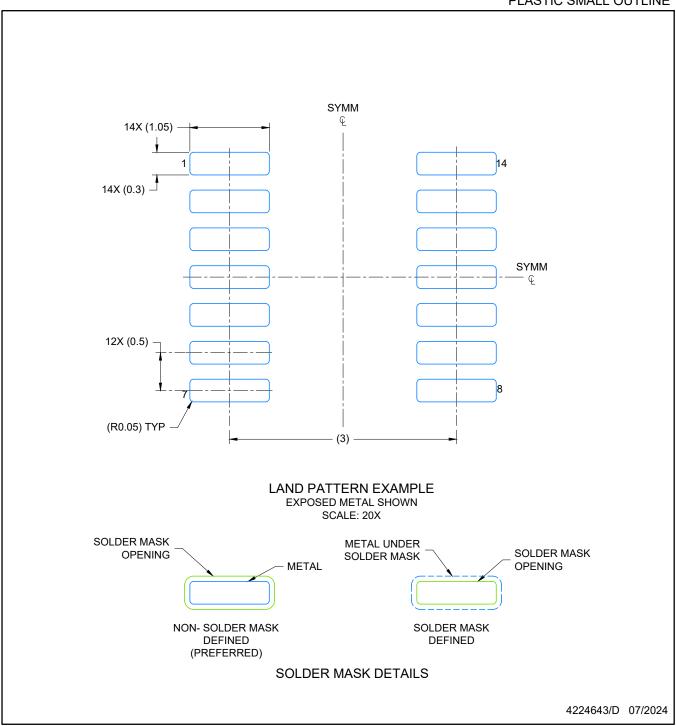

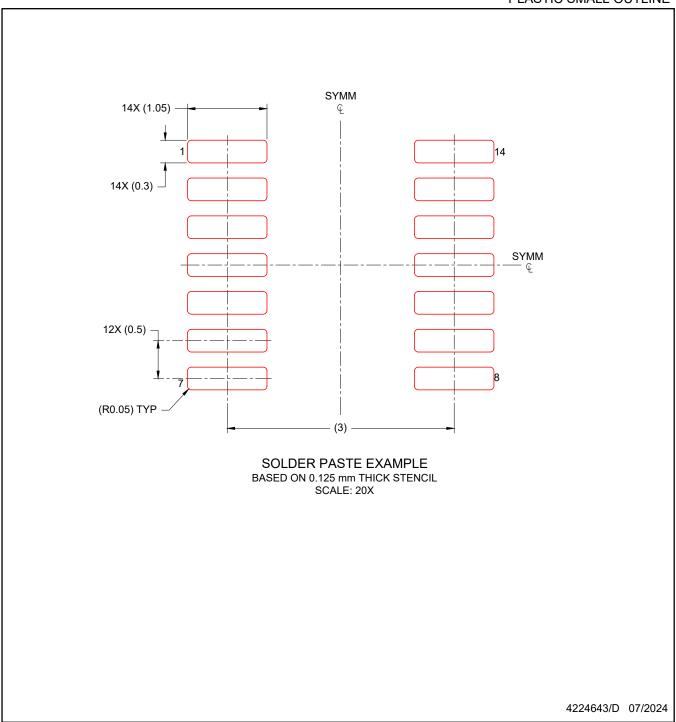

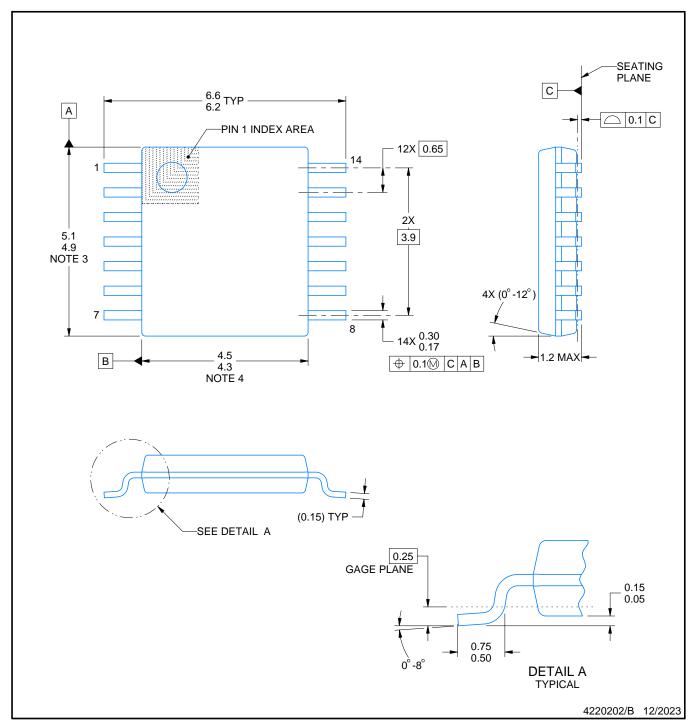

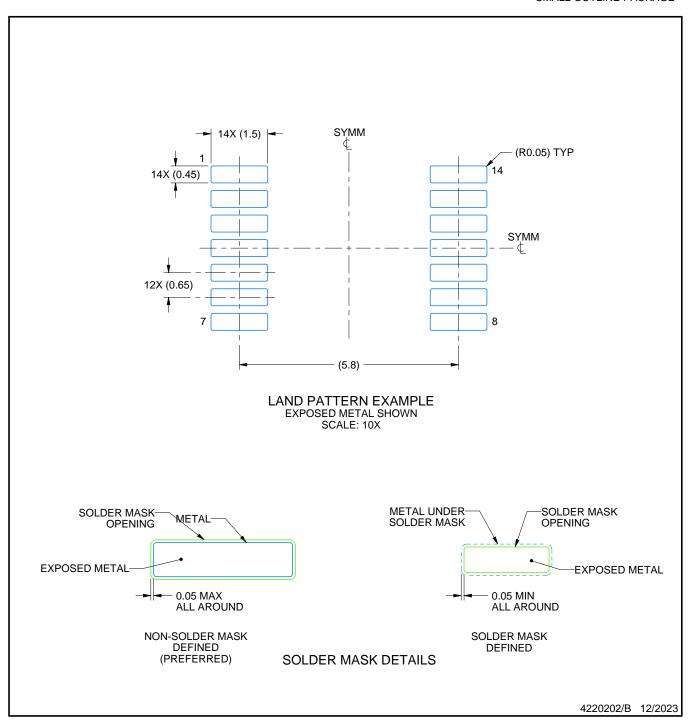

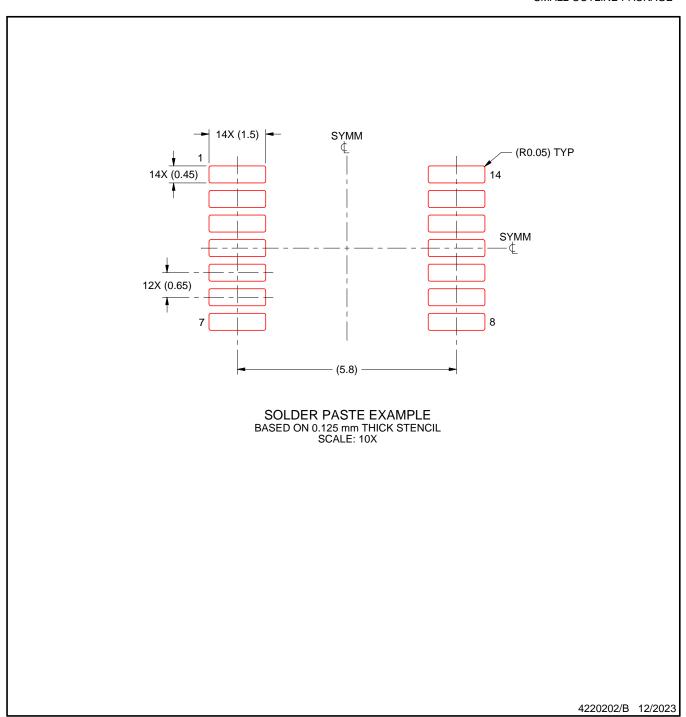

図 6-9. TLV9044 D, PW and DYY Packages 14-Pin SOIC, TSSOP and SOT-23 Top View

表 6-5. Pin Functions: TLV9044

|      | PIN |        |                                                               |  |  |  |

|------|-----|--------|---------------------------------------------------------------|--|--|--|

| NAME | NO. | - I/O  | DESCRIPTION                                                   |  |  |  |

| IN1- | 2   | ı      | Inverting input, channel 1                                    |  |  |  |

| IN1+ | 3   | I      | Noninverting input, channel 1                                 |  |  |  |

| IN2- | 6   | I      | Inverting input, channel 2                                    |  |  |  |

| IN2+ | 5   | I      | Noninverting input, channel 2                                 |  |  |  |

| IN3- | 9   | I      | Inverting input, channel 3                                    |  |  |  |

| IN3+ | 10  | I      | Noninverting input, channel 3                                 |  |  |  |

| IN4- | 13  | I      | Inverting input, channel 4                                    |  |  |  |

| IN4+ | 12  | I      | Noninverting input, channel 4                                 |  |  |  |

| NC   | _   | _      | No internal connection                                        |  |  |  |

| OUT1 | 1   | 0      | Output, channel 1                                             |  |  |  |

| OUT2 | 7   | 0      | Output, channel 2                                             |  |  |  |

| OUT3 | 8   | 0      | Output, channel 3                                             |  |  |  |

| OUT4 | 14  | 0      | Output, channel 4                                             |  |  |  |

| V-   | 11  | I or — | Negative (low) supply or ground (for single-supply operation) |  |  |  |

| V+   | 4   | I      | Positive (high) supply                                        |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted) (1)

|                                       |                          | , , , , , , , , , , , , , , , , , , , , |                      |      |

|---------------------------------------|--------------------------|-----------------------------------------|----------------------|------|

|                                       |                          | MIN                                     | MAX                  | UNIT |

| Supply voltage, V <sub>S</sub> = (V+  | ) – (V–)                 | 0                                       | 6.0                  | V    |

|                                       | Common-mode voltage (2)  | (V-) - 0.5                              | (V+) + 0.5           | V    |

| Signal input pins                     | Differential voltage (2) |                                         | V <sub>S</sub> + 0.2 | V    |

|                                       | Current (2)              | -10                                     | 10                   | mA   |

| Output short-circuit (3)              |                          | Continue                                | ous                  |      |

| Operating ambient temper              | erature, T <sub>A</sub>  | -55                                     | 150                  |      |

| Junction temperature, T <sub>J</sub>  |                          |                                         | 150                  | °C   |

| Storage temperature, T <sub>ste</sub> | g                        | -65                                     | 150                  | °C   |

|                                       |                          |                                         |                      |      |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Input pins are diode-clamped to the power-supply rails. Input signals that may swing more than 0.5 V beyond the supply rails must be current limited to 10 mA or less.

- (3) Short-circuit to ground, one amplifier per package.

## 7.2 ESD Ratings

|        |                                            |                                                                     | VALUE | UNIT |

|--------|--------------------------------------------|---------------------------------------------------------------------|-------|------|

| V      | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±3000 | V    |

| V(ESD) |                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                |                             | MIN  | MAX  | UNIT |

|----------------|-----------------------------|------|------|------|

| Vs             | Supply voltage, (V+) – (V–) | 1.2  | 5.5  | V    |

| VI             | Input voltage range         | (V-) | (V+) | V    |

| T <sub>A</sub> | Specified temperature       | -40  | 125  | °C   |

## 7.4 Thermal Information for Single Channel

|                       |                                              |        | TLV9041,    | TLV9041S      |                |      |

|-----------------------|----------------------------------------------|--------|-------------|---------------|----------------|------|

|                       | THERMAL METRIC (1)                           | _      | BV<br>T-23) | DCK<br>(SC70) | DPW<br>(X2SON) | UNIT |

|                       |                                              | 5 PINS | 6 PINS      | 5 PINS        | 5 PINS         |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 235.4  | 214.6       | 233.8         | 478.7          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 135.1  | 134.2       | 130.7         | 219.4          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 103.2  | 95.6        | 79.7          | 345.1          | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 75.6   | 73.8        | 51.6          | 32.9           | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 102.7  | 95.3        | 79.1          | 343.4          | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a    | n/a         | n/a           | 192.7          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Thermal Information for Dual Channel

|                       |                                              |             |        | TLV9042 |               |                | TLV9042S       |      |

|-----------------------|----------------------------------------------|-------------|--------|---------|---------------|----------------|----------------|------|

| THERMAL METRIC (1)    |                                              | D<br>(SOIC) |        |         | PW<br>(TSSOP) | DGK<br>(VSSOP) | RUG<br>(X2QFN) | UNIT |

|                       |                                              |             | 8 PINS | 8 PINS  | 8 PINS        | 8 PINS         | 10 PINS        |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 148.3       | 203.8  | 99.8    | 203.1         | 196.6          | 196.9          | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 89.8        | 123.9  | 122.2   | 91.9          | 87.5           | 87.6           | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 91.6        | 121.6  | 66.0    | 133.8         | 118.5          | 117.8          | °C/W |

| Ψυτ                   | Junction-to-top characterization parameter   | 38.6        | 21.7   | 13.8    | 23.7          | 25.7           | 3.4            | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 90.9        | 199.6  | 65.9    | 132.1         | 116.8          | 117.6          | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | n/a    | 41.9    | n/a           | n/a            | n/a            | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.6 Thermal Information for Quad Channel

|                       |                                              |             | TLV9044, TLV9044S |                    |      |  |  |  |  |  |

|-----------------------|----------------------------------------------|-------------|-------------------|--------------------|------|--|--|--|--|--|

|                       | THERMAL METRIC (1)                           | D<br>(SOIC) | PW<br>(TSSOP)     | DYY<br>(SOT-23-14) | UNIT |  |  |  |  |  |

|                       |                                              | 14 PINS     | 14 PINS           | 14 PINS            | 1    |  |  |  |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 116.4       | 135.7             | 152.5              | °C/W |  |  |  |  |  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 72.5        | 78.8              | 86.2               | °C/W |  |  |  |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 72.4        | 63.9              | 67.4               | °C/W |  |  |  |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 30.8        | 14.2              | 10.1               | °C/W |  |  |  |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 72          | 78.3              | 67.2               | °C/W |  |  |  |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | n/a               | n/a                | °C/W |  |  |  |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.7 Electrical Characteristics

For  $V_S$  = (V+) – (V–) = 1.2 V to 5.5 V (±0.6 V to ±2.75 V) at  $T_A$  = 25°C,  $R_L$  = 100 k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{O\ UT}$  =  $V_S$  / 2, unless otherwise noted.

|                      | PARAMETER                                | TEST CONDITIONS                                                                                                             |                                                     | MIN  | TYP       | MAX   | UNIT             |  |

|----------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-----------|-------|------------------|--|

| OFFSET \             | /OLTAGE                                  |                                                                                                                             |                                                     |      |           |       |                  |  |

| .,                   | Innut effect voltage                     |                                                                                                                             |                                                     |      | ±0.6      | ±2.25 | ma\ /            |  |

| V <sub>OS</sub>      | Input offset voltage                     |                                                                                                                             | T <sub>A</sub> = -40°C to 125°C                     |      |           | ±2.5  | mV               |  |

| dV <sub>OS</sub> /dT | Input offset voltage drift               |                                                                                                                             | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |      | ±0.8      |       | μV/°C            |  |

| PSRR                 | Input offset voltage versus power supply | $V_S = \pm 0.6 \text{ V to } \pm 2.75 \text{ V}$ , $V_{CM} = V_{-}$                                                         |                                                     |      | ±20       | ±100  | μV/V             |  |

|                      | Channel separation                       | f = 10 kHz                                                                                                                  |                                                     |      | ±5.6      |       | μV/V             |  |

| INPUT BIA            | AS CURRENT                               |                                                                                                                             |                                                     |      |           | '     |                  |  |

| I <sub>B</sub>       | Input bias current (1)                   |                                                                                                                             |                                                     |      | ±1        | ±12   | pA               |  |

| I <sub>OS</sub>      | Input offset current (1)                 |                                                                                                                             |                                                     |      | ±0.5      | ±10   | pА               |  |

| NOISE                |                                          |                                                                                                                             |                                                     |      |           | 1     |                  |  |

| E <sub>N</sub>       | Input voltage noise                      | f = 0.1 to 10 Hz                                                                                                            |                                                     |      | 6.5       |       | μV <sub>PP</sub> |  |

|                      |                                          | f = 100 Hz                                                                                                                  |                                                     |      | 85        |       |                  |  |

| e <sub>N</sub>       | Input voltage noise density              | f = 1 kHz                                                                                                                   |                                                     |      | 66        |       | nV/√H            |  |

|                      | derisity                                 | f = 10 kHz                                                                                                                  |                                                     |      | 64        |       |                  |  |

| i <sub>N</sub>       | Input current noise (2)                  | f = 1 kHz                                                                                                                   |                                                     |      | 20        |       | fA/√Hz           |  |

|                      | LTAGE RANGE                              | 1                                                                                                                           | I                                                   |      |           |       |                  |  |

| V <sub>CM</sub>      | Common-mode voltage range                |                                                                                                                             |                                                     | (V-) |           | (V+)  | V                |  |

|                      |                                          | $(V-) < V_{CM} < (V+) - 0.7 \text{ V}, V_S = 1.2 \text{ V}$                                                                 |                                                     | 60   | 77        |       |                  |  |

|                      | Common-mode                              | $(V-) < V_{CM} < (V+) - 0.7 \text{ V}, V_S = 5.5 \text{ V}$                                                                 | 1                                                   | 75   | 89        |       |                  |  |

| CMRR                 | rejection ratio                          | $(V-) < V_{CM} < (V+), V_S = 1.2 V$                                                                                         | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |      | 60        |       | dB               |  |

|                      |                                          | $(V-) < V_{CM} < (V+), V_S = 5.5 V$                                                                                         | 1                                                   | 57   | 72        |       |                  |  |

| INPUT IMI            | PEDANCE                                  |                                                                                                                             |                                                     |      |           |       |                  |  |

| Z <sub>ID</sub>      | Differential                             |                                                                                                                             |                                                     |      | 80    1.4 |       | GΩ    p          |  |

| Z <sub>ICM</sub>     | Common-mode                              |                                                                                                                             |                                                     | 1    | 00    0.5 |       | GΩ    p          |  |

| OPEN-LO              | OP GAIN                                  |                                                                                                                             | I                                                   |      |           |       |                  |  |

|                      |                                          | $V_S = 1.2 \text{ V}, (V-) + 0.2 \text{ V} < V_O < (V+) - 0.2 \text{ V},$<br>$R_L = 10 \text{ k}\Omega \text{ to } V_S / 2$ |                                                     |      | 98        |       |                  |  |

|                      | Open-loop voltage                        | $V_S = 5.5 \text{ V}, (V-) + 0.2 \text{ V} < V_O < (V+) - 0.2 \text{ V},$<br>$R_L = 10 \text{ k}\Omega \text{ to } V_S / 2$ |                                                     |      | 125       |       |                  |  |

| A <sub>OL</sub>      | gain                                     | $V_S = 1.2 \text{ V}, (V) + 0.1 \text{ V} < V_0 < (V_+) - 0.1 \text{ V},$ $R_L = 100 \text{ k}\Omega \text{ to } V_S / 2$   | T <sub>A</sub> = -40°C to 125°C                     |      | 105       |       | dB               |  |

|                      |                                          | $V_S = 5.5 \text{ V}, (V-) + 0.1 \text{ V} < V_O < (V+) - 0.1 \text{ V},$ $R_L = 100 \text{ k}\Omega \text{ to } V_S / 2$   |                                                     | 107  | 130       |       |                  |  |

| FREQUEN              | ICY RESPONSE                             |                                                                                                                             |                                                     |      |           | '     |                  |  |

| THD+N                | Total harmonic distortion + noise (3)    | $V_S$ = 5.5 V, $V_{CM}$ = 2.75 V, $V_O$ = 1 $V_{RMS}$ , $G$ = +1, $f$ = $R_L$ = 100 k $\Omega$ to $V_S$ / 2                 | : 1 kHz,                                            |      | 0.013     |       | %                |  |

| GBW                  | Gain-bandwidth product                   | $R_L$ = 1 MΩ connected to $V_S/2$                                                                                           |                                                     |      | 350       |       | kHz              |  |

| SR                   | Slew rate                                | V <sub>S</sub> = 5.5 V, G = +1, C <sub>L</sub> = 10 pF                                                                      |                                                     |      | 0.2       |       | V/µs             |  |

|                      |                                          | To 0.1%, V <sub>S</sub> = 5.5 V, V <sub>STEP</sub> = 4 V, G = +1, C <sub>L</sub> = 10                                       | pF                                                  |      | 25        |       |                  |  |

|                      | Sottling time                            | To 0.1%, V <sub>S</sub> = 5.5 V, V <sub>STEP</sub> = 2 V, G = +1, C <sub>L</sub> = 10                                       | pF                                                  |      | 22        |       |                  |  |

| t <sub>S</sub>       | Settling time                            | To 0.01%, V <sub>S</sub> = 5.5 V, V <sub>STEP</sub> = 4 V, G = +1, C <sub>L</sub> = 10                                      |                                                     | 35   |           | μs    |                  |  |

|                      |                                          | To 0.01%, V <sub>S</sub> = 5.5 V, V <sub>STEP</sub> = 2 V, G = +1, C <sub>L</sub> = 10                                      | 0 pF                                                | 30   |           |       |                  |  |

|                      | Phase margin                             | $G = +1$ , $R_L = 100$ k $\Omega$ connected to $V_S/2$ , $C_L = 10$ p                                                       | F                                                   |      | 65        |       | 0                |  |

|                      | Overload recovery                        | V <sub>IN</sub> × gain > V <sub>S</sub>                                                                                     |                                                     |      | 13        |       | μs               |  |

## 7.7 Electrical Characteristics (continued)

For  $V_S$  = (V+) – (V–) = 1.2 V to 5.5 V (±0.6 V to ±2.75 V) at  $T_A$  = 25°C,  $R_L$  = 100 k $\Omega$  connected to  $V_S$  / 2,  $V_{CM}$  =  $V_S$  / 2, and  $V_{OUT}$  =  $V_S$  / 2, unless otherwise noted.

|                   | PARAMETER                                        | TEST CONDITIONS                                                      |                                                                           | MIN TYP    | MAX             | UNIT     |

|-------------------|--------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|------------|-----------------|----------|

| EMIRR             | Electro-magnetic interference rejection ratio    | f = 1 GHz, V <sub>IN_EMIRR</sub> = 100 mV                            |                                                                           | 70         |                 | dB       |

| OUTPUT            |                                                  |                                                                      |                                                                           |            |                 |          |

|                   |                                                  |                                                                      | $V_S = 1.2 \text{ V},$<br>$R_L = 100 \text{ k}\Omega \text{ to } V_S / 2$ | 0.75       | 7               |          |

|                   |                                                  | Positive rail headroom                                               | $V_S = 5.5 \text{ V},$<br>$R_L = 10 \text{ k}\Omega \text{ to } V_S / 2$  | 10         | 21              |          |

|                   | Voltage output swing                             |                                                                      | $V_S = 5.5 \text{ V},$<br>$R_L = 100 \text{ k}\Omega \text{ to } V_S / 2$ | 1          | 8               | mV       |

|                   | from rail                                        |                                                                      | $V_S = 1.2 \text{ V},$<br>$R_L = 100 \text{ k}\Omega \text{ to } V_S / 2$ | 0.75       | 5               |          |

|                   |                                                  | Negative rail headroom                                               |                                                                           | 10         | 21              |          |

|                   |                                                  |                                                                      | $V_S = 5.5 \text{ V},$<br>$R_L = 100 \text{ k}\Omega \text{ to V}_S / 2$  | 1          | 8               |          |

| I <sub>SC</sub>   | Short-circuit current (4)                        | V <sub>S</sub> = 5.5 V                                               |                                                                           | ±40        |                 | mA       |

| Z <sub>O</sub>    | Open-loop output impedance                       | f = 10 kHz                                                           |                                                                           | 7500       |                 | Ω        |

| POWER             | SUPPLY                                           |                                                                      |                                                                           |            |                 |          |

| IQ                | Quiescent current per amplifier                  | V <sub>S</sub> = 5.5 V, I <sub>O</sub> = 0 A                         | T <sub>A</sub> = -40°C to 125°C                                           | 10         | 13<br>13.5      | μΑ       |

| IQ                | Quiescent current per amplifier                  | V <sub>S</sub> = 5.5 V, I <sub>O</sub> = 0 A, For TLV9041UIDBVR Only | T <sub>A</sub> = -40°C to 125°C                                           | 10         | 13.5<br>14      | μA<br>μA |

| SHUTDO            | WN                                               |                                                                      | 1A 10 0 to 120 0                                                          |            |                 | μι       |

| I <sub>QSD</sub>  | Quiescent current per amplifier                  | All amplifiers disabled, SHDN = V-                                   |                                                                           | 75         | 200             | nA       |

| Z <sub>SHDN</sub> | Output impedance during shutdown                 | Amplifier disabled                                                   |                                                                           | 43    11.5 |                 | GΩ    pF |

| V <sub>IH</sub>   | Logic high threshold voltage (amplifier enabled) |                                                                      |                                                                           | (V–) + 1 V |                 | V        |

| V <sub>IL</sub>   | Logic low threshold voltage (amplifier disabled) |                                                                      |                                                                           |            | (V–) + 0.2<br>V | ٧        |

|                   | Amplifier enable time (full shutdown) (5) (6)    | $G = +1, V_{CM} = V_S / 2, V_O = 0.9 \times V_S / 2, R_L connection$ | cted to V-                                                                | 160        |                 |          |

| t <sub>ON</sub>   | Amplifier enable time (partial shutdown) (5) (6) | $G = +1, V_{CM} = V_S / 2, V_O = 0.9 \times V_S / 2, R_L connection$ | cted to V-                                                                | 120        |                 | μs       |

| t <sub>OFF</sub>  | Amplifier disable time                           | $G = +1, V_{CM} = V_S / 2, V_O = 0.1 \times V_S / 2, R_L connection$ | cted to V-                                                                | 10         |                 | μs       |

|                   | SHDN pin input bias                              | (V+) ≥ SHDN ≥ (V–) + 1 V                                             |                                                                           | 100        |                 | rΛ       |

|                   | current (per pin)                                | (V–) ≤ SHDN ≤ (V–) + 0.2 V                                           |                                                                           | 50         |                 | pА       |

- (1) Max  $I_B$  and  $I_{OS}$  limits are specified based on characterization results. Input differential voltages greater than 2.5V can cause increased  $I_B$

- (2) Typical input current noise data is specified based on design simulation results

- (3) Third-order filter; bandwidth = 80 kHz at -3 dB.

- (4) Short circuit current is average of sourcing and sinking short circuit currents

- (5) Disable time (t<sub>OFF</sub>) and enable time (t<sub>ON</sub>) are defined as the time interval between the 50% point of the signal applied to the SHDN pin and the point at which the output voltage reaches the 10% (disable) or 90% (enable) level.

- (6) Full shutdown refers to the dual TLV9042S having both channels 1 and 2 disabled (SHDN1 = SHDN2 = V-) and the quad TLV9044S having all channels 1 to 4 disabled (SHDN12 = SHDN34 = V-). For partial shutdown, only one SHDN pin is exercised; in this mode, the internal biasing circuitry remains operational and the enable time is shorter.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

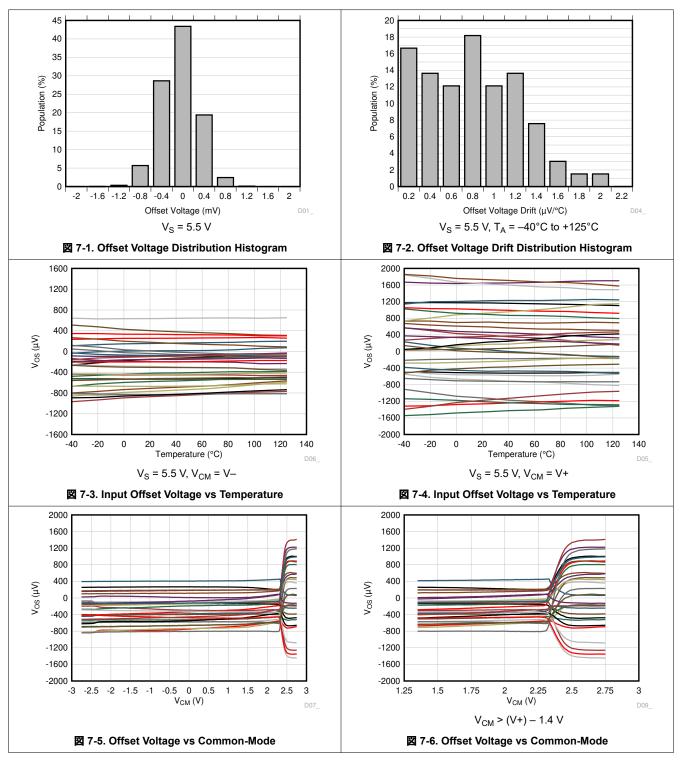

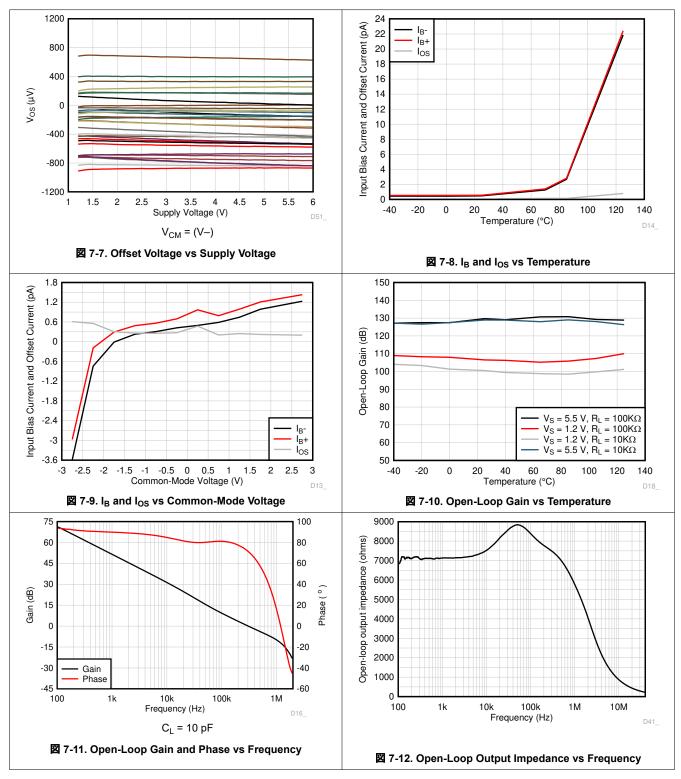

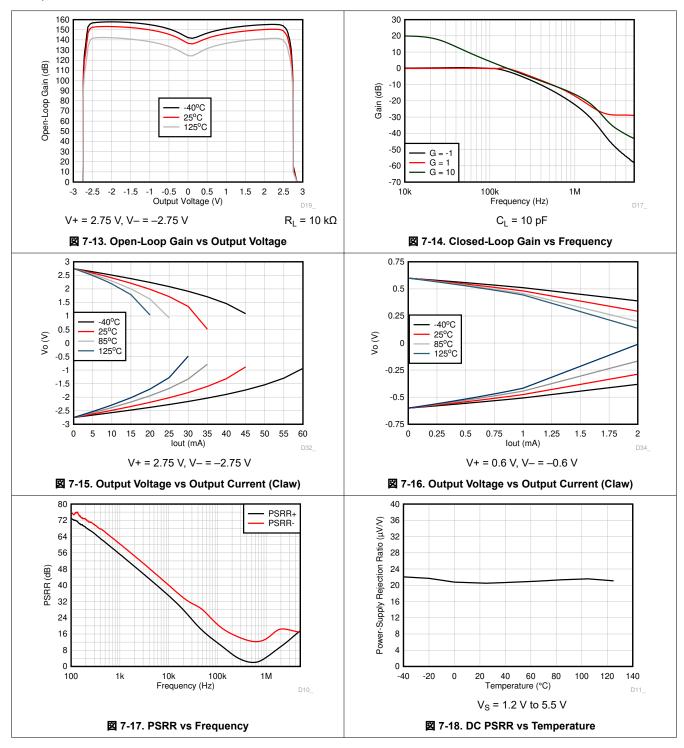

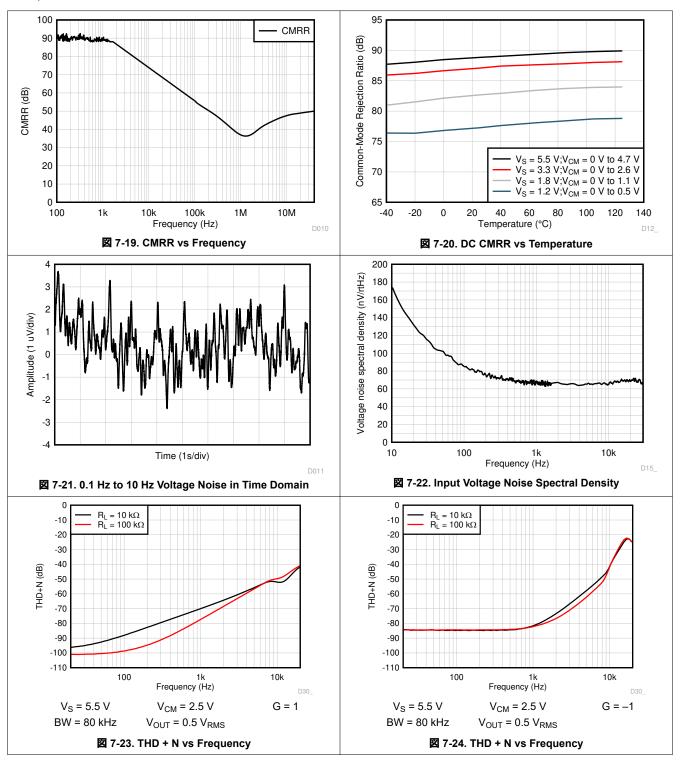

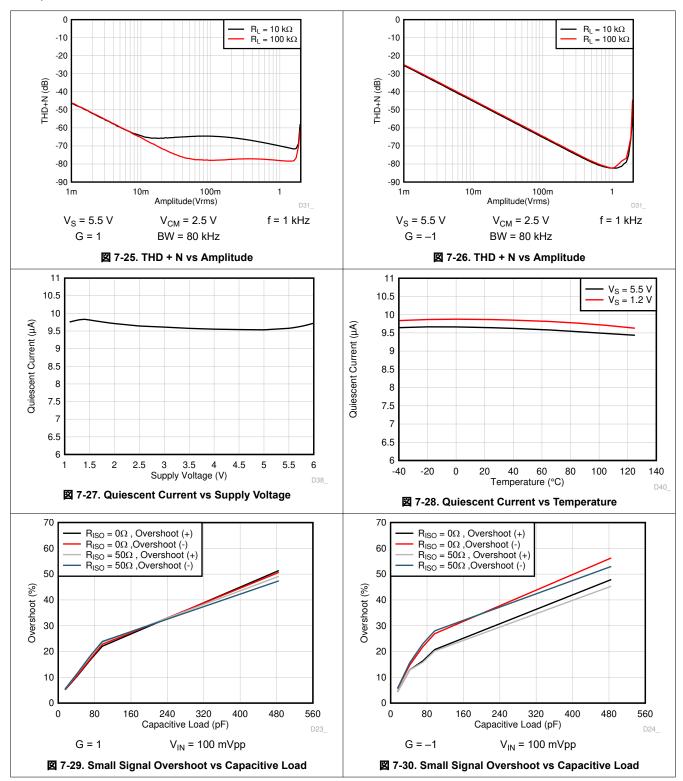

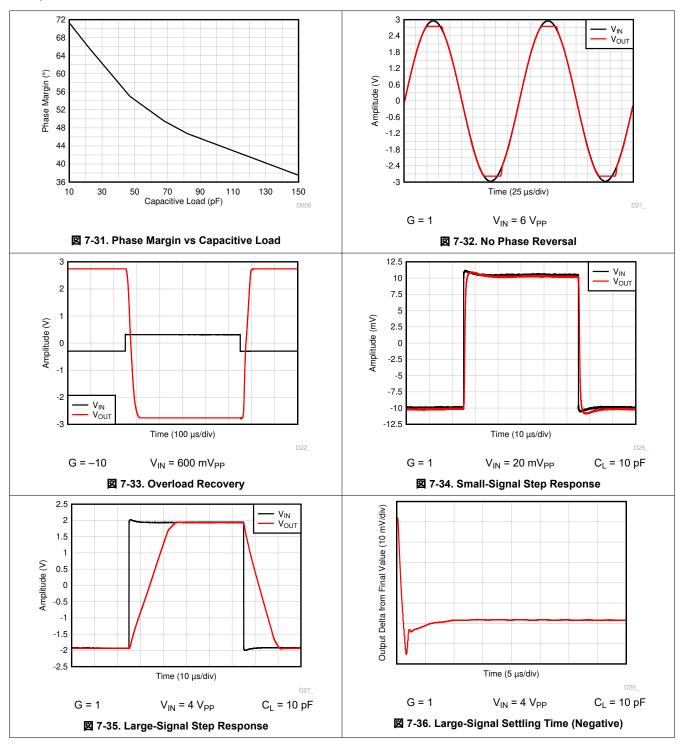

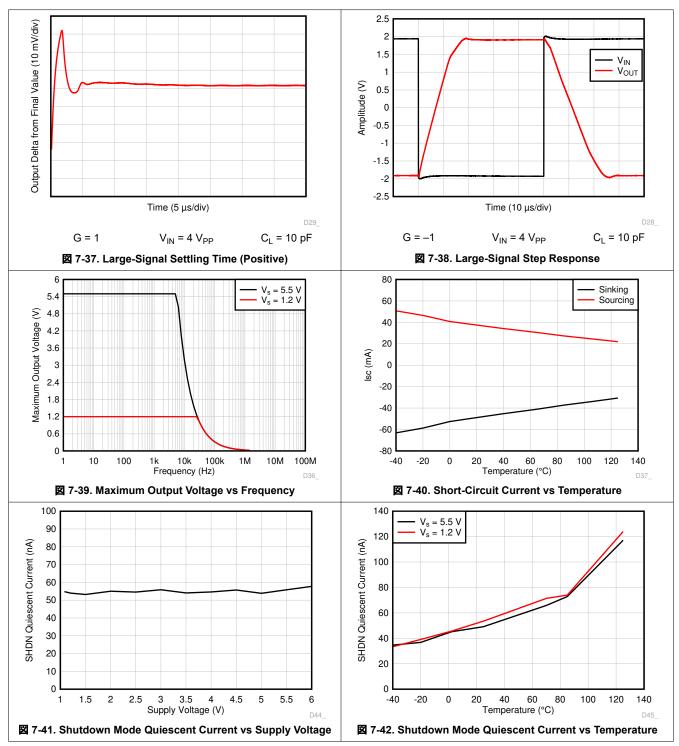

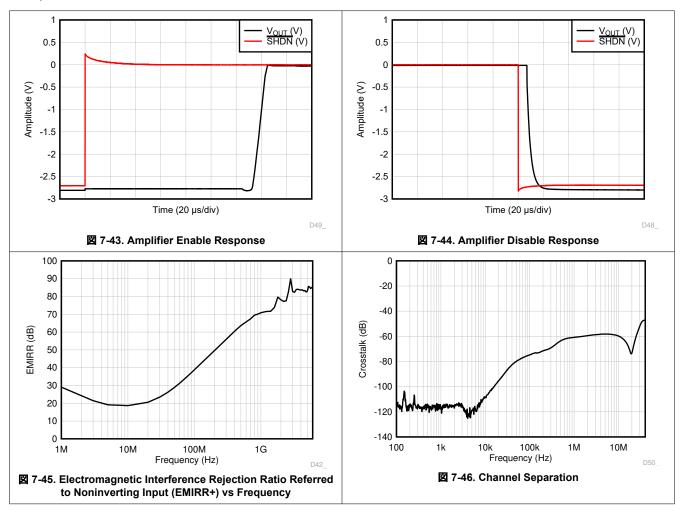

## 7.8 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

The TLV904x is a family of low-power, rail-to-rail input and output operational amplifiers specifically designed for battery powered applications. This family of amplifiers utilizes unique transistors that enable operation from ultra low supply voltage of 1.2 V to a standard supply voltage of 5.5 V. These unity-gain stable amplifiers provide 350 kHz of GBW with an  $I_Q$  of only 10  $\mu$ A. TLV904x also has short circuit current capability of 40 mA at 5.5 V. This combination of low voltage, low IQ, and high output current capability makes this device quite unique and suitable for suitable for a wide range of general-purpose applications. The input common-mode voltage range includes both rails, and allows the TLV904x series to be used in many single-supply or dual supply configurations. Rail-to-rail input and output swing significantly increases dynamic range, especially in low-supply applications, and makes these devices ideal for driving low speed sampling analog-to-digital converters (ADCs). Further, the class AB output stage is capable of driving resitive loads greater than 2-k $\Omega$  connected to any point between V+ and ground.

The TLV904x can drive up to 100 pF with a typical phase margin of 45° and features 350-kHz gain bandwidth product, 0.2-V/ $\mu$ s slew rate with 6.5- $\mu$ V $_{p-p}$  integrated noise (0.1 to 10 Hz) while consuming only 10- $\mu$ A supply current per channel, thus providing a good AC performance at a very low power consumption. DC applications are also well served with a low input bias current of 1 pA (typical), an input offset voltage of 0.6 mV (typical) and a good PSRR, CMRR, and A $_{OL}$ .

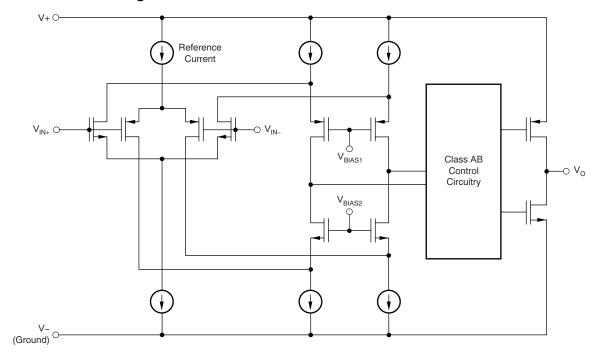

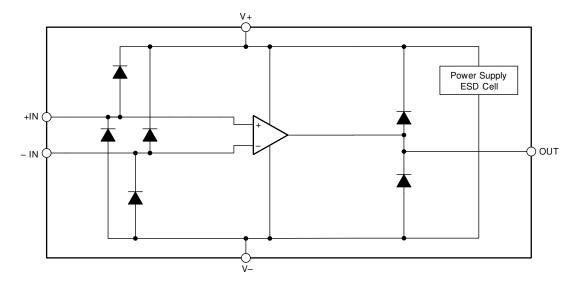

### 8.2 Functional Block Diagram

## **8.3 Feature Description**

#### 8.3.1 Operating Voltage

#### 8.3.2 Rail-to-Rail Input

The input common-mode voltage range of the TLV904x series extends to either supply rails. This is true even when operating at the ultra-low supply voltage of 1.2 V, all the way up to the standard supply voltage of 5.5 V. This performance is achieved with a complementary input stage: an N-channel input differential pair in parallel with a P-channel differential pair. Refer to セクション 8.2 for more details.

For most amplifiers with a complementary input stage, one of the input pairs, usually the P-channel input pair, is designed to deliver slightly better performance in terms of input offset voltage, offset drift over the N-channel pair. Consequently, the P-channel pair is designed to cover the majority of the common mode range with the N-channel pair slated to slowly take over at a certain threshold voltage from the positive rail. Just after the threshold voltage, both the input pairs are in operation for a small range referred to as the transition region. Beyond this region, the N-channel pair completely takes over. Within the transition region, PSRR, CMRR, offset voltage, offset drift, and THD can be degraded compared to device operation outside this region. Hence, most applications generally prefer operating in the P-channel input range where the performance is slightly better.

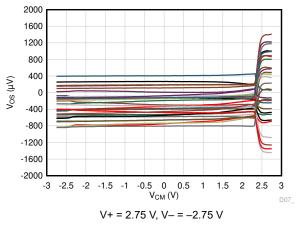

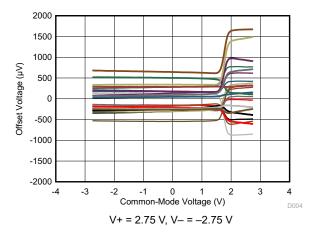

For the TLV904x, the P-channel pair is typically active for input voltages from the negative rail to (V+) - 0.4 V and the N-channel pair is typically active for input voltages from the positive supply to (V+) - 0.4 V. The transition region occurs typically from (V+) - 0.5 V to (V+) - 0.3 V, in which both pairs are on. These voltage levels mentioned above can vary with process variations associated with threshold voltage of transistors. In the TLV904x, 200-mV transition region mentioned above can vary up to 200 mV in either direction. Thus, the transition region (both stages on) can range from (V+) - 0.7 V to (V+) - 0.5 V on the low end, up to (V+) - 0.3 V to (V+) - 0.1 V on the high end.

Recollecting the fact that a P-channel input pair usually offers better performance over a N-channel input pair, the TLV904x is designed to offer a much wider P-channel input pair range, in comparison to most complimentary input amplifiers in the industry. A side by side comparison of the TLV904x and the TLV900x is provided below. Note, that the TLV900x guarantees P-channel pair operation only until 1.4 V from the positive rail while the TLV904x guarantees P-channel pair operation all the way till 0.7 V from the positive rail. This additional 700mV of P-channel input pair range for the TLV904x is particularly useful when operating at lower supply voltages (1.2 V, 1.8 V etc) where the P-channel input range usually gets limited to a great extent.

Thus the wide common mode swing of input signal can be accommodated more easily within the P-channel input pair of the TLV904x, while likely avoiding the transition region, thereby maintaining linearity.

図 8-1. TLV904x Offset Voltage vs Common-Mode

図 8-2. TLV900x Offset Voltage vs Common-Mode

#### 8.3.3 Rail-to-Rail Output

Designed as a micro-power, low-noise operational amplifier, the TLV904x delivers a robust output drive capability. A class AB output stage with common-source transistors is used to achieve full rail-to-rail output swing capability. For resistive loads up to 5 k $\Omega$ , the output typically swings to within 20 mV of either supply rail regardless of the power-supply voltage applied. Different load conditions change the ability of the amplifier to swing close to the rails.

#### 8.3.4 Common-Mode Rejection Ratio (CMRR)

The CMRR for the TLV904x is specified in several ways so the best match for a given application can be used; see the Electrical Characteristics table. First, the CMRR of the device in the common-mode range below the transition region [VCM < (V+) – 0.7 V] is given. This specification is the best indicator of the capability of the device when the application requires using one of the differential input pairs. Second, the CMRR over the entire common-mode range is specified at (VCM = 0 V to 5.5 V). This last value includes the variations measured through the transition region.

#### 8.3.5 Capacitive Load and Stability

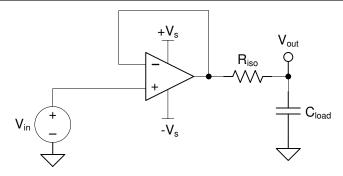

The TLV904x is designed to be used in applications where driving a capacitive load is required. As with all operational amplifiers, there may be specific instances where the TLV904x can become unstable. The particular operational amplifier circuit configuration, layout, gain, and output loading are some of the factors to consider when establishing whether or not an amplifier is stable in operation. An operational amplifier in the unity-gain (1 V/V) buffer configuration that drives a capacitive load exhibits a greater tendency to be unstable than an amplifier operated at a higher noise gain. The capacitive load, in conjunction with the operational amplifier output resistance, creates a pole within the feedback loop that degrades the phase margin. The degradation of the phase margin increases when capacitive loading increases. When operating in the unity-gain configuration, the TLV904x remains stable with a pure capacitive load up to approximately 100 pF with a good phase margin of 45° typical. The equivalent series resistance (ESR) of some very large capacitors ( $C_L$  greater than 1  $\mu$ F) is sufficient to alter the phase characteristics in the feedback loop such that the amplifier remains stable. Increasing the amplifier closed-loop gain allows the amplifier to drive increasingly larger capacitance. This increased capability is evident when measuring the overshoot response of the amplifier at higher voltage gains.

One technique for increasing the capacitive load drive capability of the amplifier operating in a unity-gain configuration is to insert a small resistor (typically 10  $\Omega$  to 20  $\Omega$ ) in series with the output, as shown in  $\boxtimes$  8-3. This resistor significantly reduces the overshoot and ringing associated with large capacitive loads. One possible problem with this technique, however, is that a voltage divider is created with the added series resistor and any resistor connected in parallel with the capacitive load. The voltage divider introduces a gain error at the output that reduces the output swing.

図 8-3. Improving Capacitive Load Drive

#### 8.3.6 Overload Recovery

Overload recovery is defined as the time required for the operational amplifier output to recover from a saturated state to a linear state. The output devices of the operational amplifier enter a saturation region when the output voltage exceeds the rated operating voltage, because of the high input voltage or high gain. Once one of the output devices enters the saturation region, the output stage requires additional time to return to the linear operating state which is referred to as overload recovery time. After the output stage returns to its linear operating state, the amplifier begins to slew at the specified slew rate. Therefore, the propagation delay (in case of an overload condition) is the sum of the overload recovery time and the slew time. The overload recovery time for the TLV904x family is approximately 13-µs typical.

#### 8.3.7 EMI Rejection

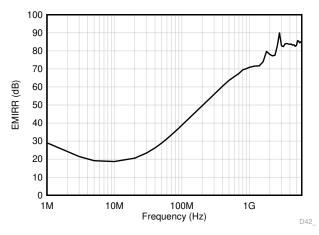

The TLV904x uses integrated electromagnetic interference (EMI) filtering to reduce the effects of EMI from sources such as wireless communications and densely-populated boards with a mix of analog signal chain and digital components. EMI immunity can be improved with circuit design techniques; the TLV904x benefits from these design improvements. Texas Instruments has developed the ability to accurately measure and quantify the immunity of an operational amplifier over a broad frequency spectrum extending from 10 MHz to 6 GHz. 図 8-4 shows the results of this testing on the TLV904x. 表 8-1 shows the EMIRR IN+ values for the TLV904x at particular frequencies commonly encountered in real-world applications. The *EMI Rejection Ratio of Operational Amplifiers* application report contains detailed information on the topic of EMIRR performance as it relates to op amps and is available for download from www.ti.com.

図 8-4. EMIRR Testing

表 8-1. TLV904x EMIRR IN+ for Frequencies of Interest

|           | 24.1                                                                                                     |       |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| FREQUENCY | FREQUENCY APPLICATION OR ALLOCATION                                                                      |       |  |  |  |  |  |

| 400 MHz   | Mobile radio, mobile satellite, space operation, weather, radar, ultra-high frequency (UHF) applications | 60 dB |  |  |  |  |  |

表 8-1. TLV904x EMIRR IN+ for Frequencies of Interest (continued)

| FREQUENCY | APPLICATION OR ALLOCATION                                                                                                                                                        | EMIRR IN+ |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| 900 MHz   | Global system for mobile communications (GSM) applications, radio communication, navigation, GPS (to 1.6 GHz), GSM, aeronautical mobile, UHF applications                        | 70 dB     |  |  |  |  |  |

| 1.8 GHz   | 1.8 GHz GSM applications, mobile personal communications, broadband, satellite, L-band (1 GHz to 2 GHz)                                                                          |           |  |  |  |  |  |

| 2.4 GHz   | 802.11b, 802.11g, 802.11n, Bluetooth®, mobile personal communications, industrial, scientific and medical (ISM) radio band, amateur radio and satellite, S-band (2 GHz to 4 GHz) |           |  |  |  |  |  |

| 3.6 GHz   | Radiolocation, aero communication and navigation, satellite, mobile, S-band                                                                                                      | 82 dB     |  |  |  |  |  |

| 5 GHz     | 802.11a, 802.11n, aero communication and navigation, mobile communication, space and satellite operation, C-band (4 GHz to 8 GHz)                                                | 85 dB     |  |  |  |  |  |

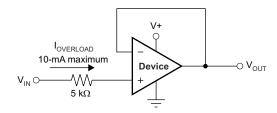

#### 8.3.8 Electrical Overstress

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but can involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

Having a good understanding of this basic ESD circuitry and its relevance to an electrical overstress event is helpful.  $\boxtimes$  8-5 shows the ESD circuits contained in the TLV904x devices. The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power supply lines, where they meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

図 8-5. Equivalent Internal ESD Circuitry

#### 8.3.9 Input and ESD Protection

The TLV904x family incorporates internal ESD protection circuits on all pins. For input and output pins, this protection primarily consists of current-steering diodes connected between the input and power-supply pins. These ESD protection diodes provide in-circuit, input overdrive protection, as long as the current is limited to 10 mA.  $\boxtimes$  8-6 shows how a series input resistor can be added to the driven input to limit the input current. The added resistor contributes thermal noise at the amplifier input and the value must be kept to a minimum in noise-sensitive applications.

図 8-6. Input Current Protection

#### 8.3.10 Shutdown Function

The TLV904xS devices feature  $\overline{SHDN}$  pins that disable the op amp, placing it into a low-power standby mode. In this mode, the op amp typically consumes less than 150 nA. The  $\overline{SHDN}$  pins are active low, meaning that shutdown mode is enabled when the input to the  $\overline{SHDN}$  pin is a valid logic low.

The  $\overline{SHDN}$  pins are referenced to the negative supply voltage of the op amp. The threshold of the shutdown feature lies around 500 mV (typical) and does not change with respect to the supply voltage. Hysteresis has been included in the switching threshold to ensure smooth switching characteristics. To ensure optimal shutdown behavior, the  $\overline{SHDN}$  pins should be driven with valid logic signals. A valid logic low is defined as a voltage between V– and V– + 0.2 V. A valid logic high is defined as a voltage between V– + 1 V and V+. To enable the amplifier, the  $\overline{SHDN}$  pins must be driven to a valid logic high. To disable the amplifier, the  $\overline{SHDN}$  pins must be driven to a valid logic low. We highly recommend that the shutdown pin be connected to a valid high or a low voltage or driven. The maximum voltage allowed at the  $\overline{SHDN}$  pins is (V+) + 0.5 V. Exceeding this voltage level will damage the device.

The  $\overline{SHDN}$  pins are high-impedance CMOS inputs. Dual op amp versions are independently controlled and quad op amp versions are controlled in pairs with logic inputs. For battery-operated applications, this feature may be used to greatly reduce the average current and extend battery life. The enable time is 160  $\mu$ s for full shutdown of all channels; disable time is 10  $\mu$ s. When disabled, the output assumes a high-impedance state. This architecture allows the TLV904xS to be operated as a gated amplifier (or to have the device output multiplexed onto a common analog output bus). Shutdown time ( $t_{OFF}$ ) depends on loading conditions and increases as load resistance increases. To ensure shutdown (disable) within a specific shutdown time, the specified 100-k $\Omega$  load to midsupply ( $V_S$  / 2) is required. If using the TLV904xS without a load, the resulting turnoff time is significantly increased.

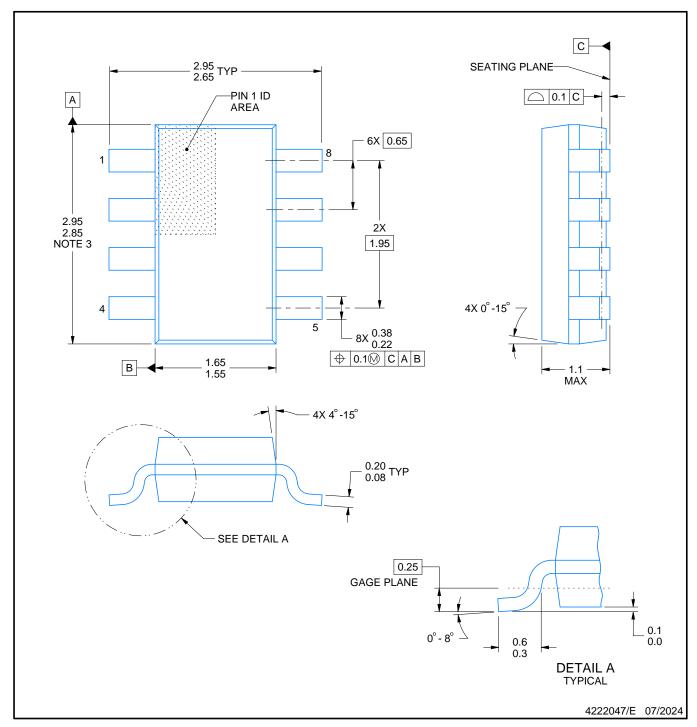

### 8.3.11 Packages With an Exposed Thermal Pad

The TLV904x family is available in packages such as the WQFN-16 (RTE) which feature an exposed thermal pad. Inside the package, the die is attached to this thermal pad using an electrically conductive compound. For this reason, when using a package with an exposed thermal pad, the thermal pad must either be connected to V— or left floating. Attaching the thermal pad to a potential other then V— is not allowed, and the performance of the device is not assured when doing so.

### 8.4 Device Functional Modes

The TLV904x devices have a single functional mode. These devices are powered on as long as the power-supply voltage is between 1.2 V ( $\pm 0.6$  V) and 5.5 V ( $\pm 2.75$  V).

The TLV904xS devices feature a shutdown pin, which can be used to place the op amp into a low-power mode. See セクション 8.3.10 for more information.

## 9 Application and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 9.1 Application Information

The TLV904x family of low-power, rail-to-rail input and output operational amplifiers is specifically designed for portable applications. The devices operate from 1.2 V to 5.5 V, are unity-gain stable, and are suitable for a wide range of general-purpose applications. The class AB output stage is capable of driving resitive loads greater than  $2-k\Omega$  connected to any point between V+ and V−. The input common-mode voltage range includes both rails and allows the TLV904x series to be used in many single-supply or dual supply configurations.

### 9.2 Typical Application

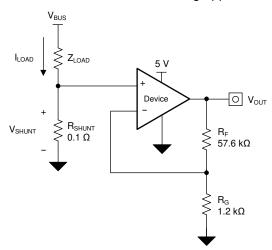

## 9.2.1 TLV904x Low-Side, Current Sensing Application

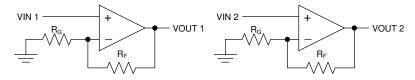

図 9-1. TLV904x in a Low-Side, Current-Sensing Application

#### 9.2.1.1 Design Requirements

The design requirements for this design are:

Load current: 0 A to 1 A

Maximum output voltage: 4.9 VMaximum shunt voltage: 100 mV

#### 9.2.1.2 Detailed Design Procedure

The transfer function of the circuit in  $\boxtimes$  9-1 is given in  $\rightrightarrows$  1.

$$V_{OUT} = I_{LOAD} \times R_{SHUNT} \times Gain$$

(1)

The load current ( $I_{LOAD}$ ) produces a voltage drop across the shunt resistor ( $R_{SHUNT}$ ). The load current is set from 0 A to 1 A. To keep the shunt voltage below 100 mV at maximum load current, the largest shunt resistor is shown using  $\pm 2$ .

$$R_{SHUNT} = \frac{V_{SHUNT\_MAX}}{I_{LOAD\_MAX}} = \frac{100mV}{1A} = 100m\Omega$$

(2)

Using  $\stackrel{\ \, }{\not \sim} 2$ ,  $R_{SHUNT}$  is calculated to be 100 m $\Omega$ . The voltage drop produced by  $I_{LOAD}$  and  $R_{SHUNT}$  is amplified by the TLV904x to produce an output voltage of approximately 0 V to 4.9 V. The gain needed by the TLV904x to produce the necessary output voltage is calculated using  $\stackrel{\ \, }{\not \sim} 3$ .

$$Gain = \frac{\left(V_{OUT\_MAX} - V_{OUT\_MIN}\right)}{\left(V_{IN\_MAX} - V_{IN\_MIN}\right)}$$

(3)

Using  $\not \equiv 3$ , the required gain is calculated to be 49 V/V, which is set with resistors R<sub>F</sub> and R<sub>G</sub>.  $\not \equiv 4$  sizes the resistors R<sub>F</sub> and R<sub>G</sub>, to set the gain of the TLV904x to 49 V/V.

$$Gain = 1 + \frac{(R_F)}{(R_G)}$$

(4)

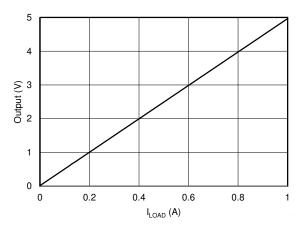

Selecting  $R_F$  as 57.6 k $\Omega$  and  $R_G$  as 1.2 k $\Omega$  provides a combination that equals 49 V/V.  $\boxtimes$  9-2 shows the measured transfer function of the circuit shown in  $\boxtimes$  9-1. Notice that the gain is only a function of the feedback and gain resistors. This gain is adjusted by varying the ratio of the resistors and the actual resistors values are determined by the impedance levels that the designer wants to establish. The impedance level determines the current drain, the effect that stray capacitance has, and a few other behaviors. There is no optimal impedance selection that works for every system; you must choose an impedance that is ideal for your system parameters.

## 9.2.1.3 Application Curve

図 9-2. Low-Side, Current-Sense Transfer Function

## 10 Power Supply Recommendations

The TLV904x family is specified for operation from 1.2 V to 5.5 V ( $\pm$ 0.6 V to  $\pm$ 2.75 V); many specifications apply from  $-40^{\circ}$ C to 125°C.  $\pm 299$  7.7 presents parameters that may exhibit significant variance with regard to operating voltage or temperature.

#### **CAUTION**

Supply voltages larger than 6 V may permanently damage the device; see the *Absolute Maximum Ratings* table.

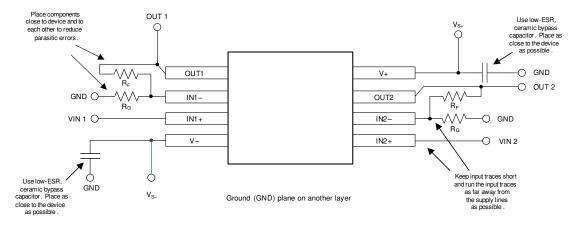

Place 0.1-µF bypass capacitors close to the power-supply pins to reduce coupling errors from noisy or high-impedance power supplies. For more detailed information on bypass capacitor placement, see セクション 11.1.

### 11 Layout

## 11.1 Layout Guidelines

For best operational performance of the device, use good printed circuit board (PCB) layout practices, including:

- Noise can propagate into analog circuitry through the power connections of the board and propagate to the

power pins of the op amp itself. Bypass capacitors are used to reduce the coupled noise by providing a lowimpedance path to ground.

- Connect low-ESR, 0.1-μF ceramic bypass capacitors between each supply pin and ground, placed as

close to the device as possible. A single bypass capacitor from V+ to ground is adequate for single-supply

applications.

- Separate grounding for analog and digital portions of circuitry is one of the simplest and most effective methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes. A ground plane helps distribute heat and reduces electromagnetic interference (EMI) noise pickup. Take care to physically separate digital and analog grounds, paying attention to the flow of the ground current.

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If these traces cannot be kept separate, crossing the sensitive trace at a 90 degree angle is much better as opposed to running the traces in parallel with the noisy trace.

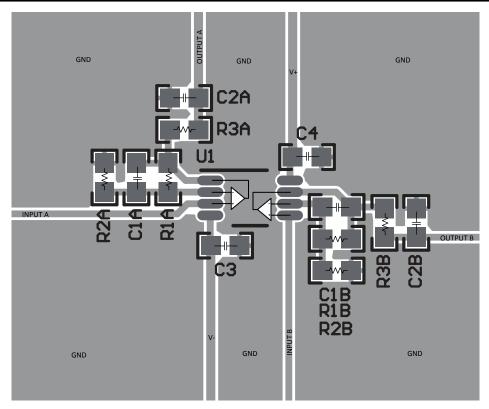

- Place the external components as close to the device as possible, as shown in ⊠ 11-2. Keeping R<sub>F</sub> and R<sub>G</sub> close to the inverting input minimizes parasitic capacitance.

- Keep the length of input traces as short as possible. Remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring may significantly reduce leakage currents from nearby traces that are at different potentials.

- · Cleaning the PCB following board assembly is recommended for best performance.

- Any precision integrated circuit can experience performance shifts resulting from moisture ingress into the

plastic package. Following any aqueous PCB cleaning process, baking the PCB assembly is recommended

to remove moisture introduced into the device packaging during the cleaning process. A low-temperature,

post-cleaning bake at 85°C for 30 minutes is sufficient for most circumstances.

#### 11.2 Layout Example

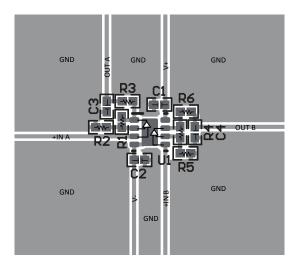

図 11-1. Schematic Representation

図 11-2. Layout Example

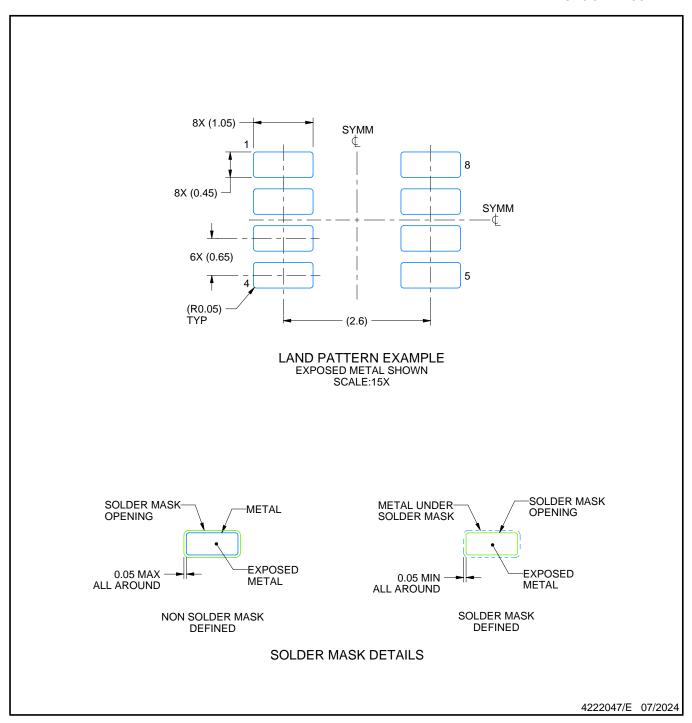

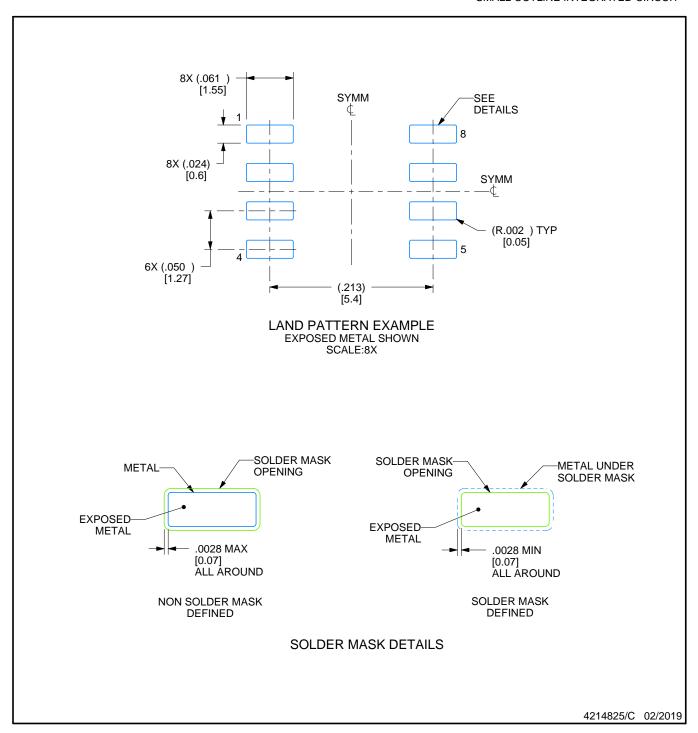

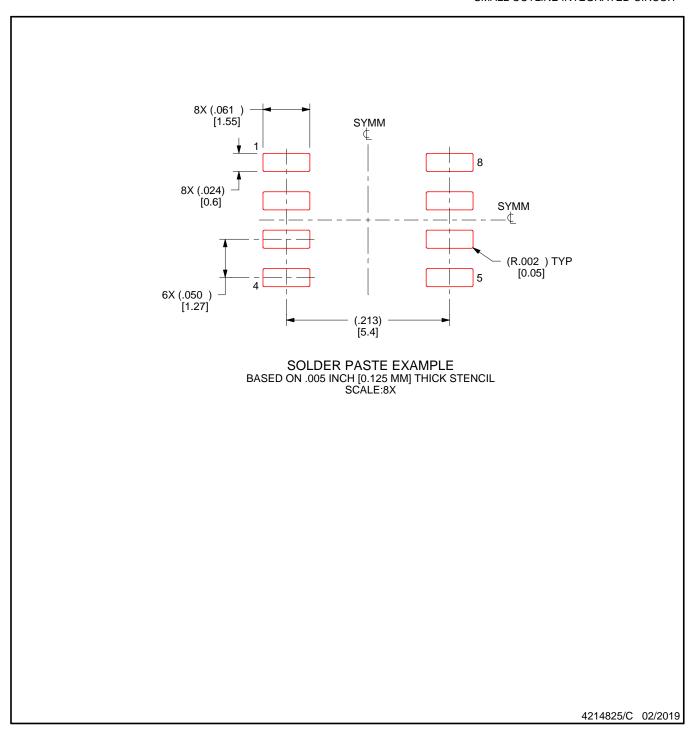

図 11-3. Example Layout for VSSOP-8 (DGK) Package

図 11-4. Example Layout for WSON-8 (DSG) Package

## 12 Device and Documentation Support

## 12.1 Documentation Support

#### 12.1.1 Related Documentation

For related documentation see the following:

- EMI rejection ratio of operational amplifiers

- QFN/SON PCB attachment

- · Quad flatpack no-lead logic packages

## 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### **Trademarks**

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

Bluetooth® is a registered trademark of Bluetooth SIG, Inc.

すべての商標は、それぞれの所有者に帰属します。

### 12.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

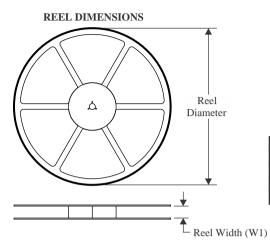

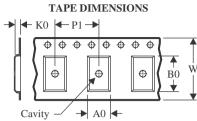

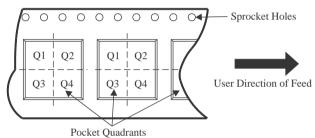

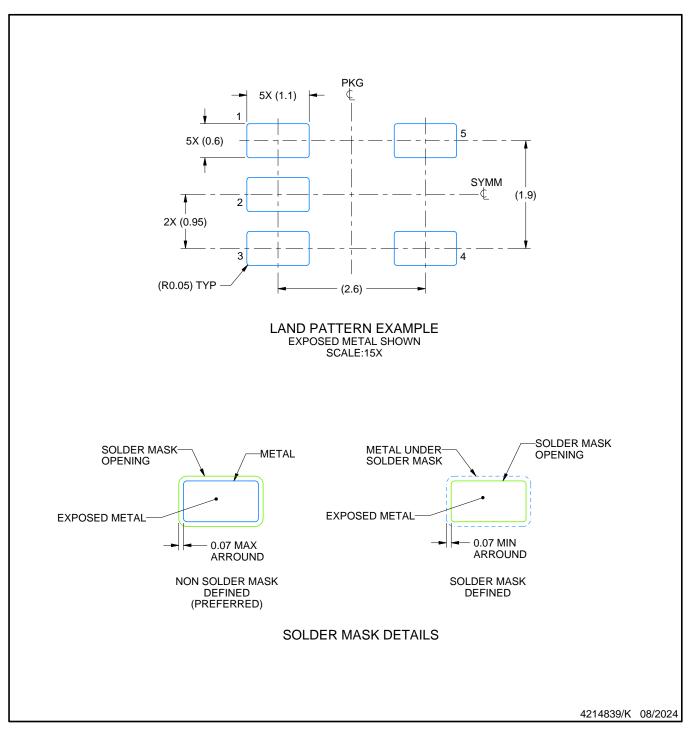

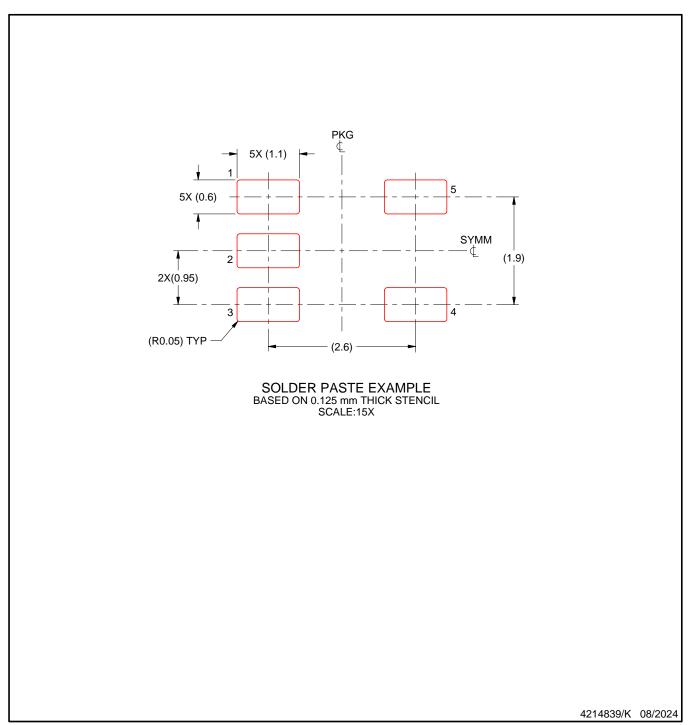

#### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

6-Dec-2025

## **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins        | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|-----------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TLV9041IDBVR          | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | T041             |

| TLV9041IDBVR.A        | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T041             |

| TLV9041IDBVRG4        | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T041             |

| TLV9041IDBVRG4.A      | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T041             |

| TLV9041IDCKR          | Active     | Production    | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 1IV              |

| TLV9041IDCKR.A        | Active     | Production    | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 1IV              |

| TLV9041IDPWR          | Active     | Production    | X2SON (DPW)   5       | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | (L, LE)          |

| TLV9041IDPWR.A        | Active     | Production    | X2SON (DPW)   5       | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | (L, LE)          |

| TLV9041IDPWRG4        | Active     | Production    | X2SON (DPW)   5       | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | L                |

| TLV9041IDPWRG4.A      | Active     | Production    | X2SON (DPW)   5       | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | L                |

| TLV9041SIDBVR         | Active     | Production    | SOT-23 (DBV)   6      | 3000   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | T41S             |

| TLV9041SIDBVR.A       | Active     | Production    | SOT-23 (DBV)   6      | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | T41S             |

| TLV9041SIDBVRG4       | Active     | Production    | SOT-23 (DBV)   6      | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T41S             |

| TLV9041SIDBVRG4.A     | Active     | Production    | SOT-23 (DBV)   6      | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T41S             |

| TLV9041UIDBVR         | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | U041             |

| TLV9041UIDBVR.A       | Active     | Production    | SOT-23 (DBV)   5      | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | U041             |

| TLV9042IDDFR          | Active     | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T042             |

| TLV9042IDDFR.A        | Active     | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T042             |

| TLV9042IDGKR          | Active     | Production    | VSSOP (DGK)   8       | 2500   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | 2H7T             |

| TLV9042IDGKR.A        | Active     | Production    | VSSOP (DGK)   8       | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 2H7T             |

| TLV9042IDR            | Active     | Production    | SOIC (D)   8          | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | T9042D           |