**TMCS1100**

JAJSHX1B - SEPTEMBER 2019 - REVISED JULY 2021

# TMCS1100 動作電圧 ±600V、高精度 1%、基本絶縁ホール・エフェクト電流セ ンサ

# 1 特長

合計エラー:±0.4% (標準値)、±0.9% (最大値)、-40°C~85°C

- 感度誤差:±0.4% - オフセット誤差:7mA

- オフセット・ドリフト: 0.04mA/℃

- 直線性誤差:0.05%

寿命と環境によるドリフト:±0.5% 未満

絶縁定格:3kV<sub>RMS</sub>

• 寿命を通じての堅牢な使用電圧:600V

双方向および単方向の電流センシング

外部基準電圧

動作電源電圧範囲:3V~5.5V

信号带域幅:80kHz

各種感度を選択可能

TMCS1100A1:50mV/A TMCS1100A2:100mV/A TMCS1100A3:200mV/A TMCS1100A4:400mV/A

安全関連の認定

- UL 1577 部品認定プログラム

- IEC/CB 62368-1

# 2 アプリケーション

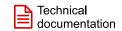

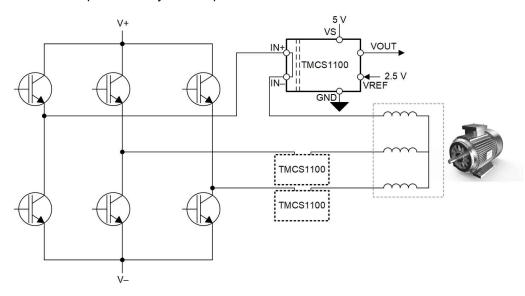

モーターおよび負荷制御

- インバータおよび H ブリッジ電流測定

- 力率補正

- 過電流保護

- DC および AC 電力監視

# 3 概要

TMCS1100 は、精度が高く、直線性に優れ、温度に対し て安定性の高い DC または AC 電流測定が可能なガル バニック絶縁ホール・エフェクト電流センサです。低ドリフト で、温度補償された信号チェーンにより、デバイスの温度 範囲全体にわたって、フルスケールで 1% 未満に誤差を 抑えています。

入力電流は 1.8mΩ の内部導体を通して流れ、そこで発 生する磁界を内蔵ホール・エフェクト・センサで測定しま す。この構造により、外部コンセントレータが不要になり、 設計が簡素化されます。導体の抵抗が小さいため、電力 損失と熱放散が最小限に抑えられます。ガルバニック絶縁 が本質的に備える優れた絶縁性により、全寿命にわたっ て 600V の動作電圧、電流パスと回路との間で 3 kV<sub>RMS</sub> の基本絶縁を達成します。内蔵の電気的シールドにより、 優れた同相除去と過渡耐性を実現しています。

出力電圧は入力電流に比例しており、4種類の感度を選 択できます。 固定感度とすることで、 TMCS1100 は 3V~ 5.5V の単一電源で動作でき、レシオメトリック誤差をなく し、電源ノイズ除去を向上させています。電流の極性は、 正の入力ピンに流れ込む方向を正としています。VREF 入力ピンにより、ゼロ電流時の出力電圧を変更でき、双方 向または単方向の電流センシングが可能です。

TMCS1100 の最大消費電流は 6mA であり、すべての感 度バリアントは -40℃~+125℃ の動作温度範囲で仕様 が規定されています。

### 製品情報(1)

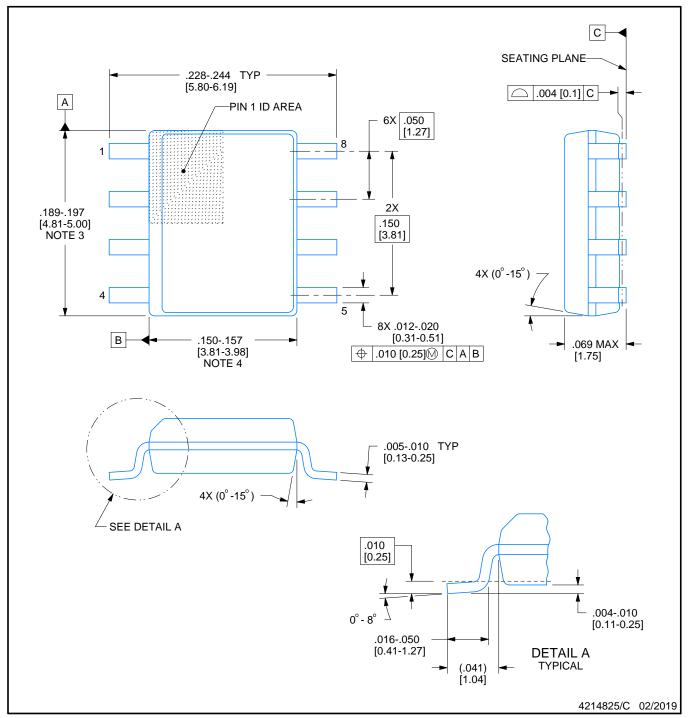

| 部品番号     | パッケージ    | 本体サイズ (公称)      |

|----------|----------|-----------------|

| TMCS1100 | SOIC (8) | 4.90mm × 3.90mm |

提供されているすべてのパッケージについては、データシートの 末尾にあるパッケージ・オプションについての付録を参照してくだ さい。

代表的なアプリケーション

Page

# **Table of Contents**

| Changes from Revision * (September 2019) to F   | Revisi  | ion A (June 2020)                                      | age |

|-------------------------------------------------|---------|--------------------------------------------------------|-----|

| • 「特長」セクションの安全関連の認定の箇条書き項                       | 目から<br> | 「予定」を削除                                                | 1   |

|                                                 |         | Ť                                                      |     |

| Changes from Revision A (June 2020) to Revisi   |         |                                                        | age |

| 4 Revision History                              |         |                                                        |     |

|                                                 |         |                                                        |     |

| 8.3 Safe Operating Area  9 Detailed Description |         | IIIOIIIauoii                                           | 4   |

| 8.2 Transient Response Parameters               |         | 14 Mechanical, Packaging, and Orderable Information    | 41  |

| 8.1 Accuracy Parameters                         |         | 13.7 Glossary                                          | 41  |

| 8 Parameter Measurement Information             |         | 13.6 Electrostatic Discharge Caution                   |     |

| 7.10 Typical Characteristics                    |         | 13.5 Trademarks                                        |     |

| 7.9 Electrical Characteristics                  | 7       | 13.4 サポート・リソース                                         |     |

| 7.8 Safety Limiting Values                      |         | 13.3 Receiving Notification of Documentation Updates   |     |

| 7.7 Safety-Related Certifications               |         | 13.2 Documentation Support                             |     |

| 7.6 Insulation Specifications                   |         | 13.1 Device Support                                    |     |

| 7.5 Power Ratings                               |         | 13 Device and Documentation Support                    | 41  |

| 7.4 Thermal Information                         |         | 12.2 Layout Example                                    | 40  |

| 7.3 Recommended Operating Conditions            |         | 12.1 Layout Guidelines                                 | 39  |

| 7.2 ESD Ratings                                 |         | 12 Layout                                              |     |

| 7.1 Absolute Maximum Ratings                    |         | 11 Power Supply Recommendations                        |     |

| 7 Specifications                                |         | 10.2 Typical Application                               |     |

| 5 Device Comparison                             |         | 10.1 Application Information                           |     |

| 4 Revision History                              |         | 10 Application and Implementation                      |     |

| 3 概要                                            |         | 9.3 Feature Description<br>9.4 Device Functional Modes |     |

| 2 アプリケーション                                      |         | 0.3 Feature Description                                | 2/  |

| <b>ラ</b> アプリゲード/コン                              |         | 9.2 Functional Block Diagram                           | 24  |

# **5 Device Comparison**

# 表 5-1. Device Comparison

| PRODUCT    | SENSITIVITY                                 | BIDIRECTIONAL LINI<br>RANGE, V <sub>R</sub> |                        | UNIDIRECTIONAL LINEAR MEASUREME<br>RANGE, V <sub>REF</sub> = V <sub>GND</sub> <sup>(1)</sup> |                              |  |

|------------|---------------------------------------------|---------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|------------------------------|--|

|            | ΔV <sub>OUT</sub> / ΔI <sub>IN+, IN</sub> _ | V <sub>S</sub> = 5 V                        | V <sub>S</sub> = 3.3 V | V <sub>S</sub> = 5 V                                                                         | V <sub>S</sub> = 3.3 V       |  |

| TMCS1100A1 | 50 mV/A                                     | ±46 A <sup>(2)</sup>                        | ±29 A <sup>(2)</sup>   | 1 A to 96 A <sup>(2)</sup>                                                                   | 1 A to 62 A <sup>(2)</sup>   |  |

| TMCS1100A2 | 100 mV/A                                    | ±23 A <sup>(2)</sup>                        | ±14.5 A                | 0.5 A to 48 A <sup>(2)</sup>                                                                 | 0.5 A to 31 A <sup>(2)</sup> |  |

| TMCS1100A3 | 200 mV/A                                    | ±11.5 A                                     | ±7.25 A                | 0.25 A to 24 A <sup>(2)</sup>                                                                | 0.25 A to 15.5 A             |  |

| TMCS1100A4 | 400 mV/A                                    | ±5.75 A                                     |                        | 0.125 A to 12 A                                                                              |                              |  |

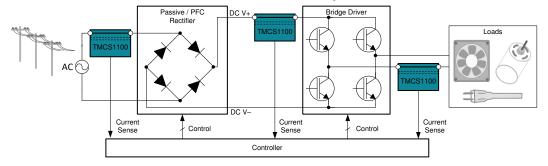

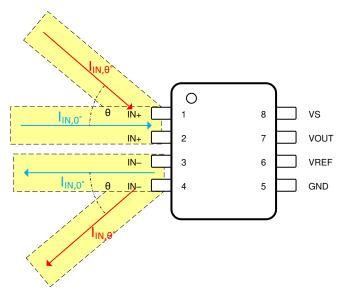

# **6 Pin Configuration and Functions**

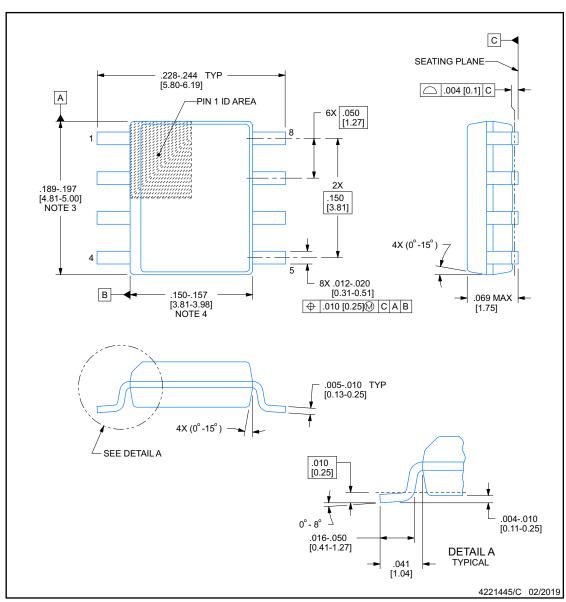

図 6-1. D Package 8-Pin SOIC Top View

表 6-1. Pin Functions

|     | PIN  | 1/0           | DESCRIPTION                           |

|-----|------|---------------|---------------------------------------|

| NO. | NAME | 1/0           | DESCRIPTION                           |

| 1   | IN+  | Analog input  | Input current positive pin            |

| 2   | IN+  | Analog input  | Input current positive pin            |

| 3   | IN-  | Analog input  | Input current negative pin            |

| 4   | IN-  | Analog input  | Input current negative pin            |

| 5   | GND  | Analog        | Ground                                |

| 6   | VREF | Analog input  | Zero current output voltage reference |

| 7   | VOUT | Analog output | Output voltage                        |

| 8   | VS   | Analog        | Power supply                          |

Linear range limited by swing to supply and ground.

Current levels must remain below both allowable continuous DC/RMS and transient peak current safe operating areas to not exceed device thermal limits. See the Safe Operating Area section.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                      |      | MIN       | MAX           | UNIT |

|------------------|----------------------|------|-----------|---------------|------|

| Vs               | Supply voltage       |      | GND - 0.3 | 6             | V    |

|                  | Analog input         | VREF | GND – 0.3 | $(V_S) + 0.3$ | V    |

|                  | Analog output        | VOUT | GND - 0.3 | $(V_S) + 0.3$ | V    |

| TJ               | Junction temperature | ·    | -65       | 150           | °C   |

| T <sub>stg</sub> | Storage temperature  |      | -65       | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                        |                                         | MIN  | NOM | MAX | UNIT            |

|----------------------------------------|-----------------------------------------|------|-----|-----|-----------------|

| V <sub>IN+</sub> ,V <sub>IN-</sub> (1) | Input voltage                           | -600 |     | 600 | V <sub>PK</sub> |

| Vs                                     | Operating supply voltage, TMCS1100A1-A3 | 3    | 5   | 5.5 | V               |

| Vs                                     | Operating supply voltage, TMCS1100A4    | 4.5  | 5   | 5.5 | V               |

| T <sub>A</sub> <sup>(2)</sup>          | Operating free-air temperature          | -40  |     | 125 | °C              |

- (1)  $V_{IN+}$  and  $V_{IN-}$  refer to the voltage at input current pins IN+ and IN-, relative to pin 5 (GND).

- (2) Input current safe operating area is constrained by junction temperature. Recommended condition based on the TMCS1100EVM. Input current rating is derated for elevated ambient temperatures.

#### 7.4 Thermal Information

|                       |                                                                                                                                                                                                                   | TMCS1100 (2) |      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|

|                       | Junction-to-ambient thermal resistance  Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter  Junction-to-board characterization parameter | D (SOIC)     | UNIT |

|                       |                                                                                                                                                                                                                   | 8 PINS       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance                                                                                                                                                                            | 36.6         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                                                                                                                                                                         | 50.7         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance                                                                                                                                                                              | 9.6          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                                                                                                                                                                        | -0.1         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter                                                                                                                                                                      | 11.7         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                                                                                                                                                      | N/A          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: TMCS1100

(2) Applies when device mounted on TMCS1100EVM . For more details, see the Safe Operating Area section.

Submit Document Feedback

# 7.5 Power Ratings

$V_S$  = 5.5 V,  $V_{REF}$  = GND,  $T_A$  = 125°C,  $T_J$  = 150°C, device soldered on TMCS1100EVM .

|                 | PARAMETER                                         | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| P <sub>D</sub>  | Maximum power dissipation (both sides)            |                                                               |     |     | 673 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (current input, side-1) | I <sub>IN</sub> = 16 A                                        |     |     | 640 | mW   |

| P <sub>D2</sub> | Maximum power dissipation by (side-2)             | $V_S = 5.5 \text{ V}, I_Q = 6\text{mA}, \text{ no VOUT load}$ |     | -   | 33  | mW   |

# 7.6 Insulation Specifications

|                   | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                                                                          | VALUE             | UNIT             |

|-------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|

| GENER             | AL                                                   |                                                                                                                                                                                                                          |                   |                  |

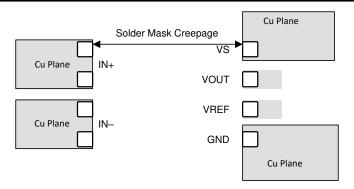

| CLR               | External clearance <sup>(1)</sup>                    | Shortest terminal-to-terminal distance through air                                                                                                                                                                       | 4                 | mm               |

| CPG               | External creepage <sup>(1)</sup>                     | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                        | 4                 | mm               |

| DTI               | Distance through the insulation                      | Minimum internal gap (internal clearance)                                                                                                                                                                                | 60                | μm               |

| CTI               | Comparative tracking index                           | DIN EN 60112; IEC 60112                                                                                                                                                                                                  | >400              | V                |

|                   | Material group                                       |                                                                                                                                                                                                                          | II                |                  |

|                   | Overveltage estagen.                                 | Rated mains voltage ≤ 150 V <sub>RMS</sub>                                                                                                                                                                               | I-IV              |                  |

|                   | Overvoltage category                                 | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                                                               | 1-111             |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage            | AC voltage (bipolar)                                                                                                                                                                                                     | 600               | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | Maximum working isolation voltage                    | AC voltage (sine wave); Time Dependent Dielectric Breakdown test, see Insulation Lifetime.                                                                                                                               | 424               | V <sub>RMS</sub> |

|                   |                                                      | DC voltage                                                                                                                                                                                                               | 600<br>4242       | V <sub>DC</sub>  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                  | $V_{TEST} = V_{IOTM} = 4242V_{PK}$ , $t = 60$ s (qualification); $V_{TEST} = 1.2 \times V_{IOTM} = 5090V_{PK}$ , $t = 1$ s (100% production)                                                                             | 4242              | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>(2)</sup>       | Test method per IEC 62368-1, 1.2/50 µs waveform,<br>V <sub>TEST</sub> = 1.3 × V <sub>IOSM</sub> = 7800V <sub>PK</sub> (qualification)                                                                                    | 6000              | V <sub>PK</sub>  |

|                   |                                                      | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM} = 4242V_{PK}, t_{ini} = 60 \text{ s};$ $V_{pd(m)} = 1.2 \times V_{IORM} = 700V_{PK}, t_m = 10 \text{ s}$                                               | ≤5                |                  |

| $q_{pd}$          | Apparent charge <sup>(3)</sup>                       | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM} = 4242 V_{PK}, t_{ini} = 60 \text{ s};$ $V_{pd(m)} = 1.2 \times V_{IORM} = 700 V_{PK}, t_m = 10 \text{ s}$                                           | ≤5                | pC               |

|                   |                                                      | Method b3: At routine test (100% production) and preconditioning (type test) $V_{ini} = 1.2 \times V_{IOTM} = 5090 V_{PK}, t_{ini} = 1 \text{ s}; \\ V_{pd(m)} = 1.2 \times V_{IOTM} = 5090 V_{PK}, t_{m} = 1 \text{ s}$ | ≤5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>(4)</sup>  | V <sub>IO</sub> = 0.4 sin (2πft), f = 1 MHz                                                                                                                                                                              | 0.6               | pF               |

|                   |                                                      | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                           | >10 <sup>12</sup> | Ω                |

| $R_{IO}$          | Isolation resistance, input to output <sup>(4)</sup> | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                                                  | >10 <sup>11</sup> | Ω                |

|                   |                                                      | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                        | >109              | Ω                |

|                   | Pollution degree                                     |                                                                                                                                                                                                                          | 2                 |                  |

| UL 1577           | 7                                                    |                                                                                                                                                                                                                          |                   | 1                |

| V <sub>ISO</sub>  | Withstand isolation voltage                          | $V_{TEST}$ = $V_{ISO}$ , t = 60 s (qualification); $V_{TEST}$ = 1.2 × $V_{ISO}$ , t = 1 s (100% production)                                                                                                              | 3000              | V <sub>RMS</sub> |

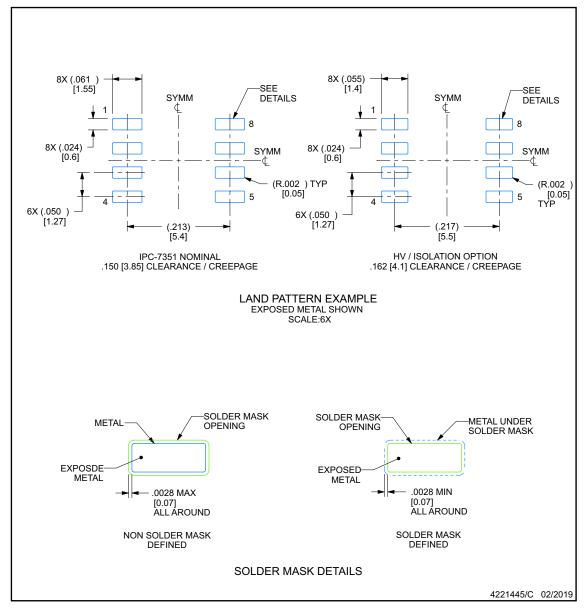

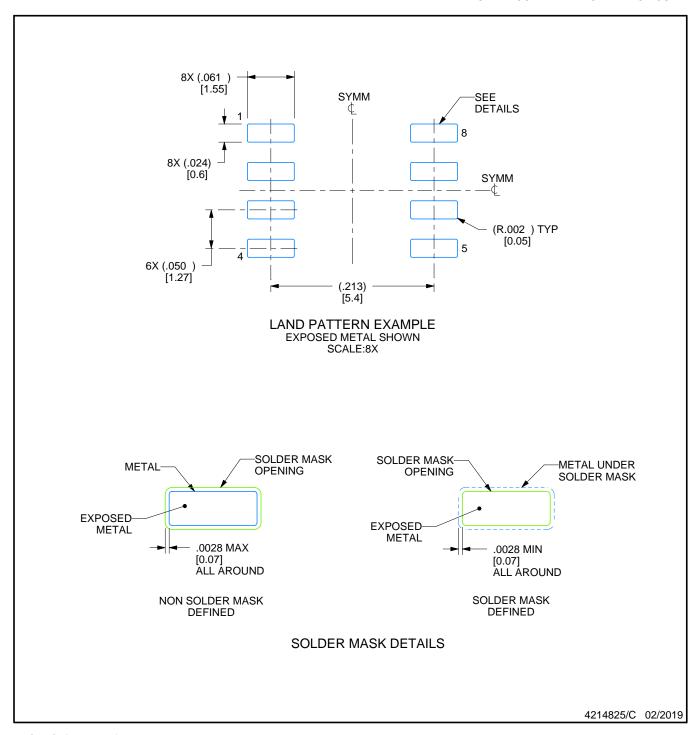

<sup>(1)</sup> Apply creepage and clearance requirements according to the specific equipment isolation standards of an application. Take care to maintain the creepage and clearance distance of the board design to make sure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

<sup>2)</sup> Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (3) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (4) All pins on each side of the barrier tied together creating a two-terminal device

### 7.7 Safety-Related Certifications

|                                       | UL                                    |

|---------------------------------------|---------------------------------------|

| UL 1577 Component Recognition Program | Certified according to IEC 62368-1 CB |

| File number: E181974                  | Certificate number: US-36733-UL       |

# 7.8 Safety Limiting Values

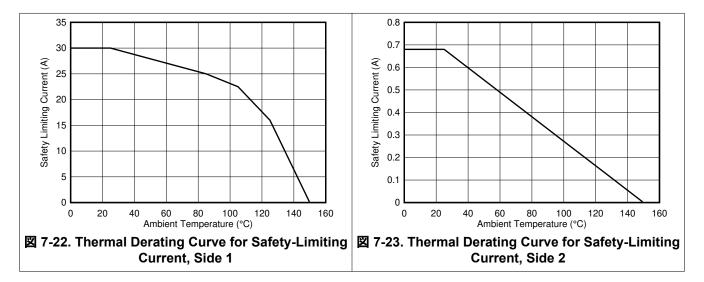

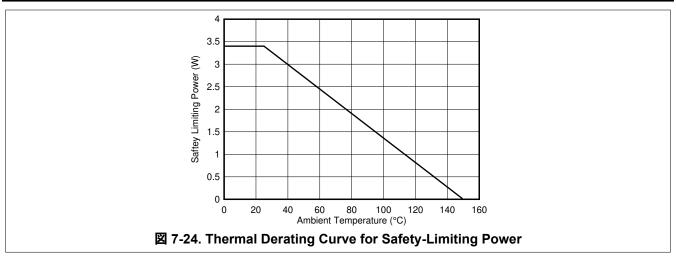

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

| PARAMETER      |                                                                 | TEST CONDITIONS                                                                                              | MIN | TYP | MAX  | UNIT |

|----------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Is             | Safety input current (side 1) <sup>(1)</sup>                    | $R_{\theta JA}$ = 36.6°C/W, $T_J$ = 150°C, $T_A$ = 25°C, see Thermal Derating Curve, Side 1.                 |     |     | 30   | ۸    |

| Is             | Safety input, output, or supply current (side 2) <sup>(1)</sup> | $R_{\theta JA} = 36.6$ °C/W, $V_I = 5$ V, $T_J = 150$ °C, $T_A = 25$ °C, see Thermal Derating Curve, Side 2. |     |     | 0.68 | Α    |

| Ps             | Safety input, output, or total power <sup>(1)</sup>             | $R_{\theta JA}$ = 36.6°C/W, $T_J$ = 150°C, $T_A$ = 25°C, see Thermal Derating Curve, Both Sides.             |     |     | 3.4  | W    |

| T <sub>S</sub> | Safety temperature <sup>(1)</sup>                               |                                                                                                              |     |     | 150  | °C   |

(1) The maximum safety temperature, T<sub>S</sub>, has the same value as the maximum junction temperature, T<sub>J</sub>, specified for the device. The I<sub>S</sub> and P<sub>S</sub> parameters represent the safety current and safety power respectively. The maximum limits of I<sub>S</sub> and P<sub>S</sub> should not be exceeded. These limits vary with the ambient temperature, T<sub>A</sub>.

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the *Thermal Information* table is that of a device installed on the TMCS1100EVM . Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.

$P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

# 7.9 Electrical Characteristics

at  $T_A = 25^{\circ}C$ .  $V_C = 5 \text{ V}$   $V_D$ = 2.5 V (unless otherwise noted)

|                 | PARAMETERS                                                                   | TEST CONDITIONS                                                                                                                            | MIN TYP | MAX    | UNIT   |

|-----------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|--------|

| OUTPUT          | Г                                                                            |                                                                                                                                            |         |        |        |

|                 |                                                                              | TMCS1100A1                                                                                                                                 | 50      |        | mV/A   |

|                 | 0 (7)                                                                        | TMCS1100A2                                                                                                                                 | 100     |        | mV/A   |

|                 | Sensitivity <sup>(7)</sup>                                                   | TMCS1100A3                                                                                                                                 | 200     |        | mV/A   |

|                 |                                                                              | TMCS1100A4                                                                                                                                 | 400     |        | mV/A   |

|                 | Sensitivity error                                                            | $0.05 \text{ V} \le \text{V}_{\text{OUT}} \le \text{V}_{\text{S}} - 0.2 \text{ V}, \text{T}_{\text{A}} = 25^{\circ}\text{C}$               | ±0.2%   | ±0.7%  |        |

|                 | Sensitivity error, including lifetime and environmental drift <sup>(5)</sup> | $0.05 \text{ V} \le \text{V}_{\text{OUT}} \le \text{V}_{\text{S}} - 0.2 \text{ V}, \text{T}_{\text{A}} = 25^{\circ}\text{C}$               | -0.47%  | ±1.02% |        |

|                 | Consiste day of the company                                                  | $0.05 \text{ V} \le \text{V}_{\text{OUT}} \le \text{V}_{\text{S}} - 0.2 \text{ V}, \text{T}_{\text{A}} = -40^{\circ}\text{C to}$<br>+85°C  | ±0.4%   | ±0.85% |        |

|                 | Sensitivity error                                                            | $0.05 \text{ V} \le \text{V}_{\text{OUT}} \le \text{V}_{\text{S}} - 0.2 \text{ V}, \text{T}_{\text{A}} = -40^{\circ}\text{C to}$<br>+125°C | ±0.5%   | ±1.15% |        |

|                 | Nonlinearity error                                                           | V <sub>OUT</sub> = 0.5 V to V <sub>S</sub> – 0.5 V                                                                                         | ±0.05%  |        |        |

|                 |                                                                              | TMCS1100A1                                                                                                                                 | ±0.4    | ±3     | mV     |

| ١,,             | Output valtage offeet error(1)                                               | TMCS1100A2                                                                                                                                 | ±0.6    | ±5     | mV     |

| V <sub>OE</sub> | Output voltage offset error <sup>(1)</sup>                                   | TMCS1100A3                                                                                                                                 | ±0.8    | ±8     | mV     |

|                 |                                                                              | TMCS1100A4                                                                                                                                 | ±2.2    | ±19    | mV     |

|                 |                                                                              | TMCS1100A1, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±3.7    | ±12    | μV/°C  |

|                 | Output walks as affect drift                                                 | TMCS1100A2, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±4      | ±19    | μV/°C  |

|                 | Output voltage offset drift                                                  | TMCS1100A3, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±8.2    | ±35    | μV/°C  |

|                 |                                                                              | TMCS1100A4, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±26     | ±138   | μV/°C  |

|                 |                                                                              | TMCS1100A1                                                                                                                                 | ±8      | ±60    | mA     |

|                 | Offset error, RTI <sup>(1)</sup> (3)                                         | TMCS1100A2                                                                                                                                 | ±6      | ±50    | mA     |

| los             |                                                                              | TMCS1100A3                                                                                                                                 | ±4      | ±40    | mA     |

|                 |                                                                              | TMCS1100A4                                                                                                                                 | ±5.5    | ±47.5  | mA     |

|                 |                                                                              | TMCS1100A1, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±74     | ±240   | μΑ/°C  |

|                 | Officet error temperature drift PTI(3)                                       | TMCS1100A2, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±40     | ±190   | μΑ/°C  |

|                 | Offset error temperature drift, RTI <sup>(3)</sup>                           | TMCS1100A3, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±41     | ±175   | μΑ/°C  |

|                 |                                                                              | TMCS1100A4, T <sub>A</sub> = -40°C to +125°C                                                                                               | ±65     | ±345   | μΑ/°C  |

| PSRR            | Power-supply rejection ratio                                                 | TMCS1100A1-A3, V <sub>S</sub> = 3 V to 5.5<br>V, V <sub>REF</sub> = V <sub>S</sub> /2, T <sub>A</sub> = -40°C to +125°C                    | ±1      | ±2     | mV/V   |

| FORK            | rower-supply rejection ratio                                                 | TMCS1100A4, $V_S = 4.5 \text{ V to } 5.5 \text{ V}$ , $V_{REF} = V_S/2$ , $T_A = -40^{\circ}\text{C}$ to +125°C                            | ±1      | ±3     | mV/V   |

| CMTI            | Common mode transient immunity                                               |                                                                                                                                            | 50      |        | kV/µs  |

| CMRR            | Common mode rejection ratio, RTI <sup>(3)</sup>                              | DC to 60Hz                                                                                                                                 | 5       |        | uA/V   |

| RVRR            | Reference voltage rejection ratio, output                                    | V <sub>REF</sub> = 0.5 V to 4.5 V, TMCS1100A1-A3                                                                                           | 1       | 3.5    | mV/V   |

|                 | referred                                                                     | V <sub>REF</sub> = 0.5 V to 4.5 V, TMCS1100A4                                                                                              | 1.5     | 8      | mV/V   |

|                 |                                                                              | TMCS1100A1                                                                                                                                 | 380     |        | μΑ/√Hz |

|                 | Noise density, RTI <sup>(3)</sup>                                            | TMCS1100A2                                                                                                                                 | 330     |        | µA/√Hz |

|                 | Noise delisity, IXTIV                                                        | TMCS1100A3                                                                                                                                 | 300     |        | μΑ/√Hz |

|                 |                                                                              | TMCS1100A4                                                                                                                                 | 225     |        | μΑ/√Hz |

| INPUT           |                                                                              |                                                                                                                                            |         |        |        |

| R <sub>IN</sub> | Input conductor resistance                                                   | IN+ to IN-                                                                                                                                 | 1.8     |        | mΩ     |

|                 | Input conductor resistance temperature drift                                 | T <sub>A</sub> = -40°C to +125°C                                                                                                           | 4.4     |        | μΩ/°C  |

| G               | Magnetic coupling factor                                                     | T <sub>A</sub> = 25°C                                                                                                                      | 1.1     |        | mT/A   |

# at $T_A = 25$ °C, $V_S = 5$ V, $V_{RFF} = 2.5$ V (unless otherwise noted)

|                     | PARAMETERS                                        | TEST CONDITIONS                                                                                                                                                                      | MIN 7              | ГҮР        | MAX                   | UNIT |

|---------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|-----------------------|------|

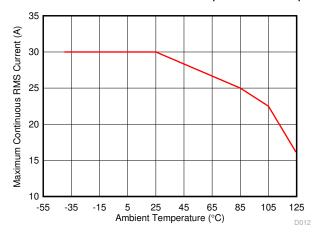

|                     |                                                   | T <sub>A</sub> = 25°C                                                                                                                                                                |                    | 30         |                       | Α    |

| I <sub>IN,max</sub> | Allewable centinuous DMS current (4)              | T <sub>A</sub> = 85°C                                                                                                                                                                |                    | 25         |                       | Α    |

|                     | Allowable continuous RMS current (4)              | T <sub>A</sub> = 105°C                                                                                                                                                               | 2                  | 22.5       |                       | Α    |

|                     |                                                   | T <sub>A</sub> = 125°C                                                                                                                                                               |                    | 16         |                       | Α    |

| V <sub>REF</sub>    | Reference input voltage                           |                                                                                                                                                                                      | $V_{GND}$          |            | Vs                    | V    |

|                     | V <sub>REF</sub> input current                    | VREF = GND, VS                                                                                                                                                                       |                    | ±1         | ±5                    | μA   |

|                     | V <sub>REF</sub> external source impedance        | Maximum source impedance of external circuit driving V <sub>REF</sub>                                                                                                                |                    |            | 5                     | kΩ   |

| VOLTA               | GE OUTPUT                                         |                                                                                                                                                                                      |                    |            | ·                     |      |

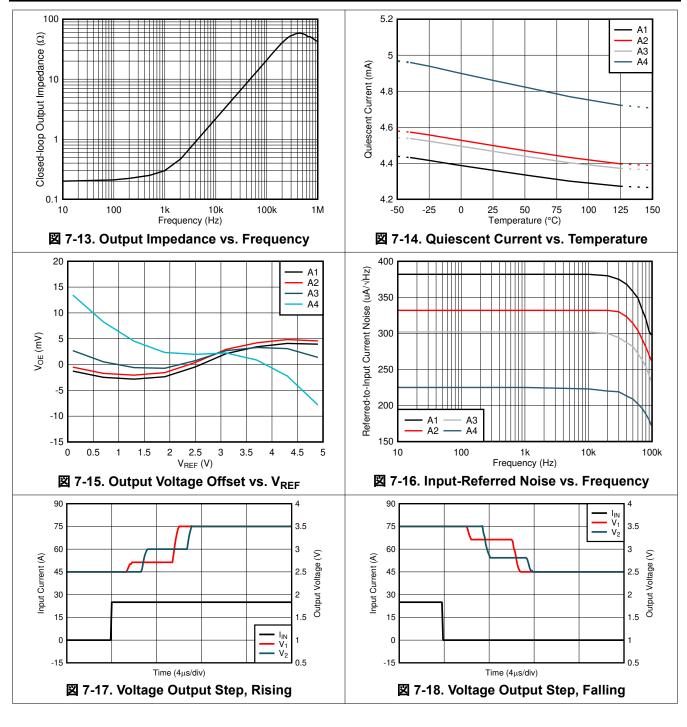

| 7                   | Classed lean author improduces                    | f = 1 Hz to 1 kHz                                                                                                                                                                    |                    | 0.2        |                       | Ω    |

| Z <sub>OUT</sub>    | Closed loop output impedance                      | f = 10 kHz                                                                                                                                                                           |                    | 2          |                       | Ω    |

|                     | Maximum capacitive load                           | No sustained oscillation                                                                                                                                                             |                    | 1          |                       | nF   |

|                     | Short circuit output current                      | VOUT short to ground, short to V <sub>S</sub>                                                                                                                                        |                    | 90         |                       | mA   |

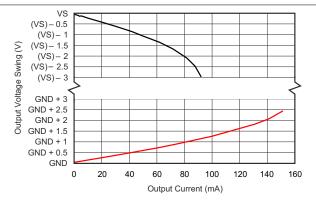

|                     | Swing to V <sub>S</sub> power-supply rail         | $R_L$ = 10 k $\Omega$ to GND, $T_A$ = -40°C to +125°C                                                                                                                                | V <sub>S</sub> - 0 | 0.02       | V <sub>S</sub> - 0.1  | V    |

|                     | Swing to GND, current driven                      | $R_L$ = 10 kΩ to GND, $T_A$ = –40°C to +125°C                                                                                                                                        | $V_{GND}$          | + 5        | V <sub>GND</sub> + 10 | mV   |

|                     | Swing to GND, zero current                        | TMCS1100A1-A3, $R_L$ = 10 k $\Omega$ to GND, $T_A$ = -40°C to +125°C, VREF = GND, $I_{IN}$ = 0 A                                                                                     | $V_{GND}$          | + 5        | V <sub>GND</sub> + 20 | mV   |

|                     |                                                   | TMCS1100A4, $R_L$ = 10 k $\Omega$ to GND, $T_A$ = – 40°C to +125°C, VREF = GND, $I_{IN}$ = 0 A                                                                                       | $V_{GN}$           | ND +<br>20 | V <sub>GND</sub> + 55 | mV   |

| FREQU               | ENCY RESPONSE                                     |                                                                                                                                                                                      |                    |            |                       |      |

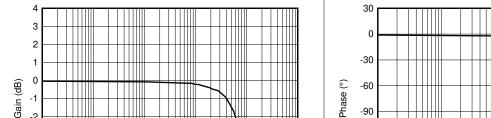

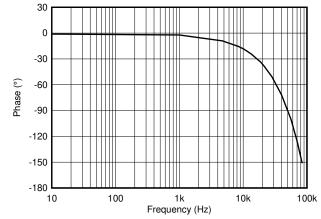

| BW                  | Bandwidth <sup>(6)</sup>                          | -3-dB Bandwidth                                                                                                                                                                      |                    | 80         |                       | kHz  |

| SR                  | Slew rate <sup>(6)</sup>                          | Slew rate of output amplifier during single transient step.                                                                                                                          |                    | 1.5        |                       | V/µs |

| t <sub>r</sub>      | Response time <sup>(6)</sup>                      | Time between the input current step reaching 90% of final value to the sensor output reaching 90% of its final value, for a 1V output transition.                                    |                    | 6.5        |                       | μs   |

| t <sub>p</sub>      | Propagation delay <sup>(6)</sup>                  | Time between the input current step reaching 10% of final value to the sensor output reaching 10% of its final value, for a 1V output transition.                                    |                    | 4          |                       | μs   |

| r,SC                | Current overload response time <sup>(6)</sup>     | Time between the input current step reaching 90% of final value to the sensor output reaching 90% of its final value. Input current step amplitude is twice full scale output range. |                    | 5          |                       | μs   |

| t <sub>p,</sub> sc  | Current overload propagation delay <sup>(6)</sup> | Time between the input current step reaching 10% of final value to the sensor output reaching 10% of its final value. Input current step amplitude is twice full scale output range. |                    | 3          |                       | μs   |

|                     | Current overload recovery time                    | Time from end of current causing output saturation condition to valid output                                                                                                         |                    | 15         |                       | μs   |

| POWER               | RSUPPLY                                           |                                                                                                                                                                                      |                    |            | '                     |      |

|                     | Ouissant surrent                                  | T <sub>A</sub> = 25°C                                                                                                                                                                |                    | 4.5        | 5.5                   | mA   |

| l <sub>Q</sub>      | Quiescent current                                 | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                                                                                 |                    |            | 6                     | mA   |

|                     |                                                   |                                                                                                                                                                                      |                    |            |                       |      |

<sup>(1)</sup> Excludes effect of external magnetic fields. See the Accuracy Parameters section for details to calculate error due to external magnetic

Product Folder Links: TMCS1100

Excluding magnetic coupling from layout deviation from recommended layout. See the *Layout* section for more information.

#### www.tij.co.jp

- (3) RTI = referred-to-input. Output voltage is divided by device sensitivity to refer signal to input current. See the *Parameter Measurement Information* section.

- (4) Thermally limited by junction temperature. Applies when device mounted on TMCS1100EVM. For more details, see the Safe Operating Area section.

- (5) Lifetime and environmental drift specifications based on three lot AEC-Q100 qualification stress test results. Typical values are population mean+1σ from worst case stress test condition. Min/max are tested device population mean±6σ; devices tested in AEC-Q100 qualification stayed within min/max limits for all stress conditions. See *Lifetime and Environmental Stability* section for more details

- (6) Refer to the *Transient Response* section for details of frequency and transient response of the device.

- (7) Centered parameter based on TMCS1100EVM PCB layout. See Layout section. Device must be operated below maximum junction temperature.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

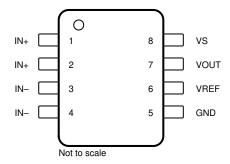

# 7.10 Typical Characteristics

-2 -3

-4

-5 -6

10

100

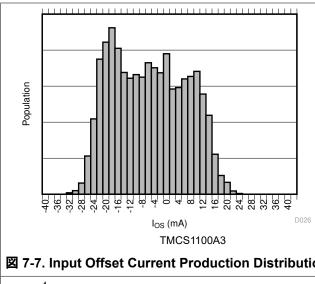

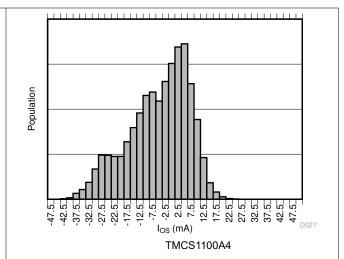

図 7-7. Input Offset Current Production Distribution 図 7-8. Input Offset Current Production Distribution

100k

1M

Frequency (Hz)

10k

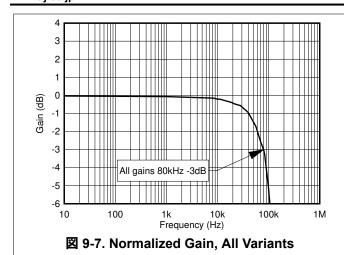

All gains 80kHz -3dB

図 7-12. Output Swing vs. Output Current

#### 7.10.1 Insulation Characteristics Curves

# **8 Parameter Measurement Information**

# **8.1 Accuracy Parameters**

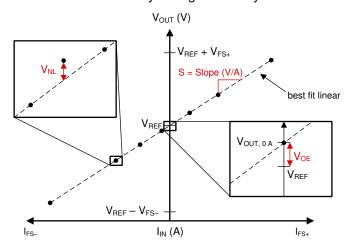

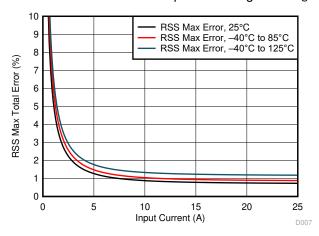

The ideal first-order transfer function of the TMCS1100 is given by  $\pm$  1, where the output voltage is a linear function of input current. The accuracy of the device is quantified both by the error terms in the transfer function parameters, as well as by nonidealities that introduce additional error terms not in the simplified linear model. See *Total Error Calculation Examples* for example calculations of total error, including all device error terms.

$$V_{OUT} = S \times I_{IN} + V_{REF} \tag{1}$$

#### where

- V<sub>OUT</sub> is the analog output voltage.

- · S is the ideal sensitivity of the device.

- I<sub>IN</sub> is the isolated input current.

- V<sub>REF</sub> is the voltage applied to the reference voltage input.

#### where

- V<sub>OUT</sub> is the analog output voltage.

- · S is the ideal sensitivity of the device.

- I<sub>IN</sub> is the isolated input current.

- V<sub>OUT.0A</sub> is the zero current output voltage for the device variant.

### 8.1.1 Sensitivity Error

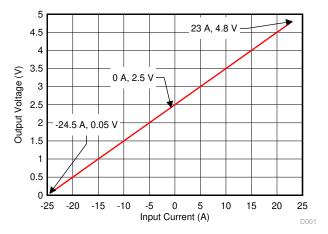

Sensitivity is the proportional change in the sensor output voltage due to a change in the input conductor current. This sensitivity is the slope of the first-order transfer function of the sensor, as shown in 🗵 8-1. The sensitivity of the TMCS1100 is tested and calibrated at the factory for high accuracy.

図 8-1. Sensitivity, Offset, and Nonlinearity Error

Deviation from ideal sensitivity is quantified by sensitivity error, defined as the percent variation of the best-fit measured sensitivity from the ideal sensitivity. When specified over a temperature range, this is the worst-case sensitivity error at any temperature within the range.

$$e_S = [(S_{fit} - S_{ideal}) / S_{ideal}] \times 100\%$$

(2)

#### where

- · e<sub>S</sub> is the sensitivity error.

- · S<sub>fit</sub> is the best fit sensitivity.

- S<sub>Ideal</sub> is the ideal sensitivity.

#### 8.1.2 Offset Error and Offset Error Drift

Offset error is the deviation from the ideal output voltage with zero input current through the device. Offset error can be referred to the output as a voltage error  $V_{OE}$  or referred to the input as a current offset error  $I_{OS}$ . Offset error is a single error source, however, and must only be included once in error calculations.

The output voltage offset error of the TMCS1100 is the error in the zero current output voltage from the VREF pin voltage as in  $\pm 3$ .

$$V_{OE} = V_{OUT,0A} - V_{REF}$$

(3)

#### where

V<sub>OUT,0A</sub> is the device output voltage with zero input current.

The offset error includes the magnetic offset of the Hall sensor and any offset voltage errors of the signal chain.

The input referred (RTI) offset error is the output voltage offset error divided by the sensitivity of the device, shown in  $\pm$  4. Refer the offset error to the input of the device to allow for easier total error calculations and direct comparison to input current levels. No matter how the calculations are done, the error sources quantified by  $V_{OE}$  and  $I_{OS}$  are the same, and should only be included once for error calculations.

$$I_{OS} = V_{OE} / S \tag{4}$$

Offset error drift is the change in the input-referred offset error per degree Celsius change in ambient temperature. This parameter is reported in  $\mu$ A/°C. To convert offset drift to an absolute offset for a given change in temperature, multiply the drift by the change in temperature and convert to percentage, as in  $\pm$  5.

$$e_{l_{OS},\Delta T}\left(\%\right) = \frac{I_{OS,25^{\circ}C} + I_{OS,drift}\left(\frac{\mu A}{{}^{\circ}C}\right) \times \Delta T}{I_{IN}}$$

(5)

#### where

- I<sub>OS,drift</sub> is the specified input-referred device offset drift.

- ΔT is the temperature range from 25°C.

# 8.1.3 Nonlinearity Error

Nonlinearity is the deviation of the output voltage from a linear relationship to the input current. Nonlinearity voltage, as shown in  $\boxtimes$  8-1, is the maximum voltage deviation from the best-fit line based on measured parameters, calculated by  $\npreceq$  6.

$$V_{NL} = V_{OUT,MEAS} - (I_{MEAS} \times S_{fit} + V_{OUT,0A})$$

(6)

### where

- V<sub>OUT,MEAS</sub> is the voltage output at maximum deviation from best fit.

- I<sub>MEAS</sub> is the input current at maximum deviation from best fit.

- S<sub>fit</sub> is the best-fit sensitivity of the device.

- V<sub>OUT 0A</sub> is the device zero current output voltage.

Nonlinearity error ( $e_{NL}$ ) for the TMCS1100 is the nonlinearity voltage specified as a percentage of the full-scale output range ( $V_{ES}$ ), as shown in  $\gtrsim 7$ .

$$e_{NL} = 100\% * \frac{V_{NL}}{V_{FS}} \tag{7}$$

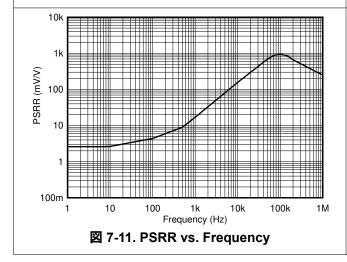

# 8.1.4 Power Supply Rejection Ratio

Power supply rejection ratio (PSRR) is the change in device offset due to variation of supply voltage from the nominal 5 V. The error contribution at the input current of interest can be calculated by  $\pm 8$ .

$$e_{PSRR}(\%) = \frac{\left|\frac{PSRR * (V_S - 5)}{S}\right|}{\left|\frac{I_{IN}}{I_{IN}}\right|}$$

(8)

#### where

- V<sub>S</sub> is the operational supply voltage.

- · S is the device sensitivity.

#### 8.1.5 Common-Mode Rejection Ratio

Common-mode rejection ratio (CMRR) quantifies the effective input current error due to a varying voltage on the isolated input of the device. Due to magnetic coupling and galvanic isolation of the current signal, the TMCS1100 has very high rejection of input common-mode voltage. Percent error contribution from input common-mode variation can be calculated by  $\stackrel{>}{\to}$  9.

$$e_{CMRR}(\%) = \left| \frac{CMRR * V_{CM}}{I_{IN}} \right|$$

(9)

### where

V<sub>CM</sub> is the maximum operational AC or DC voltage on the input of the device.

#### 8.1.6 Reference Voltage Rejection Ratio

The voltage applied to the VREF pin sets the zero current output voltage for the TMCS1100. Ideally, the zero current output voltage directly tracks  $V_{REF}$ . Light internal mismatch can cause minor errors, however. When the reference voltage deviates from half of the supply, an additional effective output offset error is introduced into the device transfer function. The reference voltage rejection ratio (RVRR) is the effective change in output offset voltage due to this deviation. Error due to reference rejection can be calculated by  $\not \equiv 10$ .

Copyright © 2022 Texas Instruments Incorporated

$$e_{V_{REF}}(\%) = \frac{\left|\frac{RVRR*(V_{REF} - \frac{V_S}{2})}{S}\right|}{I_{IN}}$$

(10)

### 8.1.7 External Magnetic Field Errors

The TMCS1100 does not have stray field-rejection capabilities, so external magnetic fields from adjacent high-current traces or nearby magnets can impact the output measurement. The total sensitivity (S) of the device is comprised of the initial transformation of input current to magnetic field quantified as the magnetic coupling factor (G), as well as the sensitivity of the Hall element and the analog circuitry that is factory calibrated to provide a final sensitivity. The output voltage is proportional to the input current by the device sensitivity, as defined in  $\pm$ 11.

$$S = G * S_{Hall} * A_{V}$$

$$(11)$$

where

- S is the TMCS1100 sensitivity in mV/A.

- G is the magnetic coupling factor in mT/A.

- S<sub>Hall</sub> is the sensitivity of the Hall plate in mV/mT.

- A<sub>V</sub> is the calibrated analog circuitry gain in V/V.

An external field,  $B_{\text{EXT}}$ , is measured by the Hall sensor and signal chain, in addition to the field generated by the leadframe current, and is added as an extra input term in the total output voltage function:

$$V_{OUT} = B_{EXT} * S_{Hall} * A_{V} + I_{IN} * G * S_{Hall} * A_{V} + V_{OUT,0A}$$

(12)

Observable from  $\not \equiv$  12 is that the impact of an external field is an additional equivalent input current signal,  $I_{BEXT}$ , shown in  $\not \equiv$  13. This effective additional input current has no dependence on Hall or analog circuitry sensitivity, so all gain variants have equivalent input-referred current error due to external magnetic fields.

$$I_{B_{EXT}} = \frac{B_{EXT}}{G} \tag{13}$$

This additional current error generates a percentage error defined by 式 14.

$$e_{B_{EXT}}(\%) = \frac{\left|\frac{B_{EXT}}{G}\right|}{I_{IN}} \tag{14}$$

#### 8.2 Transient Response Parameters

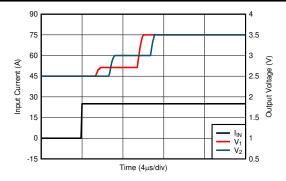

The transient response of the TMCS1100 is impacted by the 250 kHz sampling rate as defined in *Transient Response*.

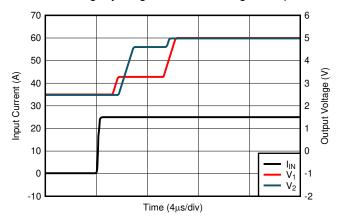

8-2 shows the TMCS1100 response to an input current step sufficient to generate a 1V output change. The typical 4us sampling window can be observed as a periodic step. This sampling window dominates the response of the device, and the response will have some probabilistic nature due to alignment of the input step and the sampling window interval.

図 8-2. Transient Step Response

### 8.2.1 Slew Rate

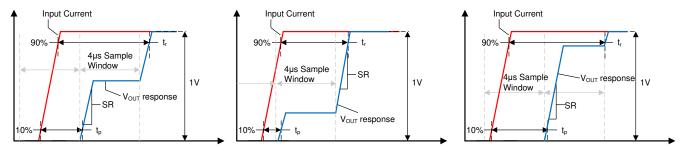

Slew rate (SR) is defined as the  $V_{OUT}$  rate of change for a single integration step's output transition, as shown in  $\boxtimes$  8-3. Because the device often requires two sampling windows to reach a full 90% settling of its final value, this slew rate is not equal to the 10%-90% transition time for the full output swing.

図 8-3. Small Current Input Step Transient Response

#### 8.2.2 Propagation Delay and Response Time

Propagation delay is the time period between the input current waveform reaching 10% of its final value and  $V_{OUT}$  reaching 10% of its final value. This propagation delay is heavily dependent upon the alignment of the input current step and the sampling period of the TMCS1100, as shown for several different sampling window cases in  $\boxtimes$  8-3.

Response time is the time period between the input current reaching 90% of its final value and the output reaching 90% of its final value, for an input current step sufficient to cause a 1-V transition on the output. 🗵 8-3 shows the response time of the TMCS1100 under three different time cases. Unless a step input occurs directly during the beginning of one sampling window the response time will include two sampling intervals.

### **8.2.3 Current Overload Parameters**

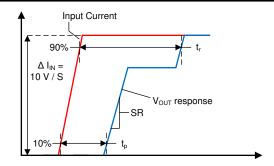

Current overload response parameters are the transient behavior of the TMCS1100 to an input current step consistent with a short circuit or fault event. Tested amplitude is twice the full scale range of the device, or 10V / Sensitivity in V/A. Under these conditions, the TMCS1100 output will respond faster than in the case of a small input current step due to the higher input amplitude signal. Response time and propagation delay are measured in a similar manner to the case of a small input current step, as shown in  $\boxtimes$  8-4.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

図 8-4. Current Overload Transient Response

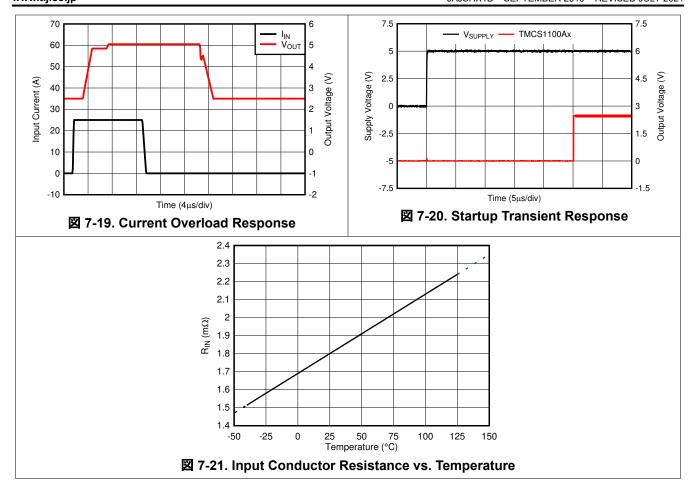

Current overload recovery time is the required time for the device output to exit a saturated condition and return to normal operation. The transient response of the device during this recovery period from a current overload is shown in  $\boxtimes$  7-19.

# 8.2.4 CMTI, Common-Mode Transient Immunity

CMTI is the capability of the device to tolerate a rising/falling voltage step on the input without disturbance on the output signal. The device is specified for the maximum common-mode transition rate under which the output signal will not experience a greater than 200-mV disturbance that lasts longer than 1 µs. Higher edge rates than the specified CMTI can be supported with sufficient filtering or blanking time after common-mode transitions.

# 8.3 Safe Operating Area

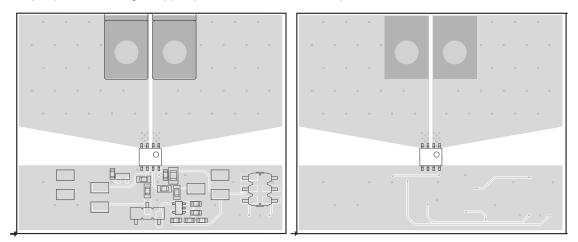

The isolated input current safe operating area (SOA) of the TMCS1100 is constrained by self-heating due to power dissipation in the input conductor. Depending upon the use case, the SOA is constrained by multiple conditions, including exceeding maximum junction temperature, Joule heating in the leadframe, or leadframe fusing under extremely high currents. These mechanisms depend on pulse duration, amplitude, and device thermal states.

Current SOA strongly depends on the thermal environment and design of the system-level board. Multiple thermal variables control the transfer of heat from the device to the surrounding environment, including air flow, ambient temperature, and printed-circuit board (PCB) construction and design. All ratings are for a single TMCS1100 device on the TMCS1100EVM, with no air flow in the specified ambient temperature conditions. Device use profiles must satisfy both continuous conduction and short-duration transient SOA capabilities for the thermal environment under which the system will be operated.

#### 8.3.1 Continuous DC or Sinusoidal AC Current

The longest thermal time constants of device packaging and PCBs are in the order of seconds; therefore, any continuous DC or sinusoidal AC periodic waveform with a frequency higher than 1 Hz can be evaluated based on the RMS continuous-current level. The continuous-current capability has a strong dependence upon the operating ambient temperature range expected in operation.

8-5 shows the maximum continuous current-handling capability of the device on the TMCS1100EVM. Current capability falls off at higher ambient temperatures because of the reduced thermal transfer from junction-to-ambient and increased power dissipation in the leadframe. By improving the thermal design of an application, the SOA can be extended to higher currents at elevated temperatures. Using larger and heavier copper power planes, providing air flow over the board, or adding heat sinking structures to the area of the device can all improve thermal performance.

図 8-5. Maximum Continuous RMS Current vs. Ambient Temperature

### 8.3.2 Repetitive Pulsed Current SOA

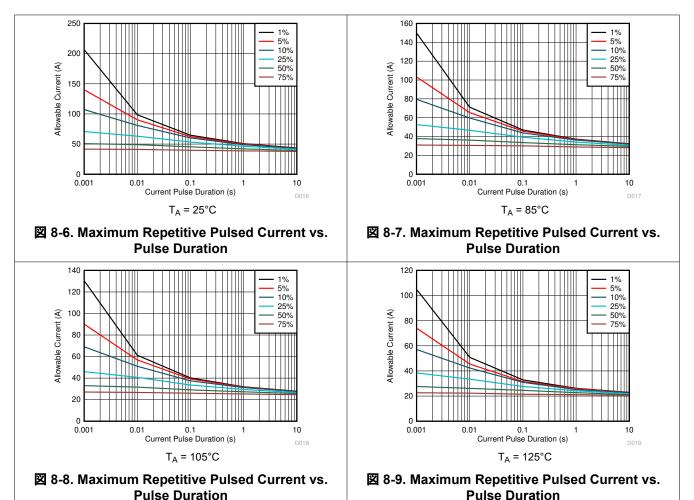

For applications where current is pulsed between a high current and no current, the allowable capabilities are limited by short-duration heating in the leadframe. The TMCS1100 can tolerate higher current ranges under some conditions, however, for repetitive pulsed events, the current levels must satisfy both the pulsed current SOA and the RMS continuous current constraint. Pulse duration, duty cycle, and ambient temperate all impact the SOA for repetitive pulsed events.  $\boxtimes$  8-6,  $\boxtimes$  8-7,  $\boxtimes$  8-8, and  $\boxtimes$  8-9 illustrate repetitive stress levels based on test results from the TMCS1100EVM under which parametric performance and isolation integrity was not impacted post-stress for multiple ambient temperatures. At high duty cycles or long pulse durations, this limit approaches the continuous current SOA for a RMS value defined by  $\npreceq$  15.

$$I_{\text{IN,RMS}} = I_{\text{IN,P}} * \sqrt{D}$$

(15)

#### where

- I<sub>IN.RMS</sub> is the RMS input current level

- I<sub>IN.P</sub> is the pulse peak input current

- D is the pulse duty cycle

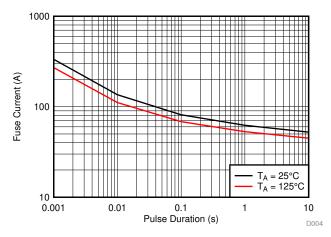

### 8.3.3 Single Event Current Capability

Single higher-current events that are shorter duration can be tolerated by the TMCS1100, because the junction temperature does not reach thermal equilibrium within the pulse duration.

8-10 shows the short-circuit duration curve for the device for single current-pulse events, where the leadframe resistance changes after stress. This level is reached before a leadframe fusing event, but should be considered an upper limit for short duration SOA. For long-duration pulses, the current capability approaches the continuous RMS limit at the given ambient temperature.

図 8-10. Single-Pulse Leadframe Capability

# 9 Detailed Description

### 9.1 Overview

The TMCS1100 is a precision Hall-effect current sensor, featuring a 600-V basic isolation working voltage, < 1% full-scale error across temperature, and an external reference voltage enabling unidirectional or bidirectional current sensing Input current flows through a conductor between the isolated input current pins. The conductor has a 1.8-m $\Omega$  resistance at room temperature for low power dissipation and a 20-A RMS continuous current handling capability up to 105°C ambient temperature on the TMCS1100EVM. The low-ohmic leadframe path reduces power dissipation compared to alternative current measurement methodologies, and does not require any external passive components, isolated supplies, or control signals on the high-voltage side. The magnetic field generated by the input current is sensed by a Hall sensor and amplified by a precision signal chain. The device can be used for both AC and DC current measurements and has a bandwidth of 80 kHz. There are multiple fixed-sensitivity device variants for a wide option of linear sensing ranges, and the TMCS1100 can operate with a low voltage supply from 3 V to 5.5 V. The TMCS1100 is optimized for high accuracy and temperature stability, with both offset and sensitivity compensated across the entire operating temperature range.

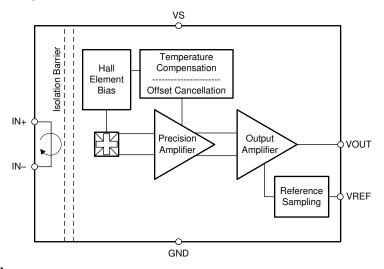

## 9.2 Functional Block Diagram

# 9.3 Feature Description

# 9.3.1 Current Input

Input current to the TMCS1100 passes through the isolated side of the package leadframe through the IN+ and IN- pins. The current flow through the package generates a magnetic field that is proportional to the input current, and measured by a galvanically isolated, precision, Hall sensor IC. As a result of the electrostatic shielding on the Hall sensor die, only the magnetic field generated by the input current is measured, thus limiting input voltage switching pass-through to the circuitry. This configuration allows for direct measurement of currents with high-voltage transients without signal distortion on the current-sensor output. The leadframe conductor has a nominal resistance of 1.8 m $\Omega$  at 25°C, and has a typical positive temperature coefficient as defined in the *Electrical Characteristics* table.

# 9.3.2 Input Isolation

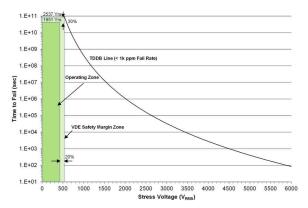

The separation between the input conductor and the Hall sensor die due to the TMCS1100 construction provides inherent galvanic isolation between package pins 1-4 and pins 5-8. Insulation capability is defined according to certification agency definitions and using industry-standard test methods as defined in the *Insulation Specifications* table. Assessment of device lifetime working voltages follow the VDE 0884-11 standard for basic insulation, requiring time-dependent dielectric breakdown (TDDB) data-projection failure rates of less than 1000 part per million (ppm), and a minimum insulation lifetime of 20 years. The VDE standard also requires an additional safety margin of 20% for working voltage, and a 30% margin for insulation lifetime, translating into a minimum required lifetime of 26 years at 509 V<sub>RMS</sub> for the TMCS1100.

Product Folder Links: TMCS1100

ibmit Document Feedback

≥ 9-1 shows the intrinsic capability of the isolation barrier to withstand high-voltage stress over the lifetime of the device. Based on the TDDB data, the intrinsic capability of these devices is 424 V<sub>RMS</sub> with a lifetime of > 100 years. Other factors such as operating environment and pollution degree can further limit the working voltage of the component in an end system.

図 9-1. Insulation Lifetime

# 9.3.3 High-Precision Signal Chain

The TMCS1100 uses a precision, low-drift signal chain with proprietary sensor linearization techniques to provide a highly accurate and stable current measurement across the full temperature range of the device. The device is fully tested and calibrated at the factory to account for any variations in either silicon or packaging process variations. The full signal chain provides a fixed sensitivity voltage output that is proportional to the current through the leadframe of the isolated input.

### 9.3.3.1 Temperature Stability

The TMCS1100 includes a proprietary temperature compensation technique which results in significantly improved parametric drift across the full temperature range. This compensation technique accounts for changes in ambient temperature, self-heating, and package stress. A zero-drift signal chain architecture and Hall sensor temperature stabilization methods enable stable sensitivity and minimize offset errors across temperature, and drastically improves system-level performance across the required operating conditions.

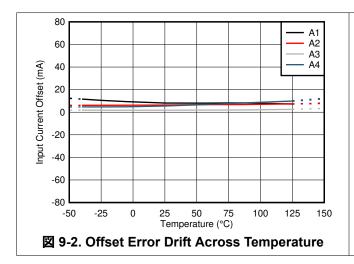

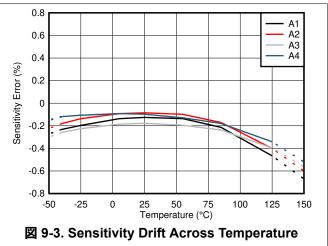

☑ 9-2 shows the offset error across the full device ambient temperature range. ☑ 9-3 shows the typical sensitivity. There are no other external components introducing errors sources; therefore, the high intrinsic accuracy and stability over temperature directly translates to system-level performance. As a result of this high precision, even a system with no calibration can reach < 1% of total error current-sensing capability.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

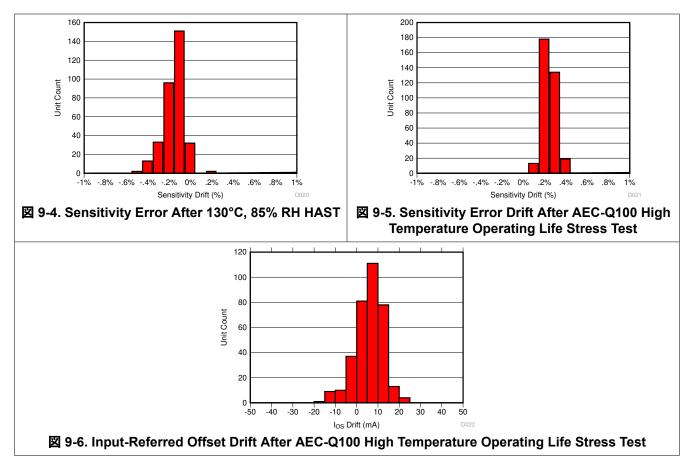

### 9.3.3.2 Lifetime and Environmental Stability

The same compensation techniques used in the TMCS1100 to reduce temperature drift also greatly reduce lifetime drift due to aging, stress, and environmental conditions. Typical magnetic sensors suffer from up to 2% to 3% of sensitivity drift due to aging at high operating temperatures. The TMCS1100 has greatly improved lifetime drift, as defined in the *Electrical Characteristics* for total sensitivity error measured after the worst case stress test during a three lot AEC-Q100 qualification. All other stress tests prescribed by an AEC-Q100 qualification caused lower than the specified sensitivity error, and were within the bounds specified within the *Electrical Characteristics* table.  $\boxtimes$  9-4 shows the total sensitivity error after the worst-case stress test, a Highly Accelerated Stress Test (HAST) at 130°C and 85% relative humidity (RH), while  $\boxtimes$  9-5 and  $\boxtimes$  9-6 show the sensitivity and offset error drift after a 1000 hour, 125°C high temperature operating life stress test as specified by AEC-Q100. This test mimics typical device lifetime operation, and shows the likely device performance variation due to aging is vastly improved compared to typical magnetic sensors.

### 9.3.3.3 Frequency Response

The TMCS1100 signal chain has a spectral response atypical of a linear analog system due to its discrete time sampling. The 250-kHz sampling interval implies an effective Nyquist frequency of 125 kHz, which limits spectral response to below this frequency. Higher frequency content than this frequency will be aliased down to lower spectrums.

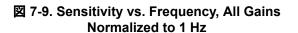

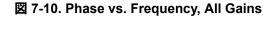

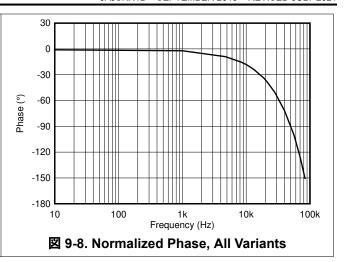

The TMCS1100 bandwidth is defined by the -3-dB spectral response of the entire signal chain which is constrained by the sampling frequency. Normalized gain and phase plots across frequency are shown below in  $\boxtimes$  9-7 and  $\boxtimes$  9-8, all variants have the same bandwidth and phase response. Signal content beyond the 3-dB bandwidth level will still have significant fundamental frequency transmission through the signal chain, but at increasing distortion levels

### 9.3.3.4 Transient Response

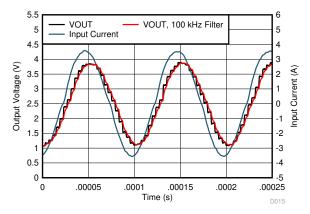

The TMCS1100 signal chain includes a precision analog front end followed by a sampled integrator. At the end of each integration cycle, the signal propagates to the output. Depending on the alignment of a change in input current relative to the sampling window, the output might not settle to the final signal until the second integration cycle. Solve 9-9 shows a typical output waveform response to a 10-kHz sine wave input current. For a slowly varying input current signal, the output is a discrete time representation with a phase delay of the integration sampling window. Adding a first order filter of 100 kHz effectively smooths the output waveform with minimal impact to phase response.

図 9-9. Response Behavior to 10-kHz Sine Wave Input Current

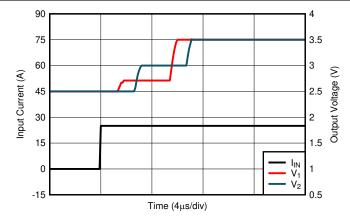

☑ 9-10 shows two transient waveforms to an input-current step event, but occurring at different times during the sampling interval. In both cases, the full transition of the output takes two sampling intervals to reach the final output value. The timing of the current event relative to the sampling window determines the proportional amplitude of the first and second sampling intervals.

図 9-10. Transient Response to Input-Current Step Sufficient for 1-V Output Swing

The output value is effectively an average over the sampling window; therefore, a large-enough current transient can drive the output voltage to near the full scale range in the first sample response. This condition is likely to be true in the case of a short-circuit or fault event.  $\boxtimes$  9-11 shows an input-current step twice the full scale measurable range with two output voltage responses illustrating the effect of the sampling window. The relative timing and size of the input current transition determines both the time and amplitude of the first output transition. In either case, the total response time is slightly longer than one integration period.

図 9-11. Transient Response to a Large Input Current Step

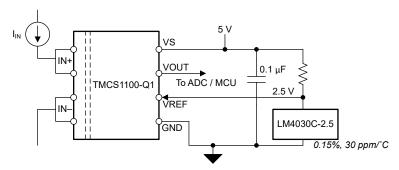

### 9.3.4 External Reference Voltage Input

The reference voltage provided externally to the TMCS1100 on the VREF pin determines the zero current output voltage,  $V_{OUT,0A}$ . This zero-current output level along with sensitivity determine the measurable input current range of the device, and allows for unidirectional or bidirectional sensing, as described in the *Absolute Maximum Ratings* table.  $\boxtimes$  9-12 illustrates the transfer function of the TMCS1100A2 with varying  $V_{REF}$  voltages of 0 V, 1.25 V, and 2.5 V. By shifting the zero current output voltage of the device, the dynamic range of measurable input current can be modified.

図 9-12. Output Voltage Relationship to Input Current With Varying VREF Voltages

The input voltage on this pin can be provided by any external voltage source or potential, such as a discrete precision reference, a voltage divider, ADC reference, or ground. The VREF pin is sampled by the internal circuitry at approximately 1 MHz, then buffered and provided to the signal chain of the device. An apparent DC load of approximately 1 µA will be observed by the external reference. To prevent errors due to sampling settling, keep the source impedance below the level specified in the *Electrical Characteristics* table.

### 9.3.5 Current-Sensing Measurable Ranges

The TMCS1100 can be configured to allow for bidirectional or unidirectional measurable current ranges based on the external voltage on the VREF pin. The output voltage is limited by  $V_{OUT}$  swing to either supply or ground. Linear output swing range to both  $V_S$  and GND is calculated by equations  $\pm$  16 and  $\pm$  17.

$$V_{OUT,max} = V_S - Swing_{VS}$$

(16)

$$V_{OUT,min} = Swing_{GND}$$

(17)

Rearranging the transfer function of the device to solve for input current, and substituting  $V_{OUT,max}$  and  $V_{OUT,min}$  yields the maximum and minimum measurable input current ranges as shown in  $\pm$  18 and  $\pm$  19.

$$I_{IN,MAX+} = (V_{OUT,max} - V_{REF}) / S$$

(18)

$$I_{IN,MAX-} = (V_{REF} - V_{OUT,min}) / S$$

(19)

# where

- $I_{IN,MAX+}$  is the maximum linear measurable positive input current.

- I<sub>IN.MAX</sub>- is the maximum linear measurable negative input current.

- S is the sensitivity of the device variant.

Setting  $V_{\mathsf{REF}}$  to the middle of the output swing range provides bidirectional measurement capability, whereas setting  $V_{\mathsf{REF}}$  close to the ground provides a unidirectional measurement. Custom ranges with nonuniform positive and negative input current ranges can be achieved by appropriately scaling the  $V_{\mathsf{REF}}$  potential relative to the full output voltage range.

#### 9.4 Device Functional Modes

#### 9.4.1 Power-Down Behavior