# TMP139 精度 0.5°C、JEDEC DDR5 グレード B、デジタル温度センサ、I<sup>2</sup>C および I<sup>3</sup>C インターフェイス付き

## 1 特長

- JEDEC JESD302-1 DDR5 グレード B 対応温度センサをサポート

- JEDEC 温度精度要求を上回る仕様:

- $\pm 0.25^\circ\text{C}$  (標準値)

- 最大  $\pm 0.5^\circ\text{C}$  ( $+75^\circ\text{C} \sim +95^\circ\text{C}$ )

- 最大  $\pm 0.75^\circ\text{C}$  ( $-40^\circ\text{C} \sim +125^\circ\text{C}$ )

- 動作温度範囲:  $-40^\circ\text{C} \sim +125^\circ\text{C}$

- 低い消費電力:

- 8.3 $\mu\text{A}$  の標準平均静止時電流

- 4.0 $\mu\text{A}$  の標準スタンバイ電流

- I/O 電源電圧: 1V

- 1.8V のコア電源

- 2 線式のシリアル・バス・インターフェイス (I<sup>2</sup>C および I<sup>3</sup>C 基本動作モード)

- I<sup>3</sup>C 基本モードで最大 12.5MHz のデータ転送速度

- アラートホスト用のインバンド割り込み (IBI)

- ホスト書き込みのパリティ・エラー・チェック機能

- ホストの読み取りおよび書き込みのパケット・エラー・チェック機能

- 11 ビット分解能:  $0.25^\circ\text{C}$  (1 LSB)

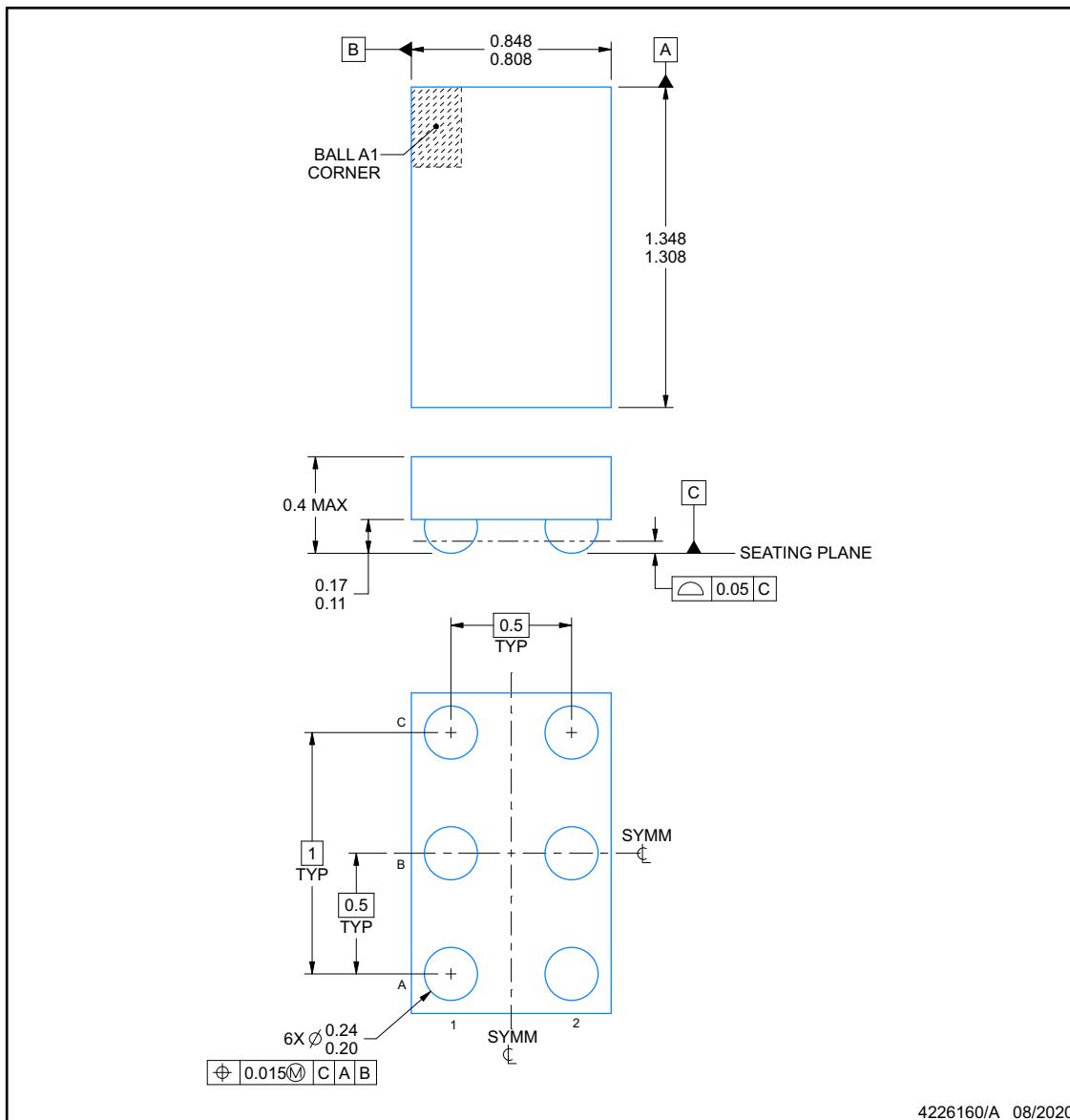

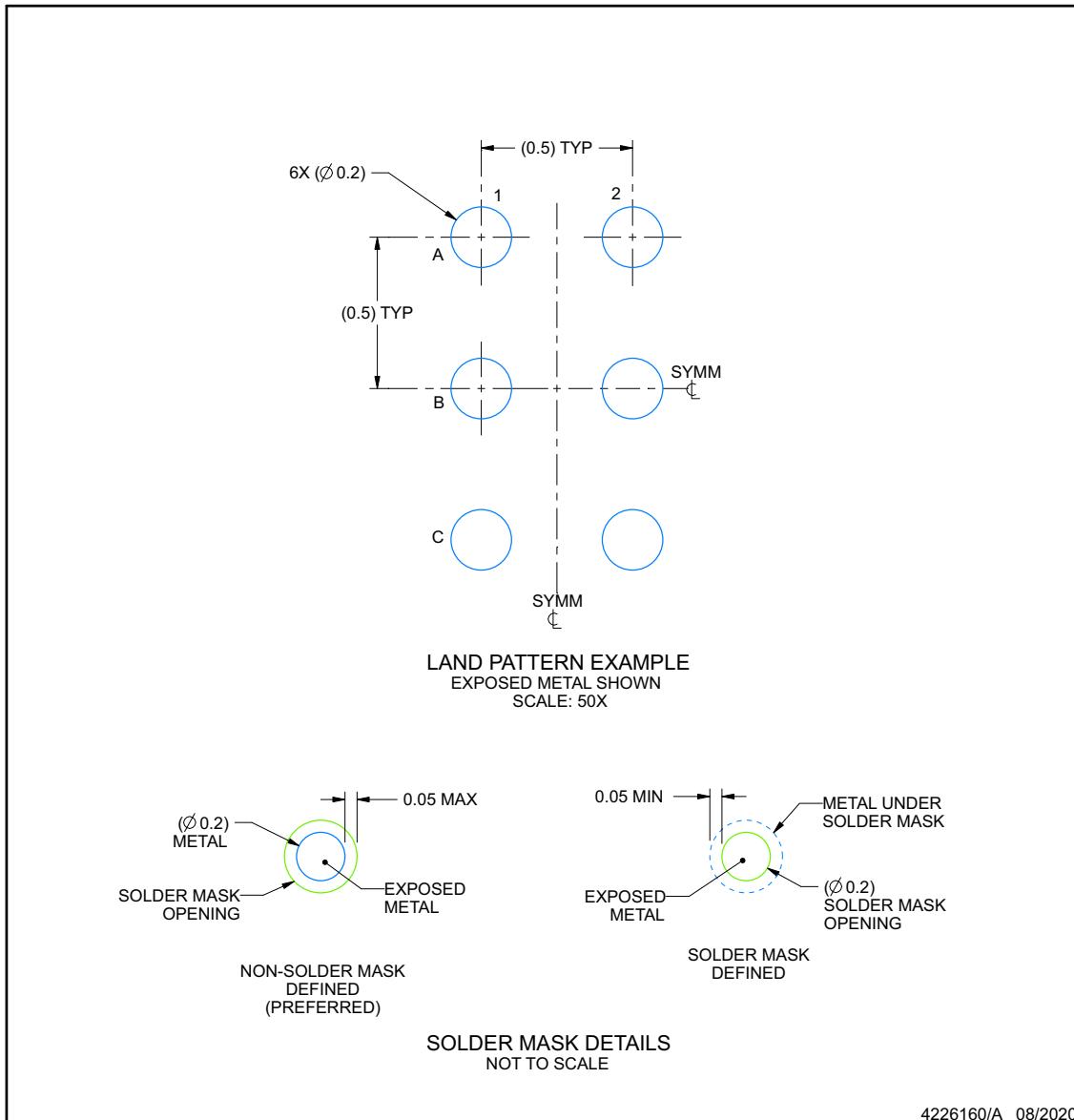

- 0.5mm ピッチの標準的な 6 ポール DSBGA (WCSP) パッケージで供給

## 2 アプリケーション

- DDR5 DIMM モジュール

- サーバー

- ノート PC

- ワークステーション

- SSD

## 3 概要

TMP139 は、I<sup>2</sup>C / I<sup>3</sup>C 準拠のデジタル・インターフェイスを搭載した高精度温度センサであり、インバンド割り込み (IBI) をサポートしています。グレード B デバイスで JEDEC JESD302-1 のインターフェイス要件をサポートする TMP139 は、仕様の温度精度要件を上回っており、より高性能な DDR5 メモリ・モジュールを実現できます。TMP139 はコンパクトな 6 ポール DSBGA パッケージで供給され、高速、高精度、低消費電力の熱監視アプリケーションを想定して設計されています。

TMP139 は、 $-40^\circ\text{C} \sim +125^\circ\text{C}$  の温度範囲全体にわたって  $\pm 0.25^\circ\text{C}$  の標準的精度を保ち、 $0.25^\circ\text{C}$  の温度分解能を持つオンチップの 11 ビット A/D コンバータ (ADC) を実現します。

TMP139 は、1.8V のコア電源と 1V の I/O 電源で動作するように設計されており、125 ミリ秒ごとに変換を行うときの標準的な平均静止時電流は 8.3 $\mu\text{A}$  と低くなります。

### パッケージ情報

| 部品番号   | パッケージ (1) | 本体サイズ (公称)        |

|--------|-----------|-------------------|

| TMP139 | DSBGA (6) | 1.328mm × 0.828mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

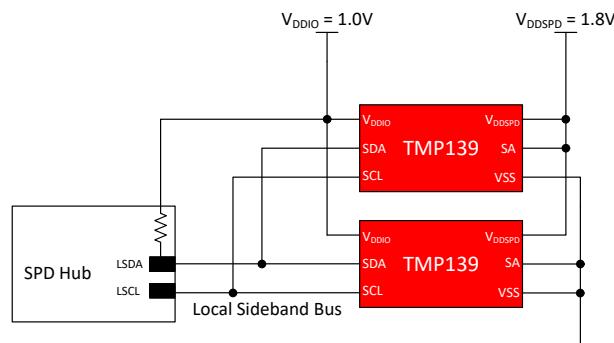

簡略回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、[www.ti.com](http://www.ti.com) で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

## 目次

|              |    |                        |    |

|--------------|----|------------------------|----|

| 1 特長         | 1  | 7.2 機能ブロック図            | 10 |

| 2 アプリケーション   | 1  | 7.3 機能説明               | 10 |

| 3 概要         | 1  | 7.4 デバイスの機能モード         | 13 |

| 4 改訂履歴       | 2  | 7.5 プログラミング            | 33 |

| 5 ピン構成および機能  | 3  | 7.6 レジスタ・マップ           | 36 |

| 6 仕様         | 4  | 8 アプリケーションと実装          | 48 |

| 6.1 絶対最大定格   | 4  | 8.1 アプリケーション情報         | 48 |

| 6.2 ESD 定格   | 4  | 8.2 代表的なアプリケーション       | 48 |

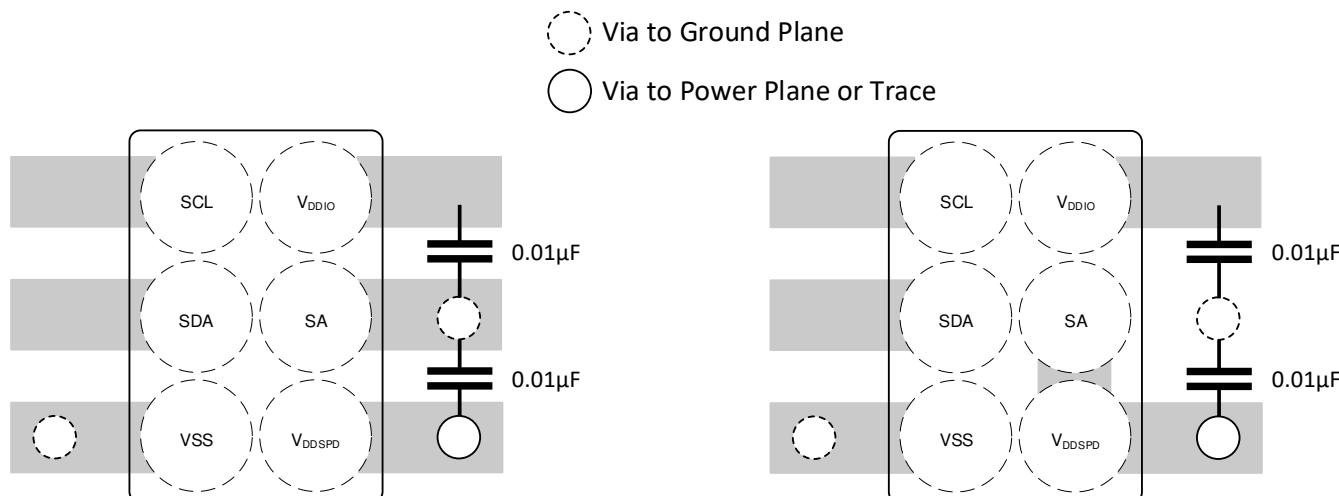

| 6.3 推奨動作条件   | 4  | 8.3 電源に関する推奨事項         | 49 |

| 6.4 熱に関する情報  | 4  | 8.4 レイアウト              | 49 |

| 6.5 電気的特性    | 5  | 9 デバイスおよびドキュメントのサポート   | 50 |

| 6.6 タイミング要件  | 6  | 9.1 ドキュメントの更新通知を受け取る方法 | 50 |

| 6.7 スイッチング特性 | 6  | 9.2 サポート・リソース          | 50 |

| 6.8 タイミング図   | 7  | 9.3 商標                 | 50 |

| 6.9 代表的特性    | 8  | 9.4 静電気放電に関する注意事項      | 50 |

| 7 詳細説明       | 10 | 9.5 用語集                | 50 |

| 7.1 概要       | 10 | 10 メカニカル、パッケージ、および注文情報 | 50 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision B (November 2022) to Revision C (May 2023) Page

|                                                      |    |

|------------------------------------------------------|----|

| • MR2 レジスタのリセット値を 04h から 06h に変更                     | 36 |

| • MR2 の DEV_REV_MINOR[2:0] ビットのリセット値を 010 から 011 に変更 | 36 |

### Changes from Revision A (February 2022) to Revision B (November 2022) Page

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| • 「製品情報」表を「パッケージ情報」に変更                                                             | 1  |

| • $I_Q$ の代表値を $4.7\mu A$ から $8.3\mu A$ に変更                                         | 5  |

| • $I_Q$ の最大値を $10\mu A$ から $12.4\mu A$ に変更                                         | 5  |

| • $I_{DDR}$ および電流の代表値のテスト条件を更新                                                     | 5  |

| • $I_{DDW}$ および電流の代表値のテスト条件を更新                                                     | 5  |

| • アクティブ電流の代表値を $92\mu A$ から $99\mu A$ に変更                                          | 5  |

| • スタンバイ電流の代表値を $0.6\mu A$ から $4\mu A$ に変更                                          | 5  |

| • スタンバイ電流の最大値を $4\mu A$ から $6.5\mu A$ に変更                                          | 5  |

| • $I_{3C}$ モードの $t_{SUSTA}$ を JESD302-1 に合わせて $19.2\text{ns}$ から $12\text{ns}$ に変更 | 6  |

| • $I_{3C}$ モードの $t_{HDSTA}$ を JESD302-1 に合わせて $38.4\text{ns}$ から $30\text{ns}$ に変更 | 6  |

| • $I_{3C}$ モードの $t_{SUSTO}$ を JESD302-1 に合わせて $19.2\text{ns}$ から $12\text{ns}$ に変更 | 6  |

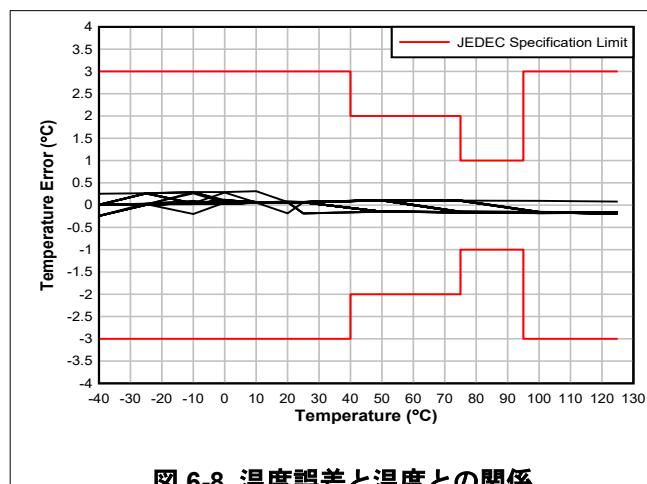

| • 図 6-8～図 6-12 を変更                                                                 | 8  |

| • 「電源に関する推奨事項」および「レイアウト」セクションを「アプリケーションと実装」セクションに移動                                | 49 |

### Changes from Revision \* (December 2020) to Revision A (February 2022) Page

|                                  |    |

|----------------------------------|----|

| • MR2 レジスタのリセット値を 02h から 04h に変更 | 36 |

| • DEF_ADDR_POINT_EN ビットの説明を変更    | 36 |

| • MR7 レジスタの説明のアドレスを変更            | 36 |

## 5 ピン構成および機能

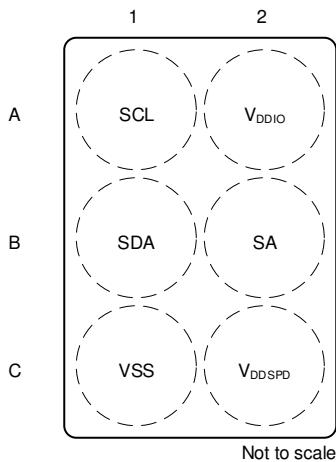

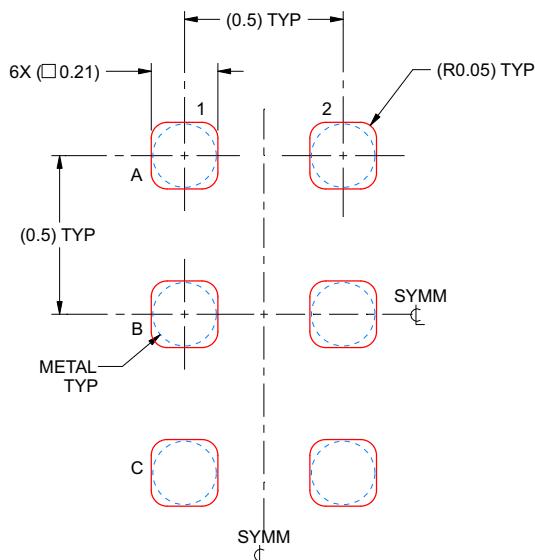

図 5-1. YAH パッケージ 6 ピン DSBGA 上面図

表 5-1. ピンの機能

| ピン                 |     | I/O | 説明                                                                                                     |

|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------|

| 名称                 | ボール |     |                                                                                                        |

| SA                 | B2  | I   | アドレス選択。V <sub>DDSPD</sub> または GND に接続します                                                               |

| SCL                | A1  | I   | シリアル・クロック                                                                                              |

| SDA                | B1  | I/O | シリアル・データ入力および出力。I <sup>3</sup> C モードでは、ピンはオープン・ドレインまたはプッシュプルになります。I <sup>2</sup> C モードではオープン・ドレインになります |

| V <sub>DDIO</sub>  | A2  | I   | センサ I/O の電源電圧                                                                                          |

| V <sub>DDSPD</sub> | C2  | I   | センサ・コアの電源電圧                                                                                            |

| VSS                | C1  | —   | グランド                                                                                                   |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                      | 最小値  | 最大値              | 単位 |

|----------------------|------|------------------|----|

| 電源電圧、( $V_{DDIO}$ )  | -0.5 | 2.1              | V  |

| 電源電圧、( $V_{DDSPD}$ ) | -0.5 | 2.1              | V  |

| 入力電圧 SA              | -0.5 | 2.1              | V  |

| 入力電圧 SCL、SDA         | -0.5 | $V_{DDIO} + 0.3$ | V  |

| 出力シンク電流 SDA          |      | ±15              | mA |

| 接合部温度、 $T_J$         | -55  | 150              | °C |

| 保存温度、 $T_{stg}$      | -65  | 150              | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 6.2 ESD 定格

|             |                                                         | 値     | 単位 |

|-------------|---------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠 <sup>(1)</sup>   | ±2000 | V  |

|             | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±1000 |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                      |             | 最小値  | 公称値 | 最大値               | 単位 |

|----------------------|-------------|------|-----|-------------------|----|

| 電源電圧                 | $V_{DDIO}$  | 0.95 | 1.0 | 1.05              | V  |

|                      | $V_{DDSPD}$ | 1.7  | 1.8 | 1.98              | V  |

| I/O 電圧               | SA          | 0    |     | $V_{DDSPD} + 0.3$ | V  |

|                      | SCL、SDA     | 0    |     | $V_{DDIO} + 0.3$  | V  |

| 自由気流での動作温度 ( $T_A$ ) |             | -40  |     | 125               | °C |

### 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>    |                     | TMP139     |  | 単位   |  |

|-------------------------|---------------------|------------|--|------|--|

|                         |                     | YAH (WCSP) |  |      |  |

|                         |                     | 6 ピン       |  |      |  |

| $R_{\theta JA}$         | 接合部から周囲への熱抵抗        | 116.6      |  | °C/W |  |

| $R_{\theta JC(top)}$    | 接合部からケース (上面) への熱抵抗 | 1.0        |  | °C/W |  |

| $R_{\theta JC(bottom)}$ | 接合部からケース (下面) への熱抵抗 | 該当なし       |  | °C/W |  |

| $R_{\theta JB}$         | 接合部から基板への熱抵抗        | 33.6       |  | °C/W |  |

| $\Psi_{JT}$             | 接合部から上面への熱特性パラメータ   | 0.4        |  | °C/W |  |

| $\Psi_{JB}$             | 接合部から基板までの特性評価パラメータ | 33.6       |  | °C/W |  |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、 $V_{DDIO} = 0.95\text{V} \sim 1.05\text{V}$ 、 $V_{DDSPD} = 1.7\text{V} \sim 1.98\text{V}$  (特に記述のない限り)、代表値は  $T_A = 25^\circ\text{C}$ 、 $V_{DDIO} = 1\text{V}$ 、 $V_{DDSPD} = 1.8\text{V}$  で測定

| パラメータ           | テスト条件                                                               | 最小値                                                  | 代表値 | 最大値        | 単位   |      |    |

|-----------------|---------------------------------------------------------------------|------------------------------------------------------|-----|------------|------|------|----|

| <b>温度入力</b>     |                                                                     |                                                      |     |            |      |      |    |

| $T_{ERR}$       | 温度精度                                                                | +75°C ~ +95°C                                        |     | $\pm 0.25$ | °C   |      |    |

|                 |                                                                     | -40°C ~ +125°C                                       |     | $\pm 0.25$ | °C   |      |    |

| $T_{RES}$       | 分解能                                                                 | 1 LSB (11 ビット)                                       |     | 0.25       | °C   |      |    |

| $T_{REPEAT}$    | 再現性 <sup>(1)</sup>                                                  |                                                      |     | 1          | LSB  |      |    |

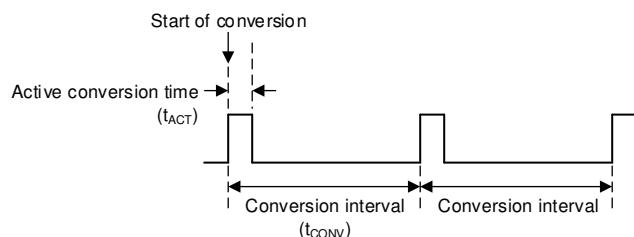

| $t_{ACT}$       | 平均変換時間                                                              |                                                      |     | 5.5        | ms   |      |    |

| $t_{CONV}$      | 変換間隔                                                                |                                                      |     | 125        | ms   |      |    |

| $T_{HYST}$      | 温度ヒステリシス                                                            |                                                      |     | 1          | °C   |      |    |

| <b>デジタル入出力</b>  |                                                                     |                                                      |     |            |      |      |    |

| $C_{IN}$        | 入力キャパシタンス <sup>(2)</sup>                                            | 入力キャパシタンス (SCL および SDA)                              |     | 4          | pF   |      |    |

| $R_{ON}$        | 出力プルアップおよびプルダウン・ドライブのインピーダンス                                        | SDA ピン                                               |     | 20         | 100  | Ω    |    |

| $I_{LI}$        | リード入力電流                                                             |                                                      |     | -1         | 0    | 1    | μA |

| $I_{LO}$        | リード出力電流                                                             |                                                      |     | -1         | 0    | 1    | μA |

| $V_{IL}$        | LOW レベル入力ロジック                                                       |                                                      |     | -0.3       | 0.3  | V    |    |

| $V_{IH}$        | HIGH レベル入力ロジック                                                      |                                                      |     | 0.7        | 1.35 | V    |    |

| $V_{HYS}$       | 入力電圧ヒステリシス                                                          | SCL ピンと SDA ピン                                       |     | 60         | 100  | mV   |    |

| $V_{OL}$        | LOW レベル出力ロジック                                                       | SDA ピン、 $I_{OL} = -3\text{mA}$                       |     | 0          | 0.3  | V    |    |

| $V_{OH}$        | HIGH レベル出力ロジック                                                      | SDA ピン、 $I_{OH} = 3\text{mA}$                        |     | 0.75       |      | V    |    |

| $SLEW\_RATE$    | 出力スルーレート <sup>(2)</sup>                                             | SDA ピン                                               |     | 0.1        | 1.0  | V/ns |    |

| <b>電源</b>       |                                                                     |                                                      |     |            |      |      |    |

| $I_Q$           | 平均電流 (シリアル・バスは非アクティブ)                                               | 変換間隔 125ms                                           |     | 8.3        | 12.4 | μA   |    |

| $I_{DDR}$       | 平均電流 (読み取り動作)                                                       | 変換間隔 125ms、読み取り温度レジスタ、 $f_{SCL} = 12.5\text{MHz}$    |     | 8.3        |      | μA   |    |

| $I_{DDW}$       | 平均電流 (書き込み動作)                                                       | 変換間隔 125ms、書き込みアラート・レジスタ、 $f_{SCL} = 12.5\text{MHz}$ |     | 8.3        |      | μA   |    |

| $I_{ACT}$       | アクティブ電流                                                             | 5.5ms のアクティブ変換時                                      |     | 99         | 140  | μA   |    |

| $I_{DD1}$       | スタンバイ電流                                                             | 連続変換時のアクティブ変換間                                       |     | 4          | 6.5  | μA   |    |

| $V_{PON}$       | パワーオン・リセットのスレッショルド                                                  | $V_{PON}$ と $V_{DDSPD(\text{MIN})}$ 間の単調な立ち上がり       |     | 1.6        |      | V    |    |

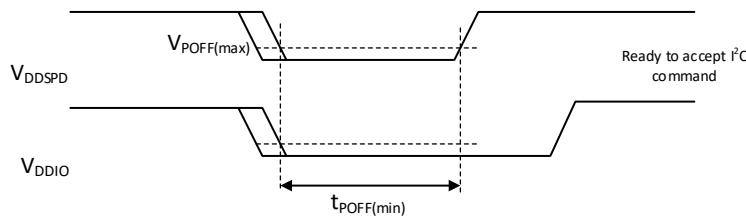

| $V_{POFF}$      | ウォーム・パワーオン・サイクルの電源オフ・リセットのスレッショルド                                   | $V_{poff}$ を超えるリングバックなし                              |     |            | 0.3  | V    |    |

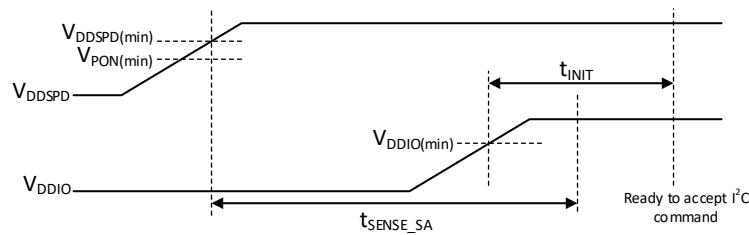

| $t_{INIT}$      | パワーオン・リセット後の初期化時間 <sup>(2)</sup>                                    | 図 7-2                                                |     |            | 10.0 | ms   |    |

| $t_{POFF}$      | ウォーム・パワー・サイクルのオフ時間 <sup>(2)</sup>                                   | 図 7-3                                                |     | 1.0        |      | ms   |    |

| $t_{SENSE\_SA}$ | 有効な $V_{DDSPD}$ 電源供給から LID コード割り当て用に SA ピンを検出するまでの時間 <sup>(2)</sup> | 図 7-2                                                |     |            | 5.0  | ms   |    |

| $t_{RST}$       | デバイスの再初期化時間 <sup>(2)</sup> (3)                                      |                                                      |     | 40         |      | μs   |    |

(1) 再現性とは、測定した温度が同じ条件の下で連続的に適用されたときに、測定値を再現する能力です。

(2) パラメータは設計により規定されています。

(3) パラメータは、RSTDAA 共通コマンド・コード用に規定されています。

## 6.6 タイミング要件

最小値と最大値の仕様は、-40°C~125°C、 $V_{DDIO} = 0.95V \sim 1.05V$  での値です (特に記述のない限り)<sup>(1)</sup>

|                               |                                                               | I <sup>2</sup> C モード - オープン・ドレイン |     | I3C モード - ブッシュブル <sup>(1)</sup> |      | 単位  |

|-------------------------------|---------------------------------------------------------------|----------------------------------|-----|---------------------------------|------|-----|

|                               |                                                               | 最小値                              | 最大値 | 最小値                             | 最大値  |     |

| $f_{SCL}$                     | SCL 動作周波数                                                     | 0.01                             | 1   | 0.001                           | 12.5 | MHz |

| $t_{HIGH}$                    | クロック・パルス幅の High 時間 (図 6-1)                                    | 260                              |     | 35                              |      | ns  |

| $t_{LOW}$                     | クロック・パルス幅の Low 時間 (図 6-1)                                     | 500                              |     | 35                              |      | ns  |

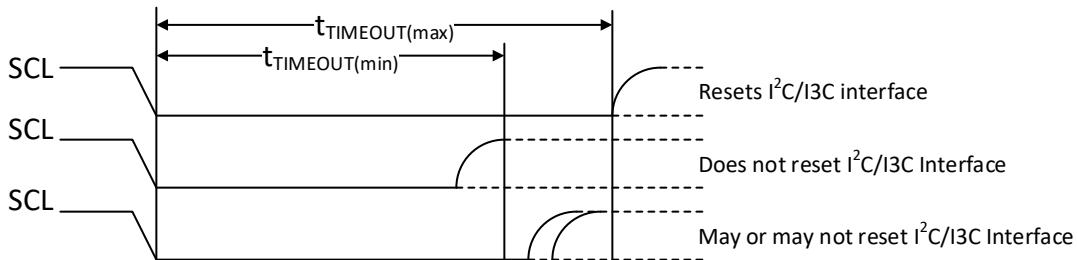

| $t_{TIMEOUT}$                 | クロック Low 検出のタイムアウト (図 7-4)                                    | 10                               | 50  | 10                              | 50   | ms  |

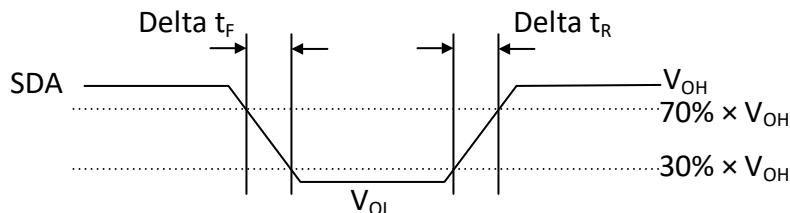

| $t_R$                         | SDA の立ち上がり時間 (図 6-1)                                          |                                  | 120 |                                 | 5    | ns  |

| $t_f$                         | SDA の立ち下がり時間 (図 6-1)                                          | 4                                | 120 |                                 | 5    | ns  |

| $t_{SUDAT}$                   | データ・セットアップ時間 (図 6-1)                                          | 50                               |     | 8                               |      | ns  |

| $t_{HDDI}$                    | データ・ホールド時間 href (図 6-1)                                       | 0                                |     | 3                               |      | ns  |

| $t_{SUSTA}$                   | スタート・コンディションのセットアップ時間 (図 6-1)                                 | 260                              |     | 12                              |      | ns  |

| $t_{HDSTA}$                   | リピート・スタート・コンディションの後のホールド時間。この期間が経過した後、最初のクロックが生成されます。 (図 6-1) | 260                              |     | 30                              |      | ns  |

| $t_{SUSTO}$                   | ストップ・コンディションのセットアップ時間 (図 6-1)                                 | 260                              |     | 12                              |      | ns  |

| $t_{BUF}$                     | ストップ・コンディションから次のスタート・コンディションまでの時間 (図 6-1)                     | 500                              |     | 500                             |      | ns  |

| $t_{AVAL}$                    | バス利用可能時間 (SDA および SCL にエッジなし)                                 |                                  |     | 1                               |      | μs  |

| $t_{IBI\_ISSUE}$              | バスが利用可能なときにイベントが検出されてから IBI 発行までの時間                           |                                  |     |                                 | 15   | μs  |

| $t_{CLR\_I3C\_CMD\_DELAY}$    | レジスタ・ステータスのクリアからスタート・コンディション付きの任意の I3C 動作までの時間、PEC はディセーブル    |                                  |     | 4                               |      | μs  |

|                               | レジスタ・ステータスのクリアからスタート・コンディション付きの任意の I3C 動作までの時間、PEC はイネーブル     |                                  |     | 15                              |      | μs  |

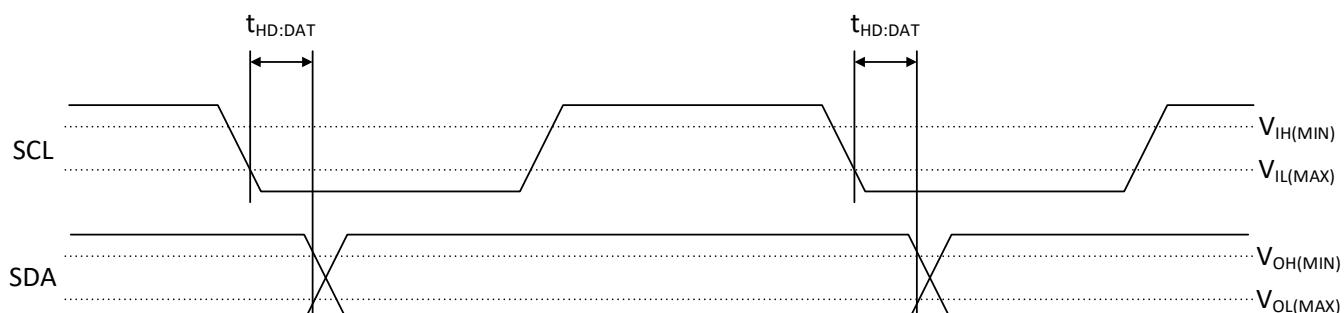

| $t_{HDDAT}$                   | SCL 立ち下がりクロック入力から SDA データ出力までのホールド時間 (図 6-4)                  | 0.5                              | 350 |                                 |      | ns  |

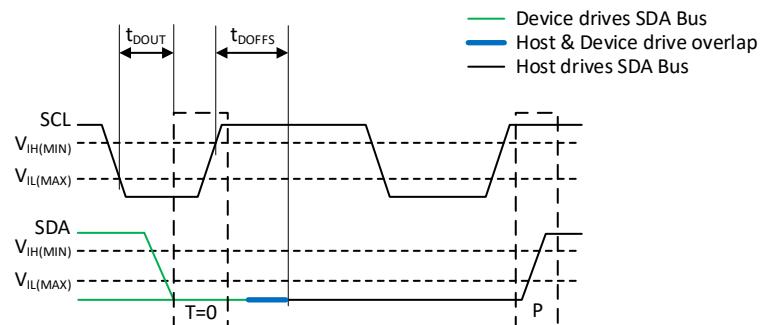

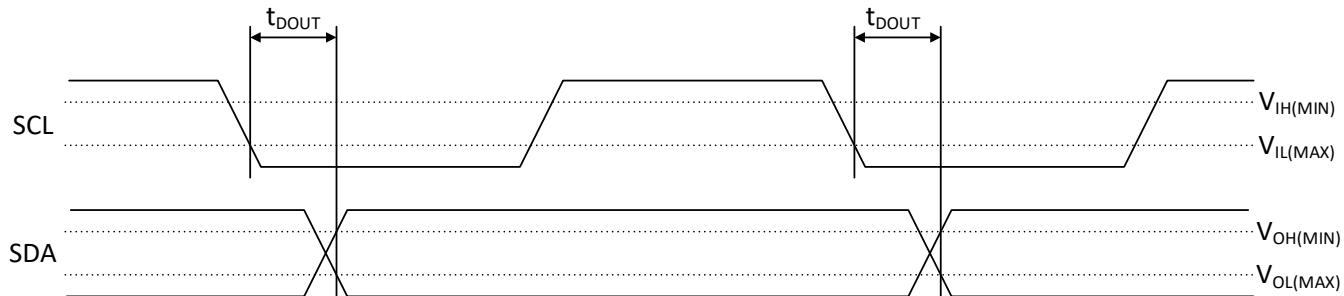

| $t_{DOUT}$                    | SCL 立ち下がりクロック入力から SDA 有効データ出力までの時間 (図 6-2、図 6-3、図 6-5)        |                                  |     | 0.5                             | 12   | ns  |

| $t_{DOFFS}$                   | SCL 立ち上がりクロック入力から SDA 出力オフまでの時間 (図 6-2、図 6-3)                 |                                  |     | 0.5                             | 12   | ns  |

| $t_{DOFFM}$                   | SCL 立ち上がりクロック入力からホスト・コントローラの SDA 出力オフまでの時間                    |                                  |     | 0.5                             | 30   | ns  |

| $t_{CL\_R\_DAT\_F}$           | SCL 立ち上がりクロック入力からホスト・コントローラの SDA Lowまでの時間 (図 6-2)             |                                  |     | 40                              |      | ns  |

| $t_{DEVCTRLCCC\_PEC\_DIS}$    | DEVCTRL CCC 後の DEVCTRL CCC またはレジスタ読み取り / 書き込みコマンドまでの遅延        | 3                                |     | 3                               |      | μs  |

| $t_{WR\_RD\_DECLAY\_PEC\_EN}$ | レジスタ書き込みコマンド後のレジスタ読み取りコマンドまでの遅延 (PEC イネーブル・モード)               |                                  |     | 8                               |      | μs  |

| $t_{I2C\_CCC\_UPDATE\_DELAY}$ | SETHID CCC または SETAASA CCC 後のほかの CCC または読み取り / 書き込みコマンドまでの遅延  | 2.5                              |     |                                 |      | μs  |

| $t_{I3C\_CCC\_UPDATE\_DELAY}$ | RSTDAA CCC または DISEC CCC 後のほかの CCC または読み取り / 書き込みコマンドまでの遅延    |                                  |     | 2.5                             |      | μs  |

| $t_{CCC\_DELAY}$              | 任意の CCC から RSTDAA CCC までの遅延                                   |                                  |     | 2.5                             |      | μs  |

(1) ホストとデバイスの  $V_{DD}$  値は同じです。値は、初期リリース時にテストされたサンプルの統計分析に基づいています。

(2) 最大  $t_{(HDDAT)}$  は、ファスト・モードでは  $0.9\mu s$  で、最大  $t_{(VDAT)}$  よりも遷移時間の分だけ短くなります。

## 6.7 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

|           |                                                    | 最小値 | 代表値           | 最大値 | 単位 |

|-----------|----------------------------------------------------|-----|---------------|-----|----|

| $t_{LPF}$ | I3C との互換性を実現するスパイク・フィルタは、I <sup>2</sup> C モードでのみ有効 |     | SCL = 12.5MHz | 50  | ns |

## 6.8 タイミング図

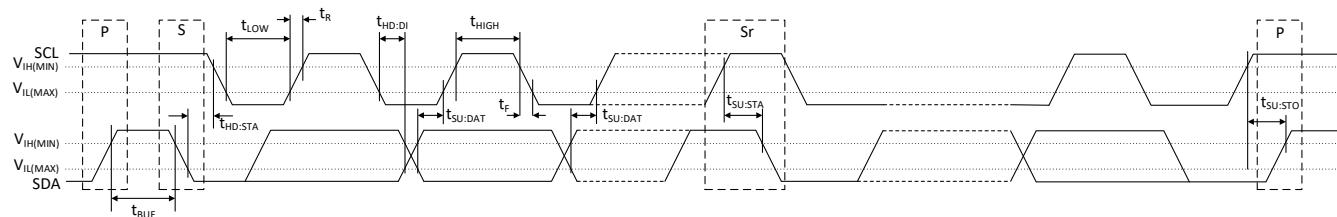

図 6-1. I<sup>2</sup>C および I<sup>3</sup>C の基本バス入力タイミング図

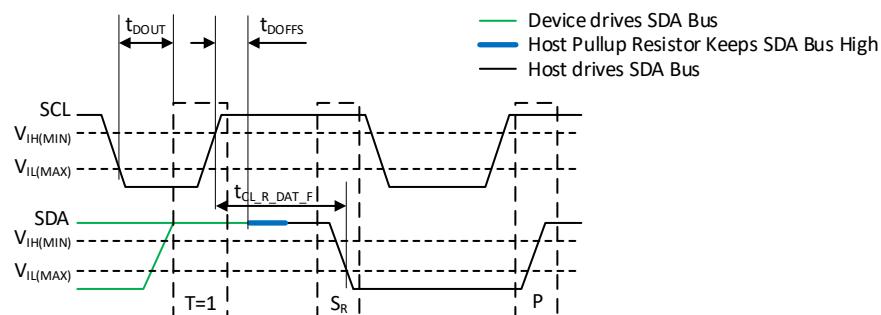

図 6-2. T = 1 ホストがリピート・スタートおよびストップで読み取りを終了するタイミング図

図 6-3. T = 0 デバイスが読み取りを終了し、ホストがストップを生成するタイミング図

図 6-4. I<sup>2</sup>C 基本バス出力のタイミング図

図 6-5. I2C 基本バス出力のタイミング図

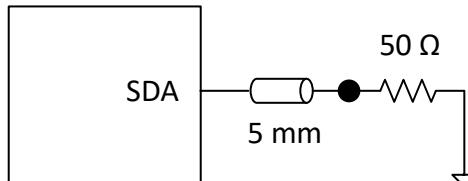

図 6-6. 出力スルーレートおよび出力タイミング基準負荷

図 6-7. 出力スルーレートの測定ポイント

## 6.9 代表的特性

図 6-8. 温度誤差と温度との関係

$V_{DDIO} = 1V, V_{IN} = 1.8V$

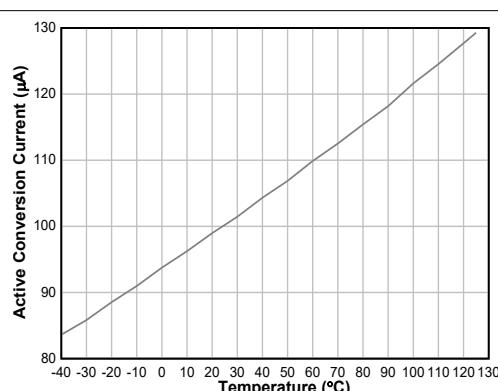

図 6-9. アクティブライト時間と温度との関係

$V_{DDIO} = 1V, V_{IN} = 1.8V$

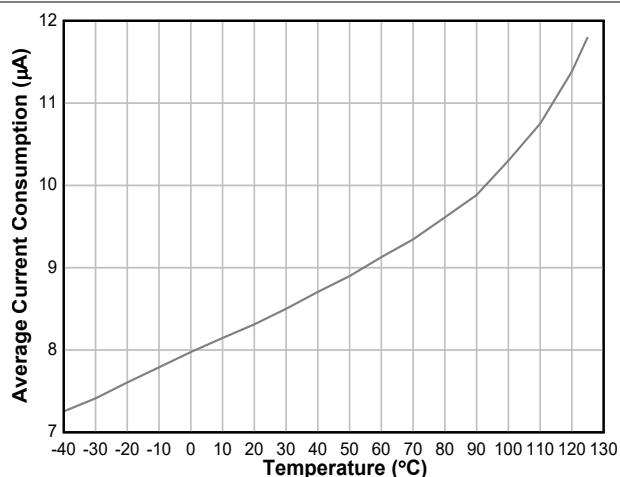

図 6-10. 平均電流と温度との関係

$V_{DDIO} = 1V, V_{IN} = 1.8V$

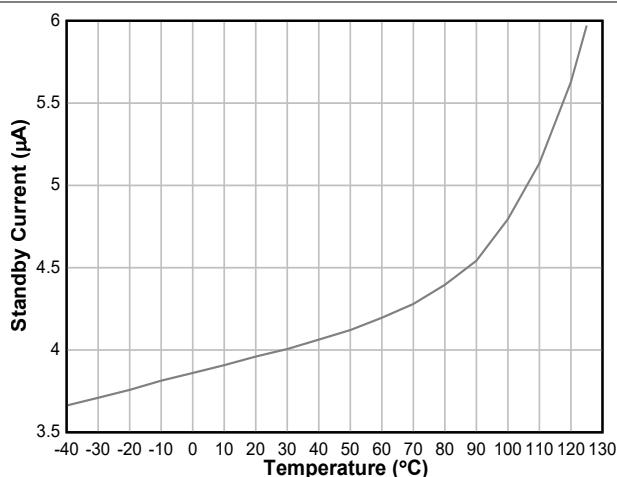

図 6-11. スタンバイ電流と温度との関係

$V_{DDIO} = 1V, V_{IN} = 1.8V$

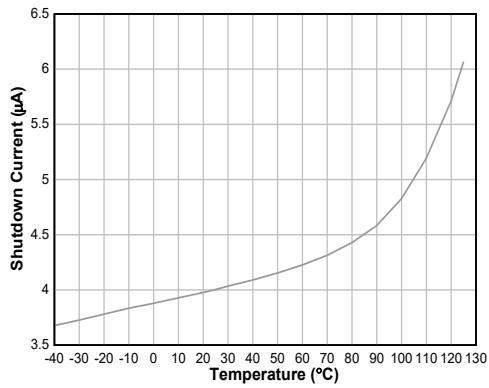

図 6-12. シャットダウン電流と温度との関係

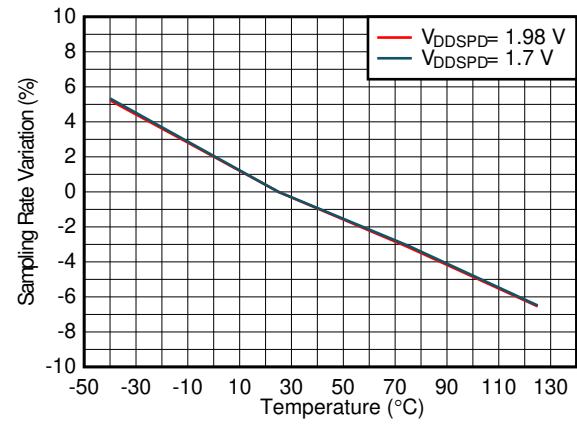

図 6-13. サンプリング・レートの変化

## 7 詳細説明

### 7.1 概要

TMP139 は、高精度の温度センサであり、パワーアップ・シーケンス、パワーダウンとデバイス・リセット、パリティおよびパケット・エラー・チェック機能、インバンド割り込み (IBI)、共通コマンド・コード (CCC) をサポートしています。

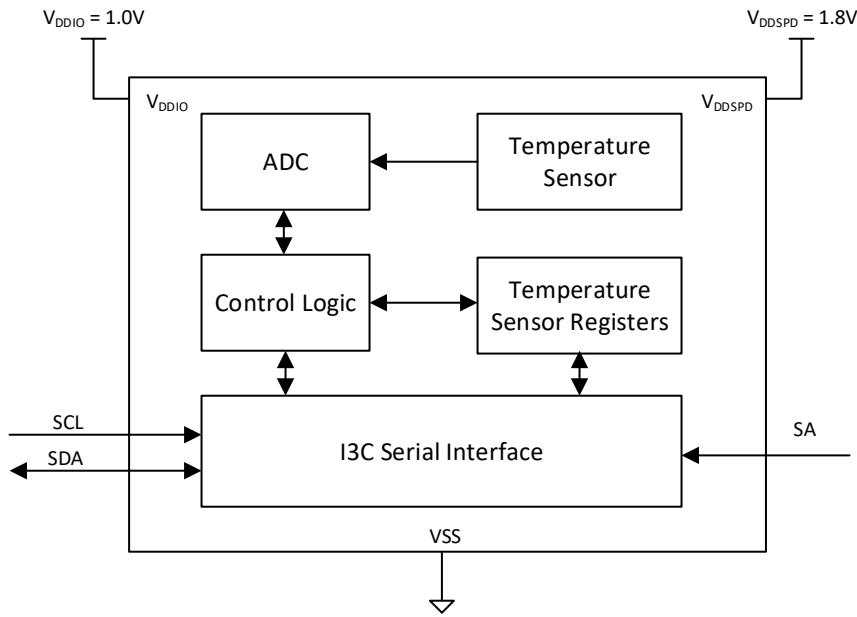

### 7.2 機能ブロック図

図 7-1. TMP139 機能ブロック図

### 7.3 機能説明

#### 7.3.1 パワーアップ・シーケンス

TMP139 には 2 つの電源ピンがあります。コア電源である  $V_{DDSPD}$  と、IO 電源である  $V_{DDIO}$  です。デバイスの正常起動を確保するためには、まず  $V_{DDSPD}$  に電源を投入し、次に  $V_{DDIO}$  を起動する必要があります。さらに、パワーオン・リセット (POR) 回路が実装されており、パワーアップ・シーケンスが正しくない場合に不適切な動作を防止します。

図 7-2 に示すように、 $V_{DDSPD}$  電源が最初に印加され、 $V_{PON(min)}$  と  $V_{DDSPD(min)}$  の間でリングバックなしに単調に立ち上がる必要があります。 $V_{DDIO}$  電源は、その次に立ち上がる必要があります、いずれかの動作が実行される前に正しいレベルに達している必要があります。

図 7-2. パワーアップ・シーケンス

$V_{DDSPD}$  および  $V_{DDIO}$  電源が最小スレッショルド値を上回ると、TMP139 は以下に示す手順を実行します。

1. 時間  $t_{SENSE\_SA}$  内に、デバイスは SA ピンをサンプリングして、デバイス・アドレスの一部を形成する LID コードを構成します。

2. 時間  $t_{INIT}$  内に、インターフェイスをイネーブルして、ホストからのコマンドを受け入れられるようにします。

デバイスは、パワーアップすると常に I<sup>2</sup>C 動作モードになります。

### 7.3.2 パワーダウンおよびデバイス・リセット

$V_{DDSPD}$  電源が低下した場合、 $V_{DDSPD(min)}$  レベル未満ではデバイスの動作は保証されません。デバイスの正常動作を確保するために、図 7-3 に示すように、アプリケーションでは、 $V_{DDIO}$  および  $V_{DDSPD}$  が  $T_{POFF}$  の期間にわたって  $V_{POFF}$  を下回るようにする必要があります。条件が満たされると、デバイスは正しくリセットされ、パワーアップ・シーケンスによってデバイスが正しく初期化されます。

図 7-3. パワーダウンおよびリセットシーケンス

### 7.3.3 温度結果および限界値

温度結果と限界値レジスタは、すべて 11 ビットの値であり、2 つの連続するレジスタに保存されます。表 7-1 に示すように、レジスタ・マップでは、下位バイト・レジスタの後に上位バイト・レジスタが続きます。データは 11 ビットの符号付き数値として表現され、温度フォーマットの最上位ビットが符号ビットになります。各温度値ビットには、重みが割り当てられており、これを使って温度値を計算できます。未使用的ビットはすべて 0 として読み取られます。また、未使用的ビットに書き込むとしても何も影響がありません。温度結果および限界値レジスタの分解能は常に 0.25°C です。デバイスの推奨動作範囲は -40°C~+125°C ですが、この値の範囲は -255.75°C~+255.75°C です。

表 7-1. 温度レジスタのフォーマット

| レジスタ・バイト | ビット 7  | ビット 6  | ビット 5  | ビット 4 | ビット 3 | ビット 2 | ビット 1  | ビット 0  |

|----------|--------|--------|--------|-------|-------|-------|--------|--------|

| 下位バイト    | 8      | 4      | 2      | 1     | 0.5   | 0.25  | 予備 = 0 | 予備 = 0 |

| 上位バイト    | 予備 = 0 | 予備 = 0 | 予備 = 0 | 符号    | 128   | 64    | 32     | 16     |

表 7-2 に、温度レジスタの読み取り値およびそれに対応する変換値(単位:°C)の例を示します。

表 7-2. 温度レジスタの例

| 温度 (°C) | 上位バイト     | 下位バイト     |

|---------|-----------|-----------|

| +255.75 | 0000 1111 | 1111 1100 |

| +125    | 0000 0111 | 1101 0000 |

| +95     | 0000 0101 | 1111 0000 |

| +85     | 0000 0101 | 0101 0000 |

| +75     | 0000 0100 | 1011 0000 |

| +1      | 0000 0000 | 0001 0000 |

| +0.25   | 0000 0000 | 0000 0100 |

| 0       | 0000 0000 | 0000 0000 |

| -0.25   | 0001 1111 | 1111 1100 |

| -1      | 0001 1111 | 1111 0000 |

| -25     | 0001 1110 | 0111 0000 |

| -40     | 0001 1101 | 1000 0000 |

| -255.75 | 0001 0000 | 0000 0000 |

### 7.3.4 バス・リセット

TMP139 はバス・リセット・メカニズムをサポートしており、デバイスがシリアル・バスをロックアップすることを防止します。バス上のデバイスは SCL を駆動しないため、バス・リセット・メカニズムは、図 7-4 に示すように SCL のタイムアウト方式を使用します。ホスト・コントローラによって SCL が LOW に保持されている期間が  $t_{TIMEOUT(max)}$  を超えた場合、TMP139 はリセットされ、次のアクションを実行します。

- インターフェイスはリセットされ、バス・リセットはストップ・コンディションと見なされるため、保留中の内部トランザクションもクリアされます。

- TMP139 は I<sup>2</sup>C 動作モードに戻り、以下のレジスタをリセットします。

- MR7 レジスタ、DEV\_HID\_CODE[2:0] は 3'b111 に設定されます。

- MR18 レジスタ、PEC\_EN、PAR\_DIS、INF\_SEL は 1'b0 に設定されます。

- MR27 レジスタ、IBI\_ERROR\_EN は 1'b0 に設定されます。

- MR52 レジスタ、PEC\_ERROR\_STATUS および PAR\_ERROR\_STATUS は 1'b0 に設定されます。

- TMP139 は、SA ピンを再サンプリングしません。

- TMP139 は、SDA ピンをフローティングにして、バス・コントローラがラインをプルアップできるようにします。

図 7-4. I<sup>2</sup>C または I3C の基本的なバス・リセット

### 7.3.5 割り込みの生成

TMP139 には専用の割り込みピンまたはアラート・ピンがありませんが、代わりに SDA ピンでのインバンド割り込み (IBI) を使用した割り込み生成をサポートしています。IBI を使用した割り込み生成は、I3C 動作モードでのみサポートされています。したがって、アプリケーションは、デバイスが IBI をイネーブルする前に、まず I3C モードで動作するようにプログラムされていることを確認する必要があります。I3C 基本バスには複数のデバイスが存在しており、それぞれが IBI を生成できるため、調停プロセスが必要です。

TMP139 が IBI を生成するのは、バスが  $t_{AVAL}$  期間にわたってアイドル状態であることを確認した場合に限ります。この条件が満たされると、デバイスは SDA ラインを  $t_{IBI\_ISSUE}$  の期間だけ LOW にプルし、IBI があることをホストに通知します。ホストは SCL を LOW に駆動して開始します。これによりバスのスタート・コンディションが生成されます。この時点では、デバイスは、R/W ビットをセットした状態でデバイス・アドレスをバスに送信します。

TMP139 が IBI を生成すると同時に、ホストが新しいバス・トランザクションを開始する状況になる可能性があります。このような場合、TMP139 とホストの間で、デバイス・アドレス・バイトでの調停が行われます。

### 7.3.6 パリティ・エラー・チェック

TMP139 によって実装されるパリティ・エラー・チェックは、奇数パリティです。I<sup>2</sup>C モードでは、サポートされている共通コマンド・コード (CCC) 以外については、パリティ・エラー・チェックはサポートされていません。I3C モードでは、CCC とホストからデバイスへのデータ転送の両方でパリティ・エラー・チェックがサポートされています。パリティ・ビットは、ホスト書き込み中にのみ送信され、TMP139 はパリティをチェックして、受信したデータまたは CCC が正しいことを確認します。このデバイスには、奇数パリティが実装されています。バイトの中で奇数個のビットが 1 になっている場合、パリティ・ビットは 0 に設定されます。バイトの中で偶数個のビットが 1 になっている場合、パリティ・ビットは 1 に設定されます。

データ転送または CCC 中にパリティ・エラーが発生した場合、TMP139 はパリティ・エラー検出後にバイトを破棄し、バス上でストップ・コンディションを待機します。

パリティ・エラーが検出された場合、デバイスは **MR48** レジスタの **IBI\_STATUS** ビットと、**MR52** レジスタの **PAR\_ERROR\_STATUS** ビットを設定します。

### 7.3.7 パケット・エラー・チェック

パケット・エラー・チェック (PEC) は、表 7-3 に示す多項式を使用して CRC-8 で実装されます。

表 7-3. PEC ルール表

| PEC ルール  | 属性                          |

|----------|-----------------------------|

| PEC 幅    | 8 ビット                       |

| PEC 多項式  | $x^8 + x^2 + x^1 + 1$ (07h) |

| 初期シード値   | 00h                         |

| 入力データの反映 | なし                          |

| 出力データの反映 | なし                          |

| XOR 値    | 00h                         |

PEC は I3C モードでのみサポートされ、デバイス・アドレス、R/W ビット、およびデータ・パケットで計算されます。PEC 機能のシード値は、バスのスタート・コンディションまたはリピート・スタート・コンディションのいずれかでゼロにリセットされます。

PEC のイネーブルまたはディセーブルによるホスト・トランザクションは、その次にバス上でストップ・コンディションが直ちに続く必要があります。これは、**MR18** レジスタの PEC 制御ビットを更新できるようにするためにです。

## 7.4 デバイスの機能モード

このセクションでは、TMP139 のシリアル・アドレス構造について、およびデバイスが I<sup>2</sup>C モードと I3C 基本モードで動作する方法 (モード間の切り替えを含む) について説明します。このセクションでは、IBI およびバス・リセット・シーケンス中の TMP139 の動作についても説明します。

### 7.4.1 変換モード

TMP139 は、起動時には、連続変換モードになっています。このモードでは、デバイスは、図 7-5 に示すように 125ms ごとに温度変換を実行します。

図 7-5. 連続変換サイクルのタイミング図

アプリケーション・ソフトウェアは、**MR26** レジスタのビット 0 をクリアすることで、変換を停止できます。ディセーブルの場合、デバイスは結果レジスタを更新しません。温度センサをディセーブルにしたとき、ホストは、デバイスへの他の書き込みを実行する前に、ディセーブルが効果を発するまで少なくとも 1 回のアクティブ変換サイクルを待つ必要があります。連続変換モードで、温度センサを再びイネーブルにした場合、ホストは、温度結果を読み取る前に、少なくとも 1 回の変換間隔を待つ必要があります。この期間中、他のレジスタへの読み取りは実行可能です。

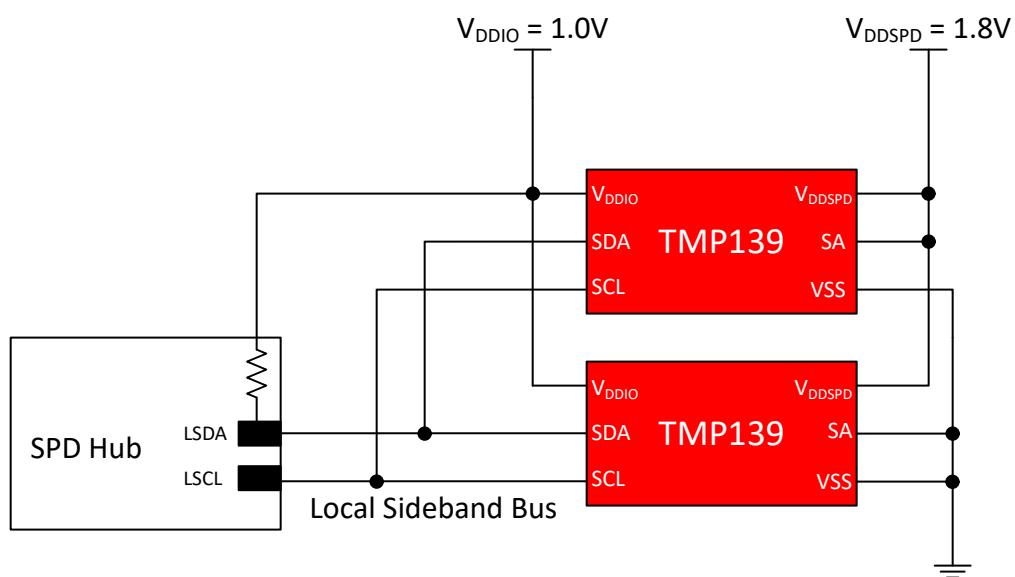

### 7.4.2 シリアル・アドレス

TMP139 には 7 ビットのシリアル・アドレスがあり、ホストは、これを I<sup>2</sup>C および I3C 基本動作モードでデバイスと通信するために使用します。表 7-4 に、TMP139 のシリアル・アドレス・フォーマットを示します。「パワー・アップ・シーケンス」で説明しているように、電源投入時に SA ピンをサンプリングします。サンプリングされた SA ピンの値を使用して、シリアル・ア

ドレスのローカル・デバイス・タイプ ID (LID) セクションとして可能な 2 つの値のいずれか一方が選択されます。LID はホスト ID (HID) と連結され、7 ビットの一意のシリアル・アドレスを形成します。

**表 7-4. シリアル・アドレス・フォーマット**

| ビット 7                  | ビット 6 | ビット 5 | ビット 4 | ビット 3        | ビット 2 | ビット 1 | ビット 0       |

|------------------------|-------|-------|-------|--------------|-------|-------|-------------|

| 0                      | SA    | 1     | 0     | 1            | 1     | 1     | R/W         |

| ローカル・デバイス・タイプ ID (LID) |       |       |       | ホスト ID (HID) |       |       | 読み出し / 書き込み |

SA ピンが GND に接続されている場合、TMP139 のシリアル・アドレスは 7'b0010111 としてエンコードされます。SA ピンが V<sub>DDSPD</sub> に接続されている場合、シリアル・アドレスは 7'b0110111 としてエンコードされます。

#### 7.4.3 I<sup>2</sup>C モードの動作

I<sup>2</sup>C 動作モードは、デバイスの電源を投入したとき、バス・リセットを実行したとき、またはデバイスが I<sup>3</sup>C 動作モードである場合に RSTDAA CCC が発行されたときの最初の動作モードです。このモードでサポートされる最大バス速度は、1.0MHz です。この動作モードでは、次の機能はサポートされていません。

1. IBI:I<sup>3</sup>C 基本モードで IBI がイネーブルになっている場合、I<sup>2</sup>C モードに切り替えると、IBI イネーブル・メカニズムがディセーブルになります。IBI を発生させるデバイス・イベントが存在する場合、デバイスは各レジスタにイベントのステータスを記録します。

2. パケット・エラー・チェック:この機能はサポートされていません。ホストが PEC バイト付きでデータの書き込みを試みる場合、PEC バイトはデータ・バイトとして扱われ、レジスタ・アドレスにインクリメント方式で書き込まれます。

3. パリティ・エラー・チェック:表 7-6 に記載されている CCC を除いて、パリティ・エラー・チェックはサポートされていません。

I<sup>2</sup>C 動作モードでは、TMP139 は、SETHID、DEVCTRL、SETAASA CCC、および PEC なしのデータ転送パケットをサポートしています。また、7'h7E および W = 0 を後に伴うスタートまたはリピート・スタートは、サポートされている CCC を発行する目的でのみ許可されます。リピート・スタートに関連するそれ以外の動作は、規格不適合とみなされます。

##### 7.4.3.1 ホスト I<sup>2</sup>C 書き込み動作

I<sup>2</sup>C 書き込み動作の場合、図 7-6 に示すように、ホスト・コントローラは、スタートまたはリピート・スタートの後、R/W ビットを 0 としてデバイス・アドレスを送信します。その後に 8 ビットのレジスタ・アドレス、さらにデータが続きます。TMP139 は、指定されたレジスタ・アドレスにデータを書き込みます。内部書き込みレジスタ・アドレス・ポインタは、データ・バイトを書き込むたびにインクリメントされます。書き込みの結果、アドレスがロールオーバーした場合、デバイスは内部書き込みレジスタ・アドレス・ポインタをリセットし、可能な場合は書き込み動作を続行します。TMP139 は、予約済みまたは読み取り専用レジスタに対するデータ・バイトに対して NACK 応答をしませんが、そのデータ・バイトを破棄し、レジスタを更新しません。

| S or Sr                     | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0   | ACK/NACK |

|-----------------------------|---|----|---|---|------|------|------|---------|----------|

| RA = Register Address [7:0] |   |    |   |   |      |      |      |         | ACK      |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      |         | ACK      |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      |         | ACK      |

| ...                         |   |    |   |   |      |      |      |         | ACK      |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      |         | ACK      |

|                             |   |    |   |   |      |      |      | Sr or P |          |

**図 7-6. I<sup>2</sup>C 書き込み動作**

##### 7.4.3.2 ホスト I<sup>2</sup>C 読み取り動作

I<sup>2</sup>C 読み取り動作の場合、ホスト・コントローラは、スタートまたはリピート・スタートの後、R/W ビットを 0 としてデバイス・アドレスを送信します。その後に 8 ビットのレジスタ・アドレスが続きます。レジスタ・アドレスが TMP139 で利用可能になると、

ホストはリピート・スタートを発行し、R/W ビットを 1 としてデバイス・アドレスを送信します。この時点で、デバイスは、ホストが NACK を送信するまで、レジスタ・アドレスをインクリメントしながらデータを送信します。読み取り動作の結果、内部読み取りレジスタ・アドレス・ポインタがロールオーバーした場合、TMP139 デバイスの動作は定義されません。

|                             |   |    |   |   |      |      |      |         |          |

|-----------------------------|---|----|---|---|------|------|------|---------|----------|

| S or Sr                     | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0   | ACK/NACK |

| RA = Register Address [7:0] |   |    |   |   |      |      |      | ACK     |          |

| Sr                          | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=1   | ACK/NACK |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      | ACK     |          |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      | ACK     |          |

| ...                         |   |    |   |   |      |      |      | ACK     |          |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      | NACK    |          |

|                             |   |    |   |   |      |      |      | Sr or P |          |

**図 7-7. I<sup>2</sup>C 読み取り動作**

#### 7.4.3.3 ホスト I<sup>2</sup>C 読み取り動作(デフォルト読み取りアドレス・ポインタ・モード)

TMP139 には 図 7-8 に示すように、デフォルト読み取りアドレス・ポインタ・モードがあり、I<sup>2</sup>C バス上の特定のレジスタを読み取ります。ホストから送信されるバイト数は、標準の I<sup>2</sup>C 読み取り動作より 2 つ少ないため、このモードではより効率的なポーリング・メカニズムを実現できます。MR18 レジスタのビット DEF\_RD\_ADDR\_POINT\_EN を使用して、モードをイネーブルにします。また、ビット DEF\_RD\_ADDR\_POINT\_Start を使用して、デフォルトの読み取りアドレス・ポインタをレジスタ・マップ内の特定のレジスタに設定します。このモードをイネーブルにすると、TMP139 は、バス上でストップ・コンディションが発生したときに、内部読み取りアドレス・ポインタを特定のレジスタに設定します。

|                                      |   |    |   |   |      |      |      |         |          |

|--------------------------------------|---|----|---|---|------|------|------|---------|----------|

| S or Sr                              | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=1   | ACK/NACK |

| Data <sub>(DEF_ADDR_POINTER)</sub>   |   |    |   |   |      |      |      | ACK     |          |

| Data <sub>(DEF_ADDR_POINTER+1)</sub> |   |    |   |   |      |      |      | ACK     |          |

| ...                                  |   |    |   |   |      |      |      | ACK     |          |

| Data <sub>(DEF_ADDR_POINTER+N)</sub> |   |    |   |   |      |      |      | NACK    |          |

|                                      |   |    |   |   |      |      |      | Sr or P |          |

**図 7-8. I<sup>2</sup>C デフォルト読み取りアドレス・ポインタ・モード**

この動作モードには、具体的には 2 つのケースがあります。第 1 のケースでは 図 7-9 に示すように、デフォルト読み取りモードの前に通常の I<sup>2</sup>C 読み取りがあります。スタートの前にストップがある場合、内部の読み取りアドレス・ポインタはデフォルト・アドレス・ポインタに設定されます。それ以降のデータ読み取りでは、そのデフォルト読み取りアドレス・ポインタに対応するデータ・バイトが TMP139 によって送信されます。ストップではなくリピート・スタートが発行された場合、TMP139 は、デフォルト読み取りアドレス・ポインタに基づいてデータを送信します。

|                                      |   |    |   |   |      |      |      |       |          |         |

|--------------------------------------|---|----|---|---|------|------|------|-------|----------|---------|

| S or Sr                              | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=0 | ACK/NACK |         |

| RA = Register Address [7:0]          |   |    |   |   |      |      |      |       | ACK      |         |

| Sr                                   | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |         |

| Data <sub>(RA)</sub>                 |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(RA+1)</sub>               |   |    |   |   |      |      |      |       | ACK      |         |

| ...                                  |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(RA+N)</sub>               |   |    |   |   |      |      |      |       | NACK     | P       |

| S                                    | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |         |

| Data <sub>(DEF_ADDR_POINTER)</sub>   |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(DEF_ADDR_POINTER+1)</sub> |   |    |   |   |      |      |      |       | ACK      |         |

| ...                                  |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(DEF_ADDR_POINTER+N)</sub> |   |    |   |   |      |      |      |       | NACK     | Sr or P |

図 7-9. I<sup>2</sup>C 通常読み取りの後にデフォルト読み取りアドレスが続く場合

第 2 のケースでは 図 7-10 に示すように、デフォルト読み取りモードの前に、通常の I<sup>2</sup>C 書き込みがあります。ストップの後に書き込みバス動作が続き、次にリピート・スタートで読み取りモードが実行される場合、TMP139 は、内部の読み取りアドレス・ポインタをデフォルト読み取りアドレスに更新して、バイトをホストに送信します。

|                                      |   |    |   |   |      |      |      |       |          |         |

|--------------------------------------|---|----|---|---|------|------|------|-------|----------|---------|

| S                                    | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=0 | ACK/NACK | P       |

| RA = Register Address [7:0]          |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(RA)</sub>                 |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(RA+1)</sub>               |   |    |   |   |      |      |      |       | ACK      |         |

| ...                                  |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(RA+N)</sub>               |   |    |   |   |      |      |      |       | ACK      |         |

| Sr                                   | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |         |

| Data <sub>(DEF_ADDR_POINTER)</sub>   |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(DEF_ADDR_POINTER+1)</sub> |   |    |   |   |      |      |      |       | ACK      |         |

| ...                                  |   |    |   |   |      |      |      |       | ACK      |         |

| Data <sub>(DEF_ADDR_POINTER+N)</sub> |   |    |   |   |      |      |      |       | NACK     | Sr or P |

図 7-10. I<sup>2</sup>C 通常書き込みの後にデフォルト読み取りアドレスが続く場合

#### 7.4.3.4 I<sup>2</sup>C モードから I3C 基本モードへの切り換え

表 7-6 に示すように、I<sup>2</sup>C モードでは、DEVCTRL、SETHID、および SETAASA の各 CCC のみがサポートされています。ホストは、SETAASA を発行してデバイスを I<sup>2</sup>C モードから I3C 基本モードに切り替える前に、DEVCTRL や SETHID を発行することができます。

ホストが SETAASA を発行すると、バス上でストップ・コンディションが検出された後、デバイスは MR18 レジスタの INF\_SEL ビットを 1'b1 に設定してこのコマンドを登録します。その後、TMP139 は I3C 基本動作モードになります。

#### 7.4.4 I3C 基本モードの動作

前のセクションで説明したように、I3C の基本動作モードは、必ず I<sup>2</sup>C 動作モードから移行します。I3C 基本モードでは、プッシュプル SDA ドライバにより、最大 12.5MHz のデータ転送速度をサポートできます。さらに、デフォルトで、またはイネーブルされた場合に、以下の機能をサポートできます。

1. IBI: デフォルトではディセーブルですが、ここでは IBI をイネーブルできます。

2. パケット・エラー・チェック: デフォルトではディセーブルですが、ホストによってイネーブルされた場合、TMP139 は、PEC 機能をサポートできます。

3. パリティ・チェック: デフォルトで常にイネーブルです。

I3C 基本動作モードでは、読み取りパケットと書き込みパケットの構成が異なる場合があります。データ・ペイロードの構造は、イネーブルになっている機能に依存します。

##### 7.4.4.1 ホスト I3C 書き込み動作、PEC なし

図 7-11 および 図 7-12 に示すように、I3C 基本書き込み動作は、I<sup>2</sup>C の書き込み動作と同じです。デバイス・アドレス・フィールドの後のすべてのバイトについて、9 番目のビットはホストから送信されるパリティ・ビットです。ホストによって IBI がイネーブルになっている場合、ホストは、デバイス・アドレスを送信する前に、7h7E および R/W = 0 で構成される IBI ヘッダ・バイトを送信する必要があります。これにより、複数のデバイスにおいてホストと通信する必要のある割り込み条件が発生した場合に、バス上の参加デバイス間での調停が可能になります。

| S or Sr                     | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

|-----------------------------|---|----|---|---|------|------|------|-------|----------|

| RA = Register Address [7:0] |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      |       | T        |

| ...                         |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      |       | T        |

|                             |   |    |   |   |      |      |      |       | Sr or P  |

図 7-11. I3C 基本モードの書き込み

| S                           | 1 | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK      |

|-----------------------------|---|----|---|---|------|------|------|-------|----------|

| Sr                          | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

| RA = Register Address [7:0] |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      |       | T        |

| ...                         |   |    |   |   |      |      |      |       | T        |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      |       | T        |

|                             |   |    |   |   |      |      |      |       | Sr or P  |

図 7-12. I3C 基本モードの書き込み、IBI ヘッダー付き

データ転送中にパリティ・エラーが発生した場合、デバイスはパリティ・エラーが検出されたバイトを含むすべてのバイトを破棄し、パリティ・エラー状態を設定します。ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、TMP139 は、デバイス・アドレスに NACK 応答して、エラー状態をホストに通知します。ホストは、TMP139 への新しい転送を実行する前に、まずパリティ・エラー状態をクリアする必要があります。IBI がイネーブルのとき、デバイスは IBI を使用して、検出されたエラー条件をホストと通信できます。ただし、IBI がイネーブルでない場合は、ホストがエラー・ステータス・レジスタをチェックして、バスでパリティ・エラーが検出されていないことを確認するよう強く推奨します。

#### 7.4.4.2 ホスト I3C 書き込み動作、PEC 付き

図 7-13 および 図 7-14 に示すように、ホストが PEC をイネーブルにすると、レジスタ・アドレスを送信した後、ホストによってさらにバイトが追加されます。追加バイトのフォーマットについては、表 7-5 で説明します。

表 7-5. コマンドの真理値表 - PEC イネーブル・モード

| CMD     | RW | コマンド名 | コマンドの説明                                |

|---------|----|-------|----------------------------------------|

| 000     | 0  | W1R   | データ・パケットで指定されたレジスタ・アドレスに 1 バイトを書き込みます  |

|         | 1  | R1R   | データ・パケットで指定されたレジスタ・アドレスから 1 バイトを読み取ります |

| 001     | 0  | W2R   | データ・パケットで指定されたレジスタ・アドレスに 2 バイトを書き込みます  |

|         | 1  | R2R   | データ・パケットで指定されたレジスタ・アドレスから 2 バイトを読み取ります |

| 010~111 | X  | RSVD  | 予約済み                                   |

ホストから送信された CMD 値が TMP139 に対して有効でない場合、デバイスは指定されたレジスタにデータを何も書き込みません。

| S or Sr                     | 0   | SA | 1   | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

|-----------------------------|-----|----|-----|---|------|------|------|-------|----------|

| RA = Register Address [7:0] |     |    |     |   |      |      |      |       | T        |

|                             | CMD |    | W=0 | 0 | 0    | 0    | 0    |       | T        |

| Data <sub>(RA)</sub>        |     |    |     |   |      |      |      |       | T        |

| ...                         |     |    |     |   |      |      |      |       | T        |

| Data <sub>(RA+N)</sub>      |     |    |     |   |      |      |      |       | T        |

| PEC                         |     |    |     |   |      |      |      |       | T        |

|                             |     |    |     |   |      |      |      |       | Sr or P  |

図 7-13. I3C 基本モードの書き込み、PEC イネーブル

| S                           | 1   | 1  | 1   | 1 | 1    | 1    | 0    | R/W=0 | ACK      |

|-----------------------------|-----|----|-----|---|------|------|------|-------|----------|

| Sr                          | 0   | SA | 1   | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

| RA = Register Address [7:0] |     |    |     |   |      |      |      |       | T        |

|                             | CMD |    | W=0 | 0 | 0    | 0    | 0    |       | T        |

| Data <sub>(RA)</sub>        |     |    |     |   |      |      |      |       | T        |

| ...                         |     |    |     |   |      |      |      |       | T        |

| Data <sub>(RA+N)</sub>      |     |    |     |   |      |      |      |       | T        |

| PEC                         |     |    |     |   |      |      |      |       | T        |

|                             |     |    |     |   |      |      |      |       | Sr or P  |

図 7-14. I3C 基本モードの書き込み、IBI ヘッダーおよび PEC イネーブル

データ転送中にパリティ・エラーが発生した場合、デバイスはパリティ・エラーが検出されたバイトを含むすべてのバイトを破棄し、パリティ・エラー状態を設定します。ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、TMP139 は、デバイス・アドレスに NACK 応答して、エラー状態をホストに通知します。ホストは、TMP139 への新しい転送を実行する前に、まずパリティ・エラー状態をクリアする必要があります。

PEC エラーが発生した場合、TMP139 はデータ・パケット全体を破棄し、PEC エラー条件を設定します。ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、TMP139 は、デバイス・アドレスに NACK

応答して、エラー状態をホストに通知します。ホストは、TMP139への新しい転送を実行する前に、まず PEC エラー状態をクリアする必要があります。

IBI がイネーブルのとき、デバイスは IBI を使用して、検出されたエラー条件をホストと通信できます。ただし、IBI がイネーブルでない場合は、ホストがエラー・ステータス・レジスタをチェックして、バスでパリティまたは PEC エラーが検出されていないことを確認するように強く推奨します。

#### 7.4.4.3 PEC なしのホスト I3C 読み取り動作

図 7-15 および 図 7-16 に示すように、I3C 基本モードの読み取りは I<sup>2</sup>C 読み取り動作と同じです。デバイスから送信されるすべてのバイトについて、9 番目のビットは T ビットです。このビットは、デバイスとホストが読み取り転送の継続をネゴシエーションするために使用されます。読み取りフェーズでは、デバイスは、立ち上がりエッジの前に T ビットを 1 に駆動して、さらに続けてバイトを送信してもよいことをホストに通知します。あるいは、T ビットを 0 に駆動して、デバイスが転送を終了しようとしていることをホストに通知できます。この場合、ホストは、バス上でストップまたはリピート・ストップを使って応答する必要があります。また、デバイスが T ビットを 1 として送信した場合に限り、ホストは T ビットを 0 に駆動することによって転送を終了できます。この場合、バス上でリピート・スタート・コンディションが発生します。また、ホストは、バス上でストップを送信することもできます。ホストによって IBI がイネーブルになっている場合、ホストは、デバイス・アドレスを送信する前に、7'h7E および R/W = 0 で構成される IBI ヘッダ・バイトを送信する必要があります。これにより、複数のデバイスにおいてホストと通信する必要のある割り込み条件が発生した場合に、バス上の参加デバイス間での調停が可能になります。

|                             |   |    |   |   |      |      |      |       |          |

|-----------------------------|---|----|---|---|------|------|------|-------|----------|

| S or Sr                     | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

| RA = Register Address [7:0] |   |    |   |   |      |      |      |       | T        |

| Sr                          | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=1 | ACK/NACK |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      |       | T=1      |

| ...                         |   |    |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      |       | T=1      |

|                             |   |    |   |   |      |      |      |       | Sr or P  |

図 7-15. I3C 基本モードの読み取り

|                             |   |    |   |   |      |      |      |       |          |

|-----------------------------|---|----|---|---|------|------|------|-------|----------|

| S                           | 1 | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK      |

| Sr                          | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |

| RA = Register Address [7:0] |   |    |   |   |      |      |      |       | T        |

| Sr                          | 0 | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=1 | ACK/NACK |

| Data <sub>(RA)</sub>        |   |    |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+1)</sub>      |   |    |   |   |      |      |      |       | T=1      |

| ...                         |   |    |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+N)</sub>      |   |    |   |   |      |      |      |       | T=1      |

|                             |   |    |   |   |      |      |      |       | Sr or P  |

図 7-16. I3C 基本モードの読み取り、IBI ヘッダー付き

リピート・スタートの前の書き込みフェーズでパリティ・エラーが発生した場合、TMP139は、トランザクションの読み取りフェーズで NACK 応答します。また、ホストがデータの読み取りを継続的に試みて、内部読み取りアドレス・ポインタが、レジスタ・マップ・テーブルの最後のレジスタである 255 に達する場合には、デバイスは、T ビットを 0 として送信します。さらに、ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、前のトランザクションでパリティ・エラーが発生している場合、TMP139は、デバイス・アドレスに NACK 応答して、エラー状態をホストに通知します。ホストは、TMP139への新しい転送を実行する前に、まずパリティ・エラー状態をクリアする必要があります。IBI がイネーブル

ルのとき、デバイスは IBI を使用して、検出されたエラー条件をホストと通信できます。ただし、IBI がイネーブルでない場合は、ホストがエラー・ステータス・レジスタをチェックして、バスでパリティ・エラーが検出されていないことを確認するよう強く推奨します。

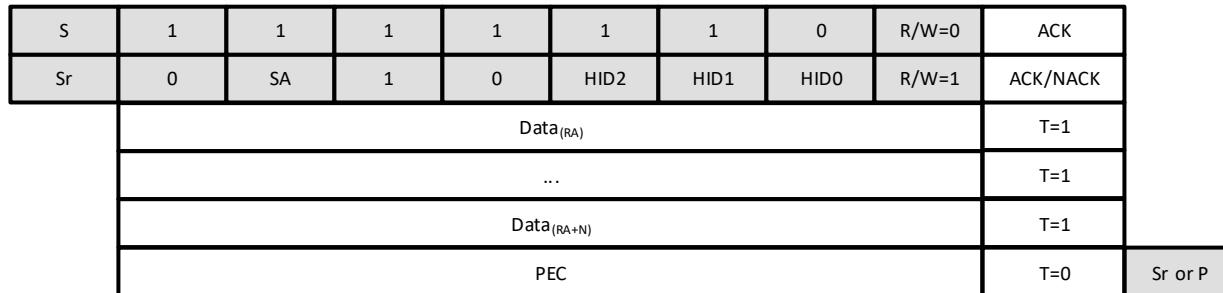

#### 7.4.4.4 ホスト I3C 読み取り動作、PEC 付き

図 7-17 および 図 7-18 に示すように、ホストが PEC をイネーブルにすると、レジスタ・アドレスを送信した後、ホストによってさらにバイトが追加されます。追加バイトのフォーマットについては、表 7-5 で説明します。CMD バイトでは 1 バイトおよび 2 バイトの読み取りのみが許可されるため、デバイスは 1 バイトのデータと PEC バイト、または 2 バイトのデータと PEC バイトを送信した後、T ビットを 0 にして読み取りフェーズを終了します。ありそうもない状況ですが、ホストがレジスタ・アドレスを 255 に設定して、2 バイトの読み取りを試みた場合、デバイスの結果は保証されません。

| S or Sr                     | 0 | SA  | 1 | 0 | HID2 | HID1 | HIDO | R/W=0 | ACK/NACK |

|-----------------------------|---|-----|---|---|------|------|------|-------|----------|

| RA = Register Address [7:0] |   |     |   |   |      |      |      |       | T        |

| CMD                         |   | R=1 |   | 0 | 0    | 0    | 0    |       | T        |

| PEC                         |   |     |   |   |      |      |      |       | T        |

| Sr                          | 0 | SA  | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |

| Data <sub>(RA)</sub>        |   |     |   |   |      |      |      |       | T=1      |

| ...                         |   |     |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+N)</sub>      |   |     |   |   |      |      |      |       | T=1      |

| PEC                         |   |     |   |   |      |      |      |       | T=0      |

|                             |   |     |   |   |      |      |      |       | Sr or P  |

図 7-17. I3C 基本モードの読み取り、PEC イネーブル

| S                           | 1 | 1   | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK      |

|-----------------------------|---|-----|---|---|------|------|------|-------|----------|

| Sr                          | 0 | SA  | 1 | 0 | HID2 | HID1 | HIDO | R/W=0 | ACK/NACK |

| RA = Register Address [7:0] |   |     |   |   |      |      |      |       | T        |

| CMD                         |   | R=1 |   | 0 | 0    | 0    | 0    |       | T        |

| PEC                         |   |     |   |   |      |      |      |       | T        |

| Sr                          | 0 | SA  | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |

| Data <sub>(RA)</sub>        |   |     |   |   |      |      |      |       | T=1      |

| ...                         |   |     |   |   |      |      |      |       | T=1      |

| Data <sub>(RA+N)</sub>      |   |     |   |   |      |      |      |       | T=1      |

| PEC                         |   |     |   |   |      |      |      |       | T=0      |

|                             |   |     |   |   |      |      |      |       | Sr or P  |

図 7-18. I3C 基本モード no 読み取り、PEC イネーブル、IBI ヘッダー付き

ホストから送信された CMD 値が TMP139 に対して有効でない場合、デバイスは読み取りフェーズで NACK 応答します。

リピート・スタートの前の書き込みフェーズでパリティ・エラーが発生した場合、TMP139 は、トランザクションの読み取りフェーズで NACK 応答します。ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、TMP139 は、デバイス・アドレスに NACK 応答して、エラー状態をホストに通知します。ホストは、TMP139 への新しい転送を実行する前に、まずパリティ・エラー状態をクリアする必要があります。

PEC エラーが発生した場合、TMP139 は、トランザクションの読み取りフェーズで NACK 応答します。ホストが同じデバイスに対してリピート・スタートで新しいトランザクション開始しようとしたとき、TMP139 は、デバイス・アドレスに NACK 応答

して、既存のエラー状態をホストに通知します。ホストは、TMP139 への新しい転送を実行する前に、まず PEC エラー状態をクリアする必要があります。

IBI がイネーブルのとき、デバイスは IBI を使用して、検出されたエラー条件をホストと通信できます。ただし、IBI がイネーブルでない場合は、ホストがエラー・ステータス・レジスタをチェックして、バスでパリティまたは PEC エラーが検出されていないことを確認するように強く推奨します。

#### 7.4.4.5 ホスト I3C 読み取り動作 (デフォルト読み取りアドレス・ポインタ・モード)

I3C 基本モードにおけるデフォルト読み取りアドレス・ポインタ・モードは、図 7-19～図 7-22 に示すとおり I<sup>2</sup>C モードと同じように動作します。また、ホストがデータの読み取りを継続的に試みて、内部読み取りアドレス・ポインタが、レジスタ・マップ・テーブルの最後のレジスタである 255 に達する場合には、デバイスは、T ビットを 0 として送信します。さらに、PEC がイネーブルでないときに限り、ホストが T ビットを 0 に駆動することによって、転送を終了することもできます。

| S or Sr | 0 | SA | 1 | 0 | HID2                   | HID1 | HIDO | R/W=1 | ACK/NACK |

|---------|---|----|---|---|------------------------|------|------|-------|----------|

|         |   |    |   |   | Data <sub>(RA)</sub>   |      |      |       | T=1      |

|         |   |    |   |   | Data <sub>(RA+1)</sub> |      |      |       | T=1      |

|         |   |    |   |   | ...                    |      |      |       | T=1      |

|         |   |    |   |   | Data <sub>(RA+N)</sub> |      |      |       | T=1      |

|         |   |    |   |   |                        |      |      |       | Sr or P  |

図 7-19. I3C 基本モード、デフォルト読み取りアドレス・イネーブル

| S  | 1 | 1  | 1 | 1 | 1                      | 1    | 0    | R/W=0 | ACK      |

|----|---|----|---|---|------------------------|------|------|-------|----------|

| Sr | 0 | SA | 1 | 0 | HID2                   | HID1 | HIDO | R/W=1 | ACK/NACK |

|    |   |    |   |   | Data <sub>(RA)</sub>   |      |      |       | T=1      |

|    |   |    |   |   | Data <sub>(RA+1)</sub> |      |      |       | T=1      |

|    |   |    |   |   | ...                    |      |      |       | T=1      |

|    |   |    |   |   | Data <sub>(RA+N)</sub> |      |      |       | T=1      |

|    |   |    |   |   |                        |      |      |       | Sr or P  |

図 7-20. I3C 基本モード、デフォルト読み取りアドレス・イネーブル、IBI ヘッダー付き

PEC がイネーブルのとき、MR18 レジスタは、送信するデフォルトのバイト数を設定します。その後、デバイスは T ビットを 0 として PEC バイトを送信します。

| S or Sr | 0 | SA | 1 | 0 | HID2                   | HID1 | HIDO | R/W=1 | ACK/NACK |

|---------|---|----|---|---|------------------------|------|------|-------|----------|

|         |   |    |   |   | Data <sub>(RA)</sub>   |      |      |       | T=1      |

|         |   |    |   |   | ...                    |      |      |       | T=1      |

|         |   |    |   |   | Data <sub>(RA+N)</sub> |      |      |       | T=1      |

|         |   |    |   |   | PEC                    |      |      |       | T=0      |

|         |   |    |   |   |                        |      |      |       | Sr or P  |

図 7-21. I3C 基本モード、デフォルト読み取りアドレス・イネーブル、PEC イネーブル

図 7-22. I<sup>2</sup>C 基本モード、デフォルト読み取りアドレス・イネーブル、PEC イネーブル、IBI ヘッダー付き

TMP139 は、前のトランザクションでエラーが発生した場合、リピート・スタート時にアドレス・フェーズを NACK 応答します。

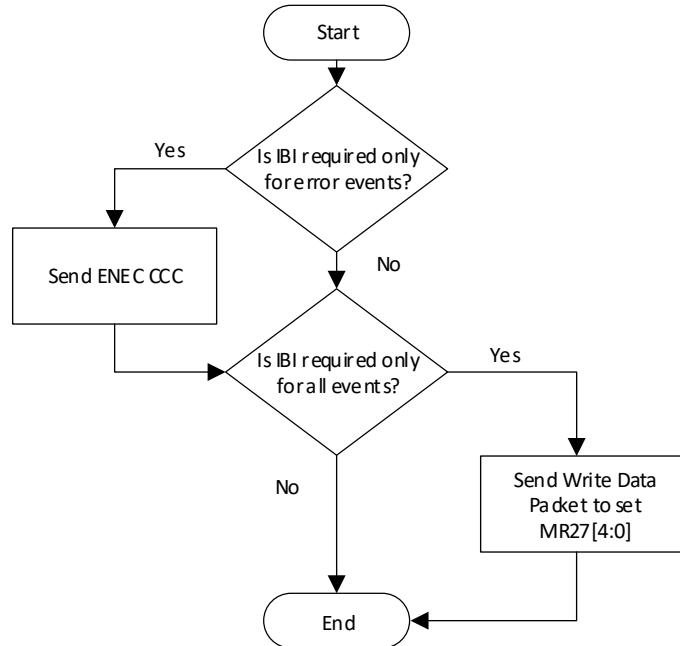

#### 7.4.5 インバンド割り込み

インバンド割り込み (IBI) は、TMP139 のイベントをホストに通知するための優れた方法です。TMP139 が生成するイベントには、次の 2 種類があります。

1. エラー・イベント: パリティまたは PEC エラーに対応するイベント。

2. 温度イベント: 温度が温度上限を上回った場合、または、温度下限を下回った場合に対応するイベント。

デフォルトでは、デバイスの電源投入時にすべての割り込みソースが無効になります。割り込みソースは、デバイスが I<sup>2</sup>C 基本動作モードのときのみイネーブルにできます。割り込みソースをイネーブルにすると、I<sup>2</sup>C 動作モードでは許可されない IBI が生成されるからです。IBI は、バスが  $t_{AVAL}$  期間にわたって非アクティブ状態になっている場合にのみ、TMP139 で要求できます。バス上の非アクティブ条件が満たされ、バス・トランザクションがない場合、TMP139 は、SDA を LOW に駆動して IBI を開始し、保留中の IBI があることをホストに通知します。

##### 7.4.5.1 インバンド割り込み調停ルール

ホスト・コントローラの準備状態と、バス上に複数のデバイスが存在するという事実に基づき、IBI の生成と調停は、以下に示すようにいくつかのルールに従う必要があります。これらの条件はすべて、バスが  $t_{AVAL}$  期間にわたって非アクティブであることを前提としています。

1. ホスト・コントローラが IBI ヘッダ付きで書き込みまたは読み取りを開始したとき、TMP139 はバス上で自分自身のアドレスの駆動を開始します。IBI ヘッダ以外の値を検出したホストは、SDA を駆動しなくなり、TMP139 は R/W ビットを 1 に設定してデバイス・ヘッダを送信できます。

2. ホスト・コントローラがデバイスから IBI を受け入れることができる場合、ホスト・コントローラはデバイス・アドレスに対して ACK 応答し、SCL の立ち下がりエッジでバスを解放し、TMP139 から送信されたバイトを受け入れます。

3. ホスト・コントローラがデバイスから IBI を受け入れることができない場合、ホスト・コントローラはデバイス・アドレスに対して NACK 応答し、バス上でストップ・コンディションを発行します。TMP139 は、 $t_{AVAL}$  期間が経過した後でなければ、別の IBI を再試行できません。

4. TMP139 よりも低いデバイス・アドレスを持つバス上のデバイスに対して、ホスト・コントローラが IBI ヘッダなしで書き込みまたは読み取りを開始した場合、デバイスはミスマッチを検出した時点でバスに参加せず、 $t_{AVAL}$  期間が経過した後に別の IBI を再試行します。

5. TMP139 よりも高いデバイス・アドレスを持つバス上のデバイスに対して、ホスト・コントローラが IBI ヘッダなしで書き込みまたは読み取りを開始した場合、このデバイスがバスの調停に成功し、ホストはバスに参加しなくなります。ホストは、ACK を送信して IBI を受け入れるか、または、NACK を送信して IBI を無視します。後者の場合、TMP139 は、 $t_{AVAL}$  期間が経過した後でなければ、別の IBI を再試行できません。

6. ホスト・コントローラが TMP139 に対して IBI ヘッダなしで書き込みまたは読み取りトランザクションを開始し、TMP139 も IBI を要求している場合、ホストまたは TMP139 のどちらかが調停に成功します。

7. ホスト・コントローラが書き込みトランザクションを開始した場合、ホスト・コントローラがバスの調停に成功し、TMP139 はバスを解放します。TMP139 は、 $t_{AVAL}$  期間が経過した後でなければ、別の IBI を再試行できません。

8. ホスト・コントローラが読み取りトランザクションを開始する場合、すべてのビットが一致しています。ただし、この時点で、ホストは読み取り要求に対する TMP139 からの ACK を期待しており、TMP139 は IBI に対するホストからの

ACK を待機しています。その結果、バス上で NACK が発生します。このような場合、TMP139 は、 $t_{AVAL}$  期間が経過した後でなければ、別の IBI を再試行できません。ただし、ホストがスタート（またはリピート・スタート）を発行し、 $t_{AVAL}$  期間前に読み出しトランザクションを試行した場合、ホストは TMP139 から ACK を受け取り、ホストの読み出しはバス上の調停に成功します。

9. 上記のように、同時に IBI を開始する複数のデバイスが存在する場合、デバイス・アドレスの最も低いデバイスがバスの調停に成功します。TMP139 がバス調停の失敗を検出した場合、 $t_{AVAL}$  期間が経過した後でなければ、別の IBI を再試行できません。

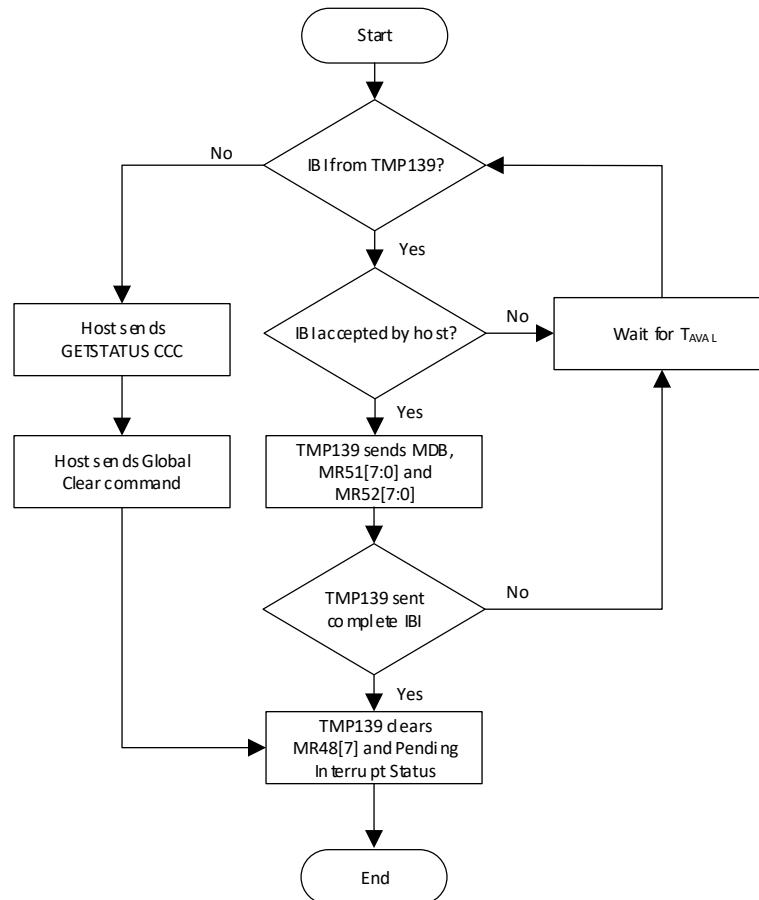

#### 7.4.5.2 インバンド割り込みバス・トランザクション

図 7-23 および図 7-24 に示すように、デバイスが IBI を送信する必要があり、バス調停に成功して、ホストによって IBI が ACK 応答された場合には、必須データ・バイト (MDB) として 8'h00 を必ず送信し、その後に MR51 および MR52 レジスタ値を送信します。最後のバイトを送信した後、T ビットを 0 に設定します。その後、ホスト・コントローラはバス上でストップ・コンディションを送信する必要があります。

| S | 0 | SA | 1 | 0 | HID2       | HID1 | HID0 | R/W=1 | ACK/NACK |   |

|---|---|----|---|---|------------|------|------|-------|----------|---|

|   |   |    |   |   | MDB = 0x00 |      |      |       | T=1      |   |

|   |   |    |   |   | MR51[7:0]  |      |      |       | T=1      |   |

|   |   |    |   |   | MR52[7:0]  |      |      |       | T=0      | P |

図 7-23. IBI ペイロード・パケット、PEC ディセーブル

PEC がイネーブルの場合、MR52 レジスタ値の後、T ビットが 0 に設定された状態で PEC バイトが送信されます。この場合も、ホストはバス上でストップ・コンディションを送信する必要があります。

| S | 0 | SA | 1 | 0 | HID2       | HID1 | HID0 | R/W=1 | ACK/NACK |   |

|---|---|----|---|---|------------|------|------|-------|----------|---|

|   |   |    |   |   | MDB = 0x00 |      |      |       | T=1      |   |

|   |   |    |   |   | MR51[7:0]  |      |      |       | T=1      |   |

|   |   |    |   |   | MR52[7:0]  |      |      |       | T=1      |   |

|   |   |    |   |   | PEC        |      |      |       | T=0      | P |

図 7-24. IBI ペイロード・パケット、PEC イネーブル

デバイスによって IBI がアサートされ、MDB、MR51、MR52、PEC (PEC モードがイネーブルの場合) バイトを含む IBI が正常に送信されると、デバイスは MR48 レジスタの IBI\_STATUS ビットを自動的にクリアします。

#### 7.4.6 コモン・コマンド・コードのサポート

TMP139 は、表 7-6 に示すように、I3C の基本仕様に記載されている CCC のサブセットをサポートしています。JESD302-1 で規定されている CCC のみがサポートされています。TMP139 は、サポートされていない CCC に対して NACK 応答する（可能な場合）か、または、一般的な I3C バスではその動作を無視するものとします。同様に、サポートされている CCC についても、TMP139 が I<sup>2</sup>C モードと I3C モードのどちらであるかによって、対応可能でない CCC が送信された場合、デバイスはその動作を無視するものとします。

TMP139 では、デバイス指定の読み取りまたは書き込み動作を処理するためには、その前に、いずれかの CCC を受信した後にバス上でストップ・コンディションが必要です。同様に、デバイス指定の読み取りまたは書き込み条件を処理する場合は、次にいずれかの CCC を発行する前に、バス上でストップ・コンディションが必要です。

TMP139 は、別のダイレクト CCC の後に、リピート・スタート・コンディション付きのダイレクト CCC を受信できます。同様に、別のブロードキャスト CCC に続いて、リピート・スタート・コンディション付きのブロードキャスト CCC を送信することも有効です。このような場合、デバイスが実行するアクションは、バス上のストップ・コンディションの後でのみ更新されます。ダイレクト CCC の後にブロードキャスト CCC が続く場合またはその逆の場合で、リピート・スタート・コンディションがあると

きには、TMP139 の動作は定義されません。たとえば、SETHID CCC の後にリピート・スタート、次に SETAASA CCC の後にストップ・コンディションを送信するのは、I<sup>2</sup>C モードでは適正な組み合わせです。しかし I3C モードにおいて、ダイレクト ENEC CCC の後にリピート・スタート、次にブロードキャスト DEVCTRL CCC を送信するのは、TMP139 に対して有効な条件ではありません。ホストは、ブロードキャスト DEVCTRL CCC を送信する前に、ENEC CCC の後でストップを発行する必要があります。

TMP139 に送信される CCC は、ブロードキャスト・コードまたはダイレクト・コードのいずれかです。すべての CCC 動作では、ホストは 7'h7E と R/W = 0 を送信し、その後に CCC およびその CCC 固有のペイロード・バイトを送信する必要があります。ダイレクト CCC の場合、ホストは、CCC バイトの後にバス上でリピート・スタートを発行し、その後にペイロード・バイトを送信しなければなりません。

**表 7-6. サポートされている CCC**

| CCC       | モード      | コード  | 説明                            | I <sup>2</sup> C モードで適用可能 | I3C モードで適用可能 |

|-----------|----------|------|-------------------------------|---------------------------|--------------|

| ENEC      | ブロードキャスト | 0x00 | イベント割り込みをイネーブル                | 不可                        | 可            |

|           | ダイレクト    | 0x80 |                               |                           |              |

| DISEC     | ブロードキャスト | 0x01 | イベント割り込みをディセーブル               | 不可                        | 可            |

|           | ダイレクト    | 0x81 |                               |                           |              |

| RSTDAA    | ブロードキャスト | 0x06 | デバイスを I <sup>2</sup> C モードに設定 | 不可                        | 可            |

| SETAASA   | ブロードキャスト | 0x29 | デバイスを I3C 基本モードに設定            | 可                         | 不可           |

| GETSTATUS | ダイレクト    | 0x90 | デバイス情報の取得                     | 不可                        | 可            |

| DEVCAP    | ダイレクト    | 0xE0 | デバイス機能の取得                     | 不可                        | 可            |

| SETHID    | ブロードキャスト | 0x61 | TMP139 が 3 ビットの HID フィールドを更新  | 可                         | 不可           |

| DEVCTRL   | ブロードキャスト | 0x62 | デバイスの設定                       | 可                         | 可            |

#### 7.4.6.1 ENEC CCC

ENEC CCC は、イベント割り込み生成をイネーブルするために、ホスト・コントローラによって発行されます。CCC は、ホスト・コントローラによってストップが発行された後に有効になります。ENEC を受信すると、TMP139 は MR27 レジスタ・ビット IBI\_ERROR\_EN を 1'b1 に更新します。

##### 注

ホスト・コントローラが ENINT ビットを 0 として送信することは規格不適合です。

図 7-25 および 図 7-26 に示すように、このコマンドは、ブロードキャスト・コマンドとして、または、TMP139 へのダイレクト・コマンドとして発行できます。

|         |      |   |   |   |   |   |   |       |                 |

|---------|------|---|---|---|---|---|---|-------|-----------------|

| S or Sr | 1    | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK/NACK        |

|         | 0x00 |   |   |   |   |   |   |       | T               |

|         | 0x00 |   |   |   |   |   |   |       | ENINT T Sr or P |

**図 7-25. ENEC CCC ブロードキャスト**

|         |      |    |   |   |      |      |      |       |                 |

|---------|------|----|---|---|------|------|------|-------|-----------------|

| S or Sr | 1    | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK        |

|         | 0x80 |    |   |   |      |      |      |       | T               |

| Sr      | 0    | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK        |

|         | 0x00 |    |   |   |      |      |      |       | ENINT T Sr or P |

**図 7-26. ENEC CCC ダイレクト**

図 7-27 および 図 7-28 に示すように、このコマンドは、PEC をイネーブルにしたブロードキャストまたはダイレクト・コマンドとして発行できます。この場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある 7'h7E および R/W = 0 のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。

|         |   |   |   |   |   |   |   |       |          |

|---------|---|---|---|---|---|---|---|-------|----------|

| S or Sr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK/NACK |

| 0x00    |   |   |   |   |   |   |   | T     |          |

| 0x00    |   |   |   |   |   |   |   | ENINT | T        |

| PEC     |   |   |   |   |   |   |   | T     | Sr or P  |

図 7-27. ENEC CCC ブロードキャスト、PEC イネーブル

|         |   |    |   |   |      |      |      |       |          |

|---------|---|----|---|---|------|------|------|-------|----------|

| S or Sr | 1 | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK |

| 0x80    |   |    |   |   |      |      |      | T     |          |

| PEC     |   |    |   |   |      |      |      | T     |          |

| Sr      | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=0 | ACK/NACK |

| 0x00    |   |    |   |   |      |      |      | ENINT | T        |

| PEC     |   |    |   |   |      |      |      | T     | Sr or P  |

図 7-28. ENEC CCC ダイレクト、PEC イネーブル

#### 注

前のトランザクションにパリティまたは PEC エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、ENEC CCC に対して NACK 応答します。

#### 7.4.6.2 DISEC CCC

DISEC CCC は、イベント割り込み生成をディセーブルするために、ホスト・コントローラによって発行されます。この CCC は、ホスト・コントローラによってストップが発行された後に有効になります。DISEC を受信すると、TMP139 は MR27 レジスタ・ビット IBI\_ERROR\_EN を 1'b0 に更新します。

#### 注

ホスト・コントローラが DISINT ビットを 0 として送信することは規格不適合です。

図 7-29 および 図 7-30 に示すように、このコマンドは、ブロードキャスト・コマンドとして、または特定のデバイスへのダイレクト・コマンドとして発行できます。

|         |   |   |   |   |   |   |   |        |          |

|---------|---|---|---|---|---|---|---|--------|----------|

| S or Sr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0  | ACK/NACK |

| 0x01    |   |   |   |   |   |   |   | T      |          |

| 0x00    |   |   |   |   |   |   |   | DISINT | T        |

|         |   |   |   |   |   |   |   |        | Sr or P  |

図 7-29. DISEC CCC ブロードキャスト

|         |      |    |   |   |      |      |      |       |          |         |

|---------|------|----|---|---|------|------|------|-------|----------|---------|

| S or Sr | 1    | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK |         |

|         | 0x81 |    |   |   |      |      |      |       | T        |         |

| Sr      | 0    | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |         |

|         | 0x00 |    |   |   |      |      |      |       | DISINT   | T       |

|         |      |    |   |   |      |      |      |       |          | Sr or P |

図 7-30. DISEC CCC ダイレクト

図 7-31 および 図 7-32 に示すように、このコマンドは、PEC をイネーブルにしたブロードキャストまたはダイレクト・コマンドとして発行できます。この場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある 7'h7E および R/W = 0 のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。

|         |      |   |   |   |   |   |   |       |          |         |

|---------|------|---|---|---|---|---|---|-------|----------|---------|

| S or Sr | 1    | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK/NACK |         |

|         | 0x01 |   |   |   |   |   |   |       | T        |         |

|         | 0x00 |   |   |   |   |   |   |       | DISINT   | T       |

|         | PEC  |   |   |   |   |   |   |       | T        | Sr or P |

図 7-31. DISEC CCC ブロードキャスト、PEC イネーブル

|         |      |    |   |   |      |      |      |       |          |         |

|---------|------|----|---|---|------|------|------|-------|----------|---------|

| S or Sr | 1    | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK |         |

|         | 0x81 |    |   |   |      |      |      |       | T        |         |

|         | PEC  |    |   |   |      |      |      |       | T        |         |

| Sr      | 0    | SA | 1 | 0 | HID2 | HID1 | HID0 | R/W=0 | ACK/NACK |         |

|         | 0x00 |    |   |   |      |      |      |       | DISINT   | T       |

|         | PEC  |    |   |   |      |      |      |       | T        | Sr or P |

図 7-32. DISEC CCC ダイレクト、PEC イネーブル

### 注

前のトランザクションにパリティまたは PEC エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、DISEC CCC に対して NACK 応答します。

#### 7.4.6.3 RSTDAA CCC

ホスト・コントローラから TMP139 に対して RSTDAA CCC を発行すると、I3C 基本モードから I2C モードに切り替わります。この CCC は、ホスト・コントローラによってストップが発行された後に有効になります。RSTDAA を受信した後、TMP139 は以下の操作を実行します。

- MR18 レジスタ・ビット INF\_SEL を 1'b0 に更新して I<sup>2</sup>C 動作モードにします。

- 以前に PEC がイネーブルになっていた場合、MR18 レジスタ・ビット PEC\_EN を 1'b0 に更新して PEC をディセーブルにします。

- 以前にパリティ・チェックがディセーブルになっていた場合、MR18 レジスタ・ビット PAR\_DIS を 1'b0 に更新してパリティ・チェックをイネーブルにします。

- 以前に IBI がイネーブルになっていた場合、MR27 レジスタ・ビット IBI\_ERROR\_EN を 1'b0 に更新して IBI をディセーブルにします。

図 7-33 に示すように、このコマンドは常にブロードキャスト・コマンドとして発行されます。

|         |   |   |   |   |   |   |   |       |          |  |  |

|---------|---|---|---|---|---|---|---|-------|----------|--|--|

| S or Sr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK/NACK |  |  |

| 0x06    |   |   |   |   |   |   |   | T     | Sr or P  |  |  |

図 7-33. RSTDAA CCC ブロードキャスト

図 7-34 に示すように、このコマンドは PEC がイネーブルの状態でも発行できます。その場合、ホスト・コントローラは、スタートまたはリピート・スタートの後に、7'h7E および R/W = 0 のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。

|         |   |   |   |   |   |   |   |       |          |  |  |

|---------|---|---|---|---|---|---|---|-------|----------|--|--|

| S or Sr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK/NACK |  |  |

| 0x06    |   |   |   |   |   |   |   | T     | Sr or P  |  |  |

| PEC     |   |   |   |   |   |   |   | T     | Sr or P  |  |  |

図 7-34. RSTDAA CCC ブロードキャスト、PEC 付き

#### 注

前のトランザクションにパリティまたは PEC エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、RSTDAA CCC に対して NACK 応答します。

#### 7.4.6.4 SETAASA CCC

ホスト・コントローラから TMP139 に対して SETAASA CCC を発行すると、I<sup>2</sup>C モードから I3C 基本モードに切り替わります。この CCC は、ホスト・コントローラによってストップが発行された後に有効になります。SETAASA を受信すると、TMP139 は、MR18 レジスタ・ビット INF\_SEL を 1'b1 に設定して I3C 基本動作モードにします。

図 7-35 に示すように、この CCC は常にブロードキャスト・コマンドとして発行され、PEC バイトはありません。これは I<sup>2</sup>C モードでのみ適用できるためです。

|         |   |   |   |   |   |   |   |       |         |  |  |

|---------|---|---|---|---|---|---|---|-------|---------|--|--|

| S or Sr | 1 | 1 | 1 | 1 | 1 | 1 | 0 | R/W=0 | ACK     |  |  |

| 0x29    |   |   |   |   |   |   |   | T     | Sr or P |  |  |

図 7-35. SETAASA CCC

#### 注

前の CCC トランザクションにパリティ・エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、SETAASA CCC に対して NACK 応答します。

#### 7.4.6.5 GETSTATUS CCC

GETSTATUS CCC は、保留中のパリティ・エラー、PEC エラー、または割り込みイベントのステータスを取得するために、ホスト・コントローラから TMP139 に対して発行されます。GETSTATUS を受信した後、TMP139 は、ステータスをクリアしません。ホストは、バス上で追加のトランザクションを発行して、ステータス・フラグを個別にクリアするか、または MR27 レジスタ CLR\_GLOBAL ビットに 1'b1 を書き込む必要があります。

このコマンドはダイレクト・モードでのみ発行されます。PEC がディセーブルの場合のコマンドを 図 7-36 に示し、PEC がイネーブルの場合のコマンドを 図 7-37 に示します。後者の場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある 7'h7E および R/W = 0 のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。TMP139 は、ホストに向けて送信されるデータ・バイトの PEC を計算します。

|         |         |    |       |   |                   |      |      |       |          |

|---------|---------|----|-------|---|-------------------|------|------|-------|----------|

| S or Sr | 1       | 1  | 1     | 1 | 1                 | 1    | 0    | R/W=0 | ACK/NACK |

| 0x90    |         |    |       |   |                   |      |      | T     |          |

| Sr      | 0       | SA | 1     | 0 | HID2              | HID1 | HIDO | R/W=1 | ACK/NACK |

|         | PEC_Err | 0  | 0     | 0 | 0                 | 0    | 0    | 0     | T=1      |

|         | 0       | 0  | P_Err | 0 | PENDING INTERRUPT |      |      |       | T=0      |

|         |         |    |       |   |                   |      |      |       | Sr or P  |

図 7-36. GETSTATUS CCC ダイレクト

|         |         |    |       |   |                   |      |      |       |          |

|---------|---------|----|-------|---|-------------------|------|------|-------|----------|

| S or Sr | 1       | 1  | 1     | 1 | 1                 | 1    | 0    | R/W=0 | ACK/NACK |

| 0x90    |         |    |       |   |                   |      |      | T     |          |

| PEC     |         |    |       |   |                   |      |      | T     |          |

| Sr      | 0       | SA | 1     | 0 | HID2              | HID1 | HIDO | R/W=1 | ACK/NACK |

|         | PEC_Err | 0  | 0     | 0 | 0                 | 0    | 0    | 0     | T=1      |

|         | 0       | 0  | P_Err | 0 | PENDING INTERRUPT |      |      |       | T=1      |

|         |         |    |       |   | PEC               |      |      |       | T=0      |

|         |         |    |       |   |                   |      |      |       | Sr or P  |

図 7-37. GETSTATUS CCC ダイレクト、PEC イネーブル

## 注

前のトランザクションにパリティまたは PEC エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、GETSTATUS CCC に対して NACK 応答します。

## 7.4.6.6 DEVCAP CCC

DEVCAP CCC は、ホスト・コントローラから TMP139 に対して発行され、サポートされているオプションのデバイス機能を取得します。その内容は 表 7-7 に示す通りです。

このコマンドはダイレクト・モードでのみ発行されます。PEC がディセーブルの場合のコマンドを 図 7-38 に示し、PEC がイネーブルの場合のコマンドを 図 7-39 に示します。後者の場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある 7'h7E および R/W = 0 のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。TMP139 は、ホストに向けて送信されるデータ・バイトの PEC を計算します。

|                 |   |    |   |   |      |      |      |       |          |

|-----------------|---|----|---|---|------|------|------|-------|----------|

| S or Sr         | 1 | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK |

| 0xE0            |   |    |   |   |      |      |      | T     |          |

| Sr              | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |

| DEVCAP_MSB[7:0] |   |    |   |   |      |      |      | T=1   |          |

| DEVCAP_LSB[7:0] |   |    |   |   |      |      |      | T=0   | Sr or P  |

図 7-38. DEVCAP CCC ダイレクト

|                 |   |    |   |   |      |      |      |       |          |

|-----------------|---|----|---|---|------|------|------|-------|----------|

| S or Sr         | 1 | 1  | 1 | 1 | 1    | 1    | 0    | R/W=0 | ACK/NACK |

| 0xE0            |   |    |   |   |      |      |      | T     |          |

| PEC             |   |    |   |   |      |      |      | T     |          |

| Sr              | 0 | SA | 1 | 0 | HID2 | HID1 | HIDO | R/W=1 | ACK/NACK |

| DEVCAP_MSB[7:0] |   |    |   |   |      |      |      | T=1   |          |

| DEVCAP_LSB[7:0] |   |    |   |   |      |      |      | T=1   |          |

| PEC             |   |    |   |   |      |      |      | T=0   | Sr or P  |

図 7-39. DEVCAP CCC ダイレクト、PEC 付き

表 7-7. DEVCAP データ・バイトの説明

| ビット             | 値     | 備考                                                        |

|-----------------|-------|-----------------------------------------------------------|

| DEVCAP_MSB[7:3] | 00000 | 予約済み                                                      |

| DEVCAP_MSB[2]   | 1     | 0 = タイマ・ベースのリセットをサポートしていません<br>1 = タイマ・ベースのリセットをサポートしています |

| DEVCAP_MSB[1:0] | 00    | 予約済み                                                      |

| DEVCAP_LSB[7:0] | 8'h00 | 予約済み                                                      |

#### 注

前のトランザクションにパリティまたは PEC エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、DEVCAP CCC に対して NACK 応答します。

#### 7.4.6.7 SETHID CCC

SETHID CCC は、ホスト・コントローラから TMP139 に対して発行され、デバイスのシリアル・アドレスの HID コードを更新します。この CCC は、ホスト・コントローラによってストップが発行された後に有効になります。SETHID を受信すると、TMP139 は、バスのストップ・コンディションが送信されたときに、[MR7](#) レジスタ・ビット DEV\_HID\_CODE[2:0] を、CCC データ・ペイロードで送信された HID[2:0] の値に更新します。

|         |   |   |   |      |      |      |   |       |         |

|---------|---|---|---|------|------|------|---|-------|---------|

| S or Sr | 1 | 1 | 1 | 1    | 1    | 1    | 0 | R/W=0 | ACK     |

| 0x61    |   |   |   |      |      |      |   | T     |         |

| 0       | 0 | 0 | 0 | HID2 | HID1 | HIDO | 0 | T     | Sr or P |

図 7-40. SETHID CCC ブロードキャスト

#### 注

前のトランザクションにパリティ・エラーがある場合に、ホストがリピート・スタートによりトランザクションを開始すると、TMP139 は、SETHID CCC に対して NACK 応答します。

#### 7.4.6.8 DEVCTRL CCC

DEVCTRL CCC は、バス上のデバイスに共通するイネーブルまたはディセーブル操作のために、ホスト・コントローラによって発行されます。TMP139 は DEVCTRL CCC を認識するものとします。

このコマンドは一般にブロードキャスト・モードで発行されますが、ユニキャストまたはマルチキャスト・モードとして発行することもできます。ホストは、RegMod フィールドを 0 に設定すると一般的なアクセスとして、RegMod を 1 に設定すると特定のレジスタ・アクセスとして、DEVCTRL CCC を発行することができます。RegMod フィールドが 0 に設定されていて、PEC がディセーブルのときの DEVCTRL CCC パケット構造を [図 7-41](#) に示します。RegMod フィールドが 0 に設定されてい

て、PEC がイネーブルのときの DEVCTRL CCC の構造を [図 7-42](#) に示します。後者の場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある  $7'h7E$  および  $R/W = 0$  のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。

| S or Sr         | 1               | 1               | 1                | 1                | 1        | 1        | 0            | R/W=0 | ACK     |

|-----------------|-----------------|-----------------|------------------|------------------|----------|----------|--------------|-------|---------|

| 0x62            |                 |                 |                  |                  |          |          |              |       | T       |

| ADDRMASK<br>[2] | ADDRMASK<br>[1] | ADDRMASK<br>[0] | ST OFFSET<br>[1] | ST OFFSET<br>[0] | PECBL[1] | PECBL[0] | REGMOD<br>=0 |       | T       |

| DEVADDR         |                 |                 |                  |                  |          |          |              | 0     | T       |

| DEVCTRL DATA 0  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 1  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 2  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 3  |                 |                 |                  |                  |          |          |              |       | T       |

|                 |                 |                 |                  |                  |          |          |              |       | Sr or P |

**図 7-41. DEVCTRL CCC、REGMOD = 0 および PEC ディセーブル**

| S or Sr         | 1               | 1               | 1                | 1                | 1        | 1        | 0            | R/W=0 | ACK     |

|-----------------|-----------------|-----------------|------------------|------------------|----------|----------|--------------|-------|---------|

| 0x62            |                 |                 |                  |                  |          |          |              |       | T       |

| ADDRMASK<br>[2] | ADDRMASK<br>[1] | ADDRMASK<br>[0] | ST OFFSET<br>[1] | ST OFFSET<br>[0] | PECBL[1] | PECBL[0] | REGMOD<br>=0 |       | T       |

| DEVADDR         |                 |                 |                  |                  |          |          |              | 0     | T       |

| DEVCTRL DATA 0  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 1  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 2  |                 |                 |                  |                  |          |          |              |       | T       |

| DEVCTRL DATA 3  |                 |                 |                  |                  |          |          |              |       | T       |

| PEC             |                 |                 |                  |                  |          |          |              |       | T       |

|                 |                 |                 |                  |                  |          |          |              |       | Sr or P |

**図 7-42. DEVCTRL CCC、REGMOD = 0 および PEC イネーブル**

RegMod フィールドが 1 に設定されていて、PEC がディセーブルのときの DEVCTRL CCC パケット構造を [図 7-43](#) に示します。RegMod フィールドが 1 に設定されていて、PEC がイネーブルのときの DEVCTRL CCC の構造を [図 7-44](#) に示します。後者の場合、ホスト・コントローラは、スタートまたはリピート・スタートの後にある  $7'h7E$  および  $R/W = 0$  のバイト以外のすべてのバイトに対して計算された PEC バイトを追加するものとします。CMD フィールドが書き込みバイトが 1 つしかないことを示している場合、オプションのレジスタ・データをホストから送信してはなりません。

| S or Sr                  | 1               | 1               | 1                | 1                | 1        | 1        | 0            | R/W=0 | ACK     |

|--------------------------|-----------------|-----------------|------------------|------------------|----------|----------|--------------|-------|---------|

| 0x62                     |                 |                 |                  |                  |          |          |              |       | T       |

| ADDRMASK<br>[2]          | ADDRMASK<br>[1] | ADDRMASK<br>[0] | ST OFFSET<br>[1] | ST OFFSET<br>[0] | PECBL[1] | PECBL[0] | REGMOD<br>=1 |       | T       |

| DEVADDR                  |                 |                 |                  |                  |          |          |              | 0     | T       |