# 9WステレオD級オーディオ・パワーアンプ DCボリューム制御付き

特長

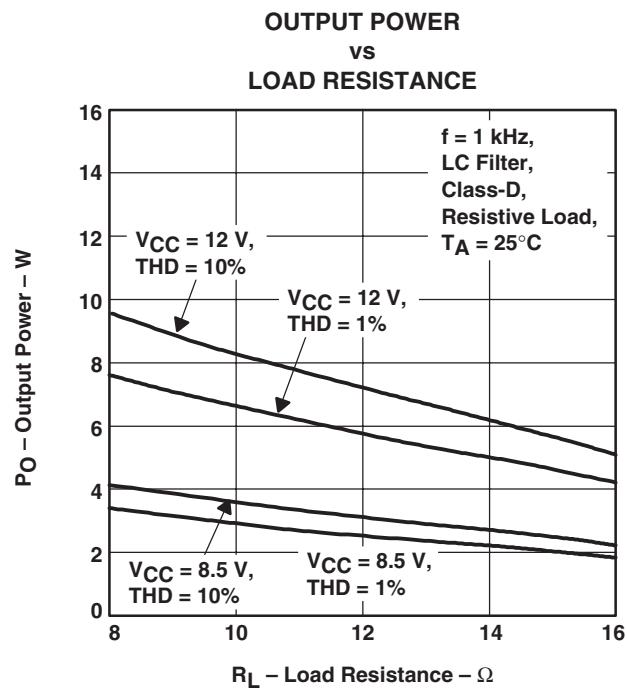

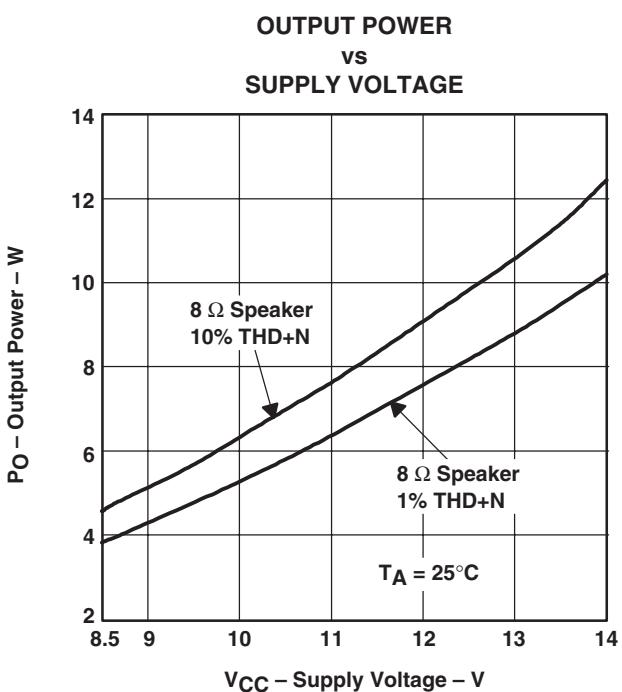

- 12V電源から8Ω負荷へ9W/チャネルの出力

- 高効率なD級動作により、ヒートシンク不要、柔軟な電源条件

- -40dBから36dBまで32段階のDCボリューム制御

- 外付けヘッドフォン・アンプ用のボリューム制御付きライン出力

- TPA6110A2用の安定化5V電源出力

- 省スペース、熱的に強化されたパワーパッド(PowerPAD<sup>TM</sup>)パッケージ

- 熱保護回路および出力短絡保護回路

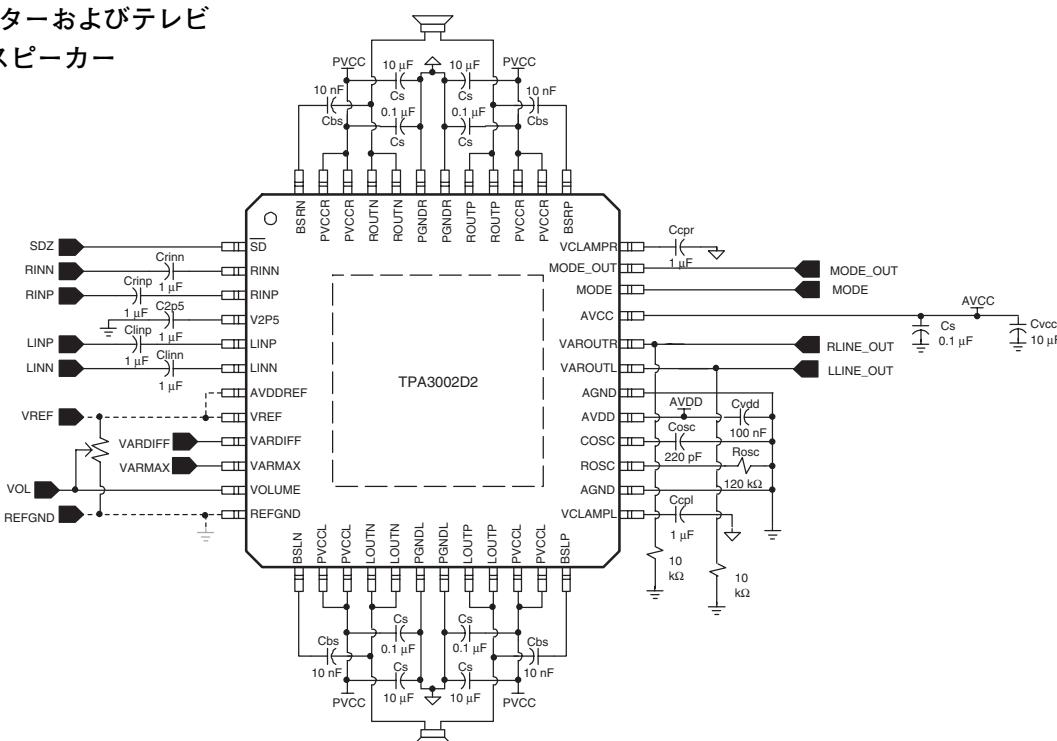

## アプリケーション

- LCDモニターおよびテレビ

- パワー・スピーカー

解 説

TPA3002D2は、ブリッジ結合型ステレオ・スピーカーを駆動する9W(チャネル当り)の高効率なD級オーディオ・アンプです。TPA3002D2は最低8Ωまでのステレオ・スピーカーを駆動できます。TPA3002D2は高効率のため、音楽演奏時に外付けのヒートシンクが不要です。

ステレオ・スピーカーのボリュームはボリューム制御端子に印加されるDC電圧で制御され、-40dBから36dBまでのゲイン範囲を提供します。ライン出力は外付けヘッドフォーン・アンプの入力を駆動し、これもまた-56dBから20dB間のゲイン範囲でDC電圧によって制御されます。

TPA3002D2は安定化5V電源を搭載し、外付けヘッドフォン・アンプに電源を供給します。

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

(日本TI)が英文から和文へ翻訳してTF成したもので、

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

助の参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## AVAILABLE OPTIONS

| T <sub>A</sub> | PACKAGED DEVICE                   |

|----------------|-----------------------------------|

|                | 48-PIN HTQFP (PHP) <sup>(1)</sup> |

| -40°C to 85°C  | TPA3002D2PHP                      |

(1) The PHP package is available taped and reeled. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA3002D2PHPR).

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

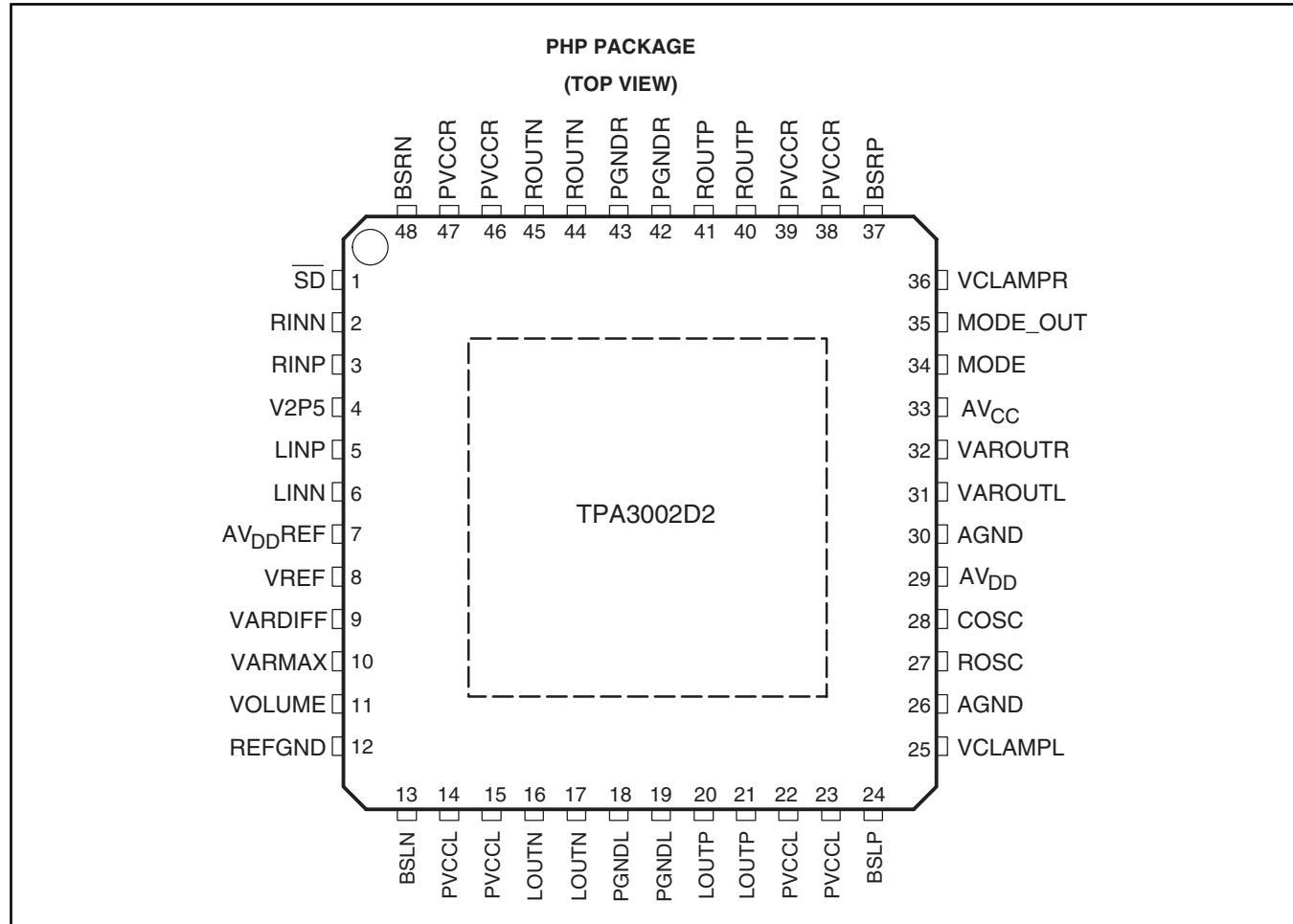

## PIN ASSIGNMENTS

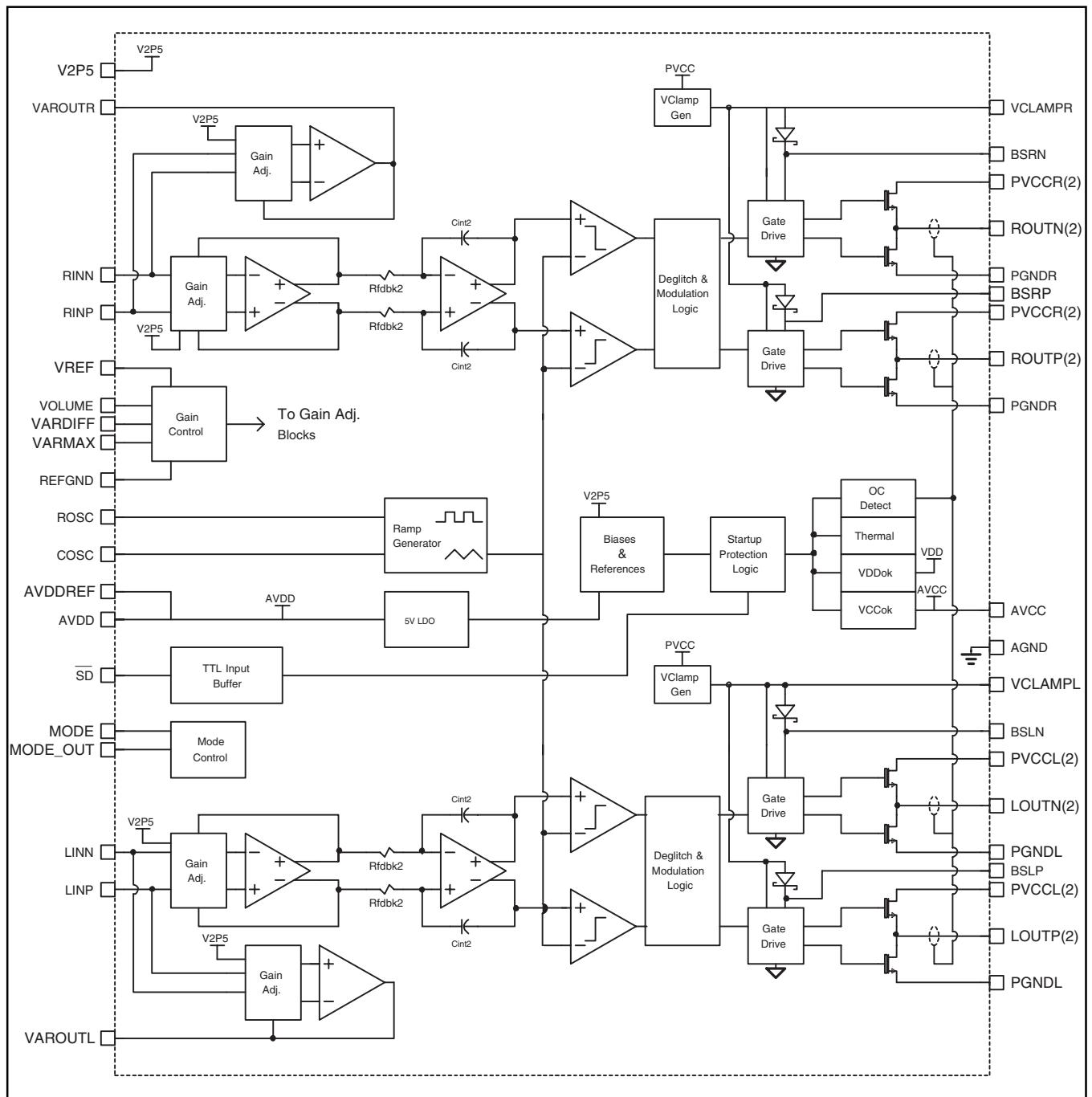

## FUNCTIONAL BLOCK DIAGRAM

## 2.3 端子機能表

| 端子名      | 番号          | I/O | 機能                                                                                                                                                                                     |

|----------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND     | 26, 30      | —   | コアのデジタル/アナログ・セルのアナログ・グランド                                                                                                                                                              |

| AVCC     | 33          | —   | 高電圧アナログ電源(8Vから14V)                                                                                                                                                                     |

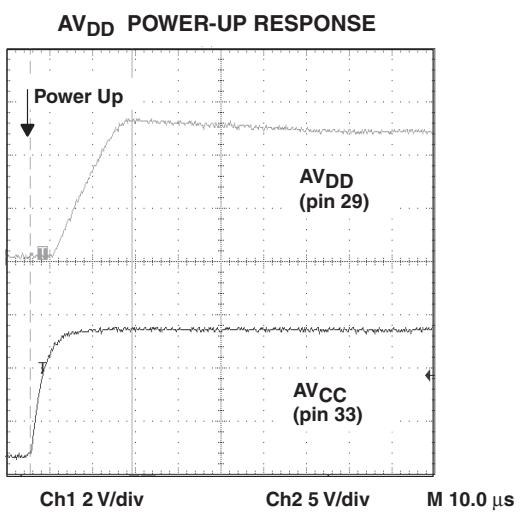

| AVDD     | 29          | O   | 電流容量が100mAの安定化5V出力                                                                                                                                                                     |

| AVDDREF  | 7           | O   | 5V基準電圧出力(隣のVREFピンに接続した場合)                                                                                                                                                              |

| BSLN     | 13          | I/O | 左チャネルの負側ハイサイドFET用のブーストストラップI/Oピン                                                                                                                                                       |

| BSLP     | 24          | I/O | 左チャネルの正側ハイサイドFET用のブーストストラップI/Oピン                                                                                                                                                       |

| BSRN     | 48          | I/O | 右チャネルの負側ハイサイドFET用のブーストストラップI/Oピン                                                                                                                                                       |

| BSRP     | 37          | I/O | 右チャネルの正側ハイサイドFET用のブーストストラップI/Oピン                                                                                                                                                       |

| COSC     | 28          | I/O | V2P5でバイアスされたランプ発生回路の三角波用のコンデンサを、充放電するためのI/Oピン                                                                                                                                          |

| LINN     | 6           | I   | 左チャネルの負差動オーディオ信号入力                                                                                                                                                                     |

| LINP     | 5           | I   | 左チャネルの正差動オーディオ信号入力                                                                                                                                                                     |

| LOUTN    | 16, 17      | O   | 左チャネルのD級ハーフH型ブリッジ負出力                                                                                                                                                                   |

| LOUTP    | 20, 21      | O   | 左チャネルのD級ハーフH型ブリッジ正出力                                                                                                                                                                   |

| MODE     | 34          | I   | モード制御入力。本ピンへのロジック・ハイレベルは、アンプを可変出力モードにし、D級出力をディスエーブルにします。本ピンへのロジック・ロー・レベルは、アンプをD級モードにし、D級ステレオ出力をイネーブルにします。D級モードでも可変出力(VAROUTLとVAROUTR)はイネーブルであり、外部アンプへのラインレベル出力として使用されます。               |

| MODE_OUT | 35          | O   | 可変出力アンプの制御出力。MODEピン(34)がロジック・ハイレベルの場合、MODE_OUTピンはロー・レベルになります。MODEピン(34)がロジック・ロー・レベルの場合、MODE_OUTピンはハイレベルになります。本ピンは、外部ヘッドフォーン・アンプのミュート制御の使用を意図しています。ヘッドフォーン・アンプのミュート制御に使用しない場合はオープンにします。 |

| PGNDL    | 18, 19      | —   | 左チャネルのH型ブリッジ用パワー・グランド                                                                                                                                                                  |

| PGNDR    | 42, 43      | —   | 右チャネルのH型ブリッジ用パワー・グランド                                                                                                                                                                  |

| PVCLL    | 14, 15      | —   | 左チャネルのH型ブリッジ用電源(デバイス内部で22, 23ピンと接続)。PVCCRあるいはAV <sub>CC</sub> と接続されていません。                                                                                                              |

| PVCLL    | 22, 23      | —   | 左チャネルのH型ブリッジ用電源(デバイス内部で14, 15ピンと接続)。PVCCRあるいはAV <sub>CC</sub> と接続されていません。                                                                                                              |

| PVCCR    | 38, 39      | —   | 右チャネルのH型ブリッジ用電源(デバイス内部で46, 47ピンと接続)。PVCLLあるいはAV <sub>CC</sub> と接続されていません。                                                                                                              |

| PVCCR    | 46, 47      | —   | 右チャネルのH型ブリッジ用電源(デバイス内部で38, 39ピンと接続)。PVCLLあるいはAV <sub>CC</sub> と接続されていません。                                                                                                              |

| REFGND   | 12          | —   | ゲイン制御回路用グランド。AGNDと接続します。ボリュームを制御するのにDACを使用する場合、DACのグランドを本ピンに接続します。                                                                                                                     |

| RINP     | 3           | I   | Positive differential audio input for right channel                                                                                                                                    |

| RINN     | 2           | I   | 右チャネルの負差動オーディオ信号入力                                                                                                                                                                     |

| ROSC     | 27          | I/O | ランプ発生回路用の電流設定抵抗。本ピンの電位は名目値で1/8 AV <sub>CC</sub> になります。                                                                                                                                 |

| ROUTN    | 44, 45      | O   | 右チャネルのD級ハーフH型ブリッジ負出力                                                                                                                                                                   |

| ROUTP    | 40, 41      | O   | 右チャネルのD級ハーフH型ブリッジ正出力                                                                                                                                                                   |

| SD       | 1           | I   | デバイスのシャットダウン信号(ロー・レベル = シャットダウン、ハイ・レベル = 動作可能)。TTLロジックレベル。AV <sub>CC</sub> の電圧まで印加可能。                                                                                                  |

| VARDIFF  | 9           | I   | D級出力と可変出力(VAROUT)のゲインの差を設定するDC電圧。VAROUTを使用しない場合は、本ピンをグランドあるいはAV <sub>DD</sub> に接続する。                                                                                                   |

| VARMAX   | 10          | I   | VAROUTの最大電圧を設定するDC電圧。VAROUTを使用しない場合は、本ピンをグランドあるいはAV <sub>DD</sub> REFに接続する。                                                                                                            |

| VAROUTL  | 31          | O   | 左チャネルのオーディオ可変出力。外部ヘッドフォン・アンプをドライブするライン出力。                                                                                                                                              |

| VAROUTR  | 32          | O   | 右チャネルのオーディオ可変出力。外部ヘッドフォン・アンプをドライブするライン出力。                                                                                                                                              |

| VCLAMPL  | 25          | —   | 左チャネルのブーストストラップ用コンデンサに供給する内部電源                                                                                                                                                         |

| VCLAMPR  | 36          | —   | 右チャネルのブーストストラップ用コンデンサに供給する内部電源                                                                                                                                                         |

| VOLUME   | 11          | I   | D級およびVAROUT出力のゲインを設定するDC電圧                                                                                                                                                             |

| VREF     | 8           | I   | ゲイン制御部のアナログ基準電圧                                                                                                                                                                        |

| V2P5     | 4           | O   | アナログ・セル用の2.5V基準電圧。同様に、シングルエンド入力時の非使用オーディオ入力への基準電圧。                                                                                                                                     |

| —        | Thermal Pad | —   | AGNDとPGNDに接続し、両グランドの(1点アースの)中心点にする。                                                                                                                                                    |

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                              |                                     | UNIT                            |

|--------------------------------------------------------------|-------------------------------------|---------------------------------|

| Supply voltage range:                                        | AV <sub>CC</sub> , PV <sub>CC</sub> | -0.3V to 15V                    |

| Input voltage range, V <sub>I</sub>                          | MODE, VREF, VARDIFF, VARMAX, VOLUME | 0V to 5.5V                      |

|                                                              | SD                                  | -0.3V to V <sub>CC</sub> + 0.3V |

|                                                              | RINN, RINP, LINN, LINP              | -0.3V to 7V                     |

| Supply current                                               | AV <sub>DD</sub>                    | 120mA                           |

|                                                              | AVDDREF                             | 10mA                            |

| Output current,                                              | VAROUTL, VAROUTR                    | 20mA                            |

| Continuous total power dissipation                           |                                     | See Dissipation Rating Table    |

| Operating free-air temperature range, T <sub>A</sub>         |                                     | -40°C to 85°C                   |

| Operating junction temperature range, T                      |                                     | -40°C to 150°C                  |

| Storage temperature range, T <sub>stg</sub>                  |                                     | -65°C to 150°C                  |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                                     | 260°C                           |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## PACKAGE DISSIPATION RATINGS

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR           | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|---------------------------|-----------------------|-----------------------|

| PHP     | 4.3 W                 | 34.7 mW/°C <sup>(1)</sup> | 2.7 W                 | 2.2 W                 |

(1) The PowerPAD must be soldered to a thermal land on the printed circuit board. Please refer to the *PowerPAD Thermally Enhanced Package* application note (SLMA002).

## RECOMMENDED OPERATING CONDITIONS

|                                                |                                                  | MIN                     | MAX        | UNIT |

|------------------------------------------------|--------------------------------------------------|-------------------------|------------|------|

| Supply voltage, V <sub>CC</sub>                | PV <sub>CC</sub> , AV <sub>CC</sub>              | 8.5                     | 14         | V    |

| Volume reference voltage                       | VREF                                             | 3.0                     | 5.5        | V    |

| Volume control pins, input voltage             | VARDIFF, VARMAX, VOLUME                          |                         | 5.5        | V    |

| High-level input voltage, V <sub>IH</sub>      | SD                                               | 2                       |            | V    |

|                                                | MODE                                             | 3.5                     |            |      |

| Low-level input voltage, V <sub>IL</sub>       | SD                                               |                         | 0.8        | V    |

|                                                | MODE                                             |                         | 2          |      |

| High-level output voltage, V <sub>OH</sub>     | MODE_OUT, I <sub>OH</sub> = 1mA                  | AV <sub>DD</sub> -100mV |            | V    |

| Low-level output voltage, V <sub>OL</sub>      | MODE_OUT, I <sub>OL</sub> = -1mA                 |                         | AGND+100mV | V    |

| High-level input current, I <sub>IH</sub>      | MODE, V <sub>I</sub> = 5V, V <sub>CC</sub> = 14V |                         | 1          | µA   |

|                                                | SD, V <sub>I</sub> = 14V, V <sub>CC</sub> = 14V  |                         | 30         | µA   |

| Low-level input current, I <sub>IL</sub>       | MODE, V <sub>I</sub> = 0V, V <sub>CC</sub> = 14V |                         | 1          | µA   |

|                                                | SD, V <sub>I</sub> = 0V, V <sub>CC</sub> = 14V   |                         | 1          | µA   |

| Oscillator frequency, f <sub>osc</sub>         |                                                  | 225                     | 275        | kHz  |

| Operating free-air temperature, T <sub>A</sub> |                                                  | -40                     | 85         | °C   |

## DC ELECTRICAL CHARACTERISTICS

$T_A = 25^\circ\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $R_L = 8\Omega$  (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                            | MIN                                                                        | TYP                   | MAX                  | UNIT                  |                  |

|--------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|------------------|

| $V_{OS}$                             | Class-D Output offset voltage<br>(measured differentially) | INN and INP connected together,<br>Gain = 36dB                             |                       | 10                   | 65                    | mV               |

| V2P5 (terminal 4)                    | 2.5-V Bias voltage                                         | No load                                                                    | 0.45x<br>$A_{V_{DD}}$ | 0.5x<br>$A_{V_{DD}}$ | 0.55x<br>$A_{V_{DD}}$ | V                |

| $A_{V_{DD}}$                         | 5-V Regulated output                                       | $I_O = 0$ to 100mA, $\bar{SD} = 2\text{V}$ , $V_{CC} = 8\text{V}$ to 14V   | 4.5                   | 5.0                  | 5.5                   | V                |

| PSRR                                 | Class-D power supply rejection ratio                       | $V_{CC} = 11.5\text{V}$ to 12.5V                                           |                       | -80                  |                       | dB               |

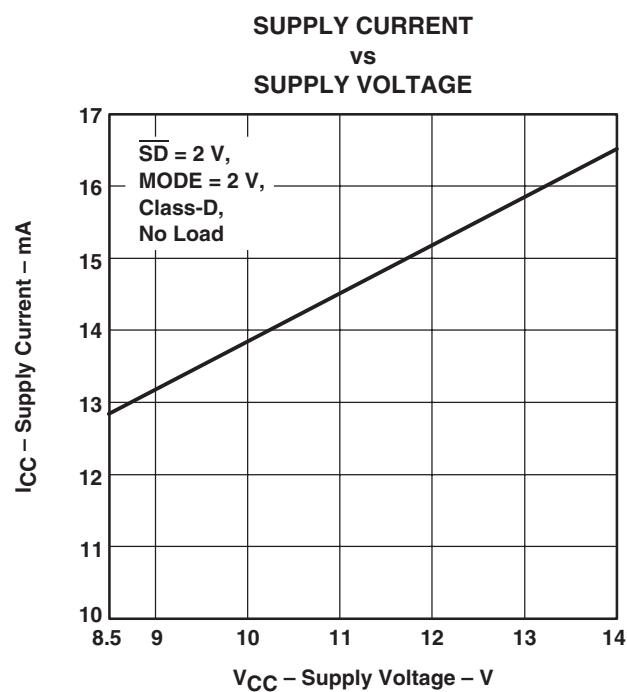

| $I_{CC(\text{class-D})}$             | Class-D mode quiescent current                             | MODE = 2V, $\bar{SD} = 2\text{V}$                                          |                       | 16                   | 28.5                  | mA               |

| $I_{CC(\text{varout})}$              | Variable output mode quiescent current                     | MODE = 3.5V, $\bar{SD} = 2\text{V}$                                        |                       | 7                    | 9                     | mA               |

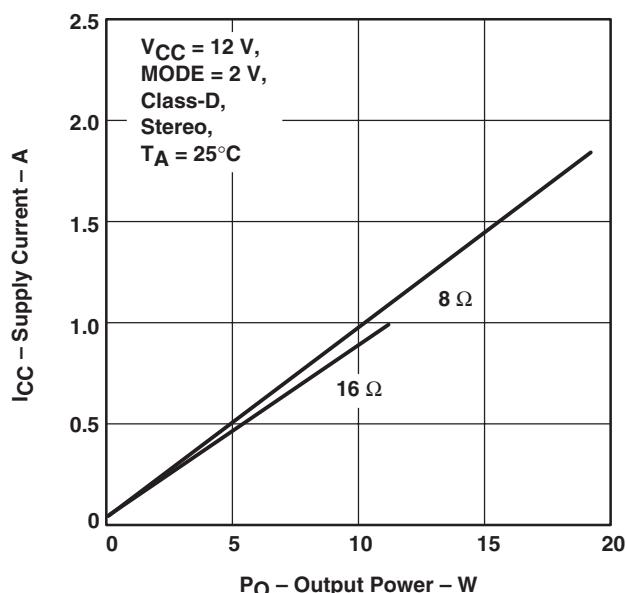

| $I_{CC(\text{class-D - max power})}$ | Class-D mode RMS current at max power                      | $R_L = 8\Omega$ , $P_O = 9\text{W}$                                        |                       | 2                    |                       | A                |

| $I_{CC(\text{SD})}$                  | Supply current in shutdown mode                            | $\bar{SD} = 0.8\text{V}$                                                   |                       | 1                    | 10                    | $\mu\text{A}$    |

| $r_{ds(\text{on})}$                  | Drain-source on-state resistance                           | $V_{CC} = 12\text{V}$ ,<br>$I_O = 1\text{A}$ ,<br>$T_J = 25^\circ\text{C}$ | High side             | 300                  |                       | $\text{m}\Omega$ |

|                                      |                                                            |                                                                            | Low side              | 250                  |                       |                  |

|                                      |                                                            |                                                                            | Total                 | 550                  | 590                   |                  |

## AC ELECTRICAL CHARACTERISTICS FOR CLASS-D OUTPUTS

$T_A = 25^\circ\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $R_L = 8\Omega$  (unless otherwise noted)

| PARAMETER                               | TEST CONDITIONS               | MIN                                                                | TYP | MAX | UNIT             |

|-----------------------------------------|-------------------------------|--------------------------------------------------------------------|-----|-----|------------------|

| $k_{SVR}$                               | Supply ripple rejection ratio | $V_{CC} = 11.5\text{V}$ to 12.5V from 10Hz to 1kHz,<br>Gain = 36dB |     | -67 | dB               |

| $P_O$                                   | Continuous output power       | THD+N = 1%, $f = 1\text{kHz}$ , $R_L = 8\Omega$                    | 7.5 |     | W                |

|                                         |                               | THD+N = 10%, $f = 1\text{kHz}$ , $R_L = 8\Omega$                   | 9   |     | W                |

| $V_n$                                   | Output integrated noise floor | 20Hz to 22kHz, No filter, Gain = 0.5dB                             | 79  |     | $\mu\text{V}$    |

|                                         |                               | 20Hz to 22kHz, A-weighted filter,<br>Gain = 13.2dB                 | -82 |     | $\text{dBV}$     |

|                                         |                               | 20Hz to 22kHz, A-weighted filter,<br>Gain = 13.2dB                 | 100 |     | $\mu\text{V}$    |

|                                         |                               | Crosstalk, Class-D-Left $\rightarrow$ Class-D-Right                | -80 |     | $\text{dBV}$     |

| Crosstalk, Class-D $\rightarrow$ VAROUT |                               | Gain = 13.2 dB, $P_O = 1\text{W}$ , $R_L = 8\Omega$                | -77 |     | dB               |

|                                         |                               | Maximum output at THD < 0.5%, Gain = 36dB                          | -63 |     | dB               |

| SNR                                     | Signal-to-noise ratio         | Maximum output at THD+N < 0.5%,<br>$f = 1\text{kHz}$ , Gain = 36dB | 96  |     | dB               |

| Thermal trip point                      |                               |                                                                    | 150 |     | $^\circ\text{C}$ |

| Thermal hysteresis                      |                               |                                                                    | 20  |     | $^\circ\text{C}$ |

## CHARACTERISTICS FOR VAROUT OUTPUTS

| PARAMETER                                | TEST CONDITIONS                   | MIN                                                                                                  | TYP    | MAX | UNIT          |

|------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|--------|-----|---------------|

| $V_{OS}$                                 | Output offset voltage             | Measured between V2P5 and VAROUT,<br>Gain = 20dB, $R_L = 10\text{k}\Omega$                           |        | 10  | mV            |

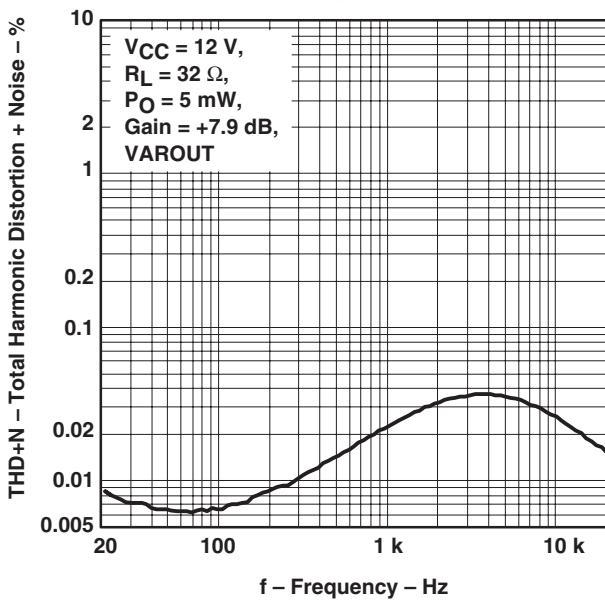

| THD+N                                    | Total harmonic distortion + noise | $A_V = 7.3\text{dB}$ , $f = 1\text{kHz}$ , $P_O = 6\text{ mW}$ , $R_L = 32\Omega$                    | 0.025% |     |               |

|                                          |                                   | $A_V = 7.3\text{dB}$ , $f = 1\text{kHz}$ , $R_L = 2\text{k}\Omega$ , $V_O = 1\text{ V}_{\text{rms}}$ | 0.002% |     |               |

| PSRR                                     | DC power supply rejection ratio   | Gain = 20dB                                                                                          |        | -74 | dB            |

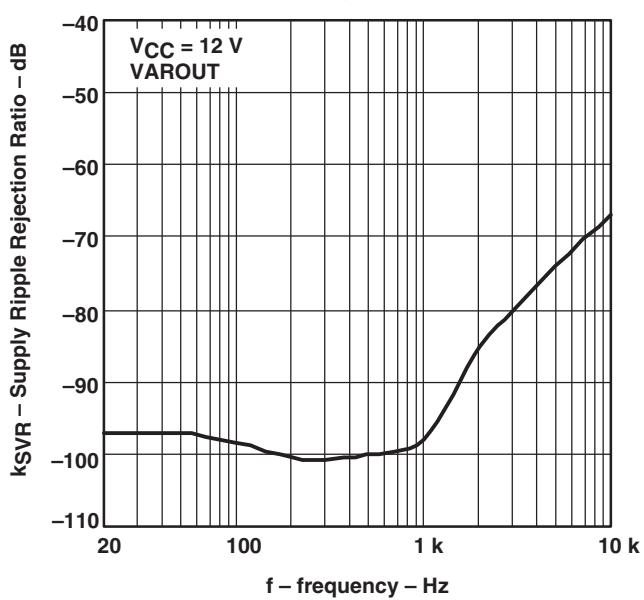

| $k_{SVR}$                                | Supply ripple rejection ratio     | Gain = 20dB, $f = 1\text{kHz}$                                                                       |        | -95 | dB            |

| Crosstalk, VAROUTL $\rightarrow$ VAROUTR |                                   | Maximum output at THD < 0.5%, Gain = 20dB                                                            | -60    |     | dB            |

| Crosstalk, VAROUT $\rightarrow$ Class-D  |                                   | Maximum output at THD < 0.5%, Gain = 20dB                                                            | -74    |     | dB            |

| $V_n$                                    | Output integrated noise floor     | 20Hz to 22kHz, Gain = 20dB                                                                           | 75     |     | $\mu\text{V}$ |

|                                          |                                   | 20Hz to 22kHz, Gain = -0.3dB                                                                         | 15     |     |               |

| VOLTAGE ON THE VOLUME PIN AS A PERCENTAGE OF VREF (INCREASING VOLUME OR FIXED GAIN) | VOLTAGE ON THE VOLUME PIN AS A PERCENTAGE OF VREF (DECREASING VOLUME) | GAIN OF CLASS-D AMPLIFIER |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| %                                                                                   | %                                                                     | dB                        |

| 0 – 4.5                                                                             | 0 – 2.9                                                               | -75 <sup>(1)</sup>        |

| 4.5 – 6.7                                                                           | 2.9 – 5.1                                                             | -40.0                     |

| 6.7 – 8.91                                                                          | 5.1 – 7.2                                                             | -37.5                     |

| 8.9 – 11.1                                                                          | 7.2 – 9.4                                                             | -35.0                     |

| 11.1 – 13.3                                                                         | 9.4 – 11.6                                                            | -32.4                     |

| 13.3 – 15.5                                                                         | 11.6 – 13.8                                                           | -29.9                     |

| 15.5 – 17.7                                                                         | 13.8 – 16.0                                                           | -27.4                     |

| 17.7 – 19.9                                                                         | 16.0 – 18.2                                                           | -24.8                     |

| 19.9 – 22.1                                                                         | 18.2 – 20.4                                                           | -22.3                     |

| 22.1 – 24.3                                                                         | 20.4 – 22.6                                                           | -19.8                     |

| 24.3 – 26.5                                                                         | 22.6 – 24.8                                                           | -17.2                     |

| 26.5 – 28.7                                                                         | 24.8 – 27.0                                                           | -14.7                     |

| 28.7 – 30.9                                                                         | 27.0 – 29.1                                                           | -12.2                     |

| 30.9 – 33.1                                                                         | 29.1 – 31.3                                                           | -9.6                      |

| 33.1 – 35.3                                                                         | 31.3 – 33.5                                                           | -7.1                      |

| 35.3 – 37.5                                                                         | 33.5 – 35.7                                                           | -4.6                      |

| 37.5 – 39.7                                                                         | 35.7 – 37.9                                                           | -2.0                      |

| 39.7 – 41.9                                                                         | 37.9 – 40.1                                                           | 0.5 <sup>†</sup>          |

| 41.9 – 44.1                                                                         | 40.1 – 42.3                                                           | 3.1                       |

| 44.1 – 46.4                                                                         | 42.3 – 44.5                                                           | 5.6                       |

| 46.4 – 48.6                                                                         | 44.5 – 46.7                                                           | 8.1                       |

| 48.6 – 50.8                                                                         | 46.7 – 48.9                                                           | 10.7                      |

| 50.8 – 53.0                                                                         | 48.9 – 51.0                                                           | 13.2                      |

| 53.0 – 55.2                                                                         | 51.0 – 53.2                                                           | 15.7                      |

| 55.2 – 57.4                                                                         | 53.2 – 55.4                                                           | 18.3                      |

| 57.4 – 59.6                                                                         | 55.4 – 57.6                                                           | 20.8                      |

| 59.6 – 61.8                                                                         | 57.6 – 59.8                                                           | 23.3                      |

| 61.8 – 64.0                                                                         | 59.8 – 62.0                                                           | 25.9                      |

| 64.0 – 66.2                                                                         | 62.0 – 64.2                                                           | 28.4                      |

| 66.2 – 68.4                                                                         | 64.2 – 66.4                                                           | 30.9                      |

| 68.4 – 70.6                                                                         | 66.4 – 68.6                                                           | 33.5                      |

| > 70.6                                                                              | >68.6                                                                 | 36.0 <sup>(1)</sup>       |

(1) Tested in production. Remaining steps are specified by design.

表1. DC Volume Control for Class-D Outputs

| VAROUT_VOLUME (V)<br>- FROM FIGURE 35 -<br>AS A PERCENTAGE OF<br>VREF (INCREASING<br>VOLUME OR FIXED GAIN) | VAROUT_VOLUME (V)<br>- FROM FIGURE 35 -<br>AS A PERCENTAGE OF<br>VREF (DECREASING<br>VOLUME) | GAIN OF VAROUT<br>AMPLIFIER |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------|

| %                                                                                                          | %                                                                                            | dB                          |

| 0 – 4.5                                                                                                    | 0 – 2.9                                                                                      | -66 <sup>(1)</sup>          |

| 4.5 – 6.7                                                                                                  | 2.9 – 5.1                                                                                    | -56.0                       |

| 6.7 – 8.91                                                                                                 | 5.1 – 7.2                                                                                    | -53.5                       |

| 8.9 – 11.1                                                                                                 | 7.2 – 9.4                                                                                    | -50.9                       |

| 11.1 – 13.3                                                                                                | 9.4 – 11.6                                                                                   | -48.4                       |

| 13.3 – 15.5                                                                                                | 11.6 – 13.8                                                                                  | -45.9                       |

| 15.5 – 17.7                                                                                                | 13.8 – 16.0                                                                                  | -43.3                       |

| 17.7 – 19.9                                                                                                | 16.0 – 18.2                                                                                  | -40.8                       |

| 19.9 – 22.1                                                                                                | 18.2 – 20.4                                                                                  | -38.3                       |

| 22.1 – 24.3                                                                                                | 20.4 – 22.6                                                                                  | -35.7                       |

| 24.3 – 26.5                                                                                                | 22.6 – 24.8                                                                                  | -33.2                       |

| 26.5 – 28.7                                                                                                | 24.8 – 27.0                                                                                  | -30.7                       |

| 28.7 – 30.9                                                                                                | 27.0 – 29.1                                                                                  | -28.1                       |

| 30.9 – 33.1                                                                                                | 29.1 – 31.3                                                                                  | -25.6                       |

| 33.1 – 35.3                                                                                                | 31.3 – 33.5                                                                                  | -23.1                       |

| 35.3 – 37.5                                                                                                | 33.5 – 35.7                                                                                  | -20.5                       |

| 37.5 – 39.7                                                                                                | 35.7 – 37.9                                                                                  | -18.0                       |

| 39.7 – 41.9                                                                                                | 37.9 – 40.1                                                                                  | -15.5                       |

| 41.9 – 44.1                                                                                                | 40.1 – 42.3                                                                                  | -13.0 <sup>(1)</sup>        |

| 44.1 – 46.4                                                                                                | 42.3 – 44.5                                                                                  | -10.4                       |

| 46.4 – 48.6                                                                                                | 44.5 – 46.7                                                                                  | -7.9                        |

| 48.6 – 50.8                                                                                                | 46.7 – 48.9                                                                                  | -5.3                        |

| 50.8 – 53.0                                                                                                | 48.9 – 51.0                                                                                  | -2.8                        |

| 53.0 – 55.2                                                                                                | 51.0 – 53.2                                                                                  | -0.3                        |

| 55.2 – 57.4                                                                                                | 53.2 – 55.4                                                                                  | 2.3                         |

| 57.4 – 59.6                                                                                                | 55.4 – 57.6                                                                                  | 4.8                         |

| 59.6 – 61.8                                                                                                | 57.6 – 59.8                                                                                  | 7.3                         |

| 61.8 – 64.0                                                                                                | 59.8 – 62.0                                                                                  | 9.9                         |

| 64.0 – 66.2                                                                                                | 62.0 – 64.2                                                                                  | 12.4                        |

| 66.2 – 68.4                                                                                                | 64.2 – 66.4                                                                                  | 14.9                        |

| 68.4 – 70.6                                                                                                | 66.4 – 68.6                                                                                  | 17.5                        |

| > 70.6                                                                                                     | >68.6                                                                                        | 20.0 <sup>(1)</sup>         |

(1) Tested in production. Remaining steps are specified by design.

表2. DC Volume Control for VAROUT Outputs

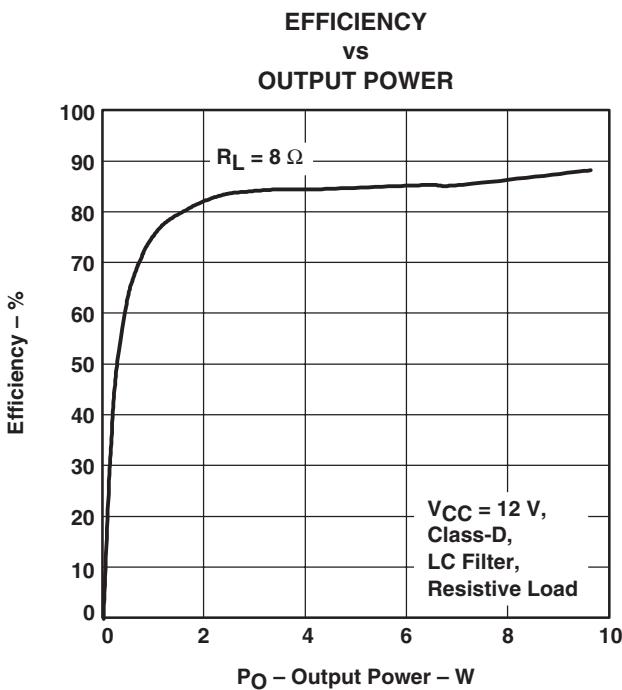

# TYPICAL CHARACTERISTICS

## TABLE OF GRAPHS

|             |                                           | FIGURE                       |

|-------------|-------------------------------------------|------------------------------|

|             | Class-D Efficiency                        | 1                            |

| $P_o$       | Class-D Output power                      | vs Output power              |

|             |                                           | vs Load resistance           |

|             |                                           | vs Supply voltage            |

| $I_{cc}$    | Class-D Supply current                    | vs Supply voltage            |

|             |                                           | vs Output Power              |

| $I_{O(sd)}$ | Shutdown supply current                   | vs Supply voltage            |

|             | Class-D Input resistance                  | vs Gain                      |

| THD+N       | Class-D Total harmonic distortion + noise | vs Frequency                 |

|             |                                           | vs Output power              |

| $k_{SVR}$   | Class-D Supply ripple rejection ratio     | vs Frequency                 |

|             | Class-D Closed loop response              |                              |

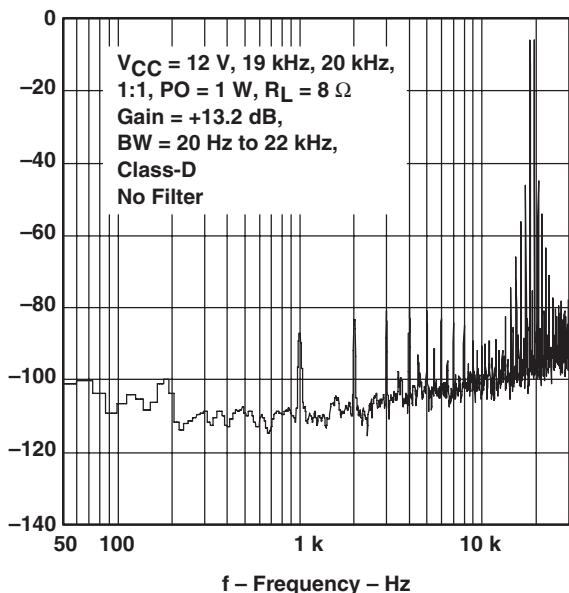

|             | Class-D Intermodulation performance       |                              |

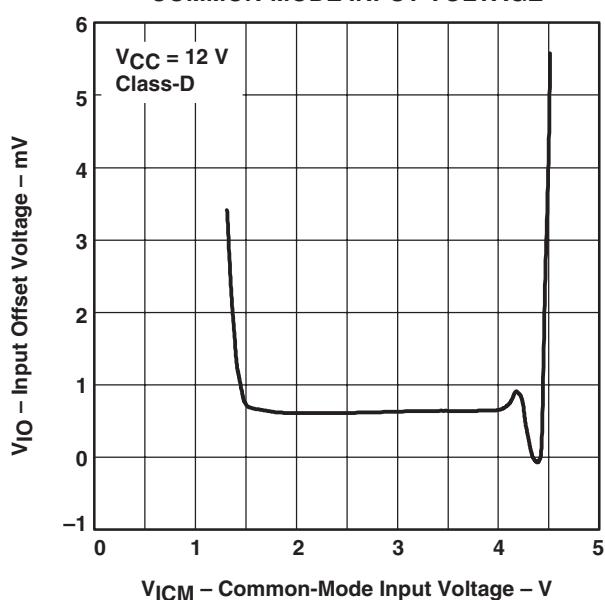

|             | Class-D Input offset voltage              | vs Common-mode input voltage |

|             | Class-D Crosstalk                         | vs Frequency                 |

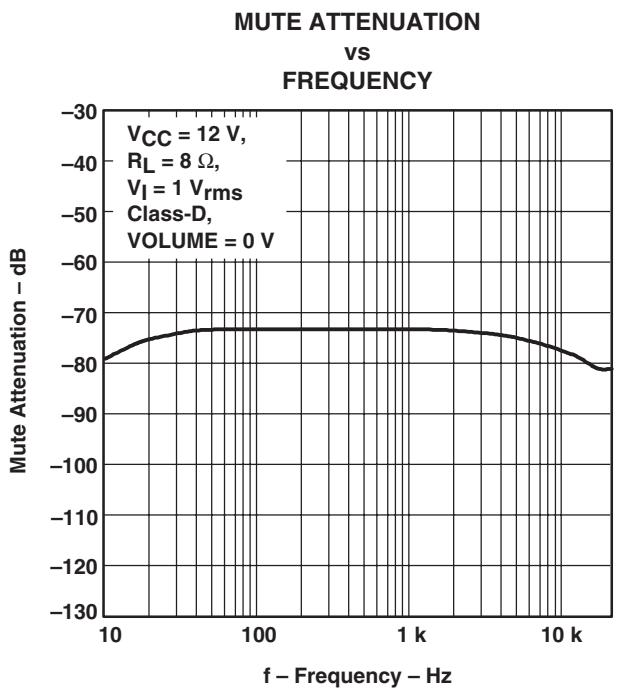

|             | Class-D Mute attenuation                  |                              |

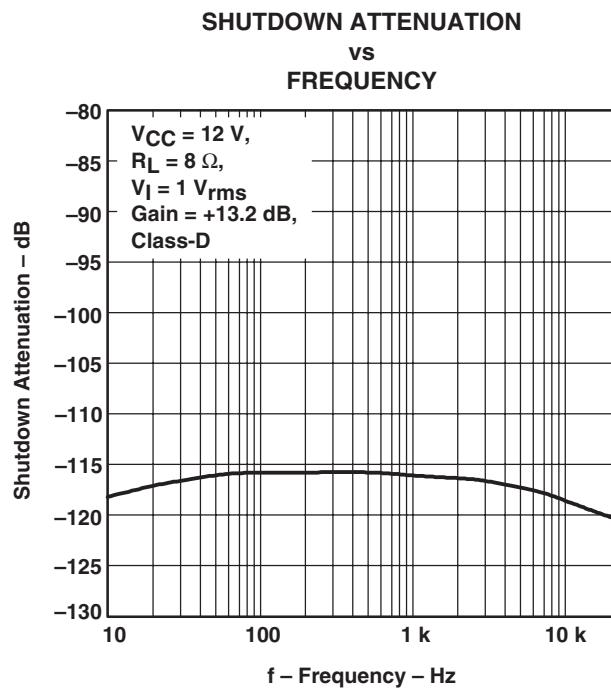

|             | Class-D Shutdown attenuation              | vs Frequency                 |

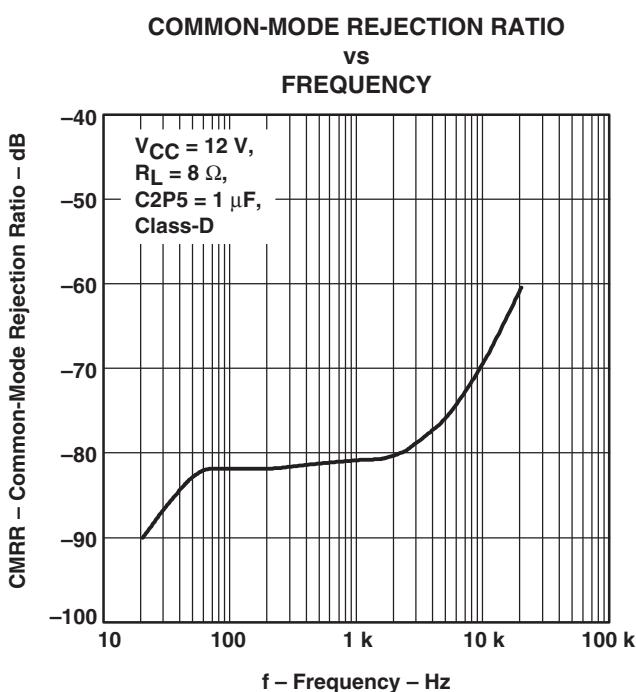

|             | Class-D Common-mode rejection ratio       | vs Frequency                 |

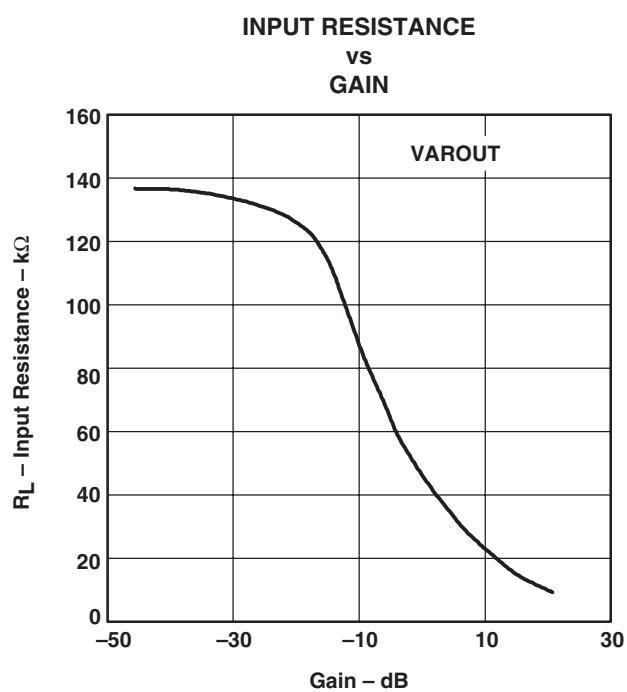

|             | VAROUT Input resistance                   | vs Gain                      |

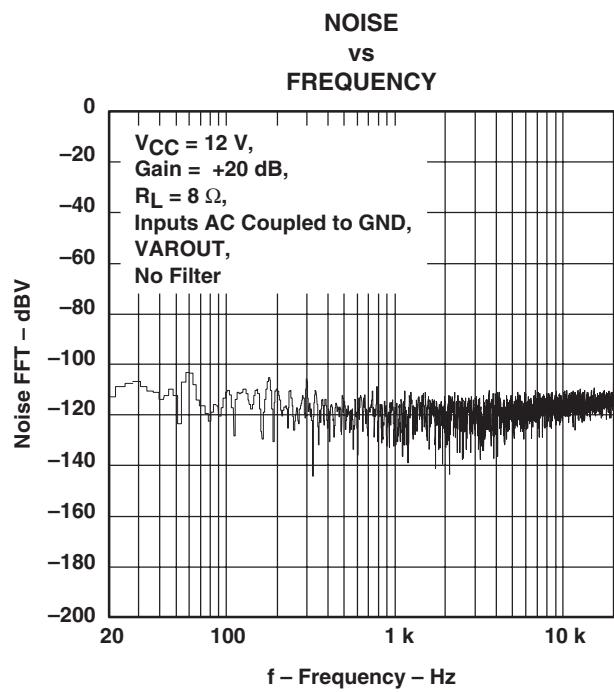

|             | VAROUT Noise                              | vs Frequency                 |

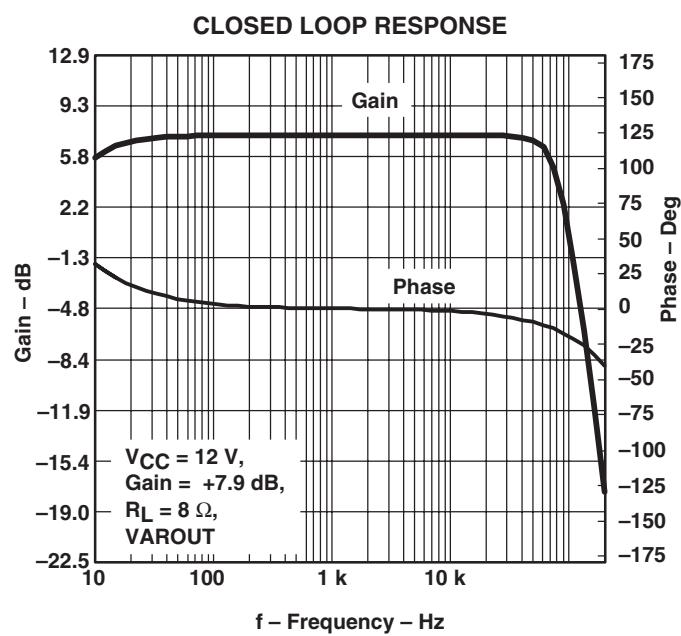

|             | VAROUT Closed Loop Response               |                              |

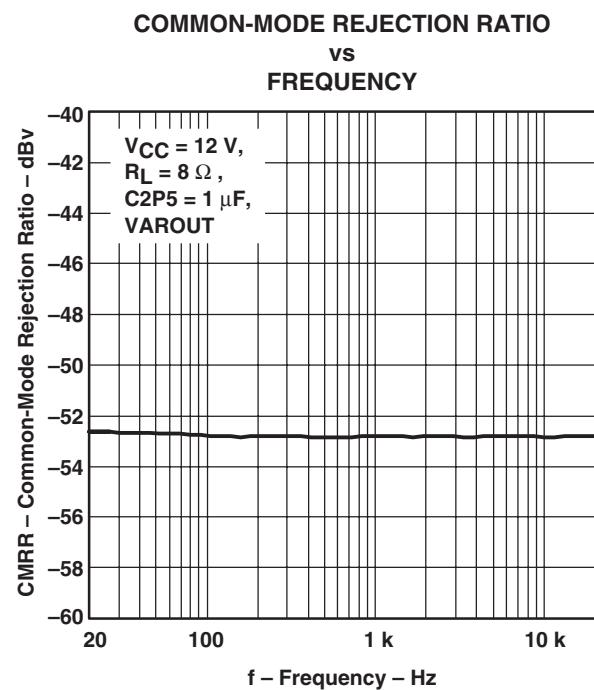

|             | VAROUT Common-mode rejection ratio        | vs Frequency                 |

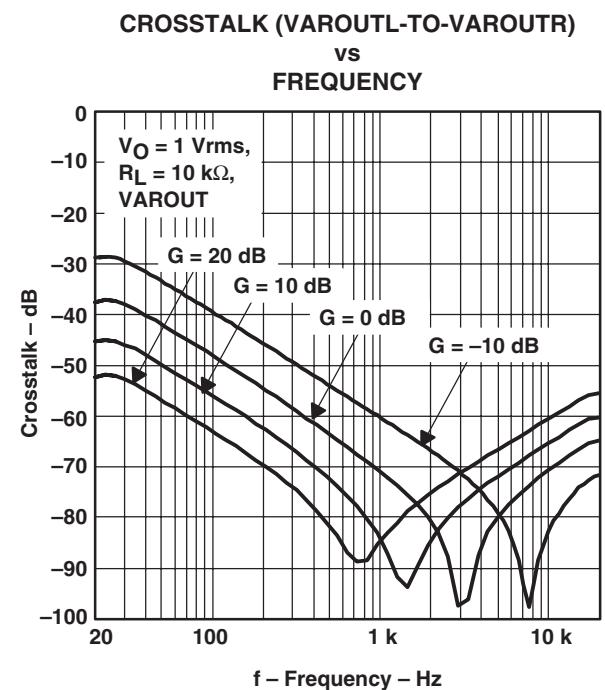

|             | VAROUT Crosstalk                          | vs Frequency                 |

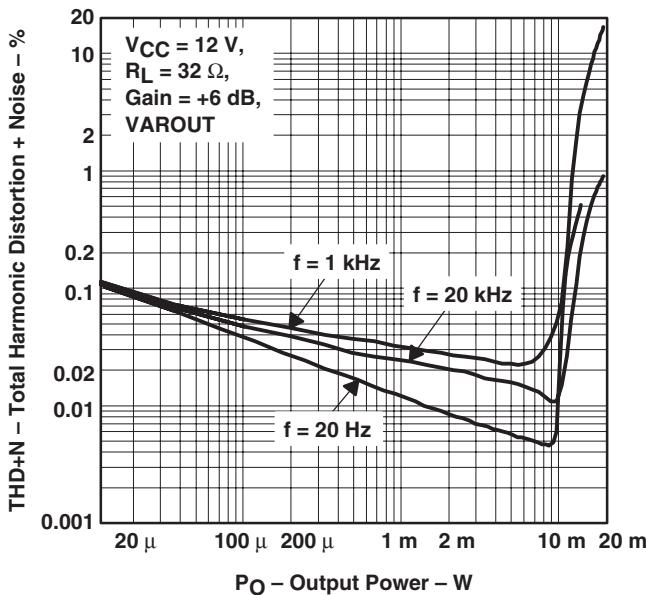

| THD+N       | VAROUT Total harmonic distortion + noise  | vs Output power              |

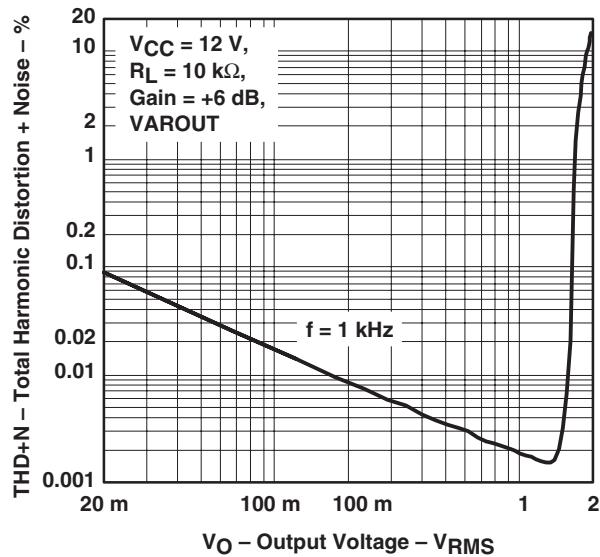

|             |                                           | vs Output voltage            |

|             |                                           | vs Frequency                 |

| $k_{SVR}$   | VAROUT Supply ripple rejection ratio      | vs Frequency                 |

図1

図2

図3

図4

SUPPLY CURRENT

vs

OUTPUT POWER

図5

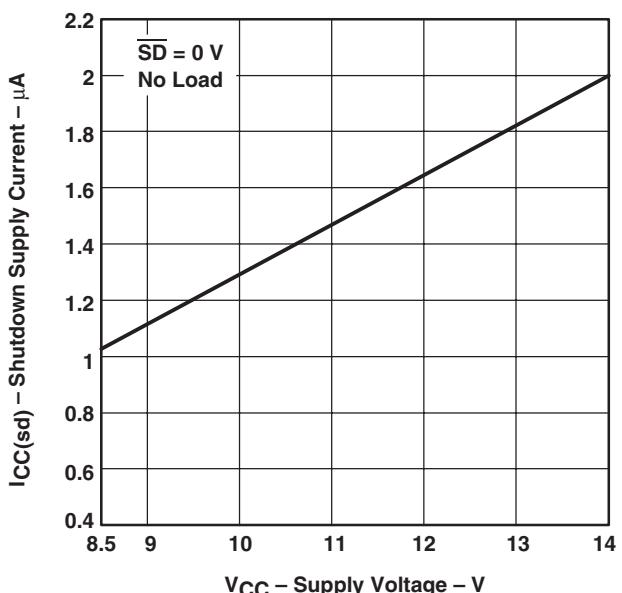

SHUTDOWN SUPPLY CURRENT

vs

SUPPLY VOLTAGE

図6

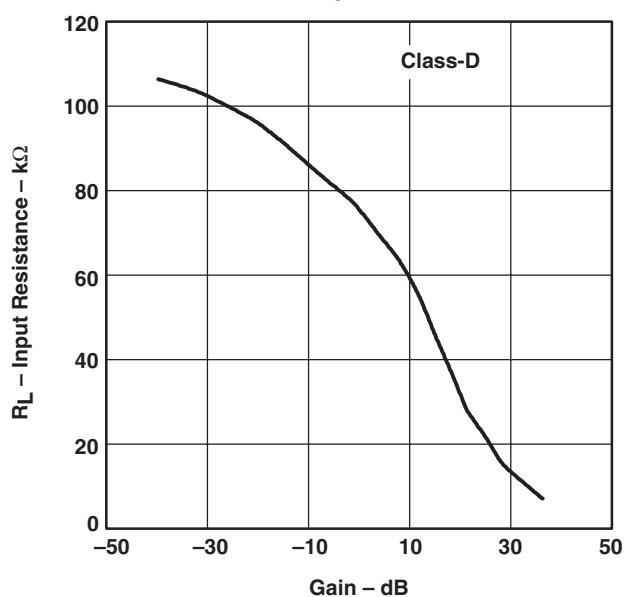

INPUT RESISTANCE

vs

GAIN

図7

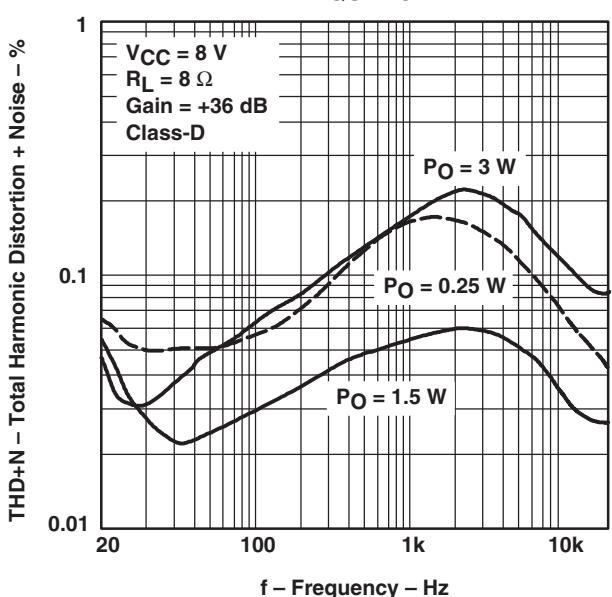

TOTAL HARMONIC DISTORTION + NOISE

vs

FREQUENCY

図8

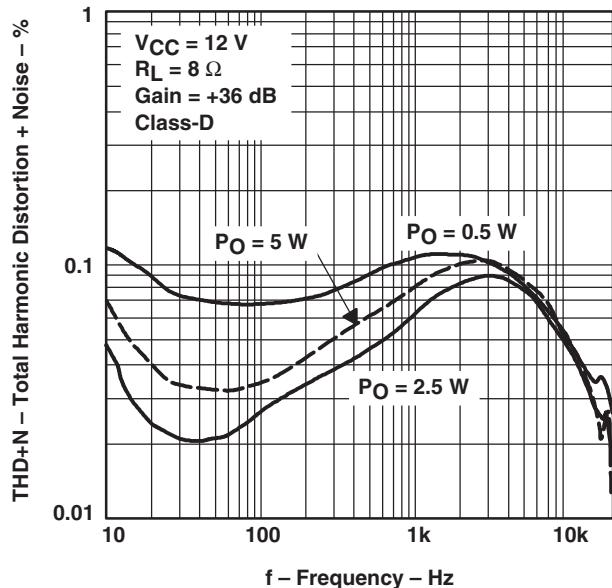

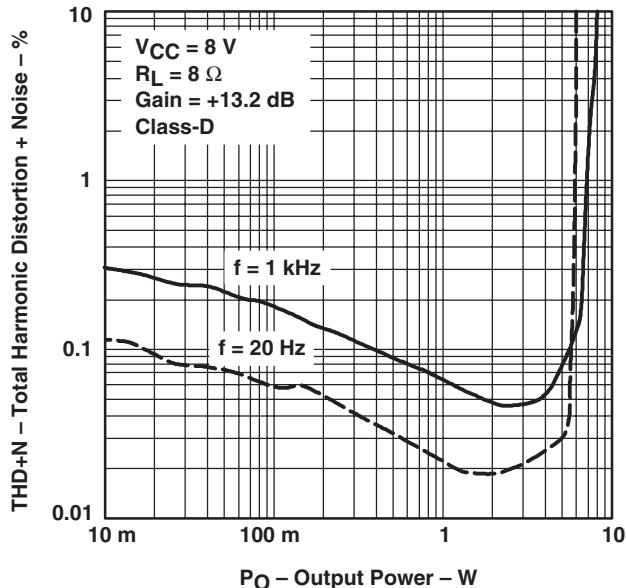

**TOTAL HARMONIC DISTORTION + NOISE

vs

FREQUENCY**

図9

**TOTAL HARMONIC DISTORTION + NOISE

vs

OUTPUT POWER**

図10

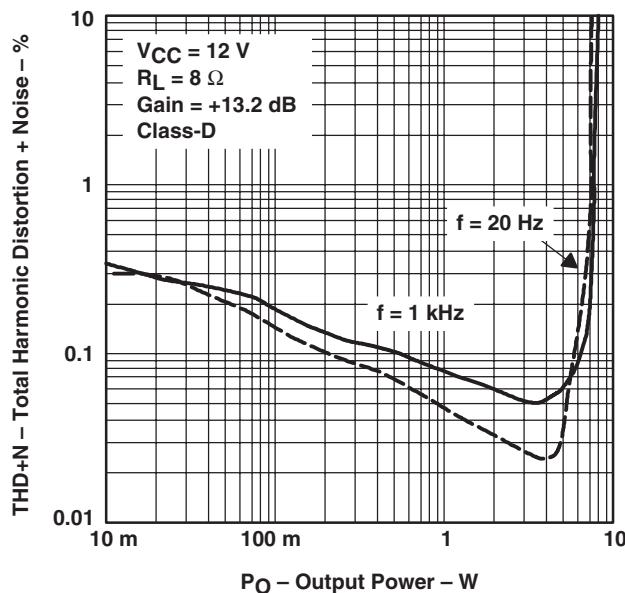

**TOTAL HARMONIC DISTORTION + NOISE

vs

OUTPUT POWER**

図11

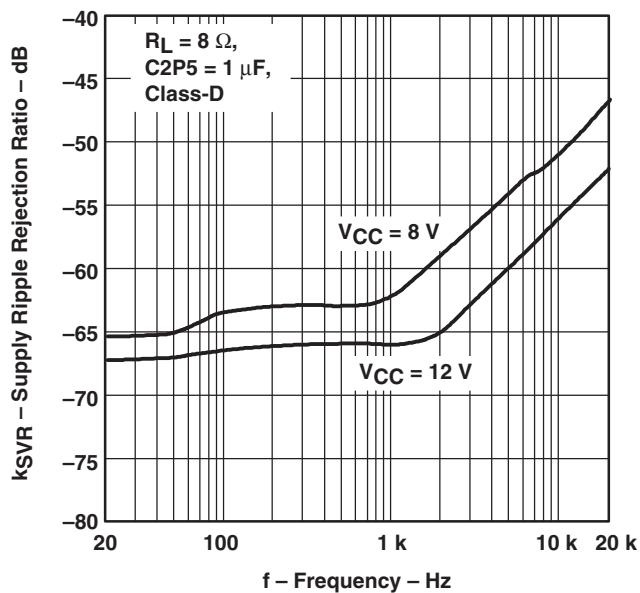

**SUPPLY RIPPLE REJECTION RATIO

vs

FREQUENCY**

図12

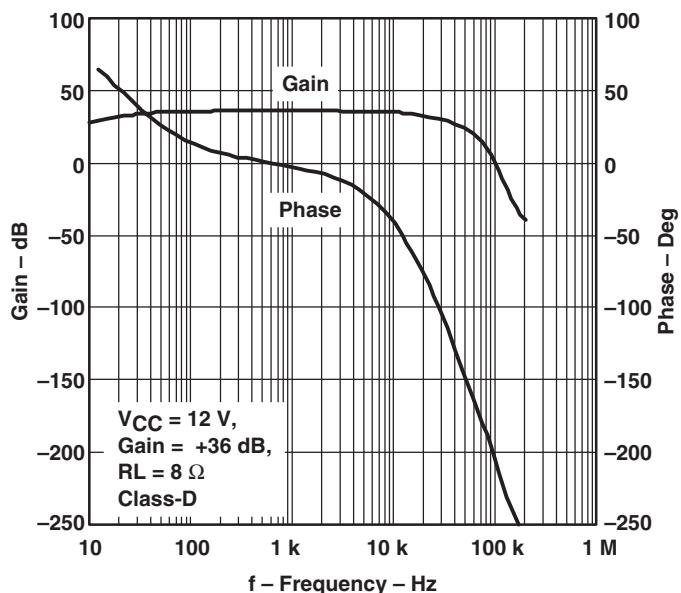

### CLOSED LOOP RESPONSE

図13

### INTERMODULATION PERFORMANCE

図14

### INPUT OFFSET VOLTAGE

vs

### COMMON-MODE INPUT VOLTAGE

図15

### CROSSTALK

vs

### FREQUENCY

図16

図17

図18

図19

図20

図21

図22

図23

図24

**TOTAL HARMONIC DISTORTION + NOISE

vs

OUTPUT POWER**

図25

**TOTAL HARMONIC DISTORTION + NOISE

vs

OUTPUT VOLTAGE**

図26

**TOTAL HARMONIC DISTORTION + NOISE

vs

FREQUENCY**

図27

**SUPPLY RIPPLE REJECTION RATIO

vs

FREQUENCY**

図28

# アプリケーション情報

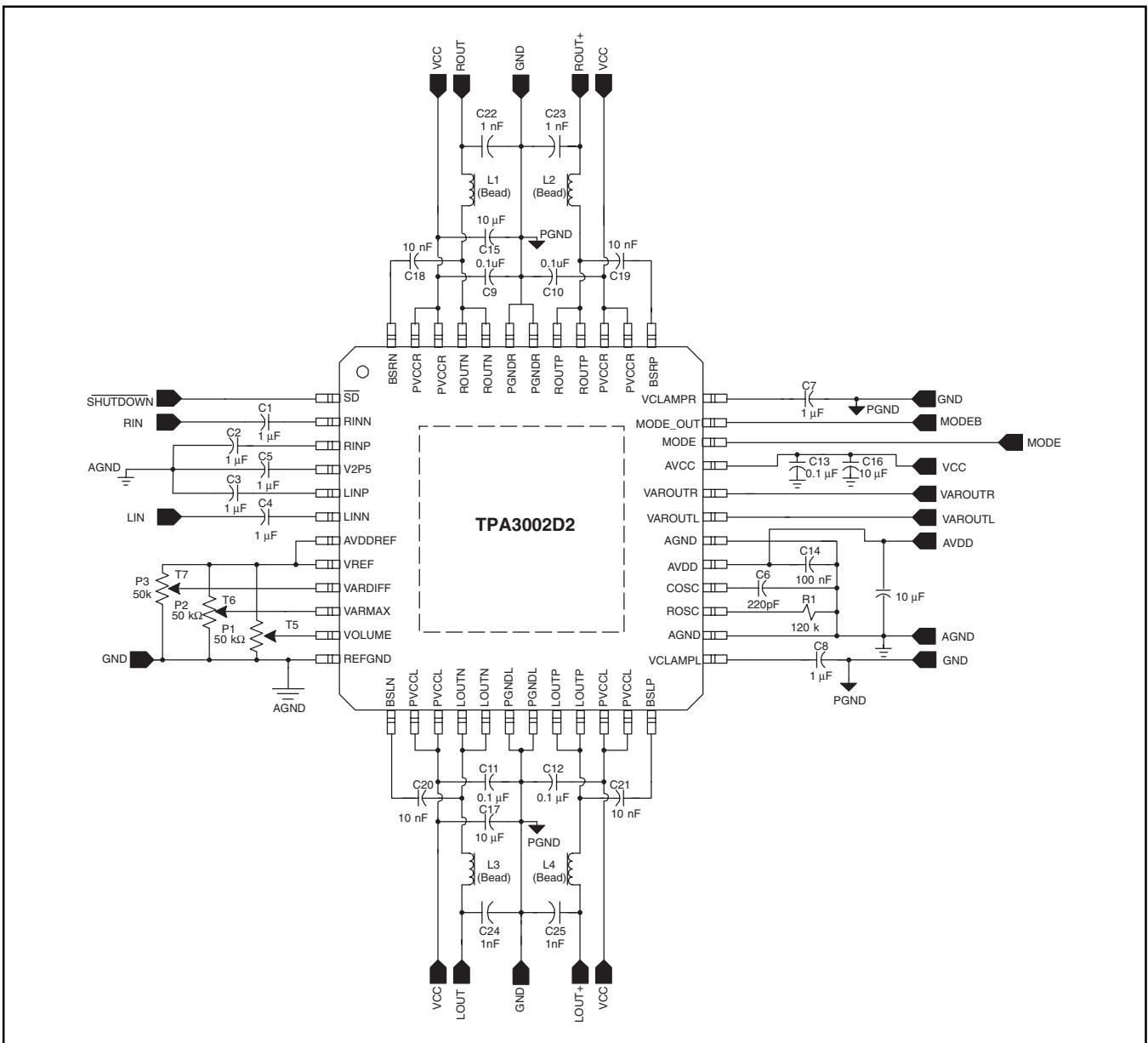

図29. Stereo Class-D With Single-Ended Inputs

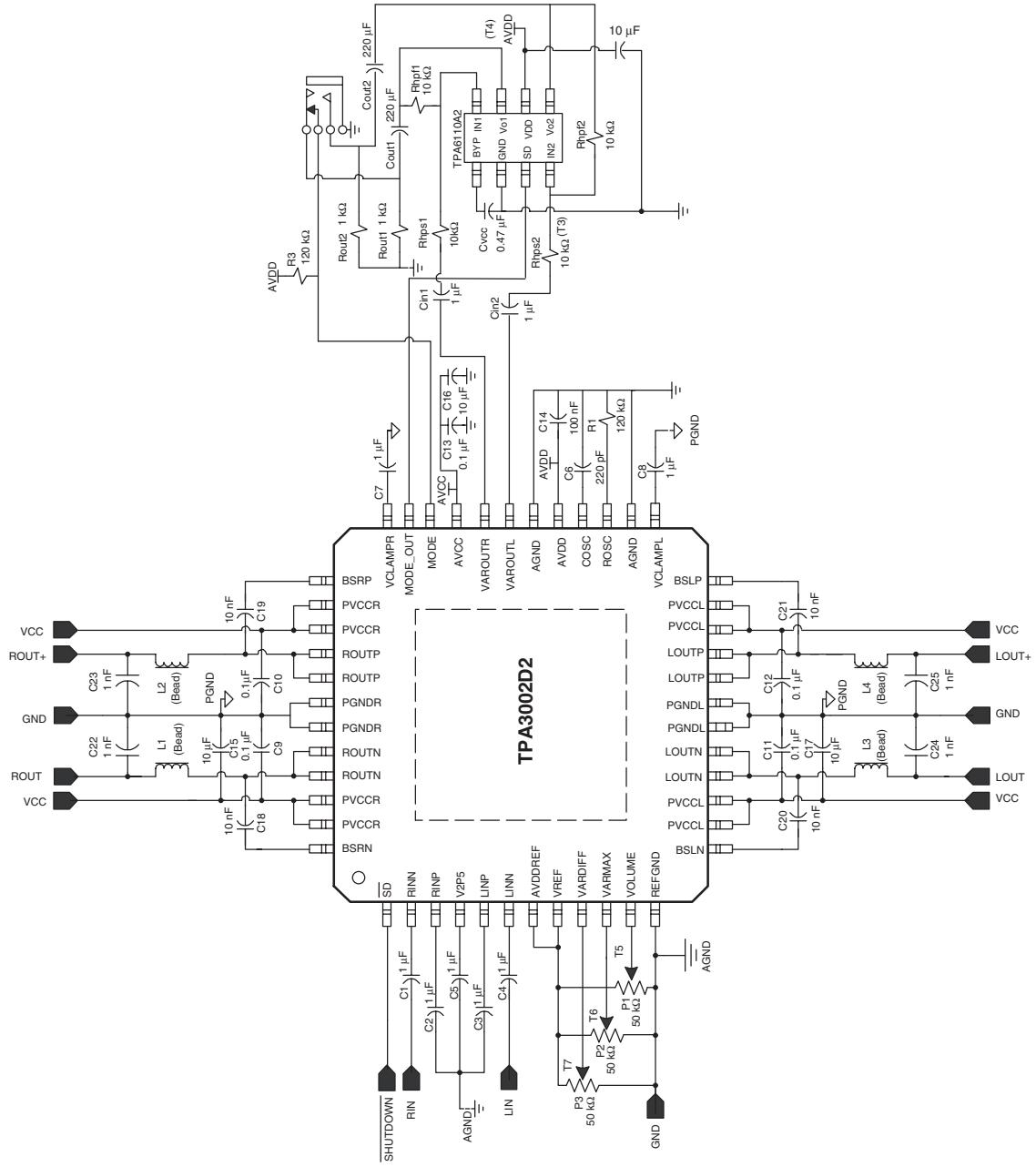

图30. Stereo Class-D With Single-Ended Inputs and Stereo Headphone Amplifier Interface

D級動作

本節ではTPA3002D2のD級動作について述べます。

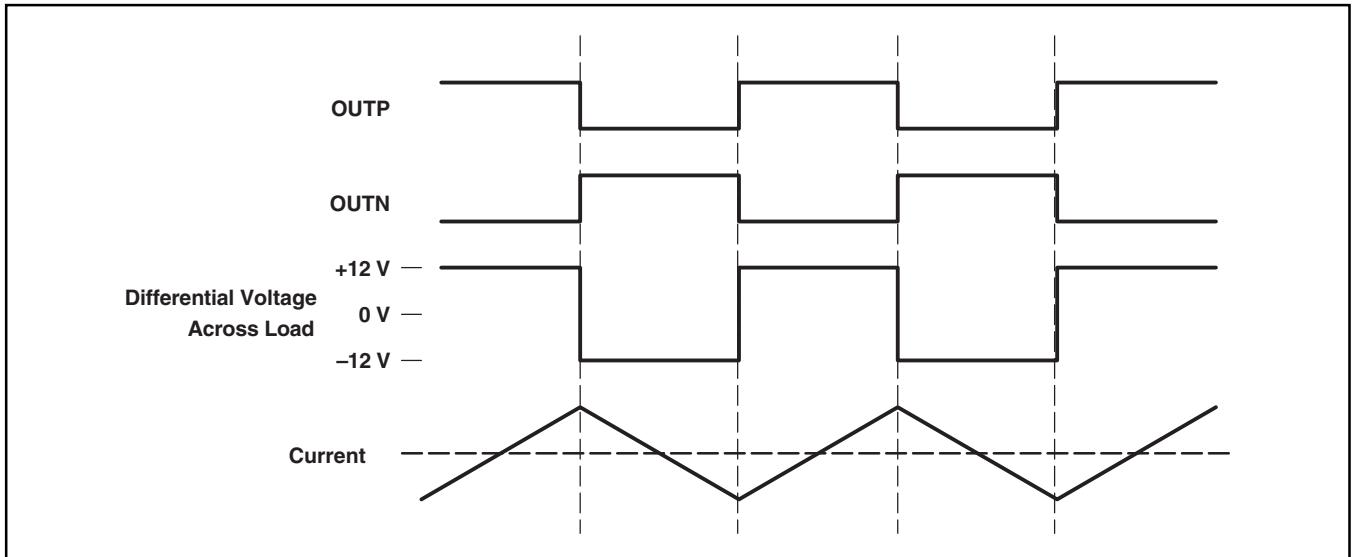

## 従来のD級変調手法

従来のD級変調手法は、TPA032D0xファミリーで用いられていますが、位相が互いに $180^\circ$ ずれた差動出力であり、グランドから電源電圧V<sub>CC</sub>まで変化します。したがって、フィルタ前の差動出力は正負の電源電圧間で変化し、フィルタされた50%のデューティサイクルで負荷に0Vがかかります。従来のD級変調手法を図31に示します。負荷に平均で0V(50%デューティサイクル)が印加されるとは言っても、負荷電流は大きく、大きな損失を生じ、大電源電流になることに注意願います。

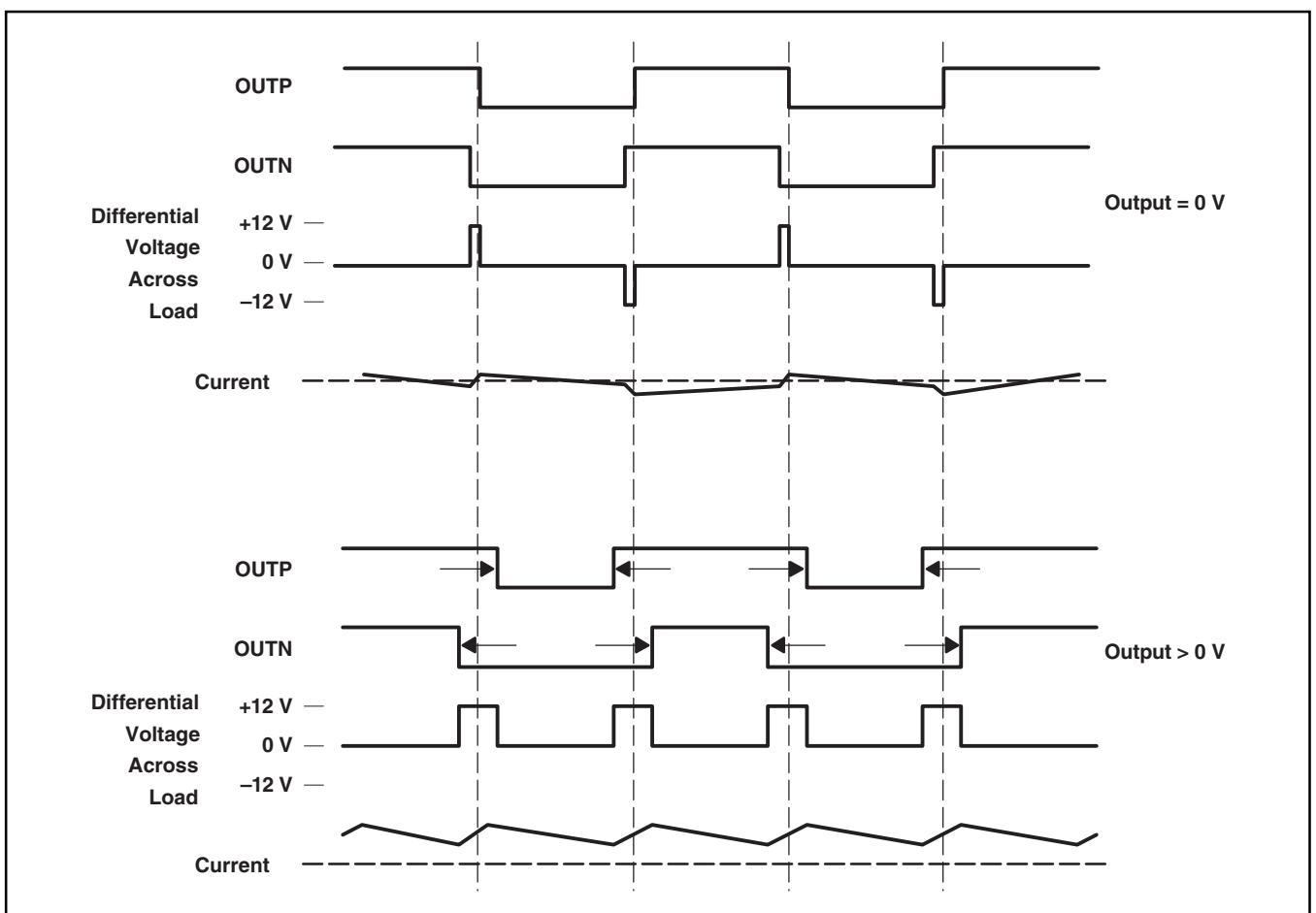

## TPA3002D2の変調手法

TPA3002D2でも、両出力が0Vから電源電圧までスイッチングする変調手法を使用しています。しかし、OUTPとOUTNは無入力時に相互に同相となります。そして、正出力電圧時のOUTPのデューティサイクルは50%以上であり、OUTN出力は50%以下になります。同様に、負出力電圧時のOUTPのデューティサイクルは50%以下であり、OUTN出力は50%以上になります。負荷にかかる電圧は大部分のスイッチング期間を通して0Vになり、スイッチング電流が激減し、負荷における $I^2R$ 損失(抵抗性の損失)を低減します。

図31. 従来のD級変調手法の、誘導性負荷に対する無入力時の出力電圧・電流波形

図32. TPA3002D2の誘導性負荷に対する出力電圧・電流波形

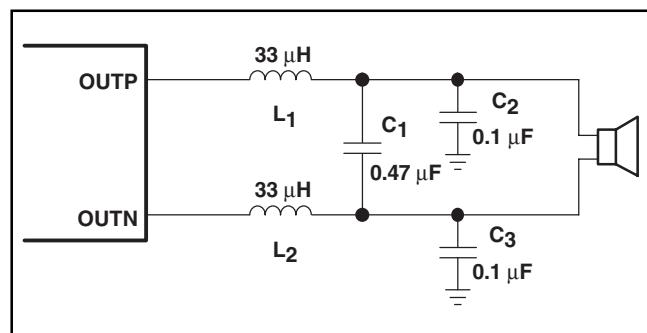

## 効率：従来のD級変調手法に必要なLCフィルタ

従来のD級アンプが出力フィルタを要する主な理由は、スイッチング波形が最大電流を生じるからです。これが負荷で大きな損失を生じ、効率を低下させます。リップル電流は電圧とその電圧の時間の積に比例するため、従来のD級変調手法のリップル電流は大きいものになります。また、従来のD級変調手法の差動電圧振幅は $2 \times V_{CC}$ となり、各電圧の時間は半サイクルになります。そこで、理想的なLCフィルタが、各半サイクルのリップル電流をその次の半サイクルのために蓄積するのに必要になります。一方、あらゆる抵抗は電力を損失します。スピーカーには抵抗性とリアクタンス性がありますが、LCフィルタはほぼ純粋なリアクタンス性です。

TPA3002D2の変調手法は、フィルタなしの負荷で非常に低損失です。なぜなら、パルス幅が非常に短く、電圧変化が $2 \times V_{CC}$ ではなく $V_{CC}$ だからです。出力電力が増加すると、パルス幅が広がり、リップル電流が増加します。リップル電流はLCフィルタで除去して効率を改善できますが、本変調手法ではほとんどのアプリケーションにおいてフィルタは必要ありません。

カットオフ周波数がD級スイッチング周波数より低いLCフィルタにすると、スイッチング電流を負荷ではなくフィルタに流すようにできます。フィルタはスピーカーより低抵抗であるため、電力損失を低減し、効率を高めることができます。

## スピーカーに方形波を印加する影響

オーディオのスペシャリストは、スピーカーに方形波を印加すべきでないと長年にわたってアドバイスしてきました。波形の振幅が十分大であり、方形波の周波数がスピーカーの帯域内の場合、方形波がボイスコイルの空隙を超えさせ、ボイスコイルを損傷することもあります。しかし、250kHzのスイッチング周波数では、オーディオ帯域以上の周波数におけるコーンの動きが $1/f^2$ に比例するため、ボイスコイルを極端に動かすことはありません。

ボイスコイルが高周波のスイッチング電流によって生じた熱を処理できない場合、損傷が起こります。スピーカーにおける電力消費の合計は、システムの全体効率に関する最初の検討で見積もることができます。出力トランジスタのオン抵抗( $r_{ds(on)}$ )がシステムの主要な損失を発生すると考えられる場合、TPA3002D2の8Ω負荷時の最大理論効率は次式(1)のようになります。

$$\text{効率(理論値 \%)} = R_L / (R_L + r_{ds(on)}) \times 100\% \\ = 8 / (8 + 0.58) \times 100\% = 93.24\% \quad (1)$$

実測による最大出力電力は、12V電源時でおよそ7.5Wです。したがって、この最悪条件での全体の供給電力理論値 $P_{(total)}$ は、次式(2)のようになります。

$$P_{(total)} = P_0 / \text{効率} = 7.5W / 0.9324 = 8.04W \quad (2)$$

実験室で実測した効率は、8Ωスピーカーを使用して89%でした。 $r_{ds(on)}$ で消費すると説明されていない電力は、実測電力から理論値電力を単に引いて計算できます。

$$\text{その他の損失} = P_{(total)}(\text{実測値}) - P_{(total)}(\text{理論値}) \\ = 8.43 - 8.04 = 0.387W \quad (3)$$

14V時の静的な電源電流は実測で14.3mAです。静的な電源電流は、デバイスの残りの全損失すなわち、バイアス損失およびスイッチング損失の合計であると仮定できます。さらに、これ以外

の残りの電力はスピーカーで消費されると仮定でき、次式(4)で計算できます。

$$P_{(dis)} = 0.387W - (14V \times 14.3mA) = 0.19W \quad (4)$$

以上の計算が、スピーカーに7.5Wを供給した最悪条件下であることに注意願います。0.19Wはスピーカーに供給した電力のわずか2.5%であるので、実際にスピーカーで消費される電力は比較的小さいものであると結論づけられます。さらに、この電力消費はほとんどのシステムのラウドスピーカー・ドライバ仕様を十分満足します。なぜなら、スピーカーの電力定格が、一般にクリッピング波形を起こす電力で定められているからです。

## どのような場合に出力フィルタを使用するか

アンプからスピーカーへの配線が短い(1インチ以下)場合、フィルタ無しでTPA3002D2を設計してください。パワード・スピーカー(スピーカーがアンプと同じ筐体内にある)は、フィルタ無しのD級の代表的なアプリケーションです。

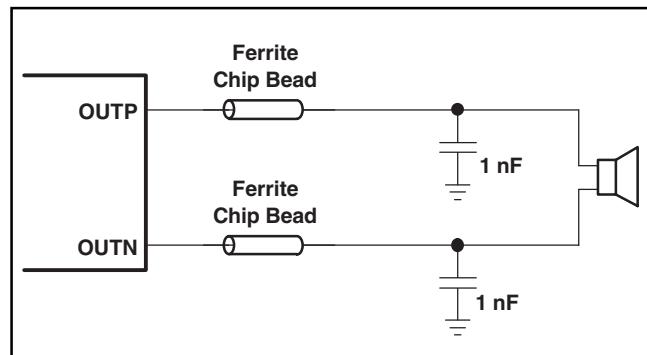

ほとんどのアプリケーションは、フェライトビーズ・フィルタを必要とします。フェライト・フィルタは、1MHz付近およびそれ以上のEMI(電磁輻射、電磁干渉)を低減します(FCCとCEは30MHz以上の電磁輻射だけをテストしています)。フェライトビーズの選定の際には、高周波時には高インピーダンスであるが、低周波時には非常に低インピーダンスのものにします。

低周波(<1MHz)EMIに敏感な回路がある場合や、長い配線がアンプとスピーカーの間にある場合は、さらにLC出力フィルタを使用します。但し、スピーカまでの伝送路がシールドされている場合や、FCCやCEの規定が無いアプリケーションの場合はこの限りではありません。

図33. 代表的なLC出力フィルタ、カットオフ周波数41kHz、スピーカー・インピーダンス8Ω

図34. 代表的なフェライトチップ・ビーズ・フィルタ

(チップビーズ例：Panasonic EXCML32A680U)

## ボリューム制御動作

VOLUME, VARDIFF, およびVARMAXと名づけられた3ピンは、スピーカーとVAROUTボリュームをドライブする場合にD級ボリュームを制御します。これらのピンはすべてDC電圧で制御され、そのDC電圧はVREFの値を超えないようにします。

D級モードでスピーカーをドライブするときは、VOLUMEピンだけがゲインを制御します。表1は、VOLUMEピンの電圧とVREF電圧との関係によって決まるD級モードのゲインのリストです。

アンプのゲインを抵抗分圧回路で固定する場合、VREFピンをAV<sub>DDREF</sub>に直接接続し、抵抗分圧回路をVREFとREFGND間に接続できます(アプリケーション情報の図29を参照)。固定ゲインでは、表1の第1列の2個のパーセンテージ数の中点に、抵抗分圧の値を計算して合わせます。例えば、10.7dBのゲインが必要な場合、分圧回路の抵抗は両方とも10kΩになります。この抵抗値のとき、 $50\% \times VREF$ の電圧がVOLUMEピンに現れ、D級ゲインが10.7dBになります。

D級ゲインの制御にDACを使用する場合、VREFとREFGNDをDACの基準電圧ピンとグランド・ピンにそれぞれ接続します。DACを使用するアプリケーションの場合、AV<sub>DDREF</sub>はオープンにしておきます。DACの基準電圧は、VREF入力を通して内部ゲイン回路の基準電圧になり、DAC出力電圧のいかなる変動もTPA3002D2のゲインに影響しません。表1の第1列のパーセンテージ数は、VOLUMEピンの電圧を増加するときに、DACの電圧を設定するのに使います。また、第2列のパーセンテージ数は、VOLUMEピンの電圧を減少するときに、DACの電圧を設定するのに使います。2つのルックアップ・テーブルは、所要のシステムのボリュームにおいて、増加・減少によるゲイン制御のソフトウェアに用います。これに関しては、以下の節でより詳しく説明します。

アナログ・ポテンショメータでゲインを制御する場合は、それをVREFとREFGNDの間に接続します。VREFは必要であればAV<sub>DDREF</sub>あるいは外部電圧源に接続できます。表1の第1と第2列を使って、ポテンショメータの回転する方向によって変化するゲインのポイントを決定します。ポテンショメータのセンタータップの電位が増加する場合、表1の第1列を参照して切換わり点を決めます。逆に、電位が減少する場合は第2列の切換わり点を参照します。

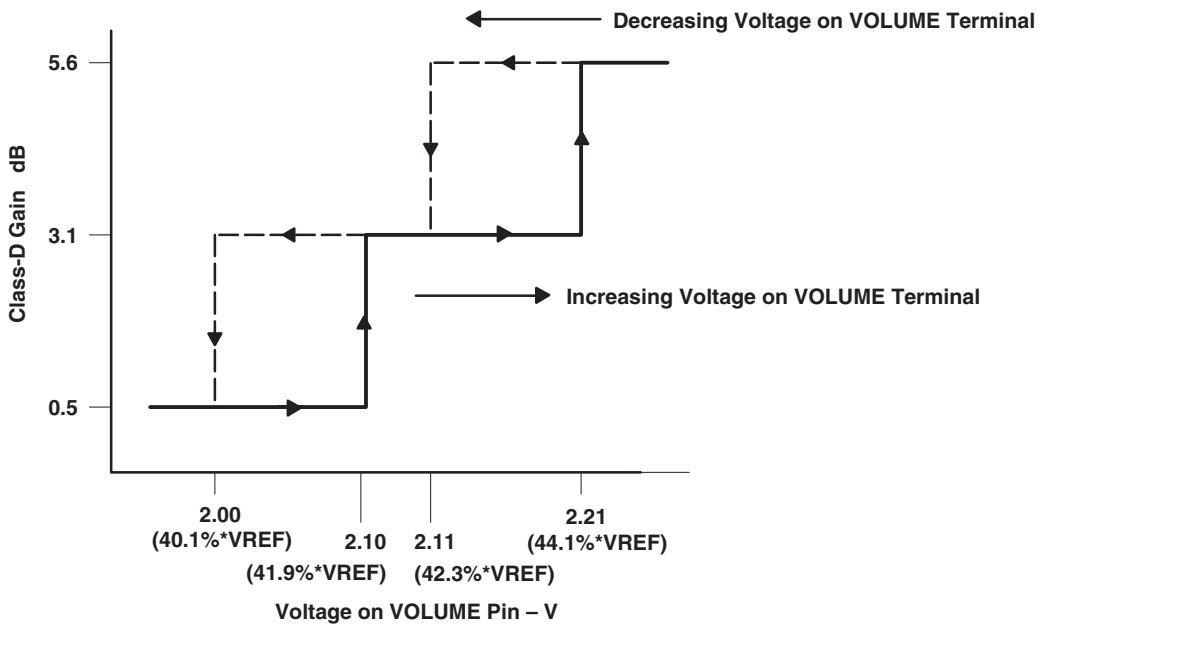

ゲインが実際に変化する切換わり点は、各点のヒステリシスのためにVOLUMEピンの電位が増加するか減少するかによって異なります。そのヒステリシスが、ゲイン制御の単調性および、あるゲイン・ステップから他のステップへ発振しないことを保証します。ボリューム制御を図式化したものを図36に示します。そのグラフは、D級ゲインに関する表1の第1列と第2列によって定義された切換わり点とともに、3つのゲイン・ステップについて示しています。破線は各ゲイン・ステップのヒステリシスを表しています。

## VARDIFFおよびVARMAX動作

TPA3002D2では、ユーザがD級ゲインとVAROUTゲインとの差を指定できます。これはヘッドフォーンを差し込むときの不快音を除去するのに必要なことです。可変出力のインターフェイスでは、VARDIFFとVARMAXピンがVAROUTチャネルのゲインを、VOLUMEピンにおける電圧によって設定されるゲインに比例したゲインに制御します。VARDIFF = 0Vの場合、D級ゲインとVAROUTゲインとの差は16dBになります。VARDIFFピンの電圧が増加するにつれて、VAROUTチャネルのゲインは低下します。TPA3002D2の内部において、VARDIFFピンの電圧がVOLUMEピンの電圧から差し引かれ、その結果がVAROUTゲインを決定するのに使用されます。

ある種のオーディオ・システムでは、VAROUTモード時のゲインを制限し、ヘッドフォーンの使用が快適なレベルにとどめることが必要になります。その目的で、VARMAXピンはVAROUTチャネルの最大ゲインを制御します。

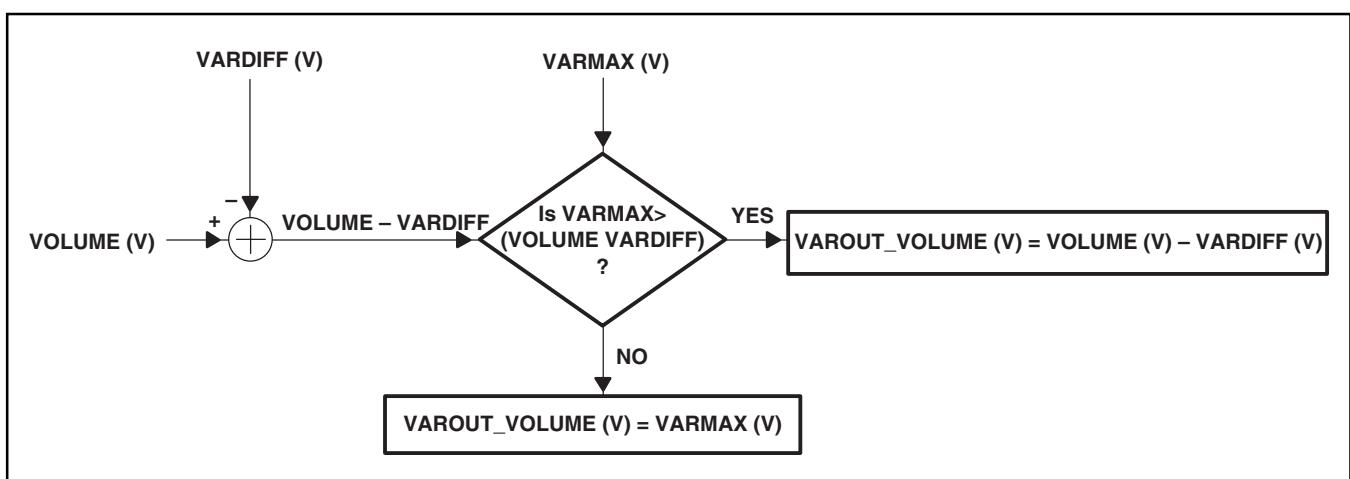

VARDIFFとVARMAXピンの機能は、互いに結合してVAROUTチャネルのゲインを決めます。その結合した機能を図35のブロック・ダイアグラムに示します。ブロック・ダイアグラムのVAROUT\_VOLUMEに得られる値はDC電圧であり、VAROUTチャネルのゲインを決定する表2に使用されます。表2は、VAROUT\_VOLUME電圧がVREF電圧と関連して決めるVAROUTモード時のゲインを記載しています。

ボリューム制御回路のタイミングは、内部の30Hzのクロックによって制御されます。このクロックは、外部のボリューム制御ピンの電圧を調整したときのゲインが変化するレートを決定します。ゲインは4クロック・サイクルごと(30Hzクロックによる目盛で133ms)に更新され、次のゲイン・ステップに移り、最終的に

図35. VAROUTボリューム制御のブロック・ダイアグラム

図36. DCボリューム制御動作 VREF = 5V

所要のゲインに達します。例えば、現在TPA3002D2がD級ゲイン・ステップの +0.53dBの場合、VOLUMEピンが最大ゲインの +36dBに調整されると、ゲインが36dBに達するのに要する時間は、14ステップ × 133ms/ステップ = 1.862秒になります。表1を参照すると、+0.53dBのゲイン・ステップから +36dBの最大ゲイン・ステップまでの間に14ステップがあります。

## MODE動作

MODEピンはTPA3002D2の出力モードを制御する入力のひとつです。本ピンがロジックのハイレベルの場合、D級出力をディスエーブルにします。また、ロジックのローレベルの場合、D級出力をイネーブルにします。VAROUT出力は、この両方のモードでアクティブであり、内部のステレオ・スピーカーをD級出力でドライブしつつ、外部のパワード・サブウーハーのラインレベル入力として使用できます。本ピンの動作レベルは仕様表にて定義してあります。

TPA6110A2のような外部ヘッドフォーン・アンプとのインターフェイスには、MODEピンをヘッドフォーン・ジャックのスイッチに接続できます。図30のように構成した場合、D級出力はヘッドフォーン・プラグをヘッドフォーン・ジャックに挿入したときにディスエーブルされます。

## MODE\_OUT動作

MODE\_OUTピンは、TPA6110A2のような外部ヘッドフォーン・アンプあるいは他のロジックとのインターフェイスに関連して、SHUTDOWNピンを制御する出力のひとつです。与えられた負荷条件での本ピンの出力電圧は、仕様表にて定義してあります。

この出力はMODEピンのロジックで制御されます。MODE入力がロジックのローレベルの場合、MODE\_OUT出力はロジックのハイレベルになります。逆に、MODEピンがロジックのハイレベルの場合、MODE\_OUTピンはローレベルになります。MODE\_OUT出力はMODE入力を単に反転したもので

TPA6110A2のSHUTDOWN入力がアクティブ・ハイ(正論理)なので、上記のように設計しました。このようにすると、TPA3002D2が内部スピーカーをD級モードでドライブするときに、TPA6110A2をシャットダウンできます。逆に、ヘッドフォーンがヘッドフォーン・ジャックに挿入され、MODE入力がハイレベルになると、MODE\_OUTピンがローレベルになって、TPA6110A2ヘッドフォーン・アンプをイネーブルにします。

## COSCとROSCの選定

スイッチング周波数は、 $R_{OSC}$ (27ピン)と $C_{OSC}$ (28ピン)に接続する部品の値で決まり、次式で計算されます。

$$f_{OSC} = 6.6 / (R_{OSC} \times C_{OSC})$$

発振周波数は $R_{OSC}$ と $C_{OSC}$ の値を調整して、225kHzから275kHzまで変えられます。この推奨値は、スイッチング周波数が250kHzで、 $C_{OSC} = 220\text{pF}$ ,  $R_{OSC} = 120\text{k}\Omega$ です。

## 内部2.5Vバイアス発生回路用コンデンサの選定

内部2.5Vバイアス発生回路(V2P5)は、D級アンプと可変アンプの両プリアンプ段に内部バイアスを供給します。外付けの入力コンデンサとこの基準電圧により、入力信号をプリアンプの最適な同相入力範囲内にバイアスできます。

V2P5ピンのコンデンサの定数選定は、最善のデバイス特性を得るのに重要です。スタートアップ時やシャットダウン状態からの回復時に、V2P5ピンのコンデンサはアンプのスタートアップのレートを決めます。V2P5コンデンサの電位が $0.75 \times V2P5$ すなわち最終値の75%のとき、デバイスはターンオンし、D級出力がスイッチングを始めます。スタートアップ時間はデボップ特性(ポップ雜音を抑える特性)に重要ではありません。なぜなら、あらゆるポップ音(電源投入時などに発生する雜音)は、スタートアップ時間ではなく、D級出力がスイッチオンした結果聞こえるからです。しかし、V2P5コンデンサには少なくとも $0.47\mu\text{F}$ を推奨します。

V2P5コンデンサの2番目の機能は、内部2.5Vバイアス発生回路の高周波雑音をフィルタすることです。

## 入力抵抗

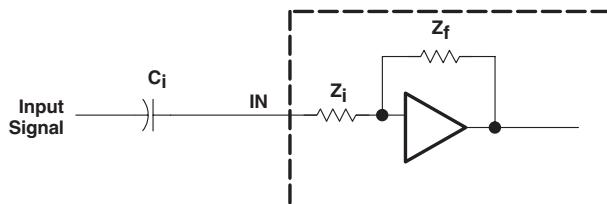

各ゲイン設定はアンプの入力抵抗を変えて行います。入力抵抗は最小値からその6倍以上まで変えられます。その結果、入力ハイパスフィルタに1個のコンデンサを使用すると、-3dBすなわちカットオフ周波数も6倍以上変化します。

-3dB周波数は式(5)で計算できます。入力インピーダンス( $Z_i$ )対ゲインの値は図7に見られます。

$$f_{-3dB} = \frac{1}{2\pi Z_i C_i} \quad (5)$$

## 入力コンデンサ $C_i$

一般的なアプリケーションでは、アンプの入力信号に最適動作のための適切な直流バイアス(V2P5)をかけられるように、入力コンデンサ( $C_i$ )が必要になります。その場合、 $C_i$ とアンプの入力インピーダンス( $Z_i$ )はハイパスフィルタを形成し、そのコーナー周波数(カットオフ周波数)は式(6)で決まります。

$$f_c = \frac{1}{2\pi Z_i C_i} \quad (6)$$

$C_i$ の値は重要であり、回路のバス(低周波)特性に直接影響します。例として、 $Z_i$ が $241\text{k}\Omega$ で、20Hzまでフラットなバス特性を必要とする仕様について考察します。式(6)を式(7)のように書き換えます。

$$C_i = \frac{1}{2\pi Z_i f_c} \quad (7)$$

式(7)より、この例では $C_i$ は $0.4\mu\text{F}$ となり、一般的に使用される値の $0.47\mu\text{F}$ のコンデンサを選ぶことになります。ゲインが既知であり一定である場合は、図7(入力インピーダンス対ゲイン)から $Z_i$ を求めて $C_i$ を計算します。このコンデンサに関するさらなる考察として、入力信号源から入力回路網( $C_i$ )と帰還回路網を通る負荷までの漏れ電流パスがあります。この漏れ電流はアンプの入力に直流オフセット電圧を生じ、使用可能な出力範囲を低減させ、高

ゲインのアプリケーションで特に問題になります。このような理由で、低リードのタンタルあるいはセラミックのコンデンサが最善の選択になります。極性のあるコンデンサを使用する場合、ほとんどのアプリケーションにおいてコンデンサの+側をアンプ入力に接続します。その理由は、アンプ入力のDCレベルが一般的の入力信号源のDCレベルよりも高い2.5Vに固定されているからです。アプリケーションにおいて、コンデンサの極性の確認が重要なことにご注意願います。

## 電源デカップリング、 $C_S$

TPA3002D2は高性能なCMOSオーディオアンプであり、出力の全高調波歪み(THD)ができるだけ低くするために、適当な電源のデカップリングを必要とします。また、電源デカップリングは、アンプとスピーカー間の配線が長い場合の発振を防止します。最適なデカップリングは、電源配線上の異なる種類の雑音に対応した、異なる2タイプのコンデンサを使用して実現します。配線上の高周波の遷移、スパイク、あるいはデジタルノイズには、かなり低い等価直列抵抗(ESR)のセラミック・コンデンサを、一般に $0.1\mu\text{F}$ でデバイスの電源ピンの極端近くに配置するのが最適です。低周波の雑音信号をフィルタするには、より大きい $10\mu\text{F}$ かそれ以上のアルミ電解コンデンサを、オーディオ・パワー・アンプの近くに配置することを推奨します。この $10\mu\text{F}$ のコンデンサは、アンプ出力が大信号遷移する際に電流を供給するローカルなストレージ・コンデンサとしても働きます。

## BSNとBSP用コンデンサ

フルH型ブリッジ出力段はNMOSトランジスタのみを使用します。したがって、適切なターンオンのために、各出力のハイサイドでブートストラップ用コンデンサが必要になります。少なくとも $25\text{V}$ 定格の $10\text{nF}$ のセラミック・コンデンサを、各出力とそれに相当する各ブートストラップ入力間に接続する必要があります。具体的には、1個の $10\text{nF}$ コンデンサをxOUTPとxBSP間に、また1個の $10\text{nF}$ コンデンサをxOUTNとxBSP間に接続します(図29のアプリケーション回路図を参照)。

The bootstrap capacitors connected between the BSxx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors attempt to hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on. However, there is a leakage path and the voltage on the bootstrap capacitors slowly decrease while the high-side is conducting.

By driving the outputs into heavy clipping with a sine wave of less than 50 Hz, the bootstrap voltage can decrease below the minimum  $V_{gs}$  required to keep the high-side output MOSFET turned on. When this occurs, the output transistor becomes a source-follower and the output drops from  $V_{CC}$  to approximately  $V_{clamp}$  (voltage on pins 25 and 36).

For the majority of applications, driving a square wave at low frequencies is not a design consideration and the recommended bootstrap capacitor value of  $10\text{nF}$  is acceptable. However, if this is a concern, increasing the bootstrap capacitors holds the gate voltage for a longer period of time and the drop in the output voltage does

not occur. A value of 220 nF is recommended with a  $51\Omega$  resistor placed in series between the outputs and bootstrap pins. The  $51\Omega$  series resistor is necessary to limit the current charging and discharging the bootstrap capacitors.

### VCLAMP用コンデンサ

NMOS出力トランジスタのゲート・ソース間電圧が許容最大値を超えないよう保証するため、2つの内部レギュレータがゲート電圧をクランプします。そこで、最小でも25V定格の $1\mu F$ のコンデンサをVCLAMPL(25ピン)とVCLAMPR(36ピン)からグランド間に各1個ずつ接続する必要があります。両方のVCLAMPの電圧は $V_{CC}$ とともに変化し、その電圧を他の回路へ供給できません。

### 内部安定化5V電源 ( $AV_{DD}$ )

$AV_{DD}$ ピン(29ピン)は内部で発生する5V電源の出力であり、発振回路、プリアンプ、およびボリューム制御回路に使用します。この内部レギュレータを安定化するために、このピンとグランド間に $0.1\mu F$ から $1\mu F$ のコンデンサを、このピンの極力近くに配置する必要があります。このレギュレータ出力は、外部ヘッドフォーン・アンプや他の回路の電源として、仕様表に指定されている電流範囲で使用できます。

### SD動作

TPA3002D2はデバイス動作にシャットダウン・モードを採用し、バッテリー電源の節約のために非使用時の電源電流( $I_{CC}$ )を絶対的に微小にする設計をしています。 $\overline{SD}$ 入力ピンは、アンプを使用している正常動作時はハイレベルに保ちます。 $\overline{SD}$ をローレベルにすると、出力を抑え、アンプを低電流状態なわち  $I_{CC(SO)} = 10\mu A$ にします。また、アンプの動作が不定になるため、 $\overline{SD}$ は決してオープンにしてはなりません。

パワーオフ時のポップ特性(電源断時に発生する雑音)を最小にするために、電源を切る前にアンプをシャットダウン・モードにしておきます。

### POWER-OFF POP REDUCTION

For the best power-off pop performance, the amplifier should be placed in the shutdown mode prior to removing the power supply voltage.

Another method to reduce power-off pop can be implemented in the hardware. A  $100\mu F$  -  $150\mu F$  capacitor can be added to the  $AV_{DD}$  terminal in parallel with the  $100-nF$  capacitor shown in Figure 29. The additional capacitance holds up the regulator voltage for a longer period of time and results in smaller power-off pop.

### 低ESRコンデンサの使用

低ESRコンデンサを本節のアプリケーション全体で推奨します。実際のコンデンサは(理想に反して)、理想コンデンサとそれに直列な抵抗の単なるモデルにできます。この抵抗にかかる電圧降下は、回路におけるコンデンサの効果を小さくします。この抵抗の等価値が低いほど、実際のコンデンサは理想コンデンサに近い動作をします。

### 出力短絡保護回路

TPA3002D2は出力に短絡保護回路があり、両出力間の短絡、出力とGNDの短絡、および出力と $V_{CC}$ の短絡時にデバイスの破壊を防止します。出力短絡を検知すると、デバイスは即座に出力ドライブをディスエーブルにします。これはラッチされた不良状態であり、リセットは $\overline{SD}$ ピンの電圧をローレベルから、正常動作時のロジックのハイレベルに変えて行う必要があります。このようにすると短絡のフラグがクリアされ、短絡状態が除去されなければ正常動作が可能になります。短絡状態が除去されていない場合は、保護回路が再度アクティブになります。

短絡保護回路の作動点は名目値で8Aに設定してあります。しかし、この作動点はプリント基板のレイアウトおよび $AV_{CC}$ と $PV_{CC}$ の分離によって変化します。 $AV_{CC}$ ピンをすべての $PV_{CC}$ ピンにできるだけ近く、広い配線パターン(20ミル以上)で接続することが重要です。このようにすると、両ピン間のインダクタンスが最小になり、短絡保護回路を名目値で作動できます。この両ピン間のインダクタンスが大きい場合、低インピーダンスの負荷を深いクリッピングにドライブしたとき、短絡保護回路が不意に作動することがあります。

図37. パワーアップ応答

### 差動入力

アンプの差動入力段は、チャネルの両入力ラインに現れるあらゆる雑音を打ち消します。TPA3002D2用EVMを差動信号源とともに使用する場合、オーディオ信号源の正側配線をINP入力に接続し、同様にオーディオ信号源からの負側配線をINN入力に接続します。TPA3002D2をシングルエンドの信号源とともに使用する場合、INP入力をコンデンサ(INNで使用しているコンデンサと同じ定数)でAC的に接地して、オーディオ信号をINN入力に接続します。シングルエンド入力アプリケーションでは、最適な雑音特性を得るために、INP入力をデバイスの入力側でなく、オーディオ信号源側でAC的に接地します。

## 熱保護回路

TPA3002D2の熱保護回路は、内部のチップ温度が150°Cを超えたときにデバイスの破壊を防止します。この作動温度はデバイスによって±15°Cの許容誤差があります。ひとたびチップ温度が熱保護の作動温度を超えると、デバイスはシャットダウン状態に入り、出力がディスエーブルになります。この不良状態はラッチされません。したがって、ひとたびチップ温度が作動温度から20°Cだけ下回ると、この熱的不良状態はクリアされます。この時点でデバイスは、外部システムからの介入なしに正常動作を開始します。

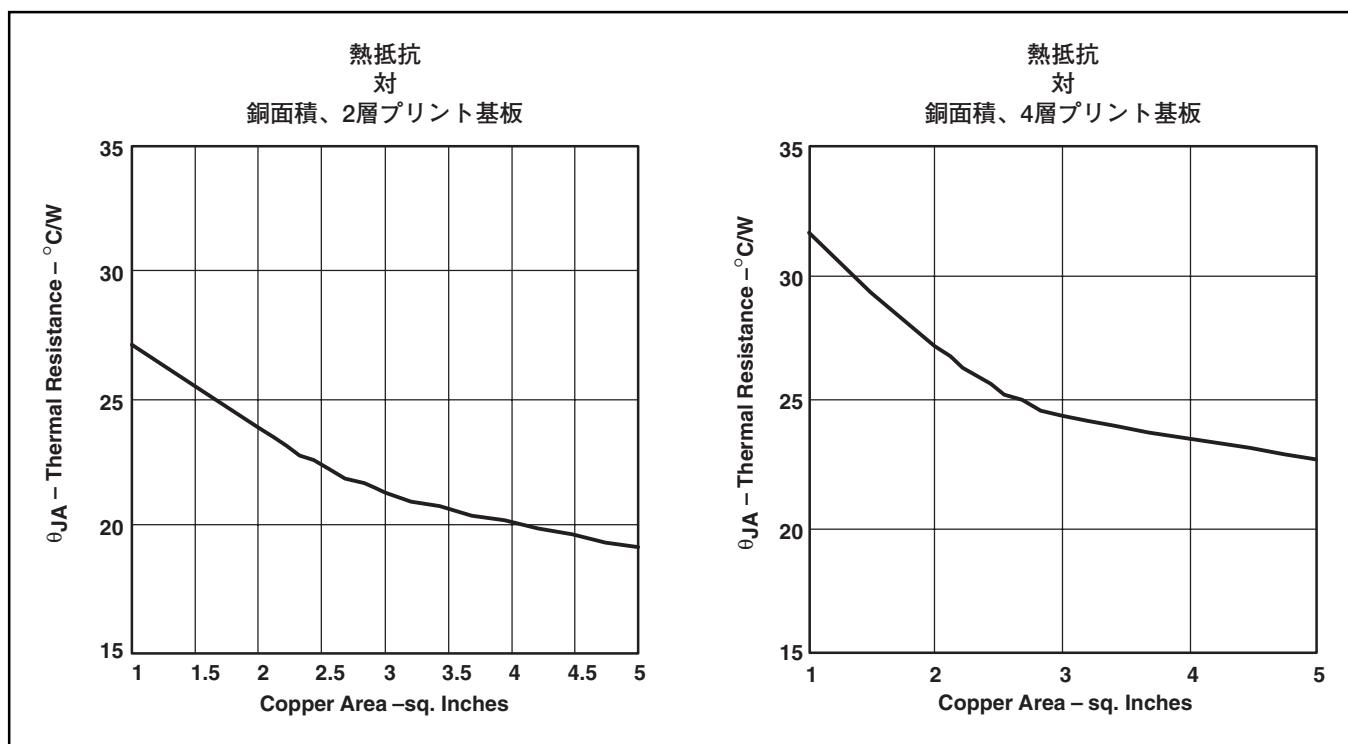

## 熱的考察：出力電力と最高周囲温度

最高周囲温度の計算には次式(8)が使えます。

$$T_{Amax} = T_{Jmax} - \Theta_{JA} P_{Dissipated}$$

ここで、 $T_{Jmax} = 150^{\circ}\text{C}$

$$\Theta_{JA} = 19^{\circ}\text{C}/\text{W}$$

(2層プリント基板、5平方インチ、銅、図39参照) (8)

(48ピンPHPパッケージのディレーティング係数は、電力消費定格表にあります。)

電力消費の見積もりには、次式(9)が使えます。

$$P_{Dissipated} = P_O(\text{average}) \times ((1 / \text{効率}) - 1)$$

効率 = ~85% (8Ω負荷時)

$$= ~75\% \text{ (4Ω負荷時)} \quad (9)$$

例題：TPA3002D2が8Ωのスピーカー(ステレオ)を7.5Wでドライブするアプリケーションにおいて、最高周囲温度は何度になるか？

$$P_{Dissipated} = 15\text{W} \times ((1 / 0.85) - 1) = 1.76\text{W}$$

(ステレオなので、 $P_O = 7.5\text{W} \times 2$ )

$$T_{Amax} = 150^{\circ}\text{C} - (19^{\circ}\text{C}/\text{W} \times 2.65 \text{ W}) = 99.65^{\circ}\text{C}$$

この計算により、周囲温度が決して超えてはならない絶対最大定格の85°Cまで、TPA3002D2は8Ωのスピーカーを7.5Wでドライブできることがわかります。

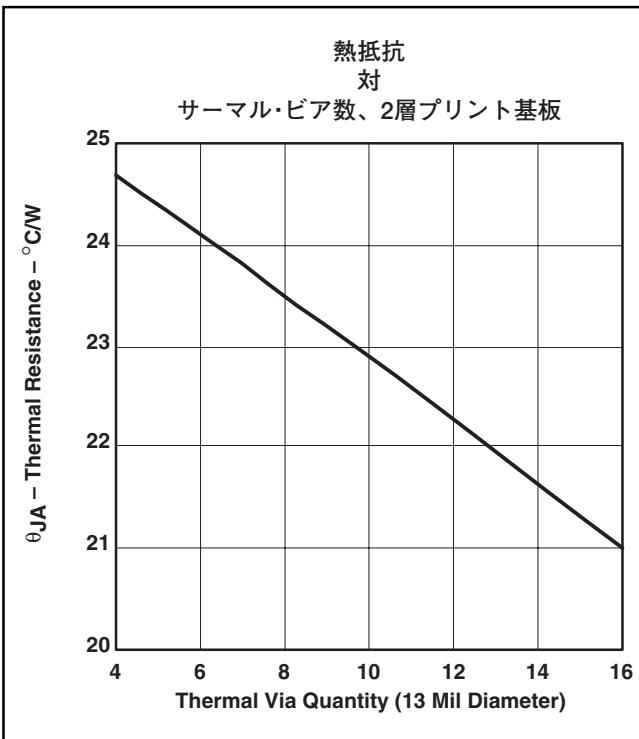

図38と図39は、TPA3002D2に関するいくつかの熱的実験の結果を示します。最適熱的特性が、より広い放熱用の銅面積と適當数のサーマル・ヴィアによって実現できることを、各特性図は示しています。

図38は2層と4層のプリント基板の2特性を示します。2層プリント基板のレイアウトは、半田面(底面)で2オンスの固定量の銅に厳密に調整しました。銅の面積はX軸上に示します。直径が13ミル(0.33mm)の9個のサーマル・ヴィアをパワーパッドの下に設け、半田面と接続しました。部品面(上面)は信号配線のパターンだけでした。

4層プリント基板のレイアウトは、中間のグランド層で2オンスの固定量の銅に厳密に調整しました。部品面は信号配線のパターンだけでした。半田面と他の中間層は空白のままにしました。直径0.33mmの9個のサーマル・ヴィアをパワーパッドの下に設け、グランドのある中間層と接続しました。

図39は、パワーパッドの下に設けたサーマル・ヴィアの個数がプリント基板の熱的特性に与える効果を示します。この実験は、半田面上に3平方インチの銅がある2層プリント基板で行いました。最適な熱特性には、少なくとも16個のヴィアを4×4の形状でパワーパッドの下に使用します。この4×4の形状のレイアウト例は、TPA3002D2EVMユーザーズ・マニュアル、SLOU115を参照願います。プリント基板のgerberファイルは、ご要求願います。

図38. 热抵抗

図39. 热抵抗

### プリント基板(PCB)のレイアウト

TPA3002D2は高周波でスイッチングするD級アンプなので、そのプリント基板(PCB)のレイアウトを下記のガイドラインに従って最適化し、最善の特性を得る必要があります。

#### ● デカップリング・コンデンサ

高周波用の0.1μFのデカップリング・コンデンサをPV<sub>CC</sub>ピン(14, 15, 22, 23, 38, 39, 46, 47ピン)とAV<sub>CC</sub>ピン(33ピン)にできるだけ近く配置します。V2P5(4ピン)用コンデンサ、AV<sub>DD</sub>(29ピン)用コンデンサ、およびVCLAMP(25, 36ピン)用コンデンサもまた、極力デバイスの近くに配置します。電源用の大きな(10μF,あるいはそれ以上)デカップリング・コンデンサはTPA3002D2のPVCCl, PVCCR、およびAV<sub>CC</sub>の各ピンの近くに配置します。

#### ● グランドのとりかた

AV<sub>CC</sub>(33ピン)デカップリング・コンデンサ、AV<sub>DD</sub>(29ピン)コンデンサ、V2P5(4ピン)コンデンサ、COSC(28ピン)コンデンサ、およびROSC(27ピン)抵抗は、それぞれアナログ・グランド(AGND, 26ピンと30ピン)に接地します。PVCCl(14, 15, 22, 23ピン)とPVCCR(38, 39, 46, 47)のデカップリング・コンデンサは、パワー・グランド(PGND, 18, 19, 42, 43ピン)に接地します。アナログ・グランドとパワー・グランドは、パワーパッドで互いに接続できます。パワーパッドはTPA3002D2のグランド接続の中心すなわち星型グランド(1点アース)として使用できます。基本的に、PGNDに単線で接続されるアイランドをパワーパッドを作ります。

#### ● 出力フィルタ

フェライトEMIフィルタ(図34)は出力ピン(10, 11, 14、および15の各ピン)にできるだけ近く配置し、最善のEMI特性を得るようにします。LCフィルタ(図33)は、出力の近くに配置しま

す。フェライトとLCの両フィルタに使用するコンデンサは、それぞれパワー・グランドに接地します。

#### ● パワーパッド

パワーパッドはプリント基板に半田付けして、適当な熱特性と最適な信頼性を得るようにします。パワーパッドのサーマル・ランドの寸法は、5mm×5mm(197ミル×197ミル)にします。パワーパッドの寸法は4.55×4.55mmです。また、4列の頑丈なヴィア(1列あたり4個のヴィア、直径が0.3302mmすなわち13ミル)を等間隔でサーマル・ランドの下に設けます。各ヴィアは、プリント基板の中間層や半田面(最下層)のしっかりした銅プレーンに接続する必要があります。各ヴィアは頑丈である必要があります、熱で浮き上がるヴィアであってはなりません。より詳細な情報は、「パワーパッド(PowerPAD) 热的に強化されたパッケージのアプリケーション・ノート(TI文献番号 SLMA002)」を参照願います。

レイアウト例として、「TPA3002D2評価用モジュール(TPA3002D2EVM)ユーザー・マニュアル (TI文献番号SLOU151)」を参照願います。EVMユーザー・マニュアルとPowerPADアプリケーション・ノートは、両方ともTIウェブサイトの<http://www.ti.com>で入手できます。

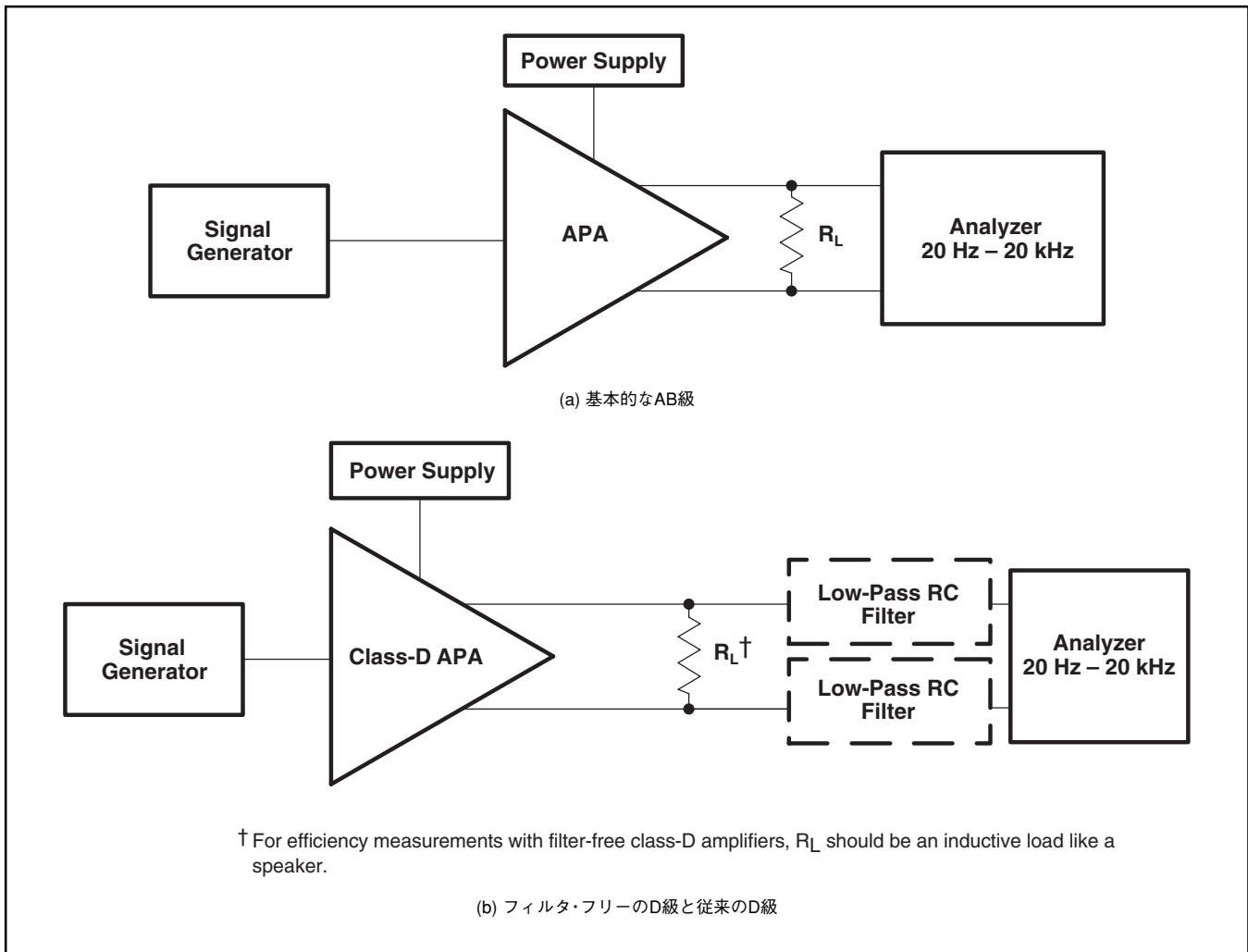

### 基本測定システム

本アプリケーション資料は、下記の基本装置を使用する方法について述べます。

- オーディオ・アナライザあるいはスペクトラム・アナライザ

- デジタル・マルチメータ(DMM)

- オシロスコープ

- ツイスト・ペア線

- 信号発生器

- 電力用抵抗

- リニア安定化電源

- フィルタ部品

- EVMあるいは他のオーディオ回路

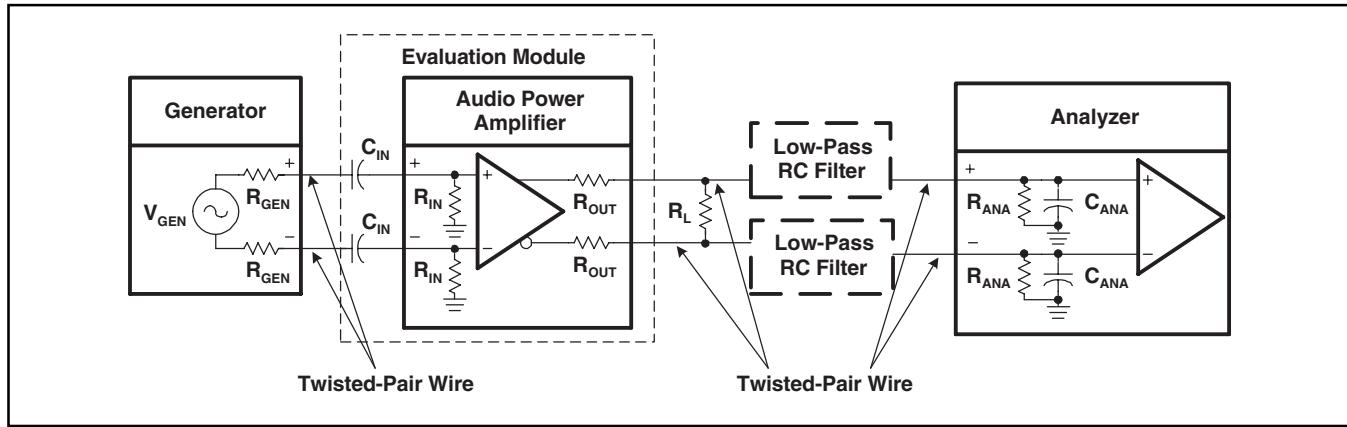

図40にAB級とD級アンプの基本的な測定システムを示します。普通、入力信号には正弦波を使用します。正弦波には高調波成分が無く、基本周波数だけで構成されているからです。次にアナライザをAPA(オーディオ・パワーアンプ)出力に接続して、電圧出力を測定します。アナライザにはオーディオ帯域全体を測定できる性能が必要です。直流安定化電源を使用して、APAの電源ピンから注入される雑音と歪みを低減します。Audio Precision社製の2オーディオ測定システム(AP-II)ならば、信号発生器とアナライザがひとつの筐体内に入っています。

信号発生器の出力とアンプ入力はAC結合(カップリング)にする必要があります。しかし、EVMには最初からACカップリング用コンデンサ(C<sub>IN</sub>)があるため、新たなコンデンサは不要です。信号発生器の出力インピーダンスは、テスト信号が減衰しないよう低い必要があります。APAの入力インピーダンスがそれほど高くない(約10kΩ)ので、これは重要なことです。逆に、アナライザの入力インピーダンスは高い必要があります。APAの出力インピーダンスR<sub>OUT</sub>は一般に数百mΩであり、電力関連の計算以外で

図40. オーディオ測定システム

は省略できます。

図40(a)はAB級アンプの測定システムを示します。AB級アンプはリニアであり、その出力信号は入力信号に対してリニアな形状であるため、AB級アンプの測定システムは比較的単純になります。AB級アンプはアナログ入力信号を受けて、アナログ出力信号を生成します。したがって、AB級アンプはAP-IIや他のアナライザの入力に直接接続できます。

以上のこととは、図40(b)に示すD級アンプにはあてはまりません。ほとんどのD級アンプの場合、オーディオ出力波形の測定にローパスフィルタが必要です。これは、D級アンプがアナログ信号を受けて、それをパルス幅変調(PWM)の出力信号に変換するからです。一部のアナライザはPWM信号を正確に処理できません。

TPA3002D2は動作時に出力フィルタを必要としない変調手法を使用していますが、測定時にはRCローパスフィルタをしばしば必要とします。これは、一部のアナライザ入力が急速に変化する方形波出力を正確に処理できず、極度に大きな歪みを記録するからです。測定用のRCローパスフィルタを使用すると変調された波形が除去されるので、アナライザは正弦波出力を測定できます。

### 差動入力とBTL出力

すべてのD級APAと多くのAB級APAは、差動入力およびブリッジタイド負荷(BTL)出力です。差動入力はチャネルごとに2つの入力ピンがあり、そのピン間の電位差を増幅します。差動入力は入力回路の同相ノイズと歪みを低減します。BTLは一般にオーディオで差動出力を説明するのに使用される言葉です。BTL出力は2つの出力ピンがあり、180度位相がずれた電圧を出力します。負荷はこの両ピン間に接続されます。このようにすると、負荷に対する出力電力を4倍にし、DCブロッキング・コンデンサが不要という利点があります。

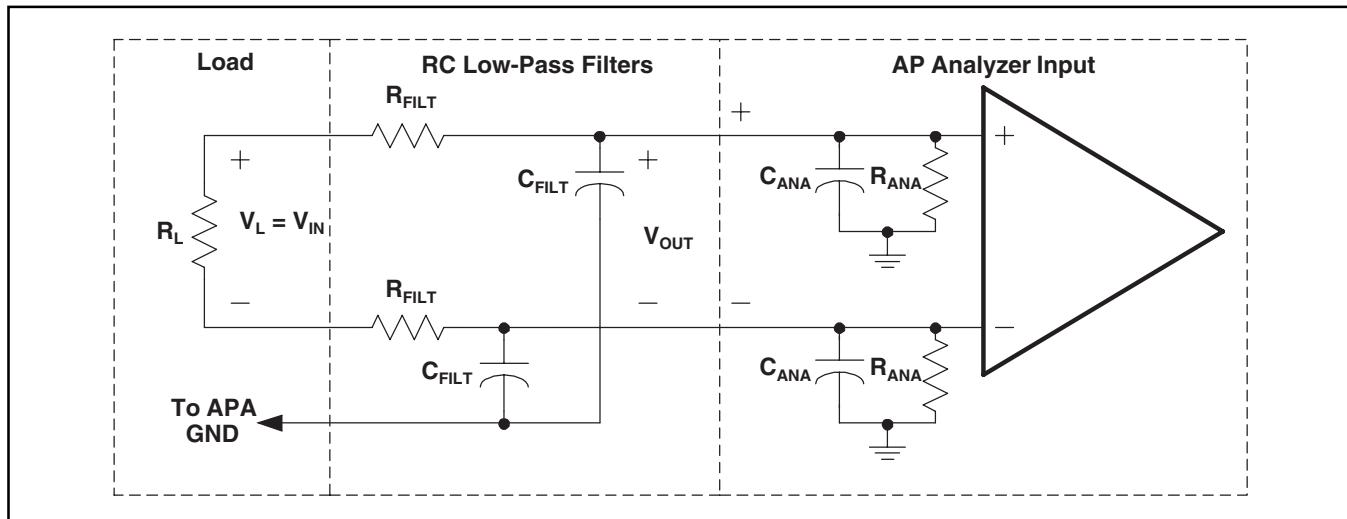

測定回路のブロック・ダイアグラムを図2に示します。差動入力は平衡入力であり、正(+)と負(-)のピンがグランドに対して等しいインピーダンスを持ちます。同様に、BTL出力は平衡出力と見なせます。

信号発生器は平衡出力である必要があります、その平衡信号によって良い結果が得られます。不平衡出力でも使用できますが、測定精度に影響するグランド・ループを形成する可能性があります。また、アナライザも平衡入力にして、システム全体を平衡にしなければなりません。平衡システムは回路のあらゆる同相ノイズを打ち消し、最も精度の高い測定を可能にします。

図41. 差動入力 – BTL出力測定回路

| P <sub>OUT</sub><br>(W) | R <sub>L</sub><br>(Ω) | AWG SIZE | DC POWER LOSS<br>(MW) | AC POWER LOSS<br>(MW) |

|-------------------------|-----------------------|----------|-----------------------|-----------------------|

| 10                      | 4                     | 18 22    | 16                    | 40                    |

| 2                       | 4                     | 18 22    | 3.2                   | 8.0                   |

| 1                       | 8                     | 22 28    | 2.0                   | 8.0                   |

| < 0.75                  | 8                     | 22 28    | 1.5                   | 6.1                   |

表3. パワー用ケーブルの推奨最小ワイヤーサイズ

図42. D級APAのための、測定用ローパスフィルタの導出回路

差動入力・BTL出力のAPAを接続する場合は、下記の一般ルールに従います。

- 平衡信号源を使用して入力信号を供給する。

- 平衡入力のアナライザを使用する。

- すべての接続はツイスト・ペア線を使用する。

- システムの周囲環境がノイジーな場合はシールドする。

- 電源からAPA、またAPAから負荷へのケーブルを大電流容量にする(表3参照)。

表3は、APA測定システムの電源および負荷用ケーブルの推奨ワイヤーサイズを示します。実際の問題は、電流がケーブルを流れで発生する直流あるいは交流電力損失です。表3の推奨値は、25°Cにおける12インチ長ワイヤー、正弦波信号に基づいたものです。

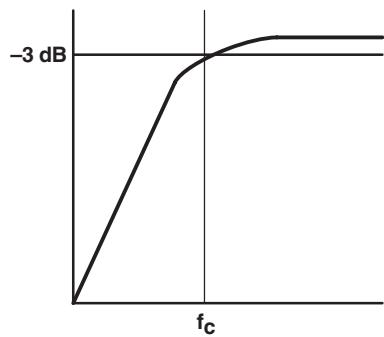

#### D級RCローパスフィルタ

アナライザがパルス幅変調のD級出力波形を処理できない場合、RCフィルタが方形波を低減するために使用されます。このフィルタは、そのカットオフ周波数をオーディオ帯域より上に設定するため、測定精度にほとんど影響しません。高周波の方形波が測定精度に与える影響は無視できます。なぜなら、その周波数が可聴周波数帯域より十分高く、スピーカーのコーンはそのような高レートに反応できないからです。また、従来の変調手法を採用するD級APA(TPA032D0x, TPA005Dxx)に使用されるLCローパスフィルタがある場合、RCフィルタは必要ありません。

RCフィルタの部品定数は、図42に示すような等価出力回路を用いて選定します。R<sub>L</sub>はAPAが試験時にドライブしている負荷インピーダンスです。アナライザの入力インピーダンス仕様は与えられており、R<sub>ANA</sub>とC<sub>ANA</sub>を代入します。このようにすると、測

定システムにおけるフィルタ部品の $R_{FILE}$ と $C_{FILT}$ が求まります。このフィルタはAPAの出力グランド・ピンすなわちパワー・グランド・ピンの近くに接地して、グランド・ループを最小にします。この回路の伝達関数を式(10)に示します。ここで、 $\omega_0 = R_{EQ}C_{EQ}$ ,  $R_{EQ} = R_{FILT}/R_{ANA}$ , および $C_{EQ} = (C_{FILT} + C_{ANA})$ です。フィルタのカットオフ周波数は測定帯域の最高周波数 $f_{MAX}$ 以上に設定し、オーディオ信号の減衰を防止します。式(11)がこのカットオフ周波数 $f_C$ になります。 $R_{FILT}$ の値は $R_L$ より十分大きくなり、負荷からシャントされる電流を最小にします。しかし、 $R_{FILT}$ と $R_{ANA}$ で構成される分圧回路によるアナライザの入力電圧の減衰が最小になるように、 $R_{FILT}$ の値を $R_{ANA}$ に比較して十分小さくします。目安として、ほとんどの測定において $R_{FILT}$ の値を小さく( $\sim 100\Omega$ )します。この値は、 $R_{ANA} \geq 10k\Omega$ の場合で測定誤差を1%より小にします。

$$\left(\frac{V_{OUT}}{V_{IN}}\right) = \frac{\left(\frac{R_{ANA}}{R_{ANA} + R_{FILT}}\right)}{1 + j \left(\frac{\omega}{\omega_0}\right)} \quad (10)$$

$$f_C = \sqrt{2} \times f_{MAX} \quad (11)$$

効率を測定する場合は例外です。 $R_{FILT}$ を10倍程度に増加し、フィルタによるシャント電流を低減しなければなりません。その場合、 $C_{FILT}$ を10分の1にしてカットオフ周波数を同じ値に保ちます。表2に推奨のフィルタ部品定数を示します。

$F_C$ を決め、 $R_{FILT}$ を選定したら、フィルタのコンデンサは式(12)を用いて計算します。その計算値のコンデンサが入手できない場合は、それより小さい容量値を選び、 $f_C$ を式(11)で計算される所要の最小値以上に保つ方が良いです。

$$C_{FILT} = \frac{1}{2\pi \times f_C \times R_{FILT}} \quad (12)$$

表2は標準部品定数に基づいた $R_{FILT}$ と $C_{FILT}$ の推奨値を示します。 $F_C$ の値は $f_{MAX}$ を20kHzとして、もともと28kHzの計算になりました。その結果 $C_{FILT}$ は57000pFと計算されました。それに最も近い値の56000pFと51000pFは入手できませんでした。そこで、その代わりに47000pFのコンデンサを使用し、 $f_C$ を所要値の28kHzより高い34kHzにしました。

| MEASUREMENT            | $R_{FILT}$ | $C_{FILT}$ |

|------------------------|------------|------------|

| Efficiency             | 1,000Ω     | 5,600pF    |

| All other measurements | 100Ω       | 56,000pF   |

表4. 代表的な測定用RCフィルタの値

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

Copyright © 2010, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊・劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 温・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供了としても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるとのこと、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier  | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|------------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPA3002D2PHP          | Active        | Production           | HTQFP (PHP)   48 | 250   JEDEC TRAY (5+1) | Yes         | NIPDAU                               | Level-4-260C-72 HR                | -40 to 85    | TPA3002D2           |

| TPA3002D2PHP.A        | Active        | Production           | HTQFP (PHP)   48 | 250   JEDEC TRAY (5+1) | Yes         | NIPDAU                               | Level-4-260C-72 HR                | -40 to 85    | TPA3002D2           |

| TPA3002D2PHPR         | Active        | Production           | HTQFP (PHP)   48 | 1000   LARGE T&R       | Yes         | NIPDAU                               | Level-4-260C-72 HR                | -40 to 85    | TPA3002D2           |

| TPA3002D2PHPR.A       | Active        | Production           | HTQFP (PHP)   48 | 1000   LARGE T&R       | Yes         | NIPDAU                               | Level-4-260C-72 HR                | -40 to 85    | TPA3002D2           |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

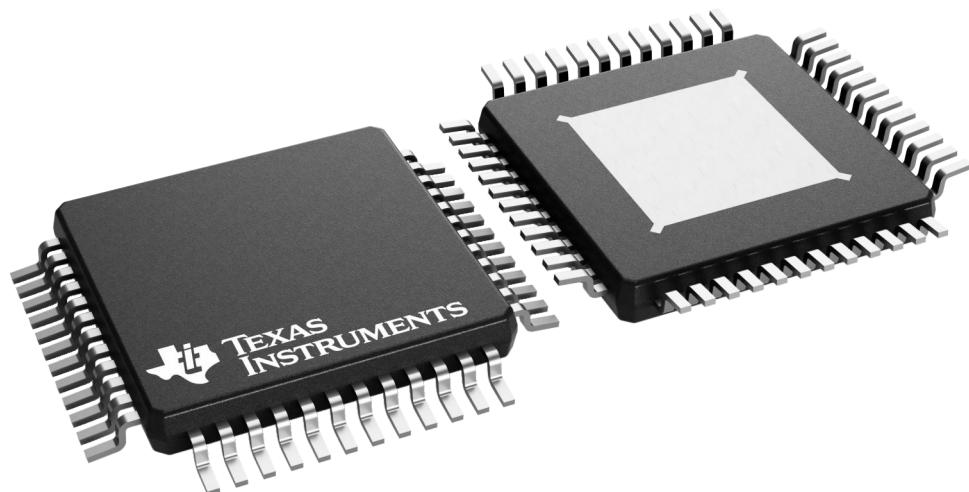

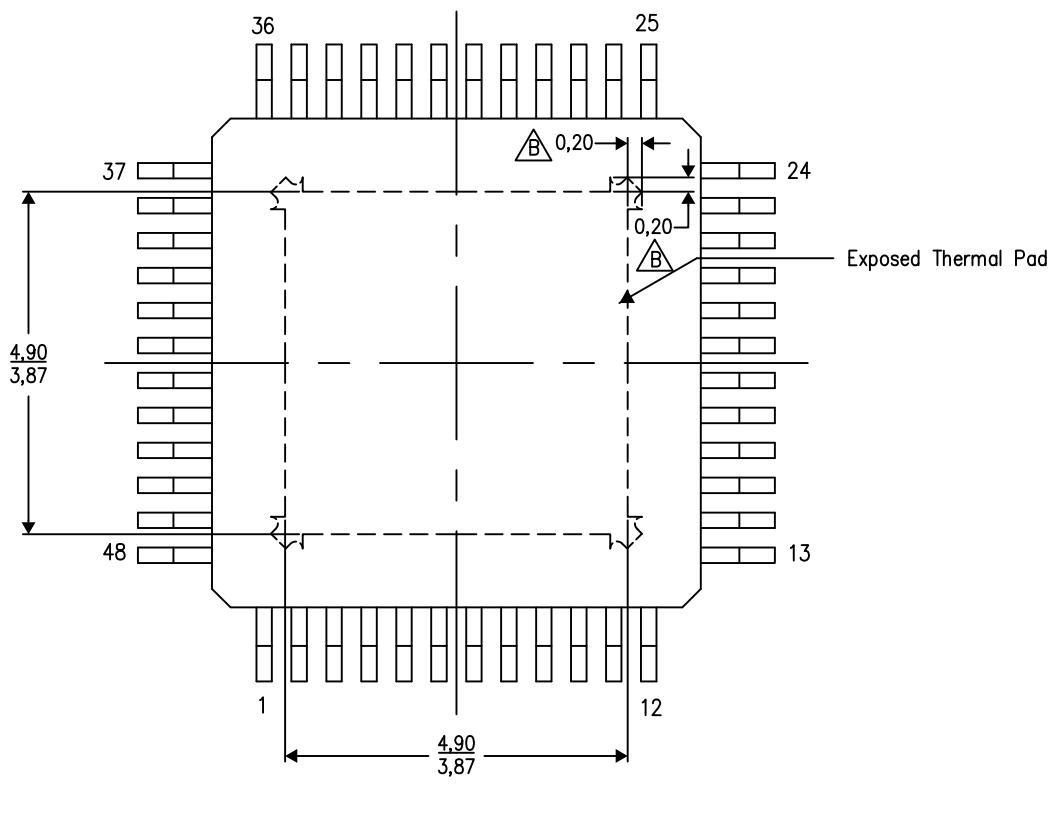

## GENERIC PACKAGE VIEW

**PHP 48**

**TQFP - 1.2 mm max height**

**7 x 7, 0.5 mm pitch**

**QUAD FLATPACK**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4226443/A

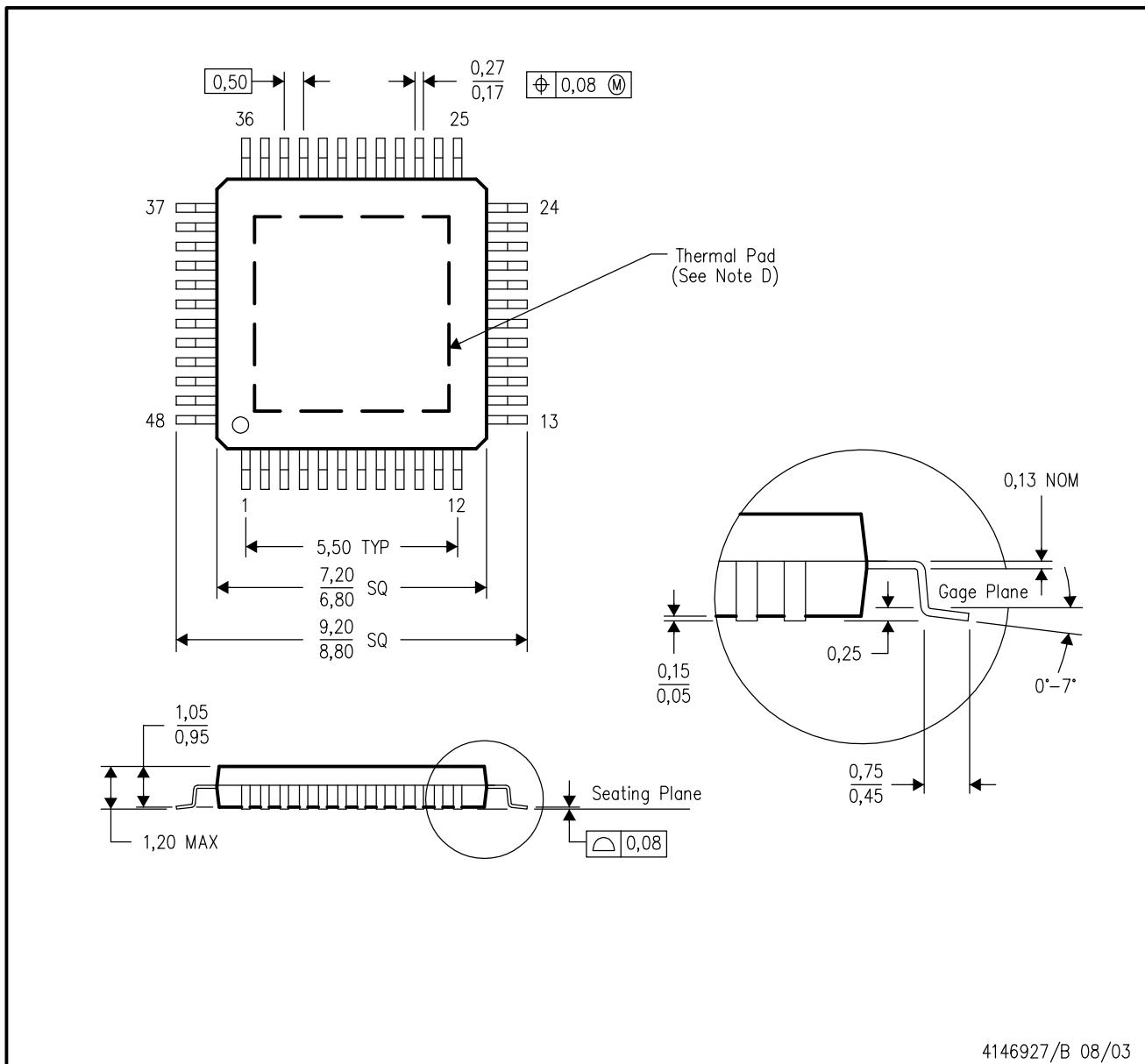

## PHP (S-PQFP-G48)

## PowerPAD™ PLASTIC QUAD FLATPACK

4146927/B 08/03

- NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

# THERMAL PAD MECHANICAL DATA

PHP (S-PQFP-G48)

PowerPAD™ PLASTIC QUAD FLATPACK

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206329-4/P 03/15

NOTE: A. All linear dimensions are in millimeters

Tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

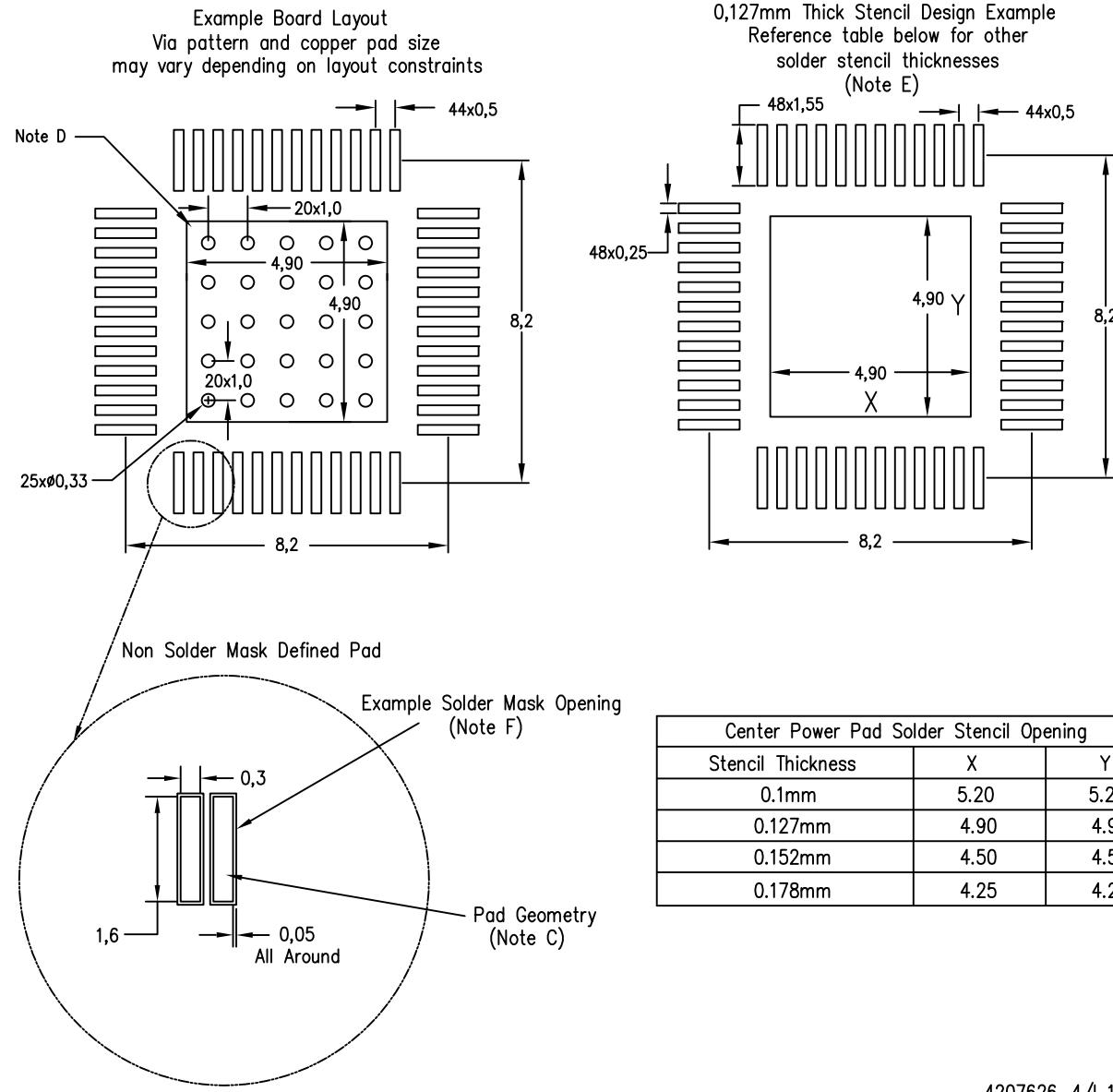

# LAND PATTERN DATA

PHP (S-PQFP-G48)

PowerPAD™ PLASTIC QUAD FLATPACK

4207626-4/I 10/15

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-7351 is recommended for alternate designs.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting options for vias placed in the thermal pad.

PowerPAD is a trademark of Texas Instruments

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月