# TPD4S480 USB Type-C® 48V EPR ポート プロテクタ: V<sub>BUS</sub> への短絡過電圧および IEC ESD 保護

## 1 特長

- 4 チャネルの V<sub>BUS</sub> への短絡過電圧保護 (CC1、CC2、SBU1、SBU2): 63V<sub>DC</sub> 許容

- 4 チャネルの IEC 61000-4-2 ESD 保護 (CC1、CC2、SBU1、SBU2)

- CC1 および CC2 過電圧保護 FET: V<sub>CONN</sub> 電力用

- CC ピンの ±65V サージ保護

- SBU ピンの +65V/-35V サージ保護

- EPR レベル V<sub>BUS</sub> を分割するためのイネーブルを搭載した内蔵 V<sub>BUS</sub> 分周回路

- 外部 EPR ブロッキング FET 制御用の FET ドライバを内蔵

- CC デッド バッテリ 抵抗の内蔵により、モバイル デバイスでのデッド バッテリ 状況に対応

- 3mm × 3mm QFN パッケージ

## 2 アプリケーション

- デスクトップ PC / マザーボード

- 標準的ノート PC

- Chromebook と WOA (Windows on Arm)

- ドッキングステーション

- ポート / ケーブル アダプタとドングル

- スマートフォン

## 3 概要

TPD4S480 は、シングル チップの USB Type-C ポート保護デバイスで、48V の V<sub>BUS</sub> への短絡過電圧および IEC ESD 保護を行います。

USB Type-C コネクタのリリース以降、USB Type-C 用でありながら、USB Type-C の仕様を満たしていない多くの製品やアクセサリがリリースされました。このような例の 1 つに USB Type-C パワー デリバリ アダプタがありますが、これは V<sub>BUS</sub> ライン上にしか高電圧を印加しません。USB Type-C に関する別の懸念として、小さなコネクタのピンが互いに近接して配置されているため、コネクタの機械的なねじれや水平方向のずれによってピン間が短絡することがあります。これによって、48V V<sub>BUS</sub> が CC および SBU ピンと短絡するおそれがあります。また、Type-C コネクタのピンが互いに近接して配置されていることから、破片や湿気により 48V V<sub>BUS</sub> ピンが CC および SBU ピンと短絡する危険も高まっています。

これらの理想的でない機器や機械的事象が存在するため、CC および SBU ピンは 5V 以下の電圧でのみ動作するにもかかわらず、48V 許容にする必要があります。TPD4S480 は CC および SBU ピンの過電圧保護を行うため、通常の動作に影響を与える前に CC および SBU ピンを 48V 許容にできます。このデバイスは、SBU および CC ラインと直列に高電圧 FET を配置します。OVP レシジョルドを超える電圧がこれらのラインに検出された場合、高電圧スイッチが開き、システムの他の部分を、コネクタに存在している高電圧の状況から絶縁します。

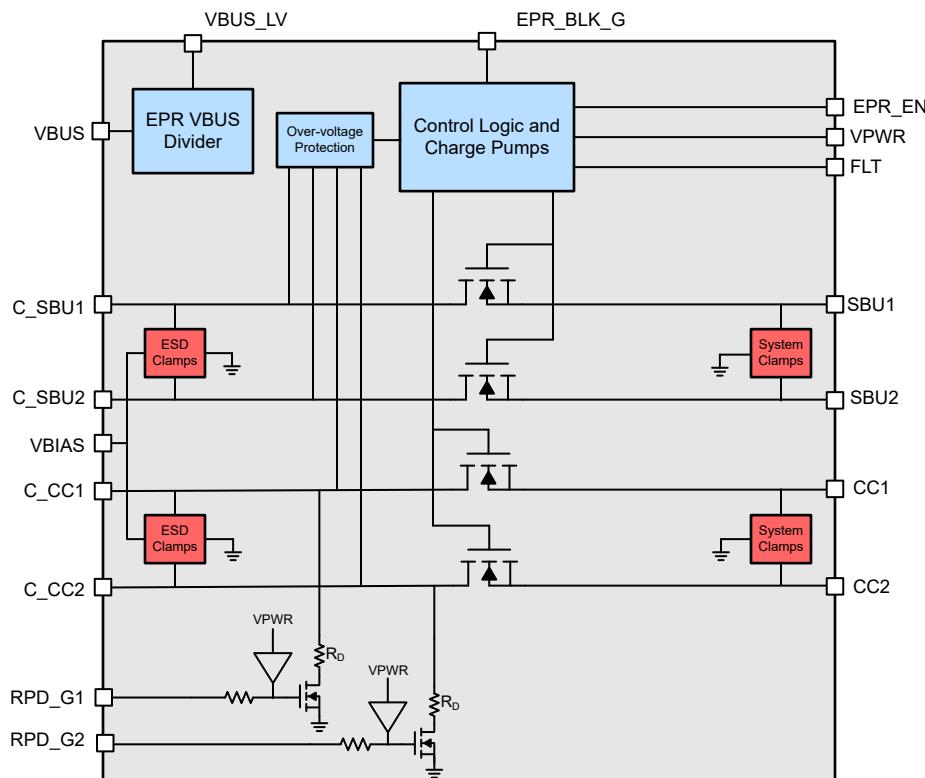

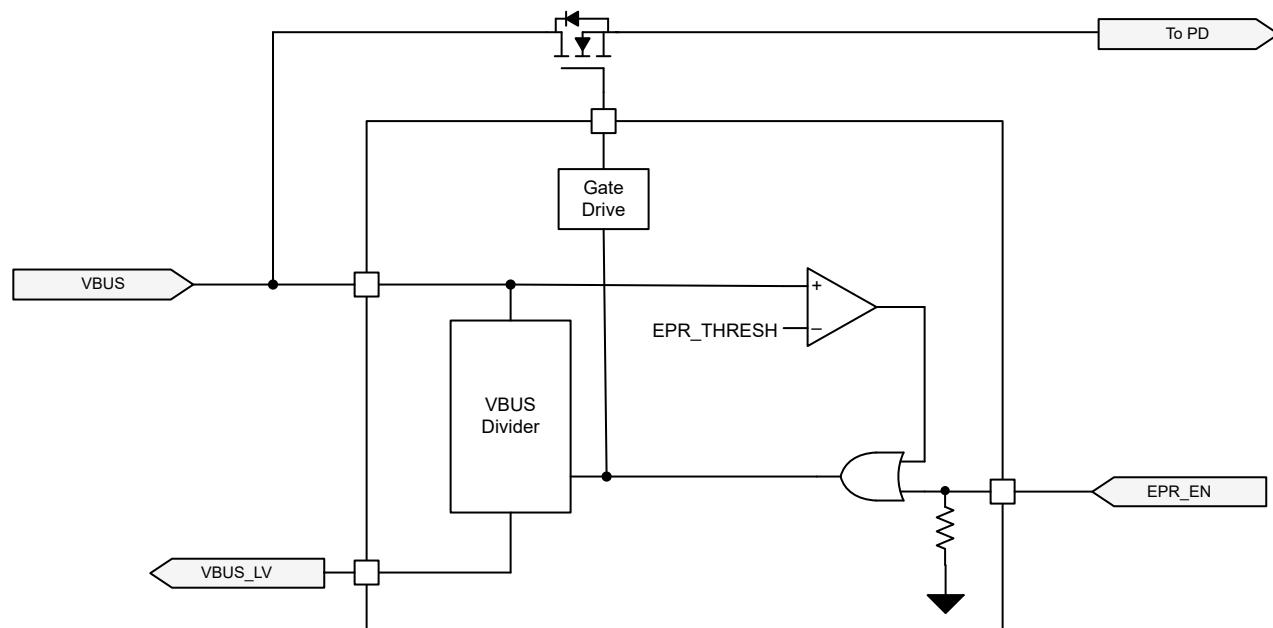

内蔵の V<sub>BUS</sub> 分圧回路と FET ドライバにより、EPR 動作に適した定格を持たない PD コントローラでも EPR 電圧範囲で安全に動作することができます。GPIO でイネーブルにしたとき、または V<sub>BUS</sub> が 24V を超えたとき自動的に、TPD4S480 はオプションの外部ブロッキング FET をディセーブルし、分圧器をイネーブルします。この動作により、20V 定格の PD コントローラが保護されるため、既存の V<sub>BUS</sub> センス回路を使用できます。

最後に、ほとんどのシステムでは外部ピンについて IEC 61000-4-2 システム レベルの ESD 保護が必要です。TPD4S480 には、CC1、CC2、SBU1、SBU2 ピンの IEC 61000-4-2 ESD 保護が内蔵されているため、コネクタの外部に高電圧 TVS ダイオードを配置する必要がありません。

### パッケージ情報 (1)

| 部品番号     | パッケージ          | 本体サイズ (公称) |

|----------|----------------|------------|

| TPD4S480 | RUK (WQFN, 20) | 3mm × 3mm  |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

### CC および SBU の過電圧保護

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## Table of Contents

|                                           |    |                                         |    |

|-------------------------------------------|----|-----------------------------------------|----|

| 1 特長.....                                 | 1  | 6.4 Device Functional Modes.....        | 14 |

| 2 アプリケーション.....                           | 1  | 7 Application and Implementation.....   | 15 |

| 3 概要.....                                 | 1  | 7.1 Application Information.....        | 15 |

| 4 Pin Configuration and Functions.....    | 3  | 7.2 Typical Application.....            | 15 |

| 5 Specifications.....                     | 5  | 7.3 Power Supply Recommendations.....   | 19 |

| 5.1 Absolute Maximum Ratings.....         | 5  | 7.4 Layout.....                         | 19 |

| 5.2 ESD Ratings—IEC Specification.....    | 5  | 8 Device and Documentation Support..... | 24 |

| 5.3 Recommended Operating Conditions..... | 5  | 8.1 Documentation Support.....          | 24 |

| 5.4 Thermal Information.....              | 6  | 8.2 ドキュメントの更新通知を受け取る方法.....             | 24 |

| 5.5 Electrical Characteristics.....       | 6  | 8.3 サポート・リソース.....                      | 24 |

| 5.6 Timing Requirements.....              | 8  | 8.4 Trademarks.....                     | 24 |

| 5.7 Typical Characteristics.....          | 9  | 8.5 静電気放電に関する注意事項.....                  | 24 |

| 6 Detailed Description.....               | 11 | 8.6 用語集.....                            | 24 |

| 6.1 Overview.....                         | 11 | 9 Revision History.....                 | 24 |

| 6.2 Functional Block Diagram.....         | 11 | 10 Mechanical, Packaging, and Orderable |    |

| 6.3 Feature Description.....              | 11 | Information.....                        | 24 |

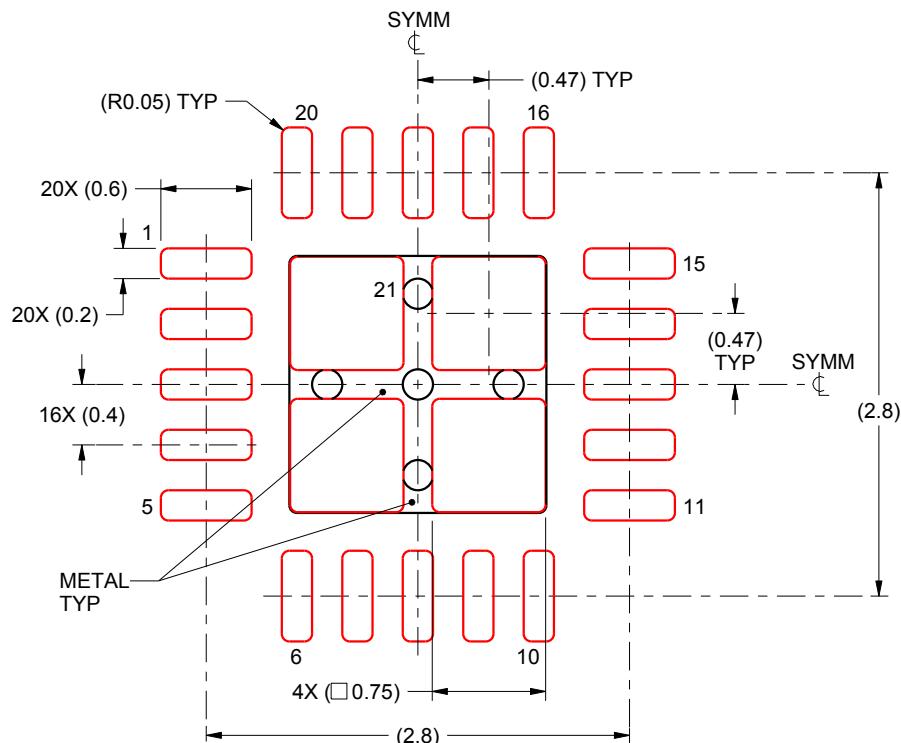

## 4 Pin Configuration and Functions

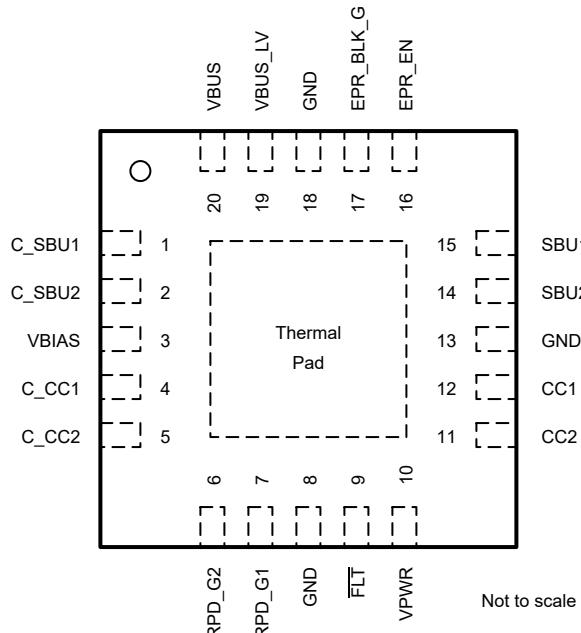

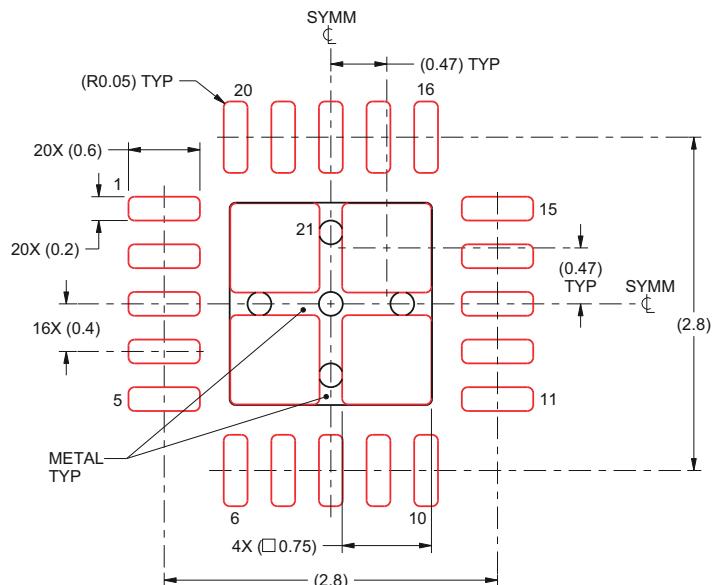

図 4-1. RUK Package 20-Pin QFN

表 4-1. Pin Functions

| PIN |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                            |

|-----|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   |                     |                                                                                                                                                                                                                        |

| 12  | CC1    | I/O                 | System side of the CC1 OVP FET. Connect to either CC pin of the CC/PD controller.                                                                                                                                      |

| 11  | CC2    | I/O                 | System side of the CC2 OVP FET. Connect to either CC pin of the CC/PD controller.                                                                                                                                      |

| 4   | C_CC1  | I/O                 | Connector side of the CC1 OVP FET. Connect to either CC pin of the USB Type-C connector.                                                                                                                               |

| 5   | C_CC2  | I/O                 | Connector side of the CC2 OVP FET. Connect to either CC pin of the USB Type-C connector.                                                                                                                               |

| 1   | C_SBU1 | I/O                 | Connector side of the SBU1 OVP FET. Connect to either SBU pin of the USB Type-C connector. Alternatively, connect to either USB2.0 pin of the USB Type-C connector to protect the USB2.0 pins instead of the SBU pins. |

| 2   | C_SBU2 | I/O                 | Connector side of the SBU2 OVP FET. Connect to either SBU pin of the USB Type-C connector. Alternatively, connect to either USB2.0 pin of the USB Type-C connector to protect the USB2.0 pins instead of the SBU pins. |

| 15  | SBU1   | I/O                 | System side of the SBU1 OVP FET. Connect to either SBU pin of the SBU MUX. Alternatively, connect to either USB2.0 pin of the USB2.0 Phy when protecting the USB2.0 pins instead of protecting the SBU pins.           |

| 14  | SBU2   | I/O                 | System side of the SBU2 OVP FET. Connect to either SBU pin of the SBU MUX. Alternatively, connect to either USB2.0 pin of the USB2.0 Phy when protecting the USB2.0 pins instead of protecting the SBU pins.           |

| 7   | RPD_G1 | I/O                 | Short to C_CC1 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND.                                                                                                       |

| 6   | RPD_G2 | I/O                 | Short to C_CC2 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND.                                                                                                       |

| 9   | FLT    | O                   | Open drain for fault reporting.                                                                                                                                                                                        |

表 4-1. Pin Functions (続き)

| PIN       |             | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                          |

|-----------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.       | NAME        |                     |                                                                                                                                                      |

| 8, 13, 18 | GND         | GND                 | Ground                                                                                                                                               |

| 3         | VBIAS       | P                   | Pin for ESD support capacitor. Place a 0.1- $\mu$ F capacitor on this pin to ground.                                                                 |

| 10        | VPWR        | P                   | 2.7V to 4.5V power supply.                                                                                                                           |

| 20        | VBUS        | I                   | Input for EPR VBUS divider. Tie to USB-C receptacle VBUS pins.                                                                                       |

| 19        | VBUS_LV     | O                   | Output of EPR VBUS divider. When EPR_EN is asserted, VBUS_LV is divided down voltage from VBUS. When EPR_EN is de-asserted VBUS_LV is equal to VBUS. |

| 16        | EPR_EN      | I                   | EPR mode enable input. When asserted EPR_BLK_G is disabled and VBUS_LV is divided VBUS.                                                              |

| 17        | EPR_BLK_G   | O                   | Gate driver output to optional VBUS blocking FET. FET is enabled when in SPR mode and disabled in EPR mode.                                          |

| -         | Thermal Pad | GND                 | Internally connected to GND. Used as a heatsink. Connect to the PCB GND plane                                                                        |

(1) I = input, O = output, I/O = input and output, GND = ground, P = power

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|            |                                         |                              | MIN  | MAX | UNIT |

|------------|-----------------------------------------|------------------------------|------|-----|------|

| $V_I$      | Input voltage                           | EPR_EN                       | -0.3 | 6.0 | V    |

| $V_I$      | Input voltage                           | VPWR                         | -0.3 | 5   | V    |

|            |                                         | RPD_G1, RPD_G2, VBUS         | -0.3 | 63  | V    |

| $V_I$      | Input voltage                           | VBUS (VPWR = 0V)             | -0.3 | 24  | V    |

| $V_I$      | Input voltage                           | VBUS (VPWR > 2.7V)           | -0.3 | 63  | V    |

| $V_O$      | Output voltage                          | FLT                          | -0.3 | 6   | V    |

|            |                                         | VBIAS                        | -0.3 | 63  | V    |

| $V_O$      | Output voltage                          | VBUS_LV                      | -0.3 | 24  | V    |

| $V_O$      | Output voltage                          | EPR_BLK_G                    | -0.3 | 30  | V    |

| $V_{IO}$   | I/O voltage                             | CC1, CC2, SBU1, SBU2         | -0.3 | 6   | V    |

|            |                                         | C_CC1, C_CC2, C_SBU1, C_SBU2 | -0.3 | 63  | V    |

| $t_{rise}$ | Input voltage rise time ( $V_I > 36V$ ) | CC1, CC2, SBU1, SBU2         | 400  |     | ns   |

| $T_J$      | Operating junction temperature          |                              | -40  | 125 | °C   |

| $T_{stg}$  | Storage temperature                     |                              | -65  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings—IEC Specification

|               |                         |                               | VALUE             | UNIT    |   |

|---------------|-------------------------|-------------------------------|-------------------|---------|---|

| $V_{(ESD)}$   | Electrostatic discharge | IEC 61000-4-2, C_CC1, C_CC2   | Contact discharge | ±8000   | V |

| $V_{(ESD)}$   | Electrostatic discharge | IEC 61000-4-2, C_CC1, C_CC2   | Air-gap discharge | ±15000  | V |

| $V_{(ESD)}$   | Electrostatic discharge | IEC 61000-4-2, C_SBU1, C_SBU2 | Contact discharge | ±8000   | V |

| $V_{(ESD)}$   | Electrostatic discharge | IEC 61000-4-2, C_SBU1, C_SBU2 | Air-gap discharge | ±15000  | V |

| $V_{(Surge)}$ | Lightning and Surge     | IEC 61000-4-5, C_CC1, C_CC2   |                   | ±65     | V |

|               |                         | IEC 61000-4-5, C_SBU1, C_SBU2 |                   | +65/-35 | V |

### 5.3 Recommended Operating Conditions

|             |                                |                                                                          | MIN | NOM  | MAX  | UNIT |

|-------------|--------------------------------|--------------------------------------------------------------------------|-----|------|------|------|

| $V_I$       | Input voltage                  | VPWR                                                                     | 2.7 | 3.3  | 4.5  | V    |

|             |                                | RPD_G1, RPD_G2                                                           | 0   |      | 5.5  | V    |

|             |                                | EPR_EN                                                                   | 0   | VPWR |      | V    |

|             |                                | VBUS                                                                     | 0   |      | 51   | V    |

| $V_O$       | Output voltage                 | FLT Pull-up resistor power rail                                          | 2.7 |      | 5.5  | V    |

| $V_{IO}$    | I/O voltage                    | CC1, CC2, C_CC1, C_CC2                                                   | 0   |      | 5.5  | V    |

|             |                                | SBU1, SBU2, C_SBU1, C_SBU2                                               | 0   |      | 4.3  | V    |

| $I_{VCONN}$ | $V_{CONN}$ Current             | Current flowing into CC1/2 and flowing out of C_CC1/2, $T_J \leq 105$ °C |     |      | 600  | mA   |

| $I_{VCONN}$ | $V_{CONN}$ Current             | Current flowing into CC1/2 and flowing out of C_CC1/2, $T_J \leq 85$ °C  |     |      | 1.25 | A    |

| $T_J$       | Operating Junction Temperature |                                                                          | -40 |      | 125  | °C   |

|                                    |                                    |                                  | MIN  | NOM | MAX              | UNIT          |

|------------------------------------|------------------------------------|----------------------------------|------|-----|------------------|---------------|

| External Components <sup>(1)</sup> | External Components <sup>(1)</sup> | FLT Pull-up resistance           | 1.7  | 300 | $\text{k}\Omega$ |               |

|                                    |                                    | VBIAS capacitance <sup>(2)</sup> | 0.04 | 0.1 | 0.14             | $\mu\text{F}$ |

|                                    |                                    | VPWR Capacitance                 | 0.3  | 1   |                  | $\mu\text{F}$ |

|                                    |                                    | VBUS_LV Capacitance              |      | 0.1 |                  | $\mu\text{F}$ |

(1) For recommended values for capacitors and resistors, the typical values assume a component placed on the board near the pin. Minimum and maximum values listed are inclusive of manufacturing tolerances, voltage derating, board capacitance, and temperature variation. The effective value presented should be within the minimum and maximums listed in the table.

(2) The VBIAS pin requires a minimum 63-VDC rated capacitor. A 100-VDC rated capacitor is recommended to reduce capacitance derating.

See the VBIAS Capacitor Selection section for more information on selecting the VBIAS capacitor.

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | TPD4S480 | UNIT                        |

|-------------------------------|----------------------------------------------|----------|-----------------------------|

|                               |                                              | QFN      |                             |

|                               |                                              | 20 PINS  |                             |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 44.7     | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 41.8     | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 17.7     | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.7      | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 17.7     | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 7.9      | $^{\circ}\text{C}/\text{W}$ |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 5.5 Electrical Characteristics

over operating junction temperature range (unless otherwise noted)

| PARAMETER               | TEST CONDITIONS                                                              | MIN                                                                                                                                                          | TYP | MAX | UNIT             |

|-------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------|

| <b>CC OVP Switches</b>  |                                                                              |                                                                                                                                                              |     |     |                  |

| $R_{ON}$                | On Resistance of CC OVP FETs                                                 | CCx = 5.5V, $T_J \leq 85^{\circ}\text{C}$                                                                                                                    | 272 | 420 | $\text{m}\Omega$ |

| $C_{ON\_CC}$            | Equivalent on Capacitance                                                    | Capacitance from CCx or C_CCx to GND when device is powered. Measure at $V_{CCx}/V_{CCx} = 0\text{V}$ to 1.2V, $f = 400\text{kHz}$ .                         | 40  | 74  | $\text{pF}$      |

| $RD\_DB$                | Dead Battery Pull-Down Resistors (only present when device is unpowered)     | $V_{C\_CCx} = 2.6\text{V}$                                                                                                                                   | 4.1 | 5.1 | $\text{k}\Omega$ |

| $V_{TH\_DB}$            | Threshold voltage of the pull-down FET in series with RD during dead battery | $I_{C\_CCx} = 80\mu\text{A}$                                                                                                                                 | 0.5 | 0.9 | 1.2 $\text{V}$   |

| $V_{OVPCC}$             | OVP Threshold on CC Pins                                                     | Place 5.5V on C_CCx. Step up C_CCx until FLT pin is asserted. Put 100mA load through the CC FET and see the FET shuts off.                                   | 5.6 | 5.9 | 6.2 $\text{V}$   |

| $V_{OVPCC\_HYS}$        | Hysteresis on CC OVP                                                         | Place 6.5 V on C_CCx. Step down the voltage on C_CCx until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for C_CCx. |     | 50  | $\text{mV}$      |

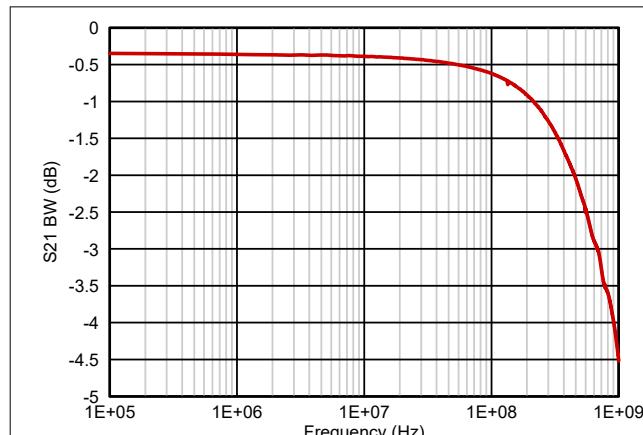

| $BW_{ON}$               | On Bandwidth Single Ended (-3dB)                                             | Measure the -3 dB bandwidth from C_CCx to CCx. Single ended measurement, 50- $\Omega$ system. $V_{cm} = 0.1\text{V}$ to 1.2 V.                               |     | 125 | $\text{MHz}$     |

| $V_{STBUS\_CC}$         | Short-to-VBUS tolerance on the CC pins                                       | Hot-Plug C_CCx with a 1 meter USB Type C Cable, place a 30- $\Omega$ load on CCx                                                                             |     | 51  | $\text{V}$       |

| $V_{STBUS\_CC\_CLAMP}$  | Short-to-VBUS System-Side Clamping Voltage on the CC pins (CCx)              | Hot-Plug C_CCx with a 1 meter USB Type C Cable. Hot-Plug voltage $C_{CCx} = 51\text{V}$ . VPWR = 3.3 V. Place a 30- $\Omega$ load on CCx.                    |     | 7   | $\text{V}$       |

| <b>SBU OVP Switches</b> |                                                                              |                                                                                                                                                              |     |     |                  |

| $R_{ON}$                | On Resistance of SBU OVP FETs                                                | $SBUx = 3.6\text{V}$ . $-40^{\circ}\text{C} \leq TJ \leq +85^{\circ}\text{C}$                                                                                | 4   | 6.8 | $\Omega$         |

## 5.5 Electrical Characteristics (続き)

over operating junction temperature range (unless otherwise noted)

| PARAMETER                                     |                                                                                | TEST CONDITIONS                                                                                                                                                                                                                    | MIN      | TYP      | MAX  | UNIT |

|-----------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|------|

| C <sub>ON_SBU</sub>                           | Equivalent on Capacitance                                                      | Capacitance from SB <sub>UX</sub> or C <sub>_SB<sub>UX</sub></sub> to GND when device is powered. Measure at V <sub>C_SBU<sub>x</sub></sub> /V <sub>SB<sub>UX</sub></sub> = 0.3V to 4.0V.                                          |          | 6        |      | pF   |

| V <sub>OVP<sub>SB<sub>U</sub></sub></sub>     | OVP Threshold on SBU Pins                                                      | Place 3.6V on C <sub>_SB<sub>UX</sub></sub> . Step up C <sub>_SB<sub>UX</sub></sub> until FLT pin is asserted.                                                                                                                     | 4.0      | 4.2      | 4.41 | V    |

| V <sub>OVP<sub>SB<sub>U</sub></sub>_HYS</sub> | Hysteresis on SBU OVP                                                          | Place 5 V on C <sub>_CC<sub>x</sub></sub> . Step down the voltage on C <sub>_CC<sub>x</sub></sub> until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for C <sub>_SB<sub>UX</sub></sub> . |          | 50       |      | mV   |

| BW <sub>ON</sub>                              | On Bandwidth Single Ended (-3dB)                                               | Measure the -3 dB bandwidth from C <sub>_SB<sub>UX</sub></sub> to SB <sub>UX</sub> . Single ended measurement, 50Ω system. V <sub>cm</sub> = 0.1V to 3.6V.                                                                         | 600      | 760      |      | MHz  |

| X <sub>TALK</sub>                             | Crosstalk                                                                      | Measure crosstalk at f = 1 MHz from SB <sub>U1</sub> to C <sub>_SB<sub>U2</sub></sub> or SB <sub>U2</sub> to C <sub>_SB<sub>U1</sub></sub> . V <sub>cm1</sub> = 3.6 V, V <sub>cm2</sub> = 0.3 V. Terminate open sides to 50Ω.      |          | -70      |      | dB   |

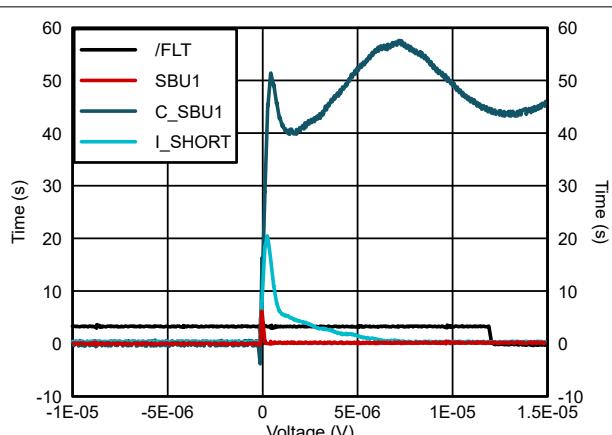

| V <sub>STBUS_SBU</sub>                        | Short-to-VBUS tolerance on the SBU pins                                        | Hot-Plug C <sub>_SB<sub>UX</sub></sub> with a 1 meter USB Type C Cable. Put a 100-nF capacitor in series with a 40-Ω resistor to GND on SB <sub>UX</sub> .                                                                         |          | 51       |      | V    |

| V <sub>STBUS_SBU_CLAMP</sub>                  | Short-to-VBUS System-Side Clamping Voltage on the SBU pins (SB <sub>UX</sub> ) | Hot-Plug C <sub>_SB<sub>UX</sub></sub> with a 1 meter USB Type C Cable. Hot-Plug voltage C <sub>_SB<sub>UX</sub></sub> = 51V. VPWR = 3.3 V. Put a 150-nF capacitor in series with a 40-Ω resistor to GND on SB <sub>UX</sub> .     |          | 7        |      | V    |

| <b>EPR Adapter</b>                            |                                                                                |                                                                                                                                                                                                                                    |          |          |      |      |

| VBUS_DIV_SPR                                  | VBUS_LV to VBUS divider ratio, SPR Mode                                        | VBUS_LV/VBUS, EPR_EN = 0, VBUS = 4.5 - 21V, I <sub>_VBUS_LV</sub> = 0-20mA                                                                                                                                                         |          | 1        |      | V/V  |

| VBUS_DIV_EPR                                  | VBUS_LV to VBUS divider ratio, EPR Mode                                        | VBUS_LV/VBUS, EPR_EN = 1, VBUS = 26.6-50.4, I <sub>_VBUS_LV</sub> = 0-20mA                                                                                                                                                         |          | 0.42     |      | V/V  |

| I <sub>_VBUS_LV</sub>                         | Current from VBUS_LV                                                           |                                                                                                                                                                                                                                    |          | 20       |      | mA   |

| V <sub>FWD_VBUS_LV</sub>                      | VBUS to VBUS_LV forward voltage drop                                           | I <sub>_VBUS_LV</sub> =20mA, VBUS=4.5V, EPR_EN=0                                                                                                                                                                                   | 456      | 700      |      | mV   |

| V <sub>FWD_VBUS_LV</sub>                      | VBUS to VBUS_LV forward voltage drop                                           | I <sub>_VBUS_LV</sub> =20mA, VBUS=26V, EPR_EN=1                                                                                                                                                                                    | 823      | 940      |      | mV   |

| V <sub>EPR_THRESH_R</sub>                     | Rising VBUS EPR enable threshold                                               |                                                                                                                                                                                                                                    | 22.7     | 24       |      | V    |

| V <sub>EPR_THRESH_F</sub>                     | Falling VBUS EPR enable threshold                                              |                                                                                                                                                                                                                                    | 22.4     | 23.4     |      | V    |

| V <sub>EPR_BLK_G</sub>                        | Gate Drive voltage for EPR_BLK_G                                               | 0 ≤ VBUS ≤ 22 V                                                                                                                                                                                                                    | 5        | 12       |      | V    |

| I <sub>EPR_BLK_G</sub>                        | Gate Driver Sourcing Current                                                   | 0 ≤ V <sub>EPR_BLK_G</sub> -V <sub>VBUS</sub> ≤ 5 V, 0 V ≤ V <sub>VBUS</sub> ≤ 22 V, measure I <sub>EPR_BLK_G</sub>                                                                                                                |          | 4        |      | μA   |

| V <sub>EPR_EN_V+</sub>                        | EPR_EN rising threshold                                                        |                                                                                                                                                                                                                                    |          | 0.7*VPWR |      | V    |

| V <sub>EPR_EN_V-</sub>                        | EPR_EN falling threshold                                                       |                                                                                                                                                                                                                                    | 0.3*VPWR |          |      | V    |

| <b>Power Supply and Leakage Currents</b>      |                                                                                |                                                                                                                                                                                                                                    |          |          |      |      |

| V <sub>PWR_UVLO</sub>                         | V <sub>PWR</sub> Under Voltage Lockout                                         | Place 1 V on VPWR and raise voltage until SBU or CC FETs turn-on.                                                                                                                                                                  | 2.1      | 2.3      | 2.6  | V    |

| V <sub>PWR_UVLO_HYS</sub>                     | V <sub>PWR</sub> UVLO Hysteresis                                               | Place 3 V on VPWR and lower voltage until SBU or CC FETs turnoff; measure difference between rising and falling UVLO to calculate hysteresis.                                                                                      | 70       | 100      | 130  | mV   |

| I <sub>_VPWR</sub>                            | V <sub>PWR</sub> supply current                                                | VPWR = 3.3 V (typical), VPWR = 4.5 V (maximum). -40°C ≤ T <sub>J</sub> ≤ +85°C.                                                                                                                                                    | 112      | 160      |      | μA   |

| I <sub>C_CC_LEAK</sub>                        | Leakage current for C <sub>_CC<sub>x</sub></sub> pins when device is powered   | VPWR = 3.3 V, V <sub>C_CC<sub>x</sub></sub> = 3.6 V, CC <sub>x</sub> pins are floating, measure leakage current into C <sub>_CC<sub>x</sub></sub> pins.                                                                            |          | 5        |      | μA   |

## 5.5 Electrical Characteristics (続き)

over operating junction temperature range (unless otherwise noted)

| PARAMETER                          |                                                               | TEST CONDITIONS                                                                                                                                                                                                                          | MIN | TYP | MAX  | UNIT               |

|------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|--------------------|

| $I_{C\_SBU\_LEAK}$                 | Leakage current for C_SBUx pins when device is powered        | VPWR = 3.3 V, $V_{C\_SBUx}$ = 3.6 V, SBUX pins are floating, measure leakage current into C_SBUx pins. Result should be same if SBUX side is biased and C_SBUx is left floating. $-40^{\circ}\text{C} \leq T_J \leq +85^{\circ}\text{C}$ |     |     | 3.2  | $\mu\text{A}$      |

| $I_{C\_CC\_LEAK\_OVP}$             | Leakage current for C_CCx pins when device is in OVP          | VPWR = 0 V or 3.3 V, $V_{C\_CCx}$ = 51 V, CCx pins are set to 0 V, measure leakage current into C_CCx pins.                                                                                                                              |     |     | 1200 | $\mu\text{A}$      |

| $I_{C\_SBU\_LEAK\_OVP}$            | Leakage current for C_SBUx pins when device is in OVP         | VPWR = 0 V or 3.3 V, $V_{C\_SBUx}$ = 51 V, SBUX pins are set to 0 V, measure leakage current into C_SBUx pins.                                                                                                                           |     |     | 720  | $\mu\text{A}$      |

| $I_{CC\_LEAK\_OVP}$                | Leakage current for CC pins when device is in OVP             | VPWR = 0 V or 3.3 V, $V_{C\_CCx}$ = 51 V, CCx pins are set to 0 V, measure leakage current out of CCx pins.                                                                                                                              |     |     | 30   | $\mu\text{A}$      |

| $I_{SBU\_LEAK\_OVP}$               | Leakage current for SBU pins when device is in OVP            | VPWR = 0 V, $V_{C\_SBUx}$ = 51 V, SBUX pins are set to 0 V, measure leakage current into SBUX pins.                                                                                                                                      | -1  |     | 1    | $\mu\text{A}$      |

| <b>/FLT Pin</b>                    |                                                               |                                                                                                                                                                                                                                          |     |     |      |                    |

| $V_{OL}$                           | Low-level output voltage                                      | IOL = 3mA. Measure voltage at FLT pin.                                                                                                                                                                                                   |     |     | 0.4  | V                  |

| <b>Over Temperature Protection</b> |                                                               |                                                                                                                                                                                                                                          |     |     |      |                    |

| $T_{SD\_RISING}$                   | The rising over-temperature protection shutdown threshold     |                                                                                                                                                                                                                                          | 150 | 175 |      | $^{\circ}\text{C}$ |

| $T_{SD\_FALLING}$                  | The falling over-temperature protection shutdown threshold    |                                                                                                                                                                                                                                          | 130 | 140 |      | $^{\circ}\text{C}$ |

| $T_{SD\_HYST}$                     | The over-temperature protection shutdown threshold hysteresis |                                                                                                                                                                                                                                          |     | 35  |      | $^{\circ}\text{C}$ |

## 5.6 Timing Requirements

|                                 |                                                                                                                                                                                                                 | MIN  | NOM  | MAX | UNIT             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------------------|

| <b>Power-On and Off Timings</b> |                                                                                                                                                                                                                 |      |      |     |                  |

| $t_{ON\_FET}$                   | Time from Crossing Rising VPWR UVLO until CC and SBU OVP FETs are on.                                                                                                                                           |      | 1.3  | 3.5 | ms               |

| $t_{ON\_FET\_DB}$               | Time from Crossing Rising VPWR UVLO until CC and SBU OVP FETs are on and the dead battery resistors are off.                                                                                                    |      | 5.7  | 9.5 | ms               |

| $dV_{PWR\_OFF}/dt$              | Minimum slew rate for CC and FETs turn off during a power off.                                                                                                                                                  | -0.5 |      |     | V/ $\mu\text{s}$ |

| <b>Over Voltage Protection</b>  |                                                                                                                                                                                                                 |      |      |     |                  |

| $t_{OVP\_RESPONSE\_CC}$         | OVP response time on the CCx pins. Time from OVP asserted until OVP FETs turn off.                                                                                                                              |      | 70   |     | ns               |

| $t_{OVP\_RESPONSE\_SBU}$        | OVP response time on the SBUX pins. Time from OVP asserted until OVP FETs turn off.                                                                                                                             |      | 80   |     | ns               |

| $t_{OVP\_RECOVERY\_CC}$         | OVP recovery time on the CCx pins. Once an OVP has occurred, the minimum time duration until the CC FETs turn back on. OVP must be removed for CC FETs to turn back on.                                         |      | 0.9  | 2.3 | ms               |

| $t_{OVP\_RECOVERY\_CC\_DB}$     | OVP recovery time on the CCx pins. Once an OVP has occurred, the minimum time duration until the CC FETs turn back on and the dead battery resistors turn off. OVP must be removed for CC FETs to turn back on. |      | 5    |     | ms               |

| $t_{OVP\_RECOVERY\_SBU}$        | OVP recovery time on the SBUX pins. Once an OVP has occurred, the minimum time duration until the SBU FETs turn back on. OVP must be removed for SBU FETs to turn back on.                                      |      | 0.62 |     | ms               |

| $t_{OVP\_FLT\_ASSERTION}$       | Time from OVP Asserted to /FLT assertion. /FLT assertion is 10% of the maximum value. Set C_CCx or C_SBUx above the maximum OVP threshold. Start the time where it passes the typical OVP threshold value.      |      | 20   |     | $\mu\text{s}$    |

| $t_{OVP\_FLT\_DEASSERTION}$     | Time from CC FET turn on after an OVP to /FLT deassertion.                                                                                                                                                      |      | 5    |     | ms               |

## 5.7 Typical Characteristics

図 5-1. SBU Bandwidth

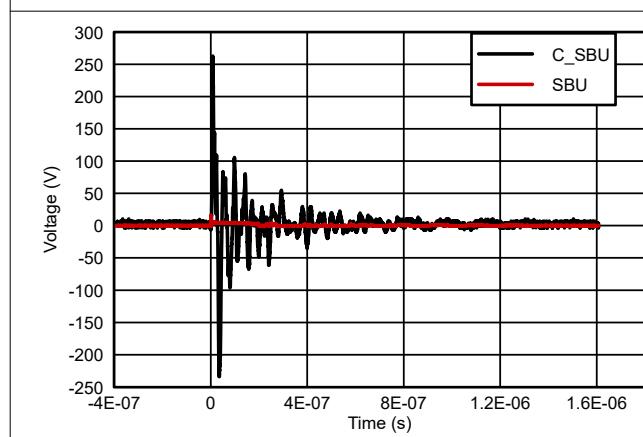

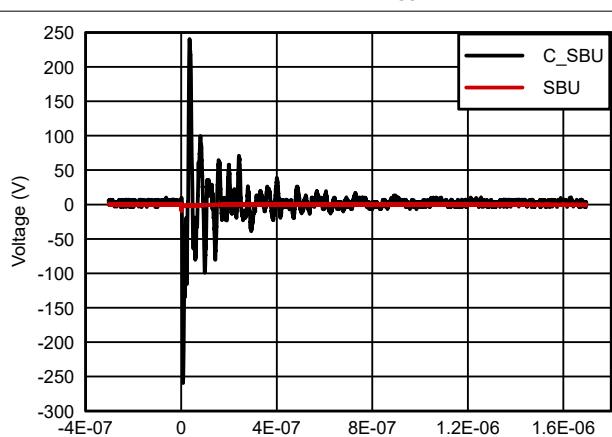

図 5-2. SBU Short-to-V<sub>BUS</sub> 48V

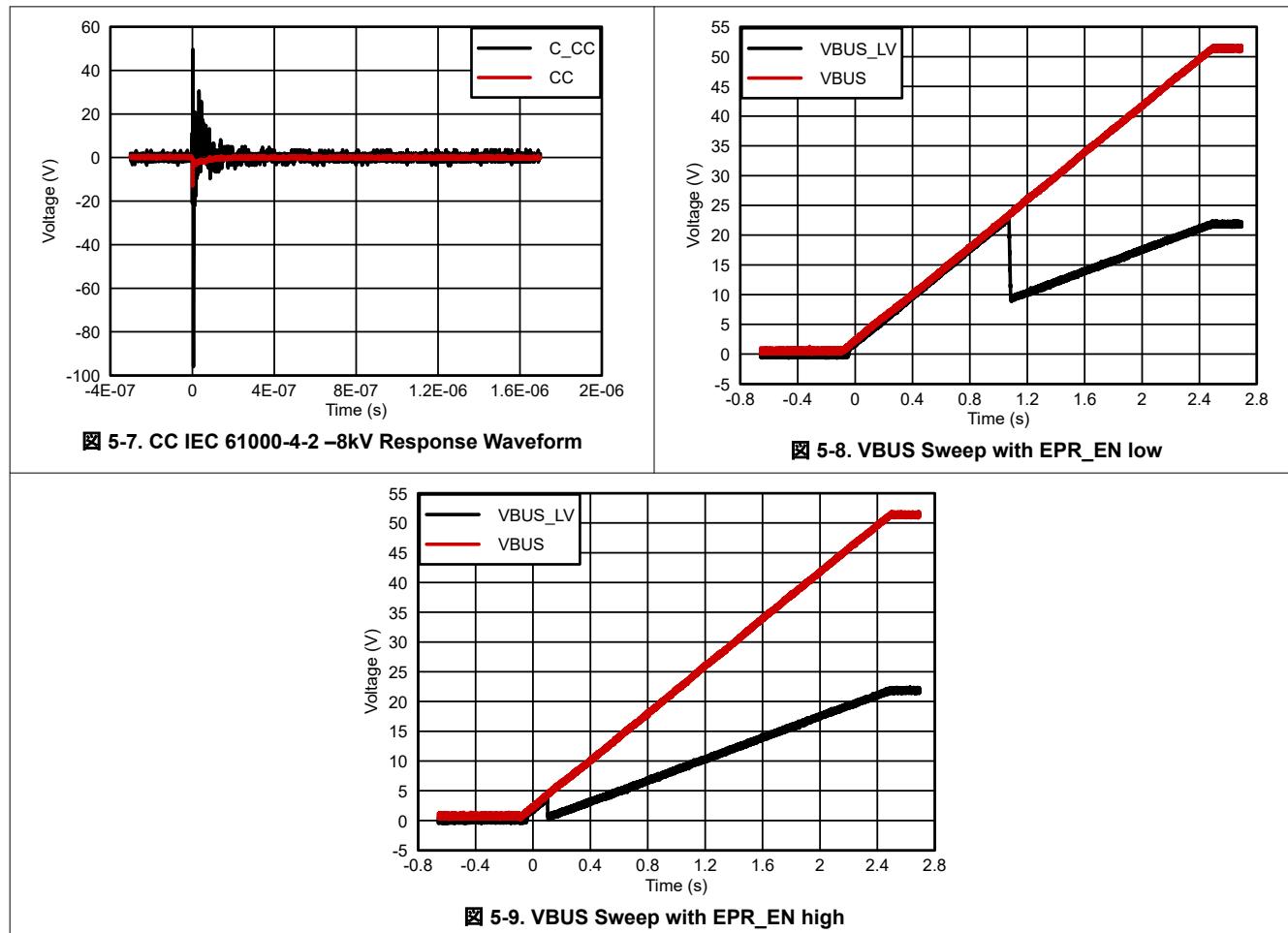

図 5-3. SBU IEC 61000-4-2 4kV Response Waveform

図 5-4. SBU IEC 61000-4-2 -4kV Response Waveform

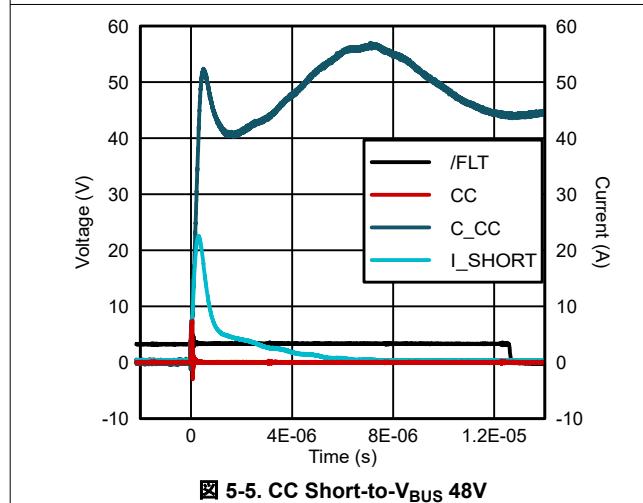

図 5-5. CC Short-to-V<sub>BUS</sub> 48V

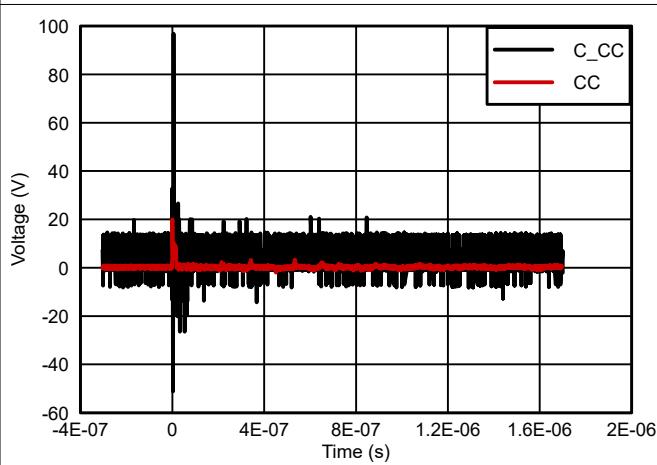

図 5-6. CC IEC 61000-4-2 8kV Response Waveform

## 5.7 Typical Characteristics (continued)

## 6 Detailed Description

### 6.1 Overview

The TPD4S480 is a single chip USB Type-C port protector that provides 48V Short-to-V<sub>BUS</sub> overvoltage and ESD protection. Due to the small pin pitch of the USB Type-C connector and non-compliant USB Type-C cables and accessories, the V<sub>BUS</sub> pins can get shorted to the CC and SBU pins inside the USB Type-C connector. Because of this short-to-V<sub>BUS</sub> event, the CC and SBU pins need to be 48V tolerant, to support protection on the full USB PD-EPR voltage range. The TPD4S480 integrates four channels of 48V Short-to-V<sub>BUS</sub> overvoltage protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector.

Additionally, IEC 61000-4-2 system level ESD protection is required to protect a USB Type-C port from ESD strikes generated by end product users. The TPD4S480 integrates four channels of IEC61000-4-2 ESD protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector. This means ESD protection is provided for all of the low-speed pins on the USB Type-C connector in a single chip by the TPD4S480. Additionally, high-voltage ESD protection that is 55V DC tolerant is required for the CC and SBU lines to simultaneously support ESD and Short-to-V<sub>BUS</sub> protection. The TPD4S480 integrates a high-voltage ESD diode designed to work in conjunction with the overvoltage protection FETs inside the device.

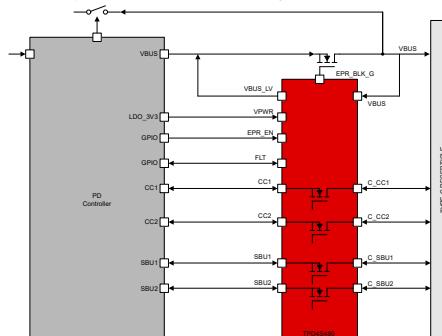

### 6.2 Functional Block Diagram

### 6.3 Feature Description

#### 6.3.1 4-Channels of Short-to-V<sub>BUS</sub> Overvoltage Protection (CC1, CC2, SBU1, SBU2 Pins or CC1, CC2, DP, DM Pins): 63-V<sub>DC</sub> Tolerant

The TPD4S480 provides 4-channels of Short-to-V<sub>BUS</sub> Overvoltage Protection for the CC1, CC2, SBU1, and SBU2 pins (or the CC1, CC2, DP, and DM pins) of the USB Type-C connector. The TPD4S480 is able to handle 63V<sub>DC</sub> on its C\_CC1, C\_CC2, C\_SBU1, and C\_SBU2 pins. This level of protection is necessary because according to the USB PD specification, with V<sub>BUS</sub> set for 48-V operation, the V<sub>BUS</sub> voltage is allowed to legally swing up to 50.4V and 50.9V on voltage transitions from a different USB PD V<sub>BUS</sub> voltage. The TPD4S480 builds

in tolerance up to 63V<sub>BUS</sub> to provide margin above this 50.9V specification to be able to support inductive ringing that may occur during a short event.

When a short-to-V<sub>BUS</sub> event occurs, ringing happens due to the RLC elements in the hot-plug event. With very low resistance in this RLC circuit, ringing up to twice the settling voltage can appear on the connector. Ringing of more than twice the DC level can be generated if any capacitor on the line derates in capacitance value during the short-to-V<sub>BUS</sub> event. This behavior means that more than 90V could be seen on a USB Type-C pin during a Short-to-V<sub>BUS</sub> event. The TPD4S480 has built in circuit protection to handle this ringing. The diode clamps used for IEC ESD protection also clamp the ringing voltage during the short-to-V<sub>BUS</sub> event to limit the peak ringing to approximately 53V. Additionally, the overvoltage protection FETs integrated inside the TPD4S480 are 63V tolerant, therefore being capable of supporting the high-voltage ringing waveform that is experienced during the short-to-V<sub>BUS</sub> event. The well designed combination of voltage clamps and 63V tolerant OVP FETs insures the TPD4S480 can handle Short-to-V<sub>BUS</sub> hot-plug events with hot-plug voltages as high as 51V<sub>DC</sub>.

The TPD4S480 has an extremely fast turnoff time of 70ns typical. Furthermore, additional voltage clamps are placed after the OVP FET on the system side (CC1, CC2, SBU1, SBU2) pins of the TPD4S480, to further limit the voltage and current that are exposed to the USB Type-C CC/PD controller during the 70ns interval while the OVP FET is turning off. The combination of connector side voltage clamps, OVP FETs with extremely fast turnoff time, and system side voltage clamps all work together to insure the level of stress seen on a CC1, CC2, SBU1, or SBU2 pin during a short-to-V<sub>BUS</sub> event is less than or equal to an HBM event.

The SBU OVP FETs are designed with to be able to optionally protect the DP, DM (USB2.0) pins in lieu of the SBU pins. Some systems designers also prefer to protect the DP, DM pins from Short-to-V<sub>BUS</sub> events due to the potential for moisture/water in the connector to short the V<sub>BUS</sub> pins to DP, DM pins. This can be especially applicable in cases where the end equipment with a USB Type-C connector is trying to be made water-proof. If desiring to protect the DP, DM pins on the USB Type-C connector from a Short-to-V<sub>BUS</sub> event, connect the C\_SBUx pins to the DP, DM pins on the USB Type-C connector, and the SBUx pins to the USB2.0 pins of the system device being protected from the Short-to-V<sub>BUS</sub> event.

### 6.3.2 CC1, CC2 Overvoltage Protection FETs 600-mA Capable for Passing VCONN Power

The CC pins on the USB Type-C connector serve many functions; one of the functions is to be a provider of power to active cables. Active cables are required when desiring to pass greater than 3 A of current on the V<sub>BUS</sub> line or when the USB Type-C port uses the super-speed lines (TX1+, TX2-, RX1+, RX1-, TX2+, TX2-, RX2+, RX2-). When CC is configured to provide power, it is called VCONN. VCONN is a DC voltage source in the range of 3V to 5.5V. If supporting VCONN, a VCONN provider must be able to provide 1.5 W of power to a cable; this translates into a current range of 273mA to 500mA (depending on the VCONN voltage level).

When a USB Type-C port is configured for VCONN and using the TPD4S480, this VCONN current flows through the OVP FETs of the TPD4S480. Therefore, the TPD4S480 has been designed to handle these currents and have an RON low enough to provide a specification compliant VCONN voltage to the active cable.

### 6.3.3 CC Dead Battery Resistors Integrated for Handling the Dead Battery Use Case in Mobile Devices

An important feature of USB Type-C and USB PD is the ability for this connector to serve as the sole power source to mobile devices. With support up to 240W, the USB Type-C connector supporting USB PD can be used to power a whole new range of mobile devices not previously possible with legacy USB connectors.

When the USB Type-C connector is the sole power supply for a battery powered device, the device must be able to charge from the USB Type-C connector even when its battery is dead. In order for a USB Type-C power adapter to supply power on V<sub>BUS</sub>, RD pulldown resistors must be exposed on the CC pins. These RD resistors are typically included inside a USB Type-C CC/PD controller. However, when the TPD4S480 is used to protect the USB Type-C port, the OVP FETs inside the device isolate these RD resistors in the CC/PD controller when the mobile device has no power. When the TPD4S480 has no power, the OVP FETs are turned off to provide overvoltage protection in a dead battery condition. Therefore, the TPD4S480 integrates high-voltage, dead battery RD pull-down resistors to allow dead battery charging simultaneously with high-voltage OVP protection.

If dead battery support is required, short the RPD\_G1 pin to the C\_CC1 pin, and short the RPD\_G2 pin to the C\_CC2 pin. This short connects the dead battery resistors to the connector CC pins. When the TPD4S480 is unpowered, and the RP pull-up resistor is connected from a power adapter, this RP pull-up resistor activates the RD resistor inside the TPD4S480, and enables  $V_{BUS}$  to be applied from the power adapter even in a dead battery condition. Once power is restored back to the system and back to the TPD4S480 on its VPWR pin, the TPD4S480 turns ON its OVP FETs in 3.5ms and then turns OFF its dead battery RD. The TPD4S480 first turns ON its CC OVP FETs fully, and then removes its dead battery RDs to make sure the PD controller RD is fully exposed before removing the RD of the TPD4S480.

If desiring to power the CC/PD controller during dead battery mode and if the CC/PD Controller is configured as a DRP, it is critical that the TPD4S480 be powered before or at the same time that the CC/PD controller is powered. It is also critical that when unpowered, the CC/PD controller also expose its dead battery resistors. When the TPD4S480 gets powered, it exposes the CC pins of the CC/PD controller within 3.5ms, and then removes its own RD dead battery resistors. Once the TPD4S480 turns on, the RD pull-down resistors of the CC/PD controller must be present immediately, in order to maintain a connection. If the power adapter does not see RD present, it can disconnect  $V_{BUS}$ . This event removes power from the device with its battery still not sufficiently charged, which consequently removes power from the CC/PD controller and the TPD4S480. Then the RD resistors of the TPD4S480 are exposed again, and connects the  $V_{BUS}$  of the power adapter to start the cycle over.

If the CC/PD Controller is configured for DRP and has started to DRP toggle before the TPD4S480 turns on, this DRP toggle is unable to maintain a connection with a power adapter. If the CC/PD controller is configured for DRP, the dead battery resistors of the PD controller need to be exposed as well, and that the resistors remain exposed until the TPD4S480 turns on. This behavior is typically accomplished by powering the TPD4S480 at the same time as the CC/PD controller when powering the CC/PD controller in dead battery operation.

If dead battery charging is not required in your application, connect the RPD\_G1 and RPD\_G2 pins to ground.

### 6.3.4 EPR Adapter

The TPD4S480 integrates additional circuitry that may be used to adapt a PD controller with pin tolerances below EPR levels for use in EPR applications. The EPR adapter consists of two components, the  $V_{BUS}$  divider and the EPR blocking FET gate driver. The EPR adapter features are enabled by asserting the EPR\_EN pin or when the  $V_{BUS}$  pin exceeds EPR\_THRESH\_R.

図 6-1. EPR Adapter

### 6.3.4.1 VBUS Divider

The VBUS divider provides a divided down output of VBUS so that an attached PD controller can safely sense EPR voltages. 表 6-1 summarizes the operating states of the VBUS divider.

**表 6-1. VBUS Divider States**

| EPR_EN | VBUS           | VBUS_LV Ratio (VBUS_LV / VBUS) | Description   |

|--------|----------------|--------------------------------|---------------|

| 0      | < EPR_THRES_R  | 1                              | SPR Operation |

| 1      | X              | 0.42                           | EPR Operation |

| X      | > EPR_THRESH_R | 0.42                           |               |

### 6.3.4.2 EPR Blocking FET Gate Driver

An NFET gate driver is integrated for controlling an external blocking FET. When in EPR mode the gate driver is disabled, isolating any non-EPR tolerant circuitry from VBUS. When in SPR mode the gate driver is enabled connecting low voltage components to VBUS.

**表 6-2. VBUS Divider States**

| EPR_EN | VBUS           | Gate Driver State | Description   |

|--------|----------------|-------------------|---------------|

| 0      | < EPR_THRES_R  | Enabled           | SPR Operation |

| 1      | X              | Disabled          | EPR Operation |

| X      | > EPR_THRESH_R | Disabled          |               |

## 6.4 Device Functional Modes

表 6-3 describes all of the functional modes for the TPD4S480. The "X" in the below table are "don't care" conditions, meaning any value can be present within the absolute maximum ratings of the data sheet and maintain that functional mode.

**表 6-3. Device Mode Table**

| Device Mode Table           |                                                         | Inputs |       |        |                                                 |                | Outputs              |         |          |                             |                             |

|-----------------------------|---------------------------------------------------------|--------|-------|--------|-------------------------------------------------|----------------|----------------------|---------|----------|-----------------------------|-----------------------------|

| MODE                        |                                                         | VPWR   | C_CCx | C_SBUx | RPD_Gx                                          | T <sub>J</sub> | FLT                  | CC FETs | SBU FETs | VBUS_LV                     | EPR_BLK_G                   |

| Normal Operating Conditions | Unpowered, no dead battery support                      | <UVLO  | X     | X      | Grounded                                        | X              | High-Z               | OFF     | OFF      | VBUS                        | Disabled                    |

|                             | Unpowered, dead battery support                         | <UVLO  | X     | X      | Shorted to C_CCx                                | X              | High-Z               | OFF     | OFF      | VBUS                        | Disabled                    |

|                             | Powered on, SPR mode                                    | >UVLO  | <OVP  | <OVP   | X, forced OFF                                   | <TSD           | High-Z               | ON      | ON       | VBUS                        | Enabled                     |

|                             | Powered on, EPR mode                                    | >UVLO  | <OVP  | <OVP   | X, forced OFF                                   | <TSD           | High-Z               | ON      | ON       | Divided VBUS                | Disabled                    |

| Fault Conditions            | Thermal shutdown                                        | >UVLO  | X     | X      | X, forced OFF                                   | >TSD           | Low (Fault Asserted) | OFF     | OFF      | Maintains EPR state         | Maintains EPR state         |

|                             | CC over voltage condition                               | >UVLO  | >OVP  | X      | X, forced OFF                                   | <TSD           | Low (Fault Asserted) | OFF     | OFF      | Maintains EPR state         | Maintains EPR state         |

|                             | SBU over voltage condition                              | >UVLO  | X     | >OVP   | X, forced OFF                                   | <TSD           | Low (Fault Asserted) | OFF     | OFF      | Maintains EPR state         | Maintains EPR state         |

|                             | IEC ESD generated over voltage condition <sup>(1)</sup> | >UVLO  | X     | X      | R <sub>D</sub> ON if RPD_Gx is shorted to C_CCx | <TSD           | Low (Fault Asserted) | OFF     | OFF      | Maintains current EPR state | Maintains current EPR state |

(1) This row describes the state of the device while still in OVP after the IEC ESD strike which put the device into OVP is over, and the voltages on the C\_CCx and C\_SBUx pins have returned to their normal voltage levels.

## 7 Application and Implementation

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 Application Information

The TPD4S480 provides 4-channels of Short-to-V<sub>BUS</sub> overvoltage protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector. Care must be taken to insure that the TPD4S480 provides adequate system protection as well as insuring that proper system operation is maintained. The following application example explains how to properly design the TPD4S480 into a USB Type-C system.

### 7.2 Typical Application

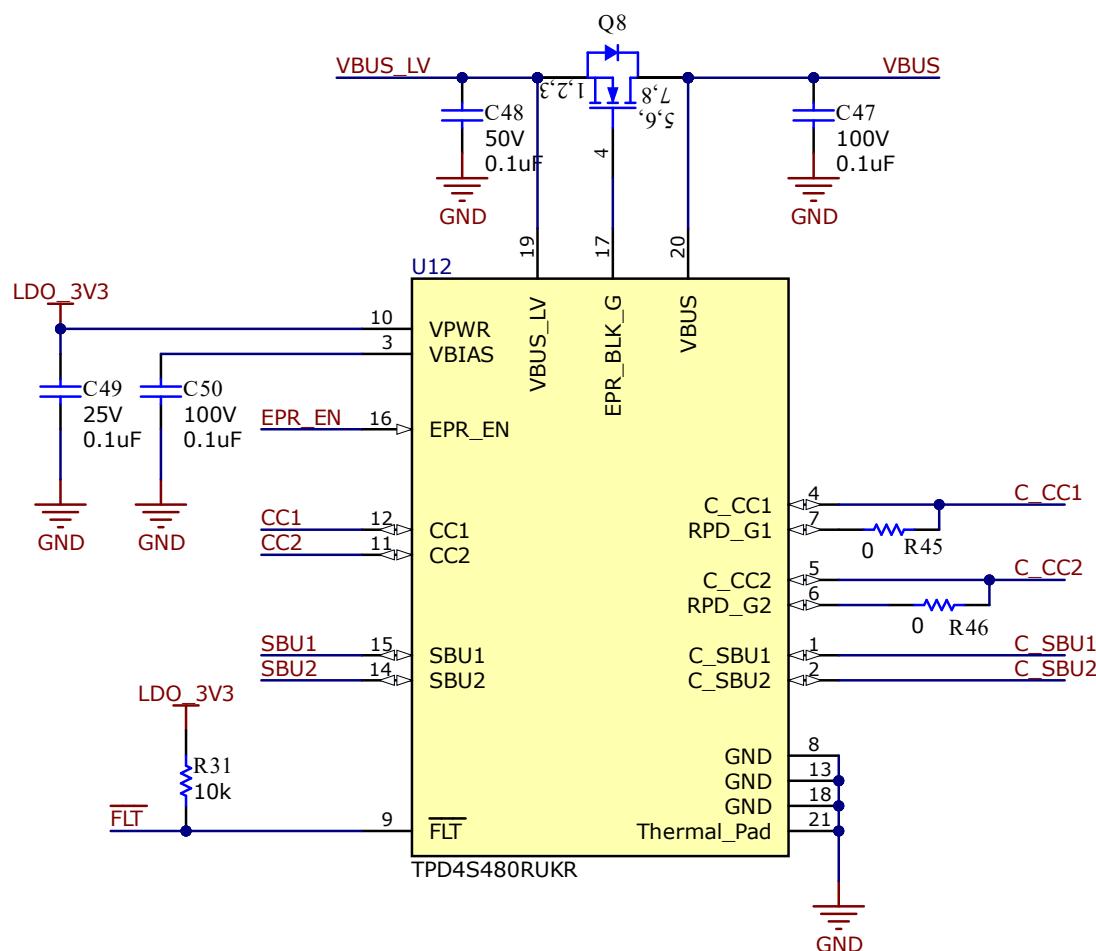

図 7-1. TPD4S480 Reference Schematic

### 7.2.1 Design Requirements

In this application example we study the protection requirements for a USB Type-C DRP Port, fully equipped with USB-PD, and 240W charging. The [TPS26750](#) is used to easily enable a DRP port. Both the CC and SBU pins are susceptible to shorting to the  $V_{BUS}$  pin. With 240W charging,  $V_{BUS}$  operates at 48V, requiring the CC and SBU pins to tolerate 48V<sub>DC</sub>. With these protection requirements present for the USB Type-C connector, the TPD4S480 is used.

表 7-1 lists the TPD4S480 design parameters.

**表 7-1. Design Parameters**

| DESIGN PARAMETER                                      | EXAMPLE VALUE |

|-------------------------------------------------------|---------------|

| $V_{BUS}$ nominal operating voltage                   | 48V           |

| Short-to- $V_{BUS}$ tolerance for the CC and SBU pins | 63V           |

| $V_{BIAS}$ nominal capacitance                        | 0.1 $\mu$ F   |

| Dead battery charging                                 | 240W          |

| Maximum ambient temperature requirement               | 85°C          |

The recommended MOSFET settings for Q8, as shown in 表 7-2, are as follows:

**表 7-2. MOSFET Selection**

| VDS (V)  | VGS (V)  | Type      | RDS (on)                                                                             |

|----------|----------|-----------|--------------------------------------------------------------------------------------|

| $>= 30V$ | $>= 15V$ | N-channel | $<= 10m\text{Ohms}$ (3A max Q8 current)<br>$<= 20m\text{Ohms}$ (1.5A max Q8 current) |

#### 7.2.1.1 EPR Design Requirements

The TPD4S480 works in conjunction with the PD controller to provide the following functionality in USB-PD EPR:

- Short to  $V_{BUS}$  protection for direct shorts to CC1 and CC2 pins of the Type-C connector.

- Short to  $V_{BUS}$  protection for the liquid detection circuitry that is connected to the SBU1 and SBU2 pins of the Type-C connector, if the liquid detection feature is implemented.

- Voltage level translation from up the EPR maximum voltage down to the operation range of the  $V_{BUS}$  pins of the PD controller.

- Gate drive for a high voltage NMOS transistor to allow the internal 5V power path to be used to source 5V in systems that only require a 5V output.

## 7.2.2 Detailed Design Procedure

### 7.2.2.1 VBIAS Capacitor Selection

As noted in the [セクション 5.3](#) table, a minimum of 63V<sub>BUS</sub> rated capacitor is required for the VBIAS pin, and a 100V<sub>BUS</sub> capacitor is recommended. The VBIAS capacitor is in parallel with the central diode clamp integrated inside the TPD4S480. A forward biased hiding diode connects the VBIAS pin to the C\_CCx and C\_SBUx pins. Therefore, when a Short-to-V<sub>BUS</sub> event occurs at 48V, 48V<sub>BUS</sub> minus a forward biased diode drop is exposed to the VBIAS pin. Additionally, during the short-to-V<sub>BUS</sub> event, ringing can occur almost double the settling voltage of 48V, allowing a potential 96V to be exposed to the C\_CCx and C\_SBUx pins. However, the internal diode clamps limit the voltage exposed to the C\_CCx and C\_SBUx pins to around 63V. Therefore, at least 63V capacitor is required to insure the VBIAS capacitor does not get destroyed during Short-to-V<sub>BUS</sub> events.

A 100V, X7R capacitor is recommended to further improve the derating performance of the capacitors. When the voltage across a real capacitor is increased, the capacitance value derates. The more the capacitor derates, the larger the ringing in the short-to-V<sub>BUS</sub> RLC circuit. The 100V X7R capacitors have great derating performance, allowing for the best short-to-V<sub>BUS</sub> performance of the TPD4S480.

### 7.2.2.2 Dead Battery Operation

For this application, we want to support 240W dead battery operation; when the device is out of battery, we still want to charge the laptop at 48V and 5A. This means that the USB PD Controller must receive power in dead battery mode. The TPS26750 has a built in LDO to supply the TPS26750 power from V<sub>BUS</sub> in a dead battery condition.

The OVP FETs of the TPD4S480 remain OFF when unpowered to provide protection in dead battery or unpowered situations. However, when the OVP FETs are OFF, this isolates the TPS26750s dead battery resistors from the USB Type-C ports CC pins. A USB Type-C power adapter must see the RD pull-down dead battery resistors on the CC pins to provide power on V<sub>BUS</sub>. Since the dead battery resistors of the TPS26750 are isolated from the USB Type-C connector CC pins, the built-in, dead battery resistors of the TPD4S480 must be connected. Short the RPD\_G1 pin to the C\_CC1 pin, and short the RPD\_G2 pin to the C\_CC2 pin.

Once the power adapter sees the dead battery resistors of the TPD4S480, 5V is applied on the V<sub>BUS</sub> pin. This provides power to the TPS26750, turning the PD controller on, and allowing the battery to begin to charge. However, this application requires 240W charging in dead battery mode, so V<sub>BUS</sub> at 48V and 5A is required. USB PD negotiation is required to accomplish this, so the TPS26750 needs to be able to communicate on the CC pins. The TPD4S480 needs to be turned on in dead battery mode as well so the PD controller can be exposed to the CC lines. To turn on the device, the TPD4S480 is powered by the internal LDO of the TPS26750, the LDO\_3V3 pin. When the TPS26750 receives power on V<sub>BUS</sub>, the TPD4S480 is turned on simultaneously.

The dead battery resistors of the PD controller also need to be present so the PD controller properly boots up in dead battery operation with the correct voltages on the CC pins.

Once this process has occurred, the TPS26750 can start negotiating with the power adapter through USB PD for higher power levels, allowing 240W operation in dead battery mode.

For more information on the TPD4S480 dead battery operation, see the [CC Dead Battery Resistors Integrated for Handling the Dead Battery Use Case in Mobile Devices](#) section of the data sheet.

### 7.2.2.3 CC Line Capacitance

USB PD has a specification for the total amount of capacitance that is required for proper USB PD BMC operation on the CC lines.

**表 7-3. USB PD cReceiver Specification**

| NAME      | DESCRIPTION             | MIN | MAX | UNIT | COMMENT                                                                                          |

|-----------|-------------------------|-----|-----|------|--------------------------------------------------------------------------------------------------|

| cReceiver | CC receiver capacitance | 200 | 600 | pF   | The DFP or UFP system shall have capacitance within this range when not transmitting on the line |

The capacitance on the CC lines must stay in between 200pF and 600pF when USB PD is being used. Therefore, the combination of capacitances added to the system by the TPS26750, the TPD4S480, and any external capacitor must fall within these limits.

#### 7.2.2.4 Additional ESD Protection on CC and SBU Lines

If additional IEC ESD protection is desired to be placed on either the CC or SBU lines, it is important that high-voltage ESD protection diodes be used. The maximum DC voltage that can be seen in USB PD is 50.4V, with 50.9V allowed during voltage transitions. Therefore, an ESD protection diode must have a reverse stand off voltage higher than 50.9V to prevent the diode from breakdown during a short-to-V<sub>BUS</sub> event.

Due to the fact that the Short-to-V<sub>BUS</sub> event applies a DC voltage to the CC and SBU pins, a deep-snap-back diode cannot be used unless its minimum trigger voltage is above 96V. During a Short-to-V<sub>BUS</sub> event, RLC ringing of up to twice the settling voltage can be exposed to CC and SBU, allowing for up to 48V to be exposed. Furthermore, if any capacitor derates on the CC or SBU line, greater ringing can occur. Since this ringing is hard to bound, it is recommended to not use deep-snap-back diodes. If the deep-snap-back diode triggers during the short-to-V<sub>BUS</sub> hot-plug event, it begins to operate in its conduction region. With a 48V V<sub>BUS</sub> source present on the CC or SBU line, this allows the diode to conduct indefinitely.

#### 7.2.2.5 FLT Pin Operation

Once a Short-to-V<sub>BUS</sub> occurs on the C\_CCx or C\_SBUx pins, the  $\overline{\text{FLT}}$  pin is asserted in 20 $\mu$ s (typical) so the PD controller can be notified quickly. If V<sub>BUS</sub> is being shorted to CC or SBU, it is recommended to respond to the event by forcing a detach in the USB PD controller to remove V<sub>BUS</sub> from the port. Although the USB Type-C port using the TPD4S480 is not damaged, as the TPD4S480 provides protection from these events, the other device connected through the USB Type-C Cable or any active circuitry in the cable can be damaged. Although shutting the V<sub>BUS</sub> off through a detach does not ensure it stops the other device or cable from being damaged, it can mitigate any high current paths from causing further damage after the initial damage takes place. Additionally, even if the active cable or other device does have proper protection, the short-to-V<sub>BUS</sub> event may corrupt a configuration in an active cable or in the other PD controller, so it is best to detach and reconfigure the port.

#### 7.2.2.6 How to Connect Unused Pins

If either the RPD\_Gx pins are unused in a design, they must be connected to GND.

### 7.2.3 EPR Application Curves

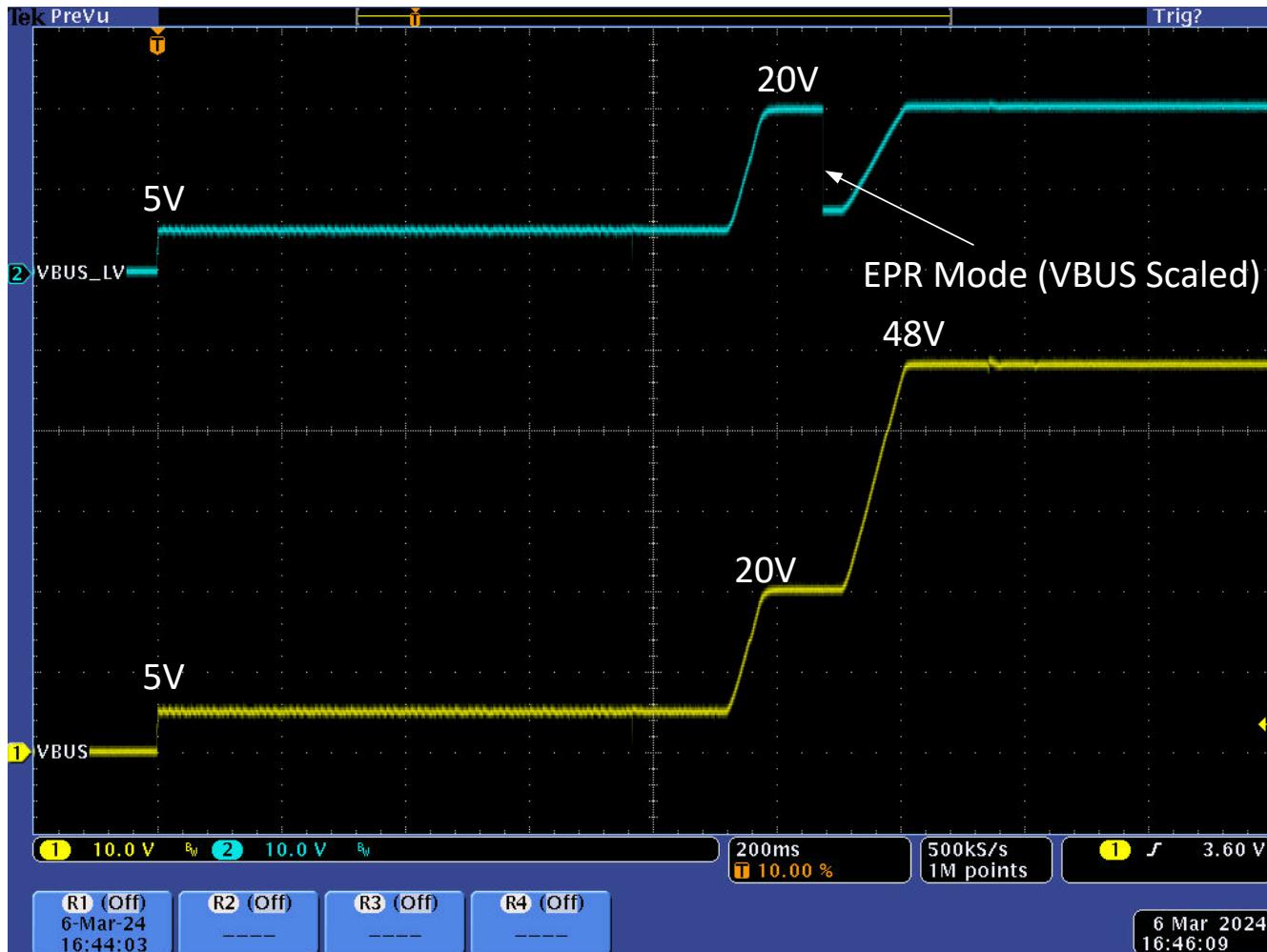

图 7-2 shows the VBUS and VBUS\_LV pins during a 5V to 48V voltage transition.

5

図 7-2. 48V EPR Contract Negotiation VBUS and VBUS LV

### 7.3 Power Supply Recommendations

The  $V_{PWR}$  pin provides power to all the circuitry in the TPD4S480. It is recommended a 1- $\mu$ F decoupling capacitor is placed as close as possible to the  $V_{PWR}$  pin. If USB PD is desired to be operated in dead battery conditions, it is critical that the TPD4S480 share the same power supply as the PD controller in dead battery boot-up (such as sharing the same dead battery LDO). See the [CC Dead Battery Resistors Integrated for Handling the Dead Battery Use Case in Mobile Devices](#) section for more details.

### 7.4 Layout

#### 7.4.1 Layout Guidelines

Proper routing and placement is important to maintain the signal integrity the USB2.0, SBU, CC line signals. The following guidelines apply to the TPD4S480 device:

- Place the bypass capacitors as close as possible to the  $V_{PWR}$  pin, and ESD protection capacitor as close as possible to the  $V_{BIAS}$  pin. Capacitors must be attached to a solid ground. This minimizes voltage disturbances during transient events such as short-to- $V_{BUS}$  and ESD strikes.

- The USB2.0 and SBU lines must be routed as straight as possible and any sharp bends must be minimized.

Standard ESD recommendations apply to the C\_CC1, C\_CC2, C\_SBU1, and C\_SBU2 as well:

- The optimum placement for the device is as close to the connector as possible:

- EMI during an ESD event can couple from the trace being struck to other nearby unprotected traces, resulting in early system failures.

- The PCB designer must minimize the possibility of EMI coupling by keeping any unprotected traces away from the protected traces which are between the TPD4S480 device and the connector.

- Route the protected traces as straight as possible.

- Eliminate any sharp corners on the protected traces between the TVS and the connector by using rounded corners with the largest radii possible.

- Electric fields tend to build up on corners, increasing EMI coupling.

#### 7.4.2 Layout Example

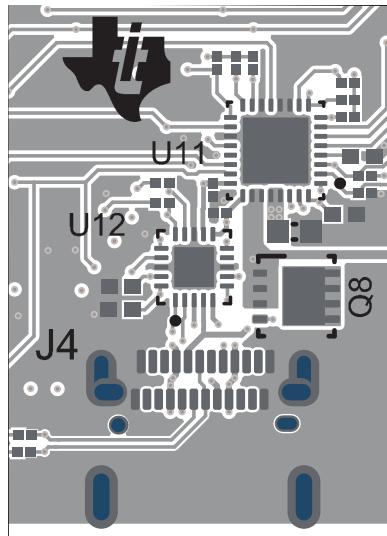

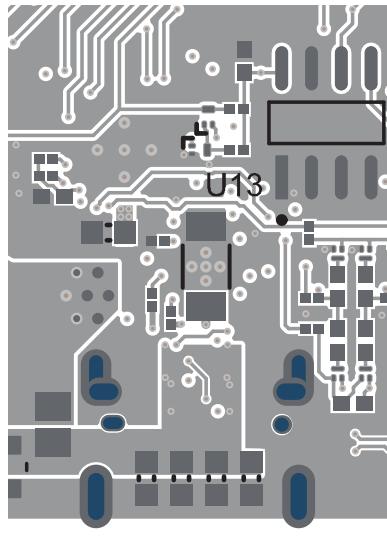

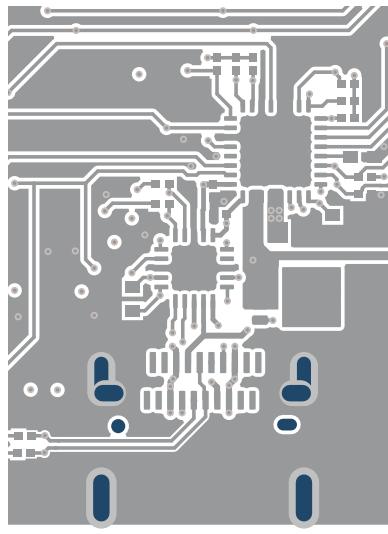

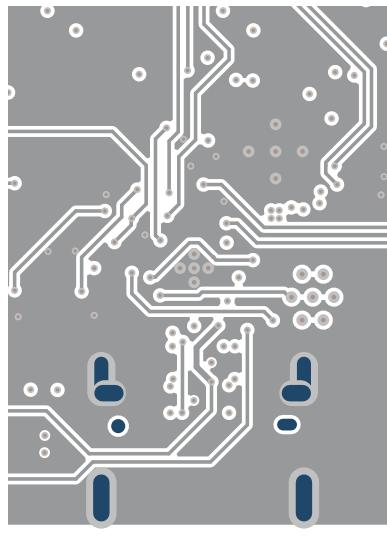

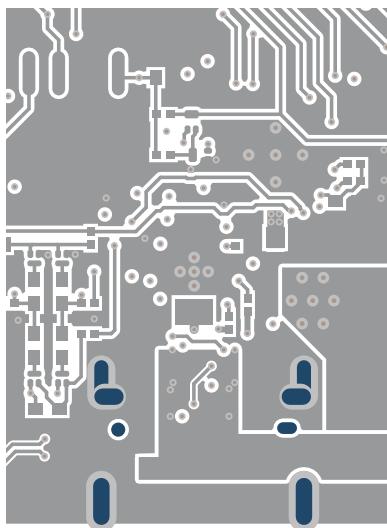

図 7-3. TPS26750 PCB Layout - Top Composite

図 7-4. TPS26750 PCB Layout - Bottom Composite

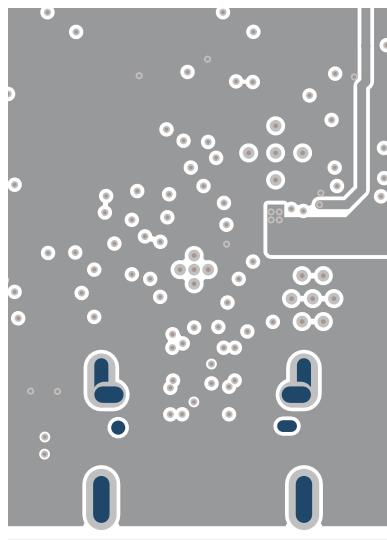

図 7-5. TPS26750 PCB Layout - Top Layer 1

図 7-6. TPS26750 PCB Layout - GND Layer 2

図 7-7. TPS26750 PCB Layout - Signal Layer 3

図 7-8. TPS26750 PCB Layout - Signal Layer 4

図 7-9. TPS26750 PCB Layout - GND Layer 5

図 7-10. TPS26750 PCB Layout - Bottom Layer 6

## 8 Device and Documentation Support

### 8.1 Documentation Support

#### 8.1.1 Related Documentation

For related documentation see the following:

[TPS26750 USB Type-C® and USB PD Controller With Integrated Power Switches Optimized for Power Applications](#)

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 8.4 Trademarks

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

[テキサス・インスツルメンツ用語集](#)

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| November 2024 | *        | Initial Release |

## 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

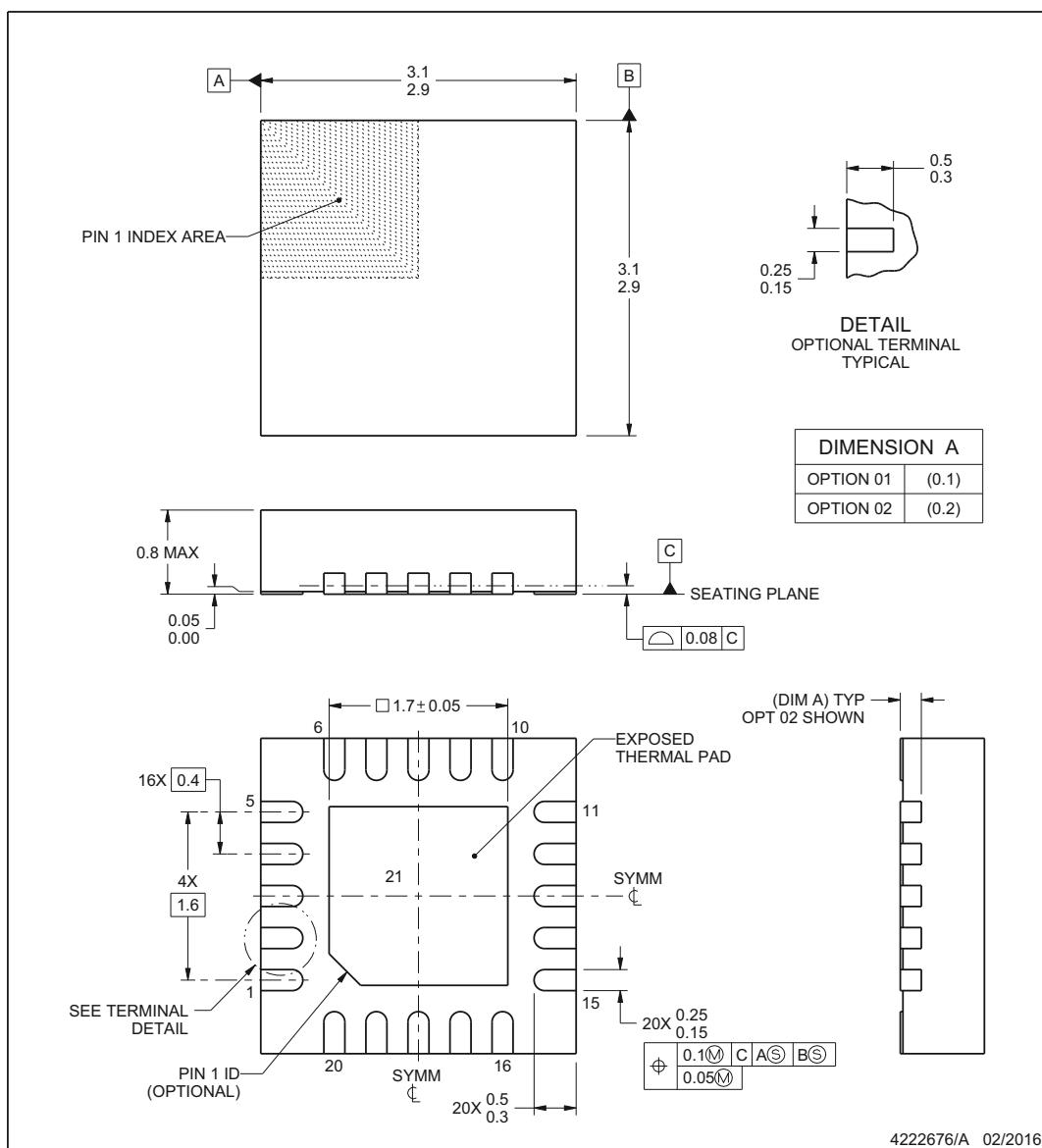

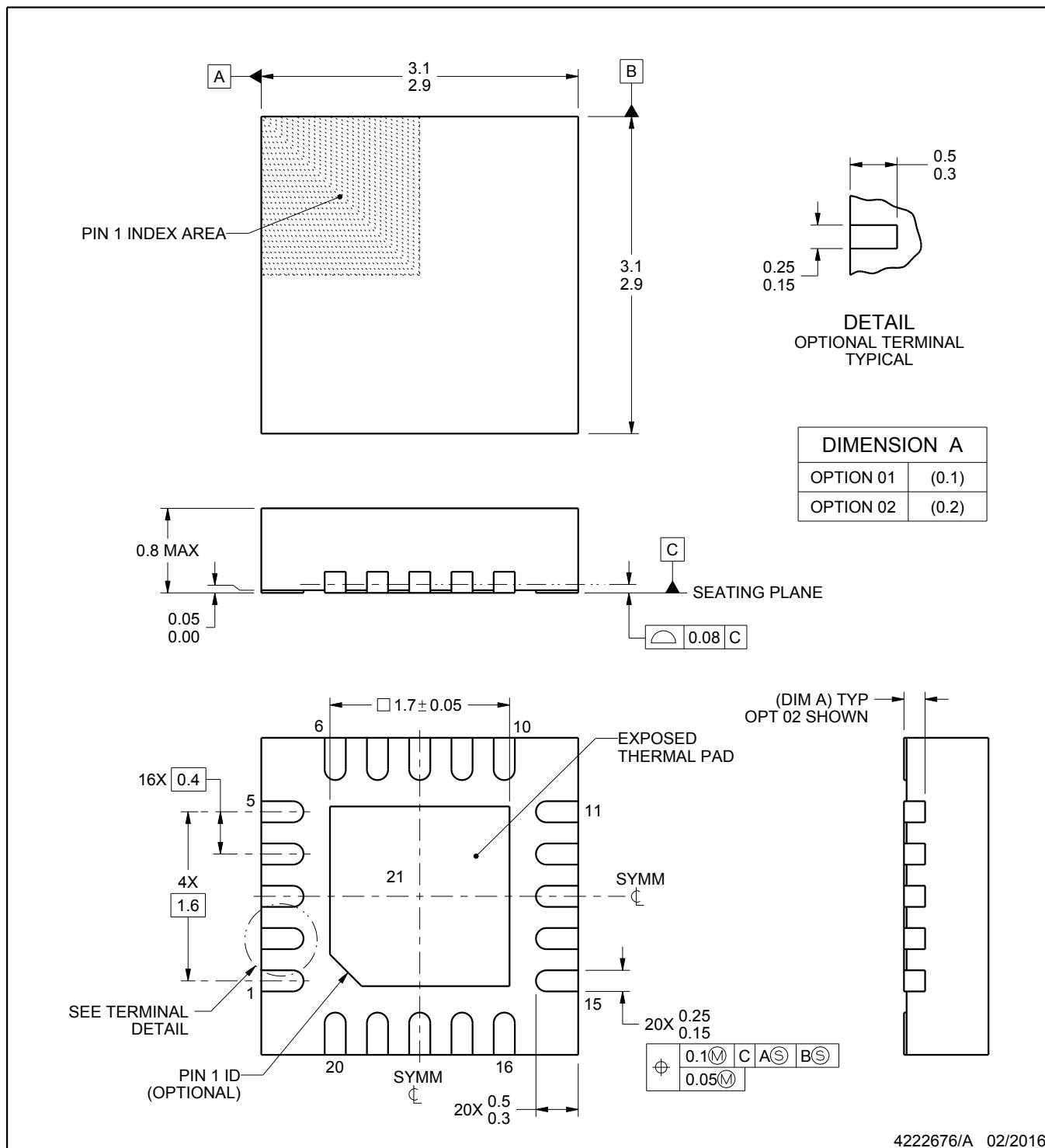

**RUK0020B**

**PACKAGE OUTLINE**

**WQFN - 0.8 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

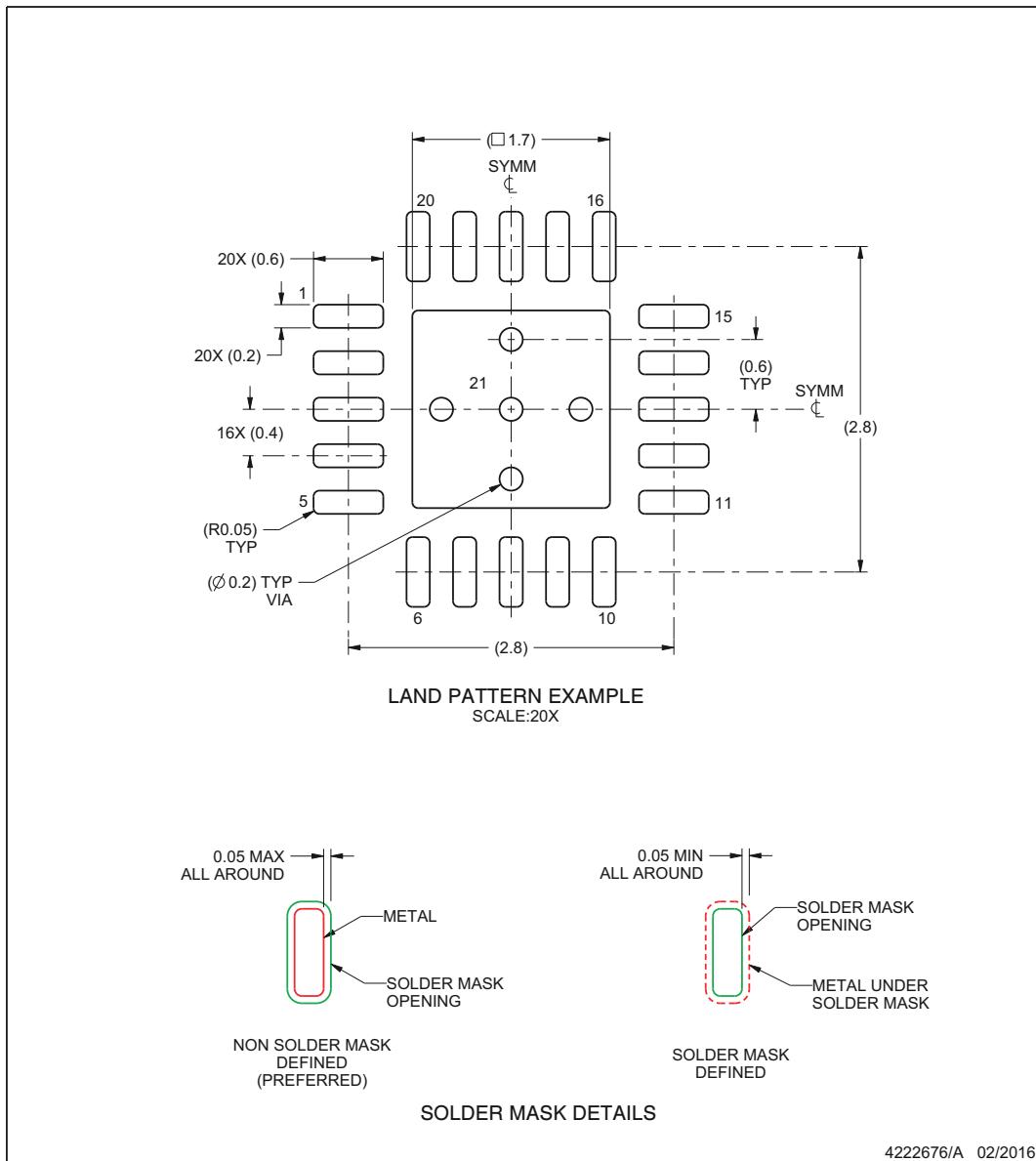

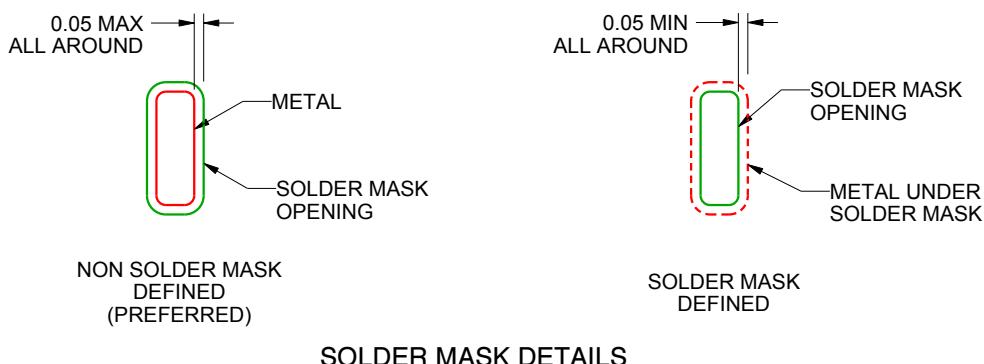

## EXAMPLE BOARD LAYOUT

### RUK0020B

**WQFN - 0.8 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

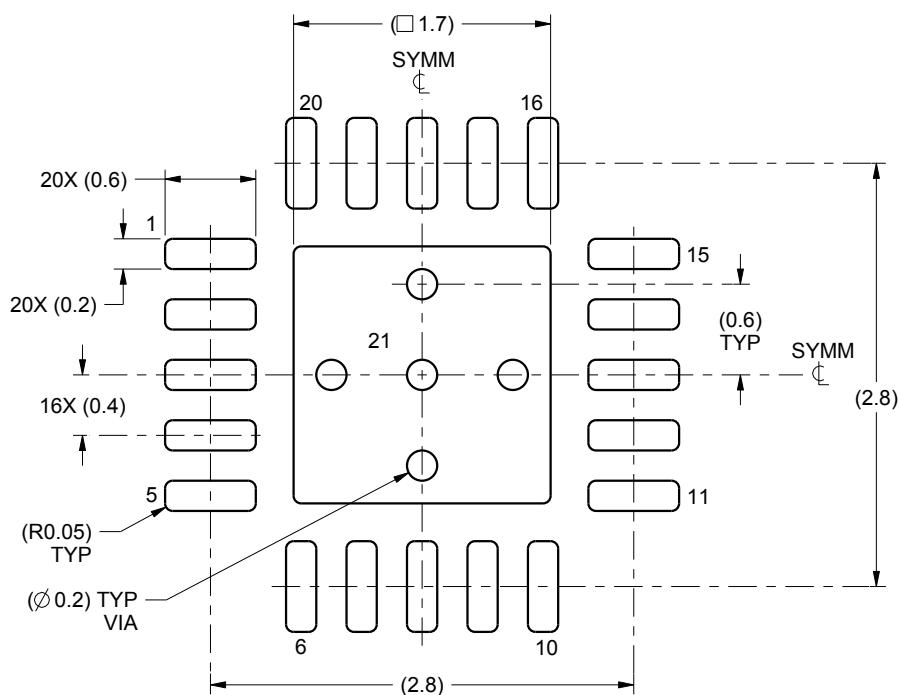

## EXAMPLE STENCIL DESIGN

**RUK0020B**

**WQFN - 0.8 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

**SOLDER PASTE EXAMPLE**

BASED ON 0.1 mm THICK STENCIL

EXPOSED PAD 21:

78% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:20X

4222676/A 02/2016

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPD4S480RUKR          | Active        | Production           | WQFN (RUK)   20 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 4S480               |

| TPD4S480RUKR.A        | Active        | Production           | WQFN (RUK)   20 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 4S480               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.