# TPL5010-Q1 AEC-Q100 ウオッチドッグ機能搭載Nano-Powerシステム・タイマ

## 1 特長

- 車載アプリケーションに対応

- 下記内容でAEC-Q100認定済み

- デバイス温度グレード1: 動作時周囲温度範囲  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$

- デバイスHBM ESD分類レベル2

- デバイスCDM ESD分類レベルC5

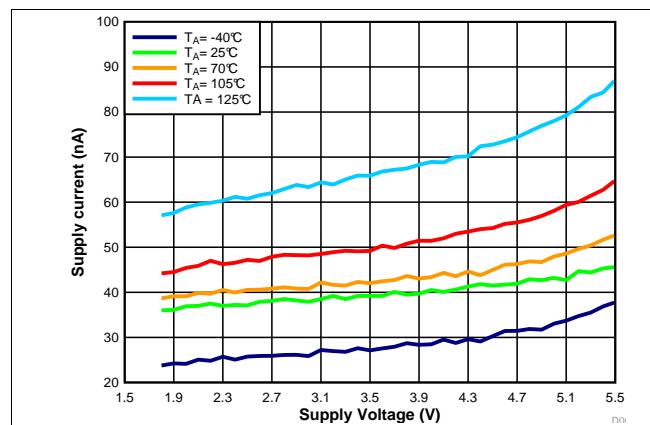

- 消費電流: 2.5Vで35nA (標準値)

- 電源電圧: 1.8V~5.5V

- 時間インターバルを100ms~7200sの範囲で選択可能

- タイマ精度: 1% (標準値)

- 時間インターバルを抵抗で選択可能

- ウォッチドッグ機能

- 手動リセット

- TPL5x10QファミリのAEC-Q100 Nano-Powerシステム・タイマ:

- TPL5010-Q1:** ウォッチドッグ機能、プログラム可能な遅延範囲

- TPL5110-Q1:** MOSドライバ、プログラム可能な遅延範囲、ワンショット機能

## 2 アプリケーション

- 電気自動車

- 常時オンのシステム

- バッテリ駆動システム

- クラッチ・アクチュエータ回路

- 車のドアハンドル回路

- スマートキー

- リモート電流センサ

- 侵入者検出

## 3 概要

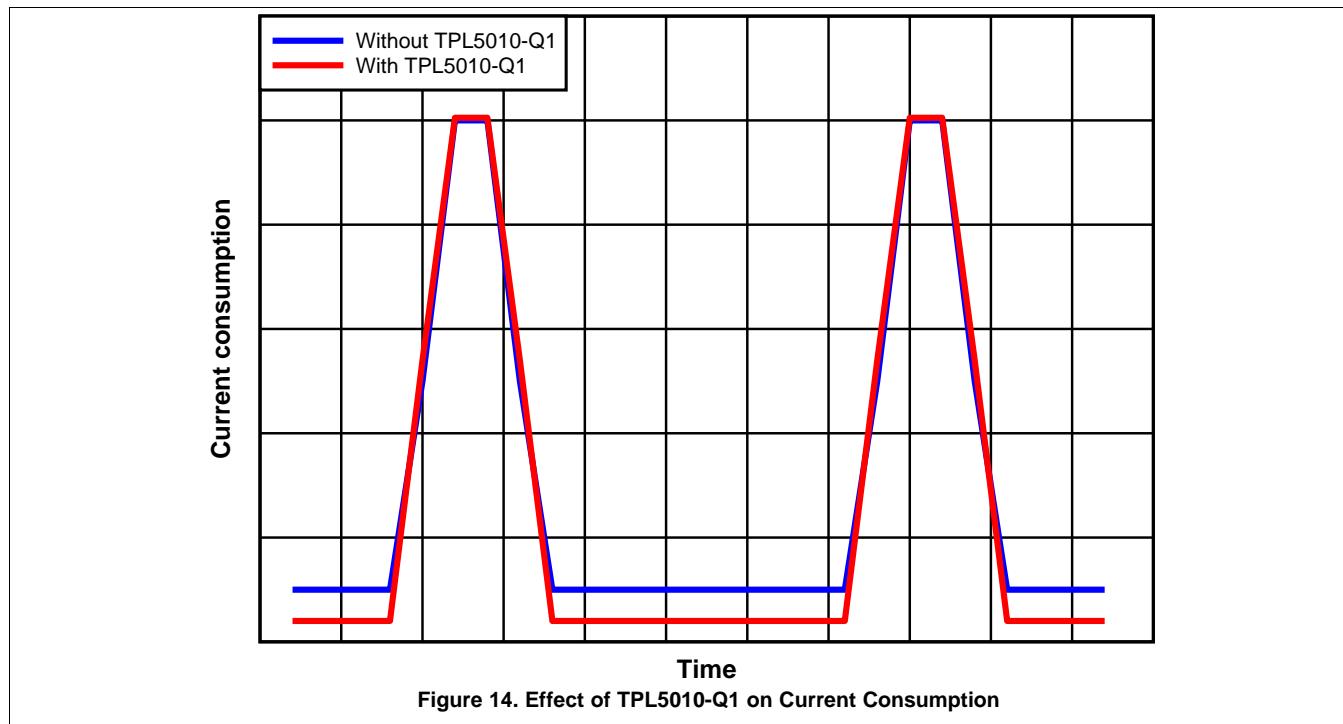

TPL5010-Q1 Nano Timerは低消費電力でAEC-Q100認定済みのタイマで、ウォッチドッグ機能を持ち、デューティ・サイクル制御またはバッテリ駆動のアプリケーションにおいて、システムのウェークアップを行うために理想的です。このようなシステムでは、マイクロコントローラのタイマを使用してシステムをウェークアップできますが、タイマのスリープ時電流が大きい場合には、スリープ・モード中にシステムの合計電流の最大60~80%がこのマイクロコントローラのタイマにより消費されることがあります。

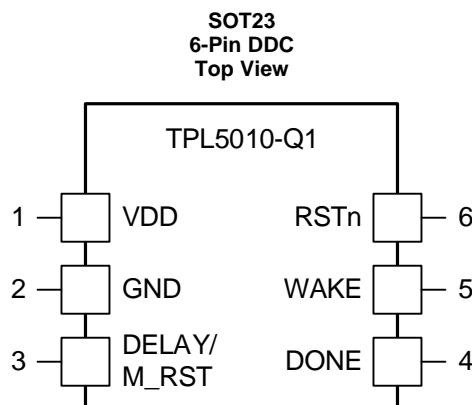

TPL5010-Q1は内蔵のマイクロコントローラのタイマに代わる機能を持ち、消費電流がわずか35nAで、マイクロコントローラを、消費電力がはるかに低いモードに移行できます。このような電力削減によりバッテリ駆動時間が延長され、より小さなバッテリを使用できるようになります。TPL5010-Q1は電力の制限が厳しいアプリケーションに理想的です。TPL5010-Q1はタイミング・インターバルを100ms~7200sの範囲で選択でき、割り込み駆動のアプリケーション用に設計されています。一部の標準(EN50271など)では、安全性のためにウォッチドッグの実装が要求されています。TPL5010-Q1を使用すると、ほぼ消費電力の増加なしに、このウォッチドッグ機能を実現できます。TPL5010-Q1は6ピンのSOT23パッケージで供給されます。

### 製品情報<sup>(1)</sup>

| 型番         | パッケージ     | 本体サイズ(公称)     |

|------------|-----------|---------------|

| TPL5010-Q1 | SOT23 (6) | 3.00mm×3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

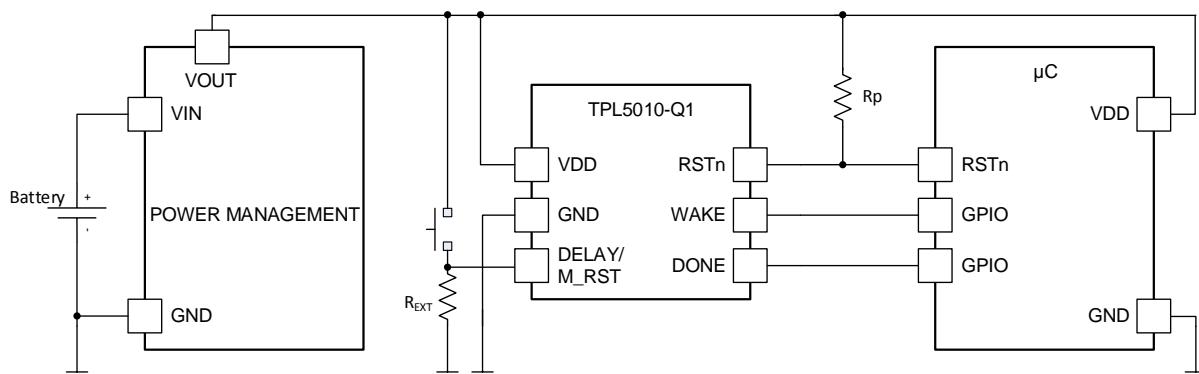

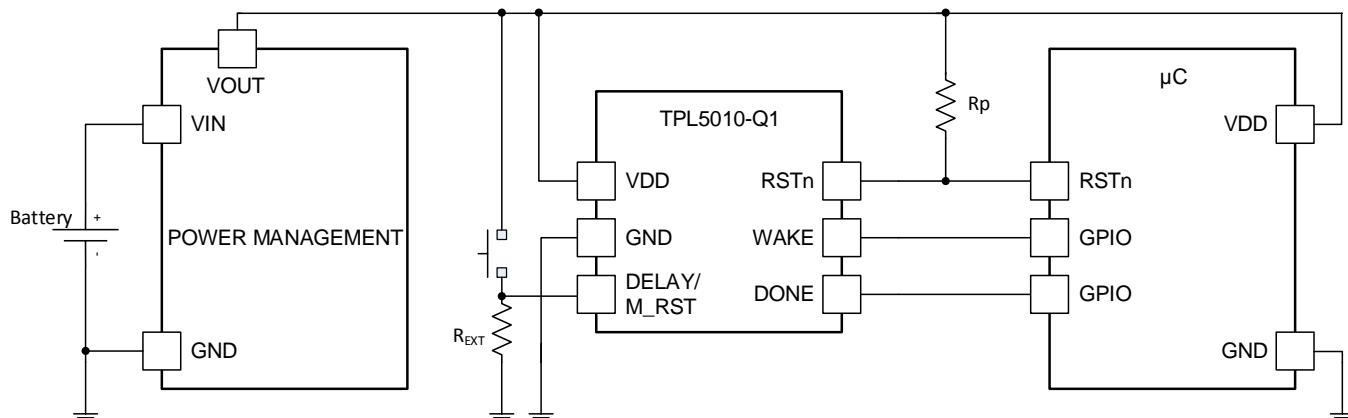

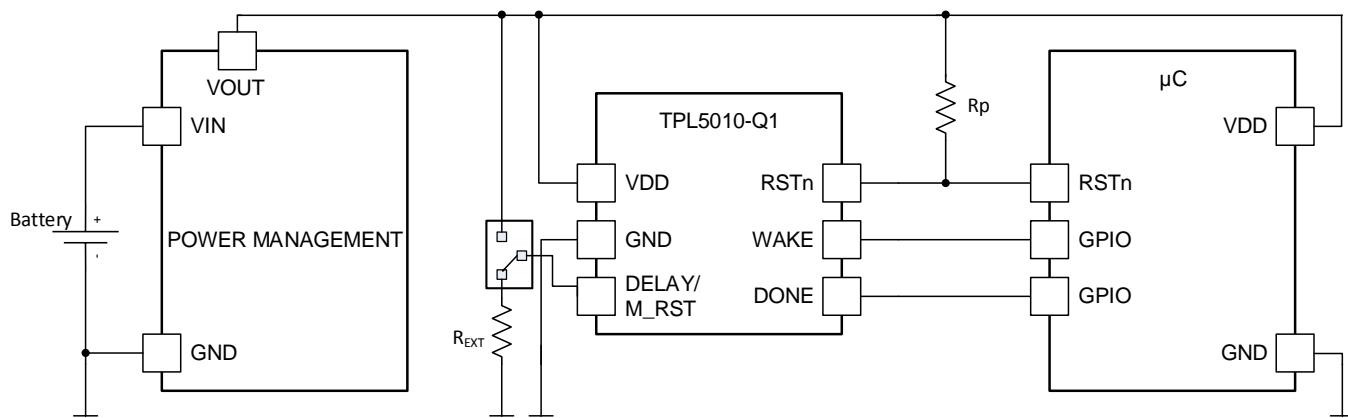

### アプリケーション概略図

## 目次

|                                          |   |                                         |    |

|------------------------------------------|---|-----------------------------------------|----|

| <b>1 特長</b>                              | 1 | 8.3 Feature Description                 | 8  |

| <b>2 アプリケーション</b>                        | 1 | 8.4 Device Functional Modes             | 9  |

| <b>3 概要</b>                              | 1 | 8.5 Programming                         | 9  |

| <b>4 改訂履歴</b>                            | 2 | <b>9 Application and Implementation</b> | 15 |

| <b>5 デバイス比較表</b>                         | 2 | 9.1 Application Information             | 15 |

| <b>6 Pin Configuration and Functions</b> | 3 | 9.2 Typical Application                 | 15 |

| <b>7 Specifications</b>                  | 4 | <b>10 Power Supply Recommendations</b>  | 17 |

| 7.1 Absolute Maximum Ratings             | 4 | <b>11 Layout</b>                        | 17 |

| 7.2 ESD Ratings                          | 4 | 11.1 Layout Guidelines                  | 17 |

| 7.3 Recommended Operating Conditions     | 4 | 11.2 Layout Example                     | 17 |

| 7.4 Thermal Information                  | 4 | <b>12 デバイスおよびドキュメントのサポート</b>            | 18 |

| 7.5 Electrical Characteristics           | 5 | 12.1 ドキュメントの更新通知を受け取る方法                 | 18 |

| 7.6 Timing Requirements                  | 6 | 12.2 コミュニティ・リソース                        | 18 |

| 7.7 Typical Characteristics              | 7 | 12.3 商標                                 | 18 |

| <b>8 Detailed Description</b>            | 8 | 12.4 静電気放電に関する注意事項                      | 18 |

| 8.1 Overview                             | 8 | 12.5 Glossary                           | 18 |

| 8.2 Functional Block Diagram             | 8 | <b>13 メカニカル、パッケージ、および注文情報</b>           | 18 |

## 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2016年9月 | *    | 初版 |

## 5 デバイス比較表

**TPL5x10QファミリのAEC-Q100 Nano-Powerシステム・タイマ**

| 型番         | 消費電流(標準値) | 特別な機能        |

|------------|-----------|--------------|

| TPL5010-Q1 | 35nA      | 低消費電力タイマ     |

|            |           | ウォッチドッグ機能    |

|            |           | 遅延範囲をプログラム可能 |

|            |           | 手動リセット       |

| TPL5110-Q1 | 35nA      | 低消費電力タイマ     |

|            |           | MOSドライバ      |

|            |           | 遅延範囲をプログラム可能 |

|            |           | 手動リセット       |

|            |           | ワンショット機能     |

## 6 Pin Configuration and Functions

**Table 1. Pin Functions**

| PIN |                 | TYPE <sup>(1)</sup> | DESCRIPTION                                          | APPLICATION INFORMATION                                                                                                  |

|-----|-----------------|---------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME            |                     |                                                      |                                                                                                                          |

| 1   | VDD             | P                   | Supply voltage                                       |                                                                                                                          |

| 2   | GND             | G                   | Ground                                               |                                                                                                                          |

| 3   | DELAY/<br>M_RST | I                   | Time Interval set and Manual Reset                   | Resistance between this pin and GND is used to select the time interval. The reset switch is also connected to this pin. |

| 4   | DONE            | I                   | Logic Input for watchdog functionality               | Digital signal driven by the µC to indicate successful processing of the WAKE signal.                                    |

| 5   | WAKE            | O                   | Timer output signal generated every $t_{IP}$ period. | Digital pulsed signal to wake up the µC at the end of the programmed time interval.                                      |

| 6   | RSTn            | O                   | Reset Output (open drain output)                     | Digital signal to RESET the µC, pull-up resistance is required                                                           |

(1) G= Ground, P= Power, O= Output, I= Input.

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                         | MIN  | MAX       | UNIT |

|------------------|-----------------------------------------|------|-----------|------|

|                  | Supply voltage (VDD-GND)                | -0.3 | 6.0       | V    |

|                  | Input voltage at any pin <sup>(2)</sup> | -0.3 | VDD + 0.3 | V    |

|                  | Input current on any pin                | -5   | 5         | mA   |

| T <sub>stg</sub> | Storage temperature                     | -65  | 150       | °C   |

| T <sub>J</sub>   | Junction temperature <sup>(3)</sup>     |      | 150       | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under [Recommended Operating Conditions](#). Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) The voltage between any two pins should not exceed 6V.

- (3) The maximum power dissipation is a function of T<sub>J</sub>(MAX), θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is PDMAX = (T<sub>J</sub>(MAX) - T<sub>A</sub>) / θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC board.

### 7.2 ESD Ratings

|                    |                         | VALUE                                             | UNIT  |

|--------------------|-------------------------|---------------------------------------------------|-------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model, per AEC Q100-002 <sup>(1)</sup> | ±2000 |

|                    |                         | Charged-device model (CDM), per AEC Q10-011       |       |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                          | MIN | NOM | MAX | UNIT |

|--------------------------|-----|-----|-----|------|

| Supply voltage (VDD-GND) | 1.8 |     | 5.5 | V    |

| Temperature              | -40 |     | 125 | °C   |

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | TPL5010-Q1 | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | SOT23      |      |

|                               |                                              | 6 PINS     |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 163        | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 26         | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 57         | °C/W |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 7.5        | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 57         | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 7.5 Electrical Characteristics

$T_A = 25^\circ\text{C}$ ,  $\text{VDD-GND}=2.5\text{ V}$  (unless otherwise stated)<sup>(1)</sup>

|                             | PARAMETER                                                   | TEST CONDITIONS                                  | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |  |  |

|-----------------------------|-------------------------------------------------------------|--------------------------------------------------|--------------------|--------------------|--------------------|------|--|--|

| <b>POWER SUPPLY</b>         |                                                             |                                                  |                    |                    |                    |      |  |  |

| IDD                         | Supply current <sup>(4)</sup>                               | Operation mode                                   | 35                 | 50                 | nA                 |      |  |  |

|                             |                                                             | Digital conversion of external resistance (Rext) | 200                | 400                | μA                 |      |  |  |

| <b>TIMER</b>                |                                                             |                                                  |                    |                    |                    |      |  |  |

| t <sub>IP</sub>             | Time interval period <sup>(5)</sup>                         | 1650 selectable time Intervals                   | Min time interval  | 100                | ms                 |      |  |  |

|                             |                                                             |                                                  | Max time interval  | 7200               | s                  |      |  |  |

| t <sub>osc</sub>            | Time interval setting accuracy <sup>(6)</sup>               | Excluding the precision of Rext                  | ±0.6%              |                    |                    |      |  |  |

|                             | Timer interval setting accuracy over supply voltage         | 1.8 V ≤ VDD ≤ 5.5 V                              | ±25                |                    | ppm/V              |      |  |  |

|                             | Oscillator accuracy                                         |                                                  | −0.5%              | 0.5%               |                    |      |  |  |

|                             | Oscillator accuracy over temperature <sup>(5)</sup>         | −40°C ≤ T <sub>A</sub> ≤ 125°C                   | 150                | ppm/°C             |                    |      |  |  |

| t <sub>DONE</sub>           | Oscillator accuracy over supply voltage <sup>(5)</sup>      | 1.8 V ≤ VDD ≤ 5.5 V                              | ±0.4               |                    | %/V                |      |  |  |

|                             | Oscillator accuracy over life time <sup>(7)</sup>           |                                                  | 0.24%              |                    |                    |      |  |  |

| t <sub>DONE</sub>           | Minimum DONE pulse width <sup>(5)</sup>                     |                                                  | 100                | ns                 |                    |      |  |  |

| t <sub>RSTn</sub>           | RSTn pulse width                                            |                                                  | 320                | ms                 |                    |      |  |  |

| t <sub>WAKE</sub>           | WAKE pulse width                                            |                                                  | 20                 | ms                 |                    |      |  |  |

| t <sub>Rext</sub>           | Time to convert Rext <sup>(5)</sup>                         |                                                  | 100                | ms                 |                    |      |  |  |

| <b>DIGITAL LOGIC LEVELS</b> |                                                             |                                                  |                    |                    |                    |      |  |  |

| VIH                         | Minimum logic high threshold DONE pin                       |                                                  | 0.7 × VDD          |                    | V                  |      |  |  |

| VIL                         | Maximum logic low threshold DONE pin                        |                                                  | 0.3 × VDD          |                    | V                  |      |  |  |

| VOH                         | Logic output high-level WAKE pin                            | I <sub>out</sub> = 100 μA                        | VDD − 0.3          |                    | V                  |      |  |  |

|                             |                                                             | I <sub>out</sub> = 1 mA                          | VDD − 0.7          |                    | V                  |      |  |  |

| VOL                         | Logic output low-level WAKE pin                             | I <sub>out</sub> = −100 μA                       | 0.3                |                    | V                  |      |  |  |

|                             |                                                             | I <sub>out</sub> = −1 mA                         | 0.7                |                    | V                  |      |  |  |

| VOL <sub>RSTn</sub>         | RSTn logic output low-level                                 | I <sub>OL</sub> = −1 mA                          | 0.3                |                    | V                  |      |  |  |

| IOH <sub>RSTn</sub>         | RSTn high-level output current                              | VOH <sub>RSTn</sub> = VDD                        | 1                  |                    | nA                 |      |  |  |

| VIH <sub>M_RST</sub>        | Minimum logic high threshold DELAY/M_RST pin <sup>(5)</sup> |                                                  | 1.5                |                    | V                  |      |  |  |

- (1) Values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

- (2) Limits are specified by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (4) The supply current excludes load and pull-up resistor current. Input pins are at GND or VDD.

- (5) This parameter is specified by design and/or characterization and is not tested in production.

- (6) The accuracy for time interval settings below 1 second is ±100 ms.

- (7) Operational life time test procedure equivalent to 10 years.

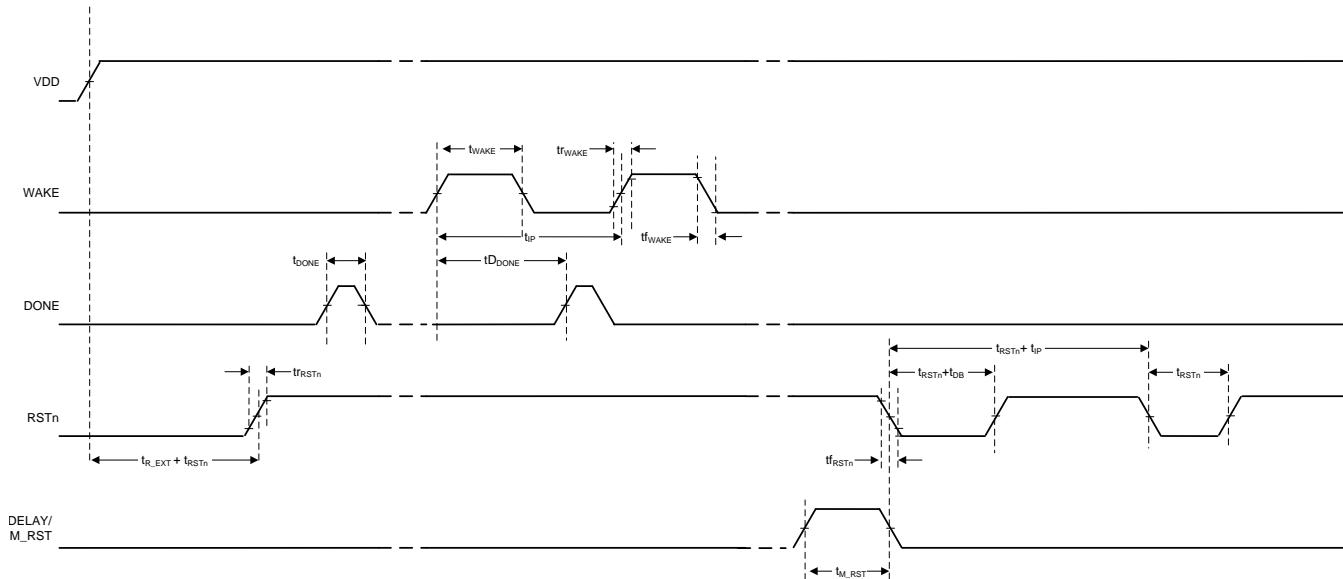

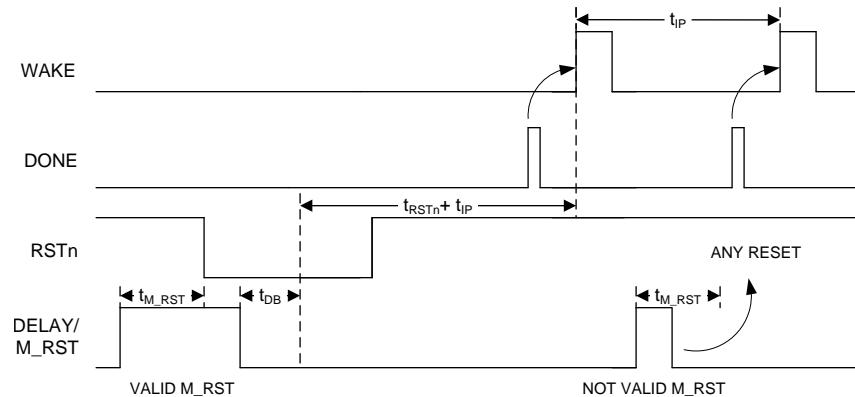

## 7.6 Timing Requirements

|              |                                           |                                        | MIN <sup>(1)</sup> | NOM <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|--------------|-------------------------------------------|----------------------------------------|--------------------|--------------------|--------------------|------|

| $tr_{RSTn}$  | Rise Time RSTn <sup>(3)</sup>             | Capacitive load 50 pF, Rpull-up 100 kΩ | 11                 |                    |                    | μs   |

| $tf_{RSTn}$  | Fall time RSTn <sup>(3)</sup>             | Capacitive load 50 pF, Rpull-up 100 kΩ | 50                 |                    |                    | ns   |

| $tr_{WAKE}$  | Rise time WAKE <sup>(3)</sup>             | Capacitive load 50 pF                  | 50                 |                    |                    | ns   |

| $tf_{WAKE}$  | Fall time WAKE <sup>(3)</sup>             | Capacitive load 50 pF                  | 50                 |                    |                    | ns   |

| $tD_{DONE}$  | DONE to RSTn or WAKE to DONE delay        | Min delay <sup>(4)</sup>               | 100                |                    |                    | ns   |

|              |                                           | Max delay <sup>(4)</sup>               |                    | $t_{IP}=20$        |                    | ms   |

| $t_{M\_RST}$ | Minimum valid manual reset <sup>(3)</sup> | Observation time 30 ms                 | 20                 |                    |                    | ms   |

| $t_{DB}$     | De-bounce manual reset                    |                                        | 20                 |                    |                    | ms   |

- (1) Limits are specified by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (2) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (3) This parameter is specified by design and/or characterization and is not tested in production.

- (4) In case of RSTn from its falling edge, in case of WAKE, from its rising edge.

**Figure 1. TPL5010-Q1 Timing**

## 7.7 Typical Characteristics

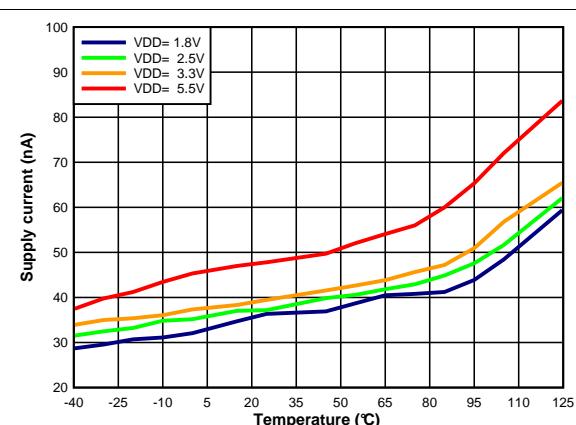

**Figure 2.  $I_{DD}$  vs  $V_{DD}$**

**Figure 3.  $I_{DD}$  vs Temperature**

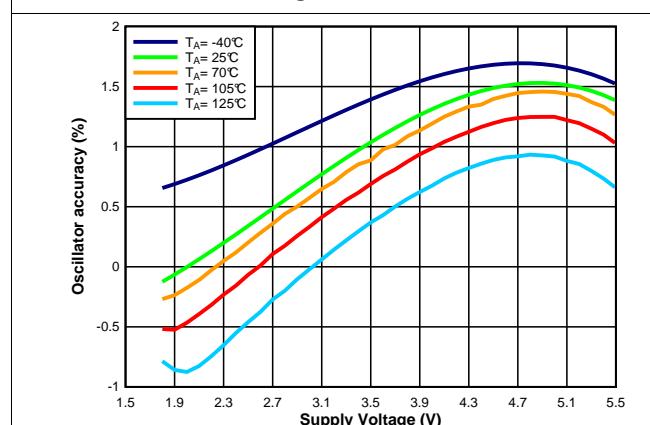

**Figure 4. Oscillator Accuracy vs  $V_{DD}$**

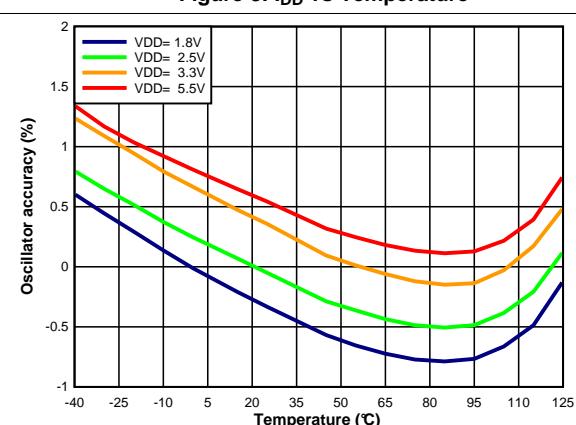

**Figure 5. Oscillator Accuracy vs Temperature**

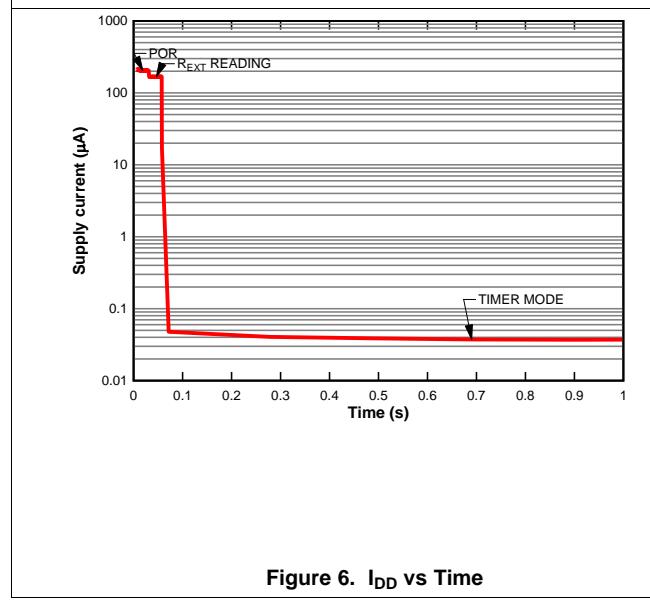

**Figure 6.  $I_{DD}$  vs Time**

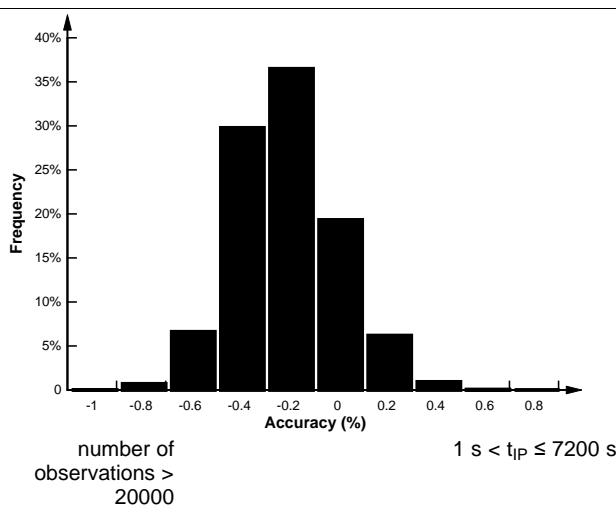

**Figure 7. Time Interval Setting Accuracy**

## 8 Detailed Description

### 8.1 Overview

The TPL5010-Q1 is a system wakeup timer with a watchdog feature, ideal for low power applications. TPL5010-Q1 is ideal for use in interrupt-driven applications and provides selectable timing from 100 ms to 7200 s.

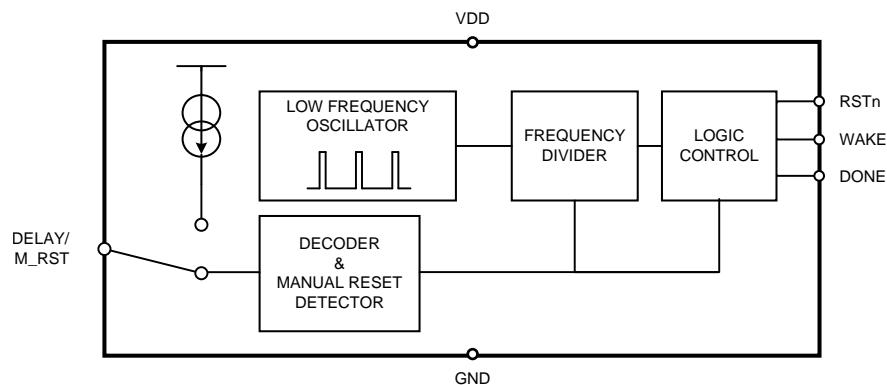

### 8.2 Functional Block Diagram

### 8.3 Feature Description

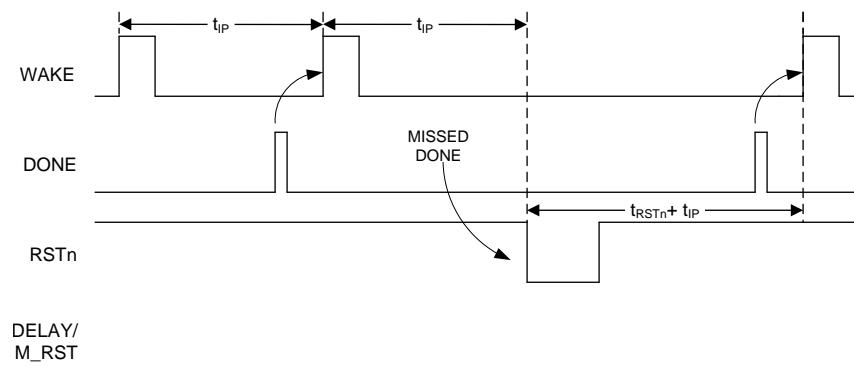

The DONE, WAKE and RSTn signals are used to implement the watchdog function. The TPL5010-Q1 is programmed to issue a periodic WAKE pulse to a  $\mu$ C which is in sleep or standby mode. After receiving the WAKE pulse, the  $\mu$ C must issue a DONE signal to the TPL5010-Q1 at least 20 ms before the rising edge of the next WAKE pulse. If the DONE signal is not asserted, the TPL5010-Q1 asserts the RSTn signal to reset the  $\mu$ C. A manual reset function is realized by momentarily pulling the DELAY/M\_RST pin to VDD.

Figure 8. Watchdog

#### 8.3.1 WAKE

The WAKE pulse is sent out from the TPL5010-Q1 when the programmed time interval starts (except at the beginning of the first cycle or if in the previous interval the DONE has not been received).

This signal is normally low.

#### 8.3.2 DONE

The DONE pin is driven by a  $\mu$ C to signal successful processing of the WAKE signal. The TPL5010-Q1 recognizes a valid DONE signal as a low to high transition; if two or more DONE signals are received within the time interval, only the first DONE signal is processed.

The DONE signal resets the counter of the watchdog only. If the DONE signal is received when the WAKE is still high, the WAKE will go low as soon as the DONE is recognized.

## Feature Description (continued)

### 8.3.3 RSTn

To implement the reset interface between the TPL5010-Q1 and the  $\mu$ C a pull-up resistance is required. 100 k $\Omega$  is recommended, to minimize current.

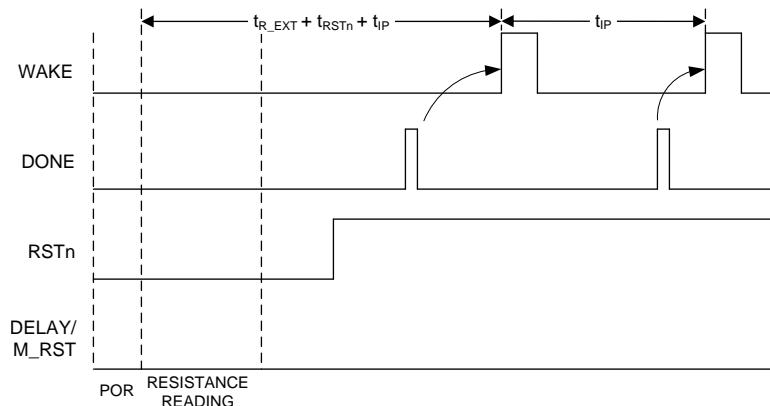

During the POR and the reading of the REXT the RSTn signal is LOW.

RSTn is asserted (LOW) for either one of the following conditions:

- 1. If the DELAY/M\_RST pin is high for at least two consecutive cycles of the internal oscillator (approximately 20 ms).

- 2. At the beginning of a new time interval if DONE is not received at least 20 ms before the next WAKE rising edge (see [Figure 8](#)).

## 8.4 Device Functional Modes

### 8.4.1 Startup

During startup, after POR, the TPL5010-Q1 executes a one-time measurement of the resistance attached to the DELAY/M\_RST pin in order to determine the desired time interval for WAKE. This measurement interval is  $t_{R\_EXT}$ . During this measurement a constant current is temporarily flowing into  $R_{EXT}$ .

**Figure 9. Startup**

### 8.4.2 Normal Operating Mode

During normal operating mode, the TPL5010-Q1 asserts periodic WAKE pulses in response to valid DONE pulses from the  $\mu$ C. If either a manual reset is applied (logic HIGH on DELAY/M\_RST pin) or the  $\mu$ C does not issue a DONE pulse within the required time, the TPL5010-Q1 asserts the RSTn signal to the  $\mu$ C and restarts its internal counters. See [Figure 8](#) and [Figure 10](#).

## 8.5 Programming

### 8.5.1 Configuring the WAKE Interval with the DELAY/M\_RST Pin

The time interval between 2 adjacent WAKE pulses (rising edges) is selectable through an external resistance ( $R_{EXT}$ ) between the DELAY/M\_RST pin and ground. The value of the resistance  $R_{EXT}$  is converted one time after POR. The allowable range of  $R_{EXT}$  is 500  $\Omega$  to 170 k $\Omega$ . At least a 1% precision resistance is recommended. See [Timer Interval Selection Using External Resistance](#) for how to set the WAKE pulse interval using  $R_{EXT}$ .

The time between 2 adjacent RESET signals (falling edges) or between a RESET (falling edge) and a WAKE (rising edge) is given by the sum of the programmed time interval and the  $t_{RSTn}$  (reset pulse width).

## Programming (continued)

### 8.5.2 Manual Reset

If VDD is connected to the DELAY/M\_RST pin, the TPL5010-Q1 recognizes this as a manual reset condition. In this case the time interval is not set. If the manual reset is asserted during the POR or during the reading procedure, the reading procedure is aborted and is re-started as soon as the manual reset switch is released. A pulse on the DELAY/M\_RST pin is recognized as a valid manual reset only if it lasts at least 20 ms (observation time is 30 ms).

A valid manual reset resets all the counters inside the TPL5010-Q1. The counters restart only when the high digital voltage at DELAY/M\_RST is removed and the next  $t_{RSTn}$  is elapsed.

Figure 10. Manual Reset

#### 8.5.2.1 DELAY/M\_RST

A resistance in the range between  $500\ \Omega$  and  $170\ k\Omega$  needs to be connected in order to select a valid time interval. At the POR and during the reading of the resistance the DELAY/M\_RST is connected to an analog signal chain through a mux. After the reading of the resistance the analog circuit is switched off and the DELAY/RST is connected to a digital circuit.

The manual reset detection is supported with a de-bounce feature which makes the TPL5010-Q1 insensitive to the glitches on the DELAY/M\_RST pin. When a valid manual reset signal is asserted on the DELAY/M\_RST pin, the RSTn signal is asserted LOW after a delay of  $t_{M\_RST}$ . It remains LOW after a valid manual reset is asserted +  $t_{DB}$  +  $t_{RSTn}$ . Due to the asynchronous nature of the manual reset signal and its arbitrary duration, the LOW status of the RSTn signal maybe affected by an uncertainty of about  $\pm 5\ ms$ .

A valid manual reset puts all the digital output signals at their default values:

- WAKE = LOW

- RSTn = asserted LOW

#### 8.5.2.2 Circuitry

The manual reset may be implemented using a switch (momentary mechanical action). The TPL5010-Q1 offers 2 possible approaches according to the power consumption constraints of the application.

## Programming (continued)

**Figure 11. Manual Reset with SPST Switch**

For use cases that do not require the lowest power consumption, using a single pole single throw switch may offer a lower cost solution. The DELAY/M\_RST pin may be directly connected to VDD with  $R_{EXT}$  in the circuit. The current drawn from the supply voltage during the reset is given by  $VDD/R_{EXT}$ .

**Figure 12. Manual Reset with SPDT Switch**

The reset function may also be asserted by switching DELAY/M\_RST from  $R_{EXT}$  to VDD using a single pole double throw switch, which will provide a lower power solution for the manual reset, because no current flows.

### 8.5.3 Timer Interval Selection Using External Resistance

In order to set the time interval, the external resistance  $R_{EXT}$  is selected according the following formula:

$$R_{EXT} = 100 \left( \frac{-b + \sqrt{b^2 - 4a(c - 100T)}}{2a} \right)$$

where

- T is the desired time interval in seconds

- $R_{EXT}$  is the resistance value to use in  $\Omega$

- a, b, c are coefficients depending on the range of the time interval

(1)

## Programming (continued)

Table 2. Coefficients for Equation 1

| SET | TIME INTERVAL RANGE (s) | a       | b         | c          |

|-----|-------------------------|---------|-----------|------------|

| 1   | 1 < T ≤ 5               | 0.2253  | -20.7654  | 570.5679   |

| 2   | 5 < T ≤ 10              | -0.1284 | 46.9861   | -2651.8889 |

| 3   | 10 < T ≤ 100            | 0.1972  | -19.3450  | 692.1201   |

| 4   | 100 < T ≤ 1000          | 0.2617  | -56.2407  | 5957.7934  |

| 5   | T > 1000                | 0.3177  | -136.2571 | 34522.4680 |

### EXAMPLE

Required time interval: 8 s

The coefficient set to be selected is the number 2. The formula becomes:

$$R_{EXT} = 100 \left( \frac{46.9861 - \sqrt{46.9861^2 + 4 * 0.1284 * (-2561.8889 - 100 * 8)}}{2 * 0.1284} \right) \quad (2)$$

The resistance value is 10.18 kΩ.

Table 3 and Table 4 contain example values of  $t_{IP}$  and their corresponding value of  $R_{EXT}$ .

Table 3. First 9 Time Intervals

| $t_{IP}$ (ms) | RESISTANCE (Ω) | CLOSEST REAL VALUE (Ω) | PARALLEL OF TWO 1% TOLERANCE RESISTORS (kΩ) |

|---------------|----------------|------------------------|---------------------------------------------|

| 100           | 500            | 500                    | 1.0 // 1.0                                  |

| 200           | 1000           | 1000                   | -                                           |

| 300           | 1500           | 1500                   | 2.43 // 3.92                                |

| 400           | 2000           | 2000                   | -                                           |

| 500           | 2500           | 2500                   | 4.42 // 5.76                                |

| 600           | 3000           | 3000                   | 5.36 // 6.81                                |

| 700           | 3500           | 3500                   | 4.75 // 13.5                                |

| 800           | 4000           | 4000                   | 6.19 // 11.3                                |

| 900           | 4500           | 4501                   | 6.19 // 16.5                                |

Table 4. Most Common Time Intervals Between 1 s to 2 h

| $t_{IP}$ | CALCULATED RESISTANCE (kΩ) | CLOSEST REAL VALUE (kΩ) | PARALLEL OF TWO 1% TOLERANCE RESISTORS (kΩ) |

|----------|----------------------------|-------------------------|---------------------------------------------|

| 1 s      | 5.20                       | 5.202                   | 7.15 // 19.1                                |

| 2 s      | 6.79                       | 6.788                   | 12.4 // 15.0                                |

| 3 s      | 7.64                       | 7.628                   | 12.7 // 19.1                                |

| 4 s      | 8.30                       | 8.306                   | 14.7 // 19.1                                |

| 5 s      | 8.85                       | 8.852                   | 16.5 // 19.1                                |

| 6 s      | 9.27                       | 9.223                   | 18.2 // 18.7                                |

| 7 s      | 9.71                       | 9.673                   | 19.1 // 19.6                                |

| 8 s      | 10.18                      | 10.180                  | 11.5 // 8.87                                |

| 9 s      | 10.68                      | 10.68                   | 17.8 // 26.7                                |

| 10 s     | 11.20                      | 11.199                  | 15.0 // 44.2                                |

| 20 s     | 14.41                      | 14.405                  | 16.9 // 97.6                                |

| 30 s     | 16.78                      | 16.778                  | 32.4 // 34.8                                |

| 40 s     | 18.75                      | 18.748                  | 22.6 // 110.0                               |

**Table 4. Most Common Time Intervals Between 1 s to 2 h (continued)**

| $t_{IP}$   | CALCULATED RESISTANCE (kΩ) | CLOSEST REAL VALUE (kΩ) | PARALLEL OF TWO 1% TOLERANCE RESISTORS (kΩ) |

|------------|----------------------------|-------------------------|---------------------------------------------|

| 50 s       | 20.047                     | 20.047                  | 28.7 // 66.5                                |

| 1 min      | 22.02                      | 22.021                  | 40.2 // 48.7                                |

| 2 min      | 29.35                      | 29.349                  | 35.7 // 165.0                               |

| 3 min      | 34.73                      | 34.729                  | 63.4 // 76.8                                |

| 4 min      | 39.11                      | 39.097                  | 63.4 // 102.0                               |

| 5 min      | 42.90                      | 42.887                  | 54.9 // 196.0                               |

| 6 min      | 46.29                      | 46.301                  | 75.0 // 121.0                               |

| 7 min      | 49.38                      | 49.392                  | 97.6 // 100.0                               |

| 8 min      | 52.24                      | 52.224                  | 88.7 // 127.0                               |

| 9 min      | 54.92                      | 54.902                  | 86.6 // 150.0                               |

| 10 min     | 57.44                      | 57.437                  | 107.0 // 124.0                              |

| 20 min     | 77.57                      | 77.579                  | 140.0 // 174.0                              |

| 30 min     | 92.43                      | 92.233                  | 182.0 // 187.0                              |

| 40 min     | 104.67                     | 104.625                 | 130.0 // 536.00                             |

| 50 min     | 115.33                     | 115.331                 | 150.0 // 499.00                             |

| 1 h        | 124.91                     | 124.856                 | 221.0 // 287.00                             |

| 1 h 30 min | 149.39                     | 149.398                 | 165.0 // 1580.0                             |

| 2 h        | 170.00                     | 170.00                  | 340.0 // 340.0                              |

#### 8.5.4 Quantization Error

The TPL5010-Q1 can generate 1650 discrete timer intervals in the range of 100 ms to 7200 s. The first 9 intervals are multiples of 100 ms. The remaining 1641 intervals cover the range between 1 s to 7200 s. Because they are discrete intervals, there is a quantization error associated with each value.

The quantization error can be evaluated according to the following formula:

$$Err = 100 \frac{(T_{DESIRED} - T_{ADC})}{T_{DESIRED}} \quad (3)$$

Where:

$$T_{ADC} = INT \left[ \frac{1}{100} \left( a \frac{R_D^2}{100^2} + b \frac{R_D}{100} + c \right) \right] \quad (4)$$

$$R_D = INT \left[ \frac{R_{EXT}}{100} \right]$$

where

- $R_{EXT}$  is the resistance calculated with [Equation 1](#)

- a, b, c are the coefficients of the equation listed in [Table 2](#)

(5)

#### 8.5.5 Error Due to Real External Resistance

$R_{EXT}$  is a theoretical value and may not be available in standard commercial resistor values. It is possible to closely approach the theoretical  $R_{EXT}$  using two or more standard values in parallel. However, standard values are characterized by a certain tolerance. This tolerance will affect the accuracy of the time interval.

The accuracy can be evaluated using the following procedure:

1. Evaluate the min and max values of  $R_{EXT}$  ( $R_{EXT\_MIN}$ ,  $R_{EXT\_MAX}$ ) with [Equation 1](#) using the selected commercial resistance values and their tolerances.

2. Evaluate the time intervals ( $T_{ADC\_MIN}[R_{EXT\_MIN}]$ ,  $T_{ADC\_MAX}[R_{EXT\_MAX}]$ ) with [Equation 4](#).

3. Find the errors using [Equation 3](#) with  $T_{ADC\_MIN}$ ,  $T_{ADC\_MAX}$ .

The results of the formula indicate the accuracy of the time interval.

The example below illustrates the procedure.

- Desired time interval ,  $T_{desired} = 600$  s

- Required  $R_{EXT}$ , from [Equation 1](#),  $R_{EXT} = 57.44$  k $\Omega$

From [Table 4](#),  $R_{EXT}$  can be built with a parallel combination of two commercial values with 1% tolerance:  $R1=107$  k $\Omega$ ,  $R2=124$  k $\Omega$ . The uncertainty of the equivalent parallel resistance can be found using [Equation 6](#).

$$uR_{\parallel} = R_{\parallel} \sqrt{\left(\frac{u_{R1}}{R1}\right)^2 + \left(\frac{u_{R2}}{R2}\right)^2} \quad (6)$$

Where  $uR_n$  ( $n=1,2$ ) represent the uncertainty of a resistance,

$$u_{Rn} = Rn \frac{Tolerance}{\sqrt{3}} \quad (7)$$

The uncertainty of the parallel resistance is 0.82%, meaning the value of  $R_{EXT}$  may range between  $R_{EXT\_MIN} = 56.96$  k $\Omega$  and  $R_{EXT\_MAX} = 57.90$  k $\Omega$ .

Using these value of  $R_{EXT}$ , the digitized timer intervals calculated with [Equation 4](#) are respectively  $T_{ADC\_MIN} = 586.85$  s and  $T_{ADC\_MAX} = 611.3$  s, giving an error range of  $-1.88\% / +2.19\%$ . The asymmetry of the error range is due to the quadratic transfer function of the resistance digitizer.

## 9 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

In battery-powered applications, one design constraint is the need for low current consumption. The TPL5010-Q1 is ideal for applications where there is a need to monitor environmental conditions at a fixed time interval. Often in these applications, a watchdog or other internal timer in a  $\mu$ C is used to implement a wakeup function. Using the TPL5010-Q1 to implement the watchdog function will consume only tens of nA, significantly improving the power consumption of the system.

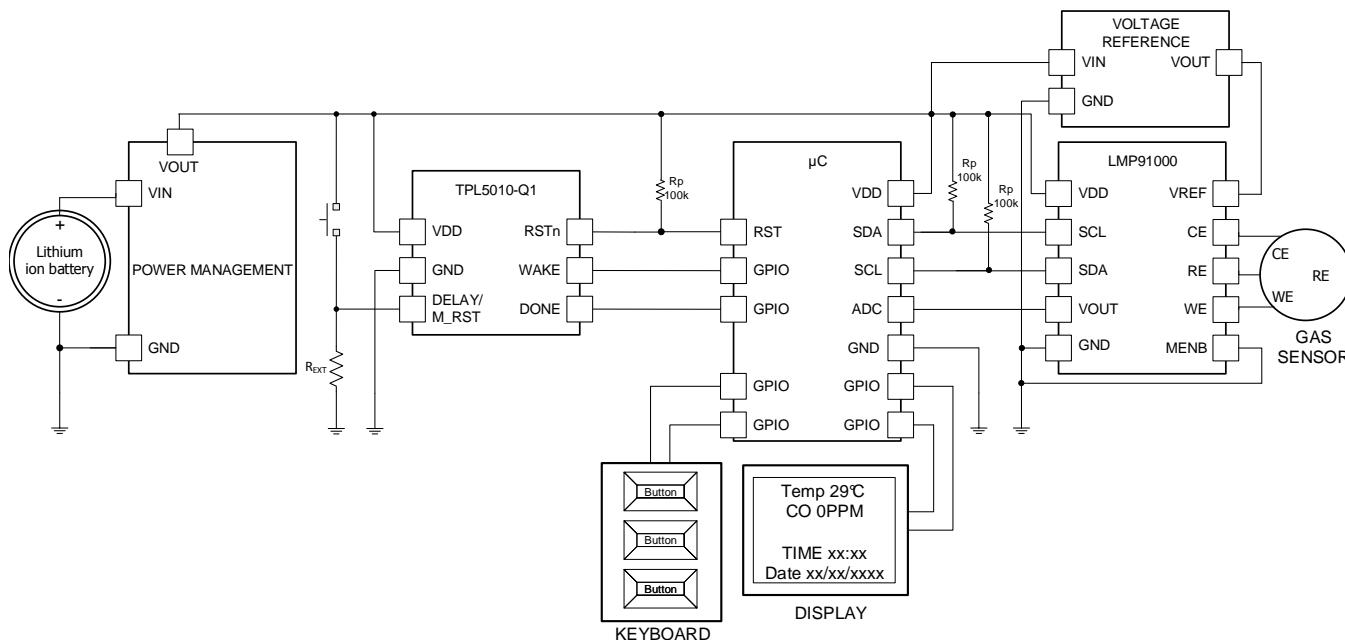

### 9.2 Typical Application

The TPL5010-Q1 can be used in conjunction with environment sensors to build a low-power environment data-logger, such as an air quality data-logger. In this application, due to the monitored phenomena, the  $\mu$ C and the front end of the sensor spend most of the time in the idle state, waiting for the next logging interval, usually a few hundred of milliseconds. [Figure 13](#) illustrates a data logging application based on a  $\mu$ C, and a front end for a gas sensor based on the LMP91000.

**Figure 13. Data-Logger**

#### 9.2.1 Design Requirements

The design is driven by the low current consumption constraint. The data are usually acquired on a rate that ranges between 1 s and 10 s. The highest necessity is the maximization of the battery life. The TPL5010-Q1 helps achieve that goal because it allows putting the  $\mu$ C in its lowest power mode. The TPL5010-Q1 will take care of the watchdog and the timing.

## Typical Application (continued)

### 9.2.2 Detailed Design Procedure

When the main constraint is the battery life, the selection of a low-power voltage reference,  $\mu$ C, and display is mandatory. The first step in the design is the calculation of the power consumption of the devices in their different mode of operations. For instance, the LMP91000 burns most of the power when in gas measurement mode, then according to the connected gas sensor it has 2 idle states: stand-by and deep sleep. The same is true for the  $\mu$ C, such as one of the MSP430 family, which can be placed in one of its lower power modes, such as LMP3.5 or LMP4.5. In this case, the TPL5010-Q1 can be used to implement the watchdog and wakeup timing functions.

After the power budget calculation it is possible to select the appropriate time interval which satisfies the application constraints and maximize the life of the battery.

### 9.2.3 Application Curves

## 10 Power Supply Recommendations

The TPL5010-Q1 requires a voltage supply within 1.8 V and 5.5 V. A multilayer ceramic bypass X7R capacitor of 0.1  $\mu$ F between VDD and GND pin is recommended.

## 11 Layout

### 11.1 Layout Guidelines

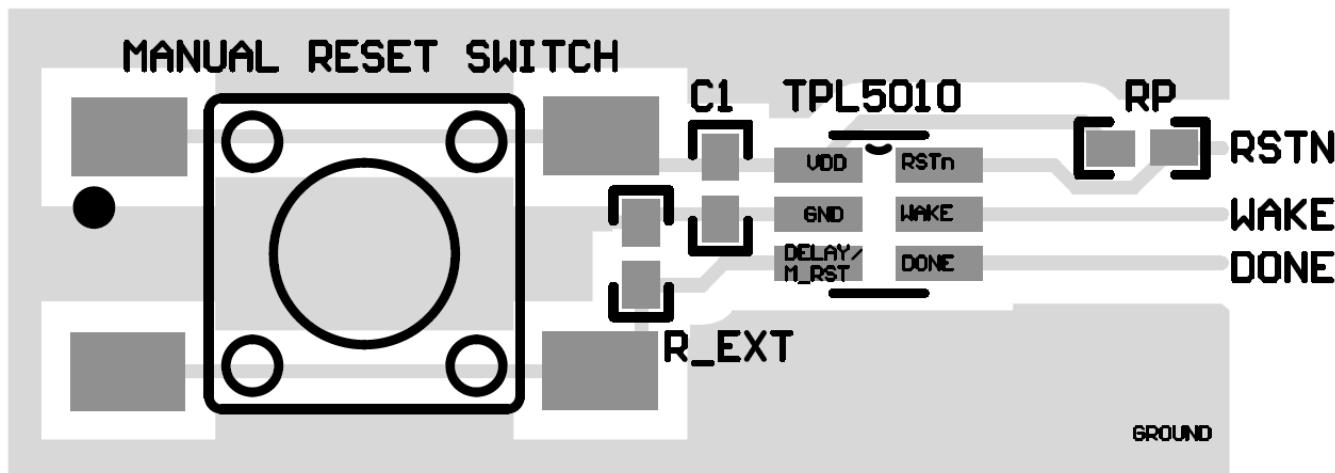

The DELAY/M\_RST pin is sensitive to parasitic capacitance. It is suggested that the traces connecting the resistance on this pin to GROUND be kept as short as possible to minimize parasitic capacitance. This capacitance can affect the initial set up of the time interval. Signal integrity on the WAKE and RSTn pins is also improved by keeping the trace length between the TPL5010-Q1 and the  $\mu$ C short to reduce the parasitic capacitance.

### 11.2 Layout Example

Figure 15. Layout

## 12 デバイスおよびドキュメントのサポート

### 12.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 12.2 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™ Online Community** *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At [e2e.ti.com](http://e2e.ti.com), you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.3 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 12.4 静電気放電に関する注意事項

これらのデバイスは、限定期的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 12.5 Glossary

[SLYZ022 — TI Glossary.](#)

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins            | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|---------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPL5010QDDCRQ1        | Active        | Production           | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | 13VX                |

| TPL5010QDDCRQ1.A      | Active        | Production           | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | 13VX                |

| TPL5010QDDCTQ1        | Active        | Production           | SOT-23-<br>THIN (DDC)   6 | 250   SMALL T&R       | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | 13VX                |

| TPL5010QDDCTQ1.A      | Active        | Production           | SOT-23-<br>THIN (DDC)   6 | 250   SMALL T&R       | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | 13VX                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a " ~ " will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPL5010-Q1 :**

- Catalog : [TPL5010](#)

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

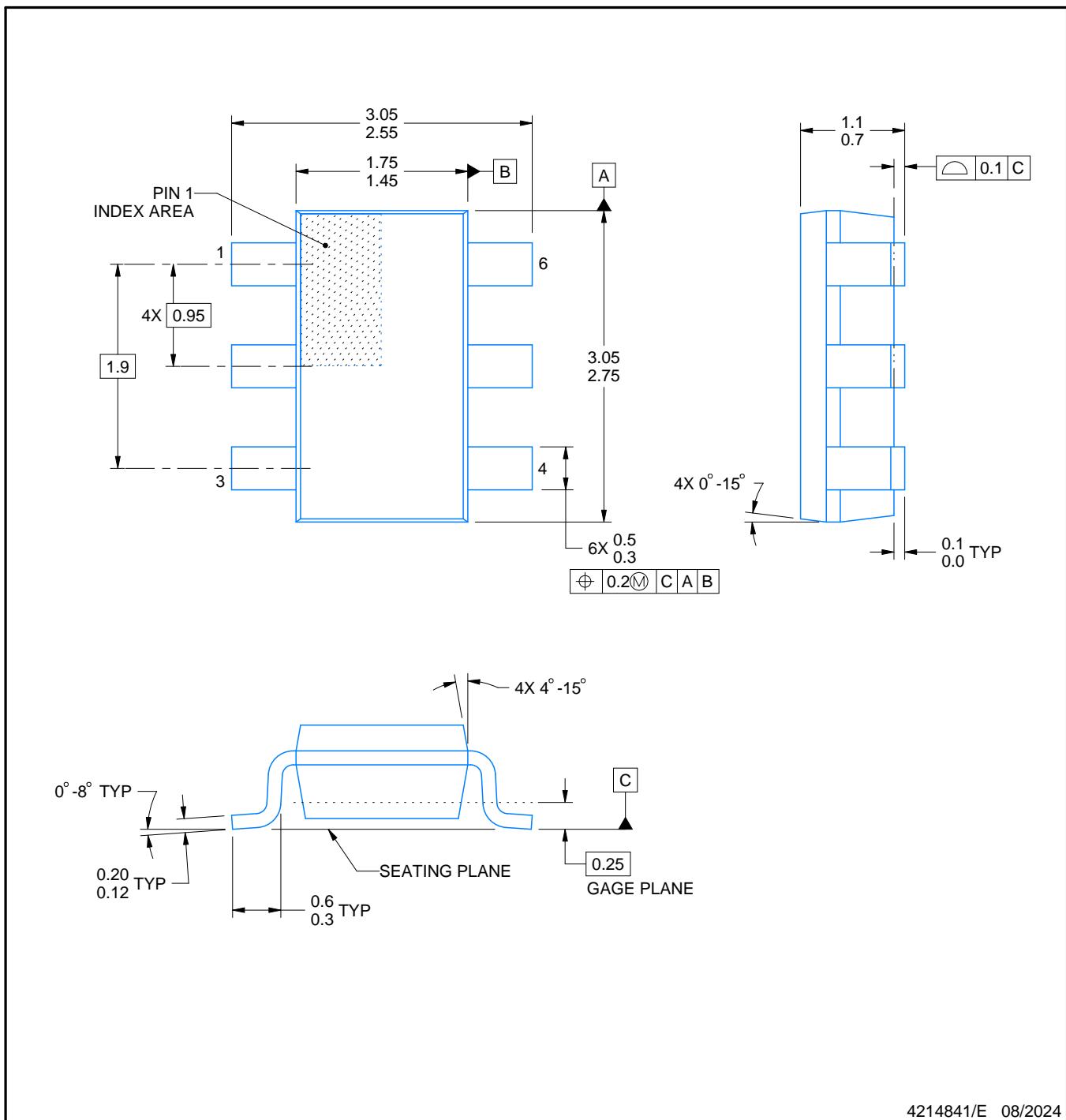

# PACKAGE OUTLINE

## SOT-23 - 1.1 max height

SMALL OUTLINE TRANSISTOR

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-193.

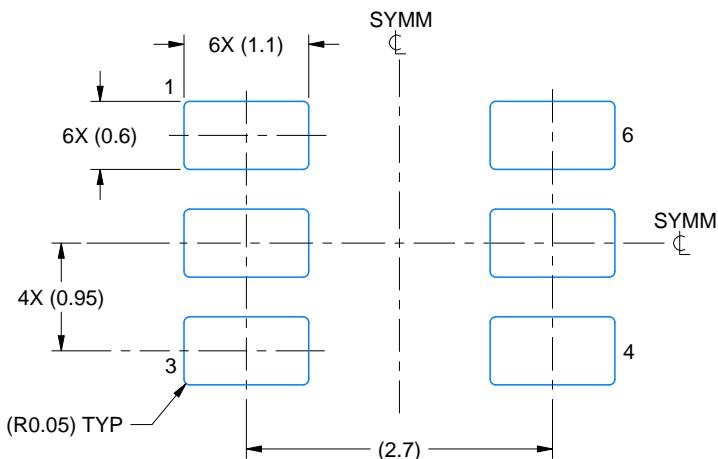

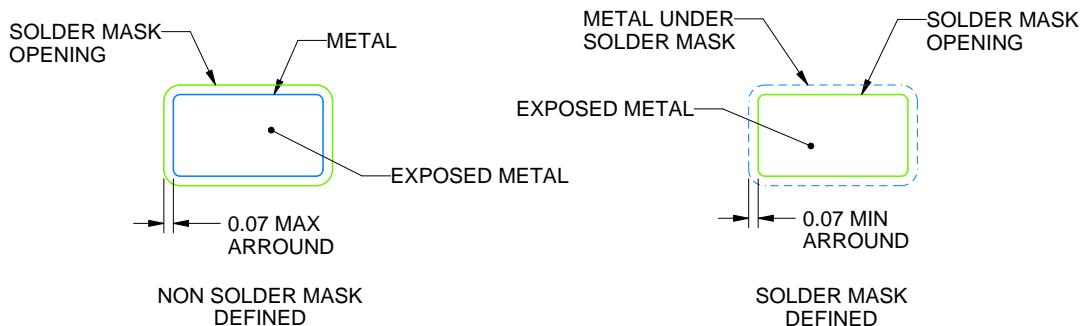

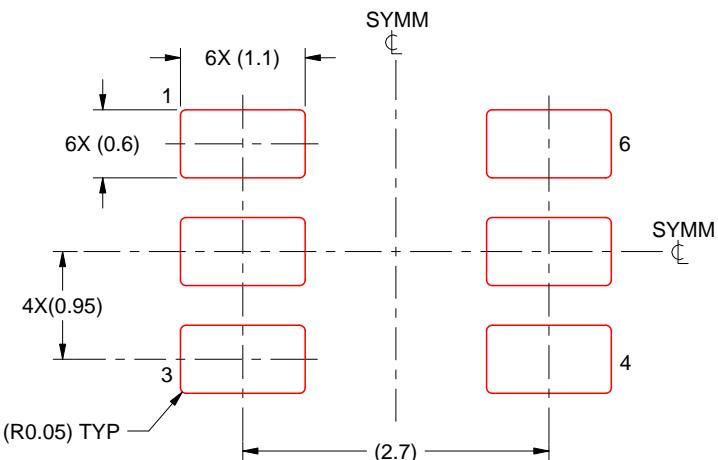

# EXAMPLE BOARD LAYOUT

DDC0006A

SOT-23 - 1.1 max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPLODED METAL SHOWN

SCALE:15X

SOLDERMASK DETAILS

4214841/E 08/2024

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DDC0006A

SOT-23 - 1.1 max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 THICK STENCIL

SCALE:15X

4214841/E 08/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月