# TPLD1201-Q1 8つのGPIOを備えた車載用プログラマブルロジックデバイス

## 1 特長

- 動作特性

- 拡張温度範囲: -40°C ~ 125°C

- 広い電源電圧範囲: 1.71V ~ 5.5V

- 車載アプリケーション認定済み

- マクロセルを構成可能

- 2ビット、3ビット、および4ビットのルックアップテーブル

- Dタイプフリップフロップおよびラッチ、リセット/セットオプションありなし

- 8ビットのパイプ遅延

- カウンタと遅延ジェネレータ

- グリッチ除去フィルタまたはエッジ検出器をプログラム可能

- ディスクリートアナログコンパレータ

- 電圧リファレンス

- 発振器

- 柔軟なデジタルI/O機能

- すべてのデジタル信号を任意のGPIOに配線可能

- デジタル入力モード: デジタル入力、シュミットトリガあり/なし、低電圧デジタル入力

- デジタル出力モード: プッシュプル、オープンドラインNMOS、トライステート

- 開発ツール

- InterConnect Studio

- 評価モジュール

- TPLDプログラミング基板

## 2 アプリケーション

- ファクトリオートメーション/制御

- 通信機器

- リテールオートメーションおよびペイメント

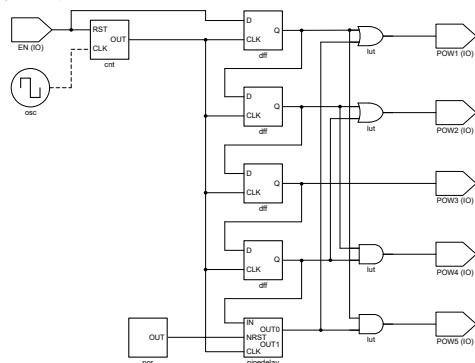

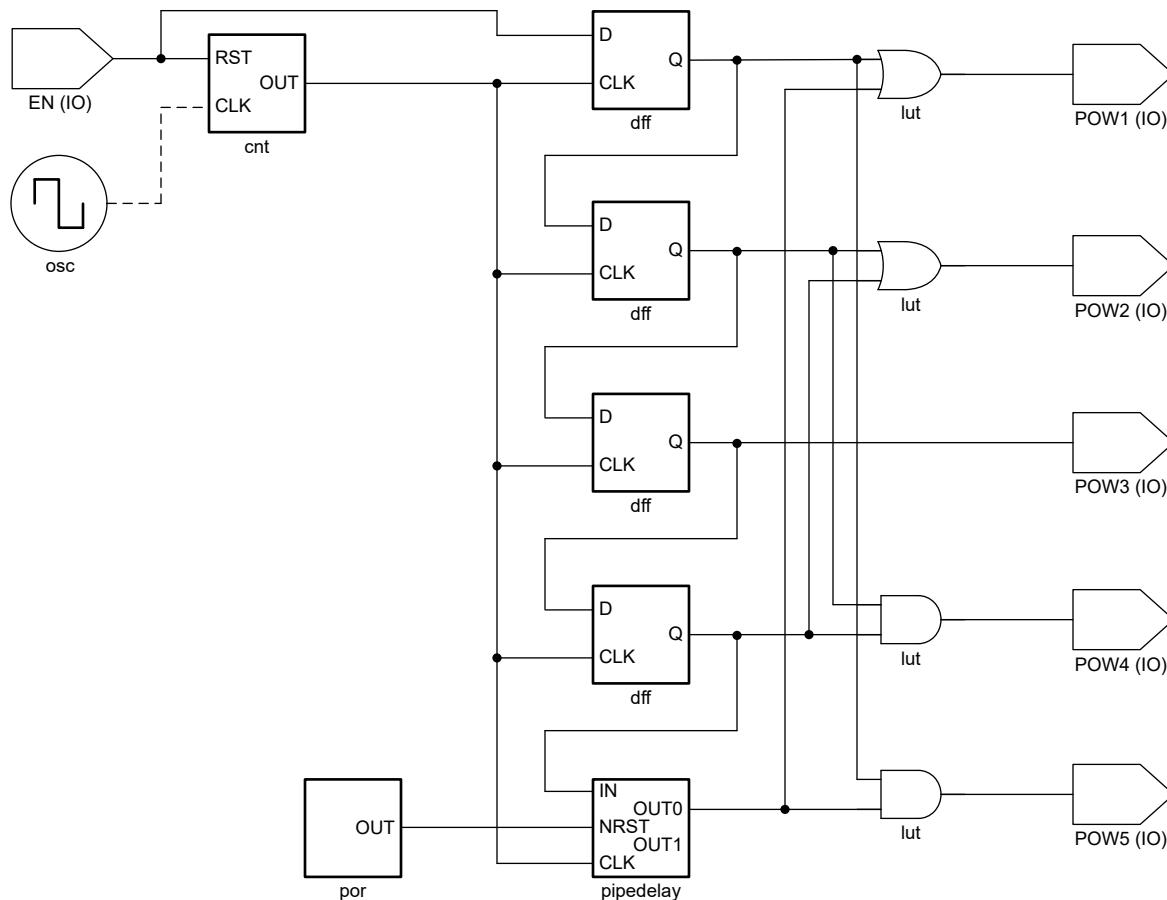

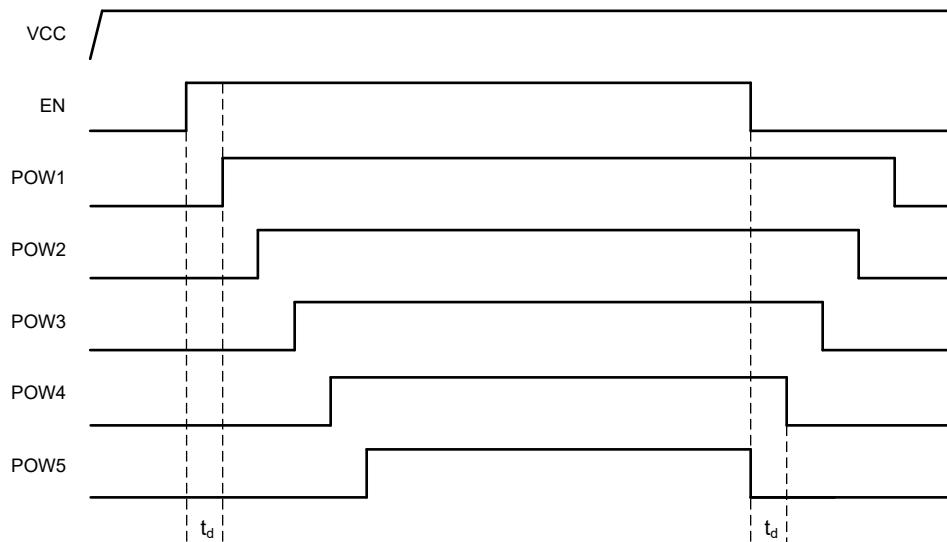

アプリケーション概略図

- 試験および測定機器

- 業務用オーディオ、ビデオ、サイネージ

- パーソナルエレクトロニクス

- 車載用

## 3 説明

TPLD1201-Q1は、組み合わせ論理、順序論理、およびアナログブロックを持つ多用途のプログラマブルロジックICを備えたテキサス・インストゥルメンツのプログラマブルロジックデバイス(TPLD)ファミリーのデバイスです。TPLDは、タイミング遅延、電圧モニタ、システムリセット、電源シーケンスIC、I/Oエクスパンダなどの共通のシステム機能を実装するための統合型低消費電力ソリューションを提供します。このデバイスは構成可能なI/O構造を採用しているため、混合信号環境で互換性を拡張し、必要な個別部品の数を減らすことができます。

システム設計者は、不揮発性メモリを一時的にエミュレートするか、InterConnect Studioを通じてワンタイムプログラマブル(OTP)を永続的にプログラミングすることにより、回路を作成し、マクロセル、I/Oピン、および相互接続を構成できます。TPLD1201-Q1はハードウェアおよびソフトウェアのエコシステムによってサポートされており、アプリケーションノート、リファレンスデザイン、設計例が提供されています。詳細および設計ツールへのアクセスについては、[ti.com](http://ti.com)をご覧ください。

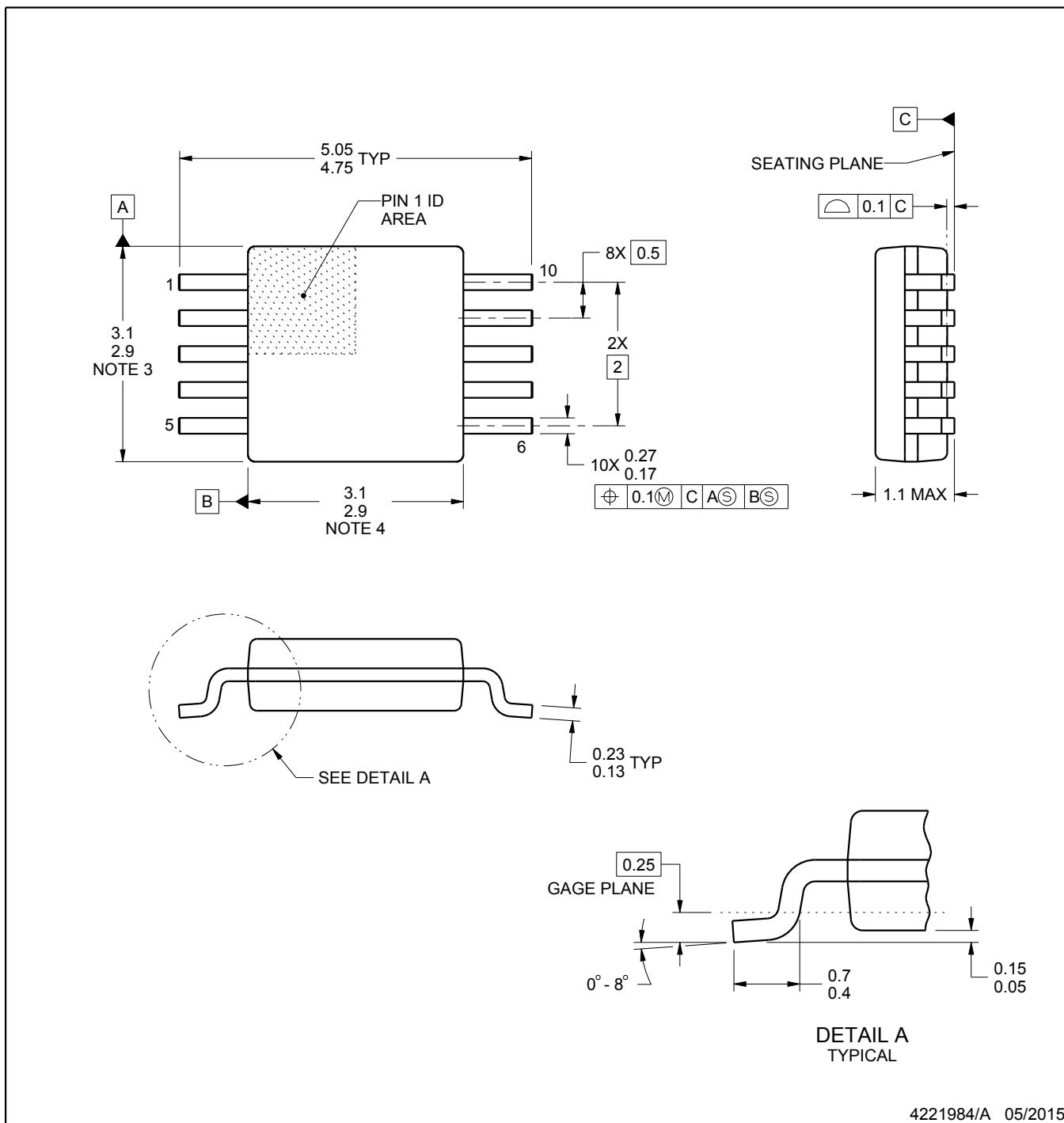

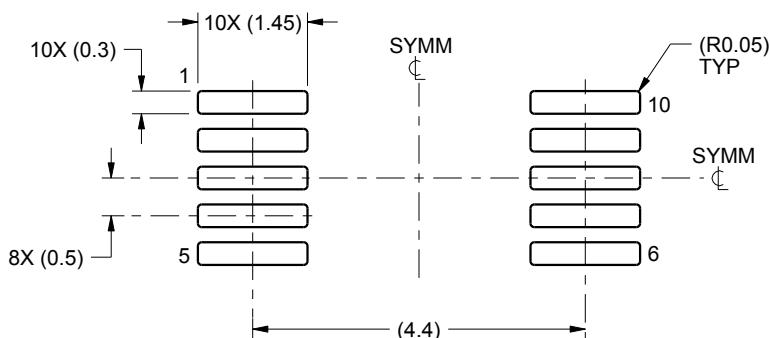

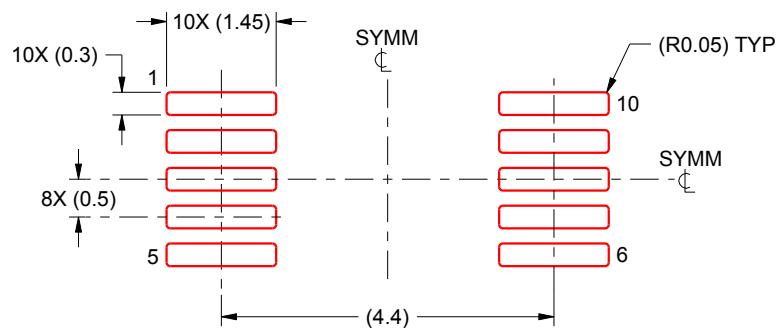

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-------------|----------------------|-------------------------|

| TPLD1201-Q1 | DGS (VSSOP、10)       | 4.9mm × 3.0mm           |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はピンも含まれます。

## 目次

|                   |    |                             |    |

|-------------------|----|-----------------------------|----|

| 1 特長.....         | 1  | 7.2 機能ブロック図.....            | 17 |

| 2 アプリケーション.....   | 1  | 7.3 機能説明.....               | 18 |

| 3 説明.....         | 1  | 7.4 デバイスの機能モード.....         | 41 |

| 4 ピン構成および機能.....  | 3  | 8 アプリケーションと実装.....          | 43 |

| 5 仕様.....         | 4  | 8.1 アプリケーション情報.....         | 43 |

| 5.1 絶対最大定格.....   | 4  | 8.2 代表的なアプリケーション.....       | 43 |

| 5.2 ESD 定格.....   | 4  | 8.3 電源に関する推奨事項.....         | 47 |

| 5.3 推奨動作条件.....   | 4  | 8.4 レイアウト.....              | 47 |

| 5.4 熱に関する情報.....  | 5  | 9 デバイスおよびドキュメントのサポート.....   | 49 |

| 5.5 電気的特性.....    | 5  | 9.1 ドキュメントの更新通知を受け取る方法..... | 49 |

| 5.6 電源電流特性.....   | 8  | 9.2 サポート・リソース.....          | 49 |

| 5.7 スイッチング特性..... | 9  | 9.3 商標.....                 | 49 |

| 5.8 代表的特性.....    | 13 | 9.4 静電気放電に関する注意事項.....      | 49 |

| 6 パラメータ測定情報.....  | 14 | 9.5 用語集.....                | 49 |

| 7 詳細説明.....       | 16 | 10 改訂履歴.....                | 49 |

| 7.1 概要.....       | 16 | 11 メカニカル、パッケージ、および注文情報..... | 49 |

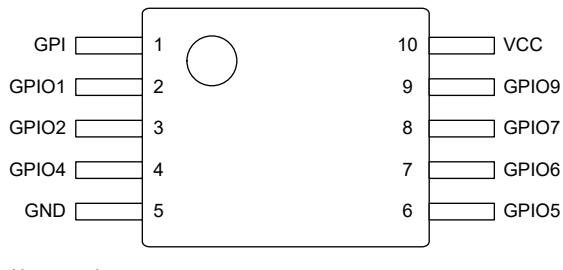

## 4 ピン構成および機能

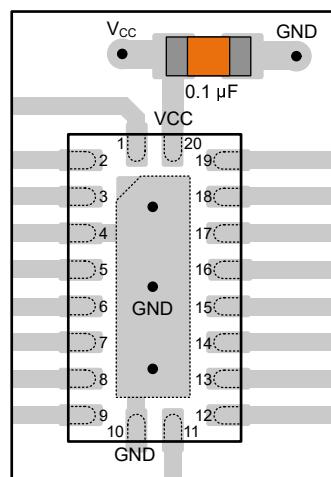

図 4-1. DGS パッケージ、10 ピン VSSOP (上面図)

表 4-1. ピンの機能

| ピン    |     |                    | 説明                                    |                                |

|-------|-----|--------------------|---------------------------------------|--------------------------------|

| 名称    | DGS | タイプ <sup>(1)</sup> | 主な機能                                  | 2 次的な機能 (ある場合)                 |

| GPI   | 1   | I                  | 汎用入力 <sup>(3)</sup>                   |                                |

| GPIO1 | 2   | I/O                | 汎用 I/O                                | ACMP0 IN+                      |

| GPIO2 | 3   | I/O                | 汎用 I/O                                | 外部 VREF IN/ACMP0 または ACMP1 IN- |

| GPIO4 | 4   | I/O                | 出力イネーブル (OE) 付きの汎用 I/O <sup>(4)</sup> | ACMP1 IN+                      |

| GND   | 5   | P                  | グランド                                  |                                |

| GPIO5 | 6   | I/O                | 汎用 I/O                                |                                |

| GPIO6 | 7   | I/O                | 汎用 I/O                                |                                |

| GPIO7 | 8   | I/O                | 出力イネーブル (OE) 付きの汎用 I/O <sup>(4)</sup> | 内部 VREF OUT                    |

| GPIO9 | 9   | I/O                | 汎用 I/O                                | 外部 OSC IN                      |

| VCC   | 10  | P                  | 電源電圧                                  |                                |

| NC    | —   | —                  | 内部接続なし <sup>(2)</sup>                 |                                |

| NC    | —   | —                  | 内部接続なし <sup>(2)</sup>                 |                                |

(1) P = 電源、I/O = 入出力、I = 入力

(2) 内部的に接続されていないピンは、グランドに接続するか、フローティングのままにします。

(3) 汎用入力 (GPI) ピンはプログラミング中の高電圧 (VPP) に耐えます。インシステム プログラミングを行う場合、このピンに接続されたペリフェラルに特に注意を払います。

(4) 出力イネーブル (OE) 接続は、接続マルチプレクサを介して利用でき、InterConnect Studio で構成できます。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|           |                              |                                    | 最小値  | 最大値            | 単位 |

|-----------|------------------------------|------------------------------------|------|----------------|----|

| $V_{CC}$  | GND を基準とした $V_{CC}$ 電源電圧     |                                    | -0.5 | 7              | V  |

| $V_I$     | 入力電圧                         |                                    | -0.5 | $V_{CC} + 0.5$ | V  |

| $V_O$     | 出力電圧                         |                                    | -0.5 | $V_{CC} + 0.5$ | V  |

| $I_{IOK}$ | 入力 / 出力クランプ電流                | $V_{IO} < 0$ または $V_{IO} > V_{CC}$ | -50  | 50             | mA |

| $I_O$     | 連続出力電流                       | $V_O = 0 \sim V_{CC}$              | -50  | 50             | mA |

| $I_{DC}$  | 平均または DC 電流 (各ピンを流れる電流) の最大値 | プッシュアップ 1X                         |      | 12             | mA |

|           |                              | プッシュアップ 2X                         |      | 17             |    |

|           |                              | オープンドレイン NMOS 1X                   |      | 18             |    |

|           |                              | オープンドレイン NMOS 2X                   |      | 28             |    |

| $T_J$     | 接合部温度                        |                                    |      | 150            | °C |

| $T_{STG}$ | 保存温度                         |                                    | -65  | 150            | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、また「推奨動作条件」に示された値を超える他のいかなる条件でも、本デバイスが正常に動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                                     | 値          | 単位 |

|-------------|------|---------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>        | $\pm 2000$ | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC 仕様 JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 1500$ |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|          |              | $V_{CC}$               | 最小値               | 最大値                 | 単位 |

|----------|--------------|------------------------|-------------------|---------------------|----|

| $V_{CC}$ | 電源電圧         |                        | 1.71              | 5.5                 | V  |

| $V_I$    | 入力電圧         |                        | 0                 | $V_{CC}$            | V  |

| $V_O$    | 出力電圧         |                        | 0                 | $V_{CC}$            | V  |

| $V_{AI}$ | アナログ入力電圧     | 正入力 (ACMP IN+)         | 0                 | $V_{CC}$            | V  |

|          |              | 負入力 (ACMP IN-、外部 VREF) | 0.15              | 1.2                 |    |

| $V_{IH}$ | High レベル入力電圧 | ロジック入力                 | $1.71V \sim 5.5V$ | $0.7 \times V_{CC}$ | V  |

|          |              |                        | $1.8V \pm 0.09V$  | 0.95                |    |

|          |              | 低電圧ロジック入力              | $3.3V \pm 0.3V$   | 1.2                 |    |

|          |              |                        | $5V \pm 0.5V$     | 1.3                 |    |

## 5.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |             |           | V <sub>CC</sub> | 最小値 | 最大値                   | 単位  |

|--------------------|-------------|-----------|-----------------|-----|-----------------------|-----|

| V <sub>IL</sub>    | Low レベル入力電圧 | ロジック入力    | 1.71V ~ 5.5V    |     | 0.3 × V <sub>CC</sub> | V   |

|                    |             |           | 1.8V ± 0.09V    |     | 0.40                  |     |

|                    |             | 低電圧ロジック入力 | 3.3V ± 0.3V     |     | 0.55                  |     |

|                    |             |           | 5V ± 0.5V       |     | 0.65                  |     |

| F <sub>(EXT)</sub> | 外部発振器周波数    |           | 1.8V ± 0.09V    |     | 8                     | MHz |

|                    |             |           | 3.3V ± 0.3V     |     | 8                     |     |

|                    |             |           | 5V ± 0.5V       |     | 8                     |     |

| T <sub>A</sub>     | 周囲温度        |           |                 | -40 | 125                   | °C  |

## 5.4 熱に関する情報

| パッケージ       | ピン | 熱評価基準 <sup>(1)</sup> |                       |                  |                 |                 |                       | 単位   |

|-------------|----|----------------------|-----------------------|------------------|-----------------|-----------------|-----------------------|------|

|             |    | R <sub>θJA</sub>     | R <sub>θJC(top)</sub> | R <sub>θJB</sub> | Ψ <sub>JT</sub> | Ψ <sub>JB</sub> | R <sub>θJC(bot)</sub> |      |

| DGS (VSSOP) | 10 | 152.7                | 60.8                  | 88.9             | 4.8             | 87.2            | —                     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 5.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 |                                                    |                                                             | テスト条件        | V <sub>CC</sub> | 最小値  | 標準値  | 最大値  | 単位 |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------|--------------|-----------------|------|------|------|----|

| <b>電源およびパワーオンリセット</b> |                                                    |                                                             |              |                 |      |      |      |    |

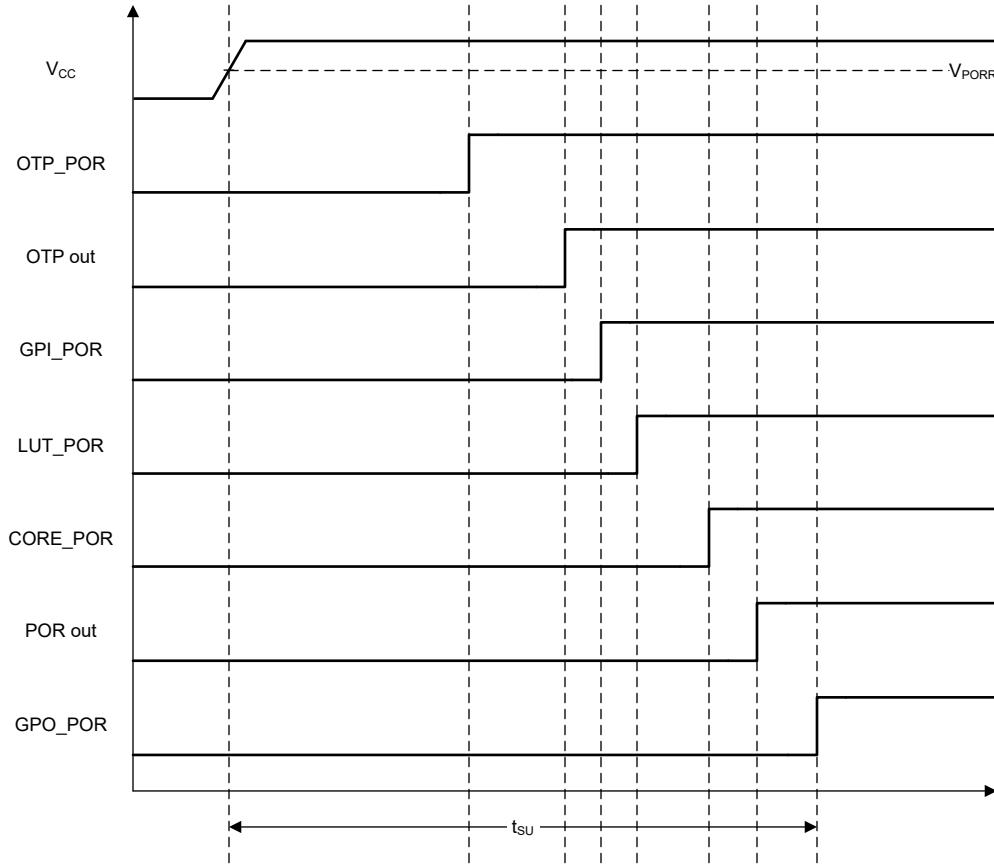

| V <sub>PORR</sub>     | パワーオンリセット電圧、V <sub>CC</sub> 立ち上がり                  | V <sub>I</sub> = V <sub>CC</sub> または GND、I <sub>O</sub> = 0 | 1.71V ~ 5.5V |                 | 1.25 | 1.30 | 1.40 | V  |

| V <sub>PORF</sub>     | パワーオンリセット電圧、V <sub>CC</sub> 立ち下がり                  | V <sub>I</sub> = V <sub>CC</sub> または GND、I <sub>O</sub> = 0 | 1.71V ~ 5.5V |                 | 1.20 | 1.26 | 1.35 | V  |

| t <sub>SU</sub>       | 起動時間                                               | V <sub>CC</sub> 立ち上がりからV <sub>PORR</sub> を超えるまで             | 1.71V ~ 5.5V |                 |      | 245  |      | μs |

| V <sub>PP</sub>       | プログラミング電圧                                          |                                                             |              |                 | 7.5  |      | 8    | V  |

| <b>デジタルIO</b>         |                                                    |                                                             |              |                 |      |      |      |    |

| V <sub>T+</sub>       | 正方向入力スレッショルド電圧                                     | シミュットトリガ付きのロジック入力                                           |              | 1.8V ± 0.09V    | 0.94 | 1.27 | V    |    |

|                       |                                                    |                                                             |              | 3.3V ± 0.3V     | 1.55 | 2.30 |      |    |

|                       |                                                    |                                                             |              | 5V ± 0.5V       | 2.21 | 3.19 |      |    |

| V <sub>T-</sub>       | 負方向入力スレッショルド電圧                                     | シミュットトリガ付きのロジック入力                                           |              | 1.8V ± 0.09V    | 0.58 | 0.94 | V    |    |

|                       |                                                    |                                                             |              | 3.3V ± 0.3V     | 1.1  | 1.79 |      |    |

|                       |                                                    |                                                             |              | 5V ± 0.5V       | 1.63 | 2.7  |      |    |

| V <sub>HYS</sub>      | シミュットトリガヒステリシス(V <sub>T+</sub> - V <sub>T-</sub> ) | シミュットトリガ付きのロジック入力                                           |              | 1.8V ± 0.09V    | 0.20 | 0.51 | V    |    |

|                       |                                                    |                                                             |              | 3.3V ± 0.3V     | 0.33 | 0.61 |      |    |

|                       |                                                    |                                                             |              | 5V ± 0.5V       | 0.42 | 0.75 |      |    |

| V <sub>HYS</sub>      | GPIヒステリシス電圧                                        | IN0に適用可能なヒステリシス電圧                                           |              | 1.71V ~ 5.5V    |      | 0.2  | V    |    |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                         | テスト条件                    | V <sub>CC</sub>                          | 最小値          | 標準値 | 最大値 | 単位  |

|----------------------|-------------------------|--------------------------|------------------------------------------|--------------|-----|-----|-----|

| V <sub>OH</sub>      | High レベル出力電圧            | I <sub>OH</sub> = -100μA | 1.8V ± 0.09V                             | 1.68         |     |     | V   |

|                      |                         |                          |                                          | 1.69         |     |     |     |

|                      |                         | I <sub>OH</sub> = -3mA   | 3.3V ± 0.3V                              | 2.60         |     |     |     |

|                      |                         |                          |                                          | 2.71         |     |     |     |

|                      |                         | I <sub>OH</sub> = -5mA   | 5V ± 0.5V                                | 3.99         |     |     |     |

|                      |                         |                          |                                          | 4.13         |     |     |     |

| V <sub>OL</sub>      | Low レベル出力電圧             | I <sub>OL</sub> = 100μA  | 1.8V ± 0.09V                             | 0.038        |     |     | V   |

|                      |                         |                          |                                          | 0.034        |     |     |     |

|                      |                         |                          |                                          | 0.045        |     |     |     |

|                      |                         |                          |                                          | 0.02         |     |     |     |

|                      |                         | I <sub>OL</sub> = 3mA    | 3.3V ± 0.3V                              | 0.1          |     |     |     |

|                      |                         |                          |                                          | 0.1          |     |     |     |

|                      |                         |                          |                                          | 0.1          |     |     |     |

|                      |                         |                          |                                          | 0.1          |     |     |     |

|                      |                         | I <sub>OL</sub> = 5mA    | 5V ± 0.5V                                | 0.12         |     |     |     |

|                      |                         |                          |                                          | 0.12         |     |     |     |

|                      |                         |                          |                                          | 0.12         |     |     |     |

|                      |                         |                          |                                          | 0.12         |     |     |     |

|                      |                         |                          |                                          | 0.12         |     |     |     |

| I <sub>I</sub>       | 入力リーク電流                 | すべてのピン                   | V <sub>I</sub> = V <sub>CC</sub>         | 1.71V ~ 5.5V |     | ±1  | μA  |

| I <sub>I</sub>       |                         |                          | V <sub>I</sub> = GND                     | 1.71V ~ 5.5V |     | ±1  |     |

| I <sub>OZ</sub>      | オフ状態 (高インピーダンス状態) の出力電流 | IO4, IO7                 | V <sub>O</sub> = 0~5.5V                  |              |     | ±1  | μA  |

| F <sub>OUT</sub>     | 最大出力周波数 (1)             | プッシュアップ 1X またはプッシュアップ 2X | 15pF の負荷容量                               | 1.8V ± 0.09V |     | 5   | MHz |

|                      |                         |                          |                                          | 3.3V ± 0.3V  |     | 12  |     |

|                      |                         |                          |                                          | 5V ± 0.5V    |     | 12  |     |

| R <sub>pu(int)</sub> | 内部プルアップ抵抗               |                          |                                          |              | 1   | MΩ  |     |

|                      |                         |                          |                                          |              | 100 | kΩ  |     |

|                      |                         |                          |                                          |              | 10  | kΩ  |     |

| R <sub>pd(int)</sub> | 内部プルダウン抵抗               |                          |                                          |              | 1   | MΩ  |     |

|                      |                         |                          |                                          |              | 100 | kΩ  |     |

|                      |                         |                          |                                          |              | 10  | kΩ  |     |

| C <sub>I</sub>       | 入力ピン容量                  | 各入力ピン                    | V <sub>I</sub> = V <sub>CC</sub> または GND | 1.71V ~ 5.5V | 1.2 | pF  |     |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                       |               |                                                                                | テスト条件                                                                                                                | V <sub>CC</sub> | 最小値 | 標準値             | 最大値  | 単位   |

|-----------------------------|---------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|------|------|

| C <sub>IO</sub>             | 入力 / 出力ピンの容量  | 各 I/O ピン                                                                       | V <sub>IO</sub> = V <sub>CC</sub> または GND                                                                            | 1.71V ~ 5.5V    |     | 2.0             |      | pF   |

| <b>アナログ コンパレータ</b>          |               |                                                                                |                                                                                                                      |                 |     |                 |      |      |

| t <sub>start</sub>          | スタート時間        | ACMP パワーオン 遅延                                                                  | バンドギャップ常時オン                                                                                                          | 1.71V ~ 5.5V    |     | 130             |      | μs   |

| V <sub>AI</sub>             | 入力電圧          | 正入力<br>負入力                                                                     |                                                                                                                      | 1.71V ~ 5.5V    | 0   | V <sub>CC</sub> | 0    | V    |

| V <sub>offset</sub>         | 入力オフセット電圧     | T <sub>A</sub> = 25°C<br>-40°C < T <sub>A</sub> ≤ 125°C                        | V <sub>HYS</sub> = 0mV、ゲイン = 1、VREF= 50mV~1200mV                                                                     | 1.71V ~ 5.5V    | -10 | 10              |      | mV   |

| dV <sub>IO</sub> /dT        | 入力オフセット電圧ドリフト | -40°C < T <sub>A</sub> ≤ 125°C                                                 | V <sub>HYS</sub> = 0mV、ゲイン = 1、VREF= 50mV~1200mV                                                                     | 1.71V ~ 5.5V    | -15 | 15              |      |      |

| I <sub>B</sub>              | 入力バイアス電流      |                                                                                |                                                                                                                      |                 |     | 1               | μA   |      |

| C <sub>ID</sub>             | 入力容量、差動       |                                                                                |                                                                                                                      |                 |     | 3               |      | pF   |

| C <sub>IM</sub>             | 入力容量、同相       |                                                                                |                                                                                                                      |                 |     | 3               |      | pF   |

| PROP                        | 伝搬遅延、応答時間     | ゲイン = 1、Vref = 50mV~1200mV、オーバードライブ = 50mV                                     | Low から High、低帯域幅イネーブル<br>High から Low 低帯域幅イネーブル<br>Low から High、低帯域幅ディセーブル<br>High から Low 低帯域幅ディセーブル                   | 1.71V ~ 5.5V    | 1.5 | 2.5             | 0.25 | 0.15 |

| <b>アナログ コンパレータ - ヒステリシス</b> |               |                                                                                |                                                                                                                      |                 |     |                 |      |      |

| V <sub>HYS</sub>            | ヒステリシス機能内蔵    | V <sub>HYS</sub> = 25mV<br>V <sub>HYS</sub> = 50mV<br>V <sub>HYS</sub> = 200mV | T <sub>A</sub> = 25°C<br>-40°C~125°C<br>T <sub>A</sub> = 25°C<br>-40°C~125°C<br>T <sub>A</sub> = 25°C<br>-40°C~125°C | 1.71V ~ 5.5V    | 16  | 21.6            | 35   | mV   |

|                             |               |                                                                                |                                                                                                                      |                 | 15  |                 | 40   |      |

|                             |               |                                                                                |                                                                                                                      |                 | 42  | 50.7            | 62   |      |

|                             |               |                                                                                |                                                                                                                      |                 | 40  |                 | 65   |      |

|                             |               |                                                                                |                                                                                                                      |                 | 170 | 202             | 240  |      |

|                             |               |                                                                                |                                                                                                                      |                 | 165 |                 | 245  |      |

| <b>アナログ コンパレータ - 入力ゲイン</b>  |               |                                                                                |                                                                                                                      |                 |     |                 |      |      |

| R <sub>sin</sub>            | 直列入力抵抗        | ゲイン = 0.5<br>ゲイン = 0.33<br>ゲイン = 0.25                                          |                                                                                                                      | 1.71V ~ 5.5V    | 1   | 0.75            | 1    | MΩ   |

| G <sub>err</sub>            | ゲイン誤差         | ゲイン = 0.5<br>ゲイン = 0.33<br>ゲイン = 0.25                                          |                                                                                                                      | 1.71V ~ 5.5V    | -1  | -1.25           | -1.5 | %    |

| <b>電圧リファレンス</b>             |               |                                                                                |                                                                                                                      |                 |     |                 |      |      |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                 |                        | テスト条件                          | V <sub>CC</sub>                         | 最小値          | 標準値   | 最大値    | 単位 |  |

|---------------------------------------|------------------------|--------------------------------|-----------------------------------------|--------------|-------|--------|----|--|

| V <sub>REF</sub>                      | 内部 V <sub>REF</sub> 誤差 | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 150mV<br>~300mV      | 1.71V ~ 5.5V | -8.5  | 8.5    | %  |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -9    | 9      |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 350mV<br>~600mV      |              | -3    | 3      |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -4    | 4      |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 650mV<br>~1000mV     |              | -2.5  | 2.5    |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -4    | 4      |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> =<br>1050mV~<br>1200mV |              | -3    | 3      |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -3.7  | 3.7    |    |  |

| V <sub>REF</sub>                      | V <sub>REF</sub> 誤差    | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 150mV<br>~300mV      |              | -10.2 | 10.2   | %  |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -11   | 11     |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 350mV<br>~600mV      |              | -5    | 5      |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -5.5  | 5.5    |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> = 650mV<br>~1000mV     |              | -3.3  | 3.3    |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -4.3  | 4.3    |    |  |

|                                       |                        | T <sub>A</sub> = 25°C          | V <sub>REF</sub> =<br>1050mV~<br>1200mV |              | -4    | 4      |    |  |

|                                       |                        | -40°C < T <sub>A</sub> ≤ 125°C |                                         |              | -5    | 5      |    |  |

| I <sub>LOAD</sub>                     | 出力電流                   |                                | 1.71V ~ 5.5V                            |              | 500   | μA     |    |  |

| dV <sub>OUT</sub> /dT                 | 出力電圧の温度ドリフト            |                                | 1.71V ~ 5.5V                            |              | 550   | ppm/°C |    |  |

| dV <sub>OUT</sub> /dI <sub>LOAD</sub> | ロード レギュレーション           |                                | 1.71V ~ 5.5V                            | 0.1          | 1     | mV/μA  |    |  |

(1) オープンドレインのスイッチング性能は、使用するプルアップ抵抗によって制限されます。

## 5.6 電源電流特性

T<sub>A</sub> = 25°C (特に記述のない限り)

| パラメータ           |       | テスト条件 | V <sub>CC</sub> = 1.8V ± 0.09V                                 |      |     | V <sub>CC</sub> = 3.3V ± 0.3V |     |      | V <sub>CC</sub> = 5V ± 0.5V |     |     | 単位 |

|-----------------|-------|-------|----------------------------------------------------------------|------|-----|-------------------------------|-----|------|-----------------------------|-----|-----|----|

|                 |       |       | 最小値                                                            | 標準値  | 最大値 | 最小値                           | 標準値 | 最大値  | 最小値                         | 標準値 | 最大値 |    |

| <b>スタンバイ</b>    |       |       |                                                                |      |     |                               |     |      |                             |     |     |    |

| I <sub>CC</sub> | 静止時電流 |       | 入力 = 静止、<br>出力 = オープン、<br>I <sub>O</sub> = 0、<br>OSC パワー<br>オフ | 3.41 |     | 3.66                          |     | 4.00 |                             | μA  |     |    |

| <b>発振器</b>      |       |       |                                                                |      |     |                               |     |      |                             |     |     |    |

## 5.6 電源電流特性 (続き)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

| パラメータ       |       |                            | テスト条件                  | $V_{CC} = 1.8V \pm 0.09V$ |     |      | $V_{CC} = 3.3V \pm 0.3V$ |      |     | $V_{CC} = 5V \pm 0.5V$ |     |     | 単位            |

|-------------|-------|----------------------------|------------------------|---------------------------|-----|------|--------------------------|------|-----|------------------------|-----|-----|---------------|

|             |       |                            |                        | 最小値                       | 標準値 | 最大値  | 最小値                      | 標準値  | 最大値 | 最小値                    | 標準値 | 最大値 |               |

| $I_{CC}$    | 静止時電流 | OSC0 有効: 25kHz             | 事前分周 = 1               | 3.21                      |     | 5.24 |                          | 10.1 |     |                        |     |     | $\mu\text{A}$ |

|             |       |                            | 事前分周 = 2               | 3.14                      |     | 5.17 |                          | 10.1 |     |                        |     |     |               |

|             |       |                            | 事前分周 = 4               | 3.53                      |     | 5.11 |                          | 10.1 |     |                        |     |     |               |

|             |       |                            | 事前分周 = 8               | 3.08                      |     | 5.28 |                          | 10.0 |     |                        |     |     |               |

|             |       | OSC0 有効: 2MHz              | 事前分周 = 1               | 42.9                      |     | 56.0 |                          | 84.9 |     |                        |     |     |               |

|             |       |                            | 事前分周 = 2               | 35.9                      |     | 49.0 |                          | 79.2 |     |                        |     |     |               |

|             |       |                            | 事前分周 = 4               | 32.5                      |     | 45.6 |                          | 75.5 |     |                        |     |     |               |

|             |       |                            | 事前分周 = 8               | 30.7                      |     | 43.8 |                          | 73.8 |     |                        |     |     |               |

| アナログ コンパレータ |       |                            |                        |                           |     |      |                          |      |     |                        |     |     |               |

| $I_{CC}$    | 静止時電流 | ディスクリート アナログ コンパレータ (ACMP) | 外部 VREF、<br>$IN+ = 0V$ | 24.8                      |     | 26.2 |                          | 26.8 |     |                        |     |     | $\mu\text{A}$ |

|             |       |                            | 追加 ACMP                | 3.2                       |     | 4.7  |                          | 4.7  |     |                        |     |     |               |

| 電圧リファレンス    |       |                            |                        |                           |     |      |                          |      |     |                        |     |     |               |

| $I_{CC}$    | 静止時電流 | 電圧リファレンス (VREF)            |                        | 16.8                      |     | 18.3 |                          | 19.9 |     |                        |     |     | $\mu\text{A}$ |

## 5.7 スイッチング特性

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

| パラメータ    |    | 始点 (入力)          | 終点 (出力)  | テスト条件 | $V_{CC}$         | 最小値  | 標準値 | 最大値 | 単位          |

|----------|----|------------------|----------|-------|------------------|------|-----|-----|-------------|

| デジタル IO  |    |                  |          |       |                  |      |     |     |             |

| $t_{pd}$ | 遅延 | デジタル入力           | プッシュプル出力 | 立ち上がり | $1.8V \pm 0.09V$ | 46.2 |     |     | $\text{ns}$ |

|          |    |                  |          | 立ち下がり |                  | 39.1 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 27.2 |     |     |             |

|          |    |                  |          | 立ち下がり | $3.3V \pm 0.3V$  | 24.5 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 22.1 |     |     |             |

|          |    |                  |          | 立ち下がり |                  | 21.1 |     |     |             |

| $t_{pd}$ | 遅延 | シュミットトリガ付きデジタル入力 | プッシュプル出力 | 立ち上がり | $1.8V \pm 0.09V$ | 49.5 |     |     | $\text{ns}$ |

|          |    |                  |          | 立ち下がり |                  | 41.5 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 29.3 |     |     |             |

|          |    |                  |          | 立ち下がり | $3.3V \pm 0.3V$  | 25.3 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 23.9 |     |     |             |

|          |    |                  |          | 立ち下がり |                  | 21.5 |     |     |             |

| $t_{pd}$ | 遅延 | 低電圧デジタル入力        | プッシュプル出力 | 立ち上がり | $1.8V \pm 0.09V$ | 45.0 |     |     | $\text{ns}$ |

|          |    |                  |          | 立ち下がり |                  | 48.1 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 25.4 |     |     |             |

|          |    |                  |          | 立ち下がり | $3.3V \pm 0.3V$  | 30.3 |     |     |             |

|          |    |                  |          | 立ち上がり |                  | 19.6 |     |     |             |

|          |    |                  |          | 立ち下がり |                  | 28.6 |     |     |             |

## 5.7 スイッチング特性(続き)

T<sub>A</sub> = 25°C (特に記述のない限り)

| パラメータ        |    | 始点<br>(入力)       | 終点<br>(出力)        | テスト条件            | V <sub>cc</sub> | 最小値          | 標準値  | 最大値 | 単位 |

|--------------|----|------------------|-------------------|------------------|-----------------|--------------|------|-----|----|

| $t_{pd}$     | 遅延 | デジタル入力           | オープンドラインの NMOS 出力 | 立ち上がり            | 1.8V ± 0.09V    |              |      |     | ns |

|              |    |                  |                   | 立ち下がり            |                 | 38.8         |      |     |    |

|              |    |                  |                   | 立ち上がり            | 3.3V ± 0.3V     |              |      |     |    |

|              |    |                  |                   | 立ち下がり            |                 | 24.3         |      |     |    |

|              |    |                  |                   | 立ち上がり            | 5V ± 0.5V       |              |      |     |    |

|              |    |                  |                   | 立ち下がり            |                 | 20.9         |      |     |    |

| $t_{pd}$     | 遅延 | ピンからの出力<br>イネーブル | OE                | ハイインピーダンスを 1 に設定 | 1.8V ± 0.09V    | 45.0         |      |     | ns |

|              |    |                  |                   |                  | 3.3V ± 0.3V     | 26.5         |      |     |    |

|              |    |                  |                   |                  | 5V ± 0.5V       | 21.7         |      |     |    |

|              |    |                  |                   | ハイインピーダンスを 0 に設定 | 1.8V ± 0.09V    | 43.2         |      |     | ns |

|              |    |                  |                   |                  | 3.3V ± 0.3V     | 22.6         |      |     |    |

|              |    |                  |                   |                  | 5V ± 0.5V       | 18.3         |      |     |    |

| 機能を設定可能なロジック |    |                  |                   |                  |                 |              |      |     |    |

| $t_{pd}$     | 遅延 | 2 ビット LUT        | IN                | OUT              | 立ち上がり           | 1.8V ± 0.09V | 1.14 |     | ns |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.32 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 3.3V ± 0.3V  | 1.14 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.31 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 5V ± 0.5V    | 1.16 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.35 |     |    |

| $t_{pd}$     | 遅延 | 3 ビット LUT        | IN                | OUT              | 立ち上がり           | 1.8V ± 0.09V | 1.31 |     | ns |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.53 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 3.3V ± 0.3V  | 1.31 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.53 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 5V ± 0.5V    | 1.31 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.53 |     |    |

| $t_{pd}$     | 遅延 | 4 ビット LUT        | IN                | OUT              | 立ち上がり           | 1.8V ± 0.09V | 1.53 |     | ns |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.86 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 3.3V ± 0.3V  | 1.53 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.86 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 5V ± 0.5V    | 1.53 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.86 |     |    |

| $t_{pd}$     | 遅延 | DFF/Latch        | CLK               | Q                | 立ち上がり           | 1.8V ± 0.09V | 1.42 |     | ns |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.44 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 3.3V ± 0.3V  | 1.42 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.44 |     |    |

|              |    |                  |                   |                  | 立ち上がり           | 5V ± 0.5V    | 1.42 |     |    |

|              |    |                  |                   |                  | 立ち下がり           |              | 1.44 |     |    |

## 5.7 スイッチング特性 (続き)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

| パラメータ        |               |                 | 始点<br>(入力) | 終点<br>(出力) | テスト条件         | $V_{cc}$      | 最小値          | 標準値          | 最大値  | 単位            |

|--------------|---------------|-----------------|------------|------------|---------------|---------------|--------------|--------------|------|---------------|

| $t_{pd}$     | 遅延            | DFF/Latch       | nRST/nSET  | Q          | 立ち上がり         | 1.8V ± 0.09V  | 1.58         |              |      | ns            |

|              |               |                 |            |            | 立ち下がり         |               | 1.58         |              |      |               |

|              |               |                 |            |            | 立ち上がり         | 3.3V ± 0.3V   | 1.58         |              |      |               |

|              |               |                 |            |            | 立ち下がり         |               | 1.58         |              |      |               |

|              |               |                 |            |            | 立ち上がり         | 5V ± 0.5V     | 1.58         |              |      |               |

|              |               |                 |            |            | 立ち下がり         |               | 1.58         |              |      |               |

| カウンタ / 遅延    |               |                 |            |            |               |               |              |              |      |               |

| $t_{pd}$     | 遅延            | カウンタ - 遅延モード    |            |            | IN の立ち上がりエッジ  | OUT の立ち上がりエッジ | 立ち下がりエッジをトリガ | 1.8V ± 0.09V | 2.21 | ns            |

|              |               |                 |            |            | IN の立ち下がりエッジ  |               | 立ち上がりエッジをトリガ |              | 2.01 |               |

|              |               |                 |            |            | IN の立ち上がりエッジ  | OUT の立ち上がりエッジ | 立ち下がりエッジをトリガ | 3.3V ± 0.3V  | 2.21 |               |

|              |               |                 |            |            | IN の立ち下がりエッジ  |               | 立ち上がりエッジをトリガ |              | 2.01 |               |

|              |               |                 |            |            | IN の立ち上がりエッジ  | OUT の立ち上がりエッジ | 立ち下がりエッジをトリガ | 5V ± 0.5V    | 2.21 |               |

|              |               |                 |            |            | IN の立ち下がりエッジ  |               | 立ち上がりエッジをトリガ |              | 2.01 |               |

| $t_{pw}$     | パルス幅          | カウンタ - エッジ検出モード |            |            | OUT の立ち上がりエッジ | OUT の立ち下がりエッジ | 立ち上がりエッジ検出   | 1.8V ± 0.09V | 57.6 | ns            |

|              |               |                 |            |            |               |               |              | 3.3V ± 0.3V  | 61.4 |               |

|              |               |                 |            |            |               |               |              | 5V ± 0.5V    | 62.0 |               |

|              |               |                 |            |            |               |               |              | 1.8V ± 0.09V | 56.0 |               |

|              |               |                 |            |            |               |               |              | 3.3V ± 0.3V  | 59.6 |               |

|              |               |                 |            |            |               |               |              | 5V ± 0.5V    | 60.4 |               |

|              |               |                 |            |            |               |               |              | 1.8V ± 0.09V | 55.9 |               |

|              |               |                 |            |            |               |               |              | 3.3V ± 0.3V  | 59.7 |               |

|              |               |                 |            |            |               |               |              | 5V ± 0.5V    | 60.5 |               |

|              |               |                 |            |            |               |               |              |              |      |               |

| 発振器          |               |                 |            |            |               |               |              |              |      |               |

| $f_{err}$    | 発振器の周波数誤差     |                 |            |            | OSC0 25kHz    | 1.8V ± 0.09V  | -5           | 5            |      | %             |

|              |               |                 |            |            |               | 3.3V ± 0.3V   | -5           | 5            |      |               |

|              |               |                 |            |            |               | 5V ± 0.5V     | -5           | 5            |      |               |

|              |               |                 |            |            | OSC0 2MHz     | 1.8V ± 0.09V  | -5           | 5            |      |               |

|              |               |                 |            |            |               | 3.3V ± 0.3V   | -5           | 5            |      |               |

|              |               |                 |            |            |               | 5V ± 0.5V     | -5           | 5            |      |               |

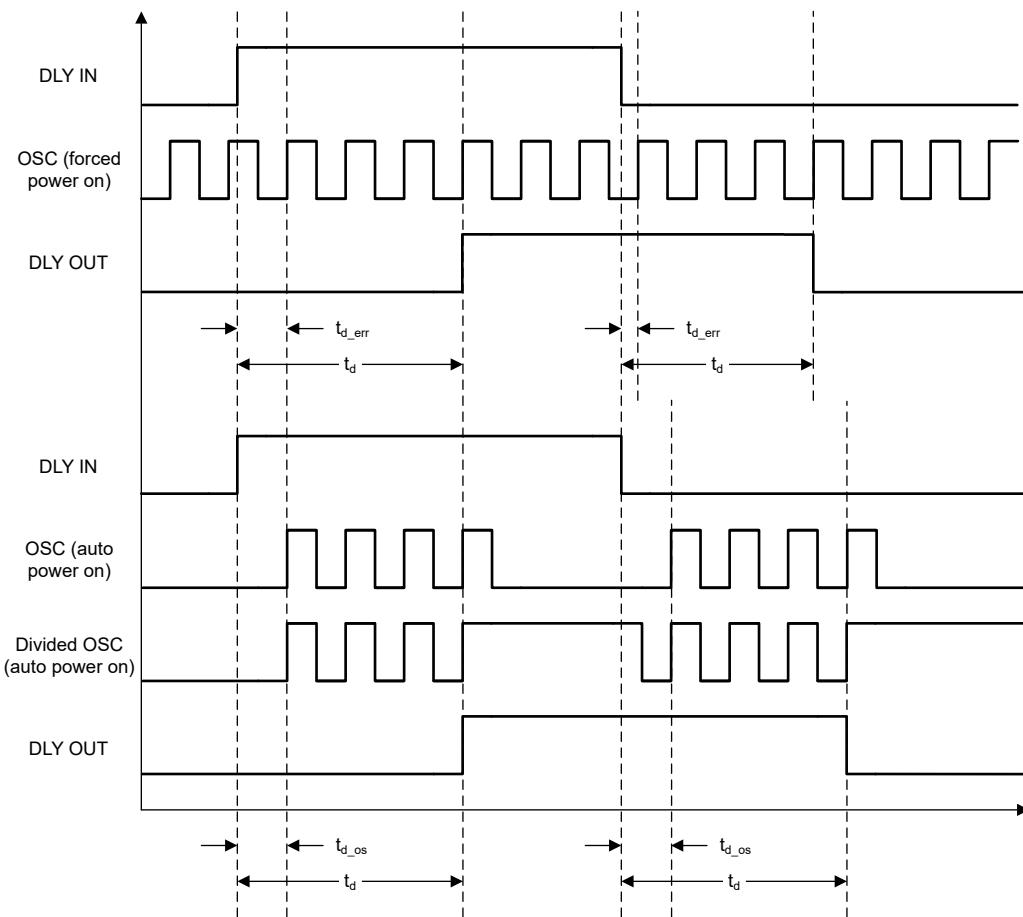

| $t_{d\_osc}$ | 発振器のスタートアップ遅延 |                 |            | OSC0 25kHz | 1.8V ± 0.09V  | 11.5          |              |              |      | $\mu\text{s}$ |

|              |               |                 |            |            | 3.3V ± 0.3V   | 10.5          |              |              |      |               |

|              |               |                 |            |            | 5V ± 0.5V     | 9.9           |              |              |      |               |

|              |               |                 |            | OSC0 2MHz  | 1.8V ± 0.09V  | 3.3           |              |              |      |               |

|              |               |                 |            |            | 3.3V ± 0.3V   | 2.7           |              |              |      |               |

|              |               |                 |            |            | 5V ± 0.5V     | 2.5           |              |              |      |               |

## 5.7 スイッチング特性 (続き)

T<sub>A</sub> = 25°C (特に記述のない限り)

| パラメータ                      |                      | 始点<br>(入力)                 | 終点<br>(出力)           | テスト条件                 | V <sub>cc</sub> | 最小値          | 標準値   | 最大値 | 単位          |

|----------------------------|----------------------|----------------------------|----------------------|-----------------------|-----------------|--------------|-------|-----|-------------|

| <i>t<sub>set_osc</sub></i> | 発振器のスタートアップ セッティング時間 |                            |                      | OSC0 25kHz            | 1.8V ± 0.09V    | 1            |       |     | μs          |

|                            |                      |                            |                      |                       | 3.3V ± 0.3V     | 1            |       |     |             |

|                            |                      |                            |                      |                       | 5V ± 0.5V       | 1            |       |     |             |

|                            |                      |                            |                      | OSC0 2MHz             | 1.8V ± 0.09V    | 7            |       |     | μs          |

|                            |                      |                            |                      |                       | 3.3V ± 0.3V     | 7            |       |     |             |

|                            |                      |                            |                      |                       | 5V ± 0.5V       | 7            |       |     |             |

| <i>t<sub>d_err</sub></i>   | 遅延誤差                 |                            |                      | OSC (強制パワー オン)        | 1.71V ~ 5.5V    | 0            | 1     |     | CLK<br>サイクル |

| プログラマブル フィルタ               |                      |                            |                      |                       |                 |              |       |     |             |

| <i>t<sub>pfit_pw</sub></i> | パルス幅                 | プログラム可能なフィルタ - エッジ検出モード    | OUT の立ち上がりエッジ        | OUT の立ち下がりエッジ         | 1 セル            | 1.8V ± 0.09V | 154.0 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 157.3 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 158.7 |     |             |

|                            |                      |                            |                      | OUT の立ち下がりエッジ         | 2 セル            | 1.8V ± 0.09V | 256.2 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 259.7 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 260.8 |     |             |

|                            |                      |                            |                      | OUT の立ち下がりエッジ         | 3 セル            | 1.8V ± 0.09V | 356.2 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 360.3 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 361.5 |     |             |

|                            |                      |                            |                      | OUT の立ち下がりエッジ         | 4 セル            | 1.8V ± 0.09V | 455.3 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 459.6 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 461.4 |     |             |

| <i>t<sub>pfit_pd</sub></i> | 遅延                   | プログラム可能なフィルタ - エッジ検出モード    |                      |                       | 任意のセル           | 1.8V ± 0.09V | 22.0  |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 21.4  |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 21.3  |     |             |

| <i>t<sub>pfit_d</sub></i>  | 遅延                   | プログラム可能なフィルタ - 両方のエッジ遅延モード | IN の立ち上がり / 立ち下がりエッジ | OUT の立ち上がり / 立ち下がりエッジ | 1 セル            | 1.8V ± 0.09V | 176.0 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 178.7 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 161.0 |     |             |

|                            |                      |                            |                      | OUT の立ち上がり / 立ち下がりエッジ | 2 セル            | 1.8V ± 0.09V | 278.2 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 281.1 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 282.1 |     |             |

|                            |                      |                            |                      | OUT の立ち上がり / 立ち下がりエッジ | 3 セル            | 1.8V ± 0.09V | 378.2 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 352.1 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 382.8 |     |             |

|                            |                      |                            |                      | OUT の立ち上がり / 立ち下がりエッジ | 4 セル            | 1.8V ± 0.09V | 477.3 |     | ns          |

|                            |                      |                            |                      |                       |                 | 3.3V ± 0.3V  | 481.0 |     |             |

|                            |                      |                            |                      |                       |                 | 5V ± 0.5V    | 482.7 |     |             |

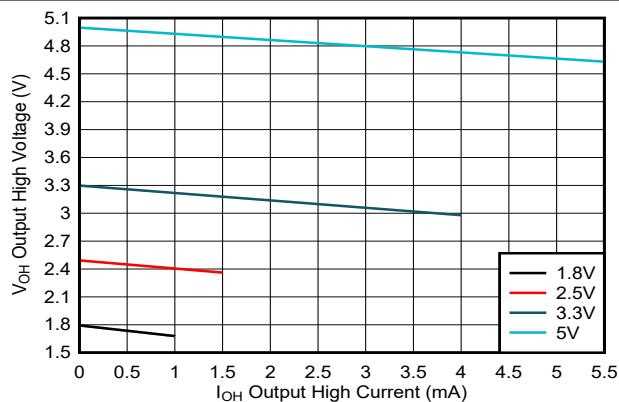

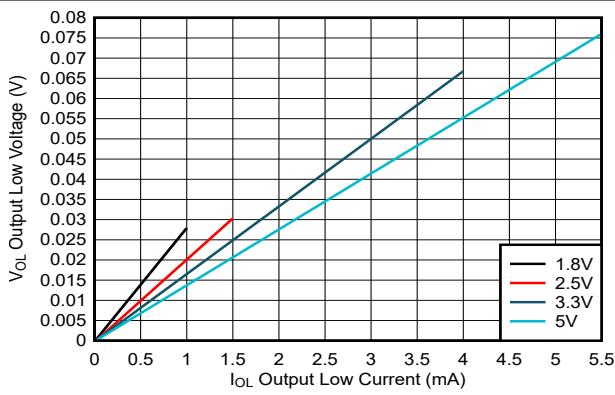

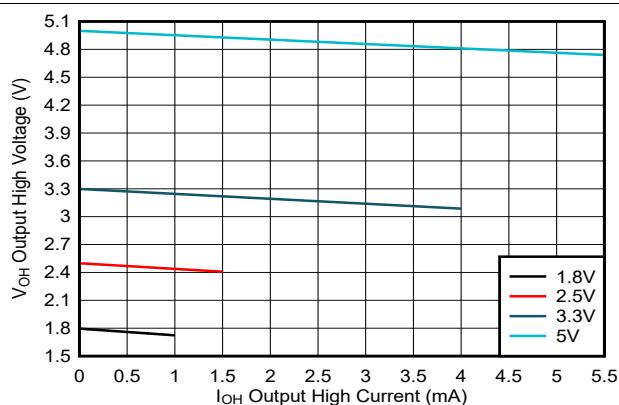

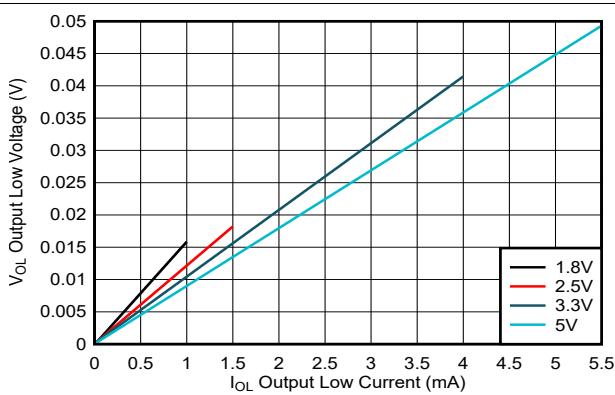

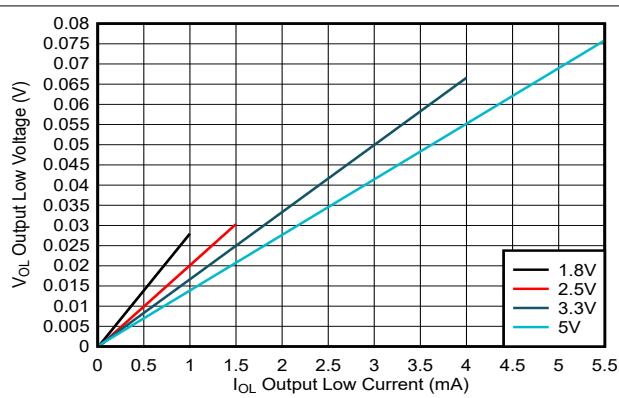

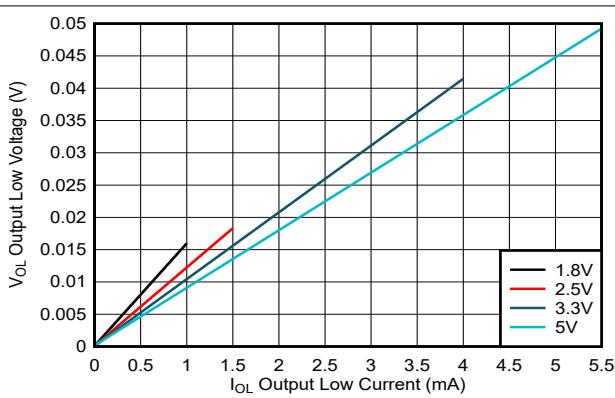

## 5.8 代表的特性

$T_A = 25^\circ\text{C}$

図 5-1. High 状態での 1X プッシュプル標準出力電圧 (V<sub>OH</sub>)

図 5-2. Low 状態での 1X プッシュプル標準出力電圧 (V<sub>OL</sub>)

図 5-3. High 状態での 2X プッシュプル標準出力電圧 (V<sub>OH</sub>)

図 5-4. Low 状態での 2X プッシュプル標準出力電圧 (V<sub>OL</sub>)

図 5-5. Low 状態での 1X オープンドレイン NMOS 標準出力電圧 (V<sub>OL</sub>)

図 5-6. Low 状態での 2X オープンドレイン NMOS 標準出力電圧 (V<sub>OL</sub>)

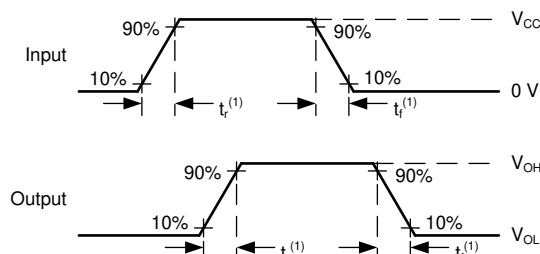

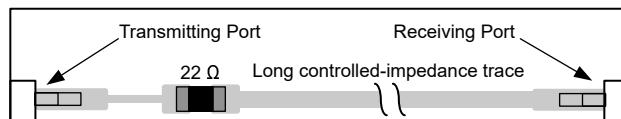

## 6 パラメータ測定情報

波形間の位相関係は、任意に選択されています。すべての入力パルスは、以下の特性を持つジェネレータによって供給されます。PRR  $\leq 1\text{MHz}$ ,  $Z_O = 50\Omega$ ,  $t_f < 2.5\text{ns}$ 。

クロック入力の  $f_{\max}$  は、入力デューティサイクルが 50% のときの測定値です。

出力は一度に 1 つずつ測定され、測定するたびに入力が 1 回遷移します。

(1)  $C_L^{(1)}$  にはプローブとテスト装置の容量が含まれます。

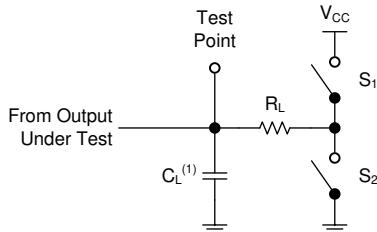

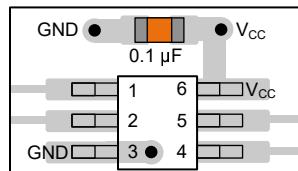

図 6-1.3 ステート出力の負荷回路

(1)  $C_L^{(1)}$  にはプローブとテスト装置の容量が含まれます。

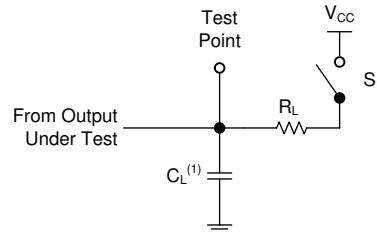

図 6-2. オープン ドレイン出力の負荷回路

(1)  $C_L^{(1)}$  にはプローブとテスト装置の容量が含まれます。

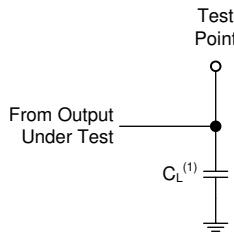

図 6-3. ブッシュプル出力のための負荷回路

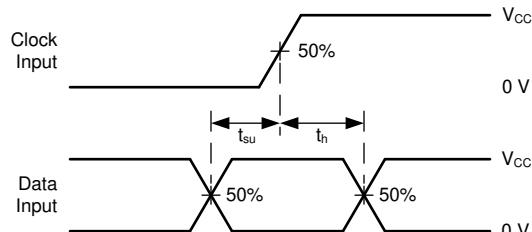

図 6-5. 電圧波形、セットアップ時間およびホールド時間

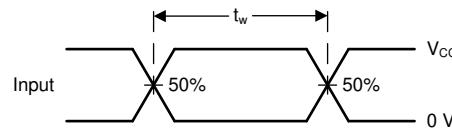

図 6-4. 電圧波形、パルス幅

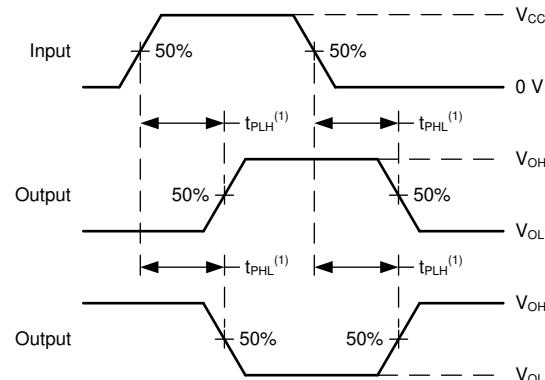

(1)  $t_{PLH}^{(1)}$  と  $t_{PHL}^{(1)}$  の大きい方が  $t_{pd}$  に相当します。

図 6-6. 電圧波形、伝搬遅延

図 6-7. 電圧波形、伝搬遅延

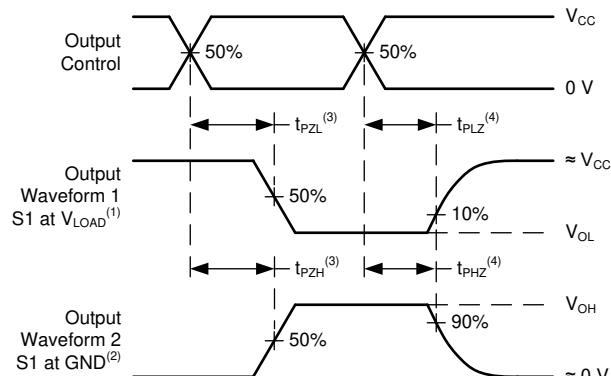

(1)  $t_{PLZ}$  と  $t_{PZL}$  の大きい方が  $t_{pd}$  に相当します。

図 6-8. 電圧波形、伝搬遅延

(1)  $t_r$  と  $t_f$  の大きい方が  $t_t$  に相当します。

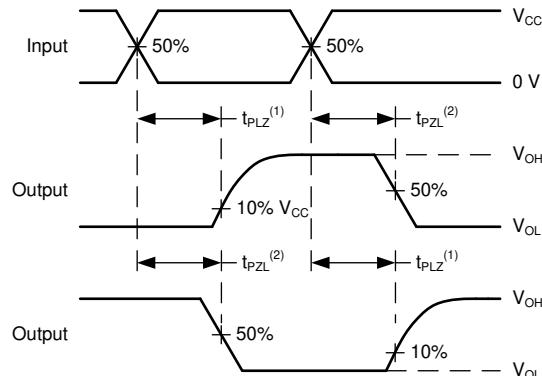

図 6-9. 電圧波形、入力および出力の遷移時間

## 7 詳細説明

### 7.1 概要

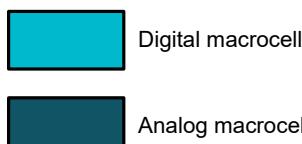

TPLD1201-Q1 は、組み合わせ論理、順序論理、アナログ ブロックを内蔵した多用途なプログラマブル ロジック IC を特長とするテキサス・インスツルメンツ プログラマブル ロジック デバイス (TPLD) ファミリのデバイスであり、一般的なシステム機能を実装するためのコンパクトな統合型低消費電力ソリューションを提供します。

TPLD1201-Q1 は、デジタル入力、デジタル出力、デジタル入出力、アナログ入出力として構成できる 1 つの GPI と 7 つの GPIO を備えています。

TPLD1201-Q1 は、内部マクロセルと I/O ピンの配線を構成するための相互接続システムを備えています。ここでは、これを接続マルチプレクサと言います。それぞれの接続マルチプレクサ入力は、デジタル I/O、ルックアップ テーブル、アナログ コンパレータ出力など、特定のデジタル マクロセル出力にハードワイヤ接続されています。接続マルチプレクサを使うと、各デジタル入力を 1 つの出力のみに接続できるため、バスの競合が発生しません。

TPLD1201-Q1 には、以下に示すマクロセルがあります。

- 機能を設定可能なロジック ブロック:

- 2 つの 2 ビット ルックアップ テーブル (LUT)

- 2 つの 3 ビット LUT

- 2 つの 2 ビット LUT または D タイプ フリップ フロップ (DFF) またはラッチ

- 2 つの 3 ビット LUT または DFF またはラッチ (リセット / セット オプション付き)

- 1 つの 3 ビット LUT またはパイプ遅延

- 1 つの 4 ビット LUT または 8 ビット カウンタ (CNT) または遅延ジェネレータ (DLY)

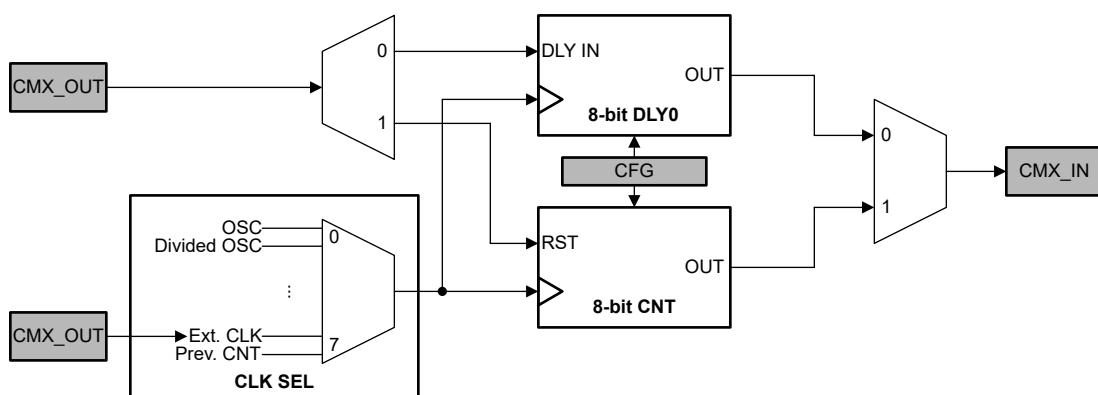

- 3 つの 8 ビット CNT/DLY

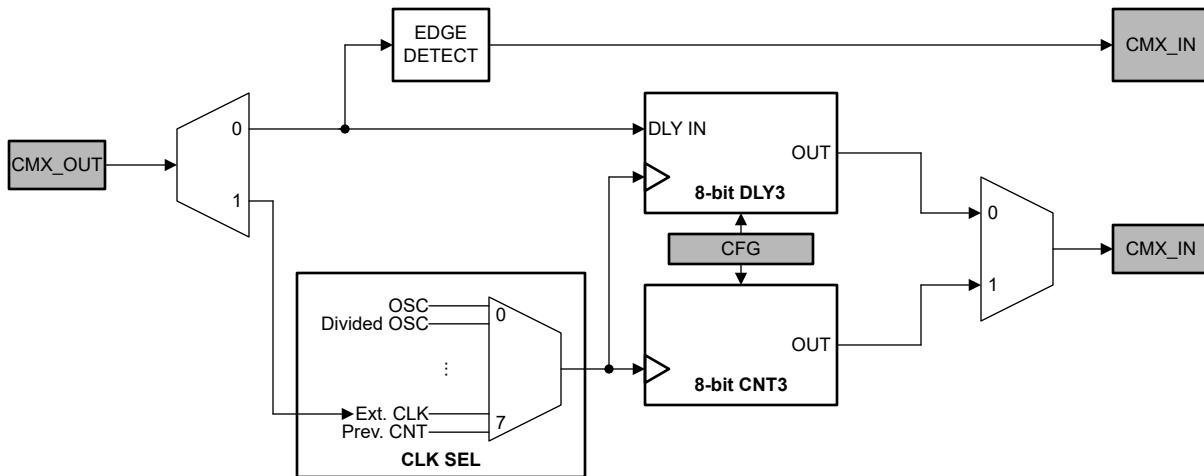

- 1 つのプログラマブル グリッヂ除去フィルタ (PFLT) またはエッジ検出器 (EDET)

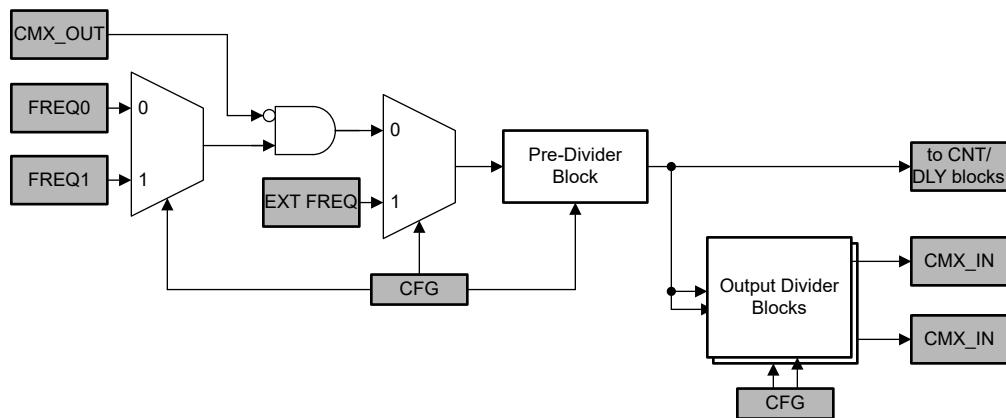

- 25kHz と 2MHz のどちらかのクロックを生成するための 1 つの発振器 (OSC)

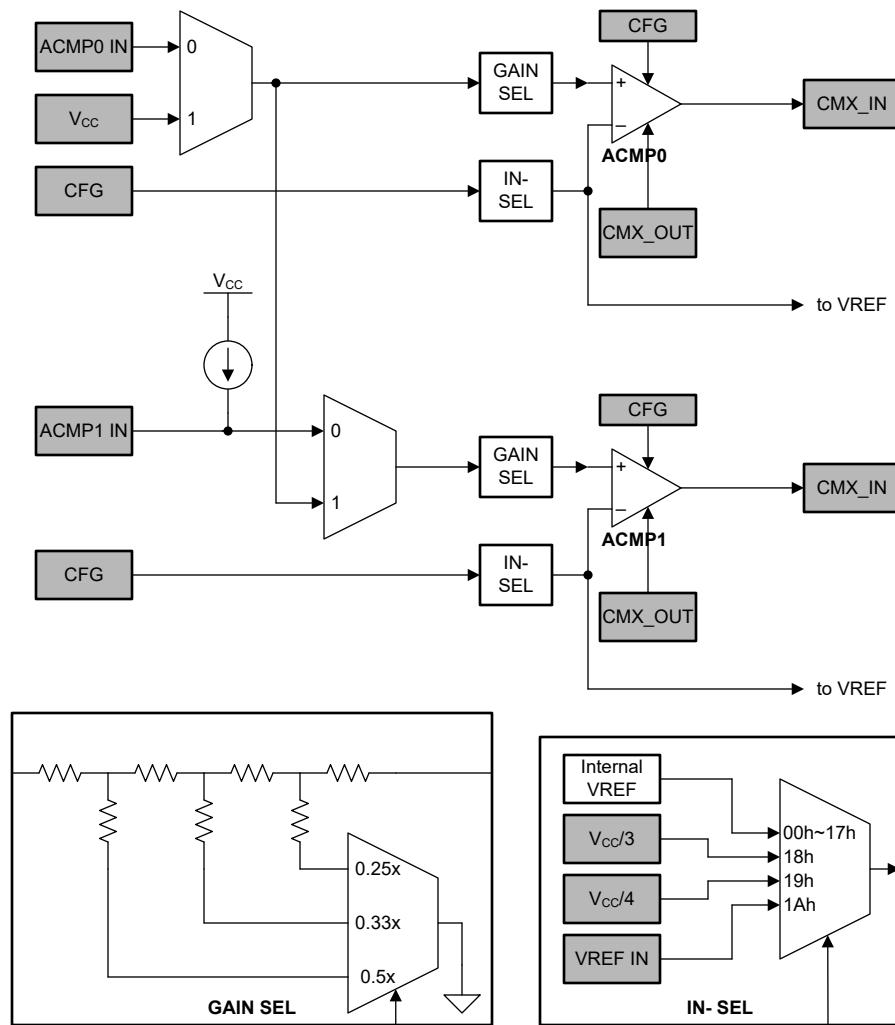

- 2 つのアナログ コンパレータ (ACMP)

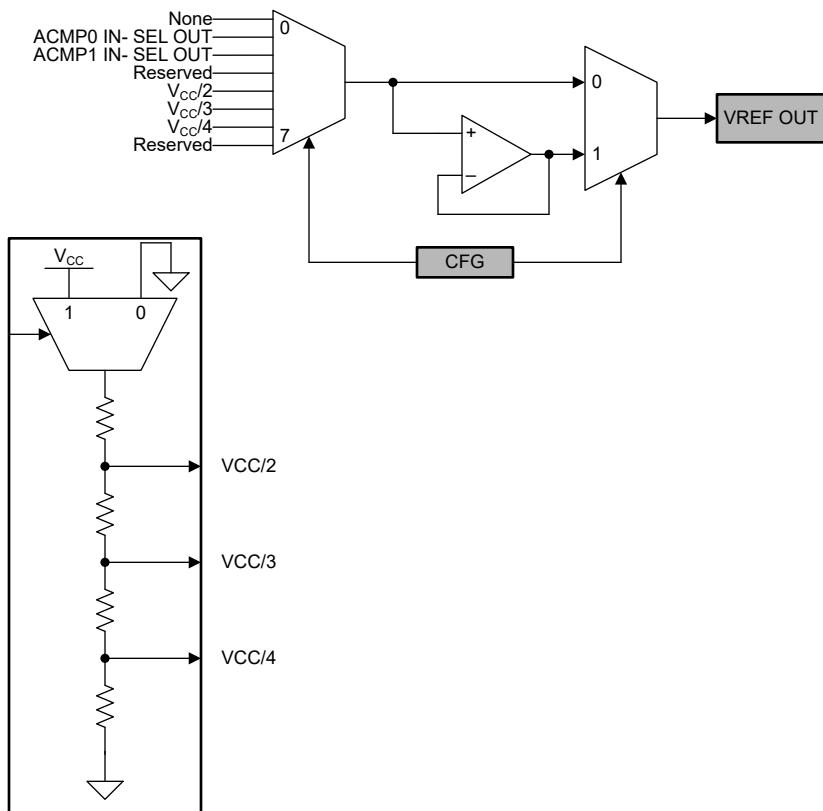

- 電圧リファレンス (VREF) (アナログ IO に出力可能)

この InterConnect Studio ソフトウェア環境では、シンプルなドラッグ アンド ドロップ インターフェイスを使用してカスタム回路設計を構築し、マクロセル、I/O ピン、相互接続を構成することができます。回路の作成に加えて、InterConnect Studio にはデジタルおよびアナログ機能のシミュレーション機能があり、設計を検証し、標準的な消費電力の推定値を提供できます。回路設計が完成した時点で、InterConnect Studio は、不揮発性メモリ内でその設計を一時的にエミュレートするか、または、ワンタイム プログラマブル (OTP) を永続的にプログラムすることができます。OTP は、ロックすることにより、内容の読み戻しを防止できます。

## 7.2 機能ブロック図

図 7-1. TPLD1201-Q1 機能ブロック図

## 7.3 機能説明

### 7.3.1 I/O ピン

TPLD1201-Q1 は 1 本の入力ピンと 7 本の多機能 I/O ピンを持っています。GPIO ピンは、ユーザー定義の入力、出力、または特殊機能のいずれかとして使用できます。

#### 7.3.1.1 入力モード

ピンを入力として構成する場合、以下のオプションを使用できます：

- ・ シュミットトリガなしのデジタル入力

- ・ シュミットトリガ付きデジタル入力

- ・ 低電圧デジタル入力

低電圧デジタル入力は、シュミットトリガなしのデジタル入力よりも  $V_{IH}/V_{IL}$  の仕様が低くなっています。これにより、低電圧デジタル入力  $V_{IH}$  および  $V_{IL}$  仕様を満たす  $V_{CC}$  より低い任意の電圧ドメインからの昇圧変換が可能です。

以下のピンは、特殊機能として動作するオプションも備えています。

- ・ IO9: 外部クロック入力

- ・ IO1: アナログコンパレータ 0 の正入力

- ・ IO2: アナログコンパレータの負入力

- ・ IO4: アナログコンパレータ 1 の正入力

- ・ IO7: 内部電圧リファレンス出力

#### 7.3.1.2 出力モード

ピンを出力として構成する場合、ドライブ強度をプログラム可能な以下のオプションを利用できます：

- ・ プッシュプル出力

- ・ オープンドレインの NMOS 出力

- ・ オープンドレインの PMOS 出力

#### 7.3.1.3 プルアップまたはプルダウン抵抗

すべての I/O ピンには、ピン構造に接続できるユーザー選択可能な抵抗のオプションがあります。これらの抵抗で選択可能な値は、 $10k\Omega$ 、 $100k\Omega$ 、 $1M\Omega$  です。これらの内部抵抗はプルアップとプルダウンのどちらかとして構成できます。InterConnect Studio で設計すると、設計で未使用のすべてのピンは、デフォルトで  $1M\Omega$  のプルダウンが接続されるように構成されます。さらに、パワーオンイベントの後、パワーオンリセットシーケンスが完了するまで、すべてのポートがハイインピーダンス状態になります。

表 7-1. ピン構成オプション

| GPIO | IO の選択 | OE | IO オプション           | 抵抗      | 抵抗値          |

|------|--------|----|--------------------|---------|--------------|

| IN0  | 未使用のピン | —  | —                  | プルダウン   | $1M\Omega$   |

|      | デジタル入力 | 0  | デジタル入力(シュミットトリガなし) | フローティング | —            |

|      |        |    | デジタル入力(シュミットトリガ付き) |         | $10k\Omega$  |

|      |        |    | 低電圧デジタル入力          | プルダウン   | $100k\Omega$ |

|      |        |    |                    |         | $1M\Omega$   |

**表 7-1. ピン構成オプション(続き)**

| GPIO     | IO の選択  | OE | IO オプション               | 抵抗      | 抵抗値   |

|----------|---------|----|------------------------|---------|-------|

| IO1, IO2 | デジタル入力  | 0  | 使用されていないピン             | プルダウン   | 1MΩ   |

|          |         |    | デジタル入力 (シュミットトリガなし)    | フローティング | —     |

|          |         |    | デジタル入力 (シュミットトリガ付き)    |         | 10kΩ  |

|          |         |    | 低電圧デジタル入力              | プルアップ   | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          |         |    |                        | プルダウン   | 10kΩ  |

|          |         |    |                        |         | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          | デジタル出力  | 1  | プッシュプル出力 (1X, 2X)      | フローティング | —     |

|          |         |    | オープンドレイン NMOS (1X, 2X) | フローティング | —     |

|          |         |    | オープンドレイン PMOS (1X, 2X) |         | 10kΩ  |

|          |         |    |                        | プルアップ   | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          |         |    |                        | プルダウン   | 10kΩ  |

|          | デジタル入出力 | 0  | アナログ入力                 | —       | —     |

|          |         |    | オープンドレイン NMOS (1X, 2X) | フローティング | —     |

|          |         |    |                        |         | 10kΩ  |

|          |         |    |                        | プルアップ   | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          |         |    |                        | プルダウン   | 10kΩ  |

|          |         |    |                        |         | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          | アナログ入出力 | —  | アナログ入出力                | フローティング | —     |

|          |         |    |                        |         | 10kΩ  |

|          |         |    |                        | プルアップ   | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

|          |         |    |                        | プルダウン   | 10kΩ  |

|          |         |    |                        |         | 100kΩ |

|          |         |    |                        |         | 1MΩ   |

表 7-1. ピン構成オプション(続き)

| GPIO     | IO の選択  | OE  | IO オプション                                                                   | 抵抗      | 抵抗値   |

|----------|---------|-----|----------------------------------------------------------------------------|---------|-------|

| IO4, IO7 | デジタル入力  | 0   | デジタル入力 (シュミットトリガなし)<br>デジタル入力 (シュミットトリガ付き)<br>低電圧デジタル入力                    | プルダウン   | 1MΩ   |

|          |         |     |                                                                            | フローティング | —     |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルアップ   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルダウン   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | フローティング | —     |

|          |         |     |                                                                            | —       | —     |

| デジタル出力   | デジタル出力  | 1/0 | プッシュプル出力 (1X, 2X)<br>オープンドレイン NMOS (1X, 2X)<br>3 ステート出力 (1X, 2X)           | フローティング | —     |

|          |         |     |                                                                            | フローティング | —     |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルアップ   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルダウン   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | フローティング | —     |

|          |         |     |                                                                            | —       | —     |

| デジタル入出力  | デジタル入出力 | 0   | デジタル入力 (シュミットトリガなし)<br>デジタル入力 (シュミットトリガ付き)<br>低電圧デジタル入力<br>アナログ入力 (IO4 のみ) | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルアップ   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | プルダウン   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 上記と共有   |       |

|          |         |     |                                                                            | フローティング | —     |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | 100kΩ   | 100kΩ |

| アナログ入出力  | アナログ入出力 | —   | アナログ入出力                                                                    | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | 100kΩ   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

|          |         |     |                                                                            | 10kΩ    | 10kΩ  |

|          |         |     |                                                                            | 100kΩ   | 100kΩ |

|          |         |     |                                                                            | 1MΩ     | 1MΩ   |

**表 7-1. ピン構成オプション(続き)**

| GPIO             | IO の選択 | OE | IO オプション                                                              | 抵抗      | 抵抗値   |

|------------------|--------|----|-----------------------------------------------------------------------|---------|-------|

| IO5, IO6,<br>IO9 | デジタル入力 | 0  | デジタル入力 (シュミットトリガなし)<br>デジタル入力 (シュミットトリガ付き)<br>低電圧デジタル入力               | プルダウン   | 1MΩ   |

|                  |        |    |                                                                       | フローティング | —     |

|                  |        |    |                                                                       | 10kΩ    | 10kΩ  |

|                  |        |    |                                                                       | プルアップ   | 100kΩ |

|                  |        |    |                                                                       | 1MΩ     | 1MΩ   |

|                  | デジタル出力 | 1  | プッシュプル出力 (1X, 2X)<br>オープンドレイン NMOS (1X, 2X)<br>オープンドレイン PMOS (1X, 2X) | 10kΩ    | 10kΩ  |

|                  |        |    |                                                                       | プルダウン   | 100kΩ |

|                  |        |    |                                                                       | 1MΩ     | 1MΩ   |

|                  |        |    |                                                                       | 10kΩ    | 10kΩ  |

|                  |        |    |                                                                       | プルアップ   | 100kΩ |

### 注

GPI/INO には、電源オン時にデバイスをリセットするオプションもあります。POR とは異なり、外部リセットによって内部ロジックと配線、入力、出力のみがリセットされます。NVM は以前の状態を保持します。GPI リセットが有効になっている場合、入力モードはシュミットトリガなしのデジタル入力に設定してください。

外部リセットを無効、レベル センシティブ、エッジトリガのいずれにするかを選択します。

レベル センシティブが選択されている場合、入力が High になると、本デバイスは、すべての内部デバイスがリセットされるリセット モードに入ります。このピンが Low になると、本デバイスはリセット パワーオン シーケンスを開始します。

エッジトリガを選択すると、立ち上がりエッジまたは立ち下がりエッジを検出するようにエッジ検出器を構成できます。そして、GPI/INO のエッジによって本デバイスはリセットされ、リセット パワーオン シーケンスが開始されます。

### 7.3.2 接続マルチプレクサ

TPLD1201-Q1 には、内部マクロセルおよび I/O ピンの配線を構成するための相互接続システムがあります。この相互接続システムは、接続マルチプレクサと呼ばれています。接続マルチプレクサには 32 の入力と 44 の出力があります。接続マルチプレクサの 32 の入力は、それぞれ、I/O ピン、LUT、アナログ コンパレータ、その他のデジタル リソース、VCC、GND などを含む特定のマクロセルにハードウェア接続されています。デジタル マクロセルへの入力は、5 ビット レジスタを使用して、これら 32 本の入力ラインのいずれかを選択します。

### 7.3.3 機能を設定可能なロジック ブロック

2 つの 2 ビット LUT と 2 つの 3 ビット LUT を含む組み合わせロジックは、TPLD1201-Q1 内のルックアップ テーブル (LUT) によってサポートされています。組み合わせ機能マクロセルの入力と出力は、OTP ビットの状態によって定義される特定のロジック機能を持つように、接続マルチプレクサによって構成されます。

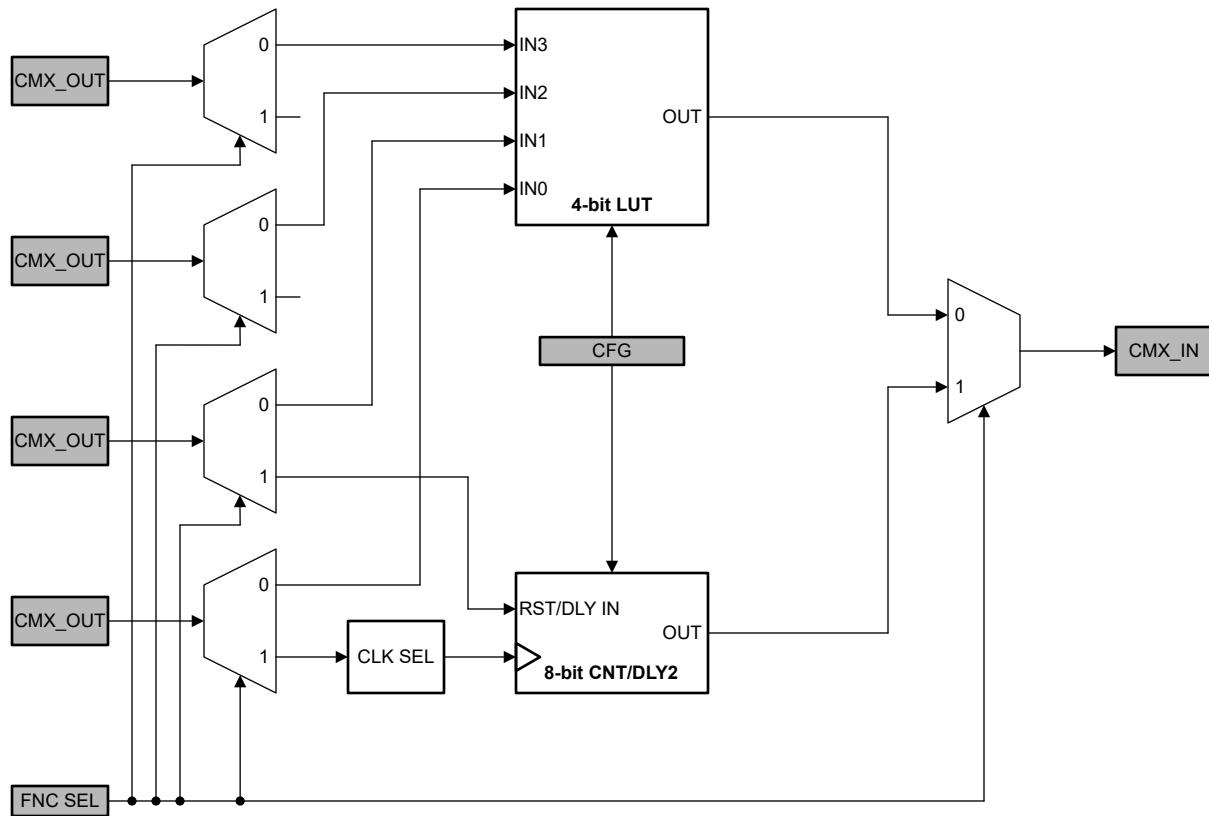

TPLD1201-Q1 は、複数のロジックまたはタイミング機能を備えた 7 つの組み合わせ機能ブロック (マクロセル) を内蔵しています。いずれの場合も、これらはルックアップ テーブル (LUT)、または別のロジックまたはタイミング機能として機能できます。これらのロジック ブロックに実装できる機能については、以下の一覧表を参照してください。

- 2 つの 2 ビット LUT

- 2 つの 3 ビット LUT

- 2 つの 2 ビット LUT または D タイプ フリップ フロップまたはラッチ

- 2 つの 3 ビット LUT または D タイプ フリップ フロップまたはラッチ (リセット / セット オプション付き)

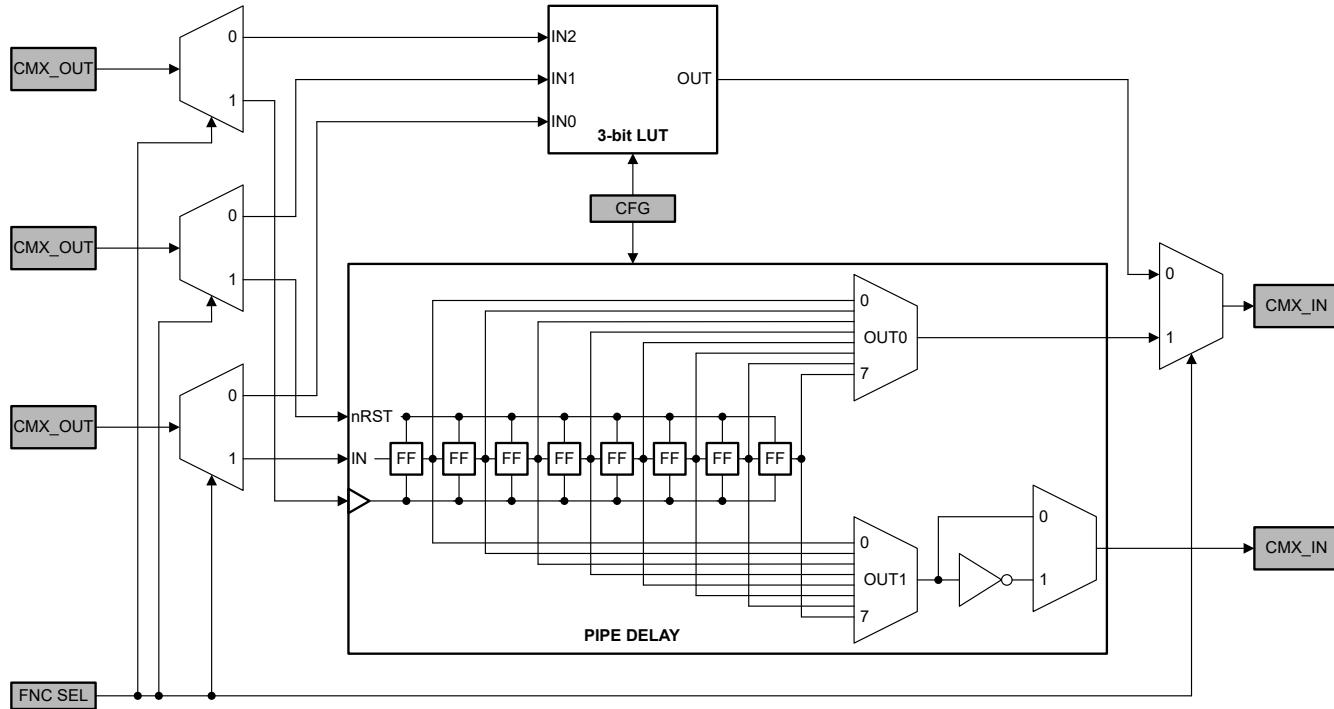

- 1 つの 3 ビット LUT またはパイプ遅延

- 1 つの 4 ビット LUT または 8 ビット カウンタまたは遅延ジェネレータ

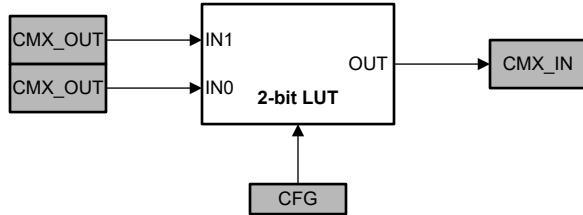

### 7.3.3.1.2 ビット LUT マクロセル

LUT 機能を実装するために使用する場合、2 ビット LUT は接続マルチプレクサから 2 つの入力信号を取り込み、1 つの出力を生成します。その出力は接続マルチプレクサに戻ります。

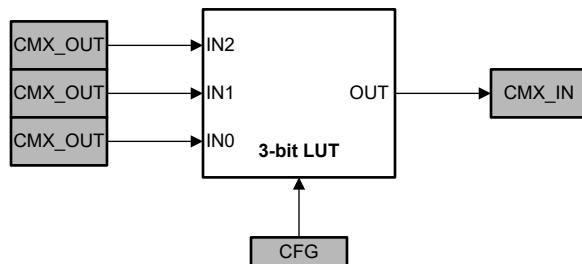

図 7-2. 2 ビット LUT のブロック図

これらの LUT は、標準デジタル ロジック機能 (AND、NAND、OR、NOR、XOR、XNOR、INV) を含む任意の 3 入力ユーザー一定義機能に構成できます。

表 7-2 に、2 ビット LUT の真理値表を示します。

表 7-2. 2 ビット LUT の真理値表

| IN1 | IN0 | OUT     |

|-----|-----|---------|

| 0   | 0   | ユーザー一定義 |

| 0   | 1   |         |

| 1   | 0   |         |

| 1   | 1   |         |

出力機能を定義するため、各 2 ビット LUT は OTP 内に 4 つのビットを備えています。

### 7.3.3.2.3 ビット LUT マクロセル

LUT 機能を実装するために使用する場合、3 ビット LUT は接続マルチプレクサから 3 つの入力信号を取り込み、1 つの出力を生成します。その出力は接続マルチプレクサに戻ります。

図 7-3.3 ビット LUT のブロック図

これらの LUT は、標準デジタル ロジック機能 (AND、NAND、OR、NOR、XOR、XNOR、INV) を含む任意の 3 入力ユーザ一定義機能に構成できます。

表 7-3 に、3 ビット LUT の真理値表を示します。

表 7-3.3 ビット LUT の真理値表

| IN2 | IN1 | IN0 | OUT    |

|-----|-----|-----|--------|

| 0   | 0   | 0   | ユーザ一定義 |

| 0   | 0   | 1   |        |

| 0   | 1   | 0   |        |

| 0   | 1   | 1   |        |

| 1   | 0   | 0   |        |

| 1   | 0   | 1   |        |

| 1   | 1   | 0   |        |

| 1   | 1   | 1   |        |

出力機能を定義するため、各 3 ビット LUT は OTP 内に 8 つのビットを備えています。

### 7.3.3.3.2 ビット LUT または D フリップ フロップ / ラッチ マクロセル

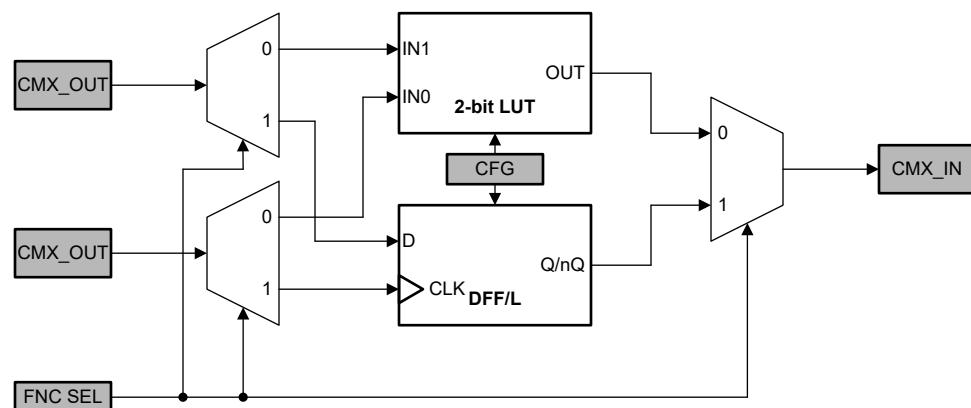

機能を設定可能なこのロジック ブロックは 2 ビット LUT と D フリップ フロップ / ラッチのどちらかとして機能できます。

図 7-4.2 ビット LUT または DFF / ラッチのブロック図

LUT 機能を実装するために使用する場合、2 ビット LUT は接続マルチプレクサから 2 つの入力信号を取り込み、1 つの出力を生成します。その出力は接続マルチプレクサに戻ります。これらの LUT は、標準デジタル ロジック機能 (AND、NAND、OR、NOR、XOR、XNOR、INV) を含む任意の 3 入力ユーザー定義機能に構成できます。

表 7-4 に、2 ビット LUT の真理値表を示します。

**表 7-4. 2 ビット LUT の真理値表**

| IN1 | IN0 | OUT    |

|-----|-----|--------|

| 0   | 0   | ユーザー定義 |

| 0   | 1   |        |

| 1   | 0   |        |

| 1   | 1   |        |

出力機能を定義するため、各 2 ビット LUT は OTP 内に 4 つのビットを備えています。

シーケンシャル ロジック素子を実装するために使用する場合、接続マルチプレクサからの 2 つの入力信号は、フリップ フロップ / ラッチのデータ (D) およびクロック (CLK) 入力に入力され、その出力は接続マルチプレクサに戻ります。このマクロセルはクロックおよび出力極性パラメータだけでなく、初期状態パラメータを持っています。

D フリップ フロップ / ラッチの動作は以下の機能説明に従います：

- クロック極性は設定可能であり、非反転 (CLKPOL = 0, CLK) または反転 (CLKPOL = 1, nCLK) に設定できます。

- CLK を使用する DFF:CLK は立ち上がりエッジでトリガされて、Q = D になります。それ以外の場合、Q は変化しません。

- nCLK を使用する DFF:CLK は立ち下がりエッジでトリガされて、Q = D になります。それ以外の場合、Q は変化しません。

- CLK を使用するラッチ:CLK が Low のとき、Q = D になります。それ以外の場合、Q は前の値を保持します (CLK が High のとき、入力 D は出力に影響を与えません)。

- nCLK を使用するラッチ:CLK が High のとき、Q = D になります。それ以外の場合、Q は前の値を保持します (CLK が Low のとき、入力 D は出力に影響を与えません)。

- 出力極性は構成可能で、非反転 (Q) または反転 (nQ) に設定できます。

表 7-5 と表 7-6 に、それぞれ D フリップ フロップと D ラッチの真理値表を示します。

**表 7-5. D フリップ フロップの真理値表**

| CLKPOL | CLK | D | Q              | nQ              |

|--------|-----|---|----------------|-----------------|

| 0      | ↓   | 0 | Q <sub>0</sub> | nQ <sub>0</sub> |

|        | ↑   | 0 | 0              | 1               |

|        | ↓   | 1 | Q <sub>0</sub> | nQ <sub>0</sub> |

|        | ↑   | 1 | 1              | 0               |

| 1      | ↓   | 0 | 0              | 1               |

|        | ↑   | 0 | Q <sub>0</sub> | nQ <sub>0</sub> |

|        | ↓   | 1 | 1              | 0               |

|        | ↑   | 1 | Q <sub>0</sub> | nQ <sub>0</sub> |

**表 7-6. D ラッチの真理値表**

| CLKPOL | CLK | D | Q     | nQ     |

|--------|-----|---|-------|--------|

| 0      | 0   | 0 | 0     | 1      |

|        | 1   | 0 | $Q_0$ | $nQ_0$ |

|        | 0   | 1 | 1     | 0      |

|        | 1   | 1 | $Q_0$ | $nQ_0$ |

| 1      | 0   | 0 | $Q_0$ | $nQ_0$ |

|        | 1   | 0 | 0     | 1      |

|        | 0   | 1 | $Q_0$ | $nQ_0$ |

|        | 1   | 1 | 1     | 0      |

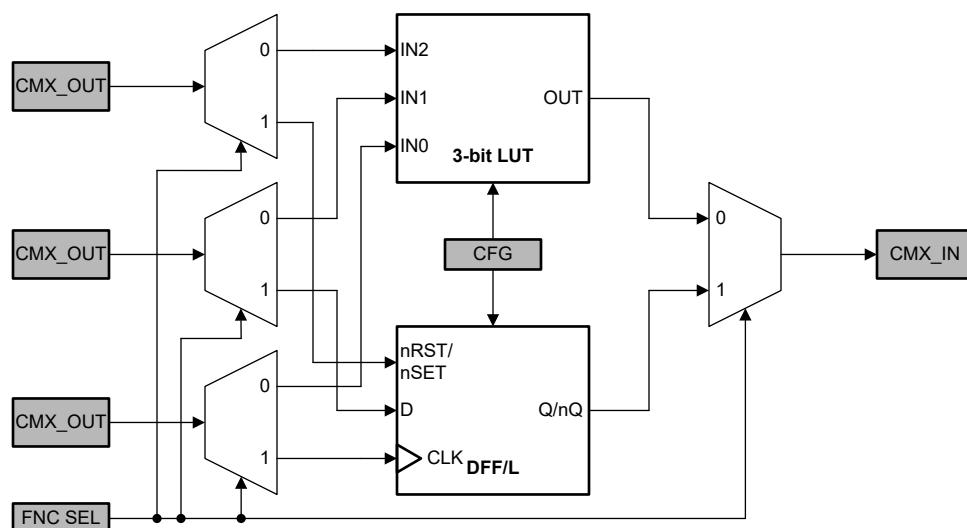

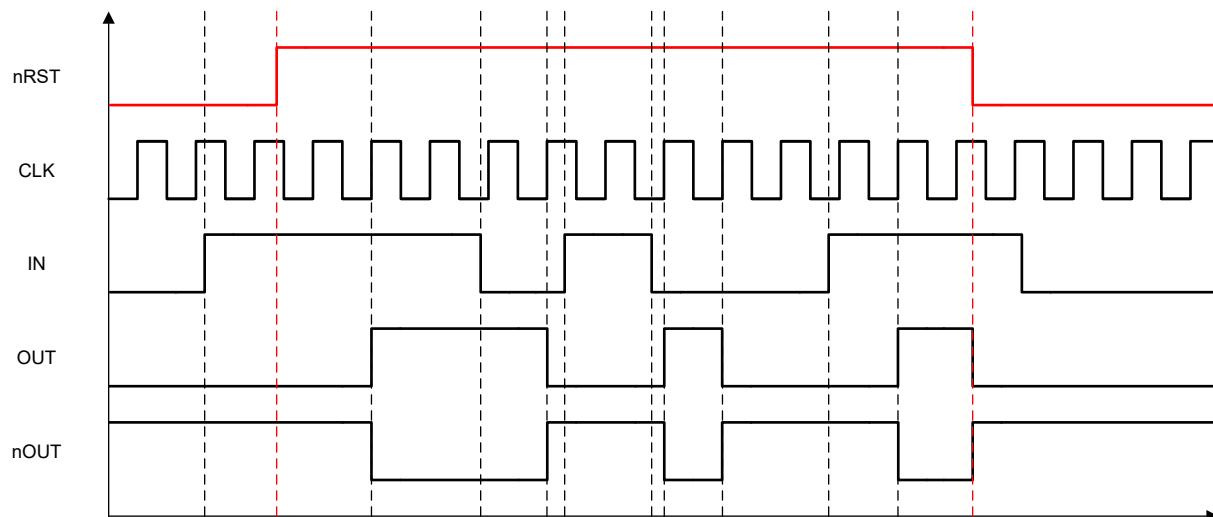

#### 7.3.3.4.3 ビット LUT または D フリップ フロップ / ラッチ (セット / リセット付き) マクロセル

機能を設定可能なこのロジック ブロックは、3 ビット LUT と D フリップ フロップ / ラッチ (セット / リセット付き) のどちらかとして機能できます。

**図 7-5. 3 ビット LUT または DFF またはラッチ (nRST または nSET 付き) のブロック図**

LUT 機能を実装するために使用する場合、3 ビット LUT は接続マルチプレクサから 3 つの入力信号を取り込み、1 つの出力を生成します。その出力は接続マルチプレクサに戻ります。これらの LUT は、標準デジタル ロジック機能 (AND、NAND、OR、NOR、XOR、XNOR、INV) を含む任意の 3 入力ユーザーディニッシュ機能に構成できます。

表 7-7 に、3 ビット LUT の真理値表を示します。

**表 7-7.3 ピット LUT の真理値表**

| IN2 | IN1 | IN0 | OUT    |

|-----|-----|-----|--------|

| 0   | 0   | 0   | ユーザ一定義 |

| 0   | 0   | 1   |        |

| 0   | 1   | 0   |        |

| 0   | 1   | 1   |        |

| 1   | 0   | 0   |        |

| 1   | 0   | 1   |        |

| 1   | 1   | 0   |        |

| 1   | 1   | 1   |        |

出力機能を定義するため、各 3 ビット LUT は OTP 内に 8 つのビットを備えています。

シーケンシャル ロジック素子を実装するために使用する場合、接続マルチプレクサからの 3 つの入力信号は、フリップ フロップ / ラッチのデータ (D)、クロック (CLK)、リセット / セット (nRST/nSET) 入力に入力され、その出力は接続マルチプレクサに戻ります。このマクロセルは初期状態、クロック極性、リセット / セット極性、出力極性のパラメータを持っています。

D フリップ フロップ / ラッチの動作は以下の機能説明に従います：

- クロック極性は設定可能であり、非反転 (CLKPOL = 0、CLK) または反転 (CLKPOL = 1、nCLK) に設定できます。

- CLK を使用する DFF:CLK は立ち上がりエッジでトリガされて、Q = D になります。それ以外の場合、Q は変化しません。

- nCLK を使用する DFF:CLK は立ち下がりエッジでトリガされて、Q = D になります。それ以外の場合、Q は変化しません。

- CLK を使用するラッチ:CLK が Low のとき、Q = D になります。それ以外の場合、Q は前の値を保持します (CLK が High のとき、入力 D は出力に影響を与えません)。

- nCLK を使用するラッチ:CLK が High のとき、Q = D になります。それ以外の場合、Q は前の値を保持します (CLK が Low のとき、入力 D は出力に影響を与えません)。

- これらの DFF / ラッチでは、アクティブ Low のリセット / セットを使うこともできます。

- nRST:入力を High にすると、DFF / ラッチは通常動作に入り、入力を Low にすると、Q は 0 にリセットされます。

- nSET:入力を High にすると、DFF / ラッチは通常動作に入り、入力を Low にすると、Q は 1 にセットされます。

- リセット / セットが不要な場合、これらの入力を V<sub>CC</sub> またはその他の常に High になっているソースに接続できます。

- 出力極性は構成可能で、非反転 (Q) または反転 (nQ) に設定できます。

表 7-8 と表 7-9 に、それぞれ D フリップ フロップと D ラッチ (リセット / セット付き) の真理値表を示します。

**表 7-8. D フリップ フロップ (nRST/nSET 付き) の真理値表**

| nRST | nSET | CLKPOL | CLK | D | Q              | nQ              |  |

|------|------|--------|-----|---|----------------|-----------------|--|

| 0    | —    | 0      | X   | X | 0              | 1               |  |

| —    | 0    |        | X   | X | 1              | 0               |  |

| 1    | 1    |        | ↓   | 0 | Q <sub>0</sub> | nQ <sub>0</sub> |  |

|      |      |        | ↑   | 0 | 0              | 1               |  |

|      |      |        | ↓   | 1 | Q <sub>0</sub> | nQ <sub>0</sub> |  |

|      |      |        | ↑   | 1 | 1              | 0               |  |

**表 7-8. D フリップ フロップ (nRST/nSET 付き) の真理値表 (続き)**

| nRST | nSET | CLKPOL | CLK | D | Q     | nQ     |  |

|------|------|--------|-----|---|-------|--------|--|

| 0    | —    | 1      | X   | X | 0     | 1      |  |

| —    | 0    |        | X   | X | 1     | 0      |  |

| 1    | 1    |        | ↓   | 0 | 0     | 1      |  |

|      |      |        | ↑   | 0 | $Q_0$ | $nQ_0$ |  |

|      |      |        | ↓   | 1 | 1     | 0      |  |

|      |      |        | ↑   | 1 | $Q_0$ | $nQ_0$ |  |

**表 7-9. D ラッチ (nRST/nSET 付き) の真理値表**

| nRST | nSET | CLKPOL | CLK | D | Q     | nQ     |  |

|------|------|--------|-----|---|-------|--------|--|

| 0    | —    | 0      | X   | X | 0     | 1      |  |

| —    | 0    |        | X   | X | 1     | 0      |  |

| 1    | 1    |        | 0   | 0 | 0     | 1      |  |

|      |      |        | 1   | 0 | $Q_0$ | $nQ_0$ |  |

|      |      |        | 0   | 1 | 1     | 0      |  |

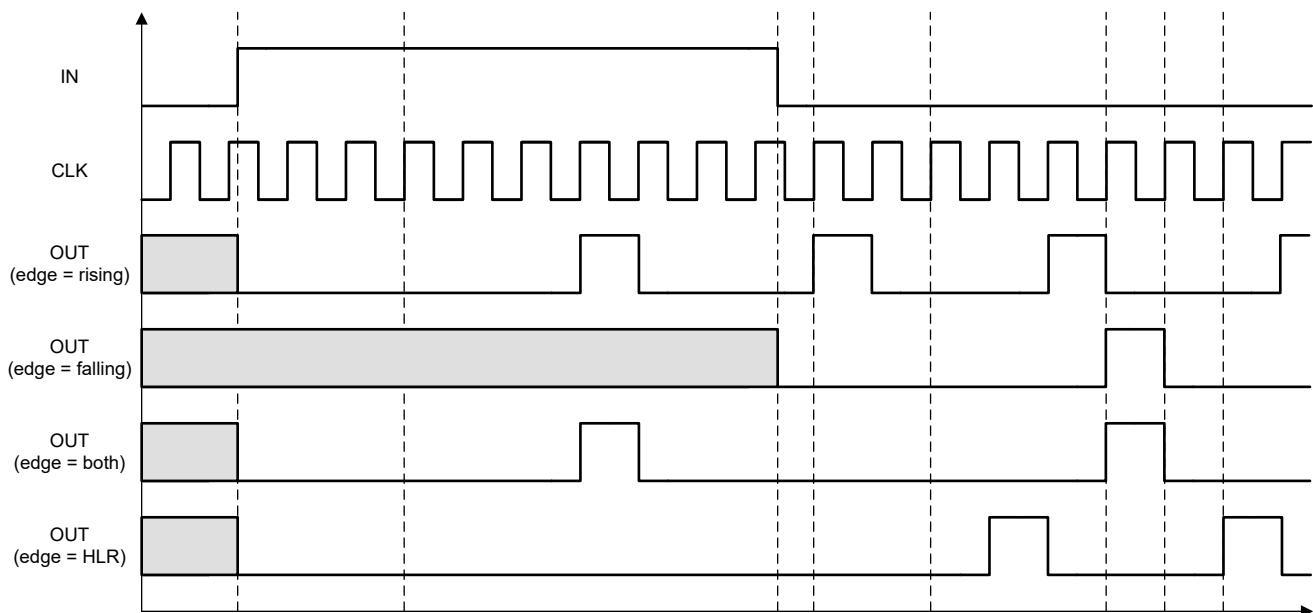

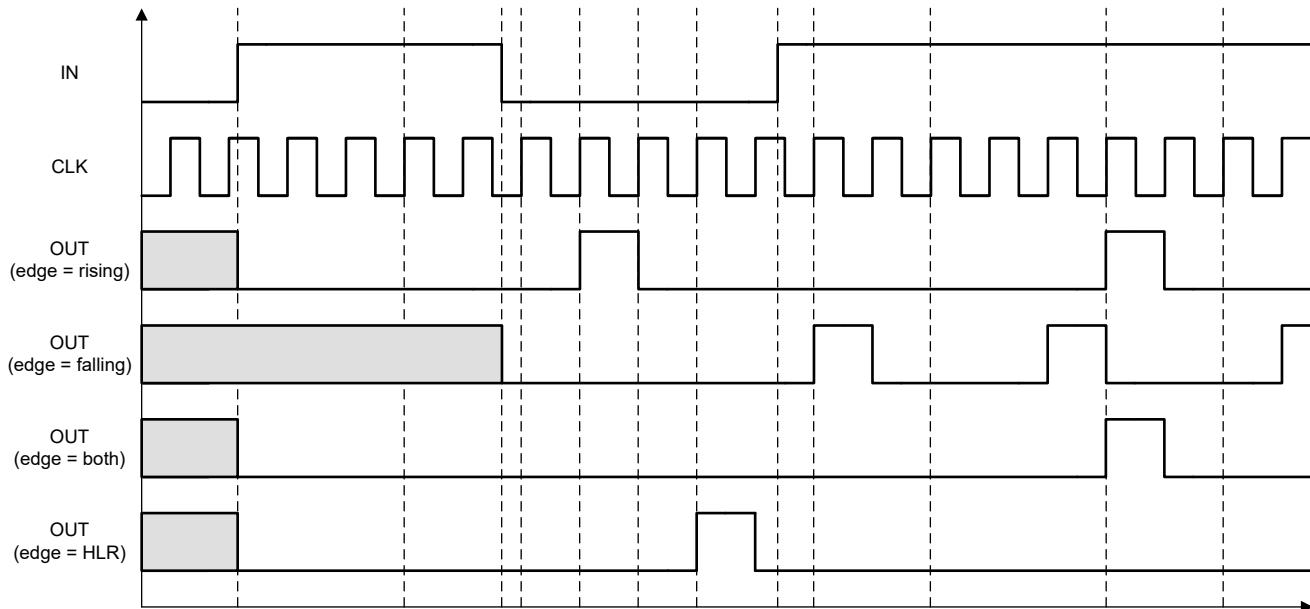

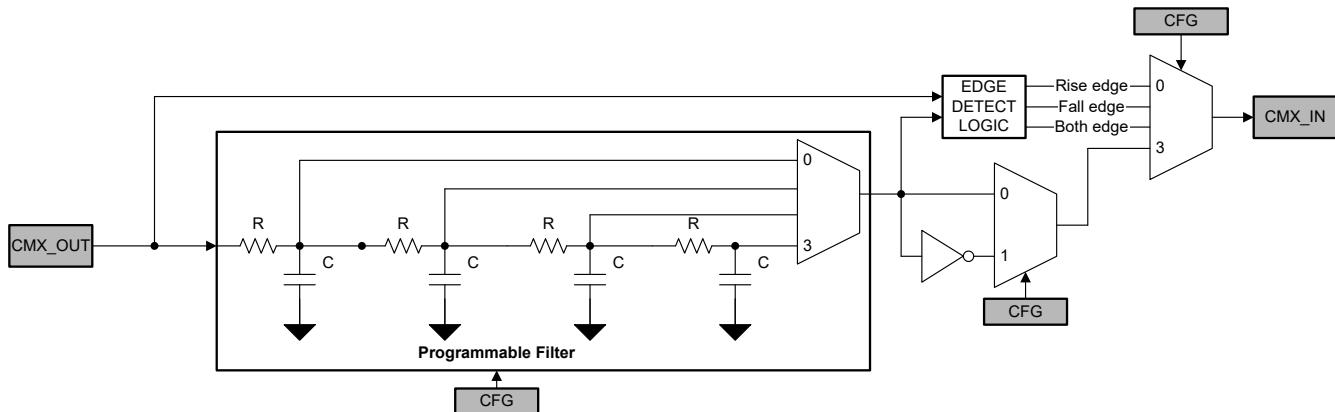

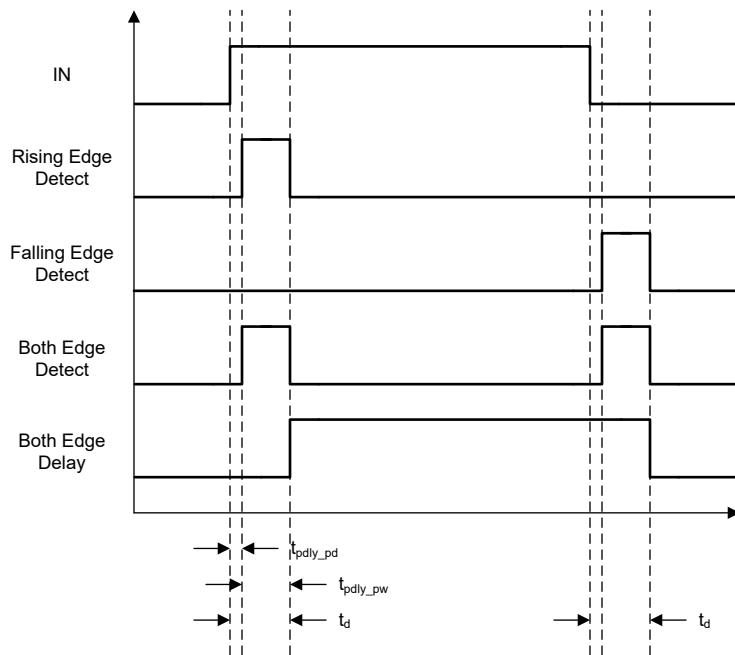

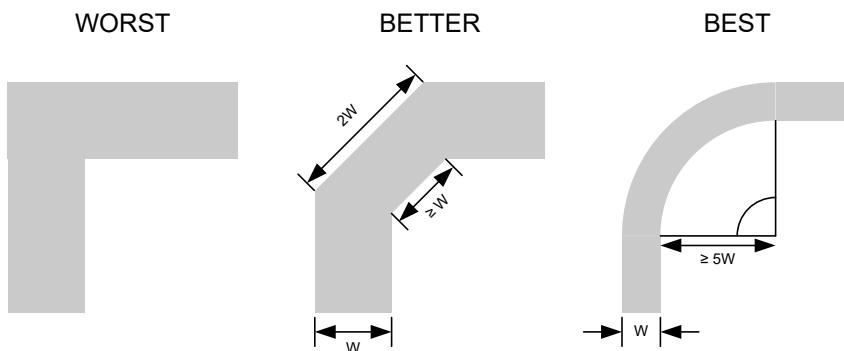

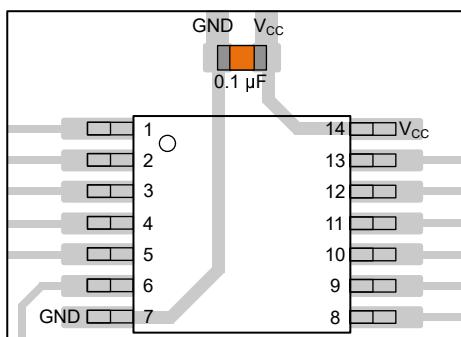

|      |      |        | 1   | 1 | $Q_0$ | $nQ_0$ |  |