**TPS40000, TPS40001

TPS40002, TPS40003

TPS40004, TPS40005**

SLUS585A

## 低入力 電圧モード 同期整流式バック・コントローラ

### 特 長

- 動作入力電圧：2.25V～5.5V

- 最小出力電圧0.7V

- 0.7V、誤差1%の内部基準電圧

- Predictive Gate Drive™を用いたNチャネルMOSFET ドライバ駆動による高効率化

- 外部から調整可能なソフトスタート及び過電流制限

- 300kHzまたは600kHzの固定周波数動作、電圧モード・コントロール

- ソース電流のみ、またはソース/シンク電流

- 10ピンMSOP PowerPAD™パッケージによる高性能化

- プリ・バイアス・スタート用バージョン

- サーマル・シャットダウン機能

- ブートストラップ・ダイオード内蔵

### アプリケーション

- ネットワーク機器装置

- テレコム機器

- 基地局

- サーバー

- DSP電源

- 電源モジュール

### 概 要

TPS4000xは、低電圧で非絶縁型同期整流式バック・レギュレータ用コントローラです。このコントローラ・ファミリは一次側バック・スイッチ用にハイサイドN型MOSFETを用います。ハイサイドNチャネルは完全にオンになるようブートストラップ回路が必要ですが、N型デバイスは与えられたデバイスのサイズやゲート電荷に対しオン抵抗が低いということはその余分な複雑さを補って余りあります。このデバイスはTIが所有権をもつPredictive Gate Drive™技術を用いて同期整流器のダイオード損失(導通及び回復の両方)を最小限に抑えるという方法でメイン・スイッチのオフから整流器のターンオン及び整流器のターンオフからメイン・スイッチのターンオンまでの遅延をコントロールし

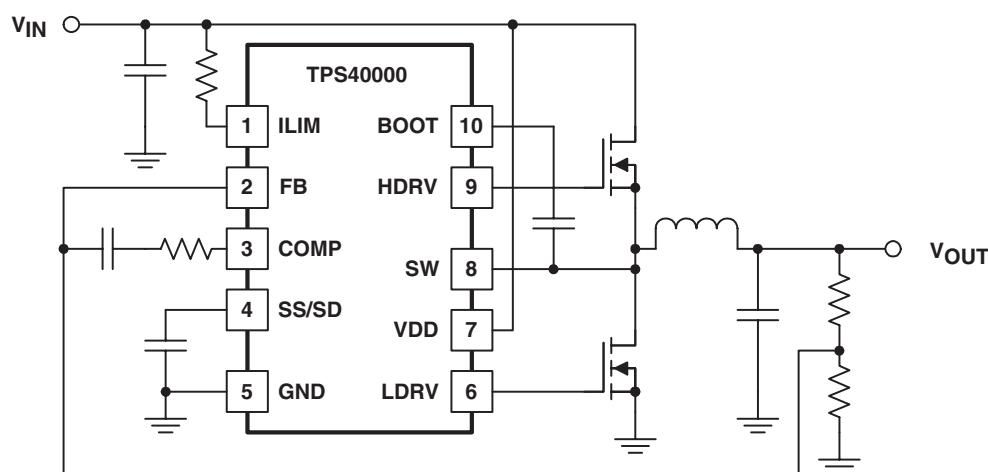

### SIMPLIFIED APPLICATION DIAGRAM

UDG 01141

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

ます。この損失を低減することは大きな意義があります、つまり、コンバータのあるパワー・レベルにおいて、小さなFETが使用できるようになります。あるいは、放熱板の使用を削減または除去することさえもできます。

電流制限のスレッショールドは1つの抵抗を接続することで調整することができます。TPS4000xコントローラは閉ループのソフトスタート機能をもっています。起動時のランプ時間はSS/SDピンに接続される1つの外付けキャパシタにより設定されます。また、SS/SDピンはシャットダウンにも使用されます。

## ORDERING INFORMATION

| T <sub>A</sub> | FREQUENCY | PACKAGED DEVICES MSOP <sup>(2)</sup> (DGQ) |                                         |                 |

|----------------|-----------|--------------------------------------------|-----------------------------------------|-----------------|

|                |           | APPLICATION                                |                                         |                 |

|                |           | SOURCE ONLY                                | SOURCE/SINK WITH PREBIAS <sup>(3)</sup> | SOURCE/SINK (3) |

| −40 °C to 85°C | 300 kHz   | TPS40000DGQ                                | TPS40001DGQ                             | TPS40004DGQ     |

|                | 600 kHz   | TPS40002DGQ                                | TPS40003DGQ                             | TPS40005DGQ     |

(2) DGQパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(すなわち、TPS40000DGQR)。発注数量単位はリールあたり2500個、チューブあたり80個です。

(3) アプリケーション情報を参照してください。

## ABSOLUTE MAXIMUM RATINGS

特に記述のない限り、動作周囲温度<sup>(1)</sup>

|                                                              | TPS4000x                               | UNIT                |

|--------------------------------------------------------------|----------------------------------------|---------------------|

| Input voltage range, V <sub>IN</sub>                         | BOOT                                   | V <sub>SW</sub> + 6 |

|                                                              | COMP, FB, ILIM, SS/SD                  | −0.3 to 6           |

|                                                              | SW                                     | −0.7 to 10.5        |

|                                                              | SW <sub>T</sub> (SW transient < 50 ns) | −2.5                |

|                                                              | VDD                                    | 6                   |

| Operating junction temperature range, T <sub>J</sub>         | −40 to 150                             | °C                  |

| Storage temperature, T <sub>stg</sub>                        | −55 to 150                             |                     |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | 260                                    |                     |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(4) PowerPADパッケージのPCBガイドラインについてはTIテクニカル・ブリーフ(文献番号SLMA002)を参照してください。

(5) PowerPAD™のヒート・スラグはGND(5ピン)に接続することができます。

# ELECTRICAL CHARACTERISTICS

over recommended operating temperature range,  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ ,  $V_{DD} = 5.0\text{ V}$ , all parameters measured at zero power dissipation (unless otherwise noted)

## input supply

| PARAMETER   |                        | TEST CONDITIONS          | MIN  | TYP  | MAX  | UNIT |

|-------------|------------------------|--------------------------|------|------|------|------|

| $V_{DD}$    | Input voltage range    |                          | 2.25 | 5.5  |      | V    |

| $V_{HGATE}$ | High-side gate voltage | $V_{BOOT} - V_{SW}$      |      | 5.5  |      |      |

| $I_{DD}$    | Shutdown current       | SS/SD = 0 V, Outputs off |      | 0.25 | 0.45 | mA   |

|             | Quiescent current      | $FB = 0.8\text{ V}$      |      | 1.4  | 2.0  |      |

|             | Switching current      | No load at HDRV/LDRV     |      | 1.5  | 4.0  |      |

| UVLO        | Minimum on-voltage     |                          | 1.95 | 2.05 | 2.15 | V    |

|             | Hysteresis             |                          | 80   | 140  | 200  | mV   |

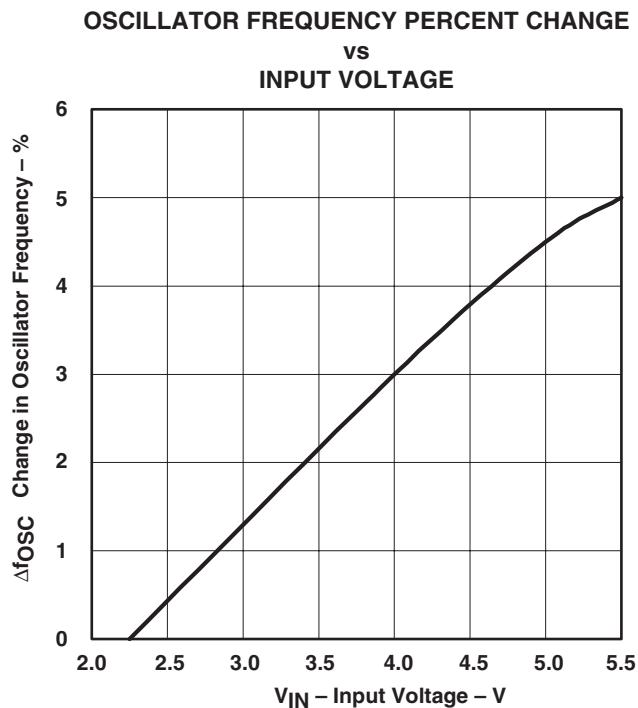

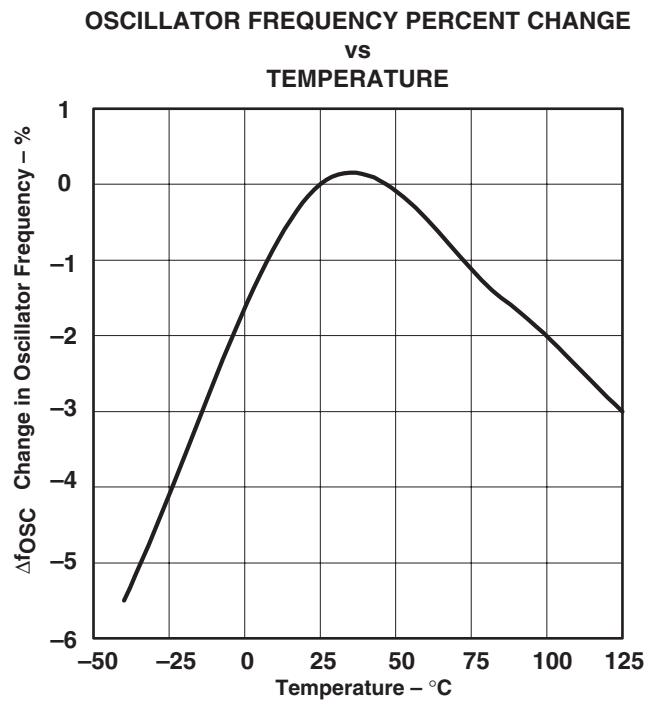

## oscillator

| PARAMETER  |                      | TEST CONDITIONS                                | MIN  | TYP  | MAX  | UNIT |

|------------|----------------------|------------------------------------------------|------|------|------|------|

| $f_{OSC}$  | Oscillator frequency | $2.25\text{ V} \leq V_{DD} \leq 5.00\text{ V}$ | 250  | 300  | 350  | kHz  |

|            |                      |                                                | 500  | 600  | 700  |      |

| $V_{RAMP}$ | Ramp voltage         | $V_{PEAK} - V_{VALLEY}$                        | 0.80 | 0.93 | 1.07 | V    |

|            | Ramp valley voltage  |                                                | 0.24 | 0.31 | 0.41 |      |

## PWM

| PARAMETER                         |                                                                      | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|-----------------------------------|----------------------------------------------------------------------|------------------------------------------|-----|-----|-----|------|

| Maximum duty cycle <sup>(2)</sup> | TPS40000<br>TPS40001<br>TPS40004<br>TPS40002<br>TPS40003<br>TPS40005 | $FB = 0\text{ V}, V_{DD} = 3.3\text{ V}$ | 87% | 94% | 97% |      |

|                                   |                                                                      |                                          | 83% | 93% | 97% |      |

| Minimum duty cycle                |                                                                      |                                          |     | 0%  |     |      |

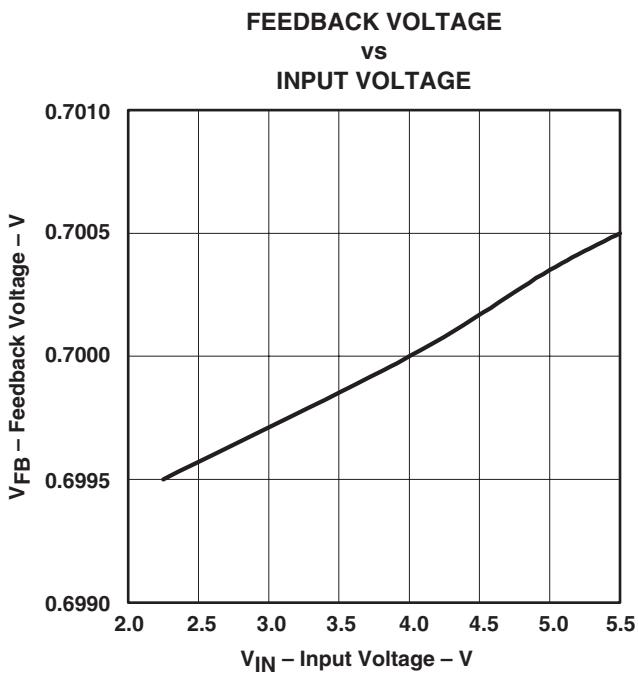

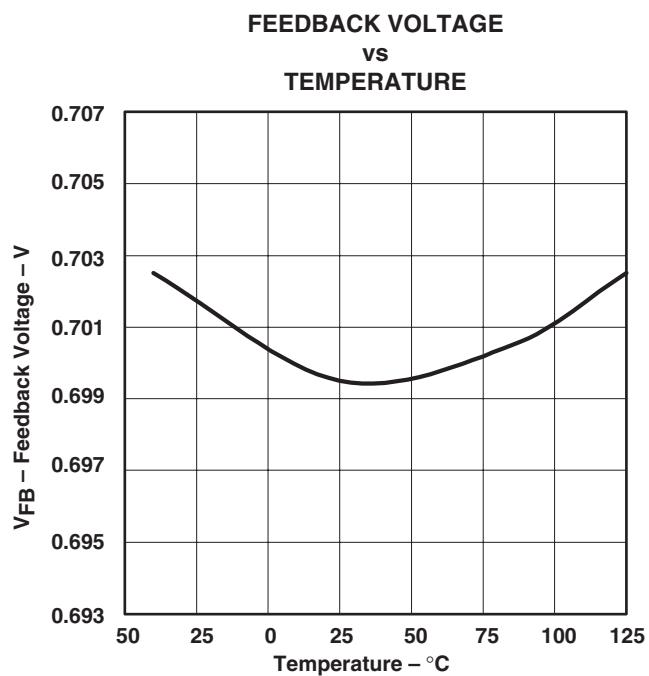

## error amplifier

| PARAMETER             |                                                | TEST CONDITIONS                           | MIN   | TYP   | MAX   | UNIT |

|-----------------------|------------------------------------------------|-------------------------------------------|-------|-------|-------|------|

| $V_{FB}$              | FB input voltage<br>$T_A = 25^{\circ}\text{C}$ | Line, Temperature                         | 0.689 | 0.700 | 0.711 | V    |

|                       |                                                |                                           | 0.693 | 0.700 | 0.707 |      |

| FB input bias current |                                                |                                           |       | 30    | 130   | nA   |

| $V_{OH}$              | High-level output voltage                      | $FB = 0\text{ V}, I_{OH} = 0.5\text{ mA}$ | 2.0   | 2.5   |       | V    |

| $V_{OL}$              | Low-level output voltage                       | $FB = V_{DD}, I_{OL} = 0.5\text{ mA}$     |       | 0.08  | 0.15  |      |

| $I_{OH}$              | Output source current                          | $COMP = 0.7\text{ V}, FB = GND$           | 2     | 6     |       | mA   |

| $I_{OL}$              | Output sink current                            | $COMP = 0.7\text{ V}, FB = V_{DD}$        | 3     | 8     |       |      |

| $G_{BW}$              | Gain bandwidth <sup>(1)</sup>                  |                                           | 5     | 10    |       | MHz  |

| $A_{OL}$              | Open loop gain                                 |                                           | 55    | 85    |       | dB   |

(1) 設計で保証されており、テストは行っていません。

(2) 入力電圧 $V_{DD}$ が $2.25\text{ V}$ の場合は、最大デューティ・サイクルは3%下がります。

# ELECTRICAL CHARACTERISTICS

over recommended operating temperature range,  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{DD} = 5.0\text{ V}$ , all parameters measured at zero power dissipation (unless otherwise noted)

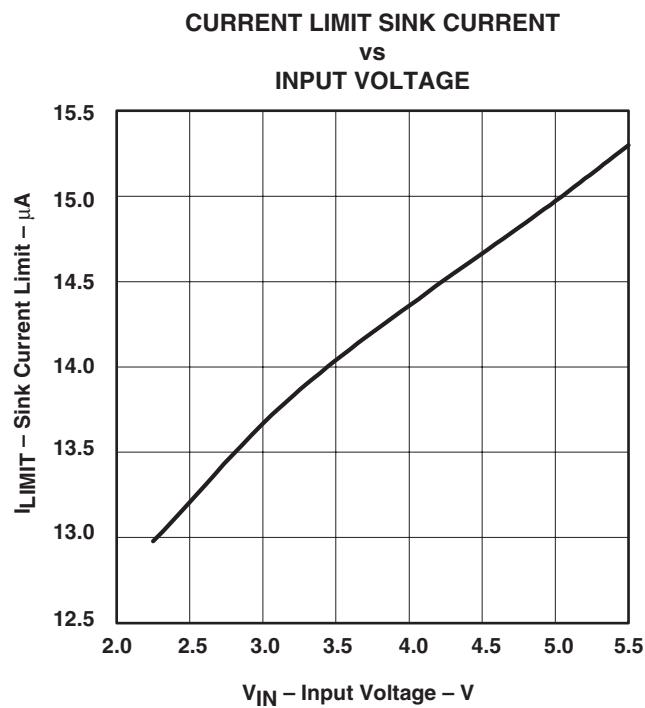

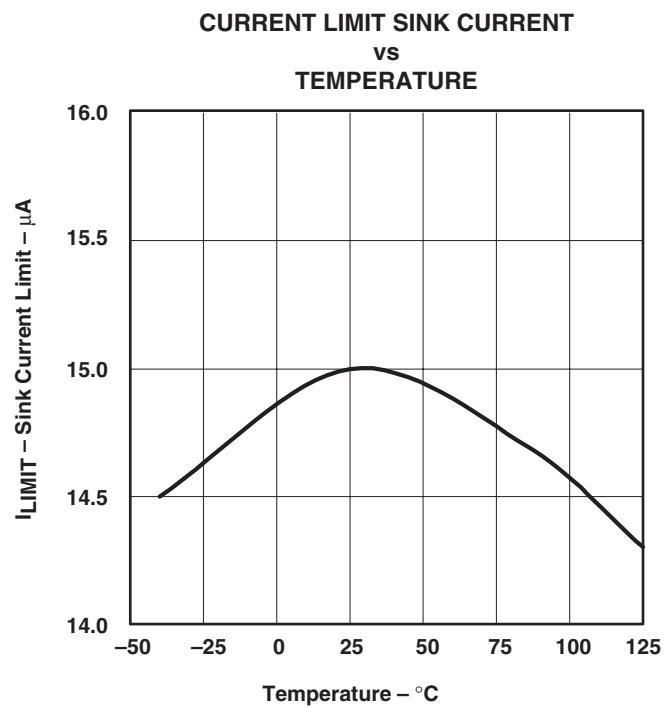

## current limit

| PARAMETER                                                             | TEST CONDITIONS                       | MIN | TYP  | MAX      | UNIT          |

|-----------------------------------------------------------------------|---------------------------------------|-----|------|----------|---------------|

| $I_{SINK}$<br>ILIM sink current                                       | $V_{DD} = 5\text{ V}$                 | 11  | 15   | 19       | $\mu\text{A}$ |

|                                                                       | $V_{DD} = 2.25\text{ V}$              | 9.5 | 13.0 | 16.5     |               |

| $V_{OS}$<br>Offset voltage SW vs ILIM <sup>(1)</sup>                  | $2.25\text{ V} \leq V_{DD} \leq 5.00$ | -20 | 0    | 20       | mV            |

| $V_{ILIM}$<br>Input voltage range                                     |                                       | 2   |      | $V_{DD}$ | V             |

| $t_{ON}$<br>Minimum HDRV pulse time in overcurrent                    | $V_{DD} = 3.3\text{ V}$               |     | 200  | 300      | ns            |

| SW leading edge blanking pulse in over-current detection              |                                       |     | 100  |          | ns            |

| $t_{SS}$<br>Soft-start capacitor cycles as fault timer <sup>(1)</sup> |                                       |     | 6    |          |               |

## rectifier zero current comparator

| PARAMETER                                                | TEST CONDITIONS      | MIN             | TYP | MAX | UNIT |    |

|----------------------------------------------------------|----------------------|-----------------|-----|-----|------|----|

| $V_{SW}$<br>Sense voltage to turn off rectifier          | TPS40000<br>TPS40002 | LDRV output OFF | -15 | -7  | -2   | mV |

| SW leading edge blanking pulse in zero current detection |                      |                 | 75  |     | ns   |    |

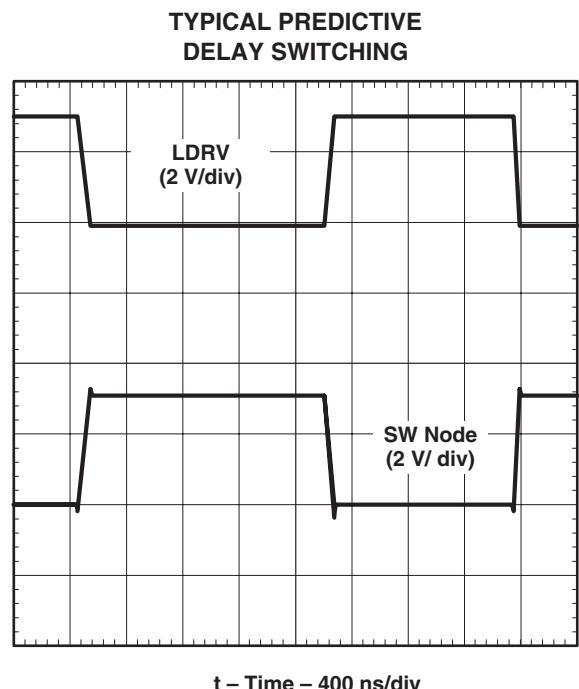

## predictive delay

| PARAMETER                                           | TEST CONDITIONS         | MIN | TYP  | MAX | UNIT |

|-----------------------------------------------------|-------------------------|-----|------|-----|------|

| $V_{SWP}$<br>Sense threshold to modulate delay time |                         |     | -350 |     | mV   |

| $T_{LDHD}$<br>Maximum delay modulation range time   | LDRV OFF – to – HDRV ON | 50  | 75   | 100 | ns   |

| Predictive counter delay time per bit               | LDRV OFF – to – HDRV ON | 3.0 | 4.5  | 6.2 | ns   |

| $T_{HDLD}$<br>Maximum delay modulation range        | HDRV OFF – to – LDRV ON | 40  | 65   | 90  | ns   |

| Predictive counter delay time per bit               | HDRV OFF – to – LDRV ON | 2.4 | 4.0  | 5.6 | ns   |

## shutdown

| PARAMETER                                   | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|---------------------------------------------|-----------------|------|------|------|------|

| $V_{SD}$<br>Shutdown threshold voltage      | Outputs OFF     | 0.09 | 0.13 | 0.18 | V    |

| $V_{EN}$<br>Device active threshold voltage |                 | 0.14 | 0.17 | 0.21 | V    |

## soft start

| PARAMETER                             | TEST CONDITIONS | MIN | TYP | MAX | UNIT          |

|---------------------------------------|-----------------|-----|-----|-----|---------------|

| $I_{SS}$<br>Soft-start source current | Outputs OFF     | 2.0 | 3.7 | 5.4 | $\mu\text{A}$ |

| $V_{SS}$<br>Soft-start clamp voltage  |                 | 1.1 | 1.5 | 1.9 | V             |

## bootstrap

| PARAMETER                                 | TEST CONDITIONS         | MIN | TYP | MAX | UNIT     |

|-------------------------------------------|-------------------------|-----|-----|-----|----------|

| $R_{BOOT}$<br>Bootstrap switch resistance | $V_{DD} = 3.3\text{ V}$ | 50  | 100 |     | $\Omega$ |

|                                           | $V_{DD} = 5\text{ V}$   | 35  | 70  |     |          |

(1) 設計で保証されており、テストは行っていません。

(2) 入力電圧  $V_{DD}$  が  $2.25\text{ V}$  の場合は、最大デューティ・サイクルは 3% 下がります。

# ELECTRICAL CHARACTERISTICS

over recommended operating temperature range,  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ ,  $V_{DD} = 5.0\text{ V}$ , all parameters measured at zero power dissipation (unless otherwise noted)

## output driver

| PARAMETER     | TEST CONDITIONS                                                    | MIN | TYP | MAX | UNIT     |

|---------------|--------------------------------------------------------------------|-----|-----|-----|----------|

| $R_{HDHI}$    | $V_{BOOT} - V_{SW} = 3.3\text{ V}$ , $I_{SOURCE} = -100\text{ mA}$ | 3   | 5.5 |     | $\Omega$ |

| $R_{HDLO}$    | $V_{BOOT} - V_{SW} = 3.3\text{ V}$ , $I_{SINK} = 100\text{ mA}$    | 1.5 | 3   |     |          |

| $R_{LDHI}$    | $V_{DD} = 3.3\text{ V}$ , $I_{SOURCE} = -100\text{ mA}$            | 3   | 5.5 |     |          |

| $R_{LDLO}$    | $V_{DD} = 3.3\text{ V}$ , $I_{SINK} = 100\text{ mA}$               | 1.0 | 2.0 |     |          |

| $t_{RISE}$    | $C_{LOAD} = 1\text{ nF}$                                           | 15  | 35  |     | ns       |

| $t_{FALL}$    |                                                                    | 10  | 25  |     |          |

| DRV rise time |                                                                    | 15  | 35  |     |          |

| DRV fall time |                                                                    | 10  | 25  |     |          |

## thermal shutdown

| PARAMETER                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT               |

|---------------------------|-----------------|-----|-----|-----|--------------------|

| $t_{SD}$                  |                 | 165 |     |     | $^{\circ}\text{C}$ |

| Hysteresis <sup>(1)</sup> |                 | 15  |     |     |                    |

## sw node

| PARAMETER | TEST CONDITIONS                            | MIN | TYP | MAX | UNIT          |

|-----------|--------------------------------------------|-----|-----|-----|---------------|

| $I_{SW}$  | Leakage current in shutdown <sup>(1)</sup> |     | 15  |     | $\mu\text{A}$ |

(1) 設計で保証されており、テストは行っていません。

(2) 入力電圧  $V_{DD}$  が  $2.25\text{V}$  の場合は、最大デューティ・サイクルは  $3\%$  下がります。

## Terminal Functions

| TERMINAL |     | I/O | 端子機能                                                                                                                                                                                                                                                                                                                                           |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. |     |                                                                                                                                                                                                                                                                                                                                                |

| BOOT     | 10  | O   | ブートストラップされた電源をハイサイドMOSFETドライバに供給し、ハイサイドMOSFETのゲートが入力電源レールより上に駆動されるようにします。                                                                                                                                                                                                                                                                      |

| COMP     | 3   | O   | 誤差増幅器の出力。                                                                                                                                                                                                                                                                                                                                      |

| FB       | 2   | I   | 誤差増幅器の反転入力。通常動作ではこのピンの電圧は内部基準電圧レベルの700mVです。                                                                                                                                                                                                                                                                                                    |

| GND      | 5   | -   | デバイスの電源帰還端子。ボード上のパワー段のグランド帰還は他の敏感な信号グランドの帰還から分離したバスにすることが必要です。                                                                                                                                                                                                                                                                                 |

| HDRV     | 9   | O   | ハイサイドNチャネルMOSFET用ゲート駆動出力。HDRVピンはハイサイドMOSFETが十分にエンハンスマント・モードとなるよう $2 \times V_{DD}$ の近辺の電圧にブートストラップされます。                                                                                                                                                                                                                                        |

| ILIM     | 1   | I   | 過電流スレッショルド電圧を設定するためこのピンとVDD間に抵抗を接続します。15μAの電流シンクにより、このピンとVDD間に電位差が生じ、過電流時にはハイサイドNチャネルMOSFETのドレイン/ソース間電圧がこの電位差を上まわります。ILIM過電流コンバレータはハイサイドMOSFETが十分にエンハンスマント・モードになるよう最初の100ns間は無効です。ILIMの電圧レベルは、 $V_{DD}$ の800mV以内、つまり、 $(V_{DD} - 0.8) \leq I_{ILIM} \leq V_{DD}$ のように設定します。                                                                    |

| LDRV     | 6   | O   | ローサイド同期整流器NチャネルMOSFETのゲート駆動出力。                                                                                                                                                                                                                                                                                                                 |

| SS/SD    | 4   | I   | ソフトスタート及び過電流異常時のシャットダウン時間がこのピンに接続されるキャパシタを充放電することで設定されます。3μAの内部電流源が外付けキャパシタを0.17Vから0.70Vに充電する時間ループのソフトスタートが起こります。ソフトスタート期間では、TPS40001とTPS40003の電流シンク能力はディスエーブルになります。SS/SD電圧が0.12V以下になると、デバイスは停止し、HDRVとLDRVは“L”レベルになります。通常動作時は、キャパシタは1.5Vに充電されています。異常状態になると、HDRVは“L”レベルに、LDRVは“H”レベルに駆動されます。ソフトスタート・キャパシタは6つの充放電サイクルを経て、7番目のサイクルでコンバータを再起動させます。 |

| SW       | 8   | O   | コンバータのスイッチ・ノードに接続します。このピンは、ハイサイドNチャネルMOSFETの過電流検出、同期整流器NチャネルMOSFETのゼロ電流検出、プレディクティブ遅延回路のレベル検出に使用されます。過電流は、ハイサイドNチャネルMOSFETがオンの時、VDDに対するSWの電圧とVDDに対するILIMの電圧を比較して決められます。ゼロ電流は、整流器NチャネルMOSFETがオンの時、グランド基準でSWの電圧を測定することで検出されます。ゼロ電流の検出はTPS40000とTPS40002のみに適用されます。                                                                                 |

| $V_{DD}$ | 7   | I   | デバイスの電源入力で、最大5.5Vです。このピンの近くに1μFまたはそれ以上の値の低ESRのデカップリング・キャパシタを配置/接続してください。                                                                                                                                                                                                                                                                       |

functional block diagram

# アプリケーション情報

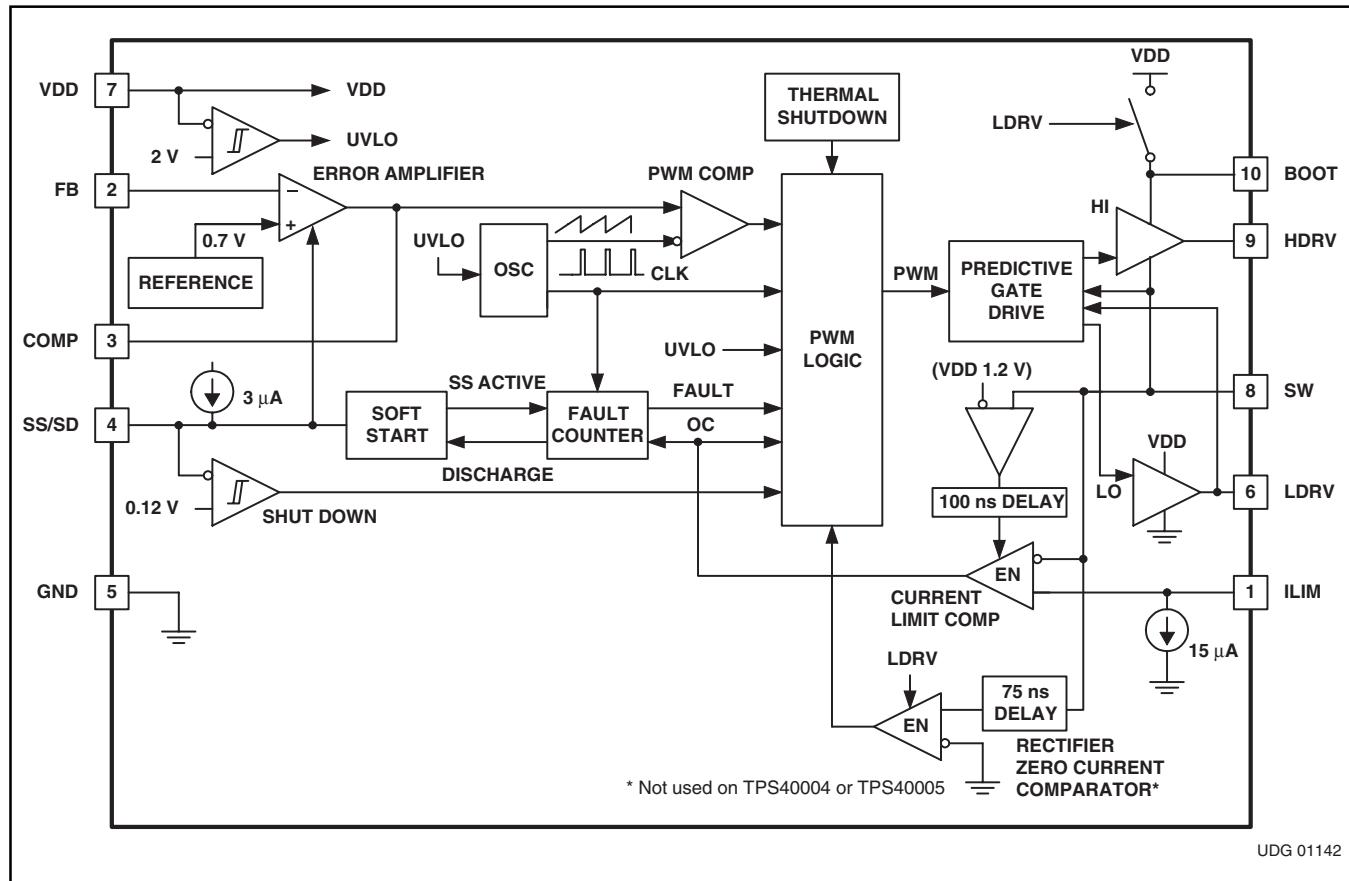

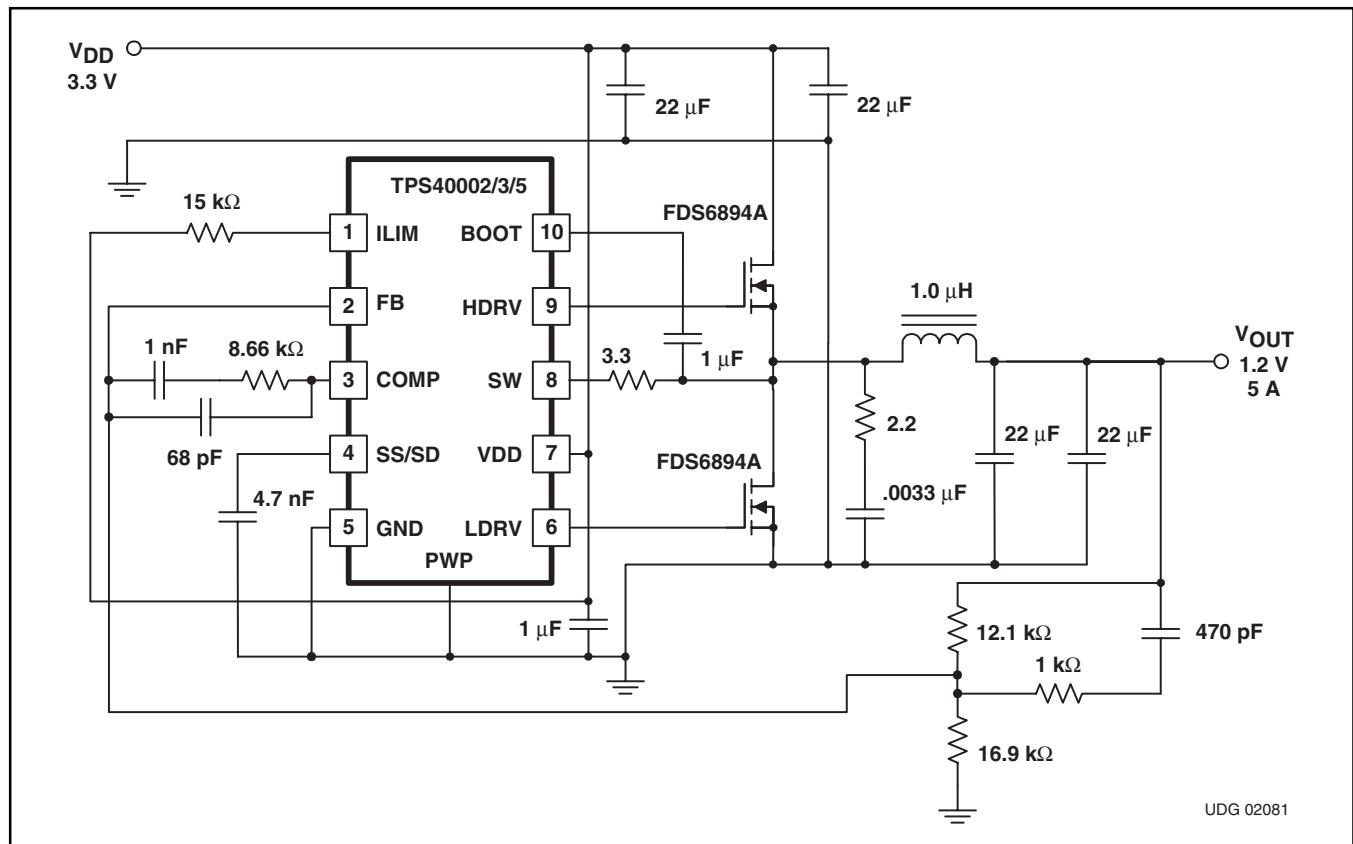

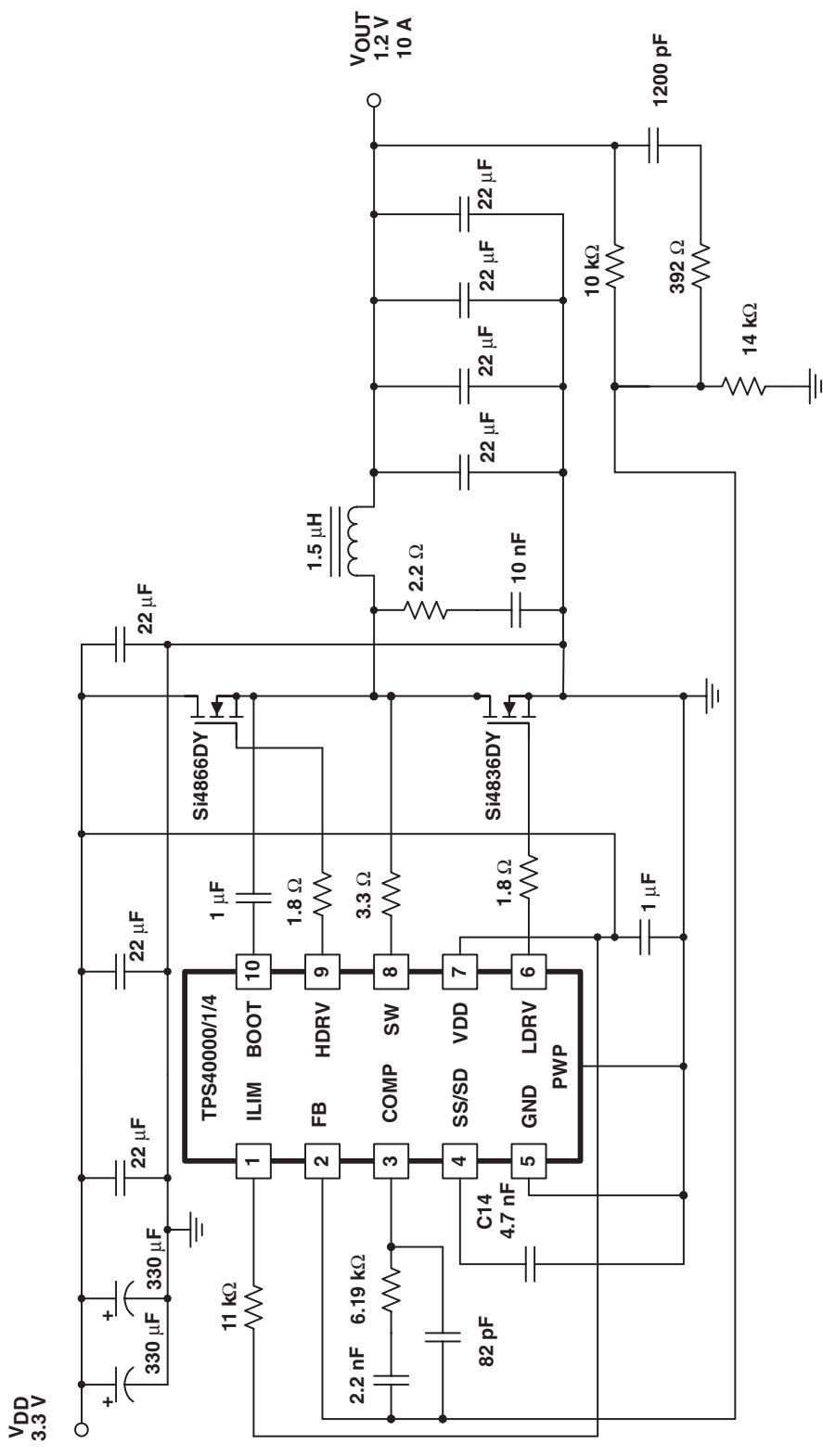

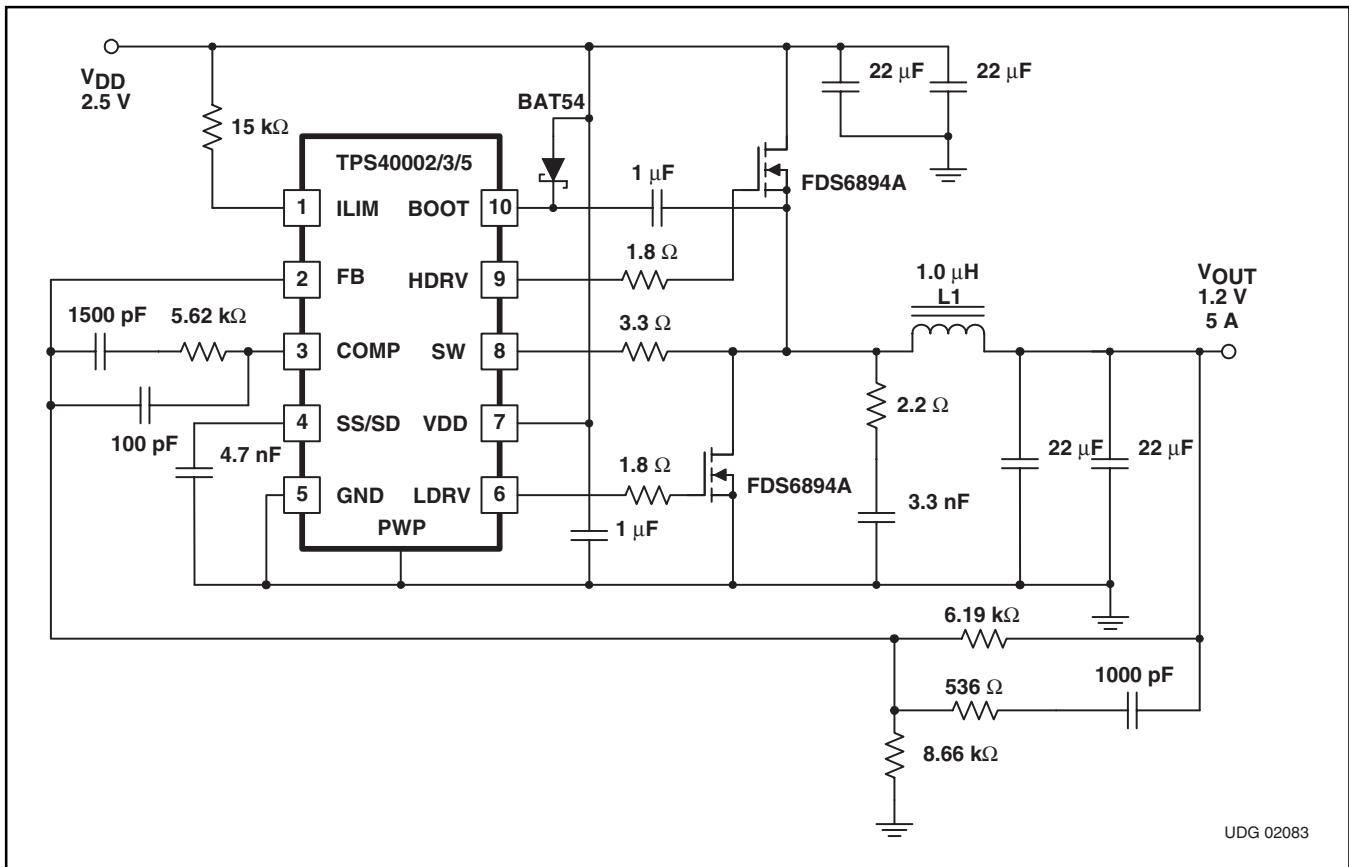

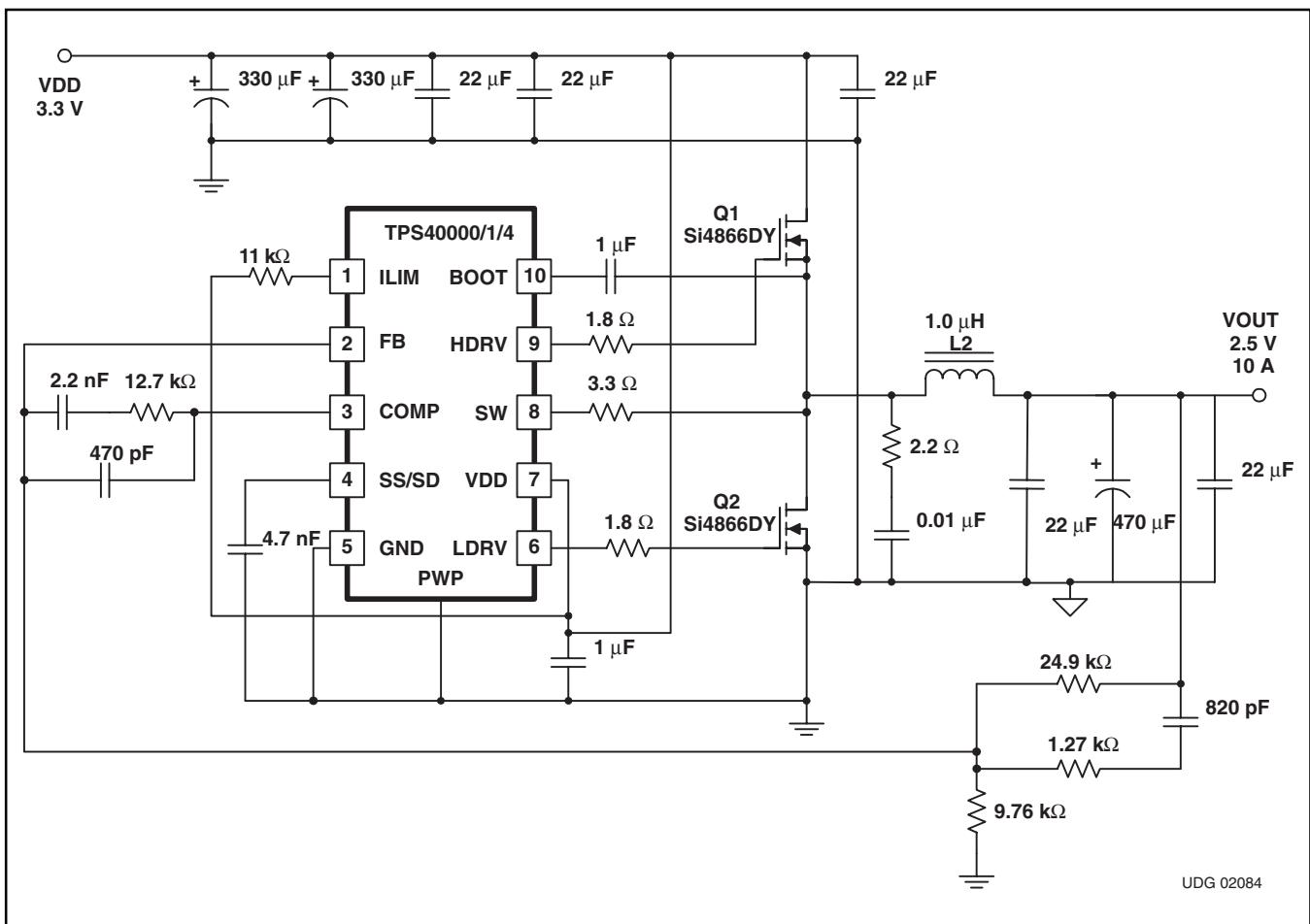

TPS4000x同期整流式バック・コントローラ・シリーズは非絶縁型分散電源システムにおける高効率のDC/DC変換に最適です。代表的なアプリケーション回路を図1に示します。

TPS40004とTPS40005は多くの汎用タイプ同期式バック・コンバータを設計するのに適したコントローラです。それぞれ常時2象限モード(ソースまたはシンク・モード)で動作します。このデバイスを選択すると、広い負荷電流範囲にわたって出力電圧の負荷過渡応答が最高の特性になります。

TPS40001とTPS40003にはさらに別の特長が追加されています。このデバイスはコンバータの起動時は1象限モード(ソース電流のみ)で動作し、次に、コンバータがレギュレーション点に達した時、コントローラは2象限モードの動作に変わります。このことは、コントローラがイネーブルになる前に出力がある電圧にプリ・バイアスされているアプリケーションに好都合です。TPS40001またはTPS40003がイネーブルの場合、起動時電流をシンクしないため、プリ・バイアス電源から電流を吸い込みません。

TPS40000とTPS40002は常時1象限モード(ソース電流のみ)で動作し、コンバータの並列化を可能にします。1象限動作により確実に1つのコンバータは並列コンバータから電流を吸い込みます。このコントローラのうちの1つを使用したコンバータは軽負荷時非同期式バック・コンバータとして動作します。出力インダクタの電流が反転しようとする時、内部のゼロ電流検出回路が同期整流器をオフにし、インダクタに流れる電流が不連続になります。

平均負荷電流がインダクタのリップル電流のピーク時振幅以上である時は、コンバータは効率を最大限にするため同期式バック・コンバータとしての動作に復帰します。

## 誤差増幅器

誤差増幅器は最小55dBの開ループ利得で5MHz以上の帯域幅をもっています。COMP出力電圧は大きな過渡応答を改善するため発振器のランプ電圧より上のレベルにクランプされます。

## 発振器

発振器は内部の抵抗とキャパシタを使用して発振周波数を設定します。ランプ波形はピーク電圧1.25V、下限電圧0.25VのPWM周波数の三角波です。PWMのデューティ・サイクルは最大95%に制限されるため、ブートストラップ・キャパシタは全サイクルで充電することができます。

## ブートストラップ/チャージ・ポンプ

VDDとBOOT間にスイッチが内蔵されています。このスイッチにより一時的な電源用に外付けのブートストラップ・キャパシタが充電されます。このスイッチの抵抗がアプリケーションにとってあまり大きすぎる場合にはVDDとBOOT間に外付けのショットキー・ダイオードを使用することができます。ブートストラップ・キャパシタのピーク電圧はほぼVDDと同じです。

図1. Typical Application Circuit

## ドライバ

HDRV/LDRVのMOSFETドライバはゲート/ソース間電圧を最大5.5Vまで駆動することができます。V<sub>IN</sub>が5Vで、適切なMOSFETを使用したとすると、20Aのコンバータが実現できます。LDRVドライバはVDDとグランド間でスイッチングし、一方、HDRVドライバはSW基準であり、BOOTとSW間でスイッチングします。BOOTとSW間の最大電圧は5.5Vです。

## 同期整流とプレディクティブ遅延

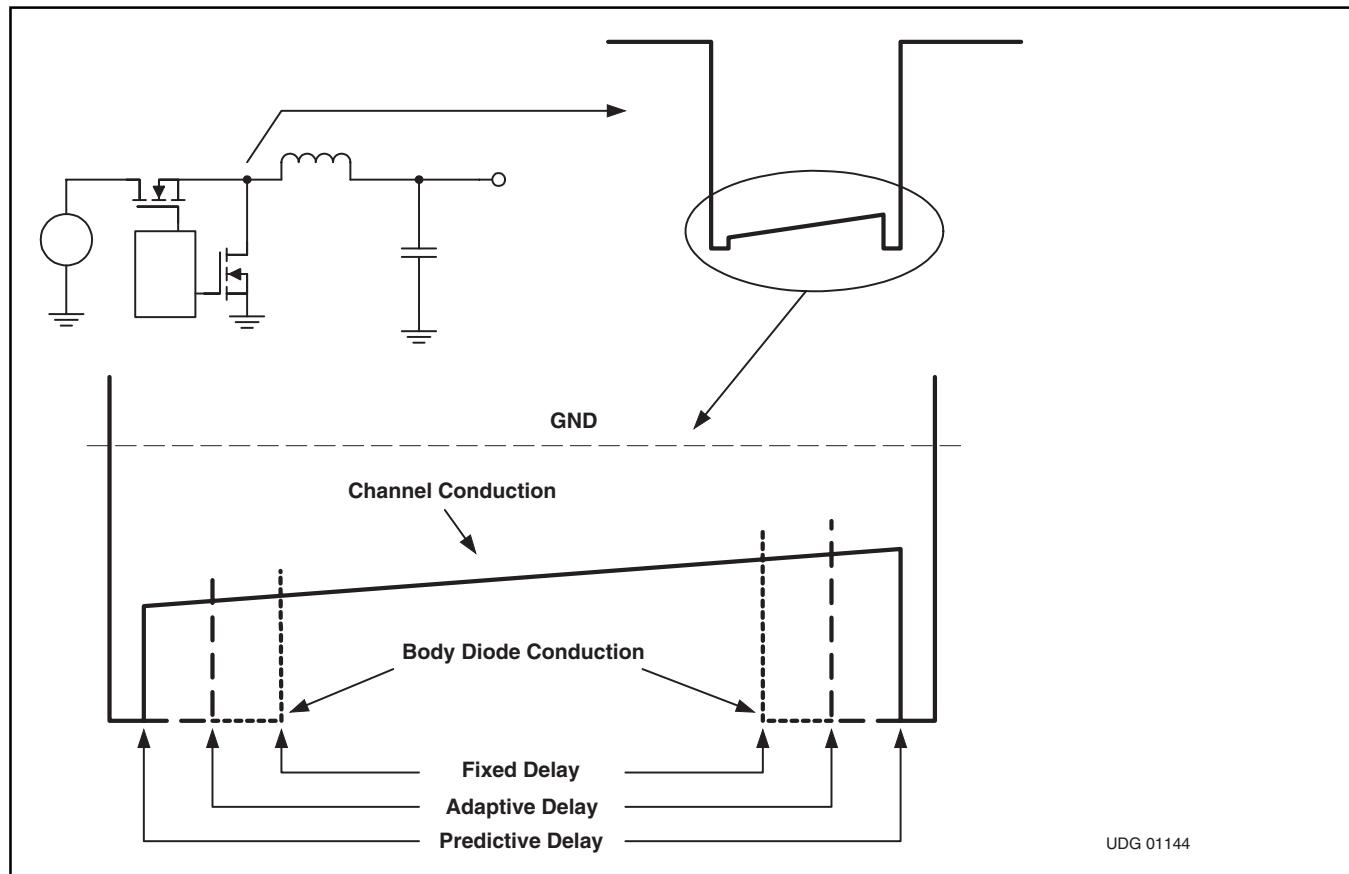

通常のバック・コンバータでは、メイン・スイッチがオフになった場合、電流はインダクタから負荷に流れます。この電流は無限大の電圧を使わなければすぐには停止できません。電流パスに電流が流れ安全なレベルに電圧レベルが維持されるには、整流器またはキャッチ・デバイスを使用します。このデバイスは従来型のダイオードでも、あるいはコントロール信号がその駆動に使用できるのであればコントロール型能動デバイスでも可能です。TPS4000xは整流器としてのNチャネルMOSFETを駆動する信号を供給します。このコントロール信号は、整流器MOSFETがオフ、メイン・スイッチがオンになる時間からの最小遅延時間、及びメイン・スイッチがオフ、整流器MOSFETがオンになる時間からの最小遅延時間が存在するよう、注意深くメイン・スイッチの駆動信号との整合性を図ります。この仕組み、つまりPredictive Gate Drive™遅延は、次のサイクルで使用されるべき遅延を調節するため電流のスイッチング・サイクルからの情報を用います。図2に、同期整流されたバック・コンバータのスイッチ・ノードの

電圧波形を示します。この図は、固定遅延の駆動体系(ターンオフからターンオンの合間の一定遅延とプリセット遅延)、アダプティブ遅延の駆動体系(電流のスイッチング・サイクルで検出された電圧をもとにした可変遅延)、プレディクティブ遅延の駆動体系の効果をそれぞれ比較したものです。

整流器の導通期間でダイオードの導通に費やされた時間が長くなるにつれ、効率が低下することに注意してください。また、図2にはプレディクティブ遅延回路がクロス導通またはショートスルーを回避すると同時にボディ・ダイオードが順方向にバイアスされるようになることを防止できるということは表されていません。このことにより、メインのMOSFETがオンになった時電力の大省力化が実現し、整流器MOSFETのボディ・ダイオードの逆回復損失が最小限に抑えられます。

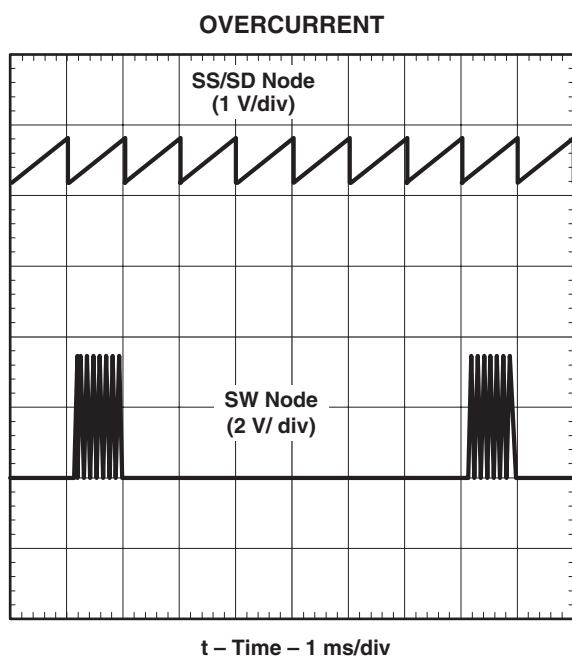

## 過電流

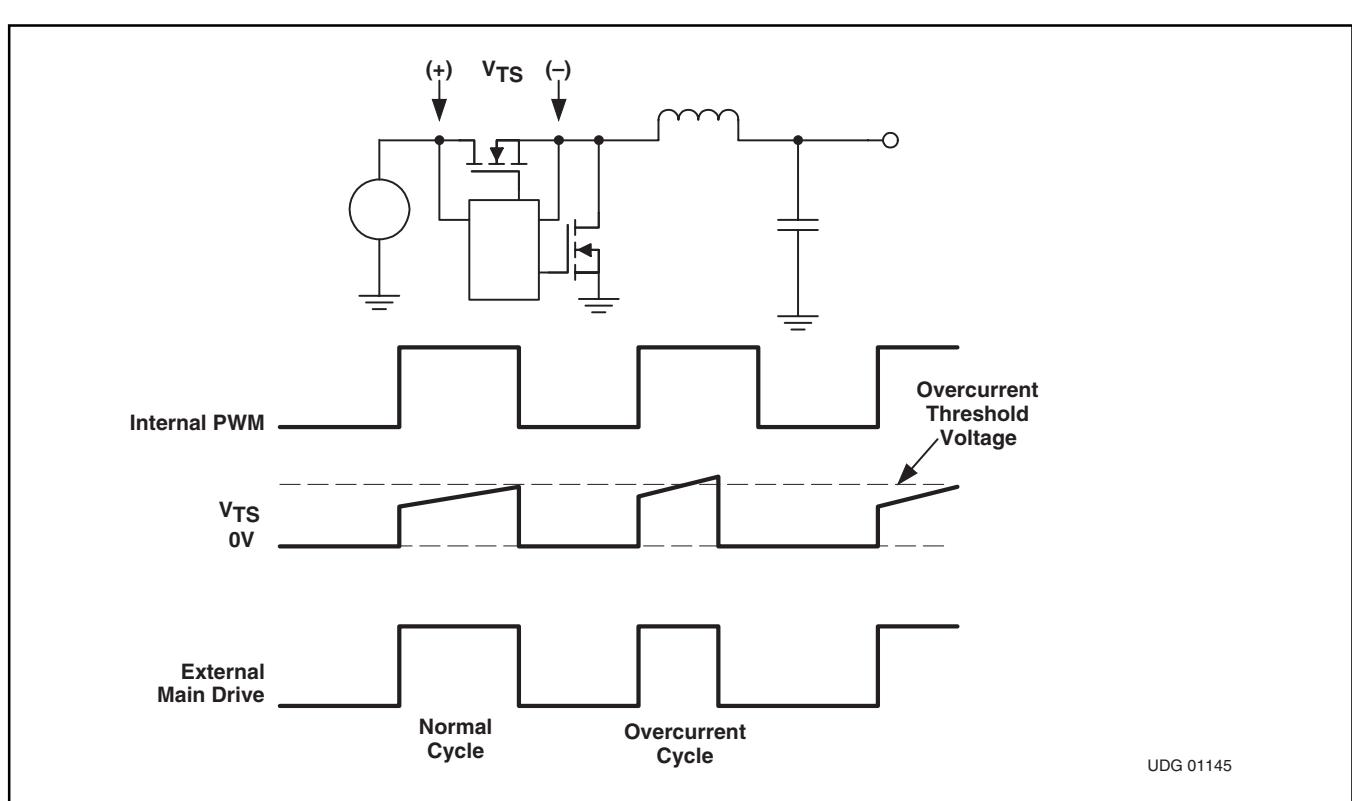

TPS4000xの過電流状態はメインのMOSFETがオンの間にその両端の電圧を検出することにより感知されます。

## 基本説明

電圧が予め設定されているスレッシホールドを越えると、電流パルスは停止し、デバイス内のカウンタが増分します。このカウンタが満杯になると異常状態が宣言され、デバイスはしばらくの間スイッチングをディスエーブルにし、その後ソフトスタート・サイクルでコンバータを再起動させようとします。

## 詳細説明

各スイッチング・サイクルで、コンパレータはハイサイドMOSFETがオンの間にその両端の電圧を観察しています。このコンパレータはSWノードが $(V_{DD} - 1.2V)$ 以上の電圧になり、その後100nsのブランкиング時間の後イネーブルになります。MOSFET端の電圧がプログラムで設定可能なスレッシホールド電圧を越えると、電流スイッチング・パルスは停止し、3ビットのカウンタが1カウント増加します。スイッチング・サイクル時、ハイサイドMOSFETの電圧が予め設定されている電圧を越えないと、このカウンタは1カウント減少します。(カウンタは7から0または0から7というような回り込みはしません)。カウンタがフル・カウントの7に達すると、デバイスは異常状態がコンバータの出力に存在することを宣言します。この異常状態では、HDRVはオフに、LDRVはオンになります、ソフトスタート・キャパシタは放電します。カウンタはソフトスタート・キャパシタ(C<sub>SS</sub>)が放電するごとに1カウントずつ減少します。ソフトスタート・キャパシタが完全に放電すると、放電回路はオフになります、キャパシタは標準の充電速度で充電することが可能となります。ソフトスタート・キャパシタが約700mVに達すると、再度放電し、過電流カウンタが1カウント減少します。キャパシタは充放電し、カウンタはカウントがゼロになるまで減少します(合計6回)。このことが起こると、ソフトスタート・キャパシタが再起動しようとする間追随するためのコンバータ用基準ランプを生成した時出力は再びイネーブルになります。

このソフトスタート期間(コントローラが異常回復を行なおうとするか、または初期起動しているかにかかわらず)では、パルスごとの電流制限は実施されますが、ソフトスタート・サイクルが完了するまで異常を宣言する過電流パルスはカウントされませ

ん。ソフトスタート時間に7スイッチング・サイクルを加えた期間中電源の短絡が起こります。パワー段の設計は熱的に影響があるのであればこのことを考慮に入れなければなりません。図3に、過電流動作の詳細を示します。

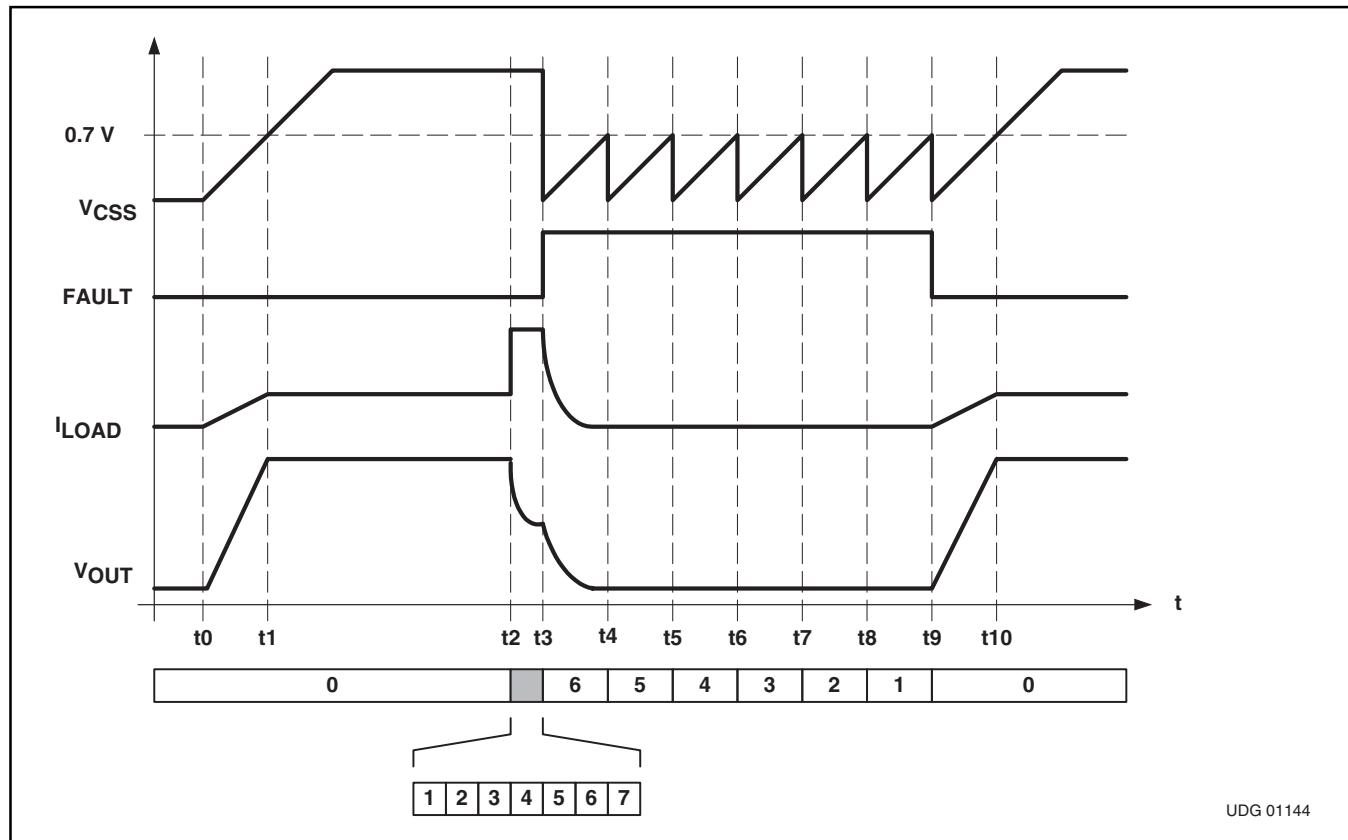

図4に、異常及び正しい異常復帰時における初期起動時の主要な信号の動作を示します。時間t0で、コンバータに電源が供給されます。ソフトスタート・キャパシタ(V<sub>CSS</sub>)の電圧が上昇し始め、t1で内部基準電圧を通過するまで基準電圧として機能します。この地点で、ソフトスタート期間は終わり、コンバータは出力を目標電圧レベルにレギュレーションします。t0からt1で、パルスごとの電流制限が実施され、t1から先では過電流パルスが考えられる異常状態を割り出す目的でカウントされます。t2で、大きな過負荷がコンバータに加わっています。この過負荷は過電流スレッシホールドを越えています。コンバータは電流の制限を開始し、出力電圧は加えられた過負荷によりあるレベルまで低下します。t2からt3の期間では、カウンタは過電流パルスをカウントしており、t3でフル・カウントの7に達します。その結果、ソフトスタート・キャパシタは放電し、カウンタは減少し、異常状態が宣言されます。

ソフトスタート・キャパシタが完全に放電した時、標準3μAの電流源により起動時と同じ速度で再び充電を開始します。キャパシタの電圧が全電荷に達した時、再び放電しカウンタは1カウント減少します。この変遷はt3からt9で起こり、t9でカウンタは0まで減少してしまいます。その結果異常ロジックはクリアされ、出力はイネーブルになり、コンバータはソフトスタート・サイクルで再起動しようとします。コンバータはt10でレギュレーション状態になります。

図3. Switch Node Waveforms for Synchronous Buck Converter

図4. Switch Node Waveforms for Synchronous Buck Converter

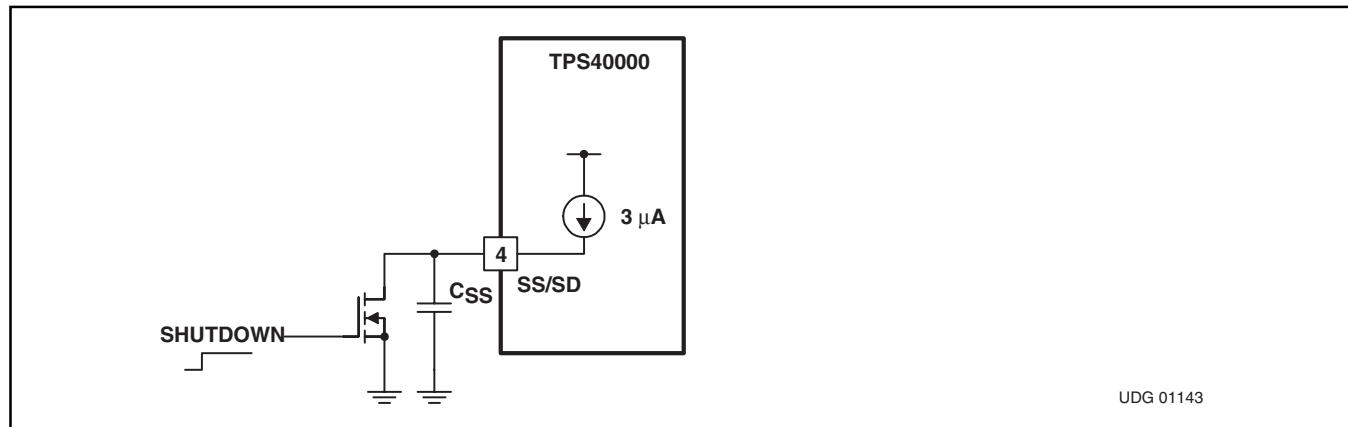

図5. Shutdown Implementation

## 電流制限の設定

VDDからILIMに抵抗を接続することにより電流制限が設定されます。デバイスに内蔵されている $15\mu\text{A}$ の電流シンクによりILIMに過電流スレッシングホールド電圧に等しい電圧の電圧降下が生じます。確実に $(V_{\text{DD}} - 0.8\text{V}) \leq V_{\text{ILIM}} \leq V_{\text{DD}}$ となるようにしてください。電流シンクの公差は正確な電流制限を行なうには大きすぎます。この主な目的はパワー・スイッチを確実に異常から保護することです。与えられたILIMシンク電流の公差とMOSFETのオン抵抗 $R_{\text{DS(on)}}$ の範囲から、コンバータに熱的に損傷を与えるような負荷が加わることは一般的に起こります。このデバイスは、負荷特性が規定されて、コントロールすることができる組み込み型コンバータに適しています。

## ソフトスタートとシャットダウン

SS/SDピンには共通して2つの機能があります。このピンの電圧が起動時誤差増幅器をコントロールする電圧です。このことにより、起動時出力キャパシタを充電するのに必要な過渡電流が低減し、正しく行なわれれば出力電圧がオーバーシュートせずに円滑な起動が可能となります。シャットダウン機能は図5に示すような手段を講じることができます。

デバイスはSS/SDピンの電圧が $120\text{mV}$ 以下に低下すると停止します。この制約のため、図5のように、コントロールするデバイスとしてMOSFETを使用することを推奨します。オープン・ドライン出力のCMOSロジックも同等の機能をします。

## 整流器のゼロ電流

TPS40000とTPS40002の両デバイスはソースのみであるため、同期整流器の逆電流を防止できます。同期整流はローサイドMOSFET端のグランド基準のSW電圧を検出することにより終了します。SWノードが $-7\text{mV}$ より大きい場合、整流は停止し、次のPWMサイクルまでオフ状態のままでです。SWノードの好ましくないノイズをフィルタで除去するために、ゼロ電流コンパレータは整流器がオンになった時から75ns無効状態になります。

TPS40001とTPS40003は、ソフトスタートがアクティブの間、ゼロ電流コンパレータをイネーブルにします(よって逆電流が防止される)が、出力がレギュレーションに達した時、つまり、ソフトスタート時間の終わりで、このコンパレータはディスエーブルになり同期整流器は電流をシンクできるようになります。

以下にいくつかのアプリケーションに対する設計案を示します。その他の設計案、詳細設計情報、有用なヒントについては <http://power.ti.com> の TPS40000 リソースにアクセスしてください。

図6. Small-Form Factor Converter for 3.3 V to 1.2 V at 5 A.

图7. High-Current Converter for 3.3 V to 1.2 V at 10 A.

UDG 02082

図8. Ultra-Low-Input Voltage Converter for 2.5 V to 1.2 V at 5 A

図9. Ultra-High-Efficiency Converter for 3.3 V to 2.5 V at 10 A

## TYPICAL CHARACTERISTICS

図10

図11

図12

図13

## TYPICAL CHARACTERISTICS

図14

図15

図16

図17

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS40000DGQ           | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAUAG                             | Level-1-260C-UNLIM                | -40 to 85    | 40000               |

| TPS40000DGQ.A         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAUAG                             | Level-1-260C-UNLIM                | -40 to 85    | 40000               |

| TPS40000DGQR          | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAUAG                             | Level-1-260C-UNLIM                | -40 to 85    | 40000               |

| TPS40000DGQR.A        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAUAG                             | Level-1-260C-UNLIM                | -40 to 85    | 40000               |

| TPS40001DGQ           | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40001               |

| TPS40001DGQ.A         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40001               |

| TPS40001DGQR          | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40001               |

| TPS40001DGQR.A        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40001               |

| TPS40002DGQ           | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40002               |

| TPS40002DGQ.A         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40002               |

| TPS40002DGQR          | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40002               |

| TPS40002DGQR.A        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40002               |

| TPS40003DGQ           | NRND          | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40003               |

| TPS40003DGQ.A         | NRND          | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40003               |

| TPS40003DGQR          | NRND          | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40003               |

| TPS40003DGQR.A        | NRND          | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40003               |

| TPS40005DGQR          | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40005               |

| TPS40005DGQR.A        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 40005               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

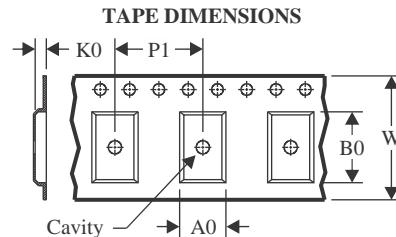

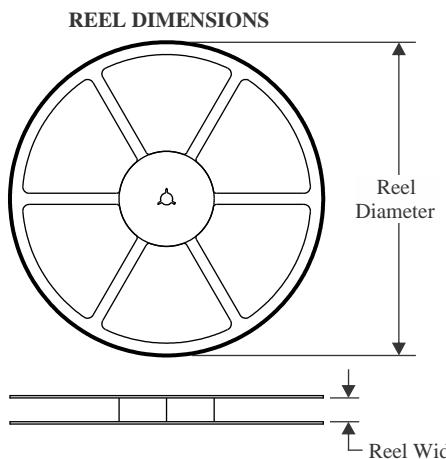

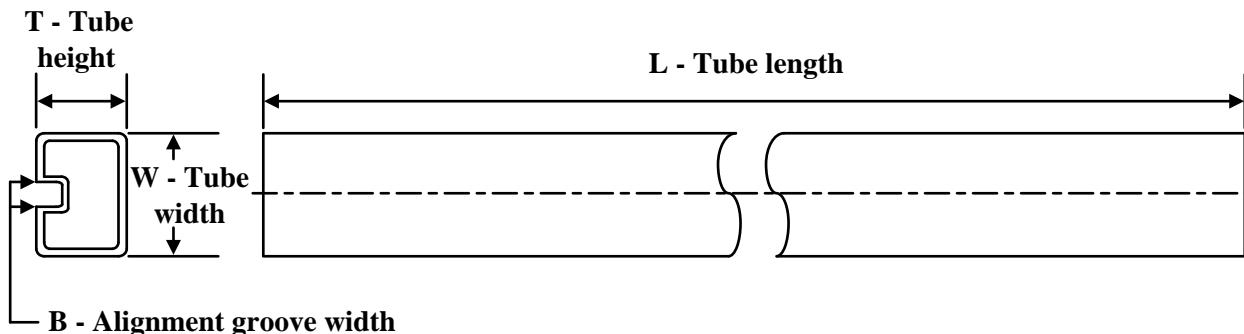

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

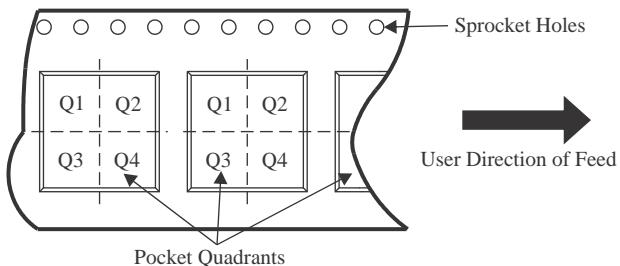

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS40000DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

| TPS40001DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

| TPS40002DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

| TPS40003DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

| TPS40005DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

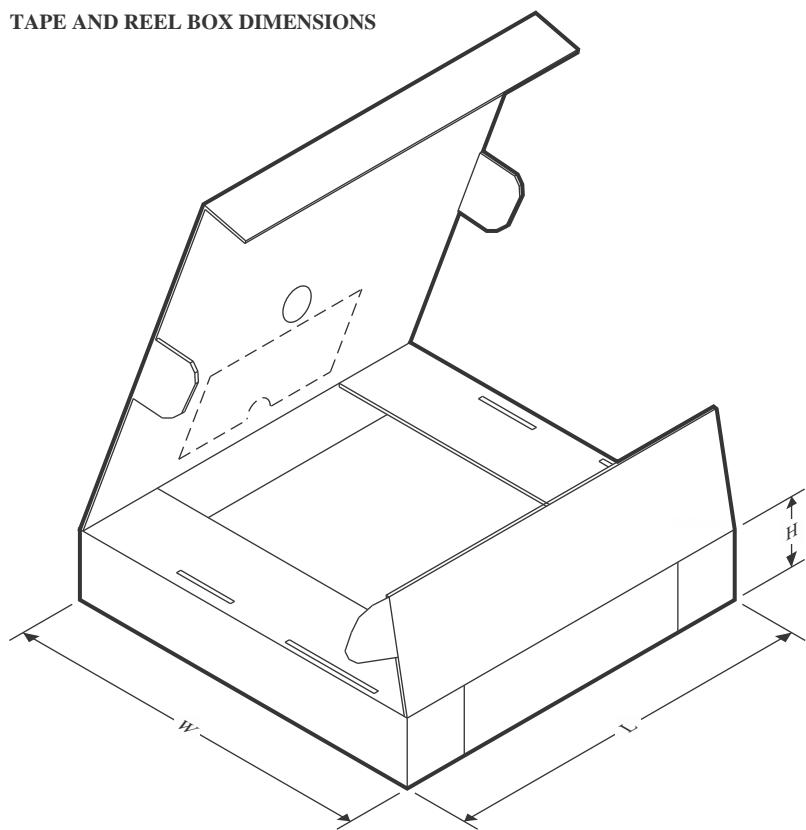

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS40000DGQR | HVSSOP       | DGQ             | 10   | 2500 | 346.0       | 346.0      | 35.0        |

| TPS40001DGQR | HVSSOP       | DGQ             | 10   | 2500 | 367.0       | 367.0      | 38.0        |

| TPS40002DGQR | HVSSOP       | DGQ             | 10   | 2500 | 346.0       | 346.0      | 35.0        |

| TPS40003DGQR | HVSSOP       | DGQ             | 10   | 2500 | 367.0       | 367.0      | 38.0        |

| TPS40005DGQR | HVSSOP       | DGQ             | 10   | 2500 | 346.0       | 346.0      | 35.0        |

## TUBE

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS40000DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40000DGQ   | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS40000DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS40000DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40001DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40001DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40002DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40002DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40003DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS40003DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

## GENERIC PACKAGE VIEW

**DGQ 10**

**PowerPAD™ HVSSOP - 1.1 mm max height**

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224775/A

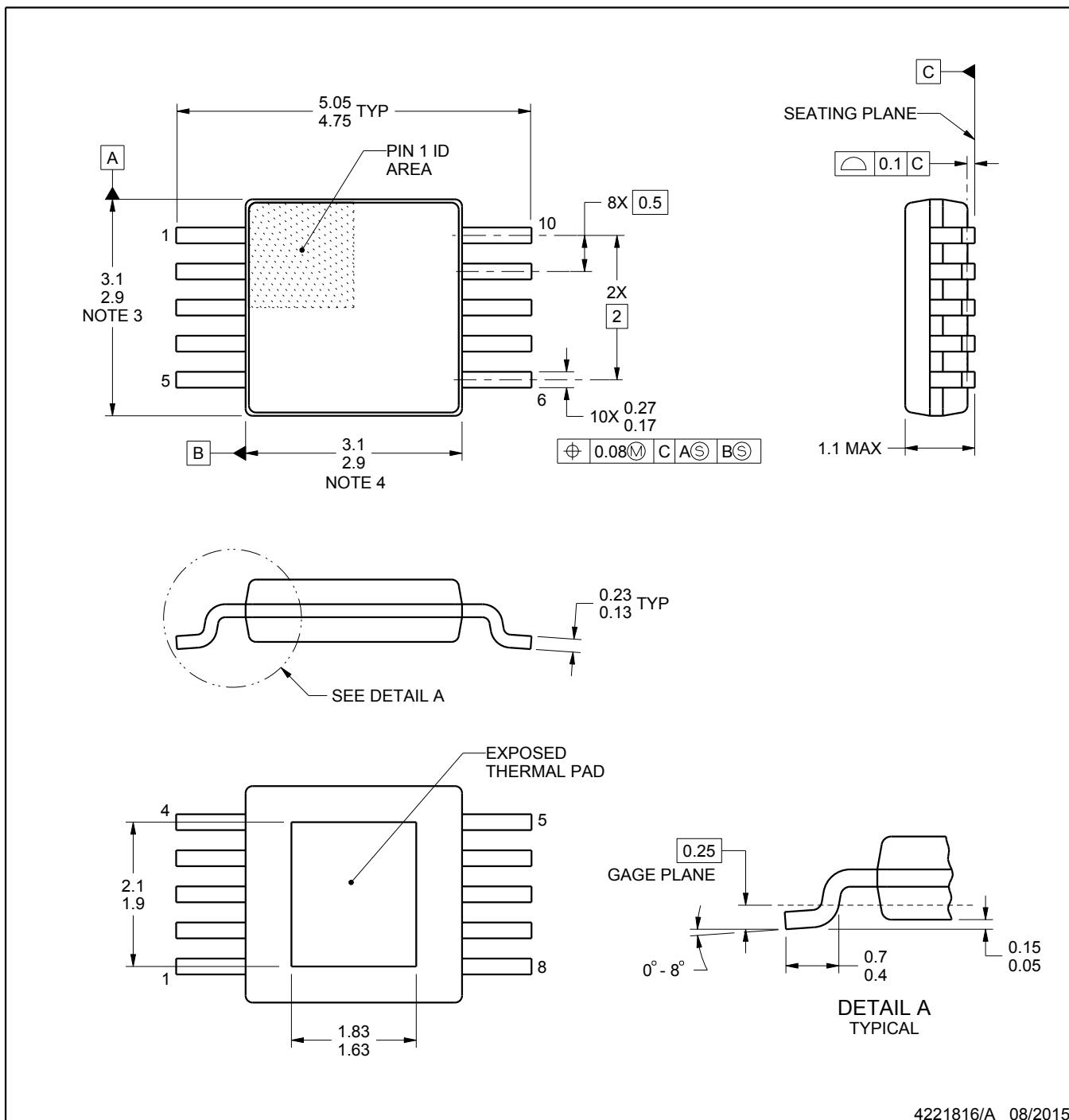

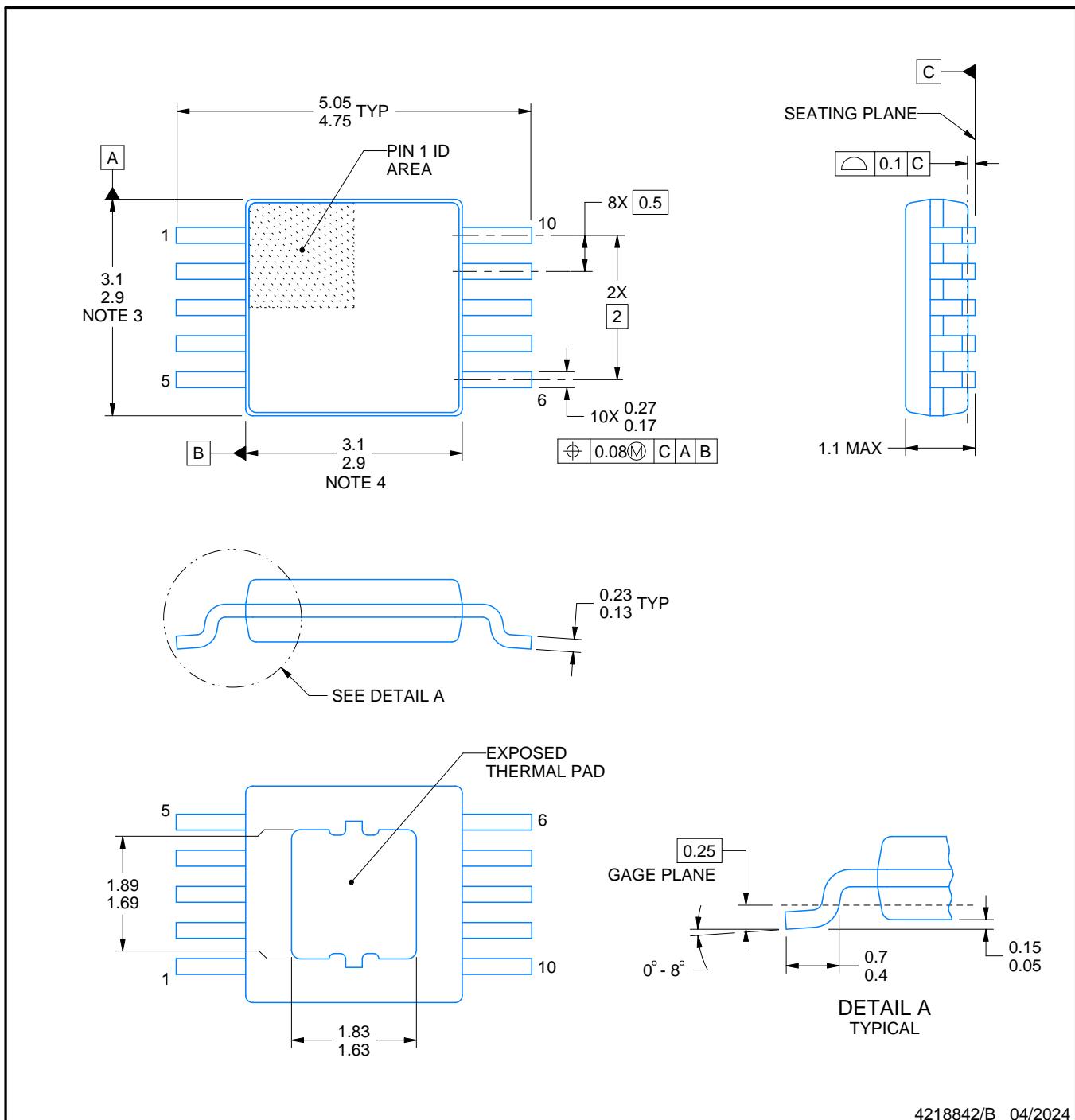

# PACKAGE OUTLINE

DGQ0010E

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

4221816/A 08/2015

PowerPAD is a trademark of Texas Instruments.

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- Reference JEDEC registration MO-187, variation BA-T.

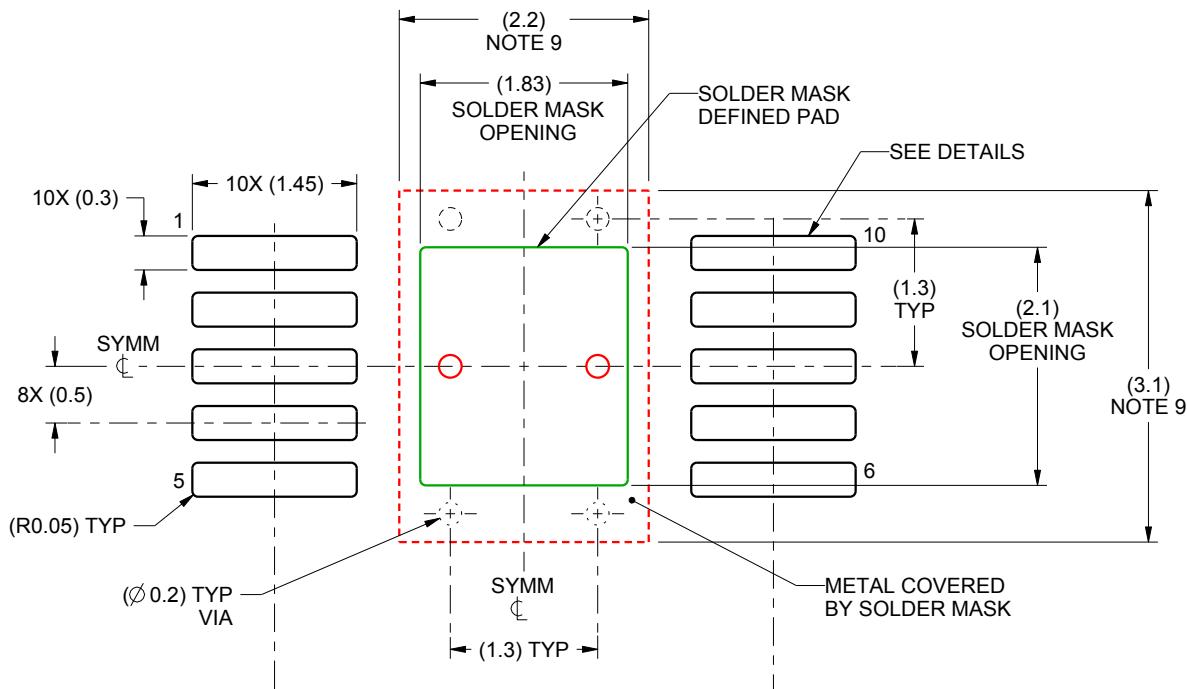

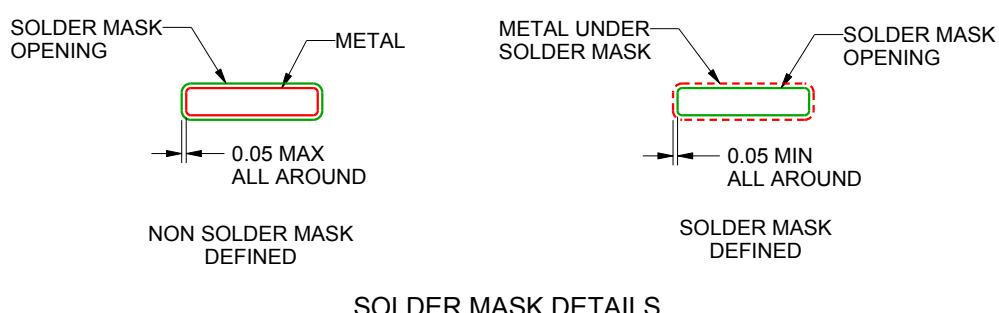

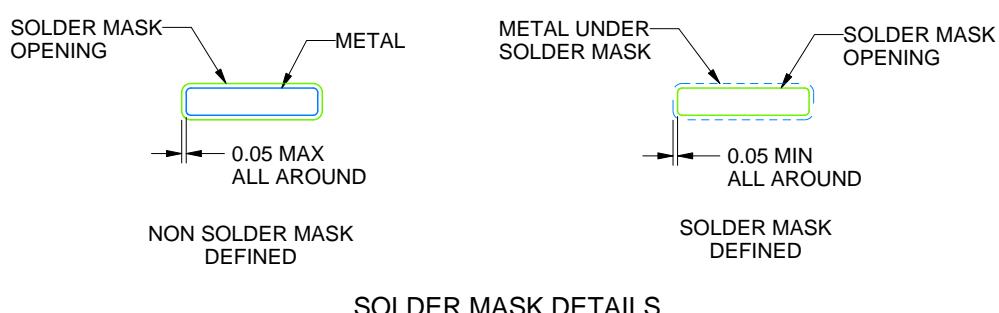

# EXAMPLE BOARD LAYOUT

DGQ0010E

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

SCALE:15X

SOLDER MASK DETAILS

4221816/A 08/2015

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

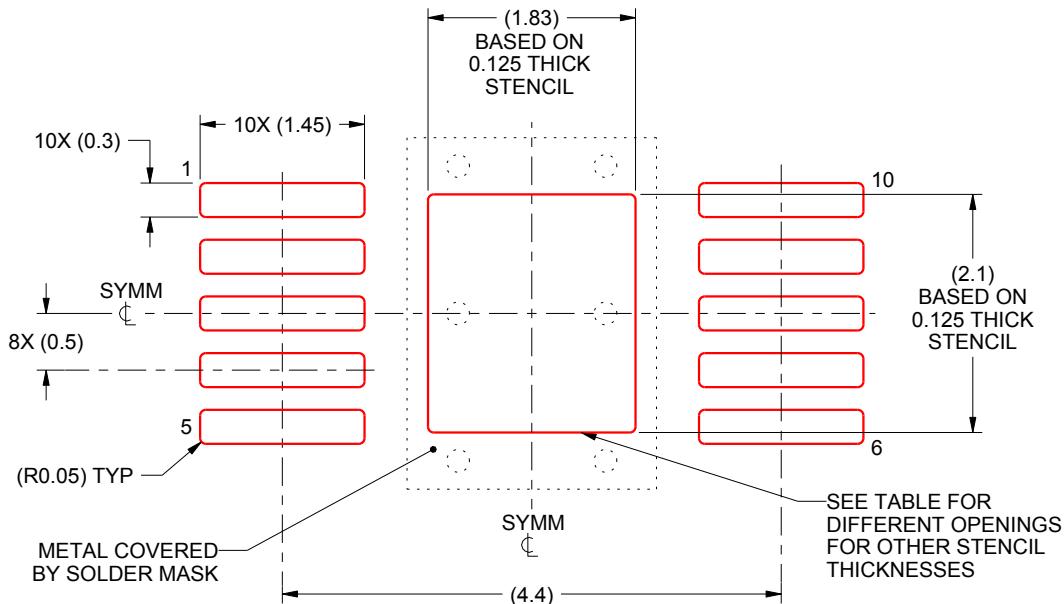

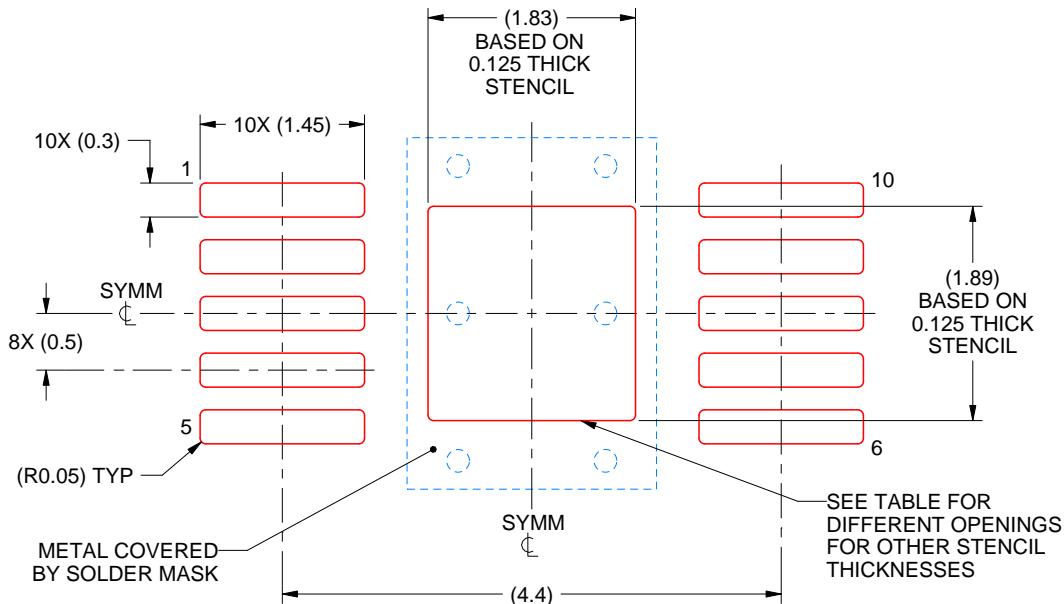

# EXAMPLE STENCIL DESIGN

DGQ0010E

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:15X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.05 X 2.35            |

| 0.125             | 1.83 X 2.1 (SHOWN)     |

| 0.150             | 1.67 X 1.92            |

| 0.175             | 1.55 X 1.77            |

4221816/A 08/2015

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

# PACKAGE OUTLINE

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

4218842/B 04/2024

PowerPAD is a trademark of Texas Instruments.

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- Reference JEDEC registration MO-187, variation BA-T.

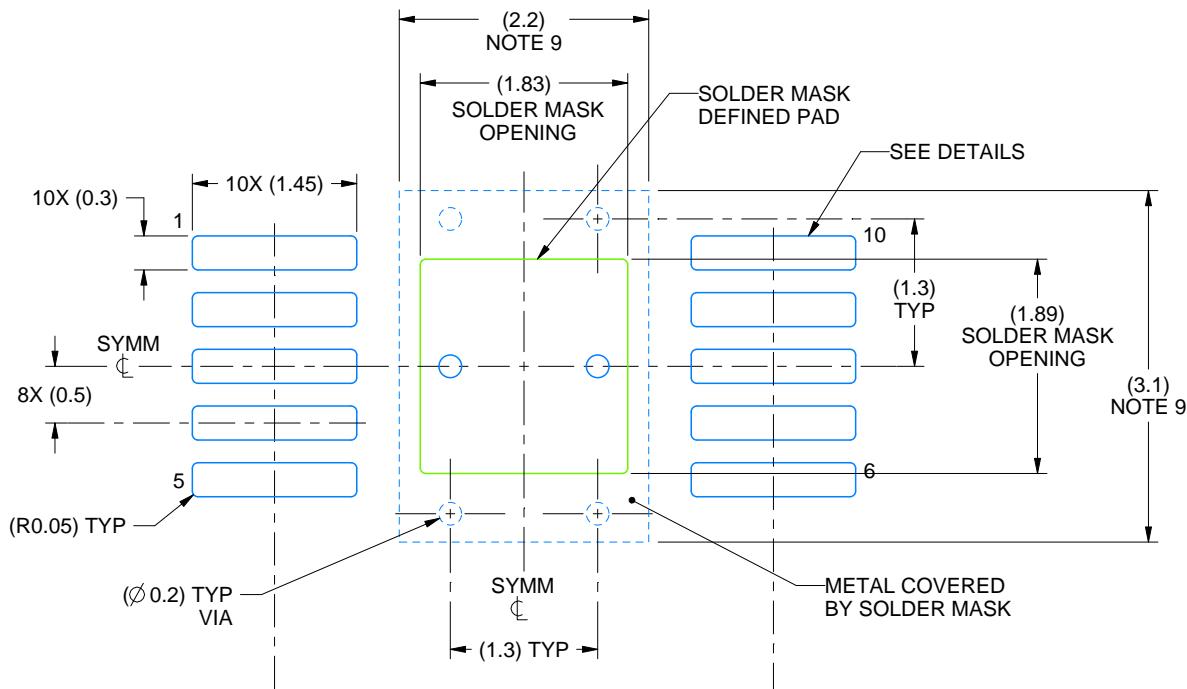

# EXAMPLE BOARD LAYOUT

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

SCALE:15X

4218842/B 04/2024

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

# EXAMPLE STENCIL DESIGN

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:15X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.05 X 2.11            |

| 0.125             | 1.83 X 1.89 (SHOWN)    |

| 0.150             | 1.67 X 1.73            |

| 0.175             | 1.55 X 1.60            |

4218842/B 04/2024

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月