## 広入力電圧範囲 同期整流式バック・コントローラ

### 特 長

- 動作入力電圧 : 8V~40V

- 入力電圧フィードフォワード補償

- 0.7V、誤差1%以下の内部基準電圧

- 最大1MHzまでプログラム可能な固定周波数の電圧モード・コントローラ

- ハイサイド及び同期式NチャネルMOSFET用ゲート駆動出力内蔵

- 16ピンPowerPAD™パッケージ ( $\theta_{JC} = 2^{\circ}\text{C}/\text{W}$ )

- サーマル・シャットダウン機能

- 外部同期可能

- プログラマブルに設定できるハイサイド電流制限

- プログラマブルに設定できる閉ループのソフトスタート

- TPS40050はソースのみ

- TPS40051はソース/シンク

- TPS40053はV<sub>OUT</sub>プリバイアス付きソース/シンク

### アプローチーション

- ネットワーキング装置

- テレコム機器

- 基地局

- サーバー

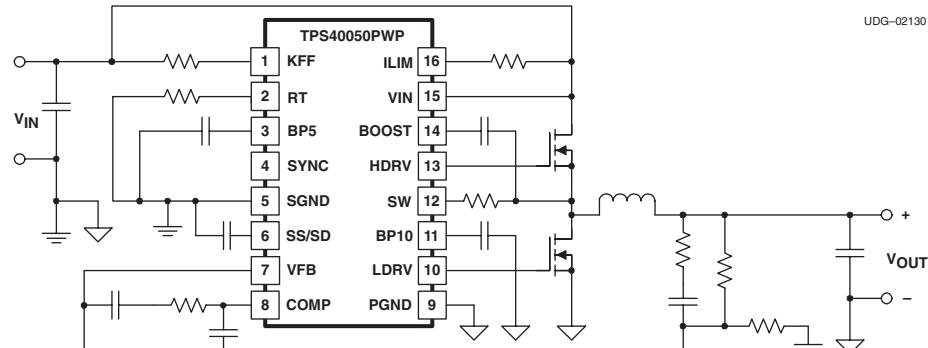

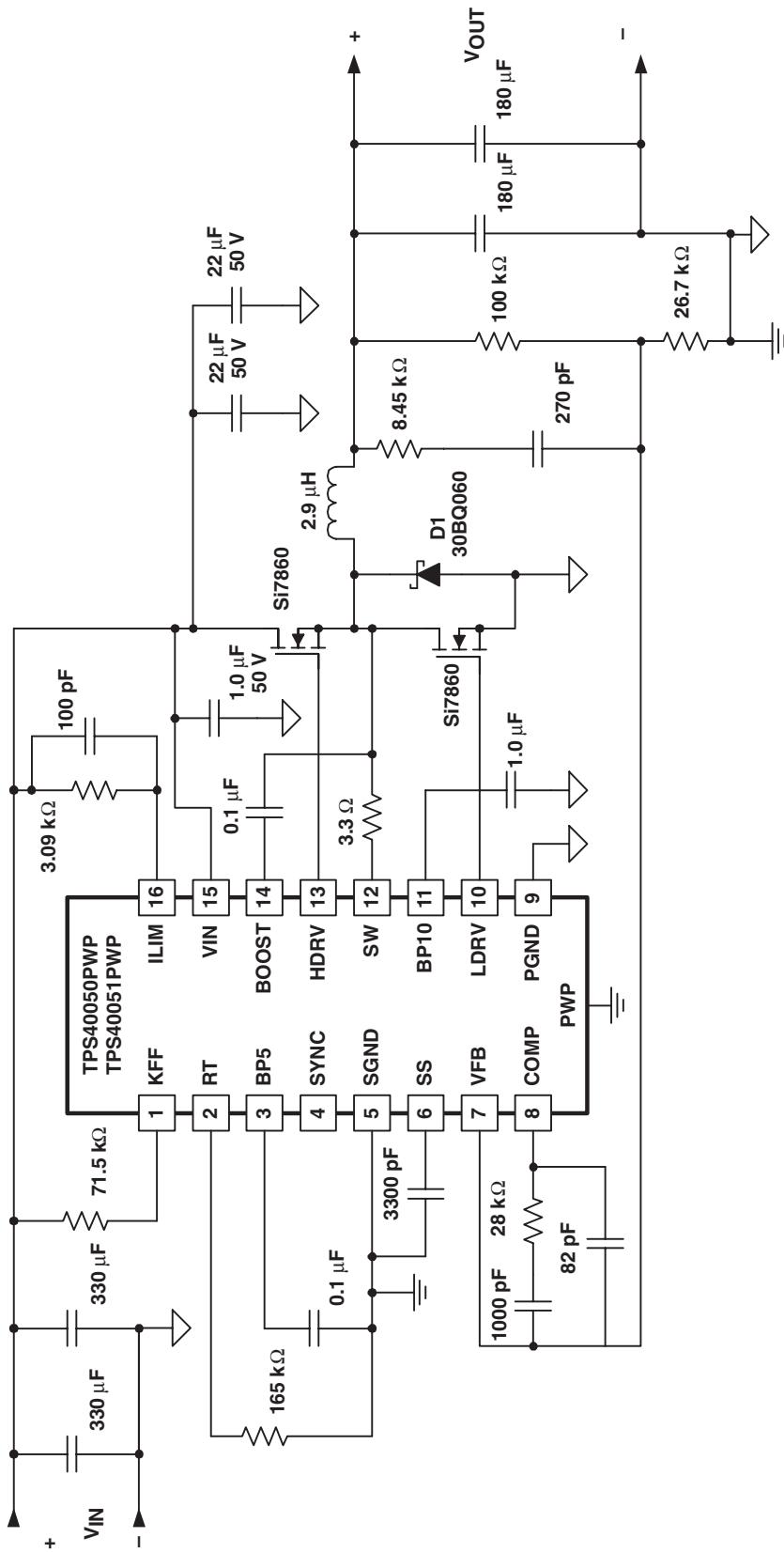

### SIMPLIFIED APPLICATION

UDG-02130

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ORDERING INFORMATION

| T <sub>A</sub> | LOAD CURRENT               | PACKAGE                             | PART NUMBER |

|----------------|----------------------------|-------------------------------------|-------------|

| -40°C to 85°C  | SOURCE                     | Plastic HTSSOP (PWP) <sup>(1)</sup> | TPS40050PWP |

|                | SOURCE/SINK                | Plastic HTSSOP (PWP) <sup>(1)</sup> | TPS40051PWP |

|                | SOURCE/SINK <sup>(2)</sup> | Plastic HTSSOP (PWP) <sup>(1)</sup> | TPS40053PWP |

(1) PWPパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(すなわち、TPS40050PWPR)。PowerPAD™の図面及びレイアウト情報についてはこのデータシートのアプリケーションの節を参照してください。

(2)ソフトスタート時はソースのみのモード(DCM)

## ABSOLUTE MAXIMUM RATINGS

特に記述のない限り、動作周囲温度<sup>(1)</sup>

|                                                              |                       | T <sub>PS40050</sub><br>T <sub>PS40051</sub><br>T <sub>PS40053</sub> | UNIT |

|--------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|------|

| Input voltage range V <sub>I</sub>                           | V <sub>IN</sub>       | 45                                                                   | V    |

|                                                              | VFB, KFF, SS, SYNC    | -0.3 to 6                                                            |      |

|                                                              | SW                    | -0.3 to 45                                                           |      |

|                                                              | SW, transient < 50 ns | -2.5                                                                 |      |

| Output voltage range, V <sub>O</sub>                         | COMP, KFF, RT, SS     | -0.3 to 6                                                            |      |

| Output current, I <sub>OUT</sub>                             | RT                    | 200                                                                  | μA   |

| Operating virtual junction temperature range, T <sub>J</sub> |                       | -40 to 125                                                           |      |

| Storage temperature, T <sub>STG</sub>                        |                       | -55 to 150                                                           | °C   |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                       | 260                                                                  |      |

(1)絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## RECOMMENDED OPERATING CONDITIONS

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Input voltage, V <sub>I</sub>                  | 8   | 40  |     | V    |

| Operating free-air temperature, T <sub>A</sub> | -40 | 85  |     | °C   |

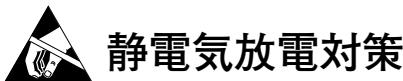

PWP PACKAGE<sup>(3)(4)</sup>

(TOP VIEW)

(3)PWPパッケージの詳細な情報についてはTIテクニカル・ブリーフ文献番号SLMA002を参照してください。

(4)PowerPAD™のヒート・スラグはSGND(5ピン)に接続するか、または、他の全ピンと電気的に絶縁してください。

# ELECTRICAL CHARACTERISTICS

$T_J = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{IN} = 24 \text{ V}_{\text{dc}}$ ,  $R_T = 90.9 \text{ k}\Omega$ ,  $I_{KFF} = 150\mu\text{A}$ ,  $f_{SW} = 500 \text{ kHz}$  (unless otherwise noted)

| PARAMETER                                      | TEST CONDITIONS                                                                             | MIN   | TYP   | MAX   | UNIT          |   |

|------------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------|-------|---------------|---|

| <b>INPUT SUPPLY</b>                            |                                                                                             |       |       |       |               |   |

| $V_{IN}$                                       | Input voltage range, $V_{IN}$                                                               | 8     |       | 40    | V             |   |

| <b>OPERATING CURRENT</b>                       |                                                                                             |       |       |       |               |   |

| $I_{DD}$                                       | Quiescent current<br>Output drivers not switching                                           |       | 1.5   | 3.0   | mA            |   |

| <b>BP5</b>                                     |                                                                                             |       |       |       |               |   |

| $V_{BP5}$                                      | Input voltage                                                                               | 4.7   | 5.0   | 5.2   | V             |   |

| <b>OSCILLATOR/RAMP GENERATOR<sup>(3)</sup></b> |                                                                                             |       |       |       |               |   |

| $f_{OSC}$                                      | Accuracy<br>$R_T = 90.9 \text{ k}\Omega$                                                    | 480   | 500   | 550   | kHz           |   |

| $V_{RAMP}$                                     | PWM ramp voltage <sup>(1)</sup><br>$V_{PEAK} - V_{VAL}$                                     |       | 2.0   |       | V             |   |

| $V_{IH}$                                       | High-level input voltage, SYNC                                                              | 2     |       | 5     |               |   |

| $V_{IL}$                                       | Low-level input voltage, SYNC                                                               |       |       | 0.8   | V             |   |

| $I_{SYNC}$                                     | Input current, SYNC<br>Pulse width, SYNC                                                    |       | 5     | 10    | $\mu\text{A}$ |   |

| $V_{RT}$                                       | RT voltage                                                                                  | 50    |       |       | ns            |   |

| Maximum duty cycle                             | $V_{FB} = 0 \text{ V}$ , $f_{SW} \leq 500 \text{ kHz}$                                      | 2.38  | 2.50  | 2.58  | V             |   |

|                                                | $V_{FB} = 0 \text{ V}$ , $500 \text{ kHz} \leq f_{SW} \leq 1 \text{ MHz}$                   | 85%   |       | 94%   |               |   |

| Minimum duty cycle                             | $V_{FB} \geq 0.75 \text{ V}$                                                                | 80%   |       | 0%    |               |   |

| $V_{KFF}$                                      | Feed-forward voltage                                                                        | 0%    | 3.35  | 3.48  | 3.65          | V |

| $I_{KFF}$                                      | Feed-forward current operating range <sup>(1)</sup>                                         | 20    |       | 1100  | $\mu\text{A}$ |   |

| <b>SOFT START</b>                              |                                                                                             |       |       |       |               |   |

| $I_{SS}$                                       | Soft-start source current                                                                   | 1.75  | 2.35  | 2.85  | $\mu\text{A}$ |   |

| $V_{SS}$                                       | Soft-start clamp voltage                                                                    |       | 3.7   |       | V             |   |

| $t_{DSCH}$                                     | Discharge time<br>$C_{SS} = 220 \text{ pF}$                                                 | 1.6   | 2.2   | 2.8   | $\mu\text{s}$ |   |

| $t_{SS}$                                       | Soft-start time<br>$C_{SS} = 220 \text{ pF}$ , $0 \text{ V} \leq V_{SS} \leq 1.6 \text{ V}$ | 115   | 155   | 205   |               |   |

| <b>BP10</b>                                    |                                                                                             |       |       |       |               |   |

| $V_{BP10}$                                     | Input voltage                                                                               | 9.0   | 9.6   | 10.3  | V             |   |

| <b>ERROR AMPLIFIER</b>                         |                                                                                             |       |       |       |               |   |

| $V_{FB}$                                       | $T_A = 25^\circ\text{C}$                                                                    | 0.698 | 0.700 | 0.704 | V             |   |

|                                                | $0^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$                                            | 0.690 | 0.700 | 0.707 |               |   |

|                                                | $-40^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$                                          | 0.690 | 0.700 | 0.715 |               |   |

| $G_{BW}$                                       | Gain bandwidth                                                                              | 3.0   | 5.0   |       | MHz           |   |

| $A_{VOL}$                                      | Open loop gain                                                                              | 60    | 80    |       | dB            |   |

| $I_{OH}$                                       | High-level output source current                                                            | 2.0   | 4.0   |       | mA            |   |

| $I_{OL}$                                       | Low-level output sink current                                                               | 2.5   | 4.0   |       |               |   |

| $V_{OH}$                                       | High-level output voltage<br>$I_{SOURCE} = 500 \mu\text{A}$                                 | 3.2   | 3.5   |       | V             |   |

| $V_{OL}$                                       | Low-level output voltage<br>$I_{SINK} = 500 \mu\text{A}$                                    | 0.20  | 0.35  |       |               |   |

| $I_{BIAS}$                                     | Input bias current<br>$V_{FB} = 0.7 \text{ V}$                                              | 100   | 200   |       | nA            |   |

(1) 設計で保証されており、テストは行っていません。

(2) すべてのパラメータは消費電力ゼロで測定されています。

(3)  $I_{KFF}$ はSYNC周波数につれ上昇し、最大デューティ・サイクルで減少します。

# ELECTRICAL CHARACTERISTICS

$T_J = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{IN} = 24 \text{ V}_{dc}$ ,  $R_T = 90.9 \text{ k}\Omega$ ,  $I_{KFF} = 150 \mu\text{A}$ ,  $f_{SW} = 500 \text{ kHz}$  (unless otherwise noted)

| PARAMETER                                                            | TEST CONDITIONS                                                                  | MIN                                    | TYP            | MAX  | UNIT             |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|----------------|------|------------------|

| <b>CURRENT LIMIT</b>                                                 |                                                                                  |                                        |                |      |                  |

| $I_{SINK}$                                                           | Current limit sink current                                                       | 8.6                                    | 10.0           | 11.5 | $\mu\text{A}$    |

| Propagation delay to output                                          | $V_{ILIM} = 23.7 \text{ V}$ , $V_{SW} = (V_{ILIM} - 0.5 \text{ V})$              | 300                                    | ns             |      |                  |

|                                                                      | $V_{ILIM} = 23.7 \text{ V}$ , $V_{SW} = (V_{ILIM} - 2 \text{ V})$                | 200                                    |                |      |                  |

| $t_{ON}$                                                             | Switch leading-edge blanking pulse time <sup>(1)</sup>                           | 100                                    |                |      |                  |

| $t_{OFF}$                                                            | Off time during a fault                                                          |                                        | 7              |      | cycles           |

| $V_{OS}$                                                             | $T_A = 25^\circ\text{C}$                                                         | -125                                   | -30            |      | mV               |

|                                                                      | $V_{ILIM} = 23.6 \text{ V}$ , $0^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$   | -140                                   | -75            | -15  |                  |

|                                                                      | $V_{ILIM} = 23.6 \text{ V}$ , $-40^\circ\text{C} \leq T_A \leq 85^\circ\text{C}$ | -140                                   |                | 10   |                  |

| <b>OUTPUT DRIVER</b>                                                 |                                                                                  |                                        |                |      |                  |

| $t_{LRISE}$                                                          | Low-side driver rise time                                                        | 48                                     | 96             |      | ns               |

| $t_{LFALL}$                                                          | Low-side driver fall time                                                        | 24                                     | 48             |      |                  |

| $t_{HRISE}$                                                          | High-side driver rise time                                                       | 48                                     | 96             |      |                  |

| $t_{HFALL}$                                                          | High-side driver fall time                                                       | 36                                     | 72             |      |                  |

| $V_{OH}$                                                             | High-level output voltage, HDRV                                                  | BOOST<br>-1.5V                         | BOOST<br>-1.0V |      | V                |

| $V_{OL}$                                                             | Low-level output voltage, HDRV                                                   | $I_{HDRV} = 0.1 \text{ A}$ (HDRV - SW) |                | 0.75 |                  |

| $V_{OH}$                                                             | High-level output voltage, LDRV                                                  | BP10<br>-1.4 V                         | BP10<br>-1.0 V |      |                  |

| $V_{OL}$                                                             | Low-level output voltage, LDRV                                                   | $I_{LDRV} = 0.1 \text{ A}$             |                | 0.5  |                  |

| Minimum controllable pulse width                                     |                                                                                  |                                        | 100            | 150  | ns               |

| <b>SS/SD SHUTDOWN</b>                                                |                                                                                  |                                        |                |      |                  |

| $V_{SD}$                                                             | Shutdown threshold voltage                                                       | Outputs off                            | 90             | 125  | 150              |

| $V_{EN}$                                                             | Device active threshold voltage                                                  |                                        | 190            | 210  | 245              |

| <b>BOOST REGULATOR</b>                                               |                                                                                  |                                        |                |      |                  |

| $V_{BOOST}$                                                          | Output voltage                                                                   | $V_{IN} = 24.0 \text{ V}$              | 31.5           | 32.5 | 33.5             |

| <b>RECTIFIER ZERO CURRENT COMPARATOR (TPS40050/TPS40053 SS ONLY)</b> |                                                                                  |                                        |                |      |                  |

| $V_{SW}$                                                             | Switch voltage                                                                   | LDRV output OFF                        | -5.5           | -0.5 | 4.5              |

| <b>SW NODE</b>                                                       |                                                                                  |                                        |                |      |                  |

| $I_{LEAK}$                                                           | Leakage current <sup>(1)</sup>                                                   |                                        |                | 25   | $\mu\text{A}$    |

| <b>THERMAL SHUTDOWN</b>                                              |                                                                                  |                                        |                |      |                  |

| $T_{SD}$                                                             | Shutdown temperature <sup>(1)</sup>                                              |                                        | 165            |      | $^\circ\text{C}$ |

|                                                                      | Hysteresis <sup>(1)</sup>                                                        |                                        | 20             |      |                  |

| <b>UVLO</b>                                                          |                                                                                  |                                        |                |      |                  |

| $V_{UVLO}$                                                           | KFF programmable threshold voltage                                               | $R_{KFF} = 39.2 \text{ k}\Omega$       | 8.19           | 9.00 | 9.58             |

|                                                                      |                                                                                  |                                        |                |      | V                |

(1) 設計で保証されており、テストは行っていません。

(2) すべてのパラメータは消費電力ゼロで測定されています。

(3)  $I_{KFF}$ はSYNC周波数につれ上昇し、最大デューティ・サイクルで減少します。

## 端子機能

| TERMINAL NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                              |

|---------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOST         | 14  | O   | ハイサイドNチャネルMOSFET用ゲート駆動電圧。BOOST電圧は入力電圧よりも9V高くなります。このピンからSWピンに0.1μFのセラミック・キャパシタを接続してください。                                                                                                                                                  |

| BP5           | 3   | O   | 5V基準電圧。このピンは0.1μFのセラミック・キャパシタでグランドにバイパスしてください。このピンは外部使用のためのものではありません。                                                                                                                                                                    |

| BP10          | 11  | O   | Nチャネル同期整流器のゲート駆動に使用される10V基準電圧。このピンは1μFのセラミック・キャパシタでバイパスしてください。このピンは外部使用のためのものではありません。                                                                                                                                                    |

| COMP          | 8   | O   | 誤差増幅器の出力で、PWMコンパレータの入力。ループ全体を補償するためフィードバック回路をこのピンからVFBピンに接続します。COMPピンは大信号の過渡応答を改善するため内部でランプのピークより上でクランプされます。                                                                                                                             |

| HDRV          | 13  | O   | ハイサイドNチャネルMOSFET用のフローティングのゲート駆動ピン。このピンの電圧はBOOST(MOSFETオン)とSW(MOSFETオフ)間で切り換わります。                                                                                                                                                         |

| ILIM          | 16  | I   | 電流制限ピンで、過電流スレッショールドを設定するのに使用されます。このピンからグランドへシンクする内部電流により、このピンとVCC間の外付け抵抗端の電圧降下が定まります。このピンの電圧は導通時ハイサイドMOSFET端の電圧降下(VIN - SW)と比較されます。                                                                                                      |

| KFF           | 1   | I   | 電圧フィードフォワード量をプログラムするためこのピンとVIN間に抵抗を接続します。このピンに流れ込む電流は内部で分割されPWMランプの勾配をコントロールするのに使用されます。                                                                                                                                                  |

| LDRV          | 10  | O   | Nチャネル同期整流器用ゲート駆動ピン。このピンの電圧はBP10(MOSFETオン)とグランド(MOSFETオフ)間で切り換わります。                                                                                                                                                                       |

| PGND          | 9   | —   | デバイスの基準パワーグランド。このピンとパワーMOSFETのソースを低インピーダンスのラインで接続します。                                                                                                                                                                                    |

| RT            | 2   | I   | 内部発振器とスイッチング周波数を設定するため、このピンからグランドに抵抗を接続します。                                                                                                                                                                                              |

| SGND          | 5   | —   | デバイスの基準信号グランド                                                                                                                                                                                                                            |

| SS/SD         | 6   | I   | ソフトスタートのプログラミング・ピン。このピンからグランドに接続するキャパシタによりソフトスタート時間がプログラムされます。キャパシタは2.3μAの内部電流源により充電されます。その結果として生じるSSピンの電圧ランプは誤差増幅器への2番目の非反転入力として使用されます。出力電圧のレギュレーションはSSピンの電圧が0.7Vの内部基準電圧に達するまでSSの電圧ランプによりコントロールされます。このピンを“L”レベルにするとコントローラがディスエーブルになります。 |

| SW            | 12  | I   | このピンはコンバータのスイッチ・ノードに接続され、過電流の検出に使用されます。TPS40050とTPS40053はこのピンをゼロ電流検出としても使用します。                                                                                                                                                           |

| SYNC          | 4   | I   | デバイスの同期入力ピン。このピンは発振器を外部のマスター周波数に同期させるのに使用することができます。                                                                                                                                                                                      |

| VFB           | 7   | I   | 誤差増幅器の反転入力。通常動作ではこのピンの電圧は内部基準電圧0.7Vと同じです。                                                                                                                                                                                                |

| VIN           | 15  | I   | デバイスの電源電圧                                                                                                                                                                                                                                |

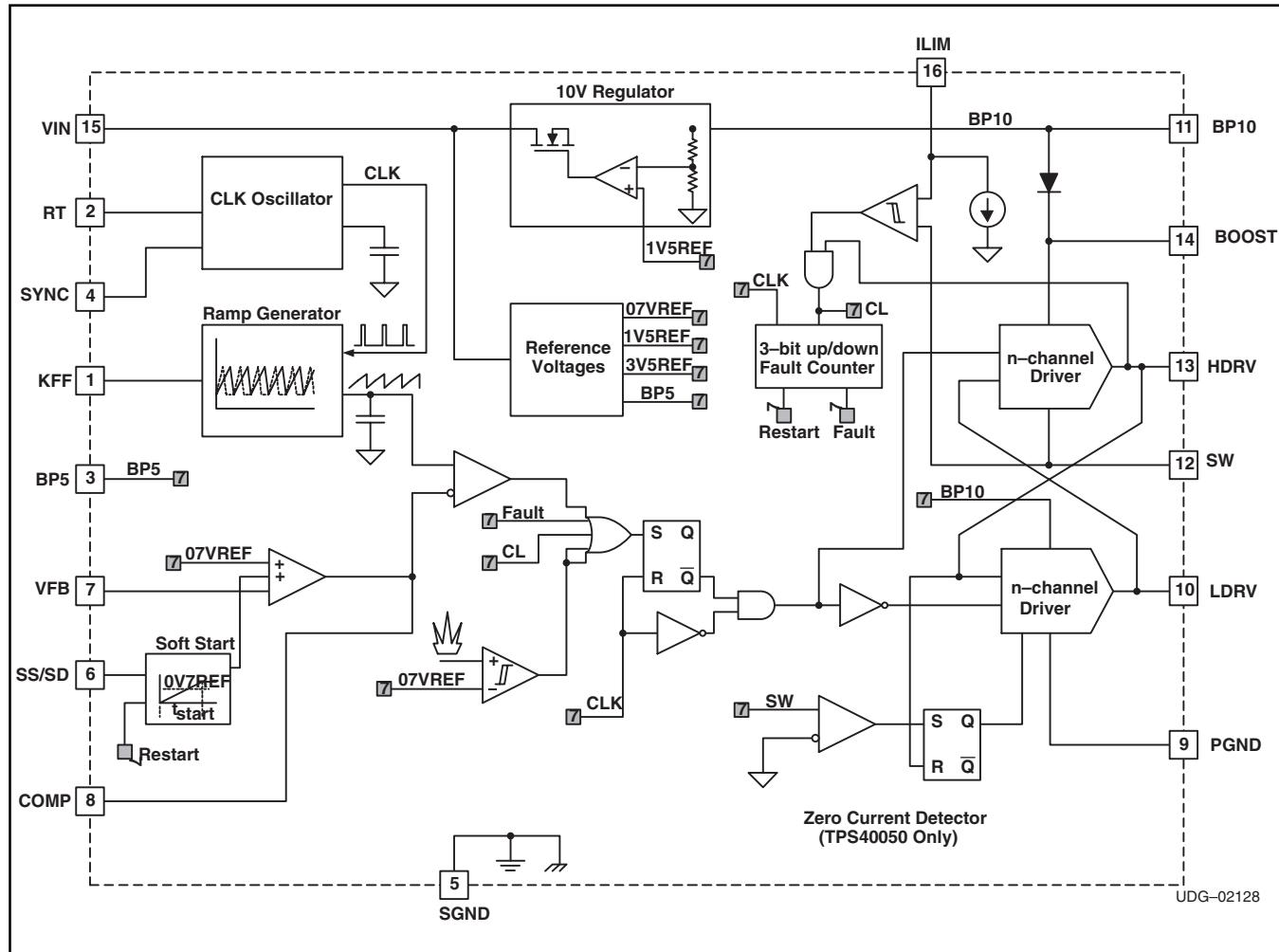

## SIMPLIFIED BLOCK DIAGRAM

## アプリケーション情報

### スイッチング周波数の設定 (クロック発振器のプログラミング)

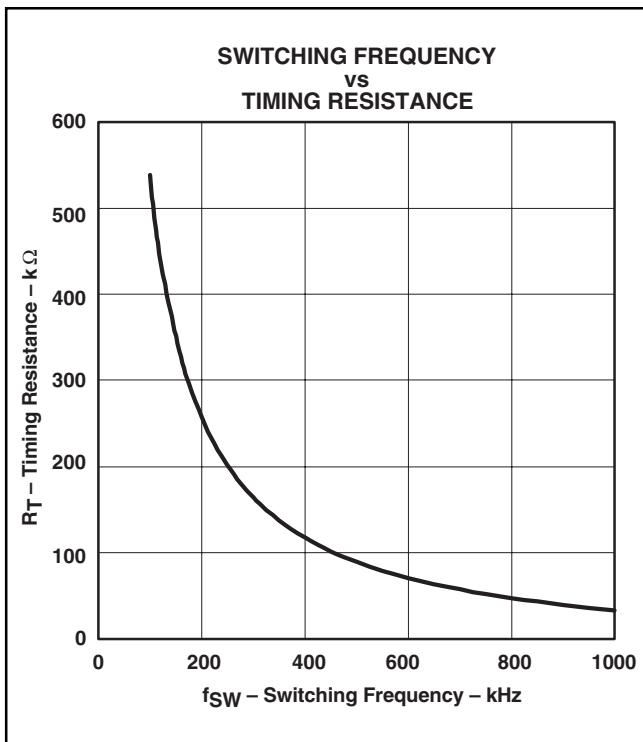

TPS4005xは独立したクロック発振器とランプ・ジェネレータ回路を内蔵しています。クロック発振器はランプ・ジェネレータ回路へのマスター・クロックとして働きます。クロック発振器のスイッチング周波数 $f_{SW}$ (単位はkHz)はグランドへの1つの抵抗( $R_T$ )で設定されます。クロック周波数は式(1)により $R_T$ (単位はkΩ)に関係しており、その相関関係を図2に示します。

$$R_T = \left( \frac{1}{f_{SW} \times 17.82 \times 10^{-6}} - 23 \right) \text{k}\Omega \quad (1)$$

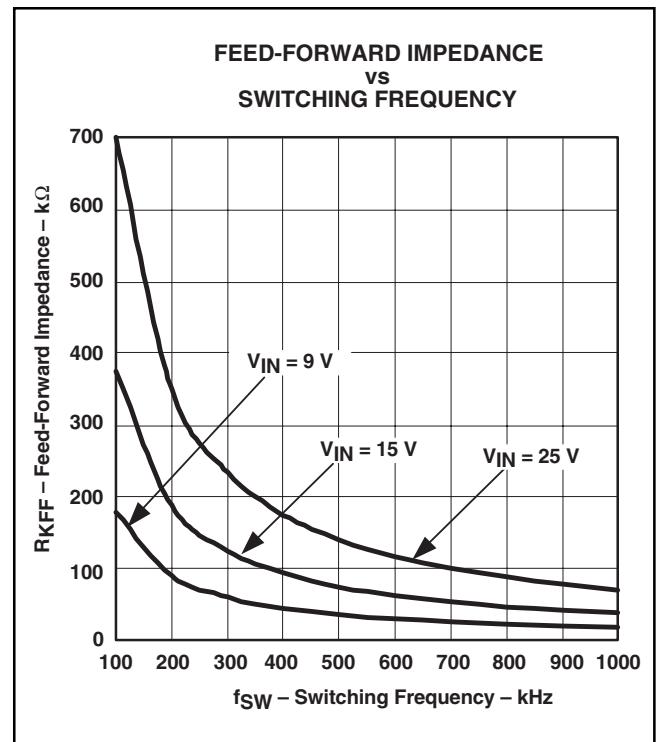

### ランプ・ジェネレータ回路のプログラミング

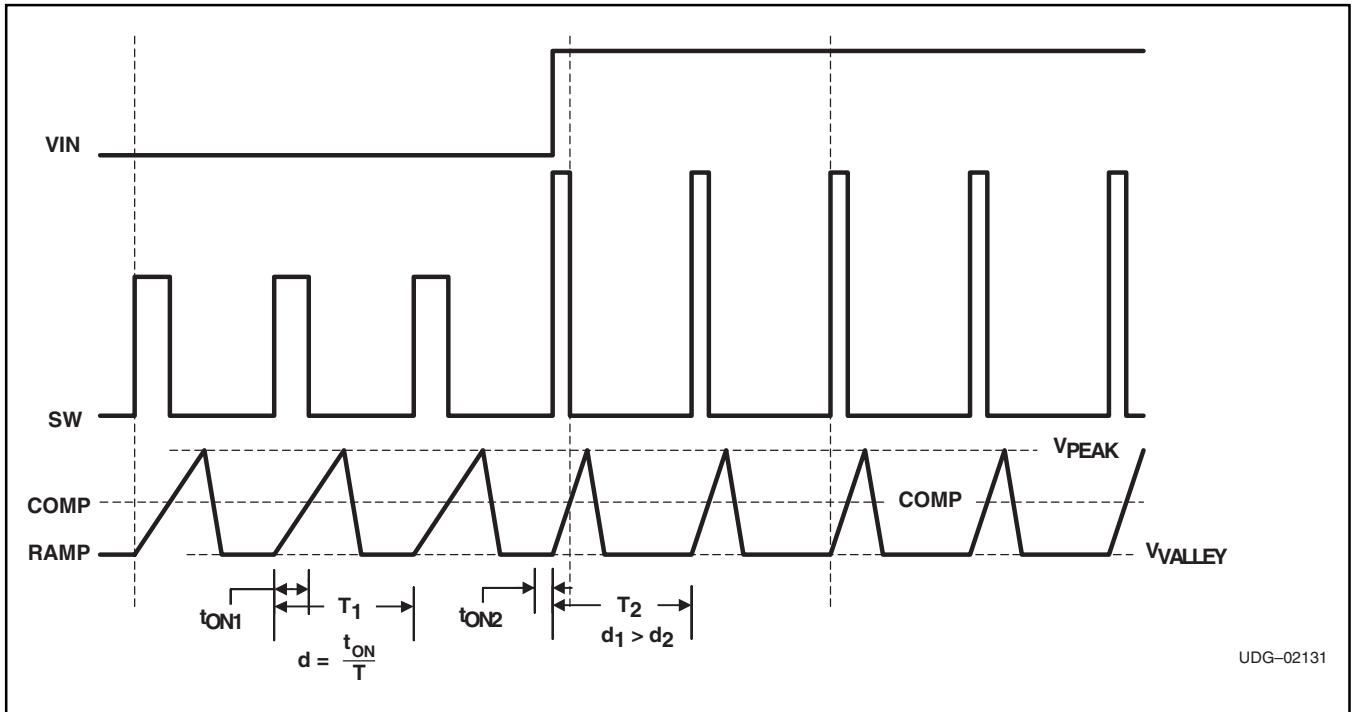

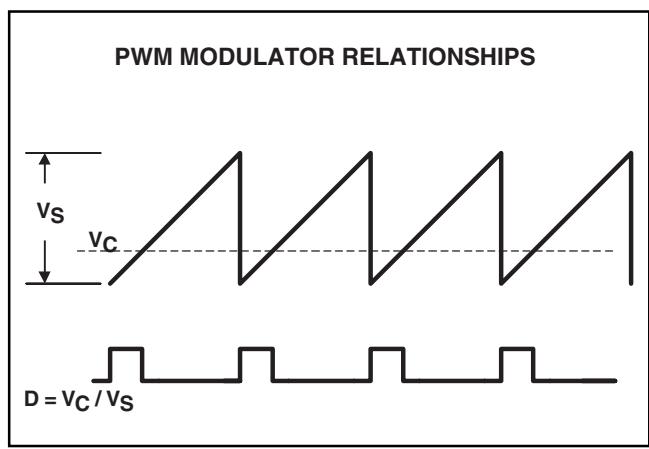

ランプ・ジェネレータ回路はPWMコンパレータにより使用される実際のランプを供給します。ランプ・ジェネレータは、ランプの振幅を一定に保ちながら、PWMランプの勾配をライン電圧により変えることで電圧フィードフォワード・コントロールを行な

います。PWMランプを直接ライン電圧により変えることで、PWMはループの遅れを待つことなしにデューティ・サイクルを変更することができるため、ラインの変動に対して優れた応答が実現します(図1参照)。

PWMランプの時間はマスター・クロック周波数の周期よりも短くなくてはならず、そうでなければPWMは起動が妨げられます。PWMランプの時間は $V_{IN}$ にプルアップされている1つの抵抗( $R_{KFF}$ )によってプログラムされます。 $R_{KFF}$ は以下のように $R_T$ と最小入力電圧 $V_{IN(min)}$ に関係しています。

$$R_{KFF} = (V_{IN(min)} - 3.5) \times (58.14 \times R_T + 1340) \Omega \quad (2)$$

但し、

- $V_{IN(min)}$ は保証された最小起動電圧です。実際の起動電圧は25°C時標準で約10%低くなります。

- $R_T$ はタイミング抵抗で単位はkΩです。

所定のスイッチング周波数 $f_{SW}$ に要する $R_{KFF}$ を示す曲線を図3に示します。

図1. Voltage Feed-Forward Effect on PWM Duty Cycle

図2.

図3.

## UVLO動作

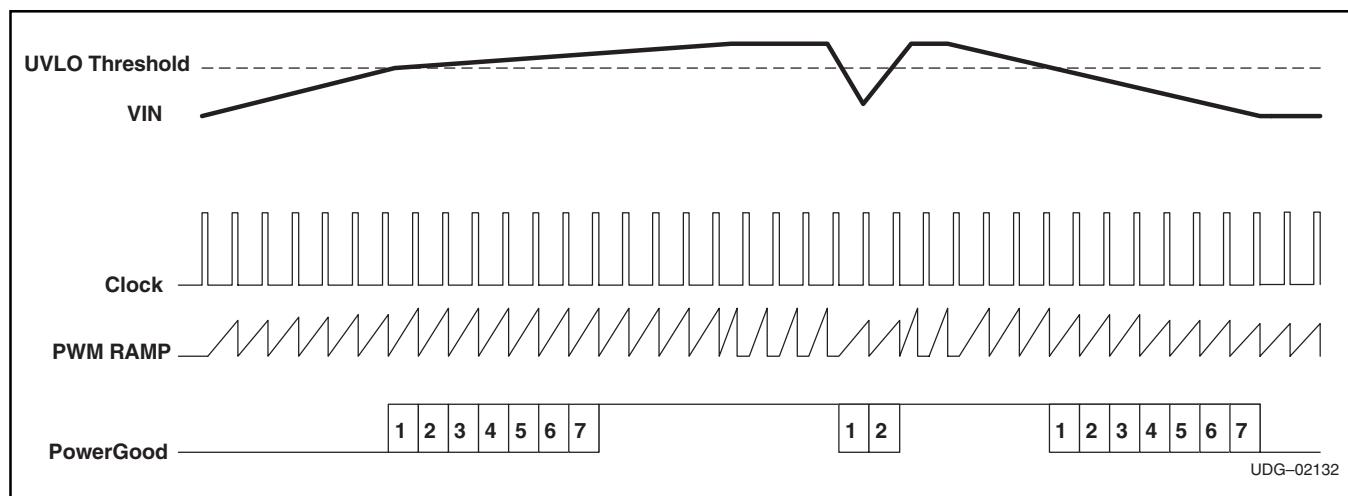

TPS4005xは調整可能な(ユーザーがプログラムできる)UVLO保護を使用しています。UVLO回路は、入力電圧がユーザーがプログラムした低電圧スレッショールドを越えるまでソフトスタートを“L”レベルに保持しています。

TPS4005xはユーザーがプログラムできる低ラインのUVLO保護としてフィードフォワード・ピンKFFを使用しています。この調整可能な低ラインのUVLOスレッショールドはPWMランプの幅を発振器のクロック周期と比較します。ランプがその全振幅の90%に達する前にTPS4005xがクロック・パルスを受け取った場合低電圧状態にあります。ランプ幅はランプの勾配の関数で、KFFピンに流れ込む電流に直接関係しています。KFFピンに流れる電流は入力電圧とKFFピンから入力電圧へ接続される抵抗の関数です。KFFピンの抵抗は式(3)で表されるように発振器の周波数を基準として求めることができます。

$$R_{KFF} = (V_{IN(min)} - 3.5) \times (58.14 \times R_T + 1340) \Omega \quad (3)$$

但し、

●  $V_{IN}$ は設定する起動(UVLO)入力電圧です。

調整可能なUVLO機能では、スパイクまたは高速のライン過渡により誤ってシャットダウンあるいはターンオンするのを防ぐため3ビットの全加算器が使用されています。加算器で、ランプ幅がクロック・サイクルよりも短いことが合計7カウントに達すると、パワーグッド信号がアクティブになります。ソフトスタートが開始し、上下のMOSFETはオフになります。

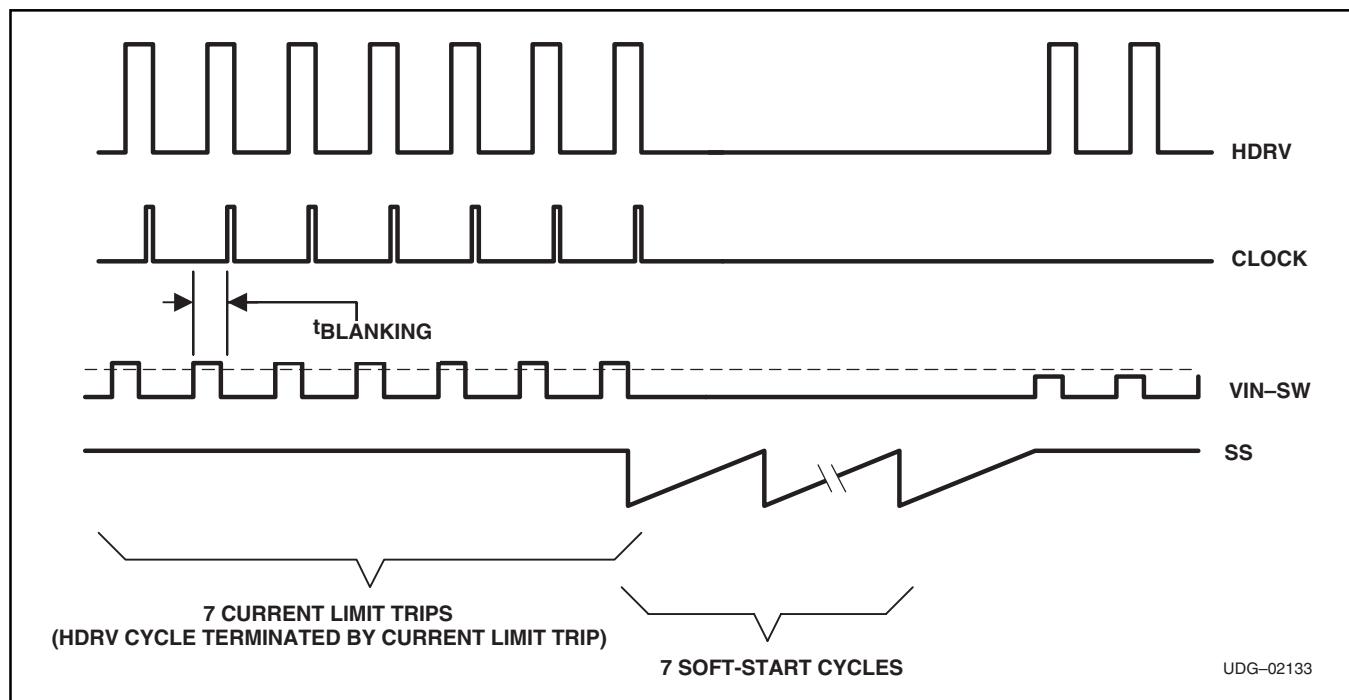

ソフトスタートが開始すると、UVLO回路は、低電圧状態を宣言する前に、ランプ幅がクロック・サイクルよりも長いことがサイクルで合計7カウント分あることを確かめなければなりません(図4参照)。

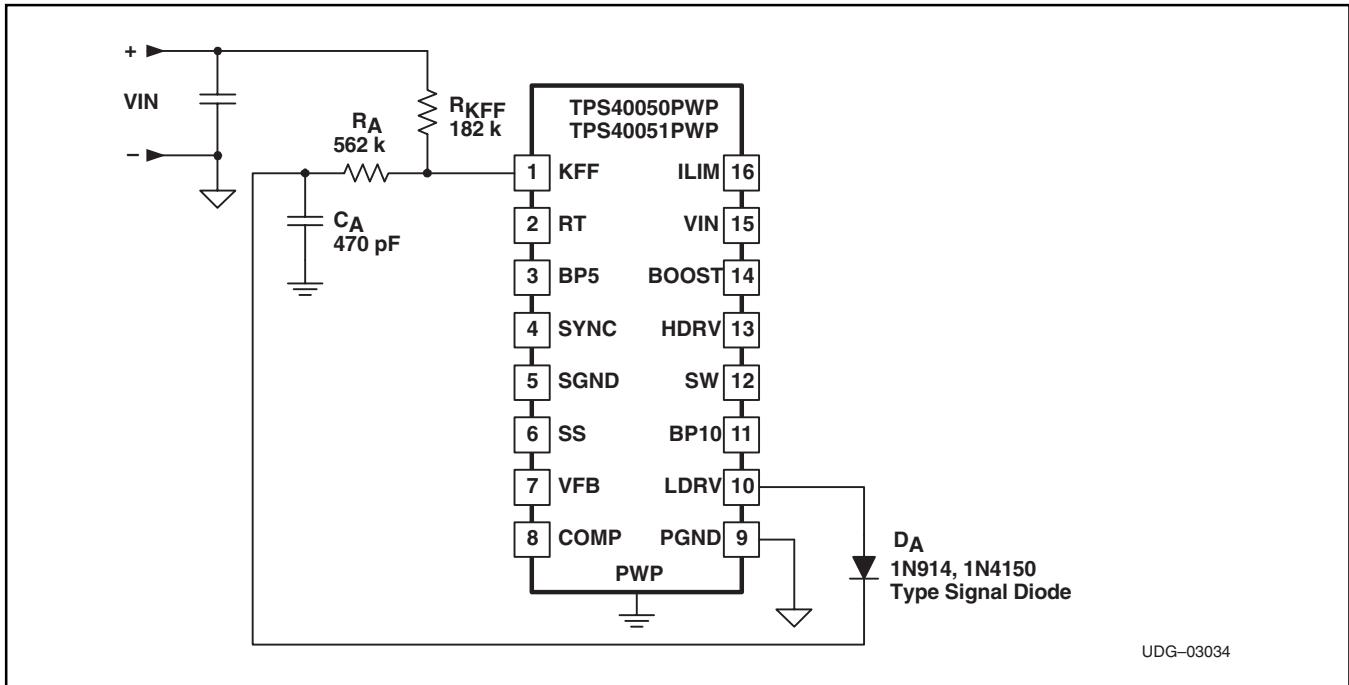

アプリケーションによってはUVLO電圧レベルで誤って再起動するのを防ぐために回路を追加することが必要とされることがあります。このことは、入力電圧ラインに高インピーダンスをもつか、あるいは $V_{IN}$ ラインに過大なリギングがあるアプリケー

ションに当てはまります。入力電圧のインピーダンスは起動時にUVLOシャットダウンやそれに続く再起動を起こすのに十分なほど入力電圧を下げる原因となります。また、過大なリギングもデバイスで検出される電圧に影響を及ぼし、UVLOシャットダウンや再起動の原因になります。簡素な回路を外付けすると迷惑なUVLOシャットダウンを防ぐためのヒステリシス量を選択することができます。

ヒステリシス電流が $I_{KFF}$ の10%、ピーク検出器が8Vにチャージされ、 $V_{IN(min)} = 18V$ とすると、 $R_A$ の値は以下の式で計算されます。

$$R_A = \frac{R_{KFF} \times (8 - 3.5)}{0.1 \times (V_{IN(min)} - 3.5)} = 565 \text{ k}\Omega \approx 562 \text{ k}\Omega \quad (4)$$

$C_A$ はスイッチング・サイクル間でピーク電圧を保持するよう選ばれます。キャパシタの電荷を0.1Vのループ、または8Vから7.9Vにならぬようには、以下の式で $C_A$ を計算します。

$$C_A = \frac{(8 - 3.5)}{(R_A \times 7.9 \times f_{SW})} \quad (5)$$

$C_A$ の値は10pF以下まで計算できますが、最大470pFまでの標準値でも十分に機能します。ダイオードは定格が20V以上の小信号のスイッチング・ダイオードまたはショットキーにすることができます。図5に小信号スイッチング・ダイオードを使用した場合の代表的例を示します。

## インダクタ値の選択

インダクタ値により、コンバータが不連続モードになる時の負荷電流だけでなく、出力キャパシタのリップル電流の大きさも決まります。インダクタンスが過度に大きいと、リップル電流は小さくなりますが、同一負荷電流では物理的寸法は大きくなります。一方、インダクタンスが過度に小さいと、リップル電流は大きくなり、同じ出力リップル電圧を満たすための要件が多くなります(または出力キャパシタが高価になります)。妥協案として望ましいのは、負荷が定格出力の10%と30%の間の値に近づくまで

図4. Undervoltage Lockout Operation

図5. Hysteresis for Programmable UVLO

コンバータが不連続モードにならない程度のインダクタンス値を選択することです。インダクタンス値の計算は以下の式(6)で表されます。

$$L = \frac{(V_{IN} - V_O) \times V_O}{V_{IN} \times \Delta I \times f_{SW}} \text{ (Henries)} \quad (6)$$

但し、

- $V_O$ は出力電圧です

- $\Delta I$ はピーク間インダクタ電流です

### 出力容量の計算

出力容量は、負荷過渡時の出力電圧偏位の要件に加え、出力リップル電圧と出力リップル電流の要件で決まります。

出力リップル電圧は出力容量とキャパシタのESRの両方の関数です。ワースト・ケース時の出力リップル電圧は式(7)で表されます。

$$\Delta V = \Delta I \left[ ESR + \left( \frac{1}{8 \times C_O \times f_{SW}} \right) \right] V_{P-P} \quad (7)$$

出力リップル電圧はESR成分により一般的に90%から95%の間です。

出力容量の要件は一般的に負荷過渡の要件に伴い増加します。ステップ負荷時、出力容量は、出力電圧を許容範囲内に保持しながら、エネルギーを負荷に供給(軽負荷から重負荷へのステップ)するか、あるいは過度のインダクタ・エネルギーを吸収(重負荷から軽負荷へのステップ)しなければなりません。容量は、負荷ステップの大きさ、ループの速度、インダクタの大きさに依存します。

重負荷から軽負荷への負荷ステップでは出力がオーバーシュートします。インダクタに蓄えられた過度のエネルギーは出力容量で吸収されなければなりません。インダクタに蓄えられたエネルギーは以下の式(8)で表されます。

$$E_L = \frac{1}{2} \times L \times I^2 \text{ (Joules)} \quad (8)$$

ここで、

$$I^2 = [(I_{OH})^2 - (I_{OL})^2] \text{ ((Amperes)}^2 \text{)} \quad (9)$$

但し、

- $I_{OH}$ は重負荷条件での出力電流です

- $I_{OL}$ は軽負荷条件での出力電流です

キャパシタのエネルギーは以下の式(10)で表されます。

$$E_C = \frac{1}{2} \times C \times V^2 \text{ (Joules)} \quad (10)$$

ここで、

$$V^2 = [(V_f)^2 - (V_i)^2] \text{ (Volts}^2\text{)} \quad (11)$$

但し、

- $V_f$ はキャパシタの最終ピーク電圧です

- $V_i$ はキャパシタの初期電圧です

式(9)を式(8)に代入し、次に式(11)を式(10)に代入し、さらにその次に式(8)が式(10)に等しいとして、 $C_O$ について解くと式(12)で表される容量が求められます。

$$C_O = \frac{L \times [(I_{OH})^2 - (I_{OL})^2]}{[(V_f)^2 - (V_i)^2]} \text{ (Farads)} \quad (12)$$

## ソフトスタートのプログラミング

TPS4005xでは起動時確実に出力上にランプがコントロールされるように閉ループの手法を使用します。ソフトスタートは内部で生成される電流源により外付けのキャパシタ( $C_{SS}$ )を充電することでプログラムされます。 $C_{SS}$ の電圧は誤差増幅器の非反転入力の1つに入ります(誤差増幅器のその他の入力はFBと0.7VのVREF)。ループは $C_{SS}$ 電圧の下端または内部基準電圧(0.7V VREF)で閉じます。 $C_{SS}$ 電圧が内部基準電圧以上に上昇すると、レギュレーションは内部基準電圧を基準として行なわれます。確実に出力電圧のランプアップをコントロールするには、ソフトスタート時間は式(13)で表されるように $L-C_0$ の時定数よりも大きくします。

$$t_{\text{START}} \geq 2\pi \times \sqrt{L \times C_0} \quad (\text{seconds}) \quad (13)$$

$t_{\text{START}}$ と起動時に必要とされる入力電流には直接的な相関関係があります。 $t_{\text{START}}$ が速くなるにつれ、起動時に大きな入力電流が必要とされます。この相関関係については次節の表題“電流制限のプログラミング”で詳細に記述されています。ソフトスタート容量 $C_{SS}$ は式(14)で表されます。

$V_{\text{IN}}$ 電源がゆっくりとランプアップする(一般的には50msから100ms)アプリケーションでは、誤ってUVLOが作動するのを防ぐためソフトスタート時間を約2ms～5msまで増加させることができます。ソフトスタート時間は、 $V_{\text{IN}}$ 電源が6Vと7Vの間を遷移する時間よりも長くしてください。

$$C_{SS} = \frac{2.3 \mu\text{A}}{0.7 \text{ V}} \times t_{\text{START}} \quad (\text{Farads}) \quad (14)$$

## 電流制限のプログラミング

TPS4005xでは過電流保護に2段の手法を使用しています。1段目はパルス毎の保護という仕組みです。電流制限はハイサイドMOSFETで実行され、ゲートが“H”レベルに駆動されている時にMOSFET端の電圧降下を検出します。MOSFETの電圧は一定の電流シンクで駆動されている時 $V_{\text{IN}}$ ピンから $ILIM$ ピンに接続されている抵抗端での降下電圧と比較されます。MOSFET端の電圧降下が $ILIM$ 抵抗端の電圧降下より大きい場合、スイッチング・パルスは即座に終了します。MOSFETは次のスイッチング・サイクルが開始するまでオフのままでです。

第2段目はフォルト・カウンタで構成されています。フォルト・カウンタは過電流パルスによって増加し、過電流パルスのないクロック・サイクルにより減少します。カウンタが7に達した時、再起動が出され7サイクルのソフトスタートが開始します。上下両方のMOSFETともこの期間オフになります。カウンタはソフトスタートのサイクルごとに減少してゆきます。カウンタがゼロに減少した時、PWMは再びイネーブルになります。障害条件が取り除かれたら、出力は正常に作動し始めます。出力に依然として障害が存在している場合、カウンタは7個の過電流パルスをカウントし、再び第2段目のフォルト・モードに入ります。代表的な過電流保護の波形については図6を参照してください。

電流制限の最小設定点( $I_{\text{LIM}}$ )は $t_{\text{START}}$ 、 $C_0$ 、 $V_0$ 、ターンオン時の負荷電流( $I_L$ )により決まります。

$$I_{\text{LIM}} = \left[ \frac{(C_0 \times V_0)}{t_{\text{START}}} \right] + I_L \quad (\text{Amperes}) \quad (15)$$

図6. Typical Current Limit Protection Waveforms

電流制限をプログラムする抵抗( $R_{ILIM}$ )は以下の式(16)を使って計算されます。

$$R_{ILIM} = \frac{I_{OC} \times R_{DS(on)}[\max]}{1.12 \times I_{SINK}} + \frac{V_{OS}}{I_{SINK}} \quad (\Omega) \quad (16)$$

但し、

- $I_{SINK}$ はILIMピンに流れ込む電流で標準値は10μAです。

- $I_{OC}$ は過電流の設定点で、DC出力電流にピーク・インダクタ電流の1/2を加えたものです。

- $V_{OS}$ は過電流コンパレータのオフセットで標準値は-48mVです。

## 外部電源への同期

TPS4005xはSYNCピンにより外部のクロックに同期することができます。TPS4005xはそのプログラムされたフリーラン周波数よりも20%高い周波数で同期させなければなりません。SYNCピンのクロック周波数は発振器回路で生成されるマスター・クロックに取って代わります。SYNCピンを“L”レベルにするとTPS4005xは $R_T$ でプログラムされる周波数でフリーランするようプログラムされます。

PWMランプのジェネレータ回路をプログラムする時は高い周波数で同期させることを考慮に入れなければなりません。PWMランプがSYNCパルスで妨げられると、UVLO状態が宣言されPWMはディスエーブルになります。一般的にはこのことは低ライン条件下のみで懸念されます。いかなる場合でも、スイッチング周波数が高い場合には $R_{KFF}$ を調整することが必要です。

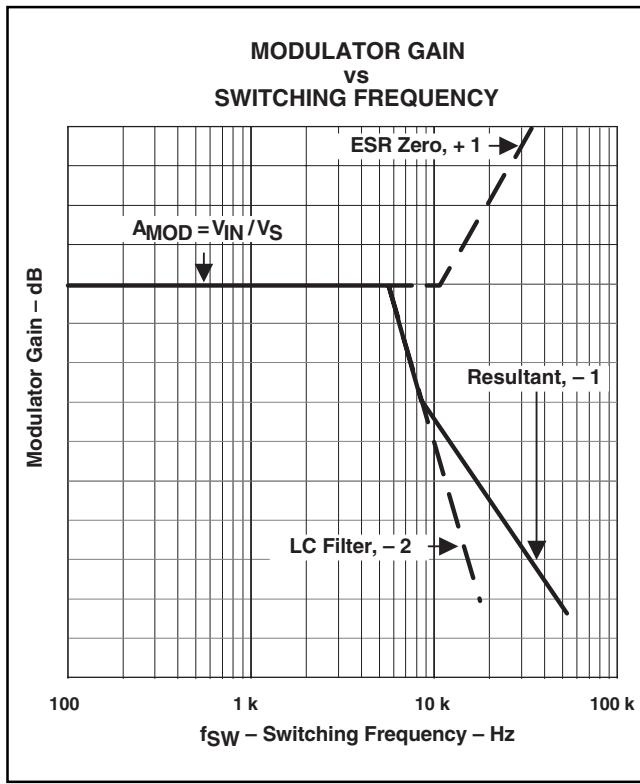

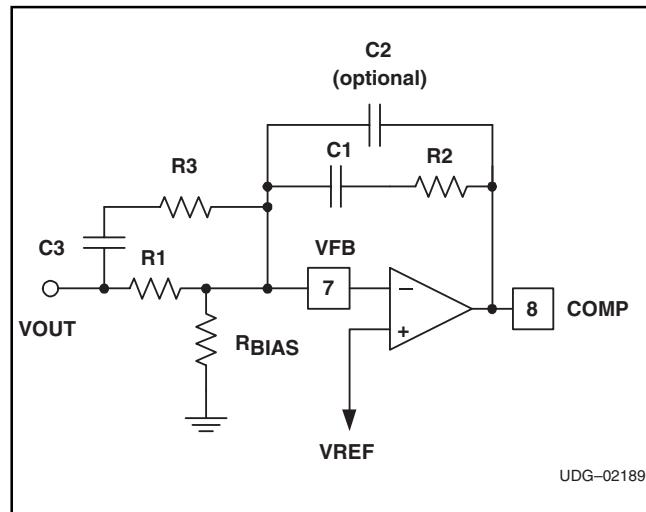

## ループ補償

電圧モードの降圧型コントローラは一般的にはタイプIIIの回路を使用して補償されます。TPS4005xは電圧フィードフォワード・コントロールを使用しているため、電圧フィードフォワード回路を含んだPWM変調器の利得が含まれなければなりません。変調器の利得を、ランプ動作を全スイッチング周期の範囲にわたせるのに必要な最小入力電圧 $V_{IN}$ とともに図7に示します。

$$A_{MOD} = \frac{V_{IN}}{V_S} \quad \text{or} \quad A_{MOD(\text{dB})} = 20 \times \log \left( \frac{V_{IN}}{V_S} \right) \quad (17)$$

図7.

デューティ・サイクルDはコントロール電圧 $V_C$ が最小ランプ電圧から最大ランプ電圧 $V_S$ に変化するにつれ0から1に変わります。また、同期式バック・コンバータの場合は、 $D = V_O/V_{IN}$ です。出力電圧に対するコントロール電圧を得るのに、変調器の利得の入力電圧とランプ電圧に置き換えると、

$$D = \frac{V_O}{V_{IN}} = \frac{V_C}{V_S} \quad \text{or} \quad \frac{V_O}{V_C} = \frac{V_{IN}}{V_S}$$

## 極とゼロの計算

電圧モード・コントロールを使用したバック・コンバータでは、出力の $L-C_O$ により二重極があります。二重極は式(18)で計算される周波数の位置にあります。

$$f_{LC} = \frac{1}{2\pi \times \sqrt{L \times C_O}} \quad (\text{Hertz}) \quad (18)$$

また、出力容量 $C_O$ とそのESRにより生成されるゼロもあります。ESRのゼロは式(19)で計算される周波数の位置にあります。

$$f_Z = \frac{1}{2\pi \times \text{ESR} \times C_O} \quad (\text{Hertz}) \quad (19)$$

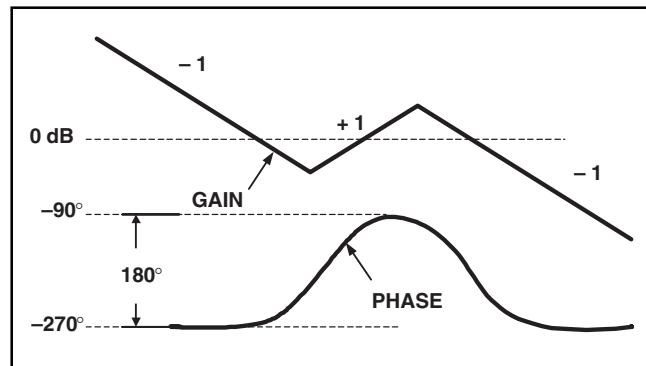

連続モードで動作する電圧フィードフォワード・コントロールをもつバック・コンバータの出力電圧対開ループ・コントロール電圧の利得 $V_O$ 対 $V_C$ のボーデ線図を図8に示します。

最大クロスオーバー周波数(0dBのループ利得)は式(20)で計算されます。

$$f_C = \frac{f_{SW}}{4} \quad (\text{Hertz}) \quad (20)$$

一般的には、 $f_C$ は $L-C_O$ の二重極とESRゼロの中間点の近くに選択されます。タイプIIIのトポロジでは+1の勾配(20dB/ディケード)であるのに対し、この周波数では、出力対コントロールの利得は-2の勾配(-40dB/ディケード)であるため、閉ループ全体では-1の勾配(-20dB/ディケード)になります。

図8に変調器の利得、L-Cフィルタ、出力キャパシタのESRゼロ、及びその結果として補償すべき応答を示します。

図9に示されるタイプIIIのトポロジには原点の極に加え2組のゼロ/極があります。タイプIIIのトポロジの利得と位相のブーストを図10に示します。2つのゼロは $L-C_O$ の二重極を補償するに使われ、位相のブーストを行ないます。二重極はESRゼロを補償するのに使われ、利得のロールオフをコントロールします。ほとんどの場合、2番目の極は取り除くことができ、増幅器の利得のロールオフは高周波で総利得をロールオフするのに使用されます。

タイプIIIの回路の極とゼロは式(21)で表されます。

$$f_{Z1} = \frac{1}{2\pi \times R2 \times C1} \quad (\text{Hertz}) \quad f_{Z2} = \frac{1}{2\pi \times R1 \times C3} \quad (\text{Hertz}) \quad (21)$$

$$f_{P1} = \frac{1}{2\pi \times R2 \times C2} \quad (\text{Hertz}) \quad f_{P2} = \frac{1}{2\pi \times R3 \times C3} \quad (\text{Hertz})$$

单一利得周波数は式(22)で表されます。

$$f_C = \frac{1}{2\pi \times R1 \times C2} \quad (\text{Hertz}) \quad (22)$$

図8.

二重ゼロ  $f_{Z1}, f_{Z2}$  と二重極  $f_{P1}, f_{P2}$  は Venable の K Factor<sup>[1]</sup> により選択され、それは以下のようになっています。

$$f_{Z1} = f_{Z2} = \frac{f_C}{\sqrt{K}} \quad \text{and} \quad f_{P1} = f_{P2} = f_C \times \sqrt{K} \quad (23)$$

ファクタ K を決めるには、単一利得周波数  $f_C$  における目標の位相余裕 M と変調器の位相シフト P が分かった後位相のブーストを計算しなければなりません。その上で、Boost = M - P - 90° で計算します。P は測定することが最善ですが、一般的な値は -140° ~ -170° の範囲です。よって、K の値は以下の式で求められます。

$$K = \left( \tan \left[ \frac{\text{Boost}}{4} + 45^\circ \right] \right)^2 \quad (24)$$

出力電圧  $V_{OUT}$  を設定するため  $R_{BIAS}$  の値を計算します。

$$R_{BIAS} = \frac{0.7 \times R_1}{V_{OUT} - 0.7} \quad (25)$$

#### 最小負荷抵抗

極端に小さいフィードバック抵抗  $R_2$  により誤差増幅器の出力の負荷をダウンさせないよう注意が必要です。誤差増幅器には  $R_2$  の大きさを決める場合に考慮しなければならないある有限の出力ソース/シンク電流があります。過度に小さな値では出力はそのフル・レンジ全体に振れることはできません。

$$R_2(\text{MIN}) = \frac{V_C(\text{max})}{I_{\text{SOURCE}}(\text{min})} = \frac{3.45 \text{ V}}{2 \text{ mA}} = 1725 \Omega \quad (26)$$

図9. Type III Compensation Configuration

図10. Type III Compensation Gain and Phase

#### BOOST及びBP10バイパス・キャパシタの計算

BOOST容量はハイサイド・ドライバに部分的な低インピーダンス電源を供給します。BOOSTキャパシタは品質が優れた高周波のキャパシタにしてください。バイパス・キャパシタの大きさは MOSFET の総ゲート電荷とバイパス・キャパシタに許容されるドリーブ量に依存します。BOOST容量は以下の式(27)で表されます。

$$C_{\text{BOOST}} = \frac{Q_g}{\Delta V} \quad (\text{Farads}) \quad (27)$$

10V基準電圧ピン BP10V は BOOST キャパシタを介して同期 MOSFET とハイサイド MOSFET の両方にエネルギーを供給する必要があります。効率上で不利な条件をすべて無視すると、BP10V の容量は以下の式(28)で表されます。

$$C_{\text{BP10}} = \frac{(Q_{gHS} + Q_{gSR})}{\Delta V} \quad (\text{Farads}) \quad (28)$$

## dv/dtにより誘発されるターンオン

MOSFETは特に高電圧( $V_{DS}$ )のアプリケーションでdv/dtによるターンオンに影響を受けやすくなっています。ターンオンは $C_{GD}$ と $C_{GS}$ で形成されるキャパシタ・デバイダにより引き起こされます。高いdv/dtとMOSFETのドレン/ソース間電圧により $C_{GD}$ に電流が流れ、ゲート/ソース間電圧を上昇させます。ゲート/ソース間電圧がMOSFETのスレッショールド電圧以上に上昇すると、MOSFETはオンになります。従って、同期整流MOSFETは $C_{GD}$ 容量が $C_{GS}$ 容量よりも小さくなるよう選んでください。上側MOSFETのゲートの帰還リードに $2\Omega$ ~ $5\Omega$ の値の抵抗を入れるとターンオンとSWノードのdv/dtを適合させ、ターンオンが誘発されることを少なくするのに役立ちます。

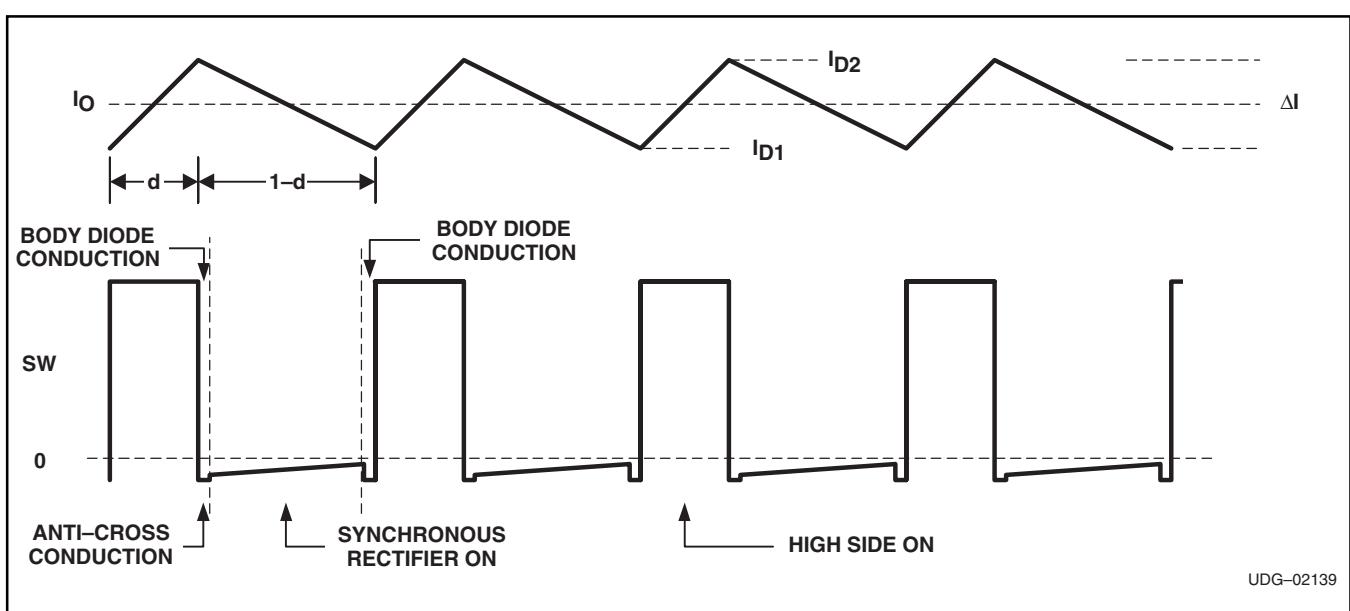

## ハイサイドMOSFETの消費電力

外付けハイサイドMOSFETで消費される電力は導通損失とスイッチング損失より構成されます。導通損失はMOSFETを流れる $I_{RMS}$ 電流とMOSFETの $R_{DS(on)}$ の関数です。ハイサイドMOSFETの導通損失は式(29)で定義されます。

$$P_{COND} = (I_{RMS})^2 \times R_{DS(on)} \times (1 + TCR \times [T_J - 25]) \text{ (Watts)} \quad (29)$$

但し、

●  $TC_R$ はMOSFET  $R_{DS(on)}$ の温度係数です

$TC_R$ はMOSFET技術と製造メーカーにより変動しますが、一般的には $0.0035\text{ppm}/\text{°C}$ ~ $0.010\text{ppm}/\text{°C}$ の範囲にあります。

ハイサイドMOSFETの $I_{RMS}$ 電流は以下の式(30)で表されます。

$$I_{RMS} = I_0 \times \sqrt{d} \text{ (Amperes RMS)} \quad (30)$$

ハイサイドMOSFETのスイッチング損失は以下の式(31)で表されます。

$$P_{SW(fsw)} = V_{IN} \times \left( \frac{I_{D1} \times ts1}{6} + \frac{I_{D2} \times ts2}{2} \right) \times f_{SW} \quad (31)$$

但し、

●  $I_{D1}$ と $I_{D2}$ はMOSFETのスイッチング時の電流の大きさです(図11参照)。

$I_{D1}$ と $I_{D2}$ はインダクタ値と負荷電流の関数です。インダクタ値は通常、標準負荷の約10%から30%が達成されるまでコンバータが連続動作モードにとどまるよう選択されます。インダクタ電流の変化は式(32)で表されます。

$$\Delta I = 2 \times I_{O(dis)} \quad (32)$$

但し、

●  $I_{O(dis)}$ はコンバータが不連続動作モードになった時の負荷電流です。

$I_{D1}$ と $I_{D2}$ は以下の式(33)で計算できます。

$$I_{D1} = I_0 - \left( \frac{\Delta I}{2} \right) \text{ and } I_{D2} = I_0 + \left( \frac{\Delta I}{2} \right) \text{ (Amperes)} \quad (33)$$

但し、

●  $\Delta I$ はインダクタのリップル電流です(図11参照)

コンバータは $I_0 = \Delta I / 2$ の時不連続モードになります。詳細についてはインダクタ値の選択の節、及び式(6)を参照してください。

過渡時間 $ts1$ と $ts2$ は選択した外付けMOSFETの関数です。 $ts1$ と $ts2$ の計算については設計例を参照してください。

MOSFETの許容最大消費電力は式(34)で決まります。

$$P_T = \frac{(T_J - T_A)}{\theta_{JA}} \text{ (Watts)} \quad (34)$$

ここで、

$$P_T = P_{COND} + P_{SW(fsw)} \text{ (Watts)} \quad (35)$$

また、 $\theta_{JA}$ はパッケージの熱抵抗です。

図11. Inductor Current and SW Node Waveforms

## 同期整流MOSFETの消費電力

同期整流MOSFETで消費される電力は、 $R_{DS(on)}$ の導通損失、ボディ・ダイオードの導通損失、逆回復損失の3つの要素より構成されています。 $R_{DS(on)}$ の導通損失は式(29)を使って求めることができます、同期整流MOSFETを流れるRMS電流は以下の式(36)で表されます。

$$I_{RMS} = I_0 \times \sqrt{1-d} \quad (\text{Amperes}_{RMS}) \quad (36)$$

ボディ・ダイオードの導通損失はアンチ・クロス導通の遅延時間にボディ・ダイオードが順方向に導通することが原因です。ボディ・ダイオードの導通損失は以下の式(37)で表されます。

$$P_{DC} = I_0 \times V_F \times t_{DELAY} \times f_{SW} \quad (\text{Watts}) \quad (37)$$

但し、

●  $V_F$ はボディ・ダイオードの順方向電圧です

●  $t_{DELAY}$ はスイッチング周期ごとの総遅延時間です

逆回復損失はボディ・ダイオードが順方向のバイアスから逆遮断状態への回復に要する時間が原因で生じます。逆回復損失は以下の式(38)で表されます。

$$P_{RR} = 0.5 \times Q_{RR} \times V_{IN} \times f_{SW} \quad (\text{Watts}) \quad (38)$$

但し、

●  $Q_{RR}$ はボディ・ダイオードの逆回復電荷です

同期整流MOSFETの総消費電力は以下の式(39)で表されます。

$$P_{SR} = P_{DC} + P_{RR} + P_{COND} \quad (\text{Watts}) \quad (39)$$

## TPS4005xの消費電力

TPS4005xの消費電力はMOSFETドライバ電流と入力電圧に大きく依存します。ドライバ電流は外付けMOSFETの総ゲート電荷 $Q_g$ に比例します。外付けのゲート抵抗を無視すると(参考資料[2]参照)ドライバの電力は式(40)で計算できます。

$$P_D = Q_g \times V_{DR} \times f_{SW} \quad (\text{Watts}) \quad (40)$$

そして、TPS40050の総消費電力は、ハイサイドと同期整流器の両方に同一のMOSFETを選択したとすると、以下の式(41)で表されます。

$$P_T = \left( \frac{2 \times P_D}{V_{DR}} + I_Q \right) \times V_{IN} \quad (\text{Watts}) \quad (41)$$

または、

$$P_T = (2 \times Q_g \times f_{SW} + I_Q) \times V_{IN} \quad (\text{Watts}) \quad (42)$$

但し、

●  $I_Q$ は静止時の動作電流です(ドライバは無視)

PowerPAD™パッケージデバイスがもつ最大の電力能力はエア・フローと同様にレイアウトにも依存します。接合部から外気への熱抵抗は、2オンスの銅配線、サーマル・パッドがはんだ付け、エア・フローなしとすると以下の値になります。

$$\theta_{JA} = 36.51^\circ\text{C}/\text{W}$$

パッケージの許容最大消費電力は式(34)により周囲温度に関係します。式(34)を式(42)に代入して、 $f_{SW}$ について解くとTPS4005xの最大動作周波数が求められます。その結果は以下の式(43)で表されます。

$$f_{SW} = \frac{\left( \left[ \frac{(T_J - T_A)}{(\theta_{JA} \times V_{DD})} \right] - I_Q \right)}{(2 \times Q_g)} \quad (\text{Hz}) \quad (43)$$

## レイアウトについての考察

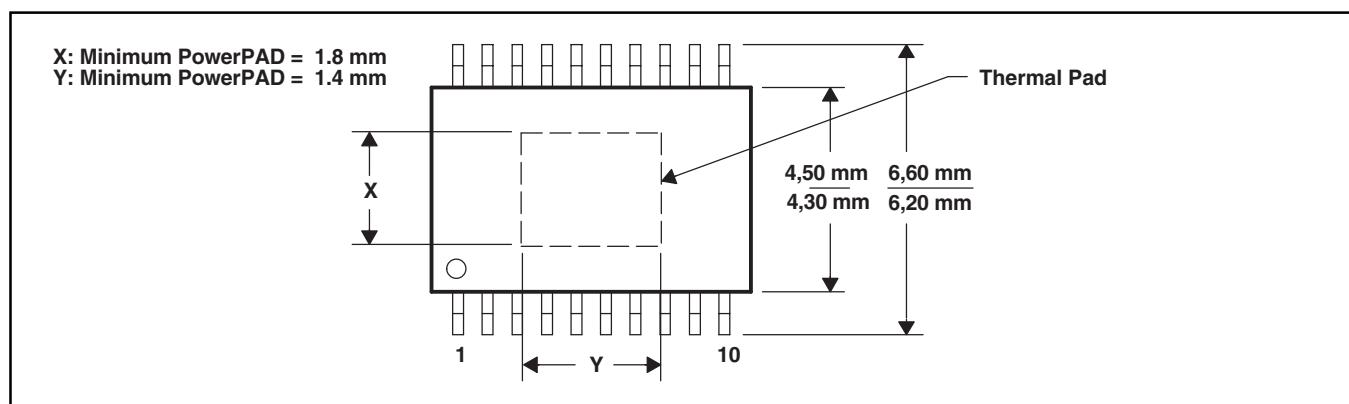

### POWERPAD™パッケージ

PowerPAD™パッケージはデバイスから熱を取り除くため低い熱抵抗を提供します。PowerPAD™はその名前の由来のとおりデバイスの底面の大きな接合用パッドにより熱抵抗が低くなります。最良の熱特性を得るには、回路ボードにはパッケージの真下にはんだ/スズめっき/銅の領域があることが必要です。この領域の大きさはPowerPAD™パッケージの寸法により決まります。16ピンのTSSOP(PWP)パッケージではこの領域は5mm × 3.4mm<sup>[3]</sup>です。

放熱用ビアは、この領域を内部または外部の銅のプレーンに接続し、また、そのビア穴はビア・バレルが銅めっきされる場合効率よく埋まるよう十分に小さな直径にしておきます。この埋め栓は、はんだリフロー時パッケージ本体とデバイスの下のはんだ/スズめっき領域との接触面からはんだが逃げるの防ぐために必要です。1オンスの銅がボード表面にめっきされ、同時にビア・バレルをめっきした場合、ビアの直径は0.33mm(13ミル)が適切です。銅めっきされる場合に放熱用ビアを埋めなければ、最小が

図12. PowerPAD Dimensions

0.1mmであるビア直径に等しい直径のはんだマスク材を使ってビアに蓋をしてください。この蓋により、はんだが放熱用ビアの中を通って逃げ、可能性として起こりうるパッケージの下にはんだのボイドができることが防止されます。PowerPAD™パッケージの詳細な情報についてはPowerPAD™ Thermally Enhanced Package<sup>[3]</sup>及びこのデータシートの最後のパッケージ寸法図面を参照してください。

## MOSFETのパッケージ

MOSFETのパッケージの選択はMOSFETの消費電力と予測される動作条件によります。一般的に、表面実装のアプリケーションでは、DPAK型のパッケージが熱抵抗( $\theta_{JA}$ )を最小にできるため、消費電力の能力が最大になります。しかし、DPAKの有効性は適切にレイアウトすることと熱管理にかかっています。MOSFETのデータシートに規定されている $\theta_{JA}$ は所定の銅面積と厚さを基準にしています。ほとんどの場合、40°C/Wの最小熱抵抗を達成するにはG-10/FR-4ボード上で1平方インチあたり2オンスの銅が必要です。ボード面積を犠牲にすると熱抵抗を低くすることができます。実装を適切に行なうことについての詳細な情報は選択するMOSFETのデータシートを参照してください。

## グランドと回路のレイアウトについての考察

TPS4005xには信号グランド(SGND)ピンと電源グランド(PGND)ピンが別々に用意されています。回路のグランドは適切に分離されていることが重要です。各グランドは、そのインピーダンスを最小限に抑えるため、できればプレーンで構成してください。出力、同期整流器、MOSFETドライバのデカッピング・キャパシタ(BP10)、入力キャパシタなどの高電力でノイズの多い回路は入力キャパシタ点でPGNDのプレーンに接続してください。

FB抵抗デバイダ、R<sub>T</sub>、ILIMなどのノイズに敏感なノードはSGNDのプレーンに接続してください。SGNDのプレーンはPGNDのプレーンに一点のみで接続するようにしてください。

部品の配置はできるだけバイパス・キャパシタ(BP10とBP5)がそれぞれの電源ピン及びグランド・ピンの近くに配置されるようにします。また、FB、RT、ILIMなどのノイズに敏感な回路は、HDRV、LDRV、BOOST、スイッチ・ノード(SW)などの高いdv/dtのノードの近くに置かないようにしてください。

## 設計例

- 入力電圧: 10Vdc~24Vdc

- 出力電圧: 3.3V ± 2%

- 出力電流: 8A(最大、定常状態時)、10A(サーボ、持続時間10ms、最大デューティ・サイクル10%)

- 出力リップル電圧: 33mV<sub>P-P</sub>(8A時)

- 出力負荷応答: 0.3V(ステップ負荷変化10%~90%)

- 動作温度: -40°C~85°C

- f<sub>SW</sub> = 300kHz

## 1. 最大/最小デューティ・サイクルの計算

$$d_{MIN} = \frac{V_{O(min)}}{V_{IN(max)}} = 0.135 \quad d_{MAX} = \frac{V_{O(max)}}{V_{IN(min)}} = 0.337 \quad (44)$$

## 2. ΔIの選択

この場合、ΔIはコンバータが標準負荷の20%で不連続モードになるよう選択します。

$$\Delta I = I_0 \times 2 \times 0.2 = 3.2 \text{ A} \quad (45)$$

## 3. ハイサイドMOSFET(Si7860DY)の電力損失の計算

式(30)より、

$$I_{RMS} = I_0 \times \sqrt{d} = 8 \times \sqrt{0.337} = 4.64 \text{ A} \quad (46)$$

式(30)を式(29)に代入して、

$$P_{COND} = I_{RMS}^2 \times R_{DS(on)} \times (1 + T_{CR} \times [T_j - 25^\circ\text{C}]) = 4.64^2 \times 0.008 \times (1 + 0.007 \times (150 - 25)) = 0.323 \text{ W} \quad (47)$$

式(33)より、

$$I_{D1} = I_0 - \frac{\Delta I}{2} = 8 - 1.6 = 6.4 \text{ A} \quad (48)$$

$$I_{D2} = I_0 + \frac{\Delta I}{2} = 8 + 1.6 = 9.6 \text{ A}$$

t<sub>S1</sub>(立上がり時間)とt<sub>S2</sub>(立下り時間)はMOSFETのデータシートのゲート電荷特性グラフより概算されます。

Q2 - Q1をゲート電圧がそのプロト電圧(V<sub>PLT</sub>)まで増加するのに要する電荷に等しいとします。この期間での等価入力容量は、

$$C_{IN} = \frac{dQ}{dV} = \frac{4 \text{ nC}}{3.5 \text{ V}} = 1143 \text{ pF} \quad (49)$$

等価容量を充電するのに要する時間は、

$$3.5 = 10 - (10 - 2) \times e^{\left(\frac{-t}{R \times C}\right)} ; t_1 = -R_X C_{IN} \ln\left(\frac{6.5}{8}\right) = 10 \times 1143 \text{ pF} \times \ln\left(\frac{6.5}{8}\right) = 2.4 \text{ ns} \quad (50)$$

但し、Rは実効ゲート駆動抵抗で10Ωです。

ドレイン/ソース間電圧V<sub>DS</sub>が降下するのにかかる時間はデータシートのゲート電荷グラフより求めることができます。プロト領域のこの期間での電荷の変化は、

$$\Delta Q = Q_3 - Q_2 = 9.5 - 5 = 4.5 \text{ nC} \quad (51)$$

この期間ではV<sub>GS</sub>は一定に保たれています。従って、MOSFETのゲート駆動は以下の電流をもつ一定の電流ソースのようにみえます。

$$I_{DRV} = \frac{V_{DRV} - V_{GS}}{R_{DRV}} = \frac{10 - 3.5}{10} = 650 \text{ mA} \quad (52)$$

ここでV<sub>DS</sub>が降下するのにかかる時間を計算することができます。

$$t_2 = \frac{\Delta Q}{I_{DRV}} = \frac{4.5 \text{ nC}}{0.65 \text{ A}} = 6.9 \text{ ns} \quad (53)$$

総立上がり時間は、

$$t_{S1} = t_r = t_1 + t_2 = 2.4 \text{ ns} + 6.9 \text{ ns} = 9.3 \text{ ns} \quad (54)$$

同様に立下がり時間も以下のように求めることができます。

$$t_3 = (Q3 - Q2) \times \frac{R_{DRV}}{V_{PLT}} = 4.5 \text{ nC} \times \frac{7.5\Omega}{3.5 \text{ V}} = 9.6 \text{ ns} \quad (55)$$

$$t_4 = -R_{DRV} \times C_{IN} \times \ln \left( \frac{3.5}{10} \right) = 12 \text{ ns} \quad (56)$$

総立下がり時間は、

$$t_{S2} = t_f = t_3 + t_4 = 9.6 \text{ ns} + 12 \text{ ns} = 21.6 \text{ ns} \quad (57)$$

$t_{S1}, t_{S2}, I_{D1}, I_{D2}$ を式(31)に代入すると、

$$P_{SW}(f_{SW}) = 24 \times \left( \frac{9.3 \text{ ns} \times 6.4}{6} + \frac{21.6 \text{ ns} \times 9.6}{2} \right) \times 300 \text{ kHz} = 818 \text{ mW} \quad (58)$$

式(34)を並び替えて式(35)を代入するとMOSFETの接合部温度が求められます。

$$T_J = (P_{COND} + P_{SW}) \times \theta_{JA} + T_A$$

#### 4. 同期整流器の損失の計算

同期整流MOSFETには、導通損失、ダイオード逆回復損失の2つの損失要素があります。導通損失はアンチ・クロス導通遅延に伴うデッドタイム時のボディ・ダイオードの導通損失に加えIRMS損失にも起因します。

式(36)より同期整流器を流れるIRMS電流は、

$$I_{RMS} = I_0 \times \sqrt{1 - d} = 8 \times \sqrt{1 - 0.135} = 7.44 \text{ A}_{RMS} \quad (59)$$

式(29)より同期MOSFETの導通損失は、

$$P_{COND} = I_{RMS}^2 \times R_{DS(on)} = 7.44^2 \times 0.008 \times (1 + 0.007(150 - 25)) = 0.83 \text{ W} \quad (60)$$

式(37)よりボディ・ダイオードの導通損失は、

$$P_{DC} = I_0 \times V_{FD} \times t_{dead} \times f_{SW} = 8.0 \text{ A} \times 0.8 \text{ V} \times 100 \text{ ns} \times 300 \text{ kHz} = 0.192 \text{ W} \quad (61)$$

式(38)よりボディ・ダイオードの逆回復損失は、

$$P_{RR} = 0.5 \times Q_{RR} \times V_{IN} \times f_{SW} = 0.5 \times 40 \text{ nC} \times 24 \text{ V} \times 300 \text{ kHz} = 0.144 \text{ W} \quad (62)$$

式(39)より同期整流MOSFETで消費される総電力は、

$$P_{SR} = P_{RR} + P_{COND} + P_{DC} = 0.144 + 0.83 + 0.192 = 1.17 \text{ W} \quad (63)$$

85°Cにおける同期整流器の接合部温度は、

$$T_J = P_{SR} \times \theta_{JA} + T_A = (1.17) \times 40 + 85 = 132^\circ\text{C} \quad (64)$$

標準的なアプリケーションでは、同期整流MOSFETをショットキー・ダイオードと並列にするとボディ・ダイオードの導通期間と逆回復期間で消費電力が小さくなるためコンバータの総効率が約2%上昇します。

#### 5. インダクタ値の計算

インダクタ値は式(45)を使って式(6)より計算されます。

$$L = \frac{(24 - 3.3) \times 3.3}{24 \times 3.2 \times 300 \text{ kHz}} = 2.96 \mu\text{H} \quad (65)$$

2.9μHのPanasonic ETQP6F2R9LFAまたはCOEV DXM1306-2R9-Tを選択します。

#### 6. スイッチング周波数の設定

クロック周波数は $R_T$ ピンからグランドへの抵抗( $R_T$ )により設定されます。 $R_T$ の値は $f_{SW}$ (単位はkHz)を用い式(1)より求めることができます。

$$R_T = \left( \frac{1}{f_{SW} \times 17.82 \times 10^{-6}} - 23 \right) \text{ k}\Omega = 164 \text{ k}\Omega \quad (66)$$

∴ use 165 kΩ

#### 7. ランプ・ジェネレータ回路のプログラミング

PWMランプはKFFピンから $V_{IN}$ への抵抗( $R_{KFF}$ )によりプログラミングされます。また、ランプ・ジェネレータは入力UVLO電圧もコントロールします。低電圧レベルが10Vの場合、 $R_{KFF}$ は式(2)より計算することができます。

$$R_{KFF} = (V_{IN(min)} - 3.5) (58.14 \times R_T + 1340) \Omega = 71 \text{ k}\Omega \quad (67)$$

∴ use 71.5 kΩ

#### 8. 出力容量( $C_O$ )の計算

この例では、出力容量は1Aから8Aへのステップ負荷で $\Delta V = 0.3\text{V}$ という負荷応答要件により決まります。 $C_O$ は式(12)を使って求められます。

$$C_O = \frac{2.9 \mu\text{F} \times (8^2 - 1^2)}{(3.3^2 - 3.0^2)} = 97 \mu\text{F} \quad (68)$$

式(7)を使用して、出力リップルの要件に適合するのに必要なESRを計算することができます。

$$33 \text{ mV} = 3.2 \left( \text{ESR} + \frac{1}{8 \times 97 \mu\text{F} \times 300 \text{ kHz}} \right) \quad (69)$$

$$\text{ESR} = 10.3 - 3.33 = 6.97 \text{ m}\Omega \quad (70)$$

この設計例では、180μF/12mΩのPanasonic SP EEFUEOJ1B1Rキャパシタが2つ使用されています。

#### 9. ソフトスタート・キャパシタ( $C_{SS}$ )の計算

この設計では、ソフトスタート時間( $t_{START}$ )は1msが要求されています。 $C_{SS}$ は式(14)で計算することができます。

$$C_{SS} = \frac{2.3 \mu\text{A}}{0.7 \text{ V}} \times 1 \text{ ms} = 3.29 \text{ nF} = 3300 \text{ pF} \quad (71)$$

## 10. 電流制限抵抗( $R_{ILIM}$ )の計算

電流制限の設定点は、式(15)に示されるように、 $t_{START}$ ,  $V_O$ ,  $C_O$ 、起動時の $I_{LOAD}$ により決まります。この設計では、

$$I_{LIM} > \frac{360 \mu F \times 3.3}{1 \text{ ms}} + 8.0 = 9.2 \text{ A} \quad (72)$$

この設計では、 $I_{LIM}$ は最小11.0Aに設定します。式(16)より、

$$R_{ILIM} = \frac{11 \times 0.008}{1.12 \times 10 \mu A} + \frac{(-0.048)}{10 \mu A} = 7.86 \text{ k}\Omega - 4.8 \text{ k}\Omega = 3.06 \text{ k}\Omega \approx 3.09 \text{ k}\Omega \quad (73)$$

## 11. ループ補償値の計算

式(17)より電圧フィードフォワード定数( $A_{MOD}$ )を計算します。

$$A_{MOD} = \frac{10}{2} = 5.0 \quad (74)$$

$$A_{MOD(\text{dB})} = 20 \times \log(5) = 14 \text{ dB} \quad (75)$$

式(18)と式(19)より出力の極とゼロを計算します。

$$f_{LC} = \frac{1}{2\pi\sqrt{2.9 \mu H \times 360 \mu F}} = 4.93 \text{ kHz} \quad (76)$$

及び、

$$f_Z = \frac{1}{2\pi \times 0.012 \times 180 \mu F} = 73.7 \text{ kHz} \quad (77)$$

閉ループの0dBクロスオーバー周波数 $f_C$ を選択します。この例では $f_C = 20 \text{ kHz}$ です。

タイプIIIの補償回路の二重ゼロの位置を選択します。参考資料[1]により極/ゼロの配置位置はクロスオーバーで必要とされる位相ブーストにより決まります。この例では位相余裕60°が望ましい値です。この例で要求される位相ブーストは、

$$\text{Boost} = M - P - 90^\circ = 60^\circ - (-145^\circ) - 90^\circ = 115^\circ \quad (78)$$

但し、

● Mは望ましい位相余裕

● Pは変調器の位相シフト(この例では-145°)

$$K = \left( \tan \left[ \frac{115^\circ}{4} + 45^\circ \right] \right)^2 \approx 11.77 \text{ and } \sqrt{K} = 3.43 \quad (79)$$

従って、

$$f_{P1} = f_{P2} = \sqrt{K} \times 20 \text{ kHz} = 69 \text{ kHz}$$

$$\text{and } f_{Z1} = f_{Z2} = \frac{1}{\sqrt{K}} \times 20 \text{ kHz} = 5.8 \text{ kHz}$$

参考資料[1]に記載のK-Factorの計算に従うと、二重ゼロは5.8kHzに置かれ、二重極は69kHzに置かれます。式(21)と式(22)より図9の部品値について解きます。 $R1 = 100 \text{ k}\Omega$ を選択します。

式(21)より、

$$C3 = \frac{1}{2\pi \times 100 \text{ k}\Omega \times 5.8 \text{ kHz}} = 274 \text{ pF} \approx 270 \text{ pF, from } f_{Z2} \quad (80)$$

$$R3 = \frac{1}{2\pi \times 270 \text{ pF} \times 69 \text{ kHz}} = 8.54 \text{ k}\Omega \approx 8.45 \text{ k}\Omega, \text{ from } f_{P2} \quad (81)$$

$$C2 = \frac{1}{2\pi \times 100 \text{ k}\Omega \times 20 \text{ kHz}} = 79.6 \text{ pF} \approx 82 \text{ pF, from } f_C \quad (82)$$

$$R2 = \frac{1}{2\pi \times 82 \text{ pF} \times 69 \text{ kHz}} = 28.1 \text{ k}\Omega \approx 28 \text{ k}\Omega, \text{ from } f_{P1} \quad (83)$$

$$C1 = \frac{1}{2\pi \times 28 \text{ k}\Omega \times 5.8 \text{ kHz}} = 980 \text{ pF} \approx 1000 \text{ pF, from } f_{Z1} \quad (84)$$

$$R_{BIAS} = \frac{0.7 \times 100 \text{ k}\Omega}{3.3 - 0.7} = 26.9 \text{ k}\Omega \approx 26.7 \text{ k}\Omega \quad (85)$$

## ゲート駆動の構成

Si7860のもう高速のMOSFETスイッチング時間、高い $V_{DS}$ 電圧、低いゲート・スレッシホールドから $dv/dt$ によりターンオンが誘発される可能性があるため、この設計では上側MOSFETのゲート帰還に3.3Ωの抵抗が含まれています。この抵抗はスイッチ・ノードの“L”レベルから“H”レベルへの遷移を形成するのに使用することができ、 $dv/dt$ によるターンオンを誘発しにくくします。

## BOOST及びBP10Vバイパス容量の計算

バイパス・キャパシタの大きさは、使用されているMOSFETの総ゲート電荷とバイパス・キャパシタに許容されるループ量により決まります。BOOSTピンで0.5Vの電圧ループが許容されるとすると、BOOST容量は式(27)より、

$$C_{BOOST} = \frac{Q_g}{\Delta V} = \frac{13 \text{ nC}}{0.5 \text{ V}} = 26 \text{ nF} \quad (86)$$

また、BP10V容量は式(28)より、

$$C_{BP10} = \frac{Q_{gHS} + Q_{gSR}}{\Delta V} = \frac{2 \times Q_g}{\Delta V} = \frac{26 \text{ nC}}{0.5 \text{ V}} = 52 \text{ nF} \quad (87)$$

このアプリケーションでは、BOOSTバイパス・キャパシタには0.1μFのキャパシタ、BP10Vには1.0μFのキャパシタが使用されます。

図13に、この設計例で規定されている出力電流8A、入力電圧24V/出力電圧3.3VのDC/DCコンバータについて選択した部品を示します。

图13. 24-V to 3.3-V at 8-A DC-to-DC Converter Design Example

## REFERENCES

1. Venable, H. Dean, *The K Factor: A New Mathematical Tool for Stability Analysis and Synthesis* Proceedings of Powercon 10, pp A5-1 through A5-12

2. Balogh, Laszlo, *Design and Application Guide for High Speed MOSFET Gate Drive Circuits*, Texas Instruments/Unitrode Corporation, Power Supply Design Seminar, SEM-1400 Topic 2.

3. PowerPAD Thermally Enhanced Package Texas Instruments, Semiconductor Group, Technical Brief: TI Literature No. SLMA002

## 付記

### アプリケーション情報

TPS40050/51/53ファミリーは、特定のアプリケーションに対し最適化し選択使用する事が出来ます。

TPS40051は、ほとんどの応用例を含んだ同期整流降圧型レギュレータのコントローラとして選択されます。出力シンク/ソースの二つの象限の動作モードを持ち、ベストなトランジエンレスポンスを供給します。

TPS40050は出力ソースだけの一つの動作モードを持ち、他のコンバータ出力からシンクをしないことを確実にし、コンバータの並列接続を可能とします。

このコントローラは、軽負荷時に通常降圧型コンバータと同等の不連続モード動作を行います。連続モードとなるインダクター電流においては、コントローラは効率を最適化する同期整流高圧レギュレータとして動作します。

TPS40053はスタートアップ時、通常の降圧型コンバータと同じ動作を行い、出力がレギュレーション動作点に到達すると、二つシンク/ソース)モードを持つ同期整流降圧型レギュレータに移行します。

これは、コンバータがイネーブルされる以前に、出力にある“プリバイアス”された電圧を持つアプリケーションに役立ちます。

TPS40053コントローラがイネーブルとなった時、スタートアップ時に出力から電流をシンクせず、“プリバイアス”された出力電圧から電流を引き込みません。

### SWノードの抵抗と、ダイオード

コンバータのSWノードは、上側、及び下側MOSFETが同時にOFFとなる“デッドタイム”時に、マイナス電圧となります。

このマイナス電圧の大きさは、下側MOSFETのボディーダイオードと、このデッドタイム時に流れる出力電流に依存し、コントローラの動作、特に低入力電圧時に影響します。

因り、図13に示されたように、抵抗(3.3Ωから4.7Ωの範囲)とショットキーダイオードを下側FETのドレインとコントローラのSW Pin12間に付加する事が必要です。

このショットキーダイオードは、入力電圧、及びSWノードに起るリギングに適合した耐圧を持つことが必要です。30VショットキーBAT54、または40V耐圧のZetex ZのZHCS400及びVishayのSD103AWSが適切です。

これらのコンポーネントは図13でRSW及びD2で示されます。

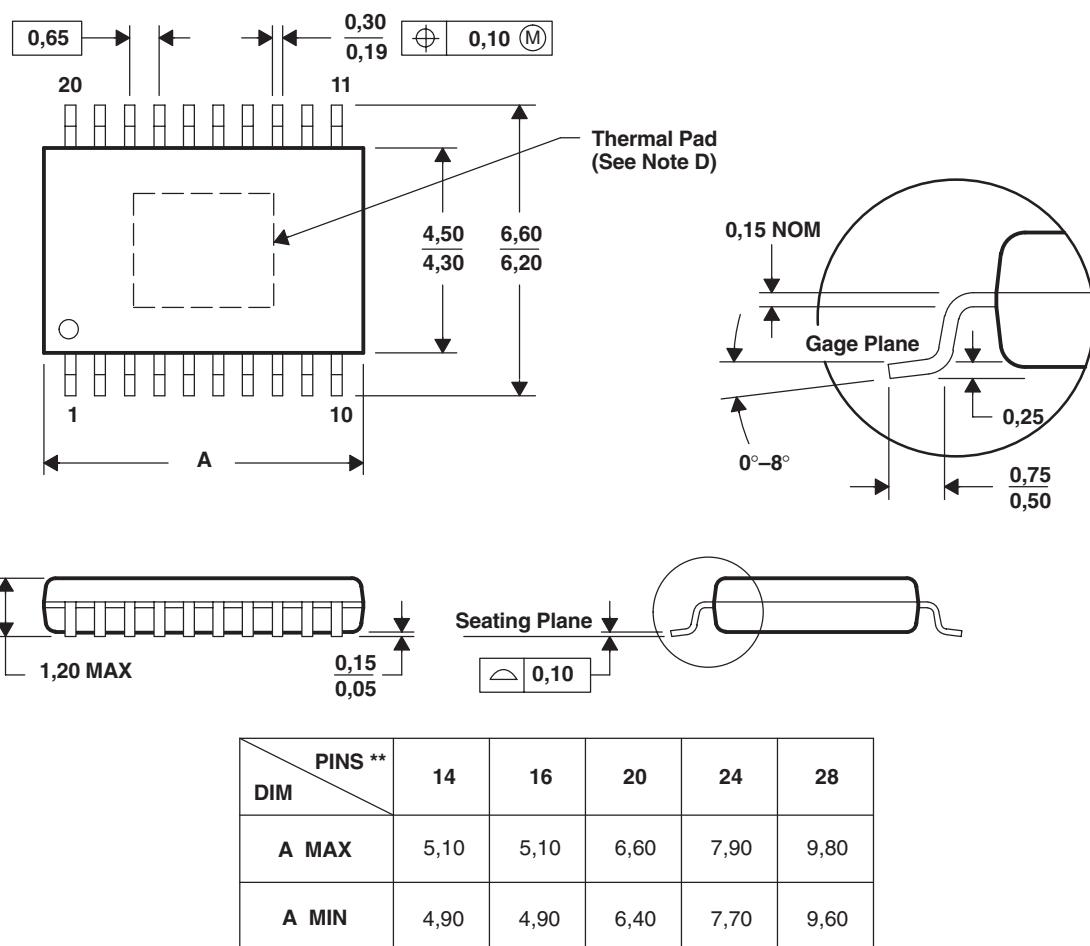

## 外観

### PWP (R-PDSO-G\*\*)

20 PINS SHOWN

### PowerPAD™ PLASTIC SMALL-OUTLINE

4073225/F 10/98

- 注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. ボディ寸法はモールド突起部を含みません。

D. パッケージの熱特性はサーマル・パッドを外部のサーマル・プレーンに接合することで改善されることがあります。

このパッドはダイの裏側と一部のリードに電気的にかつ熱的に接続されています。

E. JEDEC MO-153に準拠します。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS40050PWP           | NRND          | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40050               |

| TPS40050PWP.A         | NRND          | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40050               |

| TPS40050PWPR          | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40050               |

| TPS40050PWPR.A        | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40050               |

| TPS40051PWP           | NRND          | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40051PWP.A         | NRND          | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40051PWPG4         | NRND          | Production           | HTSSOP (PWP)   16 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40051PWPR          | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40051PWPR.A        | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40051PWPRG4        | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40051               |

| TPS40053PWPR          | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40053               |

| TPS40053PWPR.A        | NRND          | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | 40053               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

---

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS40050, TPS40051 :**

- Automotive : [TPS40050-Q1](#), [TPS40051-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

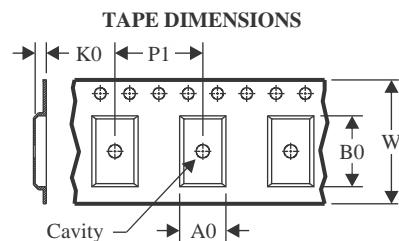

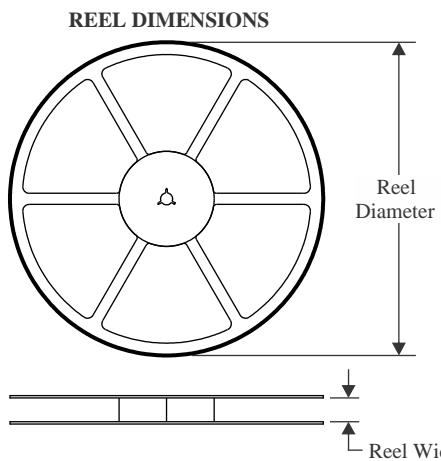

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

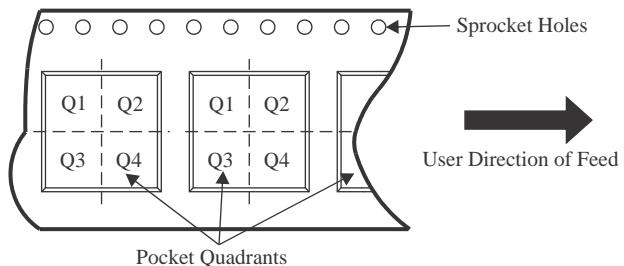

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS40050PWPR | HTSSOP       | PWP             | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TPS40051PWPR | HTSSOP       | PWP             | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TPS40053PWPR | HTSSOP       | PWP             | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

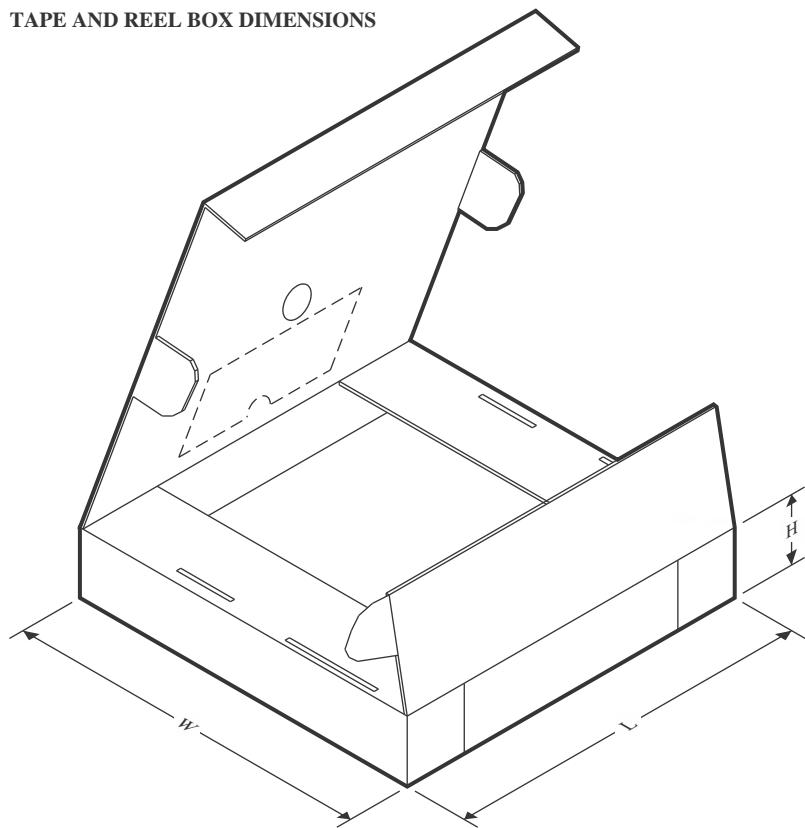

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS40050PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS40051PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS40053PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

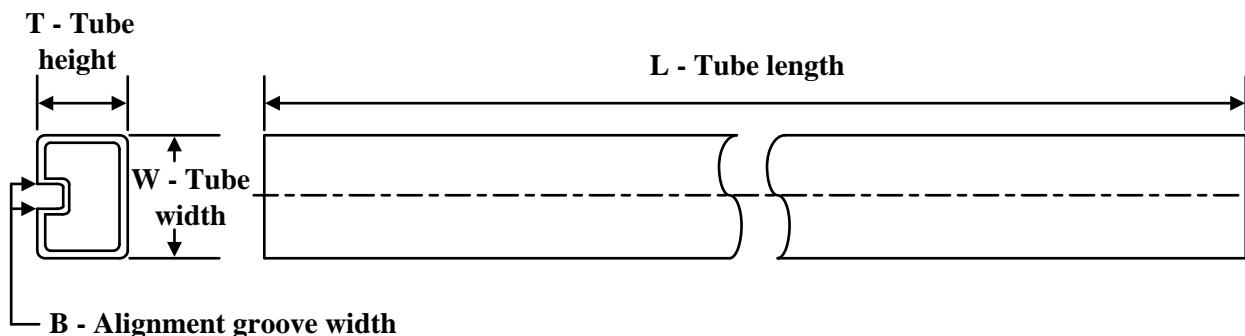

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS40050PWP   | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS40050PWP.A | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS40051PWP   | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS40051PWP.A | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS40051PWPG4 | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月