# 4.5V~18V入力電圧対応同期整流型降圧コントローラ (シーケンス/出力マージン制御付き)

## 特 長

- 入力電圧範囲：4.5V~18V

- 可変スイッチング周波数(100kHz~600kHz)の電流フィードバック・コントロール

- 出力電圧範囲：0.7V~5.5V

- 同時、レシオメトリック、シーケンシャルの起動シーケンス

- アダプティブ・ゲート・ドライブ

- リモート・センス(分離されたGND/PGNDを介して)

- NチャネルMOSFET用ゲート・ドライバ内蔵

- 5Vレギュレータ内蔵

- 24ピンQFNパッケージ

- サーマル・シャットダウン機能

- プログラム可能な過電流検出

- パワー・グッド・インジケータ

- 基準電圧：690mV、精度1%

- 出力マージン制御機能(3%、5%)

- プログラム可能なUVLO(及びプログラム可能なヒステリシス)

- 外部クロック周波数同期

## ア プ リ ケ シ ョ ン

- サーバー

- ネットワーク機器

- ケーブル・モデム/ルーター

- XDSLモデム/ルーター

- セットトップ・ボックス

- テレコム機器

- 電源モジュール

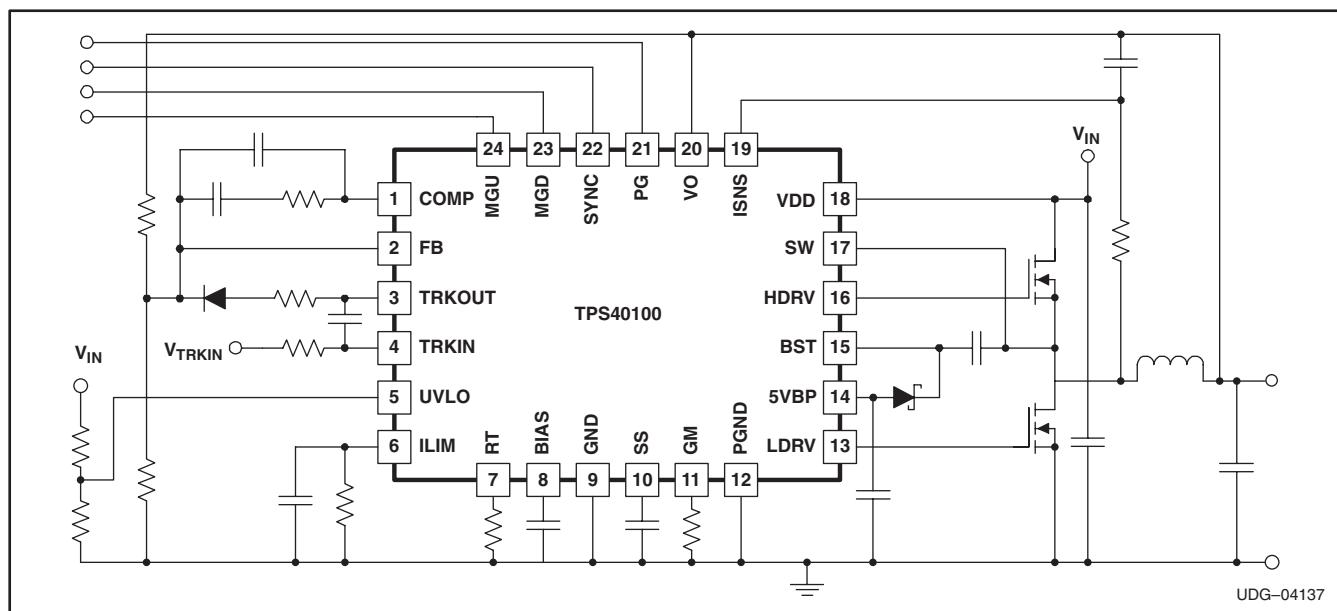

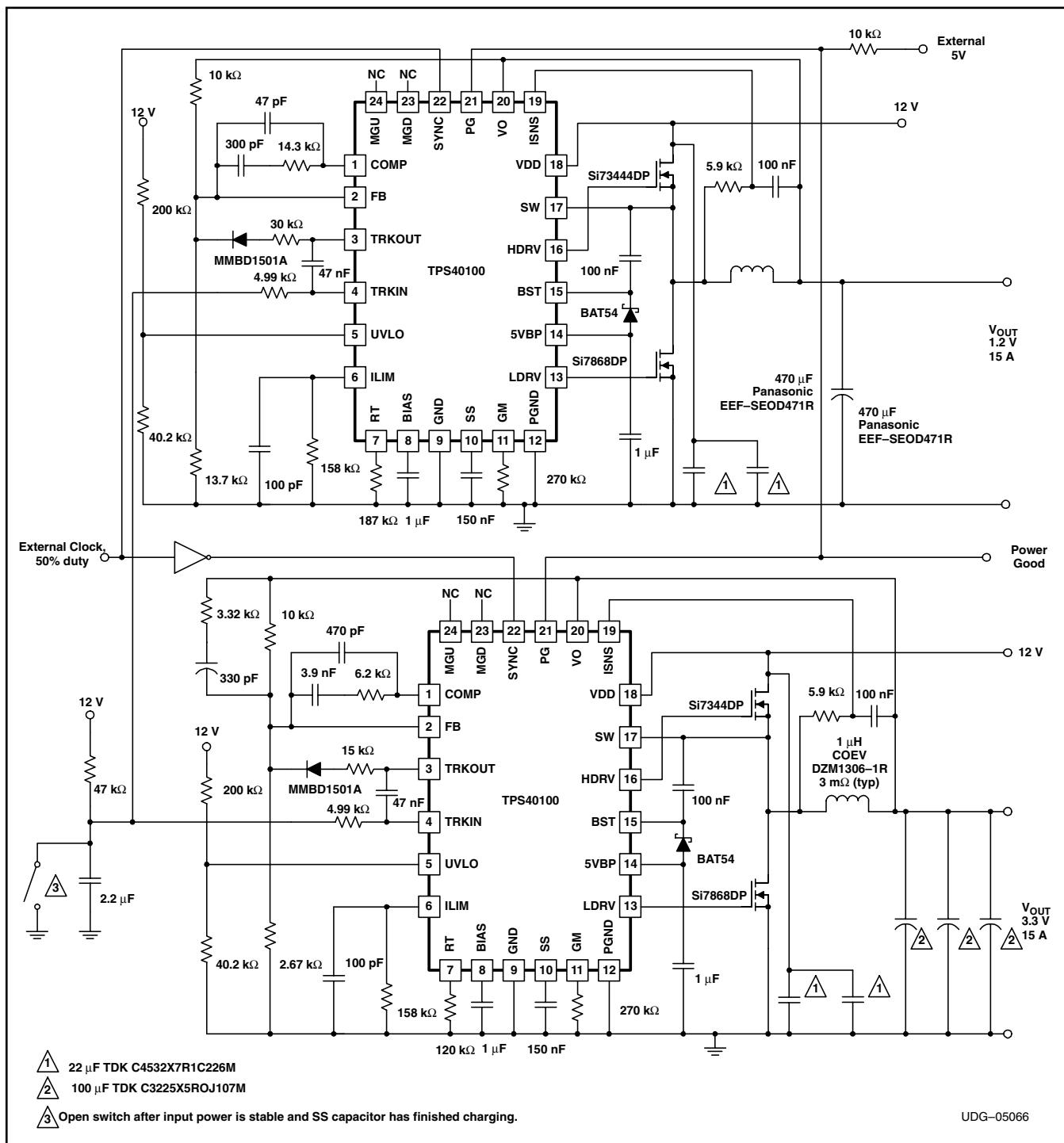

## TYPICAL APPLICATION

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 概要

TPS40100は、中間電圧入力範囲(4.5V~18V)で動作する同期式降圧型コントローラです。TPS40100にはプログラム可能な閉ループソフトスタート、プログラム可能なUVLO(及びプログラム可能なヒステリシス)、プログラム可能なインダクタ検出による電流制限の機能が用意されており、また、外部クロックに同期動作することができます。TPS40100は外付けのNチャネル・ハイサイドMOSFET及び同期整流(SR) MOSFET用にMOSFETゲート・ドライバを内蔵しています。ゲート駆動のロジックにはアダプティブのアンチクロス導通制御回路を組み込んでいるため、ハイサイドと整流MOSFETのクロス導通を抑え、整流MOSFETのダイオード導通を低減し、効率を改善します。また、外部からプログラム可能な電流制限機能を持ち、Hiccupモードによる過電流からの自動回復機能も内蔵されています。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE | PART NUMBER <sup>(1)</sup> |

|----------------|---------|----------------------------|

| −40°C to 85°C  | QFN     | TPS40100RGER               |

|                |         | TPS40100RGET               |

(1) QFNパッケージ(RGE)はテープ/リールのみで供給されています。大型テープ/リールで発注するには型番にRを付けてください(TPS40100RGER)。リールあたりの数量は3000個です。小型テープ/リールで発注するには型番にTを付けてください(TPS40100RGET)。リールあたりの数量は250個です。

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                                                                    | TPS40100                 | UNIT |

|------------------|--------------------------------------------------------------------|--------------------------|------|

| V <sub>IN</sub>  | VDD                                                                | −0.3 to 20               | V    |

|                  | 5VBP, BIAS, FB, ILIM, ISNS, LDRV, MGU, MGD, PG, SS, SYNC, UVLO, VO | −0.3 to 6                |      |

|                  | BST to SW, HDRV to SW <sup>(2)</sup>                               | −0.3 to 6.0              |      |

|                  | SW                                                                 | −1.5 to V <sub>VIN</sub> |      |

|                  | SW (transient) < 100 ns                                            | −6 to 30                 |      |

|                  | TRKIN                                                              | −0.3 to 20               |      |

|                  | GND to PGND                                                        | −0.3 to 0.3              |      |

|                  | TRKOUT                                                             | −0.3 to 8.0              |      |

| I <sub>IN</sub>  | HDRV, LDRV (RMS)                                                   | 0.5                      | A    |

|                  | HDRV, LDRV (peak)                                                  | 2.0                      |      |

|                  | FB, COMP, TRKOUT                                                   | 10 to −10                | mA   |

|                  | SS                                                                 | 20 to −20                | mA   |

|                  | PG                                                                 | 20                       |      |

|                  | GM                                                                 | 1                        |      |

|                  | RT                                                                 | 10                       |      |

|                  | V5BP                                                               | 50 <sup>(3)</sup>        |      |

| T <sub>J</sub>   | RT source                                                          | 100                      | μA   |

|                  | Operating junction temperature range                               | −40 to 125               | °C   |

| T <sub>stg</sub> | Storage temperature                                                | −55 to 150               |      |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) “BST to SW” と “HDRV to SW” は相対測定です。BSTとHDRVはSWの電圧を基準としての規定です。

(3) 5VBP電流にはゲート駆動の電流要求が含まれています。このデバイスの最大T<sub>J</sub>定格を順守してください。

## ELECTRICAL CHARACTERISTICS

$-40^{\circ}\text{C} \leq T_A = T_J \leq 85^{\circ}\text{C}$ ,  $V_{\text{VDD}} = 12\text{V}$ ,  $R_{\text{RT}} = 182\text{k}\Omega$ ,  $R_{\text{GM}} = 232\text{k}\Omega$ ,  $R_{\text{ILIM}} = 121\text{k}\Omega$  (特に記述のない限り)

| PARAMETER                                           | TEST CONDITIONS                                                                                       | MIN                                                                                                           | TYP  | MAX  | UNIT                   |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------------------------|

| <b>INPUT VOLTAGE</b>                                |                                                                                                       |                                                                                                               |      |      |                        |

| $V_{\text{VDD}}$                                    | Operating range                                                                                       |                                                                                                               | 4.5  | 18.0 | V                      |

| <b>OPERATING CURRENT</b>                            |                                                                                                       |                                                                                                               |      |      |                        |

| $I_{\text{DD}}$                                     | Quiescent current                                                                                     | $V_{\text{FB}} > 0.8\text{ V}, 0\% \text{ duty cycle}$                                                        | 1.3  | 1.8  | 2.5 mA                 |

| $I_{\text{SD}}$                                     | Shutdown current                                                                                      | $V_{\text{UVLO}} < 1\text{ V}$                                                                                |      | 500  | $\mu\text{A}$          |

| <b>5VBP</b>                                         |                                                                                                       |                                                                                                               |      |      |                        |

| Internal regulator                                  | $7\text{ V} \leq V_{\text{VDD}} \leq 18\text{ V}, 0\text{ mA} \leq I_{\text{LOAD}} \leq 30\text{ mA}$ | 4.7                                                                                                           | 5.0  | 5.3  | V                      |

|                                                     | $4.5\text{ V} \leq V_{\text{VDD}} < 7\text{ V}, 0\text{ mA} \leq I_{\text{LOAD}} \leq 30\text{ mA}$   | 4.3                                                                                                           | 5.0  | 5.3  |                        |

| <b>OSCILLATOR/RAMP GENERATOR</b>                    |                                                                                                       |                                                                                                               |      |      |                        |

| $f_{\text{SW}}$                                     | Programmable oscillator frequency                                                                     |                                                                                                               | 100  | 600  | kHz                    |

| Oscillator frequency accuracy                       |                                                                                                       | $4.5\text{ V} \leq V_{\text{VDD}} < 18\text{ V}, -40^{\circ}\text{C} \leq T_A = T_J \leq 125^{\circ}\text{C}$ | 250  | 275  | 300                    |

| $V_{\text{RAMP}}$                                   | Ramp amplitude <sup>(1)</sup>                                                                         |                                                                                                               | 0.5  |      | $V_{\text{P-P}}$       |

| $t_{\text{OFF}}$                                    | Fixed off-time                                                                                        |                                                                                                               | 100  | 150  | ns                     |

| $D_{\text{MIN}}$                                    | Minimum duty cycle                                                                                    |                                                                                                               |      | 0%   |                        |

| $t_{\text{MIN}}$                                    | Minimum controllable pulse width <sup>(1)</sup>                                                       | $C_{\text{LOAD}} = 4.7\text{ nF}, -40^{\circ}\text{C} \leq T_A = T_J \leq 125^{\circ}\text{C}$                |      | 175  | ns                     |

| $V_{\text{VLY}}$                                    | Valley voltage <sup>(1)</sup>                                                                         |                                                                                                               | 1.0  | 1.6  | 2.0 V                  |

| <b>FREQUENCY SYNCHRONIZATION</b>                    |                                                                                                       |                                                                                                               |      |      |                        |

| $V_{\text{IH}}$                                     | High-level input voltage                                                                              |                                                                                                               | 2    |      | V                      |

| $V_{\text{IL}}$                                     | Low-level input voltage                                                                               |                                                                                                               |      | 0.8  |                        |

| $I_{\text{SYNC}}$                                   | Input current, SYNC                                                                                   | $V_{\text{SYNC}} = 2.5\text{ V}$                                                                              | 4.0  | 5.5  | 10.0 $\mu\text{A}$     |

| $t_{\text{SYNC}}$                                   | Minimum pulse width, SYNC                                                                             |                                                                                                               | 50   |      | ns                     |

| $t_{\text{SYNC\_SH}}$                               | Minimum set-up/hold time, SYNC <sup>(2)</sup>                                                         |                                                                                                               | 100  |      |                        |

| <b>SOFT-START AND FAULT IDLE</b>                    |                                                                                                       |                                                                                                               |      |      |                        |

| $I_{\text{SS}}$                                     | Soft-start source (charge) current                                                                    |                                                                                                               | 13   | 20   | 25 $\mu\text{A}$       |

| $I_{\text{SS\_SINK}}$                               | Soft-start sink (discharge) current                                                                   |                                                                                                               | 3.4  | 5.0  | 6.6                    |

| $V_{\text{SSC}}$                                    | Soft-start completed voltage                                                                          |                                                                                                               | 3.25 | 3.40 | 3.75                   |

| $V_{\text{SSD}}$                                    | Soft-start discharged voltage                                                                         |                                                                                                               | 0.15 | 0.20 | 0.25 V                 |

| Retry interval time to SS time ratio <sup>(1)</sup> |                                                                                                       |                                                                                                               | 16   |      |                        |

| $V_{\text{SSOS}}$                                   | Offset from SS to error amplifier                                                                     |                                                                                                               | 300  | 500  | 800 mV                 |

| <b>ERROR AMPLIFIER</b>                              |                                                                                                       |                                                                                                               |      |      |                        |

| $\text{GBWP}$                                       | Gain bandwidth product <sup>(1)</sup>                                                                 |                                                                                                               | 3.5  | 5.0  | MHz                    |

| $\text{AVOL}$                                       | Open loop                                                                                             |                                                                                                               | 60   | 80   | dB                     |

| $I_{\text{BIAS}}$                                   | Input bias current, FB                                                                                |                                                                                                               | 50   | 200  | nA                     |

| $I_{\text{OH}}$                                     | High-level output current                                                                             |                                                                                                               | 2    | 3    | mA                     |

| $I_{\text{OL}}$                                     | Low-level output current                                                                              |                                                                                                               | 2    | 3    |                        |

| Slew rate <sup>(1)</sup>                            |                                                                                                       |                                                                                                               | 2.1  |      | $\text{V}/\mu\text{s}$ |

| <b>FEEDBACK REFERENCE</b>                           |                                                                                                       |                                                                                                               |      |      |                        |

| $V_{\text{FB}}$                                     | Feedback voltage reference                                                                            | $T_A = 25^{\circ}\text{C}$                                                                                    | 686  | 690  | 694 mV                 |

|                                                     |                                                                                                       | $-40^{\circ}\text{C} < T_A = T_J \leq 125^{\circ}\text{C}$                                                    | 683  | 697  |                        |

(1) 設計で保証されており、テストは行われていません。

(2) 外部同期回路のセットアップ時間の要求に適合するには、負のロジック・パルス幅は100nsより大きくなければなりません。

## ELECTRICAL CHARACTERISTICS

$-40^\circ\text{C} \leq T_A = T_J \leq 85^\circ\text{C}$ ,  $V_{\text{VDD}} = 12\text{V}$ ,  $R_{\text{RT}} = 182\text{k}\Omega$ ,  $R_{\text{GM}} = 232\text{k}\Omega$ ,  $R_{\text{ILIM}} = 121\text{k}\Omega$  (特に記述のない限り)

| PARAMETER                      | TEST CONDITIONS                                         | MIN                                                                                     | TYP   | MAX  | UNIT                  |

|--------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|-----------------------|

| <b>VOLTAGE MARGINING</b>       |                                                         |                                                                                         |       |      |                       |

| $V_{\text{FBMGU}}$             | Feedback voltage margin 5% up                           | $V_{\text{MGU}} \leq 500\text{ mV}$                                                     | 715   | 725  | 735                   |

|                                | Feedback voltage margin 3% up                           | $2\text{ V} \leq V_{\text{MGU}} \leq 3\text{ V}$                                        | 700   | 711  | 720                   |

| $I_{\text{MGUP}}$              | Margin-up bias current                                  |                                                                                         | 60    | 80   | 100                   |

|                                | Feedback voltage margin 5% down                         | $V_{\text{MGD}} \leq 500\text{ mV}$                                                     | 645   | 655  | 665                   |

| $V_{\text{FBMGD}}$             | Feedback voltage margin 3% down                         | $2\text{ V} \leq V_{\text{MGD}} \leq 3\text{ V}$                                        | 660   | 669  | 680                   |

|                                | Margin-down bias current                                |                                                                                         | 60    | 80   | 100                   |

| $t_{\text{MGDLY}}$             | Margining delay time <sup>(3)</sup>                     |                                                                                         | 12    | 30   | ms                    |

| $t_{\text{MGTRAN}}$            | Margining transition time                               |                                                                                         | 1.5   | 7.0  |                       |

| <b>CURRENT SENSE AMPLIFIER</b> |                                                         |                                                                                         |       |      |                       |

| $gm_{\text{CSA}}$              | Current sense amplifier gain                            | $T_J = 25^\circ\text{C}$                                                                | 300   | 333  | 365                   |

| $TC_{\text{GM}}$               | Amplifier gain temperature coefficient                  |                                                                                         | -2000 |      | ppm/ $^\circ\text{C}$ |

| $V_{\text{GMLIN}}$             | Gm linear range voltage                                 | $T_J = 25^\circ\text{C}$                                                                | -50   | 50   | mV                    |

| $I_{\text{ISNS}}$              | Bias current at ISNS pin                                | $V_{\text{VO}} = V_{\text{ISNS}} = 3.3\text{ V}$                                        | 250   |      | nA                    |

| $V_{\text{GMCM}}$              | Input voltage common mode                               |                                                                                         | 0     | 6    | V                     |

|                                |                                                         | $4.5\text{ V} \leq V_{\text{IN}} \leq 5.5\text{ V}$                                     | 0     | 3.6  |                       |

| <b>CURRENT LIMIT</b>           |                                                         |                                                                                         |       |      |                       |

| $V_{\text{ILIM}}$              | ILIM pin voltage to trip overcurrent                    |                                                                                         | 1.44  | 1.48 | 1.52                  |

| $t_{\text{ILIMDLY}}$           | Current limit comparator propagation delay              | HDRV transition from on to off                                                          | 70    | 140  | ns                    |

| <b>DRIVER SPECIFICATIONS</b>   |                                                         |                                                                                         |       |      |                       |

| $t_{\text{RHDRV}}$             | High-side driver rise time <sup>(4)</sup>               | $C_{\text{LOAD}} = 4.7\text{ nF}$                                                       | 57    | ns   |                       |

| $t_{\text{FHDRV}}$             | High-side driver fall time <sup>(4)</sup>               | $C_{\text{LOAD}} = 4.7\text{ nF}$                                                       | 47    |      |                       |

| $I_{\text{HDRVSRPKS}}$         | High-side driver peak source current <sup>(4)</sup>     |                                                                                         | 800   | mA   |                       |

| $I_{\text{HDRVSRMIL}}$         | High-side driver source current at 2.5 V <sup>(4)</sup> | $V_{\text{HDRV}} - V_{\text{SW}} = 2.5\text{ V}$                                        | 700   |      |                       |

| $I_{\text{HSDVSNPK}}$          | High-side driver peak sink current <sup>(4)</sup>       |                                                                                         | 1.3   | A    |                       |

| $I_{\text{HDRVSNMIL}}$         | High-side driver sink current at 2.5 V <sup>(4)</sup>   | $V_{\text{HDRV}} - V_{\text{SW}} = 2.5\text{ V}$                                        | 1.2   |      |                       |

| $R_{\text{HDRVUP}}$            | High-side driver pullup resistance                      | $I_{\text{HDRV}} = 300\text{ mA}$                                                       | 2.4   | 4.0  | $\Omega$              |

| $R_{\text{HDRVDN}}$            | High-side driver pulldown resistance                    | $I_{\text{HDRV}} = 300\text{ mA}$                                                       | 1.0   | 1.8  |                       |

| $t_{\text{RLDRV}}$             | Low-side driver rise time <sup>(4)</sup>                | $C_{\text{LOAD}} = 4.7\text{ nF}$                                                       | 57    | ns   |                       |

| $t_{\text{FLDRV}}$             | Low-side driver fall time <sup>(4)</sup>                | $C_{\text{LOAD}} = 4.7\text{ nF}$                                                       | 47    |      |                       |

| $I_{\text{LDRVSRPK}}$          | Low-side driver peak source current <sup>(4)</sup>      |                                                                                         | 800   | mA   |                       |

| $I_{\text{LDRVSNMIL}}$         | Low-side driver source current at 2.5 V <sup>(4)</sup>  | $V_{\text{LDRV}} = 2.5\text{ V}$                                                        | 700   |      |                       |

| $I_{\text{LSDVSNPK}}$          | Low-side driver peak sink current <sup>(4)</sup>        |                                                                                         | 1.3   | A    |                       |

|                                | Low-side driver sink current at 2.5 V <sup>(4)</sup>    | $V_{\text{LDRV}} = 2.5\text{ V}$                                                        | 1.2   |      |                       |

| $R_{\text{LDRVUP}}$            | Low-side driver pullup resistance                       | $I_{\text{LDRV}} = 300\text{ mA}$                                                       | 2.0   | 4.0  | $\Omega$              |

| $R_{\text{LDRVDN}}$            | Low-side driver pulldown resistance                     | $I_{\text{LDRV}} = 300\text{ mA}$                                                       | 0.8   | 1.5  |                       |

| $I_{\text{SWLEAK}}$            | Leakage current from SW pin                             |                                                                                         | -1    | 1    | $\mu\text{A}$         |

| <b>POWERGOOD</b>               |                                                         |                                                                                         |       |      |                       |

| $V_{\text{LPGD}}$              | Powergood low voltage                                   | $I_{\text{PGD}} = 2\text{ mA}$                                                          | 30    | 100  | mV                    |

| $t_{\text{PGD}}$               | Powergood delay time                                    |                                                                                         | 15    | 25   | 35                    |

| $V_{\text{LPGDNP}}$            | Powergood low voltage, no device power                  | $V_{\text{VDD}} = \text{OPEN}, 10\text{-k}\Omega \text{ pullup to external 5-V supply}$ | 1.00  | 1.25 | V                     |

| $V_{\text{OV}}$                | Power good overvoltage threshold, $V_{\text{FB}}$       |                                                                                         | 765   |      | mV                    |

| $V_{\text{UV}}$                | Power good undervoltage threshold, $V_{\text{FB}}$      |                                                                                         | 615   |      |                       |

(3) マージン遅延時間はマージン・コマンドが発行されてから、出力電圧がマージン電圧に移行し始めるまでの時間遅延です。

(4) 設計で保証されており、テストは行われていません。

## ELECTRICAL CHARACTERISTICS

$-40^{\circ}\text{C} \leq T_A = T_J \leq 85^{\circ}\text{C}$ ,  $V_{\text{VDD}} = 12\text{V}$ ,  $R_{\text{RT}} = 182\text{k}\Omega$ ,  $R_{\text{GM}} = 232\text{k}\Omega$ ,  $R_{\text{ILIM}} = 121\text{k}\Omega$  (特に記述のない限り)

| PARAMETER                  | TEST CONDITIONS                                                                                 | MIN                                    | TYP   | MAX   | UNIT               |   |

|----------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------|-------|-------|--------------------|---|

| <b>TRACKING AMPLIFIER</b>  |                                                                                                 |                                        |       |       |                    |   |

| $V_{\text{TRKOS}}$         | $V_{\text{TRKIN}} = V_{\text{VO}} ; V_{\text{VO}} \leq 2\text{V}$                               | 7                                      | 25    | 40    | mV                 |   |

|                            | $V_{\text{TRKOS}} = V_{\text{TRKIN}} - V_{\text{O}} ; 2\text{V} < V_{\text{VO}} \leq 6\text{V}$ | -5                                     | 25    | 40    |                    |   |

| $V_{\text{TRKCM}}$         | Input common mode, active range                                                                 | 0                                      | 6     |       | V                  |   |

| $V_{\text{TRK}}$           | $4.5\text{V} \leq V_{\text{VDD}} \leq 5.5\text{V}$                                              | 0                                      | 3.6   |       |                    |   |

|                            | $5\text{V} < V_{\text{VDD}} \leq 18\text{V}$ <sup>(5)</sup>                                     | 0                                      | 6     |       |                    |   |

| $V_{\text{HTKROUT}}$       | $V_{\text{VDD}} = 12\text{V}$                                                                   | 5.0                                    | 6.5   | 8.0   |                    |   |

|                            | $V_{\text{VDD}} = 4.5\text{V}$                                                                  | 3.2                                    | 3.6   |       |                    |   |

| $V_{\text{LTKROUT}}$       | Low-level output voltage, TRKOUT                                                                | 0                                      | 0.5   |       |                    |   |

| $I_{\text{SRCTRKOUT}}$     | Source current, TRKOUT                                                                          | 0.65                                   | 2.00  |       | mA                 |   |

| $I_{\text{SNKTRKOUT}}$     | Sink current, TRKOUT                                                                            | 1                                      | 2     |       |                    |   |

| $V_{\text{TRKDIF}}$        | Differential voltage from TRKIN to VO                                                           |                                        |       | 18    | V                  |   |

| $\text{GBWP}_{\text{TRK}}$ | Tracking amplifier gain bandwidth product <sup>(6)</sup>                                        | 1                                      |       |       | MHz                |   |

| $\text{AVOL}_{\text{TRK}}$ | Tracking amplifier open loop DC gain <sup>(6)</sup>                                             | 60                                     |       |       | dB                 |   |

| <b>PROGRAMMABLE UVLO</b>   |                                                                                                 |                                        |       |       |                    |   |

| $V_{\text{UVLO}}$          | Undervoltage lockout threshold                                                                  | 1.285                                  | 1.332 | 1.378 | V                  |   |

| $I_{\text{UVLO}}$          | Hysteresis current                                                                              | 9.0                                    | 10.0  | 10.8  | $\mu\text{A}$      |   |

| <b>INTERNAL FIXED UVLO</b> |                                                                                                 |                                        |       |       |                    |   |

| $V_{\text{UVLOFON}}$       | Fixed UVLO turn-on voltage at VDD pin                                                           | -40°C $\leq T_A < 125^{\circ}\text{C}$ | 3.850 | 4.150 | 4.425              | V |

| $V_{\text{UVLOFOFF}}$      | Fixed UVLO turn-off voltage at VDD pin                                                          |                                        | 3.75  | 4.06  | 4.35               |   |

| $V_{\text{UVLOHYST}}$      | UVLO hysteresis at VDD pin                                                                      |                                        | 85    |       | mV                 |   |

| <b>THERMAL SHUTDOWN</b>    |                                                                                                 |                                        |       |       |                    |   |

| $T_{\text{SD}}$            | Thermal shutdown temperature <sup>(6)</sup>                                                     | 130                                    | 165   |       | $^{\circ}\text{C}$ |   |

| $T_{\text{SDHYST}}$        | Hysteresis <sup>(6)</sup>                                                                       |                                        | 25    |       |                    |   |

(5) アンプは6Vまたは(VDDx0.95)のうちの小さいほうにトラッキングします。

(6) 設計で保証されており、テストは行われていません。

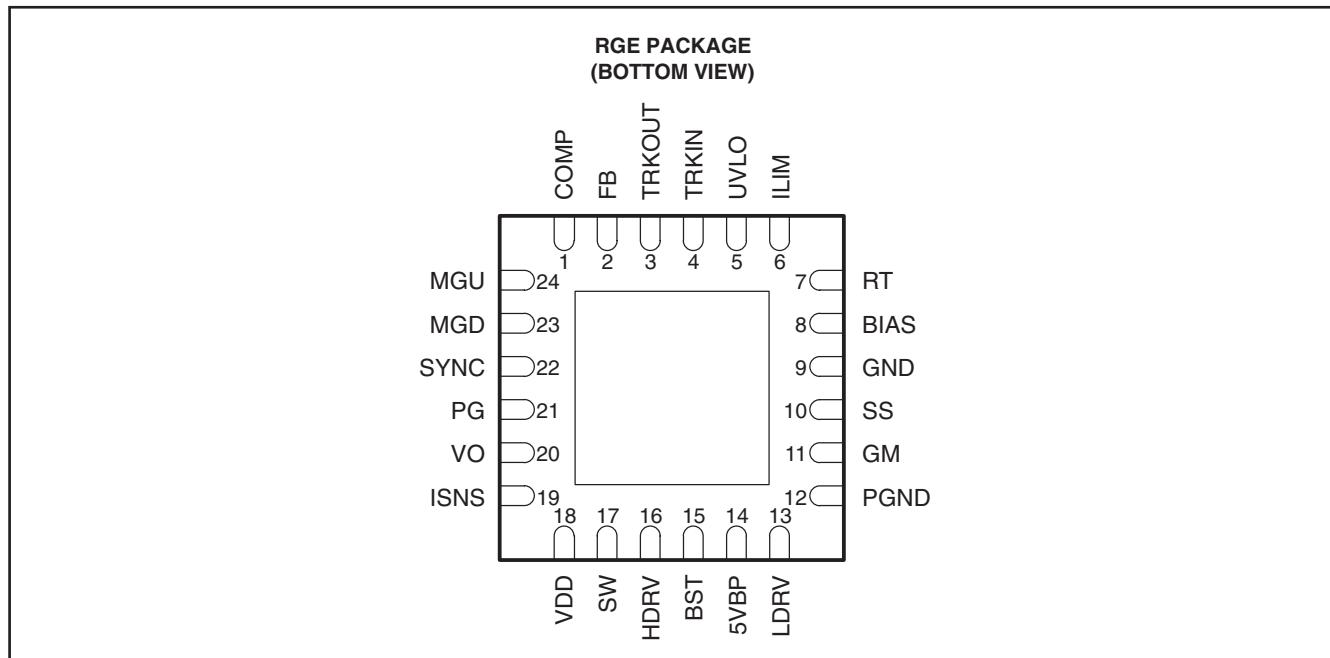

## DEVICE INFORMATION

## 端子機能

| TERMINAL |     | I/O | DESCRIPTION                                                                                                                                                                                              |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. |     |                                                                                                                                                                                                          |

| 5VBP     | 14  | O   | 内部の5Vレギュレータの出力。このピンからPGNDに1μFのバイパス・コンデンサを接続しなければなりません。このピンから外部回路へ電源を取り出すことができます。総ゲート駆動電流と外部に流れる電流によりデバイスの熱能力を越えてはいけません。                                                                                  |

| BIAS     | 8   | O   | デバイスの内部回路用バイパス電源。このピンからGNDに0.1μFまたはそれ以上のセラミック・コンデンサを接続してください。                                                                                                                                            |

| BST      | 15  | I   | ハイサイドNチャネルMOSFET用ゲート駆動電圧。外付けダイオードを5VBP(アノード)からBST(カソード)に接続しなければなりません。これにはショットキー・ダイオードを推奨します。このピンからSWピンにコンデンサを接続しなければなりません。                                                                               |

| COMP     | 1   | O   | 誤差増幅器の出力。コントロール・ループの補償用にこのピンからFBピンにフィードバック・ネットワークを接続します。                                                                                                                                                 |

| FB       | 2   | I   | 誤差増幅器への反転入力。通常動作時、このピンの電圧は内部基準電圧(約690mV)と等しくなります。                                                                                                                                                        |

| GM       | 11  | I   | 電流検出増幅器のゲインを設定するためこのピンからGNDに抵抗を接続してください。                                                                                                                                                                 |

| GND      | 9   | -   | デバイスの信号グランド。特記無き場合、全ての信号レベル回路はこのピンを基準としなければなりません。                                                                                                                                                        |

| HDRV     | 16  | O   | ハイサイドNチャネルMOSFET用フローティング・ゲート駆動ピン。                                                                                                                                                                        |

| ILIM     | 6   | O   | 過電流スレッショールドと過渡電流のライド・アウト時間を設定するのに使用される電流制限ピン。インダクタ電流に比例した内部電流源によりこのピンからGNDに接続されている抵抗の電圧が設定されます。この電圧が1.48Vに達するとデバイスにより過電流状態が宣言されます。GNDに対しこの抵抗に並列にコンデンサを挿入すると誤検出を回避する手助けとして使用可能な遅延時間が設定されます。               |

| ISNS     | 19  | I   | インダクタのDCR検出回路からの入力。この入力信号は電流フィードバック・コントロール及び過電流保護用電流検出増幅器への入力の1つです。                                                                                                                                      |

| LDRV     | 13  | O   | Nチャネル同期整流MOSFETのゲート駆動ピン。                                                                                                                                                                                 |

| MGD      | 23  | I   | 負荷ストレス試験用マージン・ダウン・ピン。このピンが10kΩより小さな抵抗を介してGNDに接続された場合、出力電圧は5%減少します。このピンを30kΩの抵抗を介してGNDに接続すると、出力電圧が3%マージン・ダウンします。                                                                                          |

| MGU      | 24  | I   | 負荷ストレス試験用マージン・アップ・ピン。このピンが10kΩより小さな抵抗を介してGNDに接続された場合、出力電圧は5%増加します。このピンを30kΩの抵抗を介してGNDに接続すると、出力電圧が3%マージン・アップします。                                                                                          |

| PG       | 21  | O   | オープン・ドラインのパワーグッド出力。FBピンの電圧が690mVより10%以上高いかまたは低い場合、UVLO状態にある場合、ソフトスタートがアクティブである場合、トラッキング状態の場合、過電流状態にある場合、チップが過熱状態の場合、このような時このピンは“L”レベルになります。                                                              |

| PGND     | 12  | -   | 内部ドライバ用パワー・グランド                                                                                                                                                                                          |

| RT       | 7   | I   | このピンからGNDに接続する抵抗により動作周波数が設定されます。                                                                                                                                                                         |

| SS       | 10  | I   | ソフトスタートのプログラム・ピン。このピンからグランドにコンデンサを接続するとソフトスタート時間がプログラムされます。また、このピンは過電流が起った時のタイムアウト機能としても使用されます。                                                                                                          |

| SW       | 17  | I   | コンバータのスイッチ・ノードに接続します。このピンはフライング・ハイサイド・ドライバのリターン・ラインです。                                                                                                                                                   |

| SYNC     | 22  | I   | 立上がりエッジでトリガされるデバイスの同期クロック入力ピン。このピンは発振器の周波数を外部マスター・クロックに同期させるのに使用できます。この機能を使用しない場合はこのピンはフローティングまたはグランドに接続することができます。                                                                                       |

| TRKIN    | 4   | I   | 複数コントローラの同時立ち上げ起動を可能にするコントロール入力。トラッキング・アンプが使用された場合、コンバータの出力は、コントロールされた小さなオフセット電圧(標準25mV)を伴って、TRKIN電圧をトラッキングします。詳細については“アプリケーション情報”の項を参照してください。                                                           |

| TRKOUT   | 3   | O   | トラッキング・アンプの出力。トラッキング機能が使用される場合、このピンはダイオードに直列の抵抗を介してFBピンに接続しなければなりません。この抵抗値はFBノードの等価インピーダンスから計算することができます。ダイオードはダイオードの逆電流による誤差を最小限に抑えるため低リードのタイプでなければなりません。トラッキング・アンプの補償についての詳細情報は“アプリケーション情報”的項を参照してください。 |

| UVLO     | 5   | I   | 低電圧ロックアウト・レベルのプログラムを行い、デバイスのシャットダウン入力として機能します。                                                                                                                                                           |

| VDD      | 18  | I   | デバイスの電源電圧。                                                                                                                                                                                               |

| VO       | 20  | I   | 出力電圧。このピンは電流モード・コントロール及び過電流保護用の電流検出増幅器への基準入力です。                                                                                                                                                          |

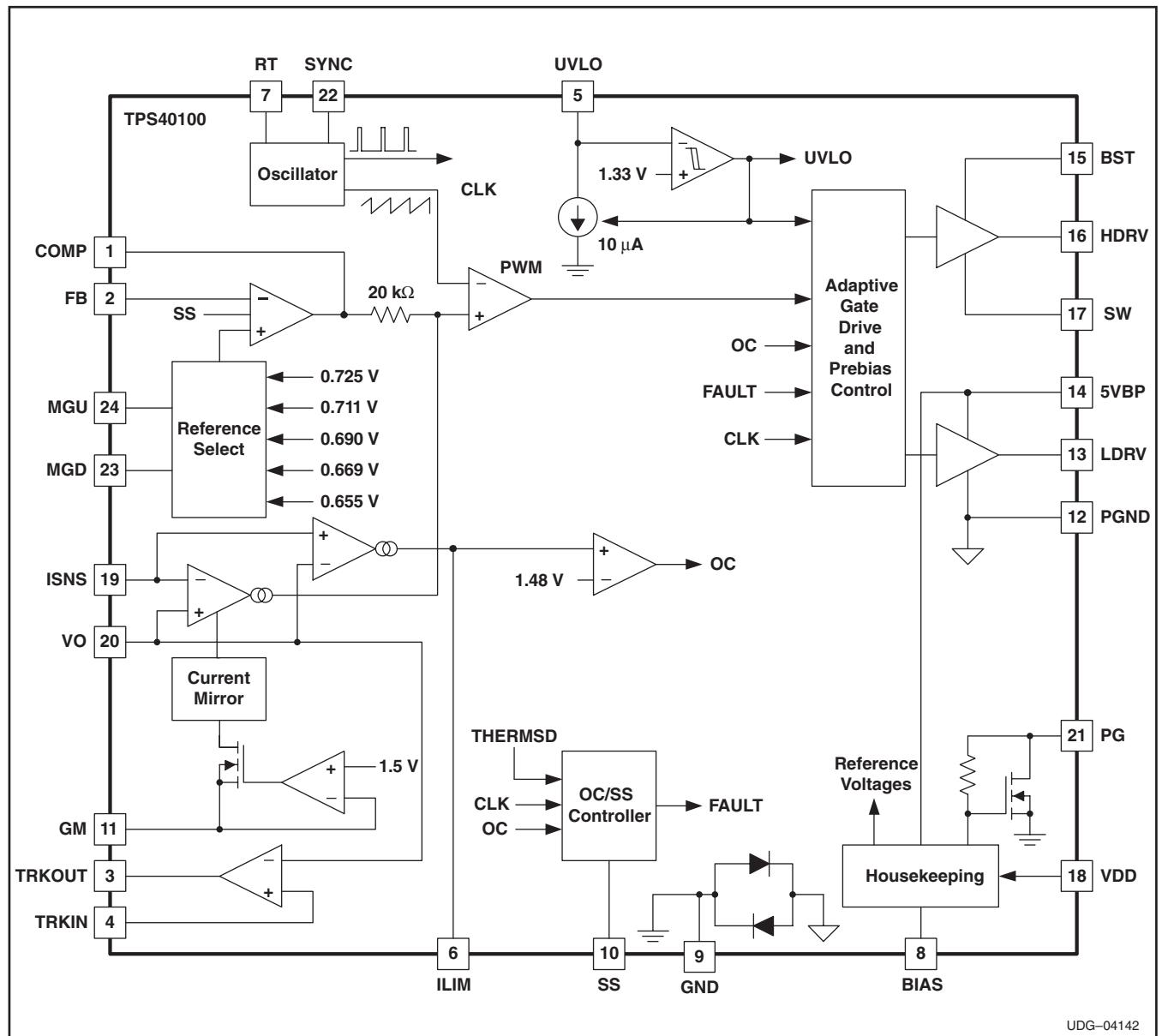

## FUNCTIONAL BLOCK DIAGRAM

UDG-04142

# アプリケーション情報

## はじめに

TPS40100は、シーケンス及び出力電圧のマージン機能を必要とするアプリケーション向けの同期式降圧型コントローラです。このコントローラは電流フィードバック・メカニズムを使用しているため容量変動の大きな負荷へのループ補償が容易になります。電流の検出(電流フィードバックと過電流の両方に対する)は完全に差動であり、インダクタの直流抵抗を使用するか(R-Cフィルタとともに)、またはインダクタに直列の別の検出抵抗を用いて行われます。過電流レベルは電流フィードバック量から独立してプログラムすることができます。アプリケーションでの柔軟性が高くなります。同様に、過電流機能は誤ったトリップを排除するためユーザーがプログラム可能なようにされており、ユーザーはアプリケーション要求に対応するよう調整することができます。コントローラは単に2つのピンのうちの1つを直接または抵抗を介してグランドに接続することで出力電圧をその標準値の±3%と±5%にマージン制御する方法を備えています。パワーグッド及びクロック同期機能が専用ピンで供給されています。ユーザーはグランドへの抵抗とコンデンサを用いてそれぞれ動作周波数と閉ループのソフトスタート時間をプログラムすることができます。出力のシーケンス/トラッキングは、シーケンシャル(1つの出力が立上がり、次に2番目が立上る)、レシオメトリック(1つまたは複数の出力が同時にレギュレーション状態に達する—起動時出力電圧は全て一定の割合で上昇する)、同時(1つまたは複数の出力が起動とともにトラッキングし最小から最大に順を追ってレギュレーション状態に達する)の3つの方法のうちの1つにより達成することができます。

図 1

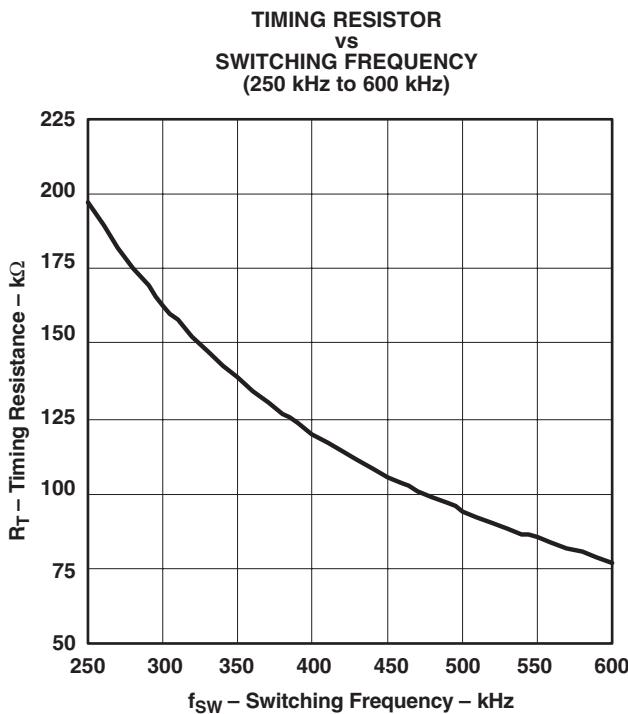

## 動作周波数のプログラム

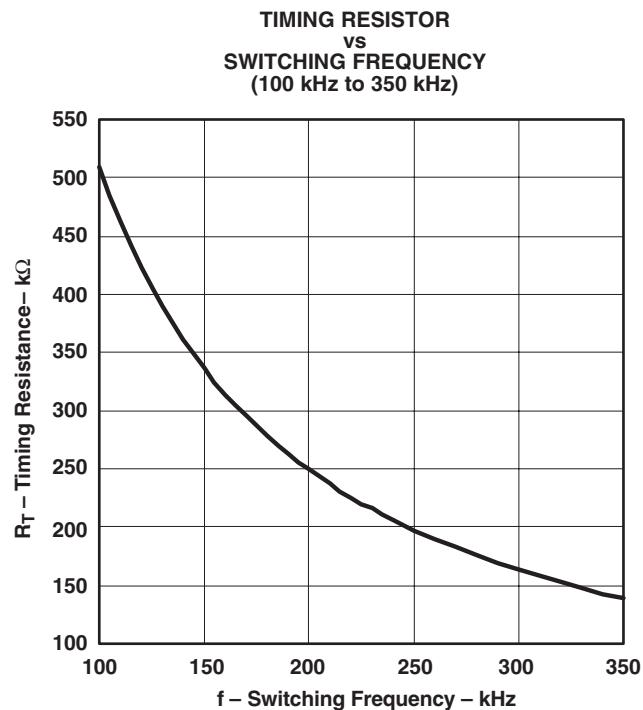

動作周波数はRTピンからGNDに抵抗を接続することで設定されます。その関係は以下のようになっています。

$$R_T = \left[ \frac{-3.98 \times 10^4}{f_{SW}^2} \right] + \left( \frac{5.14 \times 10^4}{f_{SW}} \right) - 8.6 \text{ (kΩ)} \quad (1)$$

但し、

●  $f_{SW}$ はスイッチング周波数で単位はkHzです。

●  $R_T$ の単位はkΩです。

図1と図2に式(1)で表わされるスイッチング周波数と抵抗 $R_T$ の関係を示します。ユーザーが高/低周波数の両方でより正確に見えるようスケーリングは両方の図で異なります。

図 2

## インダクタ値の選択

インダクタ値は出力コンデンサのリップル電流を決め、達成可能な過渡応答に影響を与えます。インダクタンスが大きいと、リップル電流と出力電圧リップルは減少しますが、同一電流定格では小さなインダクタンスよりも物理的に大きくなり、小さなインダクタンスの場合よりも出力電流のスルーレートを制限します。一方、インダクタンスが小さいと、リップル電流と出力電圧リップルは増加しますが、同一電流定格では大きなインダクタンスよりも物理的に小さくなります。ほとんどのアプリケーションについて、妥協案として望ましいのは、リップル電流がコンバータの全負荷電流の20%から30%となるインダクタンス値を選択することです。与えられたリップル電流に対し必要とされるインダクタンスは以下の式で求められます。

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times f_{SW} \times \Delta I} \quad (H) \quad (2)$$

但し、

- Lはインダクタンス値です (H)。

- V<sub>IN</sub>はコンバータの入力電圧です (V)。

- V<sub>OUT</sub>はコンバータの出力電圧です (V)。

- f<sub>SW</sub>はコンバータに選択されたスイッチング周波数です (Hz)。

- ΔIはインダクタのピーク間リップル電流です (A)。

## 出力容量の選択

出力容量の必要値は、存在する可能性のある負荷過渡特性に加え、要求される出力リップル電圧とインダクタのリップル電流で決まります。

出力電圧のリップルはリップル電流に直接的に依存し、出力コンデンサの2つのパラメータである総容量とコンデンサの等価直列抵抗(ESR)に影響を受けます。出力リップル電圧(ワースト・ケース)は以下の式から求められます。

$$\Delta V = \Delta I \times \left[ ESR + \left( \frac{1}{8 \times C_{OUT} \times f_{SW}} \right) \right] \quad (V) \quad (3)$$

但し、

- ΔVはピーク間の出力リップル電圧です (V)。

- ΔIはインダクタのピーク間リップル電流です (A)。

- f<sub>SW</sub>はコンバータに選択されたスイッチング周波数です (Hz)。

- C<sub>OUT</sub>は出力コンデンサの容量値です (F)。

- ESRはコンデンサC<sub>OUT</sub>の等価直列抵抗です (Ω)。

電解コンデンサの場合は、出力リップル電圧はほぼすべて(90%またはそれ以上)コンデンサのESRによります。セラミックの出力コンデンサを使用した場合は、ESRによる出力リップルへの寄与度はずっと小さく、容量値そのものがより重要になります。目的とする出力容量を得るため出力コンデンサを並列に接続することは、一般的に大きなコンデンサを1つ使用するよりもより効果的に実効ESRを低下させます。このことによりボード面積は犠牲になりますが性能は上がります。適合すべき負荷過渡要件がある場合、出力電圧のオーバーシュートとアンダーシュートを考慮しなければなりません。負荷が突然増加すると、出力電圧はインダクタの電流が新しい負荷の要求に適合するよう上昇するまで一時的に低下します。フィードバック・ループが積極的に設計されると、このアンダーシュートは最小限に抑えられます。アンダーシュートの仕様が与えられていると、必要とされる出力容量は以下の式で求められます。

$$C_{O(under)} = \frac{L \times I_{STEP}^2}{2 \times V_{UNDER} \times D_{MAX} \times (V_{IN} - V_{OUT})} \quad (F) \quad (4)$$

但し、

- C<sub>O(under)</sub>はアンダーシュートの仕様を満足するのに必要な出力容量です (F)。

- Lはインダクタ値です (H)。

- I<sub>STEP</sub>は負荷電流の変化です (A)。

- V<sub>UNDER</sub>は出力電圧の最大許容アンダーシュートです。

- D<sub>MAX</sub>はコンバータの最大デューティ・サイクルです。

- V<sub>IN</sub>は入力電圧です。

- V<sub>OUT</sub>は出力電圧です。

同様に、負荷電流が突然大きな値から小さな値になった場合、出力電圧はオーバーシュートします。出力電圧はインダクタの電流が新しい負荷電流に低下するまで上昇します。与えられたオーバーシュート量に必要とされる容量は以下の式で求められます。

$$C_{O(\text{over})} = \frac{L \times I_{\text{STEP}}^2}{2 \times V_{\text{OVER}} \times V_{\text{OUT}}} \quad (\text{F}) \quad (5)$$

但し、

- $C_{O(\text{over})}$ はオーバーシュートの仕様を満足するのに必要な出力容量です(F)。

- Lはインダクタ値です(H)。

- $I_{\text{STEP}}$ は負荷電流の変化です(A)。

- $V_{\text{OVER}}$ は出力電圧の最大許容オーバーシュートです。

- $V_{\text{OUT}}$ は出力電圧です。

出力容量の必要値は $C_{O(\text{under})}$ と $C_{O(\text{over})}$ の大きいほうの値です。インダクタのリップル電流が分かると、スイッチング周波数、必要とされる負荷ステップ、許容出力電圧の偏位により負荷過渡の観点から必要な出力容量の計算が可能となります。出力容量の実際の値とタイプはリップルと過渡の両方の仕様を満足させるものです。

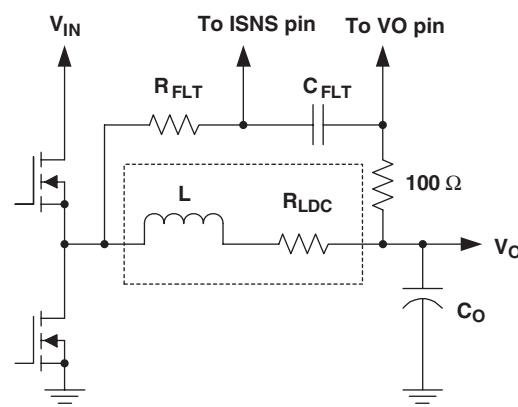

### 電流検出フィルタ回路の計算

TPS40100はインダクタの抵抗 $R_{\text{LDC}}$ 端の電圧を検出することで電流のフィードバック情報を入手します。このことを行うためには、検出した電圧がインダクタの実際の電流を代表できるようフィルタを構築しなければなりません。このフィルタは図3に示されているようにインダクタ端に接続された直列のR-C回路で構成されます。

$R_{\text{FLT}} \cdot C_{\text{FLT}}$ 時定数が $L/R_{\text{LDC}}$ 時定数に一致すると、 $C_{\text{FLT}}$ 端の電圧は $R_{\text{LDC}}$ 端の電圧に等しいことになります。 $R_{\text{FLT}}$ は10kΩまたはそれ以下にしておくことを推奨します。 $C_{\text{FLT}}$ はこの条件に適合するよう任意に選択することができます(推奨は100nF)。 $R_{\text{FLT}}$ は以下の式で計算することができます。

$$R_{\text{FLT}} = \frac{L}{R_{\text{LDC}} \times C_{\text{FLT}}} - 100 \quad (\Omega) \quad (6)$$

但し、

- $R_{\text{FLT}}$ は電流検出フィルタの抵抗です(Ω)。

- $C_{\text{FLT}}$ は電流検出フィルタの容量です(F)。

- Lは出力インダクタンスです(H)。

- $R_{\text{LDC}}$ は出力インダクタの直流抵抗です(Ω)。

ボード上にレイアウトする場合、 $C_{\text{FLT}}$ をできるだけVOピンとISNSピンの近くに配置することでより優れた特性が得られます。この2つの抵抗をデバイスの近くにもってくるほど、ノイズを拾いやすいハイ・インピーダンスの配線長が減少します。VOUTからデバイスのVOピンに100Ωの抵抗を接続するのは、コンバータの出力が短絡した時出力電圧がグランドを割り込んだ場合に電流を制限するためです。

UDG-04150

図3. Current Sensing Filter Circuit

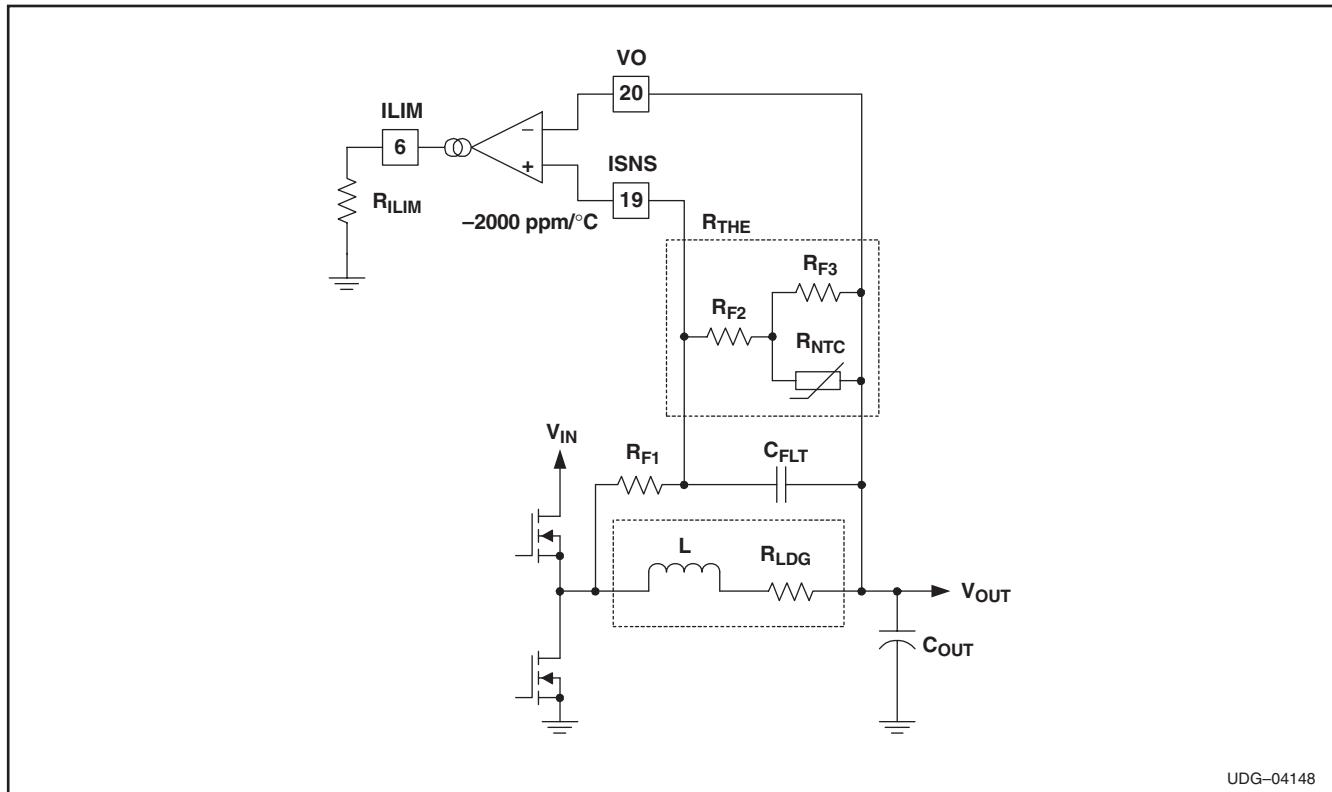

## 温度によるインダクタの抵抗変化の補償

検出されるインダクタの抵抗は銅巻線の抵抗です。この値は温度により変化し、温度係数は約4000ppm/°Cです。TPS40100の電流検出アンプのゲインは固定で約-2000ppm/°Cの温度係数をもっています。インダクタとデバイスの間で良好な熱結合が存在するよう回路が物理的に配置されていれば、熱の移動は相殺される傾向にあります。熱の結合が完全であれば、正味の温度係数は2000ppm/°Cです。一方、この結合が不完全であれば、正味の温度係数は2000ppm/°Cから4000ppm/°Cとなります。ほとんどのアプリケーションではこれで十分です。必要なら、温度ドリフトは補償することができます。以下の補償体系では、デバイスの温度上昇はインダクタの温度上昇に正比例すると仮定しています。これが当てはまなければ、補償の精度は落ちます。また、デバイスの温度上昇対インダクタの温度上昇には一般的に時間の遅れも存在するため、補償で予測される以上の過渡誤差が生じる可能性もあります。

また、図3の100Ωの抵抗について明らかにされていませんが、これは出力電圧が異常状態時グランドを割り込んだ場合に必要となります。これはR<sub>FLT</sub>の実効値を100Ω増加させる以外に計算には影響を及ぼしません。

インダクタの相対抵抗変化は以下の式より求められます。

$$R_{REL(L)} = 1 + TC_L \times (T_L - T_{BASE}) \quad (7)$$

(dimensionless)

但し、

- R<sub>REL(L)</sub>はT<sub>BASE</sub>時の抵抗を基準とした場合のT<sub>L</sub>時のインダクタの相対抵抗です。

- TC<sub>L</sub>は銅の温度係数で4000ppm/°Cまたは0.004です。

- T<sub>L</sub>はインダクタの銅温度です(°C)。

- T<sub>BASE</sub>は基準温度で、一般的には最低周囲温度です(°C)。

電流検出アンプの相対ゲインは以下の類似式より求められます。

$$gm_{(REL)} = 1 + TC_{GM} \times (T_{IC} - T_{BASE}) \quad (8)$$

(dimensionless)

但し、

- gm<sub>REL</sub>はT<sub>BASE</sub>時のゲインを基準とした場合のT<sub>IC</sub>時のアンプの相対ゲインです。

- TC<sub>GM</sub>はアンプのゲインの温度係数で-2000ppm/°Cまたは-0.002です。

- T<sub>IC</sub>はデバイスの接合部温度です(°C)。

- T<sub>BASE</sub>は基準温度で、一般的には最低周囲温度です(°C)。

デバイスの温度上昇は通常インダクタの温度上昇に関係しています。この2つの温度上昇の関係はほとんどの場合直線の関係として概算することができます。

$$T_{IC} - T_{BASE} = (T_L - T_{BASE}) \times k_{THM} \quad (9)$$

但し、

- T<sub>IC</sub>はデバイスの接合部温度です(°C)。

- T<sub>BASE</sub>は基準温度で、一般的には最低周囲温度です(°C)。

- T<sub>L</sub>はインダクタの銅温度です(°C)。

- k<sub>THM</sub>はデバイスの温度上昇をインダクタの温度上昇に関連付ける定数で、いかなる設計に対しても実験で決めなければなりません。

これらの条件を用いると、温度によるインダクタの実効抵抗は以下のようになります。

$$R_{REL(eff)} = R_{REL(L)} \times gm_{REL} = [1 + TC_L(T_L - T_{BASE})] \times [1 + k_{THM} \times TC_{GM} \times (T_L - T_{BASE})] \quad (10)$$

(dimensionless)

図4. Compensation for Temperature Coefficient of the Inductor Resistance

$R_{REL(eff)}$ は補償を行う場合に補償されなければならない相対実効抵抗です。図4の回路に電流制限での熱移動を補償する方法を示します。NTCサーミスタ ( $R_{NTG}$ ) をインダクタにうまく結合させなければなりません。 $C_{FLT}$ はできるだけデバイスに近づけて配置しなければなりません。

最初のステップは減衰比 $\alpha$ を決めることです。この比は1に近くなければなりませんが、あまり近すぎてもいけません。1にあまりにも近すぎると、回路には高インピーダンスと過度に高いサーミスタ値が必要となります。一方、 $\alpha$ が低過ぎると、電流信号は必要なまでに減衰します。この推奨値は0.8です。

$$\alpha \approx 0.8 \frac{R_{THE}}{R_{THE} + R_{F1}} \quad (\text{dimensionless}) \quad (11)$$

$R_{THE}$ は $R_{F2}-R_{F3}-R_{NTG}$ 回路の等価抵抗で以下の式で求められます。

$$R_{THE} = R_{F2} + \frac{R_{F3} \times R_{NTG}}{R_{F3} + R_{NTG}} \quad (\Omega) \quad (12)$$

基準温度 ( $T_{BASE}$ ) は熱平衡のための所定の最低温度、つまり予想される最低周囲温度となるよう選択しなければなりません。この基準温度におけるインダクタの抵抗を実効抵抗の計算に使用しなければなりません。 $T_{BASE}$ での電流検出アンプの予想ゲインは過電流用部品 ( $R_{ILIM}$ ) の計算に使用しなければなりません。

次のステップは、補償がデバイスとインダクタの銅線の反応に適合する2つの温度T1とT2を決めることです。これらが選択されると、NTCサーミスタが選択でき、そのデータシートからこの2つの温度における値 $R_{NTC(T1)}$ と $R_{NTC(T2)}$ が求められます。回路の部品値は以下の式により計算することができます。

$$R_{F1} = \frac{L}{R_{LDC(Tbase)} \times C_{FLT} \times \alpha} \quad (\Omega) \quad (13)$$

$$R_{LDC(T1)} = R_{LDC(Tbase)} \times R_{REL(effT1)} \quad (\Omega) \quad (14)$$

$$R_{LDC(T2)} = R_{LDC(Tbase)} \times R_{REL(effT2)} \quad (\Omega) \quad (15)$$

$$R_{THE(T1)} = \frac{\alpha \times R_{LDC(Tbase)} \times R_{F1}}{R_{LDC(T1)} - \alpha \times R_{LDC(Tbase)}} \quad (\Omega) \quad (16)$$

$$R_{THE(T2)} = \frac{\alpha \times R_{LDC(Tbase)} \times R_{F1}}{R_{LDC(T2)} - \alpha \times R_{LDC(Tbase)}} \quad (\Omega) \quad (17)$$

$$a = 1 - \frac{R_{NTC(T1)} - R_{NTC(T2)}}{R_{THE(T1)} - R_{THE(T2)}} \quad (\text{dimensionless}) \quad (18)$$

$$b = R_{NTC(T1)} + R_{NTC(T2)} \quad (\Omega) \quad (19)$$

$$c = R_{NTC(T1)} \times R_{NTC(T2)} \quad (\Omega^2) \quad (20)$$

$$R_{F3} = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a} \quad (\Omega) \quad (21)$$

$$R_{F2} = \frac{R_{THE(T1)} \times (R_{F3} + R_{NTC(T1)}) - R_{F3} \times R_{NTC(T1)}}{R_{F3} + R_{NTC(T1)}} \quad (\Omega) \quad (22)$$

但し、

- Lは出力インダクタンスの値です(H)。

- $C_{FLT}$ は電流検出フィルタ・コンデンサの値(F)です。

- $\alpha$ は式(11)から選択された減衰比です。

- $R_{THE(T1)}$ と $R_{THE(T2)}$ は温度T1とT2における $R_{THE}$ 回路の等価抵抗です。

- $R_{LDC(Tbase)}$ は温度T<sub>BASE</sub>におけるインダクタの直流抵抗で、単位はΩです。

- $R_{LDC(T1)}$ と $R_{LDC(T2)}$ は温度T1とT2におけるインダクタの抵抗です。

- $R_{REL(effT1)}$ と $R_{REL(effT2)}$ はT<sub>base</sub>に対するT1、T2でのインダクタの相対抵抗です。

- $R_{NTC(T1)}$ と $R_{NTC(T2)}$ は温度T1とT2におけるNTCサーミスタの実効抵抗です。

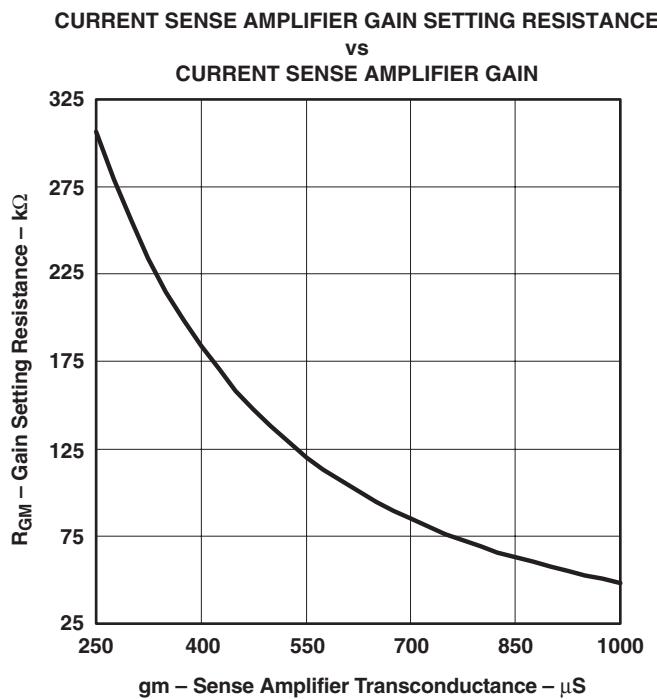

## 電流フィードバックの構築

ある特定のアプリケーションでの電流フィードバック量はユーザーがプログラムすることができます。使用される電流フィードバック量は出力フィルタの二重極のQを低減する程度の量を目的とします。このことにより、広範囲の出力容量にわたって安定したコンバータのコントロール・ループの設計が可能となります。電流フィードバックを大きく設定すると、ほとんど実利益がもたらされず、コンバータにパルス・スキップを生じさせるだけでなく、実質的に負荷過渡応答を劣化させる可能性があります。電流フィードバックは電流検出增幅器のゲインを設定することで調整されます。このアンプはトランスクンダクタンス型で、ゲインはGMピンからGNDに以下の式で求められる抵抗を接続することで設定されます。

$$R_{GM} = \frac{3}{43.443 \times gm_{CSA}^2 + 0.01543 \times gm_{CSA} + 3.225 \times 10^{-6}} \quad (\Omega) \quad (23)$$

但し、

- $R_{GM}$ はアンプのゲインを設定する抵抗です(Ω)。

- $gm_{CSA}$ は電流検出増幅器のゲインです(S)です。

電流検出増幅器のゲインの値は、1000μSより小さく、かつ、250μSより大きくなればならず、その結果ゲイン設定抵抗は50kΩより大きくなります。第一歩として推奨するのは、電流検出増幅器のゲインを標準の280μSに設定することでその結果 $R_{GM}$ は279kΩになります。この値はほとんどのアプリケーションに十分に順応します。図5に、電流検出増幅器のゲイン設定抵抗対電流検出増幅器のゲインを示します。

図 5

## コンバータの出力ゲインのコントロール

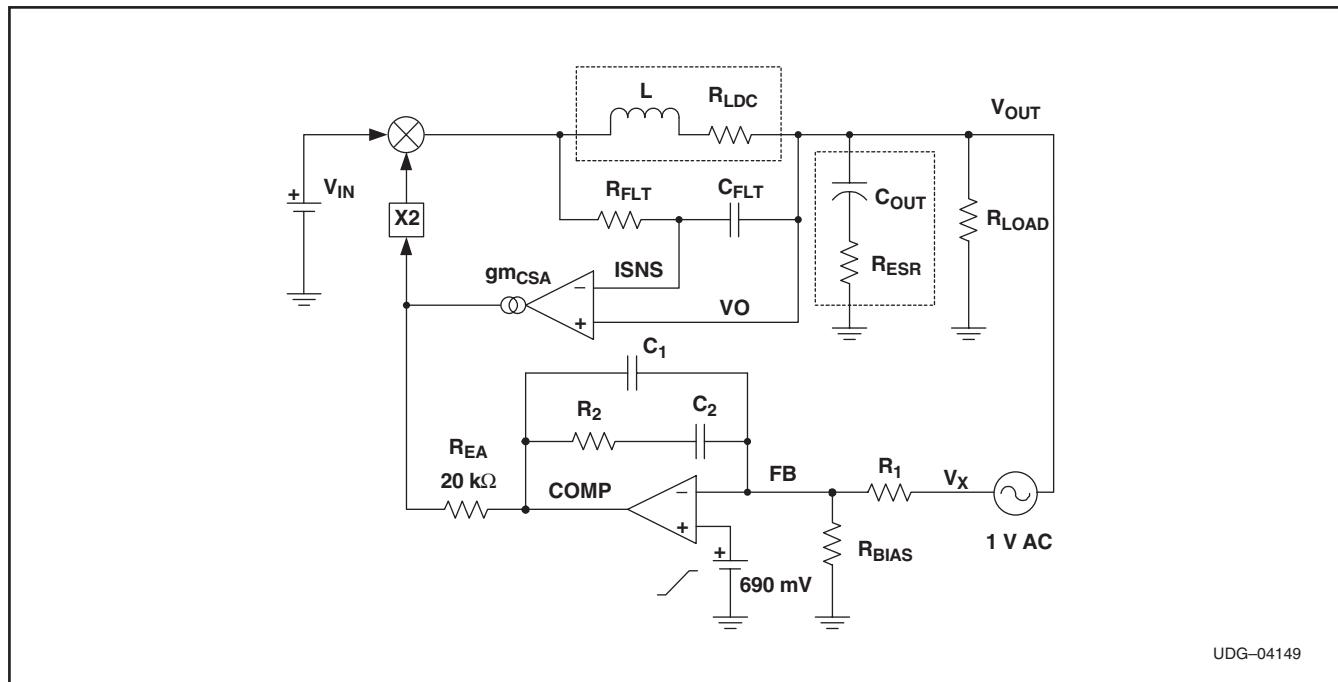

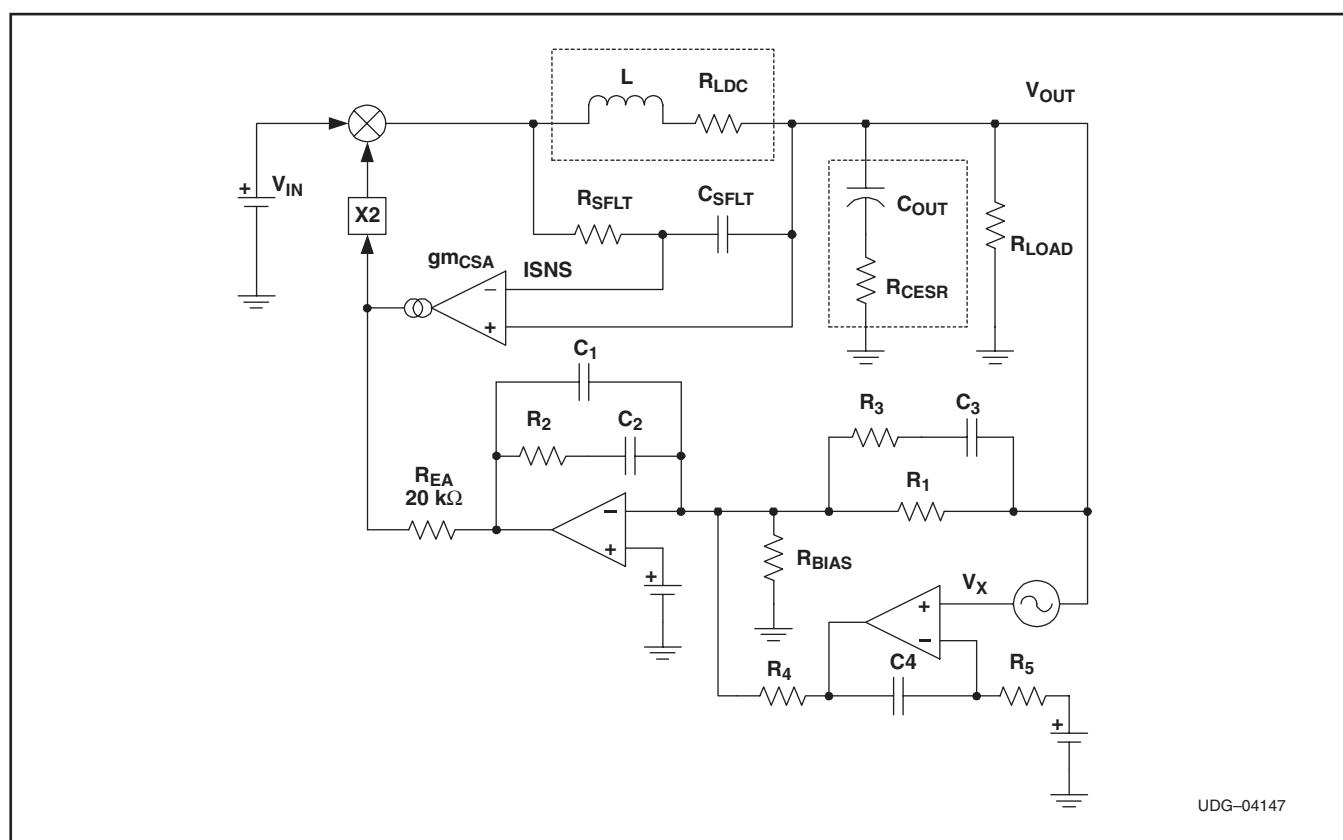

TPS40100をベースとしたコンバータの出力ゲインのコントロールの良好な第一次近似式が得られるモデルを図6に示します。このモデルは交流及び過渡応答プロットを生成するためシミュレータと連動して使用することができます。“X2”と標記

されているブロックはゲイン2の簡易標記です。アンプgmは電流検出増幅器(CSA)用に選択されたgmに等しいゲインをもつ簡素な電圧コントロールの電流源です。

分析にもとづき、このモデル(図6)の出力ゲインのコントロールは以下のように表すことができます。

$$K_{CO}(s) = \frac{V_{IN} \times K_{PWM} \times K_{FILT}(s)}{1 + Y(s) \times K_{CS} \times K_{PWM} \times V_{IN}} \quad (\text{dimensionless}) \quad (24)$$

K<sub>FILT</sub>(s)は出力フィルタの伝達関数です。

$$K_{FILT}(s) = \frac{R_{LOAD}}{R_{LDC} + R_{LOAD}} \times \frac{R_{ESR} \times C_{OUT} \times s + 1}{\frac{L \times C_{OUT} + R_{LOAD}}{R_{LDC} + R_{LOAD}} \times s^2 + \frac{L + C_{OUT} \times (R_{LOAD} \times R_{ESR} + R_{LDC} \times R_{LOAD} + R_{LDC} \times R_{ESR})}{R_{LOAD}} \times s + 1} \quad (\text{dimensionless}) \quad (25)$$

通常、R<sub>LDC</sub> << R<sub>LOAD</sub>であるため、以下の近似式が適用できます。

$$K_{FILT}(s) = \frac{R_{ESR} \times C_{OUT} \times s + 1}{L \times C_{OUT} \times s^2 + \left[ \frac{L + R_{LOAD} \times C_{OUT} \times (R_{ESR} + R_{LDC})}{R_{LOAD}} \right] \times s + 1} \quad (26)$$

Y(s)は電流信号の伝達関数で、インダクタ固有の時定数は電流検出フィルタ回路の時定数に一致していると仮定します。

$$Y(s) = \frac{1 - K_{FILT}(s)}{\frac{L}{R_{LDC}} \times s + 1} \quad (\text{dimensionless}) \quad (27)$$

$K_{CS}$ は電流フィードバック・ループにおける電流検出増幅器のゲインです。

$$K_{CS} = gm_{CSA} \times 20 \text{ k}\Omega \quad (\text{dimensionless}) \quad (28)$$

但し、各記号の定義は以下のとおりです(式(24)から式(28))。

- $V_{IN}$ は入力電圧です(V)。

- $K_{PWM}$ はパルス幅変調器のゲインで2です。

- $R_{LOAD}$ は等価負荷抵抗です( $\Omega$ )。

- $R_{LDC}$ はインダクタの直流抵抗です( $\Omega$ )。

- $L$ は出力フィルタのインダクタンスです(H)。

- $C_{OUT}$ は出力フィルタの容量です(F)。

- $R_{ESR}$ は出力フィルタ・コンデンサの等価直列抵抗です( $\Omega$ )。

- $gm_{CSA}$ は電流検出増幅器のゲインです(S)。

- 20k $\Omega$ は電流検出増幅器が逆作用するインピーダンスです(ブロック図より)。

これらの式の評価にコンピュータを利用した計算ツールを用いることを強く推奨します。

## ループの補償(タイプII)

最初のステップはループの目標クロスオーバー周波数を選択することです。過度に高いクロスオーバー周波数を選択すると、コンバータにパルス・スキップを生じさせる一因となります。パルス・スキップを回避するためクロスオーバー周波数と電流フィードバック量のバランスを保たなければなりません。推奨するループの最大クロスオーバー周波数はスイッチング周波数の1/5です。

$$f_C \leq \frac{f_{SW}}{5} \quad (\text{Hz}) \quad (29)$$

但し、

- $f_C$ はループのクロスオーバー周波数です。

- $f_{SW}$ はスイッチング周波数です。

図 6. Averaged Model for a Converter Based on the TPS40100

UDG-04149

分析モデルまたはシミュレーション・モデルのうちのどちらかを使用して、選択ループのクロスオーバー周波数における出力ゲインのコントロールを決めます。補償器のゲインはこのゲインの逆数です。

$$K_{COMP(co)} = \frac{1}{|K_{CO}(fc)|} \text{ (Hz)} \quad (30)$$

但し、

- $K_{COMP(co)}$ はクロスオーバー周波数における補償器の所要ゲインです。

- $K_{CO(fc)}$ はクロスオーバー周波数における出力伝達関数のコントロール値です。

モデルを使用して応答をシミュレーションすると、出力ゲインのコントロールは  $V_X/V_{OUT}$  です。交流電圧源を所定の範囲にわたってスイープし  $V_X/V_{OUT}$  をプロットします。

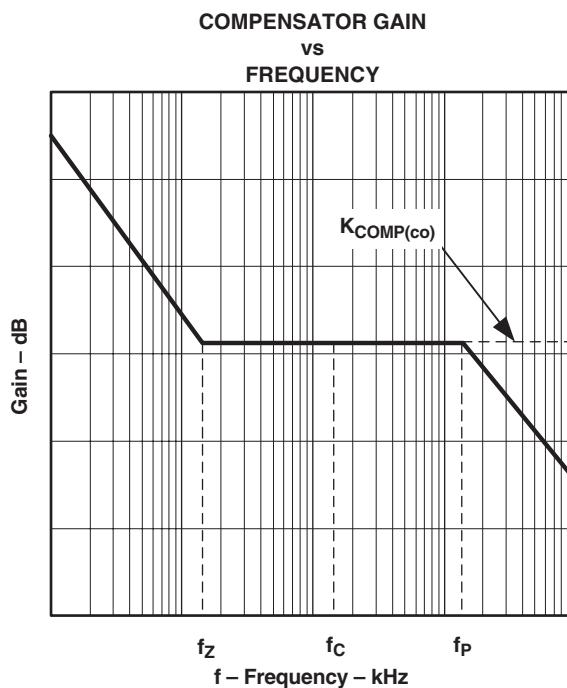

選択されたループのクロスオーバー周波数及び出力コンデンサの特性によってはタイプIIまたはタイプIIIのどちらかの補償器が必要となることがあります。出力容量に十分なESRがあれば、ESRゼロからの位相シフトを使用してタイプIIIの補償器をなくすことができる可能性があります。図6のモデルではタイプIIが使用されています。この場合、補償器の応答は図7のようになります。

まず、 $R_1$ を選択します。これはいくらか任意に選択されますが、一旦選択すると残りの部品に影響を与えます。この推奨値は  $10k\Omega$  です。

$R_2$ はクロスオーバー周波数において補償器から必要とされるゲインより求められます。

$$R_2 = K_{LF} \times R_1 \text{ (\Omega)} \quad (31)$$

一般的に推奨されることとは、極周波数をクロスオーバー周波数より10倍高くし、ゼロ周波数をクロスオーバー周波数より1/10低くすることです。

$$f_P = f_C \times 10 = \frac{1}{2\pi \times R_2 \times C_1} \text{ (Hz)} \quad (32)$$

$$f_Z = \frac{f_C}{10} = \frac{1}{2\pi \times R_2 \times C_2} \text{ (Hz)} \quad (33)$$

図 7

## ループの補償（タイプIII）

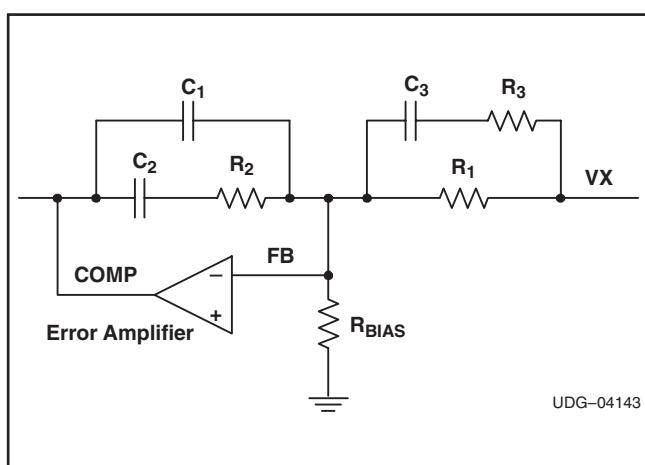

出力コンデンサにESRゼロからの位相シフトを使用するのに十分なESRがない場合にはタイプIIIの補償器が必要となります。セラミック出力コンデンサのみを用いているほとんどの設計がこれに該当します。図8に示されているように $R_1$ に並列に直列R-C回路を挿入します。

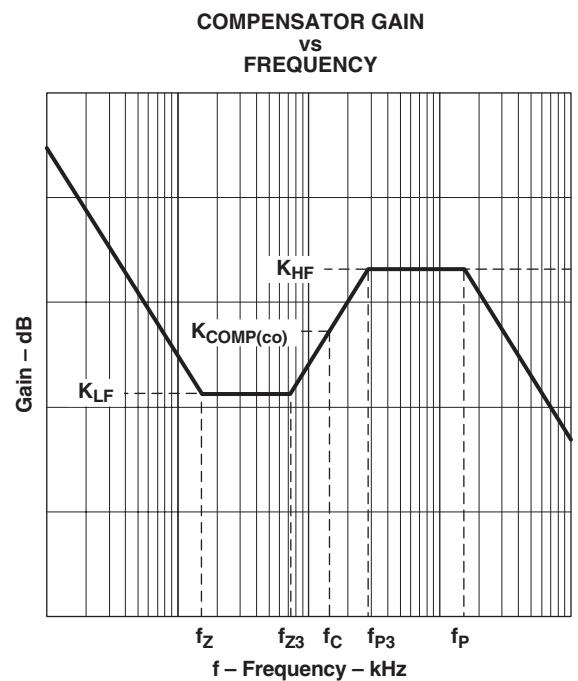

これは $C_3$ と $R_3$ を追加したことを除いては図6と同じ補償器です。この回路の代表的な応答を図9に示します。

タイプIIIの補償器を用いる理由は、 $f_{Z3}$ と $f_{P3}$ の間のゲインの上昇勾配に付随した位相進みを利用することです。クロスオーバー周波数はこの2つの周波数の間に位置していなければなりません。生成される位相進み量は、 $f_{Z3}$ と $f_{P3}$ がどの位離れているかによります。概して、 $f_{Z3}$ が $f_C$ の1/2で $f_{P3}$ が $f_C$ の2倍であれば、生成される $f_C$ における位相進み量はほとんどのアプリケーションで十分な量があります。状況によって多少の程度の差はあります。

必要とされる特別の位相進みを選択する例として、出力ゲインの位相のコントロールの見積もりを $f_C$ で-145°と仮定します。タイプIIの補償器では、元の極として $f_C/10$ でゼロ、 $10 \times f_C$ で極であるため $f_C$ での位相遅れは約11.5°です。このことは位相余裕が僅か23.5°であることになり、安定性にとって望ましくありません。 $f_{Z3}$ と $f_{P3}$ をそれぞれクロスオーバー周波数の1/2と2倍に置くことで $f_C$ での位相進みが約36°加わり新しい位相余裕は59.5°になります。

このタイプの補償器の値を計算するにはまず $R_1$ を選択します。この場合もいくらか任意に選択します。10kΩが推奨値です。

必要とされる位相余裕を得るためにタイプIIの補償以上に必要な特別の位相進みを選択し、極とゼロを追加するために必要となる乗数を計算します。

$$K_3 = \tan(\Theta_{LEAD}) + \sqrt{\tan(\Theta_{LEAD}) + 1} \quad (34)$$

(dimensionless)

但し、

- $\Theta_{LEAD}$ は特別な極とゼロを追加することにより生成される必要な特別の位相進みです。

- $K_3$ は新規の極とゼロの位置を得るために $f_C$ に適用される乗数です。

$f_{Z3}$ と $f_{P3}$ の位置は以下のようになります。

$$f_{Z3} = \frac{f_C}{K_3} \text{ (Hz)} \quad (35)$$

$$f_{P3} = f_C \times K_3 \text{ (Hz)} \quad (36)$$

但し、

- $K_3$ は新規の極とゼロの位置を得るために $f_C$ に適用される乗数です。

- $f_{Z3}$ は $R_3$ と $C_3$ を加えたことにより生じたゼロです。

- $f_{P3}$ は $R_3$ と $C_3$ を加えたことにより生じた極です。

図 8. Type III Compensator Schematic

図 9

$f_C$ における補償器より必要とされるゲイン $K_{COMP(co)}$ は式(30)で求められるタイプIIの補償と同じです。ゲイン $K_{LF}$ (図9参照)は以下の式で求められます。

$$K_{LF} = \frac{K_{COMP(co)}}{K_3} \text{ (dimensionless)} \quad (37)$$

よって $R_2$ は以下の式で求められます。

$$R_2 = K_{LF} \times R_1 \quad (\Omega) \quad (38)$$

高周波のゲインは以下のようになります。

$$K_{HF} = K_{COMP(co)} \times K_3 \text{ (dimensionless)} \quad (39)$$

よって、

$$R_3 = \frac{R_1 \times R_2}{K_{HF} \times R_1 - R_2} \quad (\Omega) \quad (40)$$

$$C_3 = \frac{1}{2\pi \times R_3 \times f_{P3}} \quad (F) \quad (41)$$

残りの極とゼロは前述と同様に $f_C$ の10倍及び $1/10$ に位置しています。式(31)と式(32)は前述のように $C_1$ と $C_2$ を解くのに使用することができます。

## トラッキングの構築とトラッキング・コントロール・ループの設計

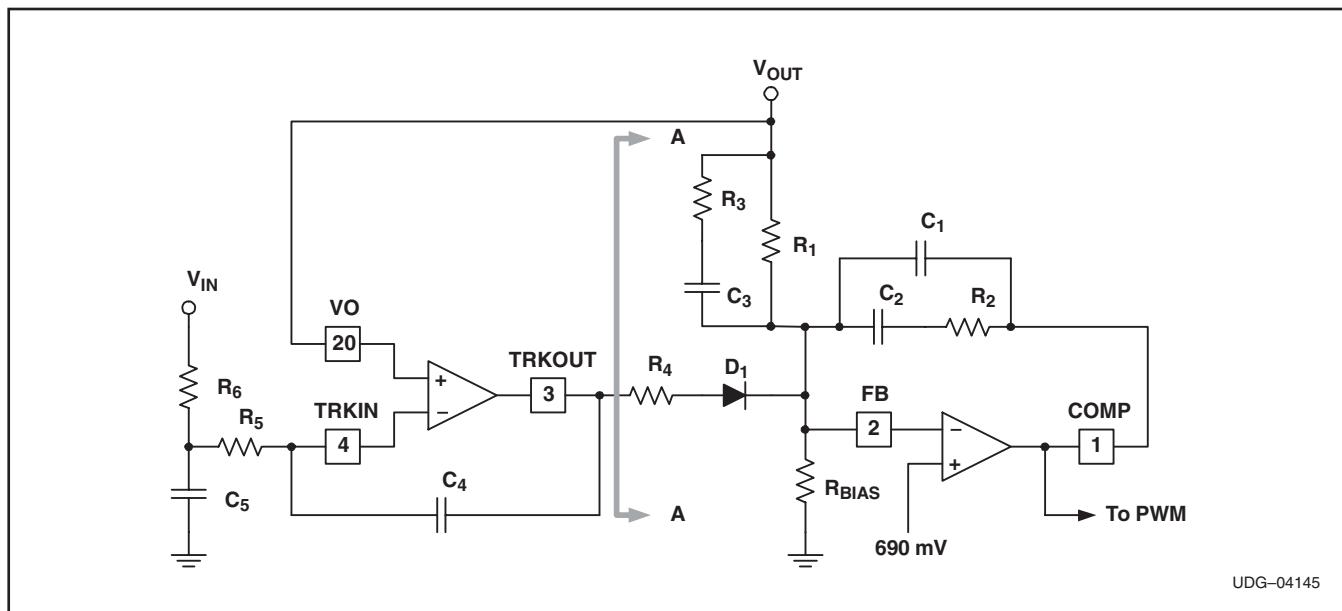

TPS40100の起動トラッキング機能は、TRKINピンに印加される基準電圧により出力電圧を制御するもう1つのコントロール・ループです。この基準電圧は一般的に外付けのR-C回路により生成されるランプ電圧です。複数のコンバータのR5、C5、R6(図10参照)の接合点を互いに接続することで起動時コンバータの出力電圧を同時にトラッキングすることができます。コントロールされた方法で共通の接合点をプルダウンし、それからコンバータへの電源を取り除くか、またはUVLOピンをグランドに落としてコンバータをオフにすることでコントロールされたパワー・ダウントが実行されます。当該回路の一部を図10に示します。

まず、 $R_4$ の値を選択します。この回路が正しく機能するには、トラッキング・アンプ出力は出力電圧( $V_{OUT}$ )が0Vの時FBピンが少なくとも690mVに達するようにする必要があります。このことは出力電圧がトラッキング・アンプによりゼロにされるということです。これにより $R_4$ の最大値が設定されます。

$$R_4 < \frac{[V_{HTRKOUT(min)} - V_{DIODE} - V_{FB}]}{V_{FB}} \times \frac{R_1 \times R_{BIAS}}{R_1 + R_{BIAS}} \Omega \quad (42)$$

図 10. Tracking Loop Control Schematic

但し、

- $V_{HTRKOUT(min)}$ はトラッキング・アンプの最小出力電圧です（電気的特性表参照）

- $V_{DIODE}$ はD<sub>1</sub>に選択したデバイスの順方向電圧です。

- $V_{FB}$ は基準電圧の値です(690mV)。

$R_4$ がこの値よりもずっと小さな値では、いたずらにトラッキング・ループのゲインを増加させ、補償をより困難にし潜在的な非線形のコントロールの問題を生じさせるため、これを選んではいけません。 $R_1-R_{BIAS}$ 列のインピーダンスが漏れ電流の影響が生じないほど十分低い場合、D<sub>1</sub>をショットキーすることができます。ショットキー・ダイオードの漏れ電流は高温時に大きく上昇することに注意してください。高温時の動作と高い精度が重要である場合には、D<sub>1</sub>には標準または低い漏れ電流の接合ダイオード、またはトランジスタのベース/エミッタ接合を使用してください。

$R_4$ が選択されると、図10の“A部”の閉ループ電源のゲインが分かります。このゲインはR<sub>1</sub>とR<sub>4</sub>の比です。

$$\frac{dV_{OUT}}{dV_{TRKOUT}} = -\frac{R_1}{R_4} \text{ (dimensionless)} \quad (43)$$

トラッキング・ループ自身は電圧コントロール・ループのクロスオーバー周波数よりずっと低いクロスオーバー周波数でなければなりません。一般的には、トラッキング・ループのクロスオーバー周波数はループの相互作用を避けるため電圧ループのクロスオーバー周波数の1/10またはそれより低くします。回路にあるダイオードによりトラッキング・ループには非線形のコントロール・メカニズムが生じることに注意してください。この非

線形のメカニズムが存在していることによりコントロール・ループの設計がより厳しくなります。もっとも簡単な方法は単にこのループの帯域幅を必要程度のみに制限することです。

$R_4$ に向かう電圧ループのゲインとトラッキング・ループの要求されるクロスオーバー周波数が分かると、R<sub>5</sub>とC<sub>4</sub>は以下の式で求められます。

$$R_5 \times C_4 = \frac{R_4}{2\pi \times R_1 \times f_{cTRK}} \quad (s) \quad (44)$$

但し、

- $f_{cTRK}$ はトラッキング・ループの要求されるクロスオーバー周波数です。

R<sub>5</sub>とC<sub>4</sub>の実際の値はインピーダンス・レベルと部品の大きさでバランスをとります。いかなる範囲の値も適用できますが、概して、R<sub>5</sub>はR<sub>6</sub>の20%以下で10kΩより小さくすべきです。このように行われると、トラッキング・ループのゲインの計算にR<sub>6</sub>を無視することに支障がなくなります。一般的な使用方法ではR<sub>6</sub>は100kΩから500kΩにしなければなりません。

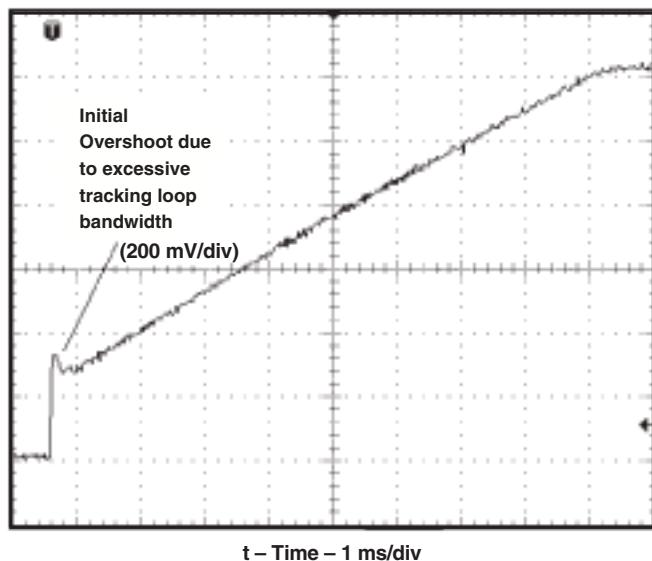

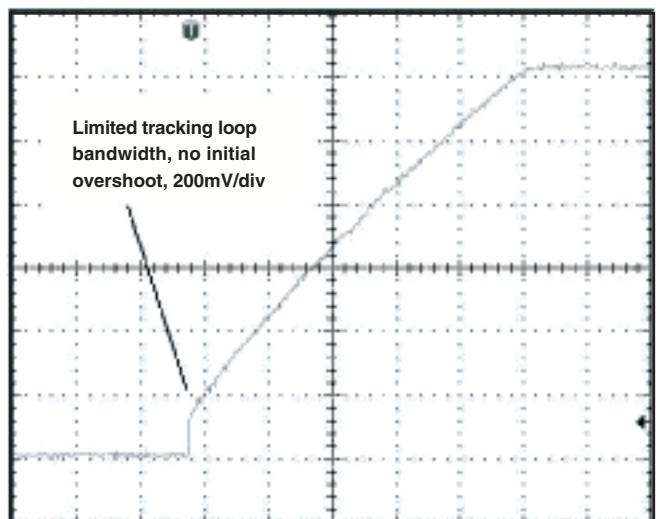

トラッキングがコントロールされている起動時の始めに出力にオーバーシュートの突出波形がある場合には、トラッキング・ループの帯域幅が高すぎることが考えられます。帯域幅を低減させると起動開始時のオーバーシュートを減少させるのに役立ちます。図11と図12を参照してください。

図 11. Excessive Tracking Loop Bandwidth

図 12. Limited Tracking Loop Bandwidth

トラッキングのランプ時間は $C_5$ をコンバータの出力電圧と同じ電圧に充電するのに要する時間です。

$$t_{TRK} = -R_6 \times C_5 \times \ln\left(1 - \frac{V_{OUT}}{V_{IN}}\right) \text{ (s)} \quad (45)$$

但し、

- $V_{OUT}$ はコンバータの出力電圧です。

- $V_{IN}$ は $R_6$ の上側に印加される電圧です。

- $t_{TRK}$ は目的とするトラッキング・ランプ時間です。

これらの式を用いて、ループのインピーダンス・レベルと部品の大きさが特定のアプリケーションに対しバランスがとれるようトラッキング・ループを設計することができます。インピーダンスが高いとループがノイズの発生に影響をより受けやすくなり、一方、インピーダンスが低いと大きなコンデンサが必要となることに注意してください。

図13にトラッキング・ループを使用するために拡張した電圧ループのスパイク・モデルを示します。

このモデルを使用するために、交流電圧源は所定の周波数範囲でスイープされます。開ループの交流応答は $V_X/V_{OUT}$ です。

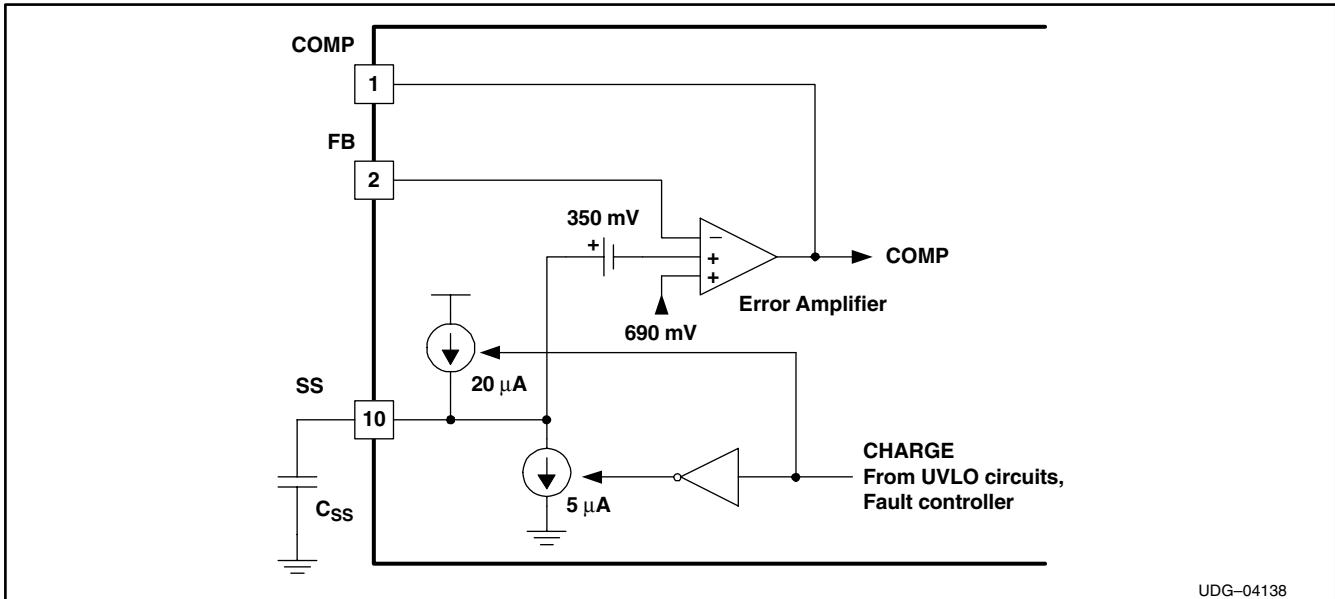

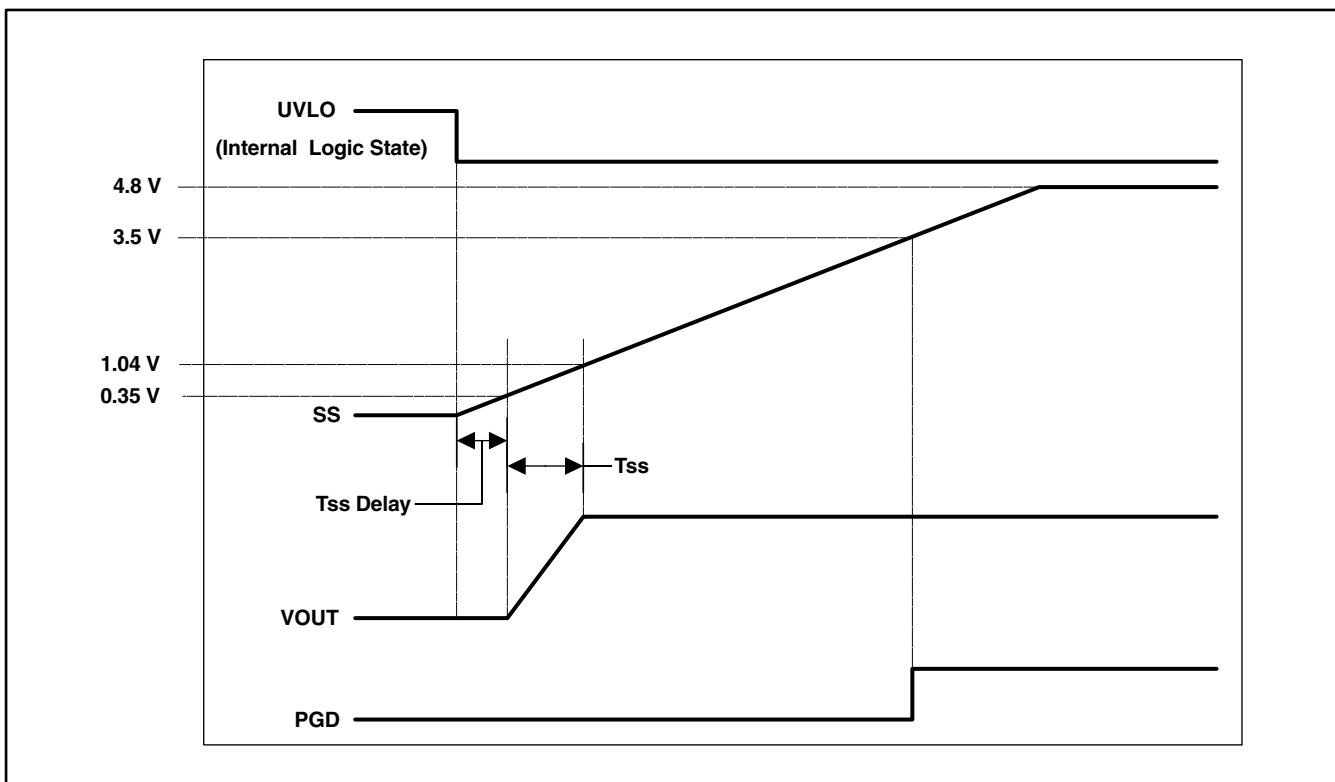

## ソフトスタート時間のプログラム

TPS40100のソフトスタート時間は単一のコンデンサを選択することで全てユーザーがプログラムすることができます。SSピンはこのコンデンサを充電するため $20\mu\text{A}$ のソース電流を流します。実際の出力の上昇時間はこの $20\mu\text{A}$ のソース電流が $690\text{mV}$ 程コンデンサを充電するのに要する時間です。実際のSS

ピンの電圧から誤差増幅器に印加される電圧のオフセットにより初めにいくらかの遅れが存在します。図15を参照してください。ソフトスタートは閉ループ方式で行われ、これは誤差増幅器がソフトスタート期間常に出力電圧をコントロールし、フィードバック・ループはデューティ・サイクル制限のソフトスタート構成で起こるようなオーブンにはならないということを意味しています。誤差増幅器には2つの非反転入力があり、1つは $690\text{mV}$ の基準電圧、もう1つはオフセットを持ってSSピン電圧です。この2つのうちの低い方の電圧を用いて、誤差増幅器のFBピンがコントロールされます。SSピンの電圧が上昇して約 $1.04\text{V}$ を越えた時(その結果、SS端子が接続される誤差増幅器の "+" 入力が $690\text{mV}$ より大きくなり)、 $690\text{mV}$ の基準電圧が主入力となり、コンバータはその最終レギュレーション電圧に達したことになります。

出力電圧に対し与えられたソフトスタート・ランプ時間に必要とされる外付けコンデンサは以下の式で求められます。

$$C_{SS} = T_{SS} \times \frac{20 \mu\text{A}}{V_{FB}} \text{ (F)} \quad (46)$$

但し、

- $T_{SS}$ は目的とするソフトスタート・ランプ時間です (S)。

- $C_{SS}$ はSSピンに必要な容量です (F)。

- $V_{FB}$ は基準電圧のフィードバック・ループです ( $690\text{mV}$ )。

図 13. AC Behavioral Model for Tracking Control Loop

図 14. Error Amplifier and Soft-Start Functional Diagram

図 15. Relationship Between UVLO(InternalLogicState), SS, VOUT and PGD at Startup

## ソフトスタートとトラッキング起動間の相互作用

TPS40100は起動のコントロールに2つの方法を供給しているため(閉ループのソフトスタートとトラッキング)、確実にこの2つの方法が互いに干渉しないよう注意を払わなければなりません。この2つの方法は同時に出力を試みたりコントロールしたりすることはできません。トラッキングが使用される場合、トラッキング・アンプへの基準電圧入力(TRKIN)はソフトスタートが完了するまで低レベルに保持しておくか、またはSSピンの電圧を少なくとも1.04Vより高くしておきます。このことにより、確実にソフトスタート回路はトラッキング回路と同時には起動のコントロールを行うことはしないようになります。ソフトスタートが起動のコントロールを行おうとする場合には以下の2つの選択肢があります。

- トラッキング・アンプ出力をFBノードから切り離します(これが推奨する解決策で、必要ならトラッキング・アンプは他のシステム用に使用することができます)。

- トラッキング・アンプ出力をFB回路に接続保持します—この場合トラッキング・アンプへの基準電圧はVDDに接続しなければなりません。このことにより、トラッキング・アンプの出力(TRKOUT)は常に低レベル状態となるため、トラッキング回路がコンバータの起動に与える影響が排除されます。

また、トラッキングが起動をコントロールすることができる時、ソフトスタートは任意で短時間に設定してはいけません。こうすると、ソフトスタートが急速に上昇し、トラッキング・ループ(必ず低い帯域幅)が出力電圧をゼロ電圧にコントロールするのに十分な速度で応答できないため、電源がコンバータに印加された時出力電圧は跳ね上がります。言い換えると、ソフトスタートのランプ・レートは、無効となるようにトラッキング・ループの能力範囲内でなければなりません。

## 過電流保護

過電流特性はILIMピンからGNDに並列のR-C回路を接続することで決まります。ILIMピンは電流検出アンプのトランジスタコンダクタンスとISNSとGND間の電圧に比例するソース電流を流します。この電流によりILIMにR-C回路の電圧が生じます。ILIMピンの電圧が1.48Vに達すると、過電流状態が宣言され、出力は一定期間スイッチングを停止します。この期間はソフトスタート・コンデンサを制御された電流で放電するのに要する時間により決まります。過電流レベルを設定するには以下の式を用います。

$$R_{ILIM} = \frac{V_{ILIM}}{gm_{CSA} \times R_{LDC} \times I_{OC}} \quad \Omega \quad (47)$$

但し、

- $V_{ILIM}$ は過電流コンパレータのスレッシホールドです(標準1.48V)。

- $I_{OC}$ は設定する過電流レベルです。

- $gm_{CSA}$ は電流検出アンプのトランジスタコンダクタンスです。

- $R_{LDC}$ はインダクタの等価直列抵抗です(または検出抵抗値)。

- $R_{ILIM}$ はILIMからGNDへの抵抗の値です。

過電流回路の応答時間はILIMピンのR-C時定数と過電流のレベルで決まります。応答時間は以下の式で求められます。

$$t_{OC} = -R_{ILIM} \times C_{ILIM} \times \ln\left(1 - \frac{1}{n}\right) \quad (s) \quad (48)$$

但し、

- $t_{OC}$ は過電流を宣言する前の応答時間です。

- $R_{ILIM}$ ( $\Omega$ )と $C_{ILIM}$ (F)はILIMピンに接続される部品です。

- $n$ は過電流の乗数です。過電流がプログラムされるレベルの2倍であれば、 $n$ は2です。

ILIMの時定数を適切に設定することにより、過電流応答の短時間の過渡検出をフィルタることができます。さらに過負荷及び短絡に対する保護を提供することができます。電流検出増幅器の $gm$ は約-2000ppm/ $^{\circ}$ Cの温度係数があります。これはインダクタの銅線抵抗の温度係数、約+4000ppm/ $^{\circ}$ Cをオフセットする手助けになります。正味の温度係数は+2000ppm/ $^{\circ}$ Cになります。よって、コントローラとインダクタ間は良好な熱結合がなされていると仮定すると、温度が100 $^{\circ}$ C上昇すると、過電流スレッシホールドは20%低下します。必要なら前述したように温度補償を行うことができます。

過電流状態が検出された時、コントローラはスイッチングを停止し、ハイサイドMOSFETとローサイドMOSFETの両方ともオフにします。ソフトスタート・コンデンサは過電流状態時、充電レートの25%の電流で放電され、コンバータはソフトスタート・ピンが、ソフトスタート回路が再度充電を開始し、コンバータが再始動するポイントの200mVに達するまで待機状態となります。通常動作では、ソフトスタート・コンデンサは出力が初期異常である時約3.5Vに充電されています。このことは過電流検出されて最初の再起動が試みられるまでの最小待ち時間が以下のようになることを意味しています。

$$t_{RESTART} = \frac{3.3 \times C_{SS}}{I_{SSDIS}} \quad (s) \quad (49)$$

但し、

- $t_{RESTART}$ は最初の再起動時間です(s)。

- $C_{SS}$ はソフトスタート容量です(F)。

- $I_{SSDIS}$ はソフトスタート放電電流です(5 $\mu$ A)。

出力異常が持続しており、再始動時再び過電流が検出されると、両方のMOSFETともオフになり、ソフトスタート・コンデンサは3.5Vまで充電を続け、それから200mVまで放電してから再始動が行われます。

UDG-04139

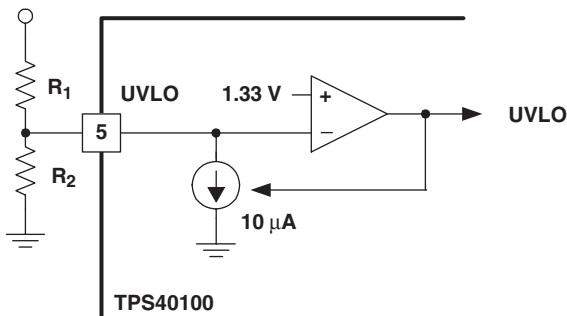

図 16. UVLO Circuit Functional Diagram

## UVLOのプログラム

TPS40100はユーザーにプログラム可能なUVLOレベルとプログラム可能なヒステリシスを提供します。機能的な観点からのUVLO検出回路図を図16に示します。

この回路をプログラムするためには、まず、目的とするヒステリシスの量(起動電圧とシャットダウン電圧の差)を選択します。

$$R_1 = \frac{V_{HYST}}{I_{UVLO}} \Omega \quad (50)$$

次に、ターンオン電圧(V<sub>on</sub>)を選択し、R<sub>2</sub>について解きます。

$$R_2 = \frac{V_{UVLO} \times R_1}{V_{ON} - V_{UVLO} - R_1 \times I_{UVLO}} \Omega \quad (51)$$

但し、

- V<sub>HYST</sub>はプログラマブルUVLO回路のヒステリシスの目標レベルです。

- I<sub>UVLO</sub>は低電圧ロックアウト回路のヒステリシス電流です(10μA typ)。

- V<sub>UVLO</sub>はUVLOコンパレータのスレッショルド電圧です(1.33V typ)。

## 電圧のマージン制御

TPS40100はユーザーが一時的に出力電圧を標準出力の3%上下、または5%上下に変化させることを可能にしています。このことは、MGUピンあるいはMGDピンを直接または抵抗を介してGNDに接続することにより実現します。表1を参照してください。

出力電圧を調整する際に考慮すべき重要な点がいくつかあります。

- これらのピンのうちの1つを常にオープン回路以外にしておかなければなりません。この表に記載していない状態は妥当でない状態で、これが行われると回路の動作は不安定になります。

- マージン・ピンを使用して出力電圧を変更する時、マージン・ピンの状態を変える前に、それ以前のマージンの移行を完了させることができます非常に重要です。

- マージン状態を変更するのに機械的な方法(スイッチ、“乾式”タイプのリレー接点などの機械的な接点)を用いてはいけません。接点のバウンスにより動作が不安定になります。

| GNDへの抵抗(kΩ)      |                  | 出力電圧 |

|------------------|------------------|------|

| R <sub>MGU</sub> | R <sub>MGD</sub> |      |

| オープン             | オープン             | 標準   |

| < 10 kΩ          | オープン             | +5%  |

| オープン             | < 10 kΩ          | -5%  |

| 25kΩ to 37kΩ     | オープン             | +3%  |

| オープン             | 25kΩ to 37kΩ     | -3%  |

表 1. Output Voltage Margining States

## 同期

TPS40100は回路の自走周波数より高速の外部のクロックと同期させることができます。SYNCピンは発振器への立上がりエッジ・トリガーで、現在のサイクルを終了させ、次のスイッチング・サイクルを開始させます。同期周波数は自走周波数の120%程度にすることを推奨します。このガイドラインに従うこととでデバイスのパルス幅変調器によるノイズやジッターの問題が減少します。この回路は自走周波数のさらに高い倍数の周波数にも同期させることができますが、このことによりPWMに加わる発振器からのランプの振幅が比例して減少することになり、その結果ノイズ感度とPWMゲインが増加し、場合によってはコントロール・ループの安定性に影響を与えてしまうことに注意してください。

SYNCピンに加わるパルスは、そのパルスが“H”レベルまたは“L”レベルのどちらにあってもパルス幅が少なくとも100nsある限りデューティ比はいくらでもかまいません。レベルは“L”レベルとみなされる0.8V以下の電圧及び“H”レベルとみなされる2V以上の電圧とロジック・コンパチブルです。

## パワーグッド表示

PGDピンはオープン・ドレイン出力で、次のいずれかの条件を満足するとGNDレベルに低下します(入力電圧は4.5Vより高いと仮定)。

- ソフトスタートがアクティブ ( $V_{SS} < 3.5V$ )。

- トラッキングがアクティブ ( $V_{TRKOUT} > 0.7V$ )。

- $V_{FB} < 0.61V$

- $V_{FB} > 0.77V$

- $V_{UVLO} < 1.33V$

- 過電流状態が存在している。

- チップの温度が165°Cより高い。

短期間の過渡条件やノイズによって、PGDが“H”レベル状態からGNDに低下し、パワー“NOT”グッド状態を表示することが無い様に、フィルタ(20μs)が内蔵されています。

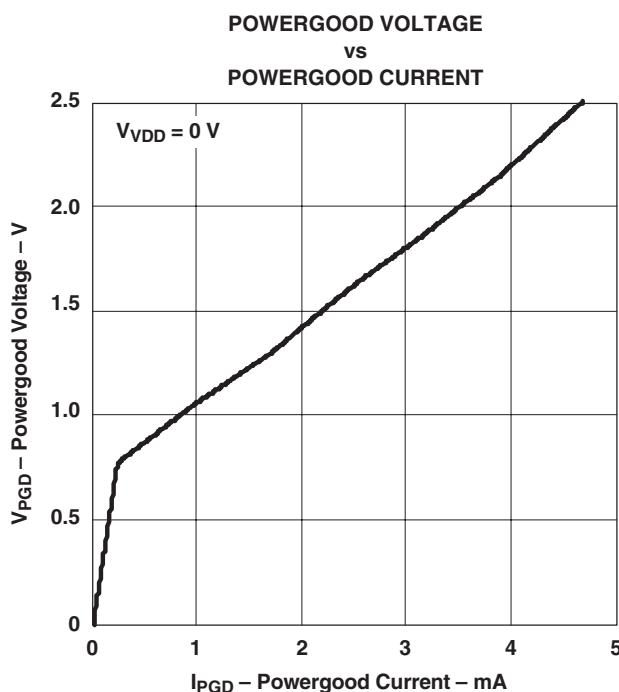

PGDピンは入力電源がない場合“L”レベルになろうとします。VDDピンがオープン回路であると、PGDの電圧は一般的に図17で示されるような動作をします。

図 17

## プリバイアス動作

アプリケーションによっては、出力がプリバイアスされている状態において、コンバータ起動時に出力から電流をシンクしないことが要求されます。同期式降圧型コンバータは本質的にシンク電流を流すため、このような動作を行わないような方法が考慮されなければなりません。このような動作を必要とするアプリケーションには、一般的に複数の電圧レールを必要とするプロセッサやASIC用の電源があります。このコントローラで使用される方法は、スタートアップランプ電圧で制御された出力電圧が既存の出力電圧より高くなるまでローサイドまたは整流MOSFETをオンにしないことです。これは内部のパルス幅変調器(PWM)の最初の出力パルスをモニタすることにより検知されます。このコントローラは閉ループの起動を使用しているため、PWMの最初の出力パルスは出力電圧が既存の電圧より高くなるよう制御されるまで発生しません。このことにより、コントローラは効果的にスタートアップ・シーケンス時にソース電流を流すことのみに制限されます。もし既存の電圧がコンバータの設定された出力レギュレーション電圧よりも高い場合、コンバータはソフトスタート時間が満了した時動作を開始し、シンク電流を流します。

## リモート・センス

TPS40100は、負荷レギュレーションの改善のため負荷電圧を間接的に検出することができます。これは出来るだけ負荷の近くから、フィードバックラインとGNDラインをとることで可能となります。

**注：GNDピンへの配線が長いとコントローラの動作が不安定になります。**

これはパルス幅が広くなったジッターとして現われ始めます。まずは、GNDピンの接続はPGNDから6インチ以内にしなければなりません。不安定動作が生じ始める実際の距離はアプリケーションやレイアウトに依存するため、個々の基準で評価しなければなりません。コントローラの出力パルスに25ns以上のジッターがあり、GNDピンが負荷グランドに接続されている場合、PGNDピンに近づけてGNDピンを接続すると(その結果負荷レギュレーションがいくらか犠牲になります)特性が改善することがあります。いずれにしても、フィードバック・ラインを負荷点で接続するといかなる問題も生じません。レイアウトについては、フィードバック・デバイダはデバイスに近づけて配置すべきで、配線はそこから負荷点に引き回します。

## Application Schematics

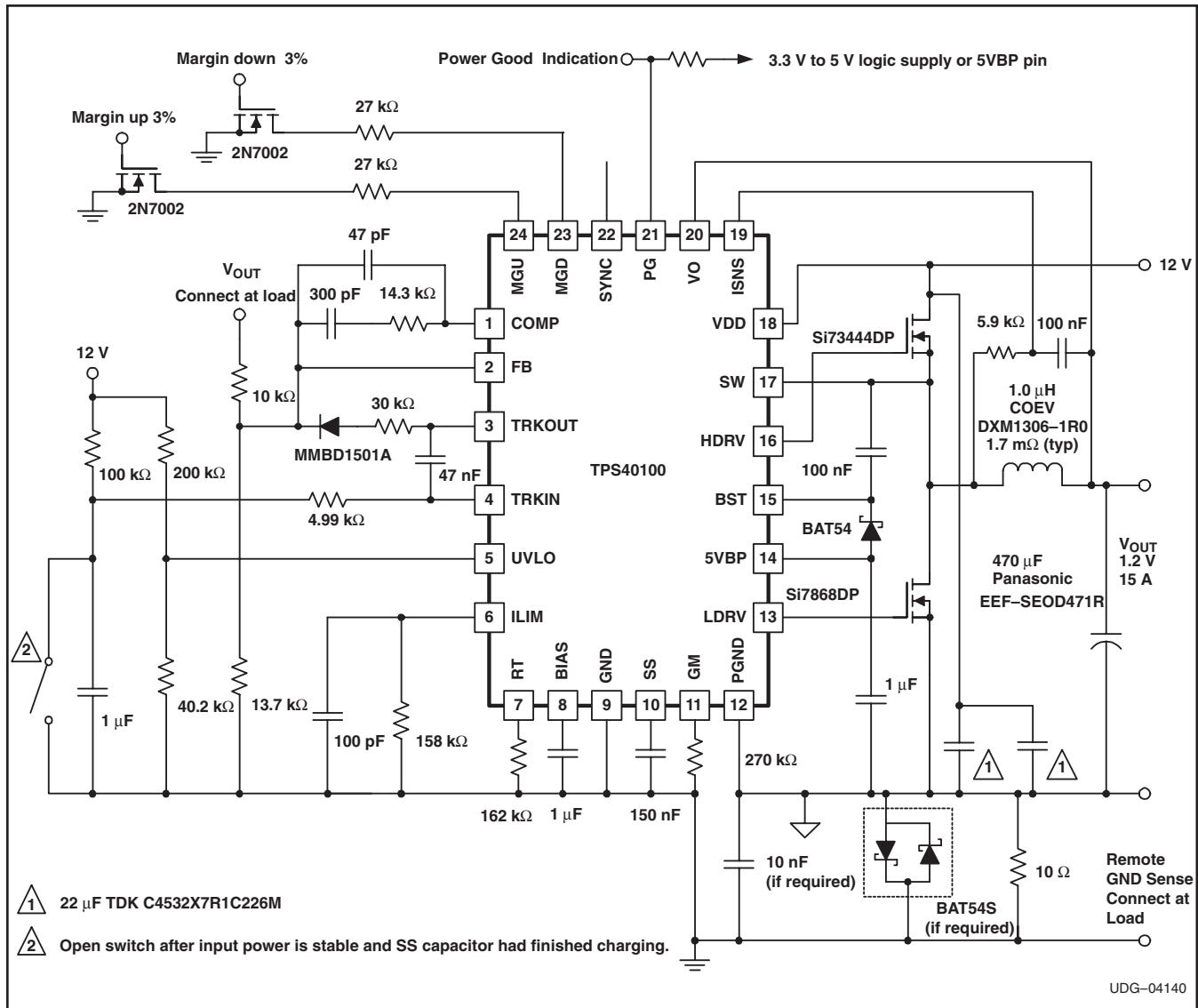

図 18. 300-kHz, 12-V to 1.2-V Converter With Tracking Startup Capability and Remote Sensing

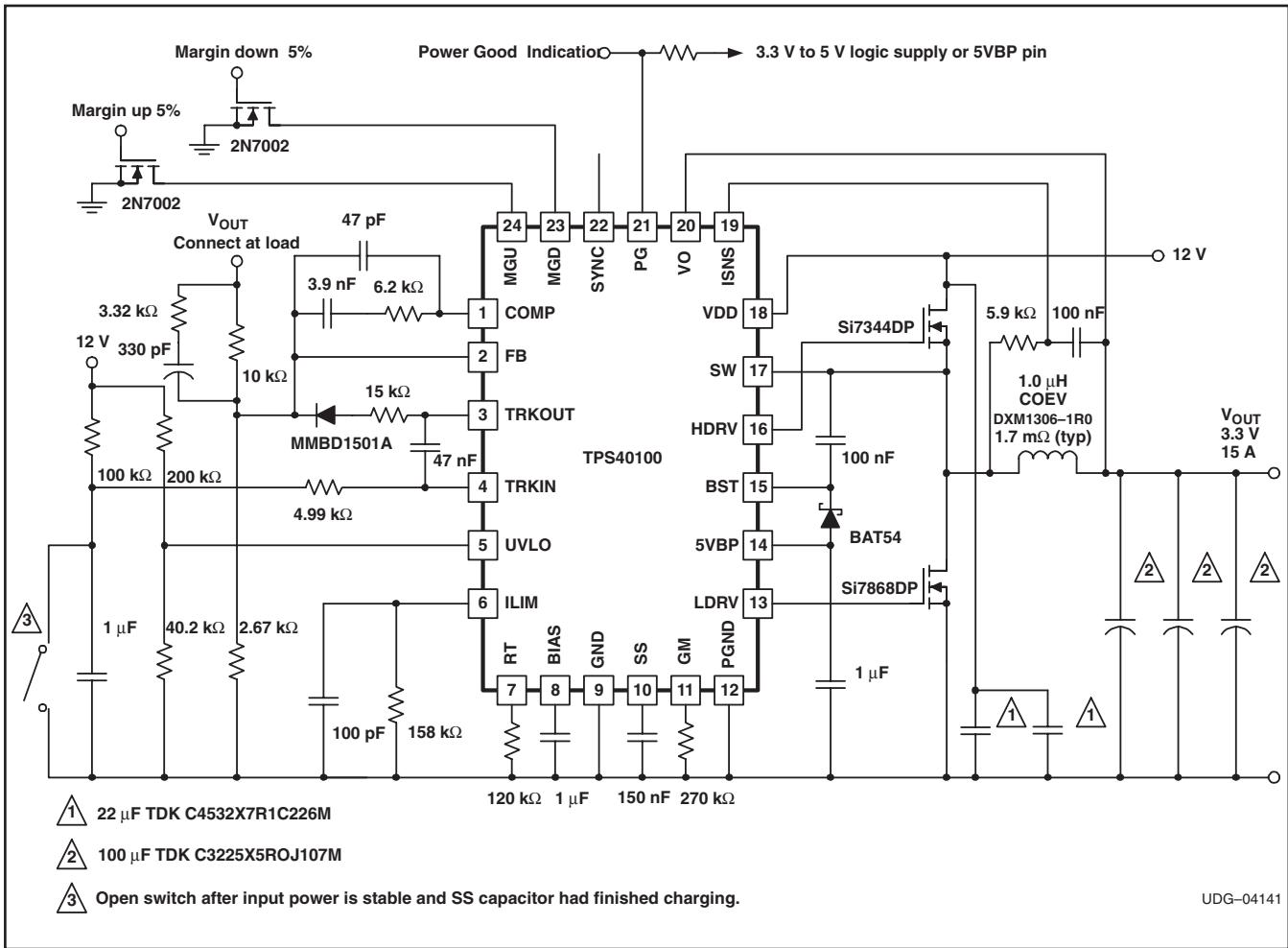

FIG 19. 400-kHz, 12-V to 3.3-V Converter With Tracking Capability and 5% Margining

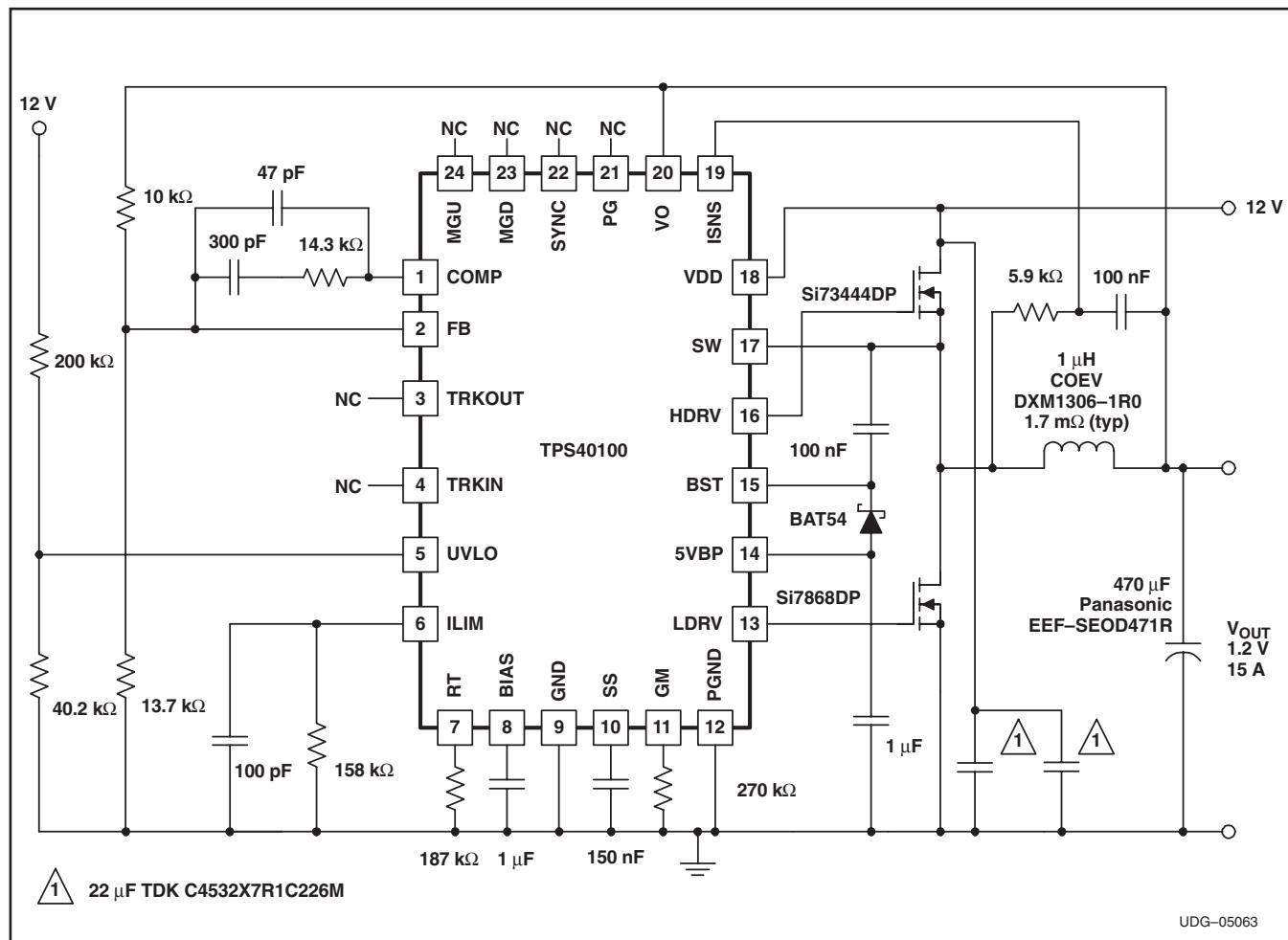

图 20. Minimal Application for 12-V to 1-V Converter

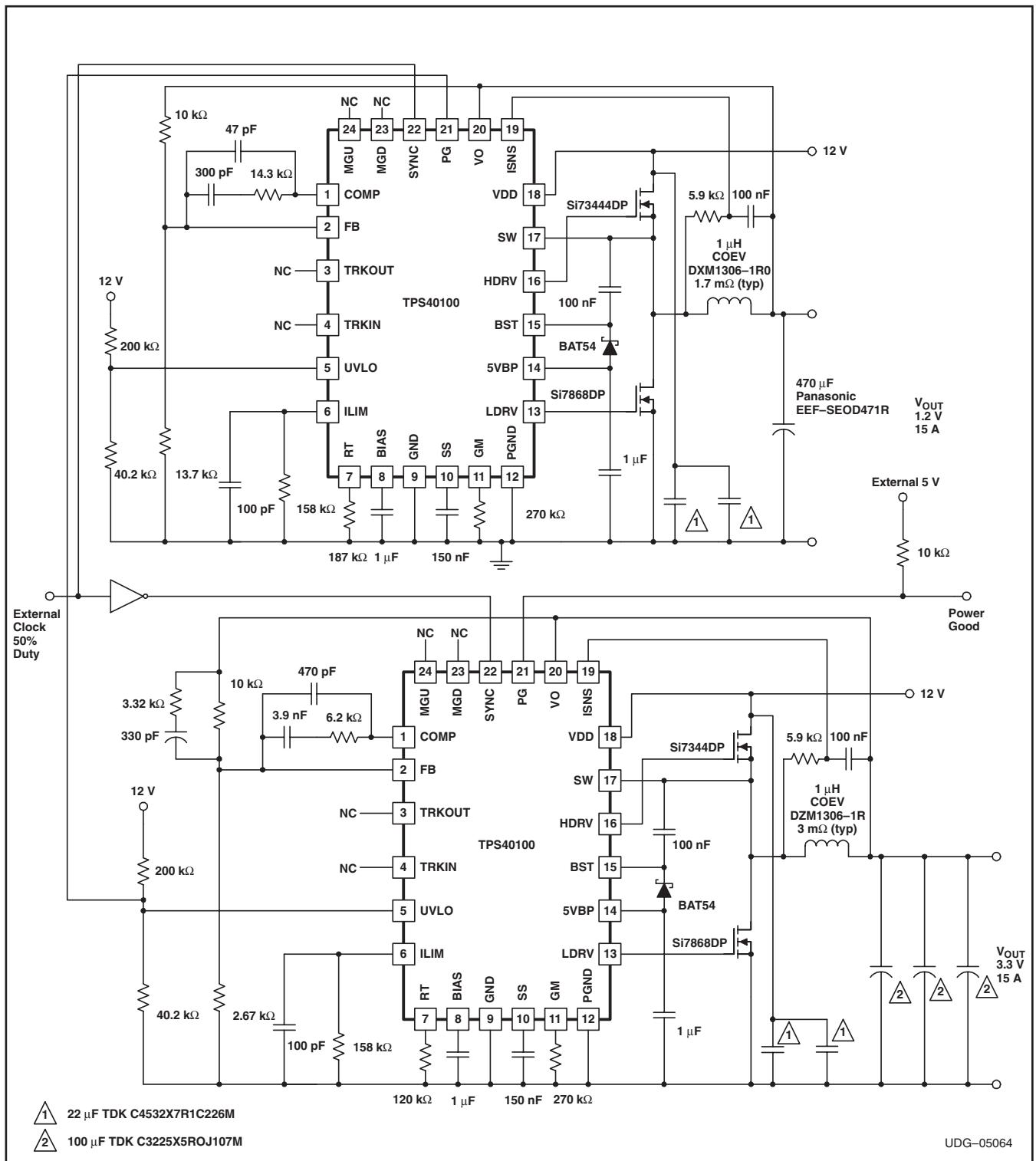

図 21. Sequenced Supplies, With Oscillators 180 Degrees Out of Phase

图 22. Tracking Supplies

# PACKAGE OPTION ADDENDUM

## PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL            | Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|----------------|--------------------------|

| TPS40100RGER     | ACTIVE                | QFN          | RGE             | 24   | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

| TPS40100RGERG4   | ACTIVE                | QFN          | RGE             | 24   | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

| TPS40100RGET     | ACTIVE                | QFN          | RGE             | 24   | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

| TPS40100RGETG4   | ACTIVE                | QFN          | RGE             | 24   | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 | YEAR                     |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS) : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Green (RoHS & no Sb/Br) : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項：**このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事實を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じるTIの責任は、TIによって年次ベースで顧客に販売される、このドキュメント発行時点でのTI製品の合計購入価格を超えることはありません。

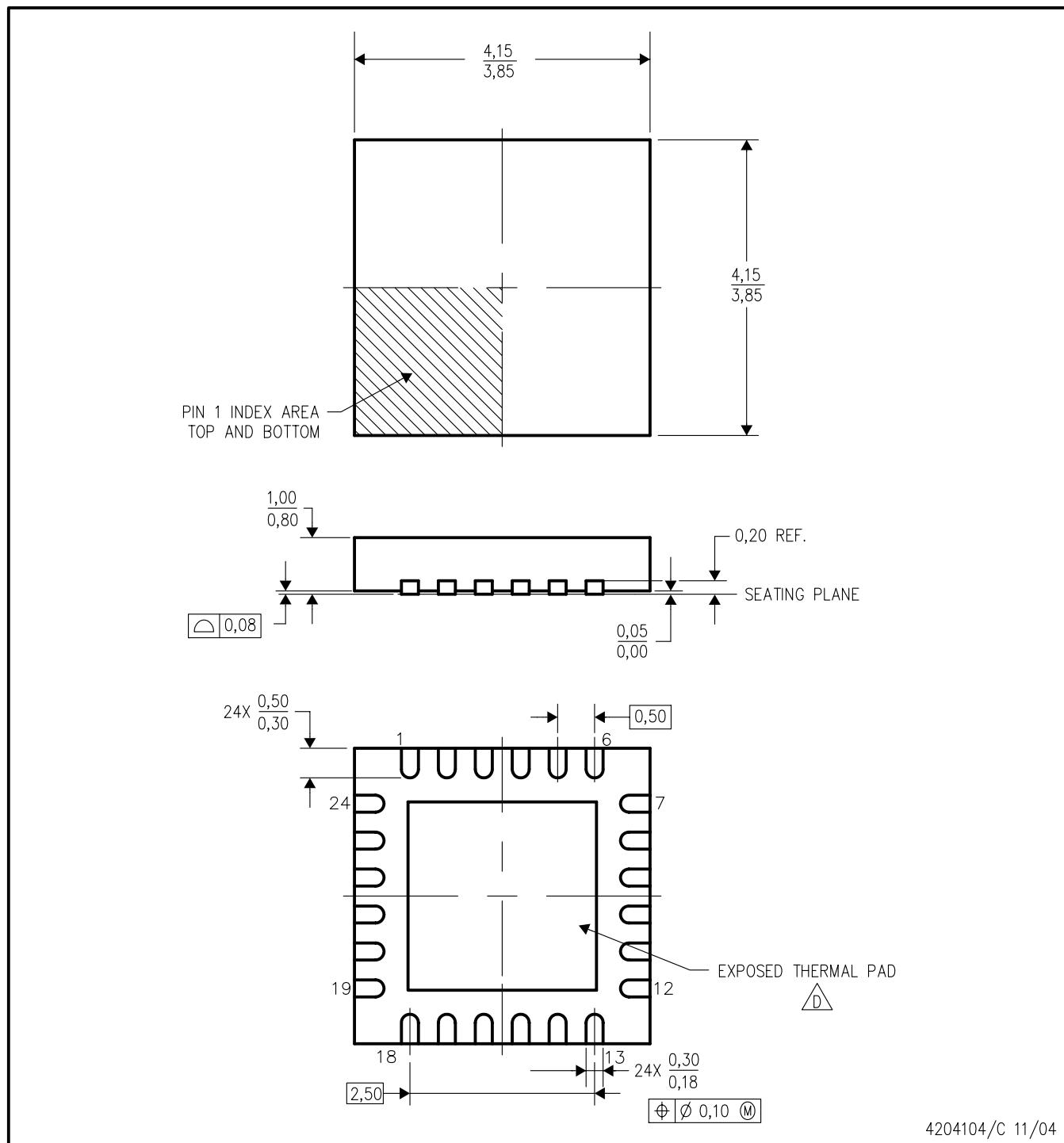

# メカニカル・データ

RGE (S-PQFP-N24)

PLASTIC QUAD FLATPACK

注: A. 全ての線寸法の単位はミリメートルです。寸法/公差はASME Y14.5M-1994によります。

B. 図は予告なく変更することがあります。

C. クワッド・フラットパック・ノーリード(QFN)パッケージ構成です。

△ パッケージのサーマル・パッドは熱的/機械的特性のためボードにはんだ付けしなければなりません。

露出しているサーマル・パッドの寸法についての詳細はデータシートを参照してください。

E. JEDEC MO-220に準拠します。

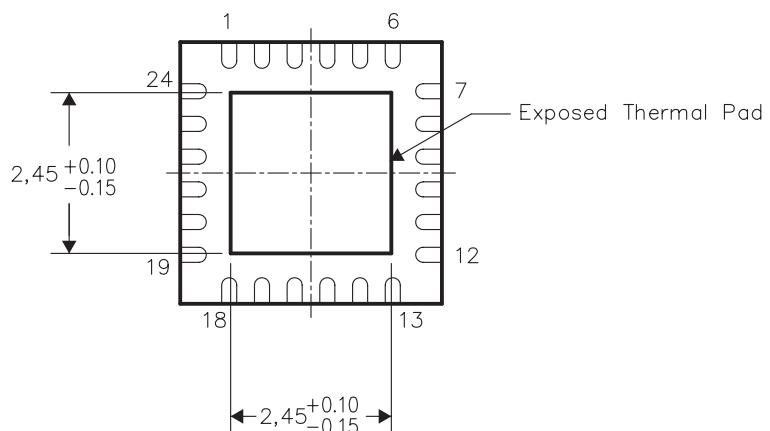

# サーマルパッド・メカニカル・データ

RGE (S-PQFP-N24)

## 熱情報

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板(PCB)に直接はんだ付けされなければならず、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはグランド・プレーンまたはPCBに設計された特別なヒートシンク構造に直接接続することができます。この設計により、集積回路(IC)からの熱移動が最適化されます。

クワッド・フラットパック・ノーリード(QFN)パッケージとその利点についての情報はアプリケーション・レポート“Quad Flatpack No-Lead Logic Packages” TI文献番号SCBA017を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージの露出したサーマル・パッドの寸法は以下の図に示されています。

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

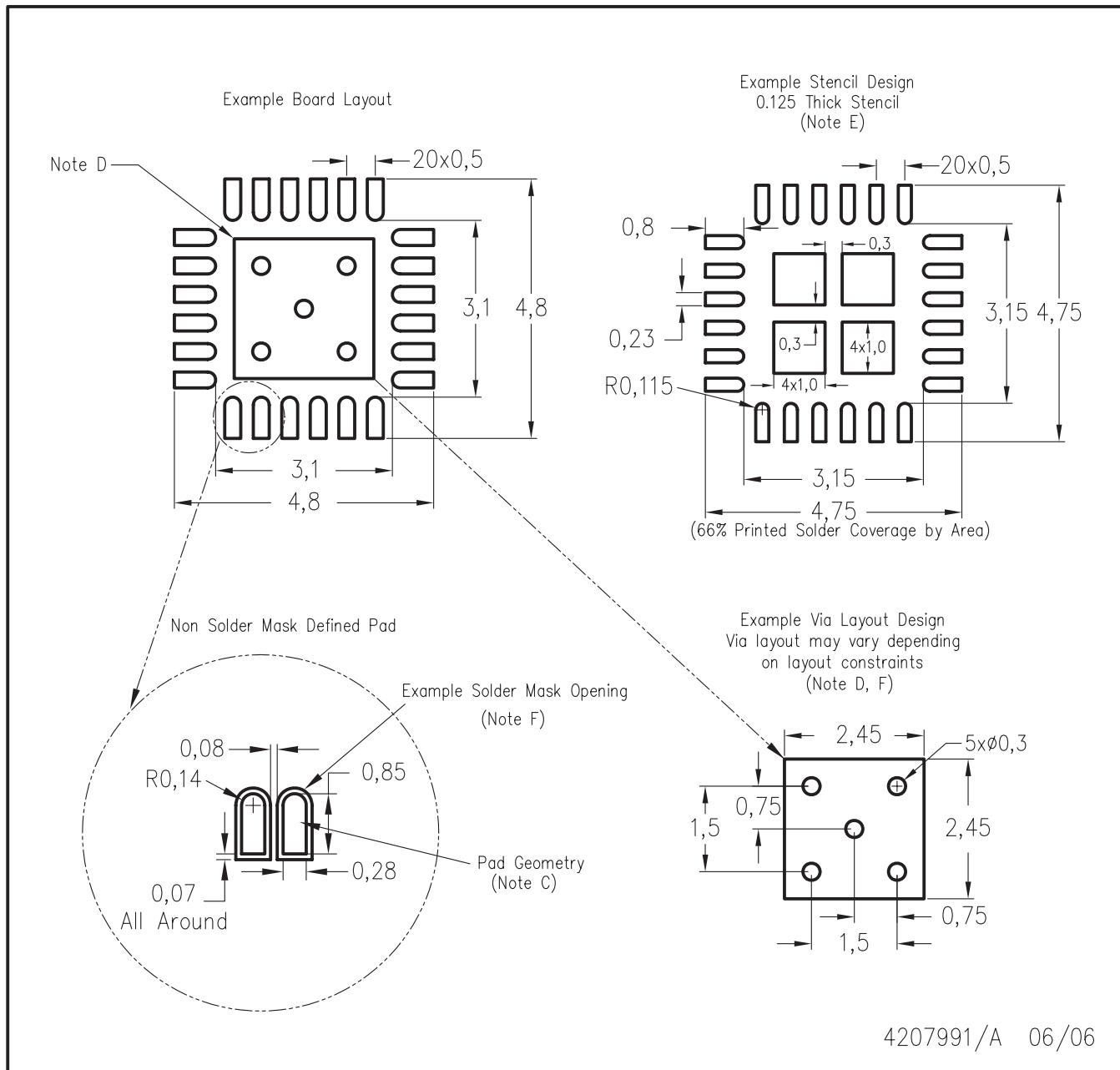

# LAND PATTERN

RGE (S-PQFP-N24)

- 注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 出版番号IPC7351は設計代案についての推奨です。

D. このパッケージはボードのサーマル・パッドにはんだ付けされるよう設計されています。個別の熱情報、ビアの要件、推奨するボード・レイアウトについてはアプリケーション・ノート “Quad Flat-Pack Packages” TI文献番号SCBA017とSLUA271、及びプロダクト・データシートを参照してください。これらの文献はホームページwww.ti.comで入手できます。

E. レーザーカットの開口部に台形の壁をつけ、角に丸みをつけるとペースト離れがよくなります。カスタマはステンシルの設計についてボード製作側に提案しなければなりません。ステンシルを設計する際の考察についてはIPC-7525を参照してください。

F. カスタマははんだマスクの推奨許容値やサーマル・パッドに置くビアの推奨ビア・テンディングについてボード製作側に連絡しなければなりません。

(SBVS073b)

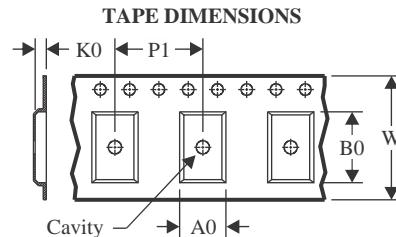

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

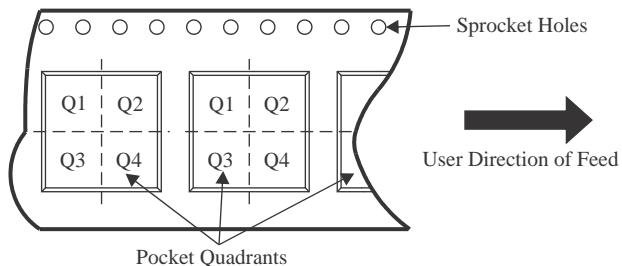

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

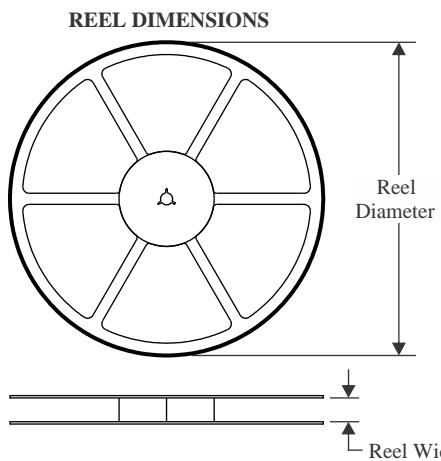

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS40100RGER | VQFN         | RGE             | 24   | 3000 | 330.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| TPS40100RGER | VQFN         | RGE             | 24   | 3000 | 330.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| TPS40100RGET | VQFN         | RGE             | 24   | 250  | 180.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

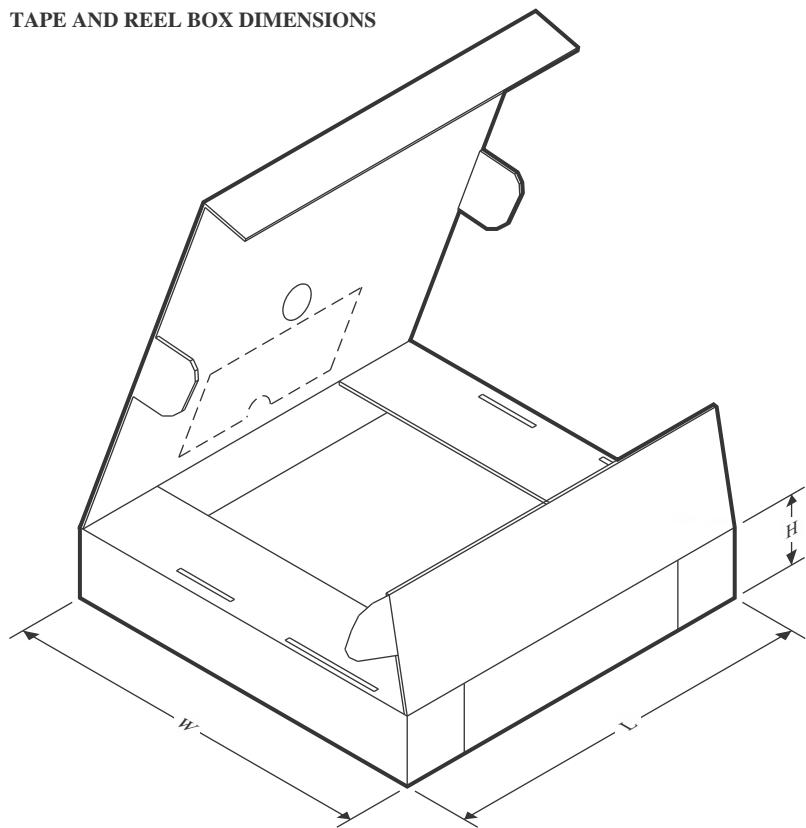

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS40100RGER | VQFN         | RGE             | 24   | 3000 | 346.0       | 346.0      | 33.0        |

| TPS40100RGER | VQFN         | RGE             | 24   | 3000 | 353.0       | 353.0      | 32.0        |

| TPS40100RGET | VQFN         | RGE             | 24   | 250  | 210.0       | 185.0      | 35.0        |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated