# デュアルまたは2フェーズ、 スタッカブル・コントローラ

## 1 はじめに

### 1.1 特長

- VDD: 4.5V~15V、内部5Vレギュレータ

- V<sub>OUT</sub>: 0.7V~5.8V

- 1MHzで15V入力を0.7V出力に変換

- デュアル出力または2フェーズのインタリーブ動作、16フェーズまでスタッカブル

- プリバイアス出力をサポート

- プログラミング可能なスイッチング周波数: 最大1MHz/フェーズ

- 0.5%内部トリミングされた0.7Vリファレンス

- シャットダウン電流: 10µA

- 強制電流シェアリング<sup>(1)</sup>による電流モード制御

- 電源段動作範囲: 1V~40V

- 異なる入力電圧レールからのパワー・シェアリング(例: 5Vからマスター、12Vからスレーブ)

- リモート・センス差動増幅器

- プログラミング可能な入力低電圧ロックアウト

- 抵抗またはインダクタDCR電流センス

- TPS40120と組み合わせて6ビットのデジタル制御出力を実現

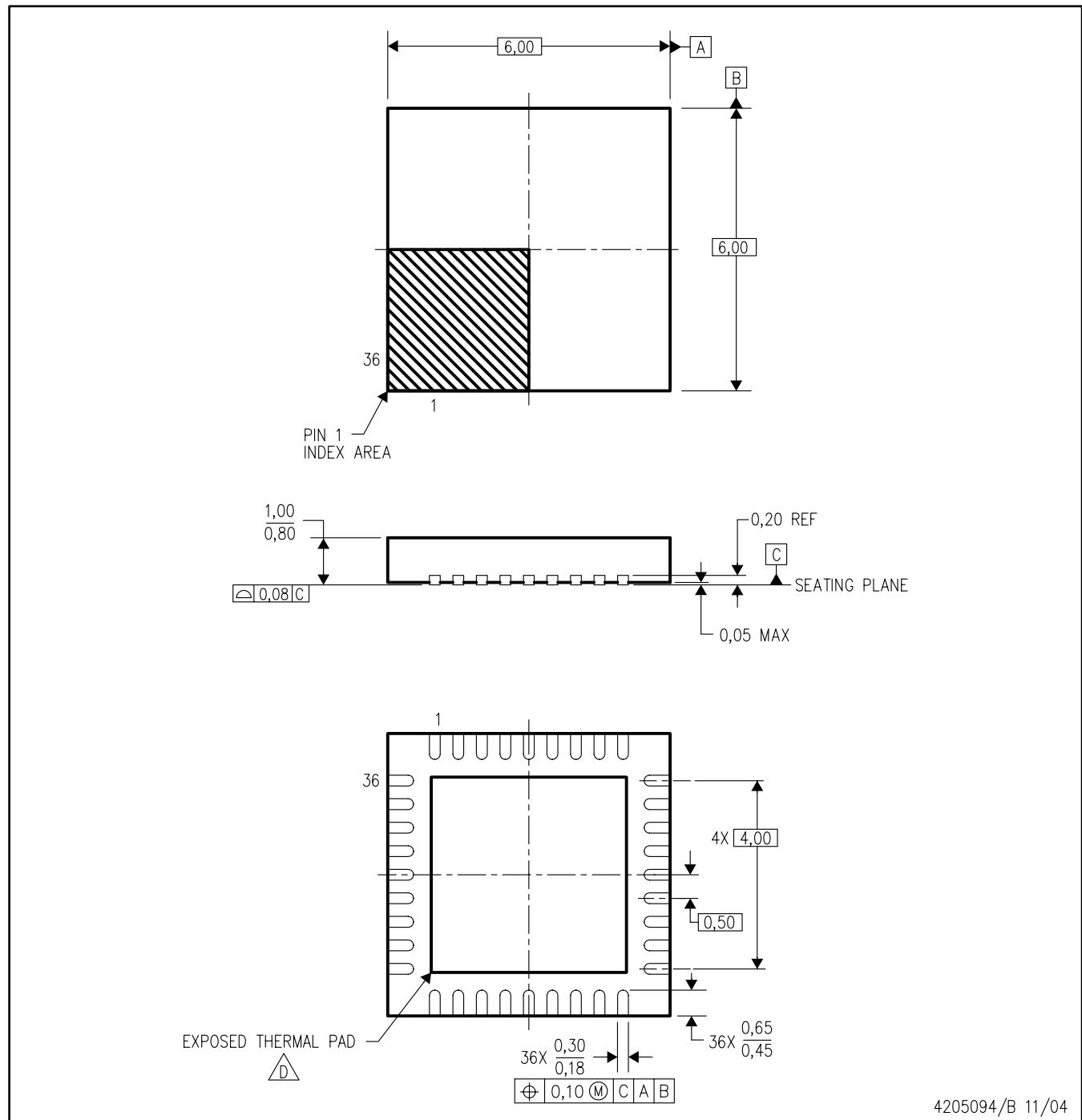

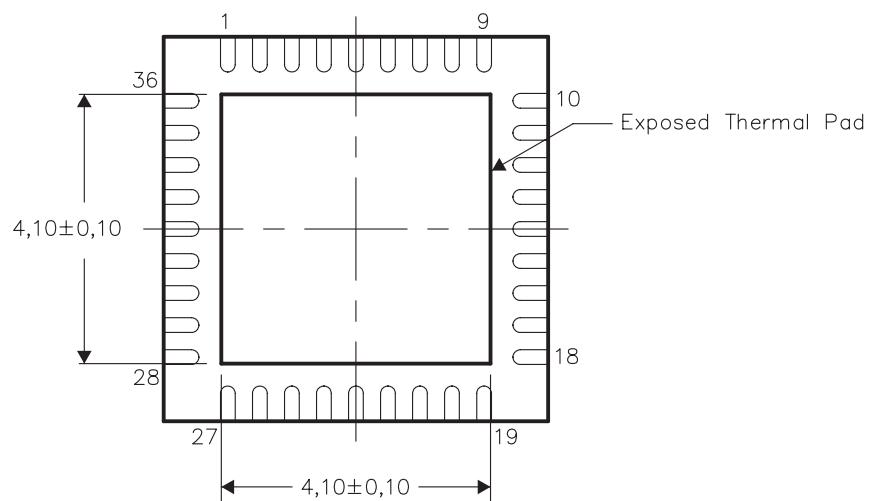

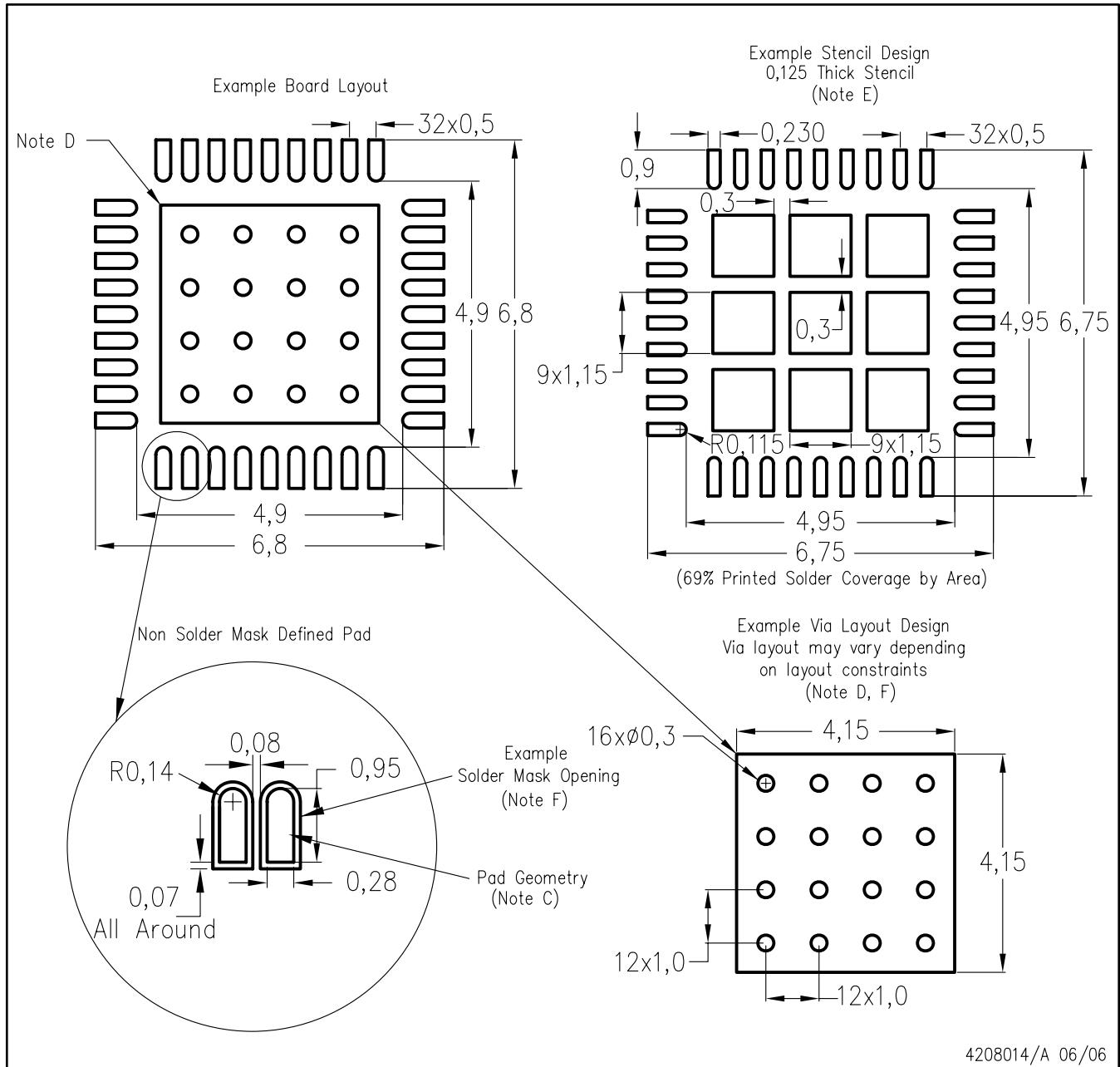

- 36ピンQFNパッケージ

(1) 特許出願中

### 1.2 アプリケーション

- グラフィック・カード

- インターネット・サーバ

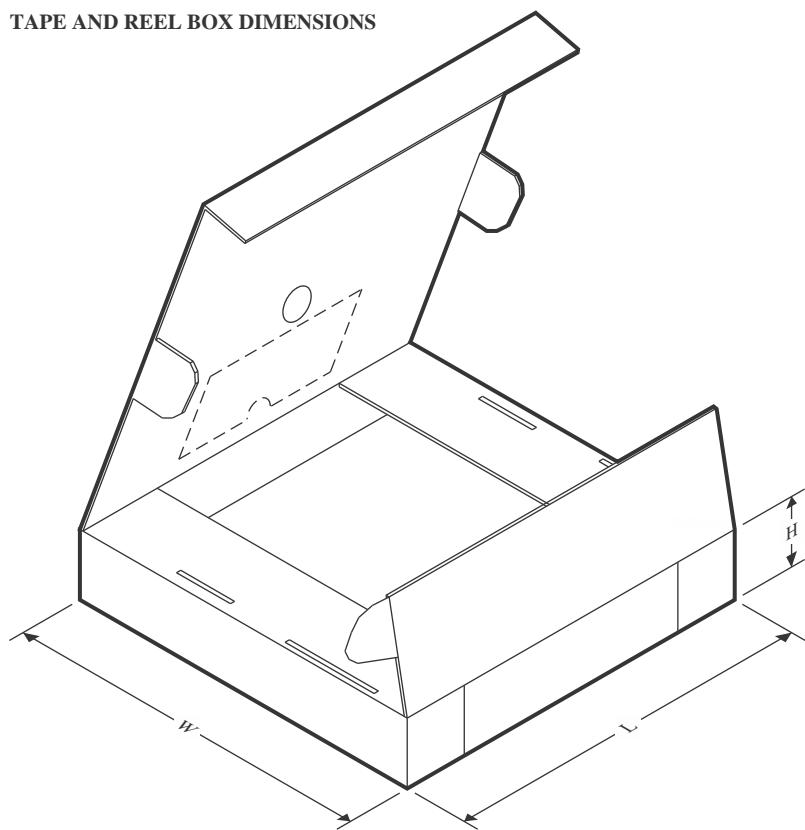

### 1.4 製品情報

| パッケージ                                   | TAPE AND REEL QTY. | PART NUMBER  |

|-----------------------------------------|--------------------|--------------|

| Plastic Quad Flatpack 36-pin RHH (PQFP) | 250                | TPS40140RHHT |

|                                         | 3000               | TPS40140RHHR |

PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

- ネットワーク機器

- 通信機器

- DC給電システム

### 1.3 概要

TPS40140は、単一出力の2フェーズ電源、または2つの独立した出力をサポートする電源として構成可能な、多機能同期バック・コントローラです。いくつかのTPS40140コントローラをスタッカブルすることで、最大16フェーズのマルチフェーズ単一出力電源を構成できます。または、それぞれ独立した出力を提供する複数のコントローラをインタリーブ・パターンに同期化することにより、入力リップル電流を改善することができます。

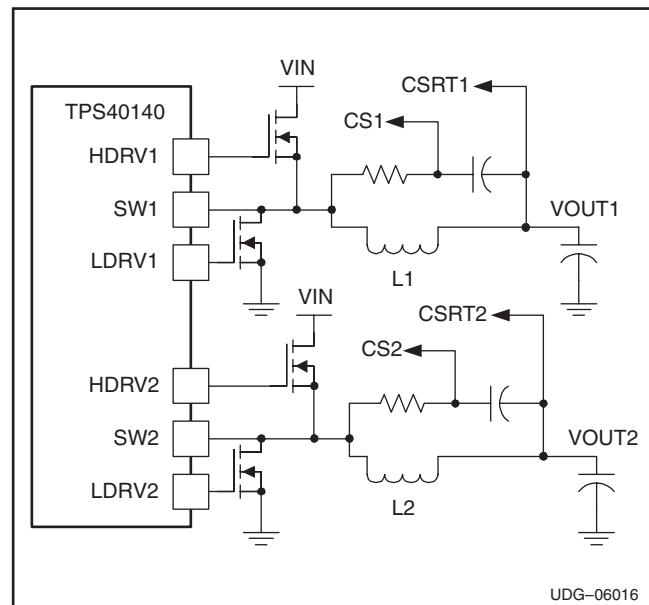

UDG-06016

TPS40140は、1MHzで15V入力を0.7V出力に変換することができます。

各フェーズは、最大1MHzのスイッチング周波数で動作します。1デバイス内の2つのフェーズは、180°位相差をもって動作します。複数デバイスのスタッカブル構成では、マスターを基準とした各スレーブの位相シフトをプログラミングできます。

## 静電気放電対策

これらのデバイスは、限定的なESD（静電破壊）保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## 2 デバイス定格

### 2.1 絶対最大定格

動作温度範囲内(特に記述のない限り)

|                             |                            | VALUE          | 単位          |

|-----------------------------|----------------------------|----------------|-------------|

| Input voltage range         | VDD, UVLO_CE1, UVLO_CE2    | -0.3 to 16     | V           |

|                             | SW1, SW2                   | -1 to 44       |             |

|                             | SW1, SW2, transient < 50ns | -5             |             |

|                             | BOOT1, BOOT2, HDRV1, HDRV2 | $V_{SW} + 6.0$ |             |

| All other pins              |                            | -0.3 to 6.0    |             |

| Output current              | RT                         | 200            | $\mu A$     |

| Junction Temperature, $T_J$ | Operating                  | -40 to 125     | $^{\circ}C$ |

| Junction Temperature, $T_J$ | Storage                    | -55 to 150     | $^{\circ}C$ |

### 2.2 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                                |                            | MIN  | TYP            | MAX | 単位          |

|--------------------------------|----------------------------|------|----------------|-----|-------------|

| Input voltage                  | VDD, UVLO_CE1, UVLO_CE2    | -0.3 | 15             |     | V           |

|                                | SW1, SW2                   | -1   | 40             |     |             |

|                                | BOOT1, BOOT2, HDRV1, HDRV2 |      | $V_{SW} + 5.5$ |     |             |

|                                | All other pins             | -0.3 | 5.5            |     |             |

| Maximum output current         | RT                         |      | 25             |     | $\mu A$     |

| Operating free-air temperature |                            | -40  | 85             |     | $^{\circ}C$ |

### 2.3 静電放電(ESD)保護

|                  | パラメータ | MIN  | TYP | MAX | 単位 |

|------------------|-------|------|-----|-----|----|

| Human body model |       | 3000 |     |     | V  |

| CDM              |       | 1500 |     |     | V  |

### 2.4 パッケージ定格消費電力<sup>(1)</sup>

| THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT (°C/W) | $T_A = 25^{\circ}C$ POWER RATING (W) | $T_A = 85^{\circ}C$ POWER RATING (W) |

|-------------------------------------------------|--------------------------------------|--------------------------------------|

| 48                                              | 2                                    | 0.8                                  |

(1) RHHパッケージの詳細な情報およびテスト方法については、TIテクニカル・ブリーフ文献番号SLUA271を参照してください。

## 2.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 、(特に記述のない限り)、 $V_{VDD} = 7\text{V}$ 、 $V_{BP5} = 5\text{V}$ 、UVLO\_CE1、UCLO\_CE2 :  $10\text{k}\Omega$ 、BP5にプルアップ、 $f_{SW} = 300\text{kHz}$  (特に記述のない限り)

| パラメータ                                            | テスト条件                                                 | MIN                                   | TYP   | MAX    | 単位               |

|--------------------------------------------------|-------------------------------------------------------|---------------------------------------|-------|--------|------------------|

| <b>VDD INPUT SUPPLY</b>                          |                                                       |                                       |       |        |                  |

| Operating Voltage Range                          |                                                       | 4.5                                   | 12    | 15     | V                |

| Shutdown Current                                 | UVLO_CE1 = UVLO_CE2 = GND                             |                                       | 1     | 10     | $\mu\text{A}$    |

| <b>BP5 INPUT SUPPLY</b>                          |                                                       |                                       |       |        |                  |

| Operating Voltage Range                          |                                                       | 4.5                                   | 5.0   | 5.5    | V                |

| BP5 Operating Current                            |                                                       | 2                                     | 3     | 5      | mA               |

| Rising BP5 Turn-On                               |                                                       | 4.0                                   | 4.25  | 4.45   | V                |

| BP5 Turn-Off Hysteresis                          |                                                       | 100                                   | 220   | 400    | mV               |

| Standby Mode Current <sup>(1)</sup>              | UVLO_CEx = 1.7V                                       |                                       | 2.8   |        | mA               |

| <b>VREG</b>                                      |                                                       |                                       |       |        |                  |

|                                                  | 7 V < $V_{DD} < 15\text{V}$                           | 4.5                                   | 5.1   | 5.5    | V                |

|                                                  | Output current                                        | 0                                     |       | 100    | mA               |

| <b>OSCILLATOR, RT</b>                            |                                                       |                                       |       |        |                  |

| Phase Frequency Accuracy                         | $R_{RT} = 110\text{k}\Omega$                          |                                       | 300   |        | kHz              |

| Phase Frequency Set Range                        |                                                       | 150                                   |       | 1000   | kHz              |

| RT <sup>(1)</sup>                                | $25\text{k}\Omega \leq R_{RT} \leq 500\text{k}\Omega$ |                                       | 0.7   |        | V                |

| <b>UNDERVOLTAGE LOCKOUT (UVLO_CE1, UVLO_CE2)</b> |                                                       |                                       |       |        |                  |

| Enable threshold, standby mode                   | Internal 5VREG regulator enabled                      | 0.5                                   | 1.0   | 1.5    | V                |

| UVLO threshold                                   | PWM Switching enabled                                 | 1.9                                   | 2     | 2.1    | V                |

| UVLO hysteresis                                  | At the UVLO_CEx pin                                   |                                       | 40    |        | mV               |

| UVLO_CE1, UVLO_CE2 bias current <sup>(1)</sup>   |                                                       |                                       |       | 1      | $\mu\text{A}$    |

| <b>PWM</b>                                       |                                                       |                                       |       |        |                  |

| D                                                | Maximum duty cycle per channel <sup>(1)</sup>         | 2-phase, 4-phase, 8-phase or 16-phase |       | 87.5%  |                  |

|                                                  |                                                       | 3-phase, 6-phase, or 12-phase         |       | 83.3%  |                  |

| <b>VSHARE</b>                                    |                                                       |                                       |       |        |                  |

|                                                  | $i_{VSHR} = 0$                                        | 1.785                                 | 1.8   | 1.815  | V                |

| (1)                                              | $-30\mu\text{A} < i_{VSHR} < 50\mu\text{A}$           | 1.785                                 | 1.8   | 1.815  | V                |

| <b>ERROR AMPLIFIER CH1, ERROR AMPLIFIER CH2</b>  |                                                       |                                       |       |        |                  |

| Input Common Mode Range <sup>(1)</sup>           |                                                       | 0                                     | 0.7   | 2.0    | V                |

| Input Bias Current <sup>(1)</sup>                | $V_{FB} = 0.7\text{V}$                                |                                       | 10    |        | nA               |

| FBx Voltage <sup>(1)</sup>                       |                                                       | 0.6965                                | 0.700 | 0.7035 | V                |

| Output Source Current                            | $V_{COMP} = 1.1\text{V}$ , $V_{FB} = 0.6\text{V}$     | 1                                     | 2     |        | mA               |

| Output Sink Current                              | $V_{COMP} = 1.1\text{V}$ , $V_{FB} = \text{BP5}$      | 1                                     | 2     |        | mA               |

| BW <sup>(1)</sup>                                |                                                       | 8                                     | 12    |        | MHz              |

| Open Loop Gain <sup>(1)</sup>                    |                                                       | 60                                    | 90    |        | dB               |

| <b>VOLTAGE TRACKING (TRK1, TRK2)</b>             |                                                       |                                       |       |        |                  |

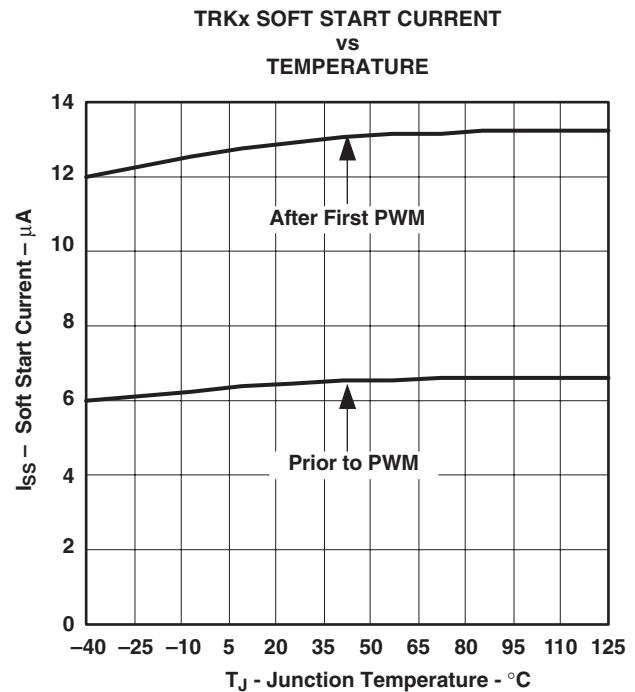

| SS source current                                | After EN, before PWM and during hiccup mode           | 5                                     | 6.0   | 7.3    | $\mu\text{A}$    |

|                                                  | After first PWM pulse                                 | 10                                    | 12.5  | 15     | $\mu\text{A}$    |

| Fault Enable Threshold <sup>(1)</sup>            |                                                       |                                       | 1.4   |        | V                |

| Internal Clamp Voltage <sup>(1)</sup>            |                                                       |                                       | 2.4   |        | V                |

| SS sink resistance <sup>(1)</sup>                | Pull-down resistance                                  |                                       |       | 1      | $\text{k}\Omega$ |

(1) 設計で確認されています。実製品の100%検査は行っていません。

## 電気的特性

$T_J = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 、(特に記述のない限り)、 $V_{\text{VDD}} = 7\text{V}$ 、 $V_{\text{BP5}} = 5\text{V}$ 、 $\text{UVLO\_CE1}$ 、 $\text{UCLO\_CE2} : 10\text{k}\Omega$ 、 $\text{BP5}$ にプルアップ、 $f_{\text{SW}} = 300\text{kHz}$  (特に記述のない限り)

| パラメータ                                            | テスト条件                                                                                                                                 | MIN   | TYP    | MAX   | 単位            |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|---------------|

| <b>CURRENT SENSE AMPLIFIERS (CS1, CS2)</b>       |                                                                                                                                       |       |        |       |               |

| Differential input voltage                       |                                                                                                                                       | -60   | 60     |       | mV            |

| Input offset voltage                             | CS1, CS2, Trimmed                                                                                                                     | -2.0  | 0      | 2.0   | mV            |

| Ac Gain transfer to PWM COMP                     | $5\text{ mV} < V_{\text{CS}} < 60\text{ mV}$ , $V_{\text{CSRT}} = 1.5\text{ V}$                                                       | 12    | 13     | 14    | V/V           |

| Input common mode <sup>(1)</sup>                 |                                                                                                                                       | 0     |        | 5.8   | V             |

| CSA Input bias current                           |                                                                                                                                       |       | 100    |       | nA            |

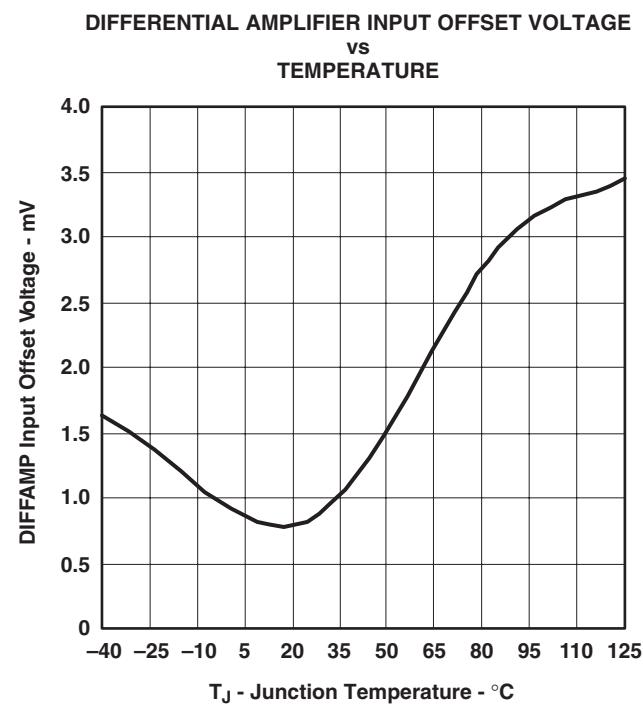

| <b>DIFFERENTIAL AMPLIFIER (DIFFO)</b>            |                                                                                                                                       |       |        |       |               |

| Gain                                             | $1.0\text{ V} < V_{\text{OUT}} < 5.8\text{ V}$                                                                                        | 0.997 | 1      | 1.003 | V/V           |

| Input Common Mode Range <sup>(1)</sup>           |                                                                                                                                       | 0     |        | 5.8   | V             |

| Output Source Current <sup>(1)</sup>             | $V_{\text{OUT}} - V_{\text{VGSNS}} = 2\text{ V}$ , $V_{\text{DIFFO}} > 1.98\text{ V}$ , $V_{\text{DD}} - V_{\text{OUT}} > 2\text{ V}$ |       |        | 2     | mA            |

| Output Source Current <sup>(1)</sup>             | $V_{\text{OUT}} - V_{\text{VGSNS}} = 2\text{ V}$ , $V_{\text{DIFFO}} > 2.02\text{ V}$ $V_{\text{DD}} - V_{\text{OUT}} = 1\text{ V}$   |       |        | 1     |               |

| Output Sink Current <sup>(1)</sup>               | $V_{\text{OUT}} - V_{\text{VGSNS}} = 2\text{ V}$ , $V_{\text{DIFFO}} > 2.02\text{ V}$                                                 |       |        | 2     |               |

| Unity gain bandwidth <sup>(1)</sup>              |                                                                                                                                       | 5     | 8      |       | MHz           |

| Input Impedance, non inverting <sup>(1)</sup>    | $V_{\text{OUT}}$ to GND                                                                                                               |       | 60     |       | k $\Omega$    |

| Input Impedance, inverting <sup>(1)</sup>        | GSNS to DIFFO                                                                                                                         |       | 60     |       |               |

| <b>GATE DRIVERS</b>                              |                                                                                                                                       |       |        |       |               |

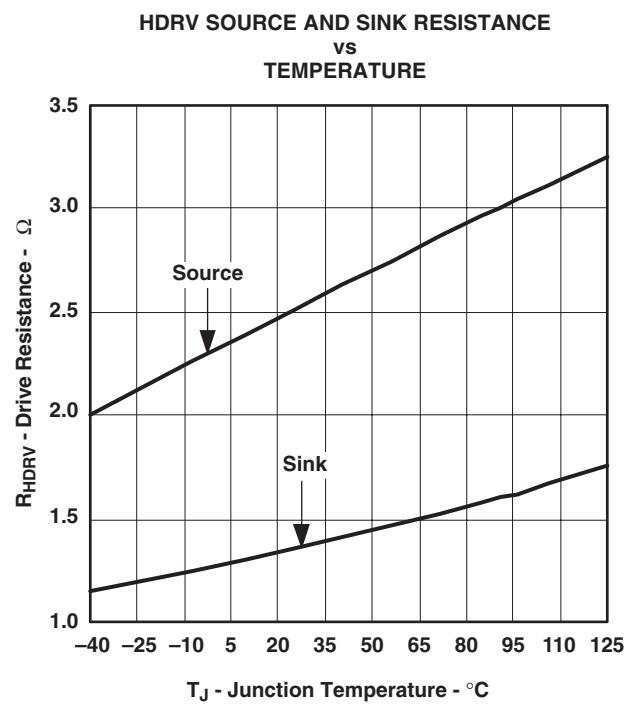

| HDRV1, HDRV2 Source On Resistance                | $V_{\text{BOOT1}}, V_{\text{BOOT2}} = 5\text{ V}$ , $V_{\text{SW1}} = V_{\text{SW2}} = 0\text{ V}$ , Sourcing 100 mA                  | 1     | 2      | 3     | $\Omega$      |

| HDRV1, HDRV2 Sink On Resistance                  | $V_{\text{VREG}} = 5\text{ V}$ , $V_{\text{SW1}} = V_{\text{SW2}} = 0\text{ V}$ , Sinking 100 mA                                      | 0.5   | 1.2    | 2     |               |

| LDRV1, LDRV2 Source On Resistance                | $V_{\text{VREG}} = 5\text{ V}$ , $V_{\text{SW1}} = V_{\text{SW2}} = 0\text{ V}$ , Sourcing 100 mA                                     | 1     | 2      | 3     |               |

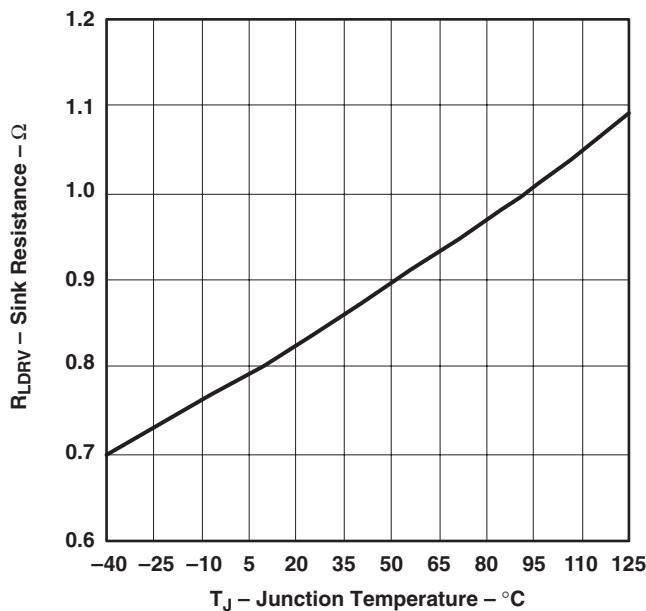

| LDRV1, LDRV2 Sink On Resistance                  | $V_{\text{VREG}} = 5\text{ V}$ , $V_{\text{SW1}} = V_{\text{SW2}} = 0\text{ V}$ , Sinking 100 mA                                      | 0.3   | 0.65   | 1     |               |

| $t_{\text{RISE}}$ HDRVx rise time <sup>(1)</sup> | $C_{\text{LOAD}} = 3.3\text{ nF}$                                                                                                     |       | 25     | 75    | ns            |

| $t_{\text{FALL}}$ HDRVx fall time <sup>(1)</sup> | $C_{\text{LOAD}} = 3.3\text{ nF}$                                                                                                     |       | 25     | 75    |               |

| $t_{\text{RISE}}$ LDRVx rise time <sup>(1)</sup> | $C_{\text{LOAD}} = 3.3\text{ nF}$                                                                                                     |       | 25     | 75    |               |

| $t_{\text{FALL}}$ LDRVx fall time <sup>(1)</sup> | $C_{\text{LOAD}} = 3.3\text{ nF}$                                                                                                     |       | 20     | 60    |               |

| Minimum Controllable On-Time                     | $C_{\text{LOAD}} = 3.3\text{ nF}$                                                                                                     |       | 50     |       |               |

| <b>OUTPUT UNDERVOLTAGE FAULT</b>                 |                                                                                                                                       |       |        |       |               |

|                                                  | $V_{\text{FB}}$ relative to $V_{\text{REF}}$                                                                                          | -19%  | -16.5% | -14%  |               |

| Undervoltage delay <sup>(1)</sup>                |                                                                                                                                       |       | 3      |       | $\mu\text{s}$ |

| <b>CURRENT LIMIT</b>                             |                                                                                                                                       |       |        |       |               |

| $I_{\text{ILIM}}$ Output current                 |                                                                                                                                       | 18.8  | 20     | 21.2  | $\mu\text{A}$ |

| <b>POWER GOOD</b>                                |                                                                                                                                       |       |        |       |               |

| PGOOD transition low threshold                   | $V_{\text{FB}}$ rising relative to $V_{\text{REF}}$                                                                                   | 10%   | 12.5%  | 15%   |               |

| PGOOD transition low threshold                   | $V_{\text{FB}}$ falling relative to $V_{\text{REF}}$                                                                                  | -15%  | -12.5% | -10%  |               |

| PGOOD trip hysteresis                            |                                                                                                                                       | 2%    |        | 5%    |               |

| PGOOD Delay <sup>(1)</sup>                       |                                                                                                                                       |       | 10     |       | $\mu\text{s}$ |

| Low level output voltage, VOL                    | $I_{\text{PGOOD}} = 4\text{ mA}$                                                                                                      |       | 0.35   | 0.4   | V             |

| PGOOD Bias Current                               | $V_{\text{PGOOD}} = 5.0\text{ V}$                                                                                                     | -2    | 1      | 2     | $\mu\text{A}$ |

(1) 設計で確認されています。実製品の100%検査は行っていません。

## 電気的特性

$T_J = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 、(特に記述のない限り)、 $V_{\text{VDD}} = 7\text{V}$ 、 $V_{\text{BP5}} = 5\text{V}$ 、UVLO\_CE1、UCLO\_CE2 :  $10\text{k}\Omega$ 、BP5にプルアップ、 $f_{\text{SW}} = 300\text{kHz}$  (特に記述のない限り)

| パラメータ                                         | テスト条件                          | MIN   | TYP  | MAX   | 単位                 |

|-----------------------------------------------|--------------------------------|-------|------|-------|--------------------|

| <b>RAMP</b>                                   |                                |       |      |       |                    |

| Ramp Amplitude <sup>(1)</sup>                 |                                | 0.421 | 0.5  | 0.526 | V                  |

| <b>VIN BALANCE</b>                            |                                |       |      |       |                    |

| $V_{\text{IN}}$ Balance Gain, $A_{\text{VB}}$ |                                | 0.23  | 0.25 | 0.27  | V/V                |

| <b>THERMAL SHUTDOWN</b>                       |                                |       |      |       |                    |

| Shutdown Temperature <sup>(1)</sup>           |                                | 155   |      |       | $^{\circ}\text{C}$ |

| Hysteresis <sup>(1)</sup>                     |                                | 30    |      |       |                    |

| <b>DIGITAL CLOCK SIGNAL (CLKIO)</b>           |                                |       |      |       |                    |

| Pull-up resistance <sup>(1)</sup>             | $I_{\text{OH}} = 5\text{ mA}$  | 27    |      |       | $\Omega$           |

| Pull-down resistance <sup>(1)</sup>           | $I_{\text{OL}} = 10\text{ mA}$ | 27    |      |       | $\Omega$           |

| Output leakage <sup>(1)</sup>                 | Three-state                    | 1     |      |       | $\mu\text{A}$      |

(1) 設計で確認されています。実製品の100%検査は行っていません。

## 代表的特性

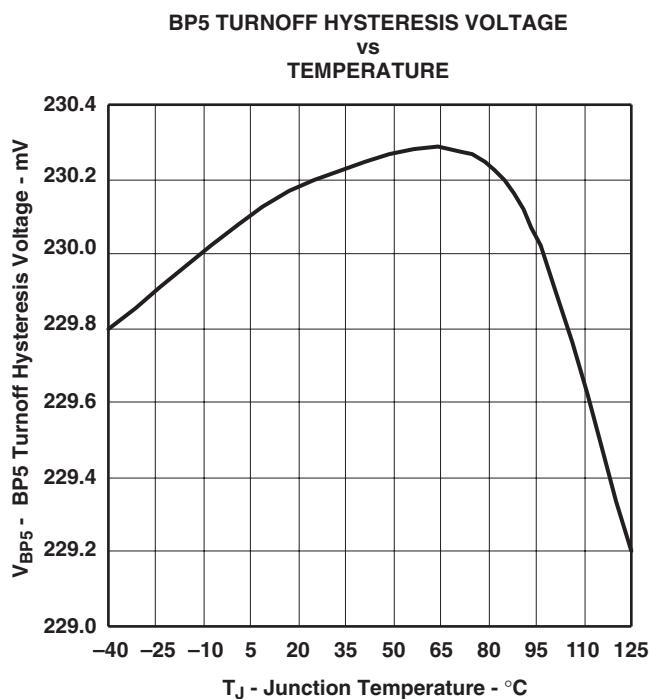

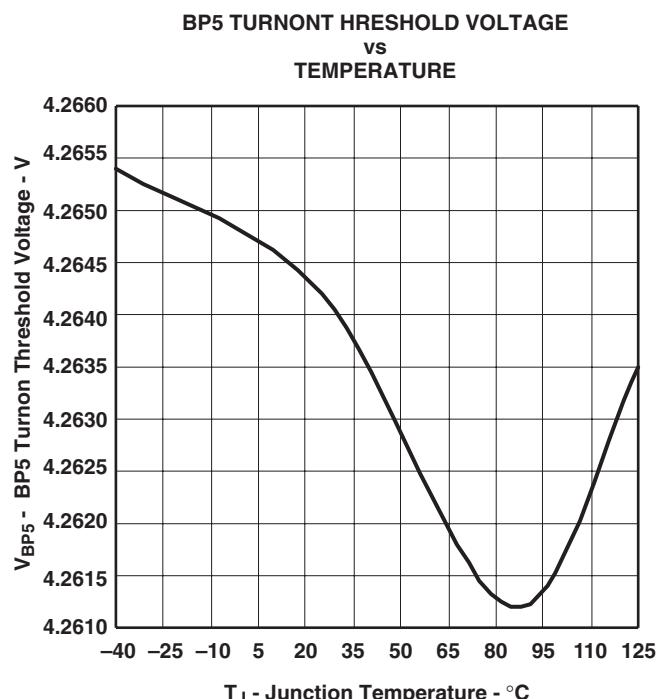

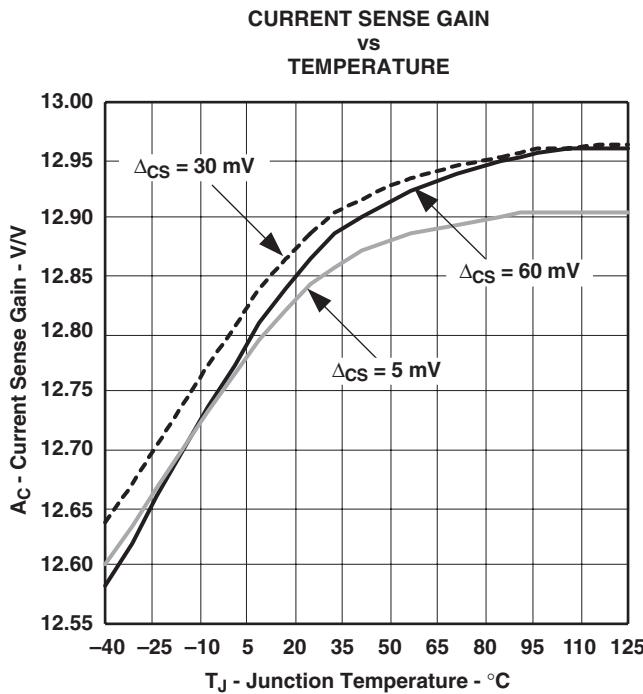

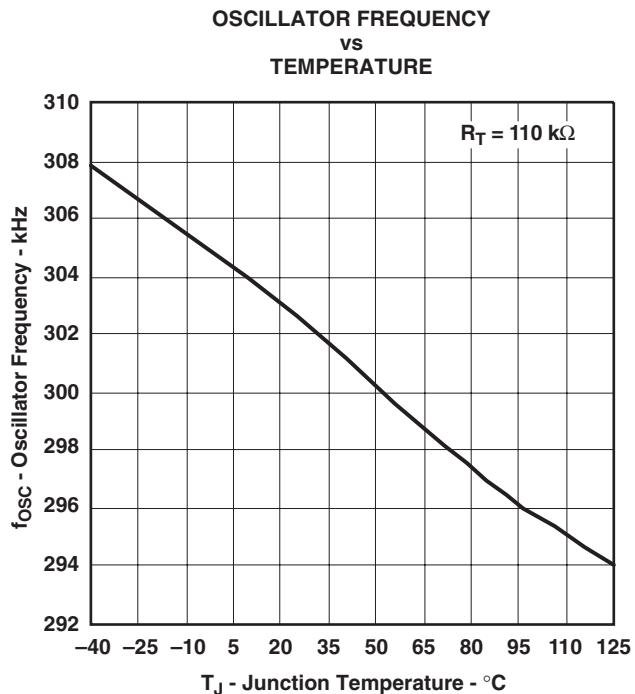

図 3-1

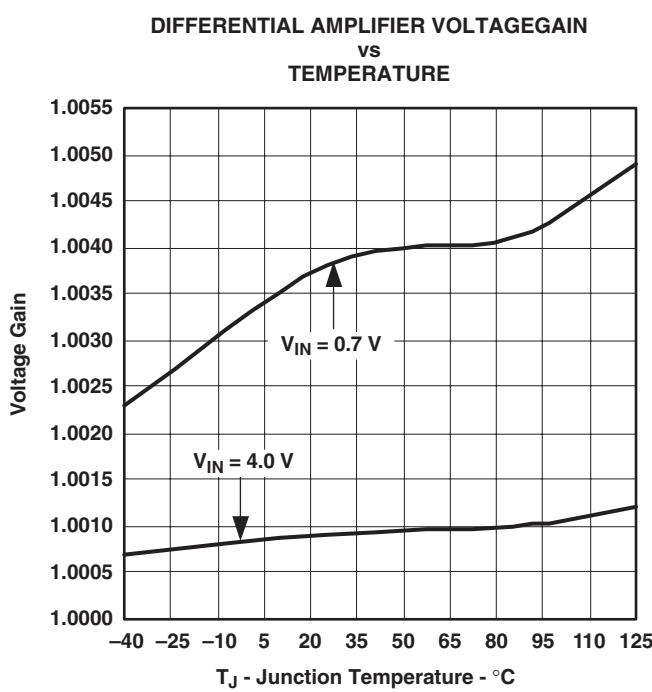

図 3-2

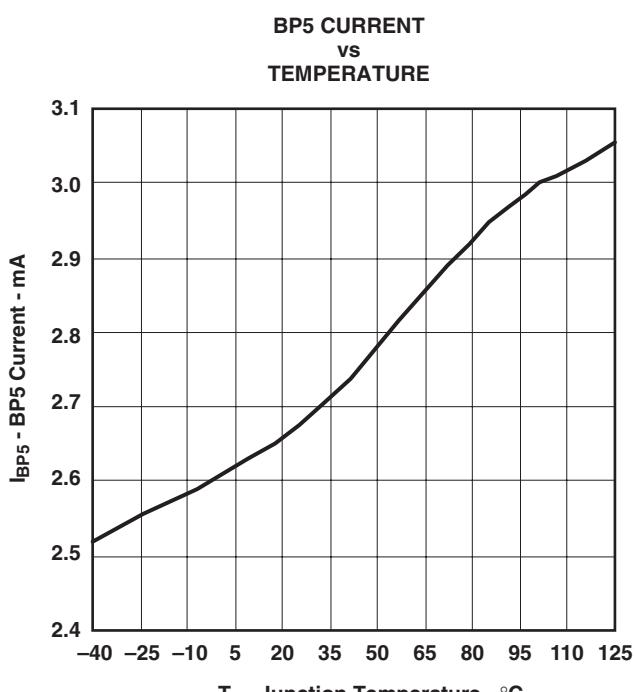

図 3-3

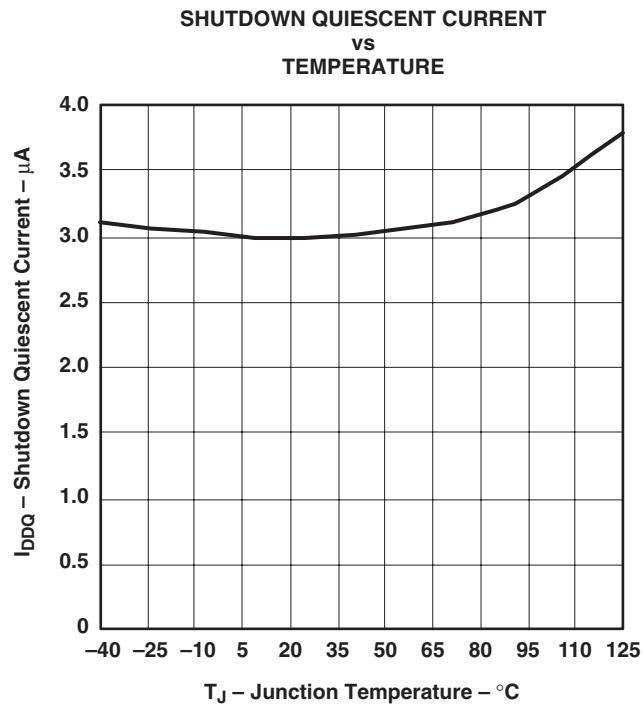

図 3-4

図 3-5

図 3-6

図 3-7

図 3-8

図 3-9

図 3-10

LDRV SINK RESISTANCE

vs

TEMPERATURE

図 3-11

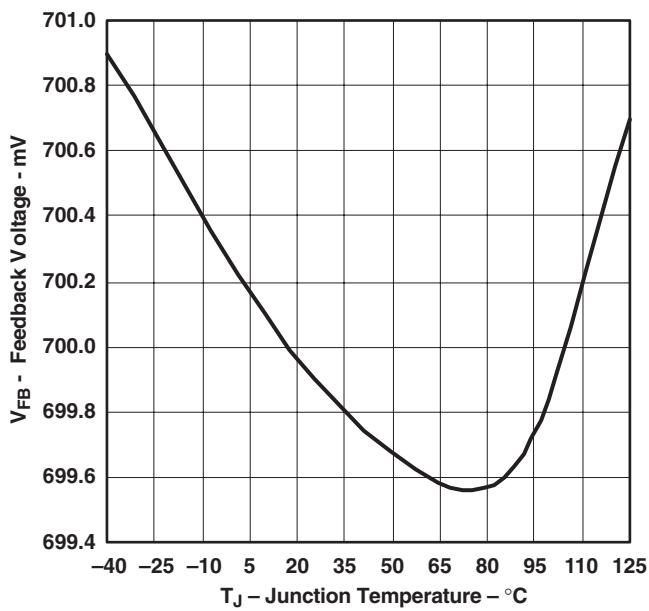

FEEDBACK VOLTAGE

vs

TEMPERATURE

図 3-12

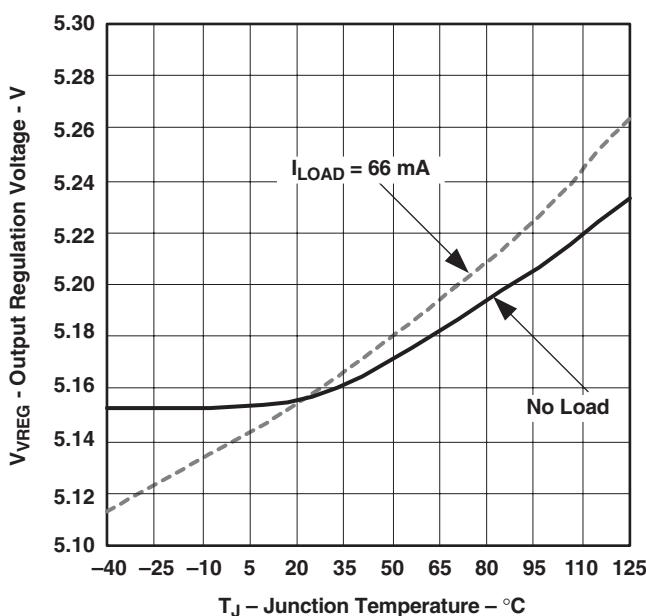

V<sub>REG</sub> OUTPUT VOLTAGE

vs

TEMPERATURE

図 3-13

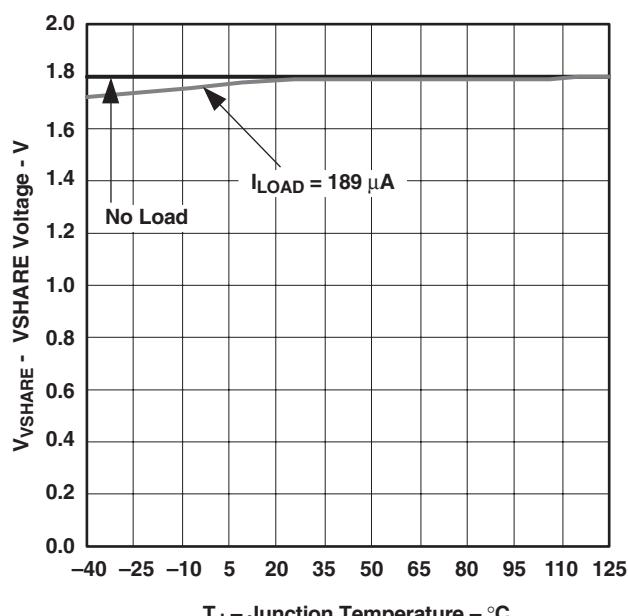

V<sub>SHARE</sub> VOLTAGE

vs

TEMPERATURE

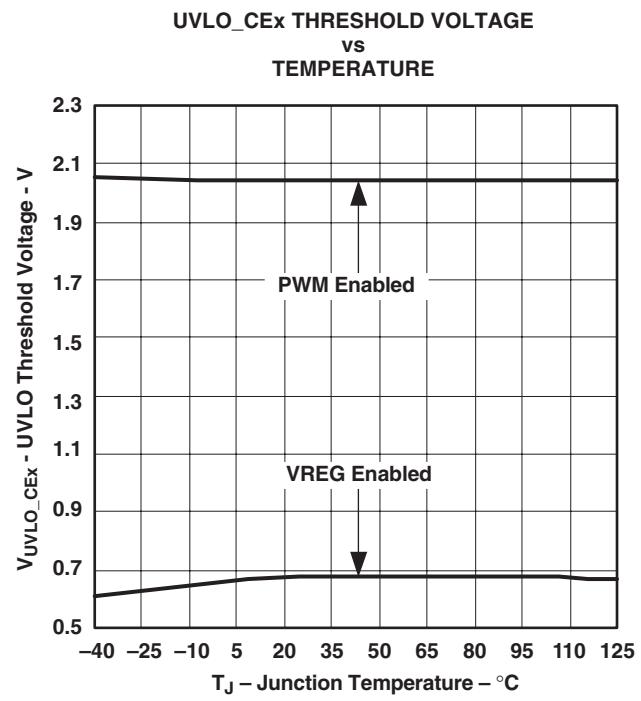

図 3-14

図 3-15

## 4 デバイス情報

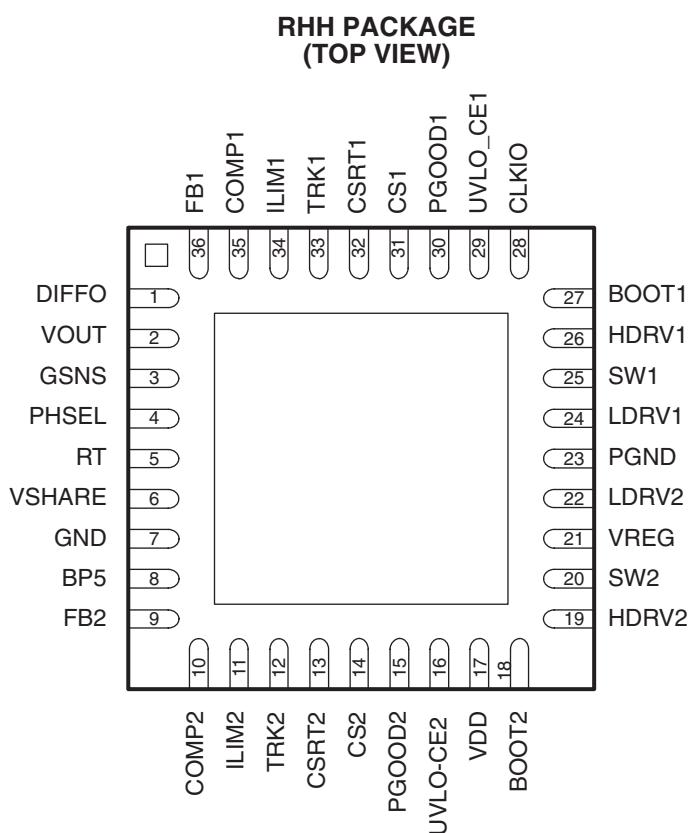

## 4.1 端子構成

パッケージは36ピンのPQFP(RHH)パッケージです。注：サード・マル・パッドは電気的なグランド接続です。

TPS40140は、單一コントローラとして、または、マルチコントローラ構成に‘スタック’して動作可能な汎用コントローラです。TPS40140には、マルチ・フェーズ(單一出力)構成、または、独立した2つの出力電圧を生成するデュアル構成として使用できる2つのチャネルがあります。單一コントローラの2つのチャネルは、常に180°位相がずれた状態でスイッチングします。クロック・マスター、電圧マスター、クロック・スレーブ、電圧スレーブの詳細については、以下を参照してください。

ピンの一部は動作モードを設定するために使用し、他のピンの定義は選択したモードに基づいて変化します。

多くの場合、CH1またはCH2あるいはその両方で使用されるピンを表記する必要があります。使用するピンの短縮名には、一方または両方のチャネルを表すために、ピンの名前に小文字の‘x’が付いています。たとえば、TRKxは、TRK1またはTRK2あるいはその両方を表します。

## 4.2 クロック・マスターおよびクロック・スレーブ

コントローラは、「クロック・マスター」または「クロック・スレーブ」として機能します。「クロック・マスター」という用語は、マルチ・コントローラ構成において、クロック・マスターとクロック・スレーブの間のクロック同期のためにCLKIO信号を生成するコントローラを表します。CLKIO信号は、クロック・マスターの‘RT’ピンが抵抗を介してグランド接続されるとともに、クロック・マスターのPHSELピンが抵抗または抵抗ストリングを介してグランド接続されている場合に生成されます。「クロック・スレーブ」は、RTピンをBP5に接続して構成します。これにより、クロック・スレーブにクロック・マスターからのCLKIO信号が入力されます。スレーブの位相整合は、PHSELピンに接続された抵抗ストリングによって行われます。詳細については、「クロック・マスター、PHSELおよびCLKIOの構成」で説明します。

## 4.3 電圧マスターおよび電圧スレーブ

電圧マスターは、出力電圧を監視するとともに、電圧レギュレーションのための‘COMP’信号を生成するチャネルを持ちます。電圧スレーブのチャネルは、TRK<sub>x</sub>ピンをBP5に接続して構成されます。これにより、電圧スレーブのCOMP<sub>x</sub>ピンにマス

ターからのCOMP信号が接続されます。TRK<sub>x</sub>ピンをBP5に接続すると、そのチャネルのCOMP<sub>x</sub>出力がハイ・インピーダンス状態になり、そのチャネルのレギュレーションを電圧マスターのCOMP信号によって制御できるようになります。

### 4.3.1 端子機能

| TERMINAL<br>NAME<br>NO. | I/O | 説明                                                                                                                                                                                             |

|-------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BP5 8                   | O   | VREGピンからフィルタを介した入力です。10Ωの抵抗をVREGとBP5の間に接続し、1.0μFのセラミック・キャパシタをBP5とグランドの間に接続する必要があります。                                                                                                           |

| GND 7                   | -   | デバイスの低ノイズ・グランド接続です。                                                                                                                                                                            |

| BOOT1 27                | I   | BOOT1は、PWM1のハイサイドFETドライバにブートストラップされた電源を供給し、ハイサイドFETのゲートが入力電源レールより上に駆動されるようにします。BOOT1とSW1ピンの間にキャパシタを接続し、このピンとVREGの間にショットキー・ダイオードを接続します。                                                         |

| BOOT2 18                | I   | BOOT2は、PWM2のハイサイドFETドライバにブートストラップされた電源を供給し、ハイサイドFETのゲートが入力電源レールより上に駆動されるようにします。BOOT2とSW2ピンの間にキャパシタを接続し、このピンとVREGの間にショットキー・ダイオードを接続します。                                                         |

| CLKIO 28                | O   | マスターのCLKIO周波数にスレーブ・コントローラを同期させるためのデジタル・クロック信号で、PWMのスイッチング周波数の6倍または8倍です。                                                                                                                        |

| COMP1 35                | O   | 誤差増幅器CH1の出力です。このピンの電圧によって、PWM1のデューティ・サイクルが決定されます。                                                                                                                                              |

| COMP2 10                | O   | 誤差増幅器CH2の出力です。このピンの電圧によって、PWM2のデューティ・サイクルが決定されます。                                                                                                                                              |

| CS1 31                  | I   | これらのピンは、CH1のフェーズ電流を検知するために使用されます。インダクタ電流は、外部の電流センス抵抗によって、または、外部のRC回路およびインダクタのDC抵抗を使用して検知できます。これらの信号のトレースは、電流センス素子に直接接続する必要があります。                                                               |

| CS2 14                  | I   | これらのピンは、CH2のフェーズ電流を検知するために使用されます。インダクタ電流は、外部の電流センス抵抗によって、または、外部のRC回路およびインダクタのDC抵抗を使用して検知できます。これらの信号のトレースは、電流センス素子に直接接続する必要があります。                                                               |

| CSRT1 32                | O   | CH1電流センス電圧のリターン・ポイントです。この信号のトレースは、電流センス素子に直接接続する必要があります。                                                                                                                                       |

| CSRT2 13                | O   | CH2電流センス電圧のリターン・ポイントです。この信号のトレースは、電流センス素子に直接接続する必要があります。                                                                                                                                       |

| DIFFO 1                 | O   | 差動増幅器の出力です。差動増幅器の出力電圧は最大5.8Vに制限されます。リモート・センスにより、このピンの電圧は、PCBトレースに高電流が流れる結果発生するI×Rドロップの影響を受けていない実際の出力電圧になります。VOUTピンおよびGSNSピンを、レギュレーションが必要な負荷ポイントに直接接続する必要があります。詳細については、「レイアウトについての考察」を参照してください。 |

| FB1 36                  | I   | CH1の誤差増幅器の反転入力です。閉ループ動作では、このピンの電圧は通常700mVです。このピンは、CH1のPGOOD1および低電圧についての監視も行います。                                                                                                                |

| FB2 9                   | I   | CH2の誤差増幅器の反転入力です。閉ループ動作では、このピンの電圧は通常700mVです。このピンは、CH2のPGOOD2および低電圧についての監視も行います。                                                                                                                |

| GSNS 3                  | I   | 差動増幅器の反転入力です。このピンは負荷点でグランドに接続する必要があります。差動増幅器を使用しない場合は、このピンをGNDに接続するか、またはオープンのままにします。                                                                                                           |

| HDRV1 26                | O   | CH1のハイサイドNチャネルMOSFETスイッチ用ゲート駆動出力です。出力はSW1を基準とし、ハイサイド・スイッチのドライブのためにブートストラップされます。                                                                                                                |

| HRDV2 19                | O   | CH2のハイサイドNチャネルMOSFETスイッチ用ゲート駆動出力です。出力はSW2を基準とし、ハイサイド・スイッチのドライブのためにブートストラップされます。                                                                                                                |

| ILIM1 34                | I   | CH1のサイクルごとの電流制限スレッシュホールドを設定するために使用します。ILIM1スレッシュホールドに達すると、PWMパルスが停止し、コンバータは、出力に制限された電流を供給します。                                                                                                  |

| ILIM2 11                | I   | CH2のサイクルごとの電流制限スレッシュホールドを設定するために使用します。ILIM2スレッシュホールドに達すると、PWMパルスが停止し、コンバータは、出力に制限された電流を供給します。                                                                                                  |

| LRDV1 24                | O   | CH1のローサイド同期整流用(SR)NチャネルMOSFETのゲート駆動出力です。                                                                                                                                                       |

| LRDV2 22                | O   | CH2のローサイド同期整流用(SR)NチャネルMOSFETのゲート駆動出力です。                                                                                                                                                       |

表 4-1. 端子機能

| TERMINAL<br>NAME | I/O<br>NO. |   | 説明                                                                                                                                                                    |

|------------------|------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGOOD1           | 30         | O | CH1の出力電圧のパワー・グッド・インジケータです。このオープン・ドレイン出力は、外部抵抗を介して電圧に接続されます。                                                                                                           |

| PGOOD2           | 15         | O | CH2の出力電圧のパワー・グッド・インジケータです。このオープン・ドレイン出力は、外部抵抗を介して電圧に接続されます。                                                                                                           |

| PGND             | 23         | - | コントローラの下位ゲート・ドライバ用のパワー・グランド基準です。下位MOSFETのソースからこのピンへ高電流リターン・バスが構成されます。                                                                                                 |

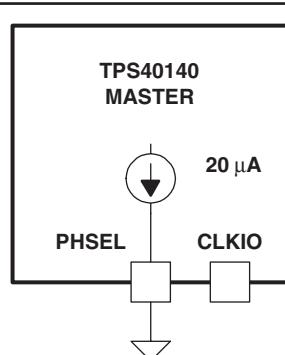

| PHSEL            | 4          | O | 20 $\mu$ Aの電流がこのピンから流れます。単一コントローラ設計では、このピンを接地する必要があります。マルチ・コントローラ構成では、このピンの電圧を設定する39k $\Omega$ の抵抗ストリングによって、スレーブの適切な位相整合が決まります。「クロック・マスター、PHSELおよびCLKIOの構成」を参照してください。 |

| VREG             | 21         | O | 内部の5Vレギュレータの出力です。4.7 $\mu$ Fのセラミック・キャパシタを、このピンとPGNDの間に接続する必要があります。                                                                                                    |

| RT               | 6          | I | このピンとグランドの間に抵抗を接続することによって、発振器の周波数を設定します。                                                                                                                              |

| SW1              | 25         | I | コンバータCH1のスイッチ・ノードに接続します。CH1の上位ゲート・ドライバのリターンです。上位MOSFETのソースからこのピンへの高電流リターン・バスが構成されます。また、このピンは、上位MOSFETの導通から下位MOSFETの導通までの間のデットタイムを最小限にするアダプティブ・ゲート・ドライブ回路によっても使用されます。  |

| SW2              | 20         | I | コンバータCH2のスイッチ・ノードに接続します。CH2の上位ゲート・ドライバのリターンです。上位MOSFETのソースからこのピンへの高電流リターン・バスが構成されます。また、このピンは、上位MOSFETの導通から下位MOSFETの導通までの間のデットタイムを最小限にするアダプティブ・ゲート・ドライブ回路によっても使用されます。  |

| TRK1             | 33         | O | 誤差増幅器CH1の非反転入力への入力です。通常、このピンは、ソフト・スタート・キャパシタまたはトラッキングされている別の電圧に接続されます。                                                                                                |

| TRK2             | 12         | O | 誤差増幅器CH2の非反転入力への入力です。通常、このピンは、ソフト・スタート・キャパシタまたはトラッキングされている別の電圧に接続されます。                                                                                                |

| UVLO_CE1         | 29         | I | $V_{IN}$ とこのピンの間の電圧デバイダによって、CH1が起動する入力電圧が決まります。電圧が0.5V～1.5Vの場合、VREGレギュレータが有効になります。電圧が2.1V以上の場合、CH1のソフト・スタートが開始されます。                                                   |

| UVLO_CE2         | 16         | I | $V_{IN}$ とこのピンの間の電圧デバイダによって、CH2が起動する入力電圧が決まります。電圧が0.5V～1.5Vの場合、VREGレギュレータが有効になります。電圧が2.1V以上の場合、CH2のソフト・スタートが開始されます。                                                   |

| VDD              | 17         | I | コントローラの5Vレギュレータおよび差動増幅器用の電源入力です。このピンとグランドの間に、1.0 $\mu$ Fのセラミック・キャパシタを接続する必要があります。                                                                                     |

| VOUT             | 2          | I | 差動増幅器の非反転入力です。このピンは、負荷ポイント近くのコンバータの出力に接続する必要があります。差動増幅器を使用しない場合は、このピンをオープンのままにします。                                                                                    |

| VSHARE           | 6          | O | 1.8Vのリファレンス出力です。                                                                                                                                                      |

表 4-1. 端子機能

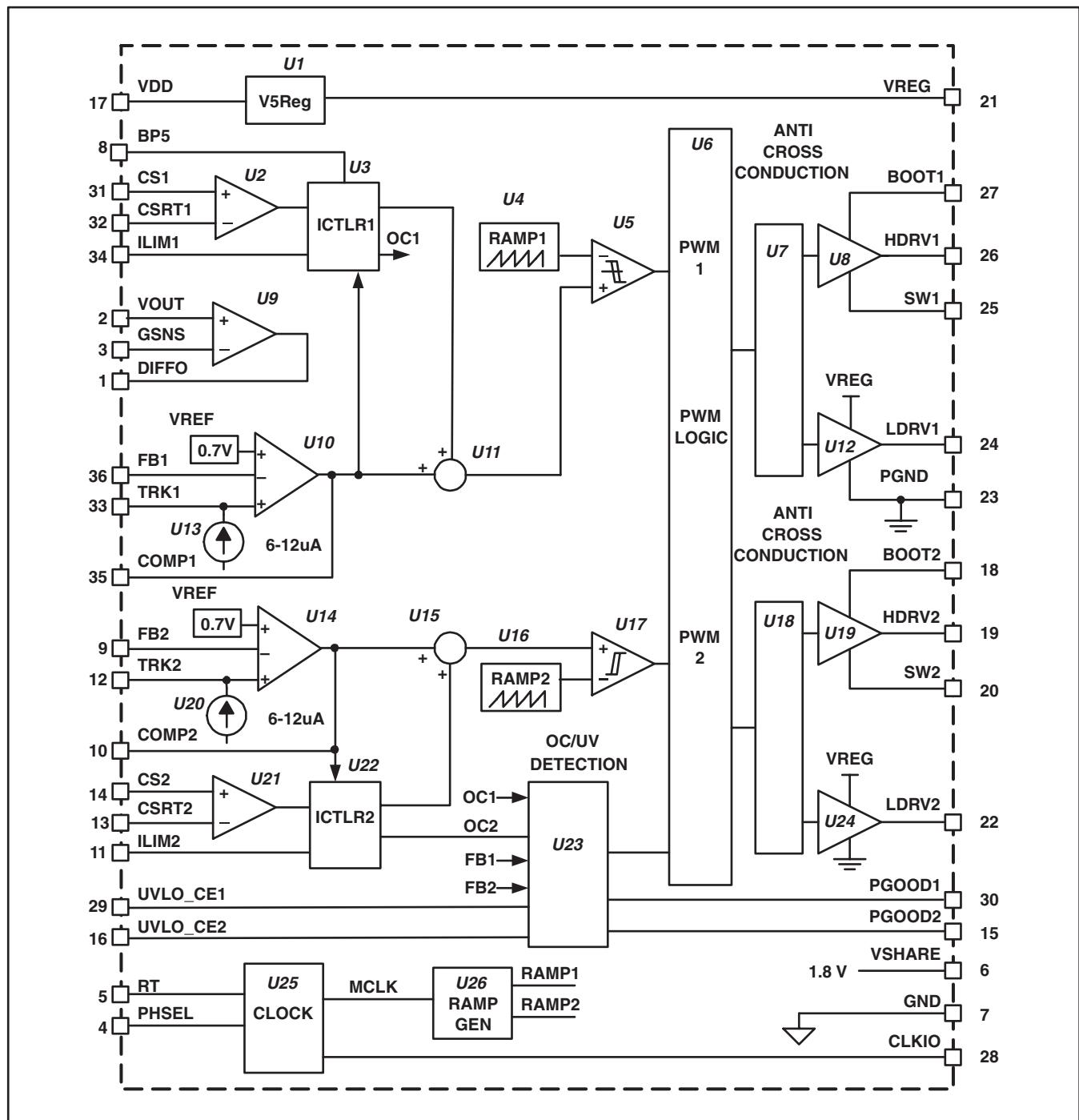

## 機能ブロック図

## 5 アプリケーション情報

### 5.1 機能説明

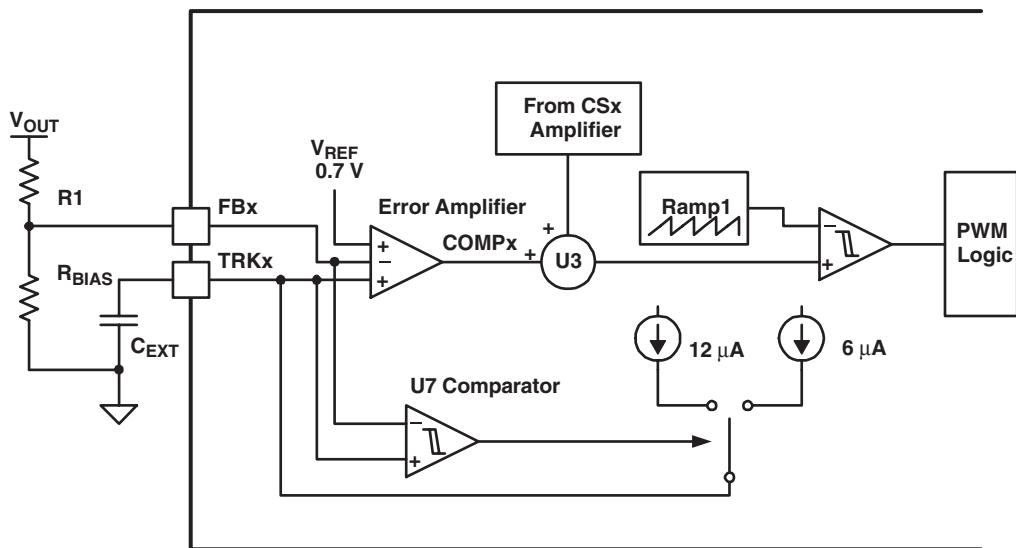

TPS40140は、プログラミング可能な固定スイッチング周波数で動作します。この製品は、強制フェーズ電流バランス機能を備えた電流帰還型コントローラです。電圧モード制御と比較すると、電流帰還型コントローラの帰還ネットワークは単純で、入力ラインの敏感性が抑えられます。フェーズ電流は、フィルタ・インダクタのDCR(直流抵抗)、または出力に直列接続された電流センス抵抗を使用して検知されます。「インダクタDCR電流センス」を参照してください。その検知された後、電流信号は増幅され、増幅された電圧誤差信号に重畠されて、電流モードPWM制御を実現します。

その他の機能としては、プログラミング可能な入力低電圧ロックアウト(UVLO)、高精度出力レギュレーション用の差動入力増幅器、ユーザがプログラミング可能な動作周波数、プログラミング可能なパルス単位の過電流保護、出力の低電圧シャットダウンおよびリスタート(再開)、キャパシタによって設定可能なソフト・スタート時間及びパワー・グッド・インジケータ機能があります。

### 5.2 データシートの構成

「アプリケーション情報」は、各モードおよび構成でTPS40140を簡単に使用できるように、いくつかのセクションに分かれています。最初の数セクションでは、すべての構成で使用する機能について説明します。残りのセクションでは、各構成(单一コントローラ、マルチ・コントローラ、マスターおよびスレーブ)に固有の機能について説明します。

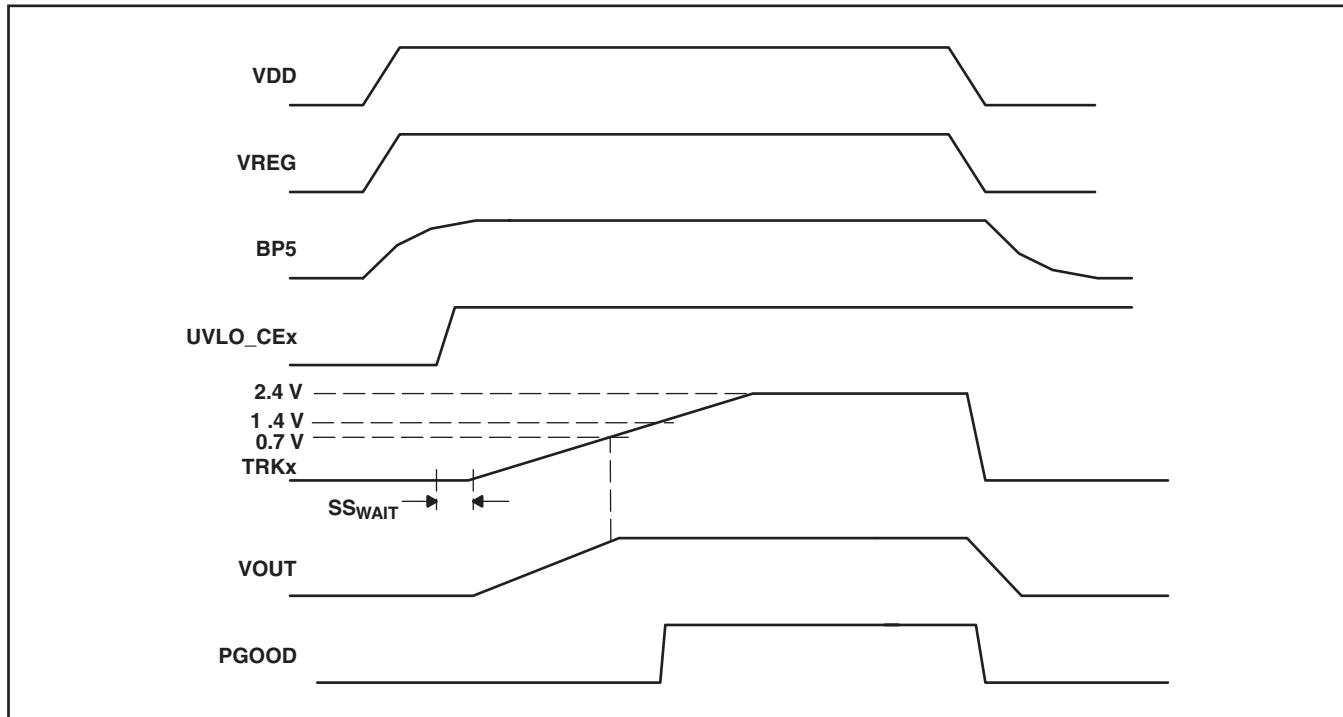

### 5.3 標準起動シーケンス

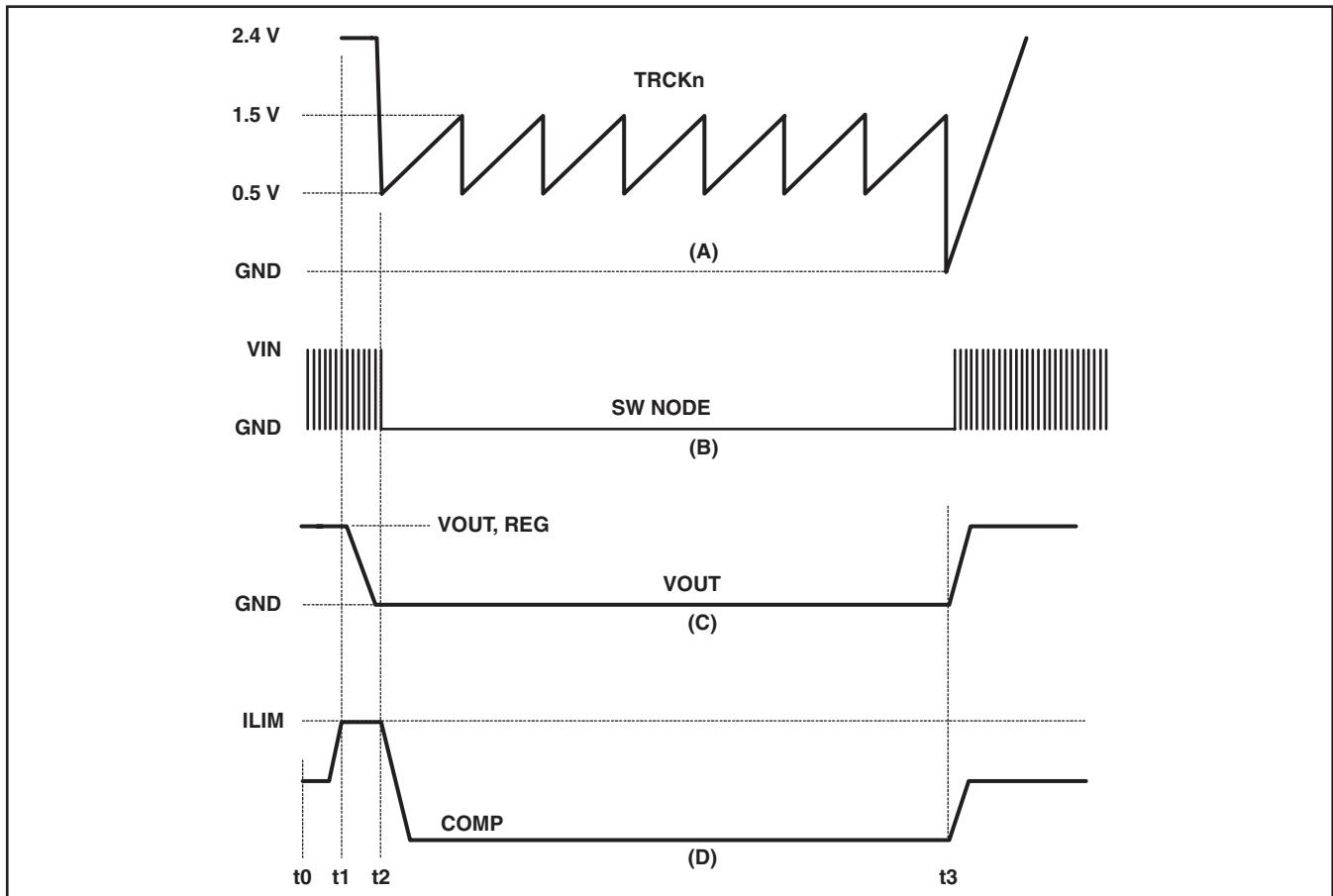

図5-1は、コントローラにVDDが印加され、それからUVLO\_CExが有効になる標準起動シーケンスを示しています。VDDが印加されなくなると、シャットダウンが行われます。

### 5.4 トランクリング(プライバイス出力なしのソフト・スタート動作)

TRKxピンに接続するキャパシタによって、パワーアップ時間が設定されます。UVLO\_CExが“ハイ”的状態で内部のパワーオン・リセット(POR)がクリアされると、キャリブレーションされた電流源から12μAの電流が流れ、ソフト・スタート・キャパシタの充電が開始されます。起動中、PGOODピンは“ロー”に維持されます。キャパシタ両端の立ち上がり電圧が、誤差増幅器U10およびU14の基準となります。ソフト・スタート電圧が基準電圧V<sub>REF</sub> = 0.7Vに達すると、コンバータの出力がレギュレーション点に達し、ソフト・スタート電圧がこれ以上に上昇しても出力に影響しなくなります。ソフト・スタート電圧が1.4Vに達すると、パワー・グッド(PGOOD)機能がクリアされ、PGOODピンに表示されます。通常、PGOODピンはこの時点で“ハイ”になります。ソフト・スタート・キャパシタの値を計算するには、式(1)を使用します。C<sub>ss</sub>の単位はファラッド、T<sub>ss</sub>の単位は秒です。

$$T_{ss} = C_{ss} \times 58 \times 10^3 \quad (1)$$

図 5-1. 標準起動およびシャットダウン・シーケンス

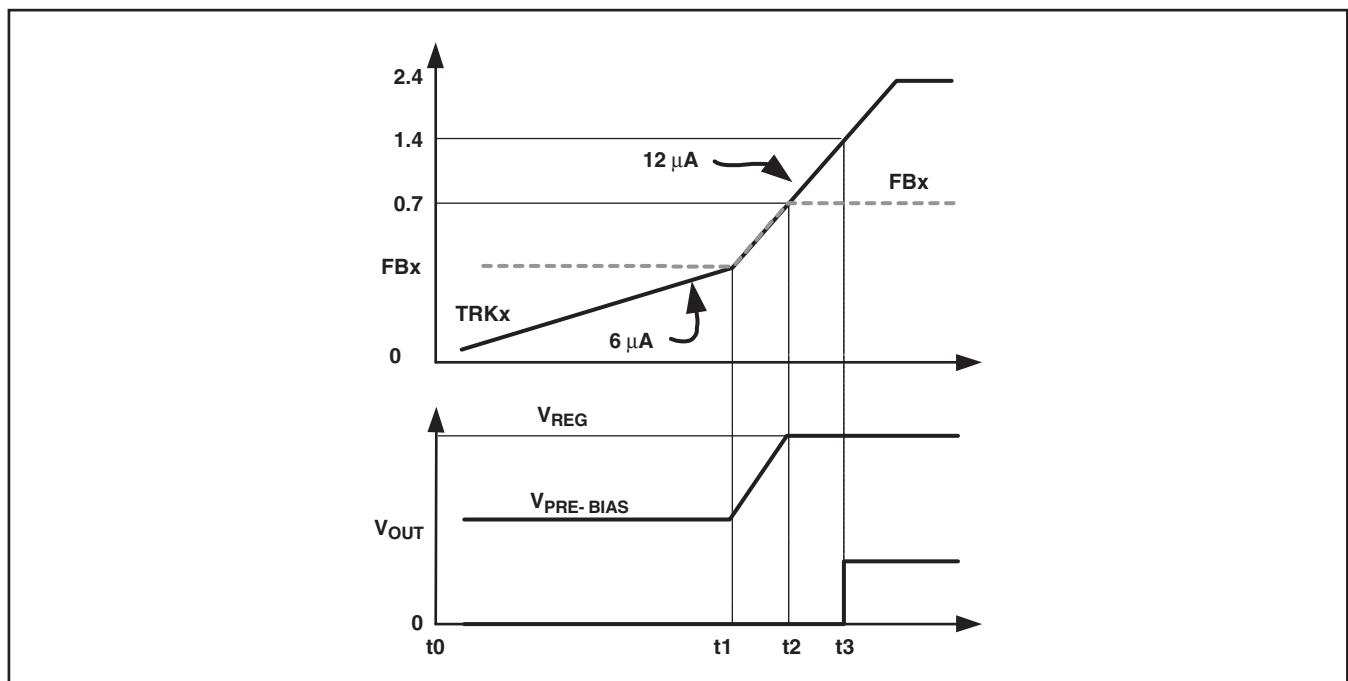

## 5.5 プリバイアス出力ありのソフト・スタート動作

プリバイアス出力をを行うために、TPS40140は、TRK<sub>x</sub>ピンに接続されたソフト・スタート・キャパシタを充電する2つのレベルのソフト・スタート電流を使用します。TRK<sub>x</sub>電圧がFB<sub>x</sub>ピンの電圧まで上昇すると、PWMのスイッチングが開始されます。最初のPWMパルスが発生すると、充電電流は12μAまで増加します。図5-2に、V<sub>OUT</sub>がプリバイアス出力の場合のTRACK<sub>x</sub>ピンの標準波形および出力電圧V<sub>OUT</sub>を示します。TRK<sub>x</sub>は、6μAの電流によって、TRK<sub>x</sub>の電圧がFB<sub>x</sub>ピンのプリバイアス電圧に等しくなるまで(時間t1)上昇します。この時点で、ソフト・スタート電流が12μAまで増加し、TRK<sub>x</sub>は傾きが増加して上昇を続けます。TRK<sub>x</sub>が時間t2で0.7Vに達すると、出力がレギュレーション状態になります。TRK<sub>x</sub>ピンの電圧は、上昇し続けます。TRK<sub>x</sub>電圧が時間t3で1.4Vになると、PGOOD<sub>x</sub>信号が有効になります。TRK<sub>x</sub>電圧は、内部でクランプされる2.4Vまで上昇を続けます。この方法によって、FB<sub>x</sub> = TRK<sub>x</sub>となるスレッシュホールドを正確に検出できます。図5-3は、実際のブロック図です。プリバイアスによるソフト・スタート時間の計算では、式(2)～式(4)に示すように、t<sub>0</sub>からt<sub>1</sub>までの時間にt<sub>1</sub>からt<sub>2</sub>までの時間を加えます。

$$t_1 = \frac{C_{SS}}{6 \mu A} \times \left( \frac{V_{OUT} \times R_{BIAS}}{R_1 + R_{BIAS}} \right) \quad (2)$$

$$t_2 = \frac{C_{SS}}{12 \mu A} \times \left( 0.7 V - \left( \frac{V_{OUT} \times R_{BIAS}}{R_1 + R_{BIAS}} \right) \right) \quad (3)$$

ここで

- C<sub>SS</sub>の単位はファラッドです。

- T<sub>SS</sub>の単位は秒です。

$$T_{SS} = t_1 + t_2 \quad (4)$$

プリバイアスがゼロの場合(V<sub>OUT</sub> = 0V)は、プリバイアスなしの場合と同じ式になります。

図 5-2. プリバイアス出力ありのソフト・スタートの波形

UDG-06031

図 5-3. プリバイアス出力時のソフトスタート内部回路構成

**設計のヒント：**プリバイアス電圧がレギュレーション電圧より高い場合、コントローラは起動しません。これは、コントローラがPWMスイッチングを開始する前に、過電圧が印加されている状態です。

## 5.6 スレーブ・チャネルを構成する場合の TRACKの機能

TRACKxピンは内部で2.4Vにクランプされます。チャネルをスレーブとして構成するには、TRACKxピンを外部で5Vにプルアップします。これにより、そのチャネルの誤差増幅器 COMPxの出力がハイ・インピーダンスになります。マスターの COMP信号でスレーブのチャネルを制御できます。

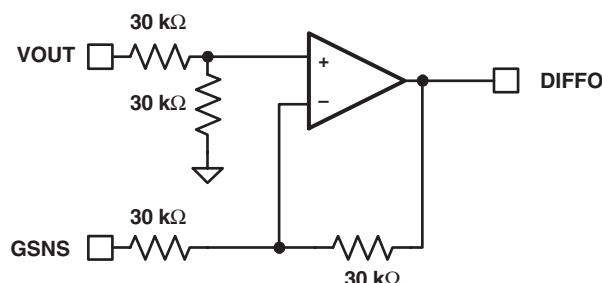

## 5.7 差動増幅器U9

ユニティ・ゲイン差動増幅器は高い帯域幅を持ち、ユーザが定義した負荷ポイントでのレギュレーションを改善し、レイアウトの制約を緩和します。出力電圧は、VOUTピンとGSNSピンの間で検知されます。出力電圧プログラミング・デバイダは、増幅器の出力ピンDIFOに接続します。

**設計のヒント：**差動増幅器の抵抗構成の関係で、入力インピーダンスを非常に低くしないと、出力電圧の設定で誤差が発生します。

## 5.8 パワー・グッド

PGOOD1およびPGOOD2ピンは、入力と出力が指定された動作範囲内であることを示します。また、UVLO\_CE1、UVLO\_CE2、TRK1、TRK2ピンも監視されます。PGOODは、入力および出力が指定された制限内の場合にハイ・インピーダンスになります。制限範囲外の状態では“ロー”になります。PGOOD信号は、対応するTRK1またはTRK2ピンの電圧が1.4Vを超えるまで“ロー”に維持されます。その後は、低電圧、過電流、または過熱によってPGOODの状態が制御されます。

図 5-4. 差動増幅器の構成

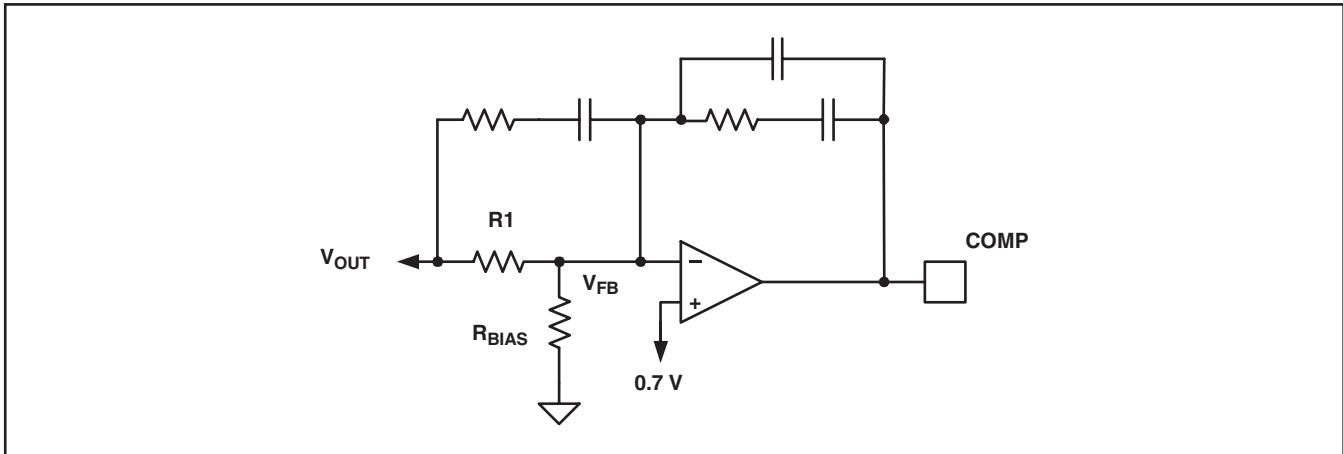

図 5-5.  $R_{BIAS}$ による出力電圧の設定

## 5.9 出力電圧の設定

図5-5に示すように、 $R1$ および $R_{BIAS}$ の2つの抵抗によって出力電圧を設定します。

$R_{BIAS}$ は式(5)で計算されます。

$$R_{BIAS} = 0.7 \times \left( \frac{R1}{(V_{OUT} - 0.7)} \right) \quad (5)$$

## 5.10 プログラミング可能な入力低電圧ロッカウト保護

UVLO\_CExピンを2Vに設定する電圧デバイダによって、コントローラが動作を開始するタイミングが決まります。UVLO\_CExピンの電圧が1Vを超えると内部レギュレータが有効になりますが、スイッチングは電圧が2Vになると開始されます。

## 5.11 パワー・オン・リセット (POR)

内部のPOR機能によって、コントローラが起動する前に、VREGおよびBP5の電圧がレギュレーション・ウィンドウの範囲内であることが保証されます。

## 5.12 過電流

過電流状態での動作については、「過電流検出およびヒップ・モード」で説明します。簡単に説明すると、コントローラが7クロック・サイクルにわたって過電流状態を検出すると、上位および下位MOSFETがオフにされ、コントローラは「ヒップ・モード」に移行します。7ソフト・スタート・サイクル後、通常のスイッチングが試行されます。過電流状態が解消されている場合は通常動作が再開しますが、解消されていない場合は上記のシーケンスが繰り返されます。

## 5.13 出力低電圧保護

「機能ブロック図」のU23によって検知されるFBピンの出力電圧が、低電圧保護スレッシュホールドである0.588V( $V_{REF}$ の84%)より低くなると、「過電流検出およびヒップ・モード」で説明するように、コントローラはヒップ・モードに移行します。

## 5.14 出力過電圧保護

出力の過電圧は、出力に現れるレギュレーション・レベルより高い電圧と定義されます。過電圧保護は、FBピンの出力電圧を監視する帰還ループによって行われます。動作中に出力電圧の過電圧状態になると、FBピンの電圧が上昇し、出力が設定レベルに戻るまで、制御ループによって上位FETがオフにされ、下位FETがオンにされます。これにより、過電圧状態のチャネルがブースト・モード構成になり、入力電圧が昇圧されることがあります。

コントローラのPWMスイッチングが開始する前に（つまり、スイッチングが全く行われていない状態で）、出力が過電圧状態になると、過電圧状態のチャネルではPWMスイッチングが開始されません。このコントローラは、プリバイアス出力での動作となります。出力がレギュレーション電圧より高いため、PWMスイッチングは行われません。

設計のヒント：過度な昇圧を防止するため、入力電圧に対して十分な負荷を確実にかけるよう注意してください。

## 5.15 CLKFLT、CLKIOピン・フォルト

CLKIO信号はマスター・コントローラからスレーブ・コントローラに供給されます。供給されない場合、スレーブ・コントローラは「スタンバイ」モードに移行します。この場合、上位および下位MOSFETはオフにされますが、内部5Vレギュレータはアクティブなままであり、VREG電圧は存在します。マスター・コントローラでCLKIO信号がオフにされているか、スレーブのCLKIO入力への接続がオープンになっている可能性があります。CLKIO信号が回復すると、通常動作が継続されます。

## 5.16 PHSELピン・フォルト

PHSELピンは通常、抵抗ストリングを介して終端されるか、グランドに直接接続されます。このストリングがオープンになると、PHSELピンの電圧が内部で4Vを超えるレベルまでプルアップされます。コントローラは‘スタンバイ’モードに移行します。この場合、上位および下位MOSFETはオフにされますが、内部5Vレギュレータはアクティブなままであり、VREG電圧は存在します。PHSEL接続が回復すると、64 PWMクロック・サイクル後に通常動作が継続されます。

## 5.17 過熱

コントローラのチップ温度が155°Cを超えたことが検出されると、上位および下位MOSFETがオフにされ、5VレギュレータVREGがオフになります。チップ温度が30°C下がると、コントローラは通常の起動シーケンスを実行します。

## 5.18 フォルト・マスキング動作

TRKxピンの電圧が1.4Vのスレッシュホールドを下回るよう外部で制限すると、コントローラは低電圧フォルトに応答せず、PGOOD出力が“ロー”に維持されます。これ以外のフォルト・モードは、有効のままであります。過電流保護については、スレッ

シュホールドを超えるたびにPWMサイクルが停止しますが、ヒップ・モードには移行しません。

## 5.19 保護およびフォルト・モード

起動時およびシャットダウン時の通常動作モードの他に、検出される各種のフォルト・モードがあります。これらのモード時の上位および下位MOSFETの状態を理解しておく必要があります。表5-1に、これらのモードおよびMOSFETの状態の概要を示します。各モードについては、表に説明します。

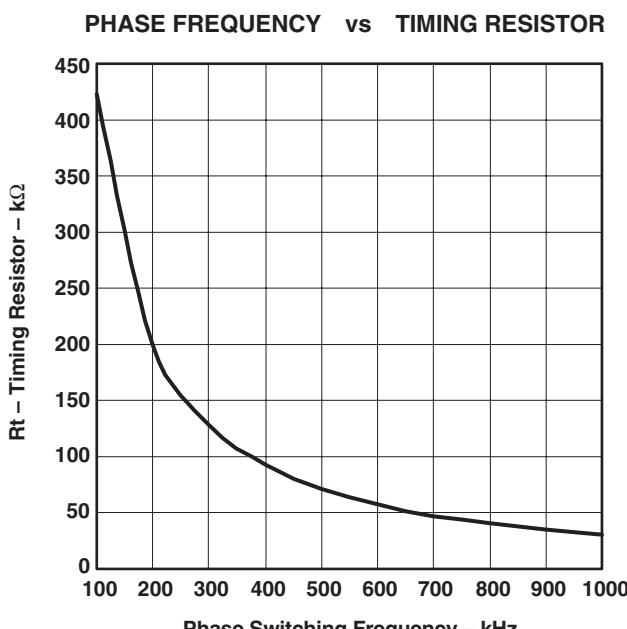

## 5.20 スイッチング周波数の設定

クロック周波数は、RTピンとグランドの間に接続するタイミング抵抗の値によってプログラミングします。式(6)を見てください。この式では、8フェーズ・システムの周波数を計算できます。6フェーズ・システムの周波数は約1.33倍高くなります。

$$R_t = 1.33 \times \left( 39.2 \times 10^3 \times f_{PH}^{-1.041} - 7 \right); \quad (6)$$

$f_{PH}$ は単一フェーズの周波数で、単位はkHzです。抵抗値 $R_t$ の単位はkΩです。図5-6を参照してください。

| MODE                                       | UPPER MOSFET     | LOWER MOSFET     |

|--------------------------------------------|------------------|------------------|

| PROGRAMMABLE UVLO_CEx = LOW                | OFF              | OFF              |

| POWER ON RESET: FIXED UVLO, BP5 < 4.25V    | OFF              | OFF              |

| OVERCURRENT                                | OFF, HICCUP MODE | OFF, HICCUP MODE |

| OUTPUT UNDERVOLTAGE                        | OFF, HICCUP MODE | OFF, HICCUP MODE |

| OUTPUT OVERVOLTAGE, PRIOR TO PWM SWITCHING | OFF              | OFF              |

| OUTPUT OVERVOLTAGE, WHILE PWM SWITCHING    | PWM SWITCHING    | PWM SWITCHING    |

| CLKFLT, MISSING CLKIO AT SLAVE             | OFF              | OFF              |

| PHSEL VOLTAGE > 4V, or open to ground      | OFF              | OFF              |

| OVERTEMPERATURE                            | OFF              | OFF              |

表5-1. フォルト・モードの概要

図5-6. フェーズ・スイッチング周波数 対  $R_t$

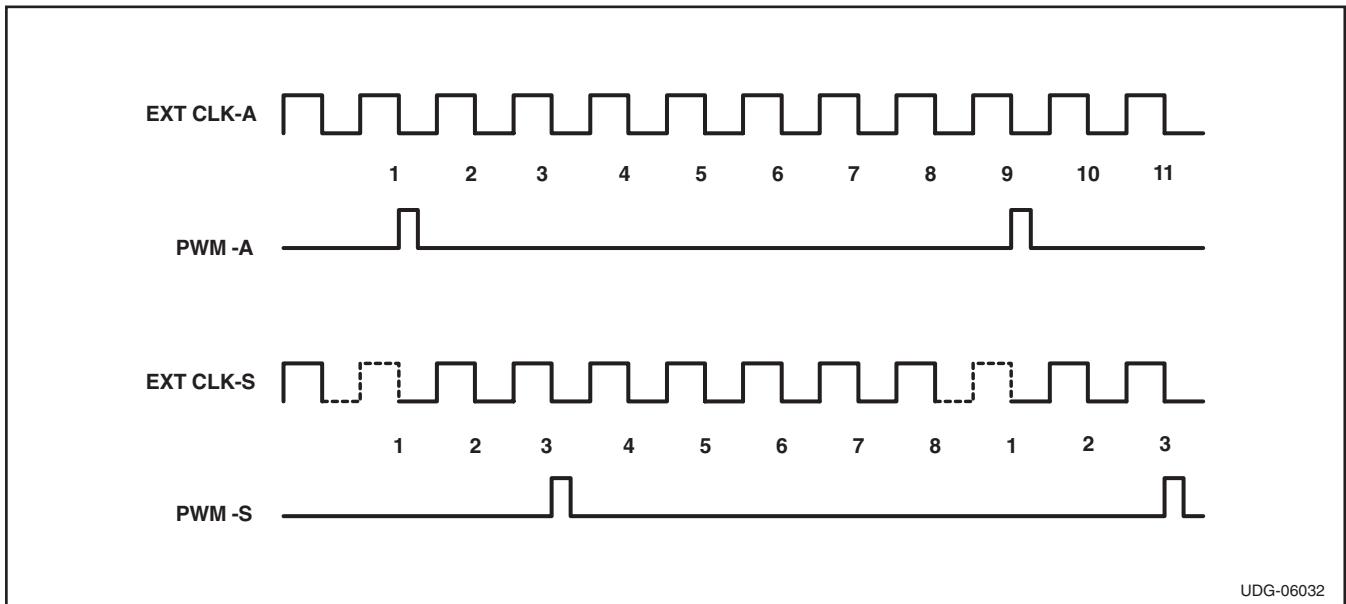

図 5-7. 単一コントローラの外部クロックへの同期

UDG-06032

## 5.21 単一コントローラの外部クロックへの同期

TPS40140には、単一コントローラを外部クロックに同期させる機能があります。クロックは、マスターのPWM周波数の6倍または8倍のパルス・ストリームでなければなりません。図5-7を参照してください。

単一コントローラの外部クロックへの同期は、クロック・スレーブのクロック・マスターへの同期に似ています。RTピンをBP5に接続することによって、内部クロック・ジェネレータを無効にし、単一コントローラをクロック・スレーブ・モードに移行させます。外部CLKIO信号が欠損パルスのないクロック・ストリームである場合、マスターは任意のパルスに同期するため、特定の決定的な位相同期はありません。欠損パルスがない場合、PWM周波数は外部クロックの1/8になります。外部CLKIO信号の6サイクルまたは8サイクルごとに欠損パルスがある場合、コントローラは6番目または8番目の位置の欠損パルスに基づいて同期します。欠損パルスがある場合、マスターの欠損パルスへの同期は、PHSELピンの電圧によって制御できます。「デジタル・クロック同期」を参照してください。また、2つ以上のコントローラを同一外部クロックに同期させる場合は、位相シフトさせることもできます。

図5-7は、想定される2種類の外部クロックとその結果得られるPWM信号のタイム・スライスです。EXT CLK-Aは、欠損パルスのない連続クロックであるため、PWM-A信号はクロック・ストリームのどの位置にも同期できます。PWM信号は、EXT CLK-Aの周波数の1/8です。EXT CLK-Sは、8サイクルごとに欠損パルスがある外部クロック・ストリームです。PWM-Sの位相整合は、PHSELピンの電圧に基づきます。PHSELが接地されている場合、図に示すように、PWM-S信号は欠損パルスの立ち下がりエッジに相当する位置から90°シフトされます。

## 5.22 分離した入力電圧での動作

マスター・コントローラの電源段が $V_{IN1}$ で動作し、これとは異なる $V_{IN2}$ でスレーブ・コントローラの電源段が動作するようになると(ここで $V_{IN1} > V_{IN2}$ )、便利な場合があります。これにより、システム設計者は、システム入力電圧から取り出す電流を最適化できます。出力電流のバランスを取るために、オフセットをプログラミングしてスレーブ・コントローラのILIM2に入力します。このピンの電圧により、チャネル2のオフセット電流が設定されます。

ランプ・オフセットは、スレーブのILIM2ピンに接続される抵抗 $R_{SET}$ によって決まり、次の式で求められます。

$$R_{SET} = V_{OUT} \left( \frac{1}{V_{IN2}} - \frac{1}{V_{IN1}} \right) 100 \text{ k}\Omega \quad (7)$$

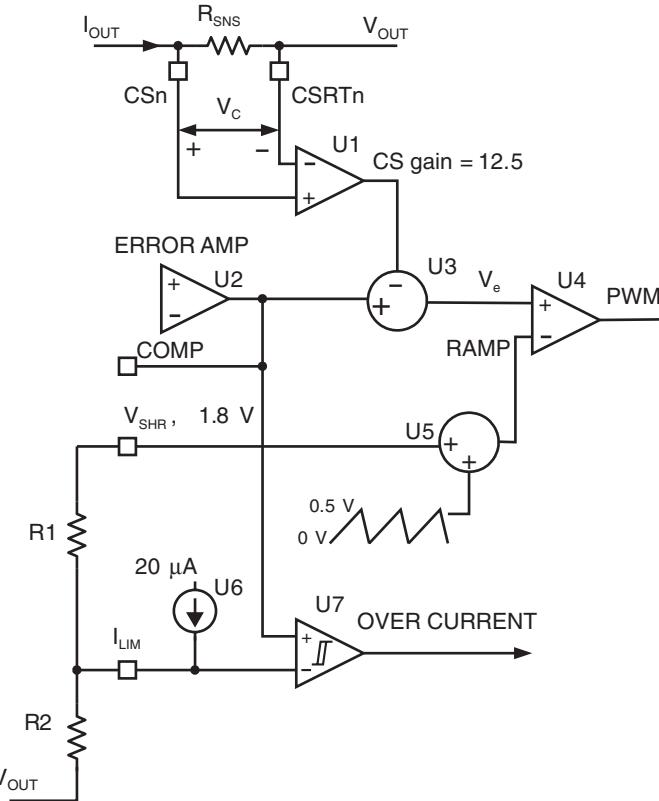

図 5-8. 出力電流センスおよび過電流検出

## 5.23 電流センス

電流センスおよび過電流検出のアーキテクチャを、図5-8に示します。

出力電流  $I_{OUT}$  が  $R_{SNS}$  を通過して、その両端に出力電流に対応する電圧  $V_C$  が生じます。また、電圧  $V_C$  は、出力インダクタと並列に配置されたRCネットワークからも取り出しができます。この電圧を12.5のゲインで増幅し、これを誤差増幅器出力COMPから減算して、 $V_e$ 電圧が生成されます。 $V_e$ 信号がスロープ補償RAMP信号と比較されて、変調器用のPWMが生成されます。出力電流が増加すると、増幅された  $V_C$  によって  $V_e$  信号が低下します。適切なデューティ・サイクル(PWM)を維持するためには、COMP信号を増加させる必要があります。したがって、COMP信号の大きさには、出力電流情報が含まれます。

$$COMP = V_e + (I_{PEAK} \times R_{SNS}) \times 12.5 \quad (8)$$

この情報は、 $I_{LIM}$ 電圧をCOMPと比較するコンパレータU7での過電流検出において必要となります。PWMで適切なデューティ・サイクルを得るために、 $V_e$ は次の式で求められる値である必要があります。

$$V_e = RAMP \times \frac{V_{OUT}}{V_{IN}} + V_{SHR} \quad (9)$$

これらの式を組み合わせると、次のようにになります。

$$COMP = RAMP \times \frac{V_{OUT}}{V_{IN}} + V_{SHR} + (I_{PEAK} \times R_{SNS}) \times 12.5 \quad (10)$$

このCOMP式から、抵抗R1およびR2がそれぞれ  $V_{SHR}$  および  $V_{OUT}$  に接続されている理由がわかります。

## 5.24 電流センスおよび電流バランス

コントローラにはピーク電流モード制御方式が備わっているため、必然的に、ある程度の電流バランス機能を持ちます。電流モードでは、サブハーモニックによる不安定を防ぐため、“スロープ補償”と呼ばれるデューティ・ファクタに応じた特定のガイドラインに、電流帰還のレベルが従う必要があります。この要件によって、より高度なフェーズ電流バランスの実現が妨げられる場合があります。問題を避けるためには、強制的にフェーズ電流をマッチングさせる別の電流ループを独自の制御方式に追加します。これにより、コントローラの小信号応答の影響を受けない高度な電流シェーリングが可能となります。これは、U3およびU22(CTLR)の中で行われます。

高帯域電流増幅器U2およびU21には、入力電圧として、専用高精度電流センス抵抗での電圧降下、RCネットワークに得られるインダクタのDCR電圧、または、インダクタのDCRから得られる熱補償された電圧のいずれかを入力できます。広範囲にわたる電流センス方法に対応することは、コストや複雑さの制約が緩和され、ローサイドMOSFET電流センスを使用するコントローラを上回る性能を提供できます。

RCネットワークの値の選択については、「インダクタDCR電流センス」を参照してください。

図 5-9. ヒカップ・モードとリカバリ動作

## 5.25 過電流検出およびヒカップ・モード

過電流発生時の入力電流と部品の消費電力を減らすために、ヒカップ・モードが実装されています。ヒカップ・モードとは、MOSFETのスイッチングが発生しない7ソフト・スタート・サイクルと、それに続く再起動試行の一連のシーケンスを表します。�トロルがクリアされていると、再起動の結果、通常動作とレギュレーションが開始されます。これを、図5-9に示します。

図5-9では、V<sub>OUT</sub>がレギュレーションされた電圧であり (C)、SW NODEで通常のスイッチングが発生し (B)、COMPが通常のレベルになっている (D) ことからわかるように、t0からt1までの間、通常動作が行われています。t1の時点で、過電流負荷が発生します。 (D) に示すように、電流が増加することによってCOMPがILIMレベルまで上昇します。COMP電圧がILIM電圧を上回っている状態が7スイッチング・サイクル続くと、コントローラはヒカップ・モードに移行します。この間、コントローラはスイッチングを行わず、スイッチングMOSFETはオフにされます。ヒカップ・モードでは、TRCKn端子に接続されるソフト・スタート・キャパシタの充放電が7サイクル実行されます。

7サイクル目の終了時に、コントローラは通常の再起動を試行します。�トロルがクリアされていれば、時間t3から、出力電圧がレギュレーション・レベルまで立ち上がります。�トロルがクリアされていない場合、COMP電圧が再びILIM電圧より高くなり、ヒカップ・モードが繰り返されます。

過電流状態が7 PWMクロック・サイクルにわたって続く場合、コンバータは上位および下位のMOSFETをオフにし、ヒカップ・モードの再起動を開始します。ヒカップ・モードでは、TRCKnピンが周期的に充放電されます。7ヒカップ・サイクル後、コントローラは通常動作に復帰するため、ソフト・スタート・サイクルを試行します。過負荷状態が持続している場合、コントローラはヒカップ・モードに戻ります。この状態が繰り返されます。

## 5.26 過電流保護レベルの計算

過電流( $I_{OC}$ )を希望する値に設定するには、いくつかの変数を調べる必要があります。入力電圧、出力電圧、出力インダクタの値とそのDC抵抗(DCR)、およびスイッチング周波数が必要です。また、ランプ電圧が0.5V、V<sub>SHARE</sub>電圧( $V_{SH}$ )が1.8Vであることがわかっています。このセクションの最後に示す、変数の一覧とその値を参照してください。

過電流設定点はDC出力電流の値として設定しますが、電流センス回路は電流のピークを監視します。したがって、次の値から計算する電流リップルが必要です。

- 入力電圧( $V_{IN}$ )

- 出力電圧( $V_{OUT}$ )

- スイッチング周波数( $f_{SW}$ )

- 出力インダクタンス( $L$ )

リップル電流は、式(11)で求められます。

$$I_{RIPPLE} = \frac{V_{IN} - V_{OUT}}{L} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}} \quad (11)$$

検出されるピーク電流は式(12)で求められ、式(14)で使用されます。

$$I_{PEAK} = \frac{I_{RIPPLE}}{2} + I_{OC} \quad (12)$$

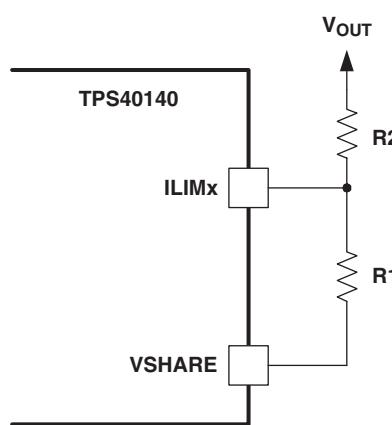

電流センス回路によって検出されるのは、この $I_{PEAK}$ 電流です。ピーク過電流保護スレッシュホールドを設定するには2つの抵抗が必要です。これらの各チャネルへの接続を図5-10に示します。

設計のヒント：抵抗R2は、出力電圧 $V_{out}$ に接続するか、差動増幅器の出力DIFFO(使用している場合)に接続します。

2つの係数 $\alpha$ および $\beta$ を使用すると、最後の式が簡単になります。これらは、式(13)および式(14)で求められます。

$$\alpha = \frac{V_{RAMP}}{V_{IN}} \quad (13)$$

$$\beta = DCR \times A_C \times I_{PEAK} + \left( \frac{V_{RAMP}}{2 \times N_{ph}} \right) \quad (14)$$

R1を式(15)に示します。

$$R1 = \frac{\beta + \alpha \times V_{SH}}{(1 - \alpha) \times I_{LIM}} \quad (15)$$

R2を式(16)に示します。

$$R2 = \frac{\beta + \alpha \times V_{SH}}{\alpha \times I_{LIM}} \quad (16)$$

ここで(以下は式(13)から式(16)に適用)

- $V_{RAMP}$ <sup>(1)</sup>はランプ振幅(0.5V typ)

- $V_{IN}$ は入力電圧

- DCRはインダクタの等価DC抵抗

- $A_C$ <sup>(1)</sup>はコンパレータへの伝達ゲイン

- $I_{OC}$ は単一フェーズのDC過電流トリップ点

- $I_{PEAK}$ は単一フェーズのピーク・インダクタ電流

- PHSEL電圧 = 1.6 V ±0.2 Vの場合 $N_{ph}$ は6、それ以外では $N_{ph} = 8$

- $V_{SHR}$ <sup>(1)</sup>はV<sub>SHARE</sub>基準電圧(1.8V typ)

- $I_{LIM}$ <sup>(1)</sup>は電流制限、出力電流(20μA typ)

(1) 変数の範囲は電気的特性に記載されています。

図 5-10. 過電流スレッシュホールド抵抗R2およびR1の選択

## 5.27 単一および複数ICの構成

コントローラは、単一出力2フェーズ・モードまたはデュアル出力電圧モードに構成できます。デュアル出力モードでは、入力電圧および出力電圧は互いに独立しています。2フェーズ・モードでは、入力電圧と出力電圧がそれぞれ互いに接続され、また、いくつか他のピンを設定する必要があります。單一コントローラの2つのフェーズは、常に180°位相がずれています。次の表で‘TO NETWORK’と記載されている項目は、制御ループ補償のために使用される通常の抵抗-キャパシタ・ネットワークを表します。これ以外の項目は、一般的にデバイスのピンに接続される部品を表します。

### 5.27.1 単一デバイス動作

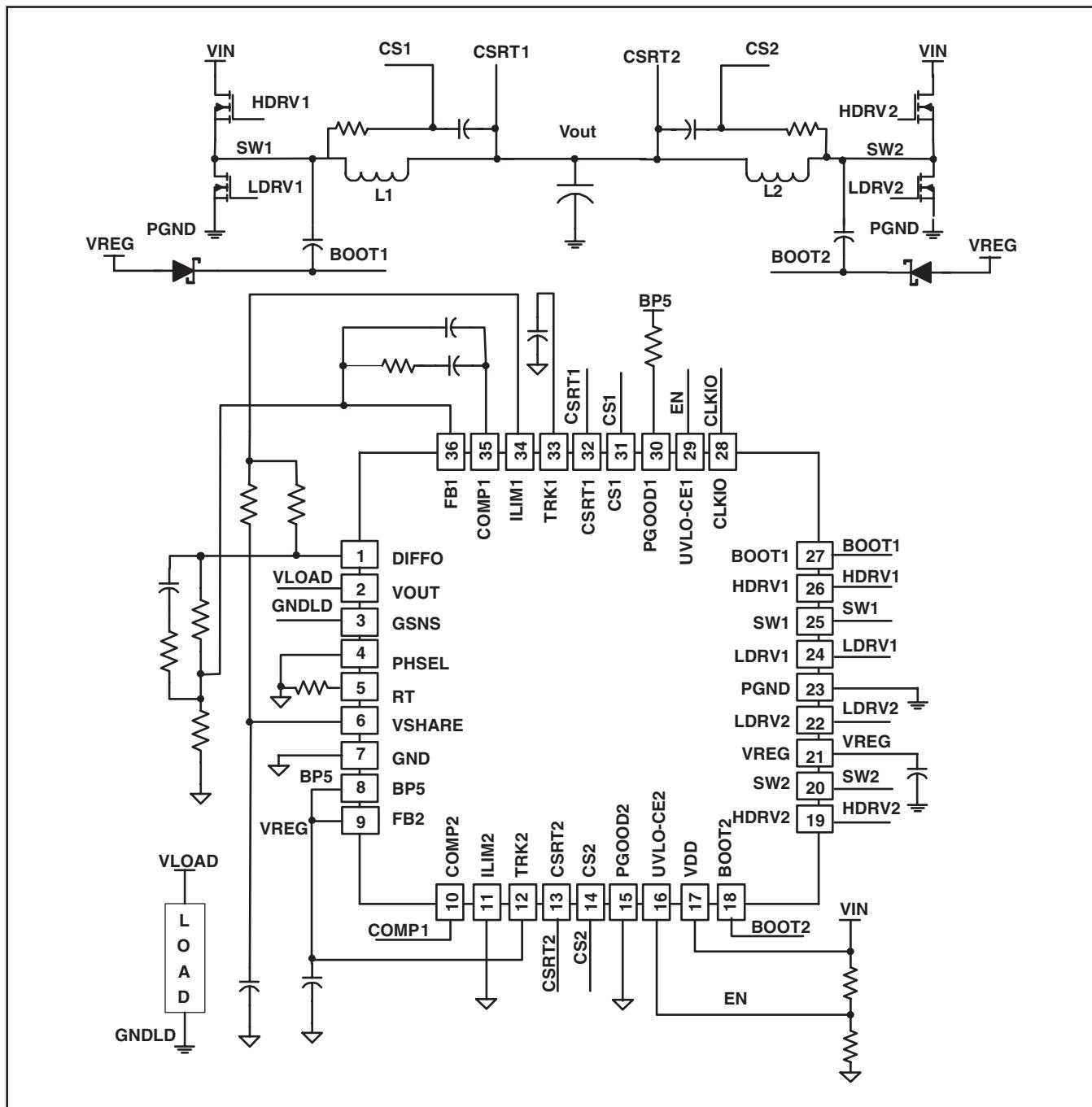

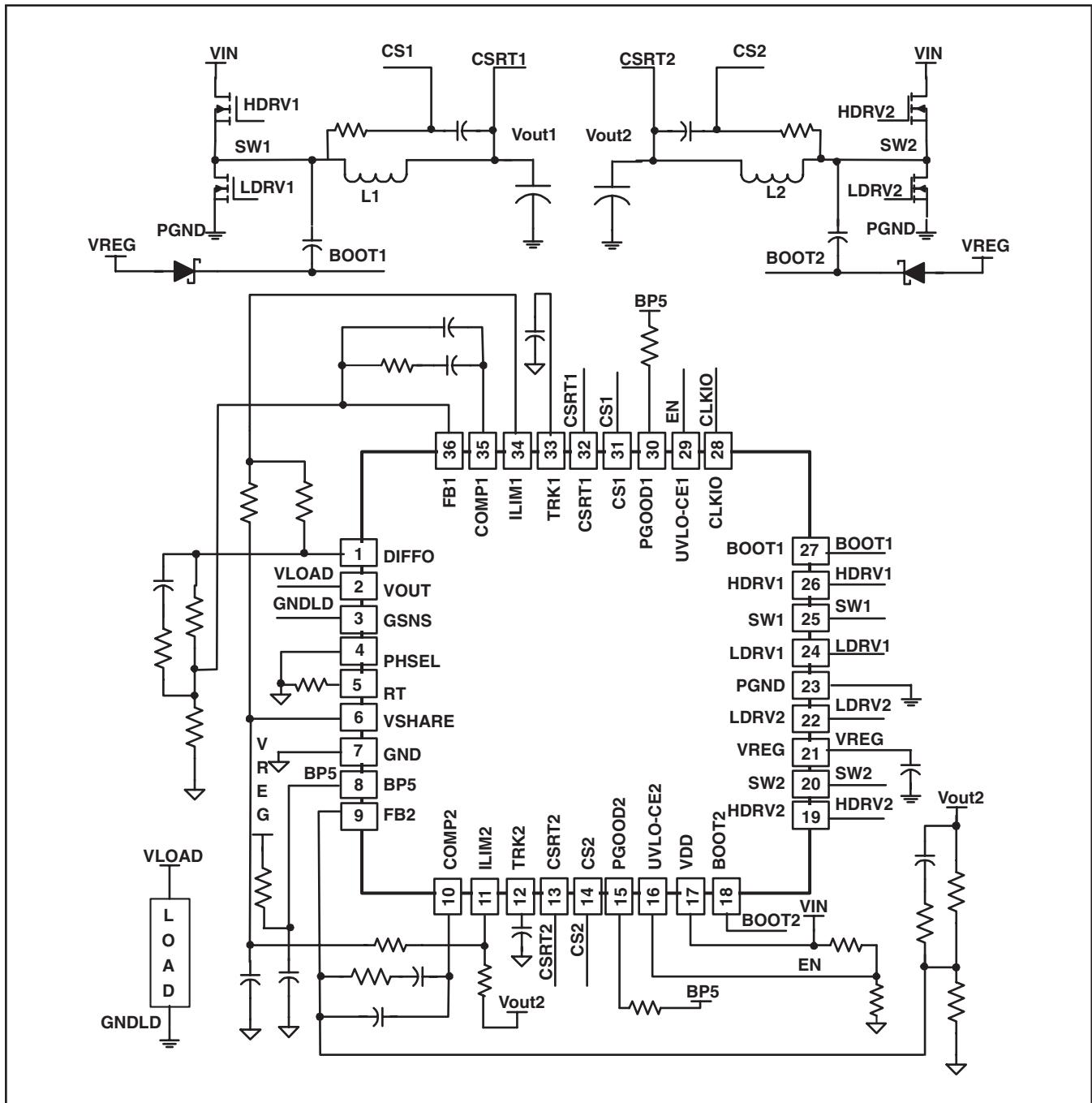

單一コントローラは2フェーズまたはデュアル出力として構成します。單一コントローラのモードおよびデバイスのピン接続の一覧を表5-2に示します。2フェーズ・モードで動作する單一コントローラの基本回路図を図5-11に示します。デュアル出力の回路図を図5-14に示します。

| DEVICE PIN | FOR 2 PHASE MODE    | FOR DUAL OUTPUT MODE |

|------------|---------------------|----------------------|

| COMP1      | TO NETWORK          | TO NETWORK           |

| COMP2      | COMP1               | TO NETWORK           |

| TRK1       | TO SS CAPACITOR     | TO SS CAPACITOR      |

| TRK2       | TO BP5              | TO SS CAPACITOR      |

| ILIM1      | TO SET RESISTORS    | TO SET RESISTORS     |

| ILIM2      | GND                 | TO SET RESISTORS     |

| FB1        | TO NETWORK          | TO NETWORK           |

| FB2        | GND                 | TO NETWORK           |

| PHSEL      | GND                 | GND                  |

| PGOOD1     | TO PULL-UP RESISTOR | TO PULL-UP RESISTOR  |

| PGOOD1     | TO PULL-UP RESISTOR | TO PULL-UP RESISTOR  |

| CLKIO      | OPEN                | OPEN                 |

表 5-2. TPS40140の單一デバイス・モード選択およびピン構成

図 5-11. 一般的なアプリケーション回路、2フェーズ・モード

図 5-12. 一般的なアプリケーション回路、デュアル・モード

## 5.27.2 マルチIC

マルチ・デバイス・システムでは、入力リップル電流、放射および伝導性放射を最小限に抑えるため、すべてのICのクロックを同期させることができます。これは、コントローラの1つを‘マスター’、残りのICを‘スレーブ’として指定して行います。マスターがシステム・クロックCLKIOを生成し、これがスレーブに供給されます。これは、最も有用なマルチIC構成であり、このデータシートで説明されています。詳細については、「クロック・マスター、PHSELおよびCLKIOの構成」で説明します。

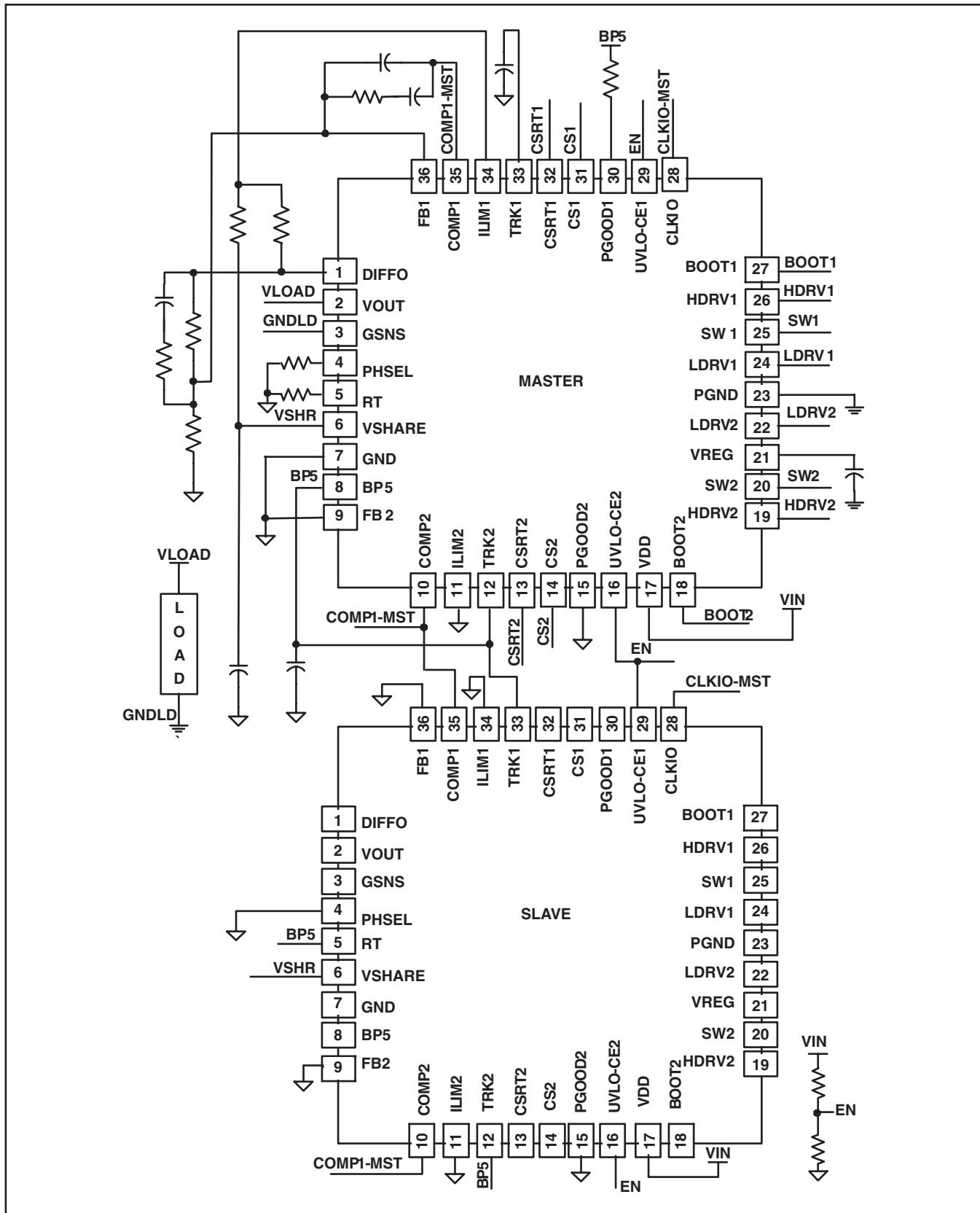

合計電流容量または出力数を増やすには、図5-15に示すように、単一のスレーブ・コントローラをマスター・コントローラに接続します。また、2フェーズ・マスターおよび2フェーズ・スレーブの構成を表5-3に示します。マスター・コントローラがあるスイッチング周波数で動作し、スレーブ・コントローラが別の独立した周波数で動作するように構成することも可能です。マルチ・フェーズ・システムでは、スレーブ・コントローラは負荷電流をマスターと共有します。

| DEVICE PIN, MASTER | MASTER, 2 PHASE     | DEVICE PIN, SLAVE | SLAVE, 2 PHASE      |

|--------------------|---------------------|-------------------|---------------------|

| COMP1              | TO NETWORK          | COMP1             | TO MASTER, COMP1    |

| COMP2              | COMP1               | COMP2             | TO MASTER, COMP1    |

| TRK1               | TO SS CAPACITOR     | TRK1              | TO BP5              |

| TRK2               | TO BP5              | TRK2              | TO BP5              |

| ILIM1              | TO SET RESISTORS    | ILIM1             | GND                 |

| ILIM2              | GND                 | ILIM2             | GND                 |

| FB1                | TO NETWORK          | FB1               | GND                 |

| FB2                | GND                 | FB2               | GND                 |

| PHSEL              | 39KΩ TO GND         | PHSEL             | GND                 |

| PGOOD1             | TO PULL-UP RESISTOR | PGOOD1            | TO PULL-UP RESISTOR |

| PGOOD1             | TO PULL-UP RESISTOR | PGOOD1            | TO PULL-UP RESISTOR |

| CLKIO              | TO SLAVE, CLKIO     | CLKIO             | TO MASTER, CLKIO    |

表 5-3. TPS40140の2つのデバイス、4フェーズ・モード選択およびピン構成

図 5-13. 一般的なアプリケーション回路、4フェーズ・モード

| DEVICE PIN, MASTER | MASTER, 2 PHASE      | DEVICE PIN, SLAVE | SLAVE, DUAL OUTPUT  |

|--------------------|----------------------|-------------------|---------------------|

| COMP1              | TO NETWORK           | COMP1             | TO NETWORK          |

| COMP2              | COMP1                | COMP2             | TO NETWORK          |

| TRK1               | TO SS CAPACITOR      | TRK1              | TO SS CAPACITOR     |

| TRK2               | TO BP5               | TRK2              | TO SS CAPACITOR     |

| ILIM1              | TO SET RESISTORS     | ILIM1             | TO SET RESISTORS    |

| ILIM2              | GND                  | ILIM2             | TO SET RESISTORS    |

| FB1                | TO NETWORK           | FB1               | TO NETWORK          |

| FB2                | GND                  | FB2               | TO NETWORK          |

| PHSEL              | 39-k $\Omega$ TO GND | PHSEL             | GND                 |

| PGOOD1             | TO PULL-UP RESISTOR  | PGOOD1            | TO PULL-UP RESISTOR |

| PGOOD1             | TO PULL-UP RESISTOR  | PGOOD1            | TO PULL-UP RESISTOR |

| CLKIO              | TO SLAVE, CLKIO      | CLKIO             | TO MASTER, CLKIO    |

表 5-4. TPS40140の2つのデバイス、2フェーズ・マスターおよびデュアル出力スレーブ構成

この構成では、マスターはPHSELピンに接続された39k $\Omega$ の抵抗によってスレーブ・コントローラが1つあることを検知し、CLKIO信号を供給します。スレーブ・コントローラは自身のPHSELピンが0Vレベルであることを検知して、マスターから90°位相がずれるよう、適切な数のCLKIOパルスを遅延させます。

また、2つのICを2フェーズ単一出力のマスターと、2つの独立した出力をもつスレーブとして構成することもできます。この場合、スレーブICは独立した2つの出力を持ちますが、これらはマスター・コントローラのクロックに同期します。構成を表5-4に示します。

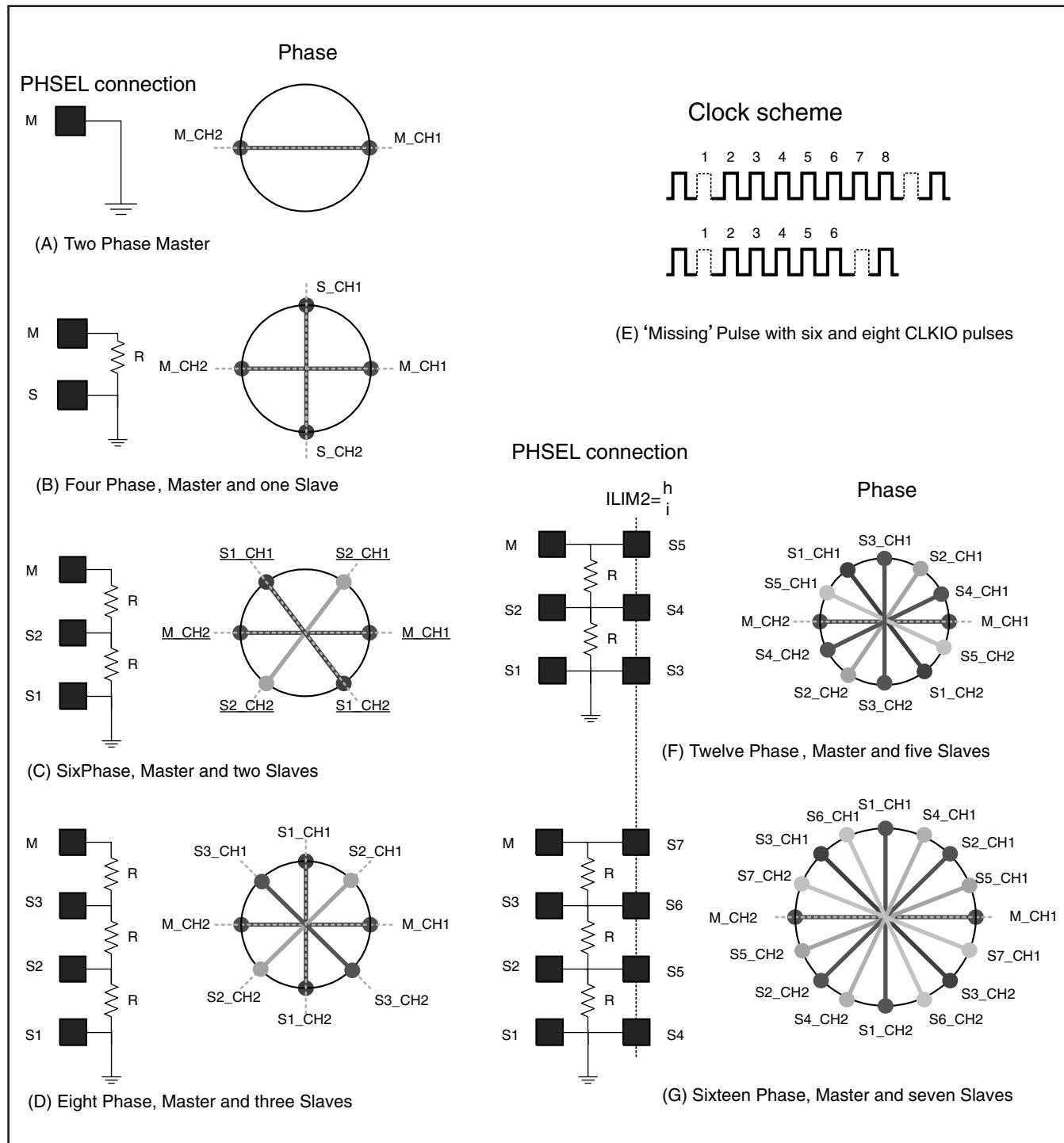

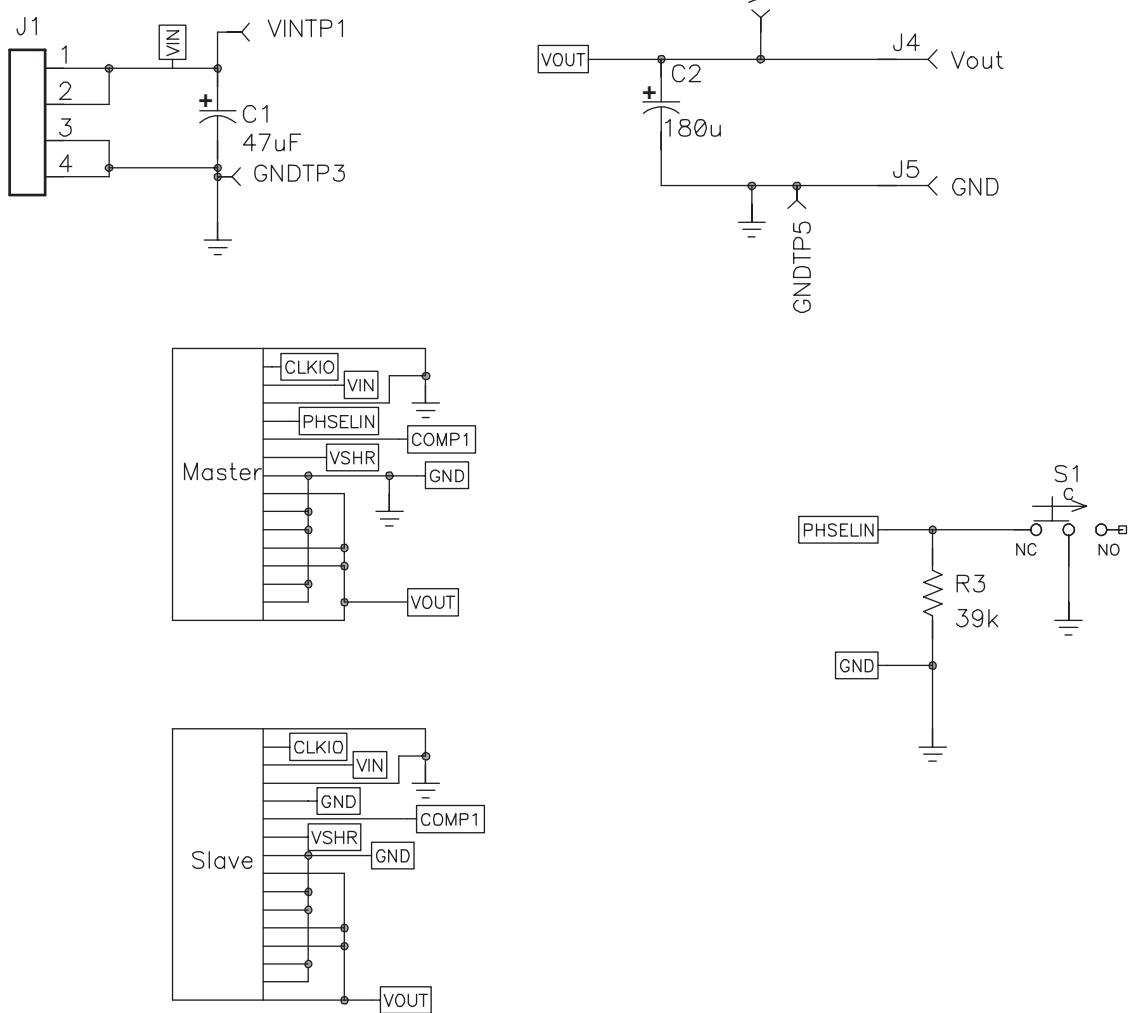

### 5.27.3 クロック・マスター、PHSELおよびCLKIOの構成

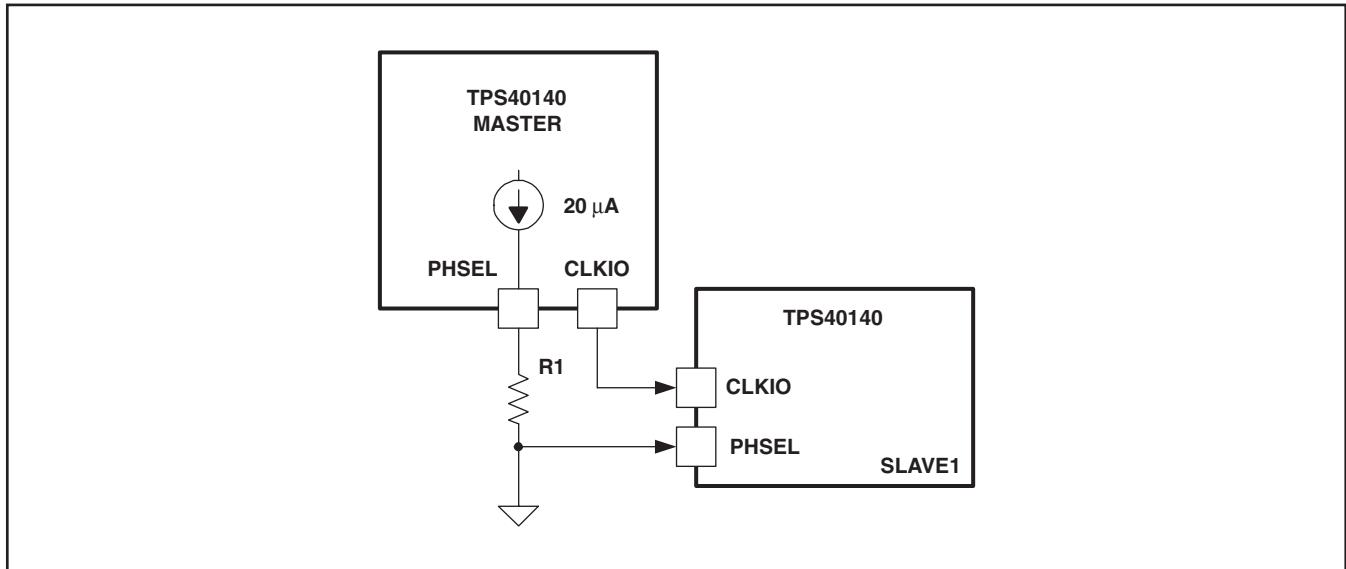

マスター・コントローラとスレーブ・コントローラとの間のクロック同期は、39k $\Omega$ の直列抵抗という簡単な構成で実現されます。マスター・コントローラのPHSELピンから出力される20 $\mu$ Aの電流源があります。フェーズのインタリーブを行うため、接続するスレーブ・コントローラの数に応じて、スレーブ

コントローラがマスターのCLKIO信号から適切に遅延するよう選択されます。任意の1つのマスターまたはスレーブ・コントローラの2つのフェーズは常に180°位相がずれています。

CLKIO信号のスイッチング周期の各サイクルは、6クロックまたは8クロックです。

柔軟性を最大限に高めるため、マスター・コントローラおよびスレーブ・コントローラは、2フェーズ構成またはデュアル出力構成のいずれか構成できます。

#### 5.27.3.1 1つのデバイスによる動作

单一デバイスの基本構成を図5-14に示します。

図 5-14. 単一コントローラのみ、2フェーズ

図 5-15. マスター・コントローラおよび1つのスレーブ・コントローラ、4フェーズ

### 5.27.3.2 2つのICによる動作

合計電流容量または出力数を増やすには、図5-15に示すように、一つのスレーブ・コントローラを追加します。

この構成では、マスターはスレーブ・コントローラが1つあることを検知して、CLKIO信号を供給します。スレーブ・コントローラは自身のPHSELピンが0Vレベルであることを検知して、マスターから90°位相がずれるよう、適切な数のCLKIOパルスを遅延させます。

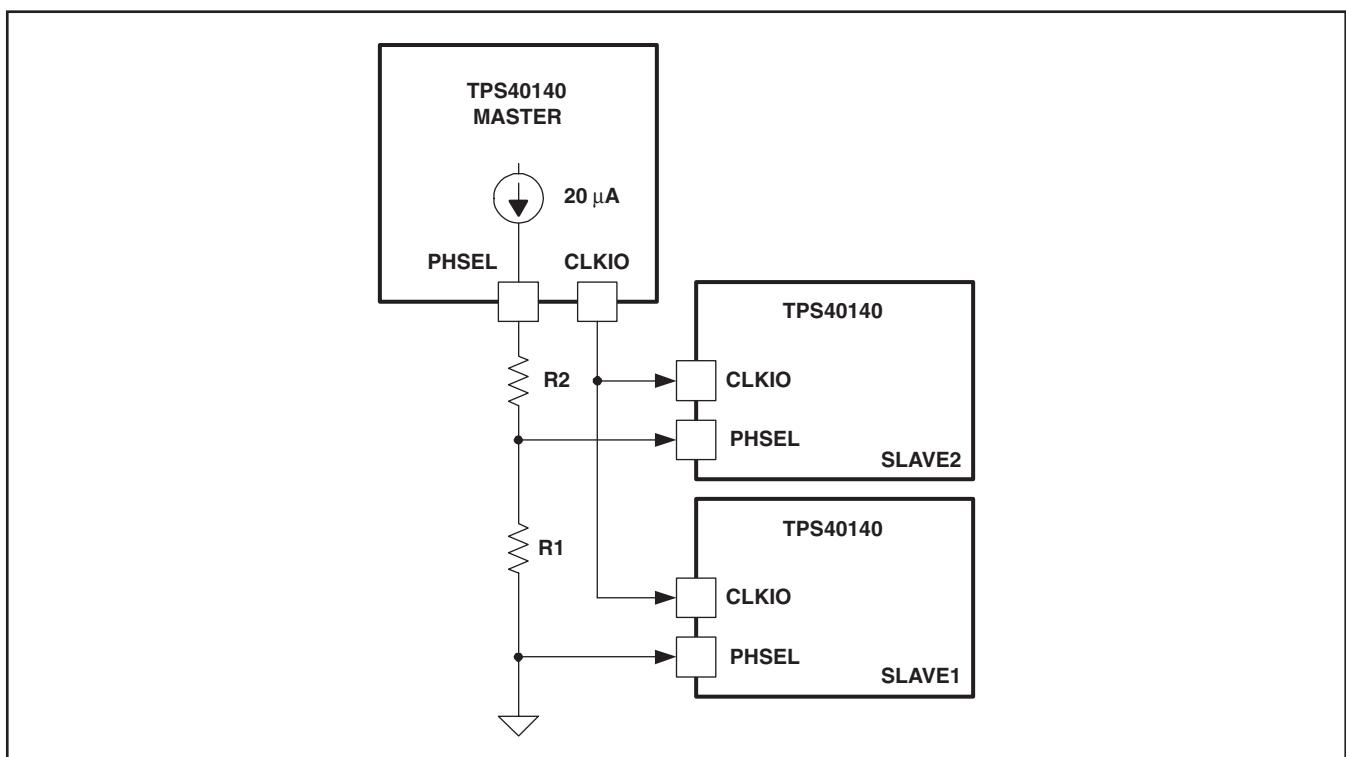

### 5.27.3.3 3つのICによる動作

合計電流容量を6フェーズまで増やすか、出力数を増やすには、図5-16に示すように、2つのスレーブ・コントローラを追加接続します。この構成では、完全なインタリーブのために、マスターとスレーブの位相は120°ずれています。CLKIO信号のスイッチング周期の各サイクルは6クロックであるため、スイッチング周期は減少しています。この6フェーズ・モードでは、スイッチング周波数は33%高くなります。

この構成では、マスターはスレーブ・コントローラが2つあることを検知して、6フェーズのCLKIO信号を供給します。スレーブ・コントローラは自身のPHSELピンの電圧を検知して、マスターから60°または120°位相がずれるよう、適切な数のCLKIOパルスを遅延させます。

図 5-16. マスター・コントローラおよび2つのスレーブ・コントローラ、6フェーズ

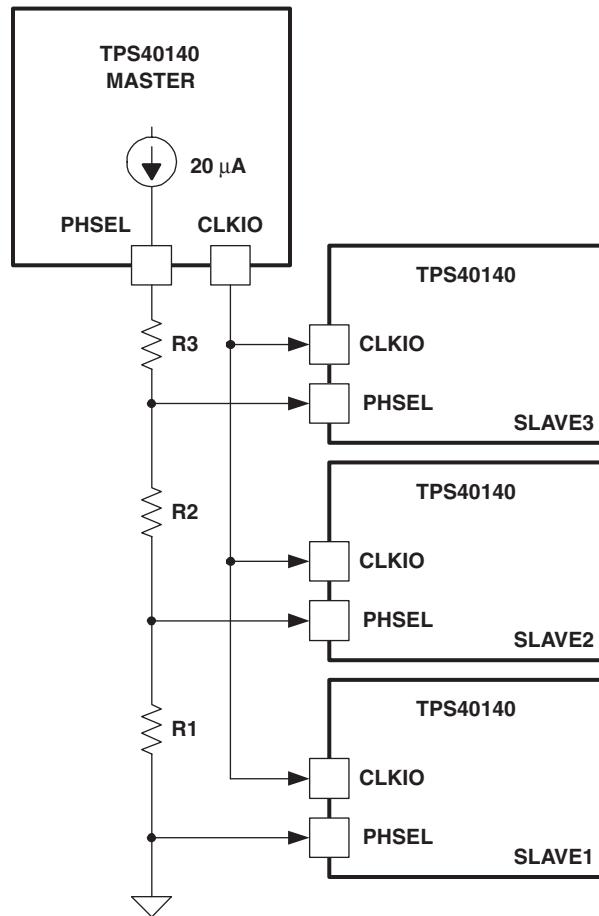

### 5.27.3.4 4つのICによる動作

合計電流容量を8フェーズまで増やすか、または出力数を増やすには、図5-17に示すように、3つのスレーブ・コントローラを追加接続します。

この構成では、マスターはスレーブ・コントローラが3つあることを検知して、8フェーズのCLKIO信号を供給します。スレーブ・コントローラは自身のPHSELピンの電圧を検知して、マスターから45°または90°位相がずれるよう、適切な数のCLKIOパルスを遅延させます。

図 5-17. マスター・コントローラおよび3つのスレーブ・コントローラ、8フェーズ

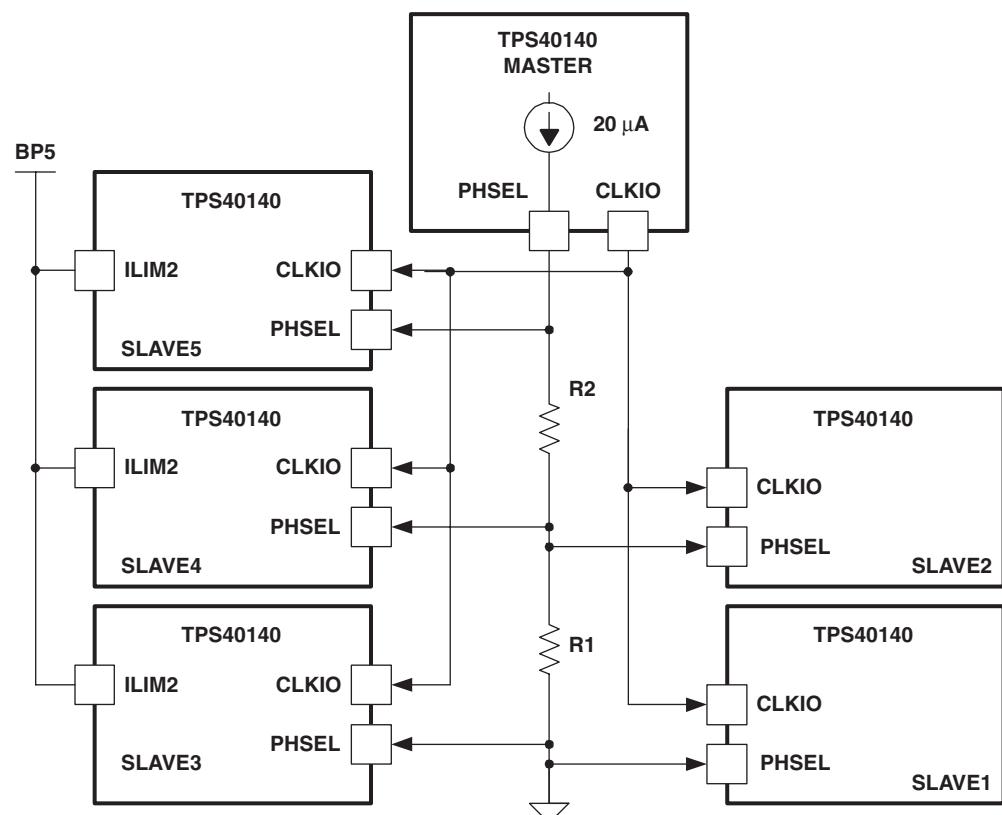

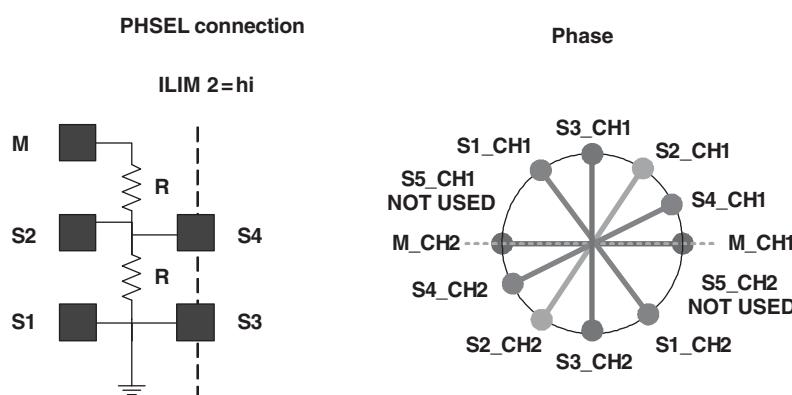

### 5.27.3.5 6つのICによる動作

合計電流容量を12フェーズまで増やすか、または出力数を増やすには、図5-18に示すように、5つのスレーブ・コントローラを追加接続します。

この構成では、マスターはスレーブ・コントローラが2つあることを検知して（抵抗が2個あるため）、6フェーズのCLKIO信号を供給します。スレーブ1およびスレーブ2は、前述のスレーブが2つの場合のように、それぞれ60°および120°でオンになります。ただし、6フェーズ・クロックで12フェーズを実現するため、CLKIO信号の両方のエッジを使用してスレーブを制御します。スレーブ3、4および5のILIM2が“ハイ”に接続されています。

るため、これらはCLKIOの立ち上がりエッジでオンになります。一方、マスターとスレーブ1および2は、CLKIOの立ち下がりエッジでオンになります。

4つのスレーブを使用する場合は、図5-18からスレーブを1つ削除するだけです。ただし、マスターと3つのスレーブの間は30°の位相差であるため、インターリープは完全ではありません。スレーブが1つ削除されたため、2つの隣接するスレーブの間が60°になります。位相整合の詳細については、図5-20を参照してください。

図 5-18. マスター・コントローラおよび5つのスレーブ・コントローラ、12フェーズ

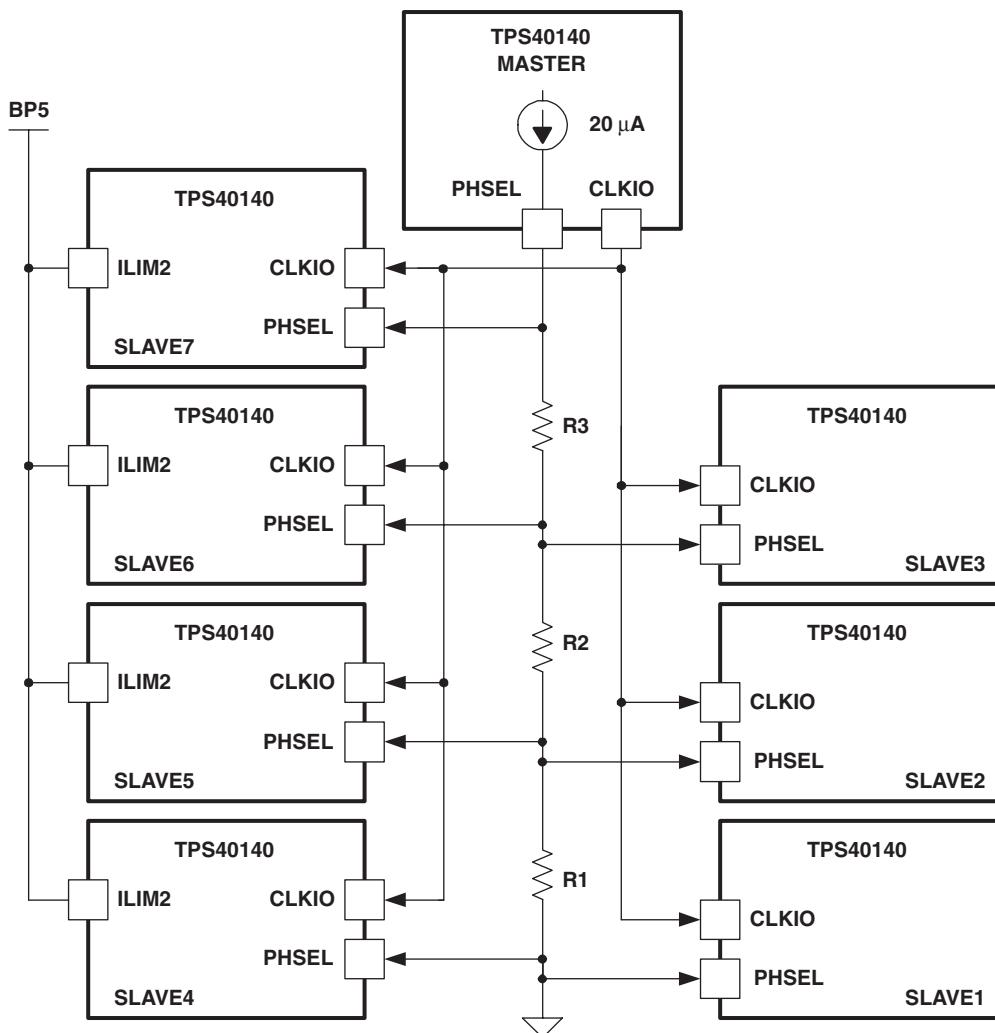

### 5.27.3.6 8つのICによる動作

合計電流容量を16フェーズまで増やすか、または出力数を増やすには、図5-19に示すように、7つのスレーブ・コントローラを追加接続します。

この構成では、マスターはスレーブ・コントローラが3つあることを検知して(抵抗が3つあるため)、8フェーズのCLKIO信号を供給します。スレーブ1、2および3は、前述のスレーブが3つの場合のように、それぞれ45°および90°でオンになります。ただし、8フェーズ・クロックで16フェーズを実現するため、CLKIO信号の両方のエッジを使用してスレーブを制御します。スレーブ4、5、6および7のILIM2は“ハイ”に接続されている

ため、これらはCLKIOの立ち上がりエッジでオンになります。一方、マスターとスレーブ1、2および3は、CLKIOの立ち下がりエッジでオンになります。6つのスレーブを使用する場合は、図5-19からスレーブを1つ削除するだけです。ただし、マスターと3つのスレーブの間は22.5°の位相差であるため、インターリープは完全ではありません。スレーブが1つ削除されるため、2つの隣接するスレーブの間が45°になります。位相整合の詳細については、図5-20を参照してください。

図 5-19. マスター・コントローラおよび7つのスレーブ・コントローラ、16フェーズ

## 5.28 デジタル・クロック同期

図5-20に、マスターおよびスレーブのクロック位相整合の要約を示します。マスターおよびスレーブは、マルチ・フェーズ単一出力構成、またはクロックに依存しない複数の独立した出力電圧レール、あるいはその両方として機能するように選択できます。

### 5.28.1 2, 4, 6, 8, 12または16フェーズの基本構成

図5-20の塗りつぶされた四角形は、マスター・コントローラ(M)または番号が付けられたスレーブ・コントローラ(S1~S7)のPHSELピンを表します。車輪型のスポーク部分のラベルは、マスター・チャネル1およびマスター・チャネル2(M\_CH1およびM\_CH2)と、番号が付けられた各スレーブのスレーブ・チャネル1およびスレーブ・チャネル2(Sn\_CH1およびSn\_CH2)を表します。任意のマスターまたはスレーブICのチャネル1とチャネル2は、常に180°位相がずれています。

図 5-20. クロック位相整合の要約

マスターおよびスレーブは、マスターとスレーブの間の抵抗ストリングに基づいて、適切に位相整合するように自動的に構成されます。すべての抵抗は39kΩ～41.2kΩです。前の図の(A)は、180°の位相差で2フェーズ動作する单一コントローラを示しています。前の図の(B)は、4フェーズ動作を示しています。これは、マスターのPHSELとGNDの間に1つの抵抗を接続し、スレーブのPHSELピンを接地することによって構成します。各チャネルは90°ずつ位相がずれています。前の図の(C)は、6フェーズ動作を示しています。これを構成するには、マスターのPHSELとGNDの間に2つの抵抗を接続します。1つ目の抵抗のタップをスレーブ2のPHSELピンに接続し、スレーブ1のPHSELピンを接地します。各チャネルは60°ずつ位相がずれています。前の図の(D)は、8フェーズ動作を示しています。これを構成するには、マスターのPHSELとGNDの間に3つの抵抗を接続します。1つ目の抵抗のタップをスレーブ3のPHSELピンに接続します。2つ目の抵抗のタップをスレーブ2のPHSELピンに接続し、スレーブ1のPHSELピンを接地します。各チャネルは45°ずつ位相がずれています。前の図の(F)は、12フェーズ動作を示しています。これを構成するには、マスターのPHSELとGNDの間に2つの抵抗を接続します。また、マスターのPHSELピンはスレーブ5のPHSELピンにも接続します。1つ目の抵抗のタップをスレーブ2およびスレーブ4のPHSELピンに接続し、スレーブ1およびスレーブ3のPHSELピンを接地します。各チャネルは30°ずつ位相がずれています。さらに、スレーブ5、スレーブ4およびスレーブ3のILIM2ピンはオープンのままにするか(内部プルアップ)、または外部でBP5に接続します。前の図の(G)は、16フェーズ動作を示しています。これを構成するには、マスターのPHSELとGNDの間に3つの抵抗を接続します。また、マスターのPHSELピンはスレーブ7のPHSELピンにも接続します。1つ目の抵抗のタップをスレーブ3およびス

レーブ6のPHSELピンに接続します。2つ目の抵抗のタップをスレーブ2およびスレーブ5のPHSELピンに接続し、スレーブ1およびスレーブ4のPHSELピンを接地します。各チャネルは22.5°ずつ位相がずれています。さらに、スレーブ7、スレーブ6、スレーブ5およびスレーブ4のILIM2ピンはオープンにするか(内部プルアップ)、または外部でBP5に接続します。

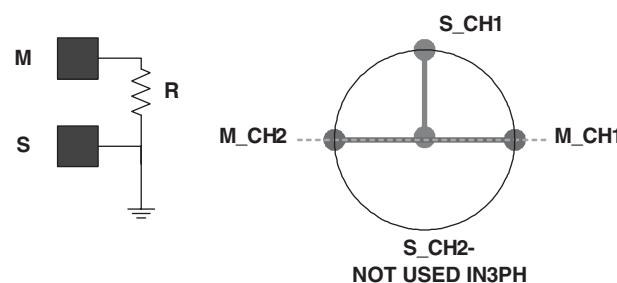

## 5.28.2 その他の数のフェーズの構成

2、4、6、8、12または16フェーズ以外の構成は、単純にいくつかのスレーブ・コントローラを接続しないだけです。マスターと接続されたスレーブとの位相整合は、前で説明したとおりです。たとえば、3フェーズ・システムは、マスターのCH1、マスターのCH2およびスレーブの1フェーズで構成できます。前の(B)を参照すると、3つのフェーズは、図5-21に示すように、マスターのCH1、マスターのCH2とスレーブのCH1またはスレーブのCH2することができます。

また、3フェーズ・システムは、マスターの1チャネルとスレーブの2チャネルでも構成できます。前の(B)を参照すると、3つのフェーズは、マスターのCH1またはマスターのCH2と、スレーブのCH1とスレーブのCH2することができます。これらのいずれの構成でも、2つのチャネル間の位相差は90°で、他のチャネルとの間の位相差は180°になります。使用されないチャネルは別の独立した出力電圧用に使用することができ、そのクロックは3フェーズ・システムで使用されていないフェーズを使います。この原理は、図5-20の「クロック位相整合の要約」に掲載されています。この原理は、図5-22のように構成できます。

たとえば、10フェーズ・システムは図5-22のように構成できます。

接続されたスレーブのチャネル間のクロックは、図のようになります。

図 5-21. フェーズ・システム：マスターの2チャネルとスレーブの1チャネル

図 5-22. スレーブ5を非接続にした10フェーズ・システム

## 5.29 設計例に関する情報

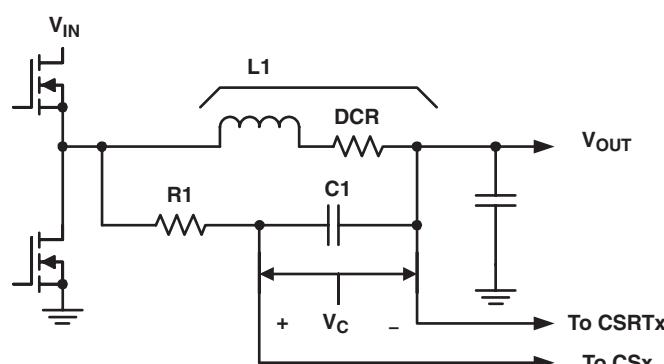

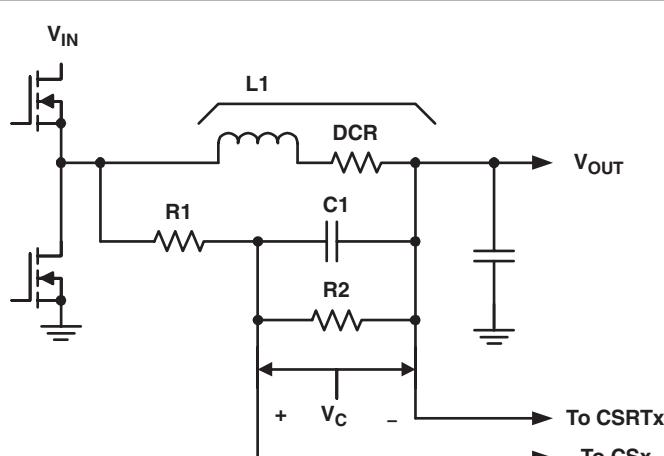

### 5.29.1 インダクタDCR電流センス

TPS40140の出力電流のサンプリングに適した方法として、インダクタDCRによる方法があります。これは、基板上の場所を占有し、効率にも影響が及ぶディスクリートの電流センス抵抗を使用する場合とは対照的に、損失のない方式です。インダクタDCRセンス回路を図5-23に示します。

インダクタL1は、インダクタンスLおよび抵抗DCRで構成されます。インダクタの時定数である  $L / DCR$  は、 $R1 \times C1$  の時定数と等しい必要があります。したがって、 $R1$  の値を求めるには、 $C1$  の値の選択 (0.1 $\mu$ Fが最適です) により、式(17)のようになります。

$$R1 = \frac{L1}{DCR \times C1} \quad (17)$$

DCの負荷が増加すると、電圧  $V_C$  の大部分は  $(I_{OC} \times DCR)$  によって決まります。ここで、 $I_{OC}$  はフェーズあたりのDC出力電流です。過電流設定点において、 $V_C$  のピーク電圧が差動入力の最大電圧 60mV を超えないようにすることが重要です。電圧  $V_C$  が 60mV を超える場合は、図5-24に示すように、抵抗  $R2$  を  $C1$  に並列接続します。 $R2$  を追加することで、式(20)に示す比率だけ等価インダクタDCRが減少します。

$R1$  と  $R2$  の並列結合は、式(19)で求められます。

$$R1 \parallel R2 = \frac{L1}{DCR \times C1} \quad (19)$$

式(20)に示す比率によって、必要な電圧減衰が得られます。

$$\frac{R2}{R1 + R2} \quad (20)$$

コントローラの電流センス増幅器に入力される電圧  $V_C$  は式(18)で計算されます。

$$V_C = (V_{IN} - V_{OUT}) \times \frac{V_{OUT}}{R1 \times C1 \times f_{SW} \times V_{IN}} + I_{OC} \times DCR \quad (18)$$

図 5-23. インダクタDCR電流センス方式

図 5-24. 電流センス増幅器の電圧を低下させる抵抗R2の使用

## 6 設計例

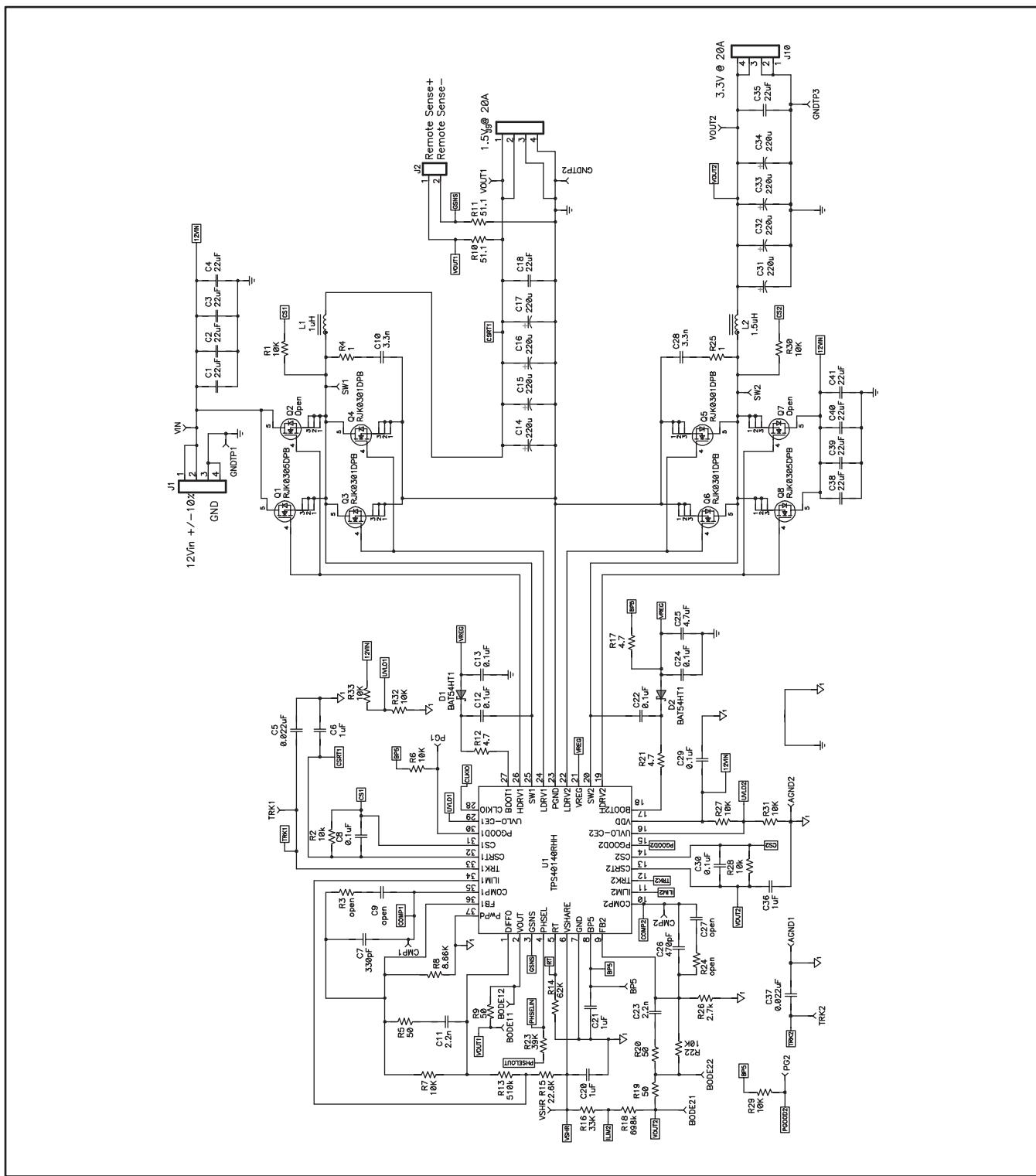

### 6.1 例1：1個のTPS40140を使用したデュアル出力構成DC/DCコンバータ (12Vから3.3Vおよび1.5V)

この例では、1個のTPS40140を使用したデュアル出力の同期バック・コンバータに対する設計プロセスおよび部品選択について説明します。設計目標パラメータを表6-1に示します。ここでは1.5V出力に対する計算値のみを示していますが、式は両方のチャネル設計に適用されます。この節の終わりに、記号の定義を示しています。

#### 6.1.1 ステップ1：インダクタの選択

インダクタは、目的のリップル電流によって決定されます。必要なインダクタは次の式で計算されます。

$$L = \frac{V_{IN(max)} - V_{OUT}}{I_{RIPPLE}} \times \frac{V_{OUT}}{V_{IN(max)}} \times \frac{1}{f_{SW}} \quad (1)$$

一般に、ピーク・ツー・ピークのインダクタ電流 $I_{RIPPLE}$ は、定格出力電流の20%前後となるよう選択します。この設計では、 $I_{RIPPLE}$ の目標値は $I_{OUT1}$ の15%です。インダクタの計算値は $0.89\mu\text{H}$ であり、実際にはVishayの $1\mu\text{H}$ 、32Aのインダクタが選択されています。したがって、インダクタのリップル電流は $2.66\text{A}$ です。

#### 6.1.2 ステップ2：出力キャパシタの選択

出力キャパシタは、一般に出力負荷過渡応答要件によって選択されます。式(2)は、負荷を増加させたときに低電圧要件に到達する最小のキャパシタ値を見積もる式です。式(3)は、負荷を減少させたときの過電圧要件に対する最小のキャパシタ値を見積もる式です。 $V_{IN(min)} < 2 \times V_{OUT}$ の場合、最小出力容量は式(2)を用いて計算できます。それ以外の場合は、式(3)を使用します。

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^2 \times L}{(V_{IN(min)} - V_{OUT}) \times V_{UNDER}} \quad (2)$$

$V_{IN(min)} < 2 \times V_{OUT}$ の場合：

$$C_{OUT(MIN)} = \frac{I_{TRAN(MAX)}^2 \times L}{V_{OUT} \times V_{OVER}} \quad (3)$$

$V_{IN(min)} > 2 \times V_{OUT}$ の場合：

この設計では、 $V_{IN(min)}$ が $2 \times V_{OUT}$ よりもずっと大きいため、式(3)を使用して最小容量を決定します。負荷過渡電流が $10\text{A}$ 、偏差が最大 $80\text{mV}$ として、必要な最小出力容量は $833\mu\text{F}$ となります。設計では、 $220\mu\text{F}$ 、 $4\text{V}$ のSPキャパシタを4個使用して、この要件を満足しています。各キャパシタのESRは $5\text{m}\Omega$ です。

キャパシタ選択のもう1つの条件は、出力リップル電圧です。出力リップルは、主に容量およびESRによって決定されます。

$$\begin{aligned} ESR_{Co} &= \frac{V_{RIPPLE(TotOUT)} - V_{RIPPLE(COUT)}}{I_{RIPPLE}} \\ &= \frac{V_{RIPPLE(TotOUT)} - \left( \frac{I_{RIPPLE}}{8 \times C_{OUT} \times f_{SW}} \right)}{I_{RIPPLE}} \end{aligned} \quad (4)$$

出力容量が $880\mu\text{F}$ の場合、キャパシタにおけるリップル電圧は $863\mu\text{V}$ と計算されます。仕様では、出力リップル電圧が $30\text{mV}$ 未満となる必要があるため、式(4)に基づき、必要な最大ESRは $9.5\text{m}\Omega$ となります。選択されたキャパシタは、この要件を満足しています。

#### 6.1.2 ステップ3：入力キャパシタの選択

入力電圧リップルは、入力容量およびESRに依存します。最小容量および最大ESRは、次の式で見積もることができます。

$$C_{IN(min)} = \frac{I_{OUT} \times V_{OUT}}{V_{RIPPLE(CIN)} \times V_{IN} \times f_{SW}} \quad (5)$$

$$ESR_{Cin} = \frac{V_{RIPPLE(CinESR)}}{I_{OUT} + \frac{1}{2} I_{RIPPLE}} \quad (6)$$

この設計では、 $V_{RIPPLE(CIN)}$ を $100\text{mV}$ 、 $V_{RIPPLE(CinESR)}$ を $50\text{mV}$ と仮定します。したがって、最小容量の計算値は $50\mu\text{F}$ 、最大ESRは $2.3\text{m}\Omega$ となります。 $22\mu\text{F}$ 、 $16\text{V}$ 、 $ESR = 2\text{m}\Omega$ のセラミック・キャパシタを4個使用することで、この要件を満足できます。

入力キャパシタに関するもう1つ重要な考慮事項は、RMSリップル電流定格です。入力キャパシタのRMS電流は、次の式で見積もることができます。

$$I_{RMS\_CIN} = \sqrt{D \times (1-D) \times I_{OUT}} \quad (7)$$

$D$ は、デューティ・サイクルです。RMS電流の計算値は、 $6.6\text{A}$ です。選択された各セラミック・キャパシタのRMS電流定格は $4.3\text{A}$ であるため、この要件を十分に満足しています。

| パラメータ        | テスト条件               | MIN                 | TYP | MAX      | 単位  |

|--------------|---------------------|---------------------|-----|----------|-----|

| $V_{IN}$     | Input voltage       |                     |     | 10.8     | V   |

| $V_{OUT1}$   | Output voltage 1    |                     |     | 1.5      | V   |

| $V_{OUT2}$   | Output voltage 2    |                     |     | 3.3      | V   |

| $V_{RIPPLE}$ | Output ripple       | $I_O = 20\text{ A}$ |     | $2\%V_O$ | V   |

| $I_{OUT1}$   | Output current 1    |                     |     | 20       | A   |

| $I_{OUT2}$   | Output current 2    |                     |     | 20       | A   |

| $f_{sw}$     | Switching frequency |                     |     | 500      | kHz |

表 6-1. 設計目標パラメータ

#### 6.1.4 ステップ4：MOSFETの選択

MOSFETの選択によって、コンバータの効率が決まります。この設計では、デューティ・サイクルが非常に小さいため、ハイサイドMOSFETではスイッチング損失が支配的であり、ローサイドMOSFETでは導通損失が支配的です。効率を最適化するために、ハイサイドMOSFETには小さなゲート電荷のものを選択し、ローサイドMOSFETには小さな $R_{DS(on)}$ を持つものを選択します。

RENESASのRJK0305およびRJK0301が、ハイサイドおよびローサイドのMOSFETとしてそれぞれ選択されています。導通損失を低減するために、2個のRJK0301を使用しています。

ハイサイドMOSFETにおける電力損失は、以下の式で計算されます。

ハイサイドMOSFETにおけるRMS電流を式(8)に示します。

$$I_{SWrms} = \sqrt{D \times \left( I_{OUT}^2 + \frac{I_{RIPPLE}^2}{12} \right)} = 7.07A \quad (8)$$

MOSFETのゲート電圧が4.5Vのとき、 $R_{DS(on)}$ は13mΩとなります。

導通損失は次のとおりです。

$$P_{SWcond} = (I_{SWrms})^2 \times R_{DS(on)}(sw) = 0.65 W \quad (9)$$

スイッチング損失は次のとおりです。

$$P_{SWsw} = \frac{I_{pk} \times V_{in} \times f_{sw} \times R_{drv} \times (Qgd_{sw} + Qgs_{sw})}{V_{gtdrv}} = 0.26W \quad (10)$$

ハイサイドMOSFETにおける合計損失の計算値は、次のようにになります。

$$P_{SWtot} = P_{SWcond} + P_{SWsw} = 0.91 W \quad (11)$$

ローサイドのSR MOSFETにおける電力損失は、以下のように計算されます。

ローサイドMOSFETにおけるRMS電流を式(12)に示します。

$$I_{SRrms} = \sqrt{(1-D) \times \left( I_{OUT}^2 + \frac{I_{RIPPLE}^2}{12} \right)} = 18.7 A \quad (12)$$

MOSFETのゲート電圧が4.5Vのとき、 $R_{DS(on)}$ は4mΩとなります。

2個のローサイドMOSFETの合計導通損失は、次のようになります。

$$P_{SRcond} = (I_{SRrms})^2 \times \frac{R_{DS(on)}(sr)}{N} = 0.7 W \quad (13)$$

Nは、MOSFETの個数です。ここでは、2です。

ボディ・ダイオードにおける合計電力損失は、次のようになります。

$$P_{diode} = 2 \times I_{OUT} \times t_d \times V_f \times f_{sw} = 0.77 W \quad (14)$$

したがって、SR MOSFETの合計損失の計算値は、次のとおりです。

$$P_{SRtot} = P_{SRcond} + P_{DIODE} = 1.47 W \quad (15)$$

#### 6.1.5 ステップ5：周辺部品設計

##### 6.1.5.1 スイッチング周波数設定 (RT : ピン5)

$$R = 1.33 \times \left( 39.2 \times 10^3 \times f_{sw}^{-1.041} - 7 \right) = 71.5 k\Omega \quad (16)$$

この設計では、62kΩの抵抗が選択されています。実際のスイッチング周波数は510kHzです。

##### 6.1.5.2 出力電圧設定 (FB1 : ピン36)

R1に10kΩを代入して、 $R_{BIAS}$ を計算します。

$$R_{BIAS} = 0.7 \times \frac{R1}{V_{OUT} - 0.7} = 8.75 k\Omega \quad (17)$$

##### 6.1.5.3 電流センス・ネットワーク設計 (CS1 : ピン31、CSRT1 : ピン32)

通常、パルス幅が小さい場合には、ループ遅延により生じる低調波を避けるために、抵抗デバイダを使用して電流帰還情報を減衰させます(「インダクタDCR電流センス」を参照)。

C1の値に0.1μFを選択し、R1とR2を等しいとすると、次の式でR1およびR2を計算できます。

$$R1//R2 = \frac{L}{DCR \times C1} = 5k\Omega \quad (18)$$

$$R1 = R2 = 10k \quad (19)$$

設計が低調波を含むかどうかを確認するための簡単な式を次に示します。

$$\frac{L}{DCR_{(eqv)}} > \frac{V_{IN} \times A_c}{2 \times V_{ramp} \times f_{sw}} \quad (20)$$

$$DCR_{(eqv)} = \frac{R2}{R1 + R2} \times DCR = \frac{DCR}{2} \quad (21)$$

この設計では、ノイズを抑えるために、CSRT1ピンに1μFのキャパシタを配置しています。これは省略しても性能が劣化することはありません。

#### 6.1.5.4 過電流保護 (ILIM1: ピン34)

「過電流保護レベルの計算」で示した抵抗選択式を単純化して、過電流設定抵抗を計算できます。DC過電流定格は25Aに設定します。

$$R1 = \frac{I_{PK} \times DCR_{eqv} \times Ac + V_{OS} + \frac{0.9}{V_{IN}}}{\left(1 - \frac{0.5}{V_{IN}}\right) \times 20 \times 10^{-6}} = 22.5 \text{ k}\Omega \quad (22)$$

$$R2 = \frac{I_{PK} \times DCR_{eqv} \times Ac + V_{OS} + \frac{0.9}{V_{IN}}}{\left(\frac{0.5}{V_{IN}}\right) \times 20 \times 10^{-6}} = 510 \text{ k}\Omega \quad (23)$$

$V_{OS}$ は内部オフセットであり、標準で約50mVです。

#### 6.1.5.5 VREG (ピン21)

ノイズをフィルタリングするために、VREGピンには4.7μFのキャパシタを接続します。

#### 6.1.5.6 BP5 (ピン8)

VREGとBP5の間には、4.7Ωの抵抗と1μFのキャパシタを配置します。

#### 6.1.5.7 PHSEL (ピン4)

このデュアル出力構成では、PHSELピンが直接GNDに接続されます。チャネル1とチャネル2は180°位相がずれています。

#### 6.1.5.8 VSHARE (ピン6)

VSHAREピンとGNDの間には1μFのキャパシタが接続されます。

#### 6.1.5.9 PGOOD1 (ピン30)

PGOOD1は、10kΩの抵抗を介してBP5に接続されます。

#### 6.1.5.10 UVLO\_CE1 (ピン29)

このピンは、抵抗デバイダを使用して入力電圧に接続されます。2つの抵抗の値は、同じ10kΩです。入力電圧が2Vを超えると、チップがイネーブルになります。

#### 6.1.5.11 CLKIO (ピン28)

デュアル出力構成ではクロック同期が不要であるため、CLKIOはフローティングです。

#### 6.1.5.12 BOOT1およびSW1 (ピン27および25)

BOOT1ピンとSW1ピンの間に、ブートストラップ・キャパシタを接続します。ブートストラップ・キャパシタの値は、ハイサイドMOSFETの合計ゲート電荷と、ブートストラップ・キャパシタで許可される降下量によって決まります。

$$C_{boot} = \frac{Qg}{\Delta V} = \frac{8nc}{0.5V} = 16nF \quad (24)$$

このアプリケーションでは、0.1μFのキャパシタが選択されています。

#### 6.1.5.13 TRK1 (ピン33)

22nFのキャパシタをTRK1ピンに接続して、1.28msのソフト・スタート時間を設定します。

$$T_{ss} = C_{ss} \times 58 \times 10^3 = 22 \times 10^{-9} \times 58 \times 10^3 = 1.28ms \quad (25)$$

#### 6.1.5.14 DIFFO、VOUT、GSNS (ピン1、ピン2、ピン3)

VOUTおよびGSNSは、リモート・センス出力コネクタに接続されます。DIFFOは、帰還抵抗デバイダに接続されます。差動増幅器を使用しない場合は、VOUTとGSNSは接地し、DIFFOはオープンにすることを推奨します。

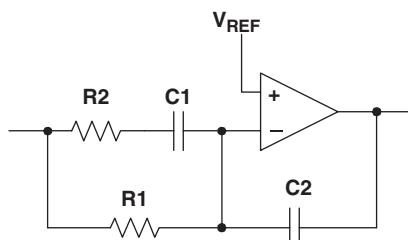

#### 6.1.6 帰還補償設計 (COMP1: ピン35)

このコントローラでは、ピーク電流モード制御が採用されています。COMP信号から出力へ、小信号モデルが形成されます。

$$G_{vc}(s) = \frac{1}{DCR \times Ac} \times \frac{1}{s \times T_s + 1} \times \frac{(s \times C_{OUT} \times ESR + 1) \times R_{OUT}}{s \times C_{OUT} \times R_{OUT} + 1} \quad (26)$$

時定数は次の式で定義されます。

$$T_s = \frac{T}{\ln \left( \frac{\frac{V_{ramp}}{T} - \frac{V_{OUT}}{L} \times DCR \times Ac}{\frac{V_{ramp}}{T} - \frac{V_{IN} - V_{OUT}}{L} \times DCR \times Ac - \frac{2 \times V_{OUT}}{L} \times DCR \times Ac} \right)} \quad (27)$$

低周波極は次の式で計算されます。

$$f_{VCP1} = \frac{1}{2 \times \pi \times C_{OUT} \times R_{OUT}} = 2.36\text{kHz} \quad (28)$$

ESRゼロは次の式で計算されます。

$$f_{ESR} = \frac{1}{2 \times \pi \times C_{OUT} \times ESR} = 176.8\text{kHz} \quad (29)$$

この設計では、タイプII補償回路を使ってループ補償を行います。

補償回路の伝達関数は次のようにになります。

$$Gc(s) = \frac{1}{R1 \times C2} \times \frac{s \times (R1 + R2) \times C1 + 1}{s \times (s \times R2 \times C1 + 1)} \quad (30)$$

ループ・ゲインの伝達関数は次のようにになります。

$$Tv(s) = Gc(s) \times Gvc(s) \quad (31)$$

目標のクロスオーバー周波数を60kHzとした場合、補償回路のゼロはクロスオーバー周波数の約1/10に設定し、補償回路の極はESRゼロに等しくします。そして、目的の帯域幅が得られるように補償回路ゲインを計算します。この設計では、補償回路のゲイン、極、およびゼロが次のように選択されます。

$$f_p = \frac{1}{2 \times \pi \times R2 \times C1} = 176.8\text{kHz} \quad (32)$$

$$f_z = \frac{1}{2 \times \pi \times (R1 + R2) \times C1} = 6\text{kHz} \quad (33)$$

$$|Tv(j \times 2 \times \pi \times f_c)| = 1 \quad (34)$$

上記の式から、補償回路ゲインは $3.978 \times 10^5$ となります。

$$A_{CM} = \frac{1}{R1 \times C} = 3.978 \times 10^5 \quad (35)$$

ここで

- $C1 = 2.6\text{nF}$

- $C2 = 250\text{pF}$

- $R2 = 350\Omega$

- $R1 = 10\text{k}\Omega$ に設定してから、他のすべての部品を計算します。

実際のラボでは、位相マージンを増やしてPWMジッタを低減するために、最終的な部品値を次のように選択します。

- $R1 = 10\text{k}\Omega$

- $C2 = 330\text{pF}$

- $R2 = 50\Omega$

- $C1 = 2.2\text{nF}$

図 6-1. タイプII補償回路

### 6.1.7 設計例のまとめ

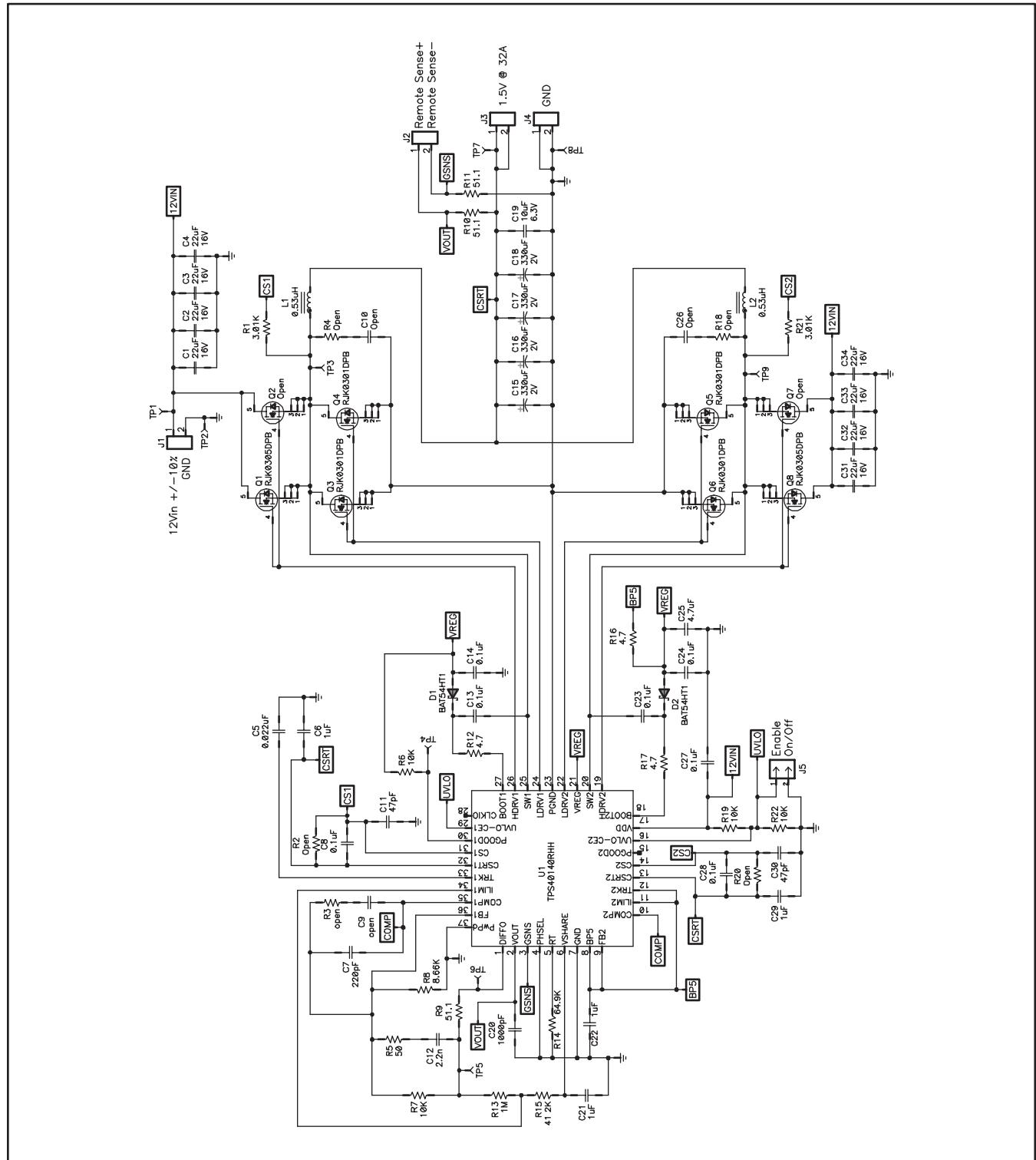

図6-2に、デュアル出力コンバータ設計の回路図を示します。

図 6-2. デュアル出力コンバータの回路図

## 6.2 例2：1個のTPS40140を使用した2フェーズ単一出力構成DC/DCコンバータ (12Vから1.5V)

この例では、1個のTPS40140を使用した2フェーズ単一出力の同期バック・コンバータに対する設計プロセスおよび部品選択を示します。設計目標パラメータを表6-2に示します。インダクタおよびMOSFETの選択式は、デュアル出力コンバータ設計の場合と同様であるため、ここでは再度示すことはしません。

### 6.2.1 ステップ1：出力キャパシタの選択

出力キャパシタは、一般に出力負荷過渡応答要件によって選択されます。デュアル出力設計例の式(3)を使用します。式の中のインダクタLは、フェーズ・インダクタンスをフェーズ数で割った値に等しくなります。

負荷過渡電流が15A、偏差が最大30mVとして、必要な最小出力容量は1.32mFとなります。設計では、330μF、2VのSPキャパシタを4個使用して、この要件を満足しています。各キャパシタのESRは6mΩです。

キャパシタ選択のもう1つの条件である出力リップル電圧は、主に容量およびESRによって決定されます。

チャネルをインタリープするため、合計の出力リップル電流は、単一フェーズのリップル電流よりも小さくなります。リップルの相殺係数は式(36)で表されます。

$$\Delta I_{OUT}(N_{PH}, D) = \frac{\prod_{i=1}^{N_{PH}} |i - N_{PH} \times D|}{\prod_{i=1}^{N_{PH}-1} (|i - N_{PH} \times D| + 1)} \quad (36)$$

ここで

Dは、単一フェーズのデューティ・サイクルです。

$N_{PH}$ はアクティブなフェーズ数であり、ここでは2です。

したがって、最大出力リップル電流は次のように計算されます。

$$I_{RIPPLE} = \frac{V_{OUT}}{L \times f_{SW}} \times \Delta I_{OUT}(N_{PH}, D) = 4.374 \text{ A} \quad (37)$$

出力容量が1.32mFの場合、キャパシタにおけるリップル電圧は828μVと計算されます。仕様では、出力リップル電圧が30mV未満となる必要があるため、式(4)に基づき、必要な最大ESRは6.7mΩとなります。選択されたキャパシタは、この要件を満足しています。

### 6.2.2 ステップ2：入力キャパシタの選択

入力電圧リップルは、入力容量およびESRに依存します。最小容量および最大ESRは、デュアル出力設計例の式(5)および式(6)で見積もることができます。

この設計では、 $V_{RIPPLE(CIN)}$ を100mV、 $V_{RIPPLE(CinESR)}$ を50mVと仮定し、インダクタ・リップル電流 $I_{RIPPLE}$ を30%と仮定します。したがって、最小容量の計算値は40μF、最大ESRは2.7mΩとなります。22μF、16V、ESR = 2mΩのセラミック・キャパシタを4個使用することで、この要件を満足できます。

入力キャパシタに関してもう1つ重要な考慮事項は、RMSリップル電流定格です。マルチフェーズのインタリープによって、入力RMS電流が低減されます。負荷電流に対する入力リップル電流のRMS値は、次の式で計算されます。

$$\Delta I_{IN(nom)}(N_{PH}, D) =$$

$$\frac{[(D - \frac{k(N_{PH}, D)}{N_{PH}}) \times (\frac{k(N_{PH}, D) + 1}{N_{PH}} - D)] + (\frac{N_{PH}}{12 \times D^2})}{\times [\frac{V_{OUT} \times (1 - D)}{L \times f_{sw} \times I_{OUT}}]^2 \times [(k(N_{PH}, D) + 1) \times (D - \frac{k(N_{PH}, D)}{N_{PH}})^3 + k(N_{PH}, D)^2 \times (\frac{k(N_{PH}, D) + 1}{N_{PH}} - D)^3]} \quad (38)$$

ここで

- $k(N_{PH}, D) = \text{floor}(N_{PH} \times D)$ 、この例では $k(N_{PH}, D) = 0$

- Floor(x)は、x以下の最大の整数を返す関数

- $N_{PH}$ はアクティブなフェーズ数、この例では $N_{PH} = 2$

したがって、この設計では、最大入力リップルRMS電流は、最小入力電圧で7.2Aと計算されます。これは、32Aの単一フェーズ・コンバータ設計と比較して、約34%低減されています。選択された各セラミック・キャパシタのRMS電流定格は4.3Aであるため、この要件を十分に満足しています。

| パラメータ                        | テスト条件       | MIN  | TYP      | MAX  | 単位  |

|------------------------------|-------------|------|----------|------|-----|

| $V_{IN}$ Input Voltage       |             | 10.8 | 12       | 13.2 | V   |

| $V_{OUT}$ Output voltage     |             |      | 1.5      |      | V   |

| $V_{RIPPLE}$ Output ripple   | $I_O = 32A$ |      | 2% $V_0$ |      | V   |

| $I_{OUT1}$ Output current    |             |      | 32       |      | A   |

| $f_{sw}$ Switching frequency |             |      | 500      |      | kHz |

表 6-2. 設計目標パラメータ

## 6.2.3 ステップ3：周辺部品設計

### 6.2.3.1 スイッチング周波数設定 (RT: ピン5)

$$R = 1.33 \times \left( 39.2 \times 10^3 \times f_{SW}^{-1.041} - 7 \right) = 71.5\text{k}\Omega \quad (39)$$

ここで、 $f_{SW}$ はフェーズのスイッチング周波数を表します。この設計では、64.9k $\Omega$ の抵抗が選択されています。実際のスイッチング周波数は490kHzです。

### 6.2.3.2 COMP1およびCOMP2 (ピン35およびピン10)

COMP1は、補償回路ネットワークに接続されます。補償回路部品の選択は、デュアル出力設計例の場合と同様です。

COMP2は、直接COMP1に接続されます。

### 6.2.3.3 TRK1およびTRK2 (ピン33およびピン12)

TRK1とGNDの間に、ソフト・スタート・キャパシタを接続します。このチャネルをスレーブとして設定する場合、TRK2は直接BP5に接続します。

### 6.2.3.4 ILIM1およびILIM2 (ピン34およびピン11)

ILIM1は、デュアル出力例と同じ設計の抵抗ネットワークに接続されます。式(22)および式(23)のピーク電流が、各フェーズのピーク電流となります。

ILIM2は接地します。

### 6.2.3.5 FB1およびFB2 (ピン36およびピン9)

FB1は、帰還ネットワークに接続されます。FB2は、GNDに接続されます。

### 6.2.3.6 PHSEL (ピン4)

この2フェーズ構成では、PHSELピンが直接GNDに接続されます。

### 6.2.3.7 PGOOD1およびPGOOD2 (ピン30およびピン15)

PGOOD1およびPGOOD2は、いずれも10k $\Omega$ の抵抗を介してBP5に接続されます。

### 6.2.3.8 CLKIO (ピン28)

2フェーズ構成ではクロック同期が不要であるため、CLKIOはオープンです。

### 6.2.3.9 DIFFO、VOUT、GSNS (ピン1、ピン2、ピン3)

VOUTおよびGSNSは、リモート・センス出力コネクタに接続されます。DIFFOは、帰還抵抗デバイダに接続されます。差動増幅器を使用しない場合は、VOUTとGSNSは接地し、DIFFOはオープンにすることを推奨します。

## 6.2.4 設計例のまとめ

図6-3に、2フェーズ単一出力コンバータ設計の回路図を示します。

図 6-3. 2フェーズ単一出力コンバータの回路図

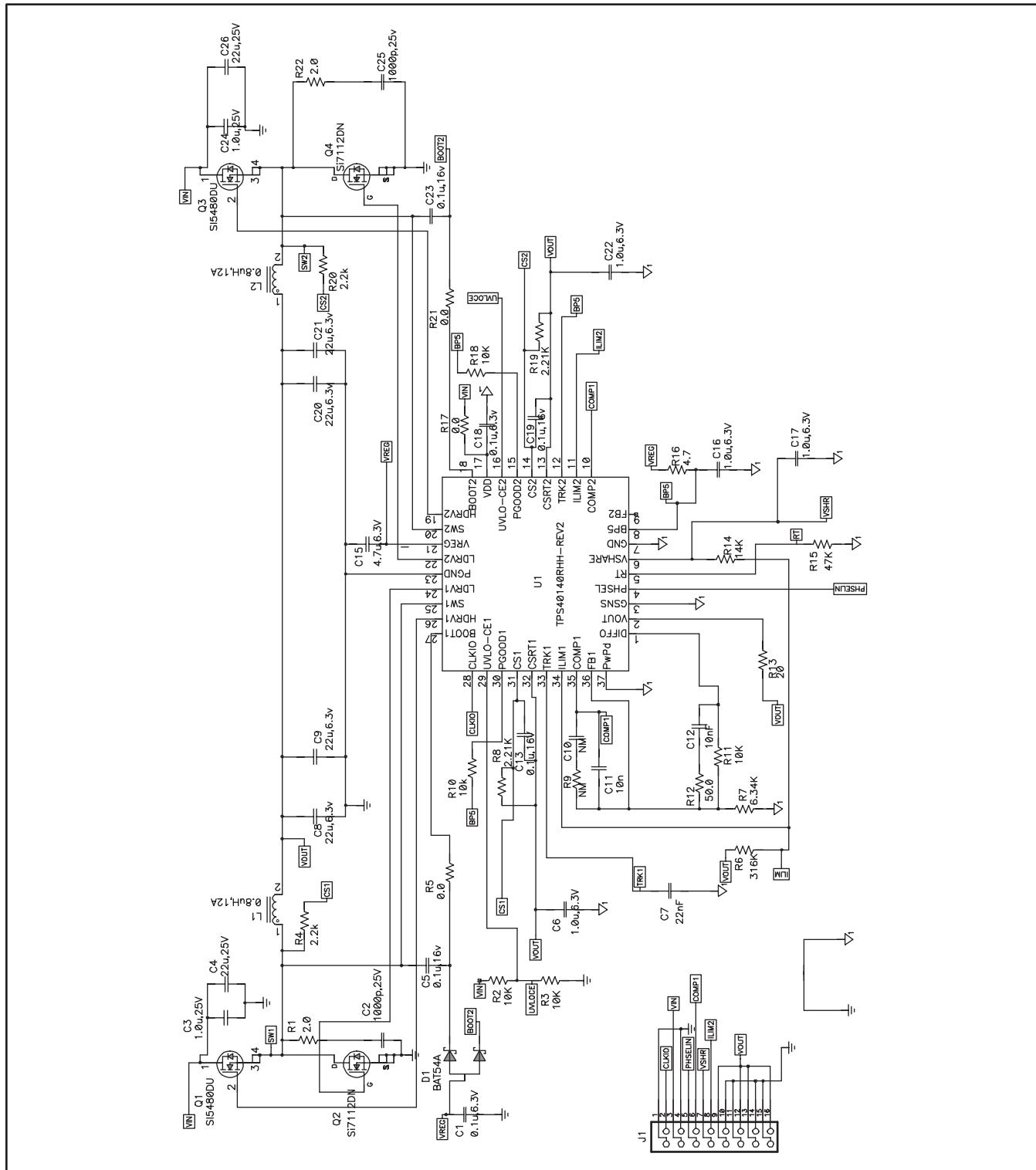

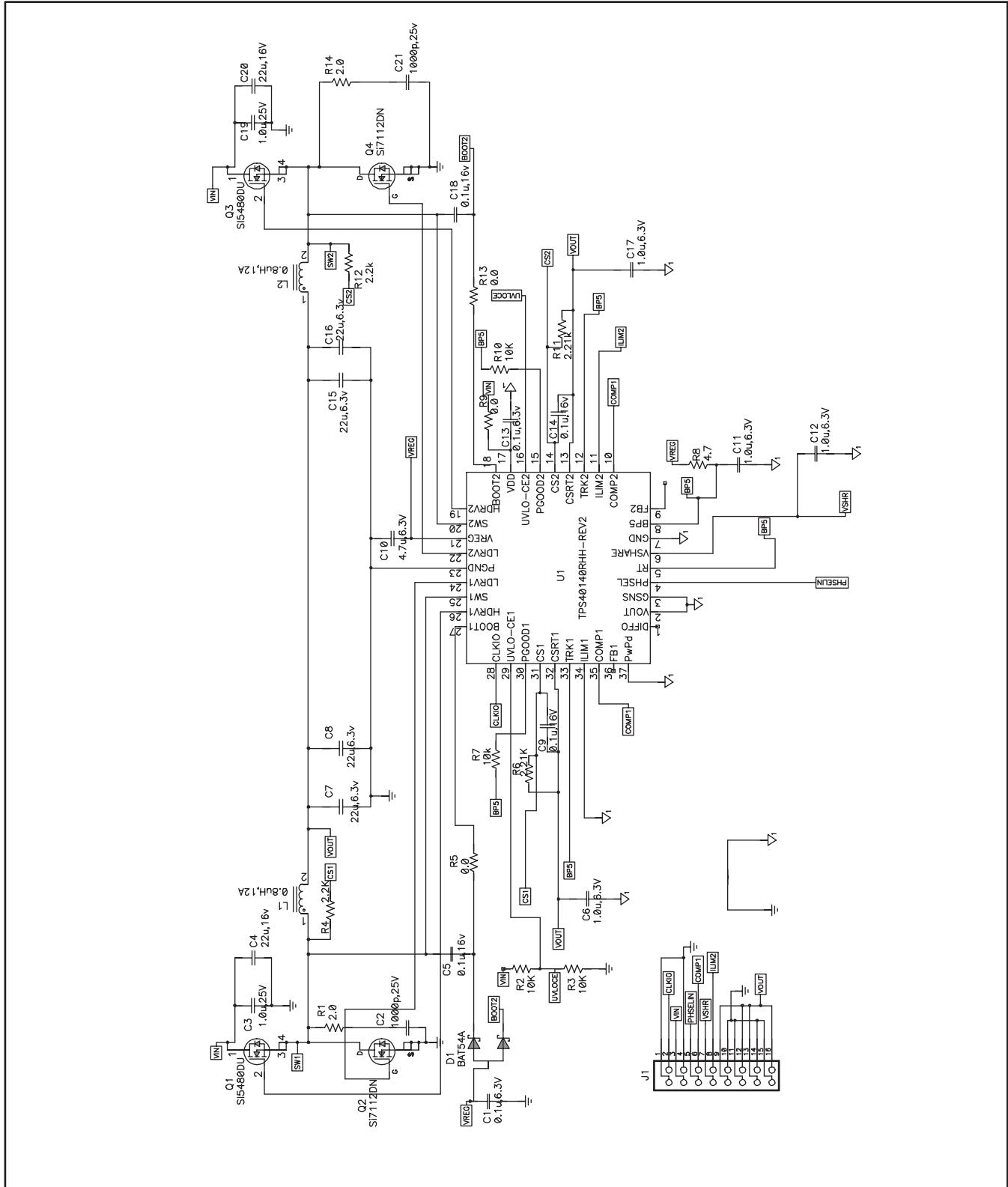

## 6.3 例3：2個のTPS40140を使用した4フェーズ単一出力構成DC/DCコンバータ (12Vから1.8V)

この例では、2個のTPS40140を使用した4フェーズ単一出力の同期バック・コンバータに対する設計プロセスおよび部品選択を示します。

ここでは、2つのモジュールを設計します。1つはマスター・モジュール、もう1つはスレーブ・モジュールです。各モジュールには2フェーズが含まれ、各フェーズが5Aを処理します。2つのモジュールをスタックすることで、4フェーズのコンバータを構成します。このコンバータにさらに追加のスレーブ・モジュールをスタックして、目的のフェーズ数を得ることができます。モジュールは、マザーボードにプラグインされます。

設計目標パラメータを表6-3に示します。

### 6.3.1 ステップ1：出力キャパシタの選択

出力キャパシタは、一般に出力負荷過渡応答要件によって選択されます。デュアル出力設計例の式(3)を使用します。また、2フェーズ設計例で説明したように、インダクタは $L/N_{PH}$ と等価です。負荷過渡電流が10A、偏差が最大30mVとして、必要な最小出力容量は370μFとなります。この設計では、180μF、6.3VのSPキャパシタをマザーボード上に1個配置します。各モジュールには、22μF、6.3Vのセラミック・キャパシタを4個配置します。合計出力容量は356μFとなります。

式(36)に基づいて、出力リップル電流の相殺係数は0.455と計算されます。

したがって、最大出力リップル電流は次のように計算されます。

$$I_{\text{RIPPLE}} = \frac{V_{\text{OUT}}}{L \times f_{\text{sw}}} \times 0.455 = 1.573\text{A} \quad (40)$$

出力容量が356μFの場合、キャパシタにおけるリップル電圧は850μVと計算されます。仕様では、出力リップル電圧が18mV未満となる必要があるため、式(4)に基づき、必要な最大ESRは11mΩとなります。選択されたキャパシタは、この要件を満足しています。

### 6.3.2 ステップ2：入力キャパシタの選択

入力電圧リップルは、入力容量およびESRに依存します。最小容量および最大ESRは、デュアル出力設計例の式(5)および式(6)で見積もることができます。

この設計では、 $V_{\text{RIPPLE}}(\text{CIN})$ を50mV、 $V_{\text{RIPPLE}}(\text{CinESR})$ を30mVと仮定し、各フェーズのインダクタ・リップル電流を50%と仮定します。したがって、最小容量の計算値は93μF、最大ESRは4.6mΩとなります。ここでは、33μF、6.3VのSPキャパシタをマザーボード上に1個配置し、22μF、6.3Vのセラミック・キャパシタを各モジュールに2個配置します。

式(38)に基づき、最大入力リップルRMS電流は、最小入力電圧で2.57Aと計算されます。選択されたキャパシタは、この要件を十分に満足しています。

### 6.3.3 ステップ3：周辺部品設計

#### 6.3.3.1 マスター・モジュール

##### 6.3.3.1.1 RT(ピン5)

このピンは、スイッチング周波数を設定する抵抗を介してGNDに接続されます。

$$R = 1.33 \times (39.2 \times 10^3 \times f_{\text{sw}}^{-1.041} - 7) = 52.2\text{k}\Omega \quad (41)$$

ここで、 $f_{\text{sw}}$ はフェーズのスイッチング周波数を表します。この設計では、47kΩの抵抗が選択されています。実際のスイッチング周波数は650kHzです。

##### 6.3.3.1.2 COMP1およびCOMP2(ピン35およびピン10)

COMP1は、補償回路ネットワークに接続されます。

COMP2は、直接COMP1に接続されます。

| パラメータ                                  | テスト条件                       | MIN  | TYP               | MAX  | 単位  |

|----------------------------------------|-----------------------------|------|-------------------|------|-----|

| $V_{\text{IN}}$<br>Input Voltage       |                             | 10.8 | 12                | 13.2 | V   |

| $V_{\text{OUT}}$<br>Output voltage     |                             |      | 1.8               |      | V   |

| $V_{\text{RIPPLE}}$<br>Output ripple   | $I_{\text{O}} = 20\text{A}$ |      | 1% $V_{\text{O}}$ |      | V   |

| $I_{\text{PH}}$<br>Phase current       |                             |      | 5                 |      | A   |

| $f_{\text{sw}}$<br>Switching frequency |                             |      | 650               |      | kHz |

| $N_{\text{PH}}$<br>Phase number        |                             |      | 4                 |      |     |

表 6-3. 設計目標パラメータ

### 6.3.3.1.3 TRK1およびTRK2 (ピン33およびピン12)

TRK1とGNDの間に、ソフト・スタート・キャパシタを接続します。このチャネルをスレーブとして設定する場合、TRK2は直接BP5に接続します。

### 6.3.3.1.4 ILIM1およびILIM2 (ピン34およびピン11)

ILIM1は、デュアル出力例と同じ設計の抵抗ネットワークに接続されます。式(22)および式(23)のピーク電流が、各フェーズのピーク電流となります。

ILIM2は接地します。

### 6.3.3.1.5 FB1およびFB2 (ピン36およびピン9)

FB1は、帰還ネットワークに接続されます。FB2は、GNDに接続されます。

### 6.3.3.1.6 PHSEL (ピン4)

この4フェーズ構成では、PHSELピンは39k $\Omega$ の抵抗を介してGNDに接続されます。

### 6.3.3.1.7 PGOOD1およびPGOOD2 (ピン30およびピン15)

PGOOD1およびPGOOD2は、いずれも10k $\Omega$ の抵抗を介してBP5に接続されます。

### 6.3.3.1.8 CLKIO (ピン28)

CLKIOは、スレーブ・モジュールの同じピンに接続されます。

### 6.3.3.2 スレーブ・モジュール

#### 6.3.3.2.1 RT (ピン5)

このピンは、BP5に接続されます。スレーブ・モジュールには、マスター・モジュールからクロックが供給されます。

#### 6.3.3.2.2 COMP1およびCOMP2 (ピン35およびピン10)

COMP1およびCOMP2は、マスター・モジュールのCOMP1またはCOMP2と一緒に直接接続されます。

#### 6.3.3.2.3 TRK1およびTRK2 (ピン33およびピン12)

TRK1およびTRK2は、直接BP5に接続されます。

#### 6.3.3.2.4 ILIM1およびILIM2 (ピン34およびピン11)

ILIM1およびILIM2は、接地されます。

#### 6.3.3.2.5 FB1およびFB2 (ピン36およびピン9)

FB1およびFB2は、GNDに接続されます。

#### 6.3.3.2.6 PHSEL (ピン4)

PHSELピンは、直接GNDに接続されます。

#### 6.3.3.2.7 PGOOD1およびPGOOD2 (ピン30およびピン15)

PGOOD1およびPGOOD2は、いずれも10k $\Omega$ の抵抗を介してBP5に接続されます。

#### 6.3.3.2.8 CLKIO (ピン28)

CLKIOは、マスター・モジュールCLKIOに接続されます。

### 6.3.4 設計例のまとめ

図6-4、図6-5、および図6-6に、4フェーズ・コンバータ設計の回路図を示します。

図 6-5. スレーブ・モジュール回路図

図 6-6. マザーボード回路図

| SYMBOL               | DESCRIPTION                                                   |

|----------------------|---------------------------------------------------------------|

| $V_{IN(min)}$        | Minimum Operating Input voltage                               |

| $V_{IN(max)}$        | Maximum Operating Input Voltage                               |

| $V_{OUT}$            | Output Voltage                                                |

| $I_{RIPPLE}$         | Inductor Peak-Peak Ripple Current                             |

| $I_{TRAN(MAX)}$      | Maximum Load Transient                                        |

| $V_{UNDER}$          | Output Voltage Undershoot                                     |

| $V_{OVER}$           | Output Voltage Overshot                                       |

| $V_{RIPPLE(TotOUT)}$ | Total Output Ripple                                           |

| $V_{RIPPLE(COUT)}$   | Output Voltage Ripple Due to Output Capacitance               |

| $V_{RIPPLE(CIN)}$    | Input Voltage Ripple Due to Input Capacitance                 |

| $V_{RIPPLE(CinESR)}$ | Input Voltage Ripple Due to the ESR of Input Capacitance      |

| $P_{SW_{cond}}$      | High Side MOSFET Conduction Loss                              |

| $I_{SW_{rms}}$       | RMS Current in the High Side MOSFET                           |

| $R_{DSON(sw)}$       | ON Drain-Source Resistance of the High Side MOSFET            |

| $P_{SW_{sw}}$        | High Side MOSFET Switching Loss                               |

| $I_{pk}$             | Peak Current Through the High Side MOSFET                     |

| $R_{drv}$            | Driver Resistance of the High Side MOSFET                     |