# TPS51375L 4.5V ~ 24V、連続電流 12A、リモートセンス、同期整流降圧コンバータ

## 1 特長

- 入力電圧範囲: 4.5V ~ 24V

- 0.6V ~ 5.5V の出力電圧

- 10mΩ および 5mΩ FET を内蔵

- 12A の連続出力電流をサポート

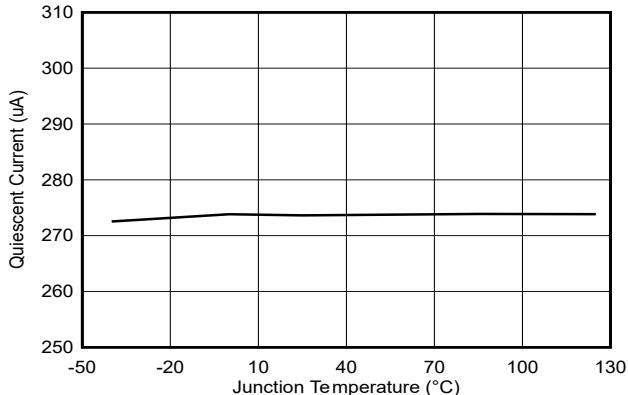

- 270uA 低静止時電流

- ±1% 基準電圧精度 (25°C)

- D-CAP3™ 制御モード アーキテクチャ制御により 0.77V 出力を

- POSCAP およびすべての MLCC 出力コンデンサをサポート

- 差動リモートセンシング

- システムスタンバイ中の ULQ™ バッテリ寿命延長機能

- 出力放電機能を内蔵

- パワーグッドインジケータを内蔵

- 600kHz の固定スイッチング周波数

- 17A 固定 OC の制限

- 固定ソフトスタート時間: 1.0ms

- 大きいデューティサイクル動作

- サイクル単位の過電流保護

- ラッチ付きの出力 OV および UV 保護

- ラッチなしの UVLO および OT 保護

- 動作時接合部温度: -40°C ~ 125°C

- 19 ピン 3.0mm × 4.0mm HotRod™ WQFN パッケージ

- WEBENCH® Power Designer により、TPS51375L を使用するカスタム設計を作成

## 2 アプリケーション

- ノート PC およびデスクトップ PC

- ウルトラブック、ハンドヘルドタブレット

- 産業用 PC、シングルボードコンピュータ

- 非軍事用ドローン

- 分散電源システム

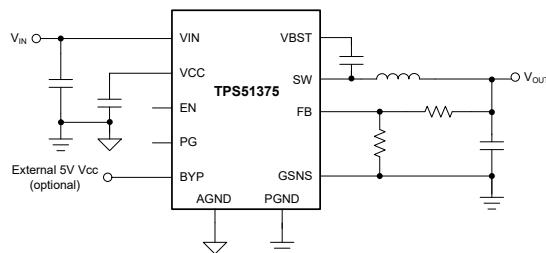

概略回路図

## 3 説明

このデバイスは、モノリシック 12A 同期整流降圧コンバータであり、高効率を実現する MOSFET が内蔵されており、また、必要な外付け部品数が最小であるため、スペースの制約が厳しい電力システムでも使いやすくなっています。TPS51375L は、内部補償を使用して高速な過渡応答と非常に優れたラインおよび負荷レギュレーションを実現する D-CAP3 制御モードを採用しています。ULQ (超低静止電流) バッテリ寿命延長機能は、低消費電力動作で長いバッテリ寿命の実現に非常に有益です。デューティ比の大きい動作により、入力電圧が低いときは負荷過渡性能が大幅に向上します。

他の機能として、差動リモートセンシング、Eco モード動作による軽負荷時の効率向上、VCC スイッチオーバー機能による軽負荷時の効率のさらなる最適化、低出力電圧時の負荷過渡改善のためのボディブレーキなどがあります。

TPS51375L はパワーグッドインジケータを内蔵しており、出力放電機能を備えています。このデバイスは、OVP、UVP、OCP、OTP、UVLO などの保護機能一式を搭載しています。このデバイスは、19 ピン 3.0mm × 4.0mm HotRod パッケージで供給され、-40°C ~ 125°C の接合部温度で動作が規定されています。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-----------|----------------------|-------------------------|

| TPS51375L | VBH (WQFN-FCRLF, 19) | 4mm × 3mm               |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンを含みます。

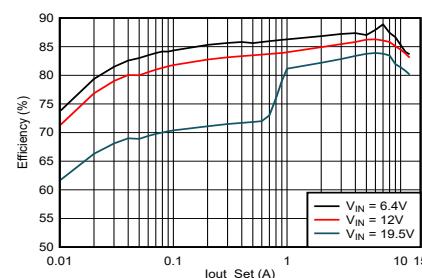

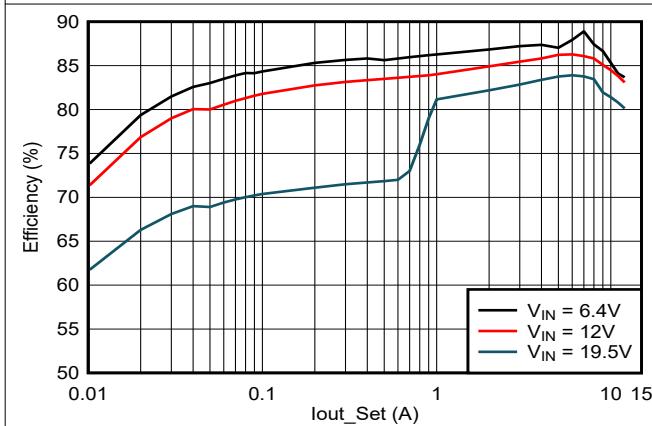

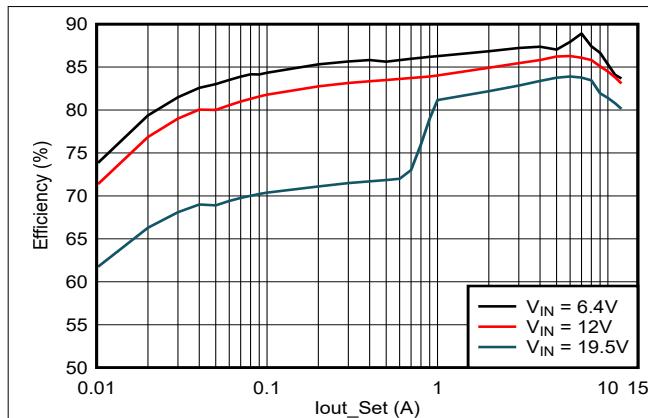

効率と出力電流との関係 ( $V_{OUT} = 0.77V$ )

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>7 アプリケーションと実装</b>          | <b>17</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>7.1 アプリケーション情報</b>         | <b>17</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>7.2 代表的なアプリケーション</b>       | <b>17</b> |

| <b>4 ピン構成および機能</b> | <b>3</b>  | <b>7.3 電源に関する推奨事項</b>         | <b>24</b> |

| <b>5 仕様</b>        | <b>4</b>  | <b>7.4 レイアウト</b>              | <b>24</b> |

| 5.1 絶対最大定格         | 4         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>26</b> |

| 5.2 ESD 定格         | 4         | <b>8.1 デバイス サポート</b>          | <b>26</b> |

| 5.3 推奨動作条件         | 4         | <b>8.2 ドキュメントのサポート</b>        | <b>26</b> |

| 5.4 熱に関する情報        | 5         | <b>8.3 ドキュメントの更新通知を受け取る方法</b> | <b>26</b> |

| 5.5 電気的特性          | 5         | <b>8.4 サポート・リソース</b>          | <b>26</b> |

| 5.6 代表的特性          | 8         | <b>8.5 商標</b>                 | <b>26</b> |

| <b>6 詳細説明</b>      | <b>11</b> | <b>8.6 静電気放電に関する注意事項</b>      | <b>27</b> |

| 6.1 概要             | 11        | <b>8.7 用語集</b>                | <b>27</b> |

| 6.2 機能ブロック図        | 12        | <b>9 改訂履歴</b>                 | <b>27</b> |

| 6.3 機能説明           | 13        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>28</b> |

| 6.4 デバイスの機能モード     | 15        |                               |           |

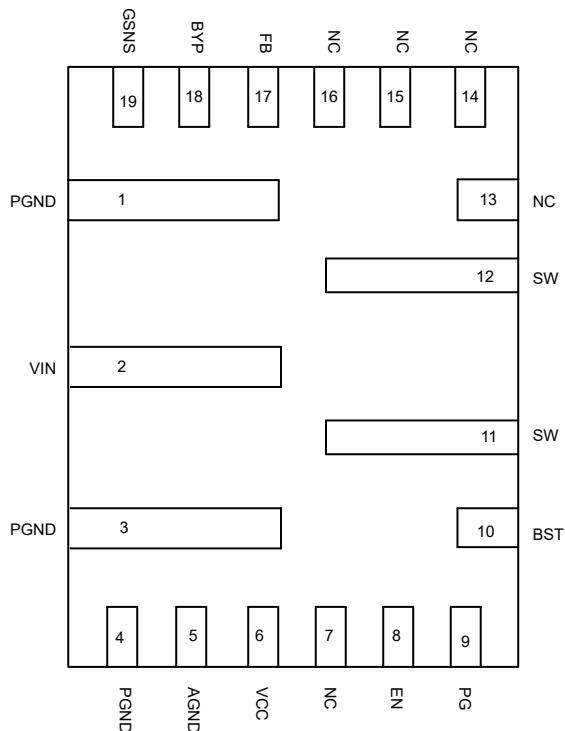

## 4 ピン構成および機能

図 4-1. 19 ピン WQFN-FCRLF、VBH パッケージ(上面図)

表 4-1. ピンの機能

| ピン   |            | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                |

|------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号         |                   |                                                                                                                                                                   |

| PGND | 1, 3, 4    | G                 | コントローラ回路および内部回路のためのパワー GND 端子                                                                                                                                     |

| VIN  | 2          | P                 | 制御回路の入力電源ピン。VIN と PGND の間に入力デカップリングコンデンサを接続します。                                                                                                                   |

| AGND | 5          | G                 | 内部アナログ回路のグランド。AGND は、AGND に近接した単一のポイントで PGND に接続します。                                                                                                              |

| VCC  | 6          | O                 | 内部 5V LDO 出力。内部アナログ回路と駆動のための電源。2.2μF のセラミックコンデンサを使用して、このピンをデカップリングして接地します。                                                                                        |

| NC   | 7, 13 ~ 16 |                   | これらのピンはフローティングにするか、GND に接続します。                                                                                                                                    |

| EN   | 8          | I                 | 降圧コンバータのイネーブル入力                                                                                                                                                   |

| PG   | 9          | O                 | パワー グッド表示ピン。過熱シャットダウン、ドロップアウト、過電圧、EN シャットダウン、またはスロースタート中に、降圧の出力電圧が範囲外になると、このピンが low にアサートされます。                                                                    |

| BST  | 10         | I                 | ブートストラップピン。電源ハイサイドゲートドライバ。このピンと SW ピンの間に 0.1μF のセラミックコンデンサを接続します。                                                                                                 |

| SW   | 11, 12     | O                 | バック用のインダクタおよびブートストラップコンデンサへのスイッチングノード接続。このピン電圧は、グランド以下のダイオード電圧から降圧コンバータの入力電圧までスイングします。                                                                            |

| FB   | 17         | I                 | 出力電圧帰還。FB は、帰還抵抗分圧回路を使用して出力電圧に接続します。                                                                                                                              |

| BYP  | 18         | I                 | 外部 5V バイパスの外部電源入力。このピンを 1uF のセラミックコンデンサを使用して GND にデカップリングします。このピンを使用しない場合は、フローティングのまにするか、このピンを GND に接続します。この BYP 外部電圧は、VIN 電圧がオンになった後で来て、VIN がオフになる前に終了する必要があります。 |

| GSN  | 19         | I                 | リモート電圧センシング構成用のリターン接続です。シングルエンド検出構成の場合、AGND への短絡。                                                                                                                 |

(1) I = 入力、O = 出力、P = 電源、G = グランド

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|          |                  | 最小値  | 最大値 | 単位 |

|----------|------------------|------|-----|----|

| 入力電圧     | VIN              | -0.3 | 28  | V  |

|          | VBST             | -0.3 | 32  | V  |

|          | VBST-SW          | -0.3 | 6   | V  |

|          | EN, FB, BYP      | -0.3 | 6   | V  |

|          | PGND, AGND, GSN  | -0.3 | 0.3 | V  |

| 出力電圧     | SW               | -1   | 28  | V  |

|          | SW (10ns の過渡)    | -3   | 28  | V  |

|          | PG, VCC          | -0.3 | 6   | V  |

| 動作時接合部温度 | T <sub>J</sub>   | -40  | 150 | °C |

| 保存温度     | T <sub>stg</sub> | -55  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      |                                                                                                                  | 値     | 単位 |

|--------------------|------|------------------------------------------------------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup><br>デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±2000 | V  |

|                    |      |                                                                                                                  | ±500  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|          |                  | 最小値  | 最大値  | 単位 |

|----------|------------------|------|------|----|

| 入力電圧     | VIN              | 4.5  | 24   | V  |

|          | VBST             | -0.3 | 29.5 | V  |

|          | VBST-SW          | -0.3 | 5.5  | V  |

|          | EN, FB, BYP      | -0.3 | 5.5  | V  |

|          | PGND, AGND, GSN  | -0.3 | 0.3  | V  |

| 出力電圧     | SW               | -1   | 24   | V  |

|          | PG, VCC          | -0.3 | 5.5  | V  |

| 連続出力電流   | I <sub>OUT</sub> |      | 12   | A  |

| 動作時接合部温度 | T <sub>J</sub>   | -40  | 125  | °C |

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>       |                                           | TPS51375L     | 単位   |

|----------------------------|-------------------------------------------|---------------|------|

|                            |                                           | VBH (WQFN-HR) |      |

|                            |                                           | 19 ピン         |      |

| $R_{\theta JA}$            | 接合部から周囲への熱抵抗                              | 67.7          | °C/W |

| $R_{\theta JA\_effective}$ | 接合部から周囲への熱抵抗 (4 層カスタム ボード) <sup>(2)</sup> | 30            | °C/W |

| $R_{\theta JC(top)}$       | 接合部からケース (上面) への熱抵抗                       | 18.2          | °C/W |

| $R_{\theta JB}$            | 接合部から基板への熱抵抗                              | 20.1          | °C/W |

| $\Psi_{JT}$                | 接合部から上面への特性パラメータ                          | 0.9           | °C/W |

| $\Psi_{JB}$                | 接合部から基板への特性パラメータ                          | 20            | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

(2) 実効  $R_{\theta JA}$  は TPS51375EVM に基づいてシミュレーションされます。

## 5.5 電気的特性

$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $V_{IN} = 12\text{V}$  (特に記述のない限り)。

| パラメータ                     |                           | テスト条件                                                           | 最小値 | 標準値 | 最大値 | 単位  |

|---------------------------|---------------------------|-----------------------------------------------------------------|-----|-----|-----|-----|

| <b>電源電流</b>               |                           |                                                                 |     |     |     |     |

| $V_{IN}$                  | 入力電圧範囲                    |                                                                 | 4.5 | 24  |     | V   |

| $I_{VIN}$                 | スイッチングなしの電源電流             | 無負荷、 $V_{EN} = 5\text{V}$ 、スイッチングなし                             | 270 |     |     | μA  |

| $I_{VINSDN}$              | シャットダウン時の電源電流             | 無負荷、 $V_{EN} = 0\text{V}$                                       | 3   |     |     | μA  |

| <b>VCC 出力</b>             |                           |                                                                 |     |     |     |     |

| $V_{CC}$                  | VCC 出力電圧                  | $V_{IN} > 5.2\text{V}$ , $I_{VCC} \leq 1\text{mA}$ 、バイパススイッチがオフ | 4.6 | 4.9 | 5.2 | V   |

| <b>帰還電圧</b>               |                           |                                                                 |     |     |     |     |

| $V_{FB}$                  | フィードバック レギュレーション電圧        | $T_J = 25^{\circ}\text{C}$                                      | 594 | 600 | 606 | mV  |

|                           |                           | $T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$            | 591 | 600 | 609 | mV  |

| <b>デューティ サイクルおよび周波数制御</b> |                           |                                                                 |     |     |     |     |

| $f_{SW}$                  | スイッチング周波数                 | CCM 動作、TPS51375L                                                | 600 |     |     | kHz |

| $t_{ON(MIN)}$             | SW の最小オン時間 <sup>(1)</sup> |                                                                 | 60  |     |     | ns  |

| $t_{OFF(MIN)}$            | SW 最小オフ時間 <sup>(1)</sup>  |                                                                 | 130 |     |     | ns  |

| <b>MOSFET とドライバ</b>       |                           |                                                                 |     |     |     |     |

| $R_{DS(ON)H}$             | ハイサイド スイッチ抵抗              | $T_J = 25^{\circ}\text{C}$                                      | 10  |     |     | mΩ  |

| $R_{DS(ON)L}$             | ローサイド スイッチ抵抗              | $T_J = 25^{\circ}\text{C}$                                      | 5   |     |     | mΩ  |

| <b>出力放電とソフトスタート</b>       |                           |                                                                 |     |     |     |     |

| $R_{DIS}$                 | 放電抵抗                      | $V_{EN} = 0\text{V}$                                            | 50  |     |     | Ω   |

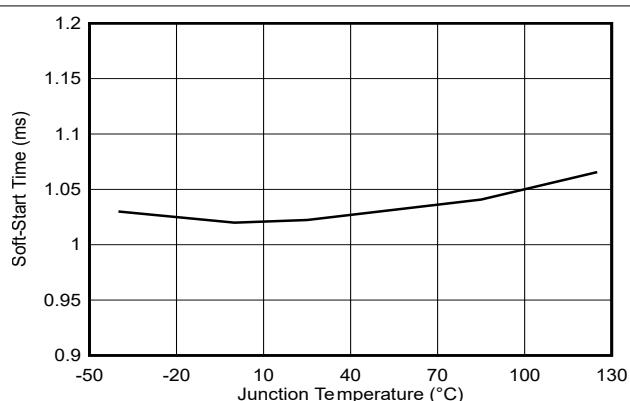

| $t_{ss}$                  | ソフト スタート時間                | 内部ソフトスタート時間                                                     | 1   |     |     | ms  |

| <b>パワーグッド</b>             |                           |                                                                 |     |     |     |     |

| $t_{PGDLY}$               | PG 遅延立ち上がり                | PG を Low から High に                                              | 160 |     |     | us  |

|                           | PG 遅延立ち下がり                | PG を High から Low に                                              | 30  |     |     | us  |

| $V_{PGTH}$                | PG スレッシュホールド              | VFB 立ち下がり (FAULT)                                               | 83  |     |     | %   |

|                           |                           | VFB 立ち上がり (グッド)                                                 | 90  |     |     | %   |

|                           |                           | VFB 立ち上がり (FAULT)                                               | 120 |     |     | %   |

|                           |                           | VFB 立ち下がり (グッド)                                                 | 115 |     |     | %   |

| $V_{PG\_L}$               | PG シンク電流容量                | $I_{OL} = 4\text{mA}$                                           |     | 0.4 |     | V   |

## 5.5 電気的特性 (続き)

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ (特に記述のない限り)。

| パラメータ      | テスト条件                                 | 最小値 | 標準値 | 最大値 | 単位            |

|------------|---------------------------------------|-----|-----|-----|---------------|

| $I_{PGLK}$ | $V_{PGOOD} = 5.5\text{V}$<br>PG リーク電流 |     |     | 1   | $\mu\text{A}$ |

## 5.5 電気的特性 (続き)

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ (特に記述のない限り)。

| パラメータ                |                                 | テスト条件                                     | 最小値  | 標準値  | 最大値 | 単位               |

|----------------------|---------------------------------|-------------------------------------------|------|------|-----|------------------|

| <b>電流制限</b>          |                                 |                                           |      |      |     |                  |

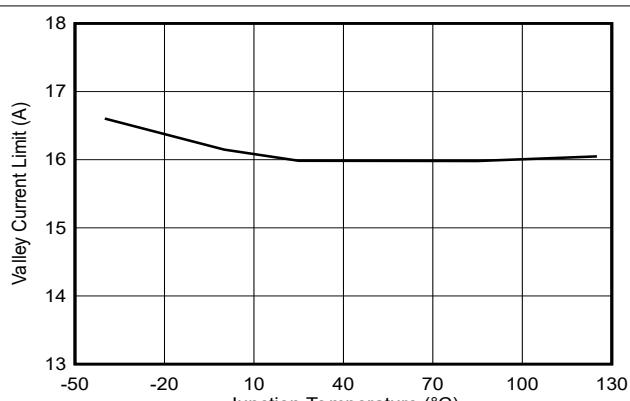

| $I_{OCL}$            | 過電流スレッショルド(バレー)                 | LS FET のバレー電流制限、 $T_J = 25^\circ\text{C}$ | 14   | 17   |     | A                |

| <b>論理スレッショルド</b>     |                                 |                                           |      |      |     |                  |

| $V_{ENH}$            | EN の High レベル入力電圧               | $T_J = 25^\circ\text{C}$                  | 1    |      |     | V                |

| $V_{ENL}$            | EN の Low レベル入力電圧                | $T_J = 25^\circ\text{C}$                  |      | 0.4  |     | V                |

| $I_{EN}$             | 内部プルダウン電流をイネーブルします              | $V_{EN} = 0.3\text{V}$                    |      | 2    |     | $\mu\text{A}$    |

| <b>出力低電圧および過電圧保護</b> |                                 |                                           |      |      |     |                  |

| $V_{OVP}$            | OVP 遷移スレッショルド                   |                                           | 120  |      |     | %                |

| $t_{OVPDLY}$         | OVP 伝搬のグリッチ除去                   |                                           | 256  |      |     | us               |

| $V_{UVP}$            | UVP 遷移スレッショルド                   |                                           | 60   |      |     | %                |

| $t_{UVPDLY}$         | UVP 伝搬のグリッチ除去                   |                                           | 200  |      |     | us               |

| <b>UVLO</b>          |                                 |                                           |      |      |     |                  |

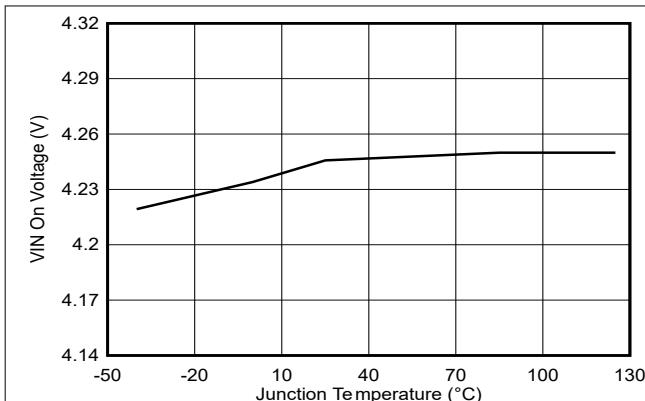

| $V_{UVLO}$           | VIN UVLO スレッショルド                | ウェークアップ                                   | 4.25 | 4.45 |     | V                |

|                      |                                 | シャットダウン                                   | 3.4  | 3.6  |     | V                |

|                      |                                 | ヒステリシス                                    | 0.65 |      |     | V                |

| <b>過熱保護</b>          |                                 |                                           |      |      |     |                  |

| $T_{OTP}$            | OTP トリップのスレッショルド <sup>(1)</sup> | シャットダウン温度                                 | 160  |      |     | $^\circ\text{C}$ |

| $T_{OTPHSY}$         | OTP ヒステリシス <sup>(1)</sup>       | ヒステリシス                                    | 20   |      |     | $^\circ\text{C}$ |

(1) 設計により規定されています。実製品の検査は行っていません。

## 5.6 代表的特性

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ (特に記述のない限り)。

図 5-1. 供給電流と接合部温度との関係

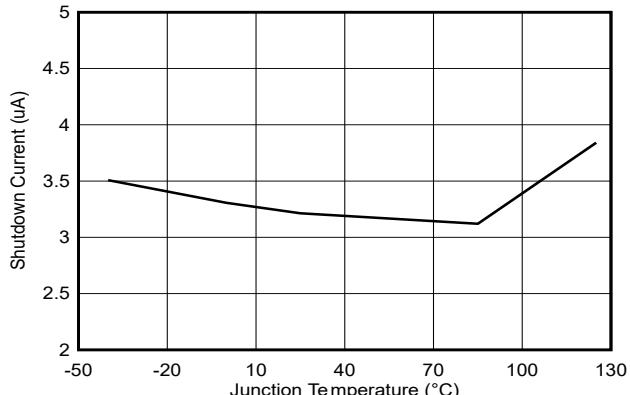

図 5-2. シャットダウン電流と接合部温度との関係

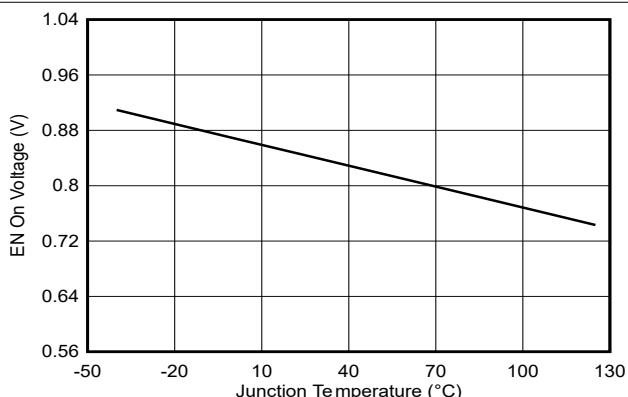

図 5-3. イネーブルオン電圧と接合部温度との関係

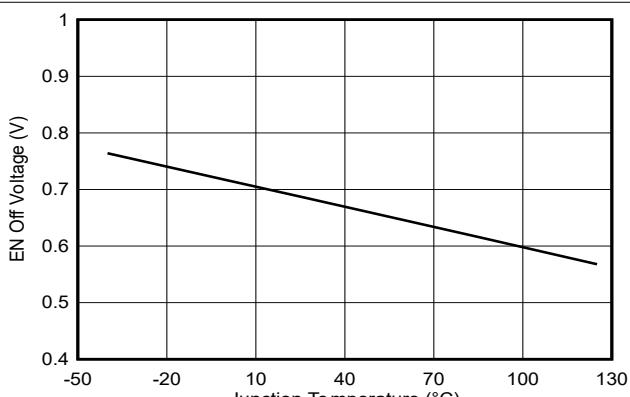

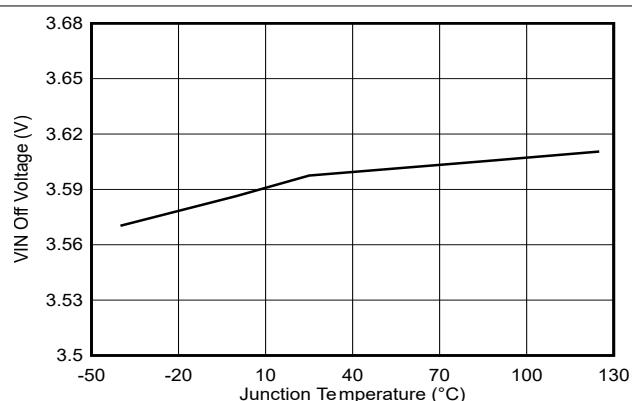

図 5-4. イネーブルオフ電圧対接合部温度

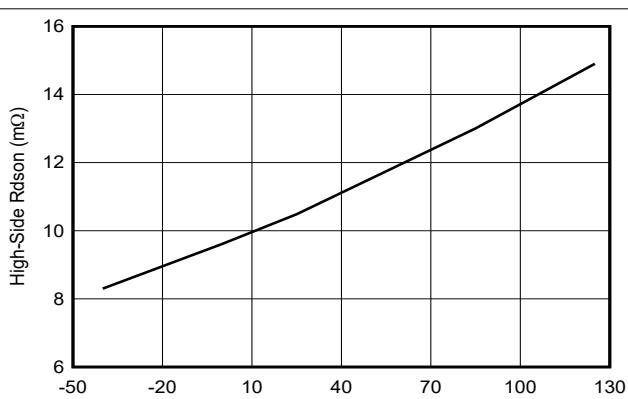

図 5-5. ハイサイド  $R_{DS(on)}$  と接合部温度との関係

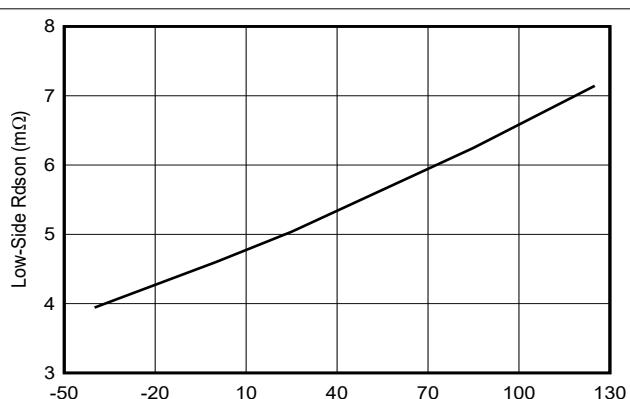

図 5-6. ローサイド  $R_{DS(on)}$  と接合部温度との関係

## 5.6 代表的特性 (続き)

$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $V_{IN} = 12\text{V}$ (特に記述のない限り)。

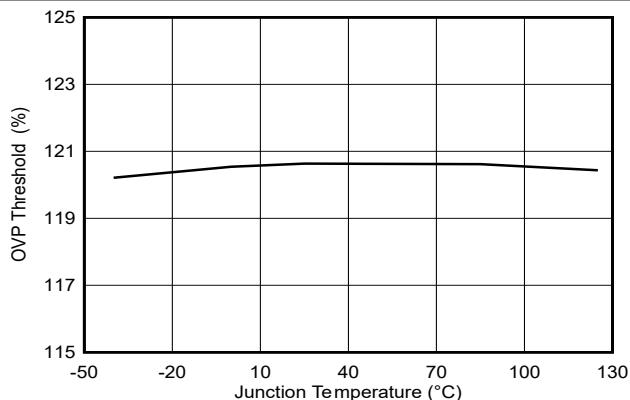

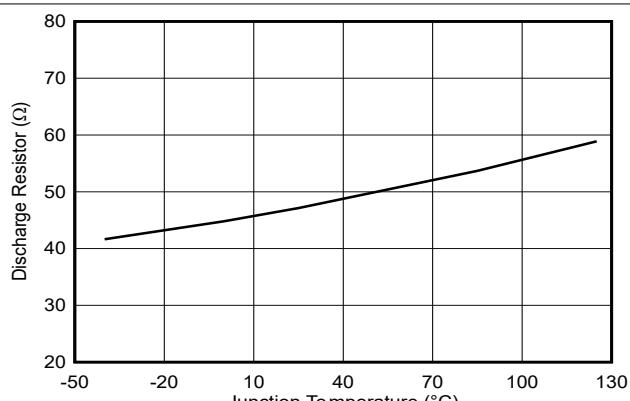

図 5-7. OVP スレッショルドと接合部温度との関係

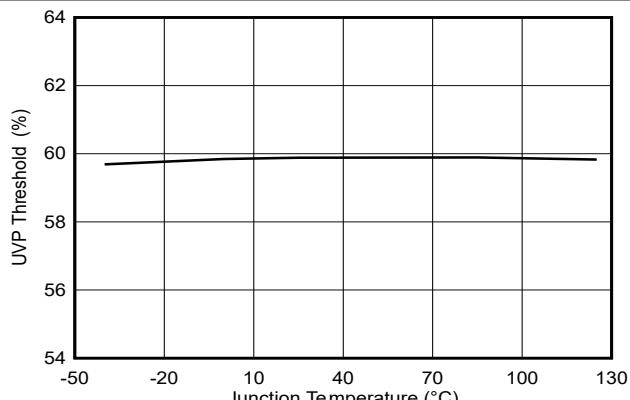

図 5-8. UVP スレッショルドと接合部温度との関係

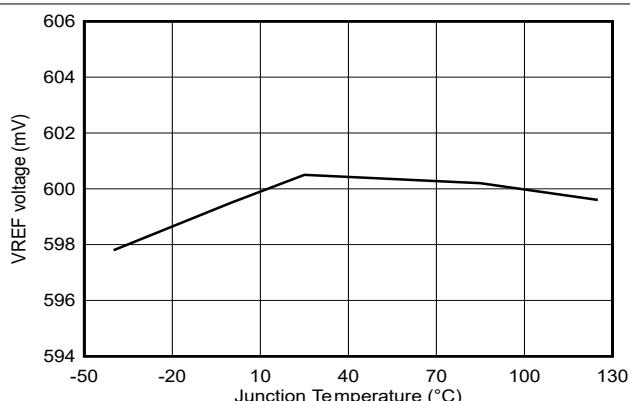

図 5-9. 接合部温度に対する VREF 電圧

図 5-10. 放電抵抗と接合部温度との関係

図 5-11. バレー電流制限とジャンクション温度

図 5-12. ソフトスタート時間と結合部温度との関係

## 5.6 代表的特性 (続き)

$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $V_{\text{IN}} = 12\text{V}$ (特に記述のない限り)。

図 5-13. VIN UVLO 立ち上がりと接合部温度との関係

図 5-14. VIN UVLO 立ち下りと接合部温度との関係

図 5-15. 効率と負荷電流との関係、

$F_{\text{SW}} = 600\text{kHz}$ ,  $V_{\text{OUT}} = 0.77\text{V}$

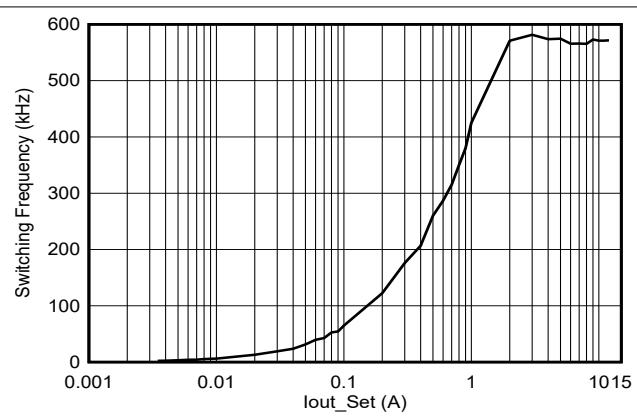

図 5-16. スイッチング周波数と負荷電流との関係、 $F_{\text{SW}} = 600\text{kHz}$

## 6 詳細説明

### 6.1 概要

TPS51375L は、12A、FET を内蔵した同期降圧コンバータで、4.5V ~ 24V の入力電圧 (VIN) で動作し、出力電圧は 0.6V ~ 5.5V です。このデバイスは、10mΩ と 5mΩ の各 MOSFET を内蔵しており、最大 12A の高効率を実現します。このデバイスは D-CAP3 制御モードを採用し、外部補償部品なしの高速過渡応答と、高精度フィードバック電圧を実現しています。この制御トポロジにより、重負荷条件での CCM (連続導通モード) と軽負荷条件での DCM、Eco-mode 動作の間をシームレスに移行できます。DCM、Eco-mode を使用すると、TPS51375L で軽負荷時に高い効率を維持できます。D-CAP3 制御モードでは、POSCAP や SP-CAP などの低等価直列抵抗 (ESR) 出力コンデンサや、超低 ESR セラミックコンデンサを使用できます。

TPS51375L は、5V VCC LDO を内蔵しており、すべての内部回路へのバイアスを生成します。低電圧誤動作防止 (UVLO) 回路は VCC ピンの電圧を監視して、内部回路を低入力電圧から保護します。外部 5V バイパス電源を使用して効率を向上させることができます。TPS51375L には EN ピンに内部プルダウン電流源があり、降圧コンバータをイネーブルするには外部プルアップ回路が必要です。

TPS51375L は 600kHz のスイッチング周波数をサポートしています。内部ソフトスタート時間は 1ms に固定されているため、設計回路を簡素化し、外部部品を低減できます。

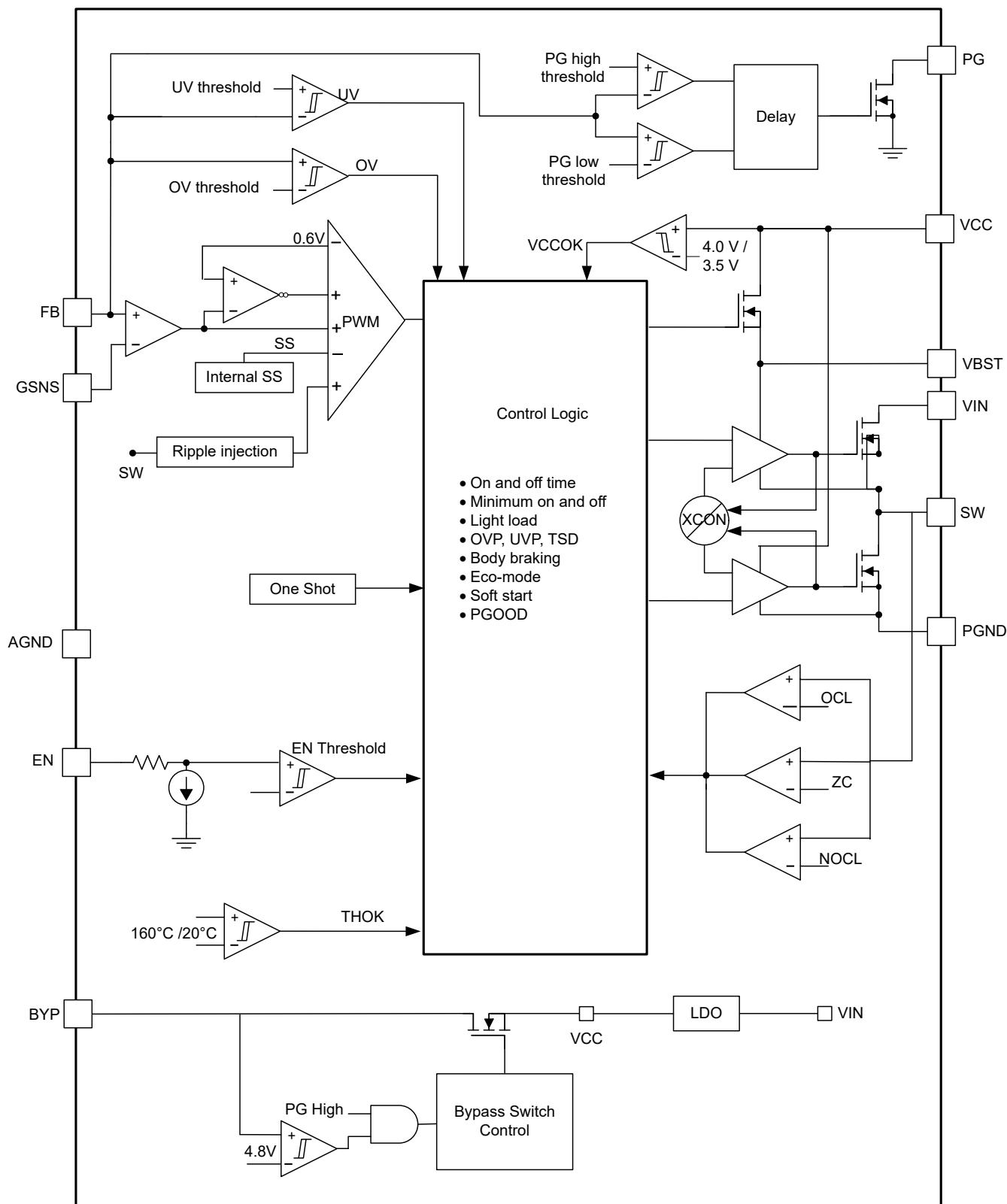

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 PWM 動作と D-CAP3™ 制御モード

降圧モジュールのメイン制御ループは、独自の D-CAP3 制御モードをサポートする適応型オン時間パルス幅変調 (PWM) コントローラとなっています。D-CAP3 制御モードは、適応型オン時間制御を、擬似固定周波数で外部部品数の少ない構成を可能にする内部補償回路と組み合わせたもので、低 ESR 出力コンデンサとセラミック出力コンデンサの両方を使用できます。D-CAP3 制御モードは、出力にほとんどリップルがない状態でも安定して動作します。TPS51375L には、出力電圧の精度を非常に高めるエラー アンプも内蔵されています。

各サイクルの開始時に、ハイサイド MOSFET がオンになります。内部のワンショット タイマが終了すると、この MOSFET がオフになります。このワンショット タイマの時間は、入力電圧範囲内で擬似固定周波数が維持されるように、コンバータの入力電圧  $V_{IN}$  に比例し、出力電圧  $V_{OUT}$  に反比例するよう設定されます。そのため、これは適応型オン時間制御と呼ばれます。帰還電圧がリファレンス電圧を下回ると、ワンショット タイマがリセットされ、ハイサイド MOSFET が再度オンになります。出力リップルをエミュレートするために、リファレンス電圧に内部リップル生成回路が追加されています。このため、多層セラミックコンデンサ (MLCC) などの超低 ESR 出力コンデンサを使用できます。D-CAP3 制御モードでは、外部の電流センス ネットワークや電圧補償回路は不要です。

内部で補償されるすべての制御トポジには、制御トポジがサポートできる出力フィルタの範囲があります。TPS51375L で使用される出力フィルタは、ローパス L-C 回路です。この L-C フィルタの 2 極周波数は、式 1 で計算されます。

$$f_P = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}} \quad (1)$$

低周波数では、出力設定点分圧抵抗回路、および TPS51375L の内部ゲインによって、全体のループ ゲインが設定されます。低周波数の L-C 二重極には、180 度の位相遅れがあります。出力フィルタ周波数では、10 進数毎にゲインが -40dB ロール オフし、位相は急速に減少します。内部リップル生成回路によって中間周波数のゼロが導入されることで、ゲインのロール オフが 10 進数毎に -40dB から -20dB に減り、位相はゼロ周波数より 10 進数毎に 90 度増加します。出力フィルタに使用するインダクタとコンデンサは、この中周波数ゼロから得られる位相ブーストによって安定性要件のための十分な位相マージンが確保されるように、二重極を中周波数ゼロに十分近く配置する必要があります。システム全体のクロスオーバー周波数は通常、スイッチング周波数 ( $F_{SW}$ ) の 1/3 未満に設定する必要があります。

### 6.3.2 リモート センス

TPS51375L デバイスは、FB および GSN ピンによるリモート センス機能を備えています。リモート センス機能は、PCB パターンで生じる可能性のある電圧降下を補償するため、定常状態動作および負荷過渡イベントにおいて VOUT 許容値を維持するのに役立ちます。FB 分圧抵抗器を遠隔地に接続すると、遠隔地での出力電圧を検知できます。FB 電圧分割抵抗器から遠隔地への接続には、パターン幅が 12mil 以上の 1 対の PCB パターンとする必要があり、0.1μF 以上の高バイパス コンデンサの両端にケルビン検出を実装する必要があります。リモート検出信号のグラウンド接続を GSNS 端子に接続する必要があります。リモートセンシング信号の VOUT 接続は、下側の帰還抵抗 RFB\_LS を GNS ピンで終端した帰還分圧抵抗に接続する必要があります。安定した出力電圧を維持し、リップルを最小限に抑えるには、インダクタや SW ノード、高周波クロック ラインなどのノイズ源から、1 対のリモート検出ラインを離して配置する必要があります。リモート検出ラインのペアを上下のグランド プレーンでシールドすることを TI は推奨します。シングルエンド Vo センシングは多くの場合、ローカル センシングに使用されます。この構成では、より高い FB 抵抗 RFB\_HS を 0.1μF 以上の高周波ローカル バイパス コンデンサに接続し、GSNS を AGND に短絡します。

### 6.3.3 ボディ ブレーキ

負荷の降圧中、コンバータは出力電圧の変化の振幅を検出します。出力電圧の変化が十分大きい場合、TPS51375L にはボディブレーキ機能が実装され、ハイサイドとローサイドの両方の FET をオフにし、ローサイド ボディダイオードを通して電力を消費できるため、オーバーシュートを低減できます。このアプローチは非常に効果的であるとともに、過渡時の効率にもある程度の影響を及ぼします。

### 6.3.4 5V LDO と BYP 機能

VCC ピンは、すべての内部回路と MOSFET ゲートドライバのバイアスを生み出す内部 5V リニア レギュレータの出力です。VCC ピンは、 $2.2\mu\text{F}$  コンデンサを使用してバイパスする必要があります。UVLO 回路は VCC ピンの電圧を監視し、VCC が UVLO しきい値を下回ると出力を無効にします。

BYP ピンに接続される外部電圧は、より高い電圧が検出された後で、内部 LDO をオーバーライドし、外部レールに切り替えることができます。このアクションにより、静止電流が入力電源ではなくこの外部レールから流れようになるため、コンバータの効率が向上します。この BYP 外部電圧は、VIN 電圧がオンになった後で来て、VIN がオフになる前に終了する必要があります。

このデバイスは、VCC スイッチオーバー機能に内蔵されており、VOUT が 4.8V より高く設定されている場合に、BYP ピンを VOUT に直接接続することをサポートしています。VCC の切り替え機能は、VOUT から電力を供給して内部 5V LDO をバイパスするように設計されています。VCC の切り替えはレギュレータのシームレスな動作であり、追加の構成は必要ありません。

VCC ピンのスイッチオーバー機能は、次の 3 つの条件が発生するとアサートされます。

- PGOOD は low にプルされません

- VOUT 電圧が 4.8V より高くなります

- BYP ピンは VOUT へ短絡しています。

このスイッチオーバー状態では、1 つ、内部スイッチオーバー MOSFET により VCC 出力が VOUT に接続されるという状況が発生します。

### 6.3.5 ソフトスタート

TPS51375L には内部に 1ms のソフト スタートがあります。EN ピンが high になると、内部ソフト スタート機能によって PWM コンパレータに対するリファレンス電圧が上昇し始めます。スタートアップ時に出力コンデンサがプリバイアスされている場合には、内部リファレンス電圧が帰還電圧  $\text{VVFB}$  より大きくなるまで、スイッチングおよび電圧上昇は開始されません。この方式により、コンバータはレギュレーション点までスムーズに上昇します。

### 6.3.6 デューティ比の大きい動作

TPS51375L は内部  $T_{ON}$  拡張機能により、大きなデューティ サイクルでの動作をサポートできます。 $V_{IN}/V_{OUT} < 1.18$  かつ  $V_{FB}$  が内部  $V_{REF}$  より低い場合、スイッチング周波数がスムーズに低下して  $T_{ON}$  が拡張され、大デューティ動作が実現されるとともに、負荷過渡性能も向上します。TPS51375L は、最大 98% のデューティ サイクルでの動作をサポートできます。

### 6.3.7 パワーグッド

Power-Good (PGOOD) ピンはオープンドレイン出力です。電圧を VCC にプルアップするため、 $100\text{k}\Omega$  のプルアップ抵抗を推奨します。 $V_{FB}$  が目標出力電圧の 90% ~ 115% になった後、200us のグリッヂ除去時間の経過後、PGOOD は high になります。PGOOD ピンがローになるのは次の場合です。

- FB ピンの電圧が目標出力電圧の 83% より低いか、120% を超えています

- 過電圧保護、UVP、サーマル シャットダウン イベントが発生します

- ソフト スタート期間中に発生します

### 6.3.8 電流保護と低電圧保護

TPS51375L には、過電流保護と低電圧保護機能が搭載されています。出力過電流保護 (OCP) は、サイクル毎のローサイド MOSFET バレー電流検出を使用して実現されています。MOSFET のドレインからソースへの間電圧を測定することで、スイッチング電流が監視されます。この電圧は、スイッチ電流に比例します。精度を向上させるため、電圧センスは温度補償されています。

ローサイド FET スイッチのオン時間中は、この電流はリニアに減少します。スイッチ電流の平均値はが、負荷電流  $I_{OUT}$  です。監視対象電圧が OCL レベルより高い場合、コンバータはローサイド FET をオンに保持し、電流レベルが OCL レベル

ル以下になるまでの間、(電圧帰還ループで必要とされる場合であっても)新しいパルスの生成を遅延させます。以降のスイッチングサイクルでは、オン時間が固定値に設定され、同じ方法で電流がモニタされます。

このようなタイプの過電流保護には、いくつかの重要な考慮事項があります。負荷電流が、ピークツーピークインダクタリップル電流の  $1/2$  だけ  $I_{OCL(Valley)}$  を加算する場合、OCP がトリガされ、出力電流が制限されます。負荷要求が、コンバータでサポートできる値を上回っているため、出力電圧が低下する傾向があります。出力電圧が目標電圧の  $60\%$  を下回ると、UVP コンパレータによって立ち下がりが検出され、 $200\mu s$  の一定時間後にデバイスがオフになります。この保護は非ラッチ方式の保護です。�ルトランチ機能は、EN を low にするか、VCC の電源を切って再投入することでリセットできます。

### 6.3.9 過電圧保護

TPS51375L には過電圧保護機能があります。出力電圧が目標電圧の  $120\%$  を超過すると、OVP コンパレータの出力が high になり、 $256\mu s$  の待ち時間後に出力が放電されてラッチされます。この機能はラッチ動作であるため、EN を low にするか、VIN の電源を切って再投入することで、この機能をリセットする必要があります。

### 6.3.10 UVLO 保護

VIN 低電圧誤動作防止 (UVLO) 保護機能は、VIN ピンの電圧を監視して、内部回路を低入力電圧から保護します。VIN 電圧が UVLO スレッショルド電圧を下回ると、デバイスの誤動作を防止するため、デバイスがオフになり、出力が放電されます。入力電圧がスレッショルドを  $650mV$  (標準値) のヒステリシスだけ上回ると、コンバータは動作を再開します。これは非ラッチ方式の保護です。

### 6.3.11 出力電圧放電

TPS51375L には  $50\Omega$  の放電スイッチがあり、出力過電圧、出力低電圧、サーマルシャットダウンなどの障害事象が発生したとき、または VIN 電圧が UVLO より低く、EN ピンの電圧がターンオンスレッショルドよりも低いときは、出力 VOUT ピン経由で出力 VOUT を放電します。

### 6.3.12 スタンバイ動作

TPS51375L は、EN ピンを低く引くことでスタンバイモードに移行できます。デバイスは、スタンバイ状態では、 $3\mu A$  のシャットダウン電流で動作します。EN ピンは内部で low にプルされます。フローティングのとき、デバイスはデフォルトで無効になっています。

### 6.3.13 サーマルシャットダウン

TPS51375L は、内部ダイの温度を監視します。温度がスレッショルド値 (通常は  $160^{\circ}C$ ) を超えると、デバイスがシャットダウンされ、出力が放電されます。これは非ラッチ方式の保護です。温度がサーマルシャットダウンしきい値を下回ると、デバイスは動作を再開します。

## 6.4 デバイスの機能モード

### 6.4.1 高度な Eco-mode 制御

軽負荷時にも高効率を維持する高度な Eco-mode 制御方式。重負荷状態から出力電流が減少すると、インダクタ電流も減少し、最終的にはそのリップル付きの谷がゼロレベルに達する点まで至ります。これは、連続導通モードと不連続導通モードの境界に当たります。ゼロインダクタ電流が検出されると、整流 MOSFET がオフになります。負荷電流がさらに減少すると、コンバータは不連続導通モードに入ります。オン時間は連続導通モードのときとほぼ同じに保持されるため、出力コンデンサを小さな負荷電流でリファレンス電圧レベルまで放電するには、より長い時間がかかります。このアクションにより、スイッチング周波数が負荷電流に比例して低下し、軽負荷時の効率が高く維持されます。式 2 を使用して、Eco-mode 動作への遷移が発生する軽負荷電流 ( $I_{OUT(LL)}$ ) を計算します。

$$I_{OUT(LL)} = \frac{1}{2 \times L_{OUT} \times F_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}} \quad (2)$$

アプリケーション要件を特定した後、インダクタのピークツーピークリップル電流が  $I_{OUT(max)}$  (アプリケーションのピーク電流) の約 20% ~ 40% になるように出力インダクタンス ( $L_{OUT}$ ) を設計します。バレー電流が負のローサイド電流制限に達しないようにインダクタのサイズを適切に調整することが重要です。

7 アプリケーションと実装

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 7.1 アプリケーション情報

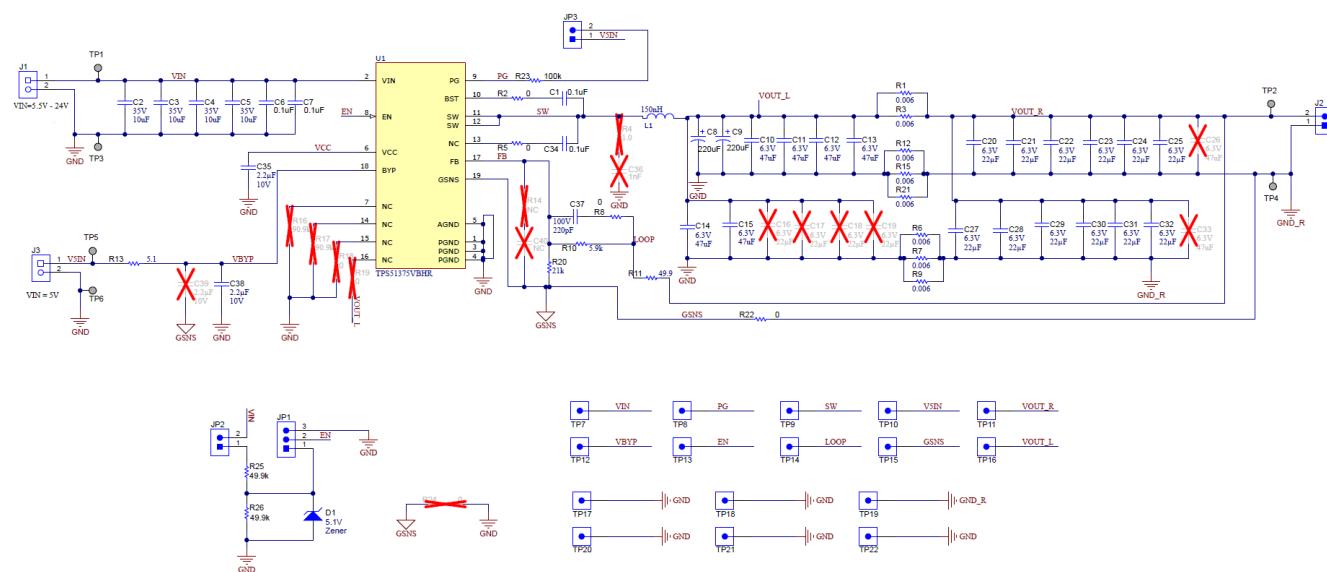

図 7-1 の回路図は、0.77V 出力の TPS51375L の代表的なアプリケーションを示しています。このデザインは、4.5V ~ 24V の入力電圧レンジを最小 0.77V に変換し、最大連続出力電流は 12A です。

## 7.2 代表的なアプリケーション

図 7-1. 0.77V、12A 連続電流リファレンスデザイン

### 7.2.1 設計要件

この例の設計パラメータを、表 7-1 に示します。

表 7-1. 設計パラメータ

| パラメータ                    |                          | 条件                 | 最小値 | 標準値  | 最大値   | 単位                |

|--------------------------|--------------------------|--------------------|-----|------|-------|-------------------|

| 出力                       |                          |                    |     |      |       |                   |

| V <sub>OUT</sub>         | 出力電圧                     |                    |     | 0.77 |       | V                 |

| I <sub>OUT</sub>         | 出力電流                     |                    |     | 12   |       | A                 |

| V <sub>IN</sub>          | 入力電圧                     |                    | 4.5 | 19.5 | 24    | V                 |

| V <sub>OUT(ripple)</sub> | 出力電圧リップル                 | 0A ~ 12 負荷         |     | 10   |       | mV <sub>P-P</sub> |

| V <sub>OUT(min)</sub>    | 最小出力電圧                   | 0A ~ 10A 負荷、10A/μs | 720 |      |       | mV                |

| V <sub>OUT(max)</sub>    | 最大出力電圧                   | 7A ~ 17A 負荷、10A/μs |     |      | 827.5 | mV                |

| F <sub>SW</sub>          | スイッチング周波数                |                    |     | 600  |       | kHz               |

| R <sub>PATH_VOUT</sub>   | V <sub>OUT</sub> パスの寄生抵抗 |                    |     | 3    |       | mΩ                |

| R <sub>PATH_GND</sub>    | GND パスの寄生抵抗              |                    |     | 1.5  |       | mΩ                |

表 7-1. 設計パラメータ (続き)

| パラメータ          |      | 条件 | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|------|----|-----|-----|-----|----|

| T <sub>A</sub> | 周囲温度 |    |     | 25  |     | °C |

## 7.2.2 詳細な設計手順

### 7.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS51375L デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インストゥルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 7.2.2.2 外付け部品の選択

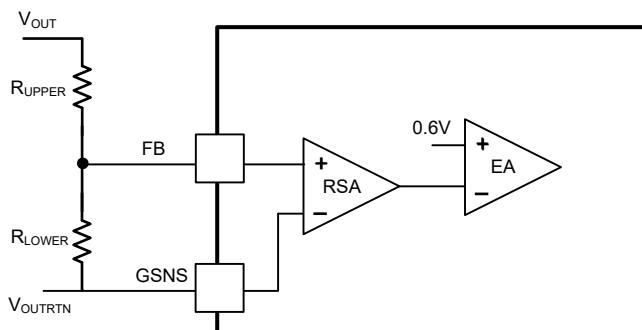

#### 7.2.2.2.1 リモート センス アンプと出力電圧の調整

専用の高速、低オフセットの計測タイプ アンプを使用して、出力電圧のリモート センシングを実施しています。以下で説明する出力電圧設定分圧抵抗を出力電圧検知ポイントから GNS ピンに接続します。中心点は FB ピンに接続します。GSN ピンは、負荷の近くの場所で、コンバータの出力電圧のリターンに接続するようにします。図 7-2 に示すように、出力電圧は、コンバータ出力 ( $V_{OUT}$ ) と FB ピンとの間の分圧抵抗回路によってプログラミングされます。公差 1% 以内の分圧抵抗を使用します。

図 7-2. リモート センス付き FB 分圧抵抗

アプリケーションの出力電圧を変更するには、上側帰還抵抗の値を変更します。この抵抗を変更することにより、出力電圧を 0.6V 以上に変更できます。式 3 を参照してください。

$$V_{OUT} = 0.6 \times \left(1 + \frac{R_{UPPER}}{R_{LOWER}}\right) \quad (3)$$

### 7.2.2.2 インダクタの選択

インダクタ リップル電流は、出力コンデンサによってフィルタリングされます。インダクタのリップル電流が大きいほど、出力コンデンサのリップル電流定格はインダクタのリップル電流よりも大きくなればならないことを意味します。推奨インダクタ値については、[表 7-3](#) を参照してください。

[式 5](#) と [式 4](#) を使用して、インダクタを流れる RMS 電流とピーク電流を計算します。インダクタがこれらの電流を処理できることを確認してください。

$$I_{L(rms)} = \sqrt{I_{OUT}^2 + \frac{1}{12} \times \left[ \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times L_{OUT} \times F_{SW}} \right]^2} \quad (4)$$

$$I_{L(peak)} = I_{OUT} + \frac{I_{OUT(ripple)}}{2} \quad (5)$$

過渡状態および短絡状態では、インダクタ電流がデバイスの電流制限まで増加する可能性があります。電流制限条件でピーク電流よりも飽和電流が大きいインダクタを選択することも安全です。

### 7.2.2.3 出力コンデンサの選択

インダクタの選択後、出力コンデンサを最適化する必要があります。D-CAP3 制御モードでは、レギュレータがデューティサイクルの変化に対して 1 サイクル以内に応答するため、大きな出力容量を必要とせずに優れた過渡性能を実現できます。推奨出力容量の範囲を [表 7-2](#) と [表 7-3](#) に示します。セラミックコンデンサの ESR は非常に低いため、ESR リップルは無視できます。そうしないと、コンデンサの最大 ESR は  $V_{OUT(ripple)}/I_{OUT(ripple)}$  未満とする必要があります。

**表 7-2. 0.77V の推奨コンポーネント値**

| <b>V<sub>OUT</sub> (V)</b> | <b>R<sub>LOWER</sub> (kΩ)</b> | <b>R<sub>UPPER</sub> (kΩ)</b> | <b>L<sub>OUT</sub> (μH)</b> | <b>C<sub>OUT(min)</sub> (μF)</b> | <b>C<sub>OUT(max)</sub> (μF)</b> | <b>R<sub>FF</sub> (kΩ)</b> | <b>C<sub>FF</sub> (pF)</b> |

|----------------------------|-------------------------------|-------------------------------|-----------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|

| 0.77                       | 21                            | 5.9                           | 0.15                        | 500                              | 1000                             | 該当なし                       | 220                        |

**表 7-3. 汎用アプリケーション向けの推奨コンポーネント値**

| <b>V<sub>OUT</sub> (V)</b> | <b>F<sub>sw</sub> (kHz)</b> | <b>L<sub>OUT</sub> (μH)</b> | <b>C<sub>OUT(min)</sub> (μF)</b> | <b>C<sub>OUT(max)</sub> (μF)</b> | <b>R<sub>FF</sub> (kΩ)</b> | <b>C<sub>FF</sub> (pF)</b> |

|----------------------------|-----------------------------|-----------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|

| 1.2                        | 600                         | 0.47                        | 176                              | 500                              | 該当なし                       | 30                         |

| 3.3                        | 600                         | 1.5                         | 88                               | 198                              | 該当なし                       | 30                         |

| 5.0                        | 600                         | 1.5                         | 88                               | 198                              | 該当なし                       | 30                         |

### 7.2.2.4 入力コンデンサの選択

TPS51375L には、電源入力ピン VIN に入力デカッピングコンデンサが必要となり、アプリケーションによってはバルクコンデンサが必要となります。[式 6](#) を使用して、必要な最小入力容量を計算します。

$$C_{IN(min)} = \frac{I_{OUT} \times V_{OUT}}{V_{IN(ripple)} \times V_{IN} \times F_{SW}} \quad (6)$$

テキサス インスツルメントでは、入力電圧ピンに、公称 44μF/35V の高品質 X5R または X7R 入力デカッピングコンデンサを使用することをお勧めします。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。コンデンサのリップル電流定格をアプリケーションの最大入力電流リップルよりも大きくする必要があります。入力リップル電流を計算するには、[式 7](#) を使用します。

$$I_{CIN(rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN(min)}} \times \frac{(V_{IN(min)} - V_{OUT})}{V_{IN(min)}}} \quad (7)$$

### 7.2.2.5 ブートストラップコンデンサの選定

適切な動作のためには、BST ピンと SW ピンの間に 0.1μF のセラミックコンデンサを接続する必要があります。DC バイアスのディレーティングを最小限に抑えるため、コンデンサの定格は 10V 以上にする必要があります。

BST コンデンサと直列に抵抗を追加することで、ハイサイド MOSFET のターンオンを低速にし、SW ピンのオーバーシュートの立ち上がりエッジのオーバーシュートを低減できます。この動作には、電力損失の増加と効率の低下というトレードオフが伴います。ベスト プラクティスとして、プロトタイプの設計に  $0\Omega$  のプレースホルダを配置します。これは、PCB レイアウトの寄生インダクタンスが通常よりも SW ピンでの電圧オーバーシュートが大きくなる場合に備えてください。この方法により、電圧をデバイスの定格内に維持し、SW ノードの高周波ノイズを低減することができます。

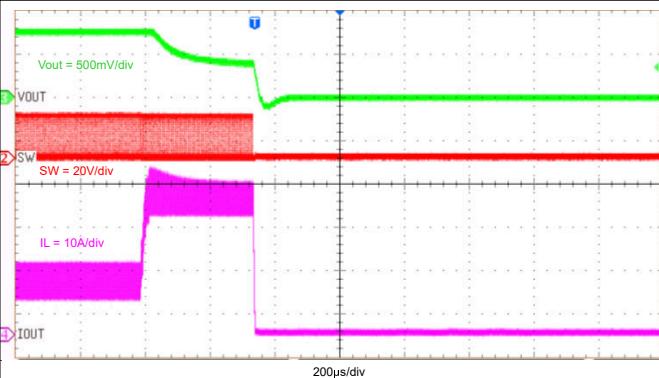

### 7.2.3 アプリケーション曲線

図 7-3 から図 7-18 は図 7-1 の回路に適用されます。 $V_{IN} = 12V$ 、 $F_{SW} = 600kHz$ 、 $T_A = 25^\circ C$ 、特に記述のない限り。

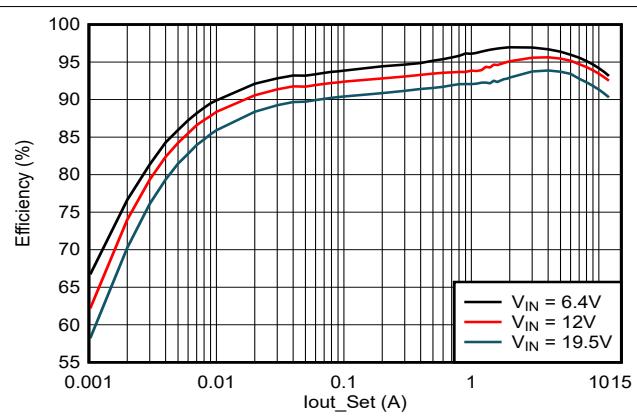

図 7-3. 効率曲線 ( $V_{OUT} = 0.77V$ )

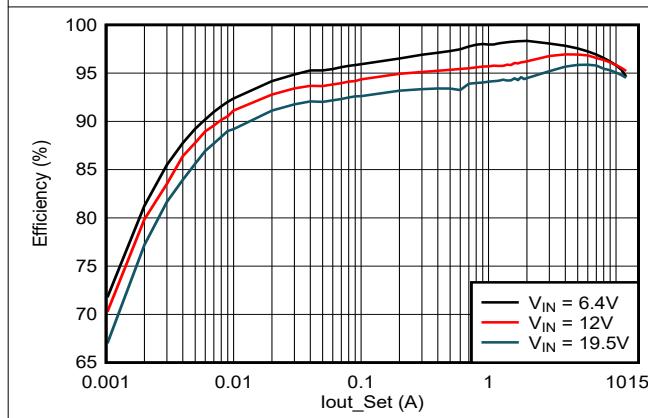

図 7-4. 効率曲線 ( $V_{OUT} = 3.3V$ )

図 7-5. 効率曲線 ( $V_{OUT} = 5V$ )

図 7-6. スイッチング周波数と出力負荷との関係

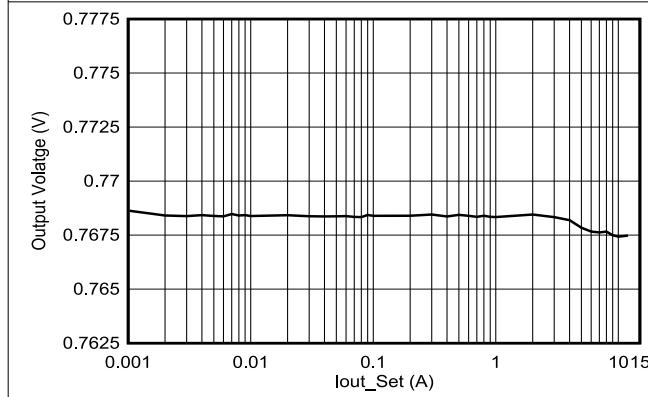

図 7-7. 負荷レギュレーション、 $V_{IN} = 12V$

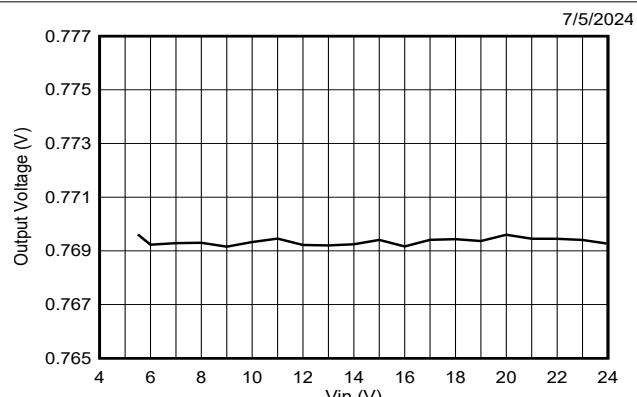

図 7-8. ラインレギュレーション、 $I_{OUT} = 12A$

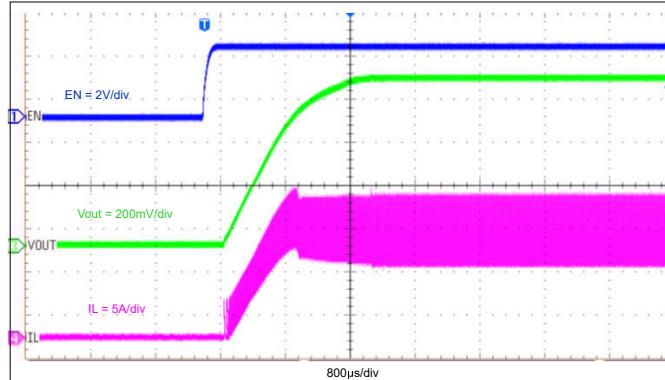

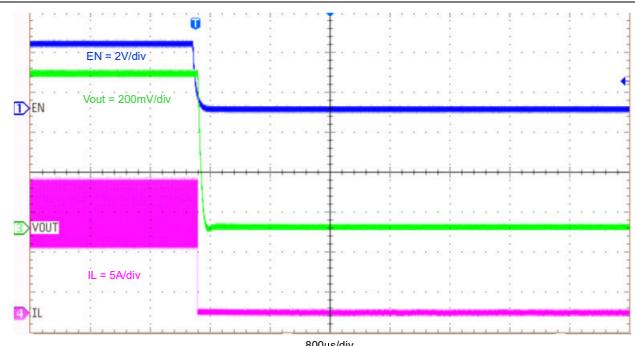

図 7-9. EN によるスタートアップ、 $I_{OUT} = 12A$

図 7-10. EN によるシャットダウン、 $I_{OUT} = 12A$

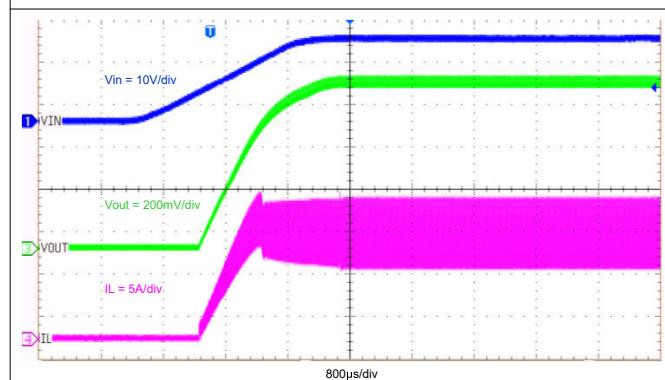

図 7-11. VIN の立ち上がり時のスタートアップ、 $I_{OUT} = 12A$

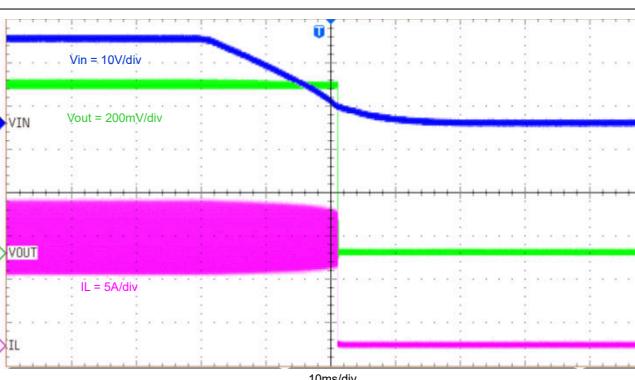

図 7-12. VIN 立ち下がり時のシャットダウン、 $I_{OUT} = 12A$

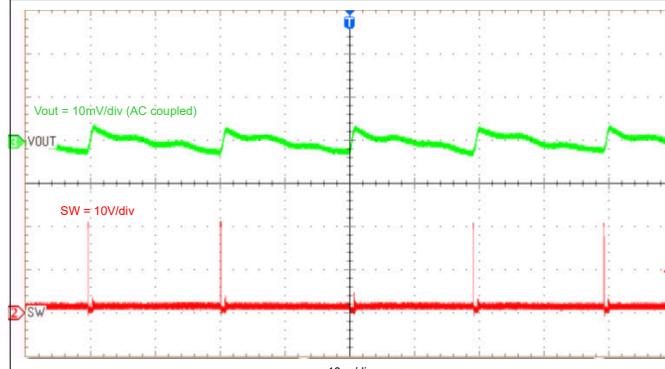

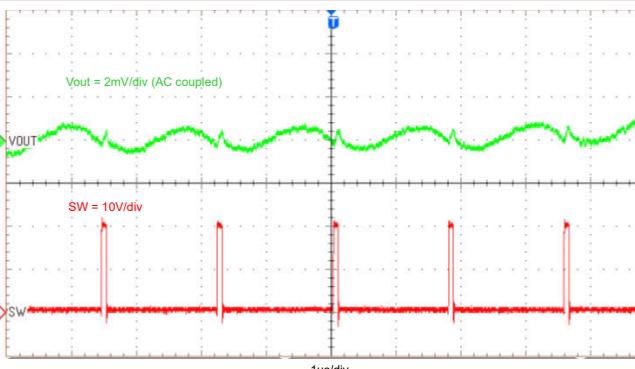

図 7-13. 出力電圧リップル、 $I_{OUT} = 0.1A$

図 7-14. 出力電圧リップル、 $I_{OUT} = 6A$

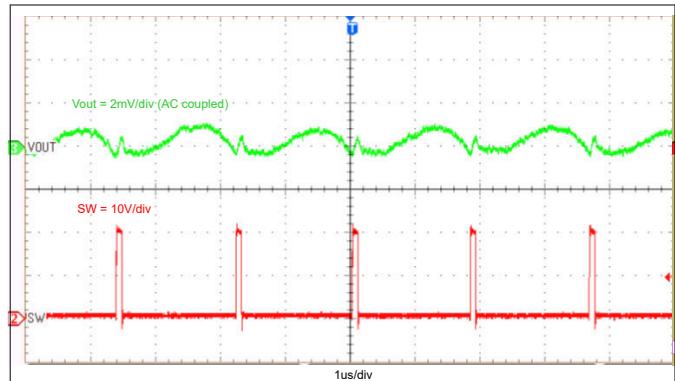

図 7-15. 出力電圧リップル、 $I_{OUT} = 12A$

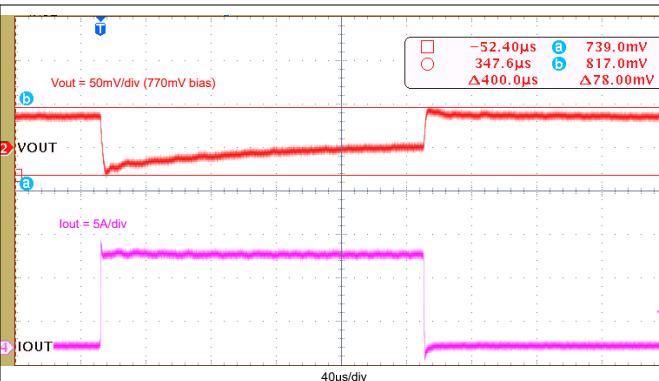

図 7-16. 過渡応答、 $0A \sim 10A$ 、

スルーレート =  $10A/\mu s$

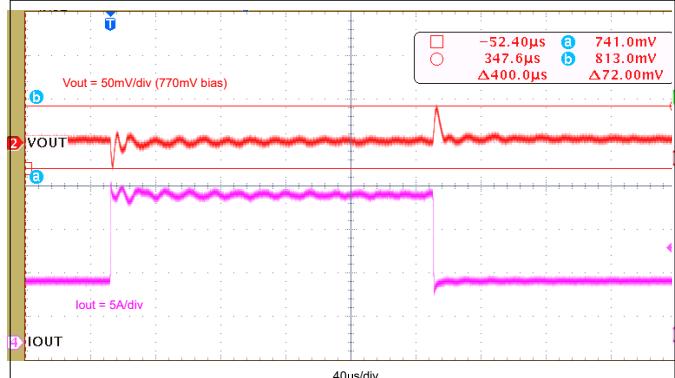

図 7-17. 過渡応答、 $7A \sim 17A$ 、

スルーレート =  $10A/\mu s$

図 7-18. 通常動作から出力のハード短絡

## 7.3 電源に関する推奨事項

TPS51375L は、安定した DC 電圧から電力を供給するよう設計されています。入力電圧範囲は 4.5V ~ 24V です。TPS51375L は、降圧コンバータです。適切に動作させるには、入力電源電圧は目的の出力電圧よりも高い必要があります。入力電源電流は、目的の出力電流に適したものでなければなりません。入力電圧電源が TPS51375L 回路から遠く離れた場所に配置されている場合は、追加の入力バルク容量をいくつかお勧めします。標準値は 100 $\mu$ F から 470 $\mu$ F です。

## 7.4 レイアウト

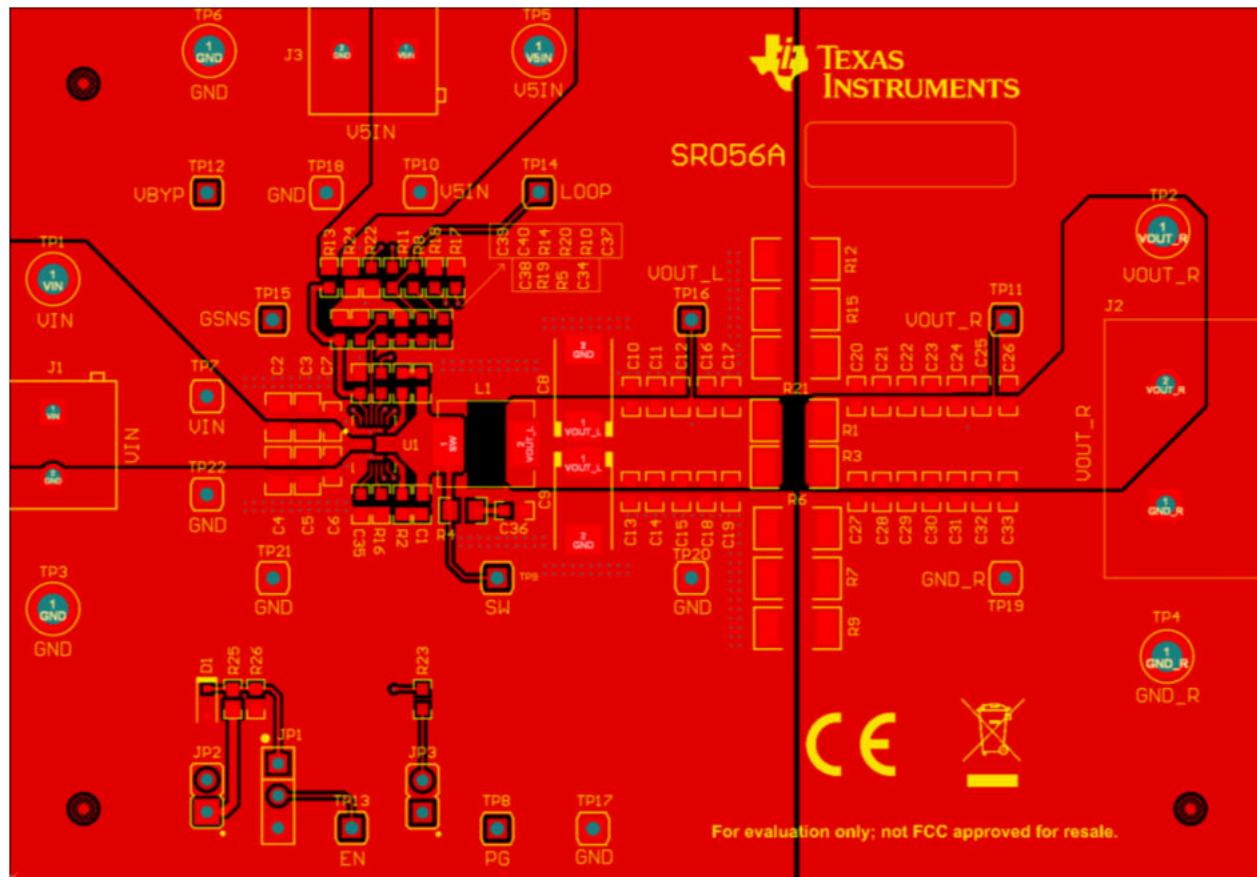

### 7.4.1 レイアウトのガイドライン

- DC/DC コンバータの PCB レイアウトは、優れた設計性能を実現するために重要であることに注意してください。PCB レイアウトが不適切な場合、適正な回路図設計の動作の妨げとなる可能性があります。コンバータが適切にレギュレートしている場合でも、PCB レイアウトが不適切では、堅牢な設計と量産できない設計という違いが生じる可能性があります。さらに、コンバータの EMI 性能は、PCB レイアウトに大きく依存します。降圧コンバータにおいて、PCB の最も重要な機能は、入力コンデンサと電源グランドによって形成されるループです。このループには、パターンのインダクタンスに応答して大きな過渡電圧を発生させる可能性がある大きな過渡電流が流れます。これらの望ましくない過渡電圧は、コンバータの正常な動作を妨げます。この事実から、このループ内のパターンは広く短くして、ループ領域をできる限り小さくし、寄生インダクタンスを低減する必要があります。

- 優れた放熱性能を実現し、最大のグランドプレーンを確保するために、4 層 PCB を使用します。例として、2 オンスの銅箔を使用した 3 インチ × 2.75 インチの上層と下層の PCB を使用しています。

- デカップリング コンデンサは、VIN と VCC の間にできる限り近づけて配置します。

- 出力インダクタとコンデンサを、IC を使用して同じ層に配置します。SW の配線は EMI を最小限に抑えるためにできる限り短くし、大電流を流すために幅プレーンにする必要があります。出力コンデンサの PGND 接続に、および出力ピンのできるだけ近くに、十分なビアを追加する必要があります。

- BST の抵抗とコンデンサは IC によるもので、BST と SW プレーンに近付けて同じ層に配置します。ラインの寄生インダクタンスを低減するため、幅が 10mil を超えるパターンを推奨します。

- 帰還は 10mil で、スイッチングノード、BST ノード、またはその他の高速デジタル信号から離して配線します。

- VIN トレースを広くして、トレースのインピーダンスを下げ、十分な電流能力を確保します。

- デバイスの下に VIN と PGND の近く、および入力コンデンサの近くに複数のビアを配置して、寄生インダクタンスを減らし、熱性能を向上させます。

### 7.4.2 レイアウト例

図 7-19 に、推奨される上面レイアウトを示します。部品リファレンス指定子は、[TPS51375 降圧コンバータ評価基板 EVM ユーザー ガイド](#)に記載されている回路と同じです。

図 7-19. 上面レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 開発サポート

##### 8.1.1.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPS51375L デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 8.2 ドキュメントのサポート

#### 8.2.1 関連資料

関連資料については、以下を参照してください。

テキサス・インスツルメンツ、[TPS51375 降圧コンバータ評価基板 EVM ユーザー ガイド](#)

### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.5 商標

D-CAP3™, ULQ™, HotRod™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.7 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

| 日付        | 改訂 | 注      |

|-----------|----|--------|

| June 2025 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS51375LVBHR         | Active        | Production           | WQFN-FCRLF<br>(VBH)   19 | 4000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 51375L              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

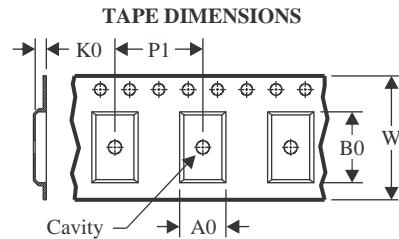

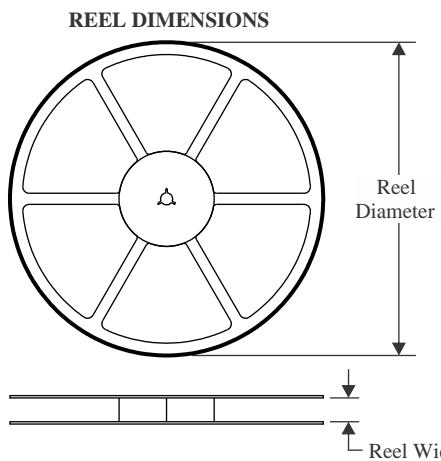

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

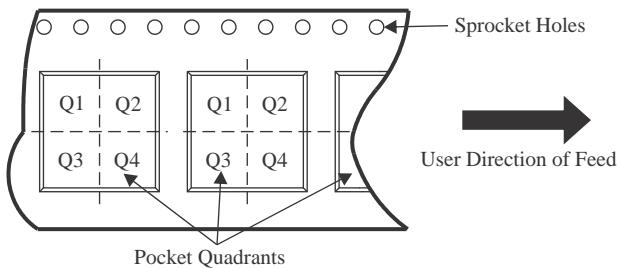

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS51375LVBHR | WQFN-FCRLF   | VBH             | 19   | 4000 | 330.0              | 12.4               | 3.3     | 4.3     | 0.85    | 8.0     | 12.0   | Q1            |

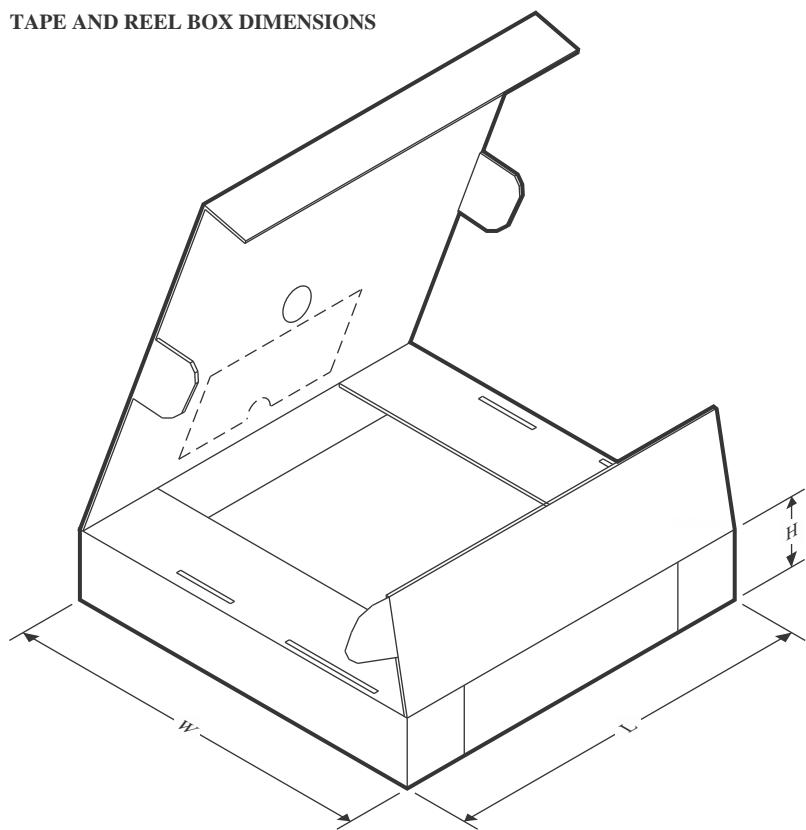

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51375LVBHR | WQFN-FCRLF   | VBH             | 19   | 4000 | 367.0       | 367.0      | 35.0        |

**VBH0019A**

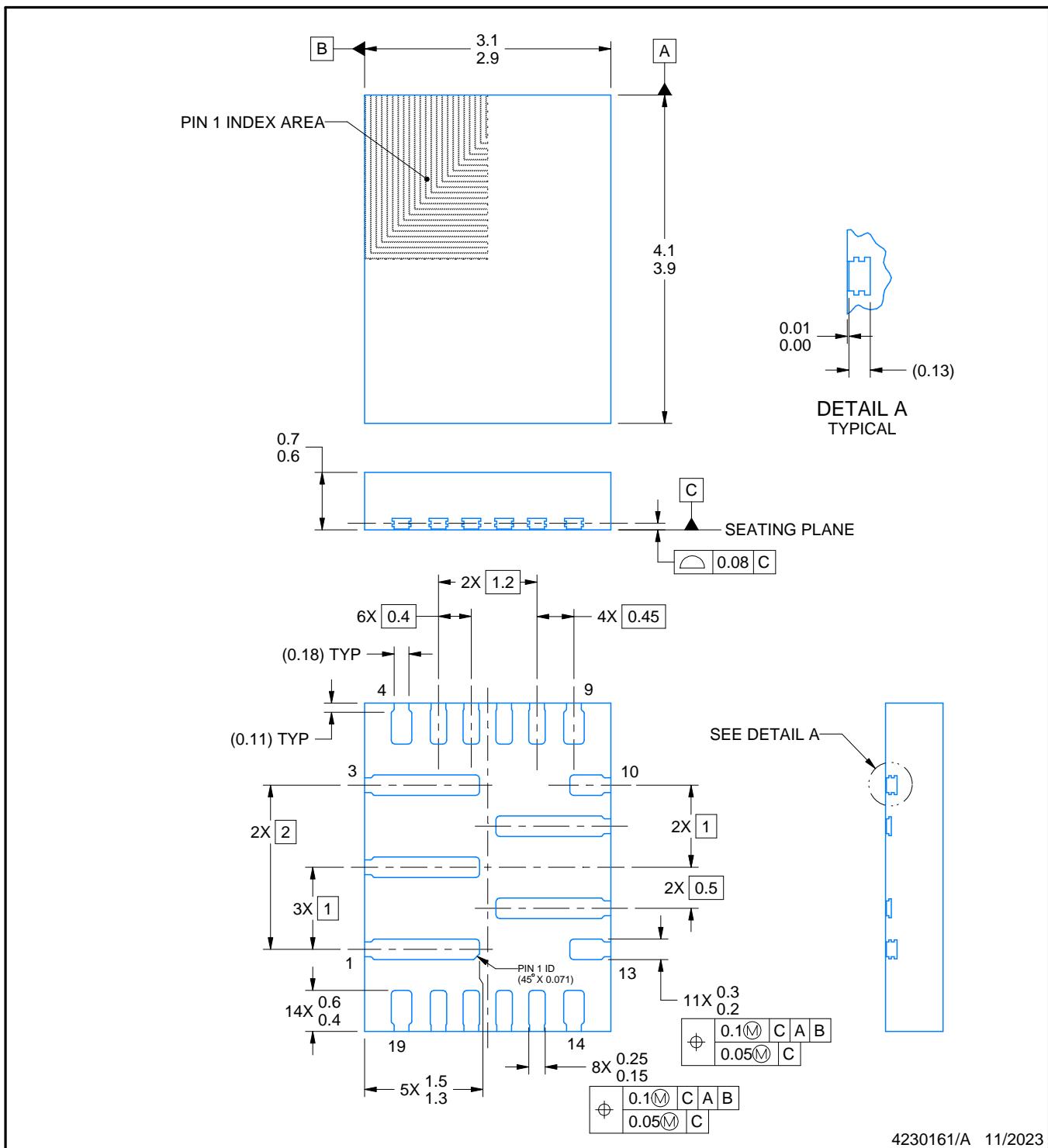

# PACKAGE OUTLINE

**WQFN-FCRLF - 0.7 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

4230161/A 11/2023

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

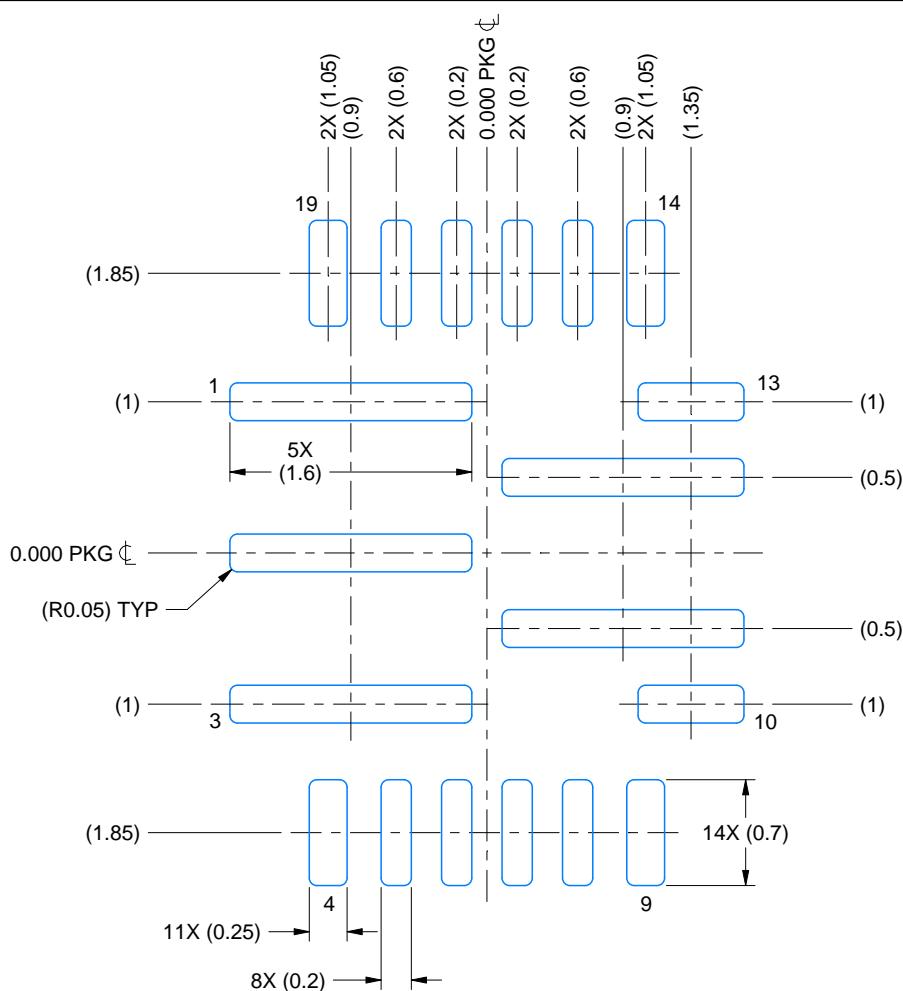

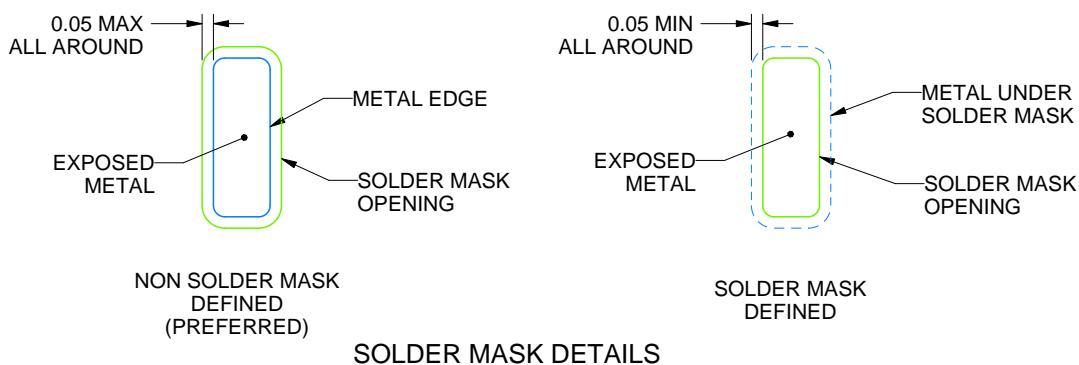

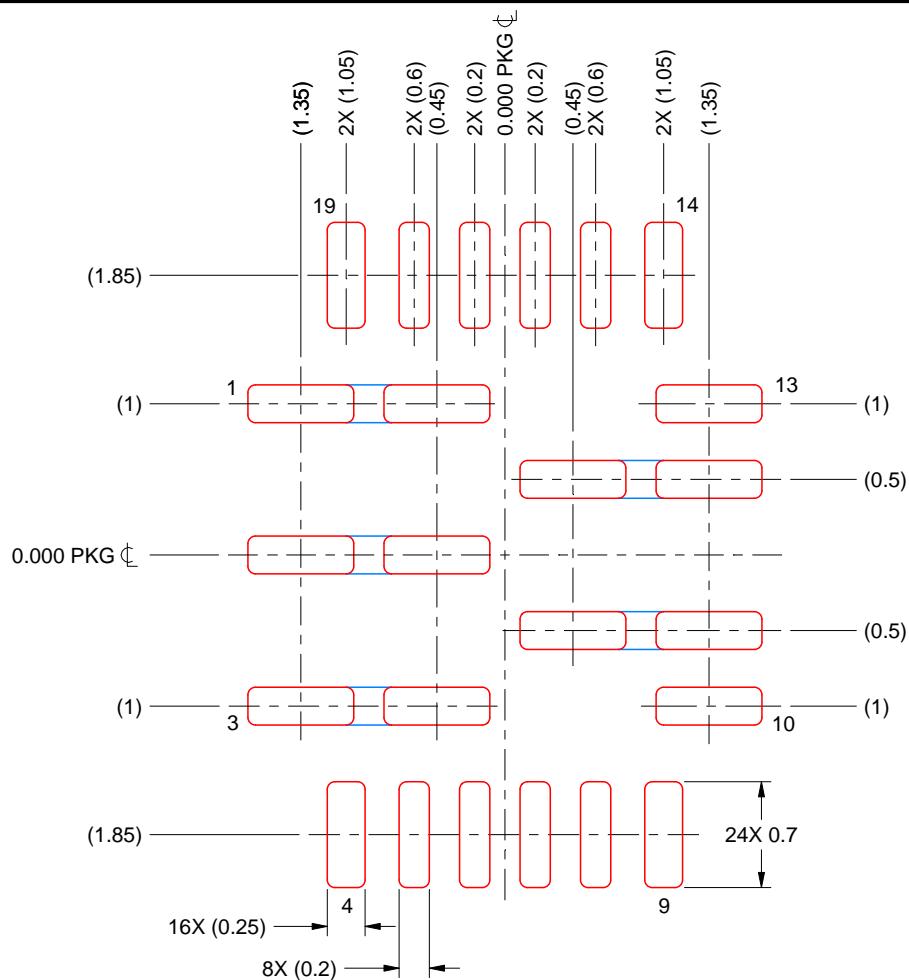

# EXAMPLE BOARD LAYOUT

VBH0019A

WQFN-FCRLF - 0.7 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

NOTES: (continued)

3. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

4230161/A 11/2023

## EXAMPLE STENCIL DESIGN

**VBH0019A**

**WQFN-FCRLF - 0.7 mm max height**

#### **PLASTIC QUAD FLATPACK - NO LEAD**

# SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE: 20X

**PRINTED SOLDER PASTE BY AREA UNDER PACKAGE

PINS 1, 2, 3, 11 & 12: 88%**

4230161/A 11/2023

## NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月