# **TPS53126**

www.tij.co.jp JAJS375

# 低電圧電源レール対応デュアル同期降圧型コントローラ

# 特長

- D-CAP2™モード制御

- 高速過渡応答

- ループ補償に外部部品が不要

- セラミック出力コンデンサを使用可能

- 高い初期リファレンス精度(±1%)

- 低出力リップル

- 幅広い入力電圧範囲:4.5V~24V

- 出力電圧範囲: 0.76V~5.5V

- ローサイドR<sub>DS(on)</sub>の電流センス

- 昇圧ダイオードを内蔵した適応型ゲート・ドライバ

- 1.2msの電圧サーボ・ソフト・スタートを内蔵

- プリバイアス付きソフト・スタート

- 選択可能なスイッチング周波数:350kHz / 700kHz

- サイクル毎の過電流制限制御

- OCPスレッショルド電圧:30mV~300mV

- 温度補償付きOCP: 4000ppm/℃ (I<sub>TRIP</sub>)

# アプリケーション

- 広範囲のアプリケーションに対する低電力システム でのポイント・オブ・ロード (POL) レギュレーション

- デジタル・テレビ用電源

- ネットワーク・ホーム・ターミナル

- デジタル・セットトップ・ボックス(STB)

- DVDプレーヤー/レコーダー

- ゲーム機など

# 概要

TPS53126は、適応型オン時間およびD-CAP2TMモードに対応したデュアル同期バック・コントローラです。TPS53126を採用することで、各種機器の電源バス・レギュレータに対して、コスト効果が高く、外部部品数の少ない、低スタンバイ電流のソリューションを実現できます。TPS53126の主制御ループではD-CAP2TMモード制御を使用し、外部部品なしで非常に高速な過渡応答が得られます。また、TPS53126には、POSCAP/SP-CAPなどの低ESR(等価直列抵抗)出力コンデンサだけでなく、超低ESRのセラミック・コンデンサにも対応できる、独自の回路が採用されています。4.5V~24Vの入力電圧、0.76V~5.5Vの出力電圧により、使いやすく効率的な動作を行います。

TPS53126は4mm  $\times$  4mmの24ピンQFN (RGE) または24ピン TSSOP (PW) パッケージで提供され、-40℃ $\sim$ 85℃の周囲温度 範囲で仕様が規定されています。

D-CAP2は、テキサス・インスツルメンツの登録商法です。

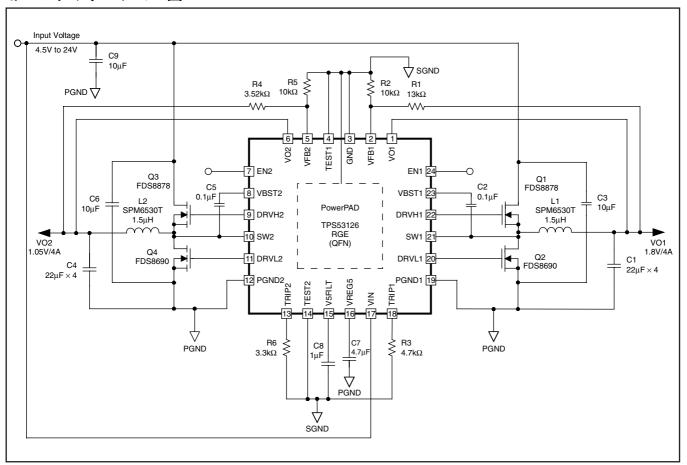

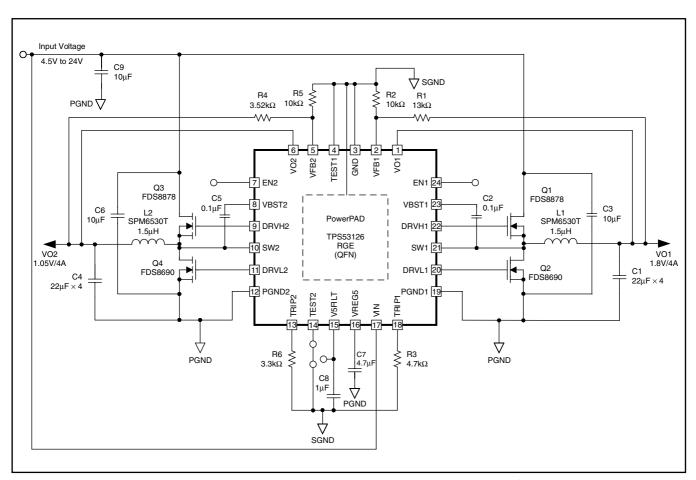

# QFNアプリケーション図

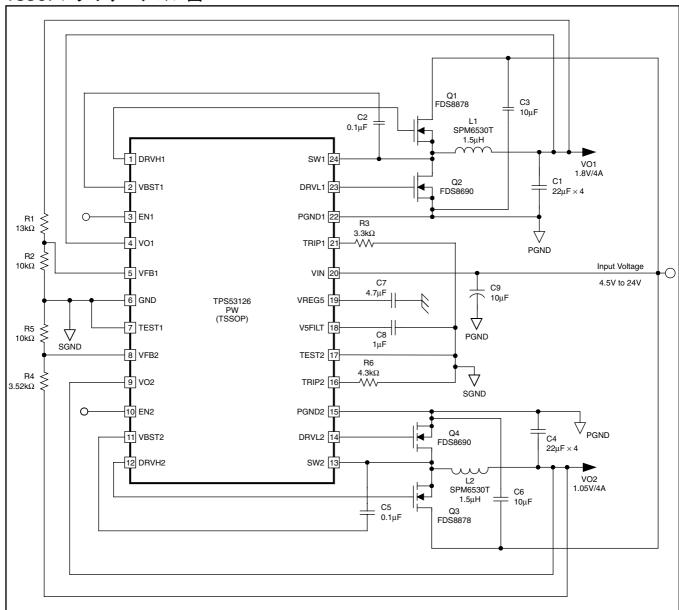

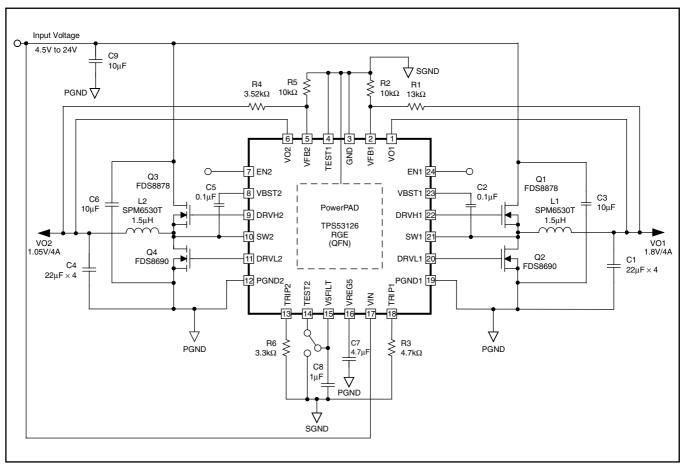

## TSSOPアプリケーション図

# 製品情報(1)(2)

| T <sub>A</sub> | パッケージ            | 発注用部品番号      | ピン数 | 供給形態    | エコ・プラン            |

|----------------|------------------|--------------|-----|---------|-------------------|

| 40°0 05°0      | プラスチックQFN        | TPS53126RGET |     | テープ・リール |                   |

|                | (Quad Flat Pack) | TPS53126RGER | 0.4 | テープ・リール | Green             |

| -40°C ∼ 85°C   | TOCOR            | TPS53126PWR  | 24  | テープ・リール | (RoHS & no Sb/Br) |

|                | TSSOP            | TPS53126PW   |     | チューブ    |                   |

<sup>(1)</sup> 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録:パッケージ・オプション」を参照するか、 TIのWebサイト (www.ti.comまたはwww.tij.co.jp) をご覧ください。 (2) すべてのパッケージ・オプションがCu NIPdAuリード / ボール仕上げとなっています。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                  |                         |                                                          | 值                  | 単位  |  |  |

|------------------|-------------------------|----------------------------------------------------------|--------------------|-----|--|--|

|                  |                         | VIN, EN1, EN2                                            | <b>−</b> 0.3 ~ 26  |     |  |  |

|                  |                         | VBST1, VBST2                                             | <b>−</b> 0.3 ~ 32  |     |  |  |

|                  | Input voltage range     | VBST1, VBST2 (wrt SWx)                                   | -0.3 ∼ 6           | V   |  |  |

|                  |                         | V5FILT, VFB1, VFB2, TRIP1, TRIP2, VO1, VO2, TEST1, TEST2 | -0.3 ∼ 6           |     |  |  |

|                  |                         | SW1, SW2                                                 | <b>−</b> 2 ~ 26    |     |  |  |

|                  |                         | DRVH1, DRVH2                                             | <b>−1</b> ~ 32     |     |  |  |

|                  | Output valtage renge    | DRVH1, DRVH2 (wrt SWx)                                   | -0.3 ∼ 6           | ] , |  |  |

|                  | Output voltage range    | DRVL1, DRVL2, VREG5                                      | -0.3 ∼ 6           | ]   |  |  |

|                  |                         | PGND1, PGND2                                             | <b>−</b> 0.3 ~ 0.3 | ]   |  |  |

| T <sub>A</sub>   | Operating ambient temp  | <b>−40</b> ~ 85                                          | $^{\circ}$         |     |  |  |

| T <sub>STG</sub> | Storage temperature ra  | <b>−</b> 55 ~ 150                                        | °C                 |     |  |  |

| TJ               | Junction temperature ra | Junction temperature range                               |                    |     |  |  |

<sup>(1)</sup> 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。 絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 定格消費電力(2オンス・トレースおよび銅パッド+半田)

| パッケージ     | T <sub>A</sub> < 25℃の電力定格 | ディレーティング係数、<br>T <sub>A</sub> = 25℃以上 | T <sub>A</sub> = 85℃の電力定格 |  |  |

|-----------|---------------------------|---------------------------------------|---------------------------|--|--|

| 24ピンQFN   | 2.33W                     | 23.3mW/°C                             | 0.93W                     |  |  |

| 24ピンTSSOP | 0.778 <b>W</b>            | 7.8m <b>W</b> /℃                      | 0.31W                     |  |  |

## 推奨動作条件

|                                              |                                    | MIN  | MAX | 単 位 |

|----------------------------------------------|------------------------------------|------|-----|-----|

| Cupaly input valtage range                   | VIN                                | 4.5  | 24  | ٧   |

| Supply input voltage range                   | V5FILT                             | 4.5  | 5.5 | V   |

|                                              | VBST1, VBST2                       | -0.1 | 30  |     |

|                                              | VBST1, VBST2 (wrt SWx)             | -0.1 | 5.5 |     |

| Input voltage range                          | VFB1, VFB2, VO1, VO2, TEST1, TEST2 | -0.1 | 5.5 | V   |

| Input voltage range                          | TRIP1, TRIP2                       | -0.1 | 0.3 | V   |

|                                              | EN1, EN2                           | -0.1 | 24  |     |

|                                              | SW1, SW2                           | -1.8 | 24  |     |

|                                              | DRVH1, DRVH2                       | -0.1 | 30  |     |

| Output voltage range                         | VBST1, VBST2 (wrt SWx)             | -0.1 | 5.5 | V   |

| Output voltage range                         | DRVL1, DRVL2, VREG5                | -0.1 | 5.5 | V   |

|                                              | PGND1, PGND2                       | -0.1 | 0.1 |     |

| T <sub>A</sub> Operating free-air temperatur | Operating free-air temperature     |      |     |     |

| T <sub>J</sub> Operating junction temperatu  | Operating junction temperature     |      |     |     |

# 電気的特性

推奨温度範囲内、VIN = 12V(特に記述のない限り)

|                          | パラメータ                               | 測定条件                                                                                                         | MIN   | TYP   | MAX   | 単位                                    |  |  |

|--------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------------------------------|--|--|

| SUPPLY C                 | CURRENT                             |                                                                                                              |       |       |       |                                       |  |  |

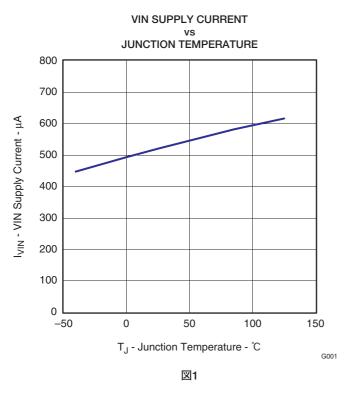

| I <sub>IN</sub>          | VIN supply current                  | VIN current, $T_A = 25^{\circ}C$ , VREG5 tied to V5FLT, EN1 = EN2 = 5V, VFB1 = VFB2 = 0.8V, SW1 = SW2 = 0.5V |       | 450   | 800   | μΑ                                    |  |  |

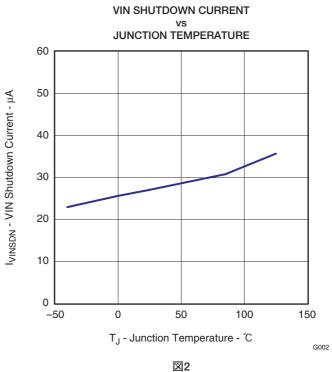

| I <sub>VINSDN</sub>      | VIN shutdown current                | VIN current, $T_A = 25$ °C, No load, EN1 = EN2 = 0V, VREG5 = ON                                              |       | 30    | 60    | μΑ                                    |  |  |

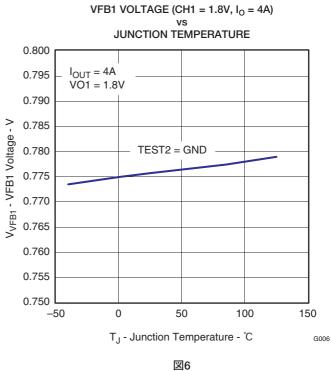

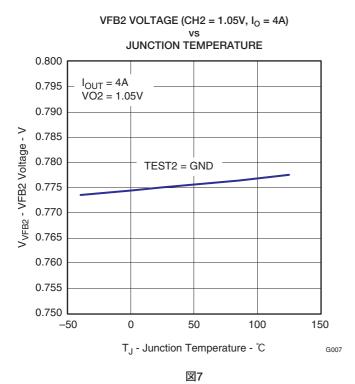

| VFB VOLT                 | AGE and DISCHARGE RESIST            | ANCE                                                                                                         |       |       |       |                                       |  |  |

| $V_{BG}$                 | Bandgap initial regulation accuracy | T <sub>A</sub> = 25°C                                                                                        | -1.0% |       | 1.0%  |                                       |  |  |

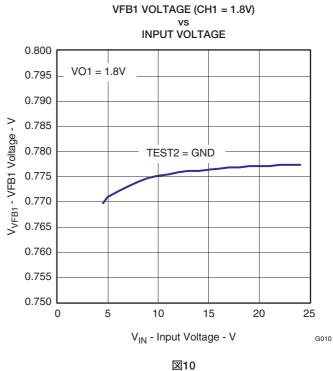

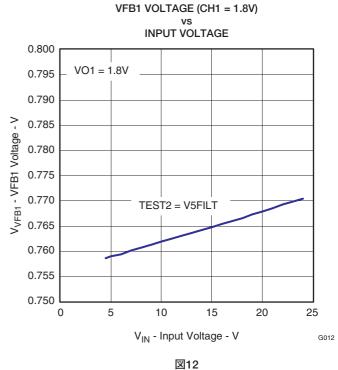

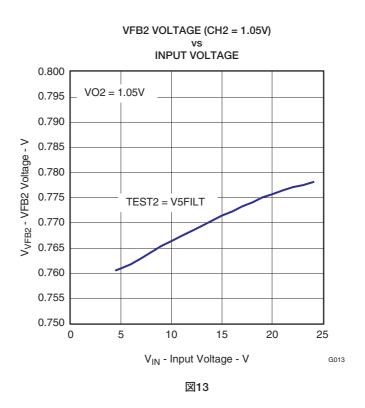

| V                        | VCDv throubold valtage              | T <sub>A</sub> = 25°C, TEST2 = 0V, SWinj = OFF                                                               | 755   | 765   | 775   | mV                                    |  |  |

| $V_{VFBTHLx}$            | VFBx threshold voltage              | $T_A = -40$ °C to 85°C, TEST2 = 0V, SWinj = OFF <sup>(1)</sup>                                               | 752   |       | 778   | IIIV                                  |  |  |

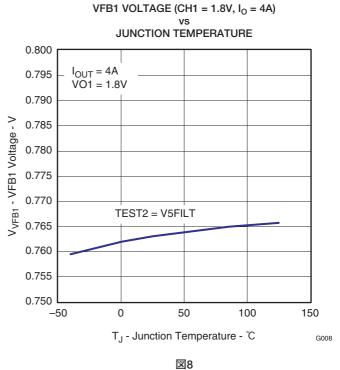

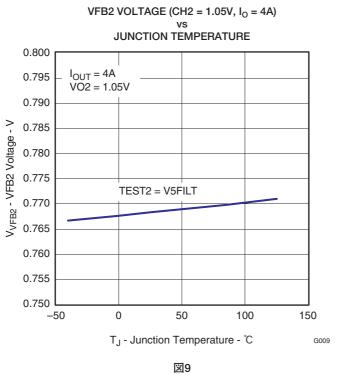

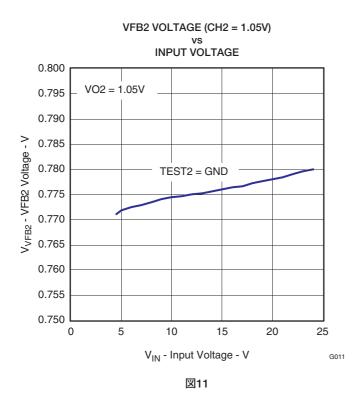

| M                        | VCDv throohold valtage              | T <sub>A</sub> = 25°C, TEST2 = V5FILT, SWinj = OFF                                                           | 748   | 758   | 768   | m\/                                   |  |  |

| $V_{VFBTHHx}$            | VFBx threshold voltage              | $T_A = -40$ °C to 85°C, TEST2 = V5FILT, SWinj = OFF <sup>(1)</sup>                                           | 745   |       | 771   | mV                                    |  |  |

| I <sub>VFB</sub>         | VFB input current                   | VFBx = 0.8V, T <sub>A</sub> = 25°C                                                                           |       | -0.01 | ±0.1  | μΑ                                    |  |  |

| R <sub>Dischg</sub>      | VO discharge resistance             | ENx = 0V, VOx = 0.5V, T <sub>A</sub> = 25℃                                                                   |       | 40    | 80    | Ω                                     |  |  |

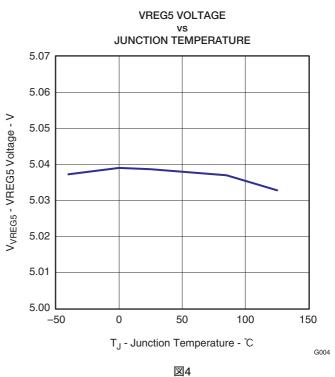

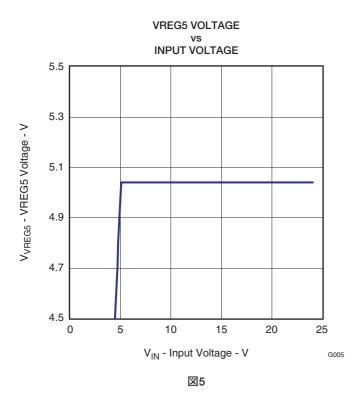

| VREG5 OL                 | JTPUT                               | ·                                                                                                            |       |       |       |                                       |  |  |

| V <sub>VREG5</sub>       | VREG5 output voltage                | T <sub>A</sub> = 25°C, 5.5V < VIN < 24V, 0 < I <sub>VREG5</sub> < 10mA                                       | 4.8   | 5.0   | 5.2   | V                                     |  |  |

| V <sub>LN5</sub>         | Line regulation                     | 5.5V < VIN < 24V, I <sub>VREG5</sub> = 10mA                                                                  |       |       | 20    | mV                                    |  |  |

| V <sub>LD5</sub>         | Load regulation                     | 1mA < I <sub>VREG5</sub> < 10mA                                                                              |       |       | 40    | mV                                    |  |  |

| I <sub>VREG5</sub>       | Output current                      | VIN = 5.5V, V <sub>VREG5</sub> = 4V, T <sub>A</sub> = 25°C                                                   |       | 170   |       | mA                                    |  |  |

|                          | N-CHANNEL MOSFET GATE D             | PRIVERS                                                                                                      |       |       |       |                                       |  |  |

| R <sub>DRVH</sub> DRV    | DDV41                               | Source, I <sub>DRVHx</sub> = -100mA                                                                          |       | 5.5   | 11    |                                       |  |  |

|                          | DRVH resistance                     | Sink, I <sub>DRVHx</sub> = 100mA                                                                             |       | 2.5   | 5     | $\frac{1}{5}$ $\Omega$                |  |  |

| R <sub>DRVL</sub> DRVL   |                                     | Source, I <sub>DBM/v</sub> = -100mA                                                                          |       |       |       |                                       |  |  |

|                          | DRVL resistance                     | Sink, I <sub>DRVLx</sub> = 100mA                                                                             |       | 2 4   |       |                                       |  |  |

|                          |                                     | DRVHx-low to DRVLx-on                                                                                        |       | 50    | 80    |                                       |  |  |

| T <sub>D</sub> Dead time |                                     | DRVLx-low to DRVHx-on                                                                                        | 20    | 40    | 80    | ns                                    |  |  |

| INTERNAL                 | BOOST DIODE                         |                                                                                                              |       |       |       |                                       |  |  |

| V <sub>FBST</sub>        | Forward voltage                     | $V_{VREG5-VBSTx}$ , $I_F = 10mA$ , $T_A = 25^{\circ}C$                                                       | 0.7   | 0.8   | 0.9   | V                                     |  |  |

| I <sub>VBSTLK</sub>      | VBST leakage current                | VBSTx = 29V, SWx = 24V, T <sub>A</sub> = 25°C                                                                |       | 0.1   | 1     | μA                                    |  |  |

|                          | TIMER CONTROL                       |                                                                                                              |       |       |       | •                                     |  |  |

| T <sub>ON1L</sub>        | CH1 on time                         | SW1 = 12V, VO1 = 1.8V, TEST2 = 0V                                                                            |       | 490   |       | ns                                    |  |  |

| T <sub>ON2L</sub>        | CH2 on time                         | SW2 = 12V, VO2 = 1.8V, TEST2 = 0V                                                                            |       | 390   |       | ns                                    |  |  |

| T <sub>OFF1L</sub>       | CH1 min off time                    | SW1 = 0.7V, T <sub>A</sub> = 25°C, VFB1 = 0.7V, TEST2 = 0V                                                   |       | 285   |       | ns                                    |  |  |

| T <sub>OFF2L</sub>       | CH2 min off time                    | SW2 = 0.7V, T <sub>A</sub> = 25°C, VFB2 = 0.7V, TEST2 = 0V                                                   |       | 285   |       | ns                                    |  |  |

| T <sub>ON1H</sub>        | CH1 on time                         | SW1 = 12V, VO1 = 1.8V, TEST2 = V5FILT                                                                        |       | 165   |       | ns                                    |  |  |

| T <sub>ON2H</sub>        | CH2 on time                         | SW2 = 12V, VO2 = 1.8V, TEST2 = V5FILT                                                                        |       | 140   |       | ns                                    |  |  |

| T <sub>OFF1H</sub>       | CH1 min off time                    | SW1 = 0.7V, T <sub>A</sub> = 25°C, VFB1 = 0.7V, TEST2 = V5FILT                                               |       | 216   |       | ns                                    |  |  |

| T <sub>OFF2H</sub>       | CH2 min off time                    | SW2 = 0.7V, T <sub>A</sub> = 25°C, VFB2= 0.7V, TEST2 = V5FILT                                                |       | 216   |       | ns                                    |  |  |

| SOFT STA                 |                                     | , , , , , , , , , , , , , , , , , , , ,                                                                      |       | -     |       |                                       |  |  |

| T <sub>ss</sub>          | Internal SS time                    | Internal soft start VFBx = 0.735V                                                                            | 0.85  | 1.2   | 1.4   | ms                                    |  |  |

| UVLO                     |                                     |                                                                                                              |       |       |       | · · · · · · · · · · · · · · · · · · · |  |  |

|                          |                                     | Wake up                                                                                                      | 3.7   | 4.0   | 4.3   | 3                                     |  |  |

| V <sub>UV5VFILT</sub>    | V5FILT UVLO threshold               | Hysteresis                                                                                                   | 0.2   | 0.3   | 0.4   | V                                     |  |  |

| LOGIC TH                 | RESHOLD                             |                                                                                                              |       |       | -     |                                       |  |  |

| V <sub>ENH</sub>         | ENx H-level input voltage           | EN                                                                                                           | 2.0   |       |       | V                                     |  |  |

| V <sub>ENL</sub>         | ENx L-level input voltage           | EN                                                                                                           |       |       | 0.3   | V                                     |  |  |

| CURRENT                  |                                     |                                                                                                              |       |       |       |                                       |  |  |

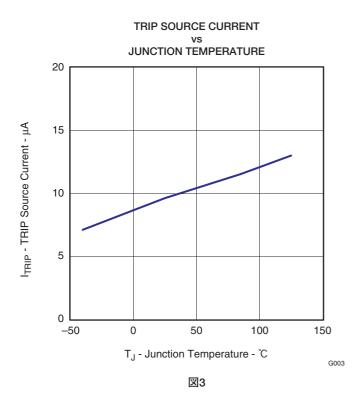

| I <sub>TRIP</sub>        | TRIP source current                 | V <sub>TRIPx</sub> = 0.1V, T <sub>A</sub> = 25°C                                                             | 8.5   | 10    | 11.5  | μΑ                                    |  |  |

| THIP                     | occioc surront                      | 1 IMIPX - 0.11, 1A - 20 0                                                                                    | 0.0   | 10    | . 1.0 | μιι                                   |  |  |

<sup>(1)</sup> 設計で確認されています。実製品のテストは行っていません。

# 電気的特性

推奨温度範囲内、VIN = 12V(特に記述のない限り)

|                                                | パラメータ                                     | 測定条件                                                                                                                          | MIN                     | TYP  | MAX  | 単 位    |  |  |

|------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|--------|--|--|

| TC <sub>ITRIP</sub>                            | I <sub>TRIP</sub> temperature coefficient | On the basis of 25°C (2)                                                                                                      |                         | 4000 |      | ppm/°C |  |  |

| V                                              | OCP compensation offset                   | $(V_{TRIPx\text{-}GND} - V_{PGNDx\text{-}SWx})$ voltage,<br>$V_{TRIPx\text{-}GND} = 60\text{mV}$ , $T_A = 25^{\circ}\text{C}$ | -15                     | 0    | 15   | m\/    |  |  |

| V <sub>OCLoff</sub>                            | OCF compensation onset                    | $(V_{TRIPx\text{-}GND} - V_{PGNDx\text{-}SWx})$ voltage,<br>$V_{TRIPx\text{-}GND} = 60\text{mV}$                              | -20                     |      | 20   | mV     |  |  |

| $V_{Rtrip}$                                    | Current limit threshold setting range     | V <sub>TRIPx-GND</sub> voltage                                                                                                | 30                      |      | 300  | mV     |  |  |

| OUTPUT UNDERVOLTAGE AND OVERVOLTAGE PROTECTION |                                           |                                                                                                                               |                         |      |      |        |  |  |

| $V_{OVP}$                                      | Output OVP trip threshold                 | OVP detect                                                                                                                    | 110%                    | 115% | 120% |        |  |  |

| T <sub>OVPDEL</sub>                            | Output OVP prop delay time                |                                                                                                                               |                         | 1.5  |      | μs     |  |  |

| V                                              | Outrout LIVD tries there also let         | UVP detect                                                                                                                    | 65%                     | 70%  | 75%  |        |  |  |

| $V_{UVP}$                                      | Output UVP trip threshold                 | Hysteresis (recovery < 20µs)                                                                                                  |                         | 10%  |      |        |  |  |

| T <sub>UVPDEL</sub>                            | Output UVP delay time                     |                                                                                                                               | 17                      | 30   | 40   | μs     |  |  |

| T <sub>UVPEN</sub>                             | Output UVP enable delay time              | UVP enable delay                                                                                                              | 1.2                     | 2    | 2.5  | ms     |  |  |

| THERMAI                                        | L SHUTDOWN                                |                                                                                                                               |                         |      |      |        |  |  |

| _                                              | Thormal abutdown throubald                | Shutdown temperature <sup>(3)</sup>                                                                                           |                         | 150  |      | °C     |  |  |

| $T_{SDN}$                                      | Thermal shutdown threshold                | Hysteresis <sup>(3)</sup>                                                                                                     | resis <sup>(3)</sup> 20 |      |      |        |  |  |

- (2) 設計で確認されています。実製品のテストは行っていません。 (3) 設計で確認されています。実製品のテストは行っていません。

# 製品情報

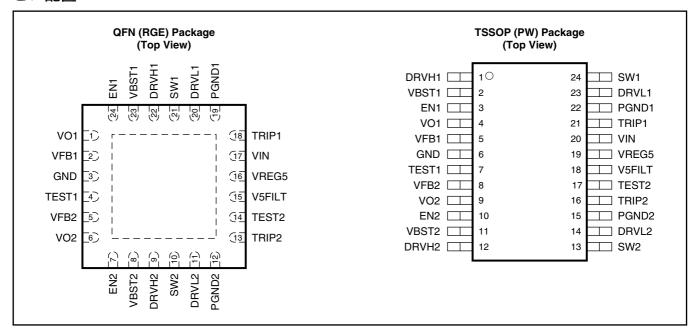

# ピン機能

| ピン           |           |             |     |                                                                                                                          |

|--------------|-----------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| 名 前          | QFN<br>24 | TSSOP<br>24 | 1/0 | 説明                                                                                                                       |

| VBST1, VBST2 | 23, 8     | 2, 11       | I   | ハイサイドNFETドライバの電源入力 (昇圧ピン)。高品質の0.1μFセラミック・コンデンサを使用してSWxにバイパスします。ハイサイドFETの駆動に順方向降下が重要である場合は、外部にショットキー・ダイオードを接続できます。        |

| EN1, EN2     | 24, 7     | 3, 10       | I   | チャネル1およびチャネル2の "H" レベル・イネーブル・ピン。                                                                                         |

| VO1, VO2     | 1, 6      | 4, 9        | ı   | オン時間調整および出力放電用の出力電圧入力。出力電圧に直接接続します。                                                                                      |

| VFB1, VFB2   | 2, 5      | 5, 8        | - 1 | D-CAP2帰還入力。抵抗分圧回路を使用して出力電圧に接続します。                                                                                        |

| GND          | 3         | 6           | - 1 | 信号グランド・ピン。PGND1、PGND2、およびシステム・グランドに1点で接続します。                                                                             |

| DRVH1, DRVH2 | 22, 9     | 1, 12       | 0   | ハイサイドMOSFETゲート・ドライバ出力。SWxを基準としたドライバがSWx(オフ)と<br>VBSTx(オン)の間で切り替わります。                                                     |

| SW1, SW2     | 21, 10    | 24, 13      | I/O | ハイサイド・ドライバと電流コンパレータの両方に対するスイッチ・ノード接続。                                                                                    |

| DRVL1, DRVL2 | 20, 11    | 23, 14      | 0   | ローサイドMOSFETゲート・ドライバ出力。PGNDを基準としたドライバがPGNDx(オフ)とVREG5(オン)の間で切り替わります。                                                      |

| PGND1, PGND2 | 19, 12    | 22, 15      | I/O | ローサイド・ドライバと電流コンパレータの両方に対するパワー・グランド接続。PGND1、PGND2、GNDは、ICの近くで強くまとめて接続します。                                                 |

| TRIP1, TRIP2 | 18, 13    | 21, 16      | ı   | 過電流トリップ点のプログラミング用ピン。このピンとGNDの間に抵抗を接続して、ローサイドR <sub>DS(on)</sub> 電流制限のスレッショルドを設定します。                                      |

| VIN          | 17        | 20          | - 1 | 5Vリニア・レギュレータの電源入力。                                                                                                       |

| V5FILT       | 15        | 18          | I   | MOSFETドライバを除く全制御回路の5V電源入力。1.0 $\mu$ F以上の高品質セラミック・コンデンサを使用してGNDにバイパスします。V5FILTは、10 $\Omega$ の内部抵抗を介してVREG5に接続されます。        |

| VREG5        | 16        | 19          | 0   | 5Vリニア・レギュレータの出力、およびMOSFETドライバの電源。4.7 $\mu$ F以上の高品質セラミック・コンデンサを使用してGNDにバイパスします。VREG5は、10 $\Omega$ の内部抵抗を介してV5FILTに接続されます。 |

| TEST1        | 4         | 7           | 0   | テスト·インターフェイス·ピン。アプリケーションでは使用しません。直接GNDに接続してください。                                                                         |

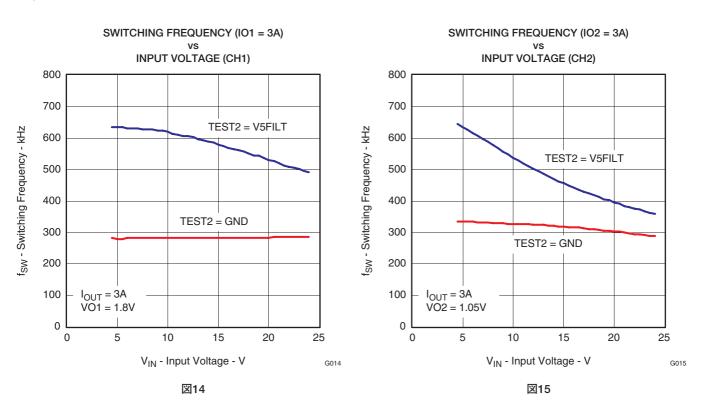

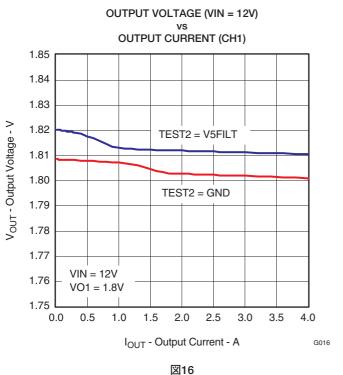

| TEST2        | 14        | 17          | ı   | 周波数選択ピン。350kHzスイッチングの場合は、GNDに接続します。700kHzスイッチングの場合は、V5FILTに接続します。                                                        |

## ピン配置

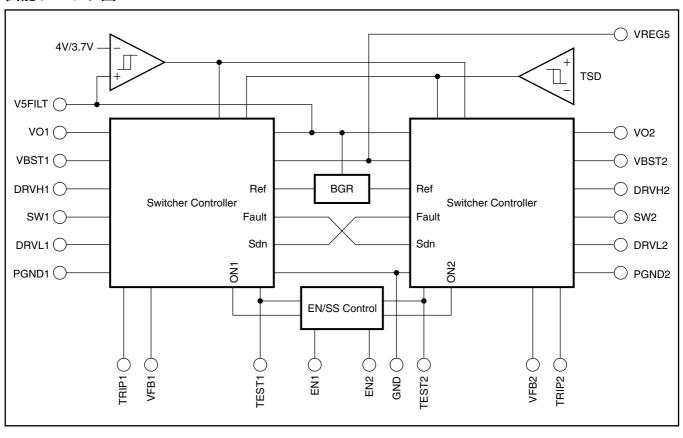

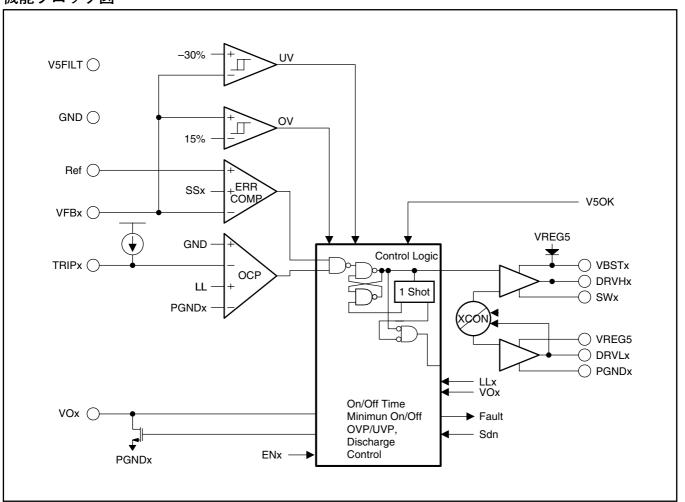

## 機能ブロック図

# 機能ブロック図

## 詳細説明

### PWM動作

TPS53126のメイン制御ループは、独自のD-CAP2モード制御をサポートする適応型オン時間パルス幅変調 (PWM) コントローラとなっています。D-CAP2モード制御は、一定オン時間制御を、擬似固定周波数で外部部品数の少ない構成を可能にする内部補償回路と組み合わせたもので、低ESRコンデンサとセラミック出力コンデンサの両方を使用できます。出力にほとんどリップルがない場合でも安定して動作します。

各サイクルの開始時に、ハイサイドMOSFETがオンになります。内部のワンショット・タイマが終了すると、このMOSFETがオフになります。このワンショット・タイマの時間は、入力電圧範囲内で擬似固定周波数を維持するために、コンバータの入力電圧(VIN)と出力電圧(VO)によって設定されます。そのため、これは適応型オン時間制御と呼ばれます。帰還電圧がリファレンス電圧を下回ると、ワンショット・タイマがリセットされ、ハイサイドMOSFETが再度オンになります。出力リップルをシミュレートするために、リファレンス電圧に内部ランプが追加され、これにより、従来のD-CAPモード制御からESRによる出力リップルが不要になります。

### ドライバ

TPS53126の各SMPSには、2つの高電流対応MOSFETドライバが含まれています。ローサイド・ドライバは、グランド基準でVREG5から電源供給されるドライバであり、ソースがPGNDに接続された、高電流、低RDS(on)のNチャネルMOSFETのゲートを駆動するように設計されています。ハイサイド・ドライバは、フローティングでSW基準のVBSTから電源供給されるドライバであり、高電流、低RDS(on)のNチャネルMOSFETのゲートを駆動するように設計されています。ハイサイド・ドライバのオン時間中にBST電圧を保持するために、SWとVBSTの間にコンデンサが配置されています。各ドライバに流れる平均電流は、ゲート電荷 (Qg AT Vgs = 5V) × スイッチング周波数 (fsw)に等しくなります。

クロス導通を防ぐため、各ドライバ遷移間でハイサイドとローサイドの両方のドライバがオフになるときに、短いデッド・タイムが設けられています。このデッド・タイムの間、インダクタ電流はMOSFETのボディ・ダイオードの一方を流れます。

#### PWM周波数と適応型オン時間制御

TPS53126は、適応型オン時間制御方式を採用し、専用の発振器は内蔵していません。入力電圧および出力電圧を使用してオン時間ワンショット・タイマを設定することにより、擬似定周波数で動作します。オン時間は、入力電圧に逆比例し、出力電圧に比例するため、デューティ比がVOUT/VINのとき周波数は一定となります。

### 5Vレギュレータ

TPS53126には、5Vの低ドロップアウト (LDO) レギュレータが内蔵され、4つすべてのドライバおよびICの内部ロジックに対してレギュレーション電圧を提供します。内部レギュレータの安定化のために、VREG5とGNDの間にコンデンサが必要です。VREG5に内部で接続された $10\Omega$ の抵抗により、レギュレータの出力をICのアナログおよびロジック入力電圧V5FILTへとフィルタリングします。VREG5からのスイッチング・ノイズをフィルタリングするために、V5FILTとGNDの間に追加のコンデンサが必要です。

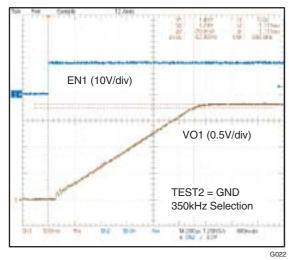

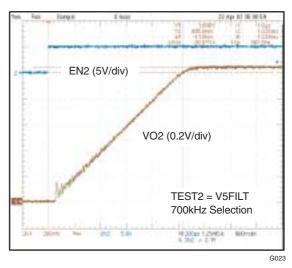

### ソフト・スタート

TPS53126には、各チャネルに対応する1.2msの電圧サーボ・ソフトスタートが内蔵されています。ENxピンが"High"になると、内部DACによってPWMコンパレータに対するリファレンス電圧が上昇し始めます。スタートアップ中には出力電圧のスムーズな制御が維持されます。TPS53126では2つのチャネルで1つのDACを共有しているため、一方のチャネルのスタートアップ中にENxピンが"High"に設定された場合、そのチャネルのソフトスタートが完了するまで、もう一方のチャネルのソフトスタートが延期されます。EN1とEN2が同時に"High"に設定された場合、両方のチャネルが同時にスタートアップします。

## プリバイアスのサポート

TPS53126は、出力コンデンサから電流をシンクしないプリバイアス・スタートアップをサポートしています。イネーブルになると、ローサイド・ドライバはソフト・スタートでプリバイアス・レベルよりも高い電圧が指定される(内部ソフト・スタートが帰還電圧 [VFB] よりも大きくなる)までオフに保持され、その後TPS53126は、最初のDRVLパルスを狭いオン時間で制限することにより、ゆっくりと同期整流を起動します。この制限されたオン時間は、完全な1-Dオフ時間に達するまで、サイクルごとに増加されます。この方式により、プリバイアス出力からの電流の初期シンクを防ぐとともに、出力電圧 (VOUT) が立ち上がり後スムーズにレギュレーション状態まで上昇し、また、制御ループがプリバイアス・スタートアップから通常モード動作へと遷移するために十分な時間が与えられます。

### プリバイスイッチング周波数の選択

TPS53126では、TEST2ピンをGNDまたはV5FILTのいずれかに接続することで、2つの異なるスイッチング周波数を選択できます。TEST2をGNDに接続すると、スイッチング周波数(fsw)が350kHzになります。TEST2をV5FILTに接続すると、スイッチング周波数が700kHzになります。

### 出力放電の制御

TPS53126では、ENxが"Low"の場合、または保護機能 (OVP、UVP、UVLO、過熱保護) によってコントローラがオフになった場合、出力が放電されます。VOxとPGNDxに接続されている内部の $40\Omega$  MOSFETを使用して出力を放電します。出力に負電圧が生じることを避けるために、出力放電中は外部ローサイドMOSFETがオンになりません。この放電により、起動時には、レギュレーション電圧が常に0Vから開始されるようになります。

### 過電流制限

TPS53126には、サイクル毎の過電流制限機能があります。この機能では、ローサイド・ドライバのオン時間中にローサイドMOSFET  $R_{DS(on)}$ での電圧降下を監視することにより、インダクタ電流の谷を制限します。インダクタ電流が過電流制限 (OCL) を上回ると、TPS53126は、センスされたインダクタ電流がOCL電流を下回るまで、次のスイッチング・サイクルの開始を遅延させます。MOSFET  $R_{DS(on)}$ の電流センスは、外部デバイスを使用せずに高精度でコスト効果の高いソリューションを実現するために利用されます。OCLをプログラミングするために、TRIPxピンを、トリップ電圧設定抵抗 (次の式を参照)を通してGNDに接続する必要があります。

$$V_{\text{trip}} = \left(I_{\text{OCL}} - \frac{(V_{\text{IN}} - V_{\text{O}})}{2 \times L1 \times f_{\text{SW}}} \times \frac{V_{\text{O}}}{V_{\text{IN}}}\right) \times R_{\text{DS(on)}}$$

(1)

$$R_{trip}(k\Omega) = \frac{V_{trip}(mV)}{I_{trip}(\mu A)}$$

(2)

トリップ電圧は、すべての動作温度にわたって $30 \text{mV}\sim 300 \text{mV}$ の範囲内である必要があります。これには、 $R_{DS(on)}$ の温度依存性に対する $4000 \text{ppm}/\mathbb{C}$ の温度スロープ補償も含まれます。負荷電流が過電流制限を超えた場合、電圧は降下を始めます。過電流状態が続くと、出力電圧が低電圧保護スレッショルドを下回り、TPS53126はシャットダウンします。

### 過電圧保護と低電圧保護

TPS53126では、帰還電圧を介して出力電圧を監視することで、過電圧と低電圧を検出しています。帰還電圧がリファレンス電圧の115%を超えると、ハイサイドMOSFETドライバがオフになり、ローサイドMOSFETドライバがオンになって、TPS53126はラッチ・オフされます。

帰還電圧がリファレンス電圧の70%より低くなると、内部のUVP遅延カウンタが動作を開始します。30μs経過後、上側と下側の両方のMOSFETドライバがオフになり、TPS53126はラッチ・オフされます。ソフト・スタート中のUVPの検出を避けるために、UVP機能はパワーオンから約2.0ms後にイネーブルになります。V5FILTがUVLOをトリガするか、ENxピンが"Low"になると、OVPおよびUVPのラッチ状態がリセットされます。

### UVLO保護

TPS53126は、V5FILTピンの電圧を監視する低電圧ロックアウト保護 (UVLO) 機能を備えています。V5FILT電圧がUVLOスレッショルド電圧を下回ると、デバイスがオフになります。シャットオフ中は、VREG5およびすべての出力ドライバがオフになり、出力放電がオンになります。UVLOは、非ラッチ方式の保護です。

### 過熱シャットダウン

TPS53126は、過熱保護シャットダウン機能を備えています。TPS53126のチップ温度がOTPスレッショルド (標準150℃)を超えると、ハイサイドとローサイドの両方のドライバがオフになり、出力電圧放電機能がイネーブルになり、デバイスはチップ温度が降下するまでオフになります。これは、非ラッチ方式の保護です。

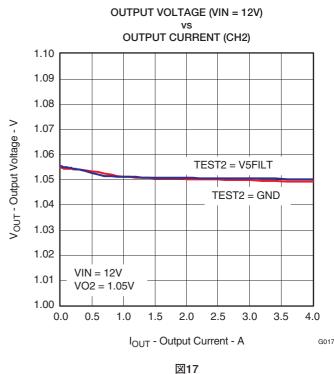

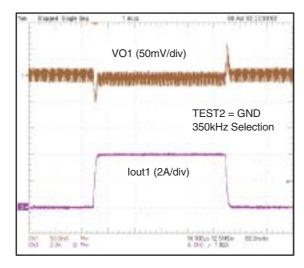

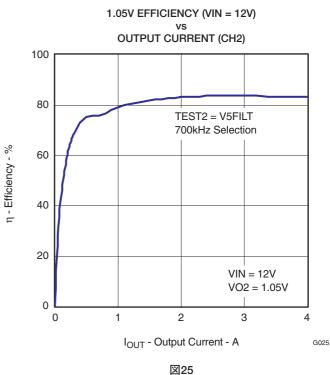

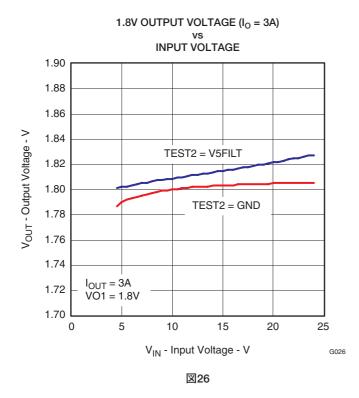

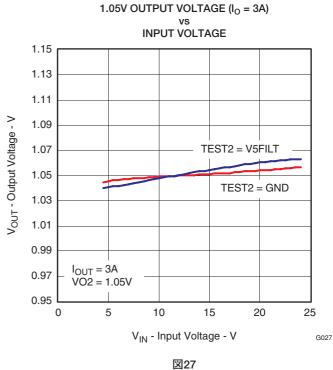

# 代表的アプリケーション性能

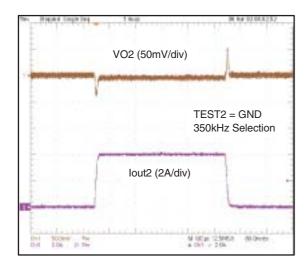

図18.1.8Vの負荷過渡応答(CH1、TEST2 = GND)

t - time - 100 $\mu$ s/div  $C_{OUT} = 22\mu F \times 2$

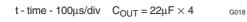

**図19.** 1.8Vの負荷過渡応答 (CH1、TEST2 = V5FILT)

t - time - 100 $\mu$ s/div  $C_{OUT}$  = 22 $\mu$ F imes 4

図20. 1.05Vの負荷過渡応答(CH2、TEST2 = GND)

$t \text{ - time - } 100 \mu \text{s/div} \quad C_{OUT} = 22 \mu \text{F} \times 2$

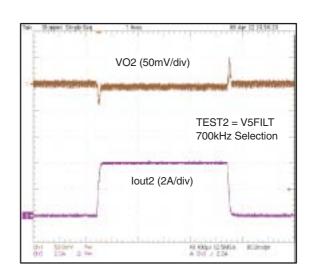

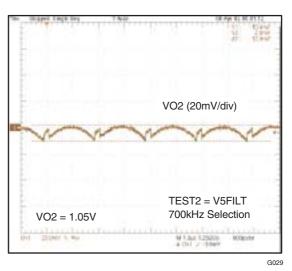

図21. 1.05Vの負荷過渡応答(CH2、TEST2 = V5FILT)

**図22.** 1.8Vのスタートアップ波形

図23.1.05Vのスタートアップ波形

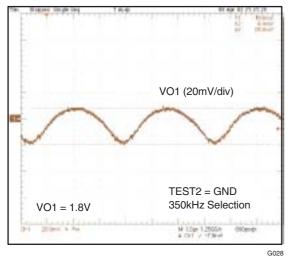

図28. 1.8Vの出力リップル電圧

図29.1.05Vの出力リップル電圧

# アプリケーション情報

図30.350kHzのスイッチング周波数を選択したときの標準アプリケーション回路(TEST2ピン = GND)

図31.700kHzのスイッチング周波数を選択したときの標準アプリケーション回路(TEST2ピン = V5FILT)

### 部品の選択

### 1. インダクタを選択します。

インダクタ値は、最大負荷で約30%のピーク・ツー・ピーク・リップル電流を提供するよう選択されます。リップル電流が大きくなると、出力リップル電圧が増加し、S/N比が向上するため、安定動作につながります。L1は式(3)を使って求められます。

$$L1 = \frac{(V_{IN(max)} - Vo1)}{I_{L1(ripple)} \times fsw} \times \frac{Vo1}{V_{IN(max)}}$$

$$= \frac{3 \times (V_{IN(max)} - Vo1)}{Io1 \times fsw} \times \frac{Vo1}{V_{IN(max)}}$$

(3)

インダクタの電流定格は、RMS(熱)電流とピーク(飽和)電流の両方をサポートする必要があります。RMSおよびピーク・インダクタ電流は次の式で見積もることができます。

$$I_{L1(ripple)} = \frac{V_{IN(max)} - Vo1}{L1 \times fsW} \times \frac{Vo1}{V_{IN(max)}}$$

(4)

$$I_{L1(peak)} = \frac{V_{trip}}{R_{DS(on)}} + I_{L1(ripple)}$$

(5)

$$I_{L1(RMS)} = \sqrt{Io1^2 + \frac{1}{2}(I_{L1(ripple)})^2}$$

(6)

注:上の計算は、一般的な基準として利用してください。過渡 応答をさらに向上させる場合は、出力インダクタンスをこ れより小さくできます。これは、出力コンデンサの選択と ともに考慮する必要があります。

#### 2. 出力コンデンサを選択します。

コンデンサの値とESRによって、出力電圧リップルの大きさおよび負荷過渡応答が決まります。セラミック出力コンデンサの使用を推奨します。

$$C1 = \frac{\Delta Iload^2 \times L1}{2 \times Vo1 \times \Delta Vos}$$

(7)

$$C1 = \frac{\Delta Iload^2 \times L1}{2 \times K \times \Delta Vus}$$

(8)

ここで

$$K = \left( (V_{IN} - Vo1) - \frac{Tmin(off)}{Ton1} \times Vo1 \right) \times \frac{Ton1}{Ton1 + Tmin(off)}$$

(9)

$$C1 = \frac{I_{L1(ripple)}}{8 \text{ Vo1(ripple)}} \times \frac{1}{f \text{sw}}$$

(10)

式 (7)、式 (8)、および式 (10) から計算された最大値よりも大きな容量値を選択してください。C1の容量は、 $66\mu F$ よりも大きい必要があります。

#### ここで

$\Delta Vos$  = 負荷過渡時に許容されるオーバーシュート電圧の大きさ  $\Delta Vus$  = 負荷過渡時に許容されるアンダーシュート電圧の大きさ Tmin(off) = 最小オフ時間

#### 3. 入力コンデンサを選択します。

TPS53126には、入力デカップリング・コンデンサと、アプリケーションによってはバルク・コンデンサが必要となります。入力コンデンサには、10μF以上の高品質セラミック・コンデンサを推奨します。コンデンサの電圧定格は、最大入力電圧よりも大きい必要があります。

#### 4. ブートストラップ・コンデンサを選択します。

TPS53126では、ハイサイド・ドライバに対してフローティング電源を提供するために、SWxとVBSTxの間にブートストラップ・コンデンサが必要となります。 $0.1\mu$ F以上の高品質セラミック・コンデンサを推奨します。電圧定格は、6Vよりも大きい必要があります。

#### 5. VREG5およびV5FILTコンデンサを選択します。

TPS53126では、VREG5レギュレータとV5FILT入力の両方をバイパスする必要があります。適切な動作のためには、VREG5ピンとGNDピンの間に $4.7\mu$ F以上の高品質セラミック・コンデンサを接続する必要があります。また、V5FILTピンとGNDピンの間に $1.0\mu$ F以上の高品質セラミック・コンデンサを接続する必要があります。両方のコンデンサについて、電圧定格は6Vよりも大きい必要があります。

#### 6. 出力電圧の分圧抵抗を選択します。

出力電圧は、出力電圧ノードとVFBxピンとの間の抵抗分圧回路によって設定されます。公差1%以内の抵抗を使用することを推奨します。 $10k\Omega \sim 100k\Omega$ のR2を選択し、式(11) および式(12)を使用してR1を計算します。

R1 =

$$\left(\frac{\text{Vo1}}{0.765 + \frac{\text{VFB1}_{(ripple)}}{2}} - 1\right) \times \text{R2} \qquad \text{(TEST2 = GND)}$$

(11)

R1 =

$$\left[\frac{\text{Vo1}}{0.758 + \frac{\text{VFB1}_{(ripple)}}{2}} - 1\right] \times \text{R2} \quad \text{(TEST2 = V5FILT)}$$

(12)

ここで

VFB1<sub>(ripple)</sub> = VFB1のリップル電圧

#### 7. 過電流制限の抵抗設定を選択します。

$$V_{trip} = \left(I_{OCL} - \frac{(V_{IN} - V_{O})}{2 \times L1 \times f_{SW}} \times \frac{V_{O}}{V_{IN}}\right) \times R_{DS(on)}$$

(13)

$$R_{trip}(k\Omega) = \frac{V_{trip}(mV)}{I_{trip}(\mu A)}$$

(14)

ここで

$R_{DS(on)}$  = ローサイドFETのオン抵抗  $I_{trip}$  = TRIPピンのソース電流 (=  $10\mu A$ )  $I_{OCL}$  = 過電流制限

### 推奨レイアウト

- 入力スイッチング電流ループは可能な限り小さくします。

- 入力コンデンサ (C3、C6) は、上側スイッチングFETの近くに配置します。また、出力電流ループは可能な限り小さくします。

- 寄生容量と寄生インダクタンスおよび放射を最小限に抑えるために、SWノードの物理的サイズを可能な限り小さく短くします。デバイスの出力と帰還ピン(FBx)の間にケルビン接続を使用します。

- アナログ部品と非スイッチング部品は、スイッチング部品 から離します。

- 信号グランドと電源グランドは一点接続します。

- デバイスの下をスイッチング電流が流れないようにしてく ださい。

## パッケージ・オプション

### パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| TPS53126PW       | ACTIVE                | TSSOP           | PW                 | 24   | 60             | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS53126PWR      | ACTIVE                | TSSOP           | PW                 | 24   | 2000           | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS53126RGER     | ACTIVE                | VQFN            | RGE                | 24   | 3000           | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS53126RGET     | ACTIVE                | VQFN            | RGE                | 24   | 250            | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY: TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free"(RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

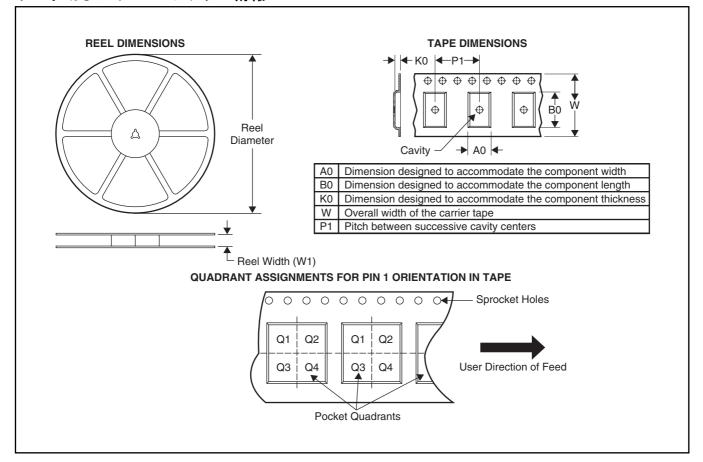

# パッケージ・マテリアル情報

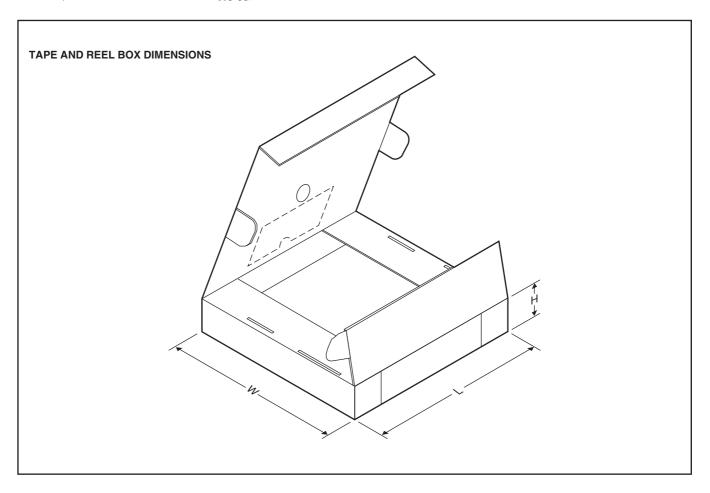

# テープおよびリール・ボックス情報

\*All dimensions are nominal

|              | an annother at a normal |                    |    |      |                          |                          |         |         |         |            |           |                  |  |  |

|--------------|-------------------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|--|--|

| Device       | Package<br>Type         | Package<br>Drawing | ı  | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |  |  |

| TPS53126PWR  | TSSOP                   | PW                 | 24 | 2000 | 330.0                    | 16.4                     | 6.95    | 8.3     | 1.6     | 8.0        | 16.0      | Q1               |  |  |

| TPS53126RGER | VQFN                    | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.3     | 4.3     | 1.5     | 8.0        | 12.0      | Q2               |  |  |

| TPS53126RGET | VQFN                    | RGE                | 24 | 250  | 180.0                    | 12.4                     | 4.3     | 4.3     | 1.5     | 8.0        | 12.0      | Q2               |  |  |

# パッケージ・マテリアル情報

### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS53126PWR  | TSSOP        | PW              | 24   | 2000 | 346.0       | 346.0      | 33.0        |

| TPS53126RGER | VQFN         | RGE             | 24   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS53126RGET | VQFN         | RGE             | 24   | 250  | 195.0       | 212.7      | 31.8        |

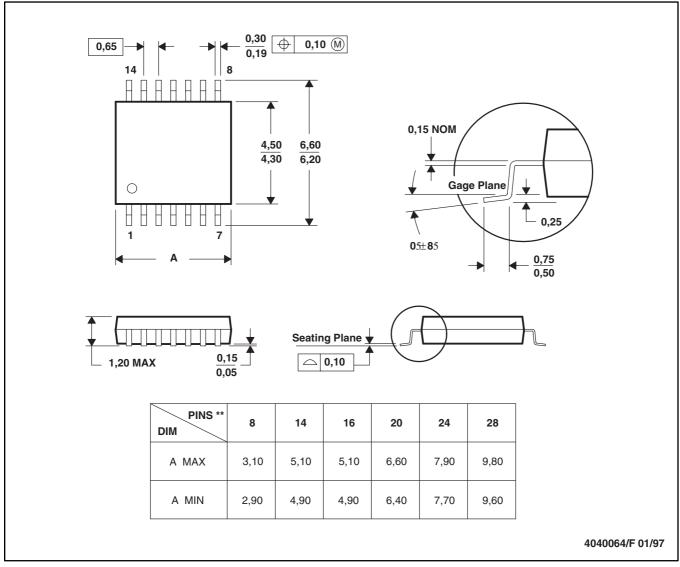

### PLASTIC SMALL-OUTLINE PACKAGE

## PW (R-PDSO-G\*\*)

### 14 PINS SHOWN

- 注:A. すべての線寸法はミリメートルです。

- B. 本図は予告なしに変更することがあります。

- C. ボディ長には、モールド・フラッシュ、突起は含まれません。 モールド・フラッシュや突起は片側で0.15を超えることはありません。

- D JEDC MO-153に準拠します。

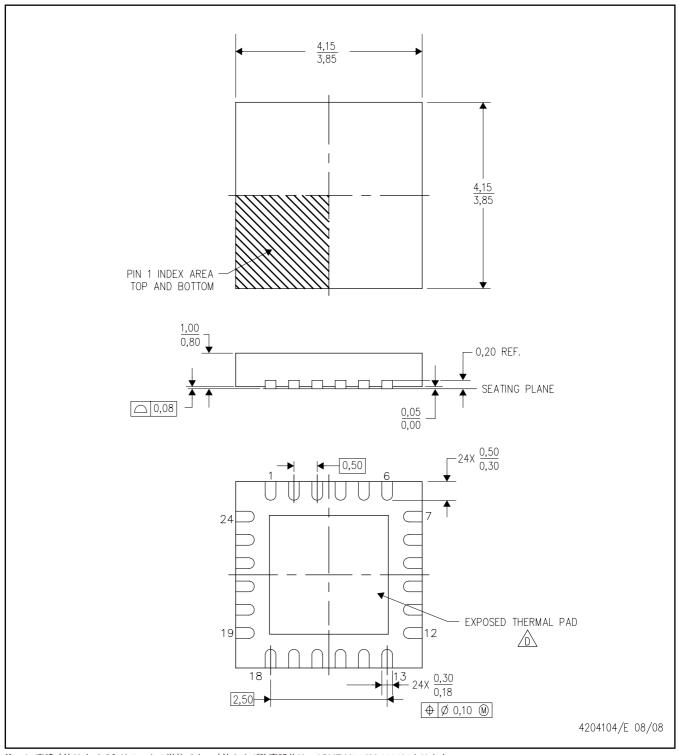

# RGE (S-PVQFN-N24)

- 注: A. 直線寸法はすべてミリメートル単位です。寸法および許容誤差は、ASME Y14.5M-1994によります。

- B. 本図は予告なしに変更することがあります。

- Ç. クゥアド・フラットパック・ノーリード (QFN) パッケージ構造。

- <u>ん</u>バッケージのサーマルパッドは、熱的および機構的特性を得るために基板に半田付けする必要があります。露出サーマルパッドの寸法に関する詳細は、 製品データシートをご覧ください。 E. JEDEC MOー220に準拠します。

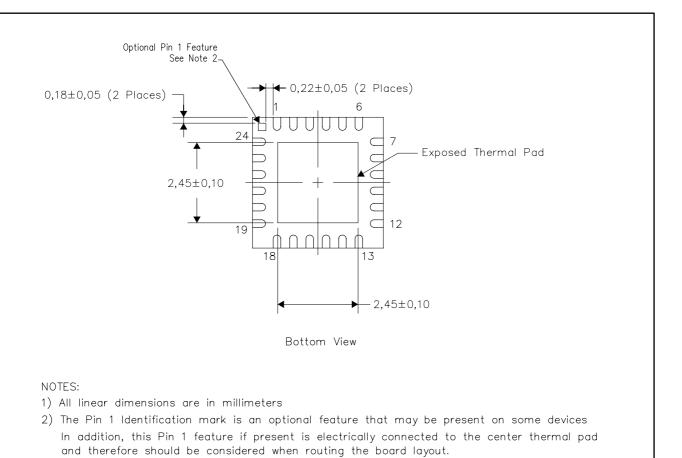

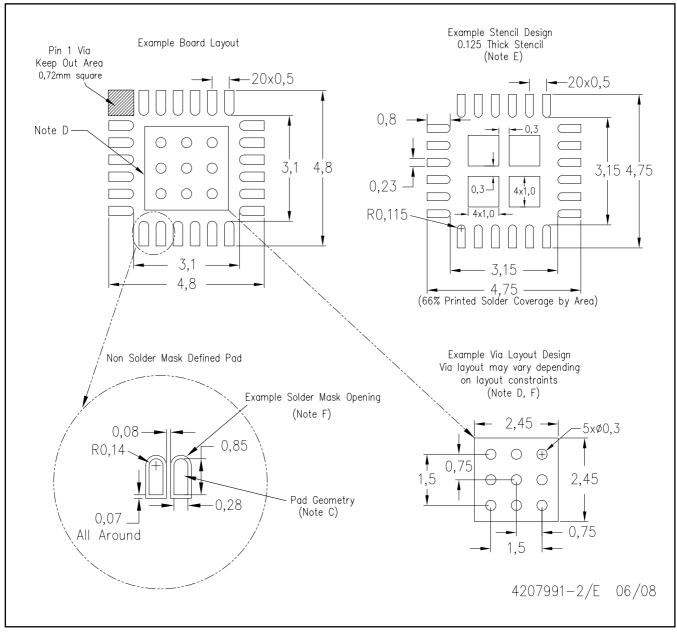

## サーマルパッド・メカニカル・データ

## RGE (S-PVQFN-N24)

### 熱的特性の情報

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板 (PCB) に直接はんだ付けされなければなりません。はんだ付けの後、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはデバイスの電気回路図に示されている銅プレーンに直接接続するか、あるいは、PCBに設計された特別なヒートシンク構造に接続することができます。この設計により、集積回路 (IC) からの熱移動が最適化されます。

クワッド・フラットパック・ノーリード (QFN) パッケージと その利点についての情報はアプリケーション・レポート "Quad Flatpack No-Lead Logic Packages" TI文献番号SLUA271を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージの露出サーマル・パッドの寸法は以下の図に 示されています。

サーマル・パッド寸法図

# ランド・パターン

# RGE (S-PVQFN-N24)

- 注:A. 直線寸法はすべてミリメートル単位です。

- B. 本図は予告なしに変更することがあります。 C. 代替設計には、IPC-7351規格を推奨します

- D. 本パッケージは、サーマルパッドを基板に半田付けするように設計されています。具体的な熱的特性情報、ヴィア条件、および推奨基板レイアウトに D. イバノア・イア・イア・イア・ファート 「クゥアド・フラット・バック・バッケージ」テキサス・インスツルメンツ文献番号SCBA017、SLUA271、および製品データシートも参照してください。これらの文献はwww.tij.co.jpもしくはwww.ti.com < http://www.ti.com > で入手できます。<br/>

E. 台形壁面やラウンドコーナーにレーザー・カッティング・アパーチャを行うと、ペーストのリリースが容易になります。推奨のステンシル設計については、基板組立元に問合せてください。ステンシル設計の検討については、IPC7525規格を参照してください。<br/>

F. 半田マスクの推奨許容差、およびサーマル・バッドに配置するビアのテンティングに関する推奨事項については、基盤組み立て拠点にお問い合わせください。

(SLUS909)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上