**TPS54311, TPS54312

TPS54313, TPS54314

TPS54315, TPS54316**

SLVS460A - March, 2003

## 3V-6V入力・3A出力、 FET内蔵の同期バックPWMスイッチャー(SWIFT™)

### 特長

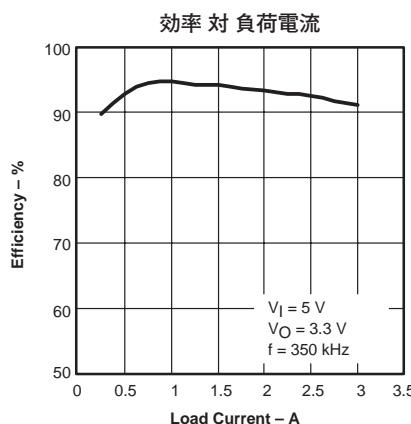

- 60mΩのMOSFETスイッチによる、3A出力ソース・シンク電流(連続)時の高効率

- 0.9V、1.2V、1.5V、1.8V、2.5V、および3.3Vの固定出力電圧デバイス 1%初期精度

- 内部補償による使いやすさ、最小の部品点数

- 高速な過渡応答

- 広帯域のPWM周波数：

固定時の周波数 350kHz、550kHz

調整可能な周波数 280kHz-700kHz

- ピーク電流制限とサーマル・シャットダウンによる負荷保護

- 集積ソリューションによる基板面積およびトータル・コストの低減

### アプリケーション

- 5Vあるいは3.3V電源の低電圧・高実装密度システム

- 高性能DSP、FPGA、ASIC、およびマイクロプロセッサの分散電源システム

- 広帯域、ネットワークおよび光コミュニケーションのインフラ

- ポータブル・コンピューティング/ノートブックPC

### 解説

DC/DCレギュレータのSWIFT™ファミリーであるTPS54311、TPS54312、TPS54313、TPS54314、TPS54315、およびTPS54316は、低入力電圧・高出力電流の同期整流降圧PWMコンバータであり、必要な能動素子をすべて集積しています。シリコン基盤上に内蔵されるものは以下の通りです。過渡状態で優れた特性を発揮する高性能誤差アンプ、入力電圧が3Vに達するまでスタート・アップさせない低電圧ロックアウト回路、内部あるいは外部から設定するラッシュ電流制限用のスロー・スタート回路であり、また、プロセッサやロジックのリセット、フォールト信号、および電源シーケンスに有効な高パワー出力です。

TPS54311-16は熱的に強化された20ピンTSSOP(PWP)のPowerPAD™(パワー・パッド)パッケージによるデバイスのため、大きなヒートシンクを必要としません。TIは、評価ボードとSWIFT™設計者用ソフトウェア・ツールを提供しますので、高性能な電源の設計の早期実現を手助けし、積極的な装置開発サイクルに対応できます。

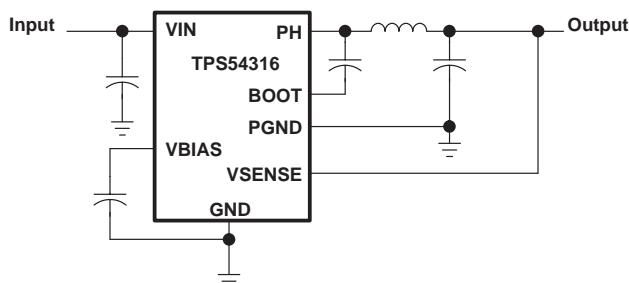

単純化した回路図

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

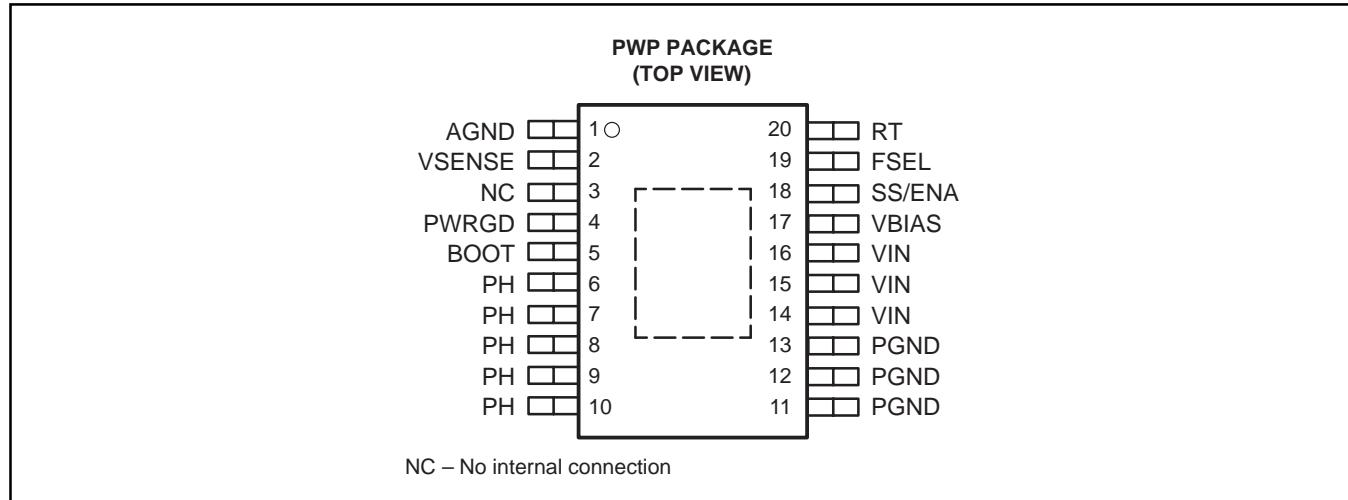

## ピン配置

## 製品オプション

| T <sub>J</sub> | OUTPUT VOLTAGE | PACKAGED DEVICES<br>PLASTIC HTSSOP (PWP) <sup>†</sup> | T <sub>J</sub> | OUTPUT VOLTAGE | PACKAGED DEVICES<br>PLASTIC HTSSOP (PWP) <sup>†</sup> |

|----------------|----------------|-------------------------------------------------------|----------------|----------------|-------------------------------------------------------|

| -40°C~125°C    | 0.9 V          | TPS54311PWP                                           | -40°C~125°C    | 1.8 V          | TPS54314PWP                                           |

|                | 1.2 V          | TPS54312PWP                                           |                | 2.5 V          | TPS54315PWP                                           |

|                | 1.5 V          | TPS54313PWP                                           |                | 3.3 V          | TPS54316PWP                                           |

<sup>†</sup>PWPパッケージはテープでリールにしたものもあります。その場合は、Rというサフィックスをデバイスタイプに付加願います(例 TPS54316PWPR)。データシートのアプリケーション・セクションにあるPowerPAD™の機構図とレイアウトを参照願います。

## ピンの機能

| TERMINAL NAME | NO.   | I/O | DESCRIPTION                                                                                                     |

|---------------|-------|-----|-----------------------------------------------------------------------------------------------------------------|

| AGND          | 1     |     | アナログ・グランド。補償網/出力分圧回路、スロー・スタートコンデンサ、VBIASコンデンサ、RT抵抗およびFSELピンの各帰線になる。PowerPAD™はAGNDに接続する。                         |

| BOOT          | 5     |     | ブーストストラップ入力。0.022μFから0.1μFの低等価直列抵抗のコンデンサをBOOTとPH間に接続し、ハイサイドFETドライバをフローティング駆動する。                                 |

| FSEL          | 19    |     | 周波数選択入力。ロジック・レベルを入力して、2つの内部設定スイッチング周波数から選択する。                                                                   |

| NC            | 3     |     | 使用しない(内部の接続なし)。                                                                                                 |

| PGND          | 11-13 |     | パワー・グランド。ローサイド・ドライバとパワーMOSFET用の大電流が流れる帰線。大面積の銅パターンのPGNDを入出力電源の帰線、および入出力(VINとVo)コンデンサの負側に接続する。                   |

| PH            | 6-10  |     | フェーズ入出力。内部のハイ・ローサイドの両パワーMOSFETおよび出力インダクタの結合点。                                                                   |

| PWRGD         | 4     |     | パワー・グッドのオープン・ドレイン出力。VSENSEがVREFの90%以上でハイ・インピーダンス、それ以外ではロー。また、SS/ENAがローあるいは内部シャットダウンがアクティブ時にも、本出力がローになることに注意。    |

| RT            | 20    |     | 周波数設定する抵抗の入力。RTとAGND間に抵抗を接続して、スイッチング周波数を設定する。                                                                   |

| SS/ENA        | 18    |     | スロー・スタートとイネーブルの入出力。デバイス動作をイネーブル・ディスエーブルするロジック入力、および外部的にスタート・アップ時間設定するコンデンサ入力の2機能のピンである。                         |

| VBIAS         | 17    |     | 内部バイアス・レギュレータの出力。内部回路にレギュレーションした電圧を供給。VBIASとAGNDの両ピン間に高品質・低等価直列抵抗の0.1μFから1.0μFのセラミック・コンデンサを接続してバイパスする。          |

| VIN           | 14-16 |     | パワーMOSFETスイッチと内部バイアス・レギュレータに供給する入力。VINピンとPGNDピン間で、高品質・低等価直列抵抗の1μFから10μFのセラミック・コンデンサをデバイス・パッケージの極力近くに接続してバイパスする。 |

| VSENSE        | 2     |     | 誤差アンプの反転入力。出力電圧(Vo)の検出点と直結する。                                                                                   |

## 絶対最大定格(特記ないかぎり仮想接合温度範囲)†

|                                                              |                         |                                    |

|--------------------------------------------------------------|-------------------------|------------------------------------|

| Input voltage range, V <sub>I</sub> :                        | VIN, SS/ENA, FSEL ..... | -0.3 V~7 V                         |

|                                                              | RT .....                | -0.3 V~6 V                         |

|                                                              | VSENSE .....            | -0.3 V~4 V                         |

|                                                              | BOOT .....              | -0.3 V~17 V                        |

| Output voltage range, V <sub>O</sub> :                       | VBIAS, PWRGD .....      | -0.3 V~7 V                         |

|                                                              | PH .....                | -0.6 V~10 V                        |

| Source current, I <sub>O</sub> :                             | PH .....                | Internally Limited                 |

|                                                              | VBIAS .....             | 6 mA                               |

| Sink current, I <sub>S</sub> :                               | PH .....                | 6 A                                |

|                                                              | SS/ENA, PWRGD .....     | 10 mA                              |

| Voltage differential:                                        | AGND to PGND .....      | ±0.3 V                             |

| Continuous power dissipation                                 | .....                   | See Power Dissipation Rating Table |

| Operating virtual junction temperature range, T <sub>J</sub> | .....                   | -40°C~125°C                        |

| Storage temperature, T <sub>STG</sub>                        | .....                   | -65°C~150°C                        |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | .....                   | 300°C                              |

† 絶対最大定格に記述される以上のストレスを加えると、デバイスは永久破壊されることがあります。これらはストレス定格だけであり、これらの条件あるいは推奨動作条件を超える条件でのデバイスのファンクション動作は含まれません。絶対最大定格の条件下に長時間デバイスをさらすと、デバイスの信頼性に影響することがあります。

## パッケージ電力消費定格‡

| PACKAGE                   | THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT | TA = 25°C<br>POWER RATING | TA = 70°C<br>POWER RATING | TA = 85°C<br>POWER RATING |

|---------------------------|------------------------------------------|---------------------------|---------------------------|---------------------------|

| 20-Pin PWP with solder    | 26.0 mW/°C                               | 3.85 W§                   | 2.12 W                    | 1.54 W                    |

| 20-Pin PWP without solder | 57.5 mW/°C                               | 1.73 W                    | 0.96 W                    | 0.69 W                    |

‡ テスト基板条件:

1. 3×3インチ、2層、厚さ0.062インチ

2. プリント基板の部品面に1.5オンスの銅配線

3. プリント基板の半田面に1.5オンスの銅のグランド・プレーン

4. 10個のサーマル・ヴィア(本データシートのアプリケーション・セクションにおける推奨ランドパターンを参照願います。)

- パッケージのより詳細な情報は、テクニカル・ブリーフ(文献番号SLMA002)を参照願います。

§ 最大電力消費は過電流保護で制限されるかもしれません。

## 他の3AのSWIFT™デバイス

| DEVICE   | OUTPUT VOLTAGE |

|----------|----------------|

| TPS54310 | 0.9 V~3.3 V    |

## 関連DC/DC製品

- UCC3585—DC/DCコントローラ

- PT5500シリーズ—3Aプラグイン・モジュール

- TPS757xx—3A低ドロップアウト・レギュレータ

# 電氣的特性

electrical characteristics,  $T_J = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ ,  $V_I = 3\text{ V}$  to  $6\text{ V}$  (unless otherwise noted)

| PARAMETER                       | TEST CONDITIONS                          | MIN                                                                                       | TYP   | MAX  | UNIT |  |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|-------|------|------|--|

| <b>SUPPLY VOLTAGE, VIN</b>      |                                          |                                                                                           |       |      |      |  |

| Input voltage range at VIN      |                                          | 3.0                                                                                       | 6.0   |      | V    |  |

| IQ                              | Quiescent current                        | Fs = 350 kHz, FSEL ≤ 0.8 V, RT open,<br>Phase pin open                                    | 6.2   | 9.6  | mA   |  |

|                                 |                                          | Fs = 550 kHz, FSEL ≤ 2.5 V, RT open,<br>Phase pin open                                    | 8.4   | 12.8 | mA   |  |

|                                 |                                          | Shutdown, SS/ENA = 0 V                                                                    | 1     | 1.4  | mA   |  |

| <b>UNDER VOLTAGE LOCK OUT</b>   |                                          |                                                                                           |       |      |      |  |

| V <sub>IT(start)</sub>          | Start threshold voltage at UVLO          |                                                                                           | 2.95  | 3.0  | V    |  |

| V <sub>IT(stop)</sub>           | Stop threshold voltage at UVLO           |                                                                                           | 2.70  | 2.80 | V    |  |

| V <sub>hys</sub>                | Hysteresis voltage at UVLO               |                                                                                           | 0.14  | 0.16 | V    |  |

| t <sub>f</sub> , t <sub>r</sub> | Rising and falling edge deglitch at UVLO | See Note 1                                                                                |       | 2.5  | μs   |  |

| <b>BIAS VOLTAGE</b>             |                                          |                                                                                           |       |      |      |  |

| Output voltage at VBIAS         | I <sub>VBIAS</sub> = 0                   | 2.70                                                                                      | 2.80  | 2.90 | V    |  |

| Output current at VBIAS         |                                          |                                                                                           |       | 100  | μA   |  |

| <b>OUTPUT VOLTAGE</b>           |                                          |                                                                                           |       |      |      |  |

| VO                              | Output voltage                           | TPS54311<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0 V                                | 0.9   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -2.5% | 2.5% |      |  |

|                                 |                                          | TPS54312<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0 V                                | 1.2   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -2.5% | 2.5% |      |  |

|                                 |                                          | TPS54313<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0V                                 | 1.5   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -2.5% | 2.5% |      |  |

|                                 |                                          | TPS54314<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0 V                                | 1.8   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -3%   | 3%   |      |  |

|                                 |                                          | TPS54315<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0V                                 | 2.5   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -3%   | 3%   |      |  |

| REGULATION                      | Line regulation                          | TPS54316<br>T <sub>J</sub> = 25°C, V <sub>IN</sub> = 5.0V                                 | 3.3   |      | V    |  |

|                                 |                                          | 3 ≤ V <sub>IN</sub> ≤ 6 V, 0 ≤ I <sub>L</sub> ≤ 3 A, -40 ≤ T <sub>J</sub> ≤ 125           | -3%   | 3%   |      |  |

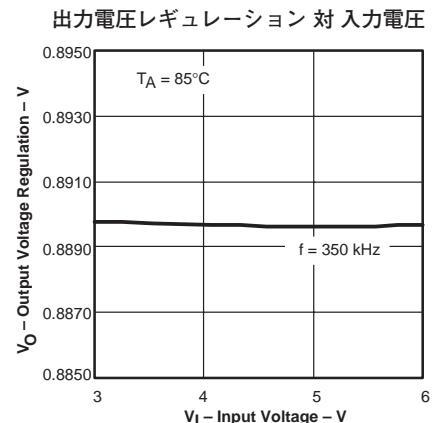

| Load regulation                 |                                          | I <sub>L</sub> = 1.5A, 350 ≤ fs ≤ 550 kHz, T <sub>J</sub> = 85°C,<br>See Note 1, 3        |       | 0.21 | %/V  |  |

|                                 |                                          | I <sub>L</sub> = 0 to 3A, 350 ≤ fs ≤ 550 kHz, T <sub>J</sub> = 85°C,<br>See Notes 1 and 3 |       | 0.21 | %/A  |  |

NOTES: 1. 設計保証

- 2. 静的な抵抗負荷のみ

- 3. 図10の回路でテスト

## 電気的特性(続き)

electrical characteristics,  $T_J = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ ,  $V_I = 3\text{ V}$  to  $6\text{ V}$  (unless otherwise noted)(continued)

| PARAMETER                                                                                   | TEST CONDITIONS                                         | MIN  | TYP  | MAX   | UNIT  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|-------|-------|

| <b>OSCILLATOR</b>                                                                           |                                                         |      |      |       |       |

| Internally set-free running frequency                                                       | SYNC <= 0.8 V, RT open                                  | 280  | 350  | 420   | kHz   |

|                                                                                             | SYNC >= 2.5V, RT open                                   | 440  | 550  | 660   |       |

| Externally set-free running frequency range                                                 | RT = 180 kΩ (1% resistor to AGND)                       | 252  | 280  | 308   | kHz   |

|                                                                                             | RT = 100 kΩ (1% resistor to AGND)                       | 460  | 500  | 540   |       |

|                                                                                             | RT = 68 kΩ (1% resistor to AGND)                        | 663  | 700  | 762   |       |

| High level threshold at FSEL                                                                |                                                         | 2.5  |      |       | V     |

| Low level threshold at FSEL                                                                 |                                                         |      |      | 0.8   | V     |

| Ramp valley                                                                                 | See Note 1                                              |      | 0.75 |       | V     |

| Ramp amplitude (peak to peak)                                                               | See Note 1                                              |      | 1    |       | V     |

| Minimum controllable on time                                                                | See Note 1                                              |      |      | 200   | ns    |

| Maximum duty cycle                                                                          | See Note 1                                              |      | 90%  |       |       |

| <b>ERROR AMPLIFIER</b>                                                                      |                                                         |      |      |       |       |

| Error amplifier open loop voltage gain                                                      | See Note 1                                              |      | 26   |       | dB    |

| Error amplifier unity gain bandwidth                                                        | See Note 1                                              | 3    | 5    |       | MHz   |

| Error amplifier common mode input voltage range                                             | Powered by internal LDO, See Note 1                     | 0    |      | Vbias | V     |

| <b>PWM COMPARATOR</b>                                                                       |                                                         |      |      |       |       |

| PWM comparator propagation delay time, PWM comparator input to PH pin (excluding dead time) | 10 mV overdrive, See Note 1                             |      | 70   | 85    | ns    |

| <b>SLOW START / ENABLE</b>                                                                  |                                                         |      |      |       |       |

| Enable threshold voltage at SS/ENA                                                          |                                                         | 0.95 | 1.20 | 1.40  | V     |

| Enable hysteresis voltage at SS/ENA                                                         | See Note 1                                              |      | 0.03 |       | V     |

| Falling edge deglitch at SS/ENA                                                             | See Note 1                                              |      | 2.5  |       | μs    |

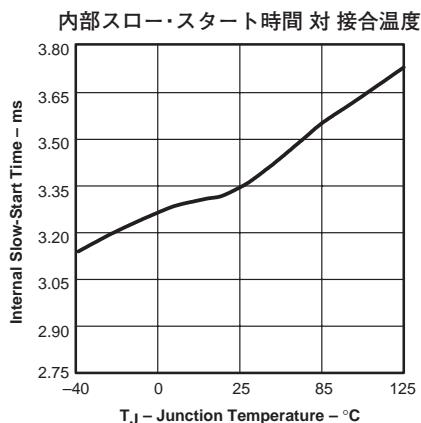

| Internal slow-start time                                                                    |                                                         | 2.6  | 3.35 | 4.1   | ms    |

| Charge current at SS/ENA                                                                    | SS/ENA = 0V                                             | 3    | 5    | 8     | μA    |

| Discharge current at SS/ENA                                                                 | SS/ENA = 1.3 V, $V_{IN} = 1.5\text{ V}$                 | 1.5  | 2.3  | 4.0   | mA    |

| <b>POWER GOOD</b>                                                                           |                                                         |      |      |       |       |

| Power good threshold voltage                                                                | $V_{SENSE}$ falling                                     |      | 90   |       | %Vout |

| Power good hysteresis voltage                                                               | See Note 1                                              |      | 3    |       | %Vout |

| Power good falling edge deglitch                                                            | See Note 1                                              |      | 35   |       | μs    |

| Output saturation voltage at PWRGD                                                          | $I_{sink} = 2.5\text{ mA}$                              |      | 0.18 | 0.30  | V     |

| Leakage current, PWRGD                                                                      | $V_{IN} = 5.5\text{ V}$                                 |      | 1    |       | μA    |

| <b>CURRENT LIMIT</b>                                                                        |                                                         |      |      |       |       |

| Current limit                                                                               | $V_{IN} = 3\text{ V}$ (see Note 1)                      | 4.0  | 6.5  |       | A     |

|                                                                                             | $V_{IN} = 6\text{ V}$ (see Note 1)                      | 4.5  | 7.5  |       |       |

| Current limit leading edge blanking time                                                    |                                                         |      | 100  |       | ns    |

| Current limit total response time                                                           |                                                         |      | 200  |       | ns    |

| <b>THERMAL SHUTDOWN</b>                                                                     |                                                         |      |      |       |       |

| Thermal shutdown trip point                                                                 | See Note 1                                              | 135  | 150  | 165   | °C    |

| Thermal shutdown hysteresis                                                                 | See Note 1                                              |      | 10   |       | °C    |

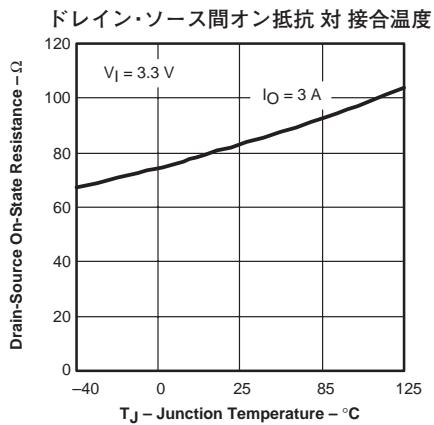

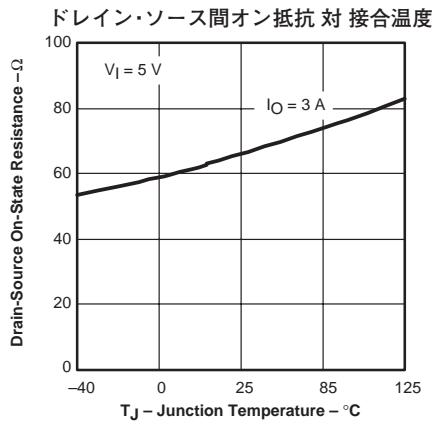

| <b>OUTPUT POWER MOSFETS</b>                                                                 |                                                         |      |      |       |       |

| Small signal drain-source on power MOSFET switches<br>RDS-ON                                | $I_O = 3\text{ A}$ , $V_{IN} = 6.0\text{ V}$ See Note 4 | 59   | 88   |       | mΩ    |

|                                                                                             | $I_O = 3\text{ A}$ , $V_{IN} = 3.0\text{ V}$ See Note 4 | 85   | 136  |       |       |

NOTES: 3. 図10の回路でテスト

4. 整合のとれたMOSFETであり、ローサイドのはテストされ、ハイサイドのは設計保証

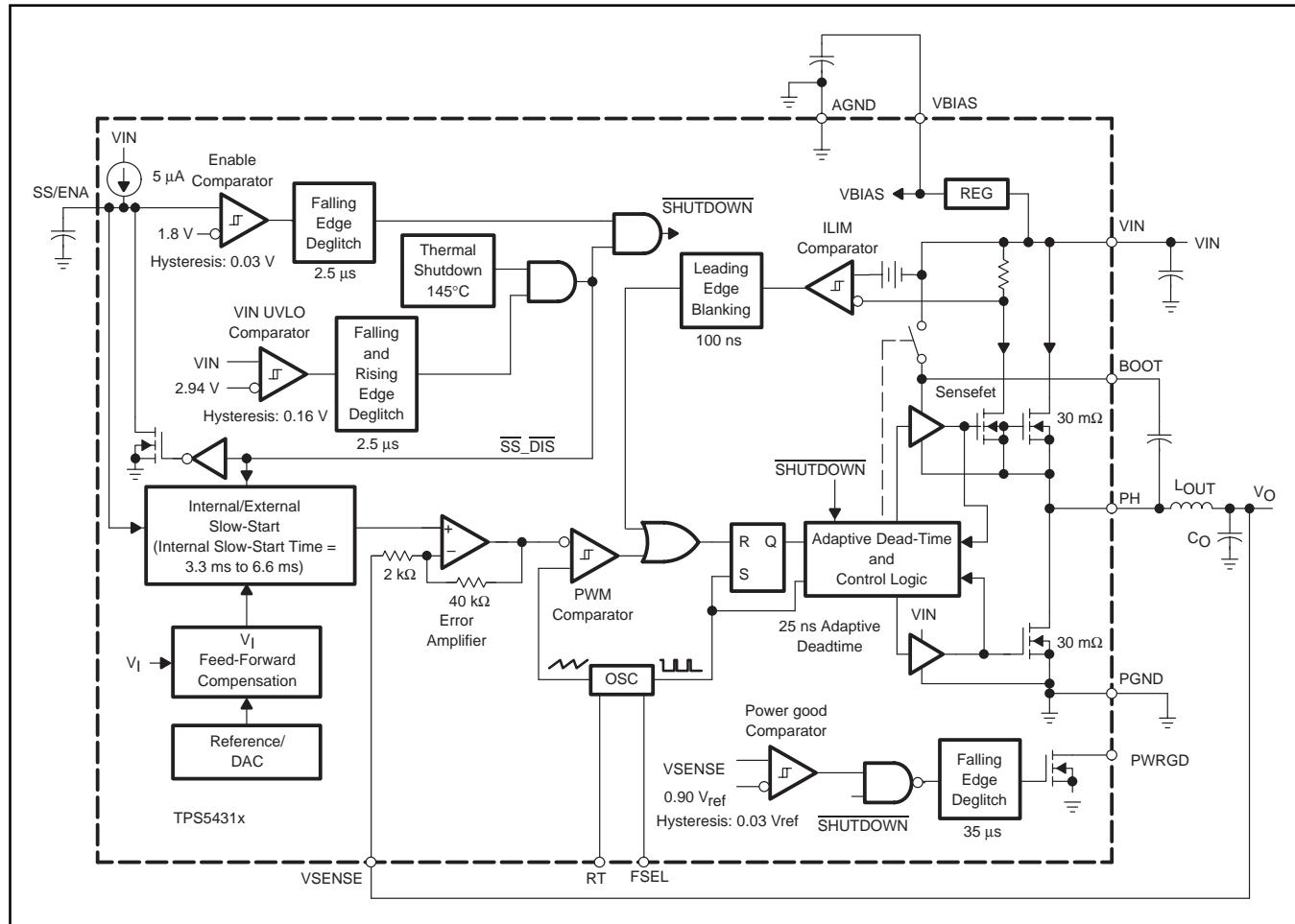

## 機能ブロック図

## 詳細解説

### 低電圧ロックアウト(UVLO)

低電圧ロックアウト回路は、入力電圧(VIN)が不十分な時にデバイスをディスエーブルに保ちます。電源投入中は、VINがUVLOのスレッシュホールド電圧(公称値2.95V)を超えるまで、内部回路を停止状態に維持します。ひとたびVINがUVLOスタートのスレッシュホールド電圧に達すると、デバイスはスタート・アップを始めます。デバイスは、VINがUVLOストップのスレッシュホールド電圧(公称値2.8V)を下回るまで動作します。このようなUVLOコンパレータのヒステリシスと、2.5µsの立ち上がり・立ち下がりエッジのデグリッチ回路が、VINに乗った雑音によるデバイスのシャットダウンの可能性を低減します。

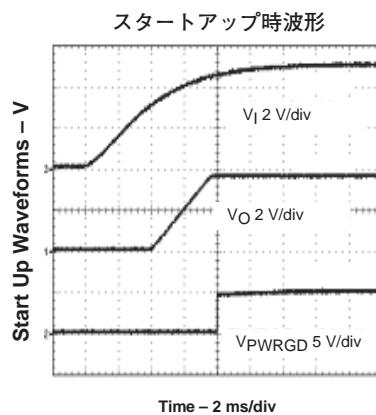

### スロー・スタート/イネーブル(SS/ENA)

スロー・スタート/イネーブルのピンには2つの機能があります。第一は、イネーブル(シャットダウン)制御としての働きであり、この電圧がスタート・スレッシュホールド電圧(約1.2V)を超えるまでデバイスを停止状態に保ちます。SS/ENAがスタート・スレッシュホールド電圧を超えると、デバイスはスタート・アップを開始します。このとき、誤差アンプに供給される基準電圧は、0Vから0.891Vまで3.35msで直線的に上昇します。同様に、デバイスの出力電圧もレギュレーションのレベルに約3.35msで到達します。このようなヒステリシス電圧と2.5µsの立ち下が

りエッジのデグリッチ回路が、雑音による誤ったイネーブルのトリガーの可能性を低減します。

SS/ENAピンの第二の機能は、このピンとAGND間に小容量コンデンサを接続して、外部からスロー・スタート時間を拡張する手段を与えることです。SS/ENAピンにコンデンサを付けると、スタート・アップに関する2つの効果があります。まず、SS/ENAピンのリリースと出力のスタート・アップ間に遅延が生じます。この遅延はスロー・スタート用コンデンサの値に比例し、SS/ENAピンの電位がイネーブル・スレッシュホールド電圧に達するまで継続します。このスタート・アップ遅延は、およそ式(1)のようになります。

$$t_d = C_{(SS)} \times \left( \frac{1.2 \text{ V}}{5 \mu\text{A}} \right) \quad (1)$$

次に、出力がアクティブになると、外部設定のスロー・スタート時間が効く前に、内部設定スロー・スタート時間のわずかな上昇が観察されます。それから、出力はスロー・スタート用コンデンサの容量値に比例して上昇します。コンデンサにより外部設定されるスロー・スタート時間は、およそ式(2)のようになります。

$$t_{(SS)} = C_{(SS)} \times \left( \frac{0.7 \text{ V}}{5 \mu\text{A}} \right) \quad (2)$$

実際のスロー・スタート時間は、内部設定の時間が若干短くなるため、上式の近似より短くなるかもしれません。

## VBIASレギュレータ(VBIAS)

VBIASレギュレータは、内部アナログ・デジタルの両ブロックに、接合温度と入力電圧の変動に依存しない安定した電源を供給します。VBIASピンには、高品質かつ低等価直列抵抗のセラミックのバイパス・コンデンサが必要です。温度変動に対して安定なX7RあるいはX5Rクラスの誘電体を推奨します。バイパス・コンデンサは極力VBIASピンの近くに配置し、AGNDに接地します。VBIASに外部の負荷をつけることは可能ですが、内部回路が最小2.70VのVBIASを必要なことと、VBIASに接続した外部負荷によるACあるいはデジタル雑音が特性を劣化させることに注意を要します。VBIASピンは外部回路の基準電圧として使うこともできます。

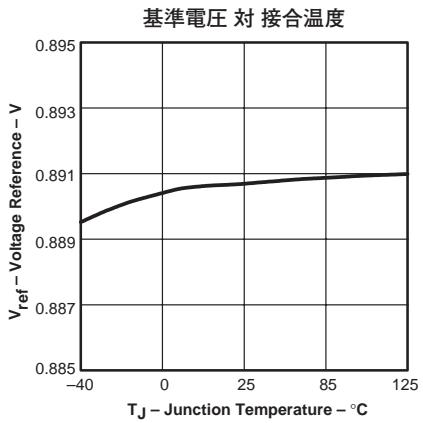

## 基準電圧

基準電圧システムは、高精度で温度に対して安定な電圧をバンドギャップ回路から作ります。スケーリング・アンプとDACを用い、各デバイスの固有出力の基準電圧を発生します。

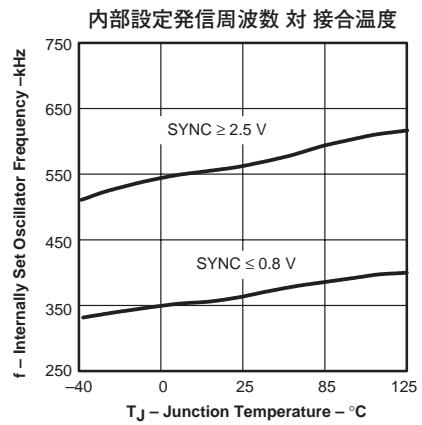

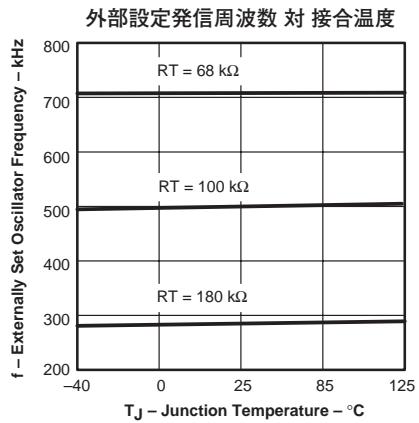

## 発振器とPWMランプ

発振周波数は、FSELピンに静的なデジタル入力を印加して、内部的に350kHzあるいは550kHzの固定値に設定できます。アプリケーションによって異なる動作周波数が必要ならば、RTピンとAGND間に抵抗を接続し、かつFSELピンをオープンにして、発振周波数を外部的に280kHzから700kHzまで調整できます。スイッチング周波数は式(3)で近似されます。ここで、RはRTとAGND間の抵抗値です。

$$\text{スイッチング周波数} = \left( \frac{100 \text{ k}\Omega}{\text{RT}} \right) \times 500 \text{ kHz} \quad (3)$$

下表に周波数選択の組み合わせを要約します。

| SWITCHING FREQUENCY               | SYNC PIN             | RT PIN                               |

|-----------------------------------|----------------------|--------------------------------------|

| 350 kHz, internally set           | Float or AGND        | Float                                |

| 550 kHz, internally set           | $\geq 2.5 \text{ V}$ | Float                                |

| Externally set 280 kHz to 700 kHz | Float                | $R = 180 \text{ k to } 68 \text{ k}$ |

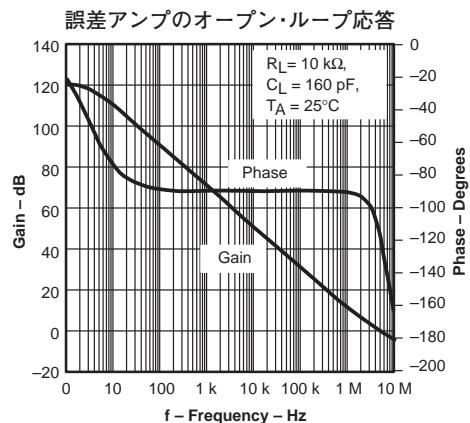

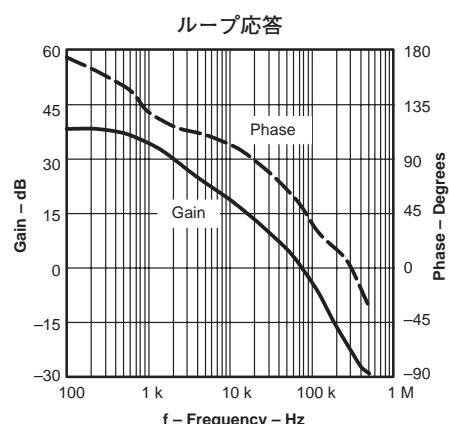

## 誤差アンプ

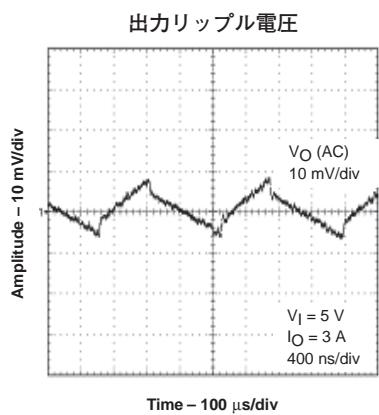

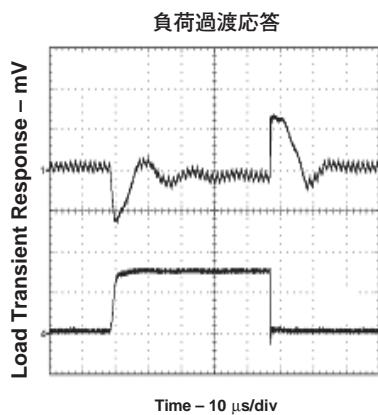

高性能で広帯域の誤差アンプは、制御ループの内部補償のために利得が限定されています。これによって、ユーザーの出力LCフィルタ用部品の選択も限定されます。4.7μHから10μHのインダクタンスが一般的な値であり、数社から入手できます。このように設計すると、非常に優れた過渡応答とともに、良好な雑音およびリップル特性を示します。過渡回復時間は一般に10から20μsの範囲です。

## PWM制御

誤差アンプ、発信器、および電流制限回路の各出力信号はPWM制御ロジック回路で処理されます。内部ブロック図を参照すると、制御ロジック回路にはPWMコンパレータ、ORゲート、PWMラッチ、およびデッドタイムと制御ロジック・ブロックの一部があります。電流制限のスレッシュホールド電圧より低い安定動作では、PWMコンパレータ出力と発振器パルスが交互にPWMラッチをリセットおよびセットします。PWMラッチがリセットされると、ローサイドFETが発振器パルス幅による最小期間だけ

オンします。この間、PWMのランプ波形は谷の電圧値まで急速に放電します。次にランプ波形が充電を始めると、ローサイドFETはオフし、ハイサイドFETがオンします。PWMランプ波形が誤差アンプの出力電圧を超えると、PWMコンパレータがラッチをリセットし、その結果ハイサイドFETがオフし、ローサイドFETがオンします。そしてローサイドFETは、次の発振器パルスがPWMランプ波形を放電するまでオンを続けます。

過渡状態では、誤差アンプ出力がPWMランプ波形の谷電圧以下やピーク電圧以上になるかもしれません。誤差アンプ出力が高い場合、PWMラッチはリセットされず、発振器パルスが制御ロジックにハイサイドFETのオフとローサイドFETのオンの信号を出すまで、ハイサイドFETはオンを維持します。このとき、出力電圧がレギュレーションの設定値に達するまで、デバイスはVSENSEにほぼ等しい電圧を供給しながら最大デューティで動作します。誤差アンプ出力が低い場合、PWMラッチは連続的にリセットされ、ハイサイドFETはオンしません。このときローサイドFETは、VSENSEの電圧が低下してPWMコンパレータの状態を反転させるまでオンし続けます。TPS54311-16は、出力がレギュレーションの設定値に達するまで連続的に電流をシンクできます。

電流制限コンパレータが100nS以上動作すると、PWMランプ波形が誤差アンプ出力を超える前にPWMラッチをリセットします。そして、ハイサイドFETはオフし、ローサイドFETはオンして、出力のインダクタのエネルギーを低減し、出力電流を減少します。この過程は、電流制限コンパレータが動作するサイクルごとに行われます。

## デッドタイム制御とMOSFETドライバ

適応性の高いデッドタイム制御は、MOSFETドライバのターン・オン時間を積極的に制御して、両方のNチャネル・パワーMOSFETにおける貫通電流を防止します。ハイサイド・ドライバは、ローサイドFETのゲート電圧が2V以下になるまでオンしません。また、ローサイド・ドライバは、ハイサイドMOSFETのゲート電圧が2V以下になるまでオンしません。ハイサイドとローサイドの両ドライバは300mAのソースおよびシンク能力で設計され、パワーMOSFETのゲートを急速にドライブできます。ローサイド・ドライバはVINから電源を供給され、ハイサイド・ドライバはBOOTピンから電源を供給されています。そのブーストストラップ回路は、外付けのBOOTコンデンサと、VINピンとBOOTピン間の内部に2.5Ωのブーストストラップ・スイッチを用いています。このブーストストラップ・スイッチはドライブ効率を高め、外付けの部品点数を節約します。

## 過電流保護

電流制限はサイクルごとにされ、ハイサイドMOSFETを流れる電流を検知し、これをプリセットの過電流スレッシュホールド電圧と比較します。ハイサイドMOSFETは、電流制限スレッシュホールド電圧に達して200ns以内にオフします。立ち上がりエッジを100nsだけブランкиングする回路が、電流制限の誤作動を防止します。電流制限の検出は、VINからPHへ流れる電流が outputフィルタに供給される場合のみに行われます。電流をシンクする場合の過負荷保護は、サーマル・シャットダウンで行われます。

## サーマル・シャットダウン

デバイスの接合温度が150°Cを超えると、デバイスはサーマル・シャットダウンを用いてパワーMOSFETをオフし、制御回路をディスエーブルにします。接合温度がサーマル・シャットダウンの動作点より10°C低下すると、デバイスはシャットダウン状態から解放され、スロー・スタート回路の制御下でスタート・アップします。サーマル・シャットダウンは過負荷状態が数mS続くと作動します。不良状態が持続すると、デバイスは次のサイクルを繰り返します。すなわち、ソフト・スタート回路の制御下でのスタート・アップ、不良状態による温度上昇、そしてサーマル・シャットダウン温度に達してのシャットダウンというサイクルです。

## パワー・グッド(PWRGD)

パワー・グッド回路はVSENSEにおける低電圧状態を監視します。VSENSEの電圧が基準電圧より10%下回ると、オープン・ドレインのPWRGD出力がローになります。また、VINがUVLOスレッシュホールド電圧を下回る、あるいはSS/ENAが低い、さらにサーマル・シャットダウンが作動した場合にもPWRGD出力がローになります。VIN = UVLOスレッシュホールド電圧、SS/ENA = イネーブル・スレッシュホールド電圧、およびVSENSE > ×90%の各場合は、オープン・ドレインのPWRGD出力がハイになります。 $V_{ref}$ の3%に相当するヒステリシス電圧と35μSの立ち下がりエッジのデグリッチ回路が、高周波雑音によるパワー・グッド・コンパレータの誤作動を防止します。

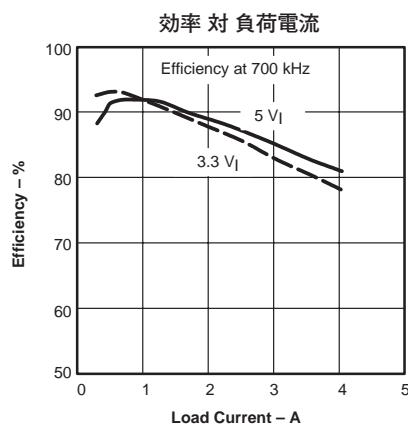

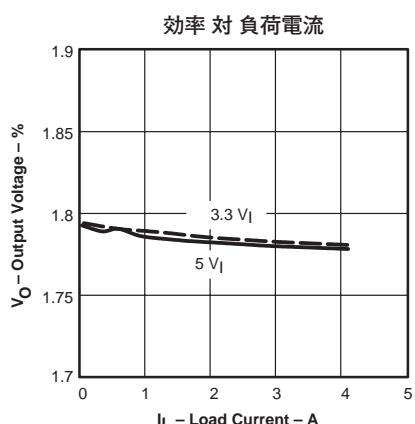

# 代表的特性

Figure1

Figure2

Figure3

Figure4

Figure5

Figure6

Figure7

Figure8

Figure9

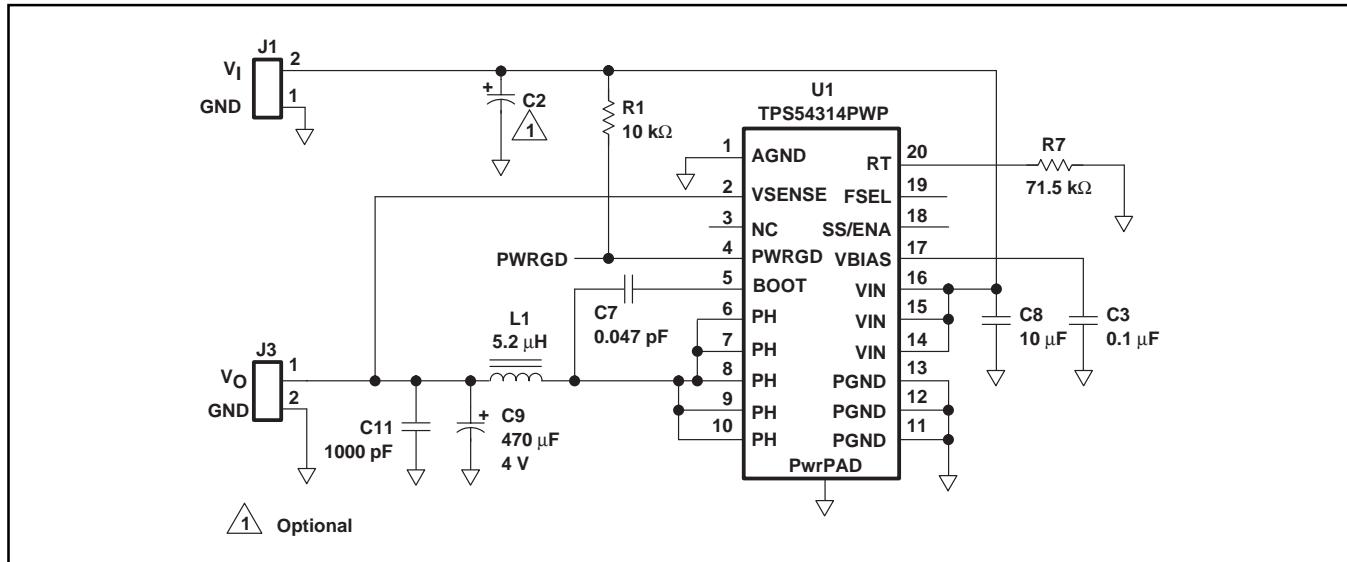

Figure10. TPS54314の回路図

## アプリケーション情報

Figure10はTPS54314の代表的なアプリケーション回路図を示します。TPS54314(図中のU1)は、公称値1.8Vの出力電圧で3Aまでの出力電流を供給できます。適切な熱特性を得るために、TPS54310の直下のPowerPAD™をプリント基板に十分に半田付けする必要があります。

### 入力電圧

回路への入力電圧は5VDC(公称値)であり、J1に供給します。オプションの入力フィルタ(C2)は220μFのPOSCAP(チップ型のタンタル電解コンデンサ)コンデンサであり、最大許容リップル電流が3Aのものです。C8はTPS54314のデカップリング・コンデンサであり、デバイスにできるだけ接近させて取りつけます。

### 帰還回路

コンバータの出力電圧をTPS54314のVSENSEピンに直接入力します。TPS54314は内部補償により、ラインおよび負荷条件の変動に対して安定な出力を供給します。

### 動作周波数

本アプリケーション回路では、FSELをオープンにし、71.5kΩの抵抗をRTとAGND間に接続して700kHzの動作周波数を選択しています。これと異なる周波数は、R7の値を式(4)にしたがって変更して設定できます。

$$R = \frac{500 \text{ kHz}}{\text{Switching Frequency}} \times 100 \text{ k}\Omega \quad (4)$$

また、動作周波数を350kHzあるいは550kHzに設定するには、RTをオープンにし、FSELピンをそれぞれAGNDあるいはVINに接続します。

### 出力フィルタ

出力フィルタは5.2μHのインダクタと470μFのコンデンサで構成されます。このインダクタは低DC抵抗(16mΩ)タイプのスミダ製CDRH104R-5R2です。コンデンサは4VのPOSCAPで、最大等価直列抵抗が40mΩのものを使用しています。出力フィルタ部品は内部補償回路網とともに、コンバータの閉ループ応答を安定なものにしています。

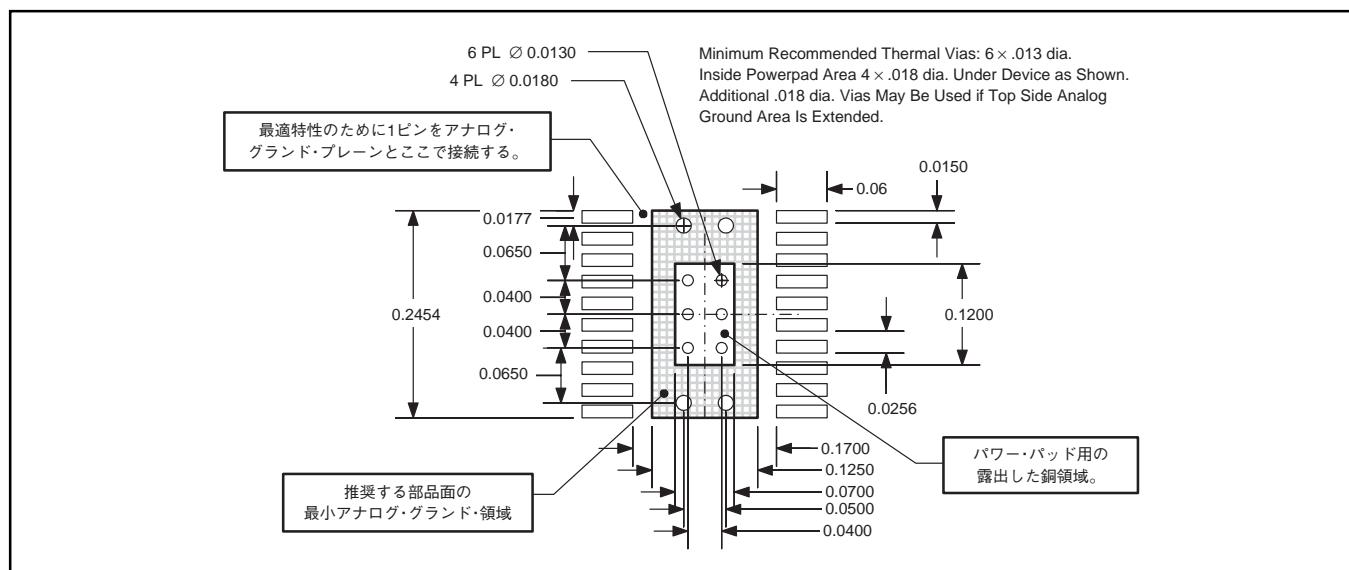

### グランドのとりかたとパワー・パッドのレイアウト

TPS54311-16にはアナログとパワーの2つの内部グランドがあります。TPS54311-16の内部では、アナログ・グランドをすべての雑音に敏感な信号に接続し、パワー・グランドは雑音を発生するパワー信号に接続しています。PowerPAD™は直接AGNDに接続する必要があります。両グランド間に入った雑音はTPS54311-16の特性を劣化させ、特に大出力電流時に顕著になります。しかし、アナログ・グランド・プレーンの雑音は、制御信号やバイアス信号に問題を発生します。したがって、これらの理由から、アナログとパワーの両グランド・プレーンを分離することを推奨します。この両プレーンはICにおいて互いに接続し、両グランド間の雑音を低減します。直接にパワー・グランド・プレーンに接続する部品は、入力コンデンサ、出力コンデンサ、入力電圧デカップリング用コンデンサ、およびTPS54311-16のPGNDピンだけです。TPS54314用評価モジュールのレイアウトは、4層基板の推奨レイアウトの代表例です。TPS54314用評価モジュールの文献は、TIのウェブサイトのTPS54314製品フォルダ、およびアプリケーション・ノートのTI文献番号SLVA111にあります。

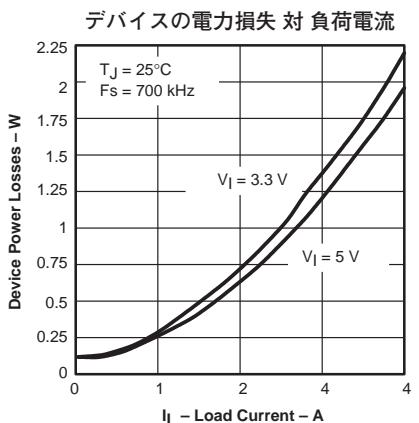

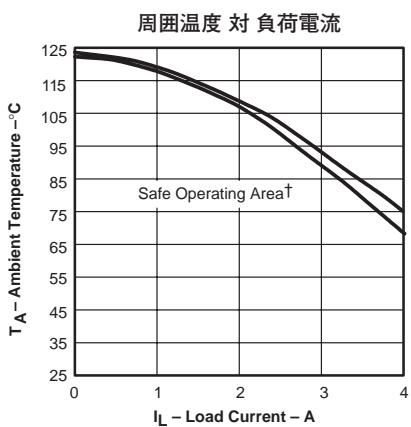

## 熱特性に関するレイアウトの考察

最大負荷電流での動作のため、アナログ・グランド・プレーンには適当な放熱領域が必要です。それには、1オンスの銅による3インチ×3インチのプレーンを推奨します。これは必須というわけではなく、周囲温度と空気流に依存します。ほとんどのアプリケーションには内部グランド・プレーンの広い領域があり、パワー・パッドはその中で最大面積のものに接続します。部品面や半田面にある他の領域も放熱に寄与するので、3A以上の動作時はすべての領域を放熱に使用します。パワー・パッドの露出領域と

アナログ・グランド・プレーン層との接続には、直径0.013インチのヴィアを用いて、ヴィアによる半田の上がりを防止します。パワー・パッド領域に6個のヴィアを作り、さらにデバイス・パッケージの直下に4個のヴィアを作ります。このパッケージ直下のヴィアのサイズは、露出したサーマル・パッド領域とは違って、0.018インチまで拡張できます。推奨するこれら10個のヴィアに加えて、熱特性を強化するヴィアをデバイス・パッケージの下以外の領域にも作ります。

Figure11. 20ピンPWP PowerPAD™用の推奨ランド・パターン

# 特性グラフ

Figure12

Figure13

Figure14

Figure15

Figure16

Figure17

Figure18

†安全動作領域は、本データシートのパッケージ電力消費定格表に記述されたテスト基板条件に適用されます。

## 外観

PWP (R-PDSO-G\*\*)

PowerPAD™ PLASTIC SMALL-OUTLINE

20 PINS SHOWN

4073225/F 10/98

- 注：A. 直線的な寸法はすべてミリメートルです。

B. 本図は通達なしに変更することがあります。

C. 本体の寸法はモールド・フラッシュや突起を含みません。

D. パッケージの熱特性は、サーマル・パッドを外部プレーンにボンディングすると強化されます。

このパッドは電気的かつ熱的にチップの背面と結合します。また、できるかぎり一部のリードとも接続させます。

E. JEDEC MO-153の規格に準拠します。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS54311PWP</a>  | Active        | Production           | HTSSOP (PWP)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54311            |

| TPS54311PWP.A                | Active        | Production           | HTSSOP (PWP)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54311            |

| <a href="#">TPS54312PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54312            |

| TPS54312PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54312            |

| TPS54312PWPRG4               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54312            |

| <a href="#">TPS54313PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54313            |

| TPS54313PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54313            |

| TPS54313PWPR1G4              | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54313            |

| TPS54313PWPR1G4.A            | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54313            |

| <a href="#">TPS54314PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54314            |

| TPS54314PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54314            |

| TPS54314PWPRG4               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54314            |

| <a href="#">TPS54315PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54315            |

| TPS54315PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54315            |

| TPS54315PWPR1G4              | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54315            |

| TPS54315PWPR1G4.A            | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TPS54315            |

| <a href="#">TPS54316PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54316            |

| TPS54316PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54316            |

| TPS54316PWPRG4               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54316            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS54311, TPS54312, TPS54313, TPS54314, TPS54315, TPS54316 :**

- Enhanced Product : [TPS54311-EP](#), [TPS54312-EP](#), [TPS54313-EP](#), [TPS54314-EP](#), [TPS54315-EP](#), [TPS54316-EP](#)

NOTE: Qualified Version Definitions:

- Enhanced Product - Supports Defense, Aerospace and Medical Applications

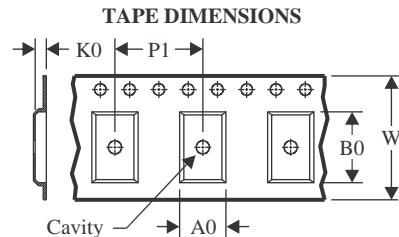

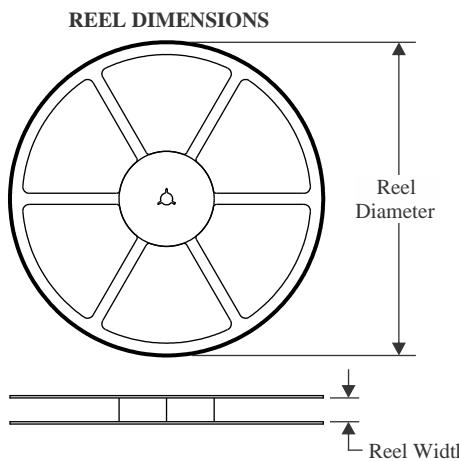

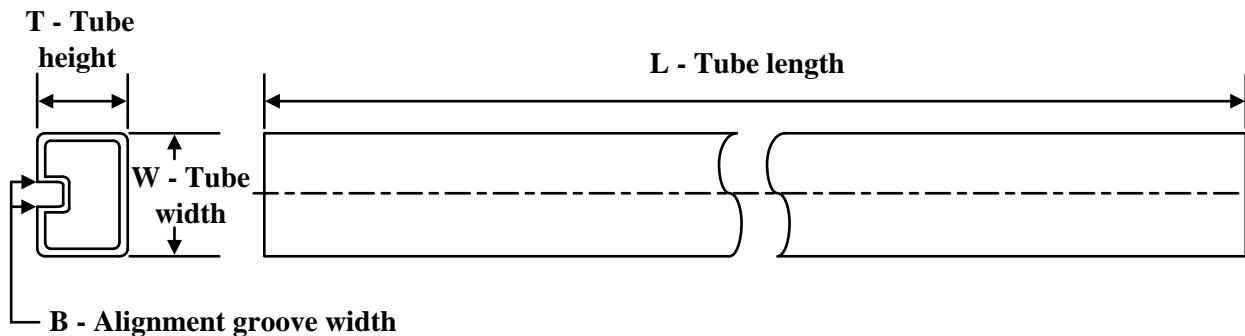

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

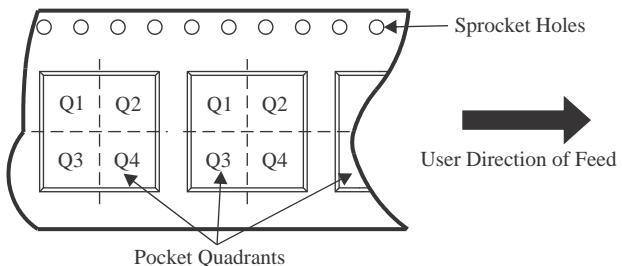

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54312PWPR    | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

| TPS54313PWPR    | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

| TPS54313PWPR1G4 | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.0     | 1.4     | 8.0     | 16.0   | Q1            |

| TPS54314PWPR    | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

| TPS54315PWPR    | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

| TPS54315PWPR1G4 | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.0     | 1.4     | 8.0     | 16.0   | Q1            |

| TPS54316PWPR    | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

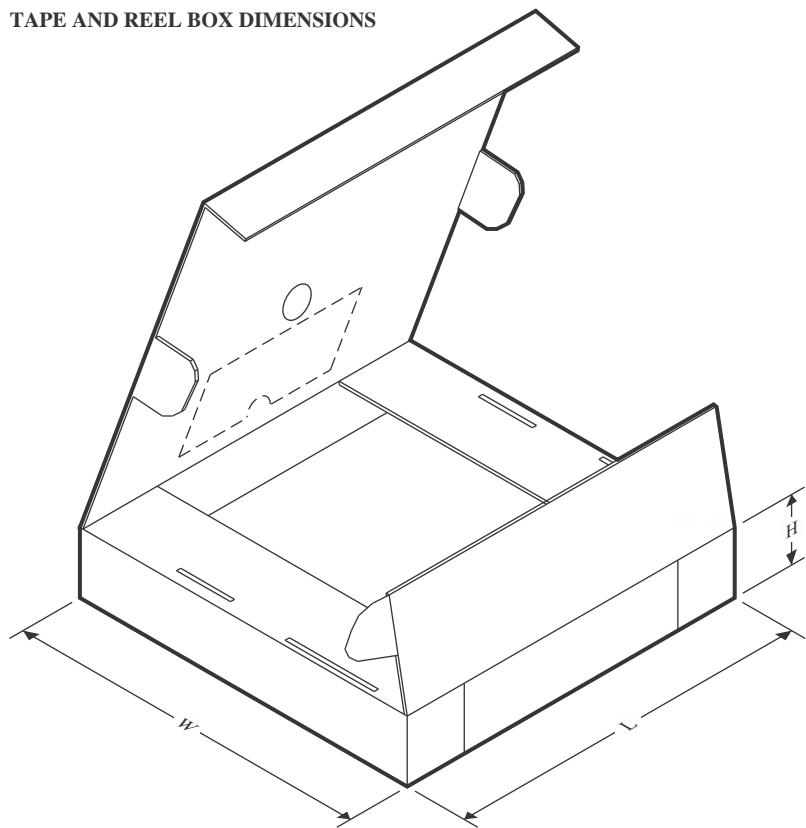

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54312PWPR    | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54313PWPR    | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54313PWPR1G4 | HTSSOP       | PWP             | 20   | 2000 | 353.0       | 353.0      | 32.0        |

| TPS54314PWPR    | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54315PWPR    | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54315PWPR1G4 | HTSSOP       | PWP             | 20   | 2000 | 353.0       | 353.0      | 32.0        |

| TPS54316PWPR    | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

## TUBE

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54311PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600         | 3.5    |

| TPS54311PWP.A | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600         | 3.5    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月