## Eco-Mode™搭載、4.5V～18V入力、 3A同期整流降圧型SWIFT™コンバータ

### 特 長

- 高速過渡応答を可能にするD-CAP2™モード

- 出力リップルが低く、セラミック出力コンデンサを使用可能

- 幅広いVIN入力電圧範囲：4.5V～18V

- 出力電圧範囲：0.76V～7.0V

- 低デューティ・サイクルのアプリケーションに対して最適化された高効率の内蔵FET

- 100mΩ(ハイサイド)および70mΩ(ローサイド)

- 高効率、シャットダウン時10µA未満

- 高い初期バンドギャップ・リファレンス精度

- 調整可能なソフト・スタート

- プリバイアス付きソフト・スタート

- スイッチング周波数(f<sub>sw</sub>)：700kHz

- サイクル毎の過電流制限

- 自動スキップEco-Mode™により軽負荷時の効率を向上

### アプリケーション

- 幅広い範囲の低電圧システム用アプリケーション

- デジタル・テレビ用電源

- 高精細Blu-ray Disc™プレーヤー

- ネットワーク・ホーム・ターミナル

- デジタル・セットトップ・ボックス(STB)

### 概 要

TPS54328は、適応型オン時間およびD-CAP2™モードに対応した同期整流バック・コンバータです。TPS54328を採用することで、各種機器の電源バス・レギュレータに対して、コスト効果が高く、部品数の少ない、低スタンバイ電流のソリューションを実現できます。TPS54328の主制御ループではD-CAP2™モード制御を使用し、外部補償部品なしで高速な過渡応答が得られます。適応型オン時間制御により、重負荷時にはPWMモード動作、軽負荷時にはEco-Mode™動作にシームレスに移行することができます。Eco-Mode™により、TPS54328は軽負荷条件時に高い効率を維持できます。また、TPS54328には、POSCAP/SP-CAPなどの低ESR(等価直列抵抗)出力コンデンサだけでなく、超低ESRのセラミック・コンデンサにも対応できる、独自の回路が採用されています。このデバイスは、4.5V～18VのVIN入力で動作します。出力電圧は、0.76V～7.0Vの範囲でプログラミングできます。また、調整可能なソフト・スタート時間も備えています。TPS54328は8ピンのDDAパッケージで提供され、-40°C～85°Cの温度範囲で動作するように設計されています。

D-CAP2, Eco-Modeは、テキサス・インスツルメンツの登録商標です。Blu-ray Discは、Blu-ray Disc Association社の登録商標です。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

ESDはこの集積回路にダメージを与えることがあります。テキサス・インスツルメンツ社は、全ての集積回路に適切なESD対策が行われることを推奨します。この適切な取扱いや取付け手順が守られない場合には、素子にダメージを与えることがあります。

ESDが与えるダメージには、素子へ微妙な性能劣化から完全な素子故障まで様々な症状に及びます。非常に些細なパラメータの変化でもその素子の仕様を満足しなくなることがあります。高詳細な集積回路はさらにESDによる影響を受けやすい場合があります。

## 製品情報<sup>(1)</sup>

| T <sub>A</sub> | パッケージ <sup>(2) (3)</sup> | オーダー可能な部品番号  | ピン | 出荷形態    |

|----------------|--------------------------|--------------|----|---------|

| −45°C ~ 85°C   | DDA                      | TPS54328DDA  | 8  | チューブ    |

|                |                          | TPS54328DDAR |    | テープ・リール |

(1) 最新のパッケージおよびご発注情報については、このデータシートの巻末にある「付録：パッケージ・オプション」を参照するか、TIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

(2) パッケージ図面、熱特性データ、記号の意味については、[www.ti.com/packaging](http://www.ti.com/packaging)を参照してください。

(3) すべてのパッケージ・オプションがCu NiPdAuリード/ポール仕上げとなっています。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                                                    |                            | VALUE |     | 単位 |

|----------------------------------------------------|----------------------------|-------|-----|----|

|                                                    |                            | MIN   | MAX |    |

| Input voltage range                                | VIN, EN                    | −0.3  | 20  | V  |

|                                                    | VBST                       | −0.3  | 26  |    |

|                                                    | VBST (10 ns transient)     | −0.3  | 28  |    |

|                                                    | VBST (vs SW)               | −0.3  | 6.5 |    |

|                                                    | VFB, SS                    | −0.3  | 6.5 |    |

|                                                    | SW                         | −2    | 20  |    |

|                                                    | SW (10 ns transient)       | −3    | 22  |    |

| Output voltage range                               | VREG5                      | −0.3  | 6.5 | V  |

|                                                    | GND                        | −0.3  | 0.3 |    |

| Voltage from GND to thermal pad, V <sub>diff</sub> |                            | −0.2  | 0.2 | V  |

| Electrostatic discharge                            | Human Body Model (HBM)     |       | 2   | kV |

|                                                    | Charged Device Model (CDM) |       | 500 | V  |

| Operating junction temperature, T <sub>J</sub>     |                            | −40   | 150 | °C |

| Storage temperature, T <sub>stg</sub>              |                            | −55   | 150 |    |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。

絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 熱特性について

|                  | THERMAL METRIC <sup>(1)</sup>                | TPS54328     | 単位   |

|------------------|----------------------------------------------|--------------|------|

|                  |                                              | DDA (8 PINS) |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 42.1         | °C/W |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 50.9         |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 31.8         |      |

| $\psi_{JT}$      | Junction-to-top characterization parameter   | 5            |      |

| $\psi_{JB}$      | Junction-to-board characterization parameter | 13.5         |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 7.1          |      |

(1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                 |                                |                        | MIN  | MAX | 単位 |

|-----------------|--------------------------------|------------------------|------|-----|----|

| V <sub>IN</sub> | Supply input voltage range     |                        | 4.5  | 18  | V  |

| V <sub>I</sub>  | Input voltage range            | VBST                   | -0.1 | 24  | V  |

|                 |                                | VBST (10 ns transient) | -0.1 | 27  |    |

|                 |                                | VBST(vs SW)            | -0.1 | 5.7 |    |

|                 |                                | SS                     | -0.1 | 5.7 |    |

|                 |                                | EN                     | -0.1 | 18  |    |

|                 |                                | VFB                    | -0.1 | 5.5 |    |

|                 |                                | SW                     | -1.8 | 18  |    |

|                 |                                | SW (10 ns transient)   | -3   | 21  |    |

|                 |                                | GND                    | -0.1 | 0.1 |    |

| V <sub>O</sub>  | Output voltage range           | V <sub>REG5</sub>      | -0.1 | 5.7 | V  |

| I <sub>O</sub>  | Output Current range           | I <sub>VREG5</sub>     | 0    | 10  | mA |

| T <sub>A</sub>  | Operating free-air temperature |                        | -40  | 85  | °C |

| T <sub>J</sub>  | Operating junction temperature |                        | -40  | 150 | °C |

## 電気的特性

動作温度範囲内(特に記述のない限り)

| パラメータ                                                  | テスト条件                                                                                                                            | MIN                                                                                            | TYP  | MAX | 単位  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-----|-----|

| <b>SUPPLY CURRENT</b>                                  |                                                                                                                                  |                                                                                                |      |     |     |

| I <sub>VIN</sub>                                       | Operating - non-switching supply current<br>V <sub>IN</sub> current, T <sub>A</sub> = 25°C, EN = 5 V,<br>V <sub>FB</sub> = 0.8 V | 800                                                                                            | 1200 |     | μA  |

| I <sub>VINSDN</sub>                                    | Shutdown supply current<br>V <sub>IN</sub> current, T <sub>A</sub> = 25°C, EN = 0 V                                              | 1.8                                                                                            | 10   |     | μA  |

| <b>LOGIC THRESHOLD</b>                                 |                                                                                                                                  |                                                                                                |      |     |     |

| V <sub>ENH</sub>                                       | EN high-level input voltage<br>EN                                                                                                | 2                                                                                              |      |     | V   |

| V <sub>ENL</sub>                                       | EN low-level input voltage<br>EN                                                                                                 |                                                                                                | 0.45 |     | V   |

| <b>V<sub>FB</sub> VOLTAGE AND DISCHARGE RESISTANCE</b> |                                                                                                                                  |                                                                                                |      |     |     |

| V <sub>FBTH</sub>                                      | V <sub>FB</sub> threshold voltage                                                                                                | T <sub>A</sub> = 25°C, V <sub>O</sub> = 1.05 V, I <sub>O</sub> = 10 mA,<br>Eco-mode™ operation | 772  |     | mV  |

|                                                        |                                                                                                                                  | T <sub>A</sub> = 25°C, V <sub>O</sub> = 1.05 V, continuous mode<br>operation                   | 749  | 765 | 781 |

| I <sub>VFB</sub>                                       | V <sub>FB</sub> input current<br>V <sub>FB</sub> = 0.8 V, T <sub>A</sub> = 25°C                                                  | 0                                                                                              | ±0.1 |     | μA  |

| <b>V<sub>REG5</sub> OUTPUT</b>                         |                                                                                                                                  |                                                                                                |      |     |     |

| V <sub>VREG5</sub>                                     | V <sub>REG5</sub> output voltage<br>T <sub>A</sub> = 25°C, 6.0 V < V <sub>IN</sub> < 18 V,<br>0 < I <sub>VREG5</sub> < 5 mA      | 5.2                                                                                            | 5.5  | 5.7 | V   |

| V <sub>LN5</sub>                                       | Line regulation<br>6 V < V <sub>IN</sub> < 18 V, I <sub>VREG5</sub> = 5 mA                                                       |                                                                                                | 25   |     | mV  |

| V <sub>LD5</sub>                                       | Load regulation<br>0 mA < I <sub>VREG5</sub> < 5 mA                                                                              |                                                                                                | 100  |     | mV  |

| I <sub>VREG5</sub>                                     | Output current<br>V <sub>IN</sub> = 6 V, V <sub>REG5</sub> = 4.0 V, T <sub>A</sub> = 25°C                                        | 60                                                                                             |      |     | mA  |

| <b>MOSFET</b>                                          |                                                                                                                                  |                                                                                                |      |     |     |

| R <sub>DS(on)h</sub>                                   | High side switch resistance<br>25°C, V <sub>BST</sub> – SW = 5.5 V                                                               | 100                                                                                            |      |     | mΩ  |

| R <sub>DS(on)l</sub>                                   | Low side switch resistance<br>25°C                                                                                               | 70                                                                                             |      |     | mΩ  |

| <b>CURRENT LIMIT</b>                                   |                                                                                                                                  |                                                                                                |      |     |     |

| I <sub>ocl</sub>                                       | Current limit<br>L <sub>out</sub> = 1.5 μH <sup>(1)</sup> , T <sub>A</sub> = -20°C to 85°C                                       | 3.5                                                                                            | 4.2  | 5.7 | A   |

(1) 実製品の検査は行っていません。

## 電気的特性

動作温度範囲内(特に記述のない限り)

| パラメータ                        |                            | テスト条件                                           | MIN  | TYP  | MAX  | 単位 |

|------------------------------|----------------------------|-------------------------------------------------|------|------|------|----|

| <b>THERMAL SHUTDOWN</b>      |                            |                                                 |      |      |      |    |

| T <sub>SDN</sub>             | Thermal shutdown threshold | Shutdown temperature <sup>(2)</sup>             | 165  |      |      | °C |

|                              |                            | Hysteresis <sup>(2)</sup>                       | 30   |      |      |    |

| <b>ON-TIME TIMER CONTROL</b> |                            |                                                 |      |      |      |    |

| t <sub>ON</sub>              | On time                    | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 1.05 V | 150  |      |      | ns |

| t <sub>OFF(MIN)</sub>        | Minimum off time           | T <sub>A</sub> = 25°C, V <sub>FB</sub> = 0.7 V  | 260  | 310  |      | ns |

| <b>SOFT START</b>            |                            |                                                 |      |      |      |    |

| I <sub>SSC</sub>             | SS charge current          | V <sub>SS</sub> = 0 V                           | 1.4  | 2.0  | 2.6  | μA |

| I <sub>SSD</sub>             | SS discharge current       | V <sub>SS</sub> = 0.5 V                         | 0.05 | 0.1  |      | mA |

| <b>UVLO</b>                  |                            |                                                 |      |      |      |    |

| UVLO                         | UVLO threshold             | Wake up V <sub>REG5</sub> voltage               | 3.45 | 3.75 | 4.05 | V  |

|                              |                            | Hysteresis V <sub>REG5</sub> voltage            | 0.19 | 0.32 | 0.45 |    |

(2) 実製品の検査は行っていません。

## 製品情報

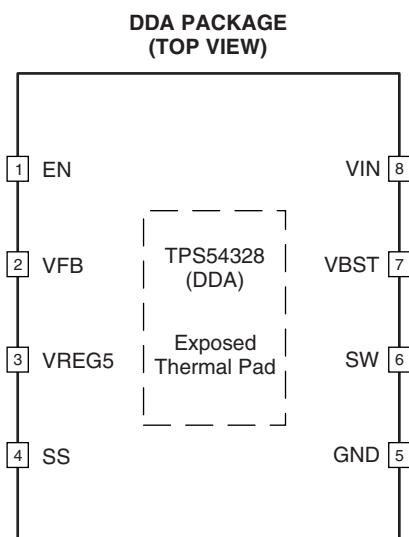

## ピン機能

| ピン               | 番号 | 説明                                                                                         |

|------------------|----|--------------------------------------------------------------------------------------------|

| 名前               |    |                                                                                            |

| EN               | 1  | イネーブル入力制御。アクティブ・ハイ。                                                                        |

| VFB              | 2  | コンバータの帰還入力。帰還分圧抵抗回路を使用して出力電圧に接続します。                                                        |

| VREG5            | 3  | 5.5V電源出力。GNDとの間にコンデンサ(標準1μF)を接続する必要があります。<br>ENが“Low”的とき、VREG5は非アクティブです。                   |

| SS               | 4  | ソフト・スタート制御。GNDとの間に外付けコンデンサを接続する必要があります。                                                    |

| GND              | 5  | グランド・ピン。スイッチング回路のパワー・グランド・リターンです。<br>ノイズに敏感なSSおよびVFBのリターンは、GNDに一点接続してください。                 |

| SW               | 6  | ハイサイドNFETおよびローサイドNFET用のスイッチ・ノード接続。                                                         |

| VBST             | 7  | ハイサイドFETゲート駆動回路の電源入力。VBSTピンとSWピンの間に0.1μFのコンデンサを接続します。<br>VREG5とVBSTの間には、内部でダイオードが接続されています。 |

| VIN              | 8  | 入力電源電圧ピン。                                                                                  |

| 露出した<br>サーマル・パッド | 裏側 | パッケージのサーマル・パッド。適切な放熱を実現するために、半田付けする必要があります。<br>GNDに接続してください。                               |

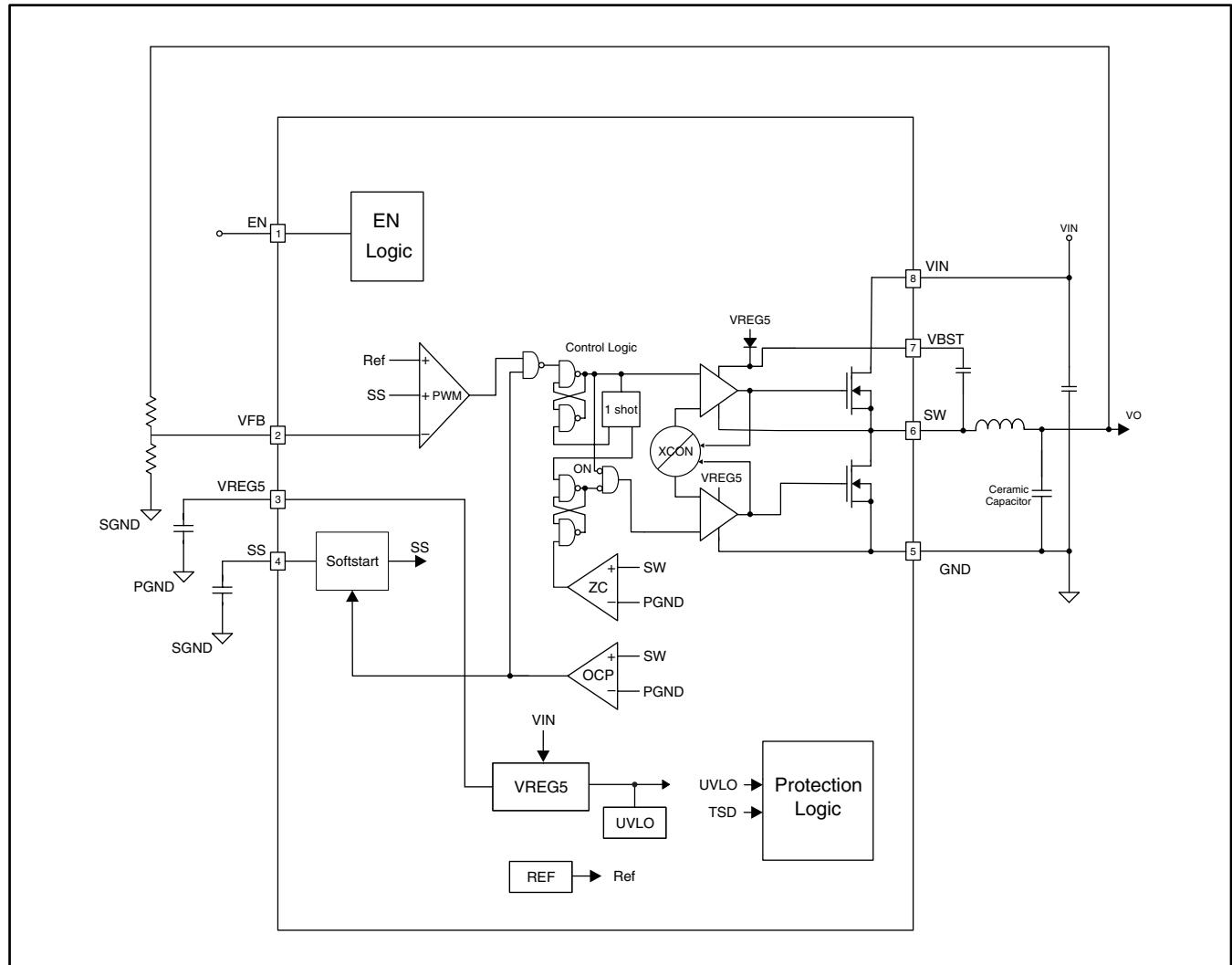

## 機能ブロック図

## 概要

TPS54328は、2つのNチャネルMOSFETを内蔵した、3Aの同期整流降圧型(バック)コンバータです。D-CAP2™モード制御を使用して動作します。D-CAP2™モード制御の高速過渡応答により、特定レベルの性能を満たすために必要な出力容量が小さくて済みます。独自の内部回路により、セラミックおよび特殊なポリマー・タイプを含めた低ESR出力コンデンサを使用可能です。

## 詳細説明

### PWM動作

TPS54328のメイン制御ループは、独自のD-CAP2™モード制御をサポートする適応型オン時間パルス幅変調(PWM)コントローラとなっています。D-CAP2™モード制御は、一定オン時間制御を、擬似固定周波数で外部部品数の少ない構成を可能にする内部補償回路と組み合わせたもので、低ESRコンデンサとセラミック出力コンデンサの両方を使用できます。出力にほとんどリップルがない状態でも安定して動作します。

各サイクルの開始時に、ハイサイドMOSFETがオンになります。

まず、内部のワンショット・タイマが終了すると、このMOSFETがオフになります。このワンショット・タイマの時間は、入力電圧範囲内で擬似固定周波数が維持されるように、コンバータの入力電圧(**VIN**)と出力電圧(**VO**)によって設定されます。そのため、これは適応型オン時間制御と呼ばれます。帰還電圧がリファレンス電圧を下回ると、ワンショット・タイマがリセットされ、ハイサイドMOSFETが再度オンになります。出力リップルをシミュレートするために、リファレンス電圧に内部ランプが追加され、これにより、D-CAP2™モード制御ではESRによる出力リップルが不要になります。

### PWM周波数と適応型オン時間制御

TPS54328は、適応型オン時間制御方式を採用し、専用の発振器は内蔵していません。入力電圧および出力電圧を使用してオン時間ワンショット・タイマを設定することにより、700kHzの擬似定周波数で動作します。オン時間は、入力電圧に逆比例し、出力電圧に比例するため、デューティ比が $V_{OUT}/V_{IN}$ のとき周波数は一定となります。

## 自動スキップEco-Mode™制御

TPS54328は、軽負荷時の効率を向上させる自動スキップEco-Mode™を備えています。重負荷状態から出力電流が減少すると、インダクタ電流も減少し、最終的にはそのリップル付きの“谷”がゼロ・レベルに達する点まで至ります。これは、連続導通モードと不連続導通モードの境界に当たります。ゼロ・インダクタ電流が検出されると、整流MOSFETがオフになります。負荷電流がさらに減少すると、コンバータは不連続導通モードに入ります。オン時間は連続導通モードのときとほぼ同じに保持されるため、出力コンデンサを小さな負荷電流でリフレンス電圧レベルまで放電するには、より長い時間がかかります。軽負荷動作電流  $I_{OUT(LL)}$ への遷移点は、式(1)で計算できます。

$$I_{OUT(LL)} = \frac{1}{2 \cdot L \cdot f_{SW}} \cdot \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{V_{IN}} \quad (1)$$

## ソフト・スタートおよびプリバイアス付きソフト・スタート

ソフト・スタート機能は調整可能です。ENピンが“High”になると、SSピンとGNDの間に接続されているコンデンサの充電が $2\mu A$ の電流によって開始されます。スタートアップ中には出力電圧のスムーズな制御が維持されます。スロー・スタート時間は式(2)で計算されます。VFB電圧は $0.765V$ 、SSピンのソース電流は $2\mu A$ です。

$$t_{SS}(ms) = \frac{C_6(nF) \times V_{REF}}{I_{SS}(\mu A)} = \frac{C_6(nF) \times 0.765}{2} \quad (2)$$

出力がプリバイアスされている状態で、スタートアップ中に出力から電流が流れ出すのを防止するために、TPS54328には独自の回路が搭載されています。ソフト・スタートでプリバイアス・レベルよりも高い電圧が指定される(内部ソフト・スタートが帰還電圧VFBよりも大きくなる)と、コントローラは、最初のローサイドFETゲート・ドライバ・パルスを狭いオン時間で開始することにより、ゆっくりと同期整流を起動します。次に、そのオン時間が $(1 - D)$ で示される時間と一致するまで( $D$ はコンバータのデューティ・サイクル)、オン時間をサイクル毎にインクリメントします。この方式により、プリバイアス出力の初期シンクを防ぐとともに、出力電圧(VO)は立ち上がり後スムーズにリギュレーション状態まで上昇し、また、制御ループがプリバイアス・スタートアップから通常モード動作へと遷移するために十分な時間が確保されます。

## 電流保護

出力過電流保護(OCP)は、サイクル毎のバレー検出制御回路を使用して実現されています。SWピンとGNDの間のローサイドFETスイッチ電圧を測定することで、スイッチ電流がモニタされます。この電圧は、スイッチ電流に比例します。精度を向上させるため、電圧センスは温度補償されます。

ハイサイドFETスイッチのオン時間中、スイッチ電流は、 $V_{IN}$ 、 $V_{OUT}$ 、オン時間、および出力インダクタ値によって決定されるリニアなレートで増加します。ローサイドFETスイッチのオン時間中は、この電流はリニアに減少します。スイッチ電流の平均値が、負荷電流 $I_{out}$ です。TPS54328はローサイドFETのオン時間の間、スイッチ電流に比例するローサイドFETスイッチ電圧を継続的にモニタします。測定された電圧が、電流制限に比例した電圧よりも高い場合は、測定電圧が電流制限に対応した電圧を下回るまで、各SWサイクルで内部カウンタがインクリメントされ、コンバータはローサイド・スイッチをオンに維持します。下回った時点では、スイッチング・サイクルが終了し、新しいスイッチング・サイクルが開始されます。以降のスイッチング・サイクルでは、オン時間が固定値に設定され、同じ方法で電流がモニタされます。過電流状態が連続7スイッチング・サイクルにわたって続いた場合、内部OCLスレッショルドがより低いレベルに設定され、可能な出力電流が減少します。1つのスイッチング・サイクルを通して、スイッチ電流が低いOCLスレッショルドを超えると、カウンタがリセットされ、OCL制限は高い値に戻ります。

このようなタイプの過電流保護には、いくつかの重要な考慮事項があります。負荷電流は、ピーク・ツー・ピーク・インダクタ電流の $1/2$ だけ過電流スレッショルドよりも高くなります。また、電流が制限されている間は、出力電圧が低下する傾向があります。これは、必要な負荷電流が、コンバータから供給される電流よりも高い場合があるためです。それによって出力電圧が降下する可能性があります。過電流状態が解消されると、出力電圧がリギュレーション電圧に戻ります。これは非ラッチ方式の保護です。

## UVLO保護

低電圧ロックアウト保護(UVLO)は、VREG5ピンの電圧を監視します。VREG5電圧がUVLOスレッショルド電圧を下回ると、TPS54328がオフになります。これは非ラッチ方式の保護です。

## 過熱シャットダウン

TPS54328は、自身の温度を監視しています。温度がスレッショルド値(標準 $165^{\circ}\text{C}$ )を超えると、デバイスがシャットダウンされます。これは非ラッチ方式の保護です。

## 標準的特性

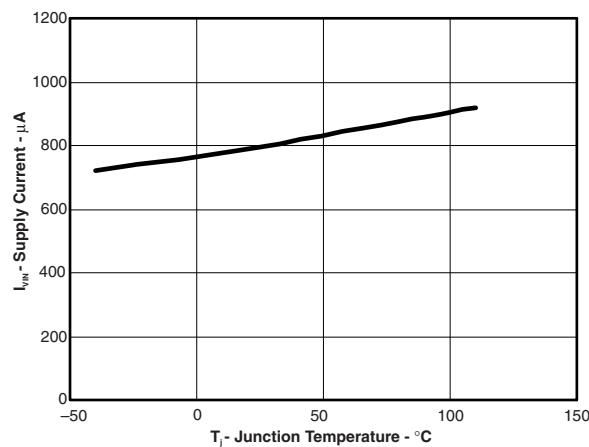

図 1. VIN電流 対 接合部温度

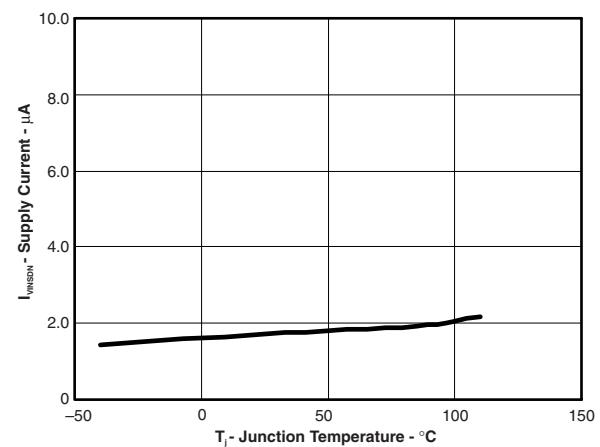

図 2. VINシャットダウン電流 対 接合部温度

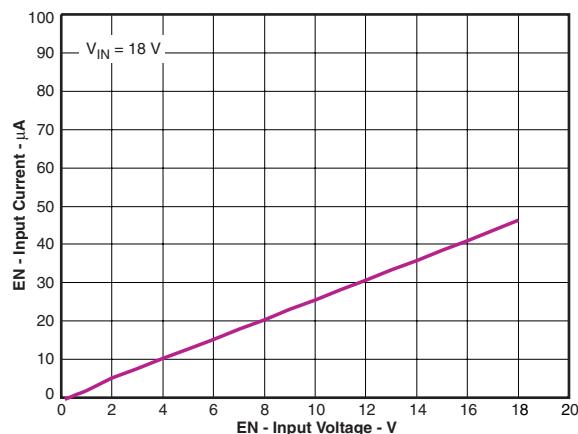

図 3. EN電流 対 EN電圧

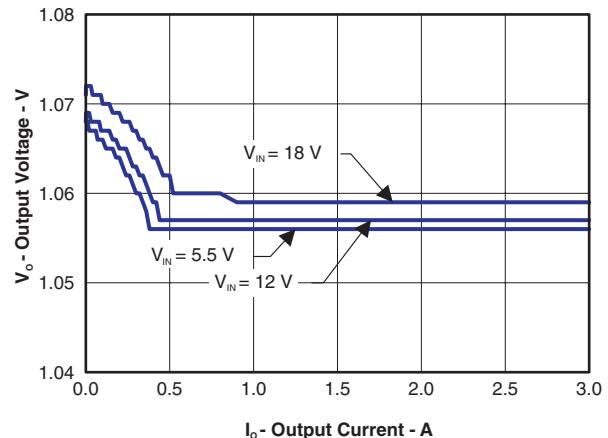

図 4. 1.05V出力電圧 対 出力電流

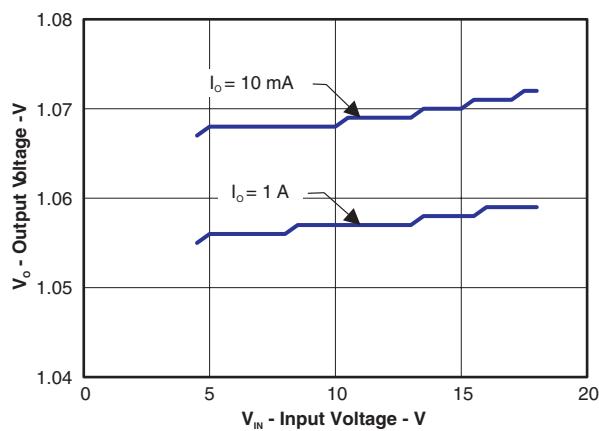

図 5. 1.05V出力電圧 対 入力電圧

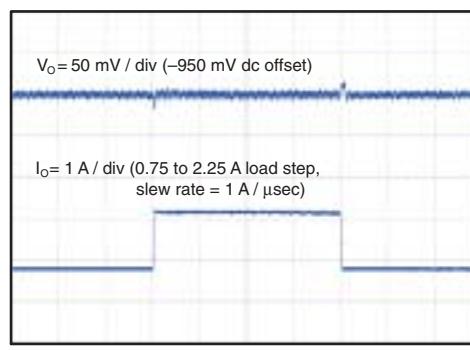

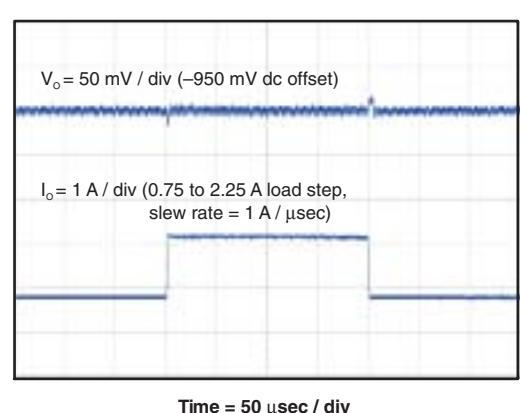

図 6. 1.05V負荷過渡応答

## 標準的特性

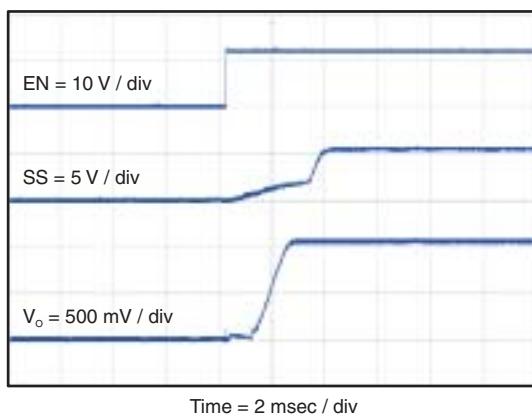

図 7. スタートアップ波形

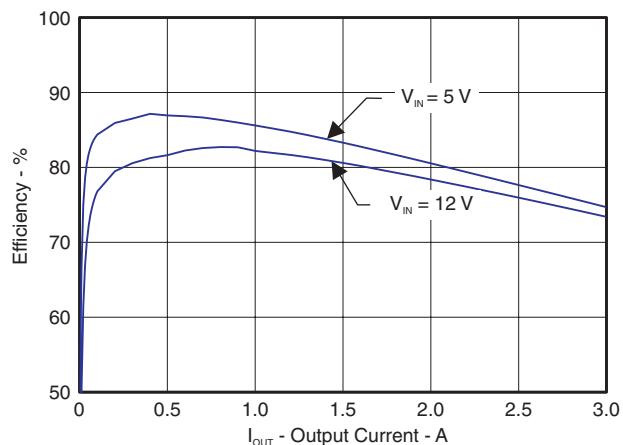

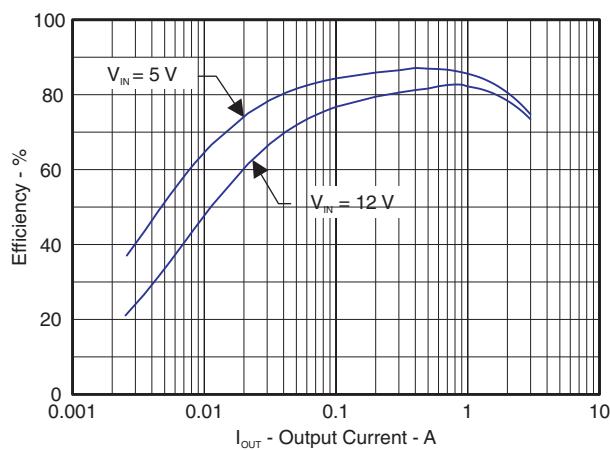

図 8. 効率 対 出力電流

図 9. 軽負荷効率 対 出力電流

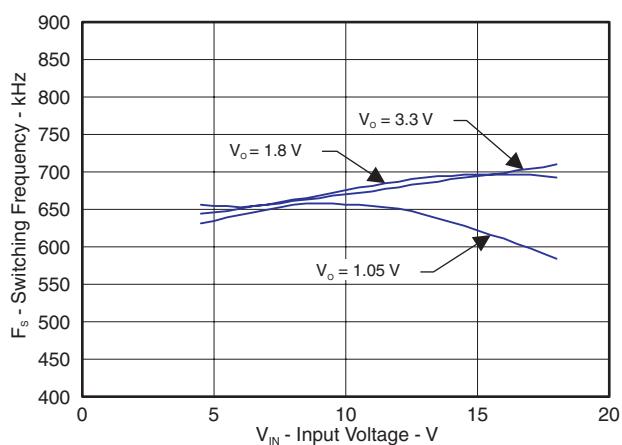

図 10. スイッチング周波数 対 入力電圧

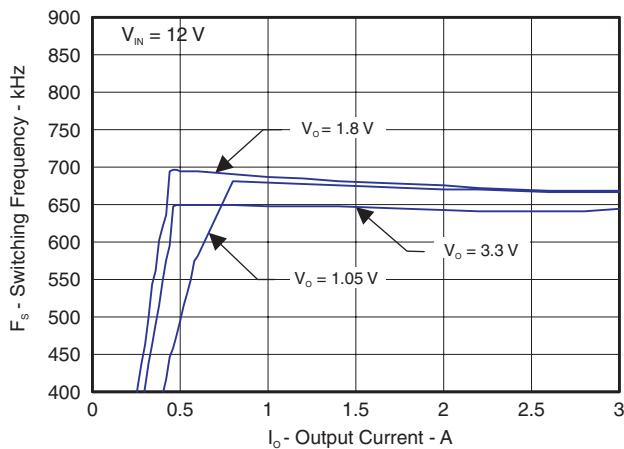

図 11. スイッチング周波数 対 出力電流

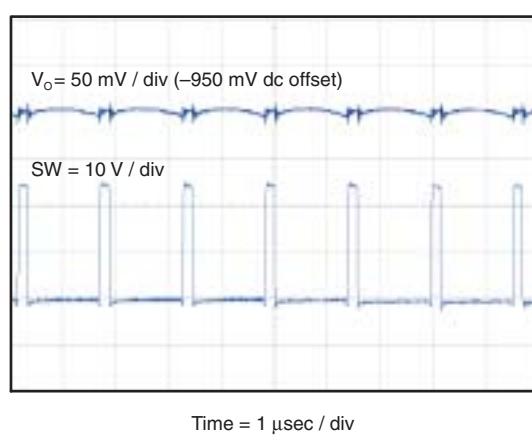

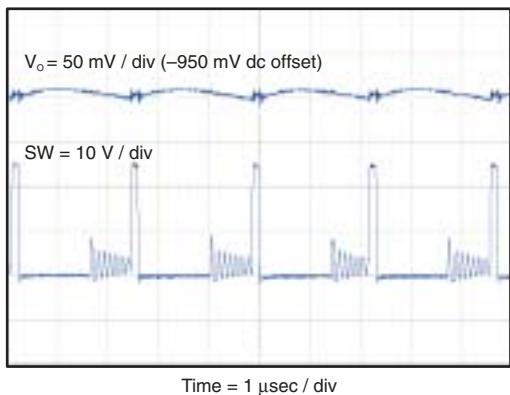

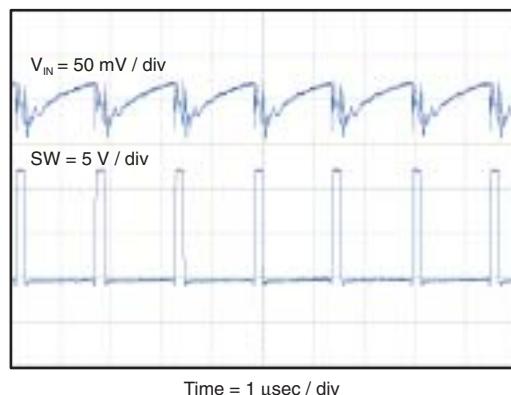

図 12. 出力電圧リップル ( $I_O = 3\text{A}$ )

## 標準的特性

図 13. DCM出力電圧リップル ( $I_0 = 30\text{mA}$ )

図 14. 入力電圧リップル ( $I_0 = 3\text{A}$ )

# 設計ガイド

## ステップ毎の設計手順

設計プロセスを開始するには、いくつかのアプリケーション・パラメータについて知っておく必要があります。

- 入力電圧範囲

- 出力電圧

- 出力電流

- 出力電圧リップル

- 入力電圧リップル

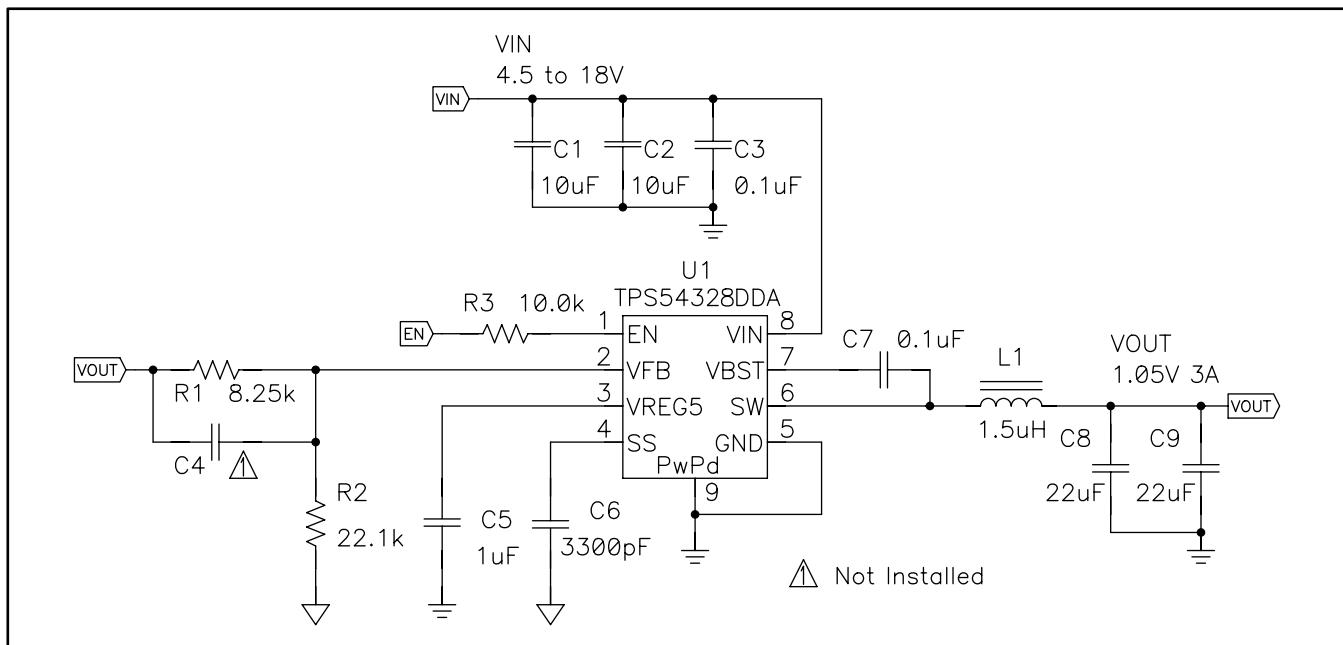

## 出力電圧抵抗の選択

出力電圧は、出力ノードとVFBピンとの間の抵抗分圧回路によって設定されます。公差1%以内の分圧抵抗を使用することを推奨します。最初は、式(3)を使用して $V_{OUT}$ を計算します。

非常に軽い負荷での効率を向上させるには、より大きな値の抵抗の使用を考慮します。ただし、抵抗が大きすぎると、ノイズの影響を受けやすくなり、VFB入力電流からの電圧誤差が目立つようになります。

$$V_{OUT} = 0.765 \times \left(1 + \frac{R_1}{R_2}\right) \quad (3)$$

## 出力フィルタの選択

TPS54328で使用する出力フィルタは、LC回路です。このLCフィルタは、下記の周波数に二重極を持ちます。

$$F_P = \frac{1}{2\pi\sqrt{L_{OUT} \times C_{OUT}}} \quad (4)$$

低周波数では、出力設定点分圧抵抗回路、およびTPS54328の内部ゲインによって、全体のループ・ゲインが設定されます。低周波数での位相は180度です。出力フィルタの極周波数では、ディケードごとにゲインが-40dBロールオフし、位相は急速に減少します。D-CAP2™によって高周波数のゼロが導入されることで、ゲインのロールオフがディケードあたり-20dBに減り、位相はゼロ周波数の1ディケード上で90度に増加します。出力フィルタに対して選択されるインダクタとコンデンサは、式(4)の二重極が高周波ゼロより低く、かつ十分近い値(位相ブーストが得られ、高周波ゼロによって回路安定化のための十分な位相マージンが得られるように)となるよう選択する必要があります。この要件を満足するための推奨値を表1に示します。

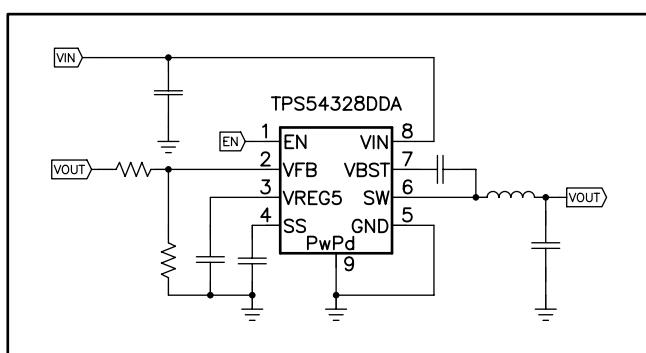

図 15. 設計例の回路図

| 出力電圧 (V) | R1 (kΩ) | R2 (kΩ) | C4 (pF) | L1 (μH) | C8 + C9 (μF) |

|----------|---------|---------|---------|---------|--------------|

| 1        | 6.81    | 22.1    |         | 1.5     | 22 - 68      |

| 1.05     | 8.25    | 22.1    |         | 1.5     | 22 - 68      |

| 1.2      | 12.7    | 22.1    |         | 1.5     | 22 - 68      |

| 1.8      | 30.1    | 22.1    | 5 - 22  | 2.2     | 22 - 68      |

| 2.5      | 49.9    | 22.1    | 5 - 22  | 2.2     | 22 - 68      |

| 3.3      | 73.2    | 22.1    | 5 - 22  | 2.2     | 22 - 68      |

| 5        | 124     | 22.1    | 5 - 22  | 3.3     | 22 - 68      |

| 6.5      | 165     | 22.1    | 5 - 22  | 3.3     | 22 - 68      |

表 1. 推奨部品値

DDCゲインは出力電圧に依存するため、出力電圧が高くなると必要なインダクタ値も増加します。1.8V以上の高出力電圧では、R1と並列にフィードフォワード・コンデンサ(C4)を追加することにより、追加の位相ブーストを実現できます。

インダクタのピーク・ツー・ピーク・リップル電流、ピーク電流、およびRMS電流は、式(5)、式(6)、および式(7)で求めることができます。インダクタの飽和電流定格は、ピーク電流の計算値より大きい必要があります。RMSまたは加熱電流定格は、RMS電流の計算値より大きい必要があります。

$f_{SW}$ には700kHzを使用します。選択したインダクタが、式(6)のピーク電流および式(7)のRMS電流の定格を満たすことを確認してください。

$$I_{IPP} = \frac{V_{OUT}}{V_{IN(max)}} \times \frac{V_{IN(max)} - V_{OUT}}{L_O \times f_{SW}} \quad (5)$$

$$I_{peak} = I_O + \frac{I_{IPP}}{2} \quad (6)$$

$$I_{Lo(RMS)} = \sqrt{I_O^2 + \frac{1}{12} I_{IPP}^2} \quad (7)$$

この設計例では、ピーク電流の計算値が3.49A、RMS電流の計算値が3.01Aです。ここでは、インダクタとしてTDKのSPM6530-1R5M100を使用し、ピーク電流定格は11.5A、RMS電流定格は11Aです。

コンデンサの値とESRによって、出力電圧リップルの大きさが決まります。TPS54328は、セラミックまたは他の低ESRコンデンサとともに使用するよう設計されています。推奨値の範囲は22μF～68μFです。出力コンデンサに対して必要なRMS電流定格は、式(8)で求められます。

$$I_{Co(RMS)} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{\sqrt{12} \times V_{IN} \times L_O \times f_{SW}} \quad (8)$$

この設計では、出力コンデンサとしてTDKのC3216X5R0J226M(22μF)を2個使用します。標準ESRはそれぞれ2mΩです。RMS電流の計算値は0.271Aであり、各出力コンデンサの定格は4Aです。

## 入力コンデンサの選択

TPS54328には、入力デカップリング・コンデンサと、アプリケーションによってはバルク・コンデンサが必要となります。デカップリング・コンデンサには、10μF以上のセラミックコンデンサを推奨します。過電流制限機能の安定性を向上させるため、ピン14とグランドの間に0.1μFのコンデンサを追加することを推奨します。コンデンサの電圧定格は、最大入力電圧よりも大きい必要があります。

## ブートストラップ・コンデンサの選択

適切な動作のためには、VBSTピンとSWピンの間に0.1μFのセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

## VREG5コンデンサの選択

適切な動作のためには、VREG5ピンとGNDピンの間に1μFのセラミック・コンデンサを接続する必要があります。セラミック・コンデンサの使用を推奨します。

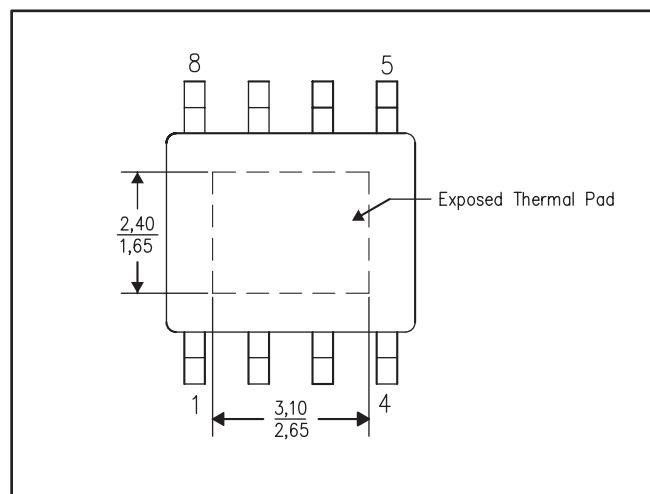

## 熱特性について

この8ピンDDAパッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。サーマル・パッドは、プリント基板(PCB)に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

露出したサーマル・パッドについての追加情報およびその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD™ Thermally Enhanced Package』(TI文献番号SLMA002)およびアプリケーション・ブリーフ『PowerPAD™ Made Easy』(TI文献番号SLMA004)を参照してください。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

図 16. サーマル・パッドの寸法

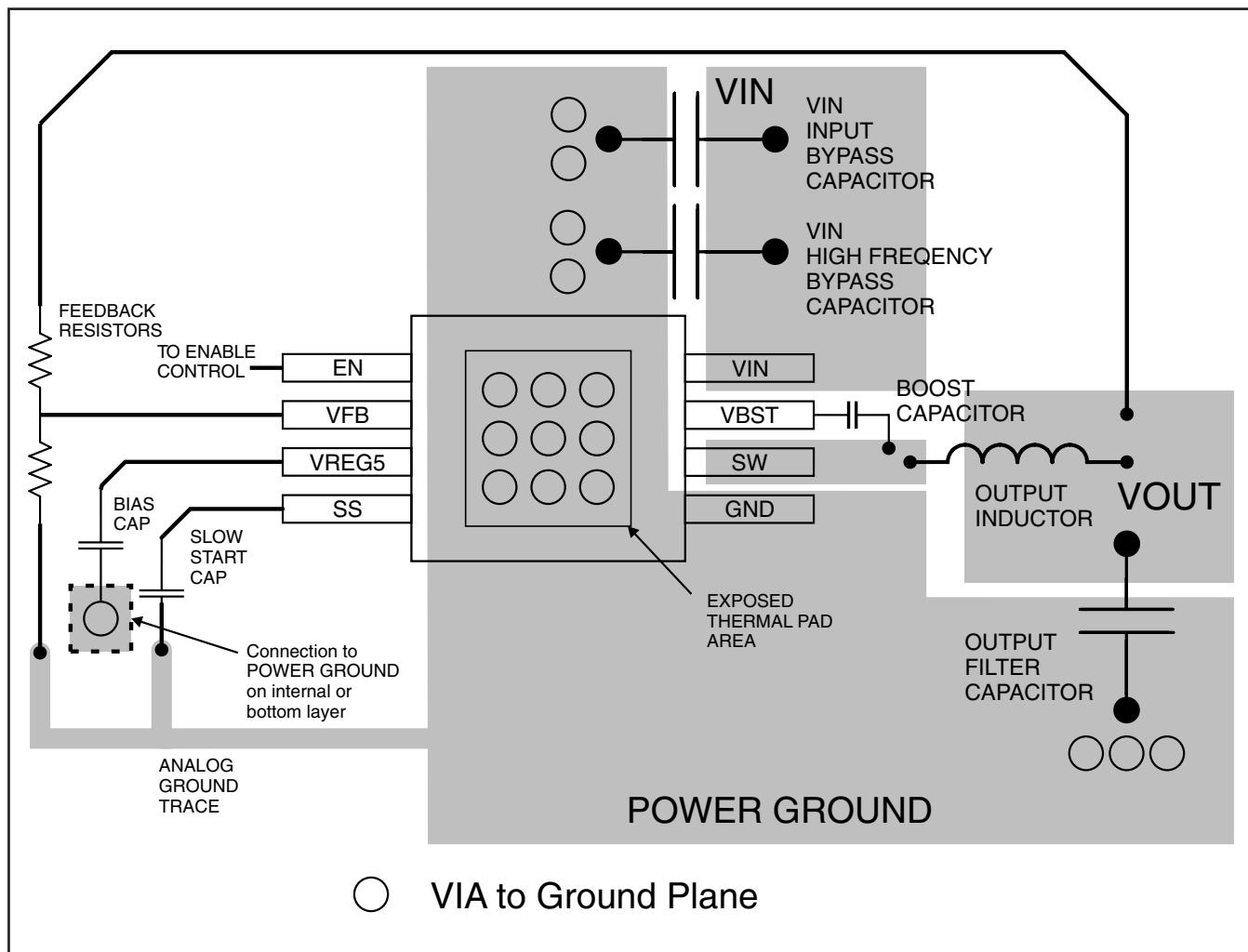

## レイアウトについての考慮事項

1. 入力スイッチング電流ループは可能な限り小さくします。

2. 寄生容量およびインダクタンスを低減し、放射を最小限に抑えるために、SWノードは物理的に可能な限り小さく、かつ短くします。出力とデバイスの帰還ピンとの間に、ケルビン接続を使用してください。

3. アナログ部品と非スイッチング部品は、スイッチング部品から離して配置します。

4. 信号グランドと電源グランドは一点接続します。

5. デバイスの下をスイッチング電流が流れないようにしてください。

6. VINおよびPGNDのパターン・ラインを幅広くします。

7. デバイスの露出したパッドは、PGNDに半田付けする必要があります。

8. VREG5コンデンサは、デバイスの近くに配置し、PGNDに接続する必要があります。

9. 出力コンデンサは、PGNDの幅広いパターンに接続する必要があります。

10. 電圧帰還ループはできる限り短くし、可能であればグラウンド・シールドを使用します。

11. VFBピンに接続される分圧回路の下側の抵抗は、SGNDに接続する必要があります。

12. VIN、SW、およびPGND接続に対しては、十分なビアを設けることを推奨します。

13. VIN、SW、およびPGNDのPCBパターンは、可能な限り幅広くします。

14. VINコンデンサは、可能な限りデバイスの近くに配置します。

図 17. PCBレイアウト

# パッケージ情報

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples (Requires Login) |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|--------------------------|

| TPS54328DDA      | ACTIVE                | SO PowerPAD  | DDA             | 8    | 75          | Green (RoHS & no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1 YEAR          |                          |

| TPS54328DDAR     | ACTIVE                | SO PowerPAD  | DDA             | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1 YEAR          |                          |

(1) マーケティング・ステータスは次のように定義されています。

**ACTIVE** : 製品デバイスが新規設計用に推奨されています。

**LIFEBUY** : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

**NRND** : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

**PREVIEW** : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

**OBSOLETE** : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) および Green (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

**TBD** : Pb-Free/Green変換プランが策定されていません。

**Pb-Free (RoHS)** : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

**Pb-Free (RoHS Exempt)** : この部品は、1)ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2)ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS)と考えられます。

**Green (RoHS & no Sb/Br)** : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項** : このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TI パーツの購入価格の合計金額を超える責任は負いかねます。

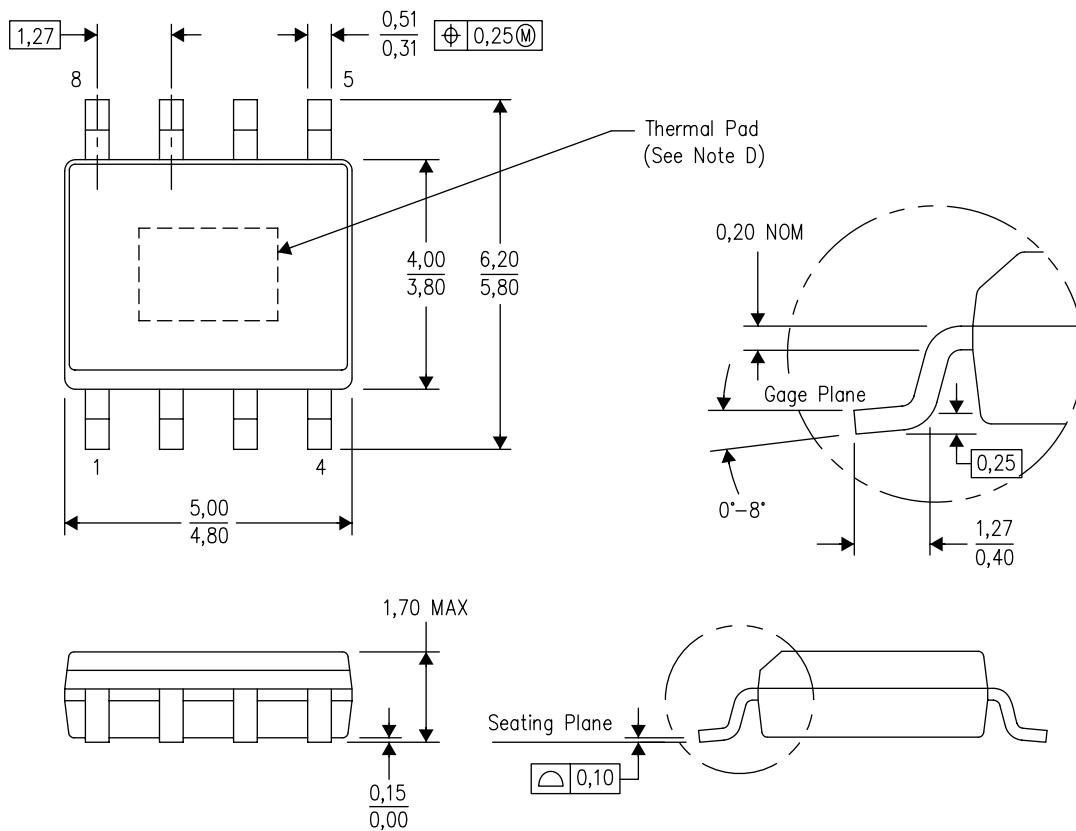

# メカニカル・データ

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL-OUTLINE

4202561/E 09/10

- 全ての線寸法の単位はミリメートルです。

- 図は予告なく変更することがあります。

- 本体寸法にはバリや突起を含みません。バリおよび突起は、各辺0,15を超えてはなりません。

- このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)を参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

- JEDEC MO-012 variationBAに適合しています。

# サーマルパッド・メカニカル・データ

DDA (R-PDSO-G8)

## 熱特性について

このPowerPAD™パッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板(PCB)に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD™パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)およびアプリケーション・ブリーフ『PowerPAD Made Easy』(TI文献番号SLMA004)を参照してください。いずれもホームページ [www.ti.com](http://www.ti.com)で入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

注：寸法はすべてミリメートル単位です。

露出サーマル・パッドの寸法

(SLVSAN2)

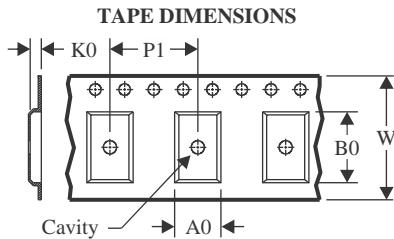

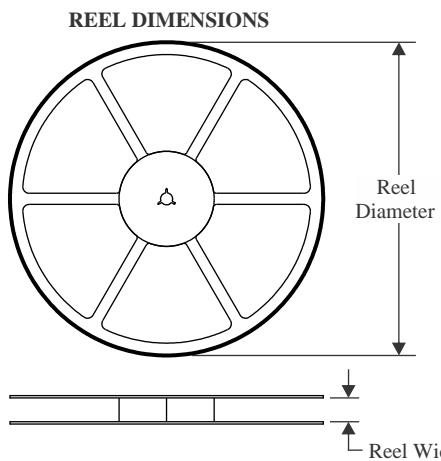

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

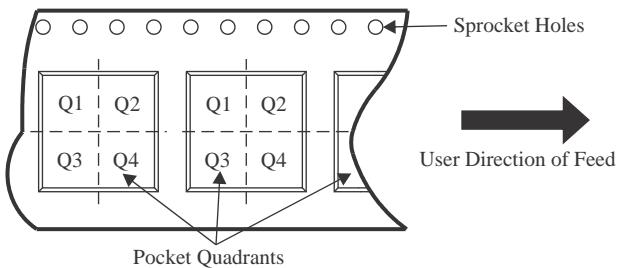

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54328DRCR | VSON         | DRC             | 10   | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TPS54328DRCT | VSON         | DRC             | 10   | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

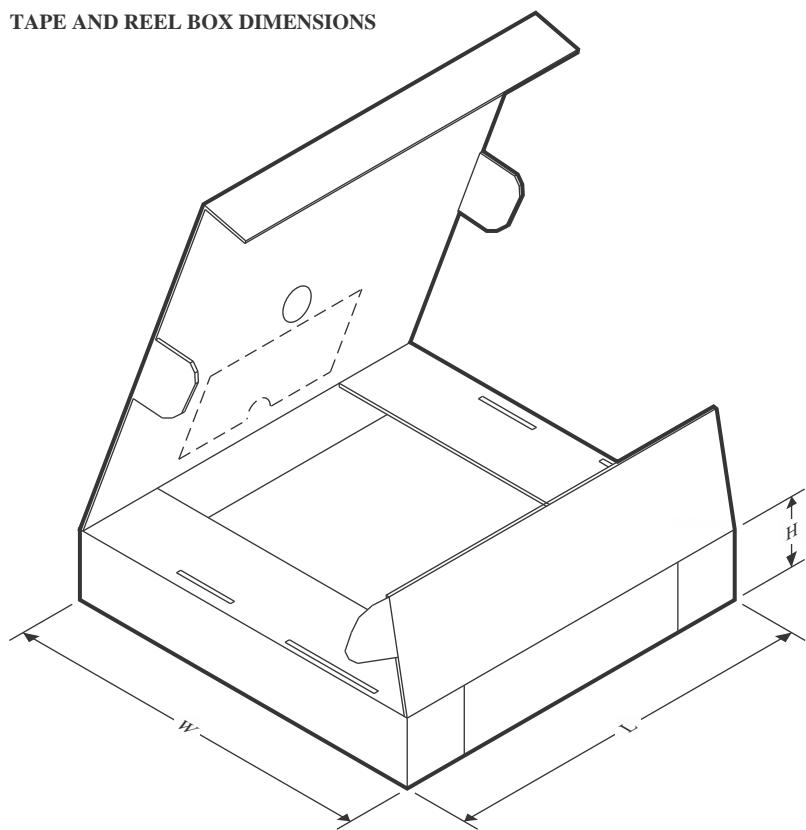

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54328DRCR | VSON         | DRC             | 10   | 3000 | 335.0       | 335.0      | 25.0        |

| TPS54328DRCT | VSON         | DRC             | 10   | 250  | 182.0       | 182.0      | 20.0        |

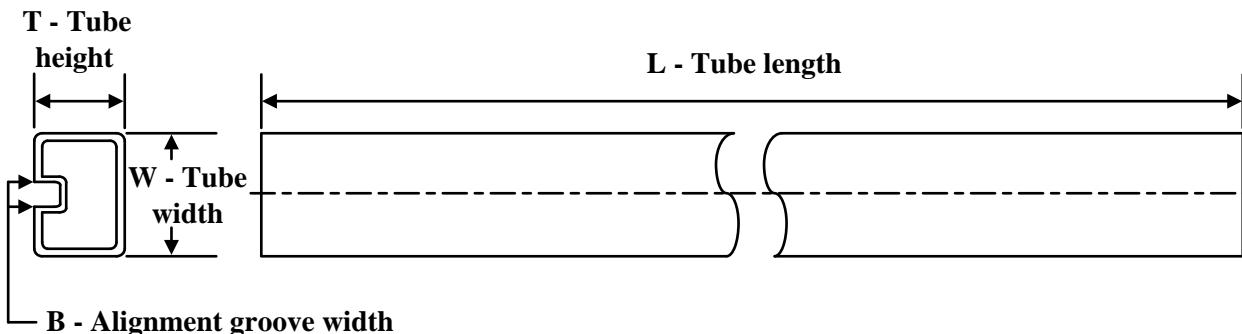

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54328DDA   | DDA          | HSOIC        | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54328DDA   | DDA          | HSOIC        | 8    | 75  | 517    | 7.87   | 635          | 4.25   |

| TPS54328DDA.A | DDA          | HSOIC        | 8    | 75  | 517    | 7.87   | 635          | 4.25   |

| TPS54328DDA.A | DDA          | HSOIC        | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| TPS54328DDA.B | DDA          | HSOIC        | 8    | 75  | 517    | 7.87   | 635          | 4.25   |

| TPS54328DDA.B | DDA          | HSOIC        | 8    | 75  | 507    | 8      | 3940         | 4.32   |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月