**TPS543620**

JAJSJT8C - MAY 2020 - REVISED JUNE 2021

# TPS543620 4V~18V 入力、6A 同期整流 SWIFT™ 降圧コンバータ、内部補償型 高度電流モード制御付き

# 1 特長

- 固定周波数、内部補償型の高度な電流モード (ACM) 制御

- 25mΩ および 6.5mΩ の MOSFET を内蔵

- 入力電圧範囲:4V~18V

- 出力電圧範囲:0.5V~7V

- 制御ループ性能を最適化する3つの選択可能な PWM ランプ・オプション

- 5 つの選択可能なスイッチング周波数:500kHz、 750kHz、1MHz、1.5MHz、2.2MHz

- 外部クロックに同期可能

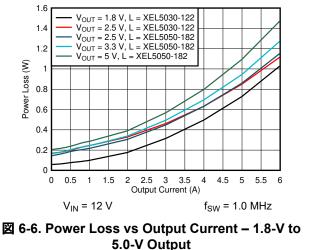

- 全温度範囲にわたって、0.5V、±0.5%の基準電圧精 度

- 選択可能なソフト・スタート時間:0.5ms、1ms、2ms、 4ms

- プリバイアスされた出力への単調なスタートアップ

- 6A および 3A 動作をサポートする選択可能な電流制 郘

- 調整可能な低電圧誤動作防止を備えたイネーブル

- パワー・グッド出力モニタ

- 出力過電圧、出力低電圧、入力低電圧、過電流、過 ٠ 熱保護

- TPS543820 および TPS543320 とピン互換

- 動作時接合部温度:-40℃~150℃

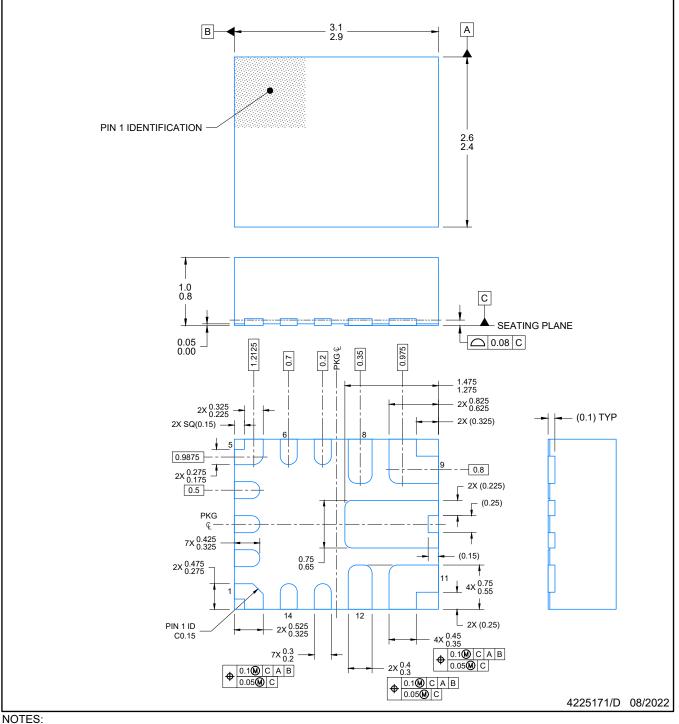

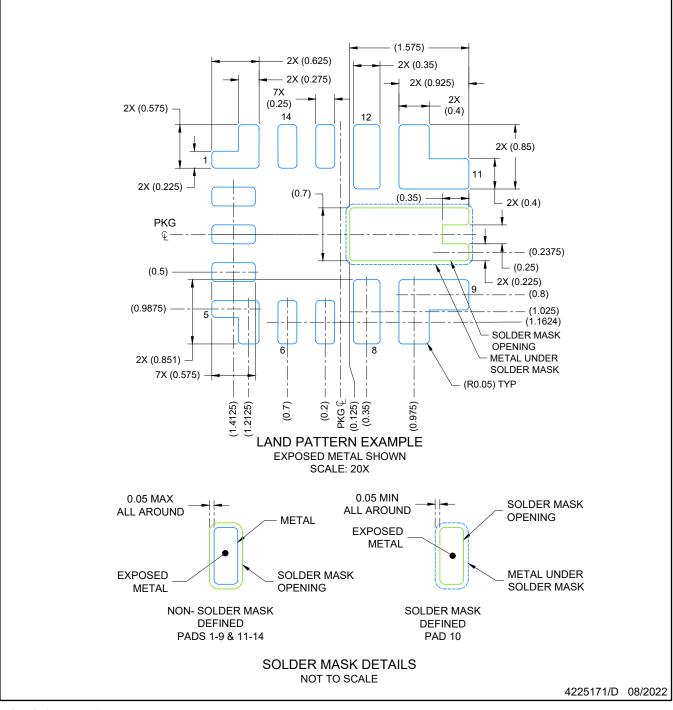

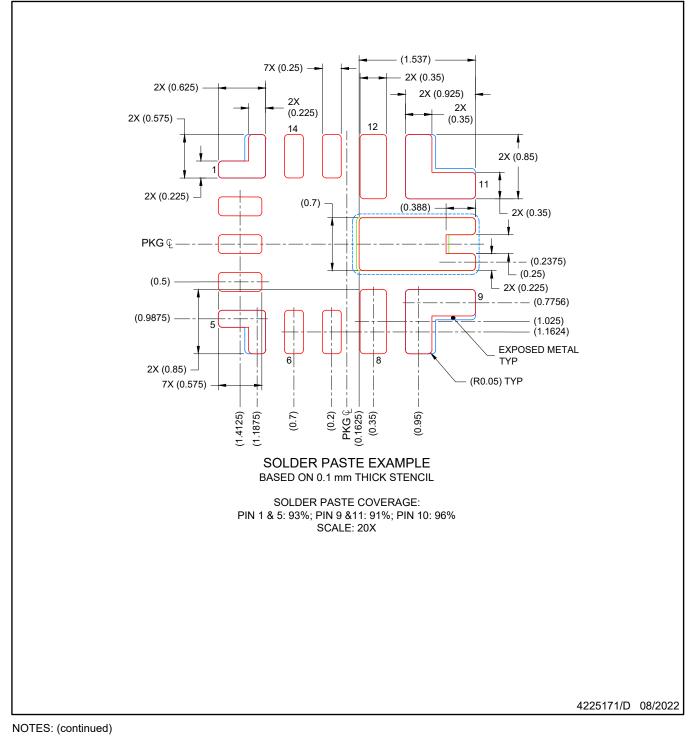

- 2.5mm × 3mm の 14 ピン VQFN-HR パッケージ、 0.5mm ピッチ

# 2 アプリケーション

- ワイヤレス・インフラと有線通信機器

- 光およびファイバ・ネットワーク

- 試驗 / 測定機器

- 医療/ヘルスケア

# 3 概要

TPS543620 は、高効率の 18V、6A 同期整流降圧コンバ ータで、内部補償された固定周波数の高度な電流モード 制御を採用しています。最大 2.2MHz のスイッチング周波 数で動作しながら、高い効率を実現できます。このデバイ スは小型の 2.5mm x 3mm HotRod<sup>™</sup> VQFN パッケージ で、高い周波数で高い効率を実現しているため、小型のソ リューション・サイズを必要とする設計に最適です。固定周 波数コントローラは 500kHz~2.2MHz で動作でき、 SYNC ピンを使用して外部クロックに同期できます。追加 機能として、高精度の基準電圧、選択可能なソフト・スター ト時間、プリバイアス出力への単調なスタートアップ、選択 可能な電流制限、EN ピンにより調整可能な UVLO、多岐 にわたるフォルト保護があります。

#### 製品情報

|           | 200 COL 11 2 1 20    |                 |

|-----------|----------------------|-----------------|

| 部品番号      | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

| TPS543620 | VQFN-HR (14)         | 2.50mm × 3.00mm |

利用可能なすべてのパッケージについては、このデータシートの (1) 末尾にある注文情報を参照してください。

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                 | 1              |

|--------------------------------------|----------------|

| 2 アプリケーション                           | 1              |

| 3 概要                                 | 1              |

| 4 Revision History                   | 2              |

| 5 Pin Configuration and Functions    | 3              |

| 6 Specifications                     | 4              |

| 6.1 Absolute Maximum Ratings         | 4              |

| 6.2 ESD Ratings                      | 4              |

| 6.3 Recommended Operating Conditions |                |

| 6.4 Thermal Information              | 4              |

| 6.5 Electrical Characteristics       | 5              |

| 6.6 Typical Characteristics          | 7              |

| 7 Detailed Description               | <mark>9</mark> |

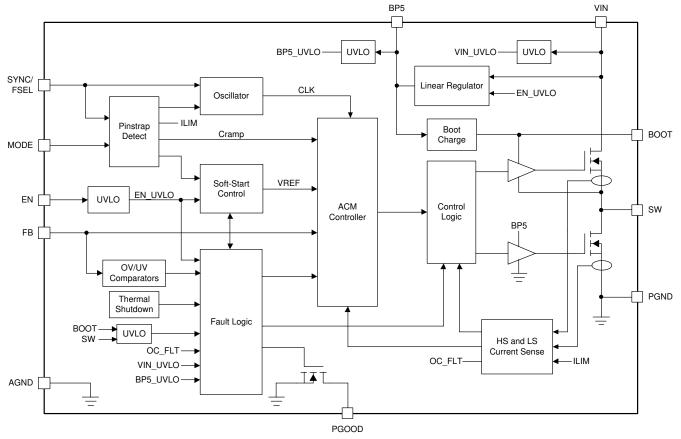

| 7.1 Overview                         | 9              |

| 7.2 Functional Block Diagram         | 9              |

| 7.3 Feature Description              |                |

| 7.4 Device Functional Modes                           | .17  |

|-------------------------------------------------------|------|

| 8 Application and Implementation                      | . 18 |

| 8.1 Application Information                           | . 18 |

| 8.2 Typical Applications                              |      |

| 9 Power Supply Recommendations                        |      |

| 10 Layout                                             |      |

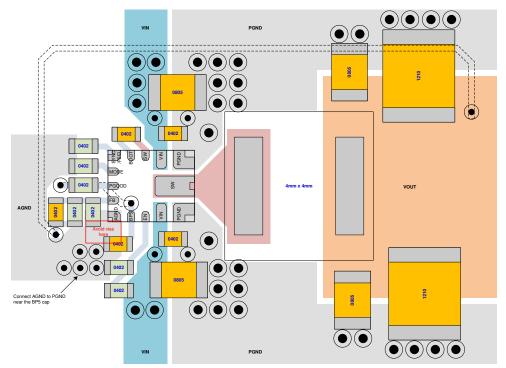

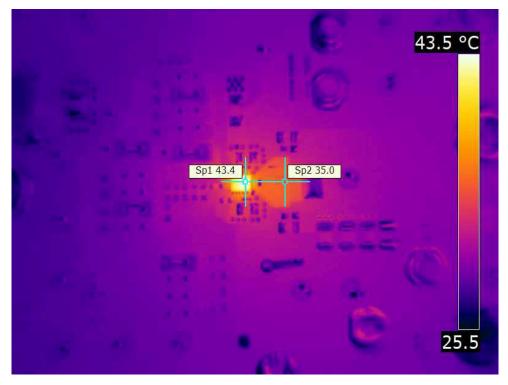

| 10.1 Layout Guidelines                                |      |

| 10.2 Layout Example                                   |      |

| 11 Device and Documentation Support                   |      |

| 11.1 Receiving Notification of Documentation Updates. | .41  |

| <b>11.2</b> サポート・リソース                                 | .41  |

| 11.3 Trademarks                                       |      |

| 11.4 Electrostatic Discharge Caution                  |      |

| 11.5 Glossary                                         |      |

| 12 Mechanical, Packaging, and Orderable               |      |

| Information                                           | .42  |

|                                                       |      |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision B (February 2021) to Revision C (June 2021) | Page |

|---|------------------------------------------------------------------|------|

| • | Changed 10-ns transient to 20-ns transient                       |      |

| • | Changed VIN to SW, transient 20 ns min value to -6               | 4    |

|   | Changed SW, transient 20 ns min value to -5                      |      |

|   | Changed max V <sub>OUT</sub> to 7 V                              |      |

|   | Added T <sub>OFF(min)</sub> max value                            |      |

| • | Added text for considering minimum off-time for fsw selection    | 19   |

| C | hanges from Revision A (November 2020) to Revision B (February 2021) | Page |

|---|----------------------------------------------------------------------|------|

| • | TPS543820 および TPS543320 ピン互換デバイスへのリンクを追加                             | 1    |

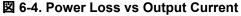

| • | Added 🗵 6-6                                                          | 7    |

| • | Updated 🗵 10-1                                                       | 38   |

| C | hanges from Revision * (May 2020) to Revision A (November 2020) | Page |

|---|-----------------------------------------------------------------|------|

| • | デバイス・ステータスを「事前情報」から「量産データ」に変更                                   | 1    |

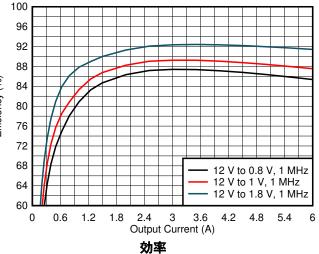

# **5** Pin Configuration and Functions

#### 表 5-1. Pin Functions

| PIN       |       | I/O | DESCRIPTION                                                                                                                                                                                                     |  |  |

|-----------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                     |  |  |

| SYNC/FSEL | 1     | I   | Frequency select and external clock synchronization. A resistor to ground sets the switching frequency of the device. An external clock can also be applied to this pin to synchronize the switching frequency. |  |  |

| MODE      | 2     | I   | A resistor to ground selects the current limit, soft start rate, and PWM ramp amplitude.                                                                                                                        |  |  |

| PGOOD     | 3     | 0   | Open-drain power good indicator                                                                                                                                                                                 |  |  |

| FB        | 4     | I   | Feedback pin for output voltage regulation. Connect this pin to the midpoint of a resistor divider to set the output voltage.                                                                                   |  |  |

| AGND      | 5     | -   | Ground return for internal analog circuits                                                                                                                                                                      |  |  |

| BP5       | 6     | 0   | Internal 4.5-V regulator output. Bypass this pin with a 2.2-µF capacitor to AGND.                                                                                                                               |  |  |

| EN        | 7     | I   | Enable pin. Float to enable, enable/disable with an external signal, or adjust the input undervoltage lockout with a resistor divider.                                                                          |  |  |

| VIN       | 8, 12 | I   | Input power to the power stage. Low impedance bypassing of these pins to PGND is critical.<br>A 10-nF to 100-nF capacitor from each VIN to PGND close to IC is required.                                        |  |  |

| PGND      | 9, 11 | -   | Ground return for the power stage. This pin is internally connected to the source of the low-side MOSFET.                                                                                                       |  |  |

| SW        | 10    | 0   | Switch node of the converter. Connect this pin to the output inductor.                                                                                                                                          |  |  |

| SW        | 13    | 0   | Return path for the internal high-side MOSFET gate driver bootstrap capacitor. Connect a capacitor from BOOT to this pin. The SW pins are connected internally.                                                 |  |  |

| воот      | 14    | I   | Supply for the internal high-side MOSFET gate driver. Connect a capacitor from this pin to SW.                                                                                                                  |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                |                                             | MIN  | МАХ | UNIT |

|------------------------------------------------|---------------------------------------------|------|-----|------|

| Input voltage                                  | VIN                                         | -0.3 | 20  | V    |

| Input voltage                                  | VIN to SW, DC                               | -0.3 | 20  | V    |

| Input voltage                                  | VIN to SW, transient 20 ns                  | -6   | 25  | V    |

| Input voltage                                  | BOOT                                        | -0.3 | 25  | V    |

| Input voltage                                  | BOOT to SW                                  | -0.3 | 6   | V    |

| Input voltage                                  | EN, PGOOD, MODE, SYNC/FSEL, FB              | -0.3 | 6   | V    |

| Output voltage                                 | SW, DC                                      | -0.3 | 20  | V    |

| Output voltage                                 | SW, transient 20 ns                         | -5   | 22  | V    |

| Operating junction temperature, T <sub>J</sub> | Operating junction temperature, $T_{\rm J}$ | -40  | 150 | °C   |

| Storage temperatur                             | e, T <sub>stg</sub>                         | -55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                | MIN | NOM | MAX  | UNIT |

|-------------------|--------------------------------|-----|-----|------|------|

| Input voltage     | V <sub>IN</sub>                | 4   |     | 18   | V    |

| Output voltage    | V <sub>OUT</sub>               | 0.5 |     | 7    | V    |

| Output current    | I <sub>OUT</sub>               |     |     | 6    | A    |

| TJ                | Operating junction temperature | -40 |     | 150  | °C   |

| f <sub>SYNC</sub> | External clock frequency       | 400 |     | 2600 | kHz  |

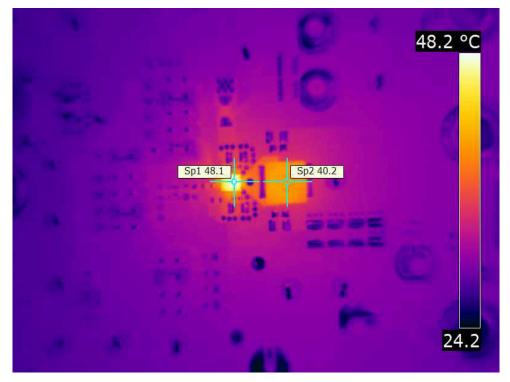

## 6.4 Thermal Information

|                       |                                              | TPS                                                      |                               |      |

|-----------------------|----------------------------------------------|----------------------------------------------------------|-------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | METRIC <sup>(1)</sup> RPY (QFN, JEDEC) RPY (QFN, TI EVM) |                               | UNIT |

|                       |                                              | 14 PINS                                                  | 14 PINS                       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 58.9                                                     | 29.1                          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 37.8                                                     | Not applicable <sup>(2)</sup> | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 7.3                                                      | Not applicable <sup>(2)</sup> | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.9                                                      | 1.8                           | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 7.2                                                      | 13.4                          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Not applicable to an EVM layout.

# **6.5 Electrical Characteristics**

$T_J = -40$  °C to +150°C,  $V_{VIN} = 4$  V - 18 V (unless otherwise noted)

|                         | PARAMETER                                                     | TEST CONDITIONS                                                                         | MIN   | TYP  | MAX   | UNIT |

|-------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|-------|------|

| SUPPLY VOLTAG           | E                                                             |                                                                                         |       |      |       |      |

| I <sub>Q(VIN)</sub>     | VIN operating non-switching supply current                    | $\rm V_{EN}$ = 1.3 V, $\rm V_{FB}$ = 550 mV, $\rm V_{VIN}$ = 12 V, 1 MHz                |       | 1200 | 1600  | μA   |

| I <sub>SD(VIN)</sub>    | VIN shutdown supply current                                   | V <sub>EN</sub> = 0 V, V <sub>VIN</sub> = 12 V                                          |       | 15   | 25    | μA   |

|                         | VIN UVLO rising threshold                                     | VIN rising                                                                              | 3.9   | 4    | 4.1   | V    |

|                         | VIN UVLO hysteresis                                           |                                                                                         |       | 150  |       | mV   |

| ENABLE AND UV           | LO                                                            | · · · · · ·                                                                             |       |      |       |      |

| V <sub>EN(rise)</sub>   | EN voltage rising threshold                                   | EN rising, enable switching                                                             |       | 1.2  | 1.25  | V    |

| V <sub>EN(fall)</sub>   | EN voltage falling threshold                                  | EN falling, disable switching                                                           | 1.05  | 1.1  |       | V    |

| V <sub>EN(hyst)</sub>   | EN voltage hysteresis                                         |                                                                                         |       | 100  |       | mV   |

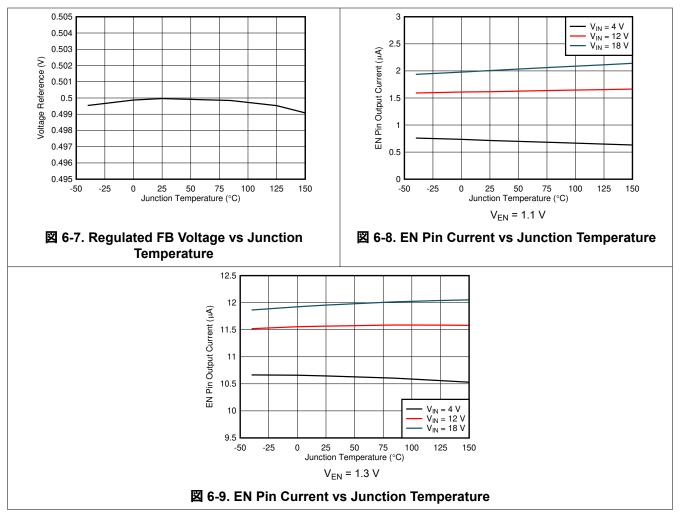

|                         | EN pin sourcing current                                       | V <sub>EN</sub> = 1.1 V                                                                 | 0.4   | 1.5  |       | μA   |

|                         | EN pin sourcing current                                       | V <sub>EN</sub> = 1.3 V                                                                 |       | 11.6 |       | μA   |

| INTERNAL LDO B          | P5                                                            | · · · · · ·                                                                             |       |      |       |      |

| V <sub>BP5</sub>        | Internal LDO BP5 output voltage                               | V <sub>VIN</sub> = 12 V                                                                 |       | 4.5  |       | V    |

|                         | BP5 dropout voltage                                           | V <sub>VIN</sub> – V <sub>BP5</sub> , V <sub>VIN</sub> = 3.8 V                          |       |      | 350   | mV   |

|                         | BP5 short-circuit current limit                               | V <sub>VIN</sub> = 12 V                                                                 |       | 75   |       | mA   |

| REFERENCE VOL           | TAGE                                                          | · · · · ·                                                                               |       |      |       |      |

| V <sub>FB</sub>         | Feedback Voltage                                              | $T_J = -40^{\circ}C$ to $150^{\circ}C$                                                  | 497.5 | 500  | 502.5 | mV   |

| I <sub>FB(LKG)</sub>    | Input leakage current into FB pin                             | $V_{\text{FB}}$ = 500 mV, non-switching, $V_{\text{VIN}}$ = 12 V, $V_{\text{EN}}$ = 0 V |       | 1    |       | nA   |

| SWITCHING FREC          | QUENCY AND OSCILLATOR                                         |                                                                                         |       |      |       |      |

| f <sub>sw</sub>         | Switching frequency                                           | R <sub>MODE</sub> = 24.3 kΩ                                                             | 450   | 500  | 550   | kHz  |

| f <sub>SW</sub>         | Switching frequency                                           | R <sub>MODE</sub> = 17.4 kΩ                                                             | 675   | 750  | 825   | kHz  |

| f <sub>sw</sub>         | Switching frequency                                           | R <sub>MODE</sub> = 11.8 kΩ                                                             | 900   | 1000 | 1100  | kHz  |

| f <sub>SW</sub>         | Switching frequency                                           | R <sub>MODE</sub> = 8.06 kΩ                                                             | 1350  | 1500 | 1650  | kHz  |

| f <sub>SW</sub>         | Switching frequency                                           | R <sub>MODE</sub> = 4.99 kΩ                                                             | 1980  | 2200 | 2420  | kHz  |

| SYNCHRONIZATI           | ON                                                            |                                                                                         |       |      |       |      |

| V <sub>IH(sync)</sub>   | High-level input voltage                                      |                                                                                         | 1.8   |      |       | V    |

| V <sub>IL(sync)</sub>   | Low-level input voltage                                       |                                                                                         |       |      | 0.8   | V    |

| SOFT-START              |                                                               | · · ·                                                                                   |       |      |       |      |

| t <sub>SS1</sub>        | Soft-start time                                               | R <sub>MODE</sub> = 1.78 kΩ                                                             |       | 0.5  |       | ms   |

| t <sub>SS2</sub>        | Soft-start time                                               | R <sub>MODE</sub> = 2.21 kΩ                                                             |       | 1    |       | ms   |

| t <sub>SS3</sub>        | Soft-start time                                               | R <sub>MODE</sub> = 2.74 kΩ                                                             |       | 2    |       | ms   |

| t <sub>SS4</sub>        | Soft-start time                                               | R <sub>MODE</sub> = 3.32 kΩ                                                             |       | 4    |       | ms   |

| POWER STAGE             |                                                               | · · · · ·                                                                               |       |      |       |      |

| R <sub>DS(on)HS</sub>   | High-side MOSFET on-resistance                                | T <sub>J</sub> = 25°C, V <sub>VIN</sub> = 12 V, V <sub>BOOT-SW</sub> = 4.5 V            |       | 25   |       | mΩ   |

| R <sub>DS(on)LS1</sub>  | Low-side MOSFET on-resistance: high<br>current limit selected | $T_J$ = 25°C, V <sub>BP5</sub> = 4.5 V, R <sub>MODE</sub> = 1.78 kΩ                     |       | 6.5  |       | mΩ   |

| R <sub>DS(on)LS2</sub>  | Low-side MOSFET on-resistance: low current limit selected     | $T_J = 25^{\circ}C, V_{BP5} = 4.5 V, R_{MODE} = 22.1 k\Omega$                           |       | 13.9 |       | mΩ   |

| VBOOT-SW(UV_r)          | BOOT-SW UVLO rising threshold                                 | V <sub>BOOT-SW</sub> rising                                                             |       | 3.2  |       | V    |

| VBOOT-SW(UV_f)          | BOOT-SW UVLO falling threshold                                | V <sub>BOOT-SW</sub> falling                                                            |       | 2.8  |       | V    |

| T <sub>ON(min)</sub>    | Minimum ON pulse width                                        | I <sub>OUT</sub> > ½ I <sub>L_PK-PK</sub>                                               |       | 30   | 37    | ns   |

| T <sub>OFF(min)</sub>   | Minimum OFF pulse width <sup>(1)</sup>                        |                                                                                         |       | 115  | 140   | ns   |

| CURRENT SENSE           | AND OVERCURRENT PROTECTION                                    | · · · · · ·                                                                             |       |      | I     |      |

| IOC_HS_pk1              | High-side peak current limit                                  | R <sub>MODE</sub> = 1.78 kΩ                                                             | 8.6   | 9    | 9.6   | Α    |

| IOC_HS_pk2              | High-side peak current limit                                  | R <sub>MODE</sub> = 22.1 kΩ                                                             | 4.2   | 4.5  | 4.8   | Α    |

| I <sub>OC_LS_src1</sub> | Low-side sourcing current limit                               | R <sub>MODE</sub> = 1.78 kΩ                                                             | 6.4   | 7.3  | 8.1   | А    |

| IOC LS src2             | Low-side sourcing current limit                               | R <sub>MODE</sub> = 22.1 kΩ                                                             | 3.65  | 4.2  | 4.65  | A    |

|                         | Low-side sinking current limit                                | Current into SW pin                                                                     | 2.95  |      |       | A    |

#### $T_J = -40$ °C to +150°C, $V_{VIN} = 4$ V - 18 V (unless otherwise noted)

|                         | PARAMETER                                                     | TEST CONDITIONS                                                | MIN | ТҮР               | MAX | UNIT               |

|-------------------------|---------------------------------------------------------------|----------------------------------------------------------------|-----|-------------------|-----|--------------------|

| OUTPUT OVER             | VOLTAGE AND UNDERVOLTAGE PROTECTION                           | NS .                                                           |     |                   | I   |                    |

| V <sub>OVP</sub>        | Overvoltage-protection (OVP) threshold voltage                | V <sub>FB</sub> rising                                         |     | 120               |     | % V <sub>REF</sub> |

| V <sub>UVP</sub>        | Undervoltage-protection (UVP) threshold voltage               | V <sub>FB</sub> falling                                        |     | 80                |     | % V <sub>REF</sub> |

| POWER GOOD              |                                                               |                                                                |     |                   |     |                    |

|                         | PGOOD threshold                                               | V <sub>FB</sub> rising (Fault)                                 | 113 | 116               | 119 | % V <sub>REF</sub> |

|                         | PGOOD threshold                                               | V <sub>FB</sub> falling (Good)                                 | 105 | 108               | 111 | % V <sub>REF</sub> |

|                         | PGOOD threshold                                               | V <sub>FB</sub> rising (Good)                                  | 89  | 92                | 95  | % V <sub>REF</sub> |

|                         | PGOOD threshold                                               | V <sub>FB</sub> falling (Fault)                                | 81  | 84                | 87  | % V <sub>REF</sub> |

| I <sub>PGOOD(LKG)</sub> | Leakage current into PGOOD pin when open drain output is high | V <sub>PGOOD</sub> = 4.7 V                                     |     |                   | 5   | μA                 |

| V <sub>PG(low)</sub>    | PGOOD low-level output voltage                                | I <sub>PGOOD</sub> = 2 mA, V <sub>IN</sub> = 12 V              |     |                   | 0.5 | V                  |

|                         | Min VIN for valid PGOOD output                                |                                                                |     | 0.9               | 1   | V                  |

| HICCUP                  |                                                               |                                                                |     |                   |     |                    |

|                         | Hiccup time before re-start                                   |                                                                |     | 7*t <sub>SS</sub> |     | ms                 |

| OUTPUT DISCI            | HARGE                                                         |                                                                |     |                   |     |                    |

| R <sub>Dischg</sub>     | Output discharge resistance                                   | $V_{VIN}$ = 12 V, $V_{SW}$ = 0.5 V, power conversion disabled. |     | 100               |     | Ω                  |

| THERMAL SHU             | JTDOWN                                                        | ·                                                              |     |                   |     |                    |

| T <sub>SDN</sub>        | Thermal shutdown threshold <sup>(1)</sup>                     | Temperature rising                                             |     | 165               | 175 | °C                 |

| T <sub>HYST</sub>       | Thermal shutdown hysteresis <sup>(1)</sup>                    |                                                                |     | 12                |     | °C                 |

(1) Specified by design. Not production tested.

100

96

92

88

76

72

68

64

60

0

0.5 1 1.5 2

(%) 84

Efficiency 80

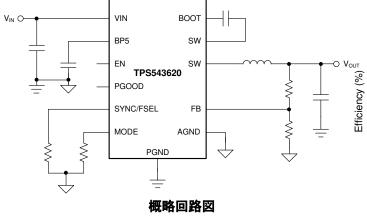

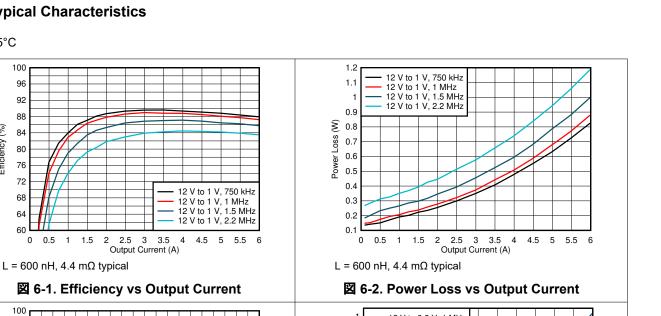

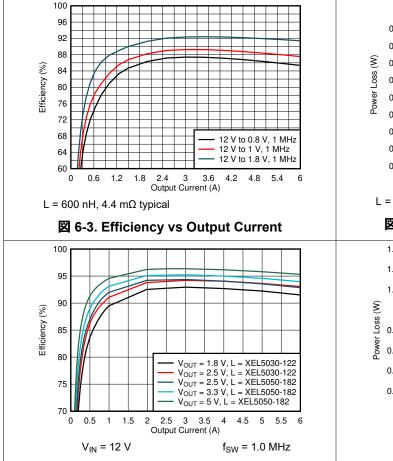

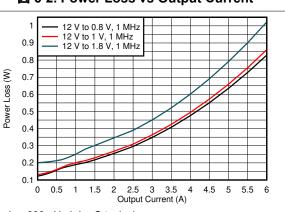

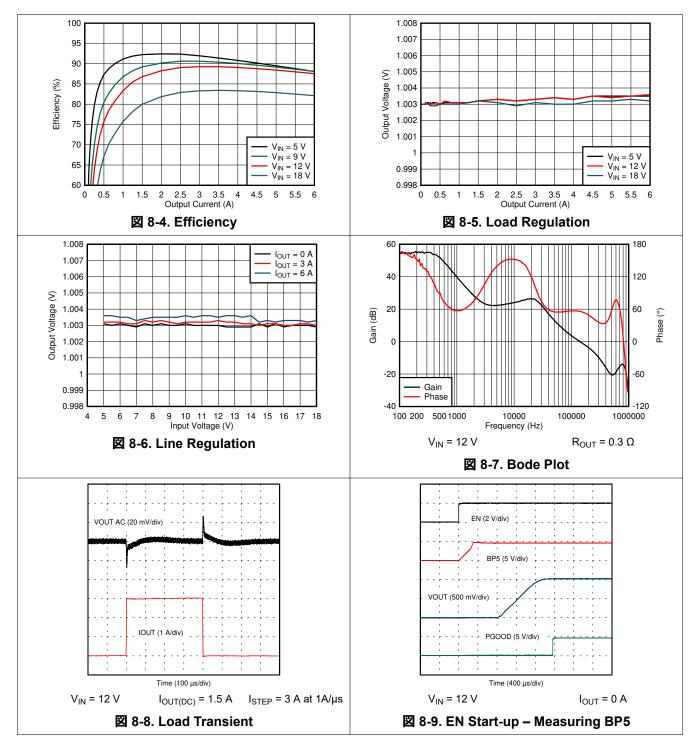

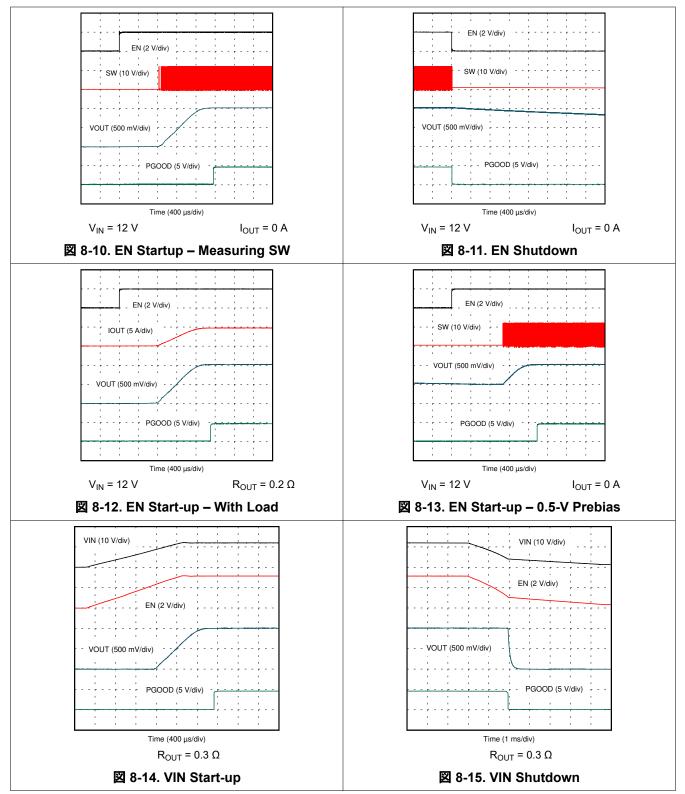

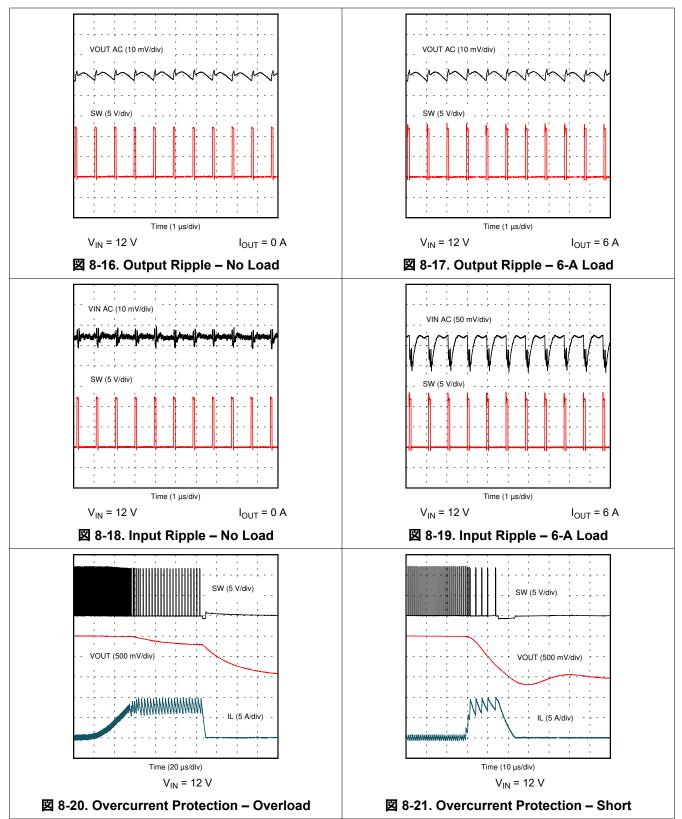

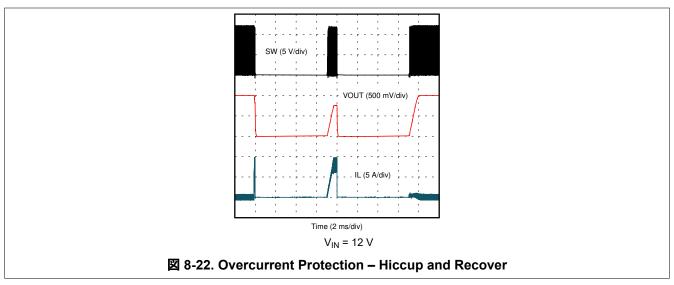

# 6.6 Typical Characteristics

図 6-5. Efficiency vs Output Current – 1.8-V to 5.0-V Output

JAJSJT8C - MAY 2020 - REVISED JUNE 2021

**TPS543620**

# 7 Detailed Description

# 7.1 Overview

The TPS543620 device is a 6-A, high-performance, synchronous buck converter with two integrated N-channel MOSFETs. The TPS543620 has a maximum operating junction temperature of 150°C, making it suitable for high-ambient temperature applications such as wireless infrastructure. The input voltage range is 4 V to 18 V and the output voltage range is 0.5 V to 7 V. The device features a fixed-frequency Advanced Current Mode control with a switching frequency of 500 kHz to 2.2 MHz, allowing for efficiency and size optimization when selecting output filter components. The switching frequency of the device can be synchronized to an external clock applied to the SYNC pin.

Advanced Current Mode (ACM) is an emulated peak current control topology. It supports stable static and transient operation without complex external compensation design. This control architecture includes an internal ramp generation network that emulates inductor current information, enabling the use of low-ESR output capacitors such as multi-layered ceramic capacitors (MLCC). The internal ramp also creates a high signal-to-noise ratio for good noise immunity. The TPS543620 has three ramp options (see topilor 7.3.6 for details) to optimize the internal loop for various inductor and output capacitor combinations with only a single resistor to AGND. The TPS543620 is easy-to-use and allows low external component count with fast load transient response. Fixed-frequency operation also provides ease-of-filter design to overcome EMI noise.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 VIN Pins and VIN UVLO

The VIN pin voltage supplies the internal control circuits of the device and provides the input voltage to the power stage. The input voltage for VIN can range from 4 V to 18 V. The device implements internal UVLO circuitry on the VIN pin. The device is disabled when the VIN pin voltage falls below the internal VIN UVLO

threshold. The internal VIN UVLO threshold has a hysteresis of 150 mV. A voltage divider connected to the EN pin can adjust the input voltage UVLO as appropriate. See セクション 7.3.2 for more details.

## 7.3.2 Enable and Adjustable UVLO

The EN pin provides on/off control of the device. Once the EN pin voltage exceeds its threshold voltage, the device begins its start-up sequence. If the EN pin voltage is pulled below the threshold voltage, the regulator stops switching and enters a low operating current state. The EN pin has an internal pullup current source, Ip, allowing it to be floated to enable the device by default. It is important to ensure that leakage currents of anything connected to the EN pin do not exceed the minimum EN pullup current or the device may not be able to start. If an application requires controlling the EN pin, an open drain or open collector output logic can be interfaced with the pin.

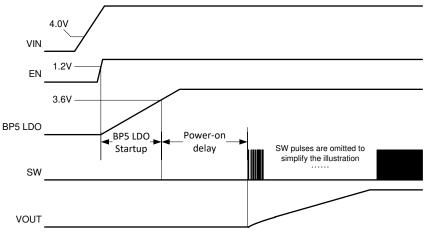

When the EN pin voltage exceeds its threshold voltage and the VIN pin voltage exceeds its VIN UVLO threshold, the device begins its start-up sequence. First, the BP5 LDO is enabled and charges the external BP5 capacitor. Once the voltage on the BP5 pin exceeds its UVLO threshold, the device enters a power-on delay. During the power-on delay, the values of the pinstrap resistors on the MODE pin (see t/2227.3.8) and SYNC/FSEL pin (see t/2227.3.8) and SYNC/FSEL pin (see t/2227.3.4) are determined and the control loop is initialized. The power-on delay is typically 600 µs. After the power-on delay, soft start begins.

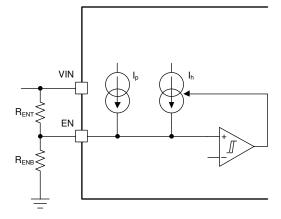

図 7-1. Start-up Sequence

An external resistor divider can be added from VIN to the EN pin for adjustable UVLO and hysteresis as shown in  $\boxtimes$  7-2. The EN pin has a small pullup current, Ip, which sets the default state of the pin to enable when no external components are connected. The pullup current is also used to control the voltage hysteresis for the UVLO function since it increases by Ih once the EN pin crosses the enable threshold. The UVLO thresholds can be calculated using  $\overrightarrow{\pi}$  1 and  $\overrightarrow{\pi}$  2. When using the adjustable UVLO function, 500 mV or greater hysteresis is recommended. For applications with very slow input voltage slew rate, a capacitor can be placed from the EN pin to ground to filter any glitches on the input voltage.

2 7-2. Adjustable UVLO Using EN

$$R_{ENT} = \frac{V_{START} \times \left(\frac{V_{ENFALLING}}{V_{ENRISING}}\right) - V_{STOP}}{I_{p} \times \left(1 - \frac{V_{ENFALLING}}{V_{ENRISING}}\right) + I_{h}}$$

(1)

$$R_{ENB} = \frac{R_{ENT} \times V_{ENFALLING}}{V_{STOP} - V_{ENFALLING} + R_{ENT} \times \left(I_{p} + I_{h}\right)}$$

(2)

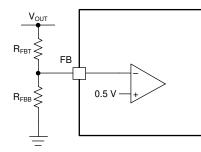

The output voltage is programmed with a resistor divider from the output (V<sub>OUT</sub>) to the FB pin shown in  $\boxtimes$  7-3. It is recommended to use 1% tolerance or better divider resistors. Starting with a fixed value for the bottom resistor, typically 10 k $\Omega$ , use  $\gtrsim$  3 to calculate the top resistor in the divider.

$$\mathbf{R}_{\mathsf{FBT}} = \mathbf{R}_{\mathsf{FBB}} \times \left(\frac{\mathbf{V}_{\mathsf{OUT}}}{\mathbf{V}_{\mathsf{REF}}} - 1\right)$$

(3)

## 7.3.4 Switching Frequency Selection

The switching frequency of the device can be selected by connecting a resistor ( $R_{FSEL}$ ) between the SYNC/ FSEL pin and AGND. The frequency options and their corresponding programming resistors are listed in  $\pm$  7-1. It is required to use a 1% tolerance resistor or better.

| R <sub>FSEL</sub> ALLOWED NOMINAL<br>RANGE (1%) (kΩ) |      |     | Fsw (kHz) |  |  |  |

|------------------------------------------------------|------|-----|-----------|--|--|--|

| ≥24.0                                                | 24.3 | 27  | 500       |  |  |  |

| 17.4-18.0                                            | 17.4 | 18  | 750       |  |  |  |

| 11.8-12.1                                            | 11.8 | 12  | 1000      |  |  |  |

| 8.06-8.25                                            | 8.06 | 8.2 | 1500      |  |  |  |

| ≤5.11                                                | 4.99 | 4.7 | 2200      |  |  |  |

### 表 7-1. Switching Frequency Selection

# 7.3.5 Switching Frequency Synchronization to an External Clock

The device can be synchronized to an external clock by applying a square wave clock signal to the SYNC/FSEL pin with a duty cycle from 20% to 80%. The clock can either be applied before the device starts up or during operation. If the clock is to be applied before the device starts, a resistor between SYNC/FSEL and AGND is not needed. If the clock is to be applied after the device starts, then the clock frequency should be within  $\pm 20\%$  of the frequency set by the SYNC/FSEL resistor. When the clock is applied after the device starts, the device will begin synchronizing to this clock after counting four consectutive switching cycles with a clock pulse present. This is shown in  $\boxed{2}$  7-4.

#### 7.3.5.1 Internal PWM Oscillator Frequency

When the external clock is present, the device synchronizes the switching frequency to the clock. Any time the external clock is not present, the device will default to the internal PWM oscillator frequency.

If the device starts up before an external clock signal is applied, then the internal PWM oscillator frequency is set by the  $R_{FSEL}$  resistor according to  $\gtrsim$  7-1. The device switches at this frequency until the external clock is applied or anytime the external clock is not present.

If the external clock is applied before the device starts up, then the  $R_{FSEL}$  resistor is not needed. The device will determine the internal clock frequency by decoding the external clock frequency.  $\gtrsim$  7-2 shows the decoding of the internal PWM oscillator frequency based on the external clock frequency.

| EXTERNAL SYNC CLOCK FREQUENCY (kHz) | DECODED INTERNAL PWM OSCILLATOR FREQUENCY (kHz) |

|-------------------------------------|-------------------------------------------------|

| 400 - 600                           | 500                                             |

| 600 - 857                           | 750                                             |

| 857 - 1200                          | 1000                                            |

| 1200 - 1810                         | 1500                                            |

| 1810 - 2640                         | 2200                                            |

#### 表 7-2. Internal Oscillator Frequency Decode

The thresholds for the external SYNC clock frequency ranges have approximately a  $\pm$ 5% tolerance. If the external clock frequency is to be within that tolerance range, it is possible for the internal PWM oscillator frequency to be decoded as either the frequency above or below that threshold. Since the internal frequency is what is used in case of the loss of the synchronization clock, it is recommended that the output LC filter and ramp selection are chosen to be stable for either frequency.  $\pm$  7-3 shows the tolerance range of the decode thresholds. If the external clock is to be within any of these ranges, it is recommended to ensure converter stability for both possible internal PWM oscillator frequencies.

| MINIMUM (kHz) | TYPICAL (kHz) | MAXIMUM (kHz) |  |  |  |  |

|---------------|---------------|---------------|--|--|--|--|

| 570           | 600           | 630           |  |  |  |  |

| 814           | 857           | 900           |  |  |  |  |

| 1140          | 1200          | 1260          |  |  |  |  |

| 1736          | 1810          | 1884          |  |  |  |  |

### 表 7-3. Frequency Decode Thresholds

#### 7.3.5.2 Loss of Synchronization

If at any time during operation, there is a loss of synchronization, the device will default to the internal PWM oscillator frequency until the synchronization clock returns. Once the clock is no longer present, the device will switch at 70% of the internal clock frequency for four consecutive cycles. After four consecutive cycles without clock pulses, the device will operate at the normal internal PWM oscillator frequency. This is demonstrated in  $\boxtimes$  7-4.

図 7-4. Clock Synchronization Transitions

## 7.3.5.3 Interfacing the SYNC/FSEL Pin

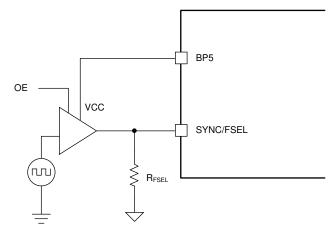

If an application requires synchronizing to a SYNC clock but the clock is unavailable before the device is enabled, a high impedance buffer is recommended to ensure proper detection of the  $R_{FSEL}$  value.  $\boxtimes$  7-5 shows the recommended implementation. The leakage current into the buffer output must be less than 5  $\mu$ A to ensure proper detection of the  $R_{FSEL}$  value. Power the buffer from the BP5 output of the device to ensure its VCC voltage is available and the buffers output is high impedance before the device tries to detect the  $R_{FSEL}$  value. When powering the buffer from the BP5 pin, the external load on the BP5 pin must be less than 2 mA.

☑ 7-5. Interfacing the SYNC/FSEL Pin with a Buffer

#### 7.3.6 Ramp Amplitude Selection

The TPS543620 uses  $V_{IN}$ , duty cycle, and low-side FET current information to generate an internal ramp. The ramp amplitude is determined by an internal ramp generation capacitor,  $C_{RAMP}$ . Three different values for  $C_{RAMP}$

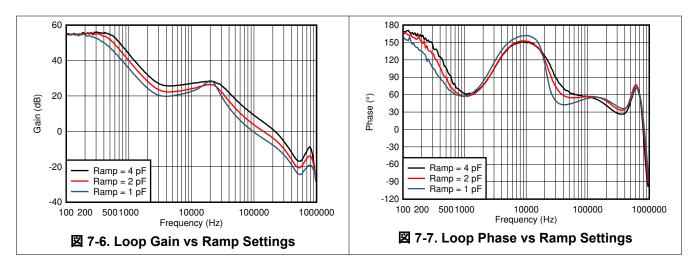

can be selected with a resistor to AGND on the MODE pin (see  $\frac{t}{2}\frac{j}{2}\frac{j}{3}\frac{7.3.8}{7.3.8}$ ). The capacitor options are 1 pF, 2 pF, and 4 pF. A larger ramp capacitor results in a smaller ramp amplitude, which results in a higher control loop bandwidth.  $\boxtimes$  7-6 and  $\boxtimes$  7-7 show how the loop changes with each ramp setting for the schematic in  $\frac{t}{2}\frac{j}{2}\frac{j}{3}\frac{j}{3}$ .

# 7.3.7 Soft Start and Prebiased Output Start-up

During start-up, the device softly ramps the reference voltage to reduce inrush currents. There are four options for the soft-start time, which is the time it takes for the reference to ramp to 0.5 V: 0.5 ms, 1 ms, 2 ms, and 4 ms. The soft-start time is selected with a resistor to AGND on the MODE pin (see  $\frac{1}{2}\sqrt{3} \sqrt{7.3.8}$ ).

The device prevents current from being discharged from the output during start-up when a prebiased output condition exists. It does this by operating in discontinuous conduction mode (DCM) during the first 16 cycles to prevent the device from sinking current. This ensures the output voltage will be smooth and monotonic during soft start.

#### 7.3.8 Mode Pin

The ramp amplitude, soft-start time, and current limit settings are programmed with a single resistor,  $R_{MODE}$ , between MODE and AGND.  $\gtrsim$  7-4 lists the resistor values for the available options. It is required to use a 1% tolerance resistor or better. See  $\frac{1}{2}2327.3.10$  for the corresponding current limit thresholds for the "High" and "Low" settings.

| R <sub>MODE</sub> (kΩ) | CURRENT LIMITS | C <sub>RAMP</sub> (pF) | SOFT-START TIME (ms) |

|------------------------|----------------|------------------------|----------------------|

| 1.78                   | High           | 1                      | 0.5                  |

| 2.21                   | High           | 1                      | 1                    |

| 2.74                   | High           | 1                      | 2                    |

| 3.32                   | High           | 1                      | 4                    |

| 4.02                   | High           | 2                      | 0.5                  |

| 4.87                   | High           | 2                      | 1                    |

| 5.9                    | High           | 2                      | 2                    |

| 7.32                   | High           | 2                      | 4                    |

| 9.09                   | High           | 4                      | 0.5                  |

| 11.3                   | High           | 4                      | 1                    |

| 14.3                   | High           | 4                      | 2                    |

| 18.2                   | High           | 4                      | 4                    |

| 22.1                   | Low            | 1                      | 0.5                  |

| 26.7                   | Low            | 1                      | 1                    |

| 表 7-4. | MODE | Pin \$ | Selection |

|--------|------|--------|-----------|

|--------|------|--------|-----------|

| R <sub>MODE</sub> (kΩ) | CURRENT LIMITS | C <sub>RAMP</sub> (pF) | SOFT-START TIME (ms) |

|------------------------|----------------|------------------------|----------------------|

| 33.2                   | Low            | 1                      | 2                    |

| 40.2                   | Low            | 1                      | 4                    |

| 49.9                   | Low            | 2                      | 0.5                  |

| 60.4                   | Low            | 2                      | 1                    |

| 76.8                   | Low            | 2                      | 2                    |

| 102                    | Low            | 2                      | 4                    |

| 137                    | Low            | 4                      | 0.5                  |

| 174                    | Low            | 4                      | 1                    |

| 243                    | Low            | 4                      | 2                    |

| 412                    | Low            | 4                      | 4                    |

# 表 7-4. MODE Pin Selection (continued)

# 7.3.9 Power Good (PGOOD)

The PGOOD pin is an open-drain output requiring an external pullup resistor to output a high signal. Once the FB pin is between 92% and 108% of the internal voltage reference, soft start is complete, and after a 256- $\mu$ s deglitch time, the PGOOD pin is de-asserted and the pin floats. A pullup resistor between the values of 10 k $\Omega$  and 100 k $\Omega$  to a voltage source that is 5.5 V or less is recommended. PGOOD is in a defined state once the VIN input voltage is greater than 1 V but with reduced current sinking capability. When the FB is lower than 84% or greater than 116% of the nominal internal reference voltage, after a 8- $\mu$ s deglitch time, the PGOOD pin is pulled low. PGOOD is immediately pulled low if VIN falls below its UVLO, the EN pin is pulled low or the device enters thermal shutdown.

#### 7.3.10 Current Protection

The protects against overcurrent events by cycle-by-cycle current limiting both the high-side MOSFET and lowside MOSFET. In an extended overcurrent condition, the device will enter hiccup. Different protections are active during positive inductor current and negative inductor current conditions.

## 7.3.10.1 Positive Inductor Current Protection

The current is sensed in the high-side MOSFET while it is conducting after a short blanking time to allow noise to settle. Whenever the high-side overcurrent threshold is exceeded, the high-side MOSFET is immediately turned off and the low-side MOSFET is turned on. The high-side MOSFET does not turn back on until the current falls below the low-side MOSFET overcurrent threshold. This effectively limits the peak current in the case of a short circuit condition. If a high-side overcurrent is detected for 15 consecutive cycles, the device enters hiccup.

The current is also sensed in the low-side MOSFET while it is conducting after a short blanking time to allow noise to settle. If the low-side overcurrent threshold is exceeded when the next incoming PWM signal is received from the controller, the device skips processing that PWM pulse. The device does not turn the high-side MOSFET on again until the low-side overcurrent threshold is no longer exceeded. If the low-side overcurrent threshold remains exceeded for 15 consecutive cycles, the device enters hiccup. There are two separate counters for the high-side and low-side overcurrent events. If the off-time is too short, the low-side overcurrent may not trip. The low-side overcurrent will, however, begin tripping after the high-side peak overcurrent limit is hit as hitting the peak current limit shortens the on-time and lengthens the off-time.

Both the high-side and low-side positive overcurrent thresholds are programmable using the MODE pin. Two sets of thresholds are available ("High" and "Low"), which are summarized in  $\frac{1}{25}$  7-5. The values for these thresholds are obtained using open-loop measurements with a DC current in order to accurately specify the values. In real applications, the inductor current will ramp and the ramp rate will be a function of the voltage across the inductor (V<sub>IN</sub> - V<sub>OUT</sub>) as well as the inductance value. This ramp rate combined with delays in the current sense circuitry can result in slightly different values than specified. The current at which the high-side overcurrent limit takes effect can be slightly lower than specified.

| 表 7-5. Overcurrent Inresholds  |                                            |                                           |  |  |  |  |

|--------------------------------|--------------------------------------------|-------------------------------------------|--|--|--|--|

| MODE PIN CURRENT LIMIT SETTING | HIGH-SIDE OVERCURRENT TYPICAL<br>VALUE (A) | LOW-SIDE OVERCURRENT TYPICAL VALUE<br>(A) |  |  |  |  |

| High                           | 9.0                                        | 7.3                                       |  |  |  |  |

| Low                            | 4.5                                        | 4.2                                       |  |  |  |  |

#### 7.3.10.2 Negative Inductor Current Protection

Negative current is sensed in the low-side MOSFET while it is conducting after a short blanking time to allow noise to settle. Whenever the low-side negative overcurrent threshold is exceeded, the low-side MOSFET is immediately turned off. The next high-side MOSFET turnon is determined by the clock and PWM comparator. The negative overcurrent threshold minimum value is 2.95 A. Similar to the positive inductor current protections, the actual value of the inductor current when the current sense comparators trip will be a function of the current ramp rate. As a result the current at which the negative inductor current limit takes effect can be slightly more negative than specified.

#### 7.3.11 Output Overvoltage and Undervoltage Protection

The device incorporates both output overvoltage and undervoltage protection. If an overvoltage is detected, the device tries to discharge the output voltage to a safe level before attempting to restart. When the overvoltage threshold is exceeded, the low-side MOSFET is turned on until the low-side negative overcurrent threshold is reached. At this point, the high-side MOSFET is turned on until the inductor current reaches zero. Then, the low-side MOSFET is turned back on until the low-side negative overcurrent threshold is repeats until the output voltage falls back into the PGOOD window. Once this happens, the device restarts and goes through a soft start cycle. The device does not wait the hiccup time before restarting.

When an undervoltage condition is detected, the device will enter hiccup where it waits seven soft-start cycles before restarting. Undervoltage protection is enabled after soft start is complete.

#### 7.3.12 Overtemperature Protection

When the die temperature exceeds 165°C, the device turns off. Once the die temperatures falls below the hysteresis level, typically 12°C, the device restarts. While waiting for the temperature to fall below the hysteresis level, the device does not switch or attempt to hiccup to restart. Once the temperature falls below this level, the device restarts without going through hiccup.

#### 7.3.13 Output Voltage Discharge

When the device is enabled, but the high-side FET and low-side FET are disabled due to a fault condition, the output voltage discharge mode is enabled. This mode turns on the discharge FET from SW to PGND to discharge the output voltage. The discharge FET is turned off when the converter is ready to resume switching, either after the fault clears or after the wait time before hiccup is over.

The output voltage discharge mode is activated by any of below fault events:

- 1. High-side or low-side positive overcurrent

- 2. Thermal shutdown

- 3. Output voltage undervoltage

- 4. VIN UVLO

#### 7.3.14 Low-Side MOSFET Resistance Scaling

When the "low" current limit is selected as described in t / 2 > 2 > 7.3.10.1, a smaller portion of the low-side MOSFET is used while the rest of the FET remains off. This increases the light-load efficiency for the lower current limits by removing a portion of the low-side MOSFET switching loss.

| MODE PIN CURRENT LIMIT SETTING         LOW-SIDE MOSFET R <sub>DS(on)</sub> (mΩ) |     |  |  |  |

|---------------------------------------------------------------------------------|-----|--|--|--|

| High                                                                            | 6.5 |  |  |  |

# 表 7-6. Low-Side MOSFET Resistance

#### 表 7-6. Low-Side MOSFET Resistance (continued)

| MODE PIN CURRENT LIMIT SETTING | LOW-SIDE MOSFET R <sub>DS(on)</sub> (mΩ) |

|--------------------------------|------------------------------------------|

| Low                            | 13.9                                     |

### 7.4 Device Functional Modes

#### 7.4.1 Forced Continuous-Conduction Mode

The TPS543620 operates in forced continuous-conduction mode (FCCM) throughout normal operation.

#### 7.4.2 Discontinuous Conduction Mode during Soft Start

During soft start, the converter operates in discontinuous conduction mode (DCM) during the first 16 PWM cycles. During this time, a zero-cross detect comparator is used to turn off the low-side MOSFET when the current reaches zero amps. This prevents the discharge of any pre-biased conditions on the output. After 16 cycles of DCM, the converter enters FCCM mode.

# 8 Application and Implementation

Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を 保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことに なります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要がありま す。

# 8.1 Application Information

The TPS543620 is a synchronous buck regulator designed for 4-V to 18-V input and 6-A load. This procedure illustrates the design of a high-frequency switching regulator using ceramic output capacitors.

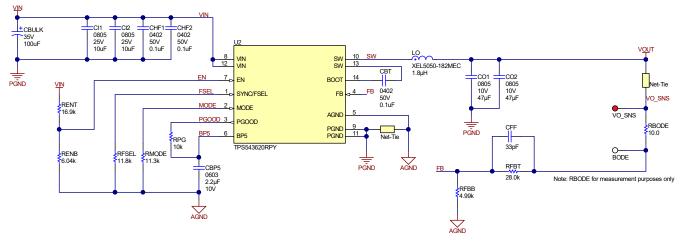

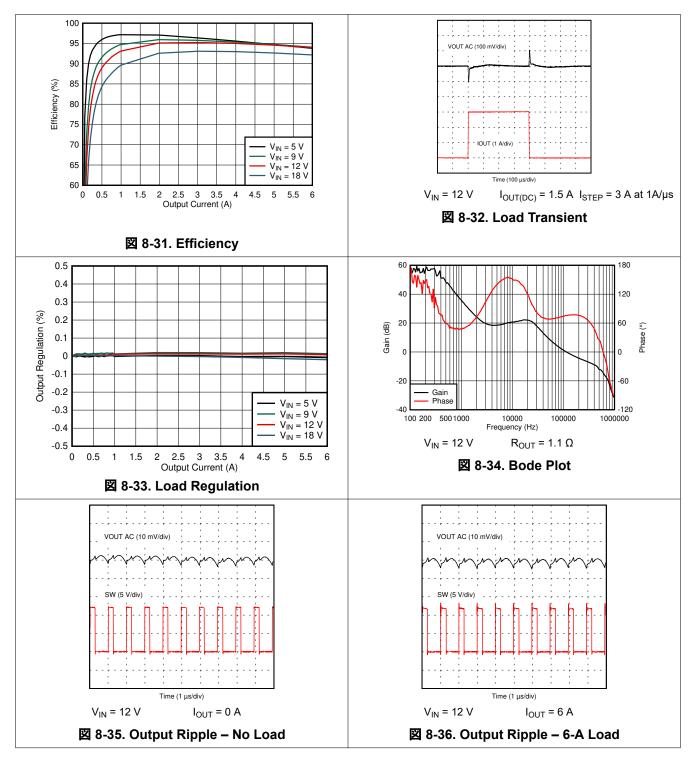

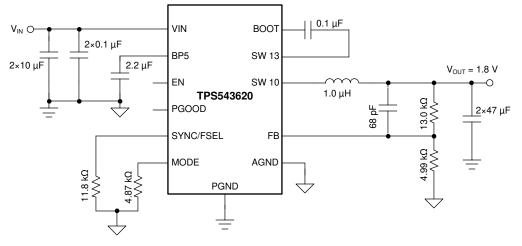

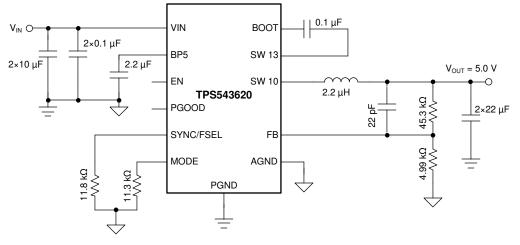

# 8.2 Typical Applications

# 8.2.1 1.0-V Output, 1-MHz Application

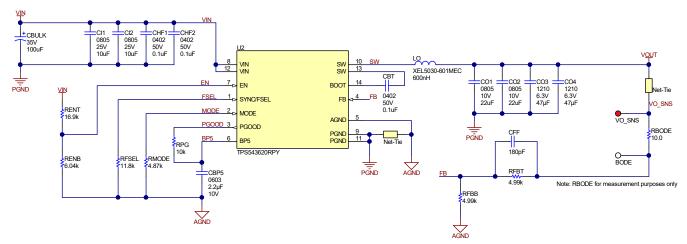

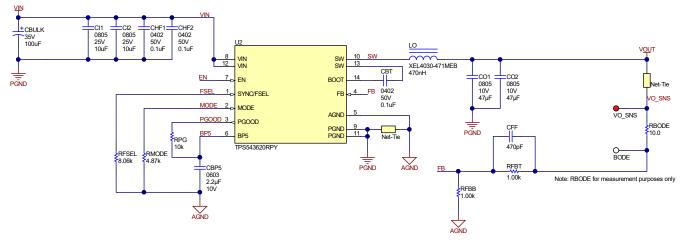

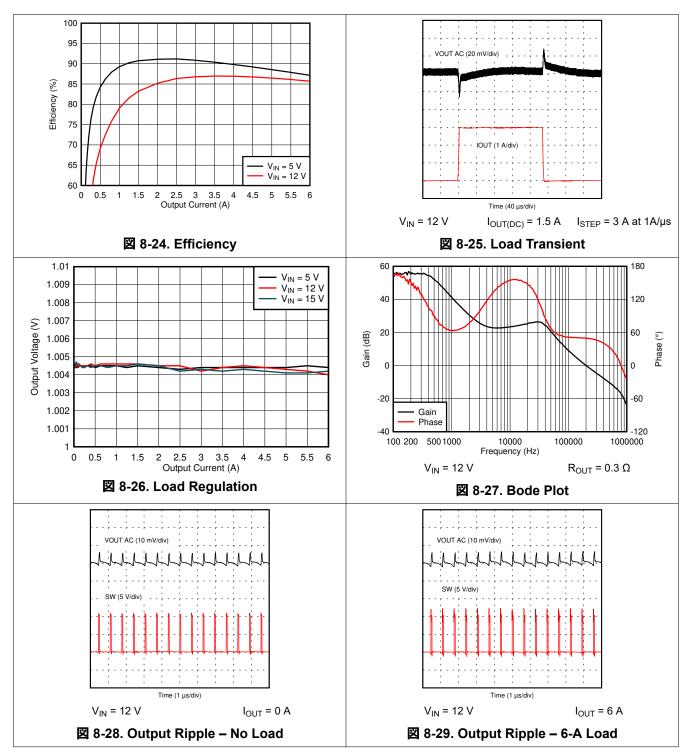

図 8-1. 12-V Input, 1.0-V Output, 1-MHz Schematic

#### 8.2.1.1 Design Requirements

For this design example, use the parameters shown in  $\frac{1}{8}$  8-1.

#### 表 8-1. Design Parameters

| PARAMETER                                 | EXAMPLE VALUE               |

|-------------------------------------------|-----------------------------|

| Input voltage range (V <sub>IN</sub> )    | 4.5 to 13.2 V, 12 V nominal |

| Output voltage (V <sub>OUT</sub> )        | 1.0 V                       |

| Output current rating (I <sub>OUT</sub> ) | 6 A                         |

| Switching frequency (f <sub>SW</sub> )    | 1000 kHz                    |

| Steady state output ripple voltage        | 10 mV                       |

| Output current load step                  | 3 A                         |

| Transient response                        | ± 30 mV (± 3%)              |

#### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Switching Frequency

The first step is to decide on a switching frequency. The TPS543620 can operate at five different frequencies from 500 kHz to 2.2 MHz. The  $f_{SW}$  is set by the resistor value from the FSEL pin to ground. Typically the highest switching frequency possible is desired because it produces the smallest solution size. A high switching frequency allows for smaller inductors and output capacitors compared to a power supply that switches at a lower frequency. The main tradeoff made with selecting a higher switching frequency is extra switching power loss, which hurts the efficiency of the regulator.

The maximum switching frequency for a given application can be limited by the minimum on-time of the regulator. The maximum  $f_{SW}$  can be estimated with  $\vec{x}$  4. Using the maximum minimum on-time of 40 ns and 13.2-V maximum input voltage for this application, the maximum switching frequency is 1890 kHz. The selected switching frequency must also consider the tolerance of the switching frequency. A switching frequency of 1000 kHz was selected for a good balance of solution size and efficiency. To set the frequency to 1000 kHz, the selected FSEL resistor is 11.8 k $\Omega$  per  $\gtrsim$  7-1.

$$f_{SW}(max) = \frac{1}{tonmin} \times \frac{V_{OUT}}{V_{IN}(max)}$$

(4)

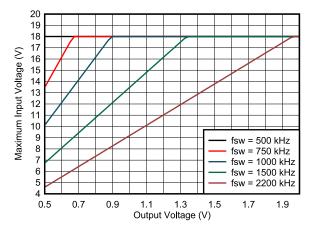

☑ 8-2 shows the maximum recommended input voltage versus output voltage for each FSEL frequency. This graph uses a minimum on-time of 45 ns and includes the 10% tolerance of the switching frequency. A minimum on-time of 45 ns is used in this graph to provide margin to the minimum controllable on-time to ensure pulses are not skipped at no load. At light loads, the dead-time between the low-side MOSFET turning off and high-side MOSFET turning on contributes to the minimum SW node pulse-width.

**図** 8-2. Maximum Input Voltage vs Output Voltage

In high output voltage applications, the minimum off-time must also be considered when selecting the switching frequency. When hitting the minimum off-time limits, the operating duty cycle will max out and the output voltage will begin to drop with the input voltage.  $\ddagger 5$  calculates the maximum switching frequency to avoid this limit. This equation requires the DC resistance of the inductor, R<sub>DCR</sub>, selected in the following step. A preliminary estimate of 10 m $\Omega$  can be used but this should be recalculated based on the specifications of the inductor selected. If operating near the maximum f<sub>SW</sub> limited by the minimum off-time, the increase in resistance at higher temperature must be considered.

$$f_{SW}(max) = \frac{V_{IN}(min) - V_{OUT} - I_{OUT}(max) \times (R_{DCR} + R_{DS(ON)\_HS})}{t_{OFF\_MIN}(max) \times (V_{IN}(min) - I_{OUT}(max) \times (R_{DS(ON)\_HS} - R_{DS(ON)\_LS}))}$$

(5)

#### 8.2.1.2.2 Output Inductor Selection

To calculate the value of the output inductor, use  $\neq$  6. K<sub>IND</sub> is a ratio that represents the amount of inductor ripple current relative to the maximum output current. The inductor ripple current is filtered by the output capacitor. Therefore, choosing high inductor ripple currents impacts the selection of the output capacitor since the output capacitor must have a ripple current rating equal to or greater than the inductor ripple current. Choosing small inductor ripple currents can degrade the transient response performance. The inductor ripple, K<sub>IND</sub>, is normally from 0.1 to 0.4 for the majority of applications giving a peak to peak ripple current range of 0.6 A to 2.4 A. The recommended minimum target Iripple is 0.3 A or larger.

For this design example,  $K_{IND} = 0.3$  is used and the inductor value is calculated to be 0.51 µH. An inductor with an inductance of 0.6 µH is selected. It is important that the RMS (Root Mean Square) current and saturation current ratings of the inductor not be exceeded. The RMS and peak inductor current can be found from  $\neq$  8 and  $\neq$  9. For this design, the RMS inductor current is 6 A, and the peak inductor current is 6.8 A. The chosen inductor is a XEL5030-601. It has a saturation current rating of 22 A, an RMS current rating of 21.4 A, and a typical DC series resistance of 4.44 mΩ.

The peak current through the inductor is the inductor ripple current plus the output current. During power up, faults, or transient load conditions, the inductor current can increase above the calculated peak inductor current level calculated in  $\neq$  9. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify the current ratings of the inductor based on the switch current limit rather than the steady-state peak inductor current.

$$L1 = \frac{Vinmax - Vout}{Io \times Kind} \times \frac{Vout}{Vinmax \times fsw}$$

(6)

Iripple =

$$\frac{\text{Vinmax} - \text{Vout}}{\text{L1}} \times \frac{\text{Vout}}{\text{Vinmax} \times f \text{sw}}$$

(7)

$$ILrms = \sqrt{lo^{2} + \frac{1}{12} \times \left(\frac{Vo \times (Vinmax - Vo)}{Vinmax \times L1 \times fsw}\right)^{2}}$$

(8)

$$ILpeak = lout + \frac{lripple}{2}$$

(9)

$\gtrsim$  8-2 shows recommended E6 standard inductor values for other common output voltages with a 1-MHz f<sub>SW</sub>. Using an inductance outside this recommended range typically works but the performance can be affected and should be evaluated. The recommended value is calculated for a nominal input voltage of 12 V. The minimum values are calculated with the maximum input voltage of 18 V. The maximum values are calculated with with an input voltage of 5-V for all but the 5-V output. For the 5-V output, an 8-V input is used.

|                      | 表 8-2. Recommended Inductor Values |                            |                                           |                                           |                            |  |  |  |

|----------------------|------------------------------------|----------------------------|-------------------------------------------|-------------------------------------------|----------------------------|--|--|--|

| OUTPUT<br>VOLTAGE (\ | SWITCHING<br>/) FREQUENCY (kHz)    | MINIMUM<br>INDUCTANCE (µH) | RECOMMENDED<br>INDUCTANCE FOR 6 A<br>(µH) | RECOMMENDED<br>INDUCTANCE FOR 3 A<br>(µH) | MAXIMUM<br>INDUCTANCE (µH) |  |  |  |

| 1                    |                                    | 0.33                       | 0.47                                      | 1                                         | 2.2                        |  |  |  |

| 1.8                  | 1000                               | 0.68                       | 1                                         | 2.2                                       | 3.3                        |  |  |  |

| 3.3                  | 1000                               | 1                          | 1.5                                       | 2.2                                       | 3.3                        |  |  |  |

| 5                    |                                    | 1.5                        | 2.2                                       | 3.3                                       | 4.7                        |  |  |  |

#### 8.2.1.2.3 Output Capacitor

**F**YAS

www.tij.co.jp

**INSTRUMENTS**

There are two primary considerations for selecting the value of the output capacitor: the output voltage ripple and how the regulator responds to a large change in load current. The output capacitance needs to be selected based on the more stringent of these criteria.

The desired response to a large change in the load current is the first criteria and is typically the most stringent. A regulator does not respond immediately to a large, fast increase or decrease in load current. The output capacitor supplies or absorbs charge until the regulator responds to the load step. The control loop needs to sense the change in the output voltage then adjust the peak switch current in response to the change in load. The minimum output capacitance is selected based on an estimate of the loop bandwidth. Typically the loop bandwidth is near  $f_{SW}$  / 10.  $\vec{r}_{s}$  10 estimates the minimum output capacitance necessary, where  $\Delta I_{OUT}$  is the change in output current and  $\Delta V_{OUT}$  is the allowable change in the output voltage.

For this example, the transient load response is specified as a 3% change in  $V_{OUT}$  for a load step of 3 A. Therefore,  $\Delta I_{OUT}$  is 3 A and  $\Delta V_{OUT}$  is 30 mV. Using this target gives a minimum capacitance of 159 µF. This value does not take the ESR of the output capacitor into account in the output voltage change. For ceramic capacitors, the effect of the ESR can be small enough to be ignored. Aluminum electrolytic and tantalum capacitors have higher ESR that must be considered for load step response.

$$C_{OUT} > \frac{\Delta I_{OUT}}{\Delta V_{OUT}} \times \frac{1}{2\pi \times \frac{f_{SW}}{10}}$$

(10)

In addition to the loop bandwidth, it is possible for the inductor current slew rate to limit how quickly the regulator responds to the load step. For low duty cycle applications, the time it takes for the inductor current to ramp down after a load step down can be the limiting factor.  $\neq$  11 estimates the minimum output capacitance necessary to limit the change in the output voltage after a load step down. Using the 0.6-µH inductance selected gives a minimum capacitance of 90 µF.

$$C_{OUT} > \frac{L_{OUT} \times \Delta I_{OUT}^{2}}{2 \times \Delta V_{OUT} \times V_{OUT}}$$

(11)

ightarrow 12 calculates the minimum output capacitance needed to meet the output voltage ripple specification. In this case, the target maximum steady state output voltage ripple is 10 mV. Under this requirement, ightarrow 12 yields 19  $\mu$ F.

$$Co > \frac{1}{8 \times fsw} \times \frac{1}{\frac{Voripple}{Iripple}}$$

where

- $\Delta I_{OUT}$  is the change in output current

- $\Delta V_{OUT}$  is the allowable change in the output voltage

- fsw is the regulators switching frequency

(12)

- Voripple is the maximum allowable steady state output voltage ripple

- Iripple is the inductor ripple current

Lastly, if an application does not have a strict load transient response or output ripple requirement, a minimum amount of capacitance is still required to ensure the control loop is stable with the lowest gain ramp setting on the MODE pin.  $\overrightarrow{x}$  13 estimates the minimum capacitance needed for loop stability. This equation sets the minimum amount of capacitance by keeping the LC frequency relative to the switching frequency at a minimum value. See  $\boxed{8}$  8-3 for the limit versus output voltage with the lowest gain ramp setting of 1 pF. With a 1-V output, the minimum ratio is 35 and with this ratio,  $\overrightarrow{x}$  13 gives a minimum capacitance of 52 µF.

$$C_{OUT} > \left(\frac{\text{Ratio}}{2\pi \times f_{SW}}\right)^2 \times \frac{1}{L_{OUT}}$$

(13)

the calculates the maximum combined ESR the output capacitors can have to meet the output voltage ripple specification and this shows the ESR should be less than 6 mΩ. In this case, ceramic capacitors are used and the combined ESR of the ceramic capacitors in parallel is much less than is needed to meet the ripple. Capacitors also have limits to the amount of ripple current they can handle without producing excess heat and failing. An output capacitor that can support the inductor ripple current must be specified. The capacitor data sheet specifies the RMS value of the maximum ripple current. the used to calculate the RMS ripple current the output capacitor needs to support. For this application, the used to calculate the RMS ripple current rating much higher than this.

$$Icorms = \frac{Vout \times (Vinmax - Vout)}{\sqrt{12} \times Vinmax \times L1 \times fsw}$$

(15)

Select X5R and X7R ceramic dielectrics or equivalent for power regulator capacitors since they have a high capacitance-to-volume ratio and are fairly stable over temperature. The output capacitor must also be selected with the DC bias and AC voltage derating taken into account. The derated capacitance value of a ceramic capacitor due to DC voltage bias and AC RMS voltage is usually found on the capacitor manufacturer's website. For this application example, two 22- $\mu$ F, 10-V, X7S, 0805 and two 47- $\mu$ F, 6.3-V, X7R, 1210 ceramic capacitors each with 2 m $\Omega$  of ESR are used. The two 22- $\mu$ F capacitors are used since they have a higher resonance frequency and can help reduce the output ripple caused by parasitic inductance. With the four parallel capacitors, the estimated effective output capacitance after derating using the capacitor manufacturer's website is 142  $\mu$ F. There is almost no DC bias derating at 1 V. This design was able to use less than the calculated minimum because the loop crossover frequency was above the f<sub>SW</sub> / 10 estimate as shown in the Load Transient graph in the *Application Curves*.

#### 8.2.1.2.4 Input Capacitor

Input decoupling ceramic capacitors type X5R, X7R, or similar from VIN to PGND that are placed as close as possible to the IC are required. A total of at least 10  $\mu$ F of capacitance is required and some applications can require a bulk capacitance. At least 1  $\mu$ F of bypass capacitance is recommended as close as possible to each VIN pin to minimize the input voltage ripple. A 0.1- $\mu$ F to 1- $\mu$ F capacitor must be placed as close as possible to both VIN pins 8 and 12 on the same side of the board of the device to provide high frequency bypass to reduce the high frequency overshoot and undershoot on VIN and SW pins. The voltage rating of the input capacitor must be greater than the maximum input voltage. The capacitor must also have a ripple current rating greater than the maximum RMS input current. The RMS input current can be calculated using  $\overrightarrow{\pi}$  16.

For this example design, a ceramic capacitor with at least a 16-V voltage rating is required to support the maximum input voltage. Two 10- $\mu$ F, 0805, X7S, 25-V and two 0.1- $\mu$ F, 0402, X7R 50-V capacitors in parallel have been selected to be placed on both sides of the IC near both VIN pins to PGND pins. Based on the capacitor manufacturer's website, the total ceramic input capacitance derates to 5.4  $\mu$ F at the nominal input voltage of 12 V. A 100- $\mu$ F bulk capacitance is also used to bypass long leads when connected a lab bench top power supply.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using  $\neq$  17. The maximum input ripple occurs when operating nearest to 50% duty cycle. Using the nominal design example values of loutmax = 6 A,  $C_{IN}$  = 5.4 µF, and  $f_{SW}$  = 1000 kHz, the input voltage ripple with the 12 V nominal input is 85 mV and the RMS input ripple current with the 4.5 V minimum input is 4.9 A.

$$\text{Icirms} = \text{Iout} \times \sqrt{\frac{\text{Vout}}{\text{Vinmin}}} \times \frac{(\text{Vinmin} - \text{Vout})}{\text{Vinmin}}$$

(16)

$$\Delta \text{Vin} = \frac{\text{loutmax} \times \left(1 - \frac{\text{Vout}}{\text{Vin}}\right) \times \frac{\text{Vout}}{\text{Vin}}}{\text{Cin} \times f_{\text{SW}}}$$

(17)

#### 8.2.1.2.5 Adjustable Undervoltage Lockout

The undervoltage lockout (UVLO) is adjusted using the external voltage divider network of  $R_{ENT}$  and  $R_{ENB}$ . The UVLO has two thresholds: one for power up when the input voltage is rising and one for power down or brownouts when the input voltage is falling. For the example design, the supply is set to turn on and start switching once the input voltage increases above 4.5 V (UVLO start or enable). After the regulator starts switching, it continues to do so until the input voltage falls below 3.95 V (UVLO stop or disable). In this example, these start and stop voltages set by the EN resistor divider were selected to have more hysteresis than the internally fixed VIN UVLO.

#### 8.2.1.2.6 Output Voltage Resistors Selection

The output voltage is set with a resistor divider created by  $R_{FBT}$  and  $R_{FBB}$  from the output node to the FB pin. It is recommended to use 1% tolerance or better resistors. For this example design, 4.99 k $\Omega$  was selected for  $R_{FBB}$ . Using  $\neq$  18,  $R_{FBT}$  is calculated as 4.99 k $\Omega$ . This is a standard 1% resistor.

$$R_{FBT} = R_{FBB} \times \left(\frac{V_{OUT}}{V_{REF}} - 1\right)$$

(18)

If the PCB layout does not use the recommended AGND to PGND connection in 22210.1, noise on the feedback pin can degrade the output voltage regulation at max load. Use a smaller R<sub>FBB</sub> of 1.00 k $\Omega$  minimizes the impact of this noise.

#### 8.2.1.2.7 Bootstrap Capacitor Selection

A 0.1-µF ceramic capacitor must be connected between the BOOT and SW pins for proper operation. The capacitor must be rated for at least 10-V to minimize DC bias derating.

A resistor can be added in series with the BOOT capacitor to slow down the turnon of the high-side MOSFET and rising edge overshoot on the SW pin. This comes with the trade off of more power loss and lower efficiency. As a best prectice, include a  $0-\Omega$  placeholder in all prototype designs in case parasitic inductance in the PCB layout results in more voltage overshoot at the SW pin than is normal. This helps keep the voltage within the ratings of the device and reduces the high frequency noise on the SW node. The recommended BOOT resistor value to decrease the SW pin overshoot is 2.2  $\Omega$ .

#### 8.2.1.2.8 BP5 Capacitor Selection

A 2.2-µF ceramic capacitor must be connected between the BP5 pin and AGND for proper operation. The capacitor must be rated for at least 10 V to minimize DC bias derating.

#### 8.2.1.2.9 PGOOD Pullup Resistor

A 10-k $\Omega$  resistor is used to pull up the power good signal when FB conditions are met. The pullup voltage source must be less than the 6-V absolute maximum of the PGOOD pin.

#### 8.2.1.2.10 Current Limit Selection

The MODE pin is used to select between two current limit settings. Select the current limit setting whose minimum is greater than at least 1.1 times the maximum steady state peak current. This is to provide margin for component tolerance and load transients. For this design, the minimum current limit should be greater than 7.45 A so the high current limit setting is selected.

#### 8.2.1.2.11 Soft-Start Time Selection

The MODE pin is used to select between four different soft-start times. This is useful if a load has specific timing requirements for the output voltage of the regulator. A longer soft-start time is also useful if the output capacitance is very large and would require large amounts of current to quickly charge the output capacitors to the output voltage level. The large currents necessary to charge the capacitor can reach the current limit or cause the input voltage rail to sag due excessive current draw from the input power supply. Limiting the output voltage slew rate solves both of these problems. The example design has the soft-start time set to 1.0 ms. With this soft-start time the current required to charge the output capacitors to the nominal output voltage is only 0.14 A.

#### 8.2.1.2.12 Ramp Selection and Control Loop Stability

The MODE pin is used to select between three different ramp settings. The most optimal ramp setting depends on V<sub>OUT</sub>,  $f_{SW}$ , L<sub>OUT</sub>, and C<sub>OUT</sub>. To get started, calculate LC double pole frequency using  $\neq$  19. The ratio between  $f_{SW}$  and  $f_{LC}$  should then be calculated. Based on this ratio and the output voltage, the recommended ramp setting should be selected using  $\boxtimes$  8-3. With a 1-V output, the 1-pF ramp is recommended for ratios between approximately 35 and 58, the 2-pF ramp is recommended for ratios between approximately 58 and 86, and the 4-pF ramp is recommended for ratios greater than approximately 86. In general, it is best to use the largest ramp capacitor the design will support. Increasing the ramp capacitor improves transient response but can reduce stability margin or increase on-time jitter.

For this design,  $f_{LC}$  is 17.5 kHz and the ratio is 57 which is on the border of the 1-pF and 2-pF ramp settings. Through bench evaluation, it was found that the design had sufficient stability margin with the 2-pF ramp so this setting was selected for the best transient response. The recommended ramp settings given by  $\boxtimes$  8-3 include margin to account for potential component tolerances and variations across operating conditions so it is possible to use a higher ramp setting as shown in this example.

Use a feedforward capacitor (C<sub>FF</sub>) in parallel with the upper feedback resistor (R<sub>FBT</sub>) to add a zero into the control loop to provide phase boost. Include a placeholder for this capacitor as the zero it provides can be required to meet phase margin requirements. This capacitor also adds a pole at a higher frequency than the zero. The pole and zero frequency are not independent so as a result, once the zero location is chosen, the pole is fixed as well. The zero is placed at 1/4 the f<sub>SW</sub> by calculating the value of C<sub>FF</sub> with  $\neq$  20. The calculated value is 128 pF — round this down to the closest standard value of 120 pF.

Using bench measurements of the AC response, the feedforward capacitor for this example design was increased to 180 pF to improve the transient response.

$$C_{FF} = \frac{1}{\pi \times R_{FBT} \times \frac{f_{SW}}{2}}$$

(20)

It is possible to use larger feedforward capacitors to further improve the transient response but take care to ensure there is a minimum of -9-dB gain margin in all operating conditions. The feedforward capacitor injects noise on the output into the FB pin. This added noise can result in increased on-time jitter at the switching node. Too little gain margin can cause a repeated wide and narrow pulse behavior. Adding a  $100-\Omega$  resistor in series with the feedforward capacitor can help reduce the impact of noise on the FB pin in case of non-ideal PCB layout. The value of this resistor must be kept small as larger values bring the feedforward pole and zero closer together degrading the phase boost the feedforward capacitor provides.

When using higher ESR output capacitors, such as polymer or tantalum, their ESR zero ( $f_{ESR}$ ) should be accounted for. The ESR zero can be calculated using  $\neq 21$ . If the ESR zero frequency is less than the estimated bandwidth of 1/10th the  $f_{SW}$ , it can affect the gain margin and phase margin. A series R-C from the FB pin to ground can be used to add a pole into the control loop if necessary. All ceramic capacitors are used in this design so the effect of the ESR zero is ignored.

$$f_{ESR} = \frac{1}{2 \times \pi \times C_{OUT} \times R_{ESR}}$$

(21)

#### 8.2.1.2.13 MODE Pin