# 3A出力、FET内蔵のトラッキング/ターミネーション同期PWMスイッチャー(SWIFT™)

## 特 長

- 外部印加の基準電圧をトラック

- 60mΩのMOSFETスイッチによる、3A出力ソース・シンク電流(連続)時の高効率

- $V_I$ の6%から90%までの出力トラッキング範囲

- 広帯域のPWM周波数：

- 固定時の周波数 350kHz

- 調整可能な周波数 280kHz-700kHz

- ピーク電流制限とサーマル・シャットダウンによる負荷保護

- 集積ソリューションによる基板面積およびトータル・コストの低減

## アプリケーション

- DDRメモリ用終端電圧

- GTLおよびSSTL高速ロジック・ファミリーの能動終端

- DAC制御の大電流出力段

- 高精度ポイント・オブ・ロード電源

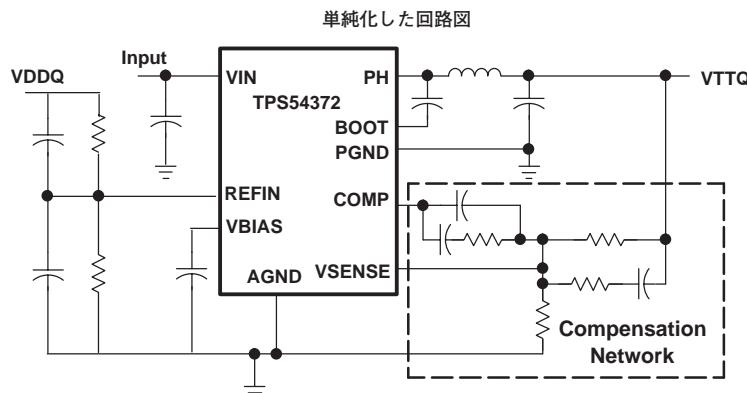

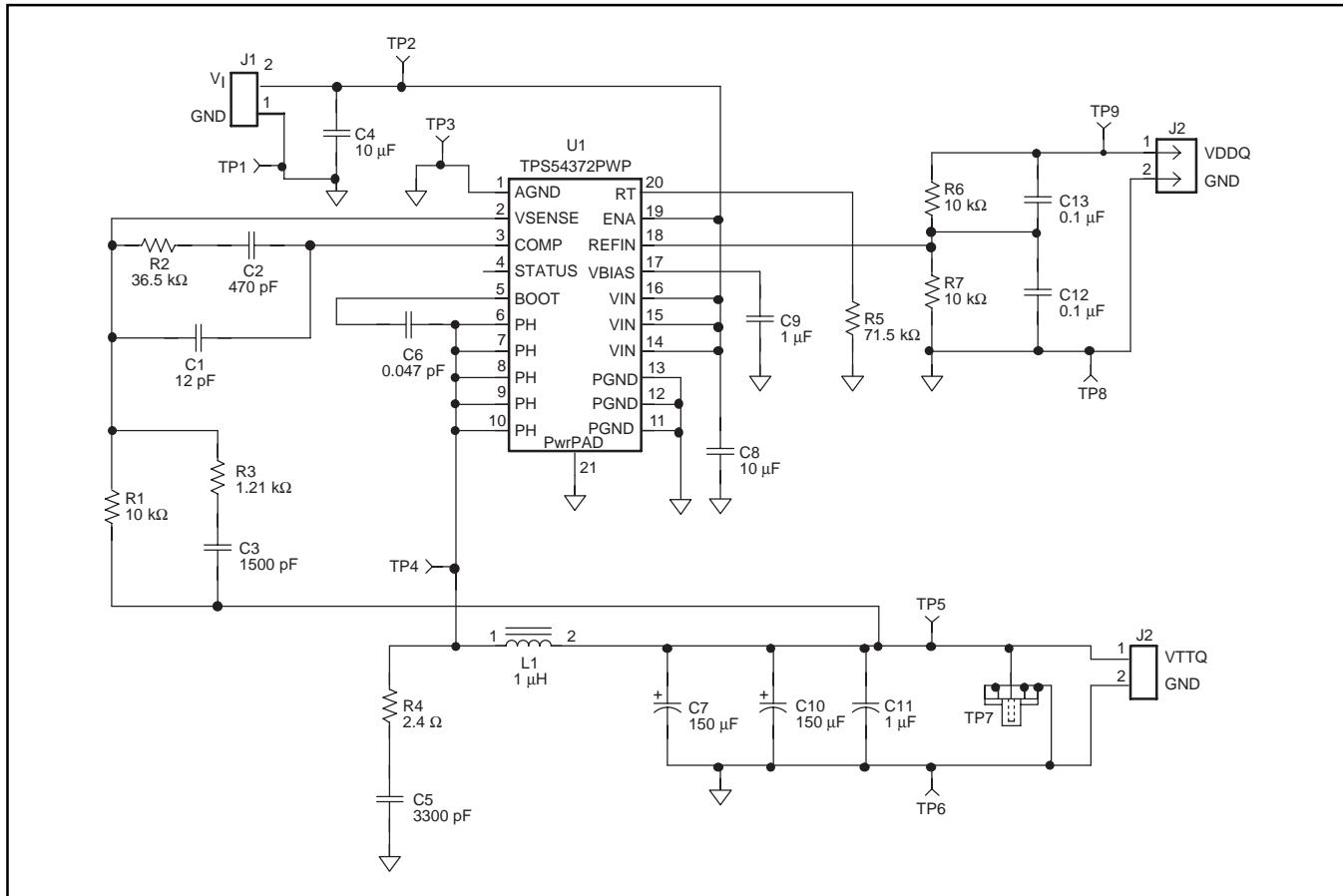

## 単純化した回路図

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## パッケージ情報/ご発注の手引き

| TA         | REFIN VOLTAGE | PACKAGE                             | PART NUMBER |

|------------|---------------|-------------------------------------|-------------|

| -40°C~85°C | 0.2 V~1.75 V  | Plastic HTSSOP (PWP) <sup>(1)</sup> | TPS54372PWP |

(1) PWPパッケージはテープでリールにしたものもあります。その場合は、Rというサフィックスをデバイスタイプに付加願います(すなわち、TPS54372PWPR)。データシートのアプリケーション・セクションにあるPowerPAD™の機構図とレイアウトを参照願います。

## 絶対最大定格

特記ないかぎり無風動作温度範囲<sup>(1)</sup>

|                                                              | TPS54372            | UNITS              |

|--------------------------------------------------------------|---------------------|--------------------|

| Input voltage range, VI                                      | VIN, ENA            | -0.3 V~7           |

|                                                              | RT                  | -0.3 V~6           |

|                                                              | VSENSE, REFIN       | -0.3 V~4           |

|                                                              | BOOT                | -0.3 V~17          |

| Output voltage range, VO                                     | VBIAS, COMP, STATUS | -0.3 V~7           |

|                                                              | PH                  | -0.6 V~6           |

| Source current, IO                                           | PH                  | Internally Limited |

|                                                              | COMP, VBIAS         | 6 mA               |

| Sink current, IS                                             | PH                  | 6 A                |

|                                                              | COMP                | 6 mA               |

|                                                              | ENA, STATUS         | 10 °C              |

| Voltage differential                                         | AGND to PGND        | ±0.3 V             |

| Operating virtual junction temperature range, TJ             |                     | -40~125 °C         |

| Storage temperature, Tstg                                    |                     | -65~150 °C         |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                     | 300 °C             |

(1)絶対最大定格に記述される以上のストレスを加えると、デバイスは永久破壊されることがあります。これらはストレス定格だけであり、これらの条件あるいは推奨動作条件を超える条件でのデバイスのファンクション動作は含まれません。また、絶対最大定格の条件下に長時間デバイスをさらすと、デバイスの信頼性に影響することがあります。

## 推奨動作条件

|                                    | MIN | NOM | MAX | UNIT |

|------------------------------------|-----|-----|-----|------|

| Input voltage, VI                  | 3   | 6   | V   |      |

| Operating junction temperature, TJ | -40 | 125 | °C  |      |

## 消費電力定格<sup>(1)(2)</sup>

| PACKAGE                   | THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT | TA = 25°C<br>POWER RATING | TA = 70°C<br>POWER RATING | TA = 85°C<br>POWER RATING |

|---------------------------|------------------------------------------|---------------------------|---------------------------|---------------------------|

| 20 Pin PWP with solder    | 26.0 °C/W                                | 3.85 W <sup>(3)</sup>     | 2.11 W                    | 1.54 W                    |

| 20 Pin PWP without solder | 57.5 °C/W                                | 1.73 W                    | 0.96 W                    | 0.69 W                    |

(1)パッケージのより詳細な情報は、テクニカル・ブリーフ(文献番号SLMA002)を参照願います。

(2)テスト基板条件

1. 3×3インチ、4層、厚さ0.062インチ

2. プリント基板の部品面に1.5オンスの銅配線

3. プリント基板の半田面に1.5オンスの銅のグランド・プレーン

4. 10個のサーマル・ヴィア(本データシートのアプリケーション・セクションにおける推奨ランドパターンを参照願います)

(3)最大電力消費は過電流保護で制限されるかもしれません。

# 電気的特性

特に記述のない限り  $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_I = 3\text{V} \sim 6\text{V}$

| PARAMETER                                                                                        |                     | TEST CONDITIONS                                                              | MIN  | TYP  | MAX   | UNIT |

|--------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------|------|------|-------|------|

| <b>SUPPLY VOLTAGE, VIN</b>                                                                       |                     |                                                                              |      |      |       |      |

| V <sub>IN</sub>                                                                                  | Input voltage range |                                                                              | 3.0  | 6.0  |       | V    |

|                                                                                                  |                     | f <sub>S</sub> = 350 kHz, RT open, PH pin open                               | 6.2  | 9.60 |       | mA   |

|                                                                                                  | Quiescent current   | f <sub>S</sub> = 550 kHz, RT = 100 kΩ, PH pin open                           | 8.4  | 12.8 |       |      |

|                                                                                                  |                     | Shutdown, SS/ENA = 0 V                                                       | 1    | 1.4  |       |      |

| <b>UNDER VOLTAGE LOCK OUT</b>                                                                    |                     |                                                                              |      |      |       |      |

| Start threshold voltage, UVLO                                                                    |                     |                                                                              | 2.95 | 3.0  |       | V    |

| Stop threshold voltage, UVLO                                                                     |                     |                                                                              | 2.70 | 2.80 |       | V    |

| Hysteresis voltage, UVLO                                                                         |                     |                                                                              | 0.14 | 0.16 |       | V    |

| Rising and falling edge deglitch, UVLO <sup>(1)</sup>                                            |                     |                                                                              | 2.5  |      |       | μs   |

| <b>BIAS VOLTAGE</b>                                                                              |                     |                                                                              |      |      |       |      |

| Output voltage, VBIAS                                                                            |                     | I(VBIAS) = 0                                                                 | 2.70 | 2.80 | 2.90  | V    |

| Output current, VBIAS <sup>(2)</sup>                                                             |                     |                                                                              |      | 100  |       | μA   |

| <b>REGULATION</b>                                                                                |                     |                                                                              |      |      |       |      |

| Line regulation <sup>(1)(3)</sup>                                                                |                     | I <sub>L</sub> = 1.5 A, f <sub>S</sub> = 350 kHz, T <sub>J</sub> = 85°C      |      | 0.07 |       | %/V  |

| Load regulation <sup>(1)(3)</sup>                                                                |                     | I <sub>L</sub> = 0 A to 3 A, f <sub>S</sub> = 350 kHz, T <sub>J</sub> = 85°C |      | 0.03 |       | %/A  |

| <b>OSCILLATOR</b>                                                                                |                     |                                                                              |      |      |       |      |

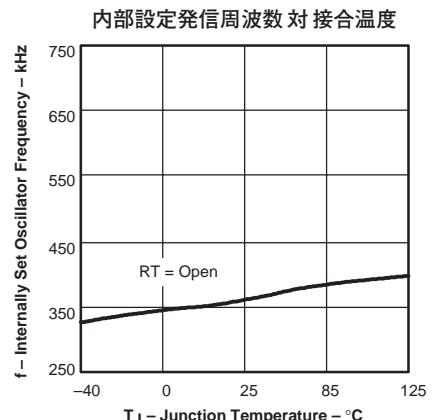

| Internally set free running frequency                                                            |                     | RT open                                                                      | 280  | 350  | 420   | kHz  |

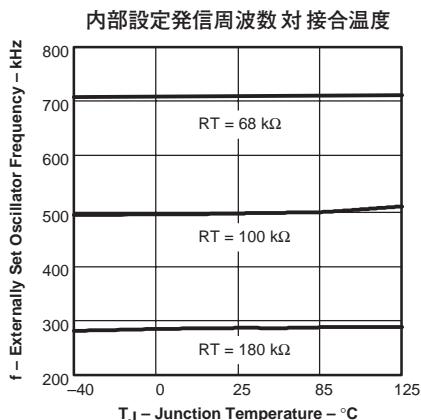

| Externally set free running frequency range                                                      |                     | RT = 180 kΩ (1% resistor to AGND)                                            | 252  | 280  | 308   | kHz  |

|                                                                                                  |                     | RT = 100 kΩ (1% resistor to AGND)                                            | 460  | 500  | 540   |      |

|                                                                                                  |                     | RT = 68 kΩ (1% resistor to AGND)                                             | 663  | 700  | 762   |      |

| Ramp valley <sup>(1)</sup>                                                                       |                     |                                                                              | 0.75 |      |       | V    |

| Ramp amplitude (peak-to-peak) <sup>(1)</sup>                                                     |                     |                                                                              | 1    |      |       | V    |

| Minimum controllable on time <sup>(1)</sup>                                                      |                     |                                                                              |      | 200  |       | ns   |

| Maximum duty cycle <sup>(1)</sup>                                                                |                     |                                                                              | 90%  |      |       |      |

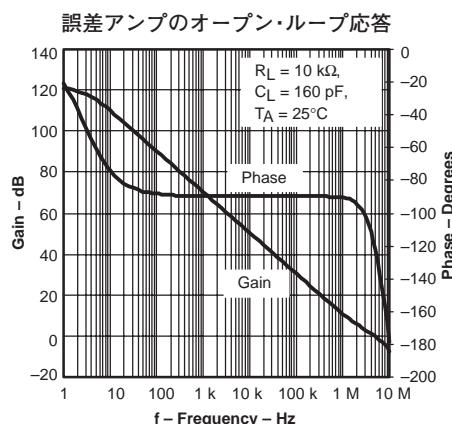

| <b>ERROR AMPLIFIER</b>                                                                           |                     |                                                                              |      |      |       |      |

| Error amplifier open loop voltage gain                                                           |                     | 1 kΩ COMP to AGND <sup>(1)</sup>                                             | 90   | 110  |       | dB   |

| Error amplifier unity gain bandwidth                                                             |                     | Parallel 10 kΩ, 160 pF COMP to AGND <sup>(1)</sup>                           | 3    | 5    |       | MHz  |

| Error amplifier common mode input voltage range                                                  |                     | Powered by internal LDO <sup>(1)</sup>                                       | 0    |      | VBIAS | V    |

| Input bias current, VSENSE                                                                       |                     | VSENSE = V <sub>ref</sub>                                                    |      | 60   | 250   | nA   |

| Output voltage slew rate (symmetric), COMP                                                       |                     |                                                                              | 1.0  | 1.4  |       | V/μs |

| <b>PWM COMPARATOR</b>                                                                            |                     |                                                                              |      |      |       |      |

| PWM comparator propagation delay time,<br>PWM comparator input to PH pin<br>(excluding deadtime) |                     | 10-mV overdrive <sup>(1)</sup>                                               |      | 70   | 85    | ns   |

(1) 設計保証

(2) 静的な抵抗負荷のみ

(3) 図8の回路で規定

## 電気的特性(続き)

特に記述のない限り  $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_I = 3\text{V} \sim 6\text{V}$

| PARAMETER                                     | TEST CONDITIONS                   | MIN  | TYP  | MAX  | UNIT             |

|-----------------------------------------------|-----------------------------------|------|------|------|------------------|

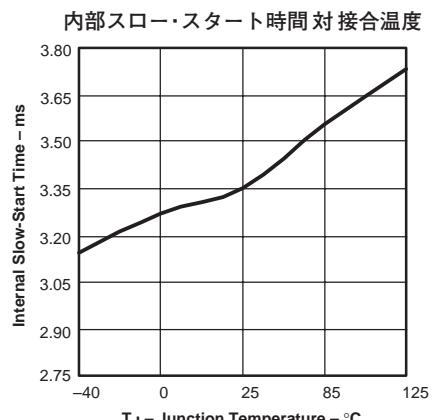

| <b>SLOW-START/ENABLE</b>                      |                                   |      |      |      |                  |

| Enable threshold voltage, ENA                 |                                   | 0.82 | 1.20 | 1.40 | V                |

| Enable hysteresis voltage, ENA <sup>(1)</sup> |                                   |      | 0.03 |      | V                |

| Falling edge deglitch, ENA <sup>(1)</sup>     |                                   |      | 2.5  |      | $\mu\text{s}$    |

| Internal slow-start time                      |                                   | 2.6  | 3.35 | 4.1  | ms               |

| <b>STATUS</b>                                 |                                   |      |      |      |                  |

| Output saturation voltage, STATUS             | $I_{\text{sink}} = 2.5\text{ mA}$ |      | 0.18 | 0.30 | V                |

| Leakage current, STATUS                       | $V_I = 3.6\text{ V}$              |      |      | 1    | $\mu\text{A}$    |

| <b>CURRENT LIMIT</b>                          |                                   |      |      |      |                  |

| Current limit                                 | $V_I = 3\text{ V}^{(1)}$          | 4    | 6.5  |      | A                |

|                                               | $V_I = 6\text{ V}^{(1)}$          | 4.5  | 7.5  |      |                  |

| Current limit leading edge blanking time      |                                   |      | 100  |      | ns               |

| Current limit total response time             |                                   |      | 200  |      | ns               |

| <b> THERMAL SHUTDOWN</b>                      |                                   |      |      |      |                  |

| Thermal shutdown trip point <sup>(1)</sup>    |                                   | 135  | 150  | 165  | $^\circ\text{C}$ |

| Thermal shutdown hysteresis <sup>(1)</sup>    |                                   |      | 10   |      | $^\circ\text{C}$ |

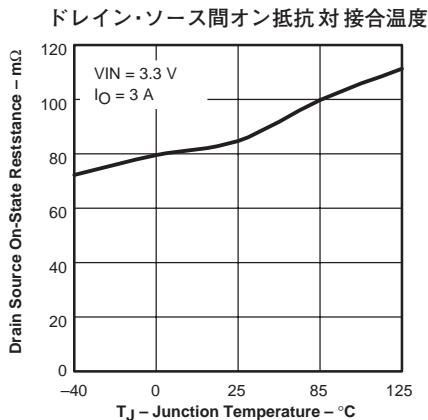

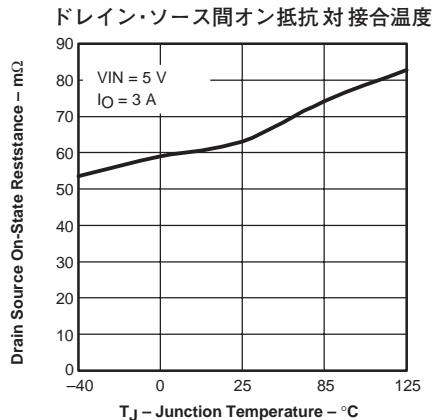

| <b>OUTPUT POWER MOSFETS</b>                   |                                   |      |      |      |                  |

| rDS(on) Power MOSFET switches                 | $V_I = 6\text{ V}^{(4)}$          |      | 59   | 88   | $\text{m}\Omega$ |

|                                               | $V_I = 3\text{ V}^{(4)}$          |      | 85   | 136  |                  |

(1) 設計保証

(2) 静的な抵抗負荷のみ

(3) 図8の回路で規定

(4) 整合のとれたMOSFETであり、ローサイドのrDS(on)はテストされ、ハイサイドのrDS(on)は設計保証

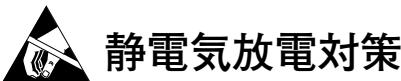

## ピン配置

## ピンの構成

| TERMINAL NAME | NO.   | DESCRIPTION                                                                                                       |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------|

| AGND          | 1     | アナログ・グランド。補償網/出力分圧回路、スロー・スタートコンデンサ、VBIASコンデンサ、およびRT抵抗の各帰線になる。PowerPAD™はAGNDに接続する。                                 |

| BOOT          | 5     | ブートストラップ入力。0.022μFから0.1μFの低等価直列抵抗のコンデンサをBOOTとPH間に接続し、ハイサイドFETドライバをフローティング駆動する。                                    |

| COMP          | 3     | 誤差アンプ出力。周波数補償網をCOMPからVSENSEに接続する。                                                                                 |

| ENA           | 19    | イネーブル入力。ロジック・レベルのハイは、発振器、PWM制御回路、MOSFETドライバをイネーブルにする。ロジック・レベルのローは動作をディスエーブルにし、デバイスを静的な低電流状態にする。                   |

| PGND          | 11-13 | パワー・グランド。ローサイド・ドライバとパワーMOSFET用の大電流が流れる帰線。大面積の銅パターンのPGNDを入出力電源の帰線、および入出力(VINとVo)コンデンサの負側に接続する。また、AGNDとの1点アースを推奨する。 |

| PH            | 6-10  | フェーズ入出力。内部のハイ・ローサイドの両パワーMOSFETおよび出力インダクタの結合点。                                                                     |

| RT            | 20    | 周波数設定する抵抗の入力。RTとAGND間に抵抗を接続して、スイッチング周波数f <sub>s</sub> を設定する。                                                      |

| REFIN         | 18    | 外部基準電圧入力。スロー・スタートおよび誤差アンプへのハイ・インピーダンス入力。                                                                          |

| STATUS        | 4     | オープン・ドレイン出力。VIN < UVLO, VBIASおよび内部基準電圧が立ち上がってない、あるいは内部シャットダウン信号がアクティブの場合にロー。それ以外はハイ。                              |

| VBIAS         | 17    | 内部バイアス・レギュレータの出力。内部回路にレギュレーションした電圧を供給。VBIASとAGNDの両ピン間に高品質・低等価直列抵抗の0.1μFから1.0μFのセラミック・コンデンサを接続してバイパスする。            |

| VIN           | 14-16 | パワーMOSFETスイッチと内部バイアス・レギュレータに供給する入力。VINピンとPGNDピン間で、高品質・低等価直列抵抗の1μFから10μFのセラミック・コンデンサをデバイス・パッケージの極力近くに接続してバイパスする。   |

| VSENSE        | 2     | 誤差アンプの反転入力。出力電圧(Vo)からの補償網および出力分圧回路を接続する。                                                                          |

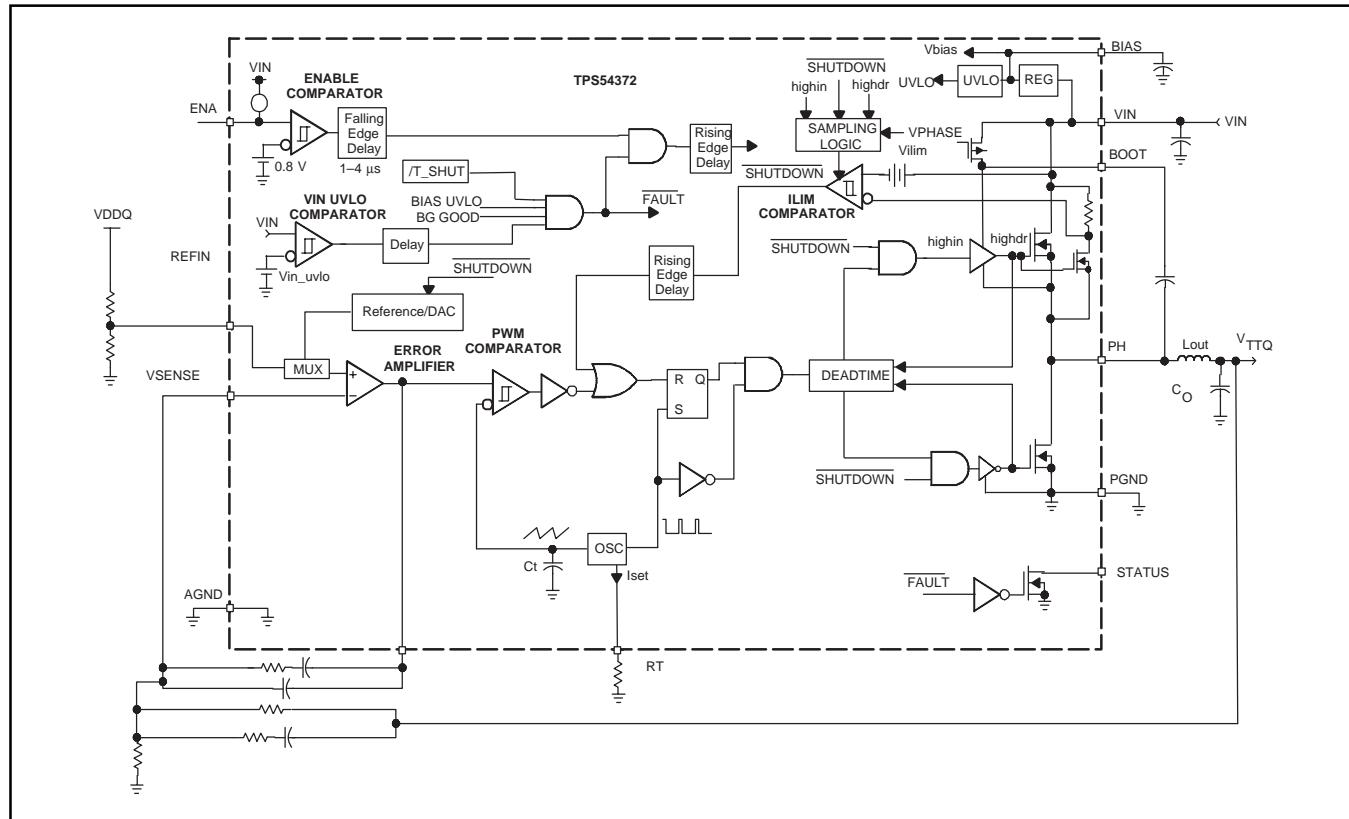

## 内部ブロック図

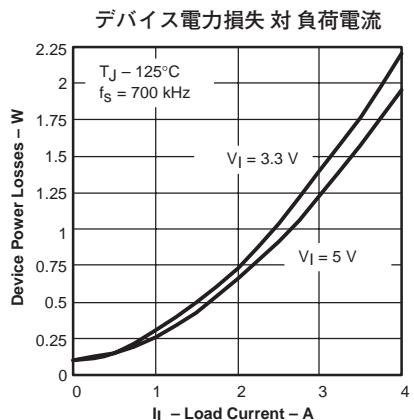

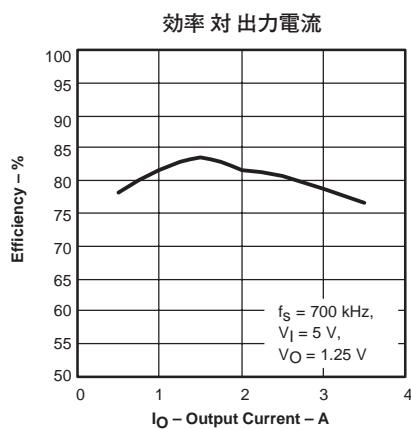

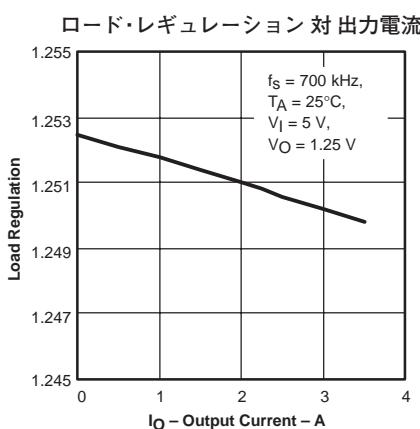

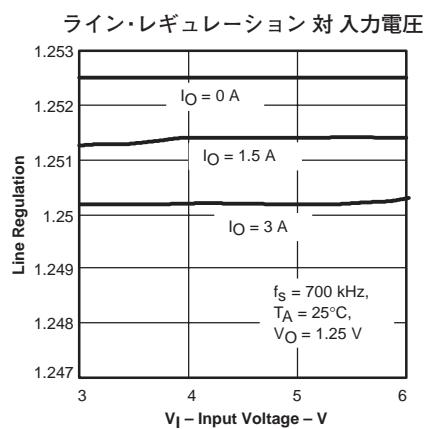

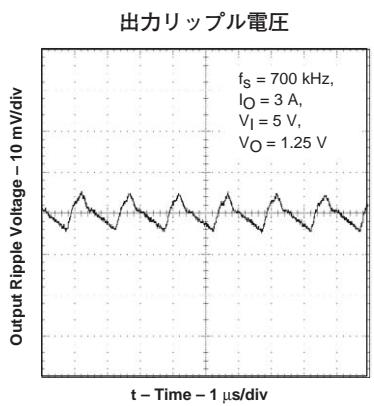

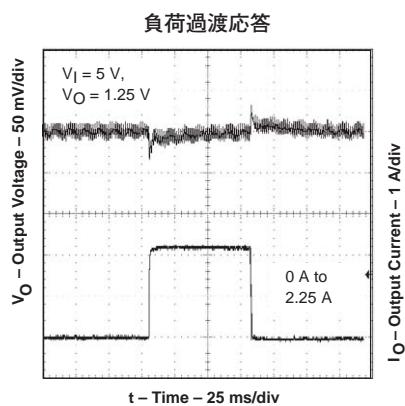

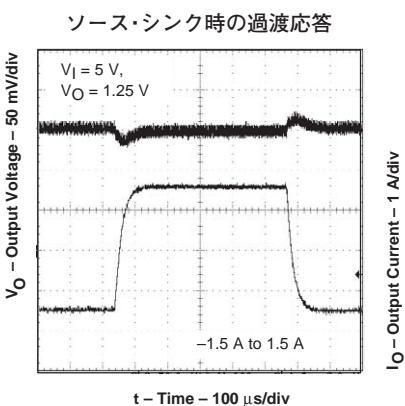

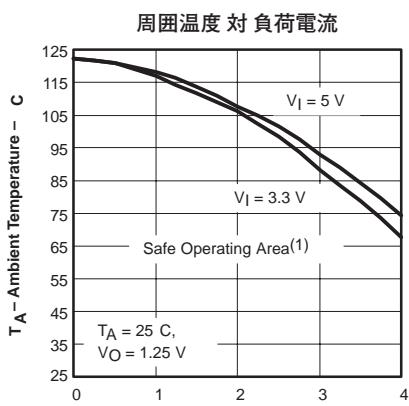

# 代表的特性

図1

図2

図3

図4

図5

図6

図7

図8. アプリケーション回路

## アプリケーション情報

図8はTPS54372の代表的なアプリケーション回路図を示します。TPS54372(図中のU1)は、VDDQの半分の出力電圧(公称値、1.25V)で3Aまでの出力電流を供給できます。適正な動作のために、TPS54372の直下のPowerPAD<sup>TM</sup>をプリント基板へ直接に半田付けする必要があります。

### 部品選定

本設計例で使用した部品の定数は、優れた過渡応答と小さな基板実装面積を実現するように選びました。特殊ポリマー・コンデンサを出力フィルタ回路に用いています。また、小型で小定数の出力インダクタを採用しています。補償回路網の部品は、閉ループの帯域を最大にし、優れた過渡応答特性を得るために選定しています。より詳細な設計情報は、www.ti.comで入手できます。

### 入力電圧

入力電圧は3.3あるいは5.0VDC(いずれも公称値)です。入力フィルタ(C4)は10μFのセラミック・コンデンサ(太陽誘電)です。同じく10μFのセラミック・コンデンサ(太陽誘電)であるC8は、TPS54372への入力電圧を高周波デカップリングします。C8は極力デバイスの近くに配置する必要があります。また、リップル電流はC4とC8の双方と、そのPGNDへの帰路を交わりますが、それが出力コンデンサC7, C10, C11を還流しないようにします。

### 帰還回路

帰還回路部品の定数は、高速な過渡応答時間を得るために選定しています。部品R1, R2, R3, C1, C2、およびC3は、ループ補償回路網を形成しています。本設計ではタイプ3のトポロジーを用いています。帰還回路網の伝達関数は、内部の誤差アンプのオープン・ループ特性で最大の閉ループ利得を得るように設定しています。閉ループのクロスオーバ周波数(ループ利得が0dBになる周波数)は、3Vから6Vの入力時で一般に80kHzから125kHzになります。

### 動作周波数

本アプリケーション回路では、71.5kΩの抵抗をRTとAGND間に接続して700kHzの動作周波数を選択しています。これと異なる周波数にするには、RT(20ピン)とアナログ・グランド間に68kΩから180kΩの抵抗を接続します。あるいは、RTをオープンにしてデフォルト値の350kHzを選びます。抵抗値を選択する場合は、式(1)で近似できます。

$$R = \frac{500 \text{ kHz}}{\text{スイッチング周波数}} \times 100 \text{ k}\Omega \quad (1)$$

## 出力フィルタ

出力フィルタは $1.0\mu\text{H}$ のインダクタと2個の $150\mu\text{F}$ のコンデンサで構成されます。このインダクタは低DC抵抗( $0.010\Omega$ )タイプのVishay製 IHLP-2525CZ-01で、 $1.0\mu\text{H}$ , 8.5A定格DC出力のものです。コンデンサは $150\mu\text{F}$ , 6.3Vの特殊ポリマー型です。

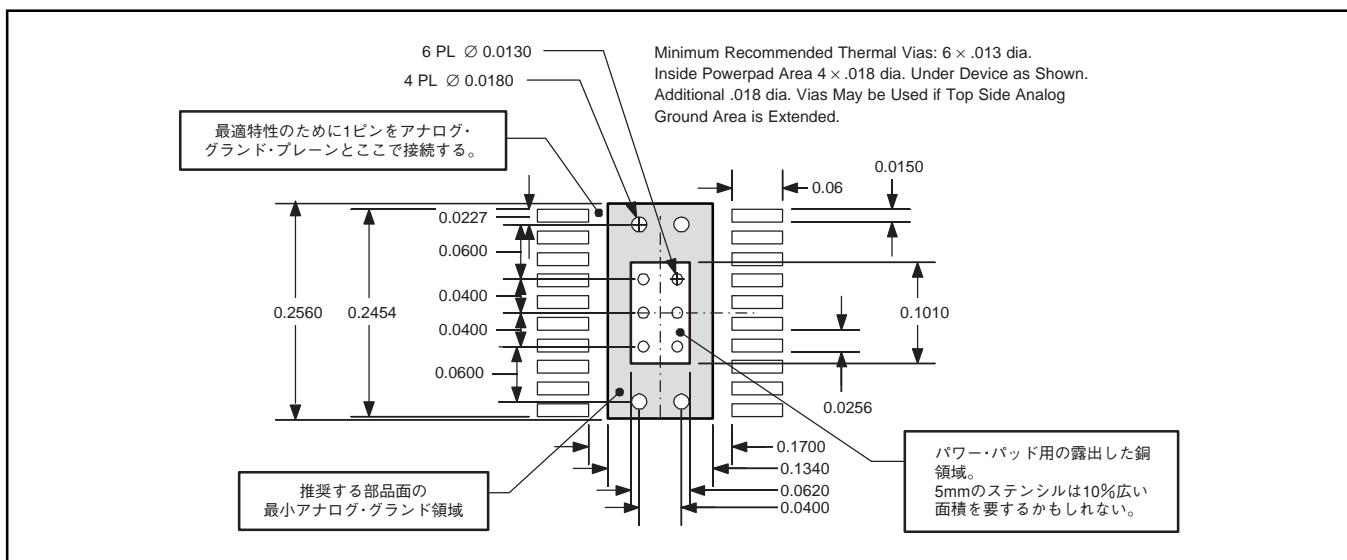

## グランドのとりかたとPowerPAD™のレイアウト

TPS54372にはアナログとパワーの2つの内部グランドがあります。TPS54372の内部では、アナログ・グランドをすべての雑音に敏感な信号に接続し、パワー・グランドは雑音を発生するパワー信号に接続しています。PowerPAD™は直接AGNDに接続する必要があります。両グランド間に入った雑音はTPS54372の特性を劣化させ、特に大出力電流時に顕著になります。しかし、アナログ・グランド・プレーンの雑音は、制御信号やバイアス信号に問題を発生します。したがって、これらの理由から、アナログとパワーの両グランド・プレーンを分離することを推奨します。この両プレーンはICにおいて互いに接続し、両グランド間の雑音を低減します。直接にパワー・グランド・プレーンに接続する部品は、入力コンデンサ、出力コンデンサ、入力電圧デカップリング用コンデンサ、およびTPS54372のPGNDピンだけです。パワー・グランド領域は、PowerPAD™を実装する領域と同様に、複数のヴィアで内部のグランド・プレーンと接続します。TPS54372用評価モ

ジュールのレイアウトは、半田面がシステムのグランド・プレーンである2層基板の推奨レイアウトの代表例です。TPS54372用評価モジュールの文献は、TI社のウェブサイトのTPS54372製品フォルダにあります。

## 熱特性に関するレイアウトの考察

最大負荷電流での動作のため、アナログ・グランド・プレーンには適当な放熱領域が必要です。それには、1オンスの銅による3インチ×3インチのプレーンを推奨します。これは必須というわけではなく、周囲温度と空気流に依存します。ほとんどのアプリケーションには内部グランド・プレーンの広い領域があり、PowerPAD™はその中で最大面積のものに接続します。部品面や半田面にある他の領域も放熱に寄与するので、3A以上の動作時はすべての領域を放熱に使用します。PowerPAD™の露出領域とアナログ・グランド・プレーン層との接続には、直径0.013インチのヴィアを用いて、ヴィアによる半田の上がりを防止します。PowerPAD™領域に6個のヴィアを作り、さらにデバイス・パッケージの直下に4個のヴィアを作ります。このパッケージ直下のヴィアのサイズは、露出したサーマル・パッド領域とは違って、0.018インチまで拡張できます。推奨するこれら10個のヴィアに加えて、熱特性を強化するヴィアをデバイス・パッケージの直下以外の領域にも作ります。

図9. 20ピンPWP PowerPAD™用の推奨ランド・パターン

# 特性グラフ

図10

図11

図12

図13

図14

図15

図16

(1)安全動作領域は、本データシートのパッケージ消費電力定格表に記述されたテスト基板条件に適用されます。

図17

## 詳細解説

### 低電圧ロックアウト(UVLO)

TPS54372は低電圧ロックアウト回路を備えており、入力電圧(VIN)が不十分な時にデバイスをディスエーブルに保ちます。電源投入中は、VINがUVLOのスレッシュホールド電圧(公称値2.95V)を超えるまで、内部回路を停止状態に維持します。ひとたびVINがUVLOスタートのスレッシュホールド電圧に達すると、デバイスはスタート・アップを始めます。デバイスは、VINがUVLOトップのスレッシュホールド電圧(公称値2.8V)を下回るまで動作します。このようなUVLOコンパレータのヒステリシスと、 $2.5\mu\text{s}$ の立ち上がり・立ち下がりエッジのデグリッチ回路が、VINに乗った雑音によるデバイスのシャットダウンの可能性を低減します。

### イネーブル(ENA)

イネーブル(ENA)ピンは、TPS54372をイネーブルあるいはディスエーブル(シャットダウン)に制御します。1.4V以上の入力でTPS54372はイネーブルになります。また、0.9V以下の入力でデバイス動作がディスエーブルになります。これらは標準的なロジックのスレッシュホールド電圧ではありませんが、TTL出力と互換性があります。

ENAがローの場合、発振器、スロー・スタート、PWM制御回路、およびMOSFETドライバはディスエーブルされ、デバイスのスタート・アップに備えた初期状態になっています。デバイスのスタート・アップはENAのローからハイへの遷移時に開始し、同時に出力電圧が0Vから始まります。

### スロー・スタート

スロー・スタート回路は、スタート・アップ時の出力電圧のスロープ(傾斜)を制御し、ラッシュ電流を制限します。内部のスロー・スタート・レートは $0.25\text{V/ms}$ (公称値)であり、その最速レートは $0.35\text{V/ms}$ になります。REFINの電圧が内部スロープより高速で立ち上がる場合、あるいはデバイス動作のイネーブル時にすでにREFINに電圧が印加されている場合、出力電圧は内部レートに従って立ち上ります。逆に、REFINがもっとゆっくり立ち上がる場合、出力電圧はREFINとほぼ等しいレートで立ち上ります。

### VBIASレギュレータ(VBIAS)

VBIASレギュレータは、内部アナログ・デジタルの両ブロックに、接合温度と入力電圧の変動に依存しない安定した電源を供給します。VBIASピンには、高品質かつ低等価直列抵抗のセラミックのバイパス・コンデンサが必要です。温度変動に対して安定なX7RあるいはX5Rクラスの誘電体を推奨します。バイパス・コンデ

ンサは極力VBIASピンの近くに配置し、AGNDに接地します。VBIASに外部の負荷をつけることは可能ですが、内部回路が最小2.70VのVBIASを必要になると、VBIASに接続した外部負荷によるACあるいはデジタル雑音が、特性を劣化させることに注意を要します。VBIASピンは外部回路の基準電圧として使うこともできます。

### 基準電圧

REFINピンには、ユーザーが設定するトラッキング電圧を入力できます。一般にこの電圧をVDDQの半分にします。この外部基準電圧の入力範囲は、 $0.2\text{V}$ から $1.75\text{V}$ です。これを超えると、内部のバンドギャップ基準電圧が外部印加の基準電圧を無効にします。

### 発振器とPWMランプ

発振周波数はRTピンをオープン(フローティング)にして、内部的に $350\text{kHz}$ の固定値に設定できます。アプリケーションによって異なる動作周波数が必要ならば、RTピンとAGND間に抵抗を接続して、発振周波数を外部的に $280\text{kHz}$ から $700\text{kHz}$ まで調整できます。そのスイッチング周波数は式(2)で近似されます。ここで、RはRTとAGND間の抵抗値です。

$$\text{スイッチング周波数} = \frac{100\text{ k}\Omega}{R} \times 500\text{ kHz} \quad (2)$$

下表に周波数選択の組み合わせを要約します。

| SWITCHING FREQUENCY                                 | RT PIN                                          |

|-----------------------------------------------------|-------------------------------------------------|

| $350\text{ kHz}$ , internally set                   | Float                                           |

| Externally set $280\text{ kHz}$ to $700\text{ kHz}$ | $R = 180\text{ k}\Omega$ to $68\text{ k}\Omega$ |

### 誤差アンプ

高性能で広帯域の誤差アンプが、TPS54372を他の大部分のDC/DCコンバータよりも優れたものにしています。これによってユーザーは、個々のアプリケーションに要する出力LCフィルタ用部品を広範に使えます。外付けの補償部品を用いて、タイプ2あるいはタイプ3の補償方式が採用できます。

## PWM制御

誤差アンプ出力、発信器、および電流制限回路からの各信号はPWM制御ロジック回路で処理されます。内部ブロック図を参照すると、制御ロジック回路にはPWMコンパレータ、ORゲート、PWMラッチ、および適応性の高いデッドタイムと制御ロジック・ブロックの一部があります。電流制限のスレッシュホールド電圧より低い安定動作では、PWMコンパレータ出力と発振器パルスが交互にPWMラッチをリセットおよびセットします。PWMラッチがセットされると、ローサイドFETが発振器パルス幅による最小期間だけオンします。この間、PWMのランプ波形は谷の電圧値まで急速に放電します。次にランプ波形が充電を始めると、ローサイドFETはオフし、ハイサイドFETがオンします。PWMランプ波形が誤差アンプの出力電圧を超えると、PWMコンパレータがラッチをリセットし、その結果ハイサイドFETがオフし、ローサイドFETがオンします。そしてローサイドFETは、次の発振器パルスがPWMランプ波形を放電するまでオンを続けます。

過渡状態では、誤差アンプ出力がPWMランプ波形の谷電圧以下やピーク電圧以上になるかもしれません。誤差アンプ出力が高い場合、PWMラッチはリセットされず、発振器パルスが制御ロジックにハイサイドFETのオフとローサイドFETのオンの信号を出すまで、ハイサイドFETはオンを維持します。このとき、出力電圧がレギュレーションの設定値に達するまで、デバイスはVSENSEにほぼ $V_{ref}$ に等しい電圧を供給しながら最大デューティで動作します。誤差アンプ出力が低い場合、PWMラッチは継続的にリセットされ、ハイサイドFETはオンしません。このときローサイドFETは、VSENSEの電圧が低下してPWMコンパレータの状態を反転させるまでオンし続けます。TPS54372は、出力がレギュレーションの設定値に達するまで連続的に電流をシンクできます。

電流制限コンパレータが100ns以上動作すると、PWMランプ波形が誤差アンプ出力を超える前にPWMラッチをリセットします。そして、ハイサイドFETはオフし、ローサイドFETはオンして、出力のインダクタのエネルギーを低減し、出力電流を減少します。この過程は、電流制限コンパレータが動作するサイクルごとに行われます。

## デッドタイム制御とMOSFETドライバ

適応性の高いデッドタイム制御は、MOSFETドライバのタン・オン時間を積極的に制御して、両方のNチャネル・パワーMOSFETのスイッチング遷移時における貫通電流を防止します。ハイサイド・ドライバは、ローサイドFETのゲート電圧が2V以下になるまでオンしません。また、ローサイド・ドライバは、ハイサイドMOSFETのゲート電圧が2V以下になるまでオンしません。ハイサイドとローサイドの両ドライバは300mAのソースおよびシンク能力で設計され、パワーMOSFETのゲートを急速に

ドライブできます。ローサイド・ドライバはVINから電源を供給され、ハイサイド・ドライバはBOOTピンから電源を供給されています。そのブートストラップ回路は、外付けのBOOTコンデンサと、VINピンとBOOTピン間の内部にある2.5Ωのブートストラップ・スイッチを用いています。この内蔵ブートストラップ・スイッチはドライブ効率を高め、外付けの部品点数を節約します。

## 過電流保護

電流制限はサイクルごとになされ、ハイサイドMOSFETを流れる電流を検知し、これをプリセットの過電流スレッシュホールド電圧と比較します。ハイサイドMOSFETは、電流制限スレッシュホールド電圧に達して200ns以内にオフします。立ち上がりエッジを100nsだけブランкиングする回路が、ハイサイドMOSFETがオンするときの電流制限の誤作動を防止します。電流制限の検出は、VINからPHへ流れる電流が出力フィルタに供給される場合のみに行われます。電流をシンクする場合の過負荷保護は、サーマル・シャットダウンで行われます。

## サーマル・シャットダウン

デバイスの接合温度が150°Cを超えると、デバイスはサーマル・シャットダウンを用いてパワーMOSFETをオフし、制御回路をディスエーブルにします。接合温度がサーマル・シャットダウンの動作点より10°C低下すると、デバイスはシャットダウン状態から自動的に解放され、スロー・スタート回路の制御下でスタート・アップします。

サーマル・シャットダウンは過負荷状態が数ms続くと作動します。不良状態が持続すると、デバイスは次のサイクルを繰り返します。すなわち、ソフト・スタート回路の制御下でのスタート・アップ、不良状態による温度上昇、そしてサーマル・シャットダウン温度に達してのシャットダウンというサイクルです。このサイクルは不良原因が除去されるまで持続します。

## ステータス

STATUSピンはオープン・ドレイン出力であり、デバイスの内部状態が適正動作に十分であることを示します。STATUSはシステム制御あるいは監視回路に接続して、タミネーションあるいはトラッキング・レギュレータとしてのスタート・アップ準備完了状態を返すのに使えます。STATUSは、TPS54372の動作時あるいはイネーブル準備完了時にハイ・インピーダンスになります。また、STATUSは以下の状況が発生するとアクティブ(ロー)になります。

- VIN < UVLOスレッシュホールド電圧

- VBIASあるいは内部基準電圧が不十分である。

- サーマル・シャットダウンが動作している。

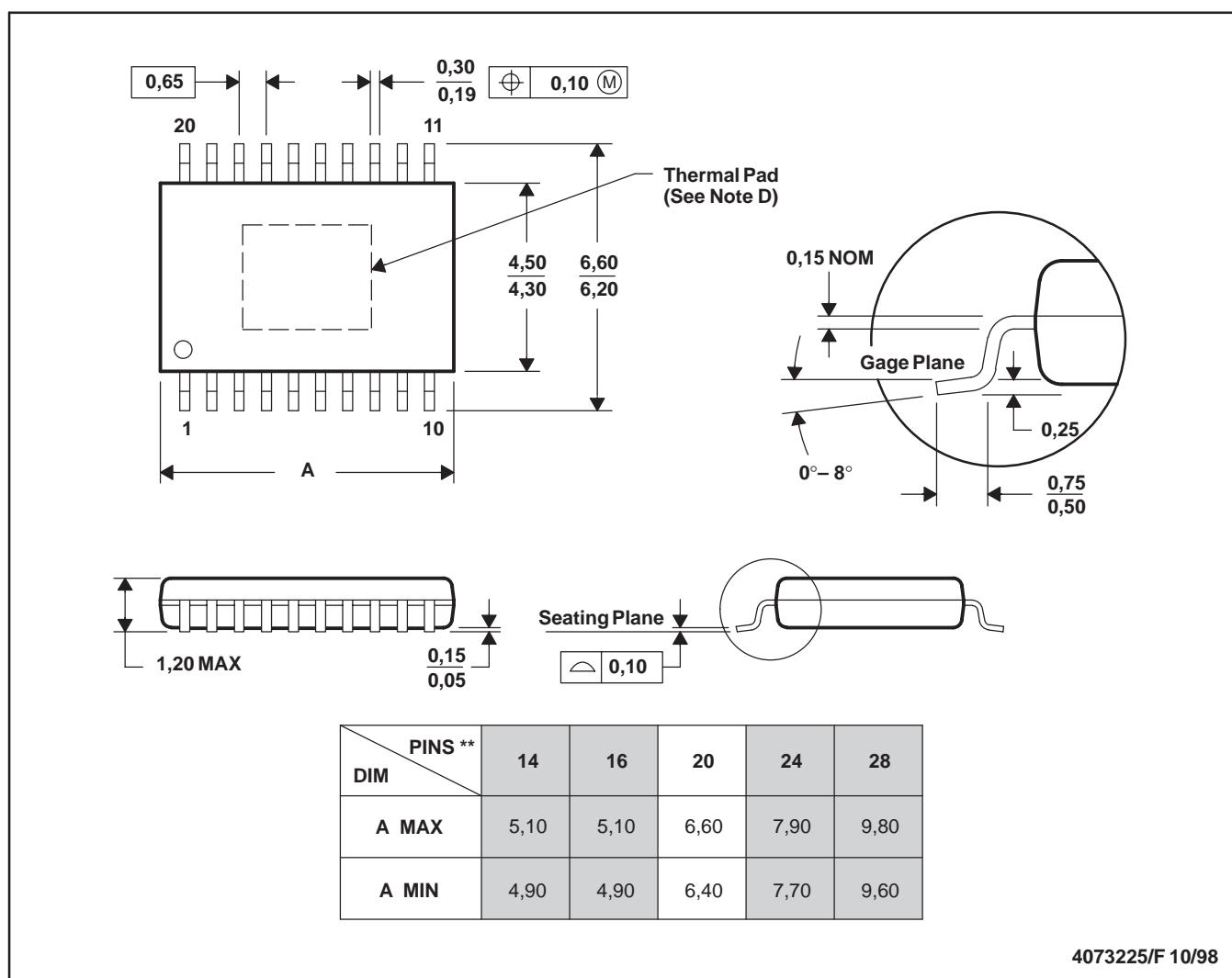

## 外観

PWP (R-PDSO-G\*\*)

20 PINS SHOWN

POWERPAD PLASTIC SMALL-OUTLINE

注：A. 直線的な寸法はすべてミリメートルです。

B. 本図は通達なしに変更することがあります。

C. 本体の寸法はモールド・フラッシュや突起を含みません。

D. パッケージの熱特性は、サーマル・パッドを外部プレーンにボンディングすると強化されます。

このパッドは電気的かつ熱的にチップの背面と結合します。また、できるかぎり一部のリードとも接続させます。

E. JEDEC MO-153の規格に準拠します。

**PACKAGING INFORMATION**

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TPS54372PWP</a>  | Active        | Production           | HTSSOP (PWP)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

| TPS54372PWP.A                | Active        | Production           | HTSSOP (PWP)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

| TPS54372PWPG4                | Active        | Production           | HTSSOP (PWP)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

| <a href="#">TPS54372PWPR</a> | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

| TPS54372PWPR.A               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

| TPS54372PWPRG4               | Active        | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | TPS54372            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS54372 :**

- Automotive : [TPS54372-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

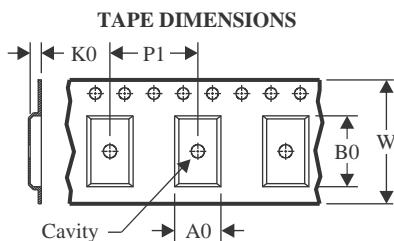

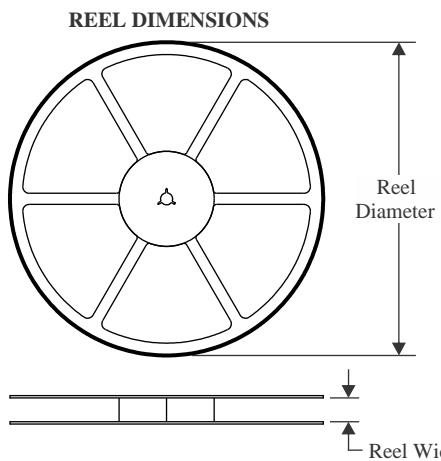

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

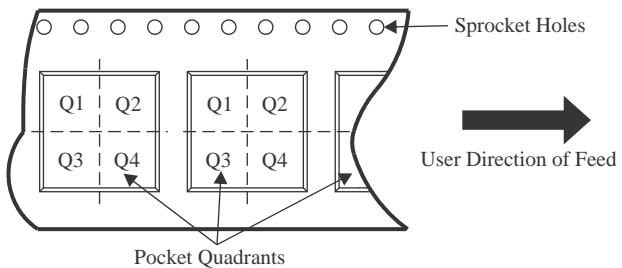

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54372PWPR | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

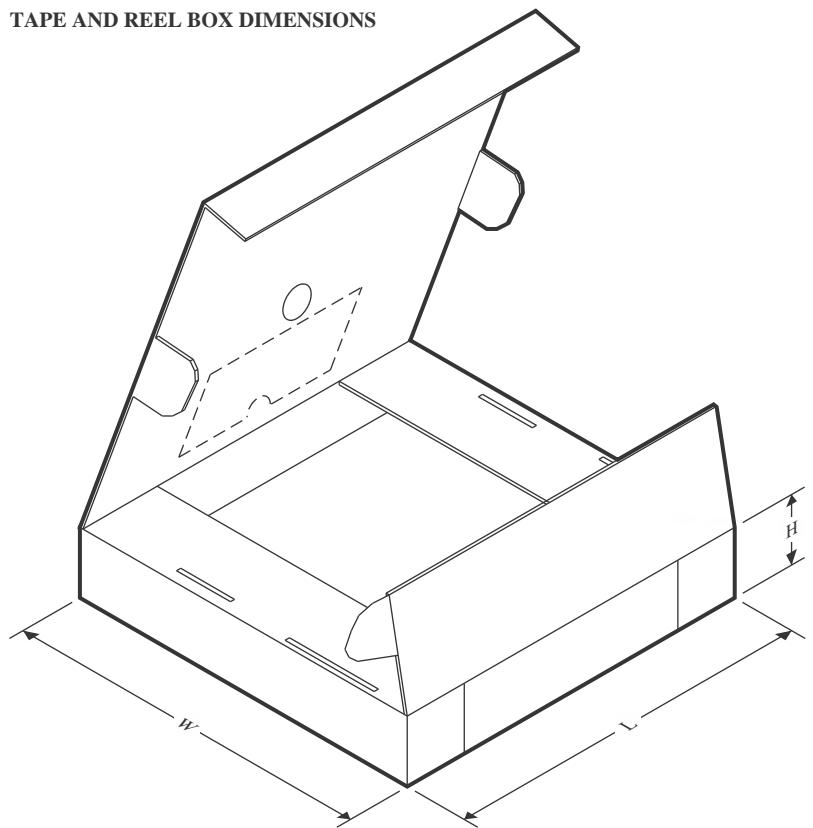

## TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54372PWPR | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

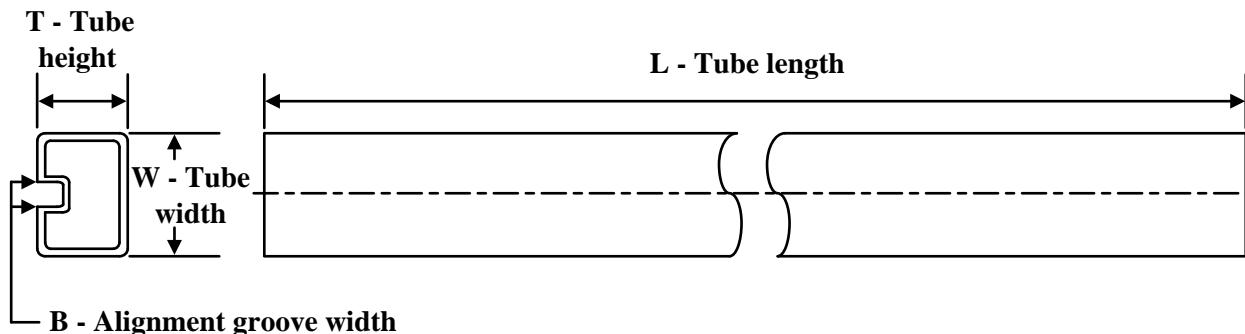

## TUBE

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54372PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600         | 3.5    |

| TPS54372PWP.A | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600         | 3.5    |

| TPS54372PWPG4 | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600         | 3.5    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月