# 4.5V ~ 20V入力、6A出力FET 内蔵同期型 PWM スイッチャ(SWIFT™)

## 特 長

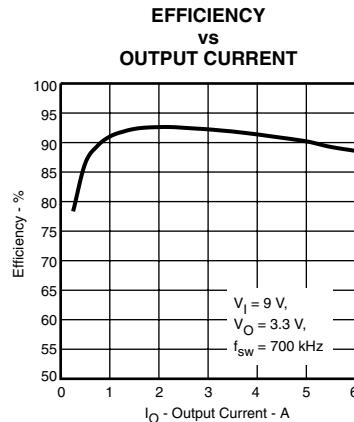

- 40mΩ MOSFETスイッチを内蔵し、6A (7.5Aピーク) 出力電流で高効率を実現

- 外部ローサイドMOSFETを使用

- 出力電圧可変 (0.891V, 1%精度の基準電圧)

- 外部クロック同期可能

- 180°の逆位同期

- 広いPWM周波数範囲：固定 250kHz/500kHz又は抵抗により可変 (250kHz~700kHz)

- 調整可能なスロースタート

- 調整可能な低電圧ロックアウト機能

- ピーク電流制限とサーマル・シャットダウン機能による負荷保護

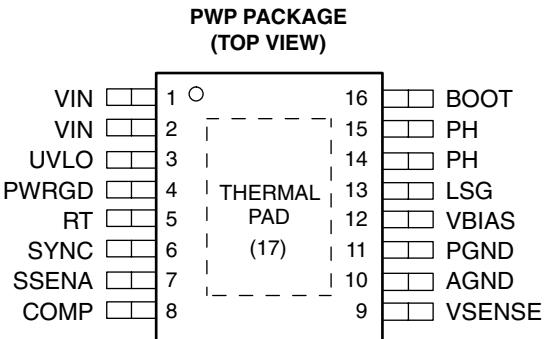

- 16ピンTSSOP PowerPAD™パッケージ

- SWIFT関連ドキュメント、アプリケーション・ノート、および設計ソフトウェアを用意

([www.ti.com/swift](http://www.ti.com/swift))

## 概 要

TPS54550は、ハイサイドMOSFETと、ローサイド外付けMOSFET用のゲート・ドライバを内蔵した、6A出力電流をサポートする同期型パックPWMコンバータです。過渡負荷条件でも最大性能を発揮できるように、高性能な電圧誤差増幅器を内蔵しており、また、出力フィルタを構成するインダクタとキャパシタの選択も柔軟に対応することができます。TPS54550には、入力電圧が4.5VになるまでTPS54550の起動を防止する低電圧ロックアウト回路、突入電流を制限するスロースタート回路、および出力状態が有効かどうかを示すパワー・グッド出力が内蔵されています。

180°の位相差を持たせて簡単に同期動作できるように、同期(SYNC)端子を入力または出力として構成することができます。TPS54550デバイスは、熱特性を改善した16ピンのTSSOP(PWP)PowerPAD™パッケージで供給されています。TIは評価モジュールとSWIFTデザイナー・ソフトウェア・ツールを提供しており、装置の短期間の開発サイクルにかなうよう高性能な電源設計が迅速に行われることを支援しています。

## ア プ リ ケ ジ シ ョ ン

- 工業用および民生用の低消費電力システム

- LCDモニタおよびTV

- コンピュータの周辺機器

- 高性能DSP、FPGA、ASIC、およびマイクロプロセッサ用のポイント・オブ・ロード・レギュレーション

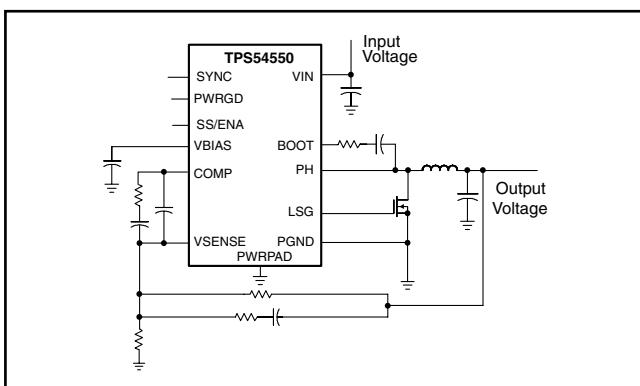

## Simplified Schematic

SWIFT、PowerPADは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

これらのデバイスは、限定的な ESD (静電破壊) 保護機能を内蔵しています。保存時または取り扱い時は、MOS ゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## ご発注の手引き

| T <sub>j</sub> | OUTPUT VOLTAGE        | PACKAGE              | PART NUMBER <sup>(1)</sup> |

|----------------|-----------------------|----------------------|----------------------------|

| -40°C to 125°C | Adjustable to 0.891 V | Plastic HTSSOP (PWP) | TPS54550PWP <sup>(2)</sup> |

(1) 最新のパッケージ情報と発注情報については、このドキュメントの末尾にある「付録: パッケージ・オプション」を参照するか、TI の Web サイト ([www.ti.com](http://www.ti.com)) を参照してください。

(2) PWP パッケージはテープ・アンド・リール形態で供給されています。

型番の末尾に R を付けてください。この製品では、TPS54550PWPR となります。

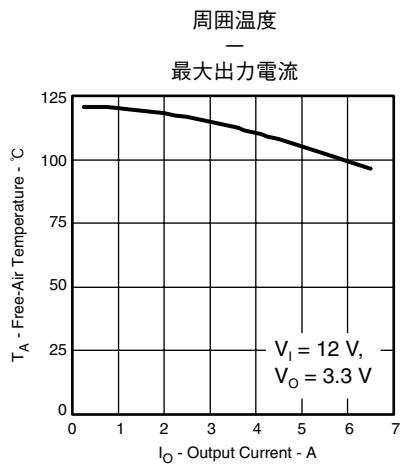

## パッケージの定格消費電力<sup>(1)</sup>

| PACKAGE                               | THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT | T <sub>A</sub> = 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------------------------------------|------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 16-Pin PWP with solder <sup>(2)</sup> | 40.1°C/W                                 | 2.49W                                 | 1.37W                                 | 1.00W                                 |

(1) 負荷軽減曲線については、図25を参照してください。

(2) テスト・ボードの条件

- a. 3インチ × 3インチ

- b. 厚さ: 0.062インチ

- c. 2PCB レイヤ

- d. 重量2オンスの銅

e. レイアウトの例については、図26, 27、およびTPS54550評価モジュールのユーザーズ・ガイドを参照してください。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                                                              |                            |              | UNIT                        |

|--------------------------------------------------------------|----------------------------|--------------|-----------------------------|

| V <sub>I</sub>                                               | VIN                        |              | -0.3 V to 21.5 V            |

|                                                              | VSENSE                     |              | -0.3 V to 8.0 V             |

|                                                              | UVLO                       |              | -0.3 V to 8.0 V             |

|                                                              | SYNC                       |              | -0.3 V to 4.0 V             |

|                                                              | SSENA                      |              | -0.3 V to 4.0 V             |

|                                                              | BOOT                       |              | V <sub>I</sub> (PH) + 8.0 V |

| V <sub>O</sub>                                               | VBIAS                      |              | -0.3 to 8.5 V               |

|                                                              | LSG                        |              | -0.3 to 8.5 V               |

|                                                              | SYNC                       |              | -0.3 to 4.0 V               |

|                                                              | RT                         |              | -0.3 to 4.0 V               |

|                                                              | PWRGD                      |              | -0.3 to 6.0 V               |

|                                                              | COMP                       |              | -0.3 to 4.0 V               |

| I <sub>O</sub>                                               | PH                         |              | -1.5 V to 22 V              |

|                                                              | PH                         |              | Internally Limited (A)      |

|                                                              | LSG (Steady State Current) |              | 10 mA                       |

| I <sub>S</sub>                                               | COMP, VBIAS                |              | 3 mA                        |

|                                                              | SYNC                       |              | 5 mA                        |

|                                                              | LSG (Steady State Current) |              | 100 mA                      |

|                                                              | PH (Steady State Current)  |              | 500 mA                      |

|                                                              | COMP                       |              | 3 mA                        |

|                                                              | SSENA, PWRGD               |              | 10 mA                       |

|                                                              | Voltage differential       | AGND to PGND | ±0.3 V                      |

| T <sub>J</sub>                                               | Junction temperature       |              | +150°C                      |

| T <sub>stg</sub>                                             | Storage temperature        |              | -65°C to +150°C             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                            |              | 260°C                       |

- (1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。

これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。

絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 静電気放電

|                      |     |             | MIN | TYP | MAX | UNIT |

|----------------------|-----|-------------|-----|-----|-----|------|

| Human Body Model     | HBM | JESD22-A114 |     |     | 1.5 | kV   |

| Charged Device Model | CDM | JESD22-C101 |     |     | 1.5 | kV   |

## 推奨動作条件

|                |                                | MIN | NOM | MAX | UNIT |

|----------------|--------------------------------|-----|-----|-----|------|

| V <sub>I</sub> | Input voltage range            | 4.5 | 20  |     | V    |

| T <sub>J</sub> | Operating junction temperature | -40 | 125 |     | °C   |

## 電気的特性

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $VIN = 4.5\text{ V} \sim 20\text{ V}$

| PARAMETER                                                          |                                                                           | TEST CONDITIONS                                 | MIN   | TYP   | MAX   | UNIT |

|--------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------|-------|-------|-------|------|

| <b>SUPPLY CURRENT</b>                                              |                                                                           |                                                 |       |       |       |      |

| $I_Q$<br>Quiescent current                                         | Operating Current, PH pin open,<br>No external low side MOSFET, RT = Hi-Z |                                                 | 10.3  |       |       | mA   |

|                                                                    | Shutdown, SSENA = 0 V                                                     |                                                 | 1.1   |       |       | mA   |

| VIN                                                                | Start threshold voltage                                                   |                                                 | 4.32  | 4.49  |       | V    |

|                                                                    | Stop threshold voltage                                                    |                                                 | 3.69  | 3.97  |       | V    |

|                                                                    | Hysteresis                                                                |                                                 | 350   |       |       | mV   |

| <b>UNDER VOLTAGE LOCK OUT (UVLO PIN)</b>                           |                                                                           |                                                 |       |       |       |      |

| UVLO                                                               | Start threshold voltage                                                   |                                                 | 1.20  | 1.24  |       | V    |

|                                                                    | Stop threshold voltage                                                    |                                                 | 1.02  | 1.10  |       | V    |

|                                                                    | Hysteresis                                                                |                                                 | 100   |       |       | mV   |

| <b>BIAS VOLTAGE (VBIAS PIN)</b>                                    |                                                                           |                                                 |       |       |       |      |

| VBIAS                                                              | Output voltage                                                            | $I_{VBIAS} = 1\text{ mA}, VIN \geq 12\text{ V}$ | 7.5   | 7.8   | 8.0   | V    |

|                                                                    |                                                                           | $I_{VBIAS} = 1\text{ mA}, VIN = 4.5\text{ V}$   | 4.4   | 4.47  | 4.5   |      |

| <b>REFERENCE SYSTEM ACCURACY</b>                                   |                                                                           |                                                 |       |       |       |      |

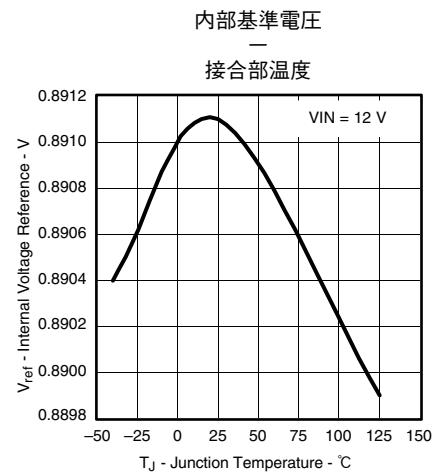

| Reference voltage                                                  | $T_J = 25^\circ\text{C}$                                                  |                                                 | 0.888 | 0.891 | 0.894 | V    |

|                                                                    |                                                                           |                                                 | 0.882 | 0.891 | 0.899 | V    |

| <b>OSCILLATOR (RT PIN)</b>                                         |                                                                           |                                                 |       |       |       |      |

| Internally set PWM switching frequency                             | RT Grounded                                                               | 200                                             | 250   | 300   | kHz   |      |

|                                                                    | RT Open                                                                   | 400                                             | 500   | 600   |       |      |

| Externally set PWM switching frequency                             | RT = 100 kΩ (1% resistor to AGND)                                         | 425                                             | 500   | 575   | kHz   |      |

| <b>FALLING EDGE TRIGGERED BIDIRECTIONAL SYNC SYSTEM (SYNC PIN)</b> |                                                                           |                                                 |       |       |       |      |

| SYNC out low-to-high rise time (10%/90%) <sup>(1)</sup>            | 25 pF to ground                                                           | 200                                             | 500   |       | ns    |      |

| SYNC out high-to-low fall time (90%/10%) <sup>(1)</sup>            | 25 pF to ground                                                           | 5                                               | 10    |       | ns    |      |

| Falling edge delay time <sup>(1)</sup>                             | Delay from rising edge to rising edge of PH pins                          | 180                                             |       |       | ns    |      |

| Minimum input pulselwidth <sup>(1)</sup>                           | RT = 100 kΩ                                                               | 100                                             |       |       | ns    |      |

| Delay (falling edge SYNC to rising edge PH) <sup>(1)</sup>         | RT = 100 kΩ                                                               | 360                                             |       |       | ns    |      |

| SYNC out high level voltage                                        | 50kΩ resistor to ground,<br>No pullup resistor                            | 2.5                                             |       |       | V     |      |

| SYNC out low level voltage                                         |                                                                           | 0.6                                             |       |       | V     |      |

| SYNC in low level threshold                                        |                                                                           | 0.8                                             |       |       | V     |      |

| SYNC in high level threshold                                       |                                                                           | 2.3                                             |       |       | V     |      |

| SYNC in frequency range <sup>(1)</sup>                             | Percentage of programmed frequency                                        | -10%                                            | 10%   |       |       |      |

|                                                                    |                                                                           | 225                                             | 770   |       | kHz   |      |

| <b>FEED-FORWARD MODULATOR (INTERNAL SIGNAL)</b>                    |                                                                           |                                                 |       |       |       |      |

| Modulator gain                                                     | $VIN = 12\text{ V}, T_J = 25^\circ\text{C}$                               | 8                                               |       |       | V/V   |      |

| Modulator gain variation                                           |                                                                           | -25%                                            | 25%   |       |       |      |

| Minimum controllable ON time <sup>(1)</sup>                        |                                                                           | 180                                             |       |       | ns    |      |

| Maximum duty factor <sup>(1)</sup>                                 | $VIN = 4.5\text{ V}$                                                      | 80%                                             | 86%   |       |       |      |

| <b>ERROR AMPLIFIER (VSENSE and COMP PINS)</b>                      |                                                                           |                                                 |       |       |       |      |

| Error amplifier open loop voltage gain <sup>(1)</sup>              |                                                                           | 60                                              | 80    |       | dB    |      |

| Error amplifier unity gain bandwidth <sup>(1)</sup>                |                                                                           | 1.0                                             | 2.8   |       | MHz   |      |

| Input bias current, VSENSE pin                                     |                                                                           | 500                                             |       |       | nA    |      |

| COMP Output voltage slew rate (symmetric) <sup>(1)</sup>           |                                                                           | 1.5                                             |       |       | V/μs  |      |

(1) 設計により規定されていますが、テストは行われておりません。

## 電気的特性

特に記述がない限り、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $VIN = 4.5\text{ V} \sim 20\text{ V}$

| PARAMETER                                   | TEST CONDITIONS                                     | MIN                                                                    | TYP  | MAX | UNIT             |

|---------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------|------|-----|------------------|

| <b>Slow Start/ENABLE (SSENA PIN)</b>        |                                                     |                                                                        |      |     |                  |

| Disable low level input voltage             |                                                     |                                                                        | 0.5  |     | V                |

| Internal slow-start time (10% to 90%)       | $f_s = 250\text{ kHz}$ , RT = ground <sup>(2)</sup> | 4.6                                                                    |      |     | ms               |

|                                             | $f_s = 500\text{ kHz}$ , RT = Hi-Z <sup>(2)</sup>   | 2.3                                                                    |      |     |                  |

| Pullup current source                       |                                                     | 1.8                                                                    | 5    | 10  | $\mu\text{A}$    |

| Pulldown MOSFET                             | $I_{I(SSENA)} = 1\text{ mA}$                        | 0.1                                                                    |      |     | V                |

| <b>POWER GOOD(PWRGD PIN)</b>                |                                                     |                                                                        |      |     |                  |

| Power good threshold                        | Rising voltage                                      | 97%                                                                    |      |     |                  |

| Rising edge delay <sup>(2)</sup>            | $f_s = 250\text{ kHz}$                              | 4                                                                      |      |     | ms               |

|                                             | $f_s = 500\text{ kHz}$                              | 2                                                                      |      |     |                  |

| PWRGD                                       | Output saturation voltage                           | $I_{sink} = 1\text{ mA}$ , $VIN > 4.5\text{ V}$                        | 0.05 |     | V                |

|                                             | Output saturation voltage                           | $I_{sink} = 100\text{ }\mu\text{A}$ , $VIN = 0\text{ V}$               | 0.76 |     | V                |

|                                             | Open drain leakage current                          | Voltage on PWRGD = 6 V                                                 | 3    |     | $\mu\text{A}$    |

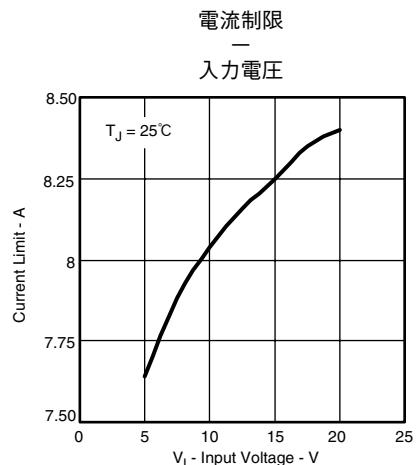

| <b>CURRENT LIMIT</b>                        |                                                     |                                                                        |      |     |                  |

| Current limit                               | $VIN = 12\text{ V}$                                 | 7.5                                                                    | 8.5  | 9.5 | A                |

| Current limit Hiccup Time <sup>(2)</sup>    | $f_s = 500\text{ kHz}$                              | 4.5                                                                    |      |     | ms               |

| <b>THERMAL SHUTDOWN</b>                     |                                                     |                                                                        |      |     |                  |

| Thermal shutdown trip point                 |                                                     | 165                                                                    |      |     | $^\circ\text{C}$ |

| Thermal shutdown hysteresis <sup>(2)</sup>  |                                                     | 7                                                                      |      |     | $^\circ\text{C}$ |

| <b>LOW SIDE MOSFET DRIVER (LSG PIN)</b>     |                                                     |                                                                        |      |     |                  |

| Turn on rise time, (10%/90%) <sup>(2)</sup> | $VIN = 4.5\text{ V}$ , Capacitive load = 1000 pF    | 15                                                                     |      |     | ns               |

|                                             | $VIN = 8\text{ V}$ , Capacitive load = 1000 pF      | 12                                                                     |      |     |                  |

| Deadtime <sup>(2)</sup>                     | $VIN = 12\text{ V}$                                 | 60                                                                     |      |     | ns               |

| Driver ON resistance                        | $VIN = 4.5\text{ V}$ sink/source                    | 7.5                                                                    |      |     | $\Omega$         |

|                                             | $VIN = 12\text{ V}$ sink/source                     | 5                                                                      |      |     |                  |

| <b>OUTPUT POWER MOSFETS (PH PIN)</b>        |                                                     |                                                                        |      |     |                  |

| Phase node voltage when disabled            | DC conditions and no load, SSENA = 0 V              | 0.5                                                                    |      |     | V                |

| Voltage drop, low side FET and diode        | $VIN = 4.5\text{ V}$ , $I_{dc} = 100\text{ mA}$     | 1.13                                                                   | 1.42 |     | V                |

|                                             | $VIN = 12\text{ V}$ , $I_{dc} = 100\text{ mA}$      | 1.08                                                                   | 1.38 |     |                  |

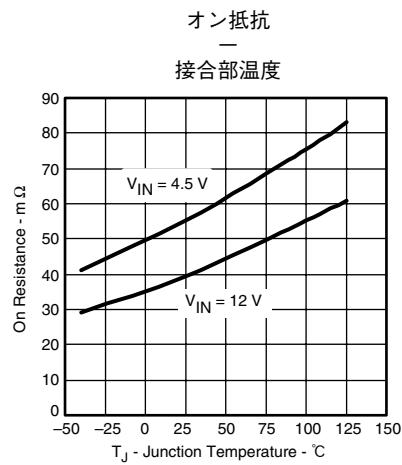

| $r_{DS(ON)}$                                | High side power MOSFET switch <sup>(3)</sup>        | $VIN = 4.5\text{ V}$ , $BOOT-PH = 4.5\text{ V}$ , $I_O = 0.5\text{ A}$ | 60   |     | $\text{m}\Omega$ |

|                                             |                                                     | $VIN = 12\text{ V}$ , $BOOT-PH = 8\text{ V}$ , $I_O = 0.5\text{ A}$    | 40   |     |                  |

(2) 設計により規定されていますが、テストは行われておりません。

(3) VINからPHピンの間の抵抗

## ピン構成

注: 1ピンマークがない場合、記号が左から右に読めるようにデバイスを回転させます。デバイスの左下すみが1ピンの位置です。

## 端子機能

| TERMINAL | DESCRIPTION |

|----------|-------------|

| NO.      | NAME        |

| 1, 2     | VIN         |

| 3        | UVLO        |

| 4        | PWRGD       |

| 5        | RT          |

| 6        | SYNC        |

| 7        | SSENA       |

| 8        | COMP        |

| 9        | VSENSE      |

| 10       | AGND        |

| 11       | PGND        |

| 12       | VBIAS       |

| 13       | LSG         |

| 14, 15   | PH          |

| 16       | BOOT        |

| 17       | PowerPAD    |

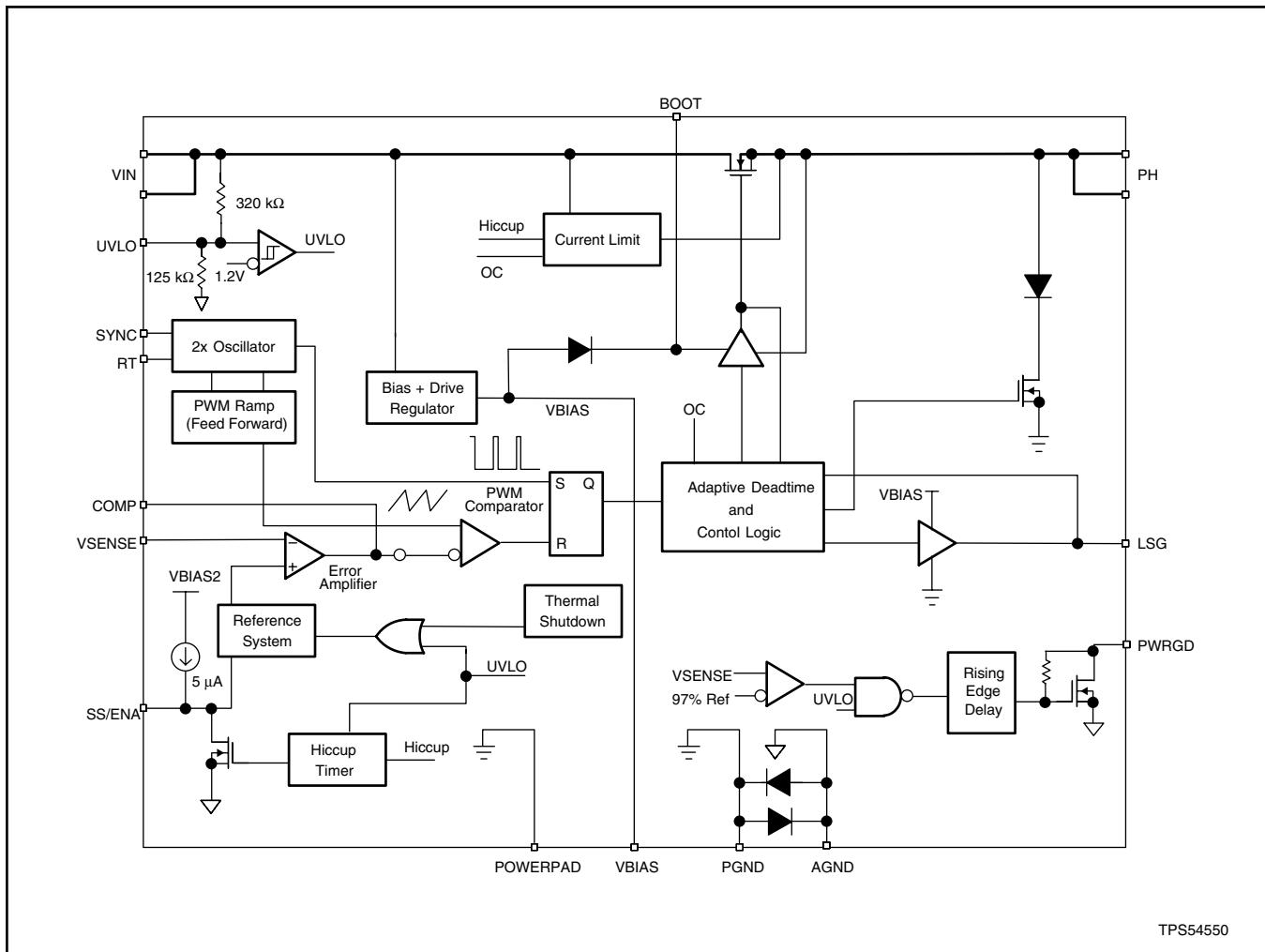

## 機能ブロック図

TPS54550

## 詳細説明

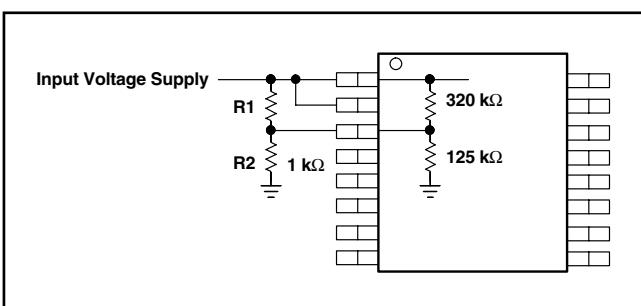

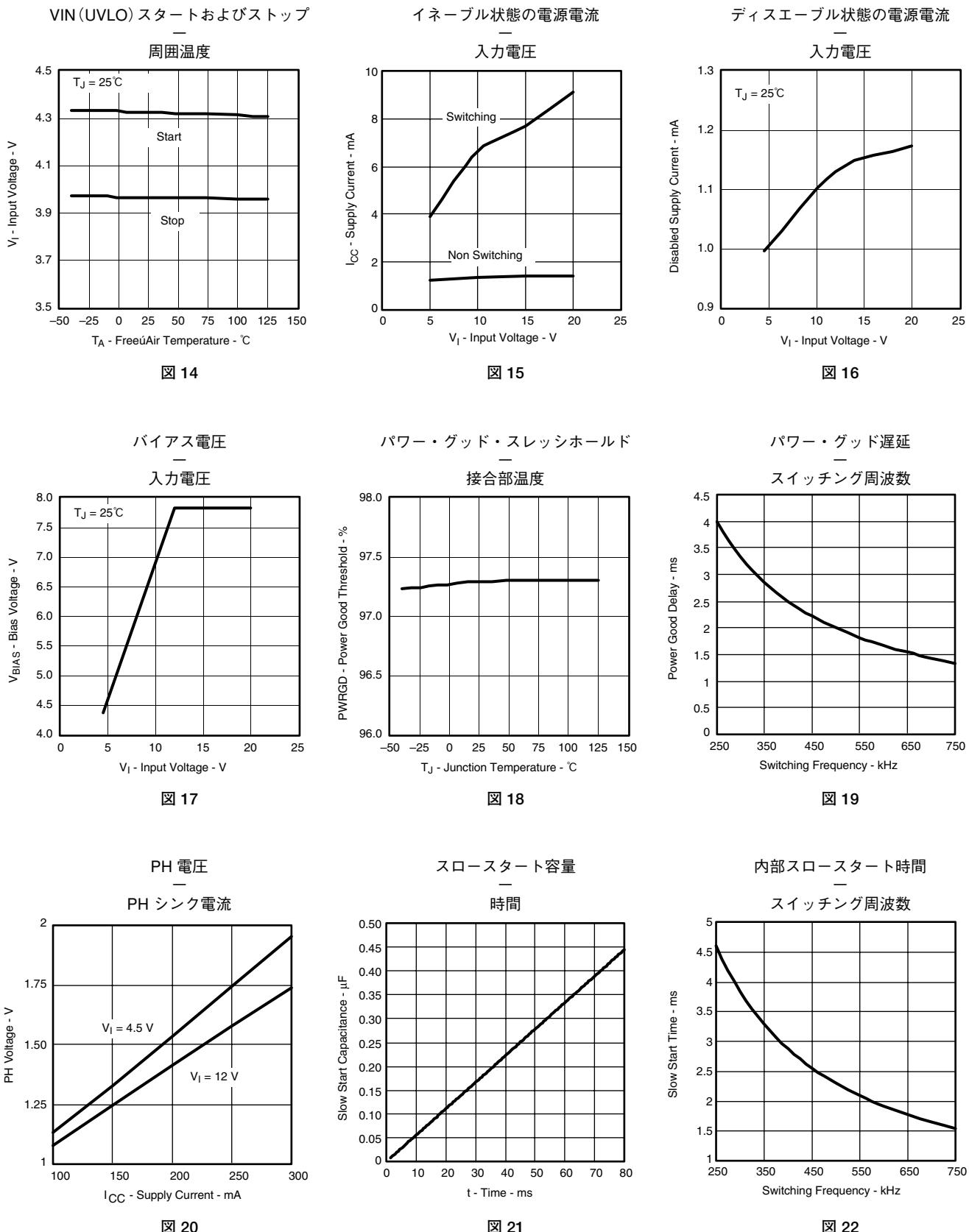

### 低電圧ロックアウト機能 (UVLO)

低電圧ロックアウト(UVLO)系には、VINとAGNDとの間に内部抵抗デバイダが配置されています。デフォルトのスタート値およびストップ値は表1にその値が記載されています。VINとグランドの間に外部抵抗デバイダを配置すると、内部設定されたUVLOスレッシュホールドが無効となります。内部のデバイダ値は、上側の抵抗が約320kΩ、下側の抵抗が約125kΩです。分圧比(デフォルトのスタート値およびストップ値)は非常に正確ですが、内部抵抗の絶対値は15%前後で変動します。外部で調整されたUVLOスレッシュホールドの精度を高くする必要がある場合は、UVLOスレッシュホールドを設定するために、もっと値の低い外部抵抗を選択してください。下側の抵抗R2には1kΩ抵抗(図1を参照)を使用することをお勧めします。どのような場合であっても、UVLOピンはVINに直接接続しないでください。

|             | スタート電圧<br>スレッシュホールド | ストップ電圧<br>スレッシュホールド |

|-------------|---------------------|---------------------|

| VIN (デフォルト) | 4.49                | 3.69                |

| UVLO        | 1.24                | 1.02                |

表1. スタート/ストップ電圧のスレッシュホールド

UVLO 抵抗の選択に使用する式は、以下のとおりです。

$$R1 = \frac{VIN(\text{start}) \times 1\text{k}\Omega}{1.24\text{V}} - 1\text{k}\Omega \quad (1)$$

$$VIN(\text{stop}) = \frac{(R1 + 1\text{k}\Omega) \times 1.02\text{V}}{1\text{k}\Omega} \quad (2)$$

低電圧ロックアウト(UVLO)スレッシュホールドを4.49Vよりも大きくする必要があるアプリケーションには、スタート電圧スレッシュホールドを調整するために、外部抵抗を追加することができます(図1を参照)。たとえば、約7.8VのUVLOスタート電圧が必要なアプリケーションでは、式(1)を使用すると、R1の計算結果は、標準抵抗値に最も近い5.36kΩになります。式(2)を使用すると、入力電圧ストップ・スレッシュホールドの計算結果は6.48Vになります。

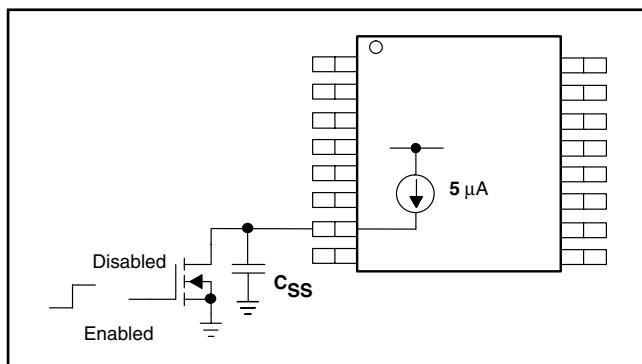

### スロースタート・イネーブル (SSENA) と 内部スロースタート

SSENAピン電圧が0.5Vを超えると、TPS54550は動作を開始します。TPS54550には、1150スイッチング・サイクルで基準電圧を最終値に上昇させるデジタル式の内部スロースタートが内蔵されています。内部スロースタート時間(10% ~ 90%)は、以下の式でおよその計算を行うことができます。

$$T_{SS\_INTERNAL}(\text{ms}) = \frac{1.15\text{k}}{f_s(\text{kHz})} \quad (3)$$

TPS54550デバイスが通常のレギュレーション状態になると、SSENAピンが“High”になります。SSENAピンが0.5Vのストップ・スレッシュホールドよりも低くなった場合は、スイッチングが停止し、内部スロースタートがリセットされます。TPS54550をディスエーブルにする必要があるアプリケーションでは、SSENAピンとのインターフェイスにオープン・ドレインまたはオープン・コレクタの出力ロジックを使用してください(図2を参照)。SSENAピンの内部にはプルアップ電流源が付いています。外部プルアップ抵抗を使用しないでください。

### スロースタート時間の延長

大きな値の出力容量を使用するアプリケーションでは、スタートアップ電流が電流制限を超えないように、スロースタート時間の延長が必要な場合があります。電流制限回路は、ハイサイドMOSFETをディスエーブルし、ハイサイドMOSFETが電流制限スレッシュホールドを超える短時間の間、内部基準電圧をリセットする仕様になっています。出力容量と負荷電流が原因でスタートアップ電流が電流制限スレッシュホールドを超える場合は、電源出力は目標の出力電圧に到達しません。スロースタート時間を延長し、スタートアップ電流を低減するために、キャパシタをSSENAピンに外付けすることができます。スロースタート容量は、以下の式で計算されます。

$$C_{SS}(\mu\text{F}) = 5.55 \times 10^{-3} T_{ss}(\text{ms})$$

| スイッチング周波数             | SYNC ピン        | RT ピン                                                                              |

|-----------------------|----------------|------------------------------------------------------------------------------------|

| 250kHz(内部設定)          | SYNC 出力信号を生成   | AGND                                                                               |

| 500kHz(内部設定)          | SYNC 出力信号を生成   | Float                                                                              |

| 250kHz ~ 700kHz(外部設定) | GNDへの10kΩ 抵抗接続 | R = 215 kΩ to 69 kΩ                                                                |

| 外部同期周波数               | 同期信号           | 他のTPS54350の同期出力信号を使用する場合、RTがフローティングで110kΩ、グランドで、237kΩ。外部同期周波数の10%~90%に匹敵するRT抵抗を使用。 |

表2. スイッチング周波数、SYNCピン、およびRTピン

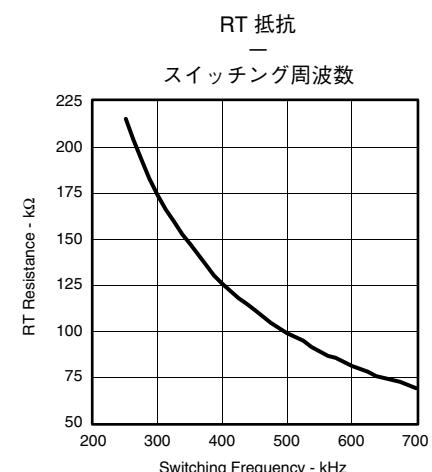

## スイッチング周波数 (RT)

TPS54550には、PWMスイッチング周波数の2倍で動作する内部オシレータが内蔵されています。内部オシレータの周波数は、RTピンによって制御されます。RTピンを接地すると、PWMスイッチング周波数はデフォルトの周波数である250kHzに設定されます。RTピンをオープンすると、PWMスイッチング周波数は500kHzに設定されます。

RTとAGNDの間に抵抗を接続すると、式(4)に従って、周波数が設定されます(図13を参照)。

$$RT(k\Omega) = \frac{46000}{f_s(kHz) - 35.9} \quad (4)$$

RTピンはSYNCピンの機能を制御します。RTピンがオープンまたは接地されると、SYNCピンは出力になります。スイッチング周波数がRTとAGNDの間の抵抗を使用してプログラムされると、SYNCは入力として機能します。

内部電圧ランプの充電電流は、設定周波数に比例して増加し、周波数の設定ポイントに関係なくフィード・フォワード・モジュレータを一定( $K_m = 8$ )に維持します。

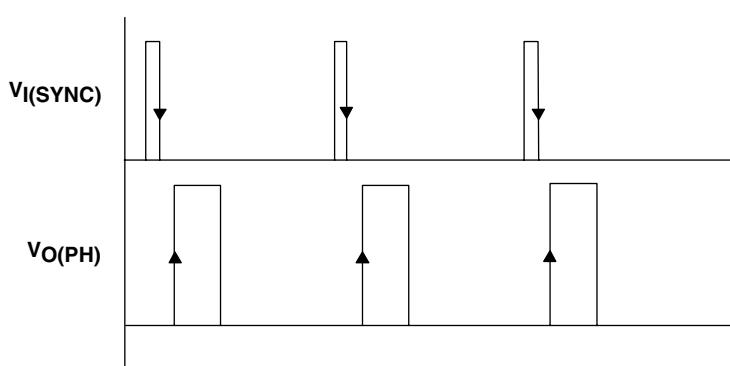

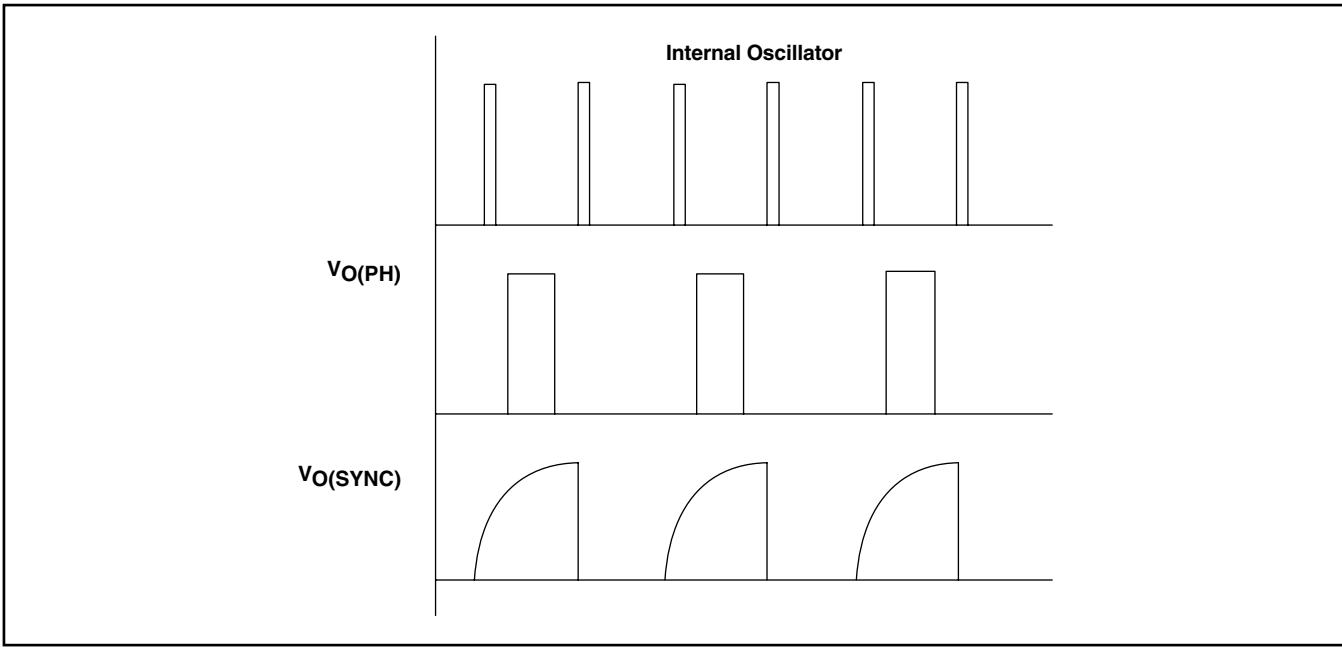

## 180° 位相ずれ同期 (SYNC)

SYNCピンは、前のセクションで説明したとおり、入力または出力として構成することができます。入力として動作しているときのSYNCピンは立ち下がりエッジのトリガ信号です(図3と図4を参照)。SYNCピンが出力として動作している場合、その信号の立ち下がりエッジは、PHピンの立ち上がりエッジに対して、約180°の位相差があります。したがって、2つのTPS54550デバイスがシステムで動作している場合、システムは入力キャパシタを共有し、単一装置の周波数の2倍でリップル電流が流れます。

180°の位相差がある2つのTPS54550デバイスが動作している場合は、全体のRMS入力電流は低下します。したがって、必要な入力キャパシタンスが下がり、効率は高くなります。

TPS54550が外部信号と同期する場合は、RTピンにタイミング抵抗を接続し、その抵抗による内部オシレータの周波数が、同期周波数の90%から110%の間となるようにプログラムされる必要があります。

注: 出力電圧が10Vよりも高い設計では、同期入力は使用しないでください。

図3. SYNC入力波形

図4. SYNC出力波形

## パワーグッド (PWRGD)

VSENSEピンが内部リファレンスと比較され、VSENSEがその内部リファレンスの97%よりも高くなり、他に異常がない場合は、PWRGDピンはハイインピーダンス状態となります。PWRGDピンが“Low”になっている場合は、異常が発生しています。PWRGDピンには、弱いプルダウンを提供するように設計されており、デバイスに電源が入っていない場合でも異常を示します。TPS54550に電源が入っていて、異常のフラグが設定されている場合には、TPS54550はPWRGDピンを“Low”にすることで、電源に問題があることを通知します。以下のイベント(単独または複合のイベント)は、電源に問題があることを表します。

- VSENSE ピンが規定範囲外

- 過電流

- サーマル・シャットダウン

- UVLO低電圧

- 入力電圧がない(弱いプルダウン)

- スロースタートの実行中

- VBIAS電圧が低い

PWRGDピンがハイインピーダンス(つまり、出力電圧有効)となった後、VSENSEピンが規定範囲外となると、PWRGDピンは、ある遅延時間の終了後に、“Low”(電源に問題がある状態)になります。この遅延時間は、スイッチング周波数の関数の1つで、以下の式(5)で計算されます。

$$T_{\text{delay}} = \frac{1000}{f_{\text{s(kHz)}}} \text{ ms} \quad (5)$$

## バイアス電圧 (VBIAS)

VBIASレギュレータは、内部のアナログ回路とローサイドのゲート・ドライバ用に安定した電源を供給します。外部のアプリケーション回路で使用するために、最大1mAの電流を流すことができます。VBIAS ピンには1.0μFのバイパス・キャパシタを接続しなければなりません。このコンデンサには、温度に対し特性値が安定しているため、X7RまたはX5Rクラスの特性の誘電体セラミック・キャパシタを推奨します。

## ブートストラップ電圧 (BOOT)

BOOTキャパシタは、1サイクルごとにVBIASキャパシタから電荷を取得します。動作には、BOOTピンとPHピンの間にキャパシタと、値の低い抵抗が必要です。ハイサイド・ドライバのブートストラップ端子には、0.1μFのバイパス・キャパシタと24Ωの抵抗が必要です。

## 誤差増幅器

VSENSEピンは誤差増幅器の反転入力です。誤差増幅器は、駆動性能が1.5mA、開ループの電圧ゲインが60dB、さらにユニティ・ゲインの帯域幅が2MHzの電圧増幅器です。

## 基準電圧

基準電圧系は、温度に対し安定なバンドギャップ回路の出力をスケーリングすることで高精度の基準信号を生成します。量産テスト時には、バンドギャップ回路とスケーリング回路は、誤差増幅器をボルテージフォロワ構成し、その出力が0.891Vとなるようにトリミングします。この手順によって、スケーリング回路と誤差増幅器の回路内のオフセット誤差がキャンセルされるため、レギュレーションが向上します。

## PWMの制御とフィード・フォワード

誤差増幅器の出力、オシレータ、および電流制限回路からの信号はPWMコントロール・ロジックで処理されます。内部ブロック図に示すように、このコントロール・ロジックにはPWMコンパレータ、PWMラッチ、およびアダプティブ・デッドタイム・コントロール・ロジックが含まれます。電流制限スレッシュホールドより低い定常状態動作では、PWMコンパレータの出力とオシレータの連続パルスが交互にPWMラッチのリセットとセットを行います。

PWMラッチがリセットされると、ローサイド・ドライバおよび内蔵プルダウンMOSFETはオシレータのパルス幅で設定される最小期間の間オン状態のままでです。この期間の間で、PWMランプはその下限電圧まで急速に放電します。ランプが再充電し始めると、ローサイド・ドライバはオフになり、ハイサイドFETがオンになります。ピークPWMランプ電圧は入力電圧と反比例し、モジュレータを一定に維持し、出力段ゲインを8V/Vに維持します。

PWMランプ電圧が誤差増幅器の出力電圧を超えると、PWMコンパレータがラッチをリセットするため、ハイサイドFETはオフ、ローサイドFETはオンになります。ローサイド・ドライバは、オシレータの次のパルスがPWMランプを放電するまでオン状態を保持します。

過渡状態では、誤差増幅器の出力はPWMランプの下限電圧より低いか、PWMピーク電圧より高い可能性があります。誤差増幅器の出力が高いと、PWMラッチはリセットされず、ハイサイドFETはオシレータのパルスがハイサイドFETをオフに、内部ローサイドFETとドライバをオンにするようコントロール・ロジックに信号を送るまでオン状態を保持します。このデバイスは出力電圧がレギュレーションの設定ポイントに達し、VSENSEの電圧が内部基準電圧とほぼ同じ電圧に設定されるまで、その最大デューティ・サイクルで動作します。一方、誤差増幅器の出力が低いと、PWMラッチは絶えずリセットされ、ハイサイドFETはオンになりません。内部ローサイドFETとローサイド・ドライバは、VSENSE電圧がPWMコンパレータに状態を変えさせる程度に減少するまでオン状態を保持します。TPS54550は、出力電圧がレギュレーションの設定ポイントに達するまで、外部のローサイドFETを使用して電流をシンクすることができます。

仕様では最小オン時間は180nsです。内部スロースタートの間隔で、内部リファレンスは0Vから0.891Vに上昇します。最初のスロースタートの間隔では、内部基準電圧は非常に低いため、いくつかのパルスが飛ばされます。これは、最小オン時間により、内部リファレンスが上昇するまで、実際の出力電圧があらかじめ設定された出力電圧よりも少し高くなるためです。

## デッドタイム・コントロール

アダプティブ・デッドタイム・コントロールは、ドライバのターンオン時間を能動的に制御することで、スイッチング過渡時にシートスルーレ電流が内蔵ハイサイドMOSFETと外部ローサイドMOSFETに流れることを防止します。ハイサイド・ドライバはローサイドMOSFETのゲート電圧が1V以下になるまでオンになりません。ローサイド・ドライバはハイサイドMOSFETのゲート電圧が1V以下になるまでオンなりません。

## ローサイド・ゲート・ドライバ (LSG)

LSGはローサイド・ゲート・ドライバの出力です。この100 mA MOSFETドライバは、このアプリケーションに適した、普及度の高いMOSFETのゲートを駆動することができます。SWIFTデザイナー・ソフトウェア・ツールを使用して、アプリケーションに最適なMOSFETを探してください。LSGピンはローサイドMOSFETのゲートに直接接続してください。ターンオン時間が極端に遅くなるため、ゲート抵抗は使用しないでください。

## サーマル・シャットダウン

接合部温度が165°Cを超えると、デバイスのサーマル・シャットダウンによりMOSFETドライバとコントローラがオフになります。デバイスは、サーマル・シャットダウンのトリップ点より7°C下がると自動的にリセットされ、スロースタート回路の制御により起動を開始します。

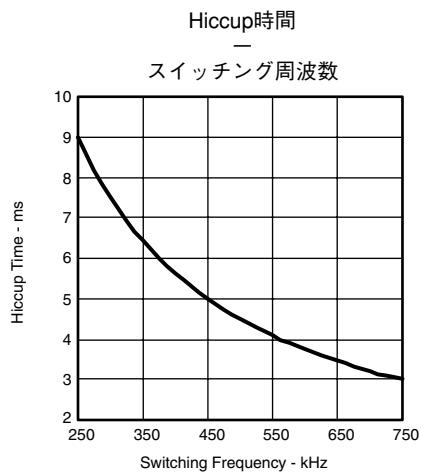

## 過電流保護

過電流保護は、ハイサイドMOSFETのドレイン - ソース間電圧を検出することにより行われ、過電流スレッシュホールド制限値に相当する電圧レベルと比較されます。ドレイン - ソース間の電圧が100nsよりも長い間、過電流スレッシュホールド制限値を超えた場合には、ハイサイドMOSFETはディスエーブルされ、SSENAピンは“Low”に低下し、デジタル式の内部スロースタートは0Vにリセットされます。SSENAは、以下の式(6)で計算される時間は、“Low”的まになります。

$$T_{HICCUP(ms)} = \frac{2250}{f_s(kHz)} \quad (6)$$

一時的な中断時間(Hiccup Time)が経過すると、SSENAピンは解放され、コンバータが内部スロースタートを開始します。

## 出力電圧の設定

TPS54550の出力電圧は、抵抗デバイダ回路を使用して、VSENSEピンに出力の一部をフィードバックすることで設定されます。図29のアプリケーション回路では、このデバイダ回路は抵抗R1およびR2で構成されます。必要な出力電圧を生成するための抵抗値を計算するには、以下の式を使用します。

$$R2 = \frac{R1 \times 0.891}{V_O - 0.891} \quad (7)$$

R1の固定値から開始して、必要なR2値を計算します。R1の固定値を10kΩと仮定した場合、一般的な出力電圧(その一部)に対する概算のR2値は、以下の表のとおりです。

| 出力電圧(V) | R2の値(kΩ) |

|---------|----------|

| 1.2     | 28.7     |

| 1.5     | 14.7     |

| 1.8     | 9.76     |

| 2.5     | 5.49     |

| 3.3     | 3.74     |

## 出力電圧の制限

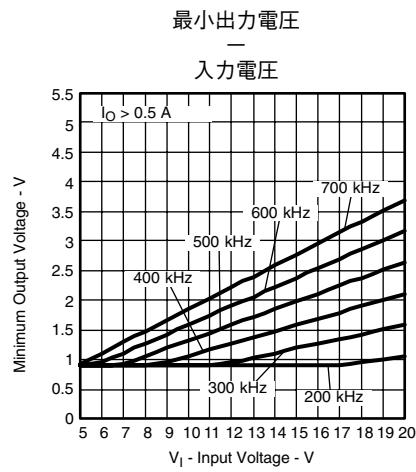

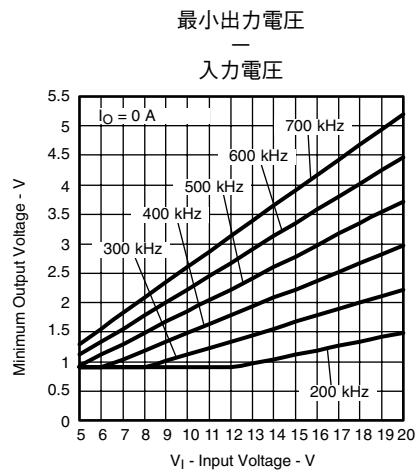

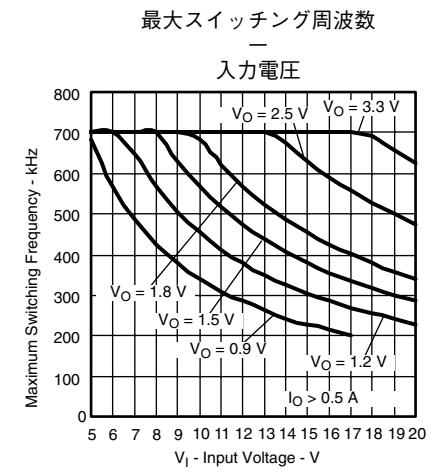

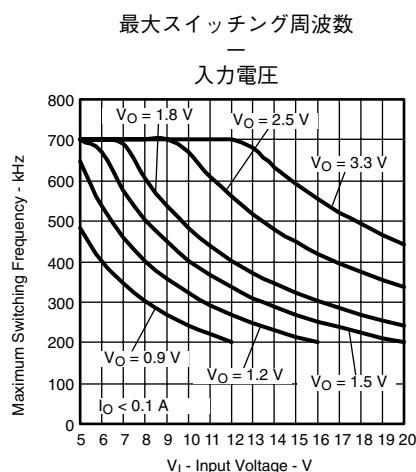

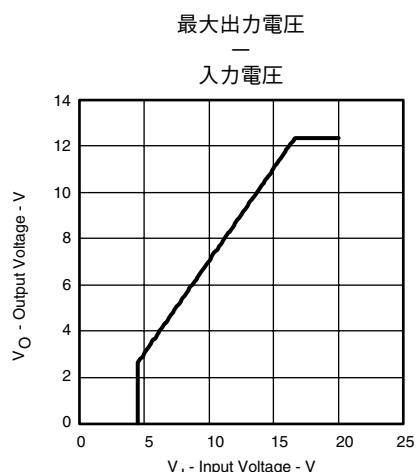

TPS54550の内部設計により、どのような入力電圧が与えられた場合でも、出力電圧には上限と下限があります。さらに、出力電圧の設定ポイント・レンジの下限は、動作周波数にも依存します。出力電圧の設定ポイントの上限は、デバイスの最大デューティ・サイクルによって制限を受けます(図12を参照)。下限は、制御可能な最小限のオン時間によって制限を受けます。このオン時間は、最大で220nsです。特定の入力電圧および動作周波数の範囲に対応する概算の最小出力電圧を、図8に示します。また、一般的な出力電圧(その一部)に対応する最大動作周波数と入力電圧との関係を図10に示します。

上記の2つの図の曲線は、出力電流が0.5Aよりも高い場合に有効です。出力電流が無負荷状態(0A)に向かって減少すると、それに伴って最小出力電圧も減少します。負荷電流が100mAよりも低いアプリケーションでは、図9と図10の曲線が該当します。これらの曲線にプロットされているデータはすべて概算であり、目標の設定ポイントを基準としたときに、実際の動作周波数に20%の偏差があることが見込まれています。

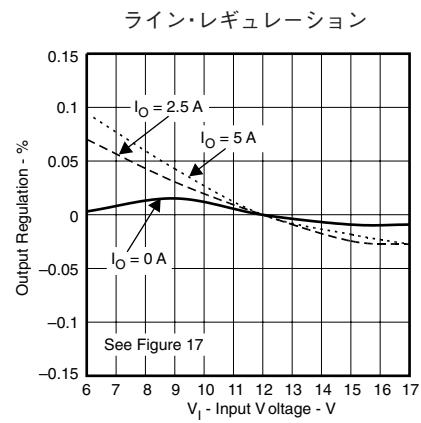

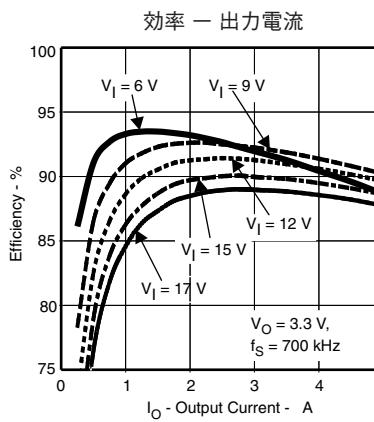

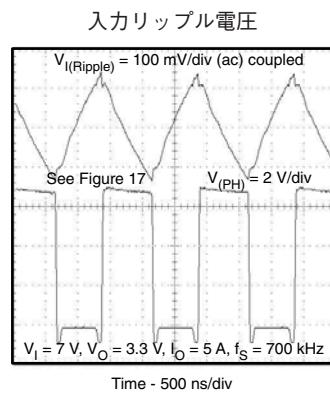

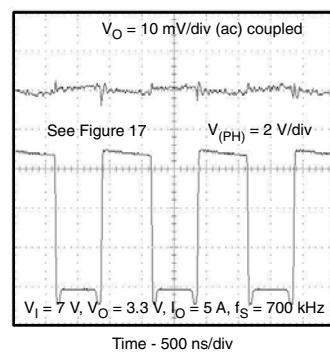

# 代表的特性

図 5

図 6

図 7

図 8

図 9

図 10

図 11

図 12

図 13

図 23

図 24

図 25

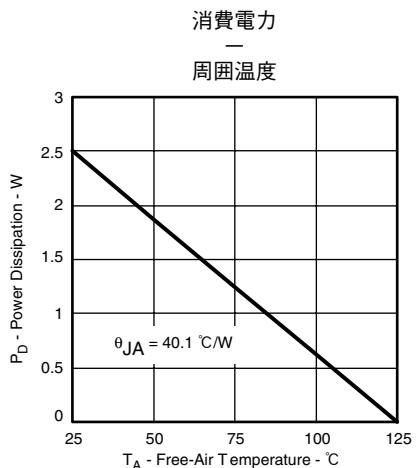

# アプリケーション情報

図26. TPS54550のPCBレイアウト

## PCBレイアウト

すべてのVINピンは、プリント基板(PCB)上で同じ領域に接続し、低ESRのセラミック・バイパス・キャパシタを使用してバイパスしてください。バイパス・キャパシタ接続、VINピン、およびローサイドMOSFETのソースによって形成されるループ領域は最小限に抑えるよう注意が必要です。推奨される最小のバイパス容量は、X5RまたはX7Rクラスの誘電体を使用した10 $\mu$ Fのセラミック・キャパシタであり、VINピンおよびローサイドMOSFETのソースにできる限り近づけて配置するのが最適です。基板レイアウトの例については、図26を参照してください。AGNDピンとPGNDピンは、ICのピン側でPCBグランド・プレーンに接続する必要があります。ローサイドMOSFETのソースはPCBグランド・プレーンに直接接続する必要があります。2つのPHピンはお互いに接続し、ローサイドMOSFETのドレインに接続する必要があります。PH接続はスイッチング・ノードであるため、MOSFETはPHピンにごく近づけて配置し、過度の容量性カップリングを避けるためにPCB導体の面積はできるだけ小さくしてください。14, 15ピンからの導体幅は0.050インチから0.075インチ、重量が1オンスから2オンスまでの銅

をお勧めします。銅のランド・パターン長は0.2インチより短くしてください。

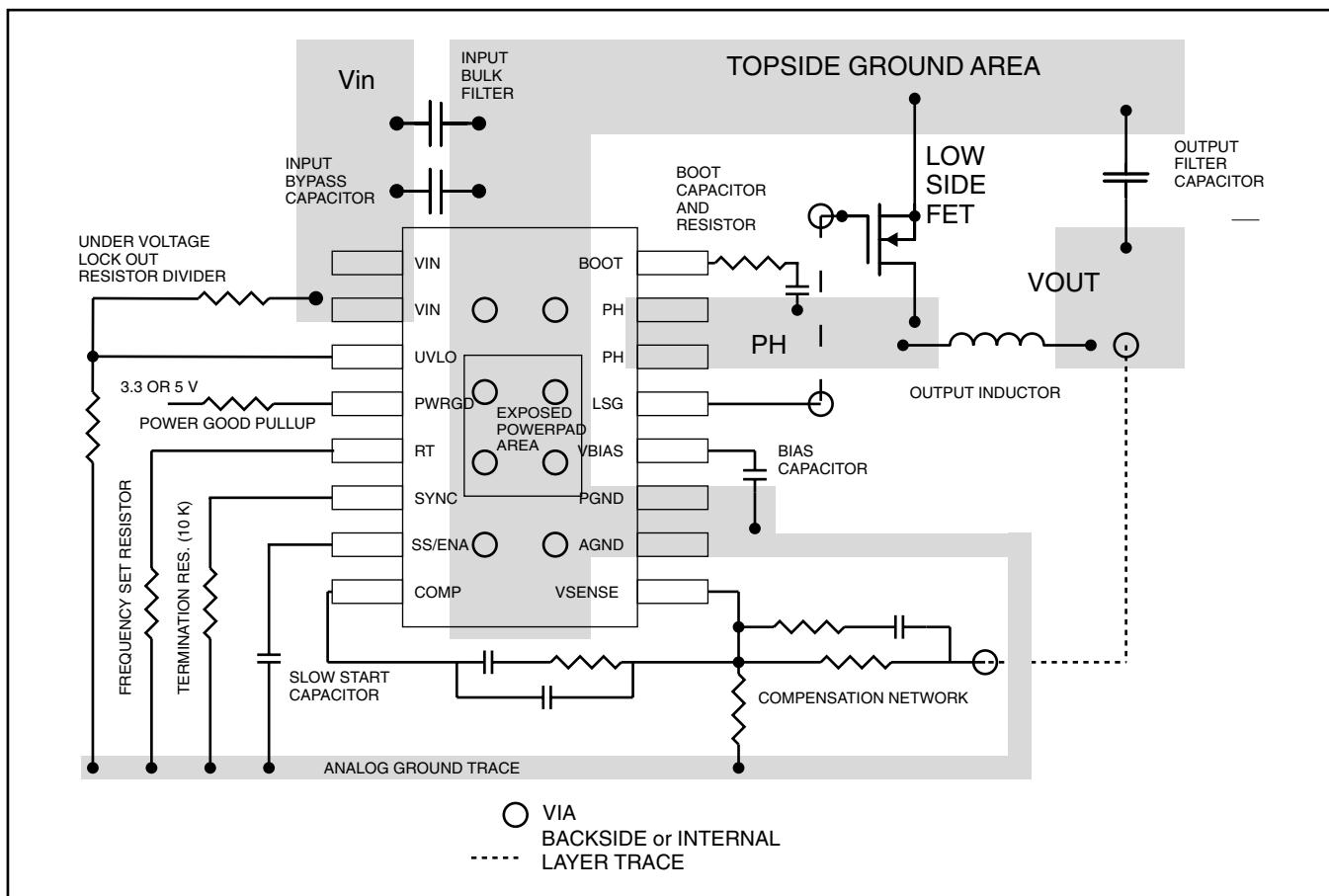

すべての定格負荷で動作するように、アナログ・グランド・プレーンは十分な熱放散面積を備えている必要があります。周囲温度とエアフローにもより、必須ではありませんが、銅のプレーンの大きさは3インチ×3インチをお勧めします。ほとんどのアプリケーションでは、大きな領域の内部グランド・プレーンを持つことができ、PowerPADはその最も面積が広い領域に接続する必要があります。最下層または最上層にある他の領域も熱を放散する手助けとなりますが、5A以上で動作させる必要がある場合には、利用可能な領域をすべて使用する必要があります。PowerPADの露出した領域からアナログ・グランド・プレーン層に接続するときは、ビアの中で半田のウイッキング(ボイド)ができるないように、直径0.013インチのビアを使う必要があります。PowerPADの領域にはビアが4つ、パッケージの外側とパッケージの真下には別のビアが4つなければなりません。放熱性能を上げるために、これよりも多いビアを追加する場合は、デバイス・パッケージの下以外の領域に配置する必要があります。

図27. PowerPADのレイアウトの熱に関する検討事項

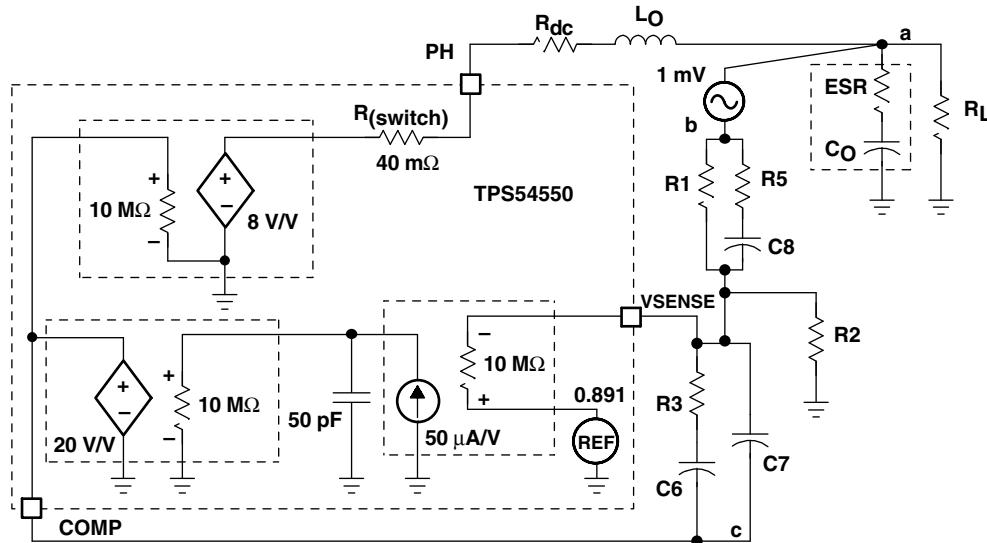

## ループ応答のモデル

図28に、TPS54550制御ループに相当するモデルを示します。このモデルは、周波数応答と動的な負荷応答を確認するために回路シミュレーション・プログラムによるモデル化が可能です。TPS54550の誤差増幅器は、開ループ・ゲインが80dB (10000V/V) の電圧増幅器です。図28に示すように、誤差増幅器は、出力に抵抗とコンデンサをもつ理想的な電圧制御の電流源としてモデル化することができます。TPS54550には、入力電圧の変動が全体のループ伝達関数に影響しないようにフィード・フォワード補償回路が内蔵されています。

フィード・フォワード・ゲインは、ゲインが8V/Vの、理想的な電圧制御の電圧源としてモデル化されます。ノードaとノードbの間の1mV AC電圧は、周波数応答の測定のための制御ループを効果的に分割します。プロットb/cは出力段の小信号応答を示します。プロットc/aは周波数補償の小信号応答を示します。プロットa/bはループ全体の小信号応答を示します。動的な負荷応答は、 $R_L$ を、時間ドメイン分析の適切な負荷ステップの振幅およびステップ・レートを持つ電流源で置き換えることで確認できます。

図28. 制御ループのモデル

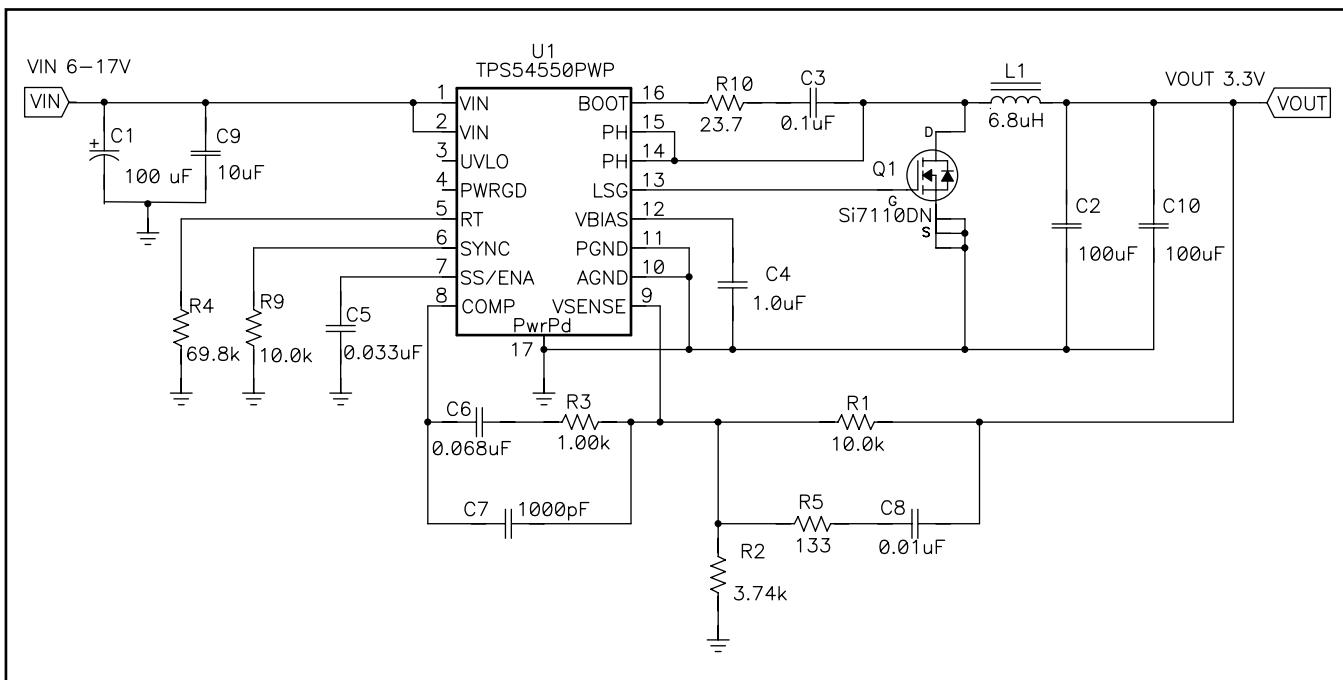

図29. アプリケーション回路、3.3V出力

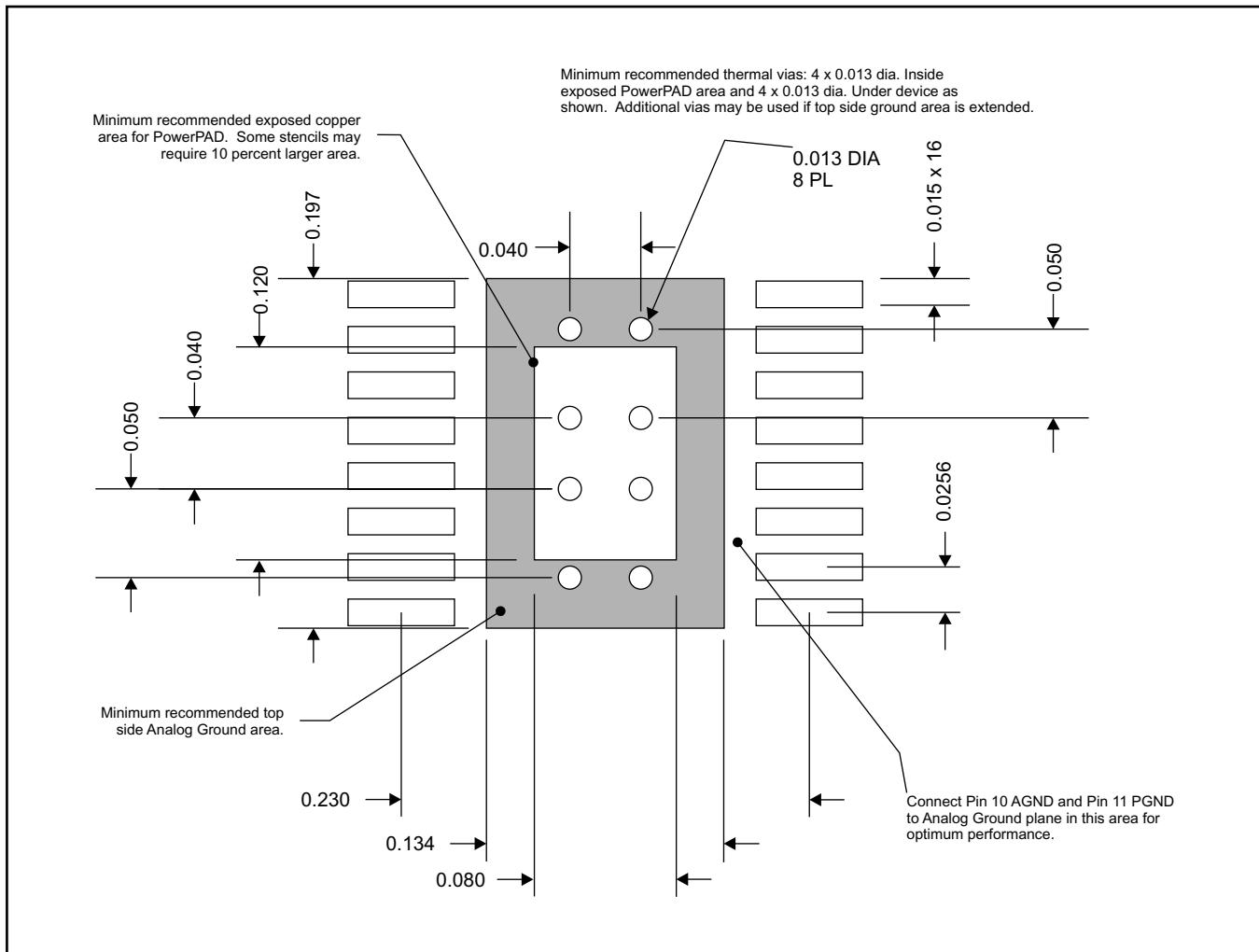

図29に、TPS54550の代表的なアプリケーションの回路図を示します。TPS54550は、3.3Vの公称出力電圧で最大5Aの出力電流を供給できます。適切な放熱性能を達成するために、デバイス底面の露出したPowerPADは、プリント基板に半田付けする必要があります。

### 設計手順

この設計手順は、TPS54550の部品の値を選択するのに使用することができます。また、SWIFTデザイナー・ソフトウェアを使用する場合には、全体の回路設計を行うことができます。SWIFTデザイナー・ソフトウェアは、設計時に、反復的な設計手順を使用し、部品の総合的なデータベースにアクセスします。ここでは、設計手順について簡単に説明します。

設計手順を開始するときに、いくつかのパラメータを決定しておく必要があります。設計者は、以下の情報を把握している必要があります。

- 入力電圧範囲

- 出力電圧

- 入力リップル電圧

- 出力リップル電圧

- 出力電流定格

- 動作周波数

ここで説明する設計の例で使用している入力パラメータは、以下のとおりです。

| 設計パラメータ                                   | 用例値      |

|-------------------------------------------|----------|

| 入力電圧範囲                                    | 6V ~ 17V |

| 出力電圧                                      | 3.3V     |

| 入力リップル電圧                                  | 300mV    |

| 出力リップル電圧                                  | 30mV     |

| 出力定格電圧                                    | 5A       |

| 動作周波数                                     | 700kHz   |

| (注): その他の制約条件として、設計は小型/薄型部品となるように行われています。 |          |

## スイッチング周波数

スイッチング周波数は、RTピンにより設定されます。RTピンを接地すると、PWMスイッチング周波数はデフォルト周波数の250kHzに設定されます。RTピンをオープンすると、PWMスイッチング周波数は500kHzに設定されます。RTとAGNDの間に抵抗を接続すると、250kHzから700kHzの間の周波数を設定できるようになります。RTの適切な値を決めるときは、式(8)を使用してください。

$$RT(k\Omega) = \frac{46000}{f_s(kHz) - 35.9} \quad (8)$$

この回路の例では、目標のスイッチング周波数は700kHzで、RTは69.8kΩです。

## 入力キャパシタ

TPS54550には、入力デカップリング・キャパシタが必要で、アプリケーションによってはバルク入力キャパシタも必要です。デカップリング・キャパシタC9の推奨最小値は10μFです。高品質のセラミック・タイプであるX5RまたはX7Rをお勧めします。電圧定格は、最大入力電圧よりも高い必要があります。その他のすべての要件を満たす限り、より小さな容量でも構いませんが、さまざまな回路で正常に動作する値は10μFです。また、TPS54550回路が入力電圧源から約2インチよりも離れている場合は、バルク容量が必要になる場合があります。このキャパシタの値はあまり重要ではありませんが、リップル電圧を含む入力電圧の最大値を処理できるように定格を満たす必要があります、また入力リップル電圧が許容できるよう出力をフィルタしなければなりません。

この入力リップル電圧は、以下の式(9)で概算することができます。

$$\Delta V_{IN} = \frac{I_{OUT(MAX)} \times 0.25}{C_{BULK} \times f_{SW}} + (I_{OUT(MAX)} \times ESR_{MAX}) \quad (9)$$

$I_{OUT(MAX)}$ は最大負荷電流、 $f_{SW}$ はスイッチング周波数、 $C_{BULK}$ はバルク・キャパシタ値、 $ESR_{MAX}$ はバルク・キャパシタの最大直列抵抗をそれぞれ表します。

最大RMSリップル電流についても確認する必要があります。ワーストケースの状態については、以下の式(10)で概算することができます。

$$I_{CIN} = \frac{I_{OUT(MAX)}}{2} \quad (10)$$

この場合、入力リップル電圧は140mV、RMSリップル電流は2.5Aになります。実際の入力電圧リップルは、レイアウトに関する寄生容量と電圧源の出力インピーダンスの影響を大きく受けます。この回路の実際の入力電圧リップルは図34に示すとおりで、計算結果の値よりも大きくなります。この値は、それでも仕様の入力制限値である300mVよりも低い値です。入力キャパシタの最大電圧は、VINの最大値に $\Delta V_{IN}/2$ を加算した値になります。選択したバルク・キャパシタとバイパス・キャパシタの定格はそれぞれ25Vで、合わせたリップル電流の受容能力は3Aよりも大きく、両方とも十分なマージンがあります。どのような環境であっても、電圧と電流の最大定格を超えないようにすることが非常に重要です。

## 出力フィルタ部品

出力フィルタとしてL1とC2の2つの部品を選択する必要があります。TPS54550は外部的に補償されるデバイスであるため、幅広いタイプと値のフィルタ部品が対応可能です。

## インダクタの選択

出力インダクタの最小値を計算するには、以下の式(11)を使用します。

$$L_{MIN} = \frac{V_{OUT(MAX)} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times K_{IND} \times I_{OUT} \times F_{SW}} \quad (11)$$

$K_{IND}$ は、最大出力電流に対するインダクタのリップル電流量を表す係数です。通常、この値は設計者の判断で自由に設定可能ですが、以下のガイドラインに従うこともできます。セラミックなどの低ESR出力キャパシタを使用している設計では、 $K_{IND} = 0.3$ を使用することができます。より高いESR出力キャパシタを使用する場合は、 $K_{IND} = 0.2$ にすると、良好な結果を得ることができます。

この設計例では、 $K_{IND} = 0.3$ を使用しており、最小インダクタ値の計算結果は3μHになります。この設計では、6.8μHが選択されています。

出力フィルタ・インダクタについては、RMS電流と飽和電流定格を超えないようにすることが重要です。RMSインダクタ電流は、以下の式(12)から求められます。

$$I_{L(RMS)} =$$

$$\sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times \left( \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.8} \right)^2} \quad (12)$$

ピーク・インダクタ電流は式(13)で決定されます。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{1.6 \times V_{IN(MAX)} \times L_{OUT} \times F_{SW}} \quad (13)$$

この設計では、RMSインダクタ電流は5.04A、ピーク・インダクタ電流は5.35Aです。

選択したインダクタはSumida CDRH105-6R8 6.8μHです。このインダクタの飽和電流定格は5.4A、RMS電流定格は5.4Aで、これらの要求を満たしています。これよりも値の小さいインダクタを使用することも可能ですが、この値を選択した理由は、電流定格の要求を満たすこのタイプの製品で、もっとも大きな値だったためです。インダクタの値がこれよりも大きいと、AC電流が低くなるため、出力電圧リップルも低くなります。通常、TPS54550と併用するときのインダクタの値は、6.8μHから47μHの間です。

### キャパシタの選択

出力キャパシタの設計で重要な要因は、DC電圧定格、リップル電流定格、および等価直列抵抗(ESR)です。DC電圧定格とリップル電流定格を超えることはできません。ESRとインダクタ電流によって出力リップル電圧量が決まるため、ESRは重要です。出力キャパシタの実際の値は重要ではありませんが、実用上の制限がいくつかあります。設計上の目的とする閉ループのクロスオーバー周波数と、出力フィルタのLCコーナー周波数との関係に注意してください。一般的に、閉ループのクロスオーバー周波数は、スイッチング周波数の1/5よりも低い周波数に維持することをお勧めします。この設計の700kHz周波数など、高いスイッチング周波数を使用する場合は、TPS54550の内部回路の制約により、実際の最大クロスオーバー周波数は約50kHzに制限されます。また、補償回路の位相ゲインを適正化するために、閉ループのクロスオーバー周波数をLCコーナー周波数よりも30%以上高くする必要があります。これにより、出力フィルタの最小キャパシタ値は、以下の値に制限されます。

$$C_{OUT} = \frac{1}{L_{OUT}} \times \left( \frac{\kappa}{2\pi f_{CO}} \right)^2 \quad (14)$$

Kは、 $f_{LC}$ と $f_{CO}$ との間の差を表す周波数乗数です。Kは1.3から15の間ですが、通常は10(1デケード差)です。目的のクロスオーバーが13kHzでインダクタが6.8μHの場合は、出力キャパシタの最小値は約39μFになります。この設計では、周波数乗数に堅実な3を使用しているため、目的の出力容量は200μFです。選択する出力キャパシタは、目的の出力電圧とリップル電圧の半分を加算した値よりも高い定格にする必要があります。ディレーティングした量もこの計算に含める必要があります。出力キャパシタの最大RMSリップル電流は、以下の式(15)で求められます。

$$I_{COUT(RMS)} = \frac{1}{\sqrt{12}} \times \left[ \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times N_C} \right] \quad (15)$$

$N_C$ は並列に配置された出力キャパシタの数です。

出力キャパシタの最大ESRは、設計の初期パラメータとして規定される、出力リップルの許容量によって決定されます。出力リップル電圧は、インダクタのリップル電流に出力フィルタのESRを乗じた値です。キャパシタのデータシートに記載されている最大規定ESRは、以下の式(16)で求められます。

$$ESR_{MAX} =$$

$$N_C \times \left( \frac{V_{IN(MAX)} \times L_{OUT} \times F_{SW} \times 0.8}{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})} \right) \times \Delta V_{p-p(MAX)} \quad (16)$$

$\Delta V_{p-p}$ はピーク・ツー・ピークの目標出力リップルです。この設計例では、C2とC10として、2つの100μFセラミック出力キャパシタが選択されています。

これらのキャパシタはTDK C3225X5R0J107Mで、定格が6.3V、最大ESRが2mΩ、およびリップル出力電流定格が3A以上です。計算結果の合計RMSリップル電流は、161mA(それぞれのRMSリップル電流は80.6mA)で、必要な最大合計ESRは43mΩです。これらの出力キャパシタは要求を大きく上回っているため、信頼性と性能が高い設計になっています。出力が設定出力の3.3Vで動作している場合、回路内での実際の容量は、公表値よりも低いことがあります。これに注意してください。

アプリケーションの要件によっては、その他のタイプのキャパシタでもTPS54550と併用しても正常に動作します。

## 補償部品

外部補償をTPS54550と併用して、幅広い出力フィルタを構成することができます。広範囲な誘導体のキャパシタ値と種類が対応しています。設計例では、R1、R3、R5、C6、C7およびC8から構成されるタイプ3補償が使用されています。また、R1とR2を組み合わせて、出力電圧を設定する分圧回路を形成しています。これらの部品の参照番号は、SWIFTデザイナー・ソフトウェアで使用されている参照番号と同じです。補償回路を設計する方法は複数あります。この手順では、ほとんどの出力フィルタの組み合わせで良好な結果を得ることができます。非常に高い閉ループのクロスオーバー周波数、セラミックなどの低ESR出力キャパシタを使用する場合、または設計者が設計手順に自身がもてない場合には、SWIFTデザイナー・ソフトウェアを使用することをお勧めします。

TPS54550の補償回路を設計するときは、検討が必要な要因がいくつかあります。補償後の誤差増幅器のゲインは、増幅器の開ループ利得特性で制限されるべきではなく、また、スイッチング周波数で過剰なゲインを発生することを避ける必要があります。また、閉ループのクロスオーバー周波数をスイッチング周波数の1/5よりも低く設定し、クロスオーバー時の位相マージンを45度より大きくする必要があります。ここに説明する一般的な手順では、ループ補償の理論については詳細に説明していませんが、この手順に従うことでこれらの要求を満たすことができます。

まず、以下の式(17)を使用して、出力フィルタのLCコーナー周波数を計算します。

$$f_{LC} = \frac{1}{2\pi \sqrt{L_{OUT} C_{OUT}}} \quad (17)$$

設計例では $f_{LC} = 4315\text{Hz}$ です。

閉ループのクロスオーバー周波数は、 $f_{LC}$ よりも高く、スイッチング周波数の1/5よりも低い必要があります。また、クロスオーバー周波数が50kHzを超えないようにする必要があります。そうしないと、誤差増幅器が目的のゲインを供給できなくなる可能性があります。この設計では、クロスオーバー周波数に13kHzが選択されています。この値は、ループ帯域幅が比較的広いときに選択されますが、安定性を確保するための位相ブーストとしては十分です。

次に、出力電圧が3.3VになるR2抵抗値を以下の式(18)で計算します。

$$R2 = \frac{R1 \times 0.891}{V_{OUT} - 0.891} \quad (18)$$

TPS54550の設計では、R1の値を1.0kΩから開始します。R2は374Ωになります。

これで、補償回路の極とゼロを設定する補償部品の値を計算できるようになりました。R1 > R5、C6 > C7と仮定すると、極とゼロの位置は式(19)から式(22)で求められます。また、原点にも極が存在し、これは以下の周波数でユニティ・ゲインを持ちます。

$$f_{Z1} = \frac{1}{2\pi R3 C6} \quad (19)$$

$$f_{Z2} = \frac{1}{2\pi R1 C8} \quad (20)$$

$$f_{P1} = \frac{1}{2\pi R5 C8} \quad (21)$$

$$f_{P1} = \frac{1}{2\pi R3 C7} \quad (22)$$

さらに、以下の周波数で単一利得をもつ原点の極があります。

$$f_{INT} = \frac{1}{2\pi R1 C6} \quad (23)$$

この極は、補償後の誤差増幅器のゲイン全体を設定するために用いられ、閉ループのクロスオーバー周波数を決定します。

タイプ3補償回路の一般的な設計方法は複数あります。これらの計算の理論については、このドキュメントでは説明していません。初期設計時には、計算結果の補償値を常に使用することが最善の方法です。次に実際の閉ループ応答を確認してください。初期の値は、個別の設計要求に合わせて調整することができます。SWIFTソフトウェア設計ツールでは、初期の回路設計に使用することもできます。

この回路では、最初の補償ゼロはLCコーナー周波数の約1/2に設定されます。2番目のゼロはそれよりも少し低くなり、LC出力フィルタの2重極以前に、位相ゲインが増加するようになります。LCコーナー周波数では全体の位相応答が180度急速に低下するため、LCコーナーの前に90度の初期フェーズを増やすことが重要です。

2つの補償極は、閉ループのクロスオーバー周波数で位相マージンが損失しないように十分高く、かつ誤差増幅器のゲインが内部オペアンプのユニティ・ゲイン帯域幅制限を越えないように低く設定されます。その次に、全体のゲインとクロスオーバー周波数を設定するために積分器の周波数が選択されます。

この結果、極周波数とゼロ周波数は以下のとおりになります。

$$f_{Z1} = 2340\text{Hz}$$

$$f_{Z2} = 1591\text{Hz}$$

$$f_{P1} = 120\text{kHz}$$

$$f_{P2} = 159\text{kHz}$$

$$f_{INT} = 234\text{Hz}$$

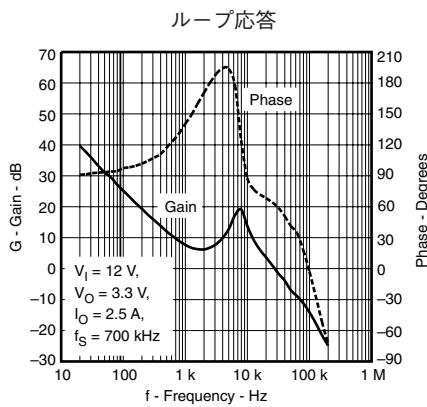

この回路で測定した結果の全体のループ応答は、図30に示すとおりです。実際の閉ループのクロスオーバー周波数は、約25kHzで想定値よりも高くなります。この原因是主に、出力フィルタ部品の実際の値と、内部フィード・フォワード・ゲイン回路の公差が変動するためです。設計全体では位相マージンが60度より大きくなり、さまざまなラインと負荷の全ての組み合わせにおいても安定した動作が達成されます。

R1に10kΩを与え、クロスオーバー周波数に13kHzを選択した結果のf<sub>INT</sub>は、以下の式(24)で計算できます。

$$f_{\text{INT}} = \frac{10^{-0.9} \times f_{\text{CO}}}{2} \quad (24)$$

また、C6の値は以下の式(25)で求められます。

$$C_6 = \frac{1}{2\pi R_1 f_{\text{INT}}} \quad (25)$$

最初のゼロf<sub>Z1</sub>は出力フィルタのLCコーナー周波数の1/2に配置されるため、R3は以下の式(26)で計算できます。

$$R_3 = \frac{1}{\pi C_6 f_{\text{LC}}} \quad (26)$$

2番目のゼロf<sub>Z2</sub>は出力フィルタのLCコーナー周波数に配置されるため、C8は式(27)で計算できます。

$$C_8 = \frac{1}{2\pi R_1 f_{\text{LC}}} \quad (27)$$

最初の極f<sub>P1</sub>は出力フィルタのESRゼロ周波数に合致するように配置されます。

この周波数は以下の式(28)で求められます。

$$f_{\text{ESR}} = \frac{1}{2\pi R_{\text{ESR}} C_{\text{OUT}}} \quad (28)$$

R<sub>ESR</sub>は、出力キャパシタの等価直列抵抗です。

この場合、ESRゼロ周波数は35.4kHzで、R5は式(29)で計算できます。

$$R_5 = \frac{1}{2\pi C_8 f_{\text{ESR}}} \quad (29)$$

最後の極は、閉ループのクロスオーバー周波数より高い周波数に配置されます。この周波数は、クロスオーバー周波数で位相が極端に低下しない大きさになります。また、この周波数は、スイッチング周波数でゲインがほとんどないか、またはまったくない状態になるように減衰します。この回路ではf<sub>P2</sub>極の位置は、閉ループのクロスオーバー周波数の4倍に設定されます。最後の補償部品の値C7は以下の式(30)で導かれます。

$$C_7 = \frac{1}{8\pi R_3 f_{\text{CO}}} \quad (30)$$

キャパシタは標準値の制限範囲でのみ有効であることに注意してください。したがって、それぞれのキャパシタには、標準値に最も近いキャパシタを選択します。この設計で測定した閉ループ応答を、図30に示します。

## バイアスおよびブートストラップ・キャパシタ

すべてのTPS54550の設計では、ブートストラップ・キャパシタC3とバイアス・キャパシタC4が必要になります。ブートストラップ・キャパシタの値は、0.1μFでなければなりません。ブートストラップ・キャパシタはPHピンとBOOTピンの間に配置します。また、24Ω抵抗をブートストラップ・キャパシタとシリーズに配置します。この抵抗は、ハイサイドFETターンオン波形のリーディング・エッジを遅くするのに使用されます。この抵抗を使用すると、スイッチング・ノードのオーバーシュートの振幅が大幅に減少します。バイアス・キャパシタは、VBIASピンとAGNDの間に接続します。値は1.0μFでなければなりません。どちらのキャパシタも、温度安定性のために、X7RまたはX5Rクラスの誘導体の高品質のセラミック・タイプにする必要があります。これらのキャパシタは、できるだけデバイスの接続ピンに近づけて配置する必要があります。

## ローサイドFET

TPS54550は外部のローサイドFETを使用して動作する仕様になっており、LSGピンはゲート駆動出力を供給します。ドレインはPHピン、ソースはPGND、ゲートはLSGへ接続します。TPS54550のゲート駆動回路は、このアプリケーションに最適な最も一般的なNチャネルFETに対応する様設計されています。SWIFTデザイナー・ソフトウェアを使って、ローサイドFETを選択するための設計上のパラメータをすべて計算することができます。ほとんどの設計に適用可能な、有効なソリューションを作成するための手順について簡単に説明します。

選択するFETは、後述するアプリケーションの絶対最大定格を満たす必要があります。

ドレインとソース間の電圧( $V_{DS}$ )はPHピンの最大電圧( $V_{INMAX} + 0.5V$ )より高い必要があります。

ゲートとソース間の電圧( $V_{GS}$ )は8Vよりも高い必要があります。

ドレイン電流( $I_D$ )は  $1.1 \times I_{OUTMAX}$ よりも高い必要があります。

ドレインとソース間のオン抵抗( $r_{DS(on)}$ )はできるだけ低い方がよく、 $30m\Omega$ 以下が望ましい値です。 $r_{DS(on)}$ の値が低いと、

高効率の設計が可能となります。ローサイドFETのオン時間は、通常、ハイサイドFETのオン時間よりも長くなることに注意してください。ローサイドFETのパラメータは慎重に設定し、全体の効率を向上させるように心がけます。

トータル・ゲートの電荷量( $Q_g$ )は50nCより小さい必要があります。ここでも同様に、 $Q_g$ 特性が低いほど、効率が改善されます。また、選択したデバイスに電力損失を消費することができることを確認してください。

この設計ではローサイドFETにVishay Siliconix SI7110 20-V NチャネルMOSFETを使用しています。このFETは、特にローサイド同期整流用として使用するように設計されています。

## パワー・グッド

TPS54550はパワー・グッド出力ピン(PWRGD)を備えています。この出力ピンはオープン・ドレイン出力で、3.3Vまたは5Vのロジック電源にプルアップすることを意図しています。このアプリケーションでは10kΩのプルアップ抵抗で良好に機能します。絶対最大値は6Vですので、最大入力電圧が6Vを超える場合には、このプルアップ抵抗をVINに接続しないように注意する必要があります。

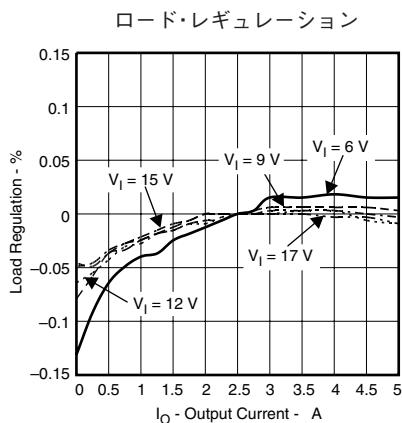

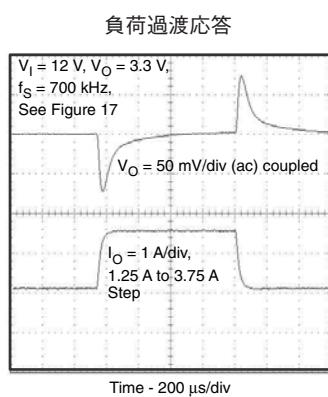

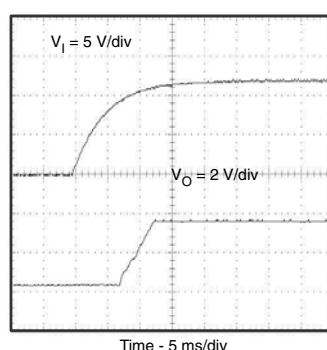

## アプリケーション特性(図29を参照)

図 30

図 31

図 32

図 33

図 34

図 35

図 36

図 37

# PACKAGE OPTION ADDENDUM

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| TPS54550PWP      | ACTIVE                | HTSSOP       | PWP             | 16   | 90          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54550PWPG4    | ACTIVE                | HTSSOP       | PWP             | 16   | 90          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54550PWPR     | ACTIVE                | HTSSOP       | PWP             | 16   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS54550PWPRG4   | ACTIVE                | HTSSOP       | PWP             | 16   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

**ACTIVE:** 製品デバイスが新規設計用に推奨されています。

**LIFEBUY:** TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

**NRND:** 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

**PREVIEW:** デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

**OBSOLETE:** TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、

Pb-Free (RoHS)、Pb-Free (RoHS Exempt: RoHS 適用除外)、およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

**TBD:** Pb-Free/Green変換プランが策定されていません。

**Pb-Free (RoHS):** TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、均質な材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

**Pb-Free (RoHS Exempt):** このコンポーネントは、次の理由のいずれかにより、RoHS指令を適用除外されています。1)ダイと

パッケージの間で、鉛ベースのフリップチップ半田突起が使用されている、または2)ダイとリードフレームの間で鉛ベースのダイ接着剤が使用されている。それ以外には、このコンポーネントは上記の定義のとおり、Pb-Free (RoHS準拠) であると考えられます。

**Green (RoHS & no Sb/Br):** TIにおける“Green”は、“Pb-Free”(RoHS 互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項:** このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

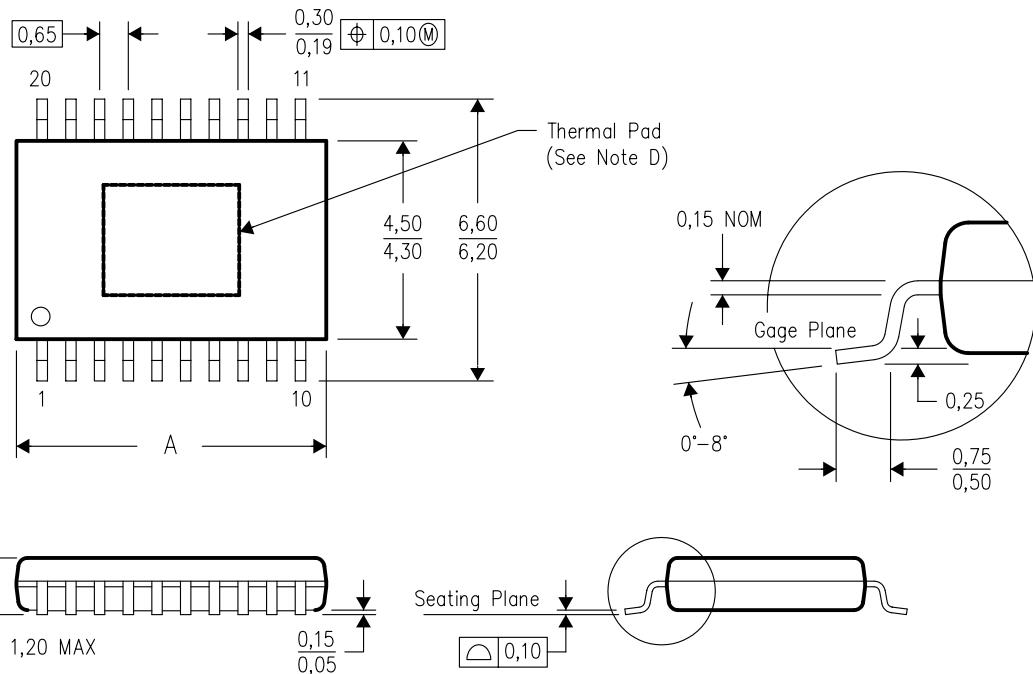

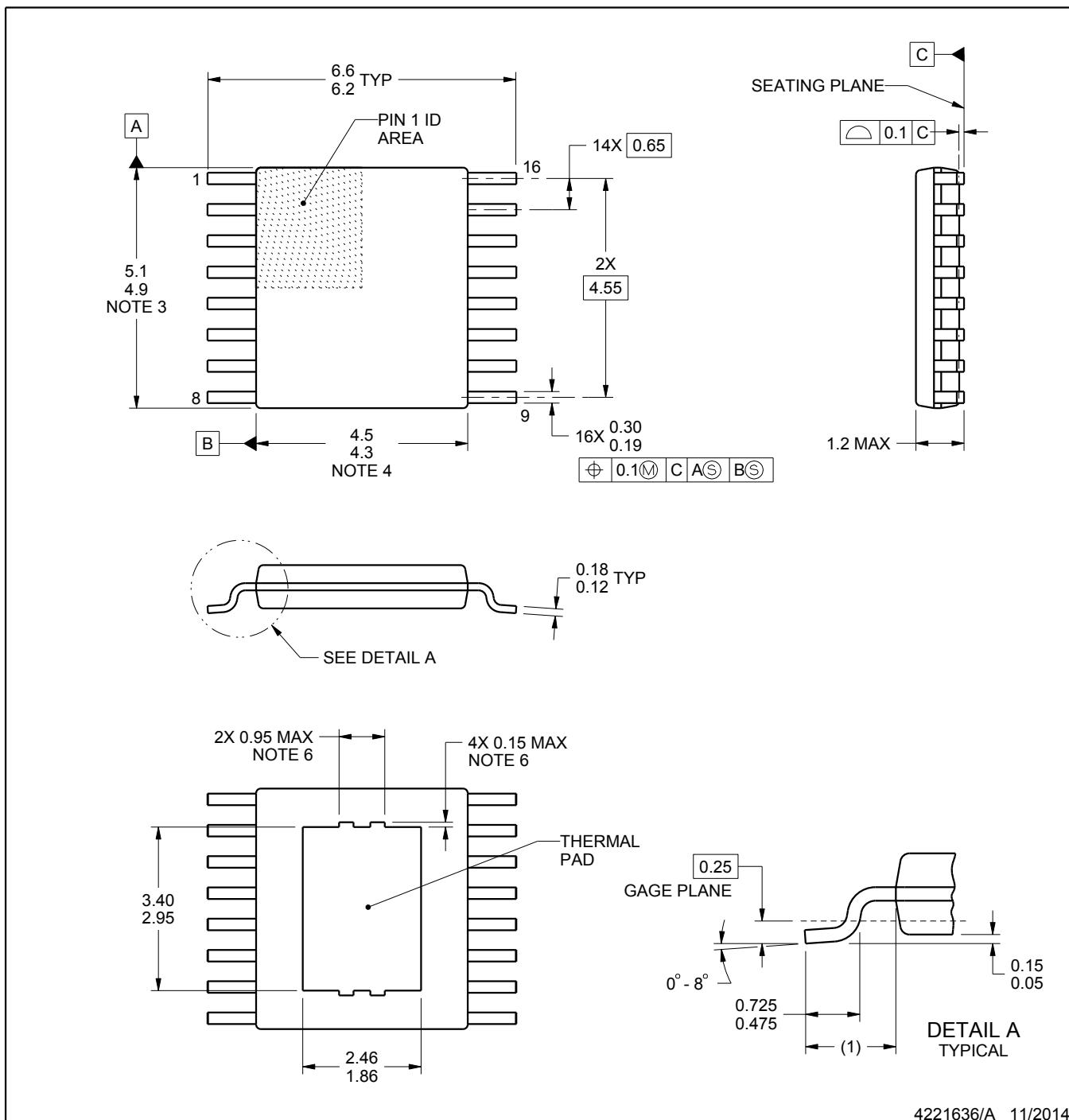

# メカニカル・データ

PWP (R-PDSO-G\*\*) 20 PIN SHOWN

PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

| DIM   | PINS ** | 14   | 16   | 20   | 24   | 28   |

|-------|---------|------|------|------|------|------|

| A MAX |         | 5,10 | 5,10 | 6,60 | 7,90 | 9,80 |

| A MIN |         | 4,90 | 4,90 | 6,40 | 7,70 | 9,60 |

4073225/H 12/05

- 注：A. 全ての線寸法はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 本寸法にはバリや突起を含みません。

- D. このパッケージは、基板上のサーマルパッドに半田付けされるように設計されています。推奨基盤レイアウトについては、テクニカル・ブリーフ“PowerPAD Thermally Enhanced Package”(TI資料番号SLMA002)を参照してください。

この資料は、ホームページwww.ti.com<http://www.ti.com>で入手できます。

- E. JEDEC MO-153に適合しています。

(SLVS623A April. 2006)

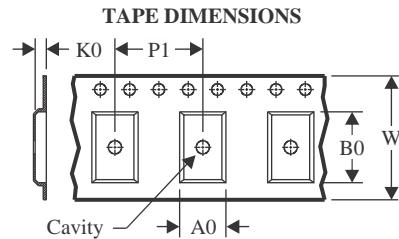

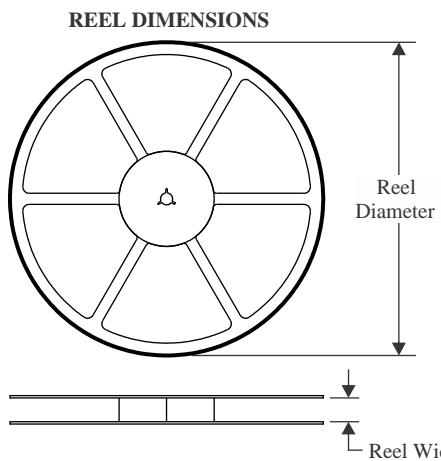

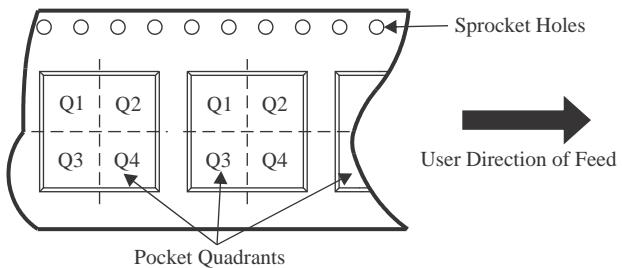

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54550PWPR | HTSSOP       | PWP             | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

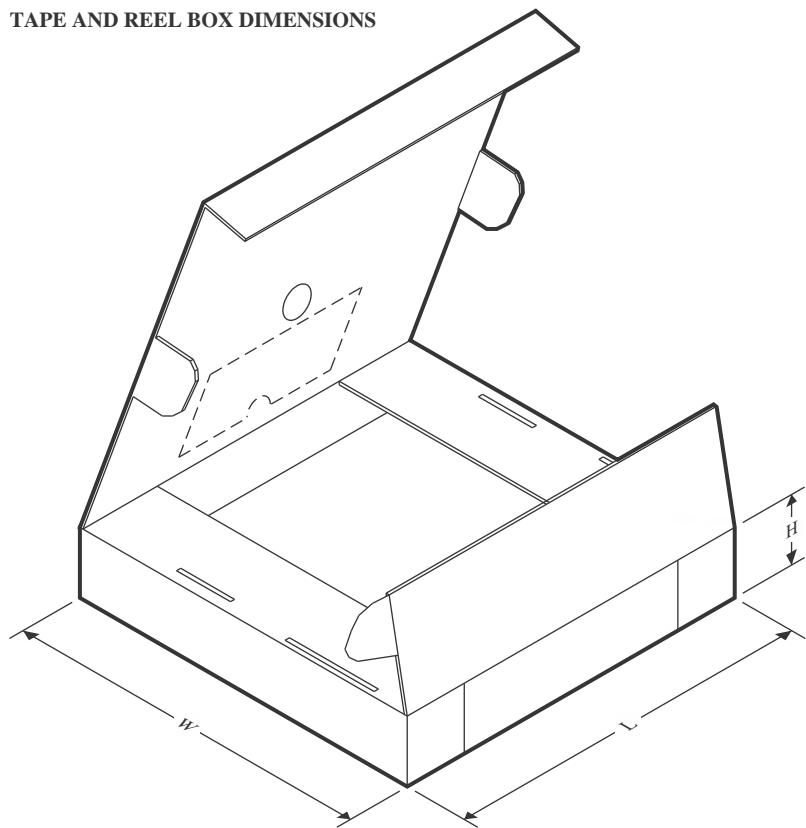

## TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54550PWPR | HTSSOP       | PWP             | 16   | 2000 | 350.0       | 350.0      | 43.0        |

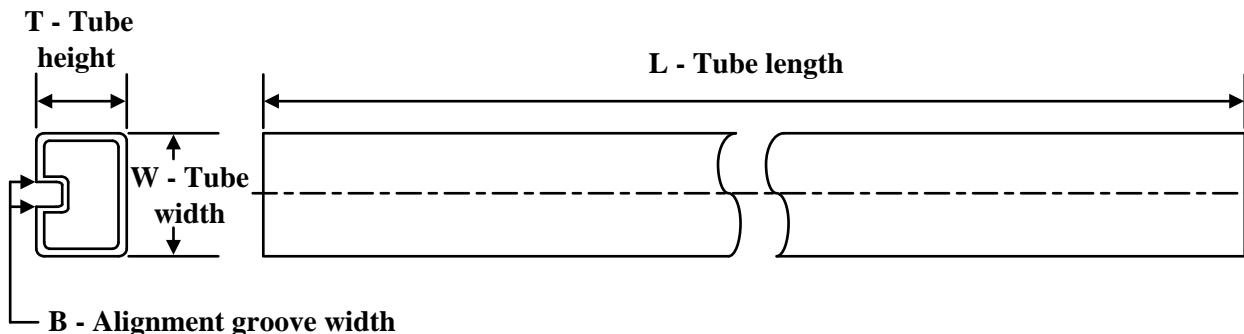

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS54550PWP   | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54550PWP.A | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| TPS54550PWPG4 | PWP          | HTSSOP       | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

## GENERIC PACKAGE VIEW

PWP 16

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4073225-3/J

## **PACKAGE OUTLINE**

PWP0016F

## **PowerPAD™ - 1.2 mm max height**

PLASTIC SMALL OUTLINE

4221636/A 11/2014

PowerPAD is a trademark of Texas Instruments.

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

5. Reference JEDEC registration MO-153.

6. Features may not present.

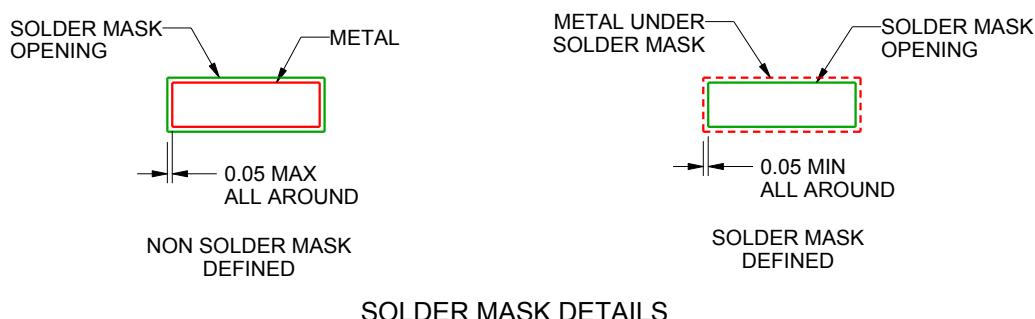

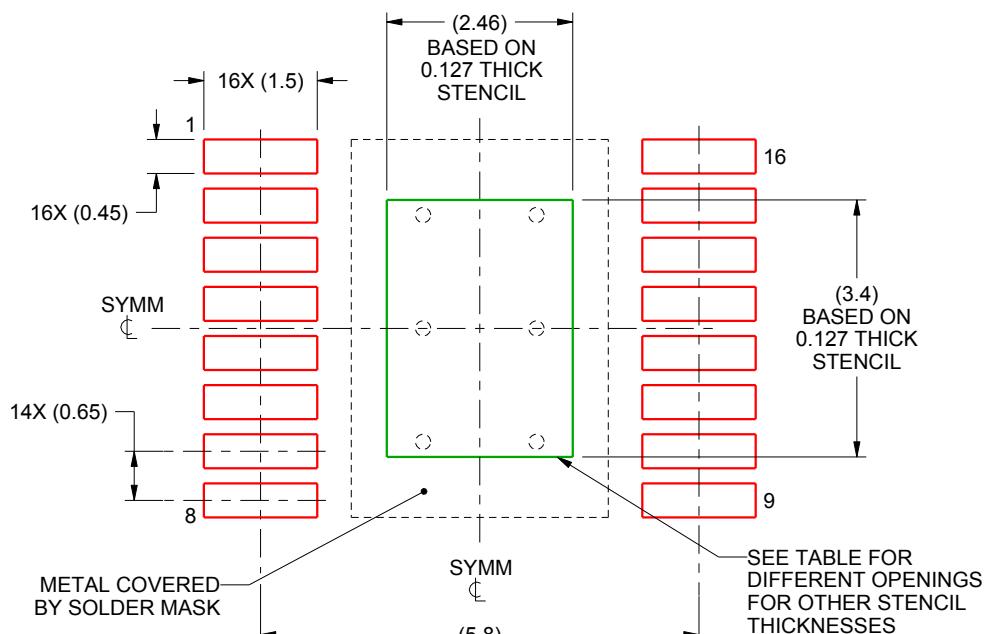

# EXAMPLE BOARD LAYOUT

PWP0016F

PowerPAD™ - 1.2 mm max height

PLASTIC SMALL OUTLINE

4221636/A 11/2014

NOTES: (continued)

7. Publication IPC-7351 may have alternate designs.

8. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

9. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

10. Size of metal pad may vary due to creepage requirement.

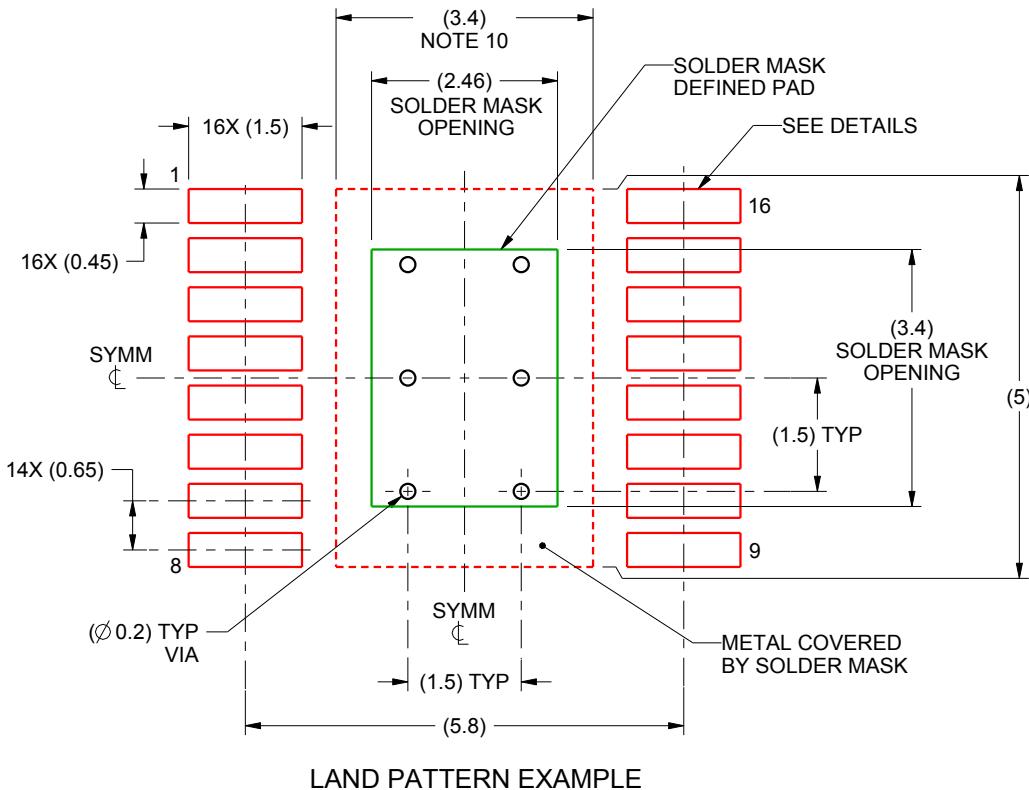

# EXAMPLE STENCIL DESIGN

PWP0016F

PowerPAD™ - 1.2 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.77 X 3.83            |

| 0.127             | 2.46 X 3.4 (SHOWN)     |

| 0.152             | 2.25 X 3.11            |

| 0.178             | 2.08 X 2.87            |

4221636/A 11/2014

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated