## TPS55285 I<sup>2</sup>C インターフェイス搭載 22V、8A 昇降圧コンバータ

### 1 特長

- USB パワー デリバリ (USB PD)用のプログラマブル電源 (PPS)サポート

- 幅広い入力電圧範囲: 2.4V ~ 22V

- スタートアップのための最低入力電圧: 3.0V

- プログラム可能な出力電圧範囲: 0.8V~15V (10mV 刻み)

- 基準電圧精度: ±1%

- ケーブルの電圧降下に対する可変出力電圧補償

- 最大 6.35A の出力電流制限を 50mA 刻みでプログラム可能

- 全負荷範囲にわたって高効率を実現

- $V_{IN} = 20V, V_{OUT} = 5V, I_{OUT} = 5A$  で 92.0% の効率

- $V_{IN} = 12V, V_{OUT} = 15V, I_{OUT} = 5A$  で 95.7% の効率

- I<sup>2</sup>C プログラミング

- 出力イネーブル (OE) のオン / オフ

- 出力電圧変化のスルーレート

- スイッチング周波数: 400kHz, 800kHz, 1.6MHz, 2.1MHz

- 軽負荷時の PFM および FPWM モードをプログラム可能

- スペクトラム拡散のイネーブル / ディスエーブル

- 出力放電のイネーブル / ディスエーブル

- 豊富な保護機能

- 入力過電圧保護

- 出力相対過電圧保護

- ヒップ モードによる出力短絡保護

- サーマル シヤットダウン保護機能

- 8A の平均インダクタ電流制限

- 小型ソリューション サイズ

- 4 個の低  $R_{DS(ON)}$  内部 MOSFET

- 最大 2.1MHz のスイッチング周波数

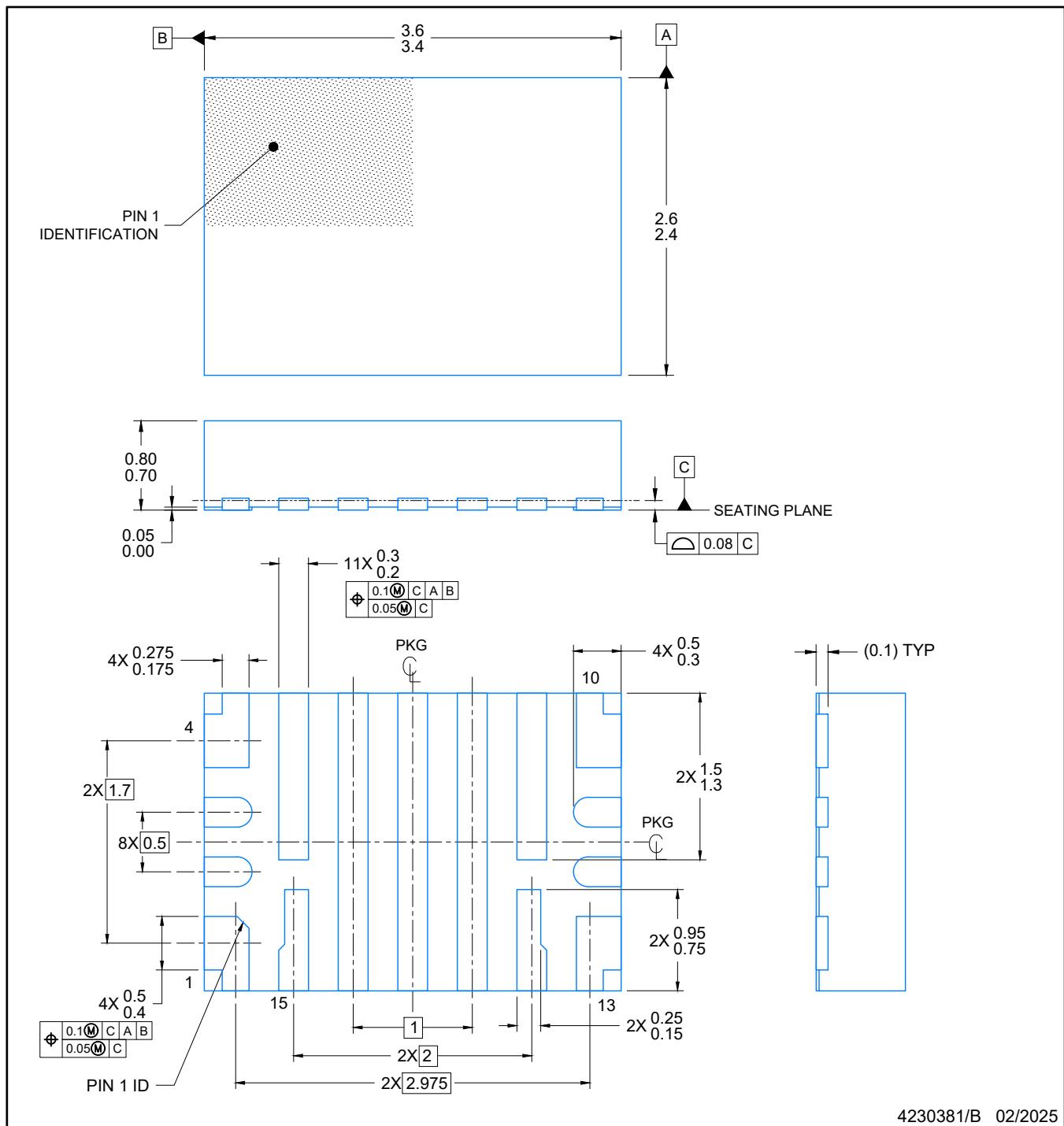

- 2.5mm × 3.5mm HotRod™ WQFN パッケージ

### 2 アプリケーション

- USB PD

- ワイヤレス充電器

- ドッキングステーション

- ノート PC

- SSD

### 3 説明

TPS55285 は、バッテリ電圧、USB Power Delivery (USB PD)、またはアダプタ電圧を複数の電源レール向けて変換する目的で最適化された、統合型の同期整流昇降圧コンバータです。TPS55285 は 4 個の 15mΩ MOSFET を内蔵しており、高効率の小型ソリューションを実現します。

TPS55285 は、2.4V (3.0V の立ち上がり) から 22V までの広い入力電圧範囲に対応しており、0.8V ~ 15V の電圧を 10mV 刻みで出力できるため、さまざまなアプリケーションをサポートできます。TPS55285 は、8A の平均インダクタ電流制限を採用し、降圧モードで最大 7A の出力電流を供給することが特徴です。ブーストモードでは、12V 入力から 60W、5V 入力から 30W を提供できます。

I<sup>2</sup>C インターフェイスにより、TPS55285 の出力電圧は動的にプログラムします。デバイスがイネーブルのとき、デフォルトの出力電圧は 5V です。I<sup>2</sup>C インターフェイスにより、出力電圧変化のスルーレート、スイッチング周波数、強制 PWM モード動作を設定できます。

TPS55285 は入力および出力の過電圧保護、平均インダクタ電流制限、サイクルごとのピーク電流制限、出力短絡保護機能を備えています。また TPS55285 は、持続的な過負荷状態での外部出力電流センサ抵抗なしの出力電流制限とヒップ モード保護機能により、安全な動作を可能にします。

TPS55285 はスイッチング周波数が高いため、小型のインダクタとコンデンサを使用できます。TPS55285 は 2.5mm × 3.5mm の QFN パッケージで供給されます。

#### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ     |

|----------|----------------------|---------------|

| TPS55285 | WQFN-HR              | 2.5mm × 3.5mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

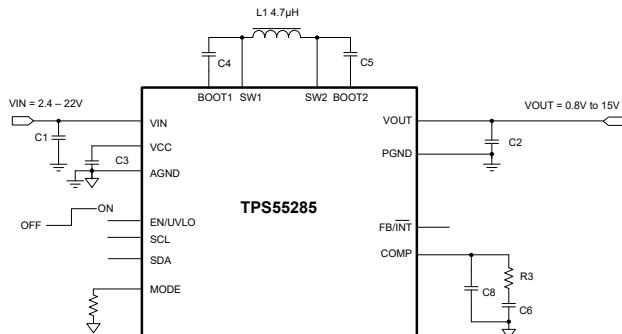

代表的なアプリケーション回路

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVS172](#)

## 目次

|                                                                 |           |                                                      |    |

|-----------------------------------------------------------------|-----------|------------------------------------------------------|----|

| <b>1 特長</b>                                                     | <b>1</b>  | 7.4 VOUT_FS レジスタ (アドレス = 4h) [リセット = 00000011b]..... | 28 |

| <b>2 アプリケーション</b>                                               | <b>1</b>  | 7.5 CDC レジスタ (アドレス = 5h) [リセット = 11110000b].....     | 29 |

| <b>3 説明</b>                                                     | <b>1</b>  | 7.6 MODE レジスタ (アドレス = 6h) [リセット = 00100000b].....    | 30 |

| <b>4 ピン構成および機能</b>                                              | <b>3</b>  | 7.7 STATUS レジスタ (アドレス = 7h) [リセット = 00000001b].....  | 31 |

| <b>5 仕様</b>                                                     | <b>5</b>  | 7.8 レジスタの要約.....                                     | 32 |

| 5.1 絶対最大定格.....                                                 | 5         | <b>8 アプリケーションと実装</b> .....                           | 33 |

| 5.2 推奨動作条件.....                                                 | 5         | 8.1 アプリケーション情報.....                                  | 33 |

| 5.3 熱に関する情報.....                                                | 5         | 8.2 代表的なアプリケーション.....                                | 33 |

| 5.4 電気的特性.....                                                  | 6         | 8.3 電源に関する推奨事項.....                                  | 41 |

| 5.5 I <sub>2</sub> C のタイミング特性.....                              | 9         | 8.4 レイアウト.....                                       | 42 |

| 5.6 代表的特性.....                                                  | 10        | <b>9 デバイスおよびドキュメントのサポート</b> .....                    | 44 |

| <b>6 詳細説明</b>                                                   | <b>12</b> | 9.1 デバイスサポート.....                                    | 44 |

| 6.1 概要.....                                                     | 12        | 9.2 ドキュメントの更新通知を受け取る方法.....                          | 44 |

| 6.2 機能ブロック図.....                                                | 13        | 9.3 サポート・リソース.....                                   | 44 |

| 6.3 機能説明.....                                                   | 14        | 9.4 商標.....                                          | 44 |

| 6.4 デバイスの機能モード.....                                             | 19        | 9.5 静電気放電に関する注意事項.....                               | 44 |

| 6.5 プログラミング.....                                                | 20        | 9.6 用語集.....                                         | 44 |

| <b>7 レジスタ マップ</b>                                               | <b>24</b> | <b>10 改訂履歴</b> .....                                 | 44 |

| 7.1 REF レジスタ (アドレス = 0h, 1h) [リセット = 10100100b, 00000001b]..... | 25        | <b>11 メカニカル、パッケージ、および注文情報</b> .....                  | 45 |

| 7.2 IOUT_LIMIT レジスタ (アドレス = 2h) [リセット = 11100100b].....         | 26        |                                                      |    |

| 7.3 VOUT_SR レジスタ (アドレス = 3h) [リセット = 00000001b].....            | 27        |                                                      |    |

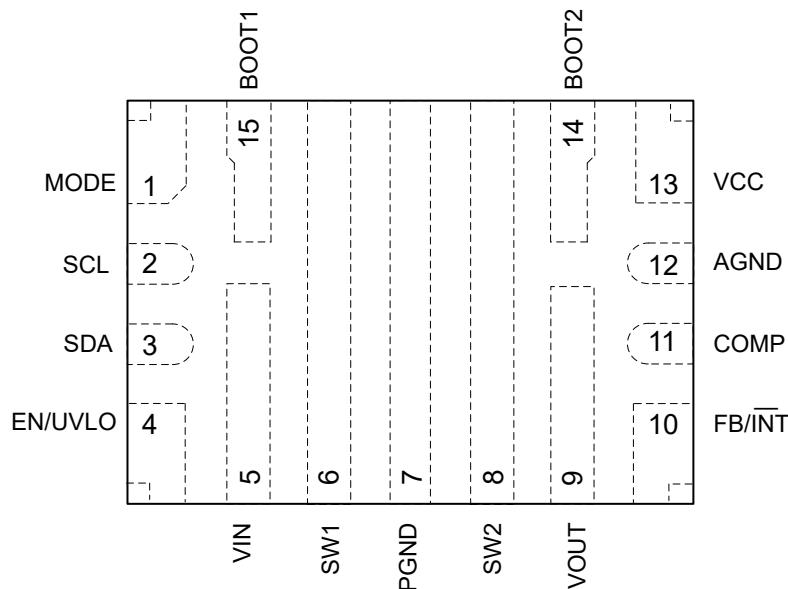

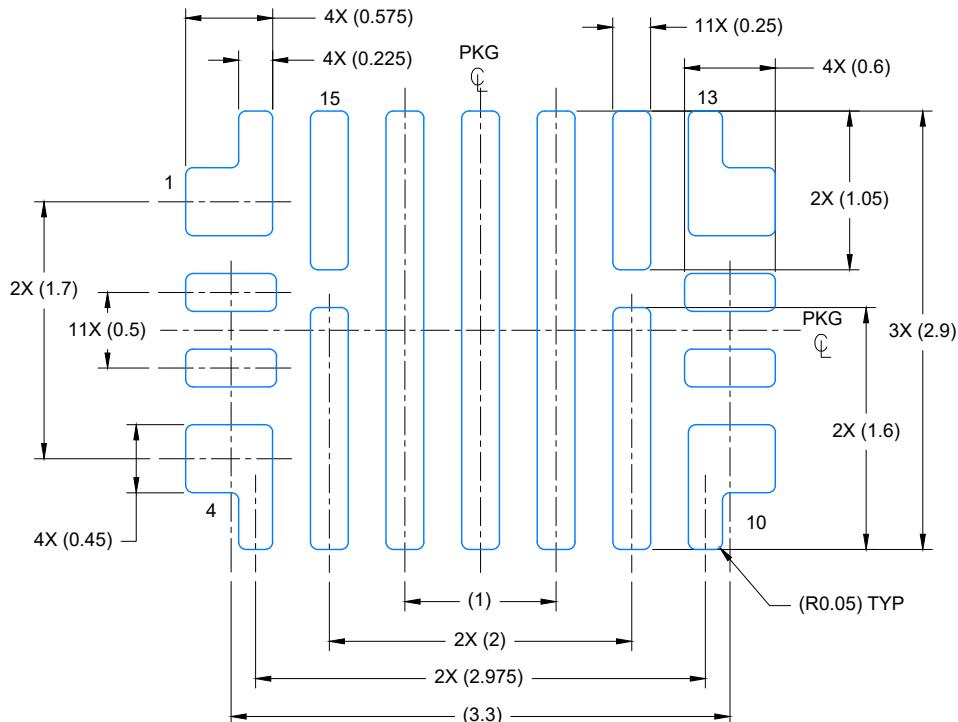

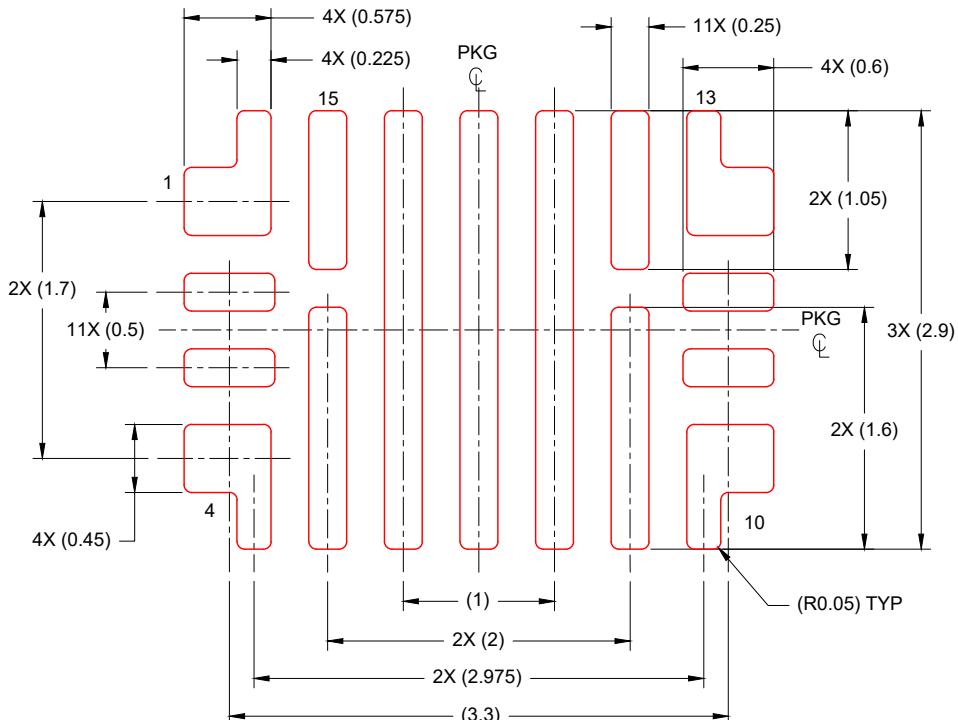

## 4 ピン構成および機能

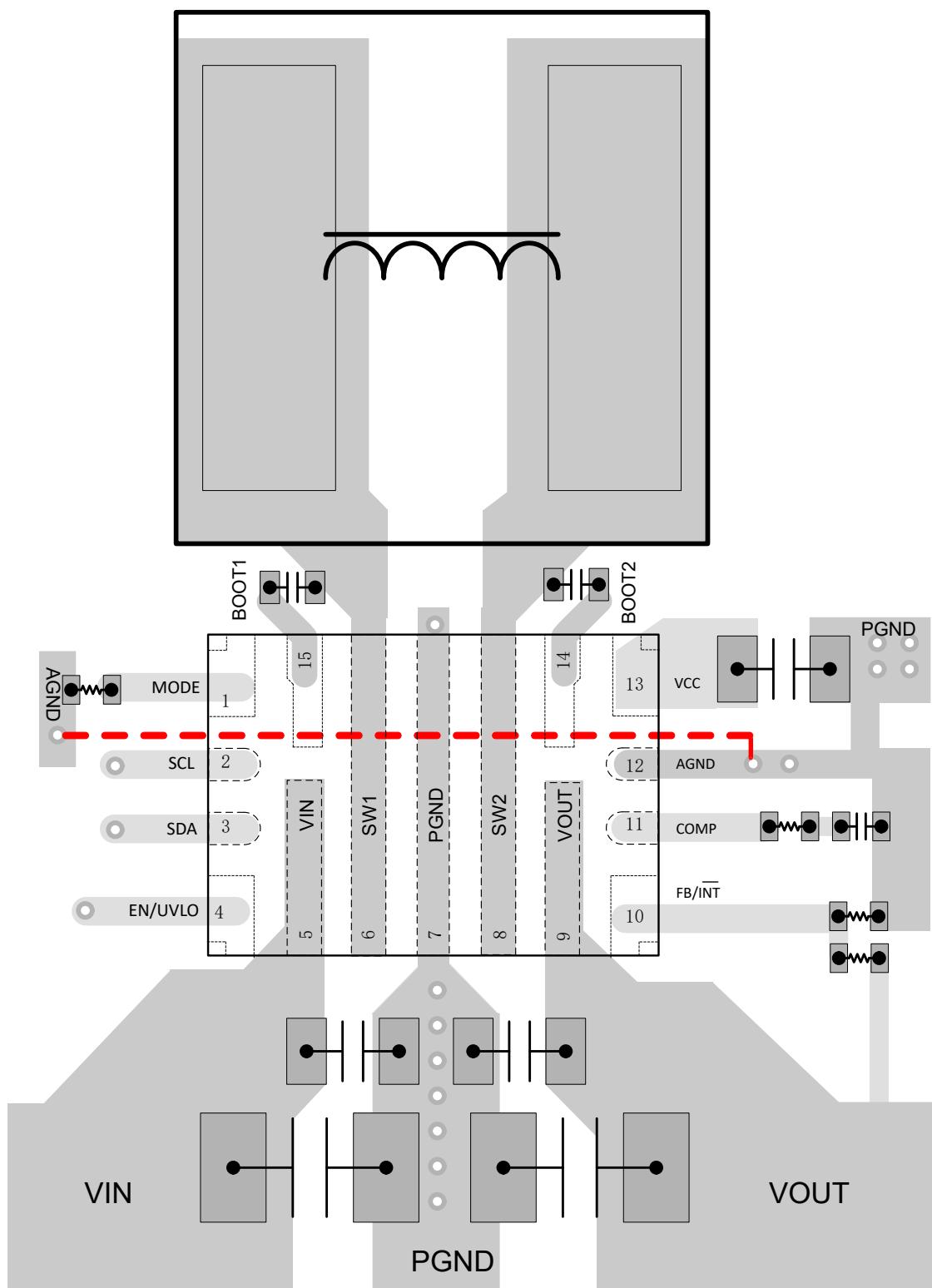

図 4-1. TPS55285 VAL パッケージ、15 ピン WQFN-HR (透過上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称 | I/O | 説明                                                                                                                                                                                                                  |

|----|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | モード      | I   | このピンと AGND との間に抵抗を配置して、TPS55285 デフォルト出力イネーブル (OE) ビットを選択します。                                                                                                                                                        |

| 2  | SCL      | I   | I <sup>2</sup> C インターフェイスのクロック。                                                                                                                                                                                     |

| 3  | SDA      | I/O | I <sup>2</sup> C インターフェイスのデータ。                                                                                                                                                                                      |

| 4  | EN/UVLO  | I   | 有効ロジック入力とプログラマブル入力電圧の低電圧ロックアウト (UVLO) 入力。ロジック "High" レベルにすると、デバイスは有効になります。ロジック "Low" レベルにすると、デバイスは無効化され、シャットダウン モードに入ります。EN/UVLO ピンの電圧がロジック "High" 電圧の 1.03V を上回った後、このピンは内部リファレンス 1.05V を持つプログラマブル UVLO 入力として機能します。 |

| 5  | VIN      | PWR | 昇降圧コンバータの入力。                                                                                                                                                                                                        |

| 6  | SW1      | PWR | 降圧側のスイッチング ノードピン。SW1 ピンは、内部降圧ローサイド パワー MOSFET のドレインおよび内部降圧ハイサイド パワー MOSFET のソースに接続されます。                                                                                                                             |

| 7  | PGND     | PWR | デバイスの電源グランド。                                                                                                                                                                                                        |

| 8  | SW2      | PWR | 昇圧側のスイッチング ノードピン。SW2 ピンは、内部昇圧ローサイド パワー MOSFET のドレインおよび内部昇圧ハイサイド パワー MOSFET のソースに接続されます。                                                                                                                             |

| 9  | VOUT     | PWR | 昇降圧コンバータの出力。                                                                                                                                                                                                        |

| 10 | FB/INT   | I/O | デバイスが外部出力電圧帰還を使用するように設定されている場合、抵抗デバイダのセンター タップに接続して、出力電圧をプログラムします。デバイスが内部帰還を使用するように設定されている場合、このピンは故障インジケータのオープン ドレイン出力です。内部故障が発生すると、このピンはロジック "Low" レベルを出力します。                                                      |

| 11 | COMP     | O   | 内部のエラー アンプの出力。このピンと AGND ピンとの間にループ補償回路を接続します。                                                                                                                                                                       |

| 12 | AGND     | -   | デバイスの信号グランド。                                                                                                                                                                                                        |

| 13 | VCC      | O   | 内部レギュレータの出力。このピンと AGND ピンとの間には、4.7μF を超えるセラミック コンデンサが必要です。                                                                                                                                                          |

| 14 | BOOT2    | O   | 昇圧側のハイサイド MOSFET ゲートドライバ用電源。このピンと SW2 ピンの間に 0.1uF のセラミック コンデンサを接続します。                                                                                                                                               |

表 4-1. ピンの機能 (続き)

| ピン |       | I/O | 説明                                                                    |

|----|-------|-----|-----------------------------------------------------------------------|

| 番号 | 名称    |     |                                                                       |

| 15 | BOOT1 | O   | 降圧側のハイサイド MOSFET ゲートドライバ用電源。このピンと SW1 ピンの間に 0.1uF のセラミック コンデンサを接続します。 |

## 5 仕様

### 5.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                         |                                         | 最小値     | 最大値     | 単位 |

|-------------------------|-----------------------------------------|---------|---------|----|

| ピンでの電圧範囲 <sup>(2)</sup> | VIN、SW1                                 | -0.3    | 27      | V  |

|                         | VOUT、SW2                                | -0.3    | 17      | V  |

|                         | BOOT1                                   | SW1-0.3 | SW1+6   | V  |

|                         | BOOT2                                   | SW2-0.3 | SW2+6   | V  |

|                         | EN/UVLO、VCC、SCL、SDA、COMP、FB/INT、MODE    | -0.3    | 6       | V  |

|                         | EN/UVLO、SCL、SDA、COMP、FB/INT、MODE        | -0.3    | VCC+0.3 | V  |

| T <sub>J</sub>          | 動作時の接合部温度、T <sub>J</sub> <sup>(3)</sup> | -40     | 150     | °C |

| T <sub>stg</sub>        | 保存温度                                    | -65     | 150     | °C |

(1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) すべての電圧値は、回路のグランドを基準としたものです。

(3) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°C を超えると、動作寿命が短くなります。

### 5.2 推奨動作条件

接合部動作温度範囲内 (特に記述のない限り)

|                  |                      | 最小値 | 公称値 | 最大値  | 単位 |

|------------------|----------------------|-----|-----|------|----|

| V <sub>IN</sub>  | 入力電圧範囲 (Vout ≥ 3.0V) | 2.4 |     | 22   | V  |

|                  | 入力電圧範囲 (Vout < 3.0V) | 3   |     | 22   | V  |

| V <sub>OUT</sub> | 出力電圧範囲               | 0.8 |     | 15   | V  |

| L                | 実効インダクタンス範囲          | 1   | 4.7 | 10   | μH |

| C <sub>IN</sub>  | 実効入力容量範囲             | 4.7 | 22  |      | μF |

| C <sub>OUT</sub> | 実効出力容量範囲             | 10  | 100 | 1000 | μF |

| T <sub>J</sub>   | 動作時接合部温度             | -40 |     | 125  | °C |

### 5.3 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | VAL (WQFN) | VAL (WQFN)          | 単位   |

|-----------------------|---------------------|------------|---------------------|------|

|                       |                     | 15 ピン      | 15 ピン               |      |

|                       |                     | 標準         | 評価基板 <sup>(2)</sup> |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 47.6       | 33                  | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 22.5       | 該当なし                | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 7.8        | 該当なし                | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.6        | 0.7                 | °C/W |

| Y <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 6.7        | 11.1                | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 該当なし       | 該当なし                | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

(2) TPS55285EVM、4 層、2oz / 1oz / 1oz / 2oz の銅箔 PCB で測定。

## 5.4 電気的特性

$T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $V_{OUT} = 15\text{V}$ 。標準値は  $T_J = 25^{\circ}\text{C}$  時に測定 (特に記述のない限り)

| パラメータ                    |                                             | テスト条件                                                                                                                                                       | 最小値   | 標準値  | 最大値   | 単位            |

|--------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------------|

| <b>電源</b>                |                                             |                                                                                                                                                             |       |      |       |               |

| $V_{IN}$                 | 入力電圧範囲                                      |                                                                                                                                                             | 2.4   | 22   | 22    | V             |

| $V_{VIN\_UVLO}$          | 低電圧誤動作防止のスレッショルド                            | $V_{IN}$ 立ち上がり                                                                                                                                              | 2.8   | 2.9  | 3.0   | V             |

|                          |                                             | $V_{IN}$ 立ち下がり、 $V_{OUT} < 3\text{V}$                                                                                                                       | 2.6   | 2.7  | 2.8   | V             |

|                          |                                             | $V_{IN}$ 立ち下がり、 $V_{OUT} \geq 3\text{V}$                                                                                                                    | 2.31  | 2.33 | 2.38  | V             |

| $V_{VIN\_OVP}$           | 入力過電圧保護スレッショルド                              | 立ち上がりスレッショルド                                                                                                                                                | 22    | 22.5 | 23    | V             |

| $V_{VIN\_OVP\_HYS}$      | 入力過電圧保護ヒステリシス                               |                                                                                                                                                             |       | 0.9  |       | V             |

| $I_Q$                    | $V_{IN}$ ピンへの静止電流                           | IC イネーブル、無負荷、スイッチングなし。 $V_{IN} = 3.0\text{V} \sim 22\text{V}$ 、 $V_{OUT} = 0.8\text{V}$ 、 $V_{FB} = V_{REF} + 0.1\text{V}$ 、 $T_J$ 最大 $125^{\circ}\text{C}$ |       | 750  |       | $\mu\text{A}$ |

|                          | $V_{OUT}$ ピンへの静止電流                          | IC イネーブル、無負荷、スイッチングなし。 $V_{IN} = 3.0\text{V}$ 、 $V_{OUT} = 3\text{V} \sim 15\text{V}$ 、 $V_{FB} = V_{REF} + 0.1\text{V}$ 、 $T_J$ 最大 $125^{\circ}\text{C}$   |       | 700  |       | $\mu\text{A}$ |

| $I_{SD}$                 | $V_{IN}$ ピンへのシャットダウン電流                      | IC ディセーブル、 $V_{IN} = 3.0\text{V} \sim 22\text{V}$ 、 $T_J$ 最大 $125^{\circ}\text{C}$                                                                          |       | 1.3  | 3.8   | $\mu\text{A}$ |

| $V_{CC}$                 | 内部電圧レギュレータ出力                                | $V_{IN} = 8\text{V}$ 、 $V_{OUT} = 15\text{V}$ 、 $I_{VCC} = 20\text{mA}$                                                                                     | 5.0   | 5.2  | 5.4   | V             |

| <b>EN/UVLO</b>           |                                             |                                                                                                                                                             |       |      |       |               |

| $V_{EN\_H}$              | EN ロジック High のスレッショルド                       | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                                                                                                     |       | 1.03 |       | V             |

| $V_{EN\_L}$              | EN ロジック Low のスレッショルド                        | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                                                                                                     | 0.4   |      |       | V             |

| $V_{EN\_HYS}$            | スレッショルド ヒステリシスをイネーブル                        | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                                                                                                     | 0.025 |      |       | V             |

| $V_{UVLO}$               | EN/UVLO ピンでの UVLO 立ち上がりスレッショルド              | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                                                                                                     | 1     | 1.05 | 1.1   | V             |

| $V_{UVLO\_HYS}$          | UVLO スレッショルド ヒステリシス                         | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                                                                                                     |       | 13   |       | mV            |

| $I_{UVLO}$               | EN/UVLO ピンでのソース電流                           | $V_{EN/UVLO} = 1.3\text{V}$                                                                                                                                 | 4.5   | 5    | 5.5   | $\mu\text{A}$ |

| <b>出力</b>                |                                             |                                                                                                                                                             |       |      |       |               |

| $V_{OUT}$                | 出力電圧範囲                                      |                                                                                                                                                             | 0.8   | 15   | 15    | V             |

| $V_{VOUT\_OVP\_FB}$      | FB 立ち上がりから検出                                |                                                                                                                                                             | 110.5 | 115  | 120   | %             |

| $V_{VOUT\_OVP\_FB\_HYS}$ | ヒステリシス                                      |                                                                                                                                                             |       | 2.3  |       | %             |

| $I_{FB\_LKG}$            | FB ピンでのリーク電流                                | $T_J$ 最大 $125^{\circ}\text{C}$                                                                                                                              |       | 100  |       | nA            |

| $I_{VOUT\_LKG}$          | $V_{OUT}$ ピンへのリーク電流                         | IC ディセーブル、 $V_{OUT} = 15\text{V}$ 、 $V_{SW2} = 0\text{V}$ 、 $T_J$ 最大 $125^{\circ}\text{C}$                                                                  | 0.13  | 20   |       | $\mu\text{A}$ |

| $I_{DISCHG}$             | 出力放電電流、OE シャットダウン                           | $V_{OUT} = 15\text{V}$ 、 $V_{CC} = 5.2\text{V}$                                                                                                             | 40    | 100  | 170   | mA            |

|                          | 出力放電電流、EN および $V_{IN}$ シャットダウン              | $V_{OUT} = 15\text{V}$ 、 $V_{CC} = 5.2\text{V}$                                                                                                             | 30    | 60   | 105   | mA            |

| <b>内部リファレンス DAC</b>      |                                             |                                                                                                                                                             |       |      |       |               |

|                          | リファレンス電圧 DAC の分解能                           |                                                                                                                                                             |       | 11   |       | ビット           |

| $V_{OUT\_FULL}$          | $V_{REF}$ が $1.129\text{V}$ に設定されているときの出力電圧 | $V_{OUT\_FS}=02\text{h}$ 、 $REF=0780\text{h}$ 、 $V_{REF}=1.129\text{V}$                                                                                     | 14.78 | 15   | 15.22 | V             |

| $V_{OUT\_FULL}$          | $V_{REF}$ が $1.129\text{V}$ に設定されているときの出力電圧 | $V_{OUT\_FS}=01\text{h}$ 、 $REF=0780\text{h}$ 、 $V_{REF}=1.129\text{V}$                                                                                     | 9.85  | 10   | 10.15 | V             |

| $V_{OUT\_FULL}$          | $V_{REF}$ が $1.129\text{V}$ に設定されているときの出力電圧 | $V_{OUT\_FS}=00\text{h}$ 、 $REF=0780\text{h}$ 、 $V_{REF}=1.129\text{V}$                                                                                     | 4.93  | 5    | 5.07  | V             |

## 5.4 電気的特性 (続き)

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $V_{OUT} = 15\text{V}$ 。標準値は  $T_J = 25^\circ\text{C}$  時に測定 (特に記述のない限り)

| パラメータ                |                                           | テスト条件                                                                                                                                                               | 最小値   | 標準値   | 最大値   | 単位               |

|----------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------------|

| $V_{OUT\_ZERO}$      | $V_{REF}$ が $45\text{mV}$ に設定されているときの出力電圧 | $V_{OUT\_FS}=03\text{h}$ , $REF=0000\text{h}$ , $V_{REF}=45\text{mV}$                                                                                               | 0.74  | 0.8   | 0.86  | V                |

|                      |                                           | $V_{OUT\_FS}=02\text{h}$ , $REF=0000\text{h}$ , $V_{REF}=45\text{mV}$                                                                                               | 0.55  | 0.6   | 0.65  | V                |

|                      |                                           | $V_{OUT\_FS}=01\text{h}$ , $REF=0000\text{h}$ , $V_{REF}=45\text{mV}$                                                                                               | 0.36  | 0.4   | 0.44  | V                |

|                      |                                           | $V_{OUT\_FS}=00\text{h}$ , $REF=0000\text{h}$ , $V_{REF}=45\text{mV}$                                                                                               | 0.18  | 0.2   | 0.22  | V                |

| 基準電圧                 |                                           |                                                                                                                                                                     |       |       |       |                  |

| $V_{REF}$            | 外部帰還使用時の FB/INT ピンでのリファレンス電圧              | REF=0780H の外部帰還                                                                                                                                                     | 1.117 | 1.129 | 1.141 | V                |

|                      |                                           | REF=058CH の外部帰還                                                                                                                                                     | 0.837 | 0.846 | 0.855 | V                |

|                      |                                           | REF=0334H の外部帰還                                                                                                                                                     | 0.501 | 0.508 | 0.514 | V                |

|                      |                                           | REF=01A4H の外部帰還                                                                                                                                                     | 0.276 | 0.282 | 0.288 | V                |

| パワースイッチ              |                                           |                                                                                                                                                                     |       |       |       |                  |

| $R_{DS(on)}$         | 降圧側のローサイド MOSFET オン抵抗                     | $V_{OUT} = 15\text{V}$ , $V_{CC} = 5.2\text{V}$                                                                                                                     | 15.5  |       |       | $\text{m}\Omega$ |

|                      | 降圧側のハイサイド MOSFET オン抵抗                     | $V_{OUT} = 15\text{V}$ , $V_{CC} = 5.2\text{V}$                                                                                                                     | 14.5  |       |       | $\text{m}\Omega$ |

|                      | 昇圧側のローサイド MOSFET オン抵抗                     | $V_{OUT} = 15\text{V}$ , $V_{CC} = 5.2\text{V}$                                                                                                                     | 15.5  |       |       | $\text{m}\Omega$ |

|                      | 昇圧側のハイサイド MOSFET オン抵抗                     | $V_{OUT} = 15\text{V}$ , $V_{CC} = 5.2\text{V}$                                                                                                                     | 14.5  |       |       | $\text{m}\Omega$ |

| 内部クロック               |                                           |                                                                                                                                                                     |       |       |       |                  |

| $f_{SW}$             | スイッチング周波数                                 | $FSW = 00\text{b}$                                                                                                                                                  | 360   | 400   | 440   | kHz              |

| $f_{SW}$             | スイッチング周波数                                 | $FSW = 11\text{b}$                                                                                                                                                  | 1900  | 2100  | 2300  | kHz              |

| $t_{OFF\_min}$       | 最小オフ時間                                    | 昇圧モード                                                                                                                                                               | 90    | 145   |       | ns               |

| $t_{ON\_min}$        | 最小オン時間                                    | 降圧モード                                                                                                                                                               | 90    | 130   |       | ns               |

| 電流制限                 |                                           |                                                                                                                                                                     |       |       |       |                  |

| $I_{LIM\_AVG}$       | 平均インダクタ電流制限                               | $V_{IN} = 8\text{V}$ , $V_{OUT} = 15\text{V}$ , $F_{SW} = 400\text{kHz}$ , FPWM                                                                                     | 7     | 8     |       | A                |

|                      |                                           | $V_{IN} = 8\text{V}$ , $V_{OUT} = 15\text{V}$ , $F_{SW} = 400\text{kHz}$ , PFM                                                                                      | 7     | 8     |       | A                |

| $I_{LIM\_PK}$        | 昇圧ハイサイドでのピークインダクタ電流制限                     | $V_{IN} = 8\text{V}$ , $V_{OUT} = 15\text{V}$ , $F_{SW} = 400\text{kHz}$ , FPWM                                                                                     | 13    |       |       | A                |

|                      |                                           | $V_{IN} = 8\text{V}$ , $V_{OUT} = 15\text{V}$ , $F_{SW} = 400\text{kHz}$ , PFM                                                                                      | 13    |       |       | A                |

| 出力電流制限               |                                           |                                                                                                                                                                     |       |       |       |                  |

| $I_{OUT\_LIMIT}$ (1) | 出力電流制限                                    | $I_{OUT\_LIMIT}$ レジスタ = 1001 0100b, $T_J = -20^\circ\text{C} \sim 85^\circ\text{C}$ , $F_{SW} = 400\text{kHz}$ , CCM, $V_{IN} = 19\text{V}$ , $V_{OUT} = 5\text{V}$ | 0.8   | 1     | 1.2   | A                |

| $I_{OUT\_LIMIT}$ (1) | 出力電流制限                                    | $I_{OUT\_LIMIT}$ レジスタ = 1011 1100b, $T_J = -20^\circ\text{C} \sim 85^\circ\text{C}$ , $F_{SW} = 400\text{kHz}$ , CCM, $V_{IN} = 19\text{V}$ , $V_{OUT} = 5\text{V}$ | 2.8   | 3     | 3.2   | A                |

|                      |                                           | $I_{OUT\_LIMIT}$ レジスタ = 1110 0100b, $T_J = -20^\circ\text{C} \sim 85^\circ\text{C}$ , $F_{SW} = 400\text{kHz}$ , CCM, $V_{IN} = 19\text{V}$ , $V_{OUT} = 5\text{V}$ | 4.7   | 5     | 5.3   | A                |

| ケーブル電圧降下補償           |                                           |                                                                                                                                                                     |       |       |       |                  |

## 5.4 電気的特性 (続き)

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $V_{OUT} = 15\text{V}$ 。標準値は  $T_J = 25^\circ\text{C}$  時に測定 (特に記述のない限り)

| パラメータ           |                                                | テスト条件                                                                           | 最小値   | 標準値   | 最大値   | 単位              |

|-----------------|------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-----------------|

| $V_{OUT\_CDC}$  | ケーブル電圧降下補償の $V_{OUT}$ 増加                       | CDC[2:0]=111、INTFB = 11b、 $I_{OUT} = 5\text{A}$                                 | 610   | 700   | 795   | mV              |

|                 |                                                | CDC[2:0]=111、INTFB = 11b、 $I_{OUT} = 1\text{A}$ 、FPWM                           | 40    | 140   | 230   | mV              |

|                 |                                                | CDC[2:0]=001、INTFB = 11b、 $I_{OUT} = 5\text{A}$                                 | 60    | 100   | 125   | mV              |

|                 |                                                | CDC[2:0]=001、INTFB = 11b、 $I_{OUT} = 1\text{A}$ 、FPWM                           |       | 15    | 48    | mV              |

| エラー アンプ         |                                                |                                                                                 |       |       |       |                 |

| $I_{SINK}$      | COMP ピン シンク電流                                  | $V_{FB} = V_{REF} + 400\text{mV}$ , $V_{COMP}=1.1\text{V}$ , $V_{CC}=5\text{V}$ |       | 20    |       | $\mu\text{A}$   |

| $I_{SOURCE}$    | COMP ピン ソース電流                                  | $V_{FB} = V_{REF} - 400\text{mV}$ , $V_{COMP}=1.1\text{V}$ , $V_{CC}=5\text{V}$ |       | 60    |       | $\mu\text{A}$   |

| $V_{CCLPH}$     | COMP ピンの High クランプ電圧                           |                                                                                 |       | 1.2   |       | V               |

| $V_{CCLPL}$     | COMP ピンの Low クランプ電圧                            |                                                                                 |       | 0.7   |       | V               |

| $G_{EA}$        | エラー アンプの相互コンダクタンス                              |                                                                                 |       | 190   |       | $\mu\text{A/V}$ |

| ソフトスタート         |                                                |                                                                                 |       |       |       |                 |

| $t_{SS}$        | ソフト スタート時間                                     |                                                                                 | 2.5   | 3.9   | 5.7   | ms              |

| スペクトラム拡散        |                                                |                                                                                 |       |       |       |                 |

| HICCUP          |                                                |                                                                                 |       |       |       |                 |

| $t_{HICCUP}$    | ヒカップ オフ時間                                      |                                                                                 |       | 76    |       | ms              |

| モード             |                                                |                                                                                 |       |       |       |                 |

| $I_{MODE}$      | MODE ピンからのソース電流                                |                                                                                 | 9     | 10    | 11    | $\mu\text{A}$   |

| $V_{MODE\_DT1}$ | MODE ピンでの検出スレッショルド電圧                           |                                                                                 | 0.571 | 0.614 | 0.657 | V               |

| $V_{MODE\_DT2}$ | MODE ピンでの検出スレッショルド電圧                           |                                                                                 | 0.322 | 0.351 | 0.380 | V               |

| $V_{MODE\_DT3}$ | MODE ピンでの検出スレッショルド電圧                           |                                                                                 | 0.169 | 0.189 | 0.209 | V               |

| ロジック インターフェイス   |                                                |                                                                                 |       |       |       |                 |

| $V_{I2C\_IO}$   | $I^2\text{C}$ の IO 電圧範囲                        |                                                                                 | 1.7   | 5.5   |       | V               |

| $V_{I2C\_H}$    | $I^2\text{C}$ 入力 High のスレッショルド                 | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                         |       | 1.2   |       | V               |

| $V_{I2C\_L}$    | $I^2\text{C}$ 入力 Low のスレッショルド                  | $V_{CC} = 3.0\text{V} \sim 5.5\text{V}$                                         | 0.4   |       |       | V               |

| $I_{FB/INT\_H}$ | 高インピーダンス出力時の $FB/\overline{INT}$ ピンへのリーコンデンサ電流 | $V_{FB/INT} = 5\text{V}$                                                        |       | 100   |       | nA              |

| $V_{FB/INT\_L}$ | $FB/\overline{INT}$ ピンの出力低電圧範囲                 | シンク 4mA 電流                                                                      | 0.03  | 0.1   |       | V               |

| PROTECTION      |                                                |                                                                                 |       |       |       |                 |

| $T_{SD}$        | サーマル シャットダウンのスレッショルド                           | $T_J$ 立ち上がり                                                                     |       | 175   |       | °C              |

| $T_{SD\_HYS}$   | サーマル シャットダウン ヒステリシス                            | $T_J$ が $T_{sd}$ を下回る                                                           |       | 20    |       | °C              |

(1) エンジニアリング サンプルの特性評価に基づいています

## 5.5 I<sup>2</sup>C のタイミング特性

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $V_{OUT} = 15\text{V}$ 。標準値は  $T_J = 25^\circ\text{C}$  時に測定 (特に記述のない限り)

| パラメータ                        |                                            | テスト条件        | 最小値 | 標準値  | 最大値 | 単位  |

|------------------------------|--------------------------------------------|--------------|-----|------|-----|-----|

| <b>I<sup>2</sup>C TIMING</b> |                                            |              |     |      |     |     |

| $f_{SCL}$                    | SCL クロック周波数                                |              | 100 | 1000 |     | kHz |

| $t_{BUF}$                    | STOP 条件と START 条件の間のバスフリーハード時間             | ファスト モード プラス | 0.5 |      |     | μs  |

| $t_{HD(STA)}$                | (繰り返し) START 条件のホールド時間                     |              | 260 |      |     | ns  |

| $t_{LOW}$                    | SCL クロックの Low 期間                           |              | 0.5 |      |     | μs  |

| $t_{HIGH}$                   | SCL クロックの High 期間                          |              | 260 |      |     | ns  |

| $t_{SU(STA)}$                | 反復開始条件のセットアップ時間                            |              | 260 |      |     | ns  |

| $t_{SU(DAT)}$                | データ セットアップ時間                               |              | 50  |      |     | ns  |

| $t_{HD(DAT)}$                | データ ホールド時間                                 |              | 0   |      |     | μs  |

| $t_{RCL}$                    | SCL 信号の立ち上がり時間                             |              |     | 120  |     | ns  |

| $t_{RCL1}$                   | START 条件の繰り返し、および ACK ビット後の SCL 信号の立ち上がり時間 |              |     | 120  |     | ns  |

| $t_{FCL}$                    | SCL 信号の立ち下がり時間                             |              |     | 120  |     | ns  |

| $t_{RDA}$                    | SDA 信号の立ち上がり時間                             |              |     | 120  |     | ns  |

| $t_{FDA}$                    | SDA 信号の立ち下がり時間                             |              |     | 120  |     | ns  |

| $t_{SU(STO)}$                | STOP 条件のセットアップ時間                           |              | 260 |      |     | ns  |

| $C_B$                        | SDA および SCL の容量性負荷                         |              |     | 200  |     | pF  |

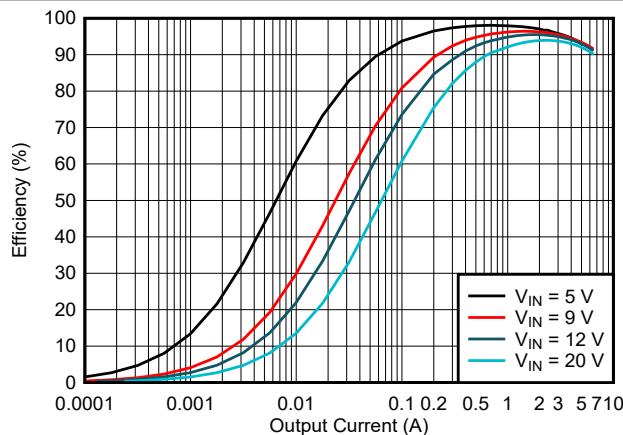

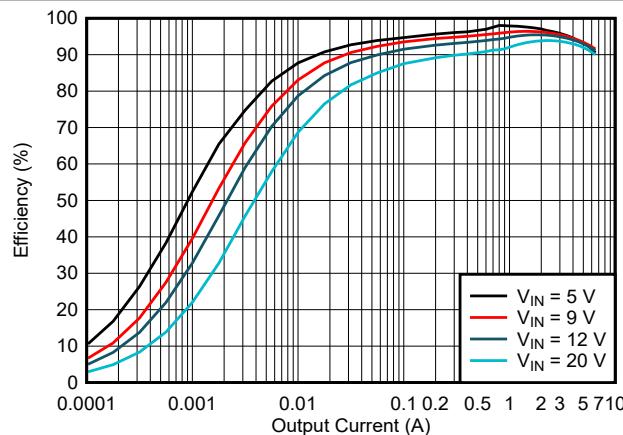

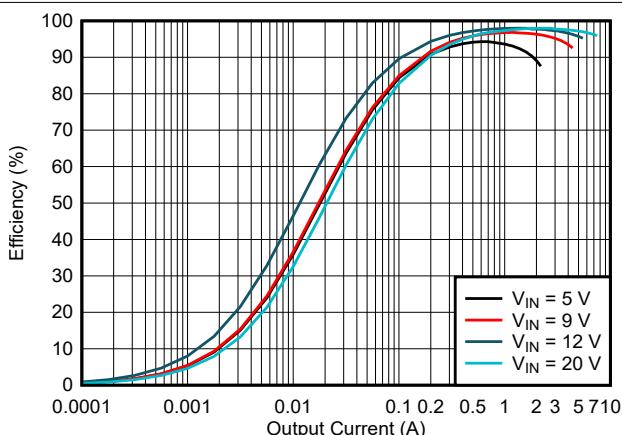

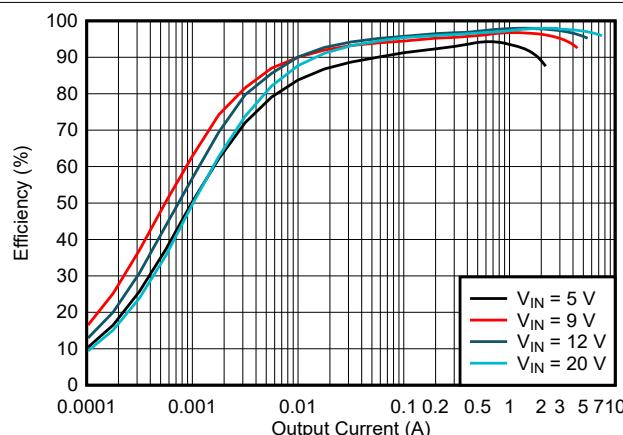

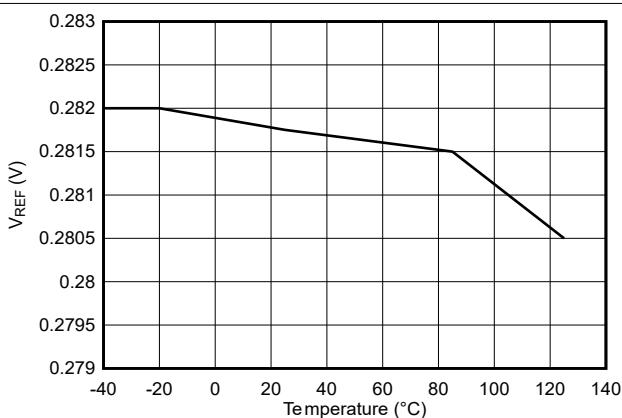

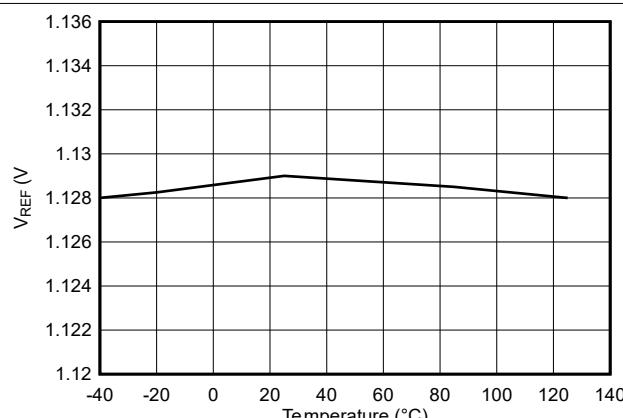

## 5.6 代表的特性

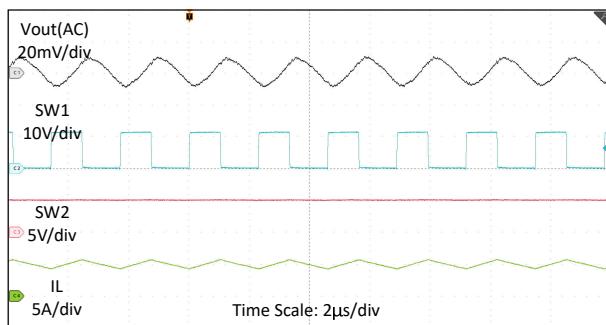

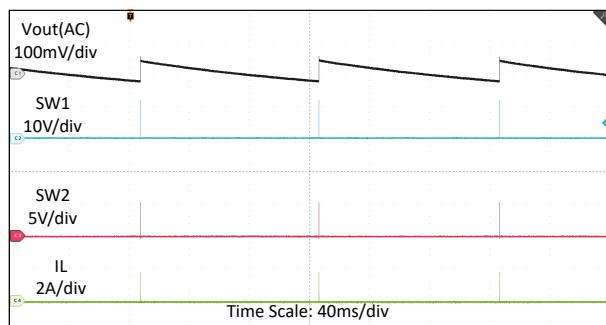

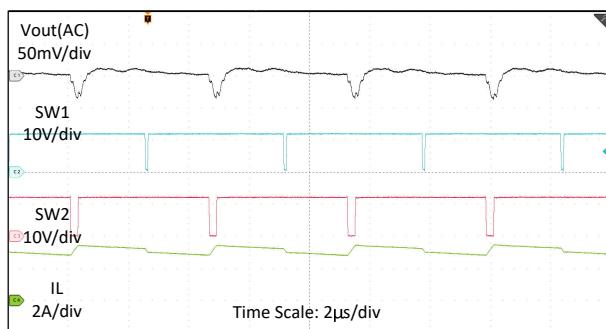

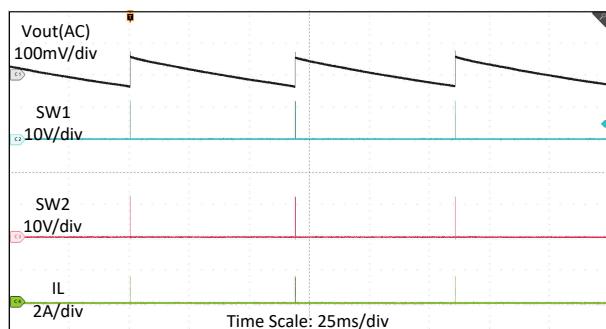

$V_{IN} = 12V$ ,  $T_A = 25^\circ C$ ,  $f_{SW} = 400\text{kHz}$  (特に記述のない限り)。

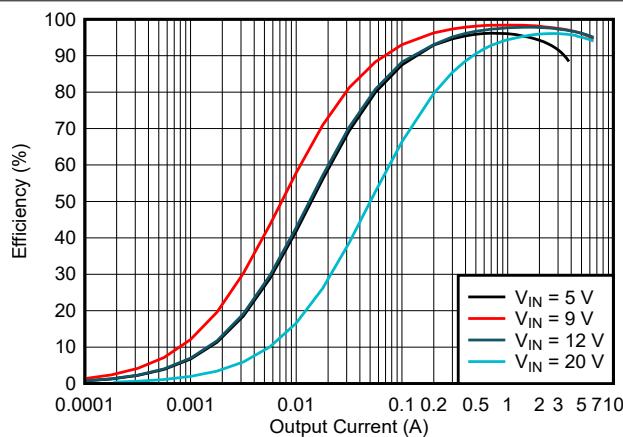

図 5-1. 効率と出力電流との関係、

$V_{OUT} = 5V$ 、FPWM

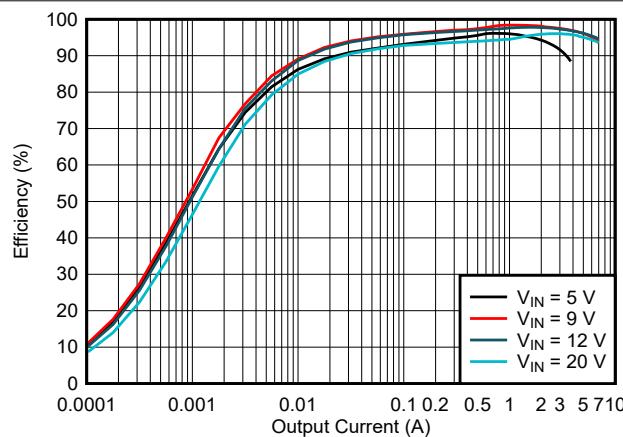

図 5-2. 効率と出力電流との関係、

$V_{OUT} = 5V$ 、PFM

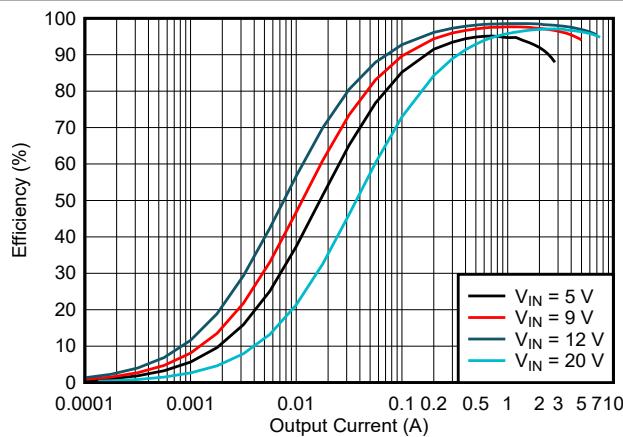

図 5-3. 効率と出力電流との関係、

$V_{OUT} = 9V$ 、FPWM

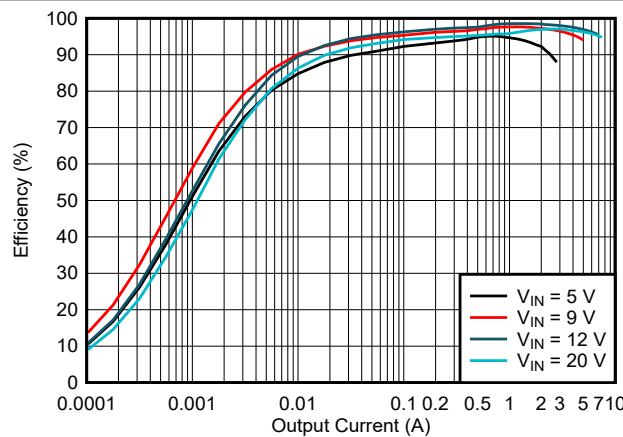

図 5-4. 効率と出力電流との関係、

$V_{OUT} = 9V$ 、PFM

図 5-5. 効率と出力電流との関係、

$V_{OUT} = 12V$ 、FPWM

図 5-6. 効率と出力電流との関係、

$V_{OUT} = 12V$ 、PFM

## 5.6 代表的特性 (続き)

図 5-7. 効率と出力電流との関係、

$V_{OUT} = 15V$ 、FPWM

図 5-8. 効率と出力電流との関係、

$V_{OUT} = 15V$ 、PFM

図 5-9. リファレンス電圧と温度との関係 ( $V_{REF} = 0.282V$ )

図 5-10. リファレンス電圧と温度との関係 ( $V_{REF} = 1.129V$ )

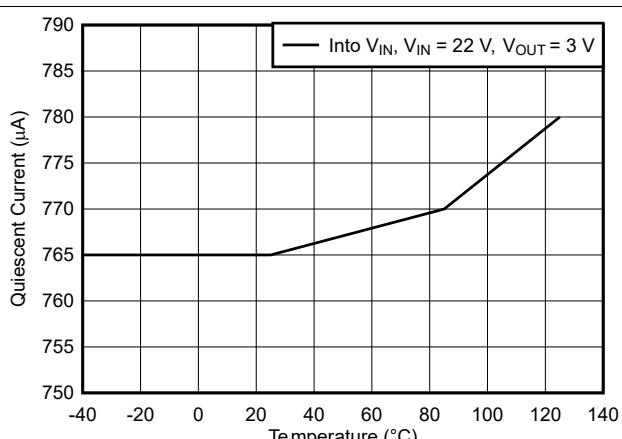

図 5-11. 静止電流と温度との関係

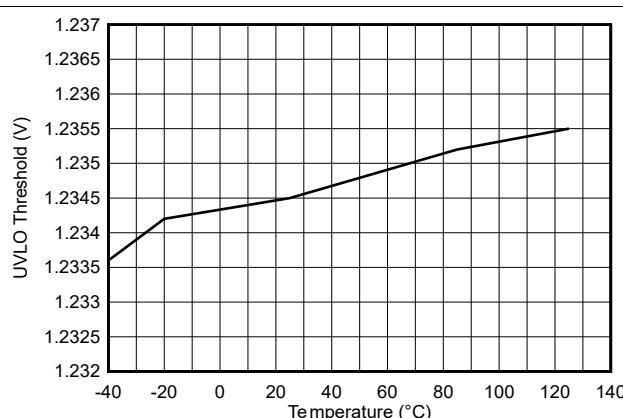

図 5-12. ENABLE/UVLO 立ち上がりリスレッショルドと温度の関係

## 6 詳細説明

### 6.1 概要

TPS55285 は、4 個の MOSFET を内蔵した 8A 昇降圧 DC/DC コンバータです。TPS55285 は、入力電圧 2.4V ~ 22V、出力電圧 0.8V ~ 15V という幅広い範囲で動作します。TPS55285 は、入力電圧と設定出力電圧に応じて、降圧モード、昇降圧モード、昇圧モード間をスムーズに遷移できます。TPS55285 は、入力電圧が出力電圧より大きい場合は降圧モードで動作し、入力電圧が出力電圧より小さい場合は昇圧モードで動作します。入力電圧が出力電圧に近いとき、TPS55285 は 1 サイクル降圧モードおよび 1 サイクル昇圧モードで交互に動作します。

TPS55285 は平均電流モード制御方式を採用しています。電流モード制御により、ループ補償が簡素化され、負荷過渡への迅速な応答と固有のライン電圧除去が可能になります。エラー アンプは、出力電圧の帰還電圧を内部リファレンス電圧と比較します。エラー アンプの出力によって、平均インダクタ電流が決まります。

TPS55285 は、中負荷から重負荷の電流では固定周波数 PWM モードで動作します。軽負荷時には、TPS55285 は内部レジスタの対応するビットを設定することで、自動的に PFM モードに遷移する、または強制的に PWM モードに移行するように構成できます。

TPS55285 は、I<sup>2</sup>C インターフェイスで内部レジスタを設定することで、出力電圧を調整できます。内部 11 ビット DAC は、DAC レジスタに書き込む値に関連するリファレンス電圧を調整します。デバイスは、外部の電流センス抵抗なしで出力電流を制限することもできます。出力電流制限は内部レジスタで設定されます。

TPS55285 には、標準 8A の平均インダクタ電流制限があります。また、インダクタのピーク電流がピーク電流制限を上回った場合は、サイクル単位のピークインダクタ電流制限も提供します。

EN/UVLO ピンでの 5µA ソース電流による 1.05V の高精度電圧レッショルドにより、ヒステリシス付きのプログラマブル入力低電圧誤動作防止 (UVLO) がサポートされます。入力電圧が 22.5V を超えると、入力過電圧保護 (OVP) 機能によってデバイスがオフになり、損傷を防止します。

出力過電圧保護 (OVP) 機能は、ハイサイド FET をオフにして、TPS55285 によって電力が供給されるデバイスの損傷を防止します。

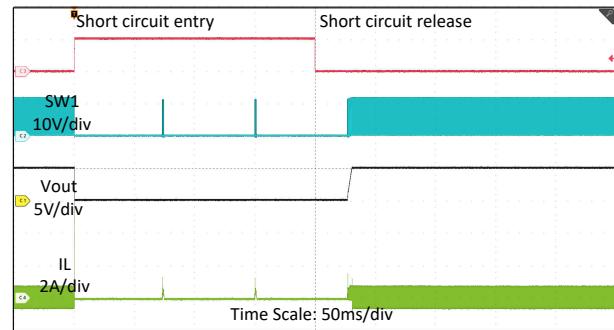

TPS55285 には、出力短絡が発生したときに電源部品の発熱を低減するためのヒップ モード オプションがあります。ヒップ モードを有効にすると、TPS55285 は 76ms の間オフになり、ソフトスタートアップを再開します。

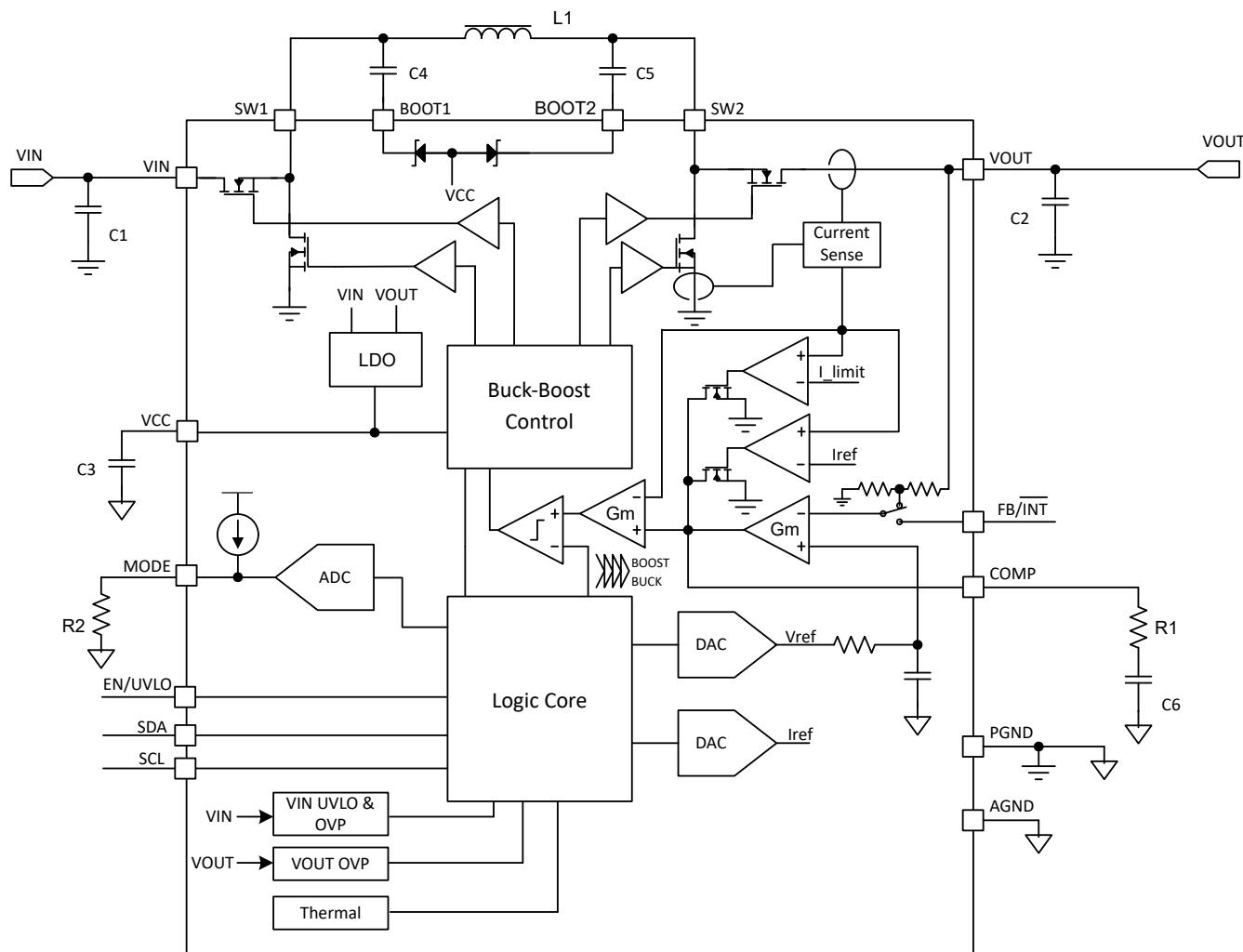

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 VCC の電源

TPS55285 には、VCC ピンで 5.2V に調整された電圧を出力する内部 LDO があります。 $V_{IN}$  が  $V_{OUT}$  より小さい場合、内部 LDO によって  $V_{IN}$  を 6.2V (ヒステリシス 0.3V) の立ち上がりスレッショルドと比較して電源が選択されます。 $V_{IN}$  が 6.2V より高い場合、LDO の電源は  $V_{IN}$  です。 $V_{IN}$  が 5.9V より低い場合、LDO の電源は  $V_{OUT}$  です。 $V_{OUT}$  が  $V_{IN}$  より小さい場合、内部 LDO によって  $V_{OUT}$  を 6.2V (ヒステリシス 0.3V) の立ち上がりスレッショルドと比較して電源が選択されます。 $V_{OUT}$  が 6.2V より高い場合、LDO の電源は  $V_{OUT}$  です。 $V_{OUT}$  が 5.9V より低い場合、LDO の電源は  $V_{IN}$  です。表 6-1 には、内部 LDO の電源の選択が示されています。

表 6-1.  $V_{CC}$  電源ロジック

| $V_{IN}$           | $V_{OUT}$          | $V_{CC}$ LDO の入力 |

|--------------------|--------------------|------------------|

| $V_{IN} > 6.2V$    | $V_{OUT} > V_{IN}$ | $V_{IN}$         |

| $V_{IN} < 5.9V$    | $V_{OUT} > V_{IN}$ | $V_{OUT}$        |

| $V_{IN} > V_{OUT}$ | $V_{OUT} > 6.2V$   | $V_{OUT}$        |

| $V_{IN} > V_{OUT}$ | $V_{OUT} < 5.9V$   | $V_{IN}$         |

### 6.3.2 デフォルトの出力イネーブル (OE) ビットステータス

MODE ピンと AGND ピンの間に異なる抵抗を配置することで、TPS55285 はデフォルトの出力イネーブル (OE) ビット値を選択します。出力イネーブル (OE) ビットは、06H レジスタでデバイス出力を制御するロジック ビットです。

デフォルトの出力イネーブル (OE) ビットが 0 に設定されている場合、 $V_{IN}$  および EN/UVLO ピンが UVLO スレッショルドを超えると、06H レジスタで出力イネーブル (OE) ビットが 1 に設定されるまで、デバイスはスイッチングしません。

デフォルトの出力イネーブル (OE) ビットが 1 に設定されている場合、04H レジスタの FB ビットも自動的に 1 に設定され、外部帰還回路が選択されます。 $V_{IN}$  および EN/UVLO ピンが UVLO スレッショルドを超えると、デバイスは 282mV  $V_{REF}$  でスイッチングを開始します。この場合、外部帰還抵抗が必要です。

表 6-2. I<sup>2</sup>C ターゲットアドレスとデフォルトの OE ビット

| 抵抗値 (kΩ)     | I <sup>2</sup> C ターゲットアドレス | デフォルトの出力イネーブル (OE) ビット |

|--------------|----------------------------|------------------------|

| 0            | 75H                        | 0                      |

| 24.9         | 75H                        | 1                      |

| 48.7         | 74H                        | 0                      |

| 82.5 またはオープン | 74H                        | 1                      |

### 6.3.3 入力低電圧誤動作防止

入力電圧が 2.4V を下回る場合、TPS55285 は無効化されます。入力電圧が 3V を上回る場合、EN ピンを 1.1V を超える高電圧にすることで、TPS55285 を有効にします。

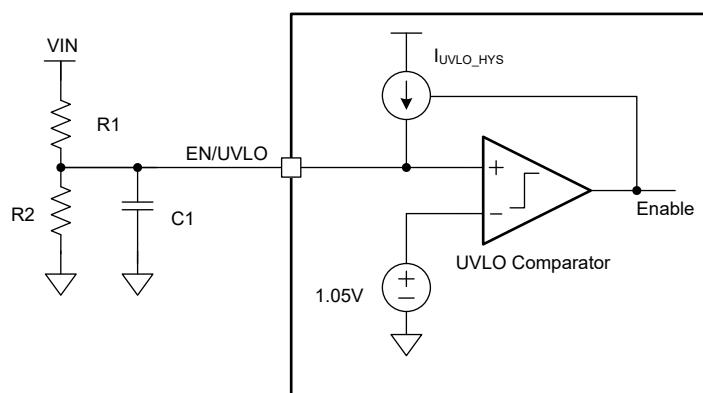

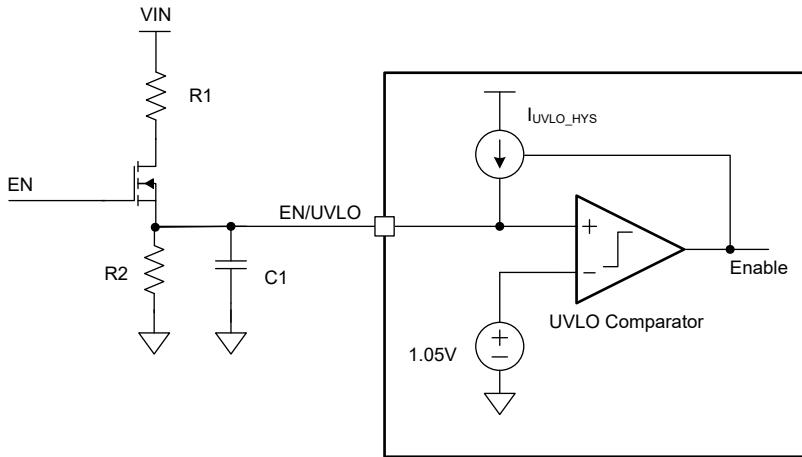

### 6.3.4 イネーブルおよびプログラム可能な UVLO

TPS55285 には、デュアル機能イネーブルおよび低電圧誤動作防止 (UVLO) 回路が搭載されています。VIN ピンの入力電圧が入力 UVLO 立ち上がりスレッショルドの 3V を超え、EN/UVLO ピンが EN ロジック high のスレッショルド  $V_{EH\_H}$  を超えたものの、イネーブル UVLO スレッショルドの  $V_{UVLO}$  を下回る場合、TPS55285 はイネーブルになりますが、スタンバイ モードのままでです。TPS55285 は、MODE ピンとグランドの間の抵抗の検出を開始します。その後、TPS55285 は、 $I^2C$  ターゲット アドレスとデフォルト OE ビットステータスを選択します。

EN/UVLO ピンには正確な UVLO 電圧スレッショルドがあり、ヒステリシス付きのプログラム可能な入力低電圧誤動作防止をサポートします。EN/UVLO ピンの電圧が UVLO スレッショルドの 1.05V より高い場合、TPS55285 は  $I^2C$  通信およびスイッチング動作がイネーブルになります。ヒステリシス電流  $I_{UVLO\_HYS}$  は EN/UVLO ピンから供給され、入力電圧が緩やかに変化するノイズによるオン/オフ チャタリングを防止するヒステリシスを提供します。

図 6-1 に示すように分圧抵抗を使用すると、ターンオン スレッショルドが 式 1 を使用して計算されます。

$$V_{IN(UVLO\_ON)} = V_{UVLO} \times \left(1 + \frac{R1}{R2}\right) \quad (1)$$

ここで、

- $V_{UVLO}$  は、EN/UVLO ピンの UVLO スレッショルド 1.05V です

UVLO オン スレッショルドとオフ スレッショルドの間のヒステリシスは、EN/UVLO 分圧抵抗回路の上側抵抗によって設定され、式 2 で求められます。

$$\Delta V_{IN(UVLO)} = I_{UVLO\_HYS} \times R1 \quad (2)$$

ここで、

- $I_{UVLO\_HYS}$  は、EN/UVLO ピンの電圧が  $V_{UVLO}$  より高い場合に EN/UVLO ピンから供給される電流です

分圧抵抗を使用して VIN UVLO スレッショルドをプログラムする場合、EN/UVLO ピンの電圧は 5.5V 未満である必要があります。

図 6-1. EN/UVLO ピンでの分圧抵抗によるプログラム可能な UVLO

NMOSFET を分圧抵抗とともに使用すると、図 6-2 に示すように、ロジック イネーブルとプログラム可能な UVLO の両方を実装します。EN のロジック high レベルは、NMOSFET Q1 のイネーブル スレッショルドと  $V_{th}$  の合計値よりも大きい必要があります。また、Q1 は、シャットダウン モード時に UVLO 分圧抵抗を介して VIN からグランドへのリーク電流を防止します。

図 6-2. ロジック イネーブルおよびプログラム可能な UVLO

### 6.3.5 ソフトスタート

入力電圧が UVLO スレッショルドを上回り、EN/UVLO ピンの電圧が有効 UVLO スレッショルドを上回っている場合、TPS55285 は I<sup>2</sup>C コントローラ デバイスからコマンドを受け入れる準備ができています。TPS55285 の内部レジスタを構成するには、I<sup>2</sup>C コントローラ デバイスが必要です。

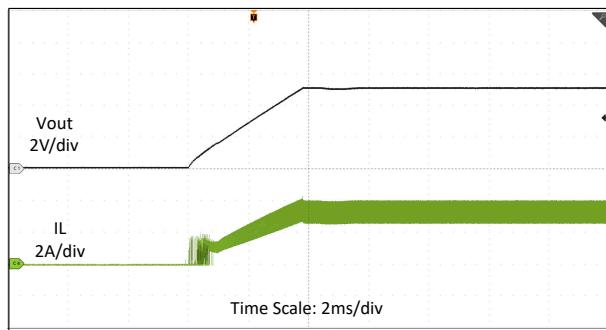

I<sup>2</sup>C コントローラ デバイスが OE ビットを 1 に設定するか、デバイスがデフォルト OE ビットが 1 であることを検出すると、TPS55285 は内部リファレンス電圧を 0V から内部レジスタ 00h および 01h で設定された電圧まで標準 3.9ms 以内に上昇させて、出力電圧の上昇を開始します。

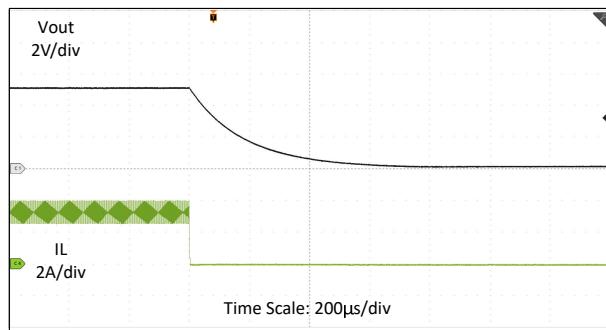

### 6.3.6 シャットダウンおよび負荷放電

EN/UVLO ピンの電圧が 0.4V を下回ると、TPS55285 はシャットダウン モードとなり、すべての機能が無効化されます。すべての内部レジスタはデフォルト値にリセットされます。EN/UVLO ピンが High ロジック レベルで、OE ビットが 0 にクリアされると、TPS55285 はスイッチング動作をオフにします。ただし、I<sup>2</sup>C インターフェイスはアクティブのままでです。

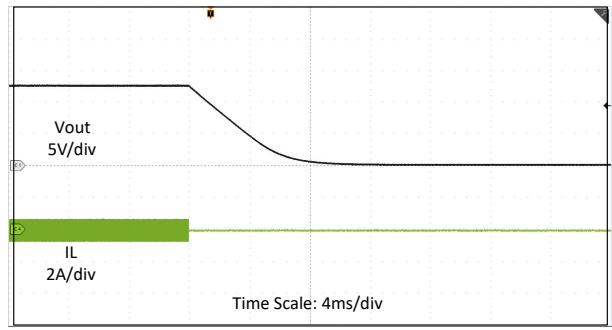

レジスタ 06h の DISCHG ビットが 1 に設定されている場合、OE ビットが 0 にクリアされると、TPS55285 は内部定電流  $I_{DISCHG}$  によって出力電圧を 0.8V 未満まで放電します。入力電圧 UVLO がトリガされるか、または EN/UVLO ピンが Low ロジック レベルまでプルされると、TPS55285 の出力電圧は、VCC が  $V_{CC\_UVLO}$  を下回るまで放電されます。

### 6.3.7 スイッチング周波数

TPS55285 は、固定周波数の平均電流制御方式を使用しています。スイッチング周波数はレジスタ 06H の FSW ビットで設定され、その選択肢には以下の 4 つがあります: 400kHz、800kHz、1.6MHz、2.1MHz。

大電力アプリケーションでのスイッチング電力損失を低減するために、スイッチ周波数を 400kHz または 800kHz に設定することを推奨します。システムが、ソリューション サイズを小型化するために、1.6MHz または 2.1MHz の高いスイッチング周波数を必要とする場合、放熱性能を向上させるために、スイッチ電流を低くして動作させることを推奨します。

最初にスイッチング周波数を設定した後で、OE ビットを有効にしてください。

### 6.3.8 スイッチング周波数のディザリング

TPS55285 には、EMI 干渉を最小限に抑えるために、FPWM モードの 06H レジスタで SPREADSPECTRUM ビットにより有効化されるオプションのスイッチング周波数ディザリング機能があります。このデバイスは三角波ジッタを使用して、スイッチング周波数を FSW ビットで設定された通常周波数の ±7% で拡散します。通常のスイッチング周波数が 400kHz の場合、三角波ジッタの周波数は 1.5kHz です。通常のスイッチング周波数が 2.1MHz の場合、三角波ジッタの周波数は 9kHz です。

### 6.3.9 インダクタ電流制限

TPS55285 は、ピーク電流と平均インダクタ電流制限の両方を実装しています。平均電流モード制御ループは、昇圧レギュラのハイサイド MOSFET の電流センス情報を使用して、最大平均インダクタ電流を 8A (標準) にクランプします。

平均電流制限に加えて、過渡時にはピーク電流制限保護が実装され、デバイスの能力を超える過電流状態からデバイスを保護します。

### 6.3.10 内部充電バス

2 つのハイサイド MOSFET ドライバは、それぞれフローティング ブートストラップ コンデンサからバイアスされます。このコンデンサは、ローサイド MOSFET がオンになると、通常、外部と内部の両方のブートストラップ ダイオードを経由して V<sub>CC</sub> により再充電されます。TPS55285 が降圧または昇圧領域でのみ動作する場合、ハイサイド MOSFET の 1 つは常時オンになります。V<sub>OUT</sub> と BOOT2 から BOOT1 へ、または V<sub>IN</sub> と BOOT1 から BOOT2 への内部充電バスによって、ブートストラップ コンデンサは V<sub>CC</sub> まで充電され、ハイサイド MOSFET はオンのままになります。

### 6.3.11 出力電圧設定

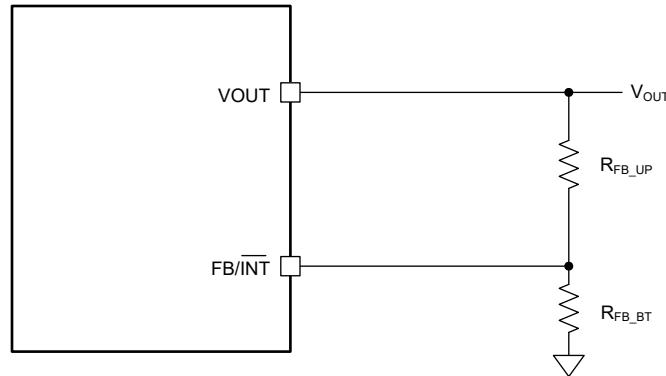

出力電圧の設定には 2 つの方法があります。帰還比を変更する方法と、リファレンス電圧を変更する方法です。TPS55285 には 11 ビット DAC が搭載されており、リファレンス電圧を 45mV ~ 1.2V の範囲でプログラムできます。また、TPS55285 では、レジスタ 04h の FB ビットを設定することで、内部帰還分圧抵抗、または外付け分圧抵抗を選択します。FB ビットが 0 に設定されている場合、出力電圧の帰還比は内部レジスタ 04h に設定されます。FB ビットが 1 に設定されている場合、出力電圧の帰還比は外付け分圧抵抗によって設定されます。

内部出力電圧帰還設定を使用する場合、レジスタ 04H の INTFB[1:0] ビットを書き込むことで、4 つの帰還比をプログラムできます。この機能により、TPS55285 は最大出力電圧を異なる値に制限します。さらに、出力電圧変化の最小ステップも、それに応じて 10mV、7.5mV、5mV、2.5mV にプログラムされます。

図 6-3 に示すように外部出力電圧帰還分圧抵抗を使用する場合、式 3 を使用して、FB/INT ピンのリファレンス電圧で出力電圧を計算します。

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{FB\_UP}}{R_{FB\_BT}}\right) \quad (3)$$

図 6-3. 外付け分圧抵抗による可変電圧設定

TI では、アップ抵抗  $R_{FB\_UP}$  には  $100\text{k}\Omega$  を使用することを推奨します。FB/INT ピンのリファレンス電圧  $V_{REF}$  は、レジスタ  $00H$  および  $01H$  に 11 ビット データを書き込むことで、 $45\text{mV} \sim 1.2\text{V}$  の範囲でプログラム可能です。

### 6.3.12 出力電流制限

TPS55285 は、外部電流検出抵抗なしで、降圧、昇降圧、昇圧モードでの出力電流制限機能をサポートしています。出力電流制限は、 $02H$  レジスタの **Current\_Limit\_Setting** ビットにより、 $500\text{mA}$  から  $6.35\text{A}$  までプログラム可能です。プログラム可能な出力電流制限ステップは  $50\text{mA}$  です。

出力電流制限は、**Current\_Limit** レジスタの **Current\_Limit\_EN** ビットを 0 にリセットすることで無効化します。

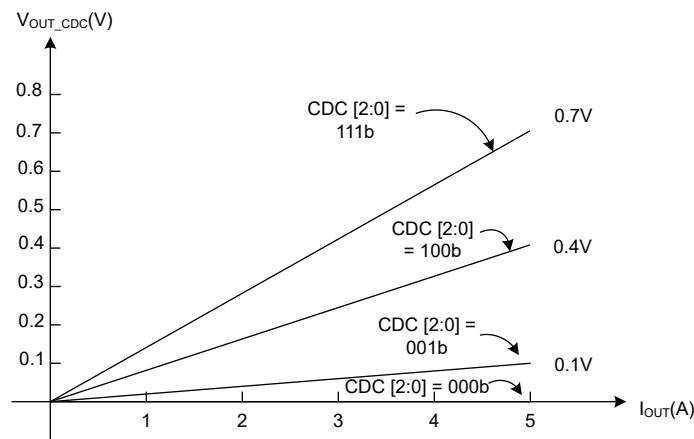

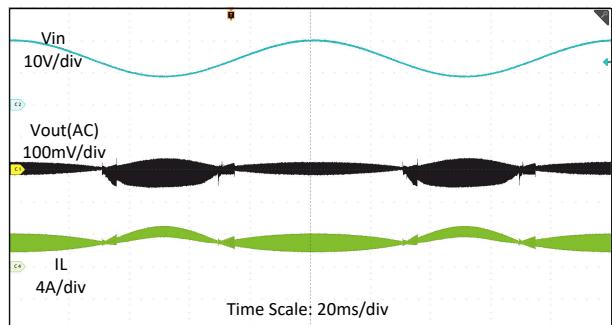

### 6.3.13 出力ケーブル電圧降下の補償

TPS55285 は、USB ポートの出力から受電デバイスまでのケーブルでの電圧降下を補償するため、出力ケーブル電圧降下補償機能を有効化することで、負荷電流に比例して出力電圧を上昇させます。

デフォルトでは、ケーブル電圧降下補償機能は無効になっています。ケーブル電圧降下補償機能を有効にするには、**CDC\_OPTION** ビットを 1 に設定します。必要な電圧補償を得るには、レジスタ  $05H$  の **CDC [2:0]** ビットに値を書き込みます。

出力電圧上昇と検出された出力電流の関係を 図 6-4 に示します。

図 6-4. 出力電圧立ち上がりと出力電流との関係

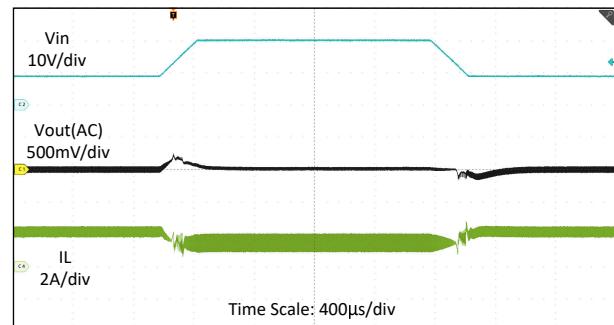

### 6.3.14 入力過電圧保護

TPS55285 は入力過電圧保護機能を備えているため、電流が出力から入力に流れ、入力ソースが FPWM モードで電流をシンクできなくなった場合に、デバイスの損傷を防止できます。VIN ピンの入力電圧が標準で  $22.5\text{V}$  を超えると、内

部ソフトスタート回路がリセットされますが、VIN OVP がトリガされても内部レジスタのすべての値は変化しません。入力電圧がヒステリシス値を入力過電圧保護スレッショルドより低下させると、コンバータは自動的に再起動します。

### 6.3.15 出力過電圧保護

TPS55285 は、抵抗で分圧された帰還電圧を監視することで、出力の過電圧状態を検出します。帰還電圧が目標電圧の 115% を超えると、デバイスは出力電圧が 2.3% のヒステリシス値を下回るまでスイッチングを停止します。この機能により、出力に接続されている回路が過剰な過電圧から保護されます。内部帰還抵抗を選択すると、TPS55285 は過電圧保護用に内部帰還電圧を検出します。

### 6.3.16 出力短絡保護機能

TPS55285 は平均インダクタ電流制限に加え、ヒップ モードに移行することで出力短絡保護機能を実装します。ヒップ モードを有効にするには、レジスタ 06h の HICCUP ビットを設定する必要があります。3.9ms のソフト スタートアップ時間の後、TPS55285 は平均インダクタ電流と出力電圧を監視します。出力短絡の発生により平均インダクタ電流が設定制限値に達し、出力電圧が 0.8V を下回ると、TPS55285 は 76ms (標準値) の間、スイッチングをシャットダウンします。その後 3.9ms の間、ソフト スタートを繰り返します。出力短絡または過電流状態において、ヒップ モードは TPS55285 の合計消費電力を低減するのに役立ちます。

### 6.3.17 サーマル シャットダウン

TPS55285 は、サーマル シャットダウン回路によって保護されており、内部接合部温度が 175°C (標準値) を超えるとシャットダウンされます。内部ソフトスタート回路はリセットされますが、サーマル シャットダウンがトリガされても、すべての内部レジスタ値は変更されません。接合部温度がサーマル シャットダウン スレッショルドより 20°C (標準値) 低いサーマル シャットダウン ヒステリシスを下回ると、コンバータは自動的に再起動します。

## 6.4 デバイスの機能モード

軽負荷時には、TPS55285 は PFM モードまたは強制 PWM モードで動作して、さまざまなアプリケーション要件を満たすことができます。PFM モードではスイッチング周波数が低下してスイッチング損失が低減されるため、軽負荷時に高い効率が得られます。FPWM モードでは、不要な低スイッチング周波数を回避するためにスイッチング周波数は変更されませんが、効率は PFM モードよりも低くなります。

デフォルトでは、TPS55285 は PFM モードで動作します。デバイスを強制 PWM モードで動作させるには、レジスタ 06h の 01 ビットを 1 に設定します。

### 6.4.1 PWM モード

FPWM モードでは、TPS55285 は軽負荷状態でスイッチング周波数を変更せずに維持します。負荷電流が減少すると、内部エラー アンプの出力も減少し、平均インダクタ電流が減少して入力から出力への電力供給が減少します。出力電流がさらに減少すると、スイッチオフ時間中にインダクタを流れる電流がゼロまで減少します。MOSFET を流れる電流がゼロであっても、ハイサイド N-MOSFET はオフになりません。したがって、インダクタ電流はゼロになった後、方向転換します。電力は出力側から入力側に流れます。この条件では効率が低くなります。ただし、固定スイッチング周波数により、軽負荷状態でスイッチング周波数が低いために発生するような可聴ノイズやその他の問題はありません。

## 6.4.2 パワー セーブ モード

TPS55285 は、PFM モードにより軽負荷時の効率を向上させます。内部レジスタで PFM 機能をイネーブルにすることで、TPS55285 は軽負荷時に PFM モードで動作します。TPS55285 が軽負荷時に動作する場合、内部エラー アンプの出力が減少してインダクタのピーク電流が下がり、負荷に供給される電力が減少します。出力電流がさらに減少すると、スイッチャオフ時間中にインダクタを流れる電流がゼロまで減少します。TPS55285 が降圧モードで動作している場合、インダクタ電流がゼロになると、降圧側のローサイド スイッチがオフになり、出力からグランドへの逆電流が防止されます。TPS55285 が昇圧モードで動作している場合、インダクタ電流がゼロになると、昇圧側のハイサイド スイッチがオフになり、出力から入力への逆電流が防止されます。TPS55285 は、出力電圧が低下するまでスイッチングを再開します。このように、PFM モードではスイッチング サイクルが短縮され、逆インダクタ電流による電力損失が解消されることで、軽負荷時に高い効率が実現します。

## 6.5 プログラミング

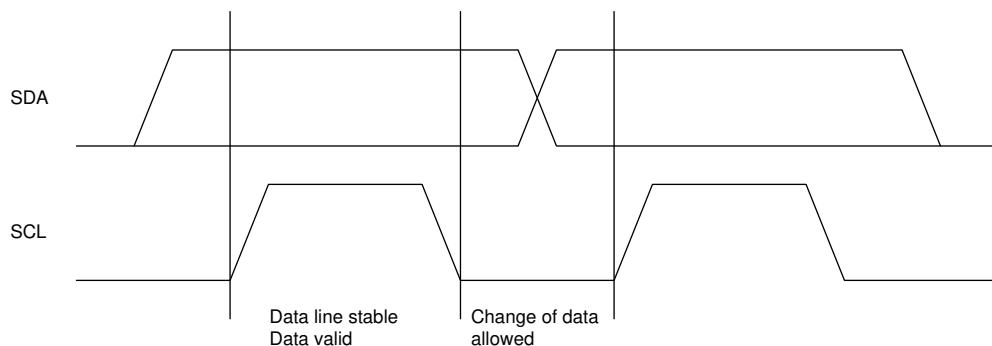

TPS55285 では、コンバータのパラメータをフレキシブルにプログラムするために、I<sup>2</sup>C インターフェイスを使用します。I<sup>2</sup>C は、双方向 2 線式のシリアル インターフェイスです。必要なバス ラインは、シリアル データライン (SDA) とシリアル クロックライン (SCL) の 2 つのみです。I<sup>2</sup>C デバイスは、データ転送を実行する際のコントローラまたはターゲットとみなされます。コントローラは、バス上でデータ転送を開始し、その転送を許可するクロック信号を生成するデバイスです。その際、アドレス指定されたデバイスはすべてターゲットとみなされます。

TPS55285 はアドレス 75h または 74h を持つターゲット デバイスとして動作します。マイコンやデジタル信号プロセッサなどのコントローラ デバイスから制御入力を受信すると、内部レジスタ 00h ~ 07h の読み取りと書き込みが行われます。TPS55285 の I<sup>2</sup>C インターフェイスは、標準モード (最大 100kbit/s) と高速モード プラス (最大 1000kbit/s) の両方をサポートしています。電流ソースまたはプルアップ抵抗経由で、SDA と SCL の両方を正の電源電圧に接続します。バスが空いていると、両方のラインが高電圧になります。

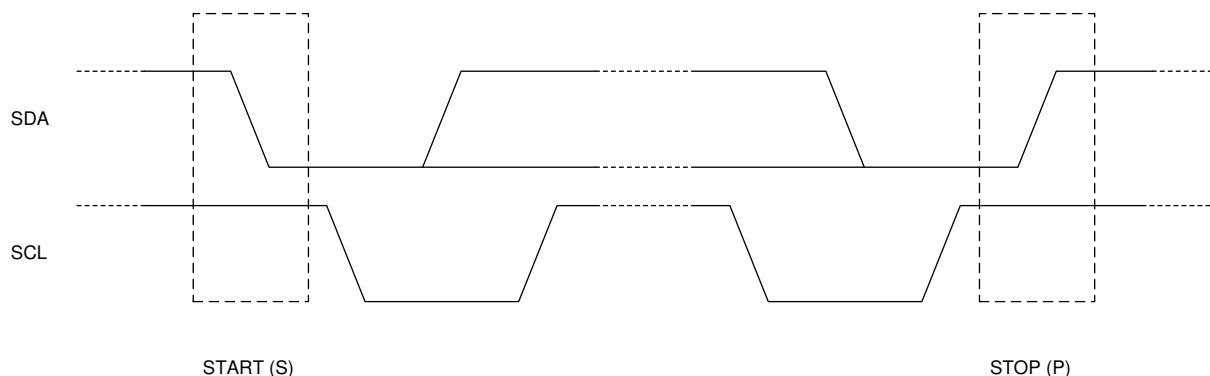

### 6.5.1 データの有効性

SDA ラインのデータは、クロックの high レベル期間中は安定している必要があります。データ ラインの high レベルまたは low レベルの状態は、SCL ラインのクロック信号が low レベルのときのみ変化可能です。転送されるデータ ビットごとに、1 つのクロック パルスが生成されます。

図 6-5. I<sup>2</sup>C データの有効性

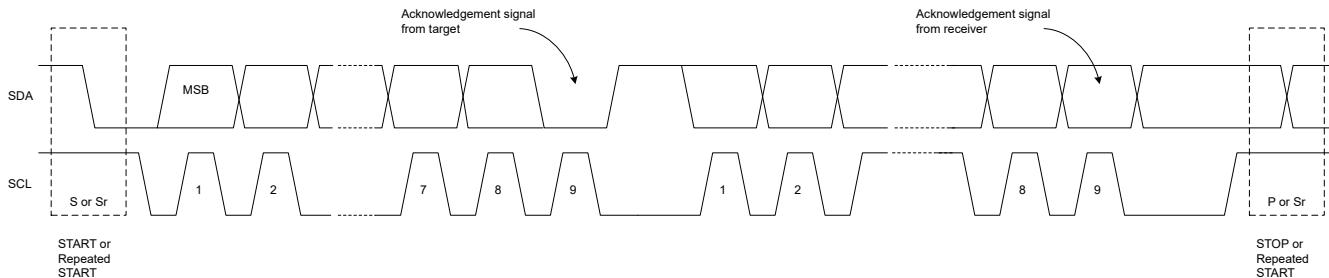

### 6.5.2 開始条件と停止条件

すべてのトランザクションは START (S) で開始され、STOP (P) により終了します。SCL が High レベルのときに SDA ラインが High レベルから Low レベルに遷移すると、START 条件が定義されます。SCL が High レベルのときに SDA ラインが Low レベルから High レベルに遷移すると、STOP 条件が定義されます。

START 条件と STOP 条件は、常にコントローラによって生成されます。バスは、START 条件の後はビジー状態とみなされ、STOP 条件の後はフリーとみなされます。

図 6-6. I<sup>2</sup>C の START 条件と STOP 条件

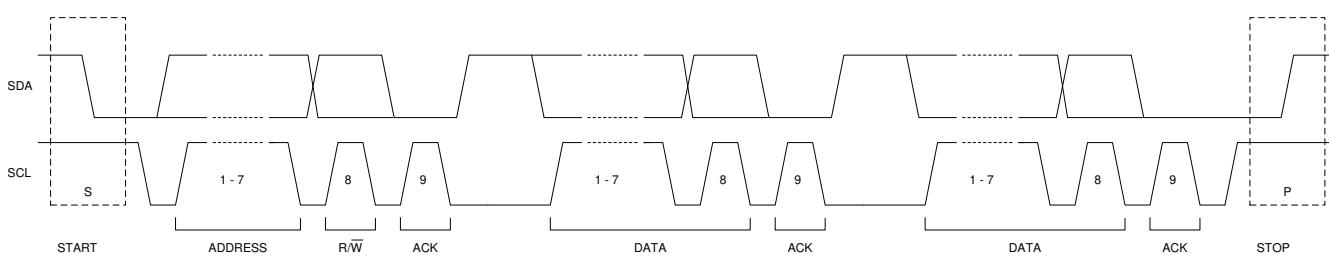

### 6.5.3 バイト フォーマット

SDA ラインの各バイトは 8 ビット長です。転送ごとに送信されるバイト数に制限はありません。各バイトには、アクノリッジ ビットが続きます。データは、最上位ビット (MSB) を先頭にして転送されます。ターゲットが他の機能を実行するまで、別の完全なデータ バイトを受信または送信しない場合、ターゲットはクロック ライン SCL を low に保持して、コントローラを強制的に待機状態 (クロック ストレッチ) に移行できます。その後、ターゲットが別のデータのバイトを処理する準備が整い、クロック ライン SCL を解放すると、データ転送が続行されます。

図 6-7. バイト フォーマット

### 6.5.4 アクノリッジ(ACK) とアクノリッジなし(NACK)

アクノリッジ (受信確認) は各バイトの後に行われます。アクノリッジ ビットによりレシーバは、バイトが正常に受信され、別のバイトが送信されることをトランスマッタに信号伝達することができます。9 番目のアクノリッジ クロック パルスを含むすべてのクロック パルスはコントローラによって生成されます。

アクノリッジ クロック パルスの間にトランスマッタは SDA ラインを解放するため、レシーバは SDA ラインを low レベルにプルし、このクロック パルスが high レベルの間は安定した low レベルを維持することができます。

アクノリッジなし信号は、9 番目のクロック パルスの間、SDA が High レベルに維持されるときです。その後コントローラは転送を中止する STOP を生成するか、新しい転送を開始する START を繰り返し生成します。

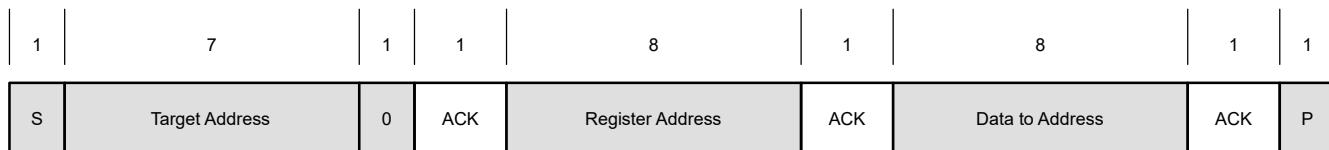

### 6.5.5 ターゲット アドレスおよびデータ方向ビット

START 後にターゲット アドレスが送信されます。このアドレスは 7 ビット長で、8 番目のビットがデータ方向ビット (ビット R/W) として続けます。0 は転送 (WRITE) を示し、1 はデータの要求 (READ) を示します。

図 6-8. ターゲット アドレスとデータ方向

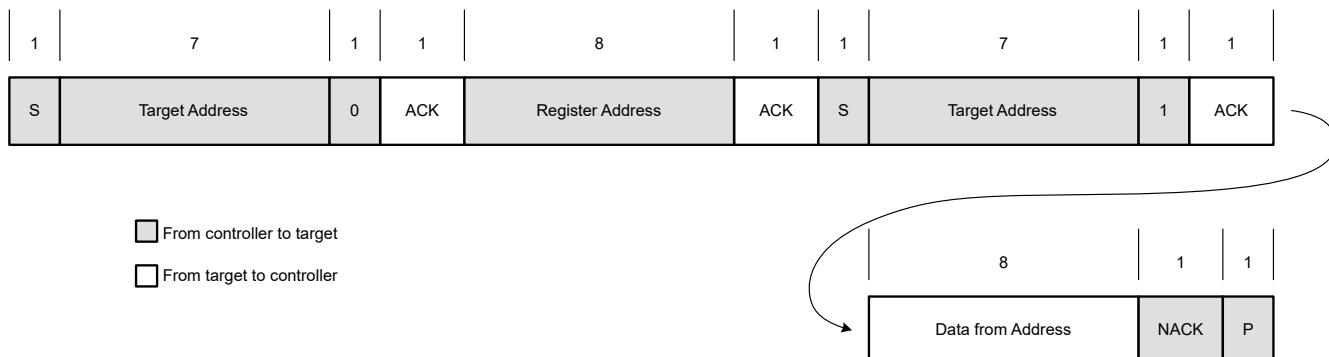

### 6.5.6 単一読み取りおよび書き込み

図 6-9 と図 6-10 に、I<sup>2</sup>C 通信のシングル バイトの書き込みとシングル バイトの読み取りのフォーマットを示します。

図 6-9. シングル バイトの書き込み

図 6-10. シングル バイトの読み取り

レジスタ アドレスが定義されていない場合、TPS55285 は NACK を返し、アイドル状態に戻ります。

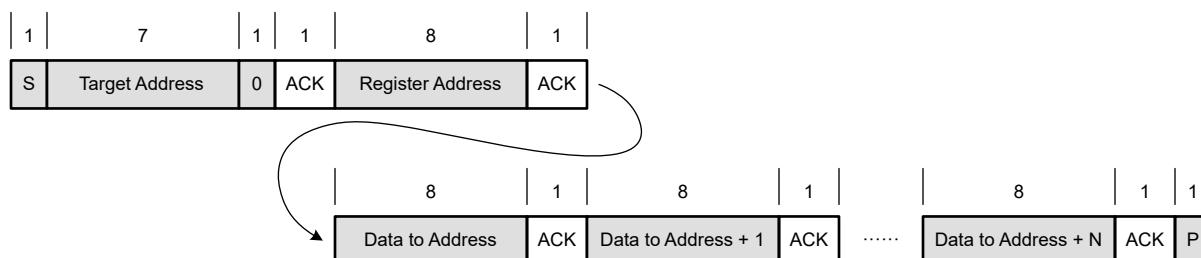

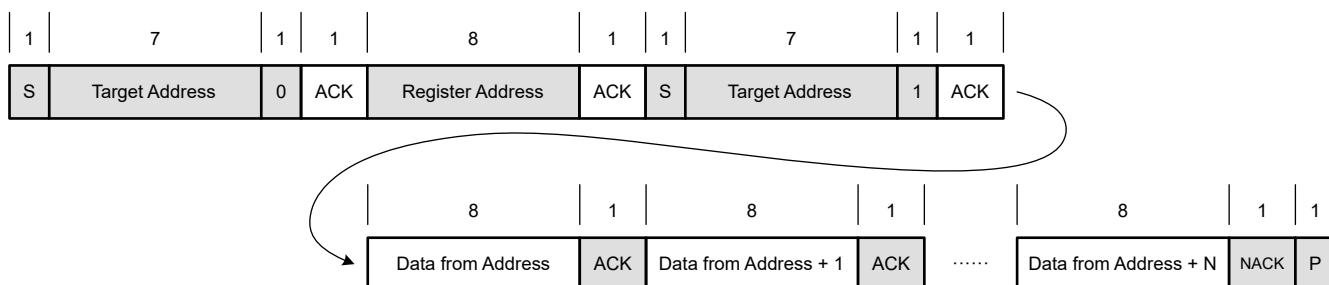

### 6.5.7 複数読み取りおよび複数書き込み

TPS55285 は、複数読み取りと複数書き込みをサポートしています。

図 6-11. マルチ バイトの書き込み

図 6-12. マルチ バイトの読み取り

## 7 レジスタ マップ

表 7-1 に、デバイスのレジスタ用のメモリマップトレジスタを示します。表 7-1 にないレジスタ オフセット アドレスはすべて予約済みと見なして、レジスタの内容は変更しないでください。

**表 7-1. デバイスのレジスタ**

| アドレス   | 略称         | レジスタ名   | セクション              |

|--------|------------|---------|--------------------|

| 0h, 1h | REF        | 基準電圧    | <a href="#">表示</a> |

| 2h     | IOUT_LIMIT | 電流制限の設定 | <a href="#">表示</a> |

| 3h     | VOUT_SR    | スルーレート  | <a href="#">表示</a> |

| 4h     | VOUT_FS    | 帰還の選択   | <a href="#">表示</a> |

| 5h     | CDC        | ケーブル補償  | <a href="#">表示</a> |

| 6h     | モード        | モード制御   | <a href="#">表示</a> |

| 7h     | STATUS     | 動作ステータス | <a href="#">表示</a> |

## 7.1 REF レジスタ (アドレス = 0h、1h) [リセット = 10100100b、00000001b]

図 7-1 と 図 7-2 に REF を示し、表 7-2 に、その説明を示します。

概略表に戻ります。

REF は TPS55285 の内部リファレンス電圧を設定します。01h レジスタは上位バイト、00h レジスタは下位バイトです。レジスタ 00h の 1LSB は、内部リファレンス電圧の 0.5645mV を表します。デフォルトのレジスタ値は 00000001 10100100b、282mV です。レジスタ値が 00000000 00000000b の場合、リファレンス電圧は 45mV です。レジスタ値が 00000111 10000000b の場合、リファレンス電圧は 1.129V です。TPS55285 の出力電圧は出力帰還比にも依存しており、レジスタ 04h での設定、または外部抵抗デバイダによる設定のいずれかになります。

内部出力電圧帰還デバイダを使用する場合、出力電圧  $V_{OUT}$  は 式 4 で計算されます

$$V_{OUT} = \frac{V_{REF}}{\text{INTFB}} \quad (4)$$

REF レジスタは、レジスタ 06h の OE ビットを設定する前に、I<sup>2</sup>C コントローラで構成されます。5V 出力電圧の場合は、REF レジスタ値を 00000001 10100100b に設定します。内部リファレンス電圧を設定するには、まずレジスタ 00h を書き込んでからレジスタ 01h を書き込みます。

図 7-1. REF\_LSB

|               |   |   |   |   |   |   |   |

|---------------|---|---|---|---|---|---|---|

| 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| VREF          |   |   |   |   |   |   |   |

| R/W-10100100b |   |   |   |   |   |   |   |

図 7-2. REF\_MSB

|          |    |    |    |    |    |          |   |

|----------|----|----|----|----|----|----------|---|

| 15       | 14 | 13 | 12 | 11 | 10 | 9        | 8 |

| 予約済み     |    |    |    |    |    | VREF     |   |

| R-00000b |    |    |    |    |    | R/W-001b |   |

表 7-2. REF レジスタ フィールドの説明

| ビット   | フィールド | タイプ | リセット             | 説明                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-11 | 予約済み  | R   | 00000b           | 予約済み                                                                                                                                                                                                                                                                                                                                                                                     |

| 10-0  | VREF  | R/W | 001<br>10100100b | 内部リファレンス電圧を設定<br>000 0000000b = 45mV リファレンス電圧<br>000 0000001b = 45.5645mV リファレンス電圧<br>000 0000010b = 46.129mV リファレンス電圧<br>.....= .....<br>001 10100100b = 282mV リファレンス電圧 (デフォルト)<br>.....= .....<br>011 00110100b = 508mV リファレンス電圧<br>.....= .....<br>101 10001100b = 846mV リファレンス電圧<br>.....= .....<br>111 1000000b = 1129mV リファレンス電圧<br>.....= .....<br>111 1111110b = 1200mV リファレンス電圧 |

## 7.2 IOUT\_LIMIT レジスタ (アドレス = 2h) [リセット = 11100100b]

図 7-3 に IOUT\_LIMIT を示し、表 7-3 に、その説明を示します。

概略表に戻ります。

IOUT\_LIMIT は、ターゲット出力電流制限を 500mA から 6.35A に設定します。1LSB は 50mA 出力電流制限ステップを表します。ビット 7 は電流制限を有効に、または電流制限を無効にします。

図 7-3. IOUT\_LIMIT レジスタ

| 7                | 6                     | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|-----------------------|---|---|---|---|---|---|

| Current_Limit_EN | Current_Limit_Setting |   |   |   |   |   |   |

| R/W-1b           | R/W-11100100b         |   |   |   |   |   |   |

表 7-3. IOUT\_LIMIT レジスタ フィールドの説明

| ビット | フィールド                 | タイプ | リセット     | 概要                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Current_Limit_EN      | R/W | 1b       | 出力電流制限を有効に、または無効にします。<br>0b = 出力電流制限が無効<br>1b = 出力電流制限が有効 (デフォルト)                                                                                                                                                                                                                                                                                                                                                                               |

| 6-0 | Current_Limit_Setting | R/W | 1100100b | 出力電流制限のターゲットを設定<br>0000000b = 500mA 出力電流制限<br>0000001b = 500mA 出力電流制限<br>0000010b = 500mA 出力電流制限<br>.....= .....<br>0001010b = 500mA 出力電流制限<br>0001011b = 550mA 出力電流制限<br>0001100b = 600mA 出力電流制限<br>0001101b = 650mA 出力電流制限<br>.....= .....<br>0010100b = 1A 出力電流制限<br>.....= .....<br>0101000b = 2A 出力電流制限<br>.....= .....<br>0111100b = 3A 出力電流制限<br>.....= .....<br>1100100b = 5A 出力電流制限 (デフォルト)<br>.....= .....<br>1111111b = 6.35A 出力電流制限 |

### 7.3 VOUT\_SR レジスタ (アドレス = 3h) [リセット = 00000001b]

図 7-4 に VOUT\_SR を示し、表 7-4 に、その説明を示します。

概略表に戻ります。

レジスタ 03h は、出力電圧変化のスルーレートと、出力電流が設定出力電流制限を超えた後の応答遅延時間を設定します。

OCP\_DELAY [1:0] ビットは、出力過電流制限に達したときの TPS55285 の応答時間を設定します。この応答時間により、TPS55285 は比較的短い時間で大電流を出力できます。デフォルト設定の 128 $\mu$ s では、TPS55285 は出力電流を即座に制限します。

SR [1:0] ビットは、出力電圧変化のスルーレートを 1.25mV/ $\mu$ s、2.5mV/ $\mu$ s、5mV/ $\mu$ s、10mV/ $\mu$ s に設定します。

図 7-4. VOUT\_SR レジスタ

| 7    | 6 | 5         | 4 | 3     | 2 | 1       | 0 |

|------|---|-----------|---|-------|---|---------|---|

| 予約済み |   | OCP_DELAY |   | 予約済み  |   | SR      |   |

| R-0b |   | R/W-00b   |   | R-00b |   | R/W-01b |   |

表 7-4. VOUT\_SR レジスタ フィールドの説明

| ビット | フィールド     | タイプ | リセット | 説明                                                                                                                                                                         |

|-----|-----------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | 予約済み      | R   | 00b  | 予約済み                                                                                                                                                                       |

| 5-4 | OCP_DELAY | R/W | 00b  | 出力過電流制限に達したときのデバイスの応答時間を設定します。<br>00b = 128 $\mu$ s (デフォルト)<br>01b = 遅延 1.024 x 3ms<br>10b = 遅延 1.024 x 6ms<br>11b = 遅延 1.024 x 12ms                                       |

| 3-2 | 予約済み      | R   | 00b  | 予約済み                                                                                                                                                                       |

| 1-0 | SR        | R/W | 01b  | 出力電圧変化のスルーレートを設定します。<br>00b = 1.25mV/ $\mu$ s の出力変化スルーレート<br>01b = 2.5mV/ $\mu$ s の出力変化スルーレート (デフォルト)<br>10b = 5mV/ $\mu$ s の出力変化スルーレート<br>11b = 10mV/ $\mu$ s の出力変化スルーレート |

## 7.4 VOUT\_FS レジスタ (アドレス = 4h) [リセット = 00000011b]

図 7-5 に VOUT\_FS を示し、表 7-5 に、その説明を示します。

概略表に戻ります。

レジスタ 04h は、内部抵抗デバイダまたは外部抵抗デバイダのどちらかによる出力電圧帰還デバイダの選択を設定し、内部帰還抵抗デバイダを使用するときの内部帰還比を設定します。

図 7-5. VOUT\_FS レジスタ

| 7      | 6      | 5 | 4        | 3 | 2 | 1       | 0 |

|--------|--------|---|----------|---|---|---------|---|

| FB     | FB_OVP |   | RESERVED |   |   | INTFB   |   |

| R/W-0b | R/W-0b |   | R-0000b  |   |   | R/W-11b |   |

表 7-5. VOUT\_FS レジスタ フィールドの説明

| ピット | フィールド    | タイプ | リセット  | 概要                                                                                                                                 |

|-----|----------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------|

| 7   | FB       | R/W | 0b    | 出力電圧帰還デバイダ<br>0b = 内部出力電圧帰還を使用。FB/INT ピンは、出力短絡保護回路、過電流ステータス、過電圧ステータスのインジケーターです (デフォルト)。<br>1b = 外部出力電圧帰還を使用。FB/INT ピンは出力電圧の帰還入力です。 |

| 6   | FB_OVP   | R/W | 0b    | 0b = FB 115% OVP を有効化 (デフォルト)<br>1b = FB 115% OVP を無効化                                                                             |

| 5-2 | RESERVED | R   | 0000b | 予約済み                                                                                                                               |

| 1-0 | INTFB    | R/W | 11b   | 内部帰還比<br>00b = 内部帰還比を 0.2256 に設定<br>01b = 内部帰還比を 0.1128 に設定<br>10b = 内部帰還比を 0.0752 に設定<br>11b = 内部帰還比を 0.0564 に設定 (デフォルト)          |

表 7-6. 出力電圧と内部リファレンスとの関係

| INTFB1 | INTFB0 | REF=0000h | REF=001Ah | REF=0050h | REF=00F0h | REF=0780h | 出力電圧ステップ |

|--------|--------|-----------|-----------|-----------|-----------|-----------|----------|

| 0      | 0      |           |           |           | 0.8V      | 5V        | 2.5mV    |

| 0      | 1      |           |           | 0.8V      |           | 10V       | 5mV      |

| 1      | 0      |           | 0.8V      |           |           | 15V       | 7.5mV    |

| 1      | 1      | 0.8V      |           |           |           | 20V       | 10mV     |

## 7.5 CDC レジスタ (アドレス = 5h) [リセット = 11110000b]

図 7-6 に CDC を示し、表 7-7 でその説明を示します。

概略表に戻ります。

レジスタ 05h は、レジスタ 07h の SC ビット、OCP ビット、OVP ビット、および TSD ビットのマスクを設定します。マスクビットが設定され、対応する故障が発生すると、デバイスは FB/INT ピンの故障表示をマスクします

また、レジスタ 05h は、検出された出力電流に対して設定出力電圧に加算される電圧立ち上がりを設定します。

**図 7-6. CDC レジスタ**

| 7       | 6        | 5        | 4        | 3          | 2 | 1        | 0 |

|---------|----------|----------|----------|------------|---|----------|---|

| SC_MASK | OCP_MASK | OVP_MASK | TSD_MASK | CDC_OPTION |   | CDC      |   |

| R/W-1b  | R/W-1b   | R/W-1b   | R/W-1b   | R/W-0b     |   | R/W-000b |   |

**表 7-7. CDC レジスタ フィールドの説明**

| ビット | フィールド      | タイプ | リセット | 説明                                                                                                                                                                                                                                                                                    |

|-----|------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SC_MASK    | R/W | 1b   | 短絡マスク<br>0b = SC 表示が無効<br>1b = SC 表示を有効化 (デフォルト)                                                                                                                                                                                                                                      |

| 6   | OCP_MASK   | R/W | 1b   | 過電流マスク<br>0b = OCP 表示が無効<br>1b = OCP 表示を有効化 (デフォルト)                                                                                                                                                                                                                                   |

| 5   | OVP_MASK   | R/W | 1b   | 過電圧マスク<br>0b = OVP 表示が無効<br>1b = OVP 表示を有効化 (デフォルト)                                                                                                                                                                                                                                   |

| 4   | TSD_MASK   | R/W | 1b   | サーマルシャットダウン マスク<br>0b = TSD 表示が無効<br>1b = TSD 表示を有効化 (デフォルト)                                                                                                                                                                                                                          |

| 3   | CDC_OPTION | R/W | 0b   | ケーブル電圧降下補償機能を無効化または有効化します<br>0b = CDC 補償を無効化 (デフォルト)<br>1b = CDC 補償を有効化                                                                                                                                                                                                               |

| 2-0 | CDC        | R/W | 000b | ケーブルの電圧降下を補償します<br>000b = 5A 出力電流で 0V の出力電圧上昇 (デフォルト)<br>001b = 5A 出力電流で 0.1V の出力電圧上昇<br>010b = 5A 出力電流で 0.2V の出力電圧上昇<br>011b = 5A 出力電流で 0.3V の出力電圧上昇<br>100b = 5A 出力電流で 0.4V の出力電圧上昇<br>101b = 5A 出力電流で 0.5V の出力電圧上昇<br>110b = 5A 出力電流で 0.6V の出力電圧上昇<br>111b = 5A 出力電流で 0.7V の出力電圧上昇 |

## 7.6 MODE レジスタ (アドレス = 6h) [リセット = 00100000b]

図 7-7 に MODE を示し、表 7-8 でその説明を示します。

概略表に戻ります。

MODE は、TPS55285 の動作モードを制御します。

DISCHG\_2 ビットは、Vout が低下したときに放電 FET を有効にするか無効にするかを制御します。DISCHG\_2 が 1 に設定されている場合、放電 FET 電流は、Vout が低下したときに FPWM モードで逆電流を低減するのに役立ちます。

図 7-7. MODE レジスタ

| 7      | 6        | 5      | 4      | 3 | 2       | 1      | 0        |

|--------|----------|--------|--------|---|---------|--------|----------|

| OE     | スペクトラム拡散 | HICCUP | DISCHG |   | FSW     | FPWM   | DISCHG_2 |

| R/W-0b | R/W-0b   | R/W-1b | R/W-0b |   | R/W-00b | R/W-0b | R/W-0b   |

表 7-8. MODE レジスタ フィールドの説明

| ビット | フィールド          | タイプ | リセット | 説明                                                                                                                                |

|-----|----------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 7   | OE             | R/W | 0b   | 出力イネーブル<br>0b = 出力ディスエーブル (デフォルト)<br>1b = 出力イネーブル                                                                                 |

| 6   | SPREADSPECTRUM | R/W | 0b   | スペクトラム拡散機能<br>0b = スペクトラム拡散機能をディスエーブル (デフォルト)<br>1b = スペクトラム拡散機能をイネーブル                                                            |

| 5   | HICCUP         | R/W | 1b   | ヒカップ モード<br>0b = 出力短絡保護時にヒカップをディスエーブル。<br>1b = 出力短絡保護時にヒカップをイネーブル (デフォルト)                                                         |

| 4   | DISCHG         | R/W | 0b   | 出力放電<br>0b = デバイスがシャットダウン モードのとき VOUT 放電をディスエーブル (デフォルト)<br>1b = VOUT 放電をイネーブル。シャットダウン モードでは、内部 100mA 電流シンクによって、VOUT がグランドに放電されます |

| 3-2 | FSW            | R/W | 00b  | スイッチング周波数<br>00b = 400kHz (デフォルト)<br>01b = 800kHz<br>11b = 1.6MHz<br>11b = 2.1MHz                                                 |

| 1   | FPWM           | R/W | 0b   | 軽負荷時の動作モードを選択します<br>0b = 軽負荷時に PFM 動作モード (デフォルト)<br>1b = 軽負荷時に FPWM 動作モード                                                         |

| 0   | DISCHG_2       | R/W | 0b   | 0b = VREF 電圧が低下すると、出力放電機能はイネーブルになります。<br>(デフォルト)<br>1b = VREF 電圧が低下すると、出力放電機能はディスエーブルになります。                                       |

## 7.7 STATUS レジスタ (アドレス = 7h) [リセット = 00000001b]

図 7-8 に、STATUS を示し、表 7-9 に、その説明を示します。

概略表に戻ります。

STATUS レジスタには、TPS55285 の動作ステータスが格納されます。SCP ビット、OCP ビット、OVP ビット、または TSD ビットのいずれかが設定され、レジスタ 05h の対応するマスク ビットも設定されると、FB/INT ピンは Low ロジック レベルを出力して状況を示します。レジスタ 07h を読み取ると、SCP ビット、OCP ビット、OVP ビット、および TSD ビットがクリアされます。レジスタ 07h が読み取られるまで、FB/INT ピンのステータスと SCP ビット、OCP ビット、OVP ビットまたは TSD ビットはリセットされます。故障状態が引き続き存在する場合、対応するビットと FB/INT ピンが再びセットされます。

図 7-8. STATUS レジスタ

| 7    | 6    | 5    | 4    | 3    | 2    | 1      | 0     |

|------|------|------|------|------|------|--------|-------|

| SCP  | OCP  | OVP  | TSD  | 予約済み | 予約済み | STATUS |       |

| R-0b   | R-11b |

表 7-9. STATUS レジスタ フィールドの説明

| ビット | フィールド    | タイプ | リセット | 概要                                                                       |

|-----|----------|-----|------|--------------------------------------------------------------------------|

| 7   | SCP      | R   | 0b   | 短絡保護回路<br>0b = 短絡なし<br>1b = 短絡発生。読み取られるまでリセットしません。                       |

| 6   | OCP      | R   | 0b   | 過電流保護<br>0b = 出力過電流なし<br>1b = 出力電流が電流制限に達しました。読み取られるまでリセットしません。          |

| 5   | OVP      | R   | 0b   | 過電圧保護<br>0b = OVP なし<br>1b = 出力電圧が OVP スレッショルドを超えていました。読み取られるまでリセットしません。 |

| 4   | TSD      | R   | 0b   | サーマル シャットダウン保護機能<br>0b = TSD なし<br>1b = サーマル シャットダウン発生。読み取られるまでリセットしません  |

| 3   | RESERVED | R   | 0b   | 予約済み                                                                     |

| 2   | RESERVED | R   | 0b   | 予約済み                                                                     |

| 1-0 | STATUS   | R   | 01b  | 動作ステータス<br>00b = 昇圧<br>01b = 降圧<br>10b = 昇降圧<br>11b = 予約済み               |

## 7.8 レジスタの要約

表 7-10 では、TPS55285 におけるレジスタのデフォルト設定を要約しています。

表 7-10. レジスタのデフォルト設定

| レジスタ・アドレス | レジスタ名      | R/W | デフォルト値   |

|-----------|------------|-----|----------|

| 00h       | VREF_LSB   | R/W | 10100100 |

| 01h       | VREF_MSB   | R/W | 00000001 |

| 02h       | IOUT_LIMIT | R/W | 11100100 |

| 03h       | VOUT_SR    | R/W | 00000001 |

| 04h       | VOUT_FS    | R/W | 00000011 |

| 05h       | CDC        | R/W | 11110000 |

| 06h       | モード        | R/W | 00100000 |

| 07h       | STATUS     | R   | 00000001 |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPS55285 は、入力電圧 2.4V ~ 22V、出力電圧 0.8V ~ 15V という幅広い範囲で動作します。TPS55285 は、入力電圧と設定出力電圧に応じて、降圧モード、昇降圧モード、昇圧モード間をスムーズに遷移できます。TPS55285 は、入力電圧が出力電圧より大きい場合は降圧モードで動作し、入力電圧が出力電圧より小さい場合は昇圧モードで動作します。入力電圧が出力電圧に近いとき、TPS55285 は 1 サイクル降圧モードおよび 1 サイクル昇圧モードで交互に動作します。高い電力の状況でスイッチング電力損失を低減するには、スイッチング周波数を 500kHz 未満に設定することを推奨します。システムが 500kHz を超える高いスイッチング周波数を必要とする場合、放熱性能を向上させるために、スイッチ電流を低くして動作させることを推奨します。

### 8.2 代表的なアプリケーション

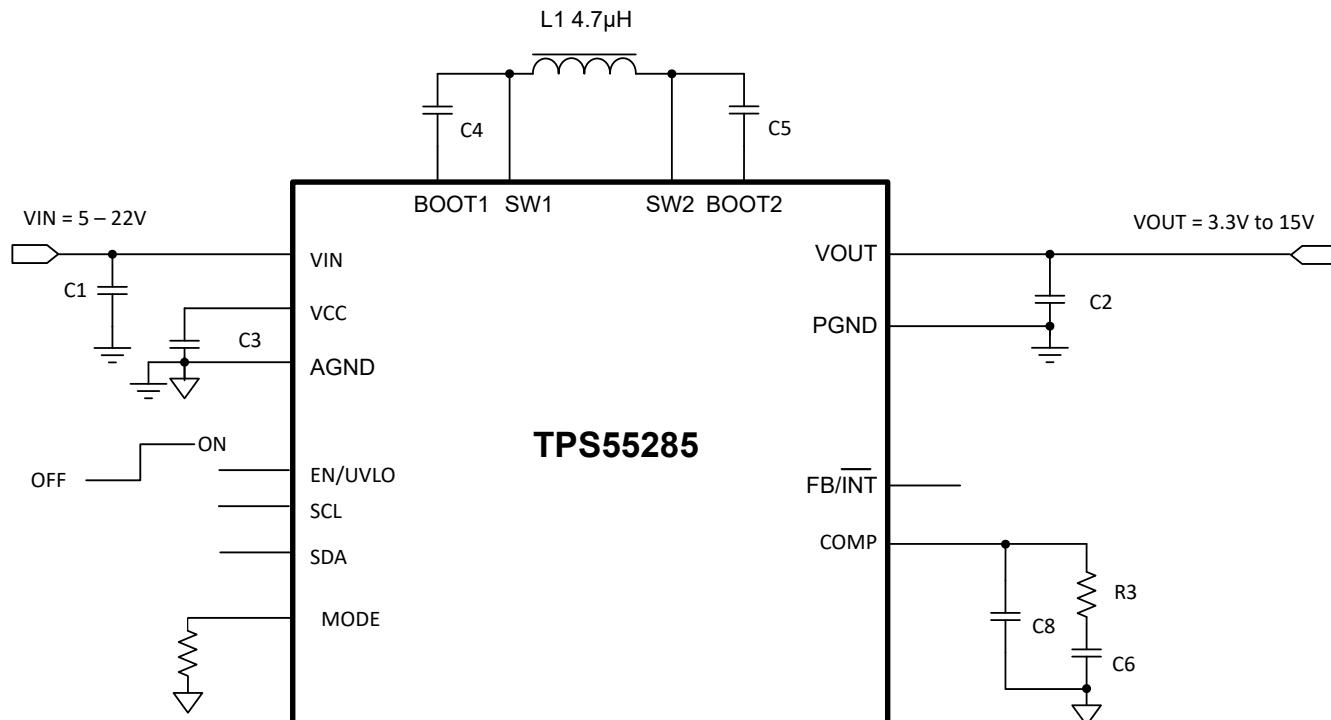

TPS55285 は、5V ~ 22V の入力電圧範囲を使用する電源アプリケーション向けの小型サイズを提供します。

図 8-1. 電源、入力電圧 5V ~ 22V

### 8.2.1 設計要件

設計パラメータを [表 8-1](#) に示します:

**表 8-1. 設計パラメータ**

| パラメータ      | 値          |

|------------|------------|

| 入力電圧       | 5V ~ 22V   |

| 出力電圧       | 3.3V ~ 15V |

| 出力電流制限     | 3A         |

| 出力電圧リップル   | ±50mV      |

| 軽荷重時の動作モード | FPWM       |

### 8.2.2 詳細な設計手順

#### 8.2.2.1 スイッチング周波数

TPS55285 のスイッチング周波数は、06H レジスタの FSW ビットで設定されます。このような大電流アプリケーションでスイッチング電力損失を低減するため、このアプリケーションでは 400kHz のスイッチング周波数が選択されています。

#### 8.2.2.2 出力電圧設定

TPS55285 には、内部リファレンス電圧を設定するための I<sup>2</sup>C インターフェイスがあります。マイコンは、I<sup>2</sup>C バスを介してリファレンス電圧レジスタに適切なデータを書き込むことにより、必要な出力電圧を簡単に設定できます。

#### 8.2.2.3 インダクタの選択

インダクタの選択は定常状態動作、過渡動作、ループの安定性に影響を及ぼすため、インダクタは電源レギュレータの設計で最も重要な部品です。インダクタには、インダクタンス、飽和電流、DC 抵抗という 3 つの重要な仕様があります。

TPS55285 は、1μH ~ 10μH のインダクタ値で動作するよう設計されています。インダクタの選択は、降圧モードと昇圧モードの両方の動作を考慮して行われます。

内部電流ループは内部補償を使用しているため、インダクタ値は 1.2/f<sub>SW</sub> より大きくなる必要があります。

降圧モードに対しては、ピークツーピークの電流リップルを最大入力電圧時の最大インダクタ電流に制限することに基づいて、インダクタを選択します。CCMにおいて、式 5 では、インダクタンスとインダクタリップル電流の関係が示されています。

$$L = \frac{(V_{IN(MAX)} - V_{OUT}) \times V_{OUT}}{\Delta I_{L(P-P)} \times f_{SW} \times V_{IN(MAX)}} \quad (5)$$

ここで、

- $V_{IN(MAX)}$  は最大入力電圧

- $V_{OUT}$  は出力電圧です。

- $\Delta I_{L(P-P)}$  はインダクタのピークツーピークリップル電流

- $f_{SW}$  はスイッチング周波数

特定のインダクタの場合、 $V_{OUT}$  が最大入力電圧の半分に等しいとき、インダクタリップル電流は最大値になります。大きいインダクタンスを選択するほどインダクタ電流リップルは小さくなり、インダクタンスが小さくなるほど、インダクタ電流リップルは大きくなります。

昇圧モードに対しては、ピークツーピークの電流リップルを最大出力電圧時の最大インダクタ電流に制限することに基づいて、インダクタを選択します。CCMにおいて、式 6 では、インダクタンスとインダクタリップル電流の関係が示されています。

$$L = \frac{V_{IN} \times (V_{OUT(MAX)} - V_{IN})}{\Delta I_{L(P-P)} \times f_{SW} \times V_{OUT(MAX)}} \quad (6)$$

ここで、

- $V_{IN}$  は入力電圧

- $V_{OUT(MAX)}$  は最大出力電圧

- $\Delta I_{L(P-P)}$  はインダクタのピークツーピークリップル電流

- $f_{SW}$  はスイッチング周波数

特定のインダクタの場合、 $V_{IN}$  が最大出力電圧の半分に等しいとき、インダクタリップル電流は最大値になります。大きいインダクタンスを選択するほどインダクタ電流リップルは小さくなり、インダクタンスが小さくなるほど、インダクタ電流リップルは大きくなります。

このアプリケーション例では、 $4.7\mu H$  インダクタを選択しています。これにより、降圧モードでは最大平均インダクタ電流の 50%、昇圧モードでは最大平均インダクタ電流の 50% という、およそその最大インダクタ電流リップルが得られます。

降圧モードでは、インダクタ DC 電流は出力電流と等しくなります。昇圧モードでは、インダクタ DC 電流は、式 7 で計算されます。

$$I_{L(DC)} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \quad (7)$$

ここで、

- $V_{OUT}$  は出力電圧です。

- $I_{OUT}$  は出力電流

- $V_{IN}$  は入力電圧

- $\eta$  は電力変換効率

昇降圧コンバータ TPS55285 の指定最大出力電流の場合、最大インダクタ DC 電流は最小入力電圧および最大出力電圧で発生します。TPS55285 が目的の出力電流キャパシティを持つように、TPS55285 のインダクタ電流制限を、計算された最大インダクタ DC 電流より高く設定します。

昇圧モードでは、インダクタリップル電流は、式 8 で計算されます。

$$\Delta I_{L(P-P)} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{L \times f_{SW} \times V_{OUT}} \quad (8)$$

ここで、

- $\Delta I_{L(P-P)}$  は、インダクタリップル電流

- $L$  はインダクタ値です。

- $f_{SW}$  はスイッチング周波数

- $V_{OUT}$  は出力電圧です。

- $V_{IN}$  は入力電圧

したがって、インダクタのピーク電流は 式 9 で計算されます。

$$I_{L(P)} = I_{L(DC)} + \frac{\Delta I_{L(P-P)}}{2} \quad (9)$$

通常、最大出力電流を得るために、インダクタのピークツーピーク電流を平均インダクタ電流の 40% 未満とすることを推奨します。インダクタの値が大きくなるほどリップルは小さくなり、インダクタ内の磁気ヒステリシス損失と EMI が減少します

が、同様に負荷過渡応答時間は長くなります。選択されたインダクタでは、計算されたピーク電流より大きい飽和電流である必要があります。

変換効率は電流パスの抵抗に依存します。スイッチング MOSFET に関するスイッチング損失と、インダクタのコア損失です。したがって、全体の効率はインダクタの DC 抵抗 (DCR)、スイッチング周波数での等価直列抵抗 (ESR)、およびコア損失の影響を受けます。表 8-2 では、TPS55285 の推奨インダクタが示されています。このアプリケーション例では、サイズが小さく、飽和電流が大きく、DCR が小さいという理由で、Coilcraft インダクタ XAL7070-472 を選択しています。

**表 8-2. 推奨するインダクタ**

| 部品番号              | L (μH) | DCR (最大値)<br>(mΩ) | 飽和電流 / 热定格電流<br>(A) | サイズ L × W × H (mm) | メーカー <sup>(1)</sup> |

|-------------------|--------|-------------------|---------------------|--------------------|---------------------|

| XAL7070-472ME     | 4.7    | 14.3              | 15.2/10.5           | 7.5 × 7.2 × 7.0    | Coilcraft           |

| VCHA085D-4R7MS6   | 4.7    | 15.6              | 16.0/8.8            | 8.7 × 8.2 × 5.2    | Cyntec              |

| IHP4040DZER4R7M01 | 4.7    | 16.5              | 17/9.5              | 10.2 × 10.2 × 4.0  | Vishay              |

(1) 「[カードパーティー製品に関する免責事項](#)」をご覧ください。

### 8.2.2.4 入力コンデンサ

降圧モードでは、入力コンデンサから高リップル電流が供給されます。入力コンデンサの RMS 電流は、式 10 で求められます。

$$I_{CIN(RMS)} = I_{OUT} \times \sqrt{\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times V_{IN}}} \quad (10)$$

ここで、

- $I_{CIN(RMS)}$  は、入力コンデンサを流れる RMS 電流

- $I_{OUT}$  は出力電流

最大 RMS 電流は、出力電圧が入力電圧の半分のときに発生し、 $I_{CIN(RMS)} = I_{OUT} / 2$  となります。セラミック コンデンサは、低 ESR で高リップル電流能力を持つため、推奨されます。合計  $20\mu F$  の実効容量が、このアプリケーションの出発点として適切です。

### 8.2.2.5 出力コンデンサ

昇圧モードでは、出力コンデンサに高リップル電流が流れます。出力コンデンサ RMS リップル電流は、式 11 で求められます。ここで、最小入力電圧と最大出力電圧は、最大コンデンサ電流に対応します。

$$I_{COUT(RMS)} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} - 1} \quad (11)$$

ここで、

- $I_{COUT(RMS)}$  は、出力コンデンサを流れる RMS 電流

- $I_{OUT}$  は出力電流

この例では、最大出力リップル RMS 電流は 2.8A です。

出力コンデンサの ESR により、出力電圧リップルが昇圧モードの 式 12 で求められます。

$$V_{RIPPLE(ESR)} = \frac{I_{OUT} \times V_{OUT}}{V_{IN}} \times R_{COUT} \quad (12)$$

ここで、

- $R_{COUT}$  は、出力キャパシタンスの ESR

また、このキャパシタンスにより、容量性出力電圧リップルが昇圧モードの 式 13 で求められます。入力電圧が最小値に達し、出力電圧が最大値に達すると、キャパシタンスによる出力電圧リップルは最大になります。

$$V_{RIPPLE(CAP)} = \frac{I_{OUT} \times \left(1 - \frac{V_{IN}}{V_{OUT}}\right)}{C_{OUT} \times f_{SW}} \quad (13)$$

通常、低 ESR、高リップル電流、小出力電圧リップルを実現するには、セラミック コンデンサとバルク電解コンデンサを組み合わせる必要があります。必要な出力電圧リップルから、式 12 と 式 13 を使用して、 $C_{OUT}$  に必要な最小実効キャパシタンスを計算します。

#### 8.2.2.6 出力電流制限

出力電流制限は、レジスタ 02h を通じて 50mA 刻みで設定します。出力電流制限の最大値は 6.35A で、出力電流制限の最小値は 500mA です。デフォルトの制限電圧は 5A です。

#### 8.2.2.7 ループ安定性

TPS55285 は平均電流制御方式を使用しています。内部電流ループは内部補償を使用しているため、インダクタ値は  $1.2/f_{SW}$  より大きくする必要があります。外部電圧ループには、外部補償が必要です。COMP ピンは内部電圧エラー アンプの出力です。COMP ピンには、抵抗とセラミック コンデンサで構成される外部補償回路が接続されています。

TPS55285 は降圧モードまたは昇圧モードで動作します。したがって、降圧と昇圧のどちらの動作モードでもループ補償が必要です。これら両方の補償のうち、ループ安定性の観点から、全体的な補償として制限の大きい方が選択されます。一般的に降圧モードまたは昇圧モードのいずれかで動作するように設計されたコンバータの場合、右半面ゼロ (RHPZ) が存在するため、昇圧モード補償設計の方が制限が大きくなります。

昇圧モードでの電力段は 式 14 でモデル化されます。