**TPS61390**

JAJSH98B - APRIL 2019 - REVISED OCTOBER 2019

# TPS61390 電流ミラーとサンプル/ホールド機能を搭載した 85V<sub>OUT</sub> の昇圧 コンバータ

## 1 特長

入力電圧範囲: 2.5V~5.5V出力電圧範囲: 85V (最大値)

• スイッチング FET の R<sub>(DS)on</sub>: 0.9Ω

• スイッチ電流制限:1000mA

• 最小 400ns のサンプル・ウィンドウ

• 応答時間 0.5µs の高光出力保護

• スイッチング周波数: 700kHz

静止電流: VIN から 110μA、VOUT から 340μA、 AVCC から 140μA

• ソフト・スタート時間: 4.8ms

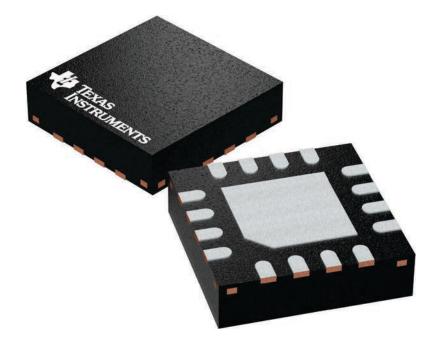

パッケージ: 3mm × 3mm × 0.75mm QFN

## 2 アプリケーション

- APD のバイアス

- 光ライン端末

- 高電圧センサの電源

## 3 概要

TPS61390 は、2.5V~5.5V の入力に対応する 85V スイッチ FET を内蔵した 700kHz パルス幅変調 (PWM) 昇圧コンバータです。スイッチング・ピーク電流は最大1000mA です。TPS61390 は高精度電流ミラーを内蔵しており、2 種類のゲイン (1:5 または 4:5) を選択できます。

さらに TPS61390 は、バースト・モードの光レシーバー・アプリケーション用のサンプル・アンド・ホールド回路を内蔵しており、APD を流れる電流を捕捉しその電流を外部の ADC に渡します。このデバイスは、強い光密度と弱い光密度の間で遷移する際に、高速の応答時間を実現しています。また、TPS61390 は、APD の電力経路と直列にFET を追加することで、応答時間 0.5 µs (標準値) の高光出力保護機能も実現できます。この保護機能は、高光出力が解除されると自動的に復帰します。

TPS61390 は、底面に露出パッドを備えた 3mm x 3mm QFN パッケージで供給されます。

## 製品情報(1)

| 型番       | パッケージ     | 本体サイズ(公称)     |

|----------|-----------|---------------|

| TPS61390 | WQFN (16) | 3.00mm×3.00mm |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

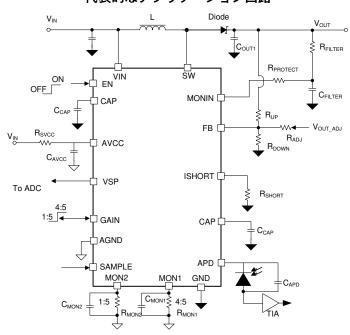

#### 代表的なアプリケーション回路

| 目 | 次 |

|---|---|

|   |   |

| 1 | 特長1                                    | 7.4 Device Functional Mode          |

|---|----------------------------------------|-------------------------------------|

| 2 | アプリケーション1                              | 8 Application and Implementation 13 |

| 3 | 概要1                                    | 8.1 Application Information         |

| 4 | 改訂履歴2                                  | 8.2 Typical Application13           |

| 5 | Pin Configuration and Functions3       | 9 Power Supply Recommendations 17   |

| 6 | Specifications4                        | 10 Layout 18                        |

|   | 6.1 Recommended Operating Conditions 4 | 10.1 Layout Guidelines18            |

|   | 6.2 Absolute Maximum Ratings 4         | 10.2 Layout Example18               |

|   | 6.3 ESD Ratings 4                      | 11 デバイスおよびドキュメントのサポート               |

|   | 6.4 Thermal Information                | 11.1 ドキュメントの更新通知を受け取る方法             |

|   | 6.5 Electrical Characteristics5        | 11.2 コミュニティ・リソース19                  |

|   | 6.6 Typical Characteristics            | 11.3 商標 19                          |

| 7 | Detailed Description9                  | 11.4 静電気放電に関する注意事項                  |

|   | 7.1 Overview9                          | 11.5 Glossary19                     |

|   | 7.2 Functional Block Diagram           | 12 メカニカル、パッケージ、および注文情報              |

|   | 7.3 Feature Description                |                                     |

|   |                                        |                                     |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision A (June 2019) から Revision B に変更

Page

#### 2019年4月発行のものから更新

Page

• ステータスを量産データに変更.......1

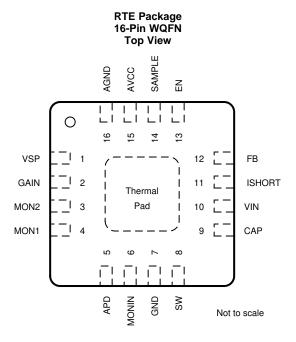

# **5 Pin Configuration and Functions**

**Pin Functions**

| PI         | N         | 1/0 | DEGODIDATION                                                                                                                                                      |

|------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.       | I/O | DESCRIPTION                                                                                                                                                       |

| VSP        | 1         | 0   | Sample/Hold voltage output with single-ended output.                                                                                                              |

|            |           |     | GAIN of the current mirror selection indicator of the sample/hold output:                                                                                         |

|            |           |     | Output low: sample/hold for current mirror gain 4 : 5;                                                                                                            |

| GAIN       | 2         | ı   | Output high: sample/hold for current mirror gain 1 : 5;                                                                                                           |

| GAIN       | 2         | ı   | This pin can also be any input pin:                                                                                                                               |

|            |           |     | Input low: sample/hold for current mirror gain 4 : 5;                                                                                                             |

|            |           |     | Input high: sample/hold for current mirror gain 1:5                                                                                                               |

| MON2       | 3         | 0   | Current mirror output pin of 1 : 5 ratio (Mirror current: APD current)                                                                                            |

| MON1       | 4         | 0   | Current mirror output pin of 4 : 5 ratio (Mirror current: APD current)                                                                                            |

| APD        | 5         | 0   | Power supply for the APD, connect this pin with the cathode of APD                                                                                                |

| MONIN      | 6         | I   | Current mirror input pin                                                                                                                                          |

| GND        | 7         | _   | Power Ground                                                                                                                                                      |

| SW         | 8         | PWR | The switching node pin of the converter. It is connected to the drain of the internal low-side power MOSFET and the source of the internal high-side power MOSFET |

| CAP        | 9         | 0   | Connecting a capacitor externally to lower the noise for current mirror.                                                                                          |

| VIN        | 10        | I   | IC power supply input                                                                                                                                             |

| ISHORT     | 11        | 0   | Programming the current limit for high optical power protection by a resistor between this pin and GND.                                                           |

| FB         | 12        | I   | Feedback voltage                                                                                                                                                  |

| EN         | 13        | I   | Enable logic input. Logic high level enables the device. Logic low level disables the device and turns it into shutdown mode                                      |

| SAMPLE     | 14        | I   | The sample trigger pin, the rising edge of this pin to trigger the sample and falling edge to hold the sampled voltage.                                           |

| AVCC       | 15        | I   | Power supply for the sample/hold circuitry                                                                                                                        |

| AGND       | 16        | _   | Analog ground for the sample / hold and current mirror circuitry                                                                                                  |

| Exposed Th | ermal Pad |     | Connect with GND, TI recommends connecting to Power GND on PCB                                                                                                    |

## 6 Specifications

## 6.1 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                              | MIN | NOM | MAX | UNIT |

|------------------|------------------------------|-----|-----|-----|------|

| $V_{IN}$         | Input voltage                | 2.5 |     | 5.5 | V    |

| $V_{OUT}$        | Output voltage               | 20  |     | 85  | V    |

| $T_{J}$          | Junction temperature         | -40 |     | 125 | °C   |

| L                | Effective Inductance         |     | 4.7 |     | μH   |

| C <sub>IN</sub>  | Effective Input Capacitance  |     | 1   |     | μF   |

| C <sub>OUT</sub> | Effective Output Capacitance |     | 0.1 |     | μF   |

## 6.2 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                | MIN  | MAX | UNIT |

|------------------|--------------------------------|------|-----|------|

| \/altaga         | SW, APD, MONIN,CAP             | -0.3 | 85  | V    |

| Voltage          | Other pins                     | -0.3 | 6   | V    |

| $T_J$            | Operating junction temperature | -40  | 125 | °C   |

| T <sub>stg</sub> | Storage temperature            | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.3 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

| M                  | Flootrostatio discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, allpins <sup>(1)</sup> | ±1500 | V    |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins (2)  | ±500  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                      |                                              | TPS61390   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                      |                                              | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 52.9       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 54.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 27.9       | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 2.0        | °C/W |

| $Y_{JB}$             | Junction-to-board characterization parameter | 27.8       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 12.8       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

Over recommended free-air temperature range,  $V_{IN} = 3.3 \text{ V}$ ,  $AV_{CC} = 3.3 \text{ V}$ ,  $V_{MONIN} = 20 \text{ V}$  to 85 V,  $T_{J} = -40 ^{\circ}\text{C}$  to 125 °C, typical values are at  $T_{A} = 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITIONS                                                                                                       | MIN   | TYP     | MAX      | UNIT |

|------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|---------|----------|------|

| POWER SUI              | PPLY                                       |                                                                                                                       |       |         |          |      |

| V <sub>IN</sub>        | Input voltage range                        |                                                                                                                       | 2.5   |         | 5.5      | V    |

|                        | Under voltage lock out                     | V <sub>IN</sub> falling                                                                                               |       | 2.4     | 2.5      | V    |

| / <sub>UVLO</sub>      | Under voltage lock out hysteresis          | V <sub>UVLO</sub> rising - V <sub>UVLO</sub> falling                                                                  |       | 200     |          | mV   |

| I <sub>Q_IN</sub>      | Quiescent current into VIN pin             | $V_{IN} = 3.3 \text{ V}, V_{FB} = V_{REF} + 0.1 \text{ V}, \text{ No}$<br>switching, -40 °C ≤ T <sub>J</sub> ≤ 85 °C  |       | 110     | 140      | uA   |

| Q_OUT                  | Quiescent current into VOUT pin            | $V_{IN} = 3.3 \text{ V}, V_{FB} = V_{REF} + 0.1 \text{ V,No}$<br>switching, -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C |       | 340     | 430      | uA   |

| Q_VCC                  | Quiescent current into AVCC pin            | AVCC = 3.3 V -40 °C ≤ T <sub>J</sub> ≤ 85 °C                                                                          |       | 140     | 180      | uA   |

|                        | Shutdown current into VIN pin              | $2.5 \text{ V} \le \text{VIN} \le 5.5 \text{ V}, \text{ EN} = 0, -40 \text{ °C} \le T_J \le 85 \text{ °C}$            |       |         | 1        | uA   |

| I <sub>SD</sub>        | Shutdown current into VOUT pin             | EN = 0, -40 °C ≤ T <sub>J</sub> ≤ 85 °C                                                                               |       |         | 1        | uA   |

|                        | Shutdown current into AVCC pin             | AVCC = 3.3 V, EN = 0, -40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C                                                       |       |         | 1        | uA   |

| OUTPUT                 |                                            |                                                                                                                       |       |         |          |      |

| V <sub>OUT</sub>       | Output voltage range                       |                                                                                                                       |       | <u></u> | 85       | V    |

| -                      |                                            | V <sub>IN</sub> = 2.5 V to 5.5 V, T <sub>J</sub> = 25 °C                                                              | 1.188 | 1.2     | 1.212    | V    |

| $V_{REF}$              | Feedback regulation reference voltage      | $V_{IN}$ = 2.5 V to 5.5 V, -40 °C ≤ $T_J$ ≤ 125 °C                                                                    | 1.182 | 1.2     | 1.218    | V    |

| I <sub>FB</sub>        | Feedback input leakage current             |                                                                                                                       |       | 1       | 25       | nA   |

| POWER SW               | ІТСН                                       |                                                                                                                       |       |         |          |      |

| R <sub>DS(on)</sub>    | Low-side FET on resistance                 | 3 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                         |       | 900     | 1300     | mΩ   |

| SWITCHING              | CHARACTERISTIC                             |                                                                                                                       |       |         | <u> </u> |      |

| $f_{SW}$               | Switching frequency                        | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 60 V                                                                      | 600   | 700     | 800      | kHz  |

| CURRENT N              | MIRROR                                     |                                                                                                                       |       |         |          |      |

| k <sub>MON1</sub>      | 4:5 Current mirror gain                    | I <sub>APD</sub> = 5 μA to 200 μA                                                                                     | 0.76  | 0.8     | 0.84     |      |

| k <sub>MON2</sub>      | 1:5 Current mirror gain                    | I <sub>APD</sub> = 100 μA to 2 mA                                                                                     | 0.19  | 0.2     | 0.21     |      |

| V <sub>MON</sub>       | MON1 / MON2 Threshold                      |                                                                                                                       | 380   | 400     | 420      | mV   |

|                        |                                            | I <sub>APD</sub> = 1 mA                                                                                               | 2.2   | 2.5     | 2.8      | V    |

| $V_{APD\_DRP}$         | Current mirror voltage drop                | I <sub>APD</sub> = 5 μA                                                                                               |       | 2.45    |          | V    |

| I <sub>BIAS</sub>      | Current mirror bias current                |                                                                                                                       | 15    | 20      | 25       | μA   |

| SAMPLE / H             | IOLD                                       |                                                                                                                       |       |         | l        |      |

| V <sub>ERROR</sub>     | Sample/hold output error steady,+/-6 sigma | $I_{APD}$ = 20 uA, GAIN = 0.8, $R_{MON}$ = 3 $k\Omega$                                                                | -15   |         | +15      | %    |

| V <sub>ERROR</sub>     | Sample/hold output error steady,+/-6 sigma | $I_{APD}$ = 500 μA, GAIN = 0.2, $R_{MON}$ = 3 kΩ                                                                      | -5    |         | +5       | %    |

| t <sub>SP_DEL</sub>    | Amplifier settling down time               |                                                                                                                       |       |         | 10       | μs   |

| t <sub>GAIN_COMP</sub> | Gain selection comparator time             | +/-20% gap of threshold                                                                                               |       |         | 8        | μs   |

| V <sub>DROP_SP</sub>   | Drop voltage during sample/hold            | Sample voltage sensing value variation at 10-100 µs, (Max-Min)/Average                                                |       |         | 1        | %    |

| CURRENT L              | IMIT                                       |                                                                                                                       |       |         |          |      |

| I <sub>LIM_SW</sub>    | Peak switching current limit               | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 60 V                                                                      | 800   | 1000    | 1200     | mA   |

|                        | High optical power current limit           | $R_{ISHORT} = 25 \text{ k}\Omega$                                                                                     | 3.7   | 4       | 4.3      | mA   |

| I <sub>SHORT</sub>     | High optical power current limit           | R <sub>ISHORT</sub> = 50 kΩ                                                                                           | 1.8   | 2       | 2.2      | mA   |

## **Electrical Characteristics (continued)**

Over recommended free-air temperature range,  $V_{IN} = 3.3 \text{ V}$ ,  $AV_{CC} = 3.3 \text{ V}$ ,  $V_{MONIN} = 20 \text{ V}$  to 85 V,  $T_{J} = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ , typical values are at  $T_{A} = 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                                    | TEST CONDITIONS                                    | MIN           | TYP MAX       | UNIT |

|-----------------------|----------------------------------------------|----------------------------------------------------|---------------|---------------|------|

| CONTROL (             | EN, SAMPLE, GAIN)                            |                                                    |               |               |      |

| V <sub>EN_H</sub>     | EN Logic high threshold                      |                                                    |               | 1.2           | V    |

| V <sub>EN_L</sub>     | EN Logic low threshold                       |                                                    | 0.4           |               | V    |

| R <sub>EN</sub>       | EN pull down resistor                        |                                                    |               | 800           | kΩ   |

| V <sub>SAMPLE_H</sub> | Sample Logic high threshold                  |                                                    |               | 0.7 x<br>AVCC | V    |

| V <sub>SAMPLE_L</sub> | Sample Logic low threshold                   |                                                    | 0.3 x<br>AVCC |               | V    |

| V <sub>GAIN_H</sub>   | Gain Logic high threshold                    |                                                    |               | 0.7 x<br>AVCC | V    |

| V <sub>GAIN_L</sub>   | Gain Logic low threshold                     |                                                    | 0.3 x<br>AVCC |               | V    |

| R <sub>GAIN_OUT</sub> | Output resistor                              |                                                    |               | 5.5           | kΩ   |

| TIMING                |                                              |                                                    |               |               |      |

| t <sub>SS</sub>       | Soft start time                              | Ref voltage 0 to 1.2V                              |               | 4.8           | ms   |

| t <sub>DELAY</sub>    | Delay time for high optical power protection | I <sub>APD</sub> = 5 mA, I <sub>SHORT</sub> = 3 mA |               | 0.5           | μs   |

| THERMAL F             | PROTECTION                                   |                                                    |               |               |      |

| T <sub>SD</sub>       | Thermal shutdown threshold                   | T <sub>J</sub> rising                              |               | 150           | °C   |

| T <sub>SD_HYS</sub>   | Thermal shutdown hysteresis                  | T <sub>J</sub> falling below T <sub>SD</sub>       |               | 20            | °C   |

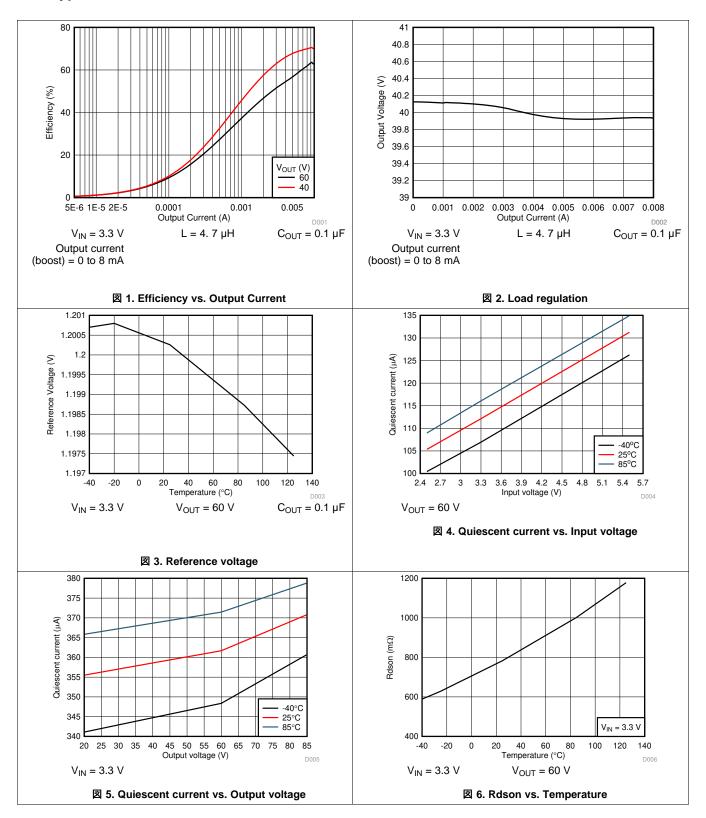

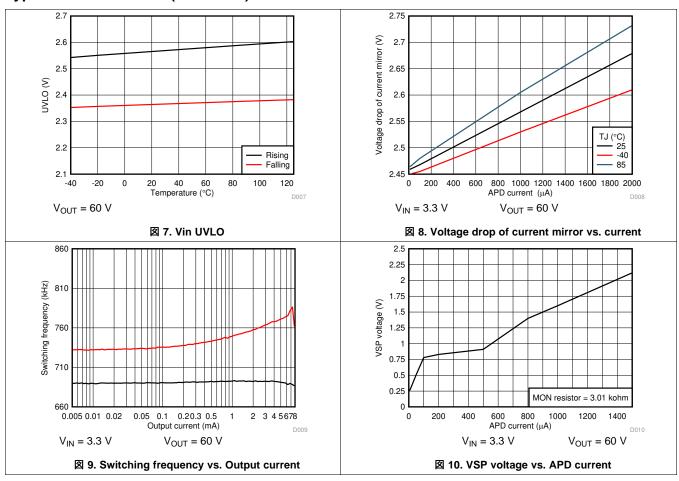

## 6.6 Typical Characteristics

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The TPS61390 is a fully integrated boost converter with an 85-V FET to convert a low input voltage to a higher voltage for biasing the APD. The TPS61390 supports an input voltage ranging from 2.5 V to 5.5 V. The device operates at a 700 kHz pulse-width modulation (PWM) crossing the whole load range.

The device can accurately mirror the APD current ranging from 0.5 uA to 2 mA. There are two ratio options for the current proportional to APD current: the MON1 (4:5) and MON2 (1:5). By connecting a resistor from the mirror output (MON1 or MON2) to GND, the current flowing through the APD is converted into the voltage crossing the resistor from MON1 / MON2 to GND.

With the sample / hold circuitry built-in and triggered by an external sampling clock, the current mirror signal (voltage) is transferred and stored on the holdup capacitor, the voltage on the holdup capacitor is then passed over to the output of an operational amplifier. An external ADC can sense the voltage of the output of the operational amplifier to measure the optical intensity.

Additionally, a high power optical protection is integrated by clamping the pre-set current limit (program by the  $I_{SHORT}$  resistor). The response time of the high optical power is typically 0.5  $\mu$ s. The device could recovery automatically when the high optical power is removed.

The device comes in a 3-mm × 3-mm QFN package with the operating junction temperature covering from –40°C to 125°C.

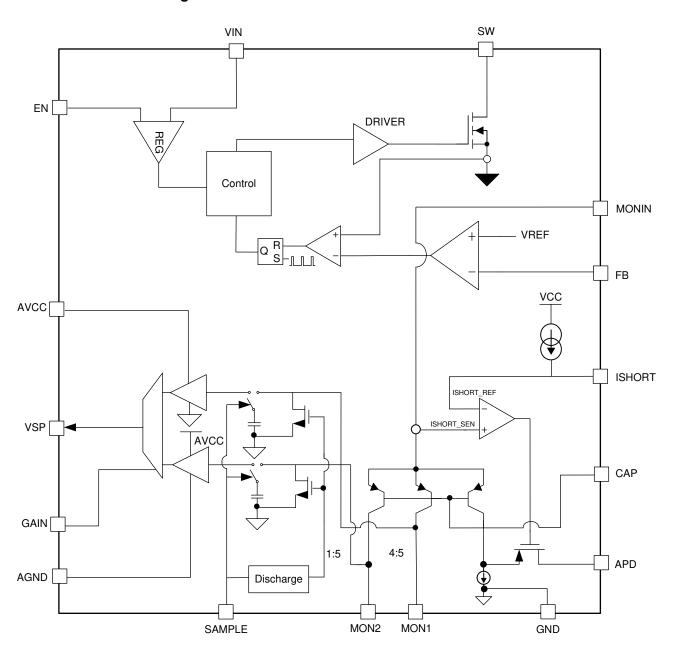

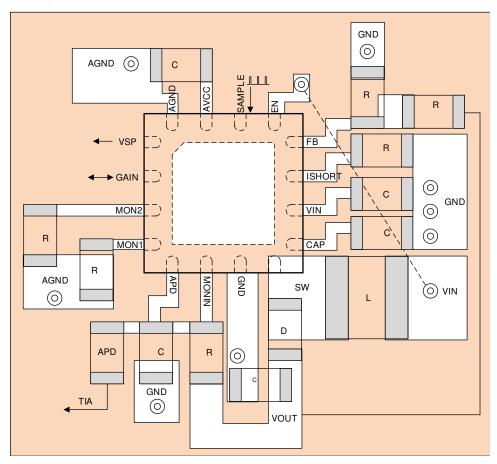

#### 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Undervoltage Lockout

An undervoltage lockout (UVLO) circuit stops the operation of the converter when the input voltage drops below the typical UVLO threshold of 2.5 V. A hysteresis of 200 mV is added so that the device cannot be enabled again until the input voltage goes up to 200 mV.

#### 7.3.2 Enable and Disable

When the input voltage is above maximal UVLO rising threshold of 2.5 V and the EN pin is pulled above the high threshold (1.2 V min.), the TPS61390 is enabled. When the EN pin is pulled below the low threshold (0.4 maximum), the device goes into shutdown mode.

#### Feature Description (continued)

#### 7.3.3 Current Mirror

There are two current mirror options for TPS61390: the gain of 4: 5 (MON1) and 1: 5 (MON2). The maximum voltage of MON1 and MON2 is 2.5 V.

#### 7.3.4 Sample and Hold

The TPS61390 has the sample-and-hold circuitry built in, including a holdup capacitor for storing the voltage capture, a FET switch, and one operational amplifier, illustrated in Functional Block Diagram.

To sample the current mirror signal, the switch connects the capacitor to the input of the common-mode operational amplifier. The amplifier converts the voltage of the capacitor to the output terminal with 4:1 ratio.

In hold mode the switch disconnects the hold-up capacitor from the operation amplifier, the voltage of the capacitor is discharged to 0 before connecting with current mirror output terminal (MON1 and MON2).

These are two ratios of the current mirror that can be selected automatically by comparing the MON1 voltage with the internal 400-mV reference. The voltage of MON1 is sampled if the MON1 voltage is below 400 mV, while the voltage of MON2 is sampled if MON1 being larger than 400 mV. The GAIN pin reports which ratio is selected for the sample and hold, the logic low (0) for MON1 while logic high (AVCC) for MON2 selected.

Also, the GAIN can be externally selected, pulling low to select the 1:5 while high for 4:5 ratio.

The voltage measured on VSP pin is calculated by 式 1 and 式 2:

$$VSP = 4 \times (0.8 \times I_{APD} \times RMON1) + 4 \times (I_{BIAS} \times RMON1)$$

#### where

- VSP is the voltage sampled on VSP pin

- I<sub>APD</sub> is the current flowing through the APD pin.

- RMON1 is the resistor connecting with MON1 pin

$$I_{BIAS}$$

is the bias current of current mirror (1)

$$VSP = 4 \times (0.2 \times I_{APD} \times RMON2) + 4 \times (I_{BIAS} \times RMON2)$$

#### where

The bias current is around 20 µA (typical) when there is no APD current flowing through. The bias voltage of MON1 or MON2 is 60 mV given a 3-kΩ MON resistor connected with MON1 or MON2. Also, the VSP voltage is reset to 250 mV prior to every sample clock coming. The maximum voltage of the MON1 is clamped to 400 mV while maximum of MON2 is 2.5 V. The maximum voltage of VSP is close to the A<sub>VCC</sub> (0.1 V lower typically), which is the supply voltage of the sample and hold circuitry.

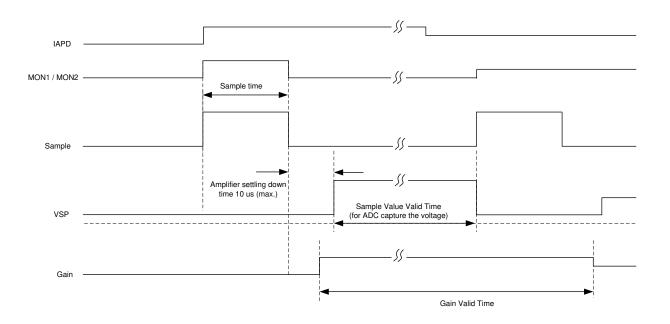

As the timing diagram shown in 2 11, the sample and hold is enabled by the rising edge of an external clock connecting to the SAMPLE pin, the holdup capacitor captures the voltage of current mirror signal (the voltage of MON1 and MON2).

At the falling edge, the sampling is stopped, and the voltage stored on the holdup capacitor is transferred to the output of the operational amplifier. The minimum time of the sampling time the TPS61390 supports is 350 ns (typically). The voltage on the stored capacitor is switched to the amplifier's input voltage. There is approximately 10-us delay time to make the output voltage of the amplifier ready.

The GAIN selector is always active and the GAIN value is captured by the falling edge of the sample signal.

(2)

#### **Feature Description (continued)**

図 11. TPS61390 Sample / Hold Circuit Timing

The output settling time of the operational amplifier is 10 µs while the maximum duration time is 100 µs with 1% derating (with the nominal voltage).

#### 7.3.5 High Optical Power Protection

There is an additional FET in series of power path connecting with the APD. When the current flowing through the APD exceeds the short protection threshold (set by connecting the resistor from I<sub>SHORT</sub> to GND), the on resistance of the FET becomes larger to clamp the current within the protection threshold by lowering the APD bias voltage. It takes typically 0.5 µs for the FET to respond in case of high optical power occurring.

When the high optical power condition releases, the TPS61390 recovers automatically back to the normal operation mode.

#### 7.4 Device Functional Mode

#### 7.4.1 PFM Operation

The TPS61390 integrates a power save mode with pulse frequency modulation (PFM) at the light load. When a light load condition occurs, the COMP pin voltage naturally decreases and reduces the peak current. When the COMP pin voltage further goes down with the load lowered and reaches the pre-set low threshold, the output of the error amplifier is clamped at this threshold and does not go down any more. If the load is further lowered, the device skips the switching cycles and reduces the switching losses and improves efficiency at the light load condition by reducing the average switching frequency.

## 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The TPS61390 is a step-up DC/DC converter with current monitor and sample / hold circuitry integrated. The following design procedure can be used to select component values for the TPS61390. This section presents a simplified discussion of the design process.

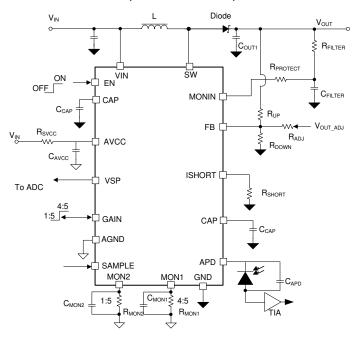

## 8.2 Typical Application

This application is designed for 2.5-V to 5.5-V input, and 60-V output user case

図 12. TPS61390 Typical Application

#### 8.2.1 Design Requirement

For this design example, use 表 1 as the design parameters.

#### 表 1. Design Parameters

| PARAMETER           | VALUE          |

|---------------------|----------------|

| Input voltage range | 2.5 V to 5.5 V |

| Output voltage      | 60 V           |

| Operating frequency | 700 kHz        |

| APD Current         | 0 to 2 mA      |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Selecting the Rectifier Diode

A Schottky diode is the preferred type for the rectifier diode due to its low forward voltage drop and small reverse recovery charge. Low reverse leakage current is important parameter when selecting the Schottky diode. The diode must be rated to handle the maximum output voltage plus the switching node ringing. Also, it must be able to handle the average output current.

#### 8.2.2.2 Selecting the Inductor

It is suggested that the TPS61390 device works in the DCM operation; otherwise the output voltage would not be delivered for low input voltage to high output voltage.

With the device working in DCM operation, the maximum inductor could be calculated by equation 式 3 and 式 4:

$$L_{MAX} = \frac{V_{IN} \times D}{f_{SW} \times I_{LIM}}$$

where

- V<sub>IN</sub> is input voltage

- D is duty cycle

- f<sub>SW</sub> is switching frequency

For instance, if  $V_{IN} = 3.3$  V,  $V_{OUT} = 60$  V,  $f_{SW} = 600$  kHz,  $I_{LIM} = 0.8$  A, the  $L_{MAX} = 6.5$   $\mu H$

However, there is minimum inductance is determined by the power delivered to the output side at given input condition.

$$L_{MIN} = 2 \times \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{\text{eff} \times f_{\text{SW}} \times I_{\text{LIM}}^2}$$

where

- V<sub>OUT</sub> is output voltage

- I<sub>OUT</sub> is output current

- · eff is the efficiency

- f<sub>SW</sub> is switching frequency

For instance, if  $I_{OUT} = 8$  mA,  $V_{OUT} = 60$  V,  $f_{SW} = 600$  kHz,  $I_{LIM} = 0.8$  A, eff = 0.6, the  $L_{MIN} = 4.2$   $\mu$ H

With the calculation aforementioned, the operating inductor is recommended between the  $L_{MIN}$  and  $L_{MAX}$ .

The 4.7 µH inductance is optimum value for using the TPS61390 in application.

#### 8.2.2.3 Selecting Output Capacitor

Use low ESR capacitors at the output to minimize output voltage ripple. Use only X5R and X7R types, which retain their capacitance over wider voltage and temperature ranges than other types. Typically use a 0.1- $\mu$ F to 1- $\mu$ F capacitor for output voltage. Take care when evaluating the derating of a ceramic capacitor under the DC bias. Ceramic capacitors can derate its capacitance at its rated voltage. Therefore, consider enough margins on the voltage rating to ensure adequate capacitance at the required output voltage.

#### 8.2.2.4 Selecting Filter Resistor and Capacitor

TI recommends an additional R-C filter be added for low ripple applications. The filter parameters is characterized based on the ripple requirement. Typically, use a  $100-\Omega$  and  $0.1-\mu F$  filter to reduce the switching output ripple.

#### 8.2.2.5 Setting the Output Voltage

The output voltage of the TPS61390 is externally adjustable using a resistor divider network. The relationship between the output voltage and the resistor divider is given by  $\pm 5$ .

$$V_{OUT} = V_{FB} \times (1 + \frac{R_{UP}}{R_{DOWN}})$$

where

- V<sub>OUT</sub> is the output voltage

- R<sub>UP</sub> the top divider resistor

- R<sub>DOWN</sub> is the bottom divider resistor

(5)

Choose  $R_{DOWN}$  to be approximately 10  $k\Omega$ . Slightly increasing or decreasing  $R_{DOWN}$  can result in closer output voltage matching when using standard value resistors. In this design,  $R_{DOWN}$  = 10  $k\Omega$  and  $R_{UP}$  = 487  $k\Omega$ , resulting in an output voltage of 60 V.

#### 8.2.2.6 Selecting Sample Window

A pulse signal is connected with SAMPLE pin; the minimum window is 350 ns while the frequency of the pulse is lower than 100 kHz.

#### 8.2.2.7 Selecting Capacitor for CAP pin

TI recommends placing a ceramic capacitor from CAP pin to GND to lower the noise for the APD current mirror. A ceramic capacitor between 10 nF and 100 nF is recommended from CAP pin to GND.

#### 8.2.2.8 Selecting Capacitor for AVCC pin

The control circuitry is powered by AVCC. A ceramic capacitor must be placed close to AVCC, with a typical capacitor value of  $2.2 \, \mu F$ .

#### 8.2.2.9 Selecting Capacitor for APD pin

A ceramic capacitor is required to make the APD current mirror more accurately against the noise coupling. The recommended values are from 100 pF to 470 pF.

#### 8.2.2.10 Selecting the Resistors of MON1 or MON2

The TPS61390 provides two currents proportional to APD current on the MON pins, 4:5 and 1:5. The voltage of the resistors connecting to the MON pins convert the APD current to voltage. The relation between APD current and the voltage on MON 1 or MON 2 pins is shown in 式 1 and 式 2.

The resistor value depends on the VSP pin voltage. While RC time constant of MON 1 and MON 2 is recommended to be 1/10 of the sample window time.

## 8.2.2.11 Selecting the Capacitors of MON1 or MON2

The capacitors are added to the MON1 or MON2 pins to decouple the noise of APD transient current. Suggested RC time (formed by the MON1 or MON2 is 1/10 with that of the sample window. With 3-k $\Omega$  R<sub>MON</sub> resistance, TI recommends a 10-pF capacitor connecting MON1 or MON2 pins to make sure the voltage on MON1 or MON2 is stable before sample signal coming.

It is recommended that RC time constant of MON 1 and MON 2 is around 1/10 of the sample window time.

#### 8.2.2.12 Selecting the Resistor of Gain pin

The GAIN pin can be configured as both input and output. If the GAIN pin is configured as output pin, TI recommends that it be directly connected with the external I/O.

If the pin is configured as the input pin to select the current mirror ratio, the pull up or pull down resistor must be lower than 1-k $\Omega$  as there is an internal 5-k $\Omega$  resistor on the GAIN pin.

#### 8.2.2.13 Selecting the Short Current Limit

The output current short-protection threshold of the TPS61390 can be programmed by an external resistor with  $\pm$  6. The short protection threshold is calculated by  $\pm$  1 and  $\pm$  2:

$$I_{SHORT} = \frac{100}{R_{SHORT}}$$

(6)

#### where

- I<sub>SHORT</sub> (mA) is the short protection threshold

- $R_{SHORT}(k\Omega)$  is the resistor connecting from ISHORT pin to GND

For instance, if  $R_{SHORT} = 25 \text{ k}\Omega$ , the  $I_{SHORT} = 4 \text{ mA}$ .

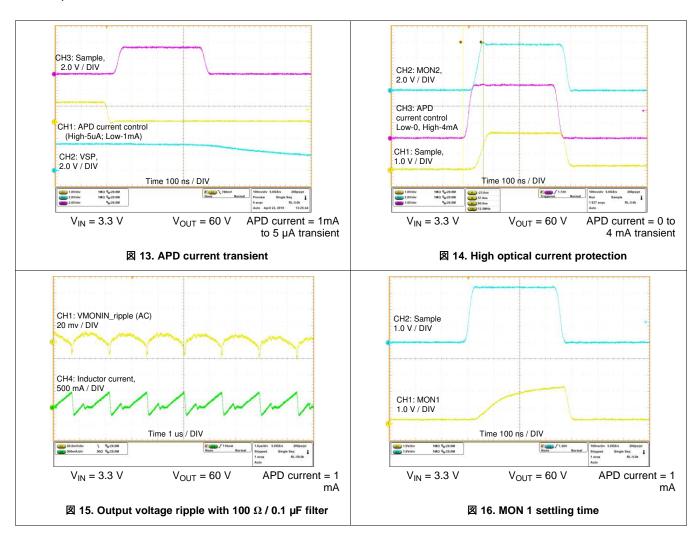

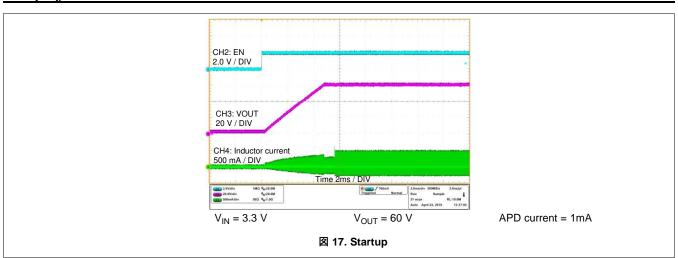

## 8.2.3 Application Curves

Typical condition  $V_{IN}=3.3~V,~V_{OUT}=60~V,~R_{SHORT}=5~k\Omega,~R_{MON1/2}=3.01~k\Omega$  and  $C_{MON1/2}=10~pF.$  Application waveforms are measured with the inductor 4.7  $\mu H$  and the output capacitance 0.1  $\mu F$  at room temperature.

## 9 Power Supply Recommendations

The device is designed to operate from an input voltage supply range between 2.5 V and 5.5 V. This input supply must be well regulated. If the input supply is located more than a few inches from the device, the bulk capacitance may be required in addition to the ceramic bypass capacitors. An electrolytic capacitor with a value of  $47 \, \mu F$  is a typical choice.

## 10 Layout

## 10.1 Layout Guidelines

The basic PCB board layout requires a separation of sensitive signal and power paths. If the layout is not carefully done, the regulator could suffer from the instability or noise problems. Use the following checklist to get good performance for a well-designed board:

- Minimize the high current path including the switch FET, rectifier FET, and the output capacitor. This loop contains high di / dt switching currents (nano seconds per ampere) and easy to transduce the high frequency noise:

- Place the noise sensitive network like sample hold and current mirror output (MON1, MON2) being far away from the SW trace;

- Split the ground for the power GND, signal GND. Use a separate ground trace to connect the sample/hold and boost circuitry. Connect this ground trace to the main power ground at a single point to minimize circulating currents.

## 10.2 Layout Example

図 18. Layout Example

## 11 デバイスおよびドキュメントのサポート

#### 11.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 11.2 コミュニティ・リソース

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 11.3 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.4 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 28-Sep-2021

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TPS61390RTER     | ACTIVE     | WQFN         | RTE                | 16   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 1XQH                    | Samples |

| TPS61390RTET     | ACTIVE     | WQFN         | RTE                | 16   | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 1XQH                    | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 28-Sep-2021

PACKAGE MATERIALS INFORMATION

www.ti.com 17-Oct-2019

## TAPE AND REEL INFORMATION

| _ |    |                                                           |

|---|----|-----------------------------------------------------------|

|   |    | Dimension designed to accommodate the component width     |

|   |    | Dimension designed to accommodate the component length    |

|   |    | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

| ſ | P1 | Pitch between successive cavity centers                   |

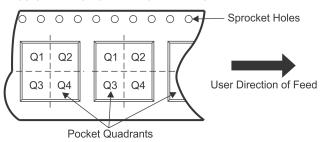

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS61390RTER | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS61390RTET | WQFN            | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 17-Oct-2019

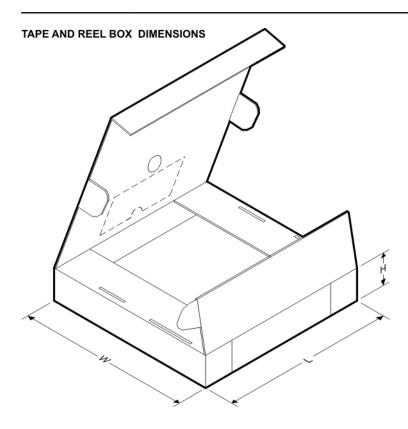

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

|--------------|--------------|-----------------|----------|------|-------------|------------|-------------|--|

| TPS61390RTER | WQFN         | RTE             | 16       | 3000 | 367.0       | 367.0      | 35.0        |  |

| TPS61390RTET | WQFN         | RTE             | 16       | 250  | 210.0       | 185.0      | 35.0        |  |

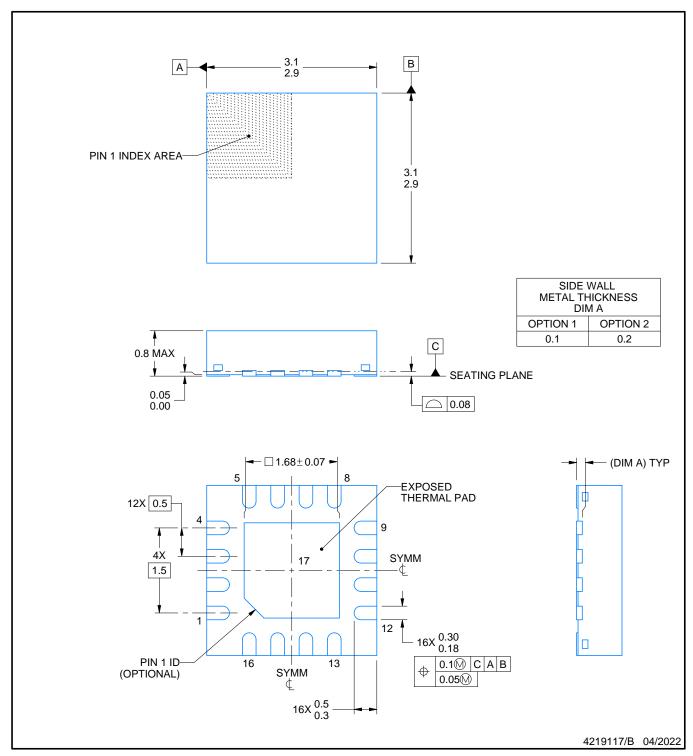

3 x 3, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

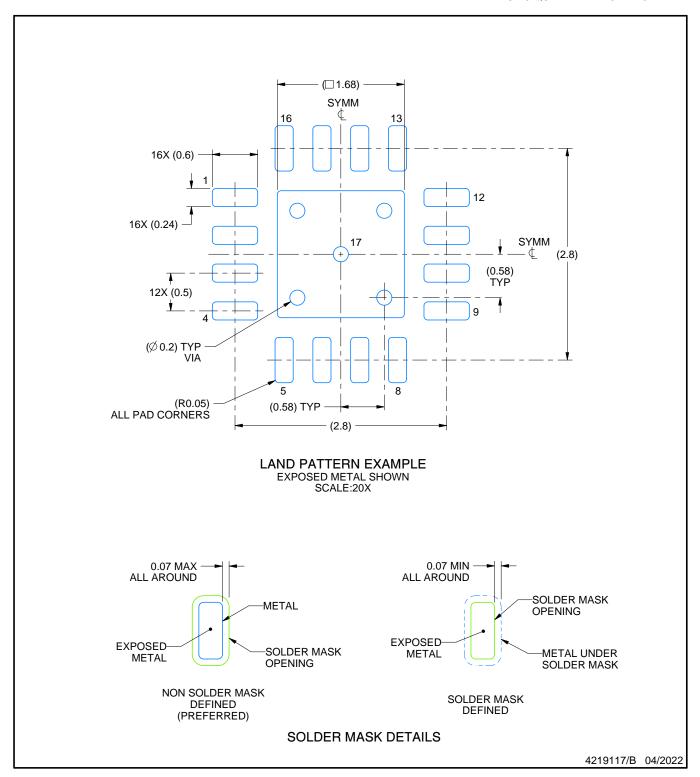

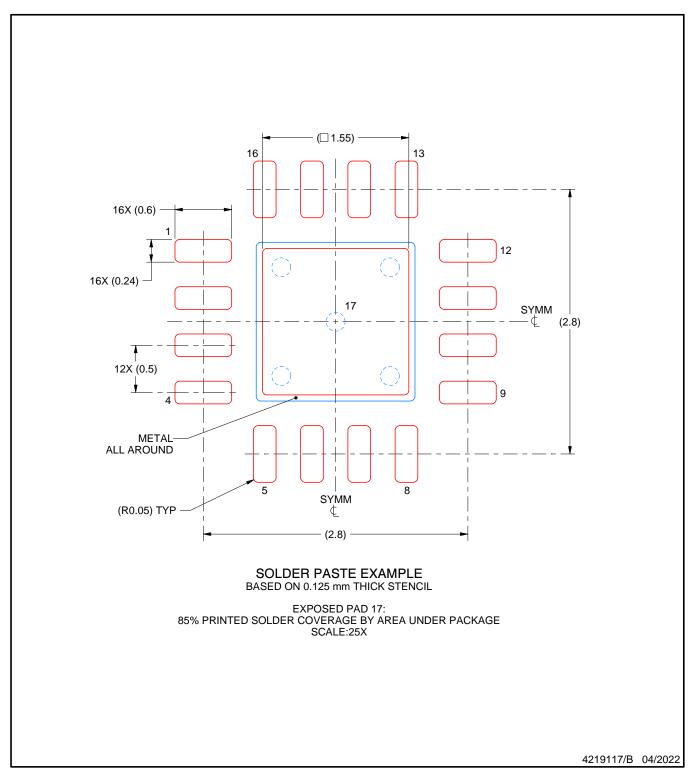

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TI はそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022. Texas Instruments Incorporated