# 800mA/1000mA, 3MHz 同期式降圧型コンバータ I<sup>2</sup>C<sup>TM</sup>互換インターフェイス/チップスケール・パッケージ

## 特 長

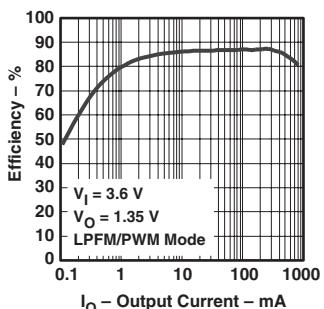

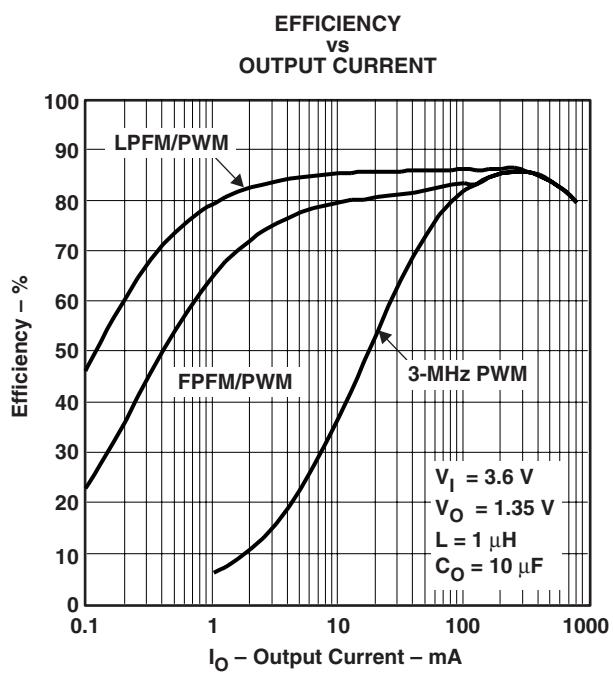

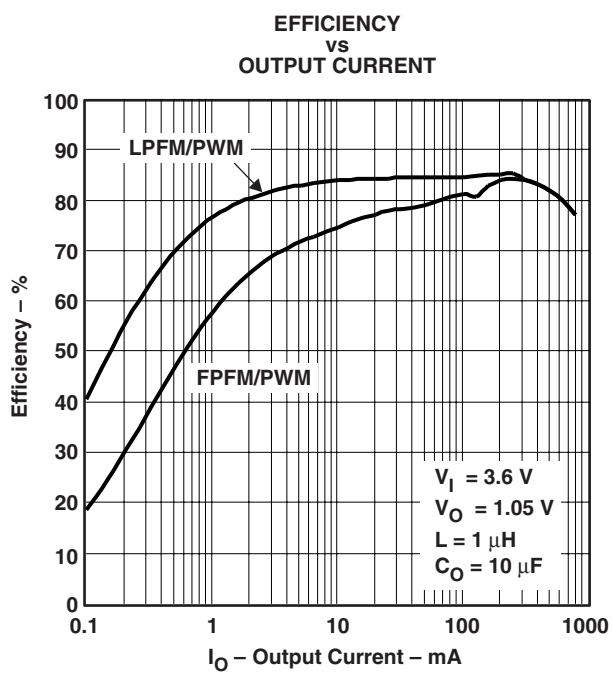

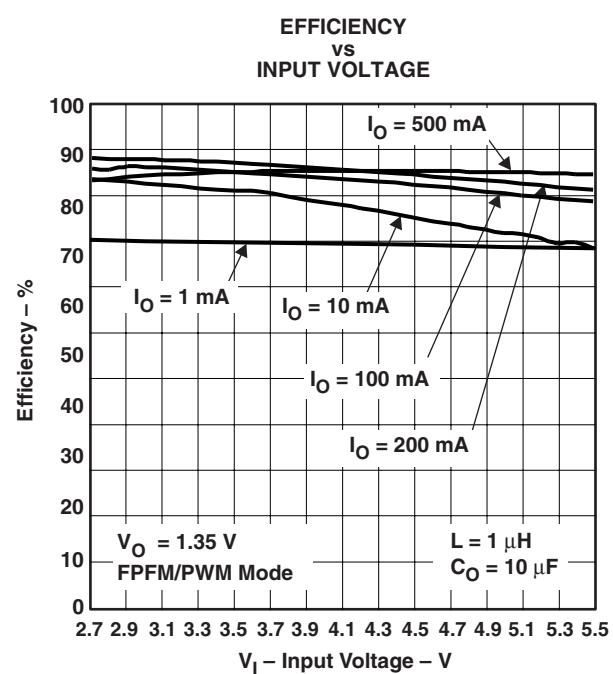

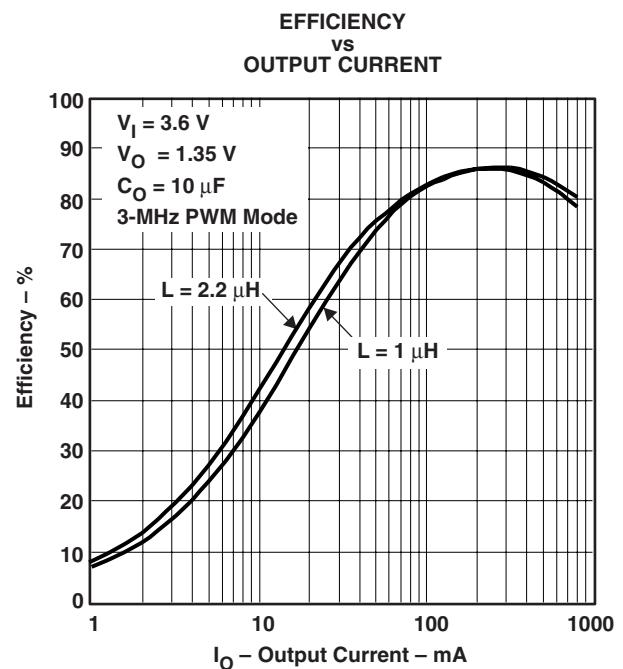

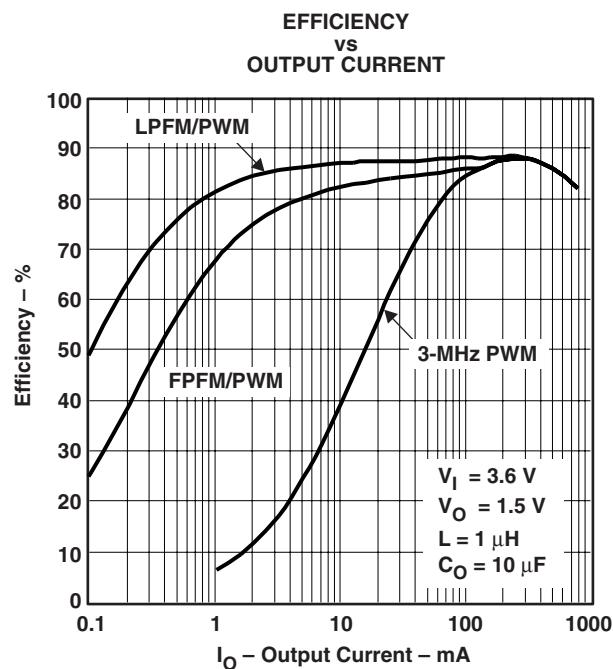

- 効率：88% (3MHz動作時)

- 出力電流：800mA ( $V_I = 2.7V$ 時)

- 3MHzの固定周波数動作

- クラス最高レベルの負荷/入力変動に対する過渡応答特性

- 厚さ1mmの電源を構成可能

- 出力電圧精度： $\pm 2\%$  (PWM動作時)

- 最小オン時間：35ns

- 効率を最適化したパワーセーブ・モード (ライトPFMモード)

- 過渡応答を最適化したパワーセーブ・モード (ファストPFMモード)

- 無負荷時消費電流： $28\mu A$  (Typ)

- I<sup>2</sup>C互換インターフェイス (最大3.4Mbps)

- 出力電圧は端子設定で選択可能

- 動作中に外部クロック信号に同期可能

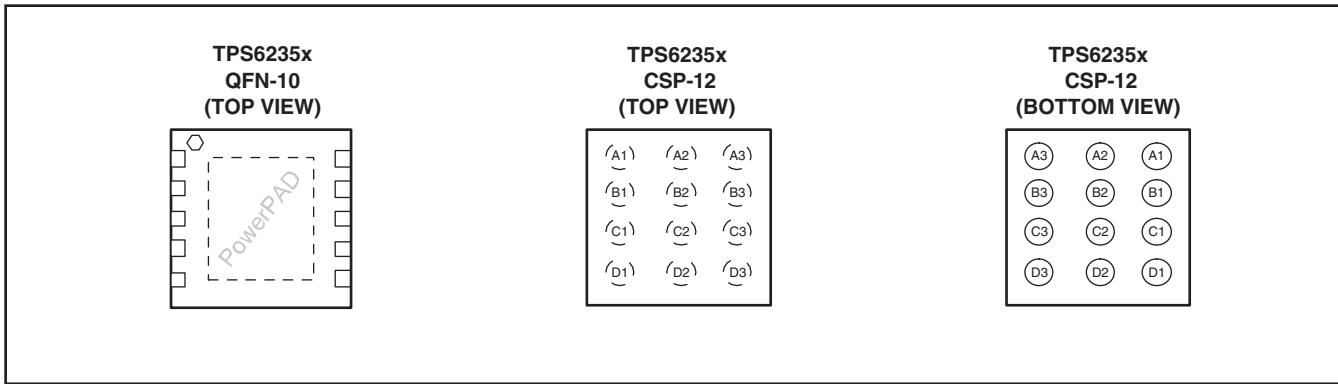

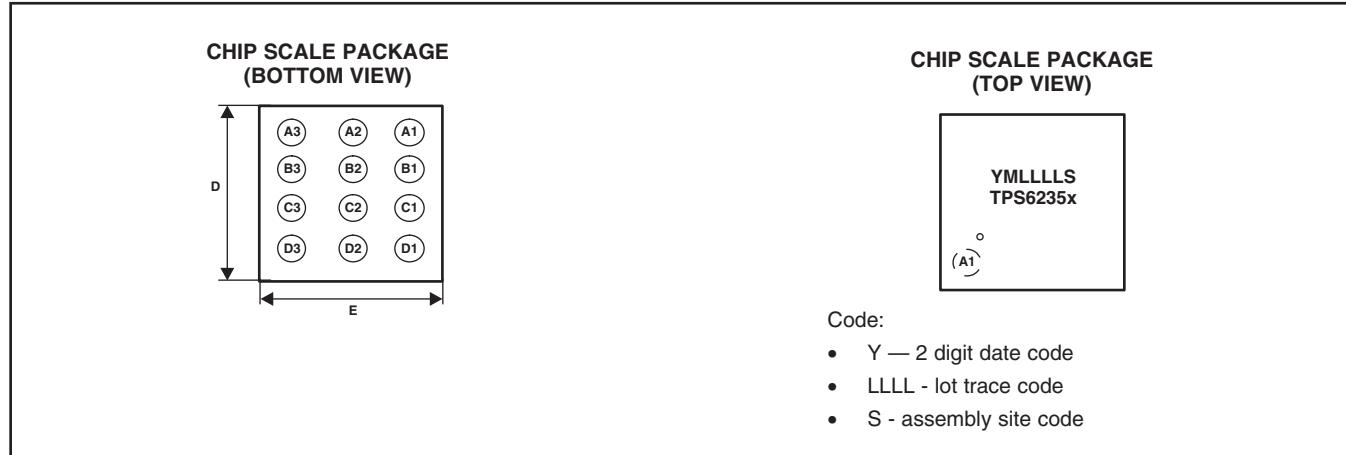

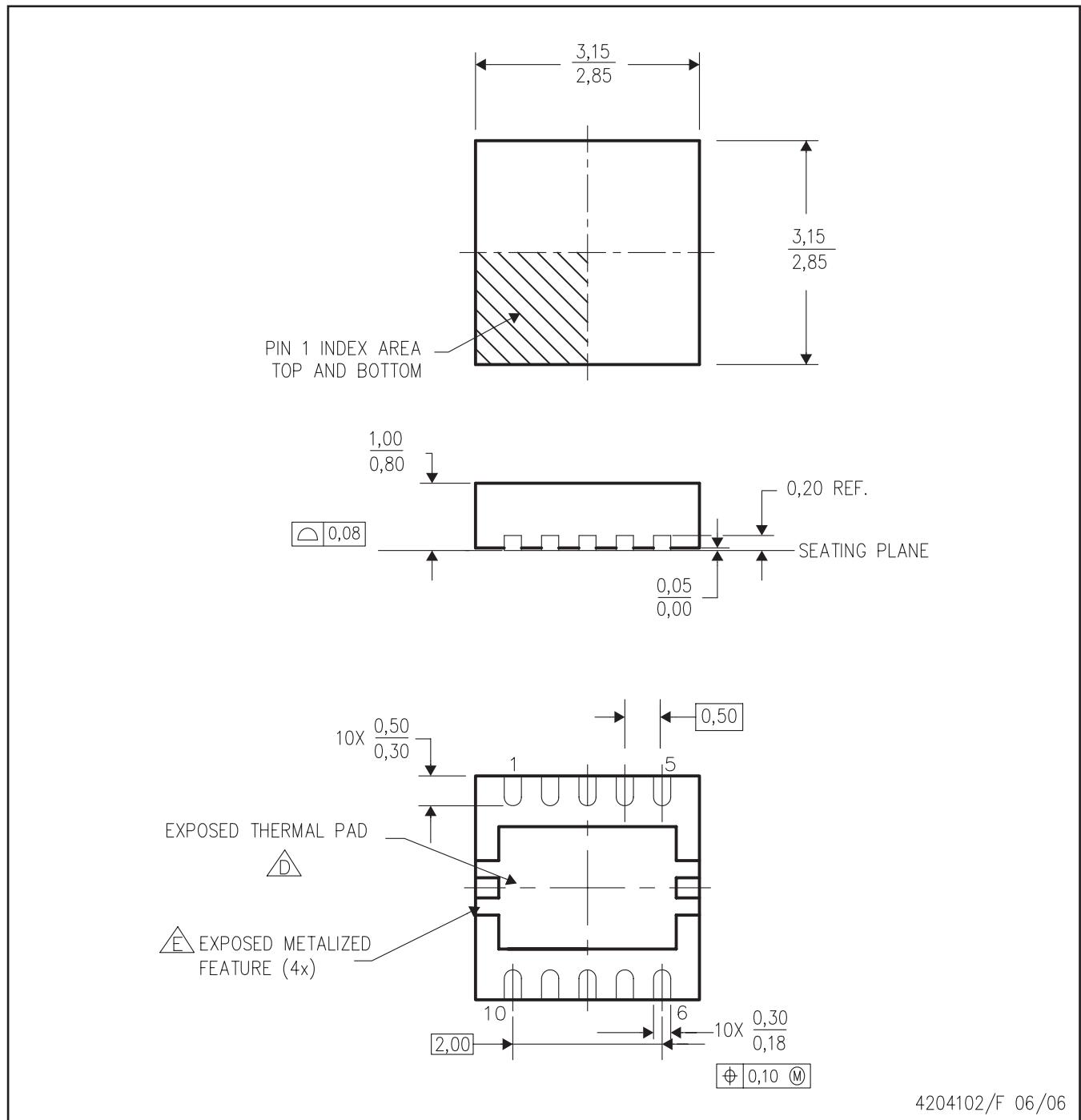

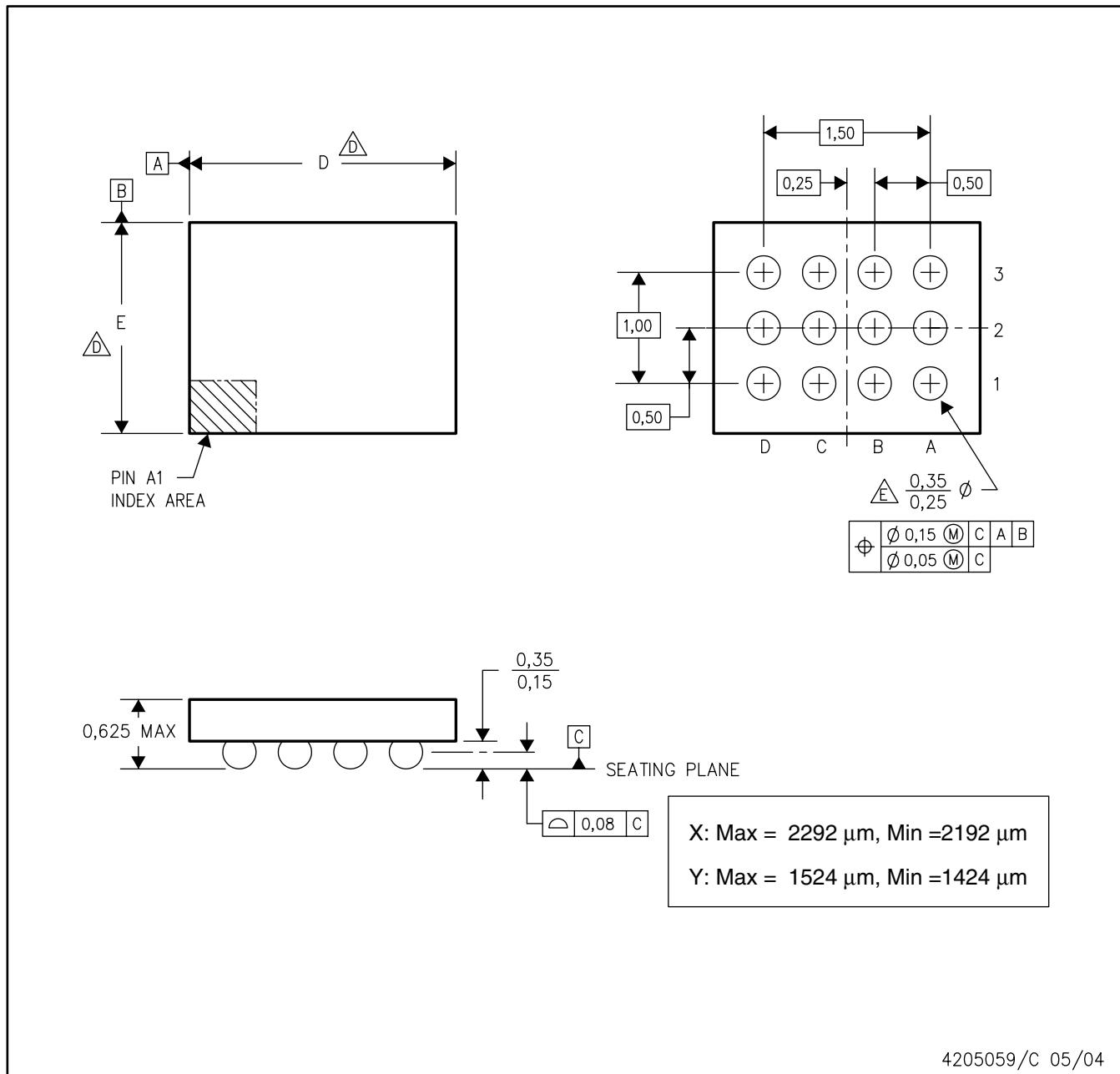

- 10ピンQFNパッケージ (3×3mm)、12ピンNanoFree<sup>TM</sup> (CSP)パッケージ

## ア プ リ ケ シ ョ ン

- SmartReflex<sup>TM</sup>準拠の電源

- スプリット電源のDSP、マイクロプロセッサ、OMAP<sup>TM</sup>、XSCALE<sup>TM</sup>

- 携帯電話、スマート・フォン

- PDA、ポケットPC

- ディジタル・カメラ

- 超小型DC/DCコンバータ・モジュール

## 概 要

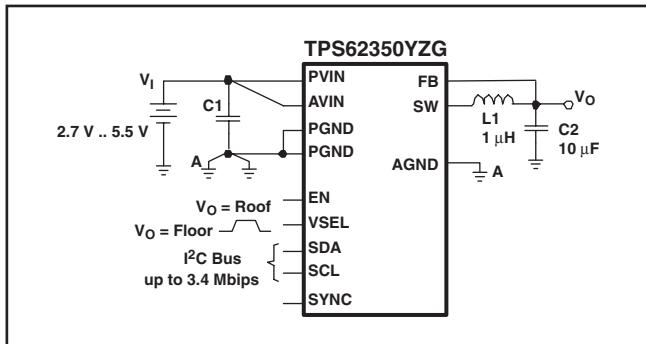

TPS6235xは、高周波の同期式降圧型DC/DCコンバータで、バッテリー駆動のポータブル・アプリケーションに最適なデバイスです。ロー・パワーのアプリケーション向けに、最大800mAの負荷電流まで対応可能で、小型で低成本のインダクタやコンデンサを使用することができます。

このデバイスは、单一セルのリチウム・イオン・バッテリーを電源とする携帯電話等のポータブル・アプリケーションに最適です。出力電圧をI<sup>2</sup>Cインターフェイス制御により最小0.6Vまで可変できるため、スマート・フォン、PDA、携帯型PC等に用いられる低電圧型のDSPやプロセッサのコア電源に対応しています。

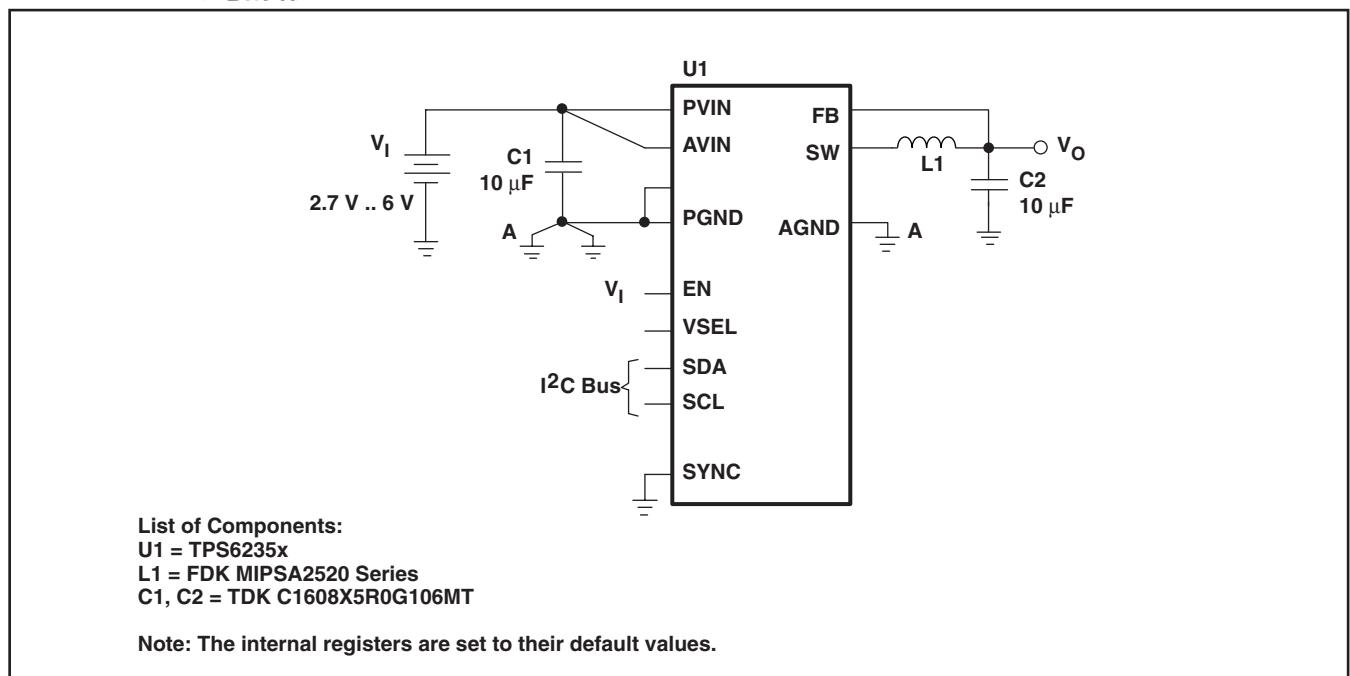

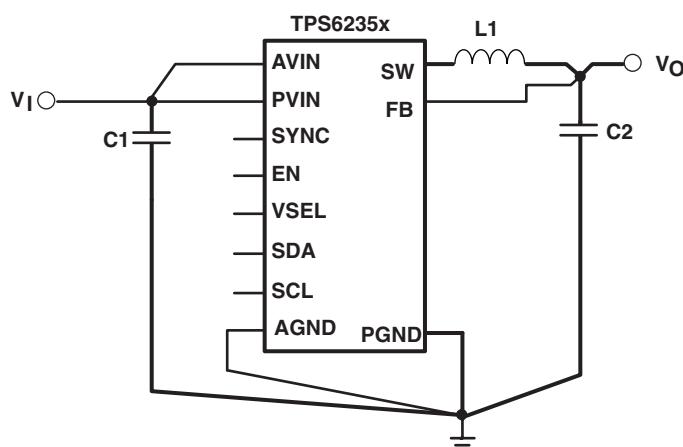

## 代表的なアプリケーション回路

EFFICIENCY vs LOAD CURRENT

NanoFree, SmartReflex, OMAP, PowerPADは、テキサス・インスツルメンツの登録商標です。

XSCALEは、Intel Corporation, I<sup>2</sup>Cは、Philips Corporationの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

TPS6235xは3MHzの固定スイッチング周波数で動作しますが、全負荷電流範囲にわたって高効率を維持するよう軽負荷電流時にはパワーセーブ・モード動作となり、効率が最適化されます。シャットダウン・モードでは、消費電流は2µA未満にまで低減します。

シリアル・インターフェイスは、ファストモード/標準モード/高速モードのそれぞれのI<sup>2</sup>C規格と互換性があり、最大3.4Mbpsの転送が可能となります。この通信インターフェイスは、最小12.5mV電圧ステップをもつ出力電圧デジタル可変機能に使用され、動作モード（ライトPFM、ファストPFM、固定PWM）の再プログラムや、出力電圧のイネーブル/ディスエーブルをコンバータの動作中に行うことができます。

## 静電気放電対策

これらのデバイスは、限定的なESD（静電破壊）保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを伝導性のフォームに入れる必要があります。

## 発注情報

| 製品型番 <sup>(1)</sup>     | 出力電圧範囲 <sup>(2)</sup> | 初期出力電圧 <sup>(2)</sup> |        | 初期値<br>EN_DCDC<br>BIT <sup>(2)</sup> | SYNC | I <sup>2</sup> C<br>LSB ADDRESS<br>BITS <sup>(2)</sup> |    | パッケージ  | 発注型式名 <sup>(3)</sup> | パッケージ捺印  |

|-------------------------|-----------------------|-----------------------|--------|--------------------------------------|------|--------------------------------------------------------|----|--------|----------------------|----------|

|                         |                       | VSEL0                 | VSEL1  |                                      |      | A1                                                     | A0 |        |                      |          |

| TPS62350 <sup>(4)</sup> | 0.75 V to 1.5375 V    | 1.05 V                | 1.35 V | 1                                    | YES  | 0                                                      | 0  | CSP-12 | TPS62350YZG          | TPS62350 |

| TPS62351                | 0.9 V to 1.6875 V     | 1.10 V                | 1.50 V | 0                                    | NO   | 1                                                      | 0  | QFN-10 | TPS62351DRC          | BNT      |

|                         |                       |                       |        |                                      | YES  | 1                                                      | 0  | CSP-12 | TPS62351YZG          | TPS62351 |

|                         |                       |                       |        |                                      | YES  | 1                                                      | 0  | CSP-12 | TPS62352YZG          | TPS62352 |

| TPS62353                | 0.75 V to 1.5375 V    | 1.00 V                | 1.20 V | 1                                    | YES  | 0                                                      | 0  | CSP-12 | TPS62353YZG          | TPS62353 |

| TPS62354 <sup>(4)</sup> | 0.75 V to 1.5375 V    | 1.05 V                | 1.30 V | 1                                    | YES  | 1                                                      | 0  | CSP-12 | TPS62354YZG          | TPS62354 |

| TPS62355 <sup>(4)</sup> | 0.75 V to 1.5375 V    | 0.90 V                | 1.15 V | 1                                    | NO   | 1                                                      | 1  | QFN-10 | TPS62355DRC          | CCP      |

| TPS62356                | 1.5 V to 1.975 V      | 1.80 V                | 1.80 V | 1                                    | YES  | 0                                                      | 0  | CSP-1  | TPS62356YZG          | TPS62356 |

(1) 全デバイスは商用温度範囲の-40°C~85°Cの動作で規定されています。

(2) 出力電圧範囲、デフォルト出力電圧、I<sup>2</sup>Cアドレスのカスタム化については工場に連絡してください。

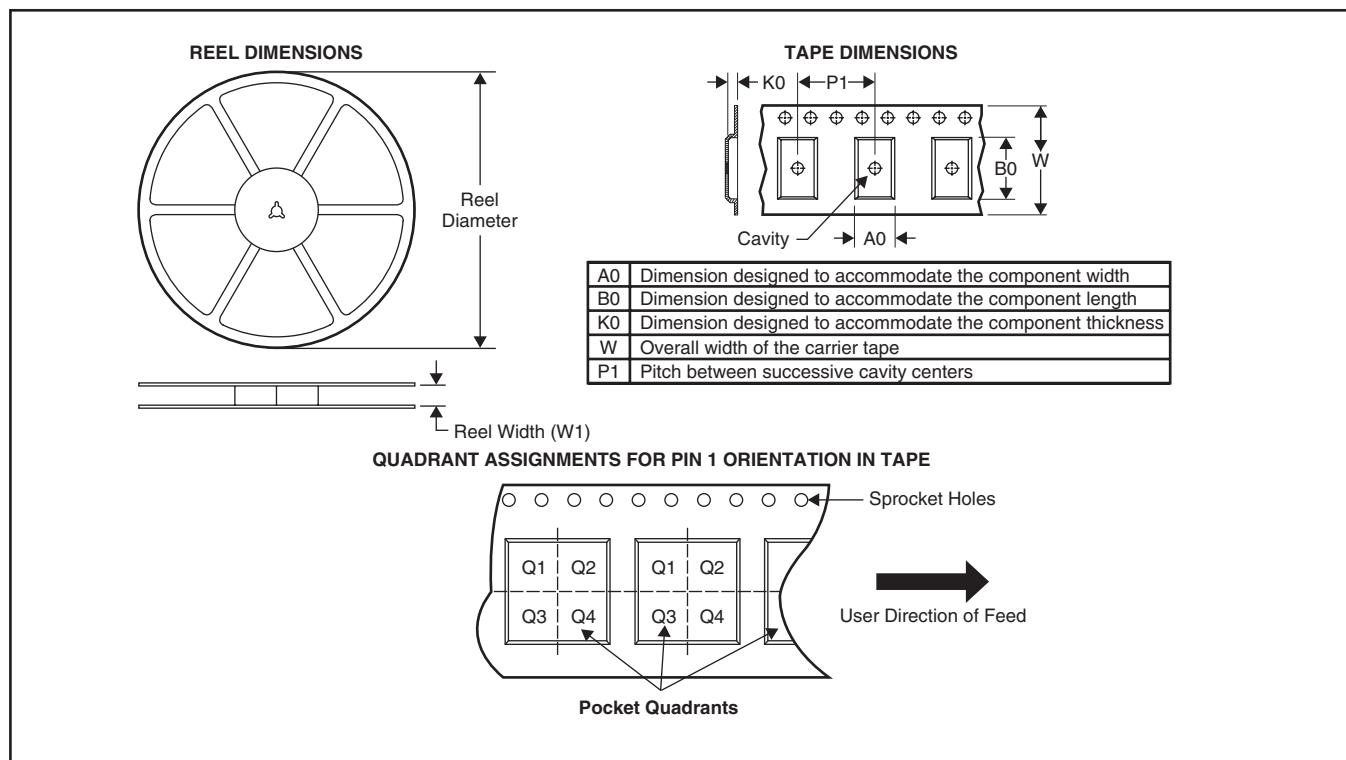

(3) YZGパッケージはテープ/リールで供給されています。型番にRを付けると（例、TPS6235xYZGR, TPS6235xDRCR）リール当たりの数量は3000個で、Tを付けると（例、TPS6235xYZGT, TPS6235xDRCT）リール当たりの数量は250個です。最新のパッケージ及び発注情報については、このデータシートの最後部のパッケージ情報またはTIウェブ・サイトwww.ti.comを参照してください。

(4) 以下のレジスタ・ビットは内部ハードウェア・ロジックにより設定されており、ユーザーはI<sup>2</sup>Cを介してプログラムすることはできません。

- VSEL0[7:6] = 11

- VSEL1[7:6] = 11

- CONTROL1[4:2] = 100

- CONTROL2[7:6] = 10, CONTROL2[4:3] = 00

## 絶対最大定格

動作温度範囲内（特に記述がない限り）<sup>(1)</sup>

|                           |                                                    | 単位                 |

|---------------------------|----------------------------------------------------|--------------------|

| V <sub>I</sub>            | Voltage at AVIN, PVIN <sup>(2)</sup>               | -0.3V to 7 V       |

|                           | Voltage at SW <sup>(2)</sup>                       | -0.3V to 7 V       |

|                           | Voltage at EN, VSEL, SCL, SDA, SYNC <sup>(2)</sup> | -0.3V to 7 V       |

|                           | Voltage at FB <sup>(2)</sup>                       | -0.3V to 4.2 V     |

| Power dissipation         |                                                    | Internally limited |

| T <sub>J</sub>            | Maximum operating junction temperature             | 150°C              |

| T <sub>stg</sub>          | Storage temperature range                          | -65°C to 150°C     |

| ESD rating <sup>(3)</sup> | Human body model                                   | 2 kV               |

|                           | Charge device model                                | 1 kV               |

|                           | Machine model                                      | 200 V              |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) 全ての電圧値は回路のグランド端子を基準にしています。

(3) 静電破壊試験条件

人体モデル：コンデンサ100pF、放電抵抗1.5kΩ

マシンモデル：コンデンサ200pF

## 推奨動作条件

動作温度範囲内 (特に記述がない限り)

|       |                                              | MIN | NOM | MAX | 単位 |

|-------|----------------------------------------------|-----|-----|-----|----|

| $V_I$ | Input voltage range                          | 2.7 | 5.5 | V   |    |

| $T_A$ | Operating temperature range (1)              | -40 | 85  | °C  |    |

| $T_J$ | Operating virtual junction temperature range | -40 | 125 | °C  |    |

(1) 消費電力が高いアプリケーションまたはパッケージの熱抵抗が低いアプリケーションでは、最大周囲温度を計算しなおす必要があります。

最大周囲温度 ( $T_A(max)$ ) は、動作ジャンクション温度の最大値 ( $T_{J(max)}$ )、アプリケーション内のデバイスの最大消費電力 ( $P_{D(max)}$ )、およびアプリケーション内のパーツ/パッケージのジャンクションと周囲の間の熱抵抗 ( $\theta_{JA}$ ) に依存し、次の式で計算されます。

$$T_{A(max)} = T_{J(max)} - (\theta_{JA} \times P_{D(max)})$$

## 損失定格<sup>(1)</sup>

| パッケージ | $R_{\theta JA}$ <sup>(2)</sup> | $T_A \leq 25^\circ C$ の電力定格 | ディレーティング係数<br>$T_A = 25^\circ C$ 超過時 |

|-------|--------------------------------|-----------------------------|--------------------------------------|

| DRC   | 49°C/W                         | 2050 mW                     | 21 mW/°C                             |

| YZG   | 89°C/W                         | 1100 mW                     | 12 mW/°C                             |

(1) 最大消費電力は  $T_{J(max)}$ 、 $\theta_{JA}$ 、 $T_A$  の関数です。許容周囲温度における許容最大消費電力は、 $P_D = [T_{J(max)} - T_A] / \theta_{JA}$  です。

(2) この熱データはhigh-Kボード (JESD51-7 JEDEC規格に準拠した4層ボード) を用いて測定されています。

## 電気的特性

動作温度範囲内、 $T_A = 25^\circ C$ 、 $V_I = 3.6 V$ 、 $EN = V_I$ 、 $VSEL = V_I$ 、 $SYNC = GND$ 、 $VSEL0[6]$  bit = 1. (特に記述がない限り)

| パラメータ                                                     |                              | テスト条件                                                        | MIN  | TYP  | MAX  | 単位        |

|-----------------------------------------------------------|------------------------------|--------------------------------------------------------------|------|------|------|-----------|

| <b>SUPPLY CURRENT</b>                                     |                              |                                                              |      |      |      |           |

| $I_Q$<br>Operating quiescent current                      | TPS62350/1/2/3/4/5           | $I_O = 0$ mA, Fast PFM mode enabled<br>Device not switching  | 110  | 150  |      | $\mu A$   |

|                                                           | TPS62356                     |                                                              | 117  | 160  |      |           |

|                                                           | TPS62350/1/2/3/4/5           | $I_O = 0$ mA, Light PFM mode enabled<br>Device not switching | 28   | 45   |      | $\mu A$   |

|                                                           | TPS62356                     |                                                              | 35   | 52   |      |           |

|                                                           | TPS62350/1/2/3/4/5/6         | $I_O = 0$ mA, 3-MHz PWM mode operation                       | 4.8  |      |      | $mA$      |

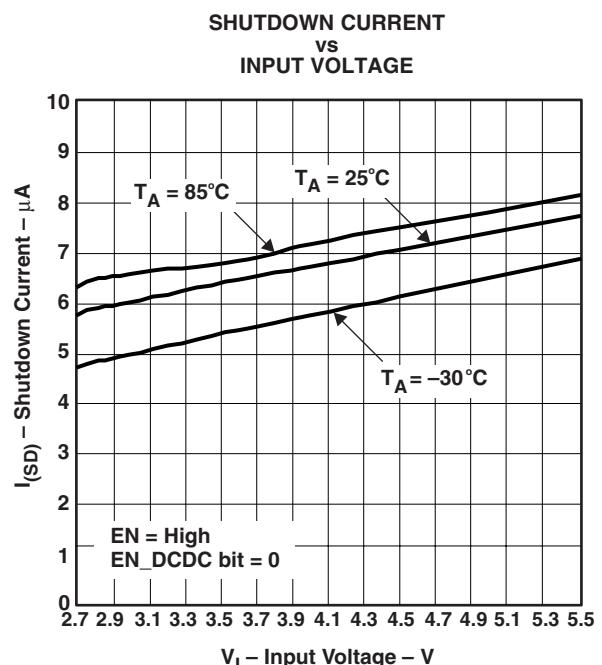

| $I_{(SD)}$<br>Shutdown current                            | EN = GND, EN_DCDC bit = X    |                                                              | 0.1  | 2    |      | $\mu A$   |

|                                                           | EN = $V_I$ , EN_DCDC bit = 0 |                                                              | 6.5  |      |      | $\mu A$   |

| $V_{(UVLO)}$<br>Undervoltage lockout threshold            |                              |                                                              | 2.20 | 2.3  |      | V         |

| <b>ENABLE, VSEL, SDA, SCL, SYNC</b>                       |                              |                                                              |      |      |      |           |

| $V_{IH}$<br>High-level input voltage                      |                              |                                                              | 1.2  |      |      | V         |

| $V_{IL}$<br>Low-level input voltage                       |                              |                                                              |      | 0.4  |      | V         |

| $I_{lkg}$<br>Input leakage current                        | Input tied to GND or $V_I$   |                                                              | 0.01 | 1    |      | $\mu A$   |

| <b>POWER SWITCH</b>                                       |                              |                                                              |      |      |      |           |

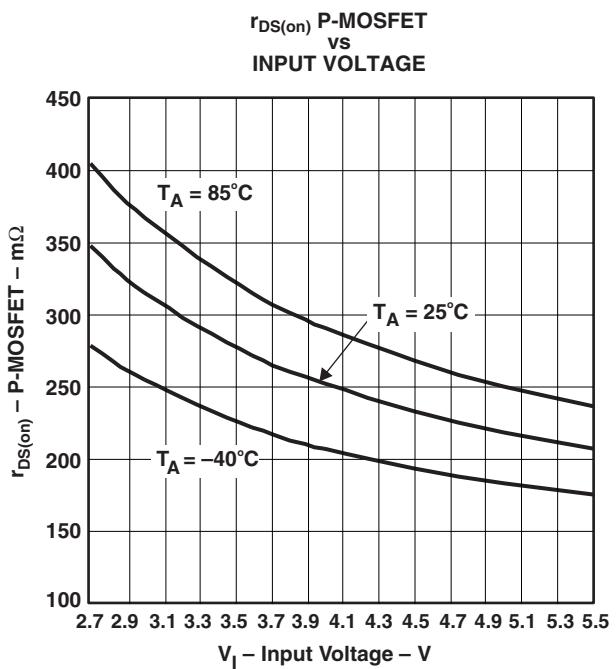

| $r_{DS(on)}$<br>P-channel MOSFET on resistance            | TPS62350/1/2/3/4/5           | $V_I = V_{(GS)} = 3.6 V$ , YZG package                       | 250  | 500  |      | $m\Omega$ |

|                                                           |                              | $V_I = V_{(GS)} = 3.6 V$ , DRC package                       | 275  | 500  |      |           |

|                                                           |                              | $V_I = V_{(GS)} = 2.7 V$ , DRC package                       | 350  | 750  |      |           |

|                                                           |                              | $V_I = V_{(GS)} = 3.2 V$ , YZG package                       | 320  | 500  |      |           |

| $I_{lkg}$<br>P-channel leakage current                    |                              | $V_{(DS)} = 6 V$                                             |      | 1    |      | $\mu A$   |

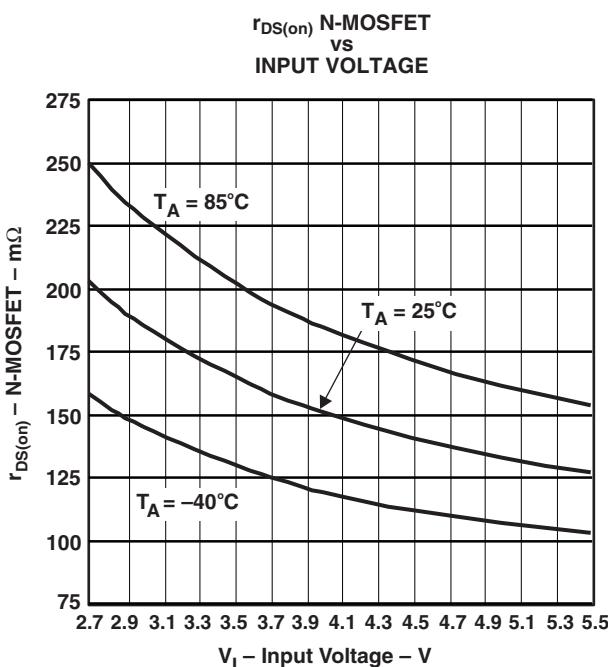

| $r_{DS(on)}$<br>N-channel MOSFET on resistance            | TPS62350/1/2/3/4/5/6         | $V_I = V_{(GS)} = 3.6 V$ , YZG package                       | 150  | 350  |      | $m\Omega$ |

|                                                           |                              | $V_I = V_{(GS)} = 3.6 V$ , DRC package                       | 165  | 350  |      |           |

|                                                           |                              | $V_I = V_{(GS)} = 2.7 V$ , YZG / DRC package                 | 210  | 500  |      |           |

| $I_{lkg}$<br>N-channel leakage current                    |                              | $V_{(DS)} = 6 V$                                             |      | 1    |      | $\mu A$   |

| $R_{(DIS)}$<br>Discharge resistor for power-down sequence |                              |                                                              |      | 15   | 50   | $\Omega$  |

| P-MOS current limit                                       | TPS62350/1/2/3/4/5           | $2.7 V \leq V_I \leq 5.5 V$                                  | 1150 | 1350 | 1600 | $mA$      |

|                                                           | TPS62356                     |                                                              | 1300 | 1550 | 1800 | $mA$      |

| N-MOS current limit (sourcing)                            | TPS62350/1/2/3/4/5           | $2.7 V \leq V_I \leq 5.5 V$                                  | 900  | 1100 | 1300 | $mA$      |

|                                                           | TPS62356                     |                                                              | 1200 | 1400 | 1700 | $mA$      |

| N-MOS current limit (sinking)                             | TPS62350/1/2/3/4/5           | $2.7 V \leq V_I \leq 5.5 V$                                  | -500 | -700 | -900 | $mA$      |

|                                                           | TPS62356                     |                                                              | -500 | -700 | -900 | $mA$      |

| Input current limit under short-circuit conditions        | TPS62350/1/2/3/4/5           | $V_O = 0 V$                                                  |      | 675  |      | $mA$      |

|                                                           | TPS62356                     |                                                              |      | 775  |      | $mA$      |

| Thermal shutdown                                          |                              |                                                              |      | 150  |      | °C        |

| Thermal shutdown hysteresis                               |                              |                                                              |      | 20   |      | °C        |

## 電気的特性

動作温度範囲内、 $T_A = 25^\circ\text{C}$ .  $V_I = 3.6 \text{ V}$ ,  $\text{EN} = V_I$ ,  $\text{VSEL} = V_I$ ,  $\text{SYNC} = \text{GND}$ ,  $\text{VSEL0}[6] \text{ bit} = 1$ . (特に記述がない限り)

| パラメータ                |                                     | テスト条件              | MIN                                                                                                                                                                                                        | TYP   | MAX    | 単位         |

|----------------------|-------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------------|

| <b>OSCILLATOR</b>    |                                     |                    |                                                                                                                                                                                                            |       |        |            |

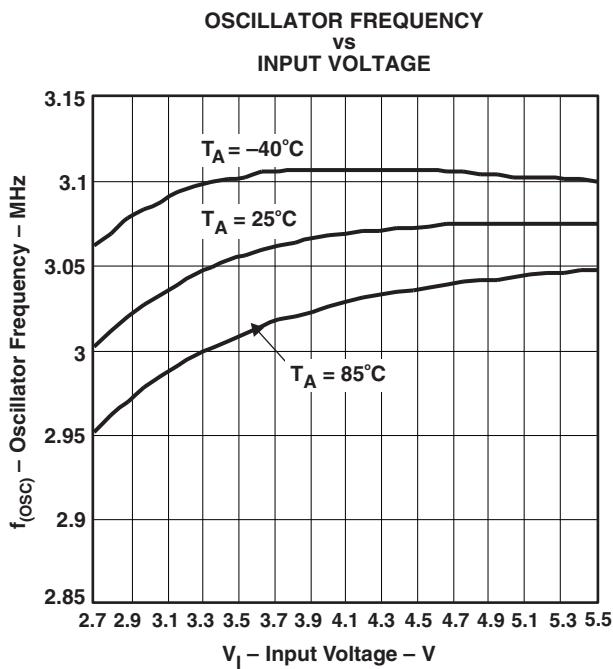

| $f_{\text{SW}}$      | Oscillator frequency                | CONTROL2[4:3] = 00 | 2.65                                                                                                                                                                                                       | 3     | 3.35   | MHz        |

| $f_{(\text{SYNC})}$  | Synchronization range               |                    | 2.65                                                                                                                                                                                                       | 3.35  |        | MHz        |

|                      | Duty cycle of external clock signal |                    | 20%                                                                                                                                                                                                        | 80%   |        |            |

| <b>OUTPUT</b>        |                                     |                    |                                                                                                                                                                                                            |       |        |            |

| $V_O$                | Output voltage range                | TPS62350           |                                                                                                                                                                                                            | 0.75  | 1.5375 | V          |

|                      |                                     | TPS62351           |                                                                                                                                                                                                            | 0.90  | 1.6875 | V          |

|                      |                                     | TPS62352           |                                                                                                                                                                                                            | 0.75  | 1.4375 | V          |

|                      |                                     | TPS62353           |                                                                                                                                                                                                            | 0.75  | 1.5375 | V          |

|                      |                                     | TPS62354           |                                                                                                                                                                                                            | 0.75  | 1.5375 | V          |

|                      |                                     | TPS62355           |                                                                                                                                                                                                            | 0.75  | 1.5375 | V          |

|                      |                                     | TPS62356           |                                                                                                                                                                                                            | 1.50  | 1.975  | V          |

| $t_{\text{on(MIN)}}$ | Minimum on-time (P-channel MOSFET)  |                    |                                                                                                                                                                                                            | 35    |        | ns         |

|                      | Resistance into FB sense pin        |                    | 700                                                                                                                                                                                                        | 1000  |        | k $\Omega$ |

| $V_O$                | Output voltage DC accuracy          | TPS62350           | $V_I = 3.6 \text{ V}$ , $V_O = 1.35 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , PWM operation                                                                                                         | -1.5% | 1.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 0.75 \text{ V}$ , $1.05 \text{ V}$ , $1.35 \text{ V}$ , $1.5375 \text{ V}$ , PWM operation | -2%   | 2%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light PFM                                                                 | -1%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.35 \text{ V}$ , $L = 1 \mu\text{H}$ , Fast PFM/PWM                                       | -2%   | 3%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.5%   |            |

| $V_O$                | Output voltage DC accuracy          | TPS62351           | $V_I = 3.6 \text{ V}$ , $V_O = 1.50 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , PWM operation                                                                                                         | -1.5% | 1.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 0.90 \text{ V}$ , $1.10 \text{ V}$ , $1.50 \text{ V}$ , $1.6875 \text{ V}$ , PWM operation | -2%   | 2%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , $V_O = 1.10 \text{ V}$ , $L = 1 \mu\text{H}$ , Light PFM                                                                 | -1%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.10 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.50 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.0%   |            |

| $V_O$                | Output voltage DC accuracy          | TPS62352           | $V_I = 3.6 \text{ V}$ , $V_O = 1.20 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , PWM operation                                                                                                         | -1.5% | 1.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 0.75 \text{ V}$ , $1.05 \text{ V}$ , $1.20 \text{ V}$ , $1.4375 \text{ V}$ , PWM operation | -2%   | 2%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light PFM                                                                 | -1%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.20 \text{ V}$ , $L = 1 \mu\text{H}$ , Fast PFM/PWM                                       | -2%   | 3%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.5%   |            |

| $V_O$                | Output voltage DC accuracy          | TPS62353           | $V_I = 3.6 \text{ V}$ , $V_O = 1.20 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , PWM operation                                                                                                         | -1.5% | 1.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 0.75 \text{ V}$ , $1.00 \text{ V}$ , $1.20 \text{ V}$ , $1.5375 \text{ V}$ , PWM operation | -2%   | 2%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , $V_O = 1.00 \text{ V}$ , $L = 1 \mu\text{H}$ , Light PFM                                                                 | -1%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.20 \text{ V}$ , $L = 1 \mu\text{H}$ , Fast PFM/PWM                                       | -2%   | 3%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.00 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.5%   |            |

| $V_O$                | Output voltage DC accuracy          | TPS62354           | $V_I = 3.6 \text{ V}$ , $V_O = 1.30 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , PWM operation                                                                                                         | -1.5% | 1.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 0.75 \text{ V}$ , $1.05 \text{ V}$ , $1.30 \text{ V}$ , $1.5375 \text{ V}$ , PWM operation | -2%   | 2%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $I_{O(\text{DC})} = 0 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light PFM                                                                 | -1%   | 4.5%   |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.30 \text{ V}$ , $L = 1 \mu\text{H}$ , Fast PFM/PWM                                       | -2%   | 3%     |            |

|                      |                                     |                    | $2.7 \text{ V} \leq V_I \leq 5.5 \text{ V}$ , $0 \text{ mA} \leq I_{O(\text{DC})} \leq 800 \text{ mA}$ , $V_O = 1.05 \text{ V}$ , $L = 1 \mu\text{H}$ , Light or Fast PFM/PWM                              | -2%   | 4.5%   |            |

## 電気的特性

動作温度範囲内、 $T_A = 25^\circ\text{C}$ 、 $V_I = 3.6\text{ V}$ 、 $\text{EN} = V_I$ 、 $\text{VSEL} = V_I$ 、 $\text{SYNC} = \text{GND}$ 、 $\text{VSEL0}[6]\text{ bit} = 1$ 。（特に記述がない限り）

| パラメータ                                                             |                                     | テスト条件                                                                                                                                                                                                                                                                                         | MIN                                                                                                            | TYP  | MAX  | 単位               |

|-------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------------------|

| $V_O$                                                             | Output voltage DC accuracy          | $V_I = 3.6\text{ V}$ , $V_O = 1.15\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$ , PWM operation                                                                                                                                                                                               | -1.5%                                                                                                          |      | 1.5% |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$V_O = 0.75\text{ V}$ , $0.9\text{ V}$ , $1.15\text{ V}$ , $1.5375\text{ V}$<br>PWM operation                                                                                           | -2%                                                                                                            |      | 2%   |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 5.5\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$<br>$V_O = 0.9\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Light PFM                                                                                                                                                 | -1%                                                                                                            |      | 4.5% |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$V_O = 1.15\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Fast PFM/PWM                                                                                                                       | -2%                                                                                                            |      | 3%   |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$V_O = 0.9\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Light or Fast PFM/PWM                                                                                                               | -2%                                                                                                            |      | 4.5% |                  |

| $V_O$                                                             | Output voltage DC accuracy          | $2.7\text{ V} \leq V_I \leq 3.2\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$3.2\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 1000\text{ mA}^{(1)}$<br>$V_O = 1.80\text{ V}$<br>PWM operation                                     | -2%                                                                                                            |      | 2%   |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 5.5\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$<br>$V_O = 1.80\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Light PFM                                                                                                                                                | -1%                                                                                                            |      | 4.5% |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 3.2\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$3.2\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 1000\text{ mA}^{(1)}$<br>$V_O = 1.80\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Fast PFM/PWM          | -2%                                                                                                            |      | 3%   |                  |

|                                                                   |                                     | $2.7\text{ V} \leq V_I \leq 3.2\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 800\text{ mA}$<br>$3.2\text{ V} \leq V_I \leq 5.5\text{ V}$ , $0\text{ mA} \leq I_{O(\text{DC})} \leq 1000\text{ mA}^{(1)}$<br>$V_O = 1.80\text{ V}$ , $L = 1\text{ }\mu\text{H}$ , Light or Fast PFM/PWM | -2%                                                                                                            |      | 4.5% |                  |

| $\Delta V_O$                                                      | DC output voltage load regulation   | $I_{O(\text{DC})} = 0\text{ mA}$ to $800\text{ mA}$ , PWM operation                                                                                                                                                                                                                           | -0.0003                                                                                                        |      |      | %/mA             |

|                                                                   | DC output voltage line regulation   | $V_I = V_O + 0.5\text{ V}$ (min $2.7\text{ V}$ ) to $5.5\text{ V}$ , $I_{O(\text{DC})} = 300\text{ mA}$                                                                                                                                                                                       | 0                                                                                                              |      |      | %/V              |

| Power-save mode ripple voltage                                    |                                     | $V_O = 0.9\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$ , $L = 1\text{ }\mu\text{H}$ , Light PFM operation                                                                                                                                                                                    | 33                                                                                                             |      |      | mV <sub>PP</sub> |

|                                                                   |                                     | $V_O = 1.05\text{ V}$ , $I_{O(\text{DC})} = 1\text{ mA}$ , $L = 1\text{ }\mu\text{H}$ , Light PFM operation                                                                                                                                                                                   | 30                                                                                                             |      |      | mV <sub>PP</sub> |

|                                                                   |                                     | $V_O = 1.10\text{ V}$ , $I_{O(\text{DC})} = 1\text{ mA}$ , $L = 1\text{ }\mu\text{H}$ , Light PFM operation, $\text{VSEL0}[6]\text{ bit} = 0$                                                                                                                                                 | 12                                                                                                             |      |      | mV <sub>PP</sub> |

|                                                                   |                                     | $V_O = 1.35\text{ V}$ , $I_{O(\text{DC})} = 1\text{ mA}$ , $L = 1\text{ }\mu\text{H}$ , Fast PFM operation                                                                                                                                                                                    | 0.025 $V_O$                                                                                                    |      |      | V <sub>PP</sub>  |

| $I_{\text{lk}g}$                                                  | Leakage current into SW pin         | $V_I > V_O$ , $0\text{ V} \leq V_{(\text{SW})} \leq V_I$ , $\text{EN} = \text{GND}$                                                                                                                                                                                                           | 0.01                                                                                                           | 1    |      | $\mu\text{A}$    |

|                                                                   | Reverse leakage current into SW pin | $V_I = \text{open}$ , $V_{(\text{SW})} = 6\text{ V}$ , $\text{EN} = \text{GND}$                                                                                                                                                                                                               | 0.01                                                                                                           | 1    |      |                  |

| DAC                                                               |                                     |                                                                                                                                                                                                                                                                                               |                                                                                                                |      |      |                  |

| Resolution                                                        |                                     | TPS62350<br>TPS62351<br>TPS62352<br>TPS62353<br>TPS62354                                                                                                                                                                                                                                      |                                                                                                                | 6    |      | Bits             |

| Differential nonlinearity                                         |                                     | Assured monotonic by design                                                                                                                                                                                                                                                                   |                                                                                                                | ±0.8 |      | LSB              |

| TIMING                                                            |                                     |                                                                                                                                                                                                                                                                                               |                                                                                                                |      |      |                  |

| Setup Time Between Rising EN and Start of I <sup>2</sup> C Stream |                                     |                                                                                                                                                                                                                                                                                               | 250                                                                                                            |      |      | μs               |

| $V_O$                                                             | Output voltage settling time        | TPS62350                                                                                                                                                                                                                                                                                      | From min to max output voltage, $I_{O(\text{DC})} = 500\text{ mA}$ , PWM operation                             | 3    |      | μs               |

| Start-up time                                                     | TPS62350                            | TPS62350                                                                                                                                                                                                                                                                                      | Time from active EN to $V_O$<br>$V_O = 1.35\text{ V}$ , $R_L = 5\Omega$ , PWM operation                        | 180  | μs   |                  |

|                                                                   |                                     |                                                                                                                                                                                                                                                                                               | Time from active EN to $V_O$<br>$V_O = 1.05\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$ , Light PFM operation | 170  |      |                  |

|                                                                   | TPS62351                            | TPS62351                                                                                                                                                                                                                                                                                      | Time from active EN_DCDC bit to $V_O$<br>$V_O = 1.5\text{ V}$ , $R_L = 5\Omega$ , PWM operation                | 45   |      |                  |

|                                                                   | TPS62352                            | TPS62352                                                                                                                                                                                                                                                                                      | Time from active EN to $V_O$<br>$V_O = 1.2\text{ V}$ , $R_L = 5\Omega$ , PWM operation                         | 175  |      |                  |

|                                                                   |                                     |                                                                                                                                                                                                                                                                                               | Time from active EN to $V_O$<br>$V_O = 1.05\text{ V}$ , $I_{O(\text{DC})} = 0\text{ mA}$ , Light PFM operation | 170  |      |                  |

(1) 消費電力が高いアプリケーションまたはパッケージの熱抵抗が低いアプリケーションでは、最大周囲温度を計算しなおす必要があります。

最大周囲温度( $T_{A(\text{max})}$ )は、動作ジャンクション温度の最大値( $T_{J(\text{max})}$ )、アプリケーション内のデバイスの最大消費電力( $P_{D(\text{max})}$ )、およびアプリケーション内のパーツ/パッケージのジャンクションと周囲の間の熱抵抗( $\theta_{JA}$ )に依存し、次の式で計算されます。

$$T_{A(\text{max})} = T_{J(\text{max})} - (\theta_{JA} \times P_{D(\text{max})})$$

## I<sup>2</sup>C インターフェイス タイミング特性<sup>(1)</sup>

| パラメータ             |                                                                                       | テスト条件                                                | MIN            | MAX  | 単位 |

|-------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|----------------|------|----|

| $f_{SCL}$         | SCL Clock Frequency                                                                   | Standard mode                                        | 100            | kHz  |    |

|                   |                                                                                       | Fast mode                                            | 400            | kHz  |    |

|                   |                                                                                       | High-speed mode (write operation), $C_B$ –100 pF max | 3.4            | MHz  |    |

|                   |                                                                                       | High-speed mode (read operation), $C_B$ –100 pF max  | 3.4            | MHz  |    |

|                   |                                                                                       | High-speed mode (write operation), $C_B$ –400 pF max | 1.7            | MHz  |    |

|                   |                                                                                       | High-speed mode (read operation), $C_B$ –400 pF max  | 1.7            | MHz  |    |

| $t_{BUF}$         | Bus Free Time Between a STOP and START Condition                                      | Standard mode                                        | 4.7            | μs   |    |

|                   |                                                                                       | Fast mode                                            | 1.3            | μs   |    |

| $t_{HD}, t_{STA}$ | Hold Time (Repeated) START Condition                                                  | Standard mode                                        | 4              | μs   |    |

|                   |                                                                                       | Fast mode                                            | 600            | ns   |    |

|                   |                                                                                       | High-speed mode                                      | 160            | ns   |    |

| $t_{LOW}$         | LOW Period of the SCL Clock                                                           | Standard mode                                        | 4.7            | μs   |    |

|                   |                                                                                       | Fast mode                                            | 1.3            | μs   |    |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 160            | ns   |    |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 320            | ns   |    |

| $t_{HIGH}$        | HIGH Period of the SCL Clock                                                          | Standard mode                                        | 4              | μs   |    |

|                   |                                                                                       | Fast mode                                            | 600            | ns   |    |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 60             | ns   |    |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 120            | ns   |    |

| $t_{SU}, t_{STA}$ | Setup Time for a Repeated START Condition                                             | Standard mode                                        | 4.7            | μs   |    |

|                   |                                                                                       | Fast mode                                            | 600            | ns   |    |

|                   |                                                                                       | High-speed mode                                      | 160            | ns   |    |

| $t_{SU}, t_{DAT}$ | Data Setup Time                                                                       | Standard mode                                        | 250            | ns   |    |

|                   |                                                                                       | Fast mode                                            | 100            | ns   |    |

|                   |                                                                                       | High-speed mode                                      | 10             | ns   |    |

| $t_{HD}, t_{DAT}$ | Data Hold Time                                                                        | Standard mode                                        | 0              | 3.45 | μs |

|                   |                                                                                       | Fast mode                                            | 0              | 0.9  | μs |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 0              | 70   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 0              | 150  | ns |

| $t_{RCL}$         | Rise Time of SCL Signal                                                               | Standard mode                                        | 20 + 0.1 $C_B$ | 1000 | ns |

|                   |                                                                                       | Fast mode                                            | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 10             | 40   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 20             | 80   | ns |

| $t_{RCL1}$        | Rise Time of SCL Signal After a Repeated START Condition and After an Acknowledge BIT | Standard mode                                        | 20 + 0.1 $C_B$ | 1000 | ns |

|                   |                                                                                       | Fast mode                                            | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 10             | 80   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 20             | 160  | ns |

| $t_{FCL}$         | Fall Time of SCL Signal                                                               | Standard mode                                        | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | Fast mode                                            | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 10             | 40   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 20             | 80   | ns |

| $t_{RDA}$         | Rise Time of SDA Signal                                                               | Standard mode                                        | 20 + 0.1 $C_B$ | 1000 | ns |

|                   |                                                                                       | Fast mode                                            | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 10             | 80   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 20             | 160  | ns |

| $t_{FDA}$         | Fall Time of SDA Signal                                                               | Standard mode                                        | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | Fast mode                                            | 20 + 0.1 $C_B$ | 300  | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –100 pF max                   | 10             | 80   | ns |

|                   |                                                                                       | High-speed mode, $C_B$ –400 pF max                   | 20             | 160  | ns |

| $t_{SU}, t_{STO}$ | Setup Time for STOP Condition                                                         | Standard mode                                        | 4              | μs   |    |

|                   |                                                                                       | Fast mode                                            | 600            | ns   |    |

|                   |                                                                                       | High-speed mode                                      | 160            | ns   |    |

| $C_B$             | Capacitive Load for SDA and SCL                                                       |                                                      |                | 400  | pF |

(1) 設計で保証されており、テストは行われていません。

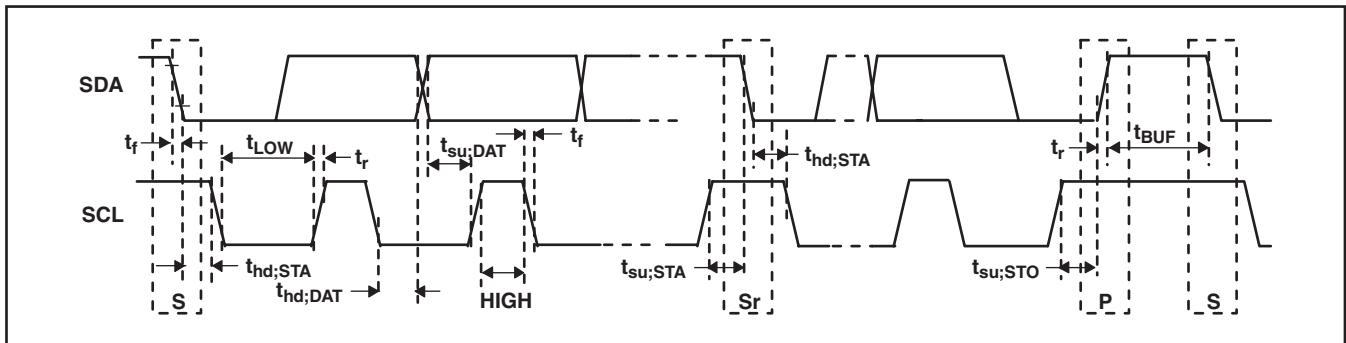

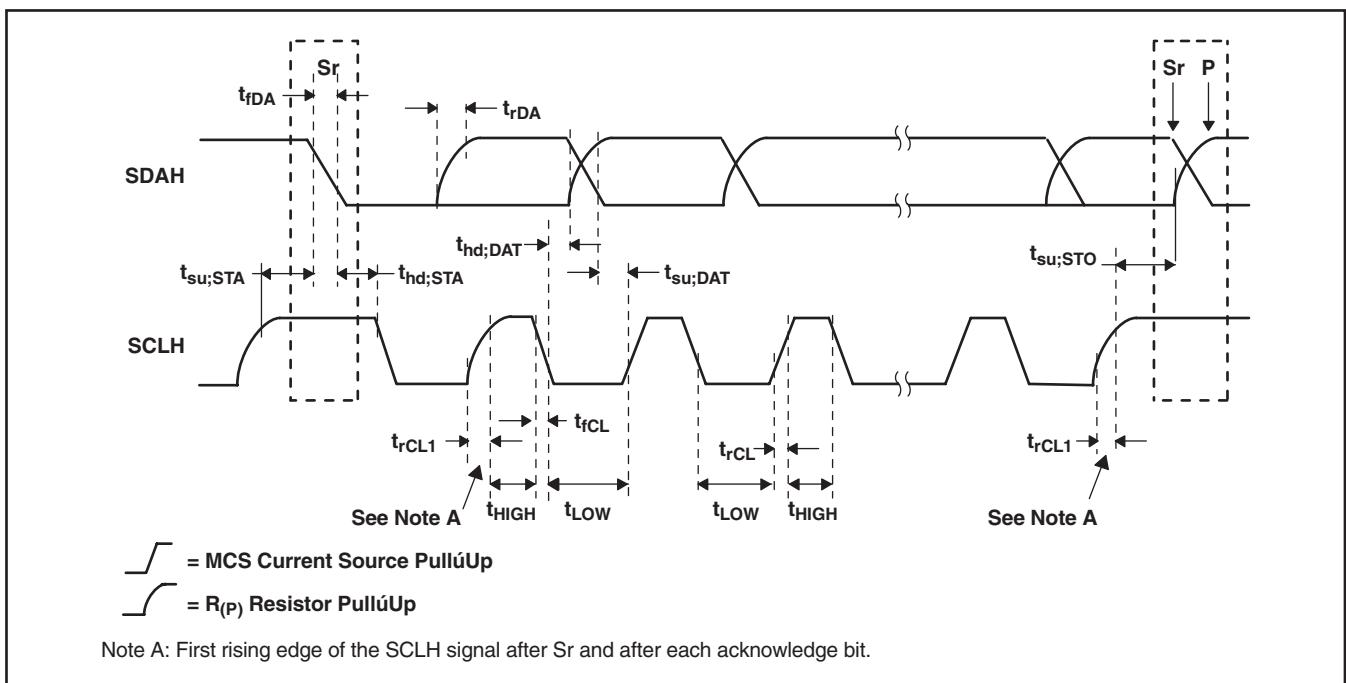

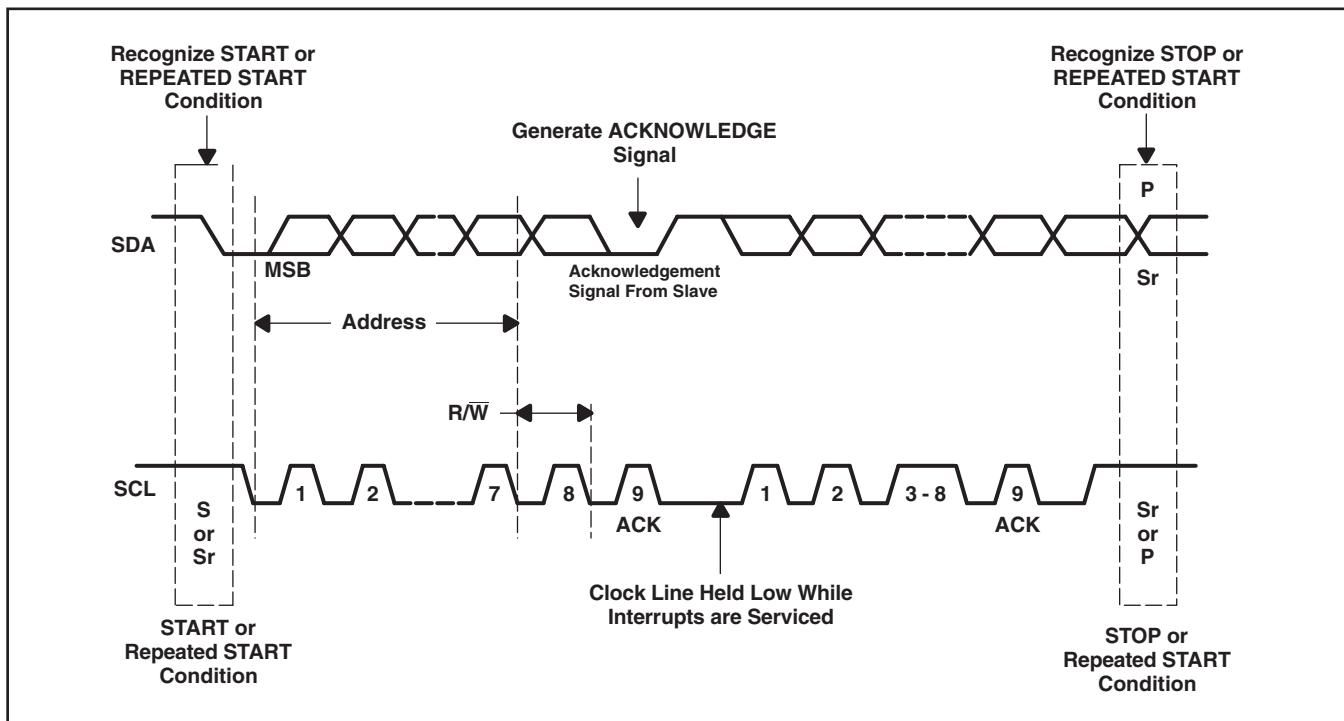

## I<sup>2</sup>C タイミング図

図 1. Serial Interface Timing Diagram for F/S-Mode

図 2. Serial Interface Timing Diagram for HS-Mode

## ピン配置

## 端子機能表

| 端子                     |         |         | I/O | 概要                                                                                                                                                                             |

|------------------------|---------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO. QFN | NO. CSP |     |                                                                                                                                                                                |

| PVIN                   | 1       | A3      |     | 出力パワー段用の電源電圧                                                                                                                                                                   |

| AVIN                   | 2       | B3      |     | デバイスの制御回路用電源電圧ピン。入力バイパス・コンデンサを直接接続してください。                                                                                                                                      |

| EN                     | 7       | C2      | I   | デバイスのイネーブル・ピン。この端子をグランドに接続するとデバイスはシャットダウン・モードになります。また、V <sub>I</sub> レベルにするとデバイスはイネーブルになります。イネーブル・ピンの立上がりエッジで、全てのレジスタがデフォルト値にリセットされます。この端子はフローティングにしてはならず、終端処理しなければなりません。      |

| VSEL                   | 5       | D2      | I   | VSEL信号は出力電圧の増減などの、アクティブ・モード(VSEL = "H" レベル)とスリープ・モード(VSEL = "L" レベル)のTPS6235xの動作モードの選択に使用されます。また、動作モードはI <sub>2</sub> Cの設定によっても変更することができます。この端子はフローティングにしてはならず、終端処理しなければなりません。 |

| SDA                    | 3       | C3      | I/O | シリアル・インターフェイスのアドレス/データ・ライン                                                                                                                                                     |

| SCL                    | 4       | D3      | I   | シリアル・インターフェイスのクロック・ライン                                                                                                                                                         |

| FB                     | 6       | D1      | I   | 出力フィードバック検出入力。FB端子はコンバータの出力に接続してください。                                                                                                                                          |

| AGND                   | 8       | C1      |     | アナログ・グランド                                                                                                                                                                      |

| SYNC                   | N/A     | B2      | I   | 外部クロック信号への同期入力。コンバータのスイッチング周波数を外部クロック信号に同期させます。この端子はフローティングにしてはならず、終端処理しなければなりません。SYNCを固定の "H" レベルまたは "L" レベルに接続してもコンバータの動作には影響は与えません。                                         |

| PGND                   | 9       | A1 B1   |     | パワー・グランド。ICの直近でAGNDと接続してください。                                                                                                                                                  |

| SW                     | 10      | A2      | I/O | コンバータのスイッチ・ピンで内部パワーMOSFETのドレインに接続されています。                                                                                                                                       |

| PowerPAD <sup>TM</sup> |         |         | N/A | 内部でPGNDに接続されています。                                                                                                                                                              |

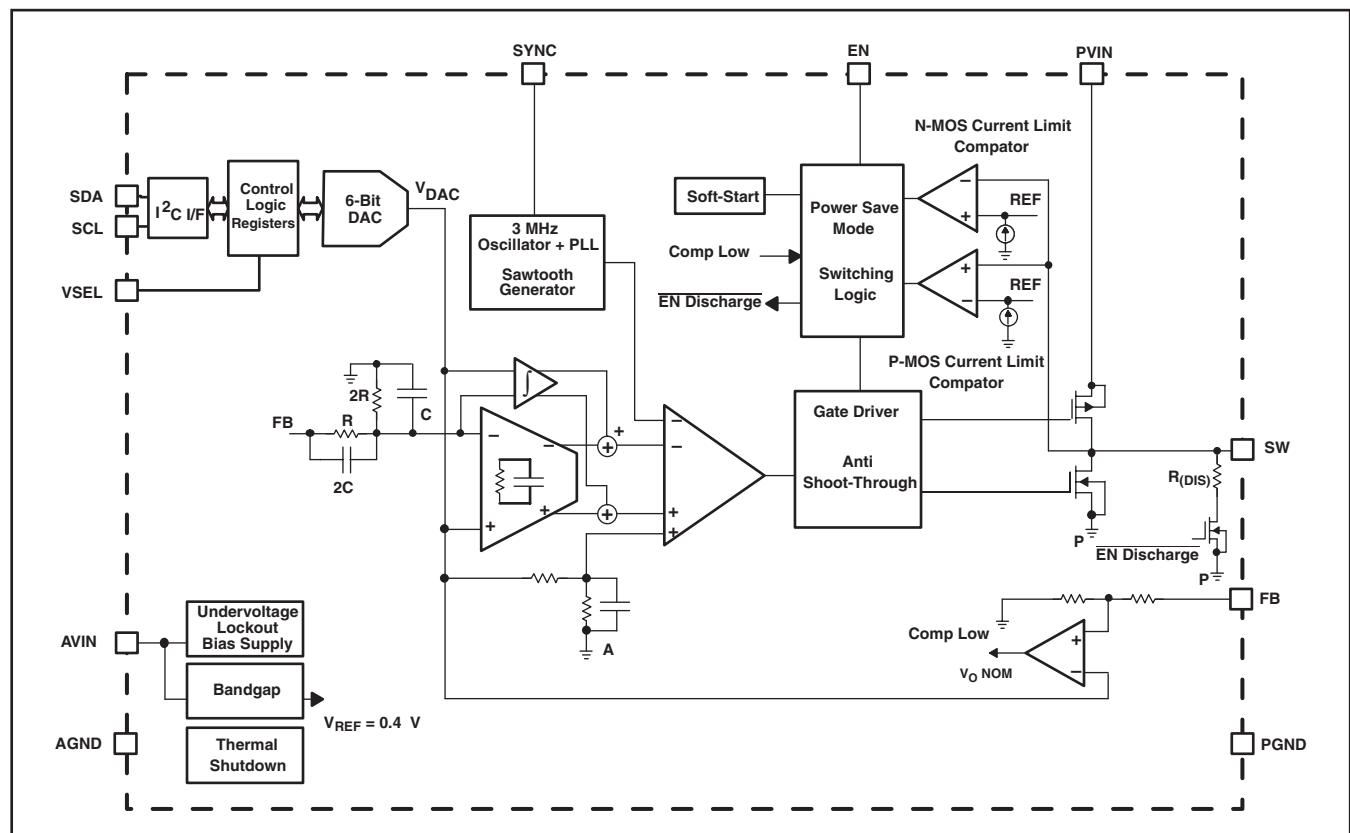

## 機能ブロック図

## パラメータ測定情報

## 標準特性

### グラフ一覧

|                                           |                                  | 図                                                                                           |

|-------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------|

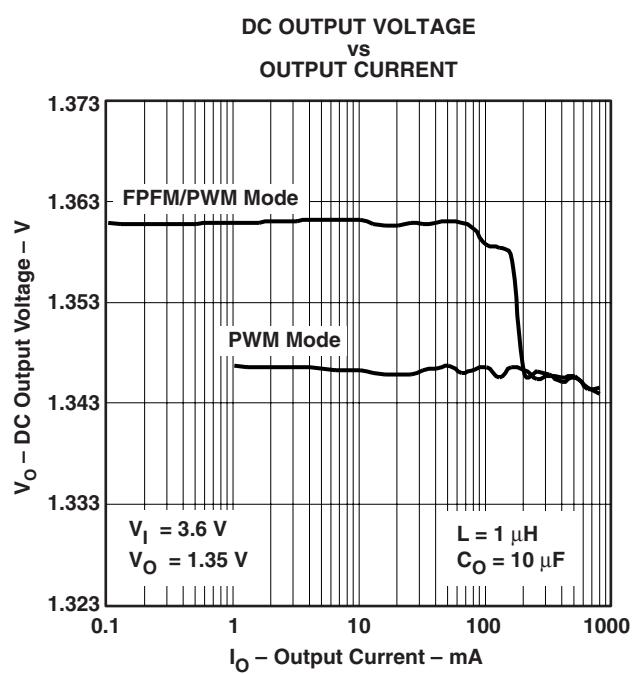

| $\eta$                                    | Efficiency                       | vs Output current<br>3, 4, 5, 6<br>vs Input voltage<br>7                                    |

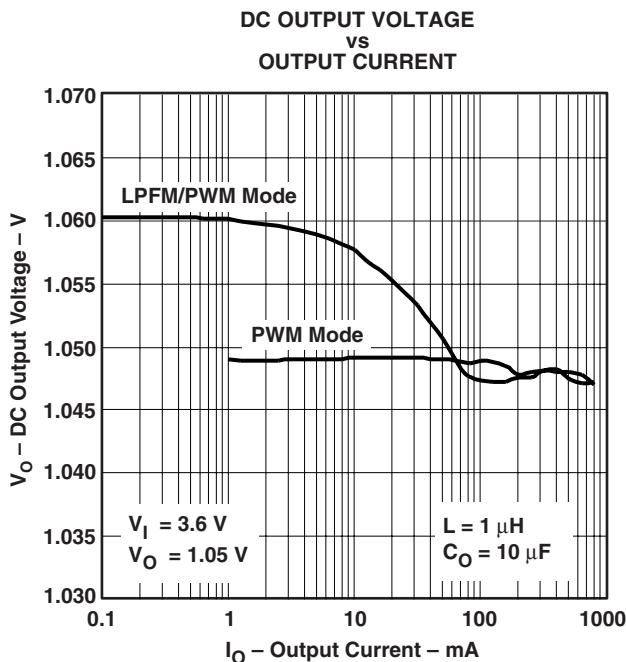

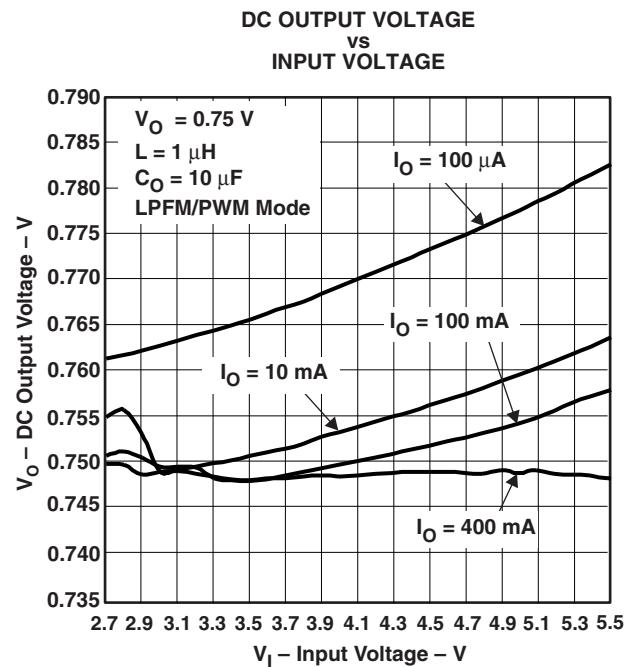

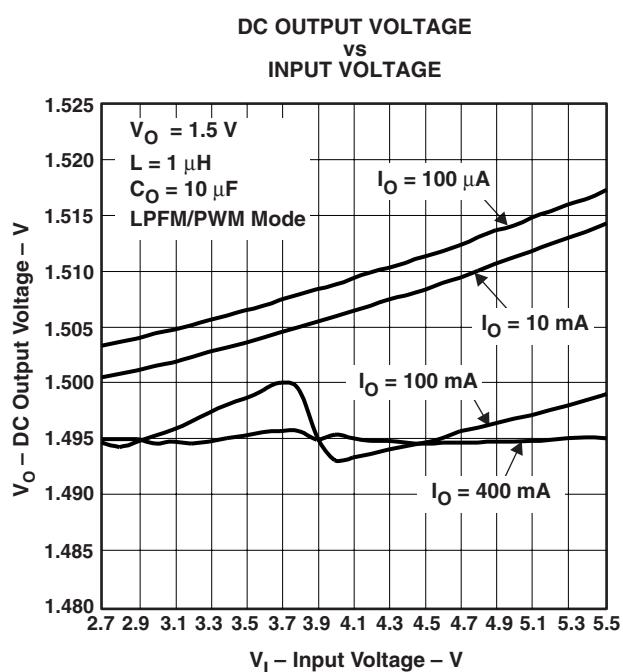

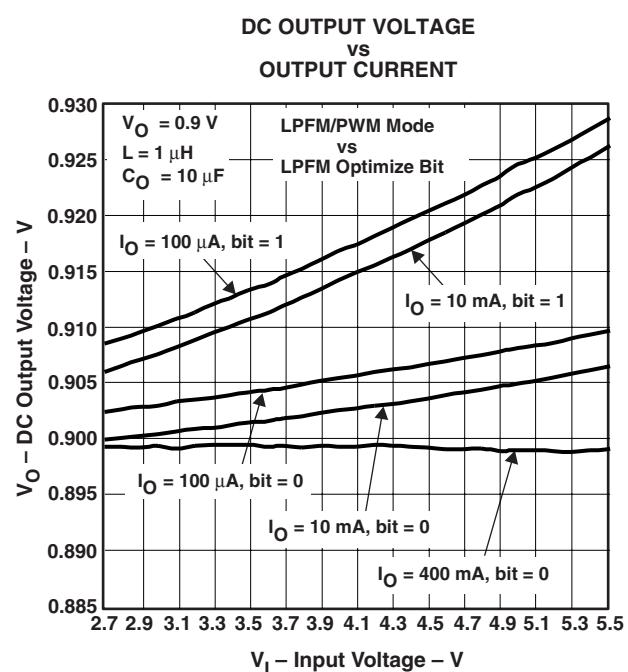

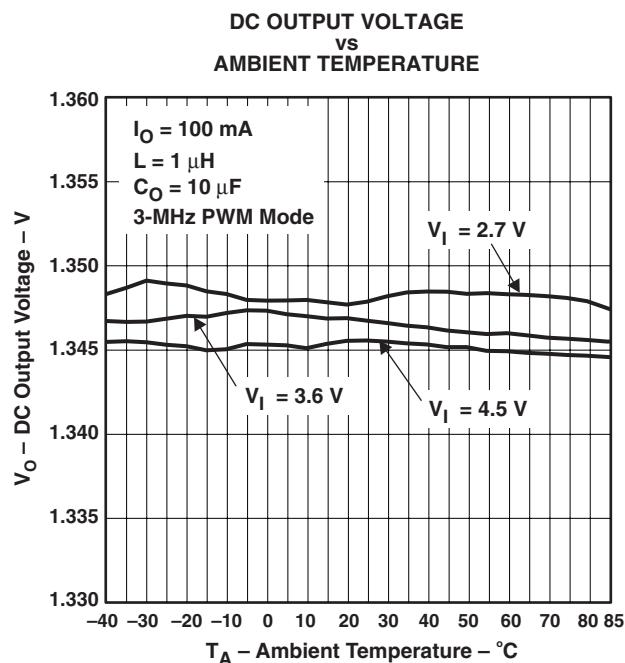

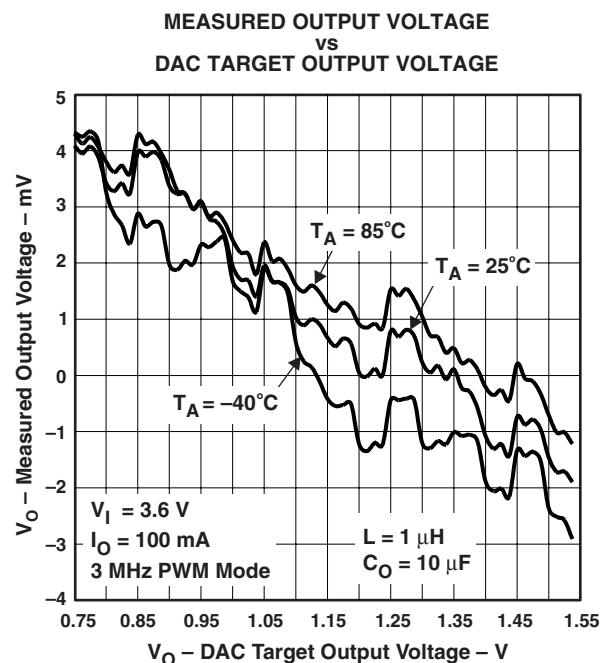

| $V_O$                                     | DC output voltage                | vs Output current<br>8, 9, 12<br>vs Input voltage<br>10, 11<br>vs Ambient temperature<br>13 |

|                                           |                                  | Measured output voltage<br>vs DAC target output voltage<br>14                               |

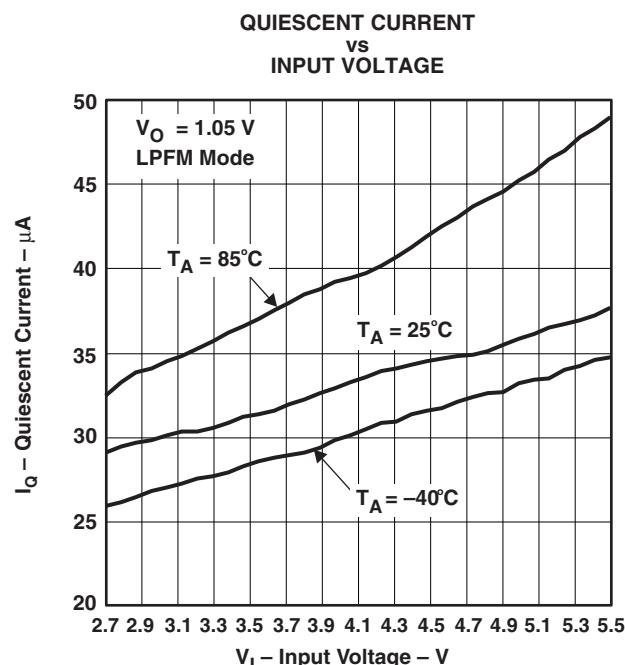

|                                           |                                  | $I_Q$ Quiescent current<br>vs Input voltage<br>15                                           |

| $I_{SD}$                                  | Shutdown current                 | vs Input voltage<br>16                                                                      |

|                                           | $f_{(OSC)}$ Oscillator frequency | vs Input voltage<br>17                                                                      |

| $r_{DS(on)}$                              | P-channel MOSFET $r_{DS(on)}$    | vs Input voltage<br>18                                                                      |

|                                           | N-channel MOSFET $r_{DS(on)}$    | vs Input voltage<br>19                                                                      |

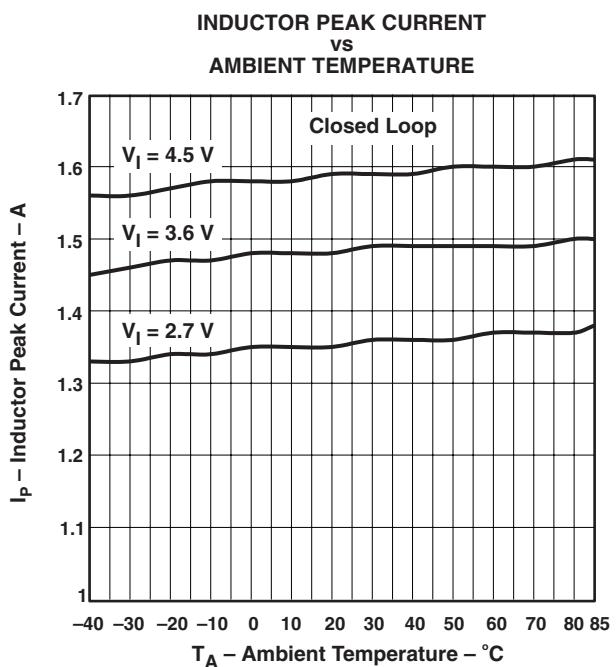

| $I_P$                                     | Inductor peak current            | vs Ambient temperature<br>20                                                                |

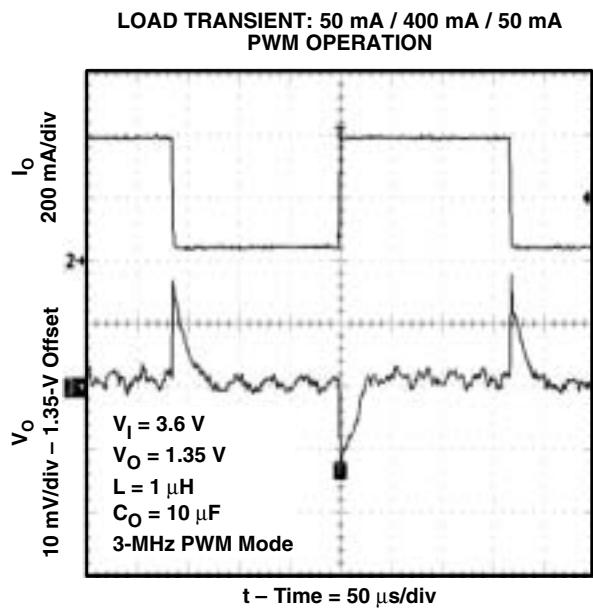

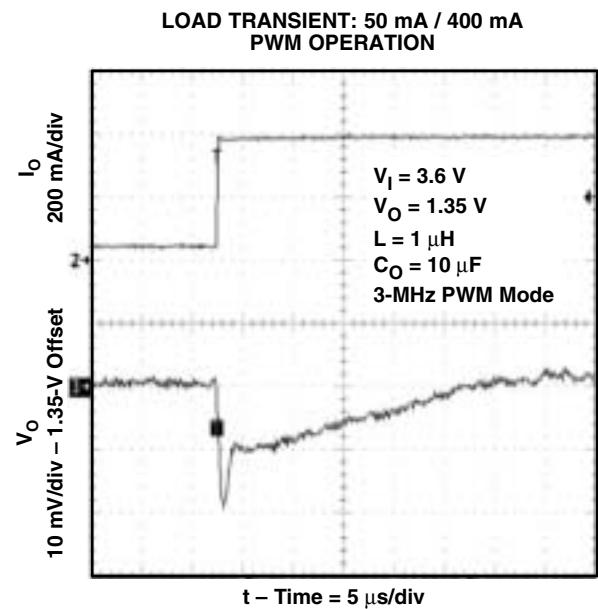

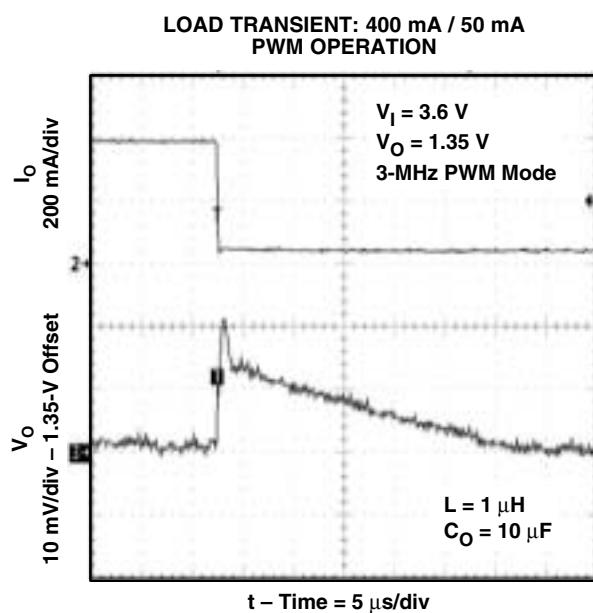

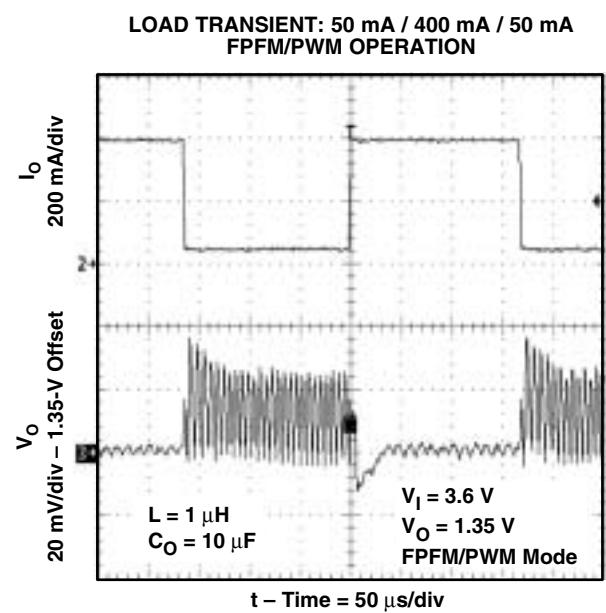

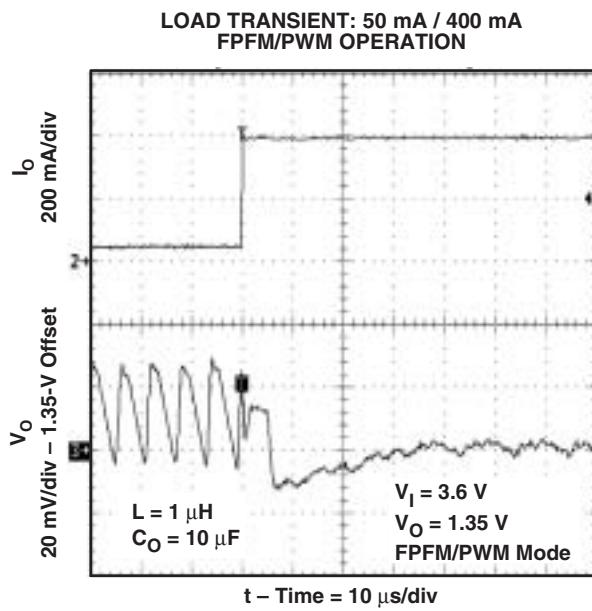

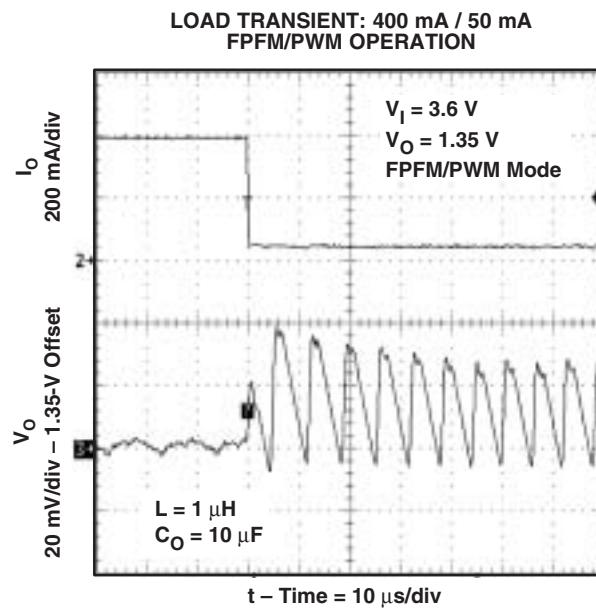

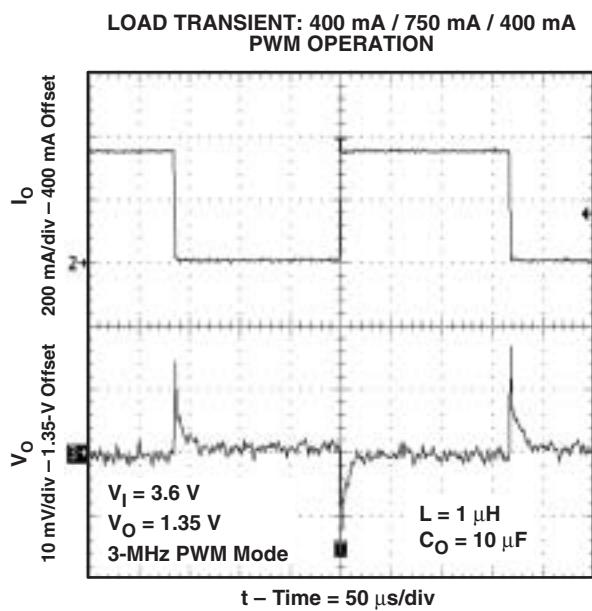

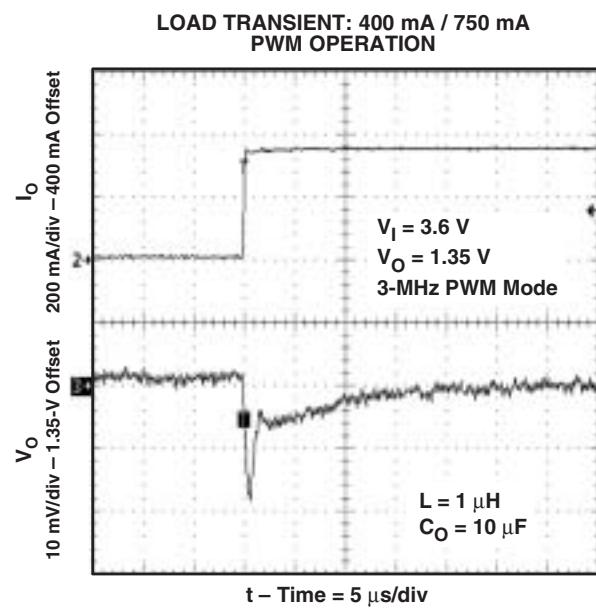

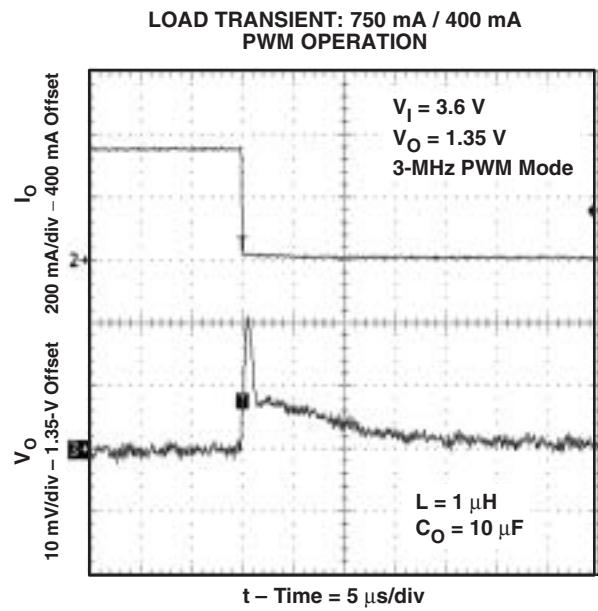

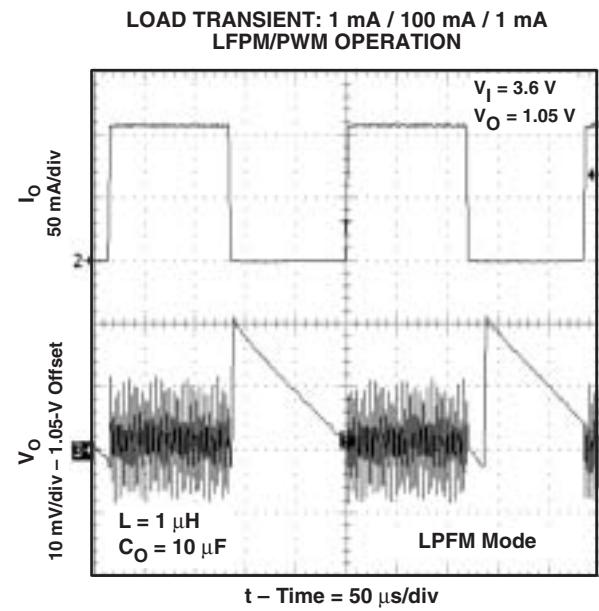

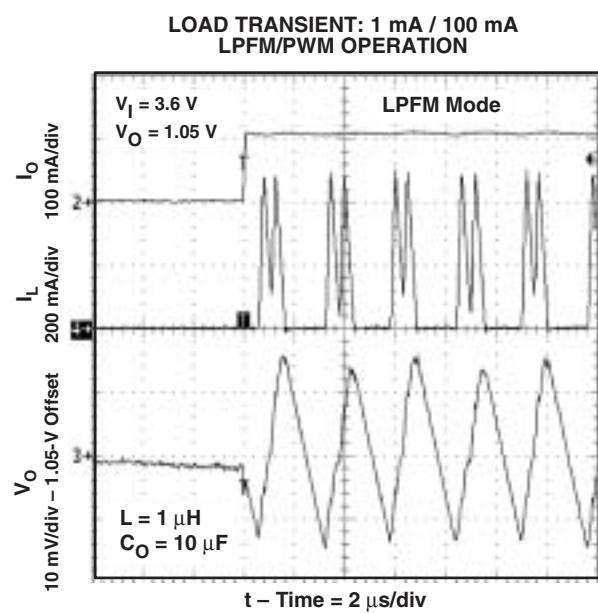

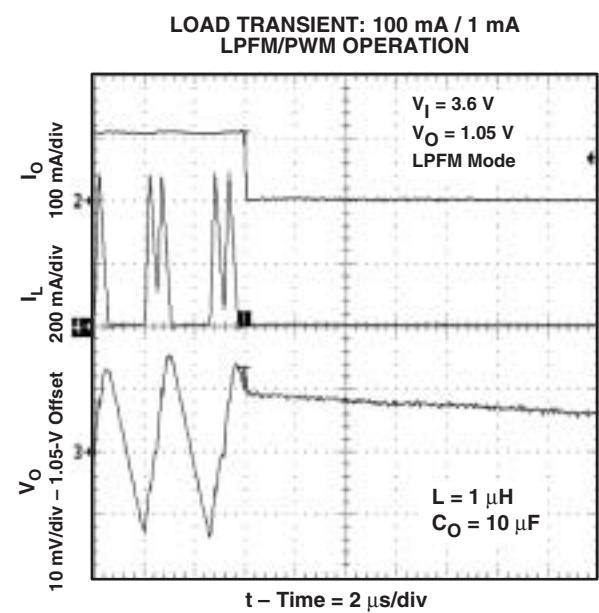

|                                           | Load transient response          | 21, 22, 23, 24, 25, 26<br>27, 28, 29, 30, 31, 32                                            |

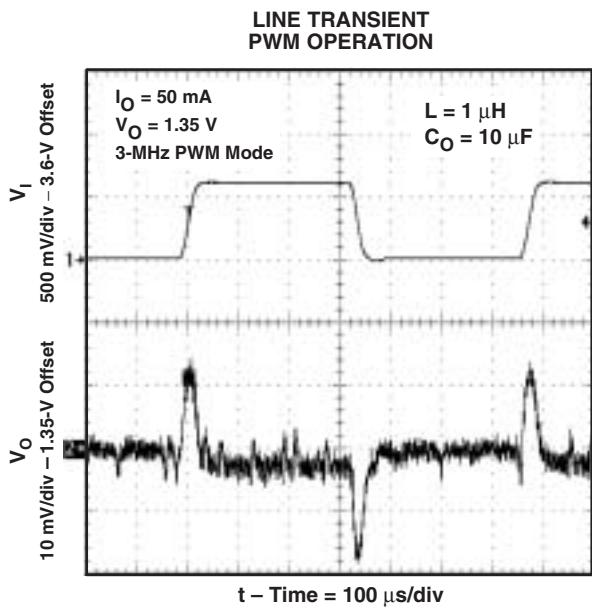

| Line transient response                   |                                  | 33                                                                                          |

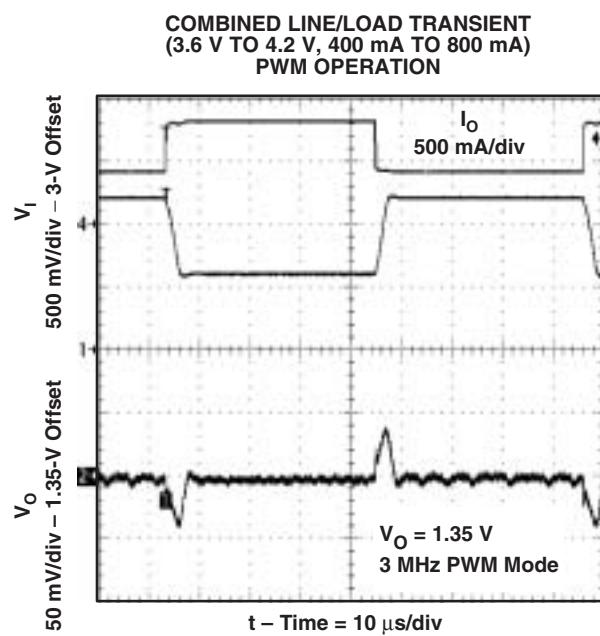

| Combined line and load transient response |                                  | 34                                                                                          |

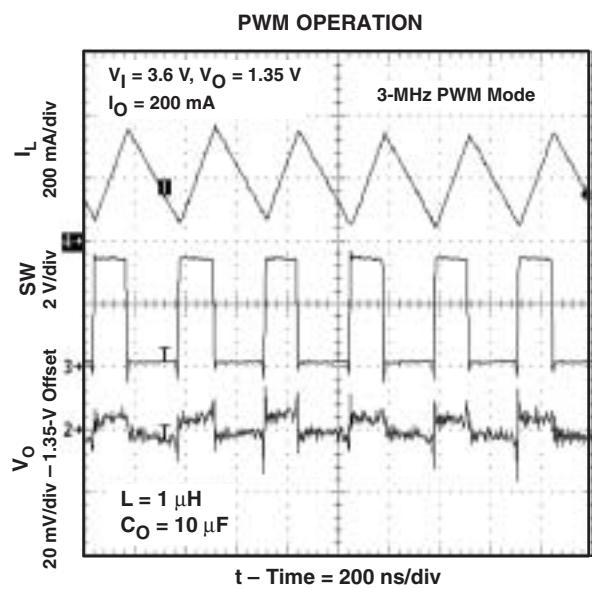

| PWM operation                             |                                  | 35                                                                                          |

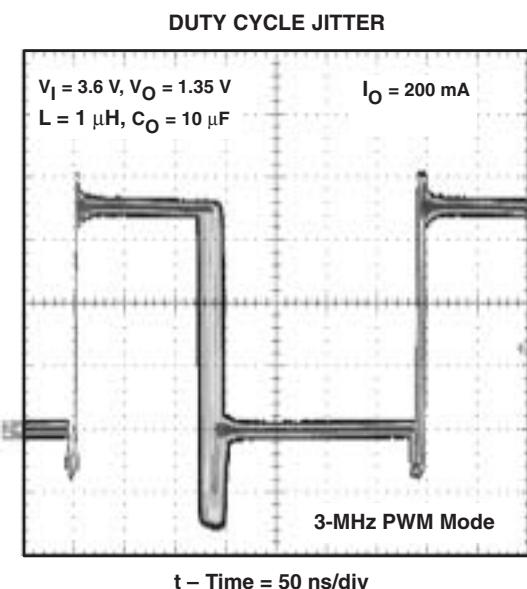

| Duty cycle jitter                         |                                  | 36                                                                                          |

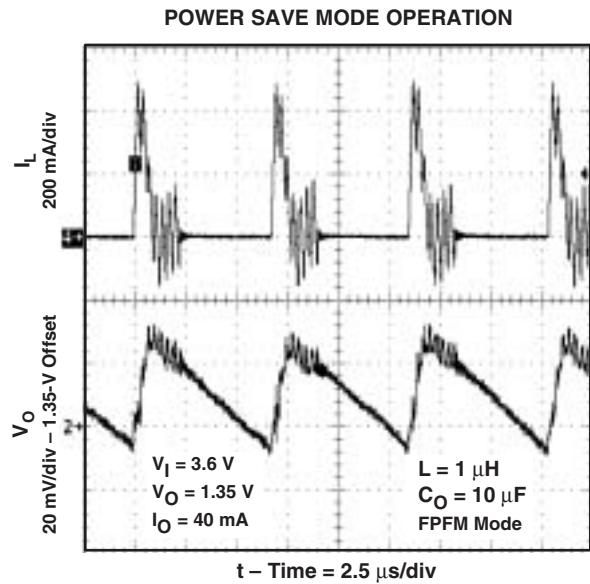

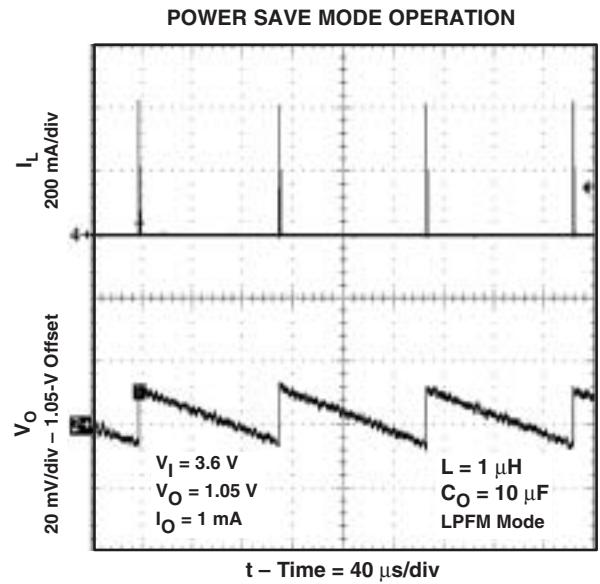

| Power-save mode operation                 |                                  | 37, 38                                                                                      |

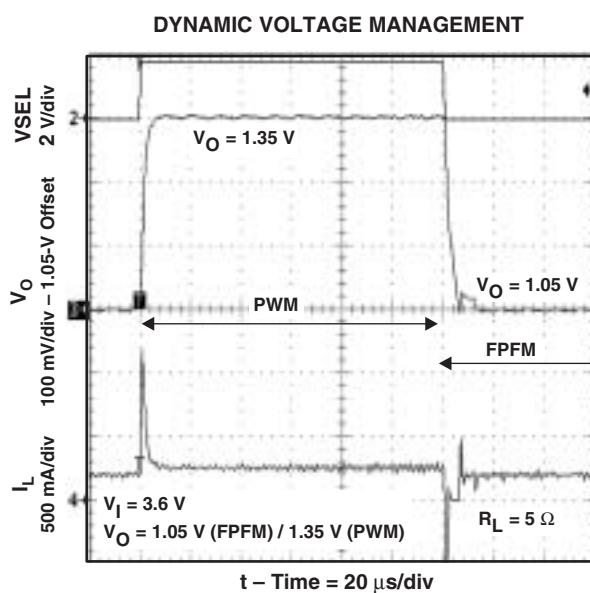

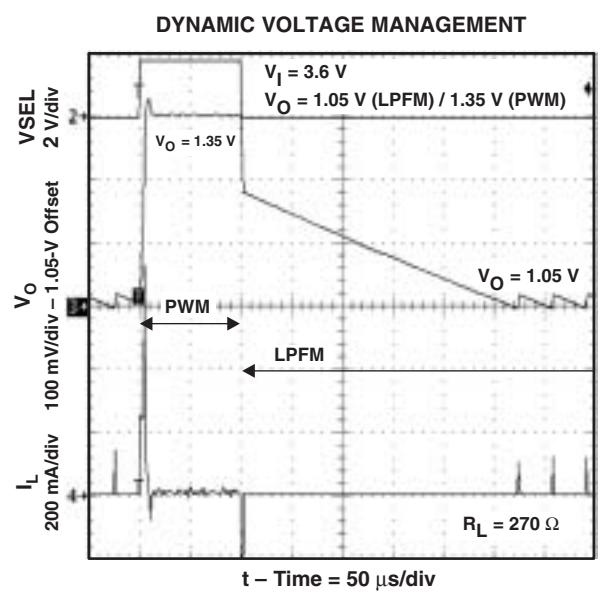

| Dynamic voltage management                |                                  | 39, 40                                                                                      |

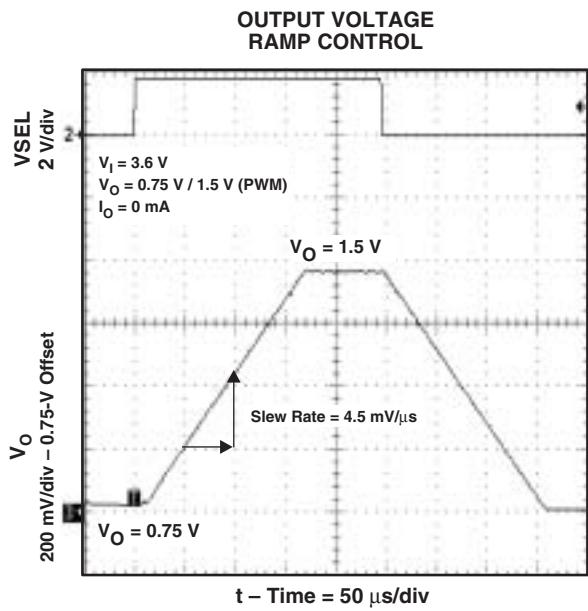

| Output voltage ramp control               |                                  | 41                                                                                          |

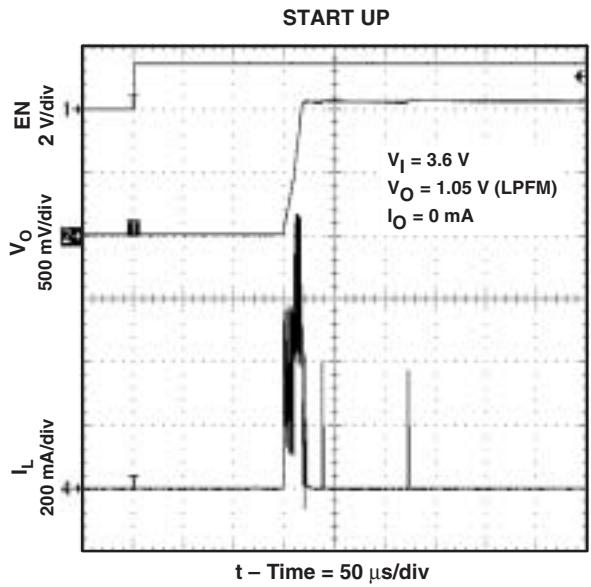

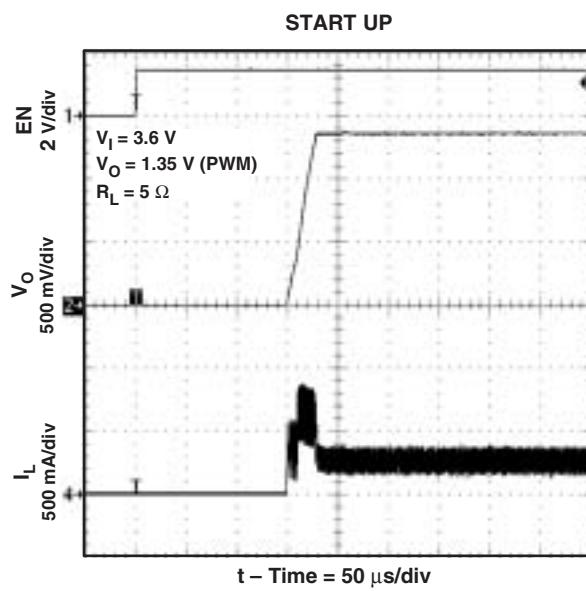

| Start-up                                  |                                  | 42, 43                                                                                      |

図 3

図 4

## 標準特性

## 標準特性

図 9

図 10

図 11

図 12

## 標準特性

図 13

図 14

図 15

図 16

## 標準特性

図 17

図 18

図 19

図 20

## 標準特性

図 21

図 22

図 23

図 24

## 標準特性

図 25

図 26

図 27

図 28

## 標準特性

図 29

図 30

図 31

図 32

## 標準特性

図 33

図 34

図 35

図 36

## 標準特性

図 37

図 38

図 39

図 40

## 標準特性

図 41

図 42

図 43

## 詳細説明

### 動作

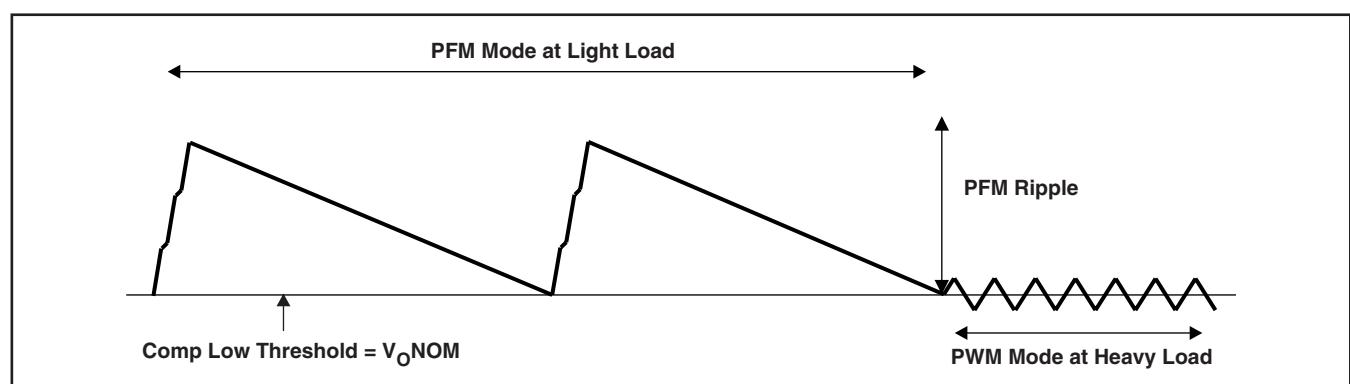

TPS6235xは同期整流方式の降圧型コンバータで、中～大負荷電流範囲では3MHz固定周波数のパルス幅変調(PWM)方式で動作します。一方軽負荷電流時には、コンバータはパルス周波数変調(PFM)方式のパワーセーブ・モードで動作します。このデバイスは、軽負荷時の超高効率に最適化したモード(ライトPFM)と、PWM動作に変わる時の過渡応答を最適化したモード(ファストPFM)の2つのパワーセーブ・モードを持っています。どちらのパワーセーブ・モードも負荷電流が増加した時に自動的にPWM動作に移行します。

TPS6235xはI<sup>2</sup>C互換のインターフェイスを内蔵しており、最大3.4Mbpsでの通信が可能です。この通信インターフェイスにより、動作中に最小12.5mV電圧ステップで出力電圧をデジタル可変を行うことが出来ます。また、動作モード(ライトPFM、ファストPFM、強制PWM)を再プログラムしたり、出力電圧のイネーブル/ディスエーブルを行うことができます。詳細についてはI<sup>2</sup>Cインターフェイス及びレジスタの説明の項を参照してください。

PWM動作時、コンバータは入力電圧フィードフォワードをもった高速応答の電圧モードで動作します。このことによりクラス最高レベルの入力及び負荷応答が実現し、極めて小さなインダクタと小型の入力/出力セラミック・コンデンサを使用することが可能になります。各スイッチング・サイクルの初めでは、PチャネルのMOSFETスイッチがオンとなり、インダクタ電流は、コンパレータが反転してコントロール・ロジックがスイッチをオフにするまで増加します。動作周波数は3MHzに設定されていますが、外部発振器またはマスターのDC/DCコンバータと動作中に外部同期運転に移行することが可能です(アプリケーション例参照)。

このデバイスは2つの電流制限を内蔵しており、1つはPチャネルMOSFET、もう1つはNチャネルMOSFETです。PチャネルMOSFETの電流がその制限電流値に達した時、PチャネルMOSFETはオフし、NチャネルMOSFETがオンとなります。また、NチャネルMOSFETの電流がN-MOS電流制限スレッシュホールドより高くなった時は、電流がその制限電流より低下するまでNチャネルMOSFETはオフのままとなります。NチャネルMOSFETの電流制限機能はインダクタ電流が減少しない場合や起動時の出力電圧が非常に低い場合などにデューティサイクルが小さくなり、ON時間中にに対してPチャネルMOSFETの過電流制限の動作遅延が問題となる場合に重要な働きをします。

### パワーセーブ・モード：ファストPFM

負荷電流の減少により、デバイスは、負荷に合わせて間欠的にパワーモードが動作するパルス・スキップ動作に自動的に切り替えます。周期的なサイクル動作により、スイッチング損失は最小限に抑えられ、デバイスは静止状態の最小電流で動作し高効率が維持されます。

ファストPFMモードでは、デバイスは、コンバータの出力電圧が設定スレッシュホールド電圧(標準はV<sub>O</sub>)を下回った時のみ動作します。コンバータは数パルス動作して出力電圧を上昇させ、インダクタ電流がゼロに達すると再びパワーセーブ・モードになります。結果として、パワーセーブ・モードでの平均出力電圧はPWMモードのときの平均値より少し高くなります。ファストPFMモードは、パルス・スキップ動作からPWM動作に遷移する時に高速応答を必要とするアプリケーションに最適です。

### パワーセーブ・モード：ライトPFM

負荷電流の減少により、デバイスは、負荷に合わせて間欠的にパワーモードが動作するライトPFMのパルス・スキップ動作に自動的に切り替えます。ライトPFMの利点は、低出力負荷時にファストPFMに比べてI<sub>Q</sub>が極めて低い(28μA)ことにより効率が大幅に高いことです。

ライトPFMモードでは、デバイスは、コンバータの出力電圧が設定スレッシュホールド電圧(標準はV<sub>O</sub>)を下回った時のみ動作します。コンバータは1つまたはいくつかのパルスで出力電圧を上昇させ、パワーセーブ・モードに戻ります。結果として、パワーセーブ・モードでの平均出力電圧はPWMモードのときの平均値より少し高くなります。

ライトPFMからPWM動作間を適切に遷移するため、ライトPFMモード時の出力電圧リップルは入力電圧に比例しています。LIGHTPFM OPTIMIZE(VSEL0[6]またはVSEL1[6])ビットを“L”レベルにセットすることで出力電圧リップルを低減することができます。しかし、これは1μH(標準)のインダクタを使用して、V<sub>I</sub>/25Ωより低い負荷電流で動作し、かつ、自動モードの遷移機能を必要としないアプリケーションでしか実現できません。

2.2μH(標準)のインダクタで動作している時、LIGHTPFM OPTIMIZE(VSEL0[6]またはVSEL1[6])ビットは常時“L”レベルにセットしておかなければなりません。この場合、自動遷移機能は負荷電流の制約を受けることはありません。

図 44. Operation in PFM Mode and Transfer to PWM Mode

## モードの選択と周波数同期

TPS6235xはSYNCピンに入力された外部クロック信号に同期運転させることができます。SYNCピンを固定状態の“H”レベルまたは“L”レベル状態にしてもコンバータの動作には影響はありません。

CONTROL1レジスタの設定により、デバイスは固定周波数動作のPWMモード、または、PWM/パワーセーブの自動切換えモードで動作させることができます。この自動切換えモードというのは、コンバータ出力が中～大負荷時には固定周波数のPWMモードで動作し、軽負荷時にはPFMモードで動作して広い負荷電流範囲にわたって高効率を維持します。詳細についてはCONTROL1レジスタの説明を参照してください。

固定周波数のPWMモードでは、優れたレギュレーションと入力/負荷過渡特性が得られます。さらに、この動作モードではノイズに敏感なアプリケーションに対するスイッチング周波数帯のフィルタを簡素化することができます。軽負荷時の効率に関しては、固定周波数のPWMモードはパワーセーブ・モードに比べて低くなります。パワーセーブ・モード(ライトまたはファストPFM)から固定PWMモードへの切り替えは動作中でも可能です。これはVSEL信号を使うか、CONTROL1レジスタを再プログラムすることで実現できます。このことにより、コンバータの動作をシステム特有の要件に適合するよう調整することができます、より効率的で柔軟性のあるパワー・マネジメントが実現します。

同期動作がイネーブル(CONTROL2[5]=1)の時、コンバータは固定周波数動作モードに設定され、PチャネルMOSFETのターンオンは外部クロックの立下りエッジに同期します。これにより、複数のコンバータをマスター/スレーブ構成で接続し、周波数マッチングを行い動作させることができます(詳細についてはアプリケーションの項を参照してください)。

CONTROL1[1:0]=00でVSEL信号が“L”レベルの時、コンバータはMODE0ビットに従って動作し、同期動作はEN\_SYNC及びHW\_nSWビットにかかわらずディスエーブルです。

## ソフトスタート

TPS6235xは内部に起動時の突入電流を制限するソフトスタート回路を持っていますので、バッテリーまたは出力インピーダンスの高い電源がコンバータの入力に接続された場合、入力電圧に起こり得る電圧降下を防ぐことができます。

TPS62350/1/3/4/5のソフトスタートはデジタル制御により350mA/675mA/1000mAの電流制限、および標準電流制限値の1350mAのステップで電流制限を増加させる事により動作します。電流制限値のステップ移行は256クロック(約88μs)毎に発生します。ただし、675mAから1000mAへの電流制限値のステップ移行は出力電圧が $0.5 \times V_{O(NOM)}$ より高い時のみ可能です(それ以下の場合は675mAの電流制限の状態を保持します)。

TPS62356のソフトスタートはデジタル制御により400mA/775mA/1150mAの電流制限、および標準電流制限値の1550mAのステップで電流制限を増加させる事により動作します。電流制限値のステップ移行は256クロック(約88μs)毎に発生します。ただし、775mAから1150mAへの電流制限値のステップ移行は出

力電圧が $0.5 \times V_{O(NOM)}$ より高い時のみ可能です(それ以下の場合は775mAの電流制限の状態を保持します)。

この機能は出力短絡時に短絡電流をより少ない値に制限する為に設けられています。この機能により、起動時間は出力コンデンサ容量と負過電流に大きく依存する事になります。

## イネーブル

このデバイスはENピンが“H”レベルにセットされた時動作を開始し、ソフトスタートにより立ち上ります。この信号はレジスタVSEL0とVSEL1で定義されているEN\_DCDCビットによりゲート・コントロールされます。ENピンの立ち上がりエッジで、全てのレジスタはデフォルト値にリセットされます。EN\_DCDCビットによりコンバータの動作をイネーブルにしても内部レジスタの設定には影響を与えません。このEN\_DCDCビットを使うと、コンバータを起動する前に出力電圧をデフォルト電圧以外の電圧値にプログラムすることができます。詳細についてはVSEL0/1レジスタの説明を参照してください。

ENピン、VSEL0[6]、VSEL1[6]ビットのいずれかを“L”レベルにすると、デバイスはシャットダウン・モードになります。このときのデバイスの待機電流値は電気的特性に示した値となります。このモードでは、PチャネルMOSFETとNチャネルMOSFETはオフとなり、内部のフィードバック用分圧抵抗が切断され、全ての内部コントロール回路がオフに切り替えられます。外部電圧源またはスーパー・キャパシタにより出力電圧がシャットダウン・モード時でも存在している時、電気的特性に規定されている逆リーク電流が流れます。正常動作を行うには、ENピンは終端処理しなければならず、フローティングにしてはなりません。

また、CONTROL2[6]ビットの設定により、デバイスがオフになった時に出力コンデンサをアクティブに放電することができます。内蔵の放電抵抗値は標準で $15\Omega$ です。 $V_O$ の出力コンデンサを放電するのに要する時間は負荷電流と出力容量値により決まります。

## 電圧とモード選択

TPS6235xの特長として出力電圧が端子の設定で選択可能なことがあります。VSELはアクティブ・モード(VSEL=“H”レベル)とスリープ・モード(VSEL=“L”レベル)間での出力デジタル可変制御に主に使用されます。出力に持たせる柔軟性を最も大きくする方法は、I<sup>2</sup>Cインターフェイス経由でVSEL信号を使ってコンバータの動作モード(例えば、固定周波数PWM、ファストPFM、ライトPFM)を再プログラムすることです。

VSELによる出力電圧とモード選択は以下のように定義されます。

**VSEL=“L”レベル**：DC/DC出力電圧はVSEL0レジスタ値により決まります。DC/DC動作モードはCONTROL1レジスタのMODE0ビットにより決まります。

**VSEL=“H”レベル**：DC/DC出力電圧はVSEL1レジスタ値により決まります。DC/DC動作モードはCONTROL1レジスタのMODE1ビットにより決まります。

## 低電圧ロックアウト

低電圧ロックアウト回路により低入力電圧時のデバイスの誤動作が防止されます。これは、不定領域でコンバータのスイッチや整流のMOSFETがオンするのを防ぎます。

## 短絡保護

出力電圧が設定値の50%より低下すると、電流制限値も50%に低減されます。短絡保護は起動時からインエーブルであるため、デバイスは出力電圧が設定値の50%を越えるまで制限電流の半分以上の電流は供給しません。このことは、モーターなどの電流シンクとして機能している負荷がコンバータの出力に接続されている場合に考慮する必要があります。

## サーマル・シャットダウン

ジャンクション温度 $T_J$ が150°C (typ.) を越えるとデバイスはサーマル・シャットダウン状態になります。このモードでは、PチャネルMOSFETとNチャネルMOSFETはオフになります。デバイスは接合部温度が再び130°C (typ.) より下がると動作を再開します。

## 動作原理

### シリアル・インターフェイスの説明

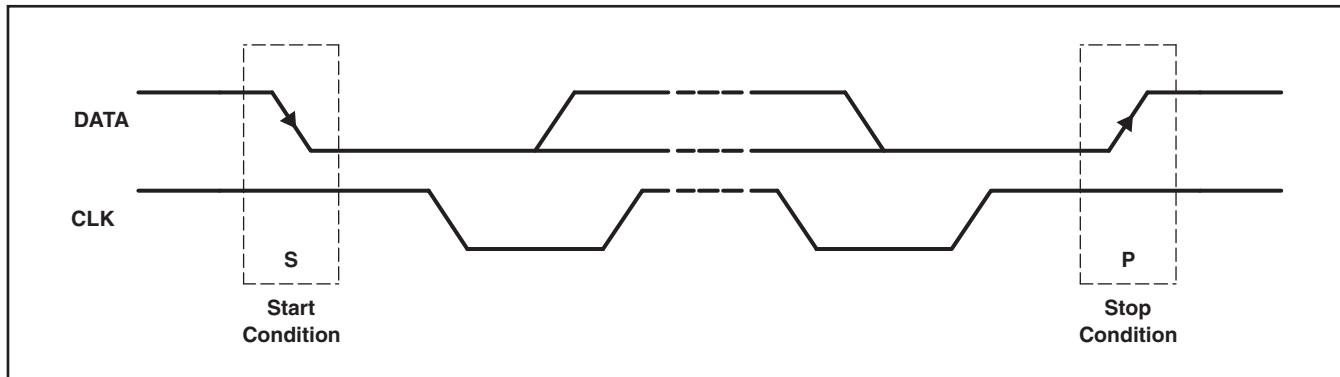

I<sup>2</sup>Cはフィリップス・セミコンダクタ社により開発された2線のシリアル・インターフェイスです(I<sup>2</sup>Cバス規格バージョン2.1/Jan2000参照)。このバスはデータ・ライン( SDA)とクロック・ライン( SCL)で構成されており、プルアップされています。バスがアイドル状態の時、SDAラインとSCLラインは“H”レベルになっています。全てのI<sup>2</sup>C互換デバイスは、オープン・ドレインのI/Oピン、SDA、SCLを介してI<sup>2</sup>Cバスに接続されます。マスター・デバイス(一般には、マイクロコントローラやデジタル・シグナル・プロセッサ)には、バスをコントロールし、SCL信号とデバイス・アドレスを生成するという重要な役割があります。また、マスター・デバイスはデータ転送のSTARTとSTOPを表す固有の状態も作ります。スレーブ・デバイスはマスター・デバイスのコントロール下でバス上のデータを送受信します。

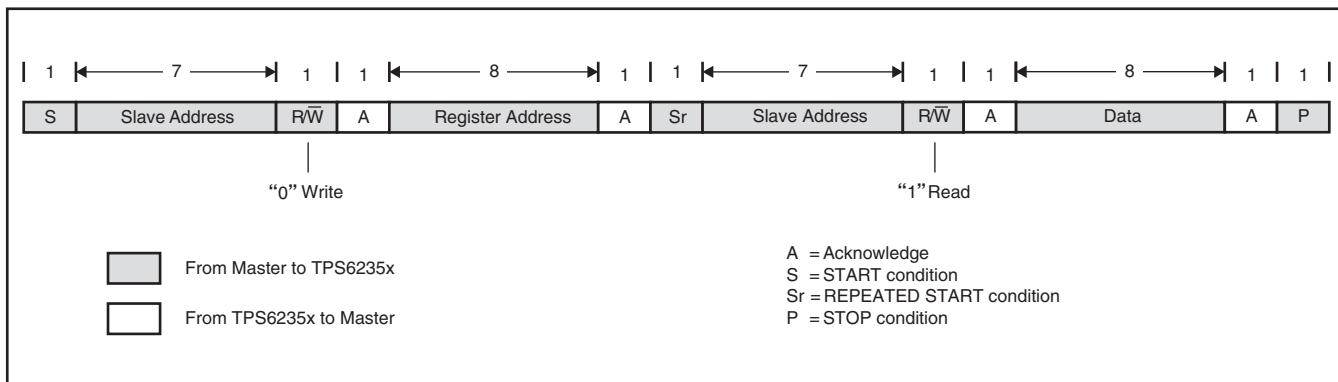

TPS6235xデバイスはスレーブとして動作し、I<sup>2</sup>Cバス規格で定義されている標準モード(100kbps)、ファスト・モード(400kbps)、高速モード(ライト・モード時最大3.4Mbps)のデータ転送モードに対応しています。このインターフェイスにより電源ソリューションに柔軟性が加わり、アプリケーション要件に応じて、ほとんどの機能を即座に新たな値にプログラムすることができます。レジスタに設定された内容は、電源電圧が2.2V(Typ)より高ければそのままの状態が保たれます。

標準モードとファスト・モードのデータ転送プロトコルは全く同じであるため、このデータシートではF/Sモードと呼ぶことにします。高速モードのプロトコルはF/Sモードと異なっているため、HSモードと呼びます。TPS6235xデバイスは7ビットのアドレッシングに対応しており、10ビットのアドレッシングとゼネラル・コール・アドレスには対応していません。

TPS6235xデバイスは、出荷検査時にプログラム可能な2LSBビットを含む7ビットのアドレスを持っており、最大4つのDC/DCコンバータを同一バスに接続することができます。5MSBは“10010”で固定されています。

### F/Sモードのプロトコル

マスター・デバイスは、スタート状態を作り出してからデータ転送を開始します。スタート状態とは、SCL = “H”時に、SDAが“H”レベルから“L”レベルに遷移した時のことです。図45を参照してください。スタート状態の認識は、全てのI<sup>2</sup>C互換デバイスでなされなければなりません。

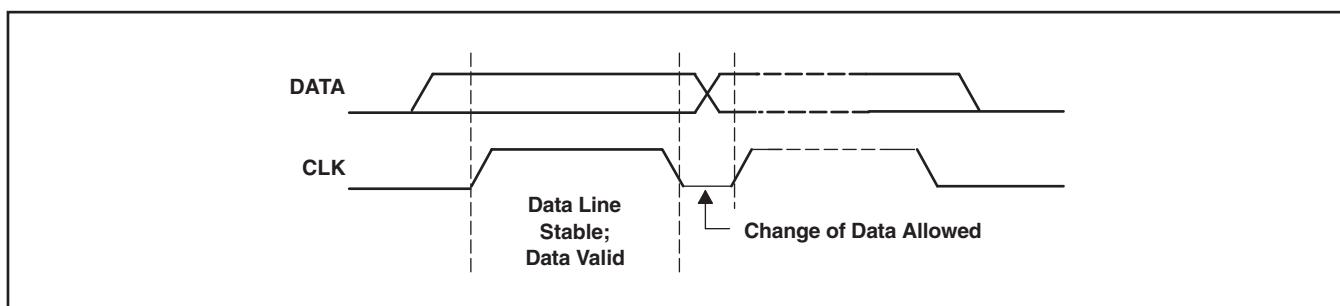

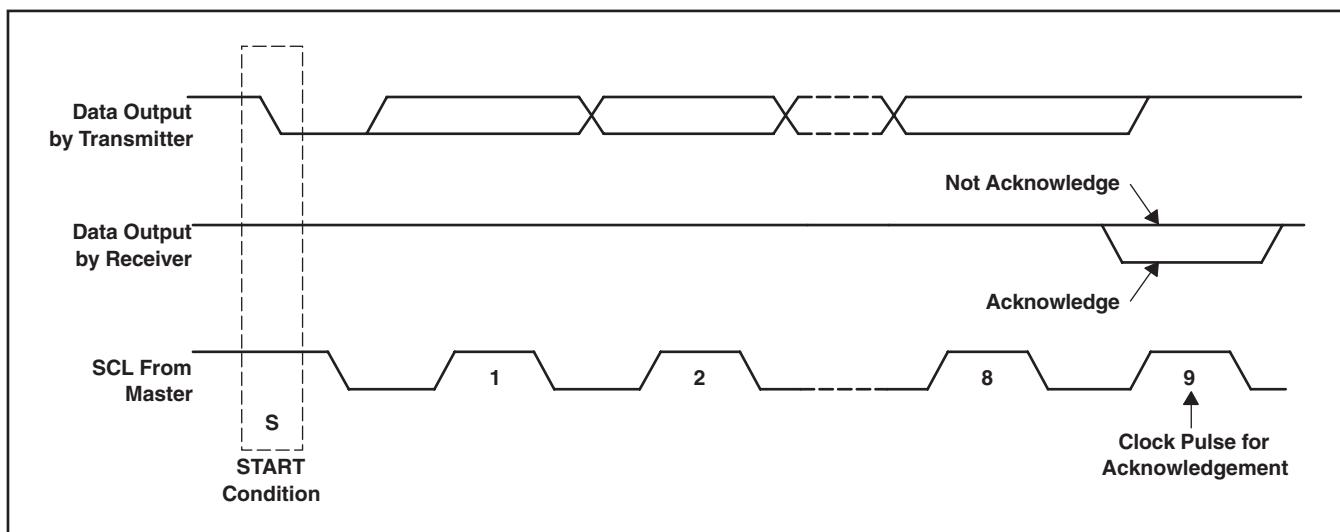

次に、マスターはSCLパルスを生成し、7ビットのアドレスとリード/ライト・ディレクション・ビットR/WをSDAラインに送信します。マスターは、全送信に対してデータが有効になるようにします。データが有効となるには、クロック・パルスの“H”レベルの全期間でSDAラインが安定している必要があります。図46を参照してください。全デバイスはマスターから送られるアドレスを認識し、それを各デバイス内部の固定アドレスと比較します。アドレスマッチングの取れたスレーブ・デバイスのみが、9番目のSCLパルスの全“H”レベル期間でSDAラインを“L”レベルにすることで、認証を受けられます。図47を参照してください。この認証信号を検出して、マスターはスレーブとの通信回線が構築されたことを知ります。

さらにマスターは、スレーブにデータを送信(R/Wビット:1)、またはスレーブからデータを受信(R/Wビット:0)するためにSCLパルスを生成します。どちらの場合にも、受信側は送信側により送られたデータを確認する必要があります。認証信号はどちらが受信側であるかによりマスターまたはスレーブのいずれかから生成されます。8ビットのデータと1ビットの認証信号から成る9ビットの有効データ列が必要である限り続きます。

データ転送の終わりを知らせるため、マスターはSCL = “H”時にSDAラインを“L”レベルから“H”レベルにしてストップ状態を生成します。図45を参照してください。これでバスは解放され、アドレッシングされているスレーブとのリンクが停止します。全てのI<sup>2</sup>C互換デバイスがストップ状態を認識しなければなりません。ストップ状態を受信した時、全デバイスはバスが解放されたことを知り、次のアドレスマッチングが行われるスタート状態を待ちます。

このデータシートに記載されていないレジスタ・アドレスからデータを読みうるとするとFFhが読み出されることになります。

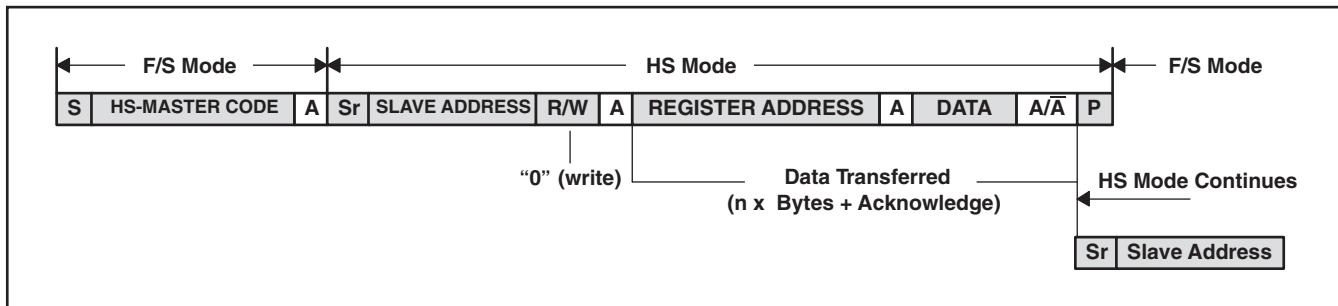

## H/Sモードのプロトコル

バスがアイドル状態の時、SDAラインとSCLラインの両方とも、プルアップにより“H”レベルになっています。

マスターは、HSマスター・コード00001XXXを含む有効シリアル・バイトが後ろに続くスタート状態を生成します。この送信は400kbps以下のF/Sモードで行われます。どのデバイスもHSマスター・コードを‘認証’することはできませんが、全デバイスはそのコードを‘認識’して内部設定を3.4Mbps動作に対応するよう切り換えなければなりません。

次に、マスターは再スタート状態を生成します(再スタート状態は始めのスタート状態のタイミングと同じです)。この再スタート状態となると、プロトコルは最大3.4Mbps転送速度が可能であることを除いてF/Sモードと同じです。ストップ状態はHSモードを終了させ、F/Sモードに対応するよう全てのスレーブ・デバイスの内部設定を切り替えます。ストップ状態の代わりに再スタート状態を使うと、HSモードでバスが確保されます。

このデータシートに記載されていないレジスタ・アドレスからデータを読もうとするとFFhが読み出されることになります。

図 45. START and STOP Conditions

図 46. Bit Transfer on the Serial Interface

図 47. Acknowledge on the I<sup>2</sup>C Bus

図 48. Bus Protocol

### TPS6235x I<sup>2</sup>C更新インターフェイス

TPS6235xは1つのレジスタを更新するのに、スタート状態、有効I<sup>2</sup>Cアドレス、レジスタ・アドレス・バイト、データ・バイトの4つを必要とします。各バイトの受信後、TPS6235xデバイスは、1つのクロック・パルスが“H”レベルの期間にSDAラインを“L”レベルにして認証を受けます。有効I<sup>2</sup>CアドレスはTPS6235xを選択し、TPS6235xは LSBバイトの立下りエッジで更新を行います。

TPS6235xがハードウェアでのシャットダウン状態にある時(ENピンがグラウンドに接続されている時)、デバイスはI<sup>2</sup>Cインターフェイスを介しては更新することはできません。逆に、ソフトウェアでのシャットダウン状態時(EN\_DCDCビット=0)には、I<sup>2</sup>Cインターフェイスはすべて機能します。

図 49. “Write” Data Transfer Format in F/S-Mode

図 50. "Read" Data Transfer Format in F/S-Mode

図 51. Data Transfer Format in H/S-Mode

## スレーブ・アドレス・バイト

| MSB |   |   |   |   |   |    | LSB |

|-----|---|---|---|---|---|----|-----|

| X   | 1 | 0 | 0 | 1 | 0 | A1 | A0  |

スレーブ・アドレス・バイトとは、マスター・デバイスから受信した 'START状態' の次に受信するバイトです。アドレスの最初の5ビット (MSB) は、工場出荷時に "10010" に初期設定されています。次の2ビット (A1, A0) はデバイス・オプションによります。例えば、TPS62350は "00" に、TPS62351は "10" に出荷時に初期設定されています。最大4タイプのTPS6235xデバイスを同一のI<sup>2</sup>Cバスに接続することができます。詳細については発注情報の表を参照してください。

## レジスタ・アドレス・バイト

| MSB |   |   |   |   |   |    | LSB |

|-----|---|---|---|---|---|----|-----|

| 0   | 0 | 0 | 0 | 0 | 0 | D1 | D0  |

スレーブ・アドレスの認証が終わると、バス・マスターはアクセスするレジスタアドレスを含む1バイトをTPS6235xに送ります。TPS6235xは双方向I<sup>2</sup>Cバス・インターフェイスを介してアクセス可能な4つの8ビット・レジスタを持っています。全ての内部レジスタはリード及びライト・アクセスの機能をもっています。

| レジスタ名                | D1, D0の値 |

|----------------------|----------|

| VSEL0 (リード/ライト) SEL0 | 00       |

| VSEL1 (リード/ライト)      | 01       |

| CONTROL1 (リード/ライト)   | 10       |

| CONTROL2 (リード/ライト)   | 11       |

表 1. レジスタの説明

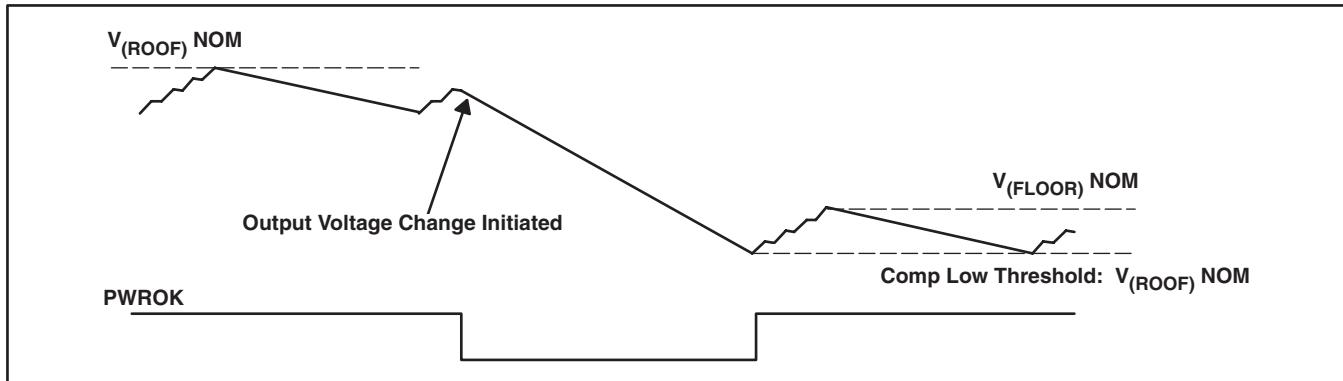

図 52. PWROK Operation (Transition to a Lower Voltage)

## 出力電圧のアクティブな制御

プロセッサのコアの消費電力を低減するため、TPS6235xはその出力電圧をコンバータ動作中にデジタル可変させることができます。これには2つのやり方があります。“ソフトウェアによる方法”ハードウェアによる方法。これはHW\_nSWビットで選択することができます（下記の制御ビットと値ビットについての詳細はレジスタの説明の項に示されています）。

### ハードウェア制御に同期した出力電圧の制御方法（HW\_nSW = 1）

アプリケーション・プロセッサにより、I<sup>2</sup>C経由で出力電圧がプログラムされます。このとき、VSEL信号の2状態（最小値[VSEL0]と最大[VSEL1]）を使います。また、アプリケーション・プロセッサは出力電圧の変化速度を制御するため、CONTROL2レジスタにDEFSLEW値も書き込みます。

この2つのレジスタは、VSEL入力に従って適切な出力電圧を供給するようI<sup>2</sup>Cを介して連続的に更新されます。出力電圧は、VSEL0またはVSEL1レジスタに書き込んだ直後に、選択した電圧変化速度で変化します。

PFMモードでは、VSEL信号を“H”レベルから“L”レベルに切り替えることで出力電圧がそれまでよりも低い電圧にプログラムされると、出力コンデンサが負荷により放電され、コンバータが電圧レギュレーションを保つためのスイッチングを開始するまでの間PWROKは“L”レベルになります。

多段ステップモードでは、出力電圧が上下にステップで変動している間は、PWROKは“L”レベルになります。その他の全ての動作状態下で、出力電圧が設定値の1.5%以下であると、PWROKは“L”レベルになります。

表2にVSEL0、VSEL1レジスタとVSEL信号に応じた出力電圧状態を示します。

### ソフトウェア設定による出力電圧の制御方法（HW\_nSW = 0）

デジタル・プロセッサは必要とされる出力電圧をI<sup>2</sup>Cインターフェイスを介して直接レジスタVSEL1に書き込みます。また、アプリケーション・プロセッサは出力電圧の変化速度をコントロールするためCONTROL2レジスタのDEFSLEW値も書き込みます。

CONTROL2レジスタのGOビットを設定後に、出力電圧は選択した変化速度で変化します。このビットは出力電圧がその目標値に達した時リセットされます。このモードでは、出力電圧の変化はVSEL信号に無関係で、VSEL0レジスタは使用しません。

PFMモードでは、出力電圧がそれまでよりも低い電圧にプログラムされると、出力コンデンサが負荷により放電され、コンバータが電圧レギュレーションを保つためのスイッチングを開始するまでの間、PWROKは“L”レベルになります。

多段ステップモードでは、出力電圧が上下にステップで変動している間は、PWROKは“L”レベルになります。その他の全ての動作状態下で、出力電圧が設定値の1.5%以下であると、PWROKは“L”レベルになります。

| VSELピン  | VSEL0レジスタ | VSEL1レジスタ | 出力電圧      |

|---------|-----------|-----------|-----------|

| “L” レベル | No action | No action | 最小        |

| “L” レベル | 新値の書き込み   | No action | 新値に変更     |

| “L” レベル | No action | 書き込み      | 最小電圧のまま不变 |

| “H” レベル | No action | No action | 最大        |

| “H” レベル | 新値の書き込み   | No action | 最大電圧のまま不变 |

| “H” レベル | No action | 新値の書き込み   | 新値に変更     |

表2. 同期スケーリングのハードウェア方策の概要(HW\_nSW=1)

## 出力電圧上昇速度制御

TPS6235xは、2つの異なるモードで動作する電圧変化速度制御機能を持っています。

- 多段ステップモード

- シングルステップモード

モード選択は、CONTROL2レジスタのDEFSLEWコントロール・ビットで行います。

多段ステップ電圧スケーリング・モード、

DEFSLEW[2:0]=[000]-[110]

多段ステップモードでは、TPS6235xは、HW\_nSWビット及び動作モード（例、固定PWM、ファストPFM、ライトPFM）とは無関係に出力電圧変化速度をコントロールします。電圧ステップ毎の時間を調整することにより、電圧上昇速度のコントロールを行っています。

ソシングルステップ電圧スケーリング・モード（デフォルト）、

DEFSLEW[2:0] = [111]

TPS6235xは、シングルステップモードでは、電圧変更が低い方から高い方へ遷移している時には、最大スルーレートで出力電圧を上昇させます。

一方、電圧設定変更により出力電圧が低い方へ遷移している時の電圧変化速度は、モード設定レジスタ（CONTROL1レジスタ参照）に設定された動作モード（固定PWM、ファストPFM、ライトPFM）により変化します。

表3に示すのは、DEFSLEWを即時移行にセットして、低い方の電圧に遷移している時の変化速度制御です。

例えば、ライトPFMまたはファストPFMで動作している場合、出力が低い方の電圧に移行するようプログラムされた時、TPS6235xは出力電圧を下降させますが、その際、電圧変化速度をコントロールしたり、ステップ電圧を入れるようなことはありません。電圧降下に要する時間は、TPS6235xの出力容量と負荷電流により決まります。システム全体からすると、アクティブな出力電圧デジタル可変を行うにはこれがもっとも効率的な方法です。

| 電圧変更時の動作モード | HW_nSW | 出力電圧ランプ・レート          |

|-------------|--------|----------------------|

| 固定PWM       | X      | 即時                   |

| ファストPFM     | X      | 下降時間は出力容量と負荷電流により決まる |

| ライトPFM      | X      | 下降時間は出力容量と負荷電流により決まる |

表3. ランプ・レート・コントロール対目標モード

## レジスタの説明

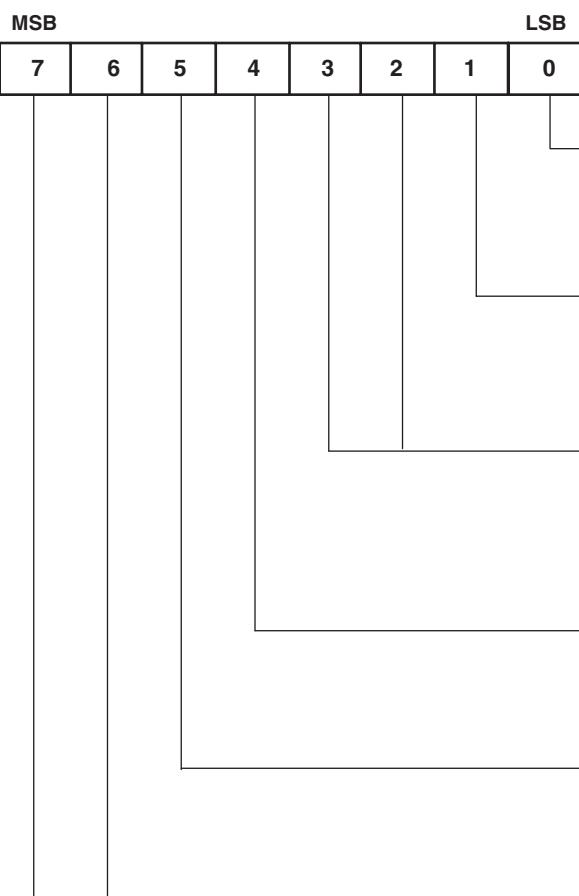

### VSEL0レジスタ(リード/ライト)

| MSB | 6 | 5 | 4 | 3 | 2 | 1 | 0 | LSB |

|-----|---|---|---|---|---|---|---|-----|

|     |   |   |   |   |   |   |   |     |

メモリ・ロケーション: 00

リセット状態: X1XX XXXX — 発注情報表参照

#### 電圧ステップ乗数、VSM0

6ビット符号なしバイナリの直線符号化

有効コード: 0~63(10進)

#### LIGHTPFM OPTIMIZE

0: 2.2μHのインダクタ向けに最適化されたライトPFM

1: 1μHインダクタ向けに最適化されたライトPFM(デフォルト)

このビットはVSEL1[6]により内部でマッピングされます。

VSEL0[6]に値を書き込むとVSEL1[6]は自動的に更新されます。

#### EN\_DCDC

このビットは外部のENピン信号をゲート・コントロールします。

0: EN信号に無関係にデバイスはシャットダウン・モード

1: ENピンが“H”レベルの時デバイスはイネーブル(デフォルト)

このビットはVSEL1[7]により内部でマッピングされます。

VSEL0[7]に値を書き込むとVSEL1[7]は自動的に更新されます。

- A. TPS62350, 51, 52, 53, 54, 55 :

出力電圧 = 最小出力電圧 + (電圧ステップ乗数0 × 12.5mV)

- B. TPS62356 :

出力電圧 = 最小出力電圧 + (電圧ステップ乗数0 × 25mV)

### VSEL1レジスタ(リード/ライト)

| MSB | 6 | 5 | 4 | 3 | 2 | 1 | 0 | LSB |

|-----|---|---|---|---|---|---|---|-----|

|     |   |   |   |   |   |   |   |     |

メモリ・ロケーション: 01

リセット状態: X1XX XXXX — 発注情報表参照

#### 電圧ステップ乗数、VSM1

6ビット符号なしバイナリの直線符号化

有効コード: 0~63(10進)

#### LIGHTPFM OPTIMIZE

0: 2.2μHインダクタ向けに最適化されたライトPFM

1: 1μHインダクタ向けに最適化されたライトPFM(デフォルト)

このビットはVSEL0[6]により内部でマッピングされます。

VSEL1[6]に値を書き込むとVSEL0[6]は自動的に更新されます。

#### EN\_DCDC

このビットは外部のENピン信号をゲート・コントロールします。

0: EN信号に無関係にデバイスはシャットダウン・モード

1: ENピンが“H”レベルの時デバイスはイネーブル(デフォルト)

このビットはVSEL0[7]により内部でマッピングされます。

VSEL1[7]に値を書き込むとVSEL0[7]は自動的に更新されます。

- A. TPS62350, 51, 52, 53, 54, 55 :

出力電圧 = 最小出力電圧 + (電圧ステップ乗数1 × 12.5mV)

- B. TPS62356 :