**TPS650864** JAJSE66E - JUNE 2017 - REVISED DECEMBER 2022

# TPS650864 設定可能なマルチレール PMU、Xilinx® MPSoC / FPGA 用

# 1 特長

- 5.6V~21V の広い V<sub>IN</sub> 範囲

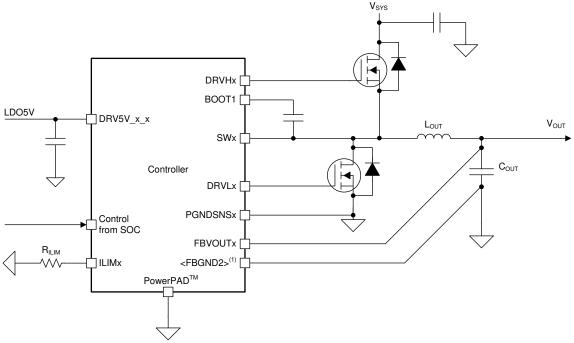

- D-CAP2™トポロジを採用した3つの可変出力電圧同

降圧型コントローラ

- 外付けの FET を使用して出力電流をスケーリング 可能、電流制限を選択可能

- I<sup>2</sup>C により、0.41V~1.67V の範囲で 10mV 刻み、 または 1V~3.575V の範囲で 25mV 刻みの DVS 制御が可能

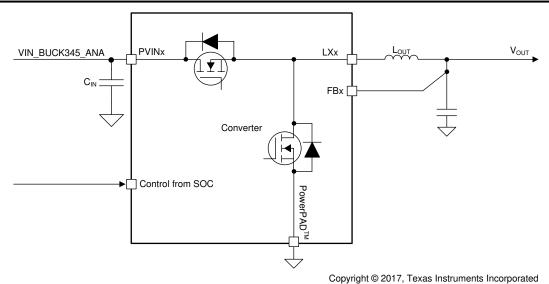

- DCS-Controlトポロジを採用した3つの可変出力電 圧同期整流降圧型コンバータ

- V<sub>IN</sub> 範囲は 3V~5.5V

- 最大 3A の出力電流

- I<sup>2</sup>C により、0.41V~1.67V の範囲で 10mV 刻み、 または 0.425V~3.575V の範囲で 25mV 刻みの DVS 制御が可能

- 出力電圧可変の 3 つの LDO レギュレータ

- LDOA1:I<sup>2</sup>C により電圧を 1.35V~3.3V の範囲で 選択可能、最大出力電流 200mA

- LDOA2 および LDOA3: I<sup>2</sup>C により電圧を 0.7V~ 1.5V の範囲で選択可能、最大出力電流 600mA

- DDR メモリ終端用の VTT LDO

- スルー・レート制御付きの3つの負荷スイッチ

- 最大 300mA の出力電流、電圧降下は公称入力 電圧の 1.5% 未満

- 入力電圧 1.8V において  $R_{DSON}$  <  $96m\Omega$

- 5V 固定出力電圧の LDO (LDO5)

- SMPS のゲート・ドライバおよび LDOA1 用の電源

- 外部 5V 降圧への自動切り替えにより高効率を実

- 工場での OTP プログラミングにより柔軟な構成が可能

- 6 つの GPI ピンを、選択した任意のレールのイネ ーブル (CTL1~CTL6) またはスリープ・モード移 行 (CTL3 および CTL6) に構成可能

- 4 つの GPO ピンを、選択した任意のレールのパワ 一・グッドに構成可能

- オープン・ドレインの割り込み出力ピン

- I<sup>2</sup>C インターフェイスにより Standard Mode (100kHz), Fast Mode (400kHz), Fast Mode Plus (1MHz) をサポート

# 2 アプリケーション

- プログラマブル・ロジック・コントローラ

- マシン・ビジョン・カメラ

- ビデオ監視

- 試験/測定機器

- 組み込み用 PC

- モーション・コントロール

- ポータブル超音波機器

### 3 概要

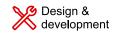

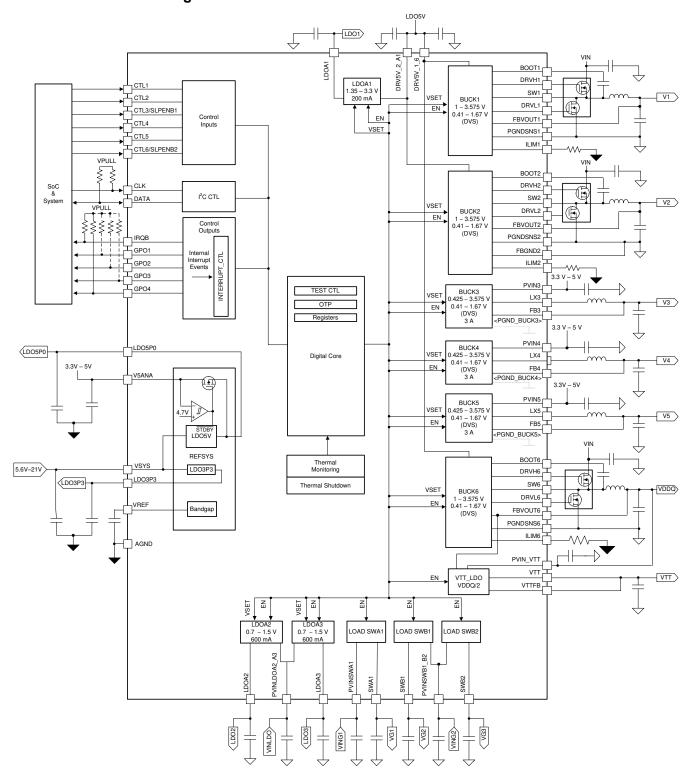

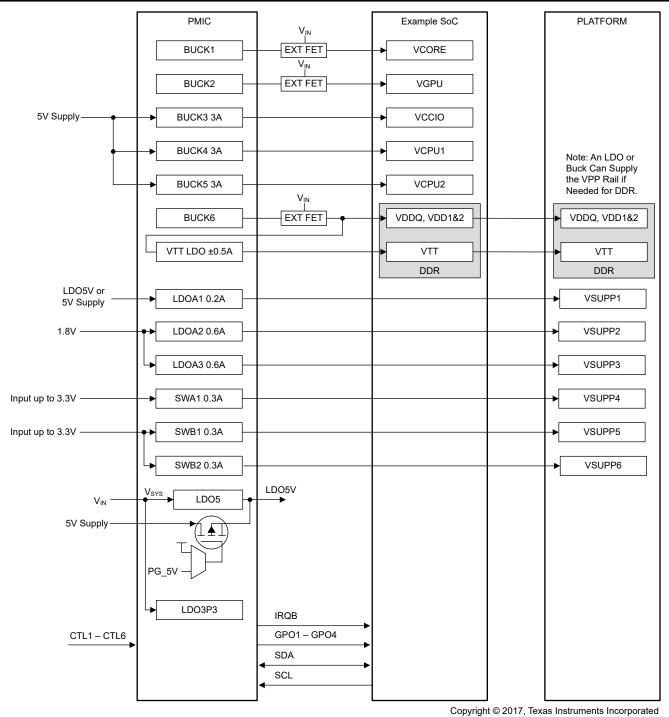

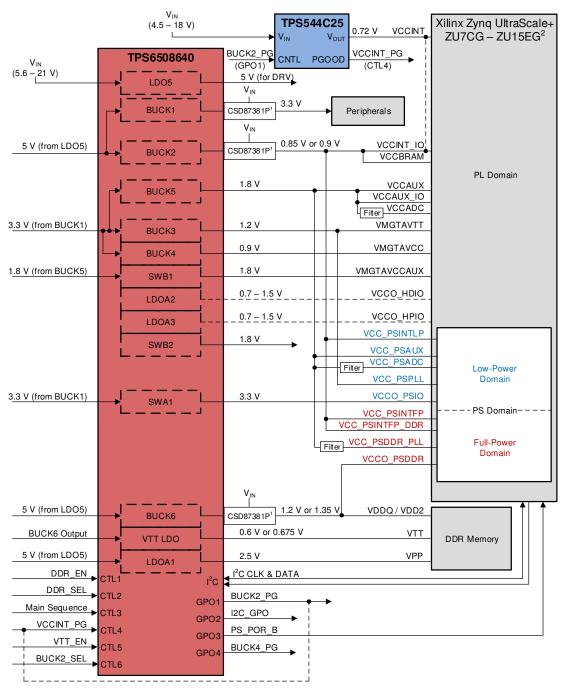

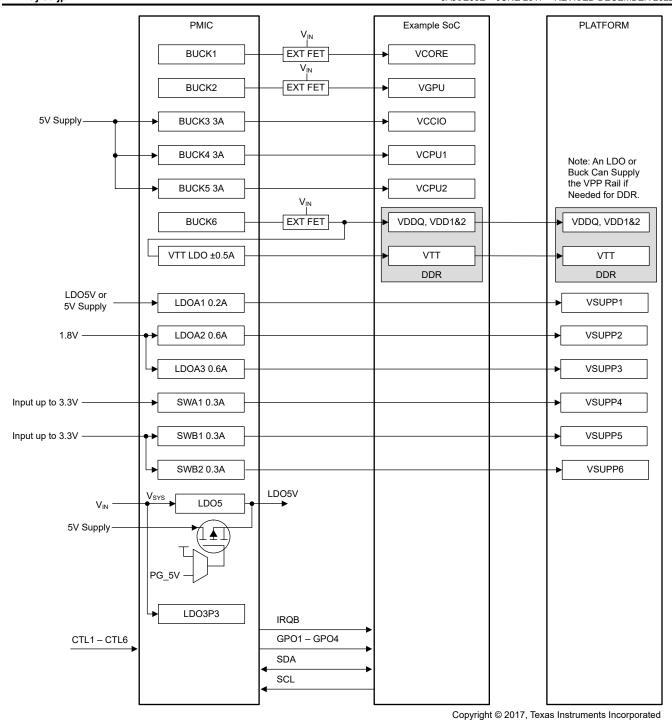

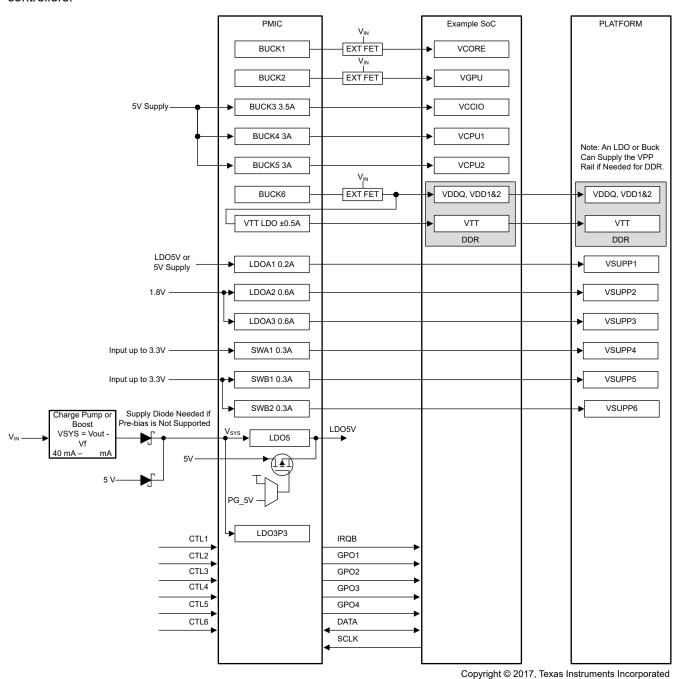

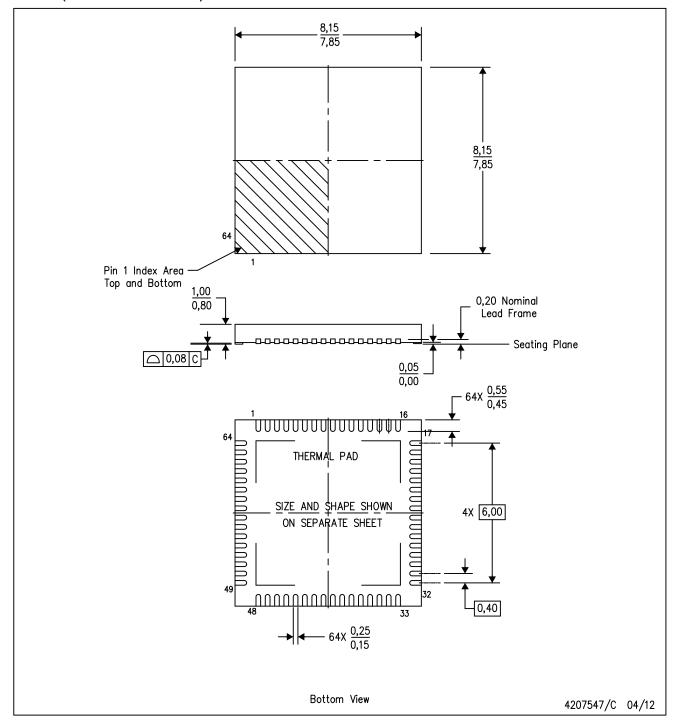

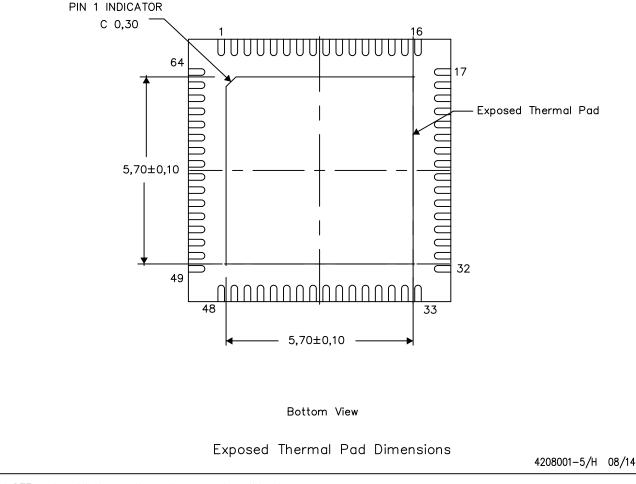

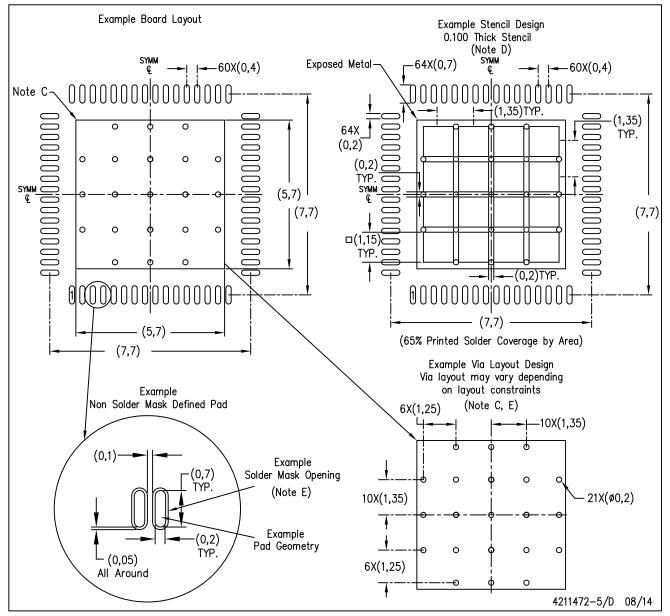

TPS650864 デバイス・ファミリは、Xilinx Zyng® マルチプ ロセッサ・システム・オン・チップ (MPSoC) およびフィール ド・プログラマブル・ゲート・アレイ (FPGA) ファミリ用に設 計されたシングルチップのパワー・マネージメント IC (PMIC) です。TPS650864 は、5.6V~21V の入力範囲 に対応することから、幅広い用途に使用できます (「デバイ ス比較表」を参照)。また、壁面電源を使用する機器や 2S、3S、4S のリチウムイオン・バッテリ・パック (NVDC ま たは非 NVDC 電源アーキテクチャ) に最適です。5V 入 力電源については、「代表的なアプリケーション」を参照し てください。 D-CAP2 および DCS-Control 高周波電圧レ ギュレータは、小型の受動素子を使用するため、ソリュー ションを小型化できます。 D-CAP2 および DCS-Control ト ポロジは過渡応答性能が非常に優れており、高速な負荷 切り替えが発生するプロセッサ・コアおよびシステム・メモリ のレールに最適です。I<sup>2</sup>C インターフェイスにより、組み込 みコントローラ (EC) または SoC を使用して単純な制御が 可能です。この PMIC は、8mm × 8mm、単一列の VQFN パッケージで供給され、放熱特性改善のためにサ ーマル・パッドが付属します。

### 製品情報(1)

| 部品番号          | パッケージ     | 本体サイズ (公称)      |

|---------------|-----------|-----------------|

| TPS650864 (2) | VQFN (64) | 8.00mm × 8.00mm |

- 詳細については、「メカニカル、パッケージ、および注文情報」を参 (1) 照してください。

- 関連製品については、「デバイス比較表」を参照してください。

# **Table of Contents**

| 1 特長                                             | 1  | 8.2 Functional Block Diagram                        | 22                 |

|--------------------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 アプリケーション                                       |    | 8.3 TPS6508640 Design and Settings                  | 24                 |

| 3 概要                                             |    | 8.4 TPS65086401 Design and Settings                 |                    |

| 4 Revision History                               |    | 8.5 TPS6508641 Design and Settings                  |                    |

| 5 Device Comparison Table                        |    | 8.6 TPS65086470 Design and Settings                 | 39                 |

| 6 Pin Configuration and Functions                |    | 8.7 SMPS Voltage Regulators                         |                    |

| 7 Specifications                                 |    | 8.8 LDOs and Load Switches                          |                    |

| 7.1 Absolute Maximum Ratings                     |    | 8.9 Power Goods (PGOOD or PG) and GPOs              | <mark>5</mark> 1   |

| 7.2 ESD Ratings                                  |    | 8.10 Power Sequencing and VR Control                | <mark>53</mark>    |

| 7.3 Recommended Operating Conditions             |    | 8.11 Device Functional Modes                        |                    |

| 7.4 Thermal Information                          | 10 | 8.12 I <sup>2</sup> C Interface                     | 58                 |

| 7.5 Electrical Characteristics: Total Current    |    | 8.13 Register Maps                                  | 62                 |

| Consumption                                      | 10 | 9 Applications, Implementation, and Layout          | 108                |

| 7.6 Electrical Characteristics: Reference and    |    | 9.1 Application Information                         | 108                |

| Monitoring System                                | 11 | 9.2 Typical Application                             | 108                |

| 7.7 Electrical Characteristics: Buck Controllers |    | 9.3 Power Supply Coupling and Bulk Capacitors       |                    |

| 7.8 Electrical Characteristics: Synchronous Buck |    | 9.4 Do's and Don'ts                                 | 119                |

| Converters                                       | 13 | 10 Device and Documentation Support                 | 120                |

| 7.9 Electrical Characteristics: LDOs             |    | 10.1 Device Support                                 | 120                |

| 7.10 Electrical Characteristics: Load Switches   |    | 10.2 Documentation Support                          | 120                |

| 7.11 Digital Signals: I <sup>2</sup> C Interface |    | 10.3 Receiving Notification of Documentation Update | tes 120            |

| 7.12 Digital Input Signals (CTLx)                |    | 10.4 サポート・リソース                                      | 120                |

| 7.13 Digital Output Signals (IRQB, GPOx)         |    | 10.5 Trademarks                                     | 120                |

| 7.14 Timing Requirements                         |    | 10.6 Electrostatic Discharge Caution                | 120                |

| 7.15 Switching Characteristics                   |    | 10.7 Glossary                                       | 121                |

| 7.16 Typical Characteristics                     |    | 11 Mechanical, Packaging, and Orderable             |                    |

| 8 Detailed Description                           |    | Information                                         | 1 <mark>2</mark> 1 |

| 8.1 Overview                                     |    |                                                     |                    |

|                                                  |    |                                                     |                    |

### 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Changes from Revision D (November 2020) to Revision E (December 2022)

**Page**

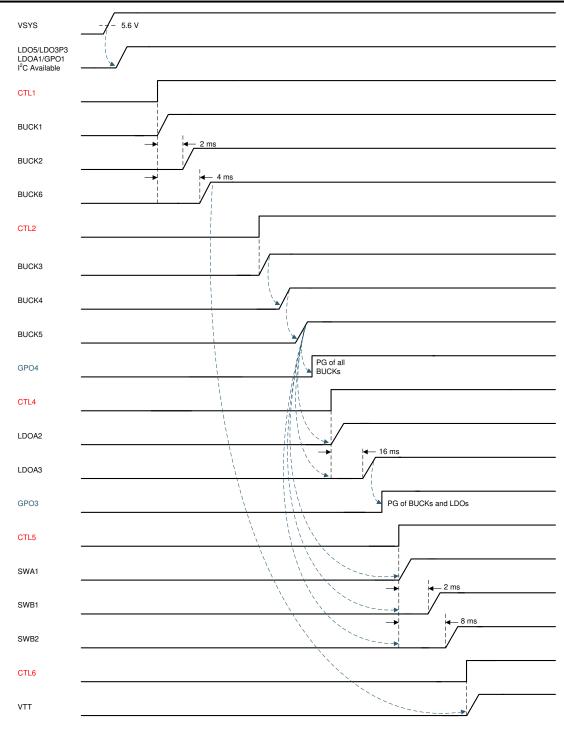

- Changed the power-up sequence for TPS6508640 in the TPS6508640 Power-Up Sequence diagram....... 24 Changed the power-down sequence for TPS6508640 in the TPS6508640 Power-Down Sequence diagram.... 24

- Changed the OTP VERSION[1:0] bits from 01 to 10 for the TPS6508640 device in the DEVICEID2 Register table 64

- Changed the OTP VERSION[1:0] bits from 00 to 01 for the TPS65086401 and TPS6506470 devices in the DEVICEID2 Register table 64

### Changes from Revision C (June 2018) to Revision D (November 2020)

文書全体にわたって表、図、相互参照の採番方法を更新......1

- Changed the incorrect LX3 pin description from connect to ground when not in use to leave floating when not

- Removed incorrect VREF notes from the middle and right DDR blocks in the *Power Map Example* figure.... 22

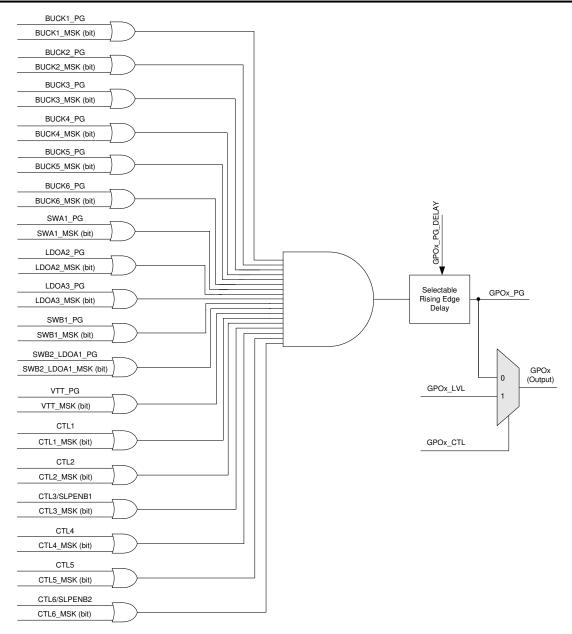

- Added when configured as push-pull, LDO3P3 is used for logic-level high to the Power Good Tree figure

- Changed the bit values for BUCK4 MODE bits in the BUCK4CTRL Register table from 0 to 1 for the TPS65086401 and TPS65086470 devices .......69

- Changed the bit values for BUCK5\_MODE bits in the BUCK5CTRL Register table from 0 to 1 for the

| • | Added links and step ranges to BUCK2SLPCTRL Register Descriptions table                                | <mark>78</mark> |

|---|--------------------------------------------------------------------------------------------------------|-----------------|

| • | Changed the bit values for BUCK3_MODE bits in the BUCK123CTRL Register table from 0 to 1 for the       |                 |

|   | TPS65086401 and TPS65086470 devices                                                                    | 82              |

| • | Removed the incorrect VREF notes from the middle and right DDR blocks in the VIN 5-V Application of    | diagram         |

|   |                                                                                                        | 108             |

| С | hanges from Revision B (December 2017) to Revision C (June 2018)                                       | Page            |

| • | データ・マニュアルに TPS6508640 および TPS6508641 を追加                                                               | 1               |

| • | Added typical MPSoC variants to Device Comparison Table                                                |                 |

| • | Added BUCKx_MODE test condition for quiescent current                                                  | 13              |

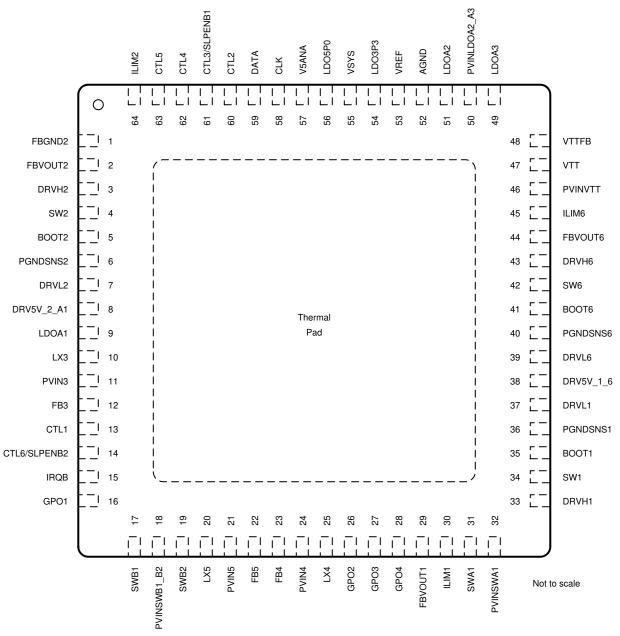

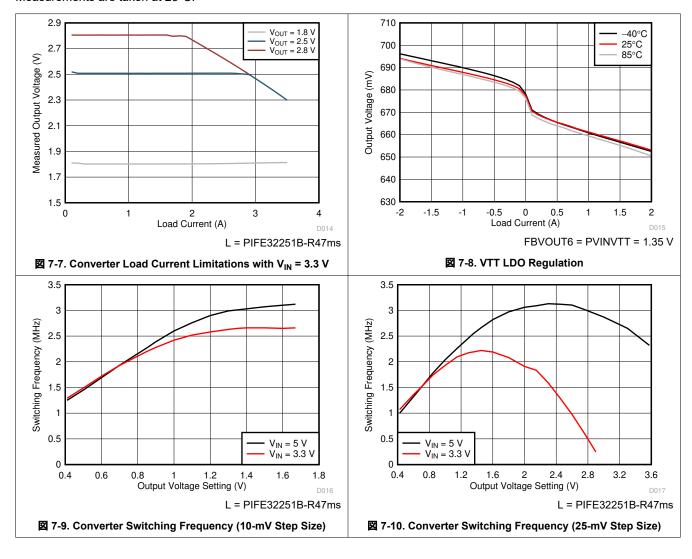

| • | Added BUCKx_MODE information to relevant graphs                                                        | 19              |

| • | Changed the TPS65086401 Power Map Example in the TPS65086401 Design and Settings section               | 29              |

| • | Changed the TPS65086470 Power Map Example in the TPS65086470 Design and Settings section               |                 |

| • | Added information regarding ILIM resistor minimum value for Force PWM condition                        | 50              |

| C | hanges from Revision A (November 2017) to Revision B (December 2017)                                   | Page            |

| • | Changed TPS65086401 from preview to production data                                                    |                 |

| C | hanges from Revision * (February 2017) to Revision A (November 2017)                                   | Page            |

| • | 製品ステータスを「製品プレビュー」から「量産データ」に変更                                                                          | 1               |

| • | Added pin connection when unused                                                                       |                 |

| • | Changed the TPS65086401 Power Map Example in the TPS65086401 Design and Settings section               | 29              |

| • | Fixed SWB1 and SWB2 current to 0.4A from 0.3A                                                          |                 |

| • | Changed typo from TPS6508470 to TPS65086470                                                            | 42              |

| • | Changed description to Sleep State from Connected Standby for consistency in the Sleep State Entry     | and             |

|   | Exit section                                                                                           | <mark>57</mark> |

| • | Changed the description of all PGOODs in the note in the Sleep State Entry and Exit section from stay  |                 |

|   | stay because the behavior can vary based on the part-number specific settings                          |                 |

| • | Added failure to reach power good within 10 ms as emergency shutdown condition to the <i>Emergency</i> |                 |

|   | Shutdown section                                                                                       |                 |

| • | Changed bit 0 in the BUCK3VID Register register to Read only (R)                                       |                 |

| • | Changed the PG_DELAY2: 2nd Power Good Delay Register description from GPO3 to GPO1, GPO2, GPO4         |                 |

| • | Fixed a typo which showed the '000' option resulting in 2.5 ms instead of 0 ms in the PG_DELAY2 Re     |                 |

|   | //                                                                                                     |                 |

|   | Descriptions table                                                                                     | 84              |

# **5 Device Comparison Table**

表 5-1 lists a brief summary of the default values for each part number stored in one-time programmable (OTP) memory. A full summary of each part number can be found in the applications section linked in the SECTION column. The step size is indicated by the values in parenthesis. If alternate voltages are available through pin-strapping, they are separated with a comma.

表 5-1. Default Values

| PART NUMBER | APPLICATION                                             | BUCK1            | BUCK2                    | BUCK3                   | BUCK4            | BUCK5            | BUCK6                             | LDOA1 | LDOA2 | LDOA3 | SECTION   |

|-------------|---------------------------------------------------------|------------------|--------------------------|-------------------------|------------------|------------------|-----------------------------------|-------|-------|-------|-----------|

| TPS6508640  | Xilinx Zynq<br>Ultrascale+<br>ZU7 - ZU15 <sup>(1)</sup> | 3.3 V<br>(25 mV) | 0.85 V, 0.9 V<br>(10 mV) | 1.2 V<br>(25 mV)        | 0.9 V<br>(25 mV) | 1.8 V<br>(25 mV) | 1.2 V, 1.35 V<br>(10 mV)          | 2.5 V | 1.5 V | 1.2 V | セクション 8.3 |

| TPS65086401 | Xilinx Zynq<br>Ultrascale+<br>ZU2 - ZU5 <sup>(1)</sup>  | 1.8 V<br>(25 mV) | 0.85 V<br>(10 mV)        | 0.85 V<br>(25 mV)       | 3.3 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.5 V, 1.2 V,<br>1.1 V<br>(10 mV) | 1.8 V | 1.2 V | 1.2 V | セクション 8.4 |

| TPS6508641  | Xilinx Zynq<br>Ultrascale+<br>ZU2 - ZU5 <sup>(1)</sup>  | Ext FB           | 0.85 V<br>(10 mV)        | 1.1 V, 1.2 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.2 V<br>(25 mV) | 1.8 V<br>(25 mV)                  | 1.8 V | 1.2 V | 1.2 V | セクション 8.5 |

| TPS65086470 | Xilinx<br>Artix 7 <sup>(1)</sup>                        | 1 V<br>(10 mV)   | 1.8 V<br>(25 mV)         | 1.2 V<br>(25 mV)        | 2.5 V<br>(25 mV) | 3.3 V<br>(25 mV) | 1.35 V, 1.5 V<br>(25 mV)          | 1.8 V | 0.7 V | 0.7 V | セクション 8.6 |

<sup>(1)</sup> Indicates the original intent of the part number. Parts can be used for alternate applications.

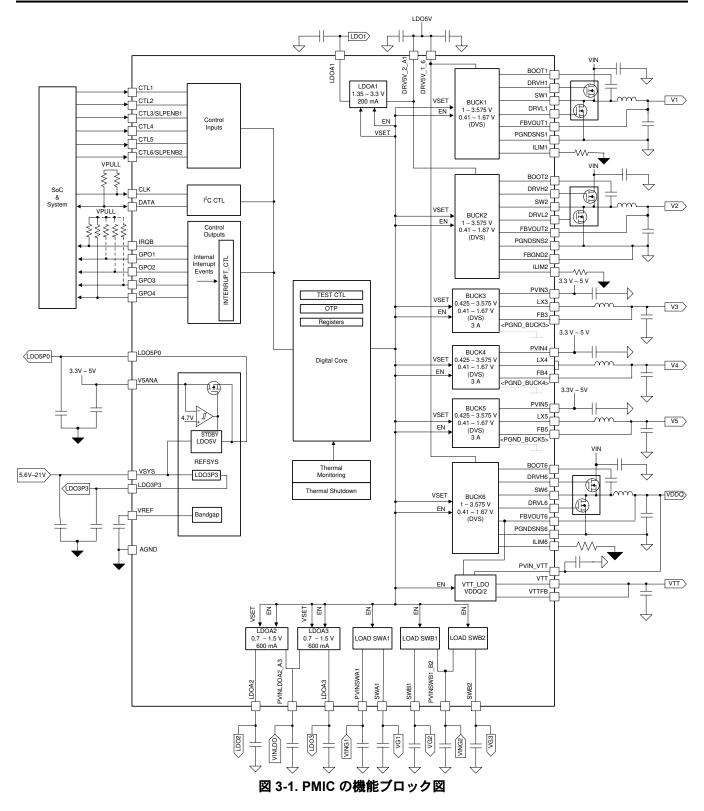

# **6 Pin Configuration and Functions**

☑ 6-1 shows the 64-pin RSK Plastic Quad Flatpack No-Lead package.

The thermal pad must be connected to the system power ground plane.

# 図 6-1. 64-Pin RSK VQFN With Exposed Thermal Pad (Top View)

表 6-1. Pin Functions

| PIN<br>NO. NAME |             | I/O | DESCRIPTION                                                                                                                               |

|-----------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

|                 |             | 1/0 | DESCRIPTION                                                                                                                               |

| SMPS REGULATORS |             |     |                                                                                                                                           |

| 1               | 1 FBGND2 I  |     | Remote negative feedback sense for BUCK2 controller. Connect to negative terminal of output capacitor. Connect to ground when not in use. |

| 2               | 2 FBVOUT2 I |     | Remote positive feedback sense for BUCK2 controller. Connect to positive terminal of output capacitor. Connect to ground when not in use. |

| 3               | DRVH2       | 0   | High-side gate driver output for BUCK2 controller. Leave floating when not in use.                                                        |

Submit Document Feedback

# 表 6-1. Pin Functions (continued)

|     | PIN              | 1/0 | DECORPORTOR                                                                                                                                                                                              |

|-----|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME             | I/O | DESCRIPTION                                                                                                                                                                                              |

| 4   | SW2              | ı   | Switch node connection for BUCK2 controller. Connect to ground when not in use.                                                                                                                          |

| 5   | BOOT2            | ı   | Bootstrap pin for BUCK2 controller. Connect a 100-nF ceramic capacitor between this pin and SW2 pin. Leave floating when not in use.                                                                     |

| 6   | PGNDSNS2         | ı   | Power GND connection for BUCK2. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |

| 7   | DRVL2            | 0   | Low-side gate driver output for BUCK2 controller. Leave floating when not in use.                                                                                                                        |

| 8   | DRV5V_2_A1       | I   | 5-V supply to BUCK2 gate driver and LDOA1. Bypass to ground with a 2.2-µF (typical) ceramic capacitor. Shorted on board to LDO5P0 pin typically. Bypass not required if BUCK2 and LDOA1 are not in use.  |

| 10  | LX3              | 0   | Switch node connection for BUCK3 converter. Leave floating when not in use.                                                                                                                              |

| 11  | PVIN3            | ı   | Power input to BUCK3 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK3 is not in use.                                                                   |

| 12  | FB3              | I   | Remote feedback sense for BUCK3 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |

| 20  | LX5              | 0   | Switch node connection for BUCK5 converter. Leave floating when not in use.                                                                                                                              |

| 21  | PVIN5            | I   | Power input to BUCK5 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK5 is not in use.                                                                   |

| 22  | FB5              | I   | Remote feedback sense for BUCK5 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |

| 23  | FB4              | ı   | Remote feedback sense for BUCK4 converter. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                          |

| 24  | PVIN4            | ı   | Power input to BUCK4 converter. Bypass to ground with a 10-µF (typical) ceramic capacitor. Bypass not required if BUCK4 is not in use.                                                                   |

| 25  | LX4              | 0   | Switch node connection for BUCK4 converter. Leave floating when not in use.                                                                                                                              |

| 29  | FBVOUT1          | I   | Remote feedback sense for BUCK1 controller. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                         |

| 30  | ILIM1            | ı   | Current limit set pin for BUCK1 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK1 not in use.                               |

| 33  | DRVH1            | 0   | High-side gate driver output for BUCK1 controller. Leave floating when not in use.                                                                                                                       |

| 34  | SW1              | I   | Switch node connection for BUCK1 controller. Connect to ground when not in use.                                                                                                                          |

| 35  | BOOT1            | I   | Bootstrap pin for BUCK1 controller. Connect a 100-nF ceramic capacitor between this pin and SW1 pin. Leave floating when not in use.                                                                     |

| 36  | PGNDSNS1         | ı   | Power GND connection for BUCK1. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |

| 37  | DRVL1            | 0   | Low-side gate driver output for BUCK1 controller. Leave floating when not in use.                                                                                                                        |

| 38  | DRV5V_1_6        | I   | 5-V supply to BUCK1 and BUCK6 gate drivers. Bypass to ground with a 2.2-µF (typical) ceramic capacitor. Shorted on board to LDO5P0 pin typically. Bypass not required if BUCK1 and BUCK6 are not in use. |

| 39  | DRVL6            | 0   | Low-side gate driver output for BUCK6 controller. Leave floating when not in use.                                                                                                                        |

| 40  | PGNDSNS6         | ı   | Power GND connection for BUCK6. Connect to ground terminal of external low-side FET. Connect to ground when not in use.                                                                                  |

| 41  | воот6            | ı   | Bootstrap pin for BUCK6 controller. Connect a 100-nF ceramic capacitor between this pin and SW6 pin. Leave floating when not in use.                                                                     |

| 42  | SW6              | I   | Switch node connection for BUCK6 controller. Connect to ground when not in use.                                                                                                                          |

| 43  | DRVH6            | 0   | High-side gate driver output for BUCK6 controller. Leave floating when not in use.                                                                                                                       |

| 44  | FBVOUT6          | I   | Remote feedback sense for BUCK6 controller and reference voltage for VTT LDO regulation. Connect to positive terminal of output capacitor. Connect to ground when not in use.                            |

| 45  | ILIM6            | ı   | Current limit set pin for BUCK6 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK6 not in use.                               |

| 64  | ILIM2            | I   | Current limit set pin for BUCK2 controller. Fit a resistor from this pin to ground to set current limit of external low-side FET. Connect to ground when BUCK2 not in use.                               |

|     | AND LOAD SWITCHE | S   |                                                                                                                                                                                                          |

| 9   | LDOA1            | 0   | LDOA1 output. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                |

| 17  | SWB1             | 0   | Output of load switch B1. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |

| 18  | PVINSWB1_B2      | ı   | Power supply to load switch B1 and B2. Bypass to ground with a 1-µF (typical) ceramic capacitor to improve transient performance. Connect to ground when not in use.                                     |

| 19  | SWB2             | 0   | Output of load switch B2. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |

| 31  | SWA1             | 0   | Output of load switch A1. Bypass to ground with a 0.1-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                    |

# 表 6-1. Pin Functions (continued)

|       | PIN                   |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO.   | NAME                  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 32    | PVINSWA1              | I   | Power supply to load switch A1. Bypass to ground with a 1-µF (typical) ceramic capacitor to improve transient performance. Connect to ground when not in use.                                                                                                                                                                                       |  |  |  |  |

| 46    | PVINVTT               | I   | Power supply to VTT LDO. Bypass to ground with a 10-µF (minimum) ceramic capacitor. Bypass not required if VTT LDO is not in use.                                                                                                                                                                                                                   |  |  |  |  |

| 47    | VTT                   | 0   | Output of load VTT LDO. Bypass to ground with 2× 22-µF (minimum) ceramic capacitors. Leave floating when not in use.                                                                                                                                                                                                                                |  |  |  |  |

| 48    | VTTFB                 | I   | Remote feedback sense for VTT LDO. Connect to positive terminal of output capacitor. Connect to ground when not in use.                                                                                                                                                                                                                             |  |  |  |  |

| 49    | LDOA3                 | 0   | Output of LDOA3. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                                                                                                                                                        |  |  |  |  |

| 50    | PVINLDOA2_A3          | I   | Power supply to LDOA2 and LDOA3. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Connect to ground when not in use.                                                                                                                                                                                                                     |  |  |  |  |

| 51    | LDOA2                 | 0   | Output of LDOA2. Bypass to ground with a 4.7-µF (typical) ceramic capacitor. Leave floating when not in use.                                                                                                                                                                                                                                        |  |  |  |  |

| 54    | LDO3P3                | 0   | Output of 3.3-V internal LDO. Bypass to ground with a 4.7-µF (typical) ceramic capacitor.                                                                                                                                                                                                                                                           |  |  |  |  |

| 56    | LDO5P0                | 0   | Output of 5-V internal LDO or an internal switch that connects this pin to V5ANA. Bypass to ground with a 4.7-µF (typical) ceramic capacitor.                                                                                                                                                                                                       |  |  |  |  |

| 57    | V5ANA                 | I   | Bias used by converters (BUCK3, BUCK4, and BUCK5) for regulation. Must be same supply as PVINx. Also has an internal load switch that connects this pin to LDO5P0 pin if 5-V is used. Bypass this pin with an optional ceramic capacitor to improve transient performance.                                                                          |  |  |  |  |

| INTER | RFACE                 |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 13    | CTL1                  | I   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 14    | CTL6/SLPENB2          | I   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state.            |  |  |  |  |

| 15    | IRQB                  | 0   | Open-drain output interrupt pin. Refer to セクション 8.13.4, IRQ: PMIC Interrupt Register, for definitions.                                                                                                                                                                                                                                              |  |  |  |  |

| 16    | GPO1                  | 0   | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 26    | GPO2                  | 0   | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 27    | GPO3                  | 0   | General purpose output that can be configured to either open-drain or push-pull arrangement. Regardless of the configuration, the pin can be programmed either to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR. |  |  |  |  |

| 28    | GPO4                  | 0   | Open-drain output that can be configured to reflect Power Good status of VRs of any choice or to be controlled by an I <sup>2</sup> C register bit by the user, which then can be used as an enable signal to an external VR.                                                                                                                       |  |  |  |  |

| 58    | CLK                   | ı   | l <sup>2</sup> C clock                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 59    | DATA                  | I/O | I <sup>2</sup> C data                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 60    | CTL2                  | I   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 61    | CTL3/SLPENB1          | ı   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin. Alternatively, when configured to active-low sleep enable, a group of VRs chosen can be entered into (L) or out of (H) sleep state where their output voltages may be different from those in normal state.            |  |  |  |  |

| 62    | CTL4                  | I   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| 63    | CTL5                  | I   | Active-high VR enable pin. A group of VRs can be assigned to be enabled at assertion or disabled at deassertion of this pin.                                                                                                                                                                                                                        |  |  |  |  |

| REFE  | RENCE                 |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 52    | AGND                  | _   | Analog ground. Do not connect to the thermal pad ground on top layer. Connect to ground of VREF capacitor.                                                                                                                                                                                                                                          |  |  |  |  |

| 53    | VREF                  | 0   | Band-gap reference output. Stabilize it by connecting a 100-nF (typical) ceramic capacitor between this pin and quiet ground.                                                                                                                                                                                                                       |  |  |  |  |

| 55    | VSYS                  | I   | System voltage detection and input to internal LDOs (3.3 V and 5 V). Bypass to ground with a 1-µF (typical) ceramic capacitor.                                                                                                                                                                                                                      |  |  |  |  |

| THER  | MAL PAD               |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| _     | Thermal pad<br>(PGND) | _   | Connect to PCB ground plane using multiple vias for good thermal and electrical performance.                                                                                                                                                                                                                                                        |  |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                                                                  | MIN                       | MAX | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|

| ANALOG                                                                                                                                           |                           |     |      |

| Input voltage from battery, VSYS                                                                                                                 | -0.3                      | 28  | V    |

| PVIN3, PVIN4, PVIN5, LDO5P0, DRV5V_1_6, DRV5V_2_A1, DRVL1, DRVL2, DRVL6                                                                          | -0.3                      | 7   | V    |

| V5ANA                                                                                                                                            | -0.3                      | 6   | V    |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2                                                                                                       | -0.3                      | 0.3 | V    |

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6                                                                                                         | -0.3                      | 34  | V    |

| SW1, SW2, SW6                                                                                                                                    | <b>-</b> 5 <sup>(2)</sup> | 28  | V    |

| LX3, LX4, LX5                                                                                                                                    | -2 <sup>(3)</sup>         | 8   | V    |

| Differential voltage, BOOTx to SWx                                                                                                               | -0.3                      | 5.5 | V    |

| VREF, LDO3P3, FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5, ILIM1, ILIM2, ILIM6, PVINVTT, VTT, VTTFB, PVINSWA1, SWA1, PVINSWB1_B2, SWB1, SWB2, LDOA1 | -0.3                      | 3.6 | V    |

| PVINLDOA2_A3, LDOA2, LDOA3                                                                                                                       | -0.3                      | 3.3 | V    |

| DIGITAL IO                                                                                                                                       |                           |     |      |

| DATA, CLK, GPO1-GPO3                                                                                                                             | -0.3                      | 3.6 | V    |

| CTL1-CTL6, GPO4, IRQB                                                                                                                            | -0.3                      | 7   | V    |

| Storage temperature, T <sub>stg</sub>                                                                                                            | -40                       | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                          |                                                                  | VALUE | UNIT |

|------------------------------------------|------------------------------------------------------------------|-------|------|

| // Flastraatatia diaaharga               | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001 <sup>(1)</sup> | ±1000 | V    |

| V <sub>ESD</sub> Electrostatic discharge | Charged Device Model (CDM), per JESD22-C101 <sup>(2)</sup>       | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Transient for less than 5 ns

<sup>(3)</sup> Transient for less than 20 ns

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                           | MIN  | NOM        | MAX           | UNIT |

|-----------------------------------------------------------|------|------------|---------------|------|

| ANALOG                                                    | ,    |            |               |      |

| VSYS                                                      | 5.6  | 13         | 21            | V    |

| VREF                                                      | -0.3 |            | 1.3           | V    |

| PVIN3, PVIN4, PVIN5, LDO5P0, V5ANA, DRV5V_1_6, DRV5V_2_A1 | -0.3 |            | 5.5           | V    |

| PGNDSNS1, PGNDSNS2, PGNDSNS6, AGND, FBGND2                | -0.3 |            | 0.3           | V    |

| DRVH1, DRVH2, DRVH6, BOOT1, BOOT2, BOOT6                  | -0.3 |            | 26.5          | ٧    |

| DRVL1, DRVL2, DRVL6                                       | -0.3 |            | 5.5           | V    |

| SW1, SW2, SW6                                             | -1   |            | 21            | V    |

| LX3, LX4, LX5                                             | -1   |            | 5.5           | V    |

| FBVOUT1, FBVOUT2, FBVOUT6, FB3, FB4, FB5                  | -0.3 |            | 3.6           | V    |

| LDO3P3, ILIM1, ILIM2, ILIM6, LDOA1                        | -0.3 |            | 3.3           | V    |

| PVINVTT                                                   | -0.3 | BUCK6 FBVC | UT6           | V    |

| VTT, VTTFB                                                | -0.3 | FBVC       | 0.5 ×<br>0UT6 | V    |

| PVINSWA1, SWA1, PVINSWB1_B2, SWB1, SWB2                   | -0.3 |            | 3.6           | V    |

| PVINLDOA2_A3                                              | -0.3 |            | 1.8           | V    |

| LDOA2, LDOA3                                              | -0.3 |            | 1.5           | V    |

| DIGITAL IO                                                |      |            | <u> </u>      |      |

| DATA, CLK, CTL1-CTL6, GPO1-GPO4, IRQB                     | -0.3 |            | 3.3           | V    |

| CHIP                                                      | ,    |            |               |      |

| Operating ambient temperature, T <sub>A</sub>             | -40  | 27         | 85            | °C   |

| Operating junction temperature, T <sub>J</sub>            | -40  | 27         | 125           | °C   |

### 7.4 Thermal Information

| /QFN) UNIT |                              |

|------------|------------------------------|

|            |                              |

| INS        |                              |

| °C/W       |                              |

| .3 °C/W    |                              |

| 4 °C/W     |                              |

| 2 °C/W     |                              |

| 4 °C/W     |                              |

| 7 °C/W     |                              |

|            | .3 °C/W 4 °C/W 2 °C/W 4 °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics: Total Current Consumption

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25$ °C) (unless otherwise noted)

|                 | PARAMETER                                                                                | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>SD</sub> | PMIC shutdown current that includes $I_Q$ for references, LDO5, LDO3P3, and digital core | V <sub>SYS</sub> = 13 V, all functional output rails are disabled |     | 65  |     | μA   |

Product Folder Links: TPS650864

# 7.6 Electrical Characteristics: Reference and Monitoring System

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25$ °C) (unless otherwise noted)

| (unless otherwise            | PARAMETER                                                               | TEST CONDITIONS                                                                                 | MIN   | TYP  | MAX      | UNIT |

|------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|------|----------|------|

| REFERENCE                    |                                                                         |                                                                                                 |       |      |          |      |

|                              | Band-gap reference voltage                                              |                                                                                                 |       | 1.25 |          | V    |

| $V_{REF}$                    | Accuracy                                                                |                                                                                                 | -0.5% |      | 0.5%     |      |

| C <sub>VREF</sub>            | Band-gap output capacitor                                               |                                                                                                 | 0.047 | 0.1  | 0.22     | μF   |

| V <sub>SYS_UVLO_5V</sub>     | VSYS UVLO threshold for LDO5                                            | V <sub>SYS</sub> falling                                                                        | 5.24  | 5.4  | 5.56     | V    |

| V <sub>SYS_UVLO_5V_HYS</sub> | VSYS UVLO threshold hysteresis for LDO5                                 | V <sub>SYS</sub> rising above<br>V <sub>SYS</sub> _uvLO_5V                                      |       | 200  |          | mV   |

| V <sub>SYS_UVLO_3V</sub>     | VSYS UVLO threshold for LDO3P3                                          | V <sub>SYS</sub> falling                                                                        | 3.45  | 3.6  | 3.75     | V    |

| V <sub>SYS_UVLO_3V_HYS</sub> | VSYS UVLO threshold hysteresis for LDO3P3                               | V <sub>SYS</sub> rising above<br>V <sub>SYS</sub> _uvLO_3V                                      |       | 150  |          | mV   |

| T <sub>CRIT</sub>            | Critical threshold of die temperature                                   | T <sub>J</sub> rising                                                                           | 130   | 145  | 160      | °C   |

| T <sub>CRIT_HYS</sub>        | Hysteresis of T <sub>CRIT</sub>                                         | T <sub>J</sub> falling                                                                          |       | 10   |          | °C   |

| T <sub>HOT</sub>             | Hot threshold of die temperature                                        | T <sub>J</sub> rising                                                                           | 110   | 115  | 120      | °C   |

| T <sub>HOT_HYS</sub>         | Hysteresis of T <sub>HOT</sub>                                          | T <sub>J</sub> falling                                                                          |       | 10   |          | °C   |

| LDO5                         |                                                                         |                                                                                                 |       |      |          |      |

| V <sub>IN</sub>              | Input voltage at V <sub>SYS</sub> pin                                   |                                                                                                 | 5.6   | 13   | 21       | V    |

| V <sub>OUT</sub>             | DC output voltage                                                       | I <sub>OUT</sub> = 10 mA                                                                        | 4.9   | 5    | 5.1      | V    |

| I <sub>OUT</sub>             | DC output current                                                       |                                                                                                 |       | 100  | 180      | mA   |

| I <sub>OCP</sub>             | Overcurrent protection                                                  | Measured with output shorted to ground                                                          | 200   |      |          | mA   |

| V <sub>TH_PG</sub>           | Power Good assertion threshold in percentage of target V <sub>OUT</sub> | V <sub>OUT</sub> rising                                                                         |       | 94%  |          |      |

| V <sub>TH_PG_HYS</sub>       | Power Good deassertion hysteresis                                       | V <sub>OUT</sub> rising or falling                                                              |       | 4%   |          |      |

| I <sub>Q</sub>               | Quiescent current                                                       | V <sub>IN</sub> = 13 V, I <sub>OUT</sub> = 0 A                                                  |       | 20   |          | μΑ   |

| C <sub>OUT</sub>             | External output capacitance                                             |                                                                                                 | 2.7   | 4.7  | 10       | μF   |

| V5ANA-to-LDO5P0              | LOAD SWITCH                                                             |                                                                                                 |       |      | •        |      |

| R <sub>DSON</sub>            | On resistance                                                           | V <sub>IN</sub> = 5 V, measured from<br>V5ANA pin to LDO5P0 pin at<br>I <sub>OUT</sub> = 200 mA |       |      | 1        | Ω    |

| V <sub>TH_PG</sub>           | Power Good threshold for external 5-V supply                            | V <sub>V5ANA</sub> rising                                                                       |       | 4.7  |          | V    |

| V <sub>TH_HYS_PG</sub>       | Power Good threshold hysteresis for external 5-V supply                 | V <sub>V5ANA</sub> falling                                                                      |       | 100  |          | mV   |

| I <sub>LKG</sub>             | Leakage current                                                         | Switch disabled,<br>V <sub>V5ANA</sub> = 5 V, V <sub>LDO5</sub> = 0 V                           |       |      | 10       | μA   |

| LDO3P3                       |                                                                         |                                                                                                 |       |      | <u> </u> |      |

| V <sub>IN</sub>              | Input voltage at V <sub>SYS</sub> pin                                   |                                                                                                 | 5.6   | 13   | 21       | V    |

|                              | DC output voltage                                                       | I <sub>OUT</sub> = 10 mA                                                                        |       | 3.3  |          | V    |

| V <sub>OUT</sub>             | Accuracy                                                                | V <sub>IN</sub> = 13 V,<br>I <sub>OUT</sub> = 10 mA                                             | -3%   |      | 3%       |      |

| I <sub>OUT</sub>             | DC output current                                                       |                                                                                                 |       |      | 40       | mA   |

| I <sub>OCP</sub>             | Overcurrent protection                                                  | Measured with output shorted to ground                                                          | 70    |      |          | mA   |

| V <sub>TH_PG</sub>           | Power Good assertion threshold in percentage of target V <sub>OUT</sub> | V <sub>OUT</sub> rising                                                                         |       | 92%  |          |      |

| V <sub>TH_PG_HYS</sub>       | Power Good deassertion hysteresis                                       | V <sub>OUT</sub> falling                                                                        |       | 3%   |          |      |

# 7.6 Electrical Characteristics: Reference and Monitoring System (continued)

over recommended free-air temperature range and over recommended input voltage range (typical values are at  $T_A = 25$ °C) (unless otherwise noted)

|                  | PARAMETER                   | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|---------------------------------------------------|-----|-----|-----|------|

| IQ               | Quiescent current           | V <sub>IN</sub> = 13 V,<br>I <sub>OUT</sub> = 0 A |     | 20  |     | μΑ   |

| C <sub>OUT</sub> | External output capacitance |                                                   | 2.2 | 4.7 | 10  | μF   |

### 7.7 Electrical Characteristics: Buck Controllers

over recommended input voltage range,  $T_A = -40^{\circ}\text{C}$  to +85°C and  $T_A = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

| F                                    | PARAMETER                                                                                                  | TEST CONDITIONS                                                                                                                                | MIN    | TYP             | MAX    | UNIT   |

|--------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|--------|--------|

| BUCK1, BUCK                          | 2, BUCK6                                                                                                   |                                                                                                                                                | '      |                 |        |        |

| V <sub>IN</sub>                      | Power input voltage for external HSD FET                                                                   |                                                                                                                                                | 5.6    | 13              | 21     | V      |

|                                      | DC output voltage VID range and options                                                                    | VID step size = 10 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111                                                                       | 0.41   | See セクシ<br>ョン 5 | 1.67   | V      |

|                                      |                                                                                                            | VID step size = 25 mV, BUCKx_VID[6:0] progresses from 0000001 to 1111111                                                                       | 1(1)   | See セクシ<br>ョン 5 | 3.575  | ٧      |

| V <sub>OUT</sub>                     | DC output voltage accuracy                                                                                 | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 100 mA to 7 A                                                     | -2%    |                 | 2%     |        |

|                                      | Total output voltage<br>accuracy (DC + ripple) in<br>DCM                                                   | I <sub>OUT</sub> = 10 mA, V <sub>OUT</sub> ≤ 1 V                                                                                               | -30    |                 | 40     | mV     |

| V <sub>FB_EXT_BUCK1</sub>            | Feedback regulation voltage                                                                                | Applies only to the Buck1 Controller if programmed for external feedback voltage adjustability                                                 | 384    | 400             | 416    | mV     |

| I <sub>FB_LKG_BUCK1</sub>            | Feedback pin leakage<br>current                                                                            | Applies only to the Buck1 Controller if programmed for external feedback voltage adjustability                                                 |        |                 | 65     | nA     |

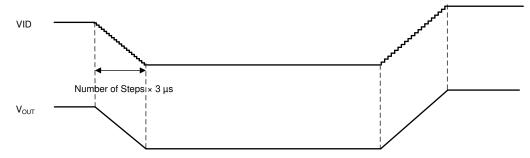

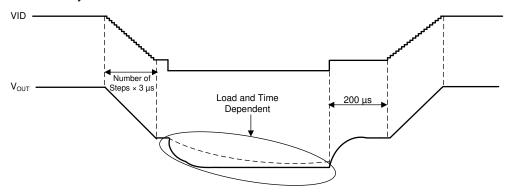

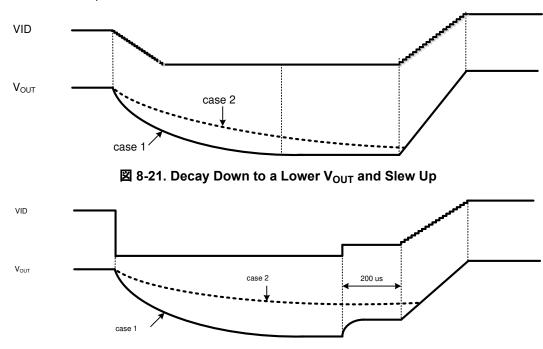

| CD(\/ \                              | Output DVS slow rate                                                                                       | VID step size = 10 mV                                                                                                                          | 2.5    | 3.125           |        | m\//uc |

| SR(V <sub>OUT</sub> )                | Output DVS slew rate                                                                                       | VID step size = 25 mV                                                                                                                          | 3.125  | 4               |        | mV/µs  |

| I <sub>LIM_LSD</sub>                 | Low-side output valley<br>current limit accuracy<br>(programmed by external<br>resistor R <sub>LIM</sub> ) |                                                                                                                                                | -15%   |                 | 15%    |        |

| I <sub>LIMREF</sub>                  | Source current out of ILIM1 pin                                                                            | T = 25°C                                                                                                                                       | 45     | 50              | 55     | μA     |

| V <sub>LIM</sub>                     | Voltage at ILIM1 pin                                                                                       | V <sub>LIM</sub> = R <sub>LIM</sub> × I <sub>LIMREF</sub>                                                                                      | 0.2    |                 | 2.25   | V      |

| ΔV <sub>OUT</sub> /ΔV <sub>IN</sub>  | Line regulation                                                                                            | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 7 A                                                               | -0.5%  |                 | 0.5%   |        |

| ΔV <sub>OUT</sub> /ΔΙ <sub>OUT</sub> | Load regulation                                                                                            | $V_{IN}$ = 13 V, $V_{OUT}$ = 1, 1.2, 1.35, 1.5, 1.8, 2.5, 3.3 V, $I_{OUT}$ = 0 A to 7 A, referenced to $V_{OUT}$ at $I_{OUT}$ = $I_{OUT\_MAX}$ | 0%     |                 | 1%     |        |

|                                      | Power Good deassertion                                                                                     | V <sub>OUT</sub> rising                                                                                                                        | 105.5% | 108%            | 110.5% |        |

| $V_{TH\_PG}$                         | threshold in percentage of target V <sub>OUT</sub>                                                         | V <sub>OUT</sub> falling                                                                                                                       | 89.5%  | 92%             | 94.5%  |        |

| D                                    | Driver DRVH resistance                                                                                     | Source, IDRVH = -50 mA                                                                                                                         |        | 3               |        | Ω      |

| R <sub>DSON_DRVH</sub>               | Direct Divertiesistance                                                                                    | Sink, IDRVH = 50 mA                                                                                                                            |        | 2               |        | Ω      |

| D                                    | Driver DRVL resistance                                                                                     | Source, IDRVL = -50 mA                                                                                                                         |        | 3               |        | Ω      |

| R <sub>DSON_DRVL</sub>               | DIVEL DIVE LESISTATION                                                                                     | Sink, IDRVL = 50 mA                                                                                                                            |        | 0.4             |        | Ω      |

|                                      | Outrat and P. I                                                                                            | BUCKx_DISCHG[1:0] = 01                                                                                                                         |        | 100             |        | Ω      |

| R <sub>DIS</sub>                     | Output auto-discharge resistance                                                                           | BUCKx_DISCHG[1:0] = 10                                                                                                                         |        | 200             |        | Ω      |

|                                      | resistance                                                                                                 | BUCKx_DISCHG[1:0] = 11                                                                                                                         |        | 500             |        | Ω      |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 7.7 Electrical Characteristics: Buck Controllers (continued)

over recommended input voltage range,  $T_A = -40^{\circ}\text{C}$  to +85°C and  $T_A = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                      | PARAMETER                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------|--------------------------------|-----------------|-----|-----|-----|------|

| C <sub>BOOT</sub>    | Bootstrap capacitance          |                 |     | 100 |     | nF   |

| R <sub>ON_BOOT</sub> | Bootstrap switch ON resistance |                 |     |     | 20  | Ω    |

<sup>(1)</sup> BUCKx\_VID[6:0] = 0000001 - 0011000

# 7.8 Electrical Characteristics: Synchronous Buck Converters

over recommended input voltage range,  $T_A = -40^{\circ}\text{C}$  to +85°C and  $T_A = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                                      | PARAMETER                                                                                                              | TEST CONDITIONS                                                                                                                                                                  | MIN   | TYP             | MAX   | UNIT  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|-------|

| BUCK3, BUCK                          | 4, BUCK5                                                                                                               |                                                                                                                                                                                  |       |                 |       |       |

| V <sub>IN</sub>                      | Power input voltage                                                                                                    |                                                                                                                                                                                  | 3.0   |                 | 5.5   | V     |

|                                      | DC output voltage VID range                                                                                            | VID step size = 10 mV,<br>BUCKx_VID[6:0] progresses from<br>0000001 to 1111111                                                                                                   | 0.41  | See セクシ<br>ョン 5 | 1.67  | V     |

|                                      | and options                                                                                                            | VID step size = 25 mV,<br>BUCKx_VID[6:0] progresses from<br>0000001 to 1111111                                                                                                   | 0.425 | See セクシ<br>ョン 5 | 3.575 | V     |

| A./                                  |                                                                                                                        | V <sub>IN</sub> = 5.0 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 1.5 A                                                                   | -2%   |                 | 2%    |       |

| V <sub>OUT</sub>                     | DC output voltage accuracy                                                                                             | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V,<br>I <sub>OUT</sub> = 1.5 A                                                                             | -2%   |                 | 2%    |       |

|                                      | $V_{IN} = 5.0 \text{ V},$ $1.8 \text{ V}, 2.5, 3$ $I_{OUT} = 100 \text{ I}$ $V_{IN} = 3.3 \text{ V},$ $1.8 \text{ V},$ | V <sub>IN</sub> = 5.0 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 100 mA                                                                | -2.5% |                 | 2.5%  |       |

|                                      |                                                                                                                        | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8 V,<br>I <sub>OUT</sub> = 100 mA                                                                            | -2.5% |                 | 2.5%  |       |

| V <sub>DCM</sub>                     | Total output voltage accuracy (DC + ripple) in DCM                                                                     | $V_{IN} = 5.0 \text{ V}, I_{OUT} = 10 \text{ mA}, V_{OUT} \le 1$                                                                                                                 | -30   |                 | 40    | mV    |

| CD()/ )                              | Output DVS slew rate                                                                                                   | VID step size = 10 mV                                                                                                                                                            | 2.5   | 3.125           | \ //  |       |

| SR(V <sub>OUT</sub> )                | Output DVS siew rate                                                                                                   | VID step size = 25 mV                                                                                                                                                            | 3.125 | 4               |       | mV/µs |

| оит                                  | Continuous DC output current                                                                                           |                                                                                                                                                                                  |       |                 | 3     | Α     |

| IND_LIM                              | HSD FET current limit                                                                                                  |                                                                                                                                                                                  | 4.3   |                 | 7     | Α     |

| lα                                   | Quiescent current                                                                                                      | V <sub>IN</sub> = 5 V, V <sub>OUT</sub> = 1 V,<br>BUCKx_MODE = 0b                                                                                                                |       | 35              |       | μΑ    |

| ΔV <sub>OUT</sub> /ΔV <sub>IN</sub>  | Line regulation                                                                                                        | V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5, 1.8,<br>2.5, 3.3 V, I <sub>OUT</sub> = 1.5 A                                                                                               | -0.5% |                 | 0.5%  |       |

| ΔV <sub>ΟυΤ</sub> /ΔΙ <sub>ΟυΤ</sub> | Load regulation                                                                                                        | V <sub>IN</sub> = 5 V, V <sub>OUT</sub> = 1, 1.2, 1.35, 1.5,<br>1.8, 2.5, 3.3 V,<br>I <sub>OUT</sub> = 0 A to 3 A, referenced to V <sub>OUT</sub><br>at I <sub>OUT</sub> = 1.5 A | -0.2% |                 | 2%    |       |

|                                      | Power Good deassertion                                                                                                 | V <sub>OUT</sub> rising                                                                                                                                                          |       | 108%            |       |       |

| V <sub>TH_PG</sub>                   | threshold in percentage of target V <sub>OUT</sub>                                                                     | V <sub>OUT</sub> falling                                                                                                                                                         |       | 92%             |       |       |

| V <sub>TH_HYS_PG</sub>               | Power Good reassertion hysteresis entering back into V <sub>TH_PG</sub>                                                | V <sub>OUT</sub> rising or falling                                                                                                                                               |       | 3%              |       |       |

|                                      | Outrot and the decimal                                                                                                 | BUCKx_DISCHG[1:0] = 01                                                                                                                                                           |       | 100             |       |       |

| R <sub>DIS</sub>                     | Output auto-discharge resistance                                                                                       | BUCKx_DISCHG[1:0] = 10                                                                                                                                                           |       | 200             |       | Ω     |

|                                      |                                                                                                                        | BUCKx_DISCHG[1:0] = 11                                                                                                                                                           |       | 500             |       |       |

## 7.9 Electrical Characteristics: LDOs

over recommended input voltage range,  $T_A = -40^{\circ}\text{C}$  to +85°C and  $T_A = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                                 | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                 | MIN                                      | TYP             | MAX  | UNIT |

|---------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|------|------|

| LDOA1                           |                                                    |                                                                                                                                                                                 |                                          |                 |      |      |

| V <sub>IN</sub>                 | Input voltage                                      |                                                                                                                                                                                 | 4.5                                      | 5               | 5.5  | V    |

| V <sub>OUT</sub>                | DC output voltage                                  | Set by LDOA1_VID[3:0]                                                                                                                                                           | 1.35                                     | See セクシ<br>ョン 5 | 3.3  | V    |

| •001                            | Accuracy                                           | I <sub>OUT</sub> = 0 to 200 mA                                                                                                                                                  | -2%                                      |                 | 2%   | V    |

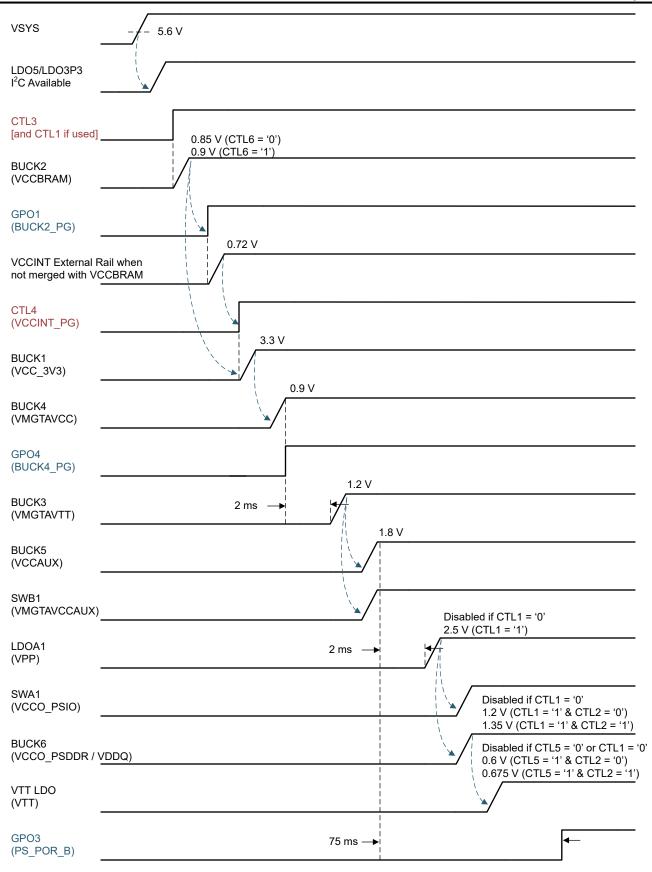

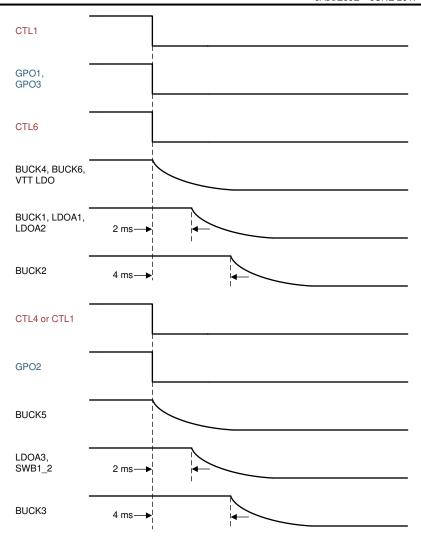

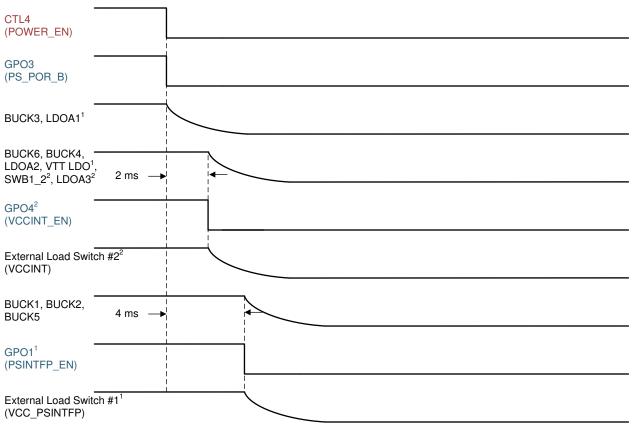

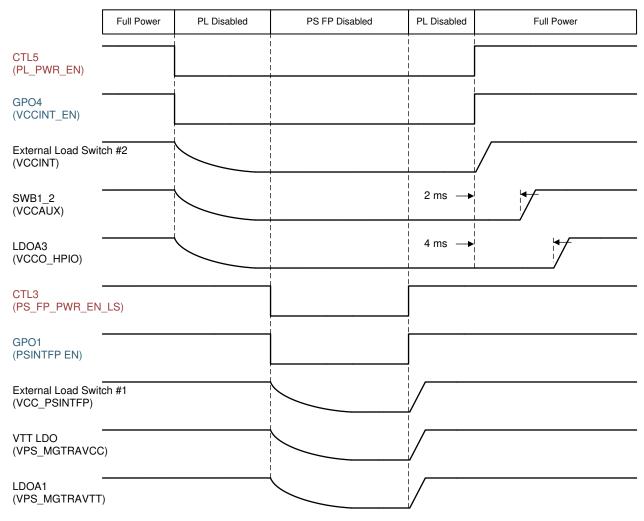

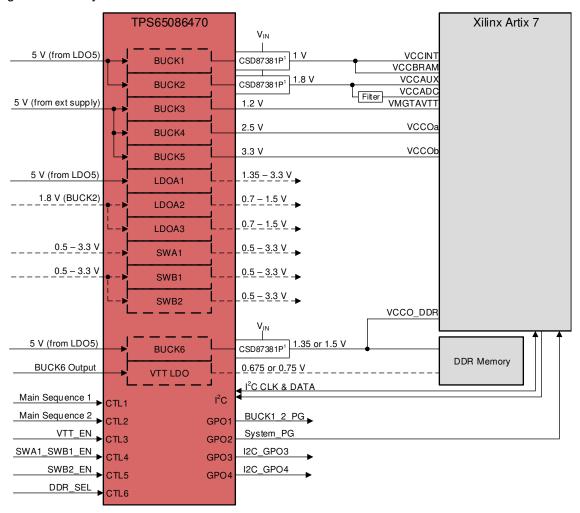

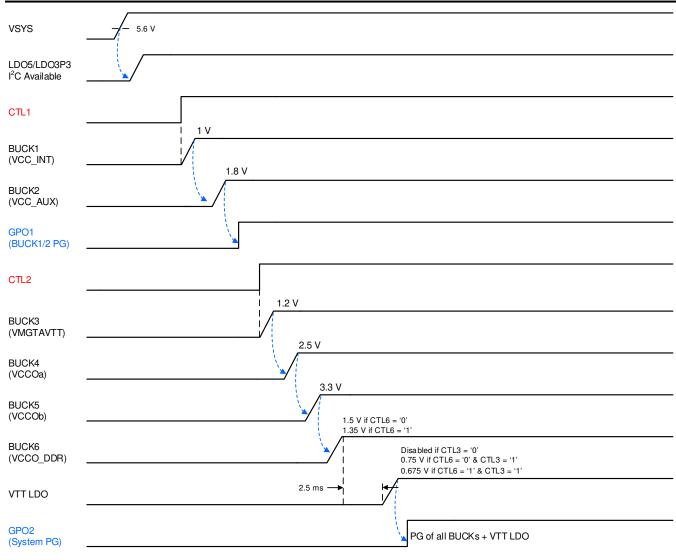

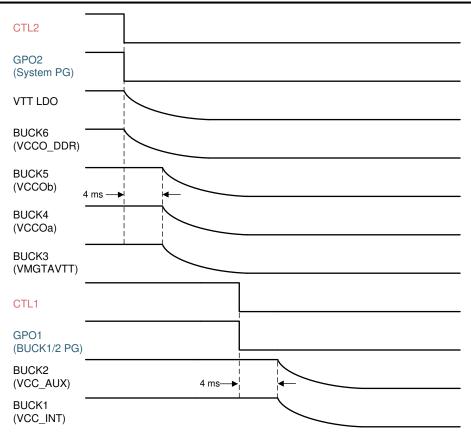

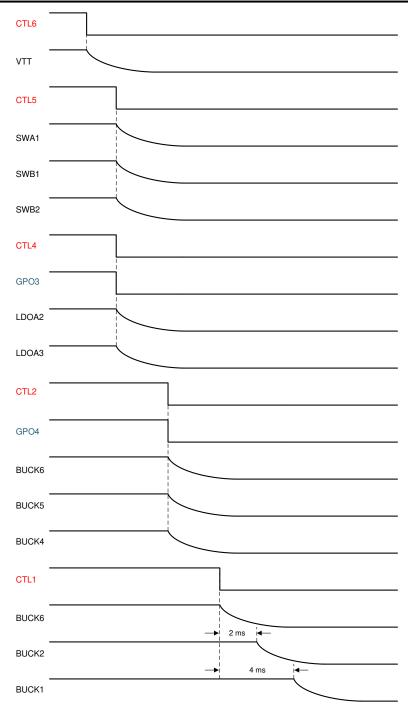

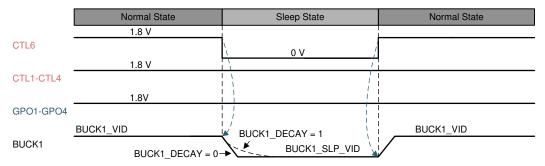

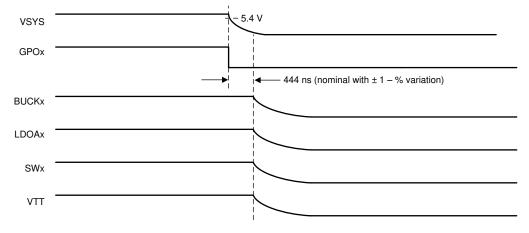

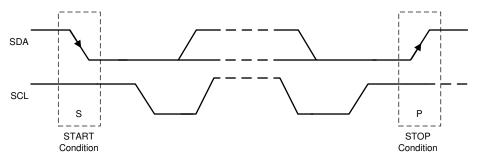

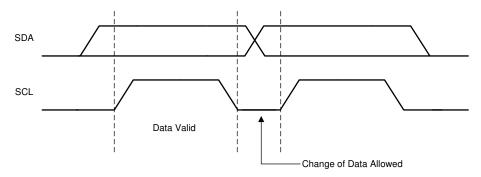

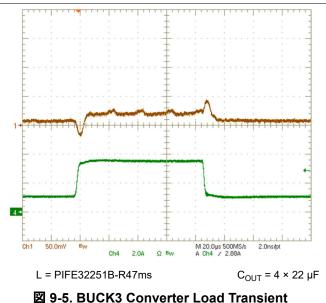

| I <sub>OUT</sub>                | DC output current                                  |                                                                                                                                                                                 |                                          |                 | 200  | mA   |