参考資料

TPS653853-Q1 JAJSCR8B - DECEMBER 2016 - REVISED FEBRUARY 2021

# 安全関連アプリケーション向けのマイコン用 TPS653853-Q1 マルチレール電 源

### 1 特長

- 車載アプリケーション向けに認定済み

- 下記内容で AEC-Q100 認定済み

- デバイス温度グレード 1:-40℃~+125℃の動作 時周囲温度範囲

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

- 機能安全準拠

- 機能安全アプリケーション向けに開発

- ASIL D までの ISO 26262 システム設計を支援す るドキュメントを提供

- ASIL D までの決定論的対応能力とハードウェア・ インテグリティ

- 入力電圧範囲

- 7~36V (初回バッテリ・パワーアップ時)

- 3.8~36V (初回バッテリ・パワーアップ後の完全な

- 最小 2.3V (ウェイクアップ後の動作中)

- 電源レール (FET 内蔵)

- 6V 同期整流昇降圧プリレギュレータ

- 5V、284mA LDO (CAN)

- 3.3V または 5V、350mA LDO (MCU)

- センサ電源またはペリフェラル用に保護された2つ

- センサ電源 1 (VSOUT1) 用の 120mA、センサ 電源 2 (VSOUT2) 用の 20mA

- 設定可能なトラッキング・モード (トラッキング入 カピン) または、3.3V または 5V 固定出力電圧

- グランドおよびバッテリへの短絡に対する保護

- チャージ・ポンプ:バッテリ電圧よりも最小で 6V、最 大で 11V 高い出力

- 監視と保護

- すべてのレギュレータ出力、バッテリ電圧、および 内部電源に対する独立した低電圧監視能および 過電圧監視機能

- 異なるバッテリ電圧入力ピンから電源を供給された 電圧監視回路 (独立したバンドギャップ・リファレン ス回路を含む)

- すべての電圧監視機能に対するセルフ・チェック機 能 (パワーアップ中に動作、加えてパワーアップ後 に外部 MCU により起動可能)

- すべての電源出力に対する電流制限機能、過熱 予告警告機能、およびシャットダウンによる過熱保 護機能

- 操舵角監視 (SAM)

- 位置センサ信号用に2つの信号コンパレータ

- 回転カウンタ

- 位置センサ信号を定期的にサンプリングする低消 費電力モード

- MCU へのセンサ信号パス用のスイッチ

- マイコン・インターフェイス

- OPEN/CLOSE ウィンドウ式、または質疑応答式の ウォッチドッグ機能

- ロックステップ MCU のエラー信号の監視

- Diagnostic 状態:デバイスのセルフ・テストおよび システム診断実行用

- SAFE 状態:システム故障検出時のデバイスおよび システム保護用

- デバイス内部発振器用のクロック・モニタ

- アナログ回路およびロジック回路の内蔵セルフ・テ スト

- 不揮発性メモリに対する CRC (デバイス・レジスタ およびシステム設定レジスタ)とSPI通信に対する CRC

- MCU 用のリセット回路

- 診断出力ピン

- SPI、コマンド + データに対する CRC 付き

- SPI レジスタによるシステム・レベルとデバイス・レベル のエラーを報告

- イネーブル・ドライブ出力:システム故障検出時の外部 パワー・ステージのディスエーブル用

- IGN ピン (イグニッション) または CAN\_WU ピン (トラ ンシーバまたはその他の機能) によるウェイクアップ

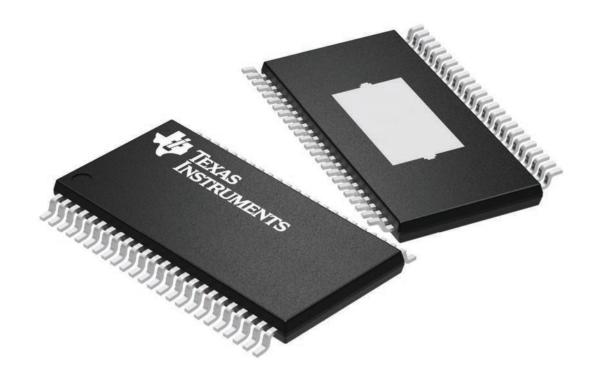

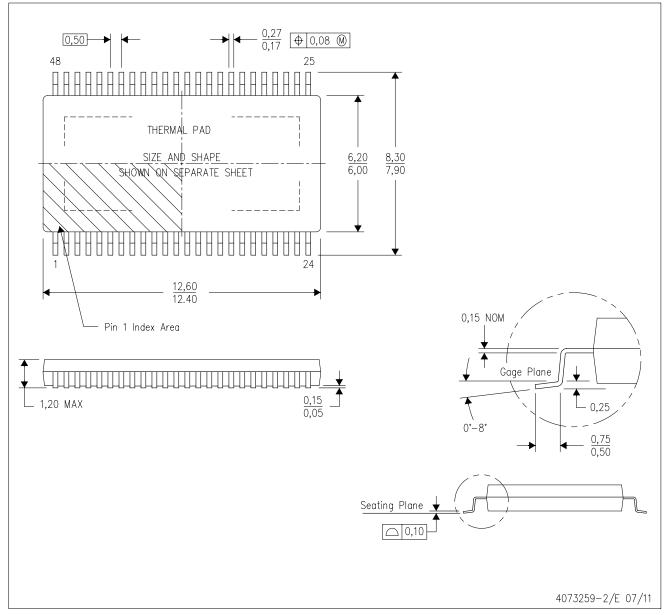

- 48 ピン HTSSOP PowerPAD™ IC パッケージ

## 2 アプリケーション

- 車載用安全性関連アプリケーション

- 産業用安全性関連アプリケーション

### 3 概要

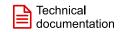

TPS653853-Q1 デバイスは、自動車業界で見られるような安全関連アプリケーションのマイコンに電源を供給するために 設計されたマルチレール電源装置です。 本デバイスは、デュアルコア・ロックステップ (LS) または疎結合 (LC) アーキテク チャを採用したマイコンをサポートしています。

TPS653853-Q1 デバイスは、MCU、CAN、FlexRay または外部センサに電源を供給する複数の電源レールを内蔵して います。内部 FET 付き昇降圧コンバータは、2.3V~36V の入力バッテリ電圧を 6V のプリレギュレータ出力に変換して

他のレギュレータに供給します。内蔵チャージ・ポンプは、内部レギュレータにオーバードライブ電圧を供給し、また、バッテリ逆接続保護として外部 NMOS FET の駆動にも使用できます。このデバイスは、イグニッション信号 (IGN ピン) からのウェイクアップ、または CAN トランシーバまたはその他の信号 (CAN\_WU ピン) からのウェイクアップをサポートしています。

このデバイスは、ECU がステアリング・ホイールの位置をモータ位置センサ経由で間接的にキャプチャする、操舵角モニタ (SAM) ユニットを備えています。専用の低消費電力モードは、たとえ ECU がスリープ・モードであっても SAM ユニットの動作を可能にします。 内蔵 SAM スイッチは、正常動作中はモータ位置センサ信号の MCU への通過を可能にし、または ECU がスリープ・モードの場合はモータ位置センサ信号からの MCU ADC 入力のデカップリングを可能にします。

デバイス内部の独立した電圧監視ユニットは、すべての内部電源レールおよびバッテリ電源からのレギュレータ出力の低電圧と過電圧を監視します。また、レギュレータの電流制限と加熱保護も実装されています。TPS653853-Q1 デバイスは、質疑応答式ウォッチドッグ、MCU エラー信号モニタ、内部発振器のクロック・モニタ、クロック・モニタのセルフ・チェック、不揮発性メモリおよび SPI 通信に対する CRC (巡回冗長検査)、デバイスの内部アナログおよびデジタル信号の監視を可能にする診断出力ピン、MCU 用リセット回路 (NRES ピン)、およびシステム故障の検出時に外部パワー・ステージを無効にする安全化出力 (ENDRV ピン) を備えています。本デバイスは起動時に内蔵セルフ・テスト (BIST) を自動的に実行します。必要に応じて、システム実行中にソフトウェア制御によって MCU が BIST を再実行することもできます。専用の診断状態では、MCU が TPS653853-Q1 の機能を確認することができます。

また TPS653853-Q1 デバイスには、SPI レジスタによるエラー報告機能があります。デバイスの SPI レジスタには、システム・レベルとデバイス・レベルの特定エラーを報告する個別のステータス・ビットがあります。デバイスが特定のエラー状態を検出すると特定のステータス・ビットが設定され、この設定状態は MCU が該当する SPI レジスタを読み出すまで保持されます。MCU は、設定されたステータス・ビットに基づいて、システムを安全な状態に保持すべきか、システムの操作を再開できるかを判定できます。

TPS653853-Q1 デバイスは 48 ピン HTSSOP PowerPAD™ IC パッケージで供給されます。

### 製品情報(1)

| 部品番号        | パッケージ       | 本体サイズ            |  |  |

|-------------|-------------|------------------|--|--|

| TPS65853-Q1 | HTSSOP (48) | 12.50mm × 6.10mm |  |  |

(1) 詳細についてはセクション 6を参照してください。

## 3.1 Typical Application Diagram

### **Table of Contents**

| 1 特長 1                                                                         | 5.2 Receiving Notification of Documentation Updates5 |

|--------------------------------------------------------------------------------|------------------------------------------------------|

| 2 アプリケーション1                                                                    | 5.3 サポート・リソース5                                       |

| 3 概要1                                                                          | 5.4 Trademarks5                                      |

| 3.1 Typical Application Diagram3                                               | 5.5 静電気放電に関する注意事項5                                   |

| 4 Revision History4                                                            | 5.6 用語集5                                             |

| 5 Device and Documentation Support5                                            | 6 Mechanical, Packaging, and Orderable Information5  |

| 5.1 Documentation Support5                                                     |                                                      |

| 資料番号末尾の英字は改訂を表しています。その改訂履歴<br>Changes from Revision A (November 2017) to Revis | - 2 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1              |

| • 「特長」セクションに機能安全準拠のステータスを追加                                                    | 1                                                    |

| <ul><li>文書全体にわたって表。図、相互参照の採番方法を更要</li></ul>                                    |                                                      |

|                                                                                | 新1                                                   |

| Changes from Revision * (December 2016) to Revis                               |                                                      |

### **5 Device and Documentation Support**

### **5.1 Documentation Support**

#### 5.1.1 Related Documentation

For related documentation see the following:

- Texas instruments, A Guide to Board Layout for Best Thermal Resistance for Exposed Packages application report

- Texas instruments, PowerPAD™ Made Easy application report

- Texas instruments, PowerPad™ Thermally Enhanced Package application report

### 5.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 5.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 5.4 Trademarks

PowerPAD™ and TI E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 5.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 5.6 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

### 6 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 20-Jan-2024

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| O3853QDCARQ1     | NRND   | HTSSOP       | DCA                | 48   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | O3853                |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Jan-2024

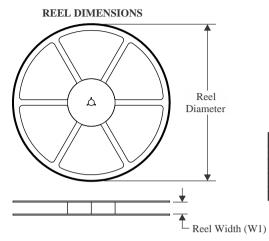

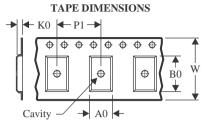

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

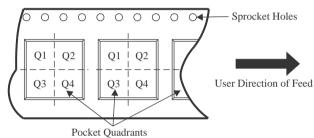

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| O3853QDCARQ1 | HTSSOP          | DCA                | 48 | 2000 | 330.0                    | 24.4                     | 8.6        | 13.0       | 1.8        | 12.0       | 24.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Jan-2024

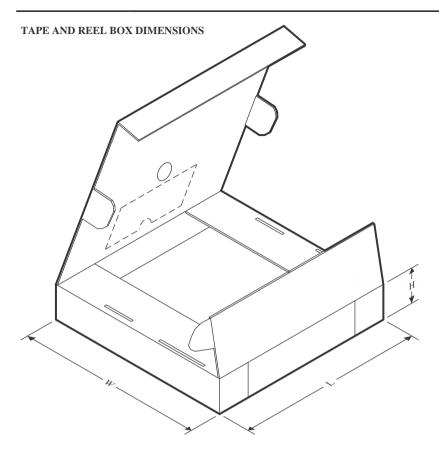

### \*All dimensions are nominal

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | O3853QDCARQ1 | HTSSOP       | DCA             | 48   | 2000 | 350.0       | 350.0      | 43.0        |  |

12.5 x 6.1, 0.5 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

## DCA (R-PDSO-G48)

## PowerPAD ™ PLASTIC SMALL-OUTLINE

NOTES:

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

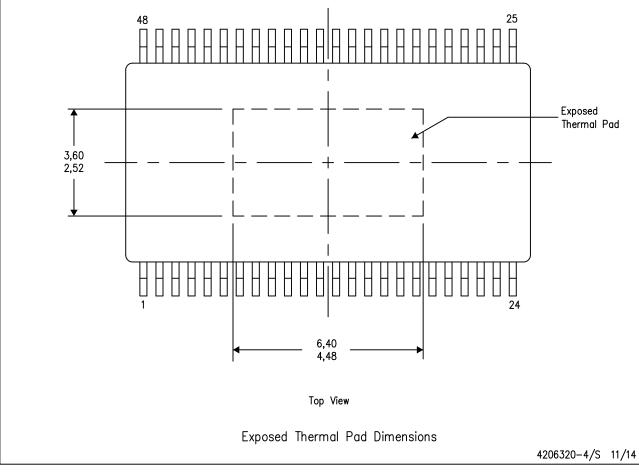

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-153

### PowerPAD is a trademark of Texas Instruments.

# DCA (R-PDSO-G48)

PowerPAD™ PLASTIC SMALL OUTLINE

### THERMAL INFORMATION

This PowerPAD package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments.

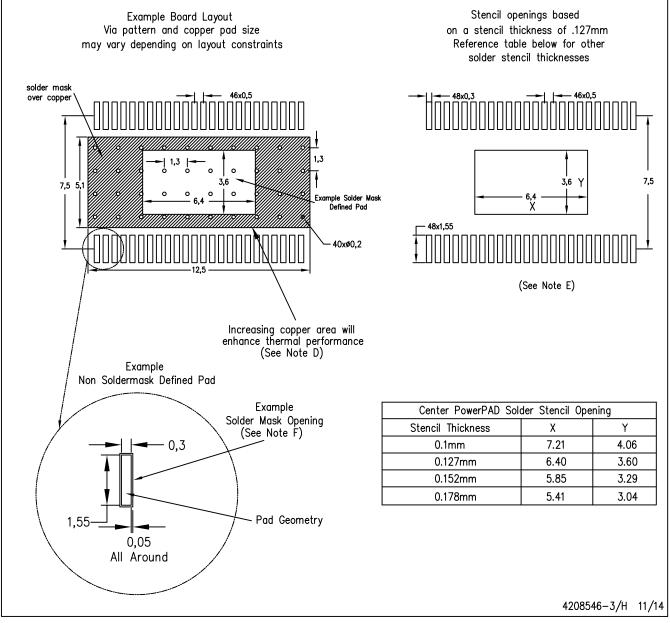

## DCA (R-PDSO-G48)

## PowerPAD ™ PLASTIC SMALL OUTLINE PACKAGE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated