## TPS99002S-Q1 システム管理および照明コントローラ

### 1 特長

- 車載アプリケーション認定済み

- 以下の結果で AEC-Q100 認定済み:

- 温度グレード 2: -40°C ~ 105°C の動作時周囲温度

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

- 機能安全品質管理**

- ASIL-Bまでの ISO 26262 機能安全システム設計に役立つ資料を入手可能

- テキサス・インスツルメンツの DLP® 製品向け車載システム管理デバイス:

- 高度な電力監視、シーケンシング、保護回路

- 2つのダイ温度モニタ、MCU 外部ウォッチドッグ タイマ、クロック周波数モニタ

- システムの過剰輝度検出

- パリティ、チェックサム、パスワード レジスタ保護搭載の SPI ポート

- 独立したシステム監視用の 2 番目の SPI ポート

- オンチップの DMD ミラー電圧レギュレータ

- +18V、+10V、-14V の DMD 制御電圧を生成

- ダイナミックレンジが広い調光および色制御: 5000:1 を超える調光比と、高いビット深度およびホワイトカラーバランスを実現

- ダイナミックレンジが広く、多くの光学デザインをサポートする、2つのトランシングピーダンス アンプ (TIA)

- フレームごとに最大 63 の時間シーケンス サンプルが可能な 12 ビット ADC

- 色およびパルス制御用の DAC およびコンパレータ機能

- LED およびシャント制御用の FET ドライバ

### 2 アプリケーション

- 広視野の拡張現実ヘッドアップ ディスプレイ (HUD) システム

- デジタル クラスタ、ナビゲーション、インフォテインメントのフロント ガラス ディスプレイ

### 3 説明

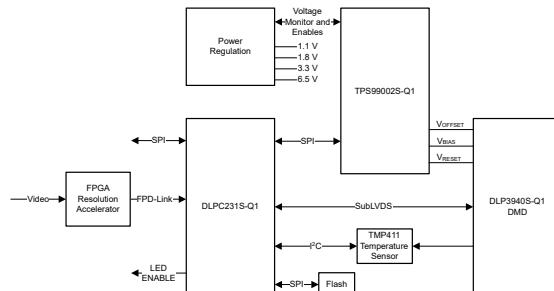

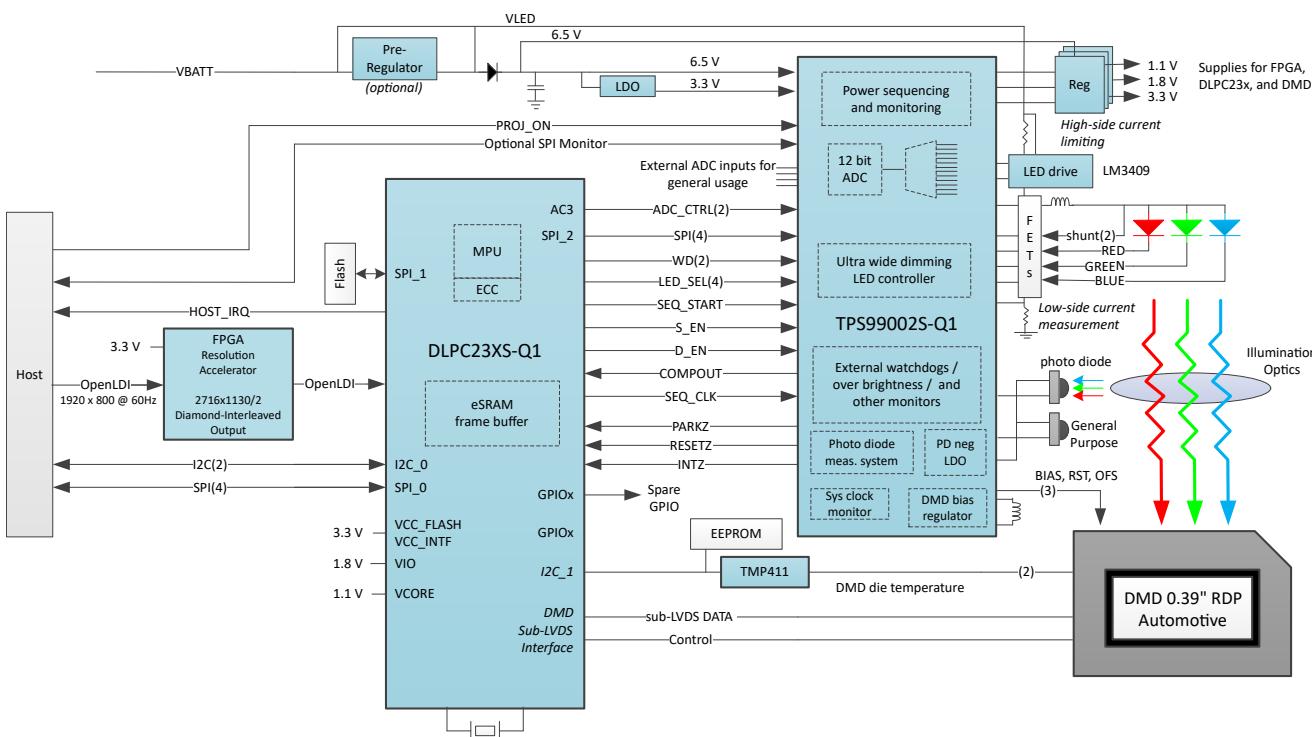

TPS99002S-Q1 システム管理および照明コントローラは、DLP394xS-Q1 チップセットの一部であり、このチップセットには、DLPC23xS-Q1 DMD ディスプレイコントローラも含まれています。このチップセットには、**ヘッドアップディスプレイ (HUD)** アプリケーションで一般的な 5000:1 のディスプレイ調光、3~15,000nit の輝度範囲、緊密な色ポイント制御という要件を十分以上にサポートするため必要なすべての機能が搭載されています。

内蔵の DMD 高電圧レギュレータは、DMD ミラー基準電圧を供給し、要求される厳しい公差を満たしています。電源シーケンス IC およびモニタは、チップセット全体について、電源オンと電源オフのイベントの確実な調整を行います。

TPS99002S-Q1 照明コントローラには、12 ビット ADC、2 つの DAC (12 ビットおよび 10 ビット)、2 つの高性能フォトダイオード信号コンディショニングトランシングピーダンス アンプ (TIA) が、照明制御システムの中核コンポーネントのとして内蔵されています。この ADC は、ビデオ フレームごとに最大 63 のイベントを自動的にサンプリングできます。

高度なシステムステータス監視回路により、ディスプレイのサブシステムの動作状況をリアルタイムで確認できます。この監視回路には、2つのプロセッサ ウォッチドッグ回路、2つのダイ温度モニタ、包括的な電源モニタによる過電圧および低電圧の検出、SPI バス トランザクション上のバイト レベル パリティによるチェックサムおよびパスワード レジスタ保護、過剰輝度の監視回路、その他の内蔵テスト機能が含まれます。

### 製品情報

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ<br>サイズ      |

|--------------|----------------------|-------------------|

| TPS99002S-Q1 | HTQFP (100)          | 14.00mm × 14.00mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

### 標準的なスタンドアロン システム

**⚠️** このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                             |           |                               |           |

|---------------------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                                 | <b>1</b>  | <b>6 詳細説明</b>                 | <b>26</b> |

| <b>2 アプリケーション</b>                           | <b>1</b>  | 6.1 概要                        | 26        |

| <b>3 説明</b>                                 | <b>1</b>  | 6.2 機能ブロック図                   | 27        |

| <b>4 ピン構成および機能</b>                          | <b>3</b>  | 6.3 機能説明                      | 28        |

| <b>5 仕様</b>                                 | <b>10</b> | 6.4 デバイスの機能モード                | 55        |

| 5.1 絶対最大定格                                  | 10        | 6.5 レジスタ マップ                  | 58        |

| 5.2 ESD 定格                                  | 10        | <b>7 アプリケーションと実装</b>          | <b>61</b> |

| 5.3 推奨動作条件                                  | 11        | 7.1 アプリケーション情報                | 61        |

| 5.4 熱に関する情報                                 | 11        | 7.2 代表的なアプリケーション              | 61        |

| 5.5 電気的特性 — トランジンピーダンス アンプのパラ<br>メータ        | 12        | <b>8 電源に関する推奨事項</b>           | <b>71</b> |

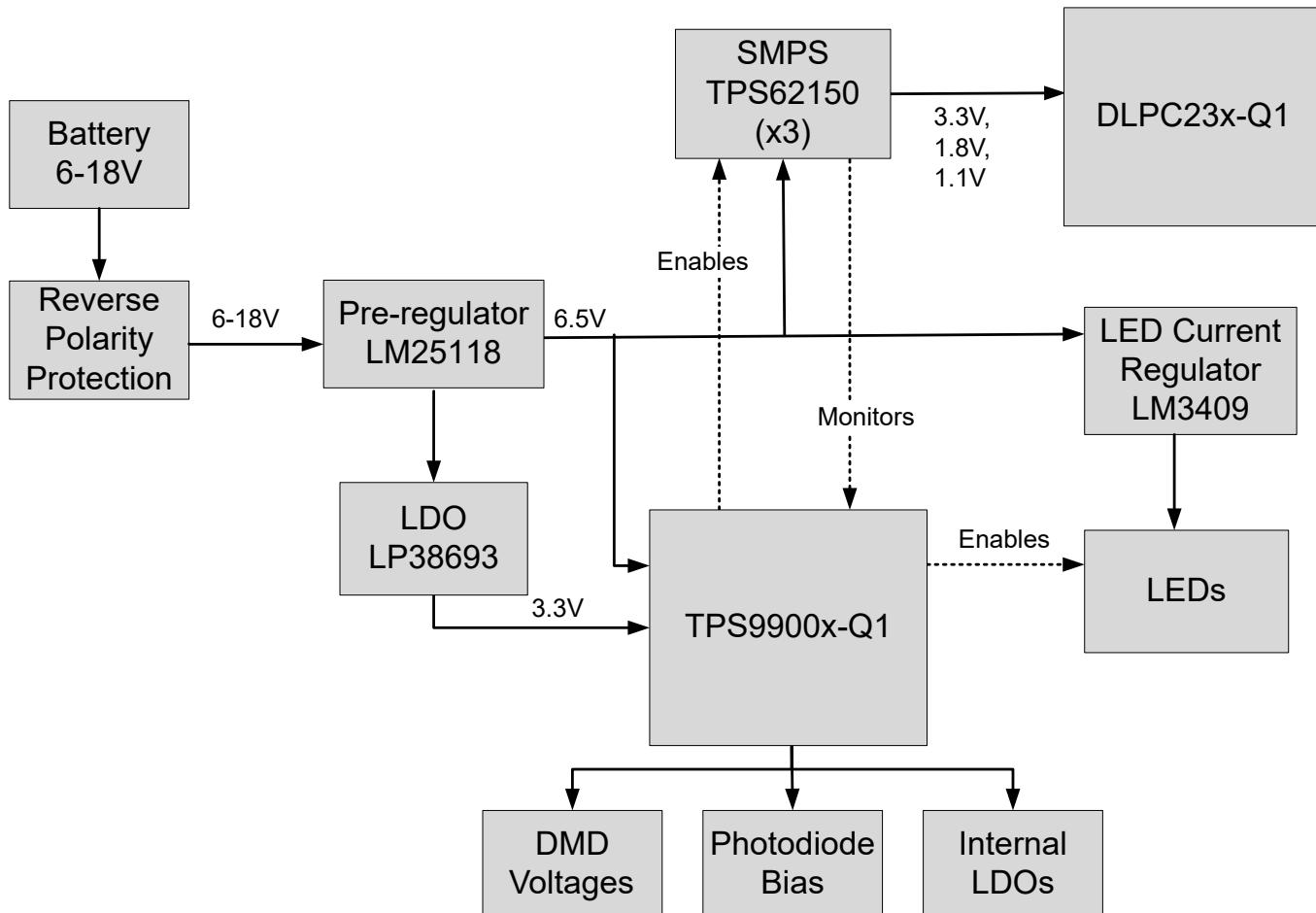

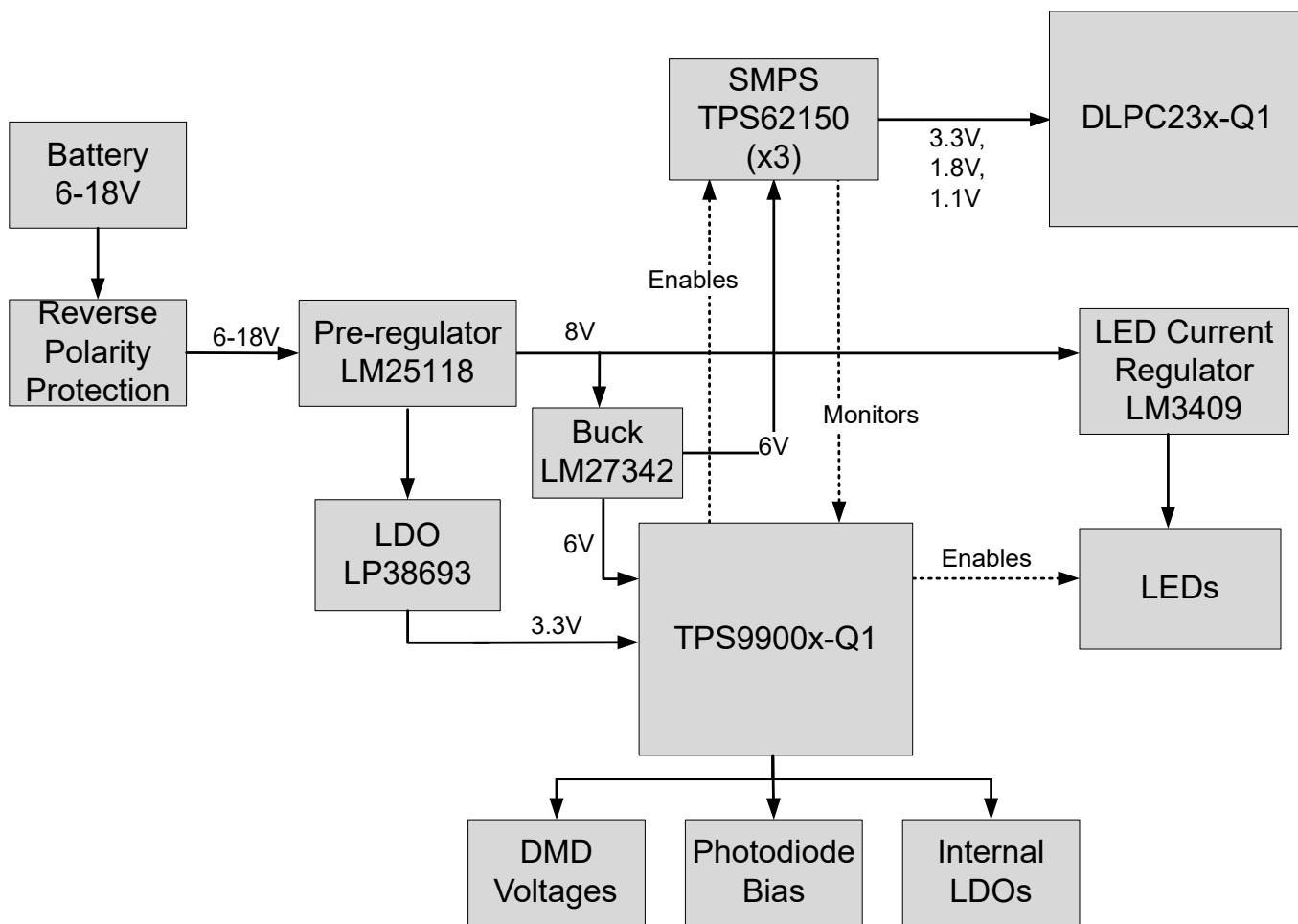

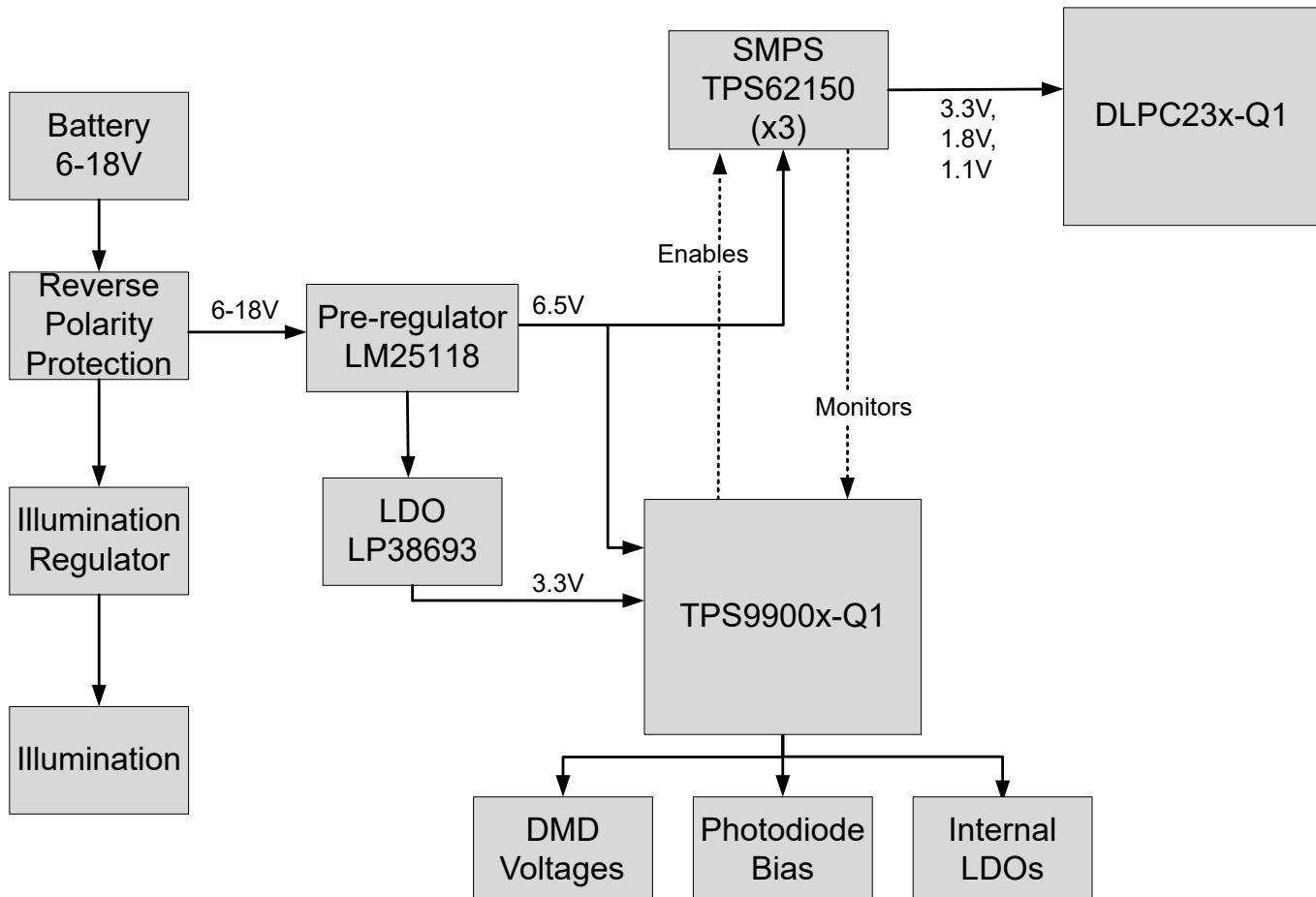

| 5.6 電気的特性:D/A コンバータ                         | 14        | 8.1 TPS99002S-Q1 電源アーキテクチャ    | 71        |

| 5.7 電気的特性:A/D コンバータ                         | 15        | 8.2 TPS99002S-Q1 の電源出力        | 71        |

| 5.8 電気的特性 — FET ゲートドライバ                     | 16        | 8.3 電源アーキテクチャ                 | 71        |

| 5.9 電気的特性 — フォトコンバータ                        | 16        | <b>9 レイアウト</b>                | <b>75</b> |

| 5.10 電気的特性 — 電圧レギュレータ                       | 17        | 9.1 レイアウトのガイドライン              | 75        |

| 5.11 電気的特性 — 温度および電圧モニタ                     | 18        | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>80</b> |

| 5.12 電気的特性 - 電流消費                           | 19        | 10.1 デバイス サポート                | 80        |

| 5.13 パワーアップのタイミング要件                         | 20        | 10.2 ドキュメントの更新通知を受け取る方法       | 80        |

| 5.14 パワーダウンのタイミング要件                         | 22        | 10.3 サポート・リソース                | 80        |

| 5.15 タイミング要件 — シーケンサ クロック                   | 24        | 10.4 商標                       | 80        |

| 5.16 タイミング要件 — ホストおよび診断ポート SPI イン<br>ターフェイス | 25        | 10.5 静電気放電に関する注意事項            | 80        |

| 5.17 タイミング要件 - ADC インターフェイス                 | 26        | 10.6 用語集                      | 80        |

| 5.18 スイッチング特性                               | 26        | <b>11 改訂履歴</b>                | <b>80</b> |

|                                             |           | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>81</b> |

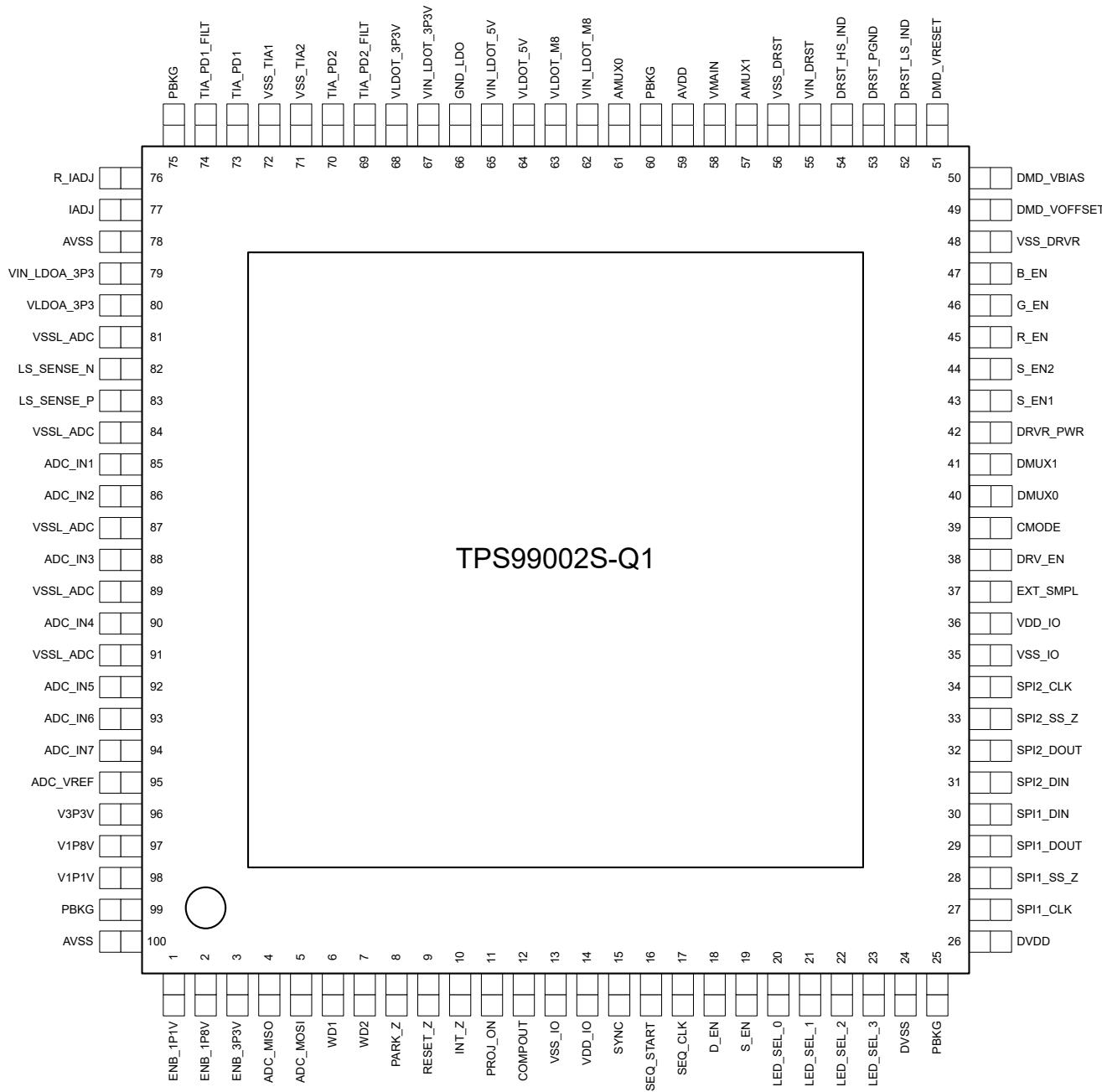

## 4 ピン構成および機能

図 4-1. PZP パッケージ 100 ピン HTQFP 上面図

表 4-1. ピン機能 – 初期化、クロック、診断

| ピン |           | タイプ | 説明                                                                                                        |

|----|-----------|-----|-----------------------------------------------------------------------------------------------------------|

| 番号 | 名称        |     |                                                                                                           |

| 6  | WD1       | I   | ウォッチドッグ割り込みチャネル 1                                                                                         |

| 7  | WD2       | I   | ウォッチドッグ割り込みチャネル 2                                                                                         |

| 8  | PARK_Z    | O   | DMD ミラー パーキング信号 (アクティブ Low)                                                                               |

| 9  | RESET_Z   | O   | DLPC23xS-Q1 への出力をリセットします。TPS99002S-Q1 を制御。                                                                |

| 10 | INT_Z     | O   | DLPC23xS-Q1 (オープンドレイン) への割り込み出力信号。TPS99002S-Q1 の ENB_3P3V 信号で制御される DLPC23xS-Q1 3.3V レールまでブルアップすることを推奨します。 |

| 11 | PROJ_ON   | I   | IC および DLP プロジェクタを有効 / 無効にする入力信号                                                                          |

| 16 | SEQ_START | I   | PWM シャドウ ラッチ制御: シーケンスの開始を示します                                                                             |

| 17 | SEQ_CLK   | I   | シーケンサ クロック                                                                                                |

| 40 | DMUX0     | O   | デジタル テスト ポイント出力                                                                                           |

| 41 | DMUX1     | O   | デジタル テスト ポイント出力                                                                                           |

| 57 | AMUX1     | O   | アナログ テスト マルチプレクサ出力 1                                                                                      |

| 61 | AMUX0     | O   | アナログ テスト マルチプレクサ出力 0                                                                                      |

**表 4-2. ピン機能 — 電源とグランド**

| ピン             |               | タイプ | 説明                                                                                                |

|----------------|---------------|-----|---------------------------------------------------------------------------------------------------|

| 番号             | 名称            |     |                                                                                                   |

| 13、35          | VSS_IO        | GND | デジタル IO インターフェイスのグランド接続                                                                           |

| 14、36          | VDD_IO        | 電源  | IO レール電源用の 3.3V 電源入力                                                                              |

| 24             | DVSS          | GND | デジタル コア グランドリターン                                                                                  |

| 25、60、75、99    | PBKG          | GND | サブストレート タイと ESD のグランドリターン                                                                         |

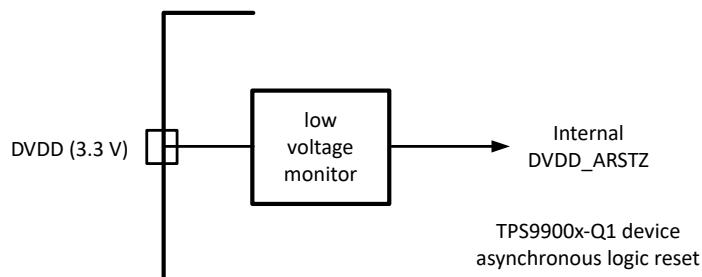

| 26             | DVDD          | 電源  | デジタル コア電源用の 3.3V 電源入力                                                                             |

| 42             | DRV_R_PWR     | 電源  | FET ドライバ電源用 6V または 3.3V 電源入力。S_EN1、S_EN2、R_EN、G_EN、B_EN 出力に電力供給                                   |

| 48             | VSS_DRV_R     | GND | FET ドライバ電源のグランド接続                                                                                 |

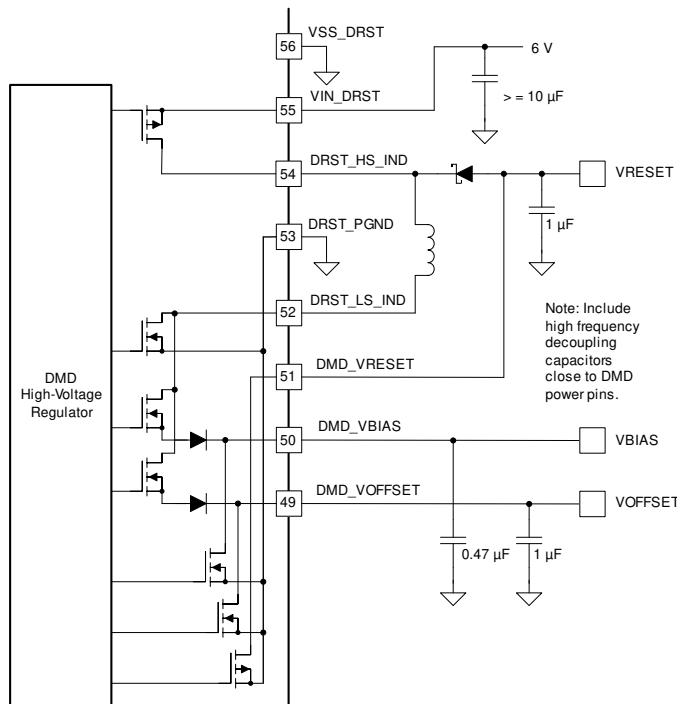

| 49             | DMD_VOFFSET   | 電源  | VOFFSET 出力レール。1μF のセラミック コンデンサを接地します。                                                             |

| 50             | DMD_VBIAS     | 電源  | VBIAS 出力レール。0.47μF のセラミック コンデンサを接地します。                                                            |

| 51             | DMD_VRESET    | 電源  | VRESET 出力レール。1μF のセラミック コンデンサを接地します。外付けダイオード経由で DRST_HS_IND に接続します。ダイオードのアノードを DMD_VRESET に接続します。 |

| 53             | DRST_PGND     | GND | DMD 電源用の電源グランド。グランドプレーンに接続                                                                        |

| 55             | VIN_DRST      | 電源  | DMD 電源用 6V 入力                                                                                     |

| 56             | VSS_DRST      | GND | DMD 電源回路のグランド                                                                                     |

| 59             | AVDD          | 電源  | アナログ回路用の 3.3V 電源入力                                                                                |

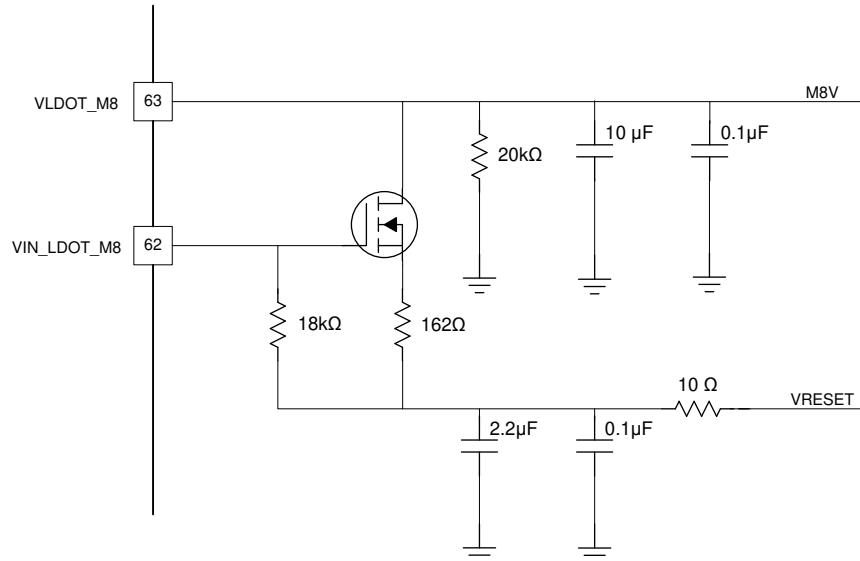

| 63             | VLDOT_M8      | 電源  | 専用 TIA インターフェイス用 –8V LDO 出力                                                                       |

| 64             | VLDOT_5V      | 電源  | 5V TIA LDO 用のフィルタ コンデンサ インターフェイス                                                                  |

| 65             | VIN_LDOT_5V   | 電源  | 5V TIA LDO 用 6V 電源入力                                                                              |

| 66             | GND_LDO       | GND | LDO のパワー グランドリターン                                                                                 |

| 67             | VIN_LDOT_3P3V | 電源  | 3.3V TIA LDO 用 6V 電源入力                                                                            |

| 68             | VLDOT_3P3V    | 電源  | 3.3V TIA LDO 用のフィルタ コンデンサ インターフェイス                                                                |

| 71             | VSS_TIA2      | GND | TIA2 専用グランド                                                                                       |

| 72             | VSS_TIA1      | GND | TIA1 専用グランド                                                                                       |

| 78、100         | AVSS          | GND | アナログ グランド                                                                                         |

| 79             | VIN_LDOA_3P3  | 電源  | 専用 ADC インターフェイス 3.3V LDO 電源用の 6V 電源入力                                                             |

| 80             | VLDOA_3P3     | 電源  | 専用 ADC インターフェイス 3.3V LDO フィルタ コンデンサ出力                                                             |

| 81、84、87、89、91 | VSSL_ADC      | GND | 外部 ADC チャネル ボンドワイヤとリード フレームの絶縁グランド                                                                |

| 95             | ADC_VREF      | 電源  | ADC リファレンス電圧出力                                                                                    |

表 4-3. ピン機能 — 電源管理

| ピン |             | タイプ | 説明                                                    |

|----|-------------|-----|-------------------------------------------------------|

| 番号 | 名称          |     |                                                       |

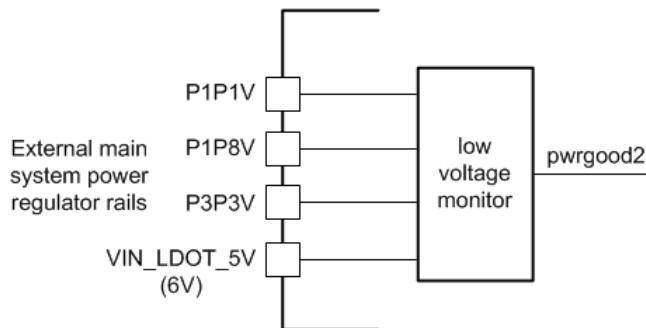

| 1  | ENB_1P1V    | O   | 1.1V 外部降圧イネーブル。3.3V 出力                                |

| 2  | ENB_1P8V    | O   | 1.8V 外部降圧イネーブル。3.3V 出力                                |

| 3  | ENB_3P3V    | O   | 3.3V 外部降圧イネーブル。3.3V 出力                                |

| 52 | DRST_LS_IND | ANA | DMD 電源インダクタ (10µH) への接続。330pF、50V コンデンサを接地します。X7R を推奨 |

| 54 | DRST_HS_IND | ANA | DMD 電源インダクタ (10µH) への接続                               |

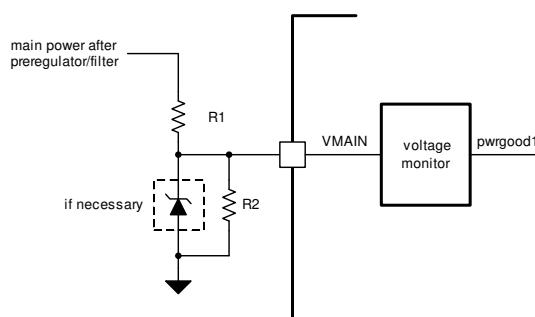

| 58 | VMAIN       | I   | メイン中間電圧監視入力。外付けの抵抗デバイダを使用して、ブラウンアウト監視用の電圧入力を設定します。    |

| 62 | VIN_LDOT_M8 | O   | 専用 TIA インターフェイス -8V LDO 外部レギュレーション FET ドライブ信号         |

| 96 | V3P3V       | I   | 外部 3.3V 降圧電圧入力                                        |

| 97 | V1P8V       | I   | 外部 1.8V 降圧電圧入力                                        |

| 98 | V1P1V       | I   | 外部 1.1V 降圧電圧入力                                        |

**表 4-4. ピン機能 — 照明制御**

| ピン |              | タイプ | 説明                                                                       |

|----|--------------|-----|--------------------------------------------------------------------------|

| 番号 | 名称           |     |                                                                          |

| 12 | COMPOUT      | O   | フォトダイオード (PD) インターフェイスの高速コンバレータ出力                                        |

| 15 | SYNC         | O   | 外部 LED 降圧ドライバ同期ストローブ出力                                                   |

| 18 | D_EN         | I   | LED インターフェイス: 降圧ハイサイド FET 駆動有効化                                          |

| 19 | S_EN         | I   | LED バイパス シャント ストローブ入力                                                    |

| 20 | LED_SEL_0    | I   | LED イネーブル ストローブ 0 入力                                                     |

| 21 | LED_SEL_1    | I   | LED イネーブル ストローブ 1 入力                                                     |

| 22 | LED_SEL_2    | I   | LED イネーブル ストローブ 2 入力                                                     |

| 23 | LED_SEL_3    | I   | LED イネーブル ストローブ 3 入力                                                     |

| 37 | EXT_SMPL     | I   | 予約済み。グランドに接続                                                             |

| 38 | DRV_EN       | O   | LM3409 の駆動有効化                                                            |

| 39 | CMODE        | O   | コンデンサの選択出力 (オーバーシュートまたはアンダーシュートを低減するため、CM モードで容量を小さくすることができます)。オープンドレイン。 |

| 43 | S_EN1        | O   | 低抵抗シャント NFET 駆動有効化 [High はシャントがアクティブを意味する]                               |

| 44 | S_EN2        | O   | 高抵抗シャント NFET 駆動有効化 [High はシャントがアクティブを意味する]                               |

| 45 | R_EN         | O   | 赤色のチャネル選択。ローサイド NFET を駆動します。                                             |

| 46 | G_EN         | O   | 緑色のチャネル選択。ローサイド NFET を駆動します。                                             |

| 47 | B_EN         | O   | 青色のチャネル選択。ローサイド NFET を駆動します。                                             |

| 69 | TIA_PD2_FILT | O   | TIA2 外部フィルタ コンデンサ - 低帯域幅サンプリング                                           |

| 70 | TIA_PD2      | I   | TIA2 フォトダイオード カソードドライバ                                                   |

| 73 | TIA_PD1      | I   | TIA1 フォトダイオード カソードドライバ                                                   |

| 74 | TIA_PD1_FILT | O   | TIA1 外部フィルタ コンデンサ - 低帯域幅サンプリング                                           |

| 76 | R_IADJ       | ANA | IADJ 電圧から電流への変換用外部抵抗                                                     |

| 77 | IADJ         | ANA | 外部 LED コントローラ駆動電流設定ポイントの調整に使用する電流出力                                      |

表 4-5. ピン機能 – シリアル ペリフェラル インターフェイス

| ピン |           | タイプ | 説明                                                                        |

|----|-----------|-----|---------------------------------------------------------------------------|

| 番号 | 名称        |     |                                                                           |

| 27 | SPI1_CLK  | I   | SPI 制御インターフェイス (DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側)、クロック入力               |

| 28 | SPI1_SS_Z | I   | SPI 制御インターフェイス (DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側)、チップ セレクト (アクティブ Low) |

| 29 | SPI1_DOUT | O   | SPI 制御インターフェイス (DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側)、送信データ出力              |

| 30 | SPI1_DIN  | I   | SPI 制御インターフェイス (DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側)、受信データ入力              |

| 31 | SPI2_DIN  | I   | SPI 診断ポート (2 次側)、受信データ入力。読み取り専用監視用                                        |

| 32 | SPI2_DOUT | O   | SPI 診断ポート (2 次側)、送信データ出力。読み取り専用監視用                                        |

| 33 | SPI2_SS_Z | I   | SPI 診断ポート (2 次側)、チップ セレクト (アクティブ Low)。読み取り専用監視用                           |

| 34 | SPI2_CLK  | I   | SPI 診断ポート (2 次側)、クロック入力。読み取り専用監視用                                         |

**表 4-6. ピン機能 – A/D コンバータ**

| ピン |            | タイプ | 説明                                                            |

|----|------------|-----|---------------------------------------------------------------|

| 番号 | 名称         |     |                                                               |

| 4  | ADC_MISO   | O   | ADC 2 線式インターフェイス - データ出力 DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側。 |

| 5  | ADC_MOSI   | I   | ADC 2 線式インターフェイス - データ入力 DLPC23xS-Q1 プライマリ、TPS99002S-Q1 2 次側。 |

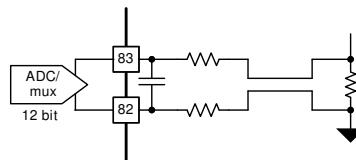

| 82 | LS_SENSE_N | I   | ローサイド電流検出 ADC 負入力。 <a href="#">表 6-2</a> を参照                  |

| 83 | LS_SENSE_P | I   | ローサイド電流検出 ADC 正入力。 <a href="#">表 6-2</a> を参照                  |

| 85 | ADC_IN1    | I   | 外部 ADC チャネル 1、 <a href="#">表 6-2</a> を参照                      |

| 86 | ADC_IN2    | I   | 外部 ADC チャネル 2、 <a href="#">表 6-2</a> を参照                      |

| 88 | ADC_IN3    | I   | 外部 ADC チャネル 3、 <a href="#">表 6-2</a> を参照                      |

| 90 | ADC_IN4    | I   | 外部 ADC チャネル 4、 <a href="#">表 6-2</a> を参照                      |

| 92 | ADC_IN5    | I   | 外部 ADC チャネル 5、 <a href="#">表 6-2</a> を参照                      |

| 93 | ADC_IN6    | I   | 外部 ADC チャネル 6、 <a href="#">表 6-2</a> を参照                      |

| 94 | ADC_IN7    | I   | 外部 ADC チャネル 7、 <a href="#">表 6-2</a> を参照                      |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                          |                                                                                                                              | 最小値  | 最大値 | 単位 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

| 入力電圧                     | VDD_IO から VSS_IO へ                                                                                                           | -0.3 | 4   | V  |

|                          | DVDD から DVSS へ                                                                                                               | -0.3 | 4   |    |

|                          | AVDD から DVSS へ                                                                                                               | -0.3 | 4   |    |

|                          | すべての「VSS」からその他の「VSS」(グランド) へ                                                                                                 | -0.1 | 0.1 |    |

|                          | グランドへのすべてのデジタル入力信号 (WD1、WD2、ADC_MOSI、PROJ_ON、SEQ_START、SEQ_CLK、SPI1_CLK、SPI1_DIN、SPI1_SS、SPI2_DIN、SPI2_CLK、SPI2_SS、EXT_SMPL) | -0.3 | 3.6 |    |

|                          | DRV_R_PWR からグランドへ                                                                                                            | -0.3 | 7.5 |    |

|                          | VIN_LDO_5V                                                                                                                   | -0.3 | 7.5 |    |

|                          | V3P3V を接地                                                                                                                    | -0.3 | 5   |    |

|                          | V1P8V を接地                                                                                                                    | -0.3 | 5   |    |

|                          | V1P1V を接地                                                                                                                    | -0.3 | 5   |    |

|                          | VIN_LDOA_3P3 を接地                                                                                                             | -0.3 | 7.5 |    |

|                          | VIN_LDOD_3P3 を接地                                                                                                             | -0.3 | 7.5 |    |

|                          | ADC_IN(7:1) を接地                                                                                                              | -0.3 | 3.6 |    |

|                          | LS_SENSE_N および LS_SENSE_P を接地                                                                                                | -0.3 | 3.6 |    |

|                          | IADJ を接地                                                                                                                     | -0.3 | 18  |    |

|                          | R_IADJ を接地                                                                                                                   | -0.3 | 5   |    |

|                          | VIN_LDOD_M8 を接地                                                                                                              | -18  | 0.3 |    |

|                          | DRST_LS_IND から DRST_PGND へ                                                                                                   | -0.3 | 27  |    |

|                          | VIN_DRST を接地                                                                                                                 | -0.3 | 7.5 |    |

|                          | VMAIN                                                                                                                        | -0.3 | 7.5 |    |

| 出力                       | INT_Z                                                                                                                        | -0.3 | 7.5 | V  |

| 動作時の接合部温度、T <sub>J</sub> |                                                                                                                              | -40  | 130 | °C |

| 保管温度、T <sub>stg</sub>    |                                                                                                                              | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                         |                                            |        | 値     | 単位 |

|-------------------------|--------------------------------------------|--------|-------|----|

| V <sub>(ESD)</sub> 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | すべてのピン | ±2000 | V  |

|                         | デバイス帯電モデル (CDM)、AEC Q100-011 準拠            | 角のピン   | ±500  |    |

|                         |                                            | 角のピン   | ±750  |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                        | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|------------------------|-----|-----|-----|----|

| <b>温度</b>      |                        |     |     |     |    |

| T <sub>A</sub> | 動作時周囲温度 <sup>(1)</sup> | -40 | 105 | 105 | °C |

| T <sub>J</sub> | 動作時接合部温度               | -40 | 125 | 125 | °C |

| <b>電圧</b>      |                        |     |     |     |    |

| VDD_IO         | IO 3.3V 電圧電源           | 3   | 3.3 | 3.6 | V  |

| DVDD           | デジタル 3.3V 電源           | 3   | 3.3 | 3.6 | V  |

| AVDD           | アナログ 3.3V 電源           | 3   | 3.3 | 3.6 | V  |

| ADC            | ADC(7:1) 入力            | 0.1 | 1.6 | 1.6 | V  |

| VIN_DRST       | DMD リセットレギュレータ入力       | 5.5 | 6   | 7   | V  |

| VIN_LDOT_5V    | 5V TIA LDO への電源入力。     | 5.5 | 6   | 7   | V  |

| VIN_LDOA_3P3V  | 3.3V ADC LDO への電源入力。   | 5.5 | 6   | 7   | V  |

| VIN_LDOT_3P3V  | 3.3V TIA LDO への電源入力。   | 5.5 | 6   | 7   | V  |

| DRVVR_PWR      | ゲートドライバ電源              | 3   | 6   | 7   | V  |

(1) 周囲温度 -40°C ~ 105°C、自由気流、AEC Q100 グレード 2。

### 5.4 热に関する情報

| 熱評価基準 <sup>(1) (2)</sup> | TPS99002S-Q1        | 単位  |      |

|--------------------------|---------------------|-----|------|

|                          | PZP (HTQFP)         |     |      |

|                          | 100 ピン              |     |      |

| R <sub>θJC(top)</sub>    | 接合部からケース (上面) への熱抵抗 | 6.9 | °C/W |

| R <sub>θJB</sub>         | 接合部から基板への熱抵抗        | 8.3 | °C/W |

| Ψ <sub>JT</sub>          | 接合部から上面への特性パラメータ    | 0.1 | °C/W |

| Ψ <sub>JB</sub>          | 接合部から基板への特性パラメータ    | 8.2 | °C/W |

| R <sub>θJC(bot)</sub>    | 接合部からケース (底面) への熱抵抗 | 0.4 | °C/W |

- (1) 従来および新しい熱評価基準値の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポート (SPRA953) を参照してください。

(2) 動作時周囲温度は、システムの熱設計に依存します。動作時の接合部温度は、周囲温度条件において仕様範囲を超えてはなりません。

## 5.5 電気的特性 – トランスインピーダンス アンプのパラメータ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                     | テスト条件                                      | 最小値                                       | 標準値   | 最大値   | 単位     |

|---------------------------|--------------------------------------------|-------------------------------------------|-------|-------|--------|

| TIA1 および TIA2             |                                            |                                           |       |       |        |

| $I_{IN\_TOT}$             | TIA1 と TIA2 の組み合わせ入力電流                     | 0                                         | 7 (3) | 7     | mA     |

| トランスインピーダンス アンプ #1 (TIA1) |                                            |                                           |       |       |        |

| $I_{IN}$                  | TIA 入力電流                                   | RGB トリム $\leq 0.5x^{(1)}$                 | 0     | 0.6   | 4.8 mA |

| $C_{IN}$                  | 合計入力容量 <sup>(2)</sup>                      | 基板、コネクタ、フォトダイオード、およびケーブルから許容される入力容量       | 10    | 50    | 140 pF |

| $TRIM_{RGB}$              | RGB トリム、通常フラックス システム                       |                                           | 0.2   | 0.5   | 1 V/V  |

| $GAINTOL_{ABS}$           | TIA ゲイン許容誤差 (絶対値)                          | 設定ごとに、規定のゲイン ターゲットの許容誤差                   | -20%  | 20%   |        |

| $GAINTOL_{REL}$           | TIA ゲイン許容誤差 (相対)                           | 他の設定との比率としての公差                            | 3%    |       |        |

| TIA1 スルーレート               |                                            |                                           |       |       |        |

| $TIA_{SLEW1}$             | 低ゲイン スルーレート、出力換算                           | $\leq 96\text{kV/A}$ ゲイン                  | 12    |       | V/μs   |

| $TIA_{SLEW2}$             | 高ゲイン スルーレート、出力換算                           | $> 96\text{kV/A}$ ゲイン                     | 5     |       | V/μs   |

| $TIA_{DELAY}$             | TIA パッドから COMPOUT パッドまでの遅延、DM 最小値、立ち下がりエンジ | 最大スルーレート入力、20pF 負荷、トリップ ポイント全体で 100mV 最小値 | 40    | 64    | ns     |

| $TIA_{DELAYCM}$           | TIA パッドから COMPOUT への遅延。CM                  | CM の最大電流                                  | 100   |       | ns     |

| TIA1 実効ゲイン                |                                            |                                           |       |       |        |

| ゲイン設定 0                   | Trim 1.0 に設定                               | 0.6                                       | 0.75  | 0.9   | kV/A   |

| ゲイン設定 1                   | Trim 1.0 に設定                               | 1.2                                       | 1.5   | 1.8   | kV/A   |

| ゲイン設定 2                   | Trim 1.0 に設定                               | 2.4                                       | 3     | 3.6   | kV/A   |

| ゲイン設定 3                   | Trim 1.0 に設定                               | 4.8                                       | 6     | 7.2   | kV/A   |

| ゲイン設定 4                   | Trim 1.0 に設定                               | 7.2                                       | 9     | 10.8  | kV/A   |

| ゲイン設定 5                   | Trim 1.0 に設定                               | 9.6                                       | 12    | 14.4  | kV/A   |

| ゲイン設定 6                   | Trim 1.0 に設定                               | 14.4                                      | 18    | 21.6  | kV/A   |

| ゲイン設定 7                   | Trim 1.0 に設定                               | 19.2                                      | 24    | 28.8  | kV/A   |

| ゲイン設定 8                   | Trim 1.0 に設定                               | 28.8                                      | 36    | 43.2  | kV/A   |

| ゲイン設定 9                   | Trim 1.0 に設定                               | 38.4                                      | 48    | 57.6  | kV/A   |

| ゲイン設定 10                  | Trim 1.0 に設定                               | 57.6                                      | 72    | 86.4  | kV/A   |

| ゲイン設定 11                  | Trim 1.0 に設定                               | 76.8                                      | 96    | 115.2 | kV/A   |

| ゲイン設定 12                  | Trim 1.0 に設定                               | 115.2                                     | 144   | 172.8 | kV/A   |

| ゲイン設定 13                  | Trim 1.0 に設定                               | 230.4                                     | 288   | 345.6 | kV/A   |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                    | テスト条件                | 最小値                       | 標準値  | 最大値   | 単位         |

|--------------------------|----------------------|---------------------------|------|-------|------------|

| トランジンピーダンス アンプ #2 (TIA2) |                      |                           |      |       |            |

| $I_{IN}$                 | TIA 入力電流             | RGB トリム $\leq 0.5x^{(1)}$ | 0    | 4.8   | mA         |

| $TRIM_{RGB}$             | RGB トリム、通常フラックス システム |                           | 0.2  | 1     | V/V        |

| TIA2 スルーレート              |                      |                           |      |       |            |

| $TIA2_{SLEW}$            | スルーレート、出力換算          | すべてのゲイン                   | 1    |       | V/ $\mu$ s |

| TIA2 E                   |                      |                           |      |       |            |

| ゲイン設定 0                  | Trim 1.0 に設定         | 0.6                       | 0.75 | 0.9   | kV/A       |

| ゲイン設定 1                  | Trim 1.0 に設定         | 1.2                       | 1.5  | 1.8   | kV/A       |

| ゲイン設定 2                  | Trim 1.0 に設定         | 2.4                       | 3    | 3.6   | kV/A       |

| ゲイン設定 3                  | Trim 1.0 に設定         | 4.8                       | 6    | 7.2   | kV/A       |

| ゲイン設定 4                  | Trim 1.0 に設定         | 7.2                       | 9    | 10.8  | kV/A       |

| ゲイン設定 5                  | Trim 1.0 に設定         | 9.6                       | 12   | 14.4  | kV/A       |

| ゲイン設定 6                  | Trim 1.0 に設定         | 14.4                      | 18   | 21.6  | kV/A       |

| ゲイン設定 7                  | Trim 1.0 に設定         | 19.2                      | 24   | 28.8  | kV/A       |

| ゲイン設定 8                  | Trim 1.0 に設定         | 28.8                      | 36   | 43.2  | kV/A       |

| ゲイン設定 9                  | Trim 1.0 に設定         | 38.4                      | 48   | 57.6  | kV/A       |

| ゲイン設定 10                 | Trim 1.0 に設定         | 57.6                      | 72   | 86.4  | kV/A       |

| ゲイン設定 11                 | Trim 1.0 に設定         | 76.8                      | 96   | 115.2 | kV/A       |

| ゲイン設定 12                 | Trim 1.0 に設定         | 115.2                     | 144  | 172.8 | kV/A       |

| ゲイン設定 13                 | Trim 1.0 に設定         | 230.4                     | 288  | 345.6 | kV/A       |

- (1) 最大入力電流は、選択したトリム値に比例して直線的に減少し、トリムが  $1.0x$  のときに  $2.4mA$  の最大値が小さくなります。

- (2) 大きな容量性負荷は、システム性能に影響を及ぼすことがあります。

- (3)  $7mA$  を超える結合 TIA 電流が必要なアプリケーションの詳細については、までお問い合わせください。

## 5.6 電気的特性 : D/A コンバータ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 | テスト条件         | 最小値                                         | 標準値 | 最大値    | 単位               |

|-----------------------|---------------|---------------------------------------------|-----|--------|------------------|

| フォトフィードバック 12 ビット DAC |               |                                             |     |        |                  |

| $V_{OUTDAC}$ Max      | 出力範囲の最大値      | 1.96                                        | 2   | 2.04   | V                |

| $V_{OUTDAC}$ Min      | 出力範囲の最小値      | -0.1                                        | 0   | 0.1    | V                |

| $t_{SET}$             | セトリング タイム     | ±2% 以内のフルレンジのステップ応答                         | 0   | 500    | ns               |

| INL                   | 積分非直線性        | -3.5                                        | 3.5 | LSB    |                  |

| DNL                   | 微分非直線性        | -3.5                                        | 3.5 | LSB    |                  |

| $V_{OFF}$             | オフセット誤差       | -100                                        | 100 | mV     |                  |

| $ZERO_{ERR}$          | ゼロスケール誤差      | -100                                        | 100 | mV     |                  |

| $GAIN_{ERR}$          | ゲイン誤差         | -5                                          | 5   | %V/コード |                  |

| $FS_{ERR}$            | フルスケール誤差      | -2                                          | 2   | %FSR   |                  |

| $ZERO_{ERRDFT}$       | ゼロスケール誤差のドリフト | -50                                         | 20  | 50     | $\mu V/^\circ C$ |

| $GAIN_{TEMP}$         | ゲイン温度係数       | -52                                         | 0   | 52     | ppm<br>FSR/°C    |

| 電流制御 10 ビット DAC       |               |                                             |     |        |                  |

| $V_{OUTDAC}$ Max      | 出力範囲の最大値      | 1.96                                        | 2   | 2.04   | V                |

| $V_{OUTDAC}$ Min      | 出力範囲の最小値      | -0.1                                        | 0   | 0.1    | V                |

| $t_{SET}$             | セトリング タイム     | ±2% 以内のフルレンジのステップ応答                         | 0   | 1000   | ns               |

| INL                   | 積分非直線性        | -2                                          | 2   | LSB    |                  |

| DNL                   | 微分非直線性        | -2                                          | 2   | LSB    |                  |

| $V_{OFF}$             | オフセット誤差       | -100                                        | 100 | mV     |                  |

| $ZERO_{ERR}$          | ゼロスケール誤差      | -100                                        | 100 | mV     |                  |

| $GAIN_{ERR}$          | ゲイン誤差         | -5                                          | 5   | %V/コード |                  |

| $FS_{ERR}$            | フルスケール誤差      | -2                                          | 2   | %FSR   |                  |

| $ZERO_{ERRDFT}$       | ゼロスケール誤差のドリフト | -50                                         | 20  | 50     | $\mu V/^\circ C$ |

| $GAIN_{TEMP}$         | ゲイン温度係数       | -52                                         | 0   | 52     | ppm<br>FSR/°C    |

| 過輝度検出 8 ビット DAC       |               |                                             |     |        |                  |

| $V_{OUTDAC}$ max      | 出力範囲の最大値      | 1.95                                        | 2   | 2.05   | V                |

| $V_{OUTDAC}$ min      | 出力範囲の最小値      | -0.1                                        | 0   | 0.1    | V                |

| $t_{OBDAC}$           | 過輝度 DAC 調整時間  | 入力コードマルチプレクサの入力が、アナログ出力で 90/10 セトリングに変化するまで |     | 1000   | μs               |

| INL                   | 積分非直線性        | -1                                          | 1   | LSB    |                  |

| DNL                   | 微分非直線性        | -0.5                                        | 0.5 | LSB    |                  |

| $V_{OFF}$             | オフセット誤差       | -100                                        | 100 | mV     |                  |

| $ZERO_{ERR}$          | ゼロスケール誤差      | -100                                        | 100 | mV     |                  |

| $GAIN_{ERR}$          | ゲイン誤差         | -5                                          | 5   | %V/コード |                  |

| $FS_{ERR}$            | フルスケール誤差      | -3                                          | 3   | %FSR   |                  |

| $ZERO_{ERRDFT}$       | ゼロスケール誤差のドリフト | -50                                         | 20  | 50     | $\mu V/^\circ C$ |

| $GAIN_{TEMP}$         | ゲイン温度係数       | -52                                         | 0   | 52     | ppm<br>FSR/°C    |

## 5.7 電気的特性 : A/D コンバータ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                           | テスト条件               | 最小値                          | 標準値   | 最大値   | 単位    |    |

|---------------------------------|---------------------|------------------------------|-------|-------|-------|----|

| <b>12-BIT ADC<sup>(1)</sup></b> |                     |                              |       |       |       |    |

| V <sub>INPUT</sub>              | 入力範囲 <sup>(2)</sup> | 0.1                          | 1.6   | 1.6   | V     |    |

| INL                             | 積分非直線性              | 有効な入力範囲内 V <sub>INPUT</sub>  | -4    | 4     | LSB   |    |

| DNL                             | 微分非直線性              |                              | -2.5  | 2.5   | LSB   |    |

| ENOB                            | 有効ビット数              |                              | 10    | 12    | ビット   |    |

| t <sub>SAMPLE</sub>             | S/H サンプリング期間        |                              | 0.4   | 5.2   | 12.8  | μs |

| t <sub>DELAY</sub>              | 変換開始前の S/H 遅延       |                              | 0.4   | 2.8   | μs    |    |

| t <sub>SHOLD</sub>              | S/H 保持期間            |                              | 102.4 | 245   | μs    |    |

| t <sub>CONV</sub>               | 変換期間                |                              | 102.4 | 102.4 | μs    |    |

| V <sub>REF</sub>                | 測定基準                | ADC リファレンス電圧を 1.6V に 2 倍しました | 0.784 | 0.8   | 0.816 | V  |

| V <sub>OFFS</sub>               | オフセット               |                              | -20   | 20    | LSB   |    |

|                                 | ゲイン誤差               | ADC_IN(7:1) 入力               | 2     | 2     | %FSR  |    |

(1) ADC 仕様は、特に記述のない限り、ADC コアの動作を指し、理想的なクロックおよび IC 入力電力条件を想定します。

(2) 結果として、無効な ADC コードが 256 未満になります

## 5.8 電気的特性 — FET ゲート ドライバ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 | テスト条件                            | 最小値                                        | 標準値    | 最大値  | 単位       |

|-----------------------|----------------------------------|--------------------------------------------|--------|------|----------|

| LED 制御信号 FET ゲート ドライバ |                                  |                                            |        |      |          |

| $Q_{SEN}$             | $S_{EN1/2}$ 負荷ゲート電荷              |                                            | 12     | 16.5 | nC       |

| $Z_{SEN}$             | $S_{EN1/2}$ プルアップ ゲート駆動出力インピーダンス | 3.3V ドメイン <sup>(1)</sup>                   |        | 12.3 | $\Omega$ |

|                       |                                  | 6V ドメイン <sup>(2)</sup>                     |        | 10.7 | $\Omega$ |

| $Z_{SEN}$             | $S_{EN1/2}$ プルダウン ゲート駆動出力インピーダンス | 3.3V ドメイン <sup>(1)</sup>                   |        | 4.85 | $\Omega$ |

|                       |                                  | 6V ドメイン <sup>(2)</sup>                     |        | 4.6  | $\Omega$ |

| $T_{SEN}$             | $S_{EN1/2}$ のプルアップ遷移時間           | 3.3V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(1)</sup> | 49.5   | 66   | 82.5     |

|                       |                                  | 6V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(2)</sup>   | 45     | 60   | 75       |

| $T_{SEN}$             | $S_{EN1/2}$ プルダウン遷移時間            | 3.3V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(1)</sup> | 20.25  | 27   | 33.75    |

|                       |                                  | 6V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(2)</sup>   | 18.75  | 25   | 31.25    |

| $Z_{RGB}$             | $RGB\_EN$ のプルアップ出力インピーダンス        | 3.3V ドメイン <sup>(1)</sup>                   |        | 50.8 | $\Omega$ |

|                       |                                  | 6V ドメイン <sup>(2)</sup>                     |        | 43.6 | $\Omega$ |

| $Z_{RGB}$             | $RGB\_EN$ プルダウン出力インピーダンス         | 3.3V ドメイン <sup>(1)</sup>                   |        | 4.85 | $\Omega$ |

|                       |                                  | 6V ドメイン <sup>(2)</sup>                     |        | 4.6  | $\Omega$ |

| $T_{RGB}$             | $RGB\_EN$ プルアップ立ち下がり遷移時間         | 3.3V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(1)</sup> | 198.75 | 265  | 331.25   |

|                       |                                  | 6V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(2)</sup>   | 180    | 240  | 300      |

| $T_{RGB}$             | $RGB\_EN$ プルダウン立ち下がり遷移時間         | 3.3V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(1)</sup> | 20.25  | 27   | 33.75    |

|                       |                                  | 6V ドメイン、最大総ゲート電荷負荷は 2.5nF <sup>(2)</sup>   | 18.75  | 25   | 31.25    |

(1) DRVR\_PWR 電源電圧は 3V~3.6V です。

(2) DRVR\_PWR 電源電圧は 5.5V~7.5V です。

## 5.9 電気的特性 — フォトコンパレータ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ             | テスト条件   | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------|---------|-----|-----|-----|----|

| フォトフィードバック コンパレータ |         |     |     |     |    |

| $V_{OFF}$         | オフセット電圧 |     | -10 | 10  | mV |

| $T_{HYST}$        | ヒステリシス  |     | 10  | 20  | mV |

## 5.10 電気的特性 – 電圧レギュレータ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                     | テスト条件                                    | 最小値                       | 標準値                | 最大値                 | 単位   |

|---------------------------|------------------------------------------|---------------------------|--------------------|---------------------|------|

| <b>VOFFSET レギュレータ</b>     |                                          |                           |                    |                     |      |

| V <sub>OUT</sub>          | 出力電圧                                     | さまざまな負荷条件                 | 9.75               | 10                  | V    |

| I <sub>OUT</sub>          | 出力電流 <sup>(2)</sup>                      |                           | 0.1 <sup>(4)</sup> | 16.3                | mA   |

| V <sub>PGTHRESHR</sub>    | パワーグッド レッショルド、<br>V <sub>OUT</sub> 立ち上がり |                           | 86%                |                     |      |

| V <sub>PGTHRESHF</sub>    | パワーグッド レッショルド、<br>V <sub>OUT</sub> 立ち下がり |                           | 66%                |                     |      |

| C <sub>OUT</sub>          | 出力コンデンサ <sup>(3)</sup>                   |                           | 1                  |                     | μF   |

| T <sub>DISC</sub>         | 放電時間                                     | C <sub>OUT</sub> = 1μF    |                    | 260                 | μs   |

| <b>VBIAS レギュレータ</b>       |                                          |                           |                    |                     |      |

| V <sub>OUT</sub>          | 出力電圧                                     |                           | 17.5               | 18                  | V    |

| I <sub>OUT</sub>          | 出力電流 <sup>(2)</sup>                      |                           | 0.1 <sup>(4)</sup> | 1.5                 | mA   |

| V <sub>PGTHRESHR</sub>    | パワーグッド レッショルド、<br>V <sub>OUT</sub> 立ち上がり |                           | 86%                |                     |      |

| V <sub>PGTHRESHF</sub>    | パワーグッド レッショルド、<br>V <sub>OUT</sub> 立ち下がり |                           | 66%                |                     |      |

| C <sub>OUT</sub>          | 出力コンデンサ <sup>(3)</sup>                   |                           | 0.47               |                     | μF   |

| T <sub>DISC</sub>         | 放電時間                                     | C <sub>OUT</sub> = 0.47μF |                    | 260                 | μs   |

| <b>VRESET レギュレータ</b>      |                                          |                           |                    |                     |      |

| V <sub>OUT</sub>          | 出力電圧                                     |                           | -14.5              | -14                 | V    |

| I <sub>OUT</sub>          | 出力電流 <sup>(1) (2)</sup>                  |                           | -17.6              | -0.1 <sup>(4)</sup> | mA   |

| V <sub>PGTHRESHR</sub>    | パワーグッド レッショルド                            |                           | 80%                |                     |      |

| C <sub>OUT</sub>          | 出力コンデンサ <sup>(3)</sup>                   |                           | 1                  |                     | μF   |

| T <sub>DISC</sub>         | 放電時間                                     | C <sub>OUT</sub> = 1μF    |                    | 260                 | μs   |

| <b>負の 8V フォトダイオード LDO</b> |                                          |                           |                    |                     |      |

| V <sub>IN</sub>           | 入力電圧                                     |                           | -10                |                     | V    |

| V <sub>OUT</sub>          | 出力電圧                                     | 無負荷                       | -8.5               | -8                  | V    |

| I <sub>OUT</sub>          | 出力電流                                     |                           | -6                 |                     | mA   |

| V <sub>IRIPPLE</sub>      | 入力リップル                                   |                           |                    | 100                 | mVpp |

- (1) VRESET 電流は、DMD と負の 8V LDO の両方に供給されます。

- (2) VOFFSET、VBIAS、VRESET は、DMD および負の 8V LDO のみに電力を供給するよう設計されており、追加の負荷には接続しないでください。

- (3) 一部のセラミックコンデンサのタイプでは、印加される DC 電圧および温度によって容量値が大幅に低下する場合があります。TI は、電圧バイアスおよび温度に対する容量損失を最小限に抑えるため、X7R 誘電体コンデンサを推奨します。また、より高い電圧定格の部品やより大きなパッケージサイズを使用すると、印加される DC 電圧での容量低減を最小限に抑えることができます。

- (4) 最小電流要件を満たすために必要なプルダウン抵抗。

## 5.11 電気的特性 – 温度および電圧モニタ

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                   | テスト条件          | 最小値                               | 標準値    | 最大値  | 単位     |

|-------------------------|----------------|-----------------------------------|--------|------|--------|

| 温度モニタ                   |                |                                   |        |      |        |

| TEMP <sub>WARN</sub>    | 過熱警告スレッショルド    | 接合部温度                             | 135    |      | °C     |

| TEMP <sub>EMRG</sub>    | 熱緊急スレッショルド     | 接合部温度                             | 150    |      | °C     |

| 1.1V 電源モニタ              |                |                                   |        |      |        |

| V <sub>TRIPN</sub>      | 負のトリップ スレッショルド | 負方向のみ                             | 0.95   | 0.98 | 1.01   |

| V <sub>TRIPHYST</sub>   | ヒステリシス         | 正方向スレッショルド、負のトリップ電圧より高い電圧         |        | 2%   |        |

| t <sub>GLITCH</sub>     | グリッヂ抑制         | 2% オーバードライブで、グリッヂのサイズは無視 (リセットなし) | 20     | 1000 | μs     |

| 1.8V 電源モニタ              |                |                                   |        |      |        |

| V <sub>TRIPN</sub>      | 負のトリップ スレッショルド | 負方向のみ                             | 1.552  | 1.6  | 1.648  |

| V <sub>TRIPHYST</sub>   | ヒステリシス         | 正方向スレッショルド、負のトリップ電圧より高い電圧         |        | 2%   |        |

| t <sub>GLITCH</sub>     | グリッヂ抑制         | 2% オーバードライブで、グリッヂのサイズは無視 (リセットなし) | 20     | 1000 | μs     |

| 3.3V 電源モニタ              |                |                                   |        |      |        |

| V <sub>TRIPN</sub>      | 負のトリップ スレッショルド | 負方向のみ                             | 2.852  | 2.93 | 3.03   |

| V <sub>TRIPHYST</sub>   | ヒステリシス         | 正方向スレッショルド、負のトリップ電圧より高い電圧         |        | 2%   |        |

| t <sub>GLITCH</sub>     | グリッヂ抑制         | 2% オーバードライブで、グリッヂのサイズは無視 (リセットなし) | 20     | 1000 | μs     |

| AVDD、DVDD、VDDIO の電源モニタ  |                |                                   |        |      |        |

| V <sub>TRIPN</sub>      | 負のトリップ スレッショルド | 負方向のみ                             | 2.74   | 2.86 | 2.98   |

| V <sub>TRIPHYST</sub>   | ヒステリシス         | 正方向スレッショルド、負のトリップ電圧より高い電圧         |        | 2%   |        |

| t <sub>GLITCH</sub>     | グリッヂ抑制         | 2% オーバードライブで、グリッヂのサイズは無視 (リセットなし) | 20     | 1000 | μs     |

| VMAIN システム入力電源モニタ       |                |                                   |        |      |        |

| V <sub>MAINTHRSH</sub>  | VMAIN スレッショルド  | VMAIN の変換に使用される外付け抵抗デバイダ          | 1.2125 | 1.25 | 1.2875 |

| t <sub>MAINGLITCH</sub> | VMAIN グリッヂ抑制   | 2% オーバードライブ時                      | 20     | 1000 | μs     |

## 5.12 電気的特性 - 電流消費

| パラメータ                                                                           | テスト条件                  | 最小値 | 標準値 <sup>(1)</sup> | 最大値 <sup>(2)</sup> | 単位 |

|---------------------------------------------------------------------------------|------------------------|-----|--------------------|--------------------|----|

| <b>3.3V 電源ピンの合計:DVDD、VDD_IO、AVDD</b>                                            |                        |     |                    |                    |    |

| システム オフ                                                                         | PROJ_ON low            |     | 1.5                | 2                  | mA |

| システム オン                                                                         | 表示オン状態、TIA はイネーブルなし    |     | 3.5                | 4                  | mA |

| TIA #1                                                                          | TIA #1 を有効にしたことによる追加電流 |     | 1                  | 1                  | mA |

| TIA #2                                                                          | TIA #2 を有効にしたことによる追加電流 |     | 1                  | 1                  | mA |

| <b>6V 電源ピンの合計:DRVVR_PWR、VIN_DRST、VIN_LDOT_5V、VIN_LDOT_3P3V、およびVIN_LDOA_3P3V</b> |                        |     |                    |                    |    |

| システム オフ                                                                         | PROJ_ON low            |     | 1                  | 2                  | mA |

| システム オン <sup>(3)</sup>                                                          | 表示オン状態、TIA はイネーブルなし    |     | 98                 | 119                | mA |

| TIA #1                                                                          | TIA #1 を有効にしたことによる追加電流 |     | 20                 | 25                 | mA |

| TIA #2                                                                          | TIA #2 を有効にしたことによる追加電流 |     | 20                 | 25                 | mA |

(1) 25°C と公称電圧で実施される代表的な測定

(2) 40°C、25°C、105°C で測定。3.3V 入力は 3V、3.3V、3.6V で測定。6V 入力は 5.5V、6V、7V で測定。これらすべての条件の最大消費電流を示しています。

(3) この数値は、DMD 電圧がこのデータシートのそれぞれのセクションに記載されている最大電流を出力するときの TPS99002S-Q1 への入力時の電流を表します。この数値は、DMD 電圧レギュレータが無負荷のときに測定される電流 (標準値 3mA、最大値 56mA) と、DMD 電圧レギュレータが最大電流 (63mA) を出力したときの 6V 電源に流れる推定電流の組み合わせです。消費電流の推定値は、式  $I_{6V} = [(18/6) \times I_{VBIAS} + (10/6) \times I_{VOFFSET} + (-14/6) \times I_{VRESET}] / \eta$  で計算されます。ここで、 $\eta = 0.9$  です。この条件での TPS99002S-Q1 の消費電力を計算するには、無負荷状態からの電流に入力電圧を乗算し、さらに DMD 電圧レギュレータからの電流に入力電圧を乗算したものに  $(1 - \eta)$  を乗算した値を加算します。

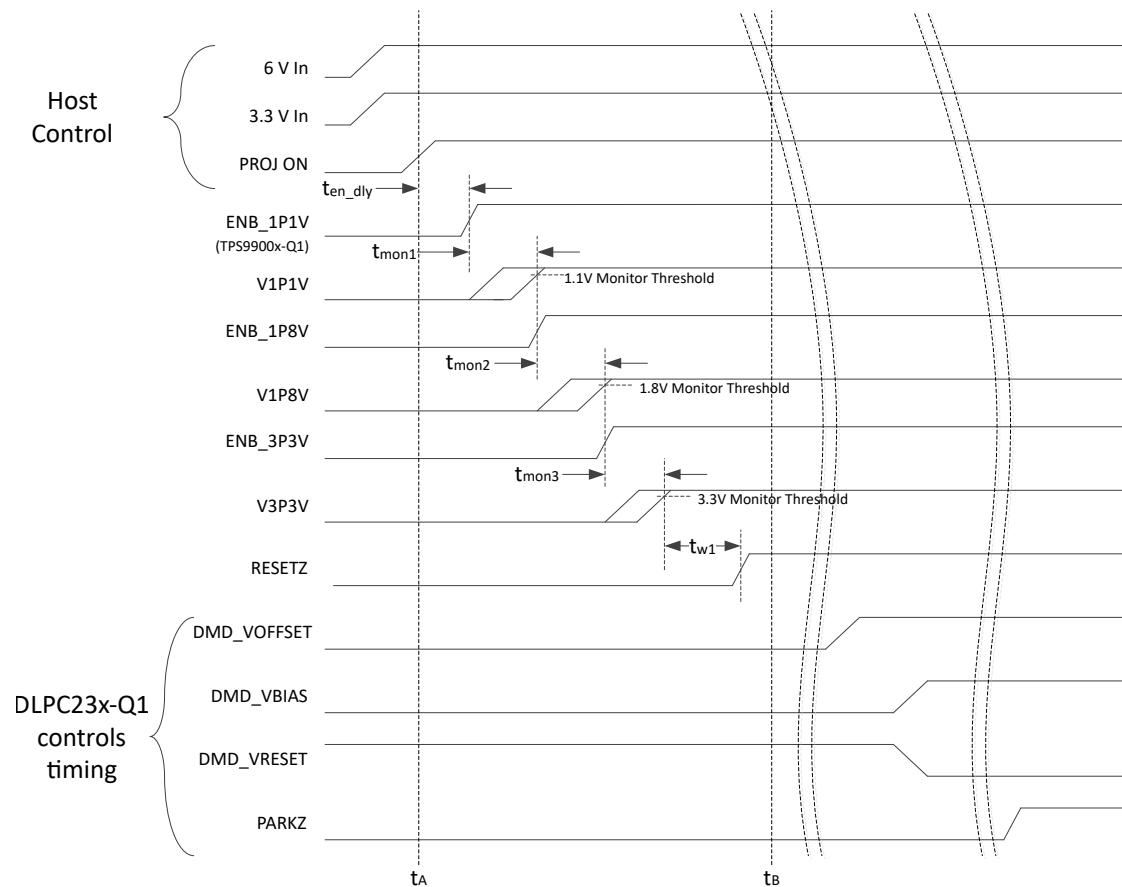

## 5.13 パワーアップのタイミング要件

|                    |                                                                                |                                            | 標準値 | 単位 |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------|-----|----|

| $t_{en\_dly}$      | PROJ_ON から 1.1V 有効化。これには、PROJ_ON $t_{glitch}$ 時間が含まれます。                        | PROJ_ON の立ち上がりエッジから 1.1V の立ち上がりエッジまでの有効化   | 11  | ms |

| $t_{mon1}$ (1) (2) | 有効化がアサートされた後、1.1V レールが電圧スレッショルドに達するまでの最大時間。この遅延長は、1.1V がスレッショルドを早期に満たしても発生します。 | ENB_1P1V の立ち上がりエッジから内部 1.1V モニタ テスト (3) まで | 10  | ms |

| $t_{mon2}$ (1) (2) | 有効化がアサートされた後、1.8V レールが電圧スレッショルドに達するまでの最大時間。この遅延長は、1.8V がスレッショルドを早期に満たしても発生します。 | ENB_1P8V の立ち上がりエッジから内部 1.8V モニタ テスト (3) まで | 10  | ms |

| $t_{mon3}$ (1) (2) | 有効化がアサートされた後、3.3V レールが電圧スレッショルドに達するまでの最大時間。この遅延長は、3.3V がスレッショルドを早期に満たしても発生します。 | ENB_3P3V の立ち上がりエッジから内部 3.3V モニタ テスト (3) まで | 10  | ms |

| $t_{w1}$ (4)       | 電圧テスト完了後の RESETZ 遅延。                                                           | RESETZ 立ち上がりエッジまでの 3.3V 監視テストの完了           | 10  | ms |

- (1) システム電源設計に必要な場合は、TPS99002S-Q1 においてそれぞれのイネーブル信号をアサートする前に、V1P1V、V1P8V、V3P3V の各レールを有効化できます。必要に応じて、ENB\_1P1V を、1.1V、1.8V、3.3V の外部電源イネーブルに接続できます。

- (2) 指定された時間内に電圧スレッショルドが満たされない場合、TPS99002S-Q1 は RESETZ をデアサートしません。この状況では、パワーアップ手順を完全に再起動する必要があります。

- (3) 各 TPS 監視テストは、電圧レールのそれぞれの電圧有効化から約 10ms で実行されます。電圧レールは、これまではいつでも、スレッショルド値に達することがあります。これは、各有効化の間に約 10ms が必要であることを意味します。1.1V、1.8V、3.3V のそれぞれの起動時間は、選択した設計や部品によって異なりますが、監視テストの前にこれらすべてが有効である必要があります。

- (4)  $t_{w1}$  は、3.3V レールが内部監視テスト(約 10ms)を超えると開始されます。3.3V がスレッショルド値になると、この時間は起動しません。この時間は、内部 TPS 監視が 3.3V をチェックした後に開始されます。テストに合格した後、RESETZ がデアサートされるまで 10ms の遅延が発生します。これは、3.3V イネーブルが有効になってから RESETZ がデアサートされるまでに約 20ms の遅延が発生することを意味します。

図 5-1. 起動タイミング

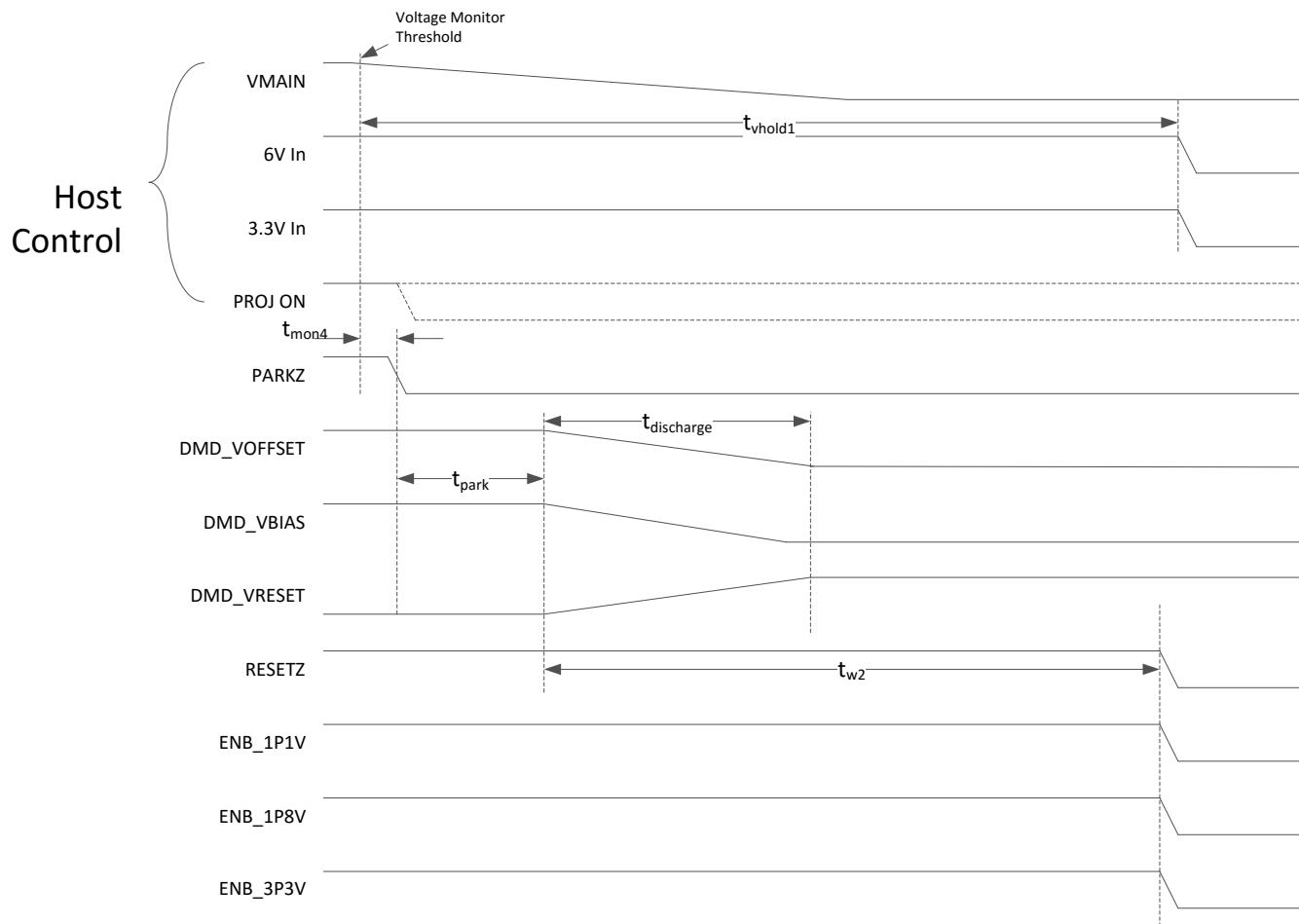

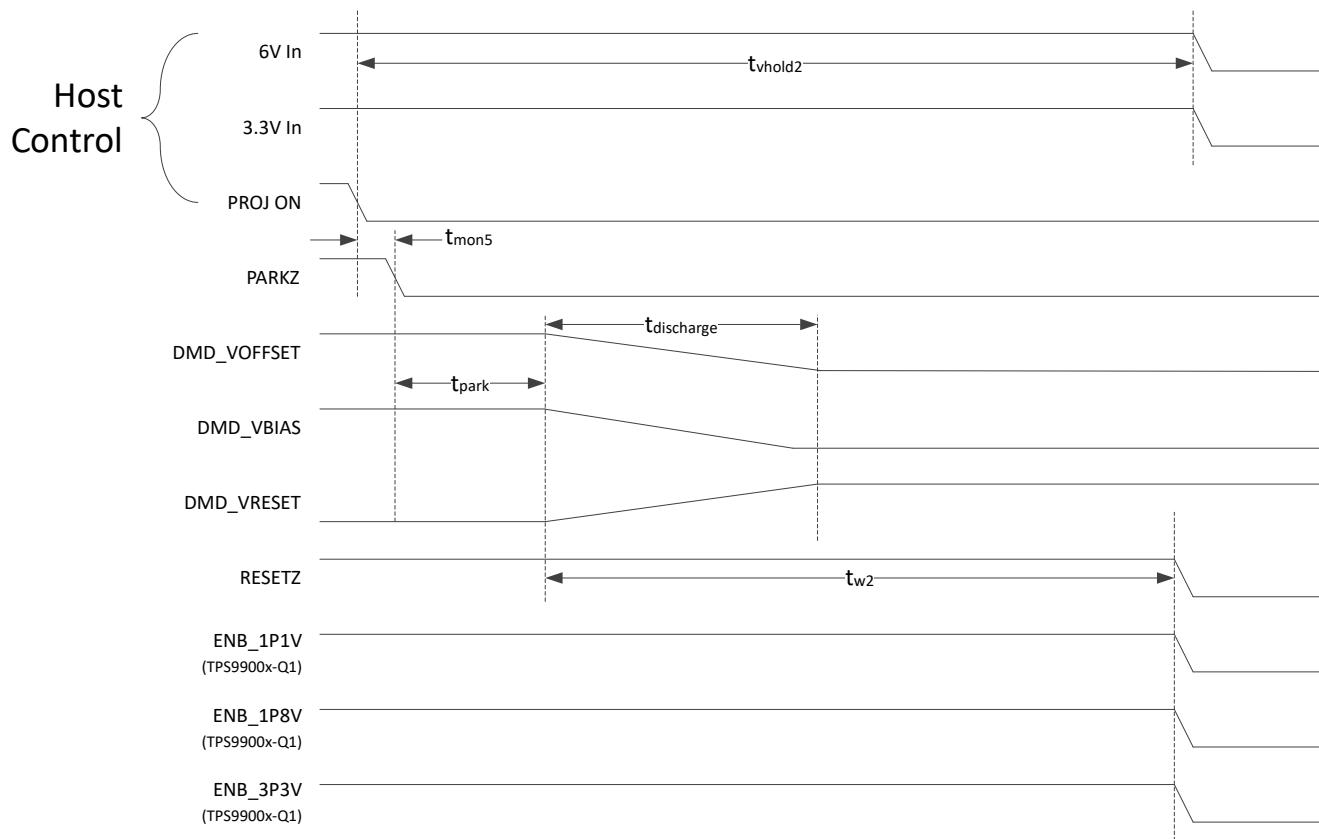

## 5.14 パワーダウンのタイミング要件

(1) を参照してください。

|                                     |                                                                                                                   | 最小値                                                                                                      | 標準値  | 最大値 | 単位 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|----|

| $t_{vhold1}$                        | VMAIN 最小スレッショルドに達した後のホスト電圧ホールド時間。<br>$t_{mon4} (\text{max}) + t_{park} (\text{max}) + t_{w2} (\text{max})$        | 6V および 3.3V の電力損失の VMAIN スレッショルド <sup>(2) (3)</sup>                                                      | 900  |     | μs |

| $t_{vhold2}$                        | PROJ_ON デアサー <sup>t</sup> 後のホスト電圧ホールド時間。<br>$t_{mon5} (\text{max}) + t_{park} (\text{max}) + t_{w2} (\text{max})$ | 6V および 3.3V の電力損失の VMAIN スレッショルド。 <sup>(2) (3)</sup>                                                     | 1.78 |     | ms |

| $t_{mon4}$                          | VMAIN 監視時間                                                                                                        | PARKZ 立ち下がりエッジまでの最小電圧トリップスレッショルド                                                                         | 52   | 120 | μs |

| $t_{mon5}$                          | PROJ_ON デアサー <sup>t</sup> 応答時間                                                                                    | PROJ_ON の立ち下がりエッジから PARKZ の立ち下がりエッジまで                                                                    |      | 1   | ms |

| $t_{park}$                          | DMD パーク時間                                                                                                         | DMD_VOFFSET 放電を開始するための PARKZ 立ち下がりエッジ                                                                    |      | 280 | μs |

| $t_{discharg}_e$ <sup>(4) (5)</sup> | DMD 電圧レールの放電時間                                                                                                    | VOFFSET $C_{out} = 1\mu\text{F}$<br>VRESET $C_{out} = 1\mu\text{F}$<br>VBIAS $C_{out} = 0.47\mu\text{F}$ | 260  |     | μs |

| $t_{w2}$ <sup>(5)</sup>             | DMD 電圧は、RESETZ デアサー <sup>t</sup> まで無効化されます                                                                        | DMD 電圧レール放電の開始から RESETZ 立ち下がりエッジまで                                                                       | 500  |     | μs |

(1) パワーダウン シーケンスを開始するには、次の 2 つの方法があります。

- VMAIN 電圧は最小スレッショルドを下回っています。これは、主電源がシステムから除去されたときに、TPS99002S-Q1 がパワーダウン シーケンスを開始することが予想される場合に一般的です。パワーダウン シーケンスの開始後、6V および 3.3V の入力レールは、指定された時間にわたって動作範囲内に維持する必要があることに注意してください。

- PROJ\_ON low。これにより、ホストコントローラは TPS99002S-Q1 へのデジタル入力を介してパワーダウンを開始できます。

- (2) 6V 入力レールには、DRV<sub>R</sub>\_PWR、VIN\_DRST、VIN\_LDOT\_5V、VIN\_LDOA\_3P3V、VIN\_LDOT3P3V が含まれます。

- (3) 3.3V 入力レールには、VDD\_IO、DVDD、AVDD が含まれます。

- (4) DMD は、VBIAS と VOFFSET の最大絶対電圧差を規定しています。この最大電圧差を下回るように、VBIAS は VOFFSET よりも早く放電する必要があります。これは、VBIAS に対してより小さい  $C_{out}$  容量を使用することで実現され、VOFFSET よりも早く放電することができます。

- (5) 情報提供のみを目的としています。

図 5-2. パワーダウンタイミング — VMAIN トリガ

図 5-3. パワーダウン タイミング — PROJ\_ON トリガ

### 5.15 タイミング要件 — シーケンサ クロック

|                |                           | 最小値 | 公称値   | 最大値 | 単位   |

|----------------|---------------------------|-----|-------|-----|------|

| $f_{SEQ\_CLK}$ | SEQ_CLK 周波数               |     | 30.00 |     | MHz  |

| $t_{JPP}$      | SEQ_CLK ジッタ (ピーク ツー ピーク)  | -3% | 3%    |     |      |

| $f_{SS}$       | SEQ_CLK で許容される拡散スペクトラム    | -2% | 0%    |     |      |

| $f_{SSMOD}$    | SEQ_CLK スペクトラム拡散変調周波数     | 25  | 100   |     | kHz  |

| $f_{SSSTEPS}$  | SEQ_CLK スペクトラム拡散変調周波数ステップ |     | 50    |     | ステップ |

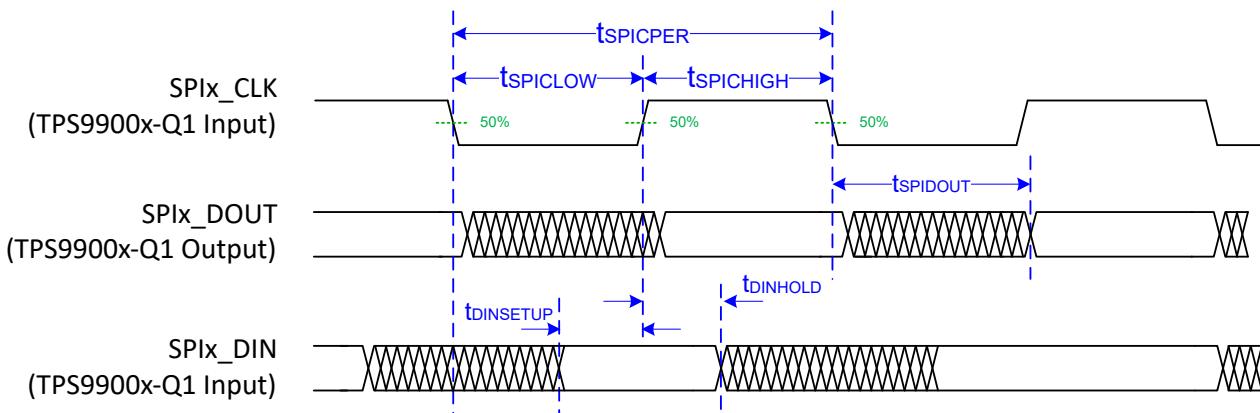

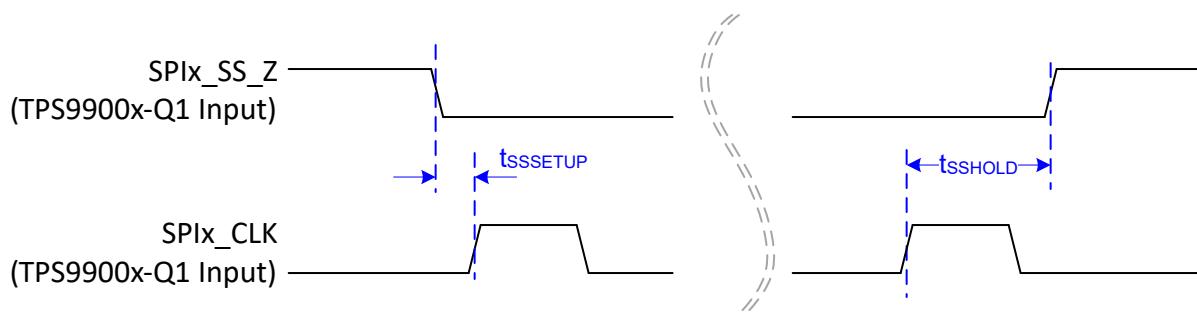

## 5.16 タイミング要件 – ホストおよび診断ポート SPI インターフェイス

|                |                                  | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|----------------------------------|-----|-----|-----|----|

| $t_{SPICPER}$  | SPI CLK サイクル時間                   | 31  | 33  |     | ns |

| $t_{SPICHIGH}$ | SPI CLK High 時間                  | 10  |     |     | ns |

| $t_{SPICLOW}$  | SPI CLK Low 時間                   | 10  |     |     | ns |

| $t_{SPIDOUT}$  | CLK の立ち下がりから DOUT まで             | 0   |     | 15  | ns |

| $t_{SSSETUP}$  | SPI SS_Z から CLK 立ち上がりまでのセットアップ時間 | 5   |     |     | ns |

| $t_{SSHOLD}$   | SPI CLK 立ち上がりから SS_Z ホールド時間まで    | 5   |     |     | ns |

| $t_{DINSETUP}$ | SPI DIN から CLK 立ち上がりまでのセットアップ時間  | 5   |     |     | ns |

| $t_{DINHOLD}$  | SPI CLK の立ち上がりから DIN ホールド時間まで    | 5   |     |     | ns |

図 5-4. DLPC23xS-Q1 診断インターフェイスのタイミング

図 5-5. チップセレクトのセットアップとホールドのタイミング

## 5.17 タイミング要件 - ADC インターフェイス

|                     |                                 | 最小値 | 公称値 | 最大値 | 単位 |

|---------------------|---------------------------------|-----|-----|-----|----|

| $t_{ADC DIN SETUP}$ | ADC DIN から CLK 立ち上がりまでのセットアップ時間 | 5   |     |     | ns |

| $t_{ADC DIN HOLD}$  | ADC CLK の立ち上がりから DIN ホールド時間まで   | 5   |     |     | ns |

| $t_{ADC DOUT}$      | CLK 立ち上がりから DOUT まで             | 0   |     | 15  | ns |

## 5.18 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ     | テスト条件     | 最小値 | 標準値  | 最大値 | 単位       |

|-----------|-----------|-----|------|-----|----------|

| 内部クロック    |           |     |      |     |          |

| $f_{osc}$ | 内部発振器の周波数 |     | 1.76 | 2   | 2.24 MHz |

## 6 詳細説明

### 6.1 概要

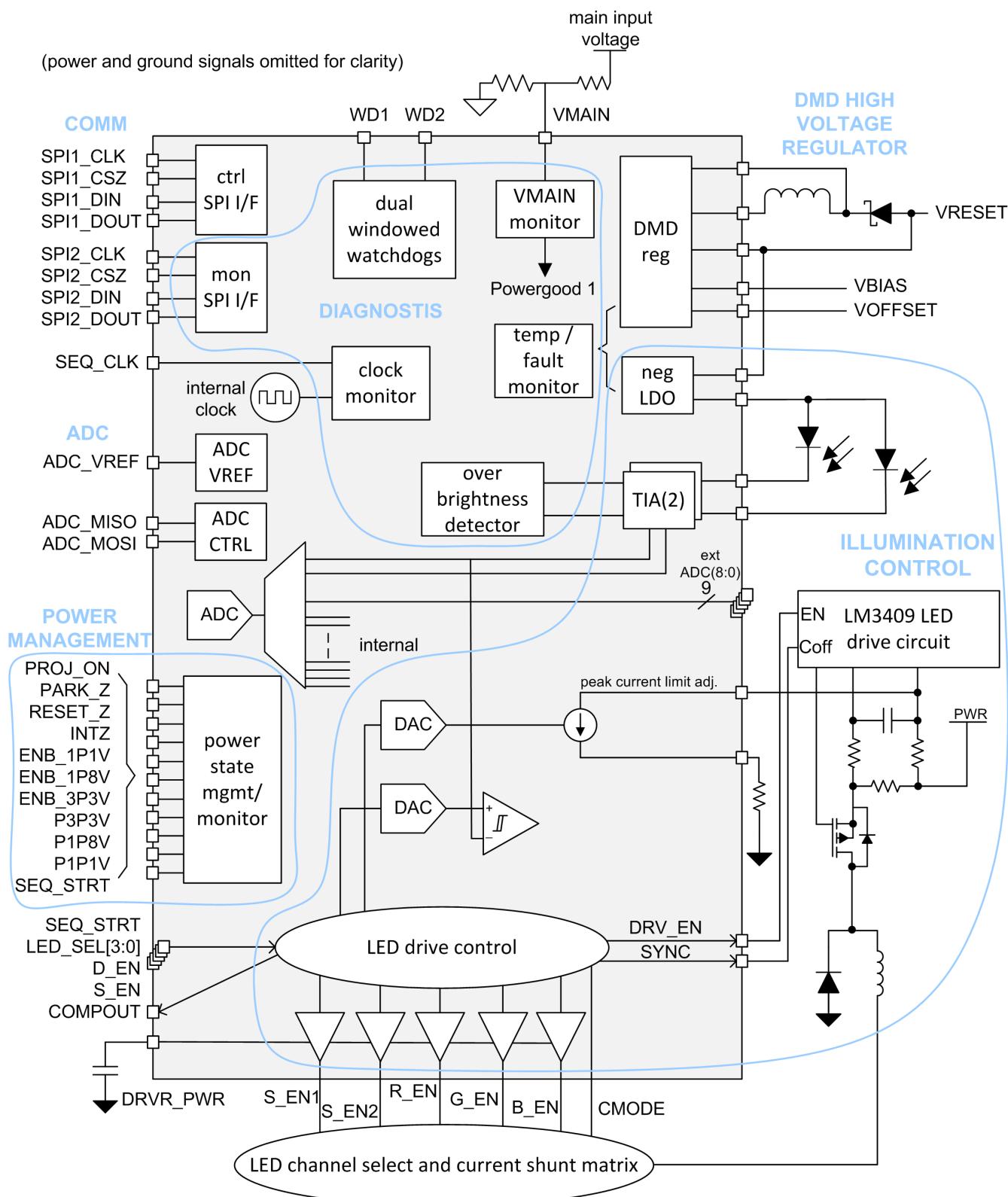

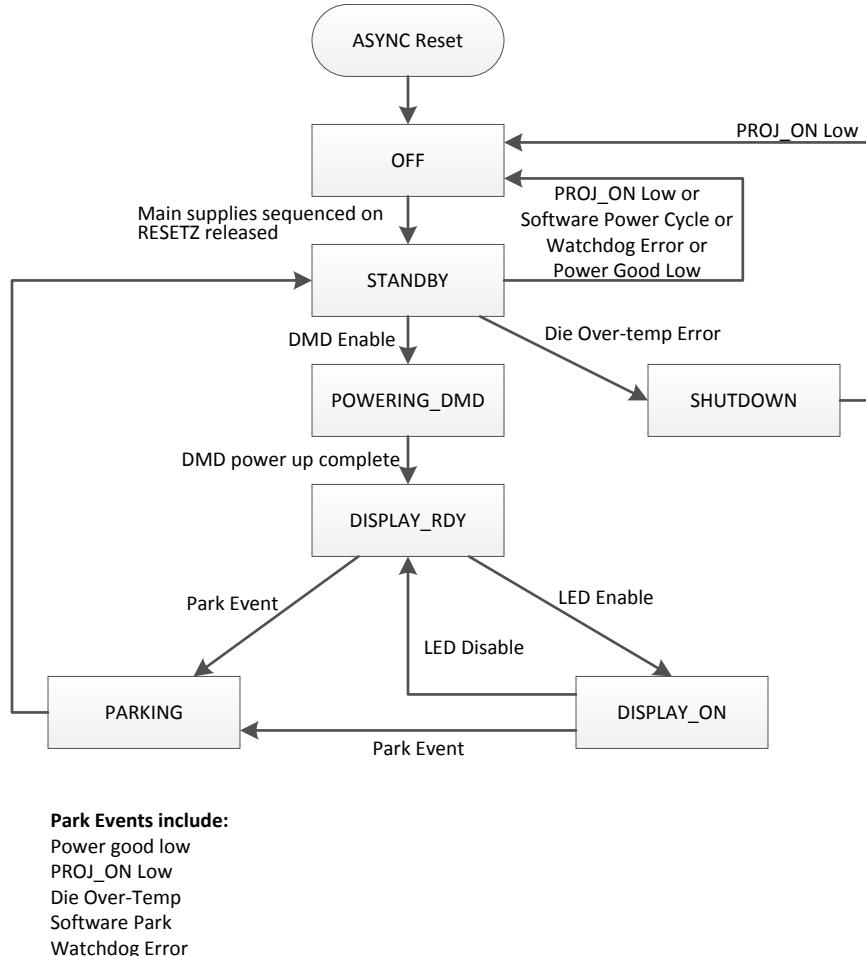

TPS99002S-Q1 は、DLP394xS-Q1 チップセットの不可欠なコンポーネントであり、このチップセットには、DLPC23xS-Q1 DMD ディスプレイコントローラも含まれています。このリファレンス デザインには、車載固有の超ワイド調光要件をサポートするための機能があります。TPS99002S-Q1 は、高電圧、高精度の 3 レールレギュレータも備えており、コスト効率の優れた方法で DMD ミラー制御電圧 (18V, 10V, -14 V) を生成します。包括的なシステム電力モニタと DMD ミラー パーキング ソリューションを搭載しており、システムの堅牢性を向上させ、コストを削減できます。さらに、TPS99002S-Q1 は、構成可能な ADC、TIA、ウォッチドッグなど多くのシステム監視および診断機能を備えています。

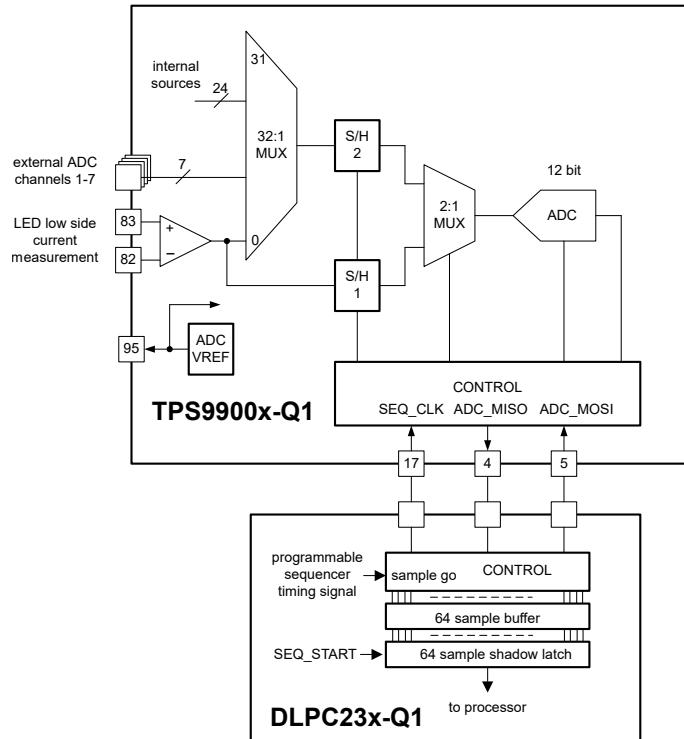

内蔵の 12 ビット ADC は、照明システム制御をサポートし、システムの動作状態に関する有用な情報を提供します。汎用 (LED 温度測定など) のために、複数の外部 ADC チャネルが含まれています。外部 ADC チャネルの 1 つには差動入力アンプが含まれ、LED 電流測定専用になっています。DLPC23xS-Q1 および TPS99002S-Q1 ADC 制御ブロックは、ビデオフレームごとに最大 63 個のサンプルをサポートし、サンプルを DMD シーケンスのタイムラインに高精度にハードウェア整列しています。この情報は、DLPC23xS-Q1 のカラー制御ソフトウェアで利用できます。このソフトウェアは、温度や LED の経年劣化による影響を緩和して、輝度と白色ポイントのターゲットを維持するために使用できます。

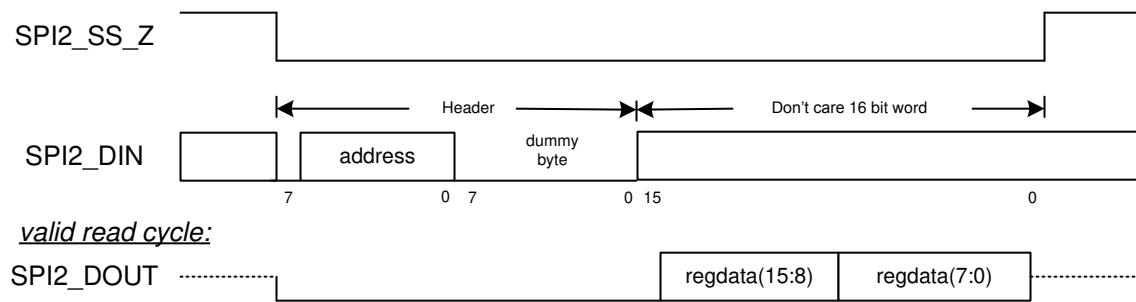

2 つの SPI バスが含まれています。1 つ目のバスはコマンドと制御を目的としており、2 つ目のバスはオプションの冗長システム状態監視用の読み取り専用バスです。SPI ポートは、バイトレベルのパリティチェックをサポートしています。

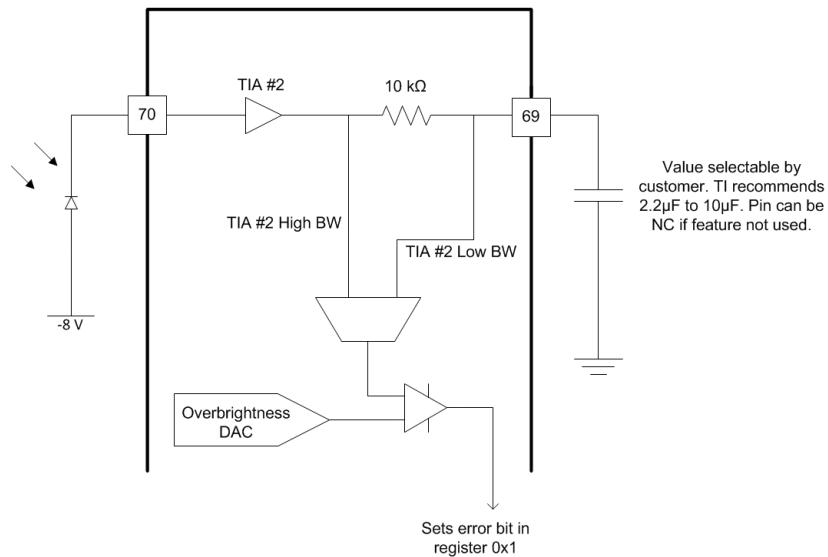

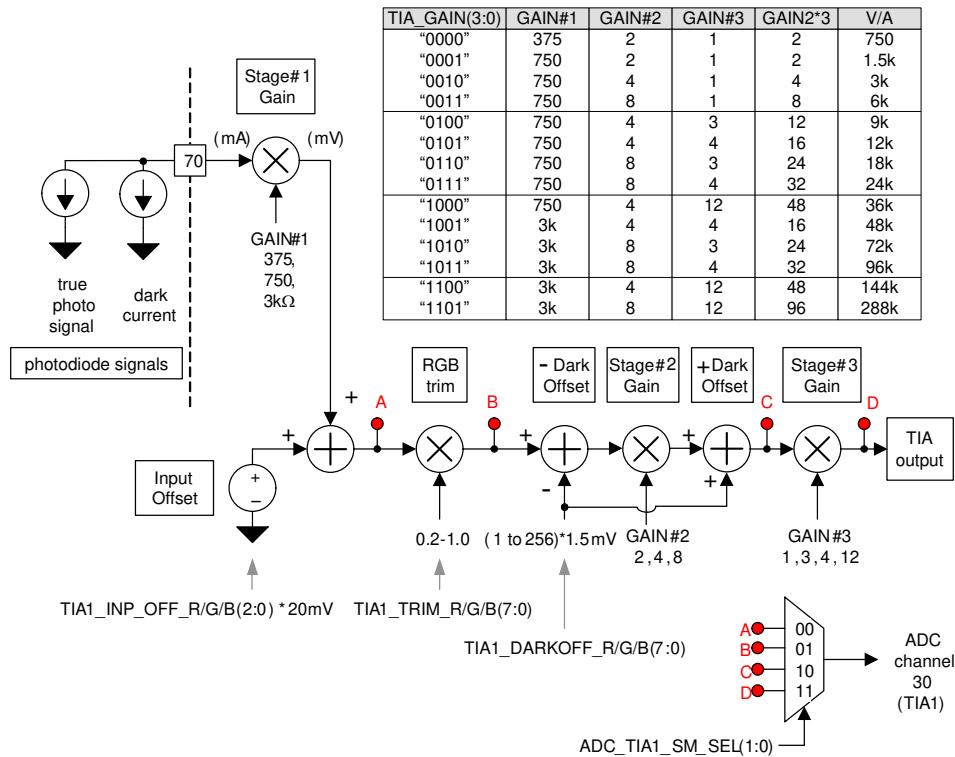

2 個のトランシスインピーダンス アンプを搭載しています。1 つ目の TIA は照明制御専用で、2 つ目の TIA は冗長性、周囲光検出、出力光検証など、一般的な使用に合わせて再構成可能です。過輝度検出器が内蔵されており、LED 輝度をハードウェアで冗長チェックできます。

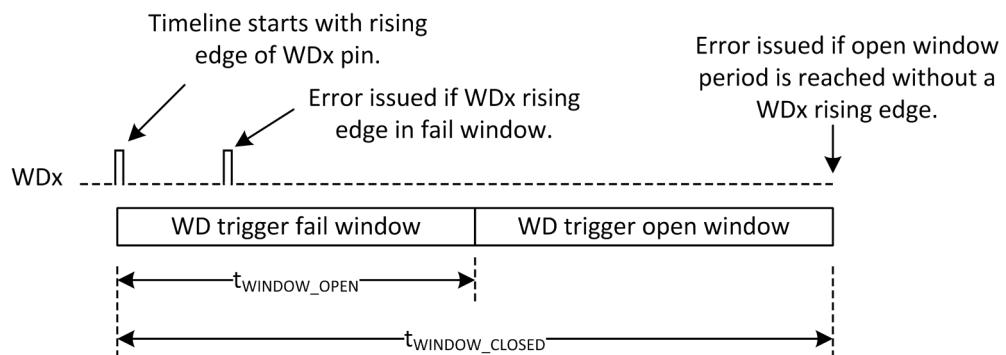

2 つのウンドウ付きウォッチドッグ回路が搭載されており、DLPC23xS-Q1 マイクロプロセッサの動作を検証し、DMD シーケンサの動作を監視します。TPS99002S-Q1 には、オンダイ温度スレッシュホールド監視機能と、内部発振器に対する (SEQ\_CLK の) 外部クロック比を検証するためのモニタ回路も含まれています。

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 照明制御

照明制御機能には、DLP サブシステム用に光を生成するのに必要なすべてのブロックが含まれています。このシステムは、広い調光範囲にわたって色と輝度の精密な制御が必要な車載アプリケーションをサポートするように設計されています。完全な調光ソリューションは、DLPC23xS-Q1 および TPS99002S-Q1 の両方に含まれるハードウェア機能と、DLPC23xS-Q1 に保存されている DMD シーケンス データで構成されています。これらの素子は連携して動作し、5000:1 全体で使用可能なシステム調光範囲を実現し、各色で最大 8 ビットをサポートします。

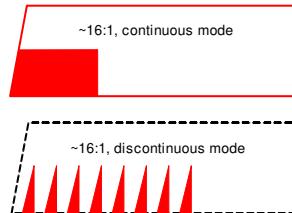

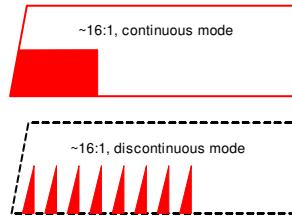

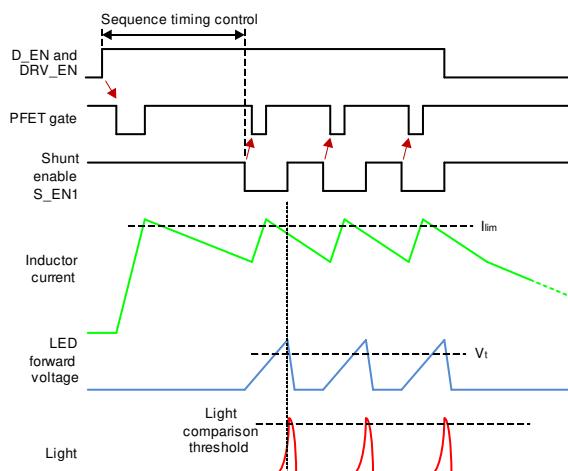

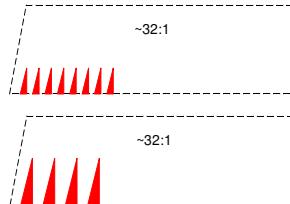

照明制御機能は 2 つの異なるモードで動作し、全調光範囲をカバーします。これらのモードは、連続モード (CM) と不連続モード (DM) です。

図 6-1. 連続モード動作と不連続モード動作の比較

#### 連続モードの機能:

- 高輝度から中輝度レベル

- 各色に対して作成される矩形波光パルス

- パルス振幅とパルス幅を変化させて輝度レベルを調整

#### 不連続モードの機能:

- 中輝度から低輝度レベル

- 各色に対して作成される一連の小さな三角波光パルス

- パルス数、パルス高さ、および LED 電流を変化させて輝度レベルを調整

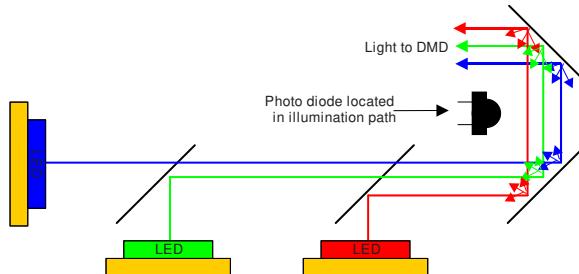

照明制御ループは、リアルタイムのフォト フィードバック制御ループを介して LED に供給される電流の安定化を行います。DLP サブシステムの照明パスに、3 つの赤 / 緑 / 青 LED すべてから光を受信する位置に広帯域フォトダイオードを配置します。連続モード動作の場合、フォト フィードバックを使用してリアルタイムのヒステリシス制御ループを作成し、各 LED の輝度レベルを設定します。不連続モードでは、フォト フィードバックによって光パルスごとにピーク輝度スレッショルドが設定されます。

照明制御をサポートするため、TPS99002S-Q1 には、多数の高性能アナログおよびミックスドシグナル ブロックが内蔵されています。これらのブロックには以下が含まれます。

- フォトダイオード電流を電圧に変換し、リアルタイムの LED 輝度を表す、高性能でダイナミックレンジが非常に広いトランジスタインピーダンス アンプ (TIA)

- フォト フィードバック制御に適した高速コンパレータ

- フォト フィードバックの参照用 12 ビット DAC

- ピーク電流制限の調整用 10 ビット DAC

- 外部のハイサイド PFET 降圧コントローラ (LM3409) の同期用 Sync および駆動イネーブル出力

- LED を選択するための外部 FET ドライバと制御ロジック (FET は外部ですが、ドライバは内部です)

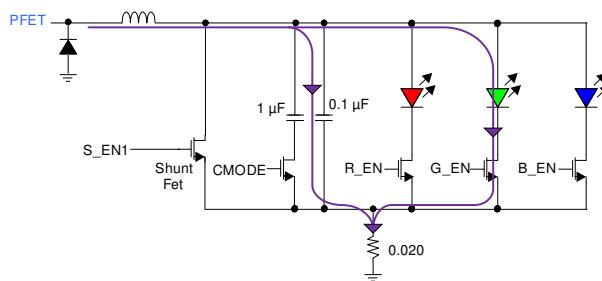

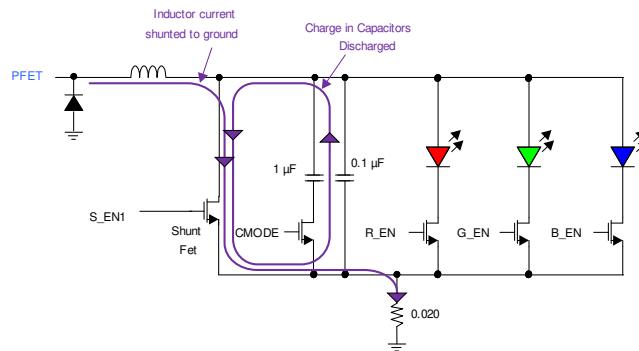

- 2 つの電流シャント(バイパス) パス FET 制御を使用して、色間で光が無効になっている間にインダクタ電流をプリリギュレーションするほか、不連続モードの動作を可能にします

- 専用の 2 線式ケルビング入力チャネルを搭載した多目的 12 ビット ADC ブロックで、LED 電流測定に特化しています

- DLPC23xS-Q1 と組み合わせて動作するハードウェア サンプル タイマ ブロックは、LED の電流および電圧、温度などの構成可能なハードウェア タイミング サンプルを提供します

- ほとんどのパラメータに対して RGB 固有の多重化設定を行うことで、カラーごとに独立した制御パラメータの最適化が可能になります

### 6.3.1.1 照明システムの高ダイナミック レンジ調光の概要

このセクションでは、一般化された概要を示し、TPS99002S-Q1 内の機能がフル チップセットとソフトウェアの高ダイナミック調光方式をどのようにサポートするかを理解するためのフレームワークを提供するた概念について説明します。

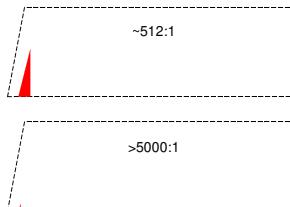

ヘッドアップ ディスプレイ (HUD) システムは通常、広い輝度範囲について、ターゲットの白色ポイント要件を満たす必要があります。広い輝度範囲をカバーするには、連続モードと不連続モードの組み合わせが必要です。連続モードでは、RGB シーケンスのデューティ サイクル、時間減衰、振幅減衰のさまざまな組み合わせを活用します。不連続モードでは、光の離散パルス数、フォトフィードバック (TIA) ゲイン、ピーク電流制限設定、光振幅 DAC 設定のさまざまな組み合わせを利用します。これらの調整は、粗調整と微調整に分類できます。

粗調整には次のものがあります。

- **照明ビン** : DMD デューティ サイクル、LED デューティ サイクル、パルス数 (DM のみ) を選択します。

- **LED 電流制限** : CM では、各 LED が動作可能な最大電流を指定します。LED の損傷を防止するために使用されます。DM では、パルスの生成に使用されるプリチャージ インダクタ電流を規定します。パルスの形状 / オーバーシュートを決定します。

- **TIA ゲイン** : TIA 設計は、幅広いフォトダイオード電流レベルに対応するため、合計 14 個の幅広いゲイン設定をサポートしています。ゲイン設定が高いと、与えられたフィードバック電圧に対する LED 出力が低くなります。

微調整には以下が含まれます。

- **フォトフィードバック DAC 設定** : この機能は、高速 12 ビット DAC を使用して実装されています。LED ターゲットの振幅を設定します。

### 6.3.1.2 照明制御ループ

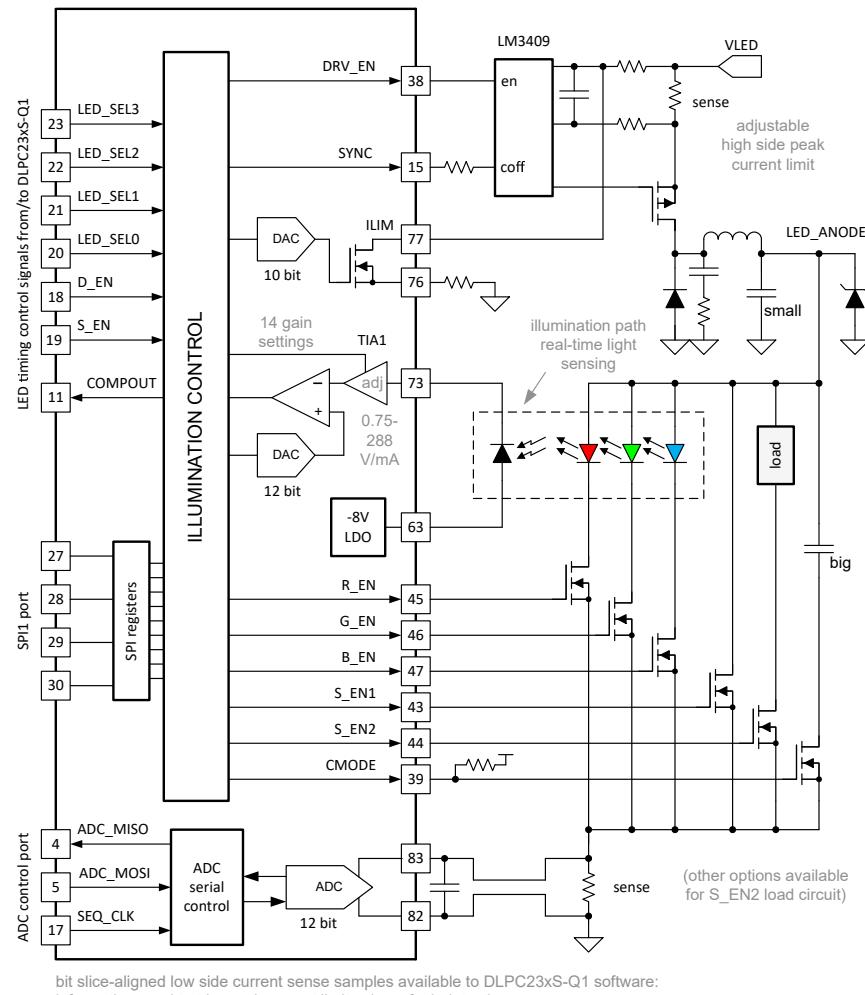

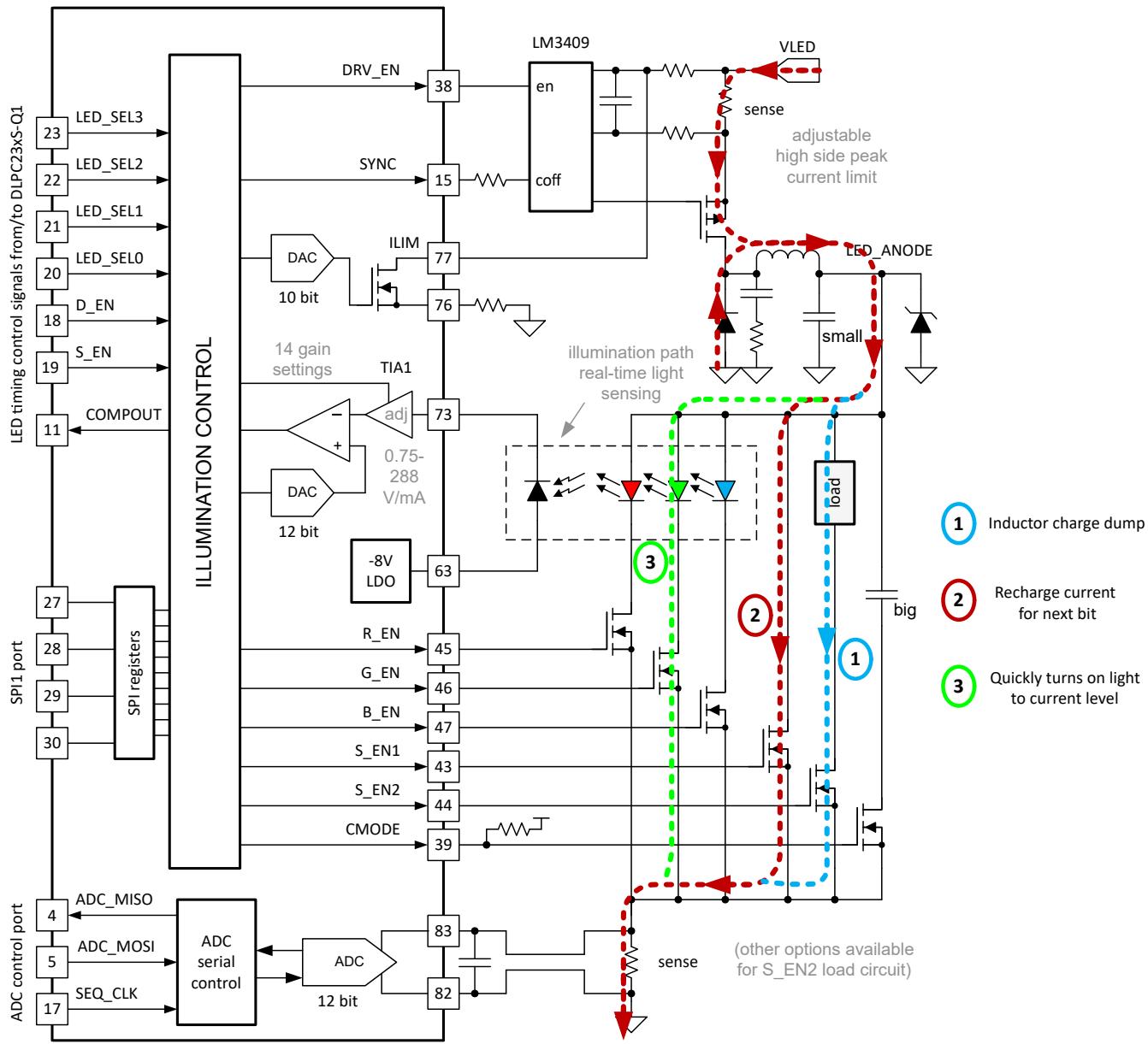

「照明制御ループ」に、照明制御ループを示します。このループは以下の機能で構成されています。

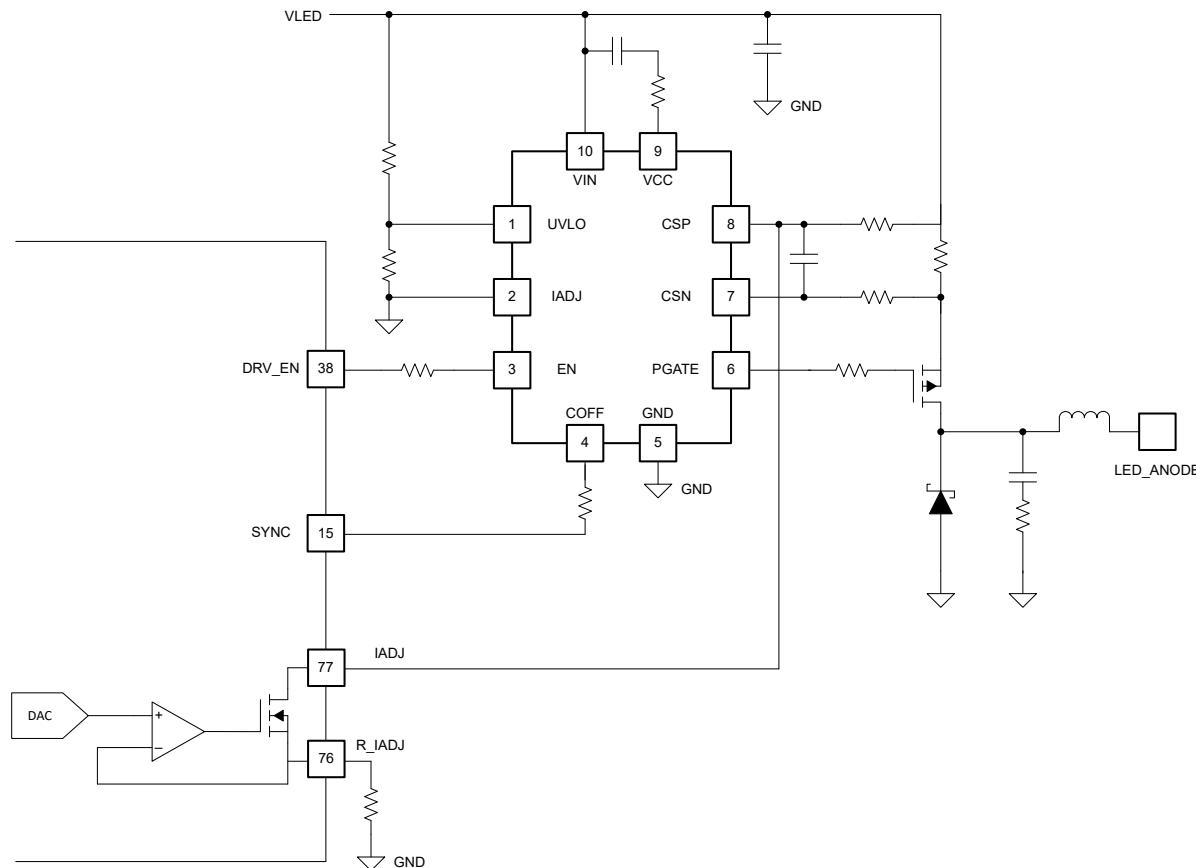

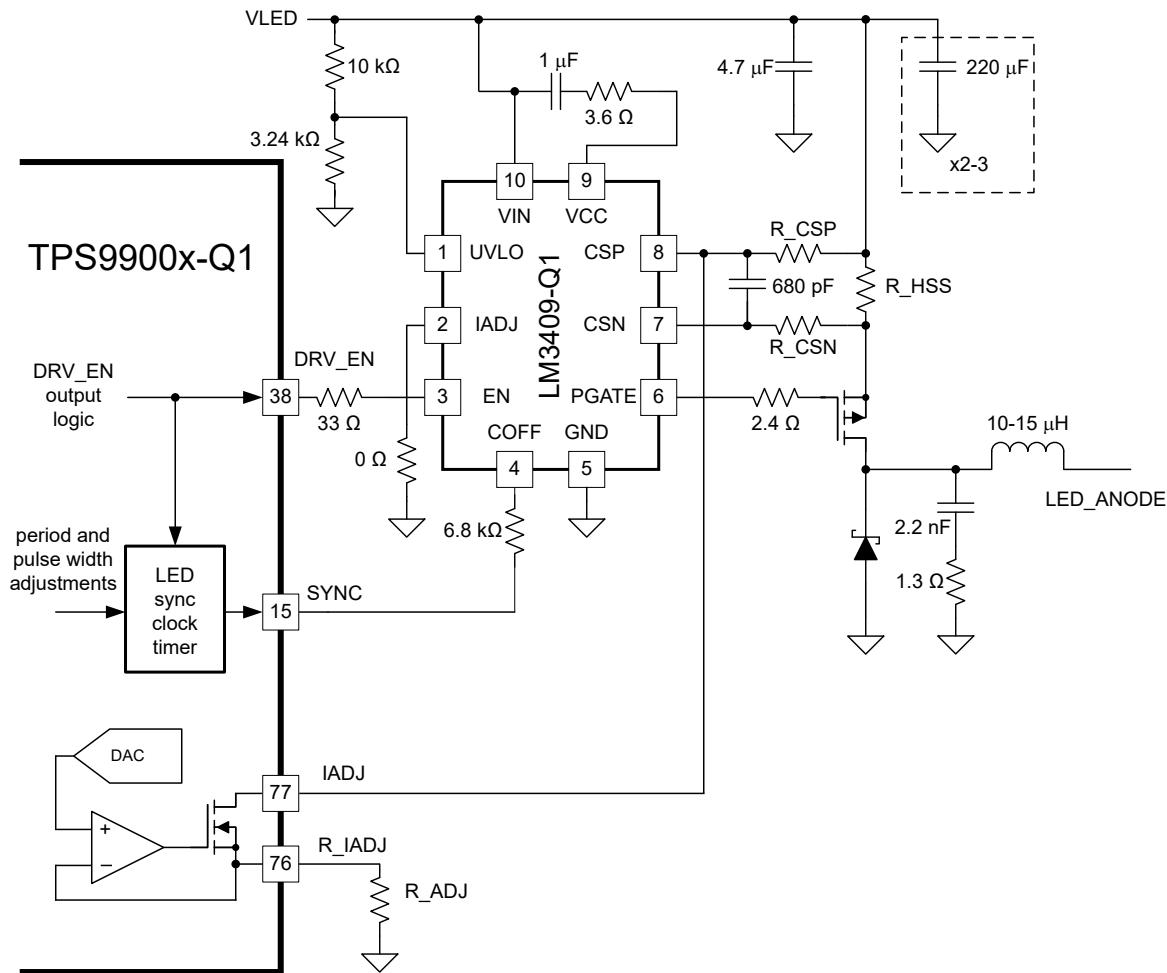

- 外部降圧コントローラ (LM3409) と関連するディスクリート部品は、メイン LED 駆動の PFET を制御し、ハイサイド センス回路を使用してピーク電流を制御および制限します。この回路は、LED ハイサイド接続 (LED\_ANODE) を駆動する制御された電流ソースを生成します。

- TPS99002S-Q1 には、10 ビットのピーク電流制限 (ILIM) 調整 DAC が内蔵されています。

- 外部 LED 駆動降圧用の同期ロジック。外部デバイスの制御されたオフ時間ピンを無効にする SYNC ピンと、外部デバイスの有効化を制御する DRV\_EN。

- フォトフィードバック信号をプログラマブル リファレンスと比較するために使用される高速コンパレータ。

- 12 ビットのフォトフィードバック比較 DAC。連続動作モードと不連続動作モードの LED 光パルス ピーク スレッショルドの基準を設定します。

- リアルタイムのフォトフィードバックには、高速で低ノイズ、広いダイナミックレンジのトランシスインピーダンス アンプ (TIA1) を使用します。0.75V ~ 288V/mA のゲインをサポートし、14 の個別ゲインステップと、1.0 ~ 0.2 ゲインの RGB 固有の追加トリムを備えています。(2 個の TIA を含む。TIA1 は照明制御機能専用です)。

- 負の LDO によりコスト効率の優れたフォトダイオード逆バイアスを供給。

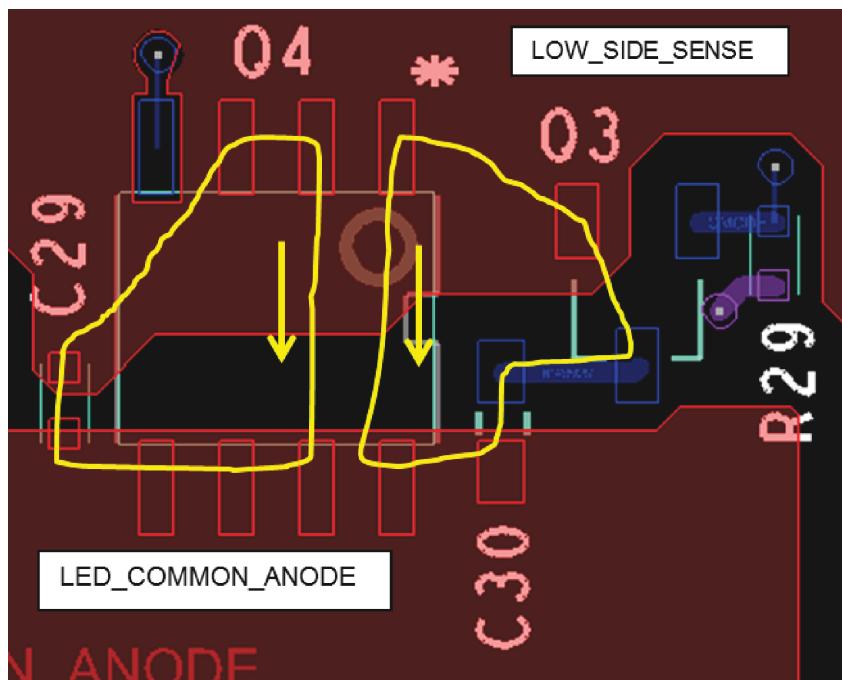

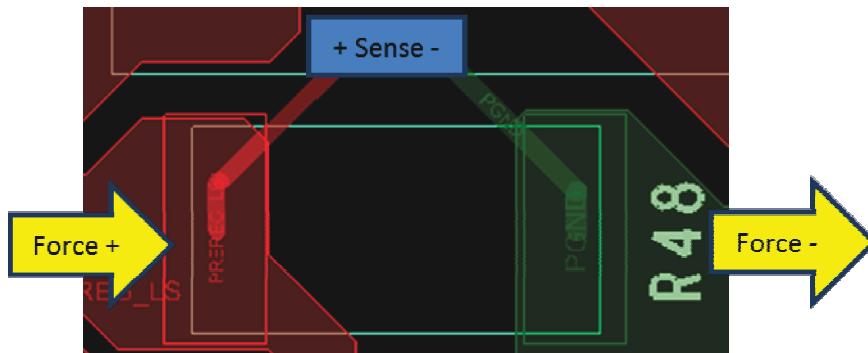

- ローサイド電流測定専用の差動入力を採用した 12 ビット ADC。

- RGB チャネル選択用の外部 FET ゲートドライバと、2 つのシャントバス選択用。シャントバスは、LED の周囲に導通パスを提供します。これらのバスは、LED が発光していないときのインダクタ電流を制御するために使用されます。制御ロジックとファームウェアは、光パルス間のギャップ中に LED を有効にする前に、インダクタの適切な電流レベルを確立します。

図 6-2. 照明制御ループ

### 6.3.1.3 連続モード動作の

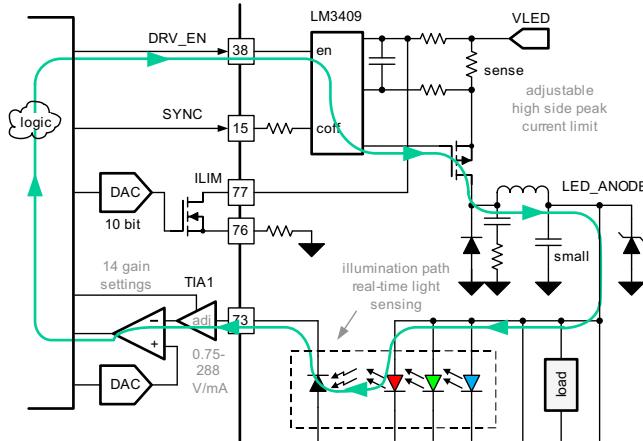

連続モード (連続光出力モード) で動作している場合、ヒステリシス制御方式が利用されます。リアルタイム アナログ光振幅測定は、フォトフィードバック ループでターゲットの光レベルを維持するために使用されます。図 6-3 は、連続モードのドライバのフォトフィードバック制御ループ パスを示しています。

図 6-3. 連続モード フォトフィードバック パス

TPS99002S-Q1 のオンチップ アナログ コンパレータは、目標の LED 光振幅を、フォトダイオード TIA 回路から取得した実際の LED 光出力電圧と比較するために使用されます。光出力がスレッショルド (12 ビット フォトフィードバック DAC 出力により設定) を下回ると、コンパレータは High レベルを出し、DRV\_EN は High になります。これによって、電源レールから LED 駆動インダクタへの接続が、LED 駆動 PFET を介して行われます。この接続により、インダクタを流れる電流が増加します。この電流は、FET が有効のとき LED を流れます。光値がスレッショルドを超えると、DRV\_EN が Low になり、PFET がオフになり、ごくわずかな遅延で電源レールへの接続が切断されます。光レベルがスレッショルドを下回ると、DRV\_EN が再び High になり、PFET が再びオンになり、LED により多くの電力が供給されます。LED 回路が有効である限り、このプロセスが繰り返されます。

ヒステリシス制御により、LED 電流にリップルが生じます。このリップルの振幅と周波数は、インダクタのインダクタンス、入力電圧、コンパレータのヒステリシス、ループ レイテンシの関数です。このヒステリシス制御アプローチの利点は、制御ループの無条件安定性です。

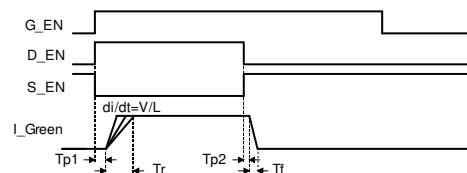

連続モード信号の例は、赤、緑、青のビット スライスの連続モード信号と光出力を示しています。LED\_SEL(3:0)、D\_EN、S\_EN1、S\_EN2 などの信号は、DLPC23xS-Q1 から送信されます。

図 6-4. 連続モードの信号の例

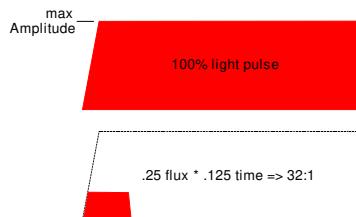

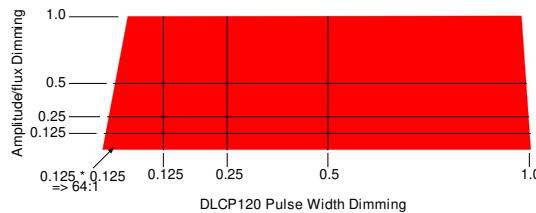

連続モードでは、振幅 / フラックス調光とパルス時間減衰の組み合わせによって調光が実現されます。振幅調光は、フォトフィードバック DAC 出力と TIA フィードバック ゲインを調整することで行われます。時間減衰は、シャント有効化 (DLPC23xS-Q1 からの S\_EN) の長さと駆動有効化 (DLPC23xS-Q1 からの D\_EN) の長さを調整することで行われます (図 6-5 を参照)。100% のビットと、32:1 調光を実現するための 時間と振幅を減衰させるビットを使用した例を図 6-5 に示します。図 6-6 は、時間調光と振幅調光の組み合わせを使用して、いくつの異なる調光レベルを実現できるかを示す、より一般的な例です。

図 6-5. 連続モード調光の図 1

図 6-6. 連続モード調光の図 2

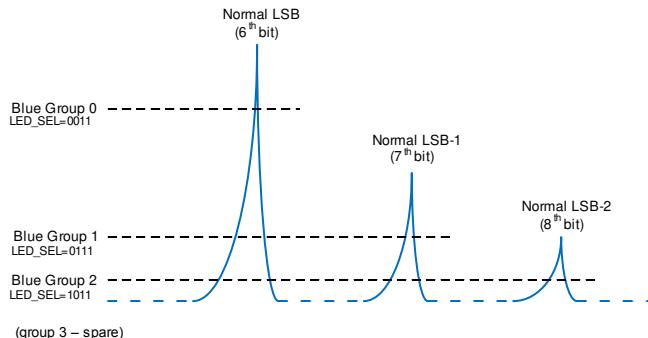

#### 6.3.1.3.1 連続モードでの出力キャパシタンス

連続モードでは、TPS99002S-Q1 からの CMODE 信号が Low に設定されるため、大容量の (ほぼ  $1\mu\text{F}$ ) コンデンサを制御する FET がオフになり、LED およびシャント FET パスと並列に小さな ( $0.1\mu\text{F}$  以下) 高周波デカップリング容量だけが残されます (照明制御ループを参照)。連続モードでより小さい容量を使用すると、コンデンサと LED の両端の電圧が急速充電され、インダクタ内の電流が LED 発光スレッショルドに達する前に目的の電流レベルをオーバーシュートしないようになります。これにより、ビットスライスの開始時に光パルスがオーバーシュートするのを防止できます。(不連続パルスモードでは、このドキュメントで後述するように、おおよそ  $1\mu\text{F}$  の容量が必要です。不連続モードでは CMODE ピンを High に設定することで、LED と並列の大容量キャパシタンスを実現できます)。

#### 6.3.1.3.2 連続モード ドライバの歪みとプランギング電流

図 6-7. 第 1 世代 / レガシー システム パルス歪みの例

第 1 世代 / レガシー システム パルス歪みの例に示すように、立ち上がり (Tr) および立ち下がり (Tf) エッジ レートが等しくないことや、ターンオン (Tp1) とターンオフ (Tp2) の伝搬遅延が等しくないことにより、実際の LED 電流パルスが歪んでいます。電流パルスの立ち上がりエッジのターンオン時間は、主にインダクタ両端の電圧と目的の電流、およびインダクタ電流の初期状態の関数です。この歪みにより、パルスの時間減衰と振幅減衰の両方が、制御設定の非線形機能になります。これにより、画像アーティファクトが発生する可能性があります。

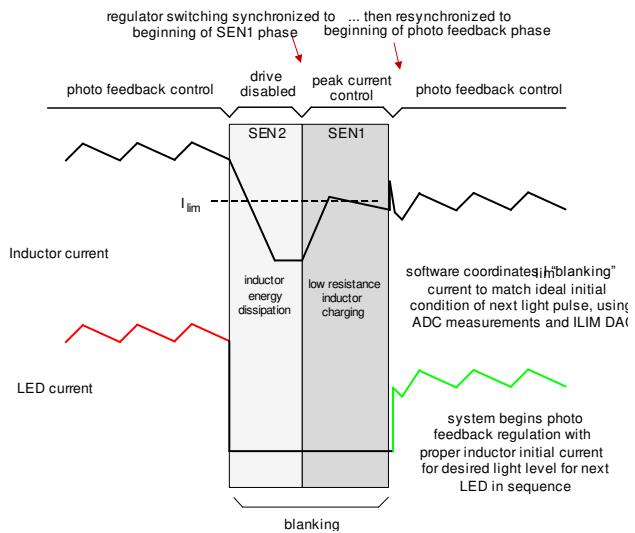

プランギング時間とは、2 つの LED セグメント間で光が output されない期間です。この時間のインダクタ電流をプランギング電流と呼びます。この電流は制御され、最適化された Tr および Tf が提供されます。

ブランкиング電流制御は、光のオーバーシュートやアンダーシュートを防止することで、画像のアーティファクトを低減します。

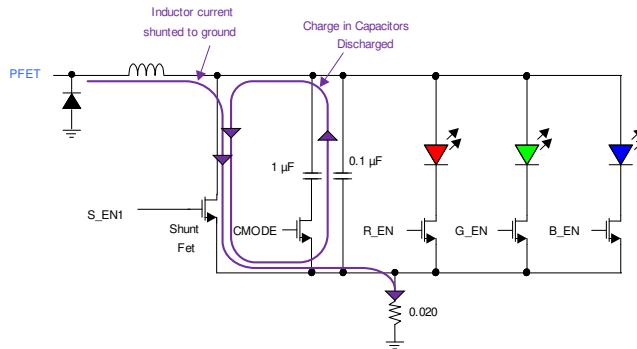

ブランкиング電流の期間は 2 つの部分に分割されます。1 つ目は、散逸シャントを使用して、前の光パルスからのインダクタ内の残留電流が低減される散逸フェーズです。2 番目のフェーズは、非散逸 (低直列抵抗) のシャントフェーズであり、LED に電流が印加される前に、次の光パルスに対して適切な電流までインダクタを充電します。このプロセスを次の図に示します。

図 6-8. ブランкиング電流放電 / 充電サイクル

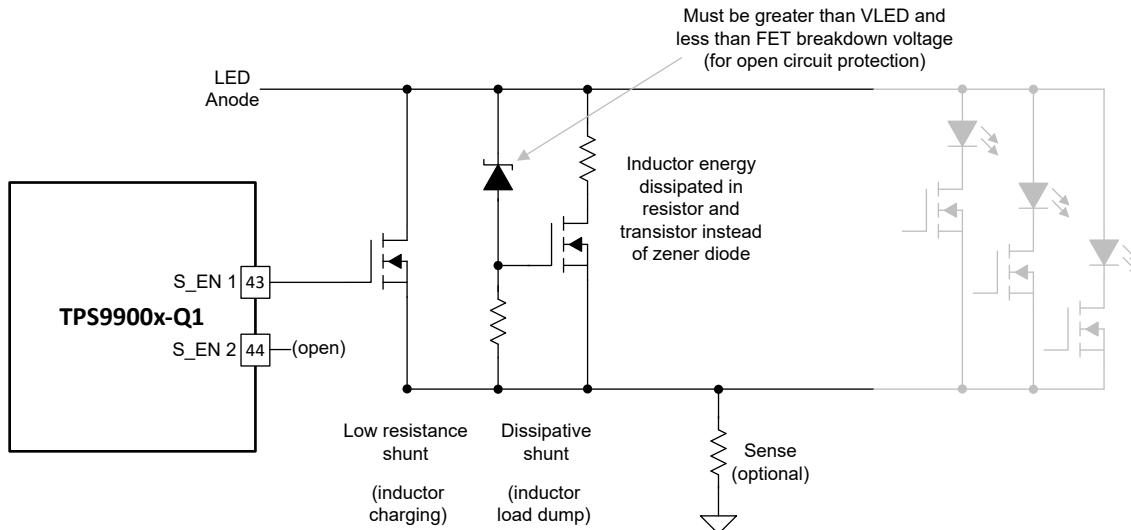

ブランкиング時間の最初のフェーズ中に、LED が切離されている間、シャント 2 (S\_EN2) が有効になります。これにより、LED の代わりに実効抵抗が大きい負荷が配置されます。インダクタの残留エネルギーがこの負荷に消費され、インダクタ電流は急速に減少します。この機能がない場合、1 つのパルスで大電流が発生すると、次のパルスで過剰な輝度が発生する可能性があります。

ブランкиング時間の第 2 フェーズ中、LED ドライバは短絡シャント (S\_EN1) を介してインダクタを充電します。ピーク電流制限に達するまで充電を続けます。ピーク電流制限は、ILIM DAC で設定されます。ピーク電流制限の設定は、DLPC23xS-Q1 ソフトウェアによって調整され、フォトフィードバック動作中の予想動作電流に一致します。(予想される電流レベルは、前のフレーム中の LED 電流の ADC 測定値から決定されます。) ブランкиング電流期間が終了すると、S\_EN1 の短絡シャントがオフになり、次の LED が有効になり、DRV\_EN 信号がトグルされ、システムはフォトフィードバック (ヒステリシス動作) に戻ります。インダクタは理想的な電流にプリチャージされ、システム容量が低くなるため、光出力の立ち上がりエッジは非常に高速で、安定したヒステリシス制御への移行はほぼ即座に行われます。その結果、矩形パルスが多くなります。次の図に、電流パスの図を示します。

図 6-10. 散逸シャント /LED 開路保護の組み合わせ 1

この場合、LED アノード電圧がツェナー電圧を超えたとき、低消費電力のツェナー ダイオードを使用して FET をオンにします。S\_EN2 イネーブルは、この構成では使用されません。代わりに、S\_EN2 ブランкиング時間の間、回路を意図的に開路状態にします。その後、保護回路がオンになり、インダクタからのエネルギーが消費されます (S\_EN1 シャントが有効になり LED アノード電圧が低下するまで)。この場合、エネルギーは負荷抵抗と FET を組み合わせて消費されます。LED アノード電圧が RGB 選択 FET ブレークダウン電圧を超えないように、ツェナー ダイオードおよび抵抗デバイダの選択には注意が必要です。(オプションで、負荷抵抗全体を削除できます。その後、消費電力は FET でのみ発生し、LED アノード電圧は、あらゆる条件下でツェナー電圧に近い値に維持されます)。回路の意図しないトリガを防止するため、ツェナー電圧は、入力 VLED 電源レールのワーストケース電圧より高くする必要があります。また、ツェナー電圧は、LED 選択 FET の Vds ブレークダウン電圧を下回っている必要があります。

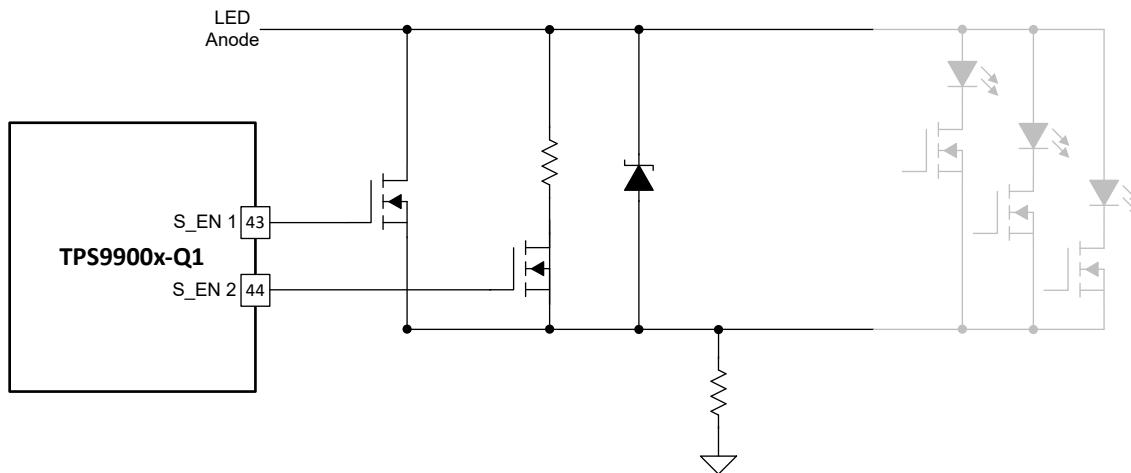

同じ機能を持つ代替回路を以下に示します。

図 6-11. 散逸シャント /LED 開路保護の組み合わせ 2

この回路では、インダクタ電流が S\_EN2 で制御される抵抗性経路を通って放電されます。

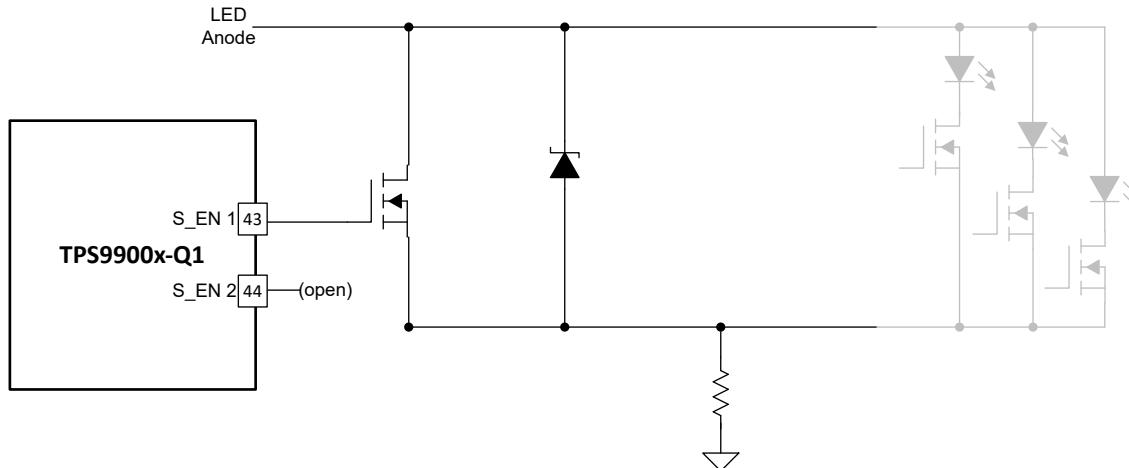

図 6-12. 散逸シャント /LED 開路保護の組み合わせ 3

この回路では、インダクタ電流がパワー ツエナーダイオードを通して放電されます。

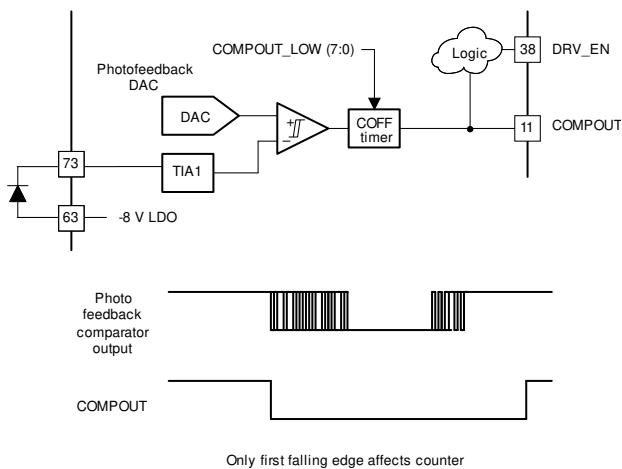

#### 6.3.1.3.4 連続モード コンスタント オフ タイム

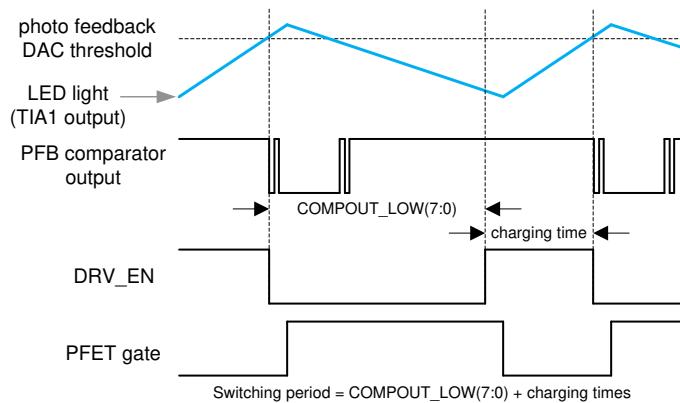

連続モード動作には、コンスタント オフ タイム機能 (図 6-13 の COMPOUT\_LOW 信号を参照) が含まれています。連続モード動作中、目標の光レベルが達成されると、DRV\_EN 信号の制御により PFET ゲート駆動がオフになり、インダクタ電流が減少し始めると光レベルは低下し始めます。一般的なヒステリシス コントローラでは、ターン オン スレッショルドに達すると、PFET がオンになり、光 / インダクタ電流が再度増加します。スイッチング周波数は、ターン オン スレッショルドとターン オフ スレッショルド、ループ遅延、ディスクリート部品値の差に依存します (インダクタのインダクタンスと電圧が最も支配的な要因)。

TPS99002S-Q1 では、動作周波数をレギュレートするため、制御が変更されます。コンスタント オフ タイマは、TPS99002S-Q1 制御ループに含まれます。フォトフィードバック コンパレータのスレッショルドに達すると、カウンタが開始されます。カウンタの長さは調整可能です。このカウンタがアクティブの間、フォトフィードバック コンパレータの出力は無視され、PFET 駆動 (TPS99002S-Q1 からの DRV\_EN 出力による) は無効になります。コンスタント オフ タイム周期カウンタがタイムアウトすると、フォトフィードバック コンパレータの出力が再度使用されて、LED 電流駆動を制御します。最小オフ時間により、ヒステリシス制御ループのスイッチング周波数の上限が規定され、回路の固有周波数から分離されます。この機能は、回路が AM 無線周波数帯域で動作しないようにするのに役立ち、また、より低いインダクタンス値のインダクタを使用できます (システムコストの削減と電力効率の向上につながります)。

図 6-13. COMPOUT\_LOW コンスタント オフ タイム

### 6.3.1.3.5 連続モード電流制限

連続モードでは、電流制限機能により、LED 電流仕様内で要求された光出力が実現できなかった場合の LED の損傷が防止されます。これは、高温が原因で発生する可能性があります。または LED が経年劣化し、同じ輝度を実現するためにより多くの電流が必要な場合です。実際にはこれが起らないように、十分な熱マージンと LED の寿命マージンを確保するようにシステムを設計する必要があります。

この制御方式では、LM3409 デバイスの内蔵電流制限機能と、TPS99002S-Q1 に搭載されている 10 ビット DAC ベースの調整機能を利用しています。これは、LED の電流の代替制限として機能します。電流制限に達しているか、フォトフィードバック制限に達しているかのどちらか低い方の場合、インダクタ駆動は無効になります。このピーク電流制限は LED ごとに設定でき、点灯アクティブ期間中のみ使用されます。(ランキング期間中、これは同じ構造を使用してランキング電流を制御しますが、ILIM DAC には異なる値がロードされます)。

電流調整メカニズムの回路図を、図 6-14 に示します。

図 6-14. IADJ ピーク電流制限の回路図

設計上、LM3409 は、IADJ ピンが Low に保持され、システムがピーク電流制限モードで動作しているときに、CSP ピンと CSN ピンの間にゼロ電圧差を生成するように設計されています。CSP ピンの電圧が CSN ピンの電圧より高い場合、PGATE ドライバは High に保持されます (PFET オフ)。

ILIM DAC がゼロ以外の電圧に設定されると、TPS99002S-Q1 デバイスの IADJ ラインに電流が発生し、CSP ピンの電圧がプルダウンされます。LM3409 デバイスが有効化され、COFF ピンの状態によって PFET 駆動がオフに保持されていない場合、電流は、センス抵抗にかかる電圧によって CSN ピンが CSP ピンの電圧以上となるまで上昇し、この時点で PFET がオフになります。

TPS99002S-Q1 の IADJ ピンの配線は、PFET ドレイン ノードなどのノイズの多いスイッチング ノードから十分に絶縁されるように注意する必要があります。

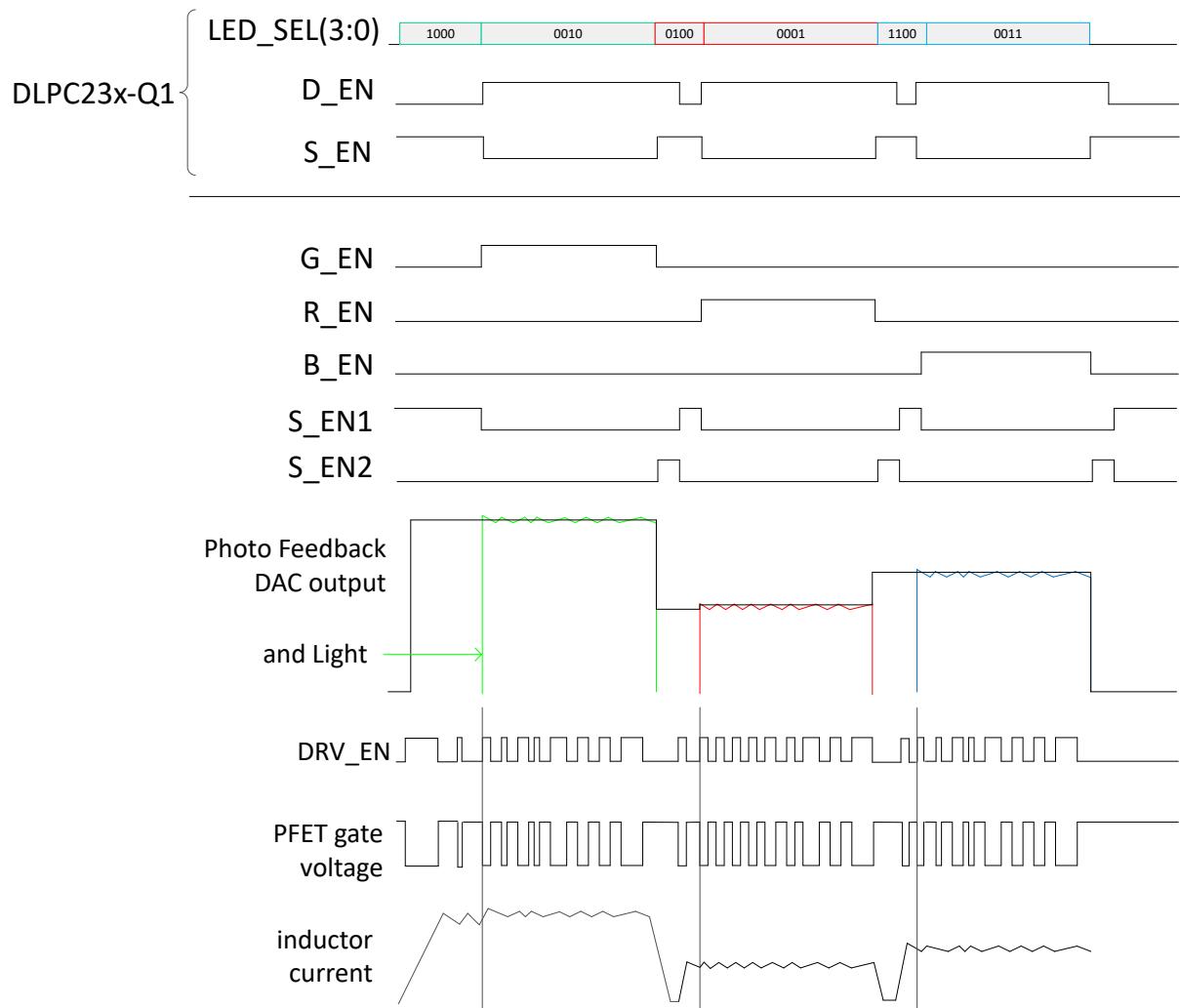

#### 6.3.1.4 不連続モードの動作

不連続モードを使用して、より低い調光レベルを実現します。図 6-15 に示すように、ビットスライス中の一定の光ブロックを、制御された振幅の一連の光パルスに置き換えます。パルス数は、DLPC23xS-Q1 ソフトウェアによって制御されます。

図 6-15. 等価の輝度での連続動作と不連続動作の比較

図 6-15 は、輝度が等価な 8 つのパルスを生成する不連続モード信号を示す図の例です。

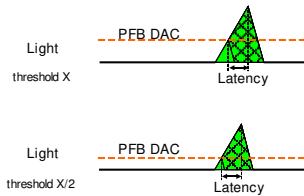

不連続モードでは、コントローラはパルス間に固定的なオフ時間で離散的な光パルスを生成します。これらのパルスが生成する光の量を正確に制御して、低い調光レベルに達することができます。一様な光パルスを生成するには、次の 2 つの制御ループを使用します。

- LED を流れる前にインダクタに目的の電流レベルを作り出すためのピーク電流制限ループ。

- 目的の光パルスレベルに達したときに各パルスを終了するフォトフィードバックループ。

初期インダクタ電流とピーク光スレッショルドは、色ごとに独立して調整可能です。図 6-16 と図 6-17 を参照してください。

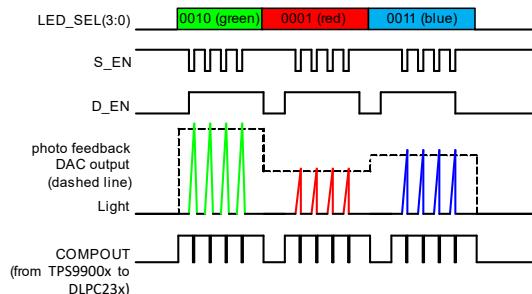

図 6-16. DLPC23xS-Q1 から TPS99002S-Q1 信号に対する不連続動作

図 6-17. 不連続モード動作インダクタ電流 / LED 電圧

不連続モードは、一連の三角波光パルスで構成されます。DLPC23xS-Q1 は、パルスの合計数を要求し、カウントする役割を果たします。ビット スライスは、低抵抗のシャント イネーブル (S\_EN1) がオンの状態から始まり、RGB カラーが選択されます。次に、DLPC23xS-Q1 が D\_EN をアサートします。これにより、TPS99002S-Q1 は LED 電流駆動 (DRV\_EN) をオンにし、(ILIM DAC でプログラムされた) ピーク電流制限に達するまで、システムはインダクタを低抵抗のシャントで充電します。その後、プログラム可能な時間が経過した後、DLPC23xS-Q1 が S\_EN を Low に駆動し、選択した LED にインダクタ電流が強制的に流れます。

TPS99002S-Q1 は、DLPC23xS-Q1 から S\_EN の立ち下がりエッジを検出し、DRV\_EN 信号のオン / オフ / オントグルを発行します。これにより、電流がインダクタを流れ、LED アノードの電圧が上昇します。LED の順方向電圧が達成されると、光が放射され始めます。フォトフィードバック ループ (TIA、フォトフィードバック コンパレータ、フォトフィードバック DAC) が目標の光スレッショルドを超えると、S\_EN1 信号が High に再度アサートされ、光パルスは終了します。

COMPOUT 信号が Low になると、DLPC23xS-Q1 にパルスが完了したことを示します。DLPC23xS-Q1 は直ちに S\_EN 出力を High に設定し (これにより TPS99002S-Q1 出力 S\_EN1 が High に設定されます)、その後、プログラム可能な時間長だけ待機します。その期間が経過した後、DLPC23xS-Q1 は、D\_EN を Low に駆動して次のビット スライスを待つか、S\_EN 出力を Low にして新しいパルスの要求を発行するかを決定します。S\_EN 出力を Low にすると、TPS99002S-Q1 は S\_EN1 を (LED を強制的に電流を流す) Low に設定し、DRV\_EN を切り替えることで、新しいピーク制限電流パルス サイクルを要求します。このプロセスは、特定のビット スライスに対して正しいパルス数が完了するまで繰り返されます。

非常に低い輝度での動作では、TPS99002S-Q1 SYNC (LM3409 COFF) タイマは無効になります。その結果、DRV\_EN は各光パルスの開始時にのみトグルされます。これにより、インダクタ電流と LED 電流が同期されます。この同期により、LED パルスの高さはあるビデオ フレームから次のビデオ フレームまでと非常に一貫性が保たれるため、ちらつきが防止されます。

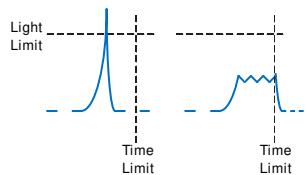

#### 6.3.1.4.1 不連続モードのパルス幅制限

TPS99002S-Q1 には、各不連続モード パルスの時間を制限する機能があります。カウントは、パルス イベント中に LED に印加される電流の時間長さを監視し、時間をプログラム可能な時間制限と比較します。ライト出力スレッショルドに達する前に時間制限が経過すると、不連続パルスは終了します。どちらの場合も (フォト レベルまたは時間制限の満了) パルスは、S\_EN1 低抵抗シャントを有効にすることで終了します。これにより、フォトフィードバックのスレッショルドに達しない場合の最大輝度が制限されます。不連続パルス幅制限に対して、独立した RGB 値がサポートされます。図 6-18 にこのプロセスを示します。

図 6-18. 不連続モードのパルス幅時間制限

#### 6.3.1.4.2 不連続動作時の COMPOUT\_LOW タイマ

不連続動作では、連続モード ケースにスイッチング周波数を設定するのと同じ COMPOUT\_LOW パラメータが、不連続動作のノイズ フィルタとして機能します。この回路は、パルスの終了に等しい光スレッショルド コンパレータの最初の立ち下がりエッジでトリガれます。その後、コンパレータ出力のそれ以降のすべての立ち上がり / 立ち下がりエッジは、事前に定義された時間だけ無視され、不連続動作に対するグリッチ抑制フィルタ機能を提供し、パルス間のタイミングを制御します。

図 6-19. COMPOUT\_LOW タイマを不連続動作でのグリッチ フィルタとして使用

#### 6.3.1.4.3 不連続動作範囲内の調光

不連続モードで動作している場合、ディスプレイの輝度を低減するために、次の 2 つの調光方式が同時に使用されます。

1. フォトフィードバック DAC 設定を使用する振幅調光。

2. ビットスライスあたりのパルス数の制御 (DLPC23xS-Q1 へのコマンドを使用し、特定のルックアップ テーブル データを選択)。

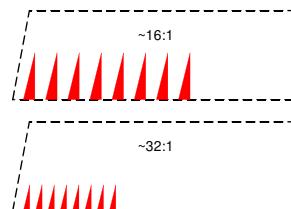

図 6-20 は、LSB あたり 8 パルス (最小ビットスライス) である最も明るい LUT データ テーブルの例です。LED パルスの高さを変調して、2:1 調光比を実現しながら、LSB ごとの 8 つのパルスを維持します。より低い調光レベルにシームレスに遷移できるように、図 6-21 に示すように、LSB ごとに 4 パルスとより大きな LED 振幅を加えた値に変更します。図 6-21 の両方の場合に生成される総光はほぼ等しくなります。システム キャリブレーションを使用して、この  $\frac{1}{2}$  の LED 振幅 フォトフィードバック DAC 設定を決定します。

図 6-20. シーケンス内の 2:1 調光

図 6-21. 不連続動作のパルス カウント変更

滑らかな調光(輝度が低下)シーケンスが継続するため、上記のプロセスは最終的に LSB あたり 1 つのパルスを使用します。図 6-22 に示すように、振幅調光は、表示輝度を絶対最小レベルまで調光するために使用されます。

図 6-22. LSB シーケンスごとに 1 つのパルスによる不連続調光

図 6-22 に示すように、LSB ごとに単一のパルスを選択すると、残りの調光はすべて、パルス高さスレッショルド低減のみを使用して発生する必要があります。

#### 6.3.1.4.4 複数のパルス高さによりビット深度を拡大

TPS99002S-Q1 を使用すると、特定のシーケンス内で最大 4 セットのフォトフィードバックスレッショルド設定がサポートされます。これは、より小さなサブ LSB ビット(通常の LSB より小さいビット)を生成する不連続動作時に便利です。

LED\_SEL(3:0) ラインは、グループ情報と色選択(およびブランкиング電流選択)を含むようにエンコードされています。

各グループを定義して、特定のカラー ビットに対するさまざまな動作を決定できます。たとえば、グループ 0 を LSB に、グループ 1 を LSB-1 の作成に使用できます。

表 6-1. LED の選択表

| LED_SEL(3:0) | 名称         | アクション                                                                                                         |

|--------------|------------|---------------------------------------------------------------------------------------------------------------|

| "0000"       | OFF        | ドライバ無効化モード S_EN1 強制 High RGB が Low に選択されます                                                                    |

| "0100"       | R BLANKING | LED_SEL(1:0) - "00" = ブランкиング                                                                                 |

| "1000"       | G BLANKING | LED_SEL(3:2):<br>"01" = 赤<br>"10" = 緑<br>"11" = 青                                                             |

| "1100"       | B BLANKING |                                                                                                               |

| "0001"       | GRP0 RED   |                                                                                                               |

| "0010"       | GRP0 GREEN |                                                                                                               |

| "0011"       | GRP0 BLUE  |                                                                                                               |

| "0101"       | GRP1 RED   | ドライバインエーブルモード:<br>LED_SEL(3:2) - グループを定義:<br>'00' - グループ 0<br>'01' - グループ 1<br>'10' - グループ 2<br>'11' - グループ 3 |

| "0110"       | GRP1 GREEN | LED_SEL(1:0):<br>"01" - 赤<br>"10" - 緑<br>"11" - 青                                                             |

| "0111"       | GRP1 BLUE  |                                                                                                               |

| "1001"       | GRP2 RED   |                                                                                                               |

| "1010"       | GRP2 GREEN |                                                                                                               |

| "1011"       | GRP2 BLUE  |                                                                                                               |

| "1101"       | GRP3 RED   |                                                                                                               |

| "1110"       | GRP3 GREEN |                                                                                                               |

| "1111"       | GRP3 BLUE  |                                                                                                               |

グループ 1 ~ 3 の RGB 選択を使用すると、図 6-23 に示すように、シーケンス内の分数 LSB を作成できます。

図 6-23. 不連続動作における拡張 LSB ピット深度

この機能と、絶対サイズの光パルスを小型化する機能と組み合わせることで、従来のシステムと同様に、実用的なビット深度制限を、TPS99002S-Q1/DLPC23xS-Q1 第 2 世代システムではカラーあたり標準的な 6 ビットから 7 ビットまたは 8 ビットに拡張できます。

#### 6.3.1.4.5 TIA ゲイン調整

TIA1 のゲインを調整して、より広い調光範囲を実現できます。TIA ゲインを大きくすると、与えられたフォト フィードバック DAC レベルに対する光出力が減少します。ゲインが大きいほど輝度範囲は狭くなりますが、目的の範囲内で分解能が高くなります。

#### 6.3.1.4.6 不連続モードでの電流制限

電流制限によって、インダクタを流れる最大電流が決定されます。電流制限を高くすると、より高いパルスの高さを実現できます。電流制限が小さいほど、各パルスの立ち上がりエッジが遅くなり、パルスのオーバーシュートが低減されます。そのため、調光レベルが低いと、電流制限は減少します。

#### 6.3.1.4.7 不連続動作での CMODE 大容量コンデンサ モード

TPS99002S-Q1 は出力信号 CMODE を提供します。この信号は、不連続な動作におけるより大きなコンデンサのスイッチングを行う FET のゲートを駆動するために使用できます。高容量モードは、不連続動作中にのみ使用されます。(高容量は連続動作で問題を引き起こすため、そのモードでは容量を最小限に抑えることが推奨されます)。容量が大きいほど、パルス生成プロセス中に LED の順方向電圧が増加する速度が遅くなります。充電速度が遅いと、発光しない状態から完全な発光状態に遷移し、時間が長くなります。適切な容量を選択するには、良好なエッジレート制御と、パルスがスレッショルドに達するまでの合計時間との間のバランスを取る必要があります。このコンデンサの温度特性に注意する必要があります。温度範囲全体で静電容量の変動が小さいため、低温 / 高温条件で、より正確で再現性の高い結果が得られます。

利点:

- パルス安定性

- 低速のパルス エッジ レートにより、低い光出力スレッショルドをサポートしています

CMODE 大容量コンデンサを使用した充放電ループは以下のとおりです。

図 6-24. シャントが有効な場合の不連続モードの電流バス

図 6-25. シャントが無効な場合の不連続モードの電流バス

### 6.3.2 過剰輝度検出

TPS99002S-Q1 には、過輝度状態を検出するため 2 つの方法があります。最初の方法は、ADC 測定値とフォトフィードバックコンパレータの出力を組み合わせて使用し、フォトフィードバックループ内の破損を検出します。別の方は、2 次フォトダイオードを使用して、HUD 画像のオーバー輝度を検出する方法です。

#### 6.3.2.1 フォトフィードバックモニタ BIST

1 次側フォトダイオードを接続解除すると、LED 出力の安定化に使用される帰還ループが遮断されます。LED を無効にできるように、このフォトダイオードの接続解除を検出する必要があります。

DLPC23xS-Q1 ソフトウェアと TPS99002S-Q1 は、フォトダイオードが接続解除されていることを検出するための、フォトフィードバックモニタの内蔵セルフテスト (BIST) を実装しています。各ビデオフレームにおいて、DLPC23xS-Q1 ソフトウェアは、LED 電流と TIA 出力の ADC 測定と COMPOUT の立ち下がりエッジを使用して、フォトダイオードの接続解除を検出します。

連続モードにおいて、DLPC23xS-Q1 ソフトウェアは、すべての LED 電流が最大であるものの、TIA の測定値が最小の場合、フォトダイオードが接続解除されていると判断します。これは、LED が電流を流している一方、フォトダイオードが LED からの光出力に応答していないことを示しています。

不連続モードでは、COMPOUT エッジを使用してフォトダイオードの切断を検出します。COMPOUT の立ち下がりエッジは、LED パルスが目標スレッショルドに達したことを示します。これは、フォトダイオードが接続されている場合にのみ可能です。したがって、フォトダイオードが接続されているかどうかを確認するために、DLPC23xS-Q1 ソフトウェアによって COMPOUT エッジが検出されます。

#### 6.3.2.2 過剰輝度 BIST

過剰輝度 BIST では、TIA2 に接続された 2 次フォトダイオードを使用して、HUD の出力画像の過輝度状態を検出します。