# TPSI3100-Q1 車載対応、17V ゲートドライバ、統合型バイアス電源、デュアル絶縁型コンパレータ内蔵、絶縁型スイッチドライバ

## 1 特長

- 外部パワー スイッチ (MOSFET, IGBT, SiC FET, SCR) を駆動

- バイアス電源を内蔵し、絶縁型の二次電源は不要

- 1.5/2.5A ピークのソースおよびシンク電流の 17V ゲートドライバ

- 5 kV<sub>RMS</sub> 強化基本絶縁

- 外部補助回路に対して最大 25mW、5V の電力を供給

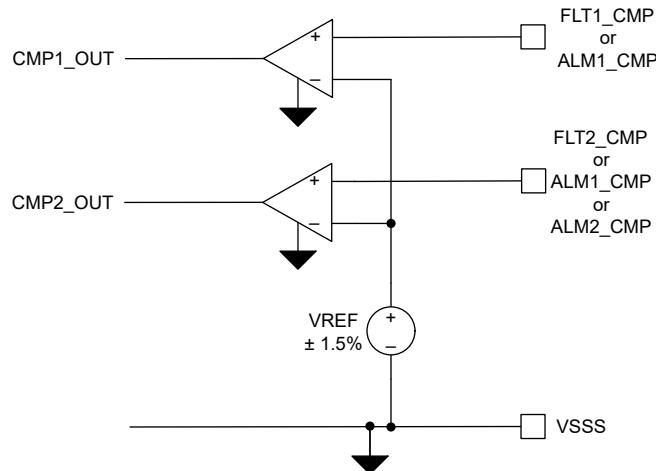

- ±1.5% の精度の電圧リファレンスを内蔵したデュアル絶縁型高速コンパレータ

- フォルトおよびアラーム インジケータ用のオープンドレイン出力

- 車載アプリケーション用に AEC Q-100 認定済み:

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 安全関連認証

- 予定:DIN EN IEC 60747-17 (VDE 0884-17) に準拠した強化絶縁耐圧: 7070V<sub>PK</sub>

- 予定:UL 1577 に準拠した絶縁耐圧: 5kV<sub>RMS</sub> (1 分間)

## 2 アプリケーション

- ソリッドステートリレー

- バッテリマネージメントシステム

- オンボードチャージャ

- ハイブリッド / 電気自動車およびパワートレインシステム

- ビルオートメーション

- ファクトリオートメーション / 制御

## 3 概要

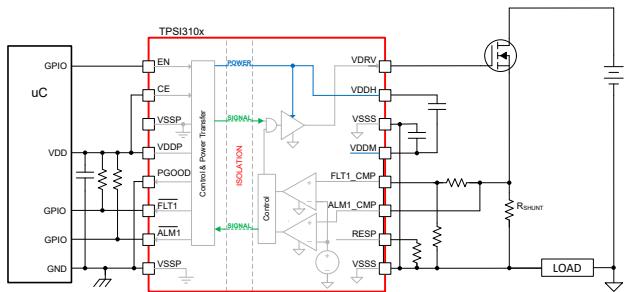

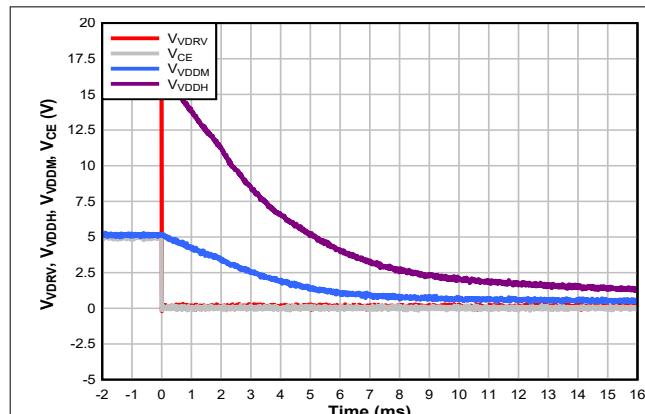

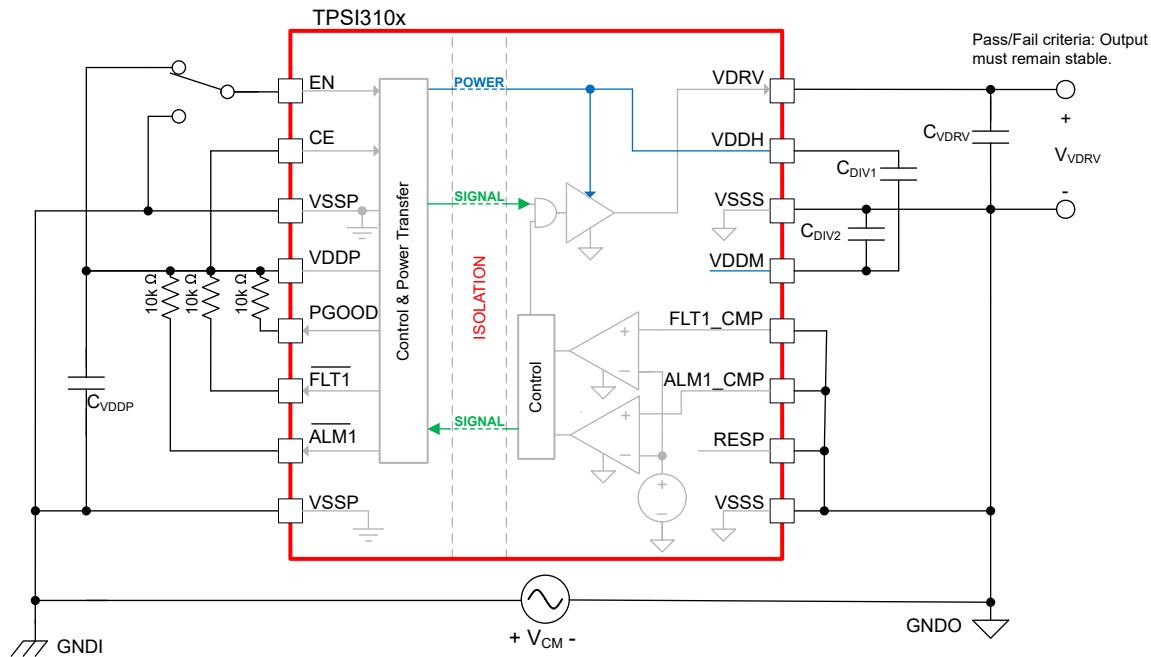

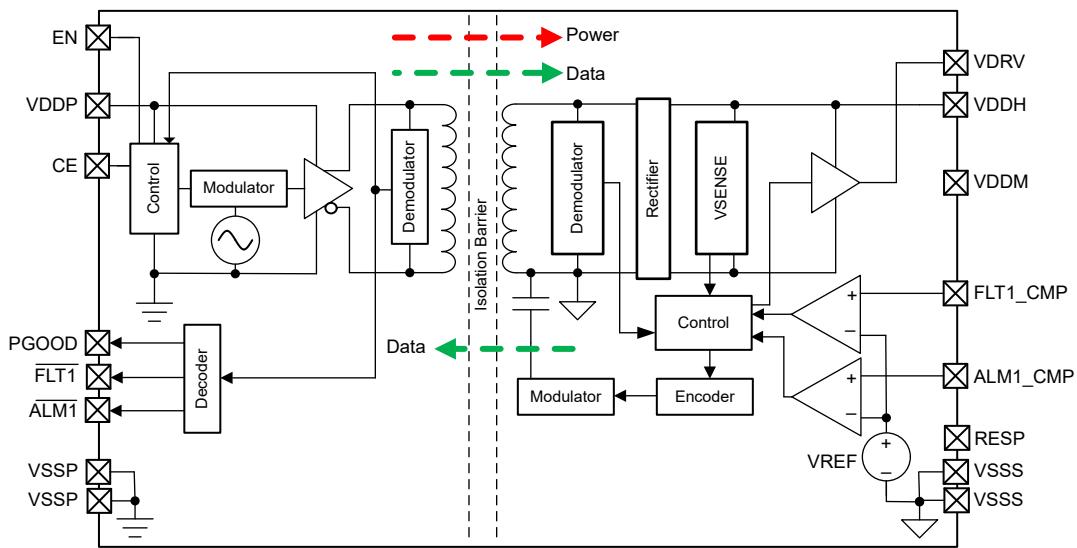

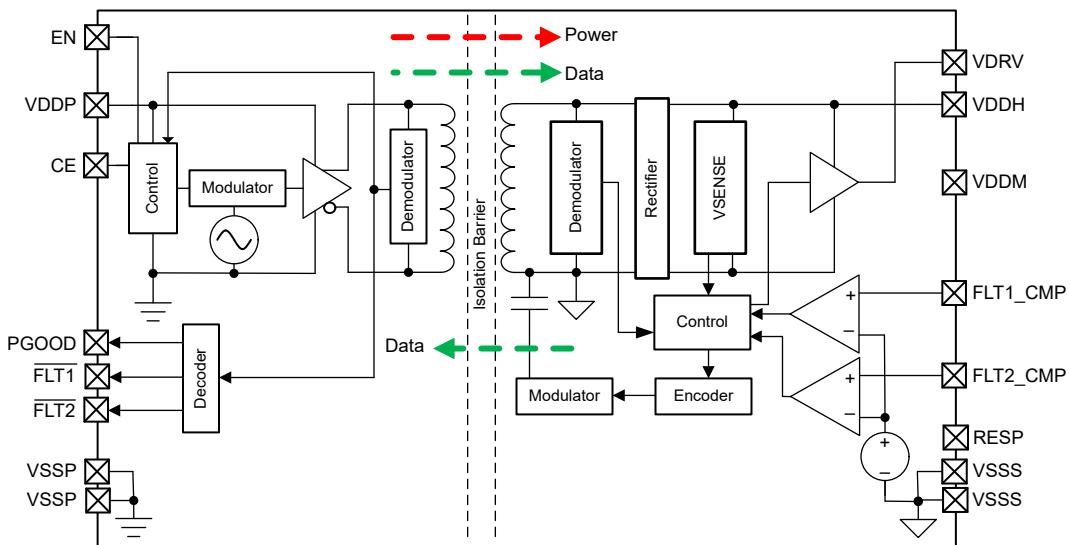

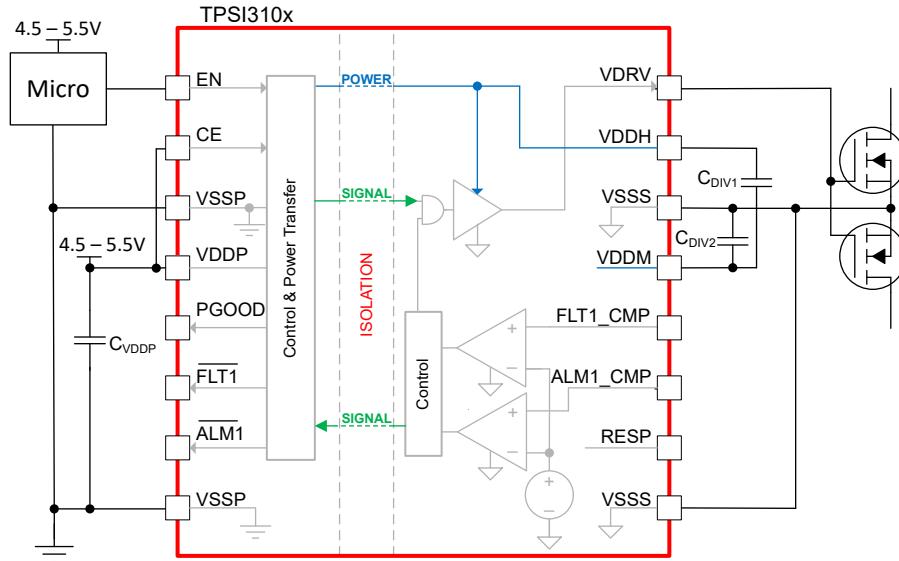

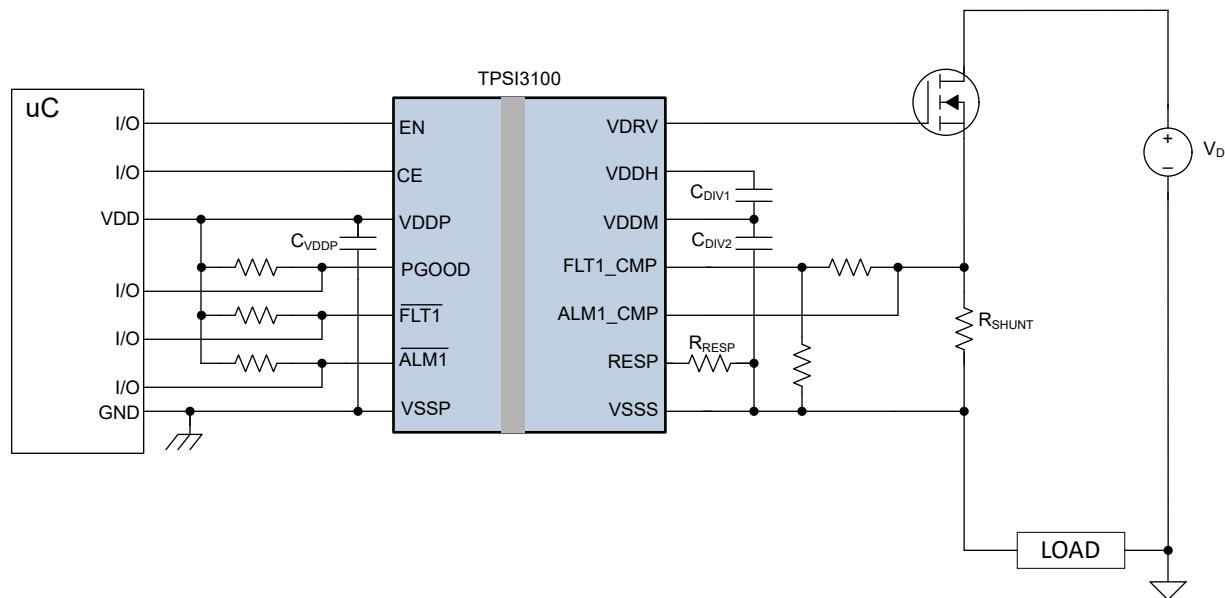

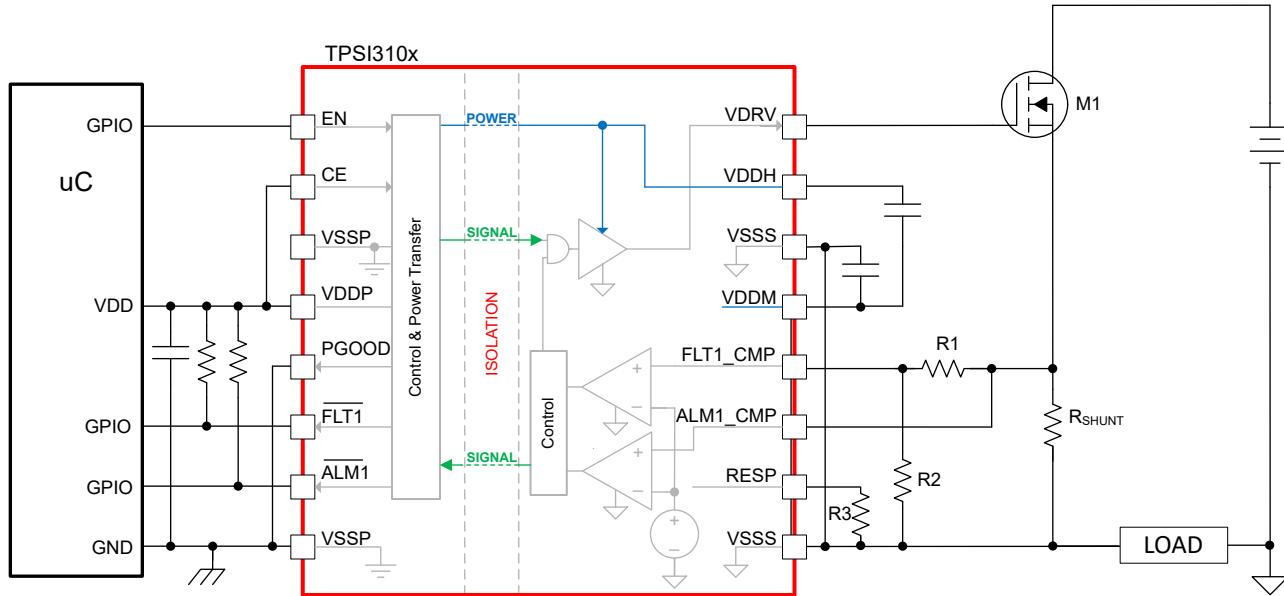

TPSI3100-Q1 は、統合型の絶縁スイッチ ドライバで、外部パワー スイッチと組み合わせることにより、完全な絶縁型ソリッドステートリレー ソリューションを形成します。ゲート駆動電圧 17V、ピーク ソース電流 / ピーク シンク電流 1.5A/2.5A という性能を備えているため、さまざまなパワー スイッチを使用して多くのアプリケーションのニーズに対応できます。TPSI3100-Q1 は、1 次側で供給された電源によって独自の 2 次バイアス電源を生成するので、絶縁型の 2 次側電源バイアスは不要です。TPSI3100-Q1 は、電流および電圧監視やリモート温度検出などの各種機能を実行するために補助回路で使用する追加電力を公称

5V のレール (VDDM) 経由で供給します。TPSI3100-Q1 の絶縁は非常に堅牢で、従来の機械式リレー や フォトカプラーに比べて高信頼性、低消費電力で、温度範囲が広くなっています。

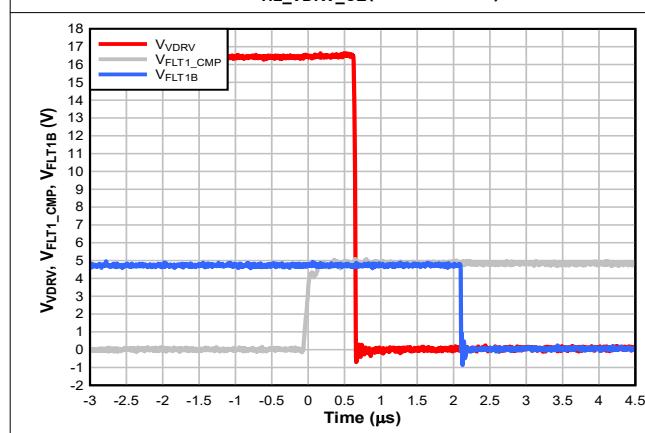

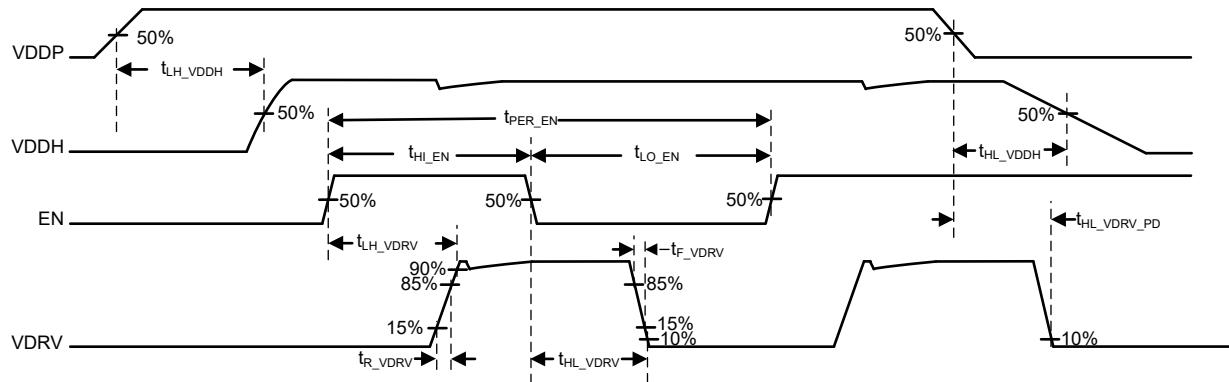

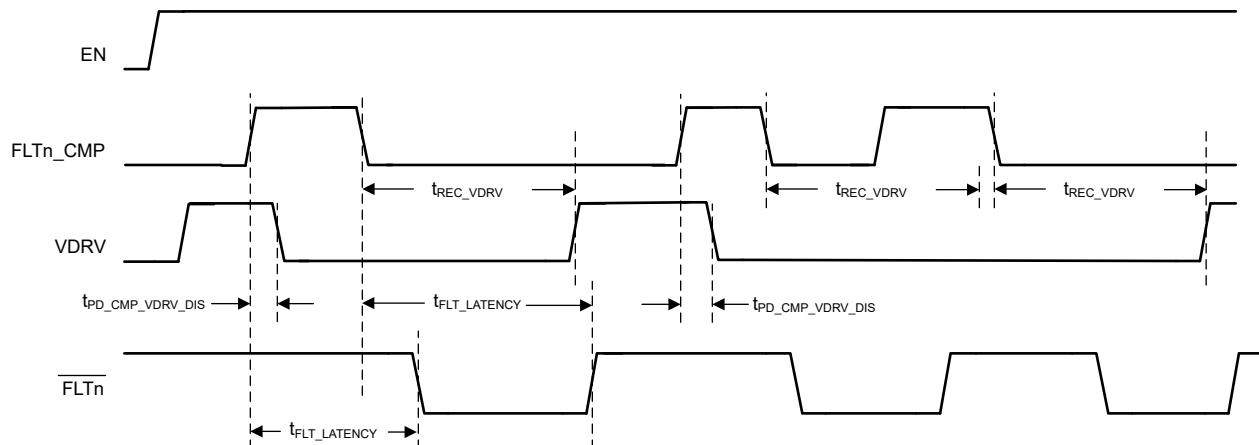

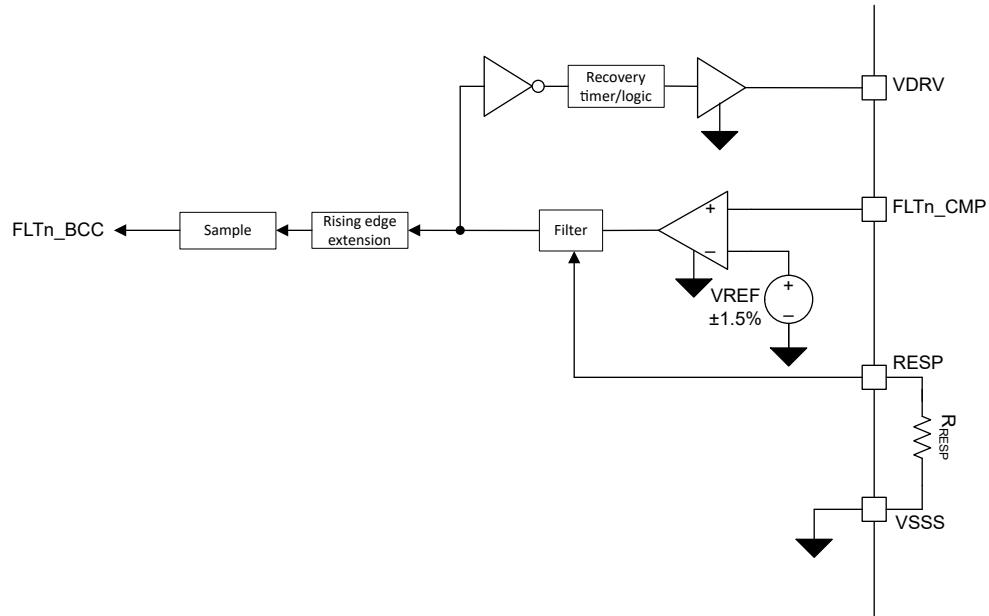

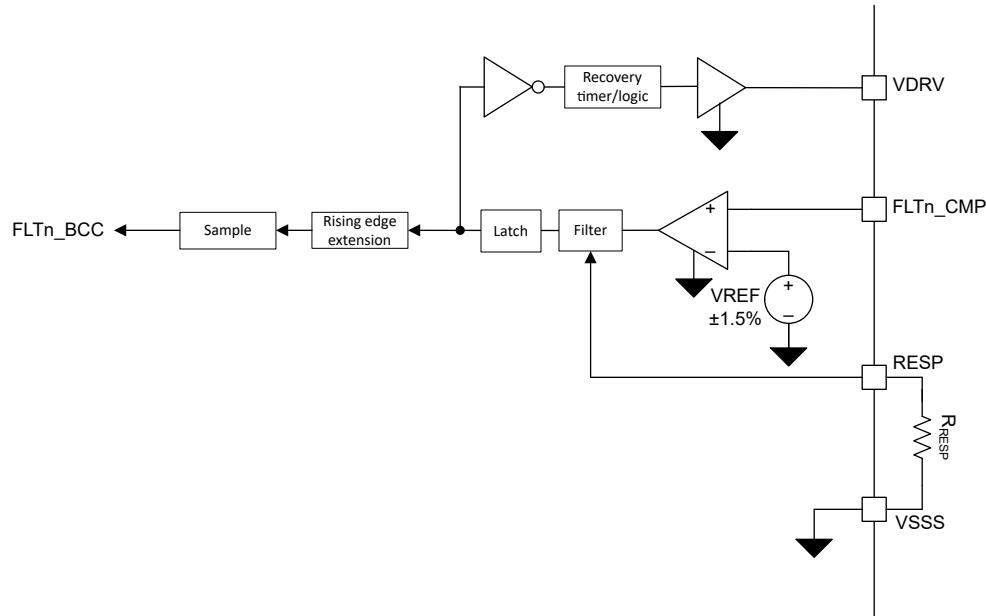

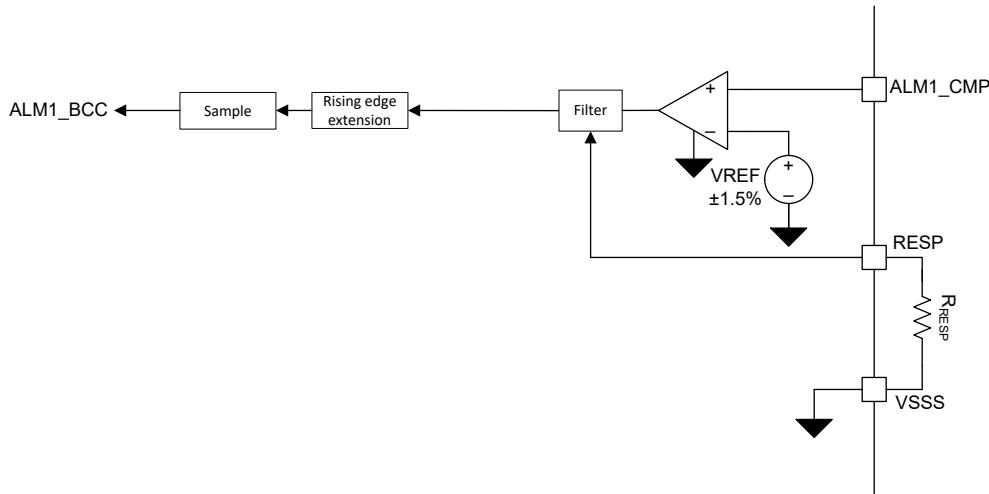

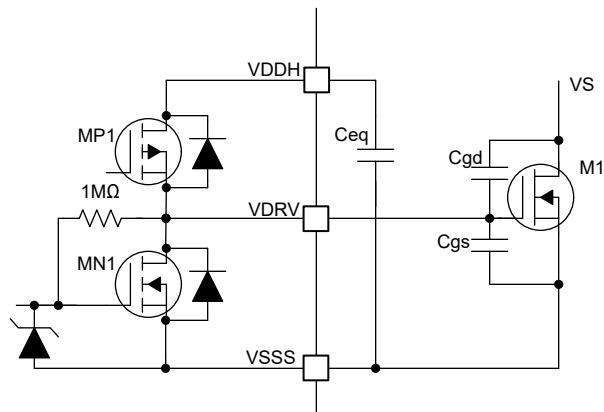

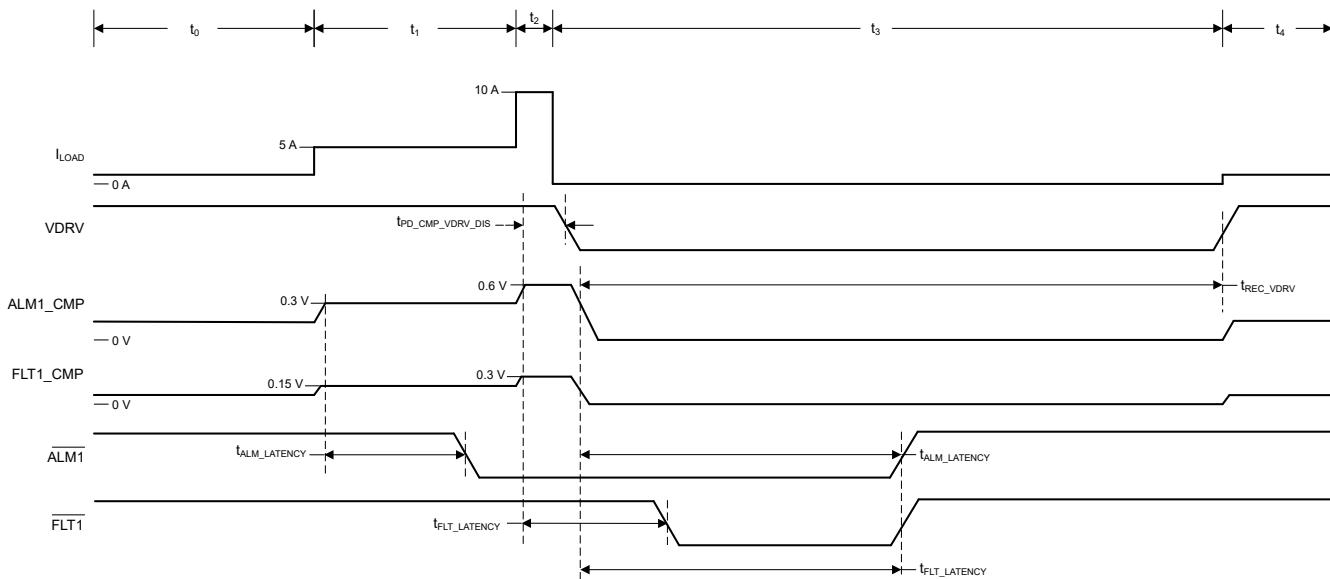

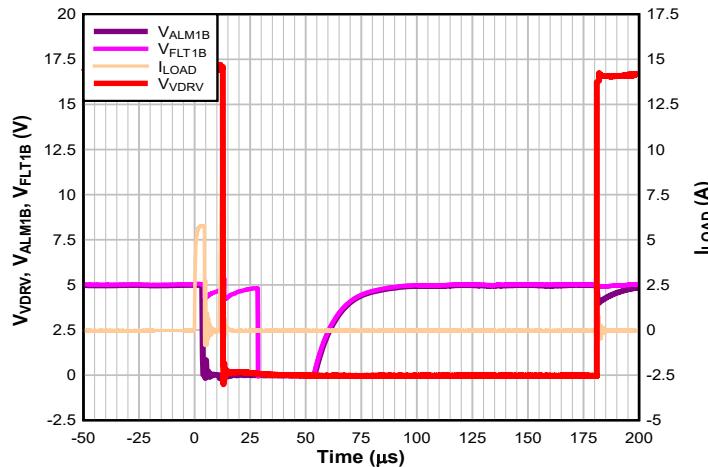

TPSI3100-Q1 には通信バックチャネルが内蔵されており、オープン ドレイン出力の PGOOD (パワー グッド)、FLT1 (フォルト 1)、ALM1 (アラーム 1) を通じて 2 次側から 1 次側にステータス情報を転送します。FLT1 および ALM1 のアサートには、共有の電圧リファレンスを内蔵したデュアル高速コンパレータが使用されます。コンパレータ入力 FLT1\_CMP が電圧リファレンスを超えると、ドライバが即座に Low にアサートされると共に FLT1 が Low に駆動され、フォルトが発生したことがシステムに示されます。これは、過電流検出などの重大なイベントが発生したときに、短いレイテンシで外部スイッチを無効にするのに便利です。コンパレータ入力 ALM1\_CMP が電圧リファレンスを超えると、ALM1 信号が Low にアサートされますが、ドライバでは何も行われません。これは、過熱や過電圧のイベントに対するアラームまたは警告インジケータとして役立ちます。

TPSI310xL-Q1 シリーズは、ラッチ ベースのフォルト インジケータを備えています。フォルトが検出されると、ドライバとフォルト インジケータが Low にアサートされ、EN が Low にアサートされるまでラッチされた状態を維持します。TPSI310x-Q1 シリーズには、ラッチなしのフォルト インジケータがあります。フォルト イベントが解消されると、FLT1 がデアサートされ、ドライバは指定された回復期間の後で EN ピンの状態に従います。それでもフォルト イベントが解消されない場合、フォルト インジケータとドライバの両方が Low にアサートされたままになります。

## 製品情報

| 部品番号         | REF (2) | コンパレータ(2)         | パッケージ (1)      |

|--------------|---------|-------------------|----------------|

| TPSI3100-Q1  | 0.31 V  | フォルト 1、アラーム 1     |                |

| TPSI3100L-Q1 | 0.31 V  | ラッチ フォルト 1、アラーム 1 | DVX (SSOP, 16) |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) [製品比較表](#)を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSG43](#)

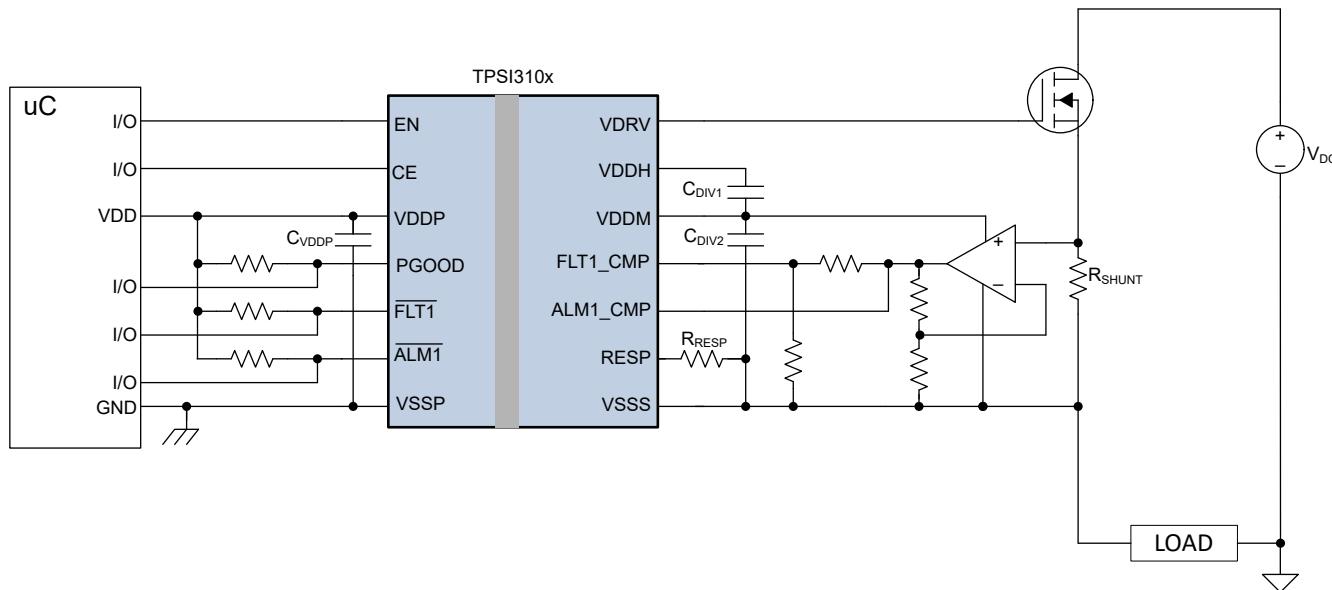

TPSI3100-Q1 の概略回路図

## Table of Contents

|                                                 |    |                                                 |    |

|-------------------------------------------------|----|-------------------------------------------------|----|

| 1 特長.....                                       | 1  | 8.1 Overview.....                               | 22 |

| 2 アプリケーション.....                                 | 1  | 8.2 Functional Block Diagram.....               | 23 |

| 3 概要.....                                       | 1  | 8.3 Feature Description.....                    | 24 |

| 4 Device Comparison Table.....                  | 4  | 8.4 Device Operation.....                       | 29 |

| 5 Pin Configuration and Functions.....          | 5  | 8.5 Device Functional Modes.....                | 33 |

| 6 Specifications.....                           | 9  | <b>9 Application and Implementation.....</b>    | 34 |

| 6.1 Absolute Maximum Ratings.....               | 9  | 9.1 Application Information.....                | 34 |

| 6.2 ESD Ratings.....                            | 9  | 9.2 Typical Application.....                    | 38 |

| 6.3 Recommended Operating Conditions.....       | 9  | 9.3 Power Supply Recommendations.....           | 42 |

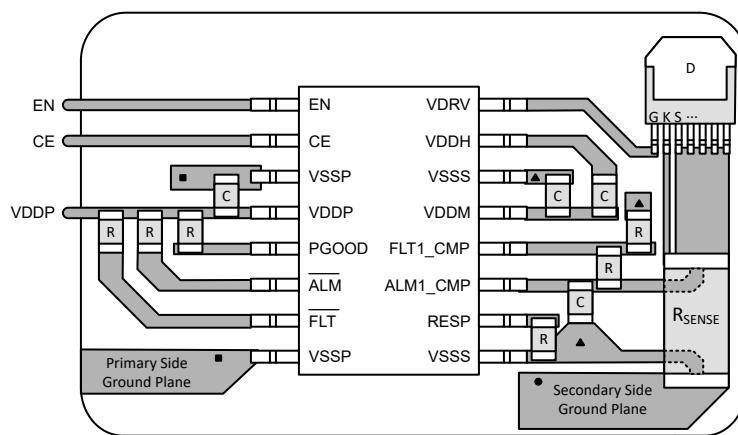

| 6.4 Thermal Information.....                    | 10 | 9.4 Layout.....                                 | 42 |

| 6.5 Power Ratings.....                          | 10 | <b>10 Device and Documentation Support.....</b> | 44 |

| 6.6 Insulation Specifications.....              | 10 | 10.1 Documentation Support.....                 | 44 |

| 6.7 Safety-Related Certifications.....          | 11 | 10.2 ドキュメントの更新通知を受け取る方法.....                    | 44 |

| 6.8 Safety Limiting Values.....                 | 12 | 10.3 サポート・リソース.....                             | 44 |

| 6.9 Electrical Characteristics.....             | 12 | 10.4 Trademarks.....                            | 44 |

| 6.10 Switching Characteristics.....             | 15 | 10.5 静電気放電に関する注意事項.....                         | 44 |

| 6.11 Insulation Characteristic Curves.....      | 17 | 10.6 用語集.....                                   | 44 |

| 6.12 Typical Characteristics.....               | 18 |                                                 |    |

| <b>7 Parameter Measurement Information.....</b> | 20 | <b>11 Revision History.....</b>                 | 44 |

| <b>8 Detailed Description.....</b>              | 22 | <b>12 Mechanical, Packaging, and Orderable</b>  |    |

|                                                 |    | <b>Information.....</b>                         | 44 |

## 4 Device Comparison Table

| VARIANT                     | REF   | COMPARATORS                      | LATCHED FAULT      |

|-----------------------------|-------|----------------------------------|--------------------|

| TPSI3100-Q1                 | 0.31V | 1 fault, 1 alarm                 | No                 |

| TPSI3103-Q1 <sup>(3)</sup>  | 1.23V |                                  |                    |

| TPSI3100L-Q1                | 0.31V |                                  | Yes                |

| TPSI3103L-Q1 <sup>(3)</sup> | 1.23V |                                  |                    |

| TPSI3110-Q1 <sup>(3)</sup>  | 0.31V | 2 faults                         | No                 |

| TPSI3113-Q1 <sup>(3)</sup>  | 1.23V |                                  |                    |

| TPSI3110L-Q1 <sup>(3)</sup> | 0.31V |                                  | Yes                |

| TPSI3113L-Q1 <sup>(3)</sup> | 1.23V |                                  |                    |

| TPSI3120-Q1 <sup>(3)</sup>  | 0.31V | 2 alarms                         | N/A <sup>(2)</sup> |

| TPSI3123-Q1 <sup>(3)</sup>  | 1.23V |                                  |                    |

| TPSI3133-Q1 <sup>(3)</sup>  | 1.23V | 1 fault <sup>(1)</sup> , 1 alarm | No                 |

(1) FLT1\_CMP input is actively pulled down when EN is low. These devices are useful for overcurrent detection using DESAT techniques primarily with IGBT power transistors.

(2) Non-applicable.

(3) Product preview.

## 5 Pin Configuration and Functions

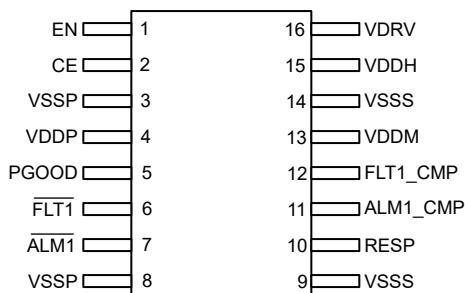

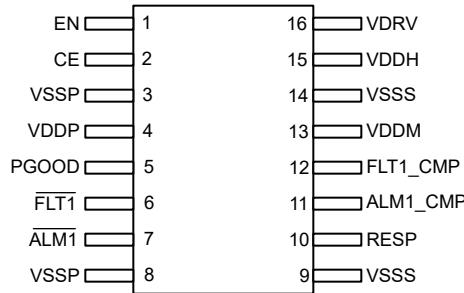

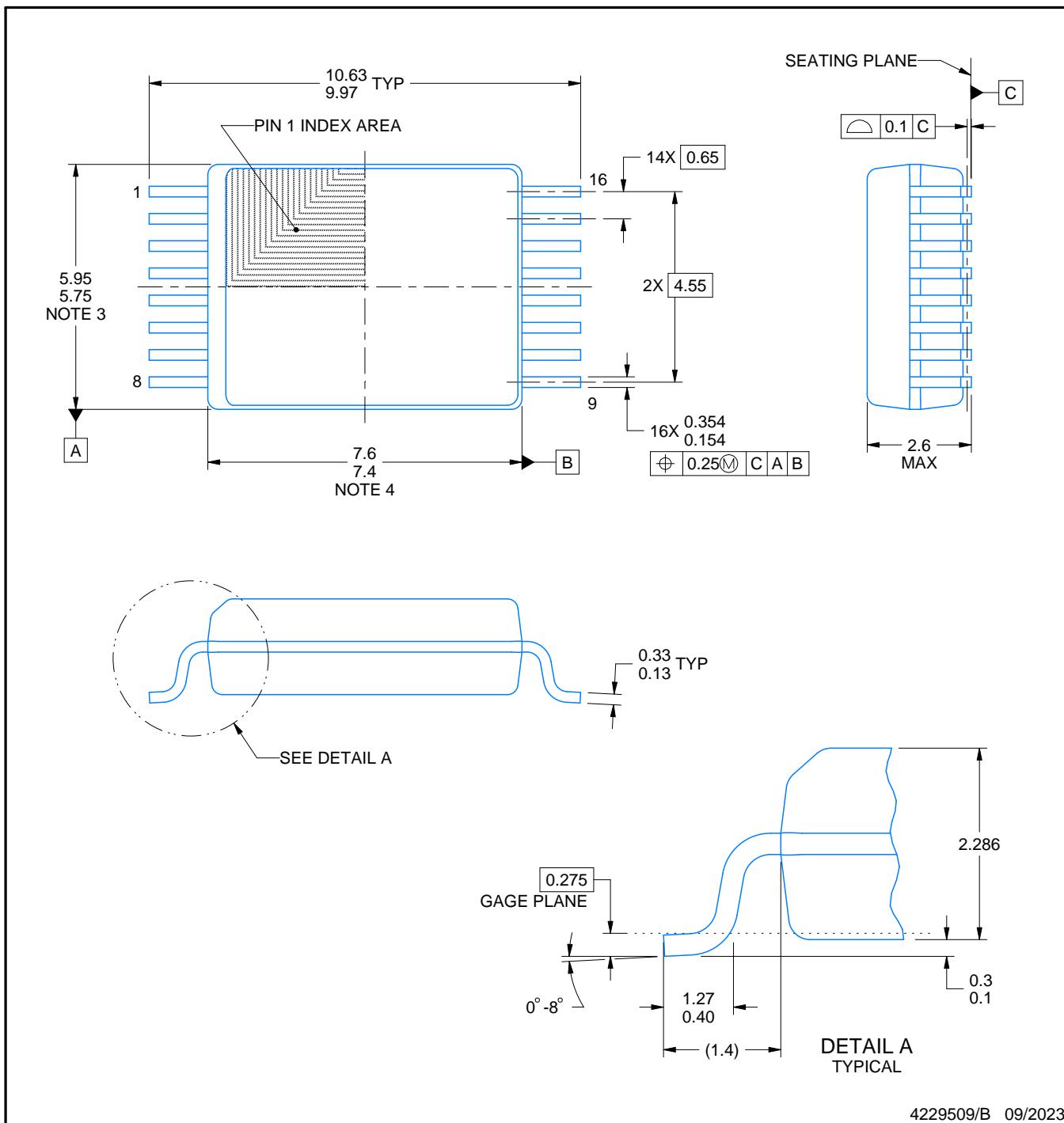

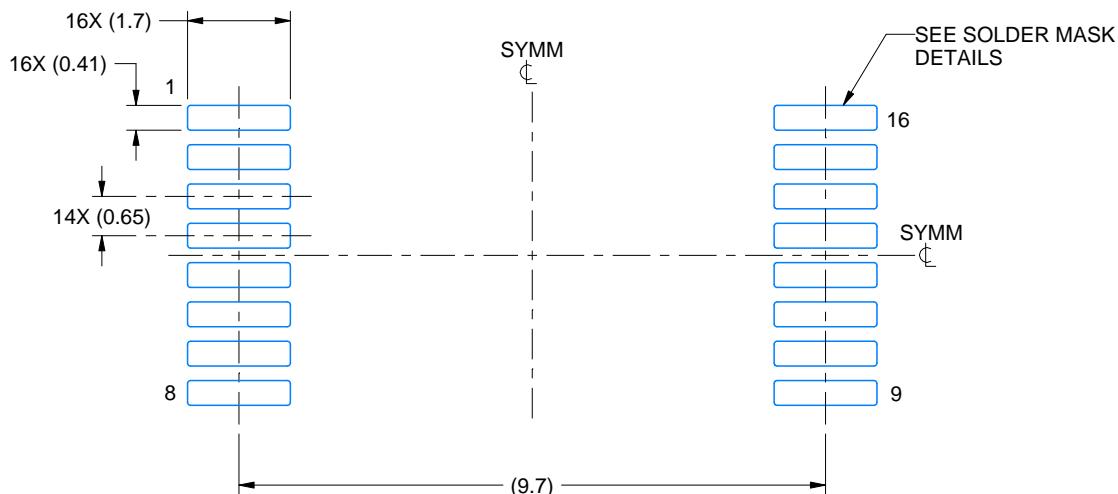

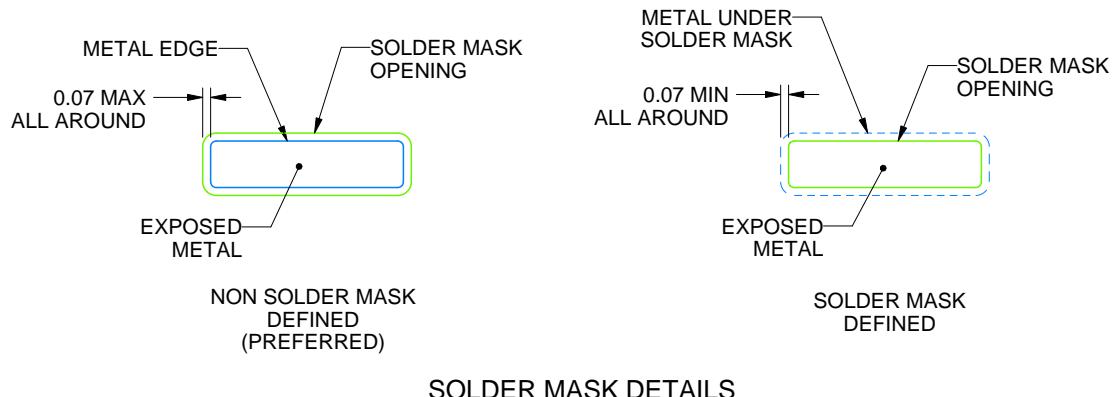

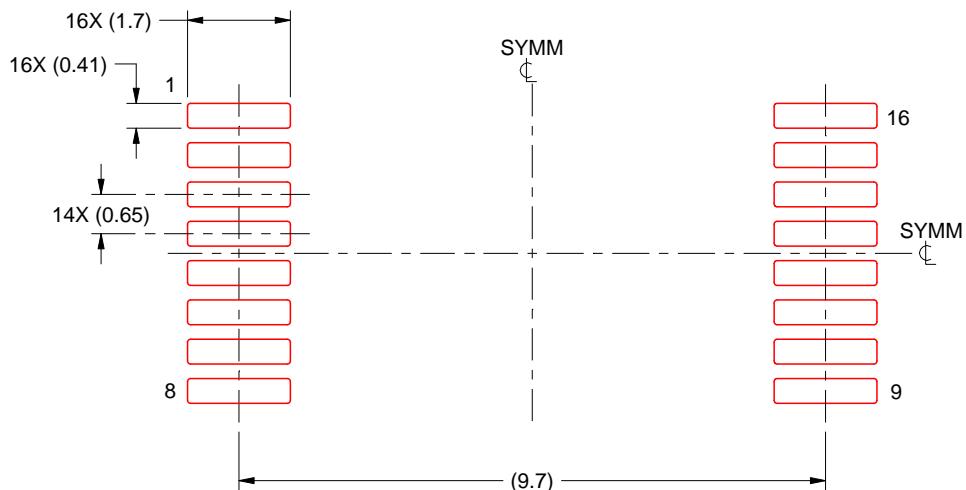

**图 5-1. TPSI310x-Q1 and TPSI310xL-Q1 DVX Package, 16-Pin SSOP (Top View)**

| PIN |          | I/O | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                        |

|-----|----------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     |     |                     |                                                                                                                                                                                                                                                                    |

| 1   | EN       | I   | —                   | Active high driver enable. Internal 500kΩ pull-down to VSSP.                                                                                                                                                                                                       |

| 2   | CE       | I   | —                   | Active high input. When asserted low, device is disabled. Tie to VDDP when not used. Internal 500kΩ pull-down to VSSP.                                                                                                                                             |

| 3   | VSSP     | —   | GND                 | Ground supply for primary side. All VSSP pins must be connected to the primary side ground.                                                                                                                                                                        |

| 4   | VDDP     | —   | P                   | Power supply for the primary side.                                                                                                                                                                                                                                 |

| 5   | PGOOD    | O   | —                   | Power good indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                   |

| 6   | FLT1     | O   | —                   | Fault 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                      |

| 7   | ALM1     | O   | —                   | Alarm 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                      |

| 8   | VSSP     | —   | GND                 | Ground supply for the primary side. All VSSP must be connected to the primary side ground.                                                                                                                                                                         |

| 9   | VSSS     | —   | GND                 | Ground supply for the secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                |

| 10  | RESP     | O   | —                   | Used in conjunction with an external resistor connected to VSSS to adjust comparator response time. When not being used, tie to VSSS.                                                                                                                              |

| 11  | ALM1_CMP | I   | —                   | Analog comparator input. When ALM1_CMP voltage exceeds internal reference voltage, ALM1 is asserted low within $t_{ALM\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS.                                                            |

| 12  | FLT1_CMP | I   | —                   | Analog comparator input. When FLT1_CMP voltage exceeds internal reference voltage, VDRV is automatically asserted low regardless of EN state and FLT1 asserted low within $t_{FLT\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 13  | VDDM     | —   | P                   | Generated mid-supply, nominal 5V.                                                                                                                                                                                                                                  |

| 14  | VSSS     | —   | GND                 | Ground supply for secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                    |

| 15  | VDDH     | —   | P                   | Generated high supply, nominal 17V.                                                                                                                                                                                                                                |

| 16  | VDRV     | O   | —                   | Active high driver output.                                                                                                                                                                                                                                         |

(1) P = power, GND = ground, NC = no connect

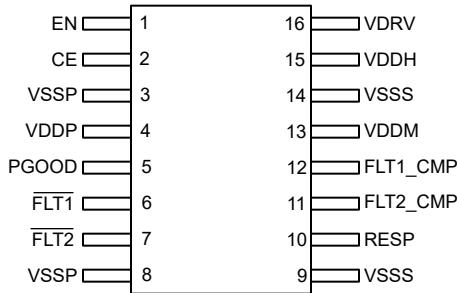

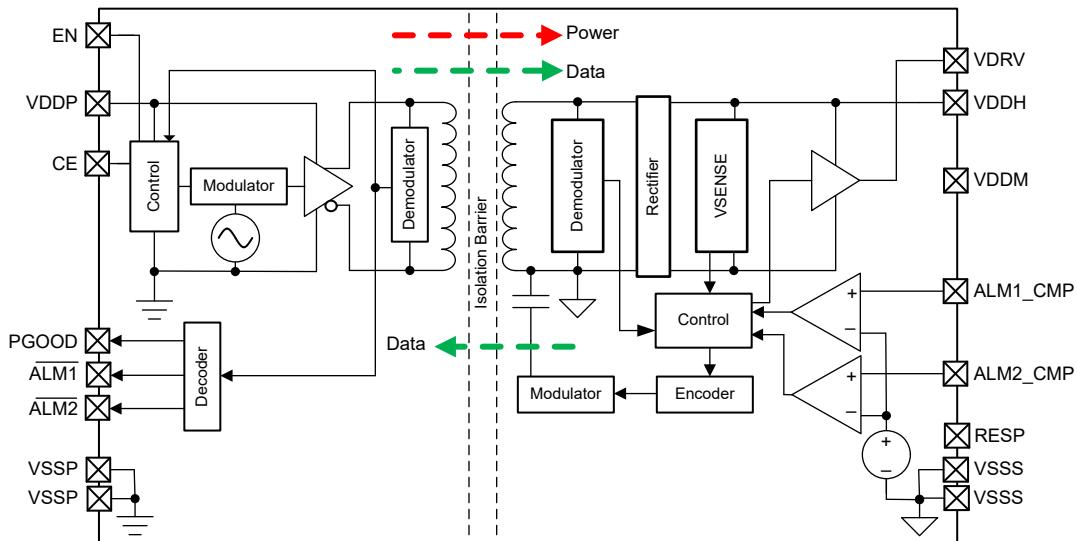

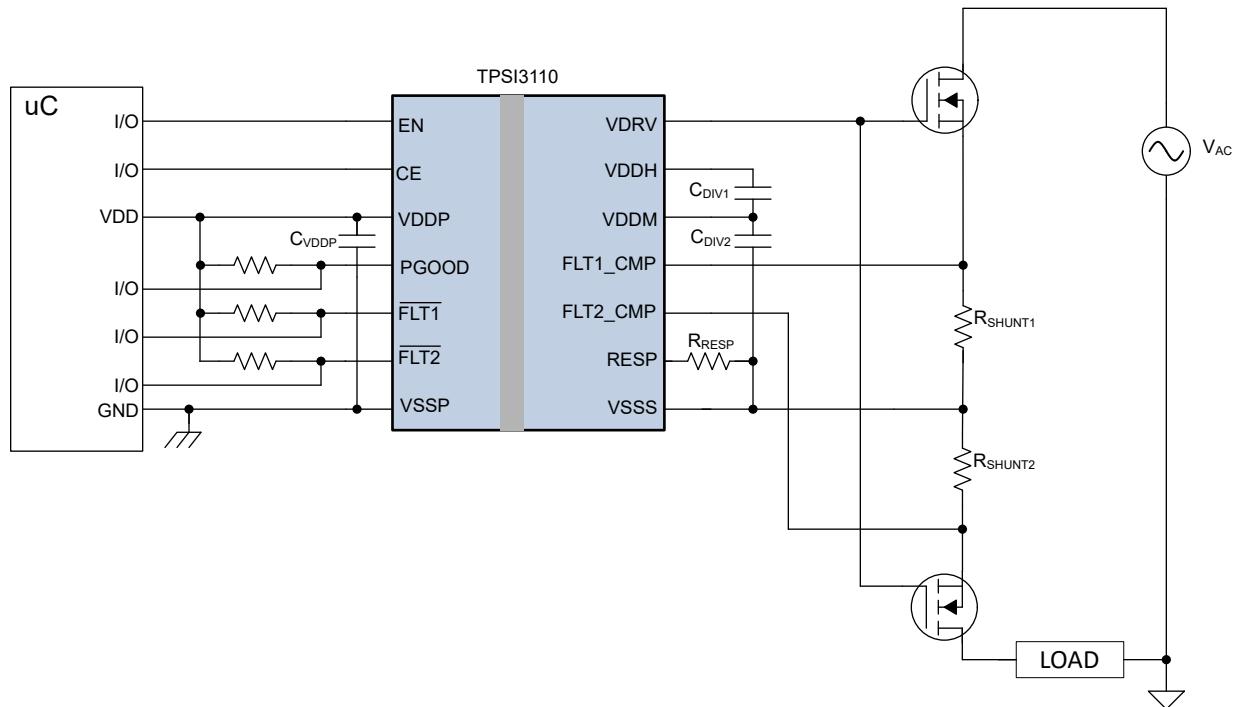

**図 5-2. TPSI311x-Q1 and TPSI311xL-Q1 DVX Package, 16-Pin SSOP (Top View)**

| PIN |          | I/O | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                        |

|-----|----------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     |     |                     |                                                                                                                                                                                                                                                                    |

| 1   | EN       | I   | —                   | Active high driver enable. Internal 500kΩ pull-down to VSSP.                                                                                                                                                                                                       |

| 2   | CE       | I   | —                   | Active high input. When asserted low, device is disabled. Tie to VDDP when not used. Internal 500kΩ pull-down to VSSP.                                                                                                                                             |

| 3   | VSSP     | —   | GND                 | Ground supply for primary side. All VSSP pins must be connected to the primary side ground.                                                                                                                                                                        |

| 4   | VDDP     | —   | P                   | Power supply for the primary side.                                                                                                                                                                                                                                 |

| 5   | PGOOD    | O   | —                   | Power good indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                   |

| 6   | FLT1     | O   | —                   | Fault 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                      |

| 7   | FLT2     | O   | —                   | Fault 2 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                      |

| 8   | VSSP     | —   | GND                 | Ground supply for the primary side. All VSSP pins must be connected to the primary side ground.                                                                                                                                                                    |

| 9   | VSSS     | —   | GND                 | Ground supply for the secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                |

| 10  | RESP     | O   | —                   | Used in conjunction with an external resistor connected to VSSS to adjust comparator response time. When not being used, tie to VSSS.                                                                                                                              |

| 11  | FLT2_CMP | I   | —                   | Analog comparator input. When FLT2_CMP voltage exceeds internal reference voltage, VDRV is automatically asserted low regardless of EN state and FLT2 asserted low within $t_{FLT\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 12  | FLT1_CMP | I   | —                   | Analog comparator input. When FLT1_CMP voltage exceeds internal reference voltage, VDRV is automatically asserted low regardless of EN state and FLT1 asserted low within $t_{FLT\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 13  | VDDM     | —   | P                   | Generated mid-supply, nominal 5V.                                                                                                                                                                                                                                  |

| 14  | VSSS     | —   | GND                 | Ground supply for secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                    |

| 15  | VDDH     | —   | P                   | Generated high supply, nominal 17V.                                                                                                                                                                                                                                |

| 16  | VDRV     | O   | —                   | Active high driver output.                                                                                                                                                                                                                                         |

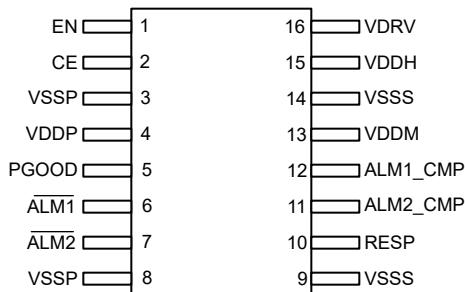

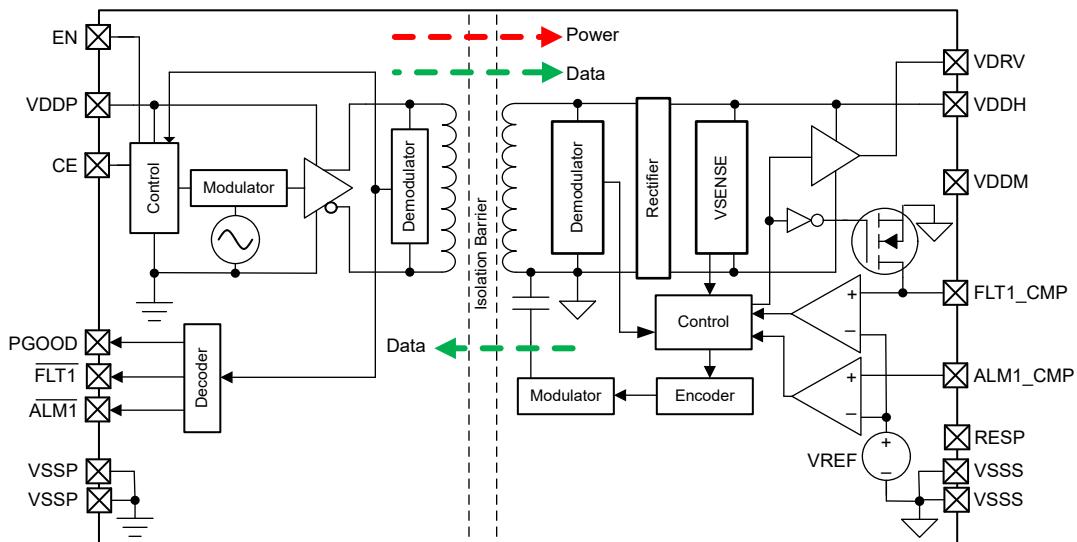

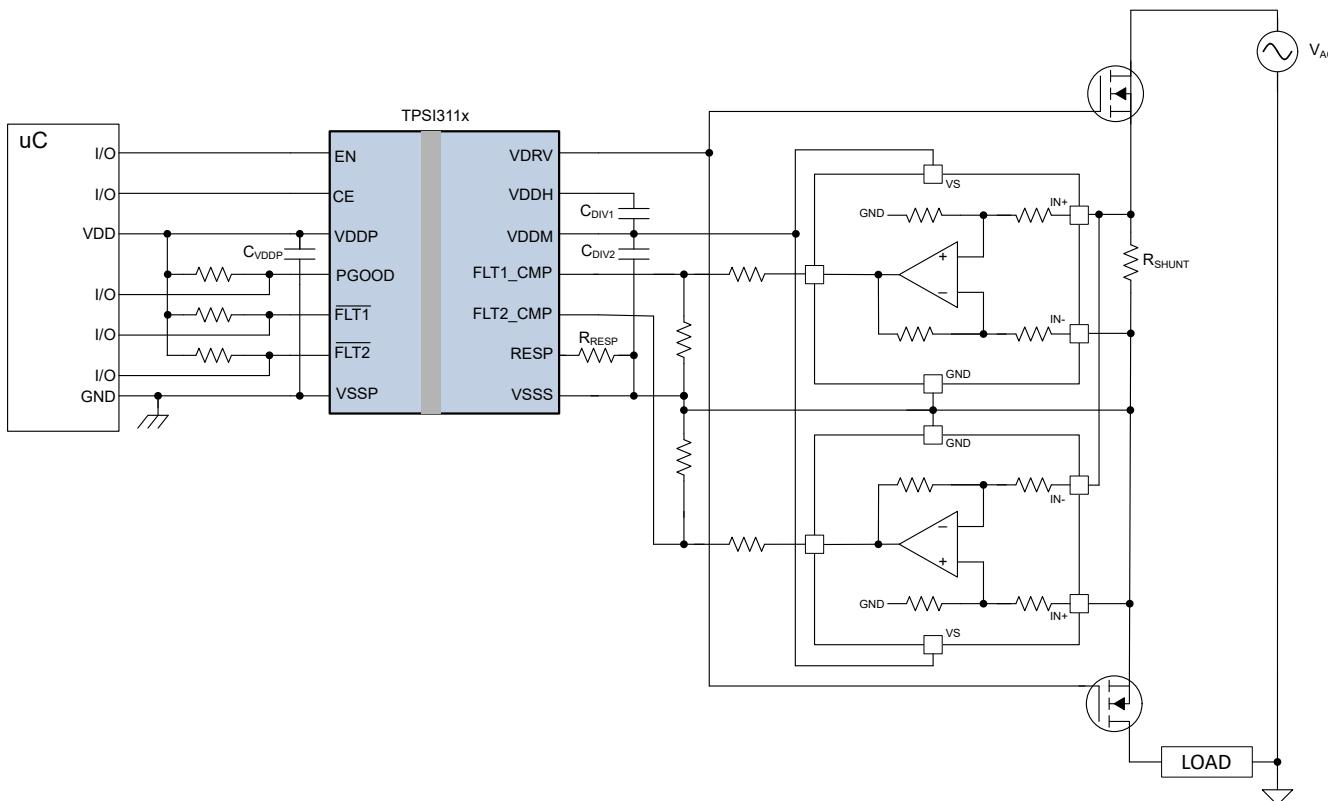

**図 5-3. TPSI312x-Q1 DVX Package, 16-Pin SSOP (Top View)**

| PIN |          | I/O | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                             |

|-----|----------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     |     |                     |                                                                                                                                                                                                         |

| 1   | EN       | I   | —                   | Active high driver enable. Internal 500kΩ pull-down to VSSP.                                                                                                                                            |

| 2   | CE       | I   | —                   | Active high input. When asserted low, device is disabled. Tie to VDDP when not used. Internal 500kΩ pull-down to VSSP.                                                                                  |

| 3   | VSSP     | —   | GND                 | Ground supply for primary side. All VSSP pins must be connected to the primary side ground.                                                                                                             |

| 4   | VDDP     | —   | P                   | Power supply for the primary side.                                                                                                                                                                      |

| 5   | PGOOD    | O   | —                   | Power good indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                        |

| 6   | ALM1     | O   | —                   | Alarm 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                           |

| 7   | ALM2     | O   | —                   | Alarm 2 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                           |

| 8   | VSSP     | —   | GND                 | Ground supply for the primary side. All VSSP pins must be connected to the primary side ground.                                                                                                         |

| 9   | VSSS     | —   | GND                 | Ground supply for the secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                     |

| 10  | RESP     | O   | —                   | Used in conjunction with an external resistor connected to VSSS to adjust comparator response time. When not being used, tie to VSSS.                                                                   |

| 11  | ALM2_CMP | I   | —                   | Analog comparator input. When ALM2_CMP voltage exceeds internal reference voltage, ALM2 is asserted low within $t_{ALM\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 12  | ALM1_CMP | I   | —                   | Analog comparator input. When ALM1_CMP voltage exceeds internal reference voltage, ALM1 is asserted low within $t_{ALM\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 13  | VDDM     | —   | P                   | Generated mid-supply, nominal 5V.                                                                                                                                                                       |

| 14  | VSSS     | —   | GND                 | Ground supply for secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                         |

| 15  | VDDH     | —   | P                   | Generated high supply, nominal 17V.                                                                                                                                                                     |

| 16  | VDRV     | O   | —                   | Active high driver output.                                                                                                                                                                              |

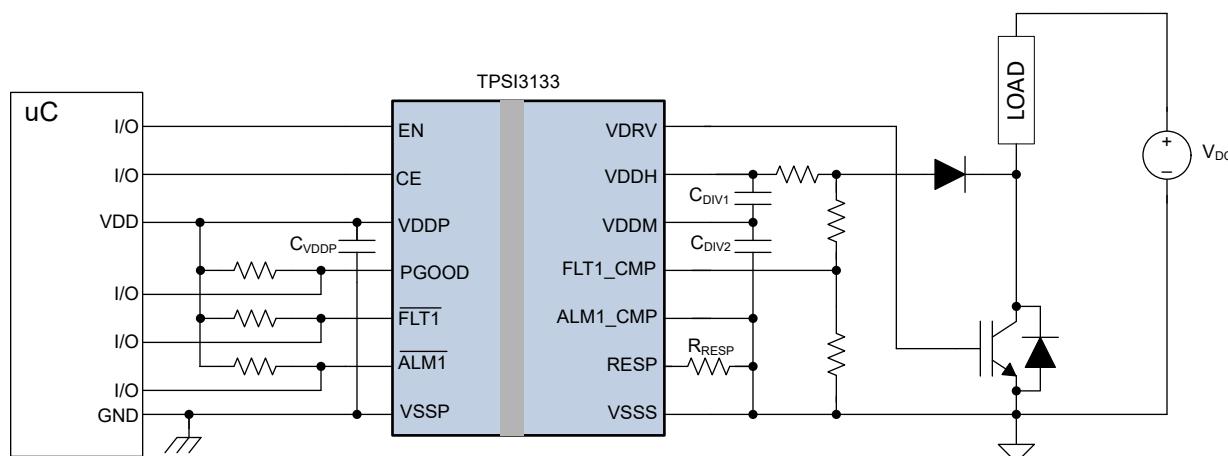

図 5-4. TPSI3133-Q1 DVX Package, 16-Pin SSOP (Top View)

| PIN |          | I/O | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     |     |                     |                                                                                                                                                                                                                                                                                                                              |

| 1   | EN       | I   | —                   | Active high driver enable. Internal 500kΩ pull-down to VSSP.                                                                                                                                                                                                                                                                 |

| 2   | CE       | I   | —                   | Active high input. When asserted low, device is disabled. Tie to VDDP when not used. Internal 500kΩ pull-down to VSSP.                                                                                                                                                                                                       |

| 3   | VSSP     | —   | GND                 | Ground supply for primary side. All VSSP pins must be connected to the primary side ground.                                                                                                                                                                                                                                  |

| 4   | VDDP     | —   | P                   | Power supply for the primary side.                                                                                                                                                                                                                                                                                           |

| 5   | PGOOD    | O   | —                   | Power good indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                                                                             |

| 6   | FLT1     | O   | —                   | Fault 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                                                                                |

| 7   | ALM1     | O   | —                   | Alarm 1 indicator. Open-drain output. When being used, requires external pull-up to VDDP. Float or tie to VSSP when not used.                                                                                                                                                                                                |

| 8   | VSSP     | —   | GND                 | Ground supply for the primary side. All VSSP pins must be connected to the primary side ground.                                                                                                                                                                                                                              |

| 9   | VSSS     | —   | GND                 | Ground supply for the secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                                                                          |

| 10  | RESP     | O   | —                   | Used in conjunction with an external resistor connected to VSSS to adjust comparator response time. When not being used, tie to VSSS.                                                                                                                                                                                        |

| 11  | ALM1_CMP | I   | —                   | Analog comparator input. When ALM1_CMP voltage exceeds internal reference voltage, ALM1 is asserted low within $t_{ALM\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS.                                                                                                                      |

| 12  | FLT1_CMP | I/O | —                   | Analog comparator input/output. When EN state is low, FLT1_CMP is actively pulled low. If EN state is high and FLT1_CMP voltage exceeds internal reference voltage, VDRV is automatically asserted low and FLT1 asserted low within $t_{FLT\_LATENCY}$ . Internal 2.8MΩ pull-down to VSSS. When not being used, tie to VSSS. |

| 13  | VDDM     | —   | P                   | Generated mid-supply, nominal 5V.                                                                                                                                                                                                                                                                                            |

| 14  | VSSS     | —   | GND                 | Ground supply for secondary side. All VSSS pins must be connected to the secondary side ground.                                                                                                                                                                                                                              |

| 15  | VDDH     | —   | P                   | Generated high supply, nominal 17V.                                                                                                                                                                                                                                                                                          |

| 16  | VDRV     | O   | —                   | Active high driver output.                                                                                                                                                                                                                                                                                                   |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| PARAMETER <sup>(1)</sup>              |                                                                                                                                 | MIN  | MAX | UNIT |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

| Primary side supply <sup>(2)</sup>    | VDDP, EN, CE, PGOOD, FLT1 (TPSI310x, TPSI311x, TPSI3133), FLT2 (TPSI311x), ALM1 (TPSI310x, TPSI312x, TPSI3133), ALM2 (TPSI312x) | -0.3 | 6   | V    |

| Secondary side supply <sup>(3)</sup>  | FLT1_CMP (TPSI310x, TPSI311x, TPSI3133), FLT2_CMP (TPSI311x), ALM1_CMP (TPSI310x, TPSI312x, TPSI3133), ALM2_CMP (TPSI312x)      | -3   | 6   | V    |

| Secondary side supply <sup>(3)</sup>  | VDRV                                                                                                                            | -0.3 | 18  | V    |

| Secondary side supply <sup>(3)</sup>  | VDDH                                                                                                                            | -0.3 | 18  | V    |

| Secondary side supply <sup>(3)</sup>  | VDDM                                                                                                                            | -0.3 | 6   | V    |

| Secondary side supply <sup>(3)</sup>  | VDDH-VDDM                                                                                                                       | -0.3 | 13  | V    |

| Secondary side supply <sup>(3)</sup>  | RESP                                                                                                                            | -0.3 | 6   | V    |

| Junction temperature, T <sub>J</sub>  | Junction temperature, T <sub>J</sub>                                                                                            | -40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub> |                                                                                                                                 | -65  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltage values are with respect to VSSP. Not all signals listed may be present pending device variant.

(3) All voltage values are with respect to VSSS. Not all signals listed may be present pending device variant.

### 6.2 ESD Ratings

|                    |                         |                                                                                           |  | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------|--|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 |  | ±2000 | V    |

|                    |                         | Charged device model (CDM), per AEC Q100-011<br>CDM ESD classification level C4B          |  | ±750  |      |

|                    |                         | Corner pins (1, 8, 9, and 16)                                                             |  | ±500  |      |

|                    |                         | Other pins                                                                                |  | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                                                                  | MIN | NOM | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VDDP              | Primary side supply voltage <sup>(1)</sup>                                                       | 4.5 | 5.5 | 5.5 | V    |

| EN                | Enable VDRV <sup>(1)</sup><br><sup>(1)</sup>                                                     | 0   | 5.5 | 5.5 | V    |

| CE                | Chip enable <sup>(1)</sup>                                                                       | 0   | 5.5 | 5.5 | V    |

| PGOOD             | Power good indicator <sup>(4) (1)</sup>                                                          | 0   | 5.5 | 5.5 | V    |

| FLT <sub>n</sub>  | Fault indicator(s). <sup>(4) (1)</sup><br>FLT1 (TPSI310x, TPSI311x, TPSI3133)<br>FLT2 (TPSI311x) | 0   | 5.5 | 5.5 | V    |

| ALM <sub>n</sub>  | Alarm indicator(s). <sup>(4) (1)</sup><br>ALM1 (TPSI310x, TPSI311x, TPSI3133)<br>ALM2 (TPSI312x) | 0   | 5.5 | 5.5 | V    |

| C <sub>VDDP</sub> | Decoupling capacitance on VDDP and VSSP <sup>(3)</sup>                                           | 1   | 20  | 20  | μF   |

## 6.3 Recommended Operating Conditions (続き)

over operating free-air temperature range (unless otherwise noted)

|                           |                                                            | MIN   | NOM | MAX  | UNIT      |

|---------------------------|------------------------------------------------------------|-------|-----|------|-----------|

| $C_{DIV1}$ <sup>(2)</sup> | Decoupling capacitance across VDDH and VDDM <sup>(3)</sup> | 0.003 |     | 15   | $\mu F$   |

| $C_{DIV2}$ <sup>(2)</sup> | Decoupling capacitance across VDDM and VSSS <sup>(3)</sup> | 0.1   |     | 40   | $\mu F$   |

| $Q_{TOTAL}$               | Total charge to be driven by VDRV.                         |       |     | 2500 | nC        |

| $R_{RESP}$                | Comparator response resistor from RESP to VSSS.            | 0     |     | 1000 | $k\Omega$ |

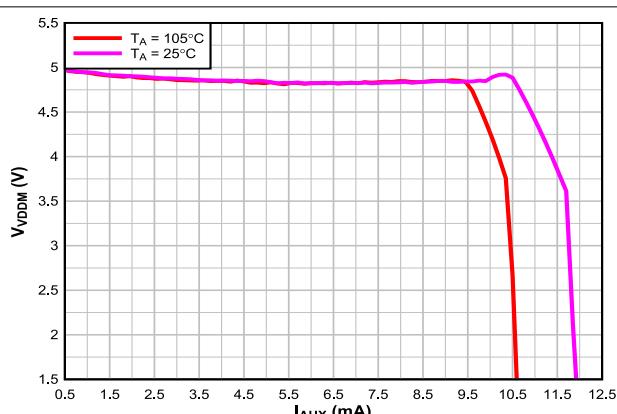

| $I_{AUX}$                 | Auxiliary current sourced from VDDM.                       | 0     |     | 5    | mA        |

| $T_A$                     | Ambient operating temperature                              | -40   |     | 125  | °C        |

| $T_J$                     | Operating junction temperature                             | -40   |     | 150  | °C        |

- (1) All voltage values are with respect to VSSP.

- (2)  $C_{DIV1}$  and  $C_{DIV2}$  should be of same type and tolerance.  $C_{DIV2}$  capacitance value should be at least three times the capacitance value of  $C_{DIV1}$  i.e.  $C_{DIV2} \geq 3 \times C_{DIV1}$ .

- (3) All capacitance values are absolute. Derating should be applied where necessary.

- (4) Open-drain fail-safe output. When being used, an external pull-up resistor greater than 20k $\Omega$  to VDDP is recommended. When not being used, float pin or connect to VSSP.

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | DEVICE     | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | DVX (SSOP) |      |

|                               |                                              | 16 PINS    |      |

| $R_{\Theta JA}$               | Junction-to-ambient thermal resistance       | 82.5       | °C/W |

| $R_{\Theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 39.3       | °C/W |

| $R_{\Theta JB}$               | Junction-to-board thermal resistance         | 42.3       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 14.7       | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 41.3       | °C/W |

- (1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics application report](#).

## 6.5 Power Ratings

| PARAMETER |  | TEST CONDITIONS                                                                                         | MIN | TYP | MAX | UNIT |

|-----------|--|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $P_D$     |  | $T_A = 25^\circ C$ , $V_{VDDP} = 5.0V$ , $f_{EN} = 1\text{kHz}$<br>square wave, $C_{VDRV} = 1\text{nF}$ |     |     | 250 | mW   |

## 6.6 Insulation Specifications

| PARAMETER                    |                                      | TEST CONDITIONS                                                   | VALUE    | UNIT    |

|------------------------------|--------------------------------------|-------------------------------------------------------------------|----------|---------|

| <b>CREEPAGE AND TRACKING</b> |                                      |                                                                   |          |         |

| CLR                          | External clearance <sup>(1)</sup>    | Shortest terminal-to-terminal distance through air                | $\geq 8$ | mm      |

| CPG                          | External creepage <sup>(1)</sup>     | Shortest terminal-to-terminal distance across the package surface | $\geq 8$ | mm      |

| DTI                          | Distance through the insulation      | Minimum internal gap (internal clearance)                         | > 120    | $\mu m$ |

| CTI                          | Comparative tracking index           | DIN EN 60112 (VDE 0303-11); IEC 60112                             | > 600    | V       |

|                              | Material group                       | According to IEC 60664-1                                          | I        |         |

|                              | Overvoltage category per IEC 60664-1 | Rated mains voltage $\leq 600V_{RMS}$                             | I-IV     |         |

|                              |                                      | Rated mains voltage $\leq 1000V_{RMS}$                            | I-III    |         |

## 6.6 Insulation Specifications (続き)

| PARAMETER                                |                                                       | TEST CONDITIONS                                                                                                                                                                          | VALUE       | UNIT      |

|------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|

| <b>DIN EN IEC 60747-17 (VDE 0884-17)</b> |                                                       |                                                                                                                                                                                          |             |           |

| $V_{IORM}$                               | Maximum repetitive peak isolation voltage             | AC voltage (bipolar)                                                                                                                                                                     | 1697        | $V_{PK}$  |

| $V_{IOWM}$                               | Maximum isolation working voltage                     | AC voltage (sine wave)                                                                                                                                                                   | 1200        | $V_{RMS}$ |

|                                          |                                                       | DC voltage                                                                                                                                                                               | 1697        | $V_{DC}$  |

| $V_{IOTM}$                               | Maximum transient isolation voltage                   | $V_{TEST} = V_{IOTM}$ ; $t = 60s$ (qualification test)                                                                                                                                   | 7070        | $V_{PK}$  |

|                                          |                                                       | $V_{TEST} = 1.2 \times V_{IOTM}$ ; $t = 1s$ (100% production test)                                                                                                                       | 8484        | $V_{PK}$  |

| $V_{IMP}$                                | Maximum impulse voltage <sup>(2)</sup>                | Tested in air;<br>1.2/50 $\mu$ s waveform per IEC 62638-1                                                                                                                                | 9230        | $V_{PK}$  |

| $V_{IOSM}$                               | Maximum surge isolation voltage <sup>(3)</sup>        | Tested in oil (qualification test);<br>1.2/50 $\mu$ s waveform per IEC 62638-1                                                                                                           | 12000       | $V_{PK}$  |

| $q_{pd}$                                 | Apparent charge <sup>(4)</sup>                        | Method a: After input-output safety test subgroup 2/3,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ;<br>$V_{pd(m)} = 1.2 \times V_{IORM} = 2036V_{PK}$ , $t_m = 10s$ .                     | $\leq 5$    | pC        |

|                                          |                                                       | Method a: After environmental tests subgroup 1,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ;<br>$V_{pd(m)} = 1.6 \times V_{IORM} = 2715V_{PK}$ , $t_m = 10s$ .                            | $\leq 5$    |           |

|                                          |                                                       | Method b1: At routine test (100% production) and preconditioning (type test), $V_{ini} = V_{IOTM}$ , $t_{ini} = 1s$ ;<br>$V_{pd(m)} = 1.875 \times V_{IORM} = 3139V_{PK}$ , $t_m = 1s$ . | $\leq 5$    |           |

| $C_{IO}$                                 | Barrier capacitance, input to output <sup>(5)</sup>   | $V_{IO} = 0.4 \times \sin(2\pi ft)$ , $f = 1MHz$                                                                                                                                         | 3           | pF        |

| $R_{IO}$                                 | Insulation resistance, input to output <sup>(5)</sup> | $V_{IO} = 500V$ , $T_A = 25^\circ C$                                                                                                                                                     | $> 10^{12}$ | $\Omega$  |

|                                          |                                                       | $V_{IO} = 500V$ , $100^\circ C \leq T_A \leq 125^\circ C$                                                                                                                                | $> 10^{11}$ |           |

|                                          |                                                       | $V_{IO} = 500V$ at $T_S = 150^\circ C$                                                                                                                                                   | $> 10^9$    |           |

|                                          | Pollution degree                                      |                                                                                                                                                                                          | 2           |           |

|                                          | Climatic category                                     |                                                                                                                                                                                          | 40/125/21   |           |

| <b>UL 1577</b>                           |                                                       |                                                                                                                                                                                          |             |           |

| $V_{ISO}$                                | Withstand isolation voltage                           | $V_{TEST} = V_{ISO} = 5000V_{RMS}$ , $t = 60s$ (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO} = 6000V_{RMS}$ , $t = 1s$ (100% production)                                            | 5000        | $V_{RMS}$ |

- (1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed-circuit board are used to help increase these specifications.

- (2) Testing is carried out in air to determine the intrinsic surge immunity of the package.

- (3) Testing is carried out in oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating a two-pin device.

## 6.7 Safety-Related Certifications

| VDE                                                                                                                                                                                    | UL                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Plan to certify according to DIN EN IEC 60747-17 (VDE 0884-17)                                                                                                                         | Plan to certify under UL 1577 Component Recognition Program |

| Reinforced insulation; Maximum transient isolation voltage, 7070V $_{PK}$ ; Maximum repetitive peak isolation voltage, 1697V $_{PK}$ ; Maximum surge isolation voltage, 12000V $_{PK}$ | Single protection, 5000V $_{RMS}$                           |

| Certificate planned                                                                                                                                                                    | Certificate planned                                         |

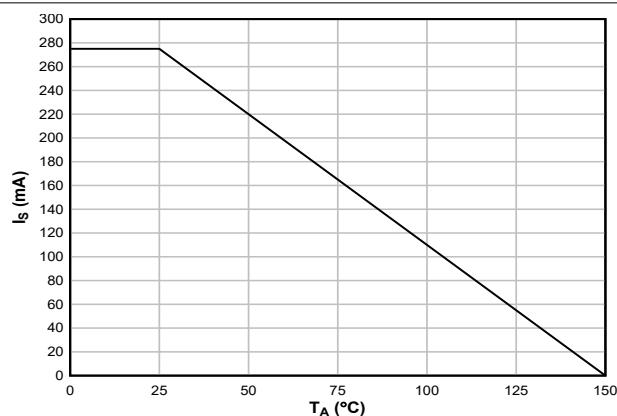

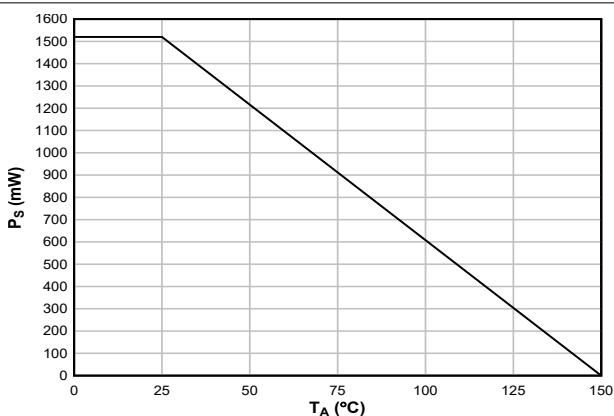

## 6.8 Safety Limiting Values

| PARAMETER <sup>(1) (2)</sup> |                                         | TEST CONDITIONS                                                                                      | MIN | TYP | MAX  | UNIT |

|------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>S</sub>               | Safety input, output, or supply current | R <sub>θJA</sub> = 82.5°C/W, V <sub>VDDP</sub> = 5.5V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C |     |     | 275  | mA   |

| P <sub>S</sub>               | Safety input, output, or total power    | R <sub>θJA</sub> = 82.5°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                           |     |     | 1.52 | W    |

| T <sub>S</sub>               | Maximum safety temperature              |                                                                                                      |     |     | 150  | °C   |

(1) Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting, dissipate sufficient power to overheat the die and damage the isolation barrier, potentially leading to secondary system failures.

(2) The safety-limiting constraint is the maximum junction temperature specified in the data sheet. The power dissipation and junction-to-air thermal impedance of the device installed in the application hardware determines the junction temperature. The assumed junction-to-air thermal resistance in the [Thermal Information](#) table is that of a device installed on a high-K test board for leaded surface-mount packages. The power is the recommended maximum input voltage times the current. The junction temperature is then the ambient temperature plus the power times the junction-to-air thermal resistance.

## 6.9 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted). Typicals at T<sub>A</sub> = 25°C. C<sub>VDDP</sub> = 1μF, C<sub>DIV1</sub> = 47nF, C<sub>DIV2</sub> = 220nF, C<sub>VDRV</sub> = 1nF, I<sub>AUX</sub> = 0mA. 50kΩ pull-ups from FLT1, ALM1, PGOOD to VDDP. R<sub>RESP</sub> = 100kΩ to VSSS.

| PARAMETER              |                                                 | TEST CONDITIONS                                                                                                                                                                                                          | MIN | TYP  | MAX | UNIT |

|------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| <b>COMMON</b>          |                                                 |                                                                                                                                                                                                                          |     |      |     |      |

| CMTI                   | Common-mode transient immunity, static.         | V <sub>CMI</sub>   = 1000V, V <sub>EN</sub> = 0V or V <sub>EN</sub> = 5V.                                                                                                                                                | 100 |      |     | V/ns |

| TSD                    | Temperature shutdown                            | V <sub>VDDP</sub> = 5V                                                                                                                                                                                                   |     | 173  |     | °C   |

| TSDH                   | Temperature shutdown hysteresis                 | V <sub>VDDP</sub> = 5V                                                                                                                                                                                                   |     | 32   |     | °C   |

| <b>SUPPLY</b>          |                                                 |                                                                                                                                                                                                                          |     |      |     |      |

| I <sub>VDDP_STBY</sub> | VDDP current in standby                         | V <sub>VDDP</sub> = 5V, EN = 0V, CE = 0V.<br>Measure average current.                                                                                                                                                    |     | 25   | 45  | μA   |

| I <sub>VDDP_LOW</sub>  | VDDP average current in steady state            | V <sub>VDDP</sub> = 5V, EN = CE = 5V.<br>Fault and alarm inputs tied to VSSP (device specific).<br>I <sub>AUX</sub> = 0mA.<br>Lowest power regulation.<br>V <sub>VDDH</sub> in steady state, measure I <sub>VDDP</sub> . |     | 5.3  |     | mA   |

| I <sub>VDDP_HIGH</sub> | VDDP average current in steady state            | V <sub>VDDP</sub> = 5V, EN = CE = 5V.<br>Fault and alarm inputs tied to VSSS (device specific).<br>Highest power regulation.<br>V <sub>VDDH</sub> in steady state, measure I <sub>VDDP</sub> .                           |     | 37   |     | mA   |

| V <sub>VDDH</sub>      | VDDH output voltage                             | V <sub>VDDP</sub> = 5V, EN = CE = 5V.<br>Fault and alarm inputs tied to VSSS (device specific).                                                                                                                          | 16  | 17   | 18  | V    |

| V <sub>VDDM</sub>      | Average VDDM voltage when not sourcing current. | V <sub>VDDP</sub> = 5V, EN = CE = 5V.<br>Fault and alarm inputs tied to VSSS (device specific).                                                                                                                          | 4.8 | 5.0  | 5.2 | V    |

| I <sub>VDDH_STBY</sub> | Average standby current of VDDH supply.         | V <sub>VDDP</sub> = 5V, EN = 0V, CE = 5V.<br>Fault and alarm inputs tied to VSSS (device specific).                                                                                                                      |     | 48   |     | μA   |

| I <sub>VDDM_STBY</sub> | Average standby current of VDDM supply.         | V <sub>VDDP</sub> = 5V, EN = 0V, CE = 5V.<br>Fault and alarm inputs tied to VSSS (device specific).                                                                                                                      |     | 105  |     | μA   |

| P <sub>OUT_VDDH</sub>  | Maximum power transfer to VDDH.                 | V <sub>VDDP</sub> = 5V, EN = 0V, CE = 5V.                                                                                                                                                                                | 42  | 72.8 |     | mW   |

## 6.9 Electrical Characteristics (続き)

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A = 25^\circ\text{C}$ .  $C_{VDDP} = 1\mu\text{F}$ ,  $C_{DIV1} = 47\text{nF}$ ,  $C_{DIV2} = 220\text{nF}$ ,  $C_{VDRV} = 1\text{nF}$ ,  $I_{AUX} = 0\text{mA}$ . 50k $\Omega$  pull-ups from  $\overline{FLT1}$ ,  $\overline{ALM1}$ ,  $\overline{PGOOD}$  to  $VDDP$ .  $R_{RESP} = 100\text{k}\Omega$  to  $VSSS$ .

| PARAMETER           | TEST CONDITIONS                                                                                                                                                                                                           | MIN                                                                                                                                                                                      | TYP  | MAX  | UNIT |   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---|

| $V_{VDDM\_IAUX}$    | $V_{VDDP} = 5\text{V}$ , $EN = 0\text{V}$ , steady state.<br>Fault and alarm inputs tied to $VSSS$ (device specific).<br>Source $I_{AUX} = 5\text{mA}$ from $VDDM$ ,<br>measure $V_{VDDM}$ .<br>$C_{DIV2} = 1\mu\text{F}$ | 4.7                                                                                                                                                                                      | 5.5  |      | V    |   |

| <b>SUPERVISORY</b>  |                                                                                                                                                                                                                           |                                                                                                                                                                                          |      |      |      |   |

| $V_{VDDP\_UV\_R}$   | $VDDP$ undervoltage threshold rising                                                                                                                                                                                      | 3.9                                                                                                                                                                                      | 4.1  | 4.35 | V    |   |

| $V_{VDDP\_UV\_F}$   | $VDDP$ undervoltage threshold falling                                                                                                                                                                                     | 3.8                                                                                                                                                                                      | 3.9  | 4.25 | V    |   |

| $V_{VDDP\_UV\_HYS}$ | $VDDP$ undervoltage threshold hysteresis                                                                                                                                                                                  |                                                                                                                                                                                          | 170  |      | mV   |   |

| $V_{VDDH\_UV\_R}$   | $VDDH$ undervoltage threshold rising                                                                                                                                                                                      | 11.9                                                                                                                                                                                     | 13   | 14.2 | V    |   |

| $V_{VDDH\_UV\_F}$   | $VDDH$ undervoltage threshold falling.                                                                                                                                                                                    | 9.6                                                                                                                                                                                      | 10.4 | 11.5 | V    |   |

| $V_{VDDH\_UV\_HYS}$ | $VDDH$ undervoltage threshold hysteresis.                                                                                                                                                                                 |                                                                                                                                                                                          | 2.5  |      | V    |   |

| $V_{VDDM\_UV\_R}$   | $VDDM$ undervoltage threshold rising                                                                                                                                                                                      | 3.4                                                                                                                                                                                      | 3.7  | 3.9  | V    |   |

| $V_{VDDM\_UV\_F}$   | $VDDM$ undervoltage threshold falling.                                                                                                                                                                                    | 3.1                                                                                                                                                                                      | 3.4  | 3.7  | V    |   |

| $V_{VDDM\_UV\_HYS}$ | $VDDM$ undervoltage threshold hysteresis.                                                                                                                                                                                 |                                                                                                                                                                                          | 0.3  |      | V    |   |

| <b>DRIVER</b>       |                                                                                                                                                                                                                           |                                                                                                                                                                                          |      |      |      |   |

| $V_{VDRV\_H}$       | $VDRV$ output voltage driven high                                                                                                                                                                                         | $V_{VDDP} = 5\text{V}$ , $EN = 5\text{V}$ .<br>$V_{VDDH}$ in steady state, no DC loading.<br>Fault and alarm inputs tied to $VSSS$ (device specific).                                    | 16   | 17   | 18   | V |

| $V_{VDRV\_L}$       | $VDRV$ output voltage driven low                                                                                                                                                                                          | $V_{VDDP} = 5\text{V}$ , $EN = 0\text{V}$ ,<br>$V_{VDDH}$ in steady state,<br>$VDRV$ sinking 10mA.<br>Fault and alarm inputs tied to $VSSS$ (device specific).                           |      | 0.1  |      | V |

| $I_{VDRV\_PEAK}$    | $VDRV$ peak output current during rise                                                                                                                                                                                    | $V_{VDDP} = 5\text{V}$ ,<br>$EN = 0\text{V} \rightarrow 5\text{V}$ ,<br>$V_{VDDH}$ in steady state,<br>measure peak current.<br>Fault and alarm inputs tied to $VSSS$ (device specific). |      | 1.5  |      | A |

|                     | $VDRV$ peak output current during fall                                                                                                                                                                                    | $V_{VDDP} = 5\text{V}$ ,<br>$EN = 5\text{V} \rightarrow 0\text{V}$ ,<br>$V_{VDDH}$ in steady state,<br>measure peak current.<br>Fault and alarm inputs tied to $VSSS$ (device specific). |      | 2.5  |      | A |

## 6.9 Electrical Characteristics (続き)

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A = 25^\circ\text{C}$ .  $C_{VDDP} = 1\mu\text{F}$ ,  $C_{DIV1} = 47\text{nF}$ ,  $C_{DIV2} = 220\text{nF}$ ,  $C_{VDRV} = 1\text{nF}$ ,  $I_{AUX} = 0\text{mA}$ . 50k $\Omega$  pull-ups from  $\overline{\text{FLT1}}$ ,  $\overline{\text{ALM1}}$ ,  $\overline{\text{PGOOD}}$  to  $\text{VDDP}$ .  $R_{RESP} = 100\text{k}\Omega$  to  $\text{VSSS}$ .

| PARAMETER                   | TEST CONDITIONS                                                                                                                                                                                                                                            | MIN                                                                                             | TYP | MAX | UNIT          |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|---------------|

| $R_{DS0N\_VDRV}$            | Driver on resistance in low state.                                                                                                                                                                                                                         | Fault and alarm inputs tied to $\text{VSSS}$ (device specific).                                 | 1.5 |     | $\Omega$      |

|                             | Driver on resistance in high state.                                                                                                                                                                                                                        | Fault and alarm inputs tied to $\text{VSSS}$ (device specific).                                 | 3.5 |     | $\Omega$      |

| $V_{ACT\_CLAMP}$            | Active clamp voltage when engaged.                                                                                                                                                                                                                         | $V_{VDDP} = 0\text{V}$ .<br>Sink $I_{VDRV} = 300\text{mA}$ .<br>Measure $VDRV$ .                | 1.9 | 2.5 | $\text{V}$    |

| <b>DIGITAL INPUT/OUTPUT</b> |                                                                                                                                                                                                                                                            |                                                                                                 |     |     |               |

| $V_{IT\_+(EN)}$             | Input threshold voltage rising on EN.                                                                                                                                                                                                                      | $V_{VDDP} = 5\text{V}$                                                                          | 2.3 | 2.5 | 2.7           |

| $V_{IT\_-(EN)}$             | Input threshold voltage falling on EN.                                                                                                                                                                                                                     | $V_{VDDP} = 5\text{V}$                                                                          | 1.7 | 1.9 | 2.0           |

| $V_{IT\_HYS(EN)}$           | Input threshold voltage hysteresis on EN.                                                                                                                                                                                                                  | $V_{VDDP} = 5\text{V}$                                                                          | 0.5 |     | $\text{V}$    |

| $V_{IT\_+(CE)}$             | Input threshold voltage rising on CE.                                                                                                                                                                                                                      | $V_{VDDP} = 5\text{V}$                                                                          | 2.3 | 2.5 | 2.7           |

| $V_{IT\_-(CE)}$             | Input threshold voltage falling on CE.                                                                                                                                                                                                                     | $V_{VDDP} = 5\text{V}$                                                                          | 1.7 | 1.9 | 2.0           |

| $V_{IT\_HYS(CE)}$           | Input threshold voltage hysteresis on CE.                                                                                                                                                                                                                  | $V_{VDDP} = 5\text{V}$                                                                          | 0.5 |     | $\text{V}$    |

| $V_{OL}$                    | Low level output voltage.<br>$\overline{\text{PGOOD}}$<br>$\overline{\text{FLT1}}$ (TPSI310x, TPSI311x, TPSI3133)<br>$\overline{\text{FLT2}}$ (TPSI311x)<br>$\overline{\text{ALM1}}$ (TPSI310x, TPSI312x, TPSI3133)<br>$\overline{\text{ALM2}}$ (TPSI32x)  | $V_{VDDP} = 4.5\text{V to } 5.5\text{V}$ ,<br>$I_{OL} = 2\text{mA}$ .<br>Outputs enabled.       | 0.4 |     | $\text{V}$    |

| $I_{OL}$                    | Low level output current.<br>$\overline{\text{PGOOD}}$<br>$\overline{\text{FLT1}}$ (TPSI310x, TPSI311x, TPSI3133)<br>$\overline{\text{FLT2}}$ (TPSI311x)<br>$\overline{\text{ALM1}}$ (TPSI310x, TPSI312x, TPSI3133)<br>$\overline{\text{ALM2}}$ (TPSI312x) | $V_{VDDP} = 4.5\text{V to } 5.5\text{V}$ ,<br>$V_{OL} = 0.4\text{V}$ .<br>Outputs enabled.      | -2  |     | $\text{mA}$   |

| $V_{OL\_FLT\_CMP}$          | Open-drain output, low level output voltage.<br>$\overline{\text{FLT\_CMP1}}$ (TPSI3133)                                                                                                                                                                   | $V_{VDDP} = 4.5\text{V to } 5.5\text{V}$ ,<br>$I_{OL} = 2\text{mA}$ ,<br>$CE = 1$ , $EN = 0$ .  | 0.1 |     | $\text{V}$    |

| $I_{OL\_FLT\_CMP}$          | Open-drain output, low level output current.<br>$\overline{\text{FLT\_CMP1}}$ (TPSI3133)                                                                                                                                                                   | $V_{VDDP} = 4.5\text{V to } 5.5\text{V}$ ,<br>$V_{OL} = 0.4\text{V}$ ,<br>$CE = 1$ , $EN = 0$ . | -2  |     | $\text{mA}$   |

| $I_{LKG}$                   | Leakage current.<br>$\overline{\text{PGOOD}}$<br>$\overline{\text{FLT1}}$ (TPSI310x, TPSI311x, TPSI3133)<br>$\overline{\text{FLT2}}$ (TPSI311x)<br>$\overline{\text{ALM1}}$ (TPSI310x, TPSI312x, TPSI3133)<br>$\overline{\text{ALM2}}$ (TPSI312x)          | $V_{VDDP} = 4.5\text{V to } 5.5\text{V}$ ,<br>Outputs disabled.                                 | 2   |     | $\mu\text{A}$ |

| $R_{EN\_PULLDOWN}$          | Internal resistor pull-down on EN.                                                                                                                                                                                                                         | $V_{VDDP} = 5\text{V}$                                                                          | 390 | 500 | 640           |

| $R_{CE\_PULLDOWN}$          | Internal resistor pull-down on CE.                                                                                                                                                                                                                         | $V_{VDDP} = 5\text{V}$                                                                          | 390 | 500 | 640           |

## 6.9 Electrical Characteristics (続き)

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A = 25^\circ\text{C}$ .  $C_{VDDP} = 1\mu\text{F}$ ,  $C_{DIV1} = 47\text{nF}$ ,  $C_{DIV2} = 220\text{nF}$ ,  $C_{VDRV} = 1\text{nF}$ ,  $I_{AUX} = 0\text{mA}$ . 50k $\Omega$  pull-ups from  $\overline{\text{FLT1}}$ ,  $\overline{\text{ALM1}}$ ,  $\overline{\text{PGOOD}}$  to  $\text{VDDP}$ .  $R_{RESP} = 100\text{k}\Omega$  to  $\text{VSSS}$ .

| PARAMETER           | TEST CONDITIONS                                                                                                                                                                                                | MIN                      | TYP  | MAX  | UNIT             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|------|------------------|

| <b>REFERENCE</b>    |                                                                                                                                                                                                                |                          |      |      |                  |

| $V_{REF}$           | Internal reference voltage.<br>TPSI3100, TPSI3110, TPSI3120 devices.                                                                                                                                           | $T_A = 25^\circ\text{C}$ |      | 0.31 | V                |

|                     | Internal reference voltage.<br>TPSI3103, TPSI3113, TPSI3123, TPSI3133 devices.                                                                                                                                 | $T_A = 25^\circ\text{C}$ |      | 1.23 | V                |

| $V_{REF\_TOL}$      | Internal reference voltage tolerance.                                                                                                                                                                          |                          | -1.5 | 1.5  | %                |

| <b>COMPARATORS</b>  |                                                                                                                                                                                                                |                          |      |      |                  |

| $R_{CMP\_PULLDOWN}$ | Internal resistor pull-down.<br>$\text{FLT1\_CMP}$ , $\text{ALM1\_CMP}$<br>(TPSI310x, TPSI3133)<br>$\text{FLT1\_CMP}$ , $\text{FLT2\_CMP}$ (TPSI311x)<br>$\text{ALM1\_CMP}$ , $\text{ALM2\_CMP}$<br>(TPSI312x) |                          | 1.3  | 2.8  | 3.8              |

|                     |                                                                                                                                                                                                                |                          |      |      | $\text{M}\Omega$ |

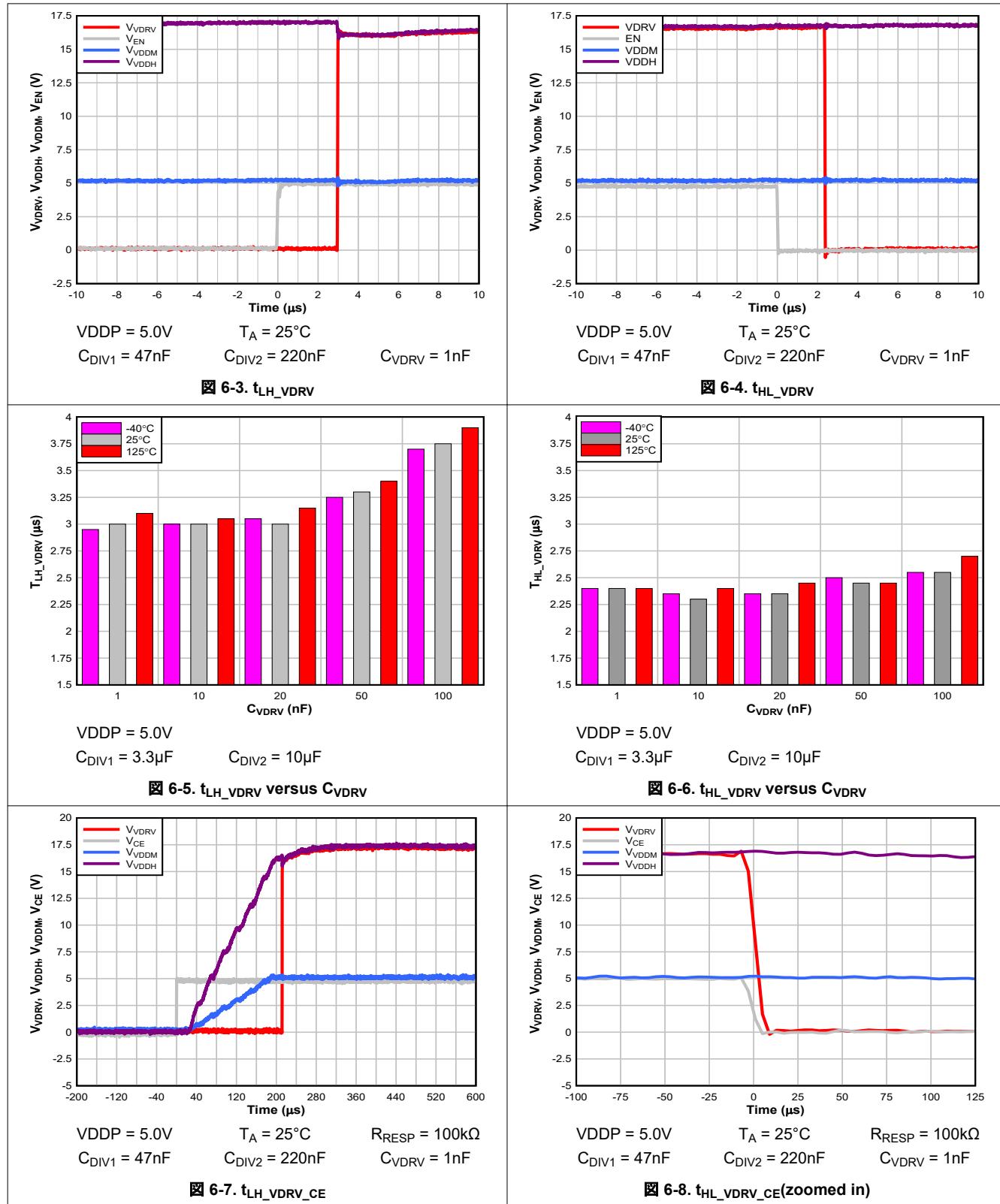

## 6.10 Switching Characteristics

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A = 25^\circ\text{C}$ .  $C_{VDDP} = 1\mu\text{F}$ ,  $C_{DIV1} = 47\text{nF}$ ,  $C_{DIV2} = 220\text{nF}$ ,  $C_{VDRV} = 1\text{nF}$ ,  $I_{AUX} = 0\text{mA}$ . 50k $\Omega$  pull-ups from  $\overline{\text{FLT1}}$ ,  $\overline{\text{ALM1}}$ ,  $\overline{\text{PGOOD}}$  to  $\text{VDDP}$ .  $R_{RESP} = 100\text{k}\Omega$  to  $\text{VSSS}$ .

| PARAMETER               | TEST CONDITIONS                                                                                                                                                                                            | MIN | TYP | MAX | UNIT          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

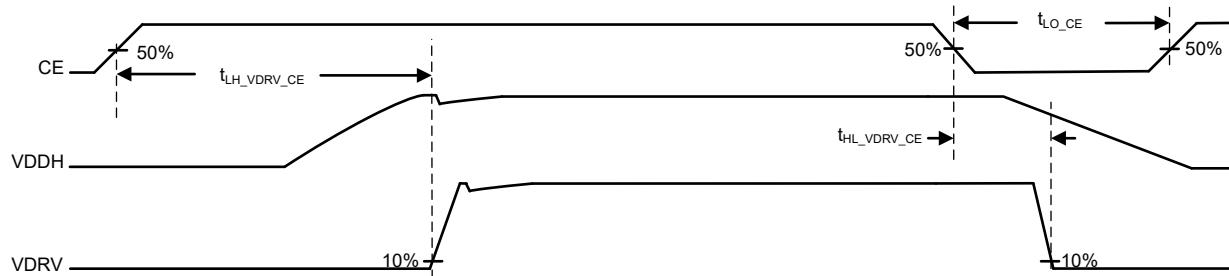

| <b>POWER and DRIVER</b> |                                                                                                                                                                                                            |     |     |     |               |