## TPSM8F7x20、4V ~ 17V、4/6A、クワッド降圧パワー モジュール

### 1 特長

- 固定周波数のピーク電流モード (PCM) 制御

- 小型フォームファクタの 12.0mm x 7.0mm x 2.4mm、オーバーモールド BGA パワーモジュール

- 4 系統の独立した同期整流降圧出力

- 2 相、3 相、4 相のスタック能力をサポートし、より大きな出力電流に対応します

- 高効率性を実現する、MOSFET、インダクタ、および基本的なパッシブ部品内蔵。

- 入力電圧範囲: 4V ~ 17V

- 出力電圧範囲: 0.6V ~ 11V

- 内部または外部補償を選択可能

- 400kHz ~ 2.2MHz の継続的な可変スイッチング周波数

- 外部クロックに同期可能

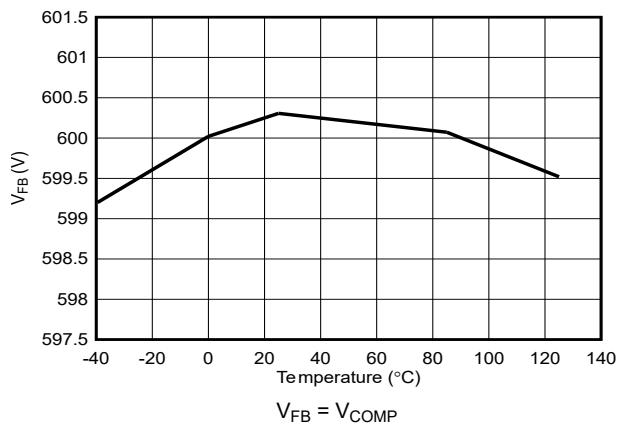

- 全温度範囲にわたって 0.6V、±0.75% の電圧リファレンス精度

- シーケンシング機能

- 可変入力 UVLO を利用可能

- パワーグッド出力監視

- 出力放電

- プリバイアス出力への単調スタートアップ

- 外部 SS ピンによりソフトスタート時間を調整可能

- 出力過電圧 (OV)、低電圧 (UV)、過電流 (OC)、サーマルシャットダウン保護機能

- MSEL1/2 ピン アナログ温度出力

- モジュール温度範囲: -40°C ~ 125°C

- WEBENCH® Power Designer** により、TPSM8F7x20 を使用するカスタム設計を作成

### 2 アプリケーション

- 試験および測定機器、航空宇宙

- 医療 / ヘルスケア

- FPGA、ASIC、DSP の I/O 電圧

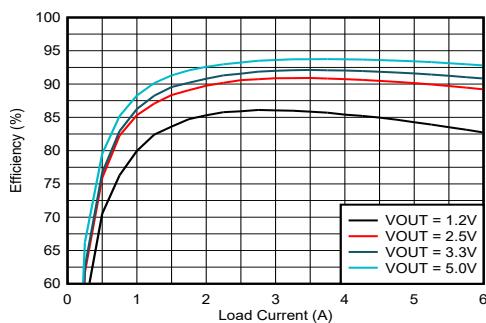

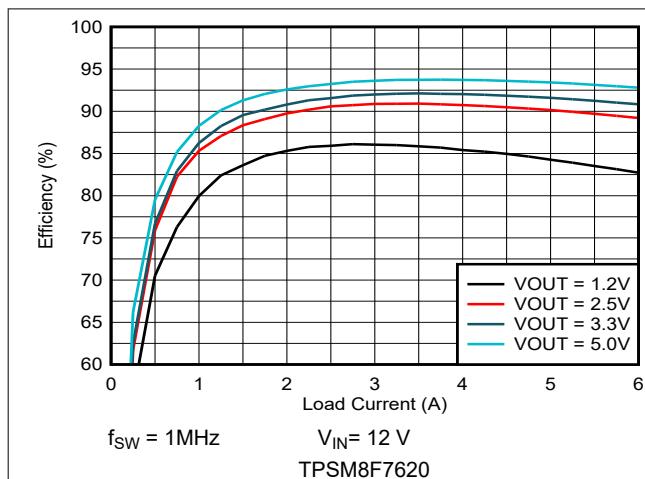

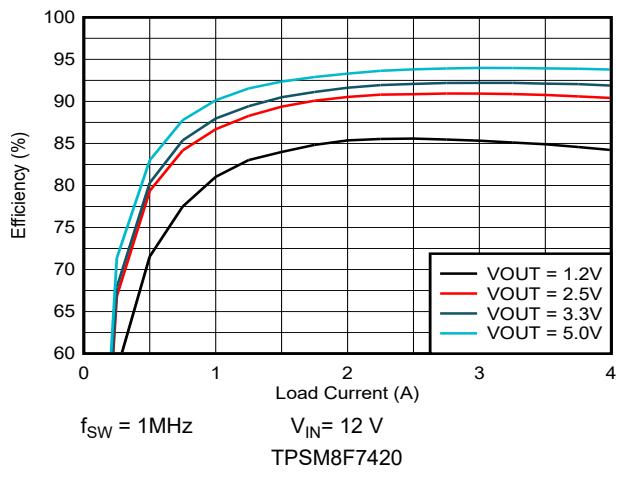

効率代表値、12V 入力、1MHz Fsw

### 3 説明

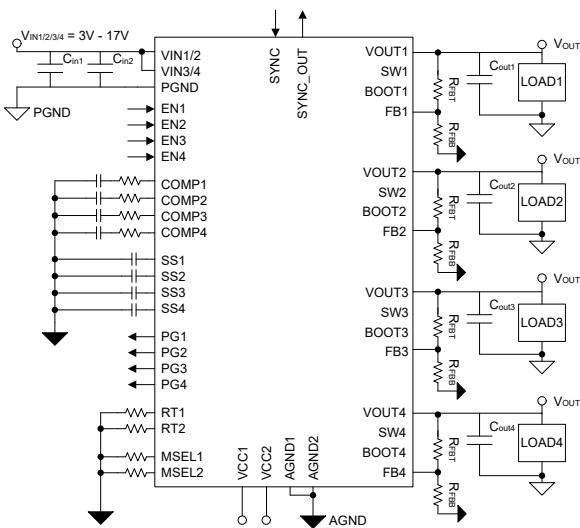

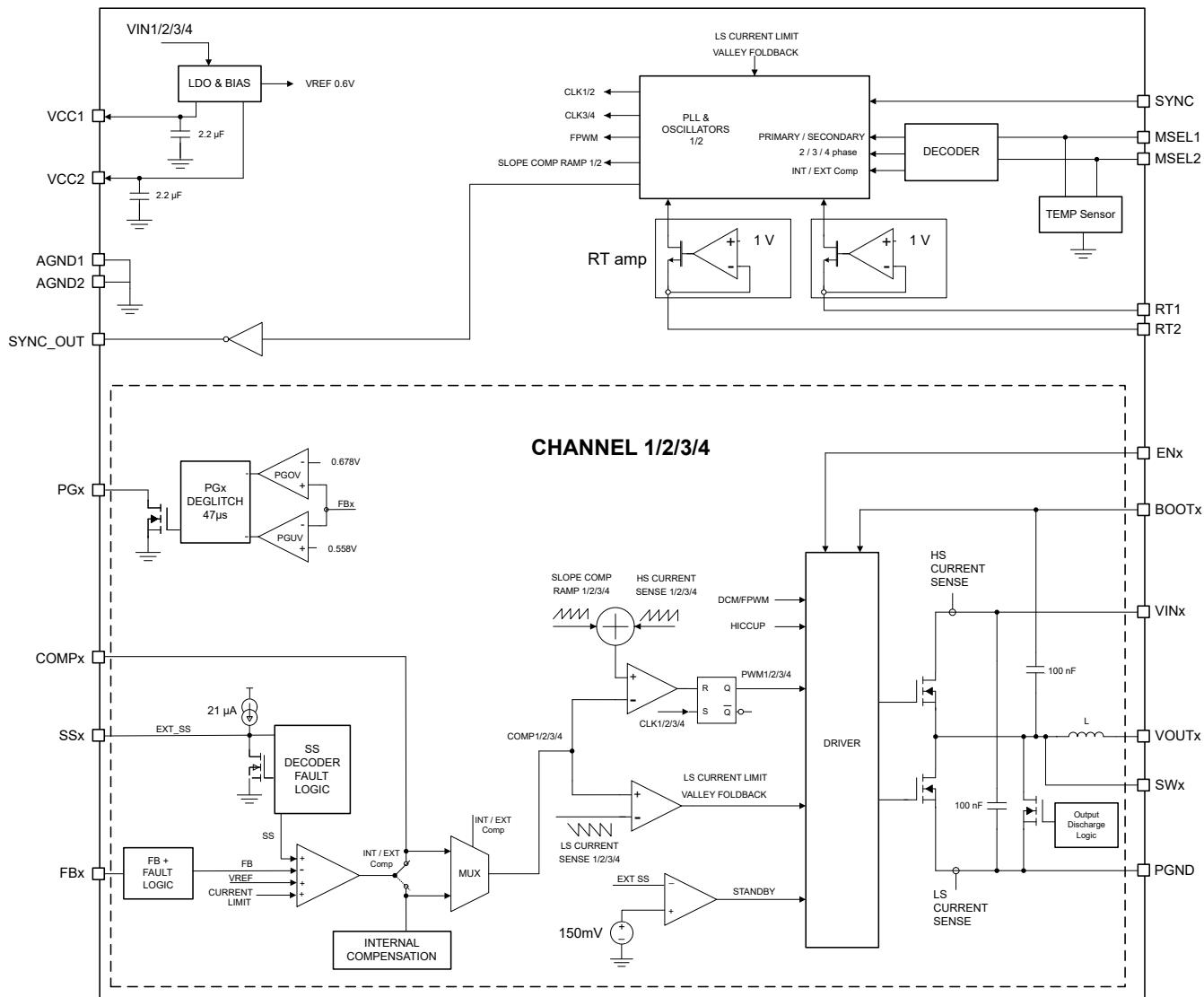

TPSM8F7x20 は、電力密度の高いクワッドチャネル降圧パワー モジュールであり、0.6V ~ 11V の広い出力電圧範囲向けに、効率的で信頼性の高い電力変換を実現するよう設計されています。このモジュールは、MOSFET、インダクタ、選択コンデンサを内蔵しているため、基板面積とレイアウトの複雑さを削減できます。このモジュールは、インターリープ位相で 2 相、3 相、4 相のスタック可能性をサポートすることで、マルチフェーズとマルチ出力両方のレールに構成できます。定常状態の条件下では、モジュールは固定周波数の FCCM で動作します。この周波数は 400kHz ~ 2.2MHz の範囲に抵抗を調整でき、外部クロックに同期可能です。

TPSM8F7x20 モジュールは、内部および外部補償による電流モード制御を採用しています。外部のソフトスタート、アクティブ出力放電、調整可能な EN、パワーグッド機能により、シーケンシング要件を簡単に満たすことができます。堅牢性を確保するため、保護機能 (出力 OV および UV、入力 UVLO、TSD、OC) もすべて搭載されています。

### 製品情報

| 部品番号 (3)   | パッケージ (1)        | パッケージ サイズ (2)  |

|------------|------------------|----------------|

| TPSM8F7420 | APG (FCCSP, 112) | 12.0mm x 7.0mm |

| TPSM8F7620 |                  |                |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 「[デバイス比較表](#)」を参照してください。

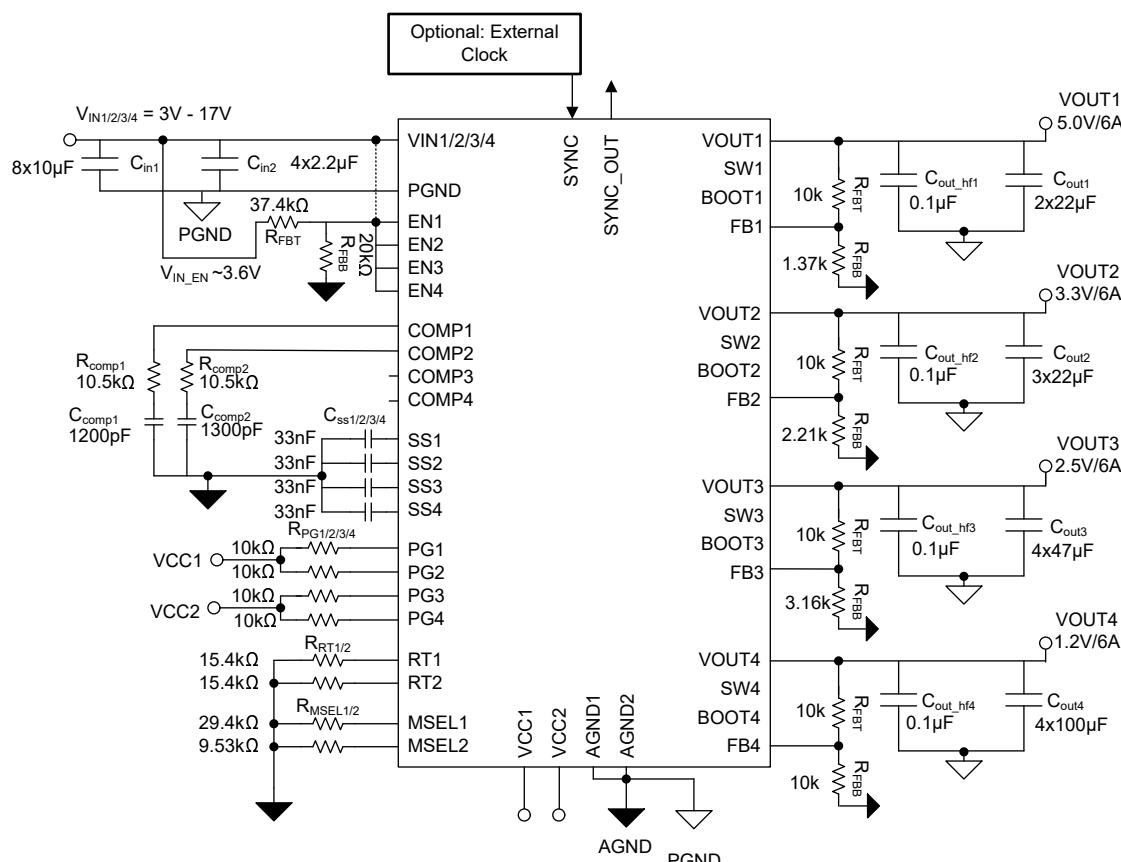

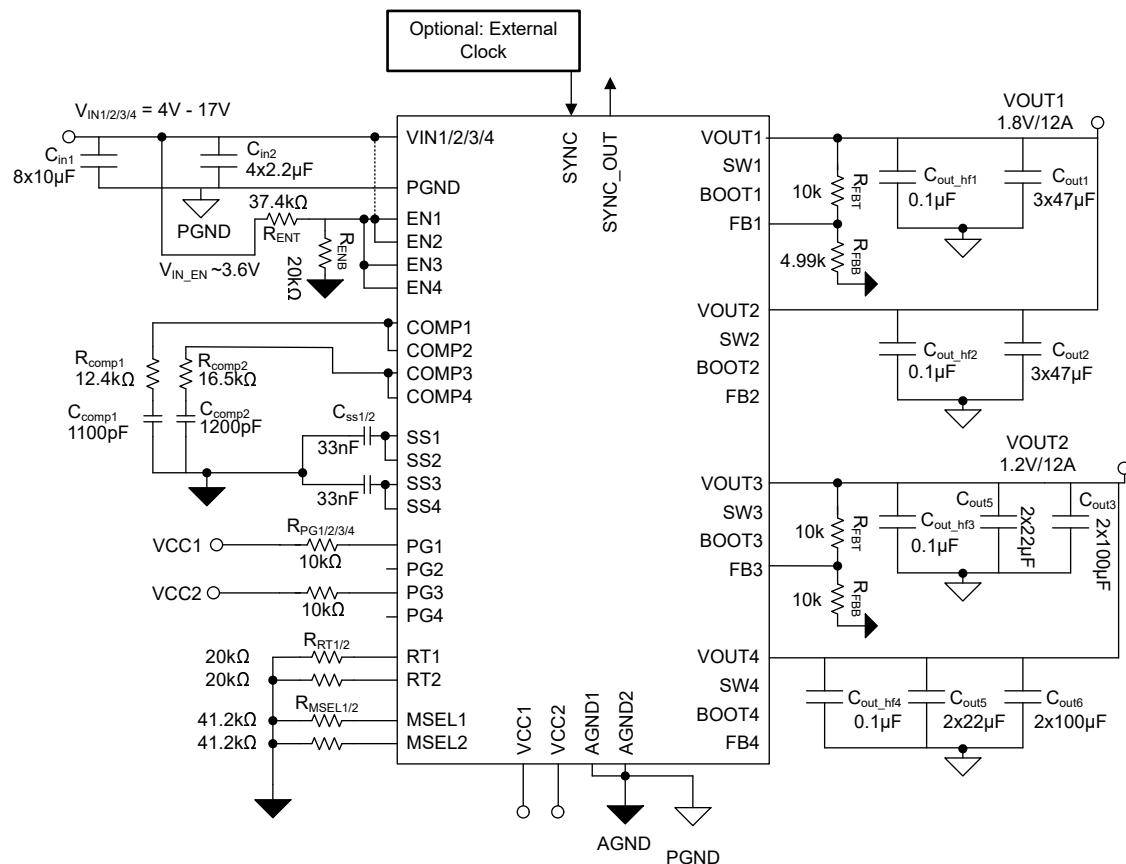

代表的な回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVS155](#)

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>27</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>27</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>27</b> |

| <b>4 デバイス比較表</b>   | <b>3</b>  | <b>8.3 2-PH アプリケーション</b>      | <b>38</b> |

| <b>5 ピン構成および機能</b> | <b>3</b>  | <b>8.4 電源に関する推奨事項</b>         | <b>43</b> |

| <b>6 仕様</b>        | <b>6</b>  | <b>8.5 レイアウト</b>              | <b>43</b> |

| 6.1 絶対最大定格         | 6         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>46</b> |

| 6.2 推奨動作条件         | 6         | 9.1 デバイス サポート                 | 46        |

| 6.3 ESD Ratings    | 6         | 9.2 ドキュメントのサポート               | 46        |

| 6.4 熱に関する情報        | 7         | 9.3 ドキュメントの更新通知を受け取る方法        | 47        |

| 6.5 電気的特性          | 7         | 9.4 サポート・リソース                 | 47        |

| 6.6 代表的特性          | 10        | 9.5 商標                        | 47        |

| <b>7 詳細説明</b>      | <b>11</b> | 9.6 静電気放電に関する注意事項             | <b>47</b> |

| 7.1 概要             | 11        | 9.7 用語集                       | 47        |

| 7.2 機能ブロック図        | 12        | <b>10 改訂履歴</b>                | <b>47</b> |

| 7.3 機能説明           | 13        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>48</b> |

| 7.4 デバイスの機能モード     | 22        |                               |           |

## 4 デバイス比較表

| デバイス       | 発注用製品型番        | 定格チャネル電流 | パッケージ       | 接合部温度範囲       |

|------------|----------------|----------|-------------|---------------|

| TPSM8F7620 | TPSM8F7620APGR | 6A       | FCCSP (112) | -40°C ~ 125°C |

| TPSM8F7420 | TPSM8F7420APGR | 4A       | FCCSP (112) | -40°C ~ 125°C |

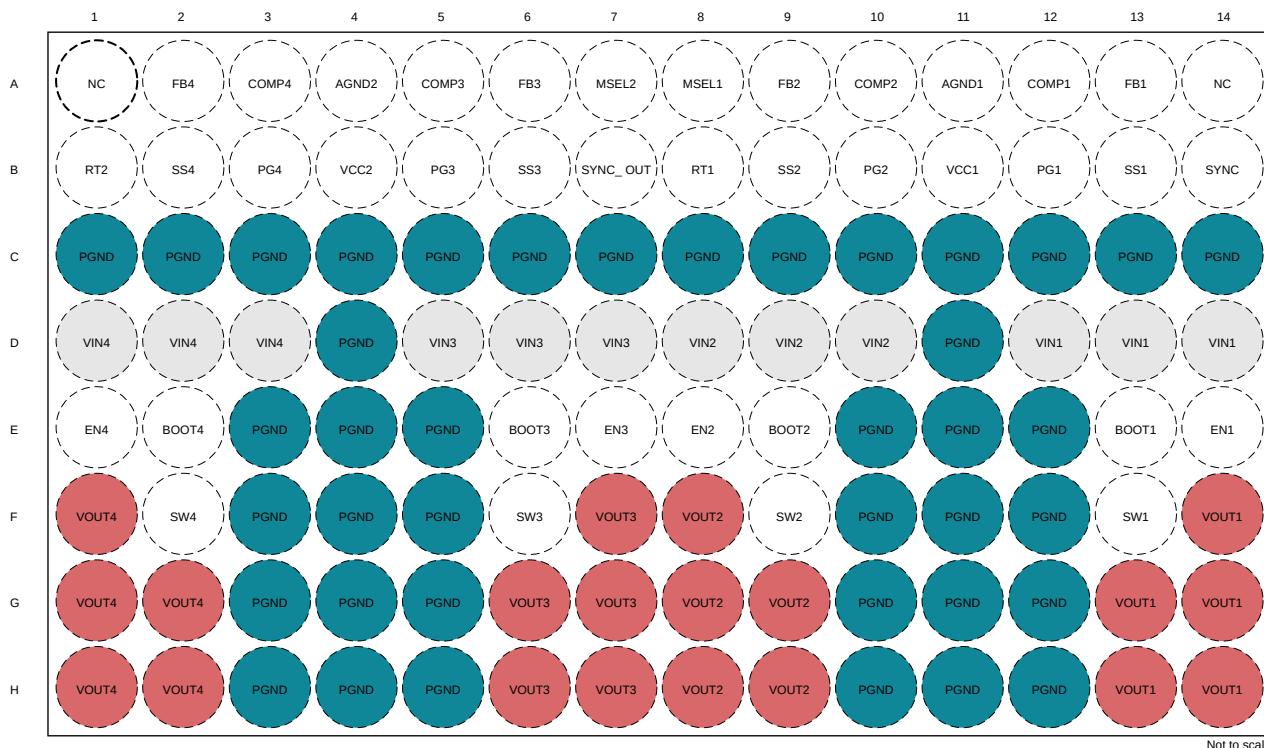

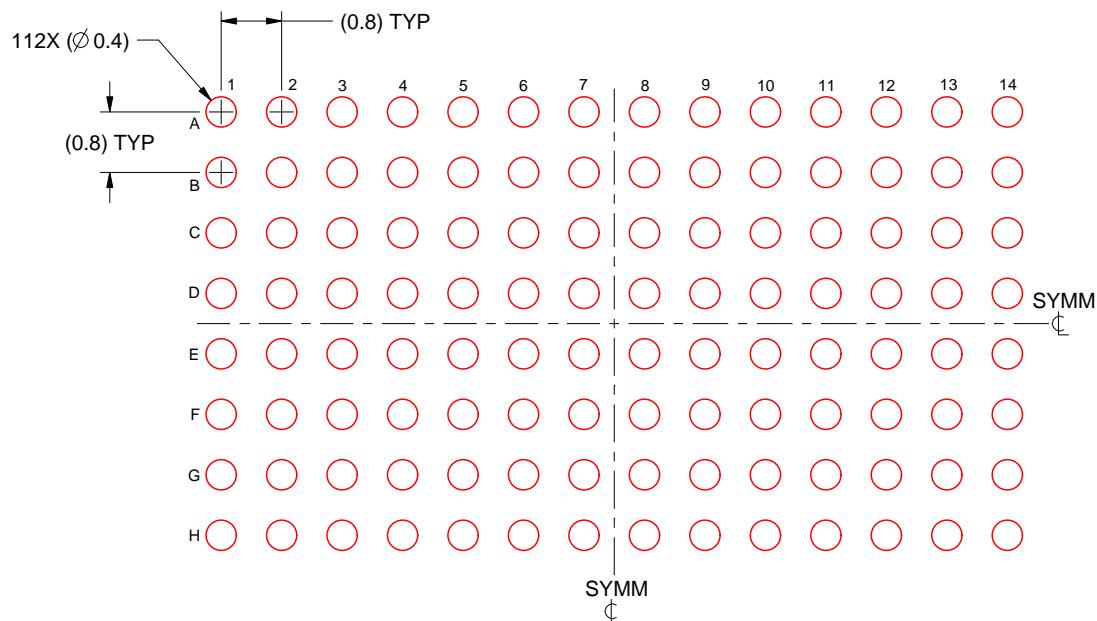

## 5 ピン構成および機能

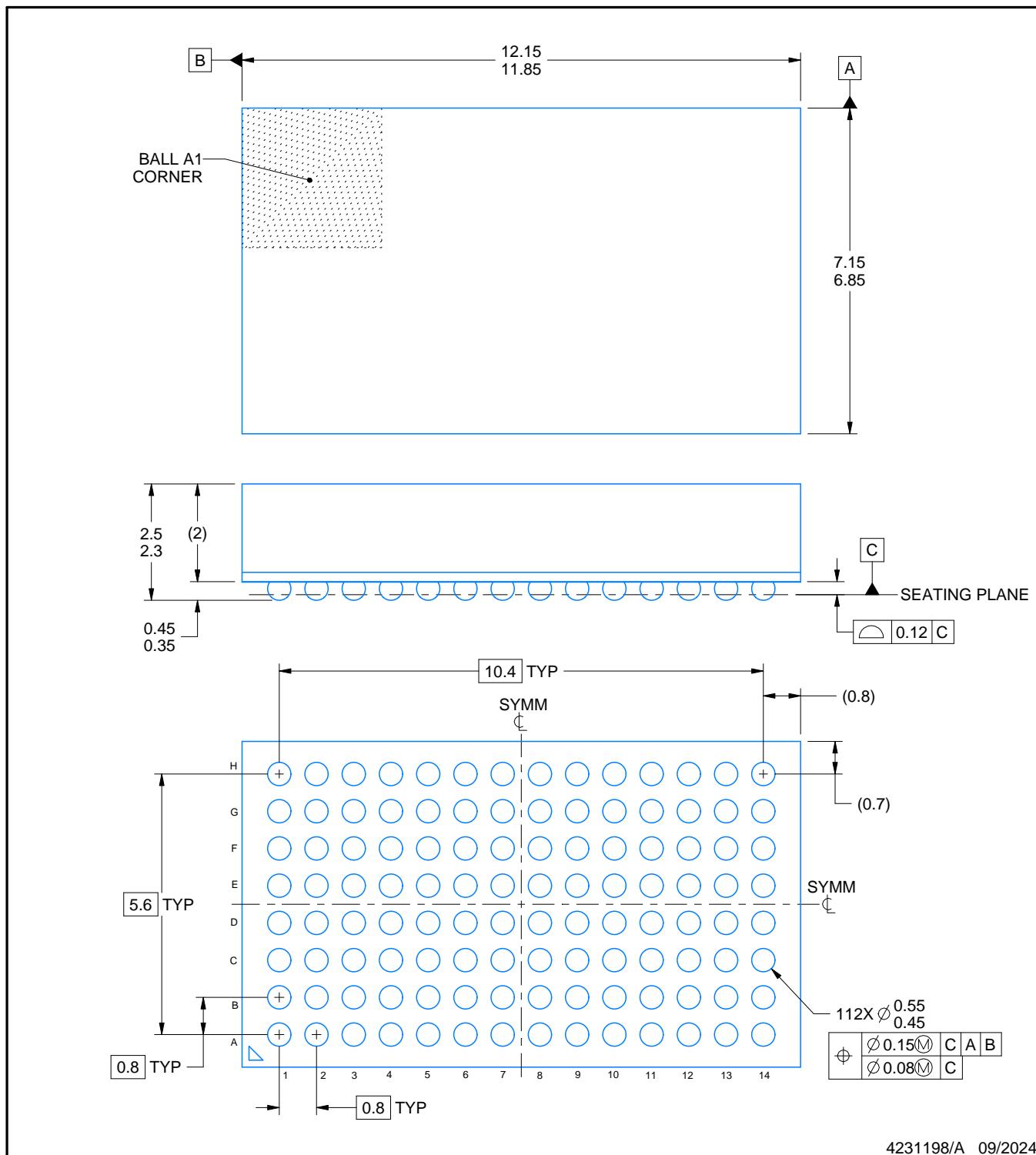

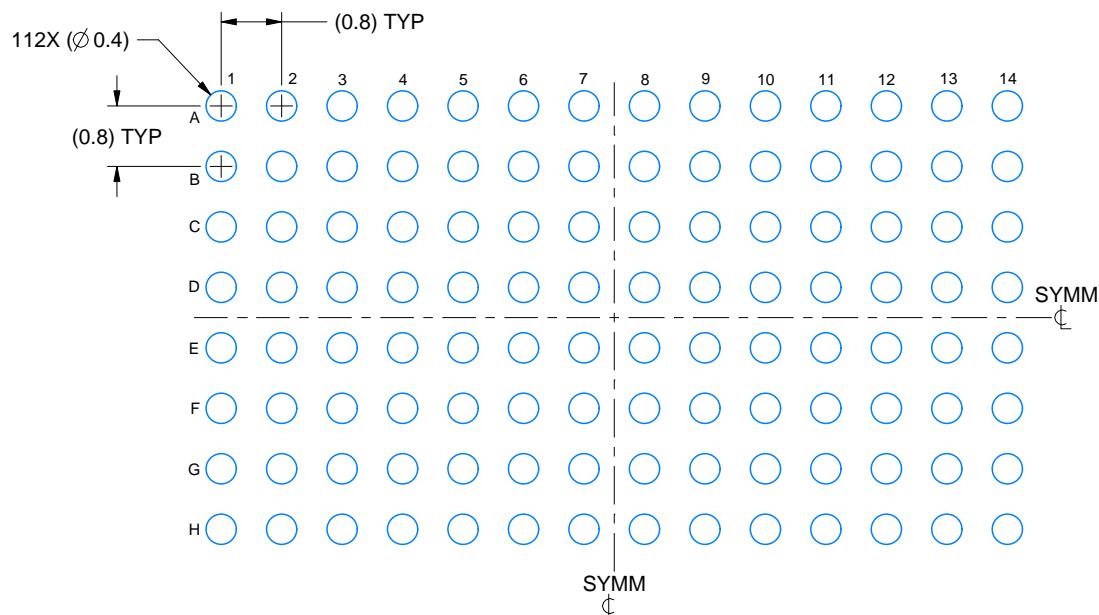

図 5-1. 112 ピン FCCSP APG パッケージ (上面図)

| 凡例    |            |

|-------|------------|

| VINx  | PGND       |

| VOUTx | その他のすべてのピン |

表 5-1. ピンの機能

| ピン                      | タイプ <sup>(1)</sup> | 説明                                                                                                                  |

|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|

| 番号                      | I                  | レギュレータへの入力電源。デカップリング入力コンデンサを VIN ピンから PGND ピンにできるだけ近づけて配置します。モジュールの各チャネルには、VIN から PGND への 100nF の内部高周波デカップリングがあります。 |

| D12, D13, D14           |                    |                                                                                                                     |

| D8, D9, D10             |                    |                                                                                                                     |

| D5, D6, D7              |                    |                                                                                                                     |

| D1, D2, D3              | O                  | VOUT の電源接続。出力コンデンサを VOUT から PGND へ、モジュールの出力ピンの近くに接続します。                                                             |

| F14, G13, G14, H13, H14 |                    |                                                                                                                     |

| F8, G8, G9, H8, H9      |                    |                                                                                                                     |

| F7, G6, G7, H6, H7      |                    |                                                                                                                     |

| F1, G1, G2, H1, H2      |                    |                                                                                                                     |

表 5-1. ピンの機能 (続き)

| ピン<br>番号                                                                                                                                                                          | 名称       | タイプ <sup>(1)</sup> | 説明                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| C1、C2、C3、C4、<br>C5、C6、C7、C8、<br>C9、C10、C11、<br>C12、C13、C14、<br>D4、D11、E3、E4、<br>E5、E10、E11、E12、<br>F3、F4、F5、F10、<br>F11、F12、G3、G4、<br>G5、G10、G11、<br>G12、H3、H4、H5、<br>H10、H11、H12 | PGND     | G                  | 電力段のグラントリターン。このピンは内部でローサイド MOSFET のソースに接続されます。                                                                                          |

| E13                                                                                                                                                                               | BOOT1    | I/O                | 内蔵のハイサイド MOSFET ゲートドライバ用電源。SW と BOOT の間に 100nF 内部コンデンサを接続します。モニタリング接続のみ。設計で NC として使用します。                                                |

| E9                                                                                                                                                                                | BOOT2    |                    |                                                                                                                                         |

| E6                                                                                                                                                                                | BOOT3    |                    |                                                                                                                                         |

| E2                                                                                                                                                                                | BOOT4    |                    |                                                                                                                                         |

| F13                                                                                                                                                                               | SW1      | O                  | モジュールのスイッチ ノード。モニタリング接続のみ。設計で NC として使用します。                                                                                              |

| F9                                                                                                                                                                                | SW2      |                    |                                                                                                                                         |

| F6                                                                                                                                                                                | SW3      |                    |                                                                                                                                         |

| F2                                                                                                                                                                                | SW4      |                    |                                                                                                                                         |

| B14                                                                                                                                                                               | SYNC     | I                  | このピンに外部クロックを入力することで、スイッチング周波数を同期させることができます。                                                                                             |

| B7                                                                                                                                                                                | SYNC_OUT | O                  | 上側と下側のチャネル ペア間の同期信号。接続する場合は、設計で NC として使用するか、他のレギュレータの同期として使用します。                                                                        |

| A8                                                                                                                                                                                | MSEL1    | I/O                | マルチファンクションセレクトピン。MSEL ピンと AGND の間にある抵抗によって内部補償と外部補償のいずれかを選択し、チャネル構成と位相を設定します。許容誤差 $\pm 1\%$ の抵抗が必要です。起動後、このピンはアナログ温度出力になります。            |

| A7                                                                                                                                                                                | MSEL2    |                    |                                                                                                                                         |

| E14                                                                                                                                                                               | EN1      | I                  | イネーブルピン。EN へのアクティブ High 入力により VOUT が有効になります。EN はフローティングのままにしないでください。                                                                    |

| E8                                                                                                                                                                                | EN2      |                    |                                                                                                                                         |

| E7                                                                                                                                                                                | EN3      |                    |                                                                                                                                         |

| E1                                                                                                                                                                                | EN4      |                    |                                                                                                                                         |

| B11                                                                                                                                                                               | VCC1     | P                  | 内部スイッチング LDO レギュレータ出力。それぞれ、VCC1、VCC2 と AGND1、AGND2 の間に内部 2.2μF コンデンサが接続されています。VCC は、PG のフルアップとして使用できます。それ以外の場合は、VCC をフローティングのままにしてください。 |

| B4                                                                                                                                                                                | VCC2     |                    |                                                                                                                                         |

| A13                                                                                                                                                                               | FB1      | I                  | 出力電圧レギュレーション用の帰還ピン。このピンを抵抗ディバイダの中間点に接続して、出力電圧を設定します。許容誤差 $\pm 1\%$ 以下の抵抗を推奨します。                                                         |

| A9                                                                                                                                                                                | FB2      |                    |                                                                                                                                         |

| A6                                                                                                                                                                                | FB3      |                    |                                                                                                                                         |

| A2                                                                                                                                                                                | FB4      |                    |                                                                                                                                         |

| A11                                                                                                                                                                               | AGND1    | G                  | アナログ グラント接続。内部電圧リファレンスとアナログ回路のグラントの帰線。AGND1 と AGND2 を低インピーダンスで接続します。                                                                    |

| A4                                                                                                                                                                                | AGND2    |                    |                                                                                                                                         |

| B8                                                                                                                                                                                | RT1      | I                  | 周波数プログラミングピン。RT と AGND の間に抵抗を配置することにより、発振器の周波数は 400kHz~2.2MHz の範囲に設定されます。許容誤差 $\pm 1\%$ の抵抗を推奨します。                                      |

| B1                                                                                                                                                                                | RT2      |                    |                                                                                                                                         |

| B13                                                                                                                                                                               | SS1      | I                  | SS ピンと AGND ピンの間に接続するコンデンサによって、ソフトスタート時間を設定します。                                                                                         |

| B9                                                                                                                                                                                | SS2      |                    |                                                                                                                                         |

| B6                                                                                                                                                                                | SS3      |                    |                                                                                                                                         |

| B2                                                                                                                                                                                | SS4      |                    |                                                                                                                                         |

**表 5-1. ピンの機能 (続き)**

| ピン<br>番号 | 名称    | タイプ <sup>(1)</sup> | 説明                                                                                                     |

|----------|-------|--------------------|--------------------------------------------------------------------------------------------------------|

| A12      | COMP1 | I/O                | 外部補償モードの GM エラー アンプ出力。マルチフェーズ モードの電流共有信号。<br>内部補償モードの場合は、フローティングのままにできます。                              |

| A10      | COMP2 |                    |                                                                                                        |

| A5       | COMP3 |                    |                                                                                                        |

| A3       | COMP4 |                    |                                                                                                        |

| B12      | PG1   | O                  | オープンドレインのパワー グッド ステータス信号。外付けプルアップ抵抗を VCC または外部電圧源に接続します。FB 電圧が指定された制限値を外れると、指定された遅延の後に PG が Low になります。 |

| B10      | PG2   |                    |                                                                                                        |

| B5       | PG3   |                    |                                                                                                        |

| B3       | PG4   |                    |                                                                                                        |

| A1、A14   | NC    | 該当なし               | 接続なし。このピンはフローティング状態のままにできます。                                                                           |

(1) I = 入力、O = 出力、P = 電源、G = グランド、N/A = 該当なし

## 6 仕様

### 6.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                     |                            | 最小値  | 最大値  | 単位 |

|---------------------|----------------------------|------|------|----|

| ピン電圧 <sup>(2)</sup> | VIN                        | -0.3 | 18   | V  |

| ピン電圧 <sup>(2)</sup> | VOUT                       | -0.3 | 15   | V  |

| ピン電圧 <sup>(2)</sup> | SW                         | -0.3 | 18   | V  |

| ピン電圧 <sup>(2)</sup> | BOOT - SW                  | -0.3 | 6    | V  |

| ピン電圧 <sup>(2)</sup> | EN                         | -0.3 | 18   | V  |

| ピン電圧 <sup>(2)</sup> | PG, MSEL, RT, FB           | -0.3 | 6    | V  |

| ピン電圧 <sup>(2)</sup> | COMP                       | -0.3 | 6    | V  |

| ピン電圧 <sup>(2)</sup> | SS                         | -0.3 | 6    | V  |

| ピン電圧 <sup>(2)</sup> | SYNC, SYNC_OUT             | -0.3 | 5.5  | V  |

| ピン電圧 <sup>(2)</sup> | VCC から AGND へ              | -0.3 | 5.5  | V  |

| ピン電圧 <sup>(2)</sup> | PGND から AGND への電圧差動        | -1   | 2    | V  |

| シンク電流               | PG                         |      | 10   | mA |

| 機械振動                | 20 ~ 2000Hz (X, Y, Z)      |      | 20   | G  |

| 機械的衝撃               | モジュールの機械的衝撃定格 (+/-X, Y, Z) |      | 1500 | G  |

| T <sub>module</sub> | 動作時のモジュール温度                | -40  | 125  | °C |

| T <sub>J</sub>      | 動作時接合部温度                   | -40  | 150  | °C |

| T <sub>stg</sub>    | 保存温度                       | -55  | 125  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 電圧値はすべて、特に記載のない限り、ネットワークのグランド端子を基準としています。

### 6.2 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                  |             |            | 最小値 | 公称値  | 最大値 | 単位  |

|------------------|-------------|------------|-----|------|-----|-----|

| V <sub>OUT</sub> | 出力電圧        |            | 0.6 | 11   |     | V   |

| V <sub>IN</sub>  | 入力電圧        |            | 4   | 17   |     | V   |

| F <sub>SW</sub>  | スイッチング周波数   |            | 400 | 2200 |     | kHz |

| I <sub>OUT</sub> | 出力電流範囲      | TPSM8F7420 | 0   | 4    |     | A   |

| I <sub>OUT</sub> | 出力電流範囲      | TPSM8F7620 | 0   | 6    |     | A   |

| T <sub>J</sub>   | 動作時のモジュール温度 |            | -40 | 125  |     | °C  |

### 6.3 ESD Ratings

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | 値    | 単位 |

|--------------------|------|----------------------------------------------------------|------|----|

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±500 |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                  | TPSM8F7x20  | 単位   |

|----------------------|------------------|-------------|------|

|                      |                  | APG (FCCSP) |      |

|                      |                  | 112 ピン      |      |

| R <sub>θJA</sub>     | 接合部から周囲への熱抵抗     | 13.6        | °C/W |

| Ψ <sub>JT</sub>      | 接合部から上面への特性パラメータ | 0.94        | °C/W |

| Ψ <sub>JB</sub>      | 接合部から基板への特性パラメータ | 7.56        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

推奨入力電圧範囲内、T<sub>J</sub> = -40°C ~ +125°C。代表値は、T<sub>J</sub> = 25°C および V<sub>IN</sub> = 12V での値です (特に記述のない限り)

| パラメータ                     | テスト条件                                      | 最小値                                                           | 標準値   | 最大値  | 単位    |     |

|---------------------------|--------------------------------------------|---------------------------------------------------------------|-------|------|-------|-----|

| <b>電源</b>                 |                                            |                                                               |       |      |       |     |

| I <sub>Q</sub>            | VIN1 + VIN2、VIN3 + VIN4、マルチフェーズモードにおける静止電流 | 非スイッチング、V <sub>EN</sub> = 2V、MSEL = 41.2kΩ、RT = 6.8kΩ、SS = 0V | 2     | 4.9  | mA    |     |

| I <sub>Q</sub>            | VIN1 + VIN2、VIN3 + VIN4、マルチ出力モードにおける静止電流   | 非スイッチング、V <sub>EN</sub> = 2V、MSEL = 29.4kΩ、RT = 6.8kΩ、SS = 0V | 4.3   | 8.2  | mA    |     |

| I <sub>SD</sub>           | VIN1 + VIN2、VIN3 + VIN4 におけるシャットダウン電源電流    | V <sub>EN</sub> = 0V                                          | 2     | 10.1 | μA    |     |

| <b>UVLO</b>               |                                            |                                                               |       |      |       |     |

| V <sub>IN_UVLO(R)</sub>   | VIN UVLO 立ち上がりスレッショルド                      | V <sub>IN</sub> 立ち上がり                                         | 3.5   | 3.8  | V     |     |

| V <sub>IN_UVLO(F)</sub>   | VIN UVLO 立ち下がりスレッショルド                      | V <sub>IN</sub> 立ち下がり                                         | 2.5   | 3    | V     |     |

| V <sub>IN_UVLO(H)</sub>   | VIN UVLO ヒステリシス                            |                                                               | 1.2   |      | V     |     |

| <b>イネーブル</b>              |                                            |                                                               |       |      |       |     |

| V <sub>EN(R)</sub>        | EN 電圧立ち上がりスレッショルド                          | EN 立ち上がり、スイッチングはイネーブル                                         | 1.125 | 1.25 | 1.375 | V   |

| V <sub>EN(F)</sub>        | EN 電圧立ち下がりスレッショルド                          | EN 立ち下がり、スイッチングはディスエーブル                                       | 0.75  | 0.84 | 1.0   | V   |

| V <sub>EN(H)</sub>        | EN 電圧ヒステリシス                                |                                                               | 0.25  | 0.4  | 0.55  | V   |

| V <sub>EN(W)</sub>        | EN 電圧ウェークアップ スレッショルド                       |                                                               | 0.4   |      | V     |     |

| I <sub>EN</sub>           | EN ピンのソース電流ポスト EN の立ち上がりスレッショルド            | V <sub>EN</sub> = V <sub>IN</sub> = 12V                       |       | 400  | nA    |     |

| <b>内部 LDO</b>             |                                            |                                                               |       |      |       |     |

| V <sub>VCC</sub>          | 内部 LDO 出力電圧                                | V <sub>IN</sub> ≥ 5V、I <sub>VCC</sub> ≤ 100mA                 | 4     | 4.4  | 5     | V   |

| I <sub>VCC</sub>          | 内部 LDO 短絡電流制限                              | V <sub>IN</sub> = 12V                                         | 130   | 220  |       | mA  |

| <b>基準電圧</b>               |                                            |                                                               |       |      |       |     |

| V <sub>FB_INT</sub>       | FB リファレンス電圧                                | 内部補償を選択、負荷電流なし。                                               | 595.5 | 600  | 604.5 | mV  |

| V <sub>FB_EXT</sub>       | FB リファレンス電圧                                | 外部補償を選択、V <sub>COMP</sub> = 0.6V                              | 595.5 | 600  | 604.5 | mV  |

| I <sub>FB(LKG)</sub>      | FB の入力リーク電流                                | V <sub>FB</sub> = 0.6V                                        |       | 10   | 250   | nA  |

| <b>エラー アンプ</b>            |                                            |                                                               |       |      |       |     |

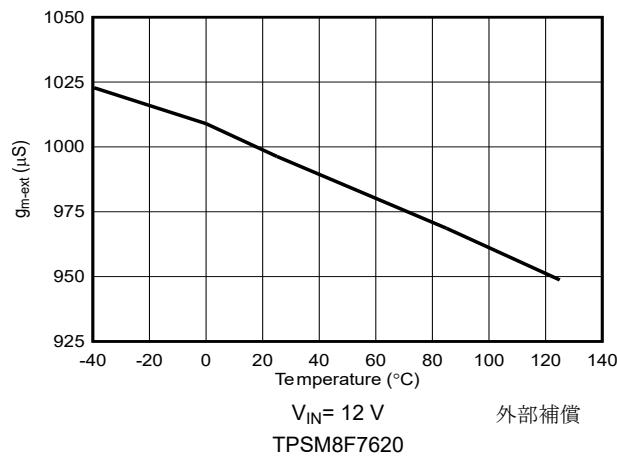

| g <sub>m-ext</sub>        | 外部 Comp の EA 相互コンダクタンス                     | V <sub>FB</sub> = V <sub>COMP</sub>                           | 840   | 1000 | 1150  | μs  |

| I <sub>COMP(src)</sub>    | 外部 Comp の EA ソース電流                         | V <sub>COMP</sub> = 1V、V <sub>FB</sub> = 0.4V                 | 100   | 155  | 400   | μA  |

| I <sub>COMP(sink)</sub>   | 外部 Comp の EA シンク電流                         | V <sub>COMP</sub> = 1V、V <sub>FB</sub> = 0.8V                 | 50    | 155  | 500   | μA  |

| <b>スイッチング周波数</b>          |                                            |                                                               |       |      |       |     |

| f <sub>SW-max(FCCM)</sub> | スイッチング周波数、FCCM 動作                          | R <sub>RT</sub> = 6.81kΩ から AGND                              | 1.95  | 2.2  | 2.4   | MHz |

| f <sub>SW (FCCM)</sub>    | 可変スイッチング周波数範囲                              | 6.81kΩ ~ 39.2kΩ から AGND への R <sub>RT</sub> 抵抗                 | 0.4   |      | 2.2   | MHz |

| <b>同期</b>                 |                                            |                                                               |       |      |       |     |

| V <sub>IH(sync)</sub>     | SYNC の High レベル スレッショルド                    |                                                               | 1.25  | 1.5  |       | V   |

| V <sub>IL(sync)</sub>     | SYNC の Low レベル スレッショルド                     |                                                               | 0.65  | 1.0  |       | V   |

| V <sub>OH(sync)</sub>     | 同期高出力電圧 (最小値)                              | SYNC_OUT ピンには負荷なし                                             | 4.4   |      |       | V   |

| V <sub>OL(sync)</sub>     | 同期低出力電圧 (最大値)                              | SYNC_OUT ピンには負荷なし                                             | 0.6   |      |       | V   |

## 6.5 電気的特性 (続き)

推奨入力電圧範囲内、 $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 。代表値は、 $T_J = 25^\circ\text{C}$  および  $V_{IN} = 12\text{V}$  での値です (特に記述のない限り)

| パラメータ                |                                    | テスト条件                                                                                                               | 最小値  | 標準値  | 最大値   | 単位               |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------|

| $f_{SYNC-2p2}$       | 2.2MHz 付近の周波数同期範囲                  | $R_{RT} = 6.81\text{k}\Omega$ から AGND                                                                               | 1.76 | 2.2  | 2.64  | MHz              |

| $f_{SYNC-0p4}$       | 400kHz 付近の周波数同期範囲                  | $R_{RT} = 39.2\text{k}\Omega$ から AGND                                                                               | 320  | 400  | 480   | kHz              |

| $t_{SYNC(IH)}$       | $V_{IL(sync)}$ を上回る外部同期信号の最小パルス幅   |                                                                                                                     |      | 50   |       | ns               |

| $t_{SYNC(IL)}$       | $V_{IL(sync)}$ を下回る外部同期信号の最小パルス幅   |                                                                                                                     |      | 50   |       | ns               |

| $t_{SYNC-SW(delay)}$ | SYNC の立ち上がりエッジから SW の立ち上がりエッジまでの遅延 |                                                                                                                     |      | 40   |       | ns               |

| <b>スタートアップ</b>       |                                    |                                                                                                                     |      |      |       |                  |

| $I_{SS(R)}$          | ソフトスタート充電電流                        | $V_{SS} = 0\text{V}$                                                                                                |      | 21   |       | $\mu\text{A}$    |

| $t_{EN}$             | EN High からスイッチング開始までの遅延            | $V_{IN} > V_{IN_{UVLO(R)}}$                                                                                         |      |      | 1300  | $\mu\text{s}$    |

| $R_{SS(F)}$          | ソフトスタート放電抵抗                        |                                                                                                                     |      | 22   | 45    | $\Omega$         |

| <b>電力段</b>           |                                    |                                                                                                                     |      |      |       |                  |

| $t_{ON(min)}$        | 最小 ON パルス幅 (1)                     | $V_{IN} = 12\text{V}$                                                                                               |      | 45   | 60    | ns               |

| $t_{OFF(min)}$       | 最小 OFF パルス幅 (1)                    | $V_{IN} = 4\text{V}$                                                                                                |      | 60   | 105   | ns               |

| <b>過電流保護</b>         |                                    |                                                                                                                     |      |      |       |                  |

| $I_{HS(OC1)}$        | ハイサイド ピーク電流制限 TPSM8F7620           | HS FET のピーク電流制限                                                                                                     | 8.2  | 9    | 9.6   | A                |

| $I_{HS(OC2)}$        | ハイサイド ピーク電流制限 TPSM8F7420           | HS FET のピーク電流制限                                                                                                     | 6.3  | 7.2  | 8.2   | A                |

| $I_{LS(OC1)}$        | ローサイドのバレー電流制限 TPSM8F7620           | LS FET のバレー電流制限                                                                                                     | 5.9  | 6.8  | 7.2   | A                |

| $I_{LS(OC2)}$        | ローサイドのバレー電流制限 TPSM8F7420           | LS FET のバレー電流制限                                                                                                     | 4.4  | 5.4  | 6.4   | A                |

| $I_{LS1(NOC)}$       | ローサイド スイッチ負電流制限 TPSM8F7620         | LS FET のシンク電流制限                                                                                                     |      | -4   | -3    | A                |

| $I_{LS3(NOC)}$       | ローサイド スイッチ負電流制限 TPSM8F7420         | LS FET のシンク電流制限                                                                                                     |      | -3.5 | -2.5  | A                |

| $V_{Hiccup-FB}$      | FB ピンのヒップアップ レッショルド                | HS FET オン時間 > 165ns                                                                                                 | 0.18 | 0.23 | 0.3   | V                |

| $t_{Hiccup-1}$       | ヒップアップに移行する前の待機時間                  |                                                                                                                     | 126  | 128  | 130   | 電流制限<br>サイクル     |

| $t_{Hiccup-2}$       | 再スタート前のヒップアップ時間                    |                                                                                                                     | 50   | 70   |       | ms               |

| <b>出力放電</b>          |                                    |                                                                                                                     |      |      |       |                  |

| $R_{Discharge}$      | 出力放電抵抗                             | $V_{IN} = 12\text{V}, V_{OUT} = 2.5\text{V}$ 、電力変換無効                                                                |      | 19.5 |       | $\Omega$         |

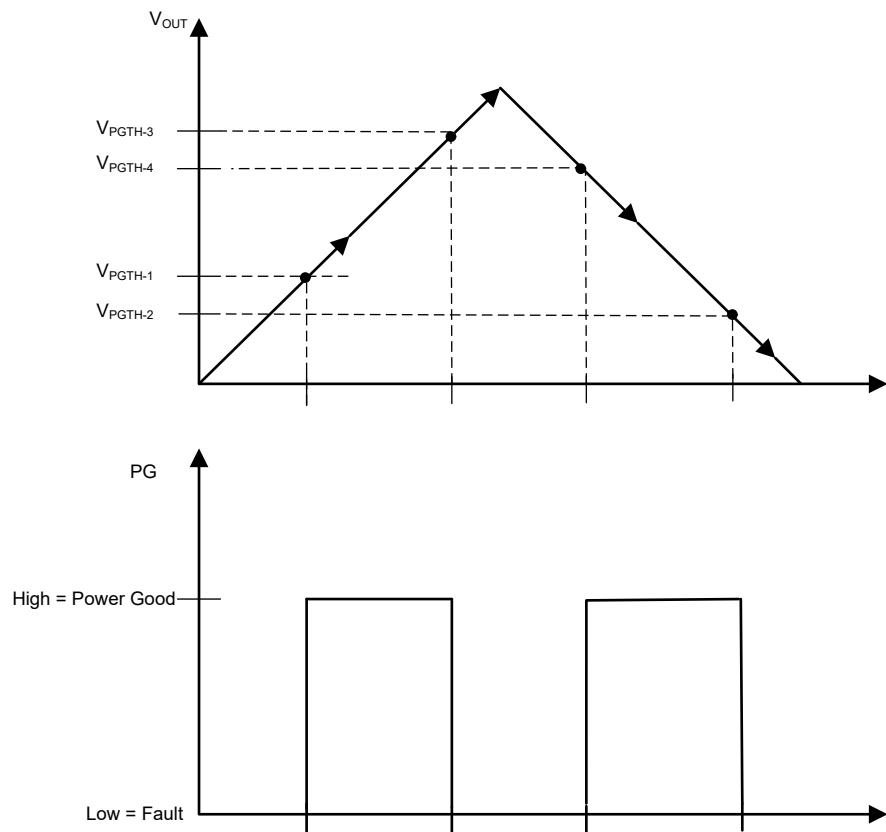

| <b>パワー グッド</b>       |                                    |                                                                                                                     |      |      |       |                  |

| $V_{PGTH-1}$         | パワー グッド (PG) スレッショルド               | PGOOD Low、 $V_{FB}$ 立ち上がり                                                                                           | 93   | 96   | 99    | % $V_{REF}$      |

| $V_{PGTH-2}$         | パワー グッド (PG) スレッショルド               | PGOOD High、 $V_{FB}$ 立ち下がり                                                                                          | 91   | 93   | 95    | % $V_{REF}$      |

| $V_{PGTH-3}$         | パワー グッド (PG) スレッショルド               | PGOOD High、 $V_{FB}$ 立ち上がり                                                                                          | 109  | 113  | 117   | % $V_{REF}$      |

| $V_{PGTH-4}$         | パワー グッド (PG) スレッショルド               | PGOOD Low、 $V_{FB}$ 立ち下がり                                                                                           | 107  | 110  | 113   | % $V_{REF}$      |

| $t_{PGOOD(R)}$       | $V_{FB}$ 有効から PGOOD High までの PG 遅延 | $V_{VOUT} = 3.3\text{V}$                                                                                            | 300  |      | 700   | $\mu\text{s}$    |

| $t_{PGOOD(F)}$       | $V_{FB}$ 無効から PGOOD Low までの PG 遅延  | $V_{VOUT} = 3.3\text{V}$                                                                                            |      | 47   |       | $\mu\text{s}$    |

| $I_{PG(LKG)}$        | オープンドレイン出力が High の PG ピンのリード電流     | $V_{PG} = 3.3\text{V}$                                                                                              |      |      | 0.075 | $\mu\text{A}$    |

| $V_{PG-D(LOW)}$      | 両方のチャネルに PG ピンが Low レベル電圧を出力します    | $I_{PG} = 1\text{mA}, V_{EN} = 0\text{V}, V_{IN} > V_{IN(PG\_VALID)}$                                               |      |      | 400   | mV               |

| $R_{PG}$             | プルダウン MOSFET 抵抗                    | $I_{PG} = 1\text{mA}, V_{EN} = 3.3\text{V}$                                                                         |      | 35   | 90    | $\Omega$         |

| $V_{IN(PG\_VALID)}$  | 有効な PG 出力の最小 VIN                   | PG の $R_{PG} = 10\text{k}\Omega$ のプルアップ抵抗、PG の $V_{PULLUP\_PG} = 3\text{V}$ の電圧プルアップ、 $V_{PG-D(LOW)} = 0.4\text{V}$ |      |      | 1.2   | V                |

| <b>サーマル シャットダウン</b>  |                                    |                                                                                                                     |      |      |       |                  |

| $T_{J(SD)}$          | サーマル シャットダウンのスレッショルド (1)           | 温度上昇                                                                                                                | 153  | 167  | 186   | $^\circ\text{C}$ |

| $T_{J(HYS)}$         | サーマル シャットダウン ヒステリシス (1)            |                                                                                                                     |      | 9    |       | $^\circ\text{C}$ |

## 6.5 電気的特性 (続き)

推奨入力電圧範囲内、 $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ 。代表値は、 $T_J = 25^\circ\text{C}$  および  $V_{IN} = 12\text{V}$  での値です (特に記述のない限り)

| パラメータ       | テスト条件          | 最小値                                   | 標準値 | 最大値 | 単位               |

|-------------|----------------|---------------------------------------|-----|-----|------------------|

| $T_{sense}$ | 温度センシングの精度 (1) | $T_A = 25^\circ\text{C}$ でのキャリブレーション後 | -10 | +10 | $^\circ\text{C}$ |

- (1) 設計により検証済み。

## 6.6 代表的特性

図 6-1. エラー アンプの GM と温度との関係

図 6-2.  $V_{FB}$  と温度との関係

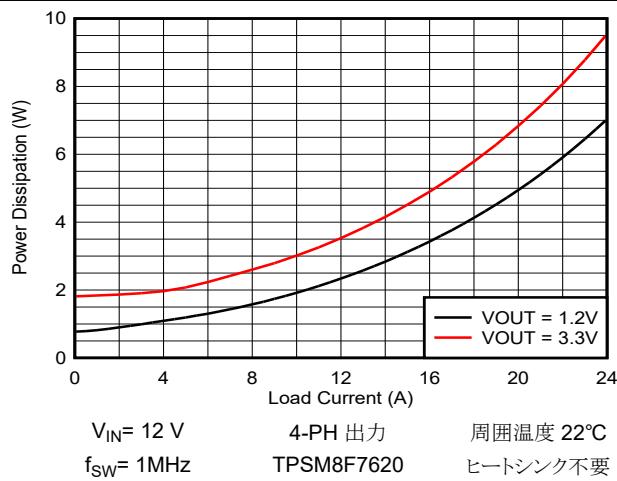

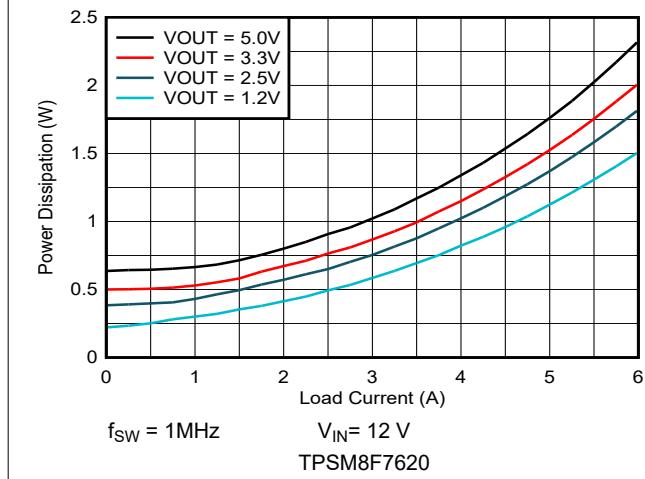

図 6-3. 消費電力 12V 入力

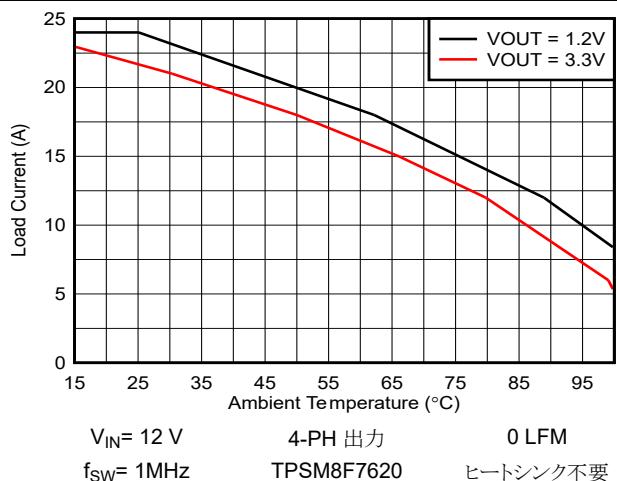

図 6-4. 最大出力電流と周囲温度との関係

## 7 詳細説明

### 7.1 概要

TPSM8F7x20 は使いやすい同期整流降圧 DC/DC 電源モジュールで、小型ソリューション サイズ、柔軟なマルチフェーズ / マルチ出力、構成可能な補償が非常に重要な幅広いアプリケーション向けに設計されています。4 系統、チャネルのパワー MOSFET、インダクタ、コンデンサ、PWM コントローラを内蔵した TPSM8F7x20 は、4V ~ 17V の入力電圧範囲で動作します。このモジュールは、TPSM8F7420/TPSM8F7620 と組み合わせて、チャネルあたり最大 4/6A を供給します。内部または外部の制御ループ補償を選択できるため、設計者は柔軟性を最大限確保しながら、出力コンデンサの量を減らし、安定性を維持することができます。

RT ピンを使用して 400kHz ~ 2.2MHz の範囲でスイッチング周波数を調整できる TPSM8F7x20 は、11V までの広い出力電圧範囲に対応しています。

このモジュールには、いくつかの EMI 低減機能が組み込まれています。

- 内蔵の高周波コンデンサのレイアウトにより、寄生インダクタンス、スイッチング電圧リンクギング、放射フィールドカップリングを最小限に抑えることが可能

- クロック同期と FPWM モードにより、負荷電流範囲全体にわたってスイッチング周波数を一定に維持可能

- 強化型ゲートドライブ制御を備えたパワー MOSFET を内蔵しているため、低ノイズの PWM スイッチングが可能

TPSM8F7x20 モジュールには、堅牢なシステム要件に対応する固有の保護機能も内蔵されています。

- 電源レールのシーケンシングと�オルト報告用のオープンドレイン パワー グッド (PG) インジケータ

- アクティブ出力電圧放電と外部ソフトスタートピンにより、予測可能なシーケンシングを実現できます

- ヒステリシス付きの高精度イネーブル入力により以下を実現する

- プログラム可能なライン低電圧誤動作防止 (UVLO)

- リモートオン/オフ特性

- サイクル単位のピーク電流制限とバレー電流制限によるヒップアップ モード過電流保護

- 自動回復機能付きサーマル シャットダウン。

TPSM8F7x20 は、外付け部品をわずかしか必要としないシンプルなレイアウト向けに設計されたピン配置を活用して、最大内部動作温度 125°C での動作が規定されています。特定の周囲環境における適合性を推定するには、[セクション 6.6](#) を参照してください。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電圧範囲 (VIN)

VIN ピン電圧は、本デバイスの内部制御回路に電源を供給し、電力段に入力電圧を供給します。VIN の入力電圧は、4V ~ 17V の範囲です。本デバイスでは、VIN ピンに内部 UVLO 回路を実装します。VIN ピンの電圧が内部の VIN UVLO スレッショルドを下回ると、本デバイスはディスエーブルになります。内部 VIN UVLO スレッショルドには、1V のヒステリシスがあります。EN ピンに接続された分圧器により、入力電圧の UVLO を必要に応じて調整できます。

スタートアップに必要な最低入力電圧は 3.5V です。ラインまたは負荷の過渡イベントにおいて、コンバータの VIN ピン (VIN1/2/3/4) の電圧が絶対最大定格である 18V を超過しないよう、十分な配慮が必要です。絶対最大定格を超える VIN ピンでの電圧リングは、IC に損傷を与える可能性があります。

VIN1/2 と VIN3/4 には別の電源から電力を供給できますが、両方の VIN 電源に同時に電源を投入することを推奨します。

### 7.3.2 バイアス電源レギュレータ (VCC)

VCC は、TPSM8F7x20 の制御回路に電力を供給するために使用される内部 LDO レギュレータの出力です。VCC の公称電圧は 4.4V です。このモジュールは VCC バイパスコンデンサを統合しているため、追加の部品が不要で、基板面積とレイアウト時間を削減できます。

不適切な動作を防止するため、VCC には、内部電圧が低すぎる場合にスイッチングを止める UVLO 保護機能が備わっています。

VCC は外部回路への電力供給に使用しないでください。VCC のロードまたは VCC のグランドへの短絡は行わないでください。VCC は、PG ピンへのプルアップとして使用できます。

### 7.3.3 デバイス構成ピン (MSEL)

MSEL ピンは、デバイス構成と補償の設定に使用します。表 7-1 に、種類の出力レール構成が 5 系統あります。これらの構成では、モジュール出力を提供するために並列に接続するチャネルとその数が指定されます。たとえば、「2+2」の構成は、合計出力電圧レールが 2 つあることを意味します。1 つ目のレールは VOUT1 と VOUT2 で構成され、2 つ目のレールは VOUT3 と VOUT4 で構成されています。「1+3」構成では、まだ 2 つの出力レールがあり、VOUT1 は単相出力、VOUT2/3/4 は互いに接続して 3 相出力を形成します。MSEL ピンを使用してデバイスを構成することで、セクション 7.3.4 で説明した位相角度に従って位相インターリーブが設定されます。

外部補償用に構成されている場合、COMP ピンは GM エラー アンプの出力になり、タイプ II 補償を制御ループで使用できます。内部補償用に構成した場合、COMP に追加の部品は必要ありません。COMP 信号はスタックの各相で共有されるため、多相構成では外部補償のみを使用できることに注意してください。詳細については「セクション 7.3.9」を参照。

MSEL ピンは接合部温度監視用としても機能します。ピンストラップ検出が完了すると、接合部温度に比例するアナログ電圧が、AGND を基準として MSEL ピンで駆動されます。詳細については「セクション 7.3.15」を参照。

表 7-1. R<sub>SEL</sub> 抵抗の選択

| CONFIG             | COMP1 | COMP2 | R <sub>MSEL1</sub> (kΩ) | COMP3 | COMP4 | R <sub>MSEL2</sub> (kΩ) |

|--------------------|-------|-------|-------------------------|-------|-------|-------------------------|

| 1+1+1+1            | 内部 1  |       | 9.53                    | 内部 1  |       | 9.53                    |

|                    | 内部 2  |       | 19.1                    | 内部 2  |       | 19.1                    |

|                    | 外部    |       | 29.4                    | 外部    |       | 29.4                    |

| 1+1+2              | 内部 1  |       | 9.53                    | 外部    |       | 41.2                    |

|                    | 内部 2  |       | 19.1                    |       |       |                         |

|                    | 外部    |       | 29.4                    |       |       |                         |

| 2+2                | 外部    |       | 41.2                    | 外部    |       | 41.2                    |

| 1+3 <sup>(1)</sup> | 内部 1  | 外部    | 56.2                    | 外部    |       | 121                     |

|                    | 内部 2  |       | 73.2                    |       |       |                         |

|                    | 外部    |       | 93.1                    |       |       |                         |

**表 7-1.  $R_{SEL}$  抵抗の選択 (続き)**

| CONFIG             | COMP1 | COMP2 | $R_{MSEL1}$ (kΩ) | COMP3 | COMP4 | $R_{MSEL2}$ (kΩ) |

|--------------------|-------|-------|------------------|-------|-------|------------------|

| 4+0 <sup>(2)</sup> | 外部    |       | 121              | 外部    |       | 121              |

(1) この構成では常に、スタンドアロンの 1 次として CH1 を使用し、多相の 1 次として CH2 を使用します

(2) この構成は、マルチフェーズ プライマリとして常に CH1 を使用します

### 7.3.4 マルチフェーズ出力構成

マルチフェーズ降圧コンバータトポジは、複数の降圧コンバータを並列接続することにより実現し、互いに  $360/N$  度離れた位相をインターリープします。N はフェーズ数です。マルチフェーズ降圧コンバータが持つ利点：

- 出力電流を N 倍に増加

- 出力電圧リップルの低減

- 入力電流リップルの低減

- 熱拡散の改善

デバイスをマルチフェーズ出力に構成するには、表 7-3 に示すように、各チャネルの SS ピン、EN ピン、COMP ピンを互いに接続する必要があります。このデバイスがサポートしているマルチフェーズ構成については、表 7-1 を参照してください。

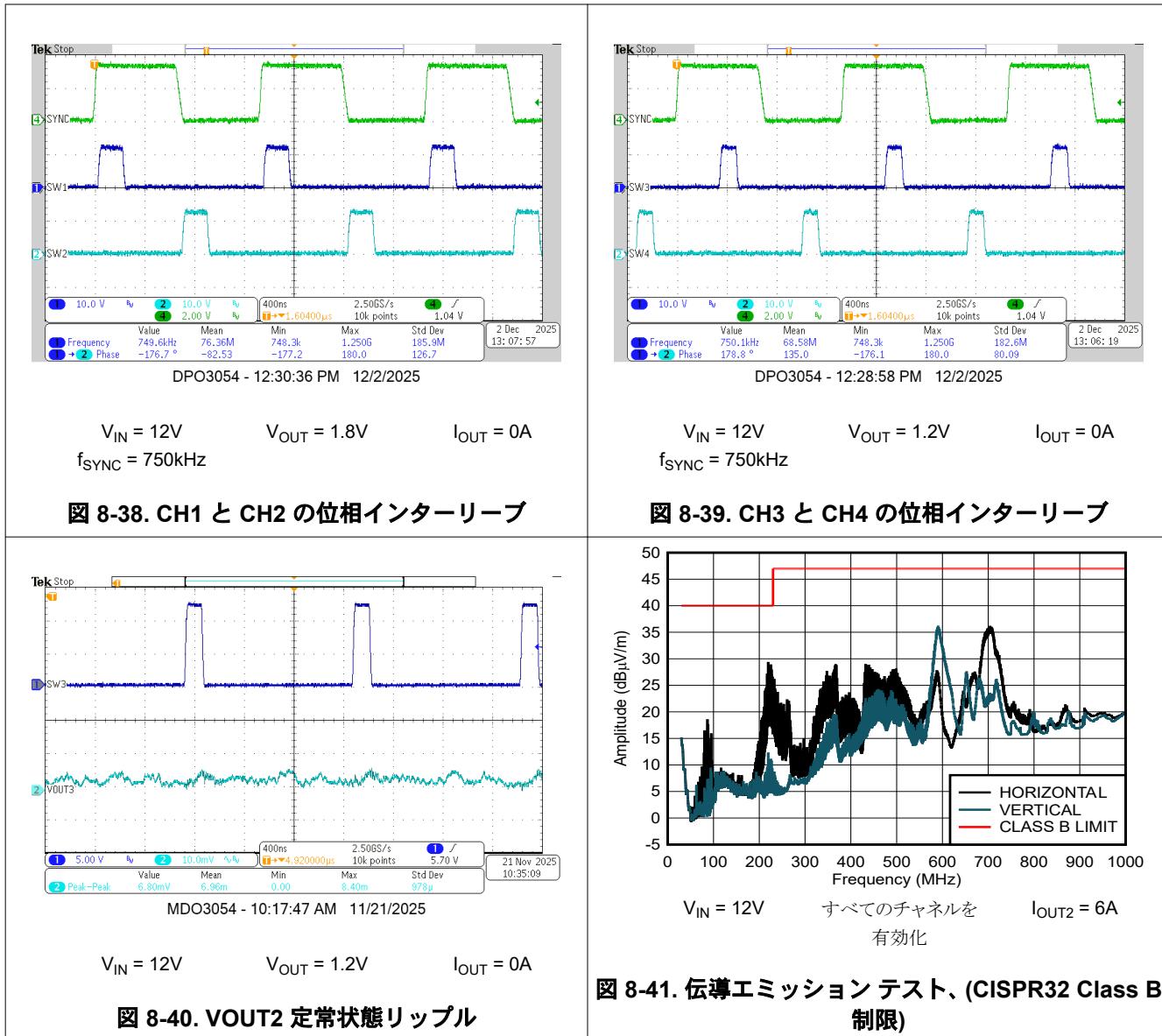

このモジュールでマルチフェーズまたはマルチ出力構成を選択する場合、表 7-2 に従って位相がインターリープされます。

**表 7-2. 構成ごとの位相インターリープ**

| CONFIG  | SW1 | SW2  | SW3  | SW4  |

|---------|-----|------|------|------|

| 1+1+1+1 | 0°  | 180° | 90°  | 270° |

| 1+1+2   |     |      |      |      |

| 2+2     |     |      |      |      |

| 4+0     |     |      |      |      |

| 1+3     | 0°  | 180° | 300° | 60°  |

TPSM8F7x20 における個々のチャネルは、スタンドアロン出力、マルチフェーズ プライマリ、マルチフェーズ セカンダリとして構成できます。マルチフェーズ スタックのプライマリ デバイスは、常にスタック内の最初のチャネルとなります。たとえば、「1+3」構成の場合、CH2 は 3 相のプライマリ チャネルに対応し、CH3/4 がマルチフェーズのセカンダリ側に対応しています。プライマリおよびセカンダリの推奨ピン接続の詳細については、表 7-3 を参照してください。

**表 7-3. マルチフェーズ ピン接続**

| ピン   | プライマリ                           | セカンダリ              |

|------|---------------------------------|--------------------|

| FB   | VOUT 抵抗デバイス                     | NC/Float           |

| EN   | VIN 分圧抵抗またはイネーブル / 制御           | プライマリの EN に接続します   |

| SS   | このピンと AGND との間に $C_{SS}$ を接続します | プライマリの SS に接続します   |

| COMP | このピンと AGND との間に補償回路を接続します       | プライマリの COMP に接続します |

| PG   | このピンと VCC の間に $R_{PG}$ を接続します   | NC/Float           |

### 7.3.5 イネーブルおよび調整可能な UVLO

TPSM8F7x20 をシャットダウン モードに移行させるには、EN1、EN2、EN3、EN4 ピンに 0.4V 未満の電圧を印加します。シャットダウン モードでは、静止電流は  $2\mu A$  (標準値) に低下します。この電圧より高く、かつ下限 EN スレッショルド未満の場合、VCC はアクティブになりますが、SW1 と SW2 のスイッチングは非アクティブのままでです。EN1 が  $V_{EN(R)}$  を上回ると、SW1 がアクティブになります。EN2 は 2 番目の出力 SW2 のスイッチングを制御します。複数出力構成では、

EN<sub>x</sub> を使用して VOUT<sub>x</sub> 出力電圧を独立してオフにできます。単一出力マルチフェーズ構成では、1 次側と 2 次側の EN を相互に接続する必要があります。

EN ピンはフローティングのままにすることはできません。動作を有効にする最も簡単な方法は、EN ピンを VIN ピンに接続することです。これにより、VIN によって内部 VCC が UVLO レベルよりも高く駆動されるときに、デバイスの自己起動が可能になります。ただし、多くのアプリケーションでは、イネーブル分圧回路を採用することで恩恵を受けることができます。これにより、高精度の入力低電圧誤動作防止 (UVLO) を実現できます。高精度 UVLO は以下の用途で使用できます：

- VIN 電圧に基づくシーケンシング

- 長い入力ケーブルと組み合わせて使用する際にデバイスが再トリガされるのを防止する

EN スレッショルドが正確であることに注意してください。立ち上がりイネーブル スレッショルドの許容誤差は 10% です。ヒステリシスの大きさは、負荷のシャットダウン時の再トリガを防止するのに十分です。その他の IC の外部ロジック出力で EN 端子を駆動して、システム電源のシーケンシングを行うこともできます。

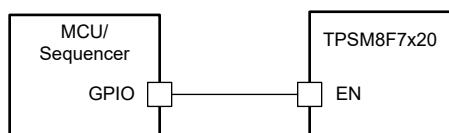

図 7-1. 外部シーケンサを使用して有効にします

図 7-2. EN ピンを使った VIN/UVLO

抵抗値は、以下の式で計算できます。

$$R_{ENB} = R_{ENT} \times \left( \frac{V_{EN(R)}}{V_{IN(on)} - V_{EN(R)}} \right) \quad (1)$$

$$V_{OFF} = V_{IN(on)} \times (1 - V_{EN(H)}) \quad (2)$$

ここで、

- $V_{IN(on)}$  =  $V_{IN}$  のターンオン電圧

- $V_{OFF}$  =  $V_{IN}$  のターンオフ電圧

### 7.3.6 可変スイッチング周波数

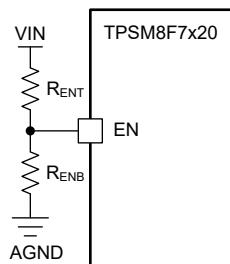

調整可能なスイッチング周波数は、RT1 および RT2 ピンから AGND に抵抗を使用して設定します。抵抗値については、下の表 7-4 を参照してください。推奨範囲外の抵抗値を使用すると、デバイスがスイッチング動作を停止する可能性があります。強制的に同期させる目的で、このピンにパルス信号を印加することはしないでください。同期が必要な場合は、SYNC ピンを使用してください。

TPSM8F7x20 には合計 4 つのスイッチング チャネルがあります。最初の 2 チャネルは RT1 によって設定され、残りの 2 チャネルは RT2 によって設定されます。各チャネルの位相が正しいことを確認するため、このモジュールのすべてのチャネルが定常状態で同じスイッチング周波数を共有する必要があります。これは、RT1 と RT2 の抵抗値は同じ 1% の抵抗値を使用する必要があることを意味します。

$$R_T[\text{k}\Omega] = \left( \frac{15.92}{f_{SW}[\text{MHz}]} - 0.526 \right) \quad (3)$$

たとえば、 $f_{SW} = 400\text{kHz}$ 、 $R_T = (15.92/0.4) - 0.526 = 39.27$  の場合、最も近い選択肢として  $39.2\text{k}\Omega$  の抵抗を選択します。

表 7-4.  $R_T$  標準値

| $R_T$ ( $\text{k}\Omega$ ) | 計算した周波数 ( $\text{kHz}$ ) |

|----------------------------|--------------------------|

| 6.81                       | 2170                     |

| 10.0                       | 1512                     |

| 15.4                       | 1000                     |

| 19.6                       | 791                      |

| 23.7                       | 657                      |

| 31.6                       | 496                      |

| 39.2                       | 402                      |

図 7-3. クロック周波数の設定

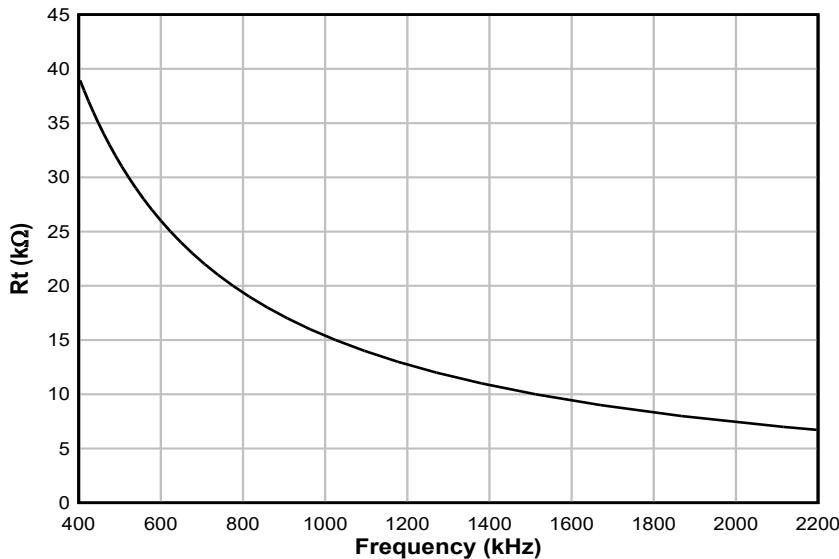

### 7.3.7 デバイス同期(SYNC)

SYNC ピンを使用して、内部発振器を外部クロックに同期します。外部クロックに同期すると、TPSM8F7x20 は FPWM で動作します。内部発振器は、正のエッジで SYNC ピンに同期することができます。内部同期パルス検出器をトリップさせるには、SYNC ピンの立ち上がりエッジ電圧が SYNC 振幅スレッショルド  $V_{IH(sync)}$  を上回る必要があります。最小 SYNC 立ち上がりパルスおよび立ち下がりパルス幅は、それぞれ  $t_{SYNC(IH)}$  および  $t_{SYNC(IL)}$  よりも長くする必要があります。

す。TPSM8F7x20 のスイッチング動作は、320kHz ~ 2.6MHz の外部クロックと同期することができます。外部クロックに同期する場合、RT ピンによってプログラムされた内部クロック周波数の約 ±20% の範囲内である必要があります。この動作により、同期が失われた場合に大きな周波数の変化が防止されます。この動作は、2 次側デバイスのスロープ補償の設定にも使用されます。

この図に、SYNC 信号を検出するために必要な条件を示します。

**図 7-4. 代表的な SYNC 波形**

#### 7.3.7.1 クロックのロック

TPSM8F7x20 は、MSEL ピンで選択した構成によって SYNC ピン入力の使用方法が異なります。「4+0」、「2+2」、で発生する多相プライマリ チャネルとして、CH1 が設定されている場合、CH1 は PLL 回路を使用して CH1 発振器周波数を同期入力にロックします。CH1 がスタンダードアロン出力になっている他の構成では、SYNC 入力が CH1 発振器に直接接続されます。さらに、PLL 回路を CH1 と CH2 との間の位相インターリーブに使用します。

SYNC ピンで有効な同期信号が検出された後、クロック ロック手順が開始されます。CH1 がスタンダードアロンの単相出力である場合、SYNC は CH1 発振器を直接接続し、スイッチング周波数を直ちに変更します。他の構成の場合、約 32 パルスの後、クロック周波数は同期信号の周波数へ突然変化します。周波数が突然調整されますが、位相は維持され、そのクロック サイクルは、デフォルトの周波数で動作する際のクロック サイクルと同期周波数で動作する際のクロック サイクルとの間の長さになります。長すぎる、または短すぎるパルスはありません。周波数が調整された後、立ち上がり同期エッジが立ち上がり SW ノードパルスに対応するように、数 10 サイクルかけて位相が調整されます。

#### 7.3.8 可変出力電圧 (FB)

TPSM8F7x20 の可変出力電圧の範囲は 0.6V ~ 最大 11V です。出力電圧を設定するには、 $R_{FBT}$  および  $R_{FBB}$  として指定された 2 つの帰還抵抗が必要です。フィードバック (FB) ピンのリファレンス電圧は 0.6V に設定され、フィードバックシステムの精度 (接合部温度範囲全体) は AGND に対して ±0.75% です。

$R_{FBT}$  の推奨範囲 10kΩ ~ 100kΩ に基づいて、下の 式 4 を使用して  $R_{FBB}$  の値を計算します。

$$R_{FBB}(k\Omega) = \frac{R_{FBT}(k\Omega)}{\frac{V_{OUT}}{0.6} - 1} \quad (4)$$

帰還抵抗が大きいほど、DC 電流の消費が小さくなることに注意してください。ただし、 $R_{FBT}$  上限抵抗値が 1MΩ を超えると、フィードバック パスはノイズの影響を受けやすくなります。一般に、帰還抵抗が大きいほど、フィードバック パスのレイアウトをより慎重に行う必要があります。帰還抵抗は、FB ピンおよび AGND ピンの近くに配置し、帰還パターンをできるだけ短く (また、PCB のノイズの多い領域から遠ざけるように) してください。詳細については、「レイアウト例」を参照してください。

#### 7.3.9 制御ループの補償 (COMP)

TPSM8F7x20 はピーク電流モード制御を採用しているため、制御ループを簡単に補償できます。COMP ピンは GM エラー アンプの出力であり、COMP と AGND との間に直列  $R_{COMP}$  -  $C_{COMP}$  を接続してタイプ II 補償を実装できます。

$R_{COMP}$  抵抗を大きくするとループ ゲインが高くなり、出力コンデンサを大きくする必要があります。 $C_{COMP}$  を小さくすると、デバイスの DC ループ応答が増加し、過渡セトリング タイムが短くなりますが、クロスオーバー周波数での位相マージンが小さくなる可能性があり、出力キャパシタンスを調整する必要がある場合があります。

### 7.3.10 スロープ補償

TPSM8F7x20 は、スロープ補償ランプを使用して、広いデューティ サイクルで安定性を維持します。ランプは、RT ピン抵抗を介してプログラムされたスイッチング周波数に比例します。ランプは次の式に従います：

$$M_a = \frac{59.54}{RT(k\Omega)} \left( \frac{A}{\mu s} \right) \quad (5)$$

TPSM8F7620 および

$$M_a = \frac{92.84}{RT(k\Omega)} \left( \frac{A}{\mu s} \right) \quad (6)$$

TPSM8F7420 の場合

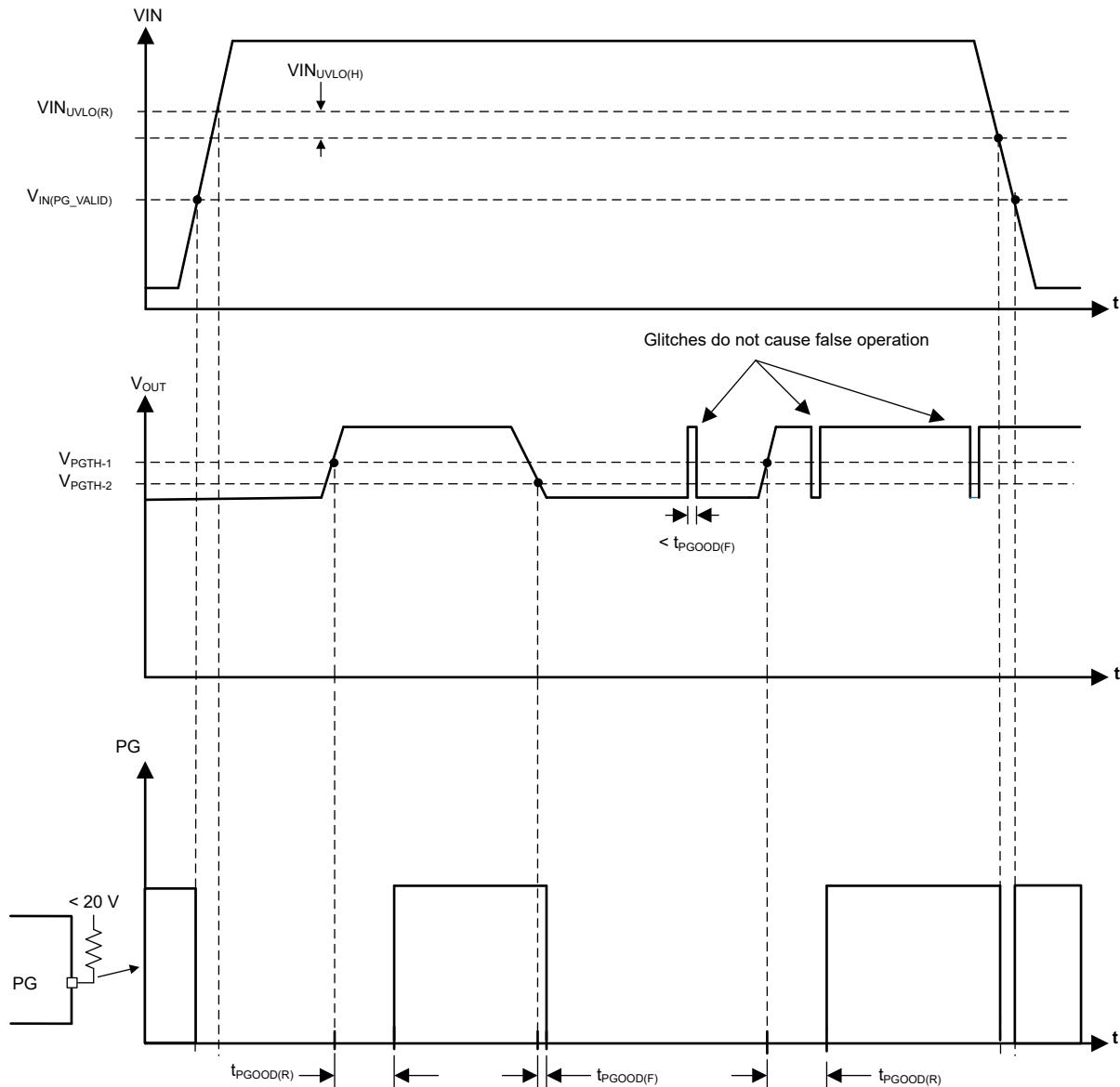

### 7.3.11 パワー グッド出力電圧の監視

TPSM8F7x20 の PG ピンは、標準のオープンドレイン パワー グッド機能に似ています。ほとんどのレギュレータでは、PG 機能と通常のパワーグッド機能に以下の 3 つの大きな違いがあります。

- リセットの解放に遅延が追加されました。[表 7-5](#) を参照してください。

- PG 出力は、部品が無効な場合にフォルトを通知します（出力をグランドにプルダウン）。

- PG は最低 1.2V の入力電圧で動作し続けます。この入力電圧を下回ると、PG 出力がハイインピーダンスになる可能性があります。

PG 信号を適切に伝達するには、PG と VCC、または外部電圧源の間に 10kΩ 以上のプルアップ抵抗が必要です。

TPSM8F7x20 には、合計 4 つのパワー グッド ピンがあります。**1+1+1+1** 構成を示す 4 つの出力を持つようにデバイスが構成されている場合、各 VOUTx に対応する PGx があります。ただし、4 出力未満の構成では、プライマリ チャネルの PG ピンのみが使用されます。たとえば、**4+0** 構成では使用される唯一のパワー グッド ピンが PG1 であり、残りはフローティングのままになります。

図 7-5. PG 静的電圧スレッショルド

図 7-6. PG のタイミング図 (OV イベントを除く)

**表 7-5. PG がフォルトを通知 (Low をプル) する条件**

| PG の立ち下がり条件                                              | PG の立ち上がり条件                             |

|----------------------------------------------------------|-----------------------------------------|

| FB が $t_{PGOOD(F)}$ よりも長い間 $V_{PGTH-2}$ を下回る             | FB が $V_{PGTH-1}$ を上回る                  |

| FB が $t_{PGOOD(F)}$ よりも長い間 $V_{PGTH-3}$ を上回る             | FB が $V_{PGTH-4}$ を下回る                  |

| サーマル シャットダウン                                             | 接合部温度が $T_{J(SD)} - T_{J(HYS)}$ 未満に低下する |

| EN が Low                                                 | EN が High になってから $t_{EN}$ が経過する         |

| VIN が $V_{INUVLO(F)}$ を下回っているが、 $V_{IN(PG\_VALID)}$ を上回る | VIN が $V_{INUVLO(R)}$ を上回る              |

過電圧検出時 (FB が  $V_{PGTH-3}$  より高い状態が  $t_{PGOOD(F)}$  以上続く場合) のフォルト通知に加え、スイッチ ノードがシャットダウンされ、SW ノードに約 1mA の小さなプルダウンが加えられます。出力過電圧フォルトが解消されると (FB が  $V_{PGTH-4}$  より低い状態)、SW ノードでスイッチングが再開されます。

PG 信号はダウンストリーム レギュレータの起動シーケンス制御や、フォルト保護、出力監視などに使用することができます。

### 7.3.12 出力放電

出力放電は常にイネーブルになり、パワーダウン シーケンスを行い、本デバイスがレギュレーションを維持していないときに負荷を保護します。出力放電がある場合、放電抵抗  $R_{Discharge}$  (標準値 19.5Ω) により、 $V_{OUT}$  が 2.5V のときに出力電圧が "Low" にプルダウンされます。出力放電機能は、サーマル シャットダウン中、UVLO 中、または EN が Low になったときに有効になります。

### 7.3.13 ソフトスタート (SS)

$V_{OUT}$  がイネーブルのときの突入電流を防止するため、TPSM8F7x20 は、可変ソフトスタート ピンを使用して、リファレンス電圧をゆっくりと上昇させます。ソフトスタート機能は、起動時の突入電流を制限し、 $V_{OUT}$  をスムーズに上昇させます。ソフトスタートは、以下のいずれかの条件によってトリガれます。

- 本デバイスをオンにするために EN が使われた。

- ヒップ待機期間から回復した。

- 過熱保護によるシャットダウンから回復した。

- IC の VIN に電力が供給されるか、VCC の UVLO が解除されています。

ソフトスタートがトリガされた後、本 IC は以下の動作を実行します。

- 出力電圧を制御するために本 IC が使用する基準電圧が、ゆっくりと 0 から上昇します。その結果、出力電圧が (それまで 0V だった場合)、 $t_{SS}$  の時間をかけて目標値の 90% に達します。

- 動作モードがダイオード エミュレーションに設定されます。これにより、電圧がすでに出力されていても、出力を Low にすることなく起動できます。

- ソフトスタート中、ヒップは無効になります

この動作により、起動時に電流が電流制限に近接する原因となる出力コンデンサと負荷条件を、ヒップをトリガすることなく使用できます。また、出力電圧がプリバイアスされている場合、出力電圧はプルダウンしません。

次の式を使って、目的のソフトスタート時間  $t_{SS}$  に基づいて、ソフトスタートコンデンサの値  $C_{SS}$  を計算できます。

$$C_{SS} = t_{SS} \times \frac{I_{SS(R)}}{V_{FB}} \quad (7)$$

ソフトスタート充電電流  $I_{SS(R)}$  および公称リファレンス電圧  $V_{FB}$  については、[電気的特性](#) を参照してください。

### 7.3.14 過電流保護 (OCP)

TPSM8F7x20 は、ピーク インダクタ電流のサイクルごとの電流制限を使用して、過電流状態から保護されています。電流は、スイッチング サイクルごとに電流制限スレッショルドと比較されます。過電流状態の間、出力電圧は低下します。

TPSM8F7x20 は、極端な過負荷が発生した場合にヒップ過電流保護を採用しています。ヒップ モードでは、モジュールがシャットダウンされ、再起動しようとする前に 70ms (標準値) オフに保持されます。それでも過電流または短絡によるフォルト状態が続く場合は、フォルト状態が解消されるまでヒップが繰り返されます。ヒップ モードは、重度の過電流状態での消費電力を低減し、過熱やデバイスが損傷する可能性を防止します。障害が解消されると、モジュールは自動的に回復し、通常動作に戻ります。

### 7.3.15 温度出力

TPSM8F7x20 は、IC の内部接合部温度を測定できます。内部デバイス温度は、本デバイスがイネーブルになりスイッチングを開始した後、MSEL1 ピンと MSEL2 ピンの電圧で測定できます。

次の式を使用して、測定された電圧を温度信号に変換します。

$$T_j = \frac{(V_{MSEL\_cal} - V_{MSEL})}{2.10208 \frac{mV}{^{\circ}C}} + T_{cal} \quad (8)$$

ここで、 $V_{MSEL\_cal}$  は  $T_{cal}$  で測定された MSEL 電圧、 $V_{MSEL}$  は接合部温度  $T_j$  を計算するために測定された MSEL 電圧です。 $T_{cal}$  は、モジュール パッケージに配置された熱電対または IR カメラを使用して測定する必要があります。このピンには、200pF 以上の容量性負荷を追加しないでください。MSEL ピンの電圧は、-40°C から 125°C までの温度範囲に対して、0.35V ~ 0.8V の範囲にあると考えられます。

### 7.3.16 サーマル シャットダウン

サーマル シャットダウンは、接合部温度を制限し、過熱に起因する損傷を防止するために使用される内蔵自己保護機能です。接合部温度が 167°C (標準値) を超えると、サーマル シャットダウンによってデバイスがオフになります。それ以上の電力消費および温度上昇を防ぎます。シャットダウン後に接合部温度が低下し、TPSM8F7x20 は接合部温度が 158°C (標準値) まで低下したときに再起動を試みます。

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウン モード

EN ピンは、TPSM8F7x20 のオン/オフ制御を行います。 $V_{EN}$  が約 0.25V を下回ると、デバイスはシャットダウン モードになります。内部 LDO とスイッチング レギュレータの両方がオフになります。シャットダウン モードでの静止電流は、2μA (標準値) まで減少します。TPSM8F7x20 は低電圧保護機能も内蔵しています。入力電圧がその UV スレッショルドを下回ると、レギュレータはオフのままになります。

### 7.4.2 スタンバイ モード

VCC バイアス電源用の内部 LDO は、レギュレータよりも低いイネーブル スレッショルドを備えています。 $V_{EN}$  が  $V_{EN(W)}$  を超え、 $V_{EN(R)}$  の高精度イネーブル スレッショルドを下回ると、内部 LDO がオンになります。スイッチング動作および電圧レギュレーションは、 $V_{EN}$  が高精度イネーブル スレッショルドを上回るまで有効なりません。

### 7.4.3 アクティブ モード

TPSM8F7x20 は、 $V_{VCC}$  および  $V_{EN}$  が関連するスレッショルドを超える場合、アクティブ モードになります。この動作を可能にする最も簡単な方法は、 $V_{EN}$  を  $V_{IN}$  に接続することです。これにより、印加された入力電圧が最小起動電圧を超えると自動的に起動できます。

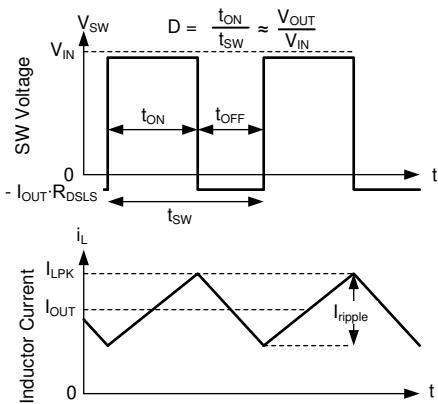

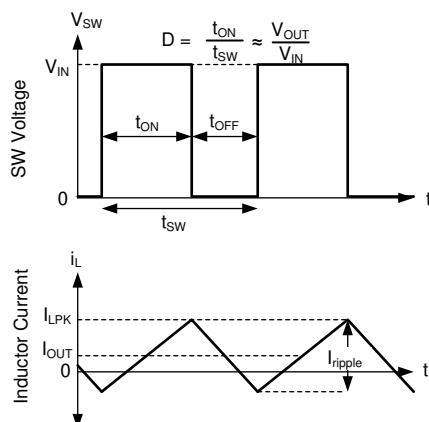

#### 7.4.3.1 ピーク電流モード動作

TPSM8F7x20 の以下の動作の説明では、[機能ブロック図](#)と図 7-7 の波形を参照しています。両方とも、内蔵ハイサイド (HS) およびローサイド (LS) NMOS スイッチを各種デューティサイクル (D) でオンにすることで、制御された出力電圧を供給します。HS スイッチのオン時間の間、SW 端子の電圧 ( $V_{SW}$ ) は  $V_{IN}$  の付近までスイングし、インダクタ電流 ( $i_L$ ) は線形的な傾きで増加します。HS スイッチは、制御ロジックによってオフにされます。HS スイッチのオフ時間 ( $t_{OFF}$ ) の間、LS スイッチはオンにされます。インダクタ電流は LS スイッチを通して放電され、LS スイッチの両端の電圧降下によって

$V_{SW}$  をグランドより低い電圧まで強制的にスイングさせます。一定の出力電圧を維持するため、レギュレータループはデューティサイクルを調整します。D は、HS スイッチのオン時間をスイッチング周期で割った値として次のように定義されます。 $D = T_{ON} / (T_{ON} + T_{OFF})$ 。

損失が無視される理想的な降圧コンバータでは、次のように D は出力電圧に比例し、入力電圧に反比例します。 $D = V_{OUT} / V_{IN}$ 。

図 7-7. 連続モード (CCM) における SW 電圧とインダクタ電流の波形

高精度の DC 負荷レギュレーションを実現するため、電圧帰還ループを使用しています。ピーク電流モード制御と電流保護のために、ピークおよびバレーインダクタ電流を検出します。負荷レベルが最小ピークインダクタ電流の 1/2 を上回っている場合、レギュレータは一定のスイッチング周波数の連続導通モードで動作します。外部的および内部的に補償された制御ネットワークは、小型外付け部品と低 ESR コンデンサを使った高速で安定した動作を実現します。

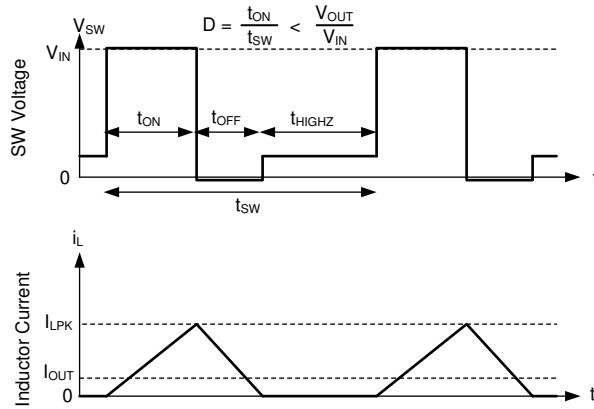

#### 7.4.3.2 ダイオード エミュレーション

ダイオード エミュレーションは、インダクタを流れる逆電流を防止します。固定ピークインダクタ電流の場合、レギュレートするために周波数をより低くする必要があります。ダイオード エミュレーションは、周波数が下がった際のリップル電流も制限します。ピークインダクタ電流が  $I_{PEAK-MIN}$  を下回ると、周波数が低下します。固定ピーク電流では、出力電流がゼロに向かって低下するにつれて、レギュレーションを維持するために周波数をゼロに近い値まで下げる必要があります。

不連続モード (DCM) では、インダクタ電流がゼロに近づくとローサイド デバイスはオフになります。その結果、出力電流が CCM でインダクタリップルの 1/2 未満になると、本デバイスは DCM で動作します。これは、ダイオード エミュレーションが機能していることと等価です。

図 7-8. PFM 動作

TPSM8F7x20 は起動時に使用する最小ピークインダクタ電流設定値を持っています。しかしながら、入力電圧を一定にした状態で、電流値が下がると、オン時間は一定になります。その後、周波数を調整することで、レギュレーションが達成されます。ソフトスタート中に DCM が有効になり、V<sub>OUT</sub> が上昇し、プライバイスされた出力が放電されるのを防止します。それ以外の場合は、軽負荷時でも強制 CCM モードで動作します。

#### 7.4.3.3 FPWM モード動作

定常状態動作では、本デバイスは常に FPWM モードで動作します。ただし、フォルト、電流制限、起動などの例外があります。

FPWM モードでは、軽負荷時に周波数が維持されます。周波数を維持するため、インダクタを流れる逆電流が制限されます。逆電流制限回路により、負の電流が制限されます。負の電流の制限値については、「電気的特性」を参照してください。

FPWM モードの連続導通 (CCM) は、I<sub>OUT</sub> が I<sub>ripple</sub> の半分未満でも可能です。

図 7-9. FPWM モード動作

FPWM モードでは、軽負荷時でも最小オン時間指示できるほど出力電圧が高ければ周波数の低減が可能です。これにより、フォルト中であっても、出力をプルアップすることを含む良好な動作が可能です。

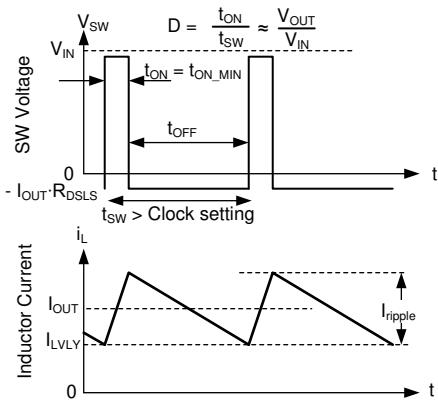

#### 7.4.3.4 最小オン時間(高入力電圧)での動作

出力電圧に対する入力電圧の比が要求するオン時間が、与えられたクロック設定のチップの最小オン時間より短い場合、TPSM8F7x20 は出力電圧をレギュレートし続けます。これは、バレー電流制御を使用して実現されます。補償回路は常に最大ピークインダクタ電流と最大バレーインダクタ電流の両方を指示します。何らかの理由でバレー電流を超過した場合、補償回路によって決定された値をバレー電流が下回るまで、クロックサイクルが延長されます。デバイスが電流制限内で動作していない場合、最大バレー電流はピークインダクタ電流よりも高く設定されます。これにより、ピーク電流のみを使ったレギュレーションに失敗しない限り、バレー制御が使われなくなります。出力電圧に対する入力電圧の比が高すぎる場合、補償回路が指示したピーク値を超える電流が流れたとしても、出力電圧をレギュレートするのに十分な速さではハイサイドデバイスをオフにすることはできません。[電気的特性](#) の  $t_{ON\_MIN}$  を参照してください。結果的に、補償回路はピーク電流とバレー電流の両方を小さくします。補償回路によって十分小さい電流が選択されると、バレー電流は、補償回路が指示した電流に一致します。これらの条件では、ローサイド素子がオンに維持され、目的のバレー電流をインダクタ電流が下回るまで、次のクロックサイクルは開始されません。オン時間は最小値に固定されているため、このタイプの動作は、COT 制御方式を採用したデバイスの動作と似ています。[バレー電流モード動作](#) を参照してください。

バレー制御モードでは、ピークインダクタ電流ではなく、最小インダクタ電流がレギュレーションされます。

図 7-10. バレー電流モード動作

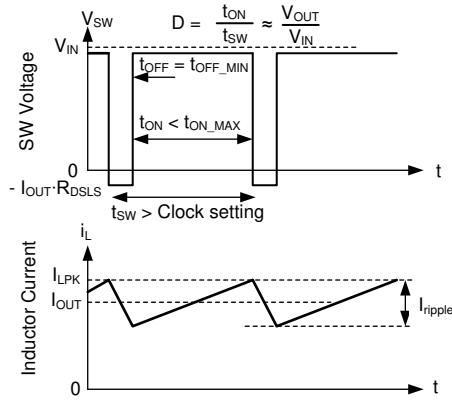

#### 7.4.3.5 ドロップアウト

ドロップアウト動作とは、必要なデューティ係数を達成するために周波数を下げ、入力電圧に対する出力電圧の比を任意の値に制御することです。与えられたクロック周波数において、デューティ係数は最小オフ時間によって制限されます。この制限値に達した後、仮にクロック周波数が維持される場合、出力電圧は低下します。TPSM8F7x20 は、出力電圧が下がるのを許容するのではなく、クロックサイクルが終わっても必要なピークインダクタ電流が達成されるまでオン時間を延長します。ピークインダクタ電流に達する、または設定済みの最大オン時間 ( $t_{ON-MAX}$ 、約 9μs) が経過すると、クロックは新しいサイクルを開始できます。その結果、最小オフ時間の存在に起因して、選択されたクロック周波数において必要なデューティ係数が達成できない場合、レギュレーションを維持するために周波数が低下します。オン時間 ( $t_{ON\_MAX}$ ) を使っても出力電圧をレギュレートできないほど入力電圧が低い場合、出力電圧は入力電圧よりもわずかに低い値に下がります。

この図は、ドロップアウト中のスイッチング波形を示しています。インダクタ電流は、目的のピーク値に達するのに通常のクロックよりも長い時間を要します。その結果、周波数は低下します。この周波数の低下は  $t_{ON\_MAX}$  によって制限されます。

図 7-11. ドロップアウト波形

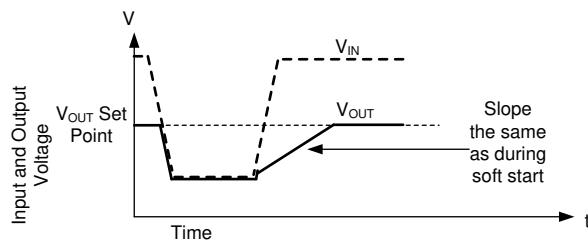

#### 7.4.3.6 ドロップアウトからの回復

一部のアプリケーションでは、目的の出力電圧よりも入力電圧が下がった後、より高い値に突然回復する場合があります。ほとんどのレギュレータは、入力電圧が急激に上昇すると、レギュレーションが達成されるまでの間、電流制限によってのみ制限されたレートで出力電圧が上昇します。入力電圧が目的の出力電圧に達すると、制御ループでのワインドアップによるオーバーシュートが発生します。出力容量が小さい（負荷が軽い）アプリケーションでは、このオーバーシュートは大きくなる可能性があります。また、レギュレータが出力電圧のレギュレーションを開始した後、大きな突入電流が入力ラインで大きな変動を引き起こす可能性があります。これは、通常、この初期突入時よりも少ない電流しか必要ありません。

TPSM8F7x20 は突入電流およびオーバーシュートを大幅に低減します。これは、入力電圧が突然上昇したときに常にソフトスタート回路を起動することで行われ、十分に下がった後で出力電圧低下を引き起します。この機能が誤って作動しないようにするには、出力電圧が 1% 以上上がるまでこの機能を使えなくする必要があります。また、この機能はドロップアウト状態または電流制限状態で動作している場合にのみ動作するため、通常の過渡応答の干渉は避けられますが、動作中に数パーセントのオーバーシュートは許容されてしまいます。出力電圧が目的のレベルに非常に近い場合、レギュレーションを開始する前にインダクタ電流が High レベルに上昇する時間がないため、オーバーシュートが低減されます。

図 7-12. ドロップアウトから復帰時の  $V_{OUT}$  オーバーシュートの防止

## 8 アプリケーションと実装

### 注

以下のアプリケーション セクションにある情報は、TI の製品仕様に含まれるものではなく、TI はその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TPSM8F7x20 同期整流降圧モジュールは、わずか数個の外付け部品を使用して、広い範囲の電源電圧を出力電圧に変換し、単相出力ごとに最大 4/6A、2 相出力の場合は最大 8/12A に変換できます。

### 8.2 代表的なアプリケーション

図 8-1.4 系統の出力アプリケーションの回路図

#### 8.2.1 設計要件

表 8-1. 設計パラメータ

| パラメータ | 値     |      |

|-------|-------|------|

| 入力電圧  | VIN   | 12V  |

| 出力電圧  | VOUT1 | 5V   |

|       | VOUT2 | 3.3V |

|       | VOUT3 | 2.5V |

|       | VOUT4 | 1.2V |

**表 8-1. 設計パラメータ (続き)**

| パラメータ        |                                              | 値                      |

|--------------|----------------------------------------------|------------------------|

| 最大出力電流       | I <sub>OUT1/2/3/4</sub>                      | 6A                     |

| スイッチング周波数    | f <sub>SW</sub>                              | 1MHz                   |

| 負荷トランジエントの調整 | V <sub>OUT3/4</sub> 負荷プロファイル: 1A ~ 4A、1A/μs。 | V <sub>OUT</sub> の ±4% |

| ソフトスタート時間    | すべてのチャネル                                     | 1ms                    |

## 8.2.2 詳細な設計手順

### 8.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPSM8F7x20 モジュールを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (V<sub>IN</sub>)、出力電圧 (V<sub>OUT</sub>)、出力電流 (I<sub>OUT</sub>) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握します。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力します。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になります。

### 8.2.2.2 モジュールの動作領域

TPSM8F7x20 は、幅広い動作範囲と柔軟性を持っています。動作領域には、考慮する必要のある制約がいくつかあります:

- 最小オン時間 (t<sub>ON(min)</sub>): SW が High にプルされたときの制御可能な最小パルス幅を指します

$$t_{ON(min)} < \frac{V_{OUT}}{V_{IN} \times f_{SW}} \quad (9)$$

- 最小オフ時間 (t<sub>OFF(min)</sub>): SW が Low にプルされたときの最小ローサイド FET オン時間を指します

$$t_{OFF(min)} < \frac{\left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{f_{SW}} \quad (10)$$

- 電流制限とインダクタ電流リップル: セクション 8.2.2.5 を参照

これらの制約により、モジュールで選択される目的の出力電圧に基づいてスイッチング周波数の選択が決定されます。特に、広い範囲の出力電圧が必要な場合や、スイッチング周波数に制限がある場合には、これらの制約が当てはまります。

### 8.2.2.3 スイッチング周波数の選択

スイッチング周波数の選択は、変換効率と設計全体のサイズとのトレードオフとなります。スイッチング周波数が低いとスイッチング損失は減少し、一般的に IC での消費電力が小さくなります。IC の消費電力が小さいとシステム効率が高くなり、IC 温度が低くなります。一方、スイッチング周波数を高くすると、より小さい容量の出力コンデンサを使用できるようになるため、よりコンパクトな設計が可能となります。

この設計では、1MHz のスイッチング周波数を使用しているため、RT に 15.4kΩ を選択しています。クアッド モジュールでは、RT1 と RT2 の両方が必要です。別のスイッチング周波数が必要な場合は、[セクション 7.3.6](#) を参照してください。

#### 8.2.2.4 出力電圧の設定

出力のレギュレーション ターゲットは、調整可能な抵抗デバイダ回路を使用してプログラムできます。分圧回路は上部と底部の帰還抵抗、 $R_{FBT}$  と  $R_{FBB}$  で構成され、出力電圧とコンバータの間のループを閉じています。コンバータは、内部アンプ入力の電圧を内部リファレンス電圧 ( $V_{FB} = 0.6V$ ) と同じ電圧に保持することで、出力電圧をレギュレートします。分圧器の合計抵抗値は、ノイズの過剰な混入と出力の過剰な負荷との折り合いを付けることで決定します。抵抗値を小さくすると、ノイズの感度は小さくなります。しかし、軽負荷効率にも小さくなります。 $R_{FBT}$  の推奨値は 25kΩ (最大値は 1MΩ) です。帰還分圧器の正確な値を計算する方法については、[式 4](#) を参照してください。分圧抵抗は公差 1% 以内としてください。

この設計では、以下の帰還分圧器を使用して、の出力電圧を 4 系統生成します。

**表 8-2. VOUT の抵抗デバイダの選択**

| 出力    | ターゲット $V_{OUT}(V)$ | $R_{FBT}(k\Omega)$ | $R_{FBB}(k\Omega)$ |

|-------|--------------------|--------------------|--------------------|

| VOUT1 | 5.0                | 10.0               | 1.37               |

| VOUT2 | 3.3                | 10.0               | 2.21               |

| VOUT3 | 2.5                | 10.0               | 3.16               |

| VOUT4 | 1.2                | 10.0               | 10.0               |

#### 8.2.2.5 インダクタ内蔵に関する考慮事項

TPSM8F7x20 モジュールは、TPSM8F7620 用の 0.68μH 固定インダクタンス、TPSM8F7420 用の 1μH 固定インダクタンスを持つインダクタを備えています。降圧コンバータのインダクタ電流リップルは [式 11](#) で与えられます。設計プロセスではリップル電流を考慮する必要があります。インダクタのリップル電流は、ハイサイドのピーク電流制限とローサイドの負の電流制限がトリップしないように、十分に小さくする必要があります。インダクタのリップル電流の半分は、ローサイドの負電流制限よりも大きく、ハイサイドのピーク電流制限から DC 負荷電流を減算した値よりも小さい必要があります。RT ピンを使って、降圧モジュールのスイッチング周波数を設定し、目的の VIN および VOUT に対してインダクタのリップル電流を十分に小さくすることができます。

$$\frac{\Delta i_L}{\Delta t} = \frac{V_{IN} \times D}{L \times f_{SW}} \quad (11)$$

#### 8.2.2.6 入力コンデンサの選択

セラミック入力コンデンサは、レギュレータに低インピーダンス ソースを供給するだけでなく、リップル電流を供給して、他の回路からスイッチング ノイズを絶縁します。TPSM8F7x20 の各  $VINx$  / グランド ピン ペアには、10μF 以上のセラミック容量が必要です。EMI 特性を向上させるために、 $2 \times 10\mu F$  以上のセラミック容量を使用してください。これは、少なくともアプリケーションが必要とする最大入力電圧を定格とする必要があります。DC バイアスのディレイティングを低減するため、最大入力電圧の 2 倍にすることを推奨します。この容量を増やすことで、入力電圧リップルを低減し、負荷過渡時の入力電圧を維持できます。

多くの場合、入力にセラミックと並列に電解コンデンサを使用することが推奨されます。これは、長い配線またはパターンを使って入力電源をレギュレータに接続する場合に特に当てはまります。このコンデンサに中程度の ESR を持つコンデンサを使うことは、長い電源配線のインダクタンスによって生じる入力電源のリンクギングを減衰させるのに有効です。この追加のコンデンサの使用は、インピーダンスが非常に高い入力電源によって生じる瞬間的な電圧低下の防止にも有効です。

入力キャパシタンスの値によって、レギュレータの入力リップル電圧が決まります。入力リップル電圧は、[式 13](#) を使って計算できます。最大の入力リップルは、デューティサイクルが 50% により近い状態で動作している時発生します。起こります。 $I_{OUT(MAX)} = 6A$ 、 $C_{IN} = 10\mu F$ 、 $f_{SW} = 1000kHz$  の公称設計例の値を使用すると、12V の入力電圧リップルは 150mV

未満を維持するようになります。入力コンデンサに DC バイアス ディレイティングを含めるようにしてください。選択した入力コンデンサに対して、12V 入力での容量は公称値から 70% 低下します。

クワッド モジュールのパワー パス配線では VIN2 と VIN3 がパッケージの外端からアクセスできないため、最下層のモジュール直下に追加のデカップリング コンデンサを配置することを推奨します。この設計では、4x2.2μF コンデンサを使用して、入力ノイズとリップルに対する追加のデカップリングを実現しています。

入力コンデンサは、最大 RMS 入力電流よりも大きなリップル電流定格を有する必要があります。RMS 入力電流は、[式 12](#) を使用して計算できます。

**表 8-3. C<sub>IN</sub> 計算表**

| 出力    | C <sub>IN(MIN)</sub> (μF) | C <sub>IN</sub> を選択します |

|-------|---------------------------|------------------------|

| VOUT1 | 5.8                       | 2x10μF                 |

| VOUT2 | 4.8                       | 2x10μF                 |

| VOUT3 | 4.0                       | 2x10μF                 |

| VOUT4 | 2.2                       | 2x10μF                 |

$$I_{CINRMS} = I_{OUT} \times \sqrt{\frac{(V_{INMIN} - V_{OUT})}{V_{INMIN}}} \times \frac{V_{OUT}}{V_{INMIN}} \quad (12)$$

$$\Delta V_{IN} = \frac{I_{OUTMAX} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \frac{V_{OUT}}{V_{IN}}}{C_{IN} \times f_{sw}} \quad (13)$$

### 8.2.2.7 ソフトスタート コンデンサ

ソフトスタート コンデンサは、目標のソフトスタート時間から計算できます。

$$C_{SS} = t_{SS} \times \frac{I_{SS(R)}}{V_{FB}} \quad (14)$$

$$C_{SS} = 1ms \times \frac{21\mu A}{0.6V} = 35nF \quad (15)$$

したがって、この設計では 0.033μF コンデンサが選択されています。1ms のソフトスタート時間は比較的高速なスタートアップとみなされるため、問題が発生する場合は、長めのソフトスタート時間を選択して突入電流をさらに制限することができます。

### 8.2.2.8 VCC および BOOT コンデンサ

TPSM8F7x20 は VCC とブートコンデンサを内蔵しています。これは、ユーザー時間と基板面積を節約し、レイアウトのミスを減らすために設計されています。VCC ピンおよび BOOT ピンに追加のコンデンサは必要ありません。

### 8.2.2.9 出力コンデンサの選択

出力電圧リップルと負荷過渡性能に合うように出力コンデンサを選択します。この設計の出力コンデンサは、過渡要件と出力電圧リップルの両方を満たすために必要なワーストケースの容量として選択しています。負荷過渡要件を満たすために出力インピーダンスが十分に低くなるように C<sub>OUT</sub> を計算できます。クロスオーバー周波数 (f<sub>co</sub>) における C<sub>OUT</sub> のインピーダンスは、最大出力インピーダンスの推定値として適切です。出力インピーダンスは、特定の負荷ステップに対して、どれだけの電圧偏差が発生するかを示します。

$$|Z_{OUT}| = \frac{\Delta V_{OUT}}{\Delta I_{step}} \quad (16)$$

ここで

- ΔV<sub>OUT</sub> は、負荷ステップからのアンダーシュートまたはオーバーシュートです。V<sub>OUT</sub> の代表的なパーセンテージ。

- $\Delta I_{step}$  は、過渡時の負荷電流の変化です。

このとき、以下の式から  $C_{OUT}$  を計算できます。

$$C_{OUT} = \frac{1}{2 \times \pi \times f_{co} \times |Z_{OUT}|} \quad (17)$$

次に、出力電圧リップル要件を使用して、出力キャパシタンスを計算します。この場合はすべての出力セラミックコンデンサを使用しているため、ESRリップルを無視できます。

$$C_{OUT} = \frac{\Delta i_{L\_ripple}}{8 \times f_{SW} \times \Delta V_{OUT\_ripple}} \quad (18)$$

このセクションで計算した 2 つの  $C_{OUT}$  値の最大値を使用して、リップルと負荷過渡性能の両方の目標を達成しています。

### 8.2.2.10 補償の選択

TPSM8F7x20 を使用して設計する際に制御ループを補償するには、2 種類のオプションがあります。COMP ピンの外部補償が最も構成能力を実現できますが、基板面積を削減し BOM 数を減らすため、2 つの内部補償オプションも用意されています。内部補償 1 はゲイン設定が高く、過渡性能の向上を目的にしています。内部補償 2 はゲイン設定が低く、安定性の維持と出力キャパシタンスの最小化を目的としています。

タイプ II 補償回路を形成する補償部品  $R_{COMP}$  および  $C_{COMP}$  は、電圧ループゲインを解析して以下の式に簡略化することで計算できます。以下の 3 つの式では、すべての変数が基本単位で表されているものとしています。

$$F_M = \frac{1}{T_s \times \left( M_a + \frac{\frac{V_{IN}}{2} - V_{OUT}}{L} \right)} \quad (19)$$

$$R_{COMP} = \frac{\frac{R_f}{N} \times 2 \times \pi \times f_{co}}{\left( \frac{R_{FB\_B}}{R_{FB\_B} + R_{FB\_T}} \right) \times GM_{MAX} \times \left( \frac{V_{IN} \times F_M}{\frac{L \times I_{OUT}}{V_{OUT}} + C \times V_{IN} \times F_M} \right)} \quad (20)$$

$$C_{COMP} = \frac{\tan \left( 65^\circ + \tan^{-1} \left( \frac{f_{co}}{\left( \frac{I_{OUT}}{2 \times \pi \times V_{OUT} \times C} \right) \times \left( 1 + \frac{V_{OUT} \times C \times F_m \times V_{IN}}{I_{OUT} \times L} \right)} \right) \right)}{2 \times \pi \times R_{COMP} \times f_{co}} \quad (21)$$

表 8-4. 制御ループ変数

| デバイス       | $R_f$  |

|------------|--------|

| TPSM8F7620 | 0.1095 |

| TPSM8F7420 | 0.1405 |

ここで

- $f_{co}$  は望ましいクロスオーバー周波数 (100kHz 未満に維持することを推奨)。

- $M_a$  は、[セクション 7.3.10](#) で定義されている勾配補償ランプ

- $R_f$  は、電流検出から COMP への電圧スケーリング係数

- $N$  は並列動作する位相の数で

内部補償を選択すると、 $R_{COMP}$  は内部的に設定されるため、望ましいクロスオーバー周波数に基づいて  $R_{COMP}$  の式を解くことで、 $C_{OUT}$  を計算できます。

**表 8-5. 内部および外部補償パラメータ**

| MSEL COMPx 設定 | 標準 GM ( $\mu\text{s}$ ) | $R_{\text{COMP}}$ ( $\text{M}\Omega$ ) | $C_{\text{COMP}}$ ( $\text{pF}$ ) |

|---------------|-------------------------|----------------------------------------|-----------------------------------|

| 外部            | 1000                    | 外部                                     | 外部                                |

| 内部 1          | 12                      | 1.4                                    | 20                                |

| 内部 2          | 12                      | 0.4                                    | 20                                |

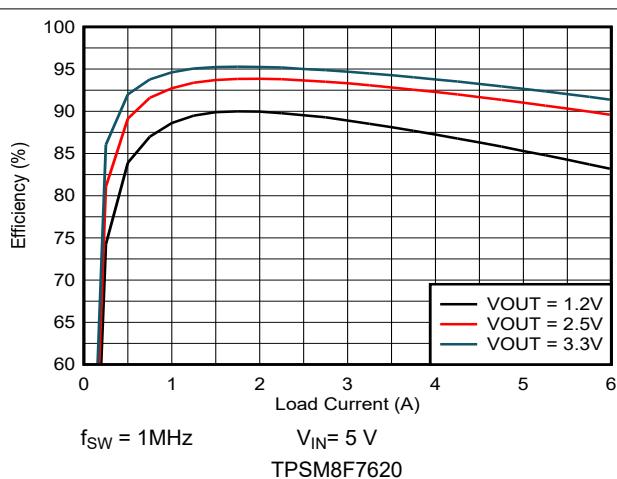

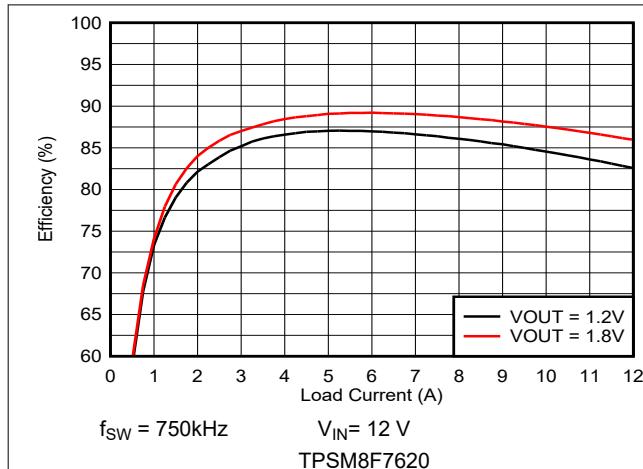

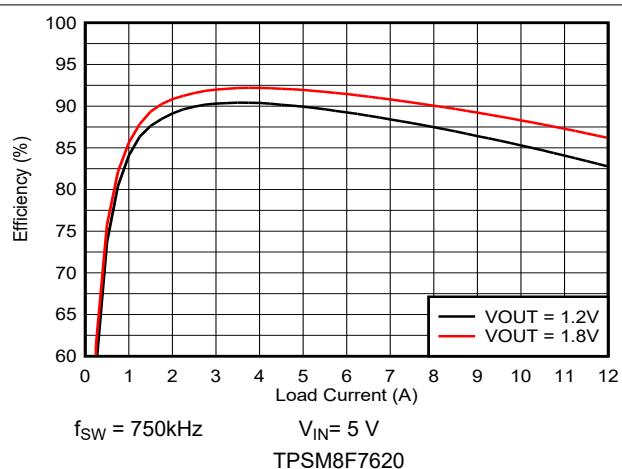

### 8.2.3 アプリケーション曲線

図 8-2. 効率と出力電流との関係

図 8-3. 効率と出力電流との関係

図 8-4. 消費電力

図 8-5. 効率と出力電流との関係

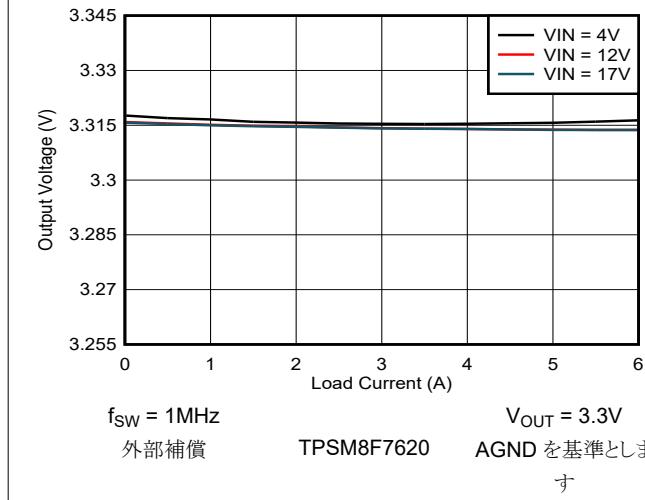

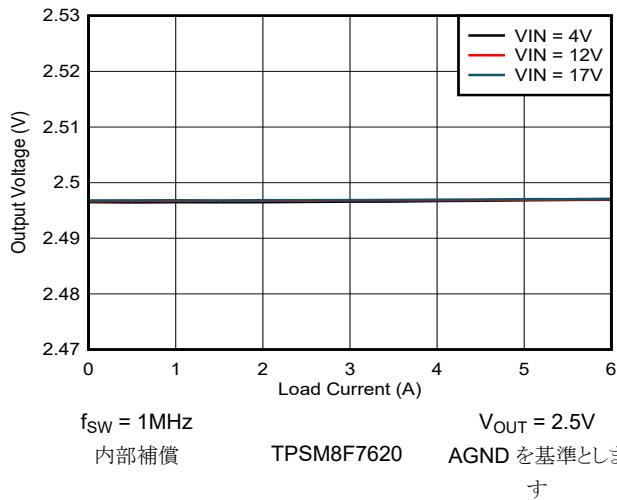

図 8-6. ロード レギュレーション

図 8-7. ロード レギュレーション

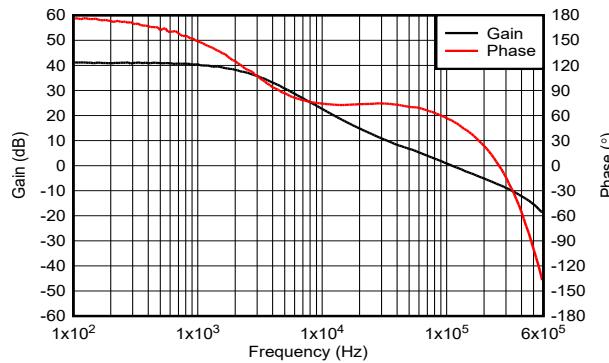

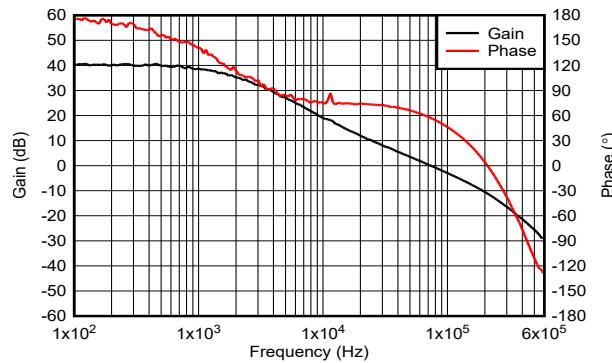

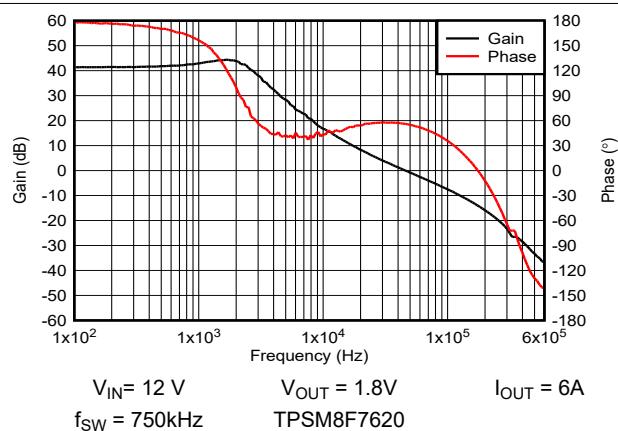

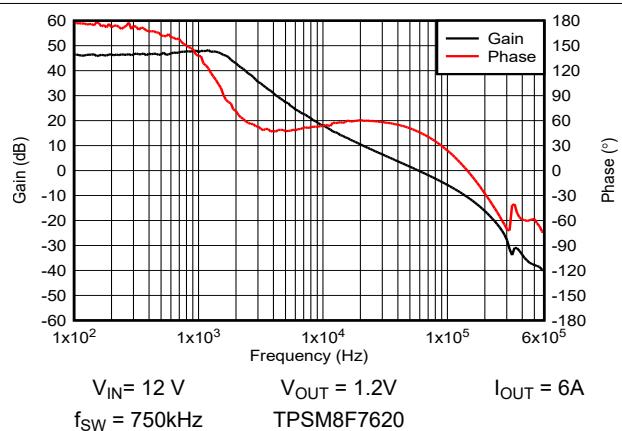

図 8-8. 電圧ループのボード線図 VOUT1

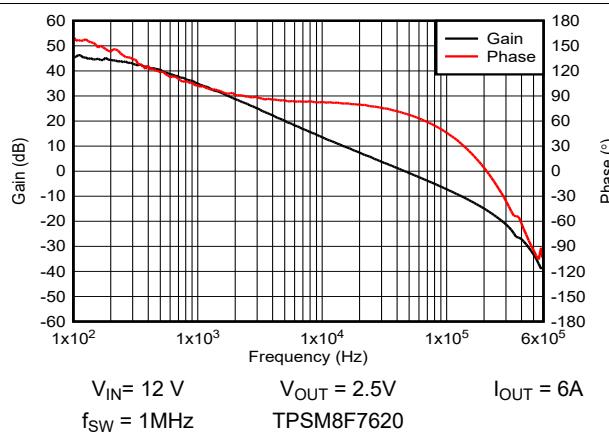

図 8-9. 電圧ループのボード線図 VOUT2

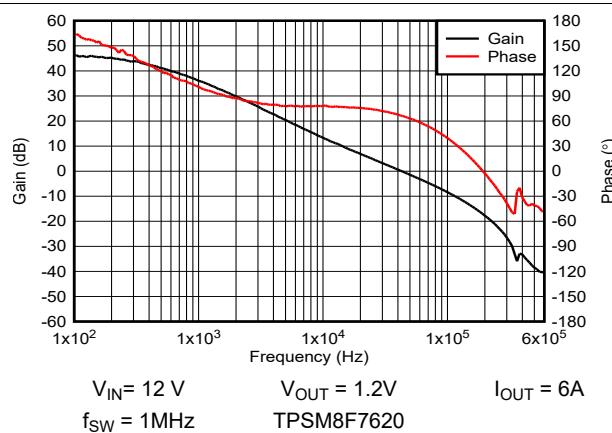

図 8-10. 電圧ループのボード線図 VOUT3

図 8-11. 電圧ループのボード線図 VOUT4

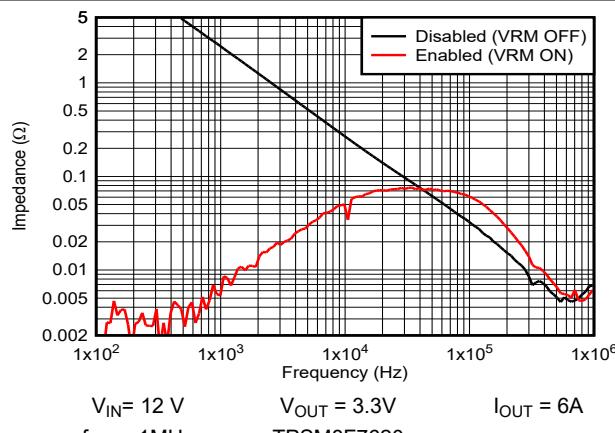

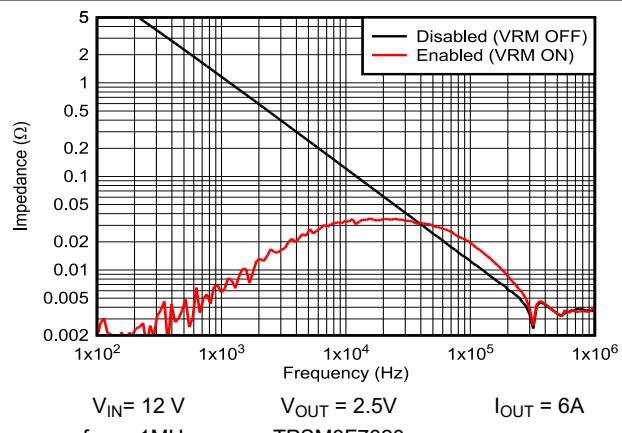

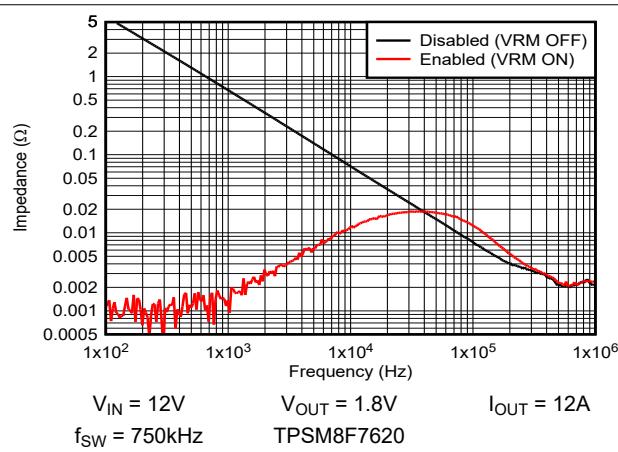

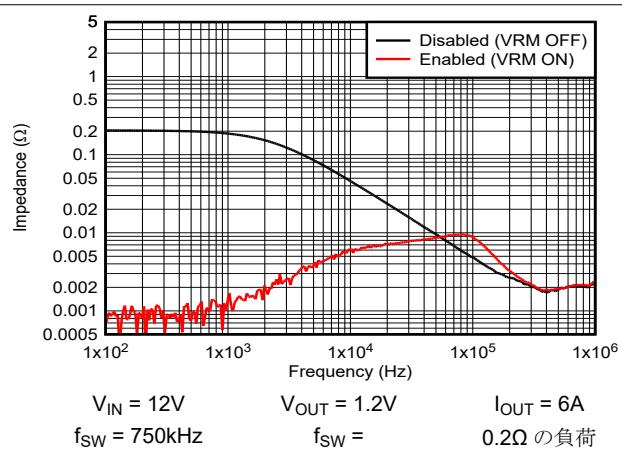

図 8-12. VOUT2 の出力インピーダンス

図 8-13. VOUT3 の出力インピーダンス

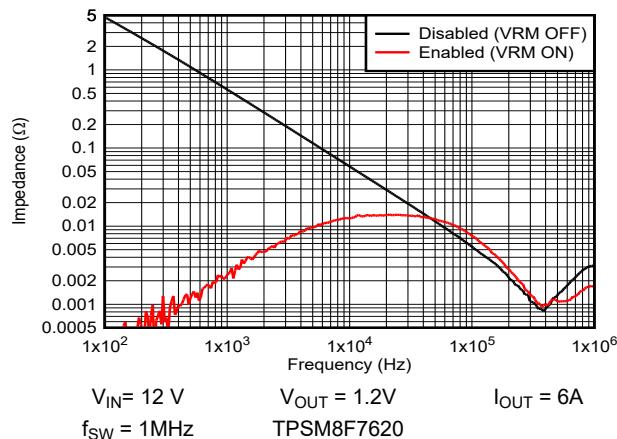

図 8-14. VOUT4 の出力インピーダンス

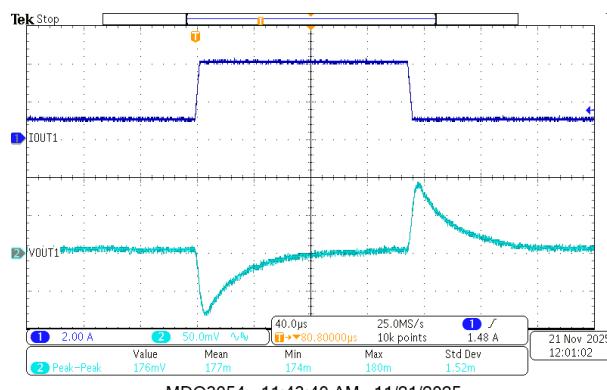

$V_{IN} = 12\text{ V}$     $V_{OUT} = 5.0\text{ V}$     $I_{OUT} = 3\text{ A} \sim 4\text{ A}, 1\text{ A}/\mu\text{s}$

$f_{SW} = 1\text{ MHz}$    TPSM8F7620

図 8-15. VOUT1 の負荷過渡応答

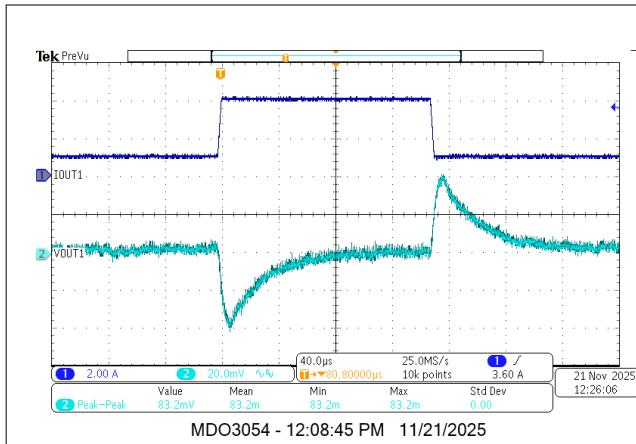

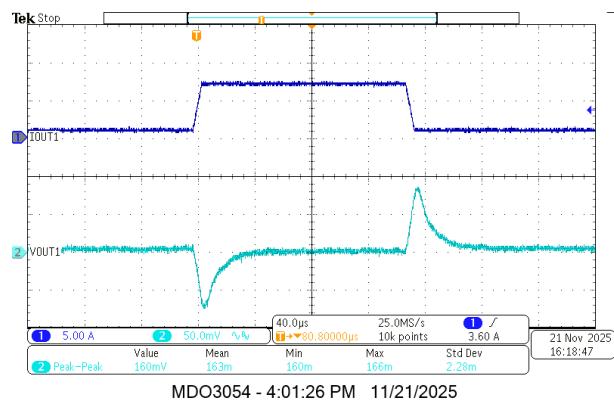

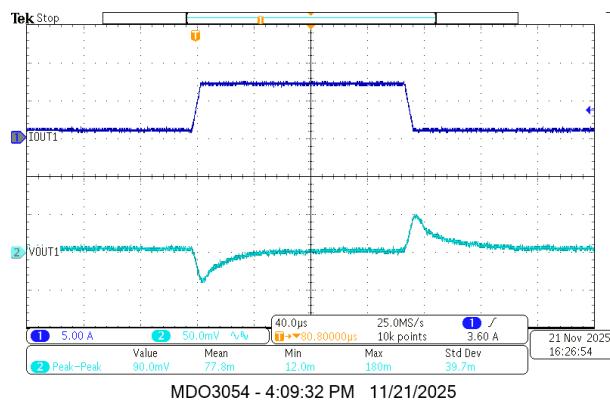

$V_{IN} = 12\text{ V}$     $V_{OUT} = 3.3\text{ V}$     $I_{OUT} = 1\text{ A} \sim 4\text{ A}, 1\text{ A}/\mu\text{s}$

$f_{SW} = 1\text{ MHz}$    TPSM8F7620

図 8-16. VOUT2 の負荷過渡応答

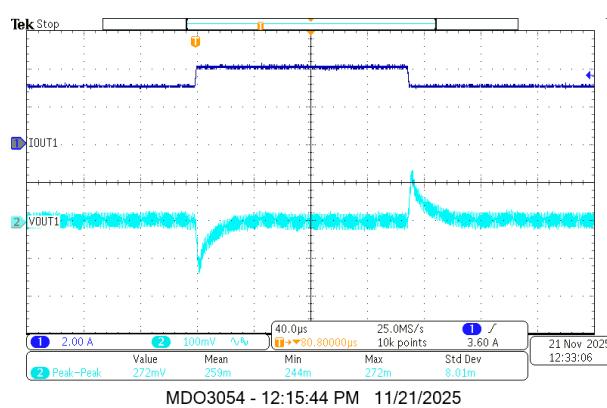

$V_{IN} = 12\text{ V}$     $V_{OUT} = 2.5\text{ V}$     $I_{OUT} = 1\text{ A} \sim 4\text{ A}, 1\text{ A}/\mu\text{s}$

$f_{SW} = 1\text{ MHz}$    TPSM8F7620

図 8-17. VOUT3 の負荷過渡応答

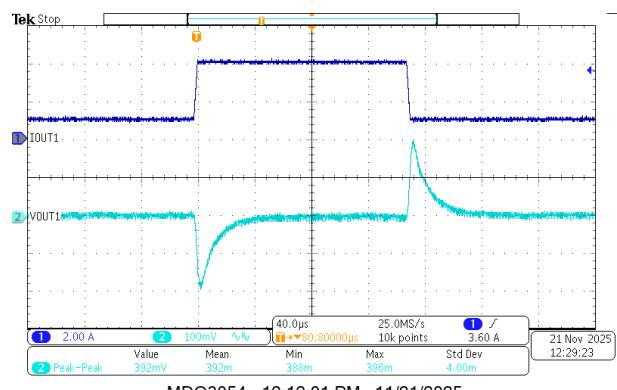

図 8-18. VOUT4 の負荷過渡応答

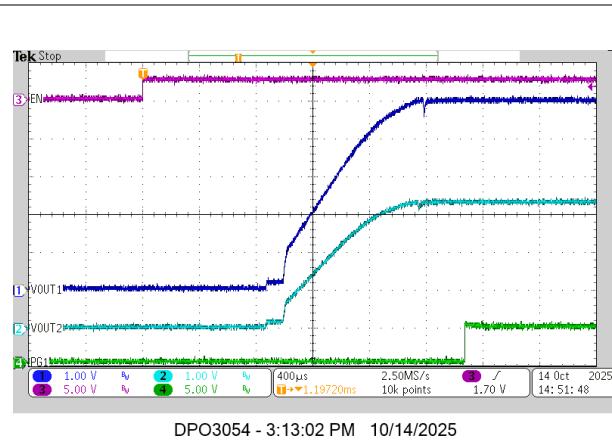

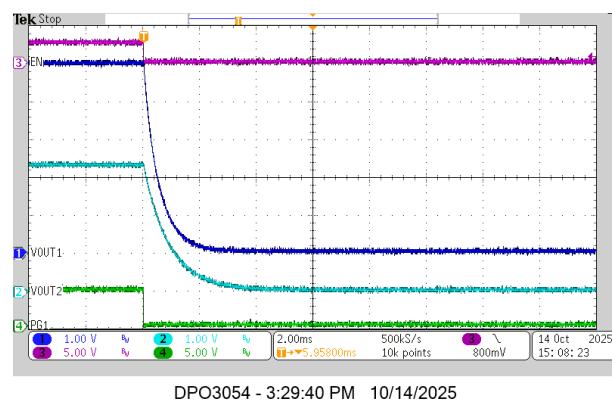

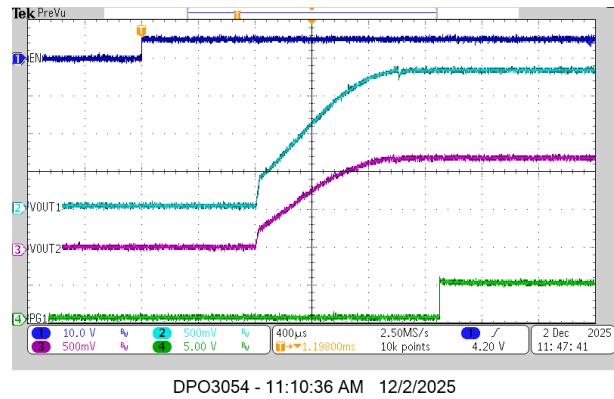

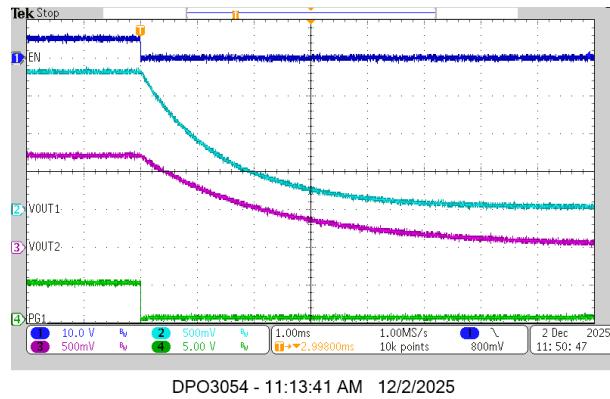

図 8-19. EN からの VOUT1 と VOUT2 の起動

図 8-20. EN からの VOUT3 と VOUT4 の起動

図 8-21. EN からの VOUT1 と VOUT2 シャットダウン

DPO3054 - 3:23:42 PM 10/14/2025

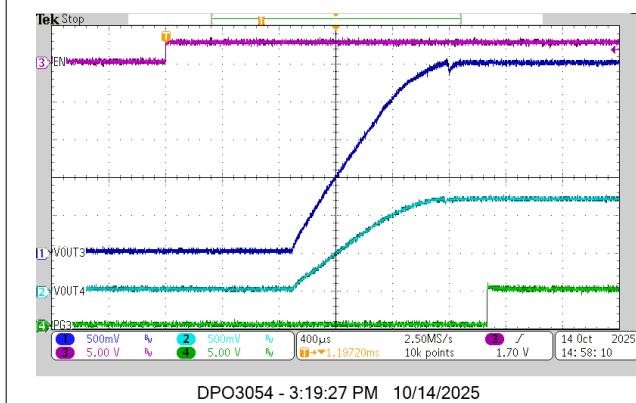

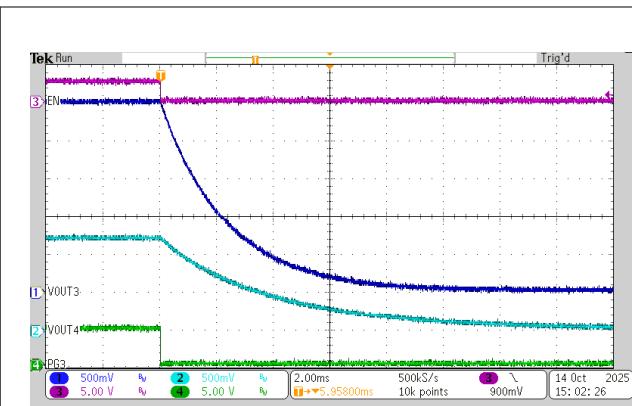

$V_{IN} = 12V$        $V_{OUT} = 2.5V \text{ & } 1.2V$        $I_{OUT} = 0A$

$f_{SW} = 1MHz$       内部補償

図 8-22. EN からの VOUT3 と VOUT4 シャットダウン

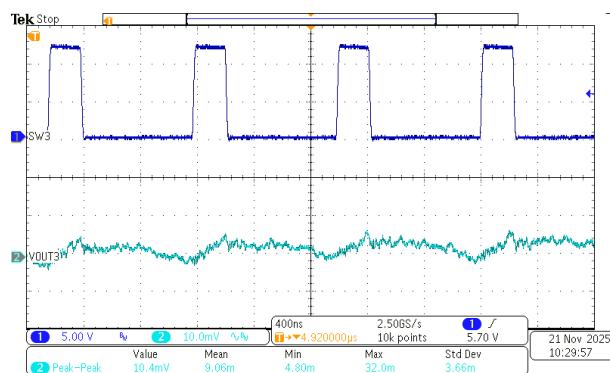

MDO3054 - 9:17:03 AM 11/21/2025

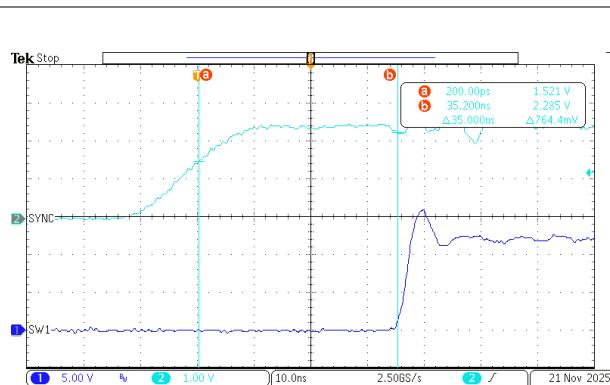

$V_{IN} = 12V$        $f_{SW} = 1MHz$

図 8-23. SYNC から SW1 への遅延

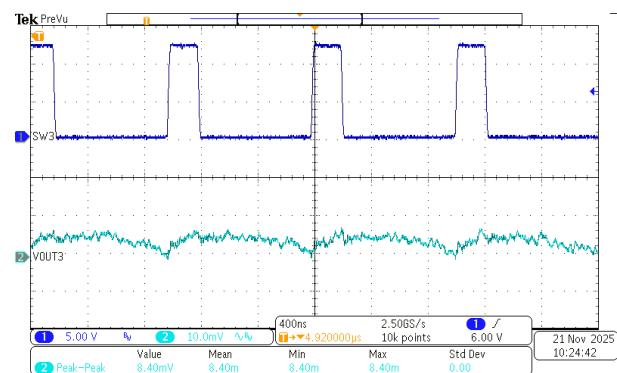

MDO3054 - 10:07:21 AM 11/21/2025

$V_{IN} = 12V$       VOUT AC 結合、

$f_{SW} = 1MHz$       20MHz BW

$f_{SW} = 1MHz$       TPSM8F7620

図 8-24. VOUT3 定常状態リップル

MDO3054 - 10:12:35 AM 11/21/2025

$V_{IN} = 12V$       VOUT AC 結合、

$f_{SW} = 1MHz$       20MHz BW

$f_{SW} = 1MHz$       TPSM8F7620

図 8-25. VOUT3 定常状態リップル

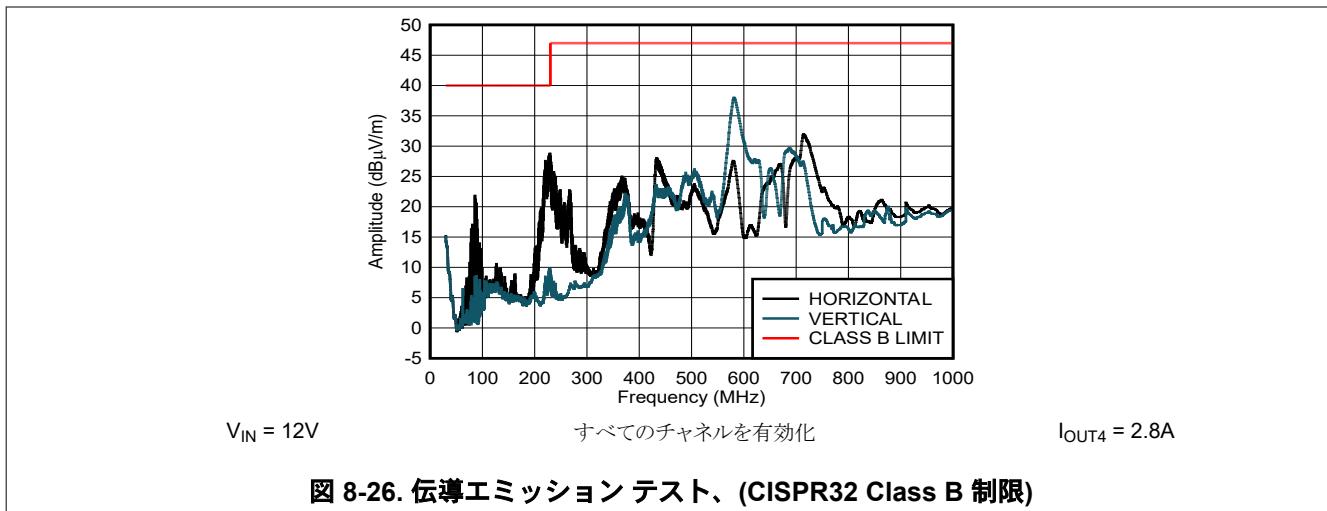

### 8.3 2-PH アプリケーション

マルチフェーズ出力を設計するには、以下の手順に従います。

**図 8-27. 2-PH + 2-PH アプリケーションの回路図**

### 8.3.1 設計要件

**表 8-6. 2-PH の設計パラメータ**

| パラメータ        |                                   | 値          |

|--------------|-----------------------------------|------------|

| 入力電圧         | VIN                               | 12V        |

| 出力電圧         | VOUT1                             | 1.8V       |

|              | VOUT2                             | 1.2V       |

| 最大出力電流       | IOUT1/2                           | 12A        |

| スイッチング周波数    | f <sub>sw</sub>                   | 750kHz     |

| 負荷トランジエントの調整 | VOUT1/2 負荷プロファイル: 1A ~ 7A, 1A/μs。 | VOUT の ±4% |

| ソフトスタート時間    | すべてのチャネル                          | 1ms        |

### 8.3.2 詳細な設計手順

TPSM8F7x20 を使用する 2 相設計の設計手順は、1 相設計の手順とよく似ています。このセクションの目的は、[セクション 8.2](#) に示すように、設計手順と単相設計の違いを説明することです。

セクション 7.3.4 のガイドラインに従って、VOUT2、EN2、SS2、COMP2 ピンはそれぞれ VOUT1、EN1、SS1、COMP1 に接続されています。CH2 はセカンダリ チャネルなので、PG と FB をフローティングにできます。CH3 と CH4 の間でも同じように接続されています。これは、CH3 と CH4 がクワッド モジュールの 2 相出力を形成するためです。ソフトスタートコンデンサは、単相設計と同じように設定されています。

スイッチング周波数は、RT ピンを使用する単相設計と同じように選択します。

多相制御ループを補償するには、[セクション 8.2.2.10](#) と同じ式を使用して RCOMP と CCOMP を求めます。スタック内の全位相数を表す N という変数があり、2 相出力の場合は 2 に設定されています。RCOMP と CCOMP の式の変数「C」には、2 相出力の合計出力キャパシタンスを使用します。

### 8.3.3 アプリケーション曲線 2-PH

図 8-28. 効率と出力電流との関係

図 8-29. 効率と出力電流との関係

図 8-30. 電圧ループのボード線図 VOUT1

図 8-31. 電圧ループのボード線図 VOUT2

図 8-32. VOUT1 の出力インピーダンス

図 8-33. VOUT2 の出力インピーダンス

図 8-34. VOUT1 の負荷過渡

図 8-35. VOUT2 の負荷過渡

図 8-36. EN からの起動

図 8-37. EN からのシャットダウン

## 8.4 電源に関する推奨事項

TPSM8F7x20 降圧モジュールは、4V ~ 17V の広い入力電圧範囲で動作するよう設計されています。入力電源の特性は、このデータシートの「**絶対最大定格**」と「**推奨動作条件**」に適合している必要があります。また、入力電源は、負荷時レギュレータ回路に必要な入力電流を供給できる必要があります。[式 22](#) を使用して平均入力電流を推定します。

$$I_{IN} = \left( \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \right) \quad (22)$$

ここで、

- $\eta$  は効率です。

モジュールが高インピーダンスを持つ長い配線や PCB パターンを経由して入力電源に接続されている場合は、安定した性能を実現するために特に注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、モジュールの動作に悪影響を及ぼすおそれがあります。具体的には、寄生インダクタンスと低 ESR のセラミック入力コンデンサの組み合わせにより、低減衰共振回路が形成され、入力電源のサイクルのオン/オフが繰り返されるたびに不安定または電圧過渡が発生する可能性があります。寄生抵抗により、負荷過渡中に入力電圧が低下する場合があります。モジュールが最小入力電圧に近い値で動作している場合、この低下によって UVLO が誤って起動され、システムがリセットされる可能性があります。

こうした問題を解決する最善策は、入力電源からモジュールまでの距離を短くして、電解入力コンデンサをセラミックと並列に使用することです。中程度の ESR を持つ電解コンデンサは、入力共振回路の振動を減衰させ、入力のすべてのオーバーシュートまたはアンダーシュートを低減するのに役立ちます。通常、入力並列ダンピングには  $47\mu F \sim 100\mu F$  の静電容量で十分であり、大きな負荷過渡時にも入力電圧を安定して保持するのに寄与します。代表的な ESR は  $0.1\Omega \sim 0.4\Omega$  であり、ほとんどの入力回路構成で十分な減衰を実現します。

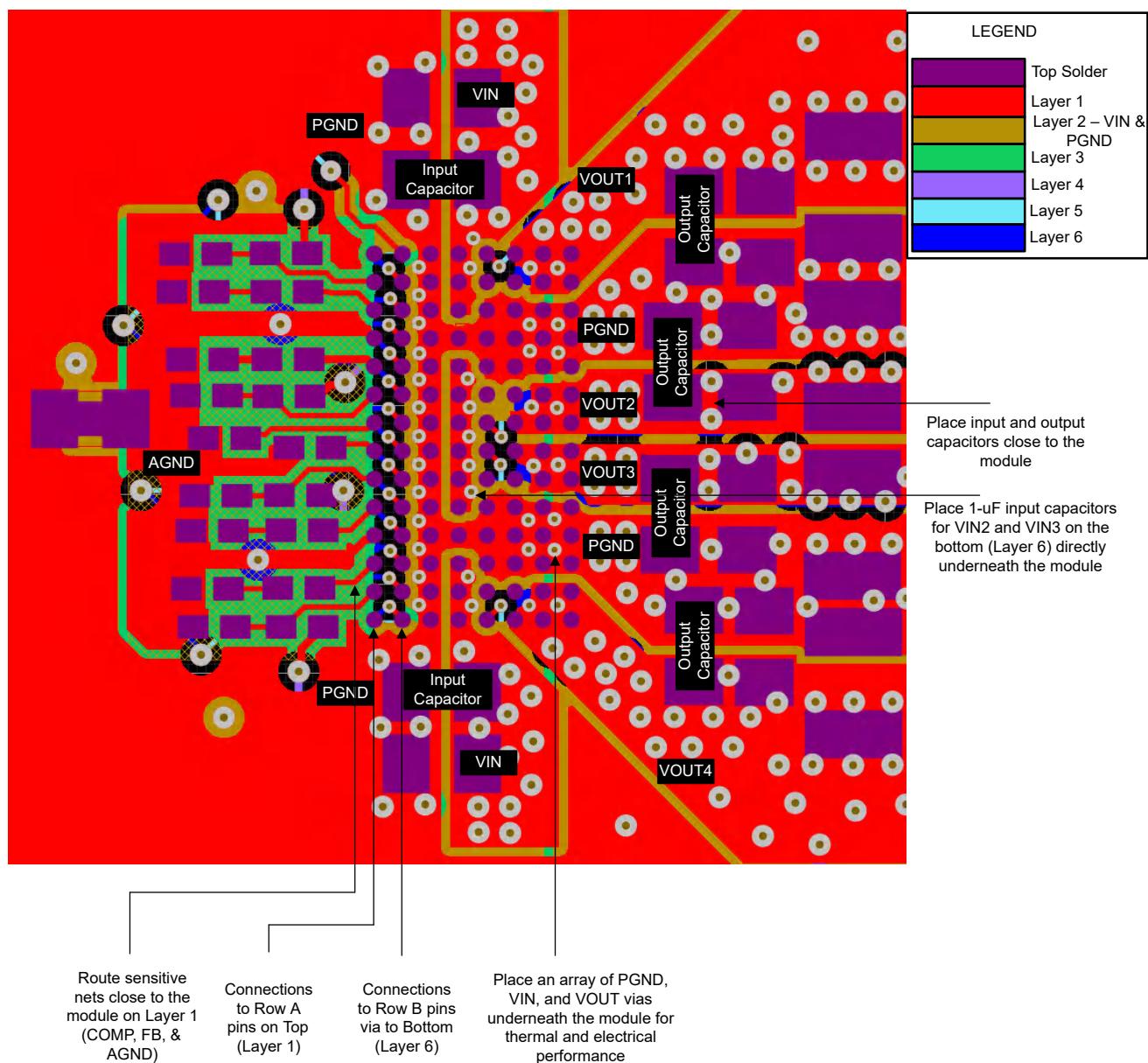

## 8.5 レイアウト

大電流、高速スイッチング モジュール回路（高い内部電圧および電流スルーレートを持つ）においては、信頼性の高いデバイス動作と設計の堅牢性を実現するために、適切な PCB 設計とレイアウトが重要です。これは主に、基板上のデバイスの EMI 性能と放熱性能に影響を与えます。

### 8.5.1 レイアウトのガイドライン

次のリストに、熱や EMI 特性を含め、DC/DC モジュールの性能を最適化できる PCB レイアウトと部品の配置に関する重要なガイドラインを要約します。[レイアウト例](#) に、TPSM8F7x20 の推奨 PCB レイアウトと、最適化された電力段および小信号部品の配置および配線を示します。

- 入力コンデンサは、VIN ピンにできる限り近づけて配置してください。高周波電流は、モジュールに内蔵された  $0.1\mu F$  コンデンサによってデカップリングされます。

- X7R または X7S の誘電体を使用した、低 ESR のセラミックコンデンサを使用してください。

- 入力コンデンサのグランドリターンパスは、モジュールの下にある PGND パッドに接続する局所的な上面プレーンで構成されている必要があります。

- VIN2 ピンと VIN3 ピンはパッケージの中央にあり、VIN を内層に配線する必要があります。また、 $2.2\mu F$  VIN コンデンサを PCB の底面または反対側に追加することは任意です。

- 出力コンデンサは、VOUT ピンにできる限り近づけて配置してください。出力コンデンサのデュアル配置と対称配置が類似しているため、リップルの低減が可能です。

- 出力コンデンサのグランドリターンパスは、モジュールの下にある PGND パッドに接続する局所的な上面プレーンで構成されている必要があります。

- VOUT ピンは内部で接続されていますが、下側の PCB 層で広いポリゴンプレーンを使用して、これらのピンを相互に接続し、負荷に接続することで、導通損失と熱ストレスを低減します。

- 帰還抵抗を FB ピンの近くに配置することで、FB パターンをできるだけ短くします。分圧抵抗を負荷ではなく FB ピン近くに配置することで、出力電圧帰還パスのノイズの影響を小さくします。FB は電圧ループ エラー アンプへの入力であり、ノイズの影響を受けやすいハイインピーダンスノードを表します。上側の帰還抵抗から必要な出力電圧レギュレーション ポイントまでパターンを配線します。

- モジュールの上層の直下にある **PCB** 層のソリッド グランド プレーンを使用します。このプレーンは、スイッチング ループ内の電流に関連する磁界を最小化することで、ノイズ シールドとして機能します。レイアウト例に示されているように、**AGND** と **PGND** を 1箇所で接続します。

- 適切なヒートシンクのために十分な **PCB** 領域を確保します。十分な銅面積を使用して、最大負荷電流および周囲温度条件に対応する低熱インピーダンスを実現します。接合部温度を 125°C 未満に維持するために、TPSM8F7x20 には十分なヒートシンクを用意してください。全定格負荷で動作する場合、上面のグランド プレーンは重要な放熱面積になります。効果的なヒートシンクと電気的導通を実現するために、モジュールの **PGND**、**VIN**、**VOUT** パッドの下に複数のビアを使用します。

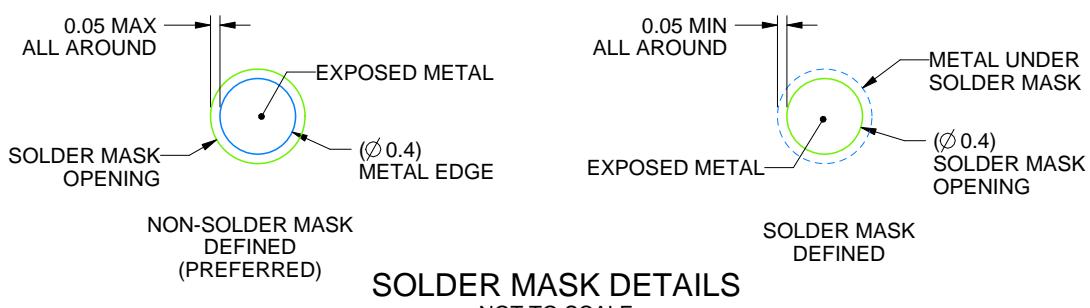

- VIN**、**PGND**、**VOUT** には **SMD** ランディング パッド、または銅箔に接続するその他のピンを使用します。他のすべての I/O および信号ピンは、「サンプル基板レイアウト」の図に記載されているように、**NSMD** を使用する必要があります。

- ドッグボーンまたはビーアインパッドのエスケープ ルーティングを使用できます。

- AGND** プレーンを **PGND** に 1箇所で接続して、グランド ループを防止します。また、同じ **AGND** 銅箔面上で低インピーダンス接続を使用して **AGND1** を **AGND2** に接続します。

#### 8.5.1.1 熱設計およびレイアウト

DC/DC モジュールを特定の温度範囲で使用できるようにするには、パッケージは接合部温度を定格制限内に維持しながら、発生する熱を効率的に除去する必要があります。TPSM8F7x20 モジュールは、豊富なアプリケーション要件に対応する小型の 7mm × 12mm 112 ピン BGA パッケージと 6.4mm × 7mm 56 ピン FCBGA パッケージで供給されます。[熱に関する情報](#) の表には、このパッケージの熱指標と、『[半導体および IC パッケージの熱指標](#)』アプリケーション ノートに記載された関連する詳細情報が要約されています。

112 ピン BGA パッケージでは、BGA ボールを介して熱が除去されます。この設計により、ヒートシンクが大幅に改善されます。熱除去サブシステムを完成させる上で、PCB 設計にサーマルランド、サーマルビア、および 1つまたは複数のグランド プレーンを含めることは不可欠です。TPSM8F7x20 の露出したパッドは、PCB 上でデバイスのパッケージの真下にある、グランドに接続された銅ランドにはんだ付けされているため、熱抵抗を非常に小さい値まで低減します。

TPSM8F7x20 はオーバーモールド パッケージ構造を採用しており、放熱特性を高めるためにヒートシンクまたはコールドプレートに接続できます。これは、デバイスの熱 SOA を増加させる効果的な方法であり、熱的制限による出力電流のディレーティングを低減できます。

可能なら、すべての層に **1oz** 以上の銅厚の 6 層基板を使用して、低インピーダンス、適切なシールド、低い熱抵抗を実現することを推奨します。サーマル ランドから内部と半田側のグランド プレーンに接続された大量のビアは、伝熱に不可欠です。PCB をマルチレイヤに積み上げる場合、通常は電力段部品下の PCB 層にソリッド グランド プレーンを配置します。この設計は、電力段の電流が流れるためのプレーンだけでなく、熱を生成するデバイスから熱を逃がす熱伝導経路を提供します。

### 8.5.2 レイアウト例

図 8-42. 標準上層部の PCB 設計

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 9.1.2 開発サポート

開発サポートについては、以下を参照してください。

- テキサス・インスツルメンツのリファレンス デザイン ライブドリについて、[テキサス・インスツルメンツ リファレンス デザイン ライブドリ](#)をご覧ください。

- テキサス・インスツルメンツの WEBENCH 設計環境については、[WEBENCH® 設計センター](#)をご覧ください。

- 低 EMI の電源を設計するには、テキサス・インスツルメンツの包括的な [EMI トレーニング シリーズ](#)をご覧ください。

- 反転昇降圧 (IBB) レギュレータを設計するには、[DC/DC 反転昇降圧モジュール](#)をご覧ください。

- TI リファレンス デザイン

- [『Kintex 7 アプリケーション向け複数出力電源ソリューション』](#)

- [『BOM \(部品表\) 点数が最小で、スペースを最適化した DC/DC 反転型電源モジュールのリファレンス デザイン』](#)

- [『小型の低ノイズ システム用の 3 ~ 11.5V<sub>IN</sub>, -5V<sub>OUT</sub>, 1.5A の反転電源モジュールのリファレンス デザイン』](#)

- 寄稿記事:

- [『DC/DC 降圧コンバータを使用した医療用画像処理アプリケーションへの電力供給』](#)

- [『How To Create A Programmable Output Inverting Buck-boost Regulator \(英語\)』](#)

#### 9.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、TPSM8F7x20 モジュールを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握します。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力します。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になります。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『[TI 降圧スイッチング DC/DC アプリケーションノートのクイックリファレンス ガイド](#)』アプリケーション ノート

- テキサス・インスツルメンツ、『[革新的な DC/DC 電源モジュール』セレクション ガイド](#)

- テキサス・インスツルメンツ、『Enhanced HotRod™ QFN パッケージ テクノロジーによる小型で低発熱の静音電源モジュールの実現』ホワイトペーパー

- テキサス・インスツルメンツ、『電源モジュール パッケージの各種オプションの利点とトレードオフ』ホワイトペーパー

- テキサス・インスツルメンツ、『電源モジュールによる低 EMI 設計の簡素化』ホワイトペーパー

- テキサス・インスツルメンツ、『ラボ計測用電源モジュール』ホワイトペーパー

- テキサス・インスツルメンツ、『DC/DC レギュレータの EMI エンジニアガイド』e-book

- テキサス・インスツルメンツ、『電源モジュールの半田付けに関する考慮事項』アプリケーションノート

- テキサス・インスツルメンツ、『DC/DC 電源モジュールを使った実用的な熱設計』アプリケーションノート

- テキサス・インスツルメンツ、『新しい熱評価基準の解説』アプリケーションノート

- テキサス・インスツルメンツ、『過去ではなく、現在の議見による AN-2020 热設計』アプリケーションノート

- テキサス・インスツルメンツ、『負出力反転昇降圧アプリケーションに TPSM53602/3/4 を使用する方法』アプリケーションノート

- テキサス・インスツルメンツ、『DC/DC コンバータの安全動作領域 (SOA) 曲線をグラフ化する方法』アプリケーションノート

## 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

## 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

## 9.5 商標

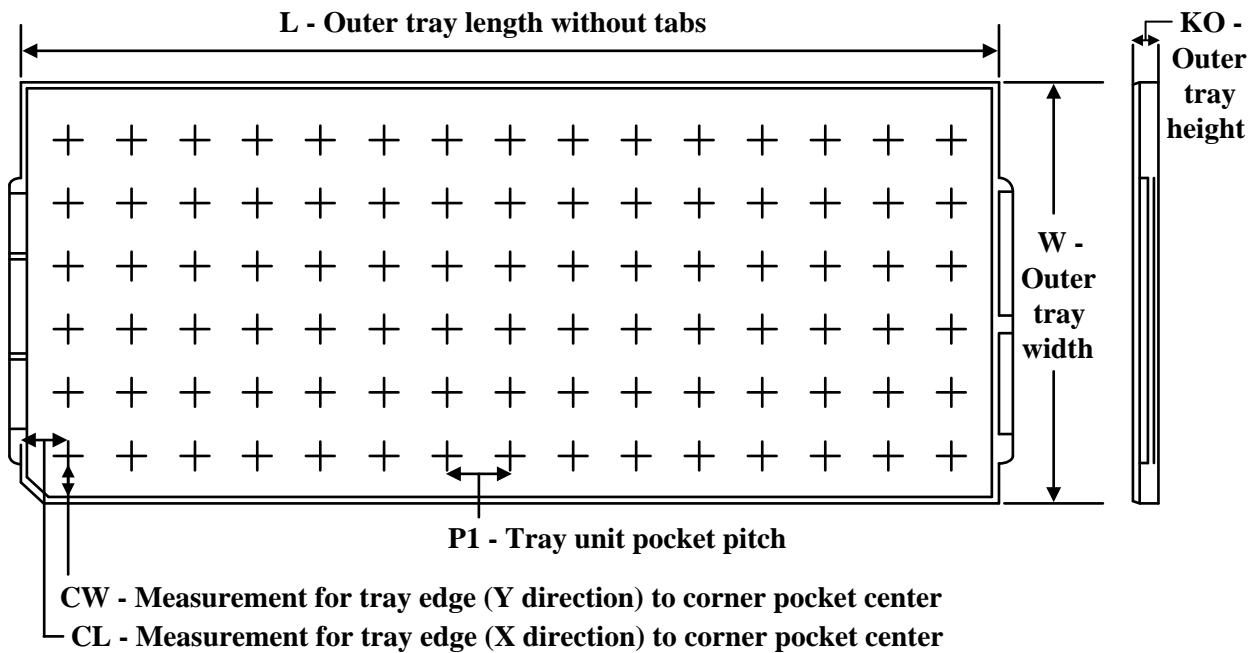

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.