# TSD5402-Q1 8W 高効率車載センサ ドライバ アンプ、保護機能と I<sup>2</sup>C 診断機能 内蔵

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み

- 温度グレード 1:-40°C~125°C, T<sub>A</sub>

- モノラル BTL デジタル パワー アンプ

- 出力電力: 8W (THD+N = 10%, 4Ω 負荷時)

- 4.5V~18V の動作範囲

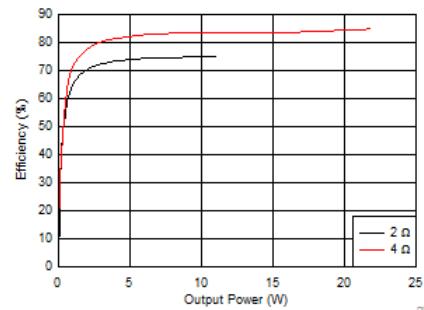

- 効率: 83% (4Ω 負荷時)

- 差動アナログ入力

- 電源ガード保護 (可変電圧リミッタ)

- 75dB 電源除去率 (PSRR)

- 負荷診断機能:

- 出力負荷の開放と短絡

- 出力と電源、出力とグランドとの間の短絡

- 保護および監視機能

- 短絡保護

- ISO-7637-2 準拠の 40V 負荷ダンプ保護

- 出力 DC レベル検出

- 過熱保護

- 過電圧および低電圧保護

- PowerPAD™ (裏面露出パッド) で熱特性を強化した 16 ピン HTSSOP (PWP) パッケージ

- 車載用 EMC 要件に合わせて設計

- ISO9000:2002 TS16949 認定済み

- スタンバイ時の負荷ダンプ保護: 40V

- スタンバイ時も遮断されない I<sup>2</sup>C

## 2 アプリケーション

- リゾルバを使用した車載用および産業用アプリケーション

- HEV/EV のインバータおよびモーター制御

- 電動パワー ステアリング (EPS)

- リアビュー ミラー モジュール

- 車載用電子ミラー

- サーボ ドライブの電力段モジュール

- 飛行制御システム

## 3 概要

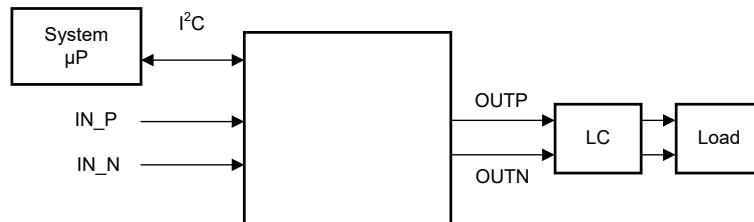

TSD5402-Q1 は Class-D センサ駆動アンプで、車載用および産業用アプリケーションに理想的です。これらのアプリケーションは、リゾルバを使用したモーター制御、ブレーキシステム、電動パワー ステアリング、サーボ、ライトコントロール表面を含みますが、これらに限定されません。広い動作電圧範囲と優れた効率を備えているため、このデバイスは設計において柔軟性が必要なアプリケーションに理想的です。負荷ダンプ保護が搭載されているため、外付け電圧クランプのコストとサイズを減らすことができ、オンボードの負荷診断機能により I<sup>2</sup>C 経由で負荷の状態が報告されます。内蔵の短絡負荷と開放負荷診断機能により、システムは外部実装を回避できます。

### 製品情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| TSD5402-Q1 | HTSSOP (16)          | 5.0mm × 6.4mm            |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

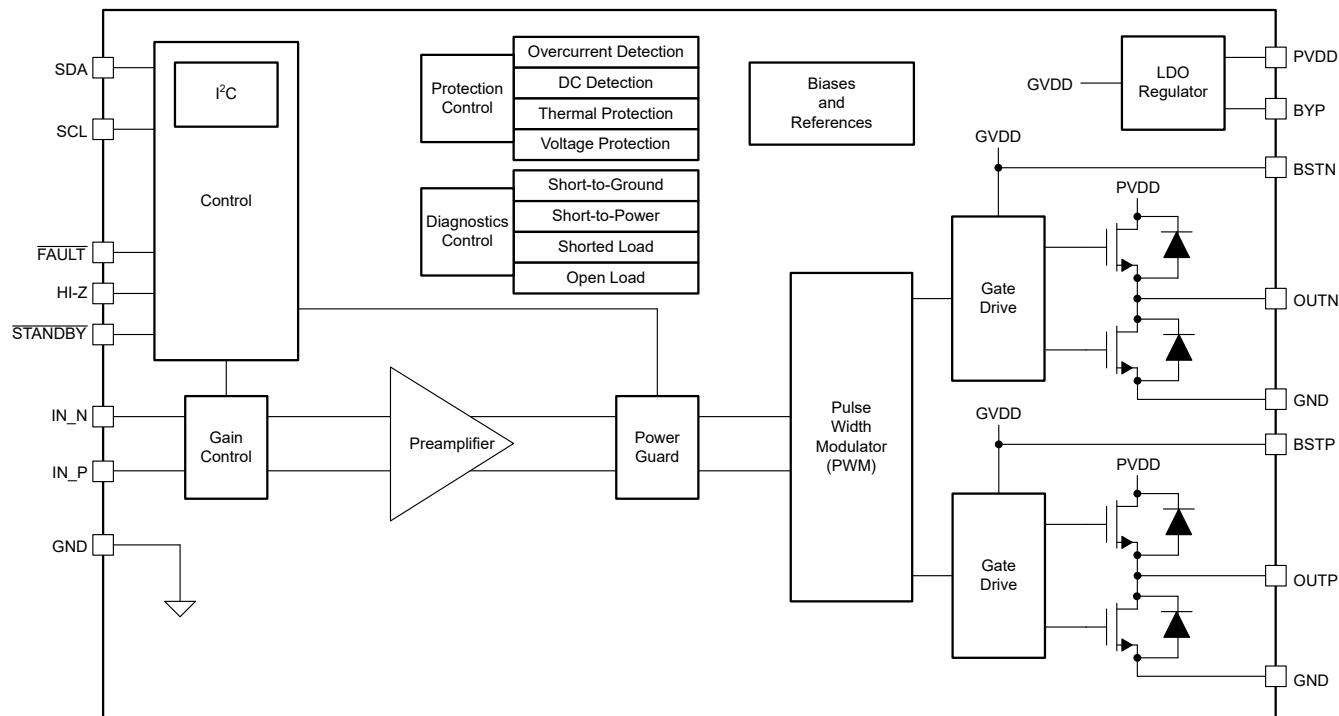

概略ブロック図

出力電力効率

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                         |    |                                        |    |

|-----------------------------------------|----|----------------------------------------|----|

| <b>1 特長</b>                             | 1  | <b>7.1 I<sup>2</sup>C アドレス レジスタの定義</b> | 19 |

| <b>2 アプリケーション</b>                       | 1  | <b>8 アプリケーションと実装</b>                   | 21 |

| <b>3 概要</b>                             | 1  | <b>8.1 アプリケーション情報</b>                  | 21 |

| <b>4 ピン構成および機能</b>                      | 3  | <b>8.2 代表的なアプリケーション</b>                | 21 |

| <b>5 仕様</b>                             | 4  | <b>8.3 電源に関する推奨事項</b>                  | 24 |

| 5.1 絶対最大定格                              | 4  | 8.4 レイアウト                              | 25 |

| 5.2 ESD 定格                              | 4  | <b>9 デバイスおよびドキュメントのサポート</b>            | 29 |

| 5.3 推奨動作条件                              | 4  | 9.1 デバイス サポート                          | 29 |

| 5.4 熱に関する情報                             | 5  | 9.2 ドキュメントのサポート                        | 29 |

| 5.5 電気的特性                               | 5  | 9.3 ドキュメントの更新通知を受け取る方法                 | 29 |

| 5.6 I <sup>2</sup> C インターフェイス信号のタイミング要件 | 7  | 9.4 サポート・リソース                          | 29 |

| 5.7 代表的特性                               | 8  | 9.5 商標                                 | 29 |

| <b>6 詳細説明</b>                           | 10 | 9.6 静電気放電に関する注意事項                      | 29 |

| 6.1 概要                                  | 10 | 9.7 用語集                                | 29 |

| 6.2 機能ブロック図                             | 10 | <b>10 改訂履歴</b>                         | 29 |

| 6.3 機能説明                                | 11 | <b>11 メカニカル、パッケージ、および注文情報</b>          | 30 |

| 6.4 デバイスの機能モード                          | 17 | 11.1 付録:パッケージ オプション                    | 31 |

| <b>7 レジスタ マップ</b>                       | 19 |                                        |    |

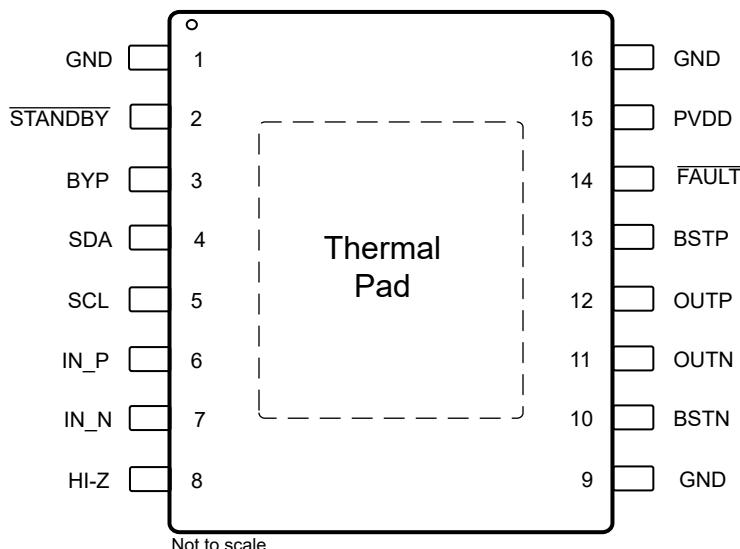

## 4 ピン構成および機能

図 4-1. PWP パッケージ、16 ピン、TSSOP (露出サーマル パッド付き) 上面図

表 4-1. ピンの機能

| ピン        |          | 種類 <sup>(1)</sup> | 説明                                                    |

|-----------|----------|-------------------|-------------------------------------------------------|

| 名称        | 番号       |                   |                                                       |

| BSTN      | 10       | AI                | 負出力ハイサイド FET のブートストラップ                                |

| BSTP      | 13       | AI                | 正出力ハイサイド FET のブートストラップ                                |

| BYP       | 3        | PBY               | 電圧レギュレータのバイパスコンデンサのピン                                 |

| FAULT     | 14       | DO                | 故障を報告するために使用されるアクティブ Low オープンドレイン出力                   |

| GND       | 1, 9, 16 | GND               | グランド                                                  |

| IN_N      | 7        | AI                | 反転アナログ入力                                              |

| IN_P      | 6        | AI                | 非反転アナログ入力                                             |

| ハイインピーダンス | 8        | DI                | DRIVE モードでの出力スイッチングを停止、アクティブ High (内部プルアップまたはプルダウンなし) |

| OUTN      | 11       | PO                | 出力 (-)                                                |

| OUTP      | 12       | PO                | 出力 (+)                                                |

| PVDD      | 15       | PWR               | 電源                                                    |

| SCL       | 5        | DI                | I <sup>2</sup> C クロック                                 |

| SDA       | 4        | DI/DO             | I <sup>2</sup> C データ                                  |

| STANDBY   | 2        | DI                | アクティブ Low STANDBY ピン (内部プルアップまたはプルダウンなし)              |

| サーマル・パッド  | —        | —                 | グランドに接続する必要があります。                                     |

(1) DI = デジタル入力、DO = デジタル出力、AI = アナログ入力、PWR = 電源、PBY = 電源バイパス、PO = 電源出力、GND = グランド

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                        |                                                     |                           | 最小値  | 最大値  | 単位 |

|----------------------------------------|-----------------------------------------------------|---------------------------|------|------|----|

| 入力電圧                                   | DC 電源電圧範囲、 $V_{(PVDD)}$                             | GND に対する相対値               | -0.3 | 30   | V  |

|                                        | パルス電源電圧範囲、 $V_{(PVDD\_MAX)}$                        | $t \leq 400\text{ms}$ の曝露 | -1   | 40   |    |

|                                        | 電源電圧ランプ レート、 $\Delta V_{(PVDD\_RAMP)}$              |                           | 15   | V/ms |    |

|                                        | SCL ピン、SDA ピン、および STANDBY ピン、FAULT ピン               | GND に対する相対値               | -0.3 | 5    | V  |

|                                        | IN_N ピン、IN_P ピン、および HI-Z ピン                         | GND に対する相対値               | -0.3 | 6.5  |    |

|                                        | BYP                                                 | GND に対する相対値               | -0.3 | 7    |    |

|                                        | BSTN、BSTP                                           | BYP に対する相対値               | -0.3 | 30   |    |

|                                        | BSTN、BSTP                                           | GND に対する相対値               | -0.3 | 36.3 |    |

| 電流                                     | OUTN、OUTP                                           | GND に対する相対値               | -0.3 | 30   |    |

|                                        | PVDD ピン、GND ピン、OUTx ピンの DC 電流、 $I_{(PVDD)}$ 、 $I_O$ |                           | ±4   | A    |    |

|                                        | すべての入力ピンの最大電流、 $I_{(IN\_MAX)}$ <sup>(2)</sup>       |                           | ±1   | mA   |    |

| オープンドレイン ピンの最大シンク電流、 $I_{(IN\_ODMAX)}$ |                                                     |                           | 7    |      |    |

| 保管温度、 $T_{stg}$                        |                                                     |                           | -55  | 150  | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、推奨動作条件に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) アナログ入力電圧と ac 結合の詳細については、セクションを参照してください。

### 5.2 ESD 定格

|             |      |                                                                | 値     | 単位 |

|-------------|------|----------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup><br>HBM ESD 分類レベル H2 | ±3500 | V  |

|             |      | デバイス帯電モデル (CDM)、AEC Q100-011 準拠<br>CDM ESD 分類レベル C5            | ±1000 |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

|                            |                                                                |                     | 最小値                                                          | 公称値  | 最大値  | 単位                    |      |   |

|----------------------------|----------------------------------------------------------------|---------------------|--------------------------------------------------------------|------|------|-----------------------|------|---|

| $V_{(PVDD\_OP)}$           | GND に対する電源電圧範囲。ac 過渡現象が見込まれるため、適切なデカップリングが必要です。 <sup>(3)</sup> | 4Ω±20%の負荷 (またはそれ以上) | 4.5                                                          | 14.4 | 18   | V                     |      |   |

|                            |                                                                | 2Ω±20% の負荷          | 5                                                            | 14.4 | 18   |                       |      |   |

| $V_{(PVDD\_RIPPLE)}$       | PVDD の最大リップル                                                   |                     | $V_{(PVDD)} < 8\text{V}$                                     |      | 1    | $V_{pp}$              |      |   |

| $V_{(HI-Z)}$               | GND に対する HI-Z 電源電圧範囲                                           |                     |                                                              |      | -0.3 | 3.3                   | 5.5  | V |

| $V_{(AIN)}$ <sup>(1)</sup> | アナログ入力信号レベル                                                    |                     | AC 結合の入力信号                                                   |      | 0    | 0.25–1 <sup>(2)</sup> | Vrms |   |

| $V_{(IH\_STANDBY)}$        | HI-Z ピンおよび STANDBY ピン ロジック レベル High の入力電圧                      |                     |                                                              |      | 2    |                       | V    |   |

| $V_{(IL\_STANDBY)}$        | HI-Z ピンおよび STANDBY ピン ロジック レベル Low の入力電圧                       |                     |                                                              |      | 0.7  |                       | V    |   |

| $V_{(IH\_SCL)}$            | SCL ピン ロジック レベル High の入力電圧                                     |                     | $R_{(PU\_I2C)} = 4.7\text{k}\Omega$ プルアップ、電源電圧 = 3.3V または 5V |      | 2.1  |                       | V    |   |

| $V_{(IH\_SDA)}$            | SDA ピン ロジック レベル High の入力電圧                                     |                     | $R_{(PU\_I2C)} = 4.7\text{k}\Omega$ プルアップ、電源電圧 = 3.3V または 5V |      | 2.1  |                       | V    |   |

|                                               |                                               |                                                                    | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>(IL_SCL)</sub>                         | SCL ピン ロジック レベル Low の入力電圧                     | R <sub>(PU_I2C)</sub> = 4.7kΩ プルアップ、電源電圧 = 3.3V または 5V             |     | 1.1 |     | V  |

| V <sub>(IL_SDA)</sub>                         | SDA ピン ロジック レベル Low の入力電圧                     | R <sub>(PU_I2C)</sub> = 4.7kΩ プルアップ、電源電圧 = 3.3V または 5V             |     | 1.1 |     | V  |

| T <sub>A</sub>                                | 周囲温度                                          |                                                                    | -40 |     | 125 | °C |

| R <sub>(L)</sub>                              | 公称負荷インピーダンス                                   | 低インピーダンス負荷を使用する場合、過電流制限を超えないようにします。                                | 2   | 4   | 60  | Ω  |

| V <sub>(PU)</sub>                             | プルアップ電源 (オープンドレイン ロジック出力用)                    | 通常動作中は、V <sub>(PU)</sub> は (V <sub>(PVDD)</sub> - 1V) を下回る必要があります。 | 3   | 3.3 | 5.5 | V  |

| R <sub>(PU_EXT)</sub>                         | オープンドレイン ロジック出力の外部プルアップ抵抗                     | オープンドレインのロジック出力と V <sub>(PU)</sub> 電源の間に接続された抵抗。                   | 10  |     | 50  | kΩ |

| R <sub>(PU_I2C)</sub>                         | SDA および SCL ピンの I <sup>2</sup> C プルアップ抵抗      |                                                                    | 1   | 4.7 | 10  | kΩ |

| C <sub>(PVDD)</sub>                           | PVDD ピンに接続する外付けコンデンサ。標準値は ±20% <sup>(3)</sup> |                                                                    |     | 10  |     | μF |

| C <sub>(BYP)</sub>                            | BYP ピンに接続する外付けコンデンサ。標準値は ±10%                 |                                                                    |     | 1   |     | μF |

| C <sub>(OUT)</sub>                            | OUT_X ピンの GND への外部容量                          |                                                                    |     |     | 4   | μF |

| C <sub>(IN)</sub>                             | アナログ入力信号と直列に接続された外部容量                         |                                                                    |     | 1   |     | μF |

| C <sub>(BSTN)</sub> 、<br>C <sub>(BSTOP)</sub> | 外付けブートストラップ コンデンサ、標準値 ±20%                    |                                                                    |     | 220 |     | nF |

(1) ゲインが 36dB、32dB、26dB、および 20dB の完全非クリッピング出力の信号入力

(2) 最大推奨入力電圧は、ゲイン設定により決定されます。

(3) セクションを参照してください。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | TSD5402      | 単位   |

|-----------------------|---------------------|--------------|------|

|                       |                     | PWP (HTSSOP) |      |

|                       |                     | 16 ピン        |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 39.4         | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 24.9         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 20           | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.6          | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 19.8         | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 2            | °C/W |

(1) 従来および最新の熱評価基準の詳細については、アプリケーション レポートを参照してください。

## 5.5 電気的特性

T<sub>C</sub> = 25°C、PVDD = 14.4V、R<sub>L</sub> = 4Ω、P<sub>(O)</sub> = 1W/ch、AES17 フィルタ、デフォルト I<sup>2</sup>C 設定 (特に記述のない限り)

| パラメータ         | テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|-------------------------------------------|-----|-----|-----|----|

| <b>動作電流</b>   |                                           |     |     |     |    |

| PVDD アイドル電流   | ドライブ モードでは、信号がありません                       | 16  |     |     | mA |

| PVDD スタンバイ 電流 | STANDBY モード、HI-Z = 0V                     | 5   | 20  |     | μA |

| <b>出力電力</b>   |                                           |     |     |     |    |

| チャネルあたりの出力電力  | 4Ω、THD+N ≤ 1%、1kHz、T <sub>C</sub> = 75°C  | 6   |     |     | W  |

|               | 4Ω、THD+N = 10%、1kHz、T <sub>C</sub> = 75°C | 8   |     |     |    |

| 高い電力効率        | 4Ω、P <sub>(O)</sub> = 8W (10% THD)        |     | 83% |     |    |

$T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $R_L = 4\Omega$ 、 $P_{(O)} = 1\text{W}/\text{ch}$ 、AES17 フィルタ、デフォルト I<sup>2</sup>C 設定 (特に記述のない限り)

| パラメータ                                         | テスト条件                                                               | 最小値   | 標準値      | 最大値  | 単位               |

|-----------------------------------------------|---------------------------------------------------------------------|-------|----------|------|------------------|

| <b>出力性能</b>                                   |                                                                     |       |          |      |                  |

| 出力のノイズ電圧                                      | $G = 20\text{dB}$ 、ゼロ入力、A ウエイト                                      | 65    |          |      | $\mu\text{V}$    |

| 同相除去比                                         | $f = 1\text{kHz}$ 、GND を基準として $100\text{mVrms}$ 、 $G = 20\text{dB}$ | 63    |          |      | $\text{dB}$      |

| 電源除去比                                         | $\text{PVDD} = 14.4\text{Vdc} + 1\text{Vrms}$ 、 $f = 1\text{kHz}$   | 75    |          |      |                  |

| 全高調波歪み + ノイズ                                  | $P_{(O)} = 1\text{W}$ 、 $f = 1\text{kHz}$                           | 0.05% |          |      |                  |

| スイッチング周波数                                     | AM 干渉回避用にスイッチング周波数を選択できます                                           | 400   |          |      | $\text{kHz}$     |

|                                               |                                                                     | 500   |          |      |                  |

| 内部同相入力バイアス電圧                                  | $\text{IN\_N}$ 、 $\text{IN\_P}$ ピンに印加される内部バイアス                      | 3     |          |      | $\text{V}$       |

| 電圧ゲイン ( $V_O / V_{IN}$ )                      | ソース インピーダンス = $0\Omega$ 、レジスタ 0x03 ビット 7–6 = 00                     | 19    | 20       | 21   | $\text{dB}$      |

|                                               | ソース インピーダンス = $0\Omega$ 、レジスタ 0x03 ビット 7–6 = 01                     | 25    | 26       | 27   |                  |

|                                               | ソース インピーダンス = $0\Omega$ 、レジスタ 0x03 ビット 7–6 = 10                     | 31    | 32       | 33   |                  |

|                                               | ソース インピーダンス = $0\Omega$ 、レジスタ 0x03 ビット 7–6 = 11                     | 35    | 36       | 37   |                  |

| <b>PWM 出力段</b>                                |                                                                     |       |          |      |                  |

| FET ドレイン - ソース抵抗                              | $T_J = 25^\circ\text{C}$                                            | 180   |          |      | $\text{m}\Omega$ |

| 出力オフセット電圧                                     | ゼロ入力信号、 $G = 20\text{dB}$                                           |       | $\pm 25$ |      | $\text{mV}$      |

| <b>PVDD 過電圧 (OV) 保護</b>                       |                                                                     |       |          |      |                  |

| PVDD 過電圧シャットダウン設定                             |                                                                     | 19.5  | 21       | 22.5 | $\text{V}$       |

| PVDD 過電圧シャットダウン ヒステリシス                        |                                                                     |       | 0.6      |      | $\text{V}$       |

| <b>PVDD 低電圧 (UV) 保護</b>                       |                                                                     |       |          |      |                  |

| PVDD 低電圧シャットダウン設定                             |                                                                     | 3.6   | 4        | 4.4  | $\text{V}$       |

| PVDD 低電圧シャットダウン ヒステリシス                        |                                                                     |       | 0.25     |      | $\text{V}$       |

| BYP                                           |                                                                     |       |          |      |                  |

| BYP ピン電圧                                      |                                                                     | 6.4   | 6.9      | 7.4  | $\text{V}$       |

| <b>パワーオンリセット (POR)</b>                        |                                                                     |       |          |      |                  |

| POR の PVDD 電圧                                 |                                                                     |       | 4.1      |      | $\text{V}$       |

| POR の PVDD 復帰ヒステリシス電圧                         |                                                                     |       | 0.3      |      | $\text{V}$       |

| <b>過熱 (OT) 保護</b>                             |                                                                     |       |          |      |                  |

| 過熱シャットダウンの接合部温度                               |                                                                     | 155   | 170      |      | $^\circ\text{C}$ |

| 接合部温度過熱シャットダウン ヒステリシス                         |                                                                     |       | 15       |      | $^\circ\text{C}$ |

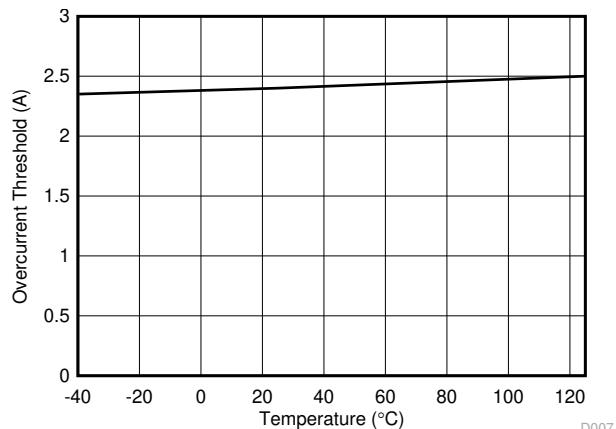

| <b>過電流 (OC) シャットダウン保護</b>                     |                                                                     |       |          |      |                  |

| 最大電流 (ピーク出力電流)                                |                                                                     |       | 2.4      |      | $\text{A}$       |

| <b>STANDBY ピン</b>                             |                                                                     |       |          |      |                  |

| STANDBY ピン電流                                  |                                                                     | 0.1   | 0.2      |      | $\mu\text{A}$    |

| <b>DC 検出</b>                                  |                                                                     |       |          |      |                  |

| DC 検出スレッショルド                                  |                                                                     |       | 2.9      |      | $\text{V}$       |

| DC 検出ステップ応答時間                                 |                                                                     |       | 700      |      | $\text{ms}$      |

| <b>異常検出通知</b>                                 |                                                                     |       |          |      |                  |

| FAULT ピンのロジックレベル High の出力電圧 (オープンドレイン ロジック出力) | 3.3V までの外部 $47\text{k}\Omega$ プルアップ抵抗                               | 2.4   |          |      | $\text{V}$       |

$T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $R_L = 4\Omega$ 、 $P_{(O)} = 1\text{W}/\text{ch}$ 、AES17 フィルタ、デフォルト I<sup>2</sup>C 設定 (特に記述のない限り)

| パラメータ                                        | テスト条件                                                         | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------------------------------|---------------------------------------------------------------|-----|-----|-----|----|

| FAULT ピンのロジックレベル Low の出力電圧 (オープンドレイン ロジック出力) | 3.3V までの外部 47kΩ プルアップ抵抗                                       |     | 0.5 | V   |    |

| <b>負荷診断</b>                                  |                                                               |     |     |     |    |

| OUT ピンから PVDD またはグランドへの短絡を検出するための抵抗          |                                                               |     | 200 |     | Ω  |

| オープン回路検出スレッショルド                              | 負荷線を含む                                                        | 70  | 95  | 120 | Ω  |

| 短絡検出スレッショルド                                  | 負荷線を含む                                                        | 0.9 | 1.2 | 1.5 | Ω  |

| <b>I<sup>2</sup>C</b>                        |                                                               |     |     |     |    |

| SDA ピン ロジック レベル High の出力電圧                   | $R_{(PU\_I^2C)} = 4.7\text{k}\Omega$ プルアップ、電源電圧 = 3.3V または 5V | 2.4 |     | V   |    |

| SDA ピン ロジック レベル Low の出力電圧                    | 3mA のシンク電流                                                    |     | 0.4 | V   |    |

| SCL ピンと SDA ピンの容量                            |                                                               |     | 10  | pF  |    |

| SDA ピンの容量                                    | STANDBY モード                                                   | 30  |     | pF  |    |

## 5.6 I<sup>2</sup>C インターフェイス信号のタイミング要件

推奨動作条件範囲内 (特に記述のない限り)

|                    |                                     | 最小値              | 公称値 | 最大値 | 単位  |

|--------------------|-------------------------------------|------------------|-----|-----|-----|

| $f_{(\text{SCL})}$ | SCL クロック周波数                         |                  | 400 |     | kHz |

| $t_r$              | SDA 信号と SCL 信号の両方の立ち上がり時間           |                  | 300 |     | ns  |

| $t_f$              | SDA 信号と SCL 信号の両方の立ち下がり時間           |                  | 300 |     | ns  |

| $t_{w(H)}$         | SCL パルス持続時間、High                    | 0.6              |     |     | μs  |

| $t_{w(L)}$         | SCL パルス持続時間、Low                     | 1.3              |     |     | μs  |

| $t_{su(2)}$        | 開始条件のセットアップ時間                       | 0.6              |     |     | μs  |

| $t_{h(2)}$         | 最初のクロック パルスが生成される前の START 条件のホールド時間 | 0.6              |     |     | μs  |

| $t_{su(1)}$        | データ セットアップ時間                        | 100              |     |     | ns  |

| $t_{h(1)}$         | データ ホールド時間                          | 0 <sup>(1)</sup> |     |     | ns  |

| $t_{su(3)}$        | 停止条件のセットアップ時間                       | 0.6              |     |     | μs  |

| $C_{(B)}$          | 各バス ラインの負荷容量                        |                  | 400 |     | pF  |

- (1) デバイスは、SCL の立ち下がりエッジの未定義領域を SDA 信号が橋渡しするために、少なくとも 300ns のホールド時間を内部的に提供する必要があります。

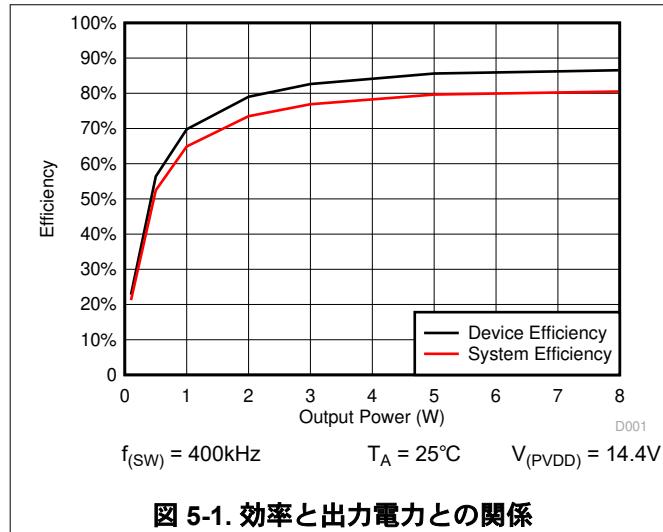

## 5.7 代表的特性

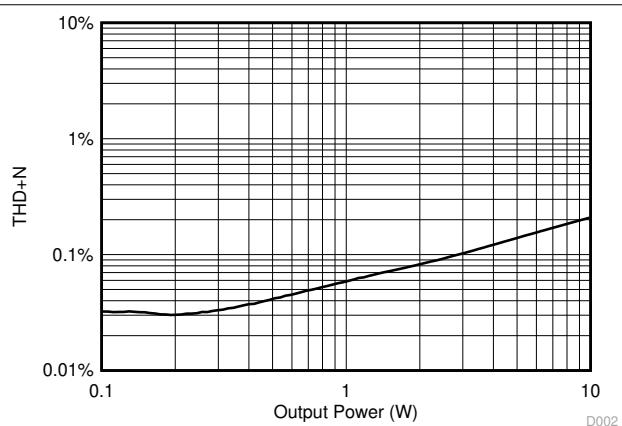

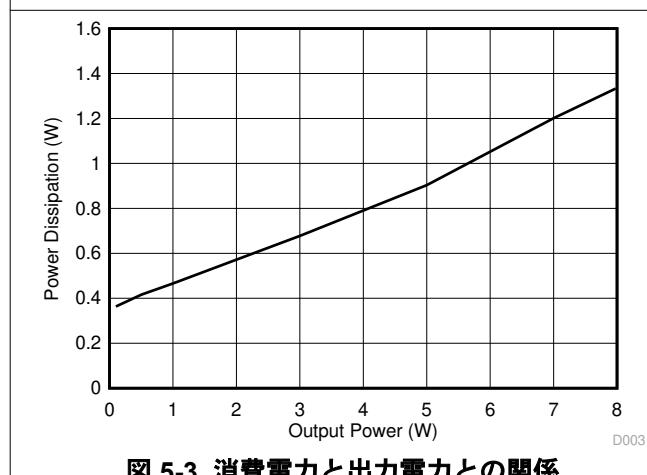

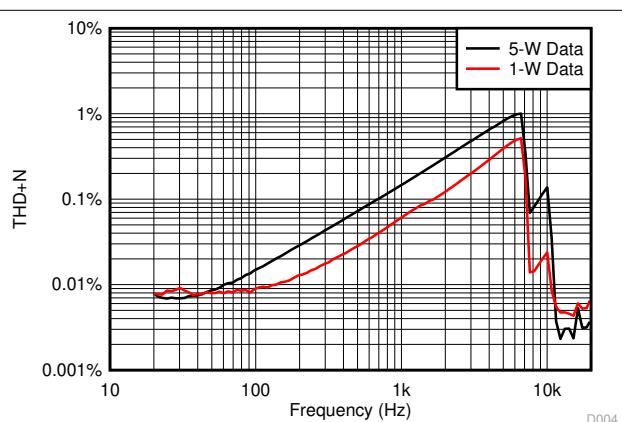

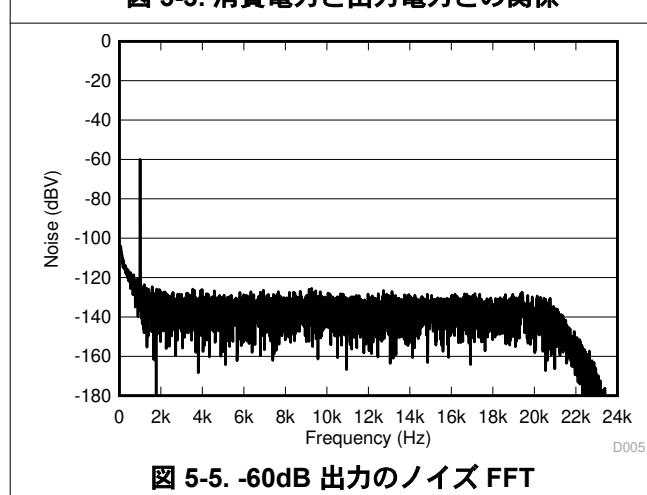

$T_C = 25^\circ\text{C}$ ,  $V_{\text{PVDD}} = 14.4\text{V}$ ,  $R_L = 4\Omega$ ,  $P_{(O)} = 1\text{W}$  / チャネル、AES17 フィルタ、1kHz 入力、デフォルト I<sup>2</sup>C 設定 (特に記述のない限り)

図 5-1. 効率と出力電力との関係

図 5-2. THD+N と出力電力との関係

図 5-3. 消費電力と出力電力との関係

図 5-4. THD+N と周波数との関係

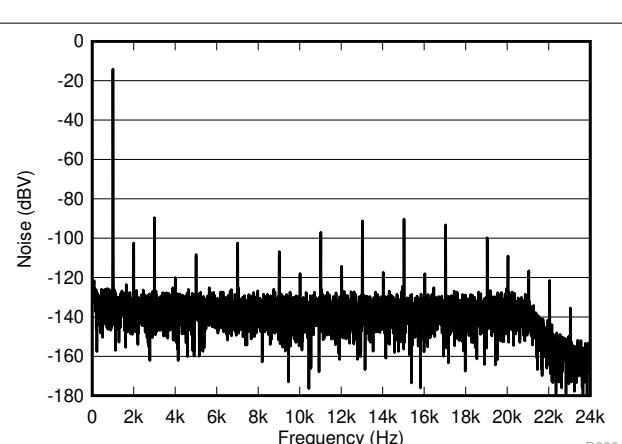

図 5-5. -60dB 出力のノイズ FFT

図 5-6. 1W 出力のノイズ FFT

図 5-7. 過電流スレッショルドと温度との関係

## 6 詳細説明

### 6.1 概要

TSD5402-Q1 は、車載用/産業用環境で使用することを目的とした、アナログ入力 Class-D センサ駆動アンプです。この基準設計は、テキサス インストルメンツが開発した超高効率の Class-D 技術と、自動車業界に固有の機能を搭載しています。Class-D 技術により、電力消費の削減、発熱の低減、電気システムのピーク電流の低減が可能になります。このデバイスは、従来の Class-AB ソリューションよりも小型で高効率の、高集積センサドライバとして機能します。

この TSD5402-Q1 デバイスには、7 つのコア設計ブロックがあります。

- PWM

- ゲートドライブ

- パワー FET

- 診断

- 保護

- 電源

- I<sup>2</sup>C シリアル通信バス

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 アナログ入力およびプリアンプ

アンプの差動入力段は、入力に現れる同相モードノイズを打ち消します。差動ソースの場合、正のリードを **IN\_P** に、負のリードを **IN\_N** に接続します。出力 **dc** オフセットを最小化し、出力電圧が適切に上昇するように、入力を **ac** 結合する必要があります。良好な過渡性能を達成するには、2つの差動入力のそれぞれで観測されるインピーダンスを同じにする必要があります。

ゲイン設定はアンプのアナログ入力インピーダンスに影響を及ぼします。標準値については、[入力インピーダンスとゲイン](#) を参照してください。

表 6-1. 入力インピーダンスとゲイン

| ゲイン   | 入力インピーダンス  |

|-------|------------|

| 20 dB | 60kΩ ± 20% |

| 26 dB | 30kΩ ± 20% |

| 32 dB | 15kΩ ± 20% |

| 36 dB | 9kΩ ± 20%  |

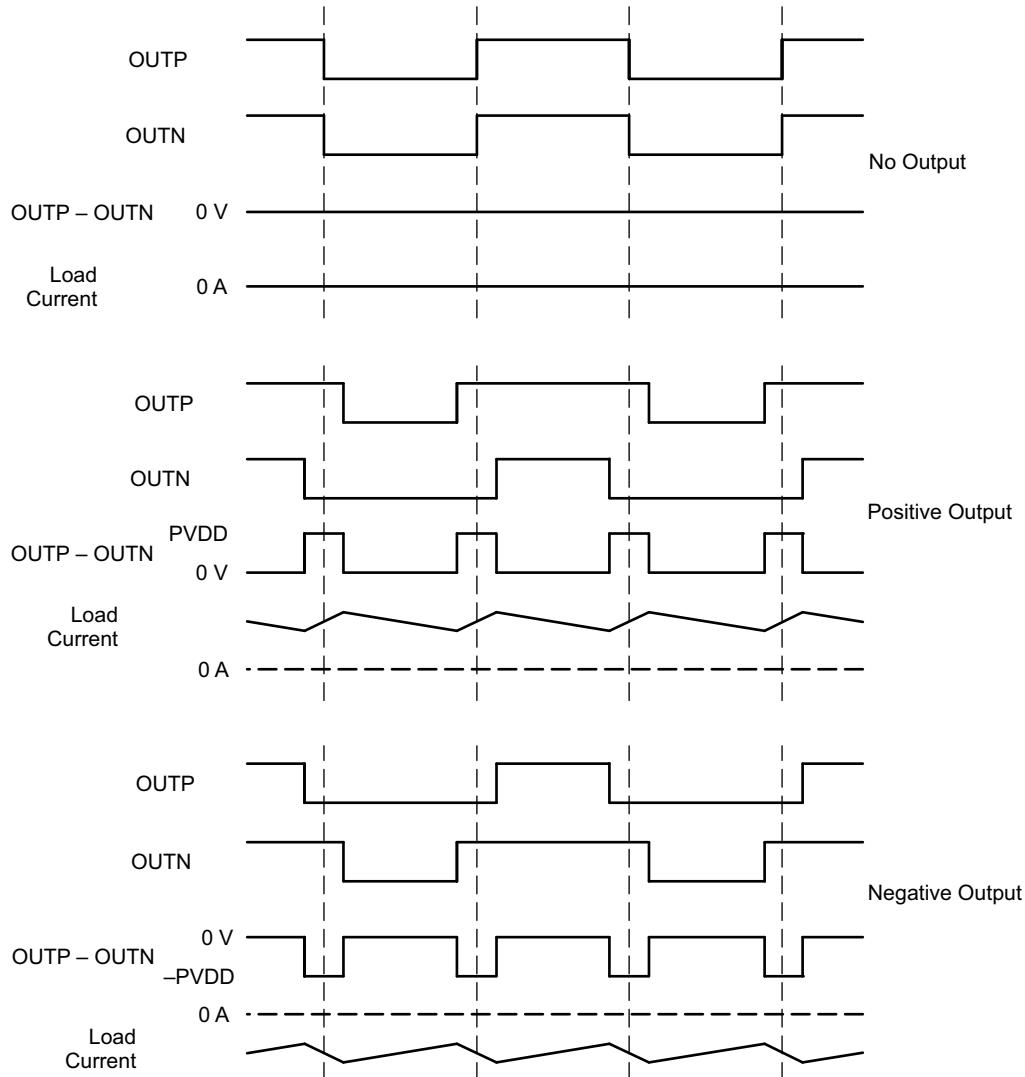

### 6.3.2 パルス幅変調 (PWM)

PWM は、プリアンプからのアナログ信号を、デューティサイクルが変化するスイッチ信号に変換します。これは、Class-D アーキテクチャを定義する重要な段階です。TSD5402-Q1において、変調器は高帯域幅、低ノイズ、低歪み、優れた安定性を備えた高度な設計です。

パルス幅変調方式により、低消費電力での効率が向上します。各出力は 0V から PVDD にスイッチングされます。OUTP ピンと OUTN ピンは入力がない場合、互いに位相が揃っているため、負荷に電流はほとんどないか、ゼロになります。正の出力電圧に対して、OUTP のデューティサイクルは 50% より大きく、OUTN デューティサイクルは 50% 未満です。負の出力電圧に対して、OUTN のデューティサイクルは 50% より大きく、OUTP デューティサイクルは 50% 未満です。負荷にかかる電圧は、スイッチング期間の大半で 0V であるため、電力損失を低減できます。

図 6-1. BD モード変調

### 6.3.3 ゲート ドライブ

ゲート ドライバは低電圧 PWM 信号を受け入れ、その信号をレベルシフトして、大電流、フルブリッジのパワー FET 段を駆動します。このデバイスは、独自の手法を使用して、EMI と性能を最適化します。

### 6.3.4 パワー FET

BTL 出力は、高効率と負荷への最大電力伝送を実現する 4 つのマッチングされた N チャネル FET で構成されています。設計上、FET はロードダンプイベント中の大きな電圧過渡に耐えます。

### 6.3.5 負荷診断

このデバイスには、出力接続の状態を検出および判定するように設計された負荷診断回路が組み込まれています。このデバイスは、以下の診断をサポートしています。

- GND への短絡

- PVDD への短絡

- 負荷の両端で短絡

- オープン負荷

このデバイスは、 $\text{I}^2\text{C}$  レジスタ読み出しによって、システムへの短絡またはオープン状態の存在を通知します。

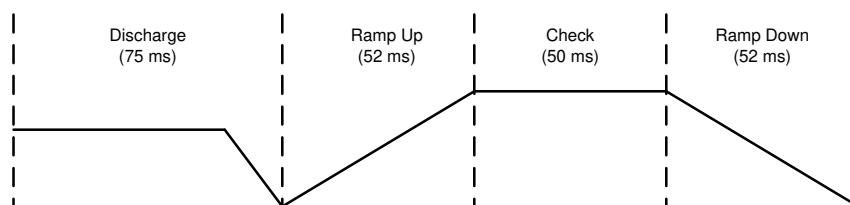

#### 6.3.5.1 負荷診断シーケンス

STANDBY がデアサートされたとき、またはデバイスが故障状態 (dc 検出、過電流、過電圧、低電圧、過熱) のときに負荷診断機能が動作します。このテスト中、出力は Hi-Z 状態になります。このデバイスは、出力が GND への短絡、PVDD への短絡、開放負荷、負荷短絡のいずれであるかを決定します。負荷診断機能は出力をバイアスするため、適切に機能させるためには容量値を制限する必要があります。[推奨動作条件](#)を参照してください。負荷診断テストの実行には約 229ms かかります。障害が発生した場合、または出力に GND との間に大きなコンデンサが存在した場合、チェックフェーズが最大 5 回繰り返されることに注意します。開放負荷を検出すると、出力は引き続き動作します。他のフォルト状態を検出すると出力が Hi-Z 状態になり、フォルト状態が解消されるまで負荷を継続的にチェックします。通常の出力条件が検出されると、信号出力が開始します。負荷診断は、他の過電圧 (OV) イベントごとに実行されます。開放負荷診断では、 $\text{I}^2\text{C}$  レポートのみが存在します。他のすべてのフォルトでは、 $\text{I}^2\text{C}$  および  $\overline{\text{FAULT}}$  ピンがアサートされます。

図 6-2 に示すように、デバイスは負荷診断テストを実行します。

図 6-3 に、出力条件に基づいて診断が負荷を判定する方法を示します。

図 6-2. イベントの負荷診断シーケンス

| Output Conditions |                                          | Load Diagnostics                          |

|-------------------|------------------------------------------|-------------------------------------------|

| OL Max            | Open Load                                | Open Load Detected                        |

| OL Min            | Open Load (OL)<br>Detection Threshold    | Normal or Open Load<br>May Be Detected    |

| SL Max            | Normal Load                              | Drive Mode                                |

| SL Min            | Shorted Load (SL)<br>Detection Threshold | Normal or Shorted Load<br>May Be Detected |

|                   | Shorted Load                             | Shorted Load<br>Detected                  |

図 6-3. 負荷診断レポートのスレッショルド

### 6.3.5.2 負荷診断中の故障

デバイスが負荷診断テスト中に故障(過熱、過電圧、低電圧など)を検出すると、デバイスは負荷診断を終了します。結果として、ポップや出力をクリックする可能性があります。

### 6.3.6 保護および監視

- **過電流シャットダウン (OCSD)** — 過電流シャットダウンにより、出力が強制的に Hi-Z になります。このデバイスは、FAULT ピンをアサートし、I<sup>2</sup>C レジスタを更新します。

- **DC 検出** — この回路は、アンプの出力での通常動作中に DC オフセットを連続的にチェックします。dc オフセットが発生すると、本デバイスは FAULT ピンをアサートし、I<sup>2</sup>C レジスタを更新します。dc 検出スレッショルドは PVDD の変化に従うことに注意してください。

- **過熱シャットダウン (OTSD)** - ダイの接合部温度が過熱スレッショルドに達すると、デバイスはシャットダウンします。このデバイスが FAULT ピンをアサートし、I<sup>2</sup>C レジスタをアサートおよび更新します。温度が安全なレベルに戻ると、回復は自動的に行われます。

- **低電圧 (UV)** — 低電圧 (UV) 保護機能は、PVDD ピンの低電圧を検出します。低電圧状態が発生すると、デバイスは FAULT ピンをアサートし、I<sup>2</sup>C レジスタをリセットします。

- **パワーオンリセット (POR)** — PVDD が POR スレッショルドを下回るとパワーオンリセット (POR) が発生します。POR イベントが発生すると、I<sup>2</sup>C バスが高インピーダンス状態になります。POR イベントから回復すると、デバイスはデフォルトの I<sup>2</sup>C レジスタ設定で自動的に再起動します。

- **過電圧 (OV) および負荷ダンプ** — OV 保護は、PVDD の高電圧を検出します。PVDD が過電圧スレッショルドに達すると、デバイスは FAULT ピンをアサートし、I<sup>2</sup>C レジスタを更新します。このデバイスは、40V の負荷ダンプ電圧スペイクに耐えられます。このデバイスは、スタンバイモードとアクティブモードの両方で負荷ダンプをサポートしています。

- **電力ガード** - この保護回路は、出力電圧を I<sup>2</sup>C レジスタ 0x03 で選択された値に制限します。この値は、正と負の両方の制限を決定します。Power Guard 機能を使用すると、バッテリ寿命を向上させたり、負荷を変位制限を超過しないように保護することができます。

- **隣接ピン短絡** — デバイスは、隣接するピン間の短絡が損傷しない設計になっています。

### 6.3.7 I<sup>2</sup>C シリアル通信バス

このデバイスは、I<sup>2</sup>C シリアル通信バスを経由して、I<sup>2</sup>C ターゲット専用デバイスとしてシステム プロセッサと通信します。プロセッサは I<sup>2</sup>C 経由でデバイスをポーリングし、動作状態を判別できます。故障状態と検出に関するすべての報告は I<sup>2</sup>C を介して行われますまた、このシステムは I<sup>2</sup>C を使用して多数の機能と動作条件を設定できます I<sup>2</sup>C インターフェイスは、STANDBY ピンが High になってから約 1ms 後にアクティブになります。

I<sup>2</sup>C インターフェイスは、次のデバイス機能を制御します。

- ゲイン設定を 20dB、26dB、32dB、36dB に変更します。

- 電源ガード保護回路のピーク電圧値の制御

- 負荷診断結果を報告します

- AM ラジオ帯域を回避するためのスイッチング周波数の変更

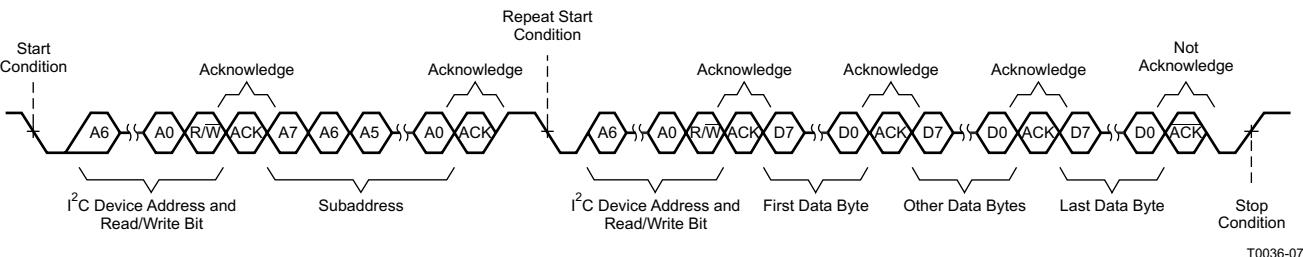

#### 6.3.7.1 I<sup>2</sup>C バス プロトコル

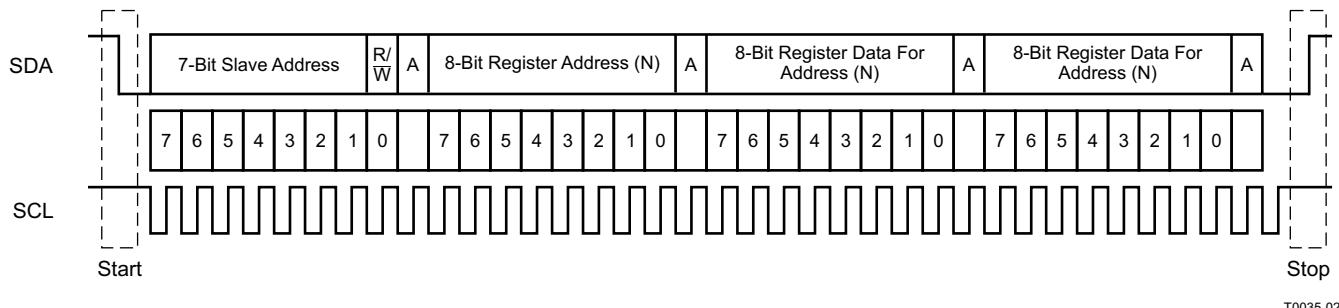

このデバイスは、IC 間 (I<sup>2</sup>C) バス プロトコルと互換性のある双方向シリアル制御インターフェイスを備えており、ランダムおよびシーケンシャルな書き込みおよび読み取り動作用に 400kbps のデータ転送レートをサポートしています。これはターゲットのみのデバイスで、マルチコントローラ バス環境やウェイト状態インサートはサポートしていません。コントローラ デバイスは、I<sup>2</sup>C 制御インターフェイスを使用して、デバイスのレジスタをプログラミし、デバイスのステータスを読み取ります。

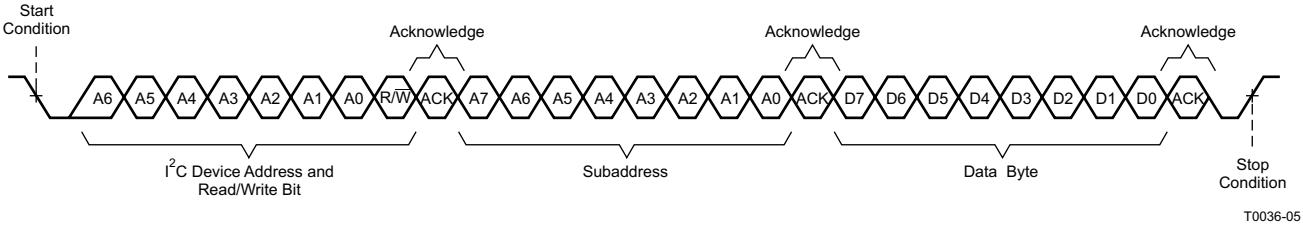

I<sup>2</sup>C バスは、SDA (データ) と SCL (クロック) の 2 つの信号を使用して、シリアル データ伝送によりシステム内の集積回路間で通信を行います。データはバス上に 1 ビットずつシリアルに送信されます。アドレスとデータはバイト (8 ビット) 形式で転送され、最上位ビット (MSB) から送信されます。さらに、受信デバイスはアクノリッジ (受信確認) ビットにより、バス上で転送された各バイトに対して受信確認を返します。各転送操作は、コントローラ デバイスがバス上にスタートコンディションを生成することで開始し、ストップ コンディションを生成することで終了します。バスは、クロックが HIGH のときに、データピン (SDA) の遷移を使用して、開始条件および停止条件を示します。SDA ラインでの HIGH から LOW への遷移は開始条件を示し、LOW から HIGH への遷移は停止条件を示します。通常のデータ ビット遷移は、クロック (SCL) が LOW のときです。[図 6-4](#) に、これらの条件を示します。コントローラ は、7 ビットのターゲット アドレスを生成し、読み取り / 書き込み (R/W) ビットを送信して他のデバイスとの通信を開始し、次にアクノリッジ (ACK) 条件を待ちます。デバイスは、アクノリッジ クロック期間に SDA LOW を保持し、アクノリッジを示します。この状態になると、コントローラ デバイスはシーケンスの次のバイトを送信します。各デバイスのアドレスは、固有の 7 ビットのターゲット アドレスと R/W ビット (1 ビット) で構成されます。すべての互換デバイスは、ワイヤード-AND 接続を使用した双方向バスを介して、同じ信号を共有します。SDA 信号と SCL 信号は、外部プルアップ抵抗を使用してバスの HIGH レベルを設定する必要があります。通信デバイスが start 条件と stop 条件の間で送信できるバイト数に制限はありません。最後のワードの転送後、コントローラ はバスを解放するための停止条件を生成します。

**図 6-4. 代表的な I<sup>2</sup>C シーケンス**

デバイスと通信するために、I<sup>2</sup>C コントローラ は、[図 6-4](#) に示すアドレスを使用します。読み取りおよび書き込みデータの送信は、シングル バイトまたはマルチ バイトのデータ転送によって行うことができます。

#### 6.3.7.2 ランダム書き込み

[図 6-5](#) にあるように、シングル バイトのデータ書き込み転送では、最初にマスター デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと読み取り / 書き込みビットが続きます。データ転送方向は、R/W ビットによって決定されます。書き込みデータ転送する場合、R/W ビットは 0 です。正しい I<sup>2</sup>C デバイス アドレスと R/W ビットを受信すると、デバイスはアクノリッジ ビットを返します。次に、コントローラ は、アドレス バイトまたはアクセスしている内部メモリアドレスに対応するアドレス バイトを送信します。デバイスは、レジスタ バイトを受信すると、再度アクノリッジ ビットを返信します。次に、コントローラ デバイスはアクセスしているメモリアドレスに書き込まれたデータ バイトを送信します。デバイスは、データ バイトを受信する

と、再度アクリッジ ビットを返信します。最後に、コントローラデバイスが停止条件を送信すると、シングル バイトデータの書き込み転送が完了します。

図 6-5. ランダム書き込み転送

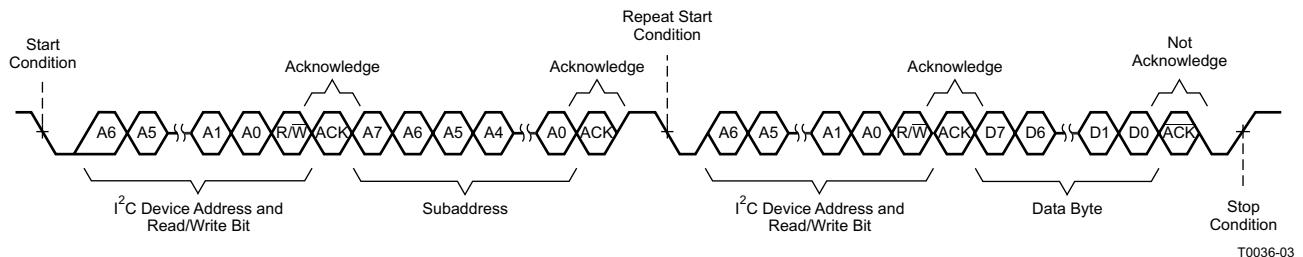

#### 6.3.7.3 ランダム読み出し

図 6-6 に示すように、シングル バイトのデータ読み取り転送では、コントローラ デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと R/W ビットを送信することで開始されます。データ読み取り転送では、コントローラ デバイスは書き込みとその後の読み取りの両方を実行します。最初に、コントローラ デバイスは書き込みを実行して、読み取る内部メモリアドレスのアドレス バイトを転送します。その結果、R/W ビットは 0 になります。このデバイスは、アドレスと読み取り / 書き込み ビットを受信すると、アクリッジ ビットで応答します。さらに、内部メモリアドレスを送信後、コントローラデバイスは別の開始条件に続いて、デバイスのアドレス、R/W ビットを送信します。このとき、R/W ビットは 1 に設定され、読み取り転送が実行されたことを示します。デバイスは、アドレスと R/W ビットを受信すると、再度アクリッジ ビットで応答します。次に、デバイスは読み取り中のメモリアドレスからデータ バイトを送信します。データ バイトを受信すると、コントローラデバイスは非応答(not-acknowledge)を送信し、その後、停止条件を出して、シングルバイトデータ読み取り転送が完了します

図 6-6. ランダム読み取り転送

#### 6.3.7.4 シーケンシャル読み出し

シーケンシャル データ読み取り転送は、図 6-7 に示すように、複数のデータ バイトをコントローラ デバイスに TSD5402-Q1 送信する点を除いて、シングル バイトデータ読み取り転送と同じです。コントローラデバイスは、最後のデータ バイトを除いて、各データ バイトを受信すると肯定応答ビットで応答し、I<sup>2</sup>C サブアドレスを自動的に 1 ずつインクリメントします。最後のデータ バイトを受信した後、コントローラデバイスは、転送を完了するために非応答(NACK)を送信し、その後に停止条件を送信します。

図 6-7. シーケンシャルリード転送

## 6.4 デバイスの機能モード

### 6.4.1 ハードウェア制御ピン

3 本のディスクリートハードウェアピンを使用して、リアルタイムで制御し、デバイスのステータスを表示できます。

- FAULT** ピン: このアクティブ Low のオープンドレイン出力ピンは、デバイスが Hi-Z モードに移行する必要のある故障条件の存在を示します。このピンをアサートすると、デバイス自体とシステムを損傷の可能性から保護します。システムは、POR を下回る PVDD 低電圧フルトを除き、I<sup>2</sup>C を介して故障の正確な性質を読み取ることができます。この場合、I<sup>2</sup>C バスは動作しなくなります。

- STANDBY** ピン: このアクティブ Low ピンをアサートするとデバイスは完全なシャットダウンに送信され、消費電流が制限されます。負荷ダンプ保護がサポートされています。I<sup>2</sup>C は非アクティブで、ブロッキングなしで (I<sup>2</sup>C バスを Low にプルしない)、デバイスのレジスタはリセットされます。

- HI-Z** ピン: このアクティブ High ピンがアサートされると、デバイスは Hi-Z モードになります。出力ピンはスイッチングを停止し、入力から出力に信号は渡されません。デバイスをドライブ モードに戻すには、このピンをデアサートします。デバイスが STANDBY 状態のときは、HI-Z ピンを Low にアサートする必要があります。

### 6.4.2 EMI に関する考慮事項

車載レベルの EMI 特性は、慎重な IC 設計と適切なシステムレベル設計の双方に依存しています。電磁干渉(EMI)の発生源を制御することは、設計のあらゆる面で主な検討事項になっていました。

この設計では、パッケージ上のリードが短いため、寄生インダクタンスが最小限に抑えられています。これにより、ダイからシステム PCB に電流が流れることによる EMI を劇的に低減できます。この設計には、EMI を引き起こす出力遷移を最適化する回路が内蔵されています。

### 6.4.3 動作モードとフルト

次の表に、動作モードと故障を示します。

表 6-2. 動作モード

| 状態名                   | 出力                       | 発振器   | I <sup>2</sup> C <sup>(1)</sup> |

|-----------------------|--------------------------|-------|---------------------------------|

| STANDBY               | ハイインピーダンス (Hi-Z)、フローティング | 停止中   | 非アクティブ、レジスタリセット、非ブロッキング         |

| 負荷診断                  | DC バイアス                  | アクティブ | アクティブ                           |

| ハイインピーダンス (Hi-Z) / 故障 | ハイインピーダンス (Hi-Z)、フローティング | アクティブ | アクティブ                           |

| 駆動                    | 出力信号によるスイッチング            | アクティブ | アクティブ                           |

(1) I<sup>2</sup>C アプリケーションについては、[SLOA264](#) を参照してください。

表 6-3. 故障とアクション

| 故障イベント                  | 故障イベントカテゴリ | 監視モード              | 報告方法                       | アクションタイプ                   | アクションの結果                    | クリア          | STANDBY               |  |  |  |

|-------------------------|------------|--------------------|----------------------------|----------------------------|-----------------------------|--------------|-----------------------|--|--|--|

| POR                     | 電圧故障       | ハイインピーダンス(Hi-Z)、駆動 | 該当なし                       | I <sup>2</sup> C + FAULTピン | スタンバイ                       | セルフクリア       | ディセーブル<br>保護あり、レポートなし |  |  |  |

| UV                      |            |                    | I <sup>2</sup> C + FAULTピン |                            | ハードストップ(ランプなし)<br>ハイインピーダンス |              |                       |  |  |  |

| OVと負荷ダンプ <sup>(1)</sup> |            |                    |                            |                            |                             |              |                       |  |  |  |

| OTSD                    | サーマル故障     | ハイインピーダンス(Hi-Z)、駆動 | I <sup>2</sup> C + FAULTピン | なし                         | Hi-Z、診断を再実行                 | セルフクリア       | ディセーブル                |  |  |  |

| OC フォルト                 | 出力チャネル故障   | 駆動                 |                            |                            | なし                          |              |                       |  |  |  |

| DC 検出                   |            |                    |                            |                            | なし                          | 次の診断サイクルでクリア |                       |  |  |  |

| 負荷診断 - 短絡               | 診断機能       | ハイインピーダンス          | I <sup>2</sup> C           |                            |                             |              |                       |  |  |  |

| 負荷診断 - オープン             |            |                    |                            |                            |                             |              |                       |  |  |  |

(1) ISO7637-1 に従ってテスト済み

## 7 レジスタ マップ

表 7-1. I<sup>2</sup>C アドレス

| 説明                    | 固定アドレス |   |   |   |   |   |   | 読み出し書き込みビット | I <sup>2</sup> C アドレス |

|-----------------------|--------|---|---|---|---|---|---|-------------|-----------------------|

|                       | MSB    | 6 | 5 | 4 | 3 | 2 | 1 |             |                       |

| I <sup>2</sup> C 書き込み | 1      | 1 | 0 | 1 | 1 | 0 | 0 | 0           | 0xD8                  |

| I <sup>2</sup> C 読み出し | 1      | 1 | 0 | 1 | 1 | 0 | 0 | 1           | 0xD9                  |

### 7.1 I<sup>2</sup>C アドレス レジスタの定義

表 7-2. I<sup>2</sup>C アドレス レジスタの定義

| アドレス | R/W | レジスタの説明          |

|------|-----|------------------|

| 0x01 | R   | ラッチされた故障レジスタ     |

| 0x02 | R   | ステータスおよび負荷診断レジスタ |

| 0x03 | R/W | 制御レジスタ           |

表 7-3. Fault レジスタ (0x01)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 機能                     |

|----|----|----|----|----|----|----|----|------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 保護によって生成された障害なし、デフォルト値 |

| -  | -  | -  | -  | -  | -  | -  | 1  | 予約済み                   |

| -  | -  | -  | -  | -  | -  | 1  | -  | 予約済み                   |

| -  | -  | -  | -  | -  | 1  | -  | -  | 負荷診断障害が発生しました。         |

| -  | -  | -  | -  | 1  | -  | -  | -  | 過電流シャットダウンが発生しました。     |

| -  | -  | -  | 1  | -  | -  | -  | -  | PVDD 低電圧が発生しました。       |

| -  | -  | 1  | -  | -  | -  | -  | -  | PVDD 過電圧が発生しました。       |

| -  | 1  | -  | -  | -  | -  | -  | -  | DC オフセット保護が発生しました。     |

| 1  | -  | -  | -  | -  | -  | -  | -  | 過熱シャットダウンが発生しました。      |

表 7-4. ステータスおよび負荷診断レジスタ (0x02)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 機能                       |

|----|----|----|----|----|----|----|----|--------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 負荷診断によって生成された障害なし、デフォルト値 |

| -  | -  | -  | -  | -  | -  | -  | 1  | PVDD への出力短絡が発生しています。     |

| -  | -  | -  | -  | -  | -  | 1  | -  | 出力がグランドに短絡しています。         |

| -  | -  | -  | -  | -  | 1  | -  | -  | オープン負荷が存在します。            |

| -  | -  | -  | -  | 1  | -  | -  | -  | 短絡負荷が存在します。              |

| -  | -  | -  | 1  | -  | -  | -  | -  | 故障状態                     |

| -  | -  | 1  | -  | -  | -  | -  | -  | 負荷診断の実行中                 |

| -  | 1  | -  | -  | -  | -  | -  | -  | Hi-Z モード                 |

| 1  | -  | -  | -  | -  | -  | -  | -  | ドライブ モード                 |

**表 7-5. 制御レジスタ (0x03)**

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 機能                                           |

|----|----|----|----|----|----|----|----|----------------------------------------------|

| 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 26dB ゲイン、スイッチング周波数は 400kHz に設定、パワーガード保護回路は無効 |

| -  | -  | -  | -  | -  | -  | -  | 1  | スイッチング周波数は 500kHz に設定                        |

| -  | -  | -  | -  | -  | 1  | 1  | -  | 予約済み                                         |

| -  | -  | 1  | 1  | 0  | -  | -  | -  | 電源保護回路は 14V ピークの出力に設定                        |

| -  | -  | 1  | 0  | 1  | -  | -  | -  | 電源保護回路は 11.8V ピークの出力に設定                      |

| -  | -  | 1  | 0  | 0  | -  | -  | -  | 電源保護回路は 9.8V ピークの出力に設定                       |

| -  | -  | 0  | 1  | 1  | -  | -  | -  | 電源保護回路は 8.4V ピークの出力に設定                       |

| -  | -  | 0  | 1  | 0  | -  | -  | -  | 電源保護回路は 7V ピークの出力に設定                         |

| -  | -  | 0  | 0  | 1  | -  | -  | -  | 電源保護回路は 5.9V ピークの出力に設定                       |

| -  | -  | 0  | 0  | 0  | -  | -  | -  | 電源保護回路は 5V ピークの出力に設定                         |

| 0  | 0  | -  | -  | -  | -  | -  | -  | ゲインは 20dB に設定                                |

| 1  | 0  | -  | -  | -  | -  | -  | -  | ゲインは 32dB に設定                                |

| 1  | 1  | -  | -  | -  | -  | -  | -  | ゲインは 36dB に設定                                |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

デバイスは、Class-D アンプを駆動する高効率のセンサです。デバイスの一般的な用途は、信号入力を増幅してセンサを駆動することです。この用途の目的は、ブリッジ接続負荷 (BTL) アプリケーションであり、シングルエンド構成のサポートではありません。このセクションでは、必要な外付け部品や、未使用ピンの接続方法など、アプリケーションでの本デバイスの使用方法について説明します。

### 8.2 代表的なアプリケーション

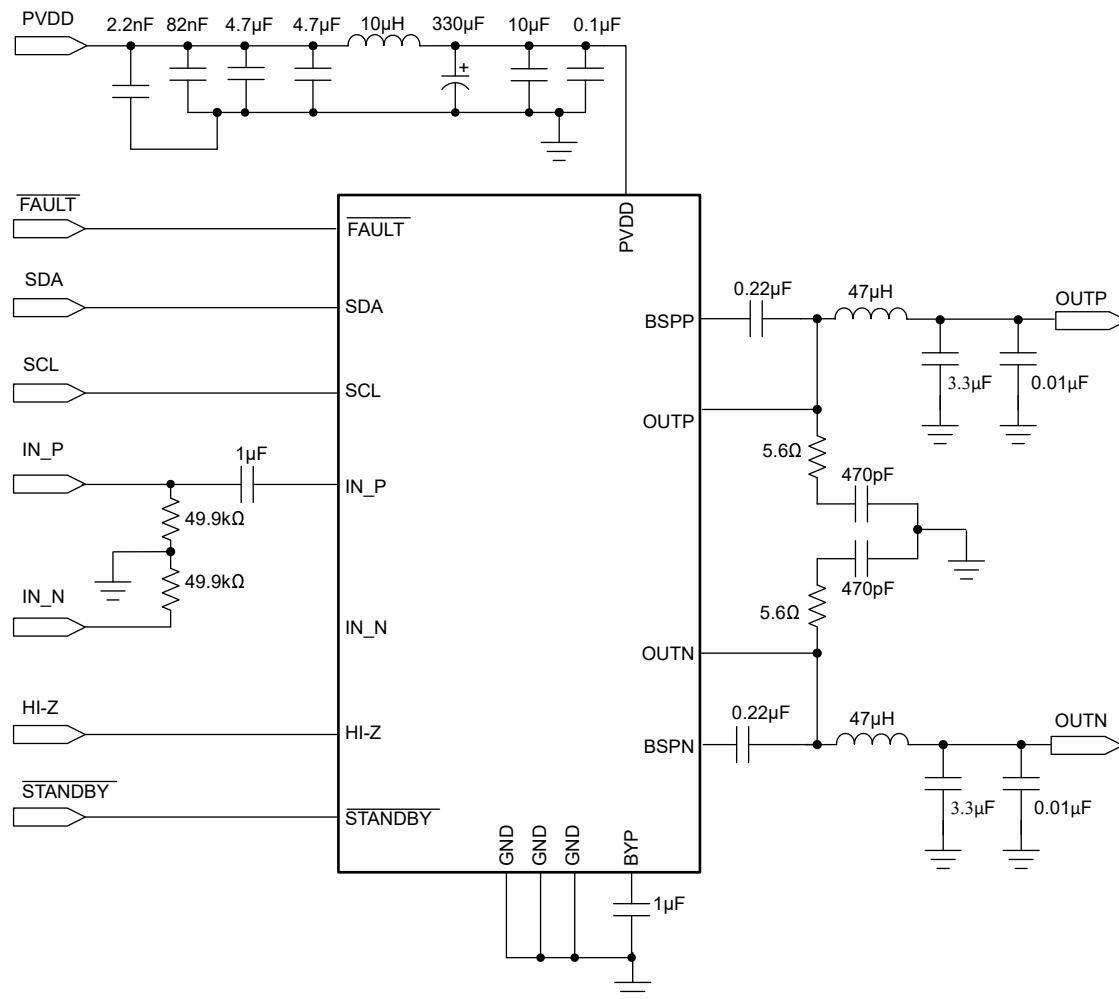

図 8-1. TSD5402-Q1 代表的なアプリケーション回路図

## 8.2.1 設計要件

以下の設計要件を使用します。

### 電源

- このデバイスは単一電源のみで動作し、推奨動作範囲に対応しています。このデバイスは、車載バッテリまたはバックアップ バッテリなどの安定化電源で動作するよう設計されています。

### 通信

- このデバイスは、ディスクリートのハードウェア制御ピンや I<sup>2</sup>C を使用して、システム コントローラと通信します。このデバイスは I<sup>2</sup>C ターゲットなので、コントローラが必要です。コントローラ I<sup>2</sup>C 準拠のデバイスがシステムに存在しない場合でも、デフォルトの設定のみでデバイスを使用できます。診断情報は、個別のレポート FAULT ピンに限定されます。

### 外付け部品

- このデバイスで使用する部品のリストを 表 8-1 に示します。

**表 8-1. サポート部品**

| EVM 記号     | 数量 | 値             | サイズ           | 説明                     | アプリケーションで使用       |

|------------|----|---------------|---------------|------------------------|-------------------|

| C7         | 1  | 10μF ± 10%    | 1206          | X7R セラミック コンデンサ、25V    | 電源                |

| C8         | 1  | 330μF ± 20%   | 10mm          | 低 ESR アルミニウム コンデンサ、25V | 電源                |

| C9、C16、C20 | 3  | 1μF ± 10%     | 0805          | X7R セラミック コンデンサ、25V    | アナログ信号入力フィルタ、バイパス |

| C10、C14    | 2  | 0.22μF ± 10%  | 0603          | X7R セラミック コンデンサ、25V    | ブートストラップ コンデンサ    |

| C11、C17    | 2  | 3.3μF ± 10%   | 0805          | X7R セラミック コンデンサ、25V    | アンプの出力フィルタリング     |

| C13、C15    | 2  | 470pF ± 10%   | 0603          | X7R セラミック コンデンサ、250V   | アンプの出力スナバ         |

| C6         | 1  | 0.1μF ± 10%   | 0603          | X7R セラミック コンデンサ、25V    | 電源                |

| C2         | 1  | 2200pF ± 10%  | 0603          | X7R セラミック コンデンサ、50V    | 電源                |

| C3         | 1  | 0.082μF ± 10% | 0603          | X7R セラミック コンデンサ、25V    | 電源                |

| C4、C5      | 2  | 4.7μF ± 10%   | 1206          | X7R セラミック コンデンサ、25V    | 電源                |

| C12、C18    | 2  | 0.01μF ± 10%  | 0603          | X7R セラミック コンデンサ、25V    | 出力 EMI フィルタリング    |

| L1         | 1  | 10μH ± 20%    | 13.5mm×13.5mm | シールド付きフェライト インダクタ      | 電源                |

| L2         | 1  | 47 μH ± 20%   | 8mm × 8mm     | 結合型インダクタ               | アンプの出力フィルタリング     |

| R5、R6      | 2  | 49.9kΩ ± 1%   | 0805          | 抵抗、0.125W              | アナログ信号入力フィルタ      |

| R4、R7      | 2  | 5.6Ω ± 5%     | 0805          | 抵抗、0.125W              | 出力スナバ             |

### 8.2.1.1 アンプの出力フィルタリング

出力 FET は、H ブリッジ構成のアンプ出力を駆動します。トランジスタは完全にオフになっているか、完全にオンになっています。その結果、入力信号の振幅に比例するデューティサイクルの方形波出力信号が生成されます。PWM 変調搬送波周波数をフィルタ処理するため、アンプの出力にはローパスフィルタが必要です。このフィルタは、2 極 ローパスフィルタを構成する誘導性素子 L と容量性素子 C が存在するため、よく L-C フィルタと呼ばれます。L-C フィルタはキャリア周波数を減衰させ、電磁放射を低減し、電源から負荷が引き込む電流波形を平滑化します。必要な負荷と応答に基づいた L-C フィルタの適切なコンポーネント選択と設計の詳細については、[Class-D LC フィルタ設計](#)を参照してください。

### 8.2.1.2 アンプの出力スナバ

スナバは、PWM 出力波形のリンギングやオーバーシュートを抑制するため、アンプの出力に配置される RC ネットワークです。オーバーシュートとリンギングは、以下のような悪影響を及ぼす可能性があります。EMI の発生源と、出力 FET または基板部品の過電圧ストレスの可能性があります。出力スナバの使用と設計の詳細については、[Class-D 出力スナバ設計ガイド](#)を参照してください。

### 8.2.1.3 ブートストラップ コンデンサ

出力段はデュアル NMOS ドランジスタを使用しているため、この回路では各出力のハイサイドが正しくオンになるようにブートストラップ コンデンサが必要です。必要なコンデンサ接続は、図 8-1 に示すように、BSTN から OUTN へ、BSTOP から OUTP へと接続します。

### 8.2.1.4 アナログ信号入力フィルタ

この回路では、アンプを適切な dc レベルにバイアスするために入力コンデンサが必要です。ハイパスフィルタは、入力コンデンサとアンプの入力インピーダンスで形成され、-3dB のコーナー周波数が次の式で決定されます。 $f = 1 / (2\pi R_{(i)} C_{(i)})$ 、ここで  $R_{(i)}$  はゲイン設定に基づくデバイスの入力インピーダンス、 $C_{(i)}$  は入力コンデンサの値です。表 8-2 に、最大の推奨入力コンデンサ値を示します。最低の周波数についてアプリケーションの要件と一致するが、記載されている値を超えないコンデンサを使用します。

**表 8-2. 推奨入力 AC カップリング コンデンサ**

| ゲイン (dB) | 標準入力インピーダンス (kΩ) | 入力静電容量 (μF) | ハイパスフィルタ (Hz) |

|----------|------------------|-------------|---------------|

| 20       | 60               | 1           | 2.7           |

|          |                  | 1.5         | 1.8           |

| 26       | 30               | 1           | 5.3           |

|          |                  | 3.3         | 1.6           |

| 32       | 15               | 5.6         | 2.3           |

| 36       | 9                | 10          | 1.8           |

### 8.2.2 詳細な設計手順

#### 詳細な設計手順

- ステップ 1: ハードウェア回路図設計: 図 8-1 をガイドとして使用して、ハードウェアをシステム回路図に統合します。

- ステップ 2: セクション 8.4.1 セクションで推奨されているレイアウトガイドラインに従い、デバイスとその補助コンポーネントをシステム PCB ファイルに統合します。

- ステップ 3: 熱設計: デバイスには露出サーマルパッドが搭載されており、適切な半田付けが必要です。詳細については、[半導体およびIC パッケージの熱メトリクスおよび PowerPAD 熱強化パッケージを参照してください](#)。

- ステップ 4: ソフトウェア開発: EVM ユーザーガイドには、デバイスの設定方法や診断情報の解釈方法などの詳細な手順が記載されています。制御レジスタの詳細については、[セクション 7](#) セクションを参照してください。

質問やサポートについては、[E2E フォーラム](#)をご覧ください。

### 8.2.2.1 未使用ピンの接続

使用しない場合でも、常にピンを固定レールに接続します。浮かせたままにしないでください。浮いた入力ピンは ESD リスクとなるため、ユーザーは各ピンについて以下のガイダンスに従う必要があります。

#### 8.2.2.1.1 ハイインピーダンス (HI-Z) ピン

アプリケーションで HI-Z ピンが使用されていない場合は、高インピーダンス抵抗を介して GND に接続します。

#### 8.2.2.1.2 STANDBY ピン

アプリケーションで STANDBY ピンが使用されていない場合は、高インピーダンス抵抗を介して 3.3V や 5V などの低電圧レールに接続します。

### 8.2.2.1.3 I<sup>2</sup>C ピン (SDA および SCL)

システムにマイクロ コントローラが存在しない場合は、I<sup>2</sup>C 通信を行わずにデバイスを使用できます。この状況では、SDA ピンと SCL ピンを 3.3V に接続します。

### 8.2.2.1.4 未使用の出力を終端する

FAULT ピンがアプリケーション内のシステム マイクロ コントローラに報告されない場合は、GND に接続します。

### 8.2.2.1.5 シングルエンド信号入力の使用

シングルエンドの信号ソースを使用する場合、正入力の入力コンデンサと等しい値のコンデンサを通して負の入力を ac グランドに接続し、信号ソースを正の入力に適用します。最高の性能を得るために、ac グランドは可能であればデバイスの入力ではなく信号ソースに配置する必要があります。

## 8.2.3 アプリケーション曲線

アプリケーションのパフォーマンス プロットについては、標準特性セクションを参照してください。

**表 8-3. グラフ一覧**

| グラフ               | 図番号   |

|-------------------|-------|

| 効率と出力電力との関係       | 図 5-1 |

| THD+N と出力電力との関係   | 図 5-2 |

| 消費電力と出力電力との関係     | 図 5-3 |

| THD+N と周波数との関係    | 図 5-4 |

| -60dB 出力のノイズ FFT  | 図 5-5 |

| 1W 出力のノイズ FFT     | 図 5-6 |

| 過電流スレッショルドと温度との関係 | 図 5-7 |

## 8.3 電源に関する推奨事項

自動車用バッテリは電圧範囲が広く、最も一般的にデバイスに電力を供給します。PVDD はフィルタリングされたバッテリ 電圧であり、出力 FET とローサイド FET ゲートドライバ用の電源です。特に低電圧と温度レベルの場合には、優れた電 源デカップリングが必要です。電気的特性セクションの PVDD 仕様を満たすために、テキサス インスツルメントでは、 PVDD ピンの近くに 10μF および 0.1μF のセラミック コンデンサとともに、より大きなバルク 330μF 電解デカップリングコ ンデンサも使用しています。

内部リニア レギュレータがアナログ回路に電力を供給し、BYP ピンに電圧を供給します。この電源には、BYP ピンに外付 けバイパスのセラミック コンデンサが必要です。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

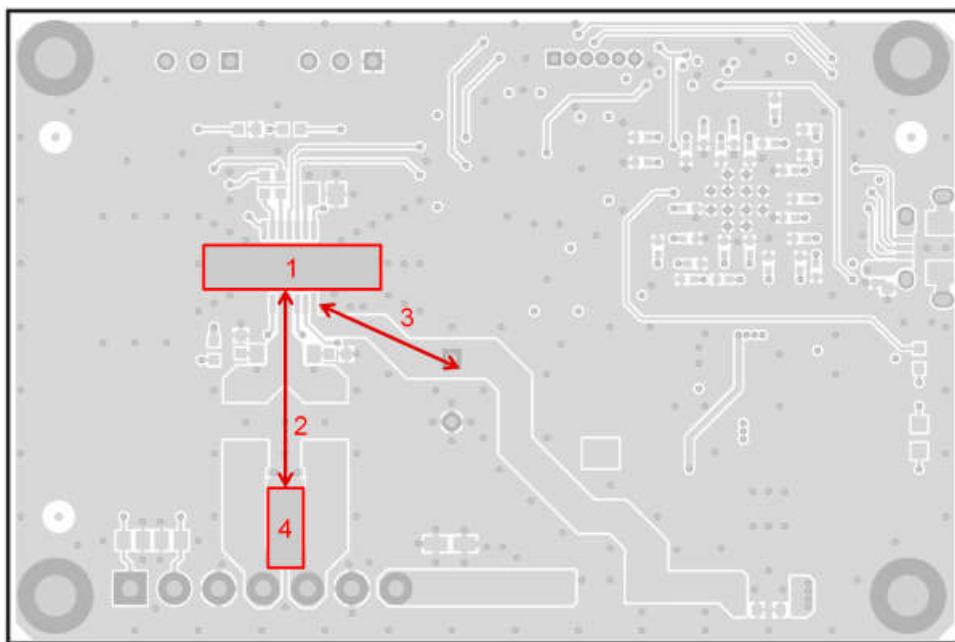

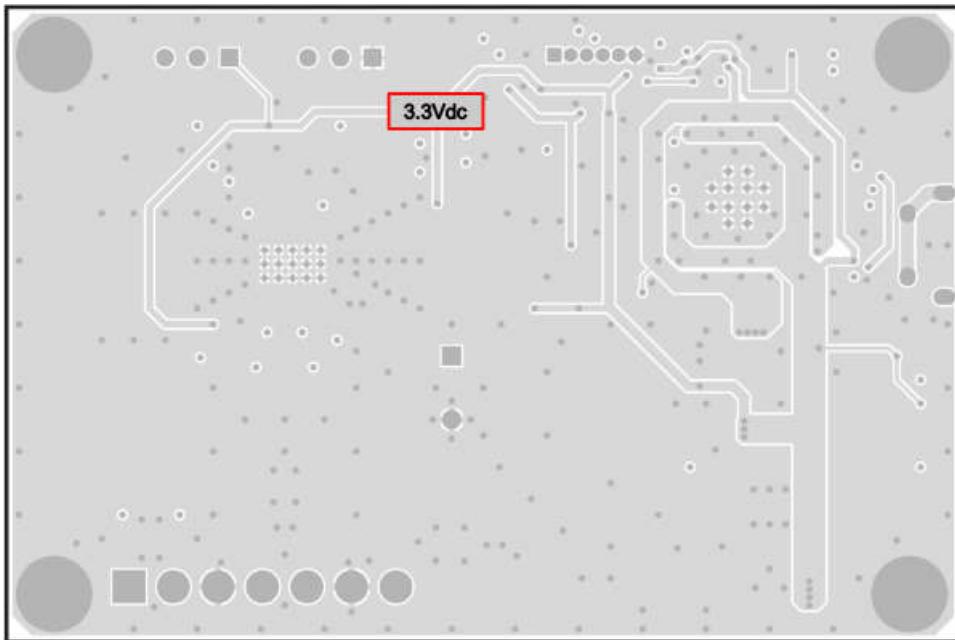

EVM のレイアウトは、放熱と EMC 性能を重視して最適化しています。この TSD5402-Q1 デバイスにはサーマル パッドがあり、優れた熱伝導および放熱特性には十分な銅の免責が必要です。レイアウトは EMC 性能にも影響を及ぼします。レイアウトディスカッションの基礎には、TSD5402Q1EVM のイラストが使用されています。

### 8.4.2 レイアウト例

#### 8.4.2.1 上層

番号 1 の前後の赤い長方形は、上層の銅箔グランドです。サーマル パッドに直接はんだ付けされたグランドは、最初に必要とされる重要な熱放散です。さらなる熱緩和のために他の層に接続するビアがありますが、ビアは熱抵抗が高くなります。TI では、トッププレイヤーを主に熱放散の目的で使用することを推奨しています。さらに、EMC 抑制のために、出力ピンから 2 次 LC フィルタへの短い配線を推奨します。2 番の矢印は、EMC の結果を向上させるための短いルートを示しています。矢印 3 で示されるように、PVDD ピンからバッテリまたは電源から LC フィルタへと短い配線を行うと、EMC 抑制も向上します。許容電流を高めるために外部層に配線します。4 番の周りの赤いボックスは、OUTP と OUTN の両方に共通のグランド プレーンを示しています。LC フィルタのコンデンサは共通グランド プレーンに配置して、同相ノイズと短いグランド ループを実現します

図 8-2. 上層

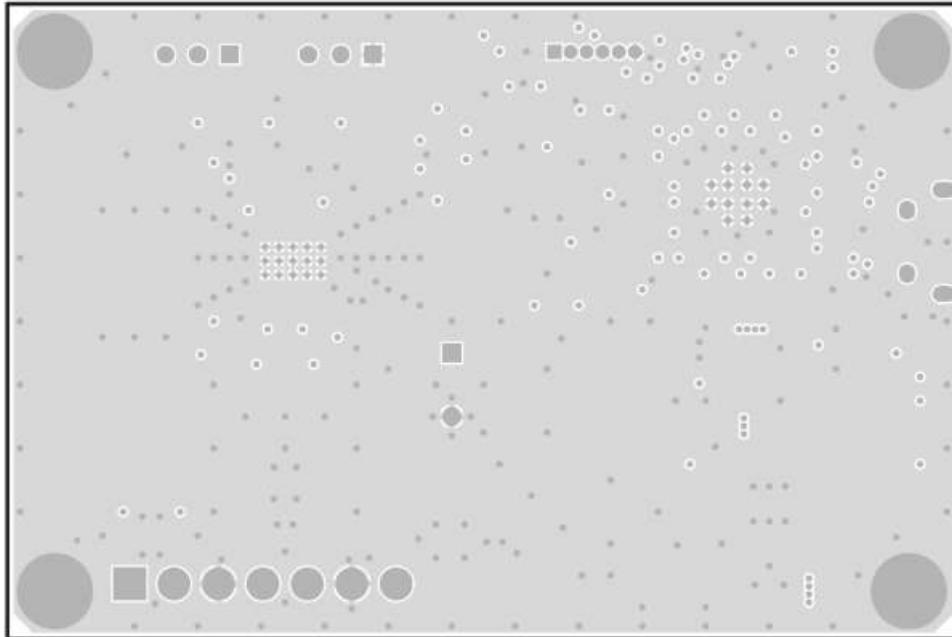

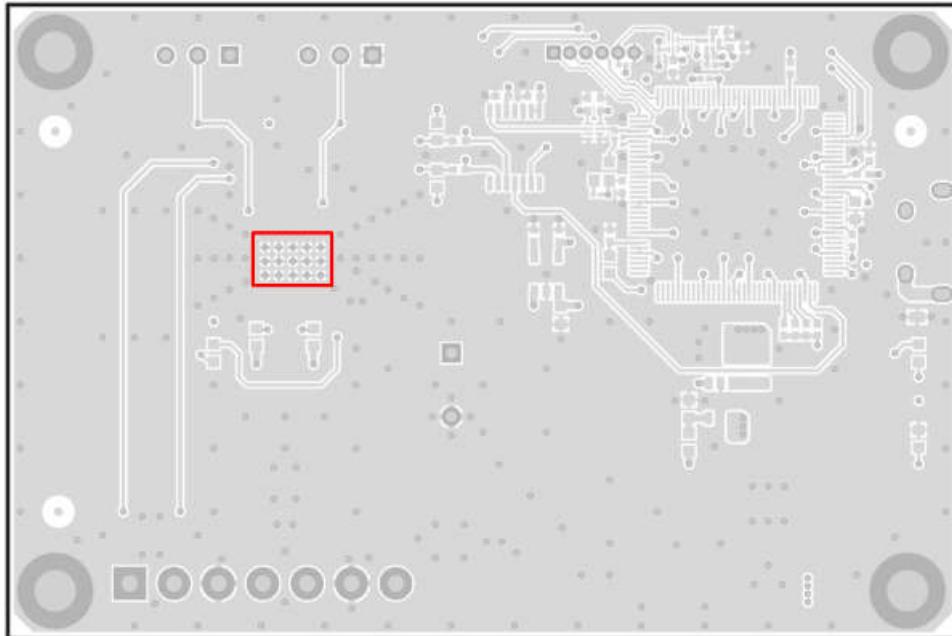

#### 8.4.2.2 第2層 - 信号層

内層にグランド プレーンを全面的に配置し、電流ループを小さく維持して、EMI を低減します。

図 8-3. 信号層

#### 8.4.2.3 第3層 - 電源層

電源プレーンには要件はありませんが、スイッチングノイズを最小限に維持し、デバイスに十分な電流を供給するために、幅の広い単一のトレースを推奨します。幅の広いパターンは、電源からの低インピーダンス経路です。正のパスとリターン(グランド) パスの両方のスイッチングノイズ(リップル電圧)を抑制するには、低インピーダンスが必要です。

図 8-4. 電源層

#### 8.4.2.4 下層 - グランド層

このデバイスは、熱特性を向上させるため底面に露出サーマル パッドを備えています。サーマル パッドから他の層に熱を伝導するには、サーマル ビアが必要です。下層は二次的な熱交換の表面であるため、サーマル ビア領域の熱抵抗を小さくする必要があります。

図 8-5. 下層

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- [Class-D LC フィルタ設計 \(SLOA119\)](#)

- [Class-D 出力スナバ設計ガイド \(SLOA201\)](#)

- [PowerPAD 熱特性強化パッケージ \(SLMA002\)](#)

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

[テキサス・インスツルメンツ E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.5 商標

PowerPAD™ and [テキサス・インスツルメンツ E2E™](#) are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

#### [テキサス・インスツルメンツ用語集](#)

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <a href="#">Changes from Revision * (September 2024) to Revision A (January 2025)</a> | <a href="#">Page</a> |

|---------------------------------------------------------------------------------------|----------------------|

| • データシートのステータスを「事前情報」から「量産データ」に変更 .....                                               | <a href="#">1</a>    |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントの改訂を伴わない場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 11.1 付録：パッケージオプション

### 11.1.1 パッケージ情報

| 発注可能なデバイス      | 供給状況 <sup>(1)</sup> | パッケージタイプ | パッケージ図 | ピン | パッケージの数量 | エコ プラン <sup>(2)</sup> | リード / ボール仕上げ <sup>(4)</sup> | MSL ピーク温度 <sup>(3)</sup> | 動作温度(°C) | デバイス マーキング <sup>(5) (6)</sup> |

|----------------|---------------------|----------|--------|----|----------|-----------------------|-----------------------------|--------------------------|----------|-------------------------------|

| TSD5402QPWPRQ1 | プレビュー               | HTSSOP   | PWP    | 16 | 2000     | 未定                    | NiPdAu                      | Level-3-260C-1<br>68 HR  | -40~125  | TSD5402                       |

- (1) マーケティング ステータスの値は次のように定義されています。

**供給中:**新しい設計への使用が推奨される量産デバイス。

**最終受注中:**テキサス・インスツルメンツによりデバイスの生産中止予定が発表され、ライフトайム購入期間が有効です。

**非推奨品:**新規設計には推奨しません。デバイスは既存の顧客をサポートするために生産されていますが、テキサス・インスツルメンツでは新規設計にこの部品を使用することを推奨ていません。

**量産開始前:**量産されていない、市販されていない、またはウェブで発表されていない未発表デバイスで、サンプルは提供されていません。

**プレビュー:**デバイスは発表済みですが、まだ生産は開始されていません。サンプルが提供される場合と提供されない場合があります。

**生産中止品:**テキサス・インスツルメンツはデバイスの生産を終了しました。

- (2) エコ プラン - 環境に配慮した計画的な分類:鉛フリー (RoHS)、鉛フリー (RoHS 適用除外)、またはグリーン (RoHS 準拠、Sb/Br 非含有) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent> でご確認ください。

**未定:**鉛フリー / グリーン転換プランが策定されていません。

**鉛フリー (RoHS):**テキサス・インスツルメンツにおける「Lead-Free」または「Pb-Free」(鉛フリー) は、6 つの物質すべてに対して現在の RoHS 要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が 0.1% を超えないという要件も含まれます。高温はんだに対応した テキサス・インスツルメンツ鉛フリー製品は、鉛フリー仕様プロセスでの使用に適しています。

**鉛フリー (RoHS 適用除外):**この部品は、1) ダイとパッケージとの間に鉛ベース フリップ チップのはんだバンプ使用、または 2) ダイとリードフレームとの間に鉛ベースの接着剤を使用、のいずれかについて、RoHS が免除されています。この部品はそれ以外の点では、上記の定義の鉛フリー (RoHS 準拠) の条件を満たしています。

**グリーン (RoHS 準拠、Sb/Br 非含有):**テキサス・インスツルメンツにおけるグリーンは、鉛フリー (RoHS 互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない(均質な材質中の Br または Sb 重量が 0.1% を超えない)ことを意味しています。

- (3) MSL、ピーク温度 -- JEDEC 業界標準分類に従った耐湿性レベル、およびピークはんだ温度です。

- (4) リード / ボール仕上げ - 発注可能なデバイスには、複数の材料仕上げオプションが用意されていることがあります。複数の仕上げオプションは、縦罫線で区切られています。リード / ボール仕上げの値が最大列幅に収まらない場合は、2 行にまたがります。

- (5) ロゴ、ロットトレースコード情報、または環境カテゴリに関する追加マークがデバイスに表示されることがあります

- (6) 複数のデバイスマーキングが、括弧書きされています。カッコ内に複数のデバイスマーキングがあり、「～」で区切られている場合、その中の 1 つだけがデバイスに表示されます。行がインデントされている場合は、前行の続きということです。2 行合わせたものが、そのデバイスマーキング全体となります。

**重要なお知らせと免責事項:**このページに掲載されている情報は、発行日現在のテキサス・インスツルメンツの知識および見解を示すものです。テキサス・インスツルメンツの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。テキサス・インスツルメンツでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。テキサス・インスツルメンツおよびテキサス・インスツルメンツのサプライヤは、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じたテキサス・インスツルメンツの責任は、このドキュメント発行時点でのテキサス・インスツルメンツ製品の価格に基づくテキサス・インスツルメンツからお客様への合計購入価格(年次ベース)を超えることはありません。

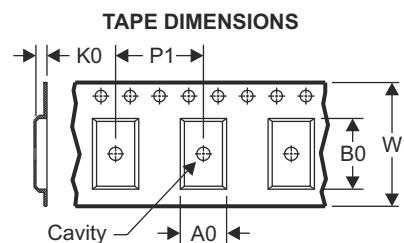

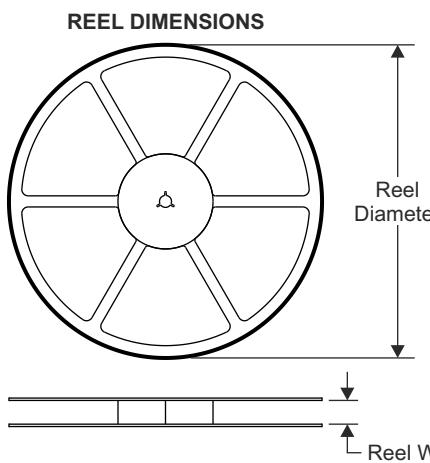

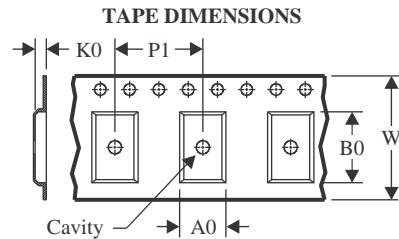

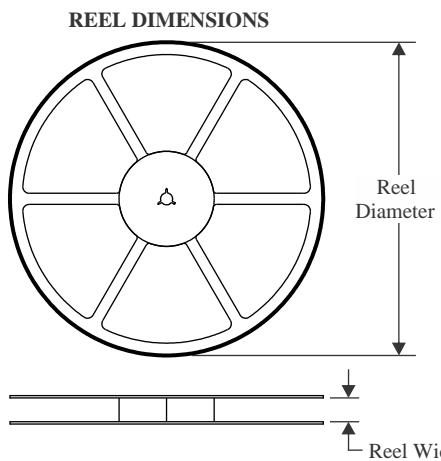

### 11.1.2 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

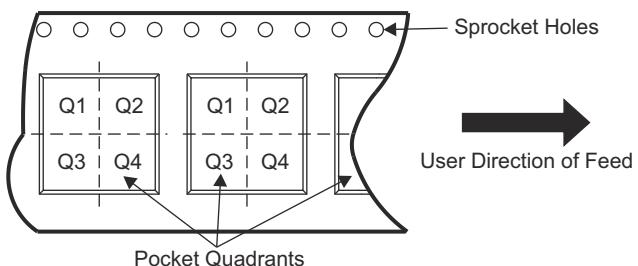

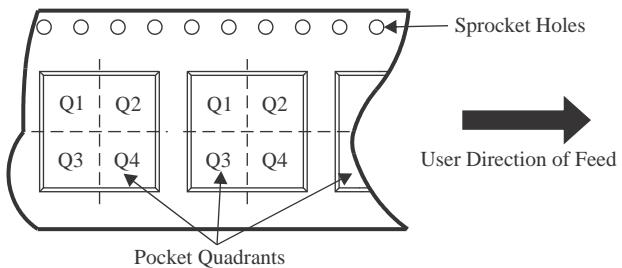

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス           | パッケージ<br>タイプ | パッケージ<br>図 | ピン | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|----------------|--------------|------------|----|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| TSD5402QPWPRQ1 | HTSSOP       | PWP        | 16 | 2000 | 330.0          | 12.4             | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1           |

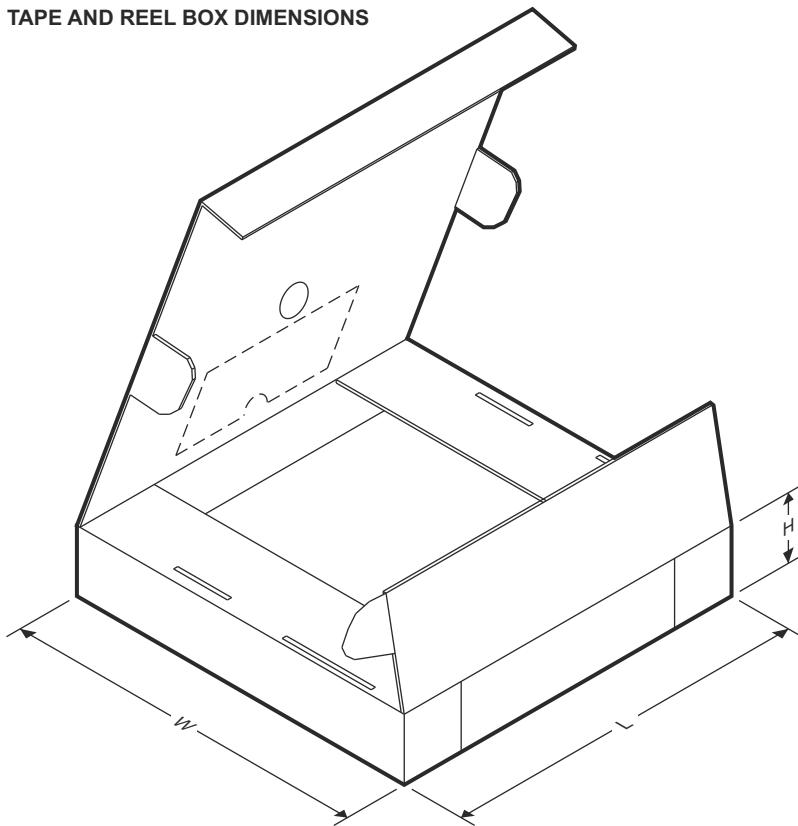

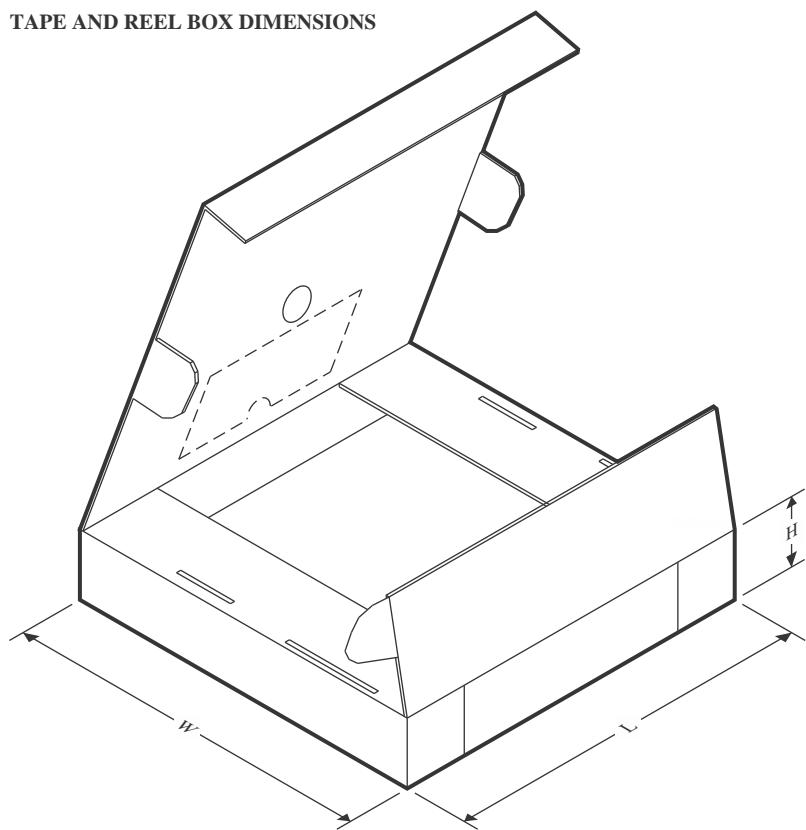

## TAPE AND REEL BOX DIMENSIONS

| デバイス            | パッケージタイプ | パッケージ図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|-----------------|----------|--------|----|------|---------|--------|---------|

| TSD54021QPWPRQ1 | HTSSOP   | PWP    | 16 | 2000 | 350.0   | 350.0  | 43.0    |

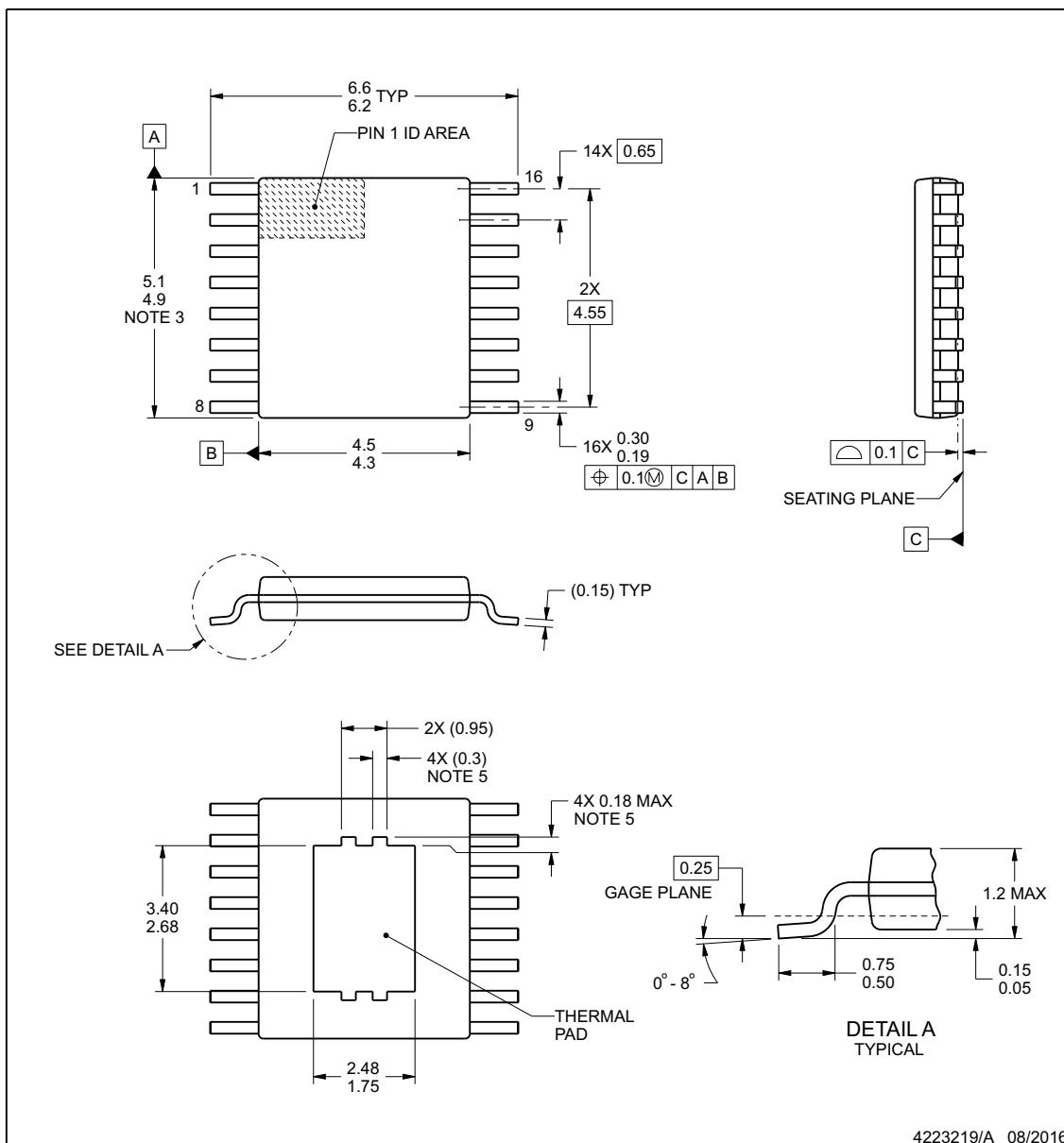

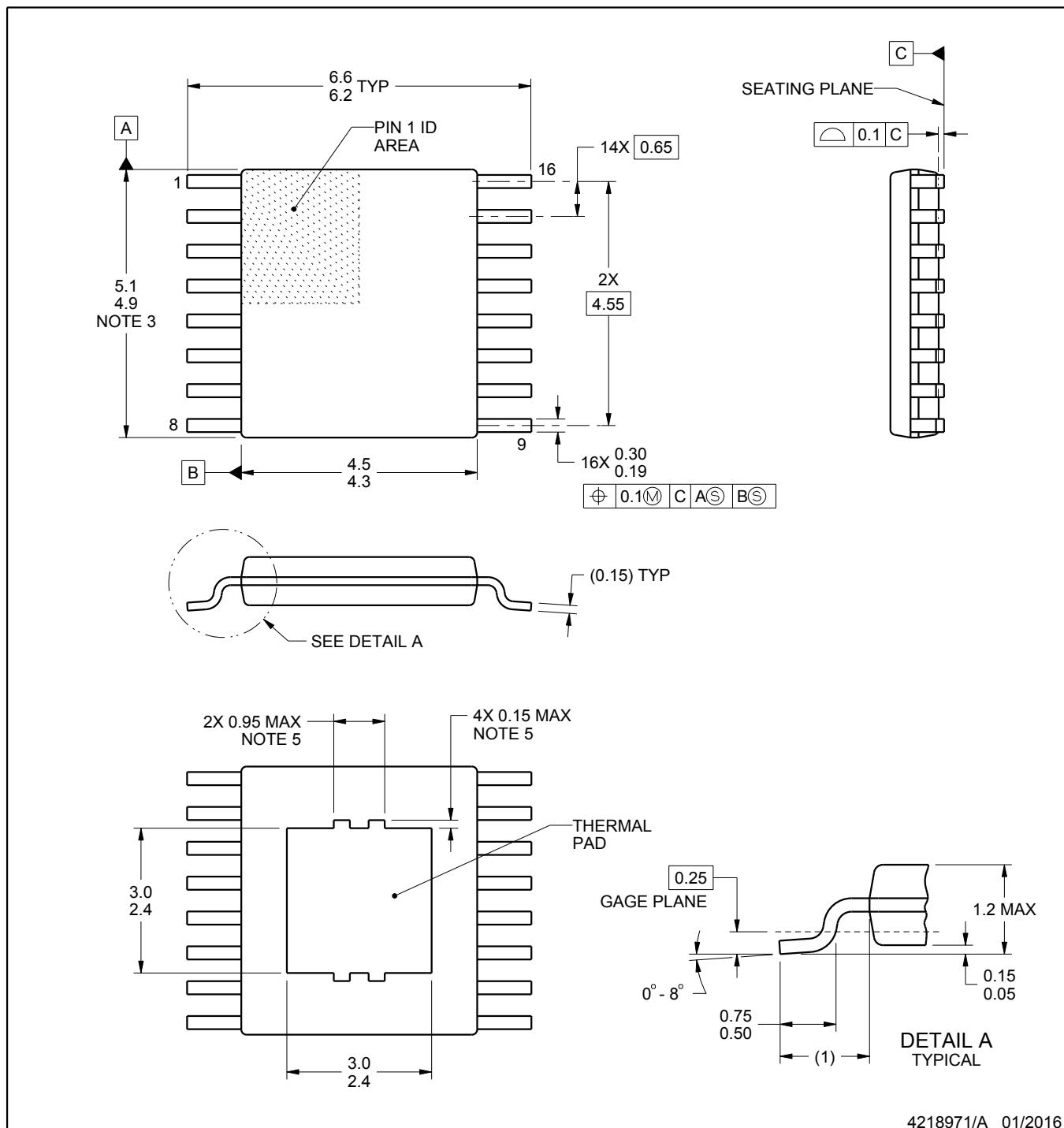

## PACKAGE OUTLINE

**PWP0016D**

**PowerPAD™ TSSOP - 1.2 mm max height**

PLASTIC SMALL OUTLINE

4223219/A 08/2016

PowerPAD is a trademark of Texas Instruments.

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ and may not be present.

[www.ti.com](http://www.ti.com)

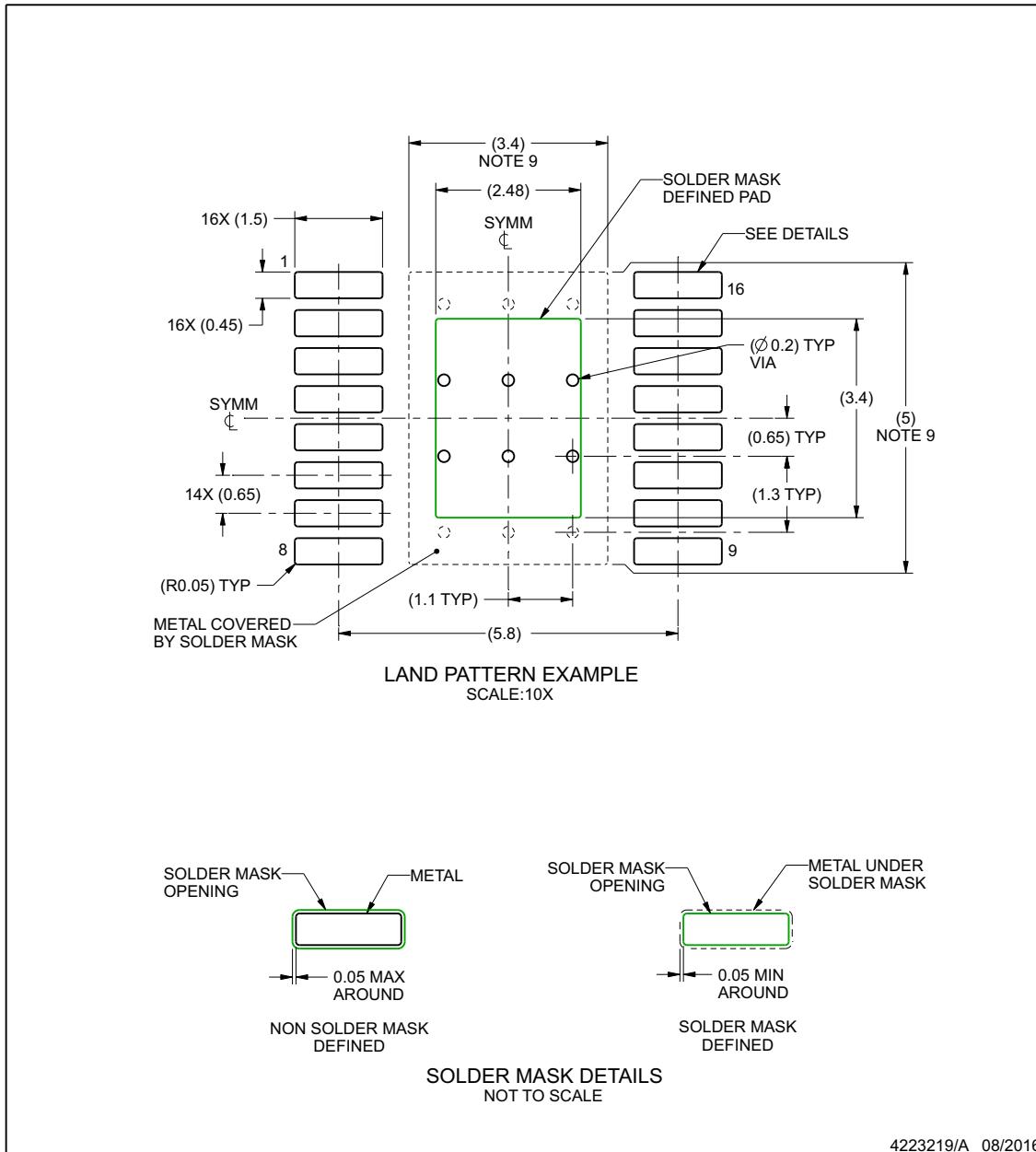

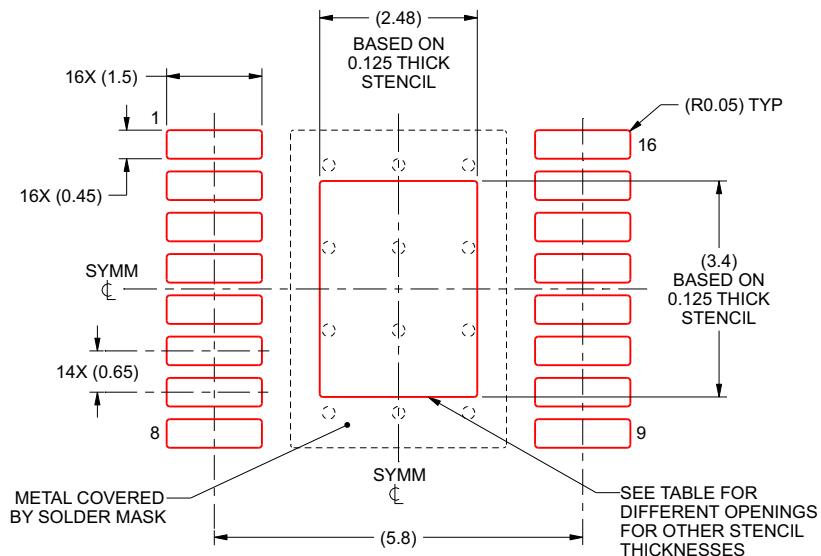

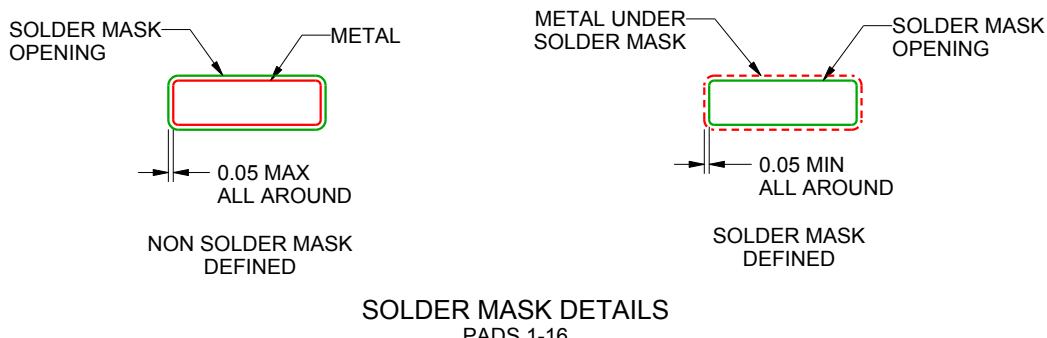

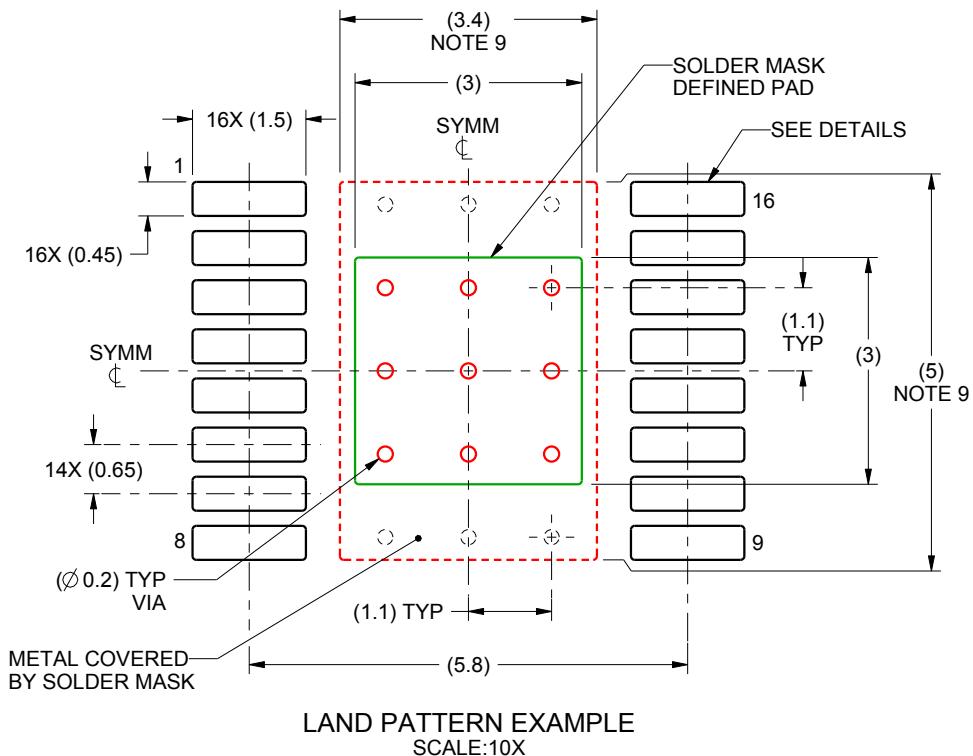

## EXAMPLE BOARD LAYOUT

**PWP0016D**

**PowerPAD™ TSSOP - 1.2 mm max height**

PLASTIC SMALL OUTLINE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

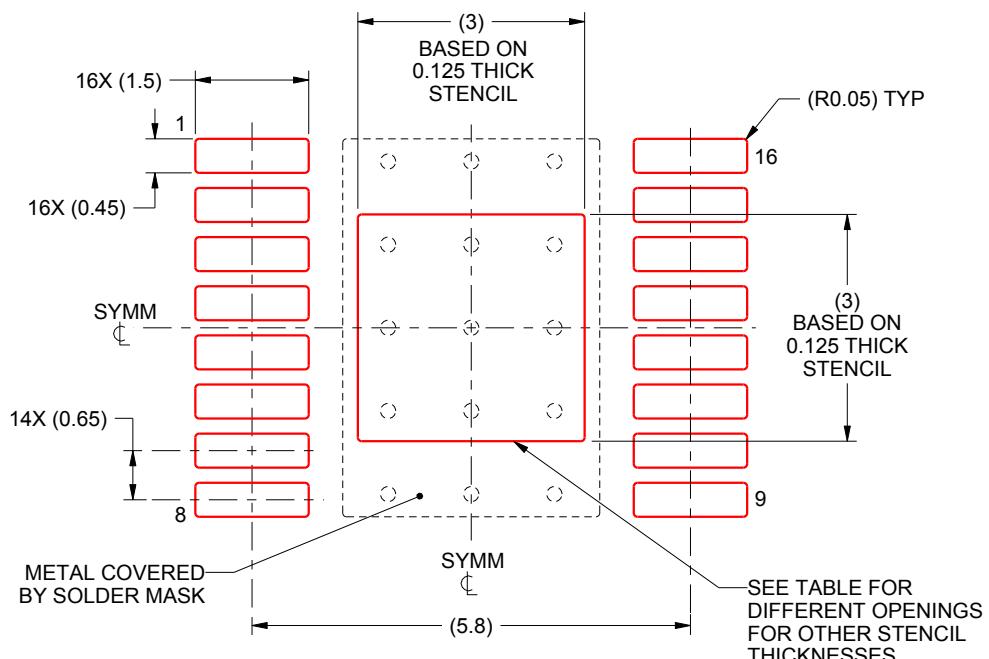

## EXAMPLE STENCIL DESIGN

PWP0016D

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.77 X 3.8             |

| 0.125             | 2.48 X 3.4 (SHOWN)     |

| 0.15              | 2.26 X 3.1             |

| 0.175             | 2.1 X 2.87             |

4223219/A 08/2016

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

[www.ti.com](http://www.ti.com)

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TSD5402QPWPRQ1        | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | TSD5402             |

| TSD5402QPWPRQ1.A      | Active        | Production           | HTSSOP (PWP)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | TSD5402             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TSD5402QPWPRQ1 | HTSSOP       | PWP             | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TSD5402QPWPRQ1 | HTSSOP       | PWP             | 16   | 2000 | 353.0       | 353.0      | 32.0        |

## GENERIC PACKAGE VIEW

PWP 16

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4073225-3/J

PWP0016B

# PACKAGE OUTLINE

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

4218971/A 01/2016

NOTES:

PowerPAD is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- Reference JEDEC registration MO-153.

- Features may not be present.

# EXAMPLE BOARD LAYOUT

PWP0016B

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

4218971/A 01/2016

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

# EXAMPLE STENCIL DESIGN

PWP0016B

PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.35 X 3.35            |

| 0.125             | 3 X 3 (SHOWN)          |

| 0.15              | 2.74 X 2.74            |

| 0.175             | 2.54 X 2.54            |

4218971/A 01/2016

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月