# TUSB2E221 USB 2.0-eUSB2 デュアル リピータ

## 1 特長

- USB 2.0 および eUSB2 (rev 1.2) 準拠

- ロースピード (LS)、フルスピード (FS)、ハイスピード (HS) をサポート

- クラス最高の高速合計ジッタ: 20ps

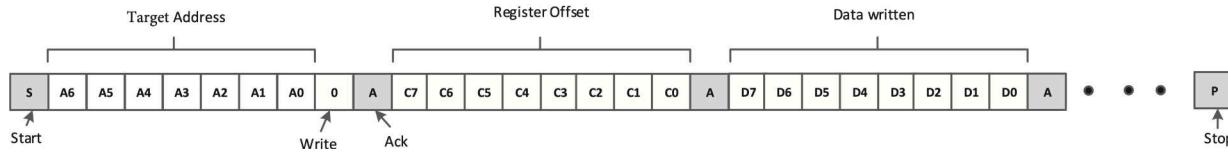

- レジスタ アクセス プロトコル レセプタ対応

- 独立型デュアル リピータ

- 2:2 クロスバー マルチプレクサ (DSBGA パッケージのみ)

- ホスト モードおよびデバイス モード (DRD) をサポート

- VIOSEL ピンを使用して、1.2V~1.8V の制御または I<sup>2</sup>C レベルを選択

- I<sup>2</sup>C かストラップ ピンかを自動検出

- USB 2.0 ハイスピード チャネル補償設定用の 3 本のストラップ ピン

- I<sup>2</sup>C デバイス インターフェイスを使用すると、より柔軟な設定が可能

- さまざまなデバイス バリアントを用意

- eUSB2 1.0V または 1.2V 信号インターフェイス

- 4 つの eUSB2 トレイス損失補償レベルで多様な 製品フォーム ファクタに対応: 2.5、5、7.5、10 インチ

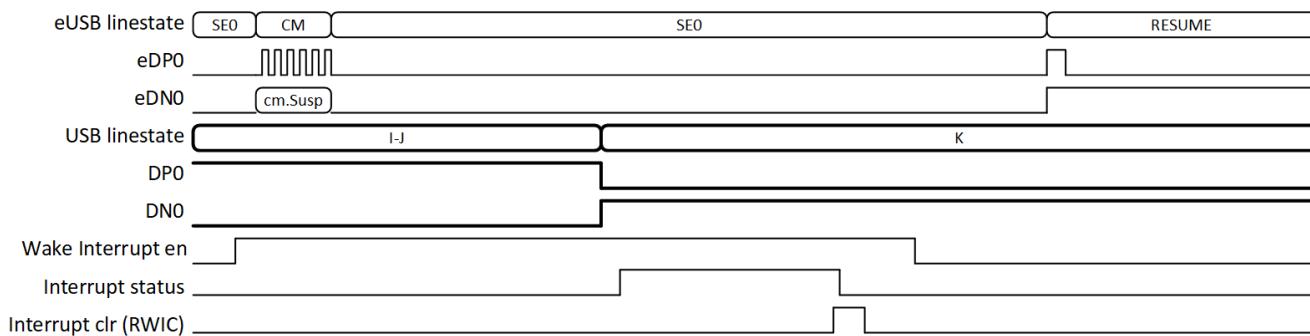

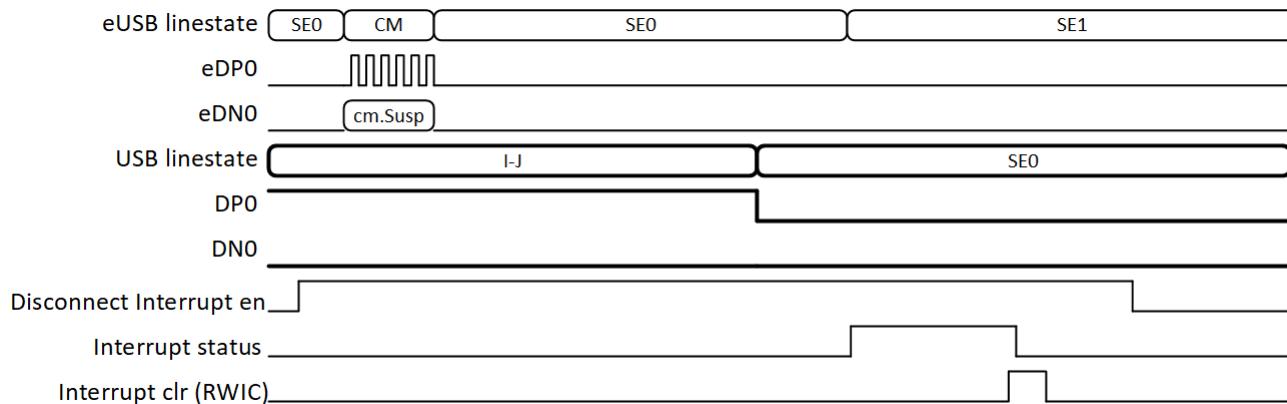

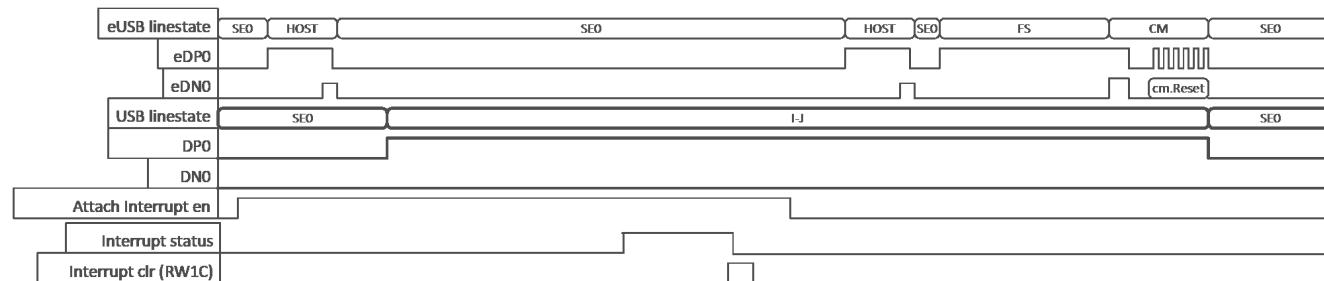

- 自動再開 ECR と L2 割り込み再開モードをサポート

- CTA-936 USB Carkit UART のサポート

- オプションの BC1.2 CDP バッテリ充電および検出サポート

- デバッグ用 EQ ピンのオプションの GPIO モードと、 EQ0/1 経由の I<sup>2</sup>C ⇄ GPIO

- I<sup>2</sup>C からアクセスできる製造試験用のデバッグ機能

## 2 アプリケーション

- 通信機器

- エンタープライズ システム

- ノート PC およびデスクトップ PC

- 産業用

- タブレット

- ポータブル エレクトロニクス

## 3 概要

TUSB2E221 は、低電圧プロセスを使用する新しいプロセッサに USB 2.0 準拠ポートを実装できます。

TUSB2E221 は、デバイス モードとホスト モードの両方をサポートする USB の eUSB2-USB 2.0 リピータです。TUSB2E221 は、USB ロースピード (LS) 信号、フルスピード (FS) 信号、ハイスピード (HS) 信号をサポートしています。

TUSB2E221 は、1.2V のシングルエンド信号で動作する eUSB2 eDSPr または eUSPr と接続するように設計されています。

TUSB2E221 は、堅牢な相互運用性、最適な性能、消費電力を実現するために、特許申請中の複数の設計を採用しています。

I<sup>2</sup>C インターフェイスを使用しないシステムでは、このデバイスは最大 17.5Ω の USB 2.0 チャネル等価直列抵抗 (ESR) に対応する 3 本のストラップ ピンによる 8 つの個別設定を提供します。このデバイスは、最大 10 インチまでのさまざまなレベルの eUSB2 トレイス長補償機能を備えるバリエントが利用可能です。

I<sup>2</sup>C インターフェイスにより、さらに柔軟にデバイスの RX および TX 設定を微調整できます。利用可能な設定は、RX イコライゼーション、RX スケルチ スレッショルド、RX 切断スレッショルド、TX 振幅、TX スルーレート、TX プリエンファシスです。

各種のデバッグ オプションが利用可能であり、3 本の EQ ピンを使用してさまざまな USB バス状態や割り込みを監視するように構成できるほか、CTA-936 UART モード制御で SoC デバッグ機能を実現できます。EQ0 および EQ1 は、汎用 I<sup>2</sup>C から GPIO へのブリッジとして使用できます。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| TUSB2E221 | VBW (WQFN, 20)       | 3mm × 3mm                |

|           | YCG (DSBGA, 25)      | 2mm × 2mm                |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

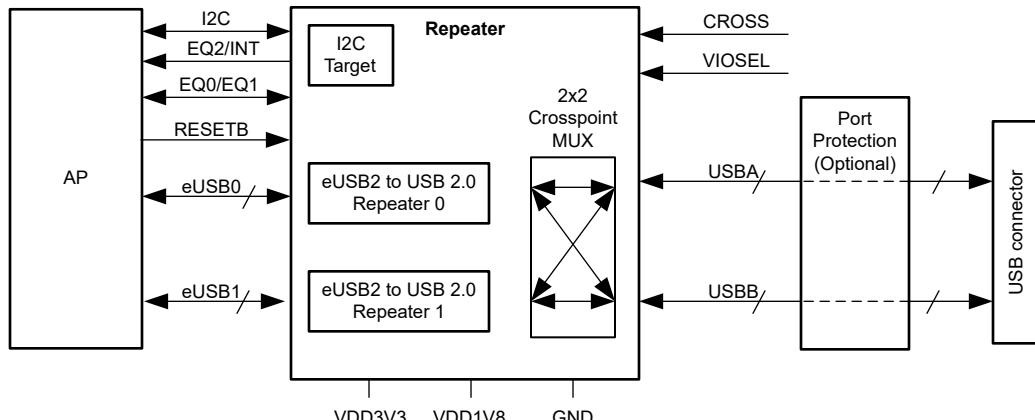

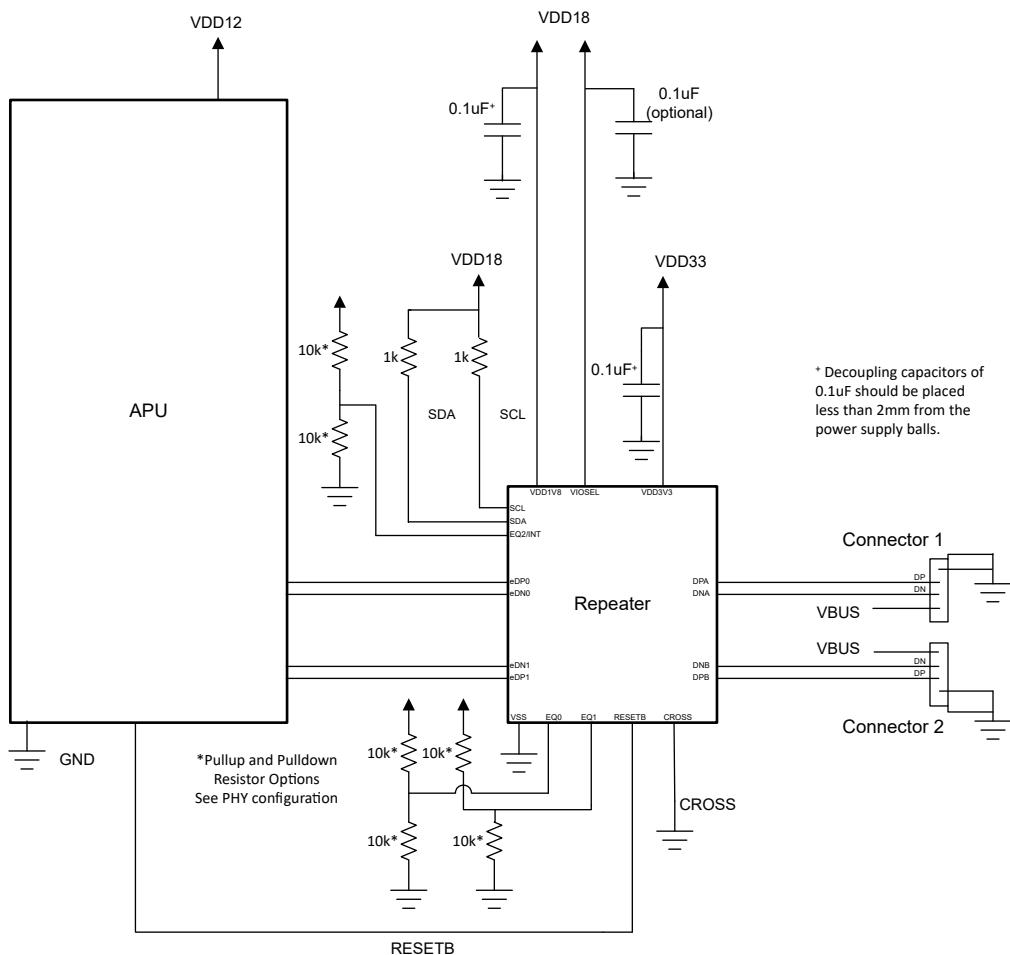

概略回路図

## 目次

|              |    |                                 |    |

|--------------|----|---------------------------------|----|

| 1 特長         | 1  | 8.4 デバイスの機能モード                  | 24 |

| 2 アプリケーション   | 1  | 8.5 プログラミング                     | 29 |

| 3 概要         | 1  | 9 レジスタ マップ                      | 33 |

| 4 デバイス バリアント | 4  | 9.1 TUSB2E221 のレジスタ             | 33 |

| 5 ピン構成および機能  | 5  | 10 アプリケーションと実装                  | 54 |

| 6 仕様         | 10 | 10.1 アプリケーション情報                 | 54 |

| 6.1 絶対最大定格   | 10 | 10.2 代表的なアプリケーション: デュアル ポートシステム | 54 |

| 6.2 ESD 定格   | 10 | 10.3 電源に関する推奨事項                 | 55 |

| 6.3 推奨動作条件   | 10 | 10.4 レイアウト                      | 56 |

| 6.4 熱に関する情報  | 11 | 11 デバイスおよびドキュメントのサポート           | 58 |

| 6.5 電気的特性    | 11 | 11.1 ドキュメントのサポート                | 58 |

| 6.6 スイッチング特性 | 17 | 11.2 ドキュメントの更新通知を受け取る方法         | 58 |

| 6.7 タイミング要件  | 19 | 11.3 サポート・リソース                  | 58 |

| 6.8 代表的特性    | 21 | 11.4 商標                         | 58 |

| 7 パラメータ測定情報  | 22 | 11.5 静電気放電に関する注意事項              | 58 |

| 8 詳細説明       | 23 | 11.6 用語集                        | 58 |

| 8.1 概要       | 23 | 12 改訂履歴                         | 59 |

| 8.2 機能ブロック図  | 23 | 13 メカニカル、パッケージ、および注文情報          | 59 |

| 8.3 機能説明     | 24 |                                 |    |

## 4 デバイス バリアント

次の表に、TUSB2E221x デバイス バリアントの主な違いを示します

**表 4-1. デバイス バリアント情報**

| 発注可能なデバイス                       | パッケージ<br>タイプ | フレーム ベース<br>LP モード <sup>(1)</sup> |

|---------------------------------|--------------|-----------------------------------|

| TUSB2E2211001YCG                | WCSP         | イネーブル                             |

| TUSB2E2211005YCG <sup>(2)</sup> |              | ディセーブル                            |

| TUSB2E2211001VBW <sup>(2)</sup> | WQFN         | イネーブル                             |

| TUSB2E2211005VBW                |              | ディセーブル                            |

(1) 「フレーム ベースの低消費電力モード」セクションを参照

(2) リリースされていません。eUSB2 1.0V 信号インターフェイス、1.2V I<sup>2</sup>C インターフェイス、1.2V GPIO インターフェイスなどのデバイス バリアントの詳細と入手可能性については、[セクション 11.3](#) を参照し、TI にお問い合わせください。

eUSB2 1.0V 信号インターフェイス、異なる 7 ビット I<sup>2</sup>C アドレス、低消費電力の内部組込みアプリケーションなどのデバイス バリアントの詳細と入手可能性については、[セクション 11.3](#) を参照してください。

**表 4-2. レジスタ マップ デフォルト**

| I <sup>2</sup> C オフセット | CAT2<br>デフォルト | CAT6<br>デフォルト |

|------------------------|---------------|---------------|

| 0x30                   | 0x79          | 0x79          |

| 0x31                   | 0x39          | 0x39          |

| 0x32                   | 0xD4          | 0xD4          |

| 0x33                   | 0x75          | 0x75          |

| 0x37                   | 0x40          | 0x40          |

| 0x38                   | 0x4C          | 0x4C          |

| 0x39                   | 0x22          | 0x22          |

| 0x10                   | 0x50          | 0x00          |

| 0x70                   | 0x79          | 0x79          |

| 0x71                   | 0x39          | 0x39          |

| 0x72                   | 0x94          | 0x94          |

| 0x73                   | 0x75          | 0x75          |

| 0x77                   | 0x40          | 0x40          |

| 0x78                   | 0x4C          | 0x4C          |

| 0x79                   | 0x22          | 0x22          |

| 0x50                   | 0x50          | 0x00          |

## 5 ピン構成および機能

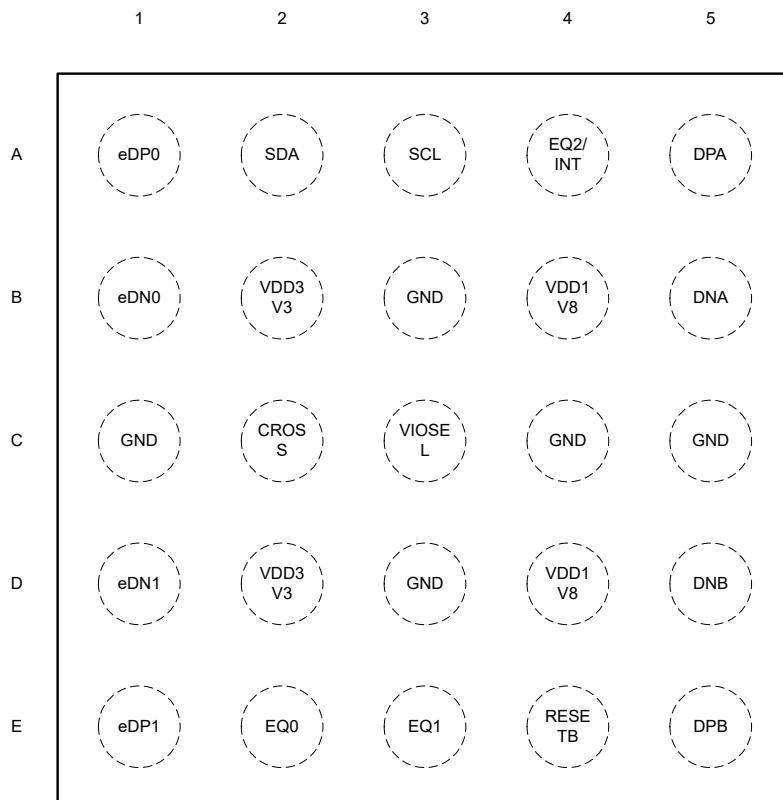

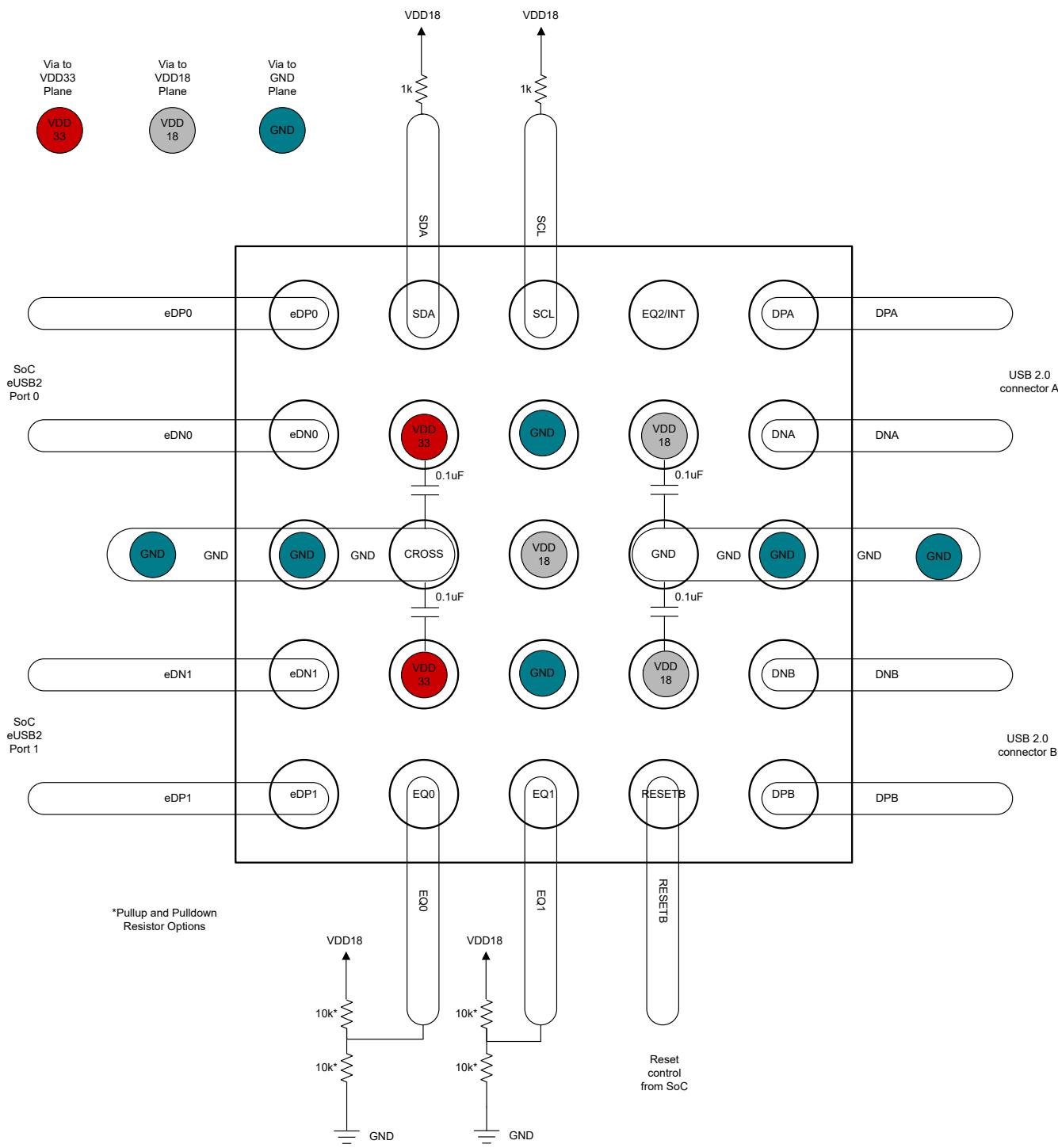

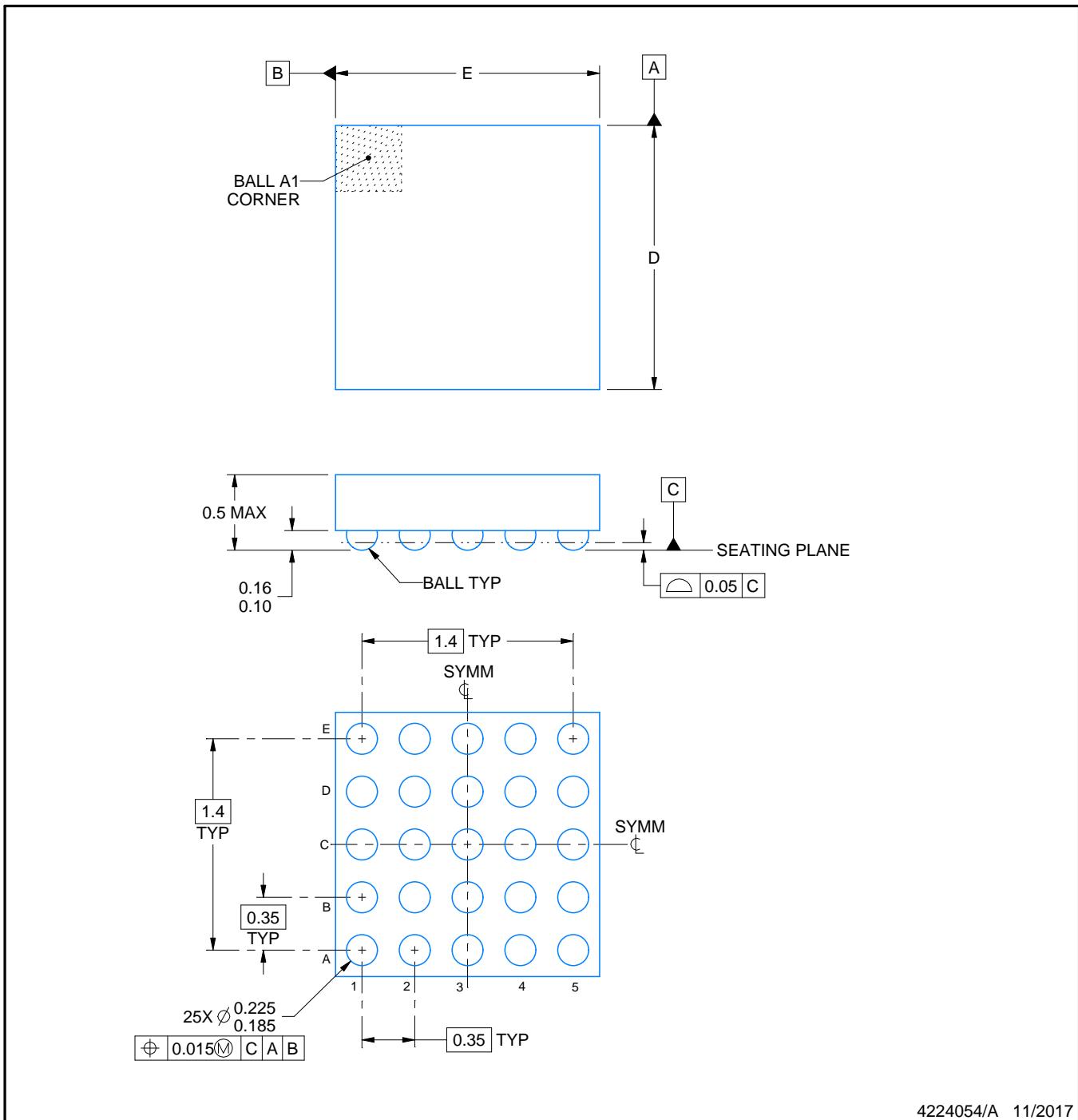

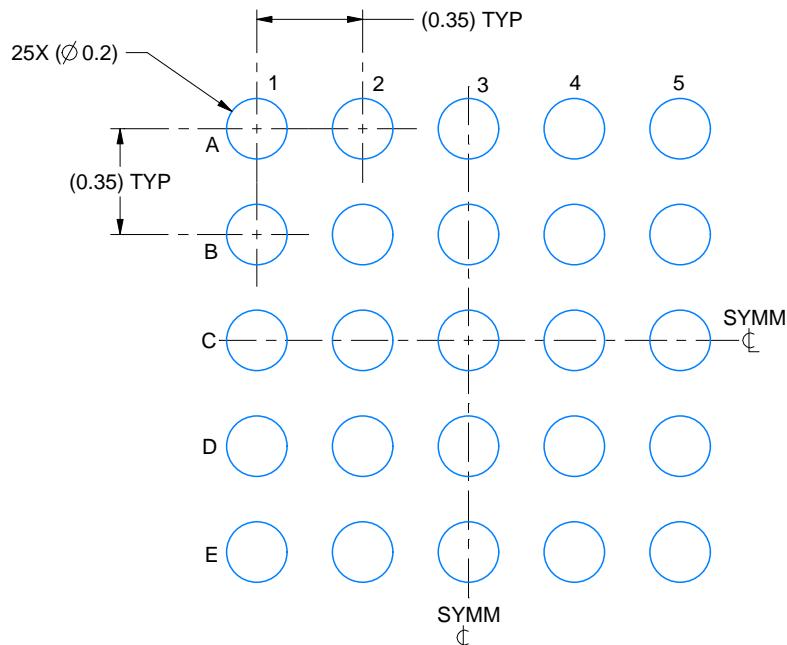

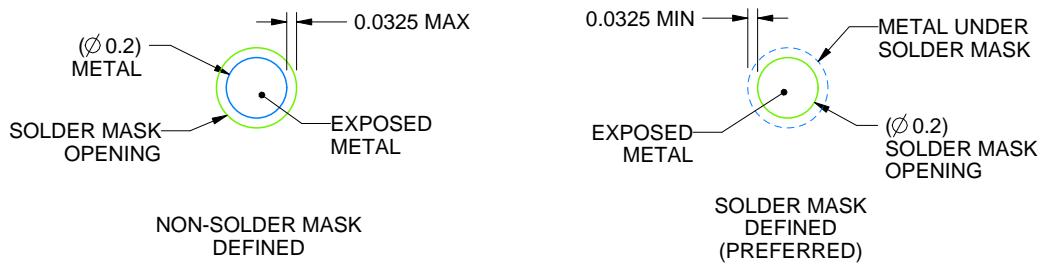

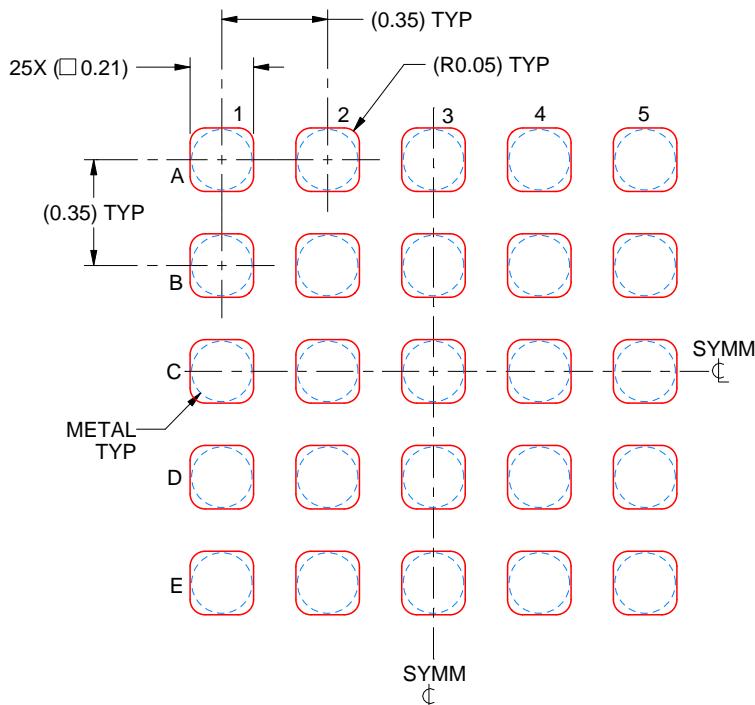

図 5-1. YCG パッケージ、25 ピン DSBGA (上面図)

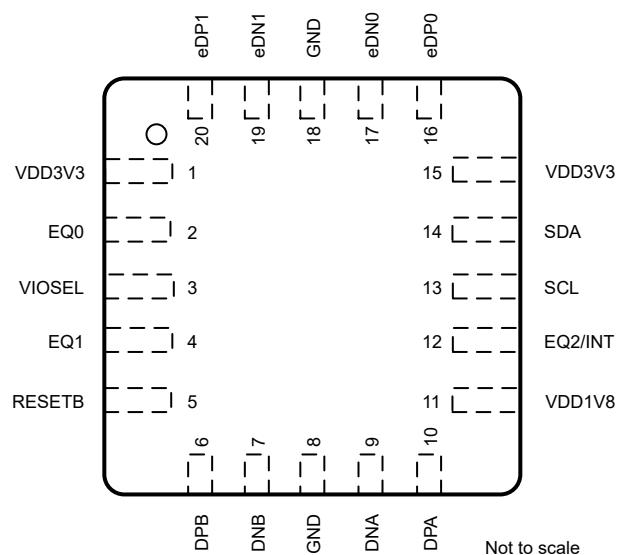

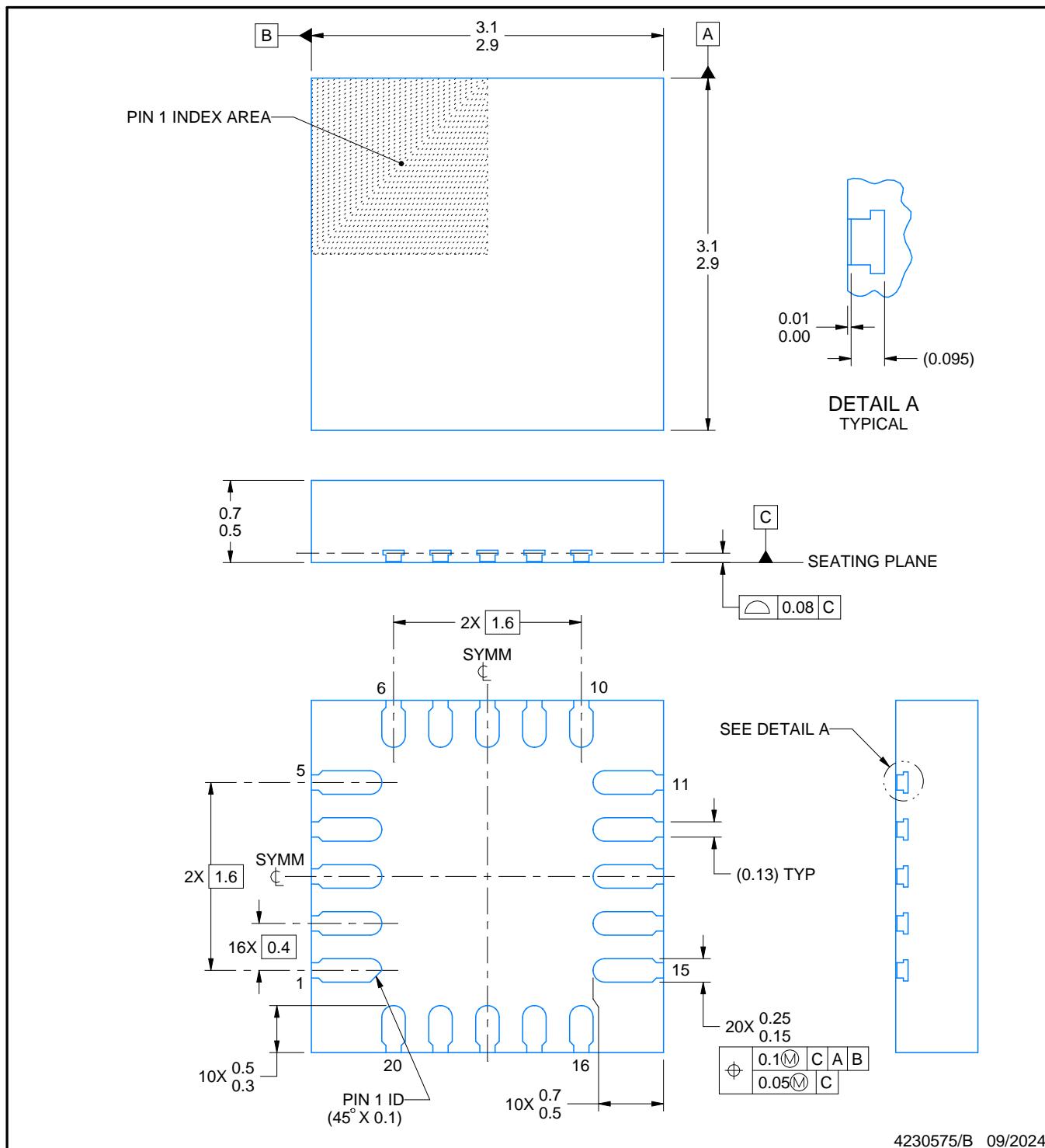

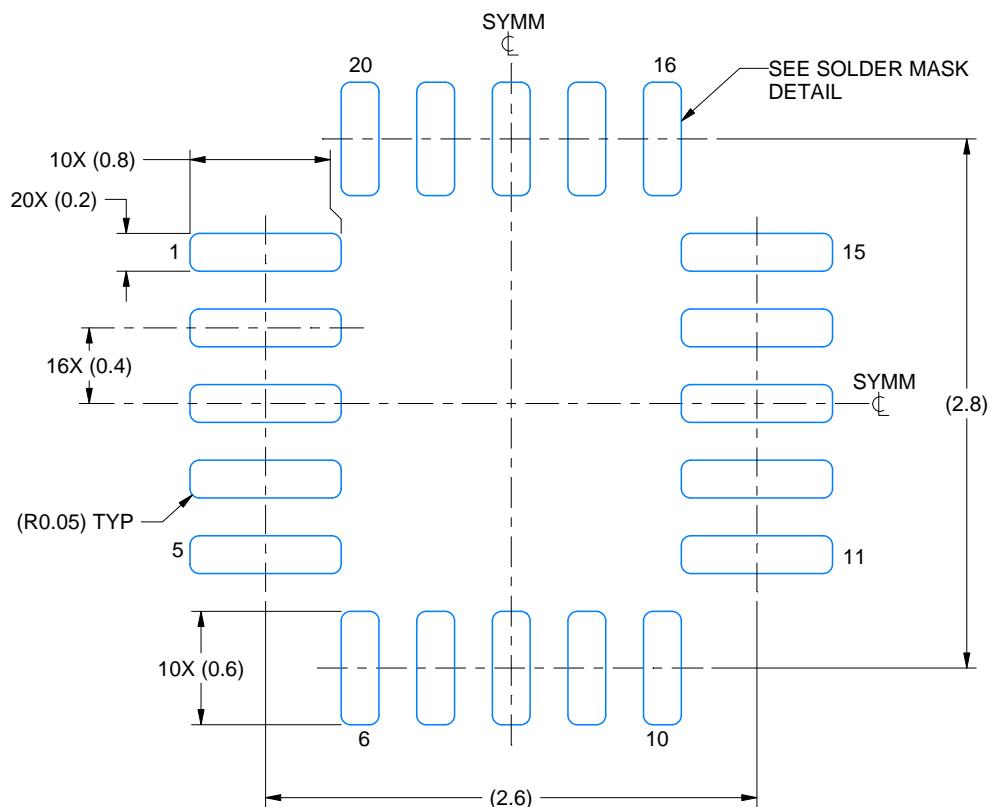

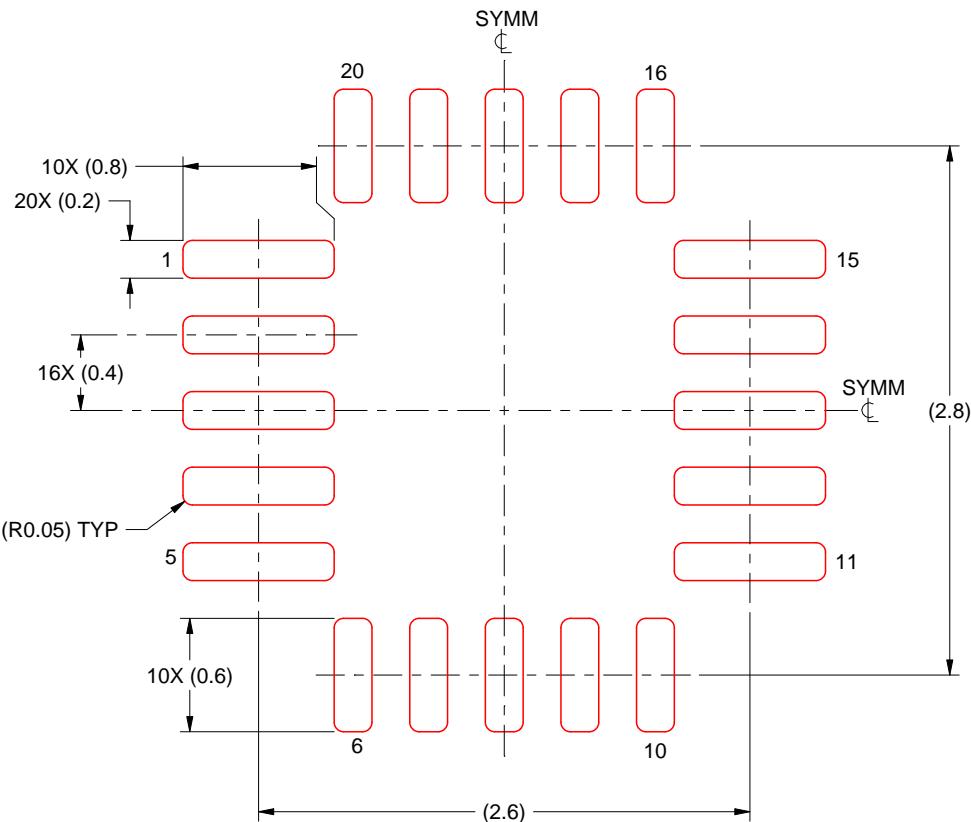

図 5-2. VBW パッケージ 20 ピン WQFN (上面図)

表 5-1. ピンの機能

| ピン      |     |     | I/O      | RESET<br>状態                     | 関連付けられた<br>ESD 供給 | 説明                                                                                                                                                                           |

|---------|-----|-----|----------|---------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | VBW | YCG |          |                                 |                   |                                                                                                                                                                              |

| CROSS   | –   | C2  | デジタル入力   | 該当なし                            | VDD3V3            | マルチブレクサの向きを示します。内部クロスバー スイッチの向きを指定するために使用されます<br>CROSS = Low: eUSB0 «→» USBA および eUSB1 «→» USBB<br>CROSS = High: eUSB0 «→» USBB および eUSB1 «→» USB A<br>RESETB のデアサート時にサンプリング |

| DNA     | 9   | B5  | アナログ I/O | ハイインピーダンス                       | VDD3V3            | USB ポート A の D- ピン                                                                                                                                                            |

| DPA     | 10  | A5  | アナログ I/O | ハイインピーダンス                       | VDD3V3            | USB ポート A の D+ ピン                                                                                                                                                            |

| DNB     | 7   | D5  | アナログ I/O | ハイインピーダンス                       | VDD3V3            | USB ポート B の D- ピン                                                                                                                                                            |

| DPB     | 6   | E5  | アナログ I/O | ハイインピーダンス                       | VDD3V3            | USB ポート B の D+ ピン                                                                                                                                                            |

| eDN0    | 17  | B1  | アナログ I/O | ハイインピーダンス                       | VDD1V8            | eUSB2 ポート 0 の D- ピン                                                                                                                                                          |

| eDP0    | 16  | A1  | アナログ I/O | ハイインピーダンス                       | VDD1V8            | eUSB2 ポート 0 の D+ ピン                                                                                                                                                          |

| eDN1    | 19  | D1  | アナログ I/O | ハイインピーダンス                       | VDD1V8            | eUSB2 ポート 1 の D- ピン                                                                                                                                                          |

| eDP1    | 20  | E1  | アナログ I/O | ハイインピーダンス                       | VDD1V8            | eUSB2 ポート 1 の D+ ピン                                                                                                                                                          |

| EQ0     | 2   | E2  | デジタル I/O | 内部プルダウン<br>1MΩ (標準値) (リセット後に無効) | VDD3V3            | (表 5-2 を参照)                                                                                                                                                                  |

| EQ1     | 4   | E3  | デジタル I/O | 内部プルダウン<br>1MΩ (標準値) (リセット後に無効) | VDD3V3            | (表 5-2 を参照)                                                                                                                                                                  |

| EQ2/INT | 12  | A4  | デジタル I/O | 内部プルダウン<br>1MΩ (標準値) (リセット後に無効) | VDD3V3            | I <sup>2</sup> C モード:システムへのオープンドレイン アクティブ Low レベルの影響を受けやすい割り込み出力<br>非 I <sup>2</sup> C モード:(表 5-2 を参照)                                                                       |

| GND     | 8   | B3  | GND      | 該当なし                            | GND               |                                                                                                                                                                              |

|         |     | C1  |          |                                 |                   |                                                                                                                                                                              |

|         |     | C4  |          |                                 |                   |                                                                                                                                                                              |

|         | 18  | C5  |          |                                 |                   |                                                                                                                                                                              |

|         |     | D3  |          |                                 |                   |                                                                                                                                                                              |

| RESETB  | 5   | E4  | デジタル入力   | 該当なし                            | VDD1V8            | アクティブ Low リセット RESETB のデアサート後、両方のリピータが有効になります。<br>eUSB2 デフォルト モードで eDSPr または eUSPr からの構成待機になります。                                                                             |

表 5-1. ピンの機能 (続き)

| ピン     |     |     | I/O        | RESET<br>状態                                 | 関連付けられた<br>ESD 供給 | 説明                                                                                                                                                                                                                                                                                                         |                                |      |                                                 |                                                                                          |  |  |

|--------|-----|-----|------------|---------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|-------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| 名称     | VBW | YCG |            |                                             |                   | SCL                                                                                                                                                                                                                                                                                                        | SDA                            | モード  |                                                 |                                                                                          |  |  |

| SCL    | 13  | A3  | デジタル I/O   | 内部プル<br>ダウン<br>1MΩ (標準値) (リセ<br>ット後に無<br>効) | VDD3V3            | I <sup>2</sup> C クロック<br>オープンドレ<br>イン I/O。                                                                                                                                                                                                                                                                 | デバイス モード マトリク<br>ス (表 5-2 を参照) | Low  | Low                                             | 非 I <sup>2</sup> C USB リピ<br>ータ (表 5-3 を参<br>照)                                          |  |  |

|        |     |     |            |                                             |                   |                                                                                                                                                                                                                                                                                                            |                                | Low  | High                                            | 非 I <sup>2</sup> C USB リピ<br>ータ (表 5-3 を参<br>照) ホスト モード<br>で BC 1.2 CDP<br>アドバタイズが有<br>効 |  |  |

| SDA    | 14  | A2  | デジタル I/O   | 内部プル<br>ダウン<br>1MΩ (標準値) (リセ<br>ット後に無<br>効) | VDD3V3            | 双方向 I <sup>2</sup> C デ<br>ータ。オープ<br>ンドレイン<br>I/O。外部抵抗<br>を通して I <sup>2</sup> C<br>レールにプル<br>アップ                                                                                                                                                                                                            | High                           | Low  | 非 I <sup>2</sup> C USB リピ<br>ータ (表 5-5 を参<br>照) |                                                                                          |  |  |

|        |     |     |            |                                             |                   |                                                                                                                                                                                                                                                                                                            |                                | High | High                                            | I <sup>2</sup> C イネーブル                                                                   |  |  |

| VDD1V8 | 11  | B4  | PWR        | 該当なし                                        | 該当なし              | 1.8V アナログ電源電圧                                                                                                                                                                                                                                                                                              |                                |      |                                                 |                                                                                          |  |  |

|        |     | D4  |            |                                             |                   | 3.3V の電源電圧                                                                                                                                                                                                                                                                                                 |                                |      |                                                 |                                                                                          |  |  |

| VIOSEL | 1   | B2  | PWR        | 該当なし                                        | 該当なし              | VIOSEL は、GPIO、CROSS、および I <sup>2</sup> C のデジタル I/O 電圧を選択するため<br>に使用されます<br>VIOSEL = VSS に設定すると、デバイスは 1.2V I/O モードになります<br>VIOSEL = VDD1V8 に設定すると、デバイスは 1.8V I/O モードになります<br>VIOSEL ピンはリアルタイム制御であり、パワーオンリセット時にラッチされ<br>るものではありません。パワーオンリセット後にこのピンが動的に変化する場合<br>は、出力電圧が 1.2V から 1.8V に変化する可能性があるため、注意してください。 |                                |      |                                                 |                                                                                          |  |  |

|        | 15  | D2  |            |                                             |                   |                                                                                                                                                                                                                                                                                                            |                                |      |                                                 |                                                                                          |  |  |

| VIOSEL | 3   | C3  | デジタル入<br>力 | 該当なし                                        | VDD3V3            |                                                                                                                                                                                                                                                                                                            |                                |      |                                                 |                                                                                          |  |  |

表 5-2. デバイス モード構成

| SCL             | SDA             | EQ0             | EQ1             | EQ2            | eUSB0                | eUSB1                | I <sup>2</sup> C インタ<br>フェイス | ホスト モードでの<br>USBA および<br>USBB CDP アド<br>バタイズ |

|-----------------|-----------------|-----------------|-----------------|----------------|----------------------|----------------------|------------------------------|----------------------------------------------|

| Low/フロー<br>ティング | Low/フロー<br>ティング | USB2 PHY 構成     |                 |                | USB リピータ             | USB リピータ             | ディセーブル                       | ディセーブル                                       |

| Low/フロー<br>ティング | High            | USB2 PHY 構成     |                 |                | USB リピータ             | USB リピータ             | ディセーブル                       | イネーブル                                        |

| High            | Low/フロー<br>ティング | eUSB PHY 構成     |                 | ハイ インピー<br>ダンス | USB リピータ             | USB リピータ             | ディセーブル                       | ディセーブル                                       |

| High            | High            | Low/フロー<br>ディング | Low/フロー<br>ディング | INT 割り込み<br>出力 | USB リピータ             | USB リピータ             | イネーブル                        | レジスタごと                                       |

| High            | High            | High            | Low/フロー<br>ディング | INT 割り込み<br>出力 | Carkit UART バイ<br>パス | USB リピータ             | イネーブル                        | レジスタごと                                       |

| High            | High            | Low/フロー<br>ディング | High            | INT 割り込み<br>出力 | USB リピータ             | Carkit UART バイ<br>パス | イネーブル                        | レジスタごと                                       |

| High            | High            | High            | High            | INT 割り込み<br>出力 | Carkit UART バイ<br>パス | Carkit UART バイ<br>パス | イネーブル                        | レジスタごと                                       |

表 5-3 で使用されている eUSB phy 構成は、デバイスとホスト間のチャネル長が 5 インチ (12.7cm) FR4 であることを前

提としています。

表 5-3. USB2 PHY 構成

| EQ0         | EQ1         | EQ2         | USB2 PHY<br>補償レベル | eUSB0/1 チャネル       | USB ESR <sup>(1)</sup><br>(Ω) |

|-------------|-------------|-------------|-------------------|--------------------|-------------------------------|

| Low/フローティング | Low/フローティング | Low/フローティング | レベル 0             | 5 インチ (12.7cm) FR4 | USB A:2.5<br>USB B:2.5        |

| High        | Low/フローティング | Low/フローティング | レベル 1             | 5 インチ (12.7cm) FR4 | USB A:10<br>USB B:10          |

| Low/フローティング | High        | Low/フローティング | レベル 2             | 5 インチ (12.7cm) FR4 | USB A:17.5<br>USB B:17.5      |

| High        | High        | Low/フローティング | レベル 3             | 5 インチ (12.7cm) FR4 | USB A:10<br>USB B:17.5        |

| Low/フローティング | Low/フローティング | High        | レベル 4             | 5 インチ (12.7cm) FR4 | USB A:2.5<br>USB B:10         |

| High        | Low/フローティング | High        | レベル 5             | 5 インチ (12.7cm) FR4 | USB A:10<br>USB B:2.5         |

| Low/フローティング | High        | High        | レベル 6             | 5 インチ (12.7cm) FR4 | USB A:17.5<br>USB B:2.5       |

| High        | High        | High        | レベル 7             | 5 インチ (12.7cm) FR4 | USB A:2.5<br>USB B:17.5       |

(1) 等価直列抵抗 (ESR) とは、スイッチやマルチプレクサなど、デバイスと USB コネクタ間のあらゆる抵抗を合わせたものです。

表 5-4. USB2 PHY 補償レベル

| 登録                            | USB2 PHY 補償レベル         |                        |                        |                        |                        |                        |                        |                        |

|-------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

|                               | レベル 0                  | レベル 1                  | レベル 2                  | レベル 3                  | レベル 4                  | レベル 5                  | レベル 6                  | レベル 7                  |

| E_EQ_Px                       | レジスタ デフ<br>オルト         |

| E_HS_TX_AMPLIT<br>UDE_Px      | レジスタ デフ<br>オルト         |

| E_HS_TX_PRE_EM<br>PHASIS_Px   | レジスタ デフ<br>オルト         |

| U_EQ_Px                       | USB A:0x0<br>USB B:0x0 | USB A:0x2<br>USB B:0x2 | USB A:0x5<br>USB B:0x5 | USB A:0x5<br>USB B:0x2 | USB A:0x2<br>USB B:0x0 | USB A:0x0<br>USB B:0x2 | USB A:0x0<br>USB B:0x5 | USB A:0x5<br>USB B:0x0 |

| U_SQUELCH_THR<br>ESHOLD_Px    | USB A:0x4<br>USB B:0x4 | USB A:0x5<br>USB B:0x5 | USB A:0x6<br>USB B:0x6 | USB A:0x6<br>USB B:0x5 | USB A:0x5<br>USB B:0x4 | USB A:0x4<br>USB B:0x5 | USB A:0x4<br>USB B:0x6 | USB A:0x6<br>USB B:0x4 |

| U_DISCONNECT_T<br>HRESHOLD_Px | USB A:0x5<br>USB B:0x5 | USB A:0x8<br>USB B:0x8 | USB A:0x8<br>USB B:0x8 | USB A:0x8<br>USB B:0x8 | USB A:0x8<br>USB B:0x5 | USB A:0x5<br>USB B:0x8 | USB A:0x5<br>USB B:0x8 | USB A:0x8<br>USB B:0x5 |

| U_HS_TX_AMPLIT<br>UDE_Px      | USB A:0x5<br>USB B:0x5 | USB A:0x9<br>USB B:0x9 | USB A:0xD<br>USB B:0xD | USB A:0xD<br>USB B:0x9 | USB A:0x9<br>USB B:0x5 | USB A:0x5<br>USB B:0x9 | USB A:0x5<br>USB B:0xD | USB A:0xD<br>USB B:0x5 |

| U_HS_TX_PRE_EM<br>PHASIS_Px   | USB A:0x0<br>USB B:0x0 | USB A:0x1<br>USB B:0x1 | USB A:0x3<br>USB B:0x3 | USB A:0x3<br>USB B:0x1 | USB A:0x1<br>USB B:0x0 | USB A:0x0<br>USB B:0x1 | USB A:0x0<br>USB B:0x3 | USB A:0x3<br>USB B:0x0 |

表 5-5. eUSB PHY 構成

| EQ0         | EQ1         | EQ2         | eUSB PHY<br>補償レベル | eUSB0<br>ESR <sup>(1)</sup><br>(Ω) | eUSB1 ESR<br>(1)<br>(Ω) | USBA (DPA/DNA)<br>ESR <sup>(1)</sup><br>(Ω) | USBB (DPB/DNB)<br>ESR <sup>(1)</sup><br>(Ω) |

|-------------|-------------|-------------|-------------------|------------------------------------|-------------------------|---------------------------------------------|---------------------------------------------|

| Low/フローティング | Low/フローティング | Low/フローティング | レベル 0             | 2.5                                | 2.5                     | 2.5                                         | 2.5                                         |

**表 5-5. eUSB PHY 構成 (続き)**

| EQ0         | EQ1         | EQ2         | eUSB PHY<br>補償レベル | eUSB0<br>ESR <sup>(1)</sup><br>(Ω) | eUSB1 ESR<br><sup>(1)</sup><br>(Ω) | USBA (DPA/DNA)<br>ESR <sup>(1)</sup><br>(Ω) | USBB (DPB/DNB)<br>ESR <sup>(1)</sup><br>(Ω) |

|-------------|-------------|-------------|-------------------|------------------------------------|------------------------------------|---------------------------------------------|---------------------------------------------|

| High        | Low/フローティング | Low/フローティング | レベル 1             | 7.5                                | 7.5                                | 2.5                                         | 2.5                                         |

| Low/フローティング | High        | Low/フローティング | レベル 2             | 15                                 | 15                                 | 2.5                                         | 2.5                                         |

| High        | High        | Low/フローティング | レベル 3             | 25                                 | 25                                 | 2.5                                         | 2.5                                         |

(1) 等価直列抵抗 (ESR) とは、スイッチやマルチプレクサなど、デバイスと USB コネクタ間、あるいはデバイスと SOC 間のあらゆる抵抗を合わせたものです。

**表 5-6. eUSB PHY 補償レベル**

| 登録                        | eUSB PHY 補償レベル |            |            |            |

|---------------------------|----------------|------------|------------|------------|

|                           | レベル 0          | レベル 1      | レベル 2      | レベル 3      |

| E_EQ_Px                   | 0x1            | 0x3        | 0x7        | 0x10       |

| E_HS_TX_AMPLITUDE_Px      | 0x3            | 0x3        | 0x5        | 0x7        |

| E_HS_TX_PRE_EMPHASIS_Px   | 0x1            | 0x2        | 0x4        | 0x6        |

| U_EQ_Px                   | レジスタ デフォルト     | レジスタ デフォルト | レジスタ デフォルト | レジスタ デフォルト |

| U_SQUELCH_THRESHOLD_Px    | レジスタ デフォルト     | レジスタ デフォルト | レジスタ デフォルト | レジスタ デフォルト |

| U_DISCONNECT_THRESHOLD_Px | レジスタ デフォルト     | レジスタ デフォルト | レジスタ デフォルト | レジスタ デフォルト |

| U_HS_TX_AMPLITUDE_Px      | レジスタ デフォルト     | レジスタ デフォルト | レジスタ デフォルト | レジスタ デフォルト |

| U_HS_TX_PRE_EMPHASIS_Px   | レジスタ デフォルト     | レジスタ デフォルト | レジスタ デフォルト | レジスタ デフォルト |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|            |                                                            | 最小値  | 最大値  | 単位 |

|------------|------------------------------------------------------------|------|------|----|

| 電源電圧範囲     | $V_{DD3V3}$                                                | -0.3 | 4.32 | V  |

| アナログ電源電圧範囲 | $V_{DD1V8}$                                                | -0.3 | 2.1  | V  |

| 電圧範囲       | DPA、DNA、DPB、DNB (OVP イネーブル)、合計数 1000 の短絡イベント、累積期間 1000 時間。 | -0.3 | 6    | V  |

| 電圧範囲       | eDP0、eDN0、eDP1、eDN1                                        | -0.3 | 1.6  | V  |

| 電圧範囲       | CROSS、RESETB、EQ0、EQ1、SCL、SDA、EQ2/INT、VIOSEL                | -0.3 | 2.1  | V  |

| 接合部温度      | $T_{J(max)}$                                               |      | 125  | °C |

| 保存温度       | $T_{stg}$                                                  | -65  | 150  | °C |

(1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      |                                                                  | 値          | 単位 |

|-------------|------|------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | $\pm 1500$ | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 500$  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                                    | 最小値  | 公称値 | 最大値  | 単位 |

|-------------------|----------------------------------------------------|------|-----|------|----|

| $V_{DD3V3}$       | 電源電圧 (VDD3V3)                                      | 3.0  | 3.3 | 3.6  | V  |

| $V_{DD1V8}$       | アナログ電源電圧 (VDD1V8)                                  | 1.62 | 1.8 | 1.98 | V  |

| $V_{I2C\_Pullup}$ | I2C および GPIO オープンドラインバス電圧 (1.2V モード)、VIOSEL=VSS    | 1.08 | 1.2 | 1.32 | V  |

| $V_{I2C\_Pullup}$ | I2C および GPIO オープンドラインバス電圧 (1.8V モード)、VIOSEL=VDD1V8 | 1.62 | 1.8 | 1.98 | V  |

| $T_A$             | 外気温度での動作時                                          | -40  |     | 85   | °C |

| $T_J$             | 接合部温度                                              | -40  |     | 105  | °C |

| $T_{CASE}$        | ケース温度                                              | -40  |     | 105  | °C |

| $T_{PCB}$         | PCB 温度 (デバイスから 1mm 離れた場所)                          | -40  |     | 92   | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                   | TUSB2E221  | TUSB2E221   | 単位   |

|-----------------------------|-------------------|------------|-------------|------|

|                             |                   | VBW (WQFN) | YCG (DSBGA) |      |

|                             |                   | 20 ピン      | 25 ピン       |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 71.9       | 73.5        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 25.9       | 0.4         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 31.7       | 18.9        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.5        | 0.2         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 30.9       | 18.9        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                 | テスト条件                                 | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------|---------------------------------------|-----|-----|-----|----|

| <b>電源</b>             |                                       |     |     |     |    |

| $P_{WC\_1\_1V8}$      | 絶対ワーストケースの消費電力 — 1 つのリピータ (VDD1V8 のみ) | 275 |     |     | mW |

| $P_{WC\_1\_3V3}$      | 絶対ワーストケースの消費電力 — 1 つのリピータ (VDD3V3 のみ) | 25  |     |     | mW |

| $P_{WC\_2\_1V8}$      | 絶対ワーストケースの消費電力 — 2 つのリピータ (VDD1V8 のみ) | 550 |     |     | mW |

| $P_{WC\_2\_3V3}$      | 絶対ワーストケースの消費電力 — 2 つのリピータ (VDD3V3 のみ) | 50  |     |     | mW |

| $P_{HS\_IOC\_1}$      | USB オーディオ ISOC 高速 — 1 つのリピータのみ        | 70  |     |     | mW |

| $P_{HS\_IDLE\_LP\_1}$ | 高速アイドル(ホストモード) — 1 つのリピータ             | 26  | 70  |     | mW |

| $P_{HS\_IDLE\_LP\_1}$ | 高速アイドル(ペリフェラルモード) — 1 つのリピータ          | 108 | 200 |     | mW |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ               |                         | テスト条件                                                                                                                                          | 最小値   | 標準値   | 最大値 | 単位            |

|---------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|---------------|

| $P_{PD}$            | 電源オフ                    | デバイス電源供給、RESETB=Low、 $T_A=25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ )。                                                                 |       | 10    |     | $\mu\text{W}$ |

| $P_{Disabled}$      | ディセーブル                  | デバイス電源供給。I2C/GPIO インターフェイスは機能しますが、アイドル状態。両方のリピータが無効で、最小消費電力状態になり、機能しません。 $T_A=25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ )。             |       | 100   |     | $\mu\text{W}$ |

| $P_{Detach\_1}$     | USB 未接続 — 1 つのリピータ      | I2C/GPIO インターフェイスはアイドル状態。1 つのリピータが無効で、1 つのリピータが eUSB PHY に接続され、USB 接続イベントを待機します。 $T_A = 25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ )    |       | 100   |     | $\mu\text{W}$ |

| $P_{Detach\_2}$     | USB 未接続 — 2 つのリピータ      | I2C/GPIO インターフェイスはアイドル状態。両方のリピータが eUSB PHY に接続され、USB 接続イベントを待機します。 $T_A = 25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ )                  |       | 150   |     | $\mu\text{W}$ |

| $P_{Suspend\_2}$    | L2 中断                   | I2C/GPIO インターフェイスはアイドル状態。USB リンクは L2。両方のリピータが再開/リモートウェークイベントを監視します。 $T_A = 25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ )                 |       | 150   |     | $\mu\text{W}$ |

| $P_{Sleep\_2}$      | L1 スリープ $P_{sleep\_2}$  | I2C/GPIO インターフェイスはアイドル状態。両方のリピータが USB 接続をサポート。USB リンクは L1。両方のリピータが L1 終了イベントを監視します。 $T_A = 25^\circ\text{C}$ 、(DP/DN 電圧 $\leq \text{VDD3V3}$ ) |       | 6     |     | $\text{mW}$   |

| $P_{LS\_Active\_1}$ | 低速アクティブ — 1 つのリピータ      | I2C/GPIO インターフェイスはアイドル状態。1 つのリピータが無効で、別のリピータが LS モード。最大遷移密度。 $T_A = 85^\circ\text{C}$ 。                                                        |       | 52    |     | $\text{mW}$   |

| $P_{FS\_Active\_1}$ | フルスピード アクティブ — 1 つのリピータ | I2C/GPIO インターフェイスはアイドル状態。1 つのリピータが無効で、1 つのリピータが FS モード。最大遷移密度。 $T_A = 85^\circ\text{C}$ 。                                                      |       | 52    |     | $\text{mW}$   |

| $P_{FS\_Active\_2}$ | フルスピード アクティブ — 2 つのリピータ | I2C/GPIO インターフェイスはアイドル状態。両方のリピータが FS モード。最大遷移密度。 $T_A = 85^\circ\text{C}$ 。                                                                    |       | 68    |     | $\text{mW}$   |

| デジタル入力              |                         |                                                                                                                                                |       |       |     |               |

| $V_{IH}$            | High レベル入力電圧            | CROSS、EQ0、EQ1 (1.2V 入力モード、VIOSEL=VSS)                                                                                                          | 0.702 |       |     | V             |

| $V_{IH}$            | High レベル入力電圧            | CROSS、EQ0、EQ1 (1.8V 入力モード、VIOSEL=VDD1V8)                                                                                                       | 1.053 |       |     | V             |

| $V_{IL}$            | Low レベル入力電圧             | CROSS、EQ0、EQ1 (1.2V 入力モード、VIOSEL=VSS)                                                                                                          |       | 0.462 |     | V             |

| $V_{IL}$            | Low レベル入力電圧             | CROSS、EQ0、EQ1 (1.8V 入力モード、VIOSEL=VDD1V8)                                                                                                       |       | 0.693 |     | V             |

| $V_{IL}$            | Low レベル入力電圧             | VIOSEL (1.8V 入力モード)                                                                                                                            |       | 0.613 |     | V             |

| $V_{IH}$            | High レベル入力電圧            | VIOSEL (1.8V 入力モード)                                                                                                                            | 1.053 |       |     | V             |

| $V_{IL}$            | Low レベル入力電圧             | RESETB (1.2V または 1.8V 入力モード)                                                                                                                   |       | 0.35  |     | V             |

| $V_{IH}$            | High レベル入力電圧            | RESETB (1.2V または 1.8V 入力モード)                                                                                                                   | 0.75  |       |     | V             |

| $I_{IH}$            | High レベル入力電流            | $V_{IH} = 1.98\text{V}$ 、 $\text{VDD3V3}=3.0\text{V}$ または $0\text{V}$ 、 $\text{VDD1V8}=1.62\text{V}$ または $0\text{V}$ 、CROSS、RESETB、EQ0、EQ1     |       | 0.5   |     | $\mu\text{A}$ |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    |             | テスト条件                                                                                          | 最小値 | 標準値 | 最大値 | 単位      |

|----------|-------------|------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| $I_{IL}$ | Low レベル入力電流 | $V_{IL} = 0V$ 、 $VDD3V3=3.0V$ または $0V$ 、<br>$VDD1V8=1.62V$ または $0V$<br>CROSS, RESETB, EQ0, EQ1 |     | 0.5 |     | $\mu A$ |

#### デジタル出力

|              |                           |                                                                                             |      |      |    |         |

|--------------|---------------------------|---------------------------------------------------------------------------------------------|------|------|----|---------|

| $V_{OH}$     | High レベル出力電圧              | EQ0, EQ11, EQ2/INT, プッシュプル I/O モード ( $I_{OH} = 20\mu A$ および最大 $3pF C_{load}$ ) (1.2V 出力モード) | 0.81 |      |    | V       |

| $V_{OH}$     | High レベル出力電圧              | EQ0, EQ1, EQ2/INT, プッシュプル I/O モード ( $I_{OH} = 20\mu A$ および最大 $3pF C_{load}$ ) (1.8V 出力モード)  | 1.21 |      |    | V       |

| $V_{OL}$     | Low レベル出力電圧               | EQ0, EQ1, EQ2/INT, プッシュプル I/O モード ( $I_{OL} = 1mA$ ) (1.2V 出力モード)                           |      | 0.25 |    | V       |

| $V_{OL}$     | Low レベル出力電圧               | EQ0, EQ1, EQ2/INT, プッシュプル I/O モード ( $I_{OL} = 1mA$ ) (1.8V 出力モード)                           |      | 0.35 |    | V       |

| $I_{OL\_PP}$ | プッシュプル モードでの Low レベル出力電流  | EQ0, EQ1, EQ2/INT (1.2V モード)<br>VIOSEL=GND, VOL=0.4                                         | 2.5  | 4    | 6  | mA      |

| $I_{OL\_PP}$ | プッシュプル モードでの Low レベル出力電流  | EQ0, EQ1, EQ2/INT (1.8V モード)<br>VIOSEL=VDD1V8, VOL=0.4                                      | 4    | 6    | 8  | mA      |

| $I_{OH\_PP}$ | プッシュプル モードでの High レベル出力電流 | EQ0, EQ1, EQ2/INT, プッシュプル I/O モード (1.2V 出力モード) VIOSEL=GND                                   | 22   |      |    | $\mu A$ |

| $I_{OH\_PP}$ | プッシュプル モードでの High レベル出力電流 | EQ0, EQ1, EQ2/INT, プッシュプル I/O モード (1.8V 出力モード) VIOSEL=VDD1V8                                | 50   |      |    | $\mu A$ |

| $I_{OL}$     | オープンドレイン モードでの出力電流        | EQ0, EQ1, EQ2/INT, VOL=0.4V, VIOSEL=VDD1V8, 1.8V モード                                        | 4    | 10   | 16 | mA      |

| $I_{OL}$     | オープンドレイン モードでの出力電流        | EQ0, EQ1, EQ2/INT, VOL=0.4V, VIOSEL=GND, 1.2V モード                                           | 4    | 9.2  | 16 | mA      |

#### I2C (SDA, SCL)

|           |                            |                                                |       |     |         |    |

|-----------|----------------------------|------------------------------------------------|-------|-----|---------|----|

| $V_{IL}$  | Low レベル入力電圧、VIOSEL=VSS     | SDA, SCL, $V_{I2C\_Pullup} = 1.08V \sim 1.32V$ | 0.387 |     | V       |    |

| $V_{IL}$  | Low レベル入力電圧、VIOSEL=VDD1V8  | SDA, SCL, $V_{I2C\_Pullup} = 1.62V \sim 1.96V$ | 0.588 |     | V       |    |

| $V_{IH}$  | High レベル出力電圧、VIOSEL=VSS    | SDA, SCL, $V_{I2C\_Pullup} = 1.08V \sim 1.32V$ | 0.833 |     | V       |    |

| $V_{IH}$  | High レベル出力電圧、VIOSEL=VDD1V8 | SDA, SCL, $V_{I2C\_Pullup} = 1.62V \sim 1.98V$ | 1.372 |     | V       |    |

| $V_{HYS}$ | 入力ヒステリシス、VIOSEL=VSS        | $V_{I2C\_Pullup} = 1.08V \sim 1.32V$           | 0.020 |     | V       |    |

| $V_{HYS}$ | 入力ヒステリシス、VIOSEL=VDD1V8     | $V_{I2C\_Pullup} = 1.62V \sim 1.98V$           | 0.098 |     | V       |    |

| $I_{IH}$  | High レベル入力リーク電流            | $V_{IH} = 1.98V$                               |       | 0.5 | $\mu A$ |    |

| $I_{IL}$  | Low レベル入力リーク電流             | $V_{IL} = 0V$                                  |       | 0.5 | $\mu A$ |    |

| $I_{OL}$  | オープンドレイン駆動強度               | $VOL = 0.4V$ , VIOSEL = VDD1V8, 1.8V モード       | 8     | 10  | 12.6    | mA |

| $I_{OL}$  | オープンドレイン駆動強度               | $VOL = 0.4V$ , VIOSEL = GND, 1.2V モード          | 6.8   | 9   | 11.9    | mA |

#### USBA (DPA, DNA), USBB (DPB, DNB)

|               |                                |                                                                    |       |     |           |           |

|---------------|--------------------------------|--------------------------------------------------------------------|-------|-----|-----------|-----------|

| $Z_{inp\_Dx}$ | GND へのインピーダンス、プルアップ / プルダウンなし  | $Vin=3.6V$ , $V_{DD3V3}=3.0V$ USB 2.0 仕様セクション 7.1.6 <sup>(1)</sup> | 390   |     | $k\Omega$ |           |

| $C_{IO\_Dx}$  | 対 GND 静電容量                     | 240MHz の VNA、ハイインピーダンスのドライバで測定                                     |       | 10  | $pF$      |           |

| $R_{PUI}$     | アップストリーム側ポートのバス プルアップ抵抗 (アイドル) | USB 2.0 仕様セクション 7.1.5 <sup>(1)</sup>                               | 0.92  | 1.1 | 1.475     | $k\Omega$ |

| $R_{PUR}$     | アップストリーム側ポート (受信側) のバス プルアップ抵抗 | USB 2.0 仕様セクション 7.1.5 <sup>(1)</sup>                               | 1.525 | 2.2 | 2.99      | $k\Omega$ |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ        |                         | テスト条件                                                 | 最小値   | 標準値 | 最大値  | 単位 |

|--------------|-------------------------|-------------------------------------------------------|-------|-----|------|----|

| $R_{PD}$     | ダウンストリーム側ポートのバス プルダウン抵抗 | USB 2.0 仕様セクション 7.1.5 <sup>(1)</sup>                  | 14.35 | 19  | 24.6 | kΩ |

| $V_{HSTERM}$ | High-Speed 時の終端電圧       | USB 2.0 仕様セクション 7.1.6.2 <sup>(1)</sup> 、高速アイドル状態の出力電圧 | -10   |     | 10   | mV |

#### USB 終端

|                 |                       |                                                                                                     |      |    |      |   |

|-----------------|-----------------------|-----------------------------------------------------------------------------------------------------|------|----|------|---|

| $Z_{HSTERM\_P}$ | ドライバ出力抵抗 (高速終端としても機能) | ( $VOH = 0 \sim 600mV$ ) USB 2.0 仕様セクション 7.1.1.1 <sup>(1)</sup> 、デフォルト、<br>$U_{HS\_TERM\_Px}$ 設定 01 | 40.6 | 45 | 49.4 | Ω |

| $Z_{HSTERM\_N}$ | ドライバ出力抵抗 (高速終端としても機能) | ( $VOH = 0 \sim 600mV$ ) USB 2.0 仕様セクション 7.1.1.1 <sup>(1)</sup> 、デフォルト、<br>$U_{HS\_TERM\_Px}$ 設定 01 | 40.6 | 45 | 49.4 | Ω |

#### USBA、USBB 入力レベル LS/FS

|           |                    |                                                                                                                              |     |     |     |   |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---|

| $V_{IH}$  | High (駆動)          | USB 2.0 仕様セクション 7.1.4 <sup>(1)</sup> (コネクタで測定)                                                                               | 2   |     |     | V |

| $V_{IHZ}$ | High (フローティング)     | USB 2.0 仕様セクション 7.1.4 <sup>(1)</sup> (ホストのダウンストリーム ポートのプルダウン抵抗が有効、および外部デバイス $1.5k\Omega \pm 5\%$ が $3.0V \sim 3.6V$ にプルアップ)。 | 2.7 |     | 3.6 | V |

| $V_{IL}$  | Low                | USB 2.0 仕様セクション 7.1.4 <sup>(1)</sup>                                                                                         |     | 0.8 |     | V |

| $V_{DI}$  | 差動入力感度 (ヒステリシスはオフ) | $ (D+)-(D-) $ 。USB 2.0 仕様の図 7-19 <sup>(1)</sup> 。<br>(コネクタで測定) $V_{CM}=0.8V \sim 2.0V$                                       |     | 0.2 |     | V |

#### USBA、USBB 出力レベル LS/FS

|              |                |                                                                                                             |     |     |  |   |

|--------------|----------------|-------------------------------------------------------------------------------------------------------------|-----|-----|--|---|

| $V_{OL}$     | Low            | USB 2.0 仕様セクション 7.1.1 <sup>(1)</sup> 、<br>( $1.425k\Omega$ の $RL$ で $3.6V$ までコネクタで測定))                      | 0   | 0.3 |  | V |

| $V_{OH}$     | High (駆動)      | USB 2.0 仕様セクション 7.1.1 <sup>(1)</sup> ( $14.25k\Omega$ の $RL$ で $GND$ までコネクタで測定)                             | 2.8 | 3.6 |  | V |

| $Z_{FSTERM}$ | ドライバ シリーズの出力抵抗 | USB 2.0 仕様セクション 7.1.1 <sup>(1)</sup> 、 $VOL$ または $VOH$ の間に測定                                                | 28  | 46  |  | Ω |

| $V_{CRS2}$   | 出力信号クロスオーバー電圧  | USB 2.0 仕様セクション 7.1.1 図 7-8 に従って測定 <sup>(1)</sup> 。アイドル状態からの最初の遷移は除外。 $DP$ で外部 $1.5k\Omega$ を $3.0V$ にプルアップ | 1.3 | 2   |  | V |

| $V_{CRS}$    | 出力信号クロスオーバー電圧  | USB 2.0 仕様セクション 7.1.1 図 7-8 に従って測定 <sup>(1)</sup> 。アイドル状態からの最初の遷移は除外                                        | 1.3 | 2   |  | V |

#### USBA、USBB 入力レベル HS

|             |                                           |                                                                                                                                                         |      |      |      |    |

|-------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| $V_{HSSQ}$  | High-Speed スケルチ / 非スケルチ検出スレッショルド          | USB 2.0 仕様セクション 7.1.7.2 (仕様はピーコク差動信号振幅を指します) <sup>(1)</sup> 、振幅を大きくして $240MHz$ で測定、<br>$U_{SQUELCH\_THRESHOLD\_Px}$ 設定 100、 $V_{CM} = -50mV \sim 500mV$ | 104  | 126  | 150  | mV |

| $V_{HSDSC}$ | High-Speed 切断検出スレッショルド                    | USB 2.0 仕様セクション 7.1.7.2 (仕様は差動信号振幅を指します) <sup>(1)</sup> 。 $(+22.4\%)$ 、<br>$U_{DISCONNECT\_THRESHOLD\_Px}$ 設定 0111、 $V_{CM} = 367mV \sim 770mV$         | 697  | 732  | 760  | mV |

| $EQ_{UHS}$  | USB 高速データ レシーバのイコライゼーション、(ジッタを使用して間接的に測定) | $240MHz$ 、 $U_{EQ\_Px}$ 設定 010                                                                                                                          | 0.62 | 1.09 | 1.57 | dB |

#### USBA、USBB 出力レベル HS

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                                          | テスト条件                                                                                                                              | 最小値  | 標準値  | 最大値  | 単位        |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| $V_{HSOD}$           | High-Speed データ信号スイング                     | 測定された p-p, 10%、<br>U_HS_TX_AMPLITUDE_Px 設定 0111、<br>PE ディスエーブル、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                      | 792  | 880  | 968  | mV        |

| $V_{HSOL}$           | 高速データ信号 Low、ドライバがオフで終端がオン (測定されたシングルエンド) | USB 2.0 仕様セクション 7.1.7.2 <sup>(1)</sup> 、PE ディスエーブル、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                  | -10  | 10   |      | mV        |

| $V_{CHIRPJ}$         | ホスト/ハブ チャープ J レベル (差動電圧)                 | USB 2.0 仕様セクション 7.1.7.2 <sup>(1)</sup> (PE ディスエーブル。スイング設定は影響しませんが、スルーレート制御は影響があります)、テスト負荷は DP の理想的な $1.5k\Omega$ ブルアップです。          | 700  | 900  | 1100 | mV        |

| $V_{CHIRPK}$         | デバイス チャープ K レベル (差動電圧)                   | USB 2.0 仕様セクション 7.1.7.2 <sup>(1)</sup> (PE ディスエーブル。スイング設定は影響しませんが、スルーレート制御は影響があります)、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。 | -900 | -760 | -500 | mV        |

| $V_{CHIRPK}$         | ホスト/ハブ チャープ K レベル (差動電圧)                 | USB 2.0 仕様セクション 7.1.7.2 <sup>(1)</sup> (PE ディスエーブル。スイング設定は影響しませんが、スルーレート制御は影響があります)、テスト負荷は DP の理想的な $1.5k\Omega$ ブルアップです。          | -900 | -700 | -500 | mV        |

| $U_{2\_TXPE}$        | High-Speed TX プリエンファシス                   | U_HS_TX_PRE_EMPHASIS_Px 設定 001、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                                      | 0.62 | 0.9  | 1.2  | dB        |

| $U_{2\_TXPE\_UI}$    | High-Speed TX プリエンファシス                   | U_HS_TX_PE_WIDTH_Px 設定 00 (PE = $2.5dB$ 設定 101 で測定)、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                 | 0.25 | 0.35 | 0.41 | UI        |

| $U_{2\_TXPE\_UI}$    | High-Speed TX プリエンファシス幅                  | U_HS_TX_PE_WIDTH_Px 設定 01 (PE = $2.5dB$ 設定 101 で測定)、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                 | 0.35 | 0.45 | 0.55 | UI        |

| $U_{2\_TXPE\_UI}$    | High-Speed TX プリエンファシス幅                  | U_HS_TX_PE_WIDTH_Px 設定 10 (PE = $2.5dB$ 設定 101 で測定)、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                 | 0.44 | 0.55 | 0.67 | UI        |

| $U_{2\_TXPE\_UI}$    | High-Speed TX プリエンファシス幅                  | U_HS_TX_PE_WIDTH_Px 設定 11 (PE = $2.5dB$ 設定 101 で測定)、テスト負荷は DP および DN の GND に対して理想的な $45\Omega$ です。                                 | 0.54 | 0.65 | 0.77 | UI        |

| $U_{2\_TXCM}$        | High-Speed TX DC コモン モード                 | PE ディスエーブルでのすべてのスイング設定                                                                                                             | 100  | 200  | 300  | mV        |

| <b>eUSB2 終端</b>      |                                          |                                                                                                                                    |      |      |      |           |

| $R_{SRC\_HS}$        | 高速送信ソース終端インピーダンス                         | eUSB2 仕様セクション 7.1.1 <sup>(2)</sup>                                                                                                 | 33   | 40   | 47   | $\Omega$  |

| $\Delta R_{SRC\_HS}$ | 高速ソース インピーダンスの不一致                        | eUSB2 仕様セクション 7.1.1 <sup>(2)</sup>                                                                                                 |      |      | 4    | $\Omega$  |

| $R_{RCV\_DIF}$       | 高速差動レシーバ終端 (リピータ)                        | eUSB2 仕様セクション 7.1.2 <sup>(2)</sup>                                                                                                 | 74   | 80   | 86   | $\Omega$  |

| $R_{PD}$             | eDP/eDN のプルダウン抵抗                         | eUSB2 仕様セクション 7.3 <sup>(2)</sup> 、LS、FS、HS 中にアクティブ                                                                                 | 6    | 8    | 10   | $k\Omega$ |

| $R_{SRC\_LSFS}$      | 送信出力インピーダンス                              | eUSB2 仕様セクション 7.2.1 <sup>(2)</sup> 、表 7-13 仕様バージョン 1.10 と一致する TX 出力インピーダンス                                                         | 28   | 44   | 59   | $\Omega$  |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                          |                                            | テスト条件                                                                                                              | 最小値   | 標準値   | 最大値  | 単位 |

|--------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------|------|----|

| $C_{IO\_eDX}$                  | 差動容量                                       | 240MHz の VNA、ハイインピーダンスのドライバで測定 (VCM = 120mV ~ 450mV)、差動で測定。                                                        |       | 3.7   | 5    | pF |

| <b>eUSB0、eUSB1 FS/LS 入力レベル</b> |                                            |                                                                                                                    |       |       |      |    |

| $V_{IL}$                       | シングルエンド入力 Low                              | eUSB2 仕様セクション 7.2.1、表 7-13 <sup>(2)</sup>                                                                          | -0.1  | 0.399 |      | V  |

| $V_{IH}$                       | シングルエンド入力 High                             | eUSB2 仕様セクション 7.2.1、表 7-13 <sup>(2)</sup>                                                                          | 0.819 | 1.386 |      | V  |

| $V_{HYS}$                      | シングルエンドヒステリシス電圧を受信                         | eUSB2 仕様セクション 7.2.1、表 7-13 <sup>(2)</sup>                                                                          | 43.2  |       |      | mV |

| <b>eUSB0、eUSB1 FS/LS 出力レベル</b> |                                            |                                                                                                                    |       |       |      |    |

| $V_{OL}$                       | シングルエンド出力 Low                              | eUSB2 仕様セクション 7.2.1、表 7-13 <sup>(2)</sup>                                                                          |       | 0.1   |      | V  |

| $V_{OH}$                       | シングルエンド出力 High                             | eUSB2 仕様セクション 7.2.1、表 7-13 <sup>(2)</sup>                                                                          | 0.918 | 1.32  |      | V  |

| <b>eUSB0、eUSB1 HS 入力レベル</b>    |                                            |                                                                                                                    |       |       |      |    |

| $V_{CM\_RX\_AC}$               | レシーバ AC 同相モード (50MHz ~ 480MHz)             | eUSB2 仕様セクション 7.1.2 (情報) <sup>(2)</sup> 、DC 同相モード範囲全体で 120mV ~ 280mV。 (TX 立ち上がり/立ち下がり時間の不一致と伝搬遅延の不一致で RX 機能をテスト済み) |       | -60   | 60   | mV |

| $C_{RX\_CM}$                   | センタータップ容量を受信                               | eUSB2 仕様セクション 7.1.2 (情報) <sup>(2)</sup>                                                                            | 15    | 50    |      | pF |

| $V_{EHSSQ}$                    | スケルチ/非スケルチ検出スレッショルド                        | eUSB2 仕様セクション 7.1.2 <sup>(2)</sup> 、(振幅を大きくして 240MHz で差動ピーク電圧として測定)、 $V_{CM} = 120mV ~ 450mV$                      | 47    | 66    | 83   | mV |

| $EQ_{\_EHS}$                   | eUSB2 高速データレシーバのイコライゼーション、(ジッタを使用して間接的に測定) | 240MHz E_EQ_P1x 設定 0010                                                                                            | 0.59  | 1.12  | 1.4  | dB |

| <b>eUSB0、eUSB1 HS 出力レベル</b>    |                                            |                                                                                                                    |       |       |      |    |

| $V_{EHSOD}$                    | 送信差動 (終端)                                  | 測定された p2p、 $R_L = 80\Omega$ 、<br>E_HS_TX_AMPLITUDE_Px 設定 100、理想的な $80\Omega$ Rx 差動終端負荷                             | 396   | 440   | 484  | mV |

| $E_{\_TXPE}$                   | High-Speed TX プリエンファシス                     | E_HS_TX_PRE_EMPHASIS_Px 設定 010                                                                                     | 1.01  | 1.29  | 1.57 | dB |

- (1) USB 2.0 プロモーター グループ 2000、USB 2.0 仕様 USB 2.0 プロモーター グループ

(2) USB インプリメンターズ・フォーラム (2018)。USB2 (eUSB2) 物理層補足を USB リビジョン 2.0 仕様に組み込み、Rev. 1.2 USB インプリメンターズ・フォーラム

## 6.6 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                          | テスト条件                     | 最小値                                                                                                             | 標準値 | 最大値   | 単位  |    |

|------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-------|-----|----|

| <b>DPA、DNA、DPB、DNB、HS ドライバのスイッチング特性</b>        |                           |                                                                                                                 |     |       |     |    |

| $T_{HSR}$                                      | 立ち上がり時間 (10%~90%)         | USB 2.0 仕様セクション 7.1.2 <sup>(1)</sup> 、<br>U_HS_TX_SLEW_RATE_Px 設定 11、DP および DN の GND 負荷に対して理想的な 45Ω、プリエンファシス無効。 | 530 | 625   | 740 | ps |

| $T_{HSF}$                                      | 立ち下がり時間 (10%~90%)         | USB 2.0 仕様セクション 7.1.2 <sup>(1)</sup> 、<br>U_HS_TX_SLEW_RATE_Px 設定 11、DP および DN の GND 負荷に対して理想的な 45Ω、プリエンファシス無効。 | 530 | 625   | 740 | ps |

| <b>DPA、DNA、DPB、DNB、FS ドライバのスイッチング特性</b>        |                           |                                                                                                                 |     |       |     |    |

| $T_{FR}$                                       | 立ち上がり時間 (10%~90%)         | USB 2.0 仕様の図 7-8、図 7-9 <sup>(1)</sup>                                                                           | 4   | 20    | ns  |    |

| $T_{FF}$                                       | 立ち下がり時間 (10%~90%)         | USB 2.0 仕様の図 7-8、図 7-9 <sup>(1)</sup>                                                                           | 4   | 20    | ns  |    |

| $T_{FRFM}$ ( $T_{FR}/T_{FM}$ )                 |                           | USB 2.0 仕様 7.1.2 <sup>(1)</sup> 、アイドル状態からの最初の遷移を除く                                                              | 90  | 111.1 | %   |    |

| <b>DPA、DNA、DPB、DNB、LS ドライバのスイッチング特性</b>        |                           |                                                                                                                 |     |       |     |    |

| $T_{LR}$                                       | 立ち上がり時間 (10%~90%)         | USB 2.0 仕様の図 7-8 <sup>(1)</sup>                                                                                 | 75  | 300   | ns  |    |

| $T_{LF}$                                       | 立ち下がり時間 (10%~90%)         | USB 2.0 仕様の図 7-8 <sup>(1)</sup>                                                                                 | 75  | 300   | ns  |    |

| <b>eDP0、eDN0、eDP1、eDN1、HS ドライバのスイッチング特性</b>    |                           |                                                                                                                 |     |       |     |    |

| $T_{EHSRF}$                                    | 立ち上がり/立ち下がり時間 (20% ~ 80%) | eUSB2 仕様セクション 7.2.1 <sup>(2)</sup> 、理想的な 80Ω Rx 差動終端 E_HS_TX_SLEW_RATE_Px 設定 = 01                               | 355 | 440   | 525 | ps |

| $T_{EHSRF\_M}$                                 | 送信立ち上がり/立ち下がりの不一致         | eUSB2 仕様セクション 7.2.1 <sup>(2)</sup> 、立ち上がり/立ち下がり不一致 = (立ち上がり - 立ち下がり時間)/(立ち上がりおよび立ち下がり時間の平均) の絶対デルタ。             |     | 25    | %   |    |

| <b>eDP0、eDN0、eDP1、eDN1、LS/FS ドライバのスイッチング特性</b> |                           |                                                                                                                 |     |       |     |    |

| $T_{ERF}$                                      | 立ち上がり/立ち下がり時間 (10% ~ 90%) | eUSB2 仕様セクション 7.2.1 <sup>(2)</sup>                                                                              | 2   | 6     | ns  |    |

| $T_{ERF\_MM}$                                  | 送信立ち上がり/立ち下がりの不一致         | eUSB2 仕様セクション 7.2.1 <sup>(2)</sup>                                                                              |     | 25    | %   |    |

| <b>I2C (SDA)</b>                               |                           |                                                                                                                 |     |       |     |    |

| $T_r$                                          | 立ち上がり時間 (STD)             | バス速度 = 100kHz、 $C_L = 200pF$ 、 $R_{PU} = 4k\Omega$ 、 $I_{OL} = \text{約 } 1mA$                                   | 600 |       | ns  |    |

| $T_r$                                          | 立ち上がり時間 (FM)              | バス速度 = 400kHz、 $C_L = 200pF$ 、 $R_{PU} = 2.2k\Omega$ 、 $I_{OL} = \text{約 } 2mA$                                 | 180 |       | ns  |    |

| $T_r$                                          | 立ち上がり時間 (FM+)             | バス速度 = 1MHz、 $C_L = 10pF$ 、 $R_{PU} = 1k\Omega$ 、 $I_{OL} = \text{約 } 4mA$                                      | 72  |       | ns  |    |

| $T_r$                                          | 立ち上がり時間 (STD)             | バス速度 = 100kHz、 $C_L = 200pF$ 、 $R_{PU} = 4k\Omega$ 、 $I_{OL} = \text{約 } 2mA$                                   |     | 1000  | ns  |    |

| $T_r$                                          | 立ち上がり時間 (FM)              | バス速度 = 400kHz、 $C_L = 200pF$ 、 $R_{PU} = 1k\Omega$ 、 $I_{OL} = \text{約 } 8mA$                                   |     | 300   | ns  |    |

| $T_r$                                          | 立ち上がり時間 (FM+)             | バス速度 = 1MHz、 $C_L = 50pF$ 、 $R_{PU} = 1k\Omega$ 、 $I_{OL} = \text{約 } 4mA$                                      |     | 120   | ns  |    |

| $T_f$                                          | 立ち下がり時間 (STD)             | バス速度 = 100kHz、 $C_L = 200pF$ 、 $R_{PU} = 2.2k\Omega$ 、 $I_{OL} = \text{約 } 4mA$                                 |     | 106.5 | ns  |    |

| $T_f$                                          | 立ち下がり時間 (FM)              | バス速度 = 400kHz、 $C_L = 200pF$ 、 $R_{PU} = 1k\Omega$ 、 $I_{OL} = \text{約 } 8mA$                                   |     | 106.5 | ns  |    |

| $T_f$                                          | 立ち下がり時間 (FM+)             | バス速度 = 1MHz、 $C_L = 90pF$ 、 $R_{PU} = 1k\Omega$ 、 $I_{OL} = \text{約 } 8mA$                                      |     | 81.5  | ns  |    |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ |               | テスト条件                                                                                              | 最小値 | 標準値 | 最大値 | 単位 |

|-------|---------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $T_f$ | 立ち下がり時間 (STD) | バス速度 = 100kHz, $C_L = 10\text{pF}$ , $R_{PU} = 4\text{k}\Omega$ , $I_{OL} = \text{約 }2\text{mA}$   | 6.5 |     |     | ns |

| $T_f$ | 立ち下がり時間 (FM)  | バス速度 = 400kHz, $C_L = 10\text{pF}$ , $R_{PU} = 2.2\text{k}\Omega$ , $I_{OL} = \text{約 }4\text{mA}$ | 6.5 |     |     | ns |

| $T_f$ | 立ち下がり時間 (FM+) | バス速度 = 1MHz, $C_L = 10\text{pF}$ , $R_{PU} = 1\text{k}\Omega$ , $I_{OL} = \text{約 }8\text{mA}$     | 6.5 |     |     | ns |

- (1) USB 2.0 プロモーター グループ 2000、USB 2.0 仕様 USB 2.0 プロモーター グループ

- (2) USB インプリメンターズ・フォーラム (2018)USB2 (eUSB2) 物理層補足を USB リビジョン 2.0 仕様に組み込み、Rev. 1.2 USB インプリメンターズ・フォーラム

## 6.7 タイミング要件

|                      |                                                                                                                                                                                                                                                                | 最小値  | 公称値  | 最大値 | 単位 |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----|

| <b>I/O タイミング</b>     |                                                                                                                                                                                                                                                                |      |      |     |    |

| $t_{GPIO\_PW}$       | INT イベントの最小 GPIO パルス幅                                                                                                                                                                                                                                          |      | 8    |     | μs |

| <b>RESET タイミング</b>   |                                                                                                                                                                                                                                                                |      |      |     |    |

| $t_{VDD1V8\_RA\_MP}$ | VDD1V8 が最小 1.62V に達するまでのランプ時間                                                                                                                                                                                                                                  |      |      | 2   | ms |

| $t_{VDD3V3\_RA\_MP}$ | VDD3V3 が最小 3.0V に達するまでのランプ時間                                                                                                                                                                                                                                   |      |      | 2   | ms |

| $t_{su\_CROSS}$      | RESETB のデアサー時の CROSS サンプリングのセットアップ時間                                                                                                                                                                                                                           | 0    |      |     | ms |

| $t_{hd\_CROSS}$      | RESETB のデアサー時の CROSS サンプリングのホールド時間                                                                                                                                                                                                                             | 3    |      |     | ms |

| $t_{aRESETB}$        | 電源供給中に RESETB が Low にアサーされてリセットを完了するまでの時間                                                                                                                                                                                                                      | 10   |      |     | μs |

| $t_{RH\_READY}$      | RESETB がデアサーされるか、(VDD1V8 および VDD3V3) が推奨される最小電圧に達した後のいずれか遅い方の時点から、デバイスが RAP および I2C 要求を受け入れる準備ができ、かつ eUSB2 インターフェイスが準備完了になるまでの時間                                                                                                                               |      |      | 3   | ms |

| $t_{RS\_READY}$      | I2C 経由でのソフトリセット後にデバイスが RAP および I2C 要求を受け入れる準備ができ、かつ eUSB2 インターフェイスが準備完了になるまでの時間                                                                                                                                                                                |      | 350  |     | μs |

| <b>リピータ タイミング</b>    |                                                                                                                                                                                                                                                                |      |      |     |    |

| $T_{J1E}$            | 2 つのリピータのいずれかが無効化された場合の eUSB2 から USB 2.0 へのリピータの合計加算ジッタ (出力ジッタ – 入力ジッタ)。(また、すべての完全な SOP ビットを含める必要があり、eUSB2 TX 立ち上がり/立ち下がり時間スキーとペア内伝搬遅延スキーで測定する必要があります、 $V_{CM\_RX\_AC}$ を参照) [RX EQ ディスエーブル、TX PE ディスエーブル、VOD 公称設定および入力または出力チャネルなし]。 <a href="#">出力セットアップ図</a> |      | 25   | 42  | ps |

| $T_{J1I}$            | 2 つのリピータのいずれかが無効化された場合の USB から eUSB2 へのリピータの合計加算ジッタ (出力ジッタ – 入力ジッタ)。[RX EQ ディスエーブル、TX PE ディスエーブル、VOD 公称設定および入力または出力チャネルなし]。 <a href="#">入力セットアップ図</a>                                                                                                          |      | 25   | 42  | ps |

| $T_{J2E}$            | 両方のリピータがアクティブな場合の eUSB2 から USB へのリピータの合計加算ジッタ (出力ジッタ – 入力ジッタ)。[RX EQ ディスエーブル、TX PE ディスエーブル、VOD 公称設定および入力または出力チャネルなし]                                                                                                                                           |      | 60   |     | ps |

| $T_{J2I}$            | 両方のリピータがアクティブな場合の USB から eUSB2 へのリピータの合計加算ジッタ (出力ジッタ – 入力ジッタ)。[RX EQ ディスエーブル、TX PE ディスエーブル、VOD 公称設定および入力または出力チャネルなし]                                                                                                                                           |      | 60   |     | ps |

| $T_{e\_to\_U\_DJ1}$  | eUSB2 から USB 2.0 へのリピータの FS ジッタから次の遷移まで (eUSB2 仕様 1.1 表 7-13 注 1 & 2: 電源および GND デルタの条件に準拠 <a href="#">(1)</a> )                                                                                                                                                | -6.0 | +6.0 |     | ns |

| $T_{U\_to\_e\_DJ1}$  | USB 2.0 から eUSB2 へのリピータの FS ジッタから次の遷移まで (eUSB2 仕様 1.1 表 7-13 Note1 & 2: 電源および GND デルタの条件に準拠 <a href="#">(1)</a> )                                                                                                                                              | -3.0 | +3.0 |     | ns |

| $T_{DJ2\_e2U}$       | eUSB2 から USB 2.0 方向へのリピータ FS ペアの遷移ジッタ (USB 2.0 +/-1ns で定義される THDJ2 に対して緩和された値)                                                                                                                                                                                 | -1.5 | +1.5 |     | ns |

| $T_{DJ2\_U2e}$       | USB 2.0 から eUSB2 方向へのリピータ FS ペアの遷移ジッタ (USB 2.0 +/-1ns で定義される THDJ2 に対して緩和された値)                                                                                                                                                                                 | -1.5 | +1.5 |     | ns |

| <b>MODE タイミング</b>    |                                                                                                                                                                                                                                                                |      |      |     |    |

| $T_{MODE\_SWI\_TCH}$ | UART バイパス モードと USB モードの間でモードを変更するために必要な時間                                                                                                                                                                                                                      |      |      | 1   | μs |

| $T_{UART\_STAR\_T}$  | UART バイパス モードに移行した後、UART データの送信を開始するために必要な時間                                                                                                                                                                                                                   |      |      | 2   | ms |

| <b>I2C (FM+)</b>     |                                                                                                                                                                                                                                                                |      |      |     |    |

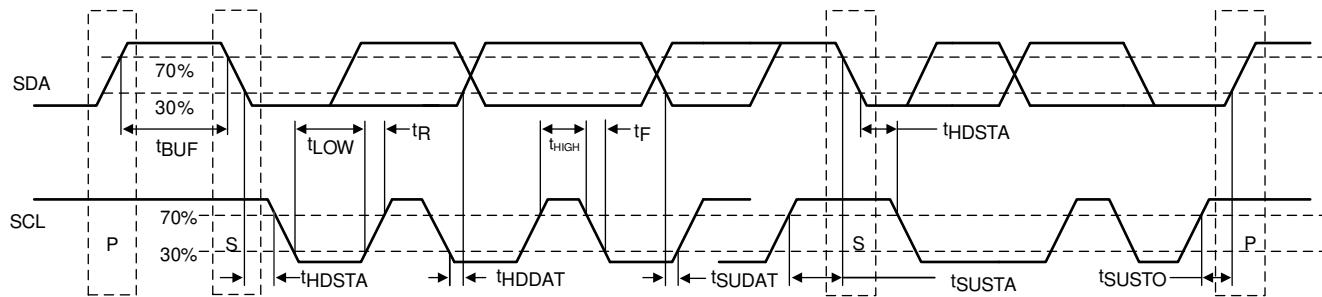

| $t_{SU\_STA}$        | スタート セットアップ時間、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+                                                                                                                                               | 260  |      |     | ns |

|                               |                                                                                                                                     | 最小値  | 公称値  | 最大値 | 単位 |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----|

| $t_{SU\_STO}$                 | ストップ セットアップ時間、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+                    | 260  |      |     | ns |

| $t_{HD\_STA}$                 | スタートホールド時間、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+                       | 260  |      |     | ns |

| $t_{SU\_DAT}$                 | データ入力または誤スタート/ストップ、セットアップ時間、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+      | 50   |      |     | ns |

| $t_{HD\_DAT}$                 | データ入力または誤スタート/ストップ、ホールド時間、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+        | 0    |      |     | ns |

| $t_{VD\_DAT}$ 、 $t_{VD\_ACK}$ | SDA 出力遅延、SCL ( $T_r=72\text{ns} \sim 120\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 81.5\text{ns}$ )、1MHz FM+                         | 20   | 450  |     | ns |

| $t_{HD\_DAT\_SL}$             | デバイスが送信中のデータホールド時間                                                                                                                  | 6.67 |      |     | ns |

| $t_{SP}$                      | グリッチ幅は抑制                                                                                                                            | 50   | 91   |     | ns |

| $t_{BUF}$                     | STOP 条件と START 条件の間のバスフリー時間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                | 0.5  |      |     | μs |

| $t_{LOW}$                     | SCL クロックの Low 期間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                           | 0.5  |      |     | μs |

| $t_{HIGH}$                    | SCL クロックの High 期間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                          | 0.26 |      |     | μs |

| <b>I2C (FM)</b>               |                                                                                                                                     |      |      |     |    |

| $t_{SU\_STO}$                 | ストップ セットアップ時間、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM                 | 600  |      |     | ns |

| $t_{HD\_STA}$                 | スタートホールド時間、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM                    | 600  |      |     | ns |

| $t_{SU\_STA}$                 | スタートセットアップ時間、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM                  | 600  |      |     | ns |

| $t_{SU\_DAT}$                 | データ入力または誤スタート/ストップ、セットアップ時間、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM   | 100  |      |     | ns |

| $t_{HD\_DAT}$                 | データ入力または誤スタート/ストップ、ホールド時間、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM     | 0    |      |     | ns |

| $t_{VD\_DAT}$ 、 $t_{VD\_ACK}$ | SDA 出力遅延、SCL ( $T_r=180\text{ns} \sim 300\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、400kHz FM                      | 20   | 900  |     | ns |

| $t_{HD\_DAT\_SL}$             | デバイスが送信中のデータホールド時間                                                                                                                  | 13.5 |      |     | ns |

| $t_{SP}$                      | グリッチ幅は抑制                                                                                                                            | 50   | 91   |     | ns |

| $t_{BUF}$                     | STOP 条件と START 条件の間のバスフリー時間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                | 1.3  |      |     | μs |

| $t_{LOW}$                     | SCL クロックの Low 期間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                           | 1.3  |      |     | μs |

| $t_{HIGH}$                    | SCL クロックの High 期間 (デバイスが許容する必要のあるホストの最小仕様)                                                                                          | 0.6  |      |     | μs |

| <b>I2C (STD)</b>              |                                                                                                                                     |      |      |     |    |

| $t_{SU\_STO}$                 | ストップ セットアップ時間、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD               | 4    |      |     | μs |

| $t_{HD\_STA}$                 | スタートホールド時間、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD                  | 4    |      |     | μs |

| $t_{SU\_STA}$                 | スタートセットアップ時間、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD                | 4.7  |      |     | μs |

| $t_{SU\_DAT}$                 | データ入力または誤スタート/ストップ、セットアップ時間、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD | 250  |      |     | ns |

| $t_{HD\_DAT}$                 | データ入力または誤スタート/ストップ、ホールド時間、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD   | 5    |      |     | μs |

| $t_{VD\_DAT}$ 、 $t_{VD\_ACK}$ | SDA 出力遅延、SCL ( $T_r=600\text{ns} \sim 1000\text{ns}$ )、SDA ( $T_f=6.5\text{ns} \sim 106.5\text{ns}$ )、100kHz STD                    |      | 3.45 |     | μs |

| $t_{HD\_DAT\_SL}$             | デバイスが送信中のデータホールド時間                                                                                                                  | 13.5 |      |     | ns |

|            |                                                      | 最小値 | 公称値 | 最大値 | 単位 |

|------------|------------------------------------------------------|-----|-----|-----|----|

| $t_{SP}$   | グリッチ幅は抑制                                             | 50  |     | 91  | ns |

| $t_{BUF}$  | STOP 条件と START 条件の間のバスフリー時間 (デバイスが許容する必要のあるホストの最小仕様) |     | 4.7 |     | μs |

| $t_{LOW}$  | SCL クロックの Low 期間 (デバイスが許容する必要のあるホストの最小仕様)            |     | 4.7 |     | μs |

| $t_{HIGH}$ | SCL クロックの High 期間 (デバイスが許容する必要のあるホストの最小仕様)           |     | 4.0 |     | μs |

(1) USB インプリメンターズ・フォーラム (2018)USB2 (eUSB2) 物理層補足を USB リビジョン 2.0 仕様に組み込み、Rev. 1.2 USB インプリメンターズ・フォーラム

## 6.8 代表的特性

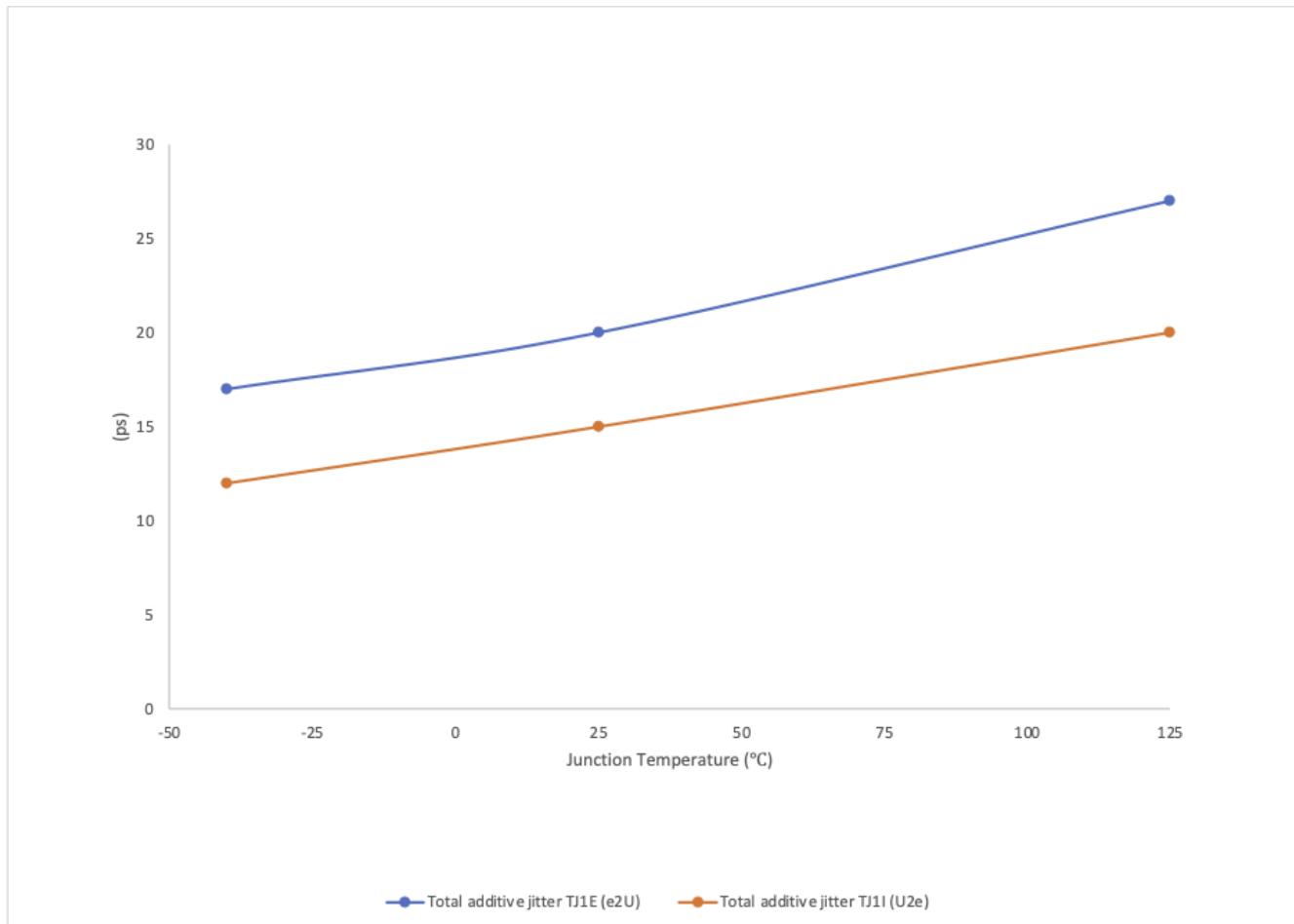

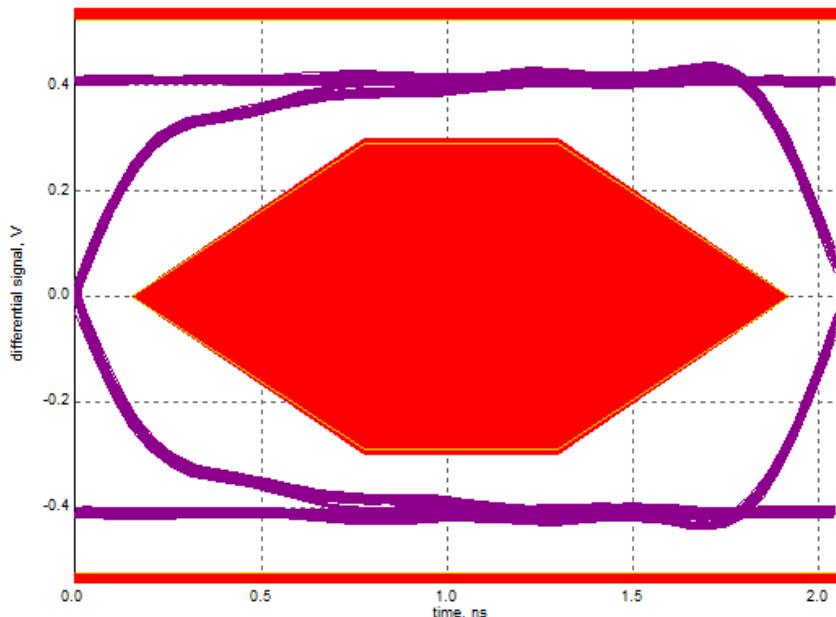

TJ1E は eUSB2 から USB への出力方向用で、TJ1I は USB から eUSB2 への入力方向用です

**図 6-1. 合計加算ジッタ (標準値)**

## 7 パラメータ測定情報

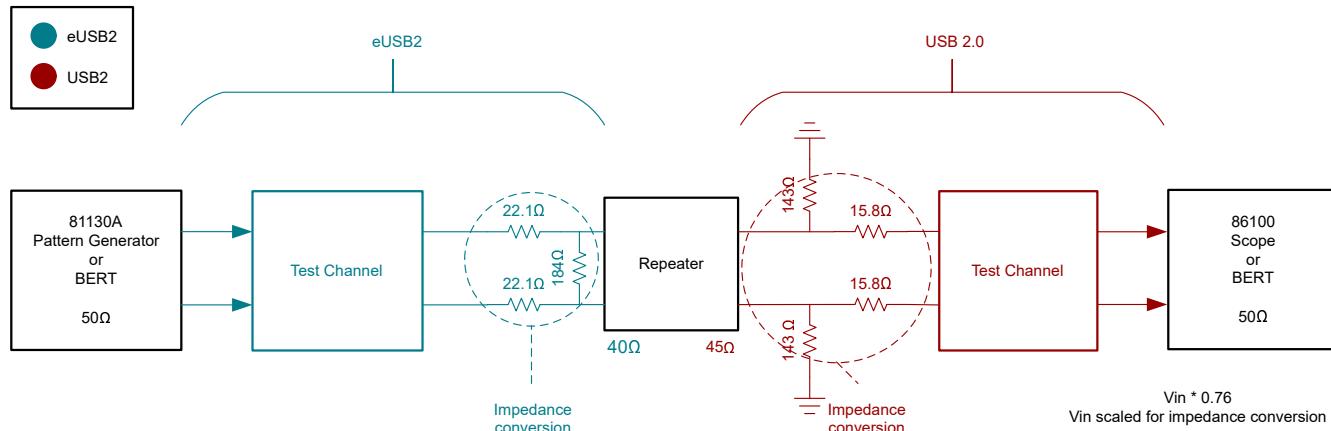

図 7-1. USB 2.0 TX 出力 (出力) ジッタ、アイ マスク テスト設定

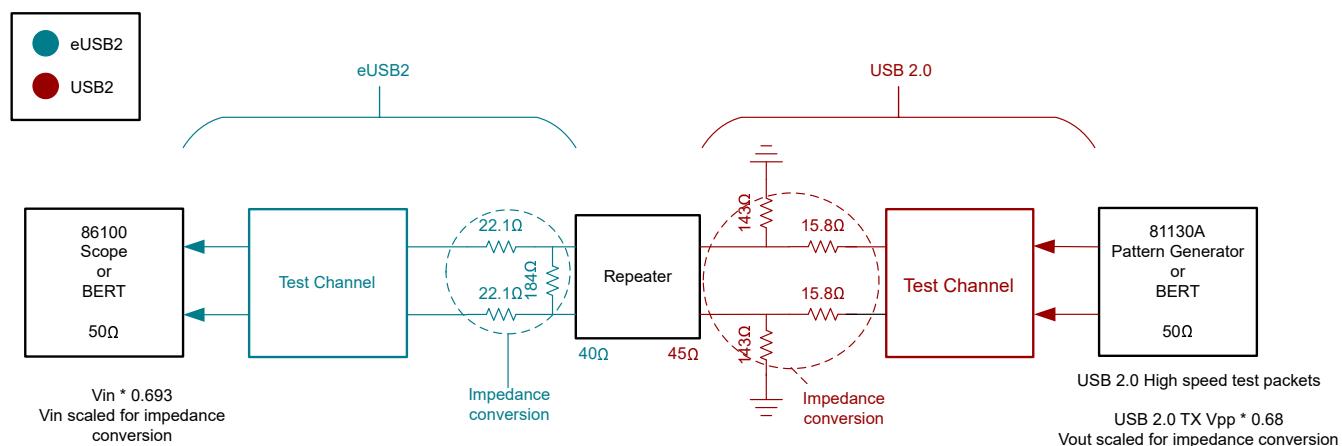

図 7-2. eUSB2 TX 出力 (入力) ジッタ、アイ マスク テスト設定

## 8 詳細説明

### 8.1 概要

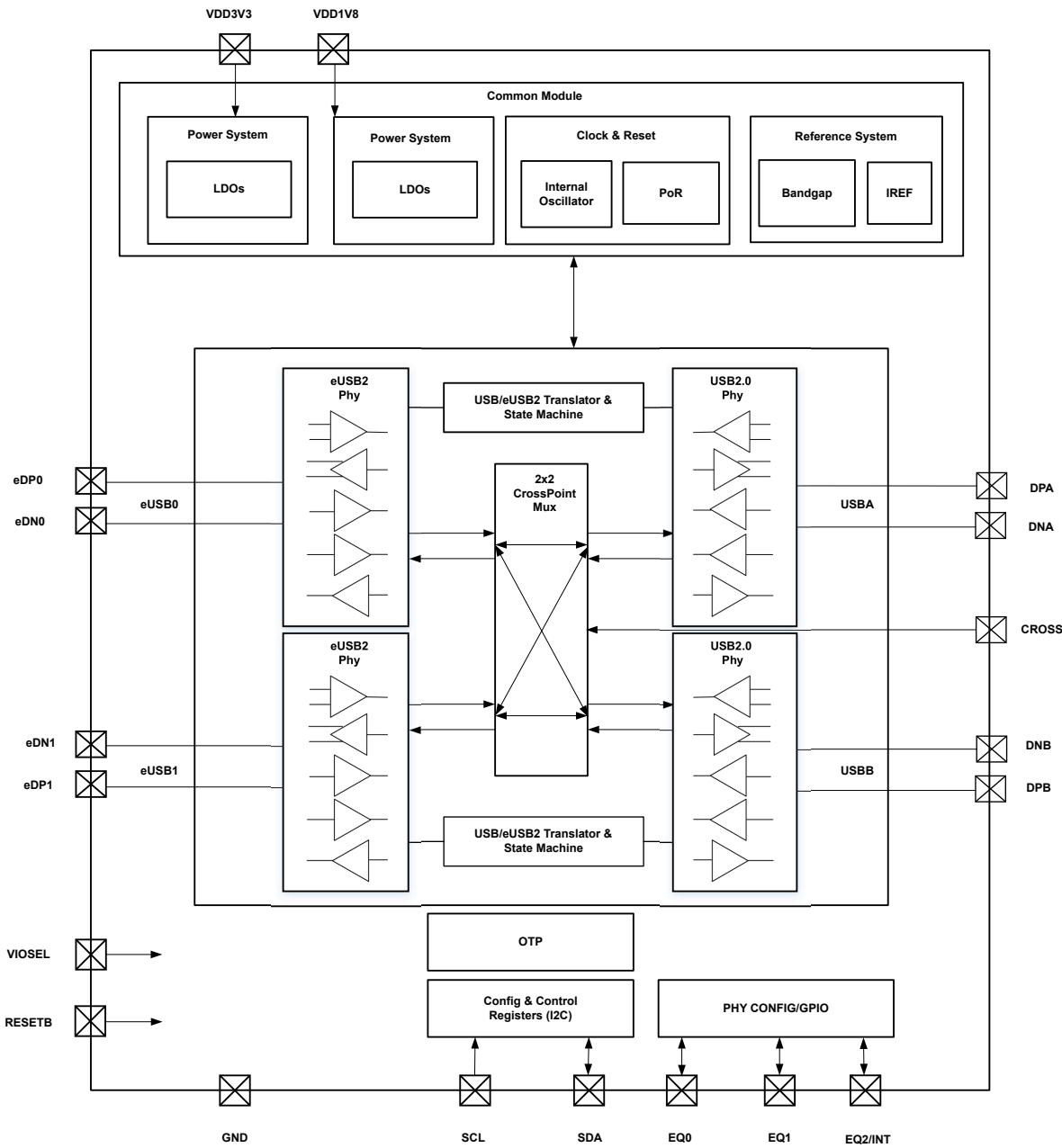

TUSB2E221 は、1 つまたは 2 つの eUSB2 ポートを備えた SoC と、USB 2.0 をサポートする外部コネクタの間に常駐する eUSB2 から USB 2.0 へのデュアル リピータです。各リピータは、ホストまたはデバイスリピータ (DRD リピータ) として個別に構成できます。

USB 2.0 ポート A および B は、リセット時に CROSS ピンを設定することで、内部クロスバー スイッチによって交換できます。パワーアップリセット後、CROSS ピンは無視されます。

### 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 USB 2.0

TUSB2E221 は、2 つの USB 2.0 ポートをサポートしています。各ポートは、低速、フルスピード、高速動作に対応しています。

### 8.3.2 eUSB2

TUSB2E221 は、低速、フルスピード、高速動作に対応する 2 つの eUSB2 ポートをサポートしています。

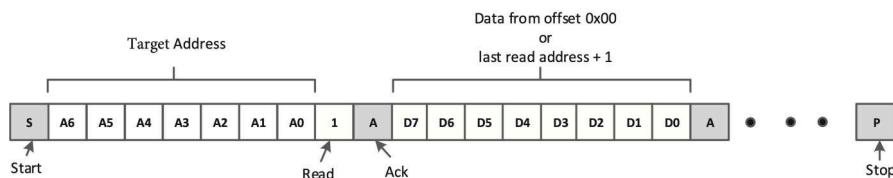

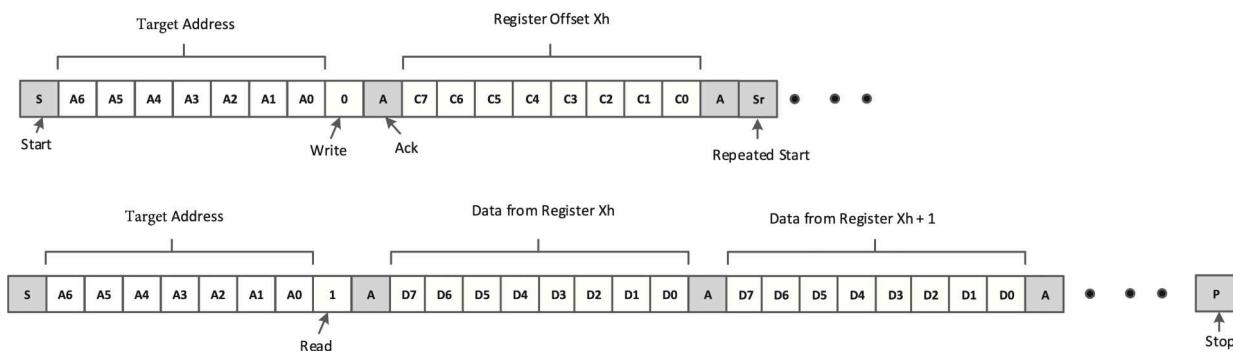

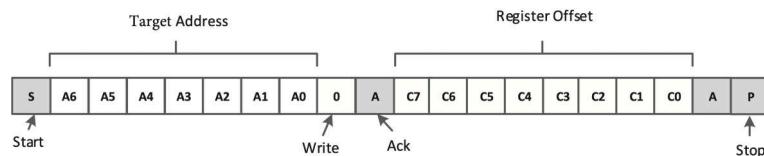

### 8.3.3 クロス マルチプレクサ