## UC284xL 高性能／低コスト電流モード PWM コントローラ

### 1 特長

- UCx84x/UCx84xA/UCx84xAQ/TLx84x/TLx84xB ファミリの出力ドライバの改善および動作/起動電流の低減

- オフラインおよび DC-DC コンバータ用に最適化

- 低いスタートアップ電流 (0.5mA 未満)

- トリムされた発振器放電電流

- 自動フィードフォワード補償

- パルス単位の電流制限

- 拡張された負荷応答特性

- ヒステリシス付きの低電圧誤動作防止

- 二重パルスの抑制

- 大電流のトーテムポール出力

- 内部調整済みバンドギャップ リファレンス

- 最大 500kHz 動作

### 2 アプリケーション

- スイッチ モード電源 (SMPS)

- DC/DC コンバータ

- パワー モジュール

- 産業用 PSU

- バッテリ駆動 PSU

### 3 概要

UC284xL 制御デバイスは、UC284x ファミリのピン互換の改良版です。このデバイスは電流モードまたはスイッチ モード電源の制御に必要な機能を備えており、36V での V<sub>CC</sub> 範囲の拡大、0.25mA での低起動電流、15mA 最大時の動作電流許容誤差の縮小、100ns でのサイクルごとの電流保護の応答速度向上などが強化されています。UC284xL の出力ドライバは、立ち上がり時間と立ち下がり時間の短縮(最大 75ns)によるスイッチング損失の低減、FET の閾値電圧から十分な余裕のある低出力レベルによるドライバ能力の強化などの点が改良されています。

#### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| UC284xL | D (SOIC, 8)          | 4.9mm × 6mm              |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ(長さ × 幅)は公称値であり、該当する場合はピントも含まれます。

Copyright © 2025, Texas Instruments Incorporated

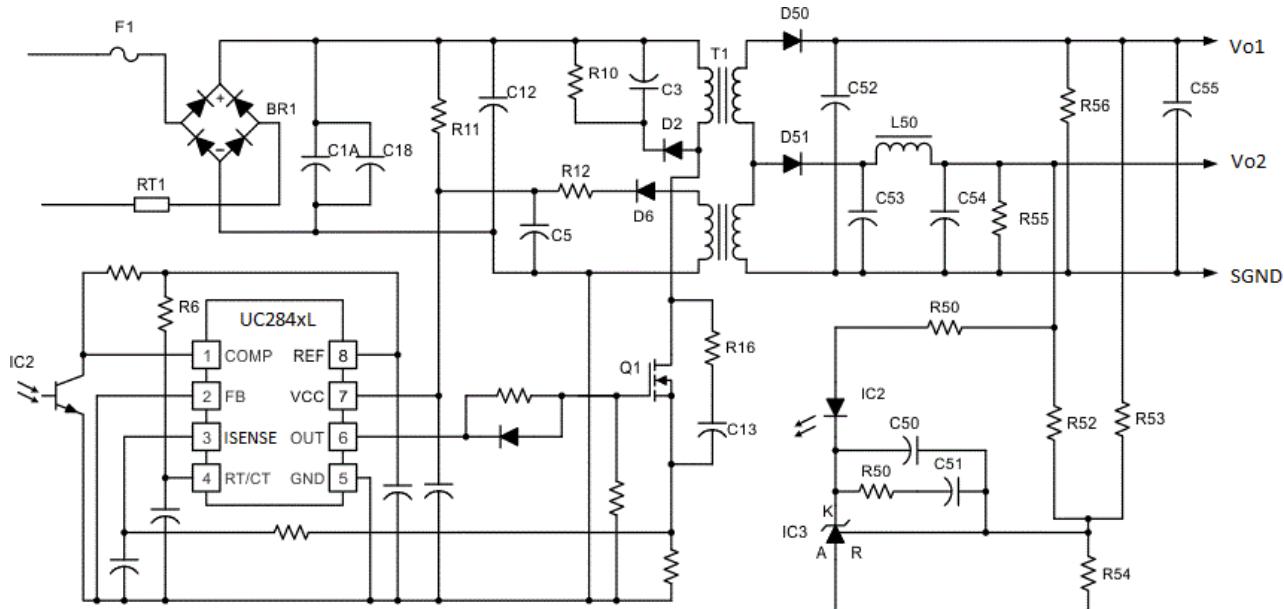

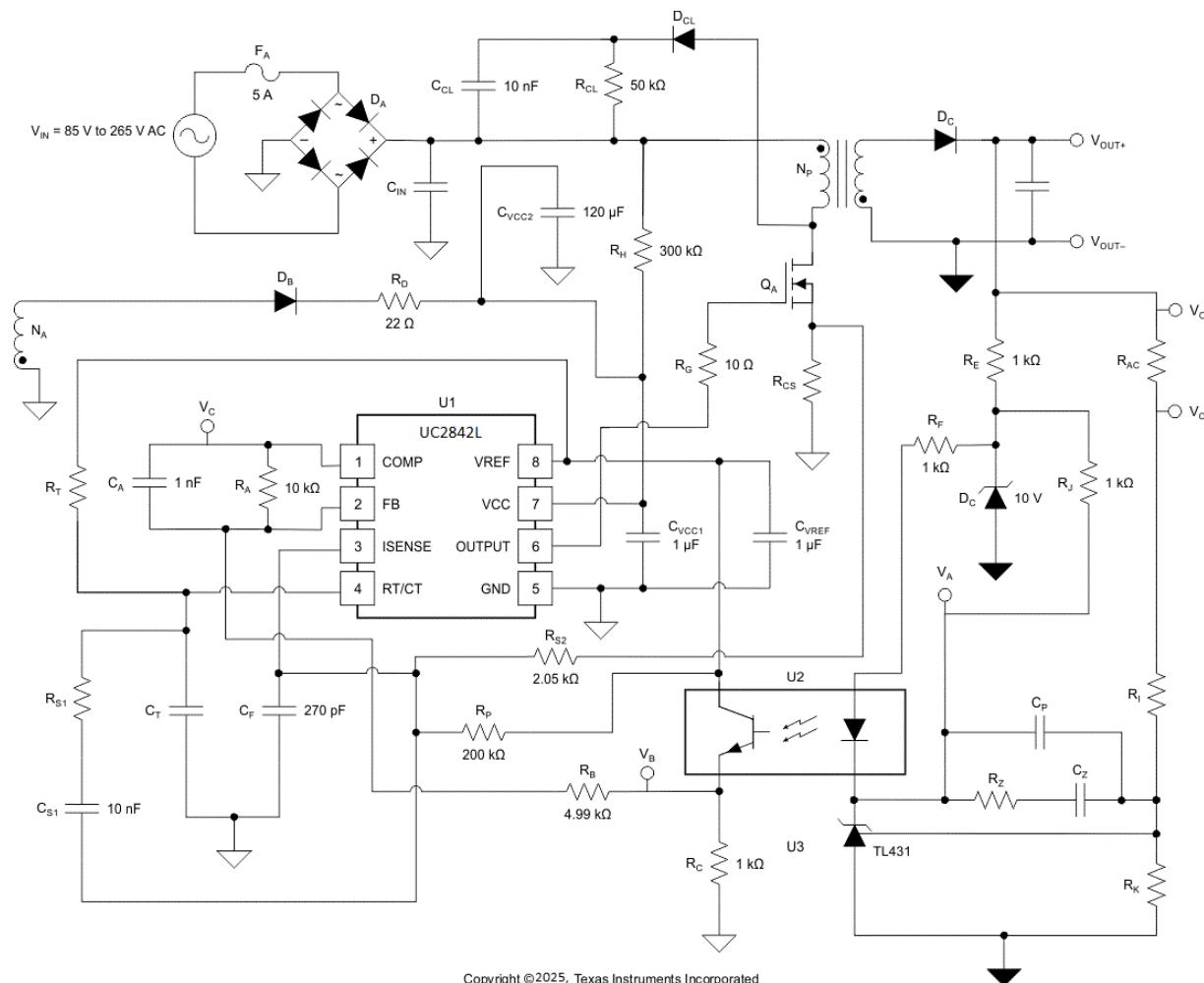

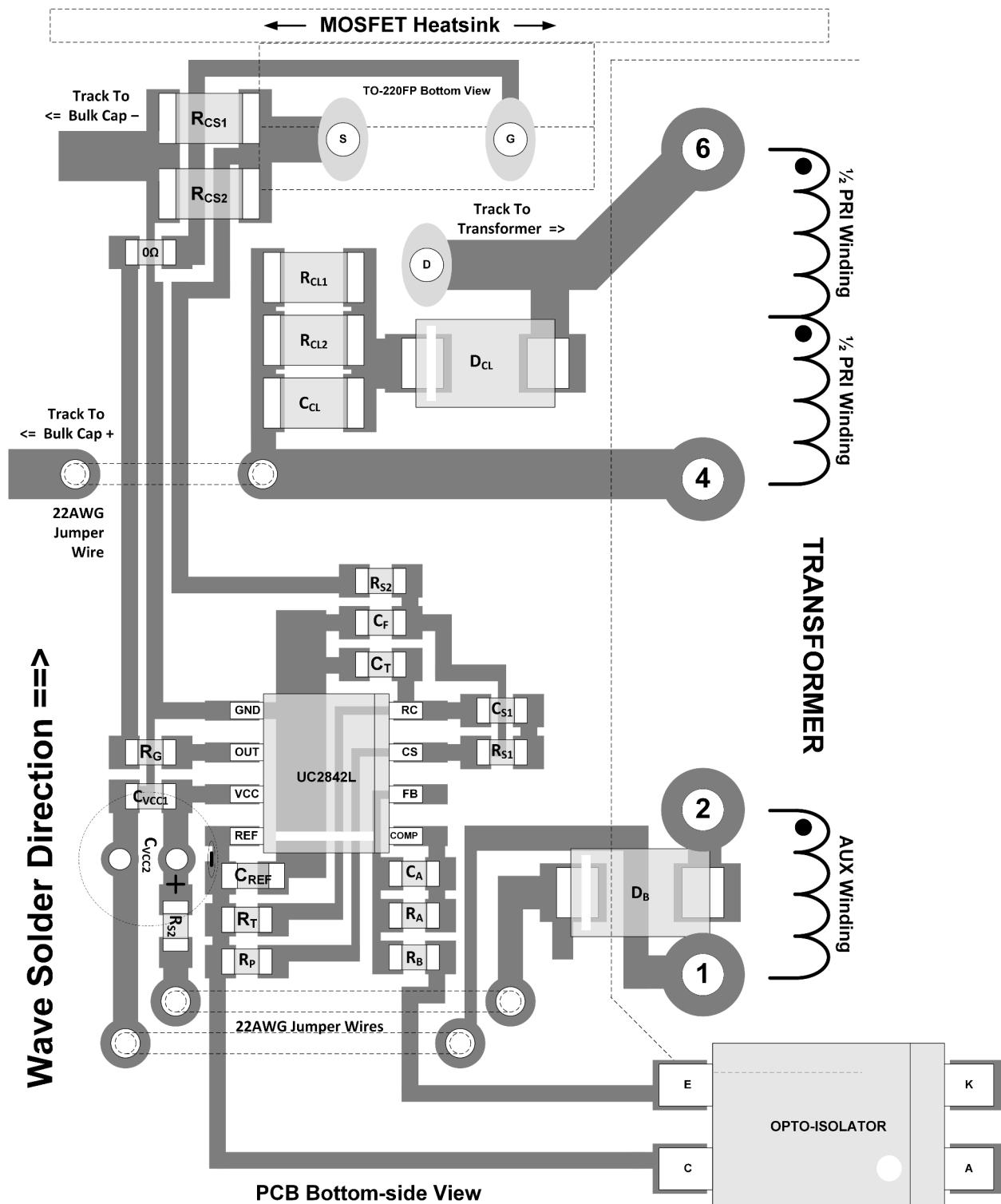

代表的なアプリケーションの図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLUSG04

## 目次

|                  |    |                             |    |

|------------------|----|-----------------------------|----|

| 1 特長.....        | 1  | 7.4 デバイスの機能モード.....         | 13 |

| 2 アプリケーション.....  | 1  | 8 アプリケーションと実装.....          | 14 |

| 3 概要.....        | 1  | 8.1 アプリケーション情報.....         | 14 |

| 4 デバイスの比較.....   | 3  | 8.2 代表的なアプリケーション.....       | 14 |

| 5 ピン構成および機能..... | 4  | 8.3 電源に関する推奨事項.....         | 22 |

| 6 仕様.....        | 5  | 8.4 レイアウト.....              | 22 |

| 6.1 絶対最大定格.....  | 5  | 9 デバイスおよびドキュメントのサポート.....   | 24 |

| 6.2 ESD 定格.....  | 5  | 9.1 デバイス サポート.....          | 24 |

| 6.3 推奨動作条件.....  | 5  | 9.2 ドキュメントのサポート.....        | 24 |

| 6.4 熱に関する情報..... | 6  | 9.3 ドキュメントの更新通知を受け取る方法..... | 24 |

| 6.5 電気的特性.....   | 6  | 9.4 サポート・リソース.....          | 24 |

| 6.6 代表的特性.....   | 8  | 9.5 商標.....                 | 24 |

| 7 詳細説明.....      | 10 | 9.6 静電気放電に関する注意事項.....      | 25 |

| 7.1 概要.....      | 10 | 9.7 用語集.....                | 25 |

| 7.2 機能ブロック図..... | 10 | 10 改訂履歴.....                | 25 |

| 7.3 機能説明.....    | 11 | 11 メカニカル、パッケージ、および注文情報..... | 25 |

## 4 デバイスの比較

表 4-1. デバイスの性能の向上

| パラメータ                               | UC284x | UC284xL |

|-------------------------------------|--------|---------|

| V <sub>CC</sub> 最大                  | 30V    | 36V     |

| CS 出力遅延                             | 150ns  | 100ns   |

| 立ち上がり / 立ち下がり時間(最大)                 | 150ns  | 75ns    |

| 出力低レベル(200mA 時)                     | 1.5V   | 0.5V    |

| 出力高レベル(200mA、V <sub>CC</sub> = 15V) | 12V    | 13.1V   |

| 起動電流                                | 0.3mA  | 0.25mA  |

| 動作電流の最大値                            | 17mA   | 15mA    |

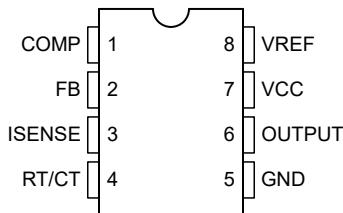

## 5 ピン構成および機能

図 5-1. D パッケージ、8 ピン SOIC (上面図)

表 5-1. ピンの機能

| ピン     |    | I/O | 説明                                                                                                                                                                                      |

|--------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |     |                                                                                                                                                                                         |

| COMP   | 1  | O   | 低インピーダンスの 1MHz 内部エラー アンプを出力します。このアンプは、ピーク電流制限または PWM コンバレータへの入力でもあり、開ループ ゲイン (AVOL) は 80dB です。このピンは最大 6mA をシンクでき、内部的に電流が制限されていません。                                                      |

| FB     | 2  | I   | エラー アンプへの入力で、パワー コンバータの電圧帰還ループを制御して安定性を確保するために使用できます。                                                                                                                                   |

| GND    | 5  | —   | コントローラの信号グランド。                                                                                                                                                                          |

| ISENSE | 3  | I   | UC284xL コントローラのピーク電流制限、PWM コンバレータへの入力。電流検出抵抗と組み合わせて使用する場合、エラー アンプの出力電圧によって、電源システムのサイクル単位のピーク電流制限が制御されます。最大ピーク電流検出信号は、内部で 1V にクランプされます。セクション 7.2 を参照してください。                              |

| 出力     | 6  | O   | 1A トーテムポール ゲートドライバの出力。このピンは、最大 1A のゲートドライバ電流をシンクおよびソースできます。ゲートドライバ電流を制限するには、ゲートドライバ抵抗を使用する必要があります。                                                                                      |

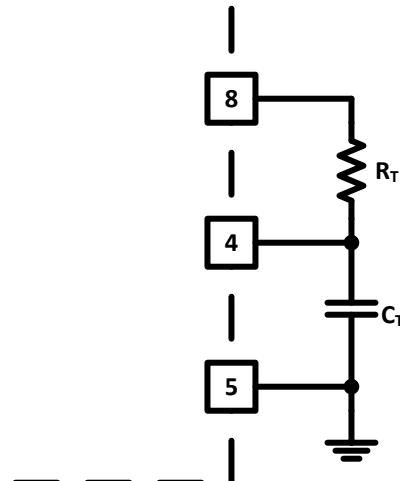

| RT/CT  | 4  | I   | 外部タイミング抵抗 (RT) とタイミング コンデンサ (CT) を使用してプログラムされる。内部発振器への入力。これらのタイミング部品の適切な選択については、セクション 7.3.5 を参照してください。TI は、470pF~4.7nF の容量値を使用することをお勧めします。また、TI は、タイミング抵抗には 5kΩ~100kΩ の値を選択することをお勧めします。 |

| VCC    | 7  | I   | ゲートドライバへのバイアス入力。このピンには、設計で使用するメイン スイッチング FET のゲート容量の 10 倍より大きいバイアス コンデンサが必要です。                                                                                                          |

| VREF   | 8  | O   | PWM コントローラのリファレンス電圧出力。このピンで供給する電力は、通常動作時に 10mA を超えないようにする必要があります。この出力は、約 100mA で短絡保護されています。このリファレンスは内部コンバレータにも使用され、1μF の高周波バイパス コンデンサが必要です。VCC コンデンサも、VREF ピンのコンデンサの 10 倍以上にする必要があります。  |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>。

|                              |             | 最小値                 | 最大値        | 単位         |

|------------------------------|-------------|---------------------|------------|------------|

| 電源電圧 <sup>(2)</sup>          | $V_{CC}$ ピン | $V_{CC}$ ツエナ<br>ー電圧 | V          |            |

| 電源電流、 $I_{CC}$               |             | 25                  | mA         |            |

| 負荷電流、 $I_{OUT}$              |             | $\pm 1$             | A          |            |

| 出力エネルギー (容量性負荷)              |             | 5                   | $\mu J$    |            |

| アナログ入力                       |             | -0.3                | 6.3        | V          |

| 最大の負電圧                       | すべてのピン      | -0.3                |            | V          |

| エラー アンプの出力シングル電流、 $I_{COMP}$ |             | 10                  | mA         |            |

| $T_A \leq 25^\circ C$ での消費電力 |             | 1                   | W          |            |

| リード温度 (半田付け、10 秒)            |             | 300                 | $^\circ C$ |            |

| 接合部温度、 $T_J$                 |             | -55                 | 150        | $^\circ C$ |

| 保管温度、 $T_{stg}$              |             | -65                 | 150        | $^\circ C$ |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートのセクション 6.3 に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 通常の動作時、 $V_{CC}$  は低インピーダンスの電源から電流制限抵抗を介して供給されます。この抵抗は、すべての動作条件において  $V_{CC}$  電圧が  $V_{CC}$  ツエナ-クランプ電圧と低電圧誤動作防止閾値の間になるように設定する必要があります。 $V_{CC}$  の最大定格は、「電気的特性」の内部ツエナ-クランプ電圧を基準に定められており、 $I_{CC}$  が 25mA を超えないように設計されています。 $V_{CC}$  と  $I_{CC}$  がこの制限値を超えると、デバイスに永続的な損傷が生じる恐れがあります。

### 6.2 ESD 定格

|             |      | 値          | 単位 |

|-------------|------|------------|----|

| $V_{(ESD)}$ | 静電放電 | $\pm 2000$ | V  |

|             |      | $\pm 1500$ |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                                 |              | 最小値  | 公称値      | 最大値 | 単位         |

|---------------------------------|--------------|------|----------|-----|------------|

| $V_{CC}$                        | バイアス電源電圧     | 18   | 30       |     | V          |

|                                 |              | 10   | 30       |     |            |

| $V_{FB}$ 、 $V_{RC}$ 、 $V_{VFB}$ | アナログ ピンの電圧   | -0.1 | 5        |     | V          |

| $V_{OUT}$                       | ゲートドライバの出力電圧 | -0.1 | $V_{CC}$ |     | V          |

| $I_{VCC}$                       | 電源バイアス電流     |      |          | 25  | mA         |

| $I_{VREF}$                      | 出力電流         |      |          | 10  | mA         |

| $f_{osc}$                       | オシレータの周波数    |      |          | 500 | kHz        |

| $T_A$                           | 自由空気での動作温度   | -40  | 125      |     | $^\circ C$ |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>                    | D (SOIC) | 単位   |

|-----------------------------------------|----------|------|

|                                         | 8 ピン     |      |

| R <sub>θJA</sub> 接合部から周囲への熱抵抗           | 117.4    | °C/W |

| R <sub>θJC(top)</sub> 接合部からケース(上面)への熱抵抗 | 51.5     | °C/W |

| R <sub>θJB</sub> 接合部から基板への熱抵抗           | 61       | °C/W |

| Ψ <sub>JT</sub> 接合部から上面への特性パラメータ        | 7.8      | °C/W |

| Ψ <sub>JB</sub> 接合部から基板への特性パラメータ        | 60.2     | °C/W |

| R <sub>θJC(bot)</sub> 接合部からケース(底面)への熱抵抗 | —        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーションレポートを参照してください。

[spra953](#)

## 6.5 電気的特性

特に記述のない限り、これらの仕様は T<sub>A</sub> = -40 ~ 125°C、T<sub>A</sub> = T<sub>J</sub>、V<sub>CC</sub> = 15V<sup>(4)</sup>、R<sub>T</sub> = 10kΩ、C<sub>T</sub> = 3.3nF の条件で適用されます。

| パラメータ                     | テスト条件                                                               | 最小値  | 標準値  | 最大値  | 単位    |

|---------------------------|---------------------------------------------------------------------|------|------|------|-------|

| <b>リファレンス</b>             |                                                                     |      |      |      |       |

| 出力電圧                      | T <sub>J</sub> = 25°C、I <sub>O</sub> = 1mA                          | 4.95 | 5    | 5.05 | V     |

| ライン レギュレーション              | 12V ≤ V <sub>IN</sub> ≤ 25V                                         |      | 6    | 20   | mV    |

| 負荷レギュレーション                | 1mA ≤ I <sub>O</sub> ≤ 20mA                                         |      | 6    | 25   | mV    |

| 温度安定性                     | (1) (6) を参照                                                         |      | 0.2  | 0.4  | mV/°C |

| 総出力変動                     | ライン、負荷、温度                                                           | 4.9  |      | 5.1  | V     |

| 出力ノイズ電圧                   | 10Hz ≤ f ≤ 10kHz、T <sub>J</sub> = 25°C <sup>(1)</sup>               |      | 50   |      | μV    |

| 長期安定性                     | T <sub>A</sub> = 125°C、1000hrs <sup>(1)</sup>                       |      | 5    | 25   | mV    |

| 出力短絡                      |                                                                     | -30  | -100 | -180 | mA    |

| <b>発振器</b>                |                                                                     |      |      |      |       |

| 初期精度                      | T <sub>J</sub> = 25°C <sup>(5)</sup>                                | 47   | 52   | 57   | kHz   |

| 電圧安定性                     | 12V ≤ V <sub>CC</sub> ≤ 25V                                         |      | 0.2  | 1    | %     |

| 温度安定性                     | T <sub>MIN</sub> ≤ T <sub>A</sub> ≤ T <sub>MAX</sub> <sup>(1)</sup> |      | 5    |      | %     |

| 振幅                        | V <sub>RT/CT</sub> のピークツーピーク <sup>(1)</sup>                         |      | 1.7  |      | V     |

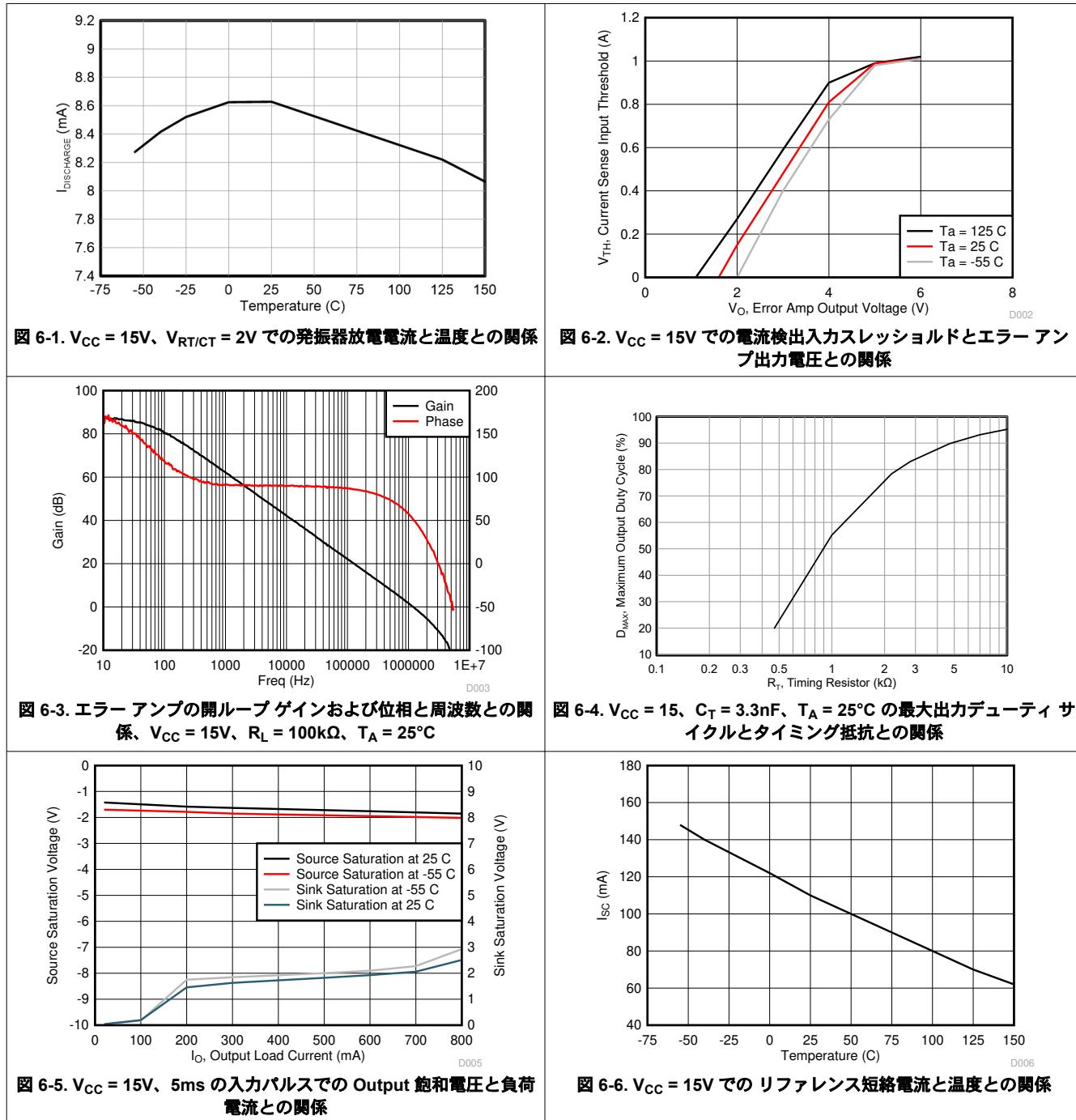

| 放電電流                      | V <sub>RT/CT</sub> = 2V <sup>(7)</sup>                              |      | 8.3  |      | mA    |

| <b>エラー アンプ</b>            |                                                                     |      |      |      |       |

| 入力電圧                      | V <sub>COMP</sub> = 2.5V                                            | 2.45 | 2.5  | 2.55 | V     |

| 入力バイアス電流                  |                                                                     |      | -0.3 | -1   | μA    |

|                           |                                                                     |      | -0.3 | -2   |       |

| A <sub>VOL</sub> 開ループ ゲイン | 2V ≤ V <sub>O</sub> ≤ 4V                                            | 65   | 90   |      | dB    |

| ユニティ ゲイン帯域幅               | T <sub>J</sub> = 25°C <sup>(1)</sup>                                | 0.7  | 1    |      | MHz   |

| CMRR 同相除去比                | 12V ≤ V <sub>CC</sub> ≤ 25V                                         | 60   | 70   |      | dB    |

| 出力シンク電流                   | V <sub>FB</sub> = 2.7V、V <sub>COMP</sub> = 1.1V                     | 2    | 6    |      | mA    |

| 出力ソース電流                   | V <sub>FB</sub> = 2.3V、V <sub>COMP</sub> = 5V                       | -0.5 | -0.8 |      | mA    |

| V <sub>OUT</sub> High     | V <sub>FB</sub> = 2.3V、R <sub>L</sub> = 15kΩ をグランドに接続               | 5    | 6    |      | V     |

| V <sub>OUT</sub> Low      | V <sub>FB</sub> = 2.7V、R <sub>L</sub> = 15kΩ を VREF に接続             |      | 0.7  | 1.1  | V     |

| <b>電流検出</b>               |                                                                     |      |      |      |       |

| ゲイン                       | (2) (3) を参照                                                         | 2.85 | 3    | 3.15 | V/V   |

| 最大入力信号                    | V <sub>COMP</sub> = 5V <sup>(2)</sup>                               | 0.9  | 1    | 1.1  | V     |

## 6.5 電気的特性 (続き)

特に記述のない限り、これらの仕様は  $T_A = -40 \sim 125^\circ\text{C}$ 、 $T_J = T_A$ 、 $V_{CC} = 15\text{V}^{(4)}$ 、 $R_T = 10\text{k}\Omega$ 、 $C_T = 3.3\text{nF}$  の条件で適用されます。

| パラメータ           | テスト条件                                            | 最小値  | 標準値  | 最大値 | 単位            |

|-----------------|--------------------------------------------------|------|------|-----|---------------|

| PSRR 電源除去比      | $12\text{V} \leq V_{CC} \leq 25\text{V}^{(2)}$   |      | 70   |     | dB            |

| 入力バイアス電流        |                                                  |      | -2   | -10 | $\mu\text{A}$ |

| 出力の遅延           | $V_{ISENSE} = 0 \sim 2\text{V}^{(1)}$            | 100  | 200  |     | ns            |

| 出力              |                                                  |      |      |     |               |

| 出力 Low レベル      | $I_{SINK} = 20\text{mA}$                         | 0.05 | 0.11 |     | V             |

|                 | $I_{SINK} = 200\text{mA}$                        | 0.55 | 1.1  |     |               |

| 出力 High レベル     | $I_{SOURCE} = 20\text{mA}$                       | 13.2 | 13.6 |     | V             |

|                 | $I_{SOURCE} = 200\text{mA}$                      | 13.1 | 13.5 |     |               |

| 立ち上がり時間         | $T_J = 25^\circ\text{C}, C_L = 1\text{nF}^{(1)}$ | 25   | 75   |     | ns            |

| 立ち下がり時間         | $T_J = 25^\circ\text{C}, C_L = 1\text{nF}^{(1)}$ | 25   | 75   |     | ns            |

| UVLO 飽和         | $V_{CC} = 5\text{V}, I_{SINK} = 10\text{mA}$     | 0.7  | 1.2  |     | V             |

| 低電圧誤動作防止        |                                                  |      |      |     |               |

| 開始スレッショルド       | UC2842L, UC2844L                                 | 15   | 16   | 17  | V             |

|                 | UC2843L, UC2845L                                 | 7.8  | 8.4  | 9   |               |

| ターンオン後の最小動作電圧   | UC2842L, UC2844L                                 | 9    | 10   | 11  | V             |

|                 | UC2843L, UC2845L                                 | 7    | 7.6  | 8.2 |               |

| PWM             |                                                  |      |      |     |               |

| 最大デューティ サイクル    | UC2842L, UC2843L                                 | 92   | 96   | 100 | %             |

|                 | UC2844L, UC2845L                                 | 46   | 48   | 50  | %             |

| 最小デューティ サイクル    |                                                  |      |      | 0   | %             |

| 総スタンバイ電流        |                                                  |      |      |     |               |

| スタートアップ電流       |                                                  | 0.25 | 0.5  |     | mA            |

| 動作電源電流          | $V_{FB} = V_{ISENSE} = 0\text{V}$                | 11   | 15   |     | mA            |

| $V_{CC}$ ツエナー電圧 | $I_{CC} = 25\text{mA}$                           | 36   |      |     | V             |

- (1) 設計で保証されますが、製品で 100% のテストは行われていません。

- (2)  $V_{FB} = 0\text{V}$  の条件で、ラッチのトリップ ポイントで測定されたパラメータ。

- (3) ゲインの定義: $A = \Delta V_{COMP} / \Delta V_{ISENSE}$ 、 $0\text{V} \leq V_{ISENSE} \leq 0.8\text{V}$ 。

- (4)  $V_{CC}$  は、開始スレッショルドより高く調整してから、15V に設定します。

- (5) 出力周波数は発振器の周波数の  $1/2$  です。

- (6) 温度安定性は平均温度係数と呼ばれることがあります、次のように表われされます。温度安定性 =  $(V_{REF(max)} - V_{REF(min)}) / (T_{J(max)} - T_{J(min)}) V_{REF(max)}$  および  $V_{REF(min)}$  は、適切な温度範囲にわたって測定された最大および最小のリファレンス電圧です。電圧の極値は、温度の極値で発生するとは限らないことに注意してください。

- (7) このパラメータは、 $R_T = 10\text{k}\Omega$  で、 $V_{REF}$  に対して測定されます。これにより、測定に約  $300\mu\text{A}$  の電流が追加されます。RT/CT ピンに流れる合計電流は、測定された値より約  $300\mu\text{A}$  大きくなります。

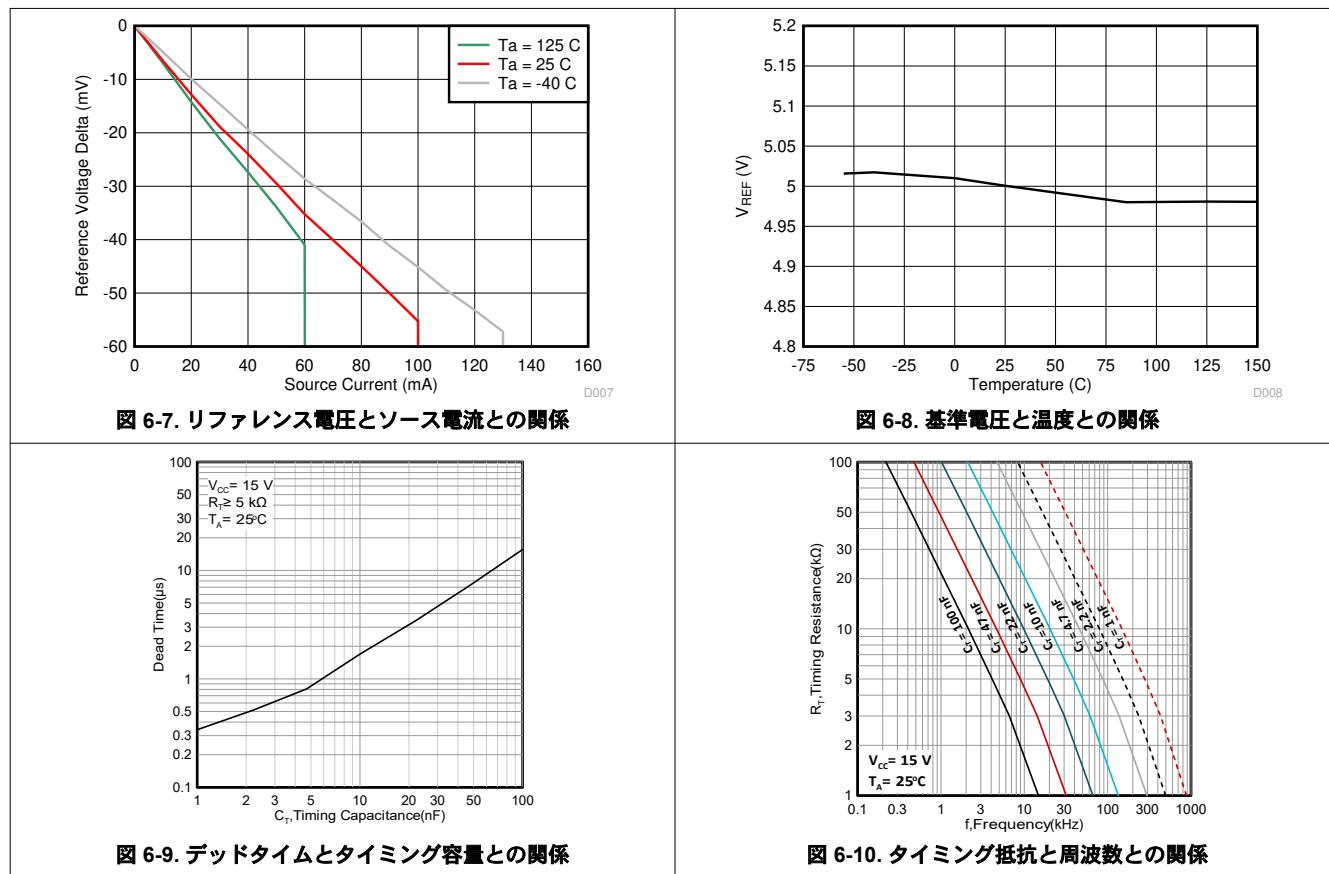

## 6.6 代表的特性

## 6.6 代表的特性 (続き)

## 7 詳細説明

### 7.1 概要

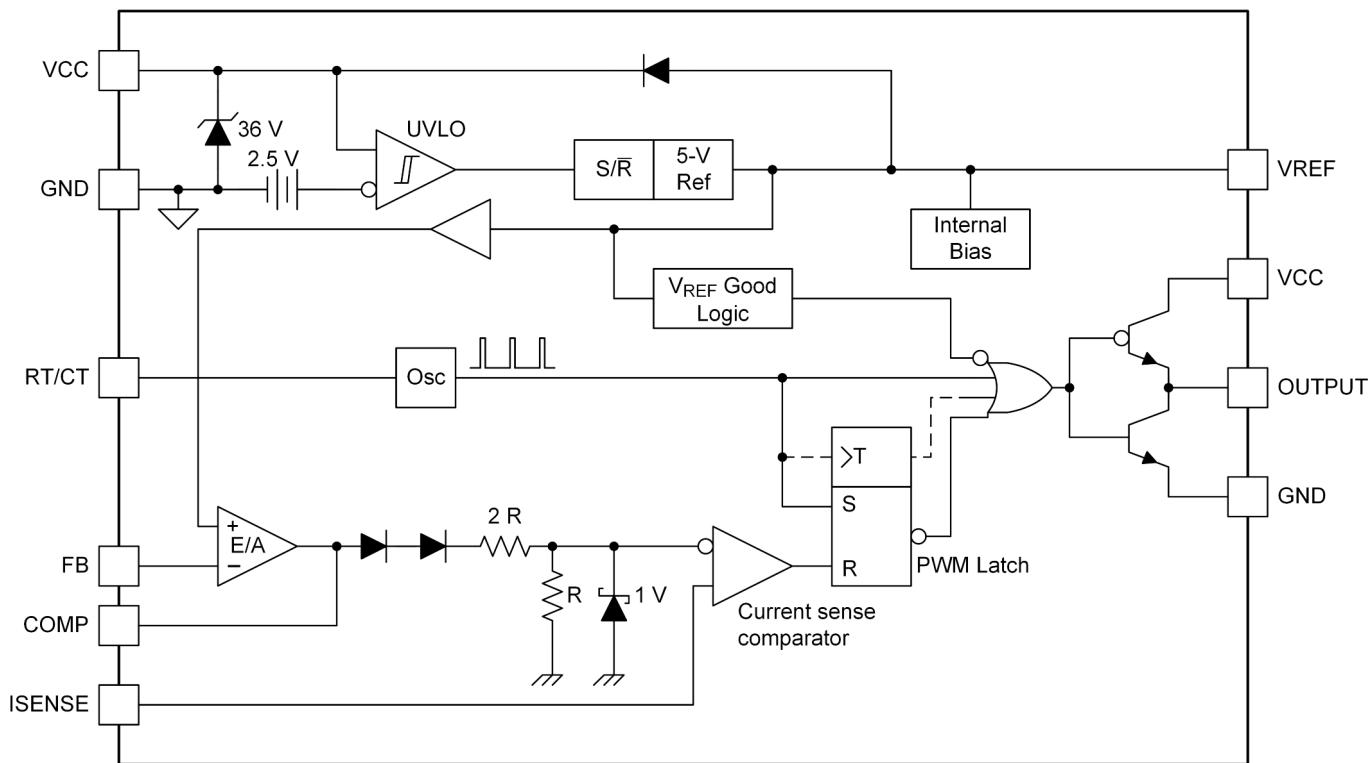

UC284xL デバイスは、固定周波数パルス幅変調 (PWM) コントローラで、500kHz のスイッチング周波数で動作するように設計されています。これらのコントローラはピーク電流モード (PCM) 用に設計されており、絶縁型および非絶縁型の電源設計に使用できます。これらのコントローラは出力から FET を直接駆動でき、最大 1A のゲートドライバ電流をソースおよびシンクできます。これらのデバイスには低インピーダンス アンプも内蔵されており、非絶縁設計で使用して、電源出力電圧と帰還ループを制御できます。

### 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 パルス単位の電流制限

パルス単位の制限は、電流モード制御スキーマに固有のものです。誤差電圧をクランプするだけで、ピーク電流の上限を設定できます。正確な電流制限により、磁気および電力半導体素子を最適化するとともに、信頼性の高い電源動作を保証できます。

### 7.3.2 電流検出回路

ピーク電流 ( $I_S$ ) は式 1 で求められます。

$$I_{S(\max)} \times \frac{1V}{R_S} \quad (1)$$

スイッチの過渡を抑制するため、小型の RC フィルタが必要な場合があります。

図 7-1. 電流検出回路図

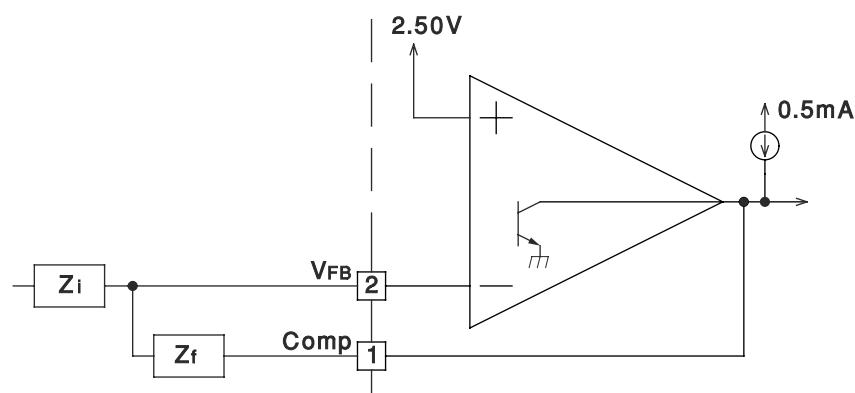

### 7.3.3 エラー アンプの構成

エラー アンプは最大で 0.8mA をソース、6mA をシンクできます。

図 7-2. エラー アンプの構成図

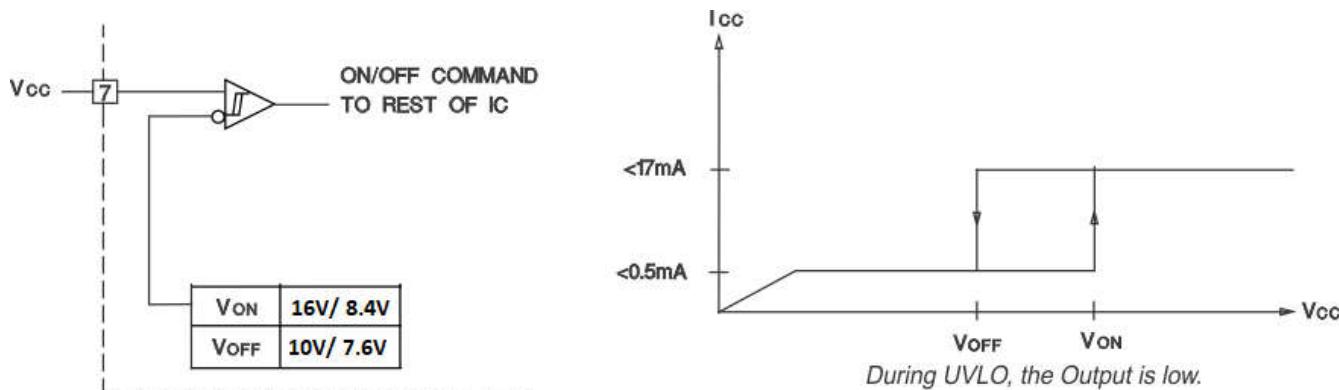

### 7.3.4 低電圧誤動作防止

UC284xL デバイスには、電源オンおよび電源オフ シーケンス中の動作を制御するため、低電圧誤動作防止保護回路が搭載されています。

UVLO 時の IC の電源電流は通常 0.25mA です。この VCC 電流は UC284x ファミリよりも大幅に少ないため、ラインからの電力が小さくなります。スタートアップ電流の低減は、IC が高電圧の DC レールで起動してから、メイントランジストの補助巻線にブートストラップする、オフライン電源で特に重要な考慮点です。その後、IC のスタートアップ電流によってサイズが設定されたスタートアップ抵抗で電力が消費されます。ターンオンスレッショルドを超えると、IC の電源電流が通常約 11mA まで増加します。UC284xL は、低電圧誤動作防止時に、電源オン時のミラー効果によってパワー MOSFET が寄生的にオンになることを防止します。この設計では、低電圧誤動作防止時の低トーテムポールトランジスタの動作が改善されているため、IC は飽和電圧が 0.7V と低いときに最大 10mA の大電流をシンクできます。

図 7-3. 低電圧誤動作防止

### 7.3.5 発振器

$$\text{For } R_T > 5 \text{ k} \quad f \approx \frac{1.72}{R_T \times C_T}$$

図 7-4. 発振器セクション

正確な最大デューティサイクルによる高周波数での正確な動作については、図 6-10 を参照してください。これは、トリムされた発振器の放電電流により、UC284xL ファミリのデバイスで実現可能になったものです。これにより、製造時の変動

による初期放電電流やデッドタイムへの影響を打ち消すことができます。UC284xL の出力周波数は発振器周波数の半分で、最大デューティサイクルは 50% です。

## 7.4 デバイスの機能モード

### 7.4.1 通常動作

この IC は、ピーク電流モード (PCM) 制御または電圧モード (VM) 制御で使用できます。コンバータが PCM で動作しているとき、電圧アンプの出力はコンバータのピーク電流とデューティサイクルをレギュレートします。IC が VM 制御で使用されるときは、電圧アンプの出力によってパワー コンバータのデューティサイクルが制御されます。内蔵のエラー アンプと外部のフィードバック回路を使用すると、システムのピーク電流とデューティサイクルをレギュレートできます。

### 7.4.2 低電圧誤動作防止 (UVLO) のスタートアップ

システムのスタートアップ時に、VCC 電圧は 0V から上昇を開始します。VCC 電圧が起動スレッショルドに達するまで、IC は UVLO モードで動作します。VCC が起動スレッショルドに達すると、デバイスはアクティブになり、リファレンス電圧は 5V まで上昇します。

### 7.4.3 UVLO ターンオフ モード

VCC へのバイアス電圧が UVLO の最小動作電圧を下回ると、PWM スイッチングが停止し、リファレンスが非アクティブになります。UVLO 起動スレッショルドより高い電圧を VCC ピンに印加することで、本デバイスを再起動できます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UC284xL コントローラは、ピーク電流モードのパルス幅変調器です。このコントローラにはオンボード アンプが搭載されており、絶縁型または非絶縁型の電源設計に使用できます。オンボードのトータルポールゲートドライバは、1A のピーク電流を供給できます。これは、最大 500kHz のスイッチング周波数で動作できる高速 PWM です。代表的な用途については、[UC2842A データシート](#)に記載されている UC284xA シリーズ を参考にできます。詳しくは、[www.ti.com/product/UC2842A](http://www.ti.com/product/UC2842A) または UCx84x/UCx84xA/UC284xAQ/TL284x/TL284xB ファミリの製品ページをご覧ください。

### 8.2 代表的なアプリケーション

オフライン フライバック コンバータでの UC2842L の代表的な用途を、[図 8-1](#) に示します。UC2842L は、1 次インダクタの電流ランプを検出する、小さな電流検出抵抗を内蔵した内部電流制御ループを使用します。この電流検出抵抗は、インダクタの電流波形を、1 次側 PWM コンパレータに直接入力される電圧信号に変換します。この内部ループによって、入力電圧の変化に対する応答が決定されます。外部電圧制御ループでは、出力電圧の一部を、エラー アンプの入力におけるリファレンス電圧と比較します。オフライン絶縁型アプリケーションで使用する場合、絶縁出力の電圧フィードバックは、2 次側のエラー アンプと、[TL431](#) などの調整可能な電圧リファレンスを使用して実現されます。この誤差信号は、コレクタが VREF ピンに接続され、エミッタが FB に接続されている光アイソレータを使用して、1 次側と 2 次側の絶縁境界をまたぐものです。外側の電圧制御ループによって、負荷の変化に対する応答が決定されます。

図 8-1. 代表的なフライバック アプリケーションの回路

## 8.2.1 設計要件

この設計例では、表 8-1 に記載されているパラメータを入力パラメータとして使用します。

**表 8-1. 設計パラメータ**

| パラメータ                      | 最小値   | 標準値   | 最大値   | 単位               |

|----------------------------|-------|-------|-------|------------------|

| 入力特性                       |       |       |       |                  |

| V <sub>IN</sub> 入力電圧 (RMS) | 85    | 265   | 265   | V                |

| f <sub>LINE</sub> ライン周波数   | 47    | 47    | 63    | Hz               |

| 出力特性                       |       |       |       |                  |

| V <sub>OUT</sub> 出力電圧      | 11.75 | 12    | 12.25 | V                |

| 出力リップル電圧                   | 50    | 50    | 50    | mV <sub>PP</sub> |

| I <sub>OUT</sub> 出力電流      | 4     | 4.33  | 4.33  | A                |

| 負荷ステップ                     | 11.75 | 11.75 | 12.25 | V                |

| システム特性                     |       |       |       |                  |

| η 最大負荷効率                   | 86%   | 86%   | 86%   |                  |

## 8.2.2 詳細な設計手順

### 8.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer を使用して、UC284x(UC284xL の同等の GPN に対応)デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 (V<sub>IN</sub>)、出力電圧 (V<sub>OUT</sub>)、出力電流 (I<sub>OUT</sub>) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 8.2.2.2 UC2842L の設計手順

このアプリケーション設計手順では、UC2842L のピーク電流モード コントローラをオフライン フライバック コンバータで、ユニバーサル入力から 12V、48W のレギュレートされた出力へ、セットアップして使用する方法を示します。

連続モードのフライバック アプリケーションで UC2842L のピーク電流モード コントローラをセットアップし、これを使用した設計を行うには、電力段に関するいくつかの事項を把握する必要があります。まず、出力電力レベル (P<sub>OUT</sub>)、効率 (η)、最小入力電圧 (V<sub>IN(min)</sub>)、ライン周波数 (f<sub>LINE</sub>)、最小バルク電圧に基づいて、必要な入力バルク容量 (C<sub>IN</sub>) を計算します。この設計例では、V<sub>BULK(min)</sub> = 95V にします。

$$V_{IN ripple} = \frac{2 \times \frac{P_{OUT}}{\eta} \times \left[ 0.25 + \frac{1}{\pi} \times \arcsin \left( \frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}} \right) \right]}{\left( 2 \times V_{IN(min)}^2 - V_{BULK(min)}^2 \right) \times f_{LINE}} \quad (2)$$

$$C_{IN} = \frac{2 \times \frac{P_{OUT}}{\eta} \times \left[ 0.25 + \frac{1}{\pi} \times \arcsin \left( \frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}} \right) \right]}{\left( 2 \times V_{IN(min)}^2 - V_{BULK(min)}^2 \right) \times f_{LINE}} \approx 180 \mu F \quad (3)$$

出力コンデンサ ( $C_{OUT}$ ) のサイズは、大信号の過渡応答時に出力電圧が 10% を超えて降下しないように設定されています。設計のこの時点では、電圧ループのクロスオーバー周波数 ( $f_C$ ) が 2.5kHz と想定します。

$$C_{OUT} \geq \frac{\frac{I_{OUT}}{f_C}}{V_{OUT} \times 10\%} \approx 1.33 mF \quad (4)$$

この設計で選択した  $C_{OUT}$  は 2200μF のコンデンサで、等価直列抵抗 (ESR) は 45mΩ です。

次に、最小入力電圧と出力電圧に基づいて、トランスの最大 1 次 / 2 次巻線比 ( $N_{PS}$ ) を計算します。

$$N_{PS} \leq \frac{V_{IN(min)} \times \sqrt{2}}{V_{OUT}} = \frac{85 V \times \sqrt{2}}{12 V} \approx 10 \quad (5)$$

その次に、UC2842A の出力電圧とバイアス電圧に基づいて、トランスの補助 / 2 次の巻線比 ( $N_{AS}$ ) を計算します。

$$N_{AS} \leq \frac{V_{VCC}}{V_{OUT}} = \frac{12\text{ V}}{12\text{ V}} = 1 \quad (6)$$

トランスの巻線比を決定すると、最小バルク電圧、デューティ サイクル (D)、反射出力電流、効率から、トランスの最小 1 次側磁化インダクタンス ( $L_{PM}$ ) を計算できます。この設計で使用するトランスは、 $L_{PM}$  が 1.7mH で、 $N_{PS} = 10$ 、 $N_{AS} = 1$ 、 $f_{sw} = 100\text{kHz}$  です。

$$D = \frac{N_{PS} \times V_{OUT}}{V_{BULK(min)} + N_{PS} \times V_{OUT}} \approx 0.56 \quad (7)$$

$$L_{PM} \geq \frac{V_{BULK(min)} \times D}{70\% \times I_{OUT} \times f_{sw}} = \frac{1.632\text{ mH}}{\eta \times N_{PS}} \approx 1.7\text{ mH} \quad (8)$$

トランスを選択したら、1 次側磁化インダクタンス リップル ( $I_{LPM}$ ) とトランス全体での反射出力電流から、トランスの 1 次側ピーク電流 ( $I_{LpPK}$ ) を計算できます。

$$I_{LPM} = \frac{V_{BULK(min)} \times D}{f_{sw} \times L_M} \approx 0.31\text{ A} \quad (9)$$

$$I_{LpPK} = \frac{I_{OUT}}{N_{PS} \times (1-D)} + \frac{I_{LM}}{2} \approx 1.1\text{ A} \quad (10)$$

1 次側ピーク電流を計算した後で、電流検出抵抗 ( $R_{CS}$ ) を選択できます。

$$R_{CS} = \frac{1\text{ V}}{I_{LpPK} \times 1.3} = 0.725\text{ }\Omega \approx 0.75\text{ }\Omega \quad (11)$$

抵抗  $R_{S1}$  および  $R_{S2}$  を使用して、設計の勾配補償を設定します。コンデンサ  $C_{S1}$  は DC ブロッキング コンデンサで、ブルアップ抵抗  $R_P$  を使用して、ノイズ耐性のため電流検出信号を多少オフセットします。 $R_P$  と  $R_{S2}$  は、電流検出信号に 50mV の DC オフセットを追加するよう、事前に選択済みです。

$R_{S1}$  は、勾配補償がフライバック インダクタのリップル電流下り勾配の 1/2 に設定されるように選択します。このために、2 次磁化インダクタンス ( $L_{SM}$ ) を計算し、 $R_{S1}$  で次の計算を行います。 $R_{S1}$  の式の 1.7V は、発振器のピーク ツー ピークのリップル電圧振幅です。

$$R_{S1} = \frac{1.7\text{ V} \times R_{S2} \times f_{sw} \times (2 \times L_{SM} \times N_{PS})}{V_{OUT} \times (1-D) \times R_{CS}} - R_{S2} = 27.72\text{ k}\Omega \approx 27.4\text{ k}\Omega \quad (12)$$

ここで、

- $R_{S2} = 2.05\text{ k}\Omega$

抵抗  $R_I$  と  $R_K$  は出力リファレンスに選択されており、 $R_K$  の値を事前に選択し、TL431 のリファレンス電圧 ( $V_{TL431REF}$ ) が分かれれば計算できます。 $R_K$  に 2.49kΩ を選択すると、 $R_I$  が計算され、この抵抗には標準の抵抗値として 9.53kΩ が選択されます。

$$R_I = \frac{R_K \times (V_{OUT} - V_{TL431REF})}{V_{TL431REF}} = \frac{2.49 \text{ k}\Omega \times (12 \text{ V} - 2.5 \text{ V})}{2.5 \text{ V}} = 9.462 \text{ k}\Omega \approx 9.53 \text{ k}\Omega \quad (13)$$

UC2842L コントローラを使用したこの設計には、多くの部品を持つ、興味深い制御ループがあります。 $G_{OPTO}(f)$  は、この設計の光アイソレータ全体についての近似伝達関数です。光アイソレータの極周波数は、 $f_P$  で表されます。この設計で使用する光アイソレータの電流伝送比は 1 で、極周波数は約 5kHz です。部品の配置とノード電圧については、図 8-1 を参照してください。補償を簡素化するため、電圧ループ ( $f_C$ ) は光アイソレータの極より低くクロスオーバーする必要があります。

$$s(f) = 2 \times \pi \times 1i \times f \quad (14)$$

$$f_P = 5 \text{ kHz} \quad (15)$$

$$G_{OPTO}(f) = \frac{\Delta V_B}{\Delta V_A} = \frac{R_C}{R_F} \times \frac{ctr}{\frac{s(f)}{2 \times \pi \times f_P} + 1} \quad (16)$$

$G_{BC}(f)$  は、光アイソレータの出力から PWM の制御電圧への推定伝達関数です。

$$G_{BC}(f) = \frac{\Delta V_C}{\Delta V_B} = \frac{R_A}{R_B} \times \frac{1}{s(f) \times R_A \times C_A + 1} \quad (17)$$

デューティサイクルは、バルク入力電圧 ( $V_{BULK}$ ) によって異なります。 $V_{BULK}$  は、通常動作時に 95V~375V の範囲で変動します。これにより、デューティサイクルは 24%~56% の範囲で変動します。

$$D = \frac{N_{PS} \times V_{OUT}}{V_{BULK} + N_{PS} \times V_{OUT}} = 0.24 \text{ to } 0.56 \quad (18)$$

$G_{CO}(f)$  は、制御 ( $V_C$ ) から出力への推定伝達関数です。ここで、変数  $Q$  は品質係数です。

$$G_{CO}(f) = \frac{\Delta V_{OUT}}{\Delta V_C} = N_{PS} \times \frac{1 - D}{1 + D} \times \left[ \frac{s(f) \times ESR \times C_{OUT} + 1}{s(f) \times R_{OUT} \times C_{OUT} + 1} \right] \times \left[ 1 - \frac{s(f) L_{SM} \times D}{R_{OUT} \times (1 - D)^2} \right] \times \frac{\frac{1}{3}}{1 + \frac{s(f)}{2 \times \pi \times f_{SW} \times Q} + \left( \frac{s(f)}{2 \times \pi \times f_{SW}} \right)^2} \quad (19)$$

品質係数 ( $Q$ ) は、1 次側の磁化インダクタンスの電圧変化 ( $S_N$ ) をデューティサイクルの関数で表したものとして定義されます。これには勾配補償 ( $S_E$ ) が追加されます。

$$S_N = \frac{V_{BULK} \times R_{CS}}{L_{PM}} \quad (20)$$

$$S_E = 1.7 \text{ V} \times \frac{R_{S2} \times f_{SW}}{R_{S1} + R_{S2}} \quad (21)$$

$$Q = \frac{1}{\pi \left[ \left( 1 + \frac{S_E}{S_N} \right) \times (1 - D) - 0.5 \right]} \quad (22)$$

電圧ループが安定していることを保証するには、フライバックコンバータの右半面のゼロ周波数 ( $f_{RHPZ}$ ) の半分よりもクロスオーバー周波数が低い必要があります。最小バルク電圧において、右半面のゼロ周波数は約 9.8kHz です。この設計例で、電圧ループの目標クロスオーバーは 1kHz です。実際の  $f_C$  は、目標よりも高い場合と低い場合があります。

$$f_{RHPZ} = \frac{(N_{PS})^2}{\frac{2 \times \pi \times Lpm}{R_{OUT}} \frac{D}{(1-D)^2}} \approx 9.8kHz \quad (23)$$

$$f_C \leq \frac{f_{RHPZ}}{2} \approx 5 kHz \quad (24)$$

$G_{CO}(f)$  の DC ゲインは、バルク入力電圧とともに変化します。抵抗  $R_Z$  は、コンバータへの入力が  $V_{BULK(min)}$  のときに電圧ループをクロスオーバーし、最大クロスオーバー周波数の  $1/5$  でクロスオーバーするよう選択します。

$$R_Z = \frac{R_I}{|G_{OPTO}(f_C/5) \times G_{BC}(f_C/5) \times G_O \times G_{CO}(f_C/5)|} = 23.95 k\Omega, a 23.7 k\Omega was used \quad (25)$$

コンデンサ  $C_Z$  は、電圧ループのクロスオーバーで  $45^\circ$  の位相マージンが追加されるよう選択します。この設計例では、 $6.8nF$  のコンデンサが使用されています。

$$C_Z = \frac{1}{2\pi \times \frac{f_C}{5} \times R_Z} \approx 6.7 nF \quad (26)$$

コンデンサ  $C_P$  は、制御ループの高周波ゲインが減衰するように選択します。

$$C_P = \frac{C_Z}{10} = 680 pF \quad (27)$$

$G_C(f)$  は、TL431 の補償の推定伝達関数です。

$$G_C(f) = \frac{\Delta V_C}{\Delta V_O} = \frac{s(f) \times R_Z \times C_Z + 1}{s(f) \times R_I \times (C_Z + C_P) \times \left( \frac{s(f) \times R_Z \times C_Z \times C_P}{C_Z + C_P} + 1 \right)} \quad (28)$$

$T_V(f)$  は、システムの閉ループ ゲインの推定される理論的な伝達関数です。実際の回路では帰還ループ応答が異なる場合があり、実際の回路の性能と信頼性を満たすため、ネットワーク アナライザで調整が必要な場合があります。帰還ループの応答は、設計パラメータのワースト ケース変動に照らして評価する必要があります。

$$T_V(f) = G_C(f) \times G_{\text{OPTO}}(f) \times G_{\text{BC}}(f) \times G_O \times G_{\text{CO}}(f_C) \quad (29)$$

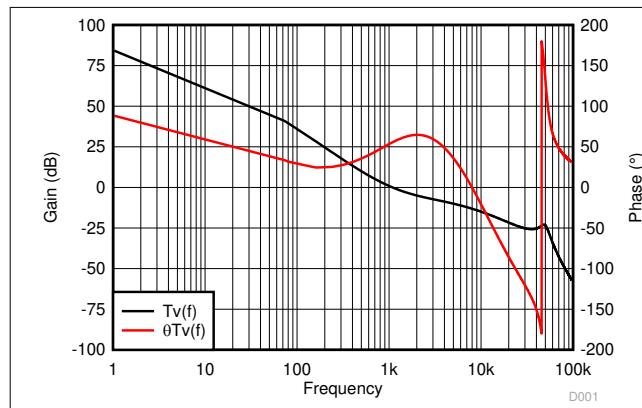

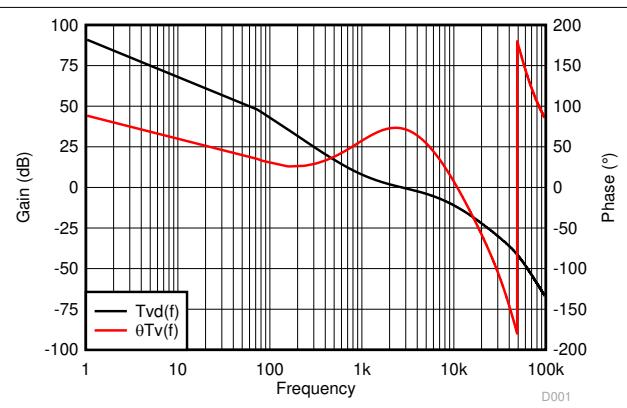

この応用例のために、この設計技法は 95V の最小入力バルク電圧で約 55° の位相マージンを持つ 1kHz での理論的な帰還ループ ( $T_V(f)$ ) クロスオーバーを生成しました。高位線での理論電圧ループは 72° の位相マージンで 2.7kHz でクロスオーバーしています。[図 8-2](#) と [図 8-3](#) を参照してください。 $T_V(f)$  は、ネットワーク アナライザで評価し、必要なら実際の回路動作に基づいてループ補償を調整する必要があります。また、過渡テストを行い、デバイスが安定していることを確認します。

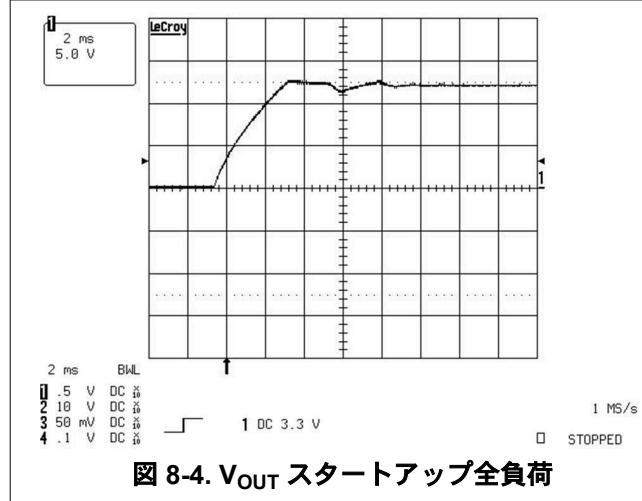

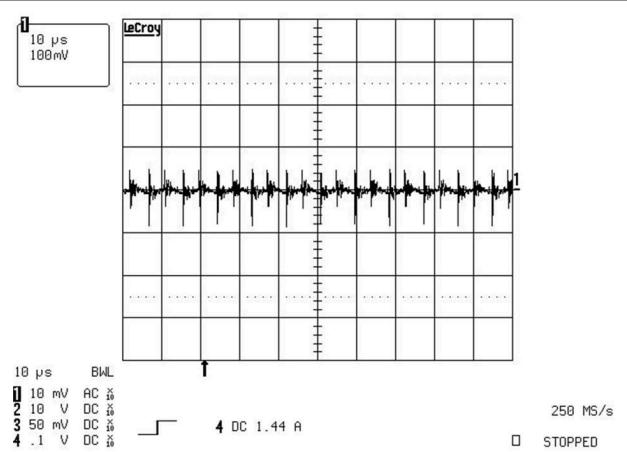

### 8.2.3 アプリケーション曲線

図 8-2. 電圧ループ ゲイン

図 8-3. 電圧ループ ゲイン

図 8-4.  $V_{\text{OUT}}$  スタートアップ全負荷

図 8-5.  $V_{\text{OUT}}$  リップル電圧

## 8.3 電源に関する推奨事項

UC284xL は、絶縁型または非絶縁型のピーク電流モード制御の電源で使用することをお勧めします。このデバイスは、降圧、昇圧、フライバック、およびフォワードコンバータベースの電源トポロジで使用できます。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

- スターグランド手法を使用する必要があります。

- 電流ループは、できるだけ短く狭い範囲に維持する必要があります。

- IC のグランドと電源グランドは、入力バルクコンデンサのリターン側で接続する必要があります。出力段からの高周波と大電流が信号グランドのパスを流れないように注意します。

- 高周波バイパスコンデンサ ( $C_{VCC1}$ ) は、VCC ピンと GND ピンとの間で、ピンにできるだけ近い場所に配置する必要があります。

- 抵抗  $R_{S2}$  とコンデンサ  $C_F$  は、電流検出信号用のローパスフィルタを形成します。 $C_F$  は、CS および GND ピンのできるだけ近くに配置する必要があります。

- コンデンサ  $C_{VREF}$  は、VREF および GND ピンのできるだけ近くに配置する必要があります。

- 単層の基板上でウェーブ半田用に配置された SMD 部品を、図 8-6 に示します。複数の層を使用する場合は、相互接続を容易にし、電流ループ領域を減らすため、一部の部品を再配置できます。半田付けプロセスで可能なら、SMD 部品を垂直方向に配置すると、相互接続やループ領域が改善される場合があります。

#### 8.4.2 レイアウト例

図 8-6. レイアウトの図

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 デバイスの命名規則

|                             |                                 |

|-----------------------------|---------------------------------|

| <b>C<sub>IN</sub></b>       | 入力バルク容量                         |

| <b>C<sub>OUT</sub></b>      | 出力容量                            |

| <b>D</b>                    | デューティサイクル                       |

| <b>ESR</b>                  | 等価直列抵抗                          |

| <b>G<sub>BC(f)</sub></b>    | 光アイソレータの出力から PWM 制御電圧への概算の伝達関数。 |

| <b>G<sub>O</sub></b>        | 制御から出力への伝達関数の DC ゲイン。           |

| <b>G<sub>OPTO(f)</sub></b>  | 設計に含まれている光アイソレータ全体にわたる近似の伝達関数。  |

| <b>I<sub>LPM</sub></b>      | トランスの 1 次側の平均電流                 |

| <b>I<sub>LpPK</sub></b>     | トランスの 1 次側のピーク電流                |

| <b>L<sub>PM</sub></b>       | トランスの 1 次側の磁化インダクタンス            |

| <b>L<sub>SM</sub></b>       | トランスの 2 次側の磁化インダクタンス            |

| <b>N<sub>PS</sub></b>       | トランスの 1 次側と 2 次側の巻線比            |

| <b>N<sub>AS</sub></b>       | トランスの補助と 2 次側の巻線比               |

| <b>T<sub>V(f)</sub></b>     | 帰還制御ループの伝達関数。                   |

| <b>V<sub>INripple</sub></b> | 入力リップル電圧                        |

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

##### 『設計レビュー: 150W 電流モード フライバック (SLUP078)』

参考設計については、UCx84x/UCx84xA/UC284xAQ/TL284x/TL284xB データシートまたは製品ページを参照してください。

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付         | 改訂 | 注  |

|------------|----|----|

| March 2025 | *  | 初版 |

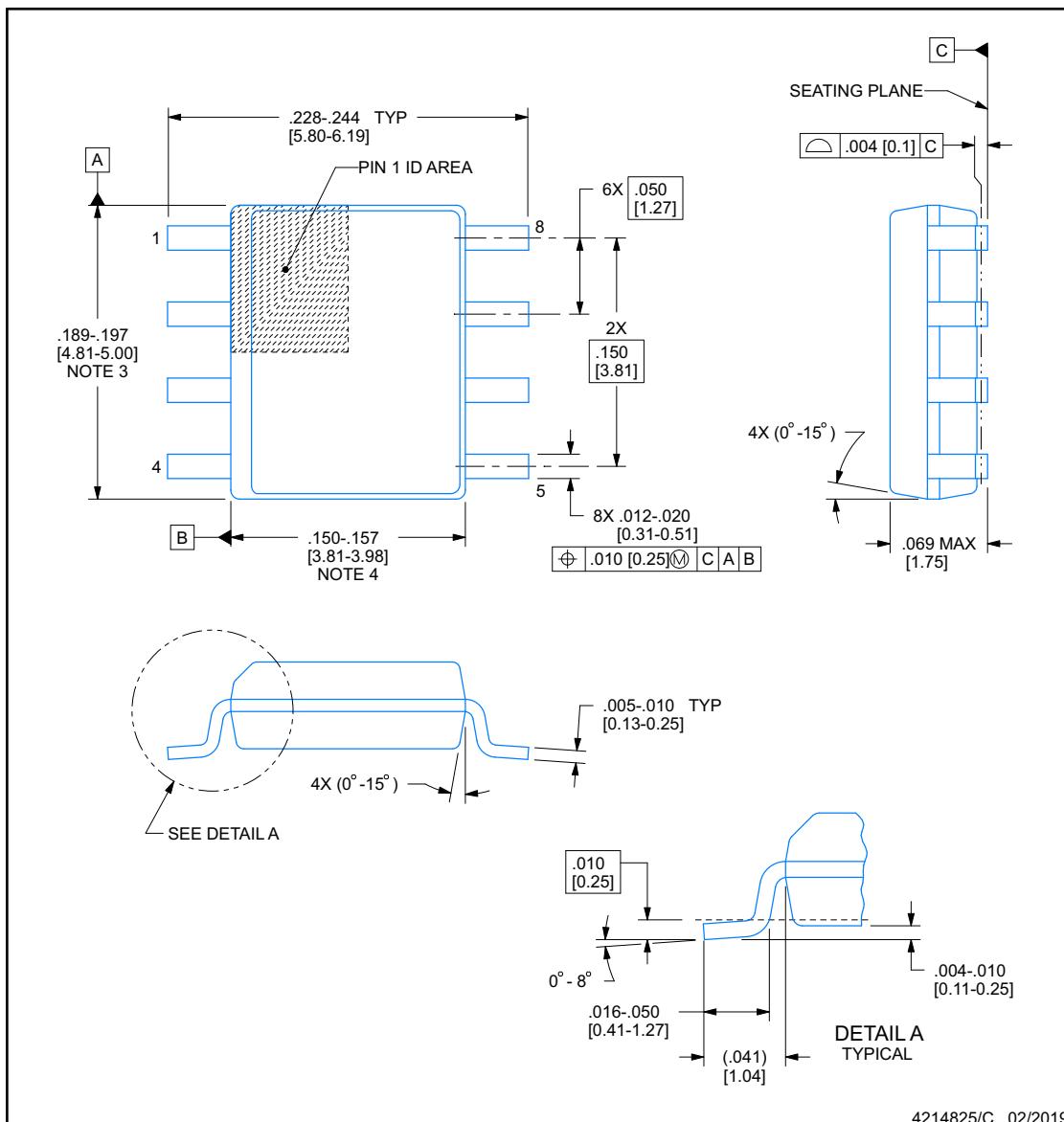

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

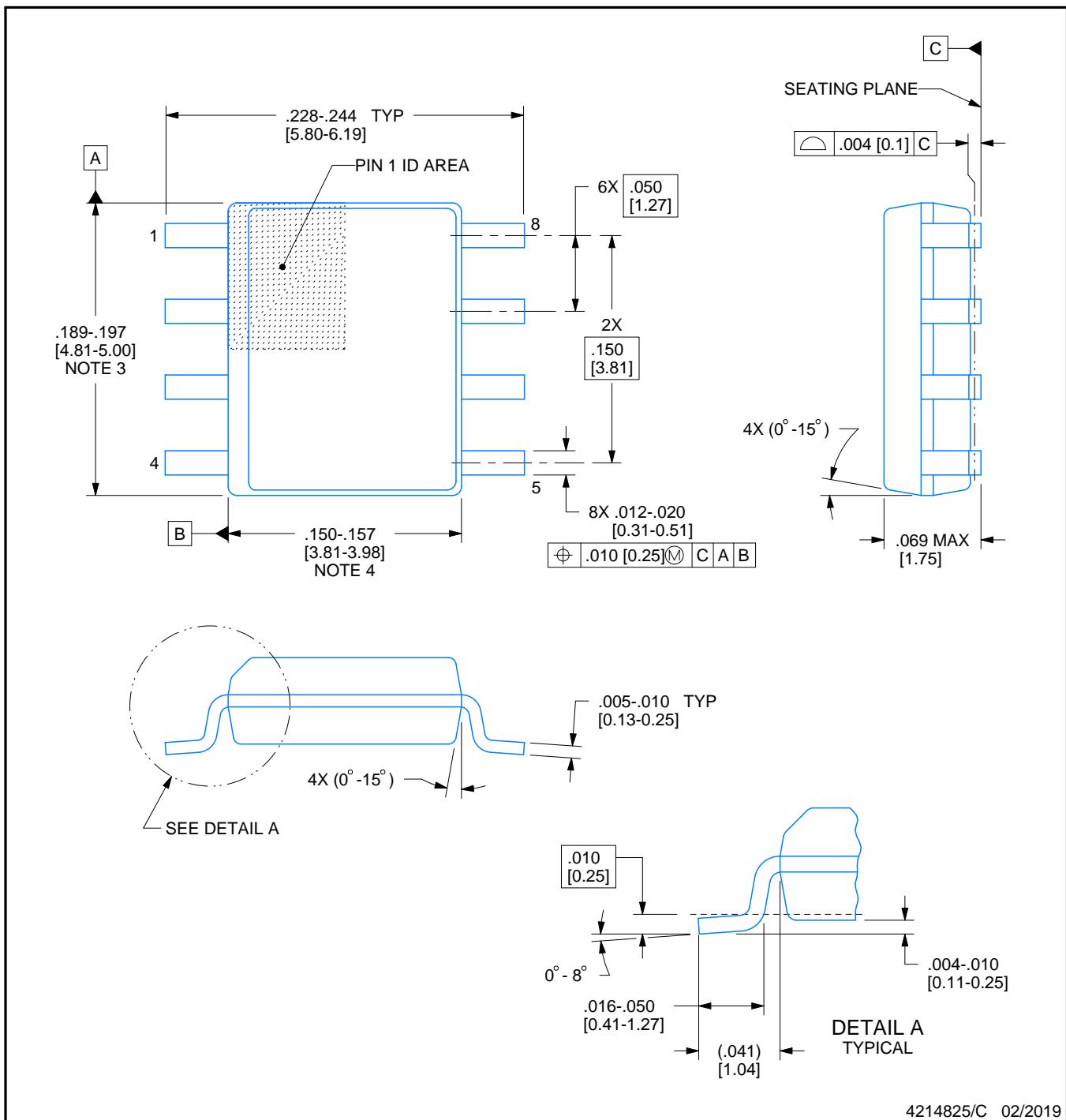

## D0008A

### PACKAGE OUTLINE

#### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

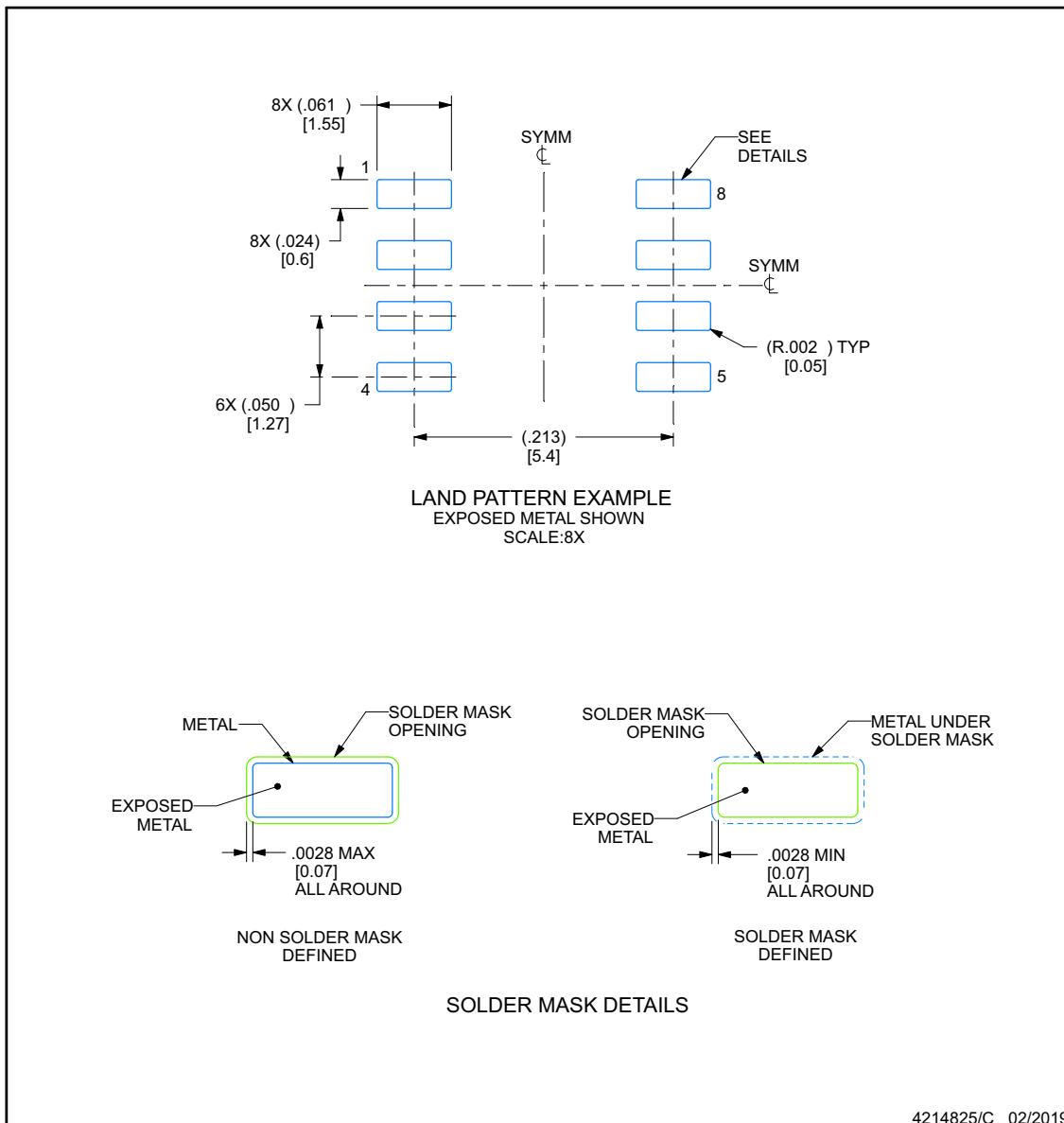

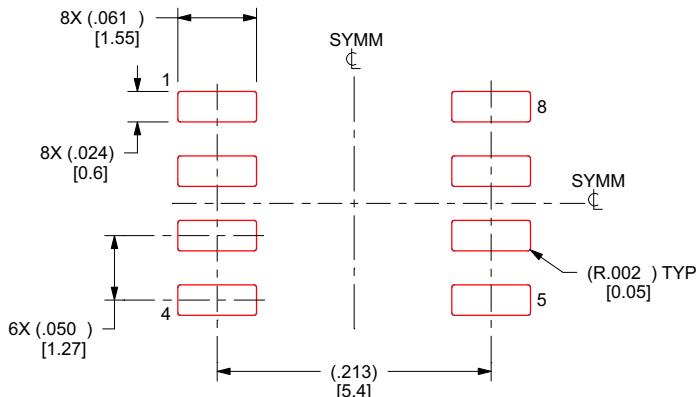

## EXAMPLE BOARD LAYOUT

**D0008A**

**SOIC - 1.75 mm max height**

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

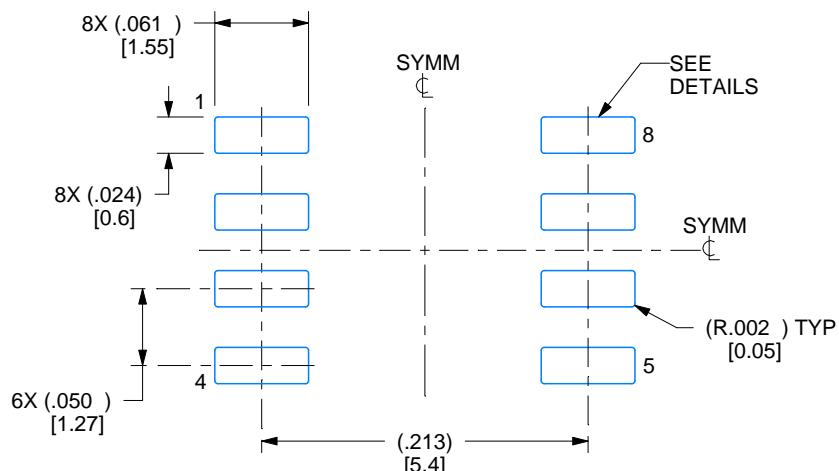

## EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number       | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UC2842LDR-8</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2842L              |

| UC2842LDR-8.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2842L              |

| <a href="#">UC2843LDR-8</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U843BL              |

| UC2843LDR-8.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U843BL              |

| <a href="#">UC2844LDR-8</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2844L              |

| UC2844LDR-8.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2844L              |

| <a href="#">UC2845LDR-8</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2845L              |

| UC2845LDR-8.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | U2845L              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UC2843L, UC2844L, UC2845L :**

- Automotive : [UC2843L-Q1](#), [UC2844L-Q1](#), [UC2845L-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

D0008A

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches.

- Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

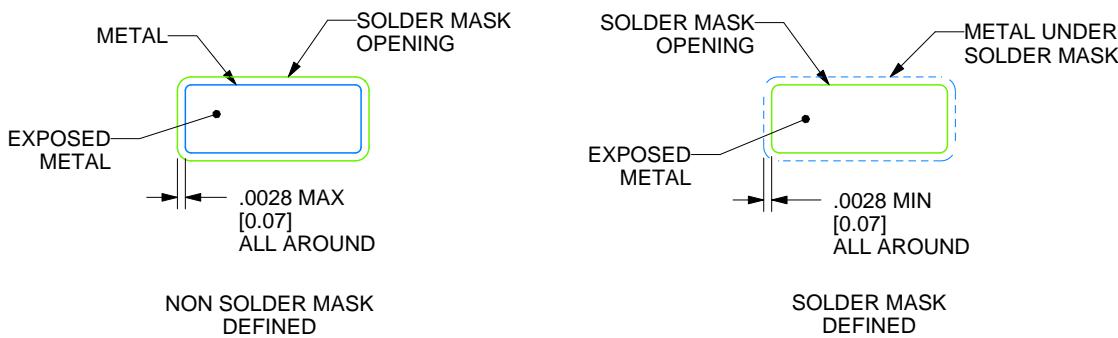

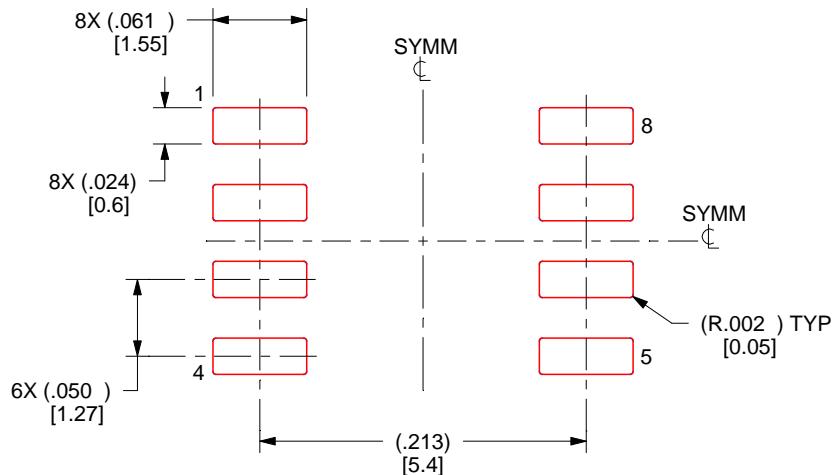

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月