## 改良型 高力率プリレギュレータ

### 特 長

- 固定周波数動作の平均電流モード・コントロール

- 平均電流制御方式にてほぼ1の力率に制御可能

- ライン電流歪みを3%以下に制限可能

- 85V～265Vの電圧入力に対応が可能

- 高精度 広負荷範囲で電力制限が可能

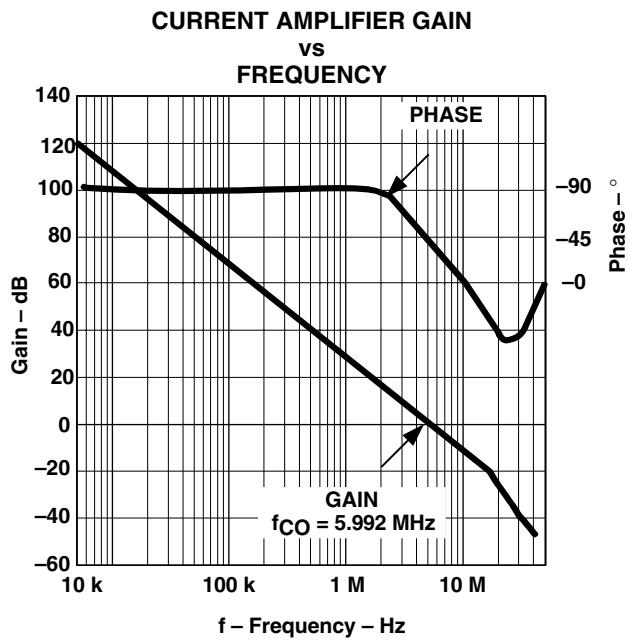

- 広帯域幅(5MHz)、低オフセットの電流検出機能

- 高精度な電流/電圧アンプ出力内蔵

- 高精度・広入力の乗算器内蔵：500mVのV<sub>AC</sub>オフセット、0V～5Vの乗算器出力同相電圧範囲

- 高精度 基準電圧V<sub>REF</sub>内蔵

- 高速で精度向上のイネーブル・コンパレータ

- UVLO回路内蔵(16V/10Vまたは10.5V/10V)

- 低起動時電流：300μA

### 概 要

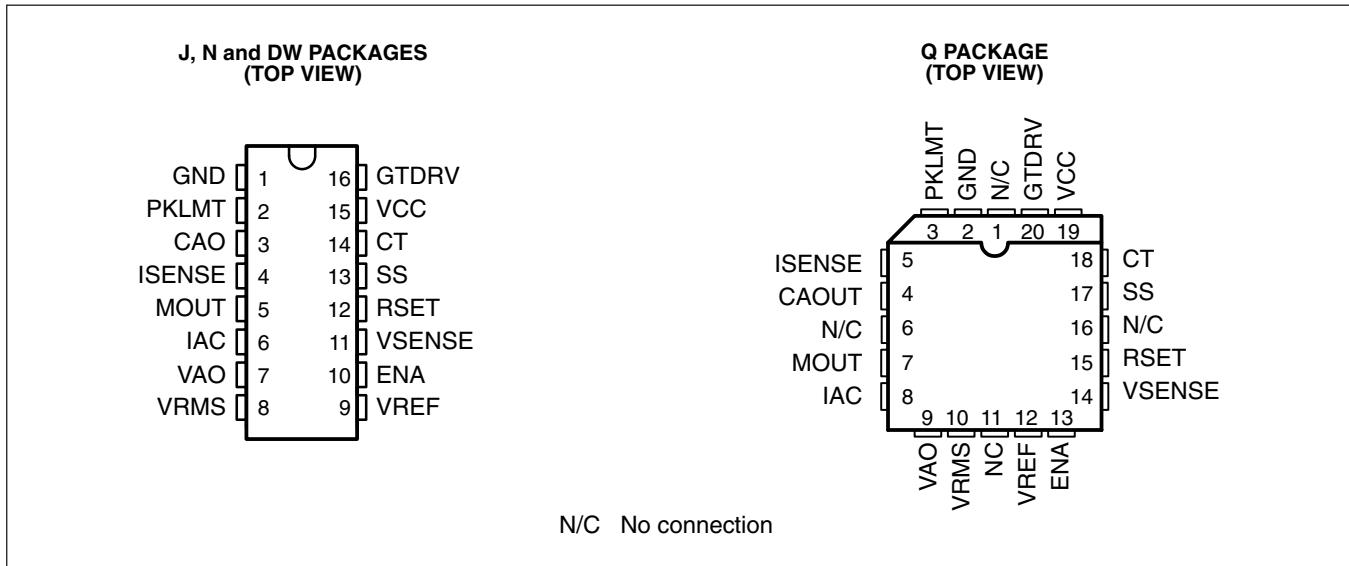

UC3854A/Bバージョンは、UC3854のピン互換で機能を拡張した製品です。UC3854と同様に、UC3854A/Bはアクティブ力率改善用のプリレギュレータに必要な全ての機能を備えています。コントローラはAC入力ライン電流の波形をAC入力ライン電圧に一致するよう成形することでほぼ1の力率を達成します。UC3854A/Bは平均電流モード・コントロールを使用しています。平均電流モード・コントロールでは、ピーク電流モード・コントロールと異なり、スロープ補償なしで安定した低歪みの正弦波ライン電流が維持することができます。その他の特長として、7.5Vで1%精度の基準電圧、固定周波数の発振器、PWM回路、ソフトスタート付き電圧アンプ、ライン電圧検出(VRMS二乗器)、入力電源電圧のクランプ、過電流コンパレータなどを内蔵しています。パッケージは16pinのN(PDIP)、DW(ワイドSOIC)、J(CDIP)及び20pinのQ(PLCC)で供給されています。各製品の温度範囲については3ページの発注情報を参照してください。

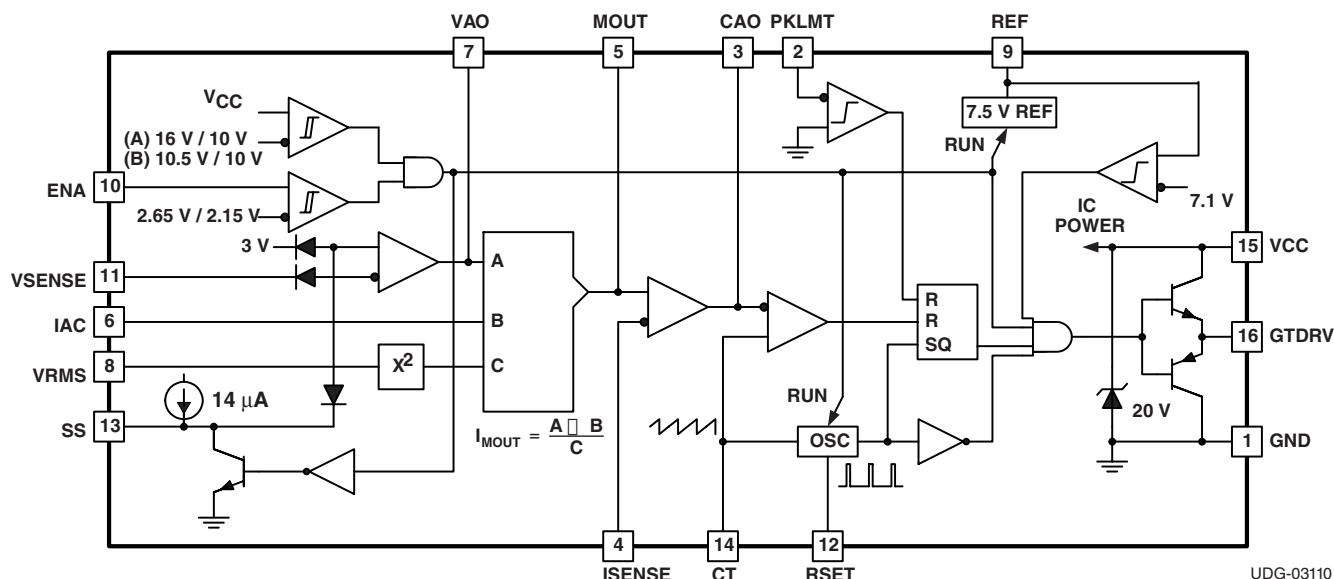

### ブロック図

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 概要(続き)

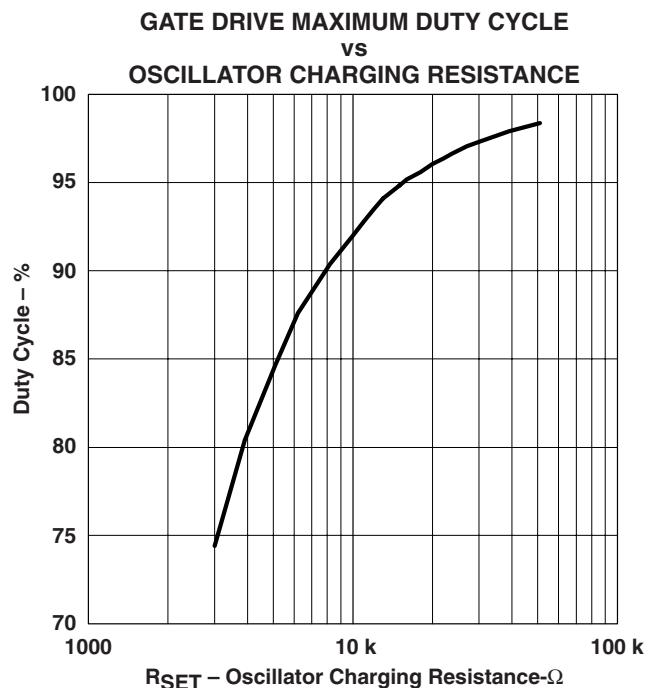

UC3854A/Bは、広帯域幅、低オフセットの電流アンプ、高速応答及び高精度に改善されたイネーブル・コンパレータ、高精度基準回路、UVLOスレッシュホールド電圧、起動時低電流を内蔵しています。また、より使いやすくかつ性能を強化した乗算回路を内蔵すなどUC3854に比べて大幅に特性が改善されるとともに外付け部品点数も削減できます。乗算器出力/電流アンプ入力の同相入力範囲も改良されており、設計者はより柔軟に大きな負荷変動電源変動に対しても安定した電流検出の選択をすることができます。RSETは発振器の充電電流のみをコントロールし、乗算器の最大出力電流のクランプには影響を与えません。この電流は常に最大 $2 \times I_{AC}$ にクランプされているため、設計が簡素化され、また、電圧低下時や超低ライン状態時に帰還電力の制限を行えます。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ABSOLUTE MAXIMUM RATINGS

特に記述のない限り、動作温度<sup>(1)</sup>

|                                                                                  |                            | UCX854A, UCX854B | UNIT |

|----------------------------------------------------------------------------------|----------------------------|------------------|------|

| Supply voltage, V <sub>CC</sub>                                                  |                            | 22               | V    |

| GTDRV current, I <sub>GTDRV</sub>                                                | Continuous                 | 0.5              | A    |

| GTDRV Current, I <sub>GTDRV</sub>                                                | 50% duty cycle             | 1.5              | A    |

| Input voltage                                                                    | VSENSE, VRMS , ISENSE MOUT | 11               | V    |

|                                                                                  | PKLMT                      | 5                | V    |

| Input current                                                                    | RSET, IAC, PKLMT, ENA      | 10               | mA   |

| Power dissipation                                                                |                            | 1                | W    |

| Junction temperature, T <sub>J</sub>                                             |                            | -55 to 150       | °C   |

| Storage temperature, T <sub>stg</sub>                                            |                            | -65 to 150       |      |

| Lead temperature, T <sub>sol</sub> , 1,6 mm (1/16 inch) from case for 10 seconds |                            | 300              |      |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。全ての電圧はGNDを基準としています。電流の極性で正は指定の端子に流入する方向、負は流出する方向を表しています。ENA入力は内部で約10Vにクランプされています。

## RECOMMENDED OPERATING CONDITIONS

|                                                |         | MIN | MAX | UNIT |

|------------------------------------------------|---------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                |         | 10  | 20  | V    |

| Operating junction temperature, T <sub>J</sub> | UC1854X |     | -55 | °C   |

|                                                | UC2854X |     | 125 |      |

|                                                | UC3854X |     | -40 |      |

|                                                |         |     | 85  |      |

|                                                |         |     | 0   |      |

|                                                |         |     | 70  |      |

## PACKAGE DESCRIPTION

## ORDERING INFORMATION

| $T_A$          | UVLO<br>TURN-ON<br>(V) | UVLO<br>TURN-OFF<br>(V) | PART NUMBERS   |                |                 |                |

|----------------|------------------------|-------------------------|----------------|----------------|-----------------|----------------|

|                |                        |                         | CDIP-16<br>(J) | PDIP-16<br>(N) | SOIC-16<br>(DW) | PLCC-20<br>(Q) |

| -50°C to 125°C | 16                     | 10                      | -              | -              | -               | -              |

|                | 10.5                   | 10                      | UC1854BJ       | -              | -               | -              |

| -40°C to 85°C  | 16                     | 10                      | UC2854AJ       | UC2854AN       | UC2854ADW       | UC2854AQ       |

|                | 10.5                   | 10                      | UC2854BJ       | UC2854BN       | UC2854BDW       | UC2854BQ       |

| 0°C to 70°C    | 16                     | 10                      | -              | UC3854AN       | UC3854ADW       | -              |

|                | 10.5                   | 10                      | -              | UC3854BN       | UC3854BDW       | -              |

(1) DW及びQパッケージはテープ/リールで供給されています。デバイス・タイプの末尾にTRを付けるとDWパッケージでは(例、UC2854ADWTR)発注数量単位はリールあたり2000個、Qパッケージではリールあたり1000個です。

## THERMAL RESISTANCE

| RESISTANCES          | PACKAGED DEVICES  |                   |                       |                      |

|----------------------|-------------------|-------------------|-----------------------|----------------------|

|                      | CDIP-16<br>(J)    | PDIP-16<br>(N)    | SOP-16<br>(DW)        | PLCC-20<br>(Q)       |

| $\theta_{JC}$ (°C/W) | 28 <sup>(2)</sup> | 45                | 27                    | 34                   |

| $\theta_{JA}$ (°C/W) | 80-120            | 90 <sup>(3)</sup> | 50-130 <sup>(3)</sup> | 43-75 <sup>(3)</sup> |

(2) 規定されている $\theta_{JC}$ のデータ値はMIL-STD-1835Bから導かれており、それには“表記されている基準値は60 × 60ミルのマイクロ回路デバイスのシリコンダイでのワースト・ケース時のもの(平均値+2シグマ)で、14,400平方ミルまでのダイ・サイズのデバイスに適用”と記載されています。14,400平方ミル以上のダイ・サイズのデバイスには、デュアル・イン・ラインでは11°C/W、フラット・パック及びピン・グリッド・アレイでは10°C/Wを使用してください。

(3)  $\theta_{JA}$ (接合部/周囲間)は、値が記載されている場合、1オンスの銅配線をもつ大きさが5平方インチのFR4のPCボードにデバイスを実装した場合のものです。抵抗値が範囲として記載されている場合は、低いほうの値は大きさが5平方インチのアルミニウムのPCボードにデバイスを実装した場合のものです。試験に使用したPWBは、厚さが0.062インチで、100 × 100ミルのプローブ・ランドが各配線端にあり、パワー・パッケージでは配線幅は0.635mm、パワー・パッケージではない場合では配線幅は1.3mmです。

## ELECTRICAL CHARACTERISTICS

$V_{CC} = 18 \text{ V}$ ,  $R_T = 8.2 \text{ k}\Omega$ ,  $C_T = 1.5 \text{ nF}$ ,  $V_{PKLMT} = 1 \text{ V}$ ,  $V_{VRMS} = 1.5 \text{ V}$ ,  $I_{IAC} = 100 \mu\text{A}$ ,  $I_{SENSE} = 0 \text{ V}$ ,  $V_{CAO} = 3.5 \text{ V}$ ,  $V_{VAO} = 5 \text{ V}$ ,  $V_{VSENSE} = 3 \text{ V}$ ,  $-40^\circ\text{C} < T_A < 85^\circ\text{C}$  for the UC2854A and UC2854B, and  $0^\circ\text{C} < T_A < 70^\circ\text{C}$  for the UC3854A and UC3854B, and  $T_A = T_J$  (unless otherwise noted)

| PARAMETER                             | TEST CONDITIONS                                                                 | MIN  | TYP  | MAX  | UNIT          |

|---------------------------------------|---------------------------------------------------------------------------------|------|------|------|---------------|

| <b>OVERALL</b>                        |                                                                                 |      |      |      |               |

| Supply current, off                   | $CAO = 0 \text{ V}$ , $VAO = 0 \text{ V}$ , $V_{CC} = V_{UVLO} - 0.3 \text{ V}$ |      | 250  | 400  | $\mu\text{A}$ |

| Supply current, on                    |                                                                                 |      | 12   | 18   | $\text{mA}$   |

| $V_{CC}$ turn-on threshold voltage    | UCx854A                                                                         | 15.0 | 16.0 | 17.5 | V             |

|                                       | UCx854B                                                                         | 8.0  | 10.5 | 11.2 |               |

|                                       |                                                                                 | 9    | 10   | 12   |               |

| $V_{CC}$ clamp                        | $I_{VCC} = I_{VCC(on)} + 5 \text{ mA}$                                          | 18   | 20   | 22   |               |

| <b>VOLTAGE AMPLIFIER</b>              |                                                                                 |      |      |      |               |

| Input voltage                         |                                                                                 | 2.9  | 3.0  | 3.1  | V             |

| $V_{SENSE}$ bias current              |                                                                                 | -500 | -25  | 500  | nA            |

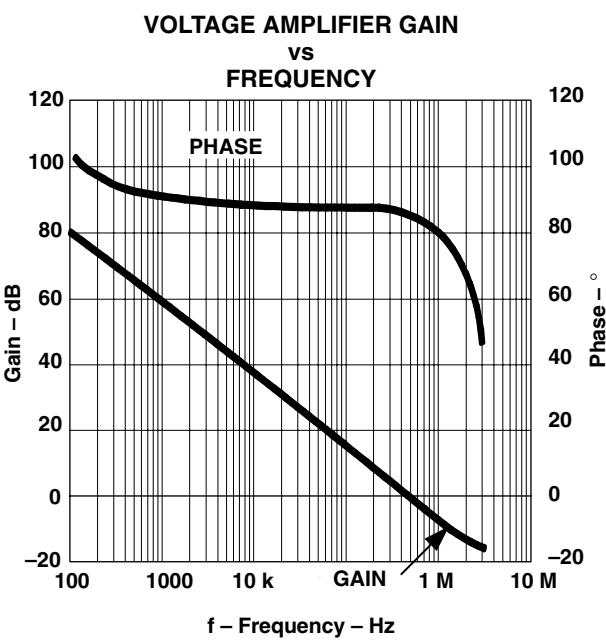

| Open loop gain                        | $2 \text{ V} \leq V_{OUT} \leq 5 \text{ V}$                                     | 70   | 100  |      | dB            |

| $V_{OH}$                              | $I_{LOAD} = -500 \mu\text{A}$                                                   |      | 6    |      | V             |

| $V_{OL}$                              | $I_{LOAD} = 500 \mu\text{A}$                                                    |      | 0.3  | 0.5  | V             |

| $I_{SC}$                              | $V_{OUT} = 0 \text{ V}$                                                         |      | 1.5  | 3.5  | $\text{mA}$   |

| Gain bandwidth product <sup>(1)</sup> | $f_{IN} = 100 \text{ kHz}$ , $10 \text{ mV}_{P-P}$                              |      | 1    |      | MHz           |

| <b>CURRENT AMPLIFIER</b>              |                                                                                 |      |      |      |               |

| Input offset voltage                  | $V_{CM} = 0 \text{ V}$ , $T_A = 25^\circ\text{C}$                               | -4   | 0    |      | mV            |

|                                       | $V_{CM} = 0 \text{ V}$ , overtemperature                                        | -5.5 | 0    |      |               |

| Input bias current, $I_{SENSE}$       | $V_{CM} = 0 \text{ V}$                                                          | -500 | 500  |      | nA            |

| Open loop gain                        | $2 \text{ V} \leq V_{OUT} \leq 6 \text{ V}$                                     | 80   | 110  |      | dB            |

| $V_{OH}$                              | $I_{LOAD} = -500 \mu\text{A}$                                                   |      | 8    |      | V             |

| $V_{OL}$                              | $I_{LOAD} = 500 \mu\text{A}$                                                    |      | 0.3  | 0.5  |               |

| $I_{SC}$                              | $V_{OUT} = 0 \text{ V}$                                                         |      | 1.5  | 3.5  | $\text{mA}$   |

| CMRR                                  |                                                                                 | -0.3 | 5.0  |      | V             |

| Gain bandwidth product <sup>(1)</sup> | $f_{IN} = 100 \text{ kHz}$ , $10 \text{ mV}_{P-P}$                              | 3    | 5    |      | MHz           |

| <b>REFERENCE</b>                      |                                                                                 |      |      |      |               |

| Output voltage                        | $I_{REF} = 0 \text{ mA}$ , $T_A = 25^\circ\text{C}$                             | 7.4  | 7.5  | 7.6  | V             |

|                                       | $I_{REF} = 0 \text{ mA}$                                                        | 7.35 | 7.50 | 7.65 |               |

| Load regulation                       | $1 \text{ mA} \leq I_{REF} \leq 10 \text{ mA}$                                  | 0    | 8    | 20   | mV            |

| Line regulation                       | $12 \text{ V} \leq V_{CC} \leq 18 \text{ V}$                                    | 0    | 14   | 25   |               |

| $I_{SC}$                              | $V_{REF} = 0 \text{ V}$                                                         | 25   | 35   | 60   | $\text{mA}$   |

(1) 設計で保証されており、テストは行われていません。

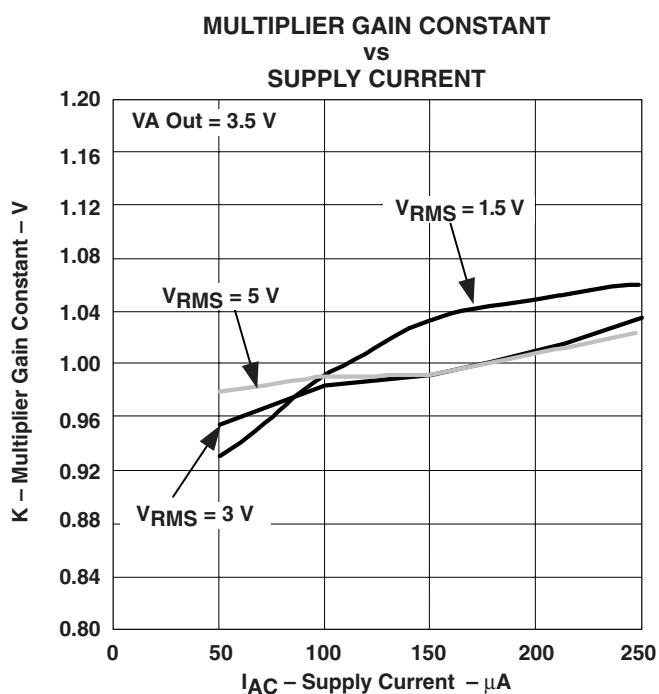

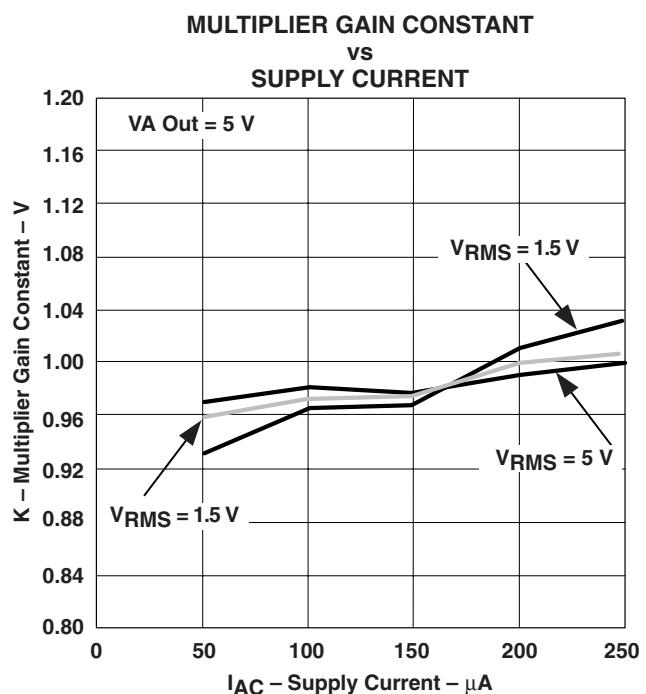

$$(2) \text{ゲイン定数。 } (K) = \frac{I_{IAC} \times (V_{VAO} - 1.5 \text{ V})}{[(V_{VRMS})^2 \times I_{MOUT}]}$$

## ELECTRICAL CHARACTERISTICS

$V_{CC} = 18 \text{ V}$ ,  $R_T = 8.2 \text{ k}\Omega$ ,  $C_T = 1.5 \text{ nF}$ ,  $V_{PKLMT} = 1 \text{ V}$ ,  $V_{VRMS} = 1.5 \text{ V}$ ,  $I_{IAC} = 100 \mu\text{A}$ ,  $I_{SENSE} = 0 \text{ V}$ ,  $V_{CAO} = 3.5 \text{ V}$ ,  $V_{VAO} = 5 \text{ V}$ ,  $V_{VSENSE} = 3 \text{ V}$ ,  $-40^\circ\text{C} < T_A < 85^\circ\text{C}$  for the UC2854A and UC2854B, and  $0^\circ\text{C} < T_A < 70^\circ\text{C}$  for the UC3854A and UC3854B, and  $T_A = T_J$  (unless otherwise noted)

| PARAMETER                                        | TEST CONDITIONS                                                               | MIN                            | TYP                     | MAX  | UNIT          |

|--------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|-------------------------|------|---------------|

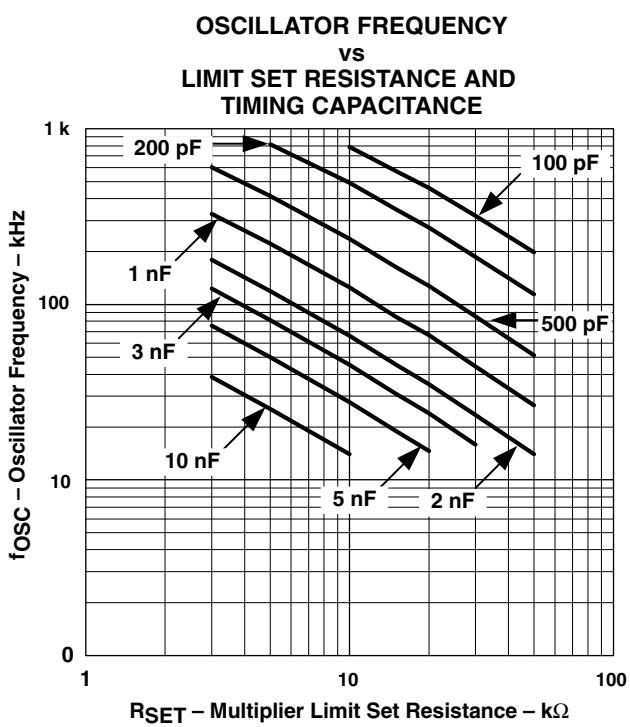

| <b>OSCILLATOR</b>                                |                                                                               |                                |                         |      |               |

| Initial accuracy                                 | $T_A = 25^\circ\text{C}$                                                      | 85                             | 100                     | 115  | $\text{kHz}$  |

| Voltage stability                                | $12 \text{ V} \leq V_{CC} \leq 18 \text{ V}$                                  |                                | 1%                      |      |               |

| Total variation                                  | Line, temperature                                                             | 80                             | 120                     |      | $\text{kHz}$  |

| Ramp amplitude (peak-to-peak)                    |                                                                               | 4.9                            | 5.9                     |      | $\text{V}$    |

| Ramp valley voltage                              |                                                                               | 0.8                            | 1.3                     |      |               |

| <b>ENABLE/SOFT-START/CURRENT LIMIT</b>           |                                                                               |                                |                         |      |               |

| Enable threshold voltage                         |                                                                               | 2.35                           | 2.55                    | 2.80 | $\text{V}$    |

| Enable hysteresis                                | $V_{FAULT} = 2.5 \text{ V}$                                                   | 500                            | 600                     |      | $\text{mV}$   |

| Enable input bias current                        | $V_{ENA} = 0 \text{ V}$                                                       | -2                             | -5                      |      | $\mu\text{A}$ |

| Propagation delay to disable time <sup>(1)</sup> | Enable overdrive = 100 mV                                                     | 300                            | ns                      |      |               |

| Soft-start charge current                        | $V_{SS} = 2.5 \text{ V}$                                                      | 10                             | 14                      | 24   |               |

| Peak limit offset voltage                        |                                                                               | -15                            | 15                      |      | $\text{mV}$   |

| Peak limit input current                         | $V_{PKLMT} = -0.1 \text{ V}$                                                  | -200                           | -100                    |      | $\mu\text{A}$ |

| Peak limit propagation delay time <sup>(1)</sup> |                                                                               | 150                            |                         |      | ns            |

| <b>MULTIPLIER</b>                                |                                                                               |                                |                         |      |               |

| Output current, $I_{AC}$ limited                 | $I_{AC} = 100 \mu\text{A}$ ,<br>$R_{SET} = 10 \text{ k}\Omega$                | $V_{RMS} = 1 \text{ V}$ ,      | -220                    | -200 | -170          |

| Output current, zero                             | $I_{AC} = 0 \mu\text{A}$ ,                                                    | $R_{SET} = 10 \text{ k}\Omega$ | -2.0                    | -0.2 | 2.0           |

| Output current, power limited                    | $V_{RMS} = 1.5 \text{ V}$ ,                                                   | $V_a = 6 \text{ V}$            | -230                    | -200 | -170          |

| Output current                                   | $V_{RMS} = 1.5 \text{ V}$ ,                                                   | $V_a = 2 \text{ V}$            |                         | -22  | $\mu\text{A}$ |

|                                                  | $V_{RMS} = 1.5 \text{ V}$ ,                                                   | $V_a = 5 \text{ V}$            |                         | -156 |               |

|                                                  | $V_{RMS} = 5 \text{ V}$ ,                                                     | $V_a = 2 \text{ V}$            |                         | -2   | $\mu\text{A}$ |

|                                                  | $V_{RMS} = 5 \text{ V}$ ,                                                     | $V_a = 5 \text{ V}$            |                         | -14  |               |

| Gain constant <sup>(2)</sup>                     | $V_{RMS} = 1.5 \text{ V}$ , $V_a = 6 \text{ V}$ ,<br>$T_A = 25^\circ\text{C}$ |                                | -1.1                    | -1.0 | -0.9          |

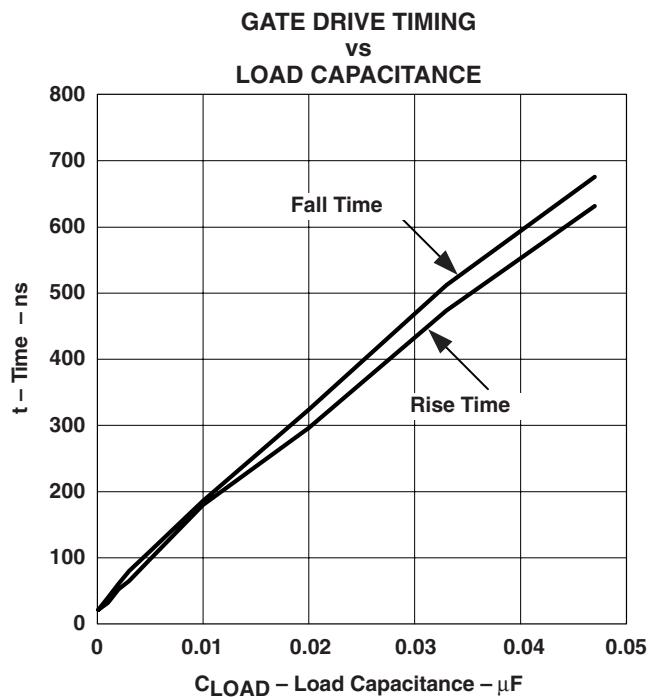

| <b>GATE DRIVER</b>                               |                                                                               |                                |                         |      |               |

| $V_{OH}$                                         | High-level output voltage                                                     | $I_{OUT} = -200 \text{ mA}$ ,  | $V_{CC} = 15 \text{ V}$ | 12.0 | 12.8          |

| $V_{OL}$                                         | Low-level output voltage                                                      | $I_{OUT} = 200 \text{ mA}$     |                         | 1.0  | 2.2           |

|                                                  |                                                                               | $I_{OUT} = 10 \text{ mA}$      |                         | 300  | 500           |

|                                                  | Low-level UVLO voltage                                                        | $I_{OUT} = 50 \text{ mA}$ ,    | $V_{CC} = 0 \text{ V}$  | 0.9  | 1.5           |

|                                                  | Output rise time <sup>(1)</sup>                                               | $C_{LOAD} = 1 \text{ nF}$      |                         | 35   | ns            |

|                                                  | Output fall time <sup>(1)</sup>                                               | $C_{LOAD} = 1 \text{ nF}$      |                         | 35   |               |

|                                                  | Output peak current <sup>(1)</sup>                                            | $C_{LOAD} = 10 \text{ nF}$     |                         | 1.0  | A             |

(1) 設計で保証されており、テストは行われていません。

$$(2) \text{ゲイン定数。 } (K) = \frac{I_{IAC} \times (V_{VAO} - 1.5 \text{ V})}{[(V_{VRMS})^2 \times I_{MOUT}]}$$

## TERMINAL FUNCTIONS

| NAME   | TERMINAL<br>PACKAGES |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|--------|----------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | J/N/DW               | Q/L |     |                                                                                                                                                                                                                                                                                                 |

| CAO    | 3                    | 4   | O   | 誤差アンプ出力およびPWM回路入力。<br>広帯域幅の電流アンプの出力及びPWMデューティ・サイクル・コンパレータへの入力。<br>この誤差アンプで生成される出力信号はPWM回路に入力されスイッチング制御に利用されます。出力振幅は0.1V~7.5Vです。                                                                                                                                                                 |

| CT     | 14                   | 18  | I   | 発振周波数設定端子。CTからGNDにコンデンサを挿入することで発振周波数を設定します。                                                                                                                                                                                                                                                     |

| ENA    | 10                   | 13  | I   | イネーブル端子。このピンに2.55Vより高い電圧を加え続けるとデバイスは動作を開始/維持します。このピンが2.05Vより低電位に下がるとデバイスは停止します。                                                                                                                                                                                                                 |

| GND    | 1                    | 2   | -   | GNDに接続される全てのバイパス/タイミング・コンデンサはできるだけ短く接続するように配慮してください。また全ての電圧はGNDを基準として測定されています。                                                                                                                                                                                                                  |

| GTDRV  | 16                   | 20  | O   | 1.5Aのピーク電流能力を持つトーテムポール型のMOSFETゲート・ドライバです。この出力はデバイスが高電源電圧でも動作できるよう内部でクランプされています。GTDRV出力に過度のオーバーシュートを生じさせる恐れのある場合にはゲート・インピーダンスとGTDRV出力ドライバ間の相互作用を防止するため、最小5Ω以上の直列ゲート抵抗を接続してください。<br>容量性負荷を駆動する際はGTDRV出力には常にある程度のオーバーシュートが予想されます。また必要に応じて順方向電圧の低いショットキーダイオードなどを接続してデバイスの寄生トランジスタの生成を防いでください。       |

| IAC    | 6                    | 8   | I   | 乗算器への電流入力で、ライン電圧に比例します。アナログ乗算器へのこの入力は電流で制御されます。乗算器はこの電流入力(IAC)からMOUTへ超低歪みで制御されているため、このピンがライン電圧を検出するのに使用されます。IACから整流された60/50Hzラインへ抵抗を挿入するのに加え、IACからVREFにも抵抗を接続してください。VREFへの抵抗が整流器への抵抗値の1/4であれば、オフセット電圧はキャンセルされ、ライン電流のクロスオーバー歪みは極めて小さくなります。                                                       |

| ISENSE | 4                    | 5   | I   | スイッチ電流検出入力。このピンは電流アンプへの反転入力です。この入力と非反転入力MOUTはGND及びGND電位以下でも機能します。これら入力は-0.5Vより下がらないようGNDへ接続するダイオードで保護してください。                                                                                                                                                                                    |

| MOUT   | 5                    | 7   | I/O | 乗算器出力及び電流検出アンプの正入力。アナログ乗算器の出力と電流アンプの非反転入力はMOUTで互いに接続されています。MOUTにも上記のISENSEと同様に端子電位が-0.5Vより低電位にならないように配慮してください。乗算器出力は電流であるため、このピンはISENSEと同様にハイ・インピーダンス入力であり、よって電流アンプはGNDノイズを除去するため差動アンプとして構成することができます。                                                                                           |

| PKLMT  | 2                    | 3   | I   | ピーク電流制限。PKLMTのスレッシュホールドは0.0Vです。この入力を電流検出抵抗の負電圧側に接続してください。負電流の検出信号をGND電位までオフセットするため抵抗をREF間に接続してください。                                                                                                                                                                                             |

| RSET   | 12                   | 15  | I   | 発振器の充電電流及び乗算器制限電流の設定。RSETからGNDに抵抗を接続することにより発振器の充電電流と乗算器の最大出力を設定します。乗算器の出力電流はRSETからグランドへの抵抗により分圧されその値は3.75Vです。                                                                                                                                                                                   |

| SS     | 13                   | 17  | I   | ソフトスタート。デバイスが停止状態またはV <sub>CC</sub> 電位が規定値以下であれば、SS電位はGNDレベルであり続けます。V <sub>CC</sub> が規定値以上になり、かつデバイスが動作状態になった場合、SSは14μAの内部電流源により充電されます。SSがVREFより下であればSSは電圧アンプへの基準入力として機能します。SSからGNDへコンデンサを接続することで、基準電圧はゆっくりと上昇し、PWMデューティ・サイクルを序々に増加させます。停止状態または電源電圧が規定値以下に降下した場合には、SSは即座に電位を放電し、PWM動作を停止状態にします。 |

| VAO    | 7                    | 9   | I   | 電圧アンプの出力                                                                                                                                                                                                                                                                                        |

| VCC    | 15                   | 19  | I   | 正電源レール                                                                                                                                                                                                                                                                                          |

| VREF   | 9                    | 12  | O   | 基準電源。ピーク制限点の設定及びデバイス内部の基準電圧として使用されます。デバイスの安定動作のためコンデンサをGND間に接続してください。                                                                                                                                                                                                                           |

| VRMS   | 8                    | 10  | I   | 乗算器への入力。このピンは入力RMS電圧を検出して乗算器に入力します。                                                                                                                                                                                                                                                             |

| VSENSE | 11                   | 14  | I   | このピンは出力からの帰還電圧を供給します。この入力は電圧誤差増幅器に接続され、電圧誤差増幅器の出力は乗算器回路へのもう1つの入力となります。                                                                                                                                                                                                                          |

# 機能説明

UC3854A/UC3854B ファミリーは、UC3854 アクティブ力率改善回路のピン互換の上位機種として設計されています。各内部回路の機能の強化により、UC3854 を使用する場合に必要とされた外付け部品を大幅に削除することができます。さらに、乗算、二乗、除算の直線性を改善することでシステム全体の性能が最大限に高められています。回路の機能強化についての詳細を以下の項で説明します。詳細な設計アプリケーションのリファレンス・データについては、アプリケーション・ノート “UC3854 Controlled Power Factor Correction Circuit Design”(文献番号SLUA144) 及び “UC3854A and UC3854B Advanced Power Factor Correction Control ICs”(文献番号SLUA177) を参照してください。

## 乗算/二乗、除算

UC3854A/B の乗算器の設計では UC3854 と同じゲイン定数( $K = -1$ )が維持されています。入力と出力電流の関係は以下の式で与えられます。

$$I_{MOUT} = I_{IAC} \times \frac{(V_{VAO} - 1.5 \text{ V})}{K \times (V_{VRMS})^2} \quad (1)$$

これは UC3854 とほぼ同じですが、回路の差異により性能やアプリケーション上に改善がなされています。相違点は IAC 入力についてです。UC3854A/B バージョンは、UC3854 で用いられた 6.0V ではなく、全動作温度範囲にわたってこのピンの電圧を約 500mV にレギュレーションします。オフセット電圧が低いため、UC3854 を用いた設計で必要とされた IAC から VREF へのラインのゼロ・クロス補償抵抗が不要となります。最大の性能を引き出すため、高ライン時の IAC への最大電流は 250 $\mu\text{A}$  です。従って、 $V_{VAC(max)}=270\text{V}$  あるとすると、

$$R_{IAC} = \frac{270 \times 1.414}{250\mu\text{A}} = 1.53 \text{ M}\Omega \quad (2)$$

UC3854A/B では  $V_{VRMS}$  ピンの直線動作範囲も改善されています。 $V_{VRMS}$  の入力範囲は 0V ~ 5.5V に広がっています。UC3854A の二乗回路は線形近似ではなくアナログ乗算器を使用しているため、精度が改善しており、不連続性が解消されています。 $V_{VRMS}$  に接続される外付けの分圧回路は低ライン時(85VAC)にても 1.5V を維持してください。このことは高ライン時(270VAC)、には  $V_{VRMS}$  電位が 4.77V になります。

電圧アンプの出力は乗算器への 3 番目の入力となり、内部で 6.0V にクランプされています。このことにより、UC3854 を用いた設計でたびたび使用されていた外付けのツェナー・ダイオードのクランプが不要になります。この入力の乗算器へのオフセット電圧は UC3854A/B では 1.5V に上げられています。

電流アンプの非反転入力と共に、乗算器の出力ピンの出力電圧範囲は、UC3854 が -0.3V から 2.5V であるのに対し、A/B バージョンでは -0.3V から 5.0V です。この改善により、UC3854A/B は電流検出信号の振幅が極めて大きいアプリケーションにも使用することができます。

## 電圧アンプ

UC3854A/B の電圧アンプの設計は 2 つの点を除いて基本的に UC3854 と同じです。1 番目の点は 内部接続についてです。電圧が低いと補償コンデンサでの電荷量が低減し、入力電圧の低下または瞬停といった大きな過度現象の特性が改善されます。また、そのことは帰還信号を流れる DC 电流も少なく抑えられます。電圧アンプの出力もまた変化します。6.0V の温度補償されたクランプ回路の内臓の他に、出力短絡電流が 2mA(Typ) に改善されています。

## 電流アンプ

平均電流 PFC コントローラの電流アンプには AC ライン電流の歪みを最小限に抑えるため低いオフセット電圧の機能が必要です。このことを念頭に置いて UC3854A/B バージョンは電流アンプでは入力オフセット電圧が 0V ~ ±3mV に改善されています。UC3854A/B の負のオフセットは、電流コマンドがゼロ(電流アンプの両入力がゼロ) では PWM 回路は MOSFET を駆動しない、ということを意味しています。また、電流アンプの帯域幅も 5MHz(Typ) に改善されています。このことは 50Hz 或いは 60Hz 入力では一般的に問題ではありませんが、400Hz 入力の航空電子のアプリケーションでは重要な項目です。

## その他

UC3854A/BA/B バージョンにはその他重要な機能強化点がいくつかあります。 $V_{CC}$  電源電圧の 20V のクランプされています。起動時の起動電流が低いので(250 $\mu\text{A}$  Typ)、起動抵抗の電力損失が大幅に緩和されます。10.5V/10V の UVLO 機能(UC3854B) により 12V の補助電源からも電源供給が可能になっています。

VREF コンパレータにより MOSFET ドライバの出力は 7.5V 基準電源がまだ立ち上がっていなければ “L” レベルのままであることが保証されます。この改善により一部の UC3854 を用いた設計で必要とされた  $P_{KLMT}$  及び乗算器の出力ピンでの外付けショットキー・ダイオードが不要になります。ディスエーブル機能の伝搬遅延は 300ns (Typ) に改善されています。

# TYPICAL CHARACTERISTICS

図 1

図 2

図 3

図 4

図 5

図 6

図 7

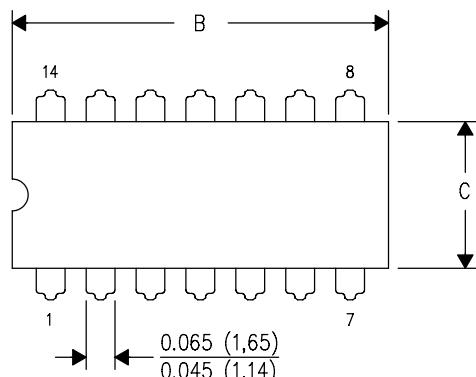

14 LEADS SHOWN

| PINS **<br>DIM | 14                     | 16                     | 18                     | 20                     |

|----------------|------------------------|------------------------|------------------------|------------------------|

| A              | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC |

| B MAX          | 0.785<br>(19,94)       | .840<br>(21,34)        | 0.960<br>(24,38)       | 1.060<br>(26,92)       |

| B MIN          | —                      | —                      | —                      | —                      |

| C MAX          | 0.300<br>(7,62)        | 0.300<br>(7,62)        | 0.310<br>(7,87)        | 0.300<br>(7,62)        |

| C MIN          | 0.245<br>(6,22)        | 0.245<br>(6,22)        | 0.220<br>(5,59)        | 0.245<br>(6,22)        |

4040083/E 03/03

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

C. このパッケージはガラス材を使用してセラミックのふたで密閉されています。

D. インデックス・ポイントはピンの識別用のみにふたの上に設けられています。

E. MIL STD 1385 GDIP1-T14, GDIP1-T16, GDIP1-T18, GDIP1-T20に準拠します。

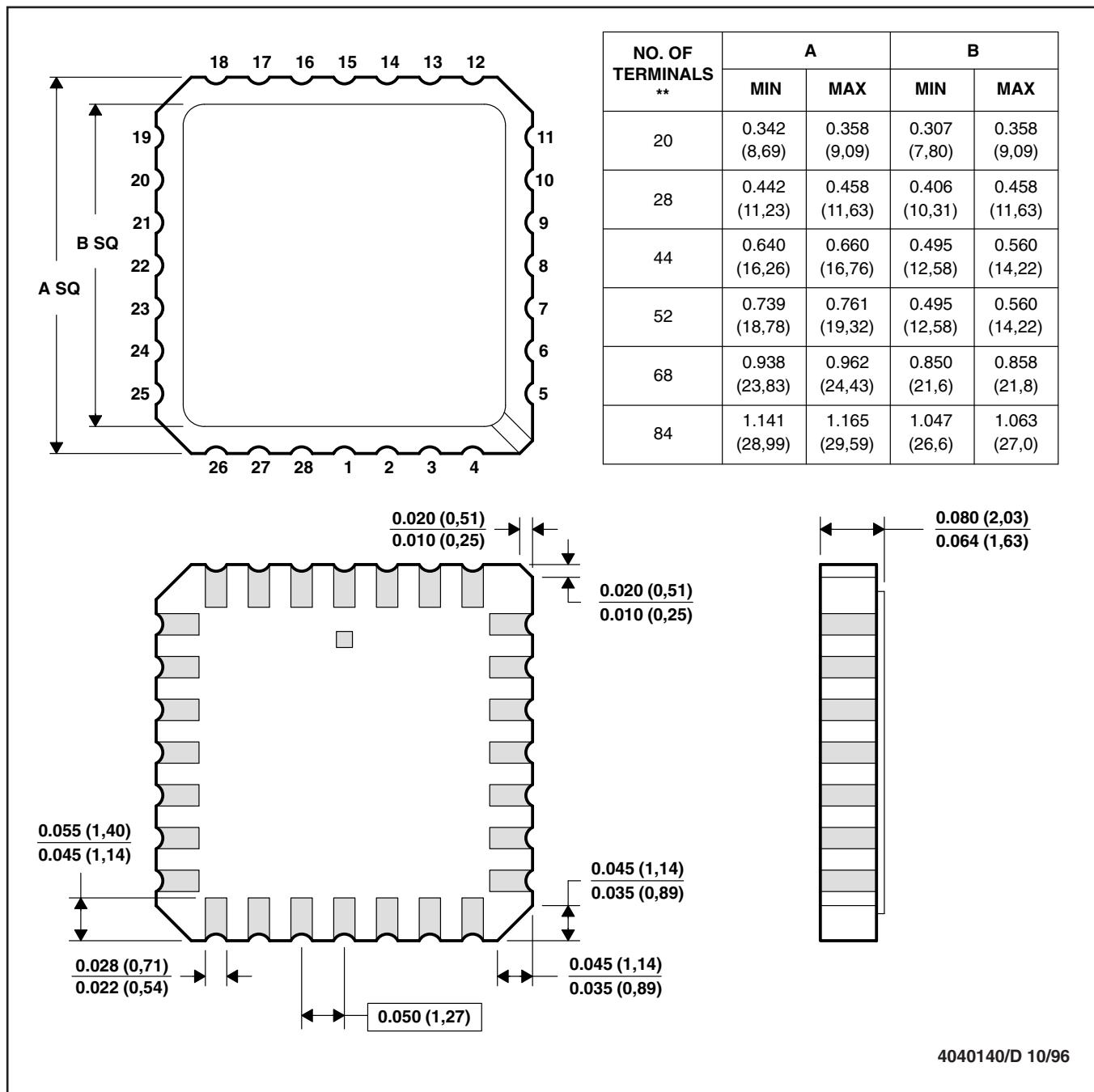

28 TERMINAL SHOWN

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

C. このパッケージは金属製のふたで密閉されています。

D. 端子は金メッキされています。

E. JEDEC MS-004に準拠します。

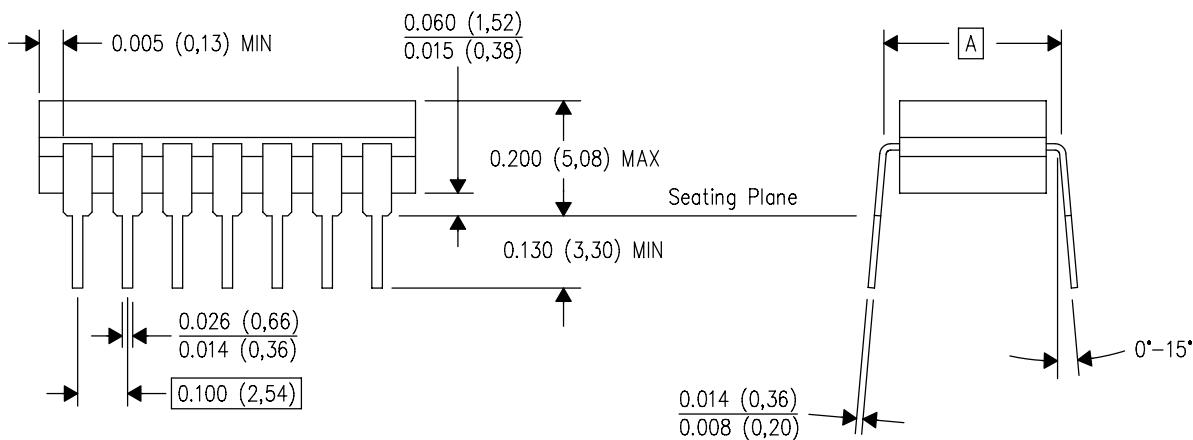

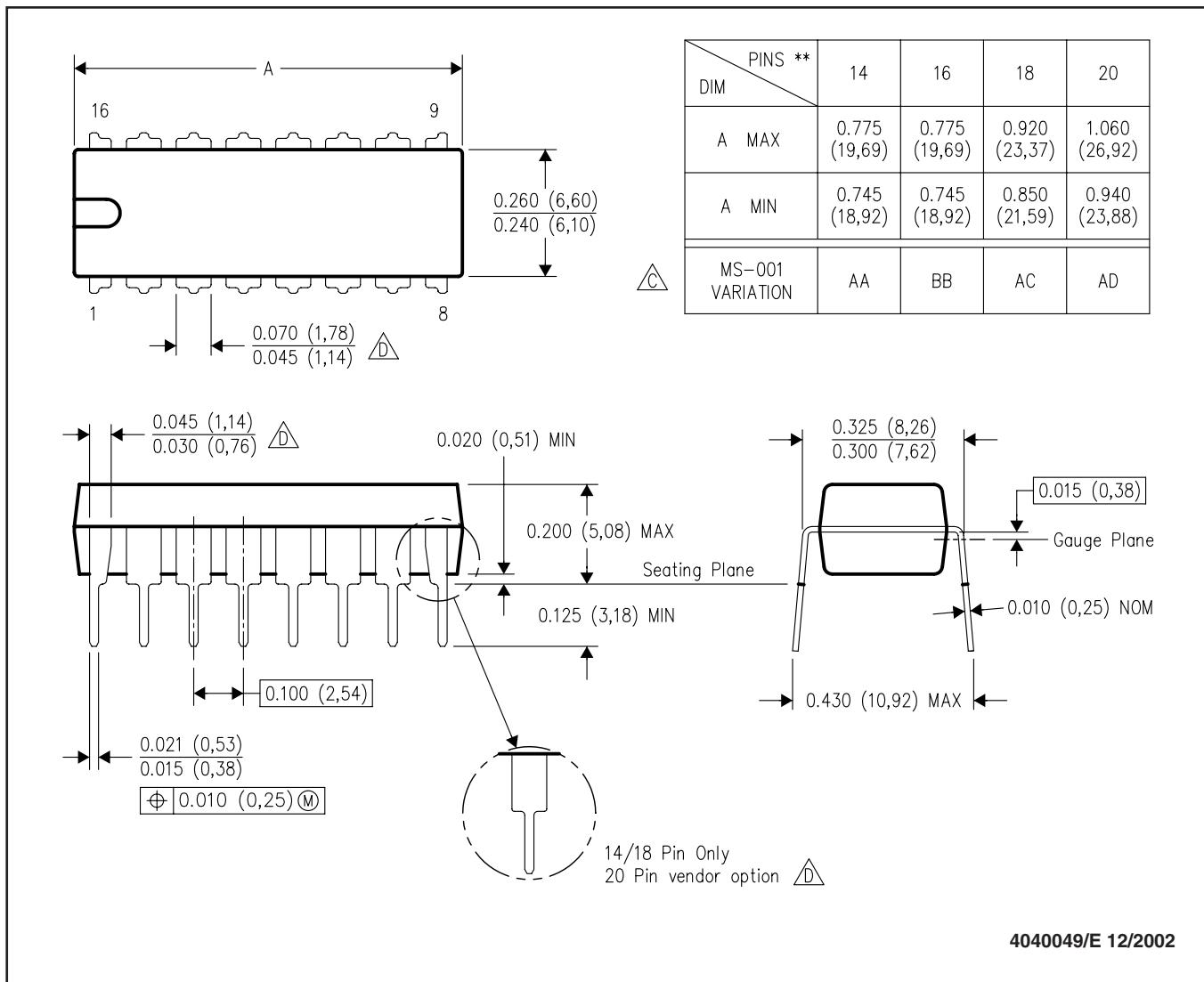

N (R-PDIP-T\*\*)

## **PLASTIC DUAL IN-LINE PACKAGE**

**16 PINS SHOWN**

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

△ JEDEC MS-001に準拠します(18/20ピンの最小ボディ長(寸法A)を除く)。

△20ピンの末端のリード・ショルダー部の幅はベンダー・オプションで、半幅または全幅です。

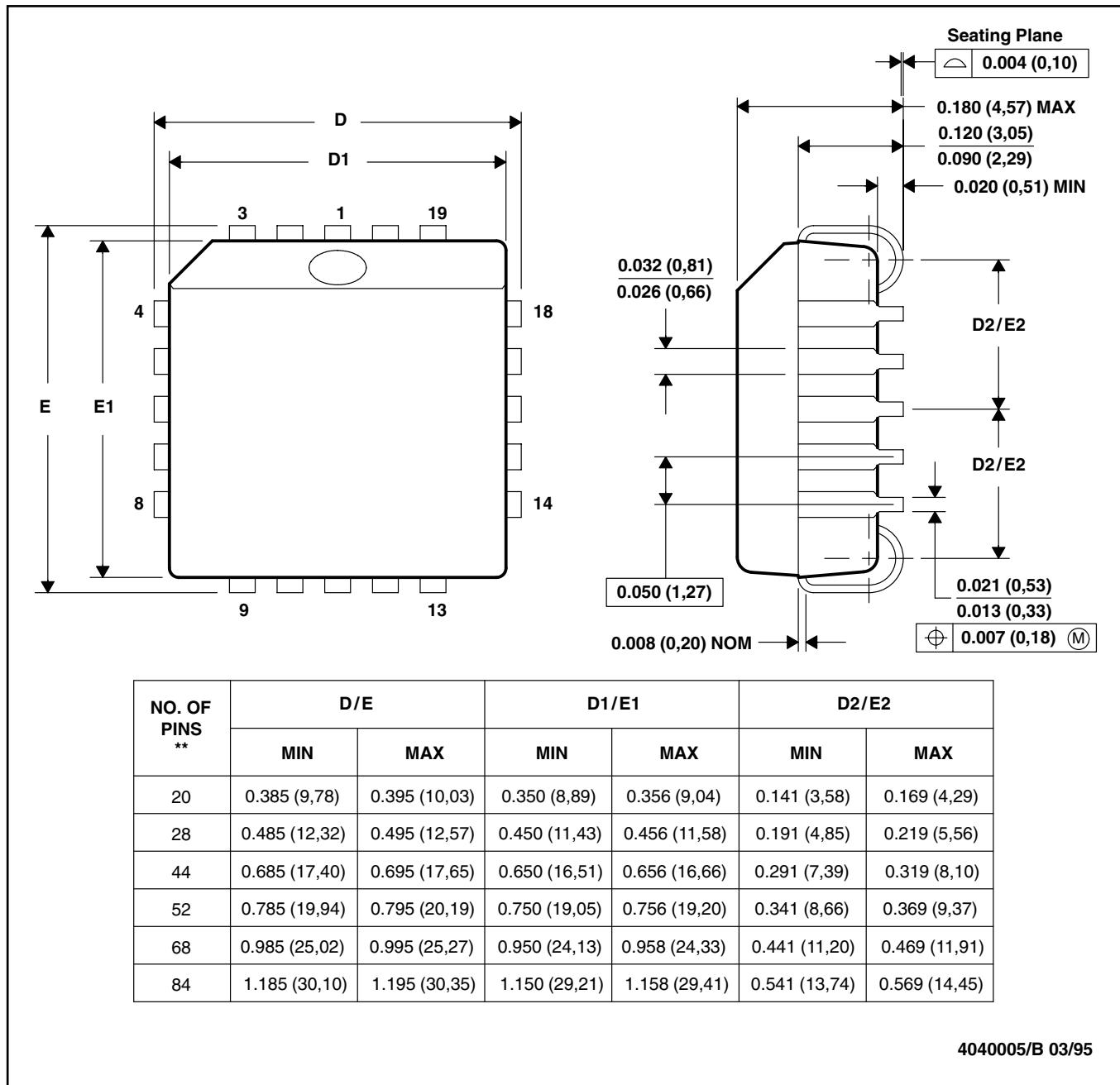

20 PIN SHOWN

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

C. JEDEC MS-018に準拠します。

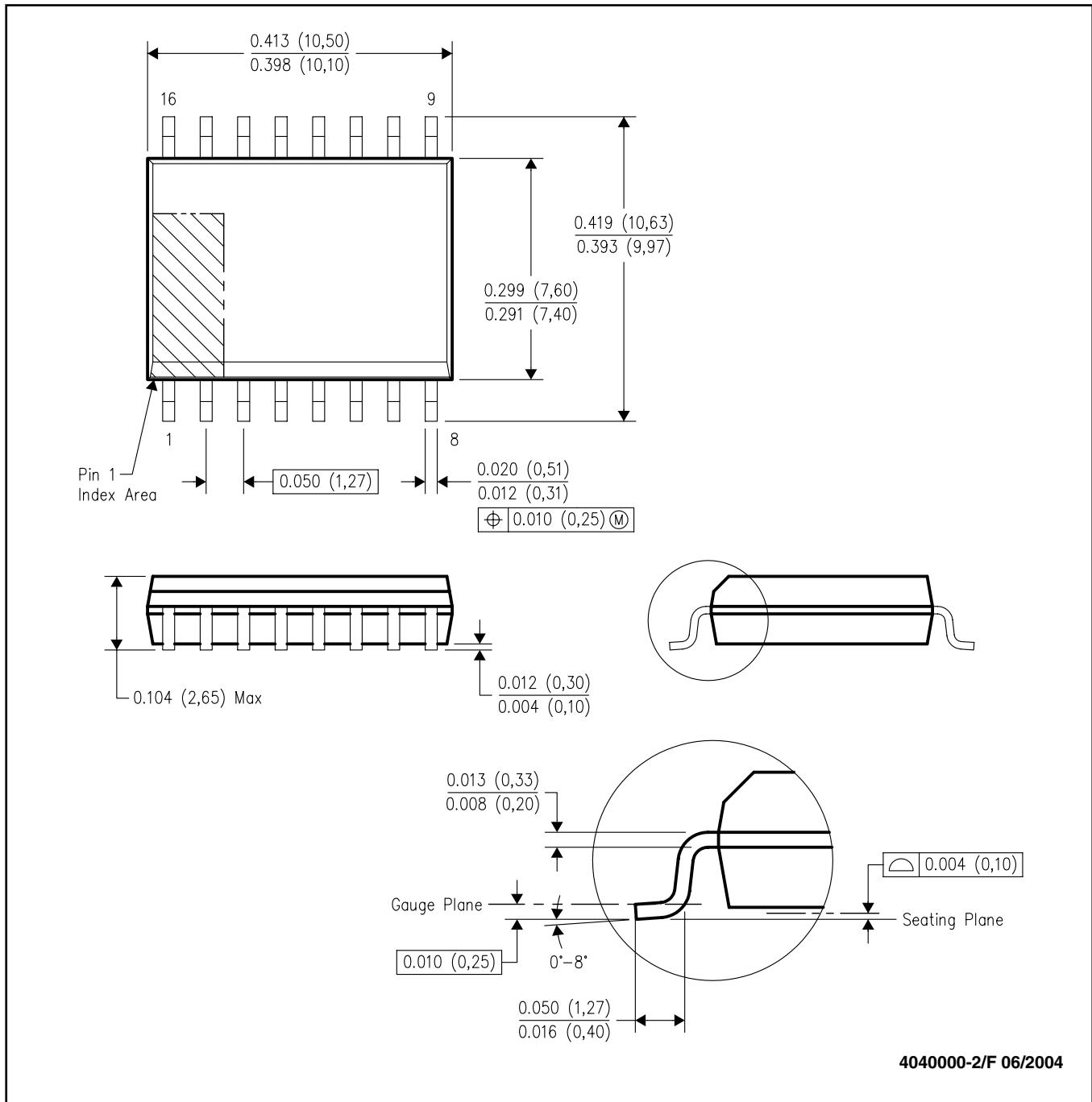

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

C. ボディ寸法はモールド突起部を含みません。また、0.006(0,15)を越えません。

D. JEDEC MS-013改AAに準拠します。

(SLUS329A)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6)                  |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|--------------------------------------|

| 5962-9326102MEA       | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-9326102ME<br>A<br>UC1854BJ/883B |

| UC1854BJ              | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | UC1854BJ                             |

| UC1854BJ.A            | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | UC1854BJ                             |

| UC1854BJ883B          | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-9326102ME<br>A<br>UC1854BJ/883B |

| UC1854BJ883B.A        | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-9326102ME<br>A<br>UC1854BJ/883B |

| UC2854ADW             | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854ADW                            |

| UC2854ADW.A           | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854ADW                            |

| UC2854ADWTR           | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854ADW                            |

| UC2854ADWTR.A         | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854ADW                            |

| UC2854AN              | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | UC2854AN                             |

| UC2854AN.A            | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | UC2854AN                             |

| UC2854ANG4            | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | UC2854AN                             |

| UC2854BDW             | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BDW.A           | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BDWG4           | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BDWTR           | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BDWTR.A         | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BDWTRG4         | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UC2854BDW                            |

| UC2854BN              | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | UC2854BN                             |

| UC2854BN.A            | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | UC2854BN                             |

| UC2854J               | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -40 to 85    | UC2854J                              |

| UC2854J.A             | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -40 to 85    | UC2854J                              |

| UC3854ADW             | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW                            |

| UC3854ADW.A           | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW                            |

| UC3854ADWG4           | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW                            |

| Orderable part number       | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UC3854ADWTR</a> | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW           |

| UC3854ADWTR.A               | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW           |

| UC3854ADWTRG4               | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854ADW           |

| <a href="#">UC3854AN</a>    | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854AN            |

| UC3854AN.A                  | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854AN            |

| UC3854ANG4                  | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854AN            |

| <a href="#">UC3854BDW</a>   | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| UC3854BDW.A                 | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| UC3854BDWG4                 | Active        | Production           | SOIC (DW)   16 | 40   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| <a href="#">UC3854BDWTR</a> | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| UC3854BDWTR.A               | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| UC3854BDWTRG4               | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | 0 to 70      | UC3854BDW           |

| <a href="#">UC3854BN</a>    | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854BN            |

| UC3854BN.A                  | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854BN            |

| UC3854BNG4                  | Active        | Production           | PDIP (N)   16  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | 0 to 70      | UC3854BN            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UC1854B, UC2854B, UC2854M, UC3854B :**

- Catalog : [UC3854B](#), [UC2854](#)

- Enhanced Product : [UC2854B-EP](#)

- Military : [UC2854BM](#), [UC1854B](#)

**NOTE: Qualified Version Definitions:**

- Catalog - TI's standard catalog product

- Enhanced Product - Supports Defense, Aerospace and Medical Applications

- Military - QML certified for Military and Defense Applications

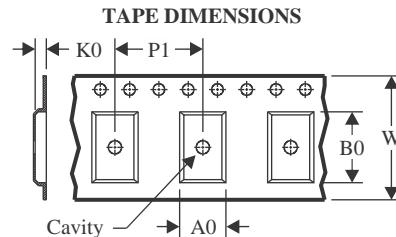

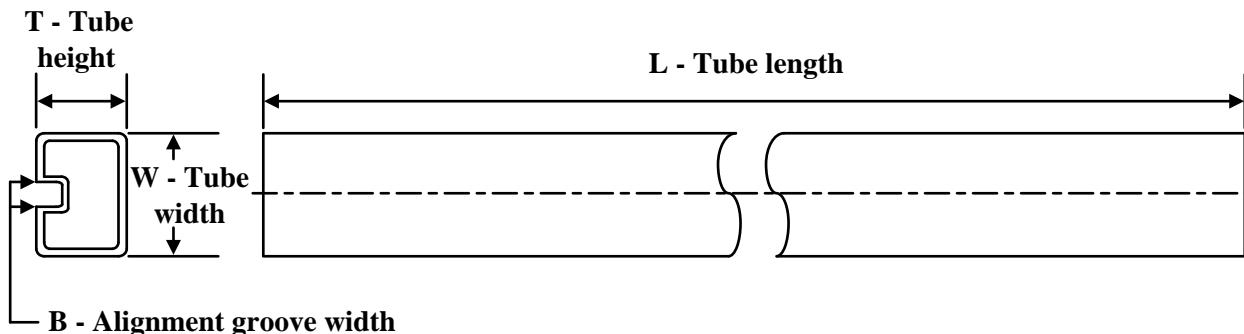

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

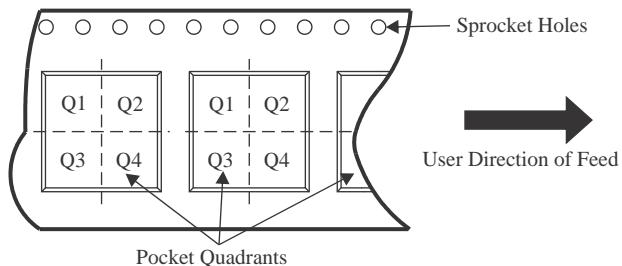

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

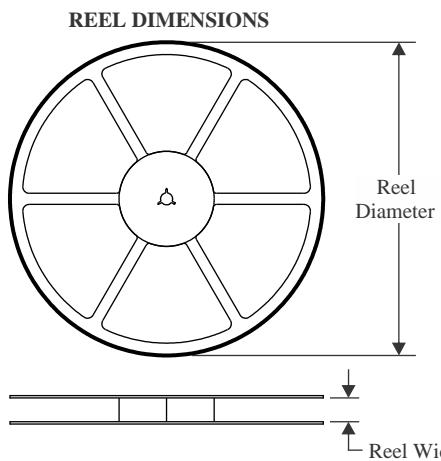

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UC2854ADWTR | SOIC         | DW              | 16   | 2000 | 330.0              | 16.4               | 10.75   | 10.7    | 2.7     | 12.0    | 16.0   | Q1            |

| UC2854BDWTR | SOIC         | DW              | 16   | 2000 | 330.0              | 16.4               | 10.75   | 10.7    | 2.7     | 12.0    | 16.0   | Q1            |

| UC3854ADWTR | SOIC         | DW              | 16   | 2000 | 330.0              | 16.4               | 10.75   | 10.7    | 2.7     | 12.0    | 16.0   | Q1            |

| UC3854BDWTR | SOIC         | DW              | 16   | 2000 | 330.0              | 16.4               | 10.75   | 10.7    | 2.7     | 12.0    | 16.0   | Q1            |

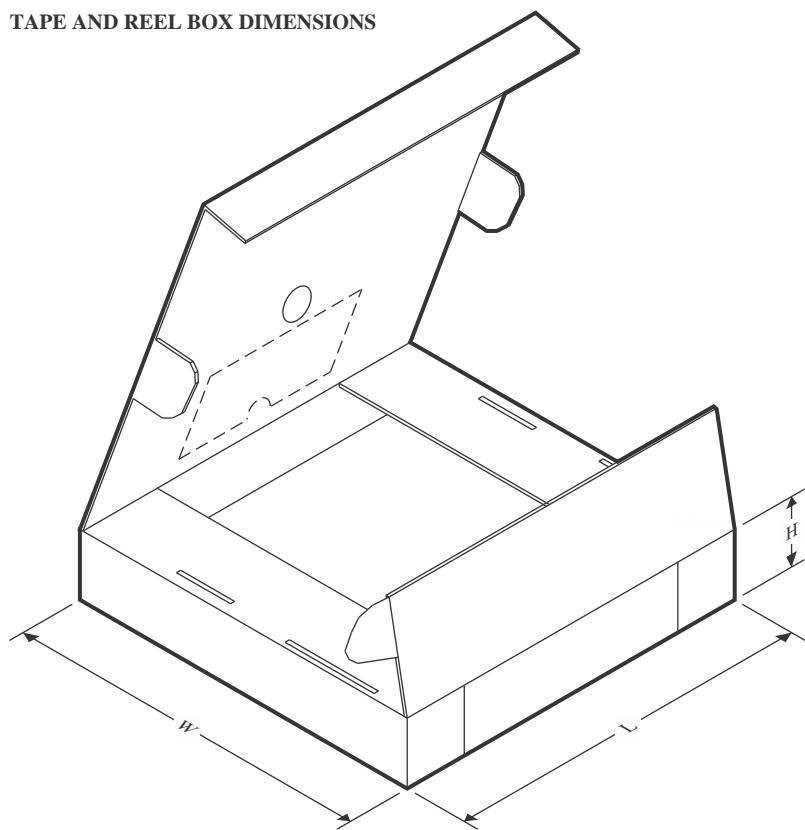

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2854ADWTR | SOIC         | DW              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

| UC2854BDWTR | SOIC         | DW              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

| UC3854ADWTR | SOIC         | DW              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

| UC3854BDWTR | SOIC         | DW              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

## TUBE

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| UC2854ADW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC2854ADW.A | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC2854AN    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC2854AN.A  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC2854ANG4  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC2854BDW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC2854BDW.A | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC2854BDWG4 | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC2854BN    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC2854BN.A  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854ADW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854ADW.A | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854ADWG4 | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854AN    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854AN.A  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854ANG4  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854BDW   | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854BDW.A | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854BDWG4 | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080         | 6.6    |

| UC3854BN    | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854BN.A  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

| UC3854BNG4  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230        | 4.32   |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月