# 高効率 二次側同期整流式 降圧型PWMコントローラ

## 特 長

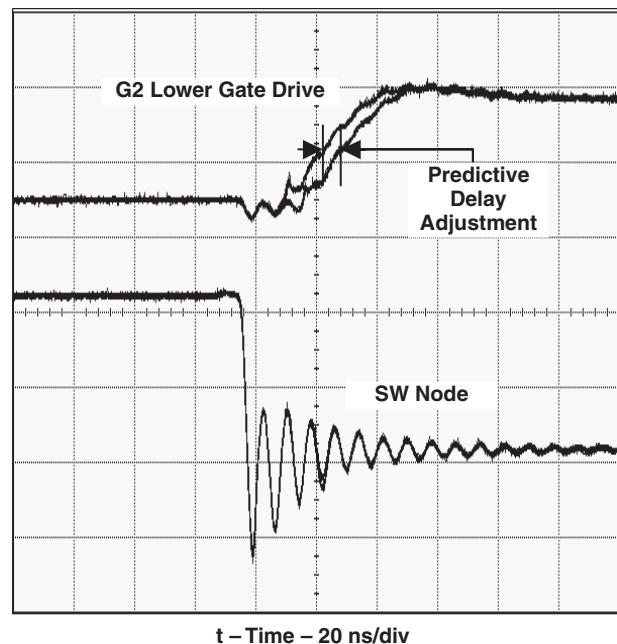

- 高効率 同期整流 降圧動作のための“Predictive Gate Drive™”機能を内蔵

- ±3A のTrueDrive™デュアル出力

- 1MHzの高周波動作が可能(SYNCINからG1出力まで70nsの遅延)

- リーディング・エッジ変調機能内蔵

- 平均電流モード・コントロール・ループを使用した過電流保護機能回路を内蔵

- 3つのモードで2.7Vから35Vでの動作が可能

- 出力段用逆電流保護機能

- プログラム可能なシャットダウン機能

- 高精度±1%の基準電圧回路内蔵

- 高利得帯域幅の誤差増幅器

- 放熱特性に優れた20ピンHTSSOP PowePAD™ パッケージ

## アプリケーション

- 多出力電源用二次側ポスト・レギュレータ(SSPR)

- カスケード型降圧・コンバータ

- バス・コンバータ及びDCトランス用ポスト・コンバータ

## 概 要

UCC2540は、高電流で低出力電圧のアプリケーションに適した二次側・同期整流式・降圧型PWMコントローラです。このデバイスはカスケード接続された絶縁型・非絶縁DC/DCコンバータの二次側コントローラ、または多出力電源用二次側ポスト・レギュレータ(SSPR)として使用することができます。

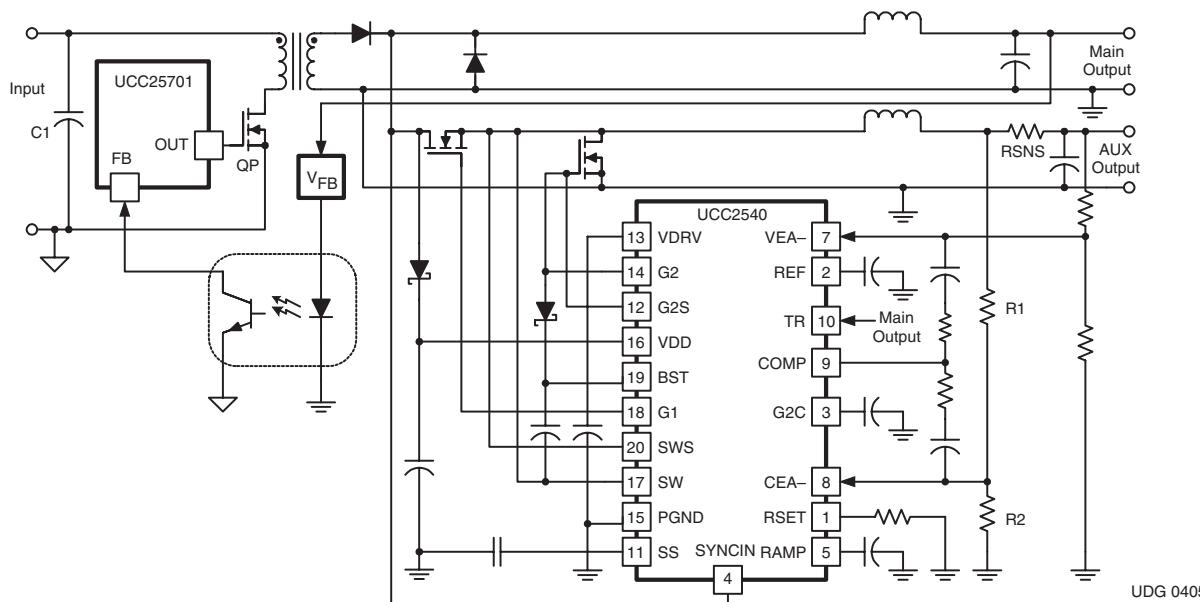

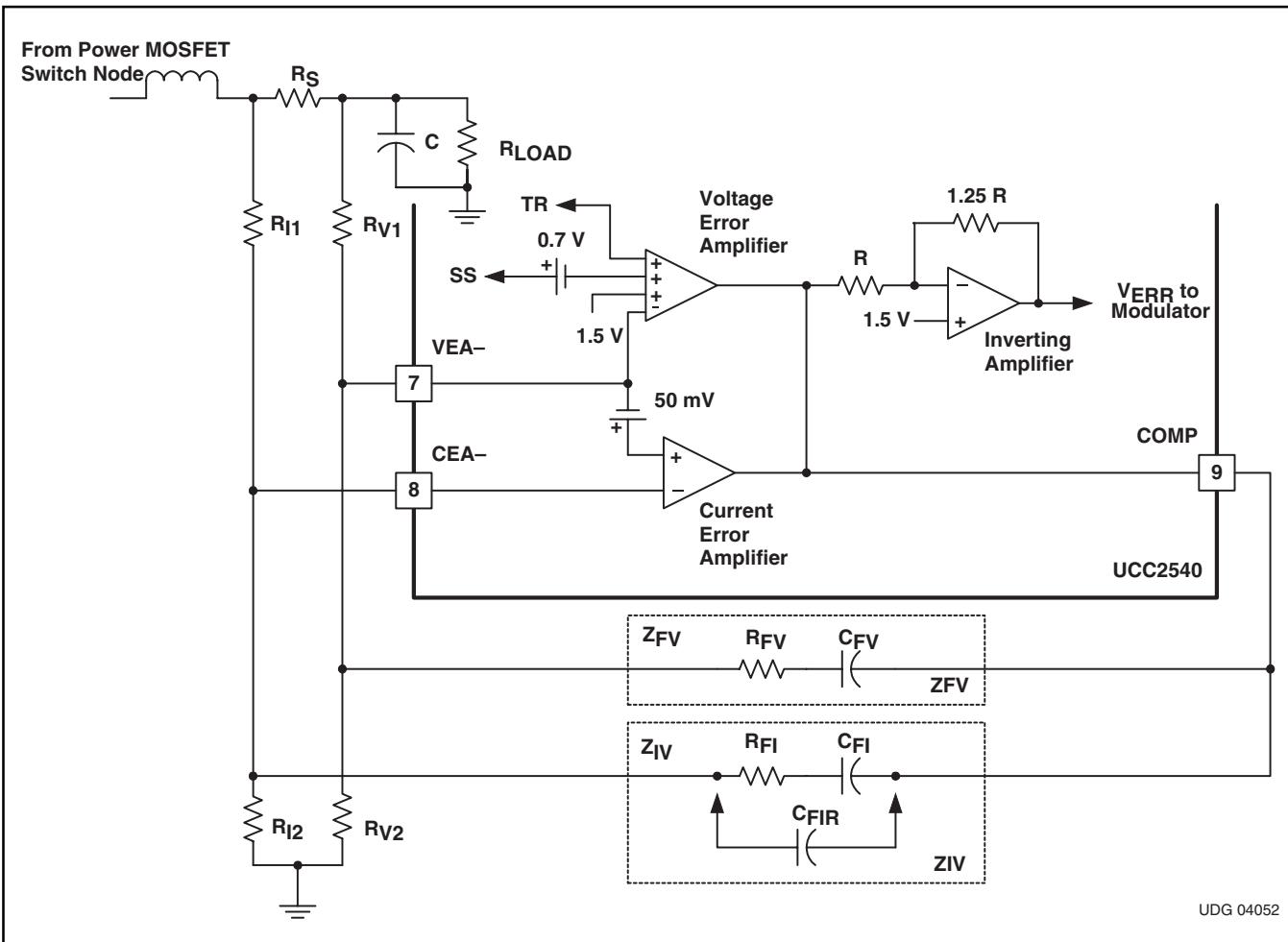

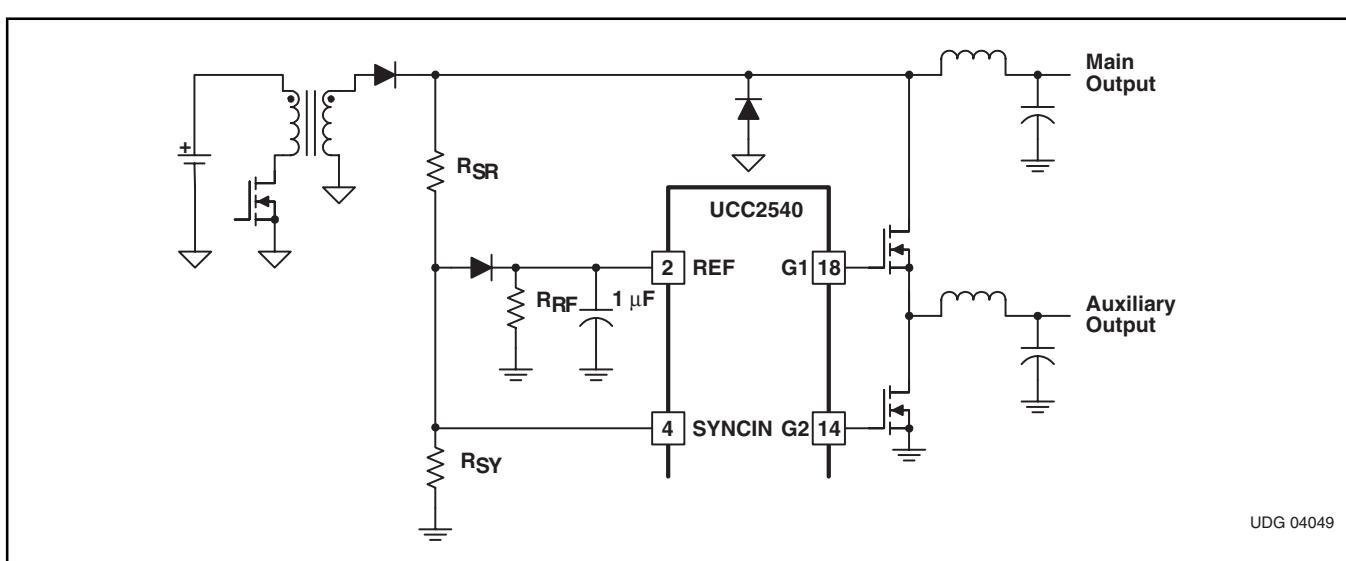

## SIMPLIFIED APPLICATION DIAGRAM

Gate Drive、TrueDriveおよびPowerPADは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

UCC2540は、一次側、またはDCトランスからの同期信号、または二次側コンバータとして動作します。高効率を実現するため、UCC2540はPredictive Gate Drive™テクノロジを搭載しており、同期整流器のボディ・ダイオードの導通損失をほぼ除去します。

UCC2540は-40°Cから105°Cの広範囲な温度範囲で使用でき、パッケージは放熱特性に優れた20ピンHTSSOP(PWP)PowerPAD™です。この小型化されたパッケージは標準の20ピンTSSOPのフットプリントを用いて、ボード上の高電流デュアル・ドライバに適応する $\theta_{JC}$ が1.4°C/Wという大幅に低い熱抵抗を実現します。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                              |                                     | <b>UCC2540</b>     | <b>UNIT</b> |

|--------------------------------------------------------------|-------------------------------------|--------------------|-------------|

| Supply voltage range, VDD                                    |                                     | 36                 | V           |

| Supply current, I <sub>VDD</sub>                             | VDD                                 | 50                 | mA          |

| Analog input voltages                                        | CEA-, COMP, G2C, RAMP, SS, TR, VEA- | -0.3 to 3.6        | V           |

|                                                              | VDRV                                | -0.3 to 9          |             |

|                                                              | G1, BST                             | SW - 0.3 to SW + 9 |             |

|                                                              | SW, SWS                             | -1 to 36           |             |

|                                                              | G2, G2S                             | -1 to 9            |             |

|                                                              | SYNCIN                              | -0.3 to 8.0        |             |

| Sink current (peak), I <sub>OUT_SINK</sub>                   | G1, G2                              | 3.5                | A           |

| Source current (peak), I <sub>OUT_SOURCE</sub>               | G1, G2                              | -3.5               |             |

| Operating junction temperature range, T <sub>J</sub>         |                                     | -55 to 150         | °C          |

| Storage temperature, T <sub>stg</sub>                        |                                     | -65 to 150         |             |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                                     | 300                |             |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) 全ての電圧はGNDを基準としています。電流の極性で正は指定の端子に流入する方向、負は流出する方向を表しています。

## RECOMMENDED OPERATING CONDITIONS

|                                                 |        | <b>MIN</b> | <b>TYP</b> | <b>MAX</b> | <b>UNIT</b>   |

|-------------------------------------------------|--------|------------|------------|------------|---------------|

| Supply voltage, VDD                             | Mode 1 | 8.5        | 35         |            | V             |

| Supply voltage, VDRV                            | Mode 2 | 4.75       | 8.00       |            |               |

| Supply voltage, REF                             | Mode 3 | 3.0        | 3.3        | 3.6        |               |

| Supply voltage bypass, C <sub>VDD</sub>         |        | 1.0        | 2.2        |            | $\mu\text{F}$ |

| Reference bypass capacitor, C <sub>REF</sub>    |        | 0.1        | 1.0        | 2.2        |               |

| VDRV bypass capacitor, C <sub>VDRV</sub>        |        | 0.2        |            |            |               |

| BST-SW bypass capacitor, C <sub>BST-SW</sub>    |        | 0.1        |            |            |               |

| Timer current resistor range, R <sub>RSET</sub> |        | 10         | 50         |            | k $\Omega$    |

| PWM ramp capacitor range, C <sub>RAMP</sub>     |        | 100        | 680        |            | pF            |

| Turn-off capacitor range, C <sub>G2C</sub>      |        | 120        | 1000       |            |               |

| COMP pin load range, R <sub>LOAD</sub>          |        | 6.5        |            |            |               |

| Junction operating temperature, T <sub>J</sub>  |        | -40        | 105        |            | °C            |

## ORDERING INFORMATION

|                 |                                |

|-----------------|--------------------------------|

| $T_A = T_J$     | HTSSOP-20 (PWP) <sup>(1)</sup> |

|                 | Bulk                           |

| -40°C to +105°C | UCC2540PWP                     |

(1) PWPパッケージはチューブ及びテープ/リールで供給され、チューブ当たりの数量は70個、リール当たりの数量は2000個です。テープ/リールの場合は型番にRを付けてください(例、UCC2540PWPR)。PowerPADの図面及びレイアウト情報についてはデータシートのアプリケーションの項を参照してください。

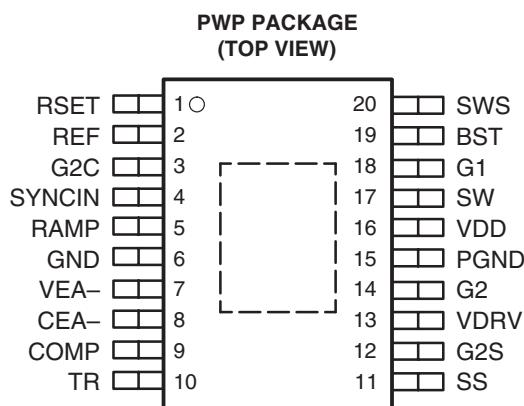

## CONNECTION DIAGRAM

注) PowerPAD™はパッケージのリードには直接接続していません。これは電気的にも熱的にもグランドとして機能するデバイスのサブストレートに接続されており、PCBのPGNDに接続してください。この露出寸法は1.3mm × 1.7mmですが、位置及びモールド・フローのばらつきにより公差は+1.05mm/-0.05mm (+41ミル/-2ミル)です。

## THERMAL INFORMATION

| PACKAGE FAMILY         | PACKAGE DESIGNATOR | $\theta_{JA}$ (°C/W)<br>(with PowerPAD) | $\theta_{JC}$ (°C/W)<br>(without PowerPAD) | $\theta_{JC}$ (°C/W)<br>(with PowerPAD) | MAXIMUM DIE TEMPERATURE |

|------------------------|--------------------|-----------------------------------------|--------------------------------------------|-----------------------------------------|-------------------------|

| PowerPAD™<br>HTSSOP-20 | PWP                | 22.3 to 32.6<br>(500 to 0 LFM)          | 19.9                                       | 1.4                                     | 125°C                   |

## ELECTRICAL CHARACTERISTICS

$V_{DD} = 12\text{ V}$ , 1- $\mu\text{F}$  capacitor from  $V_{DD}$  to GND, 1- $\mu\text{F}$  capacitor from  $BST$  to  $SW$ , 1- $\mu\text{F}$  capacitor from  $REF$  to GND, 0.1- $\mu\text{F}$  and 2.2- $\mu\text{F}$  capacitors from  $V_{DRV}$  to  $PGND$ ,  $f_{SYNCIN} = 200\text{ kHz}$ ,  $T_A = T_J = -40^\circ\text{C}$  to  $105^\circ\text{C}$ , (unless otherwise noted).

| PARAMETER                      |                                         | TEST CONDITIONS                                                                 | MIN  | TYP  | MAX  | UNIT          |

|--------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|------|------|------|---------------|

| <b>OVERALL</b>                 |                                         |                                                                                 |      |      |      |               |

| $I_{VDD}$                      | Operating current                       | DC<br>$f_S = 200\text{kHz}$ , $C_{LOAD} = 2.2\text{nF}$                         | 8    | 11   | 13   | mA            |

|                                |                                         |                                                                                 | 9    | 12   | 30   |               |

| <b>UNDERVOLTAGE LOCKOUT</b>    |                                         |                                                                                 |      |      |      |               |

| $V_{VDD}$                      | Start threshold voltage                 | MODE 1                                                                          | 8.0  | 8.5  | 9.0  | V             |

| $V_{VDD}$                      | Stop threshold voltage                  | MODE 1                                                                          | 7.5  | 8.0  | 8.5  |               |

| $V_{VDD}$                      | Hysteresis                              | MODE 1                                                                          | 0.3  | 0.5  | 0.8  |               |

| $V_{VDRV}$                     | Start threshold voltage                 | MODE 2,<br>$V_{VDD} = 4\text{V}$                                                | 4.30 | 4.65 | 4.85 |               |

| $V_{VDRV}$                     | Stop threshold voltage                  | MODE 2                                                                          | 4.0  | 4.3  | 4.6  |               |

| $V_{VDRV}$                     | Hysteresis                              | MODE 2                                                                          | 0.15 | 0.35 | 0.55 |               |

| $V_{REF}$                      | Start threshold voltage                 | MODE 3,<br>$V_{VDD} = V_{VDRV} = 2.7\text{V}$                                   | 2.75 | 3.00 | 3.20 |               |

| $V_{REF}$                      | Stop threshold voltage                  | MODE 3                                                                          | 2.25 | 2.50 | 2.70 |               |

| $V_{REF}$                      | Hysteresis                              | MODE 3                                                                          | 0.3  | 0.5  | 0.8  |               |

| <b>VOLTAGE REFERENCE (REF)</b> |                                         |                                                                                 |      |      |      |               |

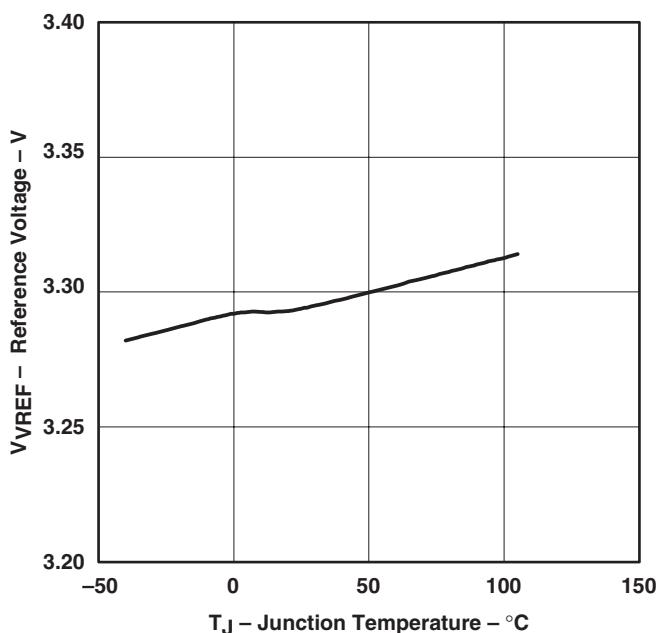

| $V_{REF}$                      | Reference output voltage                | $T_A = 25^\circ\text{C}$                                                        | 3.28 | 3.30 | 3.32 | V             |

|                                |                                         | Total variation                                                                 | 3.2  | 3.3  | 3.4  |               |

| $I_{SC}$                       | Short circuit current                   | $V_{REF} = 0\text{V}$ , $T_A = 25^\circ\text{C}$                                | 10   | 13   | 20   | mA            |

|                                | Line regulation                         | $5.25\text{V} \leq V_{REF} \leq 7.2\text{V}$                                    | 0    | 1.5  | 15   |               |

|                                | Load regulation                         | $0\text{mA} \leq I_{REF} \leq 5\text{mA}$                                       | 0    | 30   | 70   |               |

| <b>PWM (RAMP)</b>              |                                         |                                                                                 |      |      |      |               |

| $D_{MIN}$                      | Minimum duty cycle                      |                                                                                 |      |      | 0%   |               |

| $V_{RAMP}$                     | Offset voltage                          |                                                                                 | 0.10 | 0.25 | 0.45 | V             |

|                                | Timeout threshold voltage               |                                                                                 | 2.3  | 2.5  | 2.8  |               |

| $t_{DEAD}$                     | G1 deadtime at maximum duty cycle ratio | $f_{SYNC} = 200\text{kHz}$                                                      | 150  | 175  | 200  | ns            |

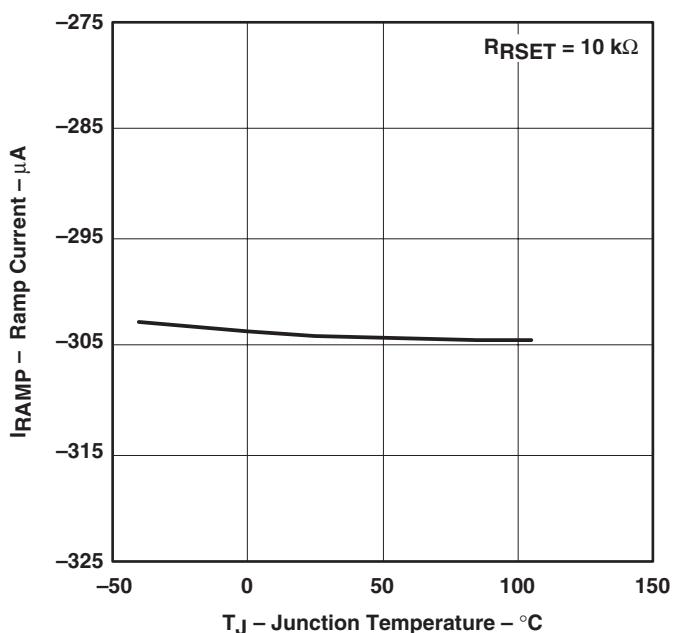

| $I_{RAMP}$                     | Ramp charge current                     | $R_{RSET} = 10\text{k}\Omega$                                                   | -325 | -300 | -275 | $\mu\text{A}$ |

| <b>CURRENT ERROR AMPLIFIER</b> |                                         |                                                                                 |      |      |      |               |

| $V_{CEA+}$                     | Offset voltage                          | Total variation                                                                 | 45   | 50   | 55   | mV            |

| GBW                            | Gain bandwidth <sup>(3)</sup>           |                                                                                 | 3    | 4    |      | MHz           |

| $V_{OL}$                       | Low-level output voltage                | $I_{COMP} = 0\text{A}$ , $V_{CEA-} = 3.3\text{V}$ , $V_{VEA-} = 2.0\text{V}$    |      |      | 0.1  | V             |

|                                |                                         | $I_{COMP} = 200\mu\text{A}$ , $V_{CEA-} = 1.5\text{V}$ , $V_{VEA-} = 1\text{V}$ | 0    | 0.60 | 0.83 |               |

| $V_{OH}$                       | High-level output voltage               | $I_{COMP} = 0\text{A}$ , $V_{CEA-} = 0\text{V}$ , $V_{VEA-} = 1\text{V}$        | 2.2  | 2.5  | 3.0  | V             |

| $A_{VOL}$                      | Open loop                               |                                                                                 | 60   | 100  | 140  | dB            |

| $I_{BIAS}$                     | Bias current                            |                                                                                 | -200 | -80  | -10  | nA            |

| $I_{SINK}$                     | Sink current                            | $V_{COMP} = 1.0\text{V}$ , $V_{CEA-} = 1.5\text{V}$ , $V_{VEA-} = 0\text{V}$    | 0.35 | 0.80 | 1.70 | mA            |

| CMR                            | Common mode input range <sup>(3)</sup>  |                                                                                 | 0    |      | 2    | V             |

(3) 設計で保証されており、テストは行われていません。

## ELECTRICAL CHARACTERISTICS

$V_{DD} = 12\text{ V}$ , 1- $\mu\text{F}$  capacitor from VDD to GND, 1- $\mu\text{F}$  capacitor from BST to SW, 1- $\mu\text{F}$  capacitor from REF to GND, 0.1- $\mu\text{F}$  and 2.2- $\mu\text{F}$  capacitors from VDRV to PGND,  $f_{SYNCIN} = 200\text{ kHz}$ ,  $T_A = T_J = -40^\circ\text{C}$  to  $105^\circ\text{C}$ , (unless otherwise noted)

| PARAMETER                                               | TEST CONDITIONS                                                                                       | MIN   | TYP   | MAX   | UNIT          |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| <b>VOLTAGE ERROR AMPLIFIER</b>                          |                                                                                                       |       |       |       |               |

| $V_{SS\_OFF}$                                           | Offset voltage from soft-start input<br>$I_{COMP} = V_{VEA-}, V_{SS-} = 1.5\text{V}$                  | 0.40  | 0.75  | 1.00  | V             |

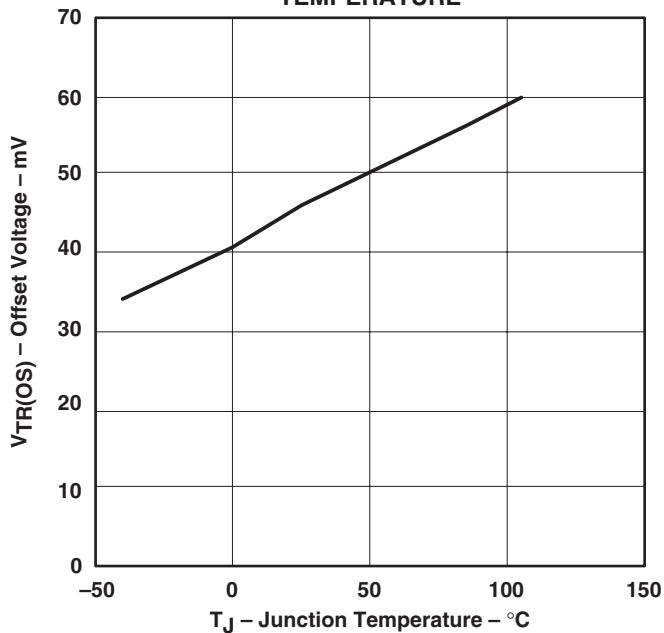

| $V_{TR\_OFF}$                                           | Offset voltage from tracking input<br>$V_{TR} = 1.0\text{V}, V_{COMP} = V_{VEA-}$                     | 25    | 48    | 70    | mV            |

| $V_{VEA+}$                                              | $0^\circ\text{C} \leq T_A \leq 105^\circ\text{C}$                                                     | 1.485 | 1.500 | 1.515 | V             |

|                                                         | Total variation                                                                                       | 1.47  | 1.50  | 1.53  |               |

| GBW                                                     | Gain bandwidth <sup>(3)</sup>                                                                         | 3     | 4     |       | MHz           |

| $V_{OL}$                                                | $I_{COMP} = 0\text{A}, V_{CEA-} = 1.75\text{V}, V_{VEA-} = 2.0\text{V}$                               |       |       | 0.1   | V             |

|                                                         | $I_{COMP} = 200\mu\text{A}, V_{CEA-} = 0\text{V}, V_{VEA-} = 1\text{V}, V_{TR} = 0\text{V}$           | 0     | 0.60  | 0.83  |               |

| $V_{OH}$                                                | High-level output voltage<br>$I_{COMP} = 0\text{A}, V_{CEA-} = 0\text{V}, V_{VEA-} = 1\text{V}$       | 2.2   | 2.5   | 3.0   |               |

| $A_{VOL}$                                               | Open loop                                                                                             | 60    | 100   | 140   | dB            |

| $I_{BIAS}$                                              | Bias current                                                                                          | -300  | -150  | -50   | $\mu\text{A}$ |

| $I_{SINK}$                                              | Sink current <sup>(4)</sup><br>$V_{COMP} = 1.0\text{V}, V_{CEA-} = 0\text{V}, V_{VEA-} = 1.5\text{V}$ | 0.35  | 0.80  | 1.70  | mA            |

| <b>CURRENT SET</b>                                      |                                                                                                       |       |       |       |               |

| $I_{OUT}$                                               | $R_{RSET} = 10\text{k}\Omega$                                                                         | -158  | -150  | -142  | $\mu\text{A}$ |

| $V_{RSET}$                                              | $R_{RSET} = 10\text{k}\Omega$                                                                         | 1.42  | 1.50  | 1.58  | V             |

| <b>SYNCHRONIZATION AND SHUTDOWN TIMER (SYNCIN, G2C)</b> |                                                                                                       |       |       |       |               |

| Timer threshold                                         |                                                                                                       | 2.3   | 2.5   | 2.7   | V             |

| SYNCIN threshold                                        |                                                                                                       | 1.50  | 1.65  | 1.80  |               |

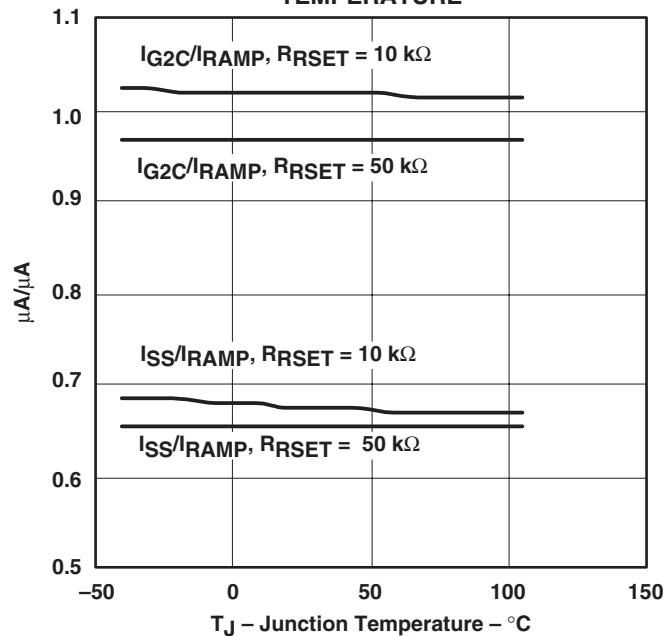

| $I_{CHG(G2C)}$                                          | $R_{RSET} = 10\text{k}\Omega$                                                                         | -325  | -300  | -275  | $\mu\text{A}$ |

| <b>SOFT-START (SS)</b>                                  |                                                                                                       |       |       |       |               |

| $I_{CH(SS)}$                                            | $R_{RSET} = 10\text{k}\Omega$                                                                         | -230  | -200  | -170  | $\mu\text{A}$ |

| $I_{DSCH(SS)}$                                          | $R_{RSET} = 10\text{k}\Omega$                                                                         | 50    | 70    | 100   |               |

| Discharge/shutdown threshold                            |                                                                                                       | 0.35  | 0.45  | 0.55  | V             |

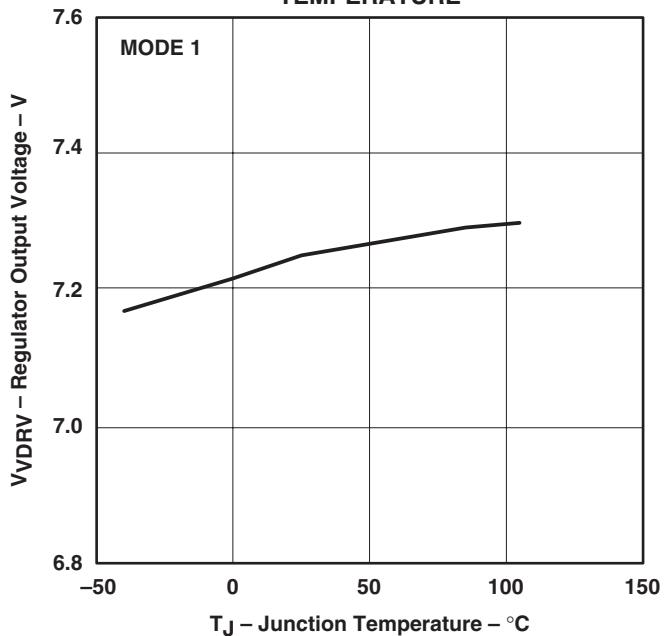

| <b>DRIVE REGULATOR (VDRV)</b>                           |                                                                                                       |       |       |       |               |

| $V_{VDRV}$                                              | $V_{VDD} = 8.5\text{V}$                                                                               | 6.87  | 7.20  | 7.53  | V             |

| Line regulation                                         | $9\text{V} \leq V_{VDD} \leq 35\text{V}$                                                              | 0     | 50    | 100   | mV            |

| Load regulation                                         | $-5\text{mA} \leq I_{VDRV} \leq 0\text{mA}$                                                           | 0     | 50    | 100   |               |

| $I_{SC}$                                                | Short-circuit current                                                                                 | 15    | 30    | 50    | mA            |

| <b>G2S GATE DRIVE SENSE</b>                             |                                                                                                       |       |       |       |               |

| G2S rising threshold voltage                            | $V_{SWS} = 0\text{V}$                                                                                 | 1.90  | 2.25  | 3.10  | V             |

| G2S falling threshold voltage                           | $V_{SWS} = 0\text{V}$                                                                                 | 1.00  | 1.25  | 1.03  |               |

| $I_{G2S}$                                               | $V_{G2S} = 0\text{V}$                                                                                 | -0.70 | -0.50 | -0.37 | mA            |

| <b>SWS GATE DRIVE SENSE</b>                             |                                                                                                       |       |       |       |               |

| SWS rising threshold voltage                            | $V_{G2S} = 0\text{V}$                                                                                 | 1.90  | 2.25  | 2.90  | V             |

| SWS falling threshold voltage                           | $V_{G2S} = 0\text{V}$                                                                                 | 1.0   | 1.2   | 1.3   |               |

| $I_{SWS}$                                               | $V_{SWS} = 0\text{V}$                                                                                 | -1.8  | -1.3  | -0.9  | mA            |

| Negative threshold voltage                              |                                                                                                       | -0.5  | -0.3  | -0.1  | V             |

(3) 設計で保証されており、テストは行われていません。

## ELECTRICAL CHARACTERISTICS

$V_{DD} = 12$  V, 1- $\mu$ F capacitor from VDD to GND, 1- $\mu$ F capacitor from BST to SW, 1- $\mu$ F capacitor from REF to GND, 0.1- $\mu$ F and 2.2- $\mu$ F capacitors from VDRV to PGND,  $f_{SYNCIN} = 200$  kHz,  $T_A = T_J = -40^\circ\text{C}$  to  $105^\circ\text{C}$ , (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS               |                                             |                         | MIN                    | TYP | MAX | UNIT |          |

|----------------------------------------|-------------------------------|---------------------------------------------|-------------------------|------------------------|-----|-----|------|----------|

| <b>G1 MAIN OUTPUT</b>                  |                               |                                             |                         |                        |     |     |      |          |

| $R_{SINK}$                             | Sink resistance               | $V_{SW} = 0\text{V}$ ,                      | $V_{BST} = 6\text{V}$ , | $V_{G1} = 0.5\text{V}$ | 0.3 | 0.7 | 1.3  | $\Omega$ |

| $R_{SRC}$                              | Source resistance             | $V_{SW} = 0\text{V}$ ,                      | $V_{BST} = 6\text{V}$ , | $V_{G1} = 5.7\text{V}$ | 10  | 25  | 45   |          |

| $I_{SINK}$                             | Sink current <sup>(3)</sup>   | $V_{SW} = 0\text{V}$ ,                      | $V_{BST} = 6\text{V}$ , | $V_{G1} = 3.0\text{V}$ | 3   |     |      |          |

| $I_{SRCE}$                             | Source current <sup>(3)</sup> | $V_{SW} = 0\text{V}$ ,                      | $V_{BST} = 6\text{V}$ , | $V_{G1} = 3.0\text{V}$ | -3  |     |      | A        |

| $t_{RISE}$                             | Rise time                     | $C_{LOAD} = 2.2\text{nF}$ , from G1 to SW   |                         |                        | 12  | 25  |      | ns       |

| $t_{FALL}$                             | Fall time                     | $C_{LOAD} = 2.2\text{nF}$ , from G1 to SW   |                         |                        | 12  | 25  |      |          |

| <b>G2 SYNCHRONOUS RECTIFIER OUTPUT</b> |                               |                                             |                         |                        |     |     |      |          |

| $R_{SINK}$                             | Sink resistance               | $V_{G2} = 0.3\text{V}$                      |                         |                        | 5   | 15  | 30   | $\Omega$ |

| $I_{SINK}$                             | Sink current <sup>(3)</sup>   | $V_{G2} = 3.25\text{V}$                     |                         |                        | 3   |     |      |          |

| $I_{SRC}$                              | Source current <sup>(3)</sup> | $V_{G2} = 3.25\text{V}$                     |                         |                        | -3  |     |      | A        |

| $t_{RISE}$                             | Rise time                     | $C_{LOAD} = 2.2\text{nF}$ , from G2 to PGND |                         |                        | 12  | 25  |      | ns       |

| $t_{FALL}$                             | Fall time                     | $C_{LOAD} = 2.2\text{nF}$ , from G2 to PGND |                         |                        | 12  | 25  |      |          |

| $V_{OH}$                               | High-level output voltage, G2 | $V_{SW} = \text{GND}$                       |                         |                        | 6.2 | 6.7 | 7.5  | V        |

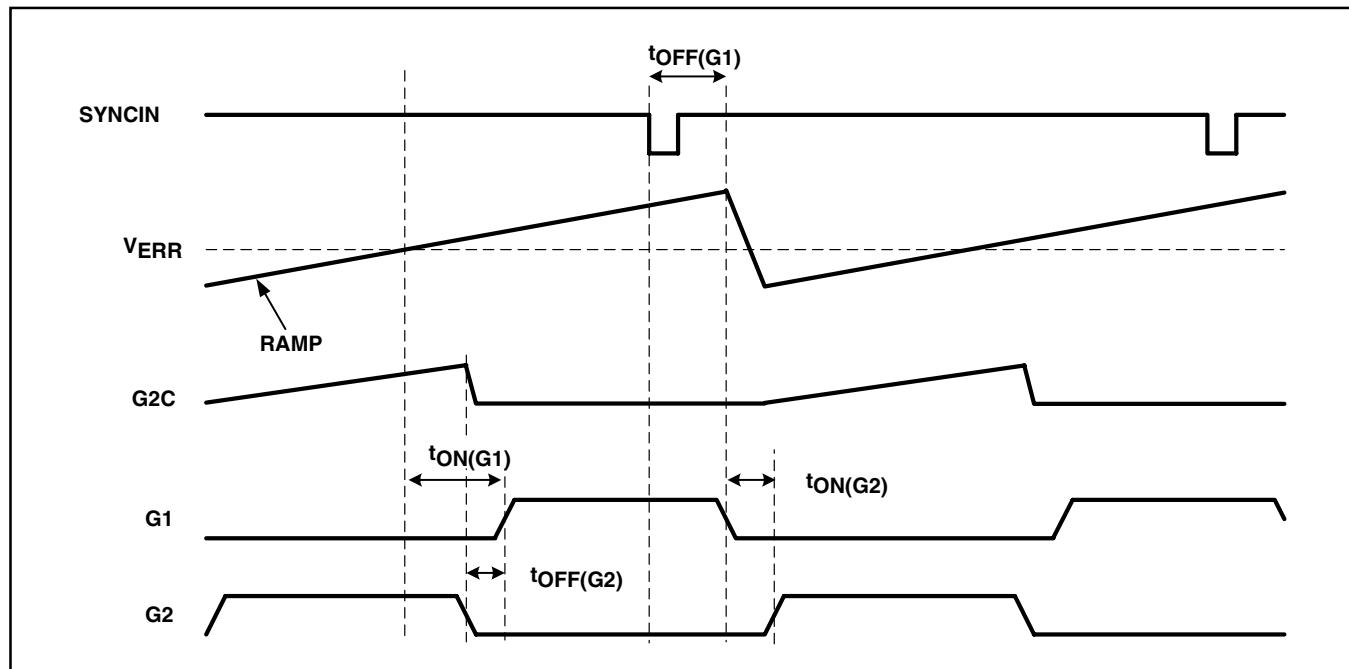

| <b>DEADTIME DELAY (see Figure 1)</b>   |                               |                                             |                         |                        |     |     |      |          |

| $t_{ON(G1)}$                           | RAMP rising to G1 rising      |                                             |                         |                        | 90  | 115 | 130  | ns       |

| $t_{OFF(G1)}$                          | SYNCIN falling to G1 falling  |                                             |                         |                        | 50  | 70  | 90   |          |

| $t_{ON(G2)}$                           | Delay control resolution      |                                             |                         |                        | 3.5 | 5.0 | 6.5  |          |

| $t_{ON(G2)}$                           | G2 on-time minimum            | wrt G1 falling                              |                         |                        | -24 |     |      |          |

| $t_{ON(G2)}$                           | G2 on-time maximum            | wrt G1 falling                              |                         |                        | 62  |     |      |          |

| $t_{OFF(G2)}$                          | G2 off-time minimum           | wrt G1 rising                               |                         |                        | -68 |     |      |          |

| $t_{OFF(G2)}$                          | G2 off-time maximum           | wrt G1 rising                               |                         |                        | 10  |     |      |          |

(3) 設計で保証されており、テストは行われていません。

図1. Predictive Gate Drive Timing Diagram

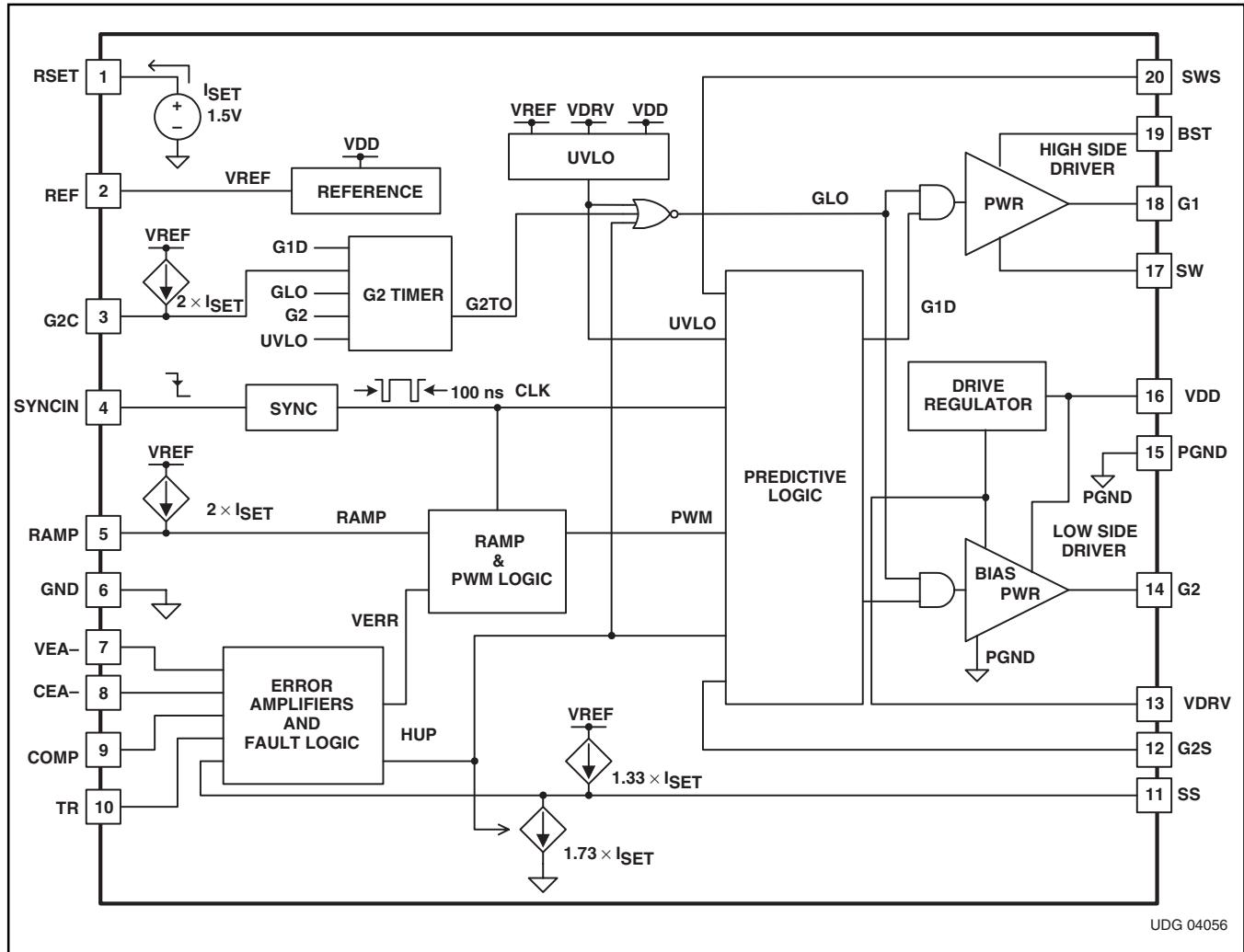

## FUNCTIONAL BLOCK DIAGRAM

## 端子機能

| TERMINAL           |     | I/O | DESCRIPTION                                                                                                                                             |

|--------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO. |     |                                                                                                                                                         |

| BST                | 19  | I   | ハイサイド側G1ゲートドライバの電源供給ピンです。“H”レベルの電圧はSR MOSFETのオン時間に外部ショットキー・ダイオードにより供給されます。コンデンサをこの端子からSW端子に外付けして使用してください。                                               |

| CEA-               | 8   | I   | 出力電流のレギュレーションに使用される電流誤差増幅器の反転入力です。                                                                                                                      |

| COMP               | 9   | I   | 位相保障用端子 電圧/電流誤差増幅器の位相保障用出力です。                                                                                                                           |

| G1                 | 18  | O   | ハイサイド・ゲート・ドライバの出力端子です。振幅はSW端子電位とBST端子電位になります。                                                                                                           |

| G2                 | 14  | O   | ローサイド・ゲート・ドライバの出力です。振幅はPGND端子電位とVDRV端子電位になります。                                                                                                          |

| G2C                | 3   | I   | 同期整流をオフにするタイマ端子です。この端子にコンデンサを接続することでG2が“Hレベル”的最大期間をプログラムすることができます。                                                                                      |

| G2S                | 12  | I   | 適切なデッドタイムを設定するためにSR MOSFETのゲート電圧を検出端子です。プレディクティブ・デッドタイム制御に利用されます。                                                                                       |

| GND                | 6   | -   | 内部制御系回路用のグランド端子です。GNDとPGNDはビアを用いてPCボードのグランドに接続してください。                                                                                                   |

| PGND               | 15  | -   | G2ドライバ用のパワーグランド端子です。PGNDはいくつかのビアを用いてPCボードのグランドに接続してください。                                                                                                |

| RAMP               | 5   | I   | ランプ補正端子です。PWMランプ(傾き)を調整するためのコンデンサを接続します。                                                                                                                |

| REF <sup>(1)</sup> | 2   | I/O | 3.3Vの基準電圧端子です。全ての内部回路はこの3.3Vから電源が供給されます。この端子は軽負荷時(1mA)での安定動作のため最小でも0.1μF以上の容量を接続してください。また、この端子は入力(モード3)として使用されるか、または通常負荷時の使用の場合には最小でも1μF以上の容量を接続してください。 |

| RSET               | 1   | I   | G2C、RAMP、SS充電、SS放電用タイマ電流のプログラム端子です。RSET端子からGNDに接続される外付け抵抗値に比例した電流が生成されます。RSETの抵抗範囲は10kΩから50kΩです(プログラム可能な標準ISET電流の範囲はそれぞれ30μAから150μAとなります)。              |

| SS                 | 11  | I   | ソフトスタート及びシャットダウン・ピンです。この端子からGNDにコンデンサを接続してソフトスタート時間を設定してください。またシャットダウン機能を行うにはこの端子からGNDにスイッチを附加してください。                                                   |

| SYNCIN             | 4   | I   | 外部同期用端子です タイミング信号を入力します。                                                                                                                                |

| SW                 | 17  | -   | G1ドライバのリターン接続端子です。                                                                                                                                      |

| SWS                | 20  | I   | 適切なデッドタイムを設定するためにSR MOSFETのゲート電圧を検出端子です。ボディ・ダイオードの導通を検出してプレディクティブ・コントローラ制御に使用されます。                                                                      |

| TR                 | 10  | I   | 電圧誤差増幅器のトラッキング入力です。使用しない場合はREFピンに接続してください。                                                                                                              |

| VDD                | 16  | I   | デバイスの電源ピン及び内部VDRVドライブ・レギュレータの入力ピンです。標準のV <sub>DD</sub> 電圧範囲は4.5Vから36Vです。このピンは最小1μF以上の容量でバイパスしてください。                                                     |

| VDRV               | 13  | I   | ドライブ・レギュレータの出力及びG2ドライバの電源ピンです。また、VDRVは内部ロジック及びコントロール回路用の電源電圧です。                                                                                         |

| VEA-               | 7   | I   | 出力電圧のレギュレーションに使用される電圧誤差増幅器の反転入力です。                                                                                                                      |

(1) REFピンはモード3の場合のみ入力です。

## アプリケーション情報

UCC2540は高効率の同期整流式降圧コントローラで、多くのポイント・オブ・ロードのアプリケーションに使用することができます。このデバイスは絶縁型バス・コントローラ(IBC)やDCトラン用のプリ・コンバータなどカスケード接続手法などのコントローラとして使用することもできます。また、UCC2540は高精度/多出力電源用の汎用の二次側レギュレータとしても使用できます。

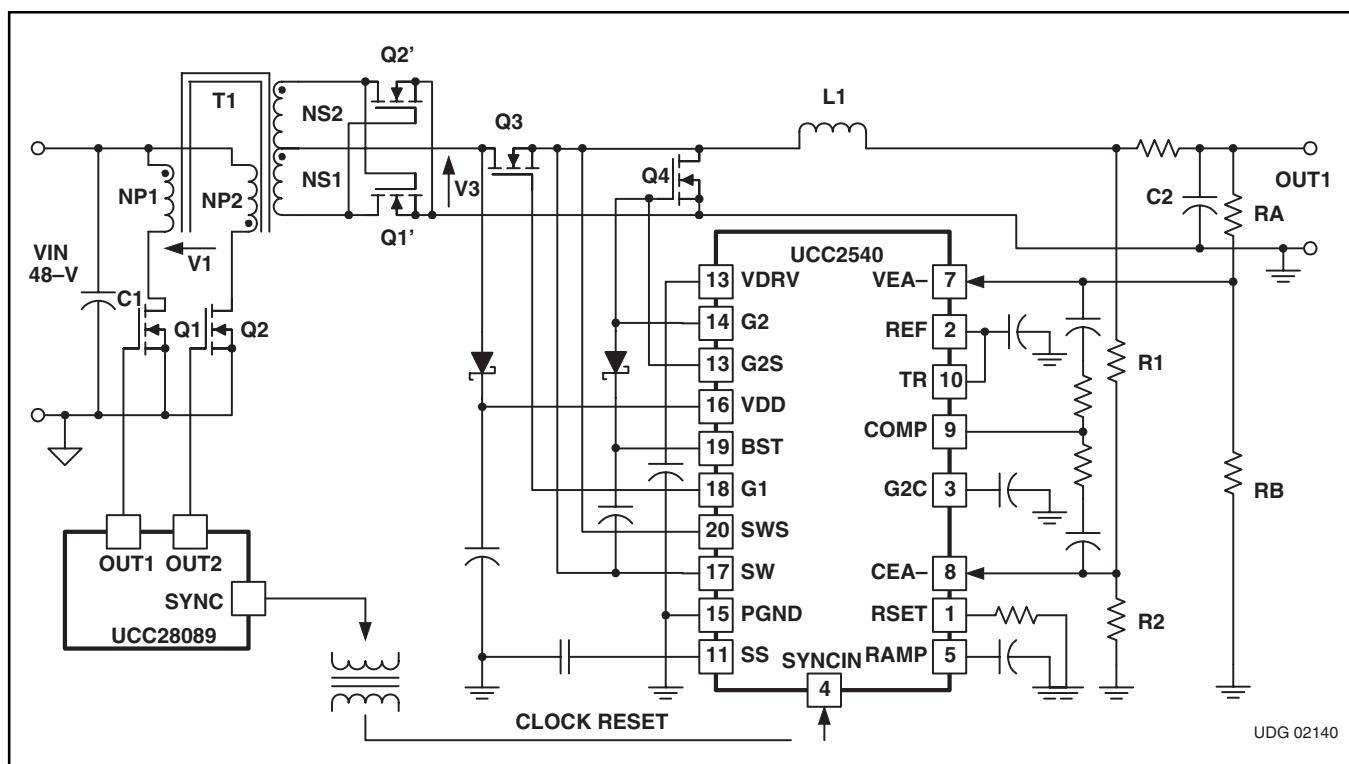

### UCC2540を2段カスケード接続プッシュプル型バック・コンバータの二次側PWMコントローラとして使用した場合

2段カスケード接続のプッシュプル型降圧制御では、テレコム用の48V電圧などの高入力バス電圧を高出力電圧に変換します。

一次側のパワー段は電圧の降圧を行う開ループのプッシュプル型コンバータで、ガルバニ方式の絶縁型の例を示しています。高いバス電圧を入力し、例えば7Vといった中間電圧に変換します。一次側プッシュプルのゲート駆動信号は市販の発振器またはUCC28089などのデューティ・サイクル50%の2チャネル制御のデバイスよりもたらされます。

二次側のパワー段は低出力電圧のレギュレーションに最適化された降圧コンバータです。一次側からの同期のためのクロック・リセット信号がトランスなどを使用して送られます。

この二次側コントロール回路には多くの利点があります。この簡素な絶縁パワー段には絶縁境界にいかなるフィードバックも必要ありません。一次側の発振器は自励式であるため、起動電源は不要です。この高周波回路はソフトスイッチング動作(全6 MOSFETスイッチに対し)やトランス・コアの最適利用を行い、また、高電流のインダクタが加わらないためフィルタへの条件が最小化されます。

一次側はプッシュプル方式のため入力段のMOSFETの直接駆動が容易に可能になります。その代わり、入力MOSFETの定格は少なくとも入力ラインのピーク電圧の2倍であることが必要です。この構成では、150V程度で適切なパワーMOSFETが多く存在するため、36Vから72Vの入力ラインのアプリケーションに効果的です。それより高い入力電圧のアプリケーションについては、入力段には交流変調を用いたハーフブリッジまたはフルブリッジがより適しているかも知れません。上に述べたように、カスケード接続の制御技術では入力パワー段に大きな柔軟性があります。また、カスケード接続の制御技術は同様に出力段にも柔軟性があります。

この制御技術の追加情報については、Power Supply Seminar SEM-1300 Topic 1: Unique Cascaded Power Converter Topology for High Current Low Output Voltage Applications [1]を参照してください。このトピックには、動作原理、設計上のトレードオフ、重要設計手順ステップなどが記載されています。

図2. Secondary-Side Controlled Cascaded Push-Pull/Buck Converter

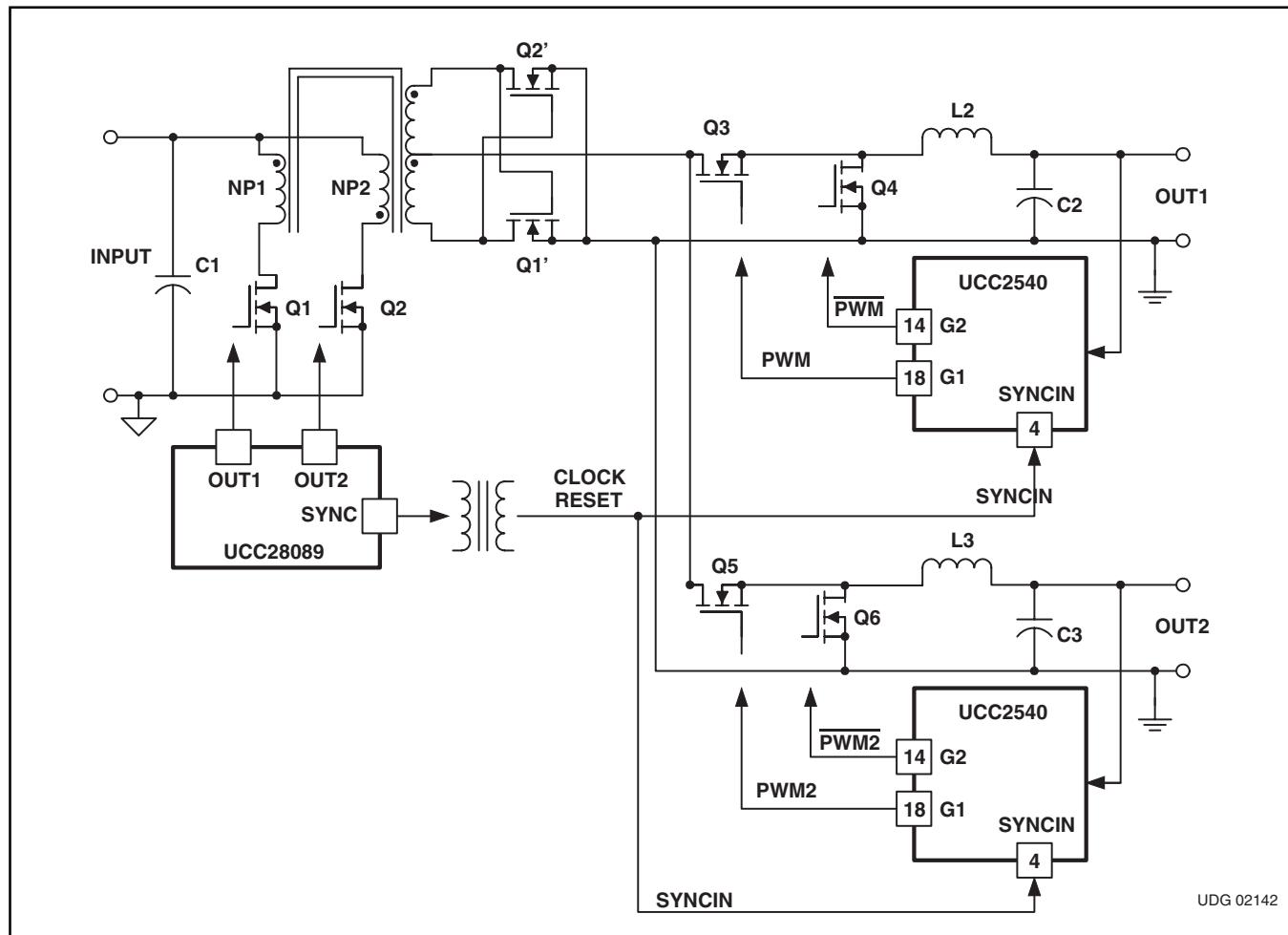

## UCC2540を多出力電源に使用した場合

その柔軟性の1つに、独立して電源を供給する補助出力用の電源回路を容易に追加することができます。カスケード接続型プッシュプル/降圧パワーコンバータの多出力の実施例を図3に示します。

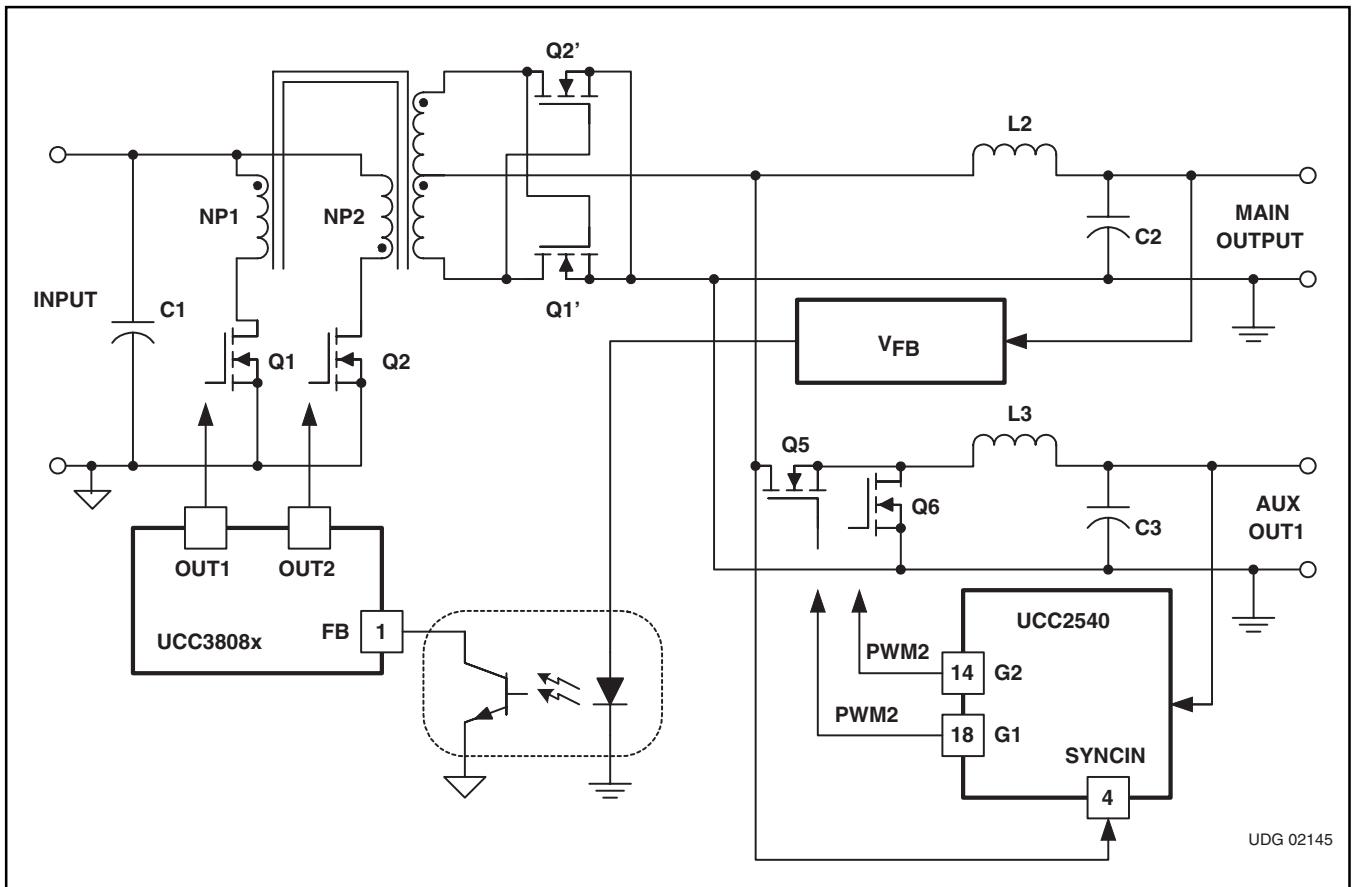

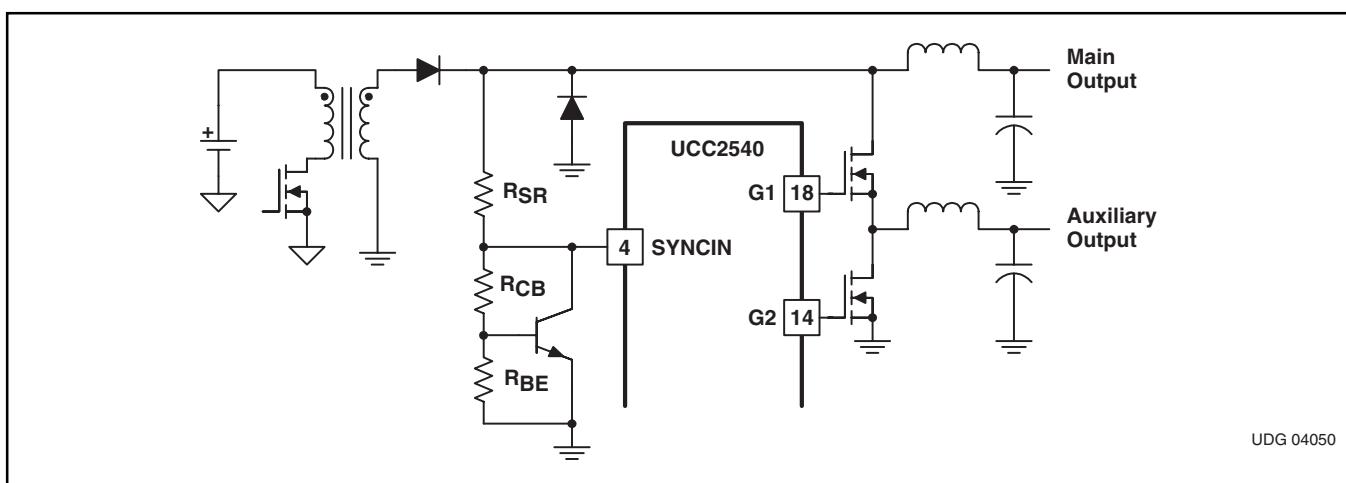

## UCC2540を二次側ポスト・レギュレータに使用した場合

UCC2540は、また、図4に示されるように、多出力電源の補助電圧を精密に制御するため二次側で通常のDC/DCコンバータとして使用することもできます。UCC2540は、一次側コントロールがフォワード、ハーフブリッジ、プッシュプルなどのいかなる制御技術を使用しても互換であるようリーディング・エッジ変調機能を内蔵しています。

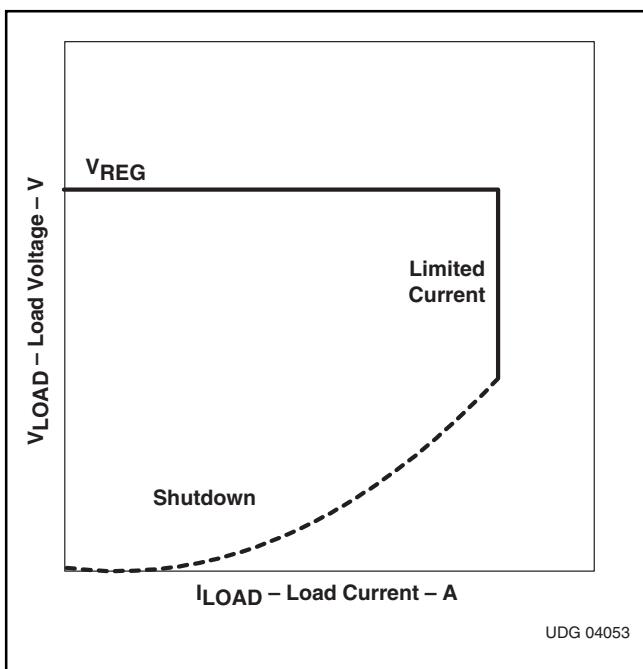

### CEA-, VEA-ピン：電流制限としゃっくり・モード(動いたり止まったりを繰り返すモード)

図5に代表的な電源の負荷の電圧対電流の特性を示します。この図では無負荷から過電流検出までの定常状態動作が示されています(ソフトスタートの再試行は図示されていません)。電圧が制

御されている状態の時、電圧誤差増幅器の出力は電流誤差増幅器よりも低いため、電圧誤差増幅器が全体の動作を制御します。一方、電流制限状態では、電流誤差増幅器の出力が電圧誤差増幅器よりも低いため、電流誤差増幅器が全体の動作を制御します。電圧コントロールと電流コントロール間の境界は、CEA-とVEA-間の電圧差が50mVを越えようとする場合に生じます。

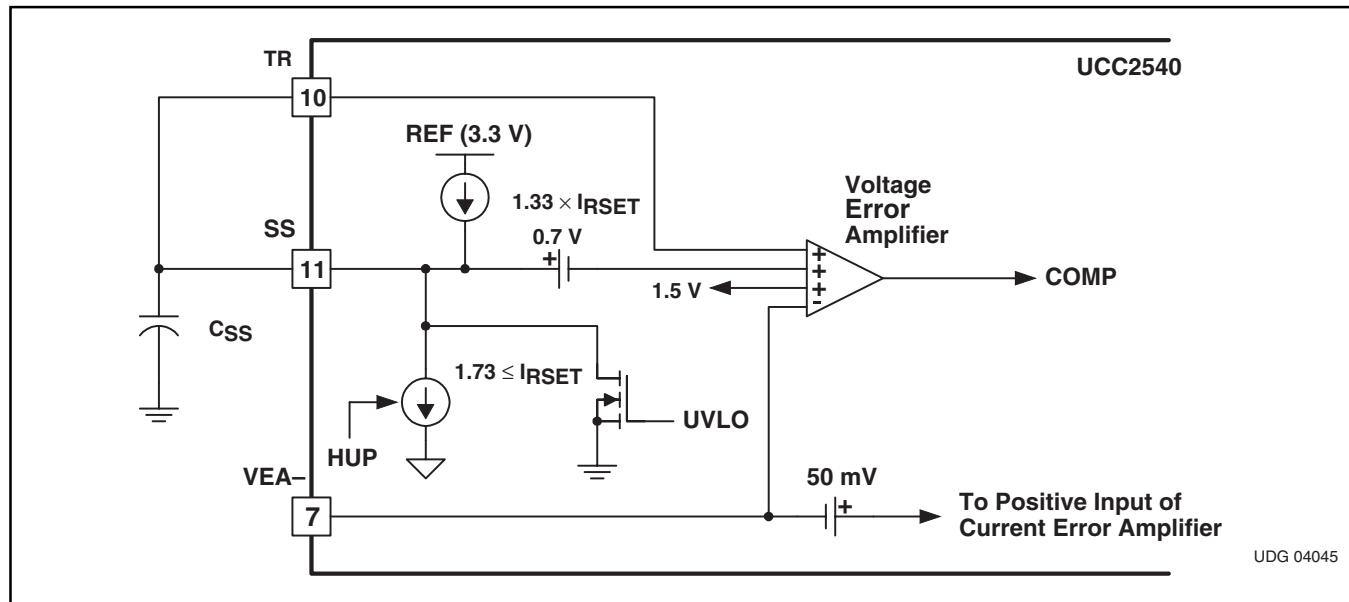

電流制限はCEA-とVEA-間の電圧差が50mVを越えた時起ります。電流がこの動作条件を越えると、UCC2540は出力電圧がその定常定格レベルの1/2に低下するまでコンバータを純粋な電流源として動作するよう制御します。次に、UCC2540はG1とG2の両出力を“L”レベルにセットして、ソフトスタート電圧をその充電レートの30%で放電するフォルトをラッチします。UCC2540はソフトスタート電圧が0.5Vより下に下がるまで再試行を禁止します。電圧誤差増幅器及び電流誤差増幅器の等価回路を図6に示します。

部品を選択するには、以下の説明のように、電圧レギュレーションのスレッシュホールド、その次に電流制限スレッシュホールドを設定します。

図3. Multiple Output Implementation of Push-Pull/Buck Cascaded Converter

図4. Multiple Output Converter with Primary Side Push-Pull Converter

図5. Typical Power Supply Load Voltage vs Current

#### 電圧対電流のプログラミング(図6参照)

1.  $R_{V1}/R_{V2}$ の比を決める。

$$\begin{aligned} R_{V1} &= \frac{V_{LOAD(\text{reg})}}{V_{VEA-} + \text{Threshold Voltage}} - 1V \\ &= \frac{V_{LOAD(\text{reg})}}{1.5 \text{ V (typ)}} - 1V \end{aligned}$$

2. 検出抵抗 $R_S$ を求める。

$$R_S = \left( 1 + \frac{R_{V1}}{R_{V2}} \right) \times \frac{V_{CEA+} \text{ offset voltage}}{I_{S(\text{max})}}$$

但し、 $I_{S(\text{max})}$ は電流制限レベルで、 $V_{CEA+}\text{offset} = 50\text{mV}(\text{typ})$

3.  $R_{V1}$ または $R_{V2}$ をどちらか小さい方が $6.5\text{k}\Omega \sim 20\text{k}\Omega$ になるよう $R_{V1}$ または $R_{V2}$ を任意に選ぶ。次にステップ1の式を使ってもう一方の抵抗値を計算する。

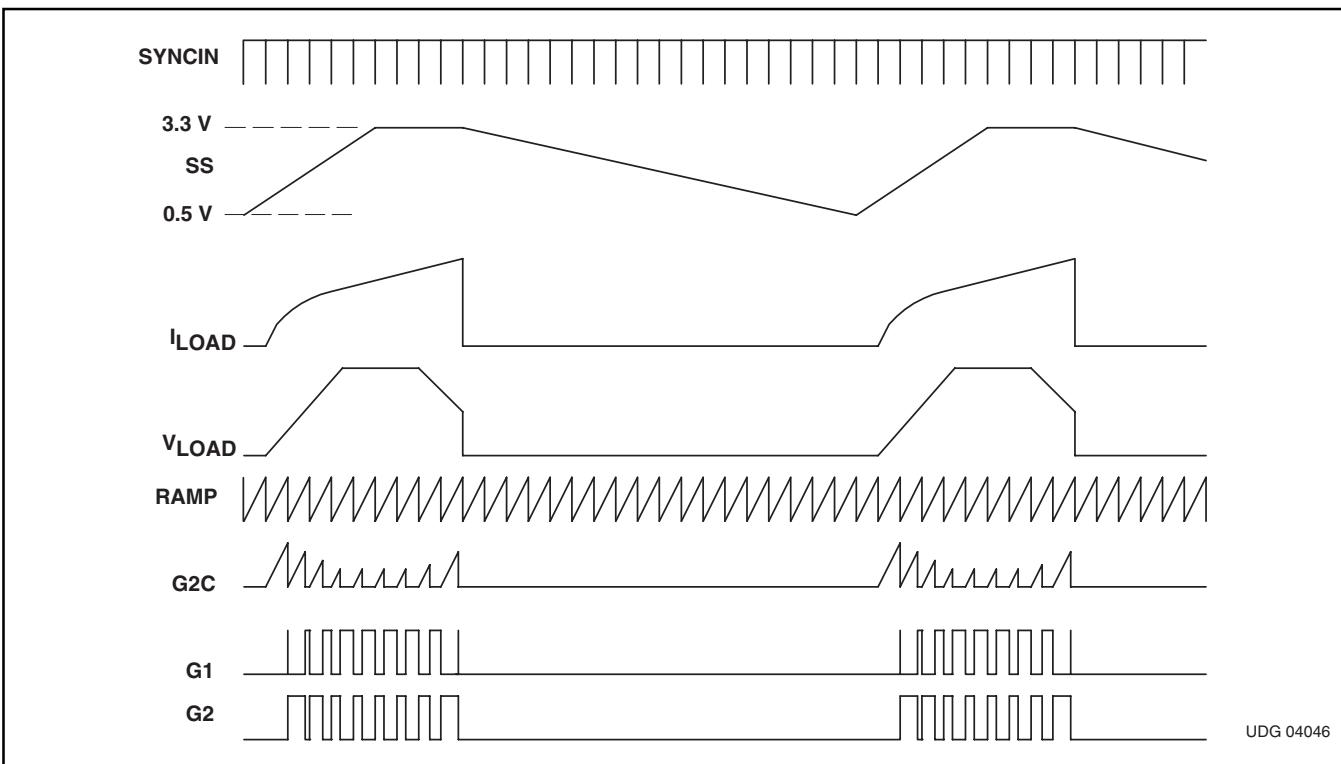

コンバータが電流制限状態にあり、出力電圧がレギュレーション出力電圧の1/2より下がると、UCC2540はしゃっくり(動作停止を繰り返す)モードになります。図7に、しゃっくり・モード時における代表的な信号を示します。

図6. Error Amplifier Configuration

図7. Typical Hiccup Mode waveforms

## COMP, VEA-, CEA-ピン：電圧/電流誤差増幅器

無負荷から全定格負荷の動作条件では、UCC2540は電圧モード・コントローラとして動作します。プログラムされた定格電流以上では、過電流保護には定電流制限と過電流リセット/リトライの2つのレベルがあります。この項では電圧コントローラ及び電流コントローラが安定して相互作用するよう、それらの設計方法についての提案を行います。図6の電圧/電流誤差増幅器の等価回路図を参照してください。図の電圧誤差増幅器には3つの非反転入力があることが示されています。3つの非反転入力(1.5V, SS, TR)のうちもっとも小さいものが有効になり非反転入力と合算され電圧誤差信号となります。2つの出力のうち低いほうが反転段を駆動し、それが次に変調器を駆動します。

定常状態の電圧コントロール動作時、電流ループのフィードバック成分はループの安定性には影響を与えません。電流制限が起こると、電圧誤差増幅器は事実上停止し、電流誤差増幅器がコントロールを引き継ぎます。定常状態の電流制限動作時は、電圧誤差増幅器のループの負のフィードバック成分が電流誤差増幅器のループの正のフィードバック成分になります。電流誤差増幅器が安定であるためには、電流誤差増幅器の帰還信号のインピーダンスが電圧誤差増幅器の帰還信号のインピーダンスより低いことが必要です。このことは、電流誤差増幅器の負の帰還の抵抗が電圧誤差増幅器の負の帰還の抵抗より小さくなければならぬということを意味しています。また、電流誤差増幅器の負の帰還のコンデンサは電圧誤差増幅器の負の帰還のコンデンサより大きい必要があります(容量は実際にはインピーダンス値というよりはむしろアドミタンス値です)。この概念は図6に示されています。

図6で電流ループが安定するために、全周波数で  $\|Z_{IV}\|$  が  $\|Z_{FV}\|$  よりも小さいことが必要です。このことは、 $R_{FI} < R_{FV}$  及び  $C_{FI} > C_{FV}$  である場合に成立します。

電流制限動作時に起こり得るもう1つの問題点とは変調器の安定性です。変調器が安定であるためには、COMP端子で測定される電流リップルの立上がり勾配がRAMP端子で測定される立上がり勾配より小さくなければなりません。このことは、 $\|Z_{FV}\|$  に対する  $\|Z_{IV}\|$  の比を選択するか、または図6のCFIRのように  $R_{FI}$  と  $C_{FI}$  に並列にコンデンサを付加することで達成できます。

### 安定したダイナミック電流ループの設計(図6参照)

1. 安定した電圧モードの設計となるよう電圧誤差増幅器を設計します。電圧誤差増幅器の負の帰還抵抗は全て最小  $15\text{k}\Omega$  を使用してください(9ピンと7ピン間)。このことは、電源の出力電圧と7ピン間の抵抗値には適用されませんし、またグランドと7ピン間の抵抗値にも適用されません。

2. 目標は電流制限状態時VEA-ピンとCEA-ピン間で  $50\text{mV}$  を維持するようコンバータを駆動するために電流制限のコントロール・ループを設計することです。電流検出素子と、目的とする電流制限レベルとなるようグランドに対するVEA-ピン、グ

ランドに対するCEA-ピンの分圧比を選択してください。

3. 電流誤差増幅器の負の帰還(9ピンと8ピン間)に、電圧誤差増幅器の負の帰還(9ピンと7ピン間)と同じ構成の部品を配置してください。但し、抵抗値は9ピンと7ピン間の対応する抵抗の約  $67\%(2/3)$  に、また、コンデンサ値は9ピンと7ピン間の対応するコンデンサの約  $150\%$  を使用してください。

4. COMP信号を確認してください。不安定である場合には、電流リップルを減衰させるために9ピンと8ピン間にコンデンサを付加(または容量を増加)してください。COMPピンの電圧が安定となるまでコンデンサの値を上昇させます。COMP電圧とRAMP電圧を比較します。安定動作では、COMP電圧リップルの立上がり勾配はRAMP電圧の立上がり勾配より小さくなります。

## RSET, RAMP, G2C, SSピン：タイマ電流の設定

RSETとGND間に抵抗を接続してタイマにベース電流を設定してください。UCC2540のブロック図にRSETピンとRAMP, G2C, SS機能用依存電流源との相互関係が示されています。RSETピンは電圧源ですが、RSETピン電流が派生しゲインが乗じられ、RAMP(ゲイン = 2)、G2C(ゲイン = 2)、SS(充電ゲイン = 1.33、正味放電ゲイン = 0.4)に分配されます。RSETピンとGND間に付加される抵抗は  $10\text{k}\Omega < RRSET < 50\text{k}\Omega$  の範囲でなければなりません。RAMP, G2C, SSのタイマはそれぞれのピンとGND間に接続されるコンデンサを選択することにより設定されます。

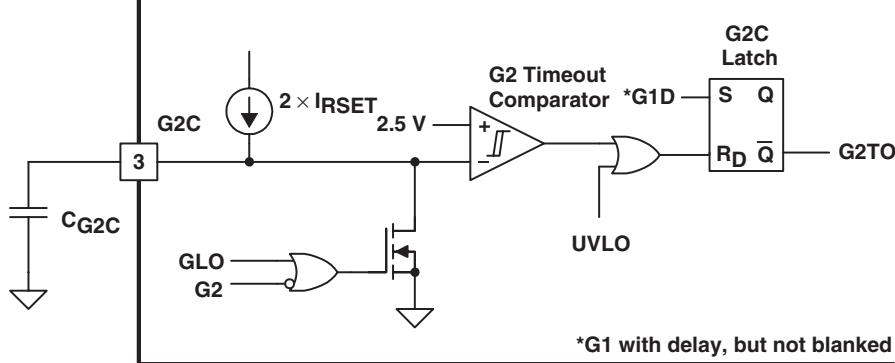

### G2Cピン：G2タイマ

G2C端子は低デューティまたはゼロ・デューティでの動作を容易にするため同期整流の最大期間を設定します。図8に、この等価回路図を示します。この機能はG2CとGND間にコンデンサを接続することで設定できます。G2CのコンデンサはRAMPピンのコンデンサよりも少し大きくなります。最良の結果を得るには、標準のG2時間制限がスイッチング周期( $T$ )の1.5倍から3倍となるよう設定します。G2タイマがその限界に達すると、G1とG2の両方とも“L”レベル出力になることに注意してください。この機能により、出力インダクタの電流がゼロデューティの状態時に極端に負になることが防止できます。式(1)を使用してG2タイムアウト(G2TO)期間を設定します。

$$C_{G2C} = \frac{2 \times V_{RSET}}{R_{RSET}} \times \frac{\text{G2 Timeout Duration}}{\text{G2C Timer Threshold}}, \text{Farads} \quad (1)$$

但し、

- $V_{RSET} = 1.5\text{V}(\text{typ})$

- $1.5\text{T} < \text{G2 タイムアウト期間} < 3T_S$

- G2Cタイマ・スレッシュホールド =  $2.5\text{V}(\text{typ})$

UDG 04047

図8. Functional diagram of the G2 Timer

UDG 04048

図9. PWM Modulator and G1 Time-Out Comparator

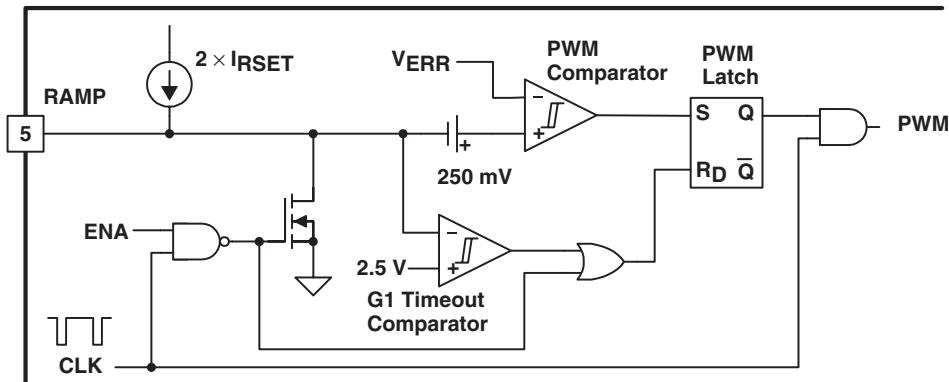

### RAMPピン：PWM変調器とG1タイマ

RAMPピンには、(1)PWM変調器のゲインをプログラムすることと、(2)メインのパワー段がSYNCパルスを発生させない場合にG1のタイムアウト期間をプログラムすることの2つ目的があります。PWM変調器とG1タイマの等価回路を図9に示します。UCC2540は誤差出力をRAMP電圧と比較するリーディング・エッジの変調器を内蔵しています。変調器の周波数はSYNCINピンを介して外部から駆動されます。RAMPピンはPWMコンパレータにのこぎり波を供給し、かつ、 $R_{SET}$ とRAMPコンデンサの値でプログラムされるG1タイムアウト保護の機能も果たします。

スイッチング・サイクルはSYNCIN信号の立下りエッジで開始し、その信号の“L”レベルは最小50ns以上です。SYNCINの立下りエッジで、RAMP機能への100nsの放電信号(CLK)が生成され、その結果、RAMPコンデンサは $2 \times I_{RSET}$ の電流源より充電することができます。

低入力電圧または電圧低下の状態では、一次側のデューティ比が100%に近づきコンバータの寄生インピーダンスがSYNCINパルスの質を低下させる可能性があります。RAMPタイミング機能によりRAMP電圧が2.5Vを越えるとG1パルスが停止します。

RAMPタイミング機能の期間は以下のように設定しなければなりません。

$$C_{RAMP} \geq \frac{\left(2 \times \frac{V_{RSET}}{R_{RSET}}\right) \times T_S}{\text{PWM}_{RAMP} \text{ timeout threshold voltage}} \quad (2)$$

但し、

- $T_S$ =スイッチング周期

- $V_{RSET} = 1.5V(\text{typ})$

- $\text{PWM}_{(RAMP)} = 2.5V(\text{typ})$

$$R_{SET} C_{RAMP} \geq \frac{1.2}{f_S} \Rightarrow \text{Gain (PWM modulator)} \geq 0.4 \quad (3)$$

G1タイマ機能を使用するためには、スイッチ・サイクルの終わりでのRAMPのピーク電圧をCRAMPとRRSETの公差が許容できる2.5Vに近づけなければなりません。つまり、PWM変調器のゲインは1/0.4Vに等しいか、または少しだけ大きくなるよう設定しなければなりません。

### SYNCINピン

SYNCINピンへ立下りエッジが加えられるとUCC2540の内部機能用の基礎信号である狭小パルスが生成されます。SYNCINパルスは、有効パルスとして登録されるためには立下りエッジに先行して最小100nsの間“H”レベル、及び立下り後最小50nsの間“L”レベルでなければなりません。タイミングが厳しいという性質により、信号遅延を回避するためSYNCIN信号の立下りエッジにフィルタを施すことは避けてください。SYNCINのピーク電圧は2.5Vから6.6Vの範囲で変動するため、ポスト・レギュレータの二次側トランジスタ電圧を簡素な抵抗分割で縮小することができます。

ライン電圧がより広範囲に変化する状態、あるいはリンクギングが大きい状態では、追加されるゲインをクランプすることが必要となることがあります。

## グランドのクランプ

リンクングまたはスパイクによりSYNCINがGND以下に低下するアプリケーションでは、ショットキー・ダイオードを用いてこのピンを保護してください(カソード側 = SYNCIN、アノード側 = GND)。

過電圧クランプ

SYNCIN信号には、リングング・レベルまたは電圧レベルにより、SYNCINのピーク電圧が絶対最大レベルの8Vになる仕様では過電圧クランプが必要となることがあります。図10のように、REFまたはVDRVをクランプ電圧として使用することができます。REFまたはVDRVは常時電流をソースすることを確認してください。REF及びVDRVの両方とも逆駆動されている場合や起動時不適切な動作モードにラッチしている場合に動作モードを検出するのに使用されます。

もう1つの過電圧クランプとして選択できることは直接SYNCINピンをクランプすることです。あいにく、ツェナー・ダイオードは過度の接合容量をもっているため、大きな遅延時間を引き起こします。しかしながら、回路はSYNCIN信号への遅延が最小で、目的とするクランプ動作を実現することができます。図11を参照してください。低ライン状態で適切な0Vから3.3Vの信号となるよう単に $R_{SR}$ と( $R_{CB} + R_{BE}$ )を選択してください。次に、SYNCINが4Vを越えた時にトランジスタがターンオンするよう $R_{RF}$ と $R_{CB}$ の比を選択してください。

図10. REF Clamp for SYNCIN. Note the REF Load Resistor.

图11. VBE Clamp for SYNCIN

## 絶縁型カスケード接続降圧制御SYNCINクランプ

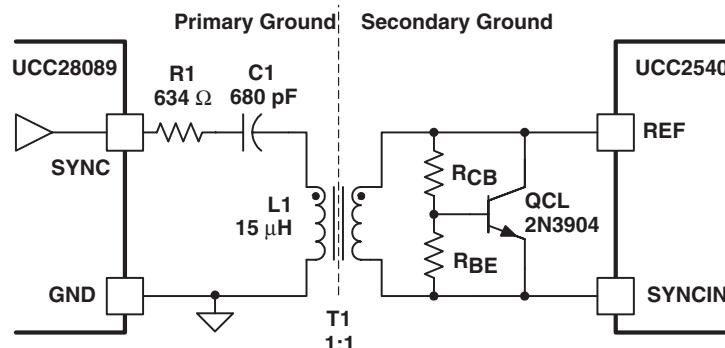

UCC2540は、UCC28089等の一次側起動コントローラと組み合った場合、カスケード接続の降圧制御の二次側コントローラとして最適です。一次側コントローラはそのデッドタイム時にパルス・エッジを送信します。UCC2540は一次側及び二次側スイッチにゼロ電圧状態をもたらすために一次側のパルスを使用します。プレディクティブ・ディレイ機能は同期整流器の逆回復損失を最小限に抑えるよう二次側の変化を調整します。パルス・エッジの情報は一次側のバイアス電圧によって変化するため、クランプすることが必要です。図12に示されている回路には、しかるべきパルス・エッジ成形回路、クランプ、1500Vの絶縁電圧が含まれています。例えば推奨するトランジスタのCOEV型番MGBT-00011-01は多くの光絶縁よりも小型です。

## VDD, VDRV, VREF, BSTピン：動作モード

UCC2540のバイアス電圧により、起動、停止、再起動条件は異なります。UCC2540を動作するには3つの形態またはモードがあります。VREFが2Vを越える起動時、モードは検出され、内部レジスタにラッチされます。このレジスタはVDD, VDRV, VREFが全て同時に1Vより低い場合にクリアされます。全てのモードはカスケード接続の降圧制御技術あるいは二次側ポスト・レギュレータ(SSPR)制御と互換性があります。モード1とモード2のメイン・バイアス電圧はトランジスタの二次側巻線などのAC電圧からダイオードやコンデンサにより供給されます。モードのまとめと各プログラム条件を表1に記載します。

- モード1、あるいは通常動作ではデバイスに対し8.5Vまたはそれ以上のバイアス電圧が必要です。このモードでは、バイアスがVDDピンを駆動します。ローサイドの駆動バイアス電圧の $V_{VDRV} = 7V$ は内部のリニア・レギュレータから生成され、VDDピンから直接電流を流します。ハイサイド・ドライバのバイアスは、G2が“H”レベルの時G2とBST間のダイオードを経てVDRVピンからG2ピンに充電されるコンデンサです。UCC2540は、 $V_{VREF}$ が2Vより上に上昇した時 $V_{VDD} > (V_{VDRV}, V_{VREF})$ であればモード1で動作します。モード1ではバイアス電圧範囲が最大幅となり、 $8.5V < V_{VDD} < 35V$ で動作可能です。このモードは既存の12VDCのバイアス電圧をもつシステムと互換性があります。また、モード1は入力ライン電圧が広範囲に変化するアプリケーションや、図13のようにバイアスが派生ライン電圧から直接得られるアプリケーションで特に有効です。

- モード2はバイアスが標準で5V(4.5V~8.0V)のアプリケーションに適しています。バイアス電圧はUCC2540のVDRV端子に印加されます。ハイサイド・ドライバのバイアスは、G2が“H”レベルの時VDRVピンからG2ピンに充電されるコンデンサです。VDDピンへのバイアス電圧は外付け電圧ダブルのチャージポンプより得られます。システムに低スレッシュホールド電圧のパワーMOSFETが使用されている場合は、VDDピンは直接VDRVピンに接続することができます。バイアス電圧は、バス・コンバータの出力、または補助電源、または制御されている電源から派生するコンバータの入力電圧です。

UDG 04051

図12. Isolation and Clamping the SYNCIN Signal for Cascaded Buck Converters

| モード | $V_{BIAS}$ 範囲 (V) | バイアス・ピン   | UVLO ON (V)       | UVLO OFF (V)     | モード要件 (起動時、 $V_{VREF} = 2V$ )               | 注                                |

|-----|-------------------|-----------|-------------------|------------------|---------------------------------------------|----------------------------------|

| 1   | 8.5~36            | VDD [16]  | $V_{VDD} = 8.5$   | $V_{VDD} = 8.0$  | $V_{VDD} > (V_{VDRV} \text{ and } V_{REF})$ | 最大幅のライン動作                        |

| 2   | 4.75~8.5          | VDRV [13] | $V_{VDRV} = 4.65$ | $V_{VDRV} = 4.3$ | $V_{VDRV} > (V_{VDD} \text{ and } V_{REF})$ |                                  |

| 3   | 3.0~3.6           | VREF [2]  | $V_{REF} = 3.0$   | $V_{REF} = 2.5$  | $V_{REF} > (V_{VDD} \text{ and } V_{VDRV})$ | 安定化バイアスと低 $V_{TH}$ のパワーMOSFETが必要 |

表1. モードとプログラム条件

- モード3はバイアス電圧が制御されている3.3V電源である同期式降圧コンバータのアプリケーション用です。これは多出力のコンバータの共通メイン出力電圧です。バイアス電圧はUCC2540のVREFピンに印加されます。UCC2540はVVREFが2Vより上に上昇した時 $V_{VREF} > (V_{VDRV}, VDD)$ が検出されればモード3で動作します。

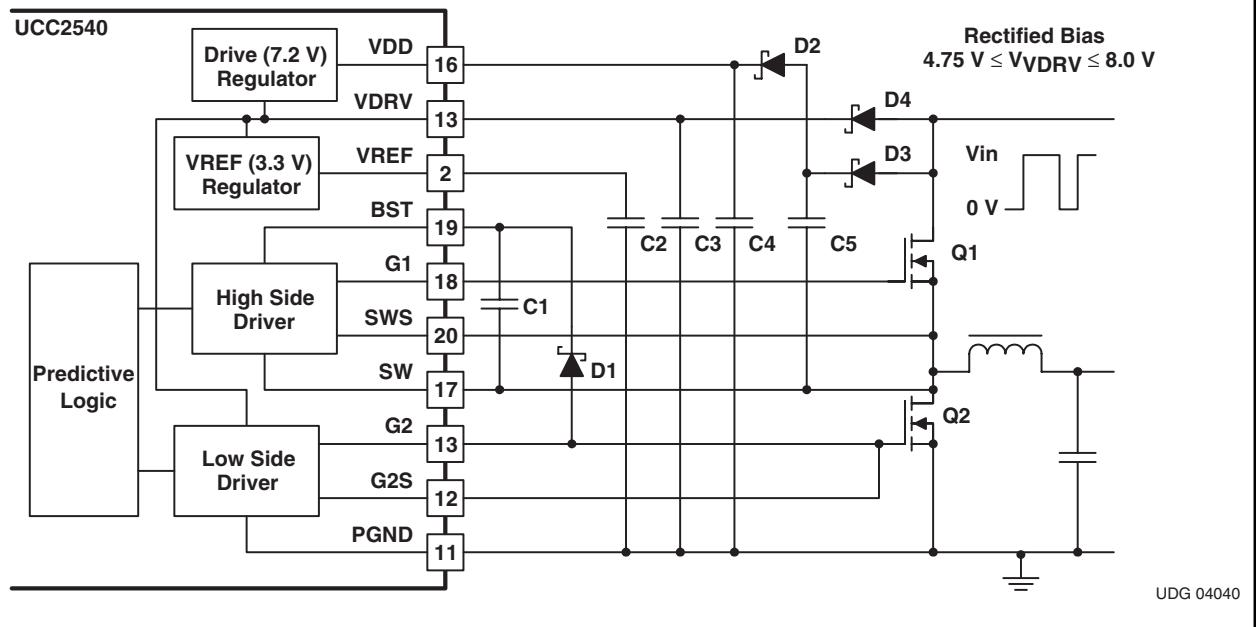

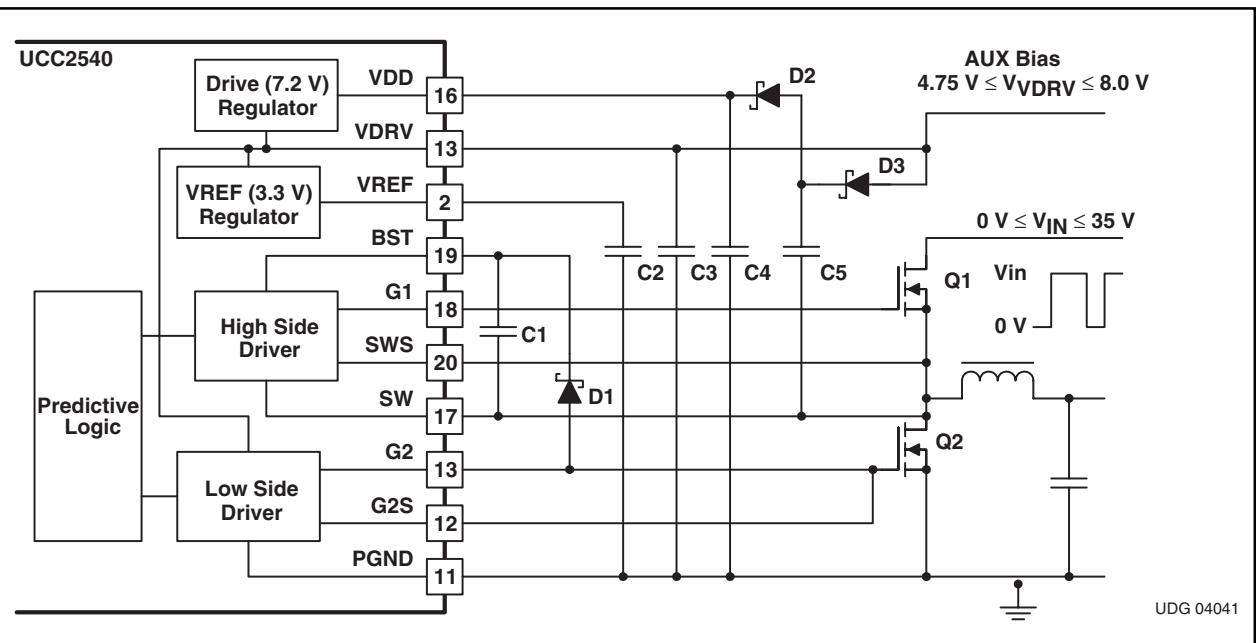

種々のモードの組み合わせ及びバイアス体系を図14から図19に示します。モード1とモード2では、図14から図17に示されるように、バイアス電圧は独立した補助電源であるか、または派生入力電圧を整流及びフィルタして生成できます。VREF電圧の公差はUCC2540がコントロールする公差であるためモード3では制御されている補助電源を使用しなければなりません。モード3では、制御されている補助電源は電源の入力電圧とは無関係(図19参照)、もしくは制御されている補助電源は電源の入力電圧と同一源とすることができます。

### チャージポンプ用コンデンサの選択

コンデンサC1からC5はUCC2540がMOSFET Q1とQ2のゲートに電荷を送ることを可能にする電荷分配回路の部品です(この項の全参照記号は図14から図19の回路図でのものです)。この項ではコンバータが正しく機能するためのC1からC5の値を選択する際の指針を紹介します。具体的なコンデンサの値は、MOSFETの特性、ダイオードD1-D4の特性、コンバータの閉ループ性能により推奨値よりも大きくなる場合もあります。3モード動作全てにはハイサイドMOSFETを駆動するためのチャージポンプ用のコンデンサとダイオード、C1及びD1が必要です。モード2とモード3ではVDDに電圧を供給するために追加のチャージポンプ用のコンデンサとダイオードが必要です。一般的に、全てのチャージポンプ用ダイオードには低い順方向電圧と高速性をもたらせるためショットキー・ダイオードを使用します。また、チャージポンプ用コンデンサにはX5R、X7RコンデンサといったESR(等価抵抗値)が低いセラミック・コンデンサを使用すべきです。

チャージポンプ用コンデンサC1の値は、パワーMOSFETのゲート電荷と容量、ミラー回路の安定のためのスレッシュホールドの電圧レベル、D1の順方向電圧降下、閉ループの応答時間に依存します。無負荷状態のハイサイド・ゲート・ドライバは標準で立上がりエッジ当たり $2nC$ の電荷と、それに加えC1から $30\mu A$ の直流電流を流します。通常、無負荷状態のハイサイド・ゲート・ドライバの負荷はハイサイド・パワーMOSFET Q1のゲート電荷要件に比べかなり微小です。C1の標準値はMOSFET Q1の入力容量

( $C_{ISS}$ )の約50~100倍です。このことにより、通常、C1に完全に再充電する十分な時間がなく、非常に大きなデューティ比での過渡動作が可能になります。C1が極端に大きいと、そのESRとESLにより起動時や過渡現象時などの再充電が妨げられます。

次に、電荷移動の方向とUCC2540の要件をもとにコンデンサC2からC5を選択します。この選択の指針を表2に示します。各コンバータの設計では表2で提案されているコンデンサの比率よりも大きな比率に調整に注意を払う必要があります。選択手順は表2の左側から始め、表の右側方向に進めてゆきますが、これは起動時の最初の数サイクルの充電フローとは逆の順序です。設計プロセスで繰り返しが必要である場合には、表の左から右の順に進めてください。

モード2及びモード3では、表2のVDDフィルタ・コンデンサのC4は、ゲートG1とG2を駆動する電荷に加えてUCC2540に $I_{VDD}$ アイドル電流(約11mA)を供給しなければなりません。コンデンサC4は、起動時の十分な動作電圧と、全動作時の $I_{VDD}$ 電流下でのその他の過渡電流に耐える程度に十分大きいことが必要です。動作周波数とMOSFETのゲート電荷( $Q_G$ )が分かると、平均 $I_{VDD}$ 電流は以下の式で見積もることができます。

$$I_{VDD} = I_{VDD(\text{idle})} + (Q_{G1} + Q_{G2}) \times f_S \quad (4)$$

- 但し、 $f_S$ はスイッチング周波数です。

ノイズの問題を防ぐため、C4は最低でも $1\mu F$ 以上であることが必要です。さらに、電荷をパワーMOSFETのゲートに送るのに十分な大きさであることが必要です。従って、C4は、表2に示されるように、多くの場合、VDRVフィルタ・コンデンサの容量の少なくとも2倍であることが示されています。

### 出力段

UCC2540は2つのゲート駆動用出力をもっており、その各々は $\pm 3A$ のピーク電流能力があります。ドライバのプルアップ/プルダウン回路はバイポーラ・トランジスタとMOSFETトランジスタを並列に接続したものです。ハイサイド及びローサイドの2つのドライバは、何よりも必要なMOSFETのスイッチング領域において3Aの高電流能力を供給します。ピーク出力電流定格はバイポーラ・トランジスタとMOSFETトランジスタとの合成電流です。出力抵抗はドライバ出力の電圧がバイポーラ・トランジスタの飽和電圧よりも小さい場合MOSFETトランジスタの $R_{DS(on)}$ となります。

| モード | ハイサイド駆動コンデンサ ( $\geq 0.1\mu F$ ) | VDRVフィルタ・コンデンサ                      | VREFフィルタ・コンデンサ      | VDDフィルタ・コンデンサ                   | 充電コンデンサ                 |

|-----|----------------------------------|-------------------------------------|---------------------|---------------------------------|-------------------------|

| 1   | $C_1 \geq 50 C_{ISS}$            | $C_3 \geq 2 \times C_1$             | $C_2 \geq 0.1\mu F$ | $C_4 \geq 1\mu F$               | n/a                     |

| 2   | $C_1 \geq 50 C_{ISS}$            | $C_3 \geq 2 \times C_1$             | $C_2 \geq 0.1\mu F$ | $C_4 \geq 1\mu F, 2 \times C_3$ | $C_5 \geq 2 \times C_4$ |

| 3   | $C_1 \geq 50 C_{ISS}$            | $C_4 \geq 1\mu F$<br>$2 \times C_1$ | $C_2 \geq 1.0\mu F$ | $C_4 \geq 1\mu F, 2 \times C_1$ | $C_5 \geq 2 \times C_4$ |

表2. チャージポンプ/バイアス・コンデンサの選択指針

出力ドライバはVDDからGNDにスイッチ可能です。また、各出力段もオーバーシュート及びアンダーシュートに対し超低インピーダンスを提供しています。このことは、ほとんどの場合、外付けショットキー・クランプ・ダイオードは不要であることを意味しています。また、出力は、500mAの逆電流にも耐えるよう設計されています。

MOSFETの安定領域での駆動電流要件の追加情報については、電源セミナSEM-1400<sup>[2]</sup>及びUCC37323/4/5のデータシート<sup>[3]</sup>を参照してください。

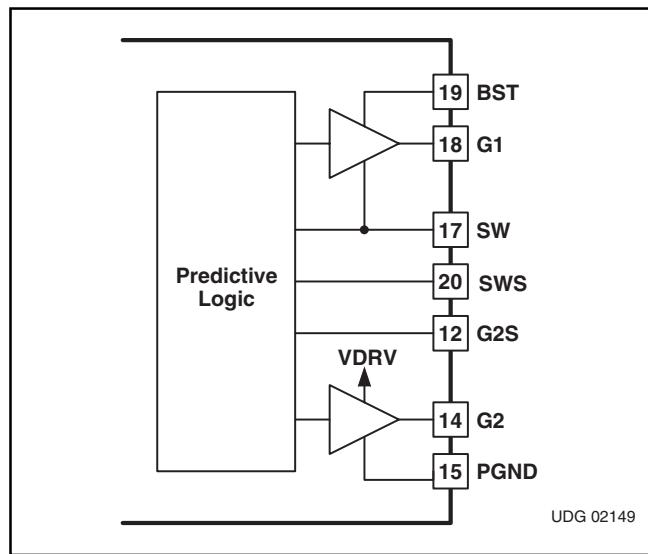

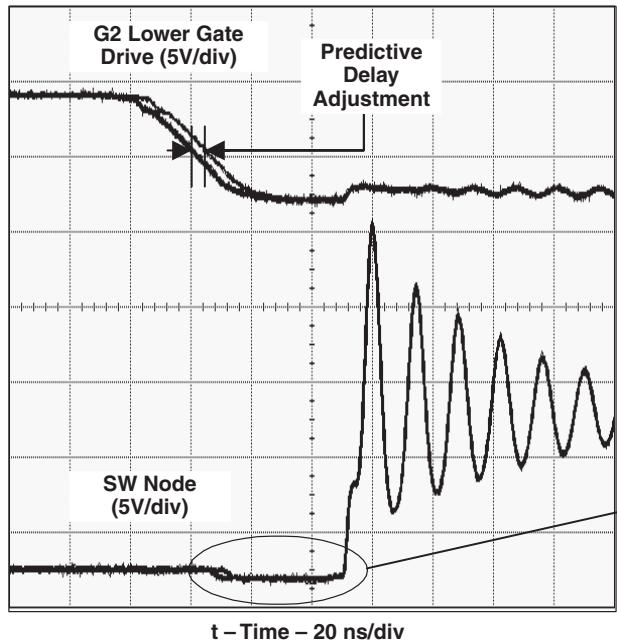

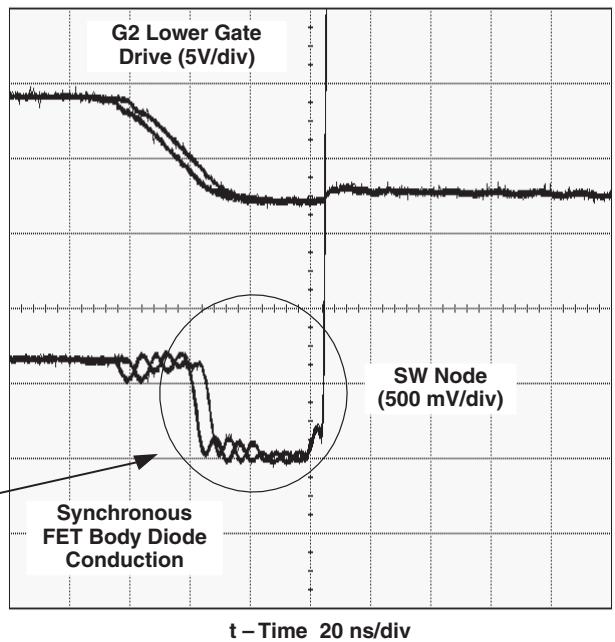

### Predictive Gate Drive™テクノロジ

Predictive Gate Drive™テクノロジは寄生ボディ・ダイオードの導通を最小限に抑えることにより効率を高めることができます。このテクノロジは寄生ボディ・ダイオードの導通を検出するのにデジタルのフィードバック・システムを利用しておらず、導通期間を最小限にするようデッドタイム遅延を調整します。この閉ループ・システムでは、色々な種類のMOSFET、温度、負荷変動による遅延に順応しながらボディ・ダイオードの導通をほぼ排除します。消費電力が最小化されるため、より高いスイッチング周波数が使用できるようになります。部品寸法が小さくできます。ナノ秒レベルの精密なゲート・タイミングにより、同期整流MOSFETの寄生ボディ・ダイオードの逆回復時間が低減し、そのことによりメイン(ハイサイド)MOSFETでの逆回復損失が減少します。最終的には、消費電力が低くなることにより信頼性が向上することになります。

図13

Predictive Gate Drive™コントロール、従来のアダプティブ遅延との効率比較、アダプティブ・コントロール技法の追加情報については、UCC27223のデータシート<sup>[3]</sup>を参照してください。

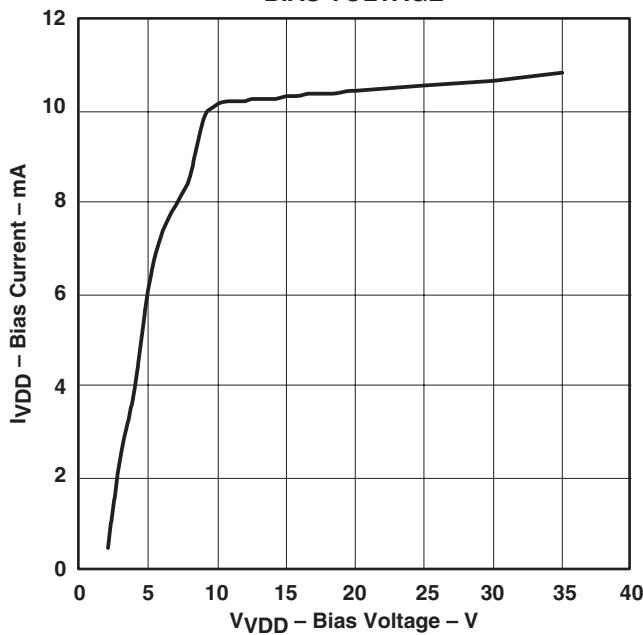

### VDDとIDD

静止時のVDD電流は低いといえ、総消費電流は出力のゲート駆動要件及びプログラムされる発振器周波数によっては大きくなります。総VDD電流( $I_{VDD}$ )は、式(4)で表されているように、静止時VDD電流とG1及びG2の出力電流の平均値の和です。動作周波数とMOSFETのゲート電荷( $Q_G$ )が分かると、ゲート当たりのドライバの出力電流は以下の式から計算できます。

$$I_G = Q_G \times f_S \quad (5)$$

但し、

- $f_S$ はスイッチング周波数です。

ノイズの問題を防ぐため、VDDピンとGNDピン間に $1\mu F$ のセラミック・コンデンサを接続してください。 $1\mu F$ のセラミック・コンデンサはできるだけUCC2540に近づけて配置してください。このコンデンサはバイアス電源の設計で用いられるエネルギー保存用電解コンデンサに対する追加分です。

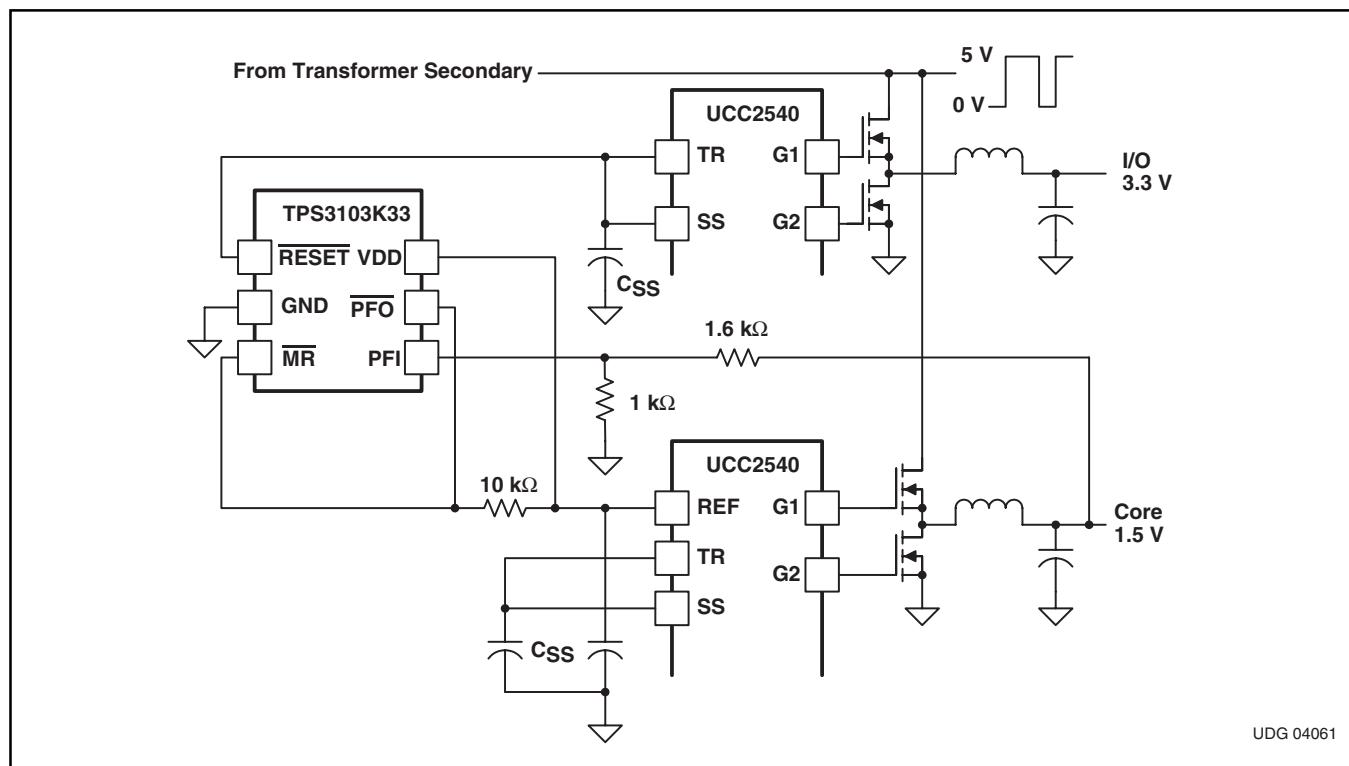

### ソフトスタートとトラッキング機能

ソフトスタート機能とトラッキング機能用に別々のピンが用意されています。この構造によりソフトスタートまたはトラッキング(シーケンス)が最小の外付け部品で簡単に実現できます。起動時の状態では、コンバータの出力は、システムが電流制限状態でなければ、SS電圧、TR電圧、1.5Vの内部基準電圧のうち低い電圧をトラッキングします。言い換えると、システムが電流制限されていないければ、電圧コントロール・ループは起動時には閉じています。図20に、ソフトスタート動作用のUCC2540構成を示します。トラッキング機能を使用しないアプリケーションでは図のようにTRピンをSSまたはREFに接続してください。リモート・シャットダウン及びシーケンシャル起動は $C_{SS}$ 端にトランジスタのスイッチを用いて容易に実現できます。

ソフトスタートは、UCC2540が相応の電圧(モード1, 2, 3参照)がUVLOレベルより上であると認識した時に開始します。次に、 $C_{SS}$ の電圧が3.3VのREF電圧にクランプされるまで直線的に増加します。

ソフトスタート電圧が約2.2V( $1.5V +$ ダイオードの電圧降下)に達した時レギュレーション状態になります。目的とするソフトスタート期間 $\Delta t_{SS}$ をプログラムするためには式(6)を使用して $C_{SS}$ コンデンサの値を選択してください。

$$C_{SS} = 1.33 \times \frac{V_{RSET}}{R_{SET}} \times \frac{\Delta t_{SS}}{\Delta V_{SS}} = 1.33 \times \frac{1.5V}{R_{SET}} \times \frac{\Delta t_{SS}}{2.2V} \text{ Farads} \quad (6)$$

UVLO異常となった場合、UCC2540の両方の出力はディスエーブルとなり、ソフトスタート・ピン(SS)はGNDに放電されます。UCC2540はUVLO異常が解除されるまで再試行しません。

TRピンを使用して、UCC2540は別のコンバータの出力電圧をトラッキングするようプログラムすることができます。トラッキングされる電圧が0Vから3.3Vの場合は、単にTRピンをVEA端子

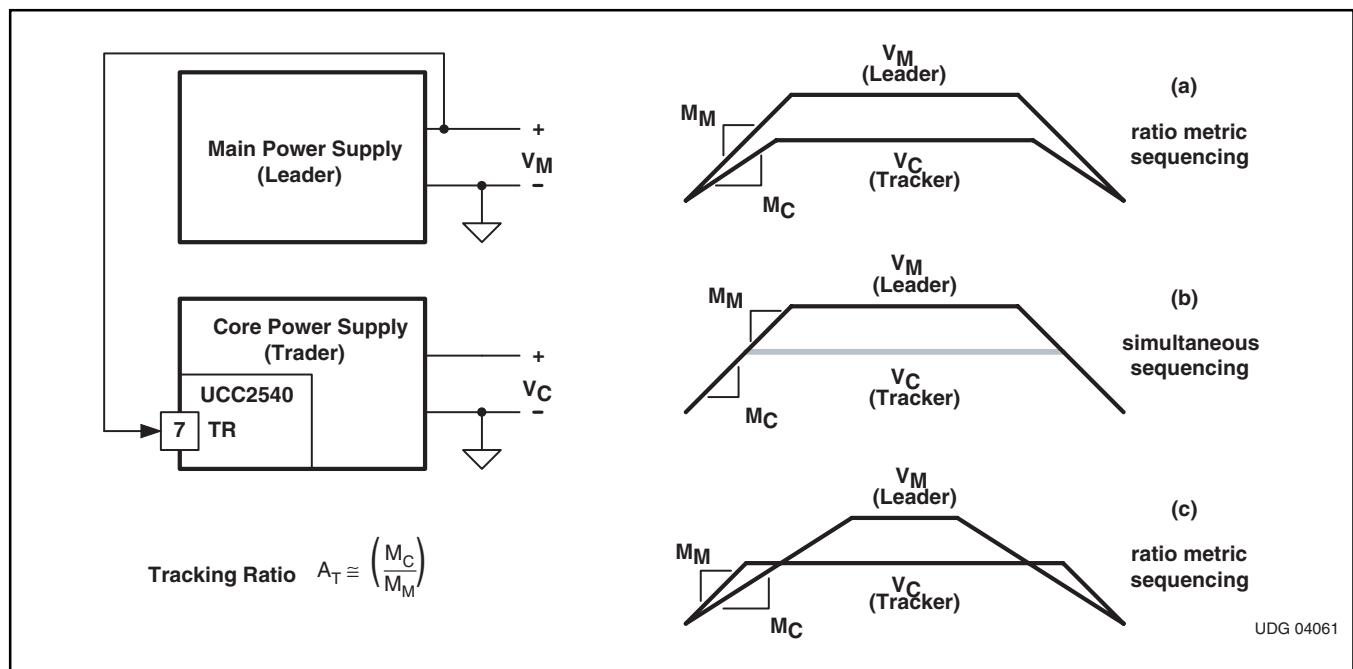

に接続されているDCインピーダンス(図6の $R_{V1} \parallel R_{V2}$ )にほぼ等しい抵抗を用いてトラッキングされる電圧に接続してください。電圧がその範囲より大きければ、この場合も前と同様に、VEA-端子に接続されているDCインピーダンスにほぼ等しい等価抵抗を用いた分圧器を使用してください。その他の方策を使用して、シーケンシャル、レシオメトリック(傾き制御トラッキング)、同時の電源トラッキング<sup>[14]</sup>を実現することができます。

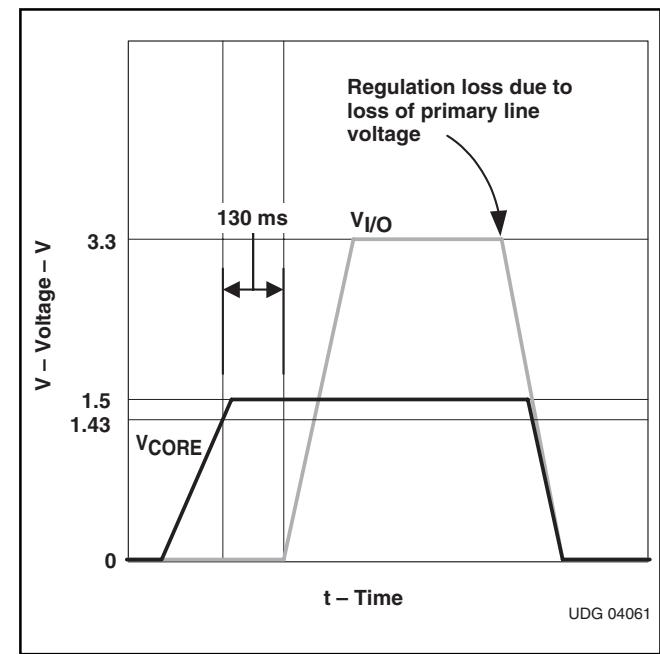

多出力電源<sup>[5]</sup>のシーケンシャルの実施例を図21に示します。負荷に1.5Vのコア電圧と3.3Vを必要とするI/Oポートをもつプロセッサが含まれているアプリケーションでは、起動時システム・レベルでのバス・コンテンション問題を解決するためにシーケンシャルが必要となります。この場合には、コアが最初に起動しなければならず、次に、130msの初期化期間の後に、ポートが起動することができます。

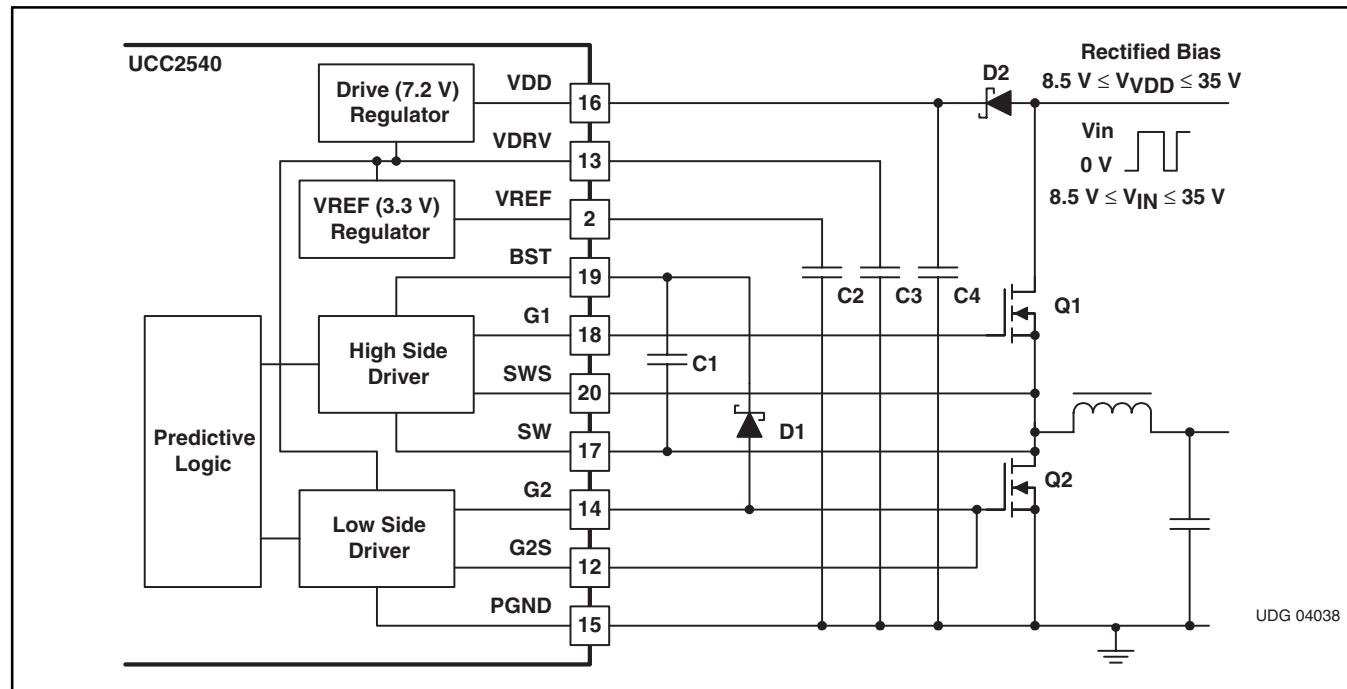

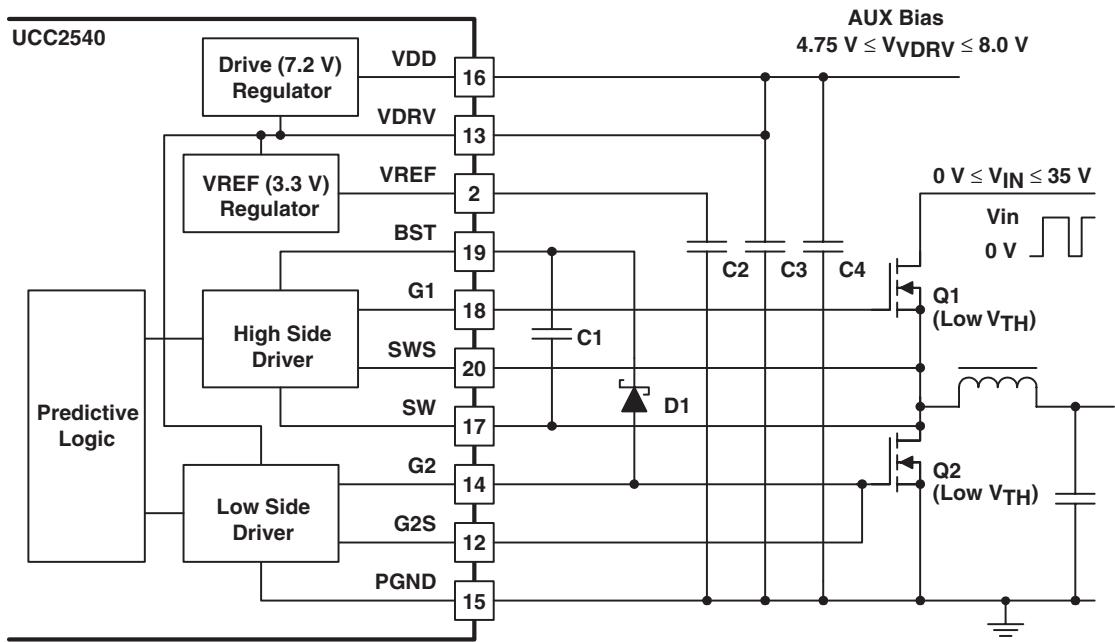

図14. Mode 1 With Rectified Biasing for Input Voltages Between 8.5 V and 35 V

図15. Mode 1 With Auxiliary Biasing for Bias Voltages Between 8.5 V and 35 V

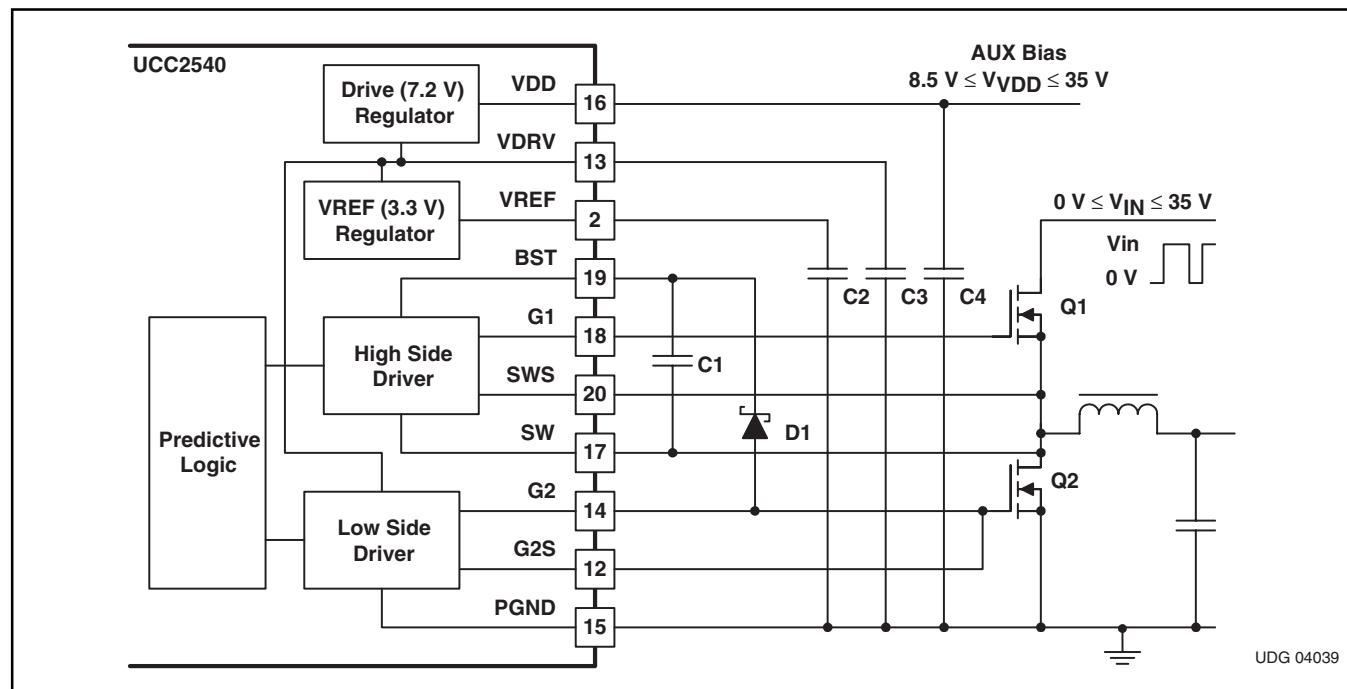

図16. Mode 2 With Rectified Biasing for Input Voltages Between 4.75 V and 8.0 V

図17. Mode 2 With Auxiliary Biasing for Bias Voltages Between 4.75 V and 8.0 V

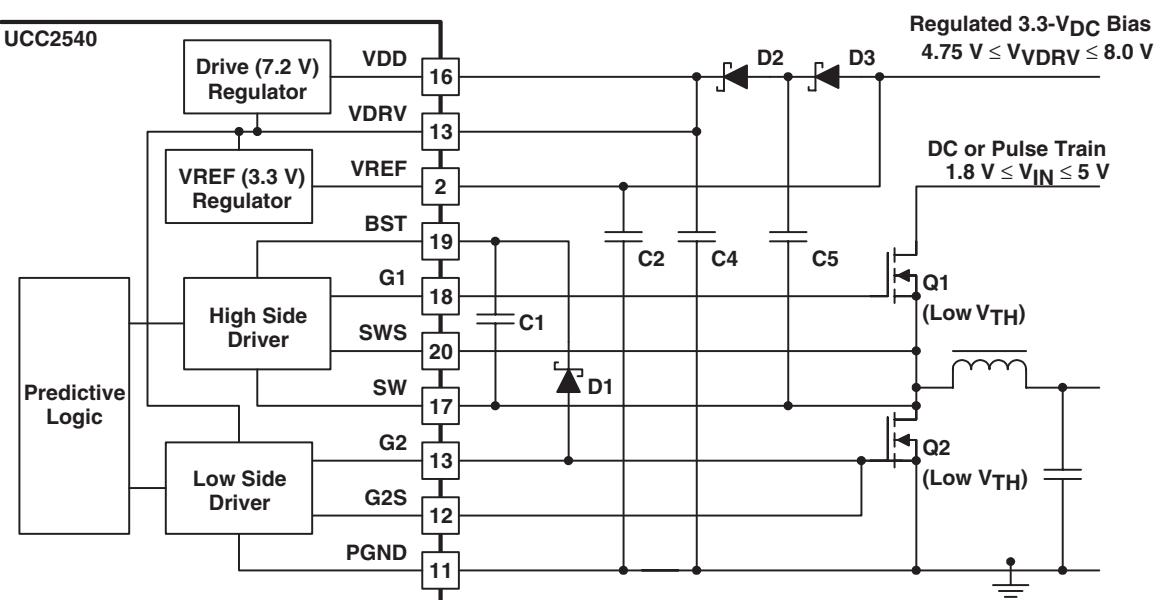

図18. Mode 2 With Auxiliary Biasing for Bias Voltages Between 4.75 V and 8.0 V and Low Threshold Power MOSFET Transistors

図19. Mode 3 With Regulated 3.3-V DC Bias

図20. Using the Soft-Start Feature

図21. Sequencing a Multiple Output Post Regulated Power Supply

TRピンを使用して、UCC2540は別のコンバータの出力電圧を自動的にトラッキングするよう設定することができます<sup>[5]</sup>。レシオメトリック方式(傾き制御)のトラッキングは出力電圧の比率が0Vから1つまたはそれ以上の出力がレギュレーションの固定点まで一定である時に行われます。SSピンに加わる外部電流がSS放電電流及び異常回復を妨げる可能性があるため、トラッキングにはTRピンのほうがSSピンよりも使い方が簡単です。当然のことながら、トラッキングされている電圧は起動時はバイアス電圧(VDD, VDRV, REF)より遅れ、シャットダウン時にはバイアス電圧よりも先行しなければなりません。さらに、トラッキングしている出力がその定常状態のDCレベルに達する前に、トラッキングされている出力はその定常状態のDCレベルに達してはいけません。図23に、もう1つの出力V<sub>M</sub>を自動的にトラッキングするために出力電圧V<sub>C</sub>をプログラムする概念を示します。

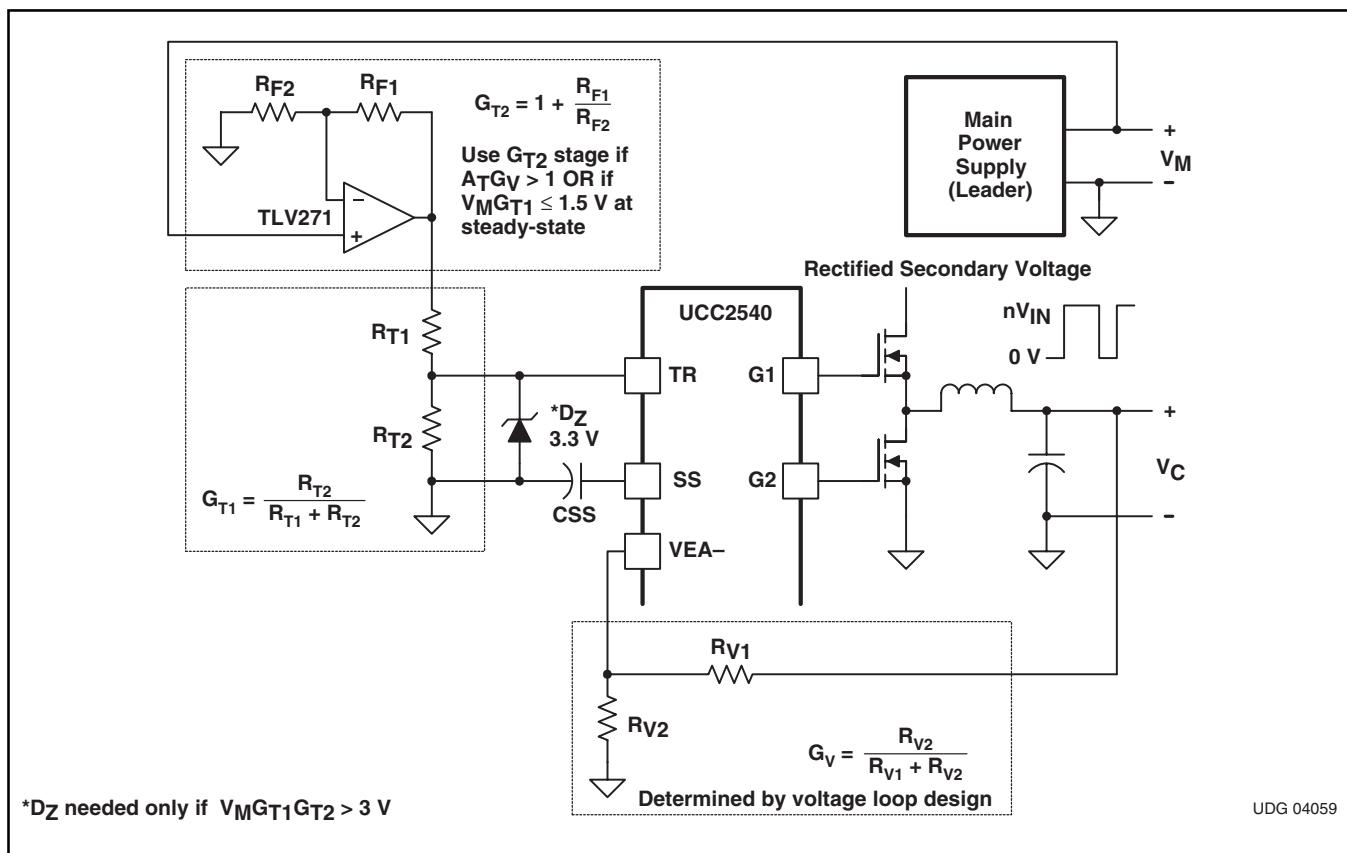

トラッキング比ATで先行する電源電圧をトラッキングするようUCC2540をプログラムする一般的な回路を図24に示します。トラッキング・プロファイル・ゲインG<sub>T1</sub>及びG<sub>T2</sub>をプログラムするには、以下に記載するレシオメトリック方式のトラッキング設計手順に従ってください。V<sub>M</sub>>1.5Vの同時シーケンスという特殊な場合は設計が簡単で、R<sub>T1</sub>=R<sub>V1</sub>、R<sub>T2</sub>=R<sub>V2</sub>と設定し、G<sub>T2</sub>は不要です。他の多くの場合では、回路はG<sub>T2</sub>用オペアンプ及びツエナー・クランプ・ダイオードを取り除いて簡素化できます。オペアンプが必要な場合、このオペアンプはレール・ツー・レール動作が可能で、通常は低電圧バイアスの製品を利用しますが、TLV271などが安価でこの両方の条件を満たしています。図24の

トラッキング回路にもソフトスタート・コンデンサC<sub>SS</sub>があることに注意してください。ソフトスタート・コンデンサC<sub>SS</sub>は短絡時の再試行動作間の時間を制限するのに有用で、主電源ではなくトラッキング電源のみで起こる異常から回復する際のオーバーシュートを防止することができます。

図22

図23. Ratio-Metric Tracking

レシオメトリック方式(傾き制御)トラッキングの設計手順(図21、図22参照)

1. トラッキング比 $A_T$ を決定する

$$A_T = \frac{M_C}{M_M} \quad (7)$$

但し、 $M_C$ と $M_M$ はそれぞれ $V_C$ と $V_M$ のソフトスタート勾配です。

2.  $G_V$ を決定する

$$G_V = \frac{R_{V2}}{R_{V1} + R_{V2}} \quad (8)$$

但し、 $R_{V2}$ と $R_{V1}$ は電圧コントロール・ループを設計する際に選択されます。

3.  $V_M \leq 1.5$ Vまたは $A_T G_V > 1$ の場合 $G_{T2}$ が必要かどうか検証する

a.  $G_{T2}$ が必要であれば、式(8)と式(9)の両方が適合するよう $G_{T2}$ を設定する

$$G_{T2} = 1 + \frac{R_{F1}}{R_{F2}} \quad (9)$$

よって、以下の両式が適合します

$$G_{T2} = \left( \frac{1.5 \text{ V}}{V_M \times G_{T1}} \right) \text{ and } G_{T2} > (A_T \times G_V) \quad (10)$$

b.  $G_{T2}$ が不要であれば $G_{T2} = 1$ に設定する

4.  $G_{T1}$ を設定する

$$G_{T1} = \frac{A_T \times G_V}{G_{T2}} = \frac{R_{T2}}{R_{T1} + R_{T2}} \quad (11)$$

5. オフセット差を最小限に抑えるため $R_{T1} \parallel R_{T2} \approx R_{V1} \parallel R_{V2}$ となるよう $R_{T1}$ と $R_{T2}$ を選択する

上記の技法を拡大適用することで、より綿密な電源のシーケンス及びトラッキングをたやすく実現することができます。この詳細情報については参考資料[5]を参照してください。

図24. Programming the UCC2540 to Track Another Output

## 熱情報

高電流の出力ドライバをもつコントローラの有効電圧範囲は、負荷への駆動パワー要件とデバイス・パッケージの熱特性に大きく影響されます。パワー・ドライバが特定の温度範囲で有用であるためには、パッケージは接合部温度を定格リミット内に保持しておくと同時に発生した熱を効率的に除去することができる必要があります。UCC2540は20ピンHTSSOP PowerPAD™パッケージで供給されています。

PowerPAD™ HTSSOP(PWP)パッケージは半導体の接合部からもっとも効率的に熱を除去する手段を提供し、ひいては長期信頼

性の改善をもたらします。参考資料<sup>[5]</sup>で図示されているように、PowerPADパッケージにはパッケージの裏面に露出したリードフレームのダイ・パッドがあります。このパッドはデバイス・パッケージの真下でPCボード上の銅に半田付けされ、 $\theta_{JC}$ を $2^{\circ}\text{C}/\text{W}$ まで下げます。このPowerPAD構造は標準のパッケージに比べ消費電力は4倍になることが参考資料<sup>[5]</sup>に示されています。PCボードは、PowerPADではない標準の表面実装パッケージよりも大きな放熱の改善を行うため、参考資料<sup>[6]</sup>で要約されているように、熱除去のサブシステムを完成するようサーマル・ランドやサーマル・ピアを用いて設計する必要があります。

## TYPICAL CHARACTERISTICS

OUTPUT REFERENCE VOLTAGE

VS

TEMPERATURE

図25

RAMP CURRENT

VS

TEMPERATURE

図26

$I_{G2C}/I_{RAMP}$  AND  $I_{SS}/I_{RAMP}$

VS

TEMPERATURE

図27

REGULATOR OUTPUT VOLTAGE

VS

TEMPERATURE

図28

## TYPICAL CHARACTERISTICS

TRACKING TO VOLTAGE ERROR AMPLIFIER OFFSET

VS

TEMPERATURE

図29

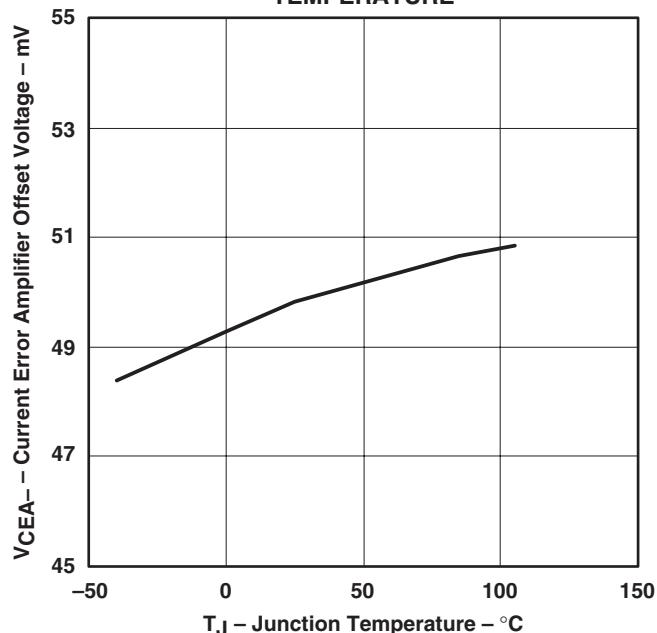

CURRENT ERROR AMPLIFIER OFFSET

VS

TEMPERATURE

図30

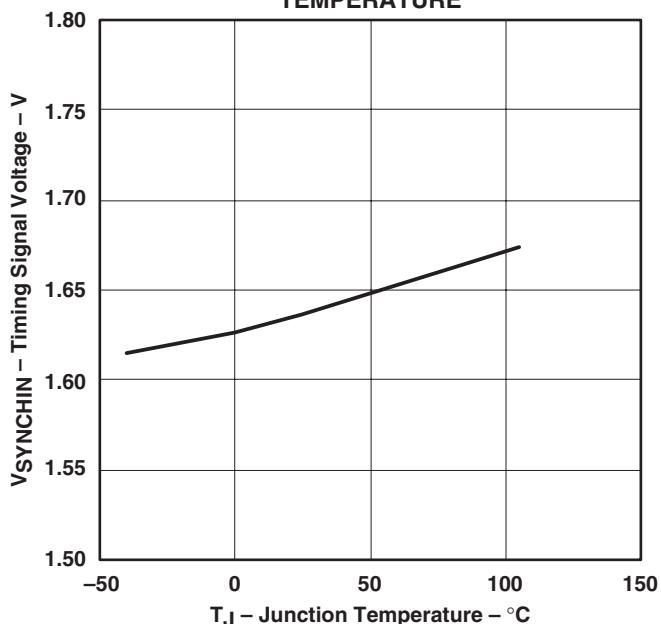

SYNCIN THRESHOLD VOLTAGE

VS

TEMPERATURE

図31

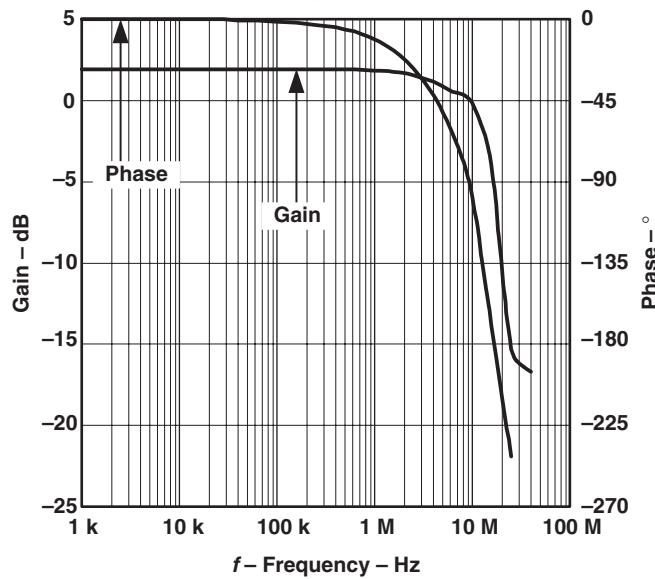

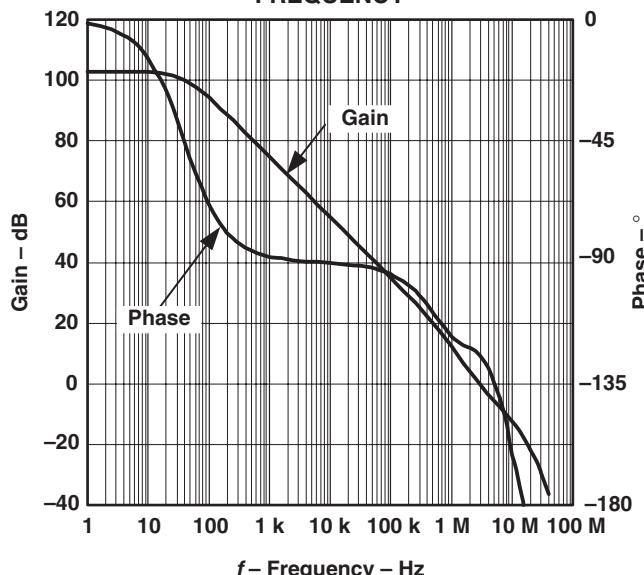

INVERTING AMPLIFIER GAIN AND PHASE

VS

FREQUENCY

図32

## TYPICAL CHARACTERISTICS

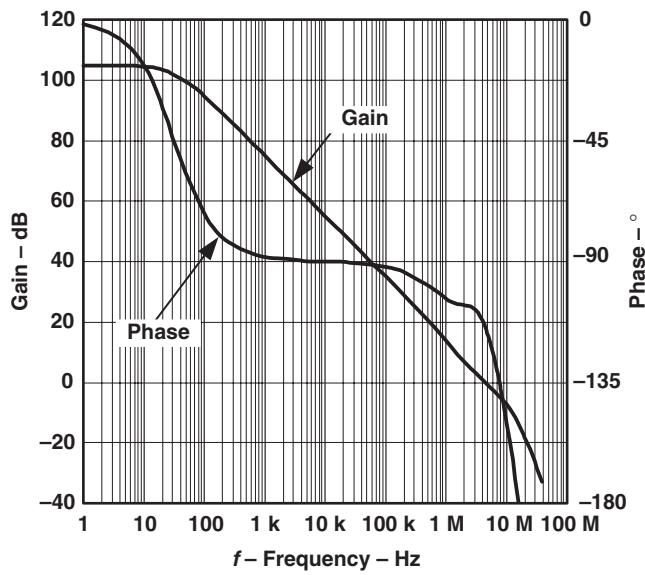

CURRENT ERROR AMPLIFIER GAIN AND PHASE

VS

FREQUENCY

図33

VOLTAGE ERROR AMPLIFIER GAIN AND PHASE

VS

FREQUENCY

図34

OPERATING CURRENT (DC)

VS

BIAS VOLTAGE

図35

## TYPICAL CHARACTERISTICS

図36. Predictive Gate Drive – G2 Falling

図37. Predictive Gate Drive – G2 Falling

図38. Predictive Gate Drive – G2 Falling

## 関連製品

- UCC28089 Primary Side Push-Pull Oscillator

- UCC27223 High Efficiency Predictive Synchronous Buck Driver with Enable

- UCC3583 Switch Mode Secondary Side Post Regulator

- UCC25701 Advanced Voltage Mode Pulse Width Modulator

- UCC3808A Low-Power Current-Mode Push-Pull PWM

- UCC38083/4/5/6 8-Pin Current-Mode Push-Pull PWM with Programmable Slope Compensation

## 參考資料

1. Power Supply Seminar SEM-1300 Topic 1: *Unique Cascaded Power Converter Topology for High Current Low Output Voltage Applications*, by L. Balogh, C. Bridge, and B. Andreycak, (SLUP118)

2. Power Supply Seminar SEM-1400 Topic 2: *Design And Application Guide For High Speed MOSFET Gate Drive Circuits*, by L. Balogh, (SLUP133)

3. Datasheet, *UCC27223 High Efficiency Predictive Synchronous Buck Driver*, (SLUS558)

4. Datasheet, *UCC37323/4/5 Dual 4-A Peak High Speed Low-Side Power MOSFET Drivers*, (SLUS492A)

5. Power Supply Seminar SEM1600 Topic 2: Sequencing Power Supplies in Multiple Voltage Rail Environments, by D. Daniels, D. Gehrke, and M. Segal, (SLUP224)

6. Technical Brief, *PowerPAD Thermally Enhanced Package*, (SLMA002)

7. Application Brief, *PowerPAD Made Easy*, (SLMA004)

8. Datasheet, *TPS3103K33 Ultra-Low Supply Current/Supply Voltage Supervisory Circuits*, (SLVS363)

9. Application Note, *A Revolutionary Power Management Solution for Highly Efficient, Multiple Output Applications*, by Bill Andreycak, (SLUA255)

10. Application Note, *Predictive Gate Drive™ FAQ*, by Steve Mappus (SLUA285)

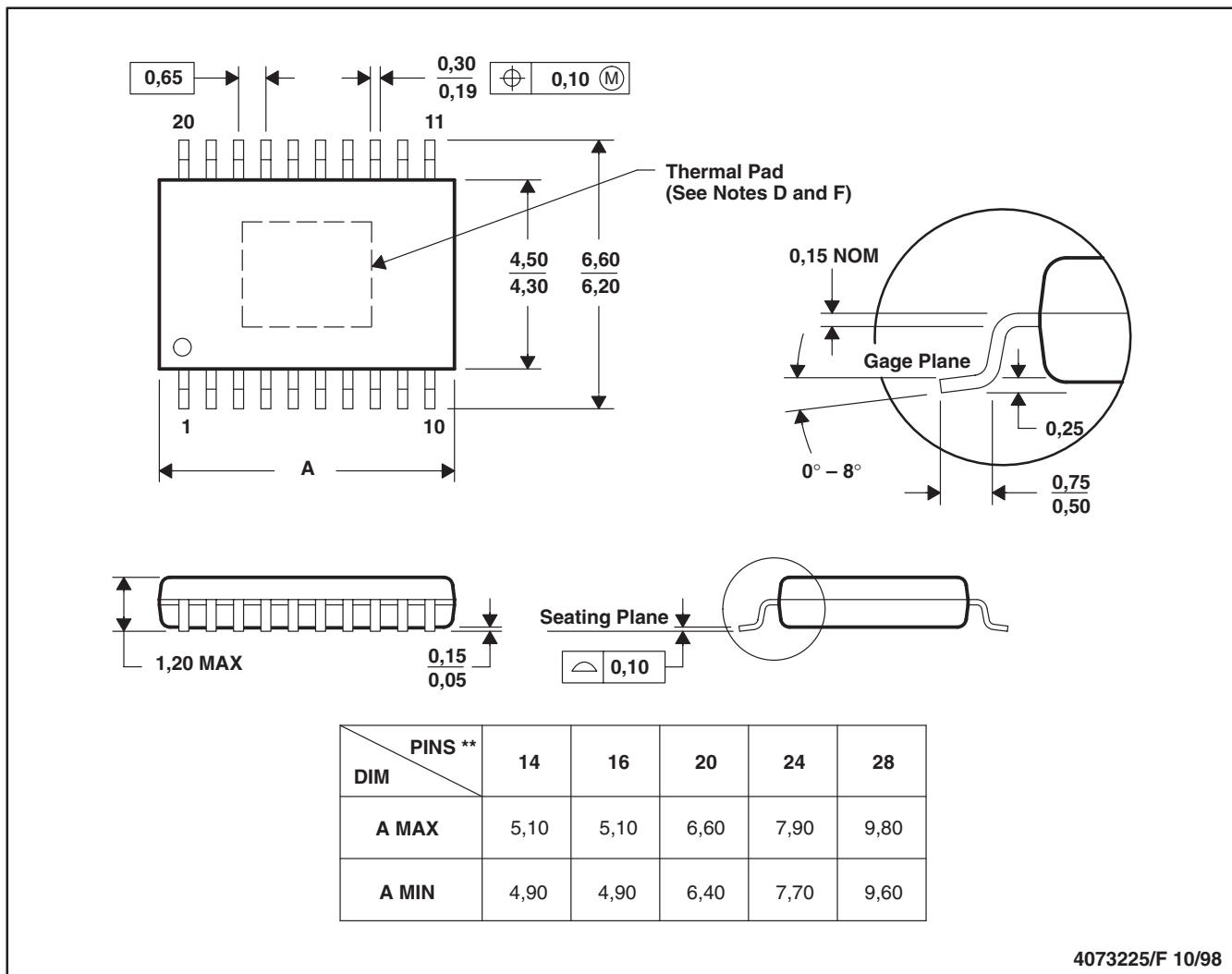

## MECHANICAL DATA

PWP (R-PDSO-G\*\*)

PowerPAD™ PLASTIC SMALL-OUTLINE

20 PINS SHOWN

4073225/F 10/98

- 注：

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. ボディ寸法はモールド突起部を含みません。

- D. パッケージの熱特性はサーマル・ダイ・パッドを外部のサーマル・プレーンに接合することで改善されることがあります。

このパッドは電気的にも熱的にもダイの裏面と、場合により選ばれたリードに接続されています。

- E. JEDEC MO-153に準拠します。

- F. PowerPAD™はパッケージのリードには直接接続していません。これは電気的にも熱的にもグランドとして機能するデバイスのサブストレートに接続されており、PCBのPGNDに接続してください。この露出寸法は1.3mm × 1.7mmですが、位置及びモールド・フローのばらつきにより公差は+1.05mm/-0.05mm(+41ミル/-2ミル)です。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCC2540PWPR           | NRND          | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UCC2540             |

| UCC2540PWPR.A         | NRND          | Production           | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | UCC2540             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月