## 高効率 同期整流方式降圧型ドライバ プレディクティブ制御 イネーブル付き

### 特 長

- ボディ・ダイオードの導通損失及び逆回復損失を最小限に抑えることによる最大効率の実現が可能

- シングルエンドPWM入力信号による同期整流方式降圧動作

- 12Vまたは5Vの入力電圧動作

- 12Vのバス・バイアス電圧の使用による3.3V入力電圧動作

- ハイサイド/ローサイド±3Aデュアル・ドライバ

- 6.5Vのゲート駆動レギュレータ内蔵

- 大電流出力が可能な±3AのTrueDrive™ゲート駆動

- 動作状態変化に柔軟に自動対応

- 放熱特性に優れた14ピンHTSSOP PowePAD™パッケージによるボード面積及び接合部温度の削減が可能

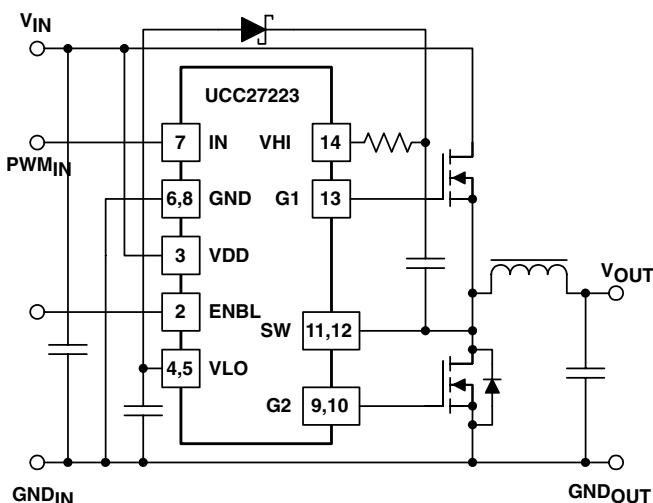

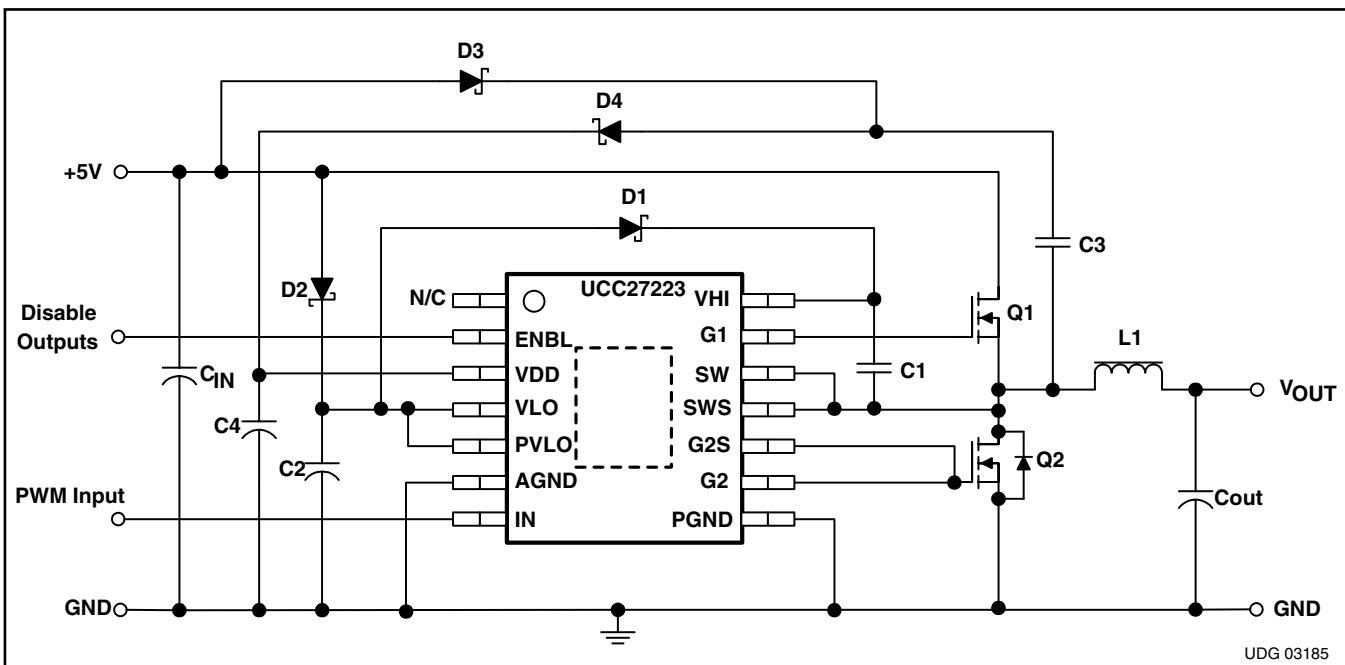

### FUNCTIONAL APPLICATION DIAGRAM

### ア プ リ ケ シ ョ ン

- TPS40K等と組み合わせた多相コンバータ

- プロセッサ電源、汎用コンピュータ、テレコム、データコム・アプリケーション用3.3V/5V/12V入力電圧の非絶縁型DC/DCコンバータ

### 概 要

UCC27223は、高効率、低出力電圧設計向けの高速同期整流方式の降圧型ドライバです。Predictive Gate Drive™ (PGD) 制御技術を用いて、ドライバは同期整流MOSFETのダイオードの導通損失及び逆回復損失を低減します。

UCC27223には、出力の動作を制御するイネーブル端子があります。また、最初のPWM入力パルスが入力されるまで出力を“L”レベルにしておくラッチ機能も内蔵されています。デバイスのRDS(on)も高周波動作に対応できるように最小限に抑えられます。

閉ループのフィードバック・システムがボディ・ダイオードの導通を検出し、導通期間を最小にするようデッドタイム遅延を調整します。このことにより、温度や負荷に依存する遅延や種々のMOSFET条件に合わせて調整しながらボディ・ダイオードの導通をほぼなくすることができます。ナノ秒レベルの精密なゲート・タイミングにより同期整流型MOSFETのボディ・ダイオードの逆回復時間が低減し、メイン(ハイサイド)MOSFETでの逆回復損失が減少します。また、ローサイドMOSFETの接合部温度が低くなるため製品の信頼性が向上します。また、消費電力が最小となるため、より高いスイッチング周波数も使用することができ、部品寸法が小さくできます。

UCC27223のパッケージは放熱特性に優れた14ピンPowePAD™で、 $\theta_{JC}$ は2°C/Wです。

Gate Drive、PowerPADは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

#### AVAILABLE OPTIONS

| T <sub>A</sub> | PWM INPUT<br>(IN) | PACKAGED DEVICES             |

|----------------|-------------------|------------------------------|

|                |                   | PowerPAD™<br>HTSSOP 14 (PWP) |

| -40°C to 105°C | NON-INVERTING     | UCC27223PWP                  |

† PWPパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(例、UCC27223PWPR)。発注数量単位はリールあたり2000個、チューブあたり90個です。

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)†‡

|                                                                              |                                                       |

|------------------------------------------------------------------------------|-------------------------------------------------------|

| Supply voltage range, VDD .....                                              | -0.3 to 20 V                                          |

| Input voltage, VHI .....                                                     | 30 V                                                  |

| SW, SWS .....                                                                | 20 V                                                  |

| Supply current, I <sub>DD</sub> , including gate drive current .....         | 100 mA                                                |

| Sink current (peak) pulsed, G1/G2 .....                                      | 4.0 A                                                 |

| Source current (peak) pulsed, G1/G2 .....                                    | -4.0 A                                                |

| Analog inputs, IN, ENBL .....                                                | -3.0 V to V <sub>DD</sub> + 0.3 V, not to exceed 15 V |

| Power Dissipation at T <sub>A</sub> = 25°C (PWP package) .....               | 3 W                                                   |

| Operating junction temperature range, T <sub>J</sub> .....                   | -55 °C to 115°C                                       |

| Storage temperature range, T <sub>stg</sub> .....                            | -65 °C to 150°C                                       |

| Lead temperature soldering 1.6 mm (1/16 inch) from case for 10 seconds ..... | 300°C                                                 |

† 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

‡ 全ての電圧はAGND及びPGNDを基準としています。電流の極性で正は指定の端子に流入する方向、負は流出する方向を表しています。

## ELECTRICAL CHARACTERISTICS

$V_{DD} = 12\text{-V}$ , 1- $\mu\text{F}$  capacitor from  $V_{DD}$  to GND, 1- $\mu\text{F}$  capacitor from VHI to SW, 0.1- $\mu\text{F}$  and 2.2- $\mu\text{F}$  capacitor from PVLO to PGND, PVLO tied to  $V_{LO}$ ,  $T_A = -40^\circ\text{C}$  to  $105^\circ\text{C}$  for the UCC27223,  $T_A = T_J$  (unless otherwise noted)

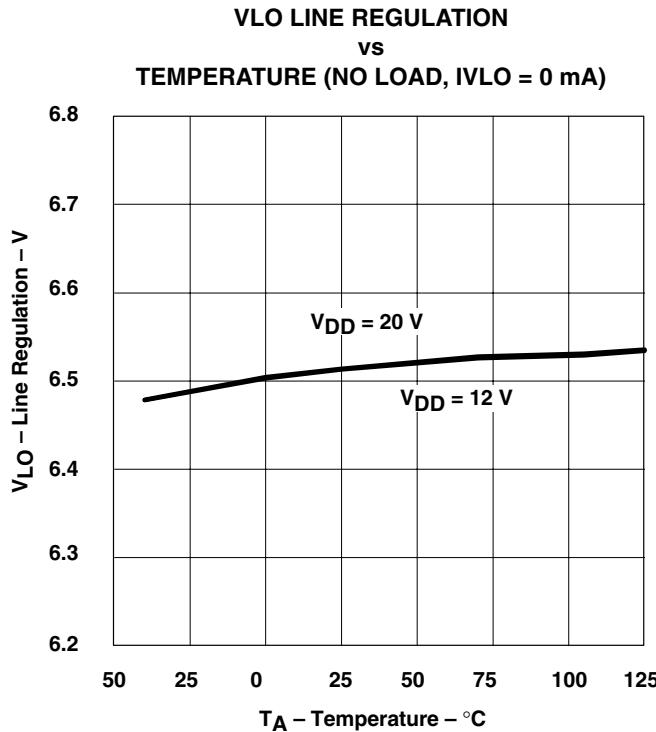

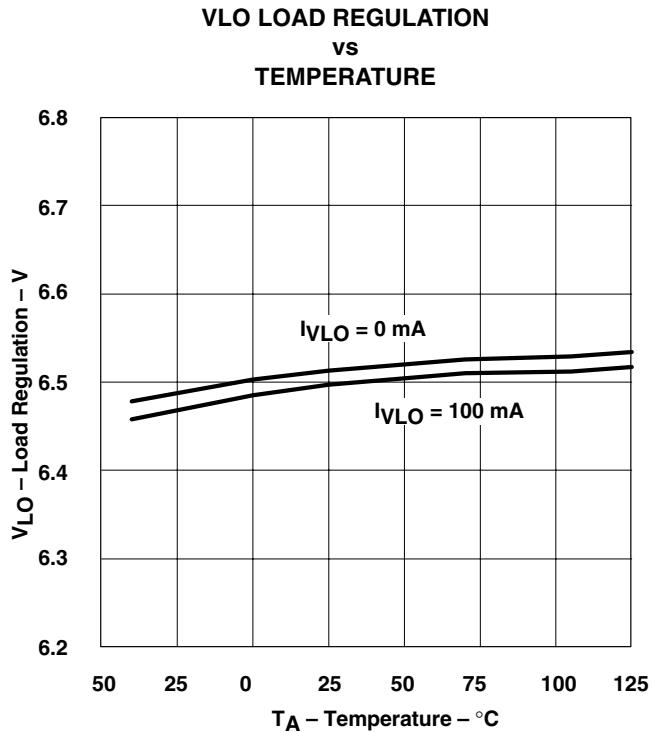

### VLO regulator

| PARAMETER                                        | TEST CONDITIONS                                       | MIN | TYP | MAX | UNIT |

|--------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| Regulator output voltage                         | $V_{DD} = 12\text{ V}$ , $I_{VLO} = 0\text{ mA}$      | 6.2 | 6.5 | 6.8 | V    |

|                                                  | $V_{DD} = 20\text{ V}$ , $I_{VLO} = 0\text{ mA}$      | 6.2 | 6.5 | 6.8 |      |

|                                                  | $V_{DD} = 10\text{ V}$ , $I_{VLO} = 100\text{ mA}$    | 6.1 | 6.5 | 6.9 |      |

| Line Regulation                                  | $V_{DD} = 12\text{ V}$ to $20\text{ V}$               |     | 2   | 10  | mV   |

| Load Regulation                                  | $I_{VLO} = 0\text{ mA}$ to $100\text{ mA}$            |     | 15  | 40  |      |

| Short-circuit current (1)                        | $V_{DD} = 8.5\text{ V}$                               |     | 220 |     | mA   |

| Dropout voltage, ( $V_{DD}$ at 5% $V_{LO}$ drop) | $V_{LO} = 6.175\text{ V}$ , $I_{VLO} = 100\text{ mA}$ | 7.1 | 7.8 | 8.5 | V    |

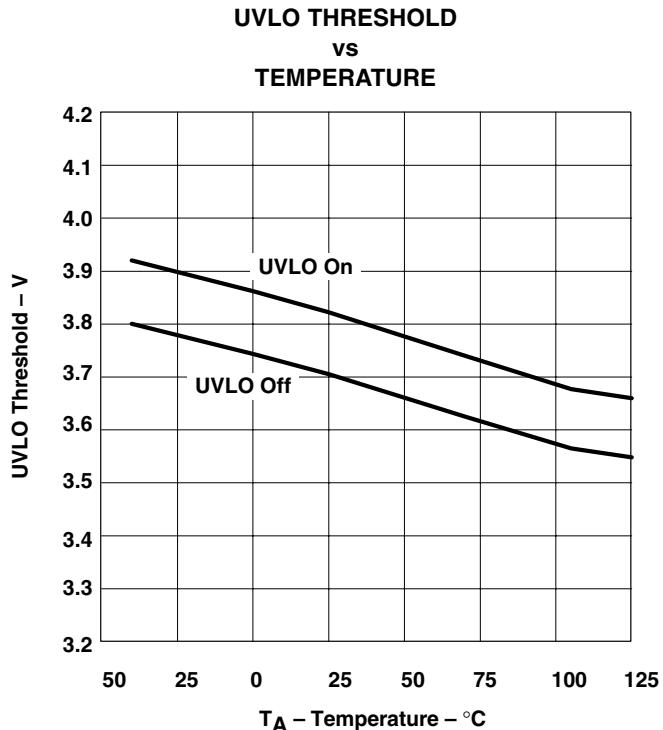

### undervoltage lockout

| PARAMETER                             | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|---------------------------------------|-----------------|------|------|------|------|

| Start threshold voltage               | Measured at VLO | 3.30 | 3.82 | 4.40 | V    |

| Minimum operating voltage after start |                 | 3.15 | 3.70 | 4.15 |      |

| Hysteresis                            |                 | 0.07 | 0.12 | 0.20 |      |

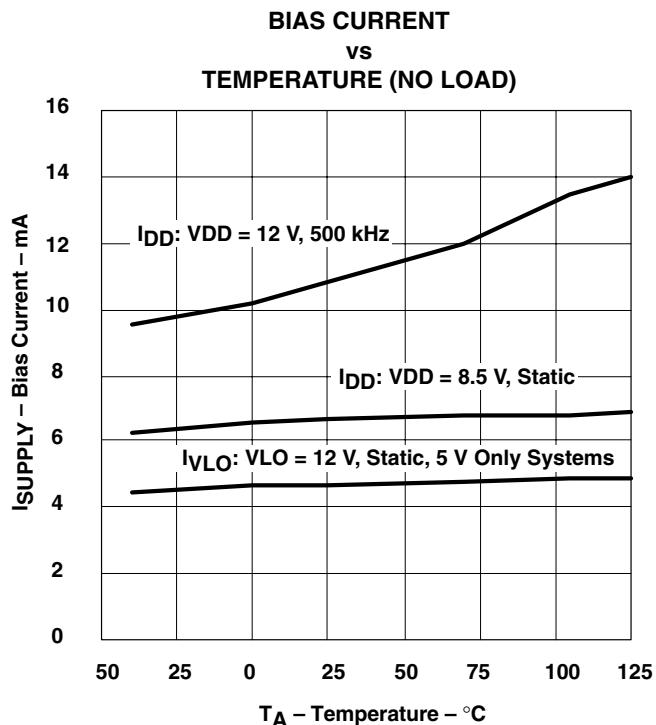

### bias currents

| PARAMETER                                                    | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| $V_{LO}$ bias current at $V_{LO}$ (ON), 5V applications only | $V_{LO} = 4.5\text{ V}$ , $V_{DD}$ = no connect | 3.6 | 4.7 | 5.8 | mA   |

| $V_{DD} = 8.5\text{ V}$                                      | 5.5                                             | 7.1 | 8.5 |     |      |

| $f_{IN} = 500\text{ kHz}$ , No load on G1/G2                 | 8                                               | 16  | 25  |     |      |

### input command (IN)

| PARAMETER                | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT          |

|--------------------------|--------------------------------------|-----|-----|-----|---------------|

| High-level input voltage | $10\text{ V} < V_{DD} < 20\text{ V}$ | 3.3 | 3.6 | 3.9 | V             |

| Low-level input voltage  | $10\text{ V} < V_{DD} < 20\text{ V}$ | 2.2 | 2.5 | 2.8 |               |

| Input bias current       | $V_{DD} = 15\text{ V}$               |     | 1   |     | $\mu\text{A}$ |

### input (SWS)

| PARAMETER                                                               | TEST CONDITIONS                                                         | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| High-level input threshold voltage                                      | $f_{IN} = 500\text{ kHz}$ , $t_{ON}$ , G2 maximum, $G2S = 0.0\text{ V}$ | 1.4  | 2.0  | 2.6  | V    |

| $f_{IN} = 500\text{ kHz}$ , $t_{ON}$ , G2 minimum, $G2S = 0.0\text{ V}$ | 0.7                                                                     | 1.0  | 1.3  |      |      |

| $f_{IN} = 500\text{ kHz}$ , $t_{ON}$ , G1 minimum                       | -100                                                                    | -300 | -500 |      |      |

| Input bias current                                                      | $SWS = 0.0\text{ V}$                                                    | -0.9 | -1.2 | -1.5 | mA   |

### input (G2S)

| PARAMETER                                                               | TEST CONDITIONS                                                         | MIN  | TYP  | MAX | UNIT |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|-----|------|

| High-level input voltage                                                | $f_{IN} = 500\text{ kHz}$ , $t_{ON}$ , G2 maximum, $SWS = 0.0\text{ V}$ | 1.4  | 2.0  | 2.6 | V    |

| $f_{IN} = 500\text{ kHz}$ , $t_{ON}$ , G2 minimum, $SWS = 0.0\text{ V}$ | 0.7                                                                     | 1.0  | 1.3  |     |      |

| $G2S = 0\text{ V}$                                                      | -370                                                                    | -470 | -570 | A   |      |

(1) 設計で保証されており、テストは行われていません。

## ELECTRICAL CHARACTERISTICS

$V_{DD} = 12\text{-V}$ , 1- $\mu\text{F}$  capacitor from  $V_{DD}$  to GND, 1- $\mu\text{F}$  capacitor from VHI to SW, 0.1- $\mu\text{F}$  and 2.2- $\mu\text{F}$  capacitor from PVLO to PGND, PVLO tied to  $V_{LO}$ ,  $T_A = -40^\circ\text{C}$  to  $105^\circ\text{C}$  for the UCC27223,  $T_A = T_J$  (unless otherwise noted)

### enable (ENBL)

| PARAMETER                              | TEST CONDITION                        | MIN  | TYP  | MAX  | UNITS            |

|----------------------------------------|---------------------------------------|------|------|------|------------------|

| $V_{IN\_H}$ , high-level input voltage | LO to HI transition                   | 2.25 | 2.45 | 2.85 | V                |

| $V_{IN\_L}$ , low-level input voltage  | HI to LO transition                   | 1.55 | 1.70 | 1.90 |                  |

| Hysteresis                             |                                       |      | 1.1  |      |                  |

| RENBL, enable impedance                | $V_{DD} = 14\text{ V}$ , ENBL = GND   | 75   | 112  | 150  | $\text{k}\Omega$ |

| $t_{D3}$ , propagation delay time(5)   |                                       |      | TBD  |      | ns               |

| $t_{D4}$ , propagation delay time(5)   |                                       |      | TBD  |      |                  |

| $t_r$ , Rise time                      | $V_{LO} = \text{PVLO} = 8.5\text{ V}$ |      | 2.5  |      | ms               |

| $t_f$ , Fall time                      | $V_{LO} = \text{PVLO} = 8.5\text{ V}$ |      | 2.5  |      |                  |

### G1 main output

| PARAMETER             | TEST CONDITIONS                                           | MIN | TYP  | MAX | UNIT     |

|-----------------------|-----------------------------------------------------------|-----|------|-----|----------|

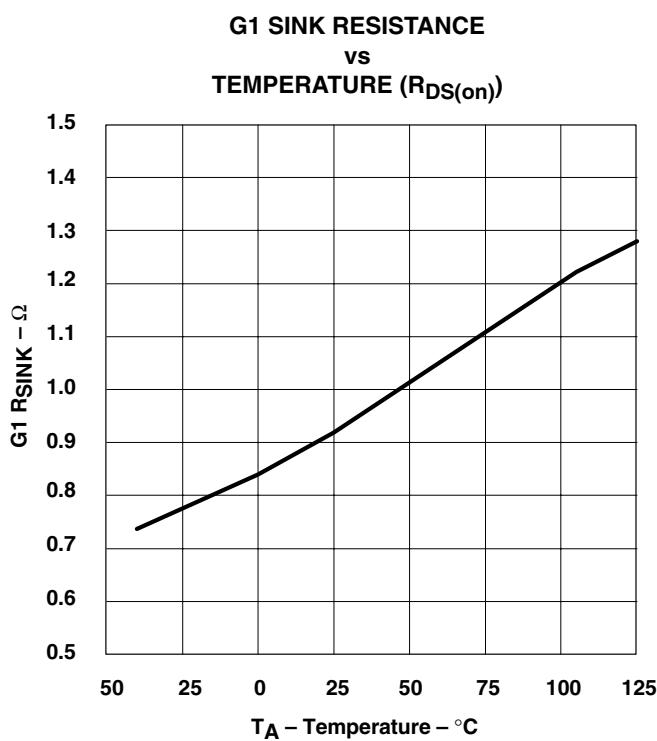

| Sink resistance       | $SW = 0\text{ V}$ , VHI = 6 V, IN = 0 V, G1 = 0.5 V       | 0.5 | 0.9  | 1.5 | $\Omega$ |

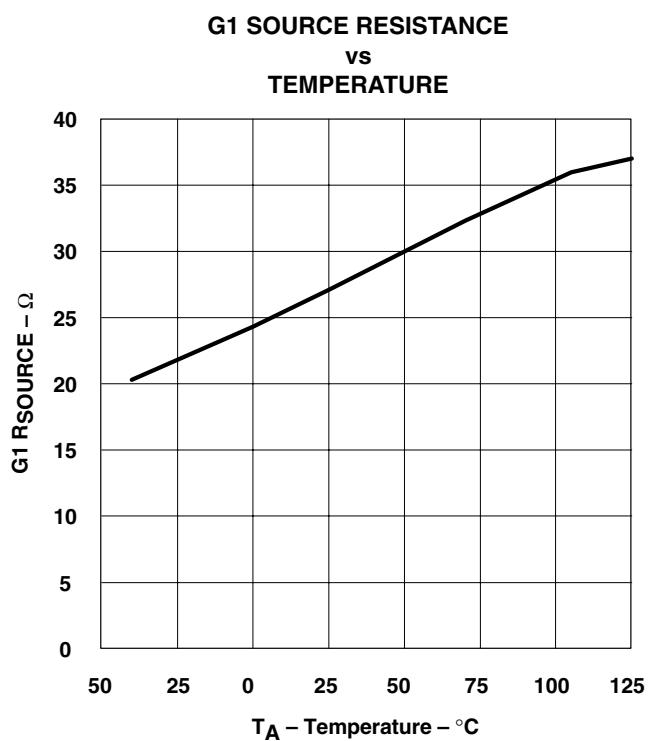

| Source resistance (2) | $SW = 0\text{ V}$ , VHI = 6 V, IN = 6.5 V, G1 = 5.5 V     | 10  | 25   | 45  |          |

| Source current (1)(2) | $SW = 0\text{ V}$ , VHI = 6 V, IN = 6.5 V, G1 = 3.0 V     | -3  | -3.3 |     |          |

| Sink current (1)(2)   | $SW = 0\text{ V}$ , VHI = 6 V, IN = 0 V, G1 = 3.0 V       | 3   | 3.3  |     | A        |

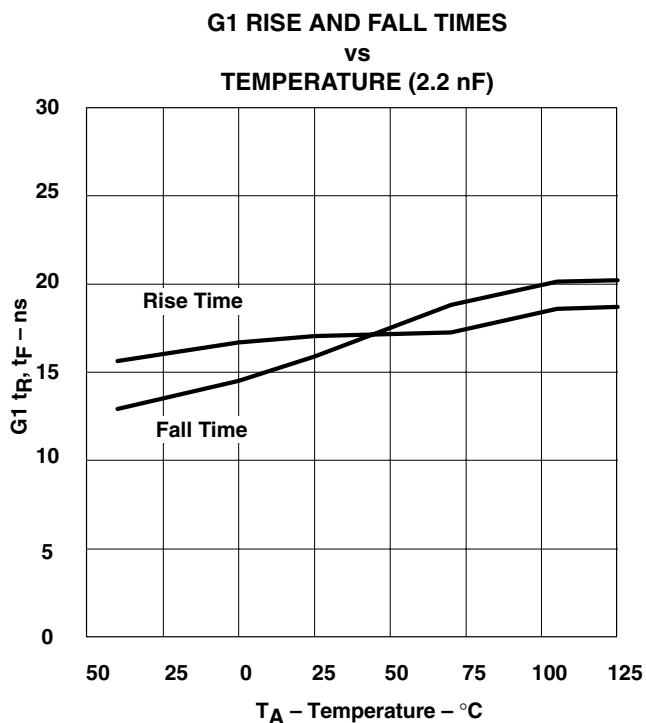

| Rise time             | $C = 2.2\text{ nF}$ from G1 to SW, $V_{DD} = 20\text{ V}$ |     | 17   | 25  |          |

| Fall time             | $C = 2.2\text{ nF}$ from G1 to SW, $V_{DD} = 20\text{ V}$ |     | 17   | 25  |          |

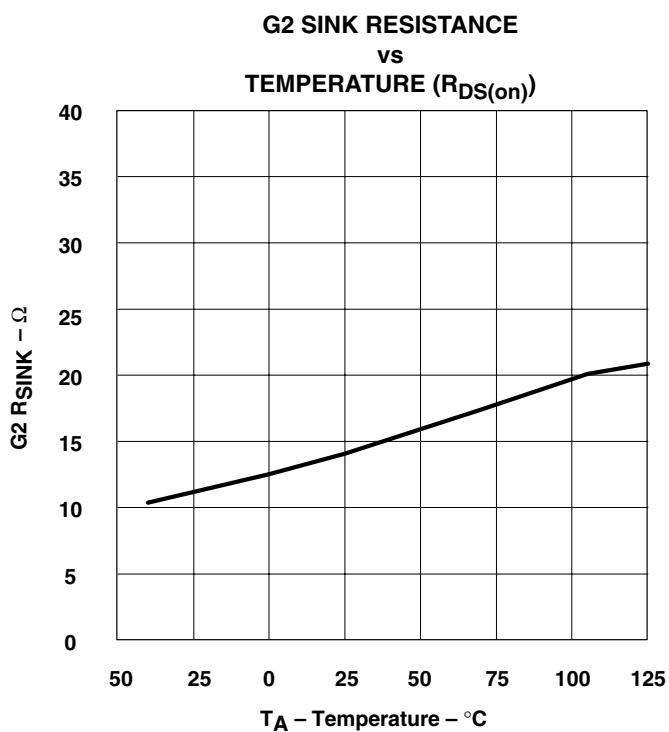

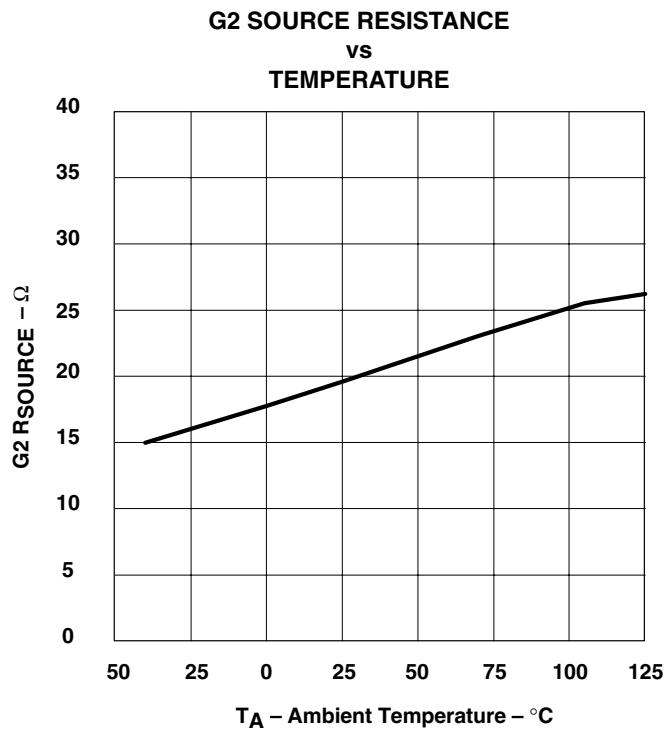

### G2 SR output

| PARAMETER             | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT     |

|-----------------------|-------------------------------------------------------------|-----|-----|-----|----------|

| Sink resistance (2)   | PVLO = 6.5 V, IN = 6.5 V, G1 = 0.25 V                       | 0.5 | 1.6 | 4.0 | $\Omega$ |

| Source resistance (2) | PVLO = 6.5 V, IN = 0 V, G2 = 6.0 V                          | 10  | 20  | 35  |          |

| Source current (1)(2) | PVLO = 6.5 V, IN = 0 V, G2 = 3.25 V                         | 3   | 3.3 |     |          |

| Sink current (1)(2)   | PVLO = 6.5 V, IN = 6.5 V, G2 = 3.25 V                       | -3  | 3.3 |     | A        |

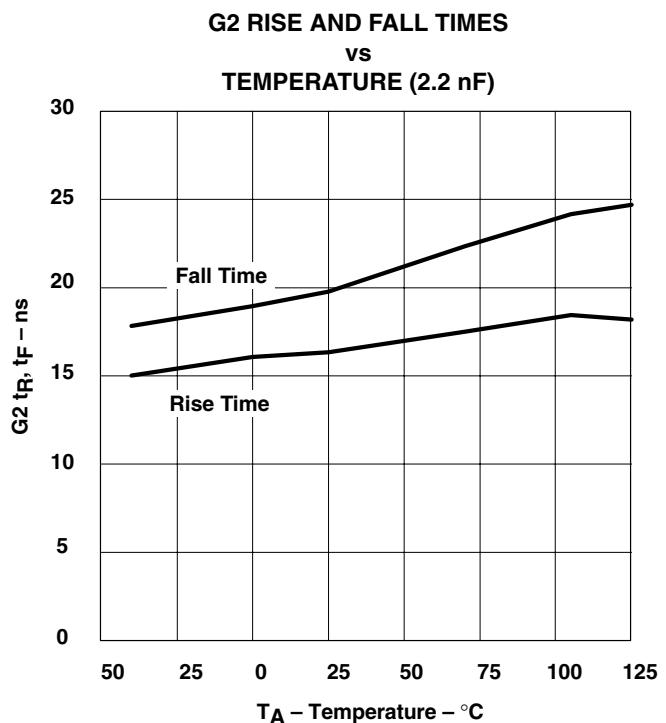

| Rise time (2)         | $C = 2.2\text{ nF}$ from G2 to PGND, $V_{DD} = 20\text{ V}$ |     | 17  | 25  |          |

| Fall time             | $C = 2.2\text{ nF}$ from G2 to PGND, $V_{DD} = 20\text{ V}$ |     | 20  | 35  |          |

### deadtime delay

| PARAMETER                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------------|-----------------|-----|-----|-----|------|

| $t_{OFF,G2}$ , IN to G2 falling |                 | 40  | 80  | 125 | ns   |

| $t_{OFF,G1}$ , IN to G1 falling |                 | 55  | 80  | 110 |      |

| Delay Step Resolution           |                 | 4.0 | 4.5 | 5.2 |      |

| $t_{ON,G1}$ minimum             |                 |     | -17 |     |      |

| $t_{ON,G1}$ maximum             |                 |     | 49  |     |      |

| $t_{ON,G2}$ minimum             |                 |     | -15 |     |      |

| $t_{ON,G2}$ maximum             |                 |     | 54  |     |      |

(1) 設計で保証されており、テストは行われていません。

(2) ドライバのプルアップ/プルダウン回路はバイポーラとMOSFETトランジスタを並列に接続しています。ピーク出力電流定格はバイポーラとMOSFETトランジスタの結合電流です。出力抵抗はドライバ出力の電圧がバイポーラ・トランジスタの飽和電圧より小さい場合MOSFETトランジスタのRDS(ON)となります。

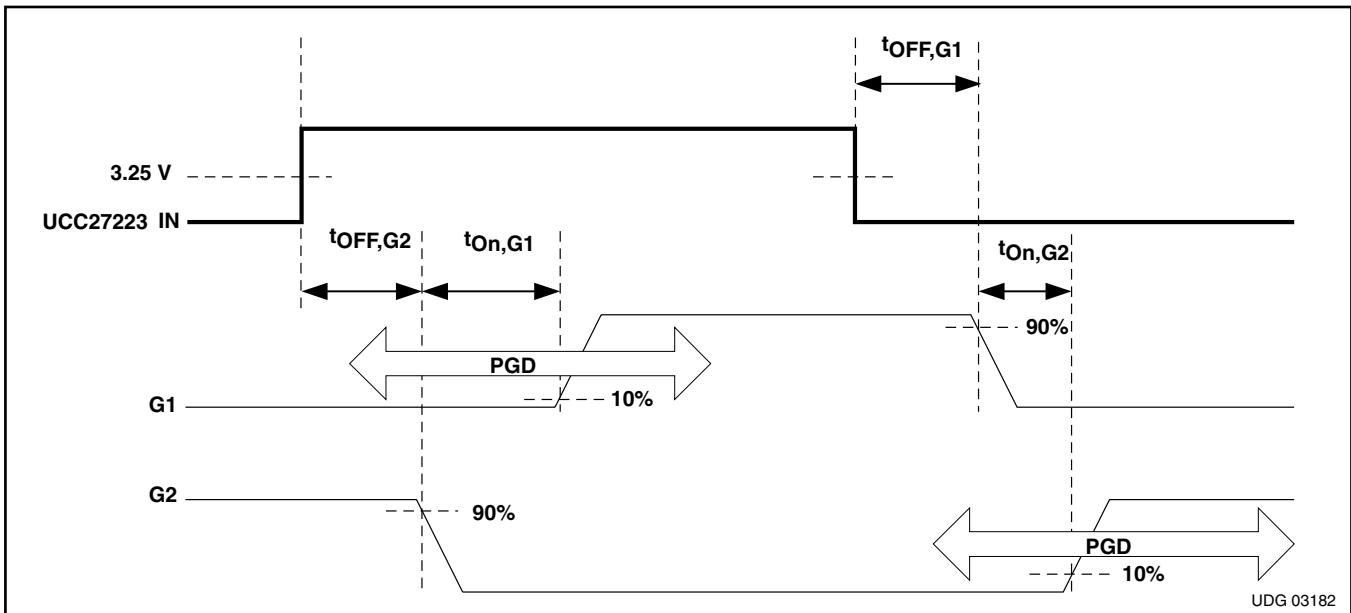

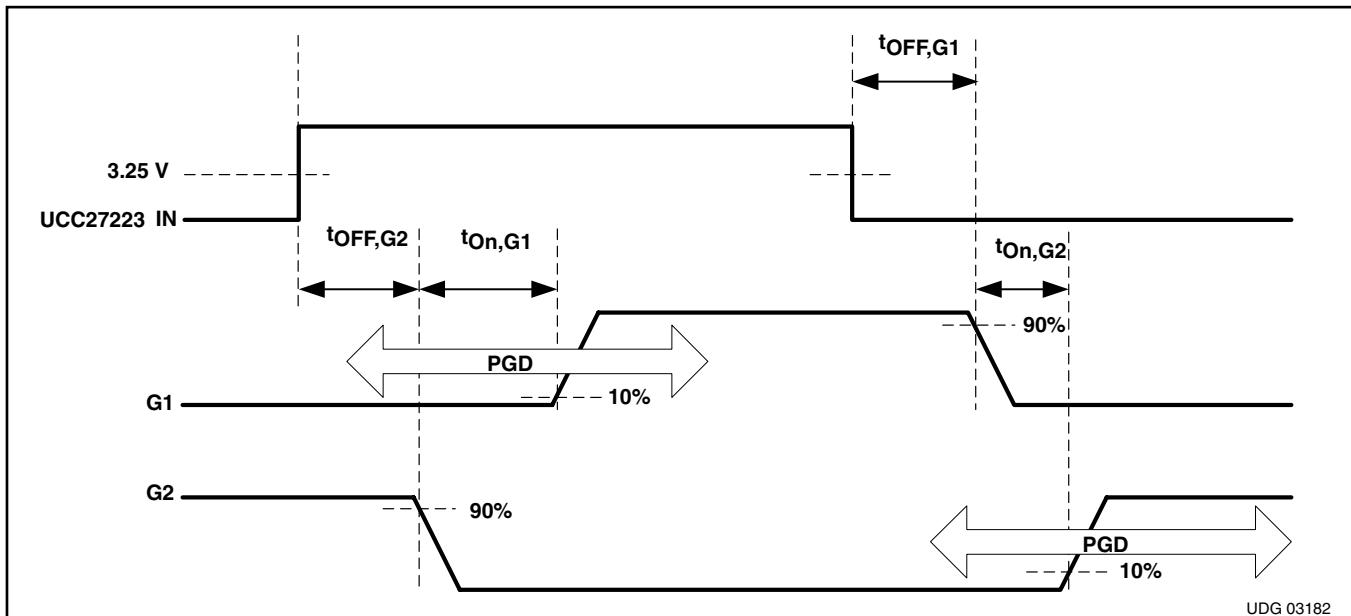

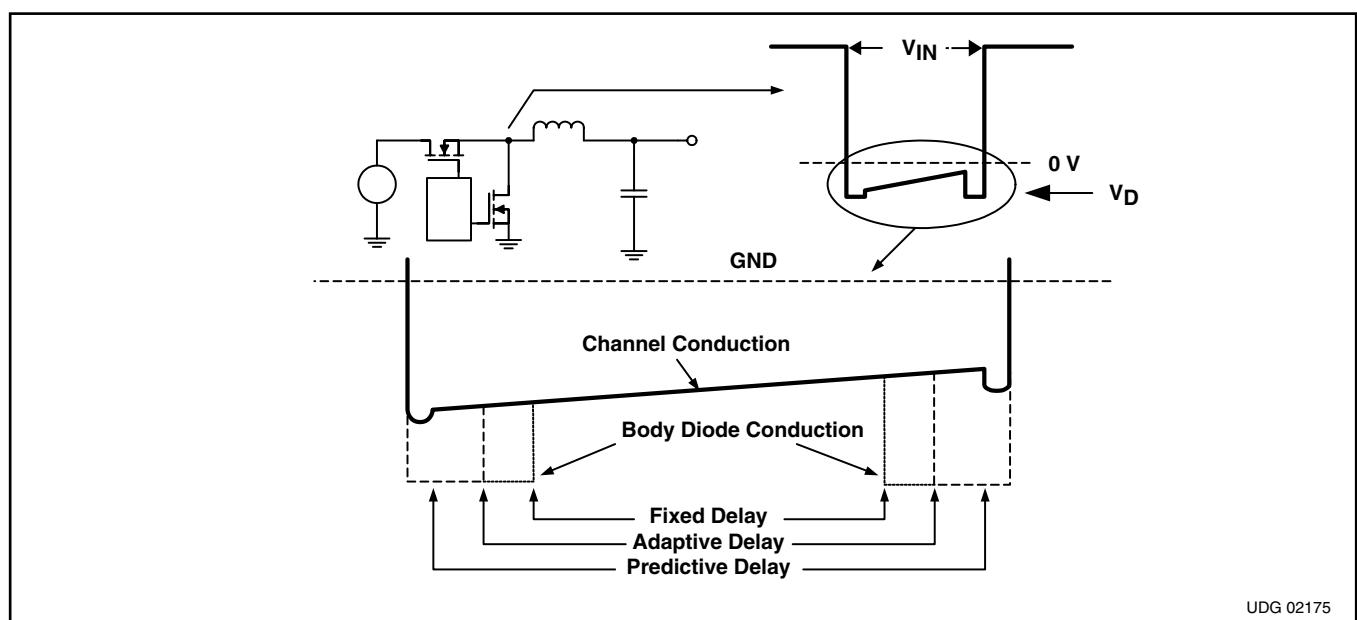

図 1. Predictive Gate Drive Timing Diagram

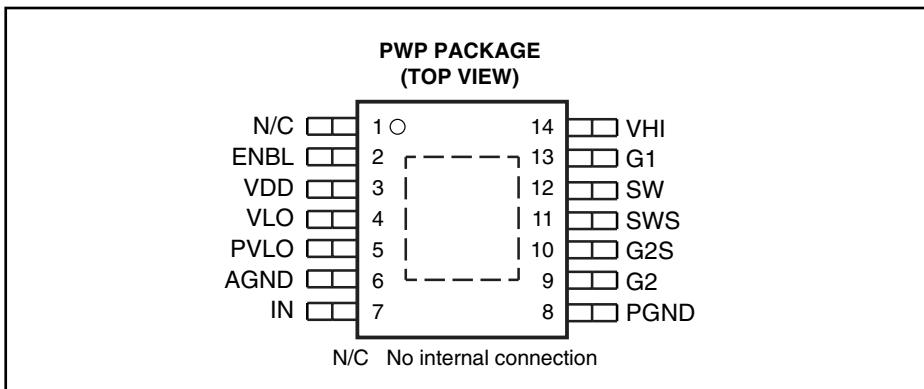

### 端子機能

| TERMINAL<br>NAME | NO. | I/O | DESCRIPTION                                                                                     |

|------------------|-----|-----|-------------------------------------------------------------------------------------------------|

| AGND             | 6   | -   | 内部制御回路用アナログ・グランドです。AGNDとPGNDはビアを用いてPCBのグランド配線に接続してください。                                         |

| G1               | 13  | O   | ハイサイド・ゲート・ドライバの出力で振幅はSWとVHI間です。                                                                 |

| G2               | 9   | O   | ローサイド・ゲート・ドライバの出力で振幅はPGNDとPVLO間です。                                                              |

| G2S              | 10  | I   | 適切なデッドタイムを設定するためにSR MOSFETのゲート電圧を検出するプレディクティブ・デッドタイム・コントローラで使用されます。                             |

| IN               | 7   | I   | デジタル入力コマンド・ピン。ロジック “H” レベルでメイン・スイッチをオン、同期整流器をオフにします。                                            |

| PGND             | 8   | -   | G2ドライバ用のグランド・リターン・ピンです。PGNDはいくつかのビアを用いてPCBのグランド配線に接続してください。                                     |

| PVLO             | 5   | I   | PVLOはG2ドライバに電源を供給します。PVLOはVLOに接続し、PCB上でバイパスしてください。                                              |

| SW               | 12  | -   | G1ドライバのリターン接続ピンです。                                                                              |

| SWS              | 11  | I   | SRのボディ・ダイオードの導通を検出するためプレディクティブ・コントローラで使用されます。MOSFETパッケージに近づけてSR MOSFETのドレインに接続してください。           |

| VDD              | 3   | I   | 内部VLOレギュレータの入力ピンです。VDD電圧範囲は8.5Vから20Vです。このピンは最小0.1μFの容量でバイパスしてください。                              |

| VHI              | 14  | I   | フローティングG1ドライバの電源供給ピンです。VHIはSR MOSFETのオン時間に外部ショットキー・ダイオードにより供給されます。外付けコンデンサによりVHIをSWにバイパスしてください。 |

| VLO              | 4   | O   | VLOレギュレータの出力及びロジック/コントロール回路用電源入力です。VLOはPVLOに接続し、PCB上で最大4.7μFのコンデンサでバイパスしてください。                  |

| ENBL             | 2   | I   | 両出力(G1とG2)の動作をコントロールするイネーブル入力ピンです。アクティブ “H” レベルの動作作用に内部で110kΩの抵抗でVLOにプルアップされています。               |

## SIMPLIFIED BLOCK DIAGRAM

## アプリケーション情報

### プレディクティブ・ゲート・ドライブ手法

Predictive Gate Drive™テクノロジはボディ・ダイオードの導通を検出するのにデジタル・フィードバック・システムを利用し、この導通を最小限にするようデッドタイム遅延を調整します。このシステムにより、種々のMOSFETの特性、伝搬及び負荷に依存する遅延に対応して調整しながら同期MOSFETのボディ・ダイオードの導通期間をほぼなくすことができ、最終結果としてパワ一段の効率が最大になります。

プレディクティブ・ディレイ・コントローラ内部の2つのフィードバック・ループは常に2つのMOSFETゲート・ドライバG1とG2

のターンオン遅延を調整しています。図2のように、ton, G1とton, G2は同期整流MOSFET Q2のボディ・ダイオードの導通が最小になるよう変化します。G1及びG2の両方のターンオフ遅延toff, G1とtoff, G2はデバイス内部の伝搬遅延により固定となっています。

プレディクティブ・ディレイ・コントローラはディジタル制御手法を用いて実行するため、時間遅延は最小に制御されます。ターンオン遅延ton, G1とton, G2はスイッチング・サイクルごとに単一ステップ(標準3ns)で変化します。G1及びG2の最小/最大ターンオン遅延は電気的特性表に規定されています。

図 2. Predictive Gate Drive Timing Diagram

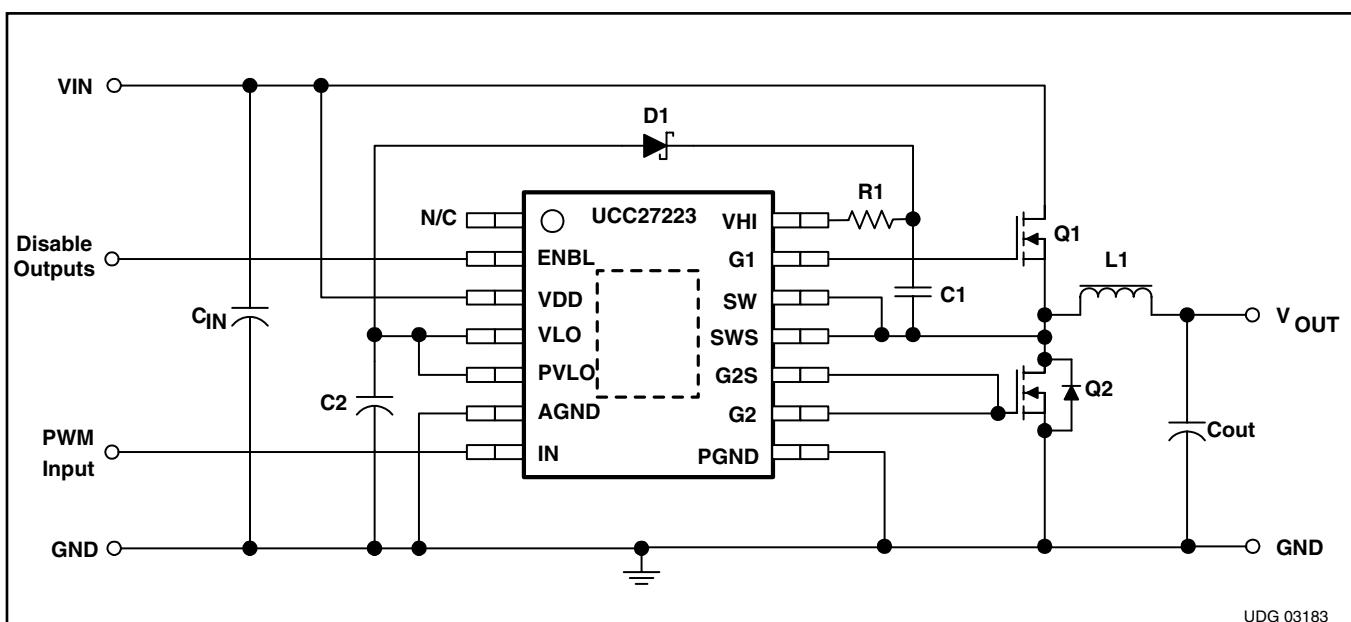

入力電圧が8.5V～20Vのシステムの代表的アプリケーション回路図を図3に示します。

図 3. System Application: 8.5-V to 20-V Input

## VHI直列抵抗R1の選択(dV/dtへの配慮)

直列抵抗R1は仕様条件によってはdV/dtを制限しメインの順方向スイッチのターンオンを減速させるのに必要となる場合もあります。12V入力の設計例では、用いられるMOSFETのタイプ及びMOSFETのハイサイド/ローサイド比によって4Ωから10ΩのR1値を利用しています。一方、5Vまたはそれより低い入力のアプリケーションでは、R1は不要な実例が多いです。

MOSFETのドレイン/ソース間電圧が急速に上昇した場合、何らかの事情でdV/dtに誘発されてデバイスがターンオンする危険性があります。このことは入力電圧が12Vまたはそれ以上の場合に特に問題となる可能性があります。Q1が急速にオンになると、Q2のドレイン/ソース間電圧は急激に上昇し、dV/dtの電圧スパイクがQ2のゲート信号上に現れます。dV/dtにより生じた電圧スパイクが所定のスレッシュホールド電圧を越えると、MOSFETは別制御信号でオフ状態に指示されているにもかかわらず一時的にオンになる可能性があります。この事象は全体の効率に悪影響を与えます。

MOSFETを適切に選択することとレイアウトを注意深く行うことでQ2へのdV/dtの影響を最小限に抑えることができます。dV/dtの影響を最小にするためのMOSFETの選択方法についての詳細は、SEM-1400, Topic 2, Appendix A, Section A5に述べられています。第二に、dV/dtの問題を悪化させる恐れのある寄生インダクタンスを最小にするよう、Q1, Q2, L1が接続しているスイッチ・ノードはできるだけ堅固に配置してください。

それでもdV/dtにより生じた電圧スパイクがQ2のゲートに存在している場合には、うっかりQ2がオンになってしまう可能性を軽減するため4Wから10WのR1値の接続を推奨します。R1を挿入するとQ1のターンオンが遅くなり、Q2のドレイン/ソース間に現れるdV/dtのレートを制限することができます。Q1のターンオンを遅くするとそのデバイスのみではスイッチング損失が少し大きくなりますが、dV/dtによるQ2のターンオンを防止することで効率が上昇できるためR1の挿入には大きな有効性があります。

Q2がdV/dtのロバスト性に対し最適に選択され、PCBレイアウトが十分に配慮された場合は、R1は全く必要がないため、高効率を保つため0Ωのジャンパーで置き換えることができます。設計者の目標とはdV/dtによるターンオン・スパイクを完全に取り除くことではなく、電圧の最大振幅が全動作条件下でMOSFETのゲート/ソース間ターンオン・スレッシュホールド電圧より小さいことを確保することです。

## バイパス・コンデンサC1の選択

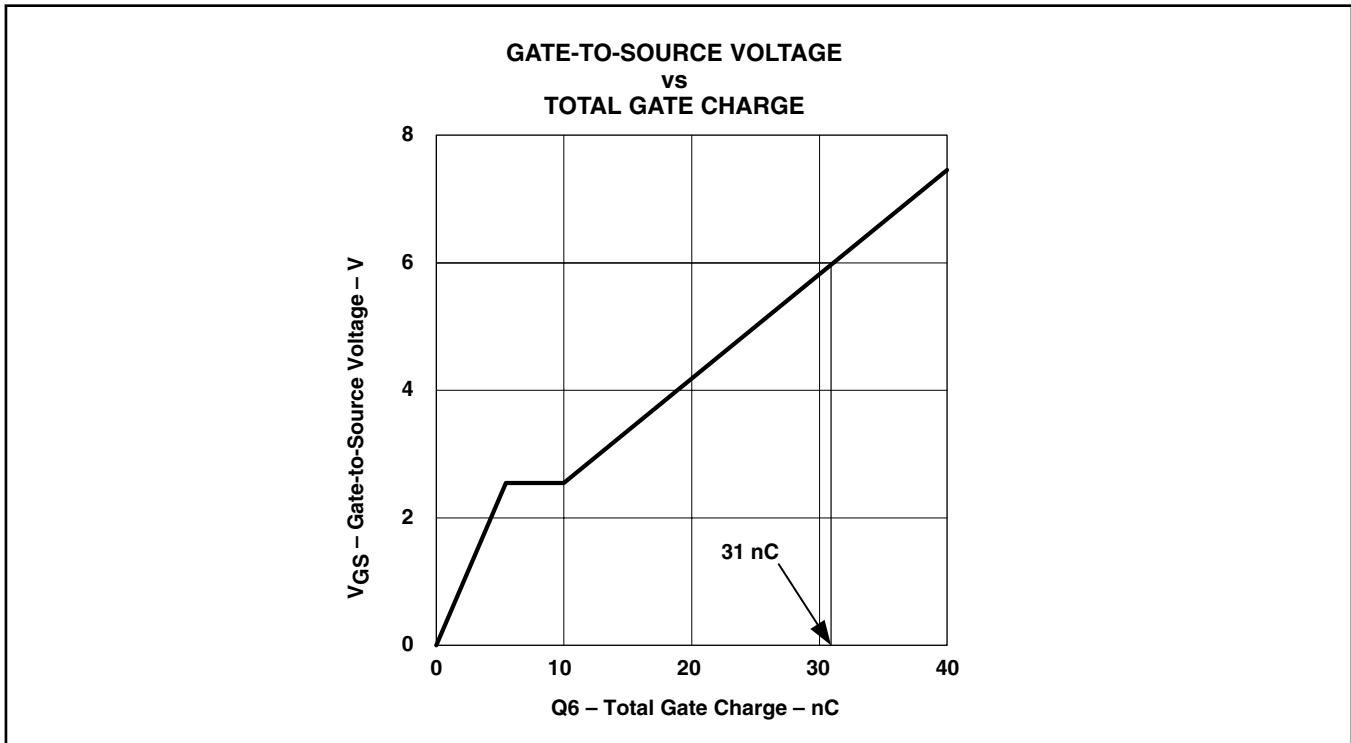

バイパス・コンデンサは、レギュレーションされる電源電位の百分率で表され、許容可能なリップル電圧をもとに選択してください。ここで示されている全てのUCC27223アプリケーション回路では、C1がメイン(ハイサイド)のゲート・ドライバ用にバイパスを行っています。Q1がオンに切り換わるたびに、Q1のゲートを約6.0Vに充電するため電荷が取り出されます。Q1のゲートに供給される電荷特性はそのメーカーのデータシートに曲線として記載されています。ゲート電荷曲線の例を図4に示します。

図4で示されているように、Q1のゲートがソースに対して6.0Vに充電されるためには約31nCのゲート電荷が必要であることが読み取れます。バイパス・コンデンサの最小値は以下の式で求められます。

$$C_{1\text{ MIN}} = \frac{Q_G}{k \times (V_{HI} - V_{SW})} \quad (1)$$

但し、kはC1でのリップルの百分率、QGはQ1のゲートをゼロから最終値(VHI-VSW)にするのに必要な総ゲート電荷です。当例のゲート電荷曲線では、量(VHI-VSW)は6.0Vとします。この値はVLOレギュレータの出力電圧から外付けショットキーダイオードD1の順方向電圧降下を差し引いた値を表しています。図4に示されているゲート電荷をもつMOSFETでは、3%のピーク間リップル電圧を保持するのに必要とされる最小容量の計算結果は最終的には172nFとなるため、180nFまたは220nFのコンデンサが使用できます。正常動作を行うにはC1の最大ピーク間リップルは0.4Vより低くするようにしてください。

## MOSFETの選択

ピーク電流定格はこのドライバにより駆動できる外付けパワーMOSFETの最大ゲート容量に制限を与えます。この制限は外付けトランジスタのターンオンまたはターンオフ時に所望のスイッチング速度を達成するため必要なゲート容量をソースまたはシンクするのに必要な時間に基づきます。従って、仕様により異なる電流定格の複数のゲート・ドライバが存在することになります。

これは、過渡には一定の時間間隔があり、ゲート駆動振幅は固定と仮定すると明確に述べられます。色々なゲート容量をもつMOSFETを、同じ時間でターンオンまたはターンオフするにはドライバからの電流能力がより大きいことが必要です。しかしUCC27223で駆動できるゲート電荷は実際には上限が存在します。TrueDrive<sup>TM</sup>出力段の電流能力とPredictive Gate Drive<sup>TM</sup>回路のダイナミック・レンジ(遅延調整範囲)を考慮すると、この上限はゲート電荷が約120nCです。

また、一部のより大きな電流のアプリケーションでは、いくつかのMOSFETを並列接続し同一ゲート駆動信号で駆動することが必要となる場合もあります。この結合ゲート容量が120nCを越えると、ゲート駆動信号の立上がり/立下がり時間が延び、UCC27223のPGD回路の遅延調整範囲に制限をかけてしまします。このことは、ある動作条件下ではPGD機能のもつ利点を制限してしまうことを意味しています。

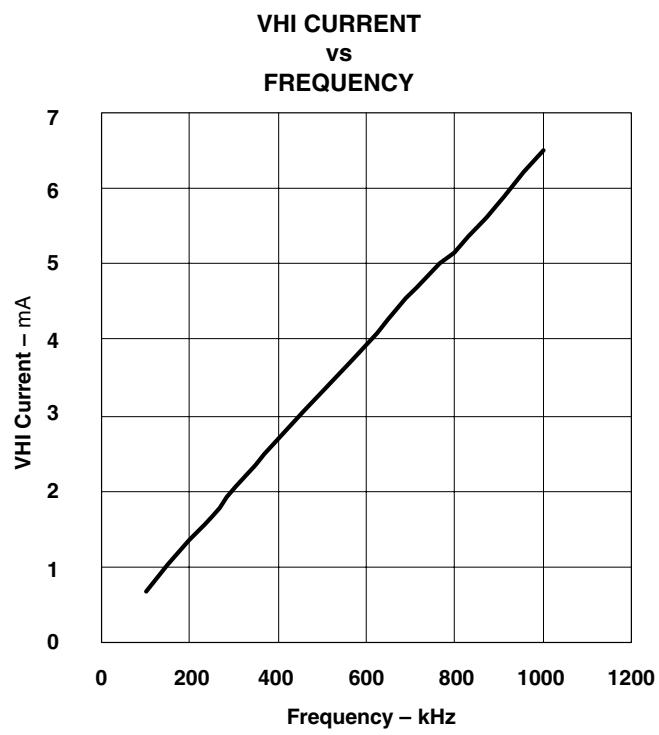

ゲート駆動回路の設計の際にさらに配慮しておくことに外付けMOSFETゲート電荷量とともに、ドライバの消費電力を決める動作周波数です。許容消費電力は、最大接合部/動作温度、及び熱/信頼性についての配慮の関数です。

## バイパス・コンデンサC2の選択

C2はブートストラップ・ダイオードによりコンデンサC1を充電するのに電流を供給するだけでなく、同期整流MOSFET Q2をターンオンするのに必要な電流も供給します。同期MOSFET

図 4

はドレイン/ソース間電圧が0Vでターンオンするため、ミラーあるいはゲート/ドレイン間電荷は存在しません。従って、同期MOSFETのゲートは単なる線形容量としてモデル化できます。この容量値はデータシートのゲート電荷曲線から分かります。図4で、ミラー安定期間を過ぎた曲線の勾配は等価的にゲート容量を示します。Y軸はボルトであるため、実際の容量は曲線の勾配の逆数です。例えば、図4の曲線の勾配はゲート電荷範囲が10nCから40nCで約2V/12nCです。よって、等価容量は $12\text{nC}/2\text{V}=6\text{nF}$ です。この等価容量を用いて、バイパス・コンデンサの最小容量は以下の式で求められます。

$$C_{2\text{MIN}} = \frac{C_{EQ}}{k} \quad (2)$$

但し、

- CEQは等価ゲート容量

- kはC2のリップル電圧で、百分率で表されます。

ピーク間リップルが3%の場合は、コンデンサC2の最小値の計算結果は200nFです。この場合は220nFのコンデンサを使用します。C2MAXは4.7μFを越えないように設定してください。計算結果の容量に加え、100nFで低ESLのバイパス・コンデンサができるだけUCC27223チップに近づけて配置してください。このコンデンサは駆動段で必要な過渡電流を供給し、ターンオン時ドライバがUVLOでシャットダウンするのを防ぎます。

### レギュレータ電流と消費電力

レギュレータ電流は2つのゲート・ドライバで必要とされる

DCまたは平均電流から計算することができます。この電流は以下の式で表されます。

$$I_{REG} = F_{SW} \times (C_{EQ} \times VLO + Q_G) \quad (3)$$

全消費電力がデバイス内部で消費され、内部のバイアス電流は無視できるものとすると、デバイスで消費される電力は以下のようになります。

$$P_{DIS} = F_{SW} \times (C_{EQ} \times VLO + Q_G) \times VDD \quad (4)$$

周波数が500kHzの設計で、Q1とQ2の両方に図4のゲート電荷特性をもつMOSFETを使用すると、平均レギュレータ電流は35mAとなり、12Vの入力動作の場合、消費電力の計算結果は420mWとなります。

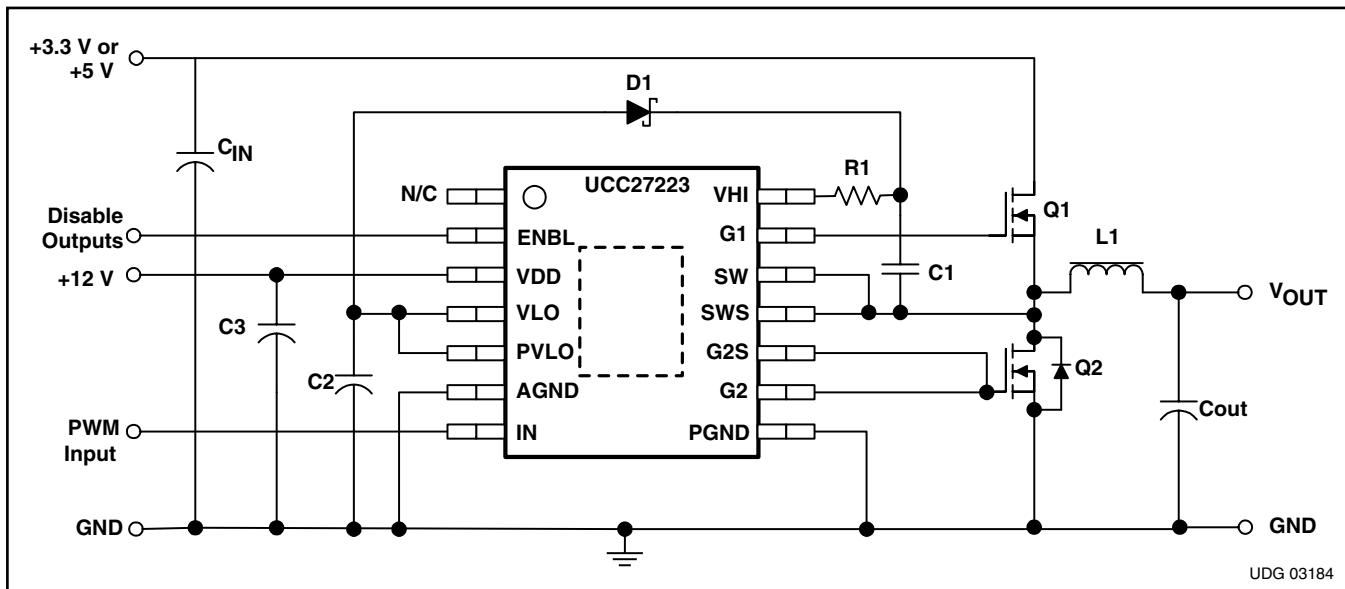

### 3.3Vまたは5V電源入力と12Vのゲート駆動を使用したシステム

図5に、電源バス入力が5Vで、ゲート駆動の電源供給に12Vが使用可能なシステムの回路図を示します。このシステムでは、両方のMOSFETに6.5Vのゲート駆動電圧が供給され、一方、パワー段は3.3Vまたは5Vのバス電圧で動作します。

直列抵抗R1は状況におうじて同期整流スイッチをオンにする誤動作の原因の急なdV/dtを制限するためメインの順方向スイッチのターンオンを減速させるのに必要に場合もあることに注意してください。dV/dtへの配慮及びR1の選択については先のセクションに記載されています。

図 5. System Application: 3.3-V or 5-V Power Input with 12 V Available for Gate Drive

## 5V入力のみのシステム

図6に示されている回路は5Vの入力バイアスで起動し、パワーMOSFETに6.5Vのゲート駆動電圧を供給します。この回路は、入力電圧を効率的に倍にし、この電圧をリニア・レギュレータの入力に印加する、D3、D4、C3から成るチャージポンプを使用しています。次に、レギュレータは倍加された入力電圧をVLOの約6.5Vに安定化します。

### D2、D3、D4の選択

ダイオードを選択するには導通ピーカー/平均電流に基

づいて行います。D2は単にコンバータの起動時C2を充電するパスを供給するだけです。例えば、汎用のショットキー・ダイオードのBAT54シリーズを使用できます。D3及びD4を選択するには、この2つのダイオードのピーク電流を考慮に入れる必要があります。まず、D3とD4の両方を流れる平均電流は式(3)で表されるレギュレータ電流と同一です。D3とD4のピーク電流は以下の式で表されます。

$$I_{D3PK} = \frac{I_{REG}}{1 - D} \quad (5)$$

$$I_{D4PK} = \frac{I_{REG}}{D} \quad (6)$$

図 6. System Application: 5-V-Only Power Input with 6.5-V Gate Drive Using Charge Pump Circuit

ほとんどのUCC27223のアプリケーションでは、時比率は50%よりずっと小さく、D3のピーク電流は極めて相応な値です。しかしながら、D4のピーク電流は非常に大きな値です。このようにピーク電流が大きいとD4には大きな電流規格をもったダイオードを使用することが必要となります。

チャージポンプの効率を適度に維持するため、ピーク電流が約40mAを下回るアプリケーション例ではBAT54タイプ等のダイオードが使用できます。ピーク電流が40mAを越えるアプリケーションでは350mA或いは500mA定格のダイオードを選定しなければなりません。

### フライング・コンデンサC3の選択

フライング・コンデンサは大きなピーク電流にさらされます。ピークのリップル電圧を低くするには、このコンデンサはC1やC2より大きくする必要があります。C3の選択はC3の許容ピークのリップルに基づいて選択してください。

$$C_{3\text{ MIN}} = \frac{I_{\text{REG}}}{F_{\text{SW}} \times k \times (V_{\text{IN}} - V_{\text{FD3}})} \quad (7)$$

但し、IREGはレギュレータの出力電流、FSWはスイッチング周波数、kはC3のリップル百分率、VFD2はD3の順方向電圧降下です。

### バイパス・コンデンサC4の選択

バイパス・コンデンサC4はチャージポンプ・ダイオードD4からピーク電流をも取り込めるような大きさにする必要があります。このコンデンサは許容リップル電圧に基づいて大きさを決めます。

$$C_{\text{MIN}} = \frac{I_{\text{REG}} \times (1 - D)}{F_{\text{SW}} \times k \times (2 \times V_{\text{IN}} - V_{\text{FD3}} - V_{\text{FD4}})} \quad (8)$$

但し、VFD3とVFD4はD3とD4の順方向電圧、kはC4に許容されるリップルの百分率です。

### イネーブル・ピンと起動時のドライバ動作

UCC27223では、アクティブ“H”レベルのENBL機能が2ピンで実行されます。このピンが“L”レベルの場合PWM入力信号の状態にかかわらずG1とG2の両出力を停止させます。ENBLピンは、オープンの場合でもチップが機能するよう内部で110kΩの抵抗でVLOに内部でプルアップされています。イネーブルのスレッシュホールド電圧はオンの場合2.45V、オフの場合1.7Vです。また、UCC27223にはロジック方式のラッチ機能があり、VDD電位がUVLOターンオン・スレッシュホールド電位以上であっても起動時両出力を“L”レベルにしておきます。両方の出力とも最初のPWM入力信号が入力されるまでは安定化のため“L”レベルを保持します。

### 同期整流とプレディクティブ・ディレイ

通常のバック・コンバータでは、メイン・スイッチがオフになった場合、電流はインダクタの負荷に流れます。この電流は無限大の電圧を使わなければすぐには停止できません。電流パスに電流が流れ安全なレベルに電圧レベルが維持されるには、整流器またはキャッチ・デバイス等を使用します。このデバイスは従来型のダイオードでも、或いはコントロール信号がその駆動に使用できるのであれば能動デバイスでも対応は可能です。UCC27223は整流器としてのNチャネルMOSFETを制御する信号を供給します。このコントロール信号は、整流器MOSFETがオフ、メイン・スイッチがオンになる時間からの最適な遅延時間、及び整流器MOSFETがオン、メイン・スイッチがオフになる時間からの最適な遅延時間が存在するよう、高精度にメイン・スイッチの駆動信号との整合性を図ります。この仕組み、つまりPredictive Gate Drive™遅延は、次のサイクルで使用されるべき遅延を調節するため現在のスイッチング・サイクルか

図 7. Switch Node Waveforms for Synchronous Buck Converter

らの情報を使用します。図7に、同期整流されたバック・コンバータのスイッチ・ノードの電圧波形を示します。この図は、固定遅延の駆動体系（ターンオフからターンオンの合間の一定遅延とプリセット遅延）、アダプティブ・ディレイの駆動体系（現在のスイッチング・サイクルで検出された電圧をもとにした可変遅延）、プレディクティブ・ディレイの駆動体系の効果をそれぞれ比較したものです。

整流器の導通期間でダイオードの導通に費やされた時間が長くなるにつれ、効率が低下することに着目してください。また、図7には表されていませんが、プレディクティブ・ディレイ回路がクロス導通または貫通電流を回避すると同時にボディ・ダイオードが順方向にバイアスされるようになることを防止できる利点があります。これは、メインのMOSFETがオンになった時電力の大きな省電力化が実現し、整流器MOSFETのボディ・ダイオードの逆回復損失が最小限に抑えらる事を意味しています。

また、メイン（順方向）MOSFETの消費電力も多少低減します。逆回復時ボディ・ダイオードはまだ順方向にバイアスされていますので、逆回復電流はドレイン/ソース間電圧が高い間順方向MOSFETを流れ、さらなるスイッチング損失が生じます。このスイッチング過渡時にPGD機能がないと、メイン・スイッチで $V_{ds} = V_{in}$ ,  $I_{ds} = I_{load} + I_{rr}$ になります。一方、PGD機能があれば、 $V_{ds} = V_{in}$ ,  $I_{ds} = I_{load}$ となります。この電流の低減によりメインMOSFETの電力がさらに節減できます。

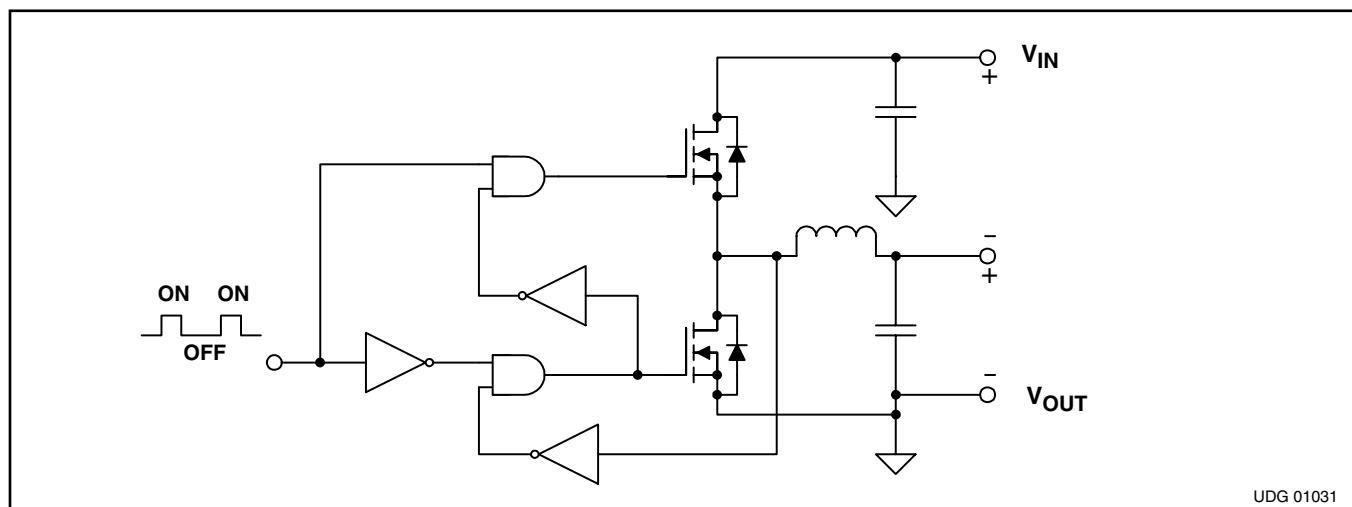

### Predictive Gate Drive手法とAdaptive Gate Drive手法の比較

最初の同期整流型コントローラには2つのゲート・ドライバのターンオン遅延制御方式がありました。このよく知られている手法の利点は単純さです。欠点としては、デバイスの温度、遅延時間のロット間等の変動を保証するのに十分な長さの遅延時間を設ける必要があることです。同期整流器のボディ・ダイオードはこのデッドタイム時導通しているため、この手法での効率はMOSFET、周囲温度、デッドタイム遅延のロット間変動により変わってしまいます。

この内部遅延時間のばらつきに対処するため、第二世代のコントローラでは2つのゲート・ドライバのターンオンを制御するのにパワー段からの状態情報を利用しました。この手法は通常Adaptive Gate Drive手法と呼ばれており、図8に示されています。

Adaptive Gate Drive手法の主な利点は種々のMOSFETや温度で変動する遅延に対し現時点での遅延調整が可能なことです。欠点は、クロス結合ループの遅延によりボディ・ダイオードの導通時間が生じることと、MOSFETのゲートをスレッシュホールド・レベルまで充電するための遅延を補償することができないことです。さらに、単にSR MOSFETのゲート電圧を監視しているため同期MOSFETのチャネルがオフかどうか判定することが困難な点にあります。一部のデバイスでは外付けコンデンサにより同期整流器のターンオフとメインMOSFETのターンオンの間に任意に遅延を付加している例もあります。この付加された遅延がボディ・ダイオードの導通損失を増加させてパワー段の効率に直接影響を与えてしまいます。この損失は同期MOSFETに集中するため、この部品のストレスや温度上昇が大きな設計上の悩みの種になります。

第三世代のプレディクティブ制御手法は、現在のサイクル毎にデッドタイムを設定するのに前回のスイッチング・サイクルからの情報を使用する点でアダプティブ手法と異なっています。それに対して、アダプティブ手法は遅延時間を設定するのに現在の状態情報を使用しています。これはフィードバック・ループの伝搬遅延が原因でボディ・ダイオードの導通が生じてしまいますがプレディクティブ制御手法は改善できます。

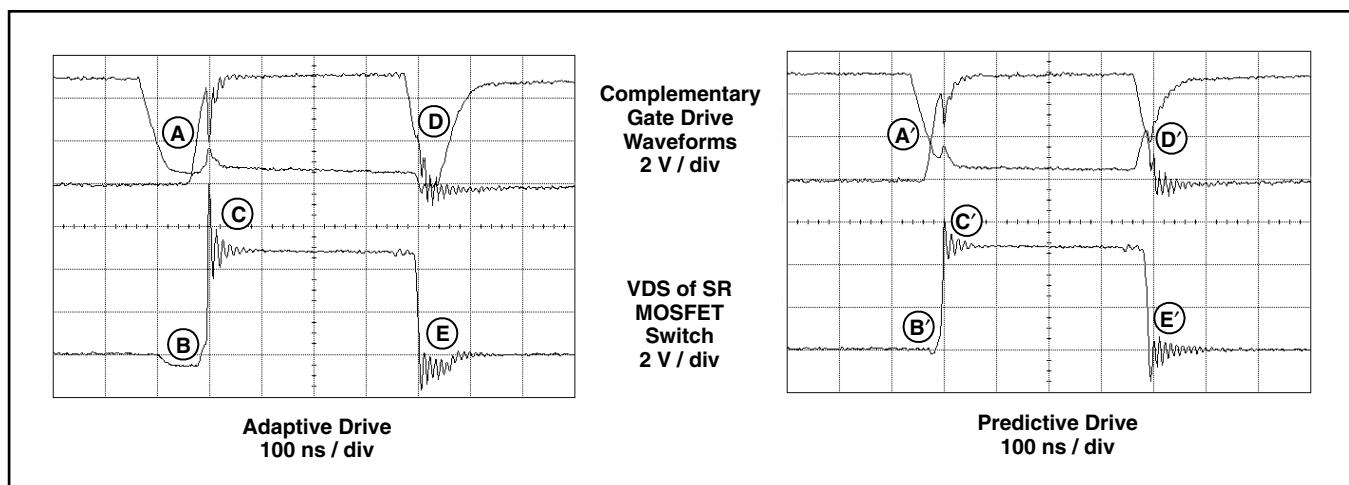

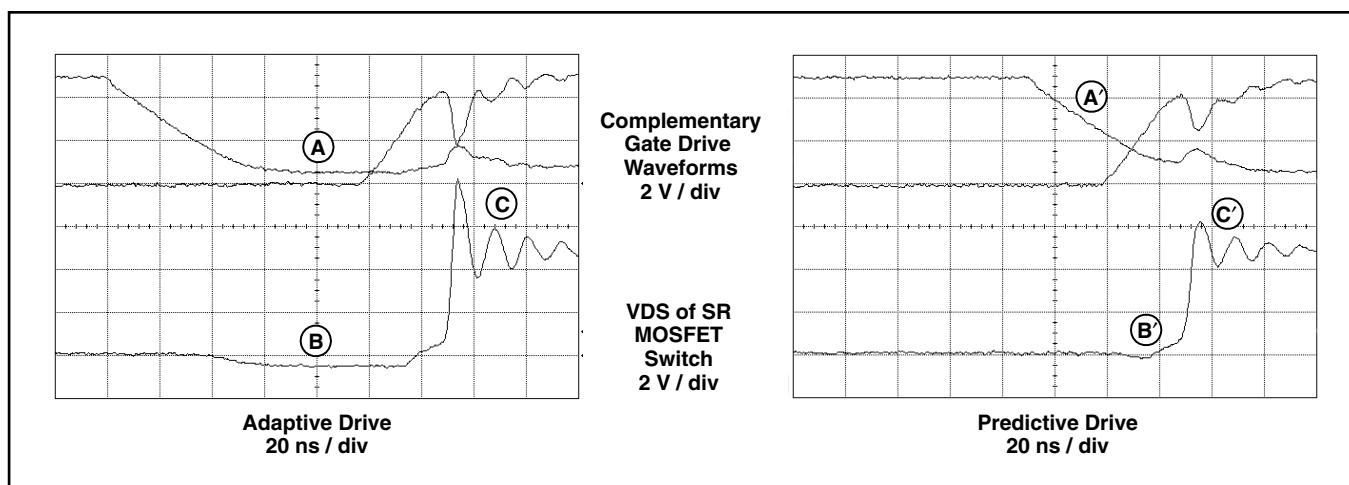

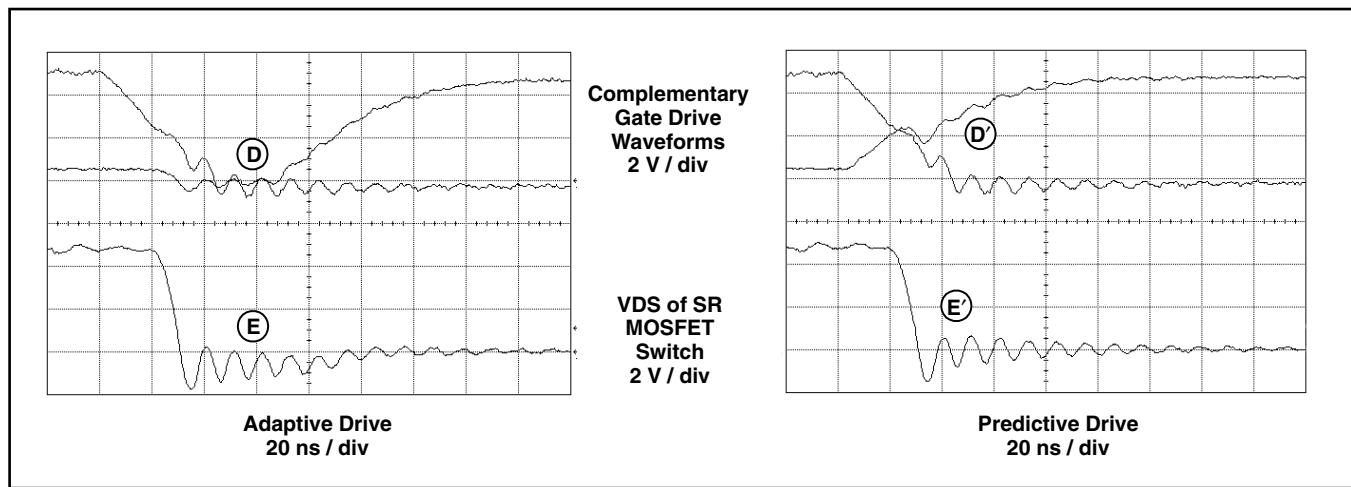

### アダプティブ手法の波形とプレディクティブ手法の波形

図9から図11に、アダプティブ手法（左側）対プレディクティブ手法（右側）のスイッチング波形を示します。主な比較領域を、アダプティブ・コントロール波形では(A)、(B)、(C)、(D)、(E)、プレディクティブ・コントロール波形では(A')、(B')、(C')、(D')、(E')で表しています。図10と図11は各過渡エッジの拡大図です。

図 8. Adaptive Gate Drive Technique

(A)で、同期整流器のゲートが“L”レベルになるのを検出してからハイサイドのゲートが“H”レベルになるまでの伝播遅延により、(B)で示されているように約60nsのボディ・ダイオードの導通が生じています。プレディクティブ・ドライブを用いると、SR MOSFETのボディ・ダイオードの導通(B)が検出されるとすぐにハイサイドのターンオン遅延はボディ・ダイオードの導通時間(B')を最適にするよう調整されます。

(A)で、同期整流器のゲート/ソース間電圧は減少しているのに対し、ハイサイドのゲート/ソース間電圧は増加しています。ハイサイドMOSFETのターンオンのタイミングを精密に行った結果を(C)と(C')に示します。プレディクティブ・ドライブ(C')のオーバーシュートとリンギングの振幅は、SR MOSFETのボディ・ダイオードの逆回復が低減しているためアダプティブ・ドライブ(C)よりずっと小さくなっています。この逆回復の低減はプレディクティブ・ドライブ手法で使用されている極めて精密なゲート・タイミング制御によってのみ可能です。

(D)で、同期整流器のドレイン/ソース間電圧の立下りからゲート/ソース間電圧の立上がりまでの伝搬遅延により、SR MOSFETのボディ・ダイオードが約60ns間導通しています(E)。プレ

ディクティブ・ドライブがイネーブルであると(D')、内在している遅延は除去され、(E')に示されているようにボディ・ダイオードの導通はほとんどありません。

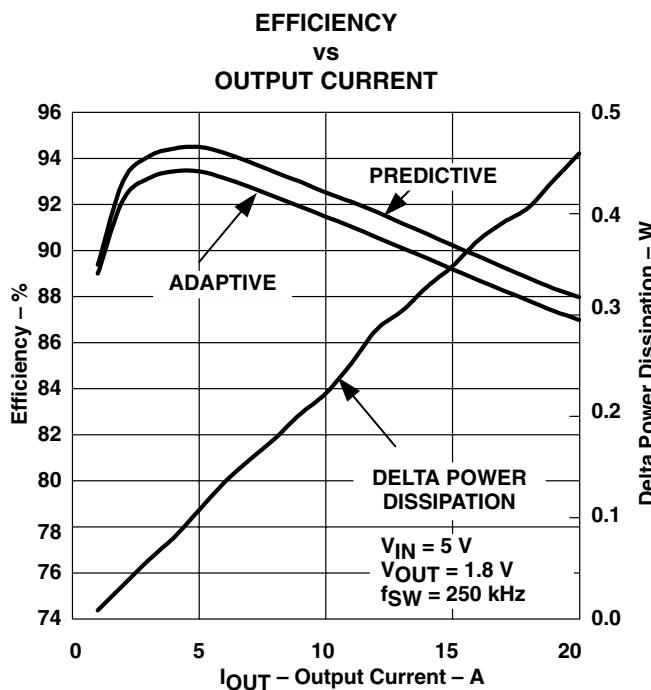

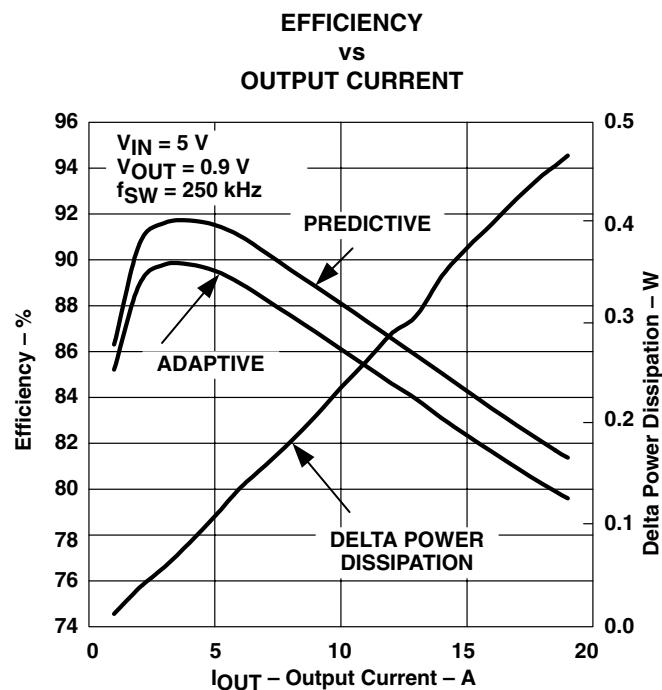

## 効率の比較

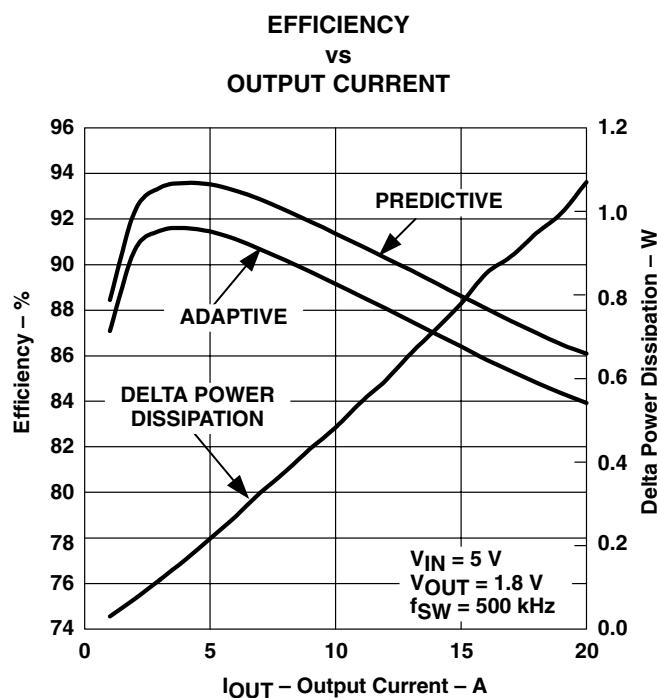

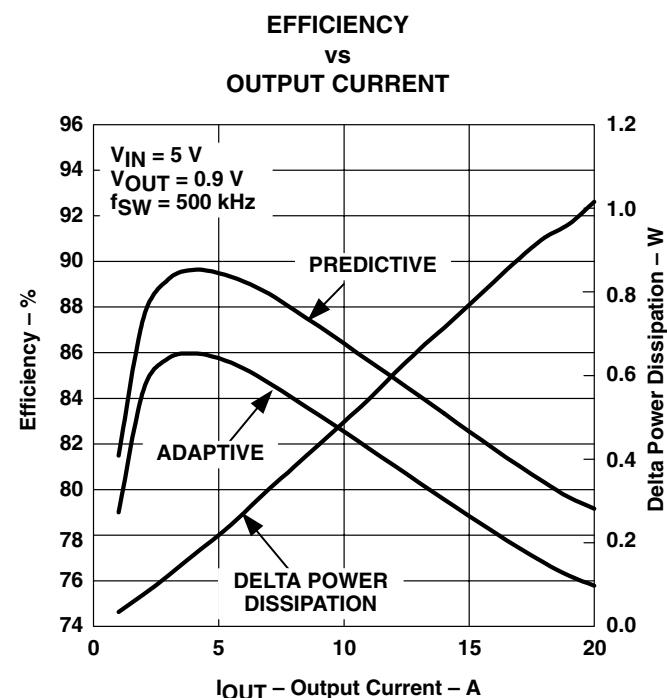

図12から図15に、プレディクティブ・ディレイ手法とアダプティブ・ディレイ手法の両方について2種類の出力電圧(0.9Vと1.8V)、2種類のスイッチング周波数(250kHzと500kHz)で効率を測定した結果を示します。

$V_{OUT}$ レベルが1.8V、スイッチング周波数が250kHzの場合プレディクティブ手法を使用すると効率が1%高くなっています(図12)。図13と図14では、 $V_{OUT}$ が1/2(0.9V)、またはスイッチング周波数が2倍の500kHzの時、効率の増加分は約2倍になることが示されています。周波数が2倍でかつ出力電圧が1/2の時、プレディクティブ手法での効率はアダプティブ手法より約4%高くなっています(図15)。従って、スイッチング周波数が増加し、出力電圧が低くなるほど、効率の増加分は大きくなります。このことにより、小型部品での設計が可能となって周波数が高くできるだけでなく、動作温度が低くなって信頼性が高くなります。

図9. Adaptive vs. Predictive Switching Waveforms

図10. Close-Up: Turn-Off of Synchronous Rectifier Switch to Turn-On of Main Switch

図 11. Close-Up: Turn-Off of Main Switch to Turn-On of Synchronous Rectifier Switch

図 12

図 13

図 14

図 15

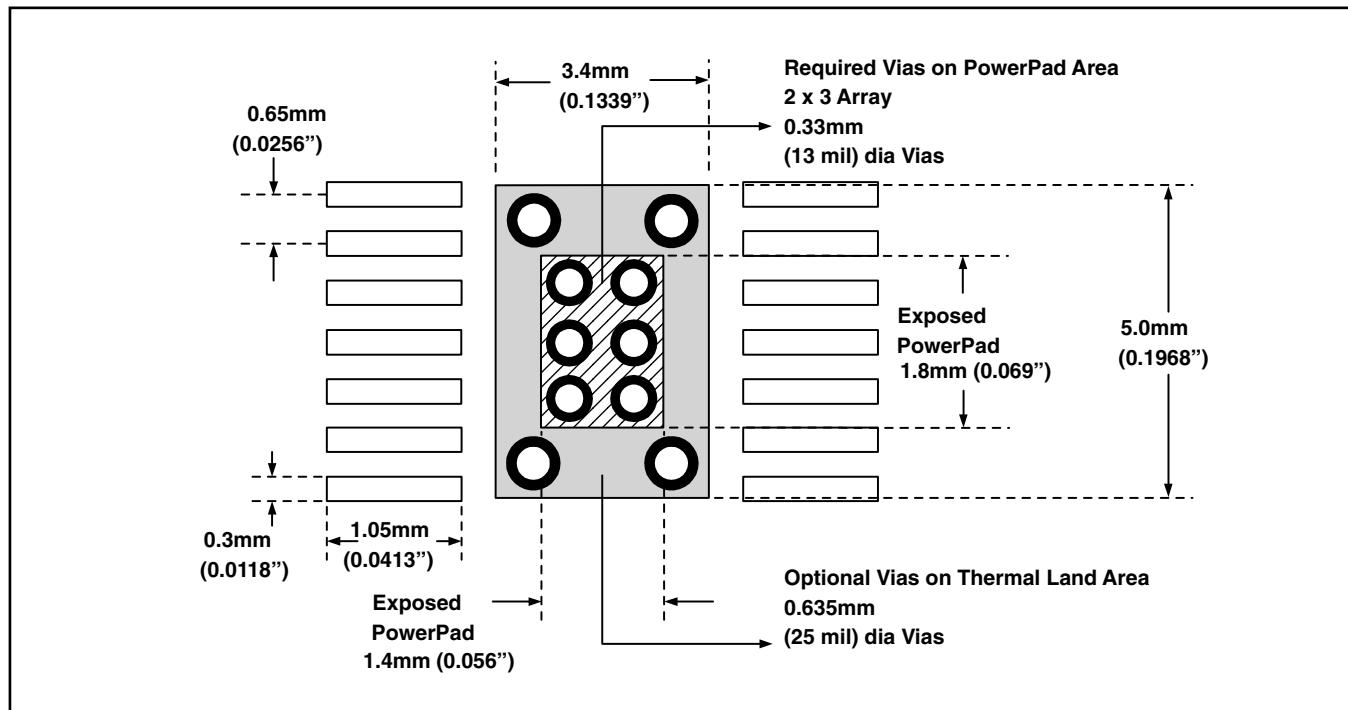

図 16. TSSOP-14 PWP Package Outline and Minimum PowerPAD™ PCB Thermal Land

## レイアウトについての考察

### パッケージング

UCC27223はTIの放熱特性に優れた14ピンPowerPAD™パッケージのみで供給されています。このパッケージは接合部/ケース間定格が $2^{\circ}\text{C}/\text{W}$ の優れたサーマル・インピーダンスをもっています。図16に斜線領域で示されているように、PowerPAD™パッケージにはパッケージの底面に位置する露出したリードフレームのダイ・パッドがあります。PowerPAD™ TSSOP 14ピン・パッケージの露出パッドの寸法は69ミル × 56ミル (1.8mm × 1.4mm) です。しかし、露出パッドの公差は位置及びモールド・フローのばらつきにより+41/-2ミル (+1.05/-0.05mm) です。PowerPAD™パッケージから効率的に熱を移動させるには図16の灰色の網掛け領域で示されているように、パッケージの直下にPCBに設計したサーマル・ランド領域が必要となります。図16に示されているように、サーマル・ランドの最小領域は5mm × 3.4mmを推奨します。この推奨最小サーマル・ランド領域がプリント基板に含まれている場合、PowerPAD™パッケージの露出部分に公差のばらつきがあったとしてもサーマル・ランド領域の範囲内にうまく収まります。さらに、図16に示されているように、2 × 3列の13ミル径のサーマル・ビアが露出PowerPAD™領域内に必要です。さらなるヒートシンク能力が要求された場合には、より大きな25ミルのビアをサーマル・ランド領域に付加することができます。

# リファレンス・デザインと評価モジュール

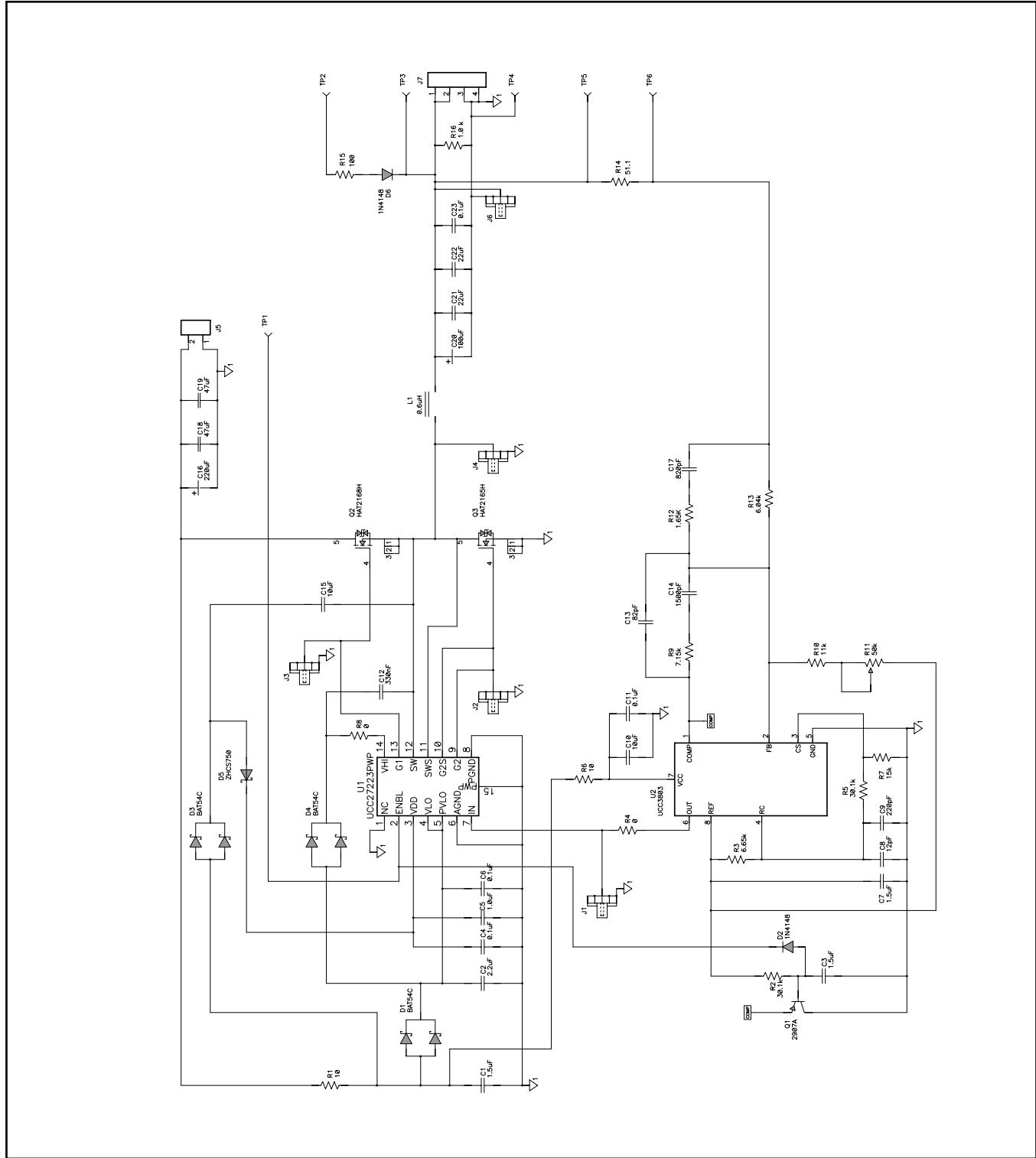

リファレンス・デザインはTI文献番号SLUU181 “5V 0.9V - 1.8V (adjustable)、20-A High Efficiency Synchronous Buck Converter Using the UCC27223 with Predictive Gate Drive™” と添付の評価モジュールUCC27223EVMに記載されています。

ここで設計では簡単なシングルエンドPWMコントローラを使用したUCC27223とそのPredictive Gate Drive™同期式降圧動作に焦点をあてています。回路図を図17に示します。

図 17. Typical Application Diagram

## TYPICAL CHARACTERISTICS

図 18

図 19

図 20

図 21

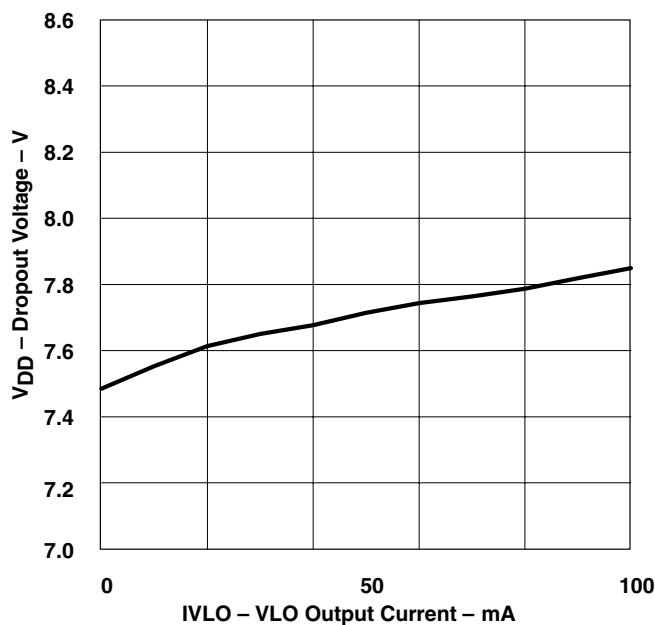

**DROPOUT VOLTAGE (VDD AT VLO = 6.175 V)

vs

OUTPUT CURRENT**

図 22

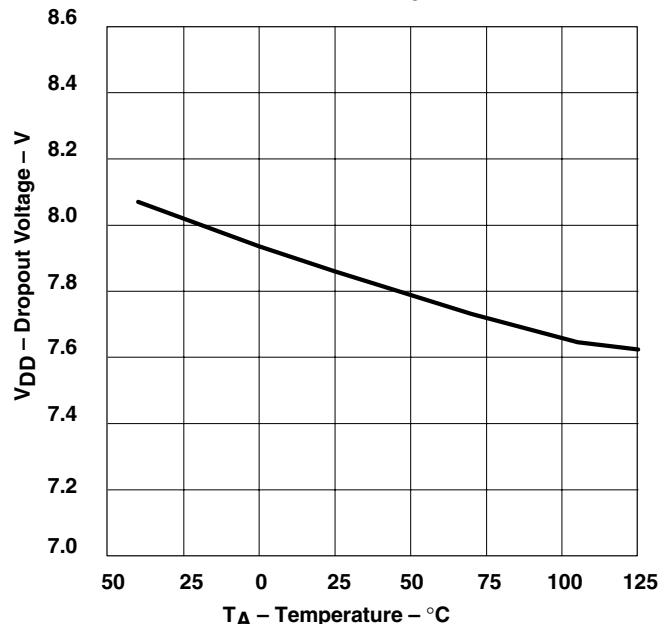

**DROPOUT VOLTAGE (VDD AT VLO = 6.175 V)

vs

TEMPERATURE ( $I_{VLO} = 100$  mA)**

図 23

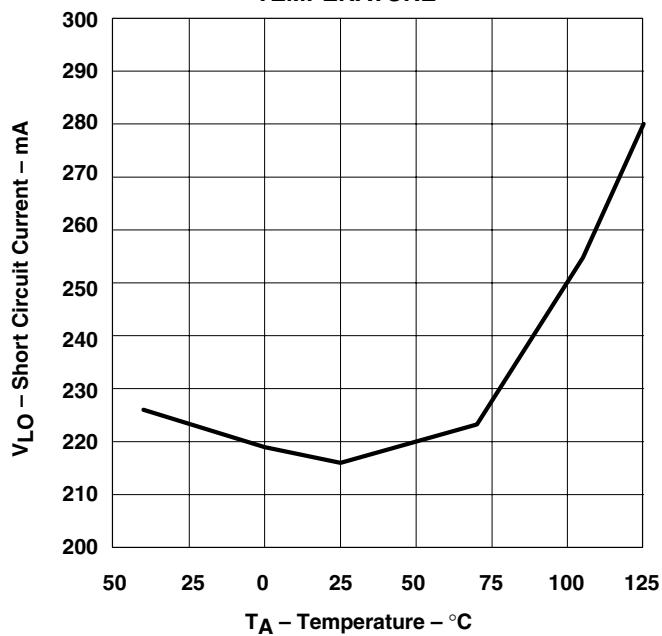

**VLO SHORT CIRCUIT CURRENT

vs

TEMPERATURE**

図 24

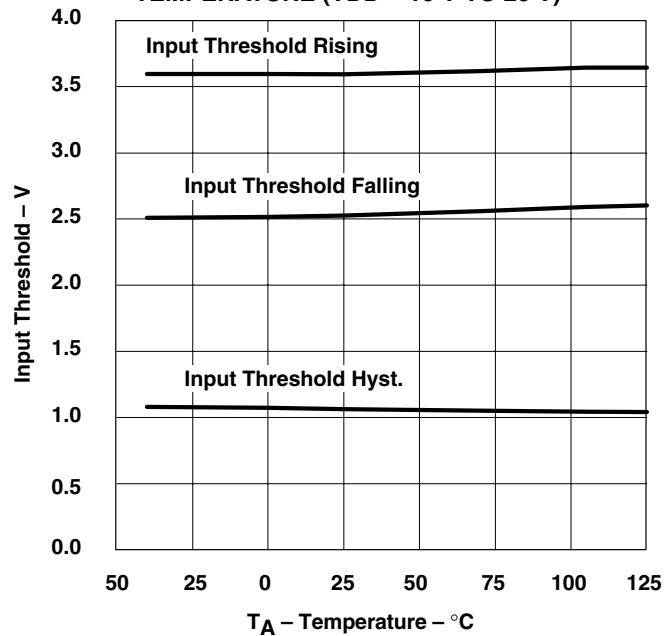

**INPUT THRESHOLD

vs

TEMPERATURE (VDD = 10 V TO 20 V)**

図 25

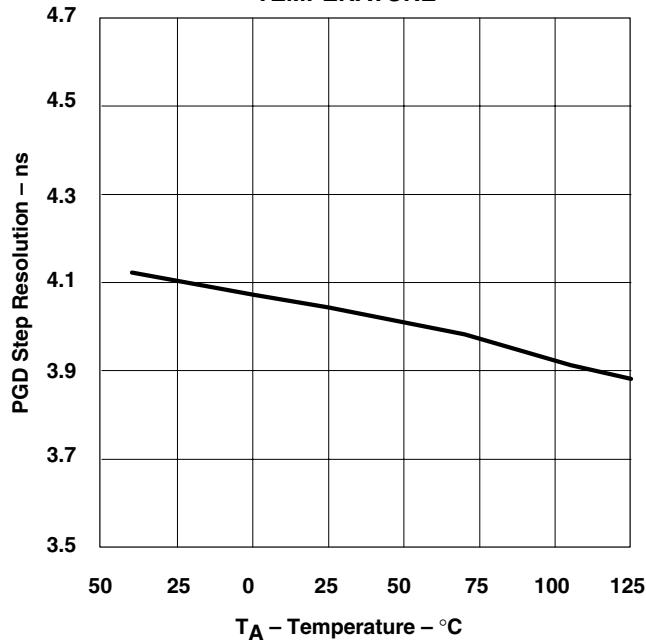

PREDICTIVE DELAY BIT WEIGHT

vs

TEMPERATURE

図 26

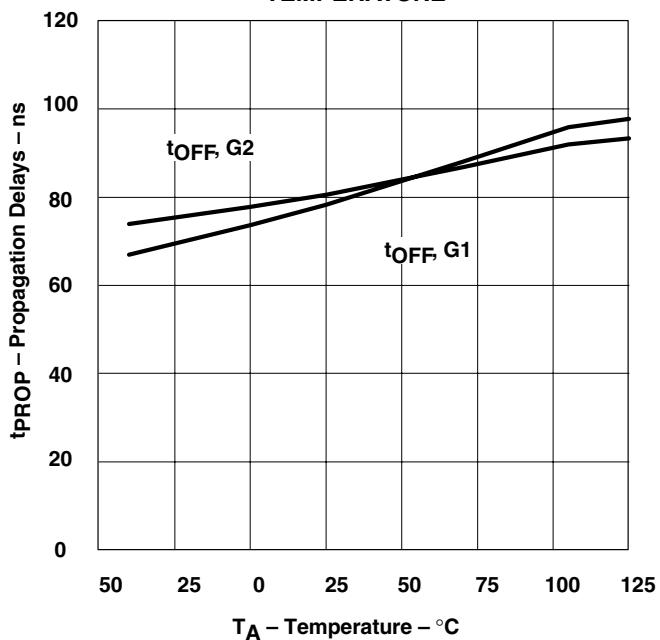

PROPAGATION DELAYS

vs

TEMPERATURE

図 27

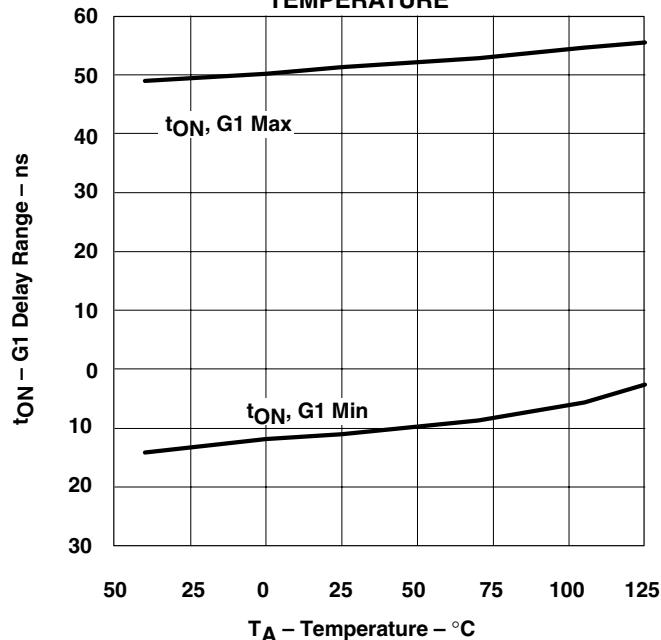

PREDICTIVE DELAY RANGE

vs

TEMPERATURE

図 28

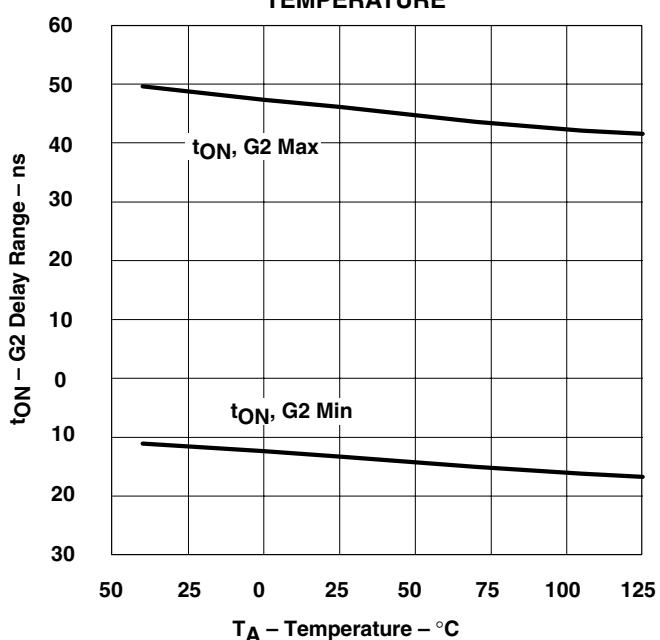

PREDICTIVE DELAY RANGE

vs

TEMPERATURE

図 29

図 30

図 31

図 32

図 33

図 34

図 35

図 36

## 関連製品

| 型番         | 内容                                  | ゲート駆動       | パッケージ                        |

|------------|-------------------------------------|-------------|------------------------------|

| TPS40090   | 高周波2、3、4相多相コントローラ                   | –           | TSSOP-24                     |

| UCC27221/2 | 高効率プレディクティブ同期式降圧型                   | $\pm 3.3$ A | PowerPAD™ HTSSOP-14          |

| TPS2830/1  | 高速同期式降圧型MOSFETドライバ(デッドタイム・コントロール付き) | $\pm 2.4$ A | PowerPAD™ HTSSOP-14, SOIC-14 |

| TPS2832/3  | 高速同期式降圧型MOSFETドライバ(デッドタイム・コントロール付き) | $\pm 2.4$ A | SOIC-8                       |

| TPS2834/5  | 同期式降圧型MOSFETドライバ(デッドタイム・コントロール付き)   | $\pm 2.4$ A | PowerPAD™ HTSSOP-14, SOIC-14 |

| TPS2836/7  | 同期式降圧型MOSFETドライバ(デッドタイム・コントロール付き)   | $\pm 2.4$ A | SOIC-8                       |

| TPS2838/9  | 同期式降圧型MOSFETドライバ(ドライブ・レギュレータ付き)     | $\pm 4$ A   | PowerPAD™ HTSSOP-16          |

| TPS2848/9  | 同期式降圧型MOSFETドライバ(ドライブ・レギュレータ付き)     | $\pm 4$ A   | PowerPAD™ HTSSOP-14          |

## 参考資料

1. *Power Supply Design Seminar SEM 1400 Topic 2: Design and Application Guide for High Speed MOSFET Gate Drive Circuits*, by Laszlo Balogh, Texas Instruments Literature Number SLUP169.

2. User's Guide: 5 V to 0.9 V 1.8 V (adjustable), 20-A High Efficiency Synchronous Buck Converter using UCC27223 with Predictive Gate Drive™, TI Literature Number SLUU181.

3. User's Guide: 12 V to 1.8 V, 20 A High-Efficiency Synchronous Buck Converter Using UCC27222 With Predictive Gate Drive™ Technology, TI Literature Number SLUU140.

4. Application Note: UCC27221/2 Predictive Gate Drive™ FAQ, TI Literature Number SLUA280.

5. Application Note: Predictive Gate Drive™ Boosts Converter Efficiency, TI Literature Number SLUA281.

6. Application Note: Increasing UCC27221/2 Gate Drive Voltage, TI Literature Number SLUA292.

**PACKAGING INFORMATION**

| Orderable part number          | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|--------------------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC27223PWP</a>    | Active        | Production           | HTSSOP (PWP)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | 27223               |

| <a href="#">UCC27223PWP.A</a>  | Active        | Production           | HTSSOP (PWP)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | 27223               |

| <a href="#">UCC27223PWPR</a>   | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | 27223               |

| <a href="#">UCC27223PWPR.A</a> | Active        | Production           | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | 27223               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月