UCC27282-Q1

JAJSHY6D - SEPTEMBER 2019 - REVISED OCTOBER 2022

### UCC27282-Q1 クロス導通保護機能を搭載し、スイッチング損失が小さい 3A 120V 車載用ハーフブリッジ・ドライバ

#### 1 特長

**TEXAS**

INSTRUMENTS

- 下記内容で AEC-Q100 認定済み

- 温度グレード 1 (T<sub>i</sub> = -40℃~150℃)

- HBM ESD 分類レベル 1B

- CDM ESD 分類レベル C3

- ハイサイド / ローサイド構成の2つのNチャネル MOSFET を駆動

- 5V (標準値)の低電圧誤動作防止

- 入力インターロック •

- イネーブル / ディスエーブル機能付き、DRC パッケー ٠ 32

- 16ns (標準値) の伝搬遅延

- 立ち上がり時間 12ns、立ち下がり時間 10ns (1.8nF 負荷時)

- 1ns (標準値) の遅延マッチング

- 入力の負電圧の絶対最大定格:-5V

- HSの負電圧の絶対最大定格:-14V

- **±3A**のピーク出力電流 •

- 絶対最大ブート電圧:120V

- ディスエーブル時の低消費電流 (7µA)

- ブートストラップ・ダイオードを内蔵

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可 能

### 2 アプリケーション

- 車載用 DC/DC コンバータ

- 電動パワー・ステアリング •

- オンボード充電器 (OBC)

- 一体型ベルト・スタータ・ジェネレータ (iBSG)

- 車載用 HVAC (エアコン) コンプレッサ・モジュール

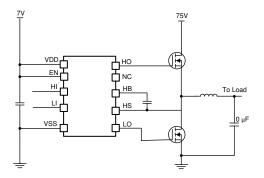

### アプリケーション概略図

#### 3 概要

UCC27282-Q1 は、100V の最大スイッチ・ノード (HS) 電 圧定格を持つ堅牢な N チャネル MOSFET ドライバで す。ハーフブリッジまたは同期整流降圧構成に基づくトポ ロジで 2 つの N チャネル MOSFET を制御できます。 UCC27282-Q1 はピーク・ソースおよびシンク電流が 3A であり、プルアップおよびプルダウン抵抗も小さいため、 MOSFET のミラー・プラトー遷移中のスイッチング損失を 最小限に抑えて大電力 MOSFET を駆動できます。各入 力が電源電圧と無関係であるため、UCC27282-Q1 はア ナログ・コントローラともデジタル・コントローラとも組み合わ せて使用できます。

入力ピンと HS ピンは大きな負の電圧に耐えられるため、 システムの堅牢性が強化されます。入力インターロックに より、ノイズの大きなアプリケーションにおいて、さらに堅牢 性とシステムの信頼性が向上します。イネーブルおよびデ ィスエーブル機能により、ドライバの消費電力を低減するこ とでシステムの柔軟性をさらに高めることができ、システム 内のフォルト・イベントに応答できます。5V UVLO により、 システムは低いバイアス電圧で動作できます。これは多く の高周波数アプリケーションに不可欠で、特定の動作モ ードでシステム効率を向上できます。伝搬遅延が短く、遅 延マッチング仕様によりデッドタイムの要件が最小化され るため、さらに効率が向上します。

ハイサイドとローサイド両方のドライバ段に低電圧誤動作 防止 (UVLO) 機能があり、VDD 電圧が指定のスレッショ ルドを下回ると、出力が強制的に LOW になります。内蔵 のブートストラップ・ダイオードにより、多くのアプリケーショ ンでは別の外付けダイオードが不要になるため、基板面 積の削減とシステム・コストの低減に役立ちます。 UCC27282-Q1 は小型のパッケージで供給されるため、 高密度の設計が可能です。

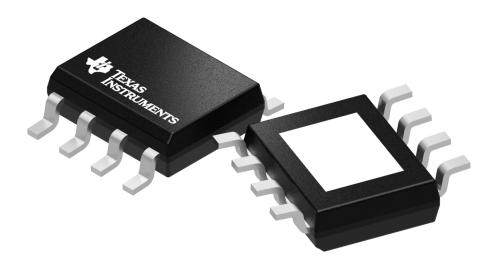

**制品情報**(1)

| 2           | 表明IFTX \/                  |  |  |  |  |  |

|-------------|----------------------------|--|--|--|--|--|

| 部品番号        | パッケージ (記号) (サイズ)           |  |  |  |  |  |

| UCC27282-Q1 | SON10 (DRC) (3mm x 3mm)    |  |  |  |  |  |

|             | SOIC8 (D) (6mm x 5mm)      |  |  |  |  |  |

|             | SOIC8-PP (DDA) (6mm x 5mm) |  |  |  |  |  |

利用可能なパッケージについては、このデータシートの末尾にあ (1) る注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

### **Table of Contents**

| 1 | 特長1                                   |     |

|---|---------------------------------------|-----|

|   | アプリケーション1                             |     |

| 3 | 概要1                                   |     |

| 4 | Revision History                      |     |

| 5 | Pin Configuration and Functions       | 5   |

| 6 | Specifications4                       | ł   |

|   | 6.1 Absolute Maximum Ratings4         | ÷   |

|   | 6.2 ESD Ratings 4                     | ÷   |

|   | 6.3 Recommended Operating Conditions4 | ÷   |

|   | 6.4 Thermal Information5              | ĵ.  |

|   | 6.5 Electrical Characteristics5       |     |

|   | 6.6 Switching Characteristics6        |     |

|   | 6.7 Timing Diagrams7                  |     |

|   | 6.8 Typical Characteristics7          |     |

| 7 | Detailed Description13                |     |

|   | 7.1 Overview13                        | )   |

|   | 7.2 Functional Block Diagram13        | i - |

| 7.3 Feature Description                               | .13  |

|-------------------------------------------------------|------|

| 7.4 Device Functional Modes                           | .16  |

| 8 Application and Implementation                      | . 17 |

| 8.1 Application Information                           | 17   |

| 8.2 Typical Application                               |      |

| 9 Power Supply Recommendations                        |      |

| 10 Layout                                             | .27  |

| 10.1 Layout Guidelines                                | 27   |

| 10.2 Layout Example                                   |      |

| 11 Device and Documentation Support                   | .28  |

| 11.1 Third-Party Products Disclaimer                  | 28   |

| 11.2 Receiving Notification of Documentation Updates. | .28  |

| 11.3 サポート・リソース                                        | .28  |

| 11.4 Trademarks                                       |      |

| 11.5 Electrostatic Discharge Caution                  | .28  |

| 11.6 Glossary                                         |      |

|                                                       |      |

#### **4 Revision History**

| Changes from Revision C (May 2022) to Revision D (October 2022)                                   | Page      |

|---------------------------------------------------------------------------------------------------|-----------|

| • 機能安全対応のリンクを追加                                                                                   | 1         |

| Changes from Revision B (March 2021) to Revision C (May 2022)                                     | Page      |

| Updated typcal peak pullup/pulldown current from +2.5A/-3.5A to ±3A in Electrical Characteristics | 5         |

|                                                                                                   | · · · · – |

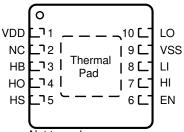

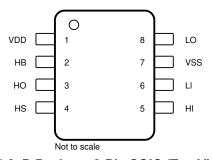

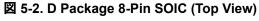

#### **5** Pin Configuration and Functions

Not to scale

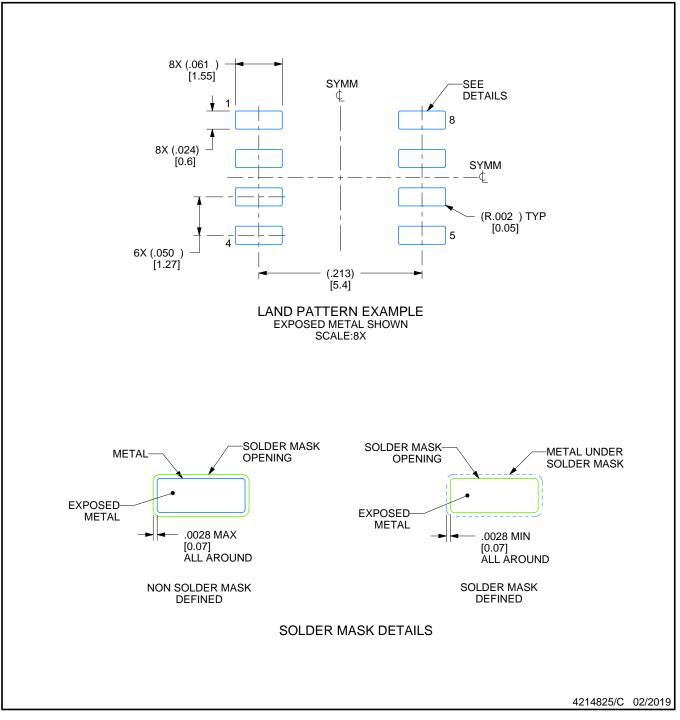

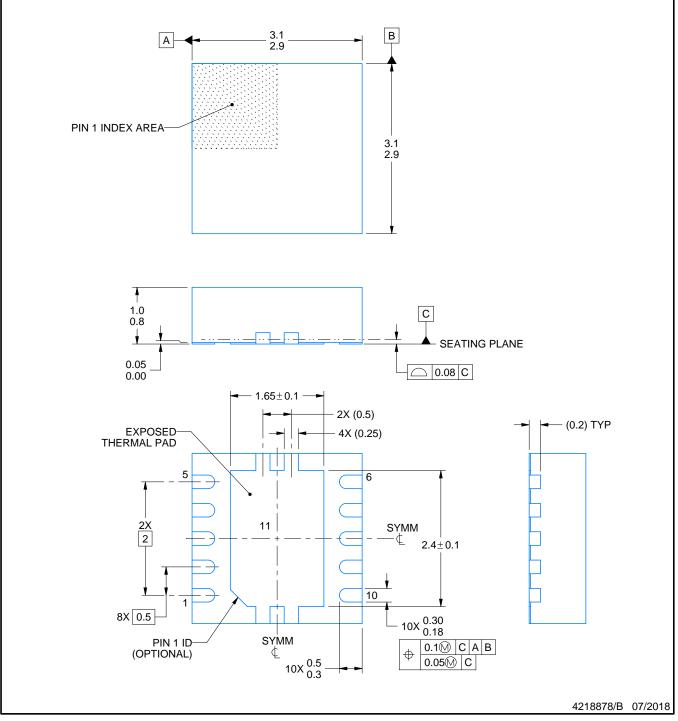

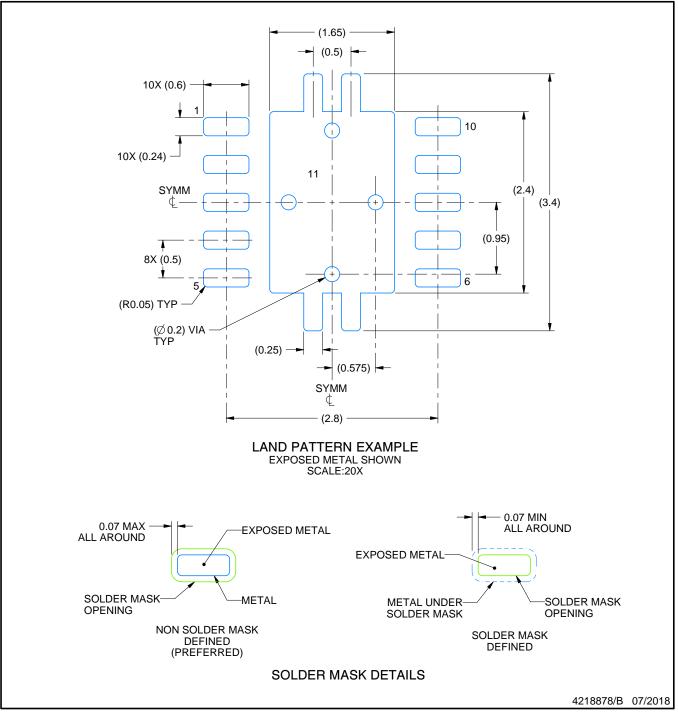

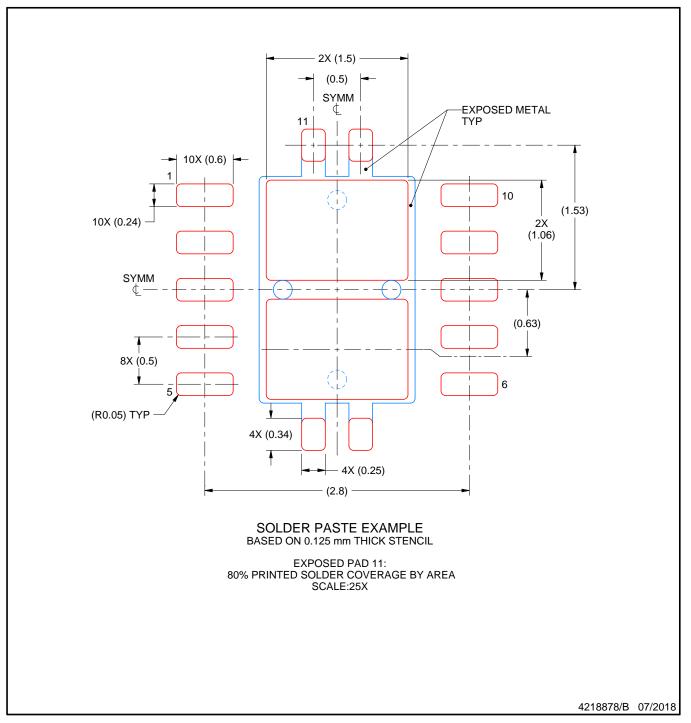

#### 図 5-1. DRC Package 10-Pin VSON With Exposed **Thermal Pad (Top View)**

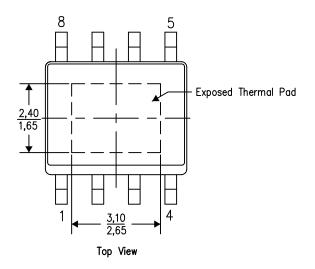

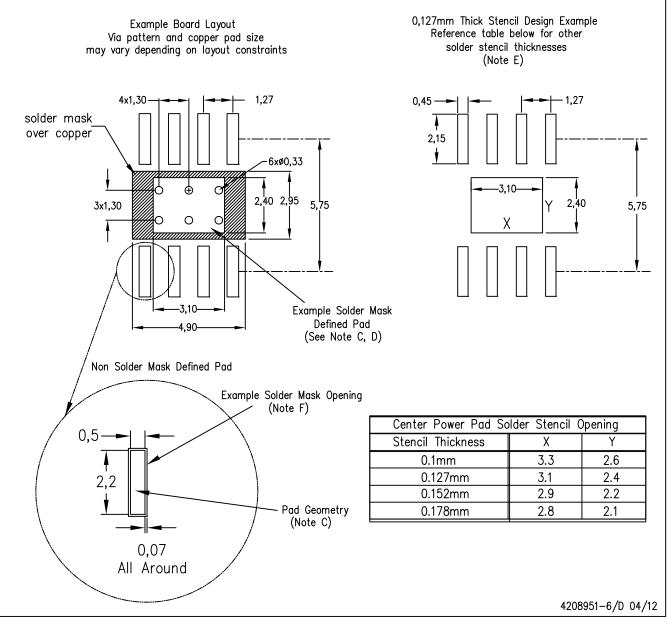

図 5-3. DDA Package 8-Pin SOIC With Exposed Thermal Pad (Top View)

| 表 5-1. Pin Functions | 表 5-1 | . Pin | Funct | tions |

|----------------------|-------|-------|-------|-------|

|----------------------|-------|-------|-------|-------|

| PIN         |     |     |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------|-----|-----|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name        | DDA | D   | DRC |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |  |

| EN          | n/a | n/a | 6   | I                  | Enable input. When this pin is pulled high, it will enable the driver. If left floating or pulled low, it will disable the driver. 1 nF filter capacitor is recommended for high-noise systems.                                                                                                                                                                                                |  |

| HB          | 2   | 2   | 3   | Р                  | High-side bootstrap supply. The bootstrap diode is on-chip but the external bootstrap capacitor is required. Connect positive side of the bootstrap capacitor to this pin. Typical recommended value of HB bypass capacitor is 0.1 $\mu$ F, This value primarily depends on the gate charge of the high-side MOSFET. When using external boot diode, connect cathode of the diode to this pin. |  |

| HI          | 5   | 5   | 7   | I                  | High-side input.                                                                                                                                                                                                                                                                                                                                                                               |  |

| НО          | 3   | 3   | 4   | 0                  | High-side output. Connect to the gate of the high-side power MOSFET or one end of external gate resistor, when used.                                                                                                                                                                                                                                                                           |  |

| HS          | 4   | 4   | 5   | Р                  | High-side source connection. Connect to source of high-side power MOSFET.<br>Connect negative side of bootstrap capacitor to this pin.                                                                                                                                                                                                                                                         |  |

| LI          | 6   | 6   | 8   | I                  | Low-side input                                                                                                                                                                                                                                                                                                                                                                                 |  |

| LO          | 8   | 8   | 10  | 0                  | Low-side output. Connect to the gate of the low-side power MOSFET or one end of external gate resistor, when used.                                                                                                                                                                                                                                                                             |  |

| NC          | n/a | n/a | 2   | —                  | Not connected internally.                                                                                                                                                                                                                                                                                                                                                                      |  |

| VDD         | 1   | 1   | 1   | Р                  | Positive supply to the low-side gate driver. Decouple this pin to VSS. Typical decoupling capacitor value is 1 $\mu$ F. When using an external boot diode, connect the anode to this pin.                                                                                                                                                                                                      |  |

| VSS         | 7   | 7   | 9   | G                  | Negative supply terminal for the device which is generally the system ground.                                                                                                                                                                                                                                                                                                                  |  |

| Thermal pad | _   | n/a | _   | _                  | Connect to a large thermal mass trace (generally IC ground plane) to improve thermal performance. This can only be electrically connected to VSS.                                                                                                                                                                                                                                              |  |

(1) P = Power, G = Ground, I = Input, O = Output, I/O = Input/Output

#### 6 Specifications 6.1 Absolute Maximum Ratings

All voltages are with respect to  $V_{ss}$  <sup>(1)</sup> <sup>(2)</sup>

|                                                     |                                  |                                | MIN                   | MAX                   | UNIT |

|-----------------------------------------------------|----------------------------------|--------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>                                     | Supply voltage                   |                                | -0.3                  | 20                    | V    |

| V <sub>EN</sub> , V <sub>HI</sub> , V <sub>LI</sub> | Input voltages on EN, HI and LI  |                                | -5                    | 20                    | V    |

| V                                                   | Output voltage on LO DC Pulses   | DC                             | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>LO</sub>                                     |                                  | Pulses < 100 ns <sup>(3)</sup> | -2                    | V <sub>DD</sub> + 0.3 | v    |

| V <sub>HO</sub>                                     | Output voltage on HO             | DC                             | V <sub>HS</sub> – 0.3 | V <sub>HB</sub> + 0.3 | V    |

|                                                     |                                  | Pulses < 100 ns <sup>(3)</sup> | V <sub>HS</sub> – 2   | V <sub>HB</sub> + 0.3 | v    |

| M                                                   | Voltage on HS                    | DC                             | -10                   | 100                   | V    |

| V <sub>HS</sub>                                     |                                  | Pulses < 100 ns <sup>(3)</sup> | -14                   | 100                   | v    |

| V <sub>HB</sub>                                     | Voltage on HB                    | <u>'</u>                       | -0.3                  | 120                   | V    |

| V <sub>HB-HS</sub>                                  | Voltage on HB with respect to HS | 3                              | -0.3                  | 20                    | V    |

| TJ                                                  | Operating junction temperature   |                                | -40                   | 150                   | °C   |

|                                                     | Lead temperature (soldering, 10  | sec.)                          |                       | 300                   | °C   |

| T <sub>stg</sub>                                    | Storage temperature              |                                | -65                   | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltages are with respect to V<sub>ss</sub>. Currents are positive into, negative out of the specified terminal.

(3) Values are verified by characterization only.

#### 6.2 ESD Ratings

|  |                                            |                         |                                                             | VALUE | UNIT |

|--|--------------------------------------------|-------------------------|-------------------------------------------------------------|-------|------|

|  | V <sub>(ESD)</sub> Electrostatic discharge | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1) (2)</sup> | ±2000 | V    |

|  |                                            | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011                | ±1500 | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification...

(2) Pins HS, HB and HO are rated at 500V HBM

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                     | <u> </u>                                       | MIN                   | NOM | MAX                  | UNIT |

|-----------------------------------------------------|------------------------------------------------|-----------------------|-----|----------------------|------|

| V <sub>DD</sub>                                     | Supply voltage                                 | 5.5                   | 12  | 16                   | V    |

| V <sub>EN</sub> , V <sub>HI</sub> , V <sub>LI</sub> | Input Voltage                                  | 0                     |     | V <sub>DD</sub> +0.3 |      |

| V <sub>LO</sub>                                     | Low side output voltage                        | 0                     |     | V <sub>DD</sub> +0.3 |      |

| V <sub>HO</sub>                                     | High side output voltage                       | V <sub>HS</sub>       |     | V <sub>HB</sub> +0.3 |      |

| V                                                   | Voltage on HS <sup>(1)</sup>                   | -8                    |     | 100                  | v    |

| V <sub>HS</sub>                                     | Voltage on HS (Pulses < 100 ns) <sup>(1)</sup> | -12                   |     | 100                  |      |

| V <sub>HB</sub>                                     | Voltage on HB                                  | V <sub>HS</sub> + 5.5 |     | V <sub>HS</sub> +16  | V    |

| V <sub>sr</sub>                                     | Voltage slew rate on HS                        |                       |     | 50                   | V/ns |

| TJ                                                  | Operating junction temperature                 | -40                   |     | 150                  | °C   |

(1)  $V_{HB-HS}$  < 16V (Voltage on HB with respect to HS must be less than 16V)

#### 6.4 Thermal Information

|                       |                                              | L      |        |         |      |

|-----------------------|----------------------------------------------|--------|--------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DDA    | D      | DRC     | UNIT |

|                       |                                              | 8 PINS | 8 PINS | 10 PINS |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 40.8   | 118.3  | 47.3    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 54.4   | 53.6   | 50.3    | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 16.4   | 63.1   | 21.3    | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 4.1    | 10.7   | 1.0     | °C/W |

| Ψ <sub>ЈВ</sub>       | Junction-to-board characterization parameter | 16.4   | 62.1   | 21.2    | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.9    | n/a    | 4.4     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### **6.5 Electrical Characteristics**

$V_{DD} = V_{HB} = V_{EN} = 12 \text{ V}, V_{HS} = V_{SS} = 0 \text{ V}$ , No load on LO or HO,  $T_J = -40^{\circ}\text{C}$  to +150°C, (unless otherwise noted)

|                     | PARAMETER                                                | TEST CONDITIONS                           | MIN | TYP  | MAX | UNIT |

|---------------------|----------------------------------------------------------|-------------------------------------------|-----|------|-----|------|

| SUPPLY              | CURRENTS                                                 |                                           |     |      |     |      |

| I <sub>DD</sub>     | VDD quiescent current                                    | $V_{LI} = V_{HI} = 0$                     |     | 0.3  | 0.4 | mA   |

| I <sub>DDO</sub>    | VDD operating current                                    | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 2.2  | 4.5 | mA   |

| I <sub>HB</sub>     | HB quiescent current                                     | V <sub>LI</sub> = V <sub>HI</sub> = 0 V   |     | 0.2  | 0.4 | mA   |

| I <sub>HBO</sub>    | HB operating current                                     | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 2.5  | 4   | mA   |

| I <sub>HBS</sub>    | HB to VSS quiescent current                              | V <sub>HS</sub> = V <sub>HB</sub> = 100 V |     | 5.0  | 50  | μA   |

| I <sub>HBSO</sub>   | HB to VSS operating current <sup>(1)</sup>               | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 0.1  |     | mA   |

| I <sub>DD_DIS</sub> | I <sub>DD</sub> when driver is disabled                  | V <sub>EN</sub> = 0                       |     | 7.0  |     | μA   |

| INPUT               |                                                          |                                           |     |      |     |      |

| V <sub>HIT</sub>    | Input rising threshold                                   |                                           | 1.9 | 2.1  | 2.4 | V    |

| V <sub>LIT</sub>    | Input falling threshold                                  |                                           | 0.9 | 1.1  | 1.3 | V    |

| VIHYS               | Input voltage Hysteresis                                 |                                           |     | 1.0  |     | V    |

| R <sub>IN</sub>     | Input pulldown resistance                                |                                           | 100 | 250  | 350 | kΩ   |

| ENABLE              |                                                          | 1                                         |     |      |     |      |

| V <sub>EN</sub>     | Voltage threshold on EN pin to enable the driver         |                                           |     | 1.54 | 2.0 | V    |

| V <sub>DIS</sub>    | Voltage threshold on EN pin to disable the driver        |                                           | 0.7 | 1.21 |     | V    |

| V <sub>ENHYS</sub>  | Enable pin Hysteresis                                    |                                           |     | 0.3  |     | V    |

| R <sub>EN</sub>     | EN pin internal pull-down resistor                       |                                           |     | 250  |     | kΩ   |

| T <sub>EN</sub>     | Time to enable the driver once the EN pin is pulled high | V <sub>EN</sub> = 2V                      |     | 18   |     | μs   |

| T <sub>DIS</sub>    | Time to disable the driver once the EN pin is pulled low | V <sub>EN</sub> = 0V                      |     | 1.5  |     | μs   |

| UNDERV              | OLTAGE LOCKOUT PROTECTION (UVLO)                         |                                           |     |      |     |      |

| V <sub>DDR</sub>    | VDD rising threshold                                     |                                           | 4.7 | 5.0  | 5.4 | V    |

| V <sub>DDF</sub>    | VDD falling threshold                                    |                                           | 4.2 | 4.5  | 4.9 | V    |

| V <sub>DDHYS</sub>  | VDD threshold hysteresis                                 |                                           |     | 0.5  |     | V    |

| V <sub>HBR</sub>    | HB rising threshold with respect to HS pin               |                                           | 3.3 | 3.7  | 4.7 | V    |

| V <sub>HBF</sub>    | HB falling threshold with respect to HS pin              |                                           | 3.0 | 3.3  | 4.4 | V    |

| V <sub>HBHYS</sub>  | HB threshold hysteresis                                  |                                           |     | 0.3  |     | V    |

#### 6.5 Electrical Characteristics (continued)

V<sub>DD</sub> = V<sub>HB</sub> = V<sub>EN</sub> =12 V, V<sub>HS</sub> = V<sub>SS</sub> = 0 V, No load on LO or HO, T<sub>J</sub> = -40°C to +150°C, (unless otherwise noted)

|                  | PARAMETER                                   | TEST CONDITIONS                                     | MIN TYP | MAX  | UNIT |

|------------------|---------------------------------------------|-----------------------------------------------------|---------|------|------|

| BOOTS            | TRAP DIODE                                  | I                                                   |         |      |      |

| V <sub>F</sub>   | Low-current forward voltage                 | I <sub>VDD-HB</sub> = 100 μA                        | 0.55    | 0.85 | V    |

| V <sub>FI</sub>  | High-current forward voltage                | I <sub>VDD-HB</sub> = 80 mA                         | 0.88    | 1.1  | V    |

| R <sub>D</sub>   | Dynamic resistance, $\Delta V_F / \Delta I$ | I <sub>VDD-HB</sub> = 100 mA and 80 mA              | 1.5     | 2.5  | Ω    |

| LO GAT           | TE DRIVER                                   |                                                     |         |      |      |

| V <sub>LOL</sub> | Low level output voltage                    | I <sub>LO</sub> = 100 mA                            | 0.085   | 0.4  | V    |

| V <sub>LOH</sub> | High level output voltage                   | $I_{LO}$ = -100 mA, $V_{LOH}$ = $V_{DD} - V_{LO}$   | 0.13    | 0.42 | V    |

|                  | Peak pullup current <sup>(1)</sup>          | V <sub>LO</sub> = 0 V                               | 3.0     |      | A    |

|                  | Peak pulldown current <sup>(1)</sup>        | V <sub>LO</sub> = 12 V                              | 3.0     |      | A    |

| HO GAT           | TE DRIVER                                   |                                                     |         |      |      |

| V <sub>HOL</sub> | Low level output voltage                    | I <sub>HO</sub> = 100 mA                            | 0.1     | 0.4  | V    |

| V <sub>HOH</sub> | High level output voltage                   | $I_{HO}$ = -100 mA, $V_{HOH}$ = $V_{HB}$ - $V_{HO}$ | 0.13    | 0.42 | V    |

|                  | Peak pullup current <sup>(1)</sup>          | V <sub>HO</sub> = 0 V                               | 3.0     |      | A    |

|                  | Peak pulldown current <sup>(1)</sup>        | V <sub>HO</sub> = 12 V                              | 3.0     |      | A    |

(1) Parameter not tested in production

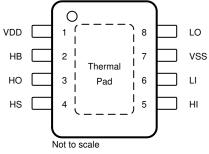

#### 6.6 Switching Characteristics

$V_{DD} = V_{HB} = 12 \text{ V}, V_{HS} = V_{SS} = 0 \text{ V}$ , No load on LO or HO,  $T_J = -40^{\circ}\text{C}$  to +150°C, (unless otherwise noted)

|                     | PARAMETER                                         | TEST CONDITIONS                                  | MIN | TYP  | MAX | UNIT |

|---------------------|---------------------------------------------------|--------------------------------------------------|-----|------|-----|------|

| PROPAG              | GATION DELAYS                                     |                                                  |     |      |     |      |

| t <sub>DLFF</sub>   | $V_{LI}$ falling to $V_{LO}$ falling              | See セクション 6.7                                    |     | 16   | 30  | ns   |

| t <sub>DHFF</sub>   | $V_{HI}$ falling to $V_{HO}$ falling              | See セクション 6.7                                    |     | 16   | 30  | ns   |

| t <sub>DLRR</sub>   | $V_{LI}$ rising to $V_{LO}$ rising                | See セクション 6.7                                    |     | 16   | 30  | ns   |

| t <sub>DHRR</sub>   | $V_{HI}$ rising to $V_{HO}$ rising                | See セクション 6.7                                    |     | 16   | 30  | ns   |

| DELAY N             | NATCHING                                          |                                                  |     |      |     |      |

| t <sub>MON</sub>    | From LO being ON to HO being OFF                  | See セクション 6.7                                    |     | 1    | 7   | ns   |

| t <sub>MOFF</sub>   | From LO being OFF to HO being ON                  | See セクション 6.7                                    |     | 1    | 7   | ns   |

| OUTPUT              | RISE AND FALL TIME                                |                                                  |     |      |     |      |

| t <sub>R</sub>      | LO, HO rise time                                  | C <sub>LOAD</sub> = 1800 pF, 10% to 90%          |     | 12   |     | ns   |

| t <sub>F</sub>      | LO, HO fall time                                  | C <sub>LOAD</sub> = 1800 pF, 90% to 10%          |     | 10   |     | ns   |

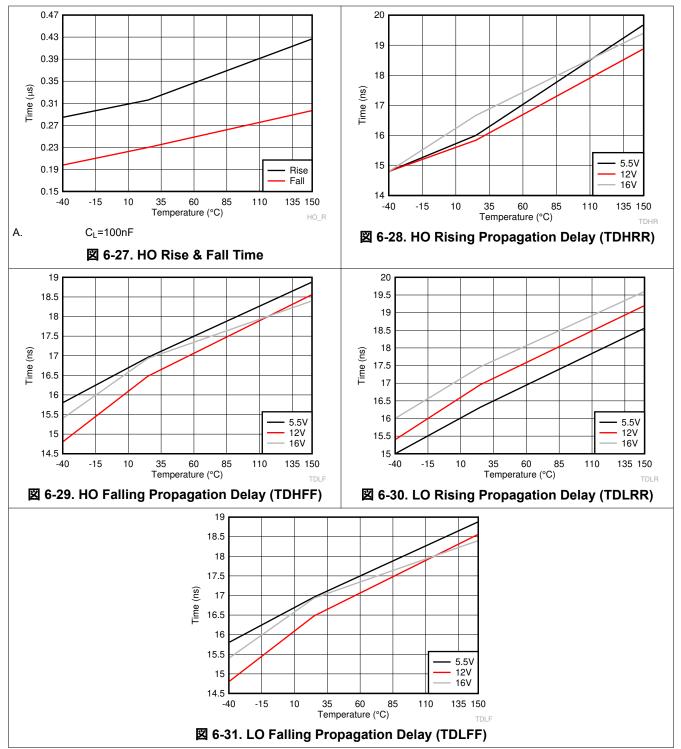

| t <sub>R</sub>      | LO, HO (3 V to 9 V) rise time                     | C <sub>LOAD</sub> = 0.1 μF, 30% to 70%           |     | 0.33 | 0.6 | μs   |

| t <sub>F</sub>      | LO, HO (3 V to 9 V) fall time                     | C <sub>LOAD</sub> = 0.1 μF, 70% to 30%           |     | 0.23 | 0.6 | μs   |

| MISCEL              | LANEOUS                                           |                                                  |     |      |     |      |

| T <sub>PW,min</sub> | Minimum input pulse width that changes the output |                                                  |     | 20   |     | ns   |

|                     | Bootstrap diode turnoff time <sup>(1)</sup>       | I <sub>F</sub> = 20 mA, I <sub>REV</sub> = 0.5 A |     | 50   |     | ns   |

(1) Parameter not tested in production

#### 6.7 Timing Diagrams

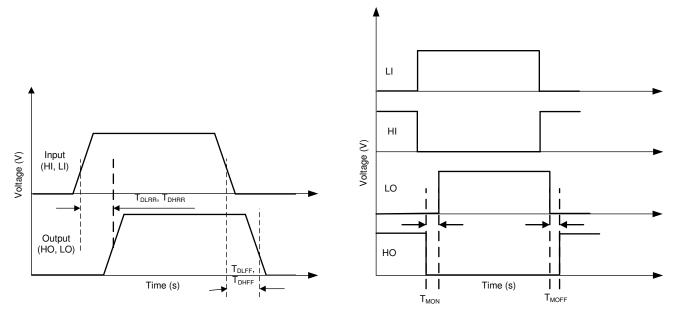

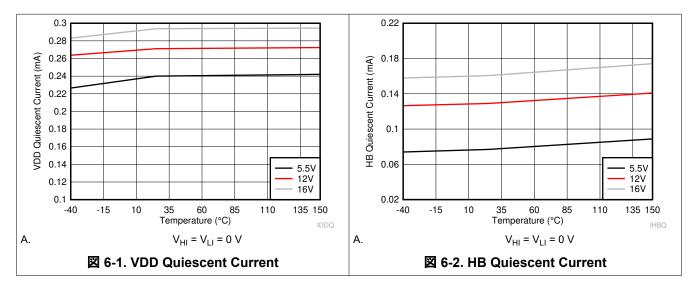

#### 6.8 Typical Characteristics

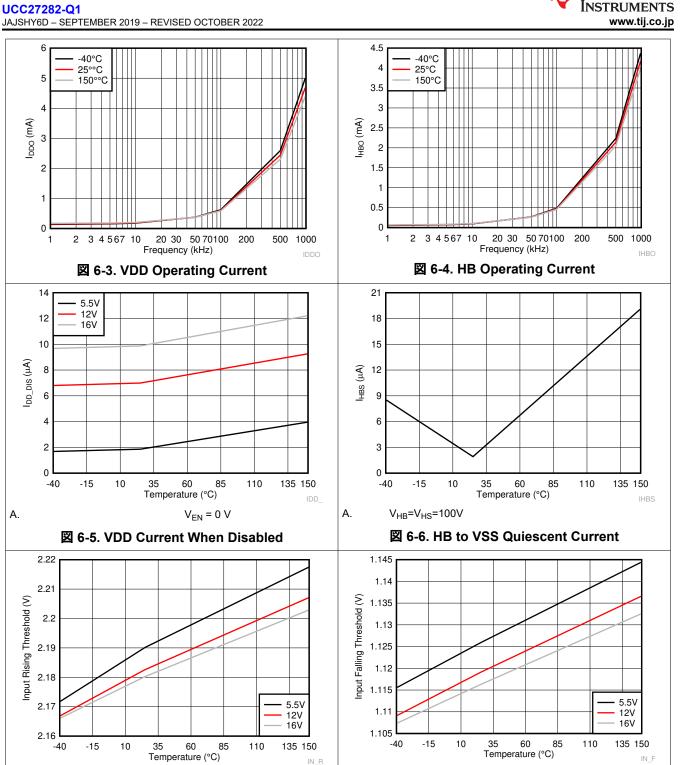

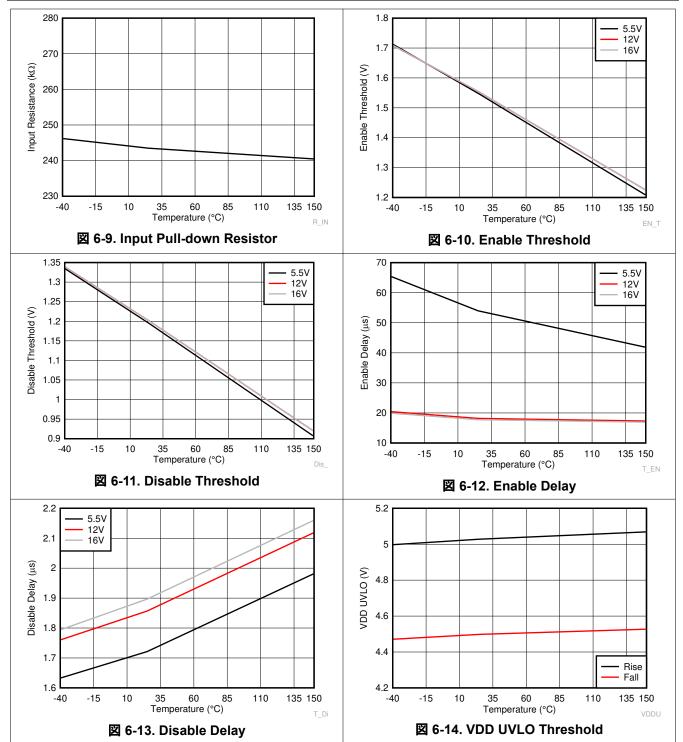

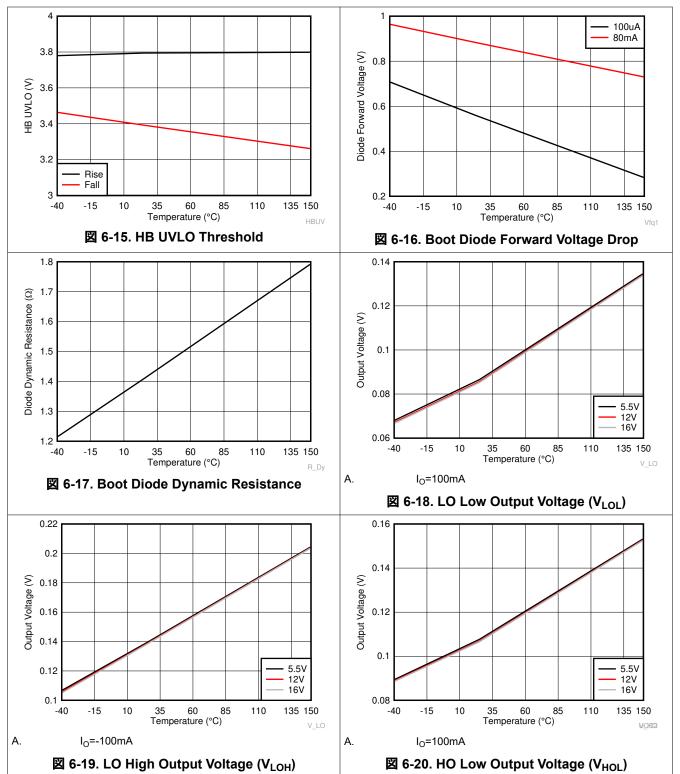

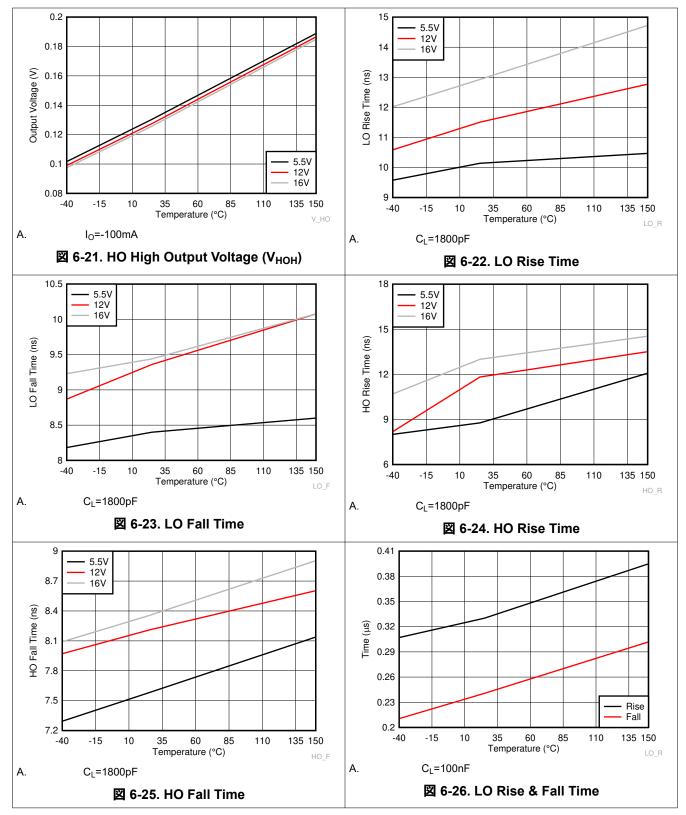

Unless otherwise specified  $V_{VDD}=V_{HB}$  = 12 V,  $V_{HS}=V_{VSS}$  = 0 V, No load on outputs

UCC27282-Q1

Α.

🛛 6-7. Input Rising Threshold

図 6-8. Input Falling Threshold

Texas

UCC27282-Q1 JAJSHY6D – SEPTEMBER 2019 – REVISED OCTOBER 2022

#### 7 Detailed Description

#### 7.1 Overview

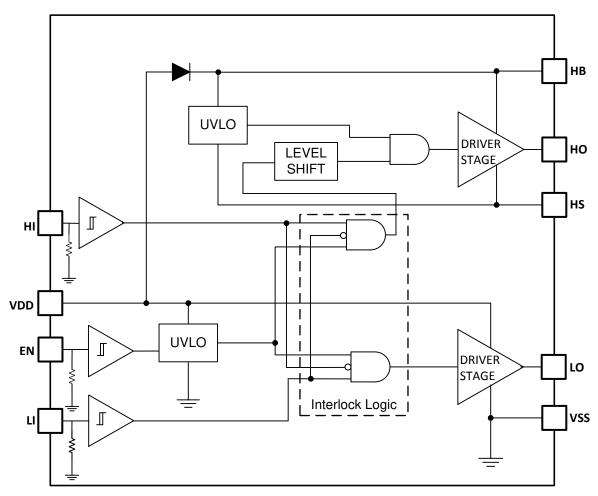

The UCC27282-Q1 is a high-voltage gate driver designed to drive both the high-side and the low-side N-channel FETs in a synchronous buck or a half-bridge configurations. The two outputs are independently controlled with two TTL-compatible input signals. The device can also work with CMOS type control signals at its inputs as long as signals meet turn-on and turn-off threshold specifications of the UCC27282-Q1. The floating high-side driver is capable of working with HS voltage up to 100 V with respect to VSS. A 100 V bootstrap diode is integrated in the UCC27282-Q1 device to charge high-side gate drive bootstrap capacitor. A robust level shifter operates at high speed while consuming low power and provides clean level transitions from the control logic to the high-side gate driver. Undervoltage lockout (UVLO) is provided on both the low-side and the high-side power rails. EN pin is provided (in DRC packaged parts) to enable or disable the driver. The driver also has input interlock functionality, which shuts off both the outputs when the two inputs overlap.

#### 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

#### 7.3 Feature Description

#### 7.3.1 Enable

The device in DRC package has an enable (EN) pin. The outputs will be active only if the EN pin voltage is above the threshold voltage. Outputs will be held low if EN pin is left floating or pulled-down to ground. An

internal 250 kΩ resistor connects EN pin to VSS pin. Thus, leaving the EN pin floating disables the device. Externally pulling EN pin to ground shall also disable the device. If the EN pin is not used, then it is recommended to connect it to VDD pin. If a pull-up resistor needs to be used then a strong pull-up resistor is recommended. For 12V supply voltage, a 10k $\Omega$  pull-up is suggested. In noise prone application, a small filter capacitor, 1nF, should be connected from the EN pin to VSS pin as close to the device as possible. An analog or a digital controller output pin could be connected to EN pin to enable or disable the device. Built-in hysteresis helps prevent any nuisance tripping or chattering of the outputs.

#### 7.3.2 Start-up and UVLO

Both the high-side and the low-side driver stages include UVLO protection circuitry which monitors the supply voltage (V<sub>DD</sub>) and the bootstrap capacitor voltage (V<sub>HB-HS</sub>). The UVLO circuit inhibits each output until sufficient supply voltage is available to turn on the external MOSFETs. The built-in UVLO hysteresis prevents chattering during supply voltage variations. When the supply voltage is applied to the VDD pin of the device, both the outputs are held low until VDD exceeds the UVLO threshold, typically 5 V. Any UVLO condition on the bootstrap capacitor ( $V_{HB-HS}$ ) disables only the high- side output (HO).

| Condition (V <sub>HB-HS</sub> > V <sub>HBR</sub> and V <sub>EN</sub> > Enable Threshold) | н | LI | НО | LO |

|------------------------------------------------------------------------------------------|---|----|----|----|

|                                                                                          | Н | L  | L  | L  |

| V = V = during device start up                                                           | L | Н  | L  | L  |

| V <sub>DD</sub> -V <sub>SS</sub> < V <sub>DDR</sub> during device start-up               | Н | Н  | L  | L  |

|                                                                                          | L | L  | L  | L  |

|                                                                                          | Н | L  | L  | L  |

| $\lambda = \lambda = \lambda = \lambda = \lambda$ ofter device start up                  | L | Н  | L  | L  |

| $V_{DD}$ - $V_{SS}$ < $V_{DDR}$ – $V_{DDH}$ after device start-up                        | Н | Н  | L  | L  |

|                                                                                          | L | L  | L  | L  |

| 表 7-1 | . VDD UVLO | Logic Operation |

|-------|------------|-----------------|

|-------|------------|-----------------|

| 表 7-2. HB UVLO Logic Operation                                                        |   |    |    |    |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|---|----|----|----|--|--|--|--|--|--|

| Condition (V <sub>DD</sub> > V <sub>DDR</sub> and V <sub>EN</sub> > Enable Threshold) | н | LI | НО | LO |  |  |  |  |  |  |

|                                                                                       | Н | L  | L  | L  |  |  |  |  |  |  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> during device start-up                          | L | Н  | L  | Н  |  |  |  |  |  |  |

|                                                                                       | Н | н  | L  | L  |  |  |  |  |  |  |

|                                                                                       | L | L  | L  | L  |  |  |  |  |  |  |

|                                                                                       | Н | L  | L  | L  |  |  |  |  |  |  |

|                                                                                       | L | Н  | L  | Н  |  |  |  |  |  |  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> – V <sub>HBH</sub> after device start-up        | Н | н  | L  | L  |  |  |  |  |  |  |

|                                                                                       | L | L  | L  | L  |  |  |  |  |  |  |

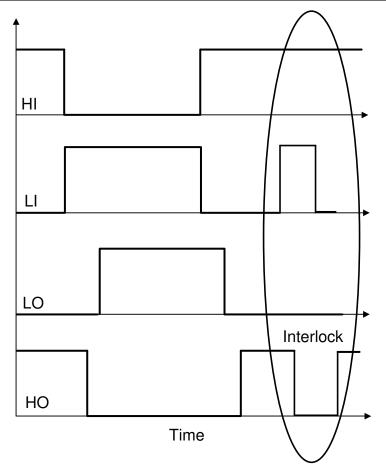

#### 7.3.3 Input Stages and Interlock

The two inputs operate independently, with an exception that both outputs will be pulled low when both inputs are high or overlap. The independence allows for full control of two outputs compared to the gate drivers that have a single input. The device has input interlock or cross-conduction protection. Whenever both the inputs are high, the internal logic turns both the outputs off. Once the device is in shoot-through mode, when one of the inputs goes low, the outputs follow the input logic. There is no other fixed time de-glitch filter implemented in the device and therefore propagation delay and delay matching are not sacrificed. In other words, there is no built-in dead-time due to the interlock feature. Any noise on the input that could cause the output to shoot-through will be filtered by this feature and the system stays protected. Because the inputs are independent of supply voltage, they can be connected to outputs of either digital controller or analog controller. Inputs can accept wide slew rate signals and input can withstand negative voltage to increase the robustness. Small filter at the inputs of the driver further improves system robustness in noise prone applications. The inputs have internal pull down resistors with typical value of 250 k $\Omega$ . Thus, when the inputs are floating, the outputs are held low.

図 7-1. Interlock or Input Shoot-through Protection

#### 7.3.4 Level Shifter

The level shift circuit is the interface from the high-side input, which is a VSS referenced signal, to the high-side driver stage which is referenced to the switch node (HS pin). The level shift allows control of the HO output which is referenced to the HS pin. The delay introduced by the level shifter is kept as low as possible and therefore the device provides excellent propagation delay characteristic and delay matching with the low-side driver output. Low delay matching allows power stages to operate with less dead time. The reduction in dead-time is very important in applications where high efficiency is required.

#### 7.3.5 Output Stage

The output stages are the interface from level shifter output to the power MOSFETs in the power train. High slew rate, low resistance, and high peak current capability of both outputs allow for efficient switching of the power MOSFETs. The low-side output stage is referenced to VSS and the high-side is referenced to HS. The device output stages are robust to handle harsh environment, such as -2 V transient for 100 ns. The device can also sustain positive transients on the outputs. The device output stages feature a pull-up structure which delivers the highest peak source current when it is most needed, during the Miller plateau region of the power switch turn on transition. The output pull-up and pull-down structure of the device is totem pole NMOS-PMOS structure.

#### 7.3.6 Negative Voltage Transients

In most applications, the body diode of the external low-side power MOSFET clamps the HS node to ground. In some situations, board capacitances and inductances can cause the HS node to transiently swing several volts below ground, before the body diode of the external low-side MOSFET clamps this swing. When used in conjunction with the UCC27282-Q1, the HS node can swing below ground as long as specifications are not violated and conditions mentioned in this section are followed.

HS must always be at a lower potential than HO. Pulling HO more negative than specified conditions can activate parasitic transistors which may result in excessive current flow from the HB supply. This may result in damage to the device. The same relationship is true with LO and VSS. If necessary, a Schottky diode can be placed externally between HO and HS or LO and VSS to protect the device from this type of transient. The diode must be placed as close to the device pins as possible in order to be effective.

Ensure that the HB to HS operating voltage is 16 V or less. Hence, if the HS pin transient voltage is –5 V, then VDD (and thus HB) is ideally limited to 11 V to keep the HB to HS voltage below 16 V. Generally when HS swings negative, HB follows HS instantaneously and therefore the HB to HS voltage does not significantly overshoot.

Low ESR bypass capacitors from HB to HS and from VDD to VSS are essential for proper operation of the gate driver device. The capacitor should be located at the leads of the device to minimize series inductance. The peak currents from LO and HO can be quite large. Any series inductances with the bypass capacitor causes voltage ringing at the leads of the device which must be avoided for reliable operation.

Based on application board design and other operating parameters, along with HS pin, other pins such as inputs, HI and LI, might also transiently swing below ground. To accommodate such operating conditions UCC27282-Q1 input pins are capable of handling absolute maximum of -5V. As explained earlier, based on the layout and other design constraints, some times the outputs, HO and LO, might also see transient voltages for short durations. Therefore, UCC27282-Q1 gate drivers can also handle -2 V 100 ns transients on output pins, HO and LO.

#### 7.4 Device Functional Modes

When the device is enabled, the device operates in normal mode and UVLO mode. See  $222 \times 7.3.2$  for more information on UVLO operation mode. In normal mode when the V<sub>DD</sub> and V<sub>HB-HS</sub> are above UVLO threshold, the output stage is dependent on the states of the EN, HI and LI pins. The output HO and LO will be low if input state is floating.

| EN       | н        | LI       | HO <sup>(1)</sup> | LO <sup>(2)</sup> |  |  |  |  |  |  |  |

|----------|----------|----------|-------------------|-------------------|--|--|--|--|--|--|--|

|          | Н        | Н        | L                 | L                 |  |  |  |  |  |  |  |

| 1        | L        | Н        | L                 | L                 |  |  |  |  |  |  |  |

| L        | Н        | L        | L                 | L                 |  |  |  |  |  |  |  |

|          | L        | L        | L                 | L                 |  |  |  |  |  |  |  |

|          | Н        | Н        | L                 | L                 |  |  |  |  |  |  |  |

| н        | L        | Н        | L                 | Н                 |  |  |  |  |  |  |  |

| п        | Н        | L        | Н                 | L                 |  |  |  |  |  |  |  |

|          | L        | L        | L                 | L                 |  |  |  |  |  |  |  |

|          | Floating | L        | L                 | L                 |  |  |  |  |  |  |  |

| н        | Floating | Н        | L                 | Н                 |  |  |  |  |  |  |  |

|          | L        | Floating | L                 | L                 |  |  |  |  |  |  |  |

|          | Н        | Floating | Н                 | L                 |  |  |  |  |  |  |  |

| Floating | Floating | Floating | L                 | L                 |  |  |  |  |  |  |  |

表 7-3. Input/Output Logic in Normal Mode of Operation

(1) HO is measured with respect to HS

(2) LO is measured with respect to VSS

#### 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

Most electronic devices and applications are becoming more and more power hungry. These applications are also reducing in overall size. One way to achieve both high power and low size is to improve the efficiency and distribute the power loss optimally. Most of these applications employ power MOSFETs and they are being switched at higher and higher frequencies. To operate power MOSFETs at high switching frequencies and to reduce associated switching losses, a powerful gate driver is employed between the PWM output of controller and the gates of the power semiconductor devices, such as power MOSFETs, IGBTs, SiC FETs, and GaN FETs. Many of these applications require proper UVLO protection so that power semiconductor devices are turned ON and OFF optimally. Also, gate drivers are indispensable when it is impossible for the PWM controller to directly drive the gates of the switching devices. With the advent of digital power, this situation is often encountered because the PWM signal from the digital controller is often a 3.3-V logic signal which cannot effectively turn on a power switch. A level-shift circuit is needed to boost the 3.3-V signal to the gate-drive voltage (such as 12 V or 5 V) in order to fully turn-on the power device, minimize conduction losses, and minimize the switching losses. Traditional buffer drive circuits based on NPN/PNP bipolar transistors in totem-pole arrangement prove inadequate with digital power because they lack level-shifting capability and under voltage lockout protection. Gate drivers effectively combine both the level-shifting and buffer-drive functions. Gate drivers also solve other problems such as minimizing the effect of high-frequency switching noise (by placing the high-current driver device physically close to the power switch), driving gate-drive transformers and controlling floating power device gates. This helps reduce power dissipation and thermal stress in controllers by moving gate charge power losses from the controller IC to the gate driver.

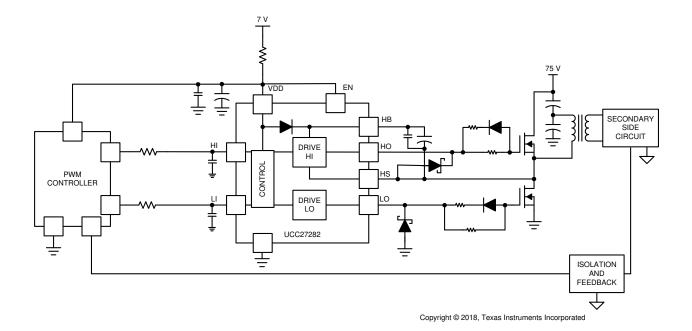

UCC27282-Q1 gate drivers offer high voltage (100 V), small delays (16 ns), and good driving capability (±3-A) in a single device. The floating high-side driver is capable of operating with switch node voltages up to 100 V. This allows for N-channel MOSFETs control in half-bridge, full-bridge, synchronous buck, synchronous boost, and active clamp topologies. UCC27282-Q1 gate driver IC also has built-in bootstrap diode to help power supply designers optimize PWB area and to help reduce bill of material cost in most applications. The driver has an enable/disable functionality to be used in applications where driver needs to be enabled or disabled based on fault condition in other parts of the circuit. Interlock functionality of the device is very useful in applications where overall reliability of the system is of utmost criteria and redundant protection is desired. Each channel is controlled by its respective input pins (HI and LI), allowing flexibility to control ON and OFF state of the output. Both the outputs are forced OFF when the two inputs overlap.

Switching power devices such as MOSFETs have two main loss components; switching losses and conduction losses. Conduction loss is dominated by current through the device and ON resistance of the device. Switching losses are dominated by gate charge of the switching device, gate voltage of the switching device, and switching frequency. Applications where operating switching frequency is very high, the switching losses start to significantly impact overall system efficiency. In such applications, to reduce the switching losses it becomes essential to reduce the gate voltage. The gate voltage is determined by the supply voltage the gate driver ICs, therefore, the gate driver IC needs to operate at lower supply voltage in such applications. UCC27282-Q1 gate driver has typical UVLO level of 5V and therefore, they are perfectly suitable for such applications. There is enough UVLO hysteresis provided to avoid any chattering or nuisance tripping which improves system robustness.

#### 8.2 Typical Application

#### 8-1. Typical Application

#### 8.2.1 Design Requirements

Table below lists the system parameters. UCC27282-Q1 needs to operate satisfactorily in conjunction with them.

#### 表 8-1. Design Requirements

| Parameter                                              | Value       |

|--------------------------------------------------------|-------------|

| MOSFET                                                 | CSD19535KTT |

| Maximum Bus/Input Voltage, V <sub>in</sub>             | 75V         |

| Operating Bias Votage, V <sub>DD</sub>                 | 7V          |

| Switching Frequency, Fsw                               | 300kHz      |

| Total Gate Charge of FET at given VDD, $Q_G$           | 52nC        |

| MOSFET Internal Gate Resistance, R <sub>GFET_Int</sub> | 1.4         |

| Maximum Duty Cycle, D <sub>Max</sub>                   | 0.5         |

| Gate Driver                                            | UCC27282-Q1 |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Select Bootstrap and VDD Capacitor

The bootstrap capacitor must maintain the V<sub>HB-HS</sub> voltage above the UVLO threshold for normal operation. Calculate the maximum allowable drop across the bootstrap capacitor,  $\Delta V_{HB}$ , with  $\neq 1$ .

$$\Delta V_{HB} = V_{DD} - V_{DH} - V_{HBL}$$

= (7 V - 1 V - (4.4 V - 0.37 V)) = 1.97 V

where

- V<sub>DD</sub> is the supply voltage of gate driver device

- V<sub>DH</sub> is the bootstrap diode forward voltage drop

- $V_{HBL}$  is the HB falling threshold (  $V_{HBR(max)} V_{HBH}$ )

In this example the allowed voltage drop across bootstrap capacitor is 1.97 V.

It is generally recommended that ripple voltage on both the bootstrap capacitor and VDD capacitor should be minimized as much as possible. Many of commercial, industrial, and automotive applications use ripple value of 0.5 V.

Use  $\neq$  2 to estimate the total charge needed per switching cycle from bootstrap capacitor.

$$Q_{\text{TOTAL}} = Q_{\text{G}} + I_{\text{HBS}} \times \left(\frac{D_{\text{MAX}}}{f_{\text{SW}}}\right) + \left(\frac{I_{\text{HB}}}{f_{\text{SW}}}\right)$$

= 52 nC + 0.083 nC + 1.33 nC = 53.41 nC (2)

where

- Q<sub>G</sub> is the total MOSFET gate charge

- I<sub>HBS</sub> is the HB to VSS leakage current from datasheet

- D<sub>Max</sub> is the converter maximum duty cycle

- I<sub>HB</sub> is the HB quiescent current from the datasheet

The caculated total charge is 53.41 nC.

Next, use  $\neq 3$  to estimate the minimum bootstrap capacitor value.

$$C_{\text{BOOT (min)}} = \frac{Q_{\text{TOTAL}}}{\Delta V_{\text{HB}}} = \frac{53.41 \text{ nC}}{1.97 \text{ V}} = 27.11 \text{ nF}$$

(3)

The calculated value of minimum bootstrap capacitor is 27.11 nF. It should be noted that, this value of capacitance is needed at full bias voltage. In practice, the value of the bootstrap capacitor must be greater than calculated value to allow for situations where the power stage may skip pulse due to various transient conditions. It is recommended to use a 100-nF bootstrap capacitor in this example. It is also recommenced to include enough margin and place the bootstrap capacitor as close to the HB and HS pins as possible. Also place a small size, 0402, low value, 1000 pF, capacitor to filter high frequency noise, in parallel with main bypass capacitor.

For this application, choose a  $C_{BOOT}$  capacitor that has the following specifications: 0.1  $\mu$ F, 25 V, X7R

As a general rule the local VDD bypass capacitor must be greater than the value of bootstrap capacitor value (generally 10 times the bootstrap capacitor value). For this application choose a  $C_{VDD}$  capacitor with the following specifications: 1  $\mu$ F, 25 V, X7R

$C_{VDD}$  capacitor is placed across VDD and VSS pin of the gate driver. Similar to bootstrap capacitors, place a small size and low value capacitor in parallel with the main bypass capacitor. For this application, choose 0402, 1000 pF, capacitance in parallel with main bypass capacitor to filter high frequency noise.

The bootstrap and bias capacitors must be ceramic types with X7R dielectric or better. Choose a capacitor with a voltage rating at least twice the maximum voltage that it will be exposed to. Choose this value because most ceramic capacitors lose significant capacitance when biased. This value also improves the long term reliability of the system.

#### 8.2.2.2 Estimate Driver Power Losses

The total power loss in gate driver device such as the UCC27282-Q1 is the summation of the power loss in different functional blocks of the gate driver device. These power loss components are explained in this section.

1.  $rac{d}{d}$  4 describes how quiescent currents (I<sub>DD</sub> and I<sub>HB</sub>) affect the static power losses, P<sub>QC</sub>.

$$P_{QC} = (V_{DD} \times I_{DD}) + (V_{DD} - V_{DH}) \times I_{HB}$$

= 7 V × 0.4 mA + 6 V × 0.4 mA = 5.2 mW

it is not shown here, but for better approximation, add no load operating current,  $I_{DDO}$  and  $I_{HBO}$  in above equation.

(4)

2. 式 5 shows how high-side to low-side leakage current (I<sub>HBS</sub>) affects level-shifter losses (P<sub>IHBS</sub>).

$$P_{\text{IHBS}} = V_{\text{HB}} \times I_{\text{HBS}} \times D = 82 \text{ V} \times 50 \text{ }\mu\text{A} \times 0.5 = 2.05 \text{ }\text{mW}$$

where

- D is the high-side MOSFET duty cycle

- $V_{HB}$  is the sum of input voltage and voltage across bootstrap capacitor.

- 3.  $\neq$  6 shows how MOSFETs gate charge (Q<sub>G</sub>) affects the dynamic losses, P<sub>QG</sub>.

$$P_{QG} = 2 \times V_{DD} \times Q_G \times f_{SW} \times \frac{R_{GD_R}}{R_{GD_R} + R_{GATE} + R_{GFET (int)}}$$

$$= 2 \times 7 V \times 52 \text{ nC} \times 300 \text{ kHz} \times 0.74 = 0.16 \text{ W}$$

where

- Q<sub>G</sub> is the total MOSFET gate charge

- f<sub>SW</sub> is the switching frequency

- R<sub>GD R</sub> is the average value of pullup and pulldown resistor

- R<sub>GATE</sub> is the external gate drive resistor

- R<sub>GFET(int)</sub> is the power MOSFETs internal gate resistor

Assume there is no external gate resistor in this example. The average value of maximum pull-up and pull down resistance of the driver output section is approximately 4  $\Omega$ . Substitute the application values to calculate the dynamic loss due to gate charge, which is 160 mW here.

4.  $rac{1}{r}$  shows how parasitic level-shifter charge (Q<sub>P</sub>) on each switching cycle affects dynamic losses, (P<sub>LS</sub>) during high-side switching.

$$P_{LS} = V_{HB} \times Q_P \times f_{SW}$$

For this example and simplicity, it is assumed that value of parasitic charge Q<sub>P</sub> is 1 nC. Substituting values results in 24.6 mW as level shifter dynamic loss. This estimate is very high for level shifter dynamic losses.

The sum of all the losses is 191.85 mW as a total gate driver loss. As shown in this example, in most applications the dynamic loss due to gate charge dominates the total power loss in gate driver device. For gate drivers that include bootstrap diode, one should also estimate losses in bootstrap diode. Diode forward conduction loss is computed as product of average forward voltage drop and average forward current.

式 8 estimates the maximum allowable power loss of the device for a given ambient temperature.

$$P_{MAX} = \frac{(T_J - T_A)}{R_{\theta JA}}$$

where

- P<sub>MAX</sub> is the maximum allowed power dissipation in the gate driver device

- T<sub>J</sub> is the recommended maximum operating junction temperature

- T<sub>A</sub> is hte ambient temperature of the gate driver device

- $R_{\theta,IA}$  is the junction-to-ambient thermal resistance

To better estimate the junction temperature of the gate driver device in the application, it is recommended to first accurately measure the case temperature and then determine the power dissipation in a given application. Then use  $\psi_{JT}$  to calculate junction temperature. After estimating junction temperature and measuring ambient temperature in the application, calculate  $\theta_{JA(effective)}$ . Then, if design parameters (such as the value of an external gate resistor or power MOSFET) change during the development of the project, use  $\theta_{JA(effective)}$  to estimate how these changes affect junction temperature of the gate driver device.

For detailed information regarding the thermal information table, please refer to the *Semiconductor and Device Package Thermal Metrics* application report.

(5)

(6)

(7)

(8)

(9)

#### 8.2.2.3 Selecting External Gate Resistor

In high-frequency switching power supply applications where high-current gate drivers such as the UCC27282-Q1 are used, parasitic inductances, parasitic capacitances and high-current loops can cause noise and ringing on the gate of power MOSFETs. Often external gate resistors are used to damp this ringing and noise. In some applications the gate charge, which is load on gate driver device, is significantly larger than gate driver peak output current capability. In such applications external gate resistors can limit the peak output current of the gate driver. it is recommended that there should be provision of external gate resistor whenever the layout or application permits.

Use  $\neq$  9 to calculate the driver high-side pull-up current.

$$I_{OHH} = \frac{V_{DD} - V_{DH}}{R_{HOH} + R_{GATE} + R_{GFET(int)}}$$

where

- I<sub>OHH</sub> is the high-side, peak pull-up current

- V<sub>DH</sub> is the bootstrap diode forward voltage drop

- R<sub>HOH</sub> is the gate driver internal high-side pull-up resistor. Value either directly provided in datasheet or can be calculated from test conditions (R<sub>HOH</sub> = V<sub>HOH</sub>/I<sub>HO</sub>)

- R<sub>GATE</sub> is the external gate resistance connected between driver output and power MOSFET gate

- R<sub>GFET(int)</sub> is the MOSFET internal gate resistance provided by MOSFET datasheet

Use  $\neq$  10 to calculate the driver high-side sink current.

$$I_{OLH} = \frac{V_{DD} - V_{DH}}{R_{HOL} + R_{GATE} + R_{GFET(int)}}$$

(10)

where

• R<sub>HOL</sub> is the gate driver internal high-side pull-down resistance

Use  $\neq$  11 to calculate the driver low-side source current.

$$I_{OHL} = \frac{V_{DD}}{R_{LOH} + R_{GATE} + R_{GFET(int)}}$$

(11)

where

• R<sub>LOH</sub> is the gate driver internal low-side pull-up resistance

Use rightarrow 12 to calculate the driver low-side sink current.

$$I_{OLL} = \frac{V_{DD}}{R_{LOL} + R_{GATE} + R_{GFET(int)}}$$

(12)

where

• R<sub>LOL</sub> is the gate driver internal low-side pull-down resistance

Both high and low-side channels of the gate driver have a peak current rating of  $\pm 3$  A. These equations help reduce the peak current if needed. To establish different rise time value compared to fall time value, external gate resistor can be anti-paralleled with diode-resistor combination as shown in  $\boxtimes$  8-1. Generally selecting an optimal value or configuration of external gate resistor is an iterative process. For additional information on selecting external gate resistor please refer to External Gate Resistor Design Guide for Gate Drivers

#### 8.2.2.4 Delays and Pulse Width

The total delay encountered in the PWM, driver and power stage need to be considered for a number of reasons, primarily delay in current limit response. Also to be considered are differences in delays between the drivers which can lead to various concerns depending on the topology. The synchronous buck topology switching requires careful selection of dead-time between the high-side and low-side switches to avoid cross conduction as well as excessive body diode conduction.

Bridge topologies can be affected by a volt-second imbalance on the transformer if there is imbalance in the high-side and low-side pulse widths in any operating condition. The UCC27282-Q1 device has maximum propagation delay, across process, and temperature variation, of 30 ns and delay matching of 7 ns, which is one of the best in the industry.

Narrow input pulse width performance is an important consideration in gate driver devices, because output may not follow input signals satisfactorily when input pulse widths are very narrow. Although there may be relatively wide steady state PWM output signals from controller, very narrow pulses may be encountered under following operating conditions.

- soft-start period

- large load transients

- short circuit conditions

These narrow pulses appear as an input signal to the gate driver device and the gate driver device need to respond properly to these narrow signals.

⊠ 8-2 shows that the UCC27282-Q1 device produces reliable output pulse even when the input pulses are very narrow and bias voltages are very low. The propagation delay and delay matching do not get affected when the input pulse width is very narrow.

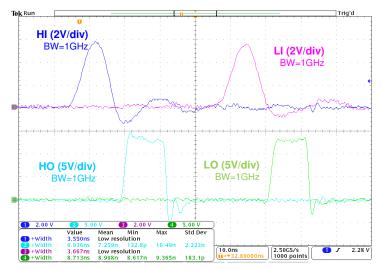

図 8-2. Input and Output Pulse Width

#### 8.2.2.5 External Bootstrap Diode

The UCC27282-Q1 incorporates the bootstrap diode necessary to generate the high-side bias for HO to work satisfactorily. The characteristics of this diode are important to achieve efficient, reliable operation. The characteristics to consider are forward voltage drop and dynamic resistance. Generally, low forward voltage drop diodes are preferred for low power loss during charging of the bootstrap capacitor. The device has a boot diode forward voltage drop rated at 0.85 V and dynamic resistance of 1.5  $\Omega$  for reliable charge transfer to the bootstrap capacitor. The dynamic characteristics to consider are diode recovery time and stored charge. Diode recovery times that are specified without operating conditions, can be misleading. Diode recovery times at no forward current (I<sub>F</sub>) can be noticeably less than with forward current applied. The UCC27282-Q1 boot diode recovery is specified as 50 ns at I<sub>F</sub> = 20 mA, I<sub>REV</sub> = 0.5 A. Dynamic impedance of UCC27282-Q1 bootstrap diode naturally

limits the peak forward current and prevents any damage if repetitive peak forward current pulses exist in the system for most applications.

In applications where switching frequencies are very high, for example in excess of 1 MHz, and the low-side minimum pulse widths are very small, the diode peak forward current could be very high and peak reverse current could also be very high, specifically if high bootstrap capacitor value has been chosen. In such applications it might be advisable to use external Schottkey diode as bootstrap diode. It is safe to at least make a provision for such diode on the board if possible.

#### 8.2.2.6 VDD and Input Filter

Some switching power supply applications are extremely noisy. Noise may come from ground bouncing and ringing at the inputs, (which are the HI and LI pins of the gate driver device). To mitigate such situations, the UCC27282-Q1 offers both negative input voltage handling capability and wide input threshold hysteresis. If these features are not enough, then the application might need an input filter. Small filter such as 10- $\Omega$  resistor and 47-pF capacitor might be sufficient to filter noise at the inputs of the gate driver device. This RC filter would introduce delay and therefore need to be considered carefully. High frequency noise on bias supply can cause problems in performance of the gate driver device. To filter this noise it is recommended to use 1- $\Omega$  resistor in series with VDD pin as shown in  $\mathbb{X}$  8-1. This resistor also acts as a current limiting element. In the event of short circuit on the bias rail, this resistor opens up and prevents further damage. This resistor can also be helpful in debugging the design during development phase.

#### 8.2.2.7 Transient Protection

As mentioned in previous sections, high power high switching frequency power supplies are inherently noisy. High dV/dt and dl/dt in the circuit can cause negative voltage on different pins such as HO, LO, and HS. The device tolerates negative voltage on all of these pins as mentioned in specification tables. If parasitic elements of the circuit cause very large negative swings, circuit might require additional protection. In such cases fast acting and low leakage type Schottky diode should be used. This diode must be placed as close to the gate driver device pin as possible for it to be effective in clamping excessive negative voltage on the gate driver device pin. Sometimes a small resistor, (for example 2  $\Omega$ , in series with HS pin) is also effective in improving performance reliability. To avoid the possibility of driver device damage due to over-voltage on its output pins or supply pins, low leakage Zener diode can be used. A 15-V Zener diode is often sufficient to clamp the voltage below the maximum recommended value of 16 V.

#### 8.2.3 Application Curves

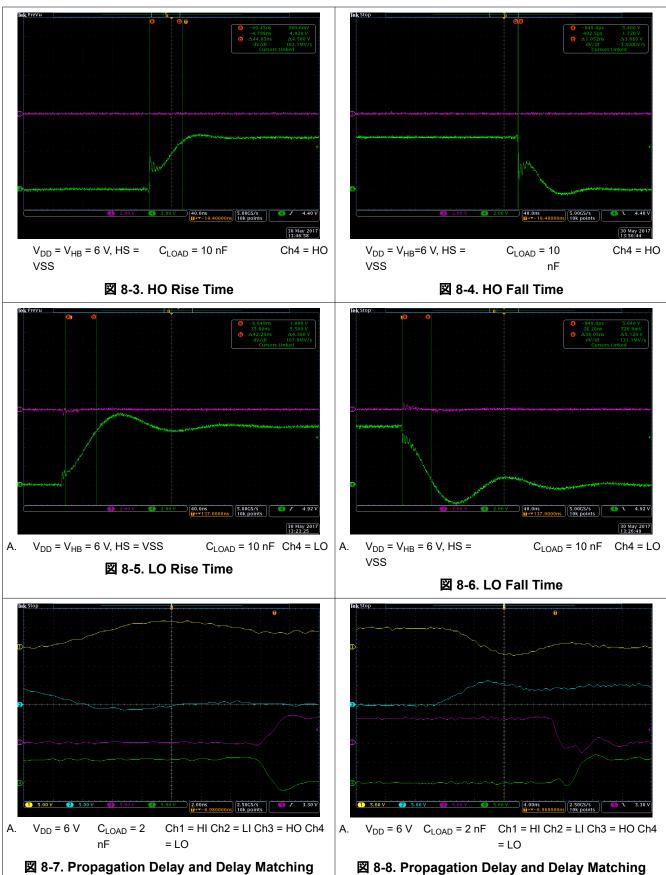

To minimize the switching losses in power supplies, turn-ON and turn-OFF of the power MOSFETs need to be as fast as possible. Higher the drive current capability of the driver, faster the switching. Therefore, the UCC27282-Q1 is designed with high drive current capability and low resistance of the output stages. One of the common way to test the drive capability of the gate driver device , is to test it under heavy load. Rise time and fall time of the outputs would provide idea of drive capability of the gate driver device. There must not be any resistance in this test circuit.  $\boxtimes$  8-3 and  $\boxtimes$  8-4 shows rise time and fall time of HO respectively of UCC27282-Q1.  $\boxtimes$  8-5 and  $\boxtimes$  8-6 shows rise time and fall time of LO respectively of UCC27282-Q1. For accuracy purpose, the VDD and HB pin of the gate driver device were connected together. HS and VSS pins are also connected together for this test.

Peak current capability can be estimated using the fastest dV/dt along the rise and fall curve of the plot. This method is also useful in comparing performance of two or more gate driver devices.

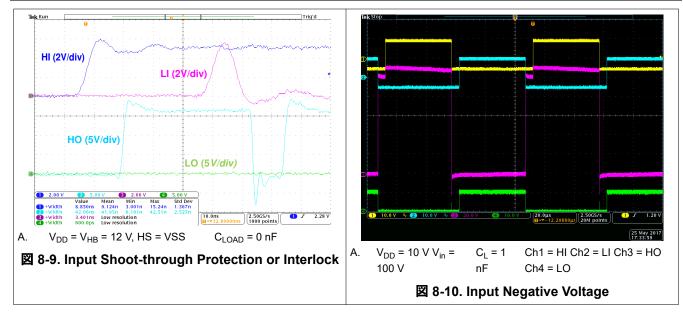

As explained in  $\forall 2 \neq 2 \geq 8.2.2.4$ , propagation delay plays an important role in reliable operation of many applications.  $\boxtimes$  8-7 and  $\boxtimes$  8-8

⊠ 8-8 shows propagation delay and delay matching of UCC27282-Q1. In many switching power supply applications input signals to the gate driver have large amplitude high frequency noise. If there is no filter employed at the input, then there is a possibility of false signal passing through the gate driver and causing shoot-through on the output. UCC27282-Q1 prevents such shoot-through. If two inputs are high at the same time, UCC27282-Q1 shuts both the outputs off. ⊠ 8-9 shows interlock feature of UCC27282-Q1 and ⊠ 8-10 shows input negative voltage handling capability of UCC27282-Q1.

#### UCC27282-Q1

JAJSHY6D - SEPTEMBER 2019 - REVISED OCTOBER 2022

#### UCC27282-Q1 JAJSHY6D – SEPTEMBER 2019 – REVISED OCTOBER 2022

#### 9 Power Supply Recommendations

The recommended bias supply voltage range for UCC27282-Q1 is from 5.5 V to 16 V. The lower end of this range is governed by the internal under voltage-lockout (UVLO) protection feature, 5 V typical, of the  $V_{DD}$  supply circuit block. The upper end of this range is driven by the 16-V recommended maximum voltage rating of the  $V_{DD}$ . It is recommended that voltage on VDD pin should be lower than maximum recommended voltage. In some transient condition it is not possible to keep this voltage below recommended maximum level and therefore absolute maximum voltage rating of the UCC27282-Q1 is 20 V.

The UVLO protection feature also involves a hysteresis function. This means that once the device is operating in normal mode, if the  $V_{DD}$  voltage drops, the device continues to operate in normal mode as far as the voltage drop do not exceeds the hysteresis specification,  $V_{DDHYS}$ . If the voltage drop is more than hysteresis specification, the device shuts down. Therefore, while operating at or near the 5.5-V range, the voltage ripple on the auxiliary power supply output should be smaller than the hysteresis specification of UCC27282-Q1 to avoid triggering device shutdown.

A local bypass capacitor should be placed between the VDD and GND pins. This capacitor should be located as close to the device as possible. A low ESR, ceramic surface mount capacitor is recommended. It is recommended to use two capacitors across VDD and GND: a low capacitance ceramic surface-mount capacitor for high frequency filtering placed very close to VDD and GND pin, and another high capacitance value surface-mount capacitor for device bias requirements. In a similar manner, the current pulses delivered by the HO pin are sourced from the HB pin. Therefore, two capacitors across the HB to HS are recommended. One low value small size capacitor for high frequency filtering and another one high capacitance value capacitor to deliver HO pulses.

UCC27282-Q1 has enable/disable functionality through EN pin. Therefore, signal at the EN pin should be as clean as possible. If EN pin is not used, then it is recommended to connect the pin to VDD pin. If EN pin is pulled up through a resistor, then the pull-up resistor needs to be strong. In noise prone applications, it is recommended to filter the EN pin with small capacitor, such as X7R 0402 1nF.

In power supplies where noise is very dominant and there is space on the PWB (Printed Wiring Board), it is recommended to place a small RC filter at the inputs. This allows for improving the overall performance of the design. In such applications, it is also recommended to have a place holder for power MOSFET external gate resistor. This resistor allows the control of not only the drive capability but also the slew rate on HS, which impacts the performance of the high-side circuit. If diode is used across the external gate resistor, it is recommended to use a resistor in series with the diode, which provides further control of fall time.

In power supply applications such as motor drives, there exist lot of transients through-out the system. This sometime causes over voltage and under voltage spikes on almost all pins of the gate driver device. To increase the robustness of the design, it is recommended that the clamp diode should be used on HO and LO pins. If user does not wish to use power MOSFET parasitic diode, external clamp diode on HS pin is recommended, which needs to be high voltage high current type (same rating as MOSFET) and very fast acting. The leakage of these diodes across the temperature needs to be minimal.

In power supply applications where it is almost certain that there is excessive negative HS voltage, it is recommended to place a small resistor between the HS pin and the switch node. This resistance helps limit current into the driver device up to some extent. This resistor will impact the high side drive capability and therefore needs to be considered carefully.

#### 10 Layout

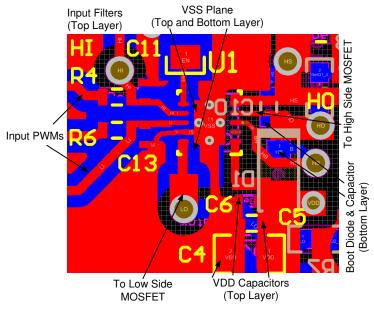

#### **10.1 Layout Guidelines**

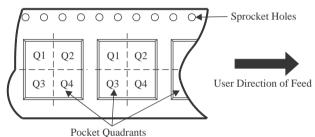

To achieve optimum performance of high-side and low-side gate drivers, one must consider following printed wiring board (PWB) layout guidelines.

- Low ESR/ESL capacitors must be connected close to the device between VDD and VSS pins and between HB and HS pins to support high peak currents drawn from VDD and HB pins during the turn-on of the external MOSFETs.

- To prevent large voltage transients at the drain of the top MOSFET, a low ESR electrolytic capacitor and a good quality ceramic capacitor must be connected between the high side MOSFET drain and ground (VSS).

- In order to avoid large negative transients on the switch node (HS) pin, the parasitic inductances between the source of the high-side MOSFET and the source of the low-side MOSFET (synchronous rectifier) must be minimized.

- Overlapping of HS plane and ground (VSS) plane should be minimized as much as possible so that coupling of switching noise into the ground plane is minimized.

- Thermal pad should be connected to large heavy copper plane to improve the thermal performance of the device. Generally it is connected to the ground plane which is the same as VSS of the device. It is recommended to connect this pad to the VSS pin only.

- Grounding considerations:

- The first priority in designing grounding connections is to confine the high peak currents that charge and discharge the MOSFET gates to a minimal physical area. This confinement decreases the loop inductance and minimize noise issues on the gate terminals of the MOSFETs. Place the gate driver as close to the MOSFETs as possible.

- The second consideration is the high current path that includes the bootstrap capacitor, the bootstrap diode, the local ground referenced bypass capacitor, and the low-side MOSFET body diode. The bootstrap capacitor is recharged on a cycle-by-cycle basis through the bootstrap diode from the ground referenced VDD bypass capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

#### 10.2 Layout Example

Copyright © 2022 Texas Instruments Incorporated

#### **11 Device and Documentation Support**

#### **11.1 Third-Party Products Disclaimer**

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### **11.2 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接 得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得るこ とができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 11.4 Trademarks

#### TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### **11.5 Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 11.6 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

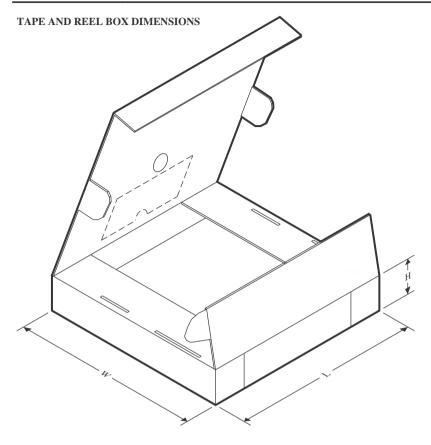

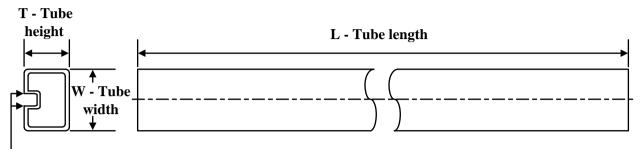

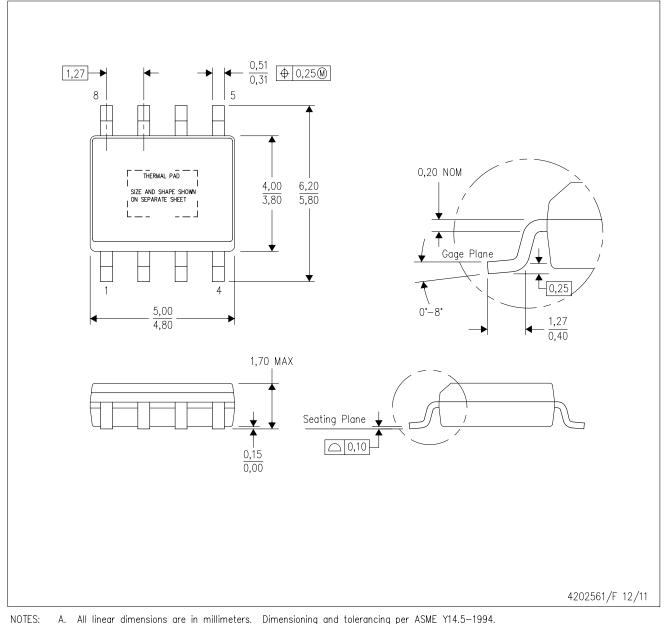

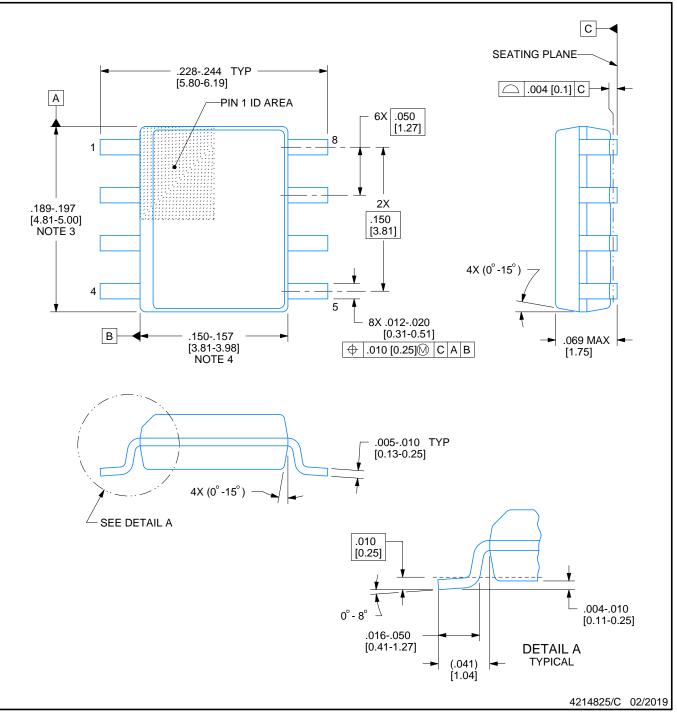

#### Mechanical, Packaging, and Orderable Information

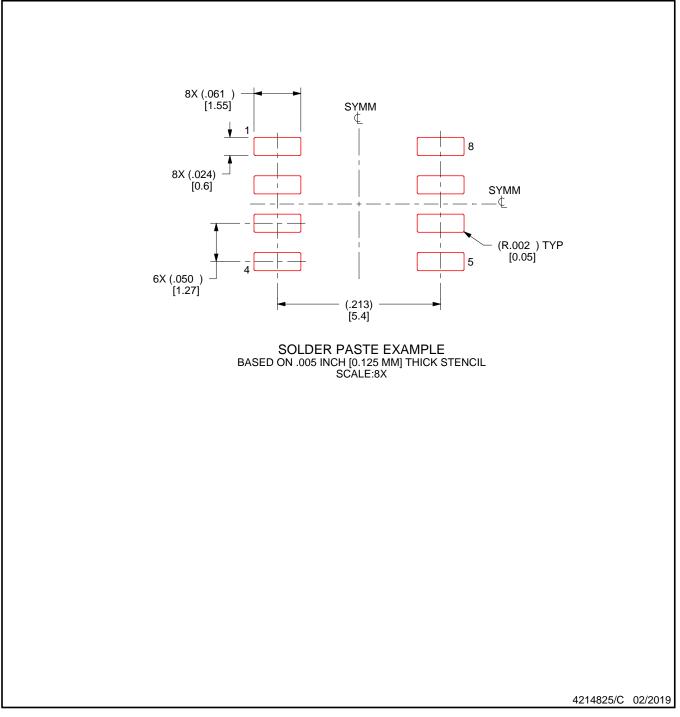

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                     |              |                |         |

| UCC27282QDDAQ1   | ACTIVE | SO PowerPAD  | DDA     | 8    | 75      | RoHS & Green | NIPDAUAG      | Level-2-260C-1 YEAR | 125 to -40   | 27282Q         | Samples |

| UCC27282QDDARQ1  | ACTIVE | SO PowerPAD  | DDA     | 8    | 2500    | RoHS & Green | NIPDAUAG      | Level-2-260C-1 YEAR | 125 to -40   | 27282Q         | Samples |

| UCC27282QDQ1     | ACTIVE | SOIC         | D       | 8    | 75      | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U282Q          | Samples |

| UCC27282QDRCRQ1  | ACTIVE | VSON         | DRC     | 10   | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U282Q          | Samples |

| UCC27282QDRCTQ1  | ACTIVE | VSON         | DRC     | 10   | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U282Q          | Samples |

| UCC27282QDRQ1    | ACTIVE | SOIC         | D       | 8    | 2500    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U282Q          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.