# Natural Interleaving™ 臨界モード 効率改善コントローラ (可聴ノイズ耐性の改善)

## NATURAL INTERLEAVINGの特長

- 軽負荷時の効率規格に準拠した簡素なフェーズ・マネージメント機能

- 2経路のフェイルセーフOVP機能により電圧検出障害により生じる出力過電圧状態を防止

- センサレス電流波形整形によるボード・レイアウトの簡素化と効率の改善

- 安全性のための突入電流制限

- 突入電流時MOSFETの導通を防止

- ブーストダイオードの逆回復現象を解消

## システムの特長

- 可聴ノイズ特性の改善

- 過電圧時のソフトスタート

- ブラウンアウト機能内蔵

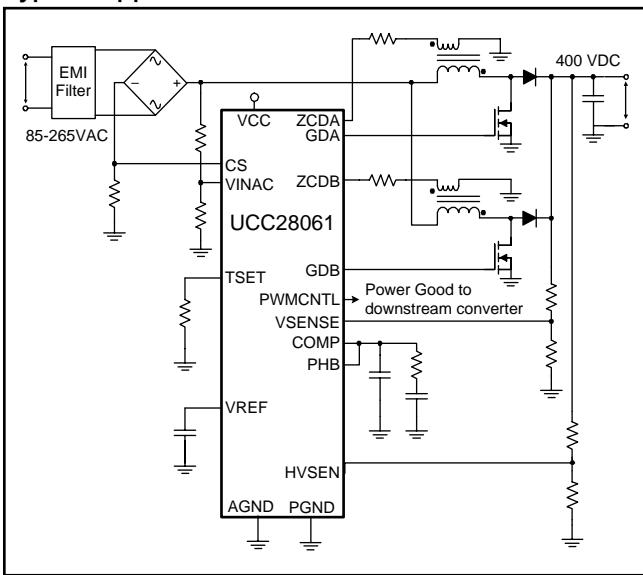

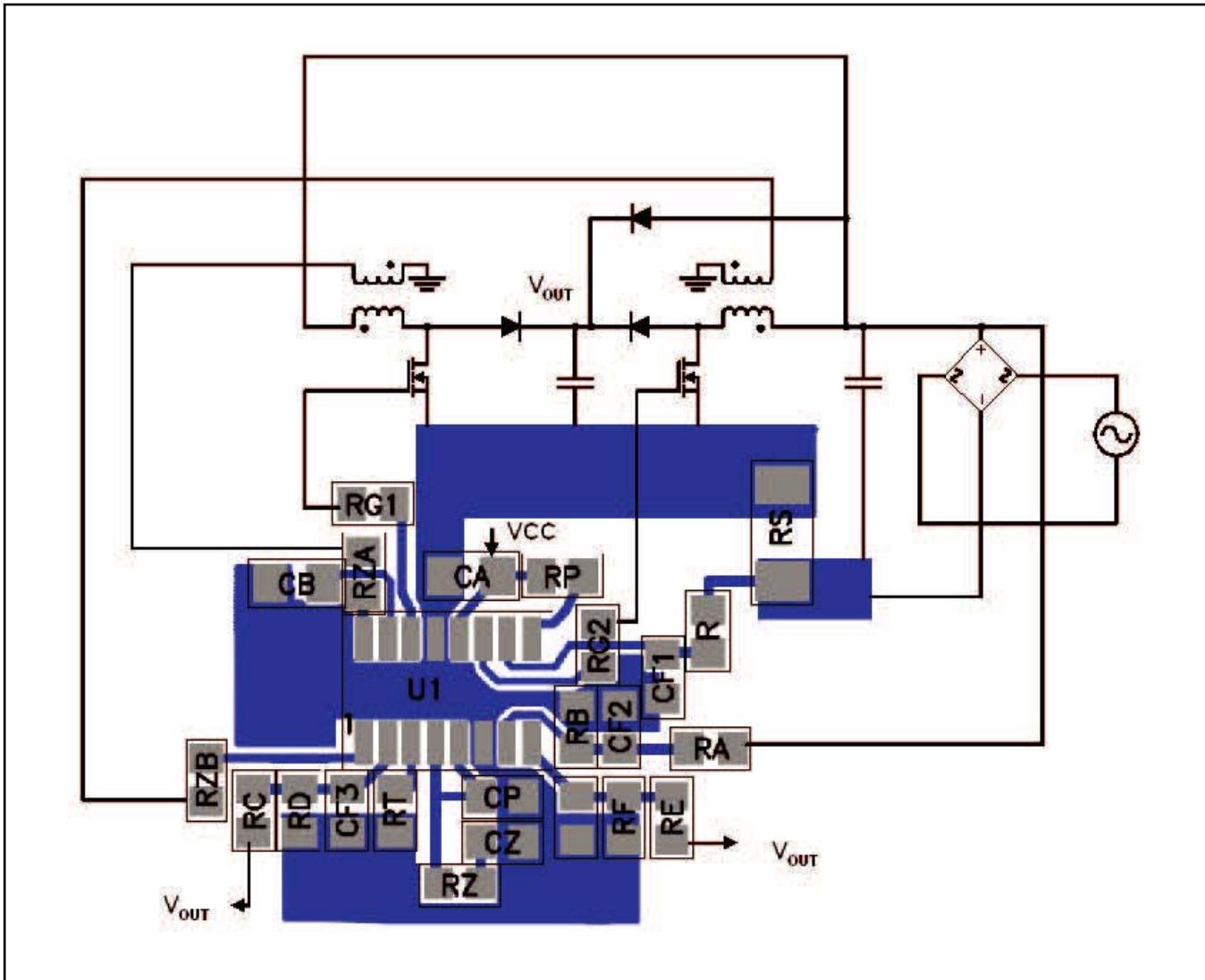

Typical Application Circuit

- 従来のシングル・フェーズ連続導通モード(CCM)よりも効率と設計の柔軟性が改善

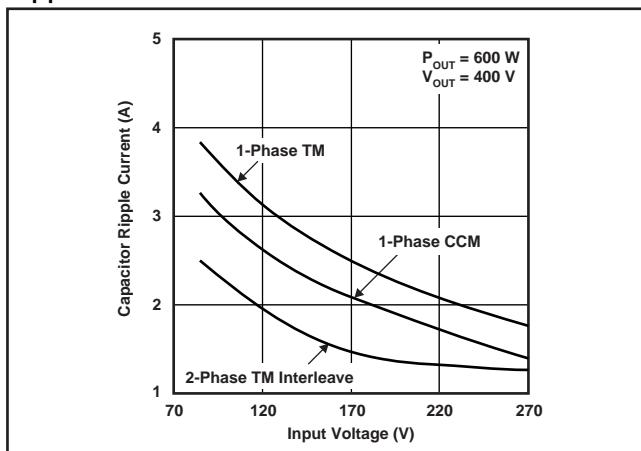

- 入力フィルタと出力コンデンサ電流のキャンセル

- 電流リップルの低減によるシステムの信頼性向上とバルク・コンデンサの小型化

- EMI用フィルタの小型化

- 大規模なスナバ回路を用いずに低コスト・ダイオードの使用が可能

- 軽負荷時効率の改善

- 過渡応答の改善

- システム・レベルの保護機能を完備

- ソース1A/シンク1.8Aのゲート・ドライバ

## アプリケーション

- 100W~800Wの電源

- ゲーム機

- セットトップボックス

- アダプタ

- LCD、プラズマ、DLP™テレビ

- 家庭用オーディオ機器

## Ripple Current Reduction

DLP、Natural Interleavingは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLUS837 翻訳版

# 目次

## 静電気放電対策

- 製品情報

- 電気的特性

- デバイス情報

- 機能ブロック図

- 代表的特性

- アプリケーション情報

- 設計例

- 補足資料

## 概要

UCC28061によるソリューションは可聴ノイズの除去が問題となる民生機器アプリケーションに適しており、従来よりも高い電力定格まで臨界モード（抵コストの部品で高効率）の利点を拡大します。Natural Interleaving手法を用いることで、両方のチャネルとも同一周波数に同期したマスター（すなわち、スレーブ・チャネルは存在しない）として動作します。この方法により本質的に強固なマッチングや高速応答が実現し、各チャネルは確実に臨界モードで動作します。

システム・レベルでの保護機能として入力プラウンアウト、出力の過電圧、オーブンループ、過負荷、ソフトスタート、フェーズ異常保護、サーマル・シャットダウンが完備しています。さらに、フェイルセーフ過電圧保護（OVP）機能により、もし検出されなければ壊滅的なデバイス破壊をもたらす恐れのある出力電圧の短絡が防止されます。

## 製品情報(1)

| PART NUMBER | パッケージ <sup>(2)</sup> | 動作温度範囲 T <sub>A</sub> |

|-------------|----------------------|-----------------------|

| UCC28061D   | SOIC 16-Pin (D)      | -40°C ~ +125°C        |

(1) 最新のパッケージ及び発注情報については、このデータシートの最後のパッケージ・オプション補遺、またはTIホームページwww.ti.comを参照してください。

(2) SOIC (D)パッケージはテープ／リールで供給されています。デバイス・タイプの末尾にRを付けてください。

UCC28061DRのリール当たりの個数は2500個です。

## 絶対最大定格<sup>(1)</sup>

All voltages are with respect to GND,  $-40^{\circ}\text{C} < T_J = T_A < +125^{\circ}\text{C}$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

|                                    |                                                                                                    | UCC28061   | 単位 |

|------------------------------------|----------------------------------------------------------------------------------------------------|------------|----|

| Input voltage range                | VCC <sup>(2)</sup>                                                                                 | -0.5 ~ +21 | V  |

|                                    | PWMCTL                                                                                             | -0.5 ~ +20 |    |

|                                    | COMP <sup>(3)</sup> , CS, PHB, HVSEN <sup>(4)</sup> , VINAC <sup>(4)</sup> , VSENSE <sup>(4)</sup> | -0.5 ~ +7  |    |

|                                    | ZCDA, ZCDB                                                                                         | -0.5 ~ +4  |    |

| Continuous input current           | VCC                                                                                                | 20         | mA |

| Input current                      | PWMCTL                                                                                             | 10         |    |

| Input current range                | ZCDA, ZCDB, VSENSE                                                                                 | -5 ~ +5    |    |

| Output current                     | VREF                                                                                               | -10        |    |

| Continuous gate current            | GDA, GDB <sup>(5)</sup>                                                                            | $\pm 25$   | °C |

| Junction temperature, $T_J$        | Operating                                                                                          | -40 ~ +125 |    |

|                                    | Storage                                                                                            | -65 ~ +150 |    |

| Lead temperature, $T_{\text{SOL}}$ | Soldering, 10s                                                                                     | +260       |    |

- (1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。

絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) VCCの電圧は内部でクランプされています。絶対最大連続VCC入力電流レベル以下に電流制限されている場合VCCは絶対最大入力電圧を越えることがあります。

- (3) 通常使用時、COMPはコンデンサと抵抗に接続され、内部で電圧振幅が制限されています。

- (4) 通常使用時、VINAC、VSENSE、HVSENは抵抗に接続され、内部で電圧振幅が制限されています。使用用途を広げることは推奨しませんが、VINAC、VSENSE、HVSENは高電圧源からのア10mAの入力電流に対する耐性をもっています。

- (5) パワーMOSFETのゲートを駆動する時GDA及びGDBの電流制限は不要ですが、浮遊インダクタンスによるリングングを低減するため小さな直列抵抗が必要になることがあります。詳細については図12と図13を参照してください。

## DISSIPATION RATINGS

| パッケージ           | THERMAL IMPEDANCE<br>JUNCTION-TO-AMBIENT | $T_A = +25^{\circ}\text{C}$ POWER RATING | $T_A = +85^{\circ}\text{C}$ POWER RATING |

|-----------------|------------------------------------------|------------------------------------------|------------------------------------------|

| SOIC 16-Pin (D) | 140°C/W <sup>(1)</sup>                   | 890mW <sup>(1)</sup>                     | 460mW <sup>(1)</sup>                     |

(1) JEDEC EIA/JESD 51-1によりテストされています。熱抵抗はボードの構造とレイアウトに大きな相関のある関数です。エアー・フローを与えることで熱抵抗は低下します。この値は単なる一般的な指針であるため、TI文献番号SPRA953 “device Thermal Metrics” を参照してください。

## 推奨動作条件

All voltages are with respect to GND,  $-40^{\circ}\text{C} < T_J = T_A < +125^{\circ}\text{C}$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

|                                                | MIN  | MAX | 単位 |

|------------------------------------------------|------|-----|----|

| VCC input voltage from a low-impedance source  | 14   | 21  | V  |

| VCC input current from a high-impedance source | 8    | 18  | mA |

| VREF load current                              | 0    | -2  |    |

| VINAC Input voltage                            | 0    | 6   | V  |

| ZCDA, ZCDB series resistor                     | 20   | 80  | kΩ |

| TSET resistor to program PWM on-time           | 66.5 | 400 |    |

| HVSEN input voltage                            | 0.8  | 4.5 |    |

| PWMCTL pull-up resistor to VREF                | 1    | 10  | kΩ |

## 静電放電(ESD)保護

|                | RATING | 単位 |

|----------------|--------|----|

| 人体モデル(HBM)     | 2000   | V  |

| デバイス帯電も出る(CDM) | 500    | V  |

## 電気的特性

At VCC = 16V, AGND = PGND = 0V, VINAC = 3V, VSENSE = 6V, HVSEN = 3V, PHB = 5V,  $R_{TSET} = 133\text{k}\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^\circ\text{C} < T_J = T_A < +125^\circ\text{C}$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

| パラメータ                              |                                                                | テスト条件                                    | MIN  | TYP   | MAX           | 単位            |

|------------------------------------|----------------------------------------------------------------|------------------------------------------|------|-------|---------------|---------------|

| <b>VCC BIAS SUPPLY</b>             |                                                                |                                          |      |       |               |               |

| VCC <sub>(shunt)</sub>             | VCC shunt voltage <sup>(1)</sup>                               | I <sub>VCC</sub> = 10mA                  | 22   | 24    | 26            | V             |

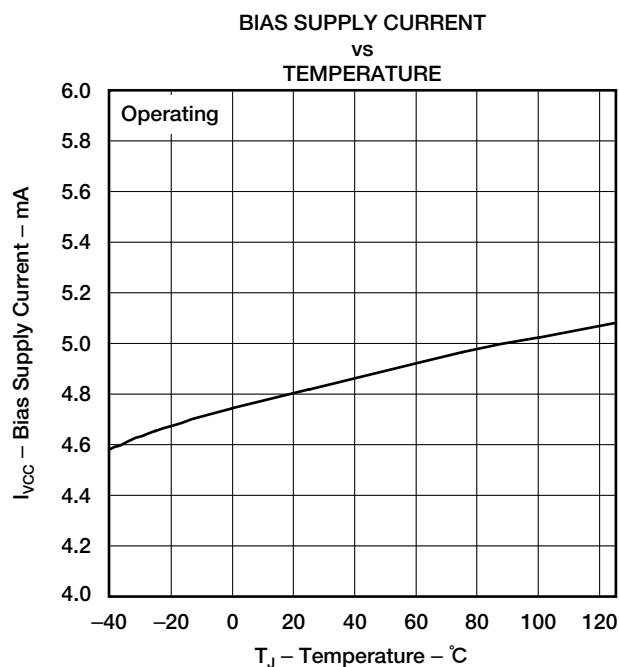

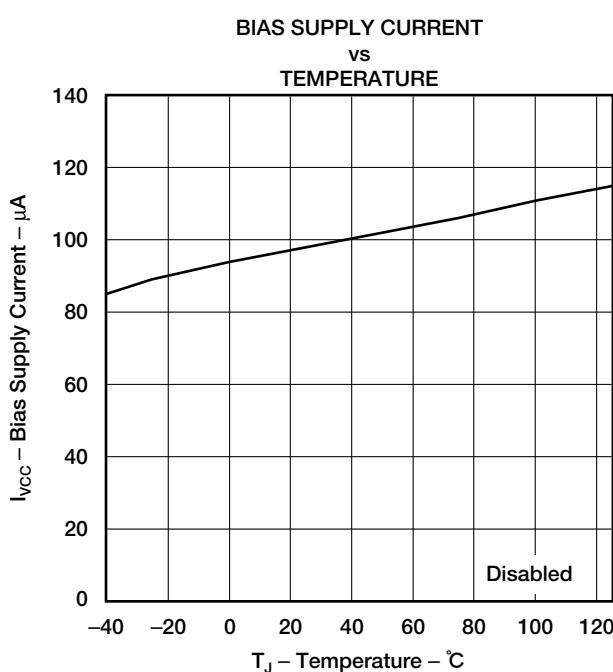

| I <sub>VCC(stby)</sub>             | VCC current, disabled                                          | VSENSE = 0V                              |      | 100   | 200           | $\mu\text{A}$ |

| I <sub>VCC(on)</sub>               | VCC current, enabled                                           | VSENSE = 6V                              |      | 5     | 8             | mA            |

| <b>UNDERVOLTAGE LOCKOUT (UVLO)</b> |                                                                |                                          |      |       |               |               |

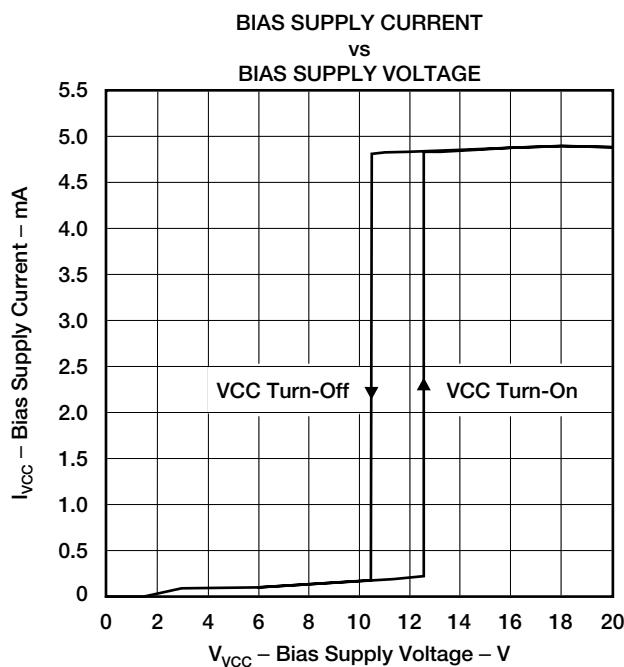

| VCC <sub>(on)</sub>                | VCC turn-on threshold                                          |                                          | 11.5 | 12.6  | 13.5          | V             |

| VCC <sub>(off)</sub>               | VCC turn-off threshold                                         |                                          | 9.5  | 10.35 | 11.5          |               |

|                                    | UVLO Hysteresis                                                |                                          | 1.85 | 2.25  | 2.65          |               |

| <b>REFERENCE</b>                   |                                                                |                                          |      |       |               |               |

| V <sub>REF</sub>                   | V <sub>REF</sub> output voltage, no load                       | I <sub>VREF</sub> = 0mA                  | 5.82 | 6.00  | 6.18          | V             |

|                                    | V <sub>REF</sub> change with load                              | 0mA $\leq$ I <sub>VREF</sub> $\leq$ -2mA |      | 1     | 6             | mV            |

|                                    | V <sub>REF</sub> change with VCC                               | 12V $\leq$ VCC $\leq$ 20V                |      | 1     | 10            |               |

| <b>ERROR AMPLIFIER</b>             |                                                                |                                          |      |       |               |               |

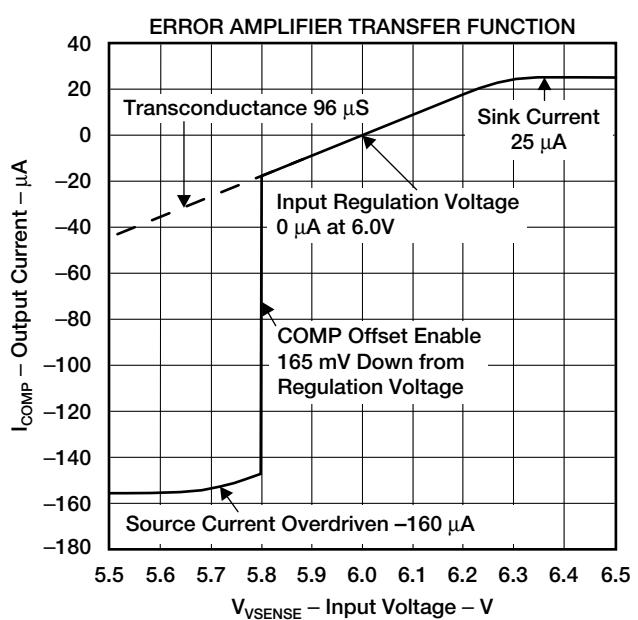

|                                    | VSENSE input regulation voltage                                | T <sub>A</sub> = +25°C                   | 5.85 | 6.00  | 6.15          | V             |

|                                    | VSENSE input regulation voltage                                |                                          | 5.82 | 6.00  | 6.18          |               |

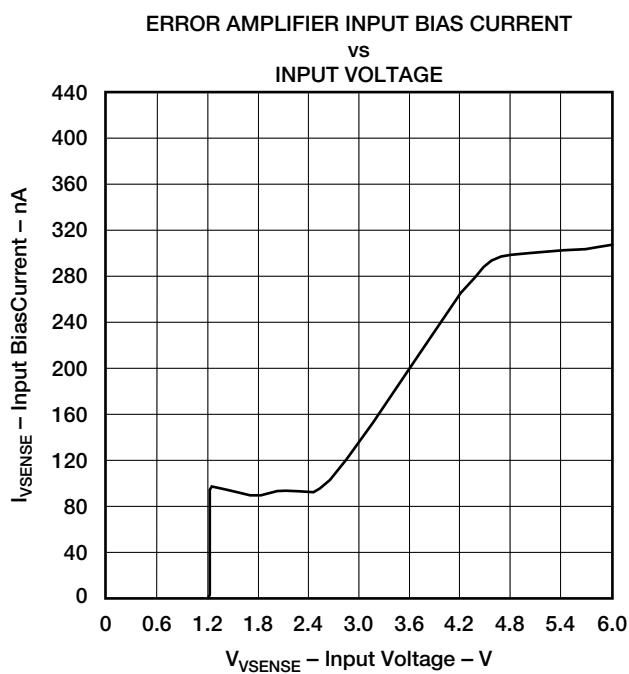

|                                    | VSENSE input bias current                                      | In regulation                            | 125  | 300   | 800           | nA            |

|                                    | COMP high voltage, clamped                                     | VSENSE = 5.8V                            | 4.70 | 4.95  | 5.10          | V             |

|                                    | COMP low voltage, saturated                                    | VSENSE = 6.2V                            |      | 0.03  | 0.125         |               |

| g <sub>m</sub>                     | VSENSE to COMP transconductance                                | COMP = 3V,<br>5.94V $<$ VSENSE $<$ 6.06V | 75   | 96    | 110           | $\mu\text{S}$ |

|                                    | COMP source current, overdriven                                | VSENSE = 5V, COMP = 3V                   | -120 | -160  | -190          | $\mu\text{A}$ |

|                                    | COMP sink current                                              | VSENSE = 6.2V, COMP = 3V                 | 7    | 20    | 32            |               |

|                                    | VSENSE threshold for COMP offset enable, from V <sub>REF</sub> | Voltage below V <sub>REF</sub>           | 135  | 185   | 235           | mV            |

| V <sub>OVP</sub>                   | VSENSE over-voltage threshold, rising                          |                                          | 6.25 | 6.45  | 6.7           | V             |

|                                    | VSENSE over-voltage hysteresis                                 |                                          | 0.1  | 0.2   | 0.4           |               |

|                                    | VSENSE enable threshold, rising                                |                                          | 1.15 | 1.25  | 1.35          |               |

|                                    | VSENSE enable hysteresis                                       |                                          | 0.02 | 0.05  | 0.2           |               |

| <b>OUTPUT MONITORING</b>           |                                                                |                                          |      |       |               |               |

| V <sub>PWMCTL</sub>                | HVSEN threshold to PWMCTL                                      | HVSEN rising                             | 2.35 | 2.50  | 2.65          | V             |

|                                    | HVSEN input bias current, high                                 | HVSEN = 3V                               | -0.5 | 0.5   | $\mu\text{A}$ |               |

|                                    | HVSEN input bias current, low                                  | HVSEN = 2V                               | 28   | 36    | 41            |               |

|                                    | HVSEN rising threshold to over-voltage fault                   |                                          | 4.64 | 4.87  | 5.1           | V             |

|                                    | HVSEN falling threshold to over-voltage fault                  |                                          | 4.45 | 4.67  | 4.80          |               |

|                                    | Phase Fail filter time to PWMCTL high                          | PHB = 5V,<br>ZCDA switching, ZCDB = 0.5V | 8    | 12    | 20            | ms            |

|                                    | PWMCTL leakage current high                                    | HVSEN = 2V, PWMCTL = 15V                 | -1   |       | 1             | $\mu\text{A}$ |

|                                    | PWMCTL output voltage low                                      | HVSENS = 3V, IPWMCTL = 5mA               |      | 0.2   | 0.5           | V             |

(1) VCC入力電圧及び電流が過度に大きいとデバイスを損傷します。このクランプはデバイスをレギュレーションされていない電源からの保護は行いません。レギュレーションされていない電源が用いられる場合は、UA78L15Aなどの固定正電圧レギュレータを使用することを推奨します。VCC電圧/電流の制限については絶対最大定格表を参照してください。

## 電気的特性

At VCC = 16V, AGND = PGND = 0V, VINAC = 3V, VSENSE = 6V, HVSEN = 3V, PHB = 5V,  $R_{TSET} = 133\text{k}\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^\circ\text{C} < T_J = T_A < +125^\circ\text{C}$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

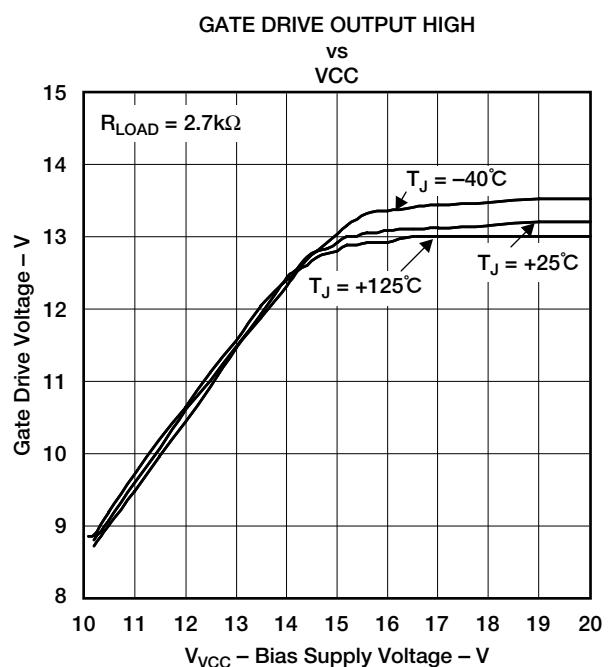

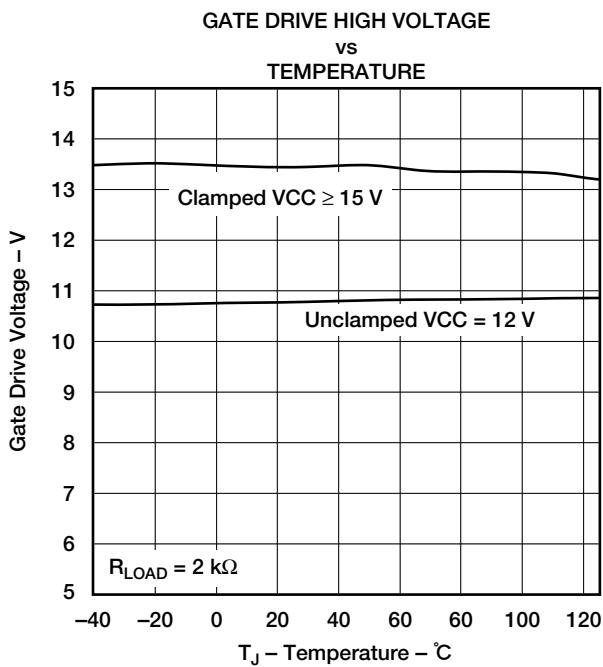

| パラメータ                           |                                                     | テスト条件                                                                          | MIN    | TYP    | MAX    | 単位            |

|---------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------|--------|--------|--------|---------------|

| <b>GATE DRIVE<sup>(2)</sup></b> |                                                     |                                                                                |        |        |        |               |

|                                 | GDA, GDB output voltage high                        | $I_{GDA}, I_{GDB} = -100\text{mA}$                                             | 11.5   | 13     | 15     |               |

|                                 | GDA, GDB output voltage high, clamped               | VCC = 20V, $I_{GDA}, I_{GDB} = -5\text{mA}$                                    | 12     | 13.5   | 15     | V             |

|                                 | GDA, GDB output voltage high, low VCC               | VCC = 12V, $I_{GDA}, I_{GDB} = -5\text{mA}$                                    | 10     | 10.5   | 11.5   |               |

|                                 | GDA, GDB on-resistance high                         | $I_{GDA}, I_{GDB} = -100\text{mA}$                                             |        | 8      | 14     | $\Omega$      |

|                                 | GDA, GDB output voltage low                         | $I_{GDA}, I_{GDB} = 100\text{mA}$                                              |        | 0.15   | 0.3    | V             |

|                                 | GDA, GDB on-resistance low                          | $I_{GDA}, I_{GDB} = 100\text{mA}$                                              |        | 2      | 3      | $\Omega$      |

|                                 | Rise time                                           | 1V ~ 9V, $C_{LOAD} = 1\text{nF}$                                               |        | 18     | 30     | ns            |

|                                 | Fall time                                           | 9V ~ 1V, $C_{LOAD} = 1\text{nF}$                                               |        | 12     | 25     |               |

|                                 | GDA, GDB output voltage UV                          | $I_{GDA}, I_{GDB} = 2.5\text{mA}$                                              |        | 1.6    | 2      | V             |

| <b>ZERO CURRENT DETECTOR</b>    |                                                     |                                                                                |        |        |        |               |

|                                 | ZCDA, ZCDB voltage threshold, falling               |                                                                                | 0.8    | 1.0    | 1.2    | V             |

|                                 | ZCDA, ZCDB voltage threshold, rising                |                                                                                | 1.5    | 1.68   | 1.88   |               |

|                                 | ZCDA, ZCDB clamp, high                              | $I_{ZCDA} = +2\text{mA}, I_{ZCDB} = +2\text{mA}$                               | 2.6    | 3.0    | 3.4    |               |

|                                 | ZCDA, ZCDB input bias current                       | ZCDA = 1.4V, ZCDB = 1.4V                                                       |        | -0.5   | 0.5    | $\mu\text{A}$ |

|                                 | ZCDA, ZCDB clamp, low                               | $I_{ZCDA} = -2\text{mA}, I_{ZCDB} = -2\text{mA}$                               | -0.4   | -0.2   | 0      | V             |

|                                 | ZCDA, ZCDB delay to GDA, GDB outputs <sup>(2)</sup> | Respective gate drive output rising 10% from zero crossing input falling to 1V |        | 45     | 100    | ns            |

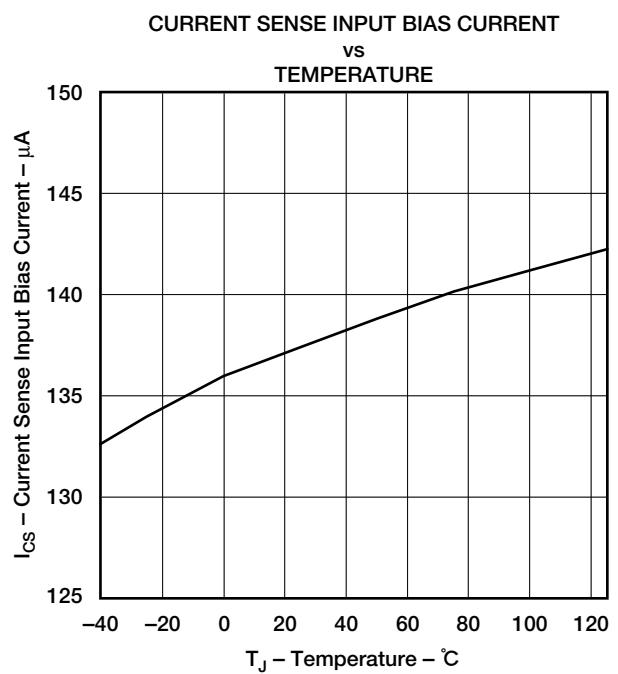

| <b>CURRENT SENSE</b>            |                                                     |                                                                                |        |        |        |               |

|                                 | CS input bias current                               | At rising threshold                                                            | -150   | -250   |        | $\mu\text{A}$ |

|                                 | CS current limit rising threshold                   |                                                                                | -0.18  | -0.20  | -0.22  | V             |

|                                 | CS current limit falling threshold                  |                                                                                | -0.005 | -0.015 | -0.029 |               |

|                                 | CS current limit response time <sup>(2)</sup>       | From CS exceeding threshold -0.05V to GDx dropping 10%                         |        | 60     | 100    | ns            |

| <b>MAINS INPUT</b>              |                                                     |                                                                                |        |        |        |               |

|                                 | VINAC input bias current                            | VINAC = 2V                                                                     | -0.5   | 0.5    |        | $\mu\text{A}$ |

| <b>BROWNOUT</b>                 |                                                     |                                                                                |        |        |        |               |

|                                 | VINAC brownout threshold                            | VINAC falling                                                                  | 1.34   | 1.39   | 1.44   | V             |

|                                 | VINAC brownout current                              | VINAC = 1V                                                                     | 5      | 7      | 9      | $\mu\text{A}$ |

|                                 | VINAC brownout filter time                          | VINAC fails to exceed the brownout threshold for the brownout filter time      | 340    | 440    | 540    | ms            |

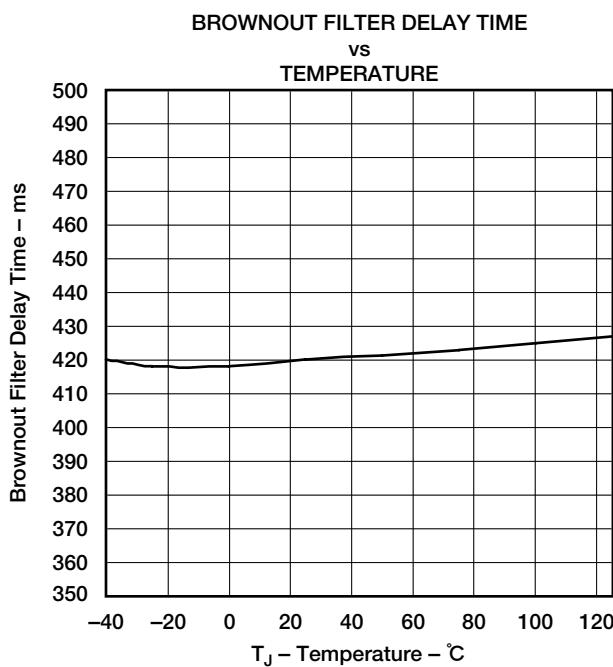

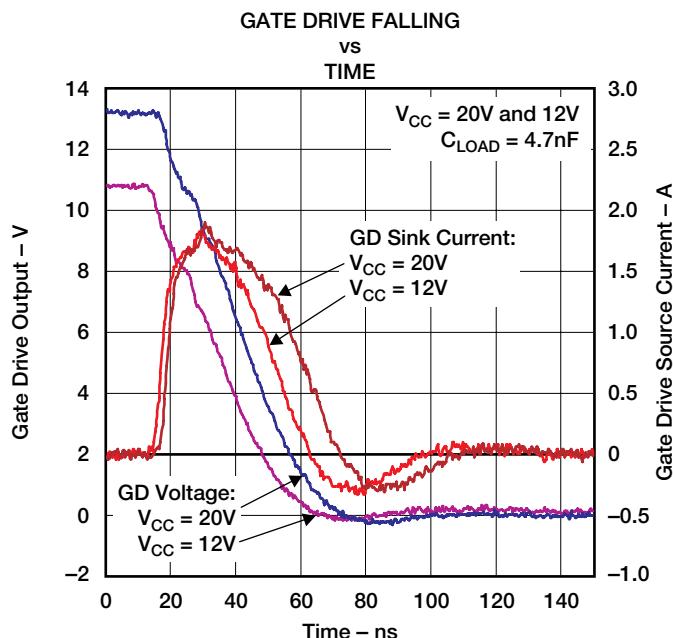

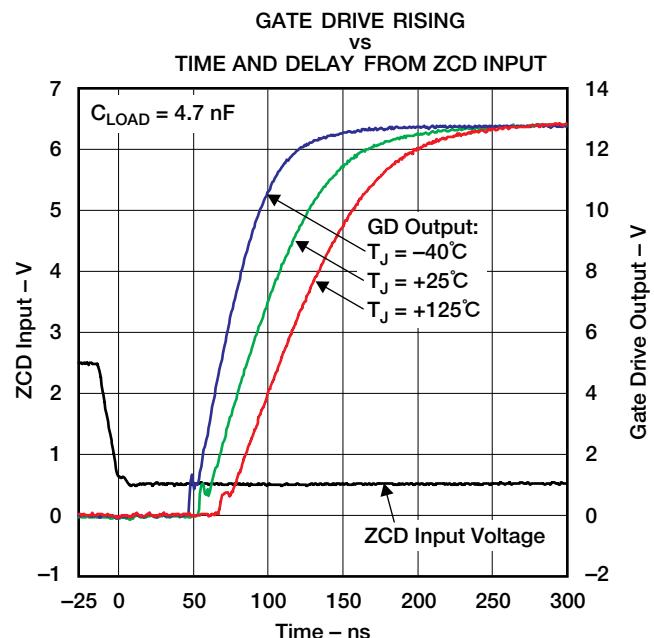

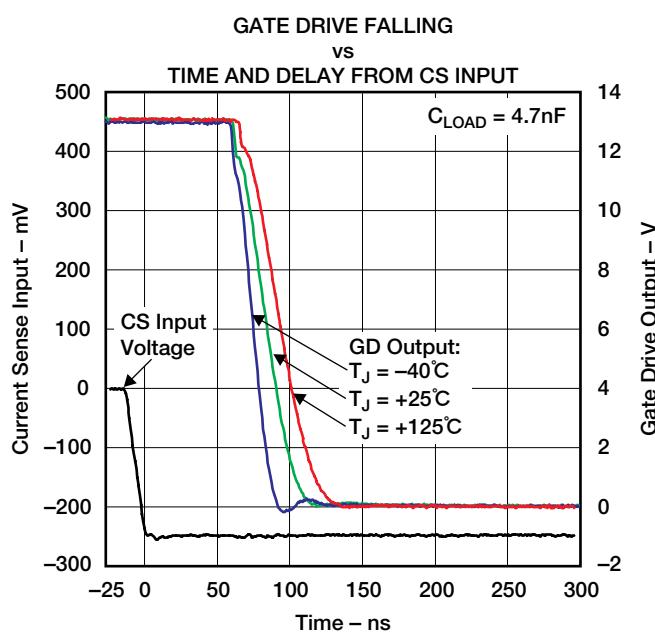

(2) 代表的なゲート波形については代表的特性の図12、図13、図14、図15を参照してください。

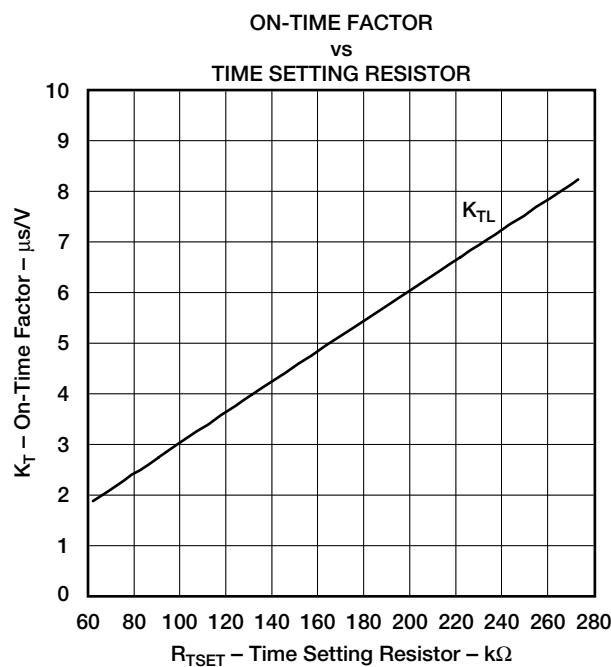

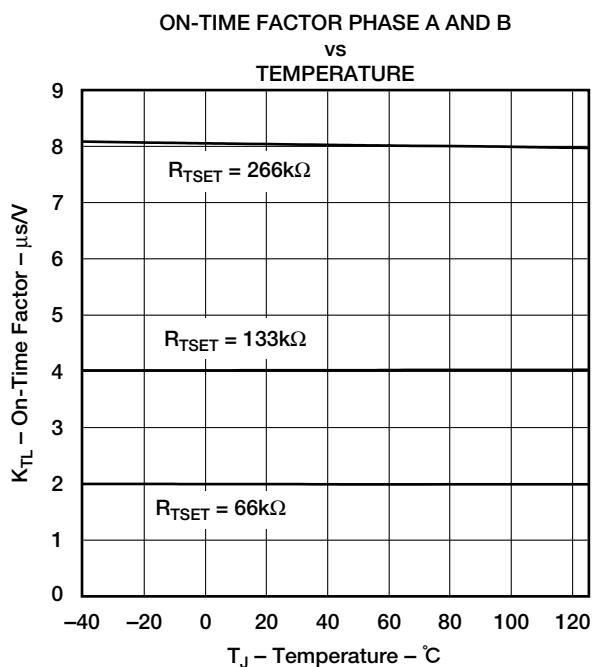

## 電気的特性

At VCC = 16V, AGND = PGND = 0V, VINAC = 3V, VSENSE = 6V, HVSEN = 3V, PHB = 5V,  $R_{TSET} = 133\text{k}\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $-40^\circ\text{C} < T_J = T_A < +125^\circ\text{C}$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

| パラメータ                        |                                                        | テスト条件                                                | MIN  | TYP | MAX | 単位                     |

|------------------------------|--------------------------------------------------------|------------------------------------------------------|------|-----|-----|------------------------|

| <b>PULSE-WIDTH MODULATOR</b> |                                                        |                                                      |      |     |     |                        |

| $K_{TL}$                     | On-time factor, phases A and B                         | VINAC = 3.2V, VSENSE = 5.8V <sup>(3)</sup>           | 3.6  | 4.0 | 4.4 | $\mu\text{s}/\text{V}$ |

| $K_{TLS}$                    | On-time factor, single-phase, A                        | VINAC = 3.2V, VSENSE = 5.8V, PHB = 0V <sup>(3)</sup> | 7.2  | 8   | 8.9 |                        |

|                              | Phase B to phase A on-time matching                    | VSENSE = 5.8V, VINAC = 3.2V                          | -6%  | 6%  |     |                        |

|                              | Zero-crossing distortion correction additional on time | COMP = 0.25V, VINAC = 1V                             | 1.2  | 2   | 2.7 | $\mu\text{s}$          |

|                              |                                                        | COMP = 0.25V, VINAC = 0.1V                           | 12.6 | 20  | 29  |                        |

|                              | PHB threshold falling, to single-phase operation       | To GDB output shutdown VINAC = 1.5V                  | 0.7  | 0.8 | 0.9 | V                      |

|                              | PHB threshold rising, to two-phase operation           | To GDB output running VINAC = 1.5V                   | 0.9  | 1.0 | 1.1 |                        |

| $T_{(min)}$                  | Minimum switching period                               | $R_{TSET} = 133\text{k}\Omega$ <sup>(3)</sup>        | 1.7  | 2.2 | 2.5 | $\mu\text{s}$          |

|                              | PWM restart time                                       | ZCDA = ZCDB = 2V <sup>(4)</sup>                      | 165  | 200 | 265 |                        |

| <b>THERMAL SHUTDOWN</b>      |                                                        |                                                      |      |     |     |                        |

|                              | Thermal shutdown temperature                           | $T_J$ , temperature rising <sup>(5)</sup>            | +160 |     |     | °C                     |

|                              | Thermal restart temperature                            | $T_J$ , temperature falling <sup>(5)</sup>           | +140 |     |     |                        |

(3) ゲート駆動のオン時間はVCOMP-125mVに比例します。オン時間の比例係数KTは2フェーズ/シングル・フェーズで異なります。

オン時間の係数KTは $R_{TSET}$ の値により直線的に変化します。最小スイッチング周期は $R_{TSET}$ に比例します。

(4) 出力のオン時間はZCDAとZCDBの両方の立下りエッジが再起動時間で検出されない場合GDAとGDBの両方で生成されます。

シングル・フェーズ・モードでは、再起動時間はZCDA入力とGDA出力に適用されます。

(5) サーマル・シャットダウンは温度が通常動作範囲より高くなった時に起こります。

通常動作温度より高い場合のデバイス性能は規定も保証もされていません。

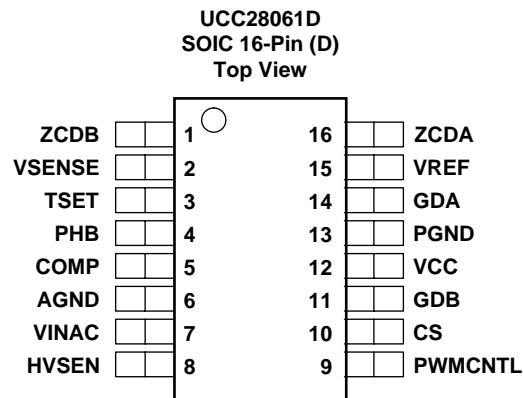

## ピン配置

## 端子機能

| TERMINAL |     |     | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AGND     | 6   | -   | アナログ・グランド：アナログ信号のバイパス・コンデンサ、補償部品、アナログ信号のリターンをこのピンに接続します。低電流のアナログ回路に干渉しないようパワー部品の大電流のノイズ信号を隔離するため一点でアナログ及び電源グランドを接続します。                                                                                                                                                                                                                                                                                                                                                                                |

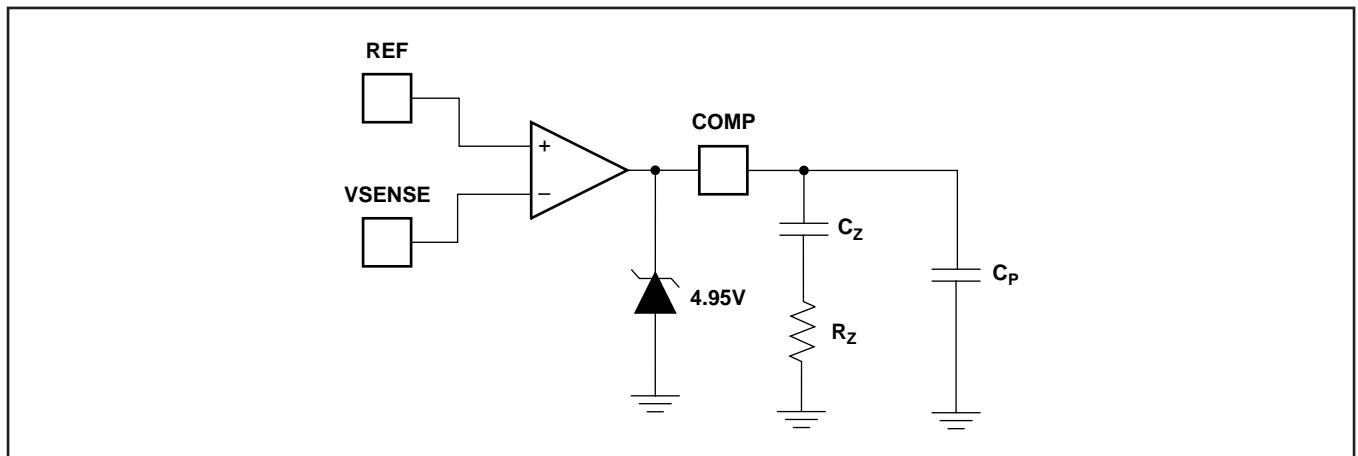

| COMP     | 5   | O   | 誤差増幅器出力：誤差増幅器はトランスコンダクタンス・アンプであるため、この出力はハイ・インピーダンスの電流源です。このピンからAGNDに電圧レギュレーション・ループの補償部品を接続します。ゲート駆動出力に現れるオン時間はこのピンの電圧から約125mVのオフセットを差し引いた電圧に比例します。ソフトスタート時(低電圧、ブラウンアウト、ディスエーブル、出力過電圧)、COMPは“L”レベルになります。ソフトスタートがクリアされCOMPが0.5V以下に放電された後にのみ通常動作は再開するため、確実に回路は低いCOMP電圧と短いオン時間で再始動します。0.5V以下に低下させ、COMPに干渉する恐れのある低インピーダンス源にはCOMPを接続しないでください。                                                                                                                                                               |

| CS       | 10  | I   | 電流検出入力：電流検出抵抗とダイオード・ブリッジの負端子をこのピンに接続します。別の配線で電流検出抵抗のリターンをAGNDに接続します。入力電流が増加するにつれ、CSの電圧はよりマイナス側に向かいます。このサイクルごとの過電流保護によりCSがCSの立上りスレッショルド(約-200mV)よりもマイナス側になった時両方のゲート・ドライバ(GDx)出力ともオフにすることで入力電流は制限されます。GD出力はCSがCSの立下りスレッショルド(約-15mV)に低下するまで“L”レベルのままでです。電流の検出はどちらかのGD出力の立下りエッジの後約100nsの間無効です。このランキングは電流がパワーFETからブースト・ダイオードに切り替わった時に生じるノイズをフィルタします。ほとんどの場合、電流検出用フィルタを追加することは必要ありません。フィルタが必要となった場合は、精度を保持するためフィルタ直列抵抗は100Ω未満にしなければなりません。突入電流状態時CSピンの電圧が過度にマイナス電圧になるのを防止するため、CSピンに低い値の抵抗を外付けして電流検出抵抗を接続します。 |

| GDA      | 14  | O   | チャネルAとチャネルBのゲート駆動出力：これらのピンを最短の接続で各フェーズのパワーFETのゲートに接続します。この接続に0.5インチ(12.6mm)より長い配線を用いる必要がある場合、配線の直列インダクタンスによりリングングが生じることがあります。このリングングはGDAとGDBに直列に5Ωから10Ωの抵抗を挿入することで低減することができます。                                                                                                                                                                                                                                                                                                                        |

| GDB      | 11  | O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HVSEN    | 8   | I   | 高電圧出力検出：UCC28061にはいかなる異常が起こっても出力を安全なレベル以上に上昇させないようフェイルセーフのOVPが内蔵されています。出力の過電圧はVSENSEとHVSENの両方で監視されており、どちらかのピンが適切な過電圧スレッショルドを越えるとPWMを停止させます。この2つの過電圧監視ピンを用いると冗長保護と耐故障性が可能になります。また、HVSENの電圧が動作範囲内にある時、HVSENはダウンストリーム・パワー・コンバータをイネーブルにすることに使用できます。HVSENの分圧比は目的とする過電圧及びパワーグッドのスレッショルドに対して選択します。HVSENの分圧インピーダンスは目的とするパワーグッド・ヒステリシスに対して選択します。動作時、HVSENは0.8Vより低くなってはいけません。HVSENが0.8Vより下がると、UCC28061は特別なテスト・モードとなり、工場テスト用のみの使用となります。ノイズにフィルタを施し誤った過電圧によるシャットダウンを防止するため、HVSENからAGNDにバイパス・コンデンサを接続することを推奨します。   |

| PGND     | 13  | -   | IC用電源グランド：このピンをゲート・ドライバのノイズをアナログ信号から分離するため短い配線でAGNDに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PHB      | 4   | I   | フェーズBイネーブル：このピンはブースト・コンバータのチャネルBをオン/オフします。チャネルAに指示されるオン時間はチャネルBがディスエーブルの時直ちに2倍となり、フェーズ・マネージメントの移行時COMP電圧を一定に保つのに役立ちます。PHBのスレッショホールドはPHBがCOMPに接続されている時効率を最良にするためライン範囲とともに変化します。また、PHBはフェーズ・マネージメントをカスタマイズできるよう外部のロジック信号からでも駆動することができます。フェーズ・マネージメントをディスエーブルにするには、PHBピンをVREFピンに接続します。                                                                                                                                                                                                                   |

## 端子機能

| TERMINAL |     |     | 説明                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O |                                                                                                                                                                                                                                                                                                                                                                                   |

| PWMCTL   | 9   | O   | PWMイネーブル・ロジック出力：このオープン・ドレイン出力はHVSENがHVSENの有効領域内にあり、ZCDA入力とZCDB入力が2フェーズ・モードで動作している場合に正しくスイッチングしている時“L”レベルになります(PHBピン参照)。そうでない場合は、PWMCTLはハイ・インピーダンスです。                                                                                                                                                                                                                              |

| TSET     | 3   | I   | タイミング設定：PWMのオン時間のプログラム入力。オン時間対COMP電圧及びゲート駆動出力の最短時間を設定するためTSETからAGNDに抵抗を接続します。                                                                                                                                                                                                                                                                                                     |

| VCC      | 12  | -   | バイアス電源入力：このピンを14Vから21Vのコントロールされたバイアス電源に接続します。また、できるだけ短いボード配線を用いてこのピンからPGNDに0.1μFのセラミック・バイパス・コンデンサを接続します。この電源はデバイス内の全ての回路に電源を供給し、直流6mAに一過渡的なパワーMOSFETのゲート充電電流を加えた電流を供給する能力をもっていなければなりません。                                                                                                                                                                                          |

| VINAC    | 7   | I   | 交流入力電圧の検出：通常動作では、このピンを整流入力電源からの抵抗分圧に接続します。VINACの電圧がブラウンアウトのフィルタ時間よりも長い時間ブラウンアウト・スレッショルドより低い時、デバイスはブラウンアウト・モードになり、両方の出力駆動ともディスエーブルになります。入力電圧の抵抗分圧比は目的とするブラウンアウト・スレッショルドに対して選択します。分圧インピーダンスはブラウンアウト・ヒステリシスに対して選択します。                                                                                                                                                                |

| VREF     | 15  | O   | 基準電圧出力：このピンからAGNDに0.1μFのセラミック・バイパス・コンデンサを接続します。VREFはVCCが低電圧の時オフになり、VSENSEはディスエーブルとなって電源電流を節約し効率を上昇させます。この6Vの直流基準電圧は他の回路をバイアスするのに使用することができ、トータル電源電流は2mA未満です。                                                                                                                                                                                                                       |

| VSENSE   | 2   | I   | 直流出力電圧検出：このピンをパワー・コンバータの出力で抵抗分圧に接続します。誤差増幅器の基準電圧は6Vです。出力電圧の分圧比は目的とする出力電圧に対して選択します。この分圧器のグランド側は良好な出力レギュレーション精度と耐ノイズ性のため短い配線でグランドを接続します。出力をディスエーブルにしVCC電流を低減するため、VSENSEピンはオープン・ドレインのロジック出力または低リードのダイオードに直列接続した6Vのロジック出力により“L”レベルにすることができます。VSENSEが接続されていないと、オープン・ループ保護機能により内部の電流源がVSENSEを“L”レベルにし、ゲート・ドライバをオフにします。                                                                  |

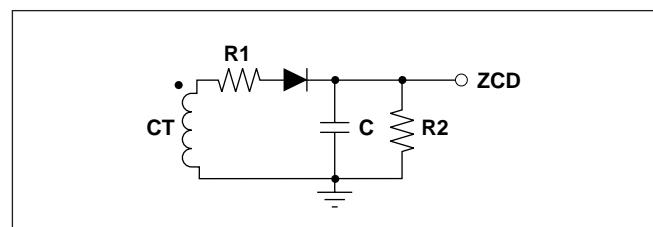

| ZCDA     | 16  | I   | ゼロ電流検出入力：これらの入力ではそれぞれのフェーズのインダクタ電流がゼロになった時立ち下りエッジとなることが想定されます。入力は0Vと3Vでクランプされます。信号はクランプ電流を±3mA未満に制限する直列抵抗を介して結合されなければなりません。これらのピンは電流制限抵抗を介して適切なブースト・インダクタのゼロ・クロス検出巻線に接続します。インダクタの巻線はこの電圧がインダクタ電流がゼロに低下した時減少するよう接続しなければなりません。インダクタ電流がゼロに低下した時、ZCD入力はゲート駆動出力を上昇させるため約1Vの立ち下りスレッショルドより低下しなければなりません。パワーMOSFETがオフになった時、ZCD入力は他のZCDの立ち下りエッジにロジックを供給するため約1.7Vの立ち上りスレッショルドより高くななければなりません。 |

| ZCDB     | 1   | I   |                                                                                                                                                                                                                                                                                                                                                                                   |

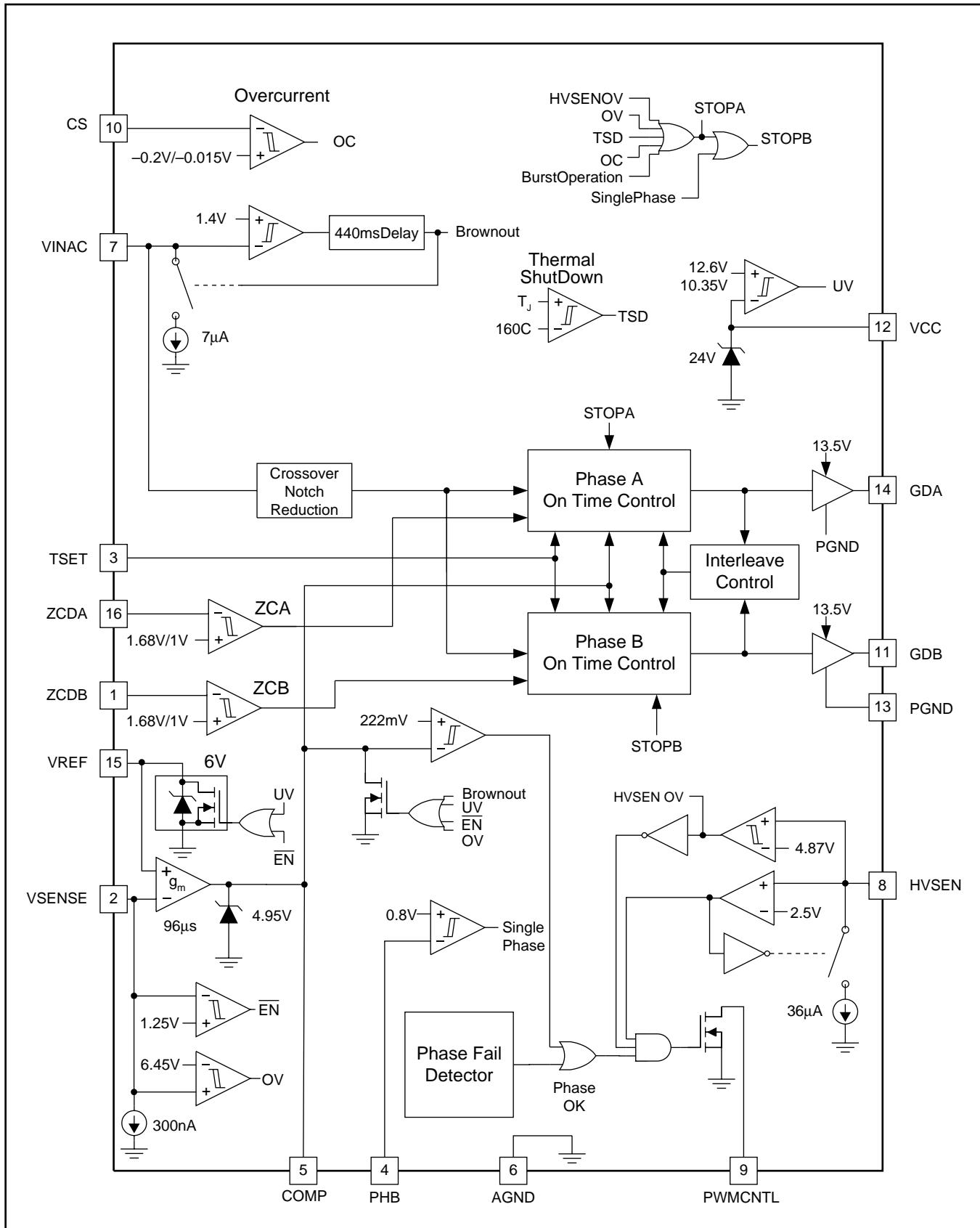

ブロック図

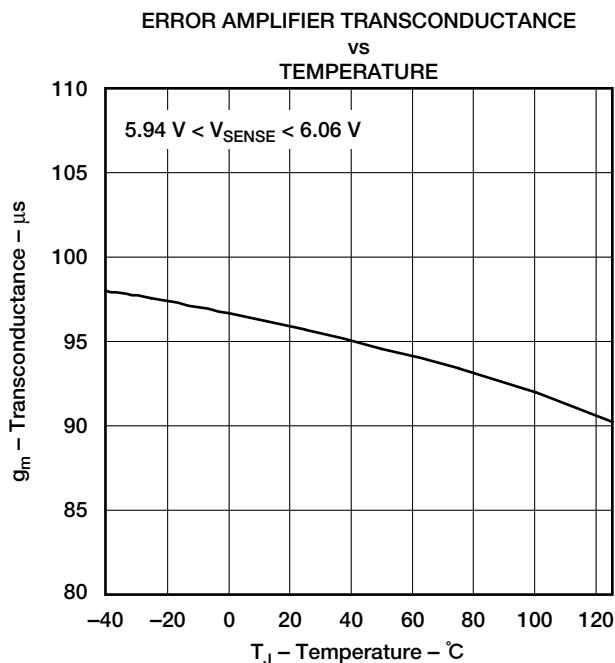

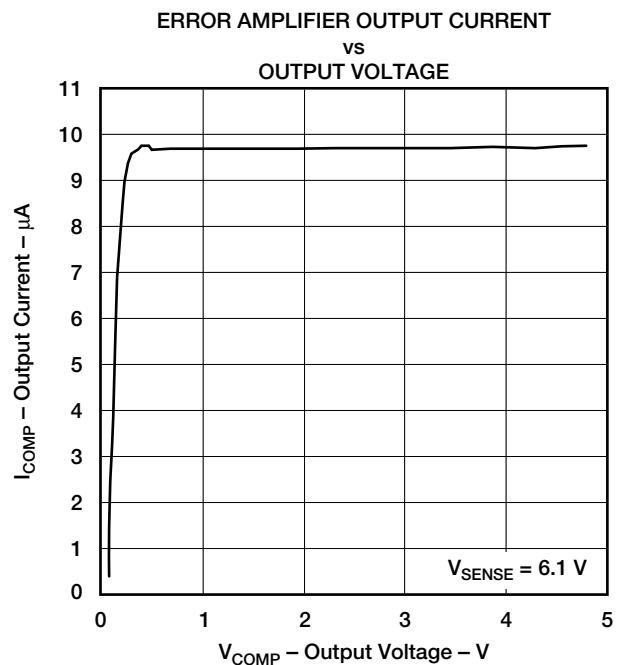

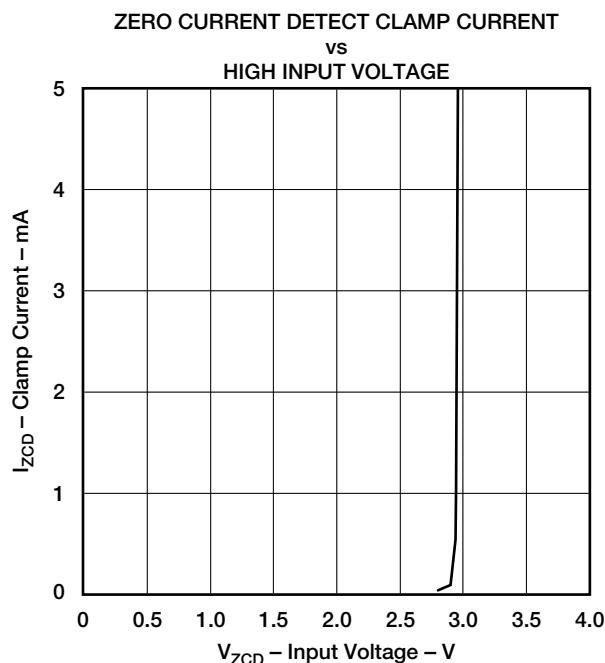

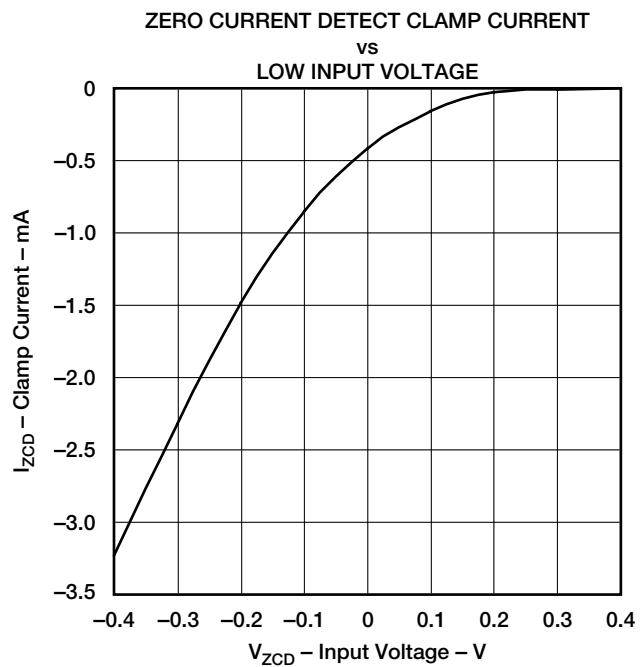

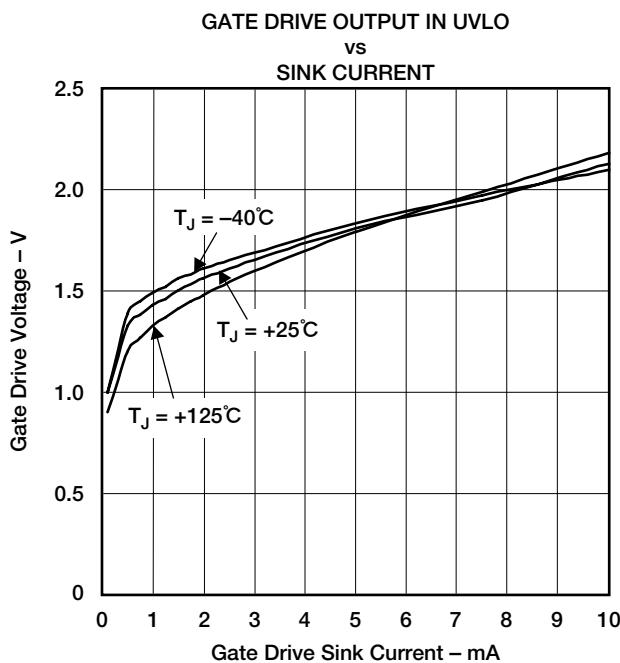

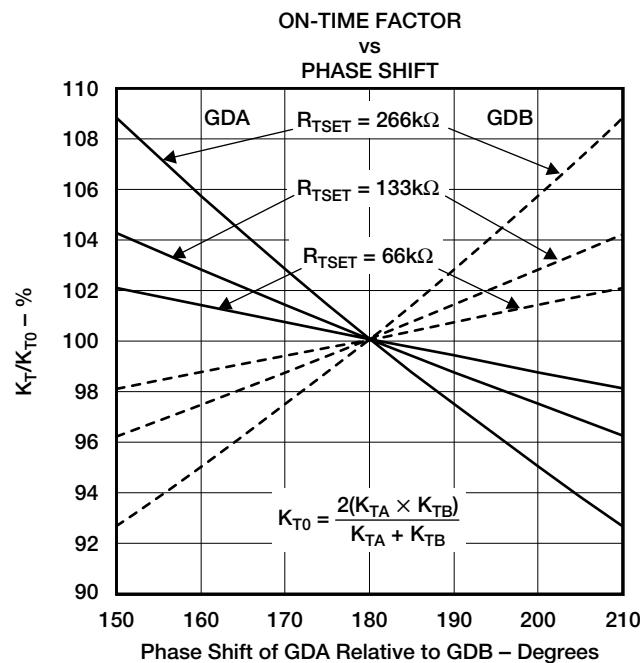

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図1

図2

図3

図4

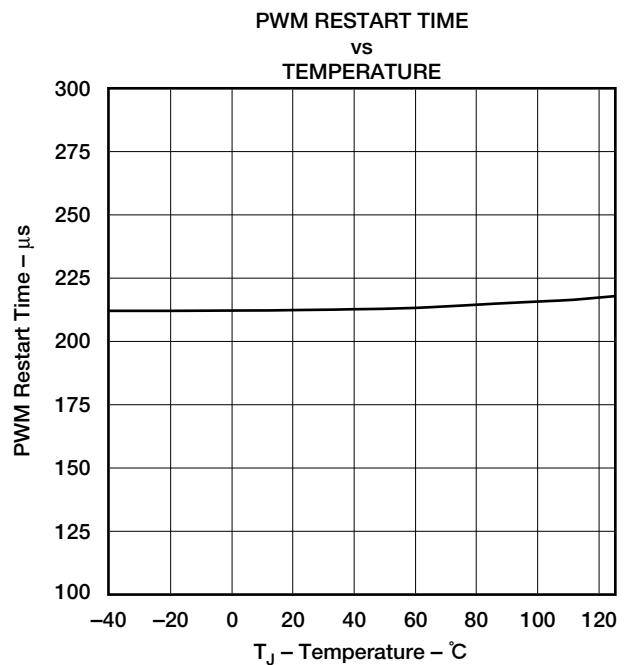

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図5

図6

図7

図8

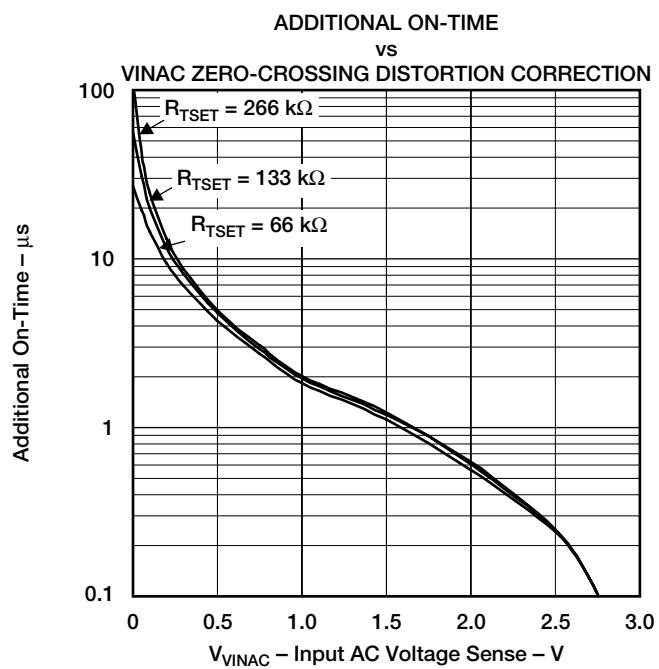

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図9

図10

図11

図12

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図13

図14

図15

図16

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図17

図18

図19

図20

## 代表的特性

At  $V_{CC} = 16V$ ,  $AGND = PGND = 0V$ ,  $VINAC = 3V$ ,  $VSENSE = 6V$ ,  $HVSEN = 3V$ ,  $PHB = 5V$ ,  $R_{TSET} = 133k\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = T_A = +25^\circ C$ , and currents are positive into and negative out of the specified terminal (特に記述のない限り)

図21

図22

図23

# アプリケーション情報

## 動作原理

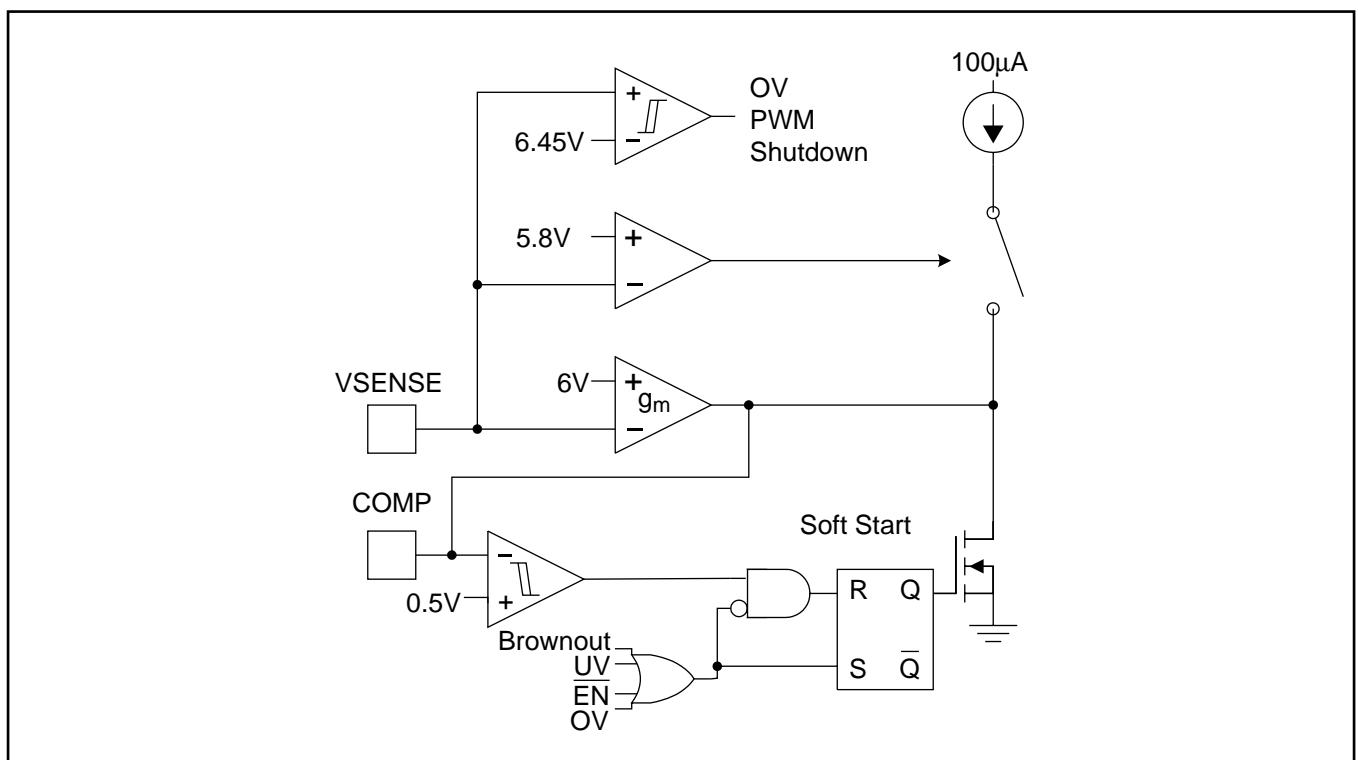

UCC28061は2つのブースト型パルス幅変調(PWM)のパワー・コンバータ用のコントロール回路を含んでいます。ブースト型PWMパワー・コンバータは誤差増幅器の出力の電圧に比例した時間ブースト・インダクタの電流を上下させます。次に各パワー・コンバータは、ゼロ電流検出入力(ZCDAとZCDB)で検出される、ブースト・インダクタの電流がゼロに減少するまでパワーMOSFETをオフにします。インダクタの電流がゼロになると、パワー・コンバータは他のサイクルを開始します。このオン/オフの繰り返しにより、式(1)に示されているように、オン時間と電源の入力電圧により設定されるピーク電流の三角波の電流が生成されます。

$$I_{PEAK}(t) = \frac{VINAC(t) \times T_{ON}}{L} \quad (1)$$

平均ライン電流は式(2)に示されているようにピーク時のライン電流のちょうど半分です。

$$I_{AVG}(t) = \frac{VINAC(t) \times T_{ON}}{2 \times L} \quad (2)$$

交流ラインの期間 $T_{ON}$ と $L$ が基本的に一定であると、各スイッチング・サイクル時結果として生じる三角波の電流波形の平均値は整流された交流ライン電圧の瞬時値に比例します。この概念によりライン周波数とほぼ1の力率で抵抗性の入力インピーダンス特性となります。

2つのPWMの出力は2つのPWMの電源ラインのリップル電流がそれぞれのPWMのリップル電流より大きく低減するよう $180^\circ$ 逆相で動作します。この設計により入出力時のリップル電流が減少し、入出力フィルタの大きさやコストの低減が可能になります。

個々のパワーセグメントとオン時間がうまく調和した場合に最適な位相バランスとなります。インダクタ値が不一致であっても位相関係に影響は与えません。

## オン時間のコントロール、最大周波数の制限、リストアート・タイマ

ゲート駆動のオン時間は式(3)に示されているように $K_T$ と呼ばれる係数により誤差増幅器の出力電圧により変化します。

$$T_{ON} = K_T (V_{COMP} - 125mV) \quad (3)$$

但し、 $V_{COMP}$ は誤差増幅器の出力電圧で、125mVは変調器のオフセットです。

2フェーズとシングル・フェーズ動作間での遷移が円滑に行われるよう、シングル・フェーズ・モードで $K_T$ は2倍に増加します。

- $K_{TLS} = 2 \times K_{TL}$  ; シングル・フェーズ動作時で有効

誤差増幅器の最大クランプ出力は4.95Vに制限されています。この値から125mVの変調器のオフセットが差し引かれオン時間は式(4)の値に制限されます。

$$T_{ON(max)} = K_T \times 4.825V \quad (4)$$

このオン時間の制限により与えられた入力電圧レベルでコンバータにより供給される最大電力が設定されます。

各フェーズのスイッチング周波数は最小時間タイマにより制限されます。最小時間タイマが経過してしまう前に電流がゼロに低下すると、ターンオンが遅れ位相電流が不連続になります。リストアート・タイマはどちらかのZCD入力が約200μsの間立下らない場合両方のフェーズを再起動させることでどんなときでも起動を確実に行います。回路が連続動作モード(CCM)で動作することを防止するため、この再起動時間では両方のフェーズ電流がゼロに戻るまでターンオンは起こりません。

オン時間の係数( $K_{TH}$ ,  $K_{THS}$ ,  $K_{TL}$ ,  $K_{TLS}$ )と最小スイッチング時間 $T_{MIN}$ はTSETピンからグランドに接続される時間設定抵抗 $R_{TSET}$ に比例し、それらは式(5)と式(6)で計算することができます。

$$K_{TL} = \frac{R_{TSET}}{133k\Omega} \times 4.0 \frac{\mu S}{V} \quad (5)$$

$$T_{MIN} = \frac{R_{TSET}}{133k\Omega} \times 2.2\mu S; \text{ Minimum Switching Period} \quad (6)$$

$R_{TSET}$ の値を適切に設定すると最小入力ライン及び最大負荷時で動作するコンバータに必要となる固定の最大オン時間 $T_{ON(max)}$ が決定されます。

## Natural Interleaving

通常動作状態でUCC28061はチャネルAとチャネルBのインダクタ電流の位相シフトがほぼ $180^\circ$ になるよう調整しているため、ライン源や出力コンデンサでのリップル電流が最小限に抑えられます。位相コントロール機能は位相と周波数の関係をもとにしてAチャネルとBチャネルのオン時間を差動的に調節します。このNatural Interleavingの手法により両方のフェーズに対しブースト・インダクタへの公差の条件が不要でコンバータは $180^\circ$ の位相シフトと臨界モード動作を実現することができます。結果として、AチャネルとBチャネルの電流シェアはインダクタの公差に比例することになります。最良の電流シェアは両方のインダクタが全く同じ値の場合に達成されます。

## フェーズ・マネージメント

軽負荷時、UCC28061は1つのフェーズを停止させることで効率を改善することができます。シングル・フェーズ動作時導通損失は増加し、スイッチング損失は減少します。ある電力レベルでは、スイッチング損失の減少量は導通損失の増加量よりも大きくなります。軽負荷時1つのフェーズをオフにすることは軽負荷時の効率規格に適合するのに特に有用です。

2フェーズ・モード(通常)で動作させるにはPHBを“H”レベルにするか、またはPHBをVREFに接続します。一方、シングル・フェーズ・モードで動作させるにはPHBをグランドに接続します

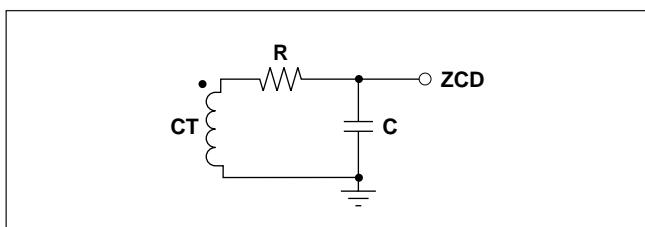

## ゼロ・クロス検出とバレー・スイッチング

臨界モードのPFC回路では、MOSFETはブースト・インダクタの電流がゼロに交差した時オンになります。

ブースト・インダクタとMOSFETドレイン・ノードの寄生コンデンサ間の共振のため、MOSFETの接合コンデンサに蓄積されたエネルギーの一部が回復し、スイッチング損失が低減します。さらに、整流入力電圧が出力電圧の半分より低い時、MOSFETの接合コンデンサに蓄積されたエネルギーの全てが回復し、ゼロ電圧スイッチング(ZVS)が実現します。適切な遅延を付加することで、MOSFETをその共振ドレン電圧の下限でオンすることができます(バレー・スイッチング)。このようにして、エネルギーの回復を最大化することができ、スイッチング損失は最小限に抑えられます。

RC時定数は一般的には経験的に得られますが、最初はドレン回路の共振期間の25%の値が適切です。図24に示されているように、遅延は簡単なRCフィルタで実現することができます。ZCDピンは内部でクランプされているため、図25を用いることでより正確な遅延を実現することもできます。

## ブラウンアウト保護

電源ラインのRMS電圧が低下すると、RMS入力電流はある特定の負荷に対し出力電圧を一定に維持するため増加します。

図24. Simple RC Delay Circuit

ブラウンアウト保護によりRMS入力電流が安全な動作レベルを越えないよう保護されます。電源ラインのRMS電圧はVINACで検出されます。VINACに加わる電圧がブラウンアウト・フィルタ時間ブラウンアウトのスレッショルドを越えることができなかった時、ブラウンアウト状態が検出され、両方のゲート駆動出力とも直ちに“L”レベルになります。ブラウンアウトの間、COMPはアクティブに“L”レベルになります。ゲート駆動出力はVINACの電圧がブラウンアウトのスレッショルドより上昇するまで“L”レベルのままであります。ブラウンアウトの後、パワー段はCOMPが上昇するとソフトスタート動作を行います。

ブラウンアウトの検出スレッショルドとそのヒステリシスは分圧比と抵抗値により設定されます。ブラウンアウト保護はVINACのピーク電圧に基づいており、そのスレッシュホールドとヒステリシスもラインのピーク電圧に基づいています。VINACのピーク電圧は簡単にRMS値に変換することができます。分圧器用の推奨抵抗値は整流入力電圧からVINACへは $3M\Omega \pm 1\%$ 、VINACからグランドへは $46.4k\Omega \pm 1\%$ です。これらの抵抗により表1に示されているようにRMS入力電圧の標準スレッショルドが設定されます。

## フェイルセーフ OVP—出力過電圧保護

フェイルセーフのOVPはいかなる異常時でも出力が安全レベルより上昇することを防止します。出力電圧を検出する冗長経路が出力の過電圧をさらに保護しています。過電圧保護は2つの独立した経路であるVSENSEとHVSENにより実行されます。どちらかの入力が過電圧状態を検出した場合コンバータは停止します。出力電圧はどちらかのループが異常であっても安全なレベルを維持しています。デバイスは両方の検出入力とも正常範囲に戻った時再びイネーブルになります。その時点でのゲート駆動出力はPWMのコントロール下でスイッチングを再開します。出力過電圧時はソフトスタートが行われることはなく、COMPピンは出力の過電圧時放電されません。

図25. More Accurate Time Delay Circuit

| スレッショルド | ブラウンアウト(RMS) |

|---------|--------------|

| 立ち下がり   | 65V          |

| 立ち上がり   | 79.8V        |

表1. ブラウンアウトのスレッショルド

## 過電流保護

ある特定の状態下(突入電流、ブラウンアウトの復帰、出力過負荷など)で、PFCのパワー段には大きな電流が流れます。パワー・デバイスはこれらの状態時にスイッチングから保護されることが重要です。

従来の電流検出方法ではコンバータの電流を検出するのにMOSFETのソースに直列にシャント抵抗を用いていたため、複数のグランド点が生じ、消費電力が大きくなっていました。さらに、MOSFETがオフの時電流情報が得られないため、ソース抵抗による電流検出方法では過電流状態時MOSFETのターンオンを繰り返すことが必要になっていました。結果として、コンバータは一時的に連続電流モード(CCM)で動作することがあり、ブースト・ダイオードの過度の逆回復電流により引き起こされる異常が生じていました。

UCC28061はトータル・インダクタ(入力)電流を連続して検出するために1つの抵抗を使用します。この方法では、インダクタ電流が過度に大きい時でもMOSFETのターンオンは完全に回避されます。MOSFETの駆動はトータル・インダクタ電流がほぼゼロに低下するまで禁止され、逆回復電流により引き起こされる異常が防止されます(これらの異常は交流ラインがブラウンアウト状態から復帰する時に生じる可能性がもっとも高くなります)。

過電流状態の後、入力電流がほぼゼロに低下した時両方のMOSFETとも同相でオンになります。2つのフェーズ電流は一時的に同相で動作するため、過電流状態後に通常動作に復帰することができるよう過電流保護のスレッショルドを各フェーズの最大電流リップル値の2倍より大きな値に設定します。

## フェーズ異常保護

UCC28061はZCDパルス列を監視することで1フェーズ異常を検出します。通常の2フェーズ動作時、1つのZCD入力が他のZCD入力が通常の切り替えを行っているのに対し約14msより長くアイドル状態のままであると、PWMCTLは“H”レベルになり、パワー段は正しく動作していないことを示します。通常のシングル・フェーズ動作時では、フェーズ異常は監視されません。UCC28061では、COMPが約222mVより低いとフェーズ異常は監視されません。

## 歪みの低減

スイッチングMOSFETのドレン/ソース端に存在する容量とブースト・インダクタ間の共振のため、従来の臨界モードの力率改善回路は入力電圧がおよそ0Vの時入力ラインから電力を吸収することができないことがありました。この制限により波形の歪みが生じ高調波歪みが増加します。ライン電流の歪みを最小可能レベルまで低減するために、UCC28061は電力の吸収を増加させこの影響を補償するよう入力電圧がおよそ0Vの時スイッチングMOSFETのオン時間を増加させます。

## 改良型誤差増幅器

電圧誤差増幅器はトランスコンダクタンス・アンプです。電圧のループ補償は誤差増幅器の出力COMPからアナログ・グランドAGNDに接続されます。推奨する補償回路を図26に示します。

過渡応答を改善するため、図27に示されているように、誤差増幅器の出力電流は誤差増幅器の入力が5.8Vより低い時100µA

増加します。この増加により負荷電流が突然増加した後に補償部品の充電が高速で行われます(代表的特性の図4も参照してください)。

UCC28061は出力過電圧が検出された時ソフトスタートを有効にし、COMPをグランドに落とします。このことにより、重負荷から軽負荷への変化に対する応答が改善されます。

図26. Typical Error Amplifier Compensation

図27. Error Amplifier Block Diagram Showing Speed-Up and Latched Soft-Start

## オープン・ループ保護

フィードバック・ループがデバイスから切斷されると、UCC28061に内蔵されている電流源がVSENSEピンの電圧をグランド方向にもってゆきます。VSENSEが1.20Vより低くなると、デバイスはディスエーブルになります。ディスエーブルになった時、電源電流は減少し、両方のゲート駆動出力とCOMPはアクティブに“L”レベルになります。VSENSEが1.25Vより高くなった時、デバイスは再度イネーブルになります。この時点で、ゲート駆動出力はPWMのコントロール下でスイッチングを開始します。

このデバイスはオープン・ドレインまたはオープン・コレクタのドライバを用いてVSENSEピンをグランドに落とすことで外部からディスエーブルすることができます。ディスエーブルの時、デバイスの電源電流は減少し、COMPはアクティブに“L”レベルになります。VSENSEが解放された時、デバイスはソフトスタートを行います。このディスエーブルの方法によりデバイスは強制的にスタンバイ・モードになり、その消費電力は最小限になります。この機能はスタンバイ時の電力が設計上で重要である場合に特に有用です。

フィードバック・ループがグランドから切斷されると、VSENSEの電圧が高くなります。VSENSEが過電圧保護のスレッショルドより高くなった時、両方のゲート駆動出力は“L”レベルになり、COMPはアクティブに“L”レベルになります。VSENSEが範囲内に戻った時、デバイスは再度イネーブルになります。この時点で、ゲート駆動出力はPWMのコントロール下でスイッチングを開始します。VSENSEピンはデバイスがこの状態で損傷しないよう内部でクランプされています。

## ソフトスタート

COMPからAGNDに接続されている補償コンデンサが低レベルから最終値に充電されるにつれ、PWMはゼロのオン時間から通常のオン時間に徐々に上昇してゆきます。このプロセスにより誤差増幅器の出力電流と補償コンデンサの値で設定される時定数でソフトスタートが実行されます。ブラウンアウト、ロジックのディスエーブル、VCCの低電圧異常が起こった場合、COMPはアクティブに“L”レベルになり、PWMはこれらの事象がクリアされた後ソフトスタートを行います。また、UCC28061は出力過電圧が検出された時ソフトスタートを有効にします。異常がごく短時間であっても、ソフトスタートは動作を再開する前に補償部品を完全に放電し、確実にソフトスタートを実行するようにします。詳細については図27を参照してください。

## 軽負荷時の動作

負荷電流が減少すると、誤差増幅器はCOMP電圧を下げることで入力電流を少なくするようにします。PHB(通常はCOMPに接続)が低入力ライン時0.8Vより下がると(高入力ライン時は1.1V)、チャネルBはスイッチングを停止し、チャネルAのオン時間はこれを補うため2倍になります。COMPが150mVより下がると、チャネルAもスイッチングを停止し、ループはヒステリック・コントロール・モードになります。PWMはレギュレーションを維持するためサイクルを省略します。

サイクルを省略する代わりに、UCC28061は負荷の減少につれオン時間をなだらかにゼロに低減させることができます。しかしながら、最大スイッチング周波数は制限されているため、非常な軽負荷では、不連続動作が可能になります。

## ダウンストリーム・コンバータへのコマンド

UCC28061では、PWMCNTLピンはPFC段とダウンストリーム・コンバータとの調整に使用されます。HVSENピンにより出力電圧が検出されます。出力電圧が目的とする範囲内にある時、PWMCNTLピンは内部でグランドに落とされ、ダウンストリーム・コンバータをイネーブルにするのに使用することができます。イネーブルのスレッショルドとヒステリシスは分圧比と抵抗値によりそれぞれ独立して調整することができます。また、HVSENピンはフェイルセーフの過電圧保護用としても使用することができます。分圧器を設計する時、このフェイルセーフの過電圧保護レベルが通常動作レベルよりも高く設定されているかどうか確認してください。

## VCC低電圧保護

VCCはPWMがその機能を開始するため低電圧スレッショルドより高くなくてはなりません。VCCが動作時このスレッショルドより低くなると、両方のゲート駆動出力とCOMPはアクティブに“L”レベルになります。VCCはPWMの機能が再開するためにはスレッショルドより高くななければなりません。

## VCC

VCCは13Vから21Vのバイアス電源に接続されます。レギュレーションが不十分な電源から電源が供給された場合、VCCに過度の電流が流れないようにするためにツェナー・ダイオードを外付けすることを推奨します。

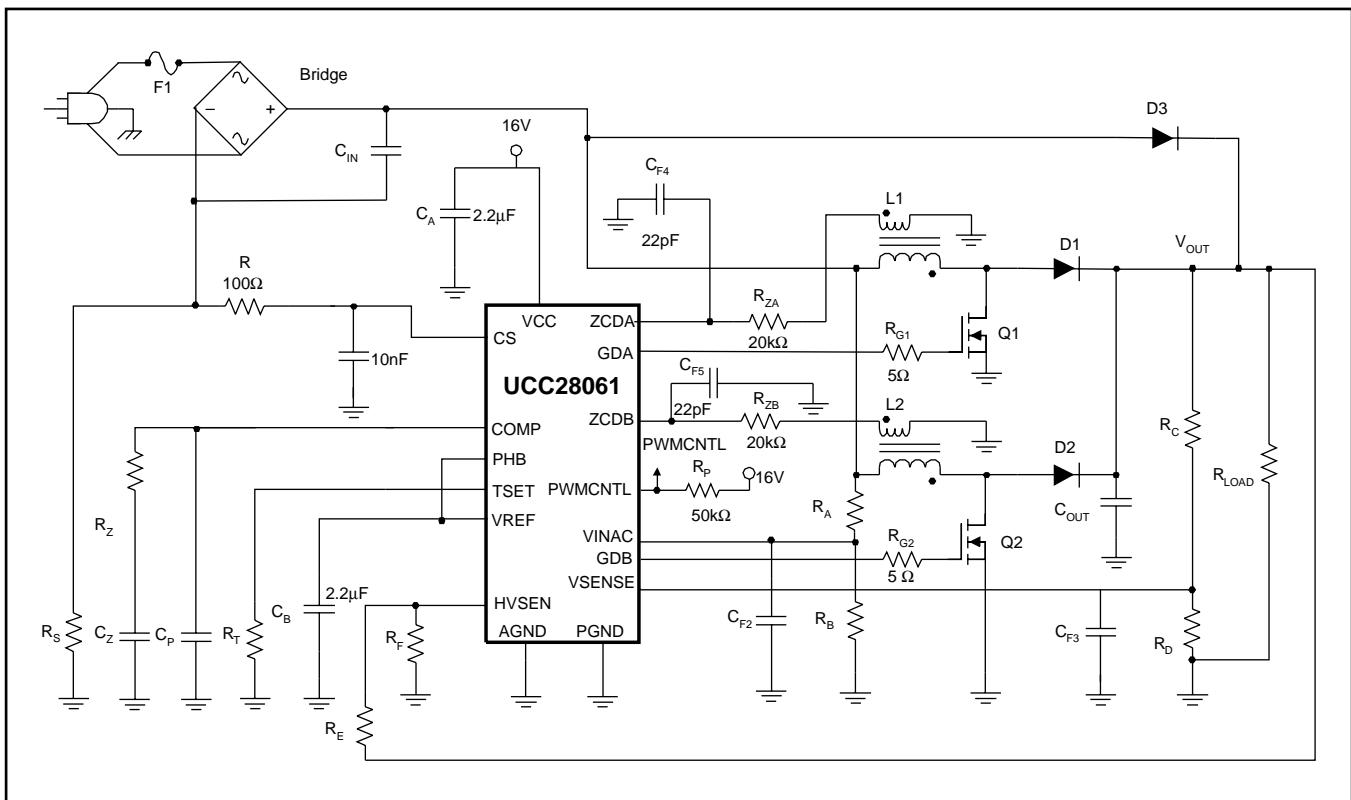

## 設計例

UCC28061PFCコントローラが2フェーズ臨界モードのインターリーブ方式PFCプリレギュレータに使用された例を図28に示します。

## 設計目標

当設計の仕様は300WのLCD TVの電力要件に基づいて選択されています。この仕様を表2に示します。

図28. Typical Transition Mode Interleaved PFC Pre-Regulator

| パラメータ      |             | MIN                  | TYP | MAX                   | 単位        |

|------------|-------------|----------------------|-----|-----------------------|-----------|

| $V_{IN}$   | RMS入力電圧     | 85 ( $V_{IN\_MIN}$ ) |     | 265 ( $V_{IN\_MAX}$ ) | $V_{RMS}$ |

| $V_{OUT}$  | 出力電圧        |                      | 390 |                       | V         |

| $f_{LINE}$ | ライン周波数      | 47                   |     | 63                    | Hz        |

| PF         | 最大負荷時の功率    | 0.90                 |     |                       |           |

| $P_{OUT}$  |             |                      |     | 300                   | W         |

| $\eta$     | 全負荷効率       | 0.92                 |     |                       |           |

| $f_{MIN}$  | 最小スイッチング周波数 | 45                   |     |                       | kHz       |

表2. 設計仕様

## 推奨するPCBとデバイスのレイアウト

インターリープ方式の臨界モードPFCシステムのアーキテクチャでは入出力リップル電流が劇的に低減するため、回路は小型で安価なフィルタを使用することができます。インターリープ方式の利点を最大限に生かすため、入出力フィルタ・コンデンサは2つのフェーズ電流が一体化した後に置かなければなりません。他のパワー・マネージメント・デバイスと同様に、プリント回路基板(PCB)をレイアウトした時は、スター・グランド手法を用いフィルタ・コンデンサができるだけデバイス・グランドに近づけておくことが重要です。ブースト・インダクタによる容量結合により生じる干渉を最小限に抑えるには、デバイスは

ブースト・インダクタから少なくとも1インチ(25.4mm)離して配置しなければなりません。また、デバイスを磁気部品の下に置かないようにすることも推奨します。タイミング条件が精密であるため、タイミング設定抵抗 $R_T$ はできるだけTSETピンの近くに置き、アナログ・グランドに戻さなければなりません。推奨する部品配置については図29を参照してください。

### 注：

PHBピンとVREFピンはボードの裏面でジャンパーで接続されています。

図29. Recommended PCB Layout

## インダクタの選択

ブースト・インダクタは低ラインのピーク時におけるインダクタのリップル電流要件に基づいて選択されます。インダクタを選択するには、式(7)に示されているように、低ラインのピーク時におけるブースト・コンバータのデューティ・サイクル( $D_{PEAK\_LOW\_LINE}$ )を計算することが必要です。

$$D_{PEAK\_LOW\_LINE} = \frac{V_{OUT} - V_{IN\_MIN} \sqrt{2}}{V_{OUT}} = \frac{390V - 85V \sqrt{2}}{390V} \approx 0.69 \quad (7)$$

低ライン状態でのコンバータの最小スイッチング周波数( $f_{MIN}$ )は低ラインのピーク時に現れ、可聴ノイズを回避するため25kHzから50kHzに設定します。当設計例では、 $f_{MIN}$ は45kHzに設定しています。

$$L_1 = L_2 =$$

$$\frac{\eta \times V_{IN\_MIN}^2 \times D_{PEAK\_LOW\_LINE}}{P_{OUT} \times f_{MIN}} = \frac{0.92(85V)^2 0.69}{300W \times 45kHz} \approx 340\mu H \quad (8)$$

当設計のインダクタのピーク電流( $I_{LPAGEK}$ )は式(9)に示されているように5.4A、RMS電流( $I_{LRMS}$ )は式(10)に示されているように2.2Aになります。

$$I_{LPAGEK} = \frac{P_{OUT} \sqrt{2}}{V_{IN\_MIN} \times \eta} = \frac{300W \sqrt{2}}{85V \times 0.92} \approx 5.4A \quad (9)$$

$$I_{LRMS} = \frac{I_{LPAGEK}}{\sqrt{6}} = \frac{5.4A}{\sqrt{6}} \approx 2.2A \quad (10)$$

このコンバータではコンバータのタイミングを構築するのに一定のオン時間( $T_{ON}$ )とゼロ電流スイッチング(ZCS)が用いられています。L1とL2の補助巻線がインダクタ電流がゼロになる時を検出します。式(11)の巻線比を選択することにより、毎スイッチング・サイクル後ZCDコンパレータをリセットするために高ラインのピーク時に少なくとも2Vが存在していることが確実になります。

$$\frac{N_P}{N_S} = \frac{V_{OUT} - V_{IN\_MAX} \sqrt{2}}{2V} = \frac{390V - 265V \sqrt{2}}{2V} \approx 8 \quad (11)$$

## ZCD抵抗の選択( $R_{ZA}, R_{ZB}$ )

ZCD抵抗の最小値は、式(12)に示されているように、内蔵のツエナー・ダイオードの最大クランプ電流定格3mAに基づいて選択されます。

$$R_{ZA} = R_{ZB} \geq \frac{V_{OUT} - N_S}{N_P \times 3mA} = \frac{390V}{8 \times 3mA} \approx 16.3k\Omega \quad (12)$$

当設計ではZCD抵抗は式(13)に示されているように20kΩに設定されています。

$$R_{ZA} = R_{ZB} = 20k\Omega \quad (13)$$

## HVSEN

HVSENピンはUCC28061のPWMCNTL出力をプログラムします。PWMCNTLのオープン・ドレイン出力はPFCの出力コンデンサが充電している間ダウンストリーム・コンバータをディスエーブルするのに使用することができます。PWMCNTLはハイ・インピーダンスで始まり、HVSENが2.5Vより高くなったら時グランドに落ちます。PWMCNTLがアクティブになる点を設定するにはブースト電圧からHVSENピン及びグランドへの抵抗分圧が必要となります。式(14)から式(18)に出力電圧がその標準値の90%以内である場合にPWMCNTLピンがアクティブになるための設定方法を示します。

$$V_{OUT\_OK} = V_{OUT} \times 0.90 \approx 351V \quad (14)$$

抵抗 $R_E$ は分圧器の上側を構成し、PWMCNTL信号のヒステリシスをプログラムします。当例では、式(15)に示されているように $R_E$ はヒステリシスが108Vとなるよう選択されます。

$$R_E = \frac{\text{Hysteresis}}{36\mu A} = \frac{108V}{36\mu A} = 3M\Omega \quad (15)$$

抵抗 $R_F$ は式(16)に示されているようにPWMCNTLのアクティブ・スレッショルドをプログラムするのに使用されます。

$$R_F = \left( \frac{2.5V}{V_{OUT\_OK} - 2.5V - 36\mu A} \right) = \frac{2.5V}{351V - 2.5V - 36\mu A} = \frac{2.5V}{3M\Omega} = 31.185k\Omega \approx 3.16k\Omega \quad (16)$$

このPWMCNTL出力は式(17)に示されている最小出力電圧( $V_{OUT\_MIN}$ )に達するまでアクティブのままであります。

$$V_{OUT\_MIN} = \frac{2.5V (R_E + R_F)}{R_F} = \frac{2.5V (3M\Omega + 31.6k\Omega)}{31.6k\Omega} \approx 240V \quad (17)$$

これらの抵抗値により、式(18)に従ってフェイルセーフのOVPスレッショルドが設定されます。

$$V_{OV\_FAILSAFE} = \frac{4.87V (R_E + R_F)}{R_F} = \frac{4.87V (3M\Omega + 31.6k\Omega)}{31.6k\Omega} \approx 467V \quad (18)$$

## 出力コンデンサの選択

出力コンデンサ( $C_{OUT}$ )は式(19)に示されているようにホールドアップ要件に基づいて選択されます。

$$C_{OUT} \geq \frac{2 \frac{P_{OUT}}{\eta} \frac{1}{f_{LINE}}}{V_{OUT}^2 - (V_{OUT\_MIN})^2} = \frac{2 \frac{300W}{0.92} \frac{1}{47Hz}}{(390V)^2 - (240V)^2} \approx 147\mu F \quad (19)$$

100μFのコンデンサを2つ並列にして出力コンデンサとして用います。

$$C_{OUT} = 200\mu F \quad (20)$$

この大きさのコンデンサの場合、出力電圧リップル( $V_{RIPPLE}$ )は式(21)に示されているように約11Vになります。

$$V_{RIPPLE} = \frac{2 \times P_{OUT}}{\eta} \frac{1}{V_{OUT} \times 4\pi \times f_{LINE} \times C_{OUT}} = \frac{2 \times 300W}{0.92 \times 390V \times 4\pi \times 47Hz \times 200\mu F} \approx 14V \quad (21)$$

ホールドアップ要件に加え、コンデンサは低周波のRMS電流( $I_{COUT\_100Hz}$ )と高周波のRMS電流( $I_{COUT\_HF}$ )への耐性をもつよう選択しなければなりません。式(22)から式(24)を参照してください。高電圧の電解コンデンサでは、通常、低周波/高周波のRMS電流定格が製品のデータシートに記載されています。

$$I_{COUT\_100Hz} = \frac{P_{OUT}}{V_{OUT} \times \eta \times \sqrt{2}} = \frac{300W}{390V \times 0.92 \times \sqrt{2}} = 0.591A \quad (22)$$

$$I_{COUT\_HF} =$$

$$\sqrt{\left(\frac{P_{OUT} 2 \sqrt{2}}{2 \times \eta \times V_{IN\_MIN}} \sqrt{\frac{4 \sqrt{2} V_{IN\_MIN}}{9\pi V_{OUT}}}\right)^2 - (I_{COUT\_100Hz})^2} \quad (23)$$

$$I_{COUT\_HF} =$$

$$\sqrt{\left(\frac{300W \times 2 \sqrt{2}}{2 \times 0.92 \times 85V} \sqrt{\frac{4 \sqrt{2} \times 85V}{9\pi \times 390V}}\right)^2} = (0.591A)^2 \approx 0.966A \quad (24)$$

## ピーク電流制限用 $R_S$ の選択

UCC28061のピーク制限コンパレータがトータル入力電流を検出し、突入電流や過負荷状態時にMOSFETを保護するのに使用されます。信頼性を高めるため、式(25)に示されているように当設計でのピーク電流制限( $I_{PEAK}$ )スレッショルドは起動時に観測される標準突入電流の120%に設定されています。

$$I_{PEAK} = \frac{2P_{OUT} \sqrt{2} (1.2)}{\eta \times V_{IN\_MIN}} = \frac{2 \times 300W \times \sqrt{2} \times 1.2}{0.92 \times 85V} \approx 13A \quad (25)$$

式(26)に示されているように、電流の検出には標準の15mΩの金属皮膜の電流検出抵抗が用いられます。電流検出抵抗の電力損失(PRS)の推定値は式(27)に示されているように通常動作時0.25Wよりも小さくなります。

$$R_S = \frac{200mV}{I_{PEAK}} = \frac{200mV}{13A} \approx 15m\Omega \quad (26)$$

$$PR_S = \left( \frac{P_{OUT}}{V_{IN\_MIN} \times \eta} \right)^2 R_S = \left( \frac{300W}{85V \times 0.92} \right)^2 \times 15m\Omega \approx 0.22W \quad (27)$$

電流検出抵抗を選択する際のもっとも重要なパラメータはサージ定格です。この抵抗はヒューズ(F1)を溶かすに要する電流より大きな短絡電流に対する耐性が必要です。 $I^2t$ (アンペア平方秒)はヒューズを溶かすに必要な電流により生じる熱エネルギーの尺度で、 $I^2t$ はRMS電流の二乗に電流が流れる時間(単位:秒)を乗じたものです。設計で短絡状態とならないようにするために $I^2t$ が14A<sup>2</sup>sの4Aのヒューズが選択されています。確実に電流検出抵抗がサージ保護に対し十分に高くなるよう、当設計では15mΩ、500mWのmetal-strip抵抗が選択されています。この抵抗は5秒間で2.5Wのサージ定格をもっています。式(27)に示されているように、この結果は833A<sup>2</sup>sになり、ヒューズが溶ける前に短絡回路を乗り切るのに十分に高い $I^2t$ です。

$$I^2t = \frac{2.5W}{0.015\Omega} \times 5s = 833A^2s \quad (28)$$

## パワー半導体の選択 (Q1, Q2, D1, D2)

Q1、Q2、D1、D2は設計の電力要件に基づいて選択されます。アプリケーション・ノートSLUU138 “UCC38050 100W Critical Conduction Power Factor Corrected (PFC) Pre-Regulator” に、臨界モードPFCプリレギュレータ用パワー半導体の選択方法が説明されています。

MOSFETの最大パルス・ドレイン電流 (Q1, Q2) を式(29)に示します。

$$I_{DM} \geq I_{PEAK} = 13A \quad (29)$$

MOSFETのRMS電流の計算式 (Q1, Q2) を式(30)に示します。

$$\begin{aligned} I_{DS} &= \frac{I_{PEAK}}{2} \sqrt{\frac{1}{6} - \frac{4\sqrt{2}V_{IN\_MIN}}{9\pi \times V_{OUT}}} \\ &= \frac{13A}{2} \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \times 85V}{9\pi \times 390V}} \approx 2.3A \end{aligned} \quad (30)$$

設計の電力要件に適合するため、Q1とQ2にはIRFB11N50A、定格500VのMOSFETを選択します。

ブースト・ダイオードのRMS電流 (D1, D2) を式(31)に示します。

$$I_D = \frac{I_{PEAK}}{2} \sqrt{\frac{4\sqrt{2}V_{IN\_MIN}}{9\pi \times V_{OUT}}} = \frac{13A}{2} \sqrt{\frac{4\sqrt{2} \times 85V}{9\pi \times 390V}} \approx 1.4A \quad (31)$$

設計の電力要件に適合するため、D1とD2にはOn SemiconductorのMURS306T3、定格600Vのダイオードを選択します。

## ブラウンアウト保護

抵抗  $R_A$  と  $R_B$  は規定最小動作入力電圧の75%でブラウンアウトの保護がアクティブになるよう選択されます。抵抗  $R_A$  はブラウンアウト・ヒステリシス・コンパレータをプログラムし、ヒステリシスが21Vとなるよう選択されます。 $R_A$  と  $R_B$  は式(32)と式(33)に示されています。

当設計例では、入力が64VRMSより低くなった時ブラウンアウトはアクティブになり、入力が79VRMSに達した時非アクティブになります。

$$R_A = \frac{\text{Hysteresis}}{7\mu\text{A}} = \frac{21\text{V}}{7\mu\text{A}} = 3\text{M}\Omega \quad (32)$$

$$R_B = \frac{1.4\text{V} \times R_A}{V_{IN\_MIN} \times 0.75\sqrt{2} - 1.4\text{V}} = \frac{1.4\text{V} \times 3\text{M}\Omega}{85\text{V} \times 0.75\sqrt{2} - 1.4\text{V}} \approx 47\text{k}\Omega \quad (33)$$

## コンバータのタイミング

式(34)に示されているように、 $K_{TL}$ をもとに正確なオン時間 ( $T_{ON}$ ) に対するタイミング抵抗  $RTSET$  を選択します。確実に正常動作を行うには、最大ブースト・インダクタンス ( $L_{1MAX}$ ) に基づいてタイミングを設定しなければなりません。当設計例では、式(35)に示されているようにブースト・インダクタはライン及び負荷状態に基づき390μHです。

$$\begin{aligned} f_{MIN} &= \frac{\eta \times (V_{IN\_MIN})^2 \left[ 1 - \frac{V_{IN\_MIN} \times \sqrt{2}}{V_{OUT}} \right]}{P_{OUT} \times L_{1MAX}} \\ &= \frac{0.92 \times (85\text{V})^2 \left[ 1 - \frac{85\text{V} \times \sqrt{2}}{390\text{V}} \right]}{300\text{W} \times 390\mu\text{H}} = 39.2\text{kHz} \end{aligned} \quad (34)$$

$$\begin{aligned} R_{TSET} &= \frac{133\text{k}\Omega \left[ 1 - \frac{V_{IN\_MIN} \times \sqrt{2}}{V_{OUT}} \right]}{4.85\text{V} \times 4\mu\text{s} \times f_{MIN}} \\ &= \frac{133\text{k}\Omega \left[ 1 - \frac{85\text{V} \times \sqrt{2}}{390\text{V}} \right]}{4.85\text{V} \times 4\mu\text{s} \times 39.2\text{kHz}} \approx 121\text{k}\Omega \end{aligned} \quad (35)$$

この結果により、式(36)に示されているように、最大周波数クランプ ( $f_{MAX}$ ) が設定され、これにより軽負荷時の効率が改善されます。

$$f_{MAX} = \frac{133\text{k}\Omega}{2\mu\text{s} \times R_T} = \frac{133\text{k}\Omega}{2\mu\text{s} \times 121\text{k}\Omega} \approx 550\text{kHz} \quad (36)$$

## $V_{OUT}$ のプログラミング

抵抗  $R_C$  はVSENSE入力バイアス電流による誤差を最小限に抑えるよう、また、PFCがディスエーブルの時電源ラインの負荷を最小限にするよう選択されます。高電圧の要件に適合させるため2つ以上の抵抗を直列接続して  $R_C$  を構築します。また、部品表の簡素化と設計コストの低減のため  $R_C$  は  $R_A$  や  $R_E$  と同じ値に選択されています。

式(37)から式(39)に示されている抵抗値に基づき、出力過電圧保護のスレッショルドは式(40)に示される値になります。

$$R_C = 3\text{M}\Omega \quad (37)$$

$$V_{REF} = 6\text{V} \quad (38)$$

$$R_D = \frac{V_{REF} \times R_C}{(V_{OUT} - V_{REF})} = \frac{6\text{V} \times 3\text{M}\Omega}{(390\text{V} - 6\text{V})} \approx 47\text{k}\Omega \quad (39)$$

$$V_{OVP} = 6.45V \frac{R_C \times R_D}{R_D} = 6.45V \frac{3M\Omega + 47k\Omega}{47k\Omega} = 418V \quad (40)$$

### ループ補償

抵抗 $R_Z$ は低周波リップルが電圧アンプの出力範囲の2%より低くなるような大きさにします。この値により、確実に効率が改善し入力電流の高調波歪みが小さくなります。

トランジスタコンダクタンス・アンプのゲインを式(41)に示します。

$$g_m = 96\mu S \quad (41)$$

分圧器のフィードバック・ゲインを式(42)と式(43)に示します。

$$H = \frac{V_{REF}}{V_{OUT}} = \frac{6V}{390V} \approx 0.015 \quad (42)$$

$$\begin{aligned} R_Z &= \frac{100mV}{V_{RIPPLE} \times H \times g_m} = \frac{100mV}{11V \times 0.015 \times 96\mu S} \\ &= 6.313k\Omega \approx 6.34k\Omega \end{aligned} \quad (43)$$

よって、式(44)に示されているように、 $C_Z$ はスイッチング周波数の1/5で45°の位相余裕が加わるよう設定されます。

$$C_Z = \frac{1}{2\pi \times \frac{f_{LINE}}{5} \times R_Z} = \frac{1}{2\pi \times \frac{47Hz}{5} \times 6.34k\Omega} = 2.67\mu F \quad (44)$$

$C_P$ は式(45)に示されているように高周波ノイズを減衰させる大きさにします。

$$C_P = \frac{1}{2\pi \times \frac{f_{MIN}}{2} \times R_Z} = \frac{1}{2\pi \times \frac{45kHz}{2} \times 6.34k\Omega} = 1.12nF \quad (45)$$

$C_Z$ と $C_P$ には式(46)と式(47)の標準値を選択しなければなりません。

$$C_Z = 2.2\mu F \quad (46)$$

$$C_P = 1nF \quad (47)$$

## 補足資料

### 関連製品

表3にUCC28061に類似した特性をもつTI製品を挙げます。

### 参考資料

以下の参考資料、設計ツール、また、設計ソフトウェアなどの補足資料へのリンクはホームページwww.power.ti.comを参照してください。

- Evaluation Module, UCC28060EVM 300W interleaved PFC Pre-regulator, SLUU280 from Texas Instruments

- Application Note, UCC38050 100-W Critical Conduction Power Factor Corrected (PFC) Pre-regulator, SLUU138 from Texas Instruments

### パッケージ・アウトラインと推奨するPCBのフットプリント

このデータシートの最後にパッケージの機械的特性として16ピンD(SOIC)パッケージの機械的寸法とPCBの推奨レイアウトが記載されています。

| デバイス名    | 機能                                           |

|----------|----------------------------------------------|

| UCC28051 | 低/中程度のパワー・アプリケーション用PFCコントローラ                 |

| UCC28019 | 8ピン連続導通モード(CCM)PFCコントローラ                     |

| UCC28060 | Natural Interleaving™デュアル・フェーズ臨界モードPFCコントローラ |

表3. 関連製品

# パッケージ・マテリアル情報

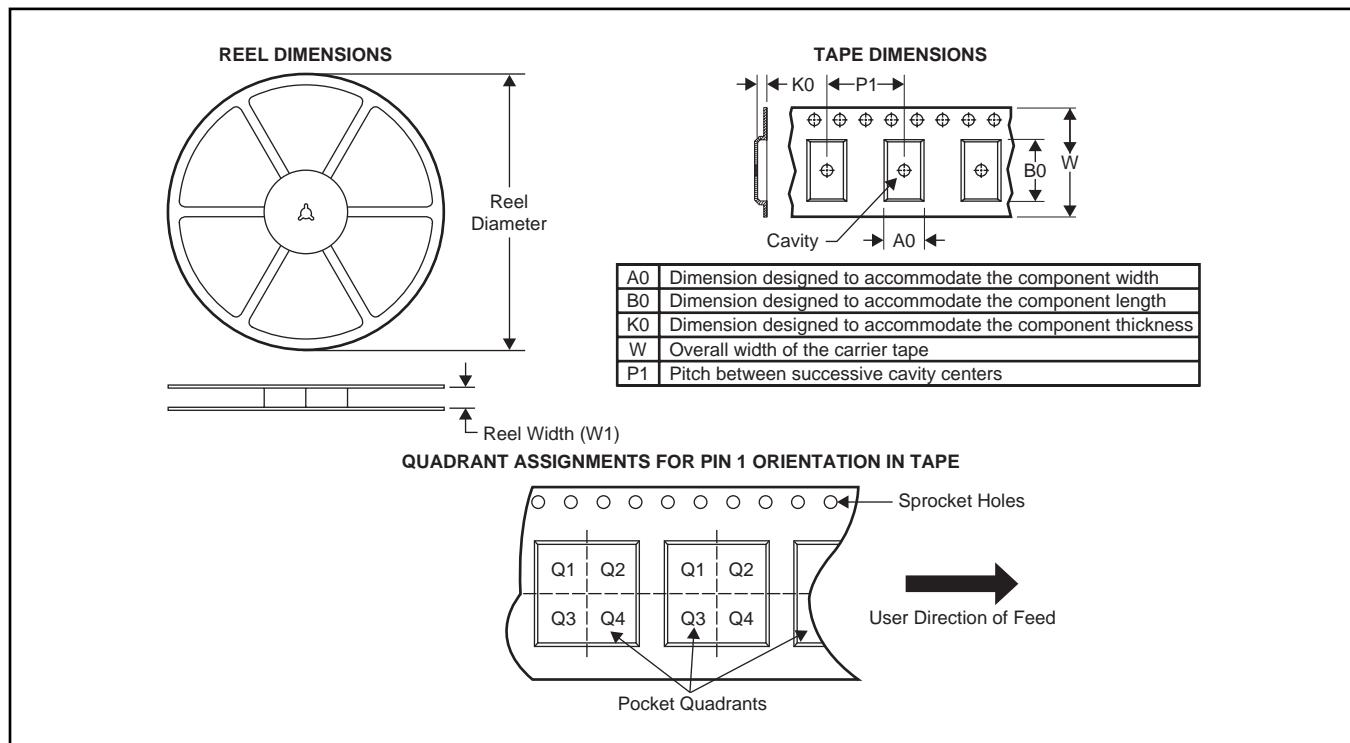

## テープおよびリール・ボックス情報

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC28061DR | SOIC         | D               | 16   | 2500 | 330.0              | 16.4               | 6.5     | 10.3    | 2.1     | 8.0     | 16.0   | Q1            |

## パッケージ・マテリアル情報

テープおよびリール・ボックス情報

\*All dimensions are nominal

| Device     | PackageType | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|-------------|-----------------|------|------|-------------|------------|-------------|

| UCC28061DR | SOIC        | D               | 16   | 2500 | 333.2       | 345.9      | 28.6        |

# メカニカル・データ

D(R-PDSO-G16)

PLASTIC SMALL-OUTLINE PACKAGE

注：A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. 図は予告なく変更することがあります。

△ボディ長はモールド突起部やゲートのバリを含みません。モールド突起部やゲートのバリは端部あたり0.006(0,15)を越えません。

△ボディ幅はリード間のバリを含みません。リード間のバリは片面あたり0.017(0,43)を越えません。

E. JEDEC MS-012改AAを参照しています。

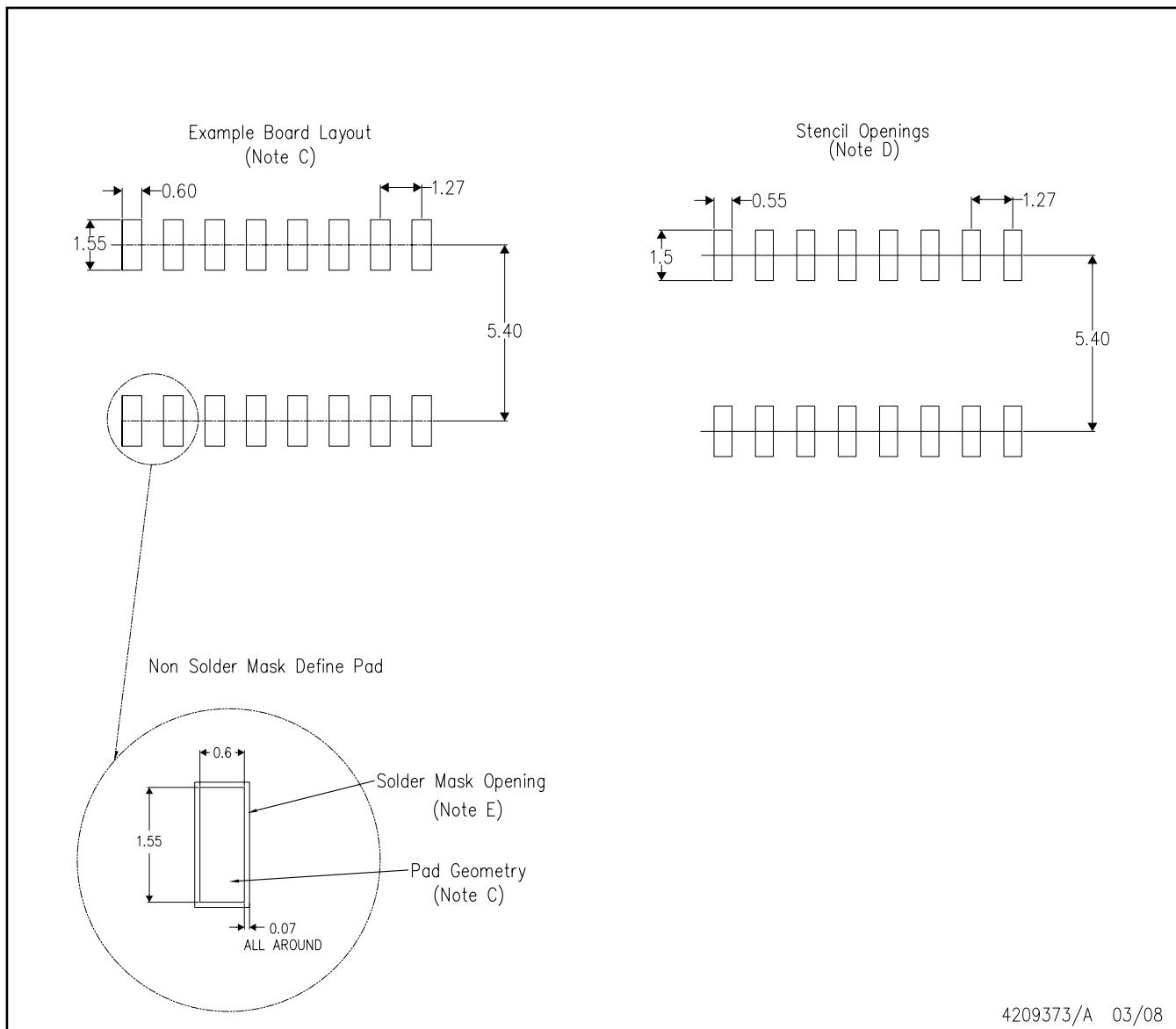

# ランド・パターン

## ランド・パターン

D (R-PDSO-G16)

注：注A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 設計代案についてはIPC7351を参照してください。

D. レーザーカットの開口部に台形の壁をつけ、角に丸みをつけるとペースト離れがよくなります。

カスタマはステンシルの設計についてボード製作側に提案しなければなりません。IPC-7525を参照してください。

E. カスタマは信号パッド間及びパッド周りのはんだマスクの許容値についてボード製作側に連絡しなければなりません。

**PACKAGING INFORMATION**

| Orderable part number      | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28061D</a>  | Active        | Production           | SOIC (D)   16  | 40   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28061            |

| UCC28061D.B                | Active        | Production           | SOIC (D)   16  | 40   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28061            |

| UCC28061DG4                | Active        | Production           | SOIC (D)   16  | 40   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28061            |

| <a href="#">UCC28061DR</a> | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28061            |

| UCC28061DR.B               | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28061            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UCC28061 :**

- Automotive : [UCC28061-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月