## プッシュプル型 高精度コントローラ(デッドタイム付き)

### 特 長

- 設定可能なデッドタイム付きプッシュプル型の高精度な発振回路を内蔵

- 大電流駆動可能なトーテムポール型のデュアル出力段により電流シンク能力1A/電流ソース能力0.5Aのプッシュプル構成可能

- プッシュプル、ハーフブリッジ、フルブリッジの制御に使用可能

- 外部同期機能端子内蔵

- 低起動時電流: 130μA、動作時電流: 1.4mA

- 過電流シャットダウン機能内蔵

- デジタル・コントロールによる過電流/リトライ機能

- 低電圧検出機能(ヒステリシス付き)

### アプリケーション

- 高効率カスケード型コンバータ

- インバータ

- 電子バラスト

- 無停電電源装置(UPS)

- 交流/直流リンク

### 概 要

UCC28089は、DC/DC或いは商用オフラインのスイッチング電源用に開発された、固定周波数動作でBiCMOSプロセスを使用した汎用コントローラです。UCC28089は2つの出力が交互に切り替わるプッシュプル構成のデュアル出力段をもっています。両出力ともT型リップルフロップ回路を使用して発振器周波数の半分の周波数で切り替わるため、デューティ・サイクルは常に50%以下に制限されています。

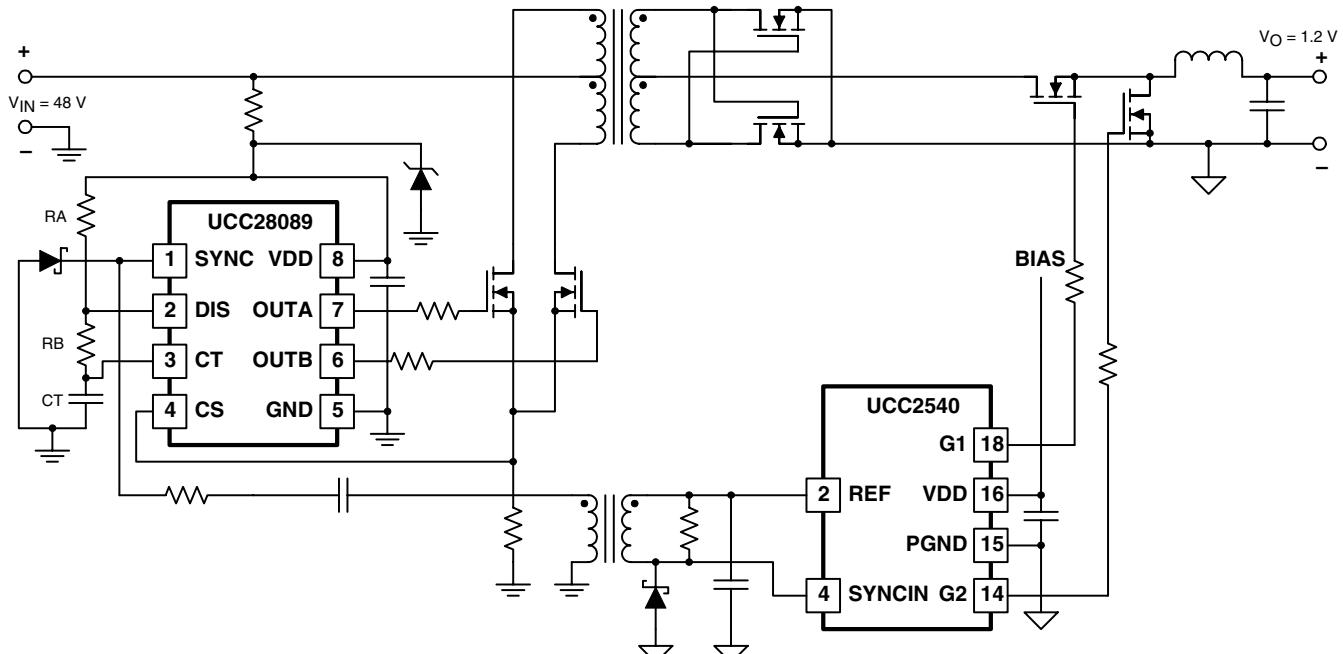

### TYPICAL APPLICATION

UDG-04112

Spartanは、Xilinxの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 概要(続き)

UCC28089は、二次側コントロールをもつカスケード型コンバータ用の一次側コントローラとして使用することにも最適化されています。このデバイスにはデッドタイムの設定機能が内蔵されています。また、外部同期出力からもデッドタイム情報等は信号として検出することができます。再起動及びソフトスタートの期間は安定かつ高性能の動作が実現できるよう発振器のクロック周波数により拡大/縮小します。

## ORDERING INFORMATION

| TEMPERATURE RANGE<br>$T_A = T_J$ | PACKAGED DEVICES† |

|----------------------------------|-------------------|

|                                  | SOIC-8 (D)        |

| -40°C to 105°C                   | UCC28089D         |

† D (SOIC-8) パッケージはテープ/リールで供給されています。リール当たりの数量は2500個で型番にRを付けてください(例、UCC28089DR)。

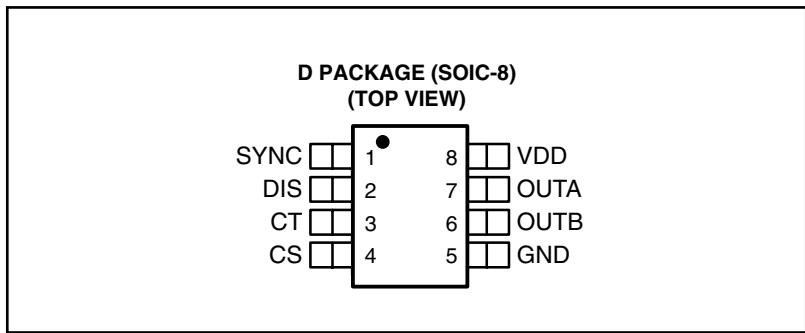

## CONNECTION DIAGRAM

また、UCC28089には一次側の低電圧保護機能(UVLO)と、過電流保護機能が備えられています。高い性能を実現するため、異常信号検出後のソフトスタート及び再起動の両方とも発振器周波数により拡大/縮小します。UVLOのターンオン/ターンオフ・スレッシュホールド電圧はそれぞれ10.5V/8.0Vです。

**ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature (unless otherwise noted)†‡

| PARAMETER                                                   | SYMBOL                   | RATING                                   | UNITS            |

|-------------------------------------------------------------|--------------------------|------------------------------------------|------------------|

| Supply voltage ( $I_{DD} < 10 \text{ mA}$ )                 | $V_{DD}$                 | 15                                       | V                |

| Supply current                                              | $I_{DD}$                 | 20                                       | mA               |

| OUTA/OUTB sink current (peak)                               | $I_{OUT}(\text{sink})$   | 1.0                                      | A                |

| OUTA/OUTB source current (peak)                             | $I_{OUT}(\text{source})$ | -0.5                                     |                  |

| SYNC sink current (peak)                                    |                          | 50                                       | mA               |

| SYNC source current (peak)                                  |                          | -50                                      |                  |

| Analog inputs (DIS, CT, CS)                                 |                          | -0.3 to $V_{DD} + 0.3$ , not to exceed 5 | V                |

| Power dissipation at $T_A = 25^\circ\text{C}$ (D package)   |                          | 650                                      | mW               |

| Power dissipation at $T_A = 25^\circ\text{C}$ (DRB package) |                          | TBD                                      |                  |

| Junction operating temperature                              | $T_J$                    | -55 to 150                               | $^\circ\text{C}$ |

| Storage temperature                                         | $T_{stg}$                | -65 to 150                               |                  |

| Lead temperature (soldering, 10 sec.)                       | $T_{sol}$                | +300                                     |                  |

† 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

‡ 全ての電圧はGNDを基準とされています。電流の極性で正は指定の端子に流入する方向、負は流出する方向を表しています。熱についての制限及びパッケージについての考察はデータブックのパッケージの項を参照してください。

**RECOMMENDED OPERATION CONDITIONS**

| Parameter                                   | Symbol           | MIN | TYP | MAX     | UNITS            |

|---------------------------------------------|------------------|-----|-----|---------|------------------|

| Supply voltage ( $I_{DD} < 10 \text{ mA}$ ) | $V_{DD}$         | 8.5 |     | 14      | V                |

| SYNC sink current (peak)                    |                  | 0   | 10  | 25      | mA               |

| SYNC source current (peak)                  |                  | -25 | -10 | 0       |                  |

| Analog inputs (DIS, CT, CS)                 |                  | 0   |     | 4       | V                |

| Timing capacitor range                      | CT               | 100 |     | 100,000 | pF               |

| Timing charge resistor range                | RA               | 32  |     | 750     | $\text{k}\Omega$ |

| Discharge resistor range                    | RB               | 0   |     | 250     |                  |

| Timing charge current                       | $I_{CHG}(RA+RB)$ | 10  |     | 300     | mA               |

| Switching Frequency                         | $f_{SW}$         |     |     | 1000    | kHz              |

| Junction temperature                        | $T_J$            | 40  |     | 105     | $^\circ\text{C}$ |

## 電気的特性

$T_A = 40^\circ\text{C}$  to  $105^\circ\text{C}$  for UCC28089,  $V_{DD} = 9\text{ V}$  (see Note 1), 1  $\mu\text{F}$  capacitor from  $V_{DD}$  to GND,  $RA = 110\text{ k}\Omega$ ,  $RB = 182\text{ }\Omega$ ,  $CT = 220\text{ pF}$ ,  $T_A = T_J$ , (unless otherwise noted).

| PARAMETER                             | TEST CONDITION                                                                       | MIN   | TYP   | MAX   | UNITS         |

|---------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| <b>Overall Section</b>                |                                                                                      |       |       |       |               |

| Startup current                       | $V_{DD} < \text{UVLO start threshold}$ (see Note 2)                                  |       | 130   | 260   | $\mu\text{A}$ |

| Operating supply current              | $CS = 0\text{ V}$ , (see Note 1, Note 2)                                             |       | 1.4   | 2.0   | $\text{mA}$   |

| <b>Undervoltage Lockout</b>           |                                                                                      |       |       |       |               |

| Start threshold                       | See Note 1                                                                           | 9.5   | 10.5  | 11.5  | $\text{V}$    |

| Minimum operating voltage after start |                                                                                      | 7.4   | 8.0   | 8.4   |               |

| Hysteresis                            |                                                                                      | 2.1   | 2.5   | 2.9   |               |

| <b>Oscillator</b>                     |                                                                                      |       |       |       |               |

| Oscillator frequency                  | 2 x OUTx frequency, Measured at output(s)                                            | 180   | 200   | 220   | $\text{kHz}$  |

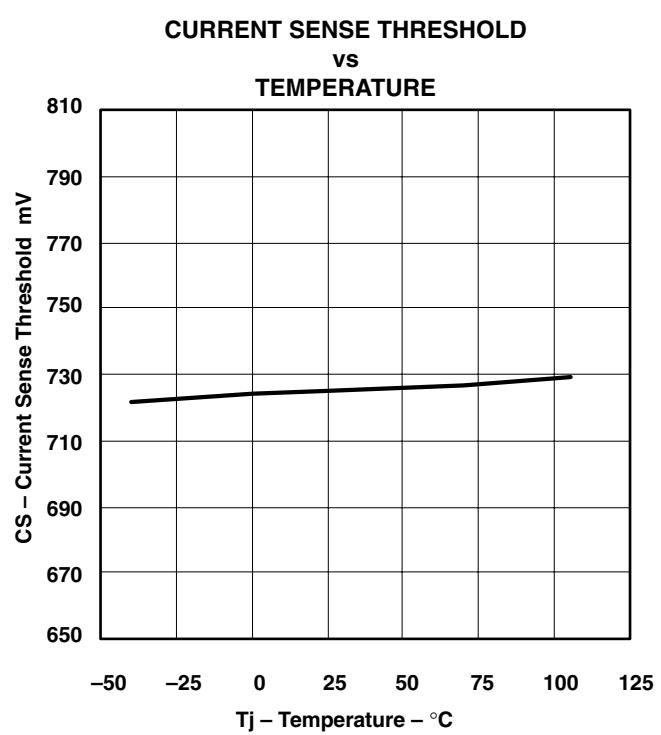

| <b>Current Sense</b>                  |                                                                                      |       |       |       |               |

| Current Shutdown threshold            | Resetting current limit                                                              | 0.650 | 0.725 | 0.800 | $\text{V}$    |

| CS to output delay                    | CS from 0 mV to 900 mV                                                               |       | 45    | 100   | $\text{ns}$   |

| <b>Output</b>                         |                                                                                      |       |       |       |               |

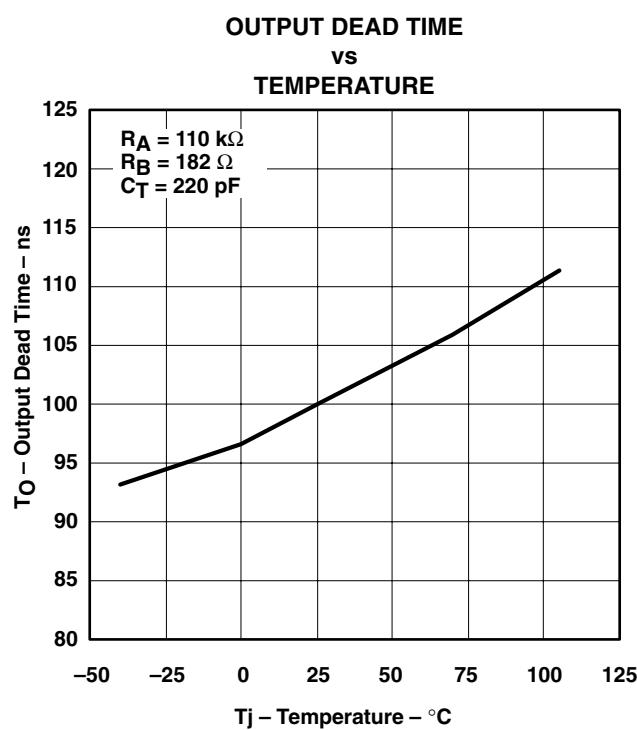

| Dead Time                             | Measured at OUTA or OUTB                                                             | 90    | 100   | 110   | $\text{ns}$   |

|                                       | Over temperature                                                                     | 80    |       | 125   |               |

| Minimum duty cycle                    | $CS = 0.9\text{ V}$                                                                  |       |       | 0     | %             |

| VOL (OUTA or OUTB)                    | $I_{OUT} = 75\text{ mA}$                                                             |       | 0.5   | 1     | $\text{V}$    |

| VOH (OUTA or OUTB)                    | $I_{OUT} = -35\text{ mA}, (V_{DD} - V_{OUT})$                                        |       | 1.0   | 1.3   |               |

| Output resistance high                | $T_A = 25^\circ\text{C}$ $I_{OUT} = -1\text{ mA}$ (see Note 4)                       | 70    | 80    | 90    |               |

| Output resistance low                 | $T_A = \text{full range}$ $I_{OUT} = -1\text{ mA}$ (see Note 4)                      | 40    | 80    | 135   | $\Omega$      |

|                                       | $T_A = 25^\circ\text{C}$ $I_{OUT} = 1\text{ mA}$ (see Note 4)                        | 6.5   | 7.5   | 8.5   |               |

|                                       | $T_A = \text{full range}$ $I_{OUT} = 1\text{ mA}$ (see Note 4)                       | 4     | 7.5   | 14    |               |

| tr, Rise Time                         | $C_{LOAD} = 1\text{ nF}$                                                             |       | 28    | 50    | $\text{ns}$   |

| tf, Fall Time                         | $C_{LOAD} = 1\text{ nF}$                                                             |       | 13    | 30    |               |

| <b>SYNC</b>                           |                                                                                      |       |       |       |               |

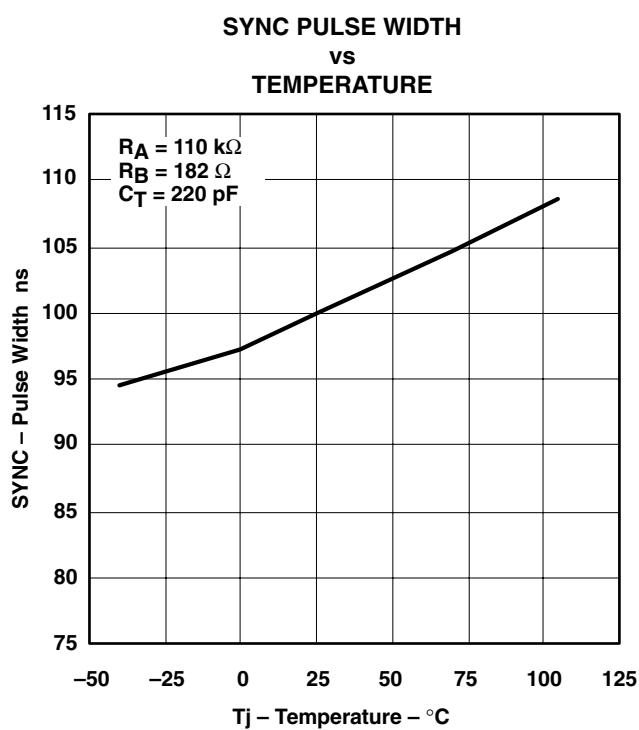

| SYNC duration                         | Measured at SYNC pin                                                                 | 75    | 95    | 115   | $\text{ns}$   |

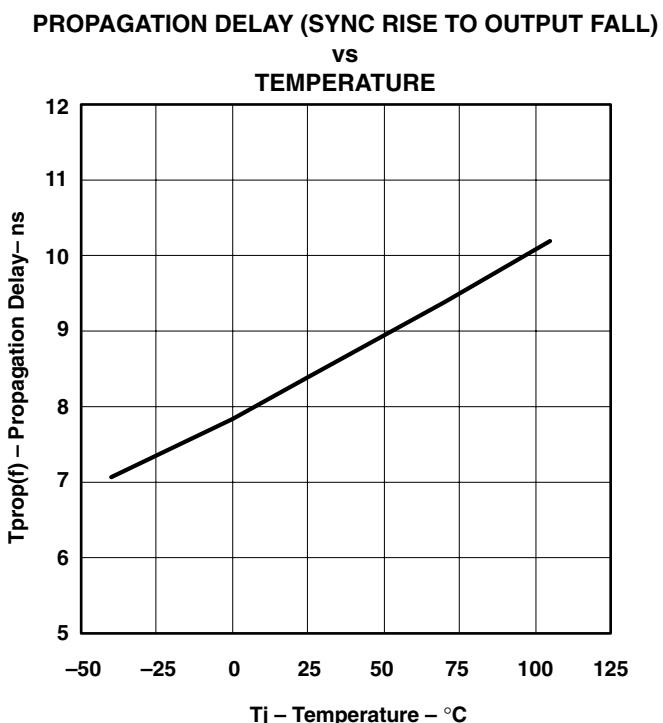

| tr, delay                             | Rising SYNC until falling OUTA or OUTB                                               | 0     | 8.5   | 30    |               |

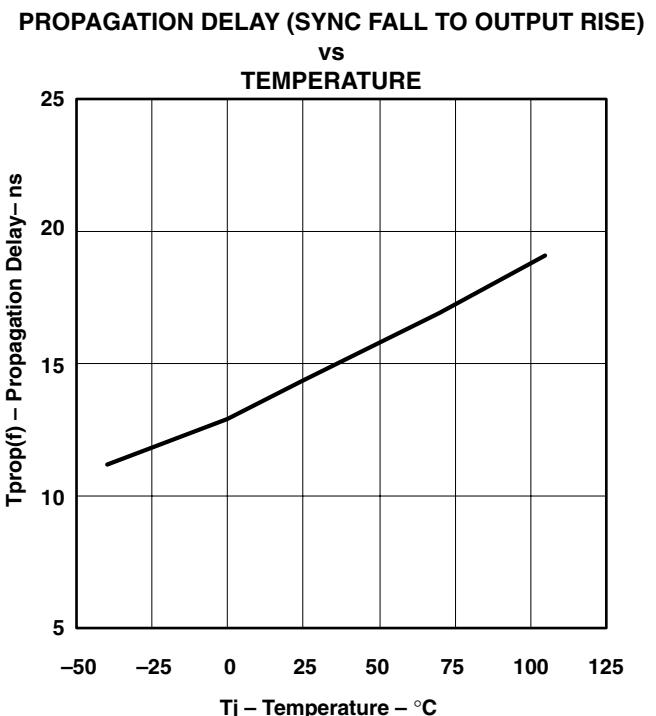

| tf, delay                             | Falling SYNC until rising OUTA or OUTB                                               | 0     | 14    | 50    |               |

| SYNC VOH                              | $I_{SYNC} = -5\text{ mA}$ ( $V_{DD} - V_{SYNC}$ )                                    |       | 0.3   | 1     | $\text{V}$    |

| SYNC VOL                              | $I_{SYNC} = 5\text{ mA}$                                                             |       | 0.3   | 1     |               |

| tr, Rise Time                         | $C_{LOAD} = 100\text{ pF}$                                                           |       | 15    | 30    | $\text{ns}$   |

| tf, Fall Time                         | $C_{LOAD} = 100\text{ pF}$                                                           |       | 15    | 30    |               |

| <b>Soft Start &amp; Fault</b>         |                                                                                      |       |       |       |               |

| OUTA/OUTB start delay time            | Cycles as measured at CT pin                                                         | 57    | 59    | 62    | cycles        |

| OUTA/OUTB soft start duration         | First output stage cycle to first full output stage cycle,<br>$CS \leq 0.6\text{ V}$ | 4     | 5     | 7     |               |

(1) 9Vに設定する前に起動スレッッシュホールド電圧より上にVDDを設定してください。

(2) 外部発振器回路の電流は含まれていません。

(3) 設計目標項目であり、テストは行われていません。

(4) ドライバのプルアップ/プルダウン回路にはバイポーラ・トランジスタとMOSFETトランジスタが並列に接続されています。ドライバ出力の電圧がバイポーラ・トランジスタの飽和電圧より低い場合、出力抵抗はMOSFETトランジスタのRDS(ON)になります。

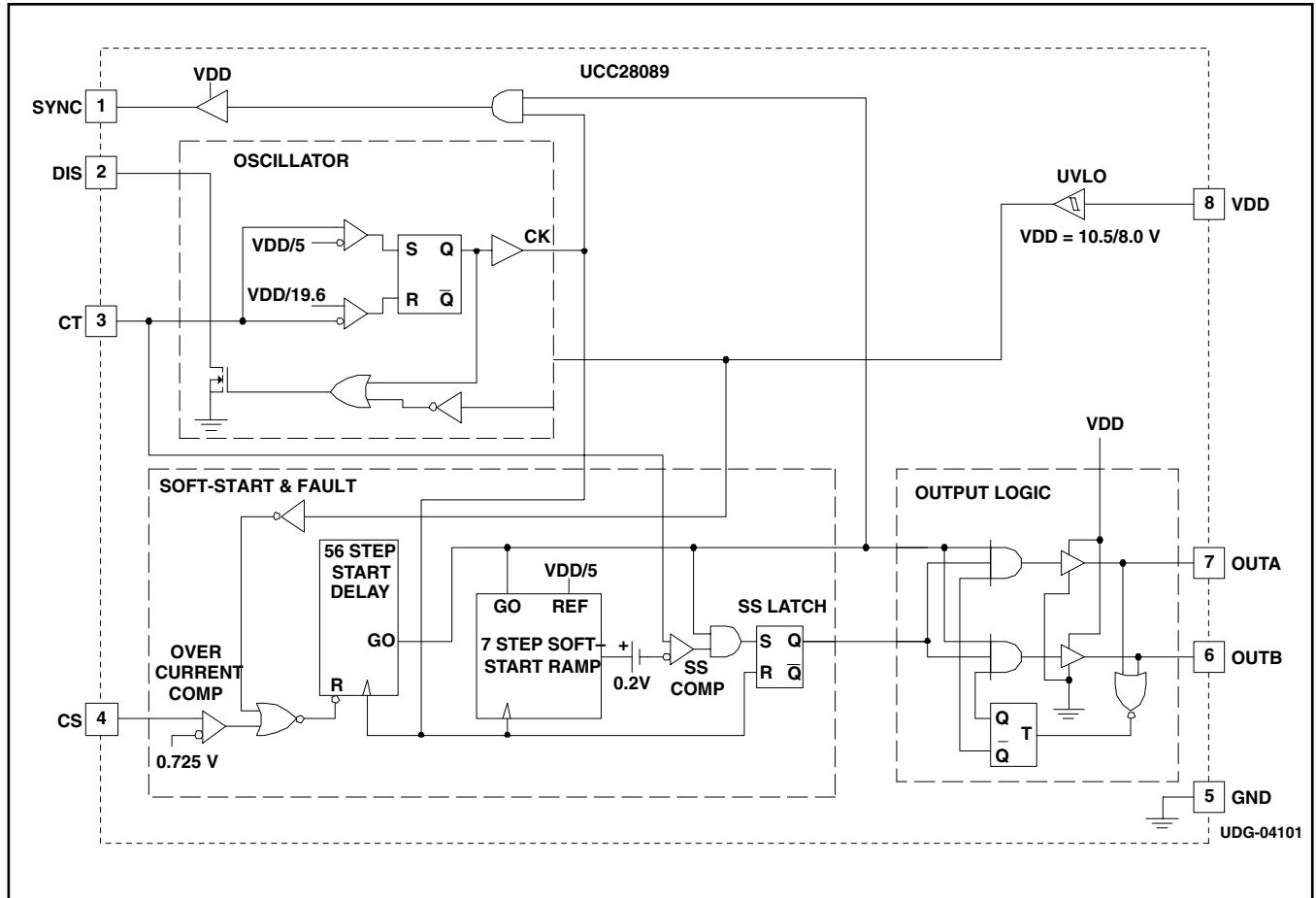

## FUNCTIONAL BLOCK DIAGRAM

| PIN # | NAME | I/O | 端子機能                                                                                                                                               |

|-------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SYNC | O   | OUTAとOUTBが動作時にはアクティブH状態です。低電圧検出時や過電流検出時等の場合はロジックレベルは“L”レベルになります。動作時、発振器の放電時間ではロジック“H”レベル (VDD) です、その他の全ての場合はロジック“L”レベル (GND) です。パルスはデッドタイム時に発生します。 |

| 2     | DIS  | I   | デッドタイムを外部から設定するための発振器タイミング・コンデンサ放電接続端子。                                                                                                            |

| 3     | CT   | I   | 発振器のタイミング・コンデンサ接続端子                                                                                                                                |

| 4     | CS   | I   | 過電流検出端子。この端子電圧が0.75V以上になった場合には過電流シャットダウン保護機能が動作します。                                                                                                |

| 5     | GND  | -   | グランド端子。アナログ／デジタル信号共通でこの端子を基準とし、出力ドライバもこの端子を介して電流を戻します。                                                                                             |

| 6     | OUTB | O   | 出力端子B。電流シンク能力が1A、ソース能力が0.5Aのドライバ出力。OUTB信号はOUTAと交互に切り替わります。                                                                                         |

| 7     | OUTA | O   | 出力端子A。電流シンク能力が1A、ソース能力が0.5Aのドライバ出力。OUTA信号はOUTBと交互に切り替わります。                                                                                         |

| 8     | VDD  | I   | このデバイス用の電源接続端子。                                                                                                                                    |

## アプリケーション情報

UCC28089は、過電流/低電圧保護機能を備え出力が交互に切り替わるデュアル・ドライバ出力をもつコントローラです。このデバイスは、ほとんどのコントロール機能が二次側で行われる絶縁型電源システムのコントローラに最適です。このデバイスはカスケード接続降圧型コンバータ[1]、交流リンクのインバータ制御方式[2]、安価な擬似インバータの制御用に特に優れた能力を発揮します。UCC28089には二次側でコントロールされるソフトスタートを妨げないように5から7サイクルの短いリーディング・エッジ変調のソフトスタート・サイクルがあります。常に再起動前に少なくとも発振器の5~6サイクル分遅れて異常信号に応答するため、オフラインの自己バイアス電源及び補助バイアス電源をもつシステムともUCC28089により信頼性が高くなります。

### 詳細機能説明

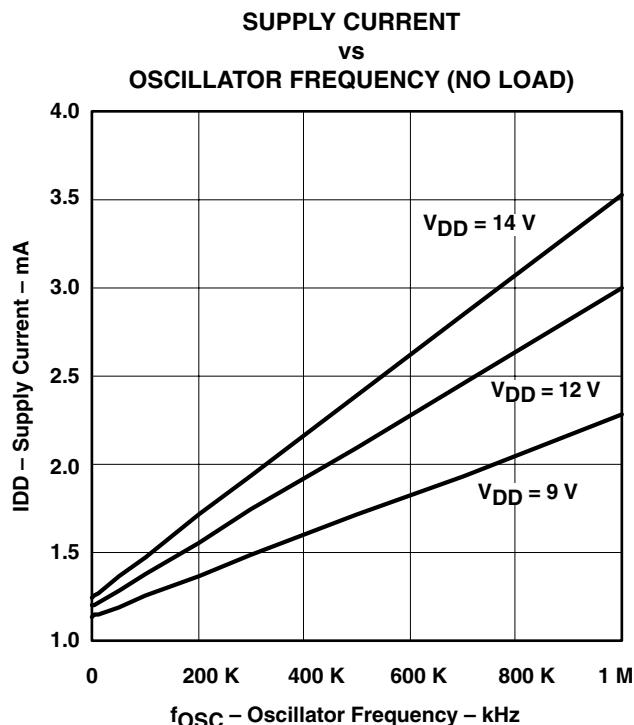

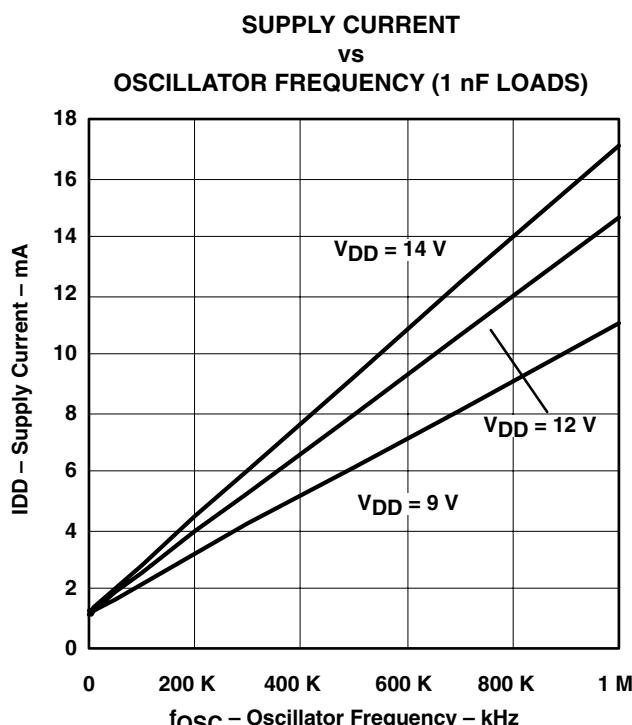

**VDD**：このデバイスの電源入力接続端子。静止電流のVDD電流は極めて小さいのですが、総消費電流は出力OUTAとOUTB電流及び設定される発振器周波数に大きく依存します。異常検出への応答時は、発振器が停止状態になるため電流は低いレベルに低下します。

動作安定、ノイズの問題を回避するため、 $1\mu F$ のセラミック・バイパス・コンデンサができるだけチップに近づけてVDD-GND間に別に接続してください。このセラミック・バイパス・コンデンサは、起動過渡時にVDD電圧を維持するために使用されるエネルギー保持用の通常のコンデンサに加えられます。

**GND**：グランド端子。アナログ/デジタル信号は共にこの端子を基準とし、出力ドライバはこの端子を介して電流を戻します。この端子をシステムグランド構成の1つの局所的なローカルグランド点として使用してください。

**OUTA、OUTB**：電流シンク能力が1A、ソース能力が0.5Aの出力ドライバ。出力パルスはOUTAとOUTBで交互に切り替わります。これはT型ラッチ回路により実現され 低デューティ比

での動作時にトランジストに形成される磁束を低減することにも役立ちます。

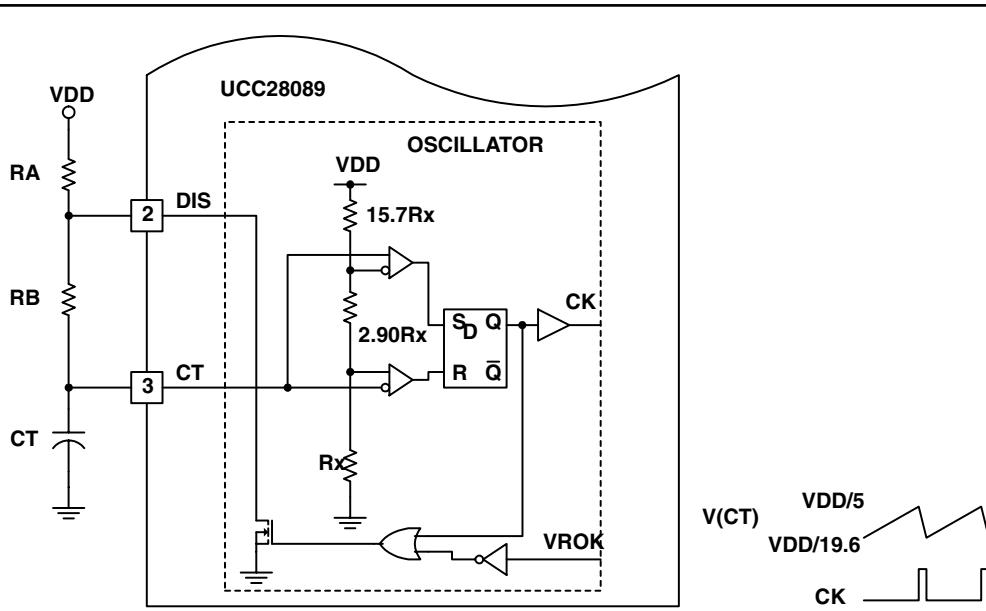

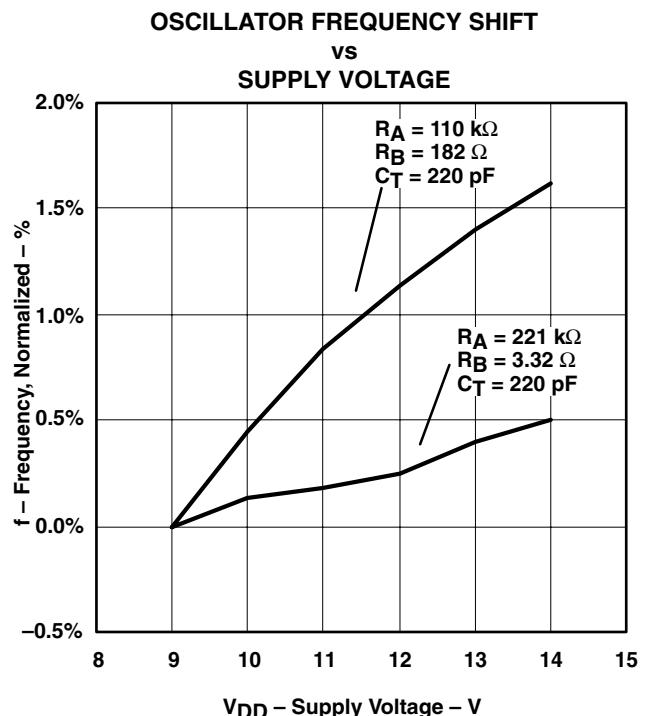

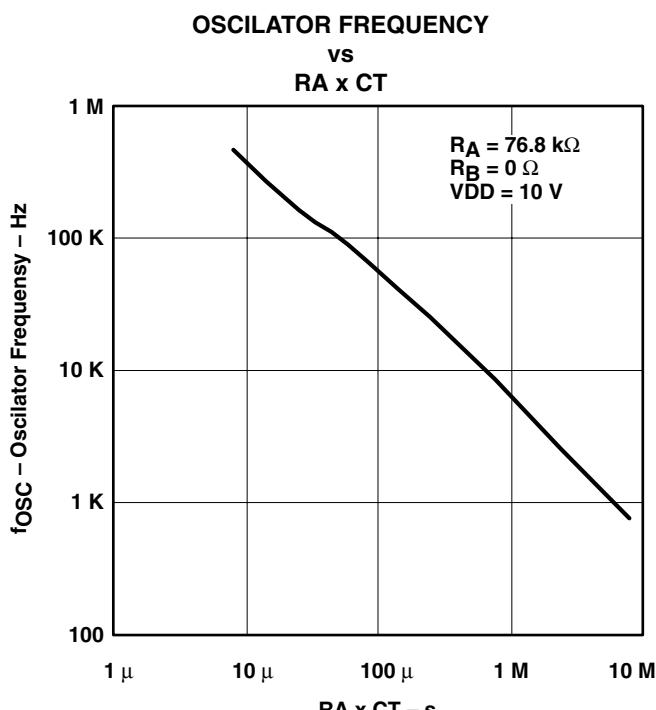

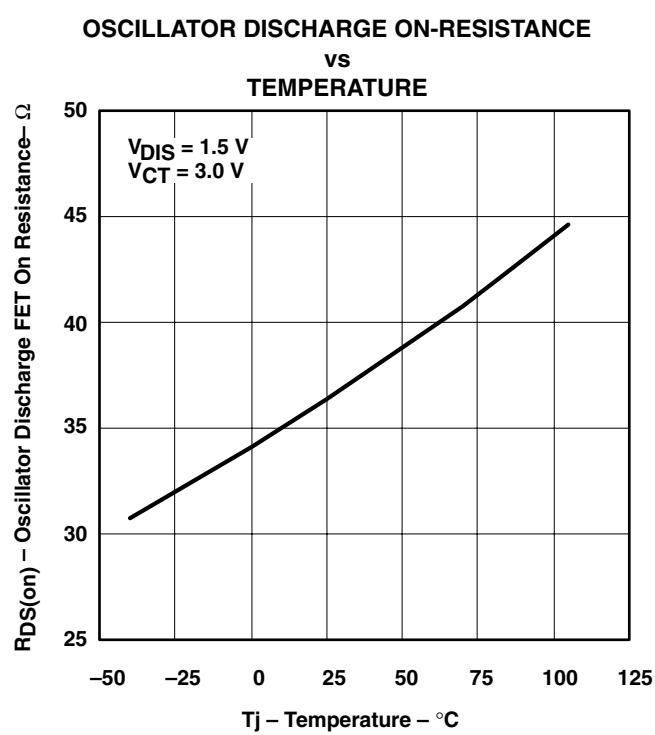

**CT、DIS**：発振器のタイミング・コンデンサ用端子及びデッドタイム設定のためのタイミング・コンデンサの放電用端子。UCC28089の発信器は、VDD電圧の変動による周波数の変化を最小限に抑えるため内部でVDDとGNDを監視し安定した動作を確保しています。図1に発振器のブロック図を示します。

推奨する発振器の最大周波数は1MHzです。ノイズの問題を回避するため、RAとRBは発振器に少なくとも $10\mu A$ の電流が流れよう設定してください。発振器をその広い設定範囲にわたってモデル化するために2つの発振器の設定の式があります。プローブのインピーダンスまたは出力ドライバの遅延による発振器への影響を回避するためSYNC端子で充電/放電時間を測定してください。

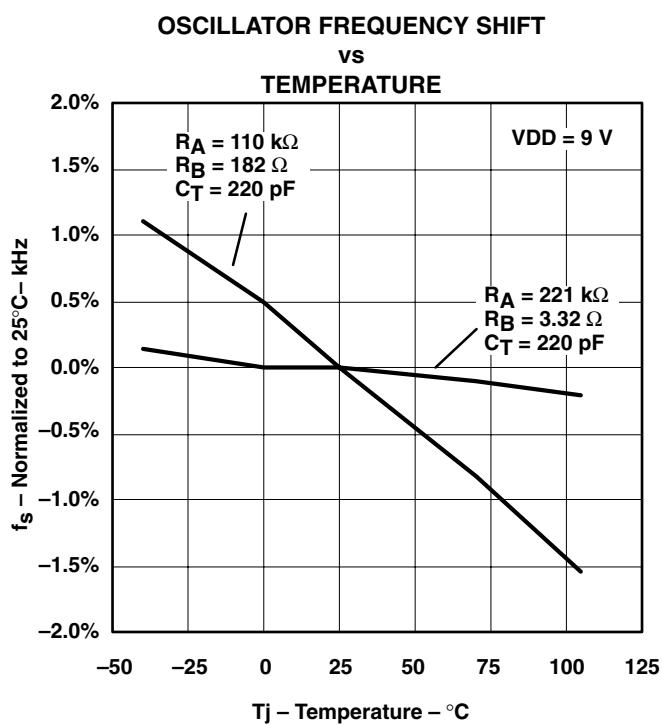

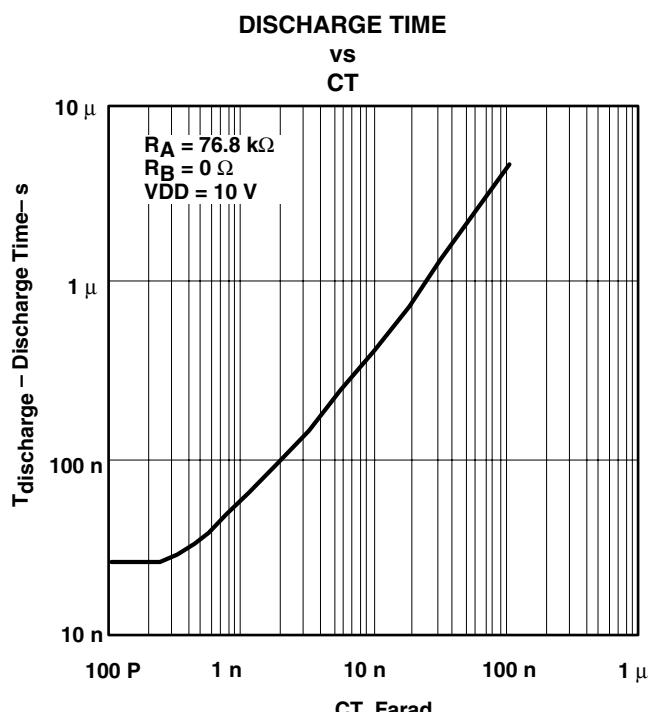

50kHzより低いスイッチング周波数及び/または $1\mu s$ より大きな放電時間では表中の1に示す近似式で十分です。表中の2に示す式に対して1に示す式を使用する場合に特有な条件とはタイミング・コンデンサの大きさと放電抵抗に関してです。1に示す式と2に示す式は実際の動作点の±20%以内の単なる近似式であることに留意してください。内部回路の周波数、充放電時間は比較的温度に関して影響を受けませんが、CTやRBは値が大きくなるにつれ温度に対する影響が大きいことに注意する必要があります。ちなみに、2に示す式は電気的特性表に記載されている動作条件に適合しています。発振器の周波数は以下の式に従い設定されます。

但し、単位はRA、RBは $\Omega$ 、CTはファラデー、foscはHz、Tcharge及びTdischargeは秒です。

発振器はCTタイミング・コンデンサの範囲が $100pF$ から $1000nF$ 、RBが $100\Omega$ 以上の場合に最適化されます。最小放電時間が求められた場合は、推奨のCT値( $100pF$ ~ $0.100\mu F$ )でDISをCTに短絡することができます。

図1. Block Diagram for Oscillator

|            | 1ST ORDER EQUATIONS                         | 2ND ORDER EQUATIONS                                                    |

|------------|---------------------------------------------|------------------------------------------------------------------------|

| Condition  | $R_A > 300 \Omega$ AND $C_T > 300\text{pF}$ | $100 \Omega < R_A < 300 \Omega$ OR $100\text{pF} < C_T < 300\text{pF}$ |

| TCHARGE    | $0.169(R_A + R_B)C_T$                       | $0.175(R_A + R_B)(C_T + 40\text{ pF}) + 20\text{ ns}$                  |

| TDISCHARGE | $1.36 R_B C_T$                              | $(1.37)(R_B + 44)(C_T + 14\text{ pF}) + 20\text{ ns}$                  |

| fOSC       | $\frac{5.9}{(R_A + 8.0 R_B)C_T}$            | $\frac{1}{T_{CHARGE} + T_{DISCHARGE}}$                                 |

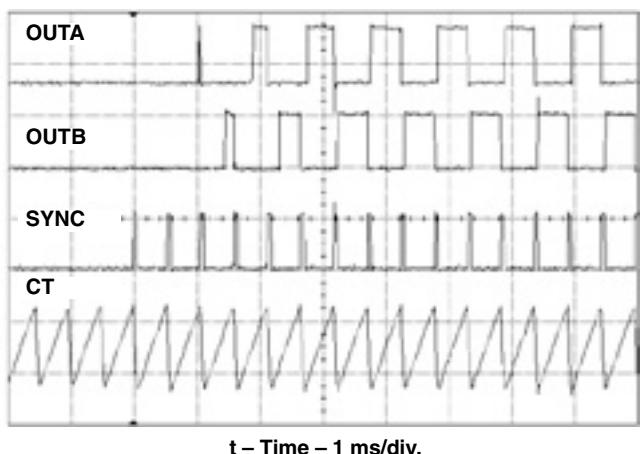

**SYNC**：このSYNC端子は二次側の降圧型コントローラなど外部回路と絶縁された回路を同期させるのに使用されます。0からVDDの出力パルスを生成します。この信号が適切なタイミングで出力されることにより一次側MOSFETでゼロ電圧スイッチングが可能になります。また、ノイズのない信号により、漏れインダクタンスの影響で誤ったトリガを引き起こす可能性のある電圧スパイクをもった同期信号がトランジスタの二次側から入る問題も解決されます。SYNCのパルス幅は発振器の放電時間で、デッドタイムにほぼ等しい大きさです。パルスの周波数は発振器の周波数です。異常状態時、SYNCパルスは停止し、SYNC出力は少なくとも発振器の56サイクルの間“L”レベルに保持されます。ソフトスタート時は、SYNCは最初の出力パルスより少なくとも発振器の1サイクル分先行して出力されます。

**CS**：電流検出回路（抵抗など）をこの端子に接続します。0.725Vの電圧スレッショールドでシャットダウンのシーケンスが開始します。

過電流異常が起こると即座にシャットダウンします。異常状態が取り除かれた後、ソフトスタートのシーケンスが完全に開始するには発振器の合計64サイクルが必要です。まず、出力とSYNCは少なくとも発振器の56サイクルの間オフに保たれます。次に、1~2個のSYNCパルスの後、ソフトスタートは発振器の次の5~7サイクルで出力のデューティ比を徐々に増加させます。

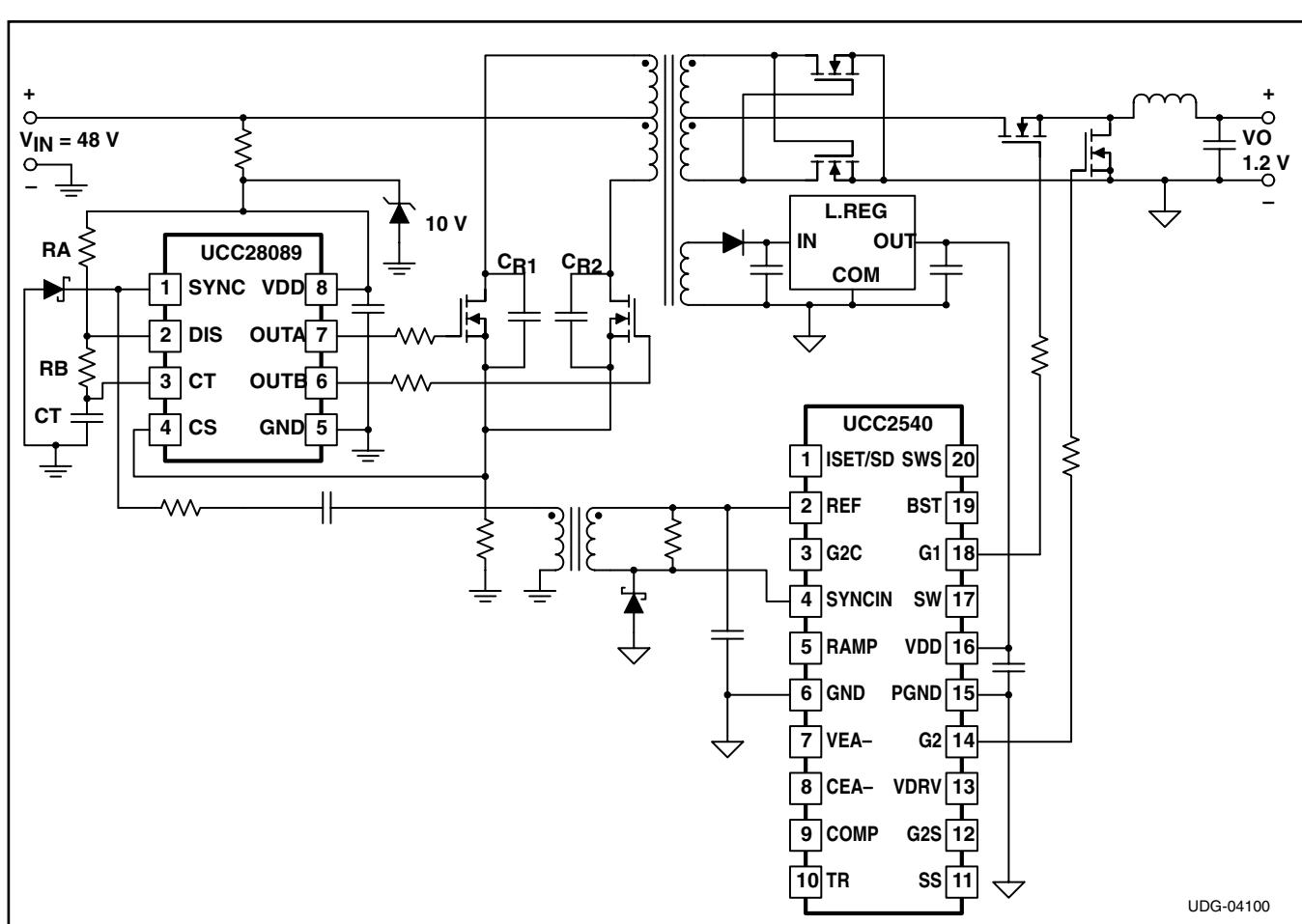

### UCC28089を2段カスケード接続プッシュプル型降圧コンバータの一次側起動コントローラとして使用した場合

カスケード接続のプッシュプル型制御は、テレコム用の48V電圧など電圧から2Vのサブ出力電圧への変換に最適です。一次側の起動コントローラとしてUCC28089、二次側のレギュレータとしてUCC2540[3]を使用した制御の概略を図2に示します。

図2. Cascaded Push-Pull Buck Two-Stage Converter

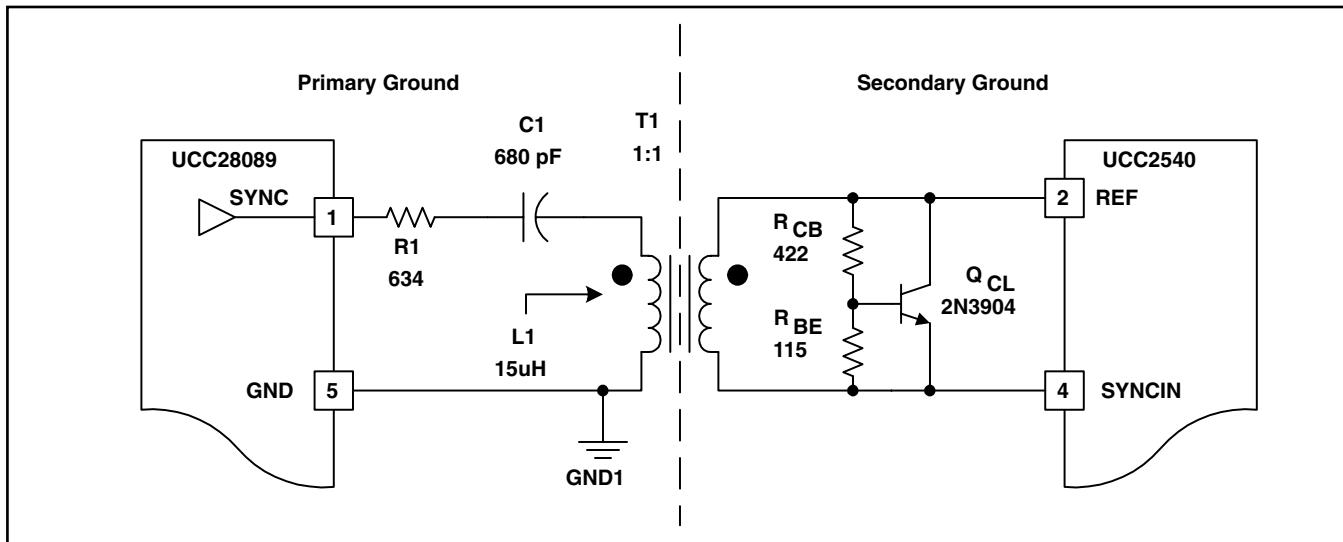

図3. Isolation and clamping the SYNC signal for Cascaded Buck Converters

UCC28089の発振器周波数を出力レギュレータの所望スイッチング周波数に等しくなるよう設定します。また、二次側のコントローラにもUCC2540のRAMP及びG2Cコンデンサ値など、対応するスイッチング周波数を設定することができます。デッドタイムがトランスの一次側漏れインダクタンス及び一次側パワーMOSFETトランジスタの総ドレイン/ソース間容量( $C_{oss}$ +浮遊容量)により形成される等価寄生L-C回路の共振周期の約1/4となるよう設定します。 $C_{oss}$ は入力ライン電圧により変動をすることに留意してください。この変動が余りにも大きく、及び/または、共振周期の1/4が100nsより小さい場合は、一次側トランジスタのドレイン/ソース間に容量を追加接続し(図2の $C_{R1}$ と $C_{R2}$ )、そのことにより容量が安定し総容量値が上がります。

二次側コントローラがパルス・エッジに対応していれば、図3のパルス・エッジのトランス回路により直径6mmまたはそれ以下のトランス・コアを用いて二次側に絶縁されたパルス・エッジ信号を供給することができます。推奨トランス(COEV #MGBT-0001101)は全スイッチング周波数に対応しており、多くの光絶縁器よりも小型です。

ピーク・パルス電圧はUCC28089のバイアス電圧に比例することに注意してください。図3の回路はクランプ回路をもっているためUCC28089バイアス電圧の全VDDバイアス電圧範囲に適しています。図3のクランプ回路( $R_{CB}$ 、 $R_{BE}$ 、 $Q_{CL}$ )はツェナー・ダイオードではなく $V_{BE}$ クランプです。クランプが50nsの狭パルス幅に影響しないほどのツェナー・ダイオードよりもかなり低い容量であるため、ここでは $V_{BE}$ クランプを使用しています。このクランプは、図2のUCC28089のVDDバイアス電圧が±5%の範囲内にレギュレーションされるアプリケーションでは1つの抵抗で置き換えることができます。

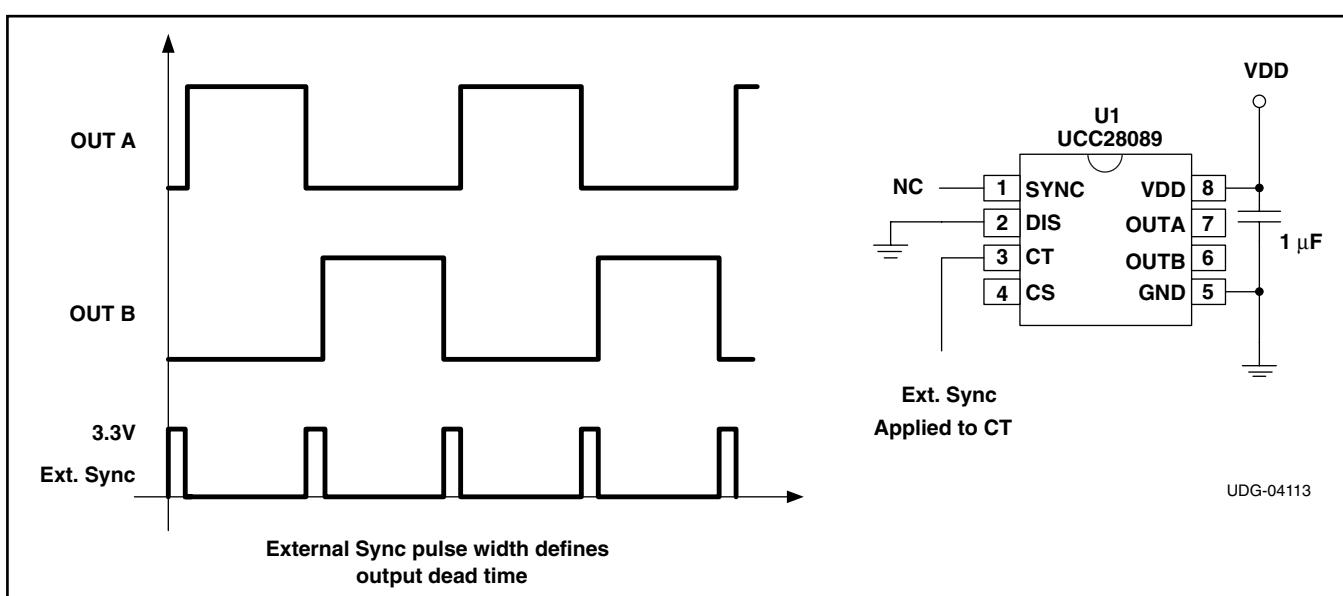

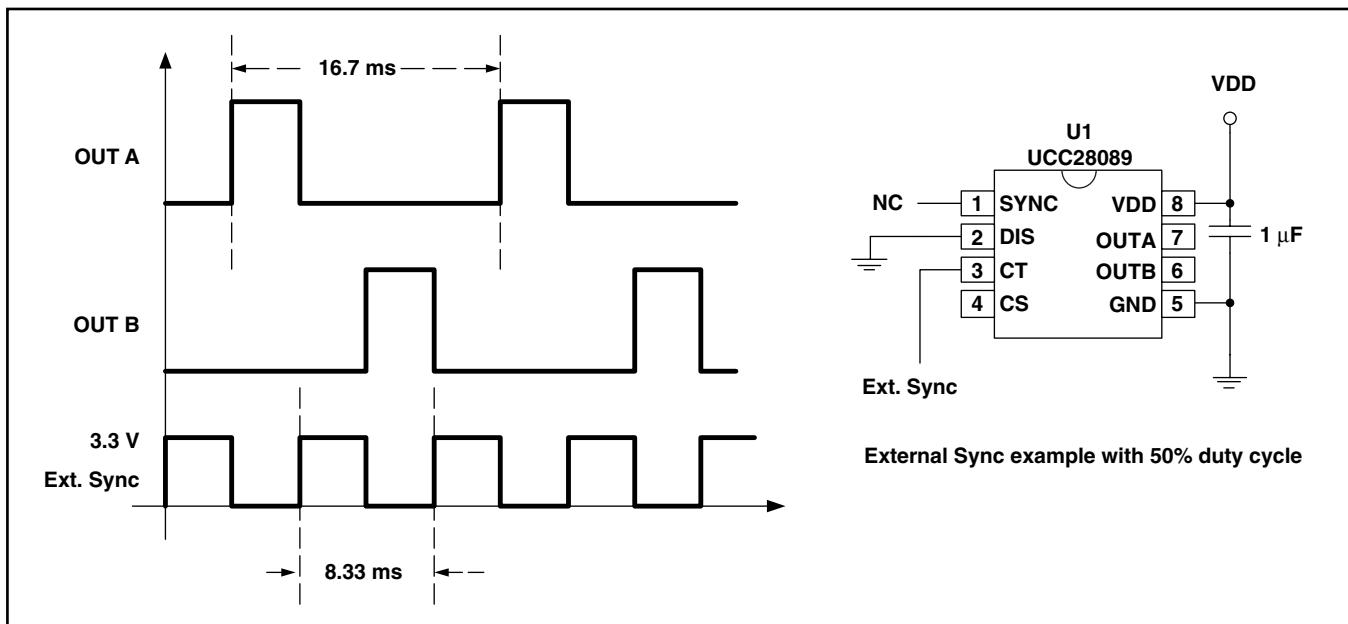

#### 複数のUCC28089の外部信号との同期

複数のUCC28089が共通クロックに同期することが必要とされるシステムでは、3.3Vのロジック・レベルの信号を直接CT端子に印加することができます(UCC28089のSYNC端子は出力同期信号のみを供給します)。図4に示されているように、外部から供給された同期パルス幅により周波数と、OUT AとOUT Bの間のデッドタイムが決まります。この構成では、放電端子DISは使用しないためグランドに接続してください。外部の同期信

図4. Synchronizing the UCC28089 to an External Signal

図5. Modified Square Wave Inverter

号は、“H” レベルの場合VDD/5の発振器のトリップ・レベルより大きく、“L” レベルの場合はCTをVDD/20より小さくしてください。

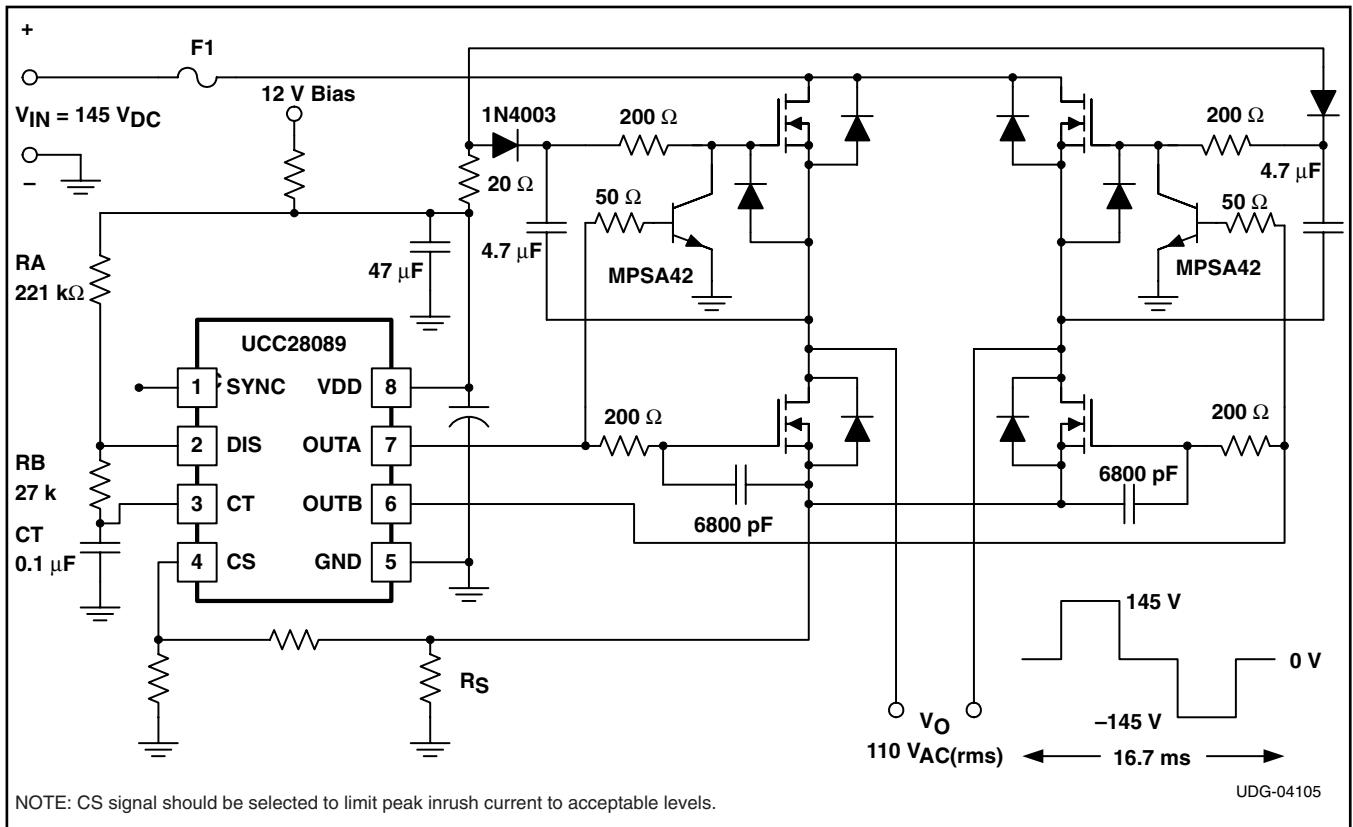

#### UCC28089を擬似方形波インバータとして使用する場合

リモートまたは直流のみの電源システムでは小型電化製品への供給のため、しばしば限られた量の60Hzの交流ライン電源が必要となることがあります。それに対応した負荷としては交直両用モーター、白熱ランプ、交流110Vからそれより低い直流電圧に変換するスイッチモード電源をもつその他電子機器などがあります。これら機器の多くは完全な正弦波のライン電圧は必要ではなく、擬似方形波電圧でも仕様を満たすことができます。図5の回路を使うと、UCC28089は一次側の過電流保護機能に加え適切な波形を供給することができます。部品RA、RB、CTは適切なデッドタイムをもつ所望の擬似方形波を設定するよう選択されます。

図5のインバータのハイサイド・ゲート・ドライバは比較的一定のデューティ比の低周波アプリケーションに適しています。ハイサイド・ゲート・ドライバのNPNトランジスタとチャージポンプ・ダイオードの電圧定格は大電圧になります(少なくとも145V+VDD)。ゲートは、ゲートからソースに示されているダイオードにより過度の負電圧から保護されています。

必要なら、60Hzの擬似方形波インバータの周波数は別個の発振器またはデジタル・コントローラから発生する外部同期信号を使用して設定することができます。図6に、CTピンに入力された120Hzの周波数で50%のデューティ・サイクルの方形波と、それによって生じたOUTA/OUTBの波形を示します。

図6. External Synchronization Example with 50% Duty Cycle Square Wave

#### 関連製品

| DEVICE  | DESCRIPTION                                                    |

|---------|----------------------------------------------------------------|

| UCC2540 | High-Efficiency Secondary-Side Synchronous-Buck PWM Controller |

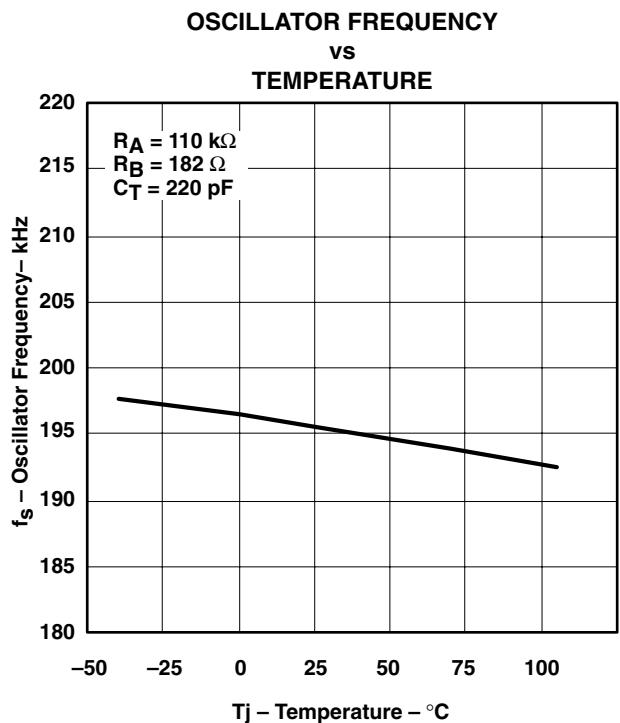

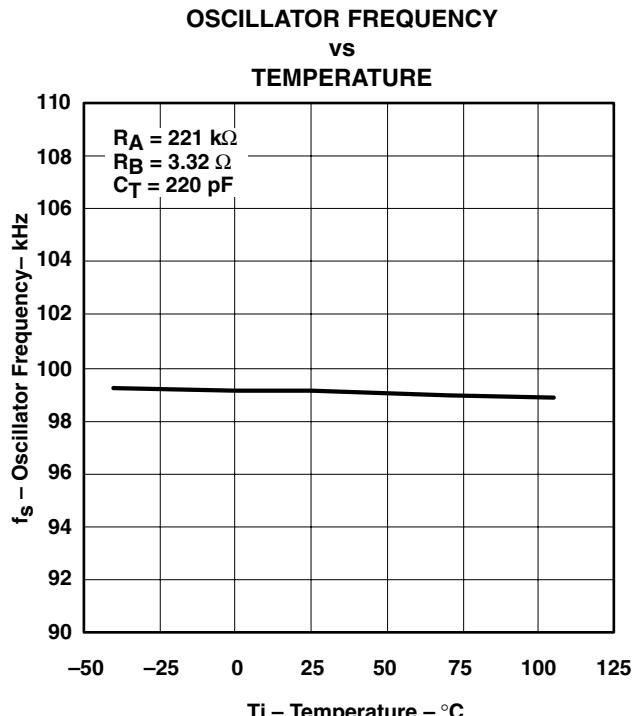

## 代表的特性

図 7

図 8

図 9

図 10

## 代表的特性(続き)

図 11

図 12

図 13

図 14

## 代表的特性(続き)

図 15

図 16

図 17

図 18

## 代表的特性(続き)

図 19

図 20

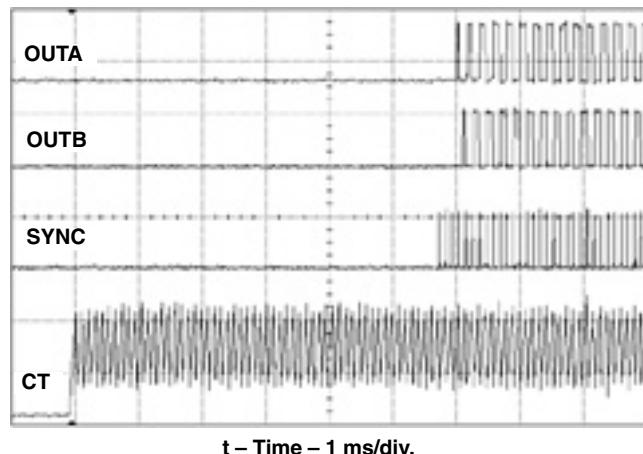

TYPICAL SOFT START WAVEFORMS

図 21

TYPICAL OVERALL START UP WAVEFORMS

図 22

## 參考資料

1. Power Supply Seminar SEM-1300 Topic 1: *Unique Cascaded Power Converter Topology for High Current Low Output Voltage Applications*, by L. Balogh, C. Bridge and B. Andreycak, Texas Instruments Literature No. SLUP133

2. *Low Cost Inverter Suitable for Medium-Power Fuel Cell Sources*, by P.T. Krein and R Balog, IEEE Power Electronics Specialists Conference Proceedings, 2002, vol. 1, pp. 321-326.

3. Datasheet, UCC2540 *High-Efficiency Secondary-Side Synchronous-Buck PWM Controller*, Texas Instruments Literature No. SLUS539

## PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup>          |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|---------------------------------------|

| UCC28089D        | ACTIVE                | SOIC         | D               | 8    | 75          | Pb-Free (RoHS)          | CU NIPDAU        | Level-2-260C-1YEAR/Level-1-220C-UNLIM |

| UCC28089DR       | ACTIVE                | SOIC         | D               | 8    | 2500        | Pb-Free (RoHS)          | CU NIPDAU        | Level-2-260C-1YEAR/Level-1-220C-UNLIM |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - May not be currently available - please check <http://www.ti.com/productcontent> for the latest availability information and additional product content details.

**None:** Not yet available Lead (Pb-Free).

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean "Pb-Free" and in addition, uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

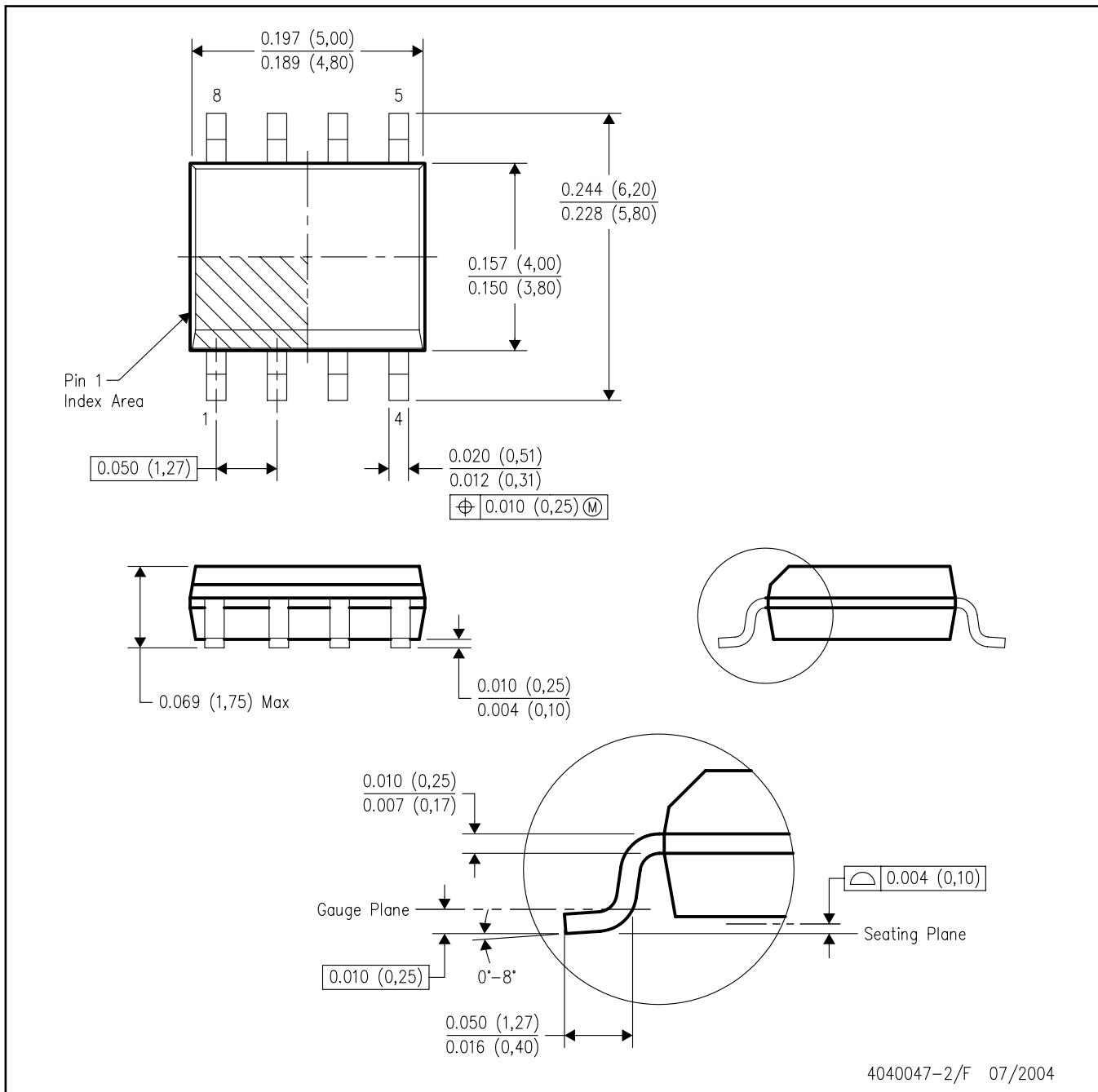

注A. 全ての線寸法の単位はインチ(ミリメートル)です。

注B. 図は予告なく変更することがあります。

注C. ボディ寸法はモールド突起部を含みません。突起部は0.006 (0,15) を越えません。

注D. JEDEC MS-012改AAに準拠します。

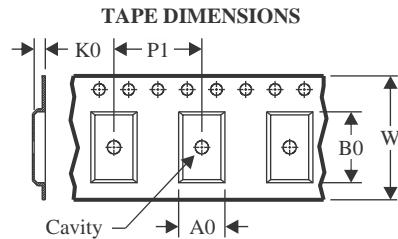

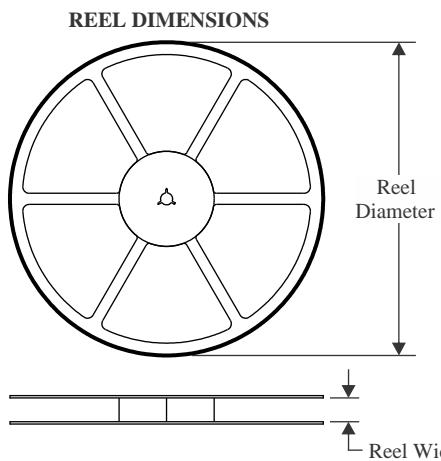

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

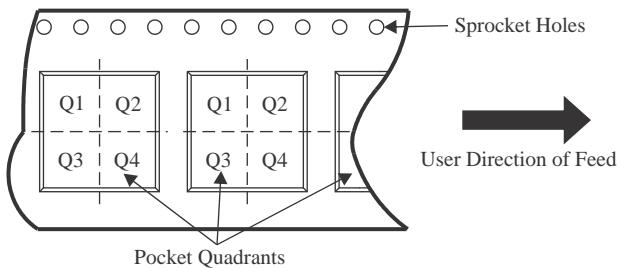

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC28089DR | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

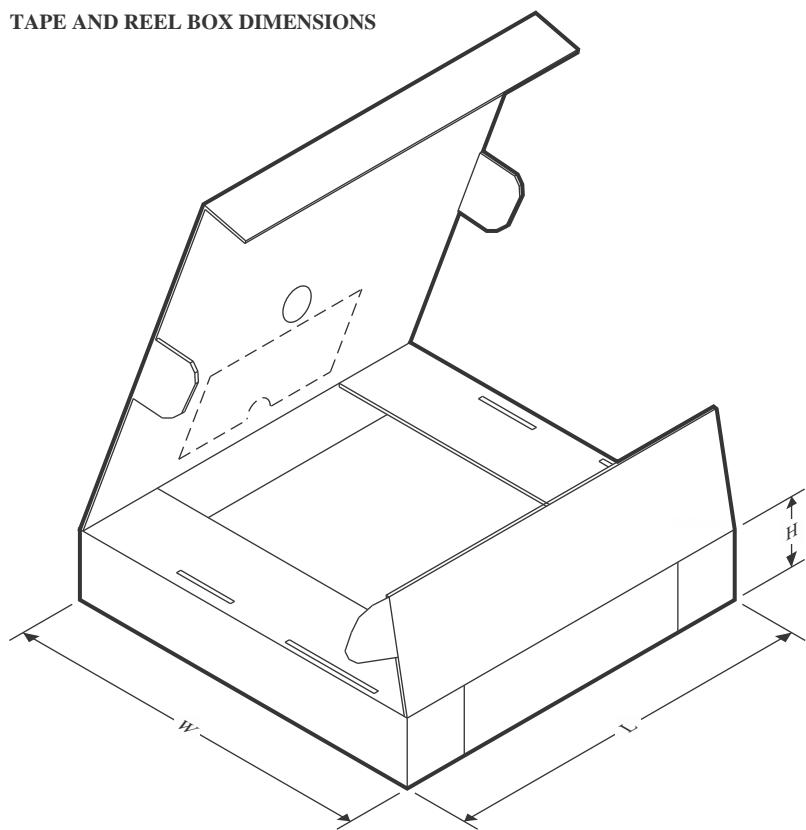

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28089DR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

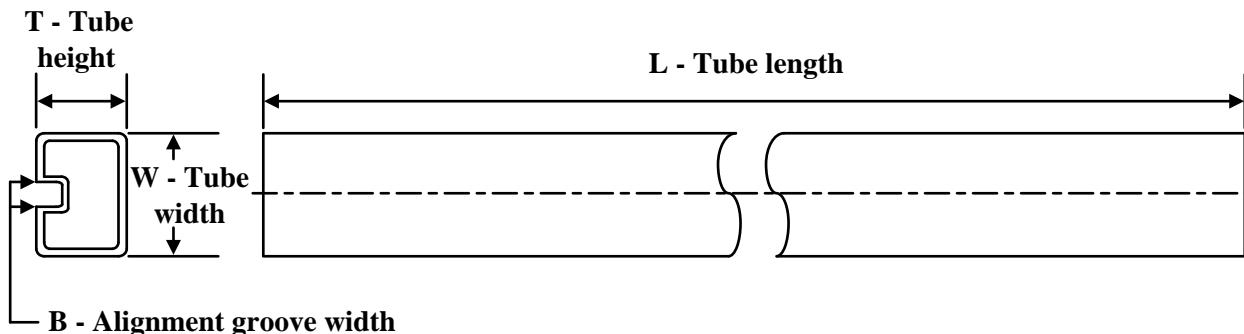

**TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| UCC28089D   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| UCC28089D.A | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated