## 高性能 PFC/PWM 混在コントローラ トレーリング・エッジ制御

### 特 長

- PFC/PWMのコントロールをワンチップに内蔵

- トレーリング・エッジPFC及びトレーリング・エッジPWM変調

- PFC/PWM ターンオンのシーケンス制御機能内蔵

- 高出力能力2A ソース/3Aシンク・ゲート駆動

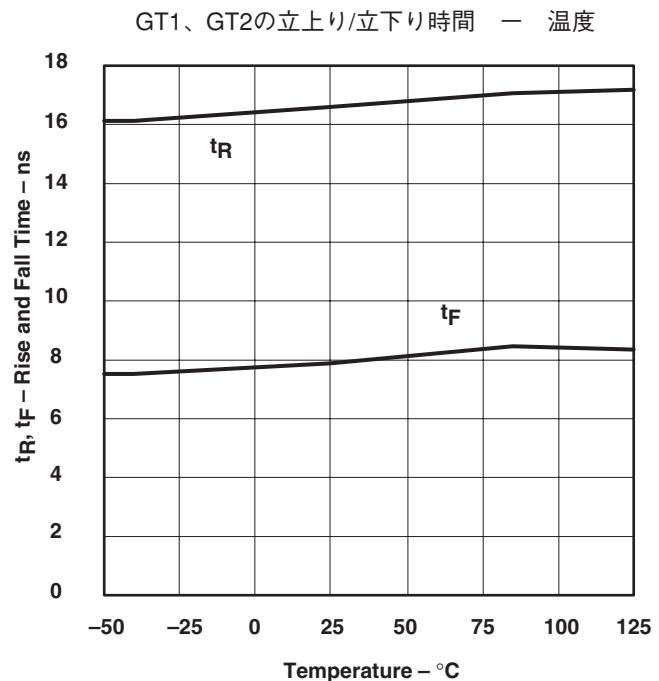

- 高速動作16nsの立ち上がり時間/7nsの立ち下がり時間 (1nF負荷)

#### PFCの特長

- 低ノイズ構成に最適な連続導通の平均電流モード制御

- 広いマルチプライヤ入力特性によりほぼ1の効率を実現可能

- 入力電圧フィードフォワード

- すぐれた過渡応答制御回路内蔵

- 正確なパワー制限

- ゼロパワー検出回路内蔵

#### PWMの特長

- Peak-Current-Modeには1:1のPFC:PWM周波数オプションがあります。

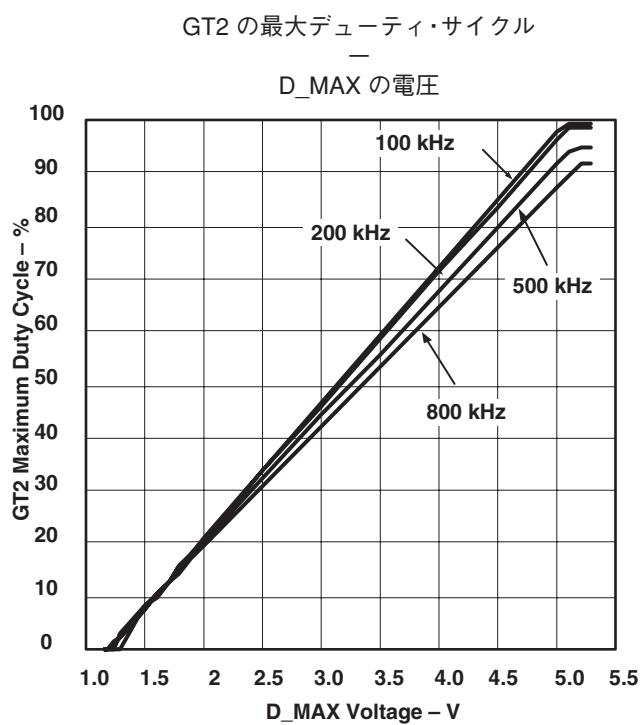

- 最大デューティ・サイクル制限を最大90%まで設定可能

- 設定可能なソフトスタート機能

### アプリケーション

- 高効率サーバー、デスクトップ電源

- 高効率テレコムAC/DCコンバータ

### 概 要

UCC28521及びUCC28528のPFC/PWM混在コントローラはIEC61000-3-2高調波電流抑制規格に準拠するオフライン電源システムの構築に必要な全ての機能を備えています。PFC段とPWM段のコントロールおよび駆動信号を1つのデバイスに組み込むことで特性やコストの面で大きな利益がもたらされています。

UCC28511に基づいて、この新型デバイスは平均電流モード・コントロールの制御方式を使用しています。UCC28521/28の主な相違点はPFC/PWM段のトレーリング・エッジ/トレーリング・エッジ(TEM/TEM)変調体系にあります。UCC28528はPWM段が立下りの電圧ではターンオフしないという点でUCC28521と異なります。UCC28528のPWMはローパワーの補助電源等向けて設計されています。

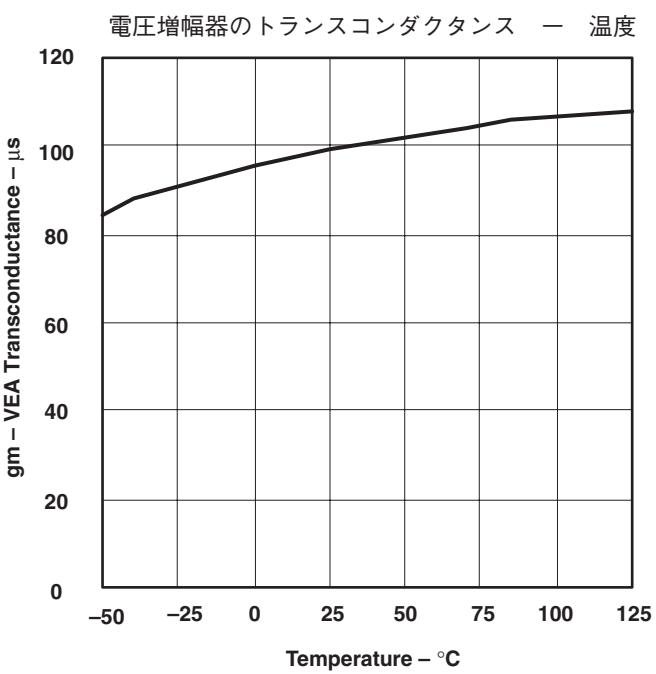

このデバイスは前世代の混在型のコントローラに対し特性面での利点があります。主なPWMの特長としては最大デューティ・サイクルが設定可能であることです。PFC段については、このデバイスではマルチプライヤの特性が改善されており、また、過渡応答特性の改善のためトランスクンダクタンス型のアンプを使用していることが特長です。

PFC部はライン電流用に基準信号を生成する3入力のマルチプライヤにあります。UCC28521/28は入力電圧および負荷条件の全ての範囲で入力電流に低歪みの基準電圧を生成することが可能な高く広い直線性の範囲を持つマルチプライヤ回路をもっています。低オフセット、高帯域な電流誤差増幅器により、実際のインダクタ電流は確実にマルチプライヤの出力制御信号に追随します。出力電圧の制御はトランスクンダクタンス・アンプを経て処理されます。

### 利用可能なアプリケーション・オプション

| PART NUMBER | PWM STAGE                                        | APPLICATION                    |

|-------------|--------------------------------------------------|--------------------------------|

| UCC28521    | PWM shuts off at 71% of the nominal bulk voltage | ac dc and main dc dc converter |

| UCC28528    | PWM does not turn off with falling bulk voltage  | ac dc and standby converter    |

bqTINYは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

回路の過渡応答は、出力電圧が設定された範囲外に低下した場合、トランスコンダクタンス型の電圧アンプの出力容量を高速で充電/放電させることにより改善しています。ヒステリシス電圧が選択可能なUVLO回路、高精度な基準電圧、OVP/イネーブル、ゼロパワー検出、ピーク電流制限、パワー制限、大電流出力のゲート・ドライバ段などの多くの機能がPFC部に内蔵されています。

PWM部の特徴としては、ピーク電流モード制御です、設定可能なソフトスタート、最大デューティ・サイクルの精密クランプ機能、ピーク電流制限、大電流出力のゲート・ドライバ段などが内蔵されています。PWM段は起動時PFC出力がその設定値の90%に達するまで抑制されています。入力ラインの低下及びオフ時、UCC28521ではPFC出力がその出力値の71%に低下するまでPWM段は動作しています。一方、UCC28528ではバイアスがUVLOターンオフ・スレッシュホールドより低くなるとPWM段は動作を停止します。

両デバイスとも20ピンのDWパッケージです。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

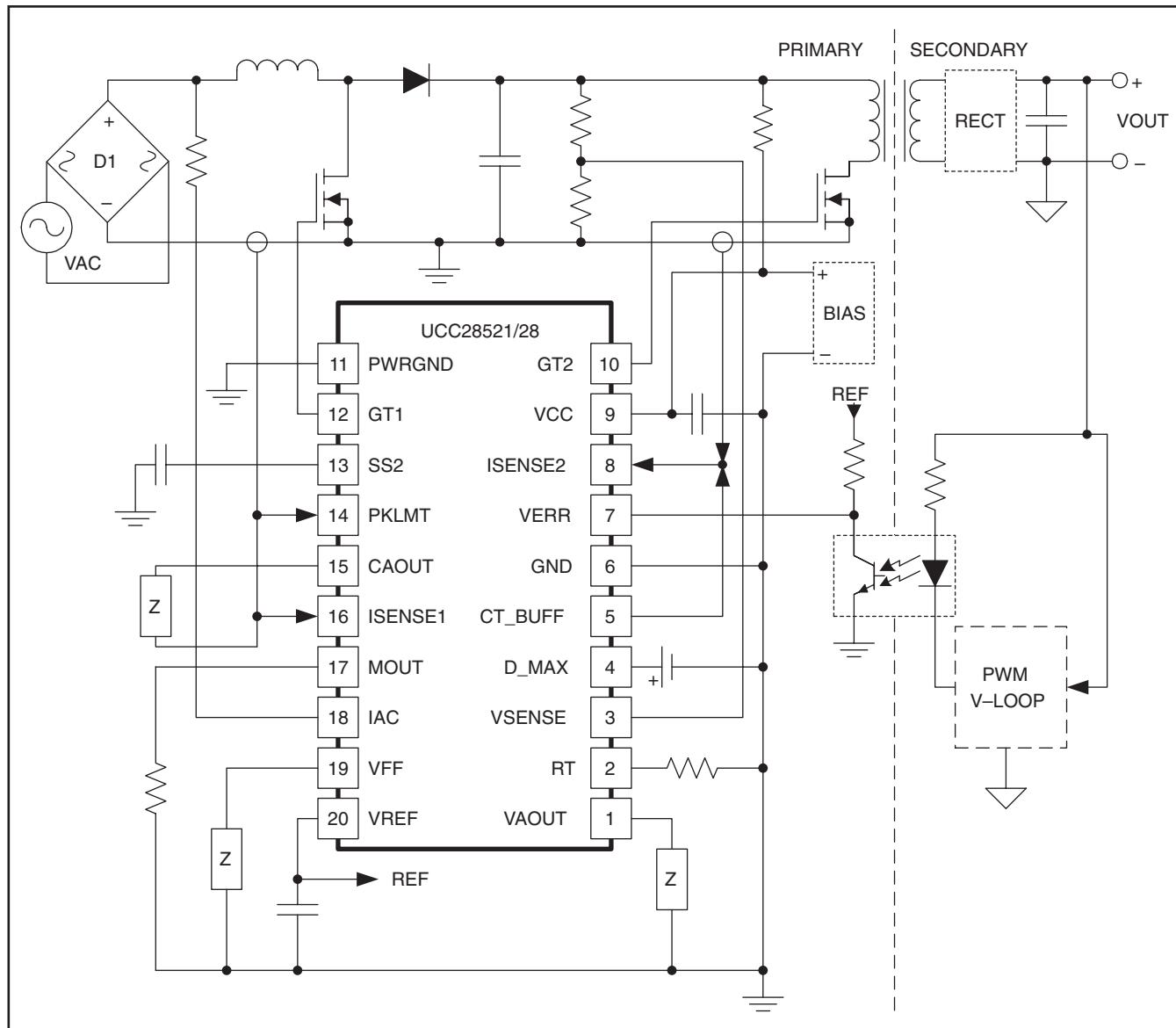

### アプリケーションの概略図

## 絶対最大定格

自由通気の全動作温度範囲に適用(特に記述のない限り)†‡

|                                         |                        |

|-----------------------------------------|------------------------|

| 供給電圧 VCC                                | 20 V                   |

| アイドル時                                   | 18 V                   |

| 動作時                                     |                        |

| ゲート駆動電流 (GT1、GT2)                       |                        |

| 連続                                      | 0.4 A                  |

| パルス                                     |                        |

| ソース                                     | -2.5 A                 |

| シンク                                     | 3.5 A                  |

| GT1、GT2 の最大電圧                           | -0.5 V to VCC + 0.3 V  |

| 入力電圧                                    |                        |

| VSENSE                                  | 0 V to 11 V            |

| D_MAX、SS2、CAOUT、ISENSE1、MOUT、VFF        | -0.5 V to VREF + 0.3 V |

| VAOUT、CT_BUFF、ISENSE2、PKLMT             | -0.5 V to 6 V          |

| ピンの電流                                   |                        |

| RT                                      | -0.5 mA                |

| VFF                                     | -5 mA                  |

| CT_BUFF                                 | 1 mA                   |

| VAOUT、VERR、ISENSE2、SS2、CAOUT、IAC        | 10 mA                  |

| ピンの最大容量                                 |                        |

| CT_BUFF                                 | 220 pF                 |

| ジャンクションの動作温度範囲、 $T_J$                   | -55 °C to 150 °C       |

| 保存温度範囲、 $T_{stg}$                       | -65 °C to 150 °C       |

| リード線温度 1.6mm(ケースから 1/16 インチ離れた場所、10 秒間) | 300 °C                 |

† 絶対最大定格以上のストレスは、恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

‡ 電流の極性で正は指定の端子に流入する方向、負は流出する方向を表しています。全ての電圧は GND を基準としています。

## 静電気放電 (ESD) 対策

| PARAMETER        | MAX | UNITS |

|------------------|-----|-------|

| Human body model | 2.5 | kV    |

| CDM              | 0.5 |       |

## 利用可能なオプション †‡

| OPTIONS                 |                  |                     |                        |                          | PACKAGED DEVICES |

|-------------------------|------------------|---------------------|------------------------|--------------------------|------------------|

| PFC:PWM FREQUENCY RATIO | UVLO TURN-ON (V) | UVLO HYSTERESIS (V) | PWM UVLO2 TURN-OFF (V) | PWM UVLO2 HYSTERESIS (V) | SOIC W 20 (DW)   |

| 1:1                     | 10.2             | 0.5                 | 5.30                   | 1.45                     | UCC28521DW       |

| 1:1                     | 10.2             | 0.5                 | -                      | -                        | UCC28528DW       |

† DW パッケージはテープ/リールで供給されています。型番に R を付けてください(例、UCC28521DWR)。リール当たりの数量は 2000 個です。

‡ 全てのデバイスの定格は -40°C ~ +105°C の場合です。

## 利用可能なオプション †

| PACKAGE                 | THERMAL IMPEDANCE JUNCTION TO AMBIENT | THERMAL IMPEDANCE JUNCTION TO CASE | $T_A < 25^\circ\text{C}$ POWER RATING | $T_A < 25^\circ\text{C}$ DERATING FACTOR | $T_A < 105^\circ\text{C}$ POWER RATING |

|-------------------------|---------------------------------------|------------------------------------|---------------------------------------|------------------------------------------|----------------------------------------|

| 8-pin plastic SOIC (DW) | 84.3 °C/W                             | 16.4 °C/W                          | 1.5 W                                 | 84.3 mW/°C                               | 0.5 W                                  |

† Dlow-K PCB\_LFM に基づいています。

## 電気的特性

特に指定がない限り、UCC2851x シリーズでは  $T_A = -40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$ ,  $T_A = T_J$ ,  $VCC = 12\text{ V}$ ,  $R_T = 156\text{ k}\Omega$ ,  $R_{CT\_BUFF} = 10\text{ k}\Omega$

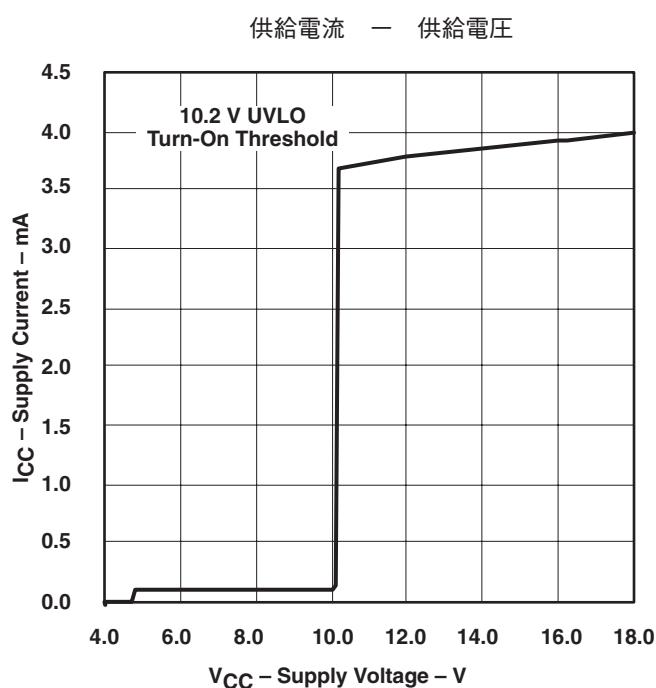

### 供給電流

| PARAMETER           | TEST CONDITIONS              | MIN | TYP | MAX | UNITS         |

|---------------------|------------------------------|-----|-----|-----|---------------|

| Supply current, off | VCC turn-on threshold 300 mV |     | 100 | 150 | $\mu\text{A}$ |

| Supply current, on  | no load on GT1 or GT2        |     | 4   | 6   | mA            |

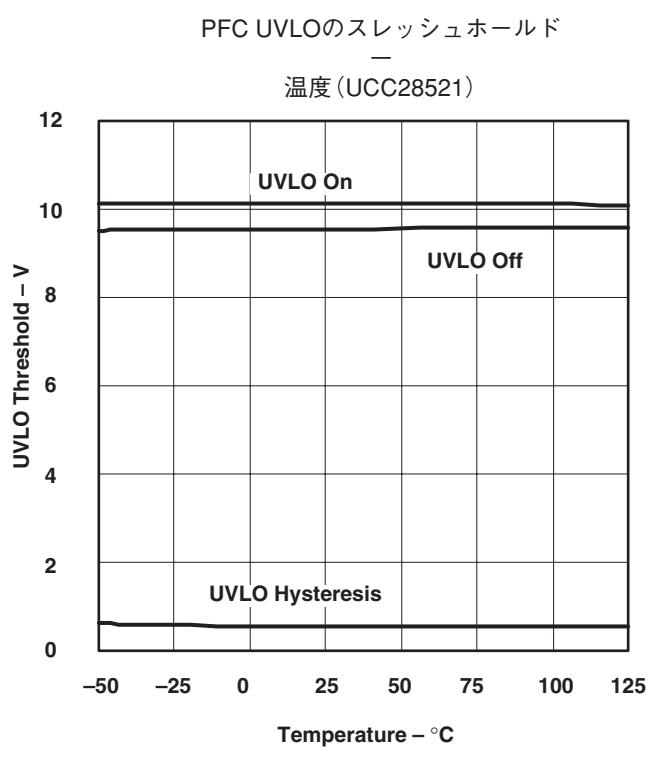

### 低電圧ロックアウト機能(UVLO)

| PARAMETER              | TEST CONDITIONS | MIN | TYP  | MAX  | UNITS |

|------------------------|-----------------|-----|------|------|-------|

| VCC turn-on threshold  | UCC28521        | 9.7 | 10.2 | 10.8 | V     |

| VCC turn-off threshold |                 | 9.1 | 9.7  | 10.6 |       |

| UVLO hysteresis        |                 | 0.3 | 0.5  | 0.8  |       |

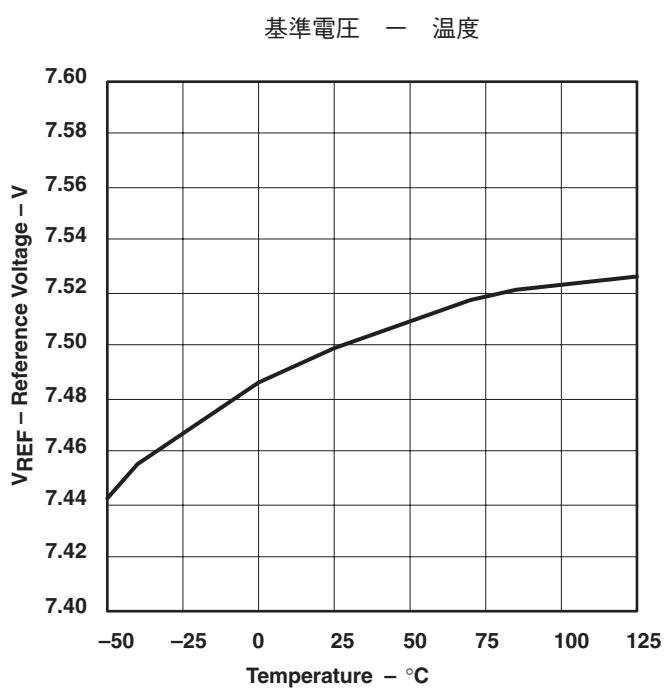

### 電圧増幅器

| PARAMETER                 | TEST CONDITIONS                                                 | MIN  | TYP  | MAX  | UNITS         |

|---------------------------|-----------------------------------------------------------------|------|------|------|---------------|

| Input voltage             | 25°C                                                            | 7.39 | 7.50 | 7.61 | V             |

|                           | Over temperature                                                | 7.35 | 7.50 | 7.65 |               |

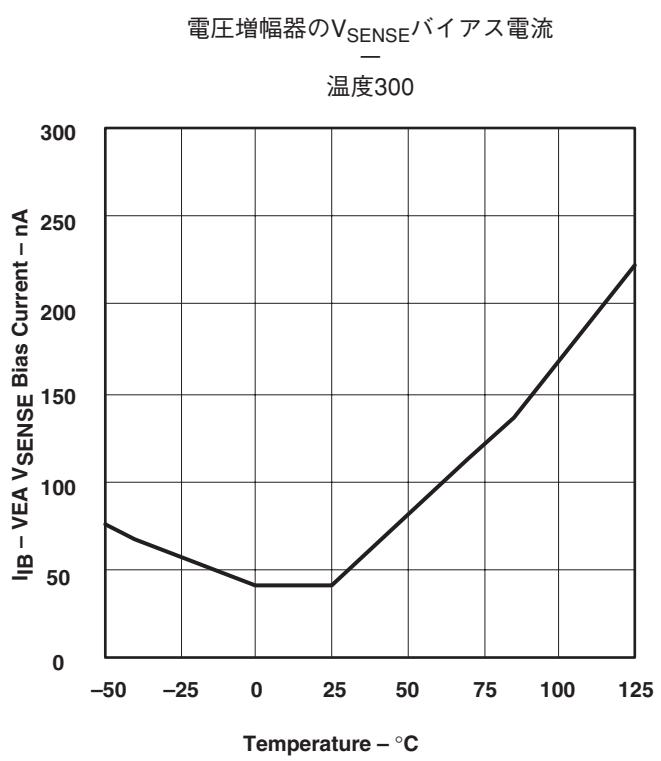

| $V_{SENSE}$ bias current  | $V_{SENSE} = V_{REF}$                                           |      | 100  | 300  | nA            |

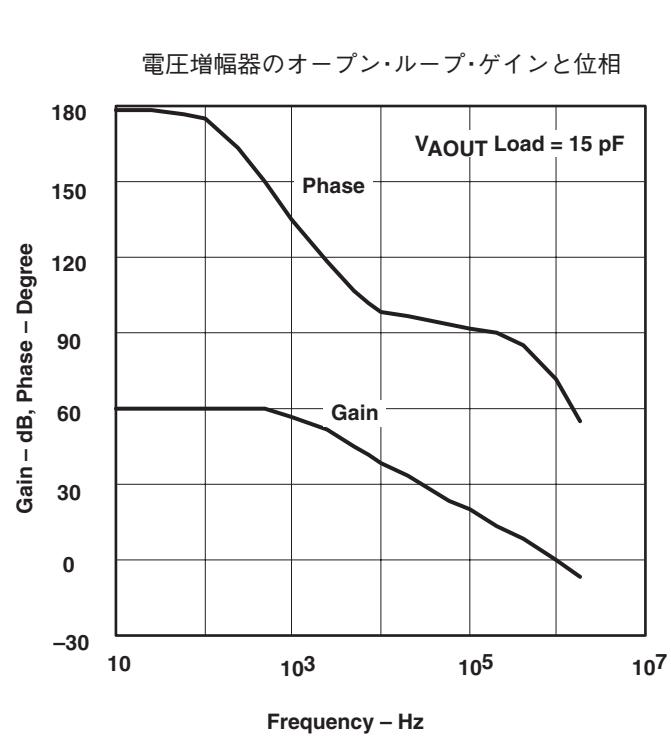

| Open loop gain            | $2\text{ V} \leq V_{AOUT} \leq 4\text{ V}$                      | 50   | 60   |      | dB            |

| High-level output voltage | $I_{LOAD} = -150\text{ }\mu\text{A}$                            | 5.3  | 5.5  | 5.6  | V             |

| Low-level output voltage  | $I_{LOAD} = 150\text{ }\mu\text{A}$                             | 0.00 | 0.05 | 0.15 |               |

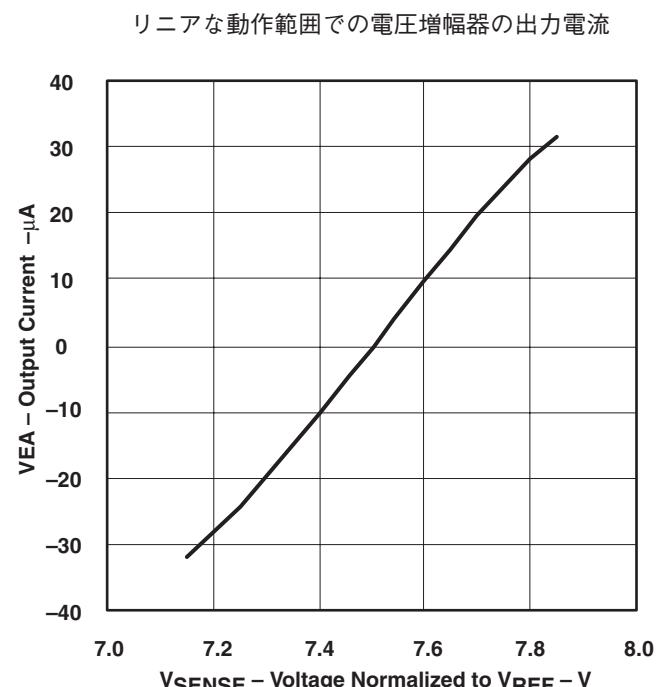

| $g_M$ conductance         | $I_{VAOUT} = -20\text{ }\mu\text{A}$ to $20\text{ }\mu\text{A}$ | 70   | 100  | 130  | $\mu\text{S}$ |

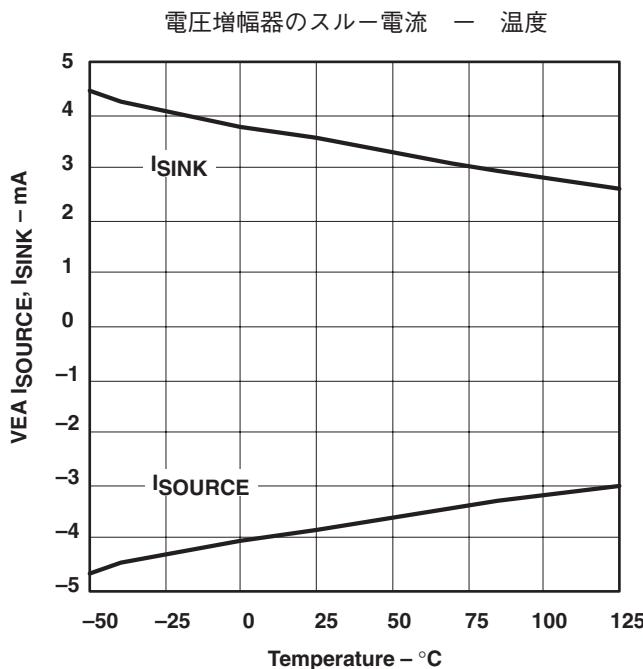

| Maximum source current    |                                                                 | -1   | -3.5 |      | mA            |

| Maximum sink current      |                                                                 | 1    | 3.5  |      |               |

### PFC段の過電圧保護とイネーブル

| PARAMETER                    | TEST CONDITIONS | MIN               | TYP               | MAX               | UNITS |

|------------------------------|-----------------|-------------------|-------------------|-------------------|-------|

| Overvoltage reference window |                 | $V_{REF} + 0.440$ | $V_{REF} + 0.490$ | $V_{REF} + 0.540$ | V     |

| Hysteresis                   |                 | 300               | 500               | 600               | mV    |

| Enable threshold             |                 | 1.7               | 1.9               | 2.1               | V     |

| Enable hysteresis            |                 | 0.08              | 0.2               | 0.3               |       |

## 電気的特性

特に指定がない限り、UCC2851x シリーズでは  $T_A = -40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$ ,  $T_A = T_J$ ,  $VCC = 12\text{ V}$ ,  $R_T = 156\text{ k}\Omega$ ,  $R_{CT\_BUFF} = 10\text{ k}\Omega$

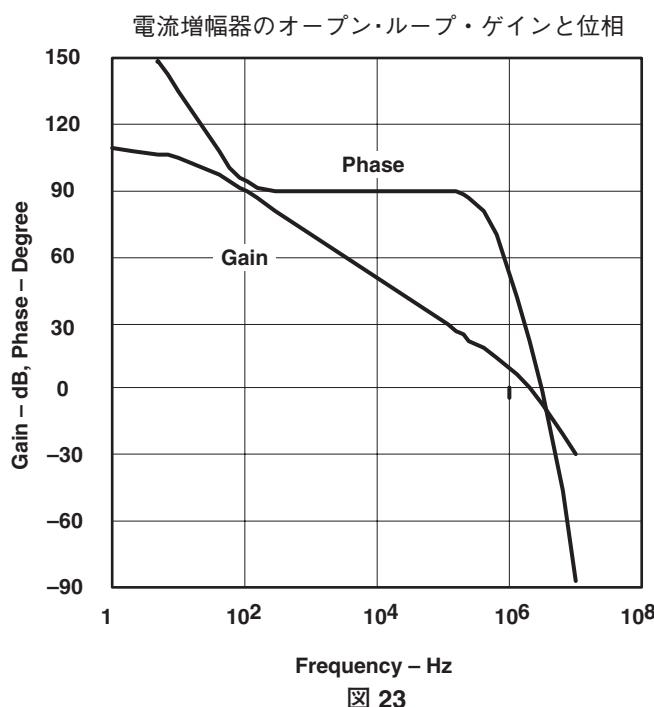

### 電流増幅器

| PARAMETER                             | TEST CONDITIONS                                                       | MIN | TYP | MAX  | UNITS |

|---------------------------------------|-----------------------------------------------------------------------|-----|-----|------|-------|

| Input offset voltage                  | $V_{CM} = 0\text{ V}$ , $V_{CAOUT} = 3\text{ V}$                      | -5  | 0   | 5    | mV    |

| Input bias current                    | $V_{CM} = 0\text{ V}$ , $V_{CAOUT} = 3\text{ V}$                      |     | -50 | -100 | nA    |

| Input offset current                  | $V_{CM} = 0\text{ V}$ , $V_{CAOUT} = 3\text{ V}$                      |     | 25  | 100  |       |

| Open loop gain                        | $V_{CM} = 0\text{ V}$ , $2\text{ V} \leq V_{CAOUT} \leq 5\text{ V}$   | 90  |     |      |       |

| Common mode rejection ratio           | $0\text{ V} \leq V_{CM} \leq 1.5\text{ V}$ , $V_{CAOUT} = 3\text{ V}$ | 80  |     |      |       |

| High-level output voltage             | $I_{LOAD} = -500\text{ }\mu\text{A}$                                  | 5.6 | 6.3 | 7.0  |       |

| Low-level output voltage              | $I_{LOAD} = 500\text{ }\mu\text{A}$                                   | 0   | 0.2 | 0.5  | V     |

| Gain bandwidth product <sup>(1)</sup> | See Note 1                                                            |     | 2.0 |      | MHz   |

### 発振器

| PARAMETER                                                     | TEST CONDITIONS                              | MIN | TYP | MAX | UNITS |

|---------------------------------------------------------------|----------------------------------------------|-----|-----|-----|-------|

| $f_{PWM}$ , PWM frequency, initial accuracy                   | $T_A = 25^{\circ}\text{C}$                   | 170 | 200 | 230 | kHz   |

| Frequency, voltage stability                                  | $10.8\text{ V} \leq V_{CC} \leq 15\text{ V}$ | -1% |     | 1%  |       |

| Frequency, total variation                                    | Line, Temp                                   | 160 |     | 240 | kHz   |

| dc-to-dc ramp peak voltage                                    |                                              | 4.5 | 5.0 | 5.5 |       |

| dc-to-dc ramp amplitude voltage <sup>(1)</sup> (peak-to-peak) |                                              |     | 4.0 |     | V     |

| PFC ramp peak voltage                                         |                                              | 4.5 | 5.0 | 5.5 |       |

| PFC ramp amplitude voltage (peak-to-peak)                     |                                              | 3.5 | 4.0 | 4.5 |       |

### 基準電圧

| PARAMETER             | TEST CONDITIONS                              | MIN  | TYP  | MAX  | UNITS |

|-----------------------|----------------------------------------------|------|------|------|-------|

| Input voltage         | 25°C                                         | 7.39 | 7.50 | 7.61 | V     |

|                       | Over temperature                             | 7.35 | 7.50 | 7.65 | V     |

| Load regulation       | $I_{REF} = 1\text{ mA}$ to $6\text{ mA}$     |      | 5    | 15   |       |

| Line regulation       | $10.8\text{ V} \leq V_{CC} \leq 15\text{ V}$ |      | 1    | 10   | mV    |

| Short circuit current | $V_{REF} = 0\text{V}$                        | -20  | -25  | -50  | mA    |

### ピーク電流の制限

| PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------|-----------------|-----|-----|-----|-------|

| PKLMT reference voltage |                 | -20 | 0   | 20  | mV    |

| PKLMT propagation delay | PKLMT to GT1    | 150 | 300 | 500 | ns    |

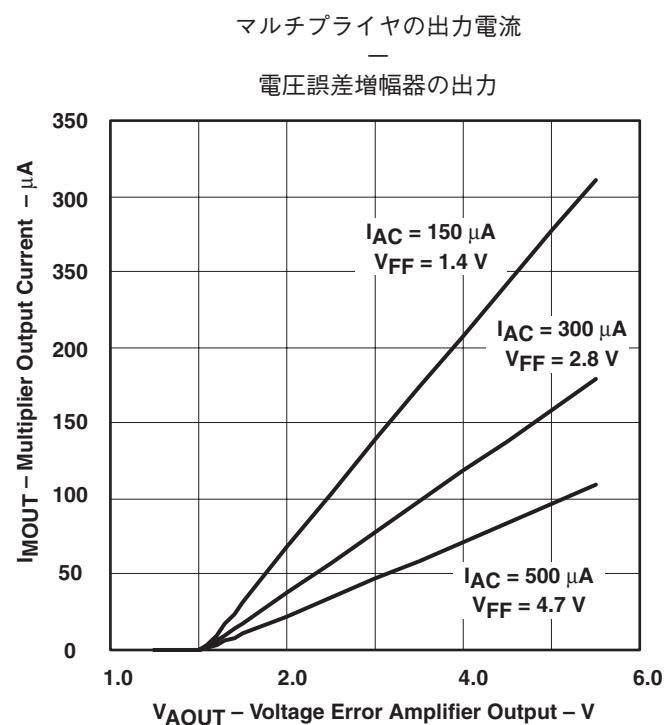

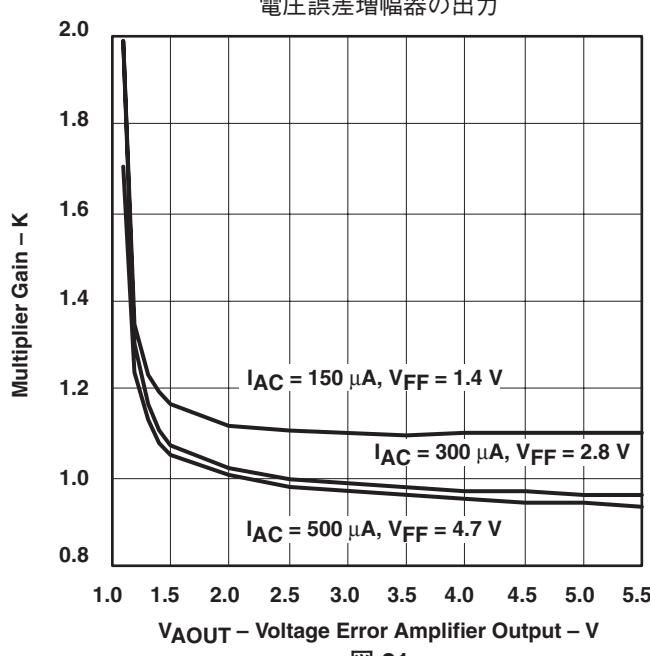

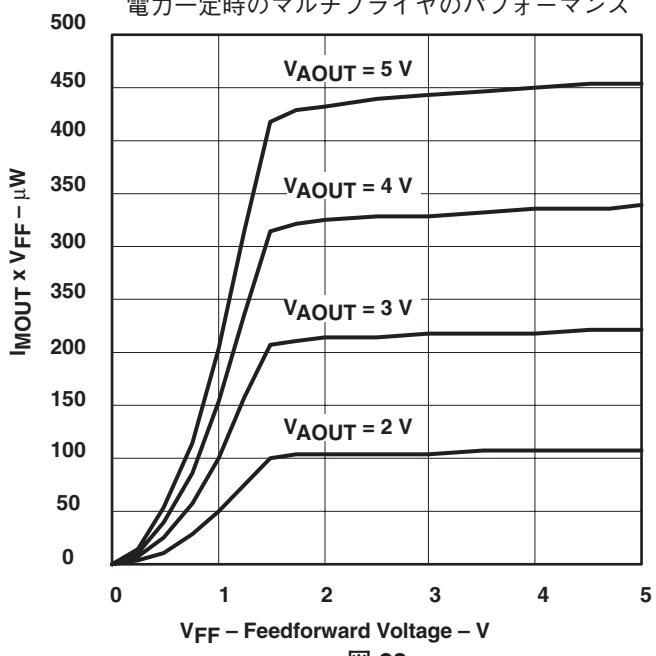

### マルチプライヤ

| PARAMETER                                        | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNITS         |

|--------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|---------------|

| $I_{MOUT}$ , high-line low-power output current  | $I_{AC} = 500\text{ }\mu\text{A}$ , $V_{FF} = 4.7\text{ V}$ , $V_{AOUT} = 1.25\text{ V}$ | -3   | -6   | -9   |               |

| $I_{MOUT}$ , high-line high-power output current | $I_{AC} = 500\text{ }\mu\text{A}$ , $V_{FF} = 4.7\text{ V}$ , $V_{AOUT} = 5\text{ V}$    | -75  | -90  | -110 |               |

| $I_{MOUT}$ , low-line low-power output current   | $I_{AC} = 150\text{ }\mu\text{A}$ , $V_{FF} = 1.4\text{ V}$ , $V_{AOUT} = 1.25\text{ V}$ | -10  | -15  | -50  |               |

| $I_{MOUT}$ , low-line high-power output current  | $I_{AC} = 150\text{ }\mu\text{A}$ , $V_{FF} = 1.4\text{ V}$ , $V_{AOUT} = 5\text{ V}$    | -245 | -290 | -330 |               |

| $I_{MOUT}$ , IAC-limited output current          | $I_{AC} = 150\text{ }\mu\text{A}$ , $V_{FF} = 1.3\text{ V}$ , $V_{AOUT} = 5\text{ V}$    | -245 | -290 | -330 |               |

| Gain constant (k)                                | $I_{AC} = 300\text{ }\mu\text{A}$ , $V_{FF} = 2.8\text{ V}$ , $V_{AOUT} = 2.5\text{ V}$  | 0.8  | 1    | 1.2  | 1/V           |

|                                                  | $I_{AC} = 150\text{ }\mu\text{A}$ , $V_{FF} = 1.4\text{ V}$ , $V_{AOUT} = 0.25\text{ V}$ |      | 0    | -0.2 | $\mu\text{A}$ |

| $I_{MOUT}$ , zero current                        | $I_{AC} = 500\text{ }\mu\text{A}$ , $V_{FF} = 4.7\text{ V}$ , $V_{AOUT} = 0.25\text{ V}$ |      | 0    | -0.2 | $\mu\text{A}$ |

|                                                  | $I_{AC} = 500\text{ }\mu\text{A}$ , $V_{FF} = 4.7\text{ V}$ , $V_{AOUT} = 0.5\text{ V}$  |      | 0    | -0.2 | $\mu\text{A}$ |

| Power limit ( $I_{MOUT} \times V_{FF}$ )         | $I_{AC} = 150\text{ }\mu\text{A}$ , $V_{FF} = 1.4\text{ V}$ , $V_{AOUT} = 5\text{ V}$    | -343 | -406 | -462 | $\mu\text{W}$ |

(1) 設計で保証されており、テストは行われていません。

## 電気的特性

特に指定がない限り、UCC2851x シリーズでは  $T_A = -40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$ ,  $T_A = T_J$ ,  $VCC = 12\text{ V}$ ,  $R_T = 156\text{ k}\Omega$ ,  $R_{CT\_BUFF} = 10\text{ k}\Omega$

### ゼロパワー

| PARAMETER                        | TEST CONDITIONS                 | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|---------------------------------|------|------|------|-------|

| Zero power comparator threshold  | Measured on VAOUT, falling edge | 0.20 | 0.33 | 0.50 | V     |

| Zero power comparator hysteresis | Measured on VAOUT, rising edge  | 40   | 90   | 140  | mV    |

### PFC ゲート・ドライバ

| PARAMETER                          | TEST CONDITIONS                                          | MIN | TYP | MAX  | UNITS    |

|------------------------------------|----------------------------------------------------------|-----|-----|------|----------|

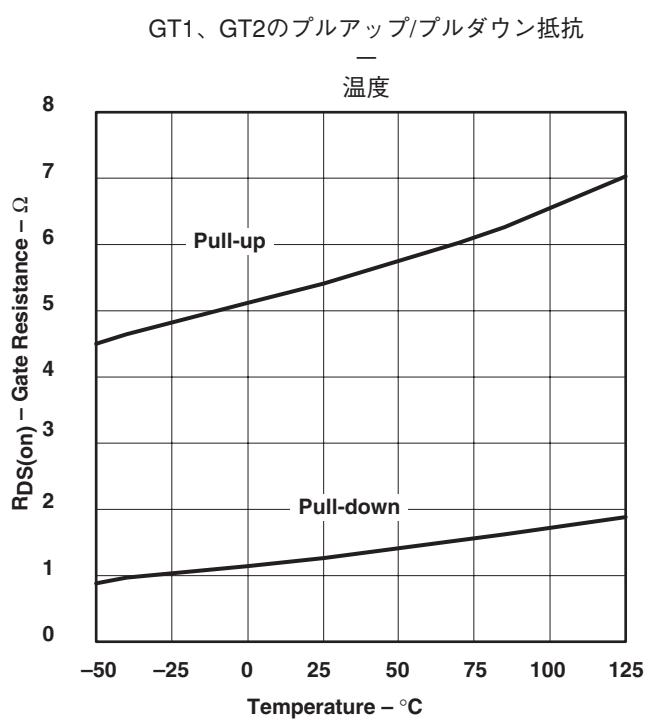

| GT1 pull-up resistance             | $-100\text{ mA} \leq \Delta I_{OUT} \leq -200\text{ mA}$ |     | 5   | 12   | $\Omega$ |

| GT1 pull-down resistance           | $I_{OUT} = 100\text{ mA}$                                |     | 2   | 10   |          |

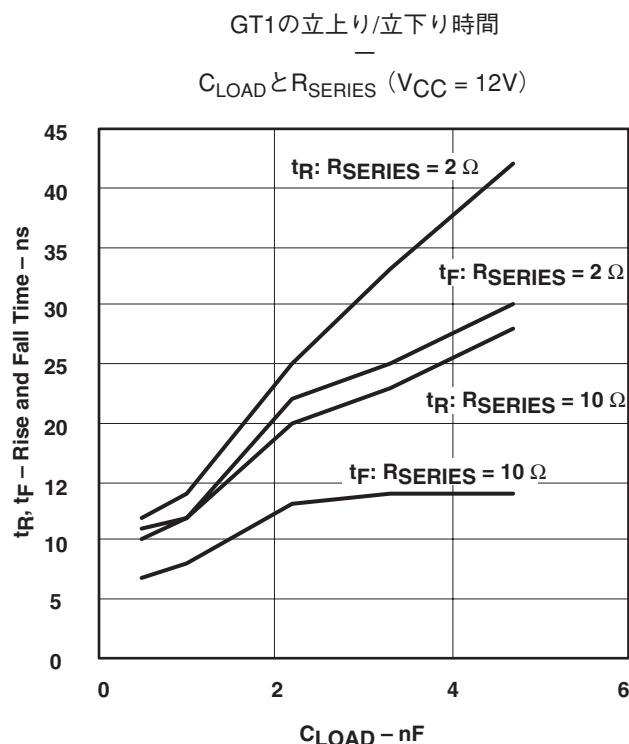

| GT1 output rise time               | $C_{LOAD} = 1\text{ nF}$ , $R_{LOAD} = 10\text{ }\Omega$ |     | 16  | 25   | ns       |

| GT1 output fall time               |                                                          |     | 7   | 15   |          |

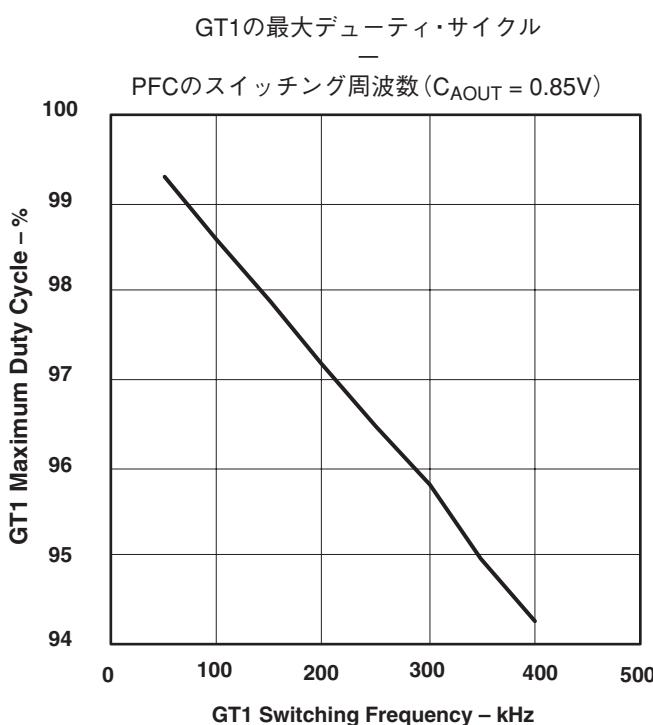

| Maximum duty cycle                 |                                                          | 93% | 95% | 100% |          |

| Minimum duty cycle (trailing edge) | See Note 1                                               | 1%  | —   | 7%   |          |

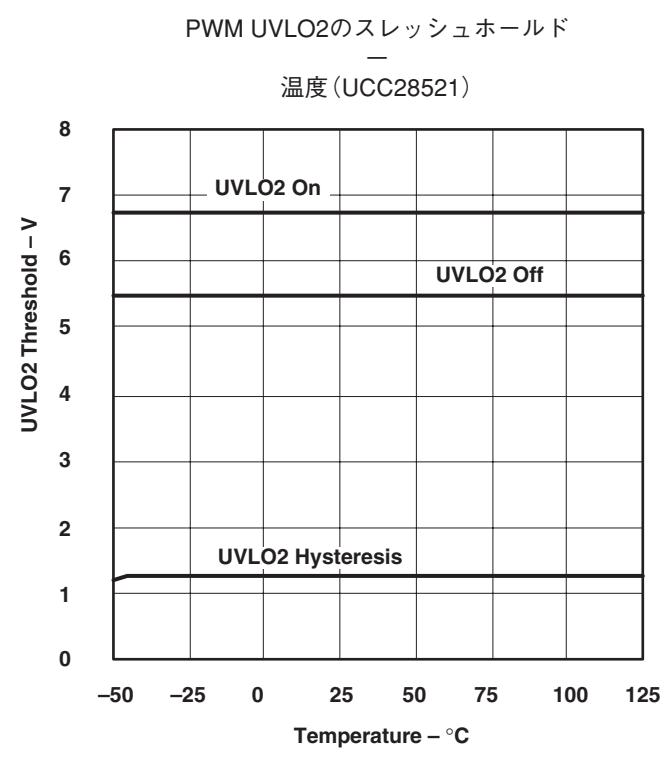

### PWM 段の低電圧ロックアウト (UVLO2)

| PARAMETER              | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|------------------------|-----------------|------|------|------|-------|

| PWM turn-on reference  | UCC28521        | 6.30 | 6.75 | 7.30 |       |

| PWM turn-off threshold | UCC28521        |      | 5.3  |      | V     |

| Hysteresis             | UCC28521        | 1.16 | 1.45 | 1.74 |       |

### PWM 段のソフトスタート

| PARAMETER             | TEST CONDITIONS                                                                              | MIN  | TYP   | MAX   | UNITS         |

|-----------------------|----------------------------------------------------------------------------------------------|------|-------|-------|---------------|

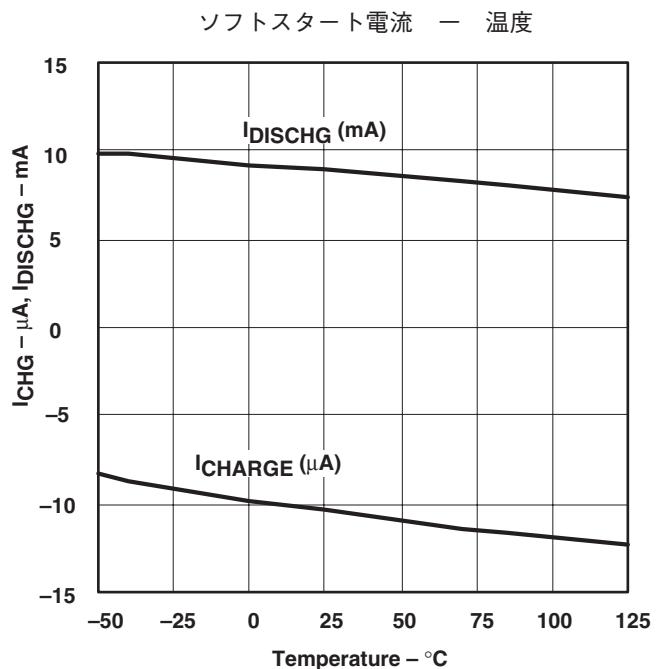

| SS2 charge current    | $V_{SENSE} = 7.5\text{ V}$ , $SS2 = 0\text{ V}$                                              | -7.0 | -10.5 | -14.0 | $\mu\text{A}$ |

| SS2 discharge current | UCC28521 $V_{SENSE} = 2.5\text{ V}$ , $SS2 = 2.5\text{ V}$ ,<br>(UVLO2 = Low, ENABLE = High) | 6    | 10    | 14    | mA            |

| Input voltage (VERR)  | UCC28521 $I_{VERR} = 2\text{ mA}$ , UVLO2 = Low                                              |      |       | 300   | mV            |

### PWM 段のデューティサイクル・クランプ

| PARAMETER          | TEST CONDITIONS           | MIN | TYP | MAX | UNITS |

|--------------------|---------------------------|-----|-----|-----|-------|

| Maximum duty cycle | $D_{MAX} = 4.15\text{ V}$ | 70% | 75% | 80% |       |

### PWM 段のパルスバイパルス電流センス

| PARAMETER                               | TEST CONDITIONS                              | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|----------------------------------------------|------|------|------|-------|

| Current sense comparator offset voltage | $I_{SENSE2} = 0\text{ V}$ , measured on VERR | 1.35 | 1.50 | 1.65 | V     |

(1) 設計で保証されており、テストは行われていません。

## 電気的特性

特に指定がない限り、UCC2851x シリーズでは  $T_A = -40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$ ,  $T_A = T_J$ ,  $VCC = 12 \text{ V}$ ,  $R_T = 156 \text{ k}\Omega$ ,  $R_{CT\_BUFF} = 10 \text{ k}\Omega$

### PWM 段の過電流制限

| PARAMETER                                 | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|-----------------|------|------|------|-------|

| Peak current comparator threshold voltage |                 | 1.15 | 1.30 | 1.45 | V     |

| Input bias current <sup>(1)</sup>         |                 | 50   |      | nA   |       |

### PWM 段のゲート・ドライバ

| PARAMETER                | TEST CONDITIONS                                           | MIN | TYP | MAX | UNITS    |

|--------------------------|-----------------------------------------------------------|-----|-----|-----|----------|

| GT2 pull-up resistance   | $-100 \text{ mA} \leq \Delta I_{OUT} \leq 200 \text{ mA}$ |     | 5   | 12  | $\Omega$ |

| GT2 pull-down resistance | $I_{OUT} = 100 \text{ mA}$                                |     | 2   | 10  | $\Omega$ |

| GT2 output rise time     | $C_{LOAD} = 1 \text{ nF}$ , $R_{LOAD} = 10 \Omega$        |     | 16  | 25  | ns       |

| GT2 output fall time     |                                                           |     | 7   | 15  | ns       |

(1) 設計で保証されており、テストは行われていません。

## 端子機能

| TERMINAL |     |       | I/O | DESCRIPTION                                                                                                                                            |  |  |

|----------|-----|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. | Stage |     |                                                                                                                                                        |  |  |

| CAOUT    | 15  | PFC   | O   | Output of the current control amplifier of the PFC stage. CAOUT is internally connected to the PWM comparator input in the PFC stage                   |  |  |

| CT_BUFF  | 5   | PWM   | O   | Internally buffered PWM stage oscillator ramp output, typically used to program slope compensation with a single resistor                              |  |  |

| D_MAX    | 4   | PWM   | I   | Positive input to set the maximum duty cycle clamp level of the PWM stage duty ratio can be between 0.09 and 0.90.                                     |  |  |

| GND      | 6   | —     | —   | Analog ground                                                                                                                                          |  |  |

| GT1      | 12  | PFC   | O   | PFC stage gate drive output                                                                                                                            |  |  |

| GT2      | 10  | PWM   | O   | PWM stage gate drive output                                                                                                                            |  |  |

| IAC      | 18  | PFC   | I   | Multiplier current input that is proportional to the instantaneous rectified line voltage                                                              |  |  |

| ISENSE1  | 16  | PFC   | I   | Non-inverting input to the PFC stage current amplifier                                                                                                 |  |  |

| ISENSE2  | 8   | PWM   | I   | Input for PWM stage current sense and peak current limit                                                                                               |  |  |

| MOUT     | 17  | PFC   | I/O | PFC multiplier high impedance current output, internally connected to the current amplifier inverting input                                            |  |  |

| PKLMT    | 14  | PFC   | I   | Voltage input to the PFC peak current limit comparator                                                                                                 |  |  |

| PWRGND   | 11  | —     | —   | Power ground for GT1, GT2 and high current return paths                                                                                                |  |  |

| RT       | 2   | —     | I   | Oscillator programming pin that is set with a single resistor to GND                                                                                   |  |  |

| SS2      | 13  | PWM   | I   | Soft start for the PWM stage                                                                                                                           |  |  |

| VAOUT    | 1   | PFC   | I/O | Output of the PFC transconductance voltage amplifier and it is internally connected to the Zero Power Detect comparator input and the multiplier input |  |  |

| VCC      | 9   | —     | I   | Positive supply voltage pin                                                                                                                            |  |  |

| VERR     | 7   | PWM   | I   | Feedback error voltage input for the PWM stage, typically connected to an optocoupler output                                                           |  |  |

| VFF      | 19  | PFC   | I   | Voltage feedforward pin for the PFC stage, sources an IAC/2 current that should be externally filtered                                                 |  |  |

| VREF     | 20  | —     | O   | Precision 7.5-V reference output                                                                                                                       |  |  |

| VSENSE   | 3   | PFC   | I   | Inverting input to the PFC transconductance voltage amplifier, and input to the OVP, ENABLE and UVLO2 comparators                                      |  |  |

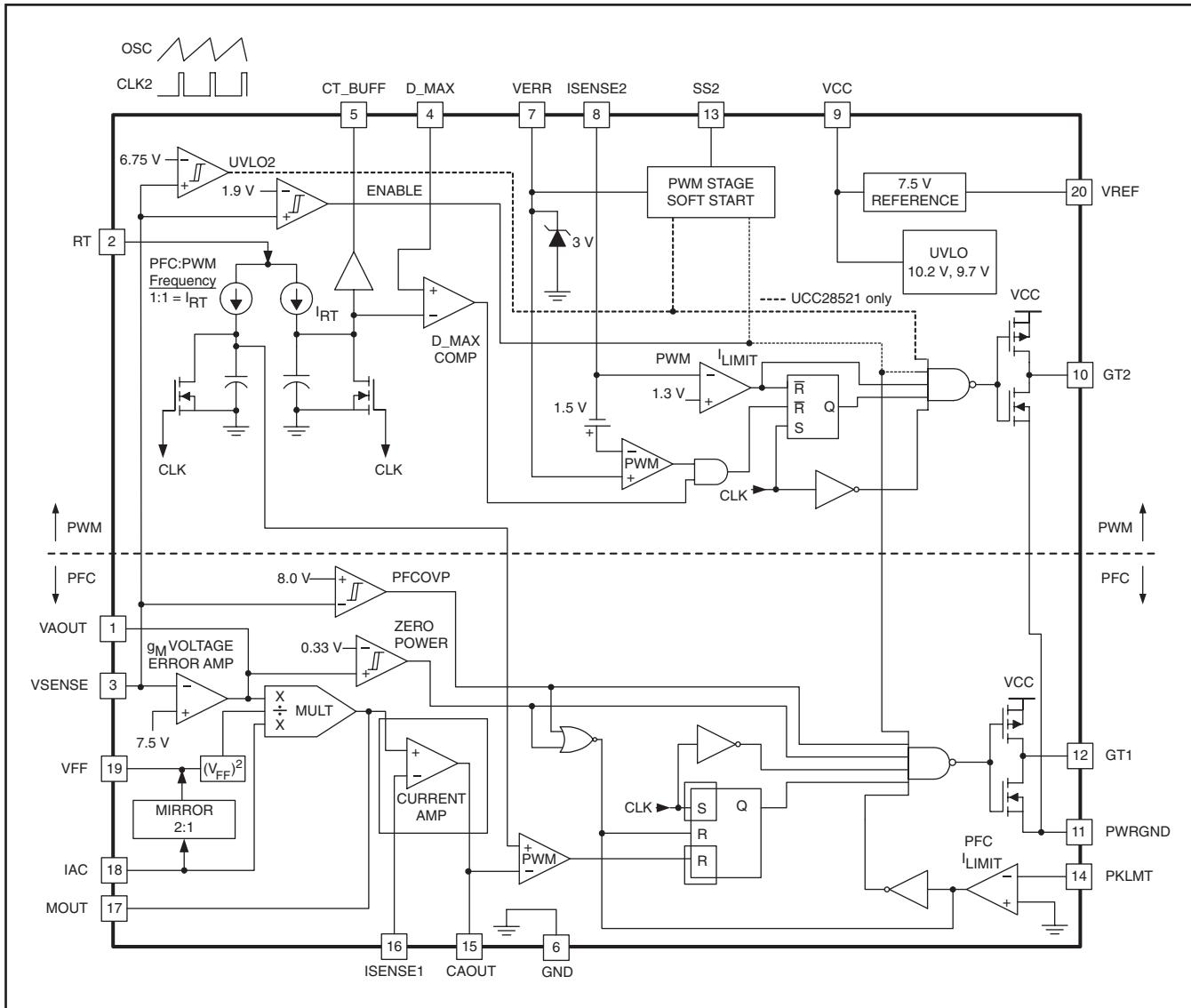

## ブロック図

## ピン機能の詳細説明

**CAOUT (15pin):** このピンは広帯域なオペアンプの出力で、入力ライン電流を検出し正しいデューティ・サイクルとなるようPFC段のPWMコンパレータに指示をします。この出力は、必要に応じて、PFCランプ・ピーク電圧より大きく振幅して最大のデューティ・サイクルを得て、またPFCランプ電圧を下回るまで振幅してデューティ・サイクルをゼロに制御します。CAOUTとMOUTの間に電流ループの位相補償部品を接続してください。

**CT\_BUFF (5pin):** 4Vの振幅をもつ発振器回路が内部でこのピンに接続されており、スロープ補償用にこのピンからISENSE2に直接接続することができます。内部バッファはこのピンに約500  $\mu$ Aの抵抗負荷を駆動することができます。

**D\_MAX (4pin):** このピンに電圧を印加することでGT2の最大デューティ・サイクルを設定することができます。最大デューティ比は0.09から0.90の間でD\_MAXに対し直線性を有します。通常、この電圧はVREFで電圧を供給され、抵抗分割により設定されます。一次近似式はCT\_BUFF周波数がほぼ200kHzの場合以下の式で算出できます。

$$D_{MAX} \approx \frac{V_{DX} - 1.15 \text{ V}}{4 \text{ V}}$$

但し、D<sub>MAX</sub>は無次元の比、

V<sub>DX</sub>はD<sub>MAX</sub>の電圧で単位はボルトです。

また、このピンはV<sub>DX</sub>を0.7Vより低くセットすることでD<sub>MAX</sub>を0に設定するのにも使用できます。

**GND(6ピン):** ICの制御系グランドです。グランド基準で測定される全ての電圧はこのピンを基準としています。VCCとVREF用のバイパス・コンデンサをできるだけ短いリード長でこのピンに接続してください。PWRGNDはこのピンと外部で接続する必要があります。最良の結果を出すためには、GNDのリターン・パスを使用する回路とPWRGNDのリターン・パスを使用する回路の間を電気的に接続するために1本の最短回路配線を使用してください。

**GT1(12ピン):** PFC段用2Aピークのソース及び3Aピークのシンク電流をもつトーテムポール型MOSFETゲート・ドライバです。容量性負荷を駆動する際GT1でのいくらかのオーバーシュートが想定されますが、GT1と外付けMOSFETの間に約2Ωのごく小さなシリーズ抵抗を挿入することでこのオーバーシュートを低減することができます。VCCがUVLOの範囲でなくVREFがオンでなければGT1はディスエーブルです。

**GT2(10ピン):** PWM段用2Aピークのソース及び3Aピークのシンク電流をもつトーテムポール型MOSFETゲート・ドライバで、GT1のドライバと同じです。

**IAC(18ピン):** このマルチプライヤ入力は整流された入力ライン電圧を検出します。IACと入力ライン電圧間の抵抗によりライン電圧はアナログ・マルチプライヤへの電流入力に変換されます。推奨する IAC の最大電流は 500μA です。

**ISENSE1(16ピン):** このピンは電流アンプの非反転入力端子です。このピンとPFC段電流検出抵抗のグランド側の間に抵抗を接続してください。このピンに接続する抵抗はMOUTピンとPFC電流検出抵抗のグランドと反対端子側との間に接続される抵抗値と等しい値でなければなりません。

**ISENSE2(8ピン):** PWM段の電流検出回路とPWMコンパレータは内部にて接続されています。電流検出回路では、ピーク電流のコントロール用は1.3Vに設定をしたピーク制限スレッシュホールドをっています。また、PWMコンパレータでは

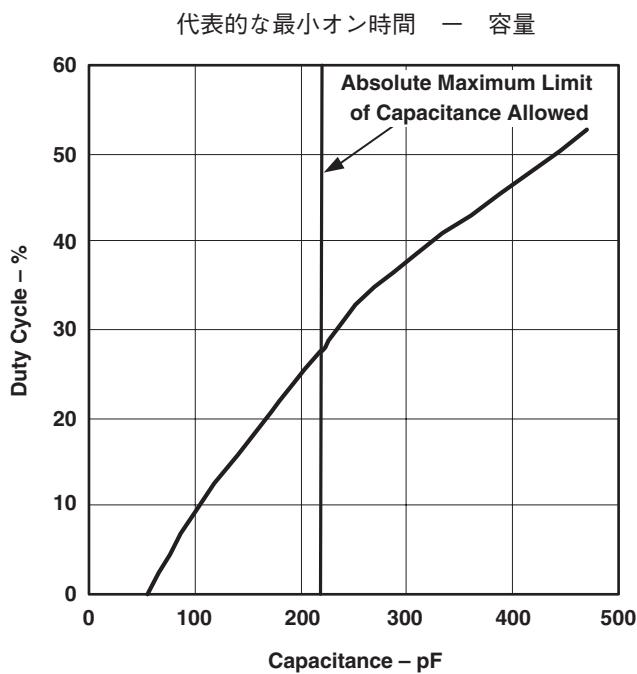

ISENSE2とPWMコンパレータ入力の間に内蔵されている1.5Vレベル・シフト回路が耐ノイズ性を高めています。また、スロープ補償用に発振器ランプもこのピンに合算されます。図31に、代表的なISENSEピンの容量とゲート2出力のパルス幅の最小制御可能リミットとの関係を示します。V<sub>ERR</sub>が最小制御可能デューティ・サイクルに相当する電圧であり、これがその後さらに減少すると、パルス幅はほぼゼロに低下します。

**MOUT(17ピン):** PFC段のマルチプライヤ出力と電流アンプ入力はこのピンで内部にて接続されています。PFC段の出力領域をMOUTピンとPFC電流検出抵抗のグランドと反対端子側との間に接続する抵抗を用いて設定してください。PFCの電流コントロール・ループを補償するためMOUTピンとCAOUTピンの間に抵抗を接続してください。マルチプライヤの出力は電流で、電流アンプの入力はハイ・インピーダンスです。マルチプライヤの出力電流は以下の式で求められます。

$$I_{MOUT} = \frac{(V_{VAOUT} - 1.0) \times I_{IAC}}{K \times (V_{VFF})^2}$$

但し、Kはマルチプライヤのゲイン定数で単位は1/Vです。I<sub>MOUT</sub>はパワー制限のためI<sub>IAC</sub>の2倍に制限されます。

**PKLMT(14ピン):** このピンを用いて PFC段のピーク電流制限を設定します。ピーク制限のスレッシュホールドは0Vです。この信号のレベルを、PFCの電流検出抵抗端で測定される所望の過電流スレッシュホールド電圧に一致する電圧にシフトするため、VREFとPFCの電流検出抵抗のグランドと反対端子側との間に抵抗分割を使用してください。

**PWRGND(11ピン):** GT1とGT2の出力ドライバ用グランドです。このグランドは外部でGNDに接続してください。

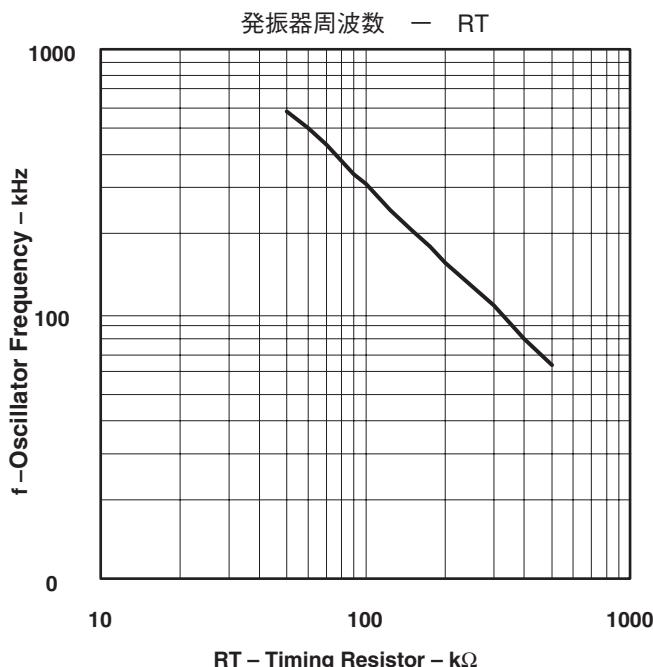

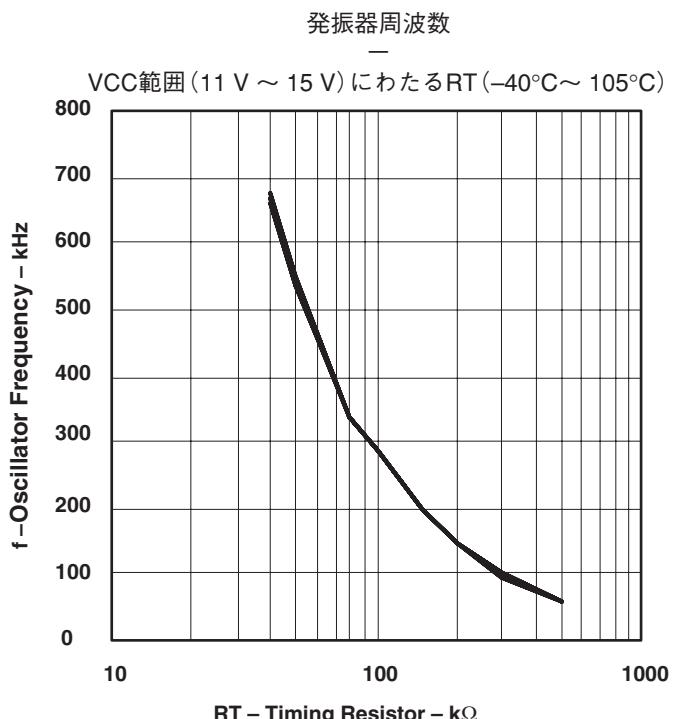

**RT(2ピン):** RTとGNDの間の抵抗によりCT\_BUFFで測定される発振器周波数が設定されます。どの選択肢であっても、PWM段はCT\_BUFFで測定される周波数で動作します。UCC28521では、PFC段はPWM段と同じ周波数で動作します。電圧は直流(標準3V)です。電圧を安定化させようとしてこのピンにコンデンサを接続しないでください。また注意として、発振器を設定する抵抗のGND側をGNDピンに近づけて接続してください。この抵抗の推奨範囲は600kHz ~ 65kHzの周波数範囲でそれぞれ45kΩ~500kΩです。以下の式に従い、抵抗RTによりCT\_BUFFで測定される発振器周波数f<sub>S</sub>が設定されます。

$$R_T = \frac{1}{31 \times 10^{-12}} \left( \frac{1}{f_S} - 2.0 \times 10^{-7} \right)$$

但し、R<sub>T</sub>の単位はΩ、f<sub>S</sub>の単位はHzです。

**SS2(13ピン):** SS2とGNDの間のコンデンサによりPWM段のゲート駆動のソフトスタート時間が設定されます。UVLO2コンパレータがPWM段をイネーブルにした場合、10.5μAの内部電流源がSS2のコンデンサを充電し起動時VERRの電圧を3Vに上昇させます。このことにより、GT2のデューティ・サイクルが0%から、以下の式で与えられるコントロールされる遅延時間t<sub>SS</sub>でデューティ・サイクル・コンパレータによりクランプされる最大まで増加します。

$$C_{SS2} = \frac{t_{SS} \times 10.5 \times 10^{-6}}{3}, \quad F(\text{ファラッド})$$

ディスエーブル・コマンドまたはUVLO2の低下が発生した場合は、SS2はPWM段のゲート駆動をディスエーブルにするよう急速にグランドに放電します。

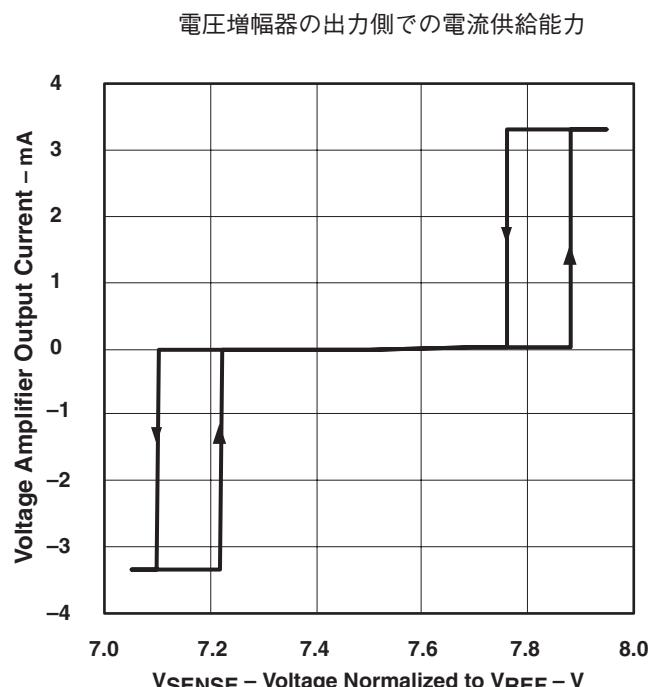

**VAOUT(1ピン):** このトランスコンダクタンス型のアンプの出力はPFC段の出力電圧をレギュレーションし、オーバーシュートを防止するため最大5.5Vで動作します。VAOUTとGNDの間に電圧補償部品を接続してください。この出力が1Vより低くなると、マルチプライヤの出力電流はゼロになります。この出力がさらに0.33Vより低下すると、ゼロパワー検出コンパレータにより確実にPFC段のゲート駆動がオフになります。直線範囲では、このピンは最大30μAまでの電流をソースまたはシンクします。スルーレートの増大機能により、直線範囲外での動作の場合、VAOUTは最大3.3mAまでの電流をソースまたはシンクすることができます。

**VCC(9ピン):** デバイスの電源電圧で、正常動作時12Vから17Vです。外付けMOSFETのゲート容量の高速充電により生じる電源電流のスパイクを吸収するため0.1μFまたはそれ以上のセラミック・コンデンサでVCCをGNDに最短に接続してください。

**VERR(7ピン):** このピンの電圧はGT2のデューティ・サイクルをコントロールし、PWM段の外付けアンプからの帰還誤差信号に接続されます。このピンは最大3Vにクランプされ、GT2に100%のデューティ・サイクルの要求を出すことができます。このピンから流出するプルアップ電流は約10μAです。

**VFF(19ピン):** このピンからの出力電流はIAC入力電流を2で割った内部カレント・ミラーよりもたらされます。次に、マルチプライヤへの入力電圧帰還信号がVFFとGNDの間に接続される外付けの単極R/Cフィルタ端に生成されます。低入力ラインでは、VFF電圧を1.4Vに設定してください。

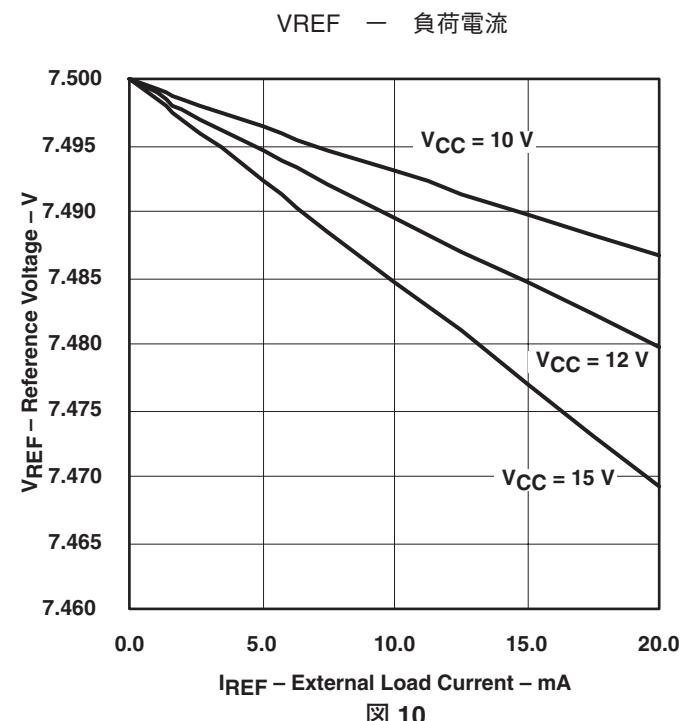

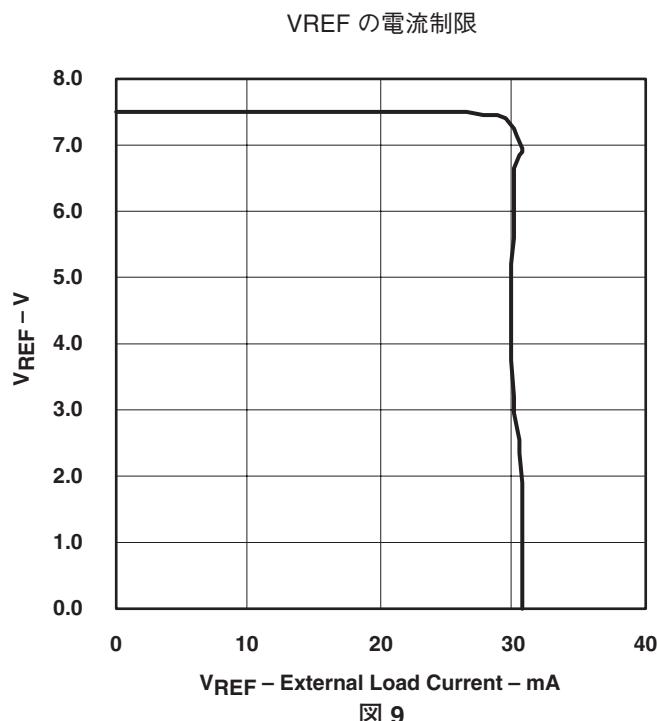

**VREF(20ピン):** このピンは内部回路に電圧を供給する7.5Vの基準電圧の出力で、外部負荷に10mA以上を供給することができます。(最大6mAを確保した時には5mVの負荷レギュレーションをもちます)。内部基準電流は25mAに制限されており、VREFがグランドに短絡した場合にICを保護します。VREFは安定化のため0.1μFから10μFのセラミック・コンデンサで直接GNDに接続してください。VCCが9.7VのUVLOスレッシュホールドより低い時VREFはディスエーブルになり0Vに保たれます。

**VSENSE(3ピン):** このピンはPFCトランスコンダクタンス型のアンプへの反転入力で、PFCへの帰還信号となります。VSENSEがその定常状態値の±0.35V以内で動作する場合、VAOUTの電流はVREF電圧とVSENSE電圧の間の差にgm係数で比例します。この範囲外では、PFC段の電圧コントロールを迅速に回復させるようスルーレートを改善するためVAOUTの電流は大きくなります。電圧コントロールの回復を行うか、そうしないかの決定はVSENSEの約120mVのヒステリシスにより内部で行われます。VSENSEは内部でPFCのOVP、イネーブル、UVLO2コンパレータに接続されています。

## アプリケーション情報

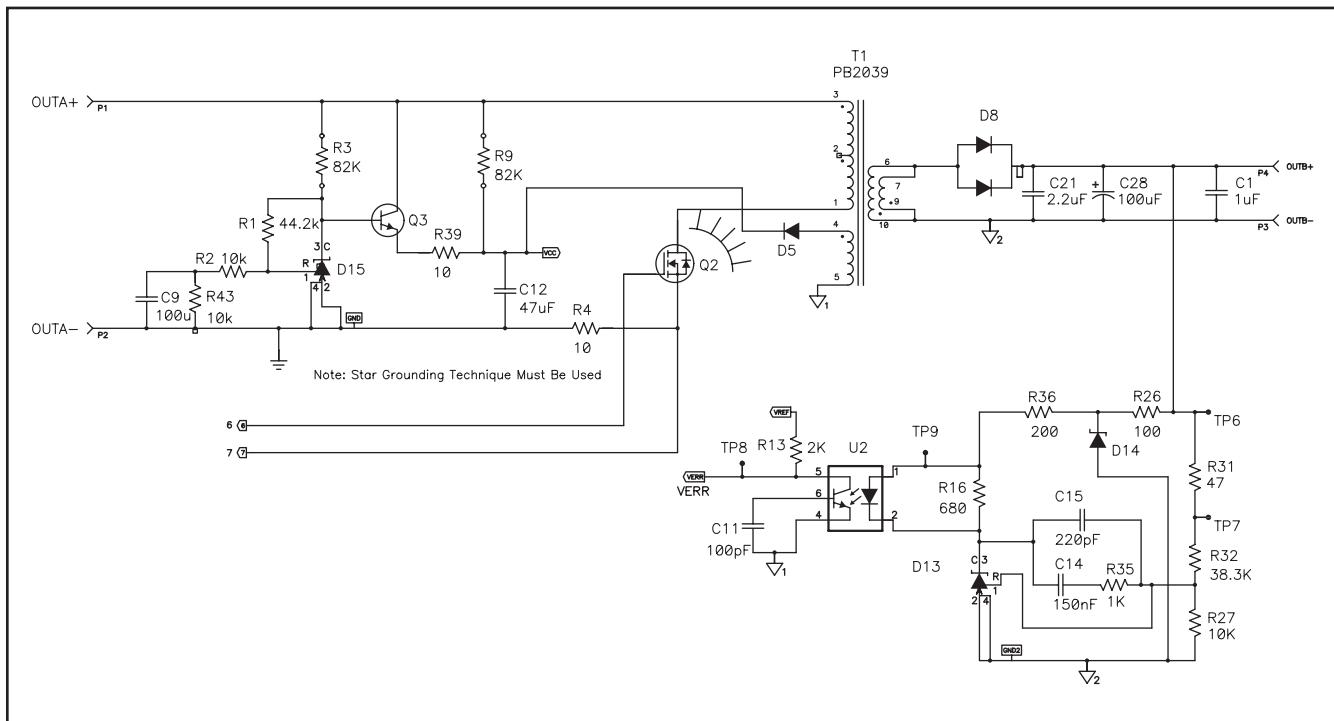

図1. 代表的なアプリケーション回路：ブーストPFCとフライバックPWMから成る電源システム

UCC28521混合コントローラはパルス幅変調器(PWM)コントローラと同期する力率改善(PFC)コントローラをワンチップに集積しています。PFCコントローラは平均電流モードで制御されるPFCの全機能を備えています。また、PWMコント

ローラはピーク電流モードで制御される絶縁型コンバータの全機能を備えています。この2つのコントローラはPFCコントローラとPWMコントローラともトレーリング・エッジ変調(TEM)された固定周波数で内部同期しています。

## 設計手順

以下の考察によりPFC/PWM混合のシステムの代表的な設計手順を進めてゆきます。設計手順はパワー段の素子から始め、PFC段のコントロール素子、PWM段のコントロール素子へと進みます。一般的な設計手順はしばしば反復を伴うということに留意しておいてください。この反復作業は通常完成したPFC/PWMシステムをシミュレーションとテストの両方またはいずれか一方を行った後に始まります。この設計手順では図1の代表的なアプリケーション回路を参照しています。

設計は出力電圧、出力電力、入力ライン電圧範囲への要求項目から始めます。効率、許容高調波電流などのその他細目は始めに与えられているか、または製品の設計サイクルを通じて明らかになってゆきます。力率改善の必要性は、EN-61000などの公的機関規格より、または利用可能なライン電力が電源システムの出力電力にほぼ等しい場合に生じます。また、保持時間の要件も設計の初期段階で必要となります。一般的に、保持時間  $t_{HU}$  は少なくとも1.5ライン・サイクルの期間とされています。

PFC/PWM段電源システムの一般的な構造は2つのスイッチモード・コンバータが縦列接続されたものです。各段にはそれぞれ付随する効率があり、また、各段は目的とする入力ライン高調波と負荷レギュレーション特性を同時に達成するためにいくつかの設定しなければならない異常制限機能をデバイス自身がもっています。PFC段は常にPWM段に十分な電力を供給するよう設計しなければなりません。PFC段のサイクルごとの電流制限はPFCの電流検出を見越しておいたため低入力ライン電圧時に電力クランプよりも少し大きな電力レベルで動作するよう設定する必要があります。このことにより、最大定格負荷の全範囲で力率改善が可能になります。瞬時的な負荷が平均負荷にほぼ等しい場合、PWM段のクランプ回路は、PFC段の平均電力クランプよりも少し低いか、または等しいレベルに電力を制限するよう設定することができます。クランプ動作のマージンは測定公差と効率を考慮に入れておかなければなりません。逆に、瞬時的な負荷が保持時間よりかなり短く大きなピークの場合は、PWM段の電流制限とデューティ比の制限はPFC段の平均電力クランプよりも高いレベルでクランプする必要があります。設計手順を簡略化するため、PWM段の平均及びピーク負荷は等しい例として示します。全ての電流制限とデューティ比の制限はPFC段の平均電力クランプよりも少し低いレベル(10%)で電力をクランプするよう設定します。

## 内部パラメータの作成

エネルギー蓄電電圧  $V_{C1}$  を選択します。PFC段は昇圧コンバータであるため、C1端の電圧は過渡負荷が発生した場合にも制御ができるよう十分な量の入力ライン電圧より大きなければなりません。通常、この電圧は85V<sub>AC</sub>から265V<sub>AC</sub>の一般的な入力ラインのアプリケーションでは約5%の約400Vです。

エネルギー蓄電電圧  $V_{C1}$  が決まると、PFC段のデューティ比の範囲  $D_1$  が設定されます。PFC段のCCM動作(連続電流モード動作)では、PFCの最小デューティ比は以下の式で求められます。

$$D_{1(\min)} = 1 - \frac{\sqrt{2} \times V_{AC\text{MIN}}}{V_{C1}} \quad (1)$$

PFC段のおおよそのスイッチング周波数を選択します。MOSFETベースのPFC段の周波数は、最大ライン電圧と最大ライン電流にもよりますが、100kHzから200kHzの範囲が妥当です。周波数を高く設定すればインダクタンスなどの低減には役立ちますがスイッチング損失の増大と負荷変動時に制御限界などを考慮する必要があります。またスイッチング周波数はQ1とD3のスイッチング損失や、またはL1の設計を最適化するために再検討することができます。

電力要求と  $V_{C1}$  の大きさなどを考慮してPWM段の適切な制御方式を選択します。簡単にするため、図1の代表的なアプリケーション回路ではPWM段はフライバック・コンバータ方式です。ほとんどの場合、PWM段の制御方式はトランス絶縁でなければならず、この制御方式で要求するパルス幅変調信号は1つのみです。これらの機能をもつ制御方式には以下のものがあります。

- 一石のフォワード・コンバータ

- 一石のフライバック・コンバータ

- 二石のフォワード・コンバータ

- 二石のフライバック・コンバータ

PWM段の標準/最大デューティ比( $D_{2(\text{nom})}$ 、 $D_{2(\text{max})}$ )とそれに関連したQ2のピーク・ドライン電流  $i_{Q2(\text{peak})}$  を、制御方式、PWMのヒステリシス、PWM段の出力電圧要求をもとに算出します。また、PWM段がPFC段と同一スイッチング周波数で動作させる事が適切かどうか、または、PWM段はPFC段のスイッチング周波数の2倍で動作させる事ができるかを推定します。最大電圧、パワーMOSFETとパワー・ダイオードの電流をもとにPWM段のスイッチング周波数を見積もります。PWM段の発振器周波数をR20の値を用いて設定します。

$$R20 = \frac{1}{31 \times 10^{-12}} \left( \frac{1}{f_{S(\text{pwm})}} - 2.0 \times 10^{-7} \right), \Omega \quad (2)$$

ほとんどのアプリケーションではPWM段は最小エネルギー蓄電容量の電圧でレギュレーションすることが求められます。最大デューティ比  $D_{2(\text{max})}$  と  $i_{Q2(\text{peak})}$  は、トランスT1のピーク電流ストレスとPWM段の他の誘導成分を見積もるため最小エネルギー蓄電電圧について計算しなければなりません。

この時点で、UCC28510ファミリーのうちのどれを選択すべきかを予測するのに十分な情報が揃いました。

## パワー段の素子

パワー段の素子の関連には、C1-C3、D1-D5、L1、R2、R5、Q1、Q2、T1があります。PWM段の素子 C2、D4、D5、Q2、T1に関しての詳細は、それらがPWM段の制御方式の選択に依存するためここでは検討しません。PWM段は選択した制御方式に同一のストレス及び損失の構造をもつ絶縁型のDC/DC制御方式です。PWM段の定常状態での平均デューティ比とQ2スイッチ電流の見積もりはPFC段のストレスの見積もりに必要です。また、ソフトスタート・コンデンサC5とバイアス電源コンデンサC3の見積もりにPWM段の固有のステップ応答が必要です。

PFC段の素子C1、C3、D1-D3、Q1の選択手順をここで詳細に検討します。一般に、PFC段の素子の選択手順は、PFC/PWM段の同期に起因するコンデンサC1を除いて、固定スイッチング周波数の標準的なPFC制御の設計の場合と同じです。

ダイオード・ブリッジD1はRMSライン電流とピーク交流ライン電圧に対する耐性をもつよう選択されます。ダイオードD2によりコンデンサC1は初期起動時L1を飽和させることなく充電し、D2はピーク突入電流と最大入力ライン電圧のピークに対する耐性をもつよう選択されます。規格または状況によっては、入力ラインに直列に突入電流制限回路を追加することも必要です。

PFC段のインダクタL1は最小入力ライン電圧で最大電流リップルを供給できるように選択します。一般的に、リップル係数  $k_{RF}$  は約0.2が選ばれます。ライン電流に過度のクロスオーバー歪みがある場合、より大きなリップル係数(0.3程度)にすると歪みは低減しますが、ライン電流にそれ以上のスイッチング時のリップルが生じます。最初は、インダクタンスは入力電力が出力電力に等しいとして見積もることができます。

$$L1 = \frac{V_{AC(min)}^2 \times D_{1(min)} \times T_{S(pfc)}}{k_{RF} \times P_{IN}} \quad (3)$$

$$\text{where, } k_{RF} = \frac{\Delta i_{L1(p-p)}}{i_{L1(max)}}$$

$$\text{and } T_{S(pfc)} \text{ is } \frac{1}{\text{switching frequency of the PFC}}$$

インダクタL1は入力ライン電流時にも飽和しないで最大RMSライン電流に対する耐性をもつよう設計しなければなりません。

パワーMOSFET Q1とダイオードD3を、固定スイッチング周波数のPFC設計に使用されるのと同じ規準で選択します。これらの素子はエネルギー蓄電電圧  $V_{C1}$  に対する耐性をもつよう十分な電圧定格と、十分な電流定格をもっていなければなりません。GT1ピンからのソース/シンク電流を制限するのにゲート駆動抵抗R9が必要です。状況によっては保護機能と特性の改善のためゲート駆動部品を追加することが必要となることがあります<sup>[10]</sup>。同じ理由でGT2ピンとQ2のゲートの間に同じようなゲート駆動抵抗R10が必要です。

PFC段の電流検出抵抗R2は1Vのダイナミック・レンジ( $V_{DYNAMIC}$ )で動作するよう選択されます。また、この検出抵抗は最大RMSライン電流で安全動作が可能となる十分に大きな電力定格をもっていなければなりません。

$$R2 = \frac{V_{DYNAMIC}}{i_{L1(max)} + 0.5 \times \Delta i_{L1(p-p)}} \quad (4)$$

$$\text{where, } i_{L1(max)} = \frac{\sqrt{2} \times P_{IN}}{V_{AC(min)}}$$

PFC段の  $I_{LIMIT}$  コンパレータのスレッシュホールドはコントローラ・デバイスのグランドが基準です。従って、PKLMTで測定されるPFC段の電流検出電圧は、PFCの瞬時電流が最大である場合、0.0Vを超えるよう正電圧でバイアスしなければなりません。このバイアス電圧は式(5)で示されているように  $R14$  と  $R7$  で設定されます。抵抗  $R14$  は任意に約10kΩを選択します。

$$\frac{R7}{R14} = \frac{1}{\frac{V_{REF}}{i_{L1(max)} \times R2} - 1} \quad (5)$$

エネルギー蓄電コンデンサC1の容量値は以下の式により保持時間要件( $t_{HU}$ )に適合するよう選択されます。

$$C1 = \frac{2P_{OUT} \times t_{HU}}{V_{C1}^2 - (V_{C1} - 0.7V_{C1})^2} \quad (6)$$

コンデンサC1は選択したエネルギー蓄電電圧の定格でなければならず、また、PFC段とPWM段の結合動作により生じるRMSリップル電流  $I_{C1(rms)}$  に対する耐性がなければなりません。GT2がMOSFET Q2をアクティブにしている間Q2の平均ドレイン電流を使用して  $I_{C1(rms)}$  を検出します。当初見積もりとして式(7)を用いて行い、次に図2を参照して精度を上げます。

$$I_{C1(rms)} = P_{OUT} \times \sqrt{\frac{16 \times V_{BOOST}}{3 - \pi \times V_{AC(max)}} - 1} \quad (7)$$

$I_{Q2}$ に対する  $I_{C1(rms)}$  の比は、1X:1Xの発振器のオプションは図3、1X:2Xの発振器オプションは図4のそれぞれのグラフを使用して求めることができます。このグラフを使うには、横軸に沿って  $V_{C1}$  に対する  $V_{AC}$  の比を見つけ、次に PWM段のデューティ比の曲線との交差点まで縦線を引きます。縦軸との交差部から横線を引いて、 $I_{Q2}$ に対する  $I_{C1(rms)}$  の比を読みます。

PWM段の電流検出抵抗R5は、最大電流時その電圧がピーク電流コンパレータのスレッシュホールド電圧(標準1.3V)となるよう選択されます。

$$R5 = \frac{V_{TH}(\text{PWM stage} \times I_{LIMIT})}{i_{Q2(\text{peak})}} \quad (8)$$

ほとんどの場合、規格またはアプリケーションの要件に適合するために入力ライン・フィルタが必要とされます。入力ライン・フィルタの設計は膨大な条件や状況に左右されるためここでの手順からは省略します。この詳細については参考資料[11]を参照してください。

## PFC段のコントロール

PFC段は3段階のプロセスで設計されます。まず、マルチプライヤのダイナミック・レンジを設定し、2番目に、平均電流コントロール・ループを安定させ、3番目に、エネルギー蓄電コンデンサの電圧をコントロールする電圧ループを安定させます。可能な限り広いマルチプライヤのダイナミック・レンジを使用することが望ましく特性に大きく影響します。電流コントロール・ループは瞬時入力ライン電圧に追随するため広い帯域幅をもたなければなりません。電圧ループは力率を落とすことがないよう交流ライン周波数の2倍以上遅く設定する必要があります。

## マルチプライヤ

マルチプライヤ(掛け算器)のダイナミック・レンジは、IACピン、VAOUTピン、VFFピンの電流及び/または電圧の関数です。マルチプライヤの全範囲を使用して選択の調整を行い、目的とするパワー制限特性を得ます。式(9)に記載されているように、 $V_{VAOUT}$ 範囲の最大条件下で $i_{IAC}(t)$ 範囲と $V_{VFF}$ 範囲を使って部品R1とR15を選択します。この選択手順はVFF電圧とMOUT電流の制限を除いてUC3854の選択プロセスと同様です<sup>[12]</sup>。この製品シリーズでは、1.4Vまたは $V_{VFF}$ のうちの大きい方で除算できるよう“二乗による除算”機能が内部で実行されます。分圧比が1.4Vレベルで制御される場合、VAOUTレベルがマルチプライヤが機能する範囲内にあれば力率改善が図られます。マルチプライヤ部が3入力のマルチプライヤでの働きよりはむしろ2入力のマルチプライヤとして機能するため力率改善はその条件の時に行われます。VFFピンの電圧はIAC電流の平均に比例することに注意してください。一般的に、設計境界として低入力ライン電圧では $V_{VFF}=1.4V$ に設定され、有効入力ライン電圧範囲が4.3:1より低い比で変わっても $V_{VFF}$ の上限は範囲内にとどまります。

$$\begin{aligned} 0 &\leq i_{IAC}(t) \leq 500 \mu\text{A}, \\ 0 &\leq V_{VAOUT}(t) \leq 5 \text{ V}, \\ 1.4 \text{ V} &\leq V_{VFF} \leq V_{VREF} - 1.4 \text{ V} \end{aligned} \quad (9)$$

選択手順は高入力ラインでの $I_{AC}$ のピーク電流が約500 $\mu\text{A}$ となるようR1を選択することから始めます。表1を参照してください。2番目に、表1に示されているようにVFF電圧が最小の場合のR15を選択します。3番目に、表1のように、第三次高調波量に適合するよう十分に小さなリップルでVFF電圧を平均化してC8を選択します。THDが3%を目標とするシステムでは、標準的にはフィードフォワード回路が入力波形に対し1.5%分の第三次高調波歪を寄与します<sup>[4]</sup>。減衰係数0.022が、この規準に適合します。最後に、最大電力、最小入力ライン電圧( $V_{FF, MIN}$ )、VAOUTがその最大レベルの5Vという条件下で、R12端の電圧が検出抵抗R2端の電圧に等しくなるよう表2のようにMOUT抵抗R12を選択します。経験的に、マルチプライヤの出力抵抗R12は、エネルギー蓄電コンデンサの電圧が最大負荷時に低下するとして少し増やしておくことが必要なことがあります。このことは部品とマルチプライヤの公差に起因しています。電流アンプのオフセットを最小限にするためには、表1に示されているように、ISENSE1ピンの抵抗R8をR12の値と同じ値に設定します。

## PFC段のコントロール

このコントローラはPFC段には平均電流ループの制御を用いています。電流制御ループは、通常は整流された正弦波の交流ライン電圧をトラッキングするのに十分速くなければなりません。PFCの電流ループを安定化させるコントローラを設計するには多くの方法があります。ここで説明されている方法はほとんどのアプリケーションで良好な結果をもたらします<sup>[5]</sup>。この方法では、式10で表されているように、システムの固有周波数と線形化された昇圧PFCのゼロの両方とも、スイッチング周波数と目的とするクロスオーバー周波数 $f_{CO(pfc)}$ の両方よりもかなり低いと仮定しています。式10の不等式の左側はC1の容量が非常に大きいため通常は真となります。

$$\frac{1 - D_{\text{PWM(min)}}}{\sqrt{L1 \times C1}} \text{ and } \frac{2P_{\text{IN}}}{C1 \times V_{C1}^2} << 2 \times \pi \times f_{CO(pfc)} << 2 \times \pi \times f_{S(pfc)} \quad (10)$$

| REFERENCE DESIGNATOR | EQUATION                                                                                       | NOTES                                                       |

|----------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| R1                   | $\frac{\sqrt{2} V_{AC(max)}}{I_{AC(peak)}}$                                                    | set $I_{AC(peak)} = 500 \mu A$                              |

| R15                  | $2 \times R1 \times \frac{V_{VFF(avgmin)}}{V_{AC(min)} \times 0.9}$                            | set $V_{VFF(avgmin)} = 1.4 V$                               |

| C8                   | $\frac{1}{2 \times \pi \times f_{AC} \times A_{FF(2)} \times R15}$                             | $A_{FF(2)} = 0.022$ for 3% THD                              |

| R12                  | $\frac{P_{IN}(R1)(R2)k}{V_{VAOUT(max)} - 1} \left( \frac{V_{VFF(min)}}{V_{AC(min)}} \right)^2$ | $k = 1$<br>$V_{VFF(min)} = 1.4V$<br>$V_{VAOUT(max)} = 5.0V$ |

| R8                   | R12                                                                                            | Always change R8 if R12 is changed                          |

表 1.

| REFERENCE DESIGNATOR | EQUATION                                                                                       | NOTES                     |

|----------------------|------------------------------------------------------------------------------------------------|---------------------------|

| R13                  | $R12 \times \frac{2 \times \pi \times f_{CO(pfc)} \times L1 \times V_{CT\_BUFF(p-p)}}{V_{C1}}$ | $V_{CT\_BUFF(p-p)} = 4 V$ |

| C6                   | $\frac{1}{R13 \times 2 \times \pi \times f_{CO(pfc)}}$                                         |                           |

| C7                   | $\frac{1}{\pi \times f_{S(pfc)}}$                                                              |                           |

表 2.

不等式の左側は中項よりも少なくとも10倍小さく、また、不等式の右側は中項よりも少なくとも5倍程度大きくしてください。50Hzから60Hzでの力率改善のためには、クロスオーバー周波数を約10kHz程度に設定することで良好な結果が得られます。PWM段のスイッチング周波数が100kHzより低いか、またはクロスオーバー周波数での補償ゲインが大きい場合は(およそ40dB以上)、これより低いクロスオーバー周波数が必要となるかもしれません。

クロスオーバー周波数を選択する際には、ゲインをクロスオーバー周波数で設定するようR13を選択し、次に、ゼロをクロスオーバー周波数に置くようC6を選択し、ポールをスイッチング周波数の半分の周波数で供給するようC7を選択します。これらの式を表2に示します。

## PFC電圧ループ

電圧ループは、電圧の補正が力率改善を妨げないよう入力ライン周波数の2倍以上の低い周波数でクロスオーバーしなければなりません。 $V_{C1}$ 検出電圧からの第二次高調波リップルは、VFF電圧のリップルと同様に、直接的に入力ライン上での第三次高調波をもたらします。

## PWM段のコントロール

PWM段のコントロール素子は標準的な電流モードの絶縁型コンバータと同じです。二次的な素子としてC12-C14、D6、R22-R25、U2、U3があり、これらは誤差増幅器、補償及び絶縁機能を行います。一次側では、VERRがホトカプラ出力U2と

プルアップ抵抗R17の間のノードに接続されます。抵抗R17はホトカプラU2の出力電流及びVERR入力からの変換ゲインを表します。

ロープ補償はISENSE2で全体の傾きを形成する抵抗R18とR11を使用して設定されます。CT\_BUFFの電圧は振幅が1Vから5Vの鋸波です。

多くのアプリケーションではトランジストの飽和を防ぐためにPWM段のデューティ比制限が必要とされます。以下の抵抗R16とR19の比率を使用して最大デューティ比を設定します。

$$\frac{R16}{R19} = \frac{V_{VREF}}{1 + 4 \times D_{PWM(max)}} - 1 \quad (11)$$

## ソフトスタート

ソフトスタート・コンデンサC5は、SS2に接続され、PWM段のソフトスタート・ランプをコントロールします。ソフトスタート・ランプはVSENSE電圧が6.75Vを超えた時開始します。ループの飽和を回避するため、ソフトスタート・ランプの速度はPWM段コンバータの開ループ応答より小さいか、または等しく設定してください。

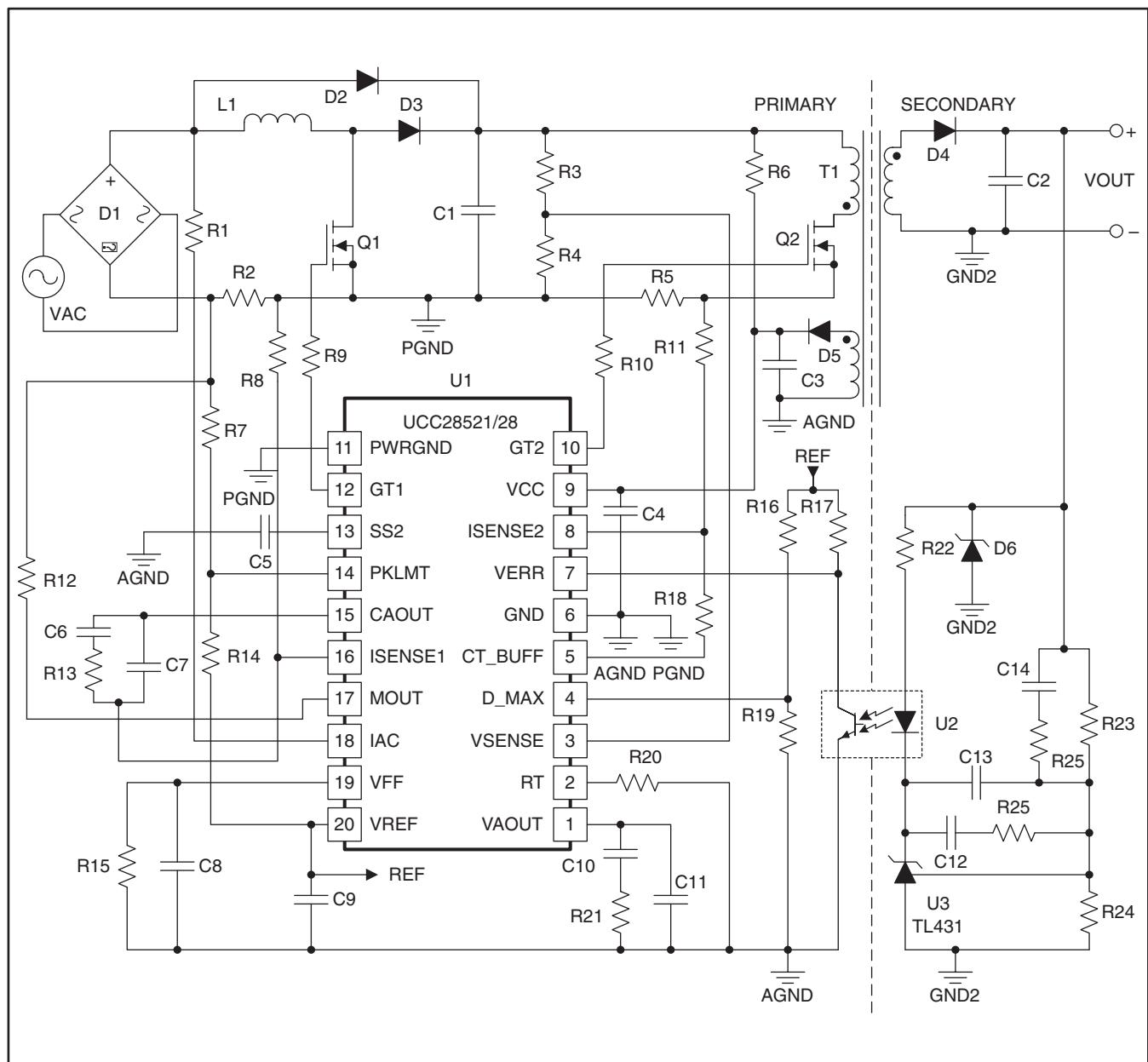

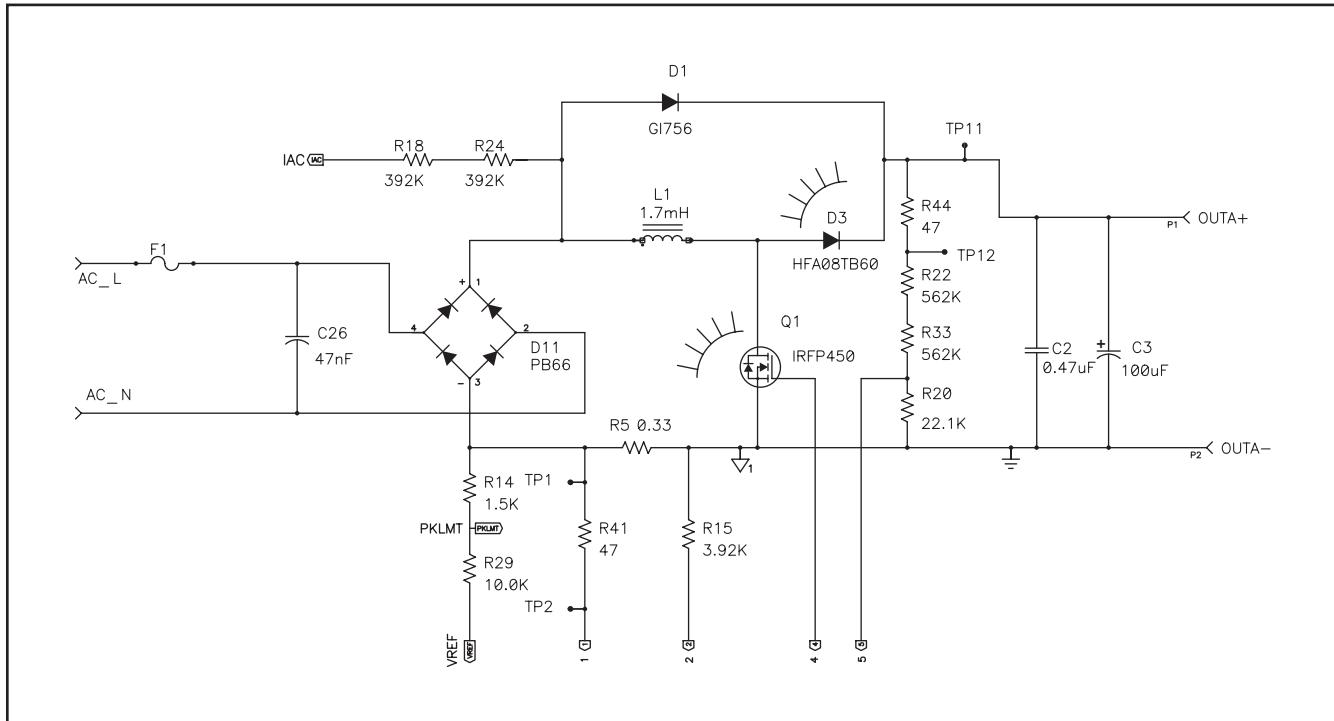

## リファレンス・デザイン

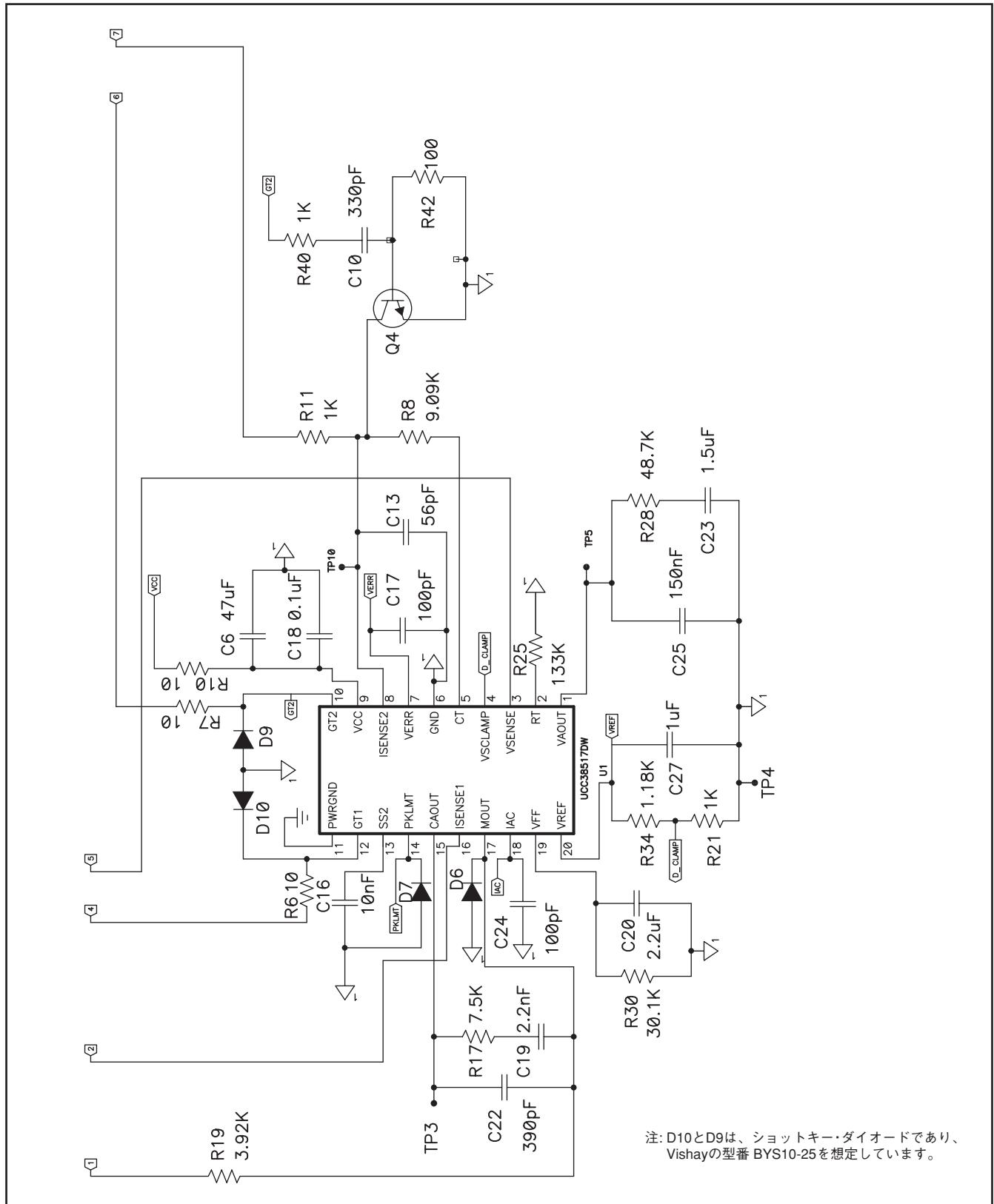

12V/8Wの出力をもつ一般的なライン入力/100W PFC出力の設計についてはUCC28517EVM (TI文献番号SLUU117) に記載されています。UCC28517はUCC28521と密接な関係のある混合デ

バイスです。UCC28517は1:2のPFC:PWM周波数オプションをもっています。回路図を図2、図3、図4に示します。詳細についてはSLUU117を参照してください (<http://www.ti.com>)。

図2. セクションA

図3. セクションB

図4. セクションC

注: D10とD9は、ショットキー・ダイオードであり、Vishayの型番 BYS10-25を想定しています。

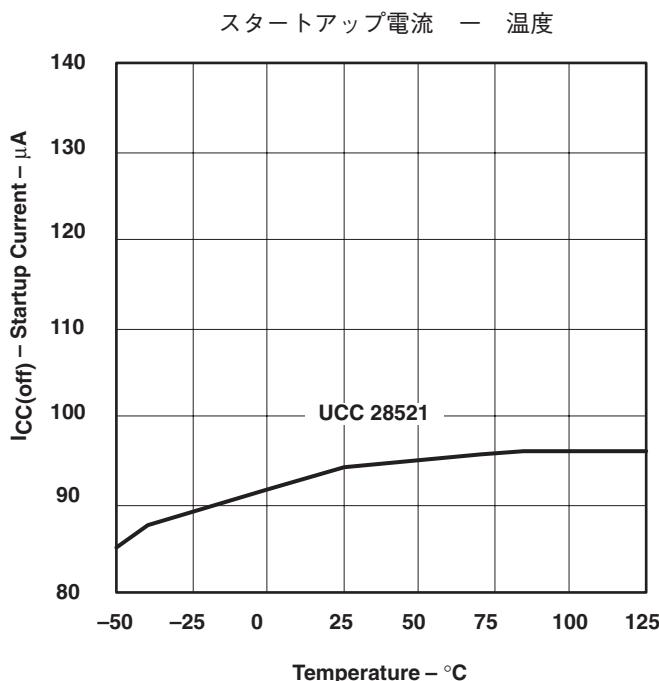

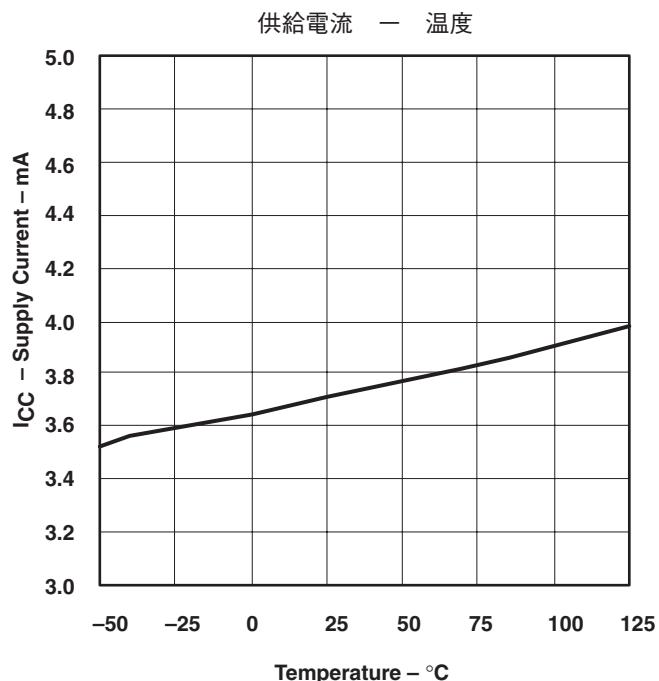

## 代表的特性

図 5

図 6

図 7

図 8

## 代表的特性

## 代表的特性

図 13

図 14

図 15

図 16

## 代表的特性

図 17

図 18

図 19

図 20

## 代表的特性

マルチプライヤのゲイン

電力一定時のマルチプライヤのパフォーマンス

## 代表的特性

図 25

図 26

図 27

図 28

## 代表的特性

図 29

図 30

図 31

## 參考資料

- Evaluation Module and associated User's Guide, UCC28521EVM, Texas Instruments Literature Number SLUU218

- Datasheet, *UCC38500/1/2/3 BiCMOS PFC/PWM Combination Controller*, Texas Instruments Literature Number SLUS419C

- Power Supply Seminar SEM 600, *High Power Factor Preregulator for Off-line Power Supplies*, L.H. Dixon, Texas Instruments Literature Number SLUP087

- Power Supply Seminar SEM 700, *Optimizing the Design of a High Power Factor Switching Preregulator*, L.H. Dixon, Texas Instruments Literature Number SLUP093

- Power Supply Seminar SEM 1500 Topic 2, *Designing High-Power Factor Off Line Power Supplies*, by James P. Noon

- Application Note, *UC3854 Controlled Power Factor Correction Circuit Design*, Texas Instruments Literature Number SLUA144

- Design Note, *Optimizing Performance in UC3854 Power Factor Correction*, Texas Instruments Literature Number SLUA172

- Design Note, *UC3854A and UC3854B Advanced Power Factor Correction Control ICs*, Texas Instruments Literature Number SLUA177

- Design Note, *UC3854A/B and UC3855A/B Provide Power Limiting with Sinusoidal Input Current for PFC Front Ends*, Texas Instruments Literature Number SLUA196

- Laszlo Balogh, *A Design and Application Guide for High Speed Power MOSFET Gate Drive Circuits*, 2001 Power Supply Design Seminar Manual SEM1400, 2001

- Bob Mammano and Bruce Carsten, *Understanding and Optimizing Electromagnetic Compatibility in Switchmode Power Supplies*, 2002 Power Supply Design Seminar Manual SEM1500, 2002

## 関連製品

| PART NUMBER    | DESCRIPTION                                     | COMMENTS                                                                                     |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|

| UCC28510-17    | Advanced BiCMOS PFC/PWM combination controllers | 1:1 or 1:2 frequency option; leading edge, trailing edge modulation, programmable PWM Max dc |

| UCC38500/1/2/3 | BiCMOS PFC/PWM combination controller           | 1:1 leading edge, trailing edge modulation, 50% PWM Max dc                                   |

| UCC3817/18     | BiCMOS power factor preregulator                | High PF, UC3854 compatible, leading edge trailing edge modulation                            |

| UCC3819        | Programmable output power factor preregulator   | Tracking boost topology for dynamic output voltage adjustments                               |

| UC3854         | High Power Factor Preregulator                  | High PF, industry standard PFC controller; 35 V <sub>CC</sub> max                            |

| UC3854A/B      | Enhanced high power factor preregulator         | Improved high PF, industry standard PFC controller; 22 V <sub>CC</sub> max                   |

| UC3855A/B      | High performance power factor preregulator      | ZVT output for lower EMI emission & higher efficiencies                                      |

| UC3853         | High power factor preregulator                  | 8-Pin package; simplified architecture to minimized external components                      |

| UCC38050       | Transition mode PFC controller                  | Constant on-time transition mode PFC controller                                              |

| UC3852         | High power factor preregulator                  | Constant off-time transition mode PFC controller; 30 V <sub>CC</sub> max                     |

## 改訂履歴

| REVISION | DATE    | CHANGE                           |

|----------|---------|----------------------------------|

| SLUS608B | 6/27/05 | Corrected CAOUT pin description. |

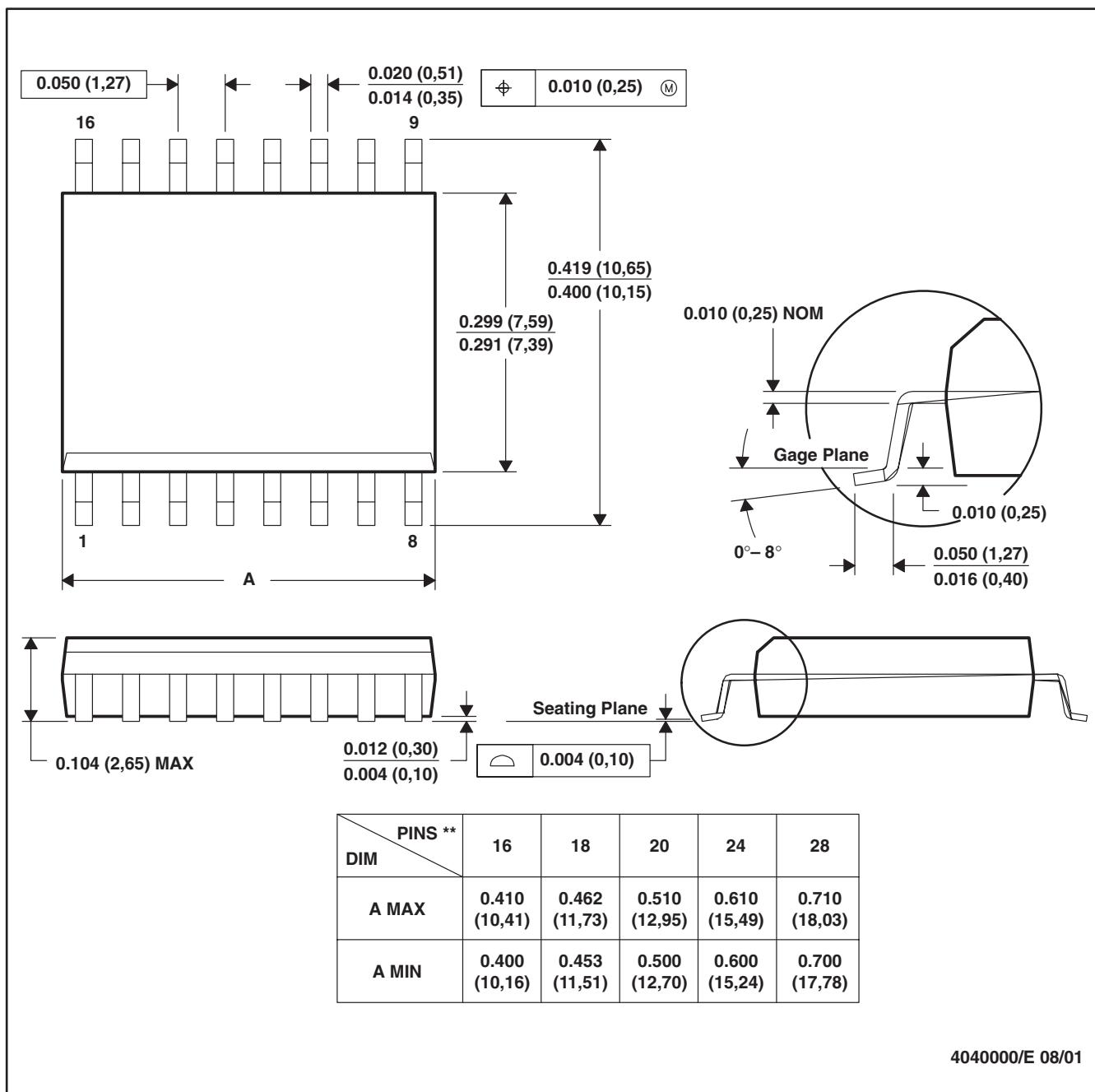

# メカニカル・データ

DW (R-PDSO-G\*\*)

16 PINS SHOWN

PLASTIC SMALL-OUTLINE PACKAGE

- 注: A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. この図は、予告なく変更されることがあります。

C. ボディ寸法はモールド突起部を含みません。突起部は0.006 (0.15) を超えません。

D. JEDEC MS-013に準拠します。

## 付録: パッケージ・オプション

### パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| UCC28521DW       | ACTIVE                | SOIC         | DW              | 20   | 25          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28521DWR      | ACTIVE                | SOIC         | DW              | 20   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28521DWRG4    | ACTIVE                | SOIC         | DW              | 20   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DW       | ACTIVE                | SOIC         | DW              | 20   | 25          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DWR      | ACTIVE                | SOIC         | DW              | 20   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DWRG4    | ACTIVE                | SOIC         | DW              | 20   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

(1) マーケティング・ステータスは次のように定義されています。

**ACTIVE** : 製品デバイスが新規設計用に推奨されています。

**LIFEBUY** : TIによりデバイスの生産中止予定が発表され、ライフトайム購入期間が有効です。

**NRND** : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

**PREVIEW** : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

**OBSOLETE** : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

**TBD** : Pb-Free/Green変換プランが策定されていません。

**Pb-Free (RoHS)** : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

**Green (RoHS & no Sb/Br)** : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項** : このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じるTIの責任は、TIによって年次ベースで顧客に販売される、このドキュメント発行時点でのTI製品の合計購入価格を超えることはありません。

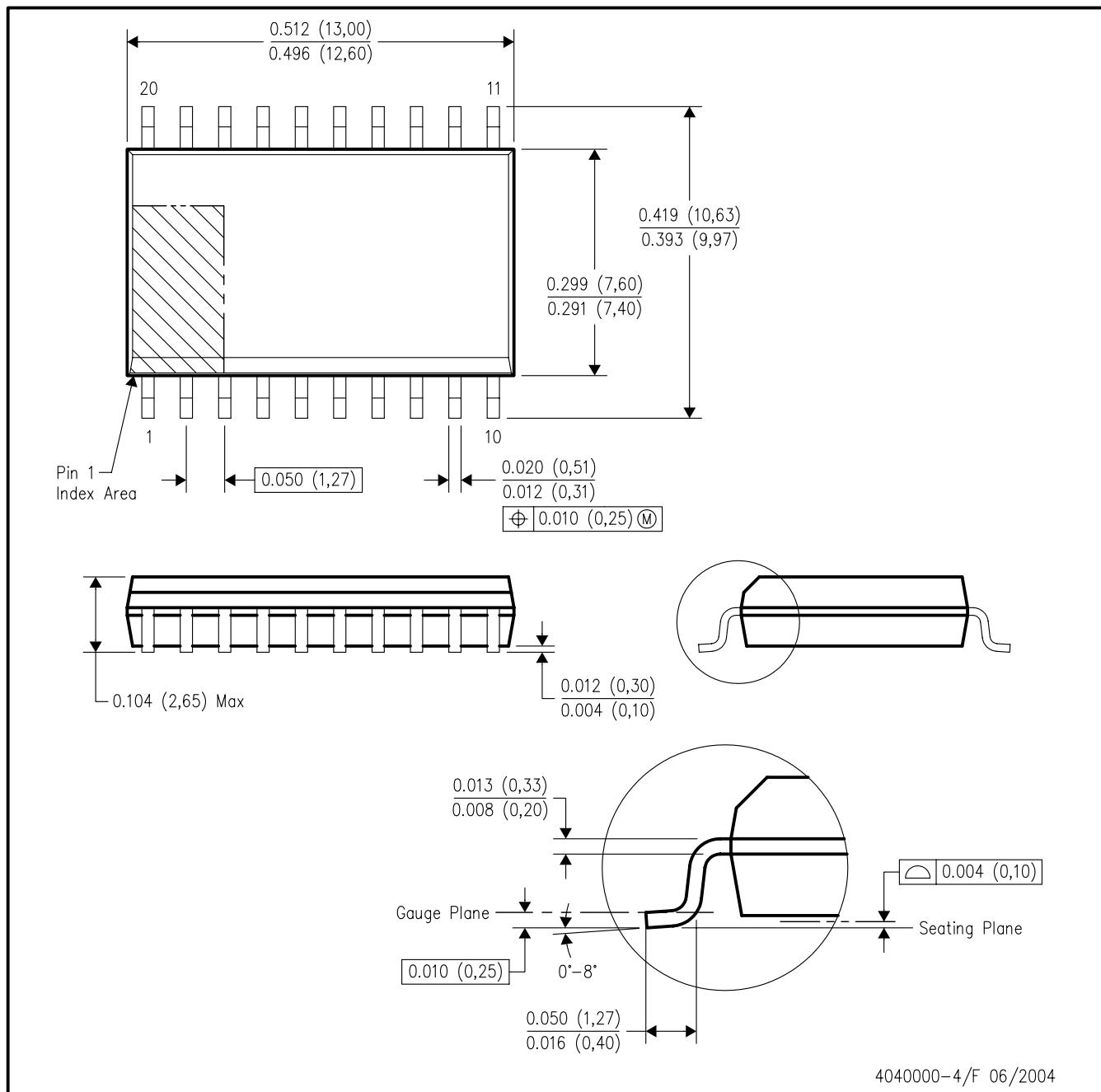

# メカニカル・データ

DW (R-PDSO-G20)

PLASTIC SMALL-OUTLINE PACKAGE

- 注: A. 全ての線寸法の単位はインチ(ミリメートル)です。

B. この図は、予告なく変更されることがあります。

C. ボディ寸法はモールド突起部を含みません。突起部は 0.006 インチ (0.15 mm) を超えません。

D. JEDEC MS-013改ACに準拠します。

(SLUS608D)

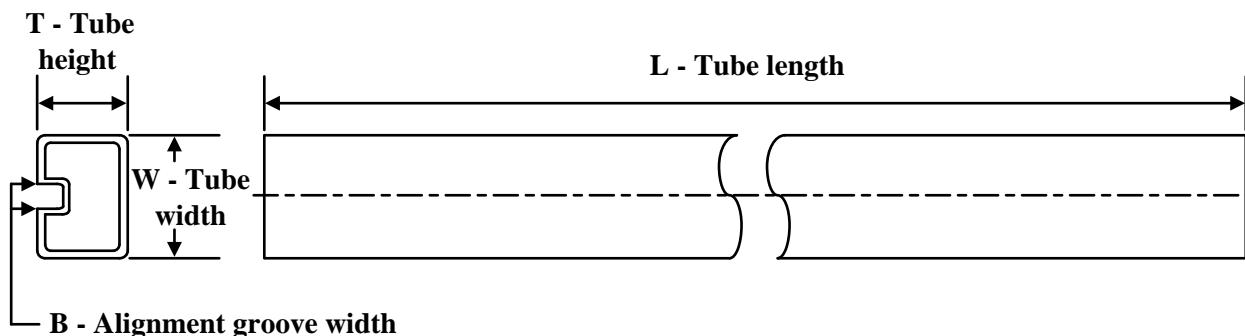

**TUBE**

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| UCC28528DW   | DW           | SOIC         | 20   | 25  | 507    | 12.83  | 5080         | 6.6    |

| UCC28528DW.A | DW           | SOIC         | 20   | 25  | 507    | 12.83  | 5080         | 6.6    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated