# UCD91160 16 レールの PMBus™ パワー シーケンサおよびシステム マネージャ

## 1 特長

- 最大 16 個のアナログ レールのシーケンス制御と監視

- 最大 8 レールの PWM マージニング

- 最大 4 つのデバイスをカスケード接続して、最大 64 レールをシーケンスします

- アクティブ トリム機能により、出力電圧を調整できます

- OV、UV、タイムアウト、GPI に起因するフォルトを監視し、それらに応答します

- フレキシブルなシーケンシングの依存関係、遅延時間、ブール論理、GPIO 構成

- 複雑なシーケンシング アプリケーションでのレールのステータス依存シーケンシング、遅延時間、LGPO ピン

- 適応型電圧識別 (AVID) 電圧レギュレータ用の 4 つのレール プロファイル

- RTC とタイムスタンプ機能を搭載した不揮発性フォルトイベント ログ

- シングルイベント フォルト ログ (100 エントリ)

- ブラックボックス フォルト ログには、すべてのレールのフォルト情報とステータスが保存されます。これには、パワー ダウン イベントが発生する前の最初のフォルトや、最後のフォルトが含まれます

- 構成アクティビティ中にレールの監視を継続して、稼働時間を最大化します

- ウオッチドッグ タイマとシステム リセットをプログラム可能

- GPI 制御レール グループ

- SEU 軽減と ECC (シングルエラー訂正 + ダブルエラー検出)

- PMBus™ 1.2 準拠

- PMBus セキュリティ プロファイル レベル 0。セキュリティ プロファイル レベル 2 で機能を有効にするためのカスタム コマンドが使用可能

## 2 アプリケーション

- 有線ネットワーク

- ワイヤレス インフラ

- データコム モジュール

- データ センターおよびエンタープライズ コンピューティング

- ファクトリ オートメーション / 制御

- 試験および測定機器

- 医療用

## 3 説明

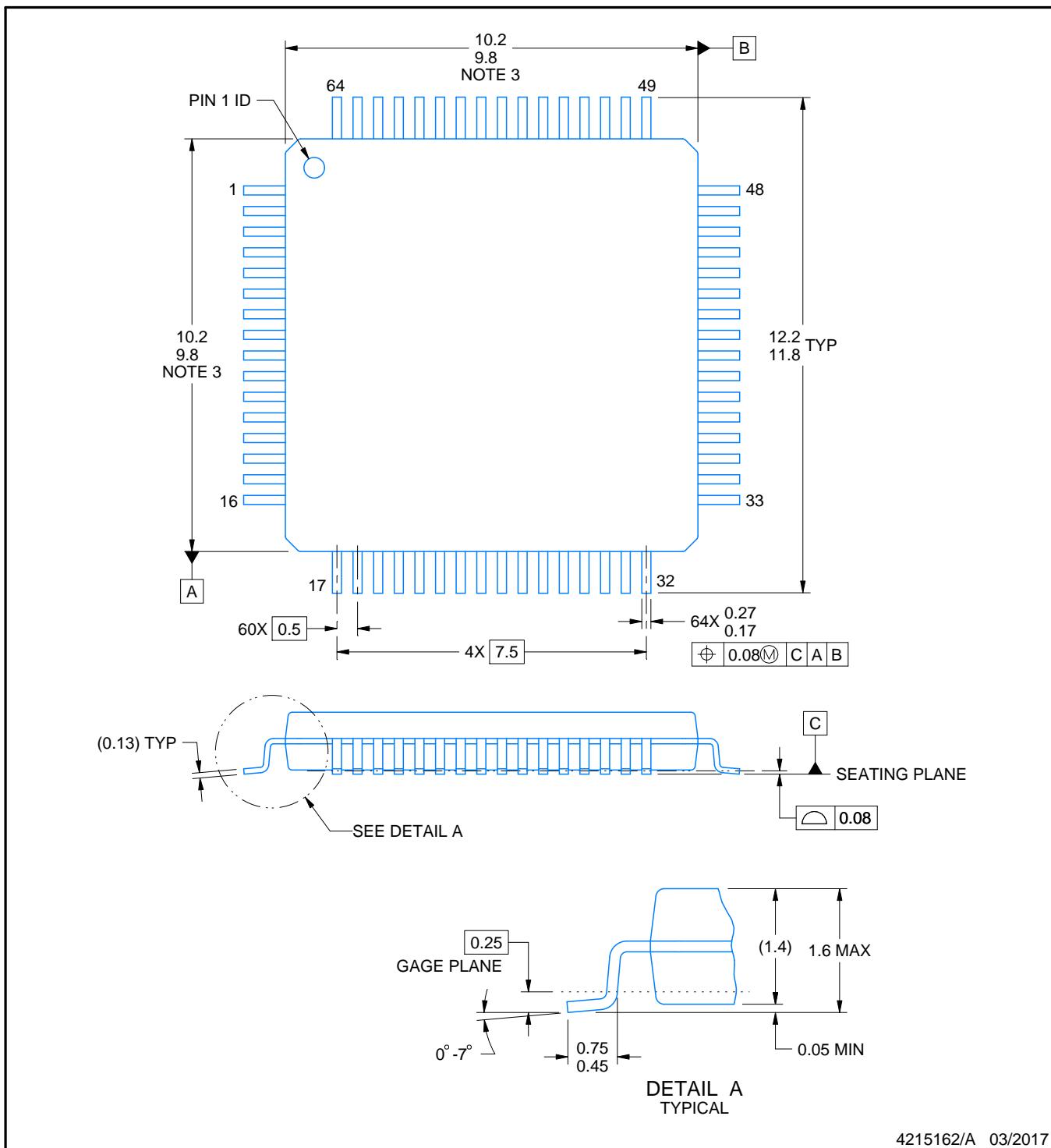

本 UCD91160 デバイスは、64 ピン QFP パッケージの 16 レール PMBus 制御電源シーケンサです。

専用ピン (MONx) は、アナログまたはデジタル モードで最大 16 個の電圧レールを監視します。16 レール イネーブル (ENx) ピンにより、レギュレータのシーケンシングを可能にします。8 本のマージニング (MARx) ピンを使用して、レギュレータをテストのために上限または下限 (マージン) にプッシュしたり、出力をアクティブにトリムして精度を向上させることができます。16 の論理 GPO (LGPOx) ピンの出力状態は、GPI、レールステータス、その他の LGPO の状態で制御できます。

不揮発性のイベント ログにより、電源のドロップアウト後もフォルト イベントが保持されます。ブラック ボックス フォルト ログには、フォルト情報とすべてのレールのステータスが保持されます。ブラック ボックスの オルト ログには、電源を切る前の最初と最後のフォルト イベントが記録されます。カスケード接続機能は、最大 64 個の電圧レールを管理する便利な方法を提供します。

ユーザー一定義のフォルト ピンによってカスケード接続されたデバイスを調整し、同期されたフォルト応答を取得します。ユーザーは、3 つの GPI を使用して、最大 8 つのグループのレール構成を選択できます。これらの構成では高度な構成と電源のインターフェイス (ACPI) 仕様に規定されているように、システムの低消費電力モードを実装できます。

Sequencer Studio™ ソフトウェアは PC ベースの直感的なグラフィック ユーザー インターフェイス (GUI) で、システムの動作パラメータすべてを構成、保存、監視できます。

**パッケージ情報表**

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|--------------|----------------------|-----------------|

| UCD91160SPMR | LQFP (64)            | 12.0mm × 12.0mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

図 3-1. アプリケーション概略図

## 目次

|                      |           |                               |           |

|----------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>          | <b>1</b>  | 6.2 機能ブロック図                   | <b>11</b> |

| <b>2 アプリケーション</b>    | <b>1</b>  | 6.3 機能説明                      | <b>12</b> |

| <b>3 説明</b>          | <b>1</b>  | 6.4 デバイスの機能モード                | <b>12</b> |

| <b>4 ピン構成および機能</b>   | <b>4</b>  | <b>7 アプリケーションと実装</b>          | <b>14</b> |

| <b>5 仕様</b>          | <b>7</b>  | 7.1 アプリケーション情報                | <b>14</b> |

| 5.1 絶対最大定格           | 7         | 7.2 代表的なアプリケーション              | <b>14</b> |

| 5.2 ESD 定格           | 7         | 7.3 電源に関する推奨事項                | <b>16</b> |

| 5.3 推奨動作条件           | 7         | 7.4 レイアウト                     | <b>16</b> |

| 5.4 熱に関する情報          | 8         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>18</b> |

| 5.5 電気的特性            | 8         | 8.1 ドキュメントの更新通知を受け取る方法        | <b>18</b> |

| 5.6 直線性パラメータ         | 8         | 8.2 サポート・リソース                 | <b>18</b> |

| 5.7 POR および BOR      | 9         | 8.3 商標                        | <b>18</b> |

| 5.8 低周波数クリスタル / クロック | 9         | 8.4 静電気放電に関する注意事項             | <b>18</b> |

| 5.9 フラッシュ メモリの特性     | 9         | 8.5 用語集                       | <b>18</b> |

| <b>6 詳細説明</b>        | <b>11</b> | <b>9 改訂履歴</b>                 | <b>18</b> |

| 6.1 概要               | 11        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>18</b> |

## 4 ピン構成および機能

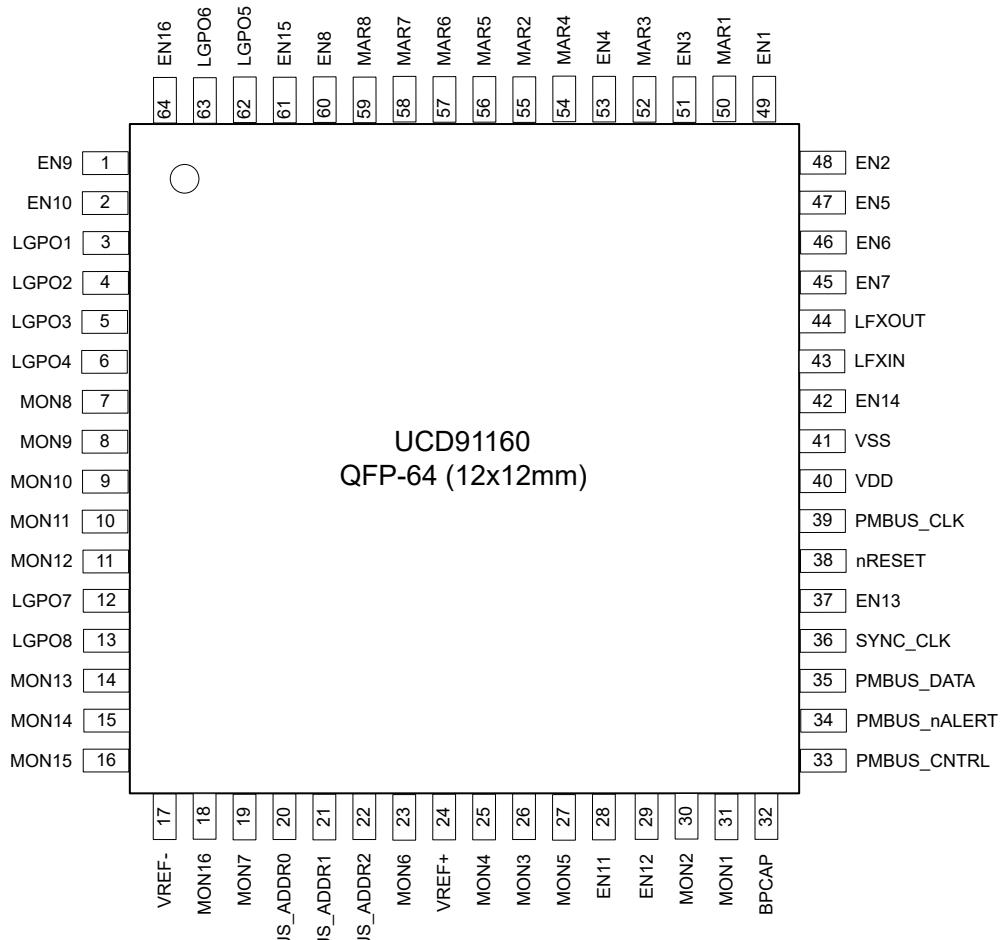

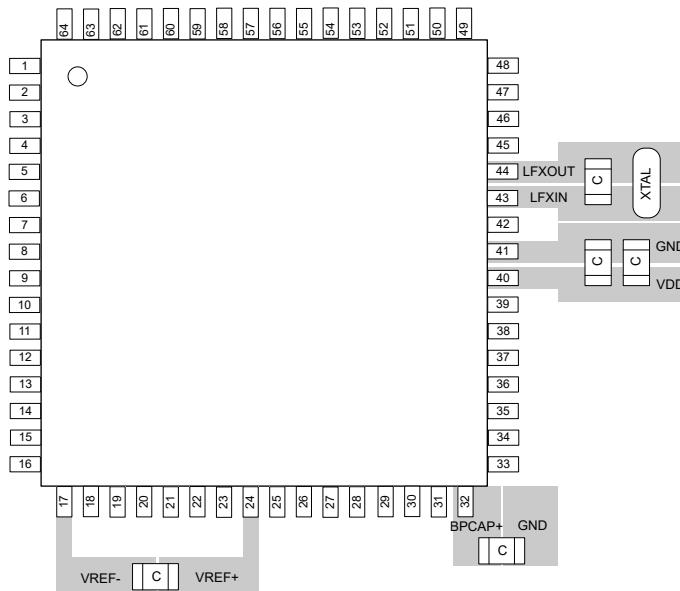

図 4-1. UCD91160PM パッケージ、64 ピン LQFP (上面図)

表 4-1. ピンの機能

| ピン                 |    | タイプ | ピン ID | 説明                               |

|--------------------|----|-----|-------|----------------------------------|

| 名称                 | 番号 |     |       |                                  |

| <b>監視入力 (MONx)</b> |    |     |       |                                  |

| MON1               | 31 | I   | 1     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON2               | 30 | I   | 2     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON3               | 26 | I   | 3     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON4               | 25 | I   | 4     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON5               | 27 | I   | 5     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON6               | 23 | I   | 6     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON7               | 19 | I   | 7     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON8               | 7  | I   | 8     | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON9               | 8  | I   | 9     | アナログモニタ (0V ~ 3.3V) <sup>1</sup> |

| MON10              | 9  | I   | 10    | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

**表 4-1. ピンの機能 (続き)**

| ピン                              |    | タイプ | ピン ID | 説明                               |

|---------------------------------|----|-----|-------|----------------------------------|

| 名称                              | 番号 |     |       |                                  |

| MON11                           | 10 | I   | 11    | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON12                           | 11 | I   | 12    | アナログモニタ (0V ~ 3.3V) <sup>2</sup> |

| MON13                           | 14 | I   | 13    | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON14                           | 15 | I   | 14    | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON15                           | 16 | I   | 15    | アナログまたはデジタルモニタ (0V ~ 3.3V)       |

| MON16                           | 18 | I   | 16    | アナログモニタ (0V ~ 3.3V) <sup>3</sup> |

| <b>レールイネーブル (ENx)</b>           |    |     |       |                                  |

| EN1(GPIO)                       | 49 | I/O | 33    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN2(GPIO)                       | 48 | I/O | 34    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN3(GPIO)                       | 51 | I/O | 35    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN4(GPIO)                       | 53 | I/O | 36    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN5(GPIO)                       | 47 | I/O | 37    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN6(GPIO)                       | 46 | I/O | 38    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN7(GPIO)                       | 45 | I/O | 39    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN8(GPIO)                       | 60 | I/O | 40    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN9(GPIO)                       | 1  | I/O | 41    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN10(GPIO)                      | 2  | I/O | 42    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN11(GPIO)                      | 28 | I/O | 43    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN12(GPIO)                      | 29 | I/O | 44    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN13(GPIO)                      | 37 | I/O | 45    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN14(GPIO)                      | 42 | I/O | 46    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN15(GPIO)                      | 61 | I/O | 47    | レールイネーブル信号、デジタル出力、または GPIO       |

| EN16(GPIO)                      | 64 | I/O | 48    | レールイネーブル信号、デジタル出力、または GPIO       |

| <b>クローズド ループ マージン ピン (MARx)</b> |    |     |       |                                  |

| MAR1(GPIO)                      | 50 | I/O | 65    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR2(GPIO)                      | 55 | I/O | 66    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR3(GPIO)                      | 52 | I/O | 67    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR4(GPIO)                      | 54 | I/O | 68    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR5(GPIO)                      | 56 | I/O | 69    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR6(GPIO)                      | 57 | I/O | 70    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR7(GPIO)                      | 58 | I/O | 71    | クローズド ループ マージン PWM 出力、または GPIO   |

| MAR8(GPIO)                      | 59 | I/O | 72    | クローズド ループ マージン PWM 出力、または GPIO   |

<sup>1</sup> MON9 はアナログ監視ピンとしてのみ使用します

<sup>2</sup> ピン 11 - MON12 はアナログ監視ピンとしてのみ使用します

<sup>3</sup> ピン 18 - MON16 はアナログ監視ピンとしてのみ使用します

**表 4-1. ピンの機能 (続き)**

| ピン                         |    | タイプ | ピン ID | 説明                                                                                                                                                   |

|----------------------------|----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                         | 番号 |     |       |                                                                                                                                                      |

| <b>PMBus COMM インターフェイス</b> |    |     |       |                                                                                                                                                      |

| PMBUS_CLK                  | 39 | I/O | 該当なし  | PMBus クロック (3.3V にプルアップする必要があります)                                                                                                                    |

| PMBUS_DATA                 | 35 | I/O | 該当なし  | PMBus データ (3.3V にプルアップする必要があります)                                                                                                                     |

| PMBUS_ALERT                | 34 | O   | 該当なし  | PMBus アラート、アクティブ Low、オープンドレイン出力 (3.3V にプルアップする必要があります)                                                                                               |

| PMBUS_CNTRL                | 33 | I   | 該当なし  | PMBus 制御 (3.3V にプルアップする必要があります)                                                                                                                      |

| PMBUS_ADDR0                | 20 | I   | 該当なし  | PMBus アドレス選択                                                                                                                                         |

| PMBUS_ADDR1                | 21 | I   | 該当なし  | PMBus アドレス選択                                                                                                                                         |

| PMBUS_ADDR2                | 22 | I   | 該当なし  | PMBus アドレス選択                                                                                                                                         |

| <b>論理汎用出力 (LGPOx)</b>      |    |     |       |                                                                                                                                                      |

| LGPO1 (GPIO)               | 3  | I/O | 81    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO2 (GPIO)               | 4  | I/O | 82    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO3 (GPIO)               | 5  | I/O | 83    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO4 (GPIO)               | 6  | I/O | 84    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO5 (GPIO)               | 62 | I/O | 85    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO6 (GPIO)               | 63 | I/O | 86    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO7 (GPIO)               | 12 | I/O | 87    | ブール論理出力、または GPIO                                                                                                                                     |

| LGPO8 (GPIO)               | 13 | I/O | 88    | ブール論理出力、または GPIO                                                                                                                                     |

| <b>入力電源、グランド、クロック</b>      |    |     |       |                                                                                                                                                      |

| LFXOUT                     | 44 | CLK | 該当なし  | 低周波水晶発振器出力                                                                                                                                           |

| LFXIN                      | 43 | CLK | 該当なし  | 低周波水晶発振器入力                                                                                                                                           |

| nRESET                     | 38 | I   | 該当なし  | アクティブ Low のデバイスリセット入力。アプリケーションで必要ない場合は、VDD にプルアップすることを推奨します。少なくとも $1.5\mu\text{s}$ の間 Low に保持してブートリセットを実行するか、1 秒の間 Low に保持してパワー オン リセット (POR) を実行します |

| SYNC_CLK                   | 36 | O   | 該当なし  | マルチ チップ カスケード接続用同期クロック I/O (5kHz)                                                                                                                    |

| VREF+                      | 24 | I   | 該当なし  | (オプション) 外部リファレンス電圧の正のノード                                                                                                                             |

| VREF-                      | 17 | P   | 該当なし  | (オプション) 外部リファレンス電圧の負のノード <sup>4</sup>                                                                                                                |

| VDD                        | 40 | P   | 該当なし  | 入力 3V ~ 3.6V 電源。レイアウトのガイドライン セクションを参照                                                                                                                |

| VSS                        | 41 | P   | 該当なし  | デバイスのグランド                                                                                                                                            |

| BPCAP                      | 32 | P   | 該当なし  | $0.47\mu\text{F}$ バイパス コンデンサ。レイアウトのガイドライン セクションを参照                                                                                                   |

<sup>4</sup> VREF ピンを使用しないときは、グランドに接続してください。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                         |                                | 最小値  | 最大値                               | 単位 |

|------------------|-------------------------|--------------------------------|------|-----------------------------------|----|

| VDD              | 電源電圧                    | VDD ピンで                        | -0.3 | 4.1                               | V  |

| V <sub>I</sub>   | 入力電圧                    | 5V 対応のオープンドレインピンに印加            | -0.3 | 5.5                               | V  |

| V <sub>I</sub>   | 入力電圧                    | 任意の通常耐圧ピンに印加                   | -0.3 | V <sub>DD</sub> + 0.3<br>(最大 4.1) | V  |

| I <sub>VDD</sub> | VDD ピンに流れ込む電流<br>(ソース)  | -40°C ≤ T <sub>j</sub> ≤ 130°C |      | 80                                | mA |

|                  | VDD ピンに流れ込む電流<br>(ソース)  | -40°C ≤ T <sub>j</sub> ≤ 85°C  |      | 100                               | mA |

| I <sub>VSS</sub> | VSS ピンから流れ出す電流<br>(シンク) | -40°C ≤ T <sub>j</sub> ≤ 130°C |      | 80                                | mA |

|                  | VSS ピンから流れ出す電流<br>(シンク) | -40°C ≤ T <sub>j</sub> ≤ 85°C  |      | 100                               | mA |

| I <sub>IO</sub>  | デバイスピンの電流               | デバイスピンによってシンクまたはソースされる電流       |      | 6                                 | mA |

| I <sub>D</sub>   | サポートされているダイオード電流        | VREF- を除くすべてのデバイスピンのダイオード電流    |      | ±2 <sup>(3)</sup>                 | mA |

| T <sub>J</sub>   | 接合部温度                   | 接合部温度                          | -40  | 130                               | °C |

| T <sub>stg</sub> | 保存温度 <sup>(2)</sup>     | 保存温度 <sup>(2)</sup>            | -40  | 150                               | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) ボード実装時のはんだ付けでは、現在の JEDEC J-STD-020 仕様に従い、ピークリフロー温度が梱包箱またはリール上のデバイスラベルに記載されている分類を超えない限り、より高い温度になつてもかまいません。

- (3) VREF- にはテスト目的で内部接続があり、このピンでは注入電流は許容されません。

### 5.2 ESD 定格

|                    |      |                                                               | 値     | 単位 |

|--------------------|------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>  | ±2000 | V  |

| V <sub>(ESD)</sub> | 静電放電 | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22C101 に準拠、すべてのピン <sup>(2)</sup> | ±500  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |                                              | 最小値 | 公称値 | 最大値 | 単位 |

|--------------------|----------------------------------------------|-----|-----|-----|----|

| VDD                | 電源電圧                                         | 2.9 | 3.6 |     | V  |

| C <sub>VDD</sub>   | VDD と VSS の間に配置されたコンデンサ <sup>(1)</sup>       |     | 10  |     | μF |

| C <sub>BPCAP</sub> | BPCAP と VSS の間に配置されたコンデンサ <sup>(1) (2)</sup> |     | 470 |     | nF |

| T <sub>A</sub>     | 周囲温度、S バージョン                                 | -40 |     | 125 | °C |

| T <sub>J</sub>     | 最大接合部温度、T バージョン                              |     |     | 125 | °C |

- (1) C<sub>VDD</sub> と C<sub>BPCAP</sub> は、それぞれ VDD/VSS 間と BPCAP/VSS 間に、本デバイスのピンにできる限り近づけて接続します。 C<sub>VDD</sub> と C<sub>BPCAP</sub> には、容量値の誤差が ±20% までの精度の低 ESR コンデンサを使う必要があります。

(2) BPCAP ピンは、 $C_{BPCAP}$  にのみ接続する必要があります。電圧を供給したり、BPCAP ピンに外部負荷を加えたりしないでください。

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | パッケージ        | 値    | 単位   |

|----------------------|---------------------|--------------|------|------|

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | LQFP-64 (PM) | 62.0 | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 |              | 21.6 | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        |              | 39.1 | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    |              | 1    | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    |              | 38.7 | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 |              | 該当なし | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。すべての代表値は 25°C で測定されており、すべての精度パラメータは 12 ビット分解能モードを使用して測定されています (特に記述のない限り)。

| パラメータ         | テスト条件                     | 最小値                                                               | 標準値                | 最大値  | 単位   |

|---------------|---------------------------|-------------------------------------------------------------------|--------------------|------|------|

| $V_{in(ADC)}$ | アナログ入力電圧範囲 <sup>(1)</sup> | すべての ADC アナログ入力ピンに適用されます                                          | 0                  | VDD  | V    |

| $V_{R+}$      | 正の ADC リファレンス電圧           | VDD から供給される $V_{R+}$                                              |                    | VDD  | V    |

| $T_s$         | チャネルごとの ADC サンプリング時間      |                                                                   | 250                |      | ns   |

| $F_s$         | ADC サンプリング周波数 (チャネルごと)    |                                                                   | 10                 |      | kspS |

| $I_{(ADC)}$   | VDD 端子に流れ込む動作電源電流         | $V_{R+} = VDD$                                                    | 1.5 <sup>(2)</sup> |      | mA   |

| $C_{S/H}$     | ADC サンプル ホールド容量           |                                                                   | 3.3                |      | pF   |

| $R_{in}$      | ADC 入力抵抗                  |                                                                   | 0.5                |      | kΩ   |

| $ENOB$        | 有効ビット数                    | 外部リファレンス                                                          | 12.3               | 12.5 | ビット  |

|               |                           | 内部リファレンス、 $V_{R+} = 2.5V$                                         | 9.9                | 10.8 |      |

| $SNR$         | 信号対雑音比                    | 外部リファレンス <sup>(3)</sup>                                           | 78                 |      | dB   |

|               |                           | 内部リファレンス、 $V_{R+} = 2.5V$                                         | 66                 |      |      |

| $PSRR_{DC}$   | 電源除去比、DC                  | 外部リファレンス <sup>(3)</sup> 、 $VDD = VDD_{(min)} \sim VDD_{(max)}$    | 62                 |      | dB   |

|               |                           | $VDD = VDD_{(min)} \sim VDD_{(max)}$<br>内部リファレンス、 $V_{R+} = 2.5V$ | 53                 |      |      |

| $PSRR_{AC}$   | 電源除去比、AC                  | 外部リファレンス <sup>(3)</sup> 、1kHz 時 $\Delta VDD = 0.1V$               | 61                 |      | dB   |

|               |                           | 1kHz 時 $\Delta VDD = 0.1V$<br>内部リファレンス、 $V_{R+} = 2.5V$           | 52                 |      |      |

(1) 有効な変換結果を得るには、選択された ADC リファレンス電圧の範囲内 ( $V_{R+} \sim V_{R-}$ ) にアナログ入力電圧範囲が含まれている必要があります。

(2) 内部リファレンス電圧 ( $V_{REF}$ ) の消費電流は、消費電流パラメータ ( $I_{(ADC)}$ ) には含まれません。

(3) 外部リファレンス電圧のすべての仕様は、 $V_{R+} = V_{REF+} = VDD = 3.3V$  かつ  $V_{R-} = V_{REF-} = VSS = 0V$  の条件で、 $V_{REF+}$  ピンの外部容量 1uF として測定されたものです。

## 5.6 直線性パラメータ

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき (特に記述のない限り)。すべての標準値は 25°C で測定されており、すべての直線性パラメータは 12 ビット分解能モードを使用して測定されています (特に記述のない限り)<sup>(1)</sup>

| パラメータ | テスト条件                                                      | 最小値                     | 標準値 | 最大値 | 単位  |

|-------|------------------------------------------------------------|-------------------------|-----|-----|-----|

| $EI$  | 積分直線性誤差 (INL)<br>外部リファレンス <sup>(2)</sup>                   | 外部リファレンス <sup>(2)</sup> | -2  | 2   | LSB |

| $E_D$ | 微分直線性誤差 (DNL)<br>ミッシング コードなしを保証<br>外部リファレンス <sup>(2)</sup> | 外部リファレンス <sup>(2)</sup> | -1  | 1   | LSB |

| $E_O$ | オフセット誤差<br>内部または外部リファレンス <sup>(2)</sup>                    |                         | -2  | 2   | mV  |

電源電圧が推奨範囲内で、自由気流の動作温度範囲内のとき(特に記述のない限り)。すべての標準値は25°Cで測定されており、すべての直線性パラメータは12ビット分解能モードを使用して測定されています(特に記述のない限り)<sup>(1)</sup>

| パラメータ                | テスト条件                   | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------|-------------------------|-----|-----|-----|----|

| E <sub>G</sub> ゲイン誤差 | 外部リファレンス <sup>(2)</sup> | -3  | 3   | LSB |    |

(1) し総合未調整誤差(TUE)は、次の式を使用して、E<sub>I</sub>、E<sub>O</sub>、E<sub>G</sub>から計算できます。TUE =  $\sqrt{E_I^2 + |E_O|^2 + E_G^2}$

注:上記の式が正確であるためには、すべての誤差を同じ単位(通常はLSB)に変換する必要があります。

(2) 外部リファレンス電圧のすべての仕様は、V<sub>R+</sub> = VREF+ = VDD、V<sub>R-</sub> = VSS = 0V、VREF+ピンの外部容量1uFとして測定されたものです。

## 5.7 POR および BOR

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                  | テスト条件              | 最小値                       | 標準値  | 最大値  | 単位   |    |

|------------------------|--------------------|---------------------------|------|------|------|----|

| dVDD/dt                | VDD(電源電圧)のスルーレート   | 立ち上がり                     | 0.1  |      | V/μs |    |

|                        |                    | 立ち下がり <sup>(2)</sup>      | 0.01 |      |      |    |

|                        |                    | 立ち下がり、STANDBY             | 0.1  |      | V/ms |    |

| V <sub>POR+</sub>      | パワーオンリセット電圧レベル     | 立ち上がり <sup>(1)</sup>      | 1.04 | 1.30 | 1.5  | V  |

| V <sub>POR-</sub>      |                    | 立ち下がり <sup>(1)</sup>      | 0.99 | 1.25 | 1.48 | V  |

| V <sub>HYS, POR</sub>  | PORヒステリシス          |                           | 30   | 58   | 74   | mV |

| V <sub>BOR+</sub>      | ブラウンアウトリセット電圧      | 立ち上がり <sup>(1)(2)</sup>   | 2.88 | 2.96 | 3.04 | V  |

| V <sub>BOR-</sub>      |                    | 立ち下がり <sup>(1)(2)</sup>   | 2.85 | 2.93 | 3.01 |    |

| V <sub>BOR, STBY</sub> |                    | STANDBYモード <sup>(1)</sup> | 2.80 | 2.92 | 3.02 |    |

| V <sub>HYS, BOR</sub>  | ブラウンアウトリセットのヒステリシス | レベル0 <sup>(1)</sup>       | 14   | 18   |      | mV |

|                        |                    | レベル1~3 <sup>(1)</sup>     | 34   | 38   |      |    |

(1) |dVDD/dt| ≤ 3V/s

(2) デバイスはRUN、SLEEP、STOPモードで動作しています。

## 5.8 低周波数クリスタル/クロック

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                    | テスト条件                   | 最小値 | 標準値   | 最大値 | 単位 |

|--------------------------|-------------------------|-----|-------|-----|----|

| <b>低周波数水晶発振器(LFXT)</b>   |                         |     |       |     |    |

| f <sub>LFXT</sub>        | LFXT周波数                 |     | 32768 |     | Hz |

| DC <sub>LFXT</sub>       | LFXTデューティサイクル           |     | 30    | 70  | %  |

| OA <sub>LFXT</sub>       | LFXT水晶発振余裕度             |     | 419   |     | kΩ |

| C <sub>L, eff</sub>      | 集積実効負荷容量 <sup>(1)</sup> |     | 1     |     | pF |

| t <sub>start, LFXT</sub> | LFXTスタートアップ時間           |     | 483   | 640 | ms |

(1) 集積実効負荷容量には、寄生ボンドおよびパッケージ容量(ピンごとに約2pF)が含まれ、C<sub>LFXIN</sub> × C<sub>LFXOUT</sub> / (C<sub>LFXIN</sub> + C<sub>LFXOUT</sub>)として計算されます。ここで、C<sub>LFXIN</sub>およびC<sub>LFXOUT</sub>は、それぞれLFXINおよびLFXOUTにおける合計容量です。

## 5.9 フラッシュメモリの特性

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                | テスト条件              | 最小値 | 標準値 | 最大値 | 単位    |

|----------------------|--------------------|-----|-----|-----|-------|

| <b>電源</b>            |                    |     |     |     |       |

| IDD <sub>ERASE</sub> | 消去動作中のVDDからの電源電流   |     | 10  |     | mA    |

| IDD <sub>PGM</sub>   | 書き込み動作中のVDDからの電源電流 |     | 10  |     | mA    |

| <b>耐久性</b>           |                    |     |     |     |       |

| NWEC                 | 消去/プログラムサイクル耐久性    |     | 10  |     | kサイクル |

## 5.9 フラッシュ メモリの特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                                | テスト条件                          | 最小値  | 標準値 | 最大値           | 単位 |  |  |

|----------------------|--------------------------------|--------------------------------|------|-----|---------------|----|--|--|

| NE <sub>(MAX)</sub>  | 故障に至るまでの全消去動作回数 <sup>(1)</sup> |                                |      | 802 | K 回の消去動作      |    |  |  |

| <b>保持</b>            |                                |                                |      |     |               |    |  |  |

| t <sub>RET_85</sub>  | フラッシュ メモリのデータ保持                | -40°C ≤ T <sub>j</sub> ≤ 85°C  | 60   | 年   |               |    |  |  |

| t <sub>RET_105</sub> | フラッシュ メモリのデータ保持                | -40°C ≤ T <sub>j</sub> ≤ 105°C | 11.4 | 年   |               |    |  |  |

| t <sub>RET_130</sub> | フラッシュ メモリのデータ保持                | -40°C ≤ T <sub>j</sub> ≤ 130°C | 2.4  | 年   |               |    |  |  |

| <b>�ルトおよびイベントのログ</b> |                                |                                |      |     |               |    |  |  |

| NF                   | �ルトが発生するまでの�ルト イベントコードの合計数     |                                |      | 64  | 100 万件のイベントログ |    |  |  |

(1) 故障に至るまでにフラッシュによってサポートされる消去動作の累積回数。セクタ消去またはバンク消去動作は、1 回の消去動作と見なします。

## 6 詳細説明

### 6.1 概要

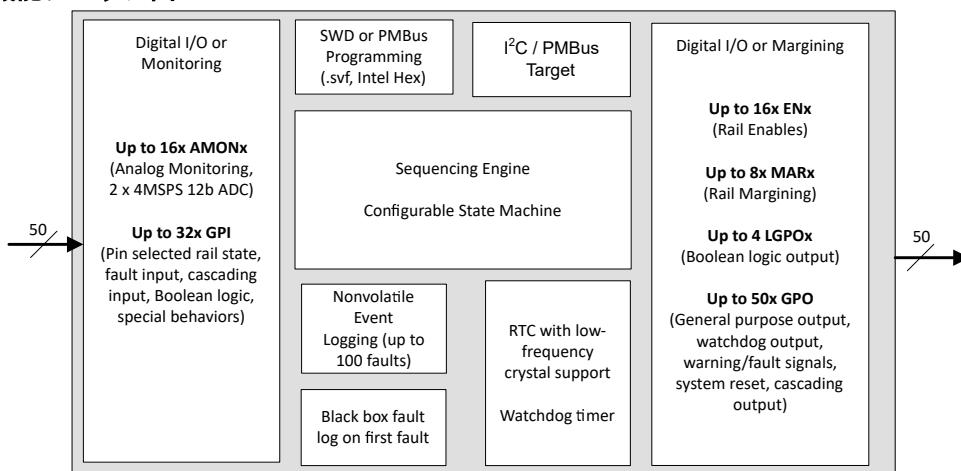

CPU、DSP、マイクロコントローラ、FPGA、ASICなどのエレクトロニクスシステムは、複数の電圧レールを備えていることがあります。正常に機能するためには、パワー オン/パワー オフの高精度シーケンスが必要です。UCD91160 は、最大 16 個の電圧レールのシーケンス制御、電圧およびフォルト状態の監視、PMBus インターフェイス経由でのシステム状態情報の報告を可能にします。

UCD91160 は、電源システムのフォルトに対して事前に設定された応答を実行することで、電子システムを保護します。フォルトが発生すると、直ちにブラック ボックス フォルト ログがトリガされて包括的なシステム ステータス レポートが保存されますが、それ以降のフォルト ログは不揮発性メモリ内に保存されます。

システムの信頼性は、4 コーナーテストで検証できます。電圧レールに、最小と最大の出力電圧で動作するように命令することができます。これをマージニングと呼びます。本デバイスは、最大 8 つの電圧レールに対して、高精度のクローズド ループ マージニングを実行できます。通常動作中、UCD91160 は、これら 8 本のピンと同じマージン処理回路を使用して、DC 出力電圧をアクティブにトリムできます。

UCD91160 には、32 本の GPIO ピンのプールがあります。これらのピンの多くは、主に ENx、MARx、LGPOx ピンなどの機能を備えていますが、汎用 I/O (GPIO) としてデバイスが外部回路と相互作用するためにも構成できます。ピンの説明表に、各ピンの主な機能を示します。GPIO の状態は、次の複数の方法で制御できます：

- コマンド制御 GPO—これらの出力は、PMBus コマンドで設定できます

- GPIO—これらのピンは、フォルトの生成、マージニングのイネーブル/ディセーブル、他の GPIO の状態への影響を与えるために使用できます。

- プール論理制御 (LGPO)—UCD91160 は、任意の GPIO を LGPO として構成できます (最大 16 の LGPO をサポート)。これらのピンの状態は、レールの状態やフォルトイベントなどの項目の状態によって異なります。

このデバイスは、カスケード、ピン選択状態、システム ウオッチドッグ、システム リセット、ランタイム クロック、リセット カウントなどの追加機能を提供します。カスケード機能は、最大 4 つ UCD91160 のデバイスをカスケード接続し、最大 128 の電圧レールを管理する便利な方法を提供します。ピン選択状態機能により、ユーザーは最大 8 つのレールの状態を定義できます。これらの状態は、高度な構成と電源のインターフェイス (ACPI) 仕様に規定されているように、システムの低消費電力モードを実装できます。

### 6.2 機能ブロック図

UCD91160 の機能ブロック図

## 6.3 機能説明

### 6.3.1 TI Sequencer Studio ソフトウェア

PC ベースのテキサス インスツルメンツ Sequencer Studio ソフトウェアは、PMBus インターフェイス経由でデバイスと通信し、低レベルの PMBus コマンドを習得しなくとも、設計エンジニアがアプリケーションの動作パラメータを構成できるようになります。ソフトウェアにより、構成がオンチップの不揮発性メモリに保存され、デバッグ作業中にシステム ステータスを観察するために使用できます。設定後、デバイスは起動時に独立して実行されます。[UCD91160 ウェブ ページ](#)から Sequencer Studio ソフトウェアをダウンロードします。

### 6.3.2 PMBUS インターフェイス

PMBus は、パワーマネージメントをサポートするために特別に設計されたシリアルインターフェイスです。PMBus インターフェイスは、I<sup>2</sup>C 物理仕様に基づいて構築された SMBus インターフェイスをベースにしています。本 UCD91160 デバイスは、PMBus 規格のリビジョン 1.3 をサポートしています。標準的な PMBus インターフェイスコマンドは、デバイスの機能をサポートしています。デバイスの固有の機能は、MFR\_SPECIFIC コマンドを使用して構成またはアクティブにするように定義されています。これらのコマンドは、[UCD91160 シーケンサおよびシステム状態コントローラ PMBUS コマンドリファレンス](#)で定義されています。最新の UCD91160 PMBus コマンドリファレンスは、ヘルプ メニュー（ヘルプ、ドキュメントとヘルプ センター、シーケンサ タブのドキュメントセクション）から Sequencer Studio ソフトウェア内にあります。

PMBus 仕様は、このデータシートで頻繁に参照されています。具体的には、このドキュメントは、PMBus 電力システム管理プロトコル仕様パート II-コマンド言語、リビジョン 1.2 (2010 年 9 月 6 日付け) です。この仕様は電力管理バスインプリメンターズフォーラムで公開されており、[www.pmbus.org](http://www.pmbus.org) から入手できます。

本 UCD91160 デバイスは、PMBus 仕様のコンプライアンスセクションのすべての要件を満たしています。このファームウェアは、SMBus のアラート機能をサポートすることを含め、SMBus 1.2 仕様に準拠しています。このハードウェアは、100kHz または 400kHz の PMBus 動作をサポートしています。

### 6.3.3 PMBUS セキュリティ

UCD91320 デバイスラインは PMBus セキュリティレベル 0 を維持し、カスタム コマンドをサポートしているため、最大 PMBus セキュリティレベル 2 の機能を実現できます。

PMBus セキュリティレベル 0 に準拠するため、UCD91320 デバイスは以下の機能のサポートを継続します：

1. **PASSKEY** コマンド

2. **ACCESS\_CONTROL** コマンド

## 6.4 デバイスの機能モード

### 6.4.1 ブラック ボックス 最初のフォルトログ

システム障害イベントの最初のフォルトは、根本原因を診断するために重要です。初期フォルトが検出されると、UCD91160 本デバイスは、この機能用に予約されている NVM の特別な領域（ブラックボックス）に各レールのステータスを記録し、保存します。デバイスは、後続のフォルトおよびモニタリング ステータスをブラックボックス フォルトログに保存せず、代わりに標準のフォルトログに記録します。BOR 電圧を超えたときの最後のフォルトログも、ブラックボックスのフォルトログに保存されます。ブラック ボックス フォルト ログを収集するには、PMBus コマンドを使用してブラック ボックス フォルト ログをクリアする必要があります。

### 6.4.2 PMBus アドレス選択

3つのデジタル入力を使用して PMBus アドレスを選択します。ピンは High または Low のいずれかに設定します。

**表 6-1. PMBus アドレス構成**

| PMBUS_ADDR2 | PMBUS_ADDR1 | PMBUS_ADDR0 | PMBUS アドレス選択済 |

|-------------|-------------|-------------|---------------|

| L           | L           | L           | 0010001b      |

| L           | L           | H           | 0010011b      |

| L           | H           | L           | 0010111b      |

| L           | H           | H           | 0110001b      |

| H           | L           | L           | 0110011b      |

| H           | L           | H           | 1110001b      |

| H           | H           | L           | 1110011b      |

| H           | H           | H           | 1110111b      |

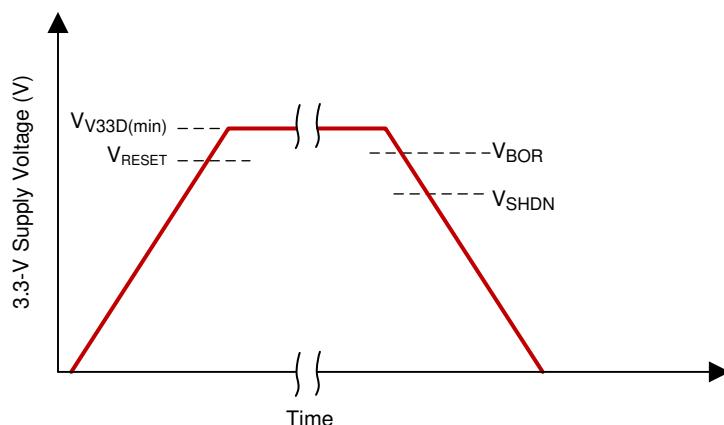

### 6.4.3 ブラウンアウト

UCD91160VDD ピンの電圧がブラウンアウトスレッショルド電圧 ( $V_{BOR}$ ) を下回ると、デバイスはブラウン アウト イベントをトリガします。ブラウン アウト イベント中、本デバイスは、ブラウン アウト イベント前に発生した NVM にフォルトログを書き込み続けます。 $VDD$  ピンの電圧がシャットダウン スレッショルド電圧 ( $V_{SHDN}$ ) を下回ると、デバイスは完全にシャットダウンされます。デバイスのシャットダウンが失われる前に NVM に書き込まれていなかったすべてのフォルトイベントが発生します。

ブラウンアウトイベントの直前に複数のフォルトが発生した場合、本デバイスは最初のフォルトイベントを NVM に書き込むために、 $500\mu s$  の容量を必要とします。書き込み機能では、ブラック ボックス フォルト ログを NVM に書き込むために、さらに  $4ms$  が必要です。最初のフォルト ログを維持するため、 $500\mu s$  のために  $VDD$  レールが  $V_{SHDN}$  より高く維持される(ブラック ボックス フォルト ログでは  $4.5ms$ )ために、十分なローカル容量を用意する必要があります。容量が大きいほど、ブラウンアウト時に、より多くのフォルトイベントを NVM に書き込むことができます。

**図 6-1. リセットおよびブラウンアウト スレッショルド**

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

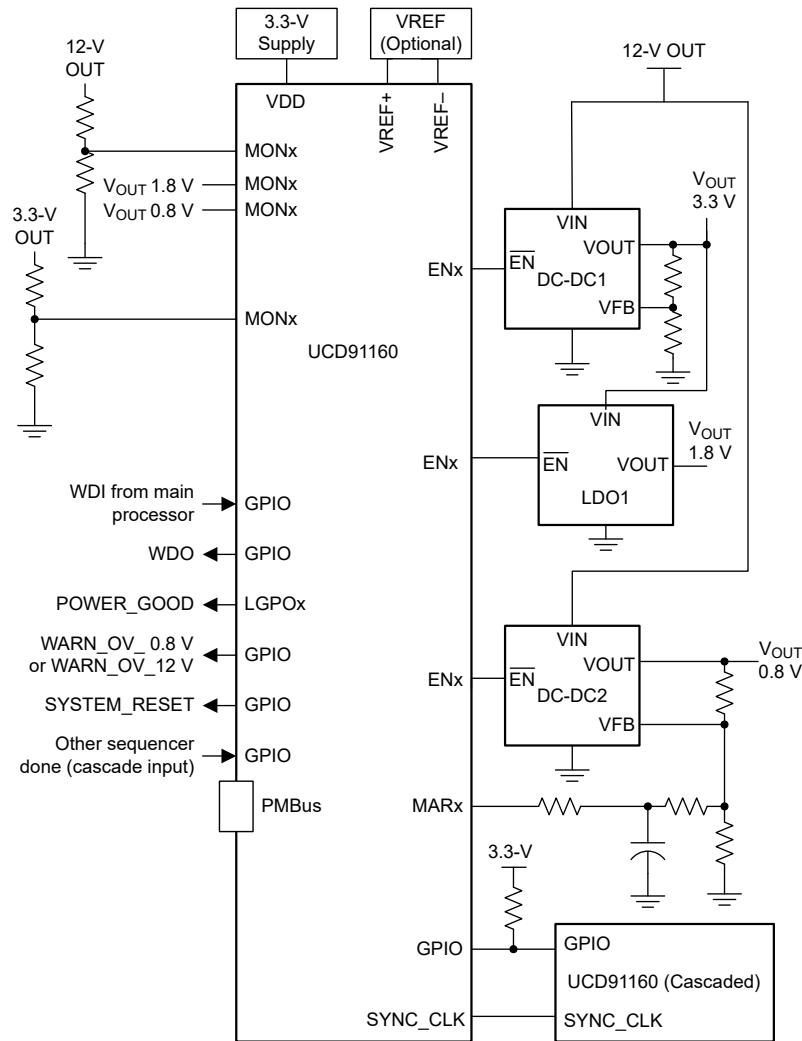

UCD91160 このデバイスは、最大 16 個の電圧レールのシーケンシングと監視を行い、最大 8 個の電圧レールをマージニングするために使用できます。最大 4 つ UCD91160 のデバイスをカスケード接続できるため、最大 64 のレールを監視し、同期されたフォルト応答を記録できます。代表的な用途には、自動試験装置、通信・ネットワーク機器、サーバー、ストレージ システムなどがあります。デバイス構成は、TI が提供する *Sequencer Studio* ソフトウェアを使用して実行できます。コーディングスキルは必要ありません。

### 7.2 代表的なアプリケーション

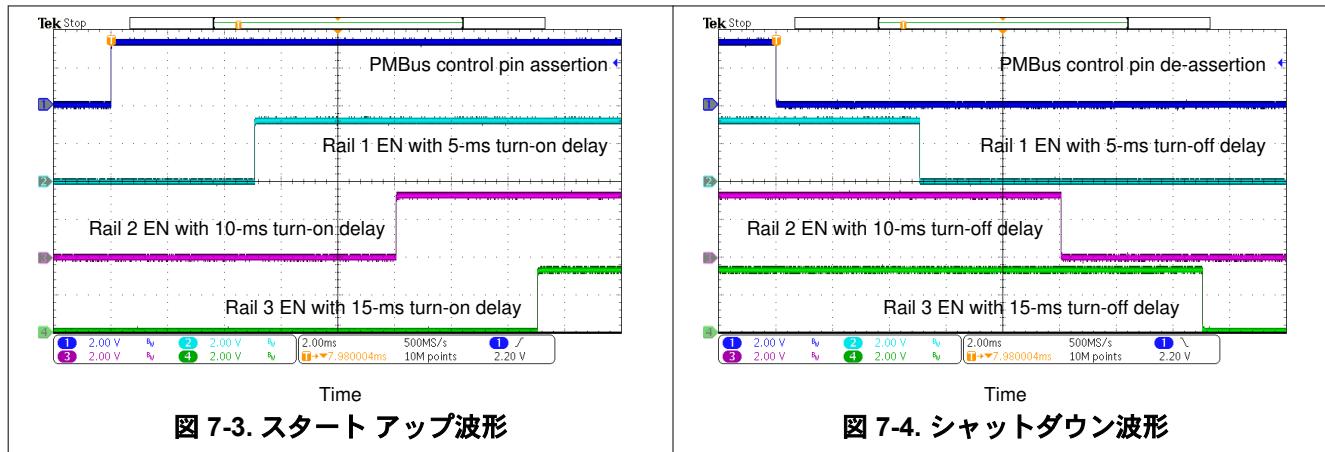

図 7-1 に、簡略化したシステム図を示します。この図では簡略化のため 3 つのレールしか示していませんが、各 UCD91160 デバイスは最大 16 のレールを管理できます。

図 7-1. システム簡略図

## 7.2.1 設計要件

UCD91160 は VDD、BPCAP、VREF+ ピンにデカップリングコンデンサが必要です。VDD、BPCAP、VREF+ の容量値は、「電気的特性」に規定されています。これらのコンデンサ設計構成を、オプションとして考慮してください。

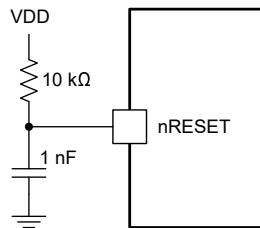

- アプリケーションで nRESET 信号を使用しない場合は、図 7-2 に示すように、VDD ピンに直接接続するか、R-C 回路によって nRESET ピンを VDD に接続する必要があります。図 7-2 に示す R-C 回路は、パワー アップ時にリセットを遅延させるためにも使用できます。アプリケーションで nRESET 外部ピンを使用する場合は、nRESET 信号のトレースをできるだけ短くする必要があります。nRESET 信号に接続されているすべての部品は、デバイスにできる限り近づけて配置します。

- nRESET ピンを 1 秒未満 Low に保持すると、BOOT リセットがトリガされ、1 秒を超えて nRESET を Low に保持すると、POR/パワー オン リセットがトリガされます。

- アナログ監視ピンは、0V ~ 3.3V の電圧レールを監視できます。MONx ピンの入力は、この範囲外にならないようにしてください。

- VDD 電源が安定し、デバイスのプログラミング中はデバイスリセットが発生しないことが必須です。デバイスのプログラミング中にトリガされたリセットにより、デバイスが破損する可能性があります。

- TI は、 $10\mu F$  と  $0.1\mu F$  の低 ESR セラミック デカップリングコンデンサを VDD ピンと VSS ピンの間に接続するとともに、これらのコンデンサを電源ピンにできる限り近づけて配置することを推奨します。ほとんどのアプリケーションでは  $10\mu F$  のバルク デカップリングコンデンサが推奨値ですが、PCB の設計とアプリケーションの要件に基づいて、必要に応じてこの容量を調整することもできます。たとえば、より値の大きいコンデンサを使用することができますが、電源レールの立ち上がり時間に影響を及ぼす可能性があります。

- BPCAP ピンには  $0.47\mu F$  のタンクコンデンサが必要であり、デバイスのグランドとの距離を最小限に抑えてデバイスの近くに配置する必要があります。他の回路は BPCAP ピンに接続しないでください。

図 7-2. R-C ネットワーク付きの nRESET ピン

## 7.2.2 詳細な設計手順

Sequencer Studio ソフトウェアを使用して、デバイス構成をオンラインまたはオフラインで設計できます（コンピュータにデバイスが接続されている場合と接続されていない場合 UCD91160）。オフライン モードでは、起動時にプロジェクトファイル (.xml) を作成するか開くかをユーザーに指示するプロンプトが表示されます。オンライン モードでは、ソフトウェアは PMBus インターフェイス経由でデバイスを自動的に検出し、デバイスから構成データを抽出します。Sequencer Studio ソフトウェアを PMBus に接続するには、TI から入手できる [USB インターフェイスアダプタ評価基板](#)が必要です。

一般的な設計手順も含まれています。手順の詳細については、セクション 6 に記載されて、Sequencer Studio ソフトウェアから簡単にアクセスできます。

1. レール セットアップ

2. レール監視構成

3. GPI による構成

4. レール シーケンス構成

5. フォルト応答構成

6. GPO による構成

7. マージニング構成

8. その他の構成には、以下のものがありますが、これらに限定されません：

- ピン選択レール状態

- ウオッチドッグ タイマ

- システム リセット

- 同期クロック

- フォルト ピン

ハードウェアへの書き込み をクリックして、変更を適用します。オンラインモードでは、**RAM をフラッシュに保存** をクリックして、新しい構成をデバイスのデータ フラッシュに永続的に保存します。

### 7.2.3 アプリケーション曲線

## 7.3 電源に関する推奨事項

3.3V 電源から UCD91160 デバイスに電力を供給します。

内部基準電圧を使用する場合、VDD は ADC リファレンスとして機能し、正確に 3.3V と想定されます。3.3V からの入力電圧の偏差は、ADC リファレンスと ADC の結果に誤差を生じさせます。したがって、3.3V 電源は厳密にレギュレートする必要があります、非常に小さな電圧変動 (負荷過渡によって生じる電圧リップルと電圧偏差を含む) のみを許容する必要があります。

外部リファレンス電圧 (VREF+) を使用する場合、3.3V 電源はセクション 5.3 およびセクション 5.5 に規定されている最小要件のみを満たす必要があります。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

- デカップリング コンデンサは、デバイスにできる限り近づけて配置してください

- BPCAP デカップリング コンデンサは、BPCAP ピンにできる限り近づけて接続してください

- マージンピン (MARx) は、高速エッジを持つ PWM 信号を出力します。これらの信号は、敏感なアナログ信号から離して配線します

### 7.4.2 レイアウト例

UCD91160 デバイスは 64 ピン LQFP パッケージで供給されます。設計で最上層にデバイスを実装する必要がある場合は、デカッピング コンデンサを最下層に配置することで、最上層のトレス配線用のスペースを確保できます。この方法については、次のレイアウト例で説明しています。図 7-5 に、上面図から最下層の部品配置を示します。さらに図 7-5、これらの重要な提案を検討してください。

1. 均一なグラウンド プレーンを使用して、VSS ピンと VREF- ピンを接続します。

2. BPCAP ピンは、共通の内部層の銅領域に接続します。

3. VSS ピンと VREF- ピンは、共通の内部層の銅領域に接続できます。

図 7-5 に、UCD91160 デバイスを最上層に、部品を最下層に配置した代表的なアプリケーションを示します。

図 7-5. レイアウト例

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.3 商標

PMBus™ is a trademark of SMIF, Inc.

Sequencer Studio™ is a trademark of TI.

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.5 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付            | 改訂 | 注      |

|---------------|----|--------|

| December 2025 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCD91160SPMR          | Active        | Production           | LQFP (PM)   64 | 1000   LARGE T&R      | -           | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | UCD91160            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

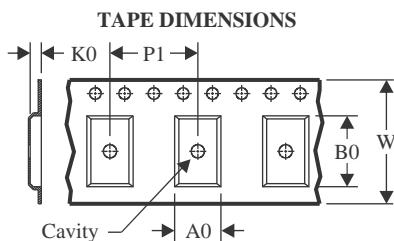

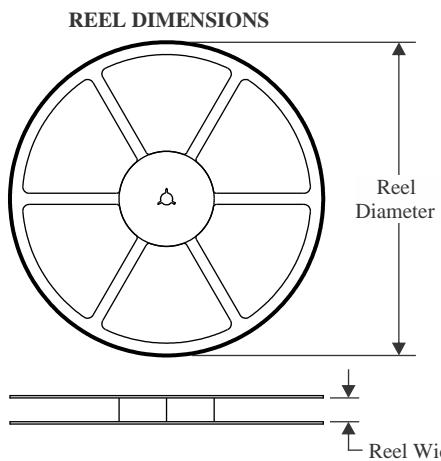

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCD91160SPMR | LQFP         | PM              | 64   | 1000 | 330.0              | 24.4               | 13.0    | 13.0    | 2.1     | 16.0    | 24.0   | Q2            |

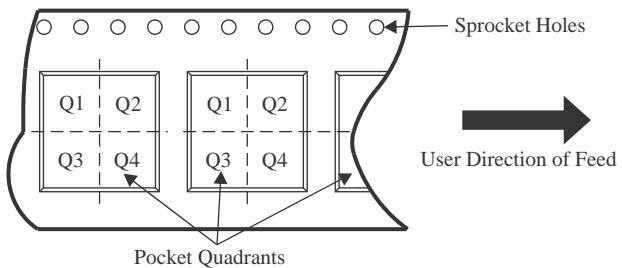

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCD91160SPMR | LQFP         | PM              | 64   | 1000 | 336.6       | 336.6      | 41.3        |

**PM0064A**

# PACKAGE OUTLINE

**LQFP - 1.6 mm max height**

PLASTIC QUAD FLATPACK

4215162/A 03/2017

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MS-026.

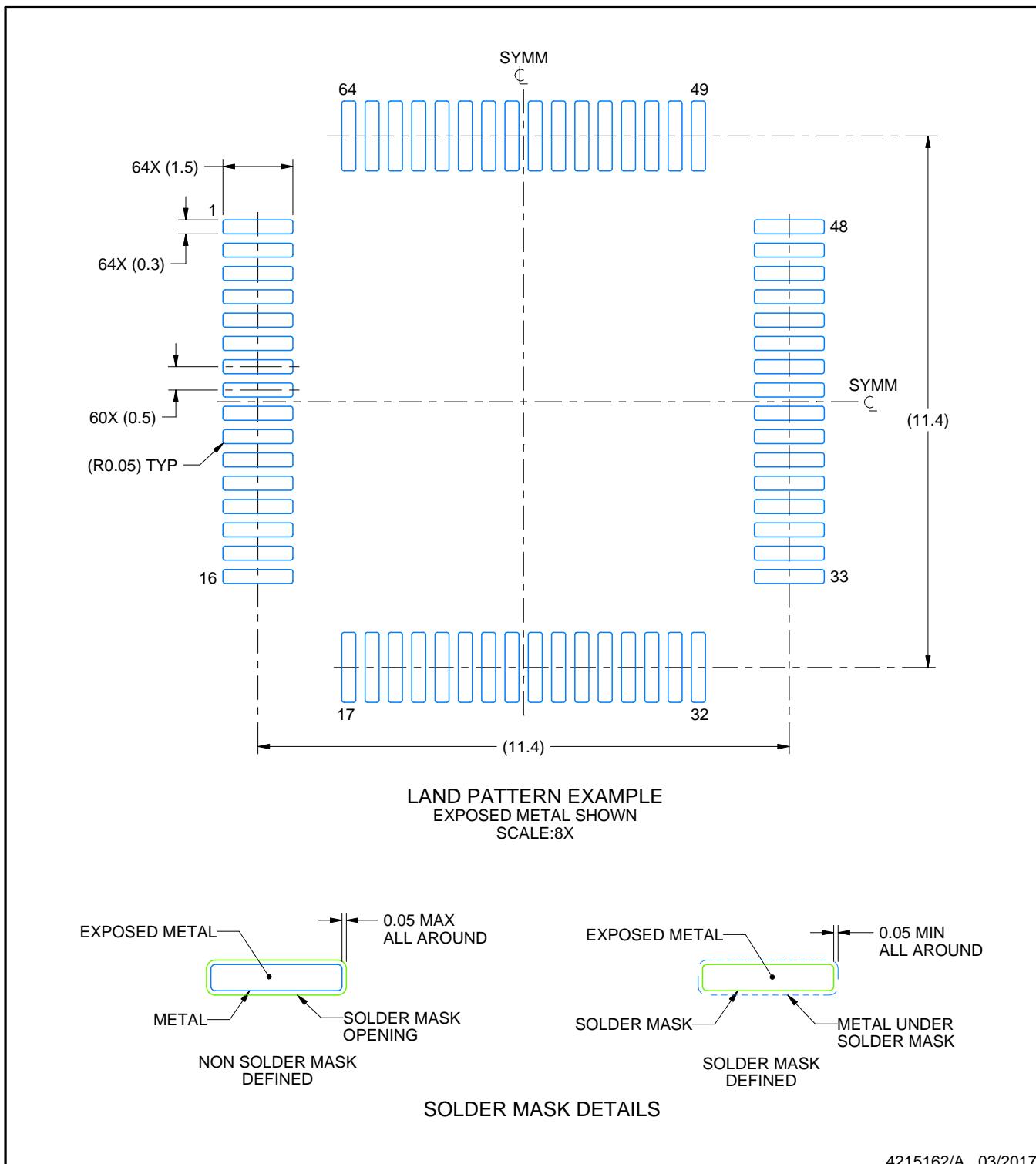

# EXAMPLE BOARD LAYOUT

PM0064A

LQFP - 1.6 mm max height

PLASTIC QUAD FLATPACK

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

7. For more information, see Texas Instruments literature number SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

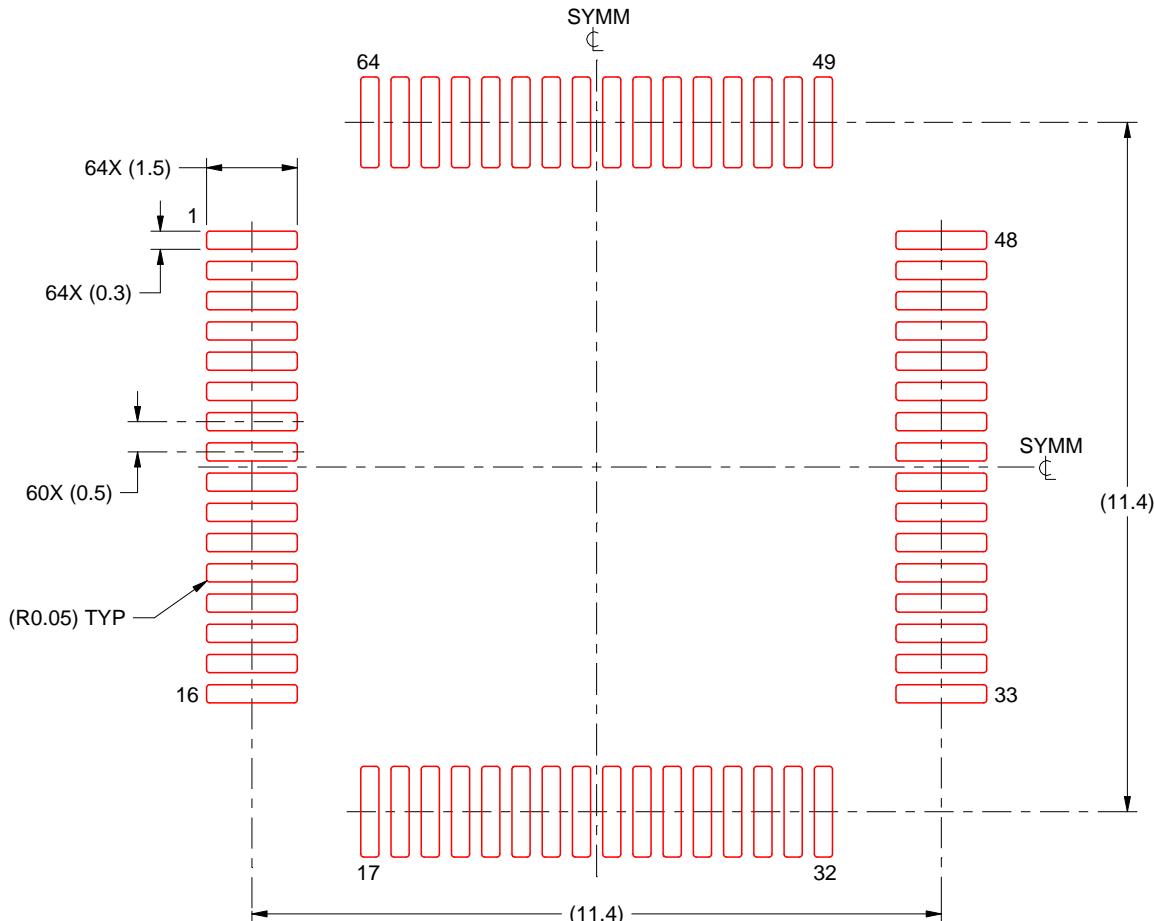

# EXAMPLE STENCIL DESIGN

PM0064A

LQFP - 1.6 mm max height

PLASTIC QUAD FLATPACK

4215162/A 03/2017

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025年10月